HIGH FREQUENCY ∑ INVERTED MESA ∑ TTL / CMOS ∑ FULL-SIZE DIP ∑ 5VDC

VOLTAGE-CONTROLLED CRYSTAL OSCILLATORS

ACVX1224

APPLICATIONS:

∑ Phase locked loops (PLLs). ∑ Gigabit ethernet, XDM.

∑ Reference signal tracking. ∑ Synthesizers.

FEATURES:

∑ 14-Pin DIP 5 Vdc. ∑ Large frequency deviation available.

∑ Tight symmetry (45/55%) available. ∑ Inverted mesa crystal.

∑ High stability. ∑ Low noise.

* Under development 160MHz to 300MHz, please call for availability.

Please call us for higher frequencies, other pulling specs.,

control voltage range or linearity.

Environmental and mechanical specifications, see appendix C. Group 1.

Marking, see appendix G.

Test circuits and waveform, see appendix B.

Value added, see appendix D.

Recommended handling, see appendix F.

Application notes, see appendix A.

ACVX1224 - Frequency - Temperature - Stability - Duty Cycle - Pulling - Value Added - Packaging

XX.XXXXX MHz

-J for ±20ppm max.

-N15 ± 150ppm min.

-S for 45 /55%

@

1

/

2Vdd

-G

Gull Wing

-QXX (Trimmed Leads)

-D for -10∞C to + 60∞C

-E for -20∞C to + 70∞C

-F for -30∞C to + 70∞C

-N for -30∞C to + 85∞C

-L for -40∞C to + 85∞C

ORDERING OPTIONS

OFFSET

PHASE

FREQUENCY

NOISE

(Hz)

(dBc/Hz)

10

-70

100

-100

1kHz

-125

10kHz

-150

100kHz

-160

PIN

FUNCTION

No.

1 Voltage Control Vc

7

GND / Case

8

Output

14

V

dd

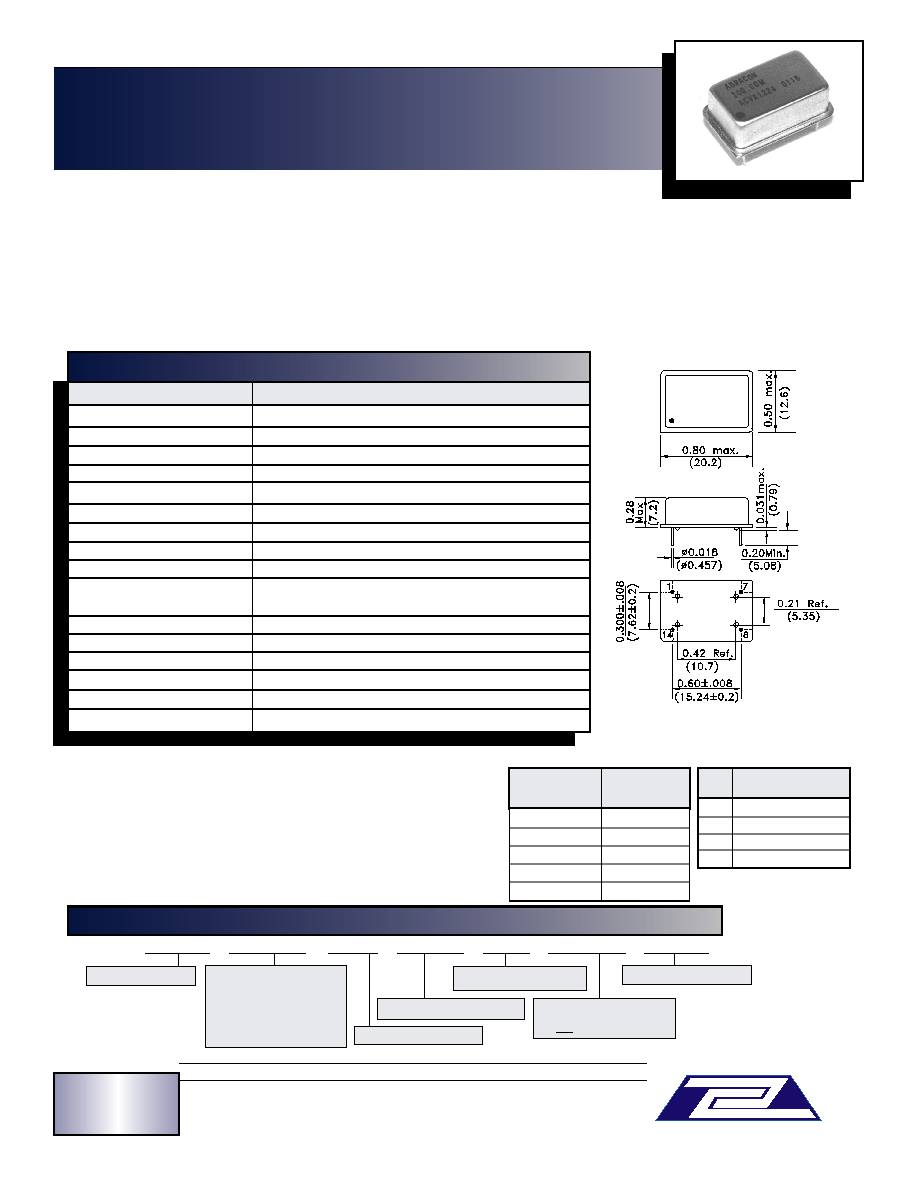

20.2 x 12.6 x 7.2 mm

Dimensions: Inches (mm)

-TY for Tray packing

29 Journey ∑ Aliso Viejo, CA 92656 ∑ USA

(949) 448-7070 ∑ F

AX

: (949) 448-8484

E-

MAIL

:

abinfo

@

abracon.com ∑

I

NTERNET

A

DDRESS

:

www.abracon.com

ABRACON IS

ISO 9001 / QS 9000

CERTIFIED

NOTE: Left blank if standard

∑ All specifications and markings subject to change without notice

ABRACON

Æ

C O R P O R A T I O N

65

TYPICAL PHASE NOISE

Frequency Range

(F

o

)

65MHz - 300MHz*

Operating Temperature (T

OPR

)

0∞C to +70∞C (See Options)

Storage Temperature (T

STO

)

-40∞C to +85∞C

Overall Frequency Stability

±25ppm max. (See Options)

Supply Voltage

(V

dd

)

5Vdc ±5%

Input Current (I

dd

) 60mA max.

Duty Cycle or Symmetry

40 / 60% max.

@ 1

/

2

V

dd

(See Options)

Rise and Fall Times (T

R

/

T

F

)

6ns max.

Output Load

TTL / CMOS (50pF or 10TTL gate)

Output Voltage

(V

OH

)

0.9 *V

dd

min.

(V

OL

)

0.4V

dc

max.

Transfer Function

Positive

Voltage Control

(Vc)

0.5Vdc to 4.5Vdc

Center Voltage

2.5Vdc ±0.5Vdc

Frequency Deviation

±100ppm min.

(See Options)

Linearity

±10% max.

Start-up Time

(T

OSC

)

10ms max.

S

S

T

T

A

A

N

N

D

D

A

A

R

R

D

D

S

S

P

P

E

E

C

C

I

I

F

F

I

I

C

C

A

A

T

T

I

I

O

O

N

N

S

S

PARAMETERS

SPECIFICATIONS