| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AD12400 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- FEATURES

- APPLICATIONS

- GENERAL DESCRIPTION

- FUNCTIONAL BLOCK DIAGRAM

- PRODUCT HIGHLIGHTS

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

12-Bit 400 MSPS

A/D Converter

AD12400

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703

© 2003 Analog Devices, Inc. All rights reserved.

FEATURES

400 MSPS sample rate

SNR of 63 dBFS @128 MHz

SFDR of 70 dBFS @128 MHz

VSWR of 1:1.5

Wideband ac-coupled input signal conditioning

Enhanced spurious-free dynamic range

Single-ended or differential encode signal

LVDS output levels

Twos complement output data

APPLICATIONS

Communications test equipment

Radar and satellite subsystems

Phased array antennas--digital beam forming

Multichannel, multimode receivers

Secure communications

Wireless and wired broadband communications

Wideband carrier frequency systems

GENERAL DESCRIPTION

The AD12400 is a 12-bit analog-to-digital converter with a

transformer-coupled analog input and digital post processing

for enhanced SFDR. The product operates at a 400 MSPS

conversion rate with outstanding dynamic performance in

wideband carrier systems.

The AD12400 requires 3.8 V analog, 3.3 V digital, and 1.5 V

digital supplies and provides a flexible encode signal that can be

differential or single-ended. No external reference is required.

The AD12400 package style is an enclosed 2.9" ◊ 2.6" ◊ 0.6"

module. Performance is rated over a 0∞C to 60∞C case

temperature range.

FUNCTIONAL BLOCK DIAGRAM

03735-0-001

ADC

A

DATA

READY

A

DATA

READY

B

DA0≠DA11

DB0≠DB11

CLK DISTRIBUTION

AD12400

POST-

PROCESSING

ADC

B

A

IN

CLOCK DISTRIBUTION

DIVIDE BY 2

ENC

ENC

Figure 1.

PRODUCT HIGHLIGHTS

1.

Guaranteed sample rate of 400 MSPS.

2.

Input signal conditioning with optimized dynamic

performance to 180 MHz.

3.

Additional performance options available--contact factory.

4.

Proprietary Advanced Filter BankTM digital post processing

from VCorpÆ Technologies, Inc.

AD12400

Rev. 0 | Page 2 of 28

TABLE OF CONTENTS

Specifications..................................................................................... 3

DC Specifications ......................................................................... 3

AC Specifications.......................................................................... 4

Explanation of Test Levels ............................................................... 5

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 8

Definitions of Specifications ......................................................... 11

Typical Performance Characteristics ........................................... 13

Theory of Operation ...................................................................... 15

Time-Interleaving ADCs ........................................................... 15

Analog Input ............................................................................... 16

Clock Input.................................................................................. 16

Digital Outputs ........................................................................... 16

Power Supplies ............................................................................ 16

START-UP AND

RESET

........................................................... 17

Lead/Lag ...................................................................................... 17

Thermal Considerations............................................................ 17

Package Integrity/Mounting Guidelines ................................. 18

AD12400 Evaluation KIT.......................................................... 19

Power Connector ................................................................... 19

Analog Input ........................................................................... 19

Encode ..................................................................................... 19

Data Outputs........................................................................... 19

Adapter Card .......................................................................... 19

Digital Post Processing Control ........................................... 19

RESET

...................................................................................... 19

Layout Guidelines........................................................................... 25

PCB Interface .............................................................................. 25

Outline Dimensions ....................................................................... 27

Ordering Guide .......................................................................... 27

REVISION HISTORY

Revision 0: Initial Version

AD12400

Rev. 0 | Page 3 of 28

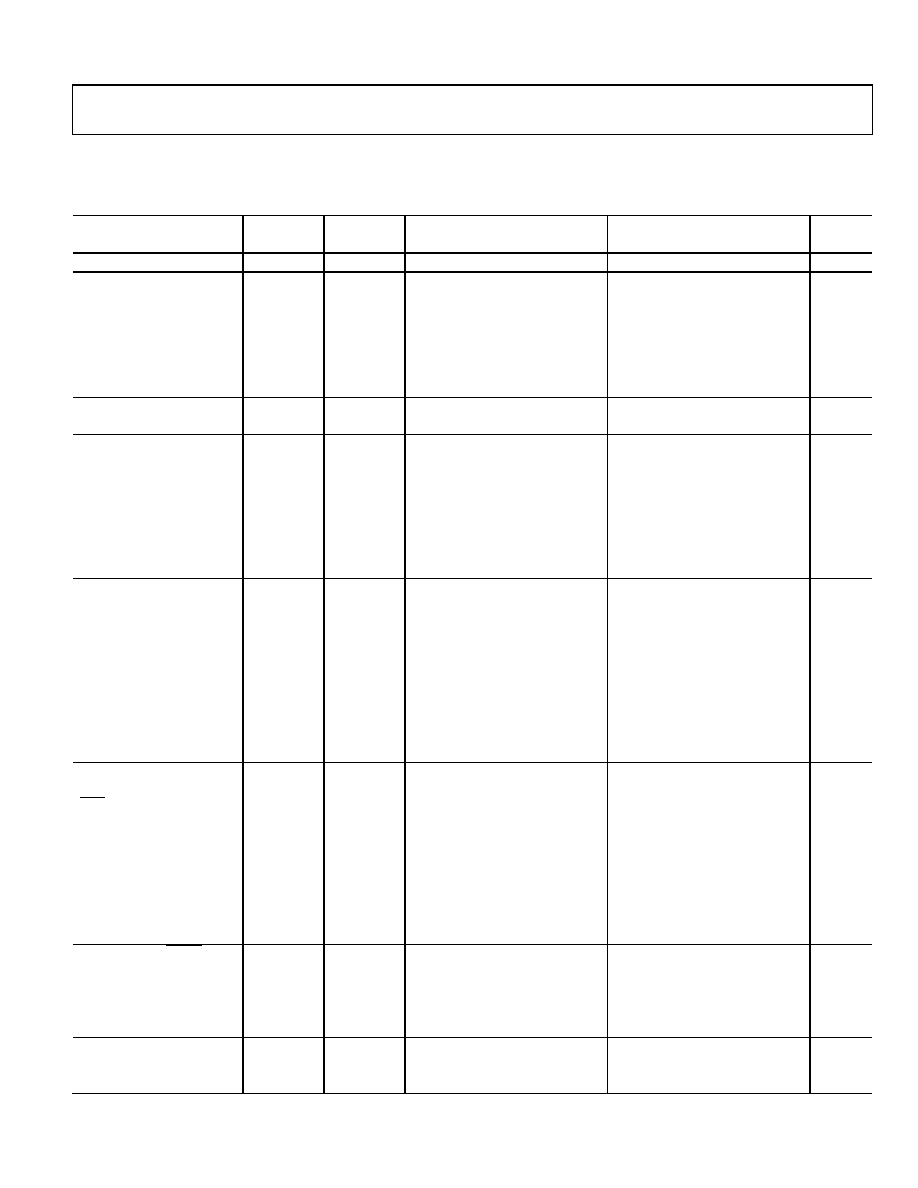

SPECIFICATIONS

DC SPECIFICATIONS

Table 1. VA = 3.8 V, VC = 3.3 V, VD = 1.5 V, Encode = 400 MSPS, 0∞C T

CASE

60∞C, unless otherwise noted.

AD12400JWS

AD12400KWS

Parameter

Case

Temp

Test

Level

Min Typ Max

Min Typ Max

Unit

RESOLUTION

12

12

Bits

ACCURACY

No Missing Codes

Full

IV

Guaranteed

Guaranteed

Offset Error

Full

I

-12

+12

-12

+12

LSB

Gain Error @ 10 MHz

Full

I

-10

+10

-10

+10

%FS

Differential Nonlinearity

(DNL)

60∞C

V

0.3

0.3

LSB

Integral Nonlinearity (INL)

60∞C

V

0.5

0.5

LSB

TEMPERATURE

DRIFT

Gain Error

60∞C

V

0.02

0.02

%/∞C

ANALOG

INPUT

(AIN)

Full-Scale Input Voltage

Range

60∞C

V

3.2

3.2

V p-p

Frequency Range

Full

IV

10

180

10

180

MHz

Flatness (10 MHz-180 MHz)

Full

IV

0.5

1

0.5

1

dB

Input VSWR (50 )

(10 MHz≠180 MHz)

60∞C

V

1.5

1.5

Analog Input Bandwidth

60∞C

V

450

450

MHz

POWER SUPPLY

1

Supply

Voltage

VA

Full

IV

3.6

3.8

3.6

3.8

V

VC

Full

IV

3.2

3.4

3.2

3.4

V

VD

Full

IV

1.475

1.575

1.475

1.575

V

Supply Current

I

VA

(VA = 3.8 V)

Full

I

0.95

1.11

0.95

1.11

A

I

VC

(VC = 3.3 V)

Full

I

400

500

400

500

mA

I

VD

(VD = 1.5 V)

Full

I

1.4

1.8

1.4

1.8

A

Total Power Dissipation

Full

I

7.0

8.5

7.0

8.5

W

ENCODE INPUTS

2

Differential Inputs (ENC,

ENC)

Input Voltage Range

Full

IV

0.4

0.4

V

Input Resistance

60∞C

V

100

100

Input Capacitance

60∞C

V

4

4

pF

Common-Mode Voltage

60∞C

V

±3

±3

V

Single-Ended

Inputs

(ENC)

Input Voltage

Full

IV

0.4

2

2.5

0.4

2

2.5

V p-p

Input Resistance

60∞C

V

50

50

LOGIC INPUTS (RESET)

3

Logic 1 Voltage

Full

IV

2.0

2.0

V

Logic 0 Voltage

Full

IV

0.8

0.8

V

Source I

IH

60∞C

V

10

10

µA

Source I

IL

60∞C

V

1

1

mA

LOGIC OUTPUTS

(DRA, DRB, Output Bits)

4

Differential Output Voltage

Full

IV

247

454

247

454

mV

AD12400

Rev. 0 | Page 4 of 28

AD12400JWS

AD12400KWS

LOGIC OUTPUTS

Output Drive Current

Full

IV

-4

+4

-4

+4

mA

Output Common-Mode

Voltage

Full

IV

1.125

1.375

1.125

1.375

V

Start-Up Time

Full

IV

600

600

ms

1

Tested using input frequency of 70 MHz. See Figure 17 for I(VD) variation vs. input frequency.

2

All ac specifications tested by driving ENC single-ended.

3

Refer to Table 5 for logic convention on all logic inputs.

4

Digital Output Logic Levels: DR V = 3.3 V, C

LOAD

= 8 pF. 3.3 V LVDS R1 = 100 .

Specifications subject to change without notice.

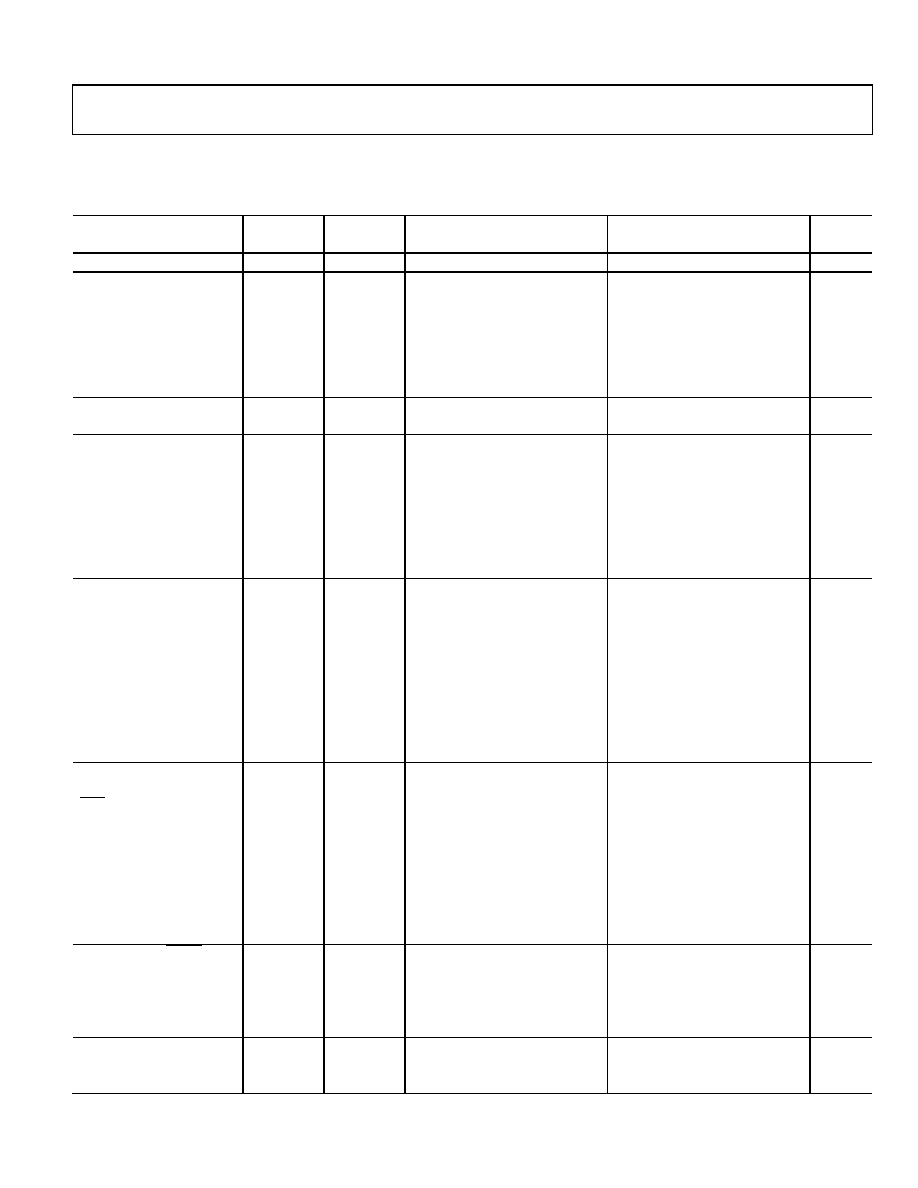

AC SPECIFICATIONS

1

Table 2. VA = 3.8 V, VC = 3.3 V, VD = 1.5 V, Encode = 400 MSPS, 0∞C T

CASE

60∞C, unless otherwise noted.

AD12400JWS

AD12400KWS

Parameter

Case

Temp Test

Level

Min Typ Max Min Typ Max Unit

DYNAMIC PERFORMANCE

2

SNR

Analog Input 10 MHz

Full

I

62

64.4

62

64.4

dBFS

@ -1.0 dBFS 70 MHz

Full

I

61.5

64

61.5

64

dBFS

128 MHz

Full

I

60

63.5

60

63.5

dBFS

180 MHz

Full

I

60

62.5

60

62.5

dBFS

SINAD

3

Analog Input 10 MHz

Full

I

61

64

61

64

dBFS

@ -1.0 dBFS 70 MHz

Full

I

60.5

64

60.5

64

dBFS

128 MHz

Full

I

59

62.5

59

62.5

dBFS

180 MHz

Full

I

57

61

57

61

dBFS

Spurious-Free Dynamic Range

3

Analog Input 10 MHz

Full

I

69

80

69

80

dBFS

@ -1.0 dBFS 70 MHz

Full

I

69

84

69

84

dBFS

128 MHz

Full

I

67

76

67

76

dBFS

180 MHz

Full

I

62

71

62

71

dBFS

Image Spur

4

Analog Input 10 MHz

Full

I

60

75

62

75

dBFS

@ -1.0 dBFS 70 MHz

Full

I

60

72

62

72

dBFS

128 MHz

Full

I

56

70

62

70

dBFS

180 MHz

Full

I

54

70

62

70

dBFS

Offset Spur

4

60∞C

V

65

65

dBFS

Analog Input @ -1.0 dBFS

Two-Tone IMD

5

F1, F2 @ -6 dBFS

60∞C

V

-75

-75

dBc

SWITCHING SPECIFICATIONS

Conversion Rate

6

Full

IV

396

400

404

396

400

404

MSPS

Encode Pulsewidth High (t

EH

)

1

60∞C

V

1.25

1.25

ns

Encode Pulsewidth Low (t

EL

)

1

60∞C

V

1.25

1.25

ns

DIGITAL OUTPUT PARAMETERS

Valid Time (t

V

)

Full

IV

1.9

2.4

3.1

1.9

2.4

3.1

ns

Propagation Delay (t

PD

)

60∞C

V

1.20

1.20

ns

Rise Time (t

R

) (20% to 80%)

60∞C

V

1

1

ns

Fall Time (t

F

) (20% to 80%)

60∞C

V

1

1

ns

AD12400

Rev. 0 | Page 5 of 28

AD12400JWS

AD12400KWS

Parameter

Case

Temp Test

Level

Min Typ Max Min Typ Max Unit

DR Propagation Delay (t

EDR

)

60∞C

V

3.88

3.88

ns

Data to DR Skew (t

EDR

- t

PD

)

60∞C

V

2.68

2.68

ns

Pipeline Latency

7

Full

IV

40

40

Cycles

Aperture Delay (t

A

)

60∞C

V

1.6

1.6

ns

Aperture Uncertainty (Jitter, t

J

)

60∞C

V

0.4

0.4

ps rms

1

All ac specifications tested with a single-ended 2.0 V p-p ENCODE.

2

Dynamic performance guaranteed for analog input frequencies of 10 MHz to 180 MHz.

3

Not including image spur.

4

Image spur will be at fs/2

≠

A

IN

and the offset spur will be at fs/2.

5

F1 = 70 MHz, F2 = 73 MHz.

6

Parts are tested with 400 MSPS encode. Device can be clocked at lower encode rates, but specifications are not guaranteed. Specifications will be guaranteed by

design for encode 400 MSPS ± 1%.

7

Pipeline latency will be exactly 40 cycles.

EXPLANATION OF TEST LEVELS

I

100% production tested.

II

100% production tested at 25∞C and sample tested at specified temperatures.

III

Sample tested only.

IV

Parameter is guaranteed by design and characterization testing.

V

Parameter is a typical value only.

VI

100% production tested at 25∞C; guaranteed by design and characterization testing for industrial temperature range; 100%

production tested at temperature extremes for military devices.