Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

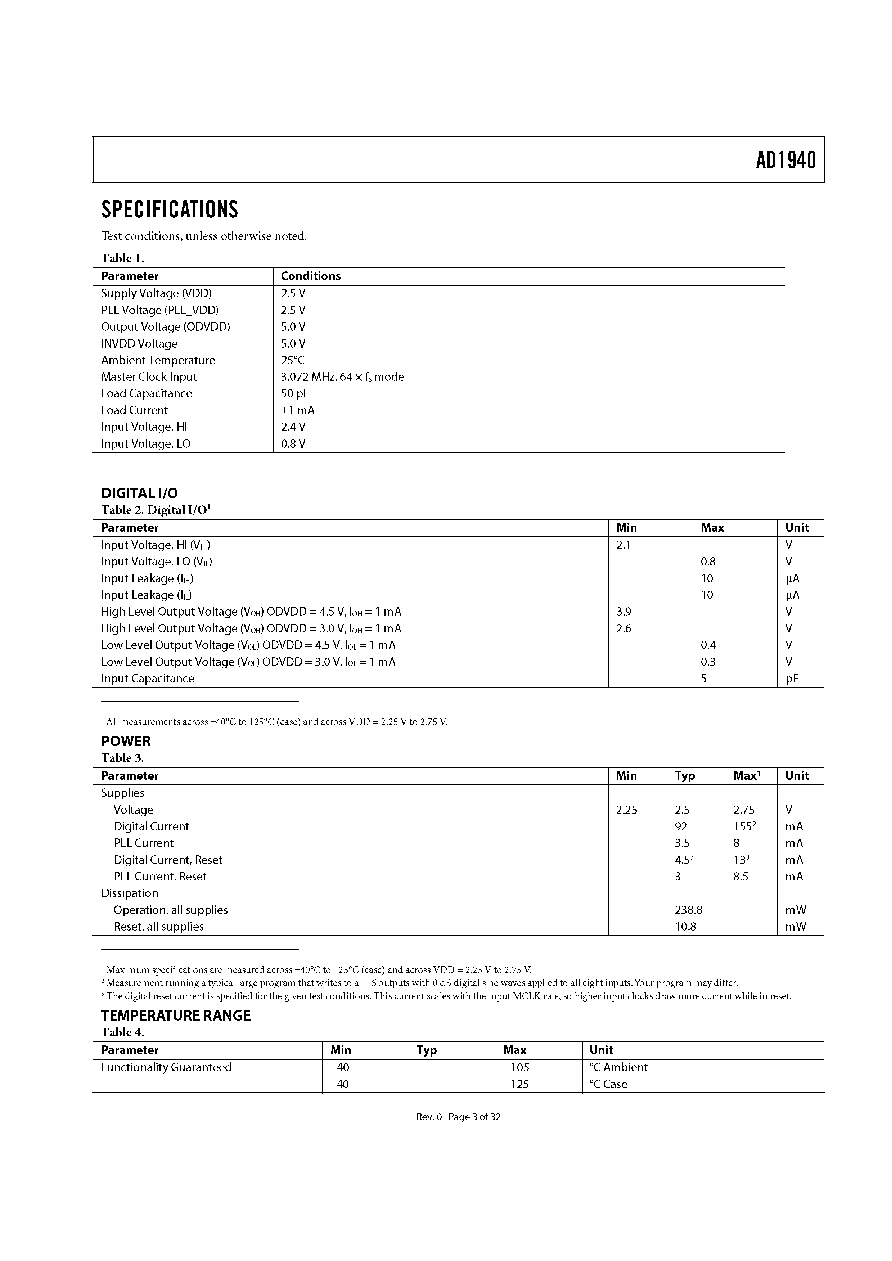

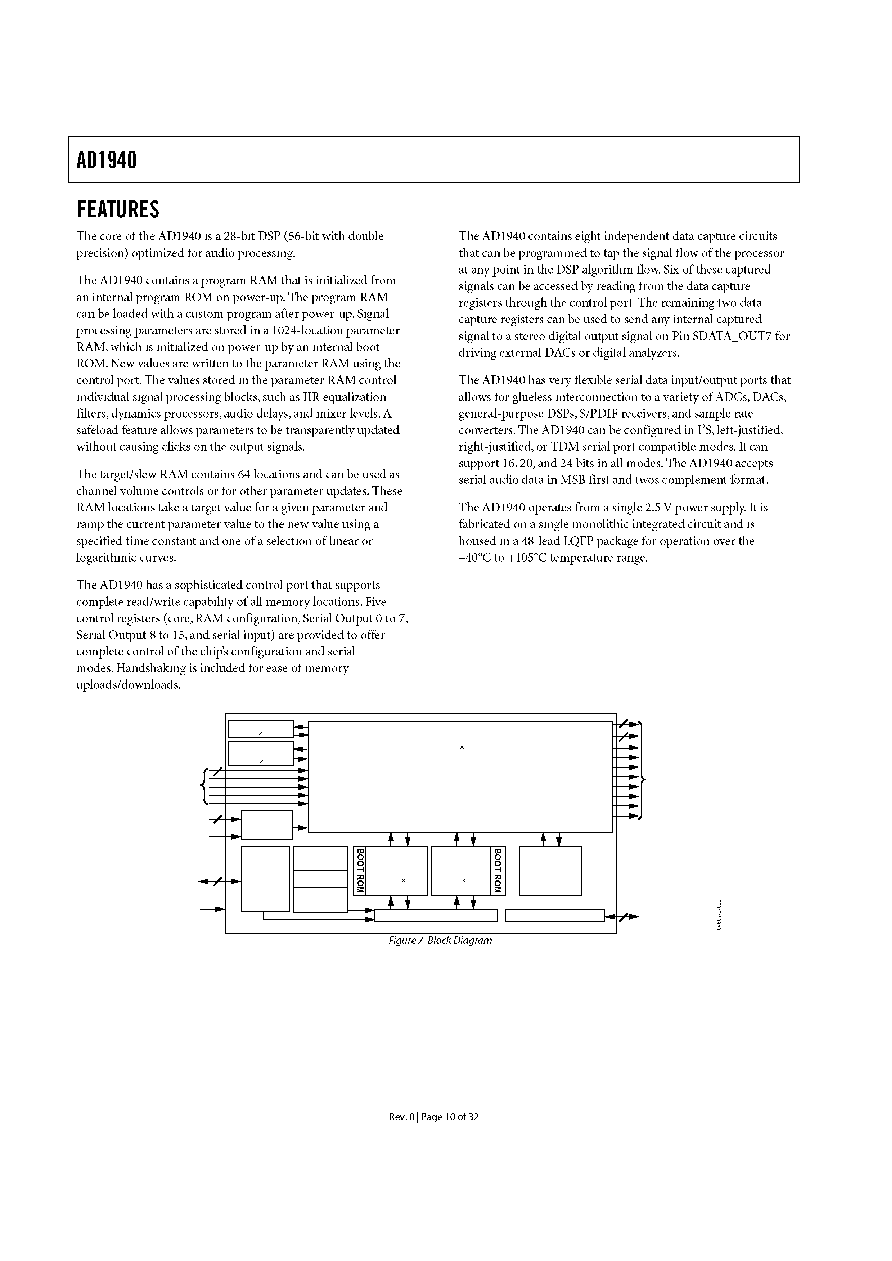

VOLTAGE

REGULATOR

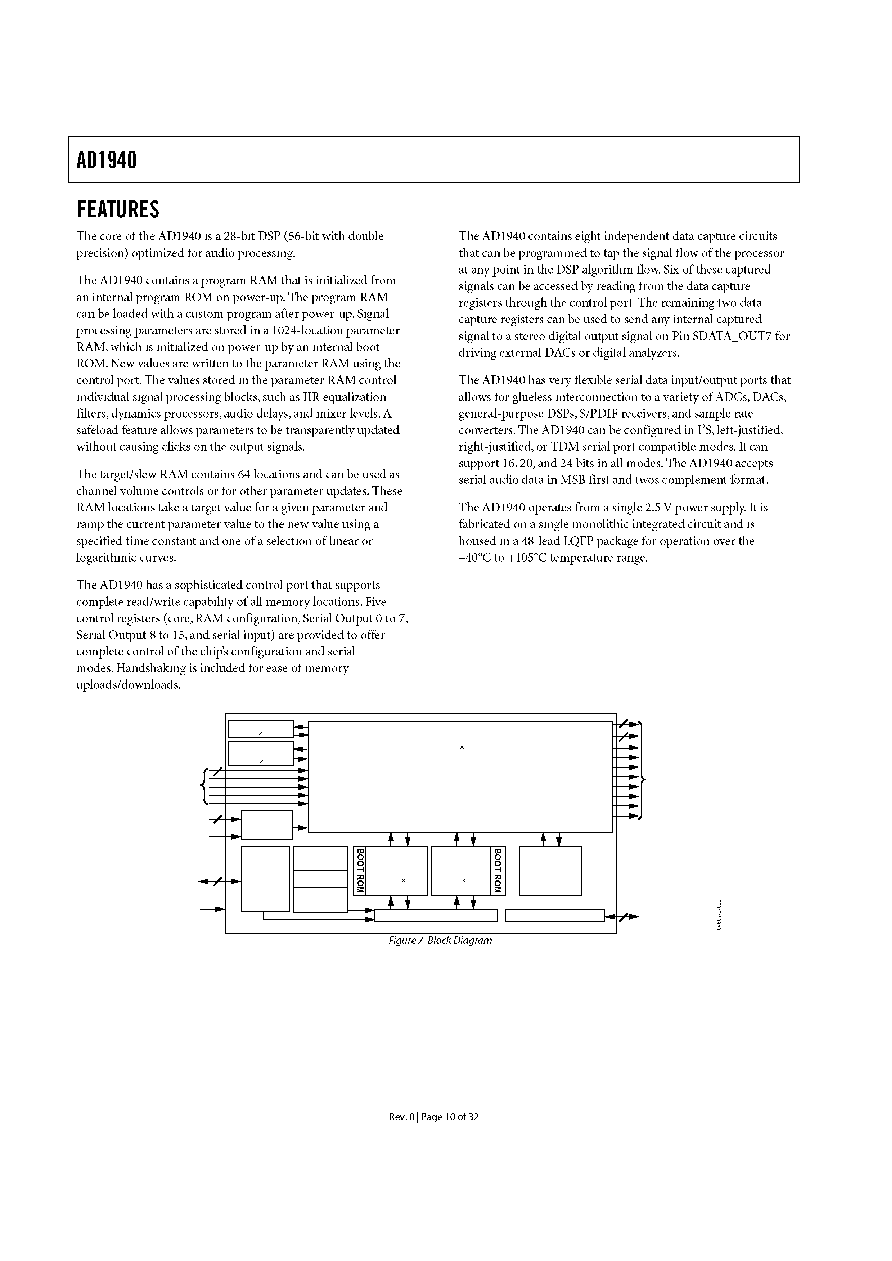

AD1940

28 28

DSP CORE

DATA FORMAT:

PLL

SERIAL

CONTROL

INTERFACE

SERIAL DATA/

TDM INPUTS

MASTER

CLOCK

INPUT

SPI I/O

RAM

ROM

SERIAL

DATA/

TDM

OUTPUTS

2

4

4

2

2

5.23 (SINGLE

PRECISION)

10.46 (DOUBLE

PRECISION)

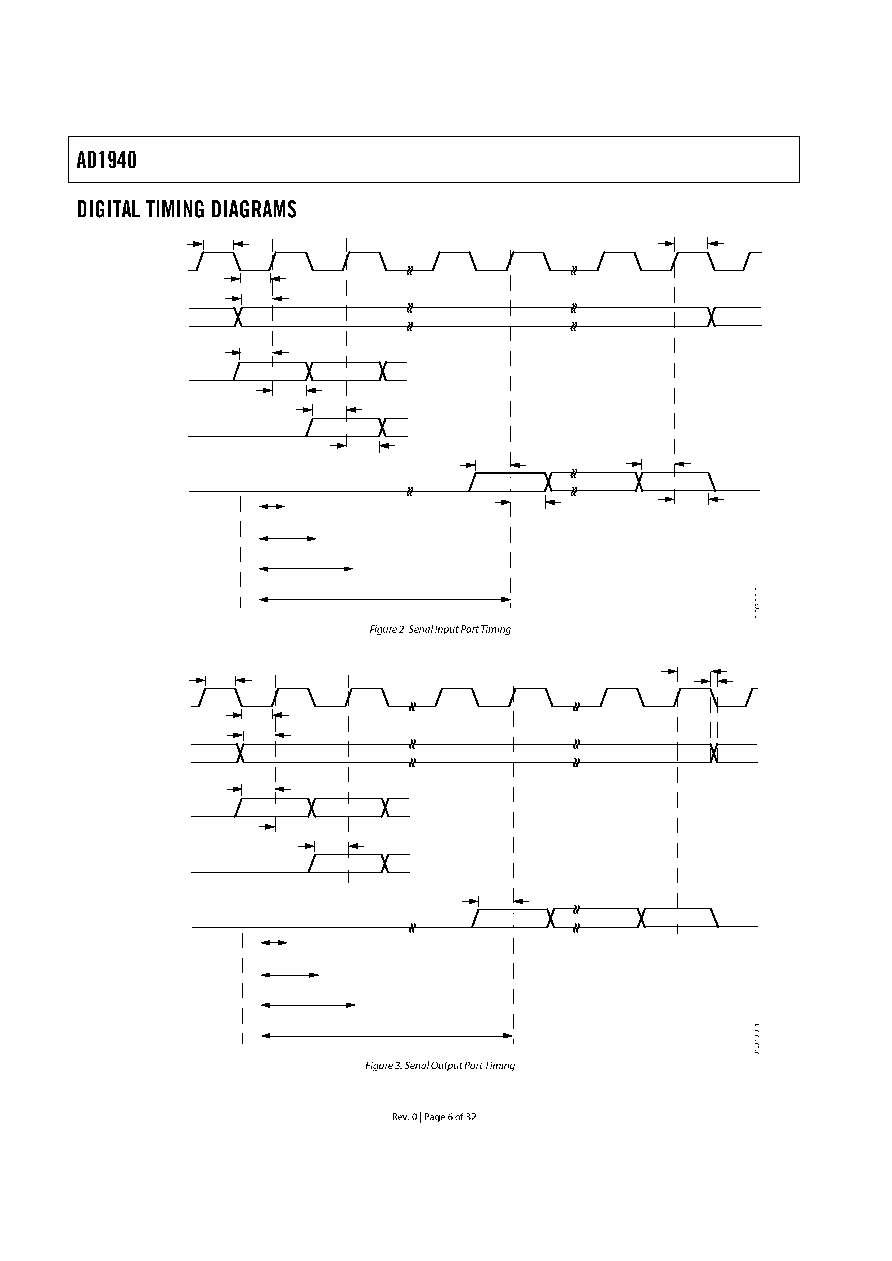

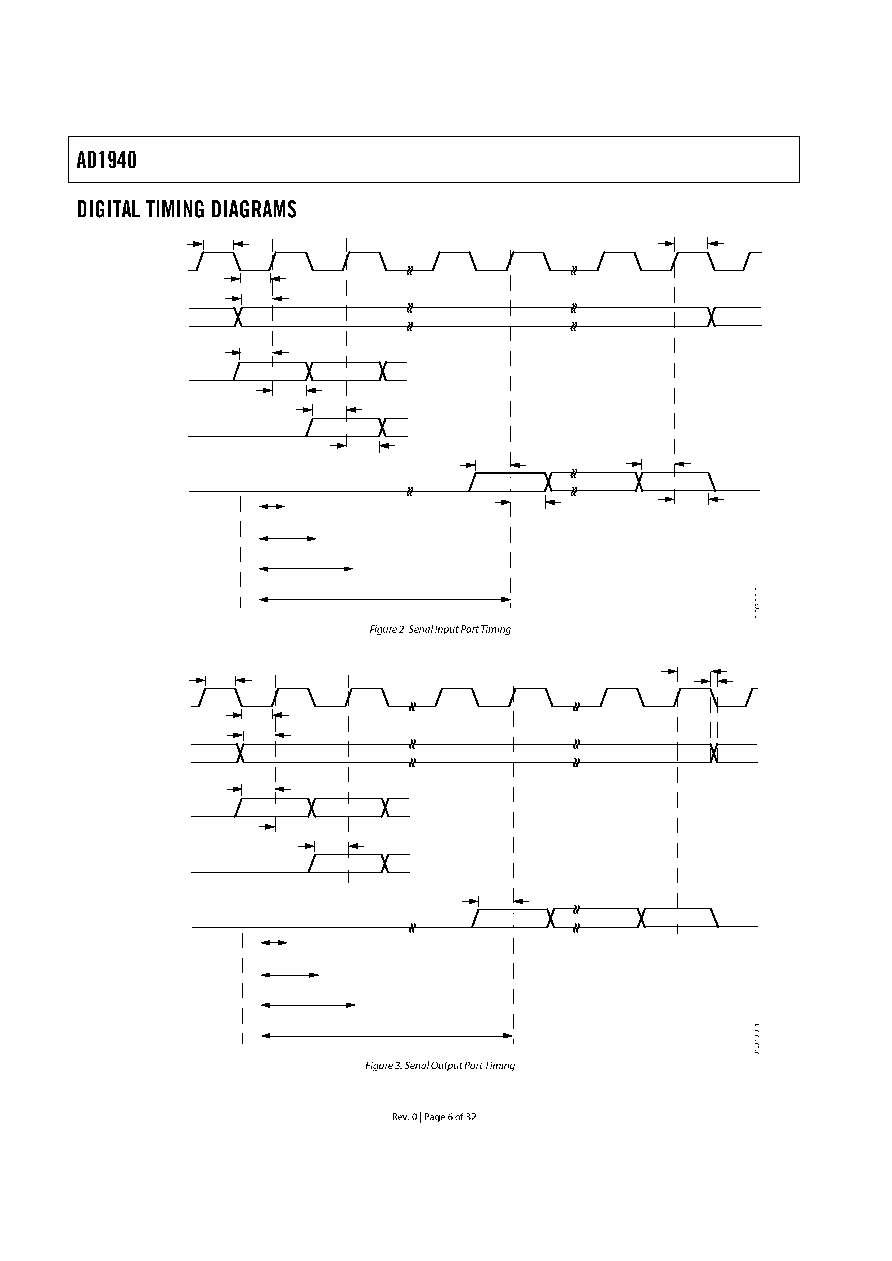

BCLK_IN

LRCLK_IN

SDATA_INX

LEFT-JUSTIFIED

MODE

LSB

SDATA_INX

I

2

S-JUSTIFIED

MODE

SDATA_INX

RIGHT-JUSTIFIED

MODE

t

BIH

MSB

MSB-1

MSB

MSB

8-BIT CLOCKS

(24-BIT DATA)

12-BIT CLOCKS

(20-BIT DATA)

14-BIT CLOCKS

(18-BIT DATA)

16-BIT CLOCKS

(16-BIT DATA)

t

LIS

t

SIS

t

SIH

t

SIH

t

SIS

t

SIS

t

SIH

t

SIS

t

SIH

t

LIH

t

BIL

BCLK_OUTX

LRCLK_OUTX

SDATA_OUTX

LEFT-JUSTIFIED

MODE

LSB

SDATA_OUTX

I

2

S-JUSTIFIED

MODE

SDATA_OUTX

RIGHT-JUSTIFIED

MODE

t

BIH

MSB

MSB-1

MSB

MSB

8-BIT CLOCKS

(24-BIT DATA)

12-BIT CLOCKS

(20-BIT DATA)

14-BIT CLOCKS

(18-BIT DATA)

16-BIT CLOCKS

(16-BIT DATA)

t

LOS

t

SDDS

t

SDDM

t

SDDS

t

SDDM

t

SDDS

t

SDDM

t

LCH

t

TS

t

BIL

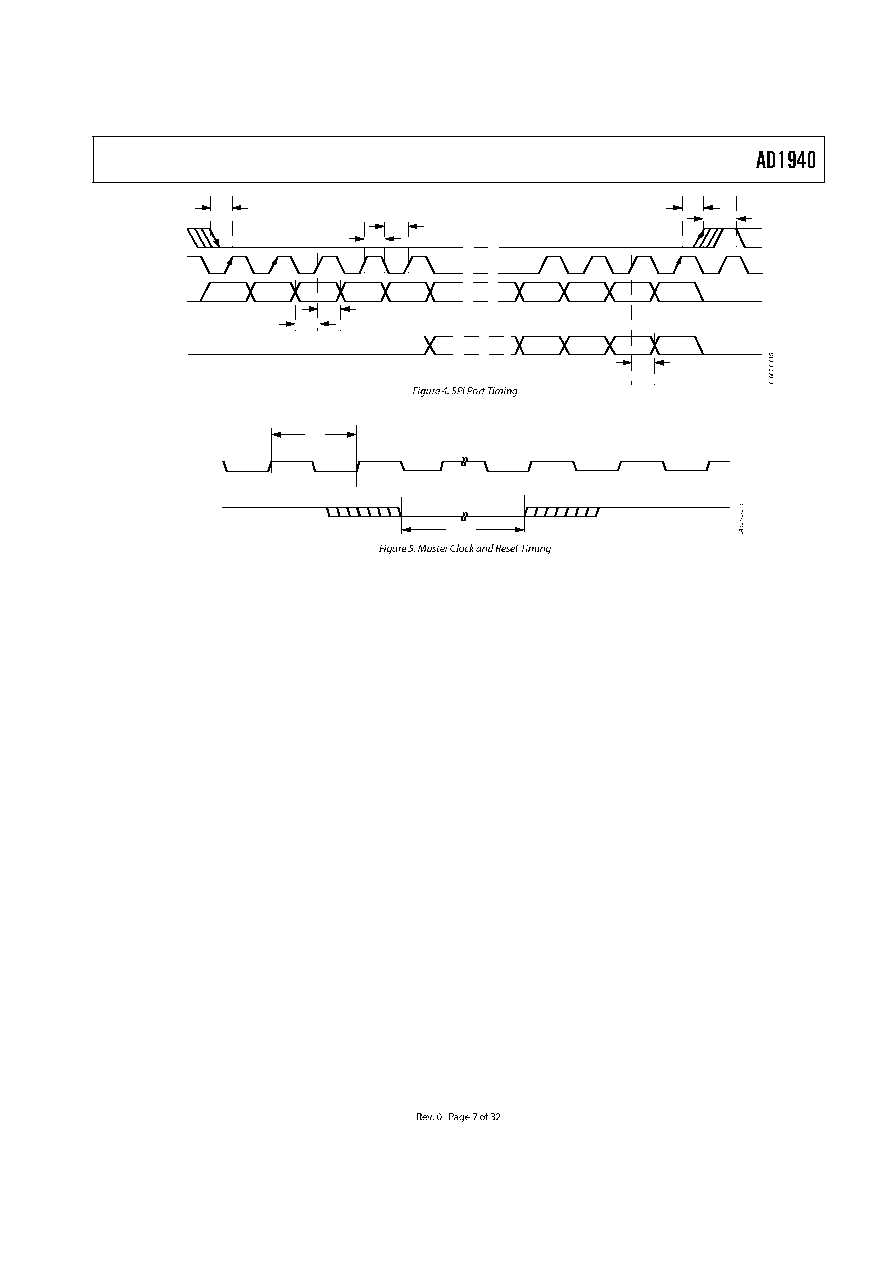

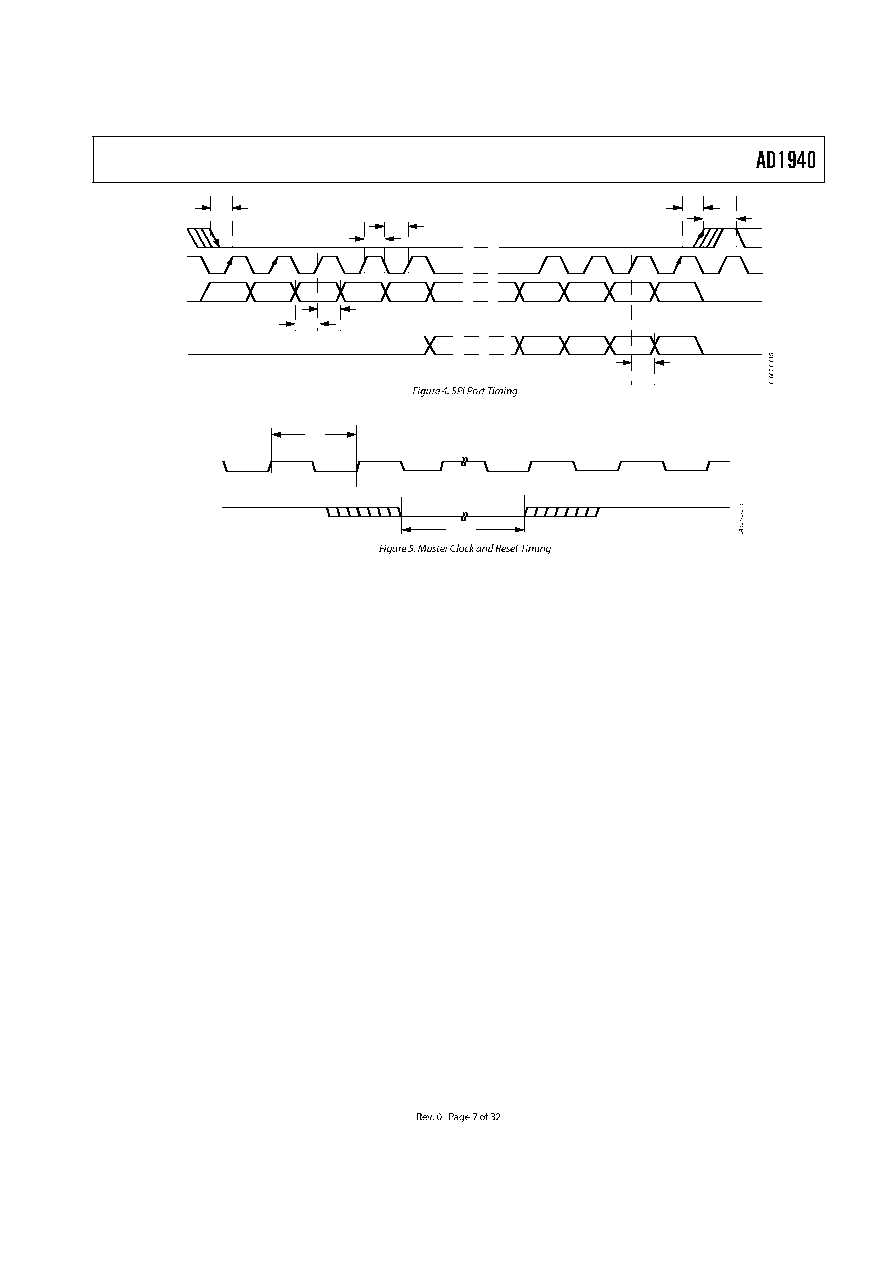

CLATCH

CCLK

CDATA

COUT

t

CLS

t

CDS

t

CDH

t

COD

t

CCPH

t

CCPL

t

CLH

t

CLPH

MCLK

RESETB

t

MP

t

RLPW

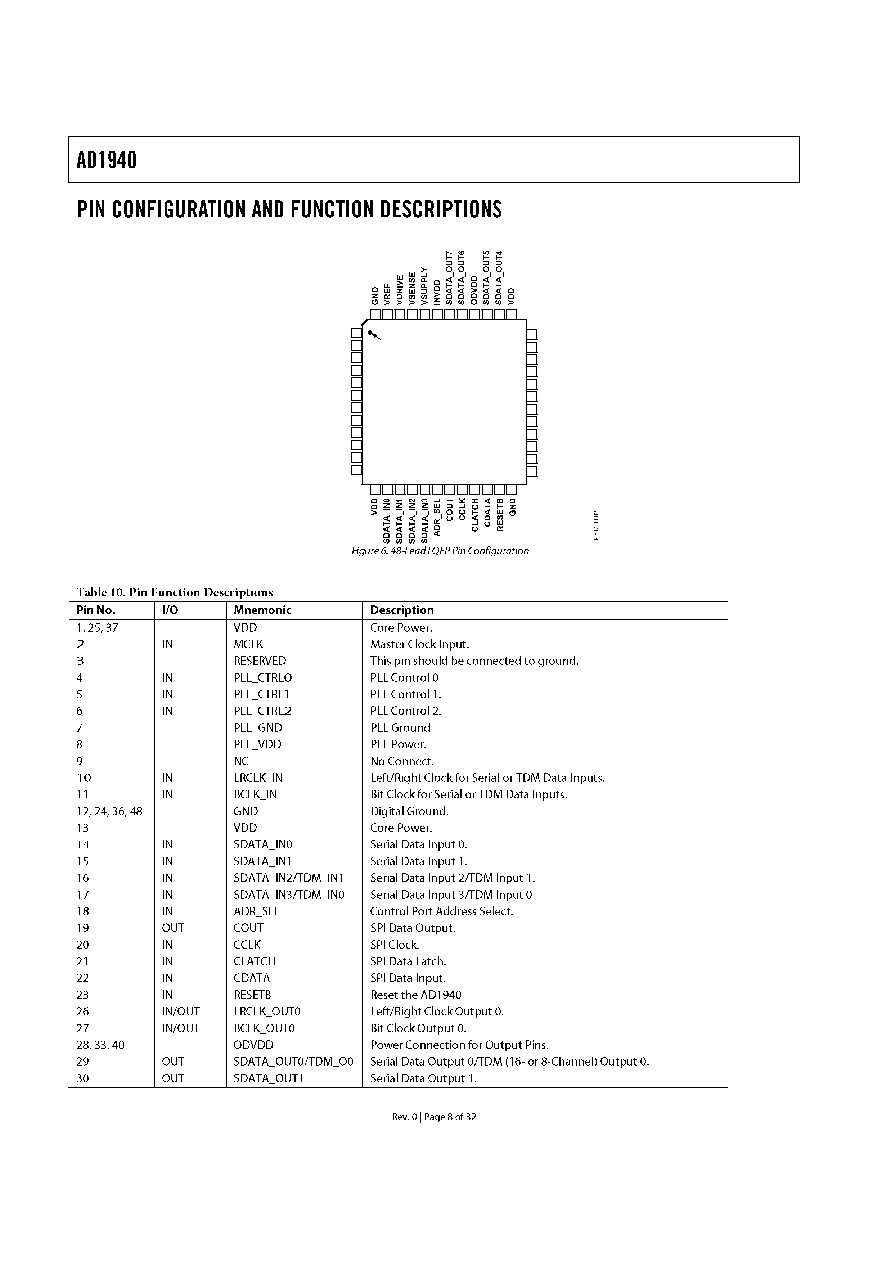

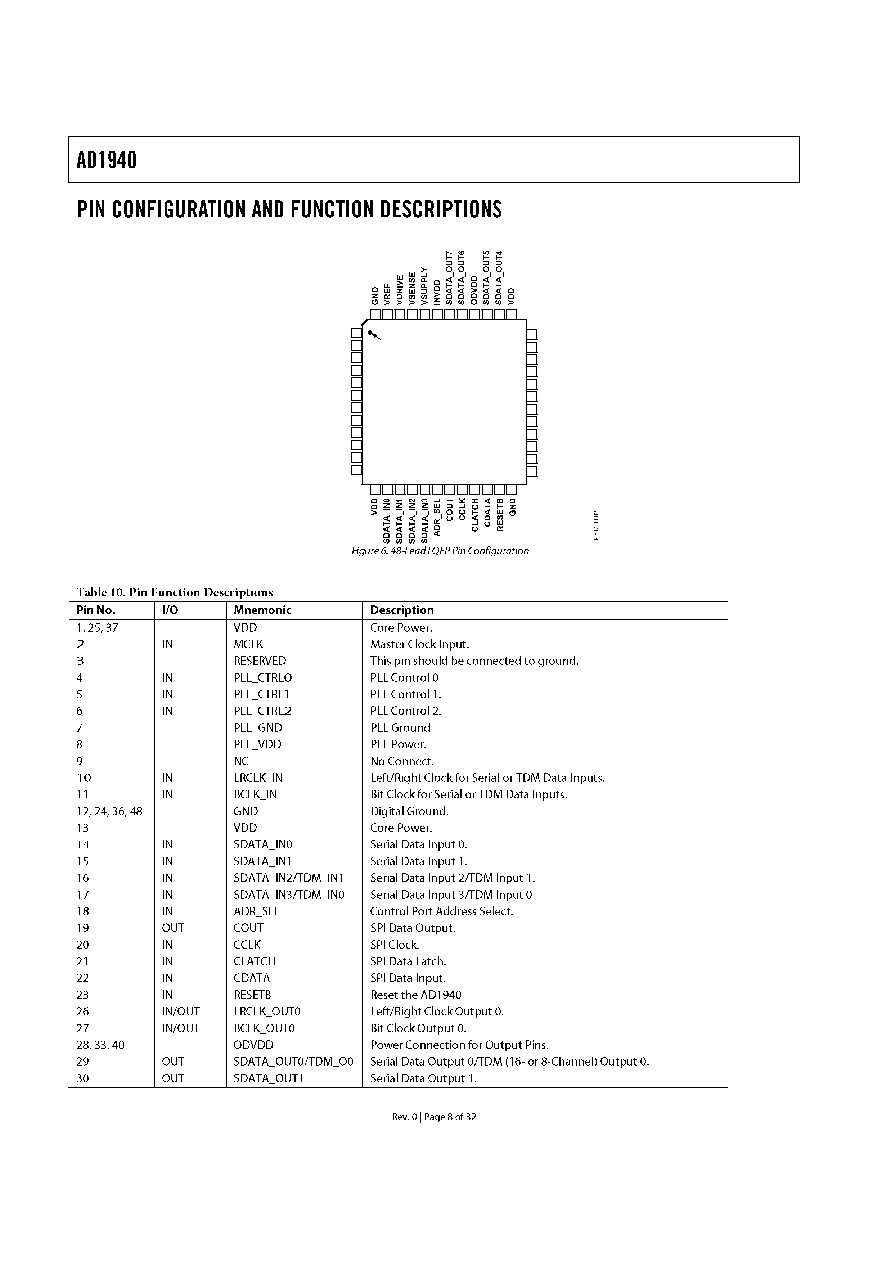

36

35

34

33

32

31

30

29

28

27

26

25

13 14 15 16 17 18 19 20 21 22 23 24

1

2

3

4

5

6

7

8

9

10

11

12

48 47 46 45 44

39 38 37

43 42 41 40

GND

BCLK_OUT1

LRCLK_OUT1

ODVDD

SDATA_OUT3

SDATA_OUT2

SDATA_OUT1

VDD

MCLK

RESERVED

PLL_VDD

NC

SDATA_OUT0

ODVDD

BCLK_OUT0

LRCLK_OUT0

GND

VDD

PIN 1

INDICATOR

PLL_CTRL0

PLL_CTRL1

PLL_CTRL2

PLL_GND

AD1940

TOP VIEW

(Not to Scale)

LRCLK_IN

BCLK_IN

NC = NO CONNECT

28 28

DSP CORE

DATA FORMAT:

5.23 (SINGLE PRECISION)

10.46 (DOUBLE PRECISION)

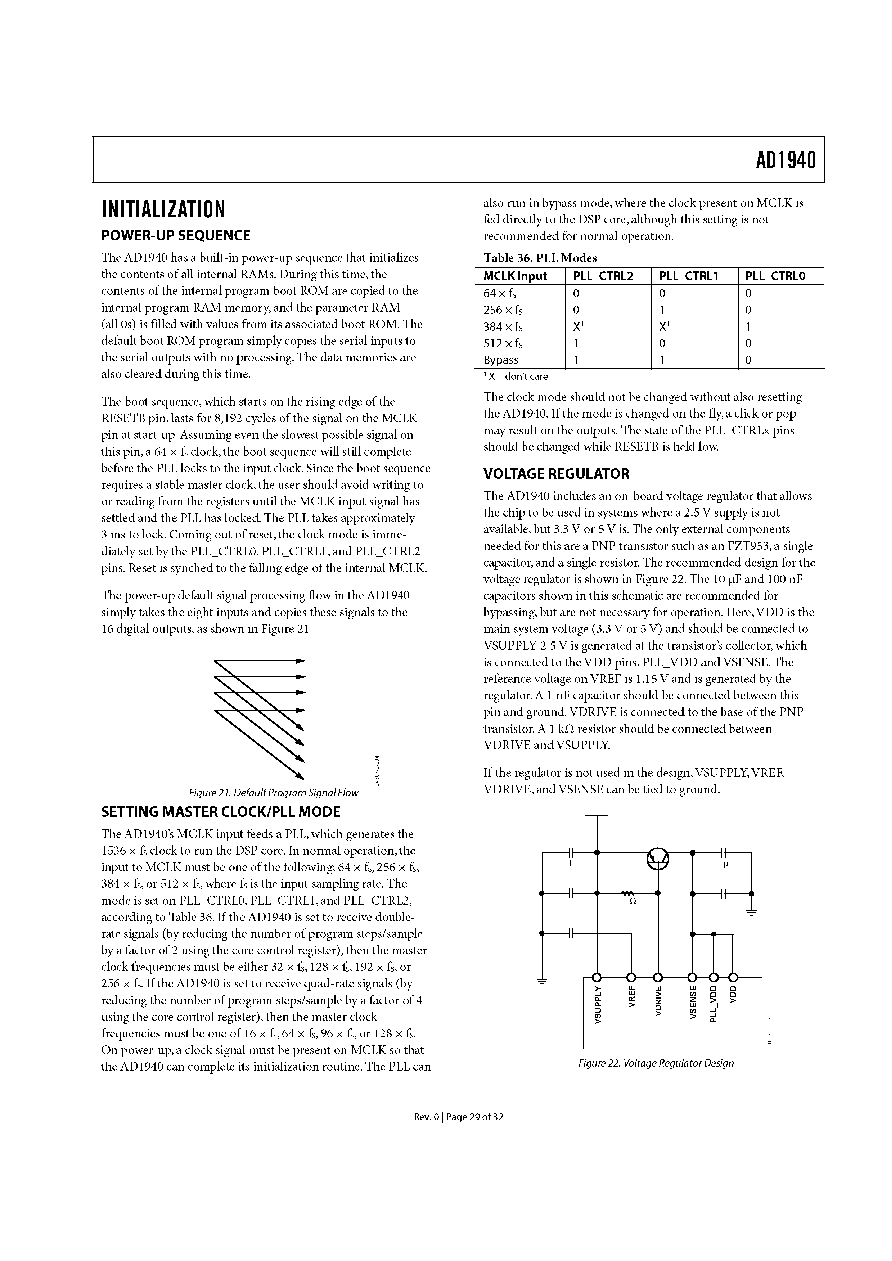

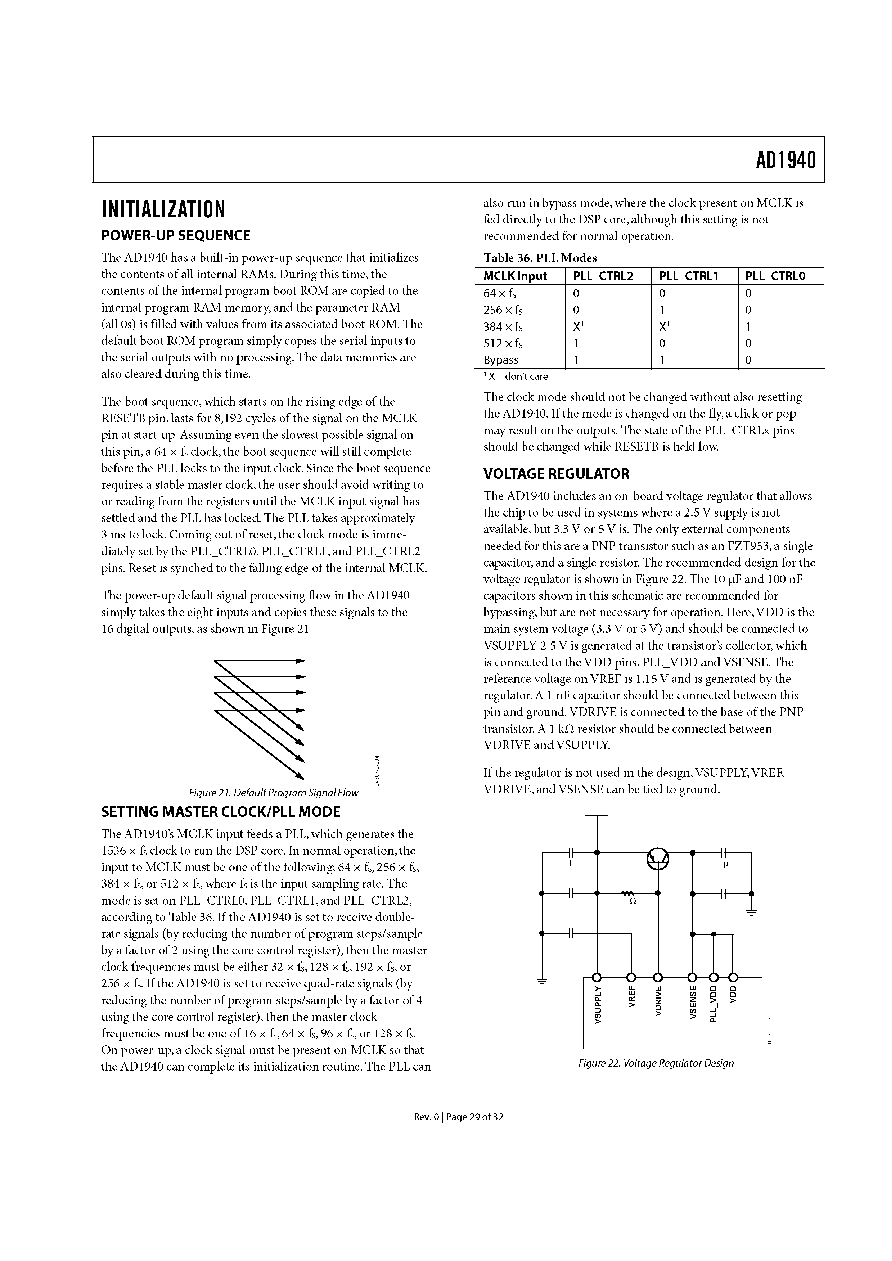

VOLTAGE REGULATOR

MEMORY CONTROLLERS

CONTROL

REGISITER

TRAP REG.

SAFELOAD

REGISTER

SERIAL

CONTROL

PORT

MCLK

PLL

DATA MEMORY

6k 28

TARGET/SLEW

RAM

64 28

SERIAL

DATA/TDM

INPUT

GROUP

PLL MODE

SELECT

MASTER

CLOCK

INPUT

SPI I/O

GROUP

RESETB

PROGRAM

RAM

1536 40

PARAMETER

RAM

1024 28

COEFFICIENT

ROM

512 28

2

2

4

4

2

2

SERIAL DATA/

TDM OUTPUT

GROUP

REGULATOR

GROUP

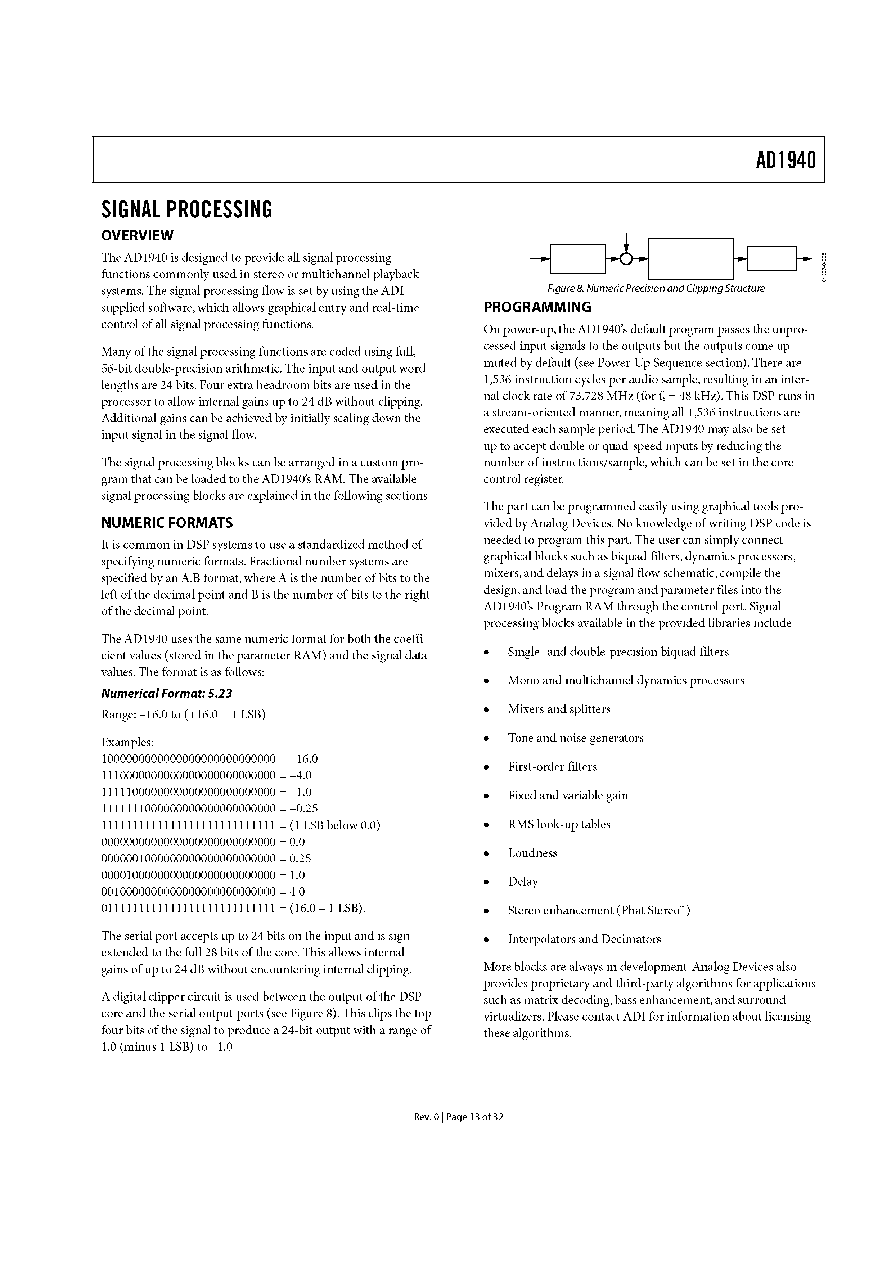

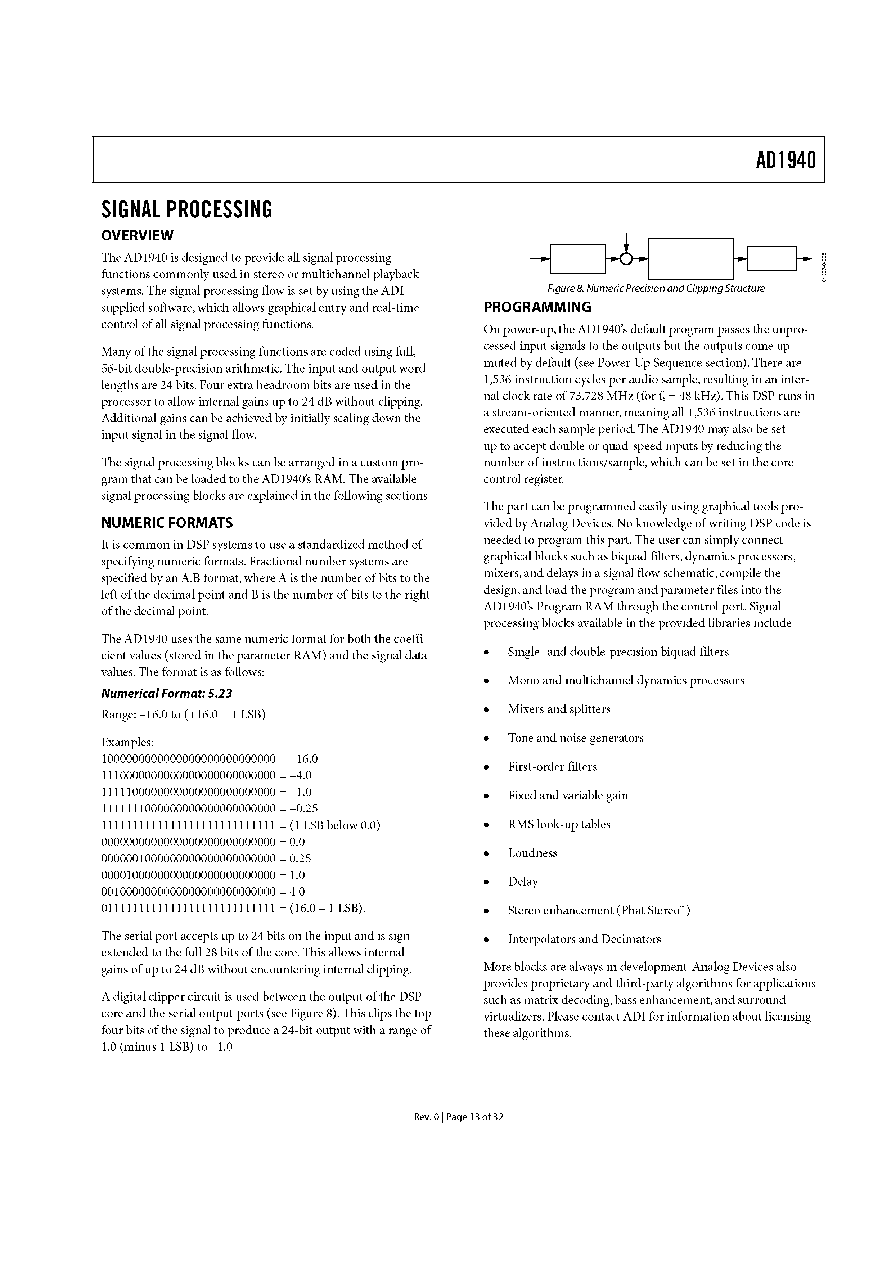

4-BIT SIGN EXTENSION

DATA IN

SERIAL PORT

1.23

5.23

SIGNAL PROCESSING

(5.23 FORMAT)

DIGITAL

CLIPPER

5.23

1.23

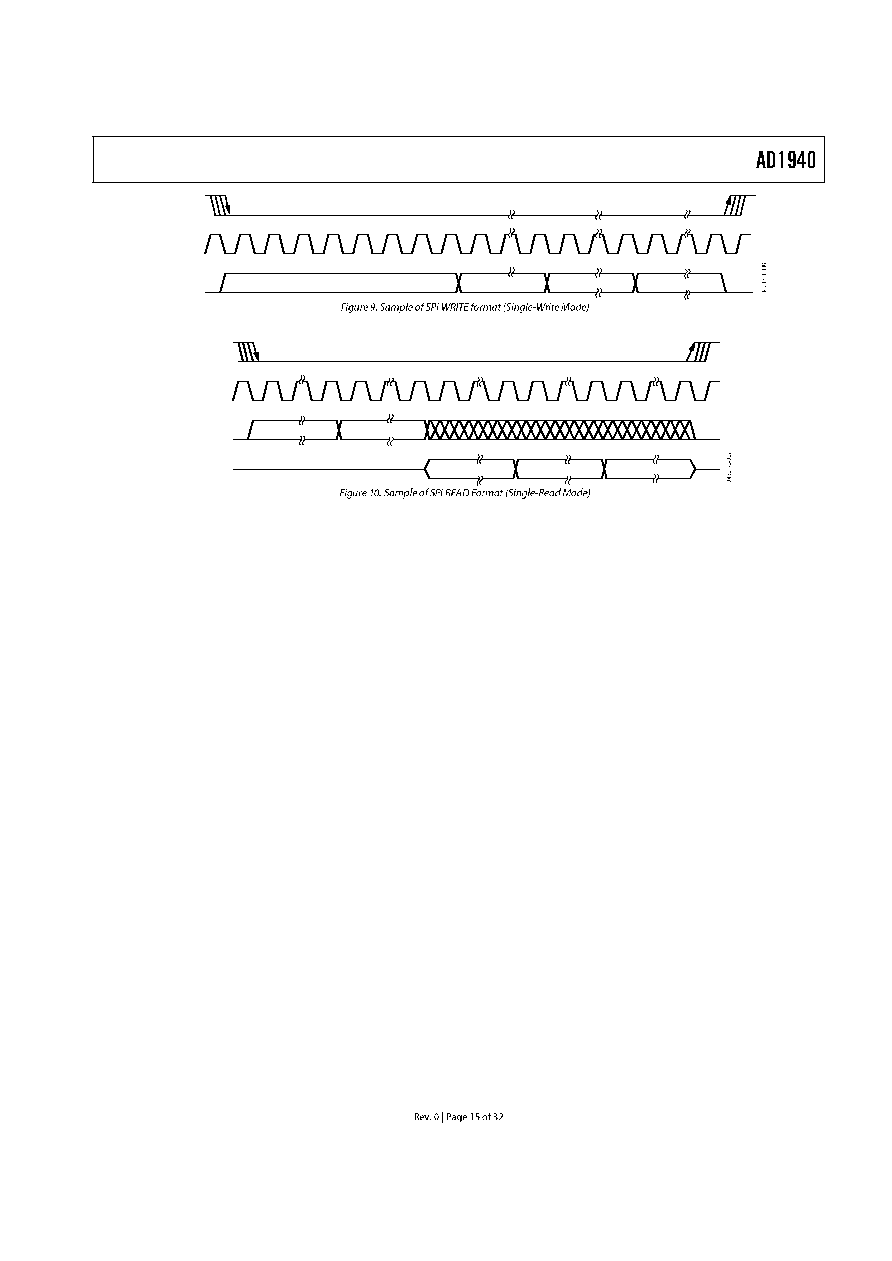

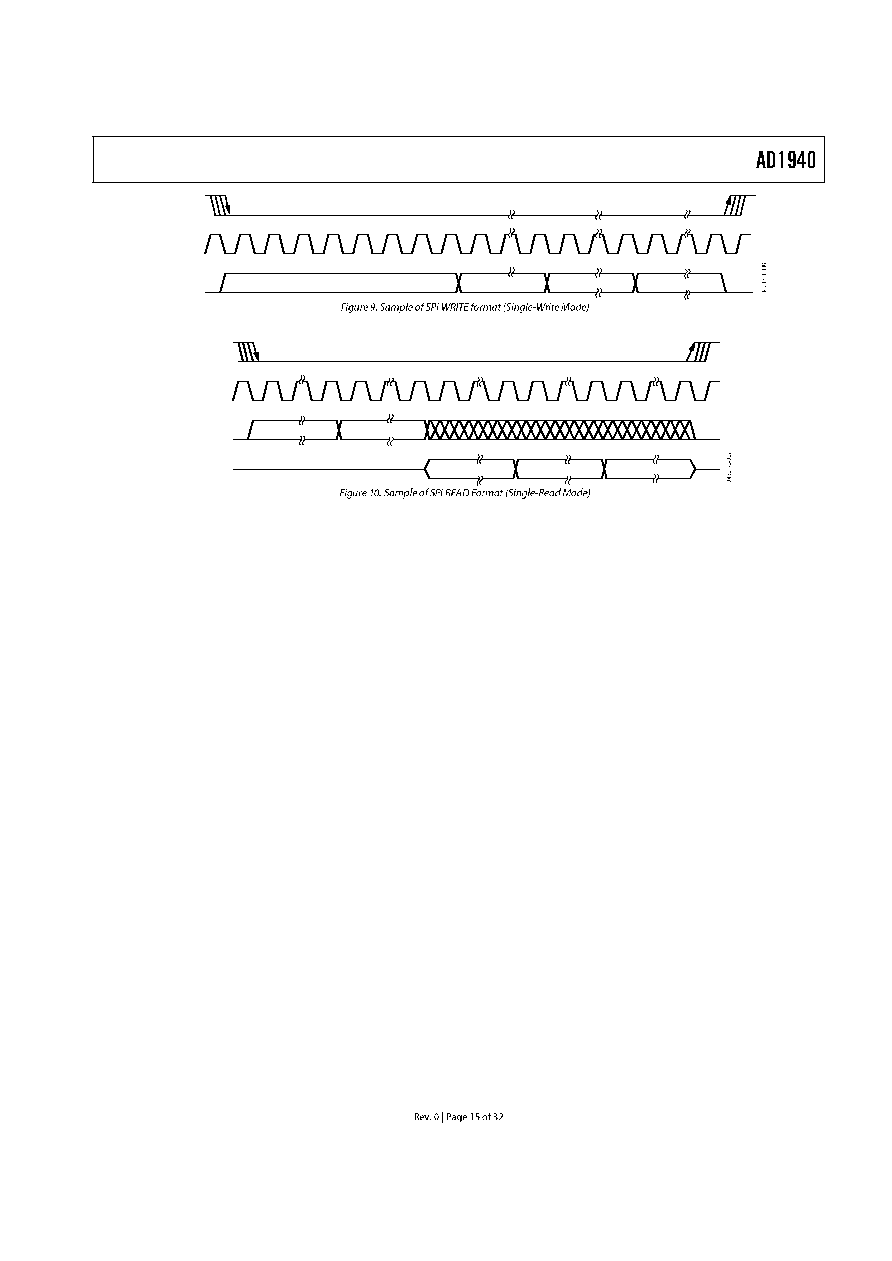

CLATCH

CCLK

CDATA

BYTE 0

BYTE 1

BYTE 2

BYTE 3

CLATCH

CCLK

CDATA

COUT

BYTE 0

BYTE 1

HI-Z

DATA

DATA

DATA

HI-Z

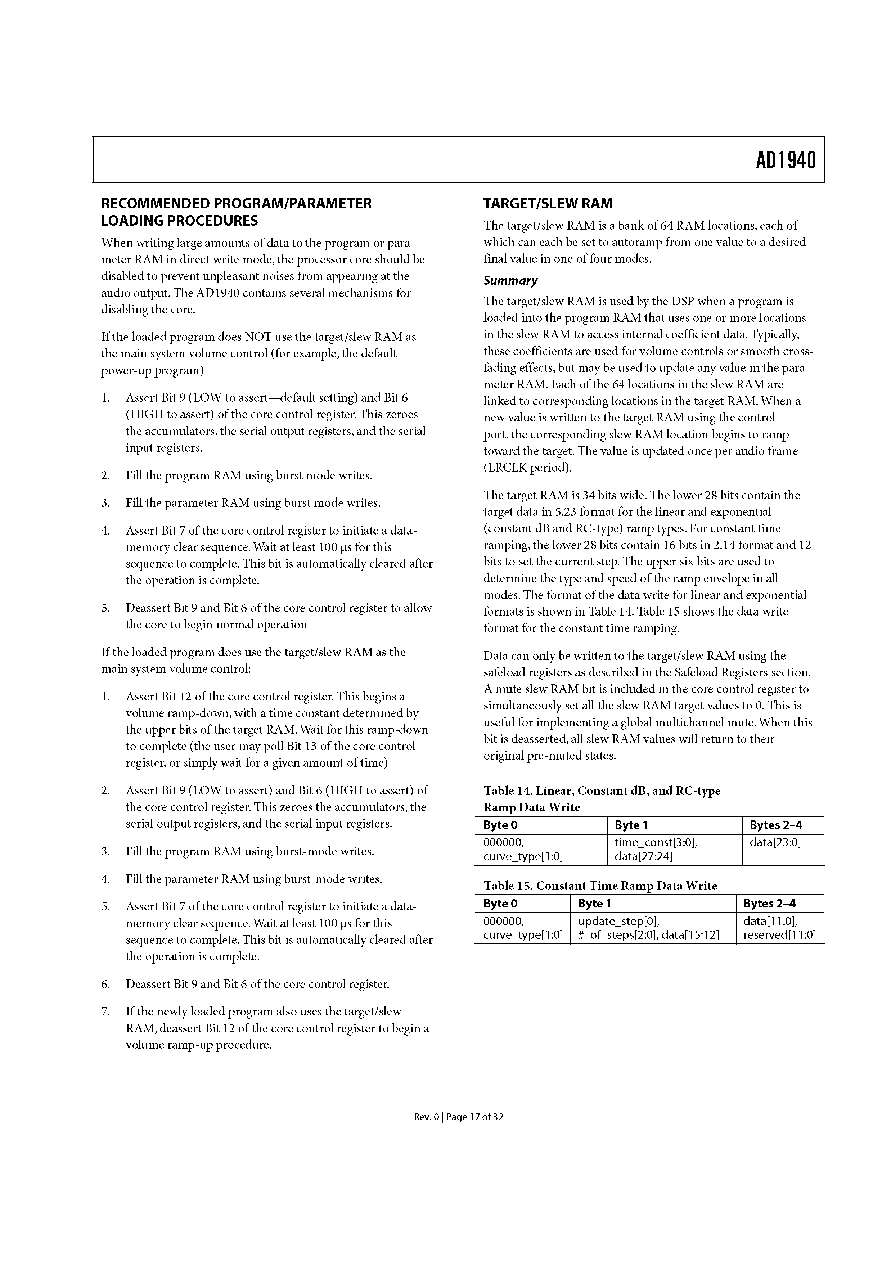

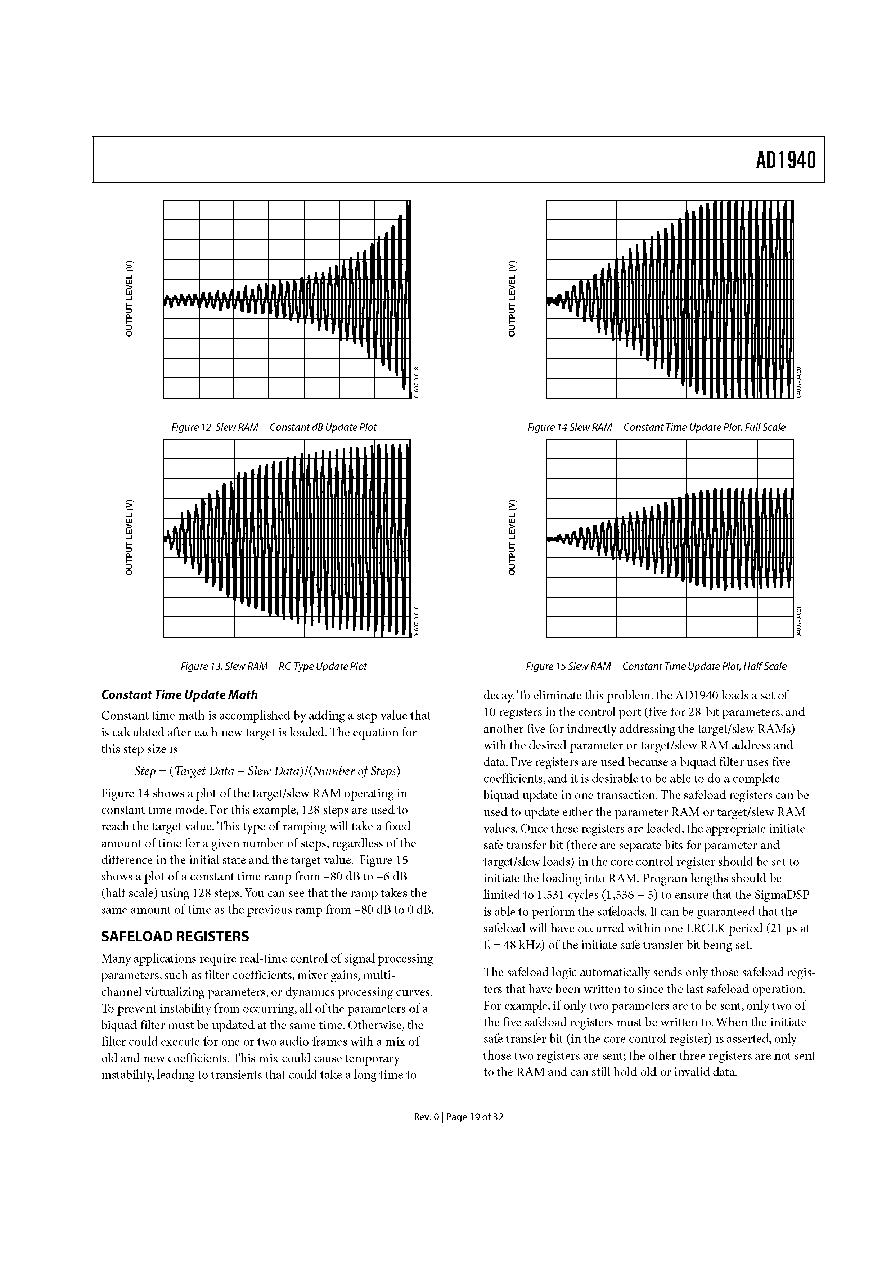

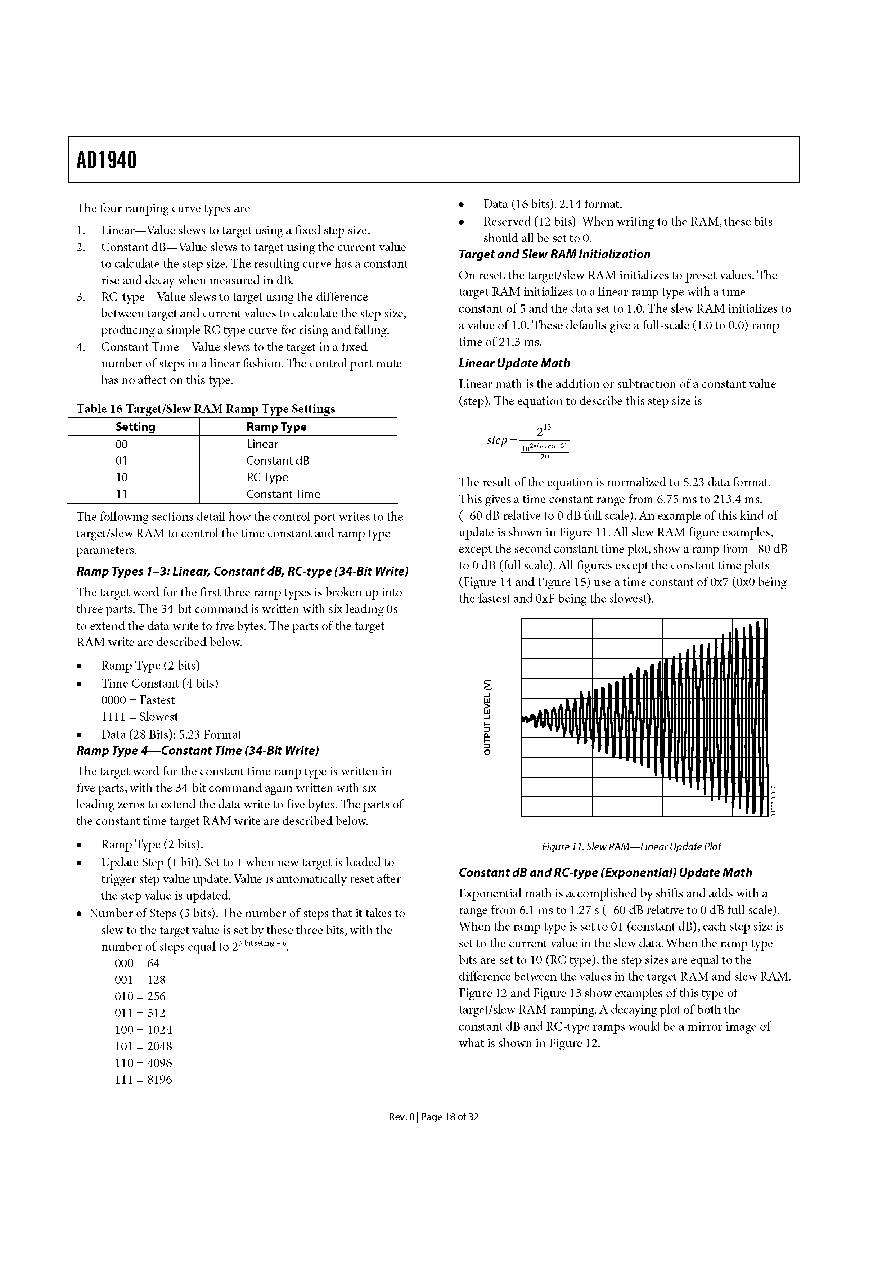

TIME (ms)

1

0.4

0.6

0.8

0.2

0

0.4

0.2

1

0.8

0.6

0

10

20

30

TIME (ms)

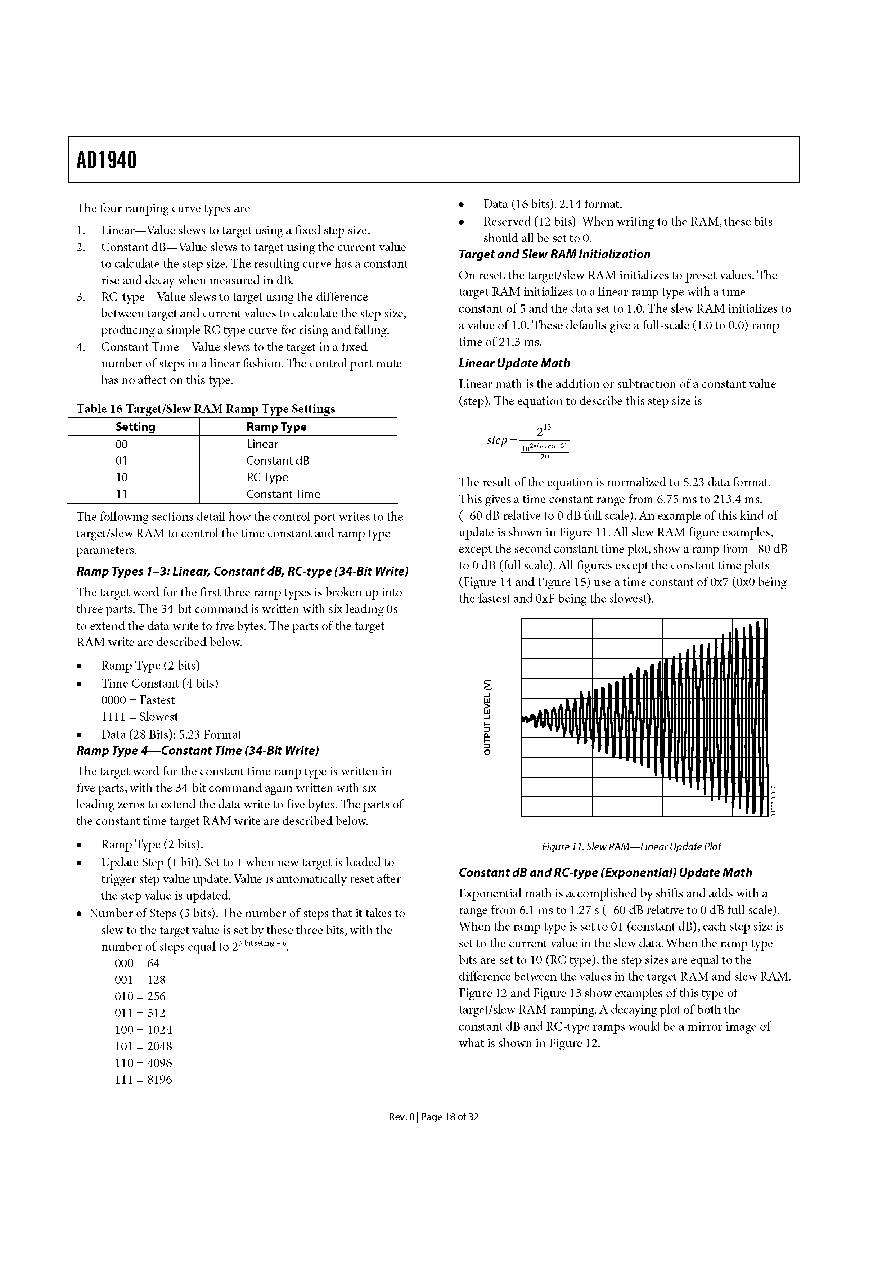

1

0.8

0.6

0.4

0.2

0

0.6

0.4

0.2

0.8

1

0

10

5

20

15

30

25

35

TIME (ms)

1

0.8

0.6

0.4

0.2

0

0.6

0.4

0.2

0.8

1

0

10

20

30

TIME (ms)

1

0.8

0.6

0.4

0.2

0

0.6

0.4

0.2

0.8

1

0

10

20

30

TIME (ms)

1

0.8

0.6

0.4

0.2

0

0.6

0.4

0.2

0.8

1

0

10

20

30

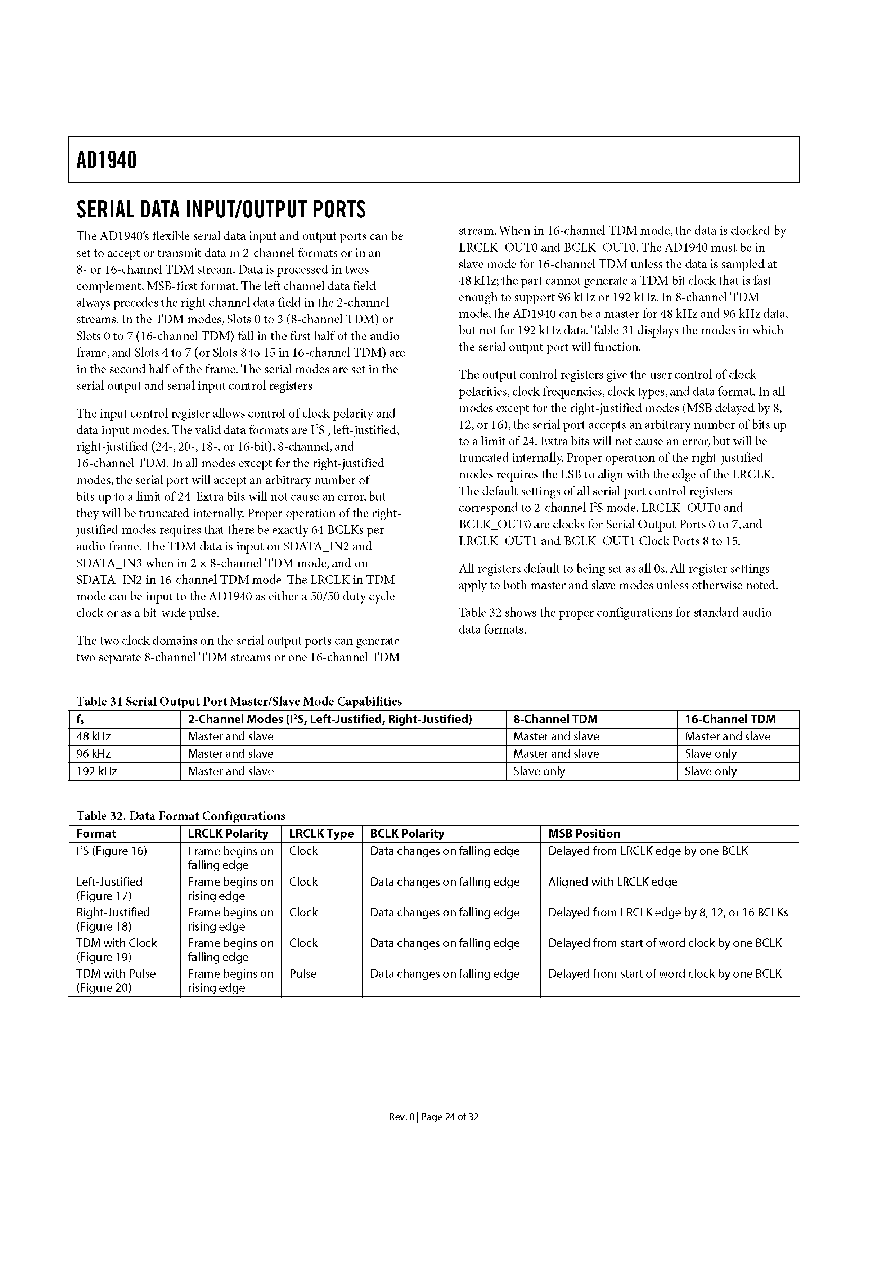

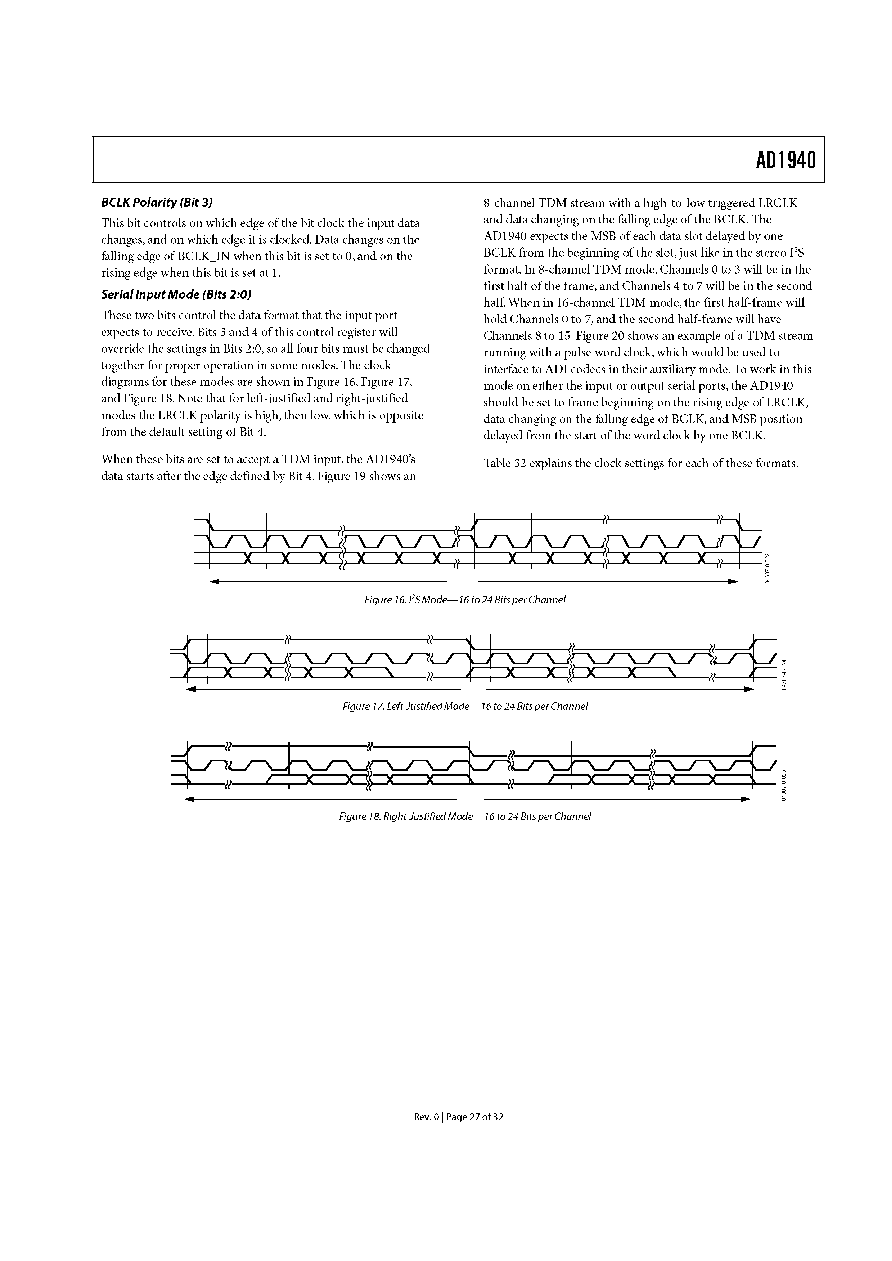

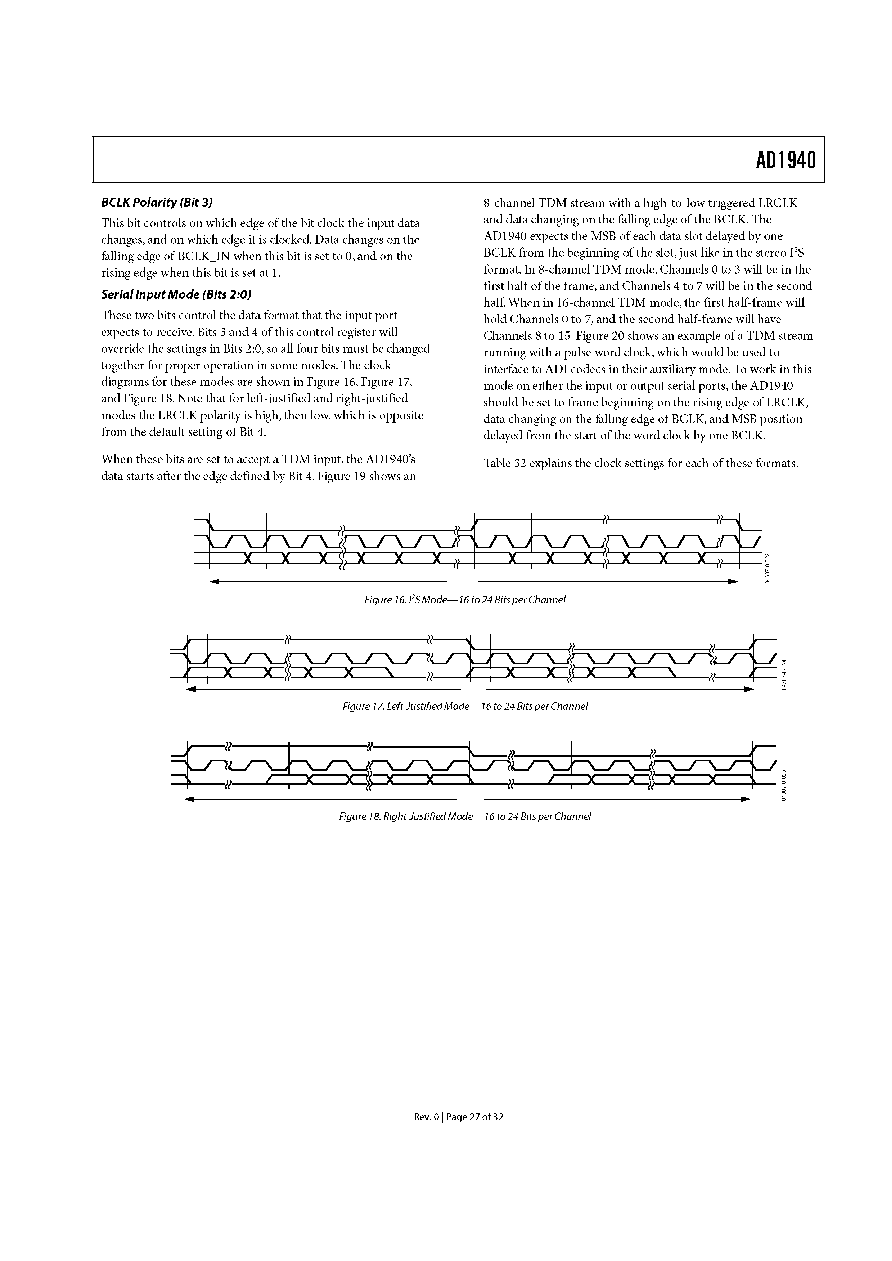

LRCLK

BCLK

SDATA

MSB

LEFT CHANNEL

LSB

MSB

RIGHT CHANNEL

LSB

1 /F

S

LRCLK

BCLK

SDATA

LEFT CHANNEL

MSB

LSB

MSB

RIGHT CHANNEL

LSB

1 /F

S

LRCLK

BCLK

SDATA

LEFT CHANNEL

MSB

LSB

MSB

RIGHT CHANNEL

LSB

1 /F

S

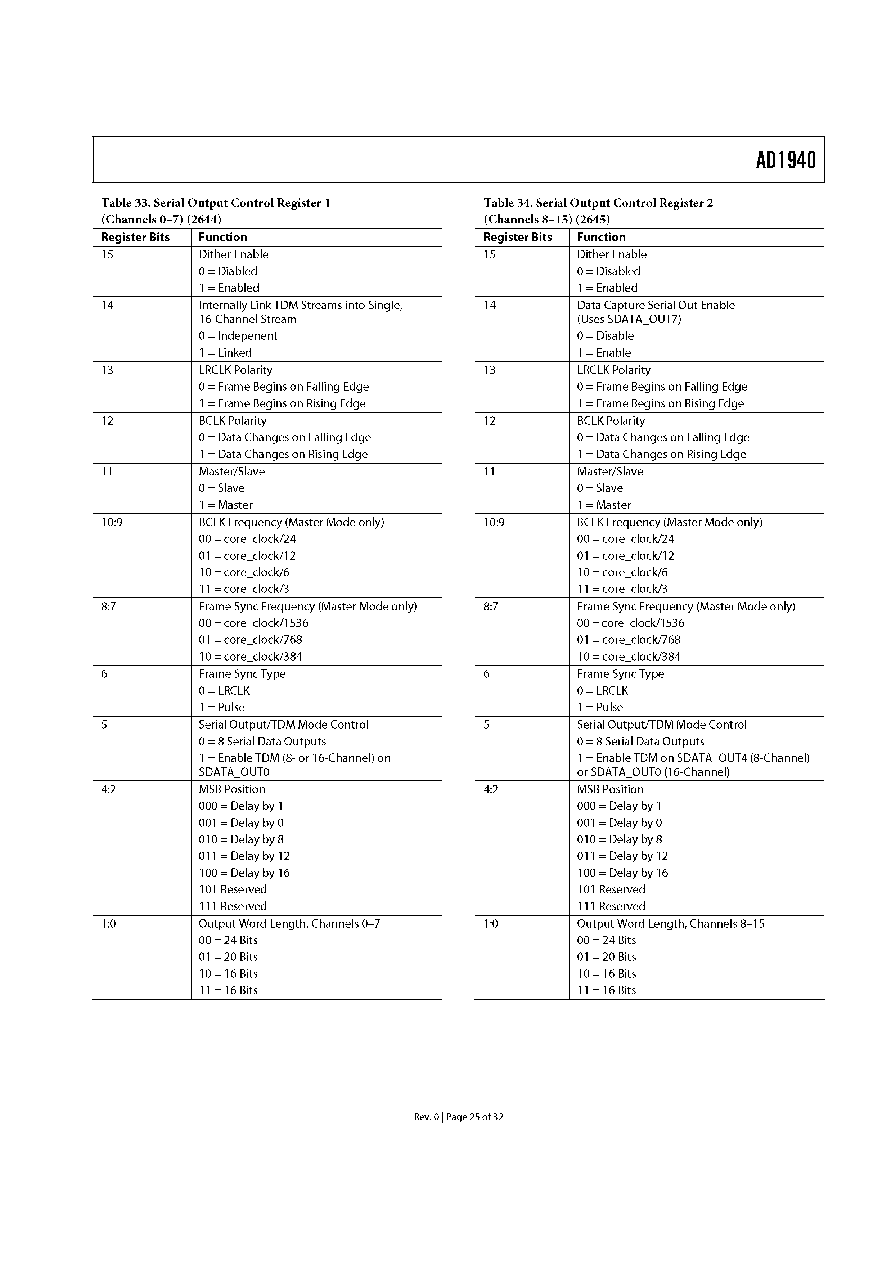

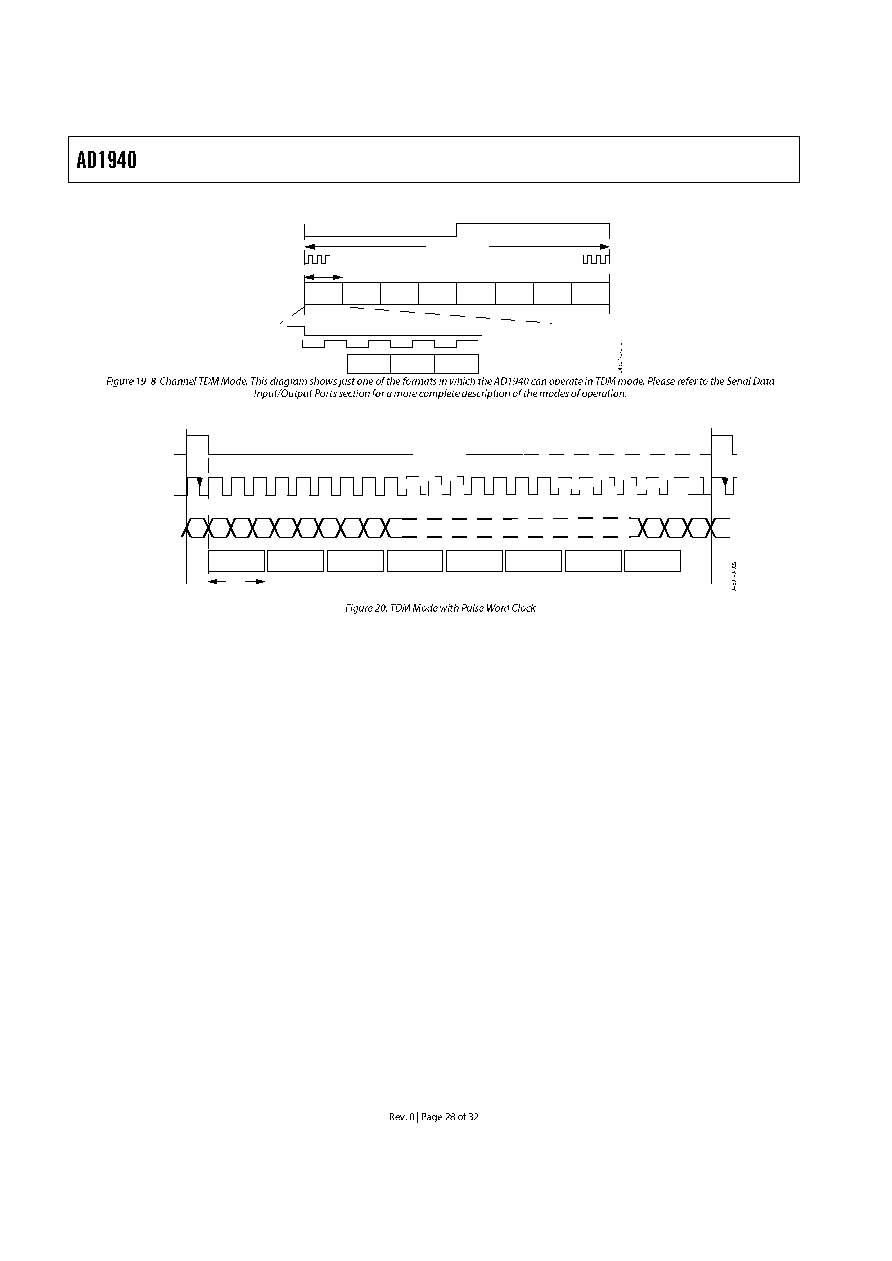

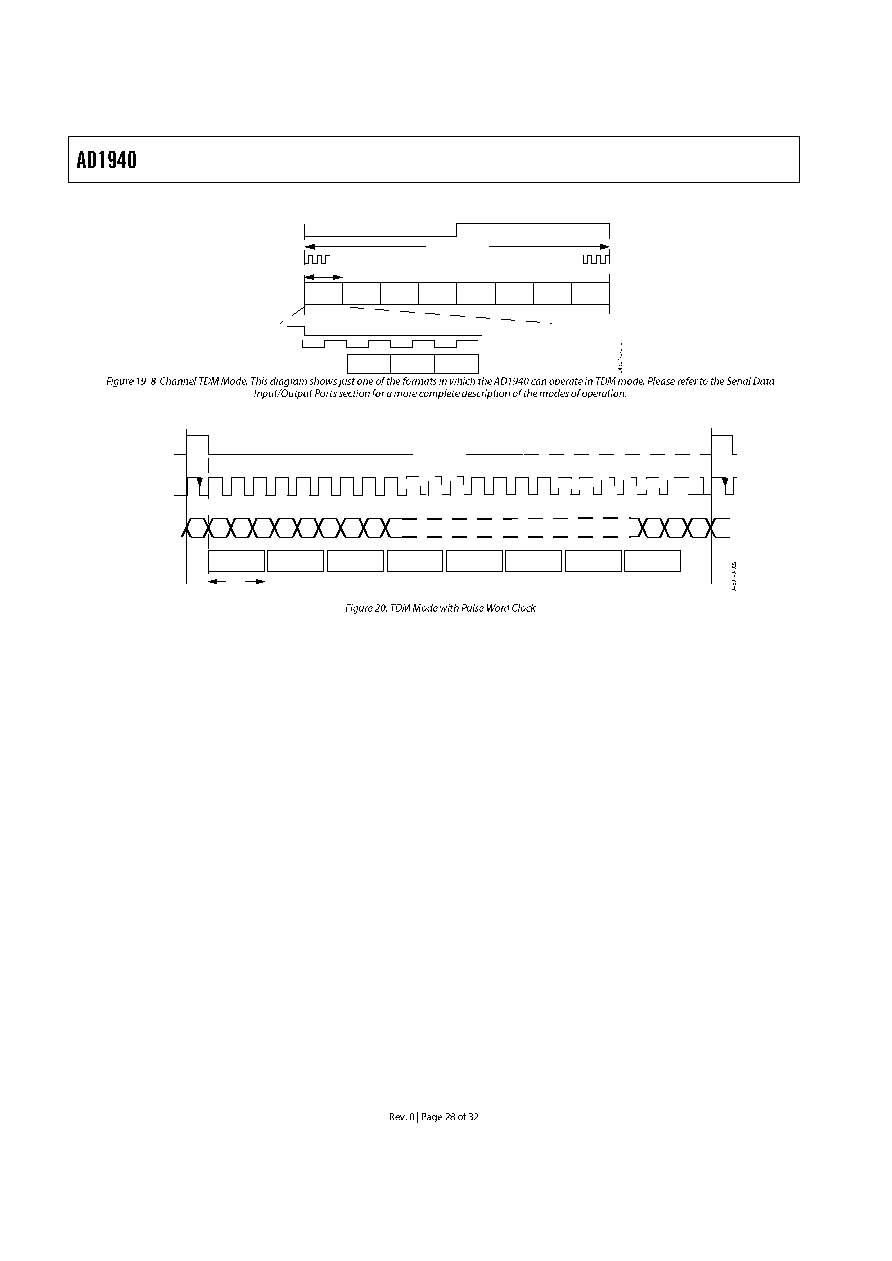

LRCLK

BCLK

DATA

SLOT 1

SLOT 2

SLOT 5

SLOT 6

32 BCLKs

MSB

MSB

1

MSB

2

256 BCLKs

SLOT 3

SLOT 4

SLOT 7

SLOT 8

LRCLK

BCLK

DATA

LRCLK

SLOT 0

SLOT 1

SLOT 2

SLOT 3

SLOT 4

SLOT 5

SLOT 6

SLOT 7

CH

0

BCLK

SDATA

MSB TDM

8TH

CH

32

BCLKs

MSB TDM

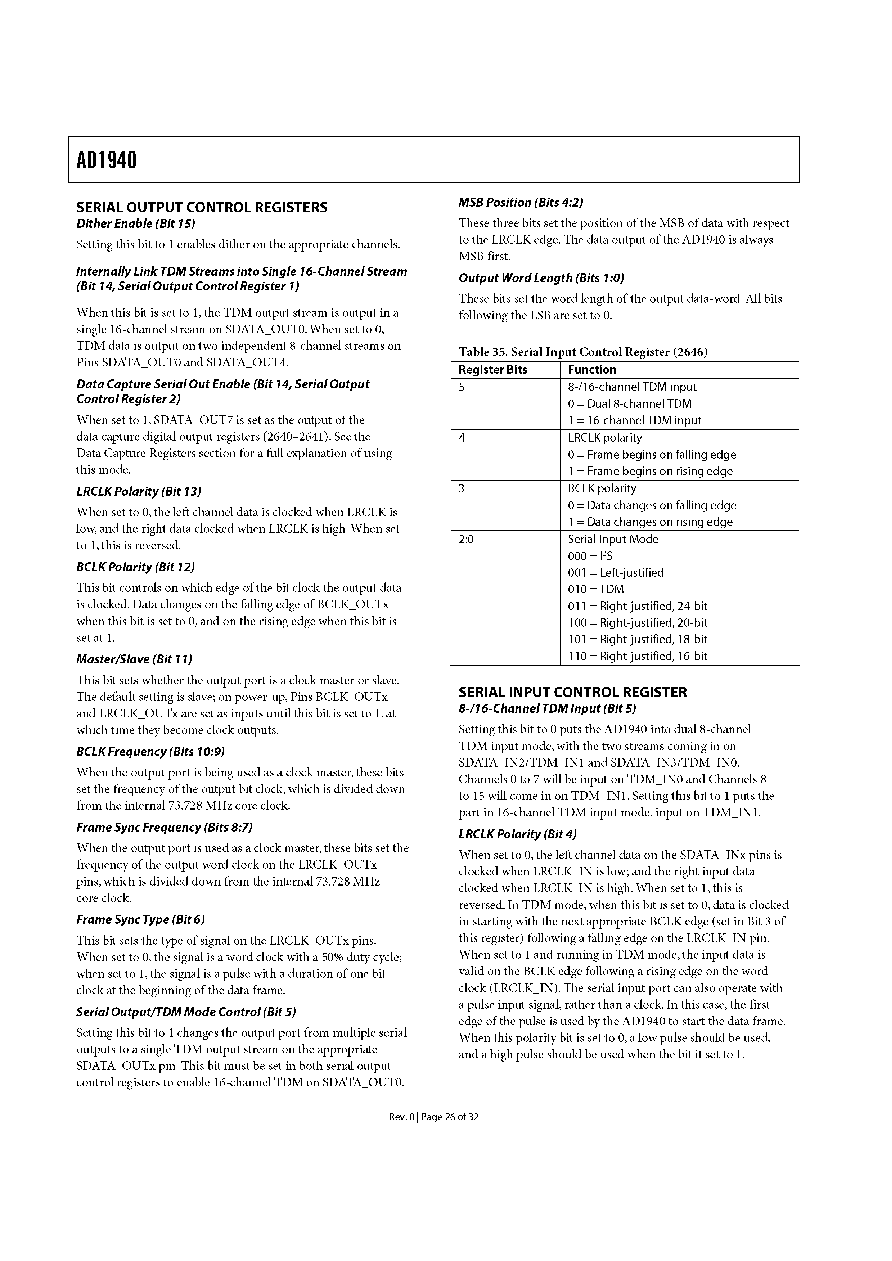

SDATA_IN0

SDATA_IN1

SDATA_IN2

SDATA_IN3

SDATA_OUT0

SDATA_OUT1

SDATA_OUT2

SDATA_OUT3

SDATA_OUT4

SDATA_OUT5

SDATA_OUT6

SDATA_OUT7

10 F

10 F

100nF

100nF

1nF

1k

AD1940

DVDD

FZT953

+

+

TOP VIEW

(PINS DOWN)

1

12

13

25

24

36

37

48

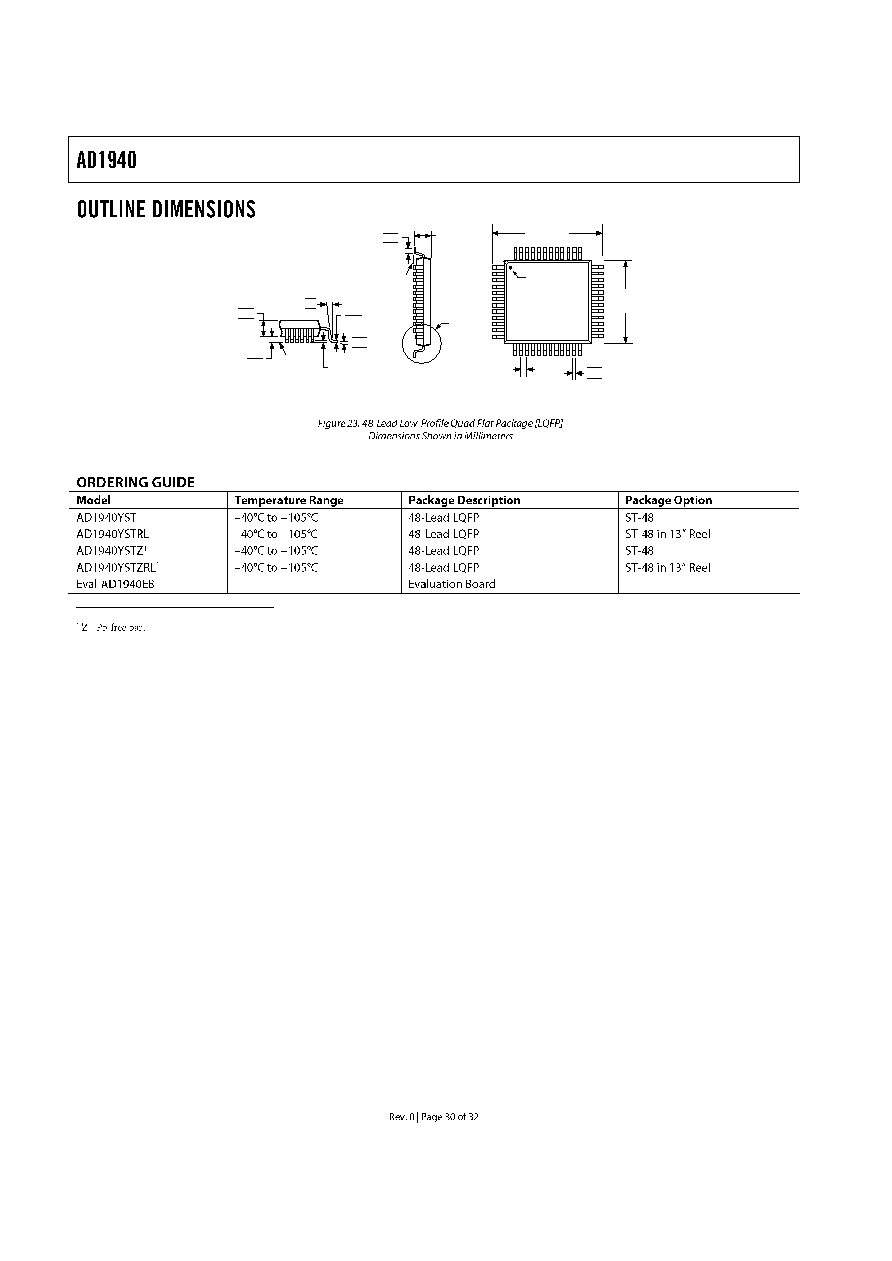

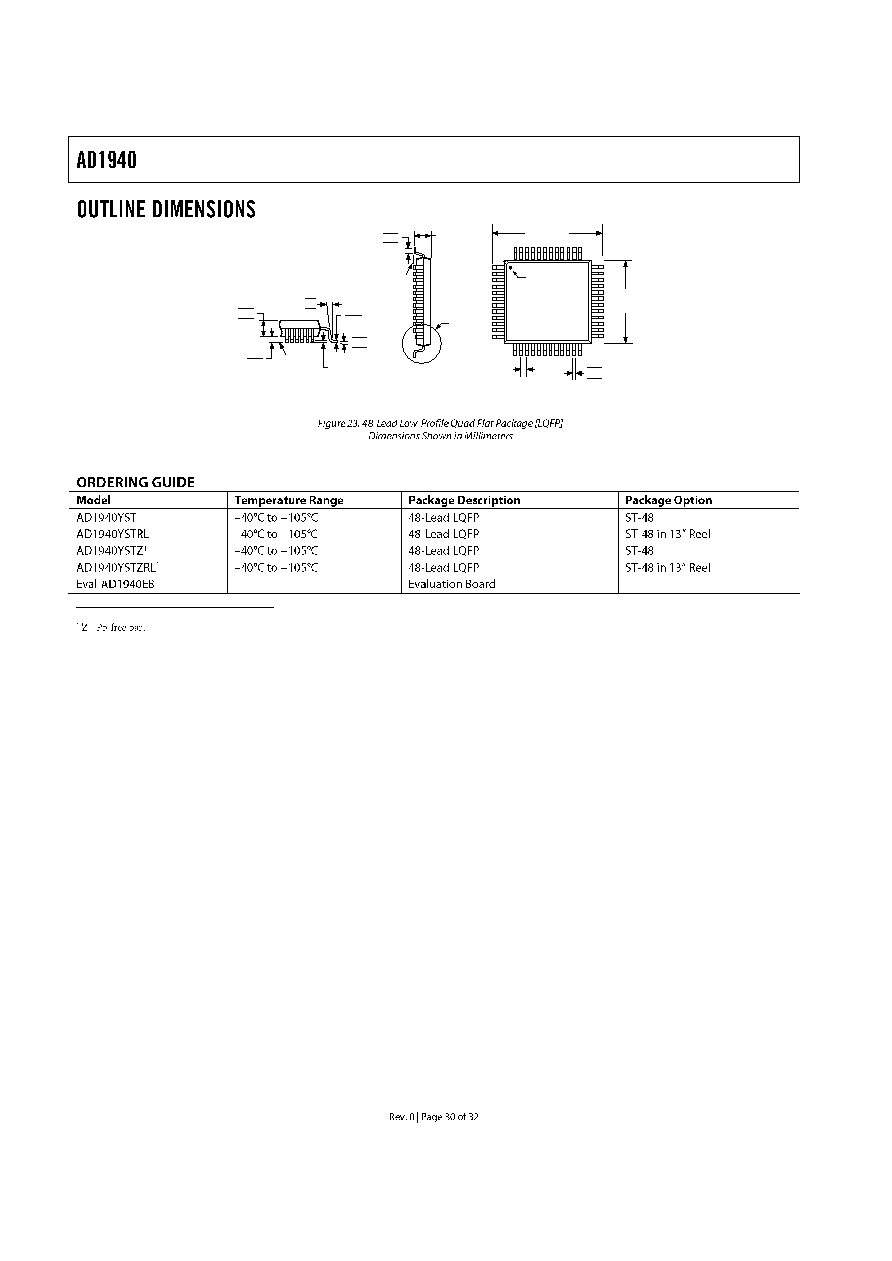

0.27

0.22

0.17

0.50

BSC

7.00

BSC SQ

SEATING

PLANE

1.60

MAX

0.75

0.60

0.45

VIEW A

9.00 BSC

SQ

PIN 1

0.20

0.09

1.45

1.40

1.35

0.08 MAX

COPLANARITY

VIEW A

ROTATED 90

°

CCW

SEATING

PLANE

10

°

6

°

2

°

7

°

3.5

°

0

°

0.15

0.05

COMPLIANT TO JEDEC STANDARDS MS-026BBC

WWW.ALLDATASHEET.COM

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com

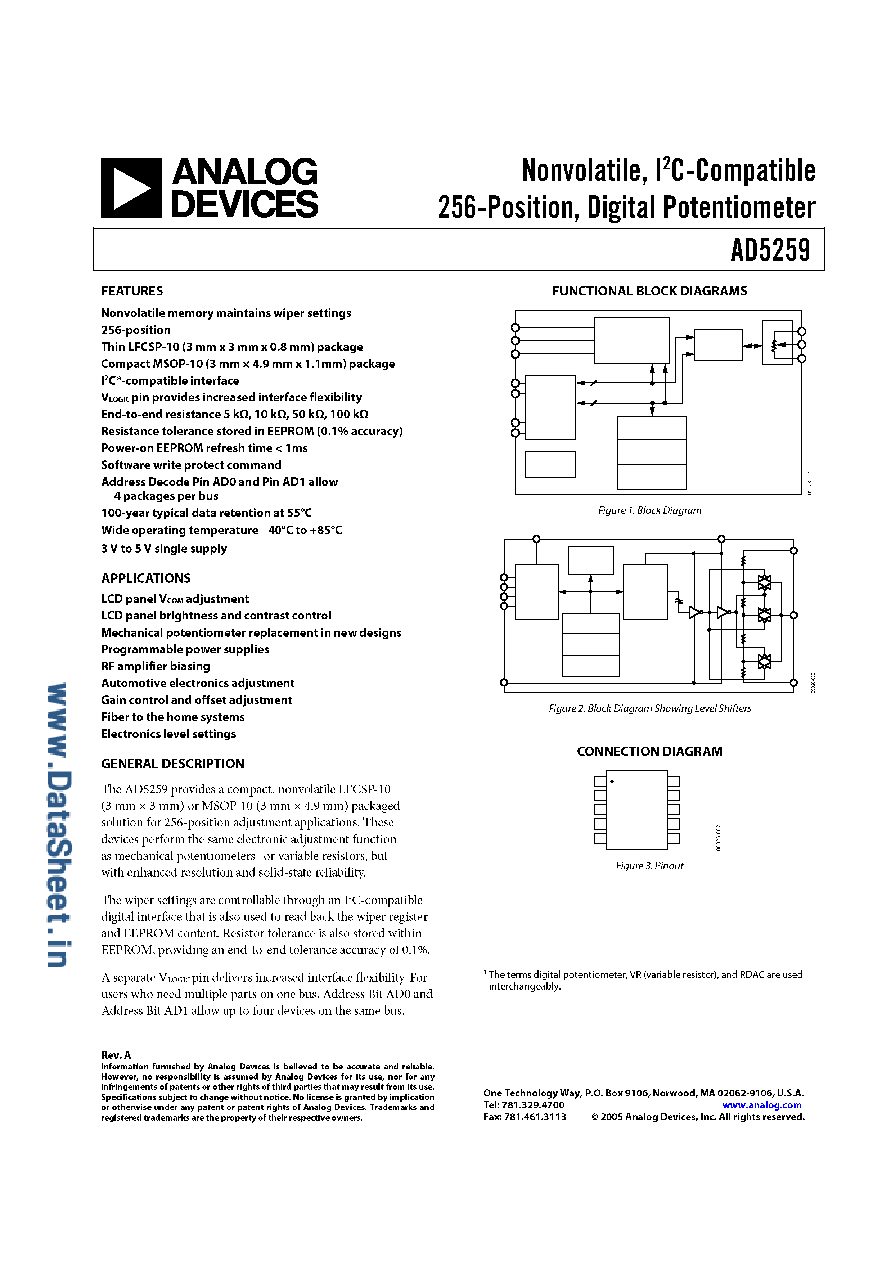

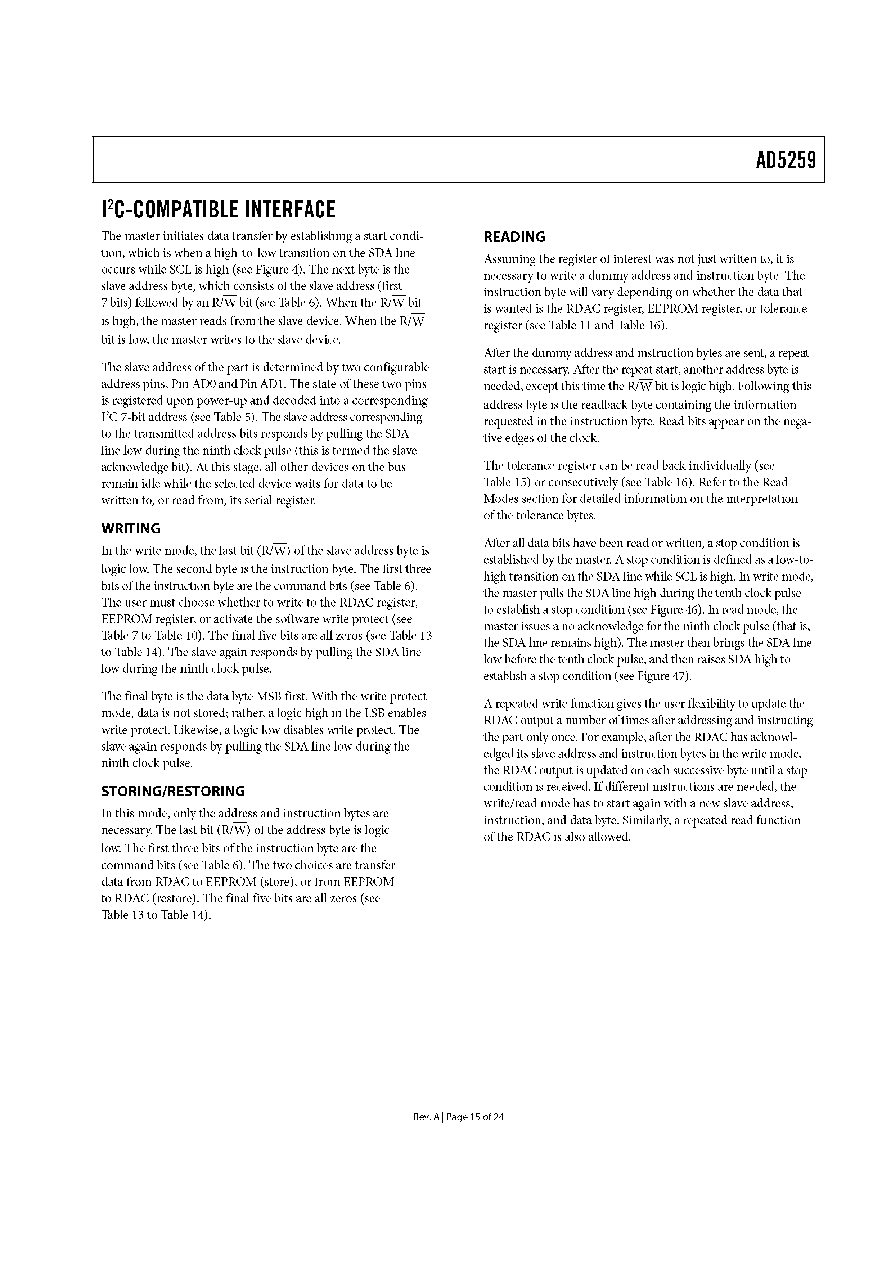

RDAC

REGISTER

RDAC

DATA

CONTROL

COMMAND

DECODE LOGIC

ADDRESS

DECODE LOGIC

CONTROL LOGIC

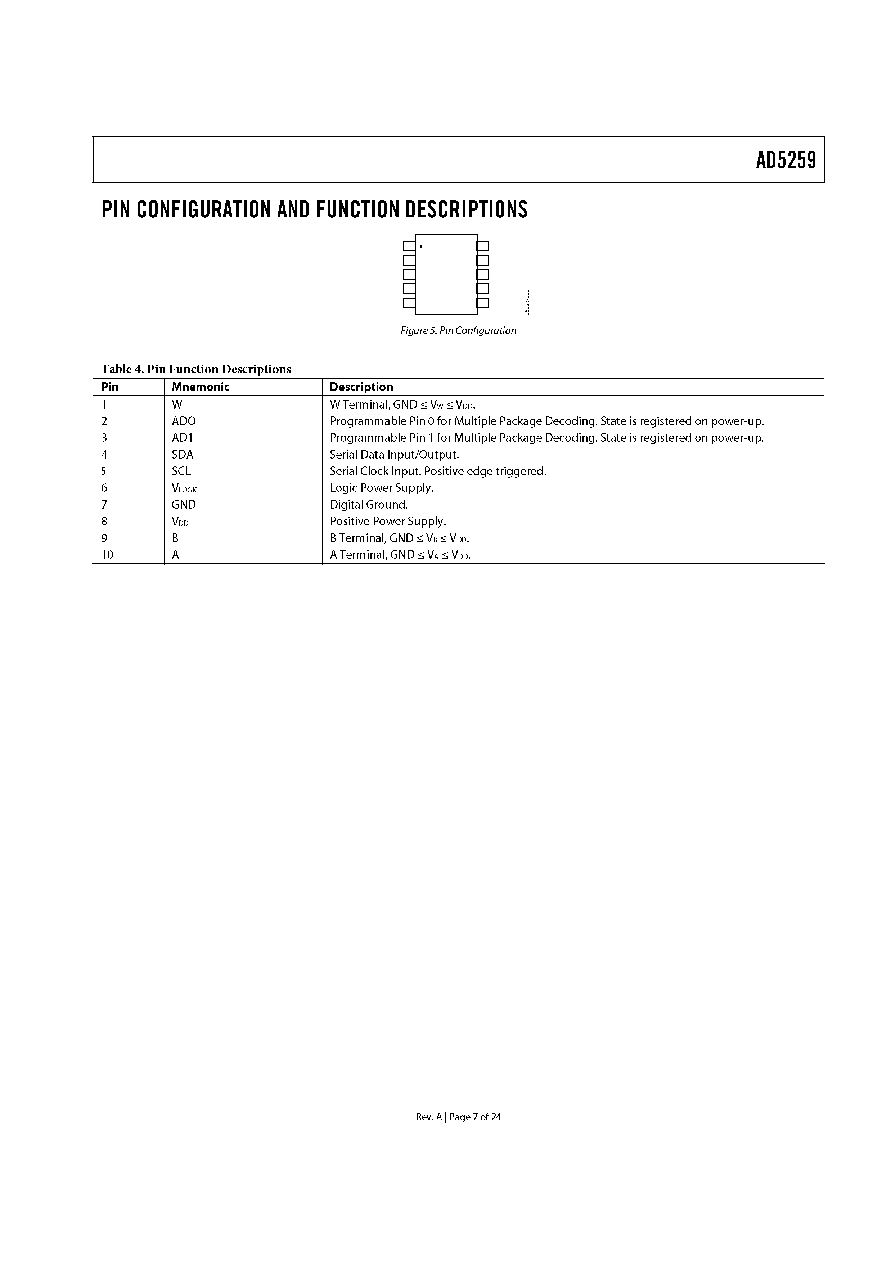

AD5259

I

2

C

SERIAL

INTERFACE

POWER-

ON RESET

A

W

B

SCL

SDA

AD0

AD1

V

DD

V

LOGIC

GND

RDAC

EEPROM

8

8

COMMAND

DECODE LOGIC

ADDRESS

DECODE LOGIC

CONTROL

LOGIC

SCL

SDA

AD0

AD1

GND

EEPROM

I

2

C

SERIAL

INTERFACE

RDAC

REGISTER

AND

LEVEL

SHIFTER

A

W

B

V

LOGIC

V

DD

AD5259

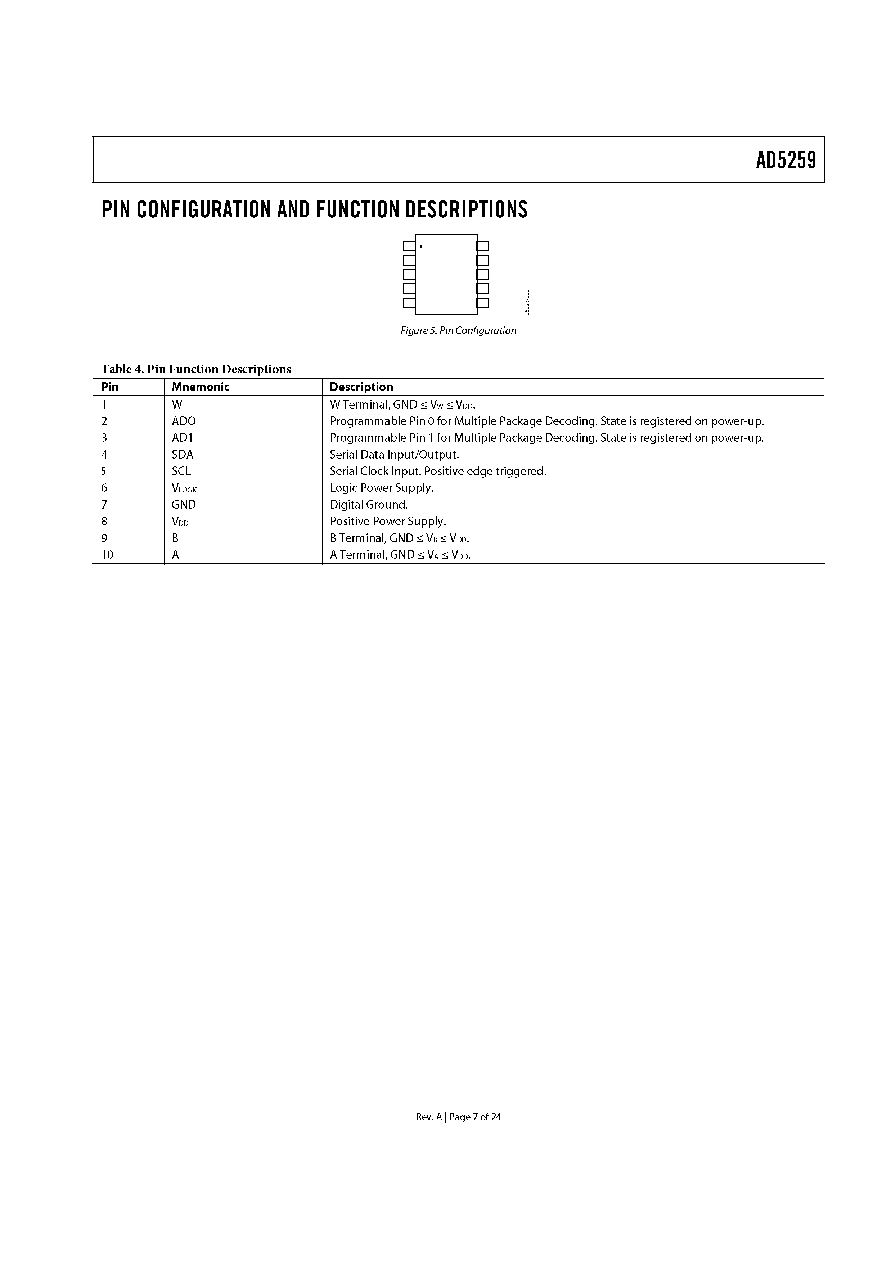

TOP VIEW

(Not to Scale)

W

1

AD0

2

AD1

3

SDA

4

SCL

5

A

B

V

DD

GND

V

LOGIC

10

9

8

7

6

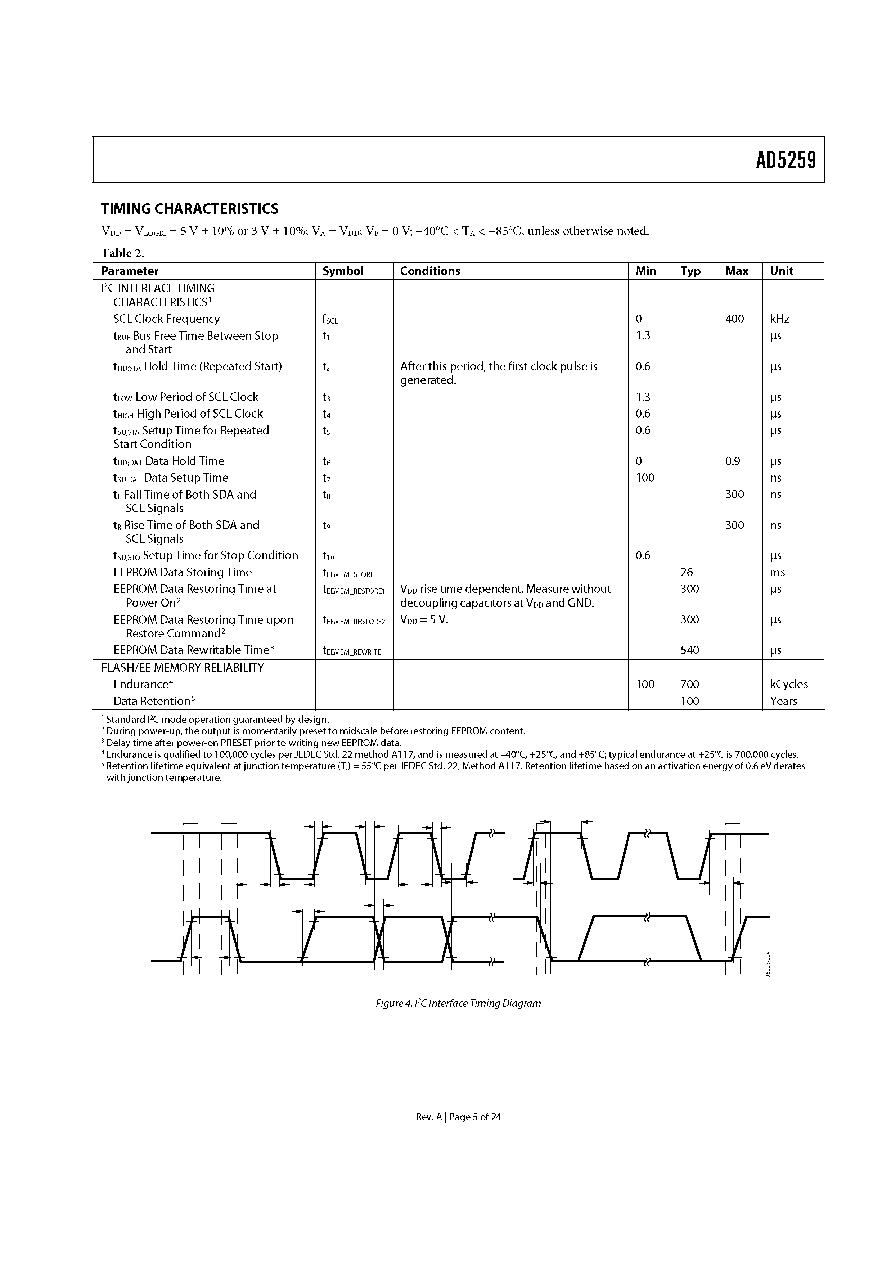

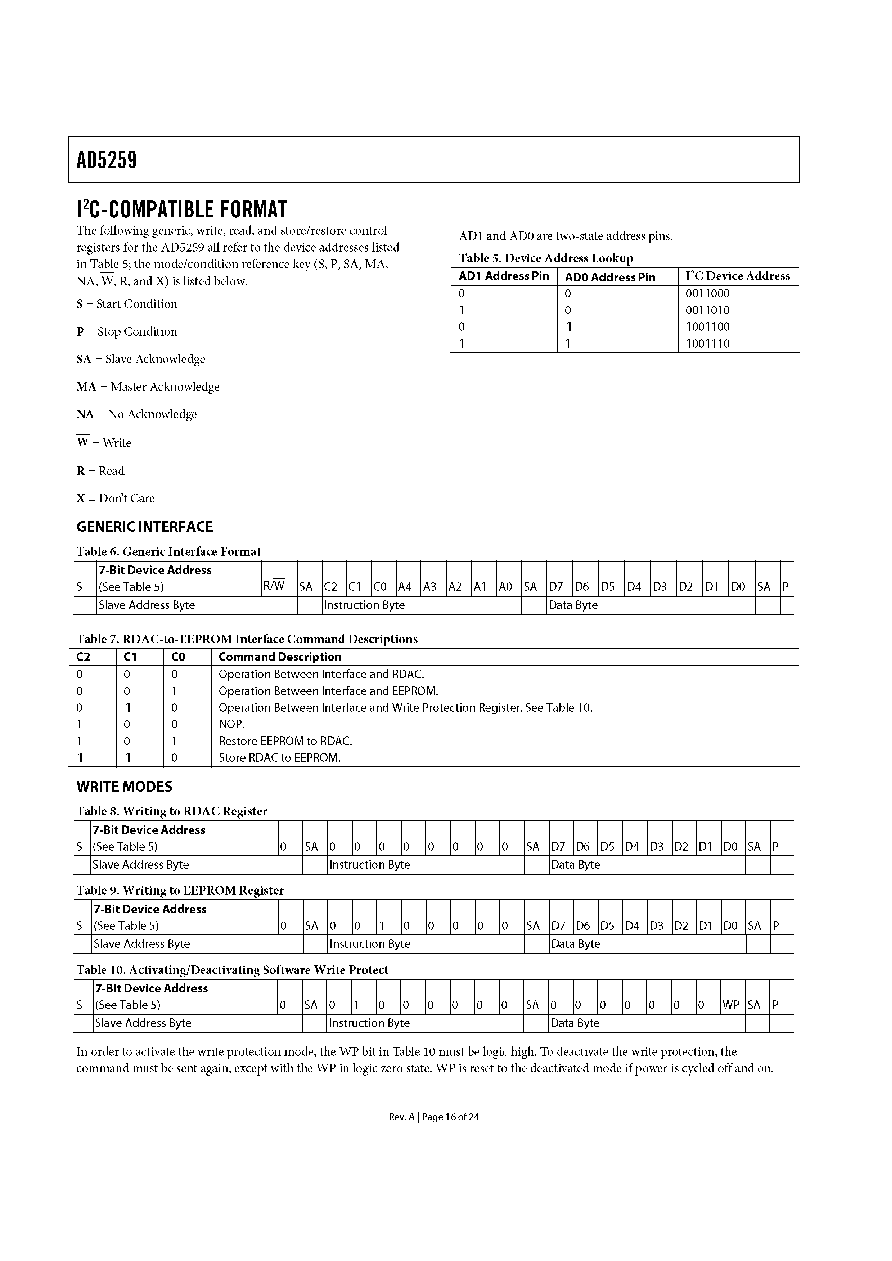

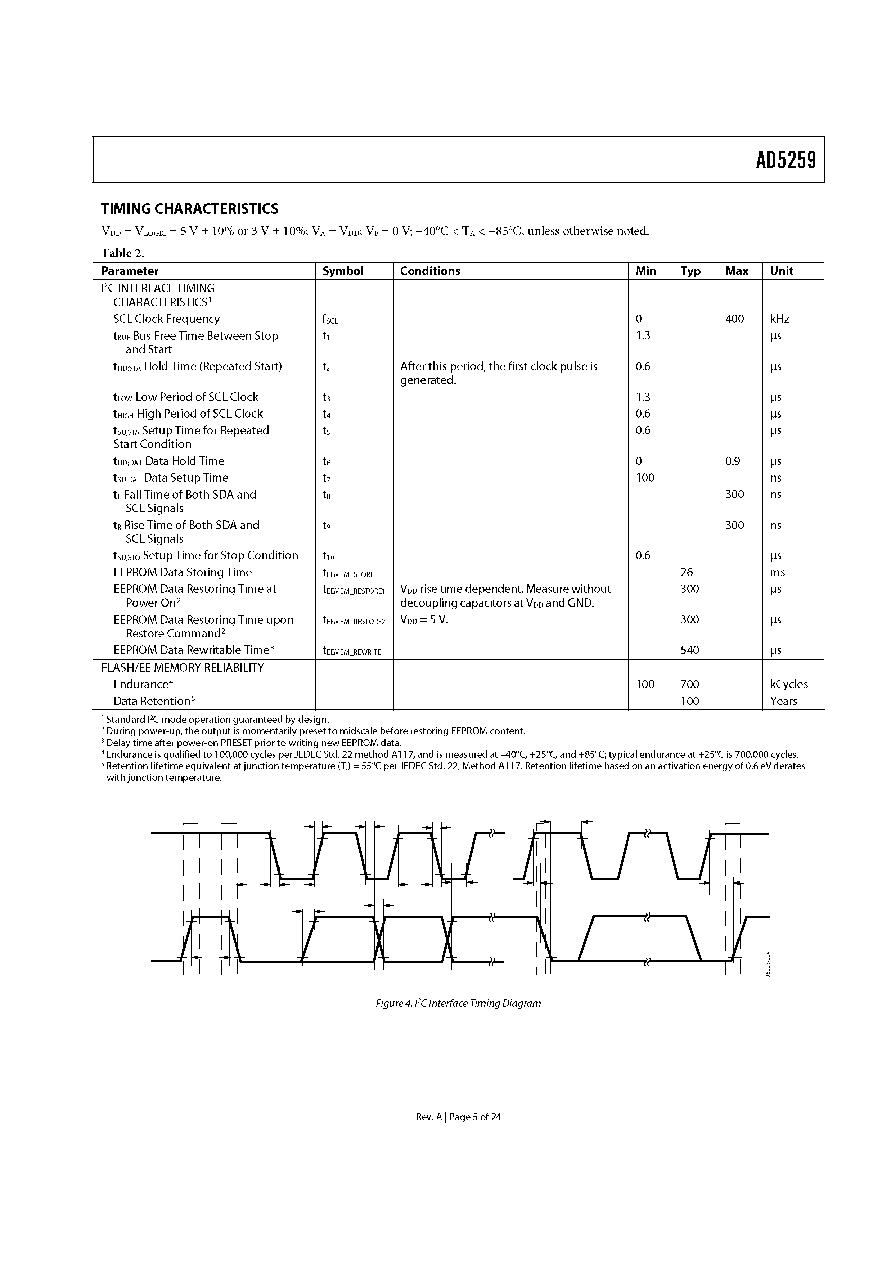

t

1

t

2

t

3

t

8

t

8

t

9

t

9

t

6

t

4

t

7

t

5

t

2

t

10

P

S

S

SCL

SDA

P

AD5259

TOP VIEW

(Not to Scale)

W

1

AD0

2

AD1

3

SDA

4

SCL

5

A

B

V

DD

GND

V

LOGIC

10

9

8

7

6

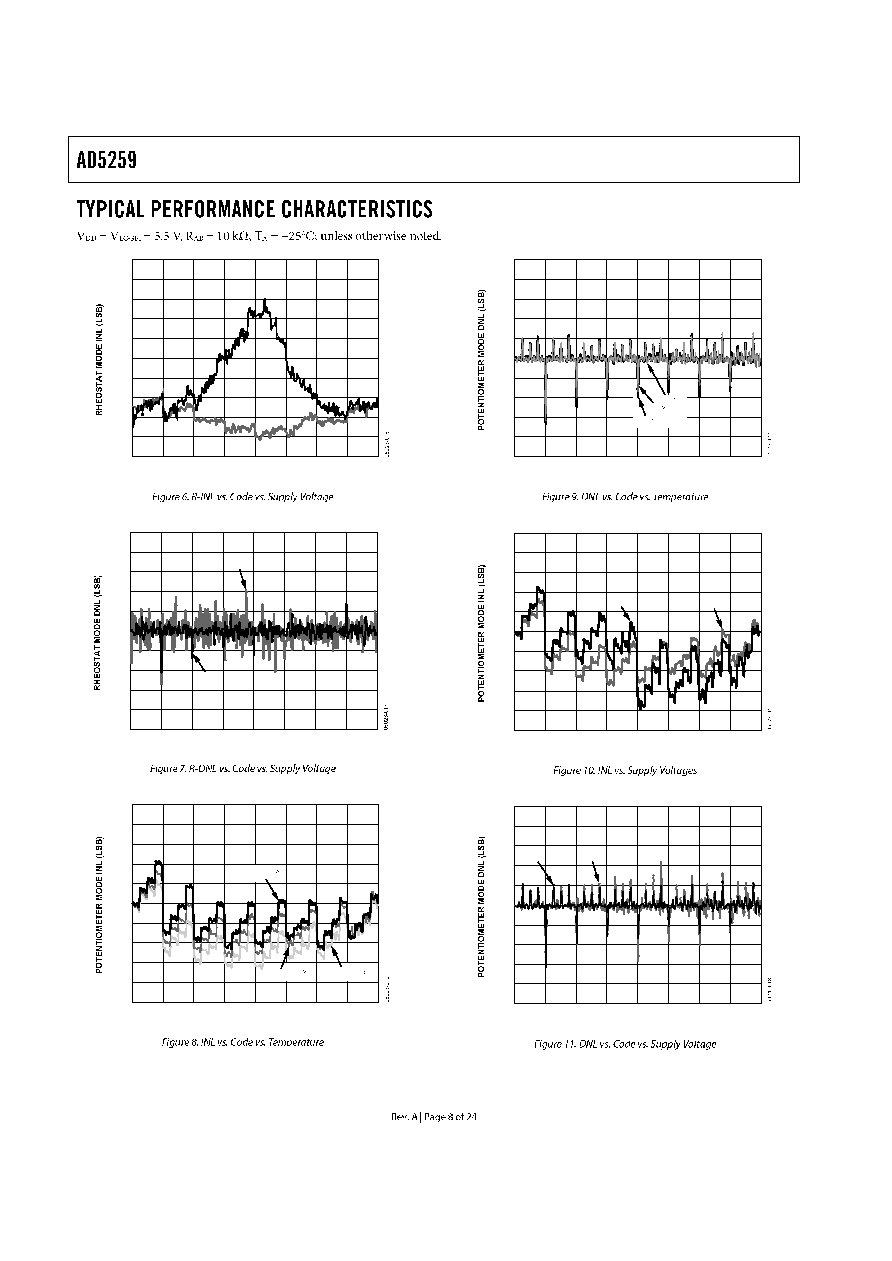

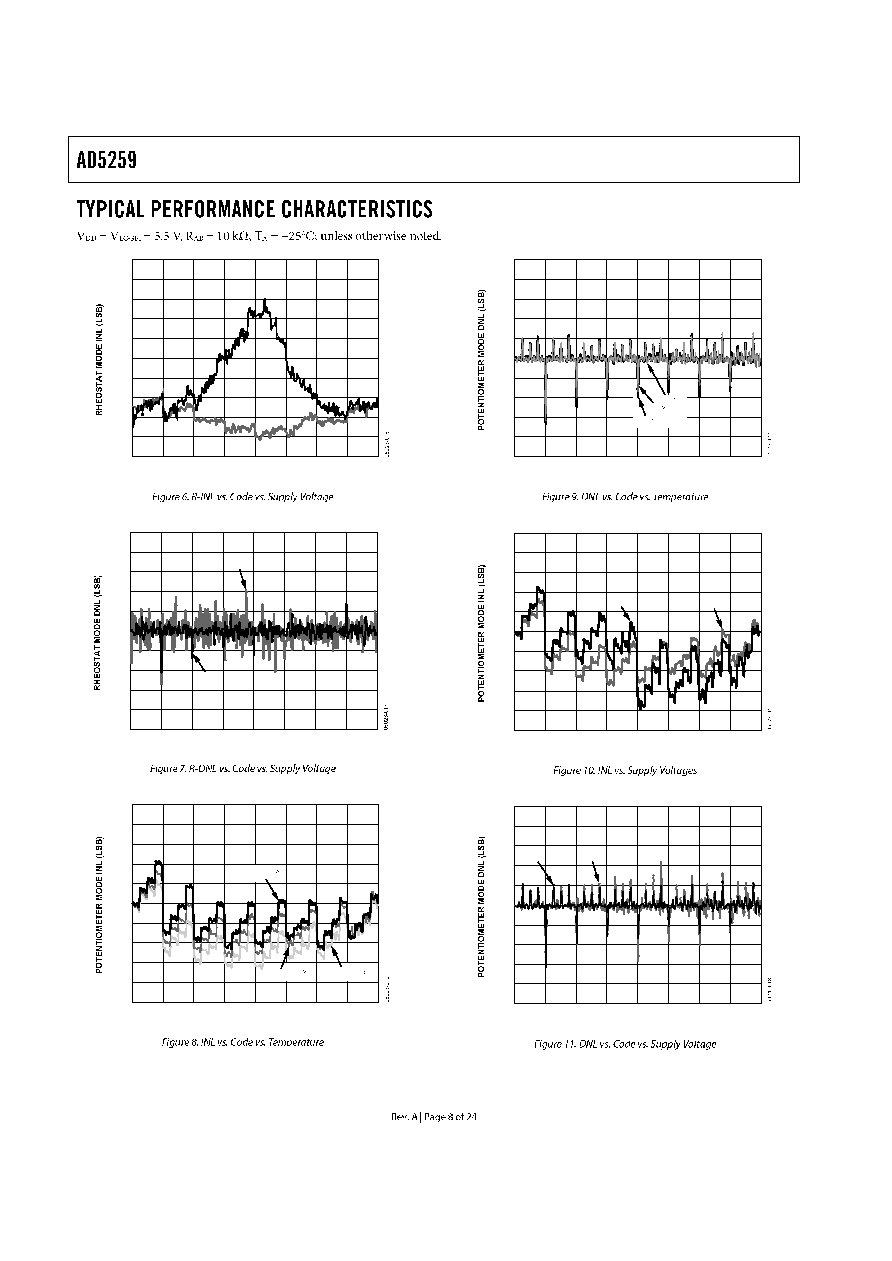

1.5

1.3

1.1

0.9

0.7

0.5

0.3

0.1

0.1

0.3

0.5

0

256

224

192

160

128

96

64

32

CODE (Decimal)

2.7V

5.5V

0.5

0.4

0.3

0.2

0.1

0

0.1

0.2

0.3

0.4

0.5

0

256

224

192

160

128

96

64

32

CODE (Decimal)

2.7V

5.5V

0.25

0.20

0.15

0.10

0.05

0

0.05

0.10

0.15

0.20

0.25

0

256

224

192

160

128

96

64

32

CODE (Decimal)

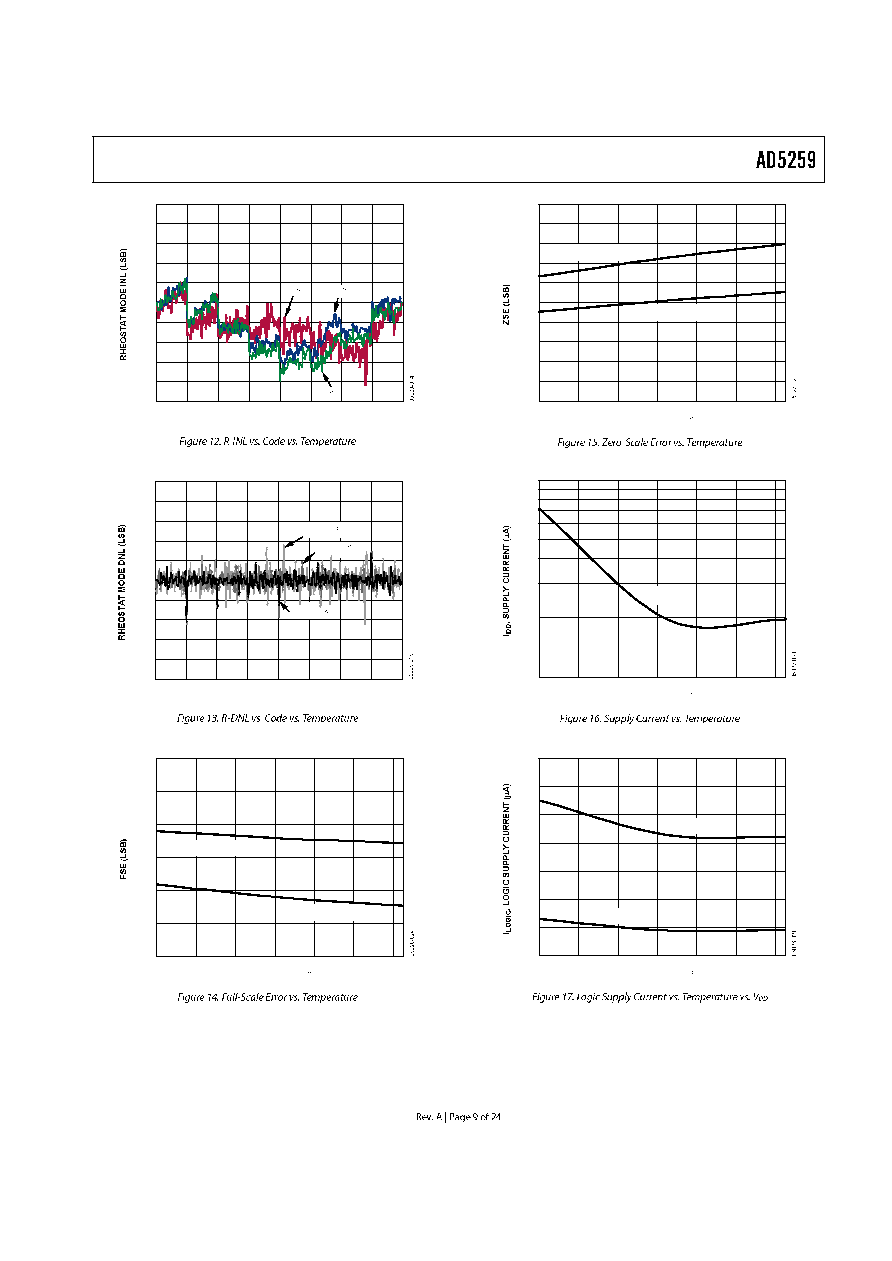

T

A

=

40 C

T

A

= +25 C

T

A

= +85 C

0.25

0.20

0.15

0.10

0.05

0

0.05

0.10

0.15

0.20

0.25

0

256

224

192

160

128

96

64

32

CODE (Decimal)

40 C

+25 C

+85 C

0.25

0.20

0.15

0.10

0.05

0

0.05

0.10

0.15

0.20

0.25

0

256

224

192

160

128

96

64

32

CODE (Decimal)

5.5V

2.7V

0.25

0.20

0.15

0.10

0.05

0

0.05

0.10

0.15

0.20

0.25

0

256

224

192

160

128

96

64

32

CODE (Decimal)

5.5V

2.7V

0.5

0.4

0.3

0.2

0.1

0

0.1

0.2

0.3

0.4

0.5

0

256

224

192

160

128

96

64

32

CODE (Decimal)

40 C

+85 C

+25 C

0.5

0.4

0.3

0.2

0.1

0

0.1

0.2

0.3

0.4

0.5

0

256

224

192

160

128

96

64

32

CODE (Decimal)

T

A

=

40 C

T

A

= +85 C

T

A

= +25 C

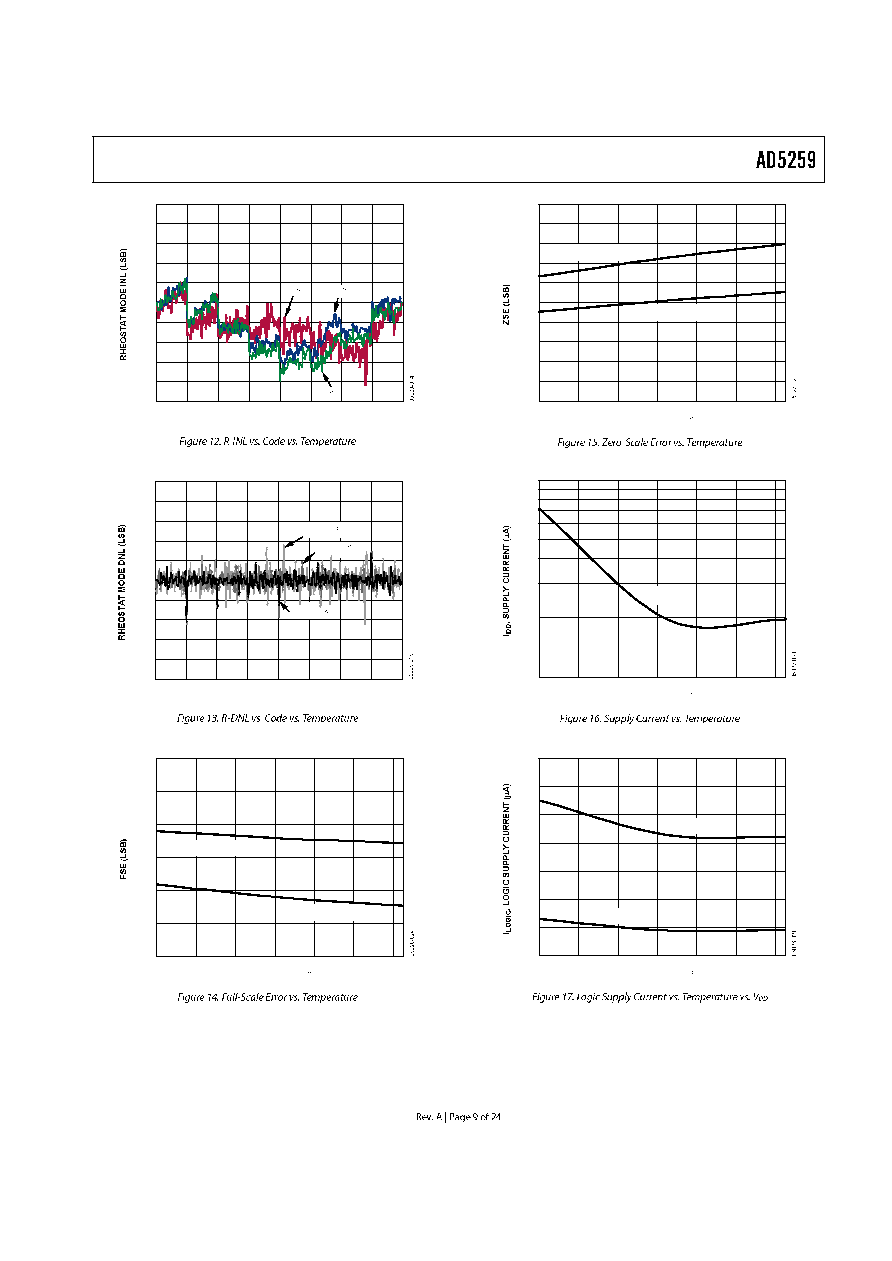

0

3.0

2.5

2.0

1.5

1.0

0.5

40

20

80

60

40

20

0

TEMPERATURE ( C)

FSE @ V

DD

= 2.7V

FSE @ V

DD

= 5.5V

2.0

1.8

1.6

1.4

1.2

1.0

0.8

0.6

0.4

0.2

0

40

20

80

60

40

20

0

TEMPERATURE ( C)

ZSE @ V

DD

= 2.7V

ZSE @ V

DD

= 5.5V

1

0.1

40

20

80

60

40

20

0

TEMPERATURE ( C)

V

DD

= 5.5V

6

1

0

1

2

3

4

5

40

20

80

60

40

20

0

TEMPERATURE ( C)

V

DD

= 2.7V

V

DD

= 5.5V

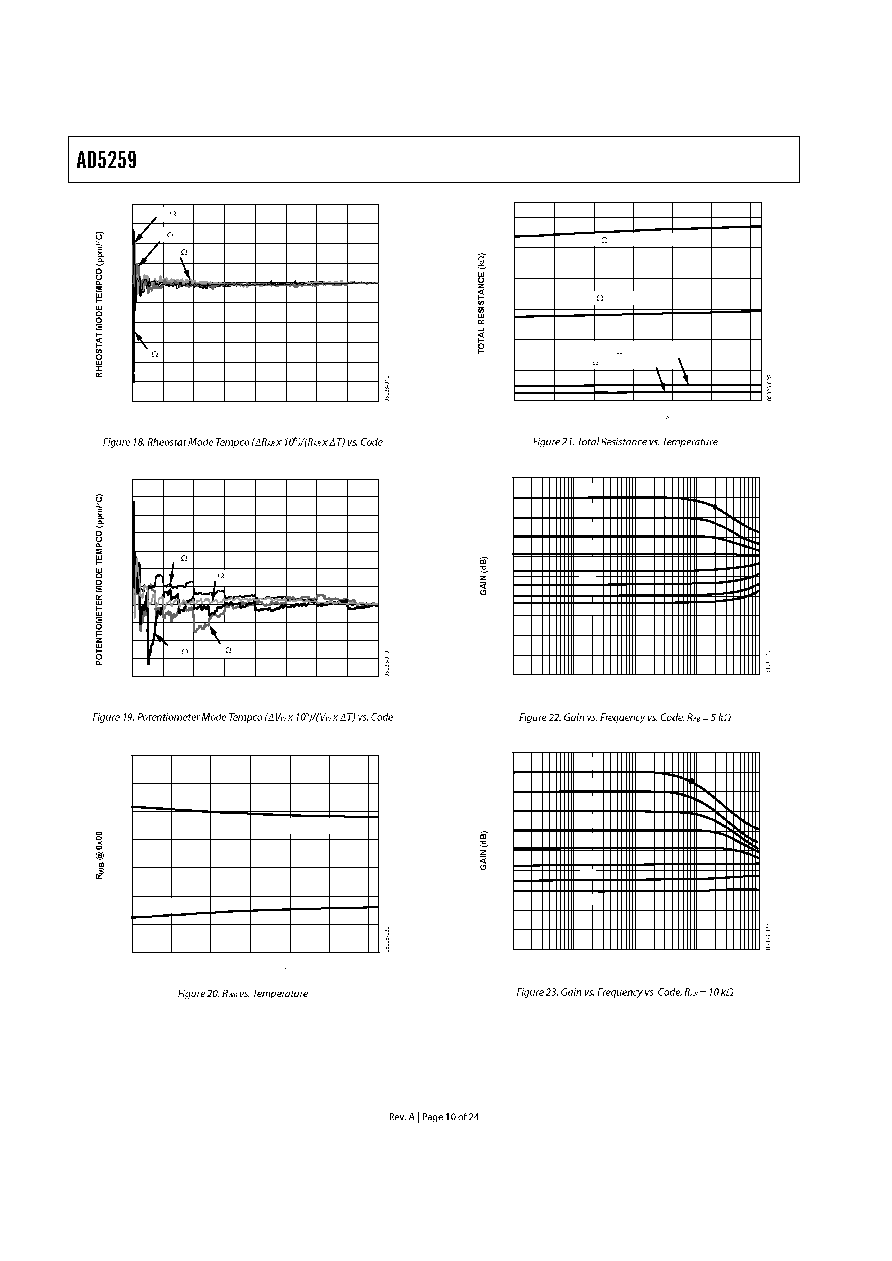

400

600

500

400

300

200

100

0

100

200

300

0

256

224

192

160

128

96

64

32

CODE (Decimal)

5k

10k

50k

100k

70

40

30

20

10

0

10

20

30

40

50

60

0

256

224

192

160

128

96

64

32

CODE (Decimal)

10k

50k

5k

100k

350

0

50

100

150

200

250

300

40

20

80

60

40

20

0

TEMPERATURE ( C)

R

WB

@ V

DD

= 5.5V

R

WB

@ V

DD

= 2.7V

120

100

80

60

40

20

0

40

20

80

60

40

20

0

TEMPERATURE ( C)

100k Rt @ V

DD

= 5.5V

50k Rt @ V

DD

= 5.5V

10k Rt @ V

DD

= 5.5V

5k Rt @ V

DD

= 5.5V

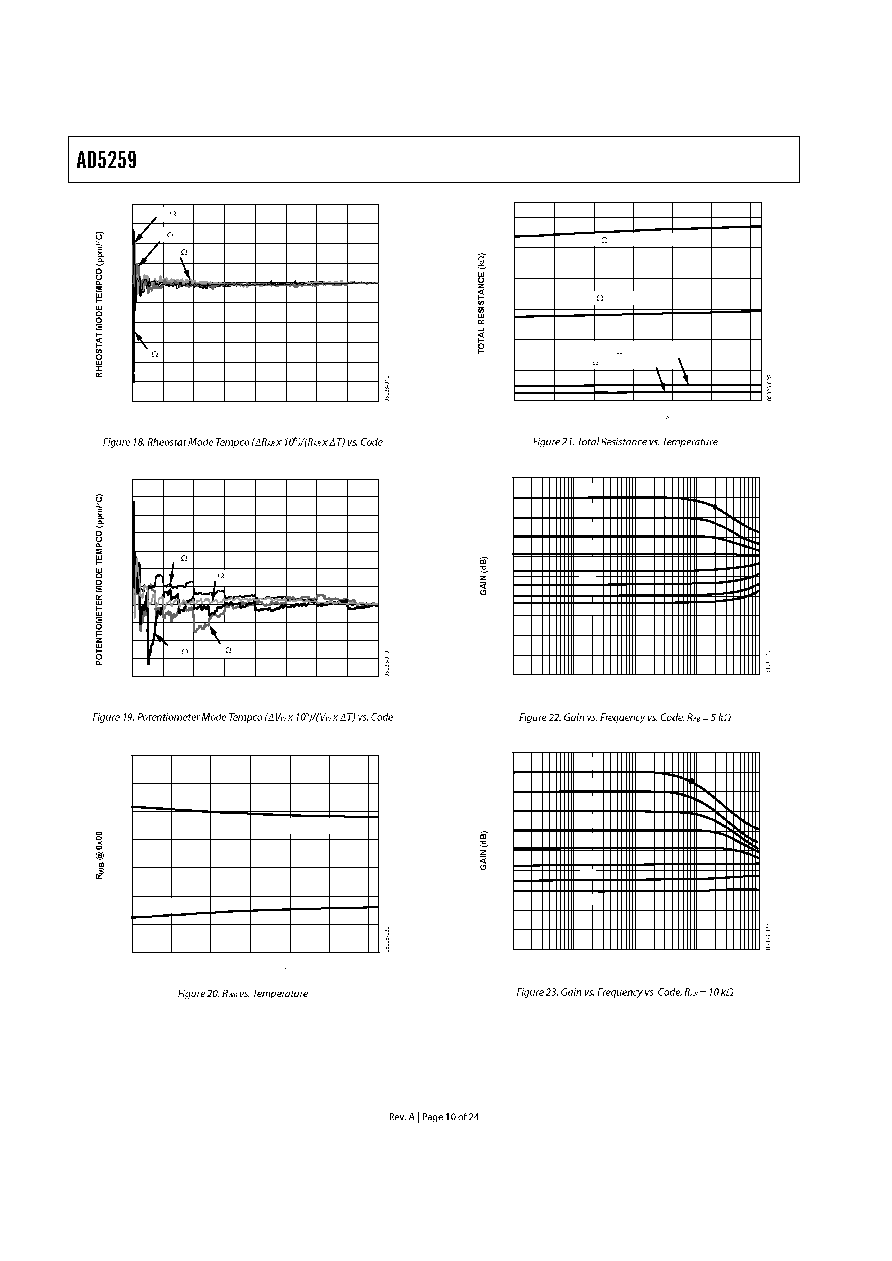

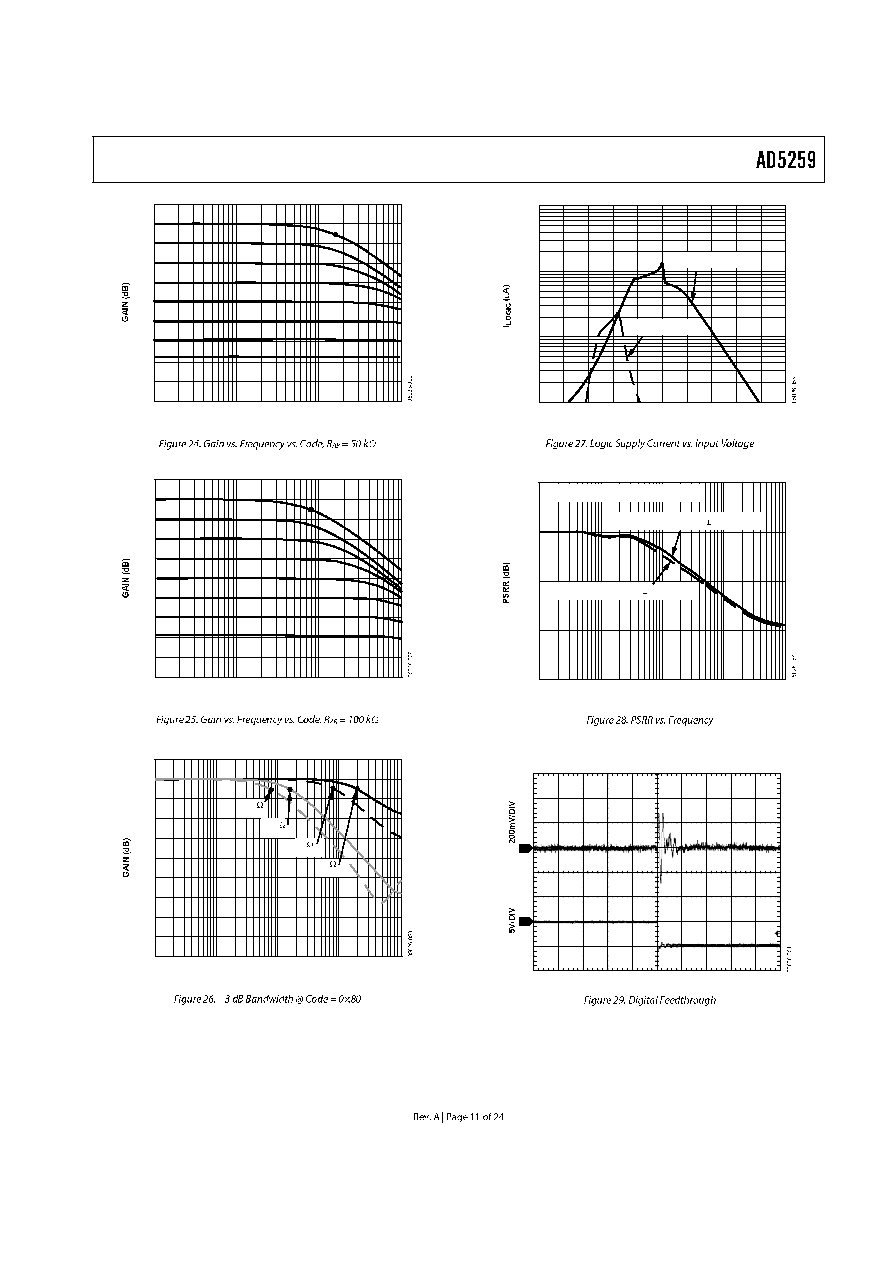

80

H

40

H

20

H

10

H

08

H

04

H

02

H

01

H

1k

10M

1M

100k

10k

60

54

48

42

36

30

24

18

12

6

0

FREQUENCY (Hz)

1k

10M

1M

100k

10k

80

H

40

H

20

H

10

H

08

H

04

H

02

H

01

H

60

54

48

42

36

30

24

18

12

6

0

FREQUENCY (Hz)

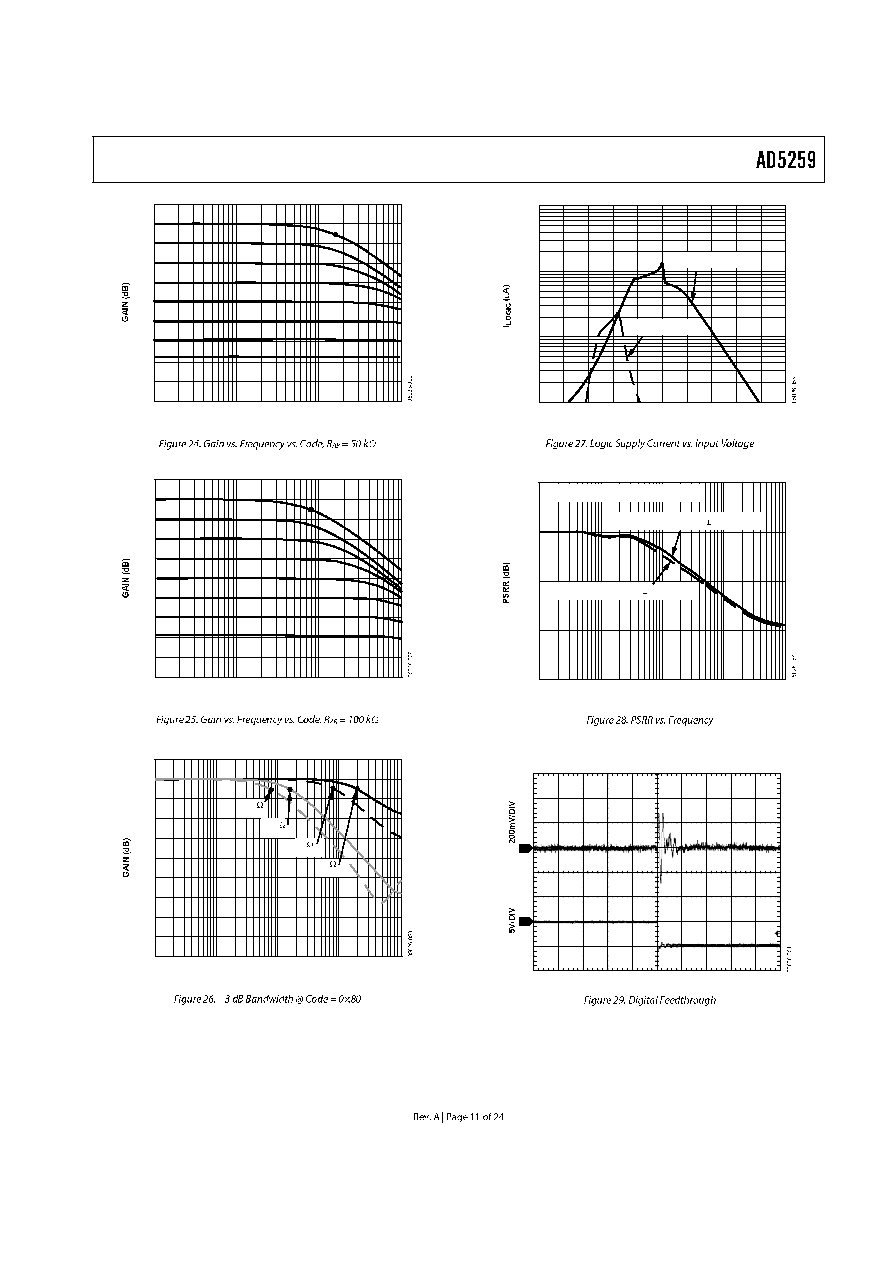

1k

1M

100k

10k

80

H

40

H

20

H

10

H

08

H

04

H

02

H

01

H

60

54

48

42

36

30

24

18

12

6

0

FREQUENCY (Hz)

1k

1M

100k

10k

80

H

40

H

20

H

10

H

08

H

04

H

02

H

01

H

60

54

48

42

36

30

24

18

12

6

0

FREQUENCY (Hz)

1k

10M

1M

100k

10k

50k

160kHz

100k

80kHz

5k

2MHz

10k

800kHz

60

54

48

42

36

30

24

18

12

6

0

FREQUENCY (Hz)

10k

1k

100

10

0

1

2

3

4

5

V

IH

(V)

V

DD

= V

LOGIC

= 5V

V

DD

= V

LOGIC

= 3V

80

60

40

20

0

100

1k

1M

100k

10k

FREQUENCY (Hz)

CODE = MIDSCALE, V

A

= V

LOGIC

, V

B

= 0V

PSRR @ V

LOGIC

= 5V DC 10% p-p AC

PSRR @ V

LOGIC

= 3V DC 10% p-p AC

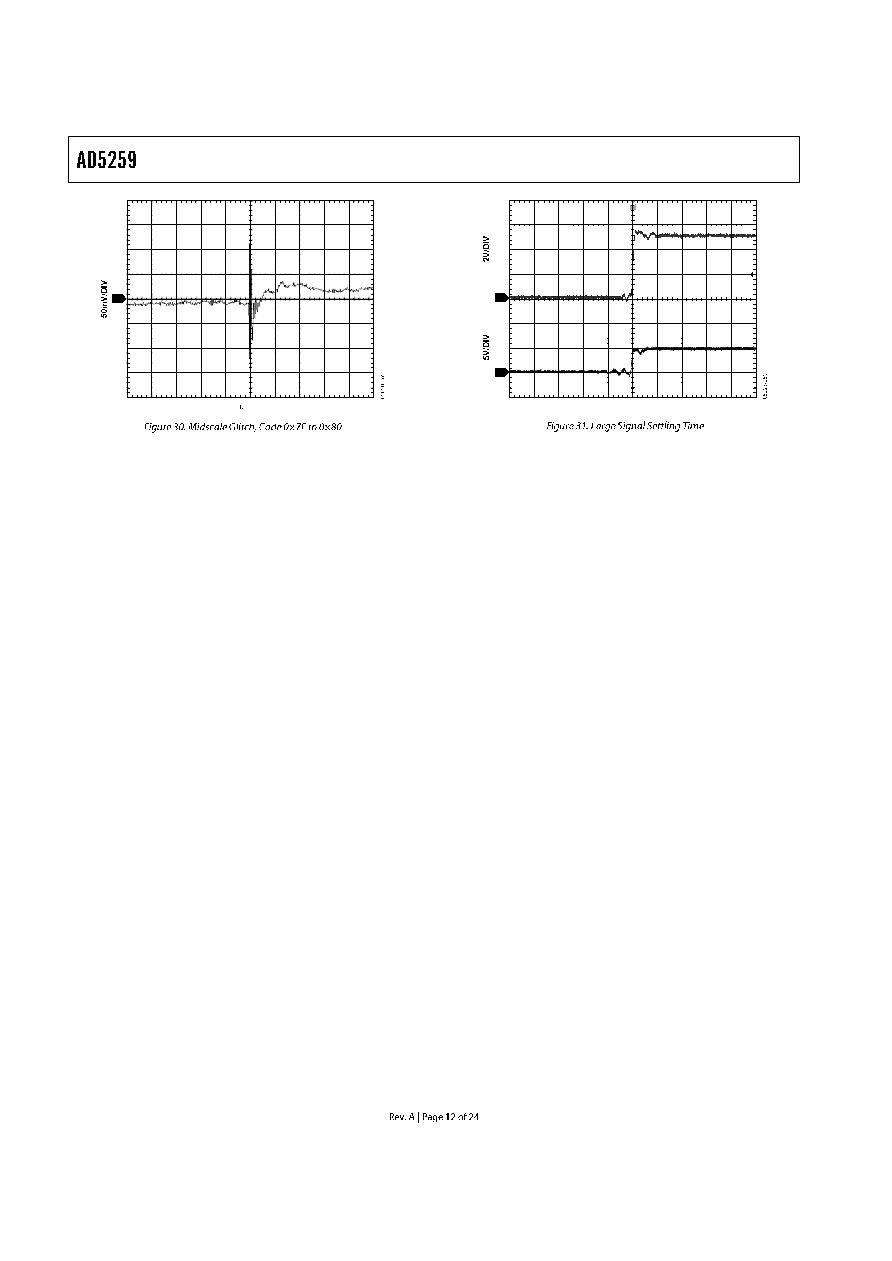

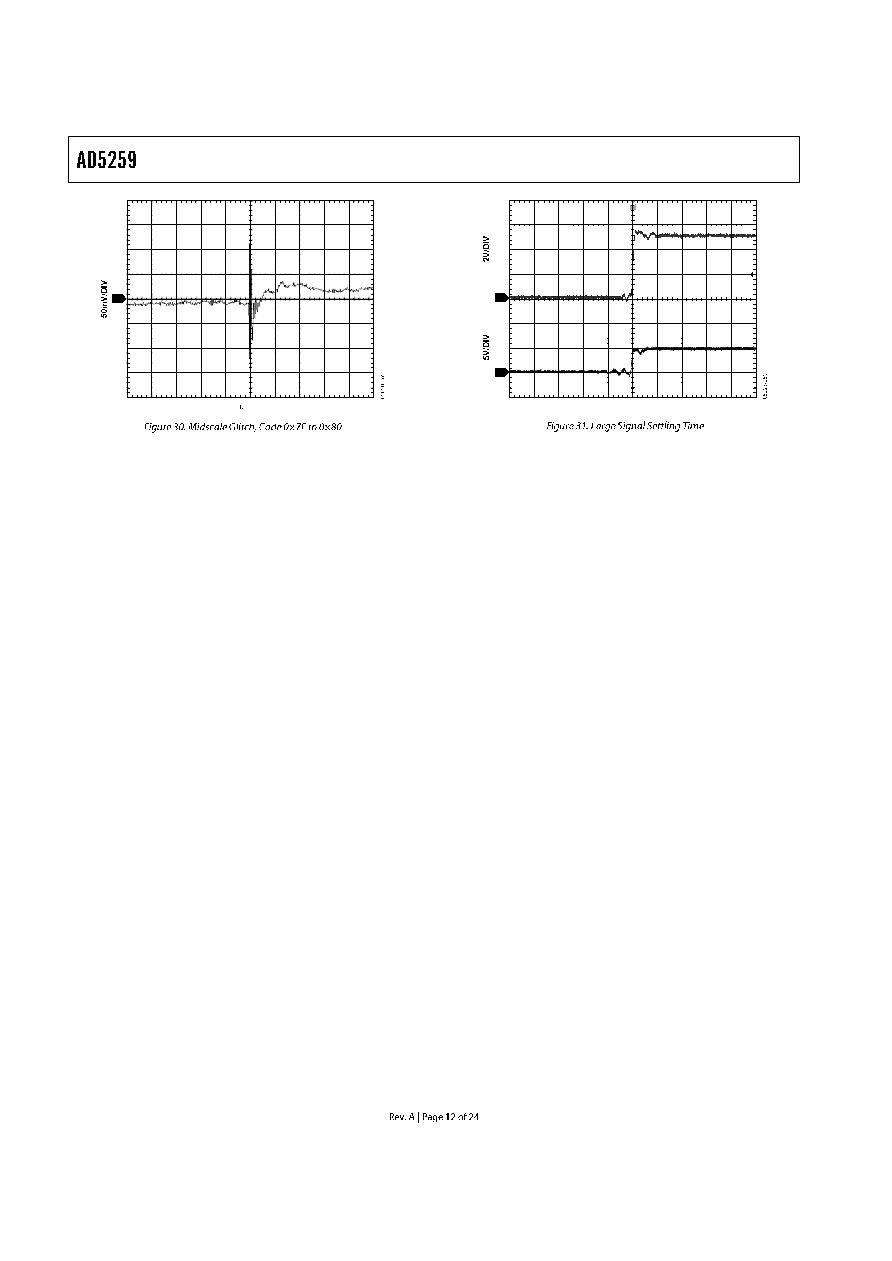

1

2

V

W

SCL

400ns/DIV

1

V

W

1 s/DIV

1

2

V

W

SCL

200ns/DIV

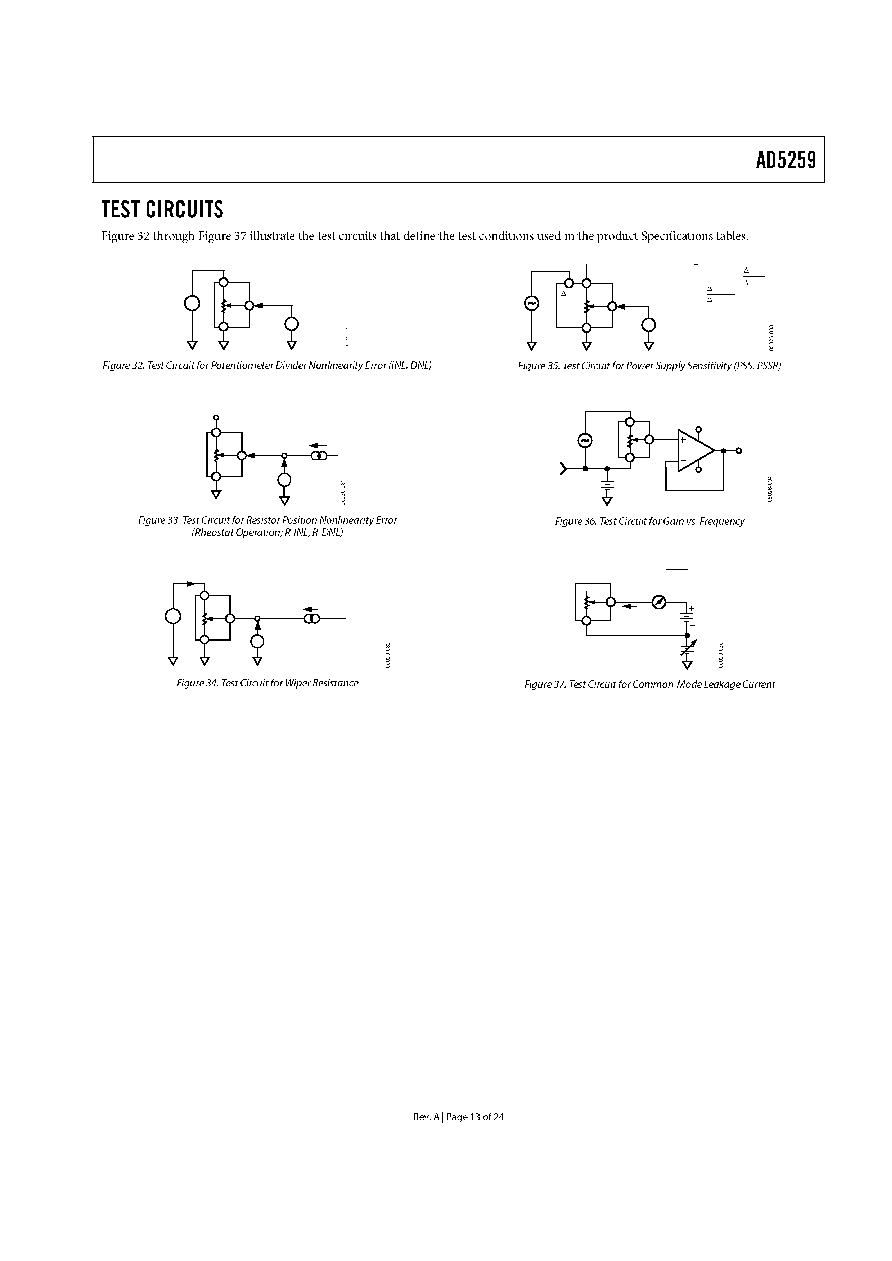

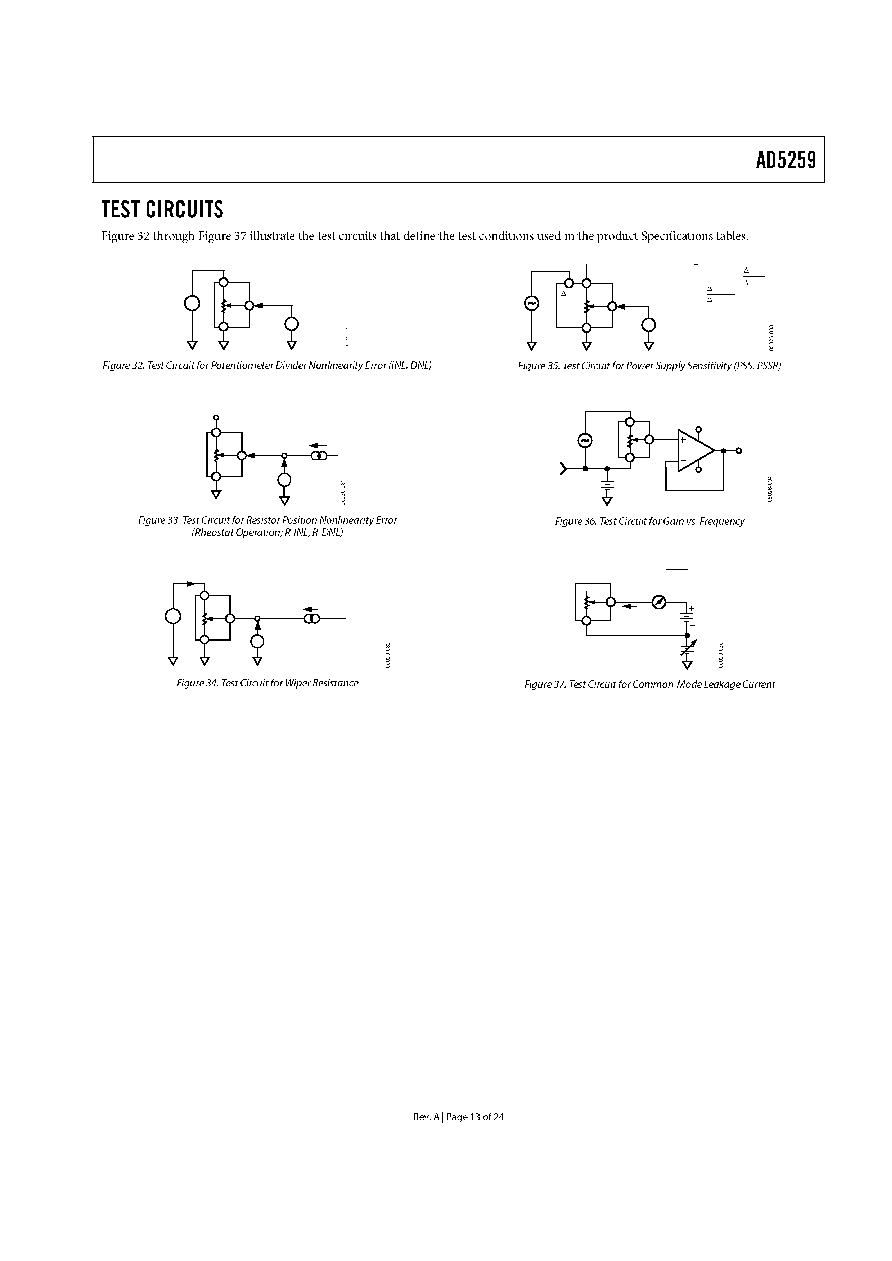

V

MS

A

W

B

DUT

V+

V+ = V

DD

1LSB = V+/2

N

NO CONNECT

I

W

V

MS

A W

B

DUT

V

MS2

V

MS1

V

W

A

W

B

DUT

I

W

= V

DD

/R

NOMINAL

R

W

= [V

MS1

V

MS2

]/I

W

V

MS

%

DUT

( )

A

W

B

V+

V

DD

%

V

MS

V

DD

V

DD

V

A

V

MS

V+ = V

DD

10%

PSRR (dB) = 20 LOG

PSS (%/%) =

+5V

5V

W

A

+2.5V

B

V

OUT

OFFSET

GND

DUT

AD8610

V

IN

W

B

DUT

I

SW

I

SW

R

SW

GND TO V

DD

CODE = 0x00

=

0.1V

0.1V

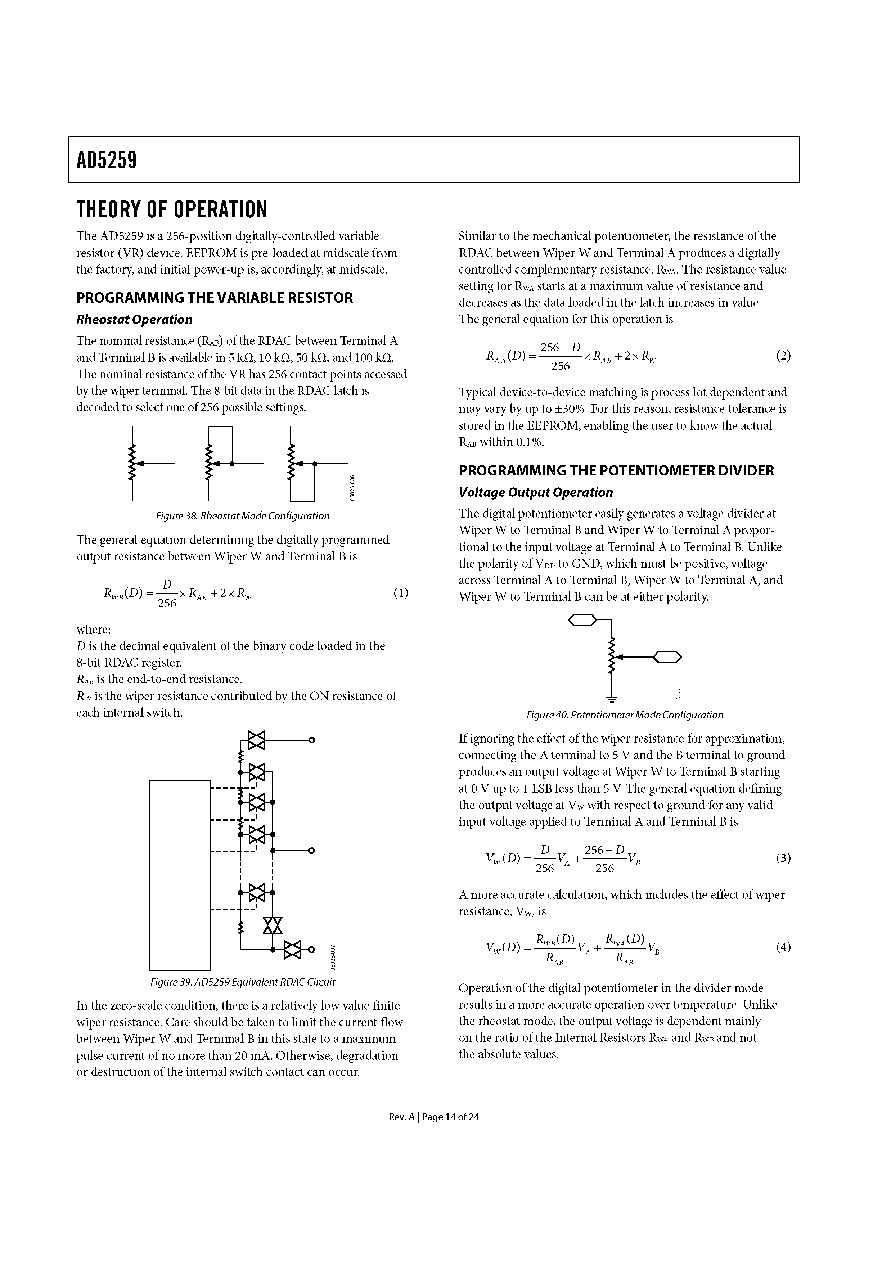

A

W

B

A

W

B

A

W

B

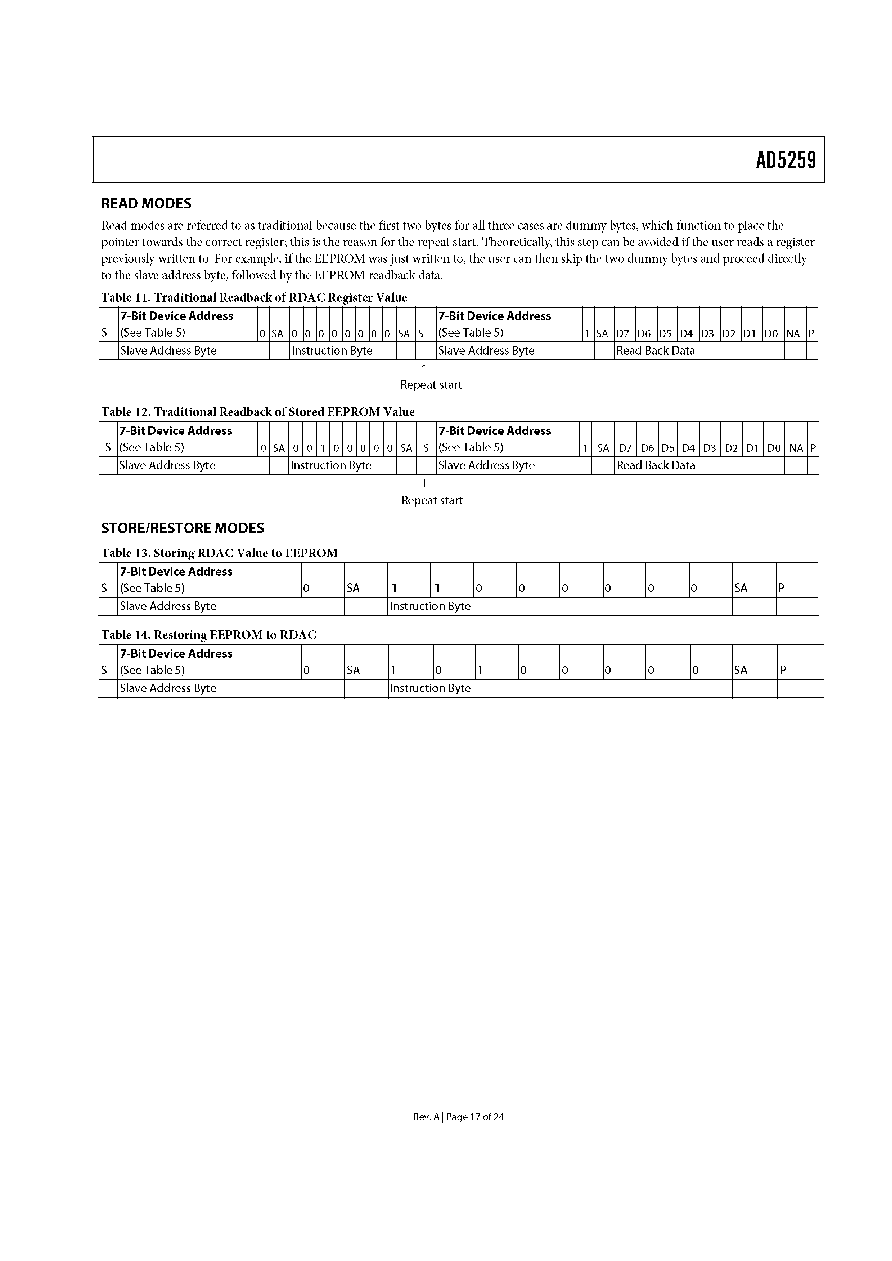

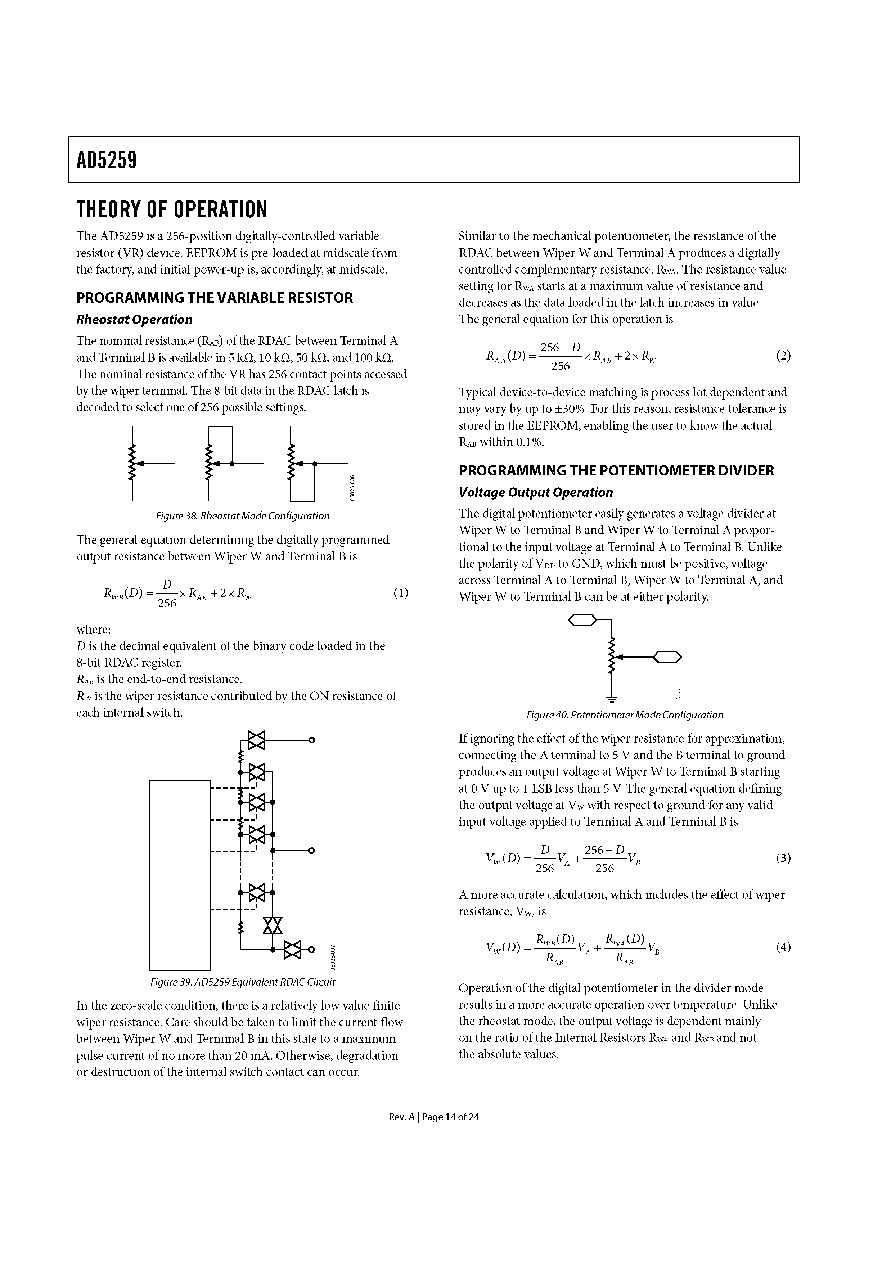

D5

D4

D3

D7

D6

D2

D1

D0

RDAC

LATCH

AND

DECODER

R

S

R

S

R

S

R

S

A

W

B

A

V

I

W

B

V

O

A

A

A

D7

D6

D5

D4

D3

D2

D1

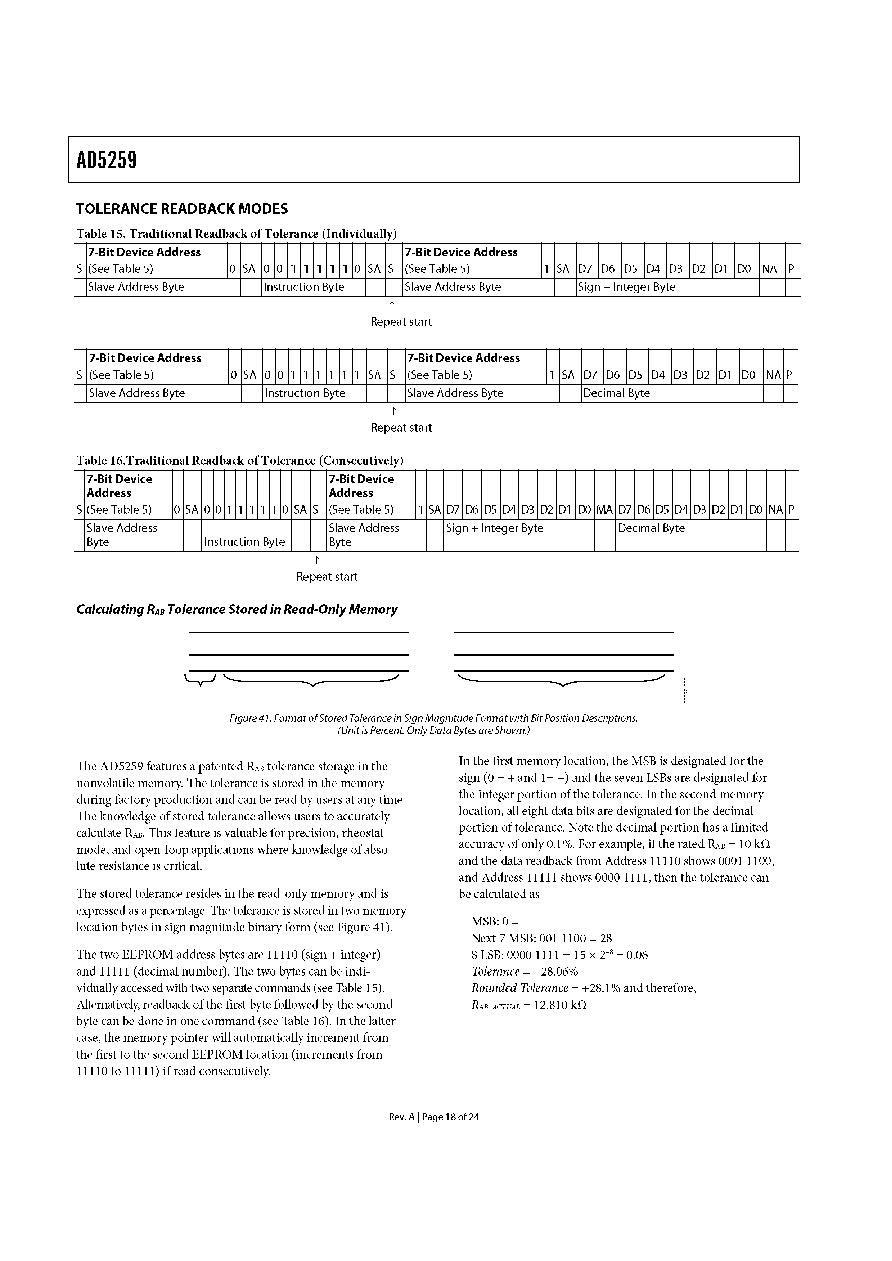

D0

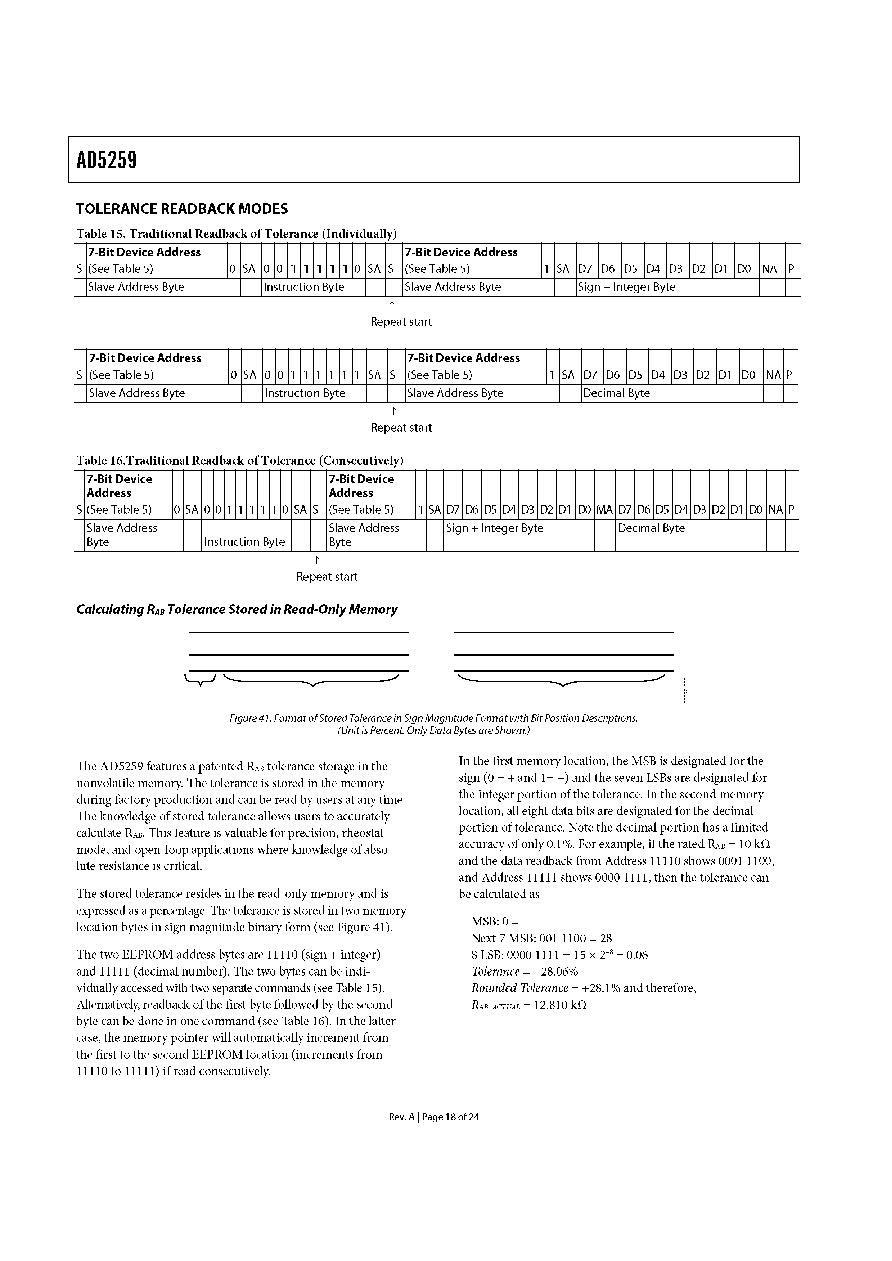

SIGN

SIGN

7 BITS FOR INTEGER NUMBER

2

6

2

5

2

4

2

3

2

2

2

1

2

0

D7

D6

D5

D4

D3

D2

D1

D0

8 BITS FOR DECIMAL NUMBER

2

8

2

1

2

2

2

3

2

4

2

5

2

6

2

7

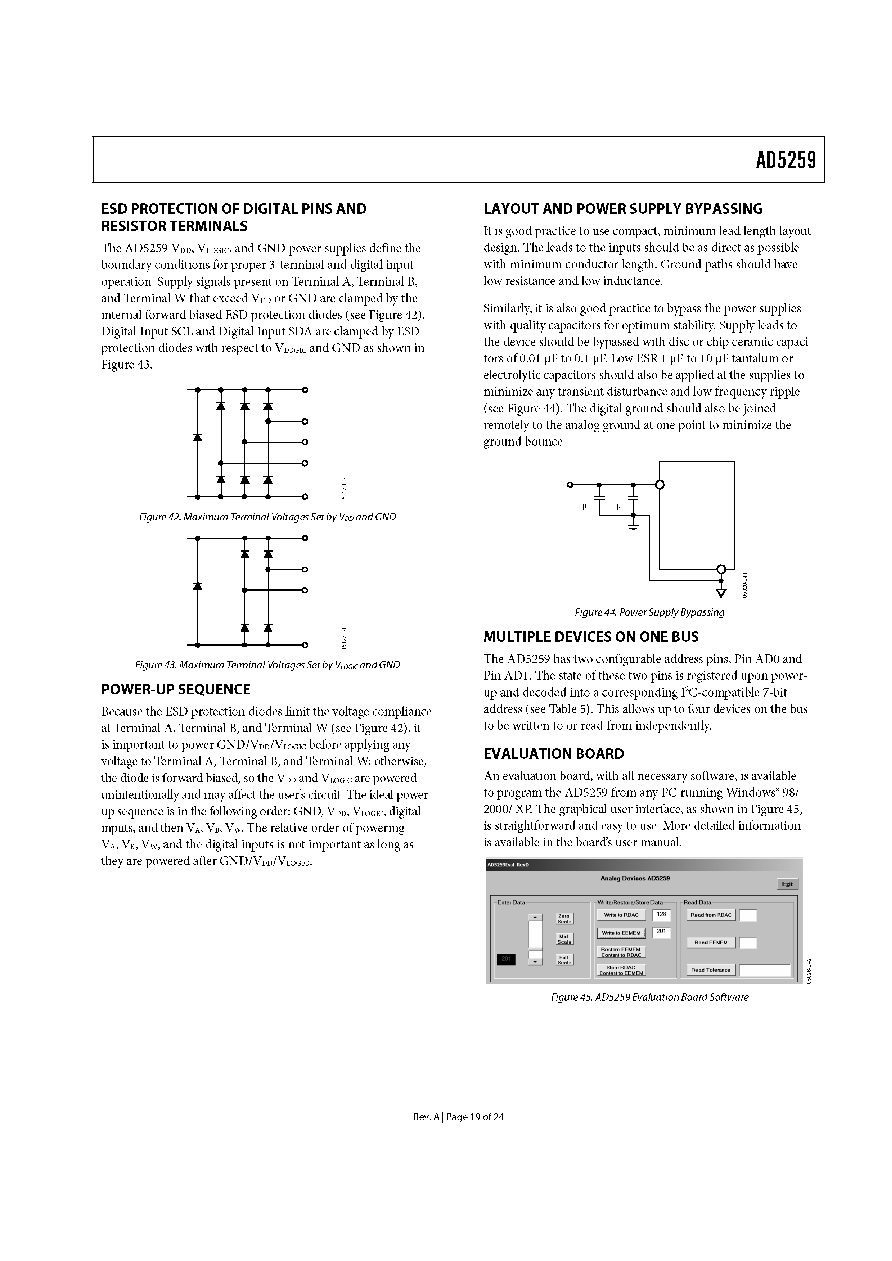

GND

A

W

B

V

DD

GND

SCL

SDA

V

LOGIC

V

DD

GND

V

DD

C2

10 F

C1

0.1 F

AD5259

+

A

B

W

R2

10k

R1

70k

R3

25k

V

DD

V

LOGIC

SCL

SDA

GND

+

U1

AD8565

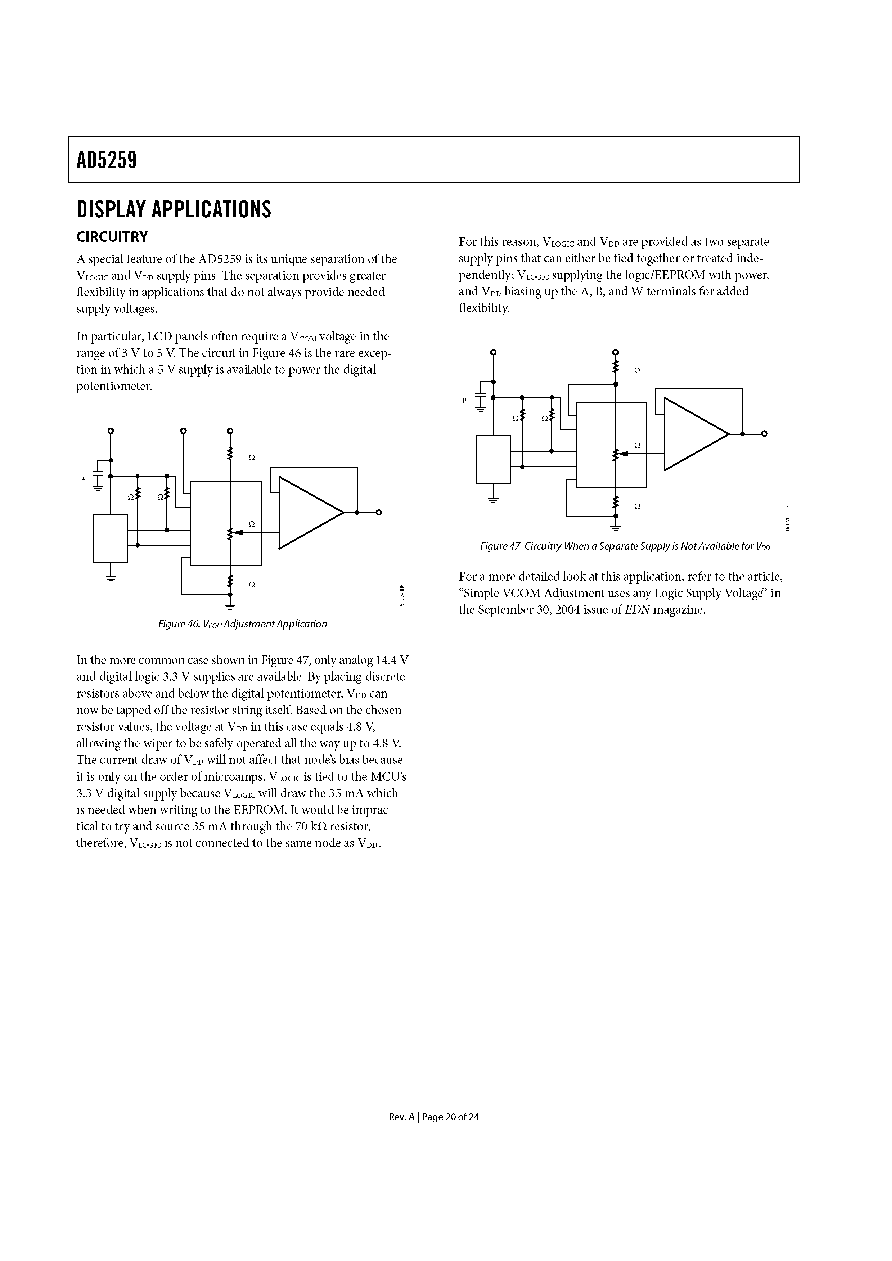

3.5V < V

COM

< 4.5V

14.4V

VCC (~3.3V)

5V

AD5259

MCU

C1

1 F

R5

10k

R6

10k

A

B

W

R2

10k

R1

70k

R3

25k

V

DD

V

LOGIC

SCL

SDA

GND

+

U1

AD8565

3.5V < V

COM

< 4.5V

14.4V

VCC (~3.3V)

AD5259

MCU

C1

1 F

R5

10k

R6

10k

SUPPLIES POWER

TO BOTH THE

MICRO AND THE

LOGIC SUPPLY OF

THE DIGITAL POT

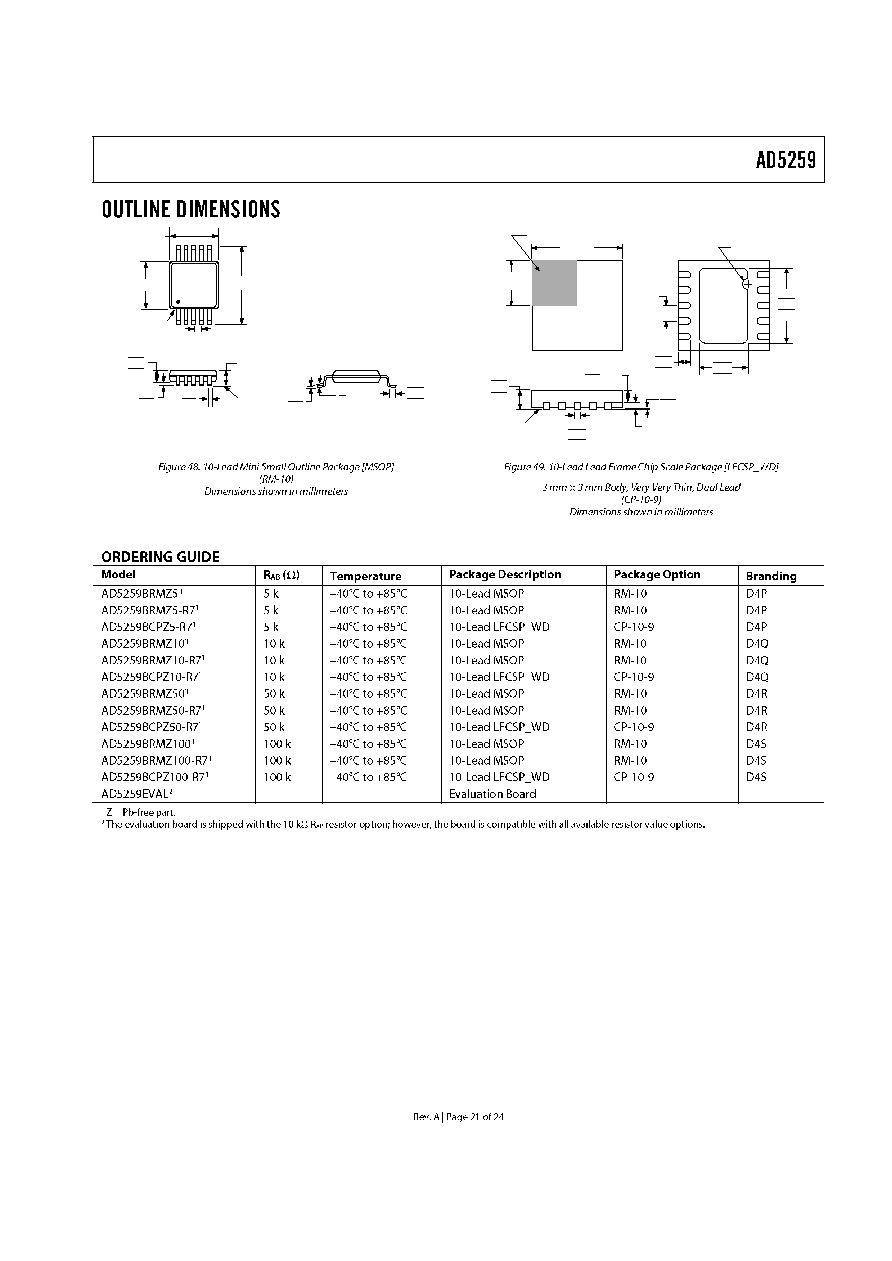

0.23

0.08

0.80

0.60

0.40

8

°

0

°

0.15

0.00

0.27

0.17

0.95

0.85

0.75

SEATING

PLANE

1.10 MAX

10

6

5

1

0.50 BSC

3.00 BSC

3.00 BSC

4.90 BSC

PIN 1

COPLANARITY

0.10

COMPLIANT TO JEDEC STANDARDS MO-187-BA

3.00

BSC SQ

INDEX

AREA

TOP VIEW

1.50

BCS SQ

EXPOSED

PAD

(BOTTOM VIEW)

1.74

1.64

1.49

2.48

2.38

2.23

1

6

10

0.50

BSC

0.50

0.40

0.30

5

PIN 1

INDICATOR

0.80

0.75

0.70

0.05 MAX

0.02 NOM

SEATING

PLANE

0.30

0.23

0.18

0.20 REF

0.80 MAX

0.55 TYP

SIDE VIEW