Document Outline

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

16 V, 4 MHz Rail-to-Rail

Output Amplifier

AD8666/AD8668

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

FEATURES

Offset voltage: 2.5 mV max

Low input bias current: 1 pA max

Single-supply operation: 5 V to 16 V

Dual-supply operation: ±2.5 V to ±8 V

Low noise: 8 nV/Hz @ 10 kHz

Wide bandwidth: 4 MHz

Rail-to-rail output

Unity gain stable

Lead-free packaging

APPLICATIONS

Sensor amplification

Reference buffers

Medical equipment

Physiological measurements

Signal filters and conditioning

Consumer audio

Photodiode amplification

ADC driver

Level shifting circuits

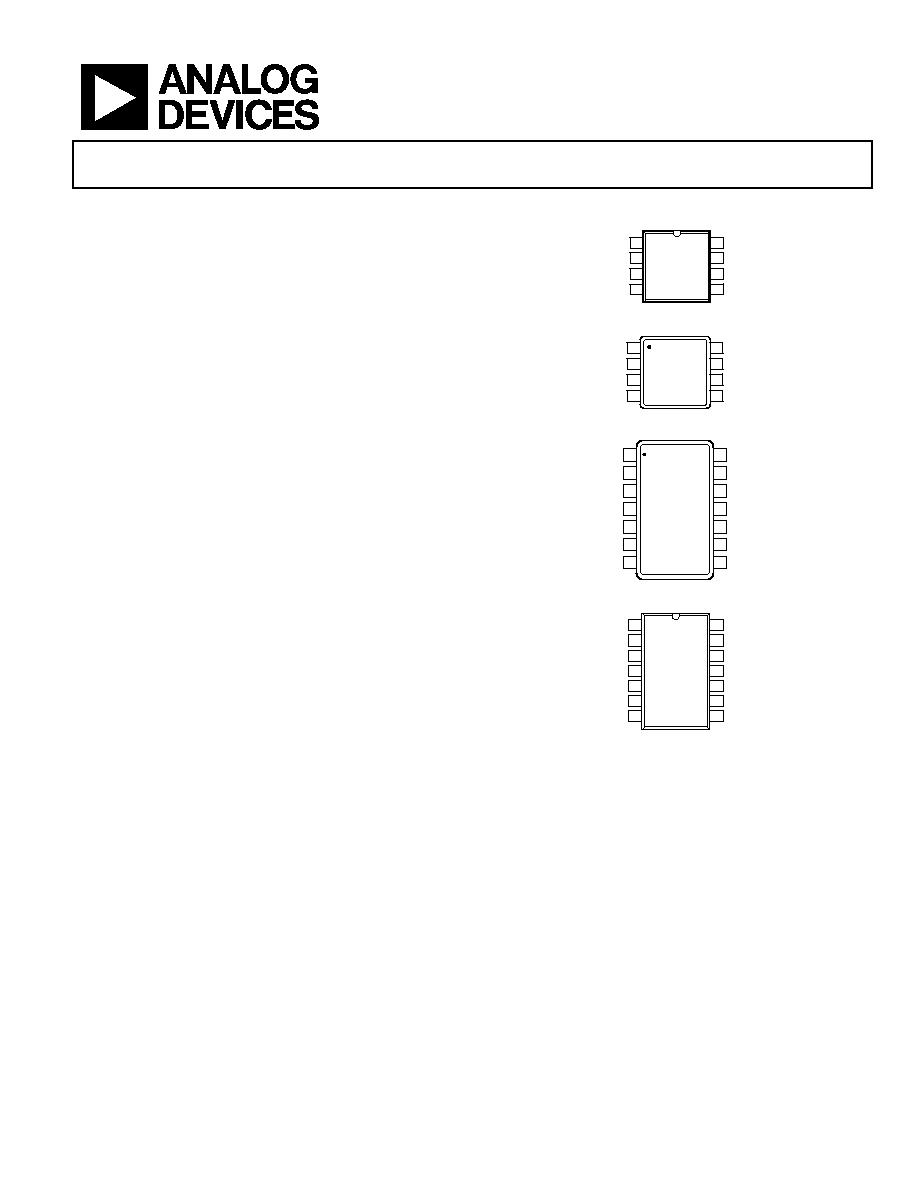

PIN CONFIGURATIONS

OUT A

1

≠IN A

2

+IN A

3

V≠

4

V+

8

OUT B

7

≠IN B

6

+IN B

5

AD8666

TOP VIEW

(Not to Scale)

06

01

8-

0

01

Figure 1. AD8666, 8-Lead SOIC_N (R-8)

OUT A

1

≠IN A

2

+IN A

3

V≠

4

V+

8

OUT B

7

≠IN B

6

+IN B

5

AD8666

TOP VIEW

(Not to Scale)

06

01

8-

0

02

Figure 2. AD8666, 8-Lead MSOP (RM-8)

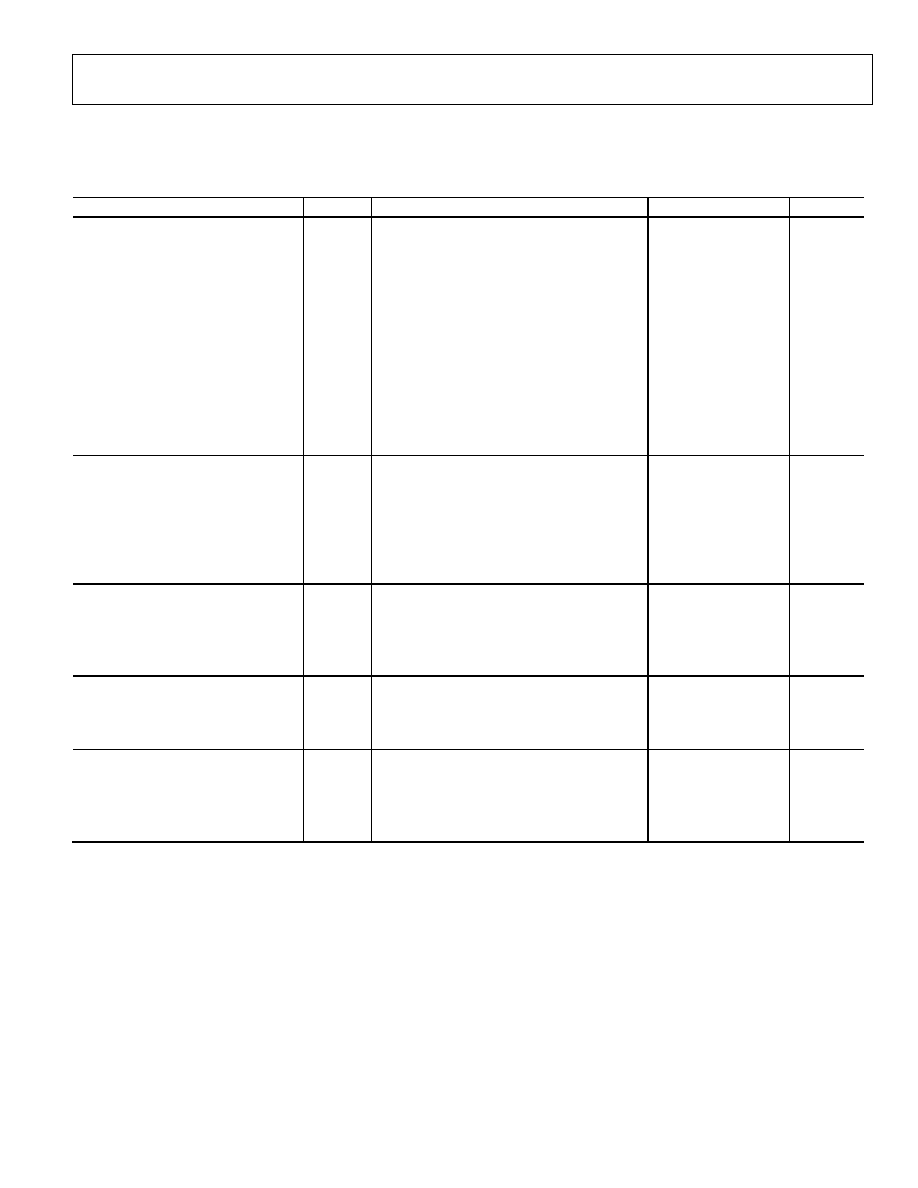

1

2

3

4

5

6

7

AD8668

≠IN A

+IN A

V+

OUT B

≠IN B

+IN B

OUT A

14

13

12

11

10

9

8

≠IN D

+IN D

V≠

OUT C

≠IN C

+IN C

OUT D

TOP VIEW

(Not to Scale)

06

01

8-

0

03

Figure 3. AD8668, 14-Lead TSSOP (RU-14)

OUT A

≠IN A

+IN A

V+

OUT D

≠IN D

+IN D

V≠

+IN B

+IN C

≠IN B

OUT B

≠IN C

OUT C

AD8648

TOP VIEW

(Not to Scale)

OUT A

AD8668

TOP VIEW

(Not to Scale)

AD8648

TOP VIEW

(Not to Scale)

6

1

2

3

4

5

7

14

13

12

11

10

9

8

AD8668

TOP VIEW

(Not to Scale)

060

18

-

0

04

Figure 4. AD8668, 14-Lead SOIC_N (R-14)

GENERAL DESCRIPTION

The AD8666/AD8668 are single supply, rail-to-rail output

amplifiers with low noise performance featuring an extended

operating range with supply voltages up to 16 V. They also

feature low input bias currents, wide signal bandwidth, and low

input voltage and current noise. For lower offset voltage, choose

the

AD8662

(dual).

The combination of offsets, very low input bias currents, and

wide supply range make these amplifiers useful in a wide variety

of cost-sensitive applications normally associated with much

higher priced JFET amplifiers. Systems utilizing high

impedance sensors, such as photo diodes, benefit from the

combination of low input bias current, low noise, and low offset

and bandwidth. The wide operating voltage range matches

today's high performance ADCs and DACs. Audio applications

and medical monitoring equipment can take advantage of the

high input impedance, low voltage and current noise, wide

bandwidth, and the lack of "popcorn" noise found in many

other low input bias current amplifiers.

The AD8666/AD8668 are specified over the extended industrial

temperature range (-40∞ to +125∞C).

AD8666/AD8668

Rev. 0 | Page 2 of 16

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications....................................................................................... 1

Pin Configurations ........................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings ............................................................5

Thermal Resistance .......................................................................5

ESD Caution...................................................................................5

Typical Performance Characteristics ..............................................6

Outline Dimensions ....................................................................... 12

Ordering Guide .......................................................................... 12

REVISION HISTORY

4/06--Rev 0: Initial Version

AD8666/AD8668

Rev. 0 | Page 3 of 16

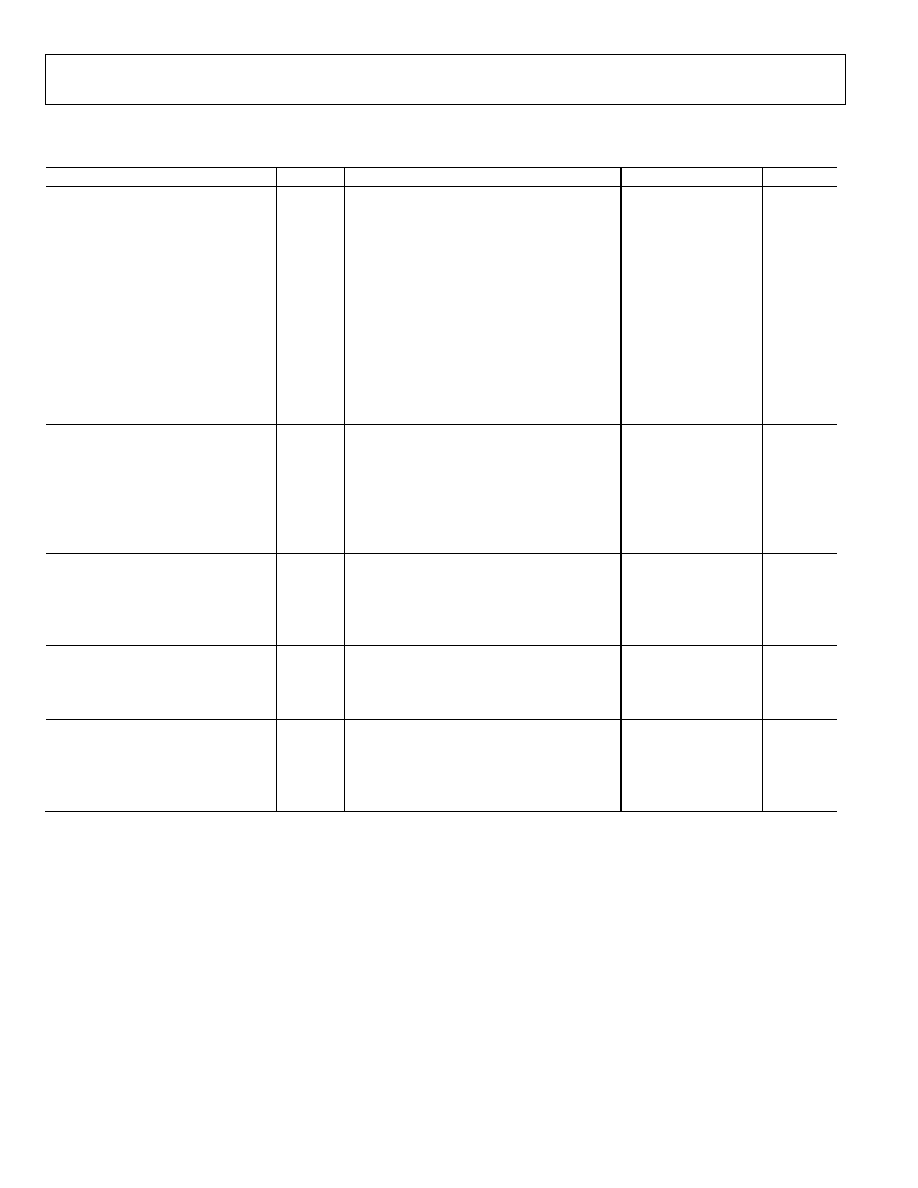

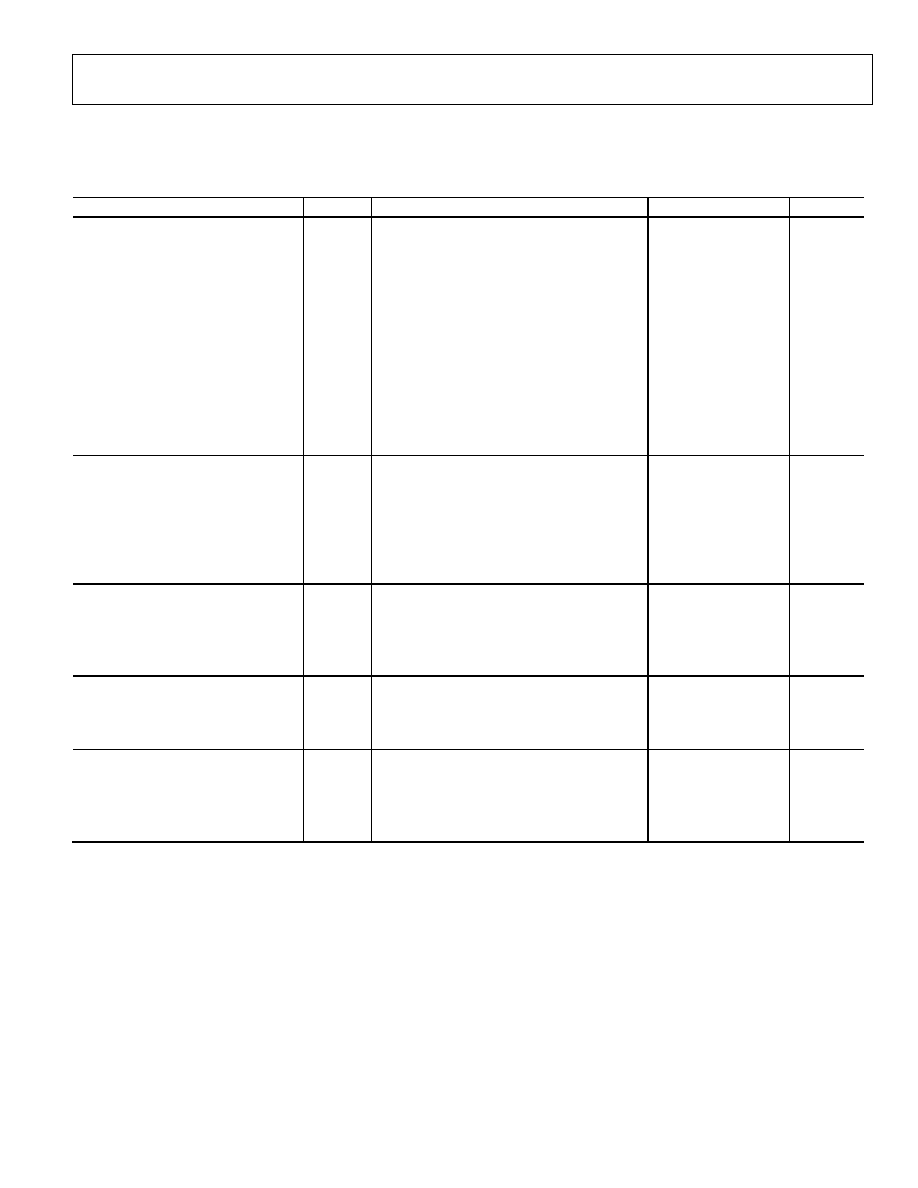

SPECIFICATIONS

V

DD

= 5.0 V, V

CM

= V

DD

/2, T

A

= 25

o

C, unless otherwise noted.

Table 1.

Parameter Symbol

Conditions

Min

Typ

Max

Unit

INPUT

CHARACTERISTICS

Offset Voltage

V

OS

V

CM

= 2.5 V

0.7

2.5

mV

V

CM

= -0.1 V to +3.0 V

3.0

mV

-40∞C

<

T

A

< +125∞C

5.0

mV

Offset Voltage Drift

V

OS

/T -40∞C

<

T

A

< +125∞C

3.0

10

V/∞C

Input Bias Current

I

B

0.2

1

pA

-40∞C

<

T

A

< +125∞C

550

pA

Input Offset Current

I

OS

0.1

0.5

pA

-40∞C

<

T

A

< +125∞C

70

pA

Input Voltage Range

V

CM

-0.1

+3.0 V

Common-Mode Rejection Ratio

CMRR

V

CM

= -0.1 V to +3.0 V

84

100

dB

-40∞C

<

T

A

< +125∞C

79

dB

Large-Signal Voltage Gain

A

VO

R

L

= 2 k, V

O

= 0.5 V to 4.5 V

68

145

V/mV

OUTPUT

CHARACTERISTICS

Output Voltage High

V

OH

I

OUT

= 1 mA

4.88

4.93

V

-40∞C

<

T

A

< +125∞C

4.86

V

Output Voltage Low

V

OL

I

OUT

= 1 mA

50

85

mV

-40∞C

<

T

A

< +125∞C

105

mV

Short-Circuit Output Current

I

SC

±19

mA

Closed-Loop Output Impedance

Z

OUT

At 1MHz, A

V

= 1

50

POWER

SUPPLY

Power Supply Rejection Ratio

PSRR

V

DD

= 5.0 V to 16 V

98

115

dB

-40∞C

<

T

A

< +125∞C

94

dB

Supply Current per Amplifier

I

SY

1.1

1.4

mA

-40∞C

<

T

A

< +125∞C

2.0

mA

DYNAMIC PERFORMANCE

Slew Rate

SR

R

L

= 2 k

3.5

V/s

Gain Bandwidth Product

GBP

4

MHz

Phase Margin

M

70

Degrees

NOISE

PERFORMANCE

Peak-to-Peak Noise

e

n

p-p

0.1 Hz to 10 Hz

2.4

V p-p

Voltage Noise Density

e

n

f = 1 kHz

10

nV/Hz

f = 10 kHz

8

nV/Hz

Channel Separation

CS

f = 10 kHz

-115

dB

AD8666/AD8668

Rev. 0 | Page 4 of 16

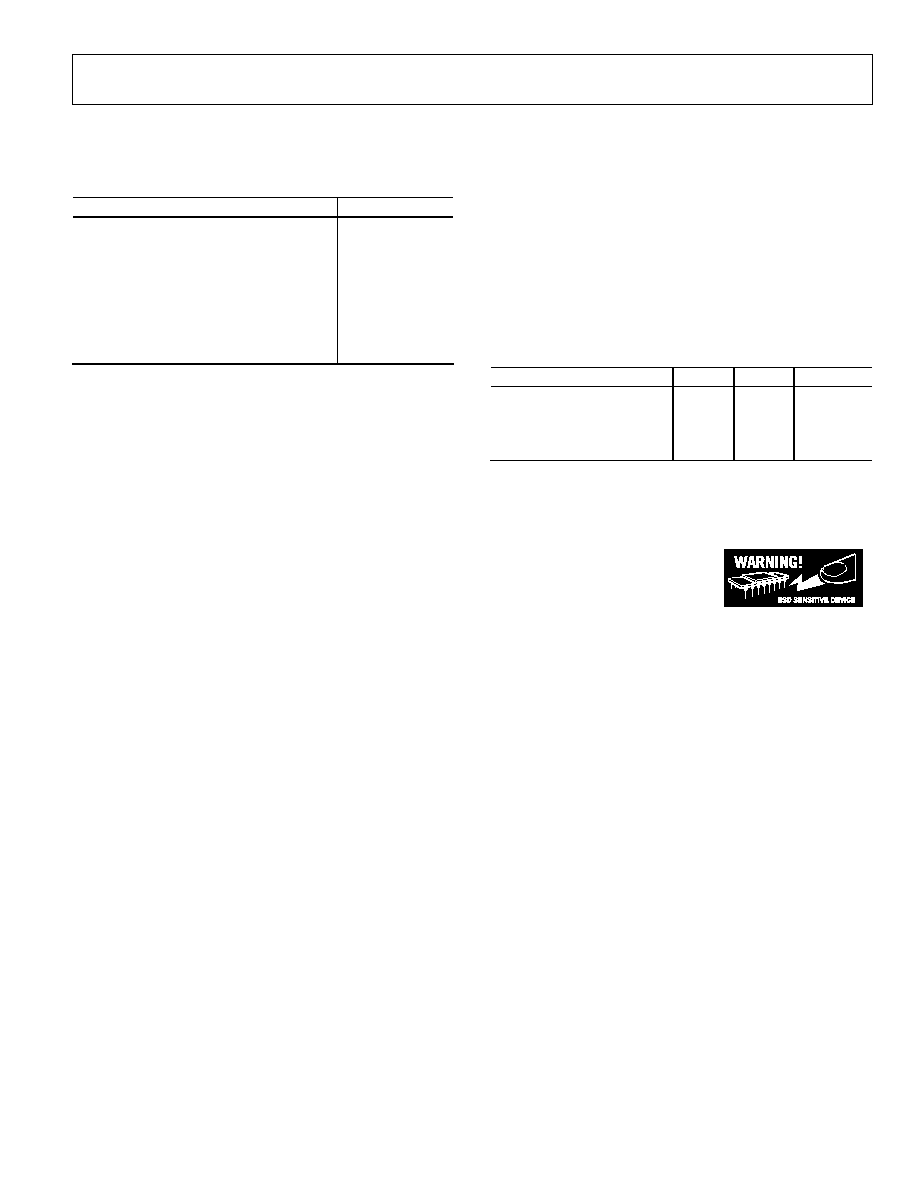

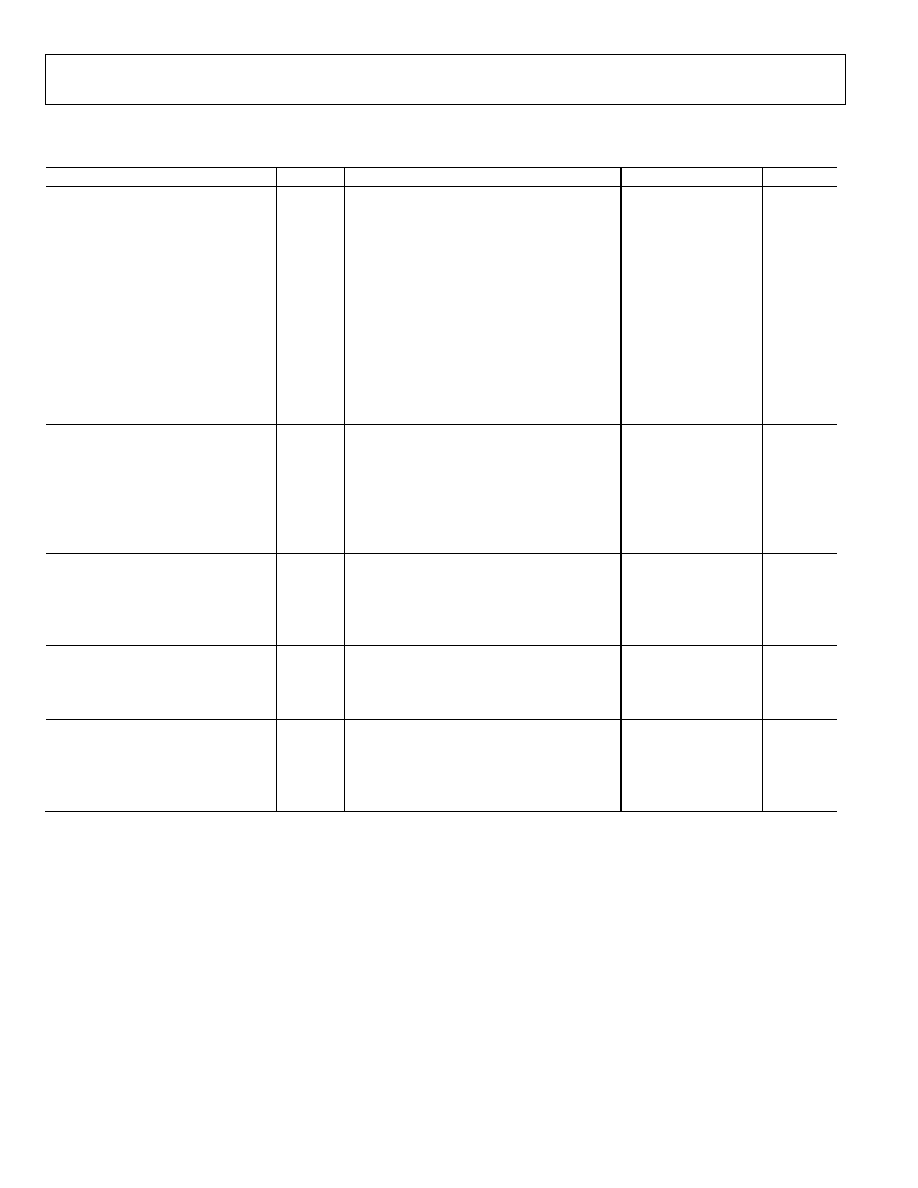

V

DD

= 16 V, V

CM

= V

DD

/2, T

A

= 25

o

C, unless otherwise noted.

Table 2.

Parameter Symbol

Conditions

Min

Typ

Max

Unit

INPUT

CHARACTERISTICS

Offset Voltage

V

OS

V

CM

= 8 V

0.6

2.5

mV

V

CM

= -0.1 V to +14.0 V

3.0

mV

-40∞C

<

T

A

< +125∞C

5.0

mV

Offset Voltage Drift

V

OS

/T -40∞C

<

T

A

< +125∞C

3.0

10

V/∞C

Input Bias Current

I

B

0.2

1

pA

-40∞C

<

T

A

< +125∞C

550

pA

Input Offset Current

I

OS

0.1

0.5

pA

-40∞C

<

T

A

< +125∞C

70

pA

Input Voltage Range

V

CM

-0.1

+14.0

V

Common-Mode Rejection Ratio

CMRR

V

CM

= -0.1 V to +14.0 V

90

110

dB

-40∞C

<

T

A

< +125∞C

80

dB

Large-Signal Voltage Gain

A

VO

R

L

= 2 k, V

O

= 0.5 V to 15.5 V

130

255

V/mV

OUTPUT

CHARACTERISTICS

Output Voltage High

V

OH

I

OUT

= 1 mA

15.94

15.96

V

-40∞C

<

T

A

< +125∞C

15.90

V

Output Voltage Low

V

OL

I

OUT

= 1 mA

22

40

mV

-40∞C

<

T

A

< +125∞C

50

mV

Short-Circuit Output Current

I

SC

±140

mA

Closed-Loop Output Impedance

Z

OUT

At 1MHz, A

V

= 1

50

POWER

SUPPLY

Power Supply Rejection Ratio

PSRR

V

DD

= 5.0 V to 16 V

98

115

dB

-40∞C

<

T

A

< +125∞C

94

dB

Supply Current per Amplifier

I

SY

1.15

1.55

mA

-40∞C

<

T

A

< +125∞C

2.0

mA

DYNAMIC PERFORMANCE

Slew Rate

SR

R

L

= 2 k

3.5

V/s

Gain Bandwidth Product

GBP

4

MHz

Phase Margin

M

73

Degrees

NOISE

PERFORMANCE

Peak-to-Peak Noise

e

n

p-p

0.1 Hz to 10 Hz

2.5

V p-p

Voltage Noise Density

e

n

f = 1 kHz

10

nV/Hz

f = 10 kHz

8

nV/Hz

Channel Separation

CS

f = 10 kHz

-115

dB

AD8666/AD8668

Rev. 0 | Page 5 of 16

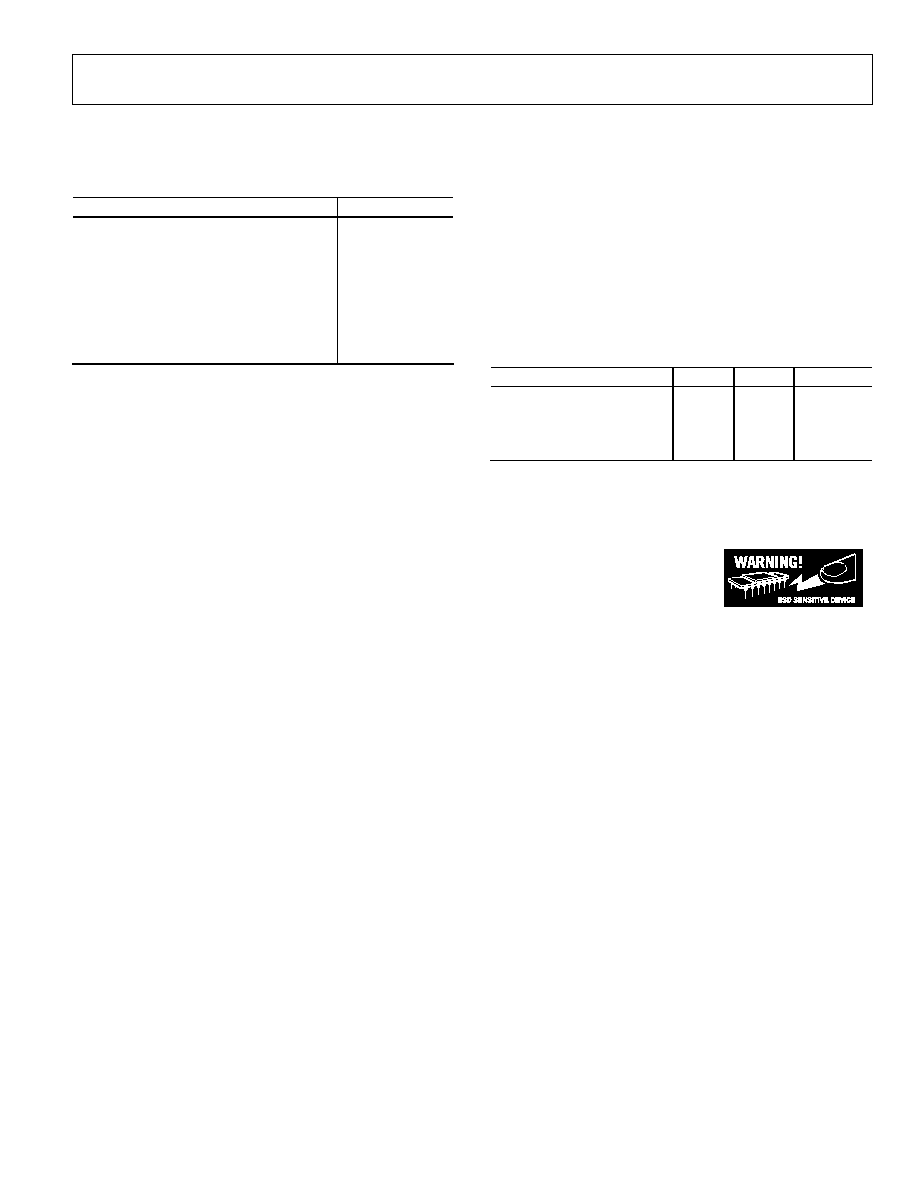

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage

18 V

Input Voltage

GND to V

DD

Differential Input Voltage

±18 V

Output Short-Circuit to GND

Indefinite

Storage Temperature Range

-65∞C to +150∞C

Operating Temperature Range

-40∞C to +125∞C

Lead Temperature (Soldering, 60 sec)

300∞C

Junction Temperature

150∞C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

Table 4. Thermal Resistance

Package Type

JA

JC

Unit

8-Lead SOIC_N (R-8)

158

43

∞C/W

8-Lead MSOP (RM-8)

210

45

∞C/W

14-Lead SOIC (R-14)

120

36

∞C/W

14-Lead TSSOP (RU-14)

180

35

∞C/W

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

AD8666/AD8668

Rev. 0 | Page 6 of 16

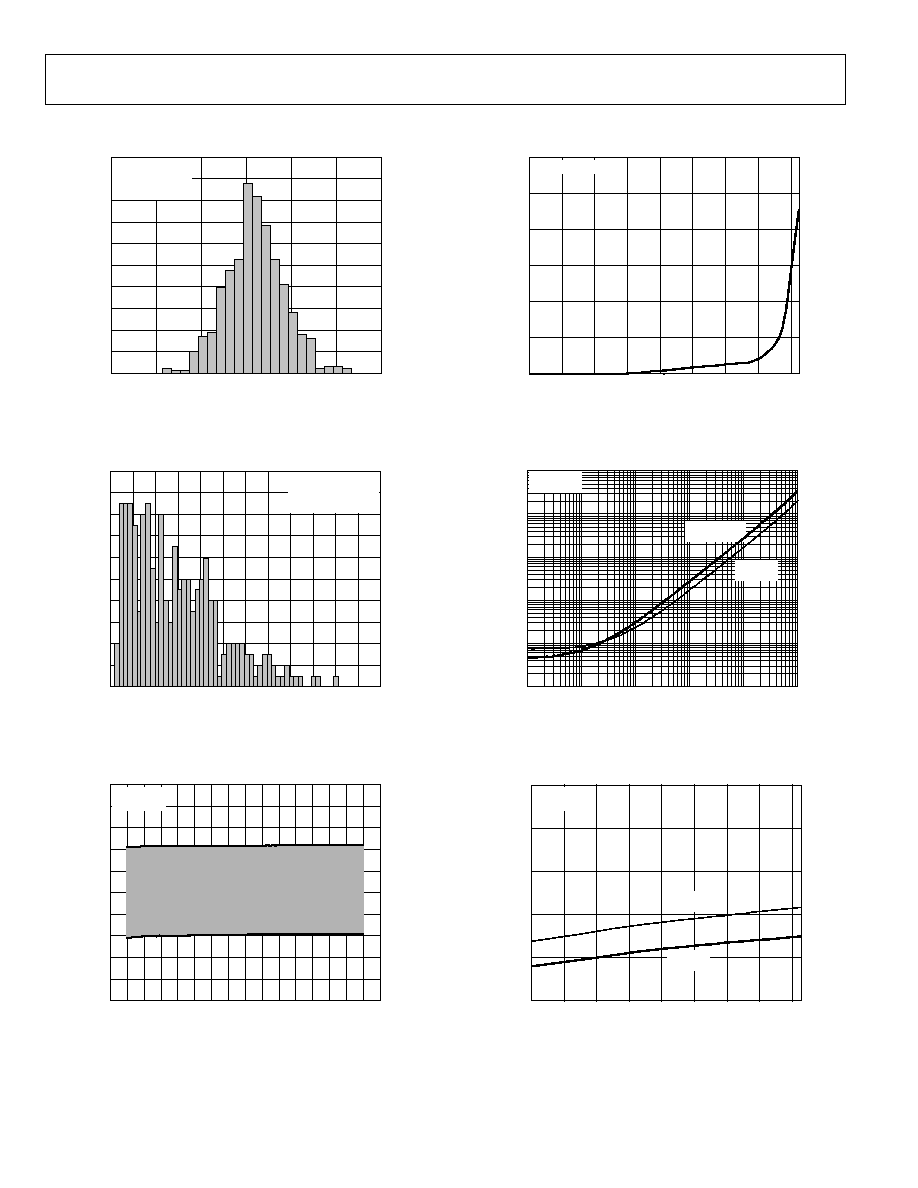

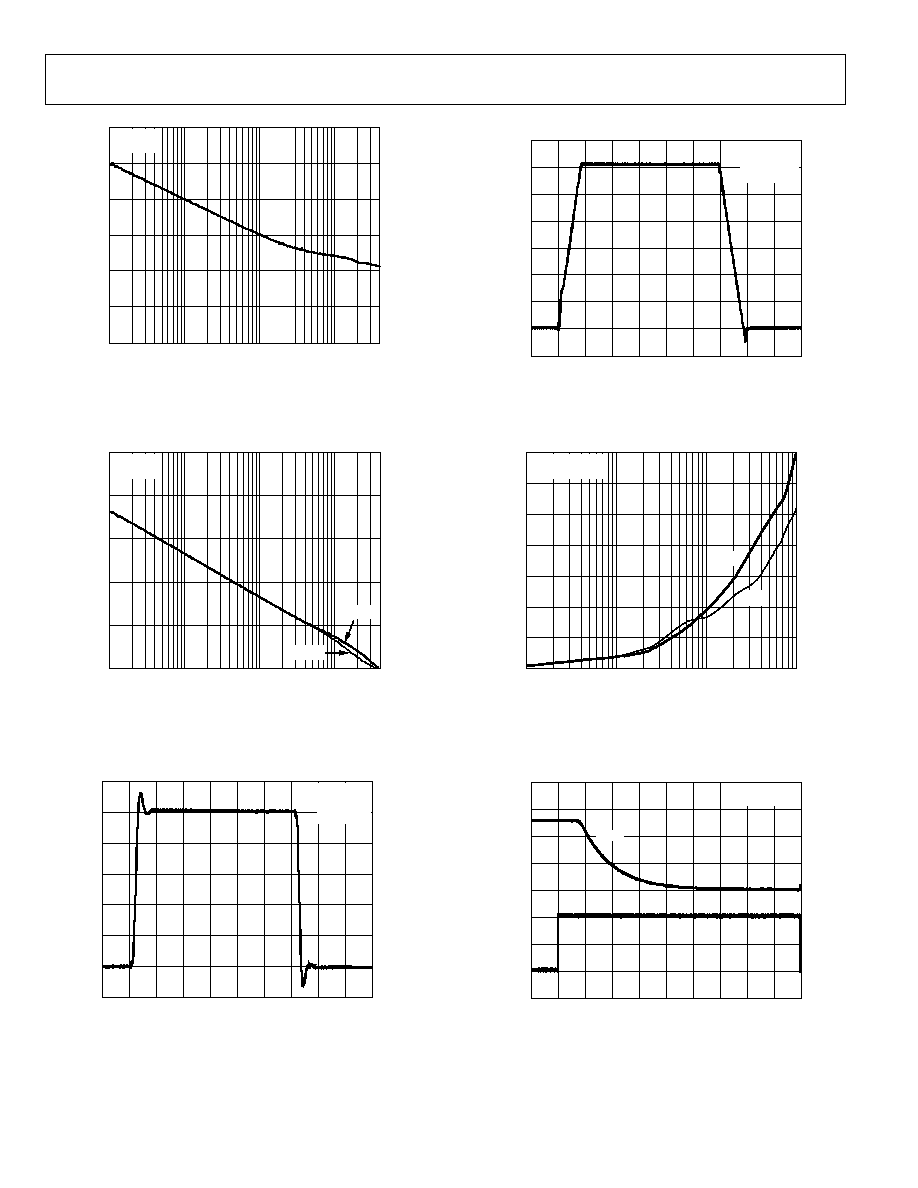

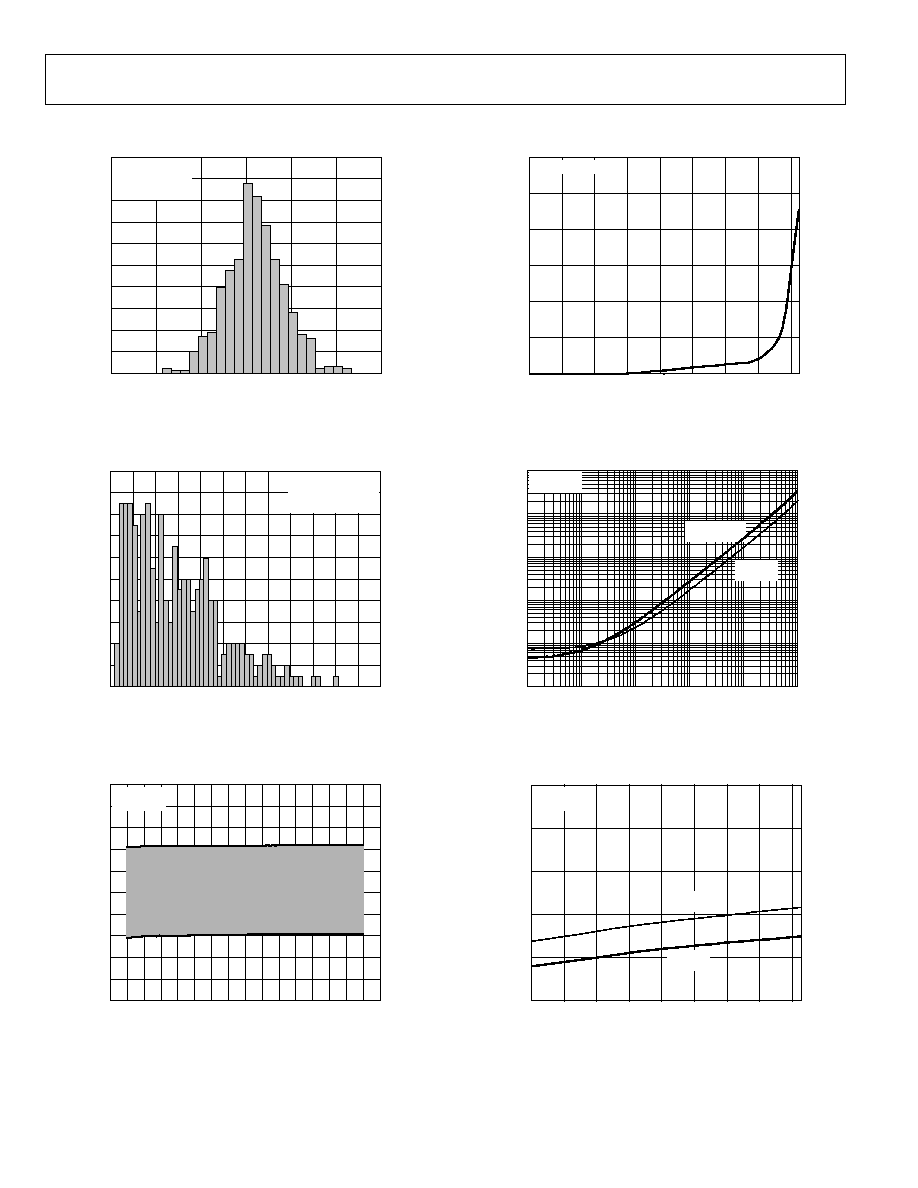

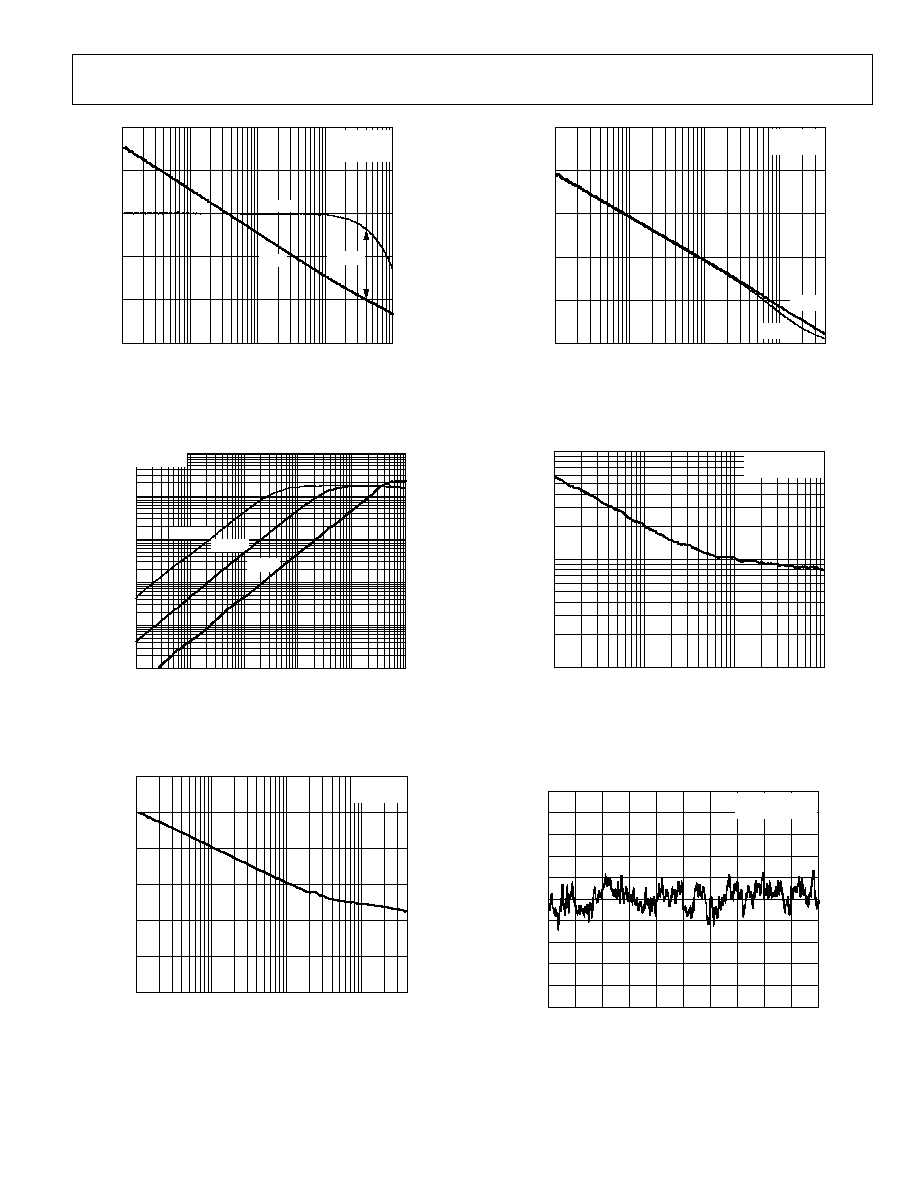

TYPICAL PERFORMANCE CHARACTERISTICS

100

0

≠3

3

INPUT OFFSET VOLTAGE (mV)

N

U

M

B

E

R

OF

A

M

P

L

IF

IE

R

S

90

80

70

60

50

40

30

20

10

≠2

≠1

0

1

2

VDD = 16V

VCM = 8V

TA = 25∞C

600 AMPLIFIERS

06

01

8-

00

5

Figure 5. Input Offset Voltage Distribution

20

0

0

12

TCVOS (µV/∞C)

N

U

MB

E

R

OF A

M

P

L

IF

IE

R

S

18

16

14

12

10

8

6

4

2

1

2

3

4

5

6

7

8

9

10

11

VDD = 16V

VCM = 8V

≠40∞C TA +125∞C

300 AMPLIFIERS

0

6

01

8-

0

06

Figure 6. V

OS

Drift (TCVOS) Distribution

5

≠5

≠1

15

INPUT COMMON-MODE VOLTAGE (V)

I

N

P

U

T

O

F

F

SET

VO

L

T

A

G

E (

m

V

)

4

3

2

1

0

≠1

≠2

≠3

≠4

0

1

2

3

4

5

6

7

8

9 10 11 12 13 14

VDD = 16V

TA +25∞C

0

60

18

-

00

7

Figure 7. Offset Voltage vs. Common-Mode Voltage

TEMPERATURE (∞C)

I

NP

UT

BI

AS

CURR

E

NT

(

p

A)

≠40

0

300

250

200

150

100

50

120

100

80

40

60

20

0

≠20

V

S

= 5V AND 16V

060

18

-

00

8

Figure 8. Input Bias Current vs. Temperature

10000

0.1

0.001

100

LOAD CURRENT (mA)

O

U

T

P

U

T

S

A

TU

R

A

TI

O

N

V

O

LT

A

G

E

(

m

V

)

VDD = 16V

TA = 25∞C

0.01

0.1

1

10

1

10

100

1000

VDD TO VOH

SOURCING

VOL

SINKING

0

60

18

-

0

09

Figure 9. Output Saturation Voltage vs. Load Current

100

0

≠40

120

TEMPERATURE (∞C)

O

UT

P

U

T

S

AT

U

RAT

I

O

N V

O

L

T

A

G

E

(

m

V

)

80

60

40

20

≠20

0

20

40

60

80

100

VDD = 16V

IOUT = 1mA

VDD TO VOH

SOURCING

VOL

SINKING

0

60

18

-

0

10

Figure 10. Output Saturation Voltage vs. Temperature

AD8666/AD8668

Rev. 0 | Page 7 of 16

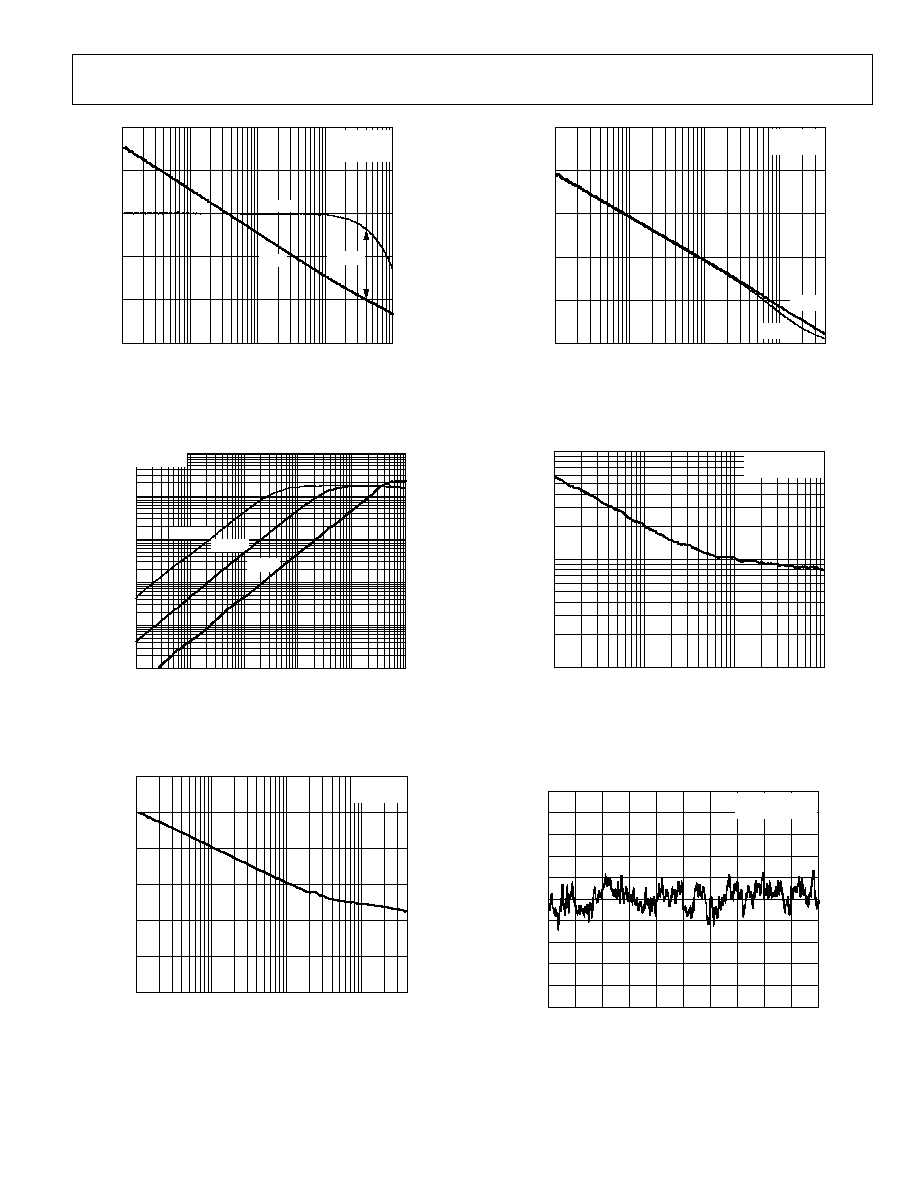

80

≠20

1k

10M

FREQUENCY (Hz)

OP

E

N

-

L

OOP

GA

IN

(

d

B

)

10k

100k

1M

60

40

20

0

0

225

O

P

E

N

-

L

O

O

P

P

HAS

E

S

H

I

F

T

(

D

eg

r

ees)

45

90

135

180

VDD = 16V

RL = 2k

CL = 10pF

M

=73∞

GAIN

PHASE

06

01

8

-

01

1

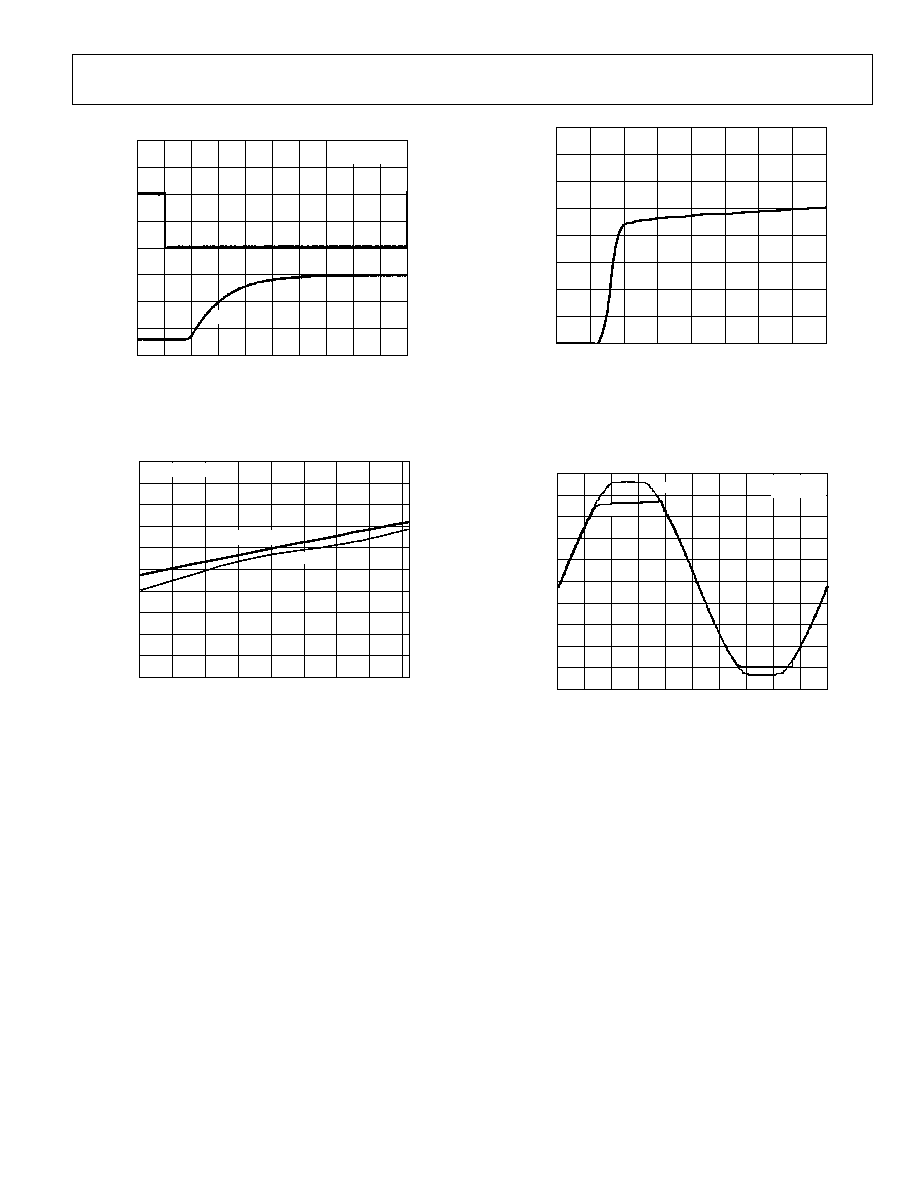

Figure 11. Open-Loop Gain and Phase vs. Frequency

1000

0.01

100

10M

FREQUENCY (Hz)

Z

OU

T

(

)

1k

10k

100k

1M

0.1

1

10

100

AV = 100

VDD = 16V

AV = 10

AV = 1

06

01

8

-

01

2

Figure 12. Closed-Loop Output Impedance vs. Frequency

120

0

1k

4M

FREQUENCY (Hz)

CM

RR (

d

B)

10k

100k

1M

100

80

60

40

20

VDD = 16V

TA = 25∞C

060

18

-

0

13

Figure 13. Common-Mode Rejection Ratio vs. Frequency

100

0

1k

4M

FREQUENCY (Hz)

P

S

RR

(

d

B)

10k

100k

1M

80

60

40

20

VDD = 16V

TA = 25∞C

PSRR≠

PSRR+

0

60

18

-

0

14

Figure 14. Power Supply Rejection Ratio vs. Frequency

100

1

10

10k

FREQUENCY (Hz)

VO

L

T

A

G

E

N

O

I

SE D

E

N

SI

T

Y (

n

V

/

Hz

)

100

1k

10

VDD = 5V TO 16V

TA = 25∞C

0

60

18

-

0

15

Figure 15. Voltage Noise Density vs. Frequency

TIME (1s/DIV)

VO

L

T

A

G

E (

1

µV

/

D

I

V

)

VDD = 5V TO 16V

TA = 25∞C

06

01

8

-

01

6

Figure 16. 0.1 Hz to 10 Hz Voltage Noise

AD8666/AD8668

Rev. 0 | Page 8 of 16

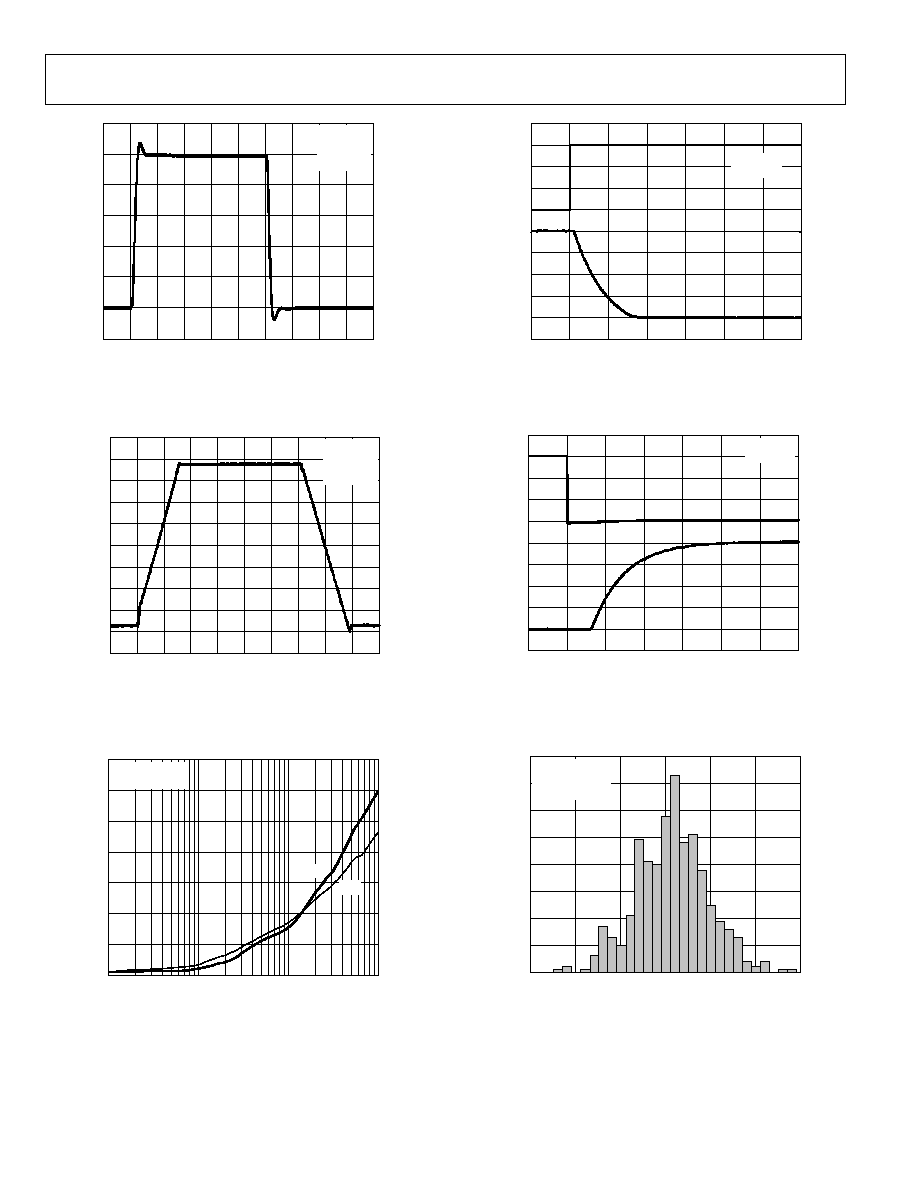

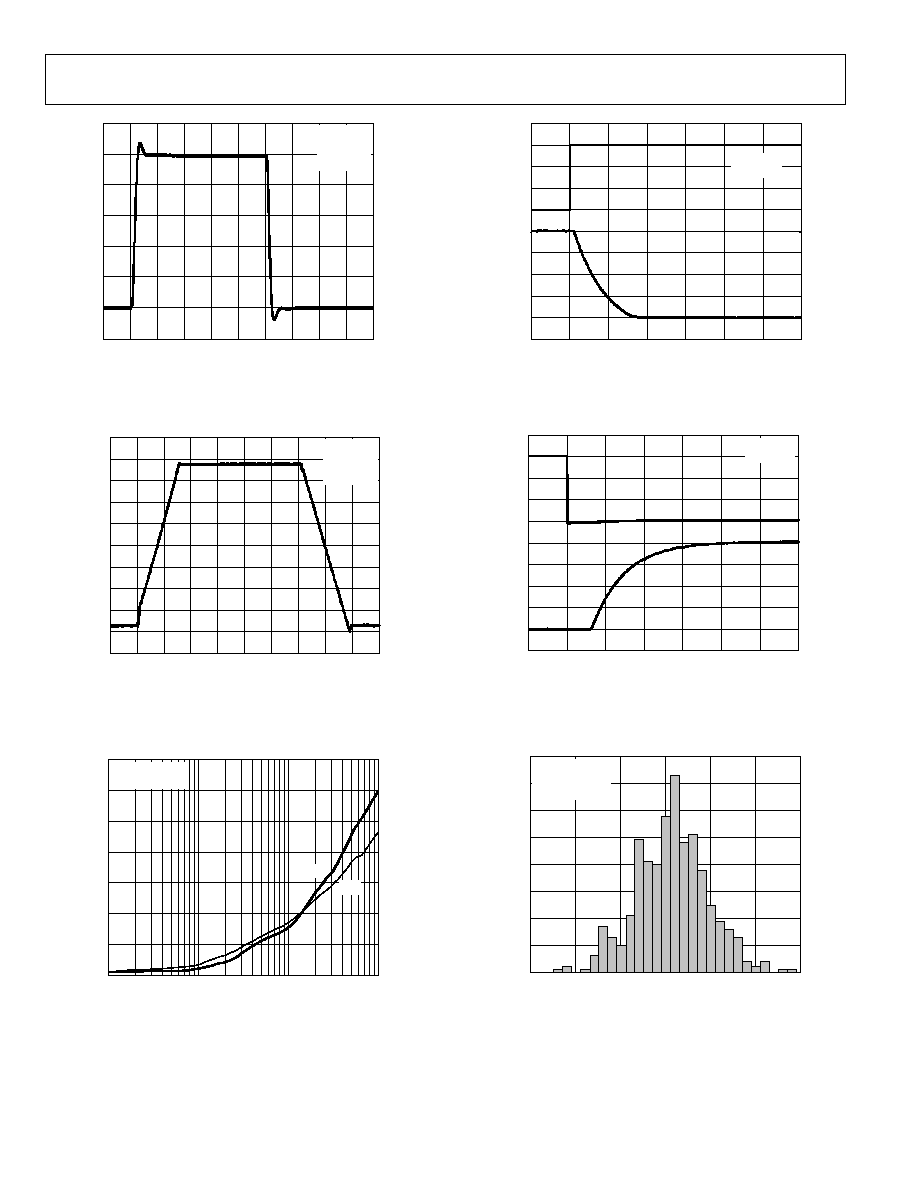

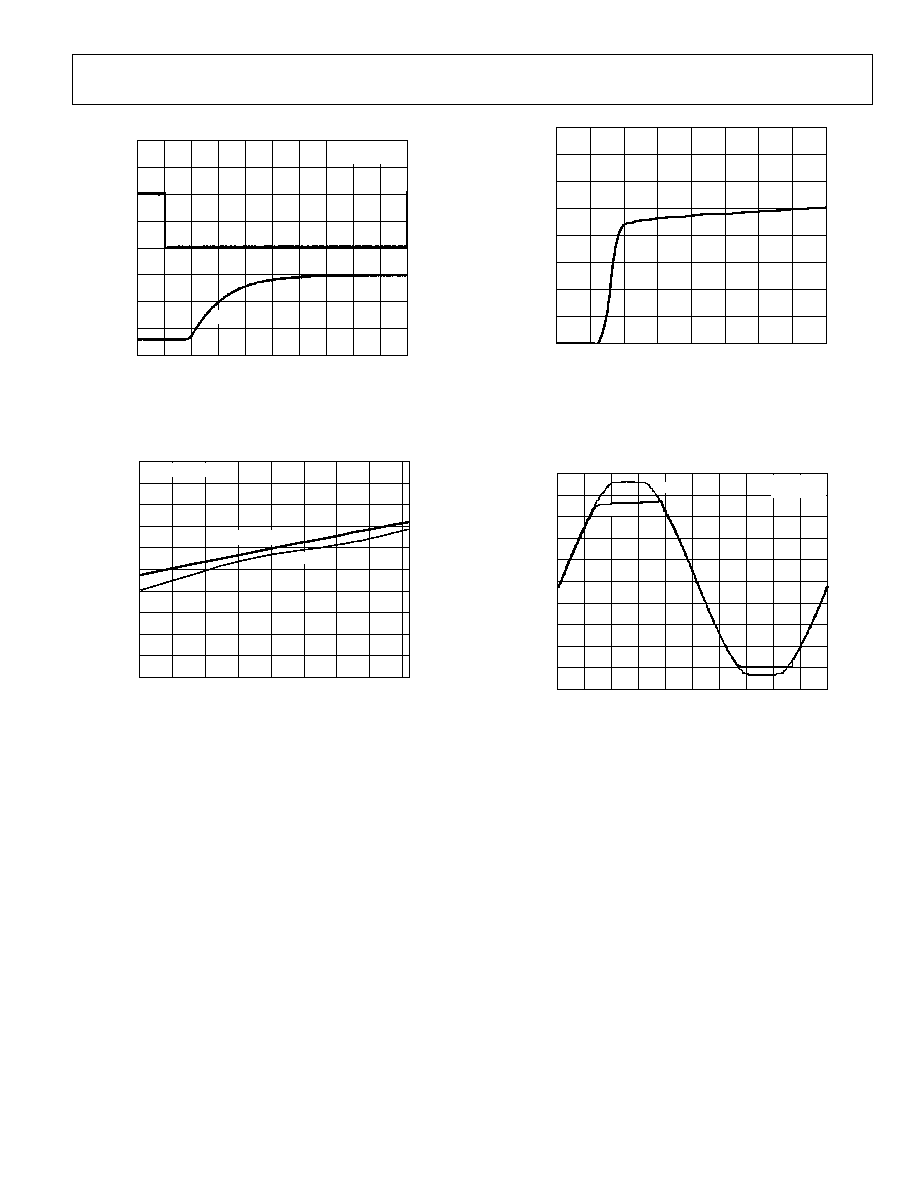

TIME (0.5µs/DIV)

VO

U

T

(

2

0

m

V/

D

I

V

)

VDD = 16V

RL = 10k

CL = 10pF

AV = +1

0

601

8-

01

7

Figure 17. Small-Signal Transient Response

TIME (2µs/DIV)

VO

U

T

(

V)

VDD = ±8V

RL = 10k

CL = 10pF

AV = +1

06

01

8-

0

18

10

≠10

≠8

≠6

≠4

≠2

2

4

6

8

0

Figure 18. Large-Signal Transient Response

70

0

1

1000

LOAD CAPACITANCE (pF)

OV

E

R

S

H

OOT

(

%

)

10

100

60

50

40

30

20

10

VDD = 16V

VIN = 100mV p-p

+OS

≠OS

0

601

8-

01

9

Figure 19. Small-Signal Overshoot vs. Load Capacitance

TIME (5µs/DIV)

0V

8V

≠100mV

0V

V

IN

V

OUT

VDD = ±8V

AV = ≠100

06

01

8

-

02

0

Figure 20. Positive Overload Recovery Time

TIME (5µs/DIV)

≠8V

0V

0V

100mV

V

IN

V

OUT

VDD = ±8V

AV = ≠100

06

01

8

-

02

1

Figure 21. Negative Overload Recovery Time

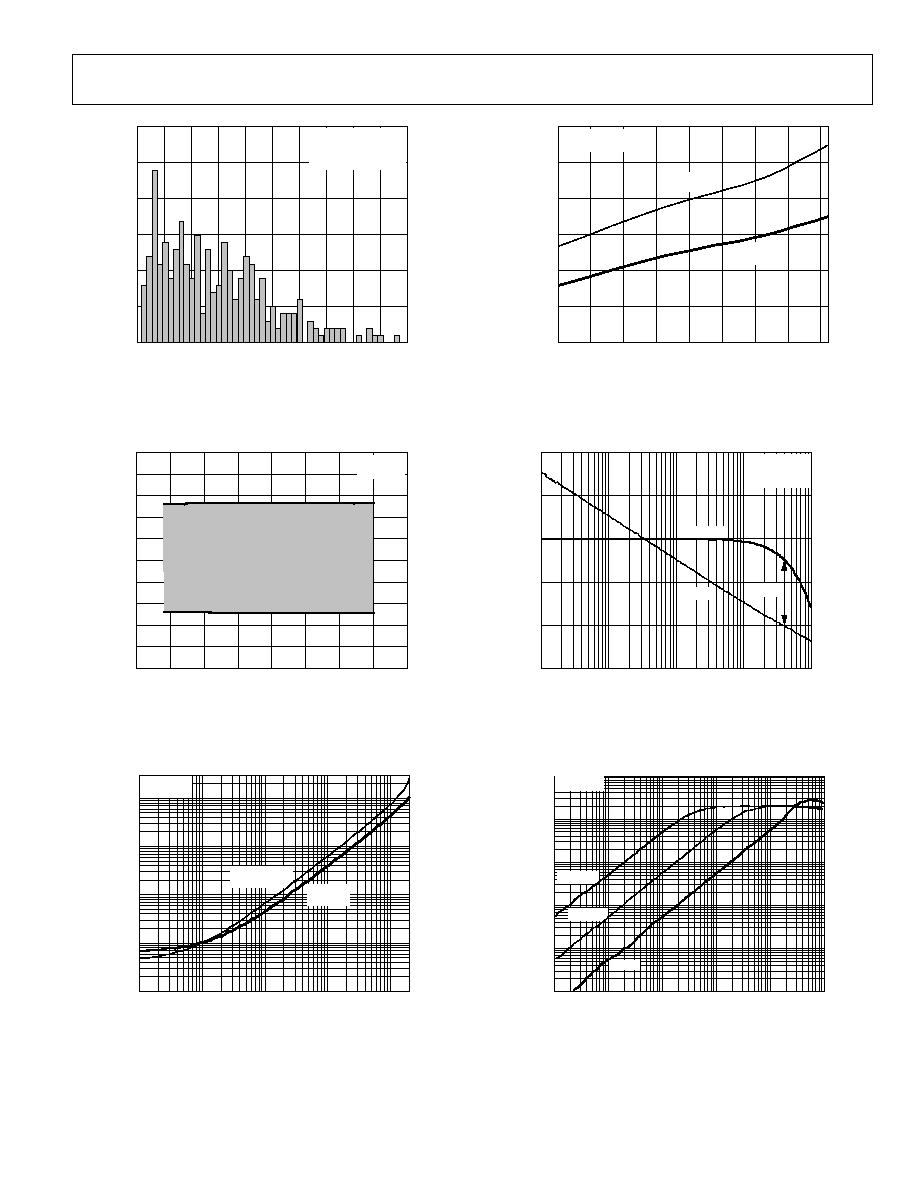

80

0

≠3

3

INPUT OFFSET VOLTAGE (mV)

N

U

M

B

E

R

OF

A

M

P

L

IFIE

R

S

70

60

50

40

30

20

10

≠2

≠1

0

1

2

VDD = 5V

VCM = 2.5V

TA = 25∞C

550 AMPLIFIERS

06

018

-

02

2

Figure 22. Input Offset Voltage Distribution

AD8666/AD8668

Rev. 0 | Page 9 of 16

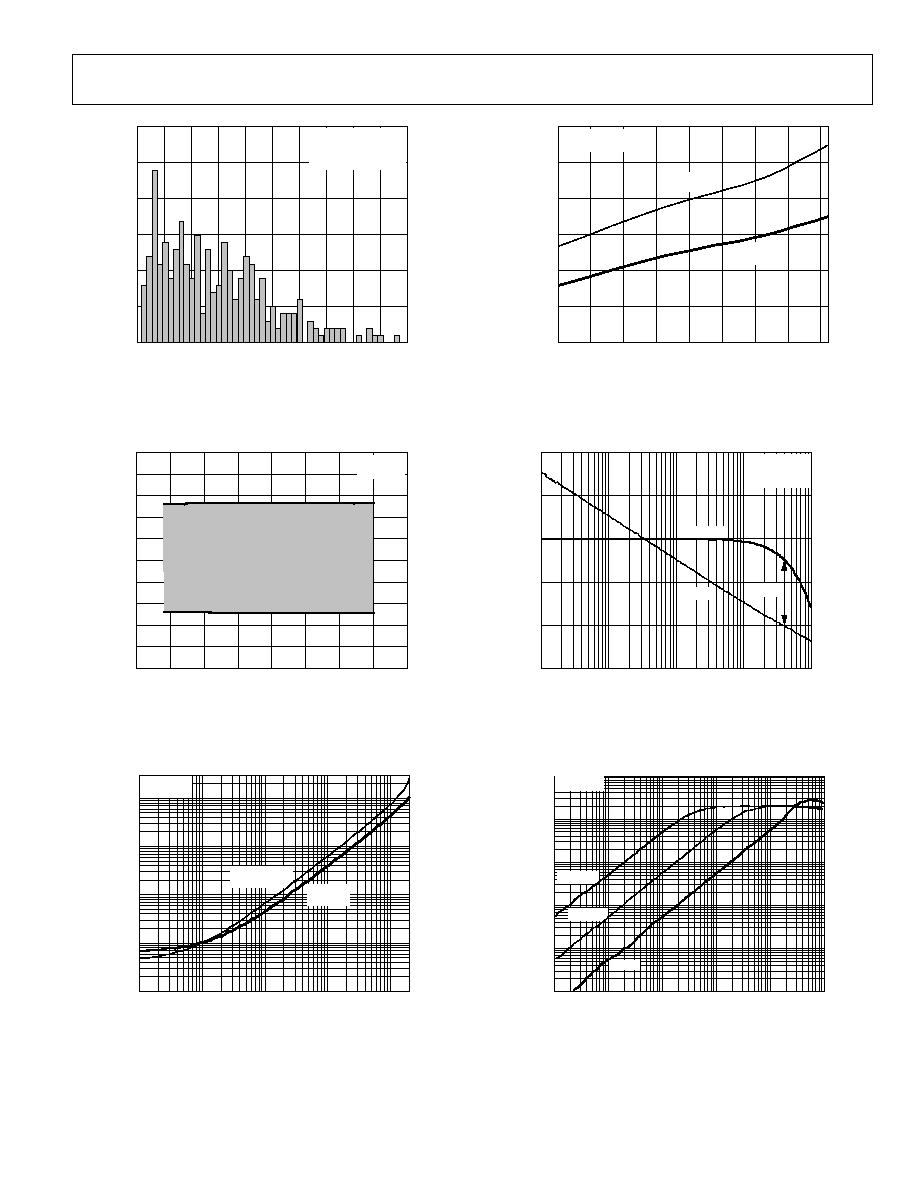

TCVOS (µV/∞C)

NUM

BE

R O

F

AM

P

L

I

F

I

E

RS

30

0

0

10

120

0

≠40

120

TEMPERATURE (∞C)

O

UT

P

UT

S

AT

URAT

I

O

N V

O

L

T

A

G

E

(

m

V

)

VDD = 5V

VCM = 2.5V

≠40∞C TA +125∞C

300 AMPLIFIERS

VDD = 5V

ILOAD = 1mA

25

20

15

10

5

100

80

60

40

20

VDD TO VOH

SOURCING

1

2

3

4

5

6

7

8

9

06

018

-

02

3

≠20

0

20

40

60

80

100

VOL

SINKING

06

018

-

02

6

Figure 23. V

OS

Drift (TCVOS) Distribution

5

≠5

≠0.5

3.5

INPUT COMMON-MODE VOLTAGE (V)

I

N

P

U

T

O

F

F

SET

VO

L

T

A

G

E (

m

V

)

4

3

2

1

0

≠1

≠2

≠3

≠4

0

0.5

1.0

1.5

2.0

2.5

3.0

VDD = 5V

TA = 25∞C

0

6

01

8-

0

24

Figure 24. Offset Voltage vs. Common-Mode Voltage

0.1

0.001

LOAD CURRENT (mA)

O

U

T

P

U

T

SA

T

U

R

A

T

I

O

N

VO

L

T

A

G

E

(m

V)

0.01

0.1

1

10 20

1

10

100

1000

3000

VDD = 5V

TA = 25∞C

VDD TO VOH

SOURCING

VOL

SINKING

060

18

-

02

5

Figure 25. Output Saturation Voltage vs. Load Current

Figure 26. Output Saturation Voltage vs. Temperature

80

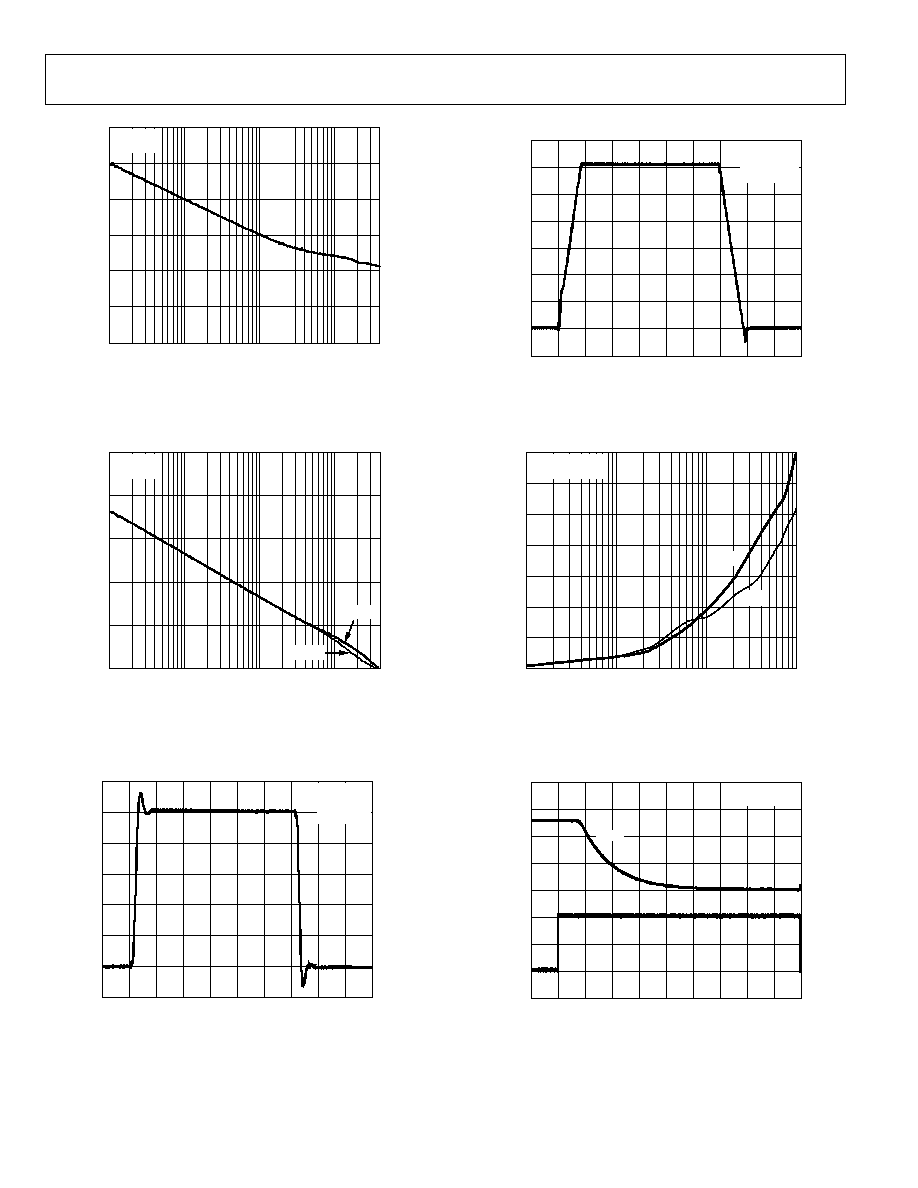

≠20

1k

10M

FREQUENCY (Hz)

OP

E

N

-

L

OOP

GA

IN

(

d

B

)

10k

100k

1M

60

40

20

0

0

225

O

P

E

N

-

L

O

O

P

P

H

AS

E

S

H

I

F

T

(

D

eg

r

ees)

45

90

135

180

M

=70∞

GAIN

PHASE

VDD = 5V

RL = 2k

CL = 10pF

0

6

01

8-

0

27

Figure 27. Open-Loop Gain and Phase vs. Frequency

1000

0.01

100

10M

FREQUENCY (Hz)

Z

OU

T

(

)

1k

10k

100k

1M

0.1

1

10

100

VDD = 5V

AV = 100

AV = 10

AV = 1

06

01

8-

02

8

Figure 28. Closed-Loop Output Impedance vs. Frequency

AD8666/AD8668

Rev. 0 | Page 10 of 16

120

0

1k

4M

FREQUENCY (Hz)

CM

RR

(

d

B

)

10k

100k

1M

100

80

60

40

20

VDD = 5V

TA = 25∞C

0

60

18

-

0

29

Figure 29. Common-Mode Rejection Ratio vs. Frequency

100

0

1k

4M

FREQUENCY (Hz)

P

S

RR (

d

B

)

10k

100k

1M

80

60

40

20

VDD = 5V

TA = 25∞C

PSRR≠

PSRR+

0

6

01

8-

0

30

Figure 30. Power Supply Rejection Ratio vs. Frequency

TIME (0.4µs/DIV)

VO

U

T

(

2

0

m

V/

D

I

V

)

VDD = 5V

RL = 100k

CL = 10pF

AV = +1

0

601

8-

03

1

Figure 31. Small-Signal Transient Response

TIME (1µs/DIV)

VO

U

T

(

V)

1.5

≠2.5

06

01

8-

0

32

1.0

0.5

0

≠0.5

≠1.0

≠1.5

≠2.0

VDD = ±2.5V

RL = 10k

CL = 10pF

AV = +1

Figure 32. Large-Signal Transient Response

70

0

1

1000

LOAD CAPACITANCE (pF)

O

VER

SH

O

O

T

(

%

)

10

100

60

50

40

30

20

10

VDD = 5V

VIN = 100mV p-p

≠OS

+OS

06

018

-

03

3

Figure 33. Small-Signal Overshoot vs. Load Capacitance

TIME (4µs/DIV)

2.5V

0V

0V

≠100mV

VDD = ±2.5V

AV = ≠100

VOUT

VIN

06

01

8-

03

4

Figure 34. Positive Overload Recovery Time

AD8666/AD8668

Rev. 0 | Page 11 of 16

TIME (4µs/DIV)

100mV

0V

0V

≠2.5V

VDD = ±2.5V

AV = ≠100

VOUT

VIN

060

18

-

03

5

Figure 35. Negative Overload Recovery Time

2.0

0

≠40

120

TEMPERATURE (∞C)

S

UP

P

L

Y

CU

RRE

NT

(

m

A

)

1.8

1.6

1.4

1.2

1.0

0.8

0.6

0.4

0.2

≠20

0

20

40

60

80

100

VOUT = VDD/2

VDD = 16V

VDD = 5V

06

01

8

-

03

6

Figure 36. Supply Current vs. Temperature

2.00

0

0

1

SUPPLY VOLTAGE (V)

S

U

P

P

L

Y

C

URRE

NT

(

m

A)

6

1.75

1.50

1.25

1.00

0.75

0.50

0.25

2

4

6

8

10

12

14

0

60

18

-

03

7

Figure 37. Supply Current vs. Supply Voltage

TIME (10µs/DIV)

VO

U

T

(V

)

VOUT

VIN

06

01

8-

0

38

10

≠10

8

6

4

2

0

≠2

≠4

≠6

≠8

VDD = ±8V

AV = +1

Figure 38. No Output Phase Reversal

AD8666/AD8668

Rev. 0 | Page 12 of 16

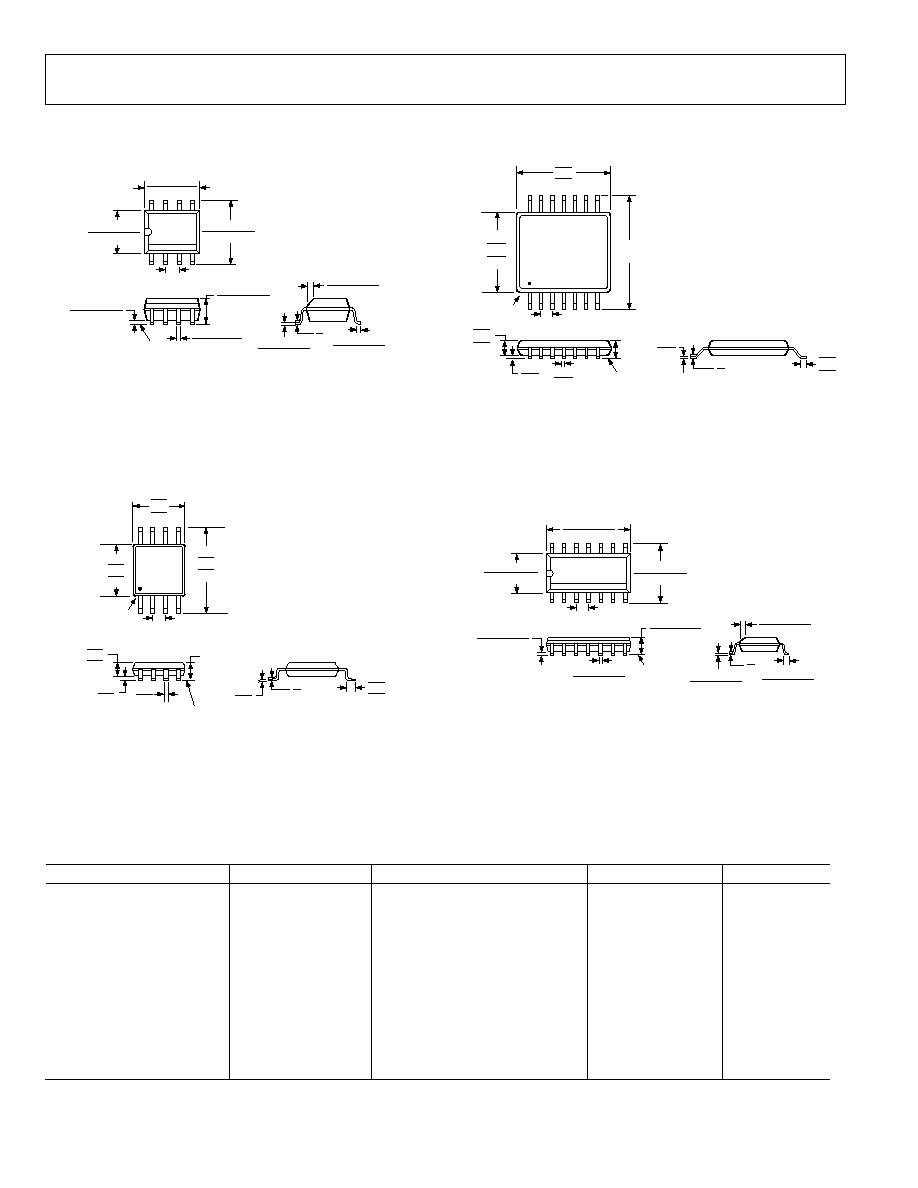

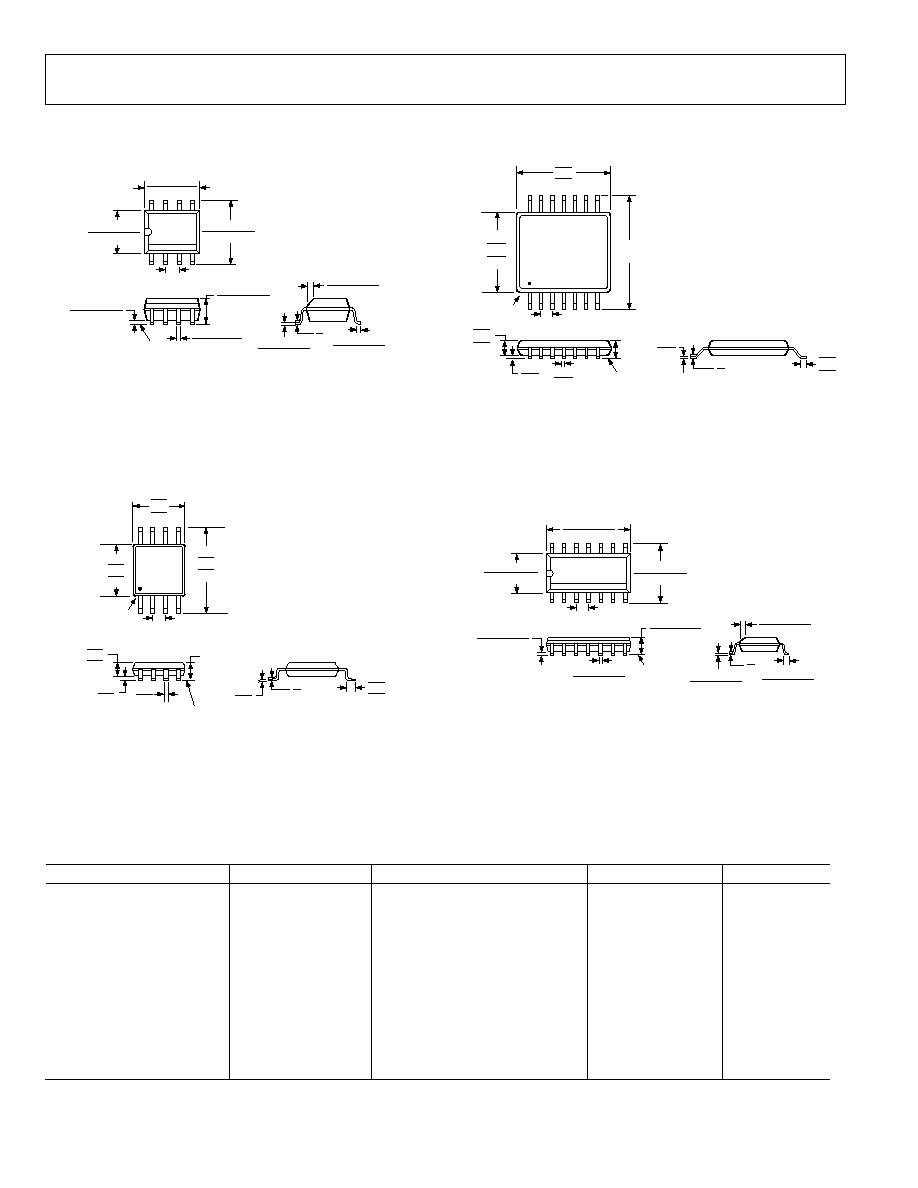

OUTLINE DIMENSIONS

0.25 (0.0098)

0.17 (0.0067)

1.27 (0.0500)

0.40 (0.0157)

0.50 (0.0196)

0.25 (0.0099)

◊ 45∞

8∞

0∞

1.75 (0.0688)

1.35 (0.0532)

SEATING

PLANE

0.25 (0.0098)

0.10 (0.0040)

4

1

8

5

5.00 (0.1968)

4.80 (0.1890)

4.00 (0.1574)

3.80 (0.1497)

1.27 (0.0500)

BSC

6.20 (0.2440)

5.80 (0.2284)

0.51 (0.0201)

0.31 (0.0122)

COPLANARITY

0.10

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

COMPLIANT TO JEDEC STANDARDS MS-012-AA

Figure 39. 8-Lead Standard Small Outline Package [SOIC_N]

Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

COMPLIANT TO JEDEC STANDARDS MO-187-AA

0.80

0.60

0.40

8∞

0∞

4

8

1

5

PIN 1

0.65 BSC

SEATING

PLANE

0.38

0.22

1.10 MAX

3.20

3.00

2.80

COPLANARITY

0.10

0.23

0.08

3.20

3.00

2.80

5.15

4.90

4.65

0.15

0.00

0.95

0.85

0.75

Figure 40. 8-Lead Mini Small Outline Package [MSOP]

(RM-8)

Dimensions shown in millimeters

4.50

4.40

4.30

14

8

7

1

6.40

BSC

PIN 1

5.10

5.00

4.90

0.65

BSC

SEATING

PLANE

0.15

0.05

0.30

0.19

1.20

MAX

1.05

1.00

0.80

0.20

0.09

8∞

0∞

0.75

0.60

0.45

COPLANARITY

0.10

COMPLIANT TO JEDEC STANDARDS MO-153-AB-1

Figure 41. 14-Lead Thin Shrink Small Outline Package [TSSOP]

(RU-14)

Dimensions shown in millimeters

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

COMPLIANT TO JEDEC STANDARDS MS-012-AB

COPLANARITY

0.10

14

8

7

1

6.20 (0.2441)

5.80 (0.2283)

4.00 (0.1575)

3.80 (0.1496)

8.75 (0.3445)

8.55 (0.3366)

1.27 (0.0500)

BSC

SEATING

PLANE

0.25 (0.0098)

0.10 (0.0039)

0.51 (0.0201)

0.31 (0.0122)

1.75 (0.0689)

1.35 (0.0531)

8∞

0∞

0.50 (0.0197)

0.25 (0.0098)

1.27 (0.0500)

0.40 (0.0157)

0.25 (0.0098)

0.17 (0.0067)

◊ 45∞

Figure 42. 14-Lead Standard Small Outline Package [SOIC_N]

Narrow Body

(R-14)

Dimensions shown in millimeters

ORDERING GUIDE

Model

Temperature Range

Package Description

Package Option

Branding

AD8666ARZ

1

-40∞C to +125∞C

8-Lead SOIC_N

R-8

AD8666ARZ-REEL

1

-40∞C to +125∞C

8-Lead SOIC_N

R-8

AD8666ARZ-REEL7

1

-40∞C to +125∞C

8-Lead SOIC_N

R-8

AD8666ARMZ-R2

1

-40∞C to +125∞C

8-Lead MSOP

RM-8

A16

AD8666ARMZ-REEL

1

-40∞C to +125∞C

8-Lead MSOP

RM-8

A16

AD8668ARZ

1

-40∞C to +125∞C

14-Lead SOIC_N

R-14

AD8668ARZ-REEL

1

-40∞C to +125∞C

14-Lead SOIC_N

R-14

AD8668ARZ-REEL7

1

-40∞C to +125∞C

14-Lead SOIC_N

R-14

AD8668ARUZ

1

-40∞C to +125∞C

14-Lead TSSOP

RU-14

AD8668ARUZ-REEL

1

-40∞C to +125∞C

14-Lead TSSOP

RU-14

1

Z = Pb-free part.

AD8666/AD8668

Rev. 0 | Page 13 of 16

NOTES

AD8666/AD8668

Rev. 0 | Page 14 of 16

NOTES

AD8666/AD8668

Rev. 0 | Page 15 of 16

NOTES

AD8666/AD8668

Rev. 0 | Page 16 of 16

NOTES

©2006 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D06018-0-4/06(0)