| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: OP497G | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

REV. D

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

a

OP497

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2002

Precision Picoampere Input Current

Quad Operational Amplifier

FEATURES

Low Offset Voltage: 50 V max

Low Offset Voltage Drift: 0.5 V/ C max

Very Low Bias Current

25 C: 100 pA max

≠55 C to +125 C: 450 pA max

Very High Open-Loop Gain: 2000 V/mV min

Low Supply Current (per Amplifier): 625 A max

Operates from 2 V to 20 V Supplies

High Common-Mode Rejection: 120 dB min

APPLICATIONS

Strain Gage and Bridge Amplifiers

High Stability Thermocouple Amplifiers

Instrumentation Amplifiers

Photo-Current Monitors

High Gain Linearity Amplifiers

Long-Term Integrators/Filters

Sample-and-Hold Amplifiers

Peak Detectors

Logarithmic Amplifiers

Battery-Powered Systems

GENERAL DESCRIPTION

The OP497 is a quad op amp with precision performance in the

space-saving, industry standard 16-lead SOlC package. Its com-

bination of exceptional precision with low power and extremely

low input bias current makes the quad OP497 useful in a wide

variety of applications.

Precision performance of the OP497 includes very low offset,

under 50

µV, and low drift, below 0.5 µV/∞C. Open-loop gain

exceeds 2000 V/mV ensuring high linearity in every application.

Errors due to common-mode signals are eliminated by the OP497's

common-mode rejection of over 120 dB. The OP497's power

supply rejection of over 120 dB minimizes offset voltage changes

experienced in battery-powered systems. Supply current of the

OP497 is under 625

µA per amplifier, and it can operate with

supply voltages as low as

±2 V.

The OP497 utilizes a superbeta input stage with bias current can-

cellation to maintain picoamp bias currents at all temperatures.

This is in contrast to FET input op amps whose bias currents start

in the picoamp range at 25

∞C, but double for every 10∞C rise in

temperature, to reach the nanoamp range above 85

∞C. Input bias

current of the OP497 is under 100 pA at 25

∞C and is under 450

pA over the military temperature range.

Combining precision, low power, and low bias current, the

OP497 is ideal for a number of applications, including instru-

mentation amplifiers, log amplifiers, photo-diode preamplifiers,

and long-term integrators. For a single device, see the OP97; for a

dual device, see the OP297.

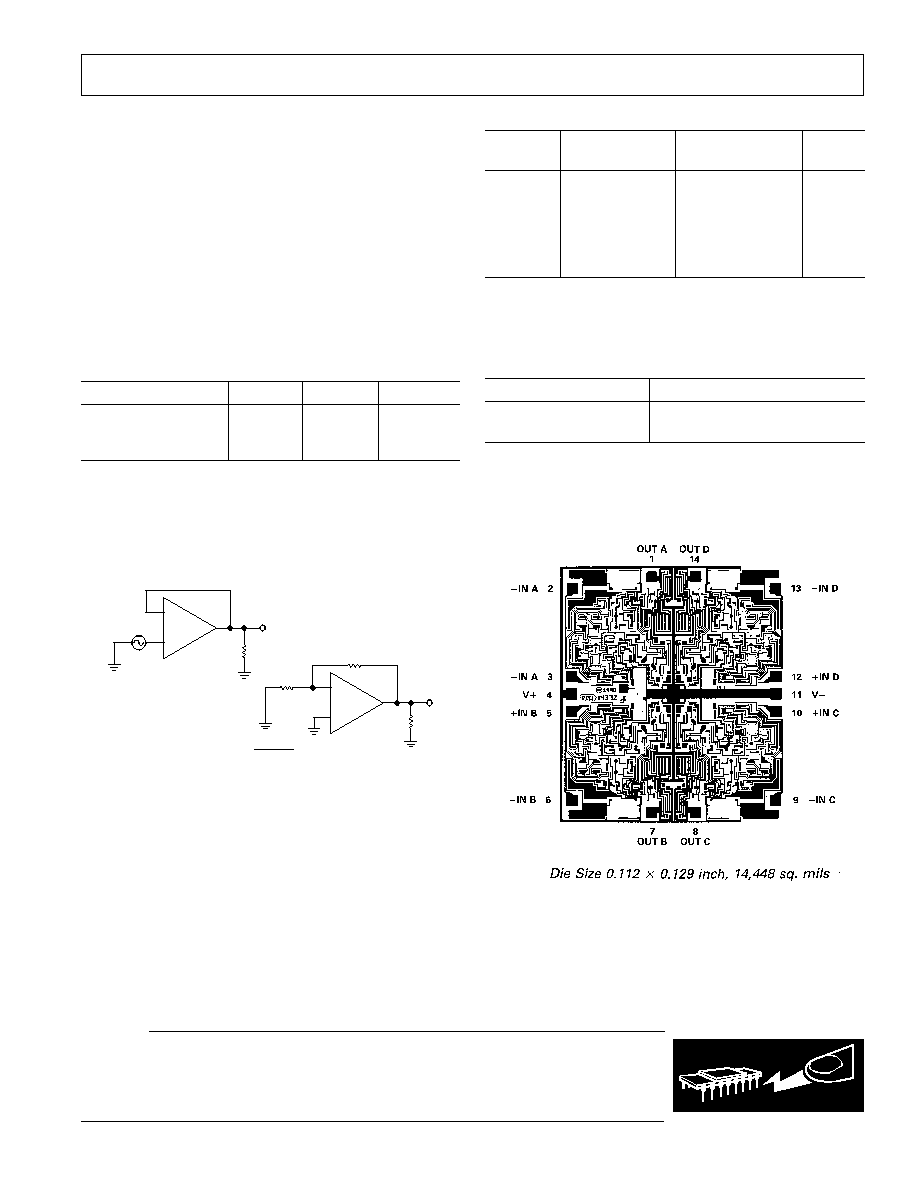

PIN CONNECTIONS

16-Lead Wide Body SOIC

(S-Suffix)

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

≠

+

NC = NO CONNECT

OUT A

≠IN A

+IN A

V+

+IN B

≠IN B

OUT B

OUT D

≠IN D

+IN D

V≠

+IN C

≠IN C

OUT C

NC

NC

≠

+

≠

+

≠

+

OP497

14-Lead Plastic Dip

(P-Suffix)

14-Lead Ceramic Dip

(Y-Suffix)

1

2

3

4

5

6

7

14

13

12

11

10

9

8

OUT A

≠IN A

+IN A

V+

+IN B

≠IN B

OUT B

OUT D

≠IN D

+IN D

V≠

+IN C

≠IN C

OUT C

≠

+

≠

+

≠

+

≠

+

OP497

V

S

= 15V

V

CM

= 0V

1000

100

10

≠75

≠50

≠25

0

25

50

75

100

125

INPUT CURRENT

≠

PA

TEMPERATURE ≠ C

≠I

B

+I

B

I

OS

Input Bias, Offset Current vs. Temperature

REV. D

≠2≠

OP497≠SPECIFICATIONS

(@ V

S

= 15 V, T

A

= 25 C, unless otherwise noted.)

A

F

C/G

Parameter

Symbol

Condition

Min Typ Max Min Typ Max

Min Typ Max

Unit

INPUT CHARACTERISTICS

Offset Voltage

Vos

20

50

40

75

80

150

µV

≠40

∞C +85∞C

70

150

120

250

≠55

∞C +125∞C

40

100

80

150

140

300

Average Input Offset

Voltage Drift

TCV

OS

T

MIN

≠ T

MAX

0.2

0.5

0.4

1.0

0.6

1.5

µV/∞C

Long-Term Input Offset

Voltage Stability

0.1

0.1

0.1

µV/Mo

Input Bias Current

I

B

V

CM

= 0 V

30

100

40

150

60

200

pA

≠40

∞ T

A

+85∞C

60

200

80

300

≠55

∞ T

A

+125∞C

80

450

110

600

130

600

Average Input Bias

Current Drift

TC

IB

≠40

∞ T

A

+85∞C

0.3

0.3

≠55

∞ T

A

+125∞C

0.5

0.7

0.7

pA/

∞C

Input Offset Current

Ios

V

CM

= OV

15

100

30

150

50

200

pA

≠40

∞ T

A

+85∞C

50

200

80

300

≠55

∞ T

A

+125∞C

35

400

60

600

90

600

Average Input Offset

Current Drift

T

C

I

OS

0.2

0.3

0.4

pA/

∞C

Input Voltage Range

1

IVR

+ 13 +14

+13 tl4

+13 +14

V

T

MIN

≠ T

MAX

+13 +13.5

+13 +13.5

+13 +13.5

Common-Mode Rejection CMR

V

CM

=

±13 V

120

140

114

135

114

135

dB

T

MIN

≠ T

MAX

114

130

108

120

108

120

Large Signal Voltage Gain A

VO

V

O

=

±10 V,

R

L

= 2 k

2000 6000

1500 4000

1200 4000

V/mV

≠40

∞ T

A

+85∞C

800

2000

800

2000

≠55

∞ T

A

+125∞C 1200 4000

1000 3000

800

3000

Input Resistance

Differential Mode

R

IN

30

30

30

M

Input Resistance

Common Mode

R

INCM

500

500

500

G

Input Capacitance

C

IN

3

3

3

pF

OUTPUT CHARACTERISTICS

Output Voltage Swing

V

O

R

L

= 2 k

±13 ±13.7

±13 ±13.7

±13 ±13.7V

R

L

= 10 k

± 13 ±14

±13 ±14

±13 ±14

T

MIN

≠ T

MAX

R

L

= 10 k

±13 ±13.5

±13 ±13.5

±13 ±13.5

Short Circuit

I

SC

±25

±25

±25

mA

POWER SUPPLY

Power Supply

PSRR

Vs =

±2 V to ±20 V 120 140

114

135

114

135

dB

Rejection Ratio

Vs =

±2.5 V to ±20 V

T

MIN

≠ T

MAX

114

130

108

120

108

120

Supply Current

I

SY

No Load

525

625

525

625

525

625

µA

(per Amplifier)

T

MIN

≠ T

MAX

580

750

580

750

580

750

Supply Voltage Range

V

S

Operating Range

±2

±20 ±2

±20

±2

±20

V

T

MIN

≠ T

MAX

±2.5

±20 ±2.5

±20

±2.5

±20

DYNAMIC PERFORMANCE

Slew Rate

SR

0.05 0.15

0.05 0.15

0.05 0.15

V/

µS

Gain Bandwidth Product

GBW

500

500

500

kHz

Channel Separation

CS

V

O

= 20 V

p-p,

fo = 10 Hz

150

150

150

dB

NOISE PERFORMANCE

Voltage Noise

e

n

p-p

0.1 Hz to 10 Hz

0.3

0.3

0.3

µV/p-p

Voltage Noise Density

e

n

= 10 Hz

17

17

17

nV/

Hz

e

n

= 1 kHz

15

15

15

nV/

Hz

Current Noise Density

i

n

= 10 Hz

20

20

20

fA/

Hz

NOTE

1

Guaranteed by CMR Test.

Specifications subject to change without notice.

REV. D

OP497

≠3≠

ORDERING GUIDE

Temperature

Package

Package

Model

Range

Description

Option

OP497AY

* ≠55

∞C to +125∞C 14-Lead Cerdip

Q-14

OP497CY

* ≠55

∞C to +125∞C 14-Lead Cerdip

Q-14

OP497FP

≠40

∞C to +85∞C

14-Lead Plastic DIP N-14

OP497FS

≠40

∞C to +85∞C

16-Lead SOIC

R-16

OP497GP

≠40

∞C to +85∞C

14-Lead Plastic DIP N-14

OP497GS

≠40

∞C to +85∞C

16-Lead SOIC

R-16

*Not for new design; obsolete April 2002.

For a military processed devices, please refer to the Standard

Microcircuit Drawing (SMD) available at www.dscc.dla.mil/

programs.milspec./default.asp.

SMD Part Number

ADI Part Number

5962≠9452101M2A

*

OP497BRC

5962≠9452101MCA

OP497BY

*Not for new designs; obsolete April 2002.

DICE CHARACTERISTICS

ABSOLUTE MAXIMUM RATINGS

1

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

±20 V

Input Voltage

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20 V

Differential Input Voltage

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

40 V

Output Short-Circuit Duration . . . . . . . . . . . . . . . . Indefinite

Storage Temperature Range

Y Package . . . . . . . . . . . . . . . . . . . . . . . . ≠65

∞C to +175∞C

P, S Package . . . . . . . . . . . . . . . . . . . . . . . ≠65

∞C to +150∞C

Operating Temperature Range

OP497A, C (Y) . . . . . . . . . . . . . . . . . . . . ≠55

∞C to +125∞C

OP497F, G (Y) . . . . . . . . . . . . . . . . . . . . . ≠40

∞C to +85∞C

OP497F, G (P, S) . . . . . . . . . . . . . . . . . . . ≠40

∞C to +85∞C

Junction Temperature

Y Package . . . . . . . . . . . . . . . . . . . . . . . . ≠65

∞C to +175∞C

P, S Package . . . . . . . . . . . . . . . . . . . . . . . ≠65

∞C to +150∞C

Lead Temperature Range (Soldering 60 sec) . . . . . . . . 300

∞C

Package Type

JA

3

JC

Unit

14-Pin Cerdip (Y)

94

10

∞C/W

14-Pin Plastic DIP (P)

76

33

∞C/W

16-Pin SOIC (S)

92

23

∞C/W

NOTES

1

Absolute Maximum Ratings apply to both DICE and packaged parts, unless

otherwise noted.

2

For supply voltages less than

± 20 V, the absolute maximum input voltage is

equal to the supply voltage.

3

HIA is specified for worst-case mounting conditions, i.e.,

JA

is specified for

device in socket for cerdip, P-DIP packages;

JA

is specified for device soldered

to printed circuit board for SOIC package.

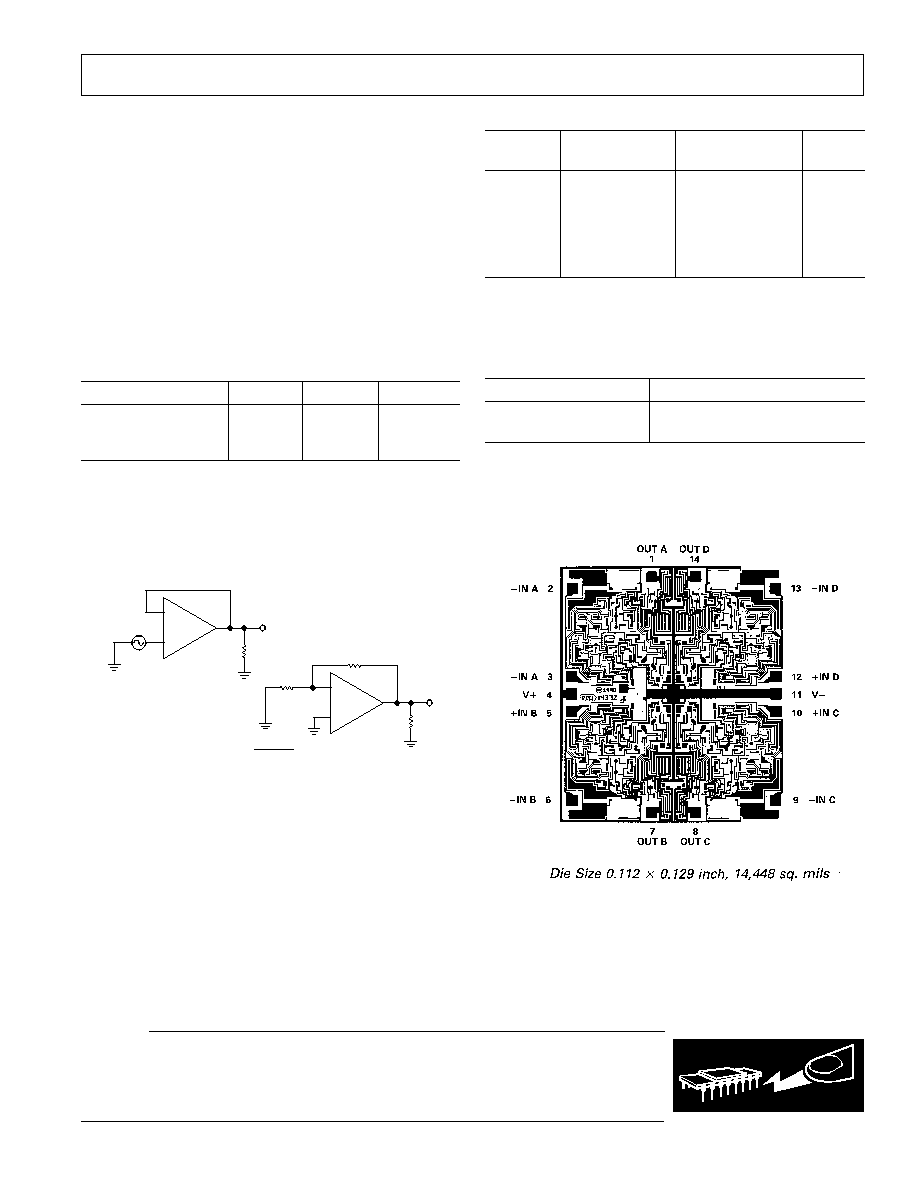

1/4

OP497

V

2

2k

V

1

20V p≠p @ 10Hz

CHANNEL SEPARATION = 20 log

V /10000

2

V

1

(

)

≠

+

50

50k

≠

+

1/4

OP497

Channel Separation Test Circuit

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the OP497 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

REV. D

OP497

≠4≠

≠Typical Performance Characteristics

(25 C, Vs = 15 V, unless otherwise noted.)

50

0

100

30

10

≠80

20

≠100

40

80

60

40

20

0

≠20

≠40

≠60

INPUT OFFSET VOLTAGE ≠ V

PERCENTAGE OF UNITS

T

A

= 25 C

V

S

= 15V

V

CM

= 0V

TPC 1. Typical Distribution of

Input Offset Voltage

TCV

OS

≠ V/ C

PERCENTAGE OF UNITS

50

0

0.8

30

10

0.1

20

0

40

0.7

0.6

0.5

0.4

0.3

0.2

V

S

= 15V

V

CM

= 0V

TPC 4. Typical Distribution of

TCV

OS

3

0

5

1

1

0

2

4

3

2

TIME AFTER POWER APPLIED ≠ Minutes

DEVIATION FROM FINAL VALUE

≠

V

T

A

= 25 C

V

S

= 15V

V

CM

= 0V

TPC 7. Input Offset Voltage

Warm-Up Drift

50

0

100

30

10

≠80

20

≠100

40

80

60

40

20

0

≠20

≠40

≠60

INPUT BIAS CURRENT ≠ pA

PERCENTAGE OF UNITS

T

A

= 25 C

V

S

= 15V

V

CM

= 0V

TPC 2. Typical Distribution of

Input Bias Current

V

S

= 15V

V

CM

= 0V

1000

100

10

≠75 ≠50 ≠25

0

25

50

75

100 125

INPUT CURRENT

≠

pA

TEMPERATURE ≠ C

≠I

B

+I

B

I

OS

TPC 5. Input Bias, Offset

Current vs. Temperature

10

100

1k

10k

100k

1M

10M

10000

1000

100

10

SOURCE RESISTANCE ≠

EFFECTIVE OFFSET VOLTAGE

≠

V

≠55 C T 125 C

A

T = +25 C

A

BALANCED OR UNBALANCED

V

S

= 15V

V

CM

= 0V

TPC 8. Effective Offset Voltage

vs. Source Resistance

INPUT OFFSET CURRENT ≠ pA

PERCENTAGE OF UNITS

60

0

60

30

10

10

20

0

50

40

50

40

30

20

T

A

= 25 C

V

S

= 15V

V

CM

= 0V

TPC 3. Typical Distribution of

Input Offset Current

70

0

15

30

10

≠10

20

≠15

60

40

50

10

5

0

≠5

COMMON-MODE VOLTAGE ≠ Volts

INPUT BIAS CURRENT

≠

pA

T

A

= 25 C

V

S

= 15V

≠I

B

+I

B

TPC 6. Input Bias Current vs.

Common-Mode Voltage

100

1k

10k

100k

1M

10M

100

10

1

0.1

SOURCE RESISTANCE ≠

EFFECTIVE OFFSET VOLTAGE

≠

V/

C

100M

BALANCED OR UNBALANCED

V

S

= 15V

V

CM

= 0V

TPC 9. Effective TCV

OS

vs.

Source Resistance

REV. D

≠5≠

OP497

1

10

100

1000

100

10

1

FREQUENCY ≠ Hz

1000

VOLTAGE NOISE DENSITY

≠

nV/

Hz

CURRENT NOISE DENSITY

≠

fA /

Hz

CURRENT NOISE

VOLTAGE NOISE

T

A

= 25 C

V

S

= 2V TO 20V

TPC 10. Voltage Noise Density

vs. Frequency

100

≠40

10M

20

≠20

1k

0

100

80

40

60

1M

100k

10k

225

180

135

90

FREQUENCY ≠ Hz

OPEN-LOOP GAIN

≠

dB

PHASE SHIFT

≠

DEG

GAIN

PHASE

V

S

= 15V

C

L

= 30pF

R

L

= 1M

T

A

= 25 C

TPC 13. Open-Loop Gain,

Phase vs. Frequency

160

0

1M

40

20

10

1

80

60

100

120

140

100k

10k

1k

100

FREQUENCY ≠ Hz

COMMON - MODE REJECTION

≠

dB

V

S

=

15V

T

A

= 25 C

TPC 16. Common-Mode

Rejection vs. Frequency

10

1

0.1

0.01

SOURCE RESISTANCE ≠

TOTAL NOISE DENSITY

≠

V/

Hz

T

A

= 25 C

V

S

= 2V TO 20V

10

2

10

3

10

4

10

5

10

6

10

7

1kHz

10Hz

TPC 11. Total Noise Density vs.

Source Resistance

LOAD RESISTANCE ≠ k

OPEN - LOOP GAIN

≠

V/ MV

V

S

= 15V

V

O

= 10V

10000

1000

100

1

10

20

T

A

= ≠55 C

T

A

= +25C

T

A

= +125 C

TPC 14. Open-Loop Gain vs.

Load Resistance

160

0

1M

40

20

10

1

80

60

100

120

140

100k

10k

1k

100

FREQUENCY ≠ Hz

POWER SUPPLY REJECTION

≠

dB

≠PSR

+PSR

V

S

=

15V

T

A

= 25 C

TPC 17. Power Supply

Rejection vs. Frequency

100

90

10

0%

1s

5mV

V

S

= 15V

T

A

= 25 C

NOISE VOLTAGE

≠

100mV/DIV

0

2

4

6

8

10

TIME ≠ Secs

TPC 12. 0.1 Hz to 10 Hz Noise Voltage

15

≠10

≠15

10

5

0

≠5

OUTPUT VOLTAGE ≠ V

DIFFERENTIAL INPUT VOLTAGE

≠

10

V/ DIV

R

L

= 2k

V

S

= 15V

V

CN

= 10V

T

A

= +125 C

T

A

= +25 C

T

A

= ≠55 C

TPC 15. Open-Loop Gain Linearity

FREQUENCY ≠ Hz

35

0

100k

15

5

1k

10

100

30

20

25

10k

OUTPUT SWING

≠

V

p-p

V

S

= 15V

T

A

= 25 C

A

VCL

= +1

1%THD

R

L

= 10k

TPC 18. Maximum Output

Swing vs. Frequency

REV. D

OP497

≠6≠

20

1.0

0.5

5

0

1.5

≠1.5

≠1.0

≠0.5

15

10

SUPPLY VOLTAGE ≠ V

INPUT COMMON-MODE VOLTAGE

≠

Volts

(REFERRED TO SUPPLY VOLTAGES)

+V

S

≠V

S

T

A

= 25 C

TPC 19. Input Common-Mode

Voltage Range vs. Supply Voltage

700

200

20

500

300

5

400

0

600

15

10

NO LOAD

SUPPLY VOLTAGE ≠ V

SUPPLY CURRENT (PER AMPLIFIER)

≠

A

+125 C

+25 C

≠55 C

TPC 22. Supply Current

(per Amplifier) vs. Supply Voltage

LOAD CAPACITANCE ≠ pF

70

0

10k

30

10

100

20

10

60

40

50

1k

OVERSHOOT

≠

%

V

S

= 15V

T

A

= 25 C

A

VCL

= +1

V

OUT

= 100mV p≠p

TPC 25. Small-Signal Overshoot

vs. Capacitance Load

LOAD RESISTANCE ≠

35

0

10k

15

5

100

10

10

30

20

25

1k

OUTPUT SWING

≠

V

p-p

V

S

= 15V

T

A

= 25 C

A

VCL

= +1

1%THD

f

O

= 1kHz

TPC 20. Maximum Output Swing

vs. Load Resistance

1000

0.001

100k

1

0.01

10

0.1

1

100

10

10k

1k

100

A

V

= +1

V

S

= 15V

T

A

= 25 C

TPC 23. Closed-Loop Output

Impedance vs. Frequency

20

1.0

0.5

5

0

1.5

≠1.5

≠1.0

≠0.5

15

10

SUPPLY VOLTAGE ≠ V

OUTPUT VOLTAGE SWING

≠

V

(REFERRED TO SUPPLY VOLTAGES)

+V

S

≠V

S

T

A

= 25 C

R

L

= 10k

TPC 21. Output Voltage Swing vs.

Supply Voltage

35

≠35

4

≠20

≠30

1

≠25

0

15

≠15

20

25

30

3

2

TIME FROM OUTPUT SHORT ≠ Mins

SHORT CIRCUIT CURRENT

≠

mA

T

A

= +125 C

T

A

= +25 C

T

A

= ≠55 C

V

S

=

15V

OUTPUT SHORTED

TO GROUND

T

A

= +125 C

T

A

= ≠55 C

T

A

= +25 C

TPC 24. Short-Circuit Current vs.

Time Temperature

≠IN

+IN

2.5k

V+

V

OUT

V≠

2.5k

TPC 26. Simplified Schematic Showing One Amplifier

REV. D

OP497

≠7≠

APPLICATIONS INFORMATION

Extremely low bias current over the full military temperature range

makes the OP497 attractive for use in sample-and-hold amplifiers,

peak detectors, and log amplifiers that must operate over a wide

temperature range. Balancing input resistances is not necessary

with the OP497. Offset voltage and TCV

OS

are degraded only

minimally by high source resistance, even when unbalanced.

The input pins of the OP497 are protected against large differen-

tial voltage by back-to-back diodes and current-limiting resistors.

Common-mode voltages at the inputs are not restricted, and may

vary over the full range of the supply voltages used.

The OP497 requires very little operating headroom about the

supply rails, and is specified for operation with supplies as low

as

± 2 V. Typically, the common-mode range extends to within

1 V of either rail. The output typically swings to within 1 V of

the rails when using a 10 k

load.

AC PERFORMANCE

The OP497's ac characteristics are highly stable over its full

operating temperature range. Unity-gain small-signal response is

shown in Figure 1. Extremely tolerant of capacitive loading on

the output, the OP497 displays excellent response even with

1000 pF loads (Figure 2).

10

90

100

0%

20mV

5 s

Figure 1. Small-Signal Transient Response

(C

LOAD

= 100 pF, A

VCL

= 1)

10

90

100

0%

20MV

5 s

Figure 2. Small-Signal Transient Response

(C

LOAD

= 1000 pF, A

VCL

= 1)

10

90

100

0%

2V

50 s

Figure 3. Large-Signal Transient Response (A

VCL

= 1)

GUARDING AND SHIELDING

To maintain the extremely high input impedances of the OP497,

care must be taken in circuit board layout and manufacturing.

Board surfaces must be kept scrupulously clean and free of mois-

ture. Conformal coating is recommended to provide a humidity

barrier. Even a clean PC board can have 100 pA of leakage currents

between adjacent traces, so guard rings should be used around

the inputs. Guard traces are operated at a voltage close to that

on the inputs, as shown in Figure 4, so that leakage currents

become minimal. In noninverting applications, the guard ring

should be connected to the common-mode voltage at the invert-

ing input. In inverting applications, both inputs remain at ground,

so the guard trace should be grounded. Guard traces should be

on both sides of the circuit board.

1/4

OP497

UNITY GAIN FOLLOWER

NONINVERTING AMPLIFIER

INVERTING AMPLIFIER

B

8

A

1

MINI-DIP

BOTTOM VIEW

≠

+

≠

+

≠

+

1/4

OP497

1/4

OP497

Figure 4. Guard Ring Layout and Connections

REV. D

OP497

≠8≠

OPEN-LOOP GAIN LINEARITY

The OP497 has both an extremely high gain of 2000 V/mv mini-

mum and constant gain linearity. This enhances the precision of

the OP497 and provides for very high accuracy in high closed-loop

gain applications. Figure 5 illustrates the typical open-loop gain

linearity of the OP 497 over the military temperature range.

15

≠10

≠15

10

5

0

≠5

OUTPUT VOLTAGE ≠ Volts

DIFFERENTIAL INPUT VOLTAGE

≠

10µ

V/ DIV

R

L

= 10k

V

S

= 15V

V

CM

= 0V

T

A

= +25C

T

A

= ≠55 C

T

A

= +125 C

Figure 5. Open-Loop Linearity of the OP497

APPLICATIONS

Precision Absolute Value Amplifier

The circuit of Figure 6 is a precision absolute value amplifier

with an input impedance of 30 M

. The high gain and low

TCV

OS

of the OP497 ensure accurate operation with microvolt

input signals. In this circuit, the input always appears as a com-

mon-mode signal to the op amps. The CMR of the OP497

exceeds 120 dB, yielding an error of less than 2 ppm.

+15V

2

3

V

IN

≠15V

4

C3

0.1 F

8

1

6

5

7

0V < V < 10V

OUT

D1

1N4148

R3

1k

R1

1k

C2

0.1 F

C1

30pF

D2

1N4148

R2

2k

1/4

OP497

1/4

OP497

Figure 6. Precision Absolute Value Amplifier

PRECISION CURRENT PUMP

Maximum output current of the precision current pump shown

in Figure 7 is

±10 mA. Voltage compliance is ±10 V with ±15 V

supplies. Output impedance of the current transmitter exceeds

3 M

with linearity better than 16 bits.

2

3

1

7

8

5

6

4

≠15V

+15V

I

OUT

10mA

≠

+

VIN

I

OUT

= = = 10mA/ V

V

IN

R5

V

IN

100

R1

10k

R2

10k

R4

10k

R3

10k

R5

10k

1/4

OP497

1/4

OP497

Figure 7. Precision Current Pump

PRECISION POSITIVE PEAK DETECTOR

In Figure 8, the CH must be of polystyrene, Teflon

*, or polyeth-

ylene to minimize dielectric absorption and leakage. The droop

rate is determined by the size of CH and the bias current of the

OP497.

2

3

1

7

8

5

6

4

≠15V

+15V

1N4148

2N930

C

H

RESET

V

IN

V

OUT

1k

1k

1k

1k

0.1 F

0.1 F

1/4

OP497

1/4

OP497

Figure 8. Precision Positive Peak Detector

SIMPLE BRIDGE CONDITIONING AMPLIFIER

Figure 9 shows a simple bridge conditioning amplifier using

the OP497. The transfer function is:

V

V

R

R

R

R

R

OUT

REF

F

=

+

The REF43 provides an accurate and stable reference voltage

for the bridge. To maintain the highest circuit accuracy, R

F

should be 0.1% or better with a low temperature coefficient.

*Teflon is a registered trademark of the Dupont Company.

REV. D

OP497

≠9≠

2

3

1

7

8

5

6

4

≠5V

+5V

REF43

6

2

4

+5V

R

R

R

2.5 V

R + R

R

F

V

OUT

V

REF

V

OUT

= V

REF

( )

R

R + R

R

F

R

1/4

OP497

1/4

OP497

Figure 9. A Simple Bridge Conditioning Amplifier Using

the OP497

NONLINEAR CIRCUITS

Due to its low input bias currents, the OP497 is an ideal log

amplifier in nonlinear circuits such as the square and square

root circuits shown in Figures 10 and 11. Using the squaring

circuit of Figure 10 as an example, the analysis begins by writing a

voltage-loop equation across transistors Q

1

, Q

2

, Q

3

, and Q

4

.

V

In

I

I

V

In

I

I

V

In I

I

I

V

In

I

I

T

IN

S

T

IN

S

T

O

S

T

REF

S

1

1

2

2

3

3

4

4

+

=

+

All the transistors of the MAT04 are precisely matched and at

the same temperature, so the I

S

and V

T

terms cancel, giving:

2InI

InI

InI

In I

I

IN

O

REF

O

REF

=

+

=

◊

(

)

Exponentiating both sides of thick equation leads to:

I

I

I

O

IN

2

REF

=

( )

Op amp A

2

forms a current-to-voltage converter which gives

V

OUT

= R2

◊ I

O

. Substituting (V

IN

/R1) for I

IN

and the above

equation for I

O

, yields:

V

R2

I

V

R1

OUT

REF

IN

2

=

1

2

3

6

7

5

C1

100pF

V+

2

3

8

1

4

V≠

V

IN

I

IN

C2

100pF

6

5

7

V

OUT

I

O

9

8

10

Q1

Q3

Q2

14

12

Q4

13

≠15V

I

REF

MAT-04E

R1

133k

R2

33k

R3

50k

R4

50k

1/4

OP497

1/4

OP497

Figure 10. Squaring Amplifier

A similar analysis made for the square-root circuit of Figure 11

leads to its transfer function:

V

R2

V

I

R1

OUT

IN

REF

=

( )( )

In these circuits, I

REF

is a function of the negative power sup-

ply. To maintain accuracy, the negative supply should be well

regulated. For applications where very high accuracy is required,

a voltage reference may be used to set I

REF

. An important con-

sideration for the squaring circuit is that a sufficiently large

input voltage can force the output beyond the operating range

of the output op amp. Resistor R4 can be changed to scale I

REF

,

or Rl and R2 can be varied to keep the output voltage within

the usable range.

1

2

3

6

7

5

C1

100pF

V+

2

3

8

1

4

V≠

6

5

7

V

OUT

I

O

9

8

10

Q1

Q3

Q2

14

12

Q4

13

≠15V

I

REF

MAT-04E

I

IN

V

IN

R1

33k

R2

33k

R5

2k

R3

50k

R4

50k

C2

100pF

1/4

OP497

1/4

OP497

Figure 11. Square-Root Amplifier

Unadjusted accuracy of the square-root circuit is better than

0.1% over an input voltage range of 100 mV to 10 V. For a

similar input voltage range, the accuracy of the squaring circuit

is better than 0.5%.

REV. D

OP497

≠10≠

OP497 SPICE MACRO-MODEL

Figure 12 and Table I show the node and net list for a SPICE

macro-model of the OP497. The model is a simplified version of

the actual device and simulates important dc parameters such as

V

OS

, I

OS

, I

B

, A

VO

, CMR, V

O

, and I

SY

. AC parameters such as slew

rate, gain and phase response, and CMR change with frequency

are also simulated by the model.

The model uses typical parameters for the OP497. The poles and

zeros in the model were determined from the actual open and

closed-loop gain and phase response of the OP497. In this way,

the model presents an accurate ac representation of the actual

device. The model assumes an ambient temperature of 25

∞C.

≠ +

≠ +

99

20

21

23

24

25

26

22

R16

D9

G4

G5

D10

G7

L1

V4

V3

G6

D8

D7

D5

D6

27

50

I

SY

V

O

R18

R19

R17

G2

R10

CCM

98

ECM

RCM1

RCM2

15

16

C5

19

CNZ

ENZ

RNZ1

RNZ2

17

18

G2

R15

20

C5

≠IN

+IN

8

9

7

2

1

C

IN

R1

R2

D1

D2

50

10

11

5

6

12

98

14

13

G1

C3

V2

C2

Q1

Q2

R6

R5

99

V1

E

REF

≠ +

R

IN2

E

OS

I

1

R

IN1

I

OS

R3

R4

D3

D4

R7

Figure 12. OP497 Macro Model

REV. D

OP497

≠11≠

* Node assignments

*

noninverting input

*

inverting input

*

positive supply

*

negative supply

*

output

*

*SUBCKT OP497 1

2

99

50 27

*

* INPUT STAGE AND POLE AT 6 MHz

*

RIN1 1

7

2500

RIN2 2

8

2500

R1

8

3

6.782E8

R2

7

3

6.782E8

R3

5

99

542.57

R4

6

99

542.57

CIN 7

8

3E-12

C2

5

6

24.445E-12

I1

4

50

0.1E-3

IOS

7

8

15E-12

EOS 9

7

POLY(1) 16

21 40E-6

1

Q1

5

8

10

QX

Q2

6

9

11

QX

R5

10

4

25.374

R6

11

4

25.374

D1

8

9

DX

D2

9

8

DX

*

EREF 98

0

21

0

1

*

*GAIN STAGE AND DOMINANT POLE AT 0.11 Hz

*

R7

1

98

2.1703E9

C3

2

98

666.67E-12

G1

98

12

5

V1

99

13

1.275

V2

11

9

1.275

D3

12

13

DX

D4

14

12

DX

*

*COMMON-MODE GAIN NETWORK WITH ZERO AT 50 MHz

*

RCM1 15

16

1E6

CCM

15

16

3.18E-9

RCM2 16

98

1

ECM

15

98

3

21

177.83E-3

* NEGATIVE ZERO AT 1.8 MHz

*

E1

17

98

12

21

1E6

R8

17

18

1E6

C4

17

18

≠88.419E-15

R9

18

98

1

*

* POLE AT 6 MHz

*

G2

98

19

18

21

1E-6

R15

20

98

1E6

C8

20

98

26.526E-15

*

* POLE AT 1.8 MHz

*

G6

98

20

19

21

1E-6

R20

20

98

1E6

C10

20

98

88.419E-15

*

* OUTPUT STAGE

*

R16

99

21

160 k

R17

21

50

160 k

ISY

99

50

331E-6

V3

23

22

1.9

D5

20

23

DX

V4

22

24

1.9

D6

24

20

DX

D7

99

25

DX

G4

25

50

20

22

5E-3

D9

50

25

DY

D8

99

26

DX

G5

26

50

22

20

5E-3

D10

50

26

DY

G6

22

99

99

20

5E-3

R18

99

22

200

G7

50

22

20

50

5E-3

R19

22

50

200

L1

22

27

0.1E-6

*

* MODELS USED

*

.MODEL QX NPN (BF = 1.25E6)

.MODEL DX (IS = 1E-15)

.MODEL DZ D(IS = 1E-15 BV = 50)

.ENDS OP497

Table I. OP497 SPICE Net-List

≠12≠

C00309≠0≠2/02(D)

PRINTED IN U.S.A.

Revision History

Location

Page

11/01--Data Sheet changed from REV. C to REV. D.

Edits to PIN CONNECTIONS headings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Deleted WAFER TEST LIMITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Edits to ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Edits to ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Edits to OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

14-Lead Ceramic DIP

(Y-Suffix)

PIN 1

1

14

8

7

0.005 (0.13)

MIN

0.098 (2.49)

MAX

0.310 (7.87)

0.220 (5.59)

0.200 (5.08)

MAX

0.060 (1.52)

0.015 (0.38)

0.200 (5.08)

0.125 (3.18) 0.023 (0.58)

0.014 (0.36)

0.100

(2.54)

BSC

0.070 (1.78)

0.030 (0.76)

0.150

(3.81)

MIN

0

∞≠15∞

0.015 (0.38)

0.008 (0.20)

0.320 (8.13)

0.290 (7.37)

0.785 (19.94) MAX

SEATING PLANE

14-Lead Epoxy DIP

(P-Suffix)

PIN 1

1

14

8

7

0.325 (8.25)

0.300 (7.62)

0.210 (5.33)

MAX

0.160 (4.06)

0.115 (2.92) 0.022 (0.558)

0.014 (0.36)

0.100

(2.54)

BSC

0.070 (1.77)

0.045 (1.15)

0.130

(3.30)

MIN

0

∞≠15∞

0.015 (0.38)

0.008 (0.20)

0.280 (7.11)

0.240 (6.10)

0.015 (0.381)

MIN

0.795 (20.19)

0.725 (18.41)

16-Lead Wide-Body SOIC

(S-Suffix)

SEATING

PLANE

0.0118 (0.30)

0.0040 (0.10)

0.0192 (0.49)

0.0138 (0.35)

0.1043 (2.65)

0.0926 (2.35)

0.050 (1.27)

BSC

16

9

8

1

0.4193 (10.65)

0.3937 (10.00)

0.2992 (7.60)

0.2914 (7.40)

PIN 1

0.4133 (10.50)

0.3977 (10.00)

0.0125 (0.32)

0.0091 (0.23)

8

0

0.0291 (0.74)

0.0098 (0.25)

45

0.0500 (1.27)

0.0157 (0.40)