| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: T7121 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Features

s

Low-cost device for B-channel (64 kbits/s) or

D-channel (16 kbits/s) data transport.

s

Optional transparent mode--no HDLC framing is

performed.

s

Frame sync (FS) allows a slot-select feature to

access an individual time slot in any TDM data

stream (e.g., Lucent Technologies Microelectronics

Group Concentration Highway Interface [CHI] or

subset).

s

Bit-masking option allows effective data rates of 8,

16, 24, 32, 40, 48, and 56 kbits/s.

s

Maximum data rate up to 4.096 MHz.

s

Serial data-transfer pins for direct connection to the

Lucent ISDN line transceiver T7250C.

s

Supports IOM2, K2, GCI, and SLD interface.

s

Parallel microprocessor interface with either multi-

plexed or demultiplexed address and data lines for

easy interface with any microprocessor.

s

Single interrupt output signal with seven maskable

interrupt conditions.

s

Programmable interrupt modes.

s

Memory-mapped read and write registers.

s

TTL/CMOS compatible input/output.

s

3-state output pins to assist system diagnostics.

s

Low-power 1.25

µ

m CMOS:

-- 30 mW typical operation at 12 MHz.

-- 5 mW standby mode (typical).

s

HDLC transceiver:

-- Stand-alone HDLC framing operation.

-- 64-byte FIFO in both transmit and receive direc-

tions.

-- Supports block-move instruction.

-- Multiple frames allowed in FIFO.

-- Programmable FIFO full- and empty-level inter-

rupt.

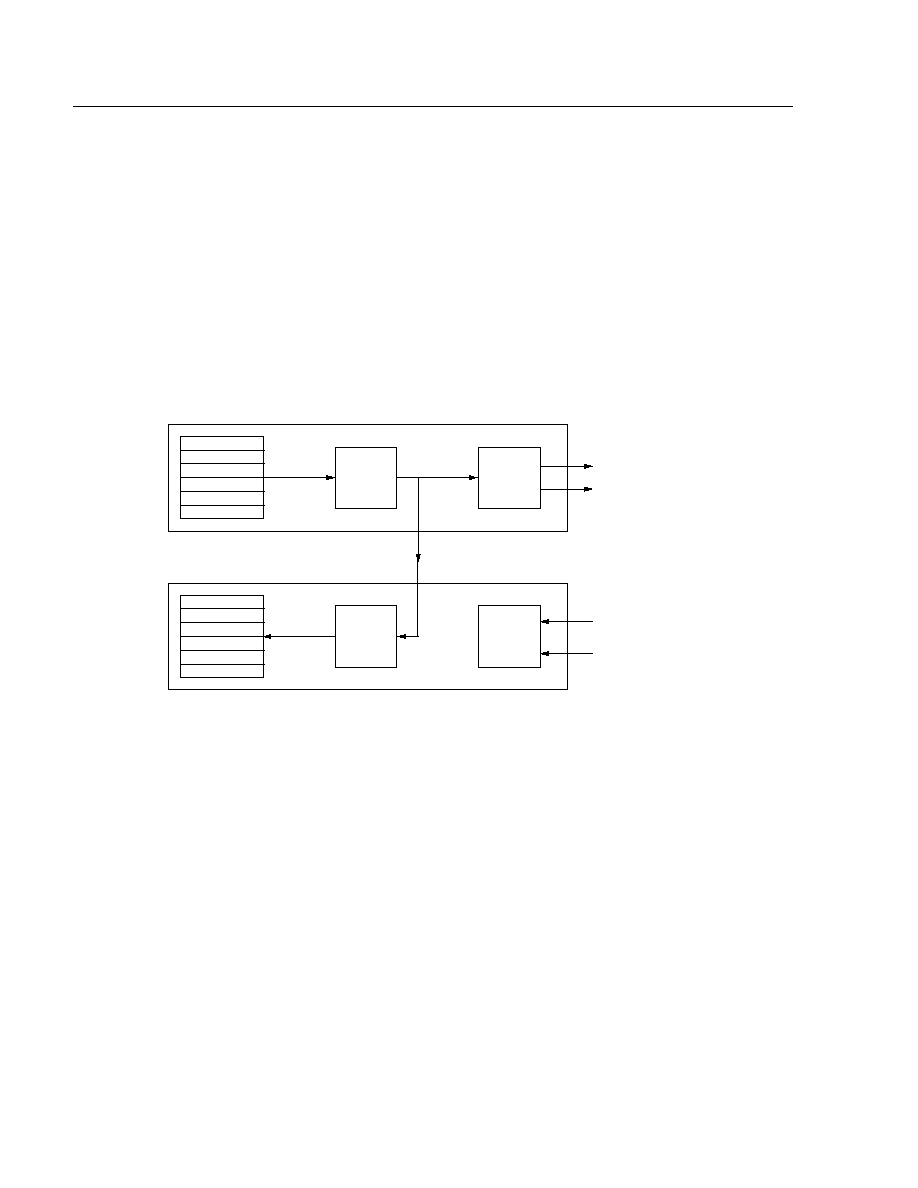

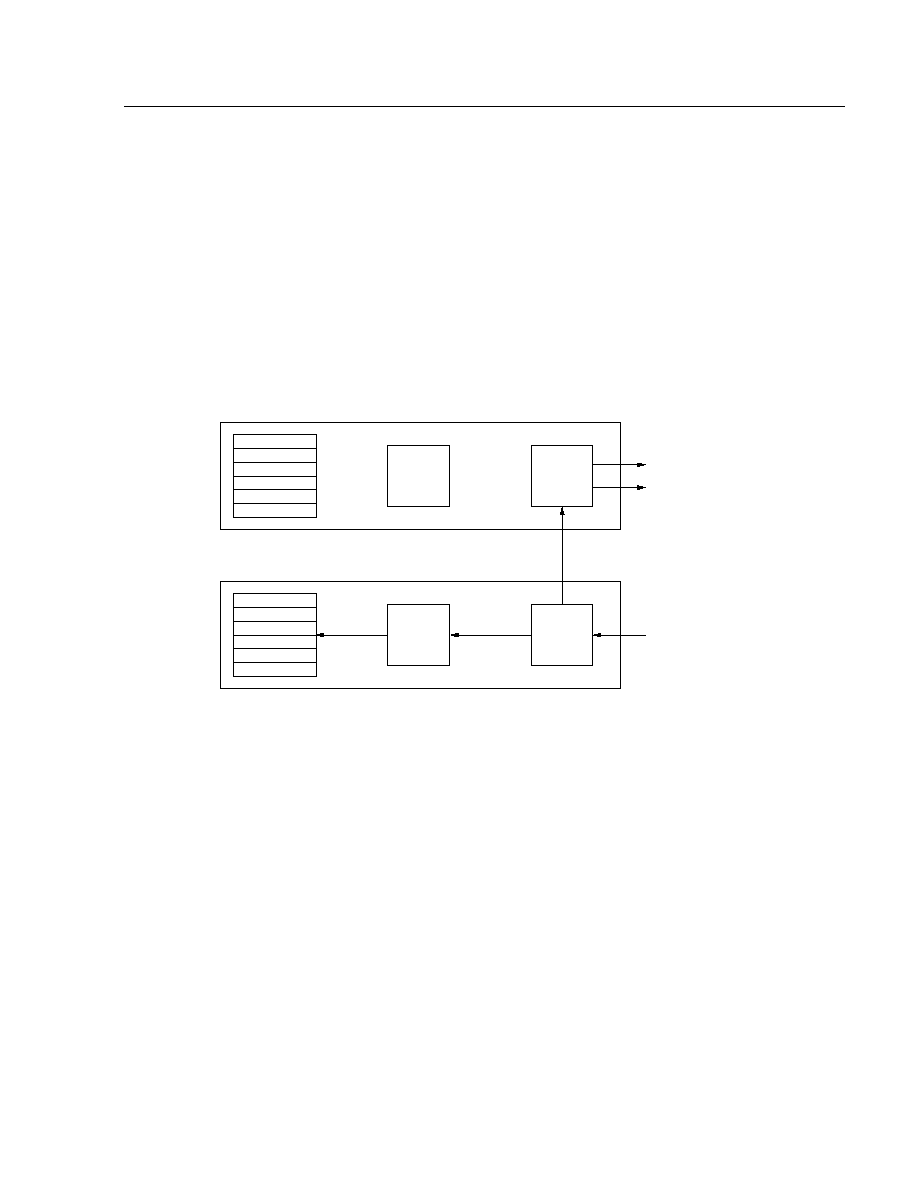

Description

The T7121 HDLC Interface for ISDN (HIFI-64) con-

nects serial communications links carrying HDLC bit-

synchronous data frames to 8-bit microcomputer sys-

tems. There is an optional transparent mode of oper-

ation in which no HDLC processing is performed on

user data. The device communicates with the system

microprocessor as a memory-mapped peripheral and

is controlled by reading and writing 19 internal regis-

ters. The chip can be instructed to interrupt the

microprocessor when it detects certain events requir-

ing microprocessor attention. The HDLC transmitter

and receiver are each buffered with 64-byte, first-in-

first-out (FIFO) memory storage. The 64-byte buffer

depth reduces the number of status polls or inter-

rupts to be processed by the microprocessor, improv-

ing overall system efficiency. The major blocks are

the microprocessor interface, transmit and receive

FIFO memory buffers, HDLC processor, and a con-

centration highway interface (see Figure 1). The

T7121 device is available in a 28-pin, plastic DIP or a

28-pin, plastic, small-outline, J-lead (SOJ) package

for surface mounting.

Table of Contents

Contents

Page

2

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Features ................................................................................................................................................................... 1

Description................................................................................................................................................................ 1

Pin Information ......................................................................................................................................................... 4

Functional Description .............................................................................................................................................. 8

Microprocessor Bus Interface ................................................................................................................................ 8

Addressing .......................................................................................................................................................... 8

Interrupts ............................................................................................................................................................. 8

Resets ................................................................................................................................................................. 9

FIFO Memory Buffers ............................................................................................................................................ 9

Transmit FIFO ..................................................................................................................................................... 9

Receive FIFO .................................................................................................................................................... 10

Block Move........................................................................................................................................................ 10

Serial Link Interface .......................................................................................................................................... 10

Enabling the Transmitter and Receiver ............................................................................................................. 10

Time-Slot Feature ............................................................................................................................................. 13

Transmission During Unassigned Time Slots ................................................................................................... 14

Bit Order During Transmission .......................................................................................................................... 14

Bit Masking........................................................................................................................................................ 16

SLD and IOM2 Examples.................................................................................................................................. 19

HDLC Operation .................................................................................................................................................. 19

Zero-Bit Insertion/Deletion (Bit Stuffing/Destuffing) .......................................................................................... 19

Transmitter FIFO ............................................................................................................................................... 21

Sending 1-Byte Frames .................................................................................................................................... 21

Transmitter Underrun ........................................................................................................................................ 21

Using the Transmitter Status and Fill Level ...................................................................................................... 21

Receiver FIFO ................................................................................................................................................... 21

Receiver Overrun .............................................................................................................................................. 23

Operational Note (T7121-EL, T7121-PL, T7121-EL2, and T7121-PL2) ............................................................ 23

Transparent Mode................................................................................................................................................ 24

Diagnostic Modes ................................................................................................................................................ 25

Loopbacks ......................................................................................................................................................... 25

3-State Mode..................................................................................................................................................... 28

Other ................................................................................................................................................................. 28

Powerdown Mode ................................................................................................................................................ 28

Registers.............................................................................................................................................................. 28

Absolute Maximum Ratings.................................................................................................................................... 45

Electrical Characteristics ........................................................................................................................................ 45

Clock Characteristics.............................................................................................................................................. 46

Timing Characteristics ............................................................................................................................................ 46

TDM Frame Timing Diagrams.............................................................................................................................. 46

Multiplexed Address and Data ............................................................................................................................. 51

Separate Address and Data................................................................................................................................. 53

Concentration Highway........................................................................................................................................ 55

Handling Precautions ............................................................................................................................................. 59

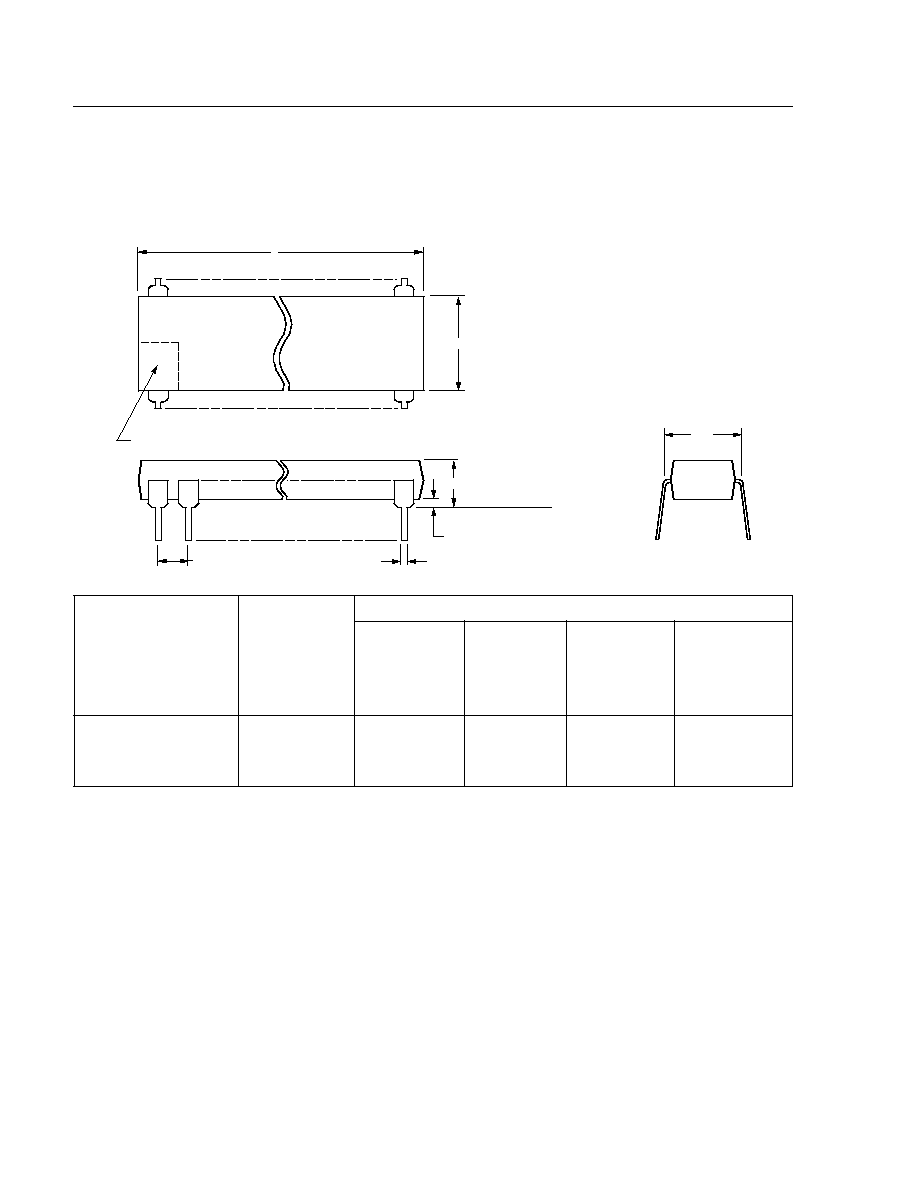

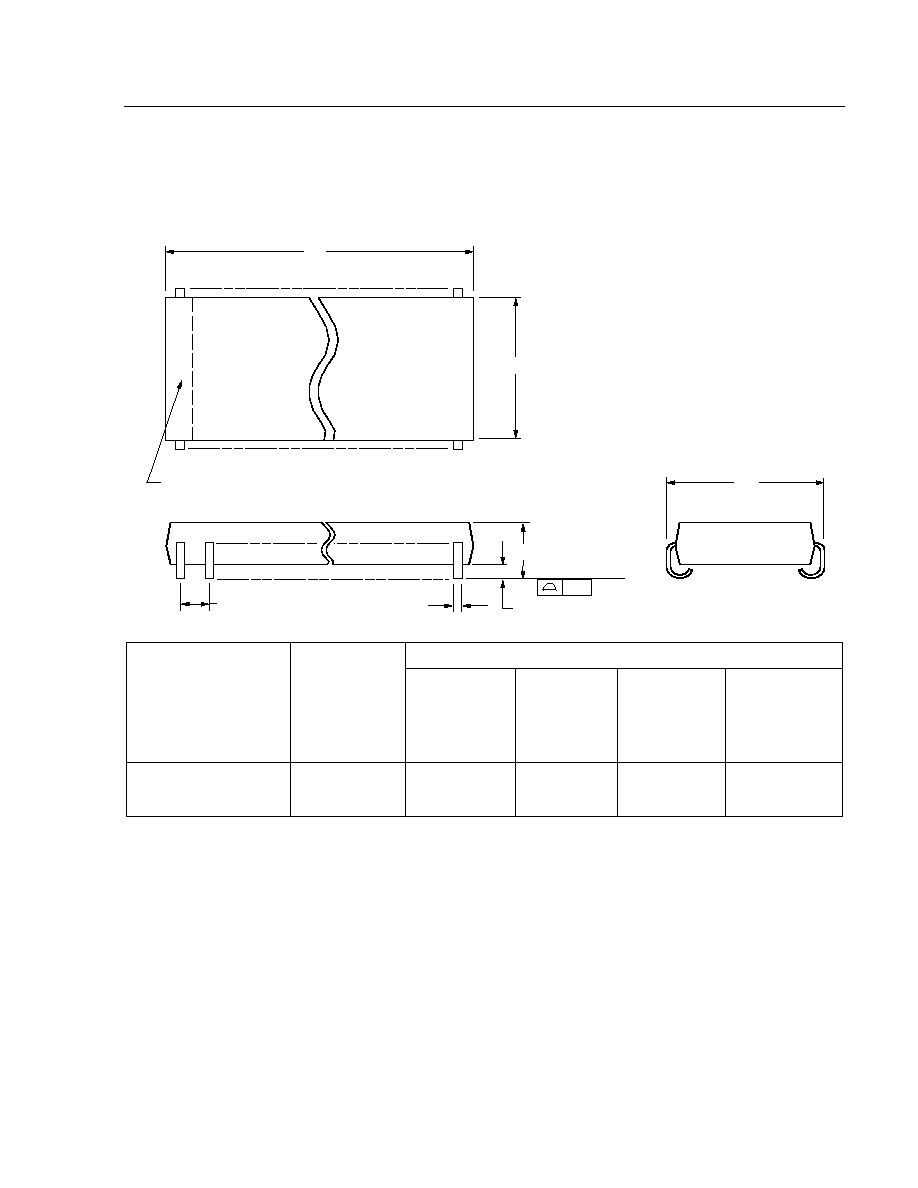

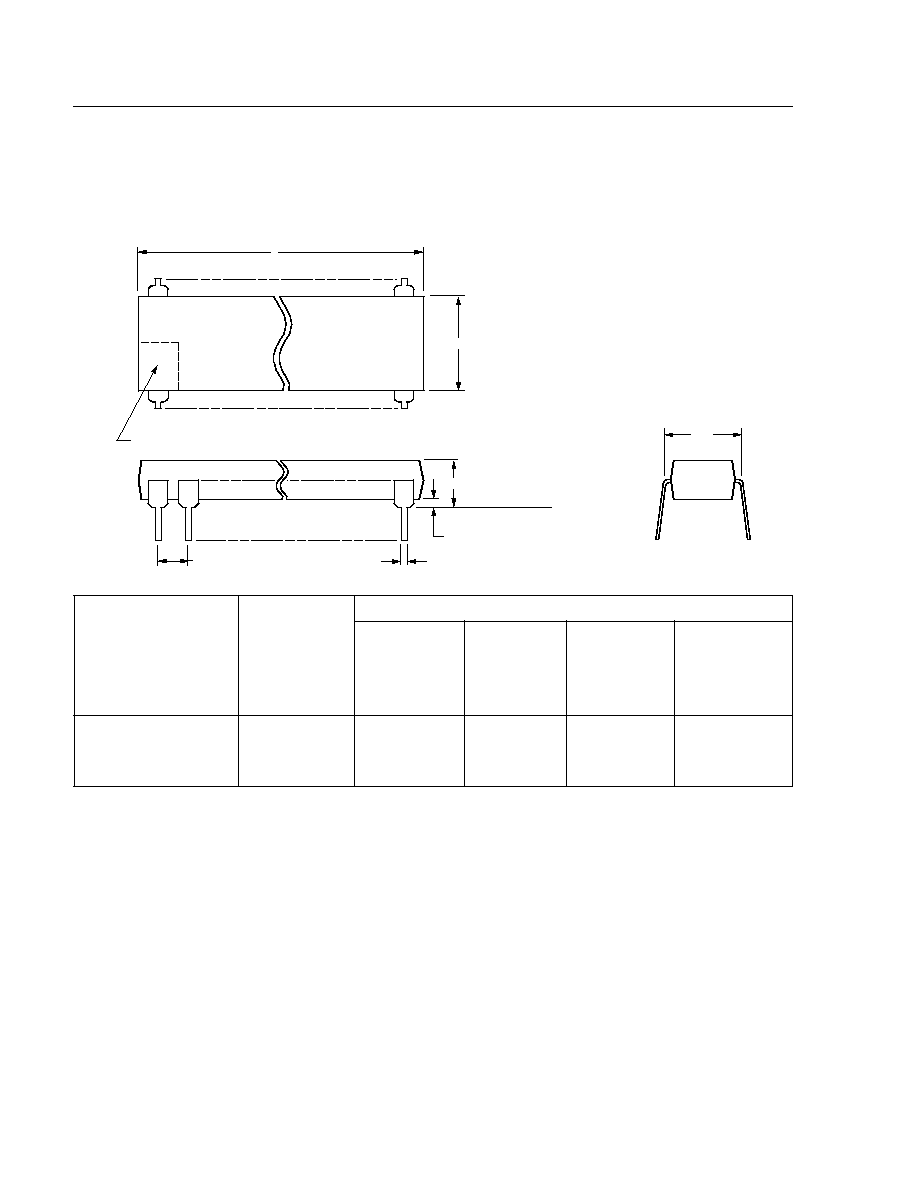

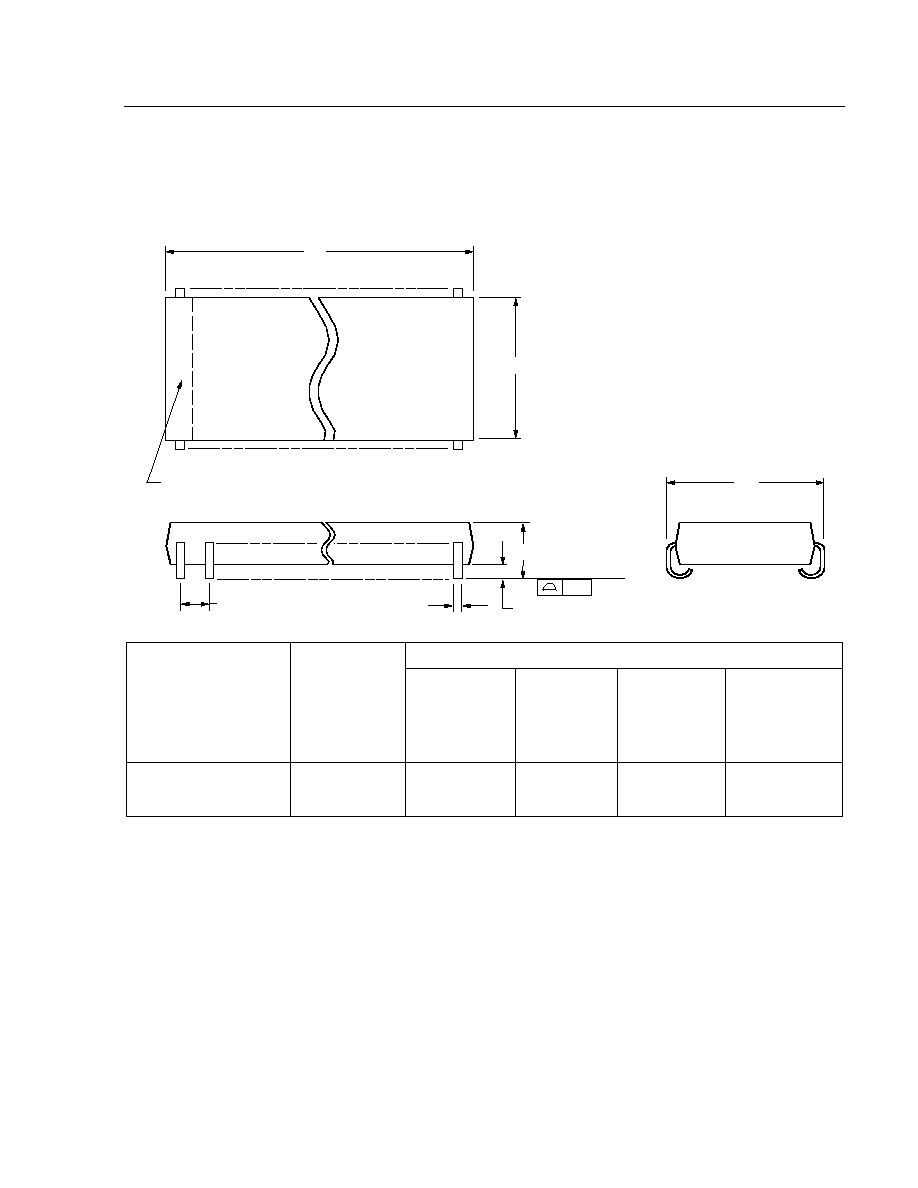

Outline Diagrams.................................................................................................................................................... 60

28-Pin, Plastic DIP ............................................................................................................................................... 60

28-Pin, Plastic SOJ, Surface Mounting................................................................................................................ 61

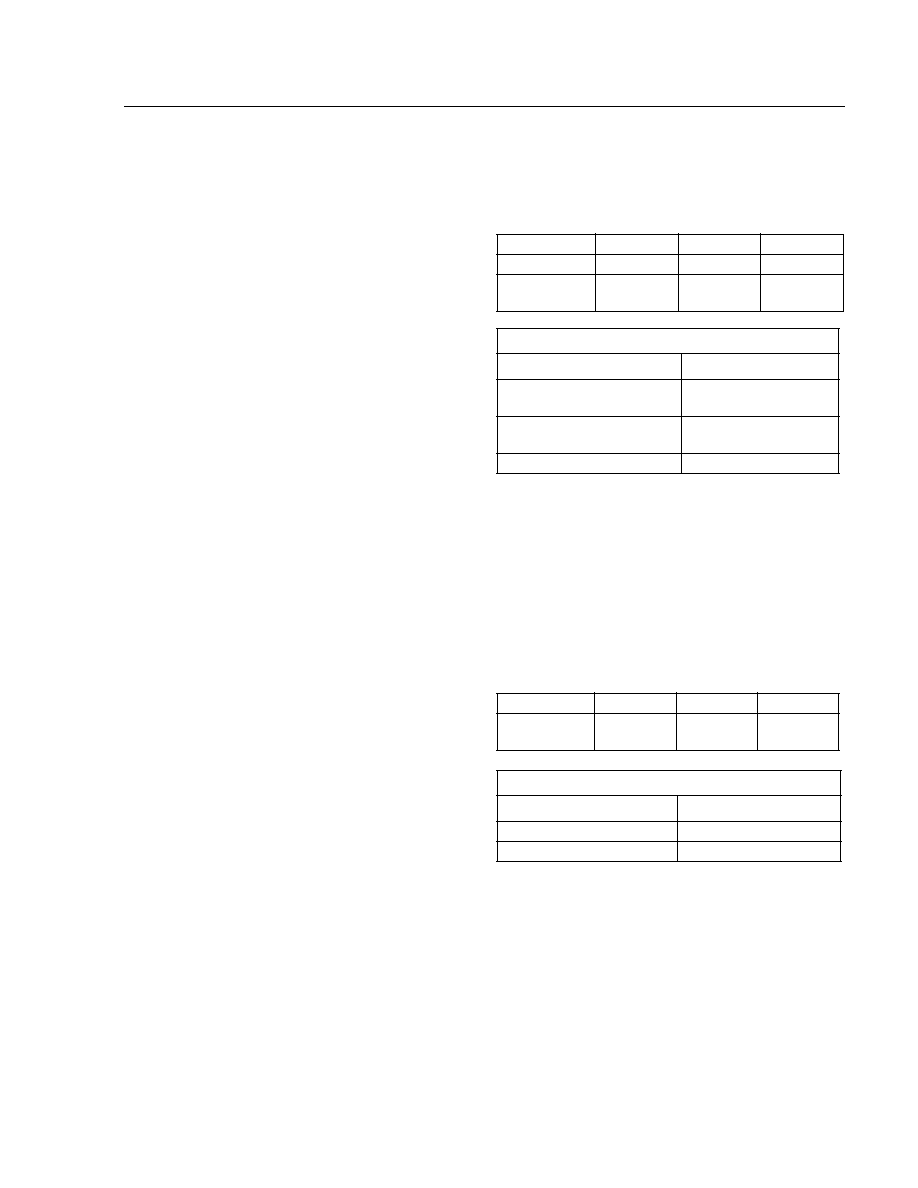

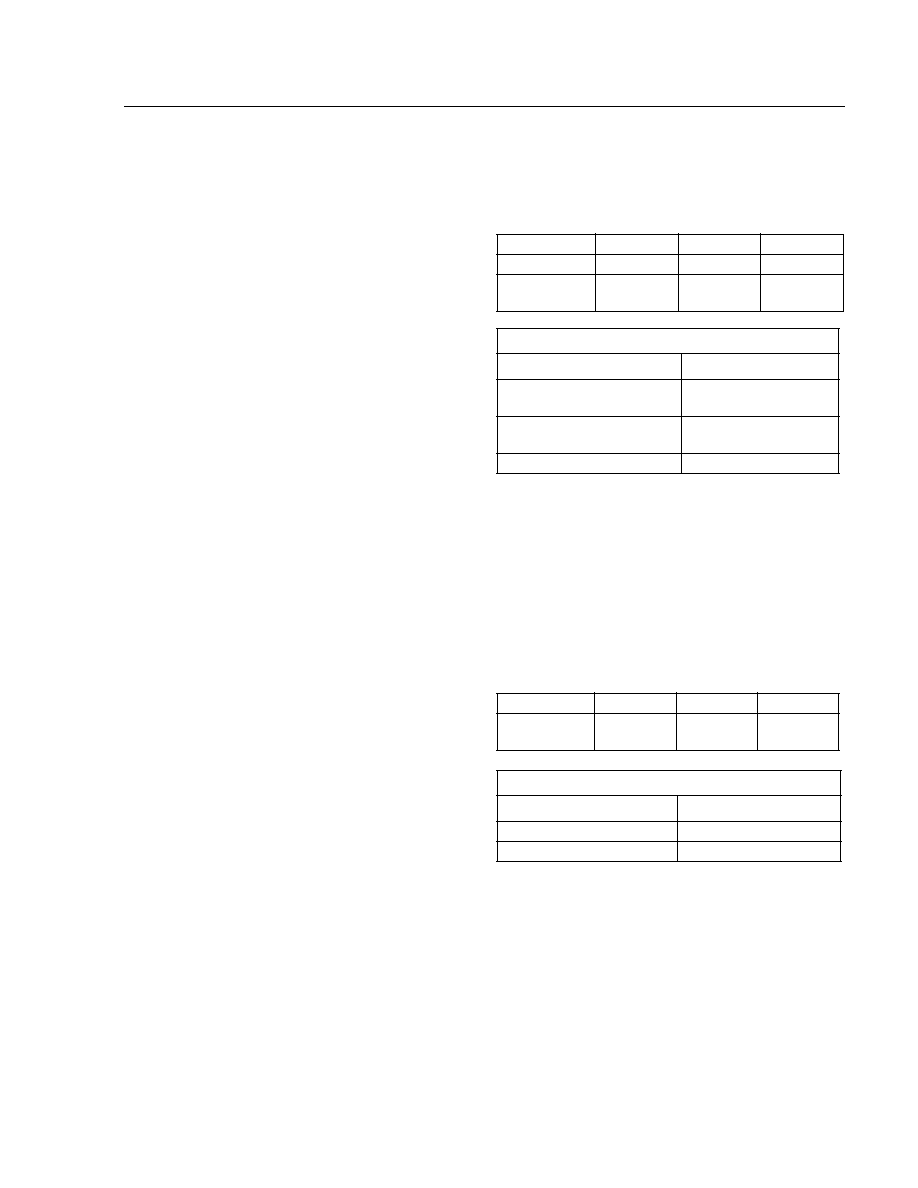

Ordering Information............................................................................................................................................... 62

Appendix................................................................................................................................................................. 63

Transparent Mode................................................................................................................................................ 63

HDLC Mode ......................................................................................................................................................... 63

General Features ................................................................................................................................................. 64

Power and Ground............................................................................................................................................... 66

Lucent Technologies Inc.

3

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Description

(continued)

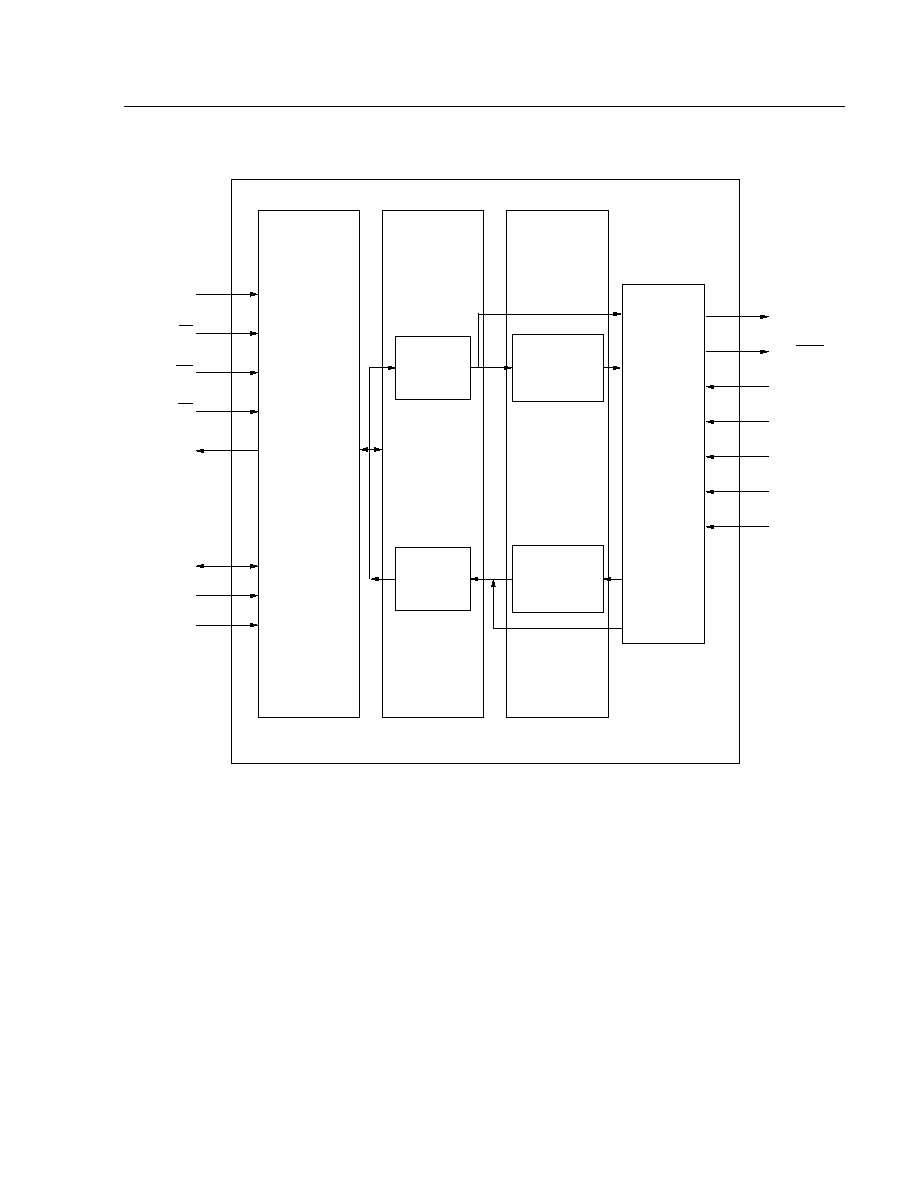

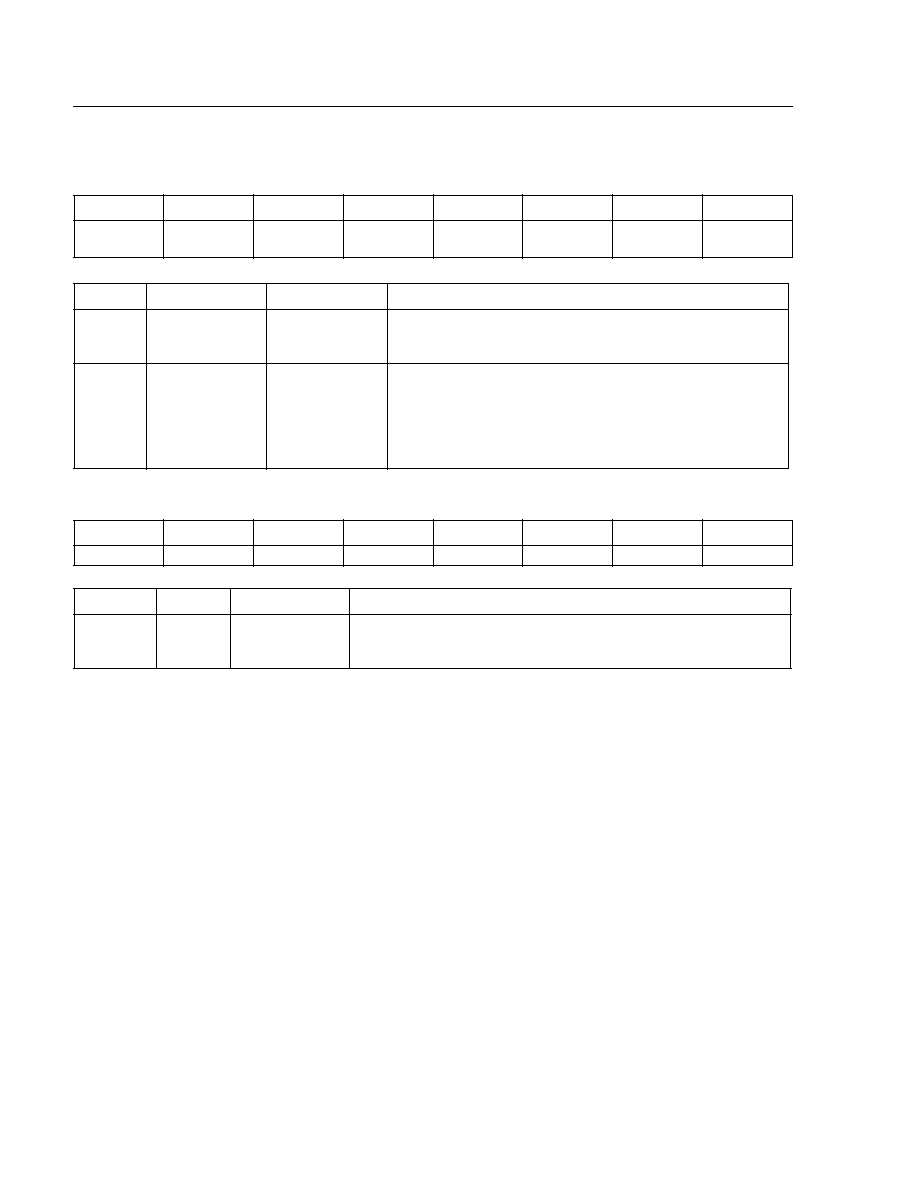

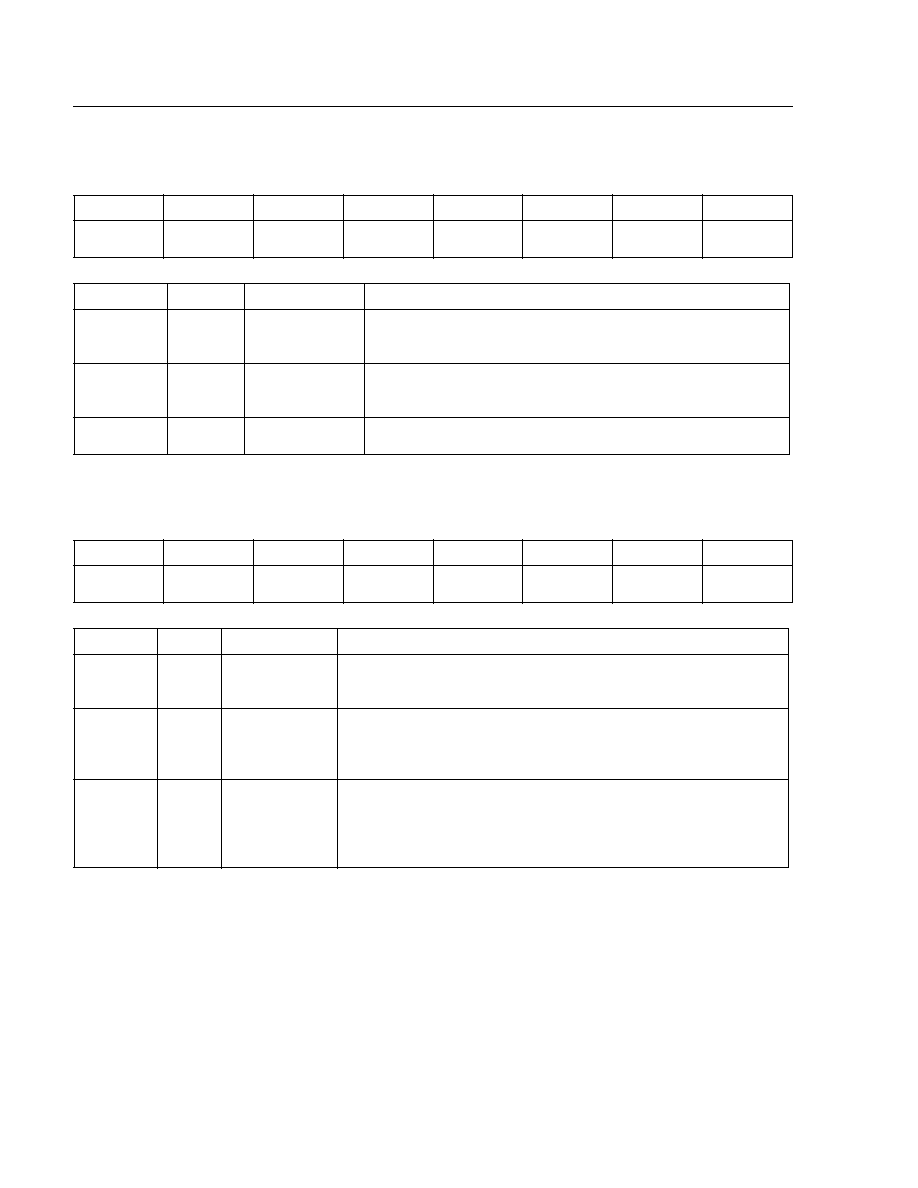

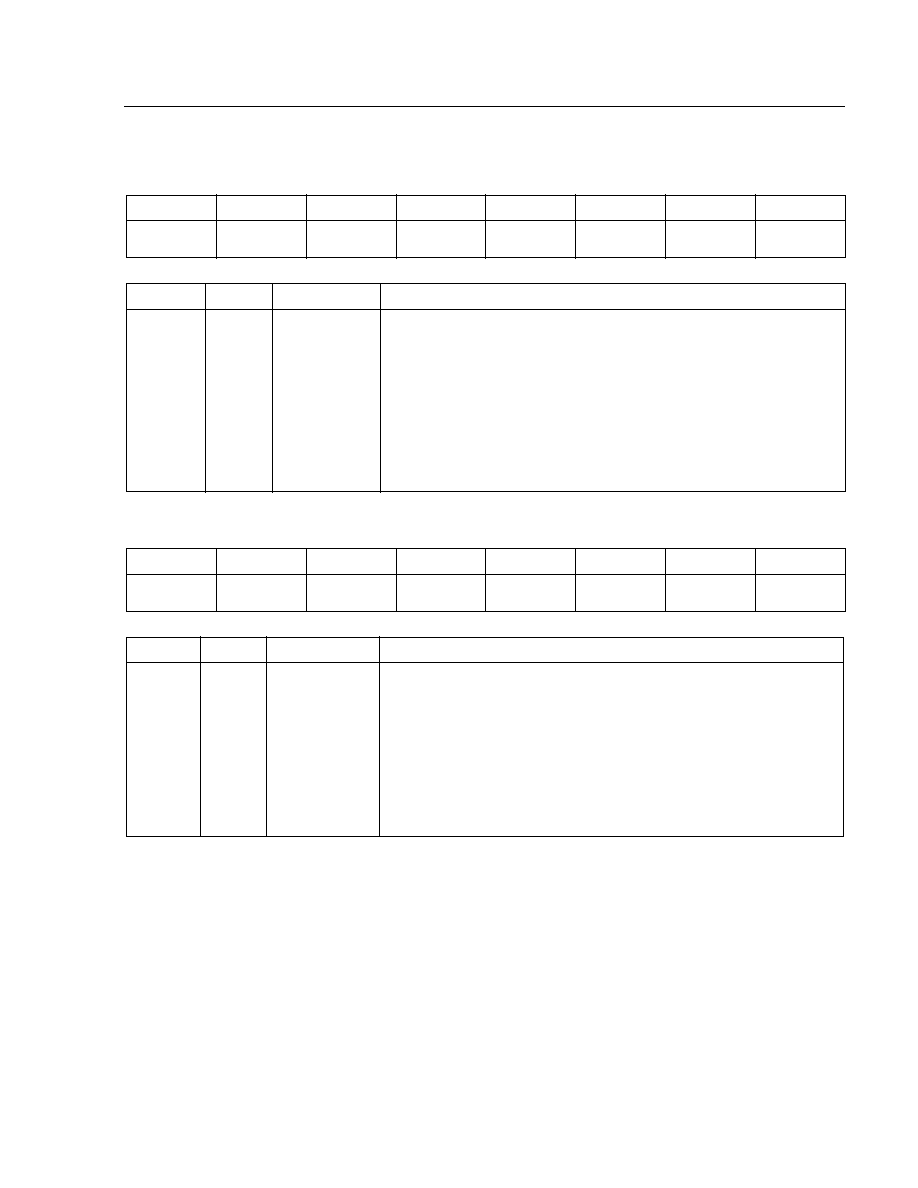

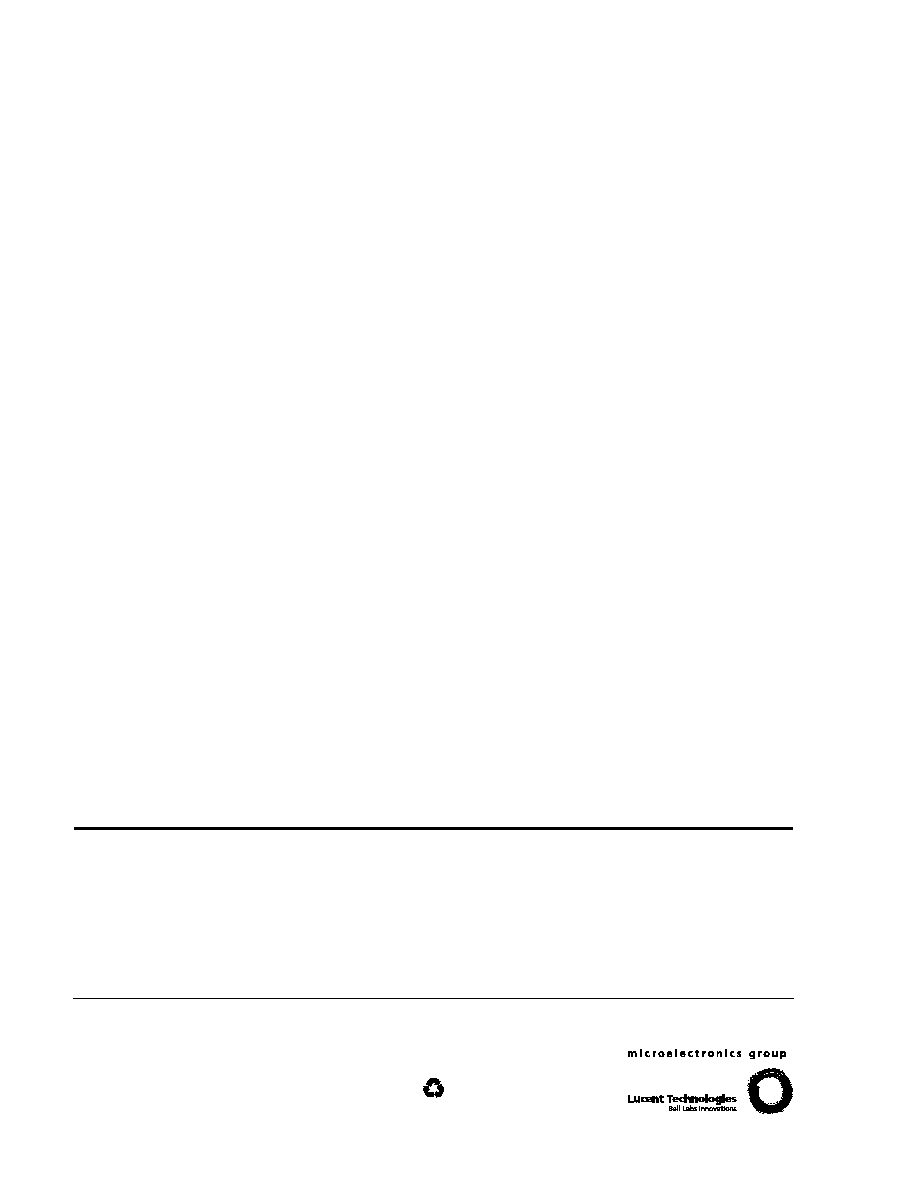

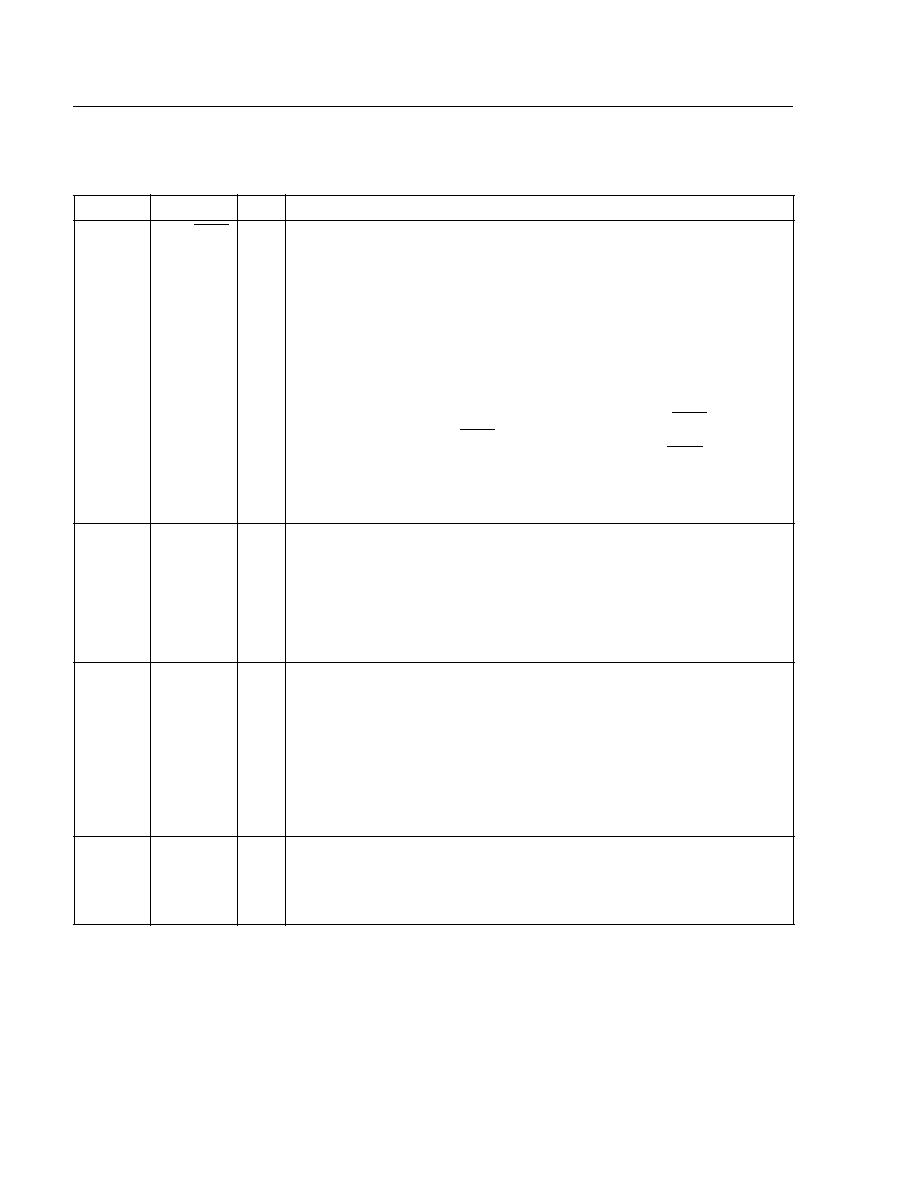

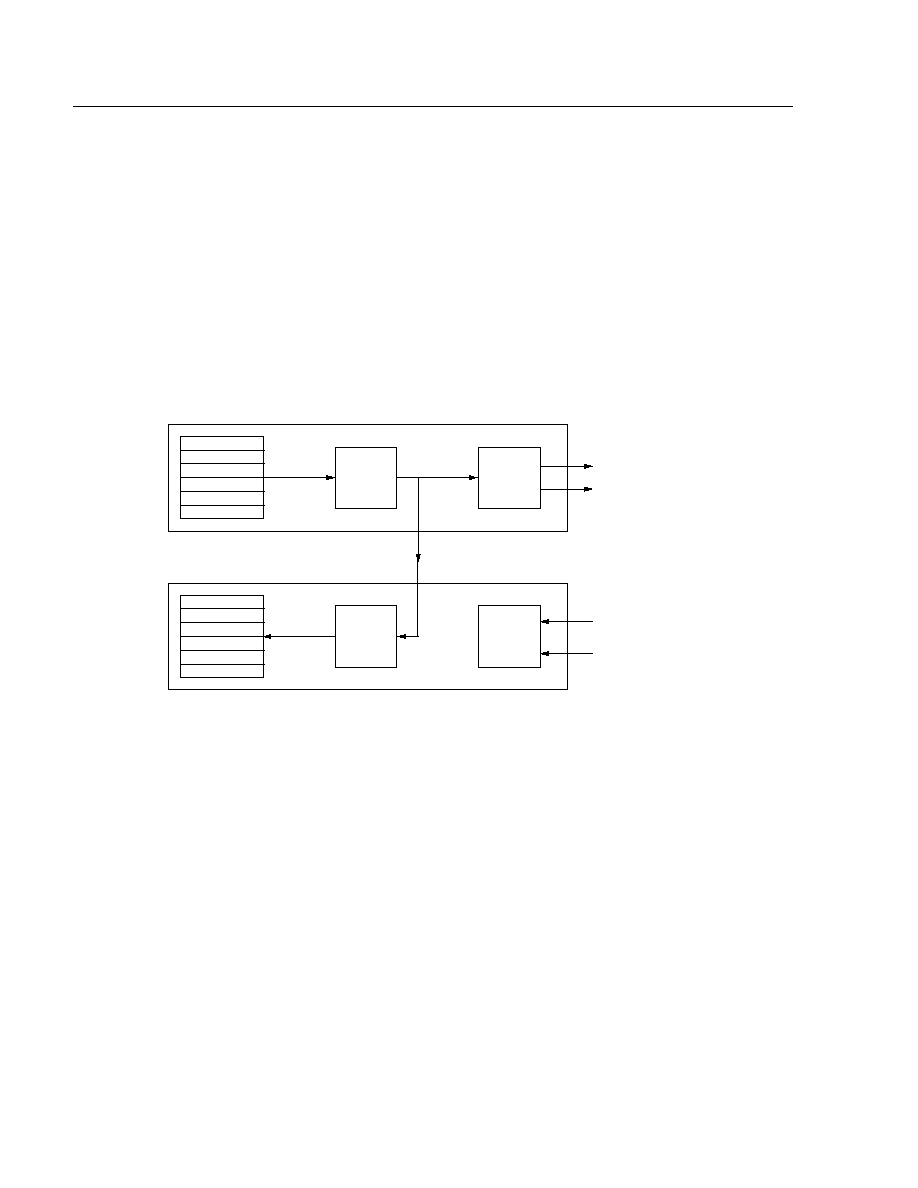

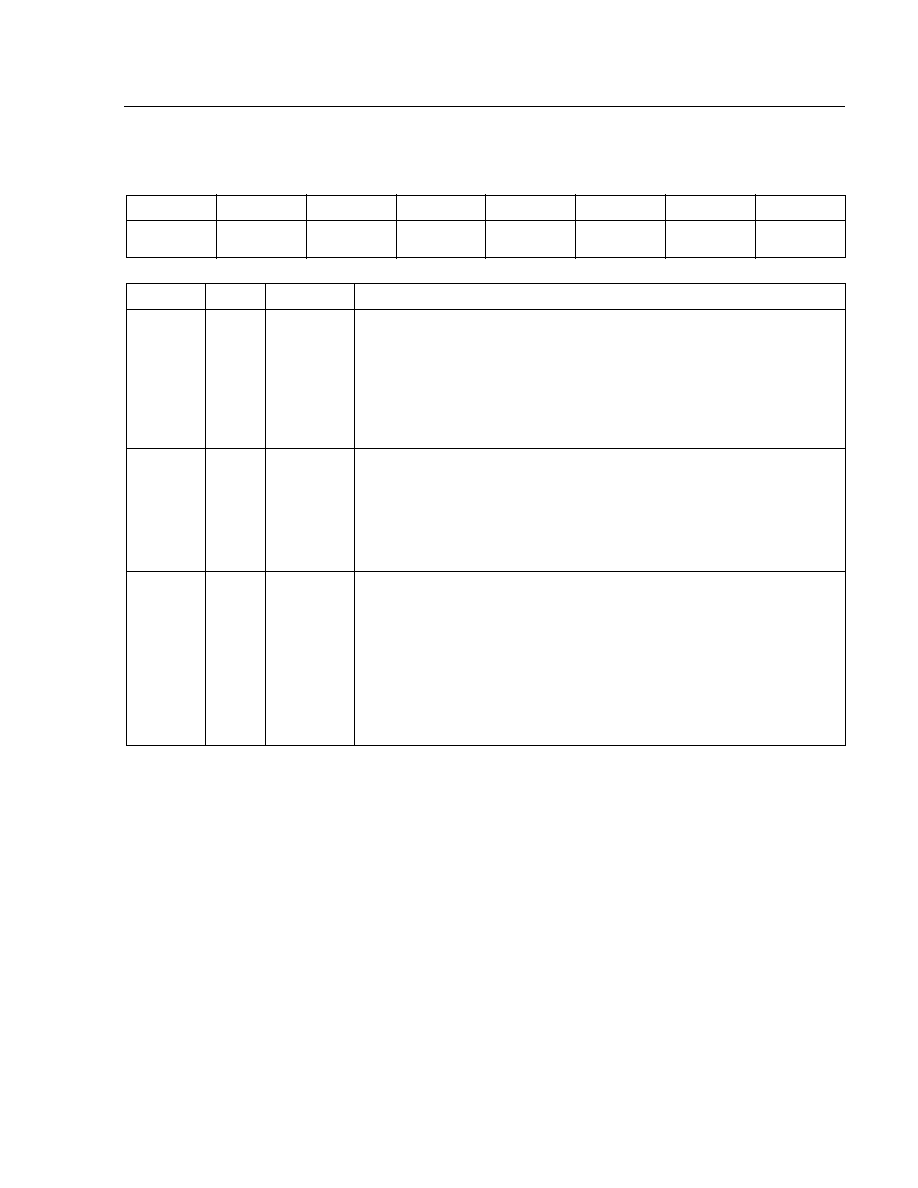

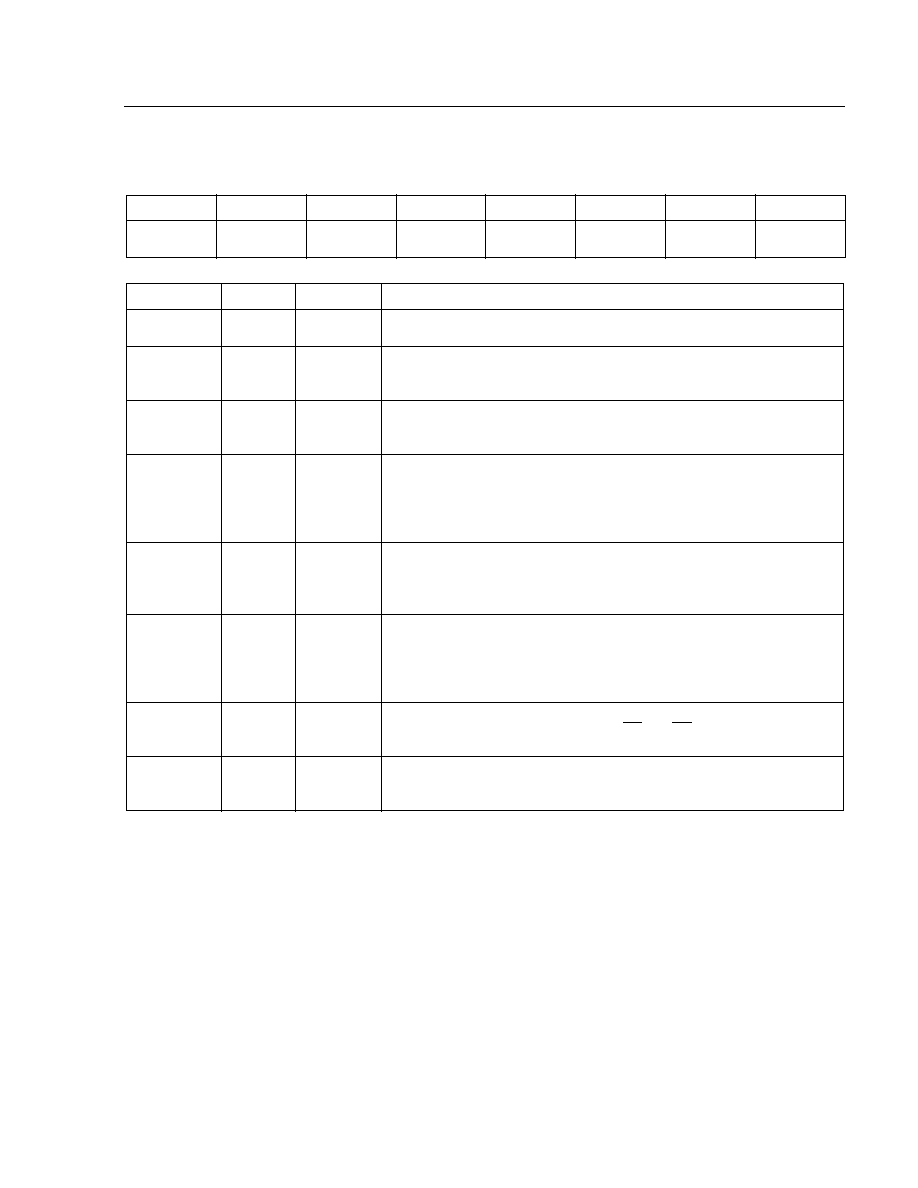

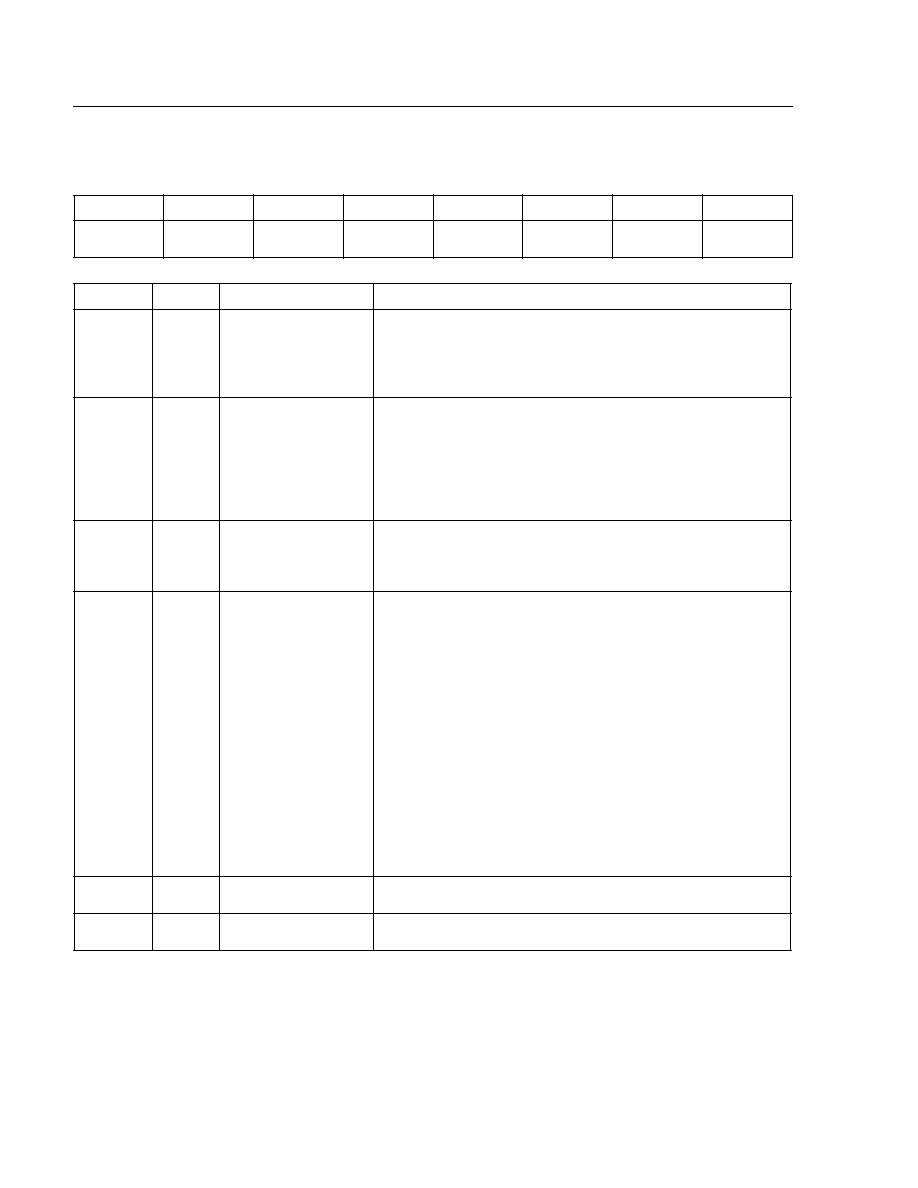

5-5027

Figure 1. Block Diagram

MICRO-

PROCESSOR

BUS

INTERFACE

INTERNAL

REGISTER

BANK

(R0--R15)

(AR11--AR13)

AND

PARALLEL

DATA I/O

MEMORY

BUFFERS

HDLC

PROCESSING

TRANSPARENT

MODE

TRANSMIT

FIFO

64 x 8

RECEIVE

FIFO

64 x 8

HDLC

TRANSMITTER

HDLC

RECEIVER

CONCEN-

TRATION

HIGHWAY

INTERFACE

TRANSPARENT

MODE

RESET

RD

WR

CS

INT

AD0--AD7

ALE

A0--A3

DXA

DXB/TSCA

CLKX

CLK

FS

DRA

CLKR/DRB

4

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

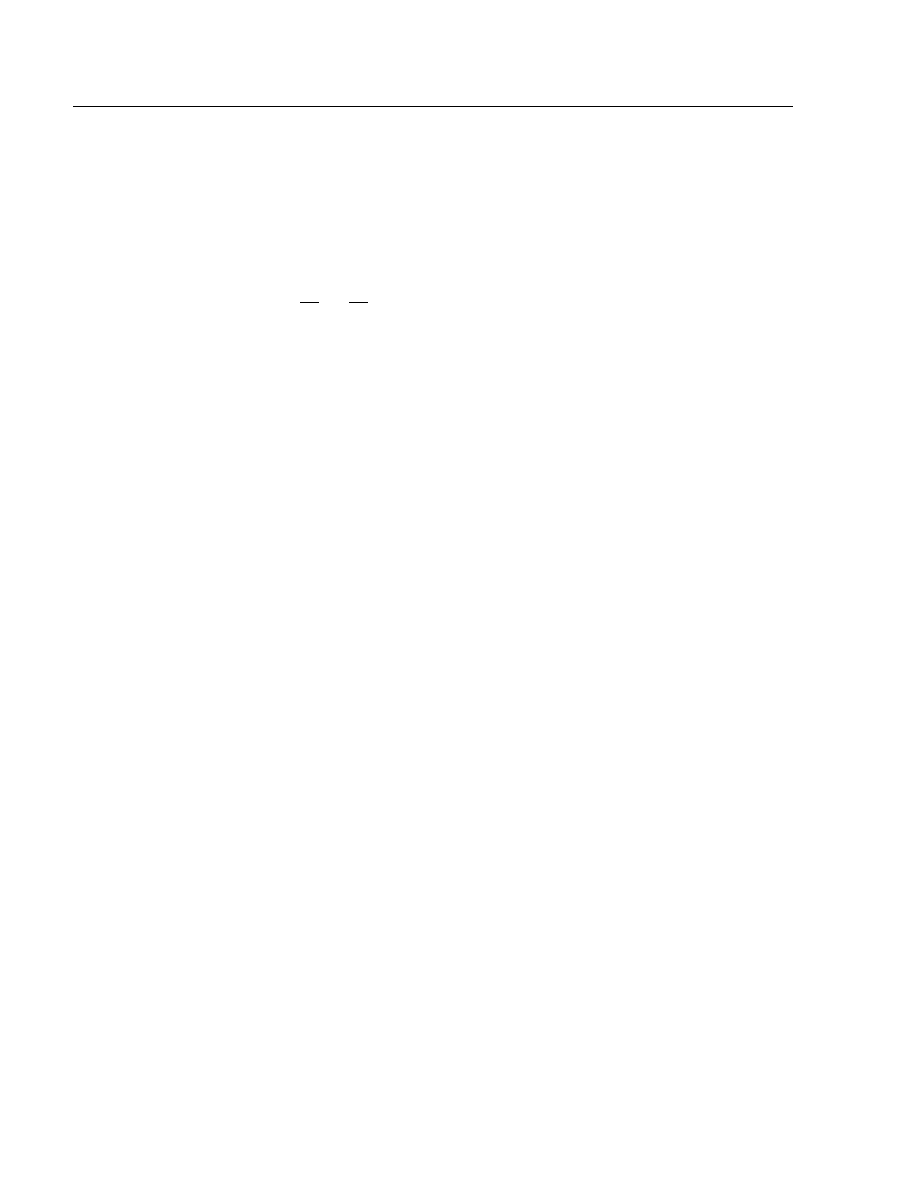

Pin Information

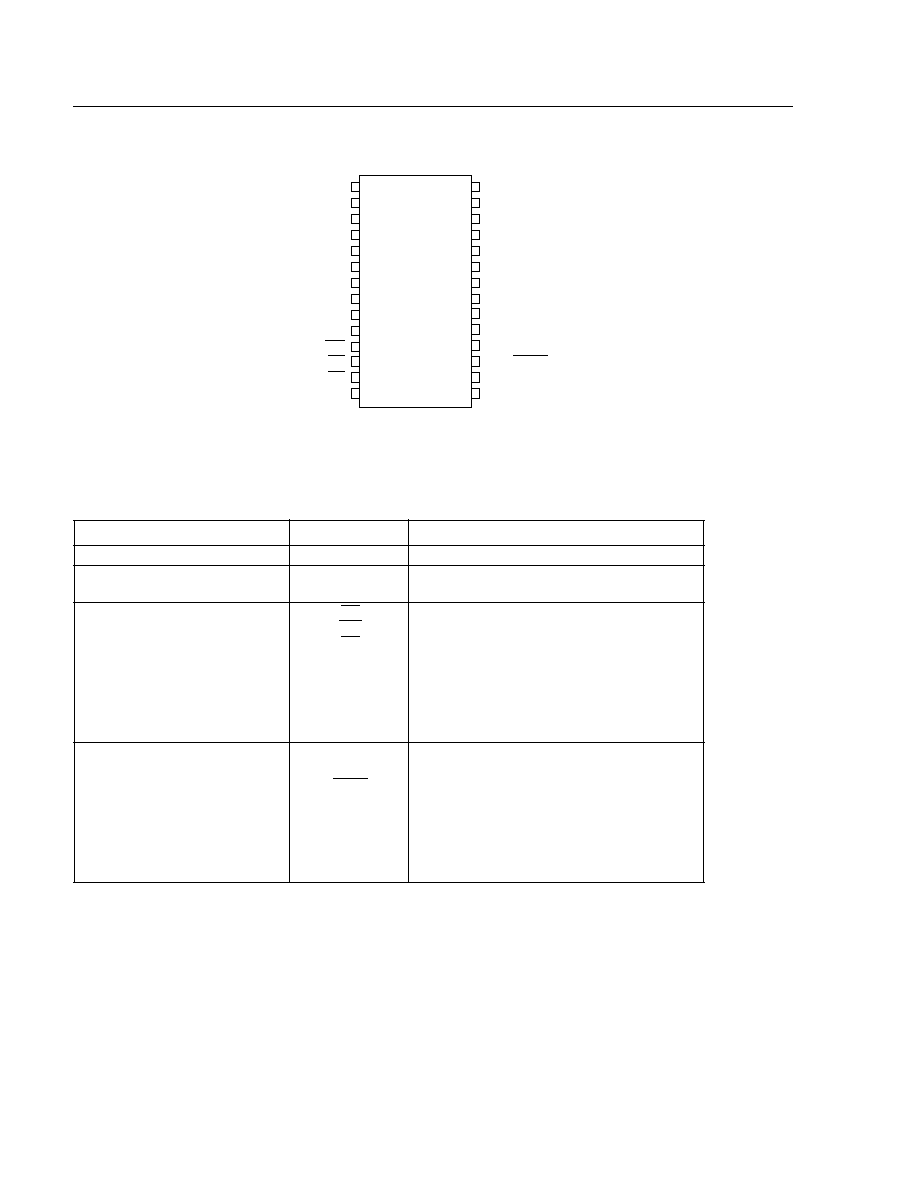

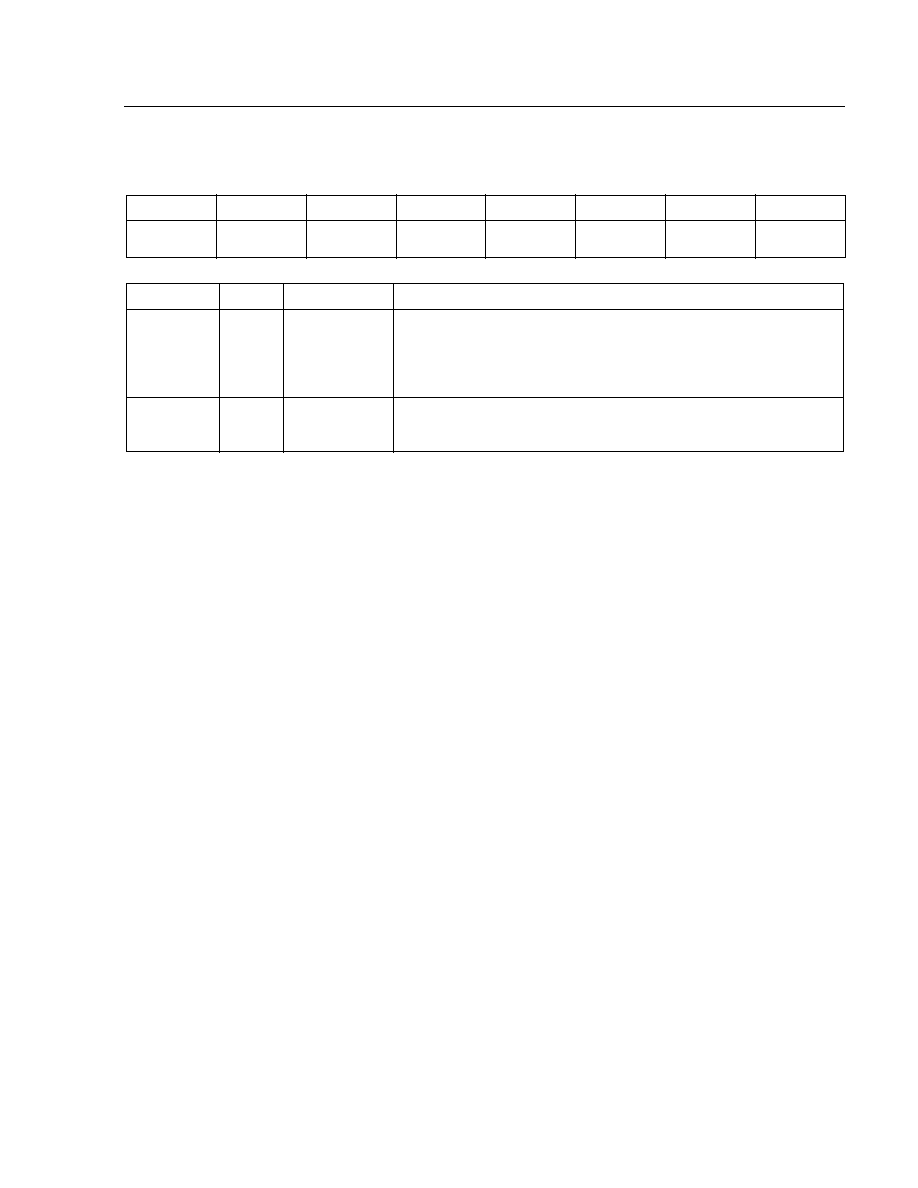

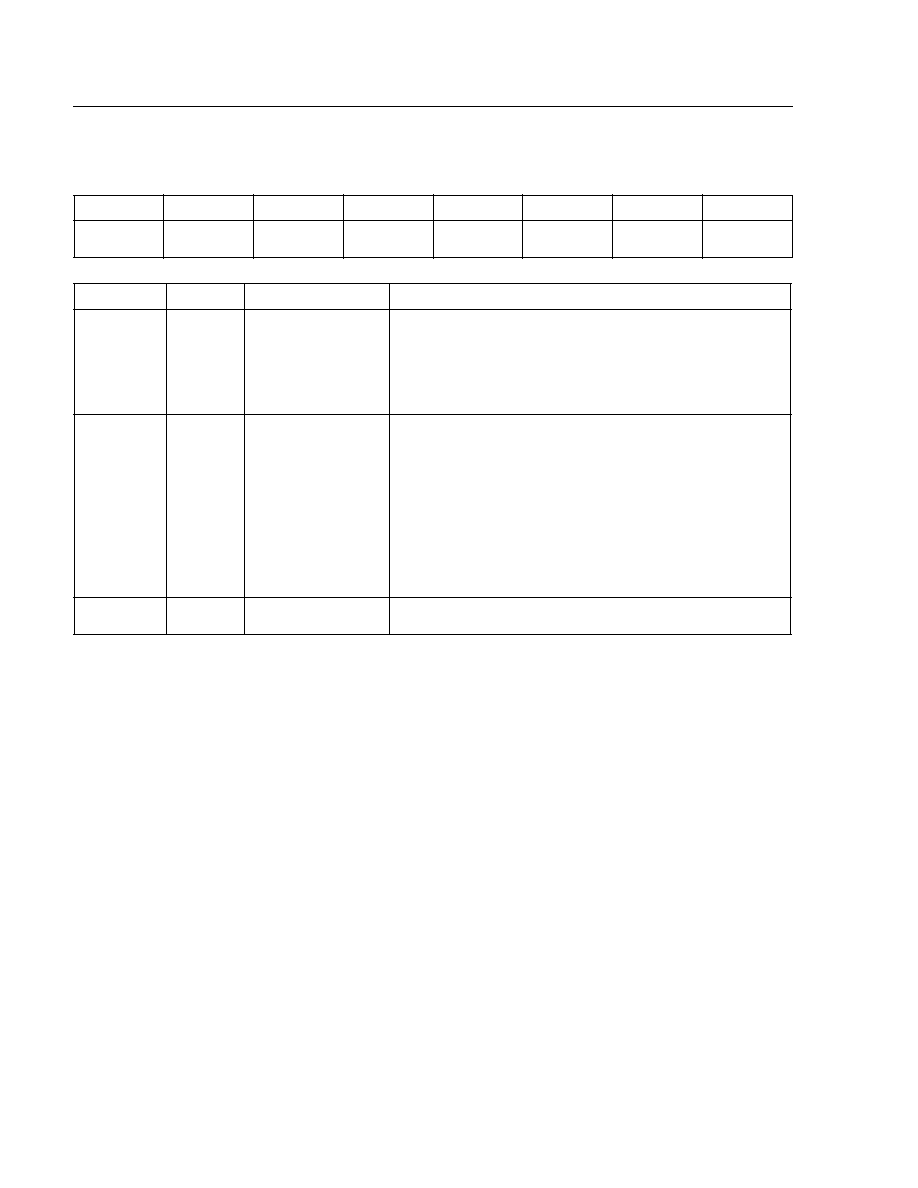

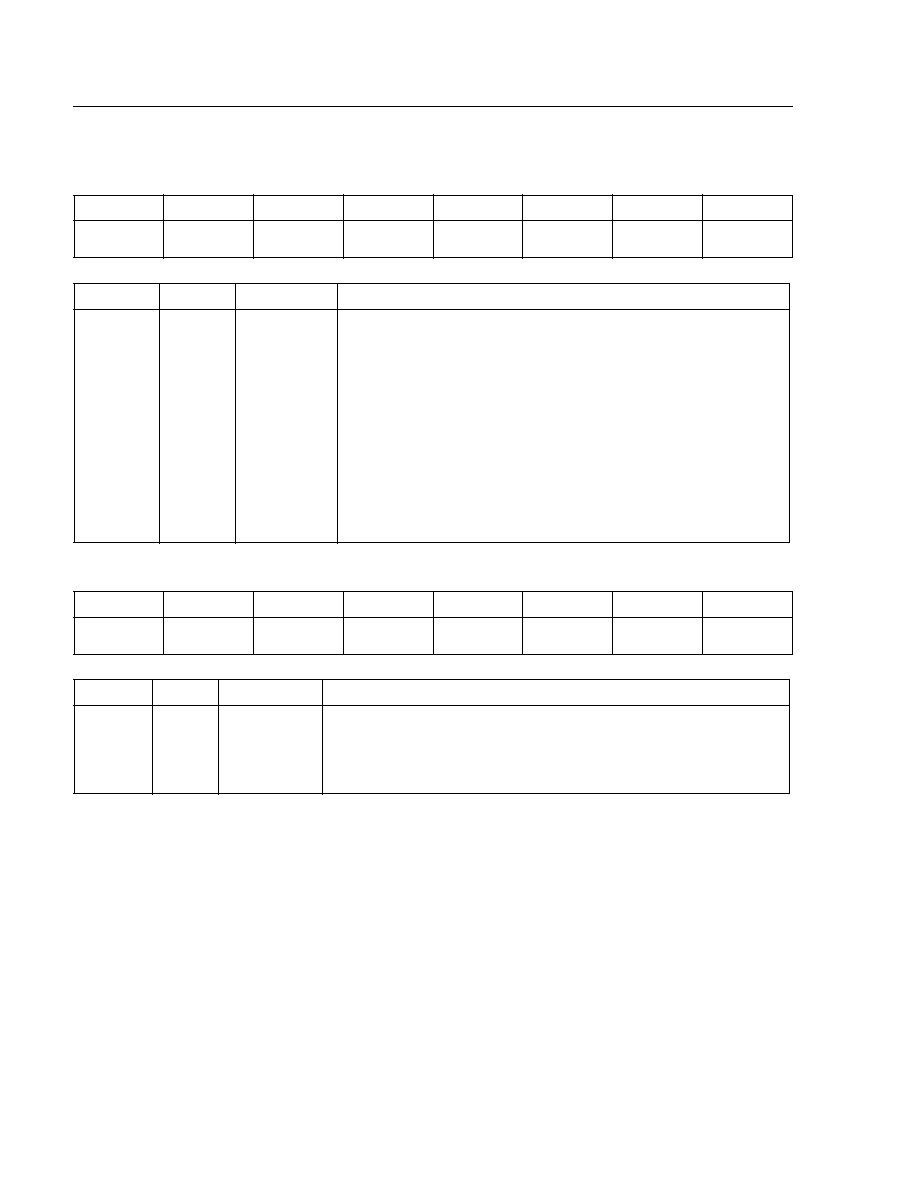

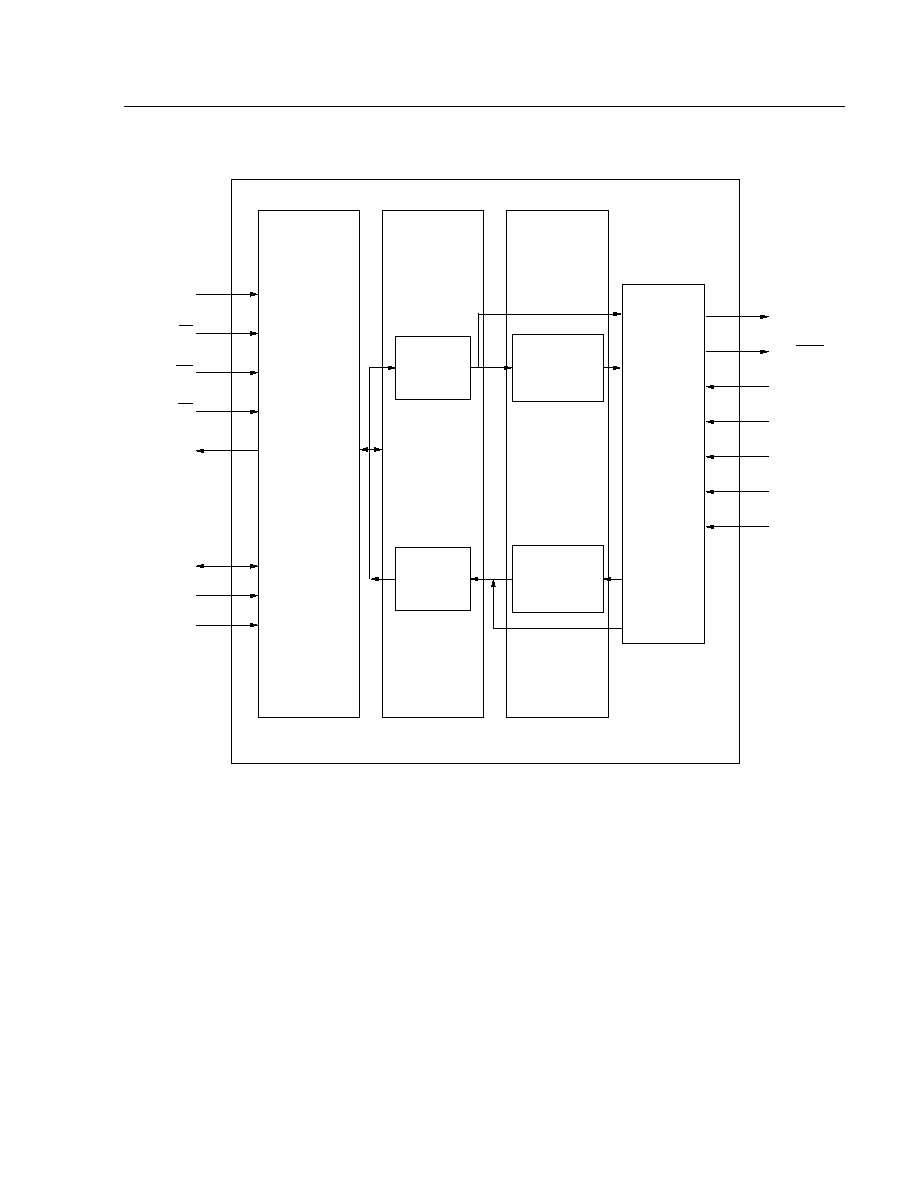

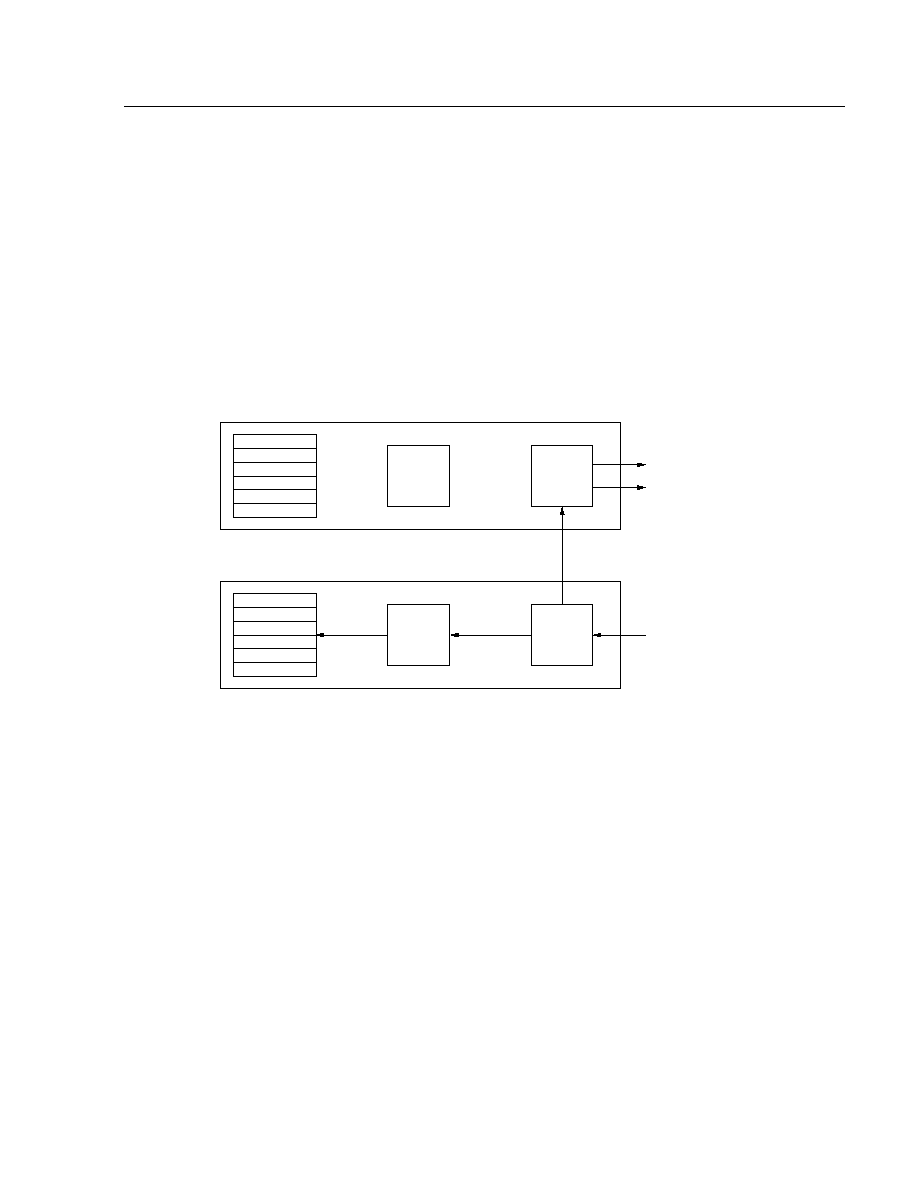

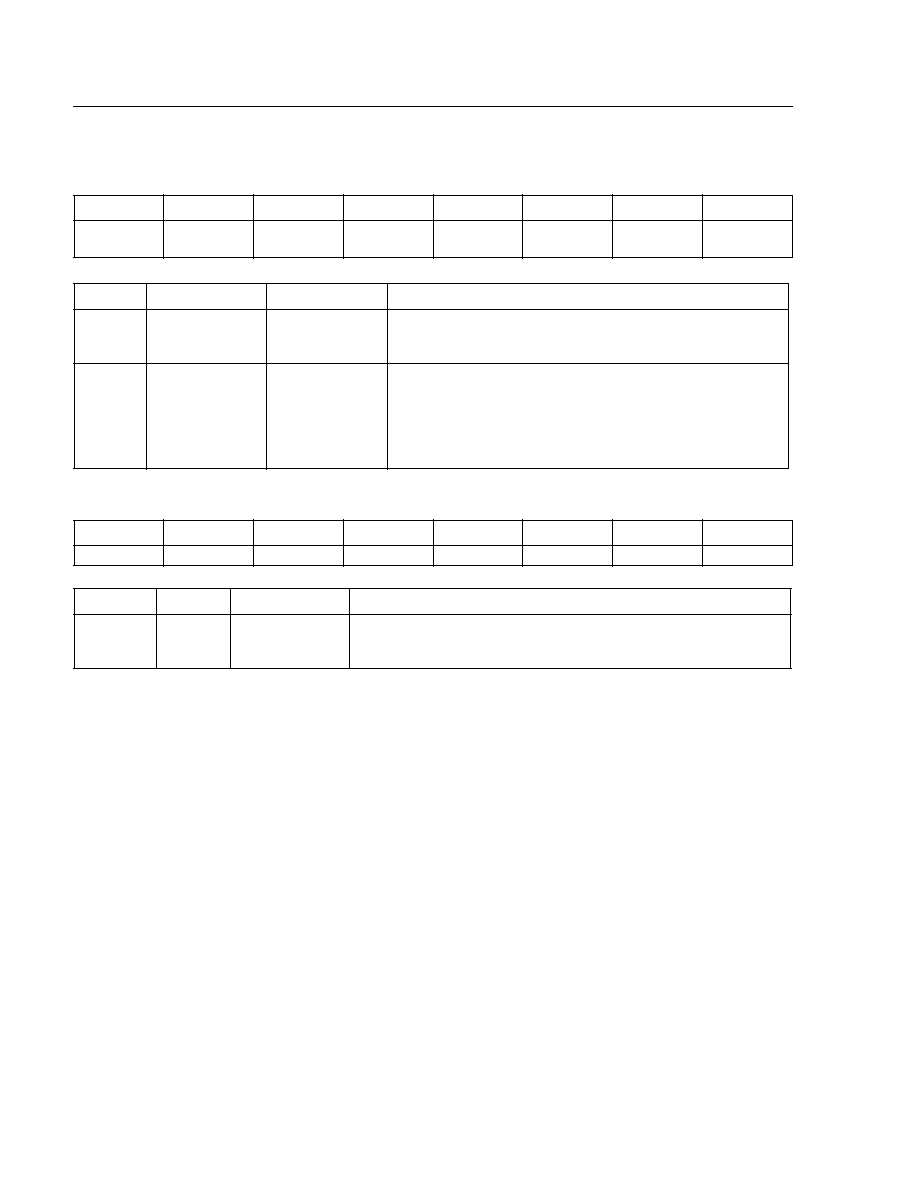

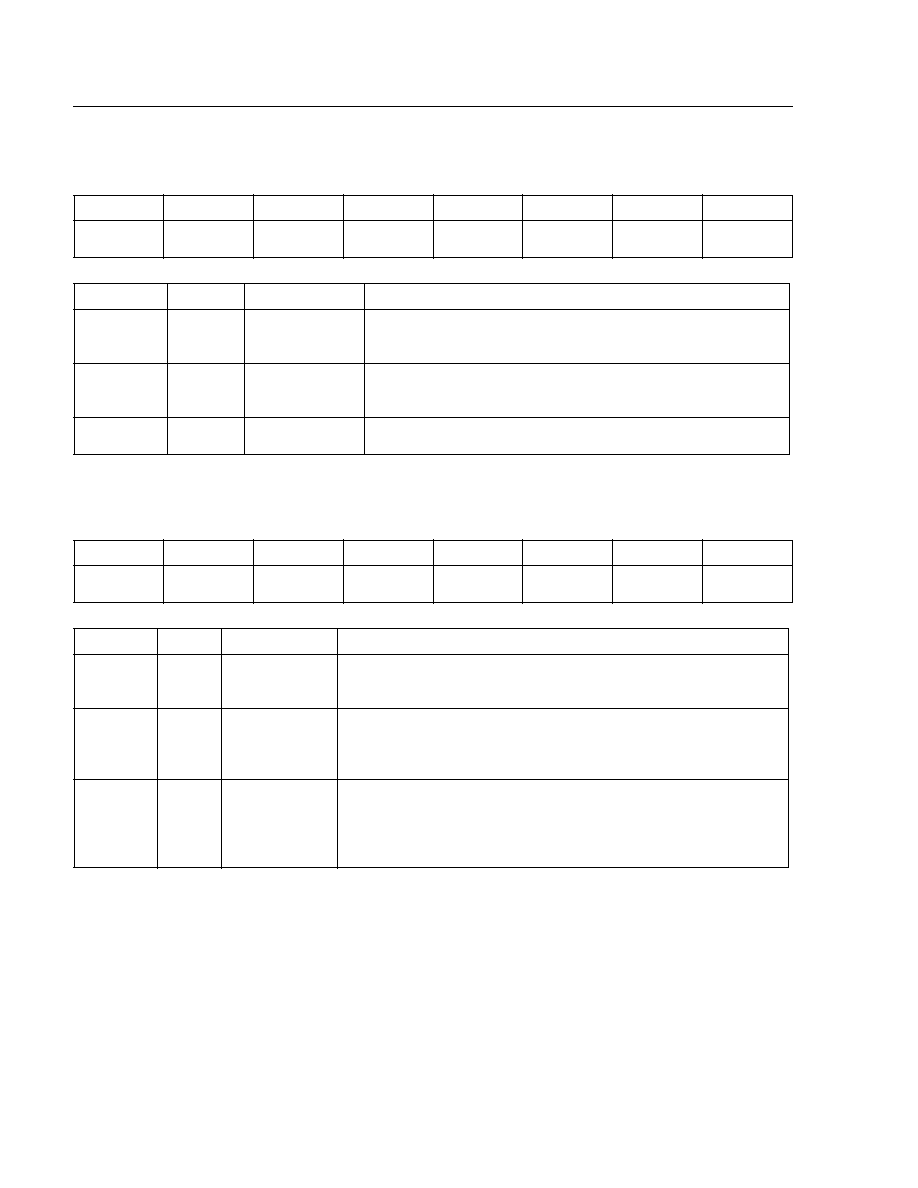

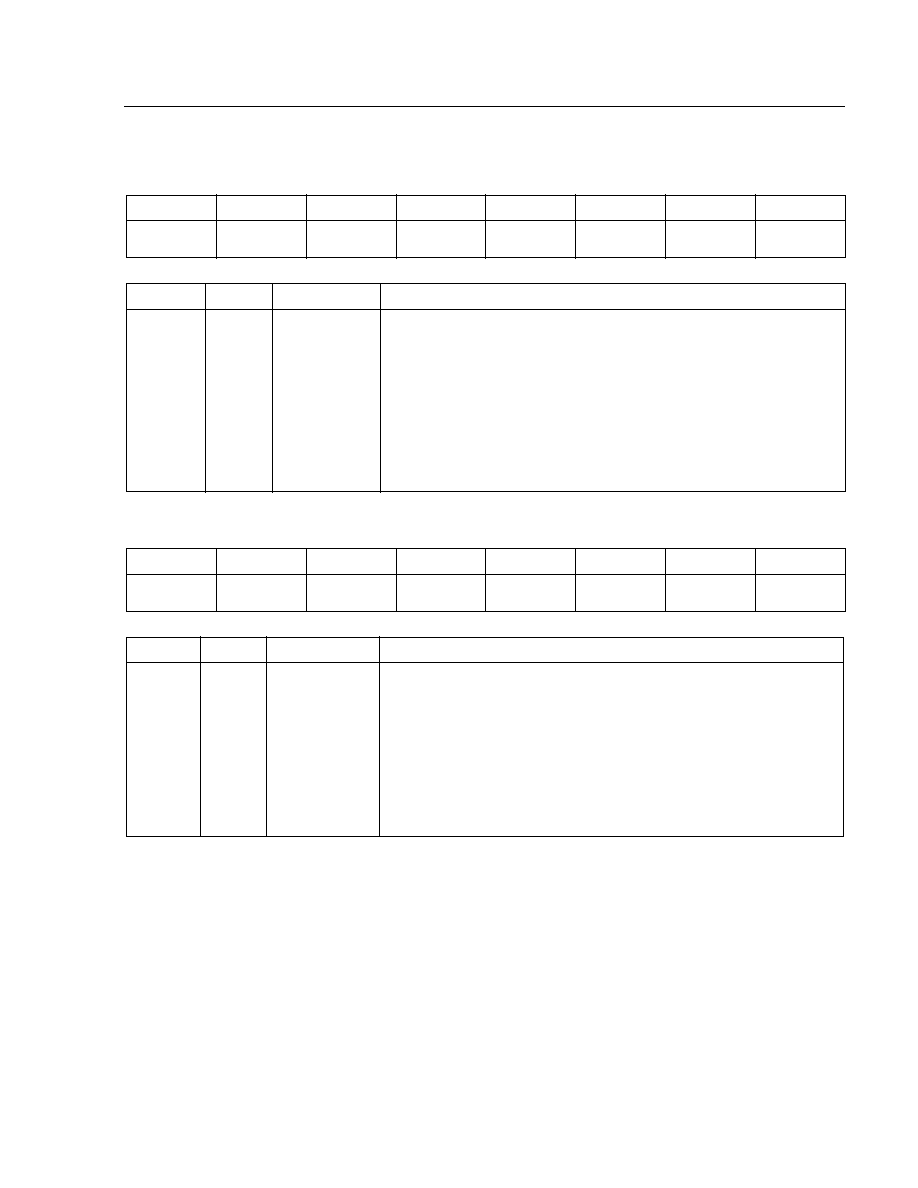

5-5028

Figure 2. Pin Diagram

Table 1. Pin Assignments

Group

Symbol

Function

Chip Clock

CLK

0 MHz--12 MHz

Power & Ground

V

DD

V

SS

5 V Power

Ground

Microprocessor Bus Interface

RD

WR

CS

INT

RESET

AD7--AD0

ALE

A3--A0

Read

Write

Chip Select

Interrupt

Reset

Address/Data Bus

Address Latch Enable

Address Bus (non-ALE addressing mode)

Serial Link Interface

DXA

DXB

TSCA

CLKX

FS

CLKR

DRA

DRB

Transmit Data A

Transmit Data B

Time-slot Control DXA

Transmit Clock

Frame Synchronization

Receive Clock

Receive Data A

Receive Data B

ALE

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

RD

CS

INT

1

2

3

4

5

6

7

8

9

10

11

12

13

14

V

DD

A2

A3

CLKR/DRB

DXA

CLKX

DXB/TSCA

FS

RESET

28

27

26

25

24

23

22

21

20

19

18

17

16

15

V

SS

WR

A0

CLK

V

SS

DRA

LUCENT

T7121

HIFI-64

A1

Lucent Technologies Inc.

5

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Pin Information

(continued)

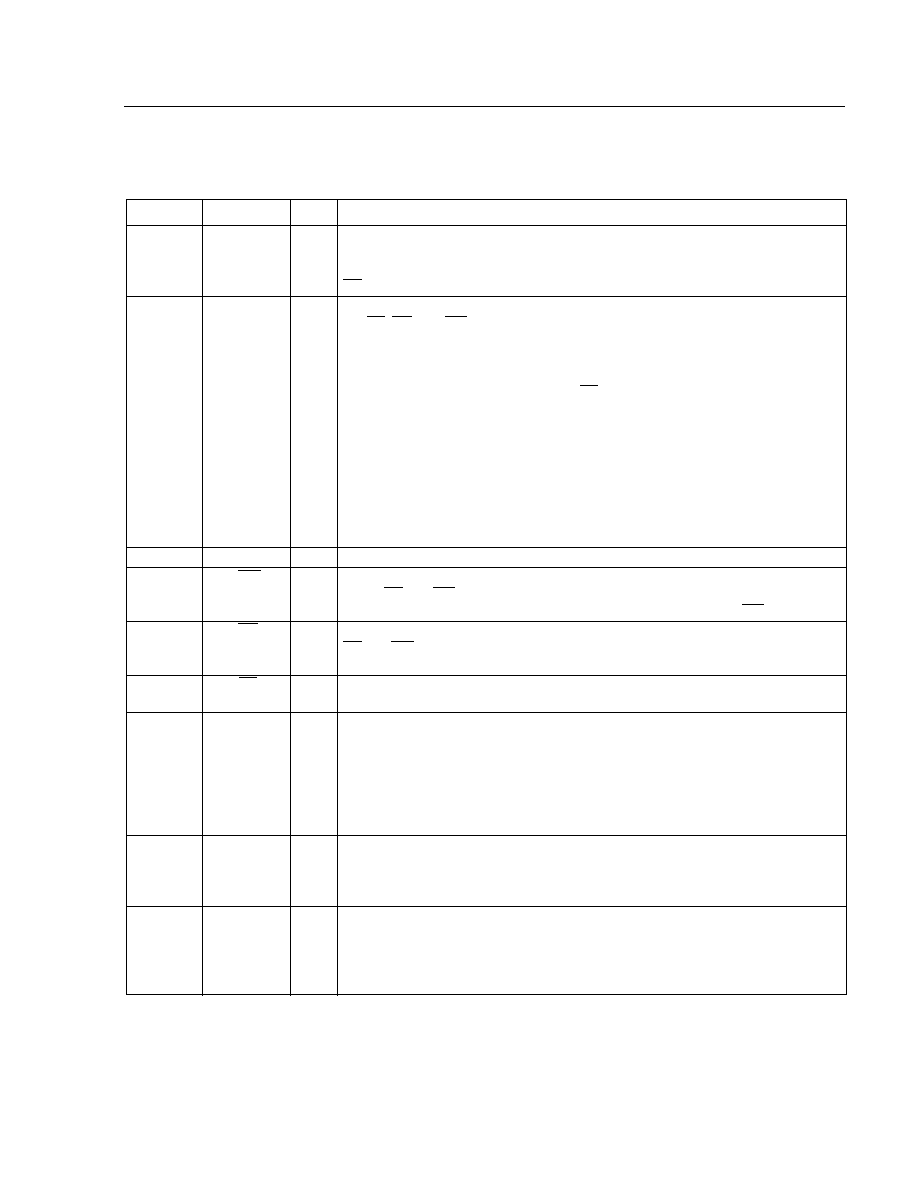

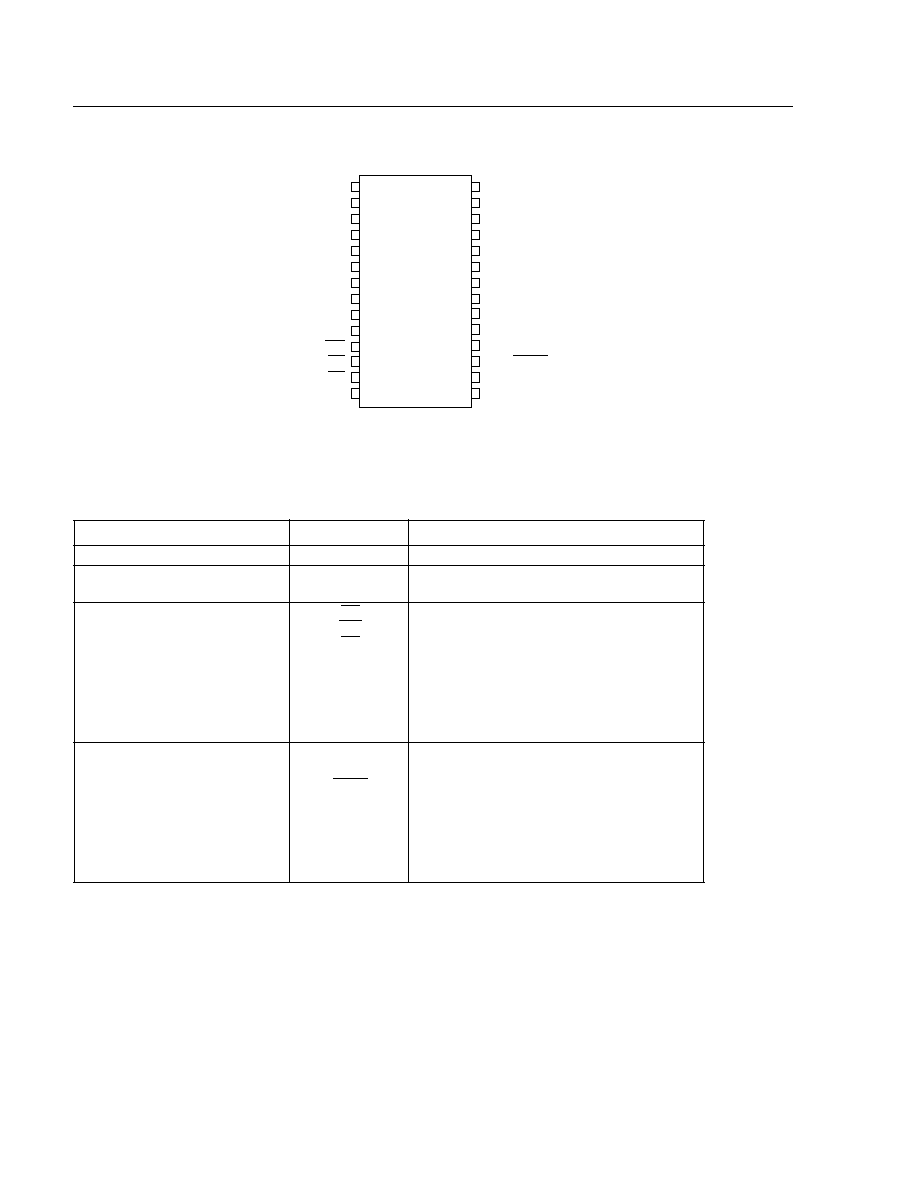

Table 2. Pin Descriptions

Pin

Symbol

Type

Name/Function

1

ALE

I

Address Latch Enable.

A high-to-low transition on this pin latches the register

address on pins AD3--AD0. ALE should be held high in the demultiplexed (sep-

arate address/data) mode. ALE latches the address regardless of the state of

CS

.

2--5,

7--10

AD0--AD7

I/O

Address/Data Bus.

The data bus direction is controlled by the logic states of

the

CS

,

RD

, and

WR

pins. Microprocessors using a multiplexed bus supply

address information during read or write cycles on AD6, AD3--AD0 synchro-

nized to the ALE signal. During read cycles, data is available to the micropro-

cessor on AD7--AD0. During write cycles, data is supplied by the

microprocessor on these lines. When

CS

is not active, the AD7--AD0 pins are

placed in a high-impedance state (3-state). AD0 is the least significant

address/data bit.

Block move is available in MUXed address and data mode by setting the BM bit

in register 0 (R0--B3) to 1 and holding AD6 high during the address cycle of the

ALE. All writes then go directly to the transmit FIFO, and all reads address the

receive FIFO. Normal ALE mode addressing is accomplished by holding AD6

low during the ALE address cycle. Block move can be disabled by clearing the

BM bit to 0.

6, 22

V

SS

--

Ground.

11

WR

I

Write (Active-Low).

This signal controls when data is written to the registers.

When

CS

and

WR

are low, valid data is supplied on lines AD7--AD0 by the

microprocessor. The chip latches the data on the rising edge of

WR

.

12

RD

I

Read (Active-Low).

This signal is used to read data from the registers. When

CS

and

WR

are low, the chip makes the requested data available on lines AD7--

AD0 to be read by the microprocessor.

13

CS

I

Chip Select (Active-Low).

This signal must be low for the internal registers to

be read or written.

14

INT

O

Interrupt.

An interrupt signal is generated when any of the interrupting condi-

tions are true. The interrupt signal remains active until the microprocessor reads

the interrupt status register (R15) if DINT (R0--B0) = 0, or until the condition

causing the interrupt is alleviated if DINT = 1. Interrupts can be masked by

appropriately setting the corresponding interrupt enable bits in the interrupt

mask register (R14). The polarity of the interrupt signal output is controlled by

the IPOL bit in register 0 (R0--B1). This pin is

not

an open-drain output.

15

RESET

I

Reset.

A high on this pin resets the device and forces a high-impedance

(3-state) condition on all outputs. All register bits are forced to their reset values.

(See Register section for more details.) A reset must be performed upon pow-

erup. A full chip reset occurs with or without a clock input.

16

FS

I

Frame Synchronization.

This signal marks the beginning of a TDM highway

frame. The polarity of the input pulse can be adjusted via the FSPOL bit in regis-

ter 0 (R0--B6). Individual time slots are assigned relative to the detection of FS

by the use of registers 7--11. When HWYEN (R0--B7) is 0, the input to this pin

is ignored.

6

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

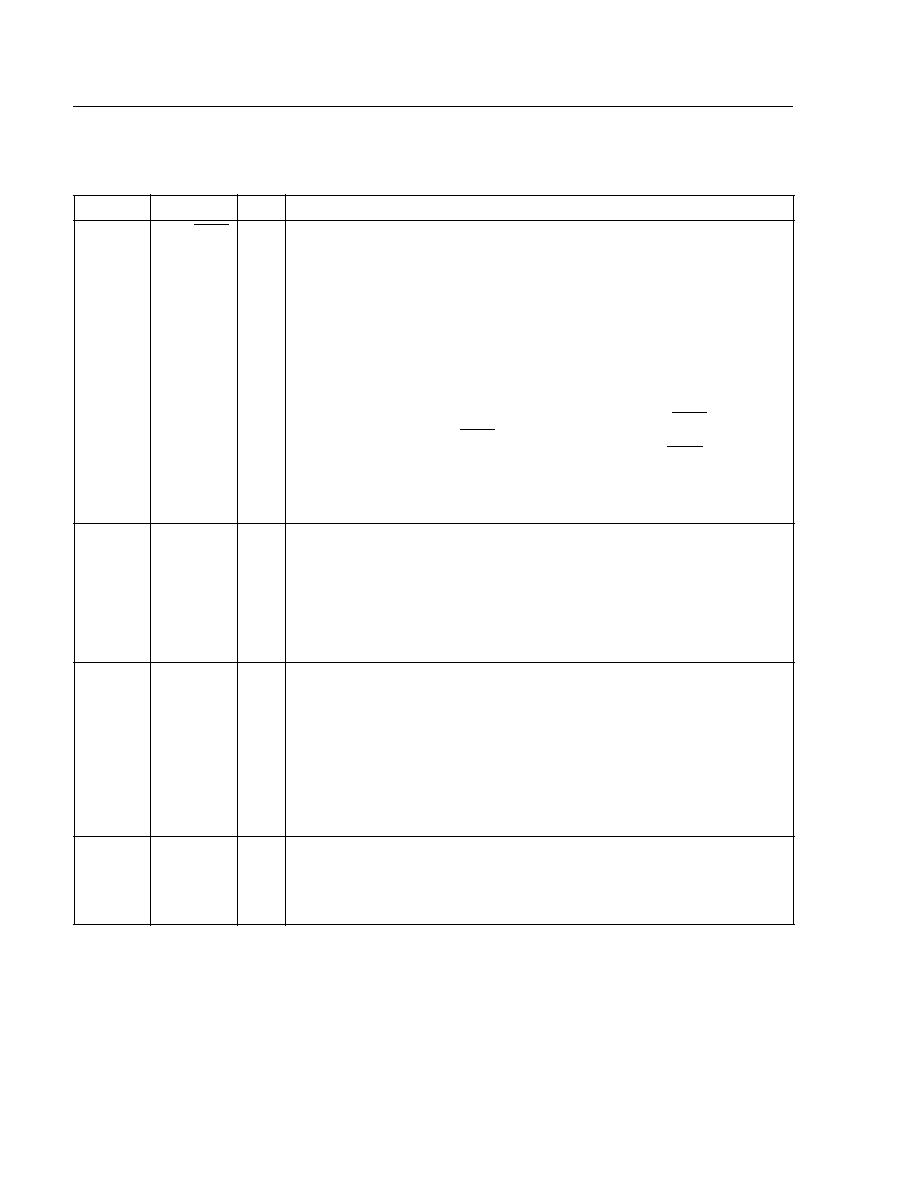

17

DXB/

TSCA

O

Transmit Data B or Time-Slot Control for DXA.

The functionality of this pin is

user-controlled by the P17CTL bit in the receiver control register (R5--B7).

Clearing the P17CTL bit to 0 selects operation as Transmit Data B. Once DXB

operation is selected, data is transmitted on DXB whenever the DXBC bit in reg-

ister 7 (R7--B6) is set to 1. Data can be configured for transmission on either

CLKX edge (CLKXI, R9--B4), optionally inverted (DXI, R10--B7) and placed in

a user-selected time slot (registers 7, 9, 10) with bit 0 or bit 7 sent first (TLBIT,

R10--B6).

DXB should be pulled up by an external resistor to prevent random data pat-

terns from propagating through other devices when DXB is 3-stated.

When P17CTL (R5--B7) is set to 1, this pin is configured as

TSCA

(active-low)

(time-slot control for DXA).

TSCA

allows use of an external 3-stating bus driver

when data is being transmitted on DXA over long distances.

TSCA

goes low dur-

ing the valid bit positions of data and is high at all other times.

When an external driver is required, DXAC (R7--B7) must be set to 1. Setting

the P17CTL bit (R5--B7) to 1 overrides the selection of DXBC (R7--B6).

18

CLKX

I

Transmit Clock.

This input clock controls the bit rate for transmitted data. Trans-

mit clock frequency must be less than the chip master clock frequency divided

by 2 (fCLKX < fCLK/2). In the reset configuration, data is transmitted on the fall-

ing edge of CLKX. Data can be transmitted by using the rising edge of CLKX by

setting the CLKX Invert bit (CLKXI) in the bit offset register (R9--B4) to 1. If the

P21CTL bit in the receiver control register (R5--B6) is set to 1, this clock is also

used to receive data. If P21CTL is 0, the transmit clock rate can be independent

of the receive clock rate.

19

DXA

O

Transmit Data A.

When the DXAC bit in register 7 (R7--B7) is set to 1, data is

transmitted on this pin. If external drivers are not required, both DXAC (R7--B7)

and DXBC (R7--B6) can be set to allow simultaneous transmission of the data

byte on both transmit data pins.

Data can be configured for transmission on either CLKX edge (CLKXI, R9--B4),

optionally inverted (DXI, R10--B7) and placed in a user-selected time slot (reg-

isters 7, 9, 10) with bit 0 or bit 7 sent first (TLBIT, R10--B6).

DXA should be pulled up by an external resistor to prevent random data pat-

terns from propagating through other devices when DXA is 3-stated.

20

DRA

I

Receive Data A.

When the DRA/B bit in register 8 (R8--B7) is cleared to 0,

data is received on this pin. Data can be optionally inverted (DRI, R11--B7),

received on a positive or negative receive clock edge (CLKRI, R9--B0), and

received during a user-selected time slot (registers 8, 9, 11) with bit 0 or bit 7

first (RLBIT, R11--B6).

Table 2. Pin Descriptions

(continued)

Pin

Symbol

Type

Name/Function

Pin Information

(continued)

Lucent Technologies Inc.

7

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

21

CLKR/DRB

I

Receive Clock or Receive Data B.

The functionality of this pin is controlled by

programming the P21CTL bit in the receiver control register (R5--B6). When

P21CTL is cleared to 0 (default), this pin is the receive data clock (CLKR).

Receive clock frequency must be less than the chip master clock frequency

divided by 2 (fCLKR < fCLK/2). Upon reset, data is received (latched) on the ris-

ing edge of CLKR. Data can be received on the falling edge of the receive clock

by clearing the CLKRI bit in register 9 (R9--B0) to 0. Receive clock rate can be

independent of transmit clock rate.

When P21CTL (R5--B6) is set to 1, this pin is configured as Receive Data B

(DRB). Clocking for receive data is obtained from CLKX, while CLKRI (R9--B0)

controls the edge of CLKX used to latch received data. In this mode, data can

be received on DRA or on DRB. DRB is selected by setting the DRA/B bit in reg-

ister 8 (R8--B7) to 1. Data can be optionally inverted (DRI, R11--B7) and

received during a user-selected time slot (registers 8, 9, 11) with bit 0 or bit 7

first (RLBIT R11--B6).

23

CLK

I

Clock.

This clock controls internal chip operation. It can be from 0 MHz to

12 MHz. Typically it is 6.144 MHz (i.e., SYSCKO from the Lucent T7250C).

Clock frequency must be greater than two times the fastest data clock fre-

quency.

24, 25, 26,

27

A3--A0

I

Address Bus.

These four address leads allow the chip to be accessed by a

microprocessor employing separate address and data leads. They are used to

select the internal registers. The ALE pin should be tied high in this mode of

operation.

These pins can be left unconnected when in the multiplexed address/data mode

(internal pull-up resistors are provided).

28

V

DD

--

+5 V Supply.

Table 2. Pin Descriptions

(continued)

Pin

Symbol

Type

Name/Function

Pin Information

(continued)

8

8

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

Microprocessor Bus Interface

Addressing

The T7121 is designed to easily interface with 8-bit

microprocessors. The microprocessor bus interface

allows parallel asynchronous access to a bank of 19

registers (R0--R15 and AR11--AR13). The bus inter-

face is compatible with most microprocessors. The reg-

isters occupy 16 continuous locations in the memory

map of a controlling microprocessor, and the registers

are accessed under the control of the following signals:

address select (A0--A3 or AD0--AD7), address latch

enable (ALE), chip select (

CS

), read (

RD

), and write

(

WR

). When multiplexed address and data lines are

used, the ALE signal is used to latch the address

present on AD0--AD3 and AD6. AD6 has a special

use in the block-move mode. See the Block Move sec-

tion under the FIFO Memory Buffers section. ALE

should be tied high when separate address and data

are used.

Registers 11, 12, and 13 have alternate meanings

depending on the value of the Alternate (ALT) bit in the

chip configuration register (R0--B4). The alternate reg-

isters are accessed by setting the ALT bit (R0--B4) to

1. All subsequent addressing of registers 11 through 13

then refers to the alternate registers (AR11--AR13).

Returning to the foreground register set is accom-

plished by clearing the ALT bit (R0--B4) to 0.

Interrupts

A programmable interrupt output, INT, is provided to

alert the microprocessor when the device needs ser-

vice. Associated with the interrupt system are the IPOL

bit in register 0 (R0--B1), the interrupt mask register

(R14), and the interrupt status register (R15). The

polarity of the INT signal (pin 14) is programmable by

setting the IPOL bit in register 0 (R0--B1). The inter-

rupt mask register can be programmed so that only

certain conditions cause the INT signal to be asserted.

The interrupt status register (R15) reveals the source of

the interrupt.

Register 14, the interrupt mask register, controls the

operation of the INT pin. Masking an interrupt means

that no transition of the INT pin is generated for any

occurrence of that interrupt condition. The INT signal is

enabled upon the first occurrence of any unmasked

interrupt condition. The INT signal remains until the

interrupt is acknowledged by reading the interrupt sta-

tus register (R15). Unmasked interrupts occurring

between the first unmasked interrupt and the status

register read do not cause a transition of the INT pin. If

a second interrupt occurs during a read of the interrupt

status register (R15), the INT signal is disabled after

the read and then reasserts itself. This deassertion can

actually be much less than one cycle, and no minimum

width is guaranteed. One method to ensure that the

second interrupt is detected is to use an edge-sensed

INT pin on the processor. If this is not available, the

interrupt service routine should reread the interrupt sta-

tus register to determine if an interrupt occurred during

the clearing of the first interrupt.

Masking all interrupts effectively disables the INT pin. It

is possible to mask a currently active interrupt. Doing

so causes a transition of the INT pin from active to

inactive if the masked interrupt was the only active

interrupt. Likewise, unmasking an interrupt that is cur-

rently asserted causes an INT pin transition from inac-

tive to active if all other unmasked interrupts were

currently inactive. Interruptable conditions are always

reported in register 15, even if the interrupt pin transi-

tion is masked. Thus, polled interrupt systems are also

supported. Note that a transition of the INT pin occurs

only if the interrupting condition is unmasked and no

other unmasked, unacknowledged interrupt exists.

The HIFI-64 allows two modes of interrupt: dynamic

and nondynamic. The mode is controlled by setting the

DINT (Dynamic INTerrupt) bit in register 0 (R0--B0). If

DINT (R0--B0) is 0 (nondynamic mode), the interrupt

bits in the interrupt status register (R15) are cleared

directly by a read of register 15. The condition causing

the interrupt must go away and come back in order to

reassert the interrupt. If DINT (R0--B0) is set to 1

(dynamic mode), the transmitter empty (R15--B1) and

receiver full (R15--B3) interrupts are cleared only

when the condition causing the interrupt has been rem-

edied (all other interrupts are cleared by reading the

interrupt status register [R15]). In addition, the INT sig-

nal (pin 14) remains enabled until the condition(s)

causing the interrupt has been remedied.

A dynamic version of the transmitter empty interrupt,

transmitter empty dynamic (TED), is provided in the

transmitter status register (R2--B7). TED behaves

dynamically regardless of the value of the DINT bit

(R0--B0). TED does not cause a transition of the INT

pin.

In transparent mode, the REOF, RIDL, and UNDABT

interrupts are disabled. TDONE is used to indicate a

transmitter underrun and can be used to determine

transmission end. Additionally, the MSTAT bit

(AR11--B3) can be used as a polled interrupt to deter-

mine the beginning of receive data. A transition of the

INT pin can be programmed for the beginning of

receive data by setting the initial receiver-full interrupt

level RIL (R5--B[5--0]) to 1 byte.

Lucent Technologies Inc.

9

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

Resets

The T7121 is fully reset by either asserting the RESET

pin (hardware reset) or by asserting both the TRES

(R6--B5) and RRES (R6--B4) bits simultaneously

when writing to register 6 (software reset). A full reset

results in all registers returning to their default condi-

tions and all logic returning to a known state. No clock

input is necessary. During a hardware reset, all outputs

are 3-stated. Thus, the RESET pin can be used for

bed-of-nails testing. During a software reset, outputs

are not automatically 3-stated. Output pin states are

determined by their default register configuration. Both

transmit data pins (DXA and DXB) 3-state since the

default register configuration is both transmit pins dis-

abled. The INT pin is high.

In addition, the transmitter and receiver can be individ-

ually reset. When TRES (R6--B5) is high and RRES

(R6--B4) is low during a write of register 6, the trans-

mitter is independently reset. The transmitter FIFO

pointers return to default values, resulting in the loss of

any untransmitted data, and the transmitter state

machine is returned to the idle state. Transmitter inter-

rupts are cleared, except for the TE (R15--B1) inter-

rupt, which is asserted and causes a transition on the

INT pin if unmasked (TEIE, R14--B1 = 1). Only trans-

mit status registers and interrupts change to reflect the

reset. Disabling the transmitter does not cause an

automatic reset. When the transmitter has been active

and then subsequently disabled, a TRES is needed to

restore it to a known state.

When TRES (R6--B5) is low and RRES (R6--B4) is

high during a write of register 6, the receiver is inde-

pendently reset. A receiver reset causes the receiver

FIFO pointers to return to their default values, resulting

in the loss of unread data in the FIFO. The receiver is

returned to a known state, and all currently asserted

receiver interrupts are cleared. The receiver should be

reset whenever it was active and subsequently dis-

abled to ensure correct operation. Only receiver status

and interrupt bits are affected in the register set. Dis-

abling the receiver does not cause a receiver reset.

FIFO Memory Buffers

The HIFI-64 is equipped with a transmit FIFO and a

receive FIFO, each with a capacity of 64 bytes.

Transmit FIFO

Data to be transmitted is loaded via the data register

(R3) into the 64-byte transmit FIFO. Multiple frames

can be placed in the FIFO. In HDLC mode, the final

byte of each frame is marked by writing the transmit

frame complete bit TFC (R1--B7). The transmitter can

also be instructed to abort a frame by using the trans-

mit abort bit TABT (R1--B6) (HDLC mode only). Trans-

mission status is available in the transmit status

register and via the transmit interrupts. The transmitter

status register (R2) indicates how many additional

bytes can be added to the FIFO. The transmitter inter-

rupt trigger level (TIL) can be programmed in the trans-

mitter control register (R1--B[5--0]) to tailor service

time intervals to the system environment. The transmit-

ter empty (TE) interrupt bit is set in the interrupt status

register (R15--B1) when the FIFO has sufficient empty

space to add the number of bytes specified in the TIL. If

the TE interrupt mask TEIE (R14--B1) is 1, the occur-

rence of a TE interrupt condition causes a transition of

the interrupt pin if no other unmasked interrupts are

currently active. In dynamic interrupt mode (DINT,

R0--B0 = 1), this interrupt remains set until the condi-

tion is cleared. In nondynamic interrupt mode

(DINT, R0--B0 = 0), this interrupt is cleared by reading

R15. A TDONE (R15--B0) interrupt occurs for each

HDLC frame completed. In the transparent mode, a

TDONE interrupt occurs when the transmit FIFO emp-

ties. In HDLC mode, an UNDABT (R15--B2) interrupt

is issued if the transmitter underruns.

There is no interrupt indication of a transmitter overrun

that is writing more data than empty spaces exist.

Overrunning the transmitter causes the last valid data

byte written to be repeatedly overwritten, resulting in

missing data in the frame.

10

10

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

Receive FIFO

Data received from the serial link interface is stored in

the 64-byte receive FIFO. In the HDLC mode, the

receiver also places a status of frame (SF) status byte

in the receiver FIFO for every completed frame

received. Whenever an SF frame status byte is present

in the receive FIFO, the EOF bit (R4--B7) is set. The

receiver queue status (RQS) bits (R4--B[6--0]) report

the number of bytes up to and including the first SF

frame status byte. If no SF frame status byte is present

in the FIFO (EOF, R4--B7 = 0), the count directly

reflects the number of data bytes available to be read.

Depending on frame size, it is possible for multiple

frames to be present in the FIFO. The receiver fill level

indicator (RIL) can be programmed in the receiver con-

trol register (R5--B[5--0]) to tailor the service time

interval to the system environment. The receiver full

(RF) interrupt bit is set in the interrupt status register

(R15--B3) when the FIFO reaches the prepro-

grammed full position. The RF interrupt condition is

reported in the interrupt register (R15--B3). If the RF

interrupt mask RFIE (R14--B3) is 1, the occurrence of

an RF interrupt condition causes a transition of the

interrupt pin if no other unmasked interrupts are

present. In dynamic interrupt mode (DINT,

R0--B0 = 1), this interrupt remains set until the condi-

tion is cleared. In nondynamic interrupt mode (DINT,

R0--B0 = 0), this interrupt is cleared by reading R15.

In the HDLC mode, an REOF interrupt is issued when

the receiver has identified the end of a frame and writ-

ten the SF status byte for that frame. An overrun inter-

rupt is generated when the receiver needs to write

either status or data to the FIFO and finds the FIFO full.

An overrun condition causes the last byte of the FIFO

to be overwritten with an SF status byte indicating the

overrun status. In the HDLC mode, an RIDL interrupt is

issued whenever 15 or more continuous 1s have been

received.

Block Move

The block-move mode is intended to support micropro-

cessors with a memory-to-memory move instruction.

Memory-to-memory move instructions can be faster

and reduce the amount of code needed to service the

FIFOs. Block-move mode allows the T7121 FIFOs to

appear as a block of memory. Systems using block

move need to allocate 16 addresses to the T7121 reg-

ister set (with AD6 = 0) and 64 addresses to the FIFOs

(with AD6 = 1). Block move is

available only in the

MUXed address and data mode

by setting the BM bit

in register 0 (R0--B3) to 1.

When block move is enabled (BM, R0--B3 = 1) and

AD6 is held high during the address cycle of the ALE,

the address is translated internally to R3, the data byte

register. All writes then go directly to the transmit FIFO,

and all reads address the receive FIFO. Normal regis-

ter addressing is accomplished by holding AD6 low

during the ALE address cycle. Block moves can be dis-

abled by clearing the BM bit (R0--B3) to 0.

Serial Link Interface

The HIFI-64 can interface to a wide variety of serial

links. In the simplest interface, the time-slot feature is

not used, and the HIFI-64 performs HDLC processing

in conjunction with three externally supplied clocks:

CLK, CLKR, and CLKX. The maximum data rate fre-

quency is 4.096 MHz, and the minimum CLK frequency

must be greater than two times the fastest data clock

frequency. In the case of a burst clock, the fastest data

clock frequency is defined as the clock frequency dur-

ing the burst.

If the time-slot feature is enabled (HWYEN,

R0--B7 = 1), the HIFI-64 is capable of controlling sep-

arate transmit and receive time slots on a wide variety

of time-division multiplexed (TDM) serial highways. In

particular, the HIFI-64 can interface to the Lucent Con-

centration Highway--a variable-speed, dual full-duplex

serial highway. The HIFI-64 can also interface to a vari-

ety of TDM highways containing 64 or fewer time slots

(primary-rate interface, SLD, K, K2, GCI, IOM, IOM2,

etc.).

The IOM, IOM2, and GCI interfaces specify the data

clock to be twice the data transmission frequency. In

order to comply with this specification, a Clock Mode

Select (CMS) bit (R8--B6) has been included. The bit

has the effect of dividing the data clock by two inter-

nally. In CMS mode, the minimum CLK frequency must

be greater than the data clock.

Enabling the Transmitter and Receiver

The HIFI-64 can transmit on either of two transmit data

pins (DXA, pin 19, and DXB, pin 17), or can broadcast

on both pins by appropriately programming the DXAC

(R7--B7) and DXBC (R7--B6) bits in the transmit time-

slot control register (R7--B6,B7). If both pins are

selected, the same data appears on both. The behavior

of pin 17, either DXB or

TSCA

, is controlled by the

P17CTL (R5--B7) bit. The P17CTL bit must be cleared

to 0 to enable transmission on DXB. Pin 17 can be con-

figured as

TSCA

by setting P17CTL to 1. When P17CTL

is set to 1, the setting of DXBC (R7--B6) is ignored.

While configured as

TSCA

, pin 17 is low continually if

HWYEN (R0--B7) = 0 and DXAC (R7--B7) = 1.

Lucent Technologies Inc.

11

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

When HWYEN = 1 and DXAC = 1, pin 17

TSCA

is low during unmasked bits of the selected time slot. Otherwise

TSCA

is high.

The transmitter begins transmission when the transmitter enable ENT bit (R6--B3) is set to 1. Once the ENT bit is

enabled, user data is transmitted on the selected transmit data pin(s) (DXA, DXB, both, or neither). If the transmit-

ter is enabled and no transmit data pin has been selected, the HIFI-64 3-states both pins and the FIFO empties as

if the data were being transmitted. When the transmitter is disabled (ENT = 0), the transmitter continuously trans-

mits 1s on the selected transmit data pin(s) (DXA, DXB, or both). If neither DXA nor DXB is selected, both pins are

3-stated. The microprocessor can load the FIFO as normal while the transmitter is disabled. Disabling the transmit-

ter does not cause a transmitter reset. When the transmitter is disabled after having been enabled, the transmitter

should be reset via a TRES (R6--B5) = 1. Table 3 summarizes the transmit pin behavior based on the four register

bits that can affect it. This table assumes that P17CTL is set to 0 and that, in TDM highway modes, at least one

data bit is unmasked.

* P17CTL = 0 is assumed.

The edge of CLKX (pin 18) used for data transmission is programmable by using CLKXI (R9--B4). Setting CLKXI

to 1 causes the T7121 to transmit data using the positive edge, while setting CLKXI to 0 enables transmission on

the negative edge (DEFAULT). Whenever the clock edge is changed, the transmitter should be reset via TRES

(R6--B5). When a gated clock is used to begin transmission on the first programmed clock edge, the opposite

clock edge must be provided first, after the reset. For example, if a gated clock with a negative edge transmission

is used, a positive edge of the clock should be provided first. This extra edge is only necessary on initial enabling of

the transmitter.

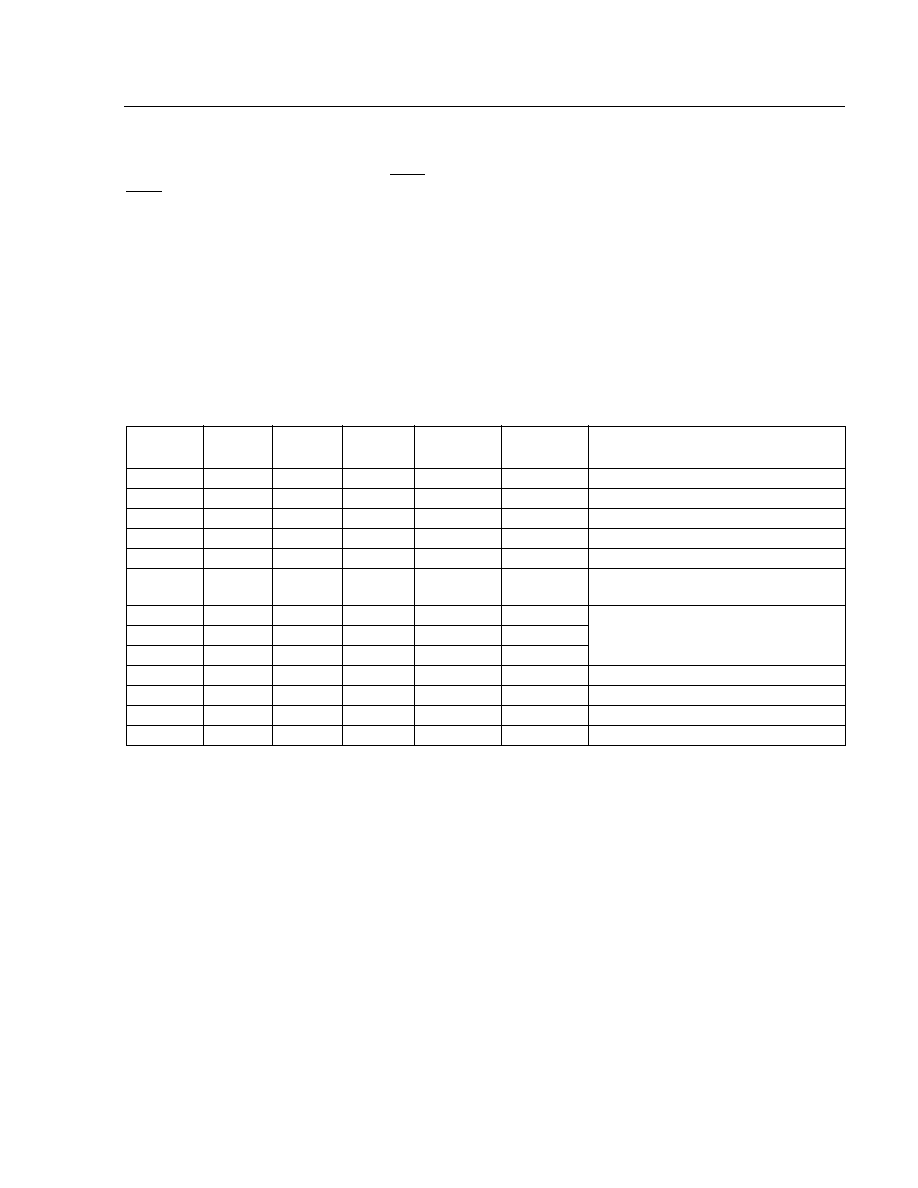

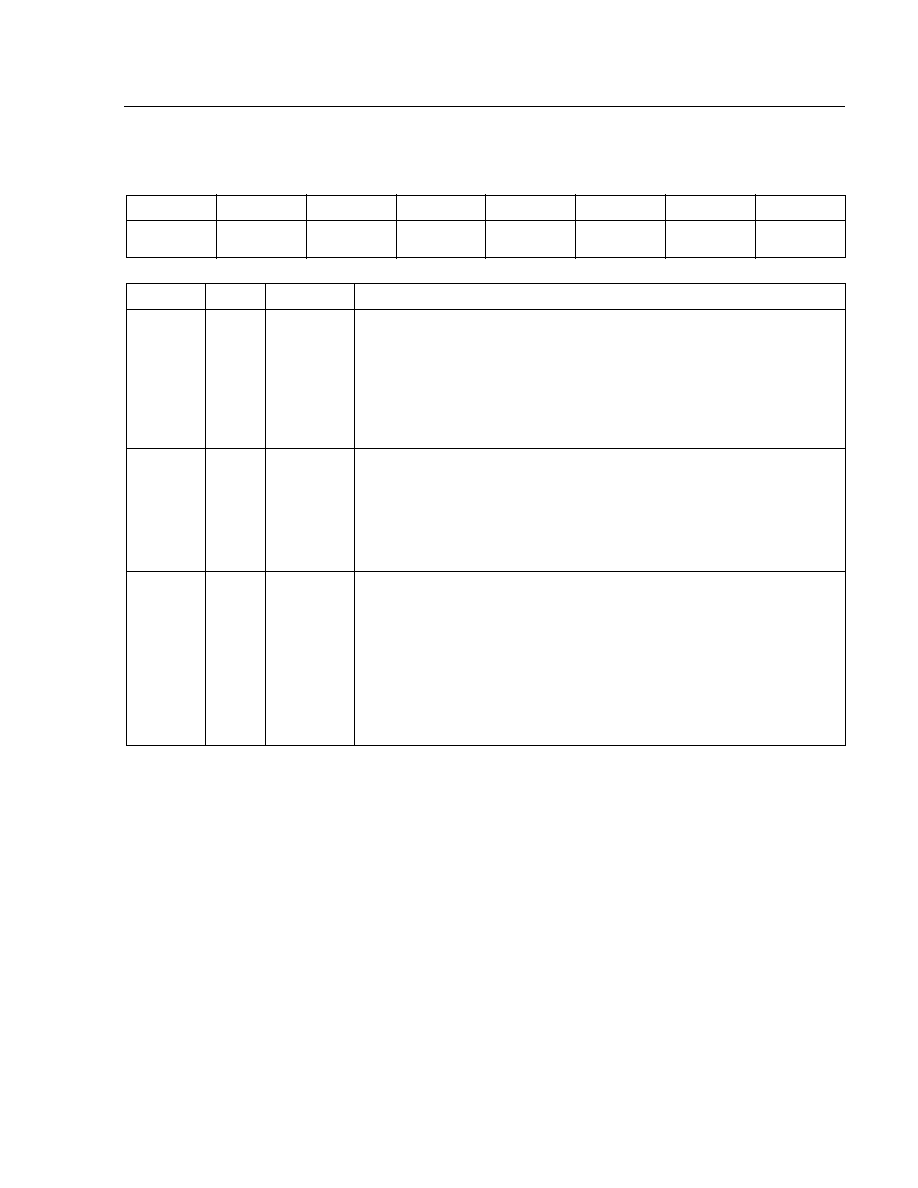

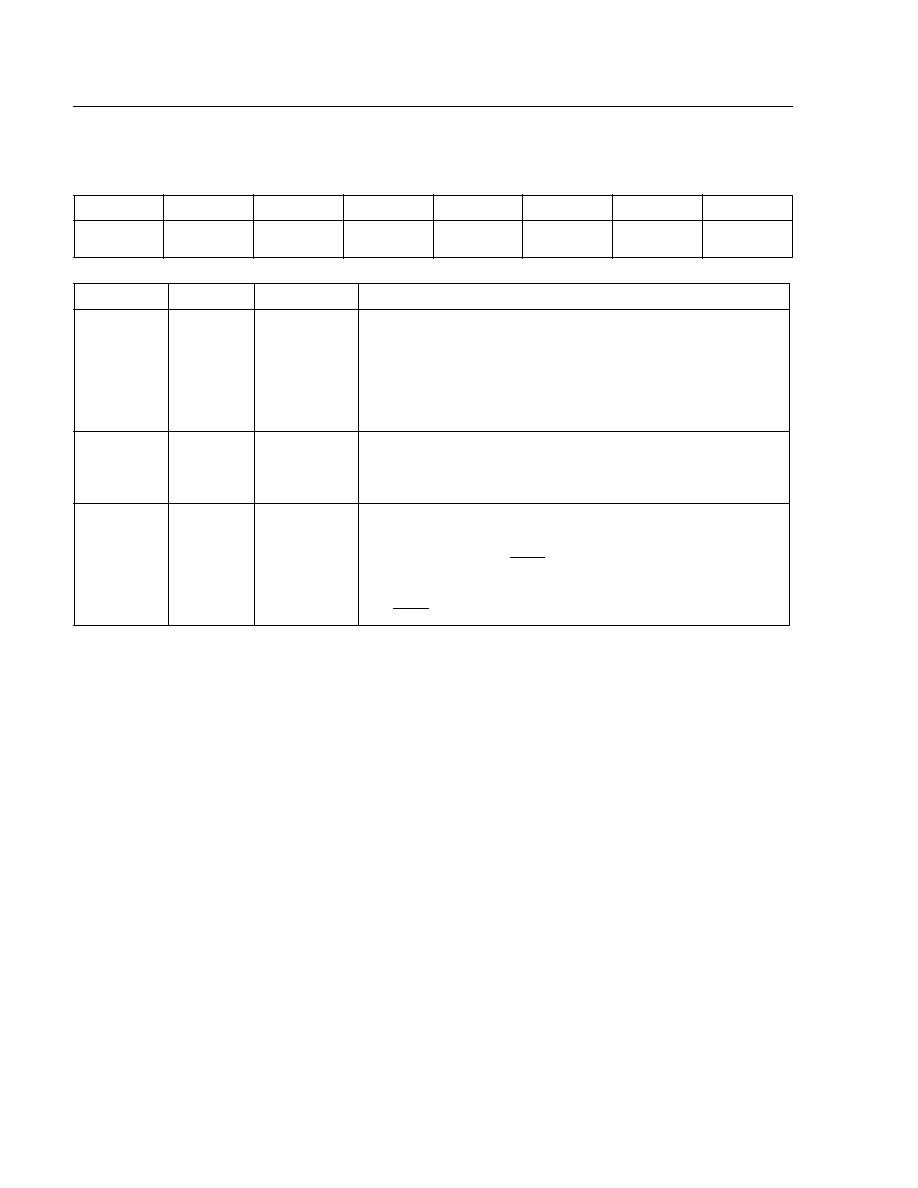

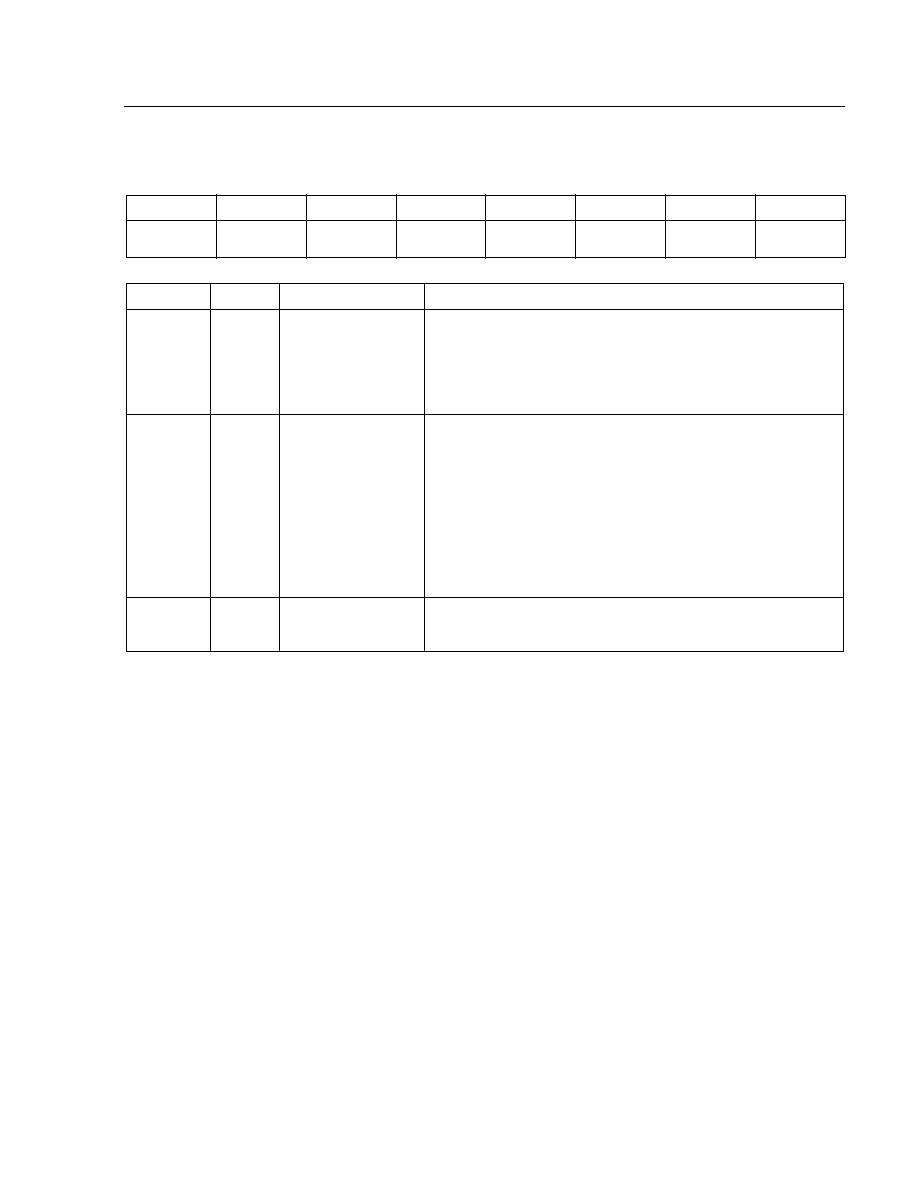

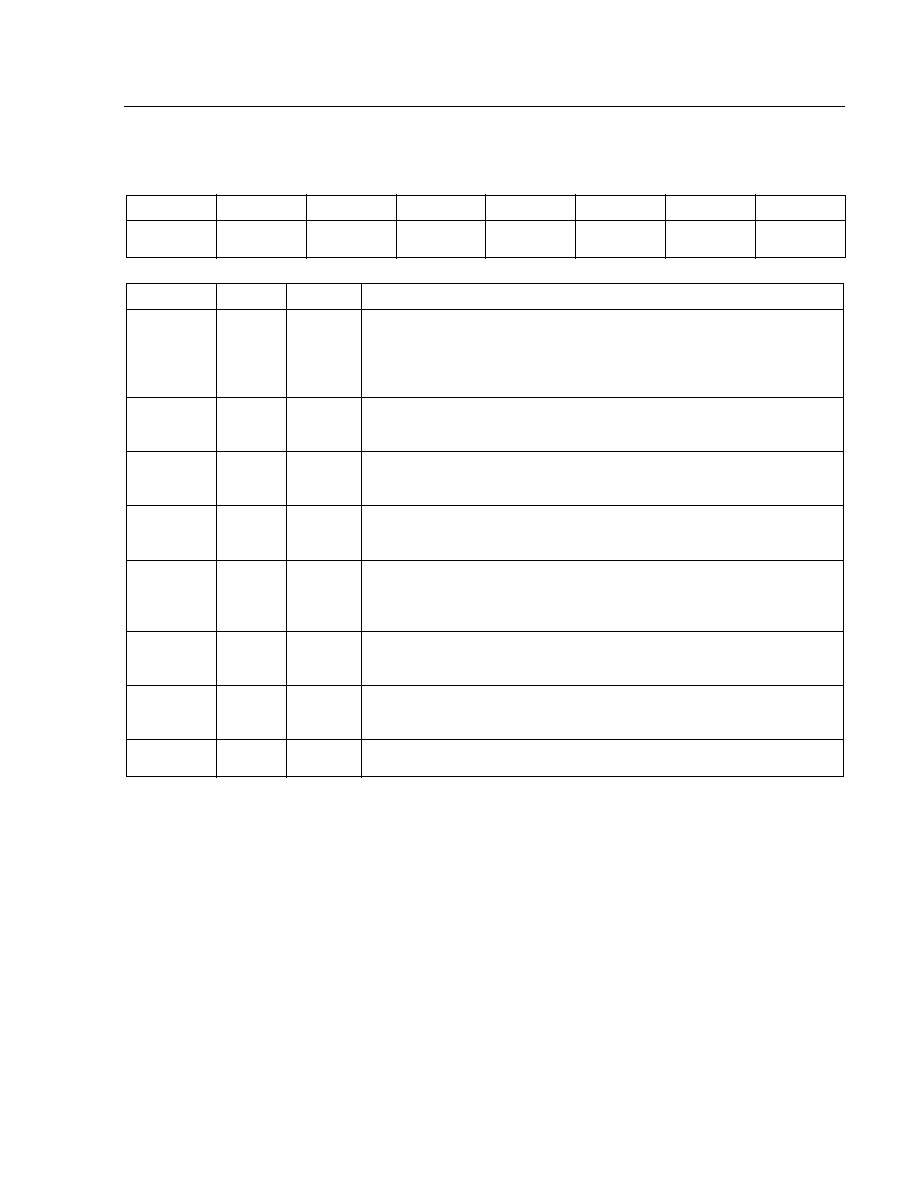

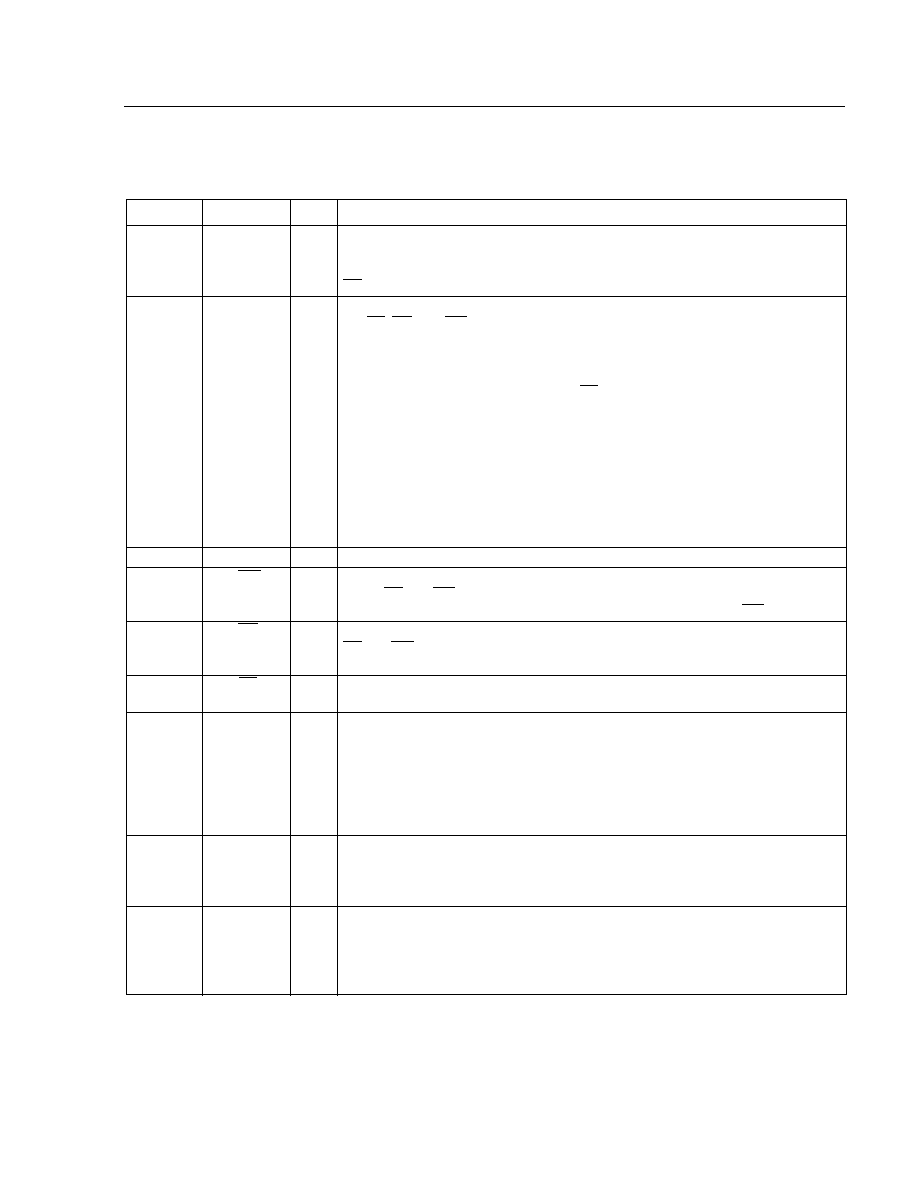

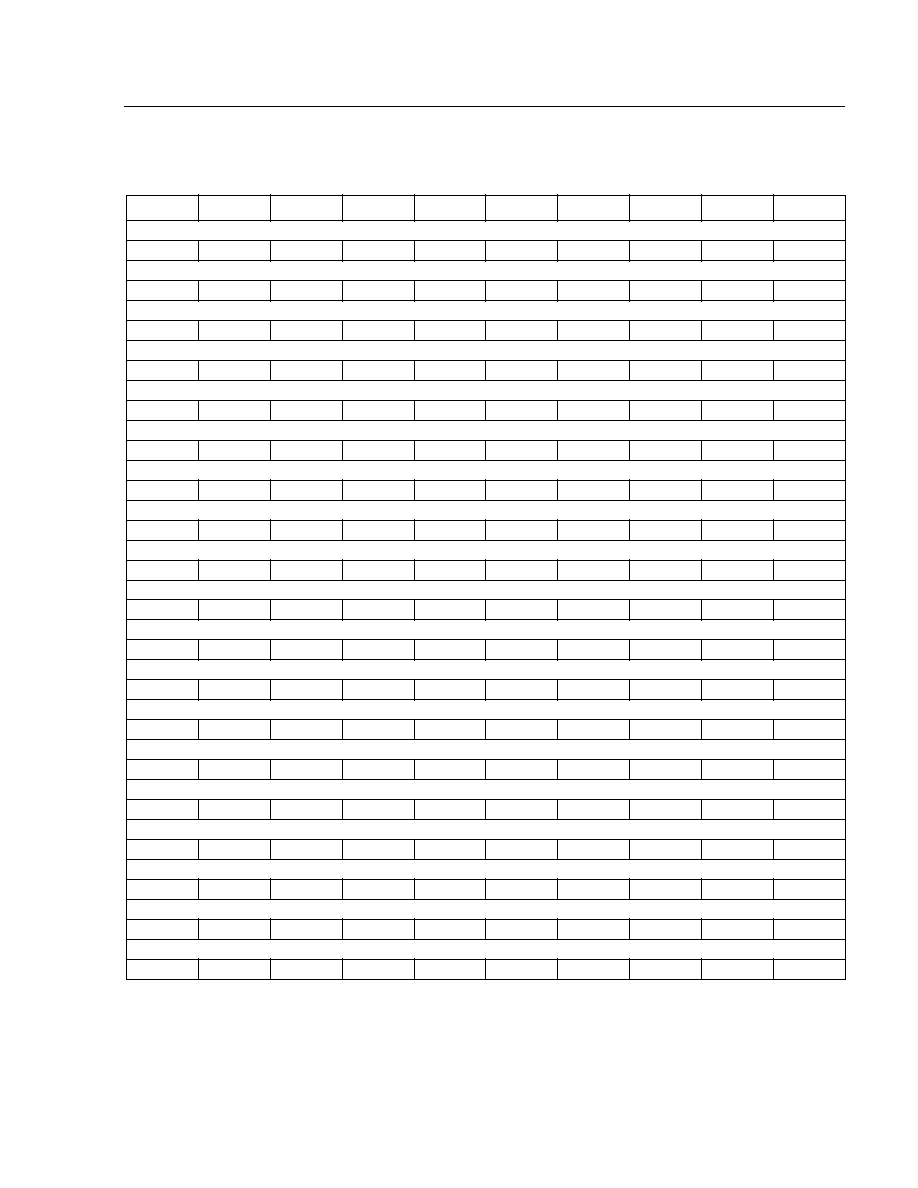

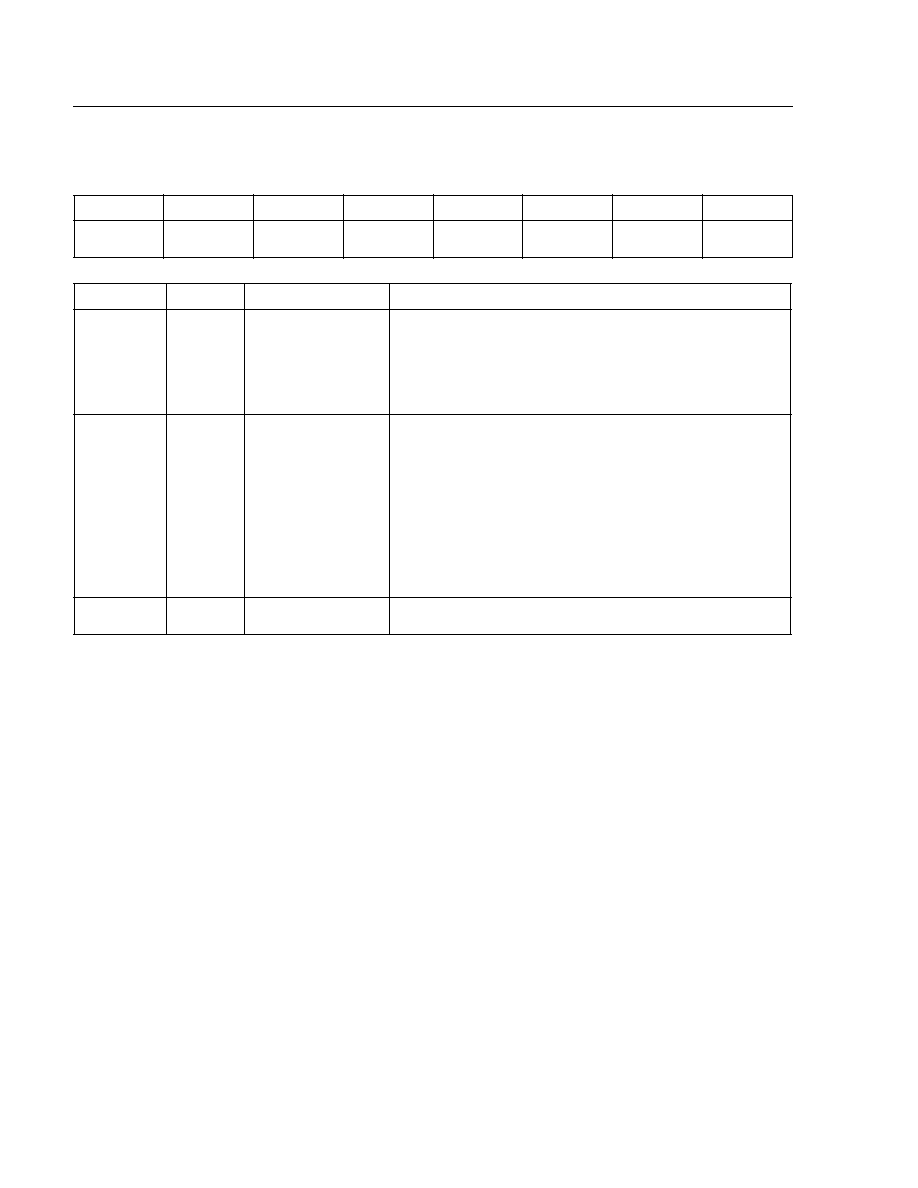

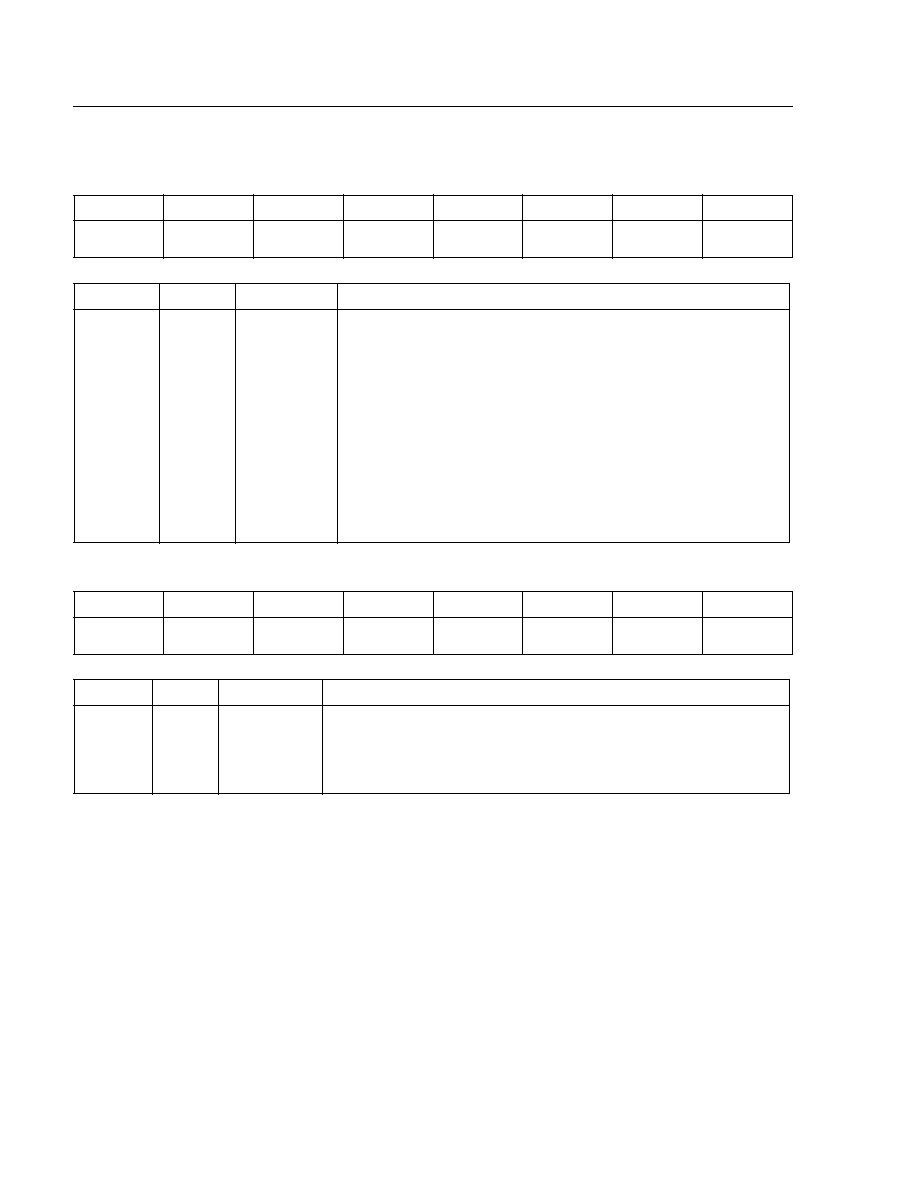

Table 3. Transmit Pin Behavior

HWYEN

(R0--B7)

ENT

(R6--B3)

DXAC

(R7--B7)

DXBC*

(R7--B6)

DXA

(Pin 19)

DXB

(Pin 17)

Comments

0

0

X

X

3-state

3-state

Reset condition.

0

1

0

0

3-state

3-state

Data can be lost.

0

1

0

1

3-state

user data

--

0

1

1

0

user data

3-state

--

0

1

1

1

user data

user data

--

1

0

0

0

3-state

3-state

Concentration highway interface

enabled.

1

0

0

1

3-state

1s

Transmit 1s during user-programmed

time slot until transmitter is enabled.

1

0

1

0

1s

3-state

1

0

1

1

1s

1s

1

1

0

0

3-state

3-state

Data can be lost.

1

1

0

1

3-state

user data

--

1

1

1

0

user data

3-state

--

1

1

1

1

user data

user data

--

12

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

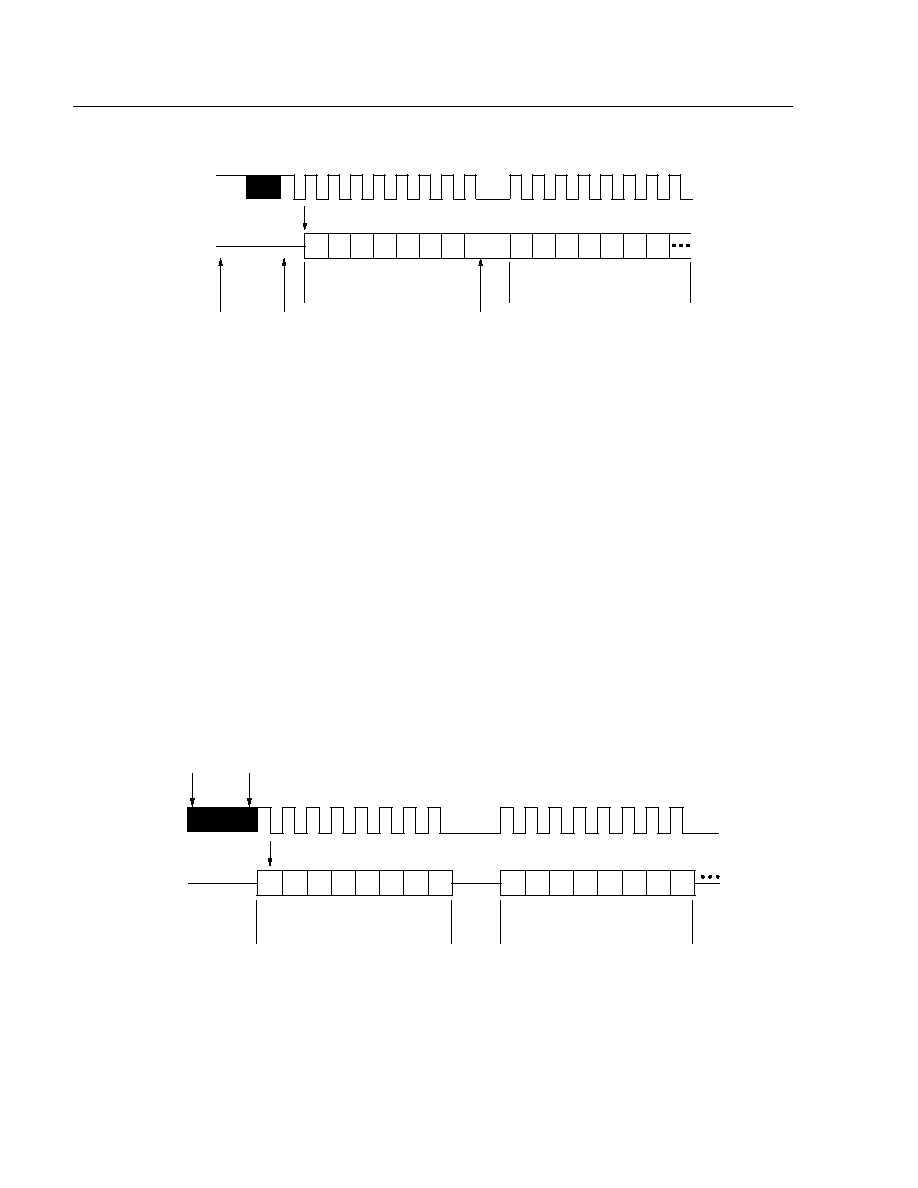

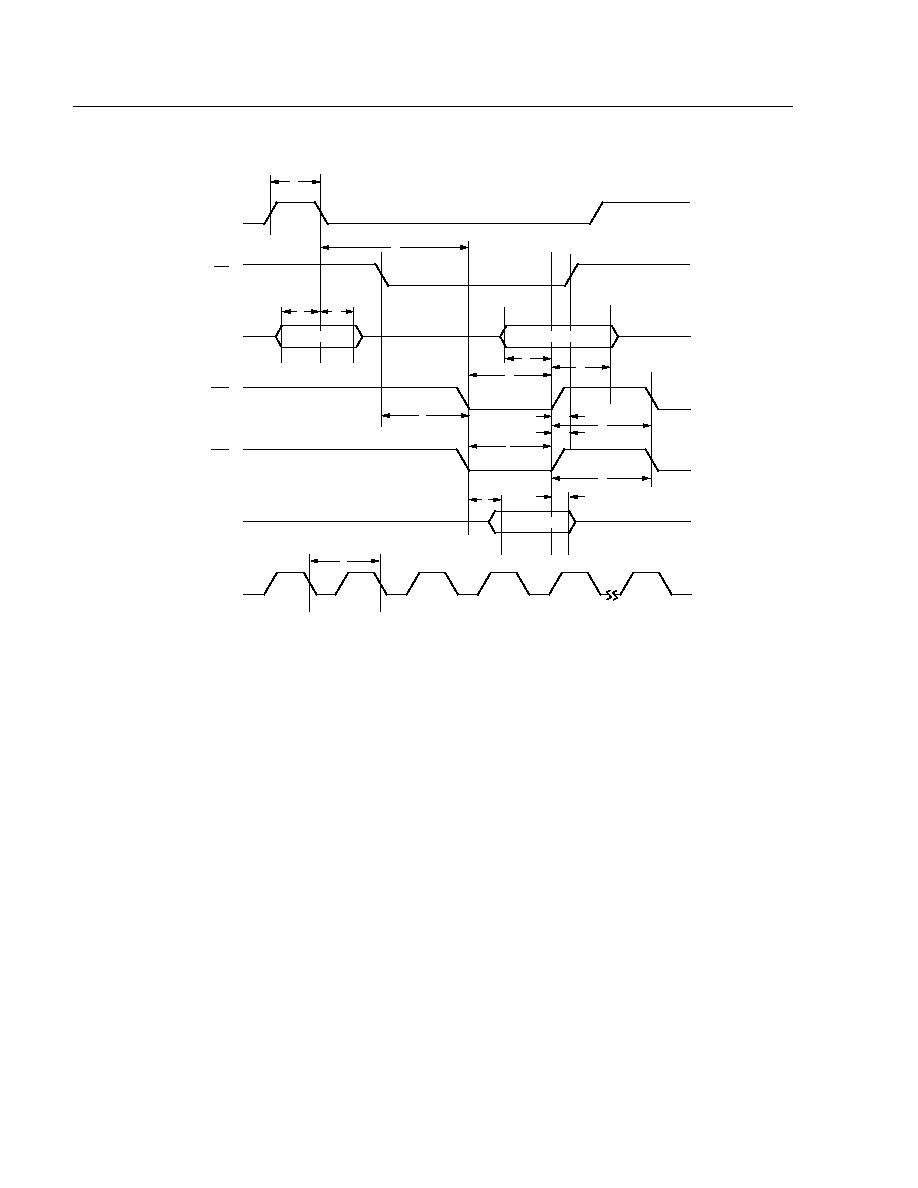

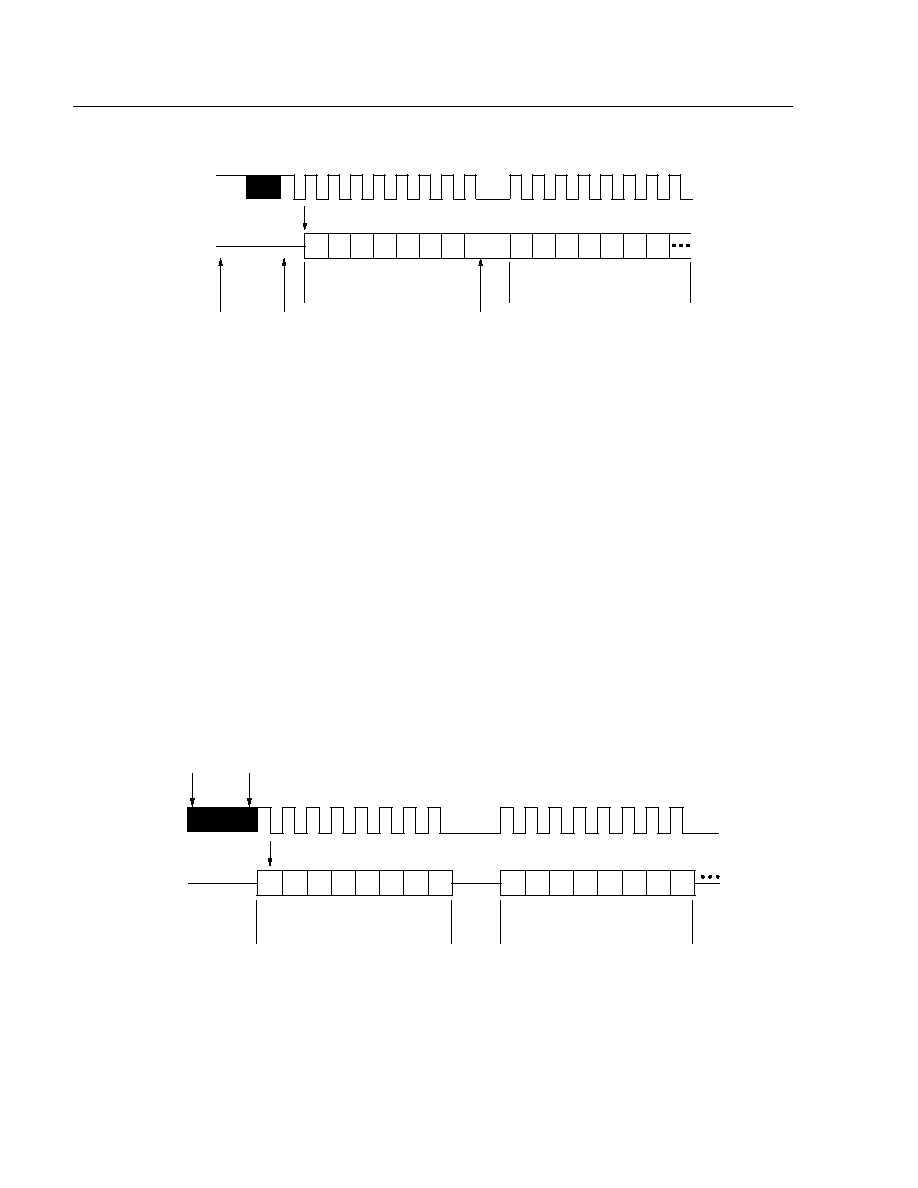

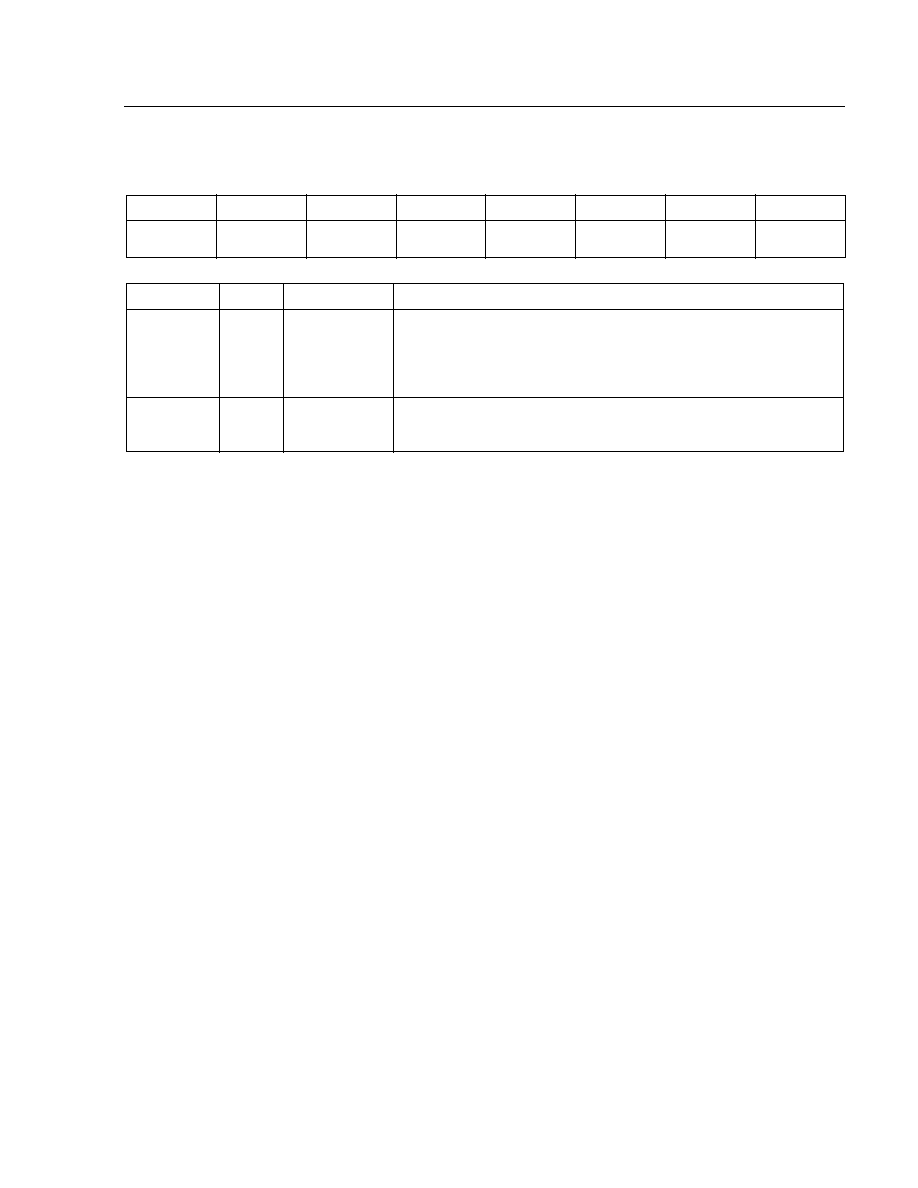

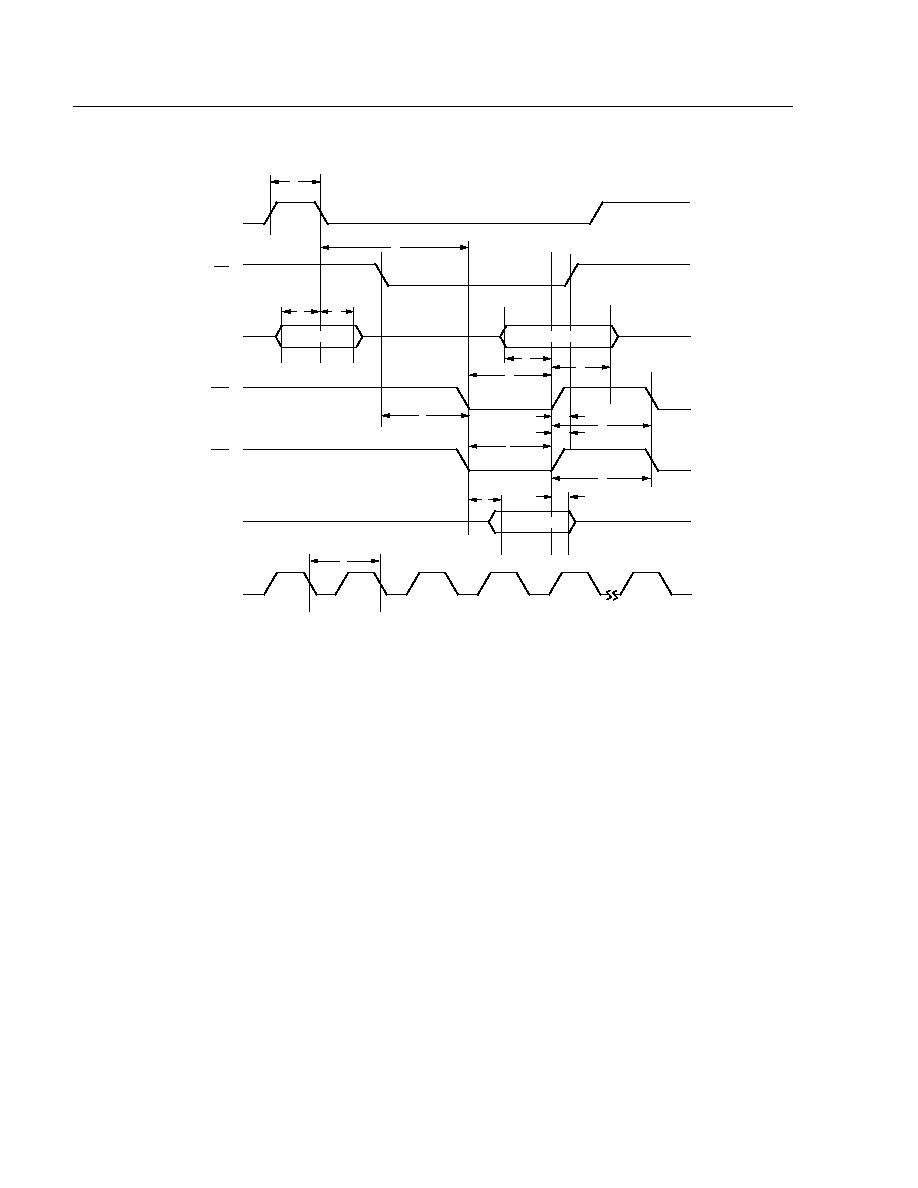

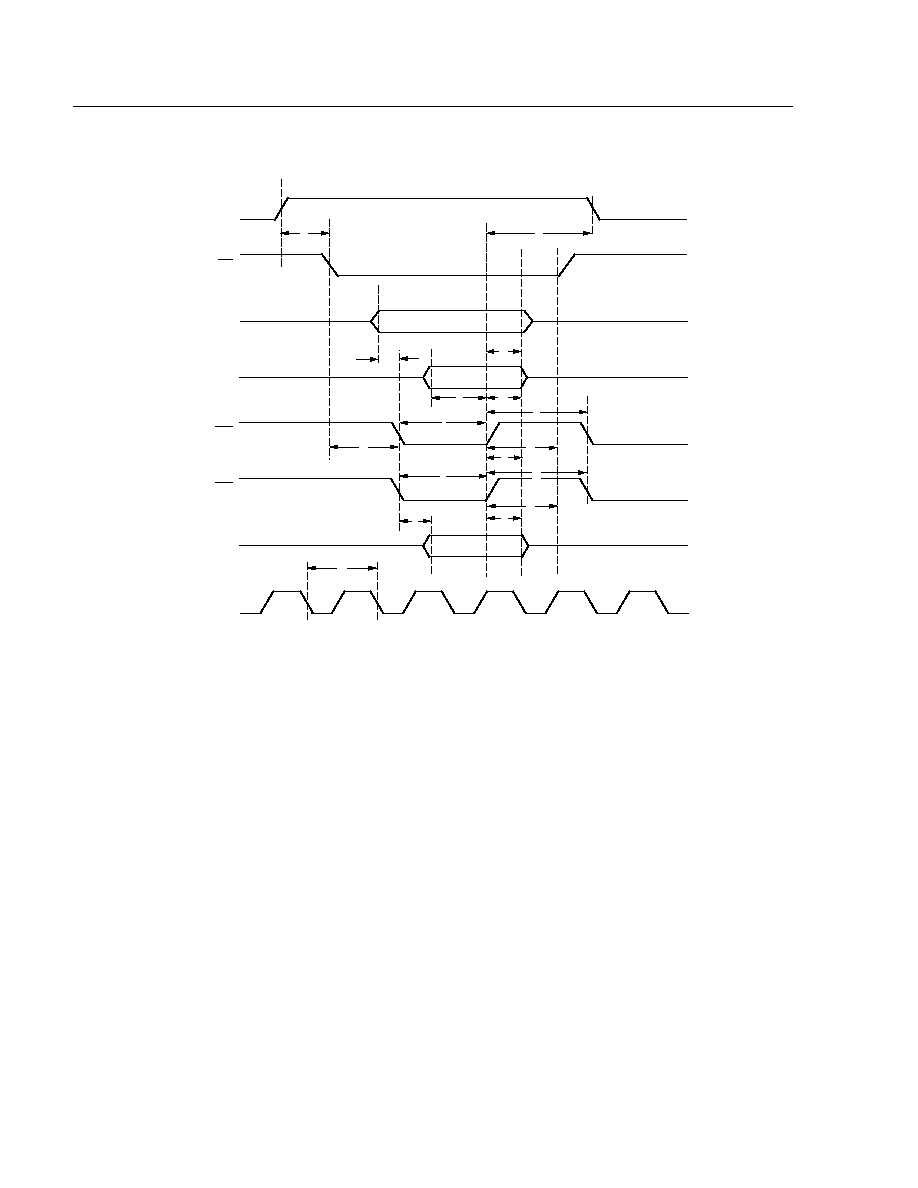

5-5029

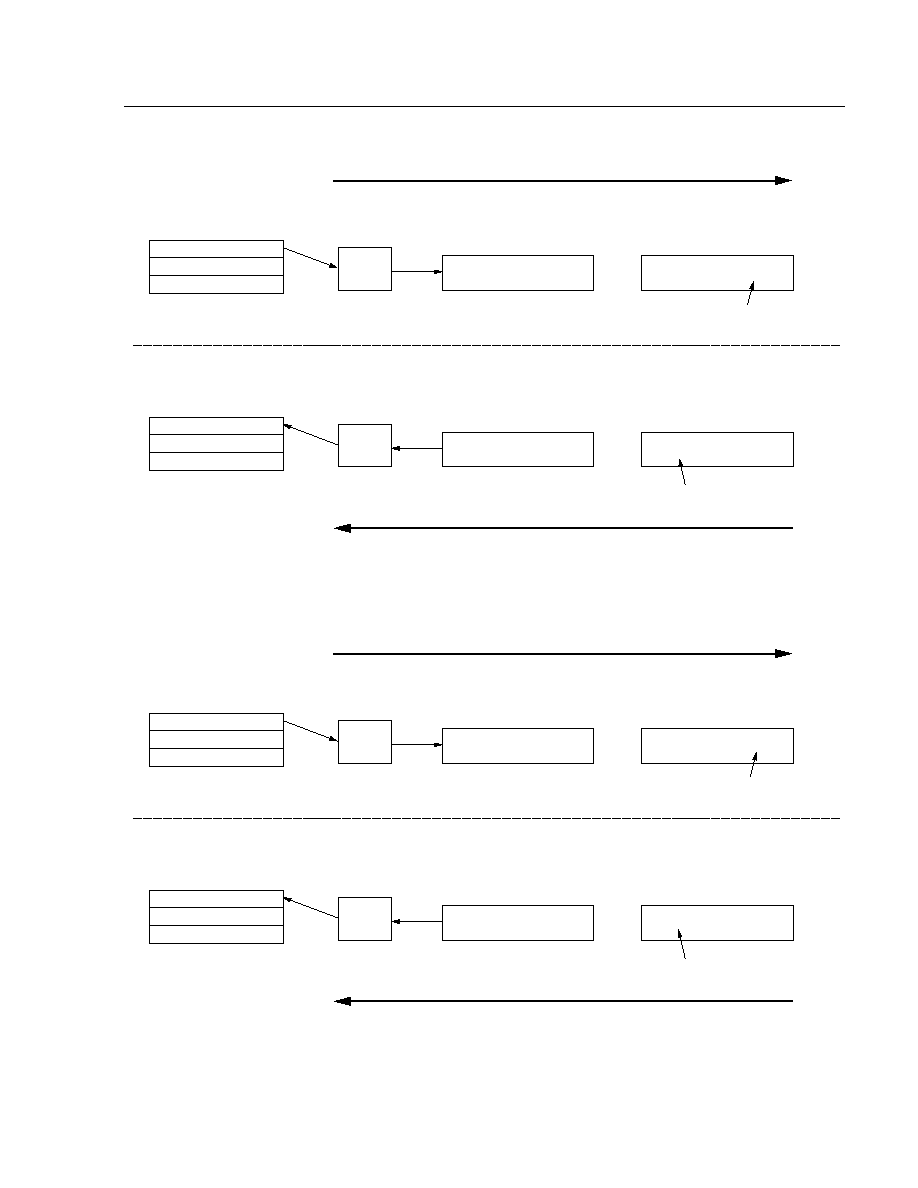

Figure 3. Transmitting with a Gated Clock

The receiver can be enabled or disabled by programming the ENR bit (R6--B2). When disabled, the receiver

ignores all serial inputs (i.e., no data loaded into the FIFO). Whatever was in the FIFO before the receiver was dis-

abled remains intact, and the microprocessor can read the contents as normal. Disabling the receiver does

not

cause a receiver reset. Whenever the receiver has been enabled and is subsequently disabled, the receiver must

be reset via RRES (R6--B4) before it is reenabled.

The HIFI-64 can receive data on either of two receive data pins (DRA, pin 20, or DRB, pin 21) depending on the

programming of the DRA/B bit in register 8 (R8--B7). The HIFI-64 can be programmed to use either the input of pin

21 (CLKR/DRB) or the input of pin 18 (CLKX) as the receive clock using P21CTL (R5--B6). Clearing P21CTL to 0

(DEFAULT) selects pin 21, while a setting of 1 selects pin 18. The selected clock can be programmed to latch

received data on either clock edge using CLKRI (R9--B0). Setting CLKRI to 1 causes the receiver to use the posi-

tive receive clock edge to latch data, while clearing CLKRI to 0 causes the receiver to use the negative edge.

Whenever the clock edge is changed, the receiver should be reset via an RRES (R6--B4). When a gated clock is

used, the receiver begins latching data on the first programmed clock edge. When a gated clock is used, separate

transmit and receive clocks must be used if data alignment to the first clock edge is required, since the transmit

clock requires an extra edge to align. See Figures 3 and 4.

5-5030

Figure 4. Receiving with a Burst Clock

CLKX

DXA

TRANSMIT 1ST BIT ON 1ST POSITIVE EDGE AFTER 1ST NEGATIVE EDGE

FIRST BYTE TRANSMITTED

SECOND BYTE TRANSMITTED

SET

CLOCK

EDGES

VIA R9

RESET

TRANSMITTER

VIA R6--B5

BIT VALUE

MAINTAINED

UNTIL NEXT EDGE

CLKR

DRA

LATCH IN 1ST RECEIVE BIT ON 1ST NETGATIVE EDGE AFTER RECEIVE RESET

FIRST DATA BYTE

SECOND DATA BYTE

SET

CLOCK

EDGES

VIA R9

RESET

RECEIVER

VIA R6--B4

B0

B7

B0

B7

Lucent Technologies Inc.

13

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

Time-Slot Feature

The HIFI-64 can be configured to interface with devices

supplying a frame-synchronization signal (FS) to indi-

cate the beginning of a single or multiple time-slot

sequence. The T7121 can be configured to interface to

TDM highways from 3 to 64 time slots.

The HWYEN bit (R0--B7) enables the time-slot feature

logic. All highway parameters should be programmed

before enabling HWYEN. When HWYEN is 0, any input

on the FS pin is ignored. When HWYEN is 1, data

transmission begins with the first programmed time slot

following the first detected frame sync, provided that at

least one of the transmit pins is enabled and at least

one transmit bit is unmasked. The first data byte trans-

mitted in all cases is FF hex. When transmit highway

parameters are changed, such as time slot, the trans-

mitter and transmit output pins should be disabled

(ENT R6--B3 = 0, DXBC R7--B6 = 0, DXAC R7--B7 =

0). This guarantees that no other time slot is corrupted

during reprogramming. When the receiver time slot is

changed, the receiver should be disabled (ENR

R6--B2 = 0). After reprogramming, 1 TDM frame is

necessary to resynchronize. When HWYEN is first

enabled, the user should wait one TDM frame between

enabling HWYEN and enabling the transmit outputs.

The highway logic is reset completely to a known state

by each FS pulse or by a full chip reset.

The T7121 provides a bit masking feature to allow sub-

rate operation. The default bit masks are FF hexadeci-

mal for the receiver bit mask (R12) and 00 hexadecimal

for the transmitter bit mask (R13). The transmitter by

default transmits no bits in the selected time slot. To

enable transmission of all 8 bits in the selected time

slot, the transmitter bit mask (R13) must be changed to

FF hexadecimal (see the Bit Masking section for more

details).

The HIFI-64 determines that an FS has occurred by

sampling the FS signal with the appropriate data clock.

The polarity of a valid FS is determined by FSPOL

(R0--B6). That is, if FSPOL is 0, the FS is considered

valid when low. When FSPOL is 1, the FS is consid-

ered valid when high. When an FS pulse is provided, at

least one FS pulse must be provided for every 512 data

clock cycles. The FE bit (R0--B5) controls the edge of

the data clock used to sample the FS signal. If FE

(R0--B5) is cleared to 0, FS is sampled on a negative

edge of the transmit and receive data clocks. If FE is

set to 1, FS is sampled on a rising edge of the transmit

and receive data clocks.

The HIFI-64 can be programmed to transmit data on

either a positive or negative edge of the data clock by

programming the CLKXI bit (R9--B4). Similarly, the

device can be programmed to sample received data on

either a positive or negative edge of the data clock by

programming the CLKRI bit (R9--B0). The timing of the

transmission or reception of the first bit relative to the

frame-sync pulse then depends on the configuration of

three bits: FE (R0--B5), CLKXI (R9--B4), and CLKRI

(R9--B0). Figure 12 in the Timing Characteristics sec-

tion shows the position of the first transmit bit and

receive bit relative to the FS for each combination of

these register bits. These register configurations are

assumed:

HWYEN (R0--B7)

=

1

FSPOL (R0--B6)

=

1

TBOF[2--0] (R9--B[7--5])

=

000

RBOF[2--0] (R9--B[3--1])

=

000

TSLT[5--0] (R7--B[5--0])

=

000000

RSLT[5--0] (R8--B[5--0])

=

000000

Figure 13 in the Timing Characteristics section shows

an example of bit masking; all other examples assume

no masking. Transmission can be over DXA and/or

DXB (depending on the configuration of the DXAC and

DXBC bits in register 7 [R7--B6,7]), and

TSCA

is

shown to illustrate transmission over DXA with an

external driver. DRA or DRB can be used to receive

incoming data (depending on configuration of the DRA/

B bit [R8--B7]).

The HIFI-64 can be programmed to delay transmission

of the first bit by using the offset registers. These are

the transmit bit offset TBOF (R9--B[7--5]), the transmit

time-slot TSLT (R7--B[5--0]), and the transmitter time-

slot offset TTSOF (R10--B[5--0]). The transmit bit off-

set register moves the transmission of the first bit for-

ward one bit at a time, up to 7 bits total. The transmitter

time-slot offset moves the first bit forward by multiples

of 8 bits. The combination of the settings of these two

registers defines the position of time slot 0. From that

point, the time slot is selected by the value of the trans-

mitter time slot TSLT (R7--B[5--0]). The first bit is

transmitted

TBOF + (8 x TTSOF) + (8 x TSLT) = N

bit times after the beginning of the TDM frame.

14

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

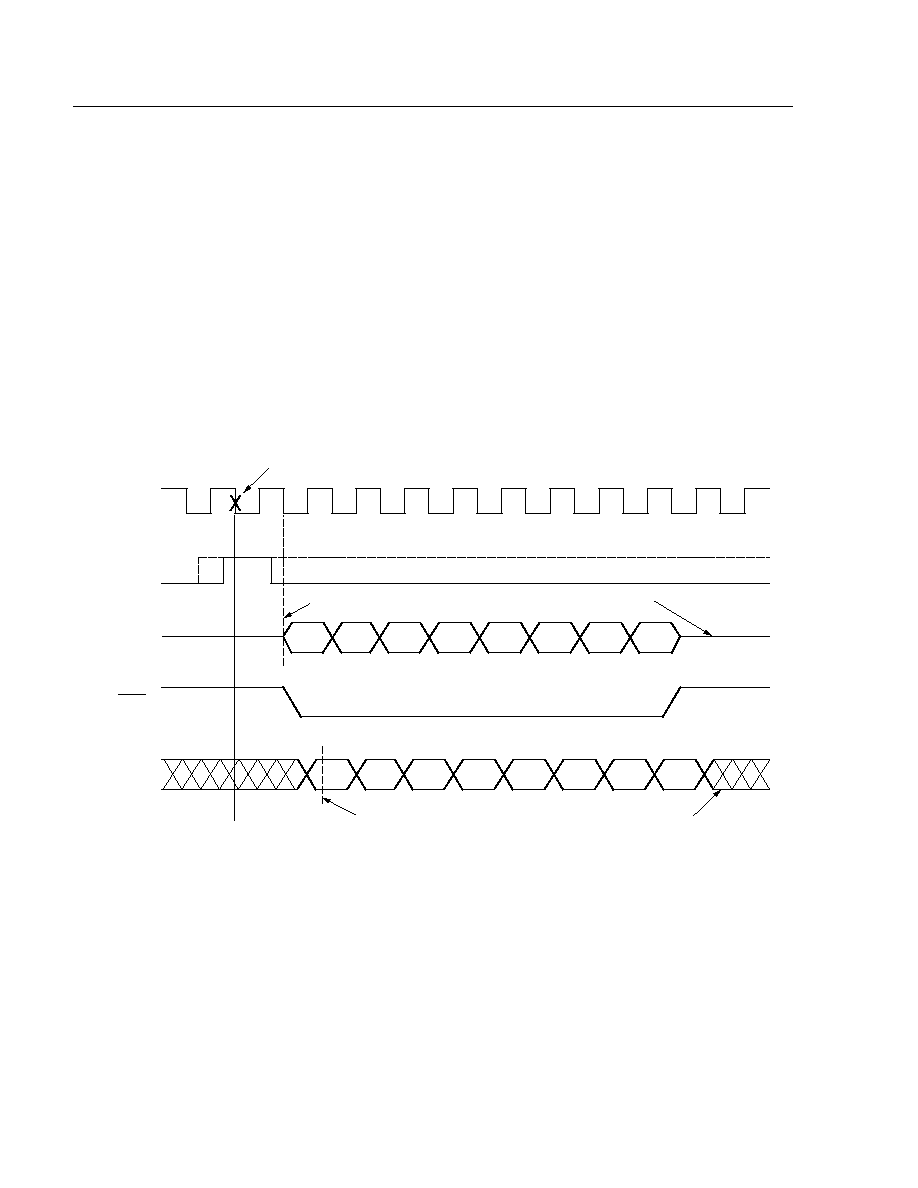

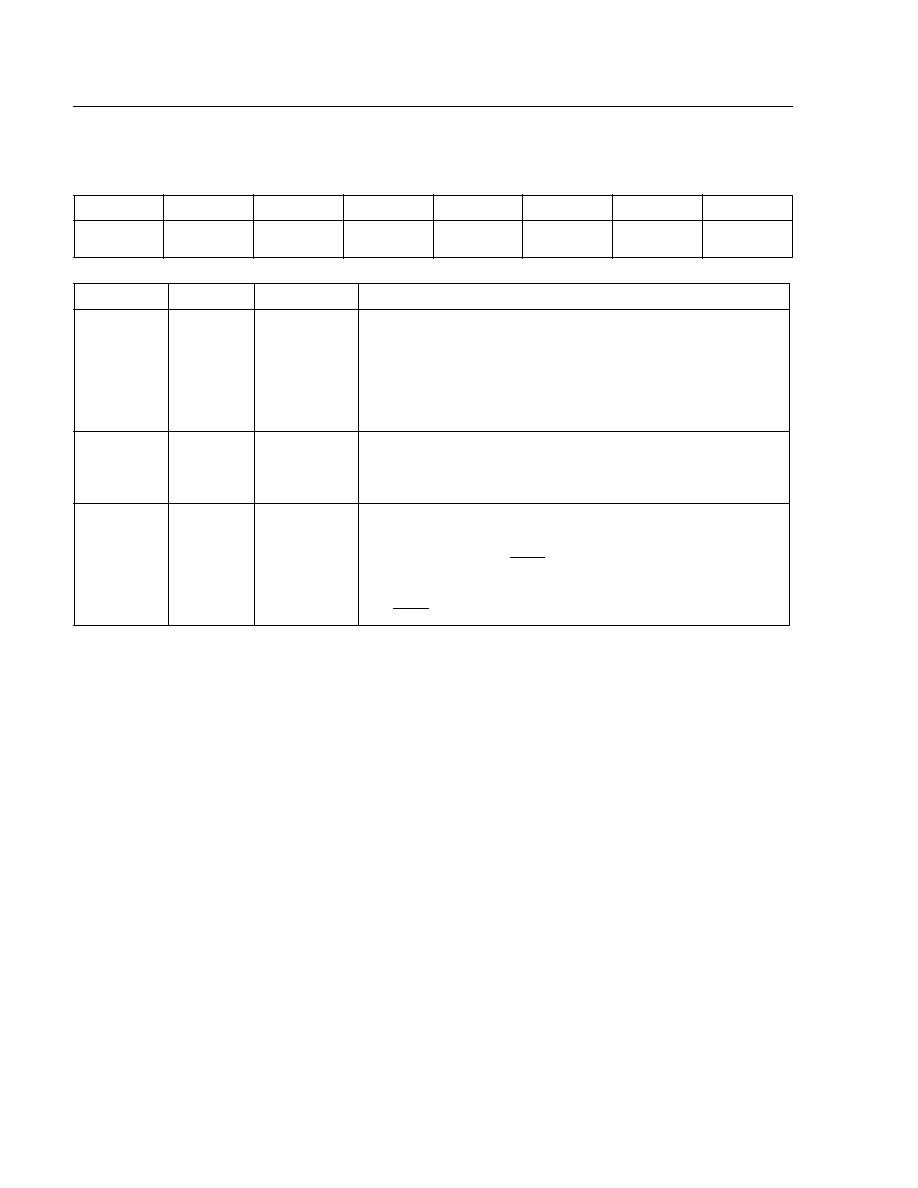

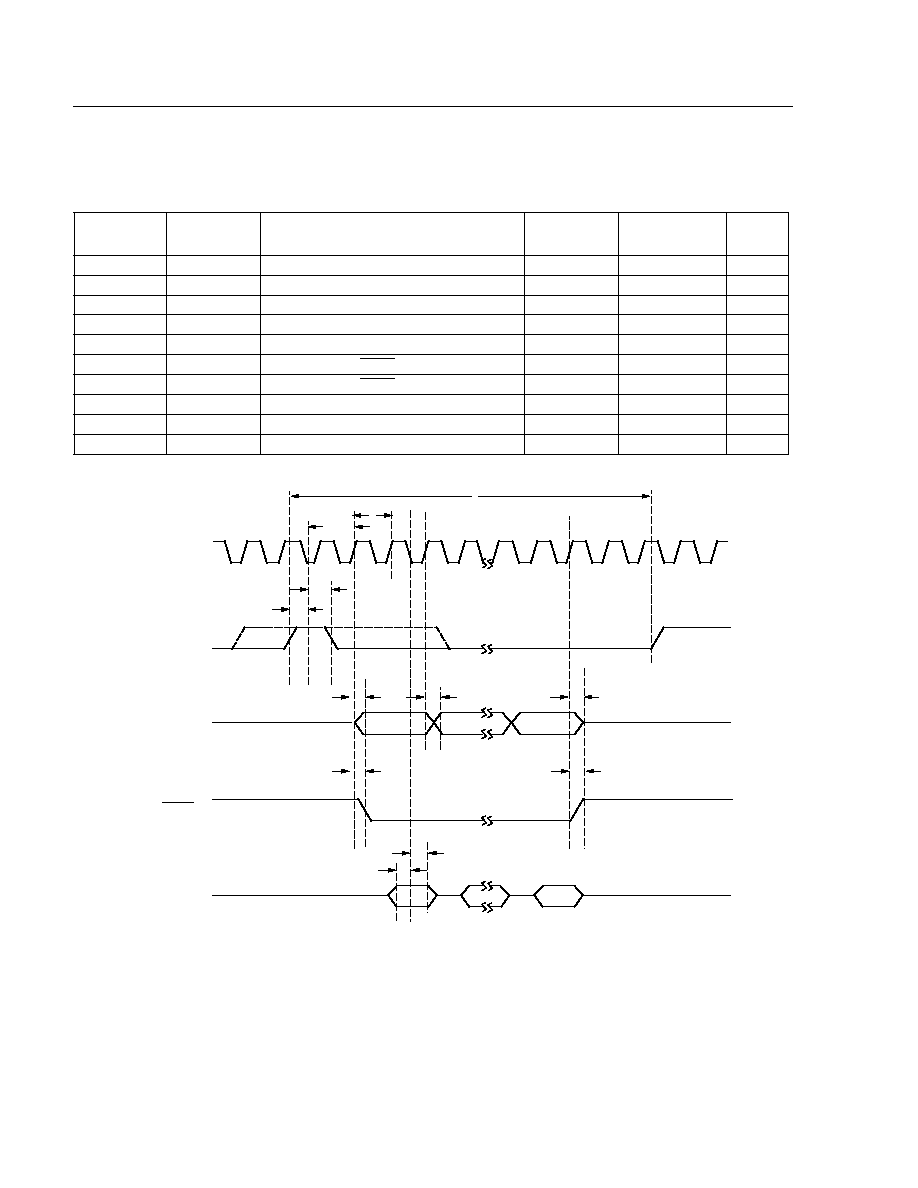

Similarly for the receiver, the receive bit offset RBOF (R9--B[3--1]) and the receive time-slot offset RTSOF

(R11--B[5--0]) determine where the first bit of the first receive time slot is found. The time slot used is selected by

the value of the receiver time-slot RSLT (R8--B[5--0]). The first bit is received

RBOF + (8 x RTSOF) + (8 x RSLT) = M

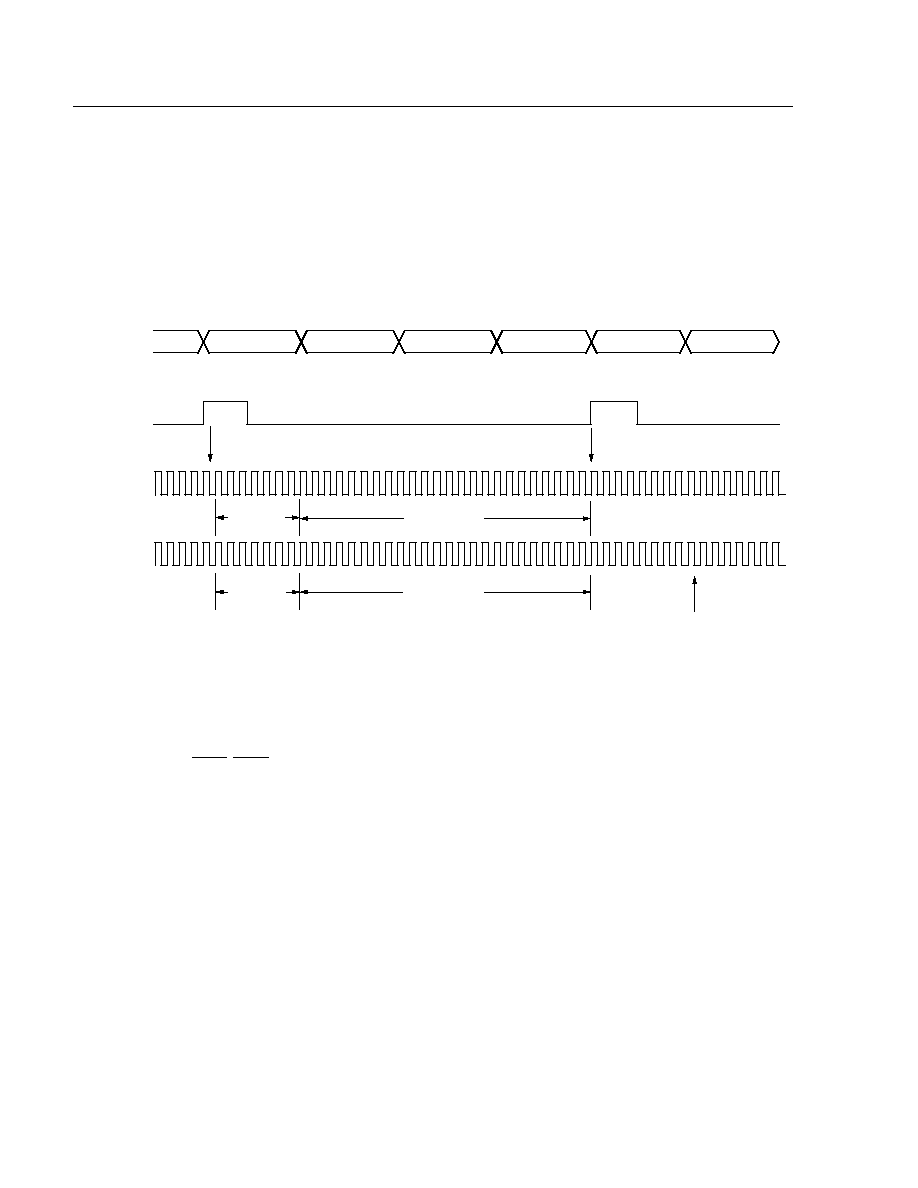

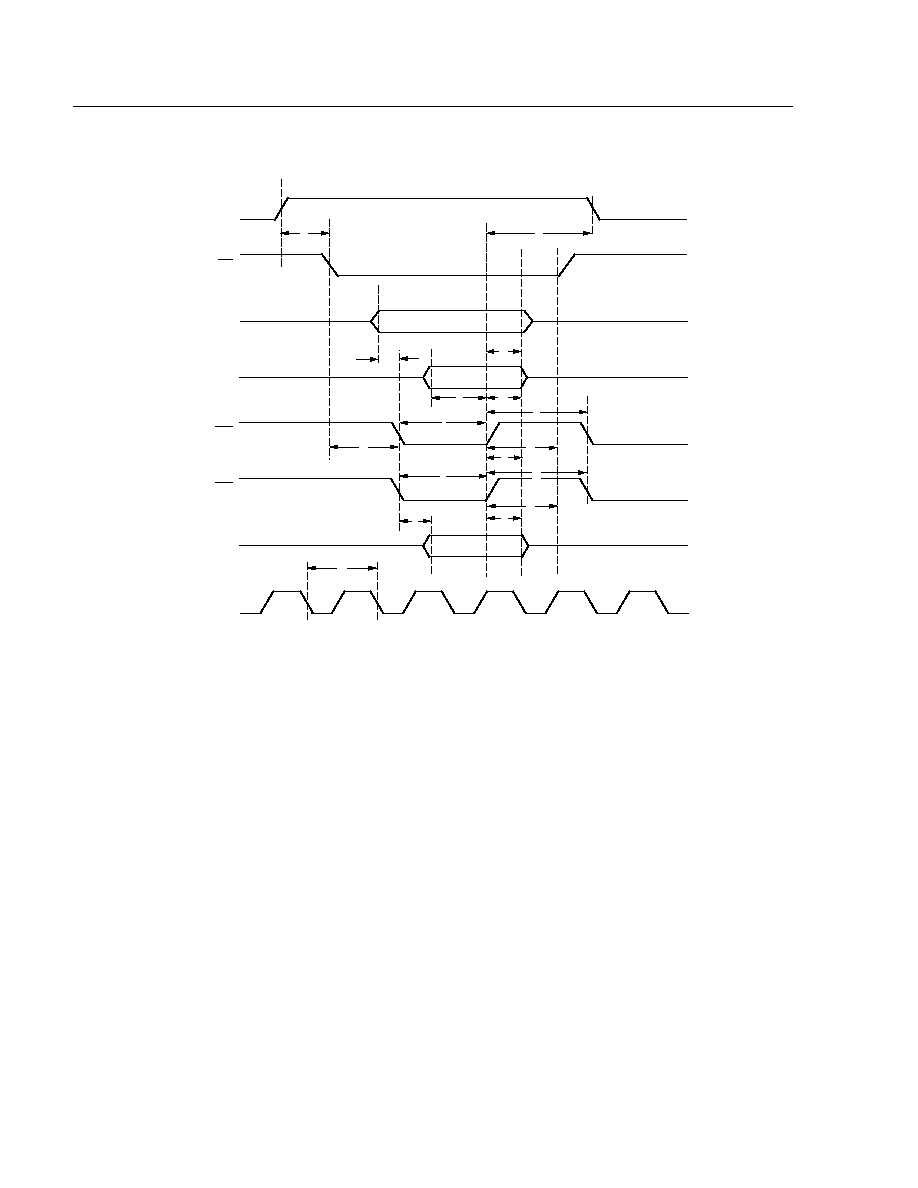

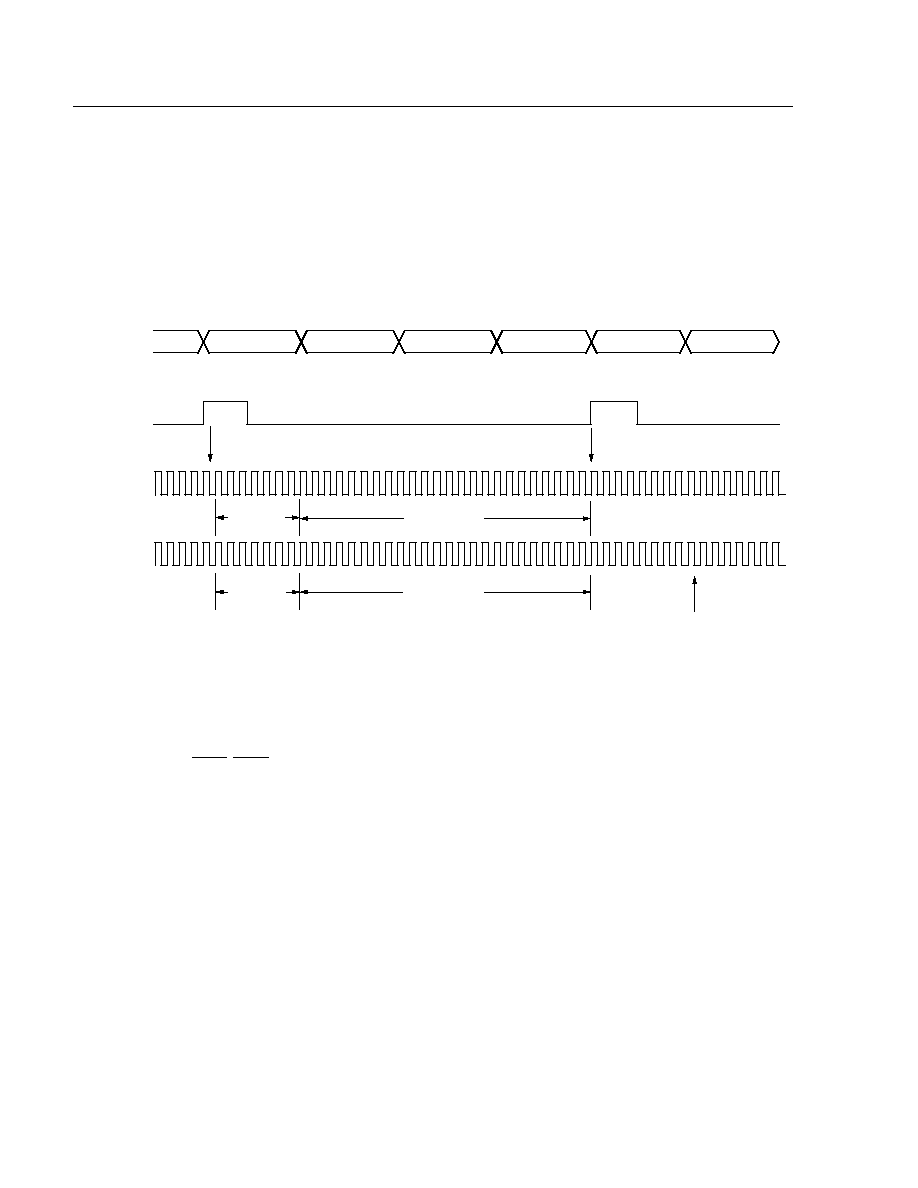

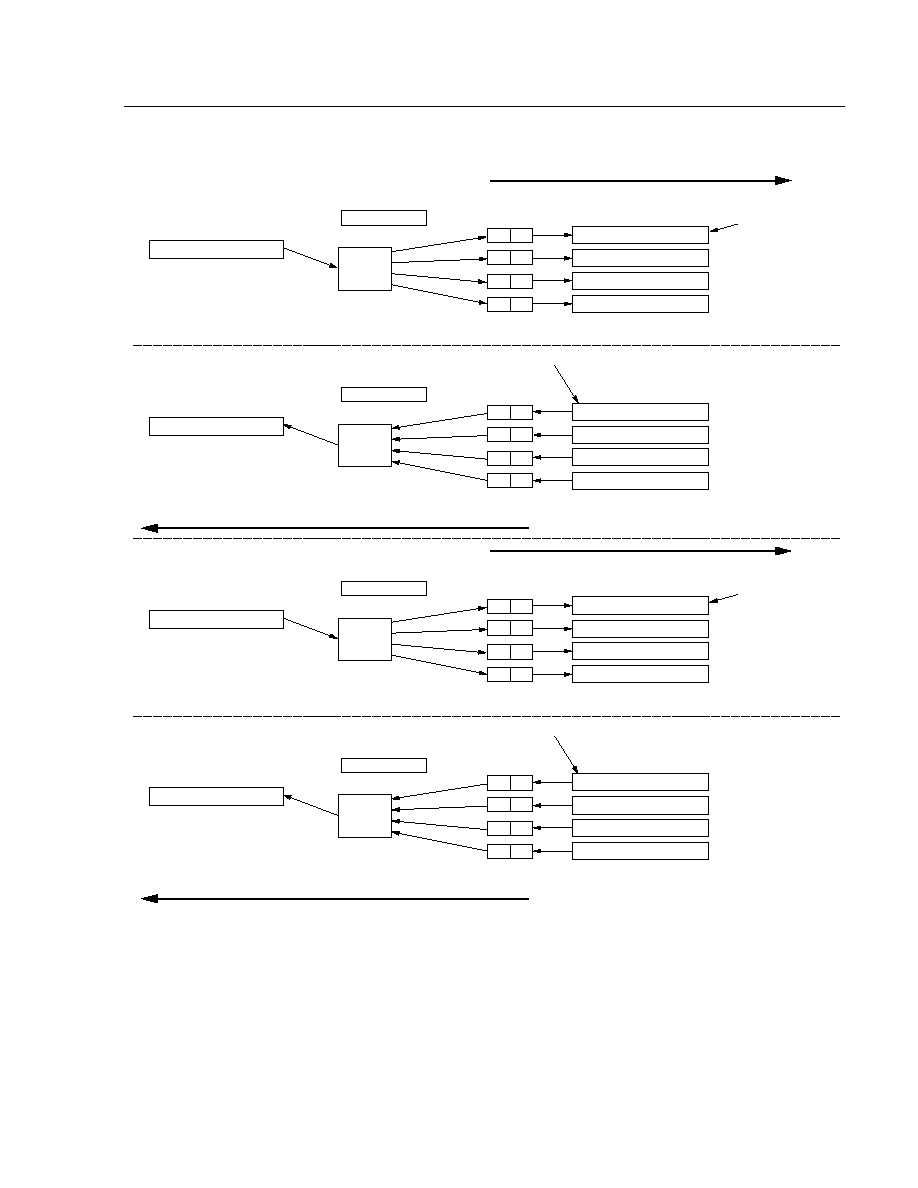

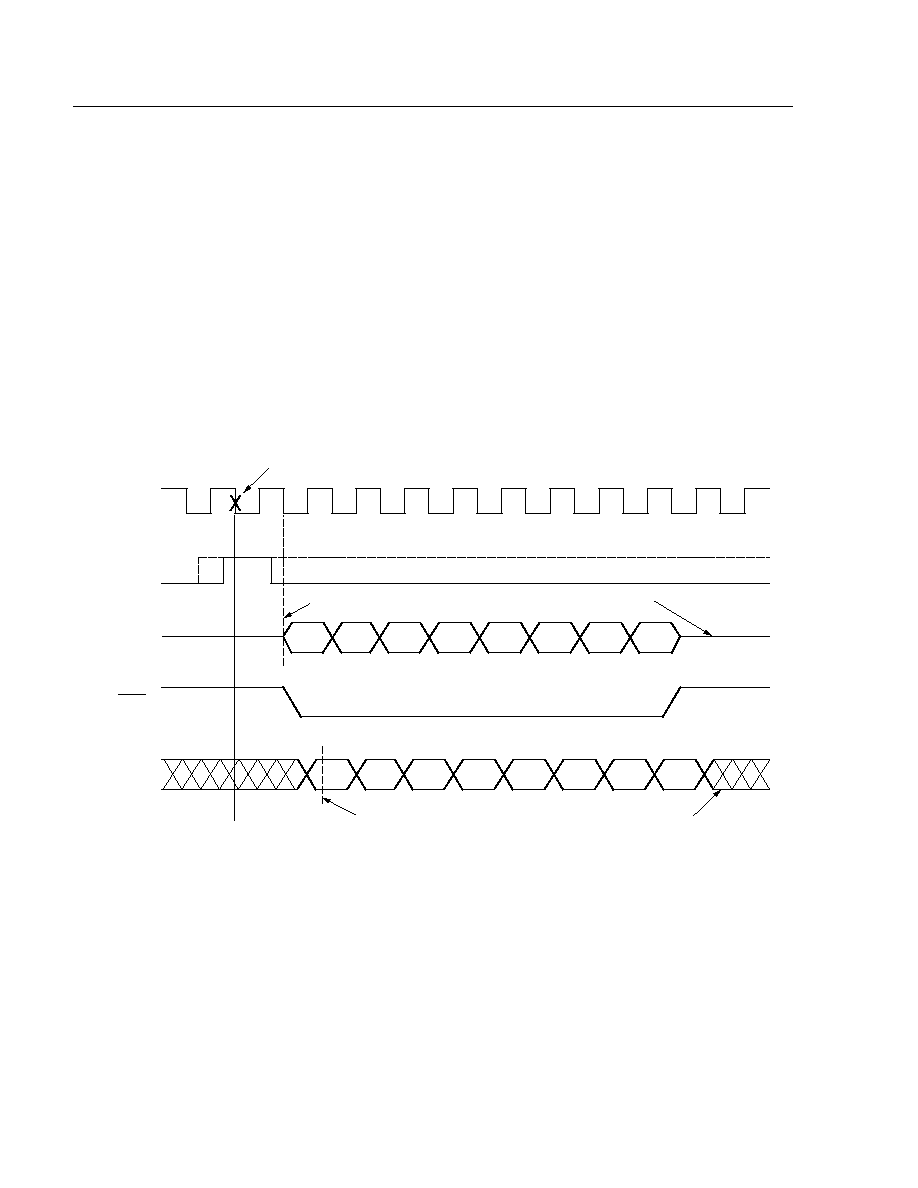

bit times after the beginning of the TDM frame. Figure 5 illustrates using the offsets to configure a system consist-

ing of four time slots, where the initial time slot aligns with the FS. For this system, FE = 0, CLKXI = 1, CLKRI = 0,

TSLT = 000000, and RSLT = 000001.

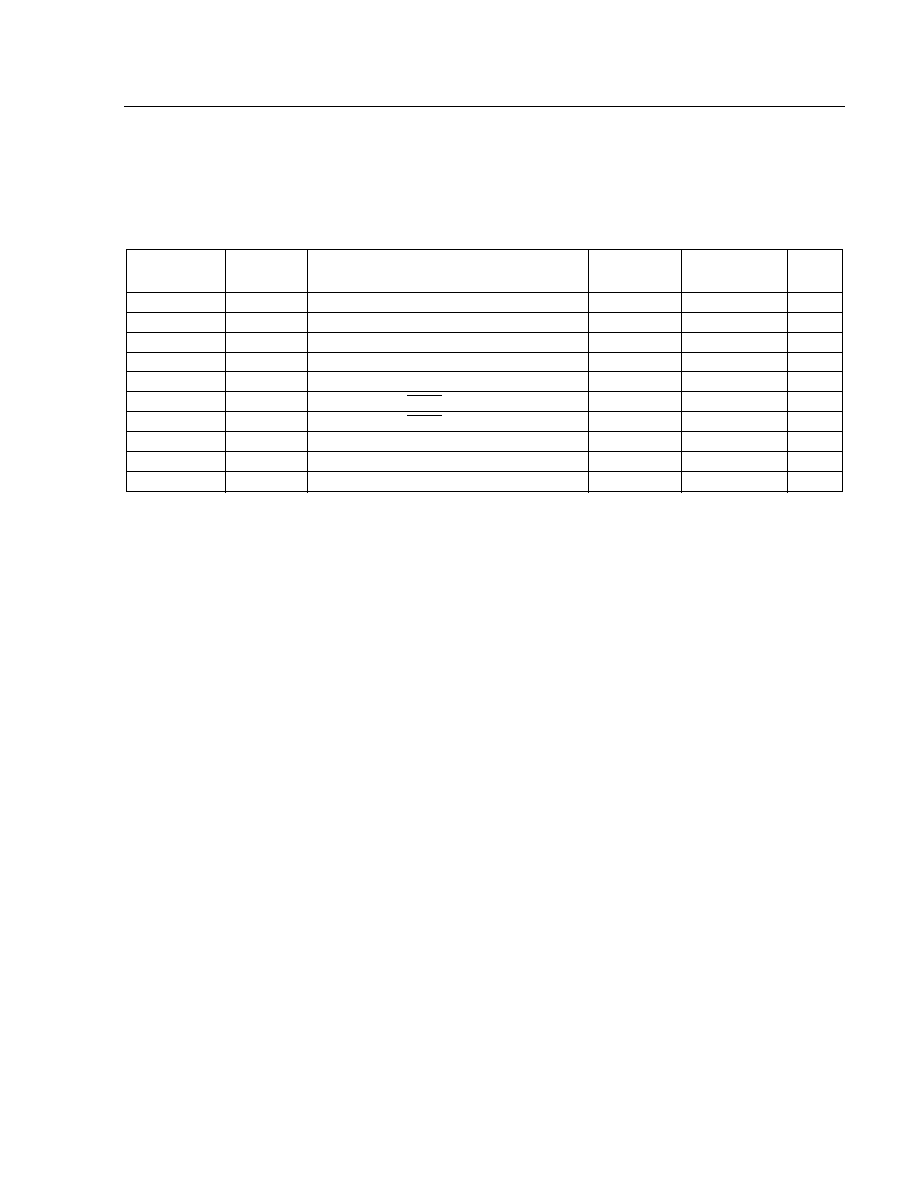

5-5031

Figure 5. Maximum Bit and Time-Slot Offsets for a Four Time-Slot System

Transmission During Unassigned Time Slots

During time slots when the HIFI-64 is not transmitting, the transmit data output 3-states (an external pull-up resistor

is recommended). This also occurs during masked bit times during a time slot (see the Bit Masking section). If pin

17 is configured to

TSCA

,

TSCA

is high during all time slots other than the assigned time slot and during masked bit

times in the assigned time slot.

Bit Order During Transmission

Data transmission is normally least significant bit (LSB) first per HDLC protocol specifications. In transparent mode,

data is also generated least significant bit first. However, when in the TDM highway mode (HWYEN R0--B7 = 1),

the order of transmission and the expected order for receiving can be reversed by programming the TLBIT and

RLBIT (R10--B6) and (R11--B6), respectively. These bits can be programmed independently of one another. In

other words, the HIFI-64 can be receiving LSB first but transmitting most significant bit (MSB) first, or vice versa.

The effect of TLBIT cleared to 0 is to reverse end-for-end the transmitter-generated data before transmission in the

time slot. All data is reversed, including flags, aborts, CRC, and user data. The effect of RLBIT cleared to 0 is to

reverse end-for-end the time-slot data before passing it to the receiver. RLBIT and TLBIT have no effect on the data

unless HWYEN (R0--B7) = 1.

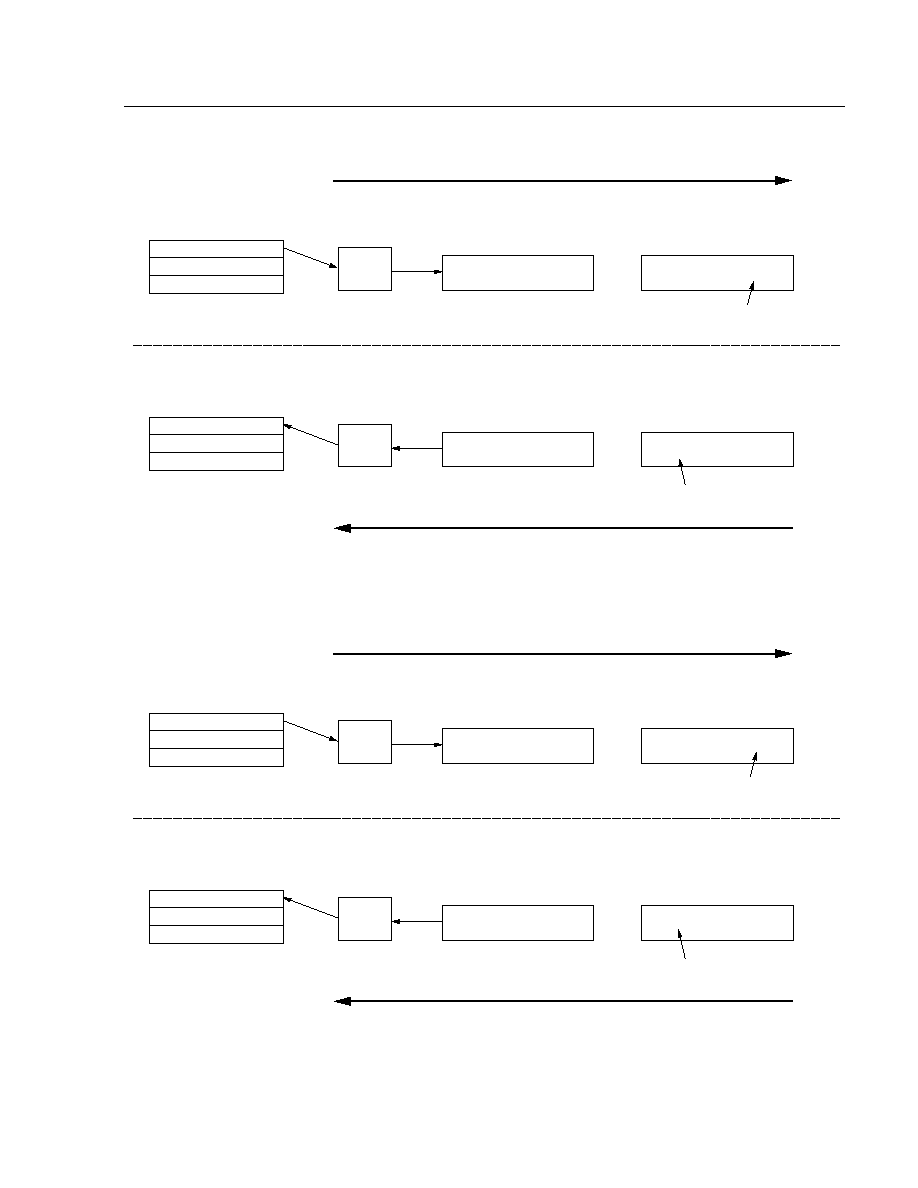

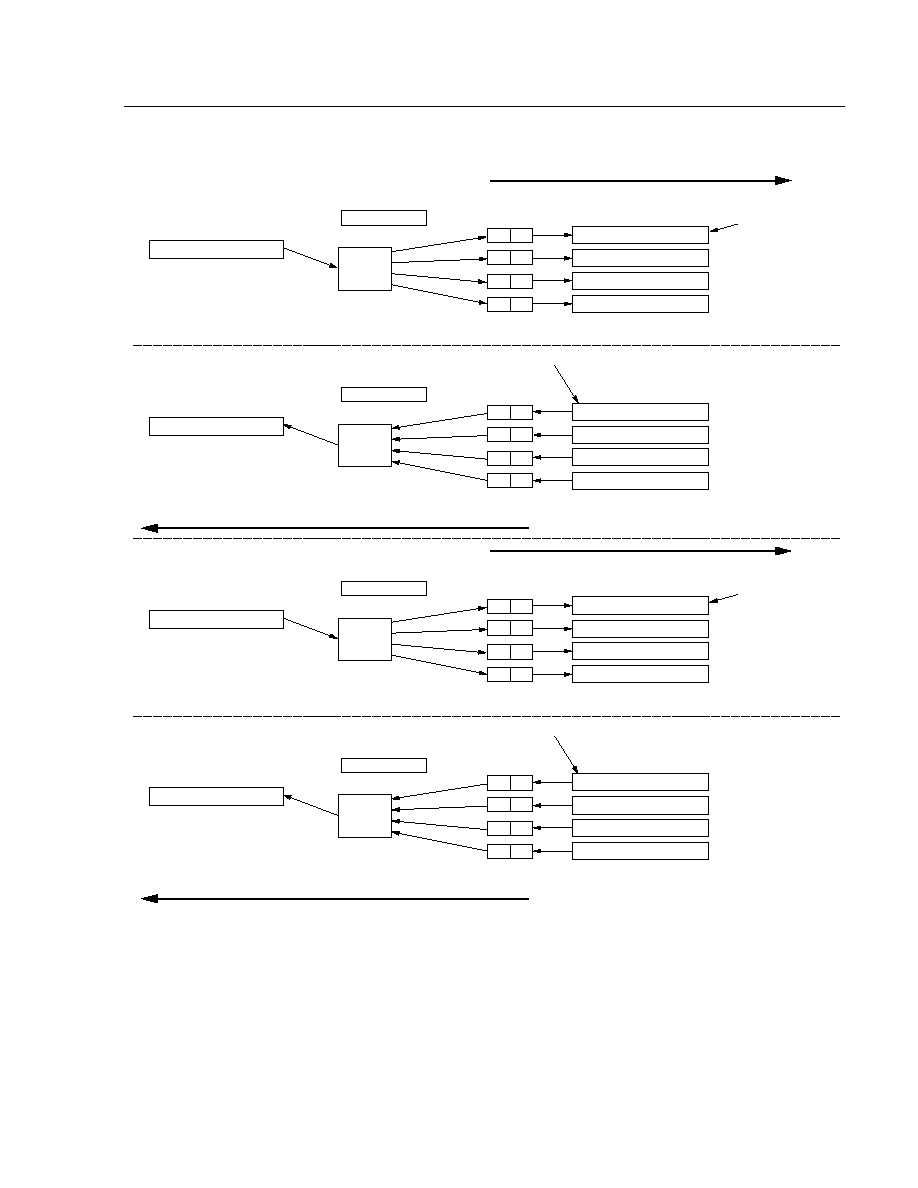

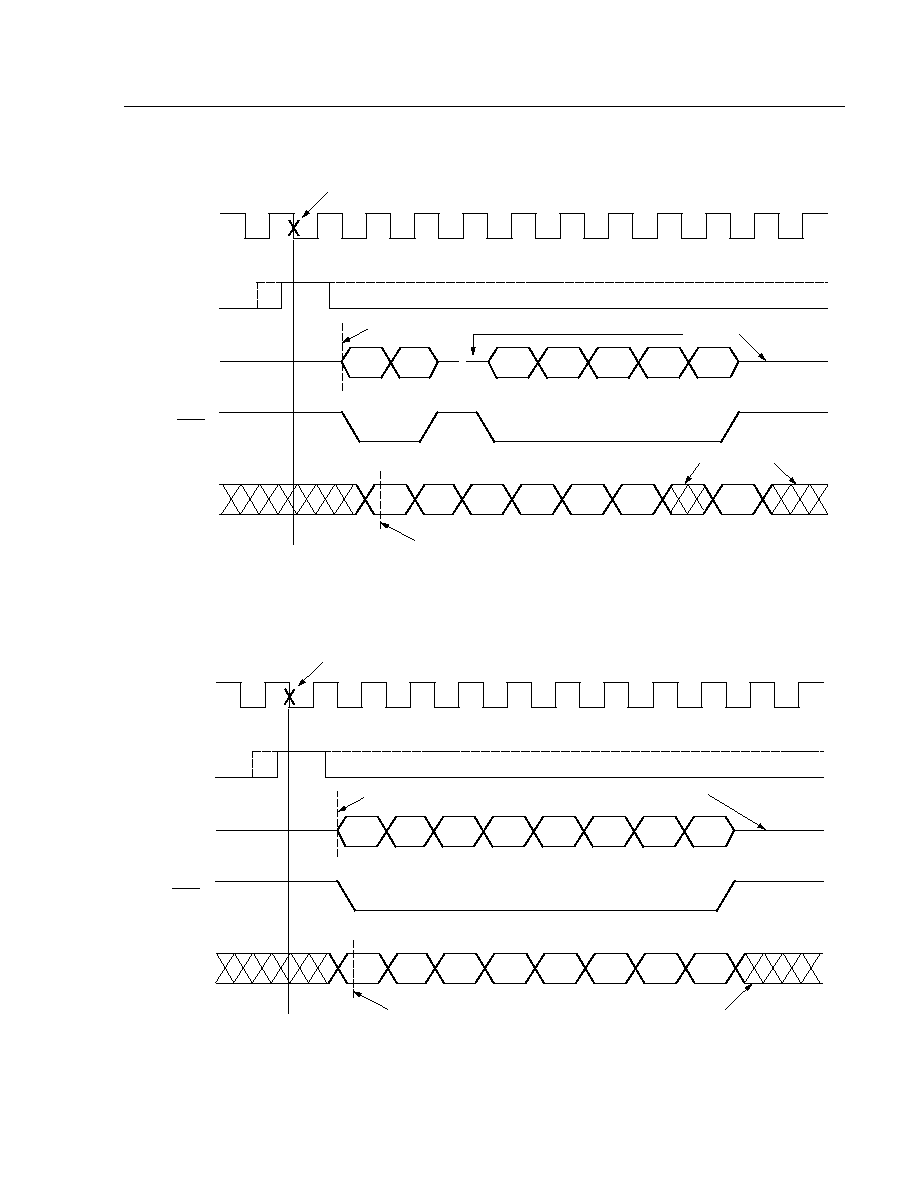

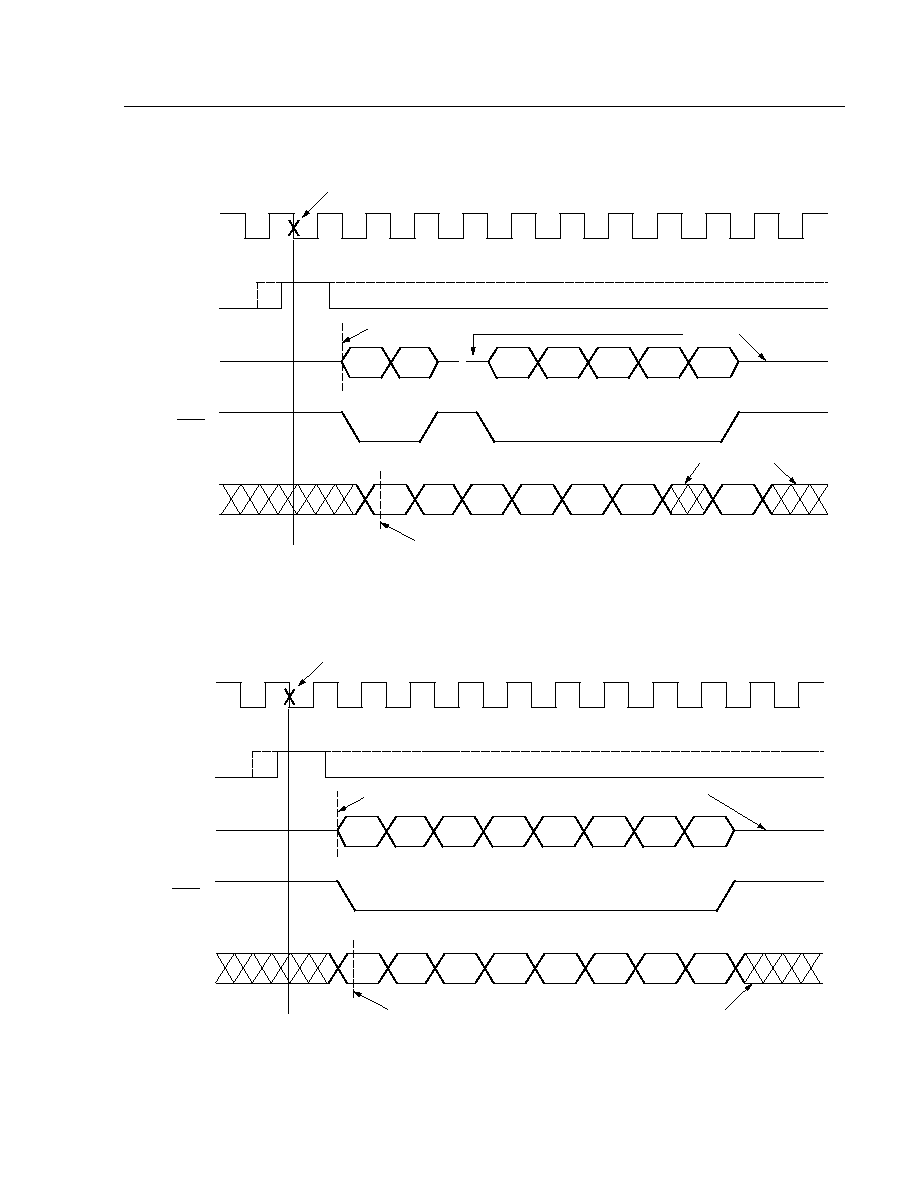

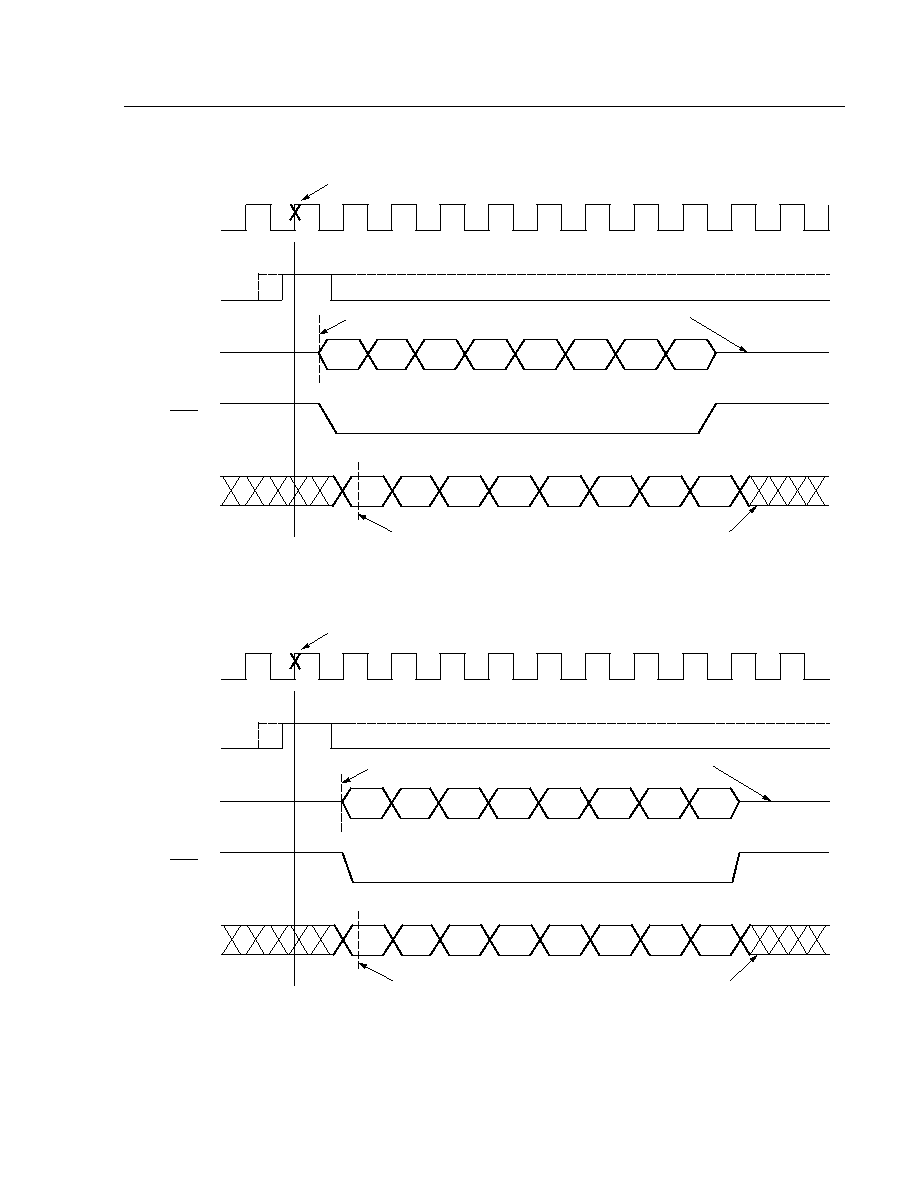

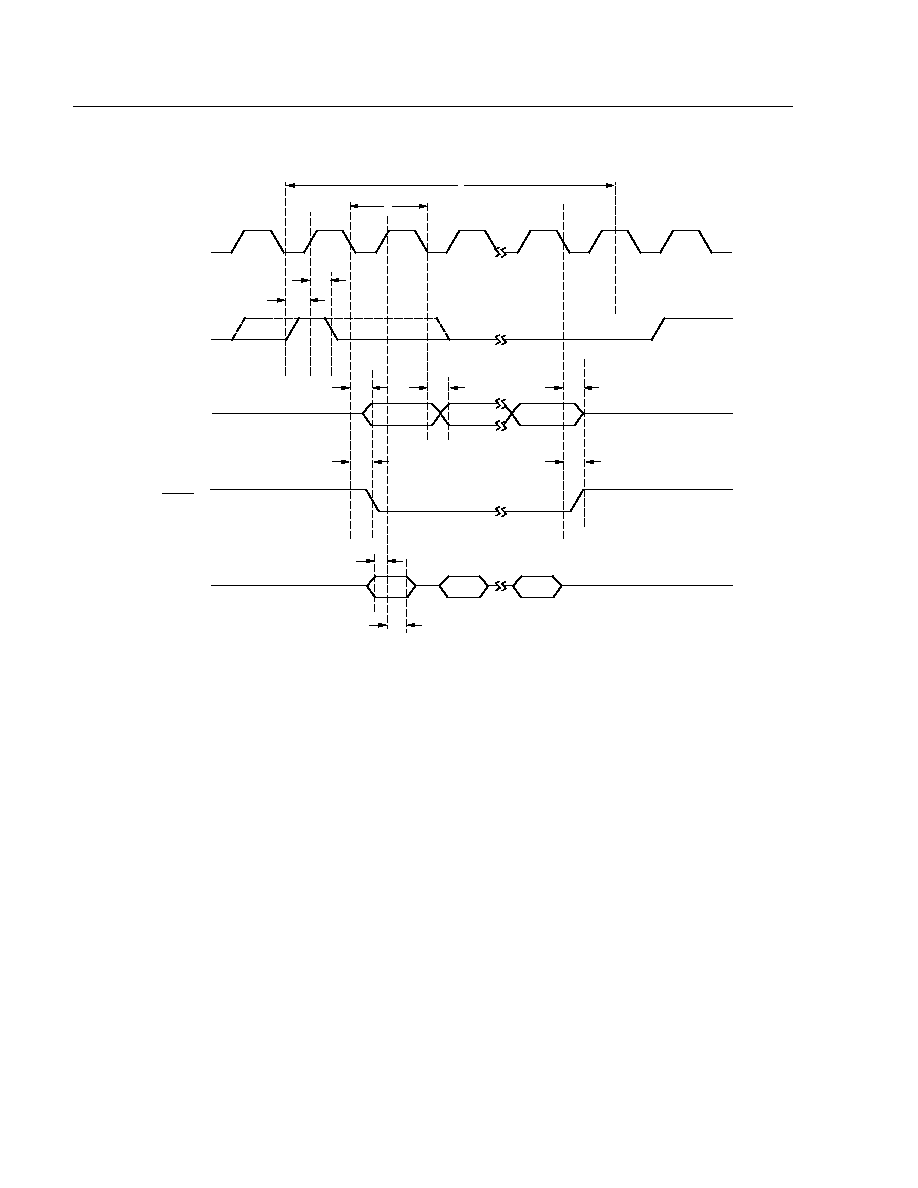

Figures 6 and 7 show how the transmission and reception of data is affected by adjusting TLBIT and RLBIT. The

convention used represents user data in the FIFO with lower-case letters and HDLC data as upper-case letters.

This convention is meant to indicate only that data in the FIFO and data transmitted or received during the time

slot(s) may not be identical bit-for-bit (i.e., zero-bit insertion and deletion--see the HDLC section of this document).

TS 0

TS 1

TS 2

TS 3

TS 0

TS 1

TDM DATA

FS

CLKX

CLKR

FIRST BIT

RECEIVED

TTSOF = 000011

RTSOF = 000011

TBOF = 111

RBOF = 111

FS LATCHED ON THIS EDGE

FIRST BIT TRANSMITTED

Lucent Technologies Inc.

15

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

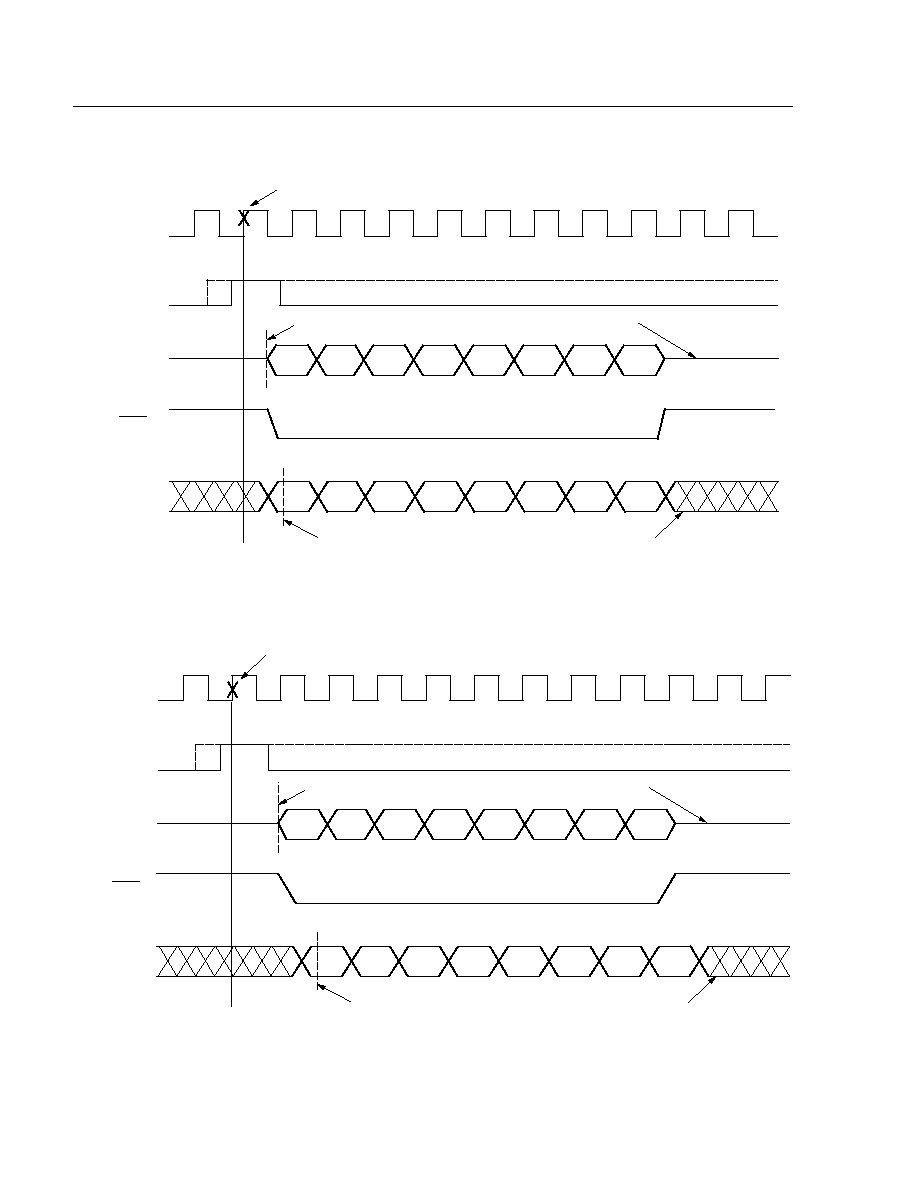

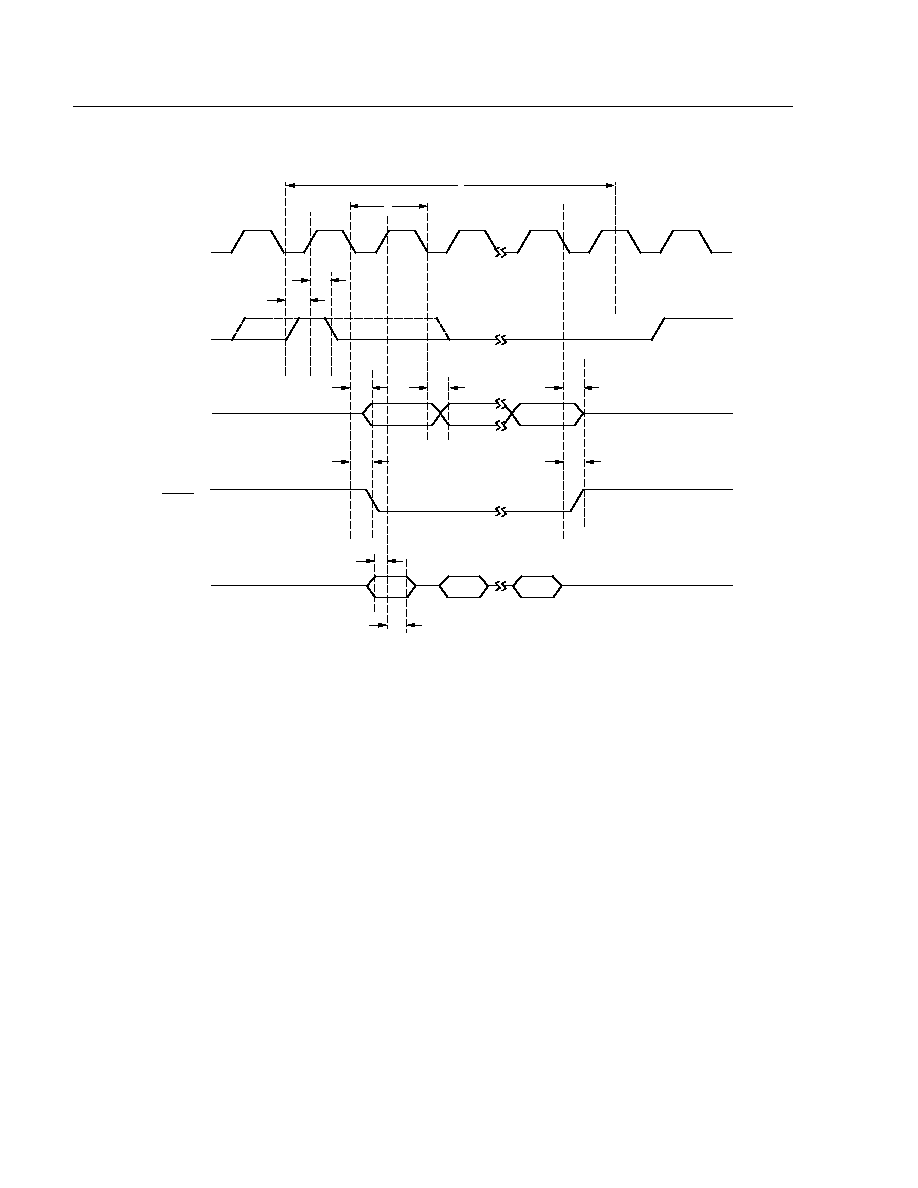

5-5032

Note: abcdefgh are not the same as ABCDEFGH due to HDLC processing.

Figure 6. Transmission and Reception of Data LSB First

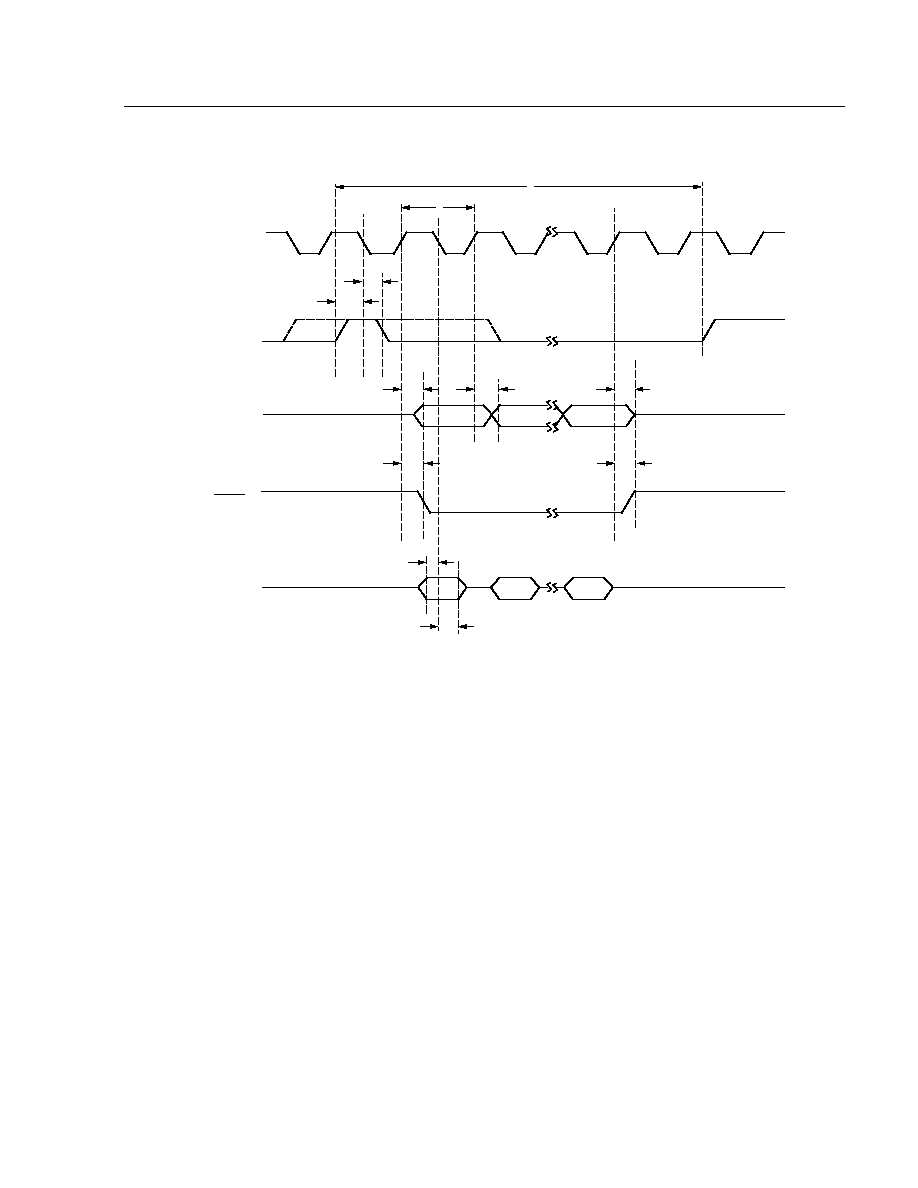

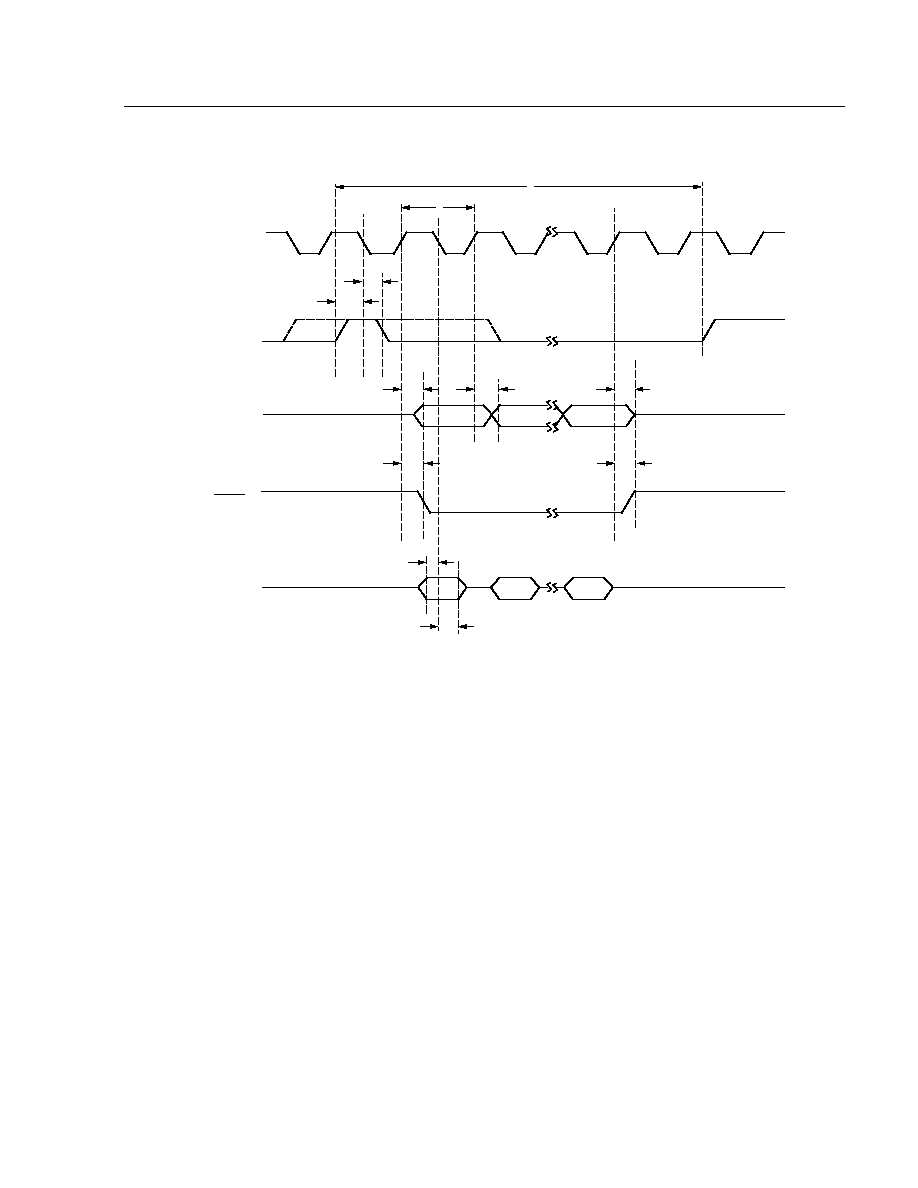

5-5033

Note: abcdefgh are not the same as ABCDEFGH due to HDLC processing.

Figure 7. Transmission and Reception of Data MSB First

a b c d e f g h

HDLC

A B C D E F G H

H G F E D C B A

TRANSMIT FIFO

TRANSMITTER HDLC

PROCESSES LSB FIRST

FIRST BIT

TRANSMITTED

TIME-SLOT DATA

MSB

BIT 7

LSB

BIT 0

MSB

BIT 7

LSB

BIT 0

DIRECTION OF TRANSMISSION

TLBIT = 1 (TRANSMIT LSB FIRST)

a b c d e f g h

HDLC

A B C D E F G H

H G F E D C B A

RECEIVE FIFO

RECEIVER HDLC

EXPECTS LSB FIRST

FIRST BIT

RECEIVED

TIME-SLOT DATA

LSB

BIT 0

MSB

BIT 7

MSB

BIT 7

LSB

BIT 0

DIRECTION OF RECEPTION

RLBIT = 1 (RECEIVE LSB FIRST)

a b c d e f g h

HDLC

A B C D E F G H

H G F E D C B A

TRANSMIT FIFO

TRANSMITTER HDLC

PROCESSES LSB FIRST

FIRST BIT

TRANSMITTED

TIME-SLOT DATA

MSB

BIT 7

LSB

BIT 0

MSB

BIT 7

LSB

BIT 0

DIRECTION OF TRANSMISSION

TLBIT = 0 (TRANSMIT MSB FIRST)

a b c d e f g h

HDLC

A B C D E F G H

H G F E D C B A

RECEIVE FIFO

RECEIVER HDLC

EXPECTS LSB FIRST

FIRST BIT

RECEIVED

TIME-SLOT DATA

LSB

BIT 0

MSB

BIT 7

MSB

BIT 7

LSB

BIT 0

DIRECTION OF RECEPTION

RLBIT = 0 (RECEIVE MSB FIRST)

16

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

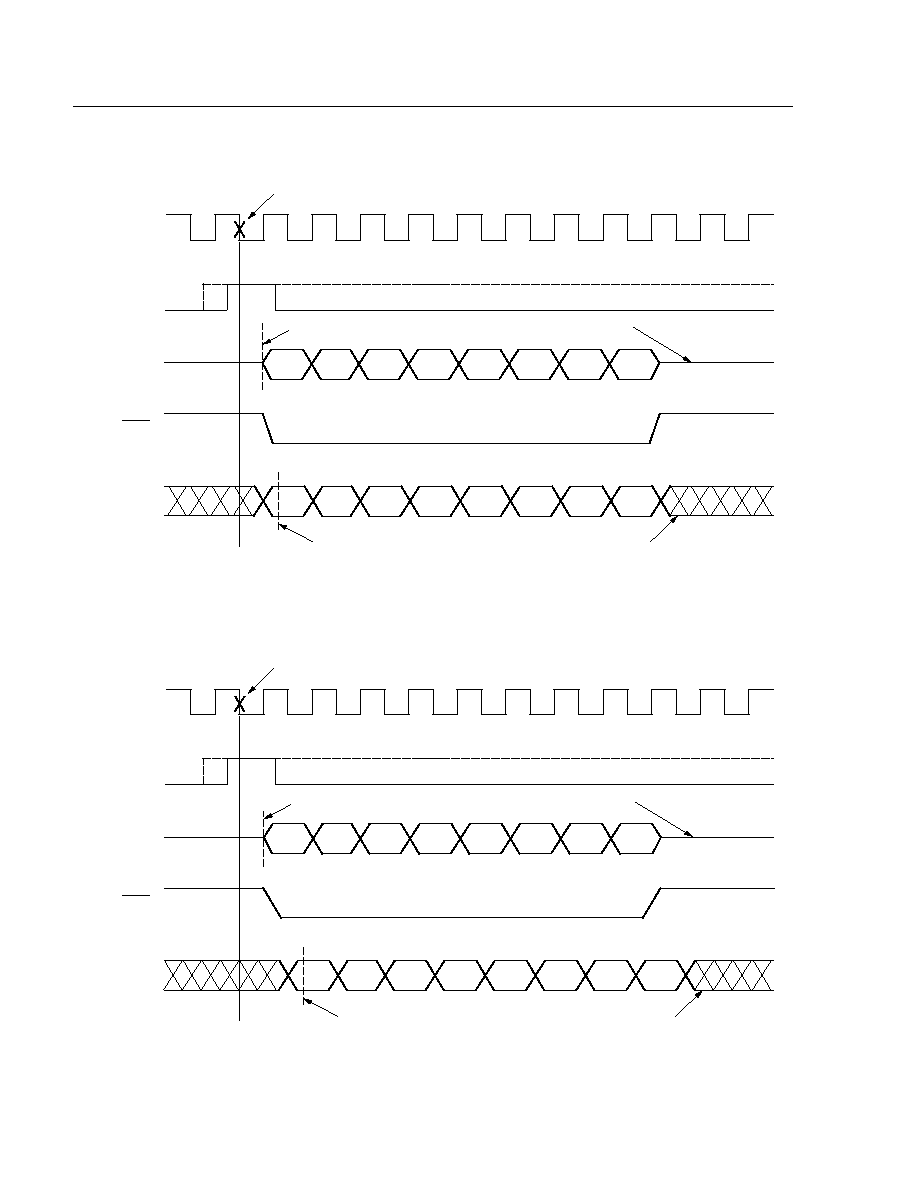

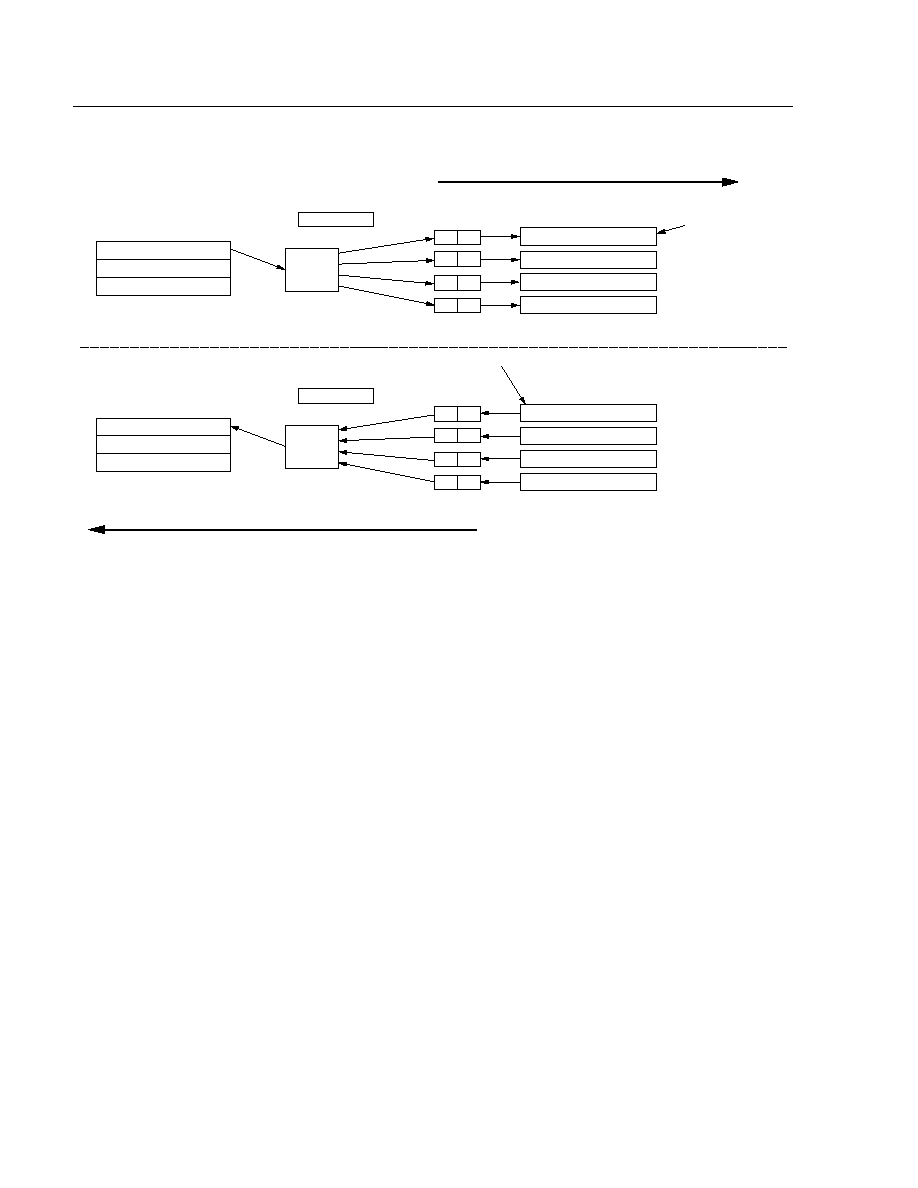

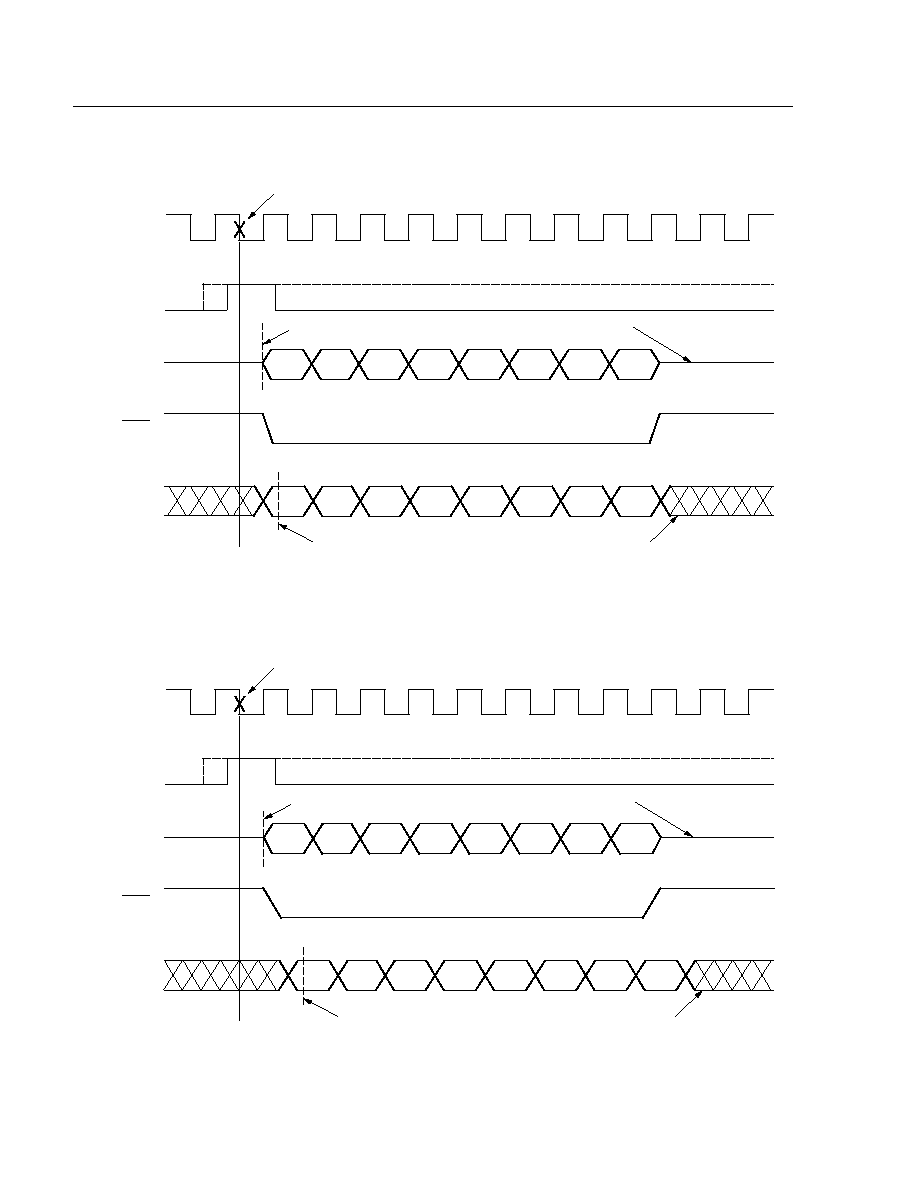

Bit Masking

When in the TDM highway mode (HWYEN, R0--B7 = 1), the HIFI-64 can be programmed to mask any combina-

tion of bits in a byte. As an example, this feature is used to process 16 kbits/s D-channel data where only 2 bits in

each byte are looked at when receiving, and where only 2 bits are transmitted during an 8-bit time slot. Using this

option, the HIFI-64 is able to support effective intermediate data rates of 8, 16, 24, 32, 40, 48, and 56 kbits/s.

The receiver ignores bit positions that are masked (cleared to 0) in the receiver bit mask register (R12). The trans-

mitter outputs high impedance (3-state) during the bit times specified (cleared to 0) in the transmitter bit mask reg-

ister (R13). The user can program any combination of bits to be masked in the receiver and transmitter

independently.

Upon chip reset, the default is as follows:

1. The receiver defaults to recognize all incoming data as valid (i.e., no masking).

2. The transmitter defaults to a state where all bits are masked.

The user must unmask the bits to be transmitted. This eliminates the problem of the HIFI-64 transmitting before the

time slot has been programmed in registers 7, 9, and 10.

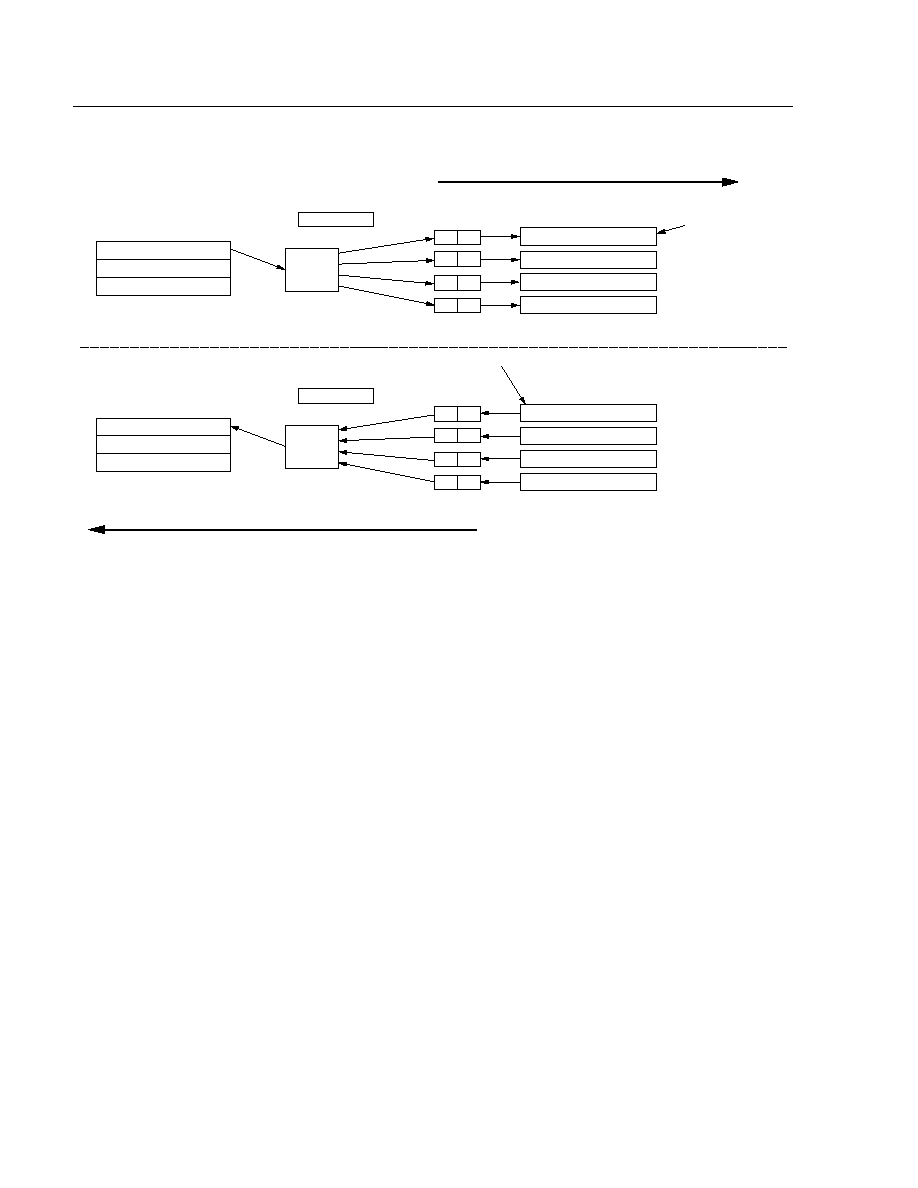

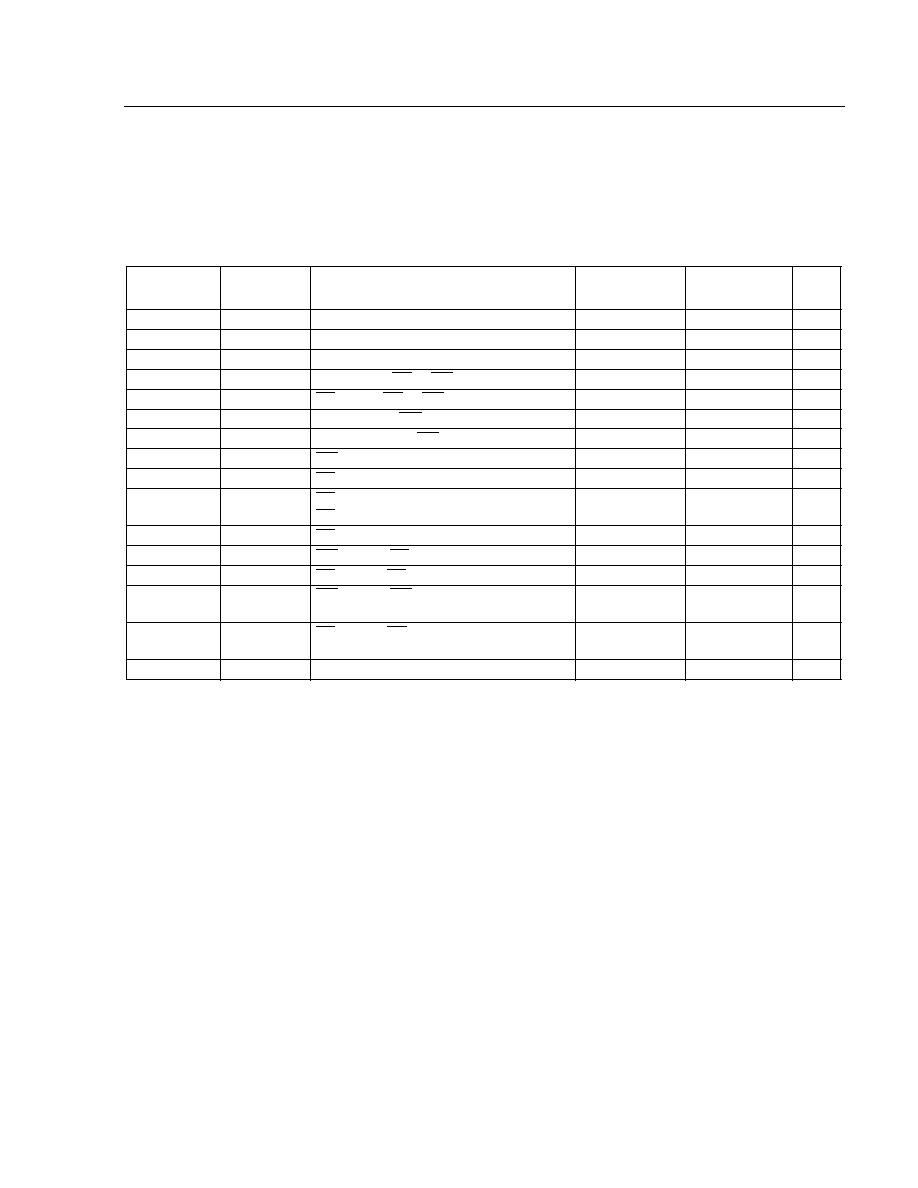

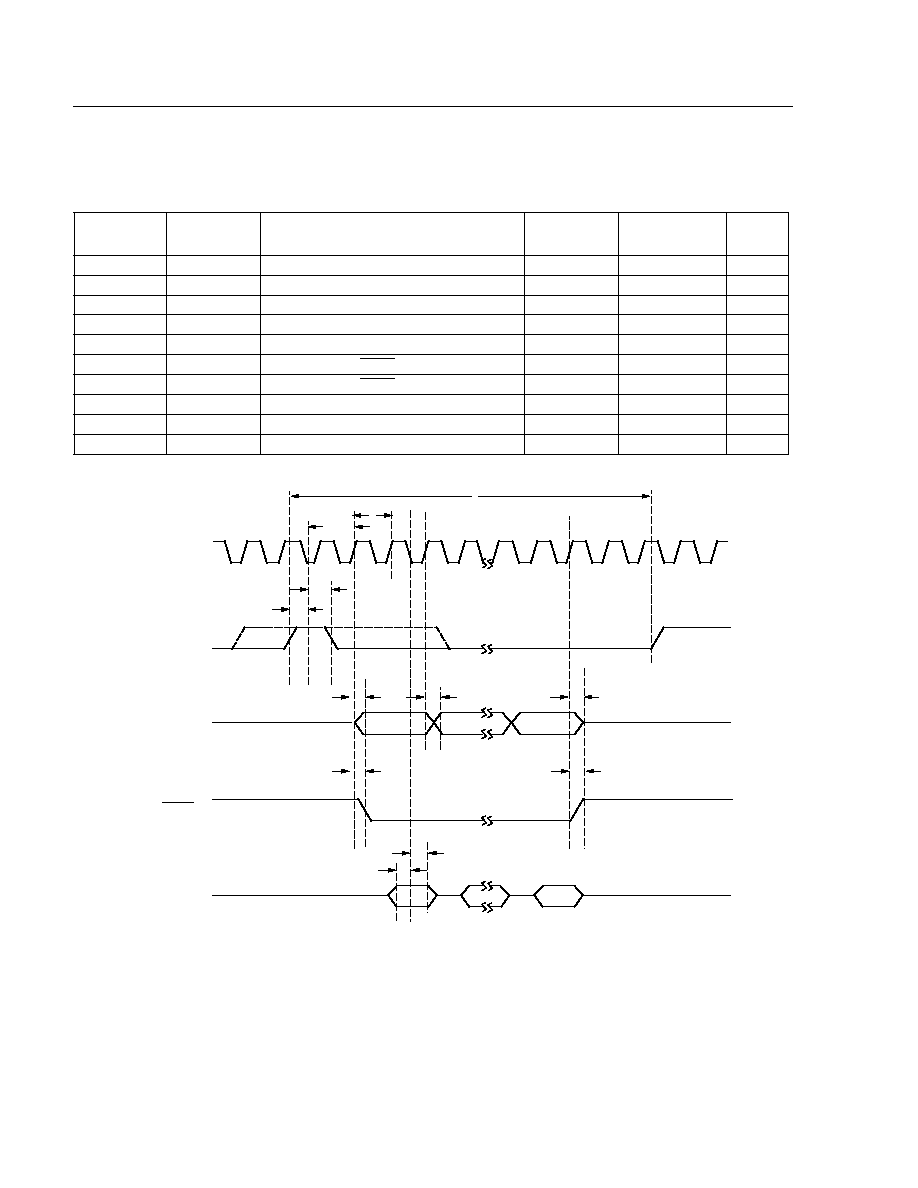

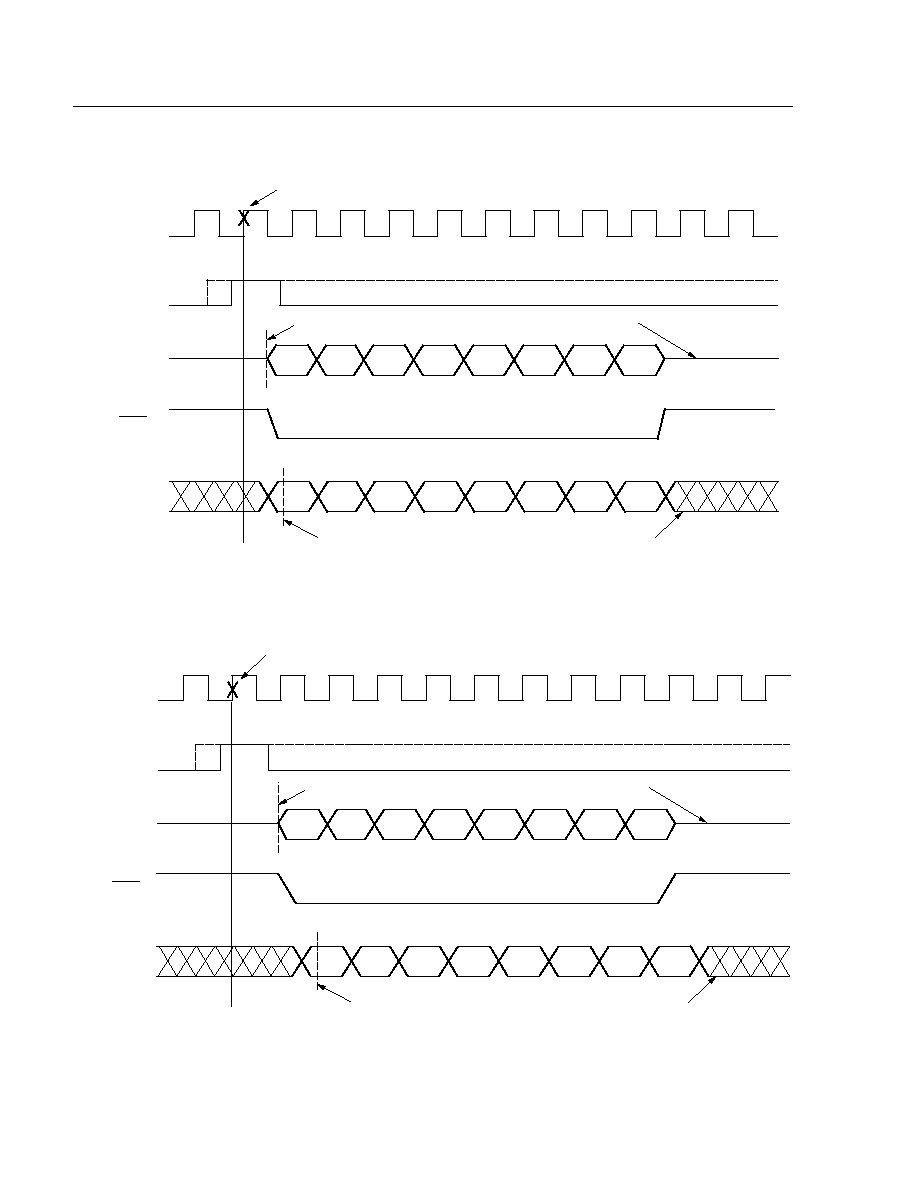

Figures 8 and 9 show how 16 kbits/s operation is achieved by using the bit-masking option.

Lucent Technologies Inc.

17

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

5-5034

Note: abcdefgh are not the same as ABCDEFGH due to HDLC processing.

Figure 8. 16 kbits/s Operation

a b c d e f g h

HDLC

3 3 3 3 3 3 * G H

TRANSMIT FIFO

TRANSMITTER HDLC

PROCESSES LSB FIRST

FIRST BIT

TRANSMITTED

TIME-SLOT DATA

MSB

BIT 7

LSB

BIT 0

DIRECTION OF TRANSMISSION

TLBIT = 1

(TRANSMIT LSB FIRST)

a b c d e f g h

HDLC

RECEIVE FIFO

RECEIVER HDLC

EXPECTS LSB FIRST

MSB

BIT 7

LSB

BIT 0

DIRECTION OF RECEPTION

TBM7

TBM0

G

H

E

F

C

D

A

B

(R13) TRANSMITTER BIT MASK

3 3 3 3 3 3 E F

3 3 3 3 3 3 C D

3 3 3 3 3 3 A B

*3 = 3-STATE.

1ST TIME SLOT

2ND TIME SLOT

3RD TIME SLOT

4TH TIME SLOT

H G X X X X X X*

FIRST BIT RECEIVED

TIME-SLOT DATA

0 0 0 0 0 0 1 1

RBM7

RBM0

H

G

F

E

D

C

B

A

(R12) RECEIVER BIT MASK

F E X X X X X X

D C X X X X X X

B A X X X X X X

*X = DON'T CARE. THESE BITS

ARE IGNORED BY THE RECEIVER.

1ST TIME SLOT

2ND TIME SLOT

3RD TIME SLOT

4TH TIME SLOT

RLBIT = 1

(RECEIVE LSB FIRST)

a b c d e f g h

HDLC

H G 3 3 3 3 3 3*

TRANSMIT FIFO

TRANSMITTER HDLC

PROCESSES LSB FIRST

FIRST BIT

TRANSMITTED

TIME-SLOT DATA

MSB

BIT 7

LSB

BIT 0

DIRECTION OF TRANSMISSION

TLBIT = 0

(TRANSMIT MSB FIRST)

a b c d e f g h

HDLC

RECEIVE FIFO

RECEIVER HDLC

EXPECTS LSB FIRST

MSB

BIT 7

LSB

BIT 0

DIRECTION OF RECEPTION

TBM7

TBM0

G

H

E

F

C

D

A

B

(R13) TRANSMITTER BIT MASK

F E 3 3 3 3 3 3

D C 3 3 3 3 3 3

B A 3 3 3 3 3 3

*3 = 3-STATE.

1ST TIME SLOT

2ND TIME SLOT

3RD TIME SLOT

4TH TIME SLOT

X*X X X X X G H

FIRST BIT RECEIVED

TIME-SLOT DATA

RBM7

RBM0

H

G

F

E

D

C

B

A

(R12) RECEIVER BIT MASK

X X X X X X E F

X X X X X X C D

X X X X X X A B

1ST TIME SLOT

2ND TIME SLOT

3RD TIME SLOT

4TH TIME SLOT

RLBIT = 0

(RECEIVE MSB FIRST)

0 0 0 0 0 0 1 1

0 0 0 0 0 0 1 1

0 0 0 0 0 0 1 1

*X = DON'T CARE. THESE BITS

ARE IGNORED BY THE RECEIVER.

18

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

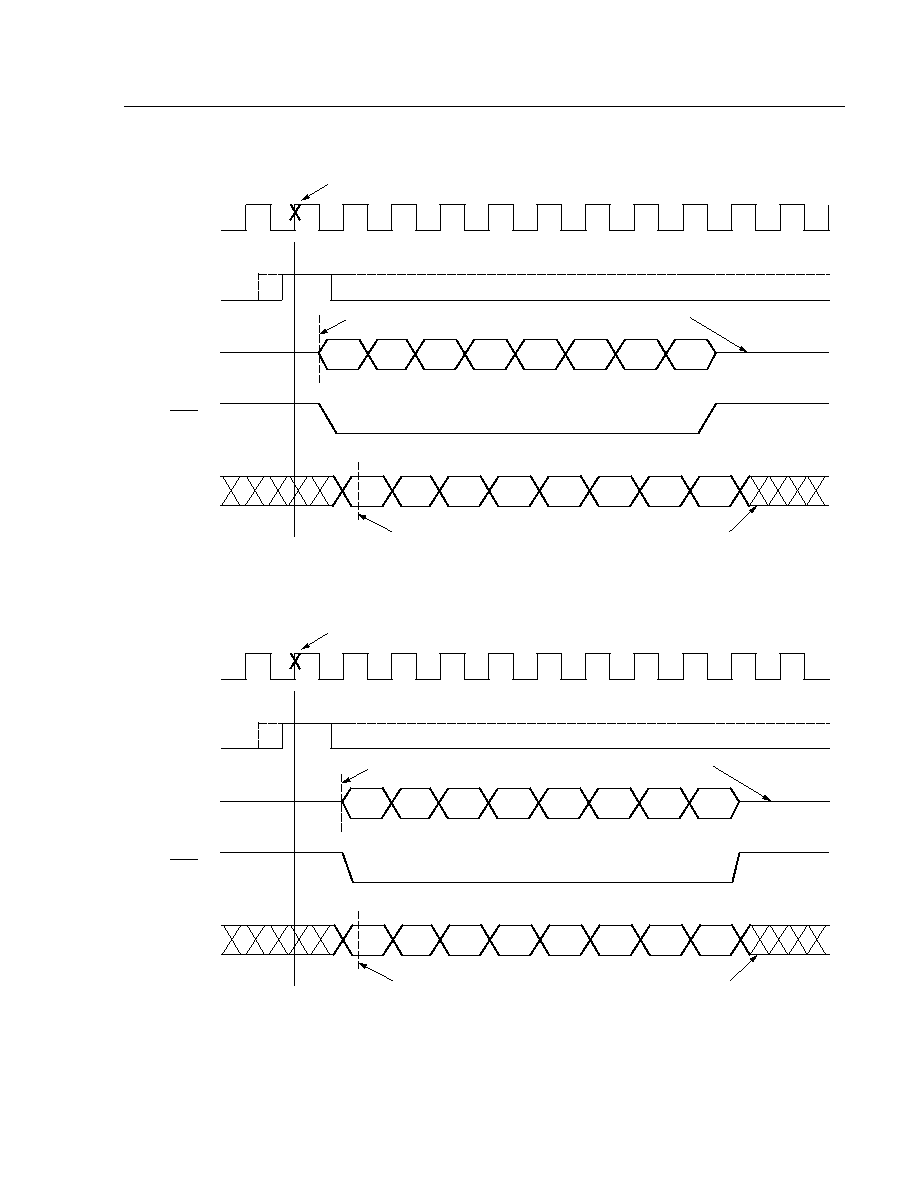

5-5035

Note: abcdefgh are not the same as ABCDEFGH due to HDLC processing.

Figure 9. 16 kbits/s Operation, MSB First

a b c d e f g h

HDLC

3 3 3 3 3 3* H G

TRANSMIT FIFO

TRANSMITTER HDLC

PROCESSES LSB FIRST

FIRST BIT

TRANSMITTED

TIME-SLOT DATA

MSB

BIT 7

LSB

BIT 0

DIRECTION OF TRANSMISSION

TLBIT = 0

(TRANSMIT MSB FIRST)

a b c d e f g h

HDLC

RECEIVE FIFO

RECEIVER HDLC

EXPECTS LSB FIRST

MSB

BIT 7

LSB

BIT 0

DIRECTION OF RECEPTION

11000000

TBM7

TBM0

G

H

E

F

C

D

A

B

(R13) TRANSMITTER BIT MASK

3 3 3 3 3 3 F E

3 3 3 3 3 3 D C

3 3 3 3 3 3 B A

*3 = 3-STATE.

1ST TIME SLOT

2ND TIME SLOT

3RD TIME SLOT

4TH TIME SLOT

G H X X X X X X*

FIRST BIT RECEIVED

TIME-SLOT DATA

11000000

RBM7

RBM0

H

G

F

E

D

C

B

A

(R12) RECEIVER BIT MASK

E F X X X X X X

C D X X X X X X

A B X X X X X X

*X = DON'T CARE. THESE BITS

ARE IGNORED BY THE RECEIVER.

1ST TIME SLOT

2ND TIME SLOT

3RD TIME SLOT

4TH TIME SLOT

RLBIT = 0

(RECEIVE MSB FIRST)

Lucent Technologies Inc.

19

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

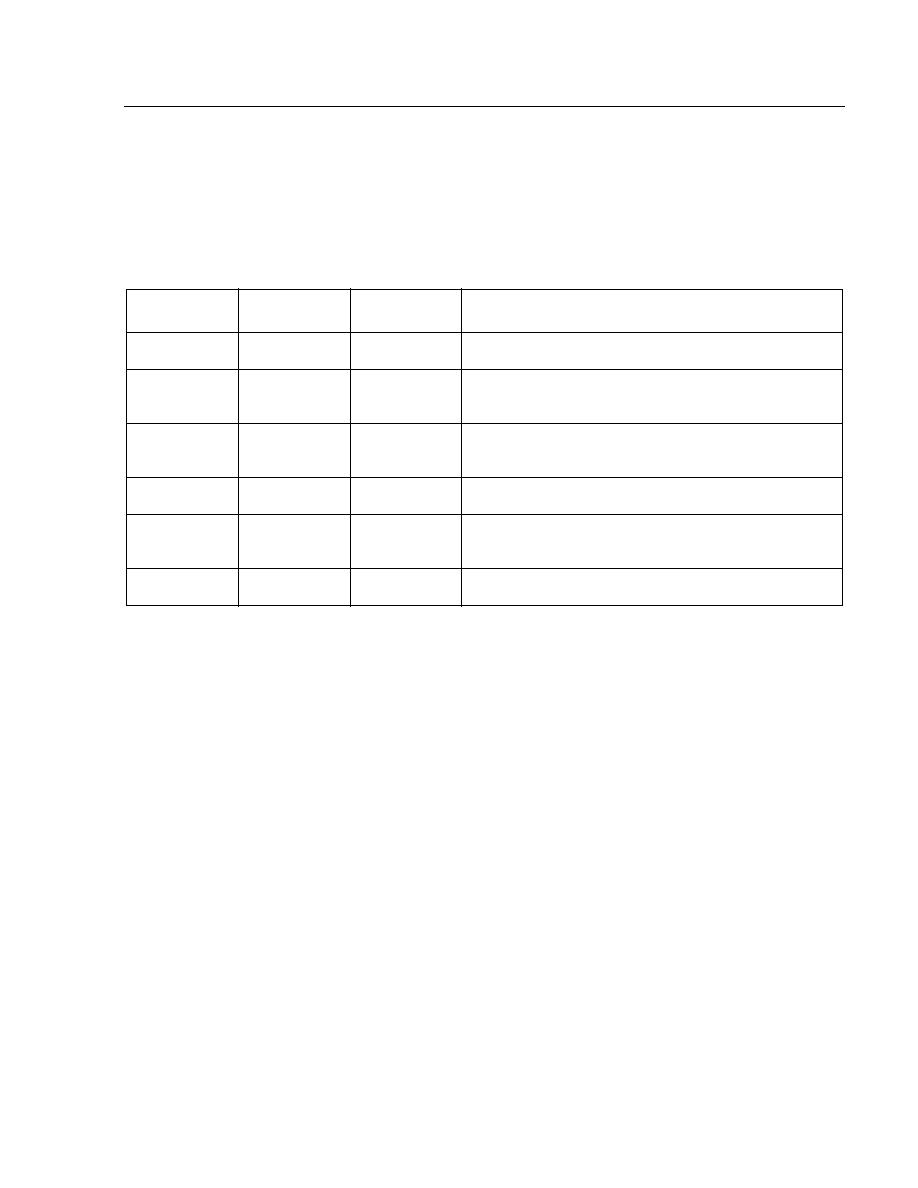

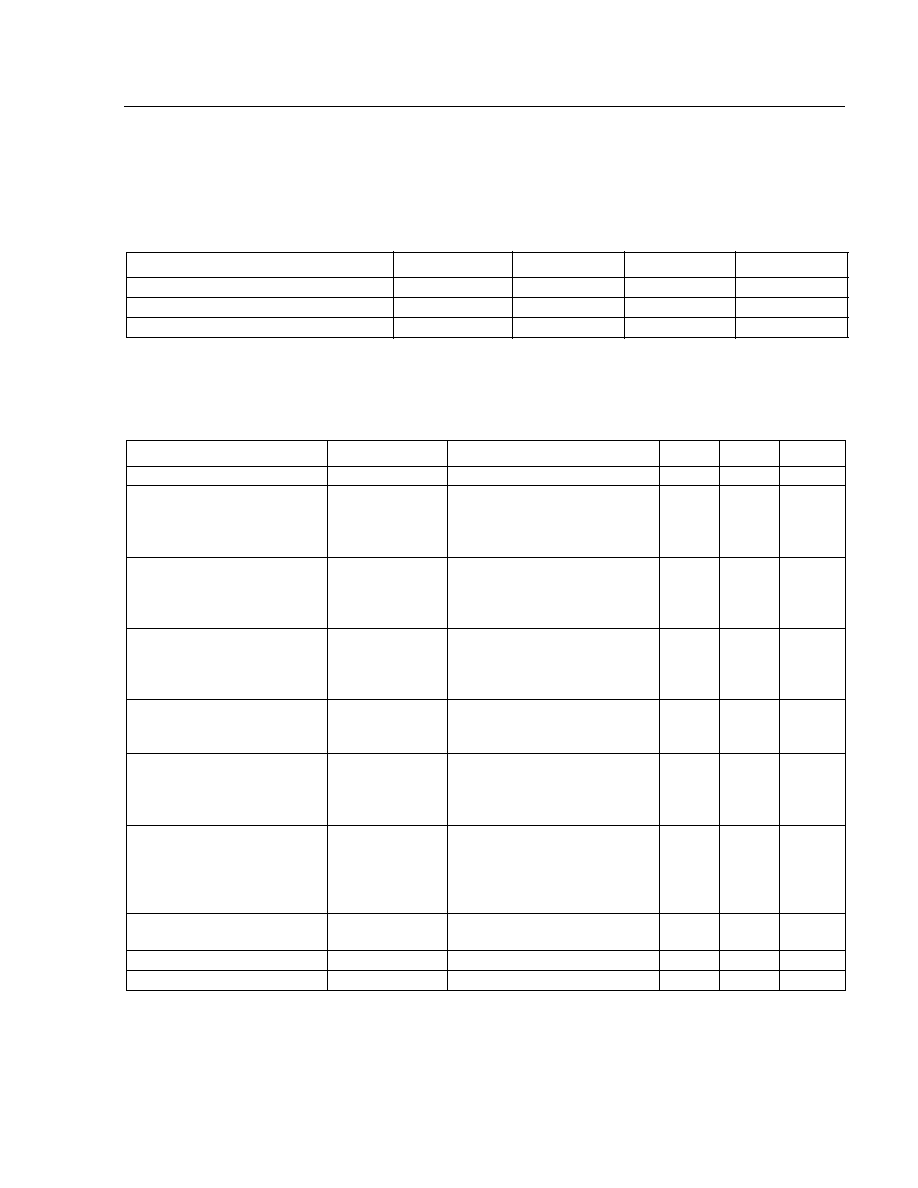

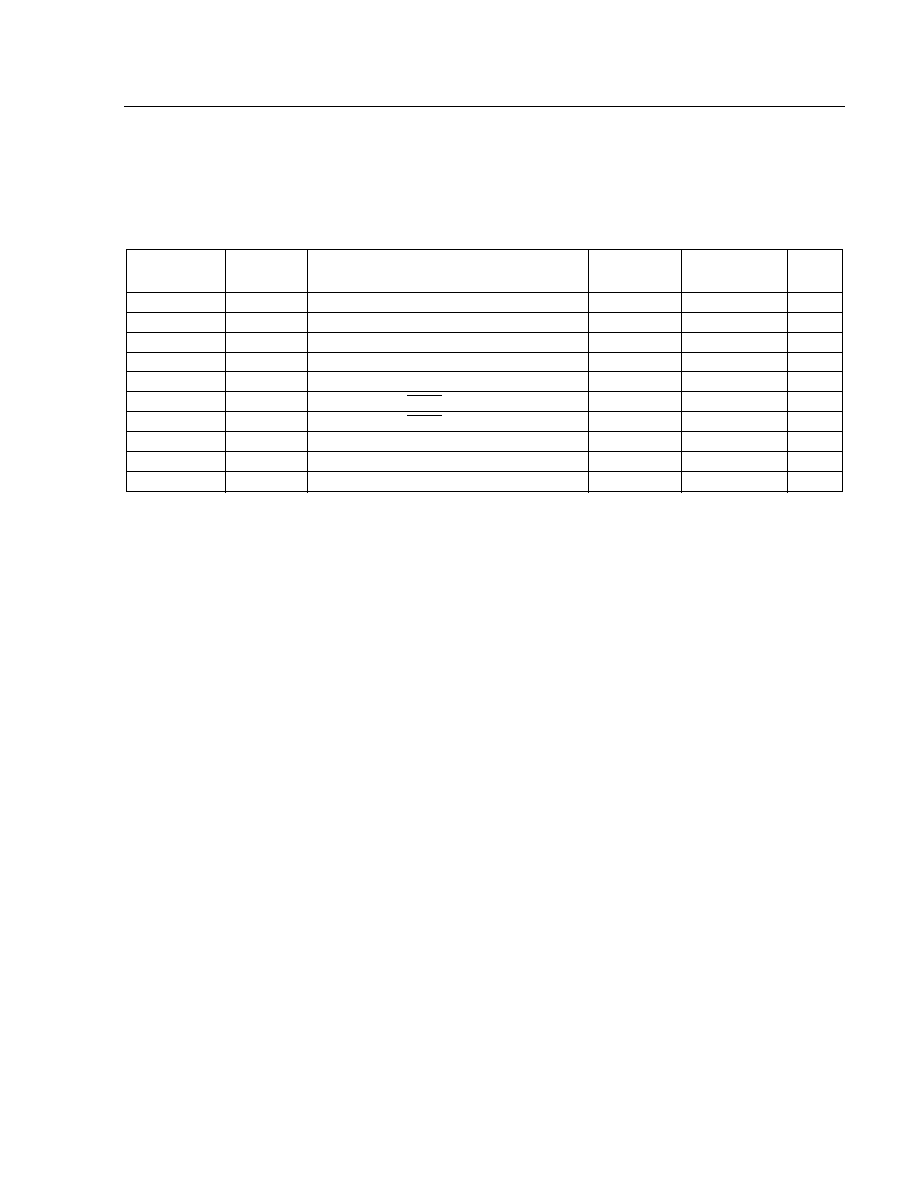

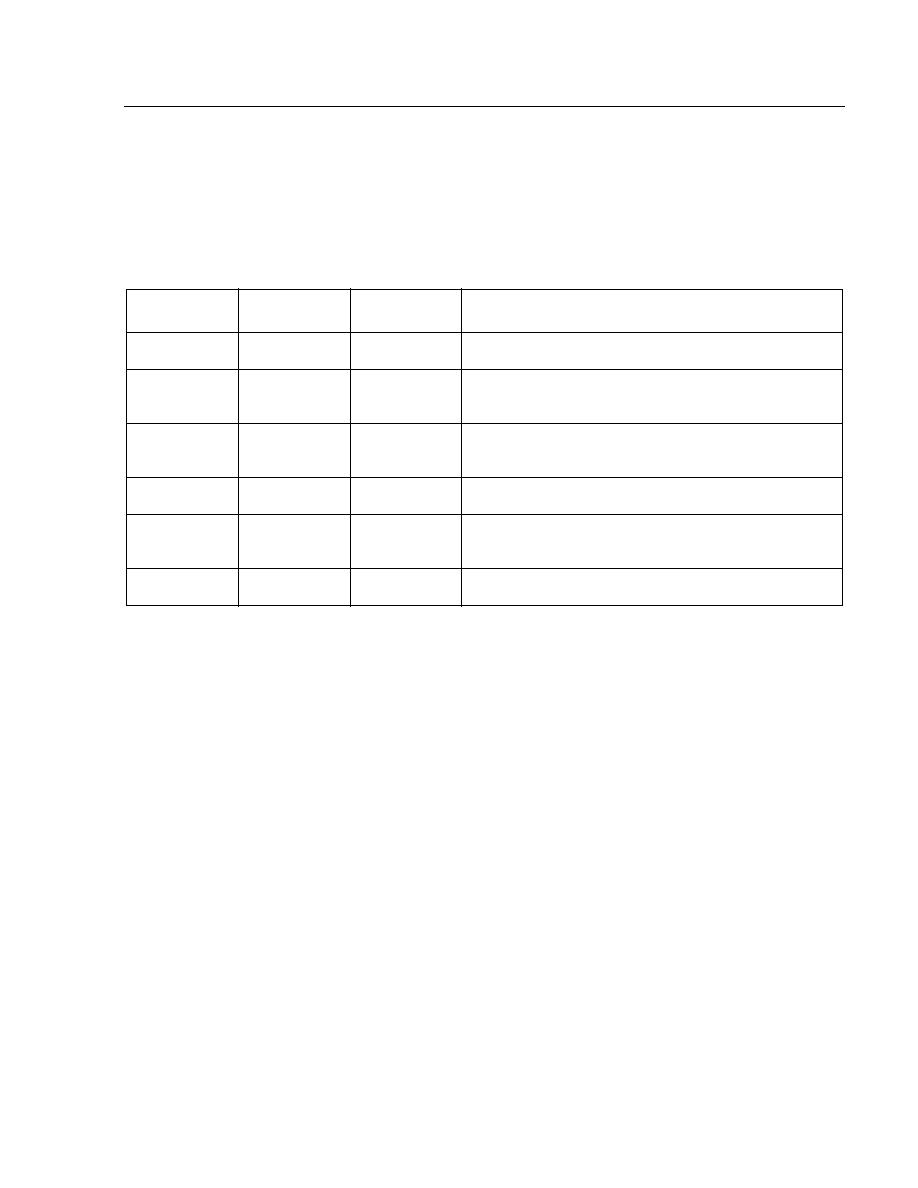

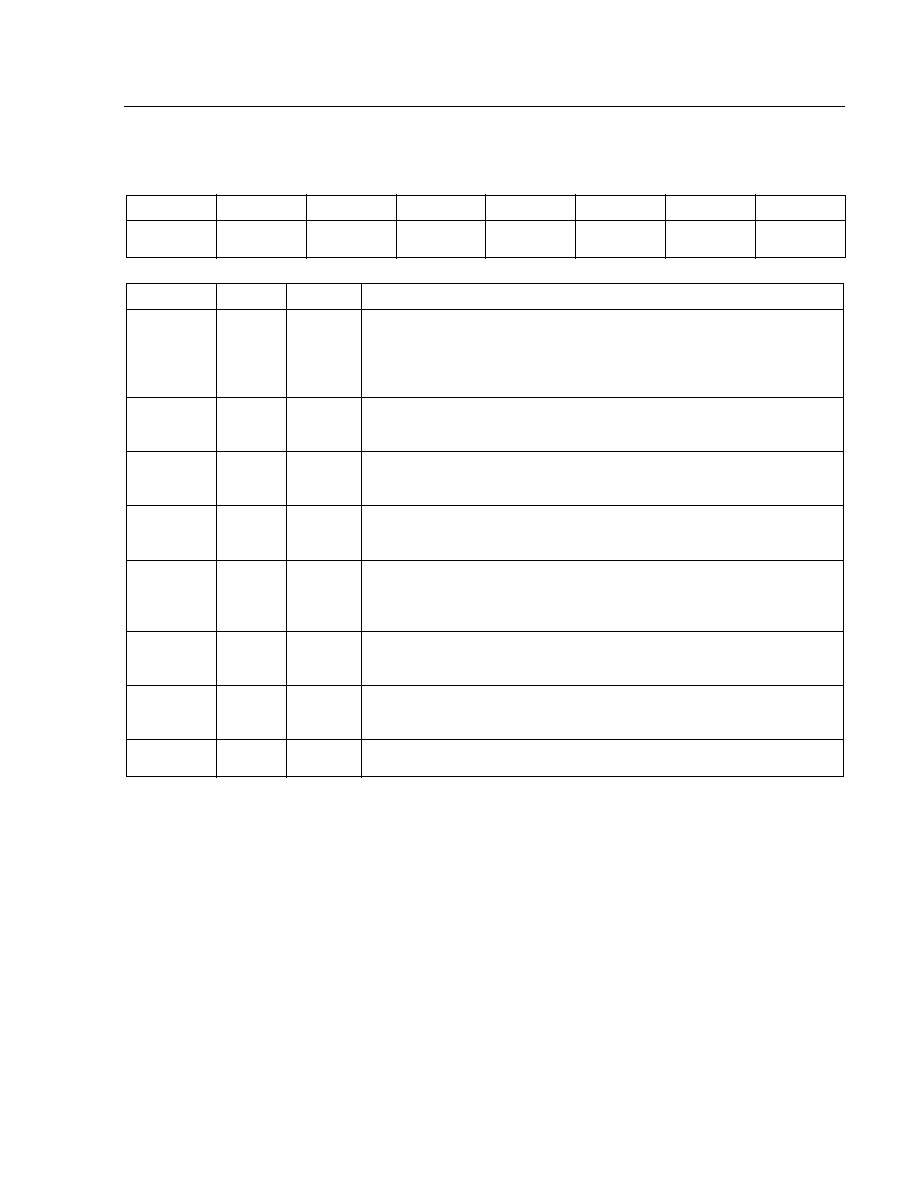

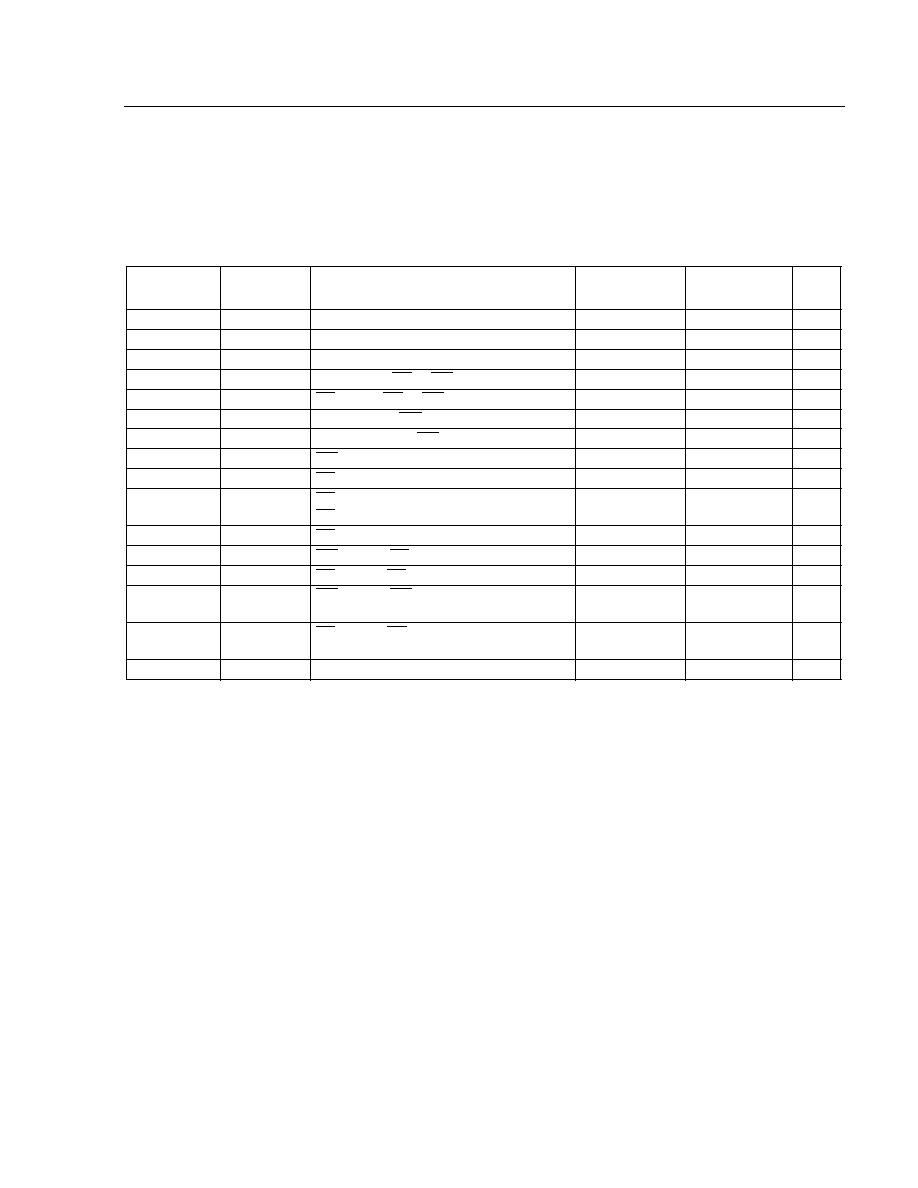

SLD and IOM2 Examples

Example register settings for configuring to SLD, IOM2, or K2 TDM highways are shown below. These settings

assume HWYEN (R0--B7) = 1 and FSPOL (R0--B6) = 1.

HDLC Operation

This section describes the standard HDLC functions performed by the HIFI-64. HDLC operation is the default

mode of operation. The transmitter accepts parallel data from the transmit FIFO, converts it to a serial bit stream,

provides bit stuffing as necessary, adds the CRC and the opening and closing flags, and sends the framed serial

bit stream on the selected transmit data pin(s). The receiver accepts serial data on the selected receive data pin,

identifies frames for proper format, reconstructs data bytes, provides bit destuffing as necessary, and loads parallel

data in the receive FIFO. HDLC frames on the serial link have the following format:

All bits between the opening flag and the CRC are considered user data bits. User data bits such as the address,

control, and information fields for LAPB or LAPD frames are fetched from the transmit FIFO for transmission.

Received user data bits are stored in the FIFO buffers. The 16 bits preceding the closing flag are the frame check

sequence or cyclic redundancy check (CRC) bits.

Zero-Bit Insertion/Deletion (Bit Stuffing/Destuffing)

The HDLC protocol recognizes three special bit patterns: flags, aborts, and idles. These patterns have the com-

mon characteristic of containing at least six consecutive 1s. A user data byte can contain one of these special pat-

terns. Transmitter zero-bit stuffing is done on user data and CRC fields of the frame to avoid transmitting one of

these special patterns. Whenever five 1s occur between flags, a 0 bit is automatically inserted after the fifth 1, prior

to transmission of the next bit. On the receive side, if five successive 1s are detected followed by a 0, the 0 is

assumed to have been inserted and is deleted (bit destuffing).

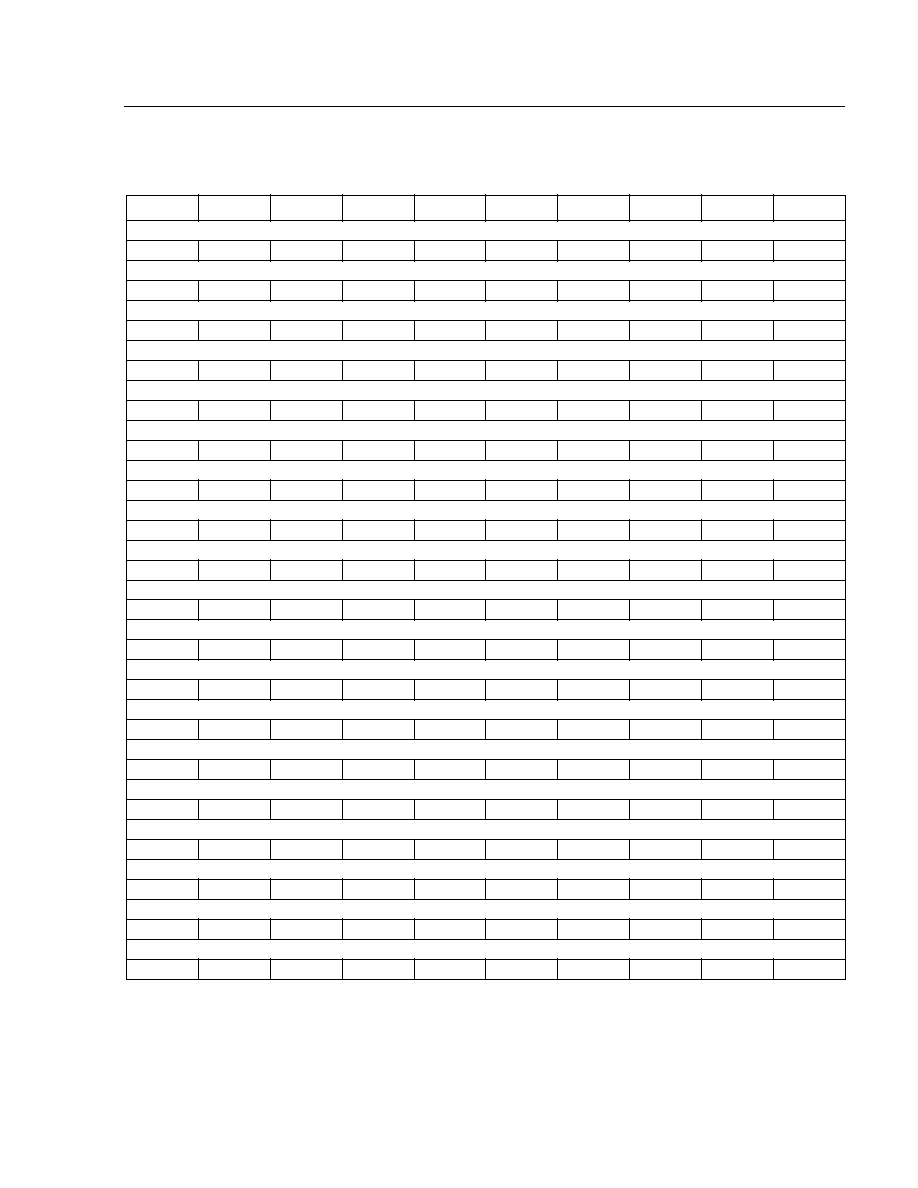

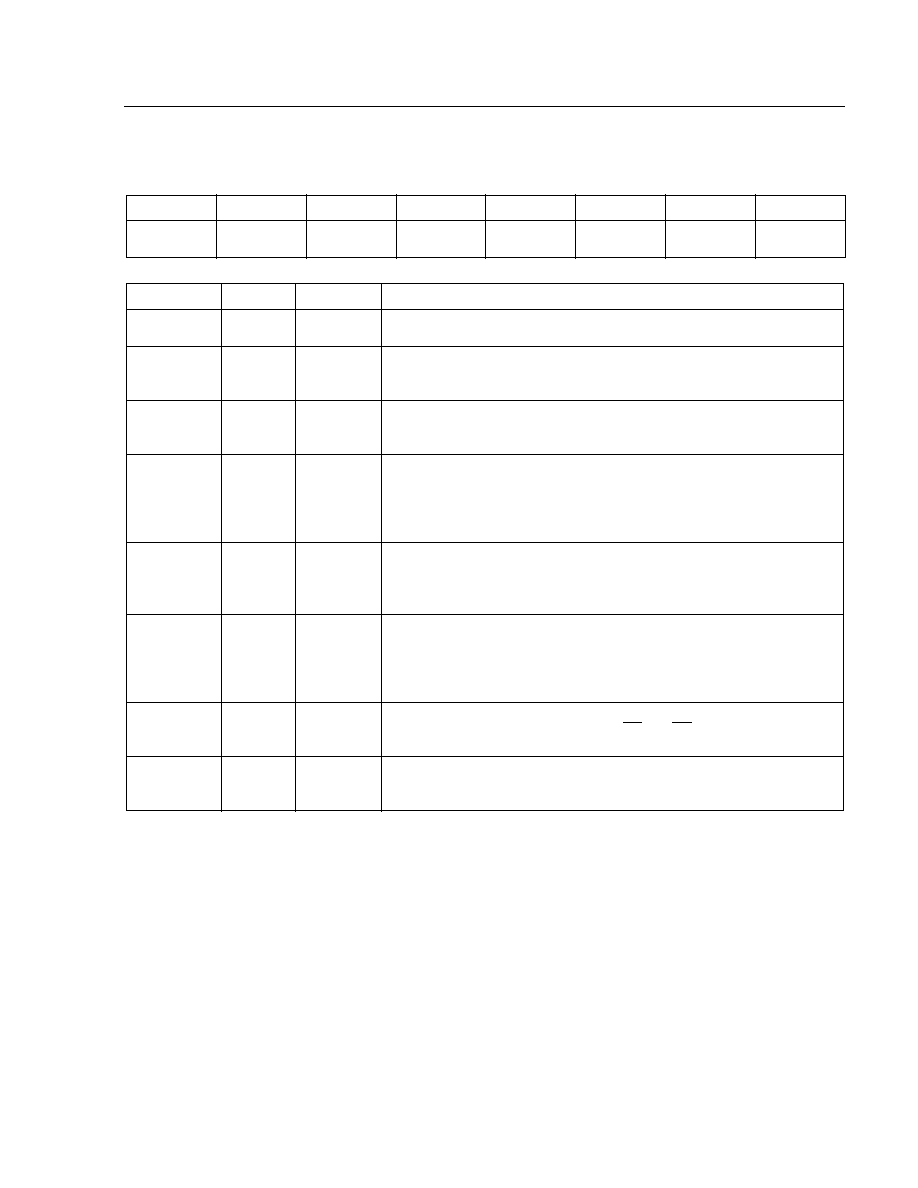

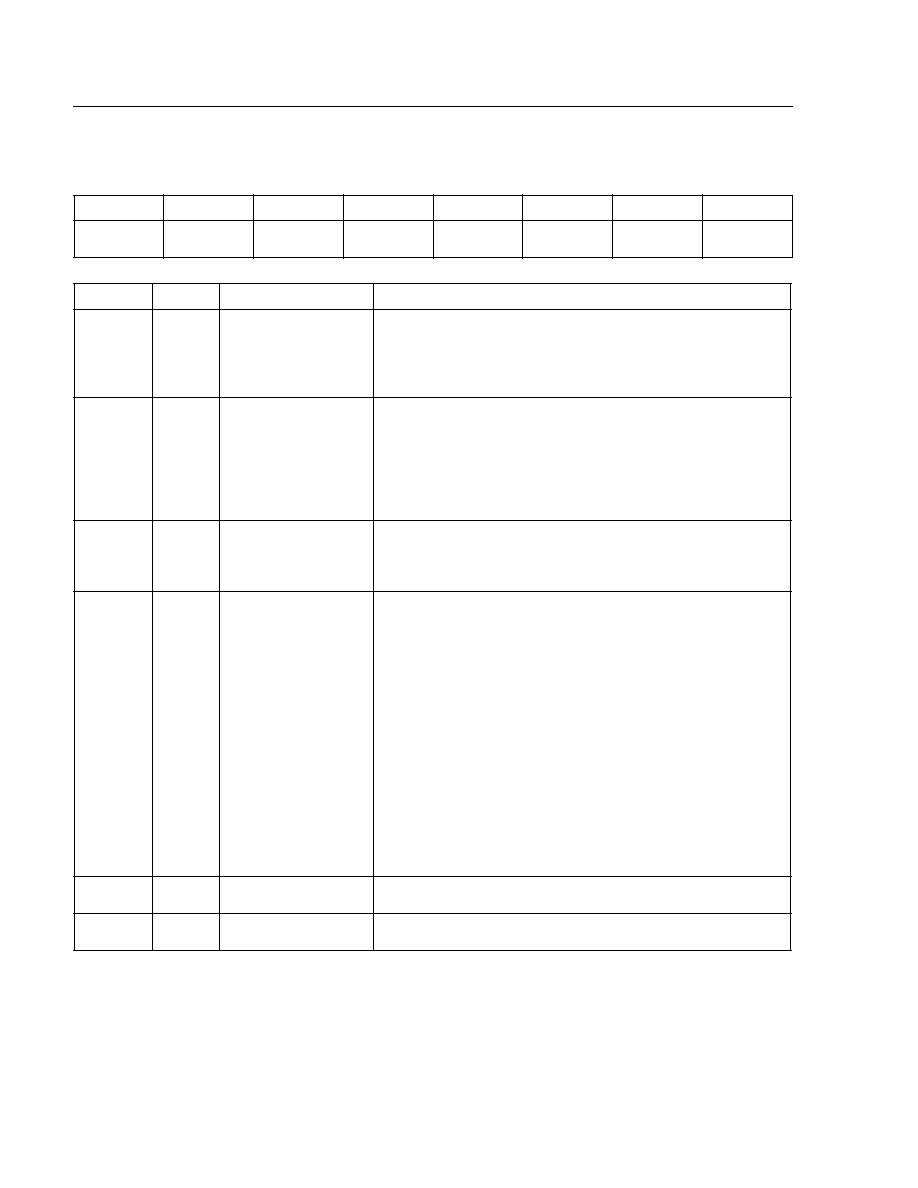

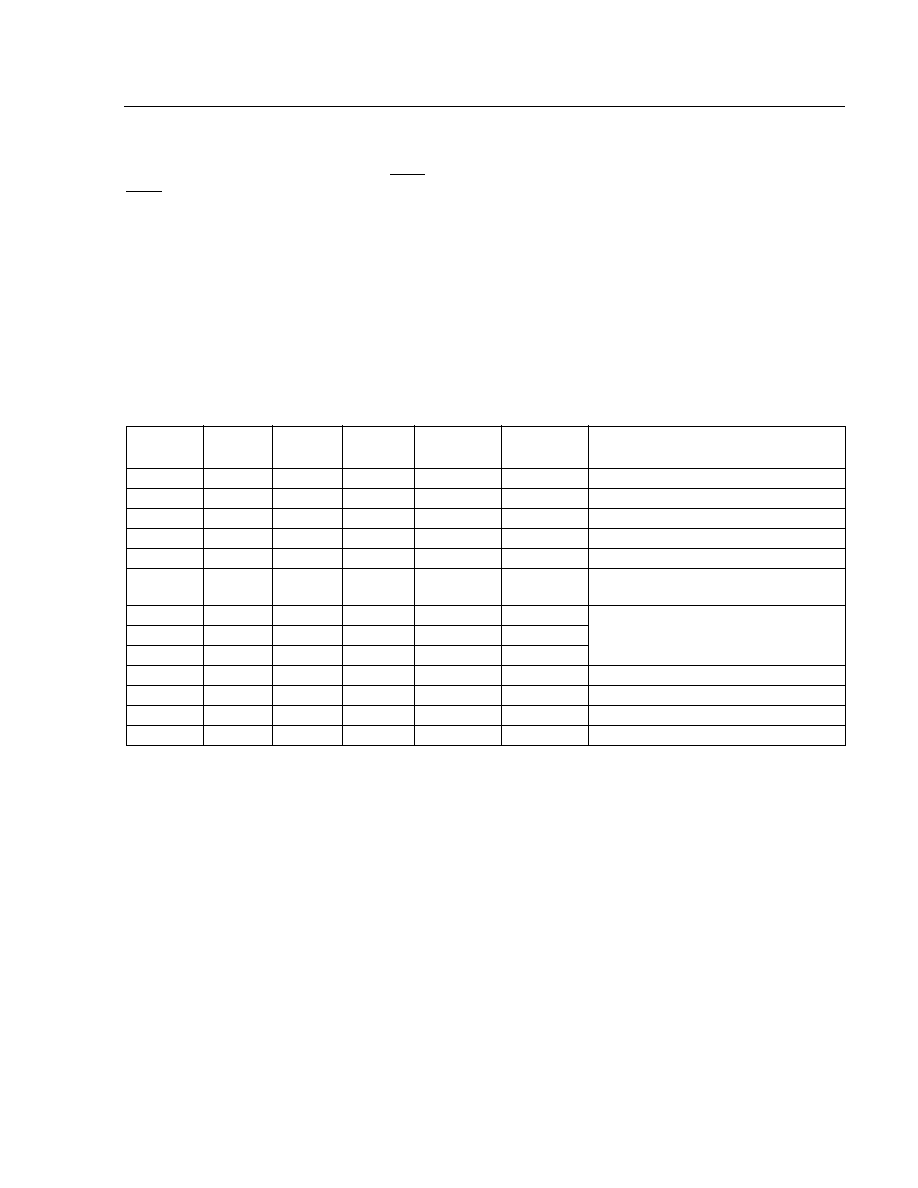

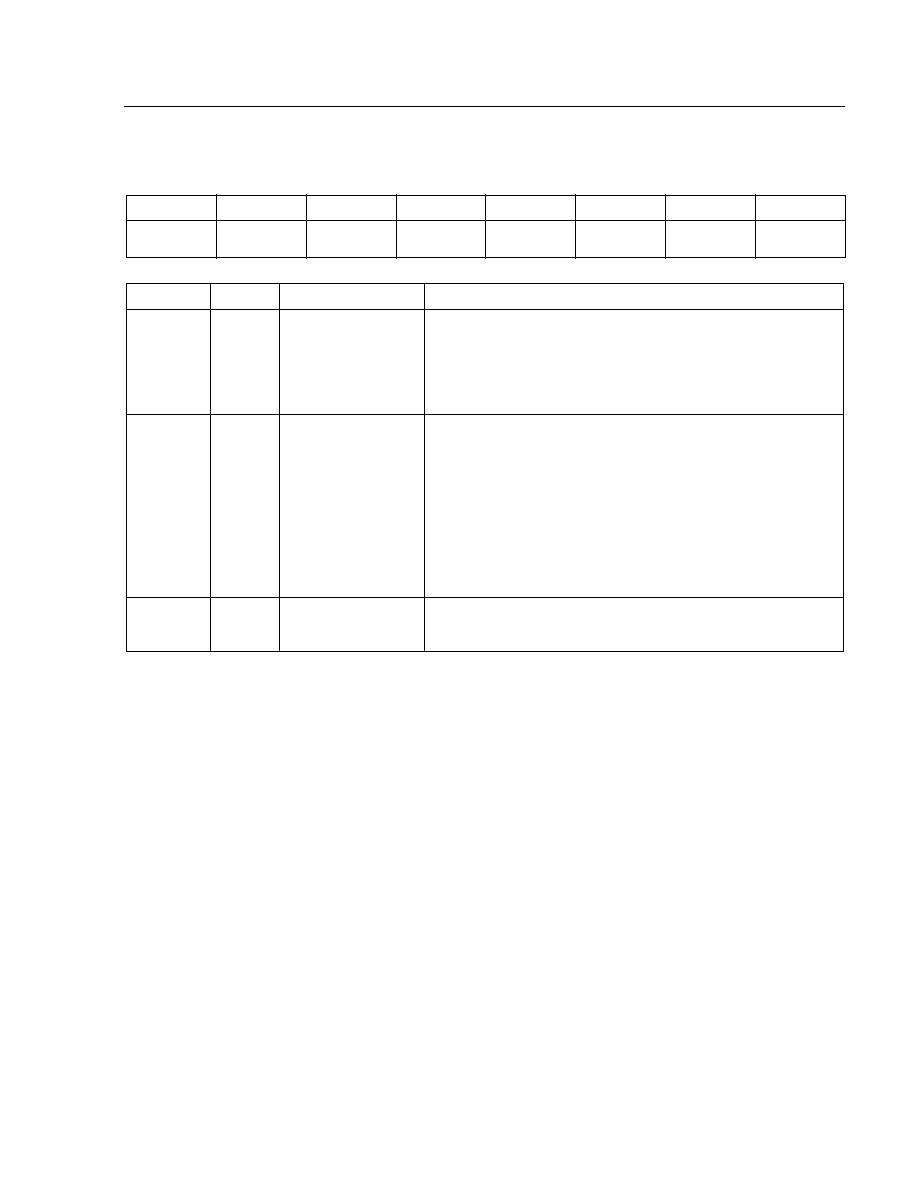

Table 4. Example Register Settings

Register

IOM2/GCI

SLD

K2

FE, (R0--B5)

0

0

0

P21CTL, (R5--B6)

1

1

1

CMS, (R8--B6)

1

0

0

CLKXI, (R9--B4)

1

1

1

TBOF[2--0], (R9--B[7--5])

111

111

111

TTSOF[5 0], (R10--B[5--0])

(# of time slots) ≠ 1

000011

000000, 000111

TSLT[5--0], (R7--B[5--0])

Desired time slot

000000--000011

000001--000111, 000000

CLKRI, (R9--B0)

0

0

0

RBOF[2--0], (R9--B[3--1])

111

111

111

RTSOF[5--0], (R11--B[5--0])

(# of time slots) ≠ 1

000011

000000, 000111

RSLT[5--0], (R8--B[5--0])

Desired time slot

000100--000111

000001--000111, 000000

Opening Flag

User Data Field

Frame Check Sequence (CRC)

Closing Flag

01111110

8 bits

16 bits

01111110

20

20

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

Flags. All flags have the bit pattern 01111110 and are

used for frame synchronization. The HIFI-64 automati-

cally sends two flags between frames. If the FLAGS bit

in the chip-configuration register (R0--B2) is cleared to

0, the 1s idle byte (11111111) is sent between frames if

no data is present in the FIFO. Once there is data in the

transmit FIFO, an opening flag is sent followed by the

frame. If the FLAGS bit (R0--B2) is set to 1, the HIFI-

64 sends continuous flags when the transmit FIFO is

empty. During transmission, two successive flags will

not share the intermediate 0. The HIFI-64 does not

transmit consecutive frames with a shared flag.

An opening flag is generated at the beginning of a

frame (indicated by the presence of data in the transmit

FIFO and the transmitter enabled). Data is transmitted

per the HDLC protocol until a byte is read from the

FIFO with TFC set. The HIFI-64 follows this byte with

the CRC sequence and a closing flag.

The receiver recognizes the 01111110 pattern as a

flag. Two successive flags may or may not share the

intermediate 0 bit and are identified as two flags (i.e.,

both 011111101111110 and 0111111001111110 are

recognized by the HIFI-64). The received data bytes

are stored in the 64-byte receive FIFO delayed by three

bytes or delayed by four bytes if operating in the TDM

highway mode (i.e., HWYEN, R0--B7 = 1). When

another flag is identified, it is treated as the closing flag.

As mentioned above, a flag sequence in the user data

or FCS fields is prevented by zero-bit insertion and

deletion. The received CRC bytes are not loaded into

the receive FIFO. The HIFI-64 receiver recognizes a

single flag between frames as both a closing and open-

ing flag.

Aborts. The bit pattern of the abort sequence is

01111111, with 0 transmitted first. A frame can be

aborted by writing a 1 to TABT (R1--B6). This causes

the last byte written to the transmit FIFO to be replaced

with the abort sequence upon transmission. Once a

byte is tagged by a write to TABT, it cannot be cleared

by subsequent writes to R1. TABT (R1--B6) and TFC

(R1--B7) should never be set to 1 simultaneously

since this causes the transmitter to enter an invalid

state that requires a transmitter reset to clear. A frame

should not be aborted in the very first byte following the

opening flag. An easy way to avoid this situation is to

first write a dummy or junk byte into the queue and then

write the abort command to the queue.

When receiving a frame, the receiver recognizes the

abort sequence whenever it receives a 0 followed by

seven consecutive 1s. This status results in the abort

bit, and possibly the bad byte count bit and/or bad CRC

bits, being set in the Status of Frame status byte which

is appended to the receive data queue. The last two

bytes of user data are assumed to be CRC bits and are

not placed in the queue. All subsequent bytes are

ignored until a valid opening flag is received.

Idles. In accordance with the HDLC protocol, the HIFI-

64 recognizes 15 or more contiguous received 1s as

idle. When the HIFI-64 receives 15 contiguous 1s, the

receiver idle bit (RIDL, R15--B6) is set in register 15.

An interrupt pin transition is generated if no other

unmasked interrupts are active and the RIDL interrupt

is unmasked; i.e., RIIE (R14--B6) = 1.

For transmission, the 1s idle byte is defined as the

binary pattern 11111111 (FF hexadecimal). If the

FLAGS control bit in the chip configuration register

(R0--B2) is 0, the 1s idle byte is sent as the time-fill

byte between frames. A time-fill byte is sent when the

transmit FIFO is empty and the transmitter has com-

pleted transmission of all previous frames. Frames are

sent back-to-back otherwise. If the FLAGS bit (R0--B2)

is set to 1, flags (01111110) are sent as the time-fill

byte between frames. 1s idle is the default time-fill byte.

Note: Regardless of the time-fill byte used, there

always is an opening and closing flag with each

frame. Back-to-back frames are separated by

two flags.

CRC. For a given frame of bits, 16 additional bits that

constitute an error-detecting code are added by the

transmitter. As called for in the HDLC protocol, the

Frame Check Sequence bits are transmitted most sig-

nificant bit first and are bit stuffed. The Cyclic Redun-

dancy Check (or Frame Check Sequence) is calculated

as a function of the transmitted bits by using the ITU-T

standard polynomial:

x

16

+ x

12

+ x

5

+ 1

At the other end, the receiver performs the same calcu-

lation on the received bits after destuffing and com-

pares the results to an expected result. An error occurs

if, and only if, there is a mismatch.

The transmitter can be instructed to transmit a cor-

rupted CRC by setting the Transmit Bad CRC bit

TBCRC (R14--B7). As long as the TBCRC bit is set,

the CRC is corrupted for each frame transmitted by log-

ically flipping the least significant bit of the transmitted

CRC.

The receiver calculates and verifies the CRC for an

incoming frame. The result of the CRC check is

reported in bit 7 of the Status of Frame byte which is

placed in the receive FIFO after the last data byte of

the frame. The CRC is not stored in the FIFO.

Lucent Technologies Inc.

21

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

Transmitter FIFO

Data associated with multiple frames can be written to

the transmit FIFO by the controlling microprocessor.

However, all frames must be explicitly tagged with a

Transmit Frame Complete (TFC) bit (R1--B7) or a

Transmit Abort (TABT) bit (R1--B6) by writing to regis-

ter 1. The TFC is tagged onto the last byte of a frame

written into the transmitter FIFO. TFC instructs the

transmitter to end the frame by attaching the CRC and

closing flag following the tagged byte. Once written, the

TFC cannot be changed by another write to R1. If TFC

is not written before the last data byte is read out for

transmission, an underrun occurs. When the FIFO is

empty, writing two data bytes to the FIFO before setting

TFC provides a minimum of eight CLKX periods to

write TFC. TABT (R1--B6) and TFC (R1--B7) should

never be set to 1 simultaneously. This causes the trans-

mitter to enter an invalid state requiring a transmitter

reset.

When the transmitter has completed a frame, with a

closing flag or an abort sequence, the TDONE

(R15--B0) bit is set to 1. If TDIE (R14--B0) is 1 and no

other prior unacknowledged interrupt exists, the INT

pin transitions.

Sending 1-Byte Frames

Sending 1-byte frames with an empty transmit FIFO is

not recommended. If the FIFO is empty, writing two

data bytes to the FIFO before setting TFC provides a

minimum of eight CLKX periods to write TFC. When

one byte is written to the FIFO, TFC must be written

within 1 CLKX period to guarantee it is effective. Thus,

1-byte frames are subject to underrun aborts. One-byte

frames cannot be aborted with TABT. Placing the trans-

mitter in 1s idle mode (FLAGS, R0--B2 = 0) lessens

the frequency of underruns. If the transmit FIFO is not

empty, then 1-byte frames present no problem.

Transmitter Underrun

After writing a byte to the transmit queue, the user has

eight CLKX cycles in which to write the next byte before

a transmitter underrun occurs. An underrun occurs

when the transmitter has finished transmitting all the

bytes in the queue, but the frame has not yet been

closed by writing TFC. When a transmitter underrun

occurs, the abort sequence is sent at the end of the last

valid byte transmitted. A TDONE interrupt is generated,

and the transmitter reports an underrun abort in the

interrupt status register (R15--B2). The transmitter

enters forced idle (sending FLAGS or IDLES based

upon the value in R0--B2) until the interrupt status reg-

ister (R15) is read.

Using the Transmitter Status and Fill Level

The Transmitter-interrupt Level bits (R1--B[5--0]) allow

the user to instruct the T7121 to interrupt the host pro-

cessor whenever the transmitter has a predetermined

number of empty locations. The number of locations

selected determines the time between transmitter

empty (TE) interrupts. The transmitter status bits

(R2--B[6--0]) report the number of empty locations in

the transmitter FIFO. The bits are encoded in binary

with bit 0 the least significant bit. Also found in register

2 is the Transmitter Empty Dynamic bit, TED (R2--B7).

This bit, like the TE interrupt bit, is set when the number

of empty locations is less than or equal to the pro-

grammed empty level. TED returns to 0 when the trans-

mitter is filled to above the programmed empty level.

Polled interrupt systems can use TED to determine

when they can write to the transmit FIFO.

Programming Note: After the transmitter is turned off,

a transmitter reset should be performed (TRES, R6, bit

5 = 1) before the transmitter is turned on. After the

receiver is turned off, a receiver reset should be per-

formed (RRES, R6, bit 4 = 1) before the receiver is

turned on. The transmitter and receiver should both be

reset individually (i.e., not at the same time) after any

concentration highway configuration change. If TRES =

RRES = 1 at the same time, a full chip reset is per-

formed: all register bits are forced to their reset values.

Receiver FIFO

The receiver status is available in two ways. First, the

queue manager creates a Status of Frame (SF) byte for

each HDLC frame and stores this status byte in the

FIFO after the last data byte of the associated frame.

Thus, a frame containing 24 user data bytes results in

25 bytes present in the receive FIFO. The SF status

byte has the following format:

STATUS OF FRAME BYTE

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

BAD CRC

ABOR

T

O

VERR

UN

BAD BYTE COUNT

0

0

0

0

22

22

Lucent Technologies Inc.

Data Sheet

April 1997

T7121 HDLC Interface for ISDN (HIFI-64)

Functional Description

(continued)

Bit 7 of the SF status byte is the CRC status bit. If an

incorrect CRC was detected, this bit is set to 1. If the

CRC was correct, the bit is 0.

Bit 6 of the SF status byte is the abort status. A high (1)

indicates the frame associated with this status byte was

aborted (i.e., the abort sequence was detected after an

opening flag and before a subsequent closing flag). An

abort can also cause bits 7 and/or 4 to go high (1). An

abort is not reported when a flag is followed by seven

1s.

If the Overrun bit (bit 5) is high, it indicates that a

receiver FIFO overrun occurred (the 64-byte FIFO size

was exceeded; see the Receiver Overrun section).

The Bad Byte Count bit (Bit 4) indicates whether or not

the bit count received was a multiple of eight (i.e., an

integer number of bytes). A high (1) indicates that the

bit count received after 0-bit deletion was not a multiple

of eight, and a low indicates that the bit count was a

multiple of eight. When a non-byte-aligned frame is

received, all bits received are present in the receive

FIFO. The byte before the SF status byte contains less

than eight valid data bits. The nondata bits are the first

bits of the received CRC. The T7121 provides no indi-

cation of how many of the bits in the byte are valid. It is

up to the user and the protocol to decide what to do

with non-byte-aligned frames.

Bits 0 to 3 of the SF status byte are not used and are

guaranteed to be 0 when read. A good frame is implied

when the SF status byte is 00 hexadecimal.

The last byte of a completed frame in the receive FIFO