| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: T7633 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- AY99-010BBAC (T7633 Device Advisory for Version 1.0 of the Device)

- Introduction

- Microprocessor Timing Requirements

- Microprocessor Interface

- Table 1. Microprocessor Interface I/O Timing Specifications

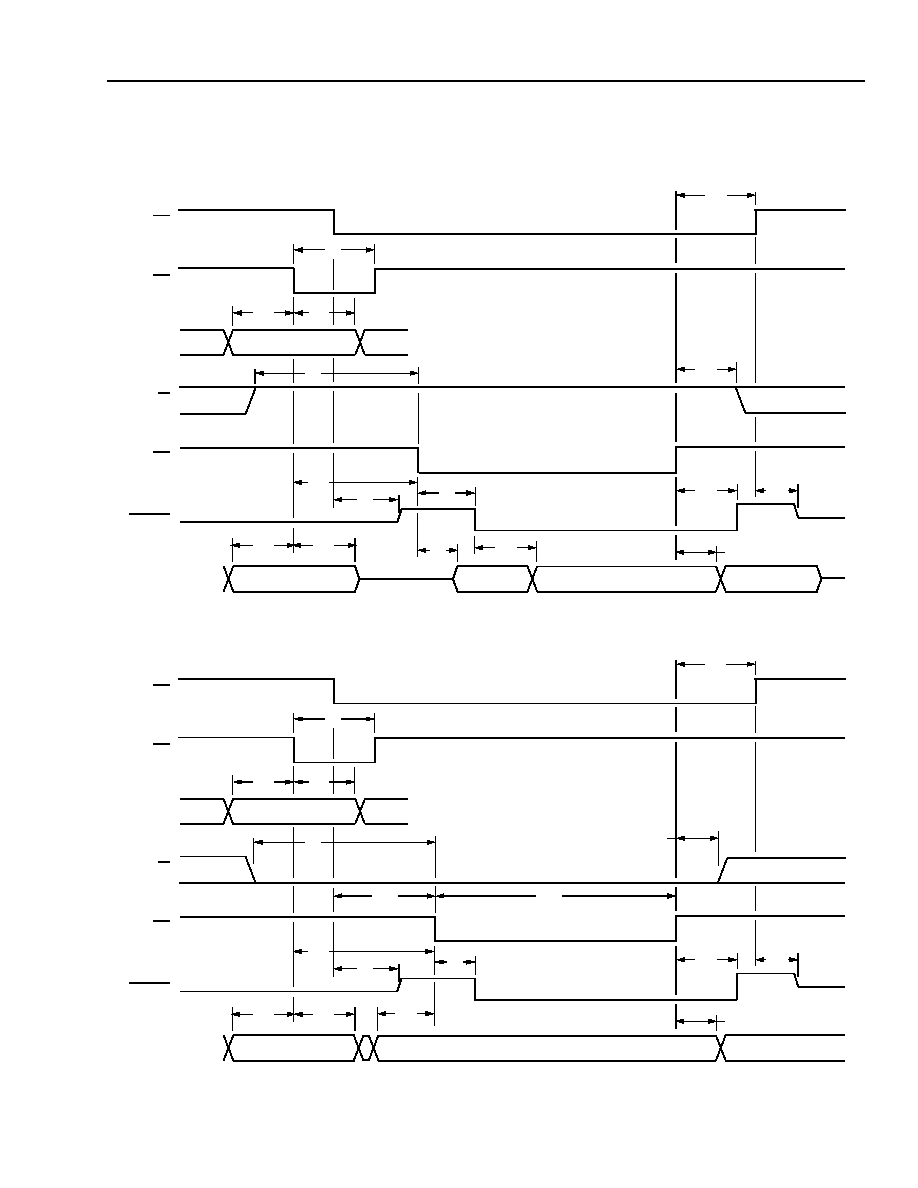

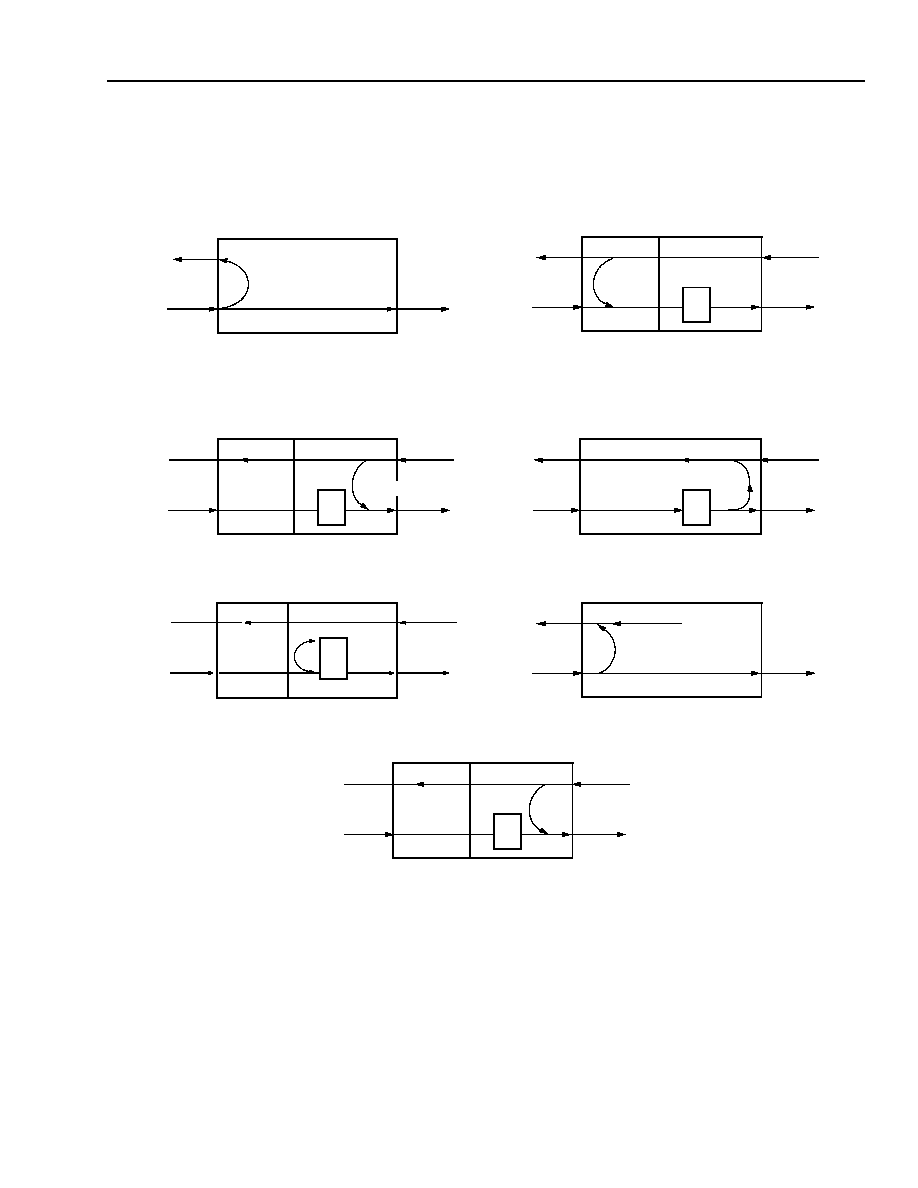

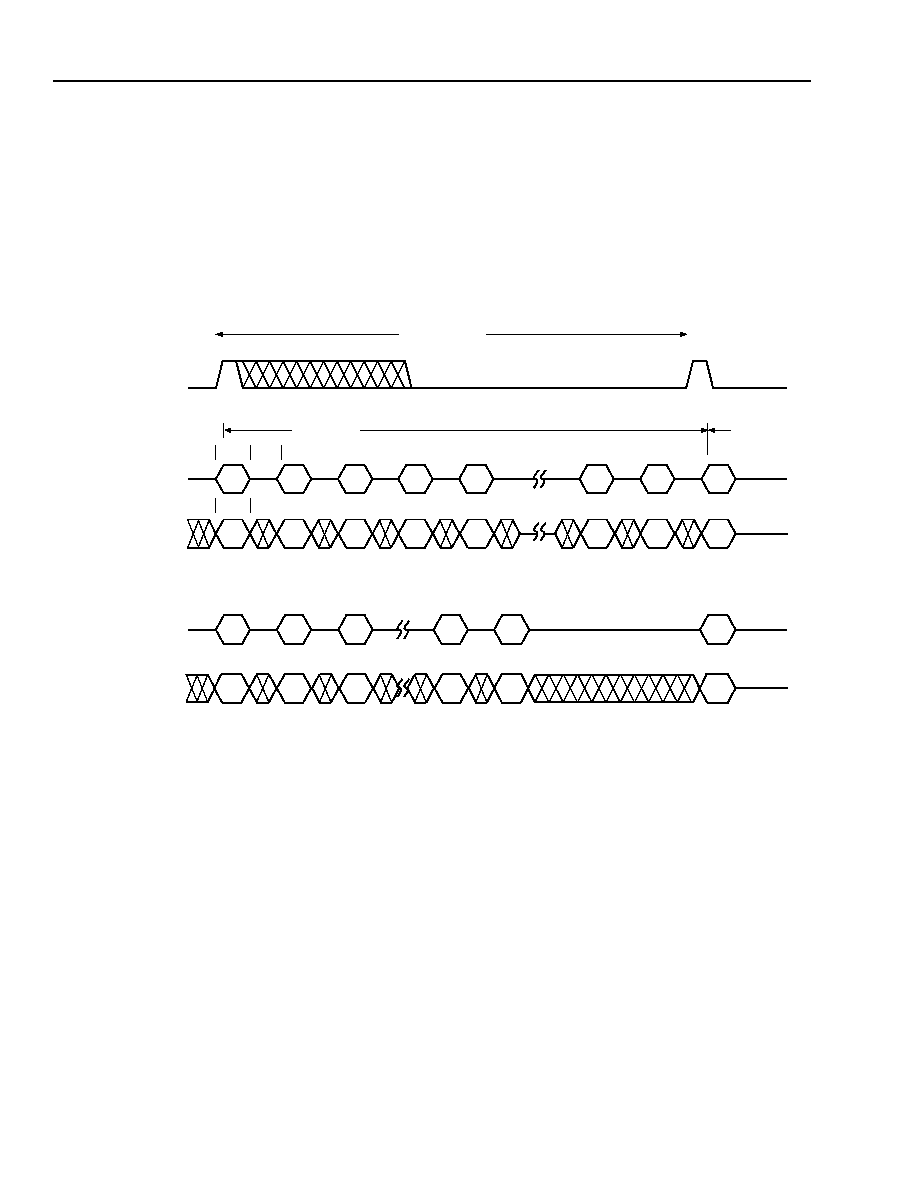

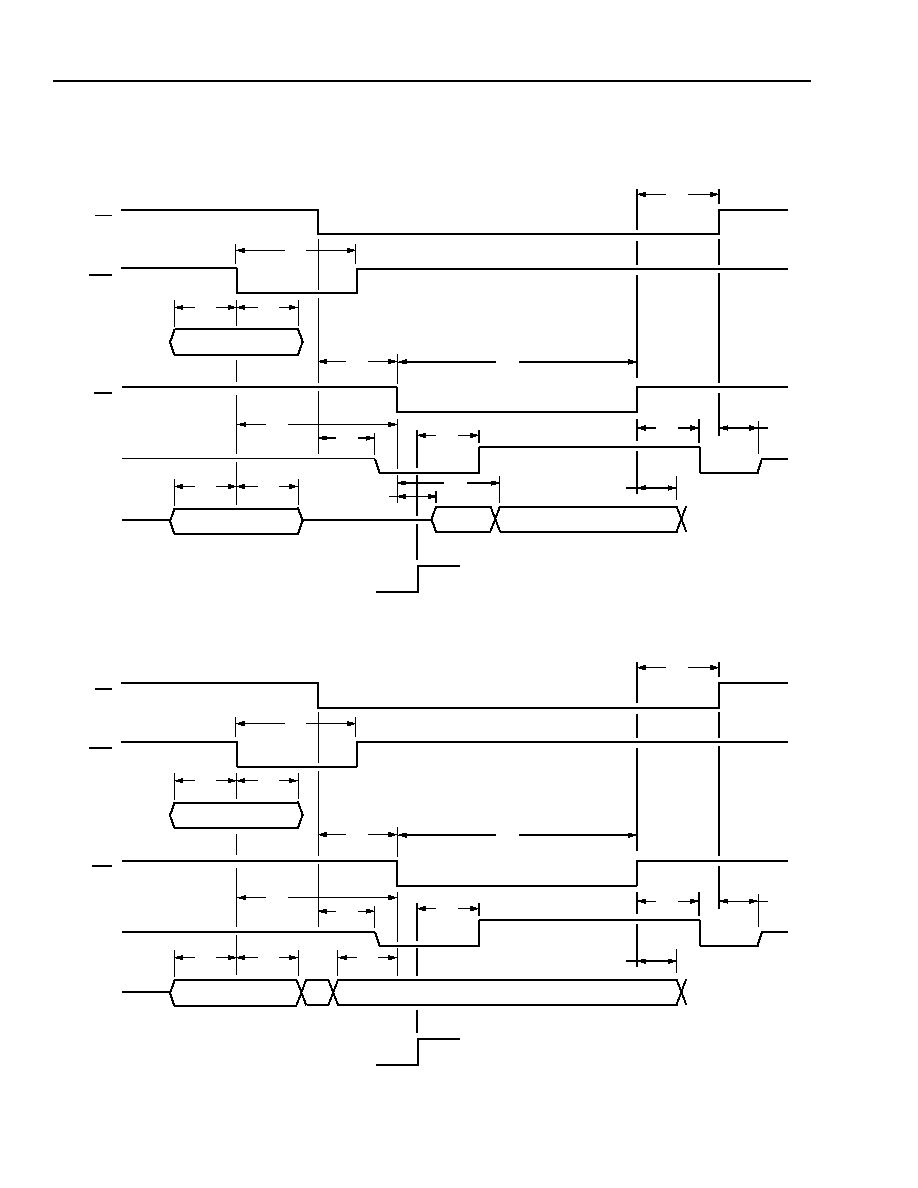

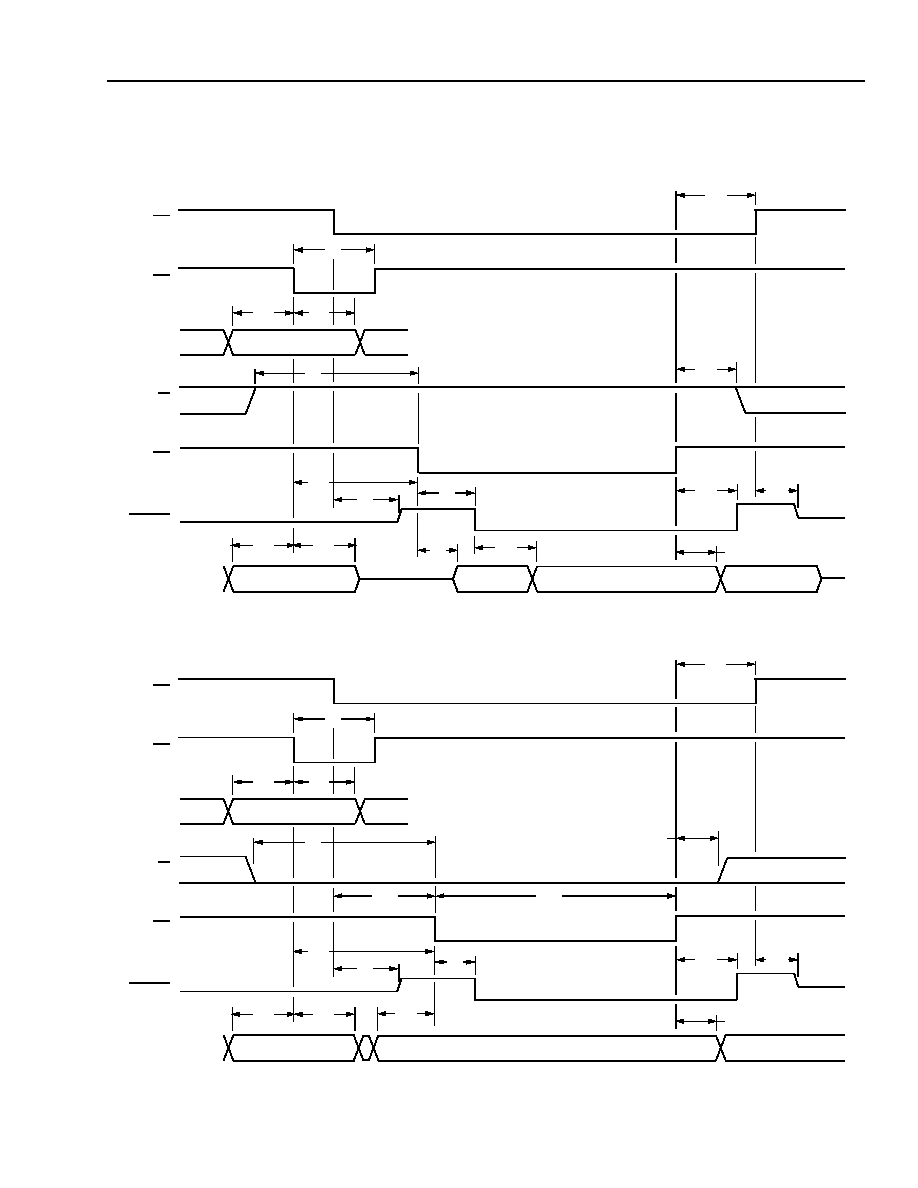

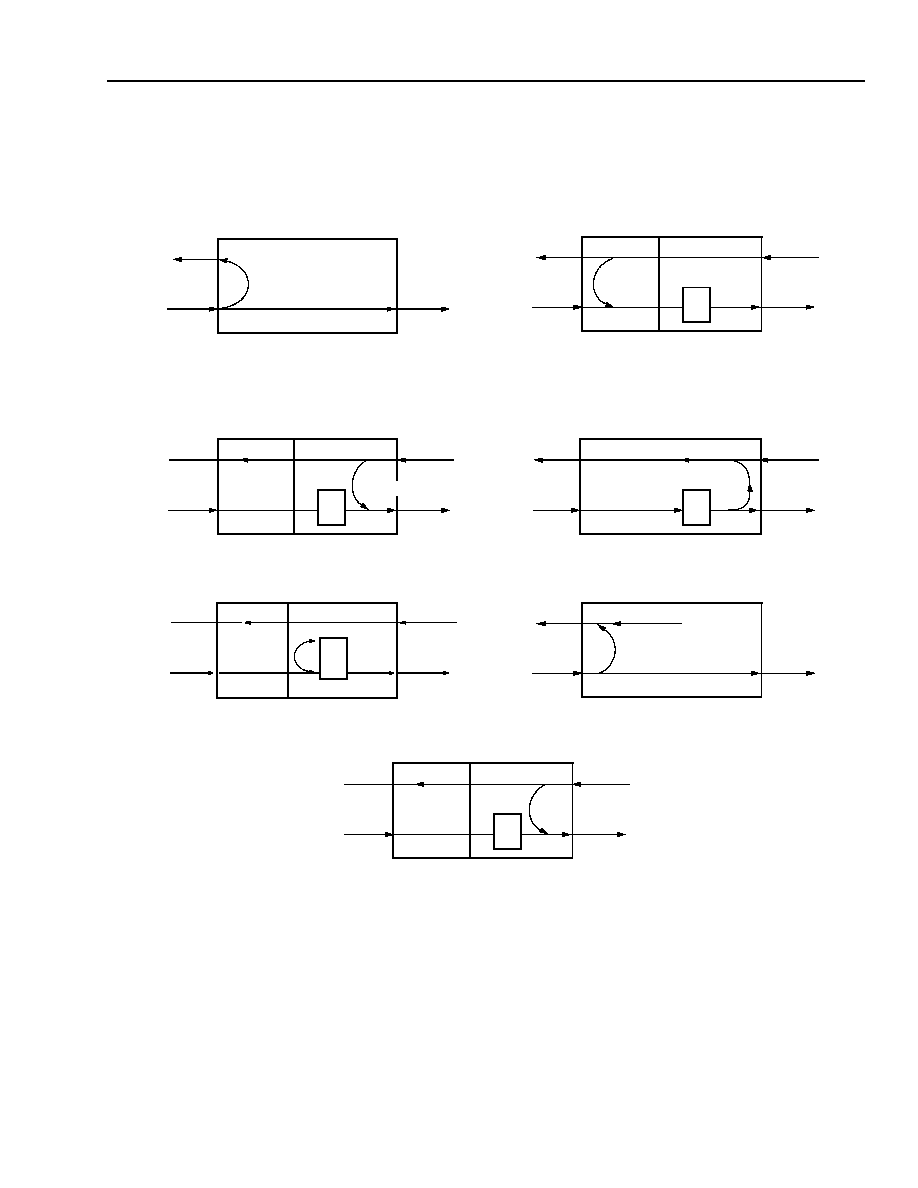

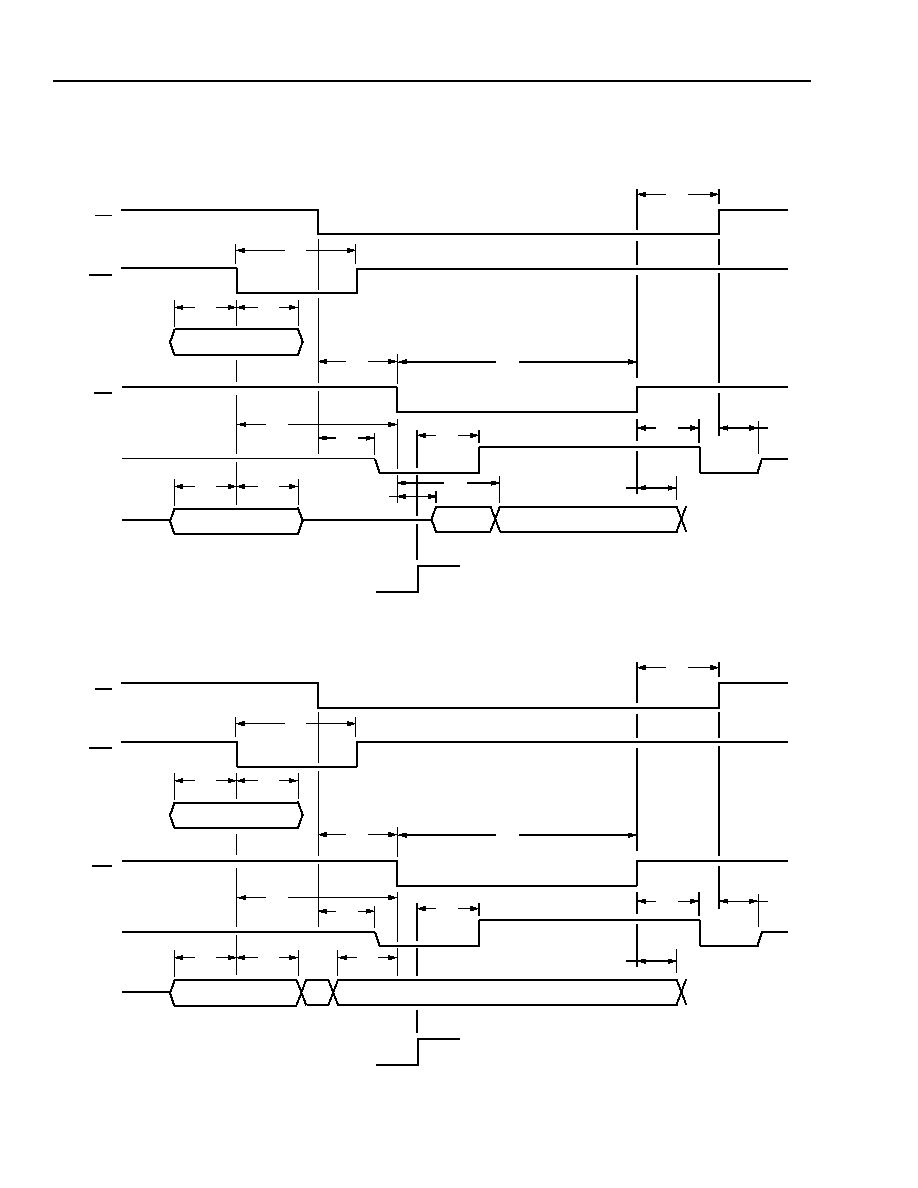

- Figure 1. Mode 1ÑRead Cycle Timing (MPMODE = 0, MPMUX = 0)

- Figure 2. Mode 1ÑWrite Cycle Timing (MPMODE = 0, MPMUX = 0)

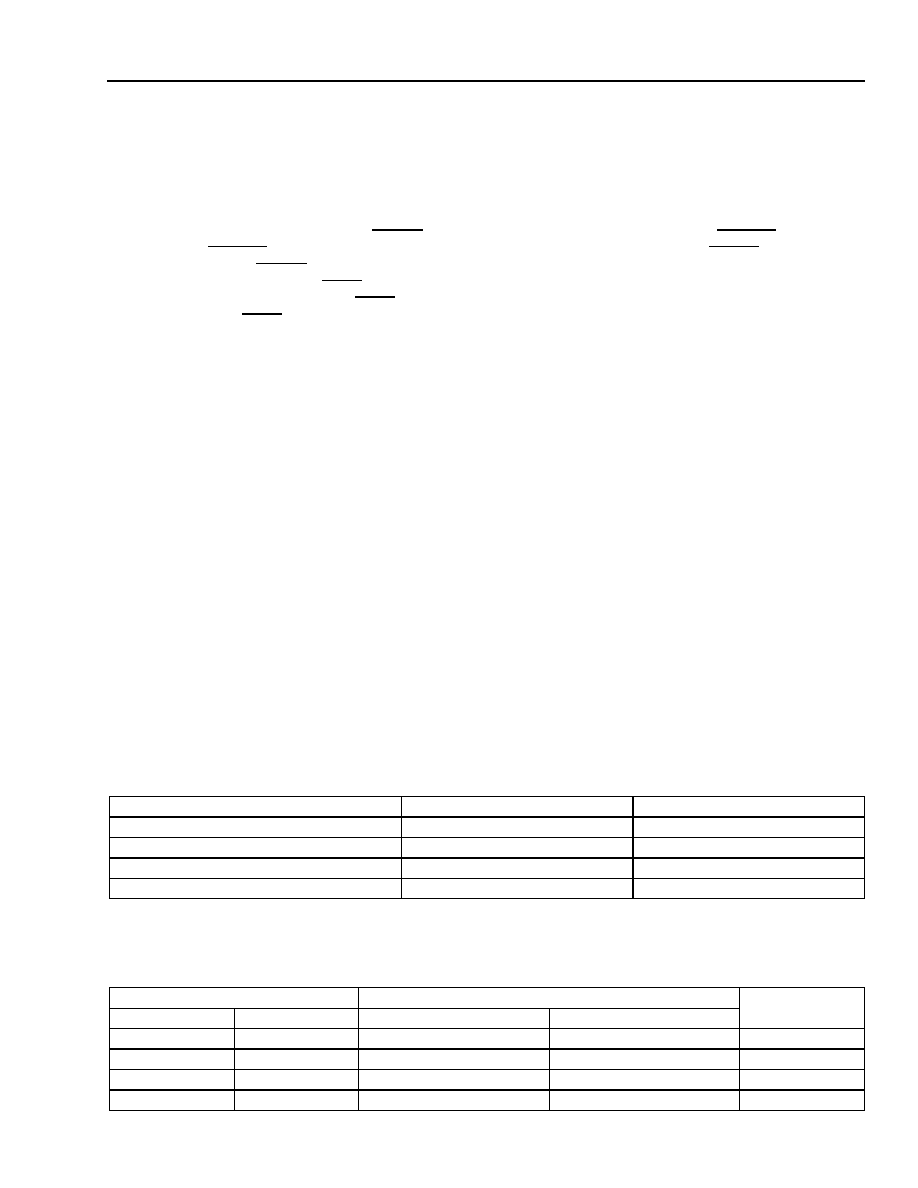

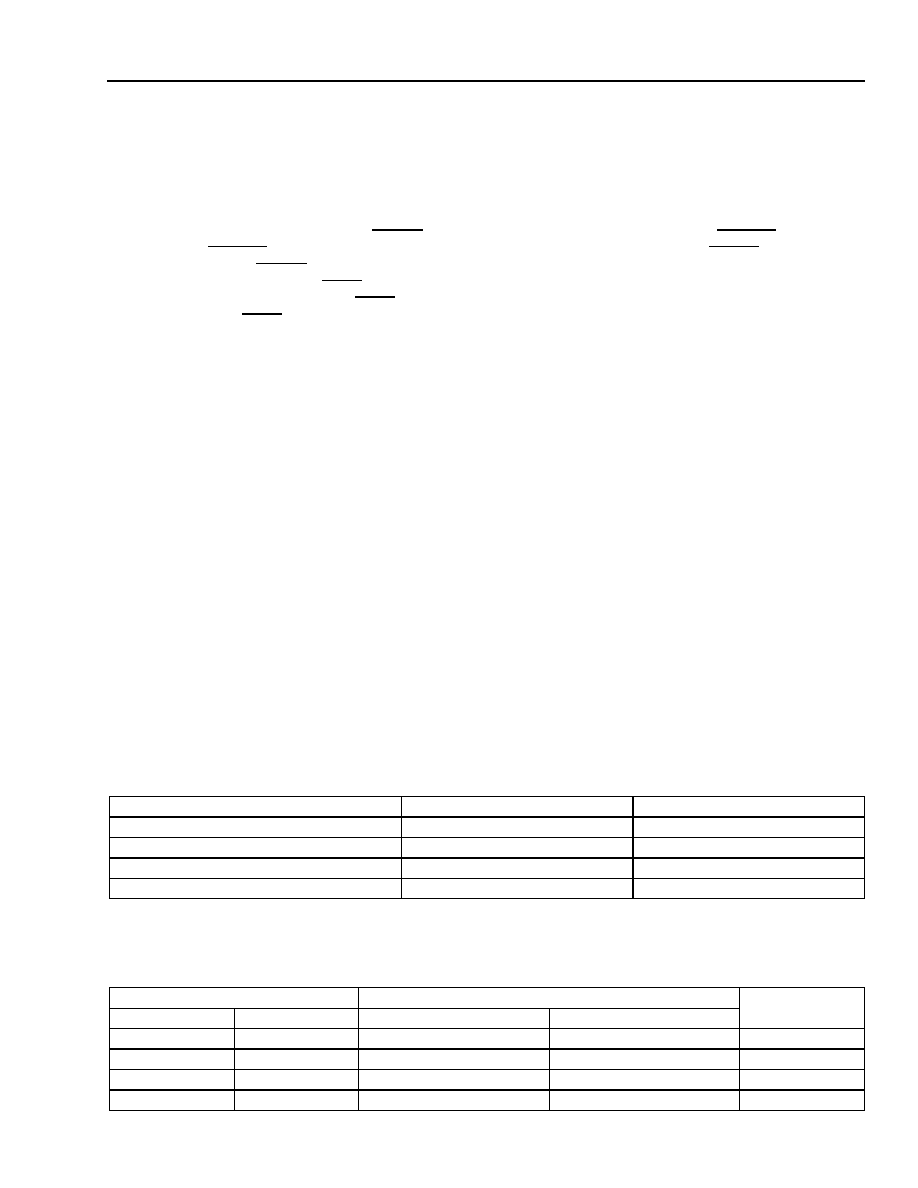

- Figure 3. Mode 2ÑRead Cycle Timing (MPMODE = 0, MPMUX = 1)

- Figure 4. Mode 2ÑWrite Cycle Timing (MPMODE = 0, MPMUX = 1)

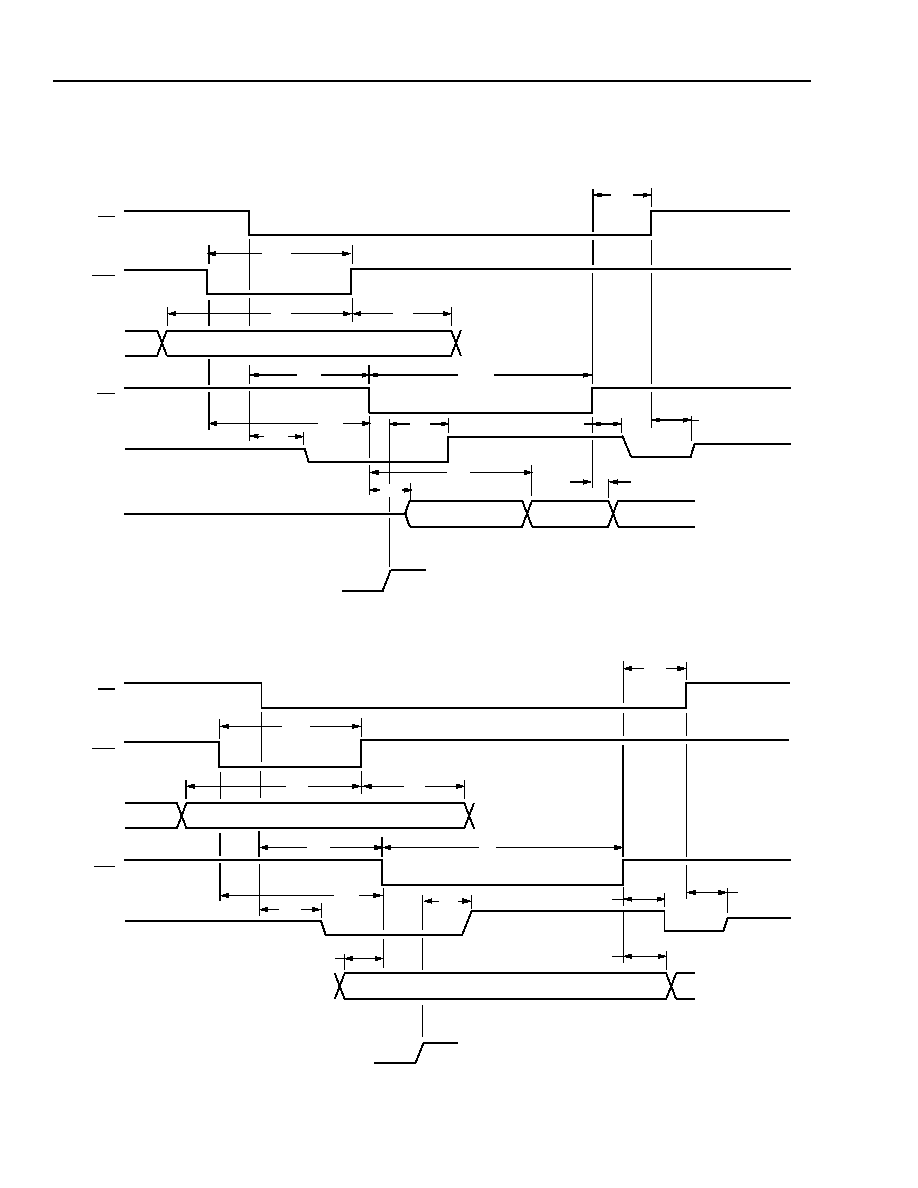

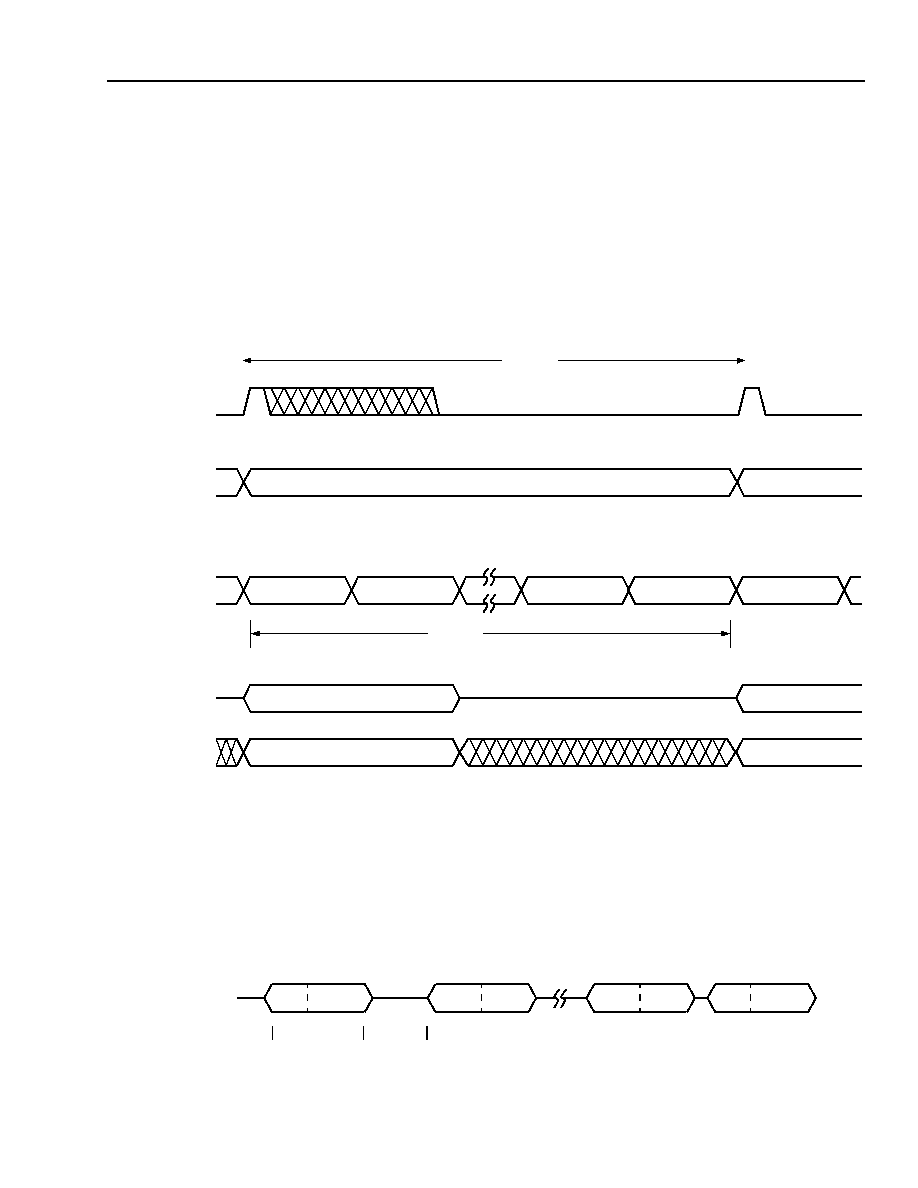

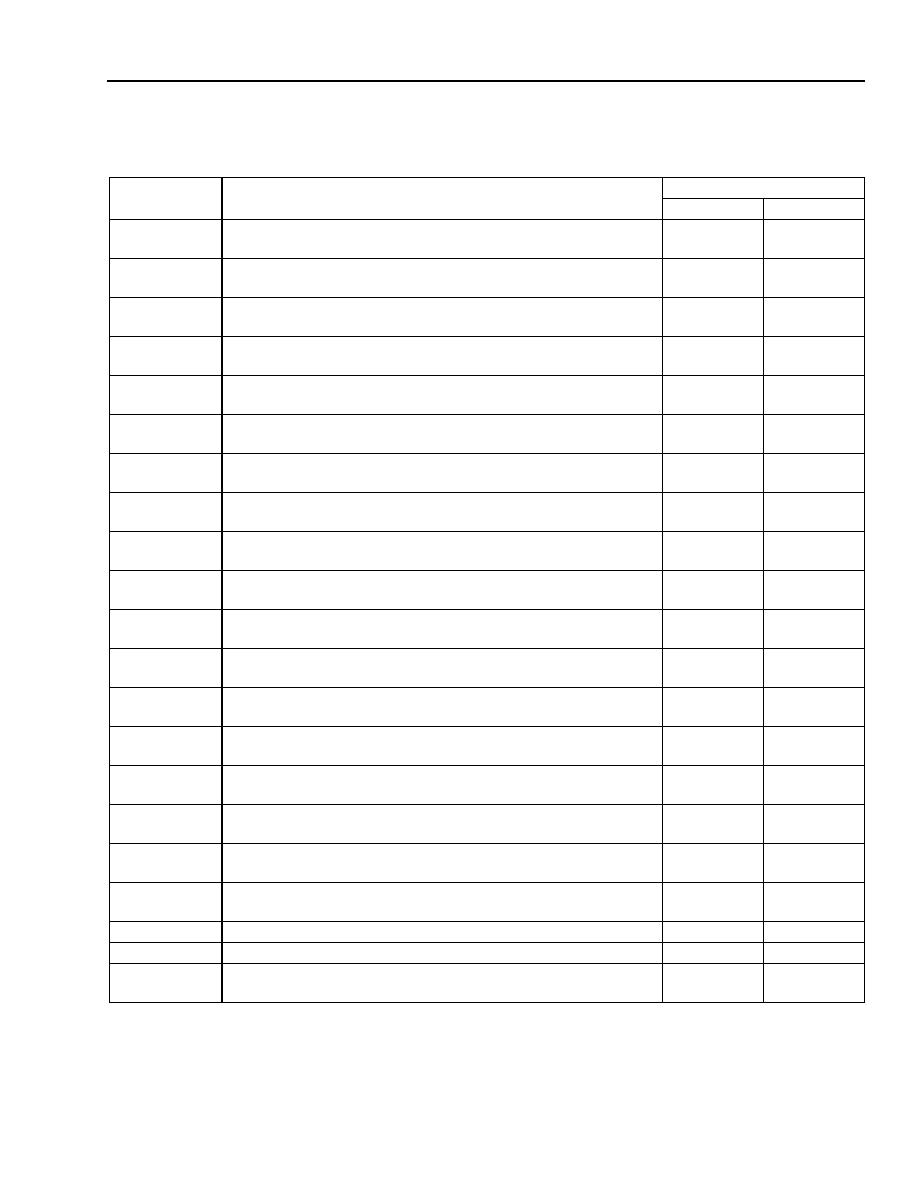

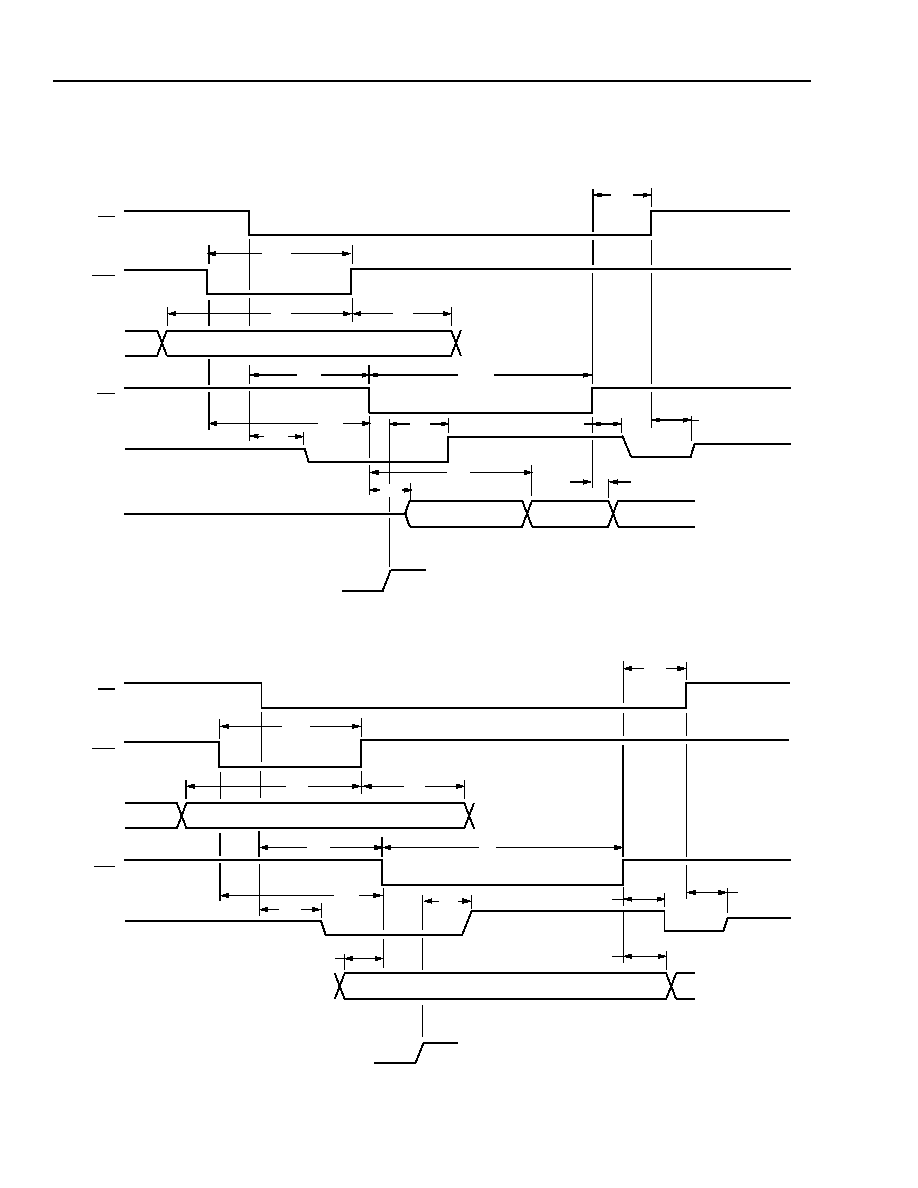

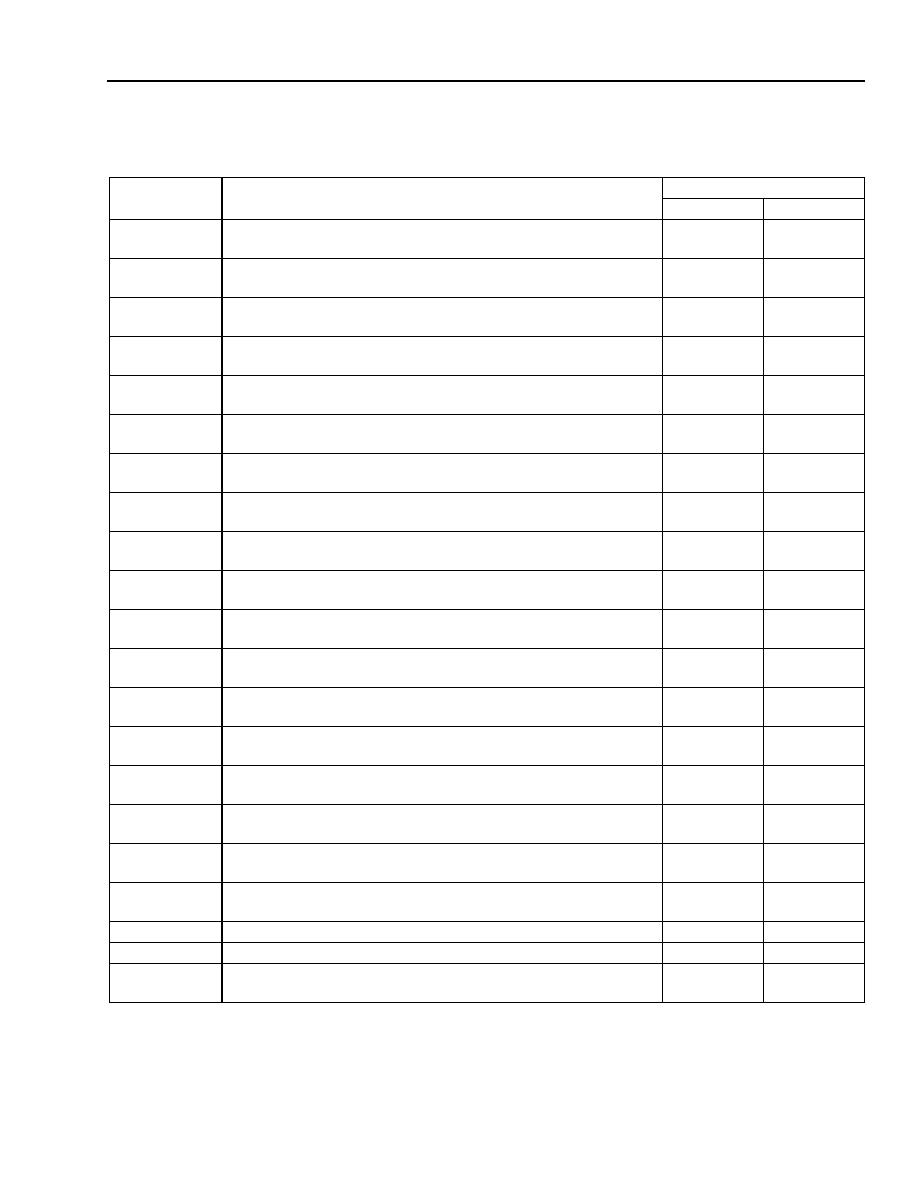

- Figure 5. Mode 3ÑRead Cycle Timing (MPMODE = 1, MPMUX = 0)

- Figure 6. Mode 3ÑWrite Cycle Timing (MPMODE = 1, MPMUX = 0)

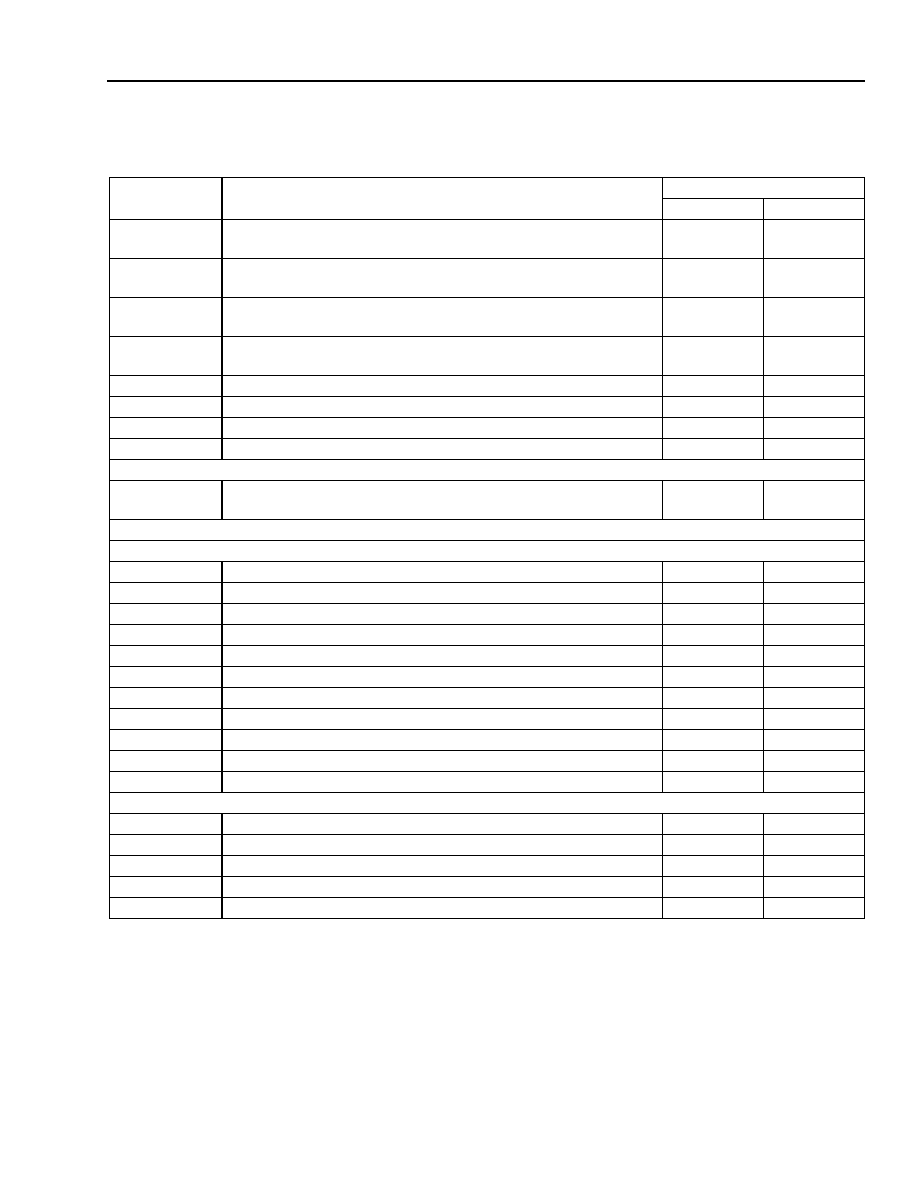

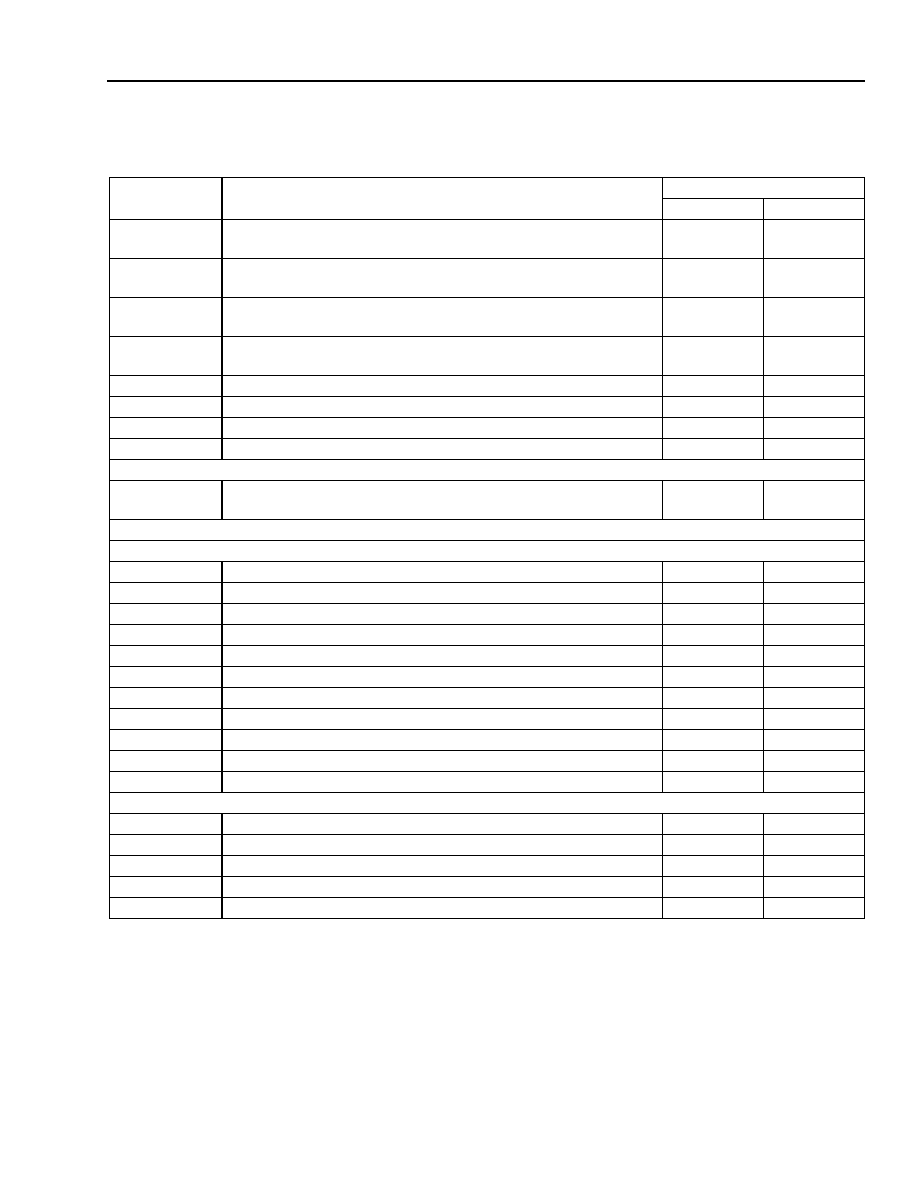

- Figure 7. Mode 4ÑRead Cycle Timing (MPMODE = 1, MPMUX = 1)

- Figure 8. Mode 4ÑWrite Cycle Timing (MPMODE = 1, MPMUX = 1)

- Data Pattern Limitation for Proper Functionality of the LIU Internal Full Local Loopback (FLLOOP)

- Asynchronous SYSCK and PLLCK with Jitter Attenuator in the Line Transmit Path

- AY99-010PDH Replaces AY99-007T1E1 to Incorporate the Following Updates

- Contact Us

- AY99-033BBAC (T7633 Device Advisory Describing Differences Between Version 1.0 and Version 2.0 of Device)

- Introduction

- Data Sheet Changes

- Device Operation Updates

- LIU Full Local Loopback (FLLOOP)

- Microprocessor Interface Timing

- Contact Us

- DS02-244BBAC (T7633 Dual T1/E1 3.3 V Short-Haul Terminator)

- Features

- List of Figures

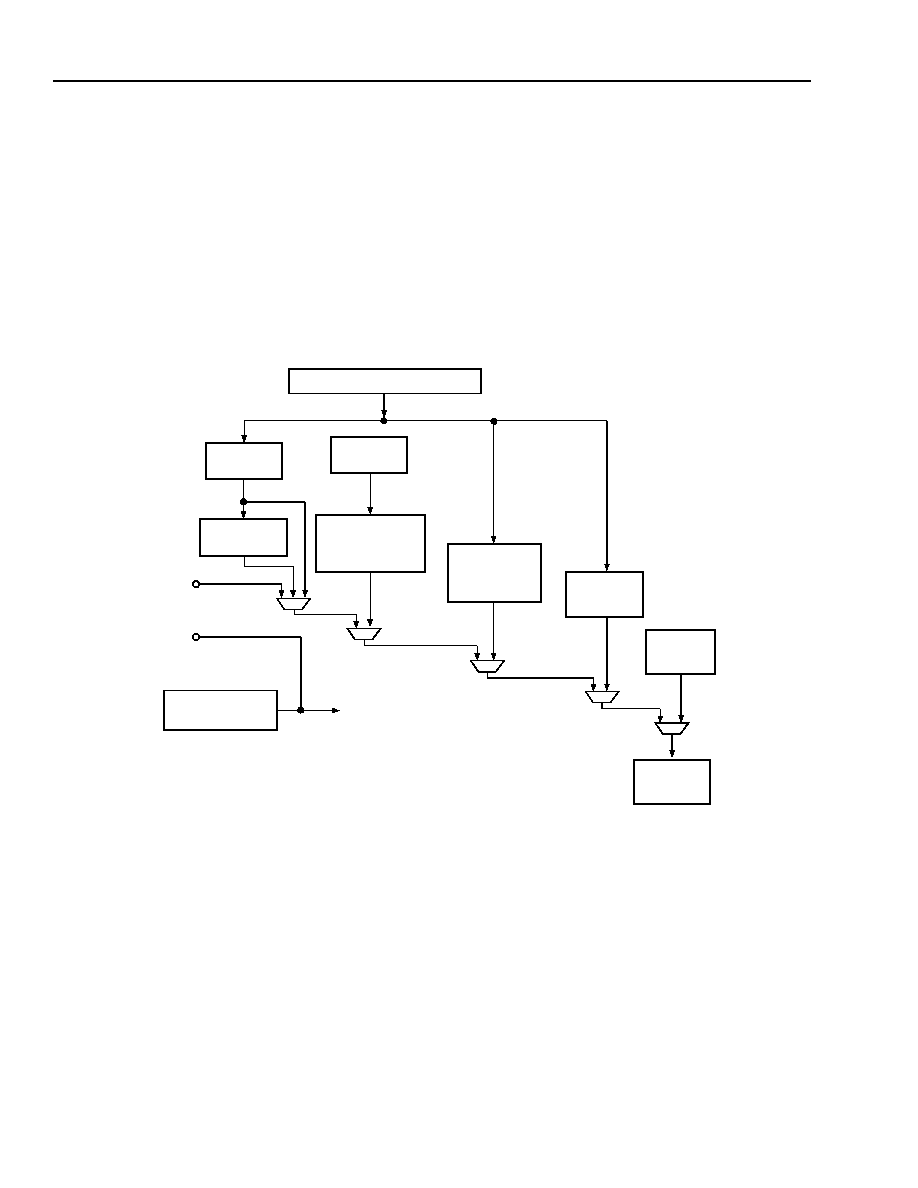

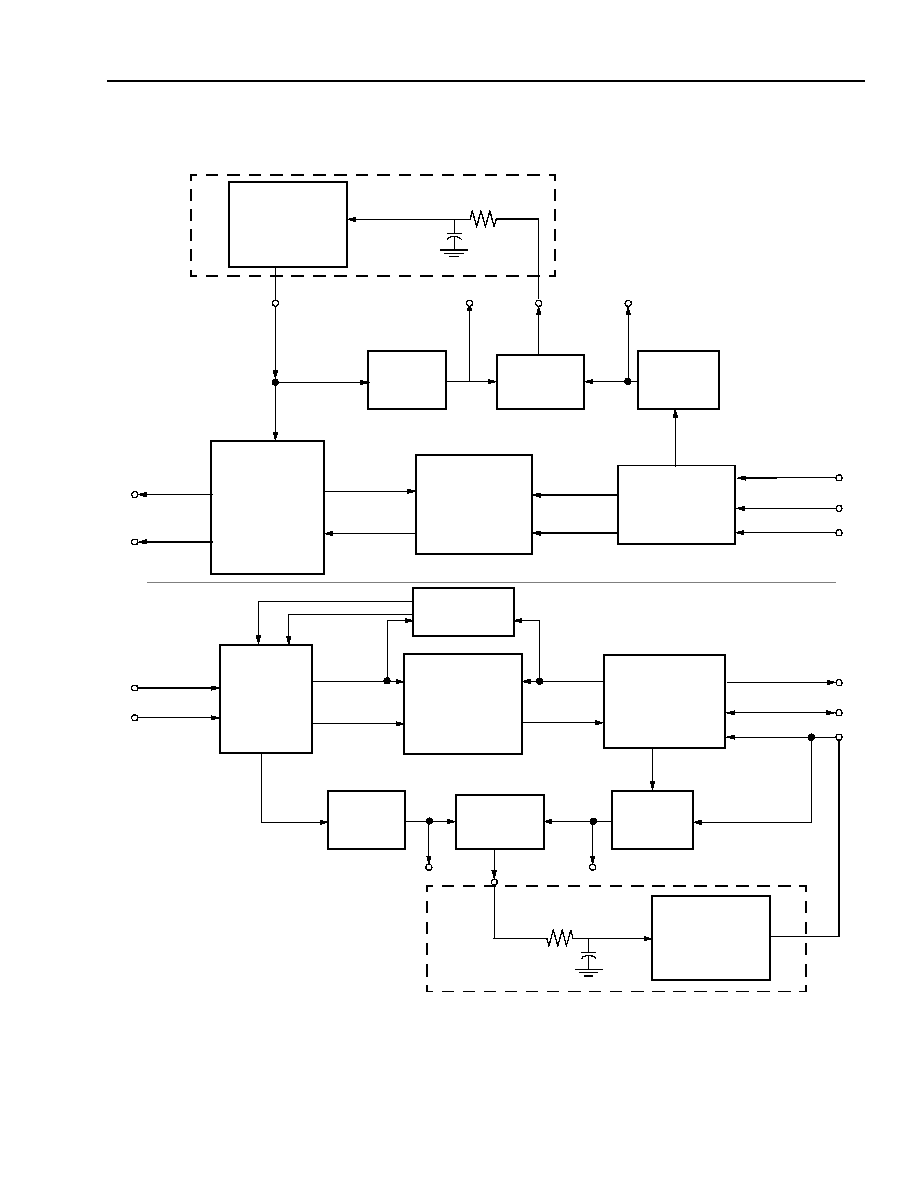

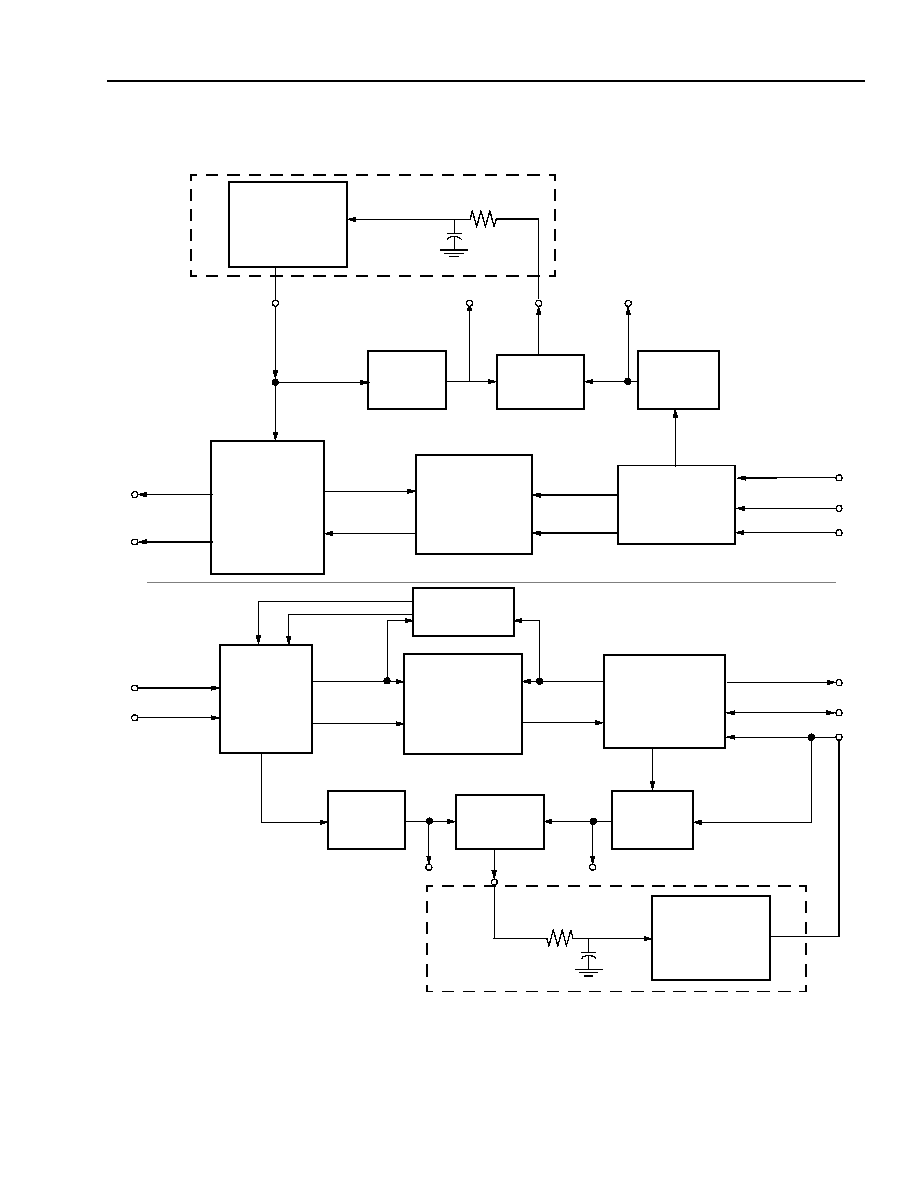

- Figure 1. T7633 Block Diagram (One of Two Channels)

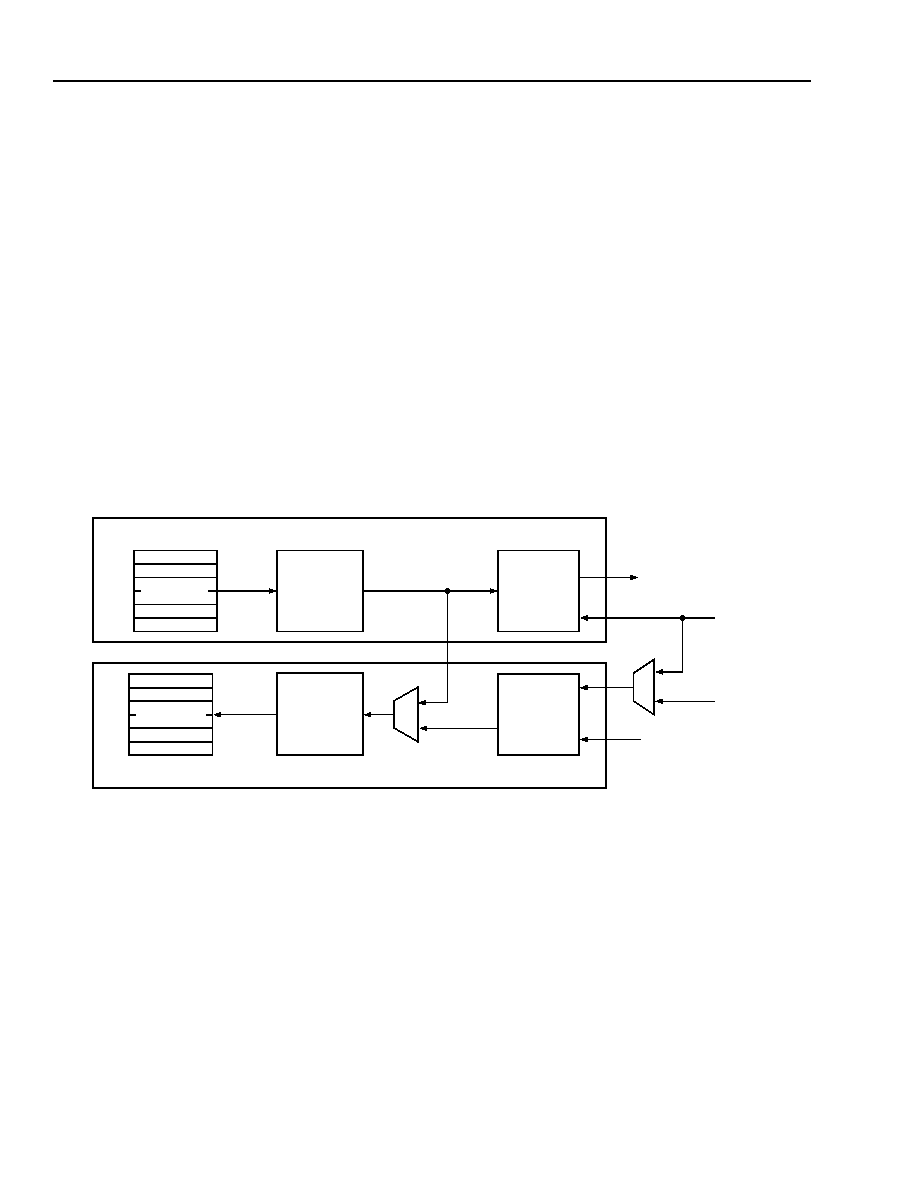

- Figure 2. T7633 Block Diagram: Receive Section (One of Two Channels)

- Figure 3. T7633 Block Diagram: Transmit Section (One of Two Channels)

- Figure 4. Pin Assignment

- Figure 5. Block Diagram of Line Interface Unit: Single Channel

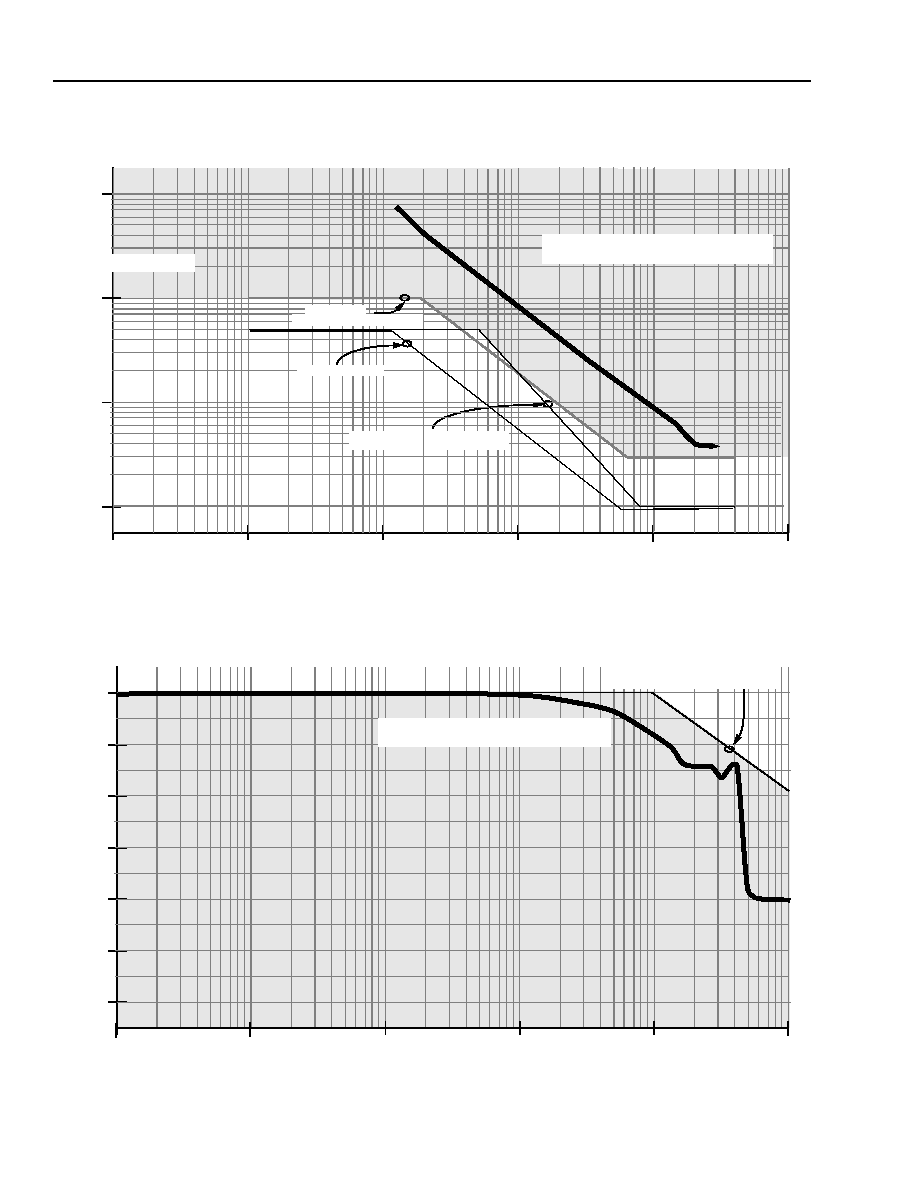

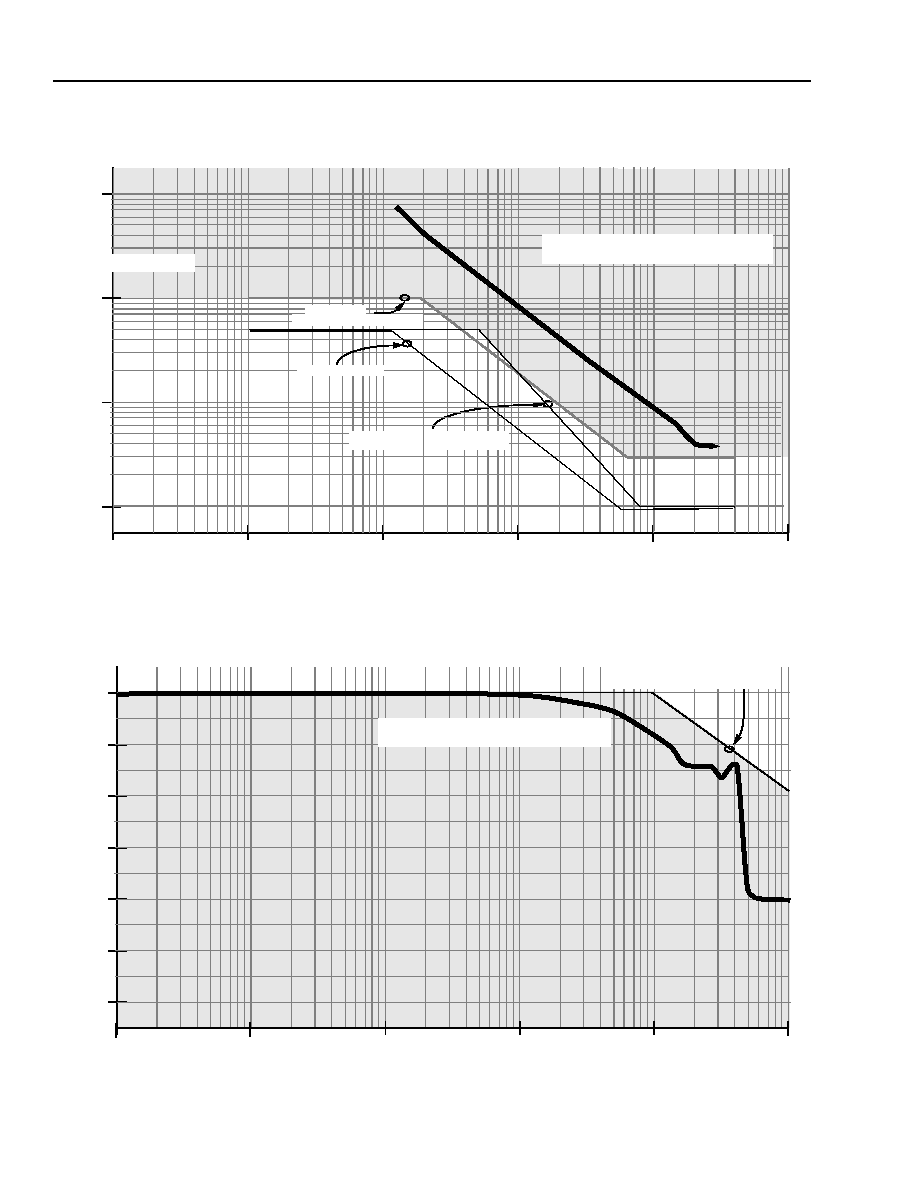

- Figure 6. T1/DS1 Receiver Jitter Accommodation Without Jitter Attenuator

- Figure 7. T1/DS1 Receiver Jitter Transfer Without Jitter Attenuator

- Figure 8. CEPT/E1 Receiver Jitter Accommodation Without Jitter Attenuator

- Figure 9. CEPT/E1 Receiver Jitter Transfer Without Jitter Attenuator

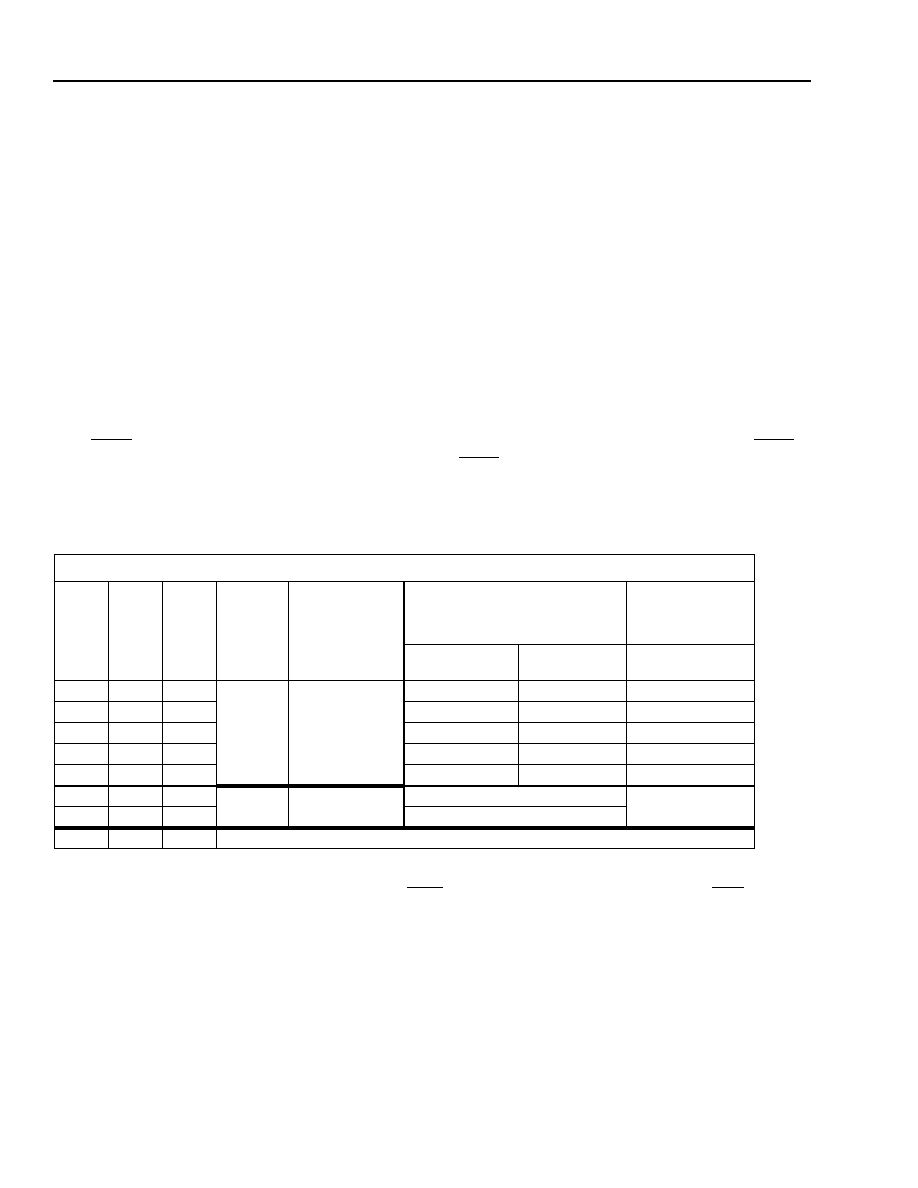

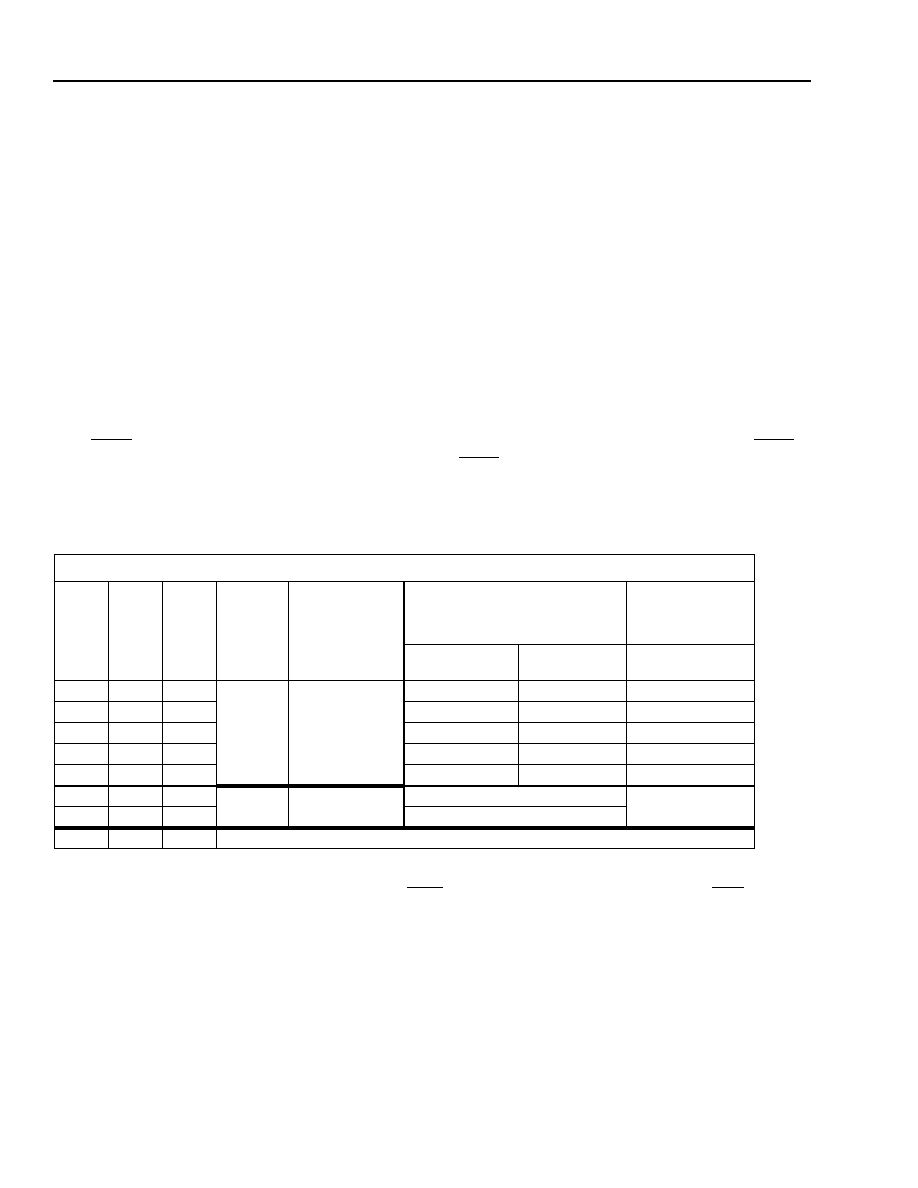

- Figure 10. DSX-1 Isolated Pulse Template

- Figure 11. ITU-T G.703 Pulse Template

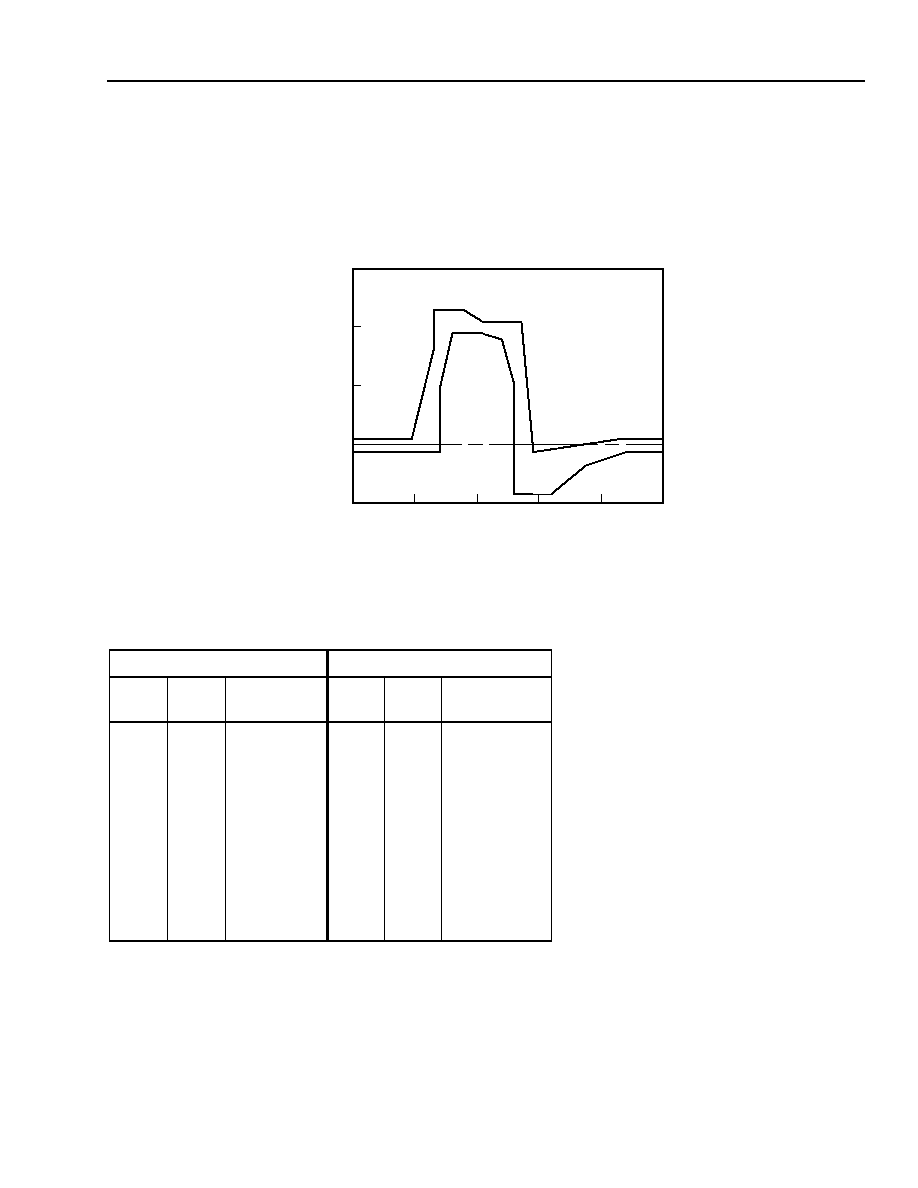

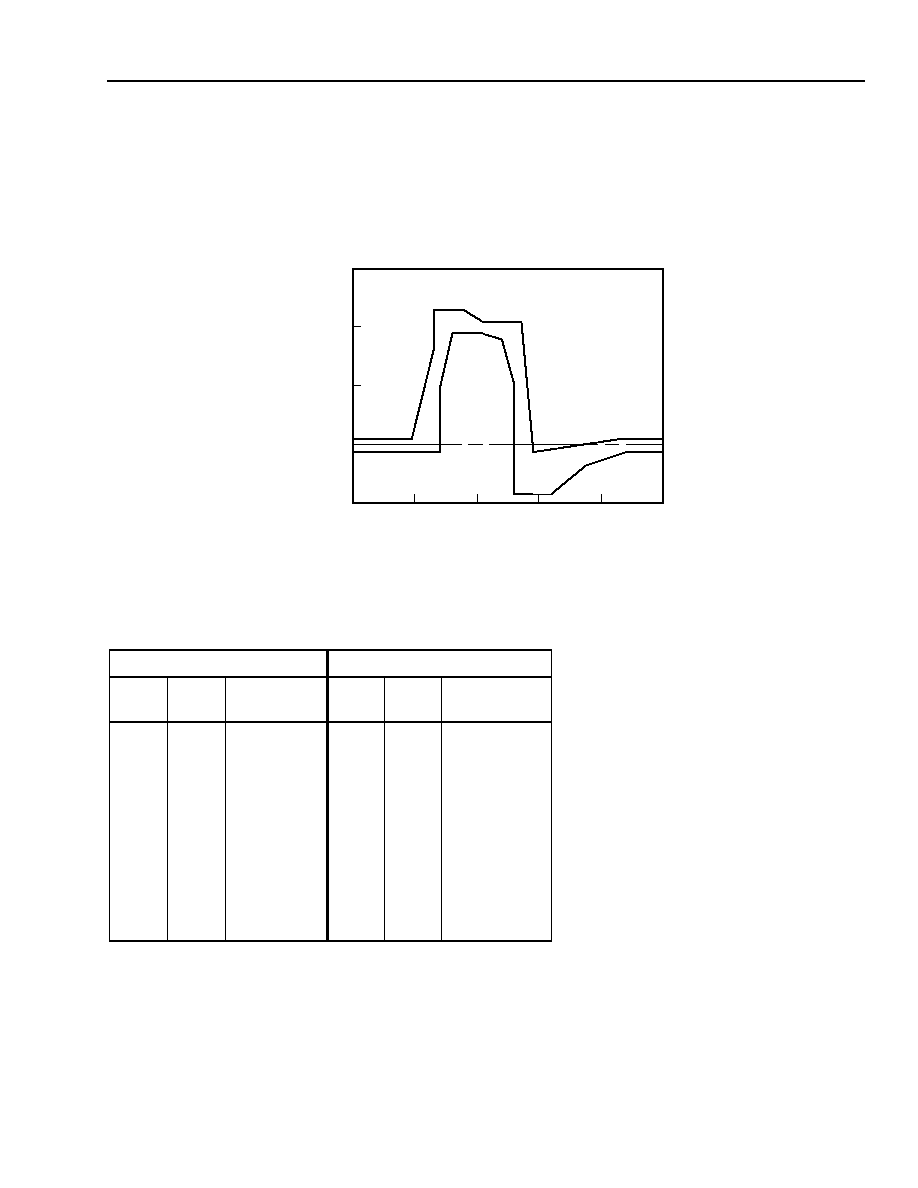

- Figure 12. T1/DS1 Receiver Jitter Accommodation with Jitter Attenuator

- Figure 13. T1/DS1 Jitter Transfer of the Jitter Attenuator

- Figure 14. CEPT/E1 Receiver Jitter Accommodation with Jitter Attenuator

- Figure 15. CEPT/E1 Jitter Transfer of the Jitter Attenuator

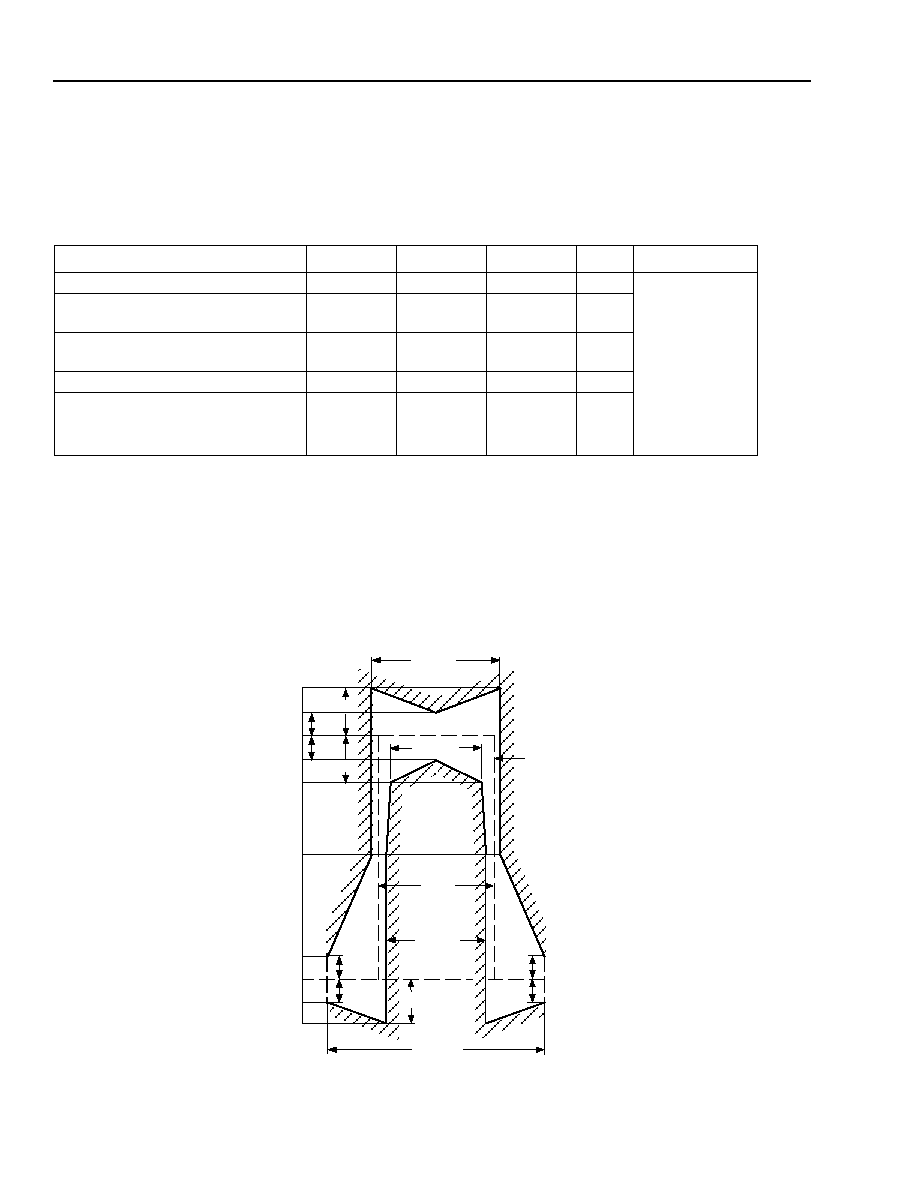

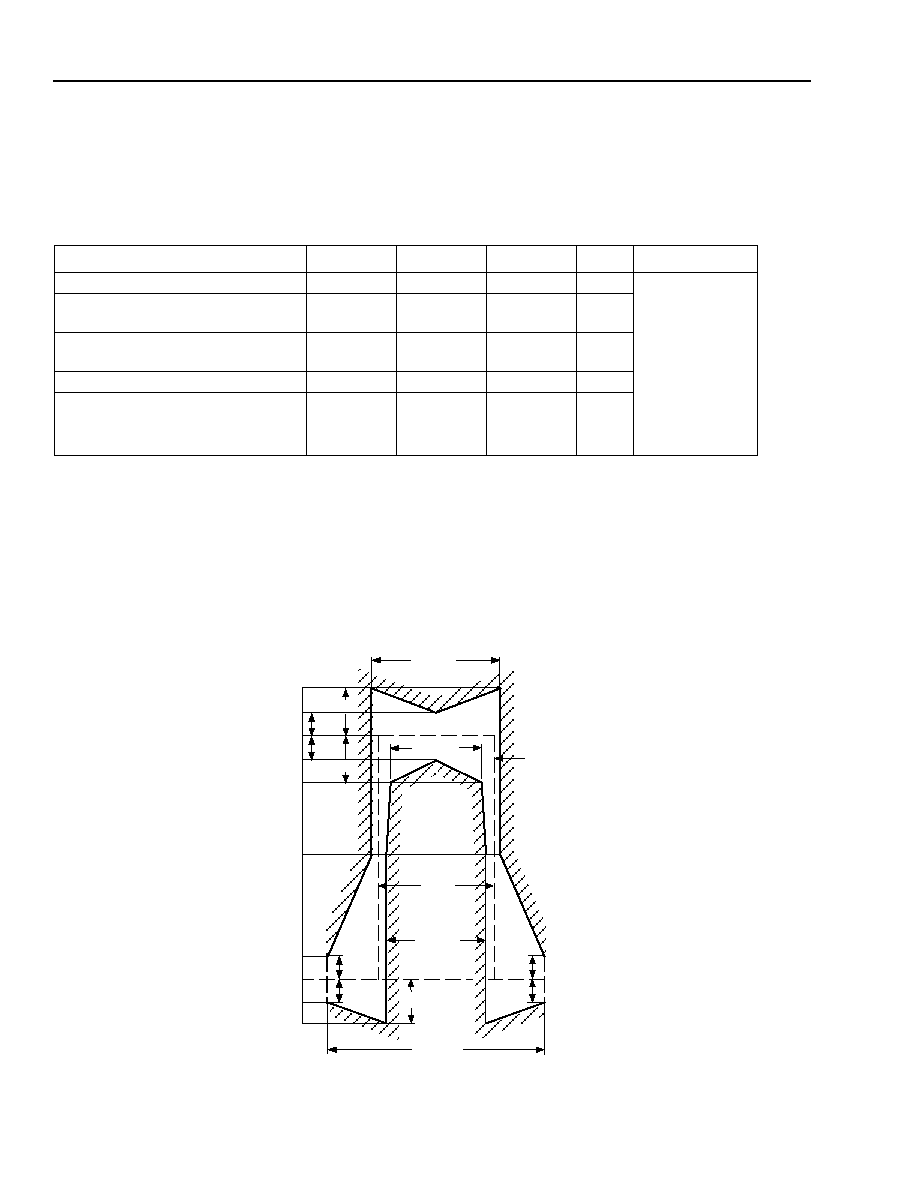

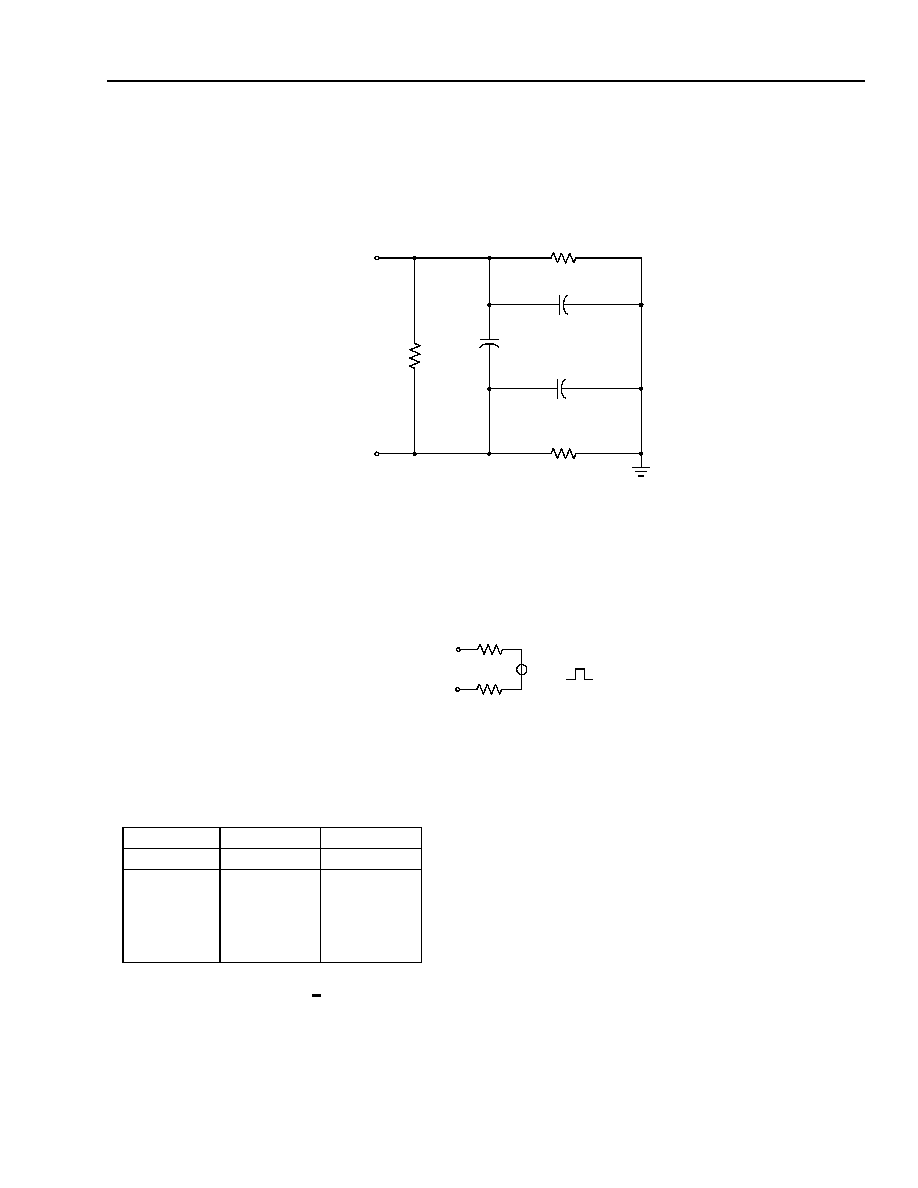

- Figure 16. Line Termination Circuitry

- Figure 17. T7633 Line Interface Unit Approximate Equivalent Analog I/O Circuits

- Figure 18. Block Diagram of Framer Line Interface

- Figure 19. Transmit Framer TLCK to TND, TPD and Receive Framer RND, RPD to RLCK Timing

- Figure 20. T1 Frame Structure

- Figure 21. T1 Transparent Frame Structure

- Figure 22. T7633 Facility Data Link Access Timing of the Transmit and Receive Framer Sections

- Figure 23. ITU 2.048 Basic Frame, CRC-4 Multiframe, and Channel Associated Signaling Multiframe S...

- Figure 24. CEPT Transparent Frame Structure

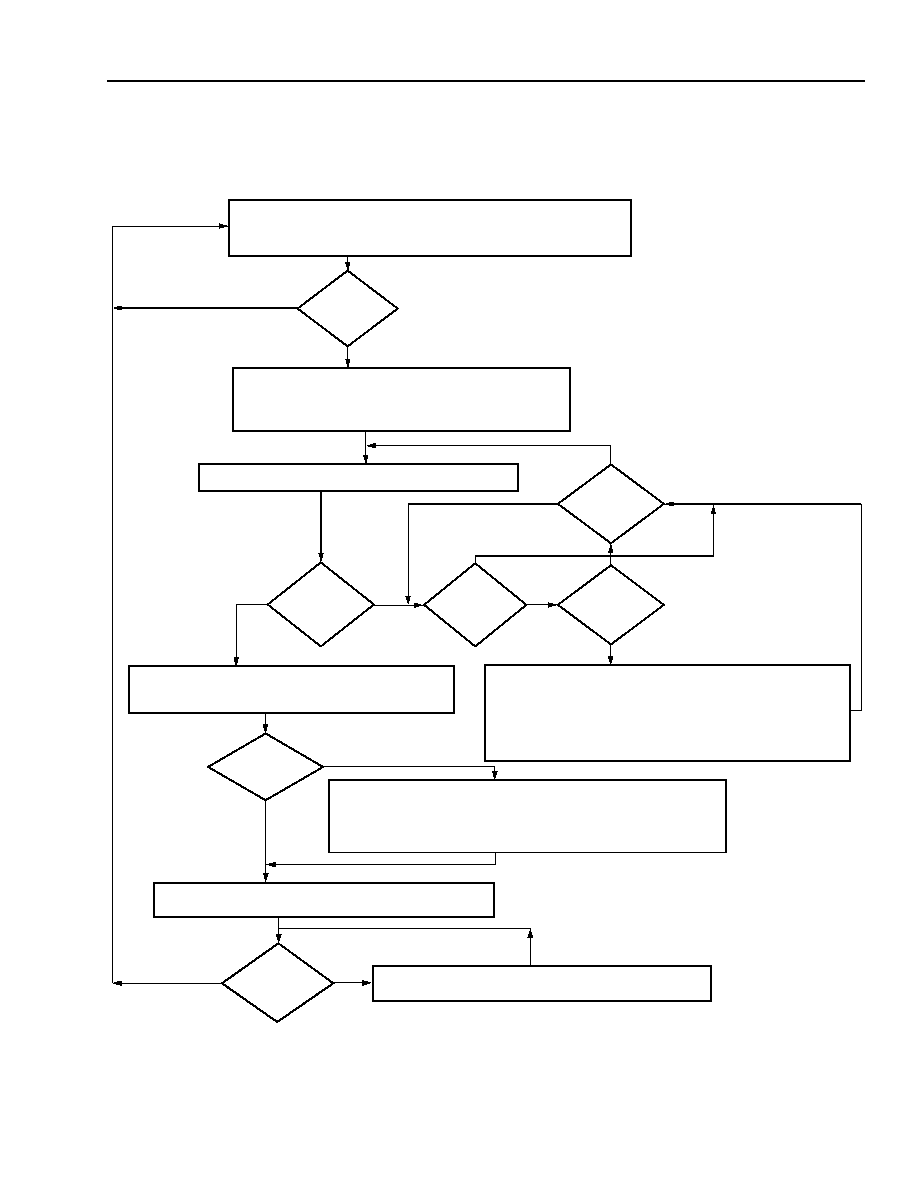

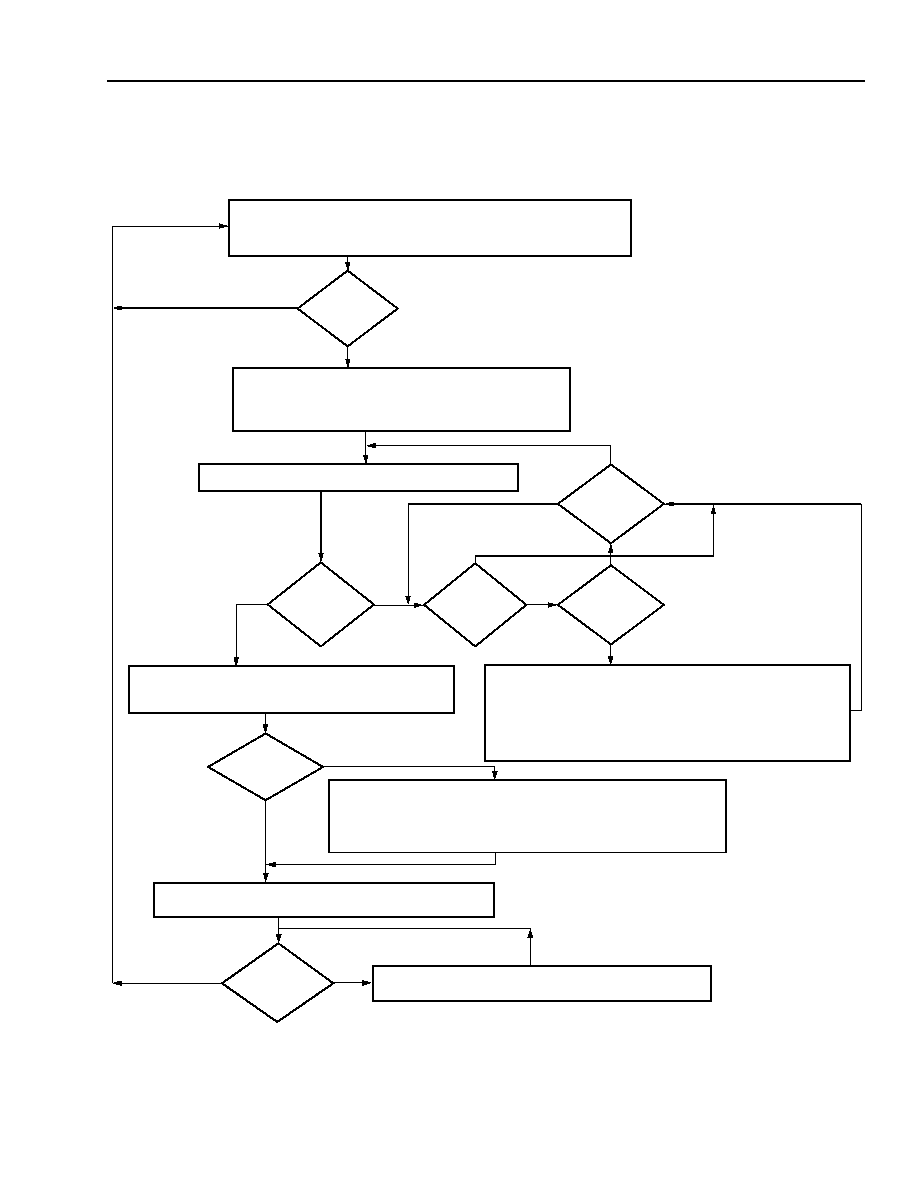

- Figure 25. Receive CRC-4 Multiframe Search Algorithm Using the 100 ms Internal Timer

- Figure 26. Receive CRC-4 Multiframe Search Algorithm for Automatic, CRC-4/Non-CRC-4 Equipment Int...

- Figure 27. Facility Data Link Access Timing of the Transmit and Receive Framer Sections in the CE...

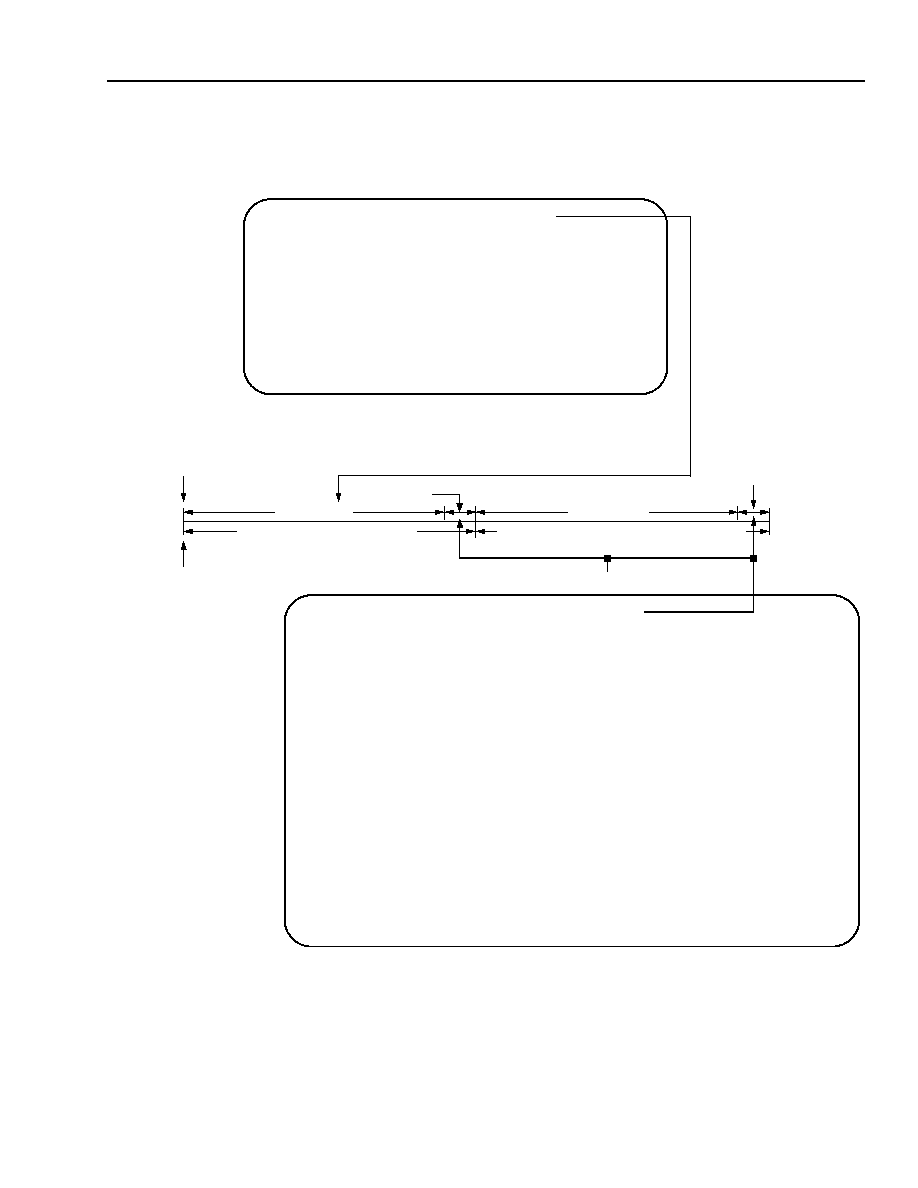

- Figure 28. Transmit and Receive Sa Stack Accessing Protocol

- Figure 29. Timing Specification for RFRMCK, RFRMDATA, and RFS in DS1 Mode

- Figure 30. Timing Specification for TFS, TLCK, and TPD in DS1 Mode

- Figure 31. Timing Specification for RFRMCK, RFRMDATA, and RFS in CEPT Mode

- Figure 32. Timing Specification for RFRMCK, RFRMDATA, RFS, and RSSFS in CEPT Mode

- Figure 33. Timing Specification for RCRCMFS in CEPT Mode

- Figure 34. Timing Specification for TFS, TLCK, and TPD in CEPT Mode

- Figure 35. Timing Specification for TFS, TLCK, TPD, and TSSFS in CEPT Mode

- Figure 36. Timing Specification for TFS, TLCK, TPD, and TCRCMFS in CEPT Mode

- Figure 37. Relation Between RLCK1 and Interrupt (Pin 99)

- Figure 38. Timing for Generation of LOPLLCK (Pin 39/143)

- Figure 39. The T and V Reference Points for a Typical CEPT E1 Application

- Figure 40. Loopback and Test Transmission Modes

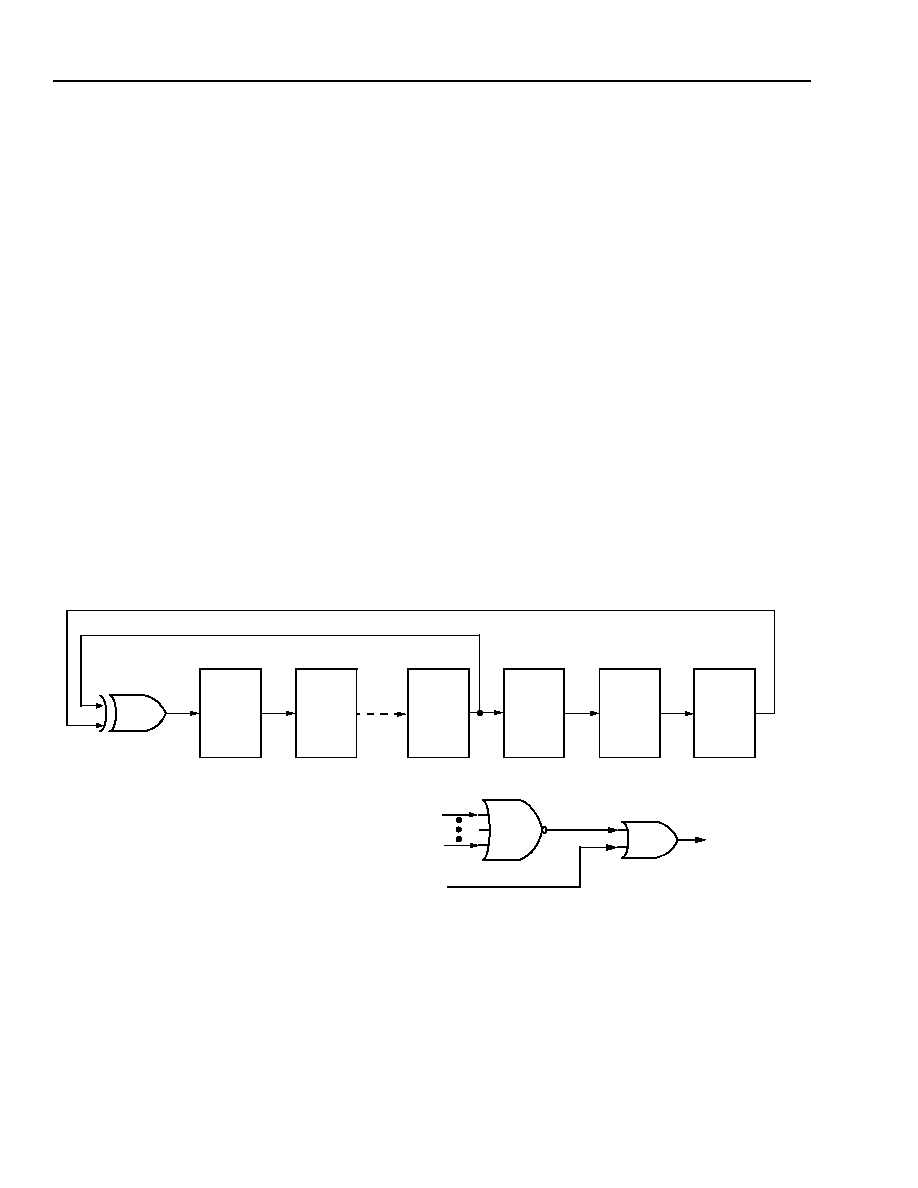

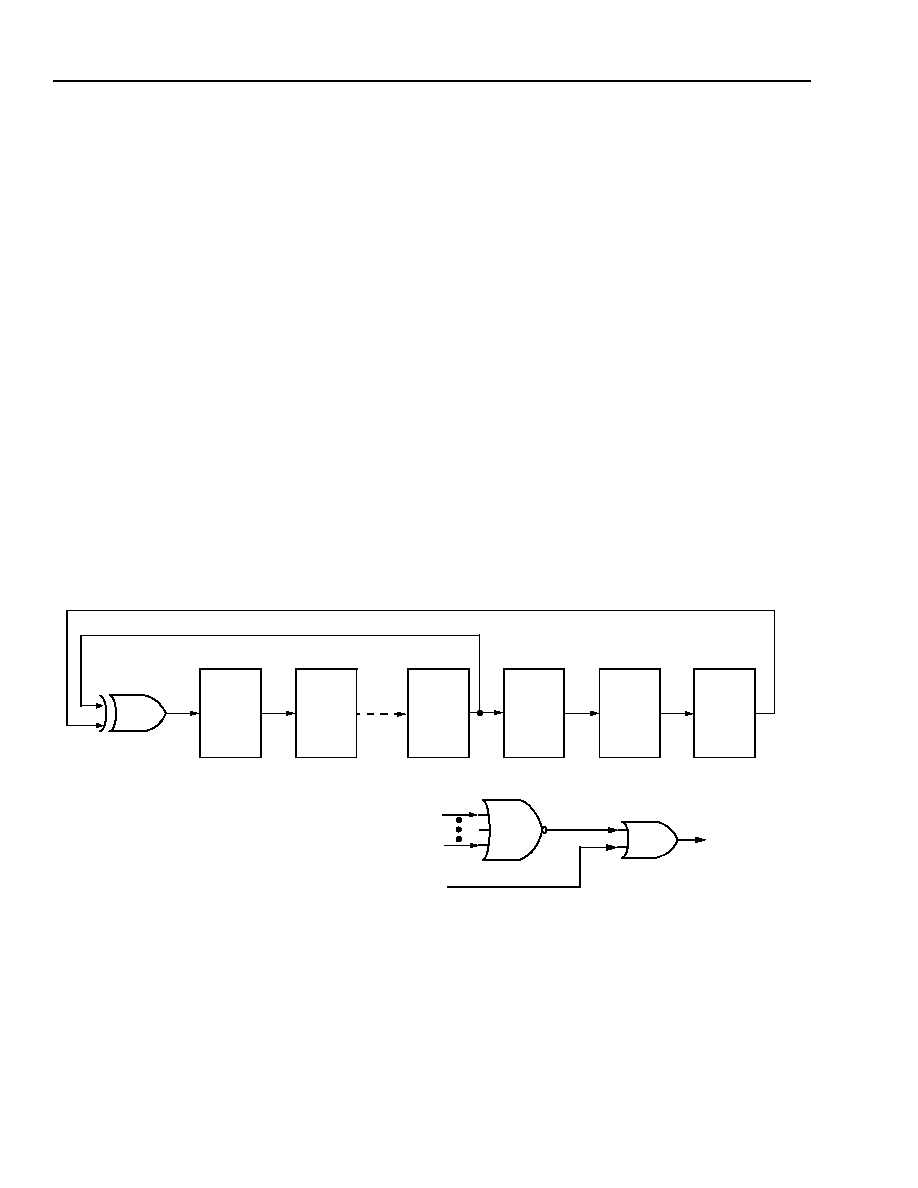

- Figure 41. 20-Stage Shift Register Used to Generate the Quasi-Random Signal

- Figure 42. 15-Stage Shift Register Used to Generate the Pseudorandom Signal

- Figure 43. T7633 Facility Data Link Access Timing of the Transmit and Receive Framer Sections

- Figure 44. Block Diagram for the Receive Facility Data Link Interface

- Figure 45. Block Diagram for the Transmit Facility Data Link Interface

- Figure 46. Local Loopback Mode

- Figure 47. Remote Loopback Mode

- Figure 48. T7633 Phase Detector Circuitry

- Figure 49. Nominal Concentration Highway Interface Timing (for FRM_PR43 bit 0Ñbit 2 = 100 (Binary))

- Figure 50. CHIDTS Mode Concentration Highway Interface Timing

- Figure 51. Associated Signaling Mode Concentration Highway Interface Timing

- Figure 52. CHI Timing with ASM and CHIDTS Enabled

- Figure 53. TCHIDATA and RCHIDATA to CHICK Relationship with CMS = 0 (CEX = 3 and CER = 4, Respect...

- Figure 54. CHI TCHIDATA and RCHIDATA to CHICK Relationship with CMS = 1 (CEX = 3 and CER = 6, Res...

- Figure 55. Receive CHI (RCHIDATA) Timing

- Figure 56. Transmit CHI (TCHIDATA) Timing

- Figure 57. Block Diagram of the T7633's Boundary-Scan Test Logic

- Figure 58. BS TAP Controller State Diagram

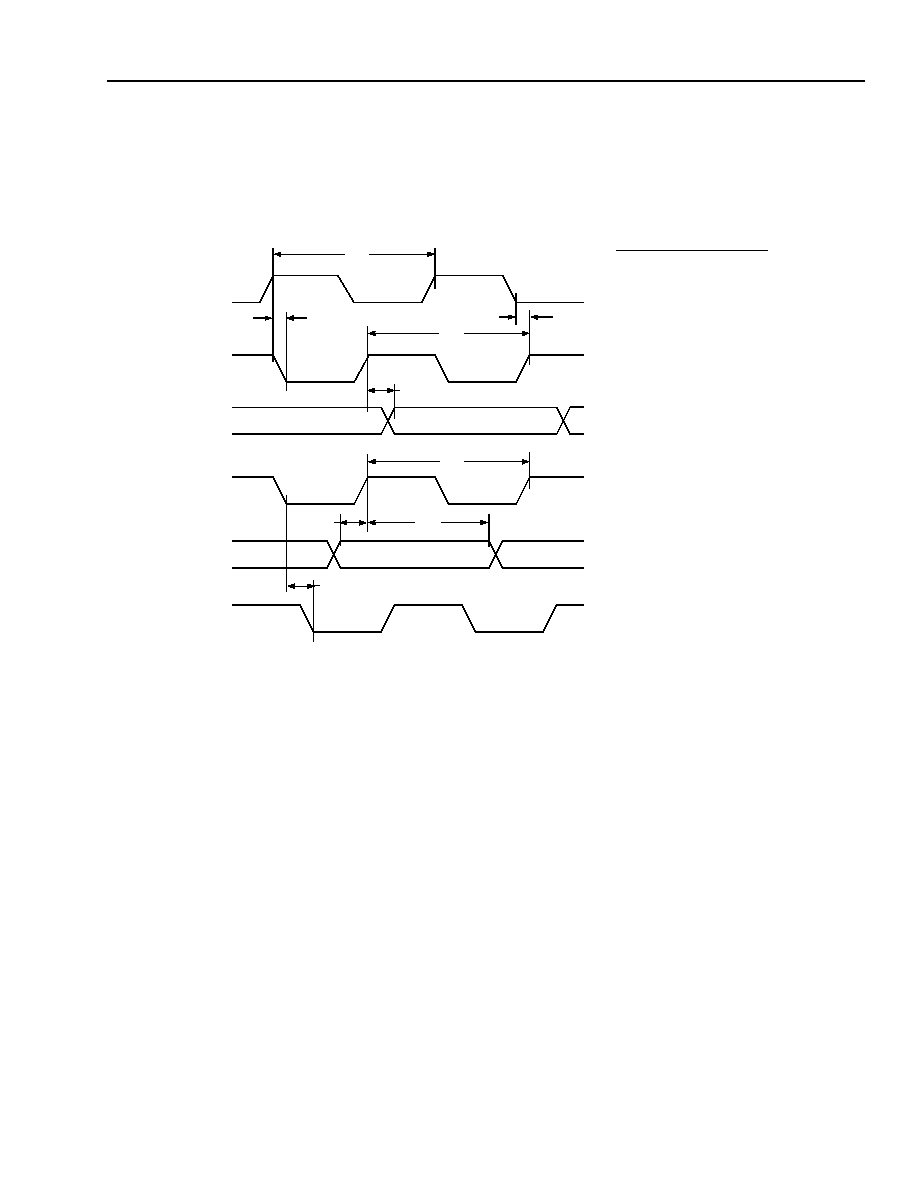

- Figure 59. Mode 1ÑRead Cycle Timing (MPMODE = 0, MPMUX = 0)

- Figure 60. Mode 1ÑWrite Cycle Timing (MPMODE = 0, MPMUX = 0)

- Figure 61. Mode 2ÑRead Cycle Timing (MPMODE = 0, MPMUX = 1)

- Figure 62. Mode 2ÑWrite Cycle Timing (MPMODE = 0, MPMUX = 1)

- Figure 63. Mode 3ÑRead Cycle Timing (MPMODE = 1, MPMUX = 0)

- Figure 64. Mode 3ÑWrite Cycle Timing (MPMODE = 1, MPMUX = 0)

- Figure 65. Mode 4ÑRead Cycle Timing (MPMODE = 1, MPMUX = 1)

- Figure 66. Mode 4ÑWrite Cycle Timing (MPMODE = 1, MPMUX = 1)

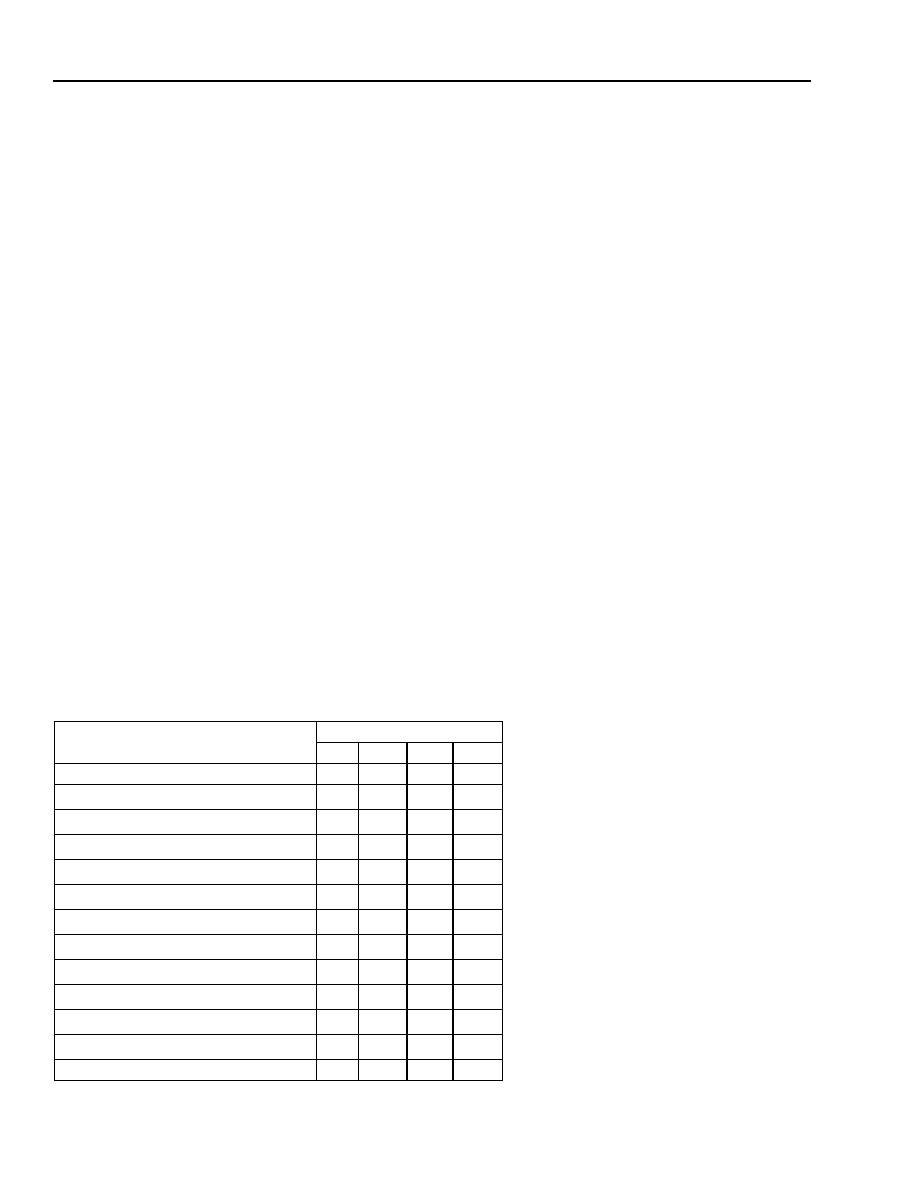

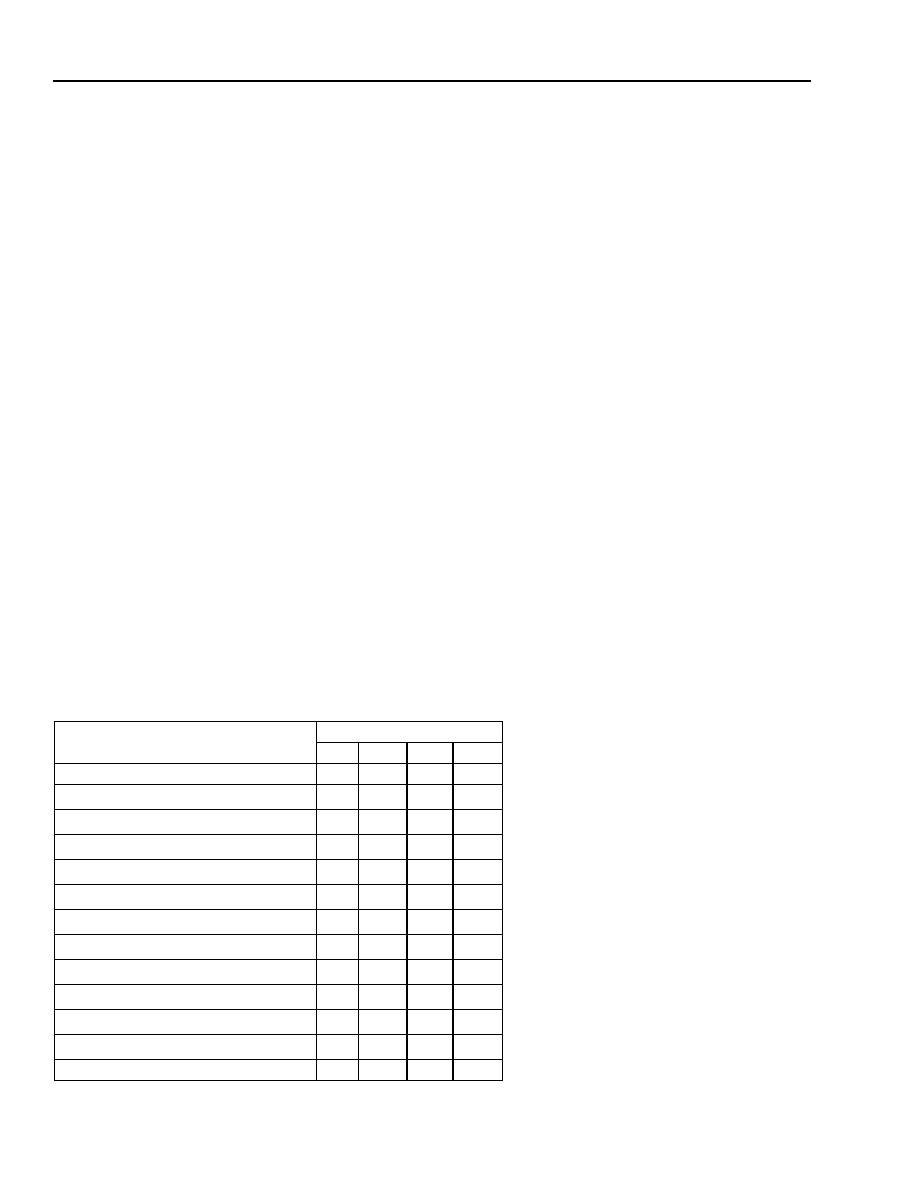

- List of Tables

- Table 1. Pin Descriptions

- Table 2. Digital Loss of Signal Standard Select

- Table 3. LOSSD and RCVAIS Control Configurations (Not Valid During Loopback Modes)

- Table 4. DS1 LIU Receiver Specifications

- Table 5. CEPT LIU Receiver Specifications

- Table 6. Transmit Line Interface Short-Haul Equalizer/Rate Control

- Table 7. DSX-1 Pulse Template Corner Points (from CB119, T1.102)

- Table 8. DS1 Transmitter Specifications

- Table 9. CEPT Transmitter Specifications

- Table 10. Loopback Control

- Table 11. SYSCK (16x, CKSEL = 1) Timing Specifications

- Table 12. SYSCK (1x, CKSEL = 0) Timing Specifications

- Table 13. Termination Components by Application1

- Table 14. AMI Encoding

- Table 15. DS1 ZCS Encoding

- Table 16. DS1 B8ZS Encoding

- Table 17. ITU HDB3 Coding

- Table 18. T-Carrier Hierarchy

- Table 19. D4 Superframe Format

- Table 20. DDS Channel-24 Format

- Table 21. SLC-96 Data Link Block Format

- Table 22. SLC-96 Line Switch Message Codes

- Table 23. Transmit and Receive SLC-96 Stack Structure

- Table 24. Extended Superframe (ESF) Structure

- Table 25. T1 Loss of Frame Alignment Criteria

- Table 26. T1 Frame Alignment Procedures

- Table 27. Robbed-Bit Signaling Options

- Table 28. SLC-96 9-State Signaling Format

- Table 29. 16-State Signaling Format

- Table 30. Allocation of Bits 1 to 8 of the FAS Frame and the NOT FAS Frame

- Table 31. ITU CRC-4 Multiframe Structure

- Table 32. ITU CEPT Time Slot 16 Channel Associated Signaling Multiframe Structure

- Table 33. CEPT IRSM Signaling Multiframe Structure

- Table 34. Transmit and Receive Sa Stack Structure

- Table 35. Associated Signaling Mode CHI 2-Byte Time-Slot Format for DS1 Frames

- Table 36. Associated Signaling Mode CHI 2-Byte Time-Slot Format for Stuffed Channels

- Table 37. Associated Signaling Mode CHI 2-Byte Time-Slot Format for CEPT

- Table 38. Red Alarm or Loss of Frame Alignment Conditions

- Table 39. Remote Frame Alarm Conditions

- Table 40. Alarm Indication Signal Conditions

- Table 41. Sa6 Bit Coding Recognized by the Receive Framer

- Table 42. Sa6 Bit Coding of NT1 Interface Events Recognized by the Receive Framer

- Table 43. AUXP Synchronization and Clear Sychronization Process

- Table 44. Event Counters Definition

- Table 45. Summary of the Deactivation of SSTSSLB and SSTSLLB Modes as a Function of Activating th...

- Table 46. Register FRM_PR69 Test Patterns

- Table 47. Register FRM_PR70 Test Patterns

- Table 48. Automatic Enable Commands

- Table 49. On-Demand Commands

- Table 50. Receive ANSI Code

- Table 51. Performance Report Message Structure*

- Table 52. FDL Performance Report Message Field Definition

- Table 53. Octet Contents and Definition

- Table 54. Receive Status of Frame Byte

- Table 55. HDLC Frame Format

- Table 56. Receiver Operation in Transparent Mode

- Table 57. Summary of the T7633ês Concentration Highway Interface Parameters

- Table 58. Programming Values for TOFF[2:0] and ROFF[2:0] when CMS = 0

- Table 59. Programming Values for TOFF[2:0] when CMS = 1

- Table 60. Programming Values for ROFF[2:0] when CMS = 1

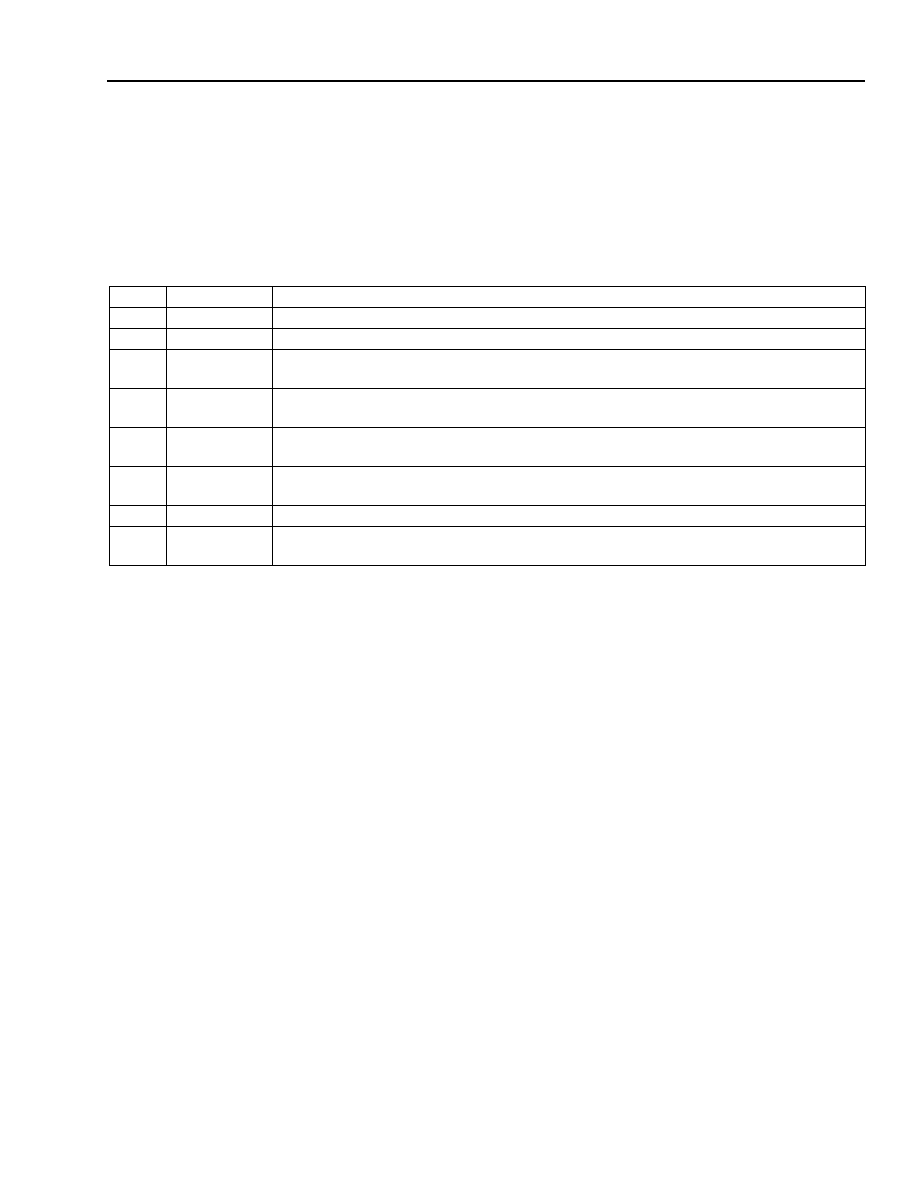

- Table 61. TAP Controller States in the Data Register Branch

- Table 62. TAP Controller States in the Instruction Register Branch

- Table 63. T7633ês Boundary-Scan Instructions

- Table 64. IDCODE Register

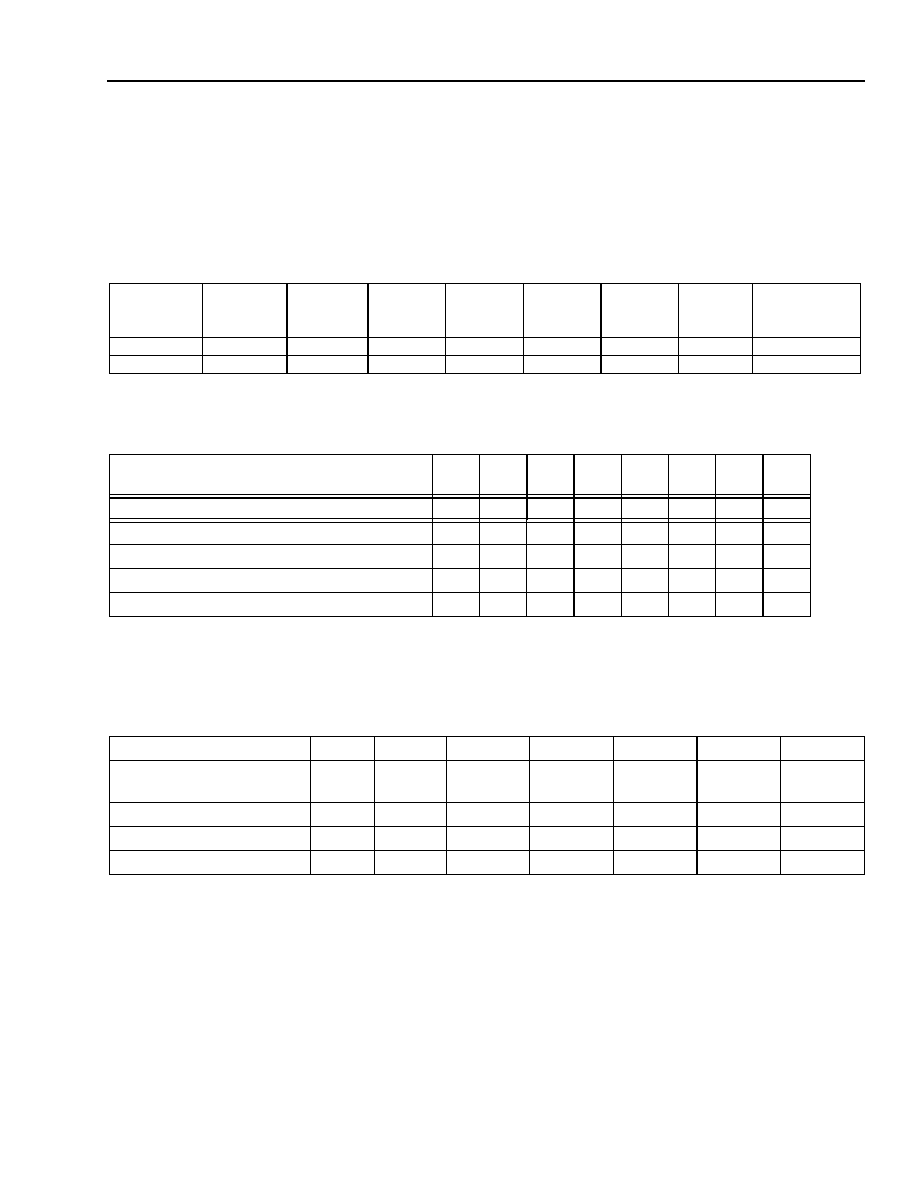

- Table 65. Microprocessor Configuration Modes

- Table 66. Mode [1Ñ4] Microprocessor Pin Definitions

- Table 67. Microprocessor Input Clock Specifications

- Table 68. T7633 Register Address Map

- Table 69. Microprocessor Interface I/O Timing Specifications�

- Table 70. Status Register and Corresponding Interrupt Enable Register for Functional Blocks

- Table 71. Asserted Value and Deasserted State for GREG4 Bit 4 and Bit 6 Logic Combinations

- Table 72. Register Summary

- Table 73. Global Register Set (0x000Ñ0x008)

- Table 74. Primary Block Interrupt Status Register (GREG0) (000)

- Table 75. Primary Block Interrupt Enable Register (GREG1) (001)

- Table 76. Global Loopback Control Register (GREG2) (002)

- Table 77. Global Loopback Control Register (GREG3) (003)

- Table 78. Global Control Register (GREG4) (004)

- Table 79. Device ID and Version Registers (GREG5ÑGREG7) (005Ñ007)

- Table 80. Line Interface Units Register Set1 ((400Ñ40F); (A00ÑA0F))

- Table 81. LIU Alarm Status Register (LIU_REG0) (400, A00)

- Table 82. LIU Alarm Interrupt Enable Register (LIU_REG1) (401, A01)

- Table 83. LIU Control Register (LIU_REG2) (402, A02)

- Table 84. LIU Control Register (LIU_REG3) (403, A03)

- Table 85. LIU Register (LIU_REG4) (404, A04)

- Table 86. LIU Configuration Register (LIU_REG5) (405, A05)

- Table 87. LIU Configuration Register (LIU_REG6) (406, A06)

- Table 88. Framer Status and Control Blocks Address Range (Hexadecimal)

- Table 89. Interrupt Status Register (FRM_SR0) (600; C00)

- Table 90. Facility Alarm Condition Register (FRM_SR1) (601; C01)

- Table 91. Remote End Alarm Register (FRM_SR2) (602; C02)

- Table 92. Facility Errored Event Register-1 (FRM_SR3) (603; C03)

- Table 93. Facility Event Register-2 (FRM_SR4) (604; C04)

- Table 94. Exchange Termination and Exchange Termination Remote End Interface Status Register (FRM...

- Table 95. Network Termination and Network Termination Remote End Interface Status Register (FRM_S...

- Table 96. Facility Event Register (FRM_SR7) (607; C07)

- Table 97. Bipolar Violation Counter Registers (FRM_SR8ÑFRM_SR9) ((608Ñ609); (C08ÑC09))

- Table 98. Framing Bit Error Counter Registers (FRM_SR10ÑFRM_SR11) ((60AÑ60B); (C0AÑC0B))

- Table 99. CRC Error Counter Registers (FRM_SR12ÑFRM_SR13) ((60CÑ60D); (C0CÑC0D))

- Table 100. E-Bit Counter Registers (FRM_SR14ÑFRM_SR15) ((60EÑ60F); (C0EÑC0F))

- Table 101. CRC-4 Errors at NT1 from NT2 Counter Registers (FRM_SR16ÑFRM_SR17) ((610Ñ611); (C10ÑC11))

- Table 102. E Bit at NT1 from NT2 Counter (FRM_SR18ÑFRM_SR19) ((612Ñ613); (C12ÑC13))

- Table 103. ET Errored Seconds Counter (FRM_SR20ÑFRM_SR21) ((614Ñ615); (C14ÑC15))

- Table 104. ET Bursty Errored Seconds Counter (FRM_SR22ÑFRM_SR23) ((616Ñ617); (C16ÑC17))

- Table 105. ET Severely Errored Seconds Counter (FRM_SR24ÑFRM_SR25) ((618Ñ619); (C18ÑC19))

- Table 106. ET Unavailable Seconds Counter (FRM_SR26ÑFRM_SR27) ((61AÑ61B); (C1AÑC1B))

- Table 107. ET-RE Errored Seconds Counter (FRM_SR28ÑFRM_SR29) ((61CÑ61D); (C1CÑC1D))

- Table 108. ET-RE Bursty Errored Seconds Counter (FRM_SR30ÑFRM_SR31) ((61EÑ61F); (C1EÑC1F))

- Table 109. ET-RE Severely Errored Seconds Counter (FRM_SR32ÑFRM_SR33) ((620Ñ621); (C20ÑC21))

- Table 110. ET-RE Unavailable Seconds Counter (FRM_SR34ÑFRM_SR35) ((622Ñ623); (C22ÑC23))

- Table 111. NT1 Errored Seconds Counter (FRM_SR36ÑFRM_SR37) ((624Ñ625); (C24ÑC25))

- Table 112. NT1 Bursty Errored Seconds Counter (FRM_SR38ÑFRM_SR39) ((626Ñ627); (C26ÑC27))

- Table 113. NT1 Severely Errored Seconds Counter (FRM_SR40ÑFRM_SR41) ((628Ñ629); (C28ÑC29))

- Table 114. NT1 Unavailable Seconds Counter (FRM_SR42ÑFRM_SR43) ((62AÑ62B); (C2AÑC2B))

- Table 115. NT1-RE Errored Seconds Counter (FRM_SR44ÑFRM_SR45) ((62CÑ62D); (C2CÑC2D))

- Table 116. NT1-RE Bursty Errored Seconds Counter (FRM_SR46ÑFRM_SR47) ((62EÑ62F); (C2EÑC2F))

- Table 117. NT1-RE Severely Errored Seconds Counter (FRM_SR48ÑFRM_SR49) ((630Ñ631); (C30ÑC31))

- Table 118. NT1-RE Unavailable Seconds Counter (FRM_SR50ÑFRM_SR51) ((632Ñ633); (C32ÑC33))

- Table 119. Receive NOT-FAS TS0 Register (FRM_SR52) (634; C34)

- Table 120. Receive Sa Register (FRM_SR53) (635; C35)

- Table 121. SLC-96 FDL Receive Stack (FRM_SR54ÑFRM_SR63) ((636Ñ63F); (C36ÑC3F))

- Table 122. CEPT Sa Receive Stack (FRM_SR54ÑFRM_SR63) ((636Ñ63F); (C36ÑC3F))

- Table 123. Transmit Framer ANSI Performance Report Message Status Register Structure

- Table 124. Received Signaling Registers: DS1 Format (FRM_RSR0ÑFRM_RSR23) ((640Ñ658); (C40ÑC58))

- Table 125. Receive Signaling Registers: CEPT Format (FRM_RSR0ÑFRM_RSR31) ((640Ñ65F); (C40Ñ C5F))

- Table 126. Summary of Interrupt Group Enable Registers (FRM_PR0ÑFRM_PR7) ((660Ñ667); (C60ÑC67))

- Table 127. Primary Interrupt Group Enable Register (FRM_PR0) (660; C60)

- Table 128. Interrupt Enable Register (FRM_PR1) (661; C61)

- Table 129. Interrupt Enable Register (FRM_PR2) (662; C62)

- Table 130. Interrupt Enable Register (FRM_PR3) (663; C63)

- Table 131. Interrupt Enable Register (FRM_PR4) (664; C64)

- Table 132. Interrupt Enable Register (FRM_PR5) (665; C65)

- Table 133. Interrupt Enable Register (FRM_PR6) (666; C66)

- Table 134. Interrupt Enable Register (FRM_PR7) (667; C67)

- Table 135. Framer Mode Bits Decoding (FRM_PR8) (668; C68)

- Table 136. Line Code Option Bits Decoding (FRM_PR8) (668; C68)

- Table 137. CRC Option Bits Decoding (FRM_PR9) (669, C69)

- Table 138. Alarm Filter Register (FRM_PR10) (66A; C6A)

- Table 139. Errored Event Threshold Definition

- Table 140. Errored Second Threshold Register (FRM_PR11) (66B; C6B)

- Table 141. Severely Errored Second Threshold Registers (FRM_PR12ÑFRM_PR13) ((66CÑ66D; C6CÑC6D))

- Table 142. ET1 Errored Event Enable Register (FRM_PR14) (66E; C6E)

- Table 143. ET1 Remote End Errored Event Enable Register (FRM_PR15) (66F; C6F)

- Table 144. NT1 Errored Event Enable Register (FRM_PR16) (670; C70)

- Table 145. NT1 Remote End Errored Event Enable Registers (FRM_PR17ÑFRM_PR18) ((671Ñ672); (C71ÑC72))

- Table 146. Automatic AIS to the System and Automatic Loopback Enable Register (FRM_PR19) (673; C73)

- Table 147. Transmit Test Pattern to the Line Enable Register (FRM_PR20) (674; C74)

- Table 148. Framer FDL Control Command Register (FRM_PR21) (675; C75)

- Table 149. Framer Transmit Line Idle Code Register (FRM_PR22) (676; C76)

- Table 150. Framer System Stuffed Time-Slot Code Register (FRM_PR23) (677; C77)

- Table 151. Primary Time-Slot Loopback Address Register (FRM_PR24) (678; C78)

- Table 152. Loopback Decoding of Bits LBC[2:0] in FRM_PR24, Bits 7Ñ5

- Table 153. Secondary Time-Slot Loopback Address Register (FRM_PR25) (679; C79)

- Table 154. Loopback Decoding of Bits LBC[1:0] in FRM_PR25, Bits 6Ñ5

- Table 155. Framer Reset and Transparent Mode Control Register (FRM_PR26) (67A, C7A)

- Table 156. Transmission of Remote Frame Alarm and CEPT Automatic Transmission of A Bit = 1 Contro...

- Table 157. CEPT Automatic Transmission of E Bit = 0 Control Register (FRM_PR28) (67C; C7C)

- Table 158. Sa4ÑSa8 Source Register (FRM_PR29) (67D; C7D)

- Table 159. Sa Bits Source Control for Bit 5ÑBit 7 in FRM_PR29

- Table 160. Sa4ÑSa8 Control Register (FRM_PR30) (67E; C7E)

- Table 161. Sa Transmit Stack (FRM_PR31ÑFRM_PR40) ((67FÑ688); (C7FÑC88))

- Table 162. SLC-96 Transmit Stack (FRM_PR31ÑFRM_PR40) ((67FÑ688); (C7FÑC88))

- Table 163. Transmit SLC-96 FDL Format

- Table 164. CEPT Time Slot 16 X-Bit Remote Multiframe Alarm and AIS Control Register (FRM_PR41) (6...

- Table 165. Framer Exercise Register (FRM_PR42) (68A; C8A)

- Table 166. Framer Exercises, FRM_PR42 Bit 5ÑBit 0 (68A; C8A)

- Table 167. DS1 System Interface Control and CEPT FDL Source Control Register (FRM_PR43) (68B; C8B)

- Table 168. Signaling Mode Register (FRM_PR44) (68C; C8C)

- Table 169. CHI Common Control Register (FRM_PR45) (68D; C8D)

- Table 170. CHI Common Control Register (FRM_PR46) (68E; C8E)

- Table 171. CHI Transmit Control Register (FRM_PR47) (68F; C8F)

- Table 172. CHI Receive Control Register (FRM_PR48) (690; C90)

- Table 173. CHI Transmit Time-Slot Enable Registers (FRM_PR49ÑFRM_PR52) ((691Ñ694); (C91ÑC94))

- Table 174. CHI Receive Time-Slot Enable Registers (FRM_PR53ÑFRM_PR56) ((695Ñ698); (C95ÑC98))

- Table 175. CHI Transmit Highway Select Registers (FRM_PR57ÑFRM_PR60) ((699Ñ69C); (C99ÑC9C))

- Table 176. CHI Receive Highway Select Registers (FRM_PR61ÑFRM_PR64) ((69DÑ6A0); (C9DÑCA0))

- Table 177. CHI Transmit Control Register (FRM_PR65) (6A1; CA1)

- Table 178. CHI Receive Control Register (FRM_PR66) (6A2; CA2)

- Table 179. Auxiliary Pattern Generator Control Register (FRM_PR69) (6A5; CA5)*

- Table 180. Pattern Detector Control Register (FRM_PR70) (6A6; CA6)*

- Table 181. Transmit Signaling Registers: DS1 Format (FRM_TSR0ÑFRM_TSR23) ((6E0Ñ6F7); (CE0ÑCF7))

- Table 182. Transmit Signaling Registers: CEPT Format (FRM_TSR0ÑFRM_TSR31) ((6E0Ñ6FF); (CE0Ñ CFF))

- Table 183. FDL Register Set (800Ñ80E); (E00ÑE0E)

- Table 184. FDL Configuration Control Register (FDL_PR0) (800; E00)

- Table 185. FDL Control Register (FDL_PR1) (801; E01)

- Table 186. FDL Interrupt Mask Control Register (FDL_PR2) (802; E02)

- Table 187. FDL Transmitter Configuration Control Register (FDL_PR3) (803; E03)

- Table 188. FDL Transmitter FIFO Register (FDL_PR4) (804; E04)

- Table 189. FDL Transmitter Mask Register (FDL_PR5) (805; E05)

- Table 190. FDL Receiver Interrupt Level Control Register (FDL_PR6) (806; E06)

- Table 191. FDL Register FDL_PR7

- Table 192. FDL Receiver Match Character Register (FDL_PR8) (808; E08)

- Table 193. FDL Transparent Control Register (FDL_PR9) (809; E09)

- Table 194. FDL Transmit ANSI ESF Bit Codes (FDL_PR10) (80A; E0A)

- Table 195. FDL Interrupt Status Register (Clear on Read) (FDL_SR0) (80B; E0B)

- Table 196. FDL Transmitter Status Register (FDL_SR1) (80C; E0C)

- Table 197. FDL Receiver Status Register (FDL_SR2) (80D; E0D)

- Table 198. Receive ANSI FDL Status Register (FDL_SR3) (80E; E0E)

- Table 199. FDL Receiver FIFO Register (FDL_SR4) (807; E07)

- Table 200. Global Register Set

- Table 201. Line Interface Unit Register Set1

- Table 202. Framer Unit Status Register Map

- Table 203. Receive Signaling Registers Map

- Table 204. Framer Unit Parameter Register Map

- Table 205. Transmit Signaling Registers Map

- Table 206. Facility Data Link Register Map

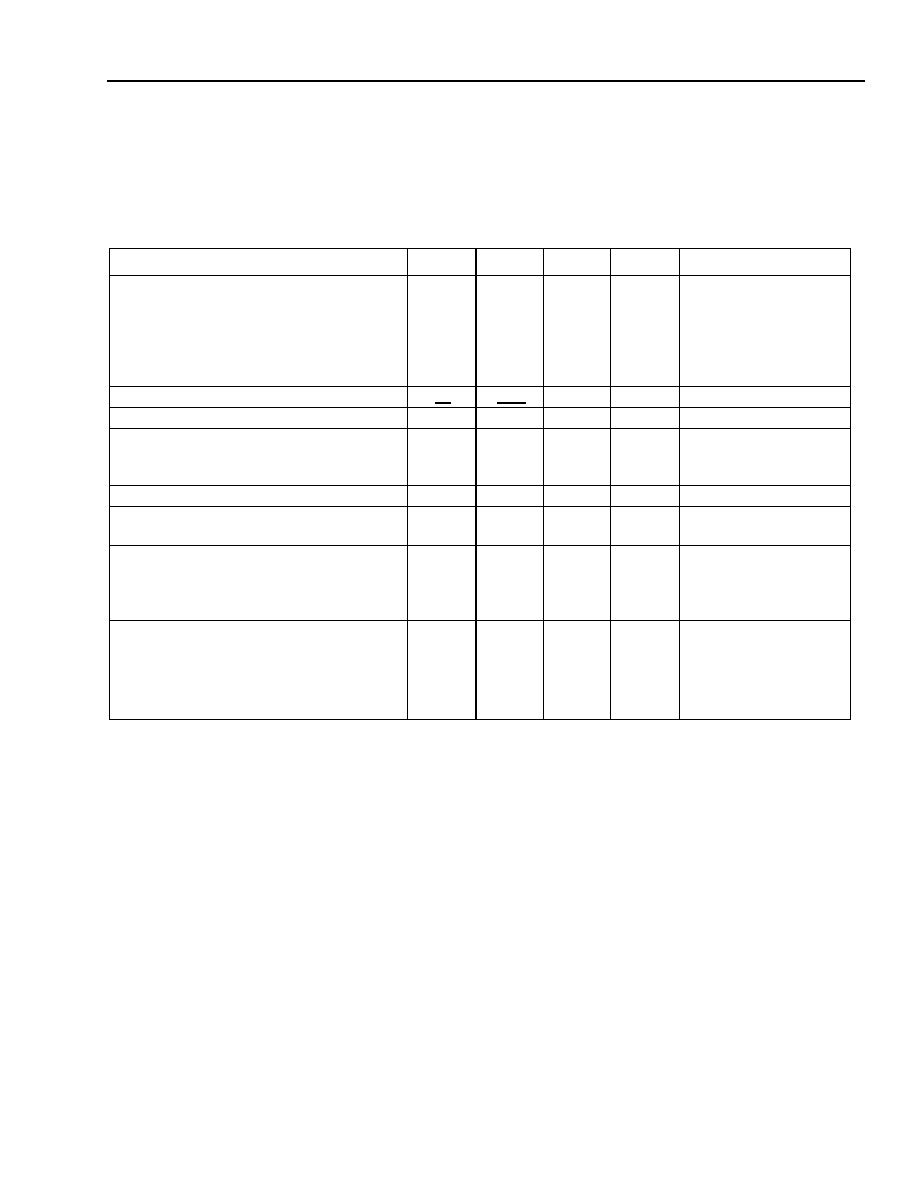

- Table 207. ESD Protection Characteristics

- Table 208. Logic Interface Characteristics (TA = Ö40 ∞C to +85 ∞C, VDD = 3.3 V ± 5%, VSS = 0)

- Feature Descriptions

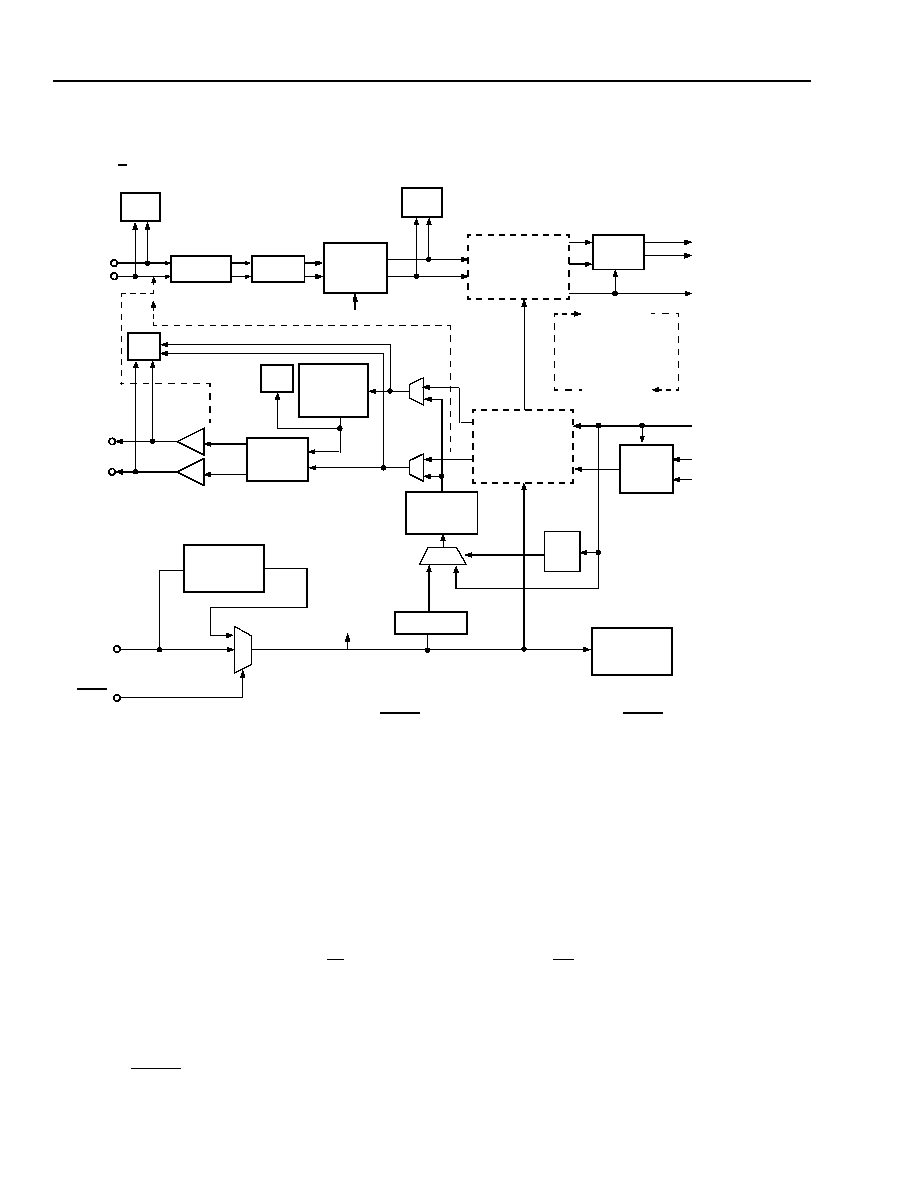

- Functional Description

- Pin Information

- Line Interface Unit: Block Diagram

- Line Interface Unit: Receive

- Line Interface Unit: Transmit

- Line Interface Unit: Jitter Attenuator

- Line Interface Unit: Loopbacks

- Line Interface Unit: Other Features

- SYSCK Reference Clock

- Line Interface Unit: Line Interface Networks

- LIU-Framer Interface

- Frame Formats

- CEPT Time Slot 0 FAS/NOT FAS Control Bits

- Signaling Access

- Auxiliary Framer I/O Timing

- Alarms and Performance Monitoring

- Facility Data Link (FDL)

- Phase-Lock Loop Circuit

- Framer-System (CHI) Interface

- Concentration Highway Interface (CHI)

- JTAG Boundary-Scan Specification

- Microprocessor Interface

- Reset

- Interrupt Generation

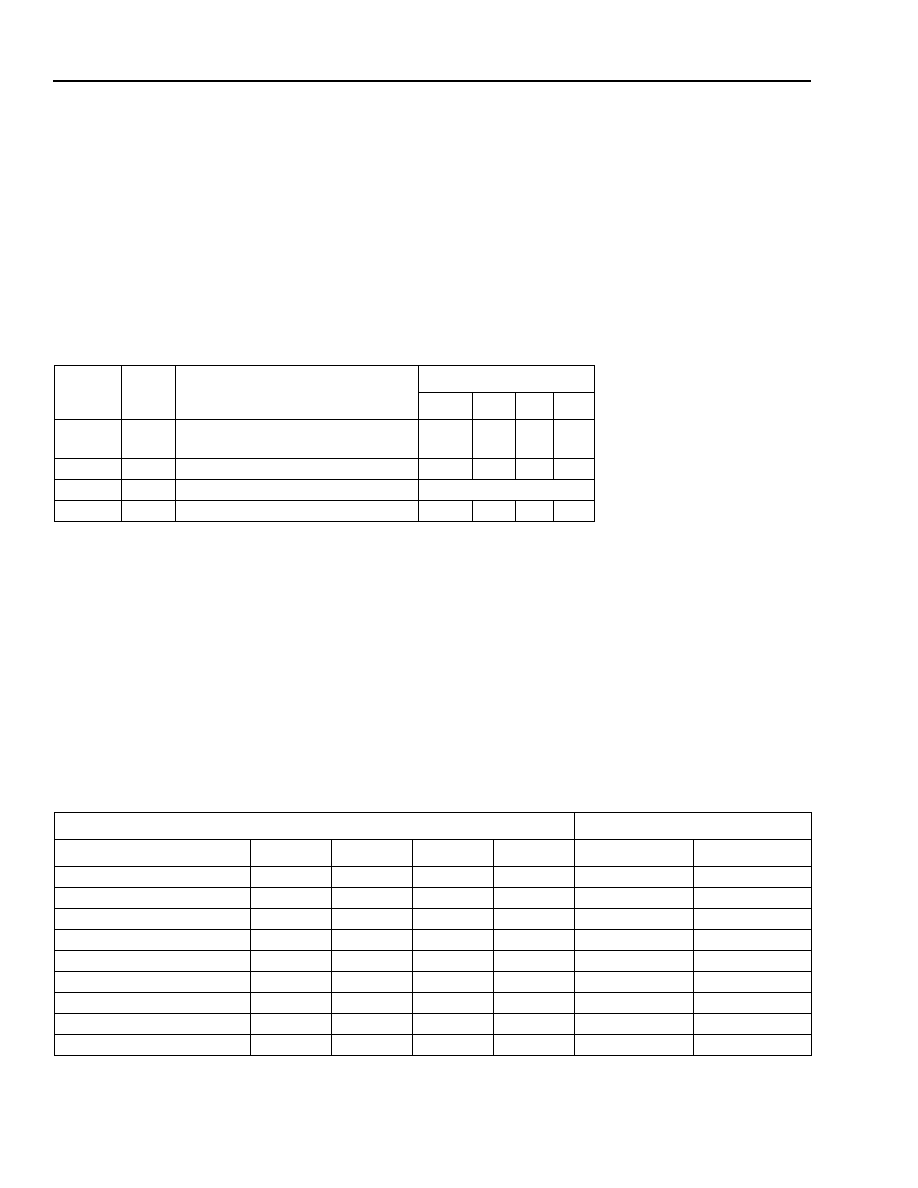

- Register Architecture

- Global Register Architecture

- Global Register Structure

- Line Interface Unit (LIU) Register Architecture

- Line Interface Alarm Register

- Line Interface Alarm Interrupt Enable Register

- Line Interface Control Registers

- Framer Register Architecture

- FDL Register Architecture

- FDL Parameter/Control Registers (800Ñ80E; E00ÑE0E)

- Register Maps

- Absolute Maximum Ratings

- Operating Conditions

- Handling Precautions

- Electrical Characteristics

- Power Supply Bypassing

- Outline Diagram

- Ordering Information

- Index

- Trademark Information

- Contact Us

Device Advisory

September 1999

T7633 Device Advisory for Version 1.0 of the Device

Introduction

This advisory applies to the T7633 Dual T1/E1 3.3 V Short-Haul Terminator as described in the May 1998

T7633 Dual T1/E1 3.3 V Short-Haul Terminator

Advance Data Sheet (DS98-244TIC).

Microprocessor Timing Requirements

This section describes a modification to the microprocessor interface timing information to guarantee proper

function of the line interface clear on read status register, LIU_REG0, at address 400 and A00 (hex).

For clear on read (COR) register LIU_REG0 to clear, the chip select (CS) and address value (AD0--AD7 and

A8--A11, or A0--A11) must be active for either of the following intervals after the completion of the read (RD)

or data strobe (DS) pulse.

1. If present, two microprocessor clock (MPCK) cycles.

s

33 MHz maximum.

s

3 MHz minimum.

2. Two internal SYSCK cycles, if MPCK is not present.

s

The internal SYSCK is a clock at 16 times the line rate (24.704 MHz for DS1 or 32.768 MHz for CEPT).

Two internal SYSCK cycles, at 16 times the line rate, are equivalent to 81 ns for DS1 and 61 ns for CEPT. If

MPCK is present, this time interval can range from 61 ns to 667 ns depending upon the particular repetition

rate selected for MPCK. The microprocessor interface timing table from the T7633 advance data sheet is

shown in Table 1, Microprocessor Interface I/O Timing Specifications on page 2 with the revised timing incor-

ported in the table (notes * and ). The timing diagrams, which did not change, are shown in Figure 1--

Figure 8.

For the case where MPCK is not present, it is recommended that the hold time between the deassertion of RD

or DS and the deassertion of CS be at least 110 ns to provide a safety margin.

This requirement is not specified in the T7633 advance data sheet.

The framer portion of the terminator internally latches the decoded register address within its logic for clearing

the framer CORs, and it does not require this timing modification.

2

Agere Systems Inc.

Device Advisory

September 1999

T7633 Device Advisory for Version 1.0 of the Device

Microprocessor Interface

I/O Timing

In modes 1 and 3, asserting ALE_AS signal low is used to enable the internal address bus. In modes 2 and 4, the

falling edge of ALE_AS signal is used to latch the address bus.

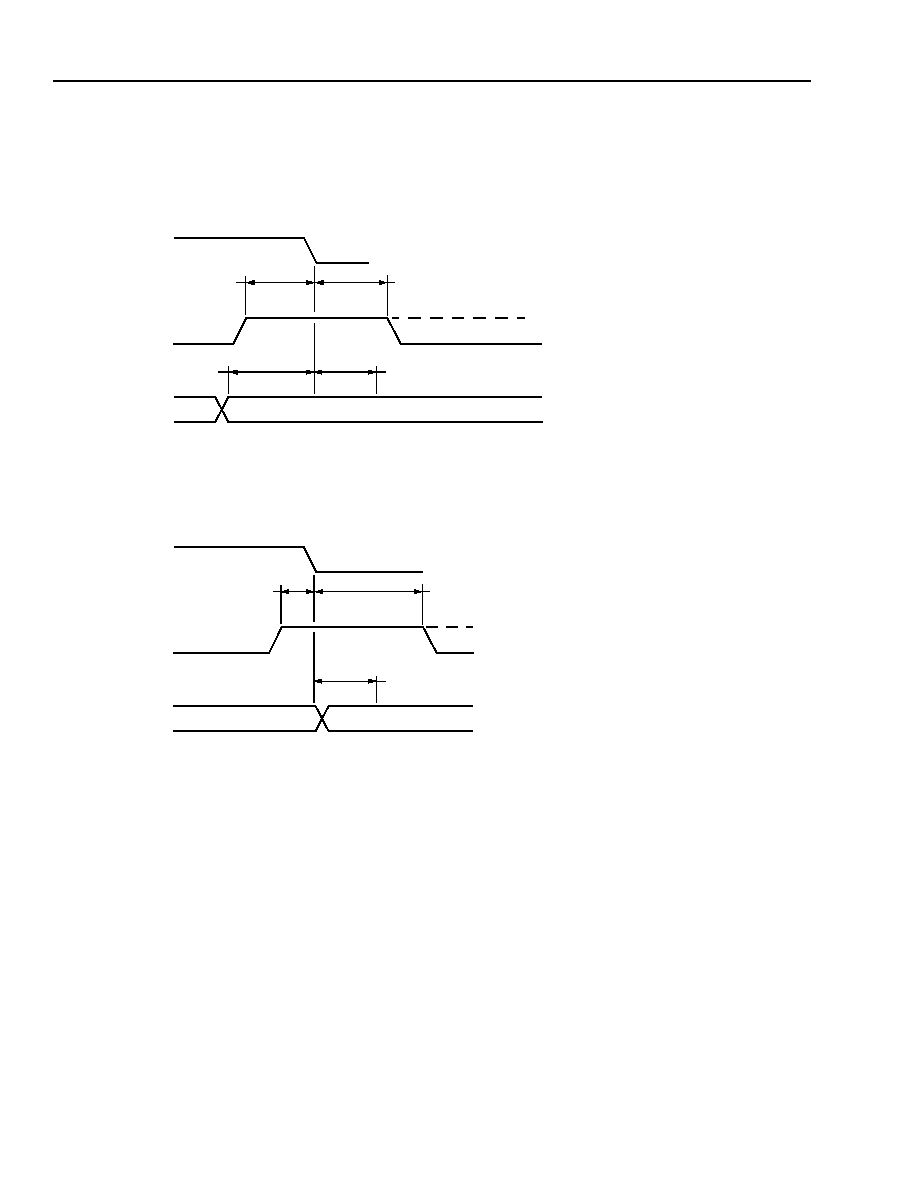

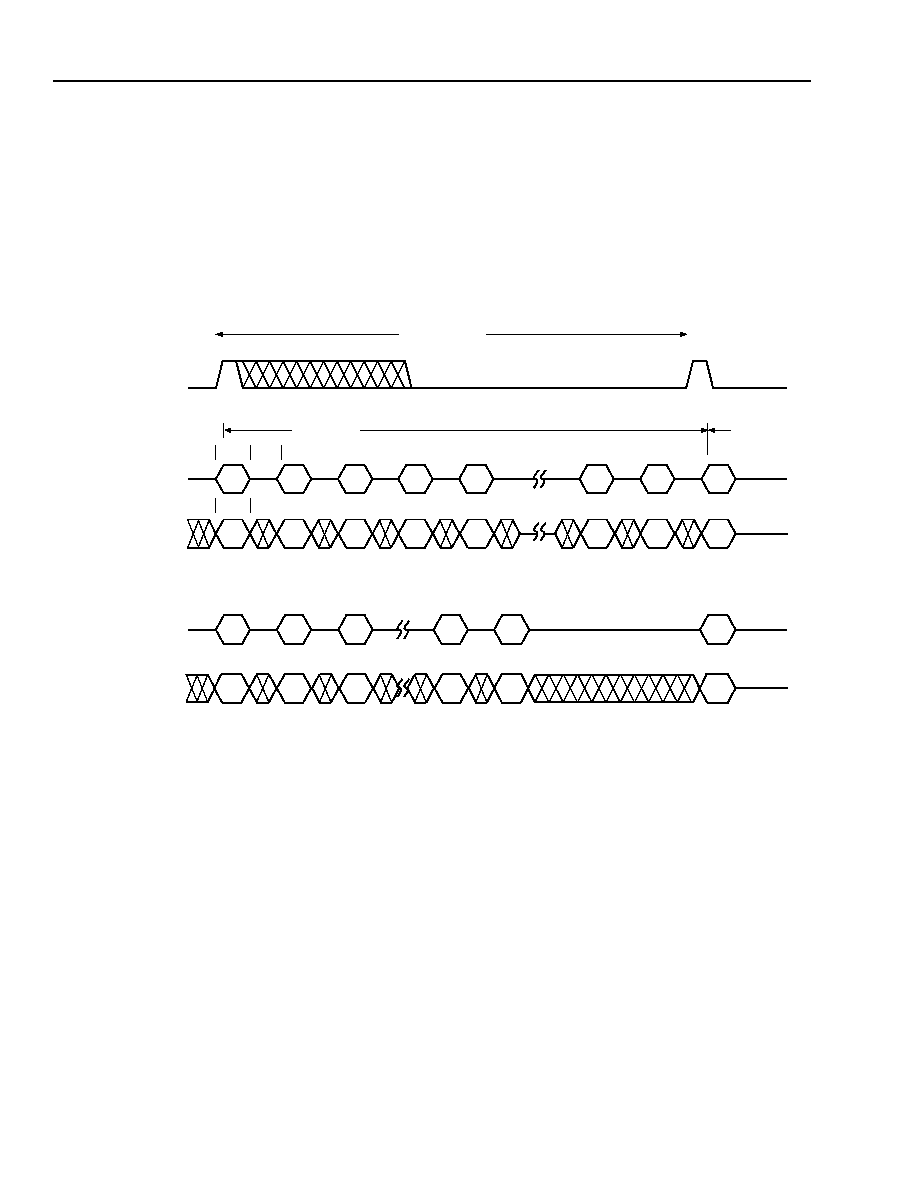

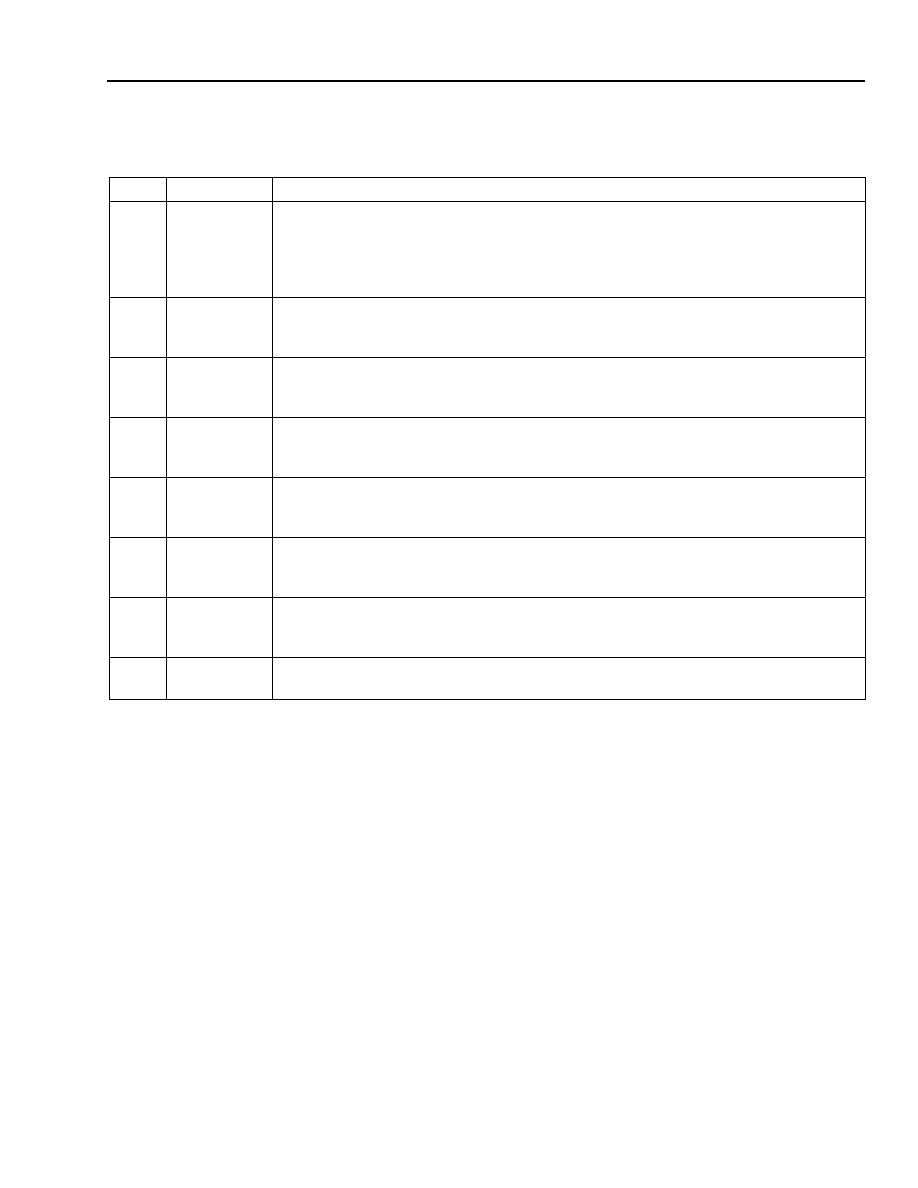

* For Figure 1:

s

If AS = 0 (AS is not used or is inactive), then the address must be valid until CS = 1 and

-- If MPCK is used (MPCK is active), then t11 must exceed two MPCK periods,

-- If MPCK is not used (MPCK is inactive), then t11 must exceed two 16x line clock periods. A t11 of 110 ns is suggested.

s

If AS is used (AS is active), then

-- If MPCK is used (MPCK is active), then t11 must exceed two MPCK periods,

-- If MPCK is not used (MPCK is inactive), then t11 must exceed two 16x line clock periods. A t11 of 110 ns is suggested.

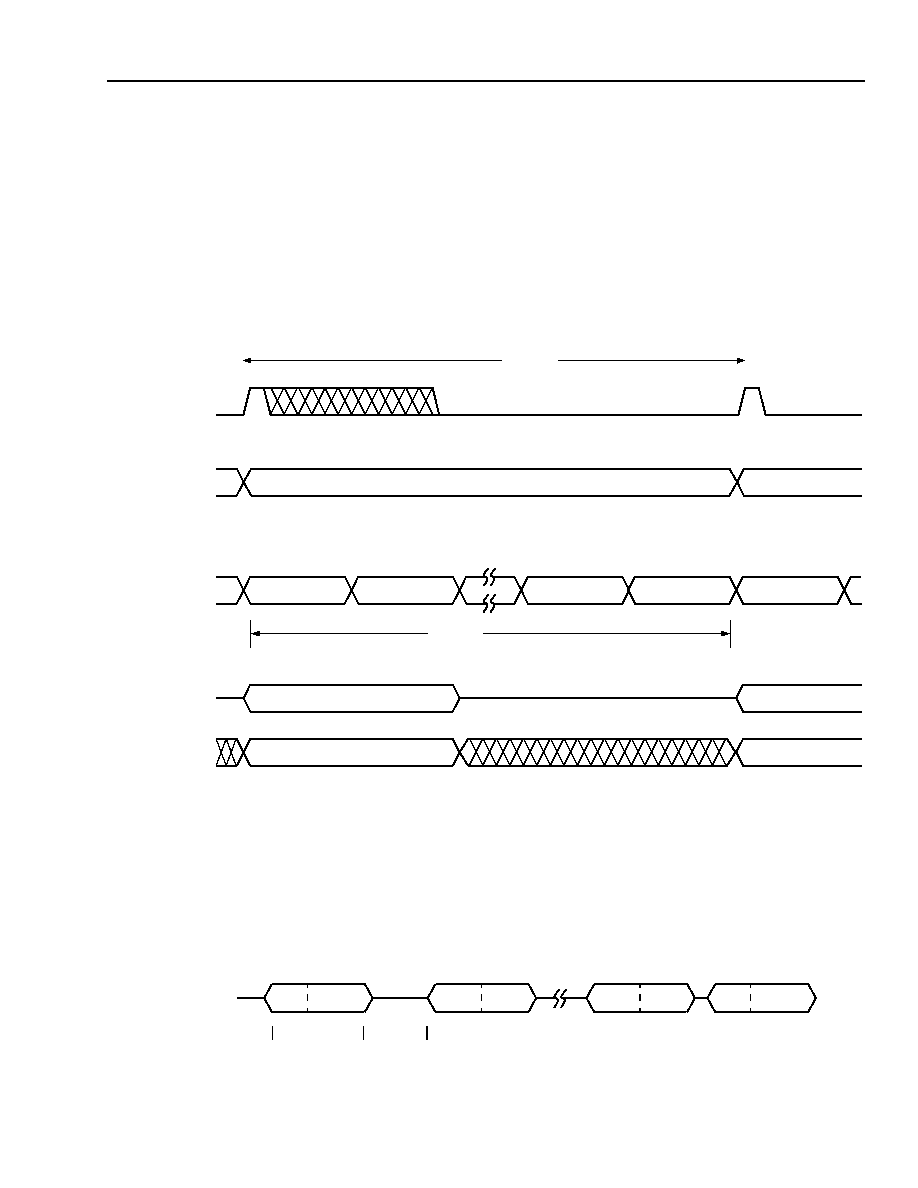

For Figure 3:

s

If MPCK is used (MPCK is active), then t11 must exceed two MPCK periods,

s

If MPCK is not used (MPCK is inactive), then t11 must exceed two 16x line clock periods. A t11 of 110 ns is suggested.

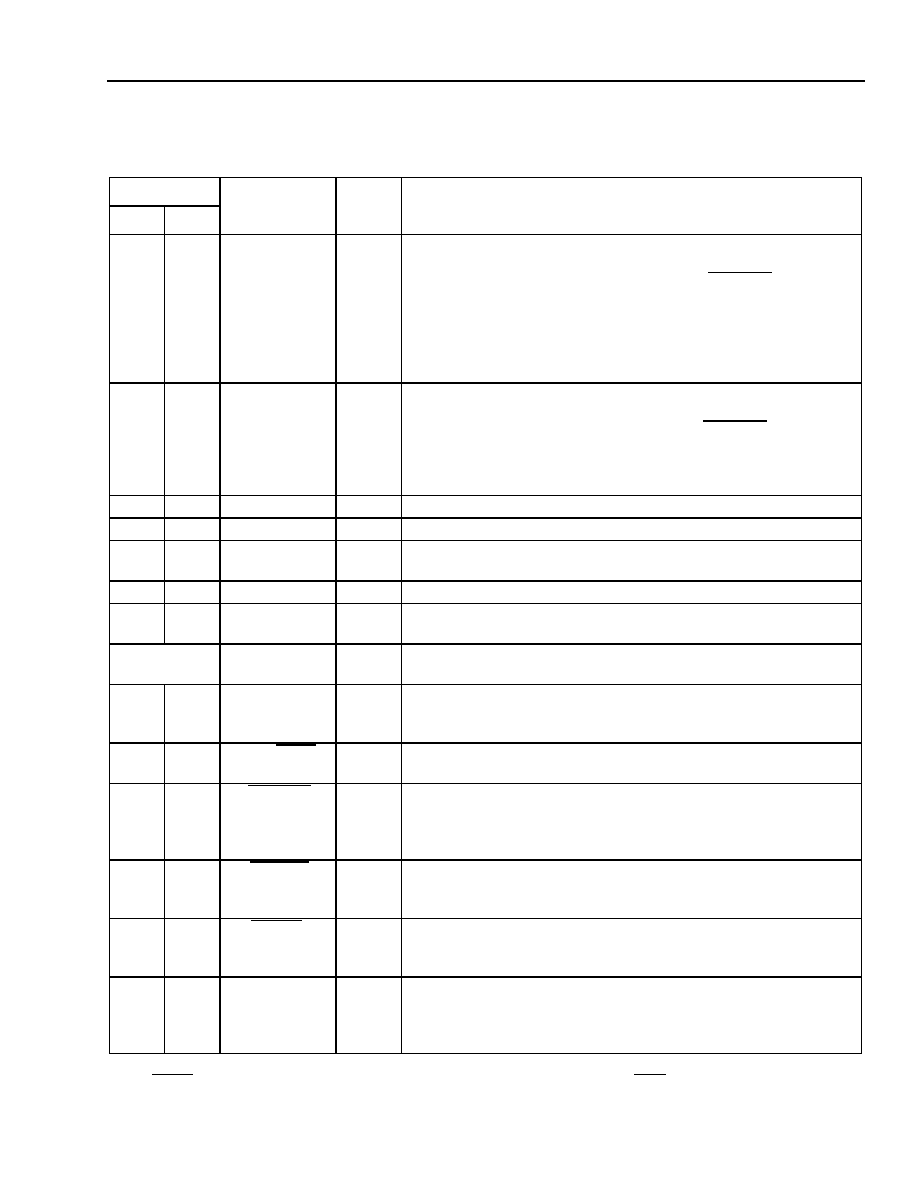

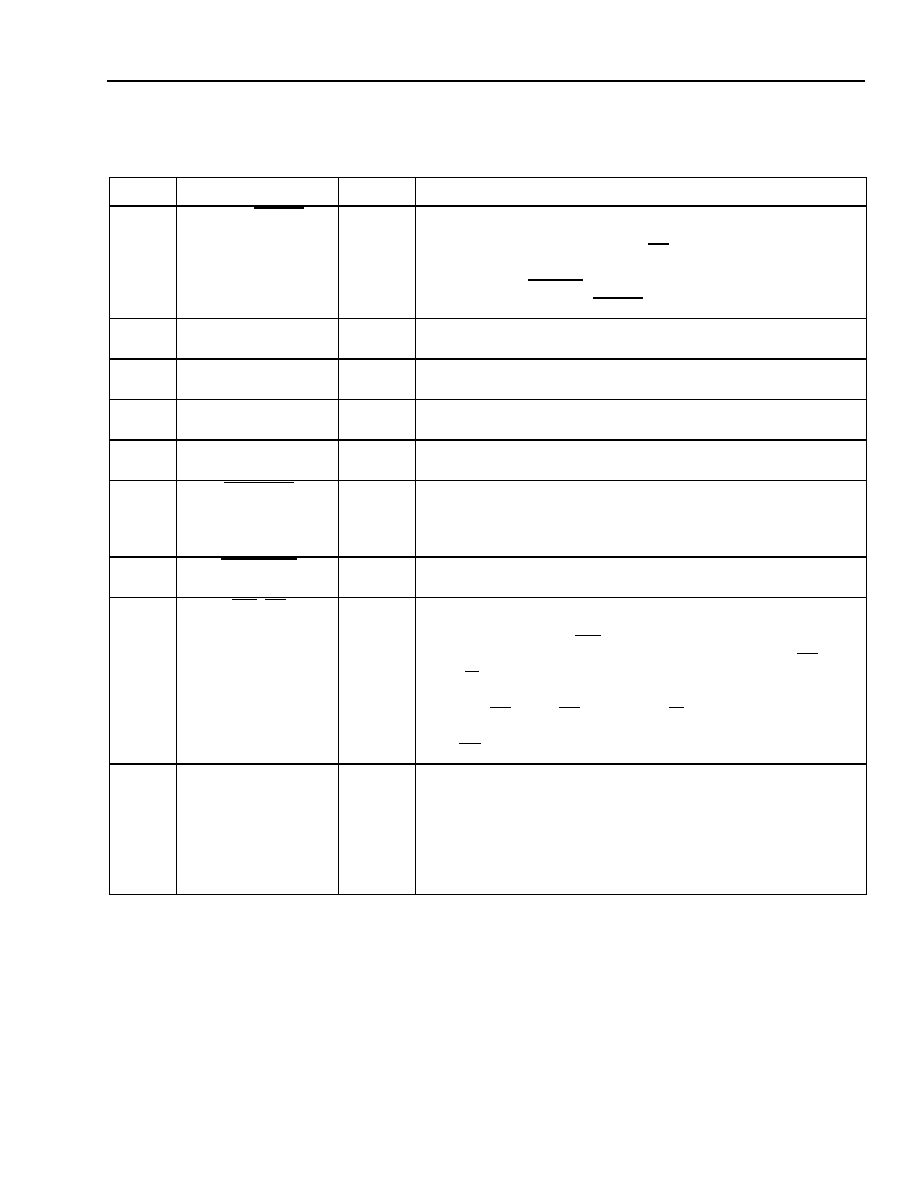

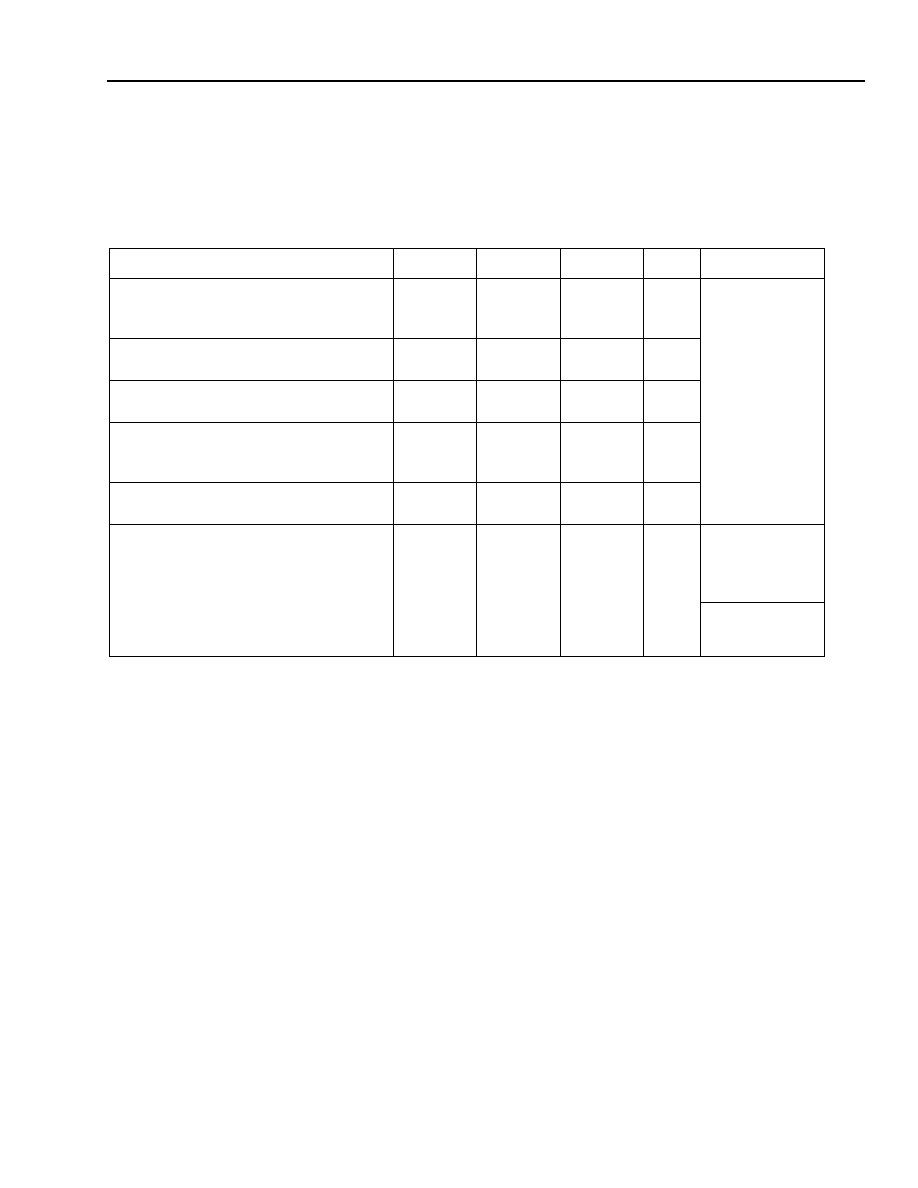

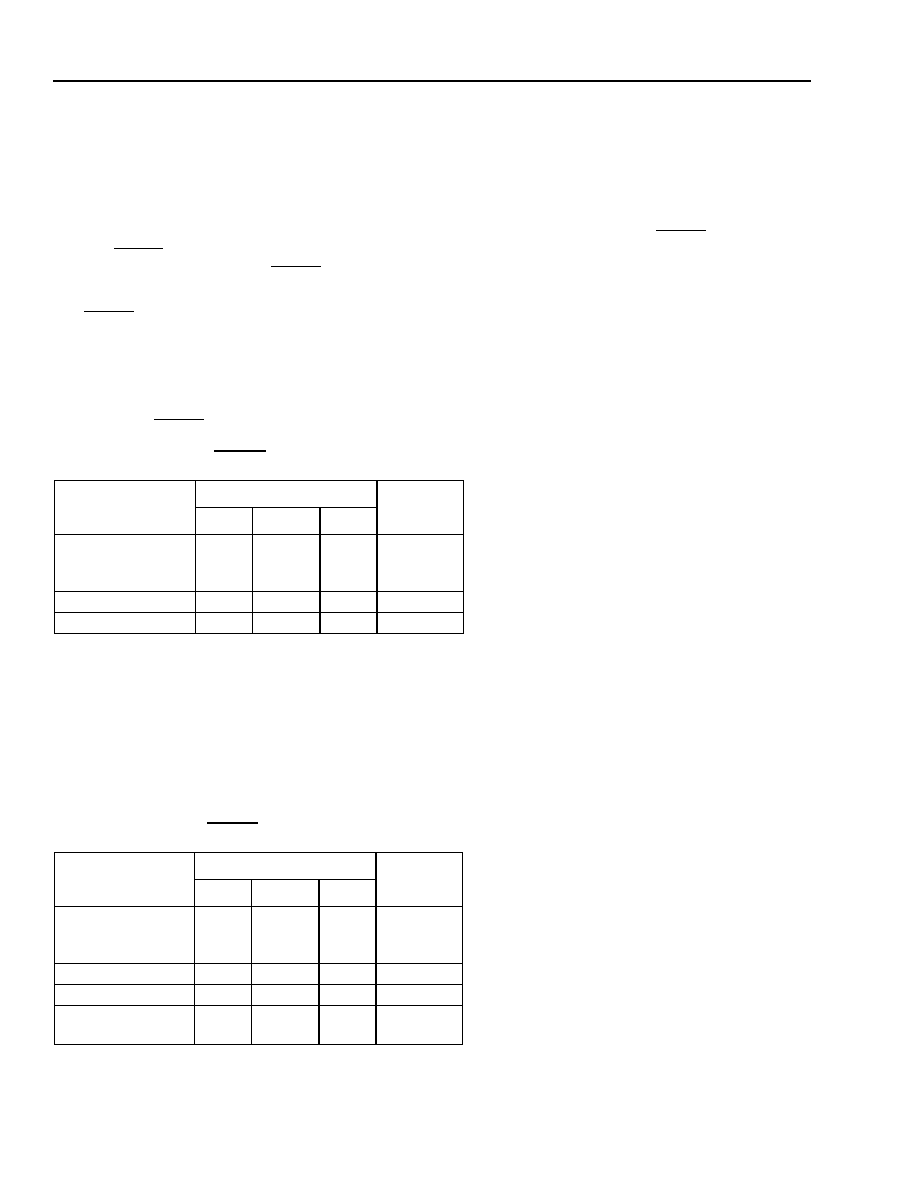

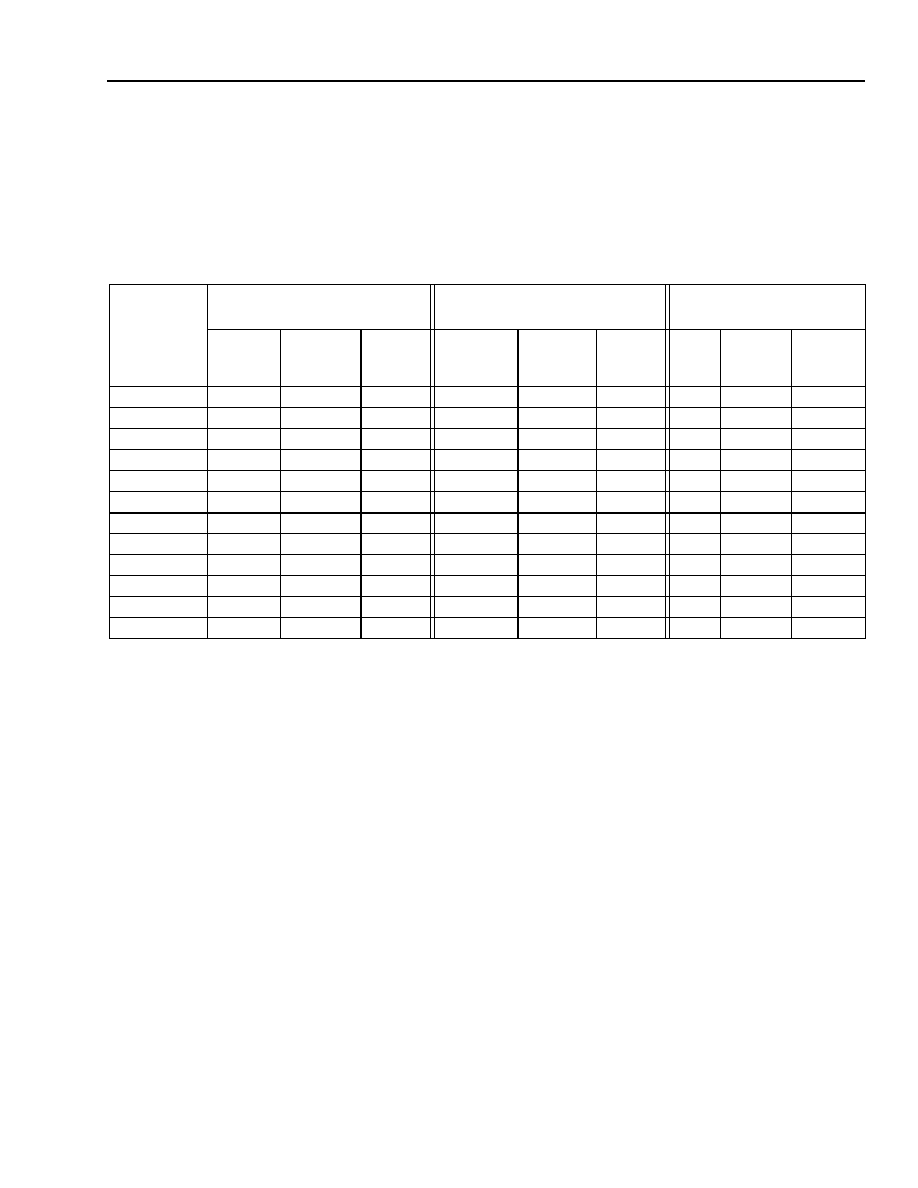

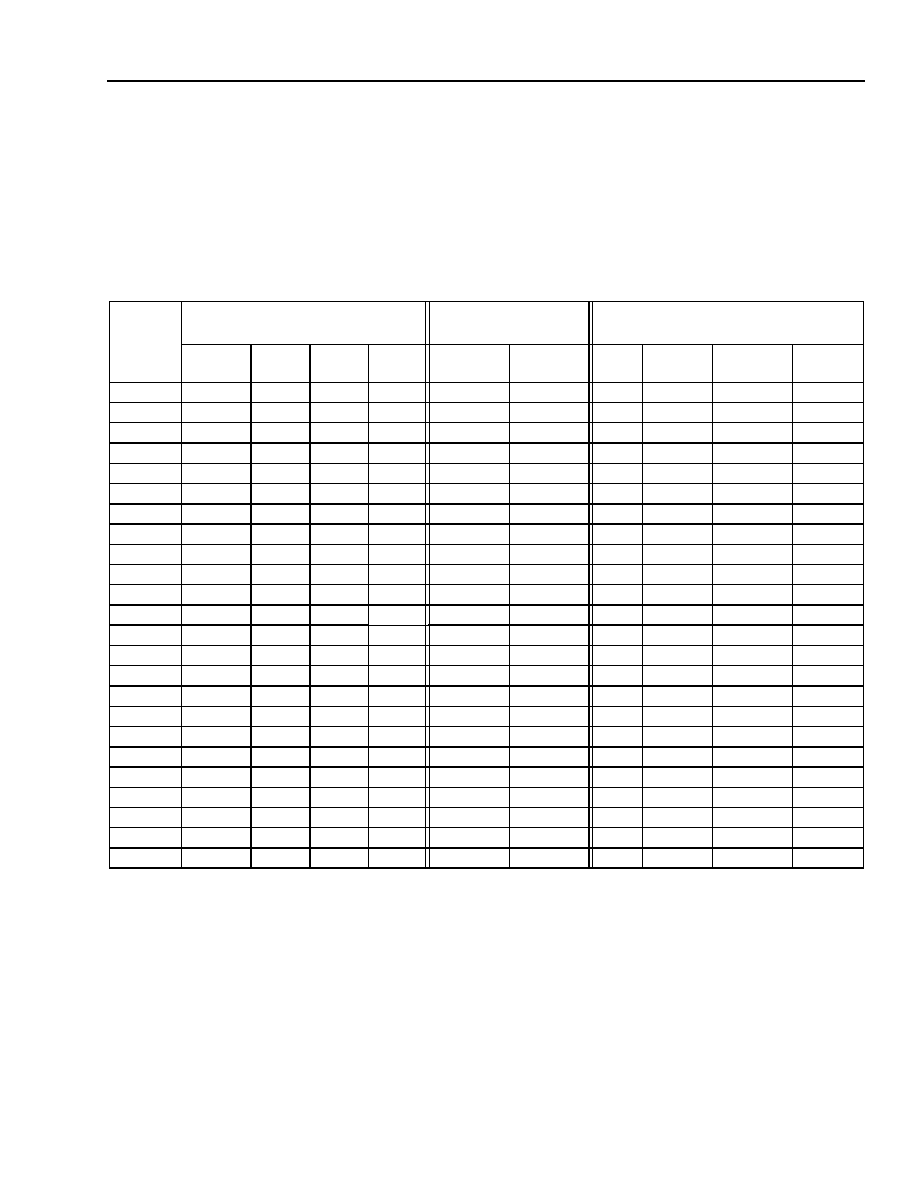

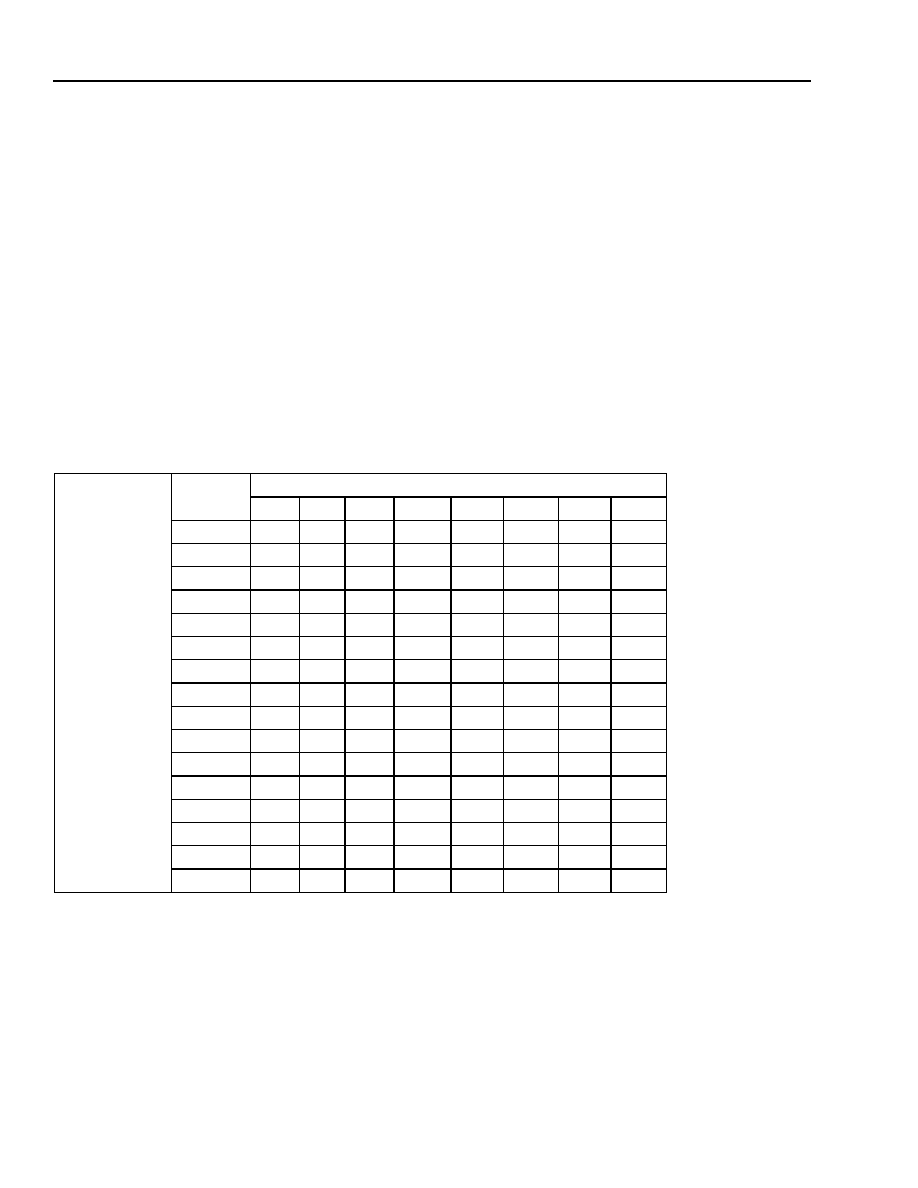

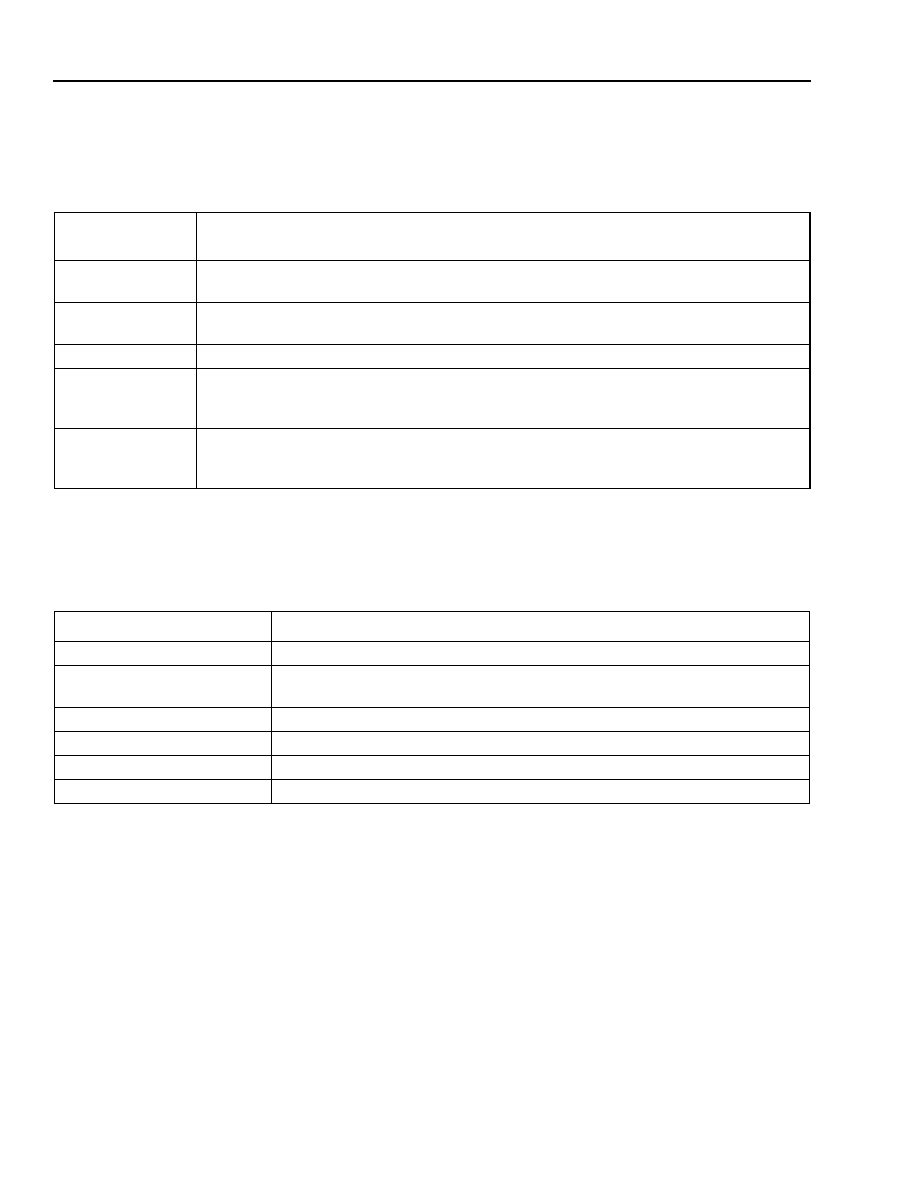

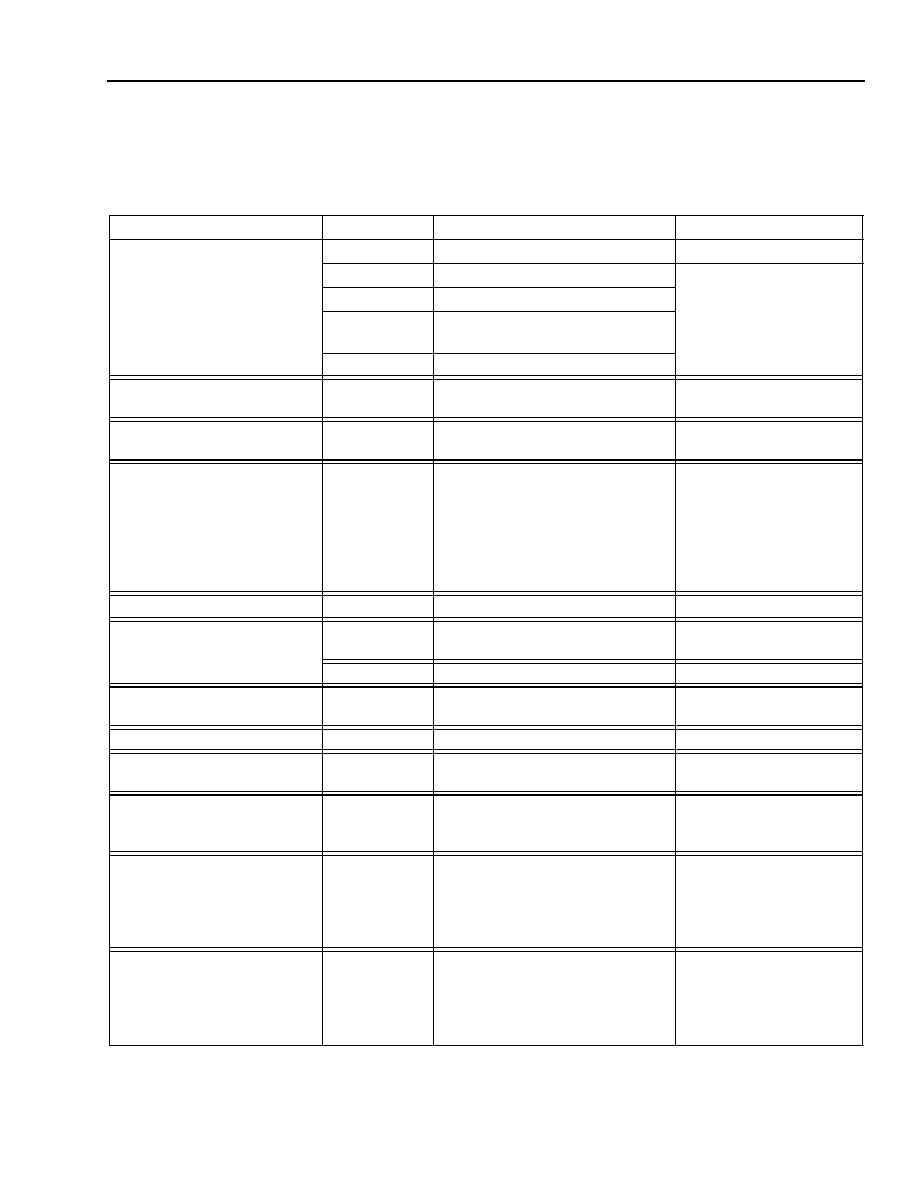

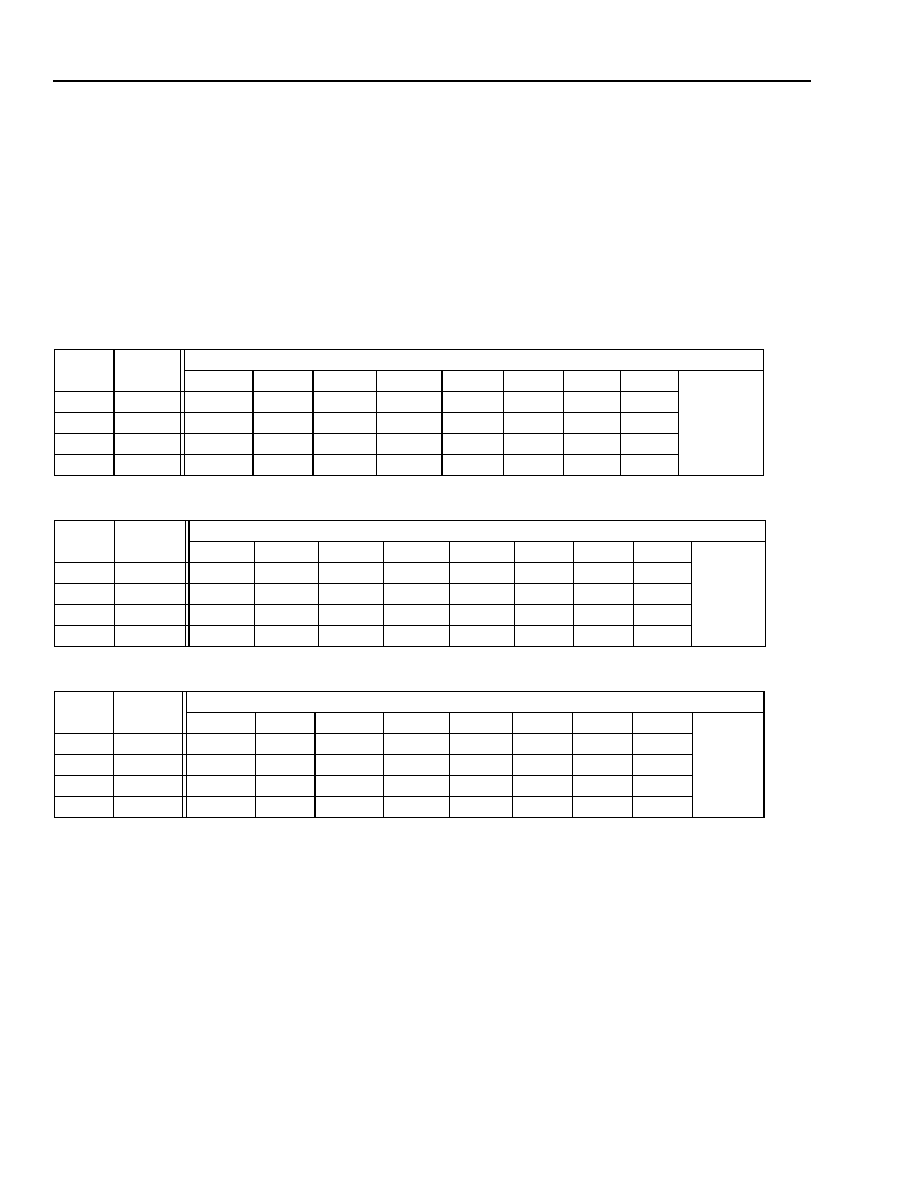

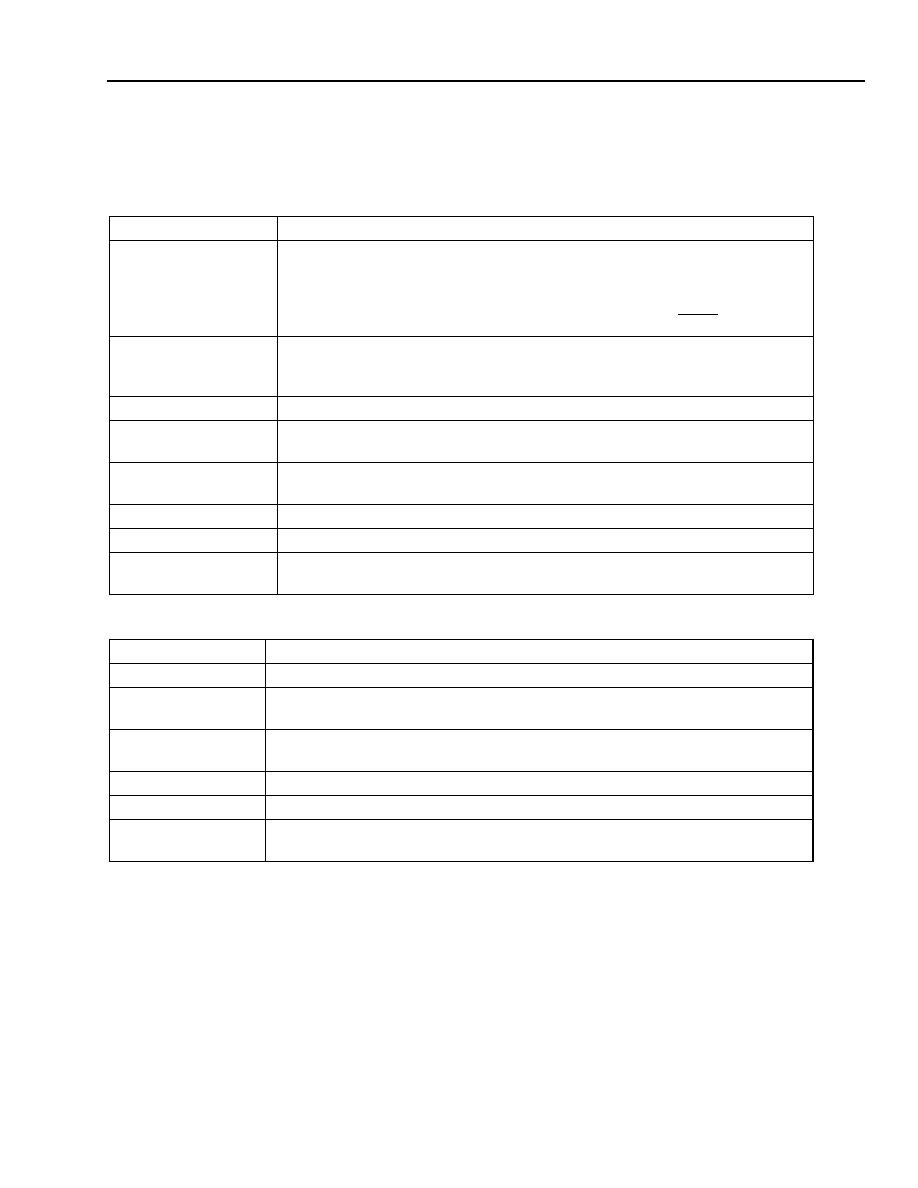

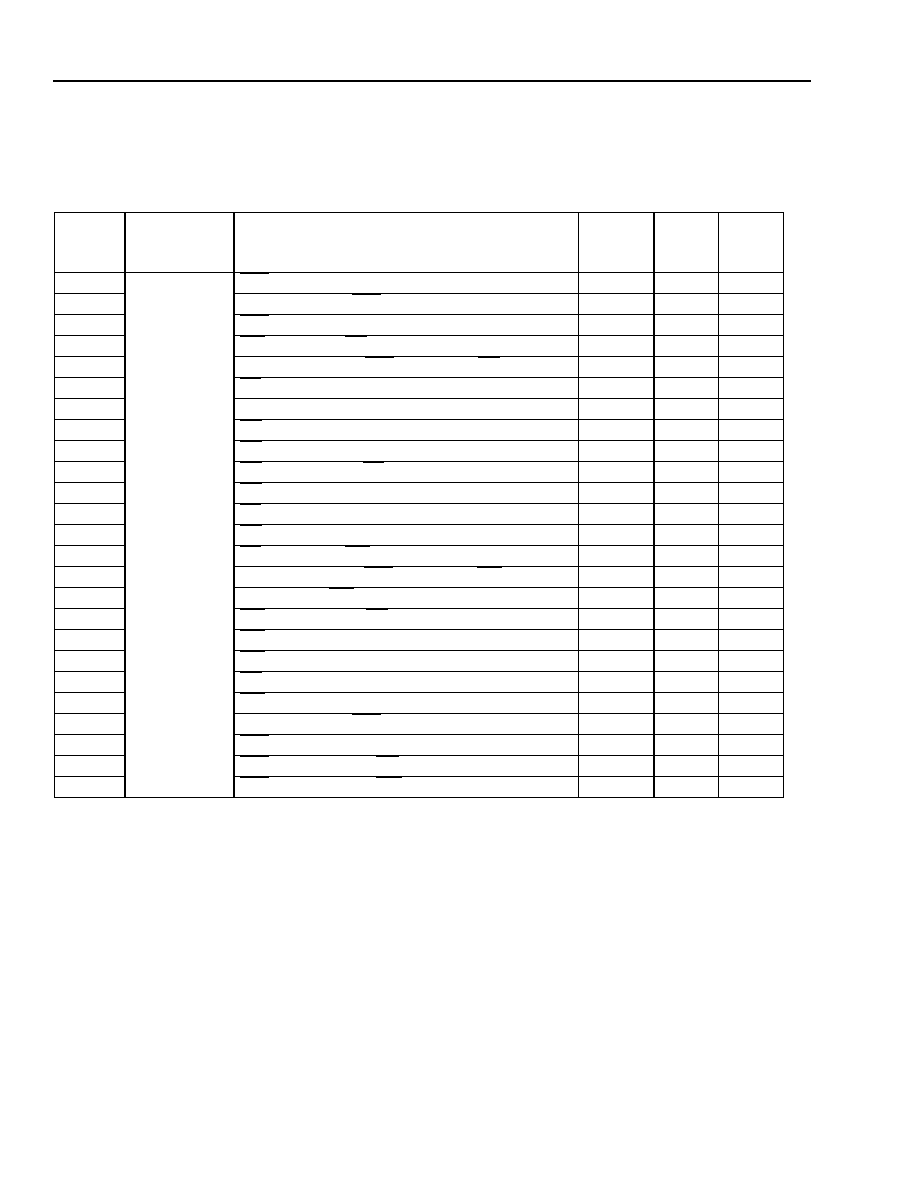

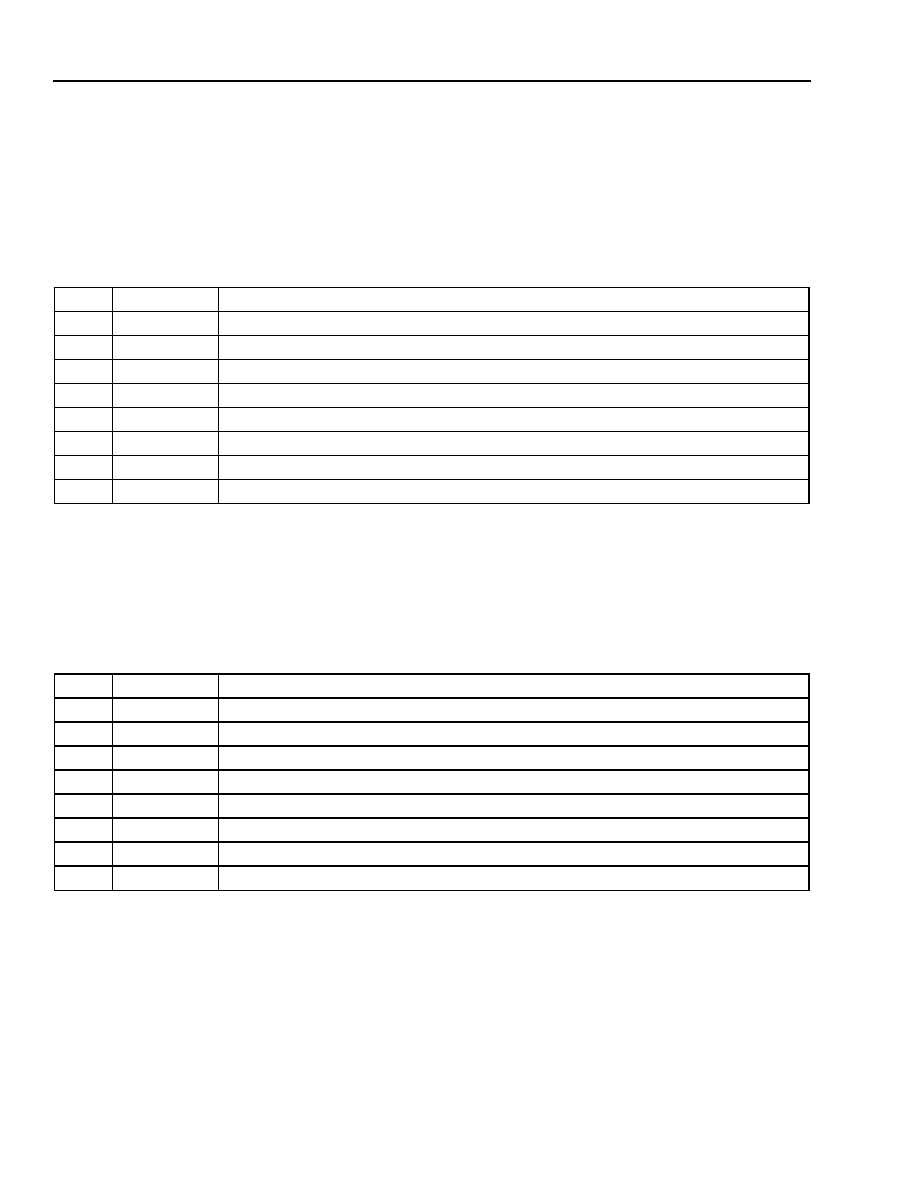

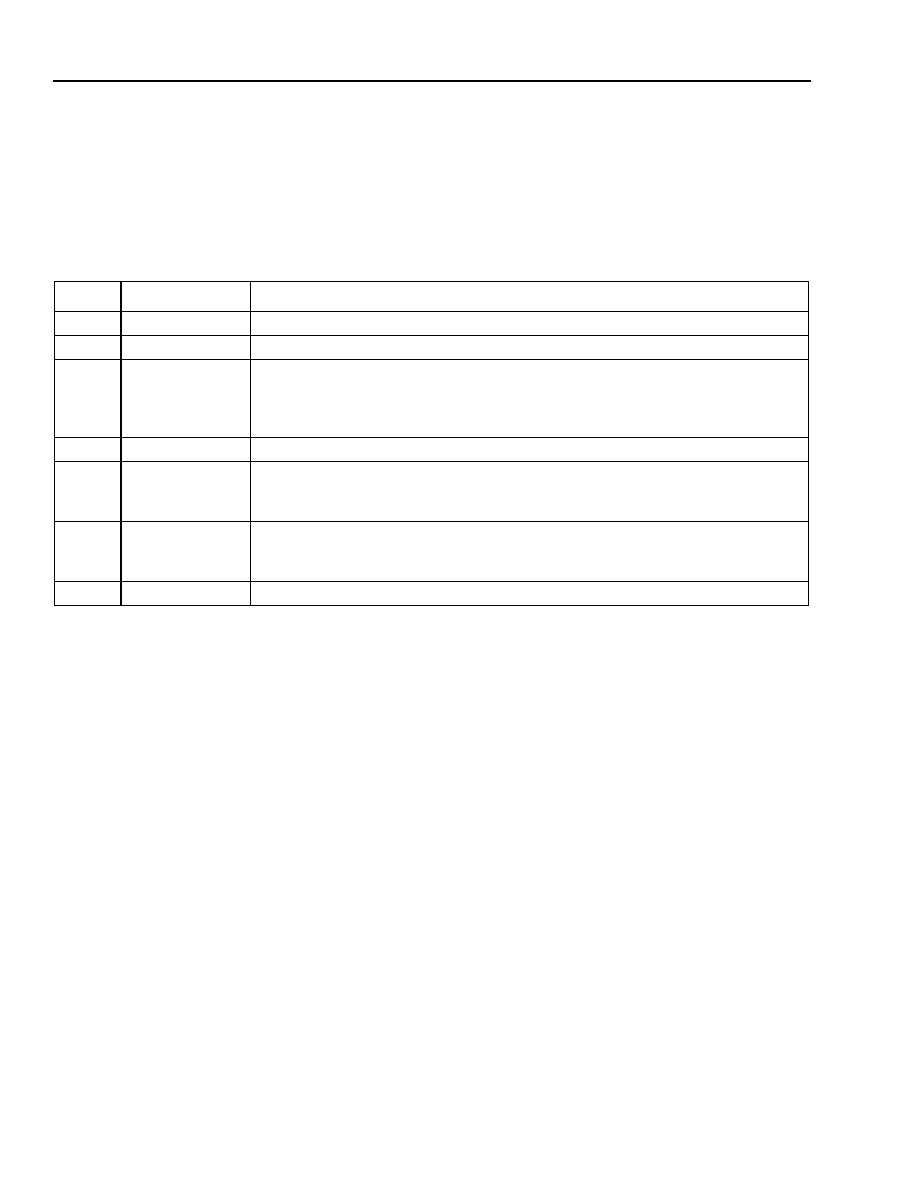

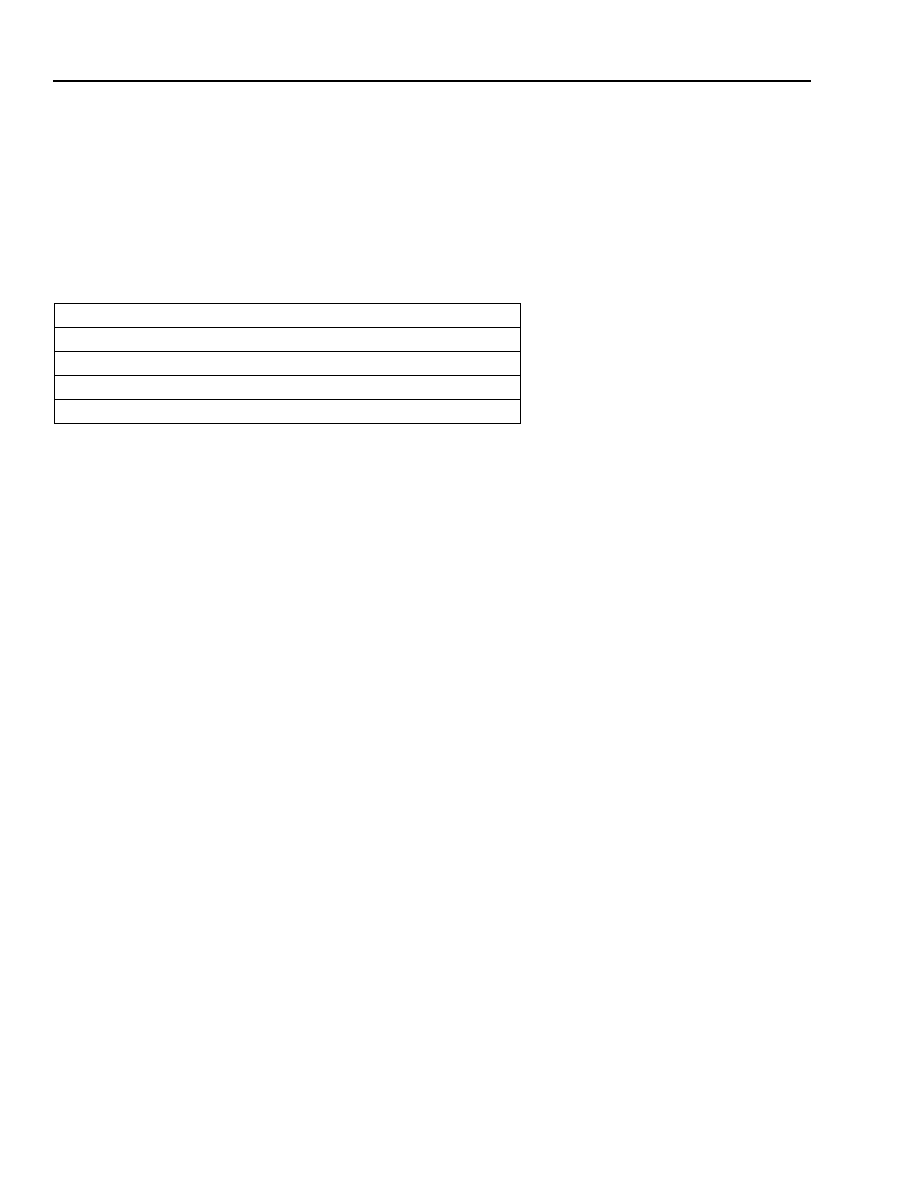

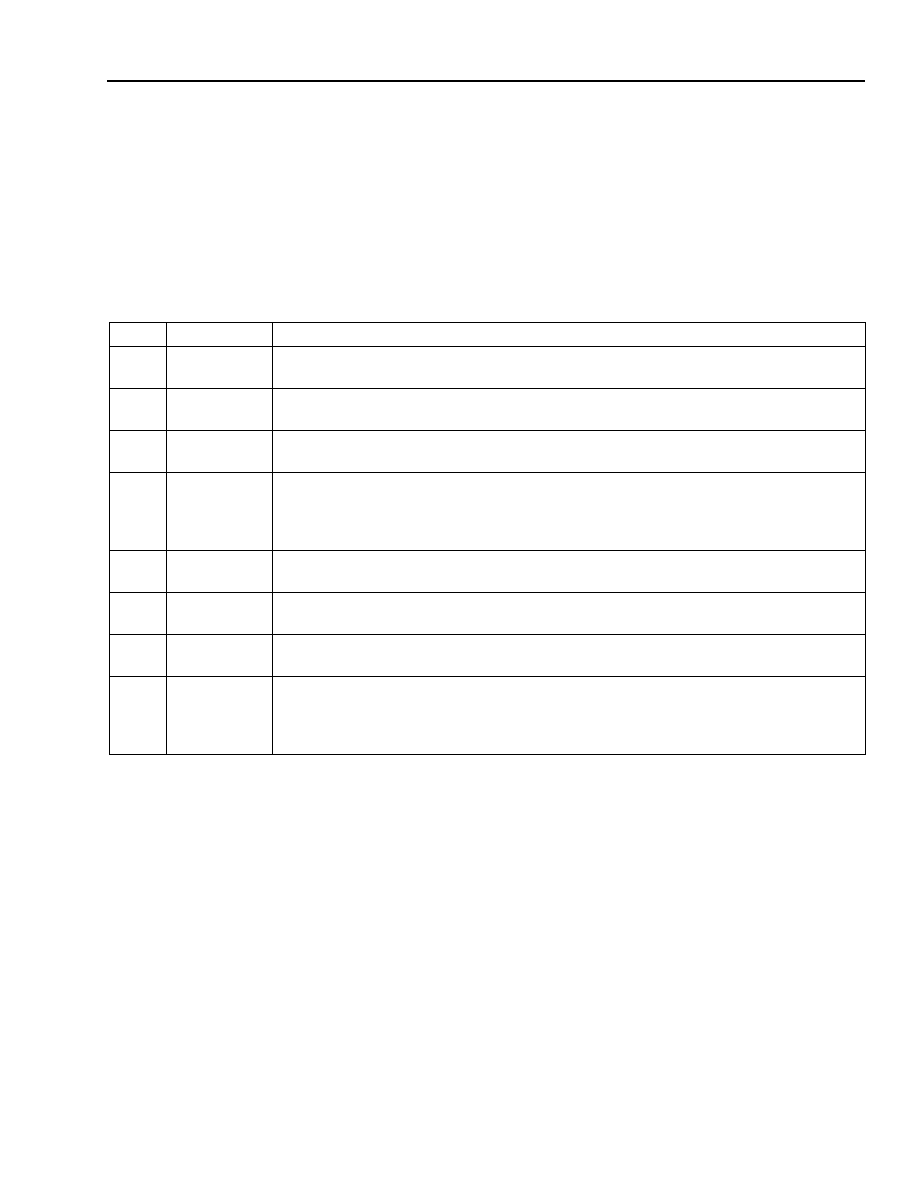

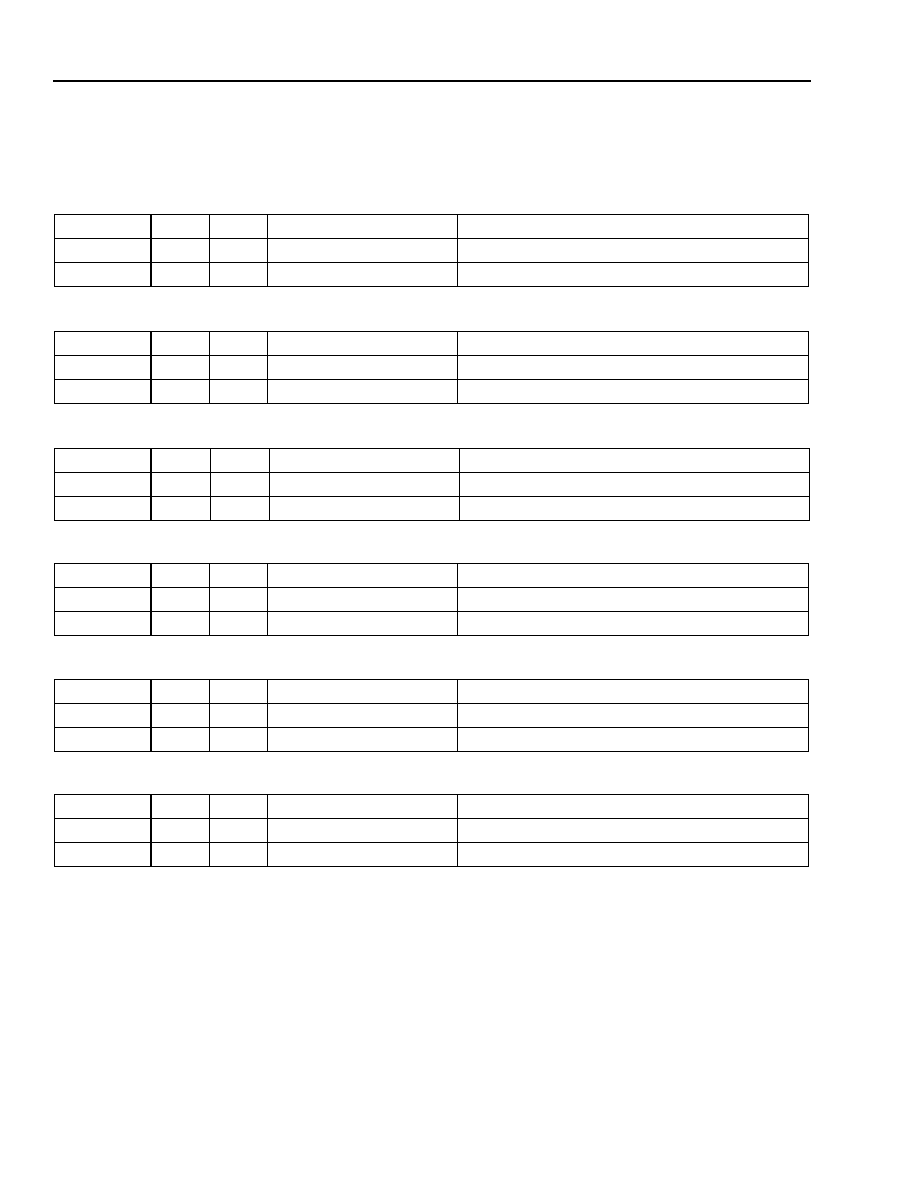

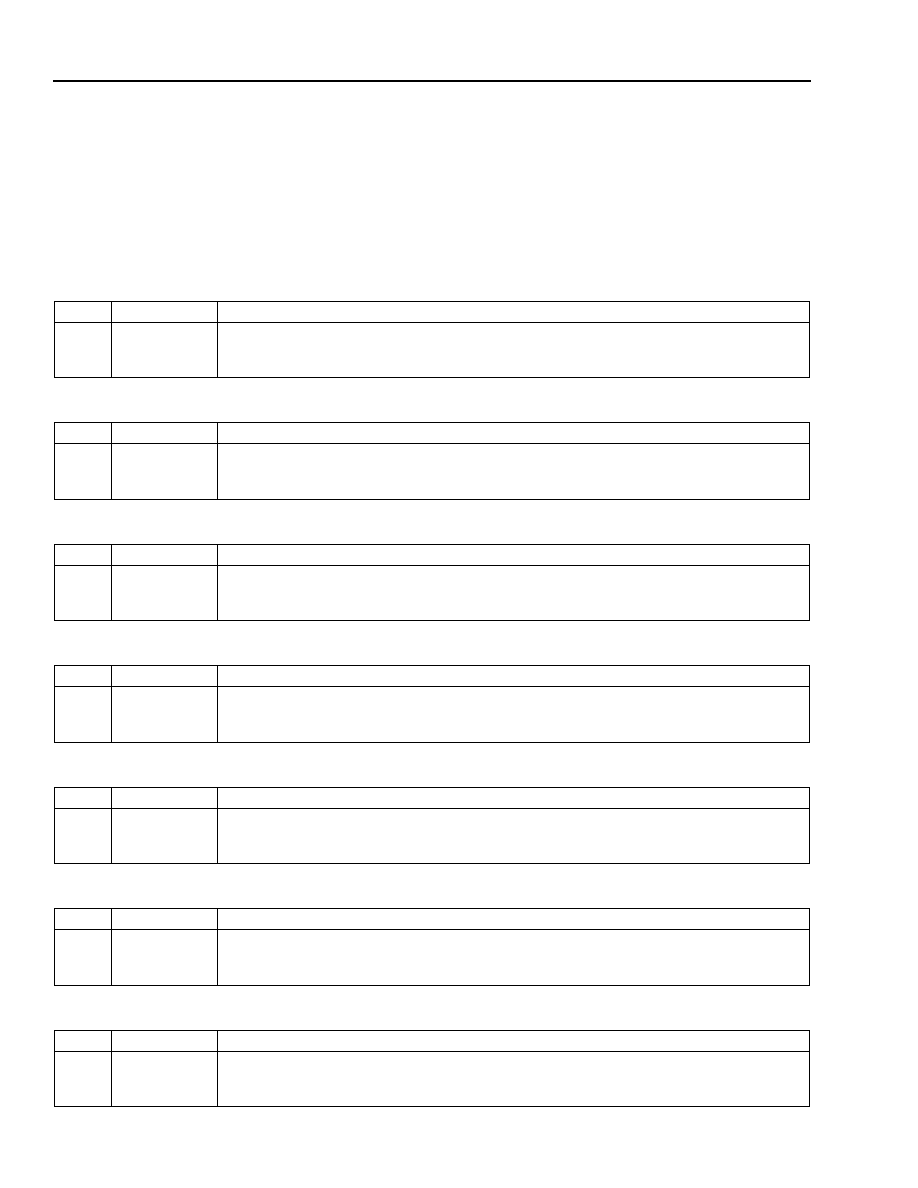

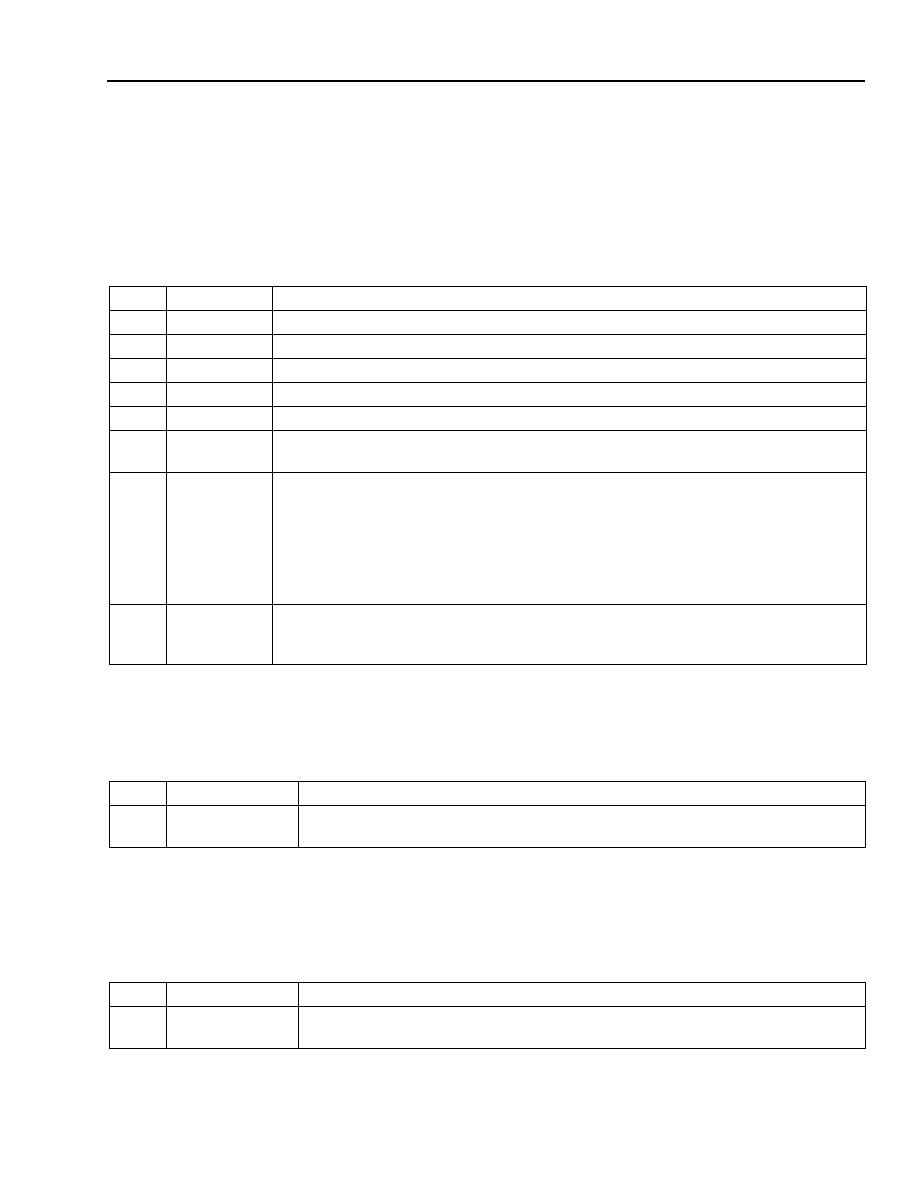

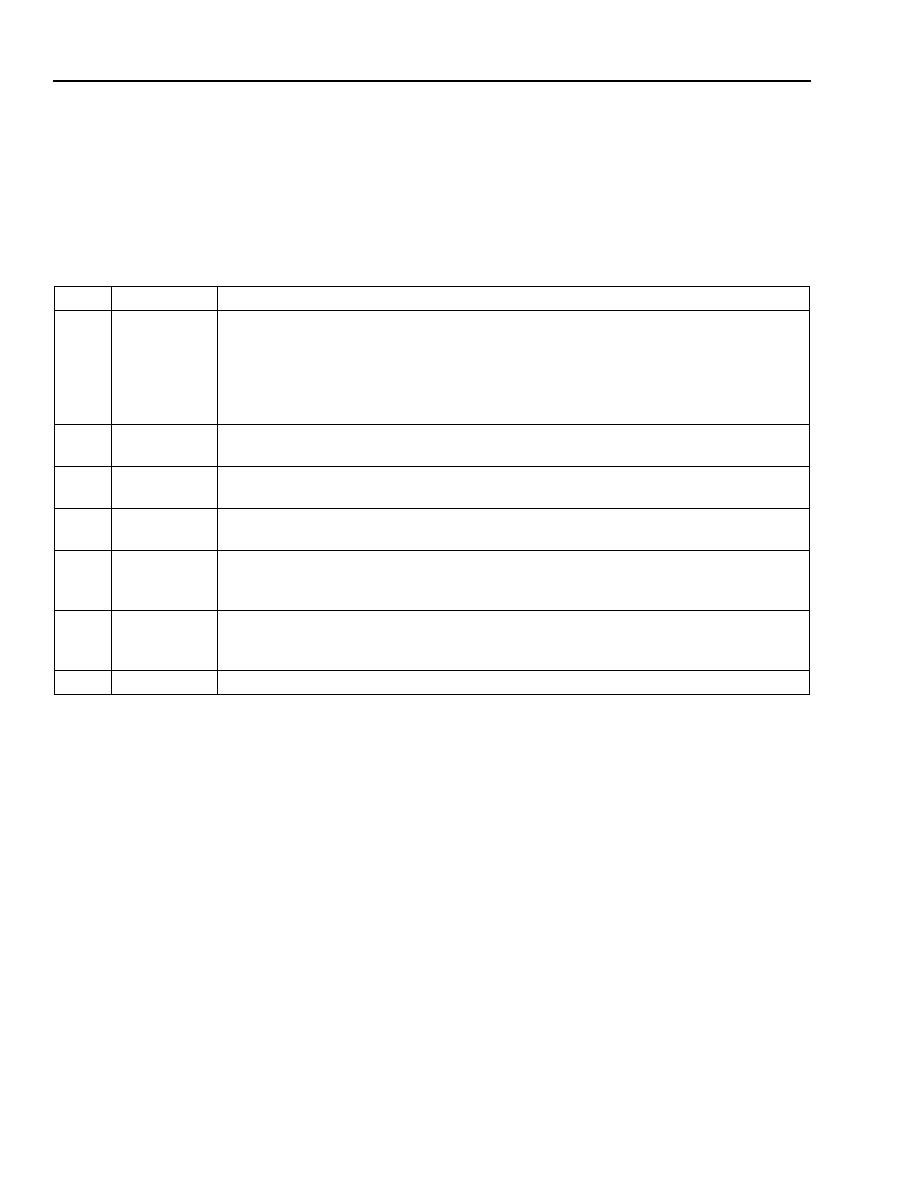

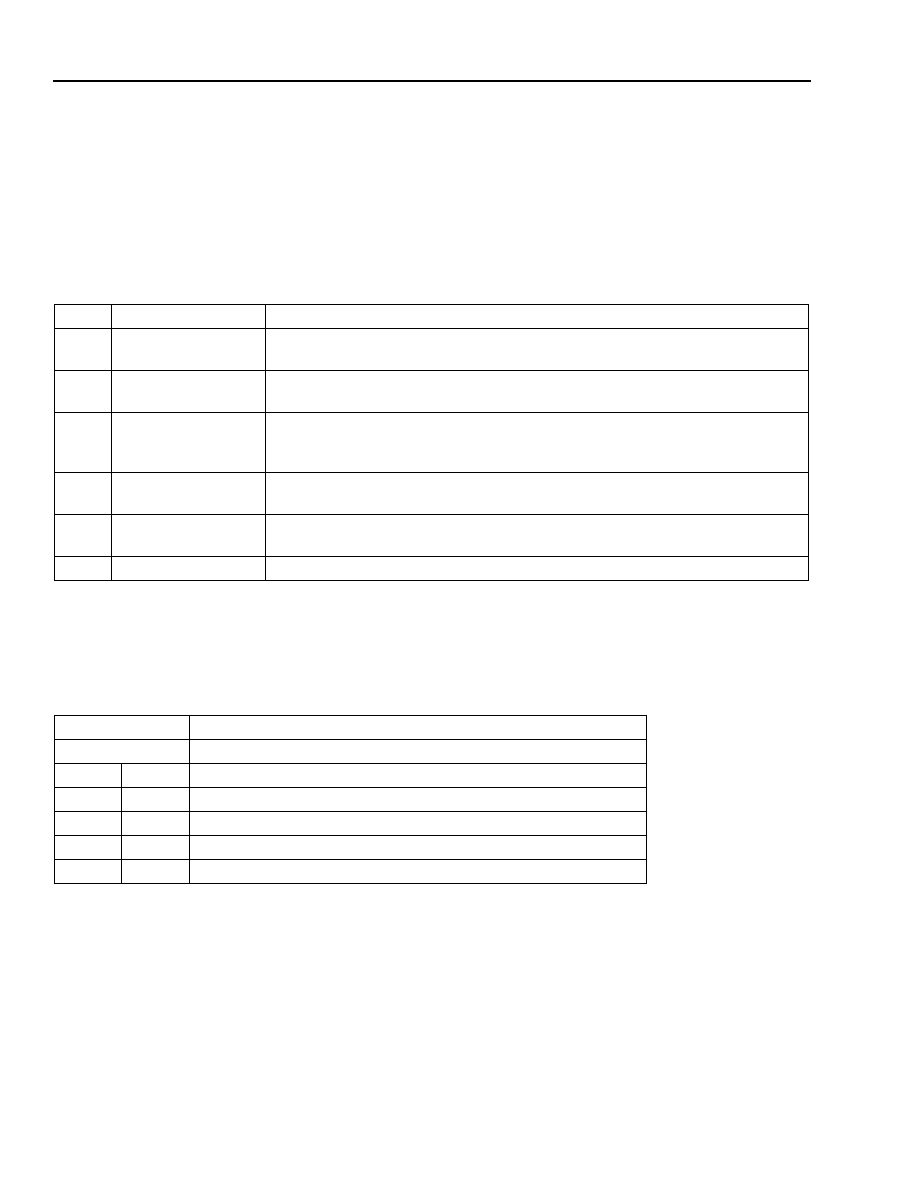

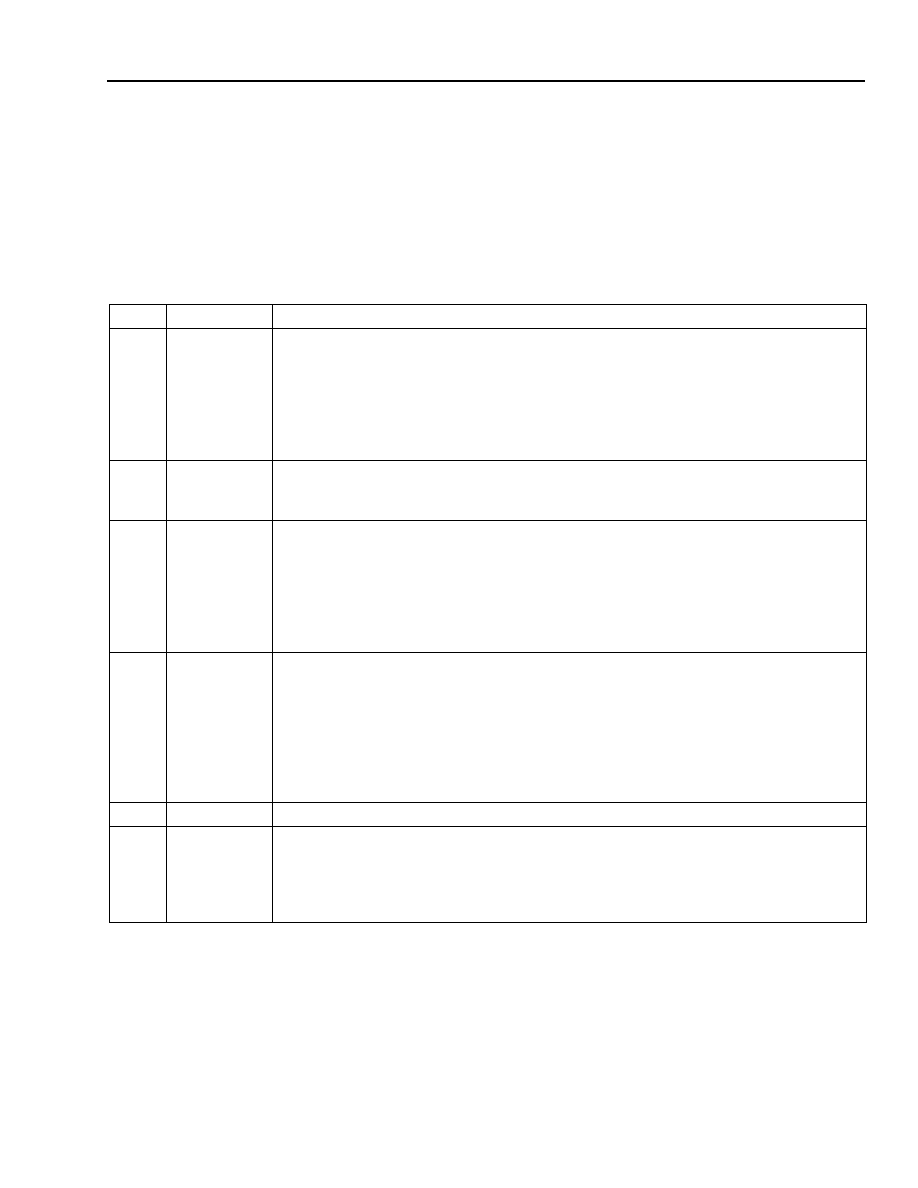

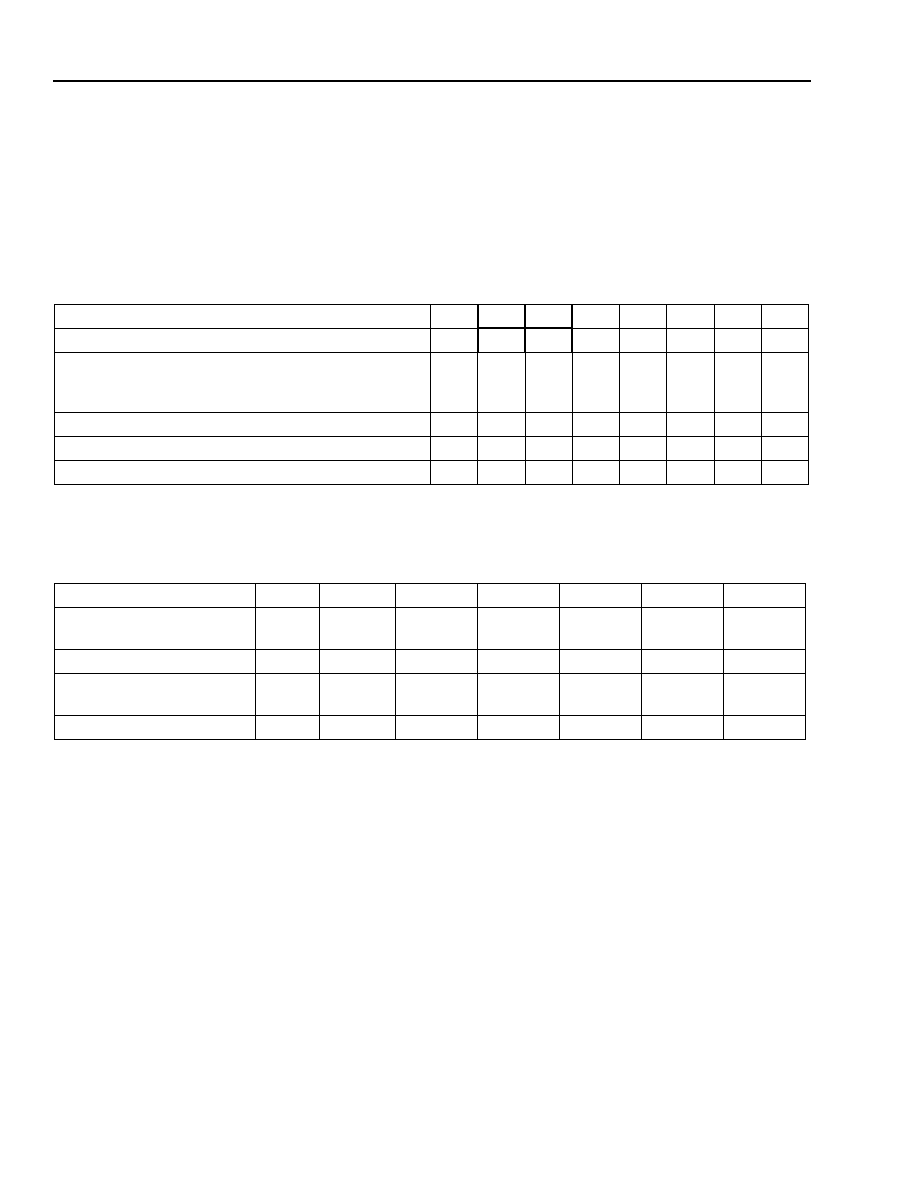

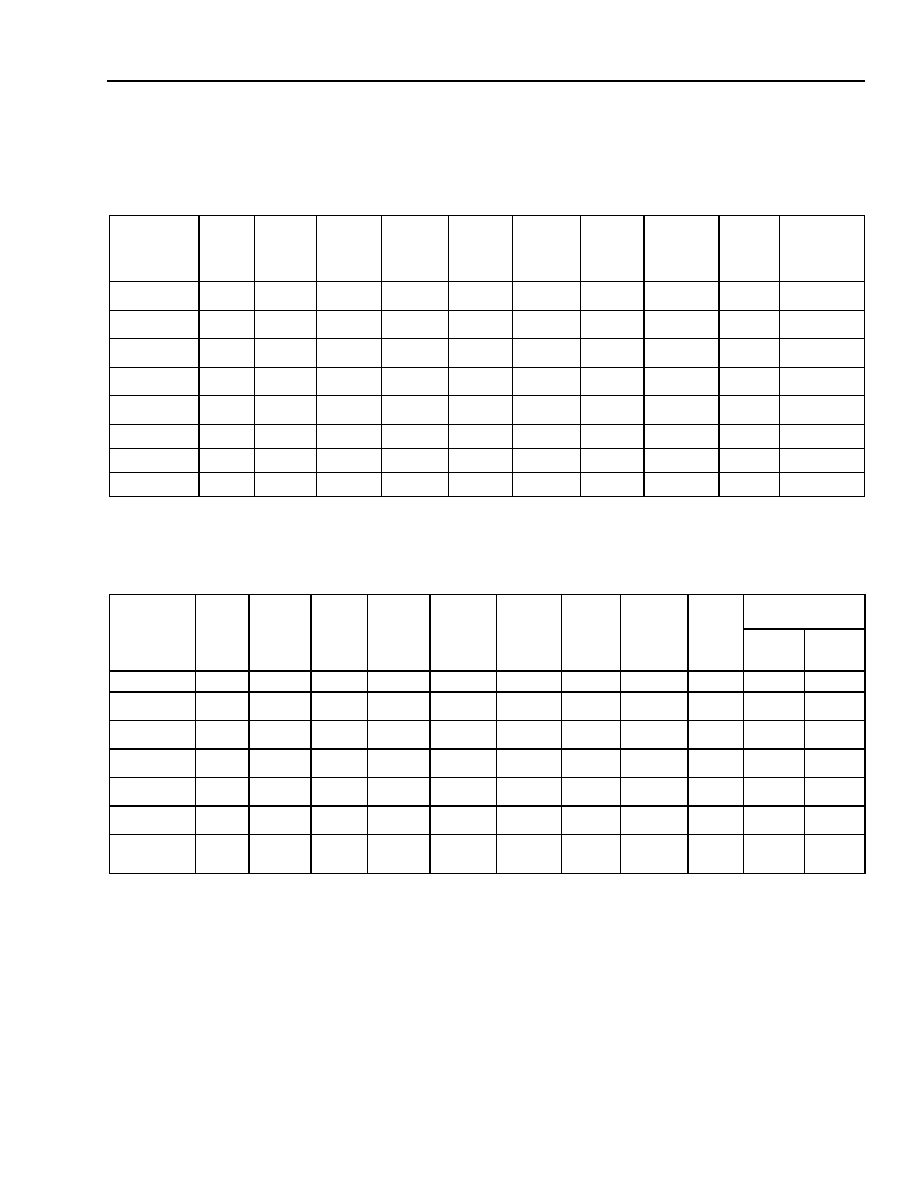

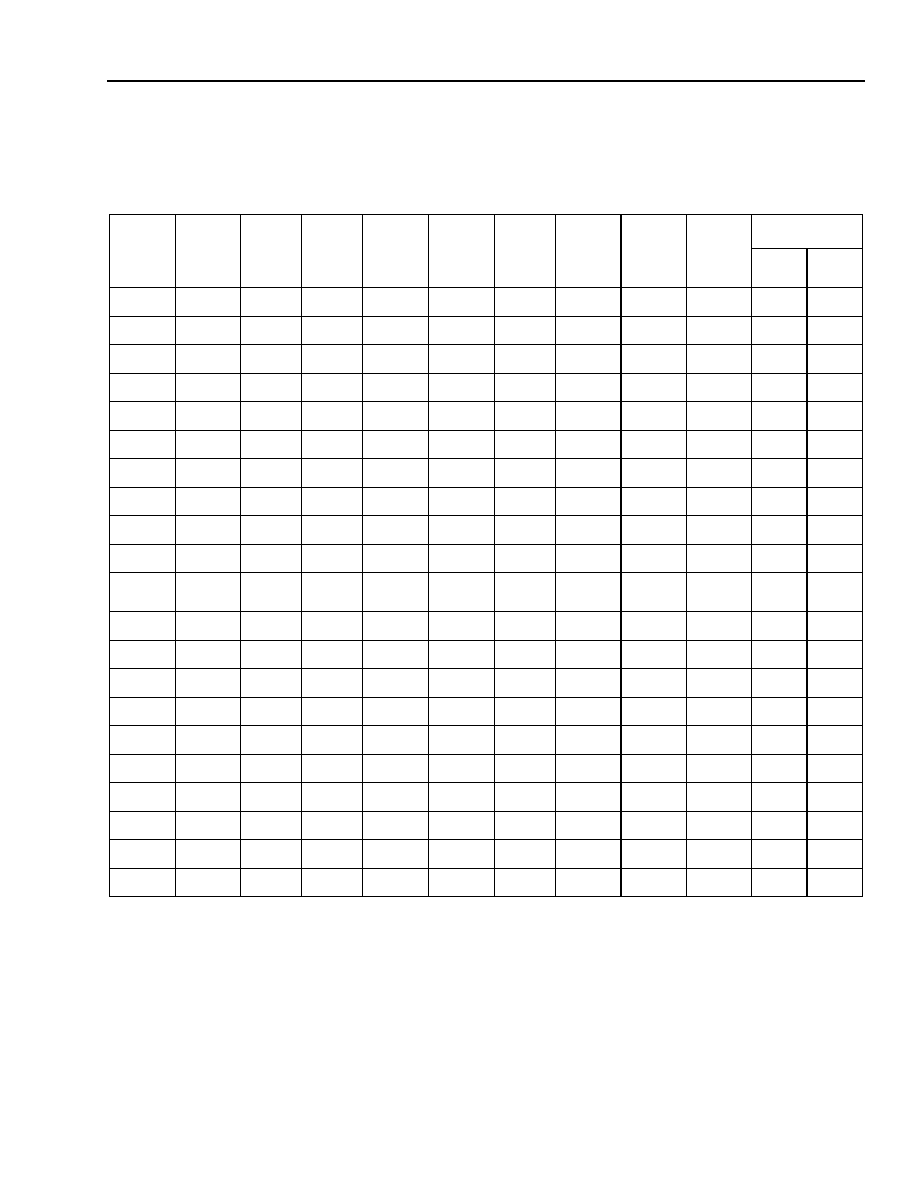

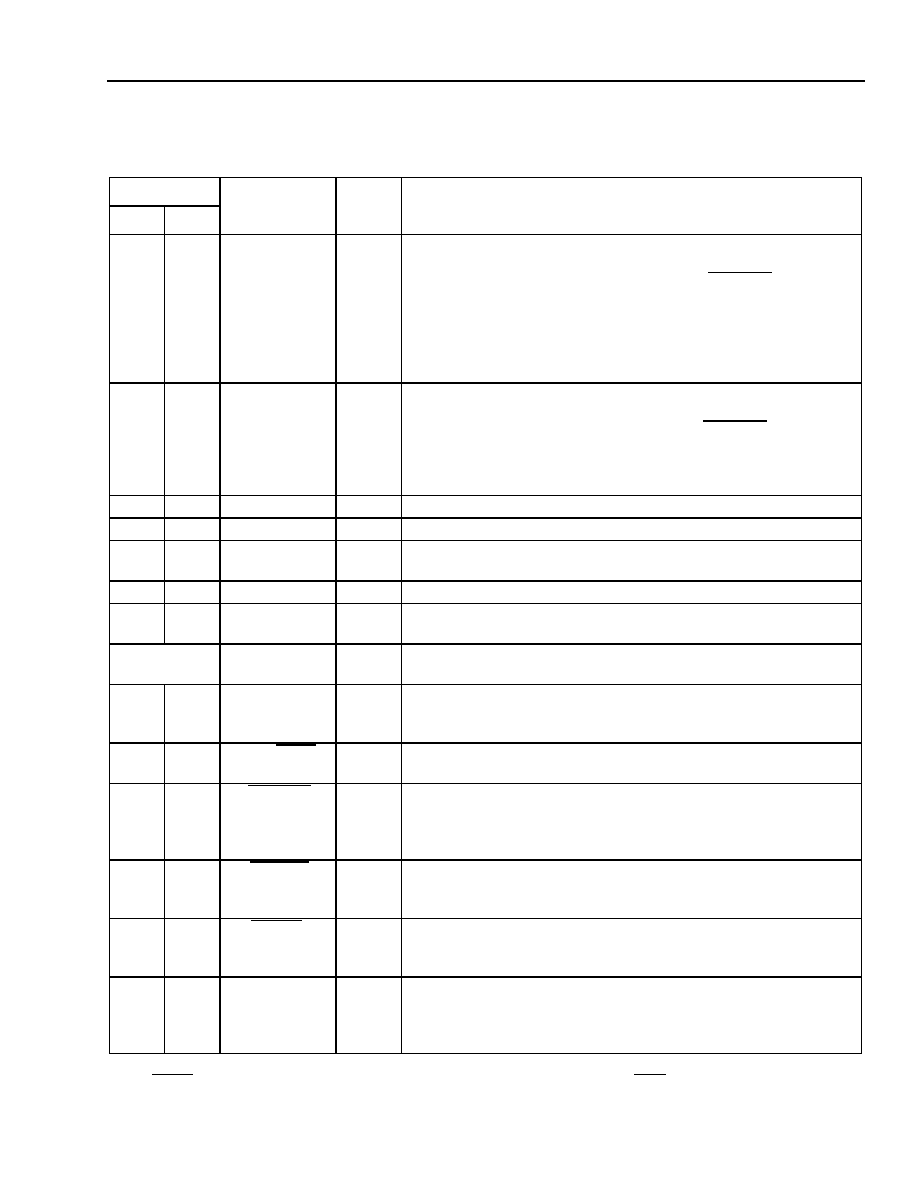

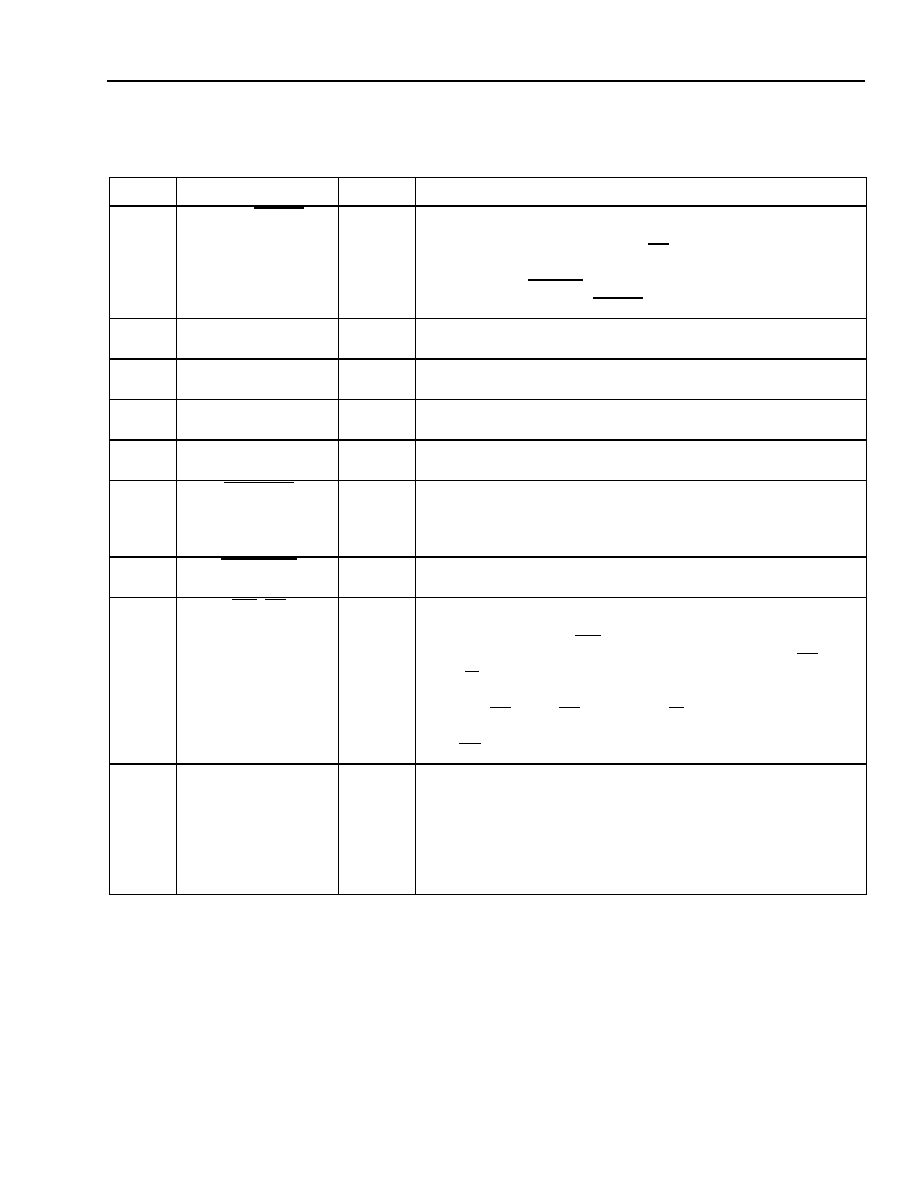

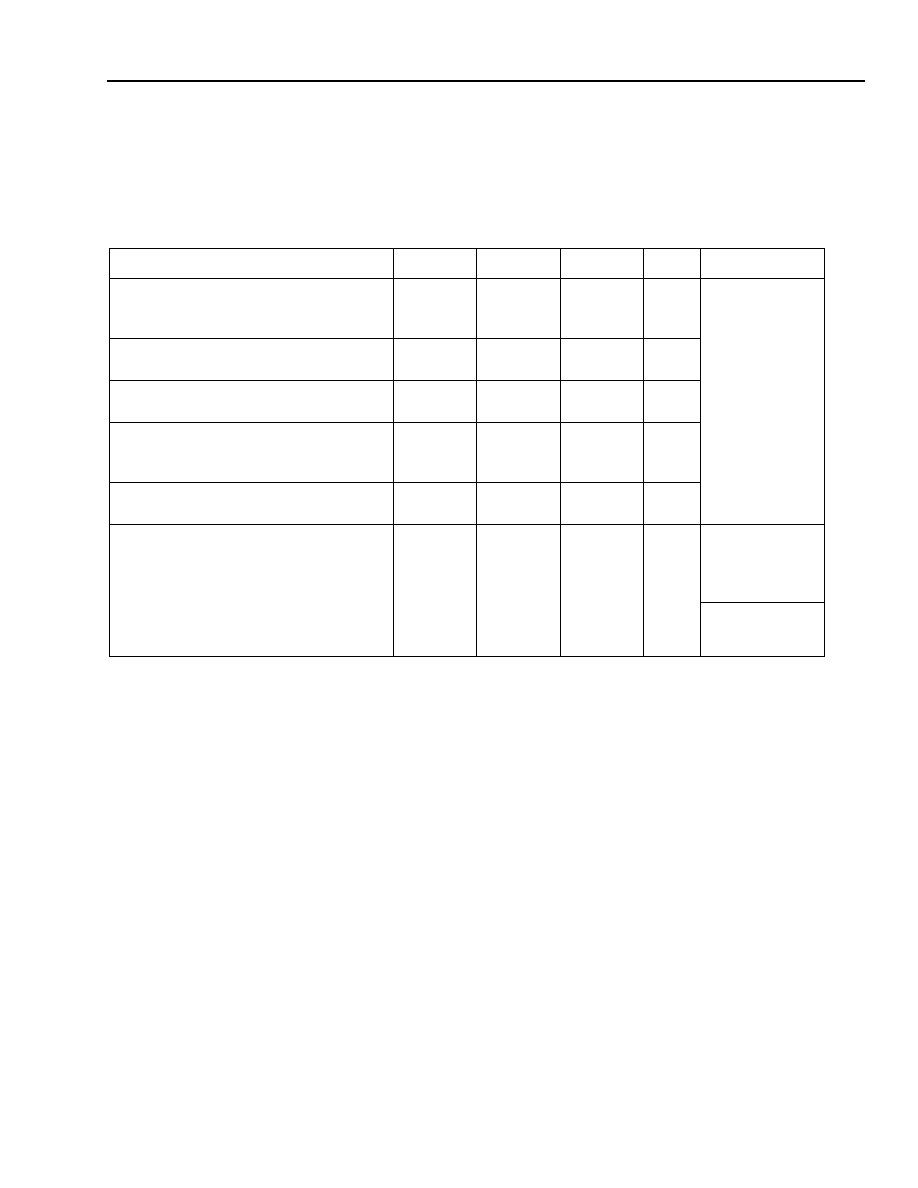

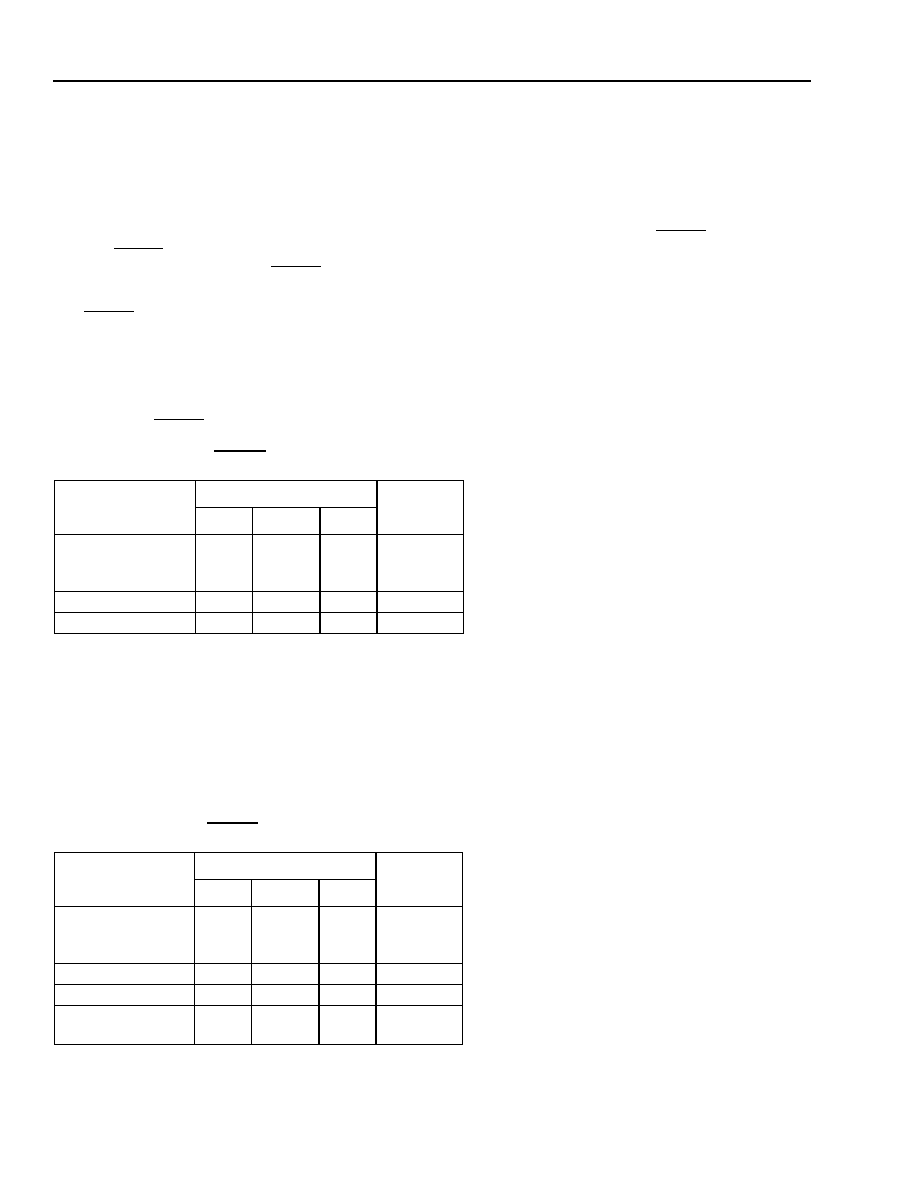

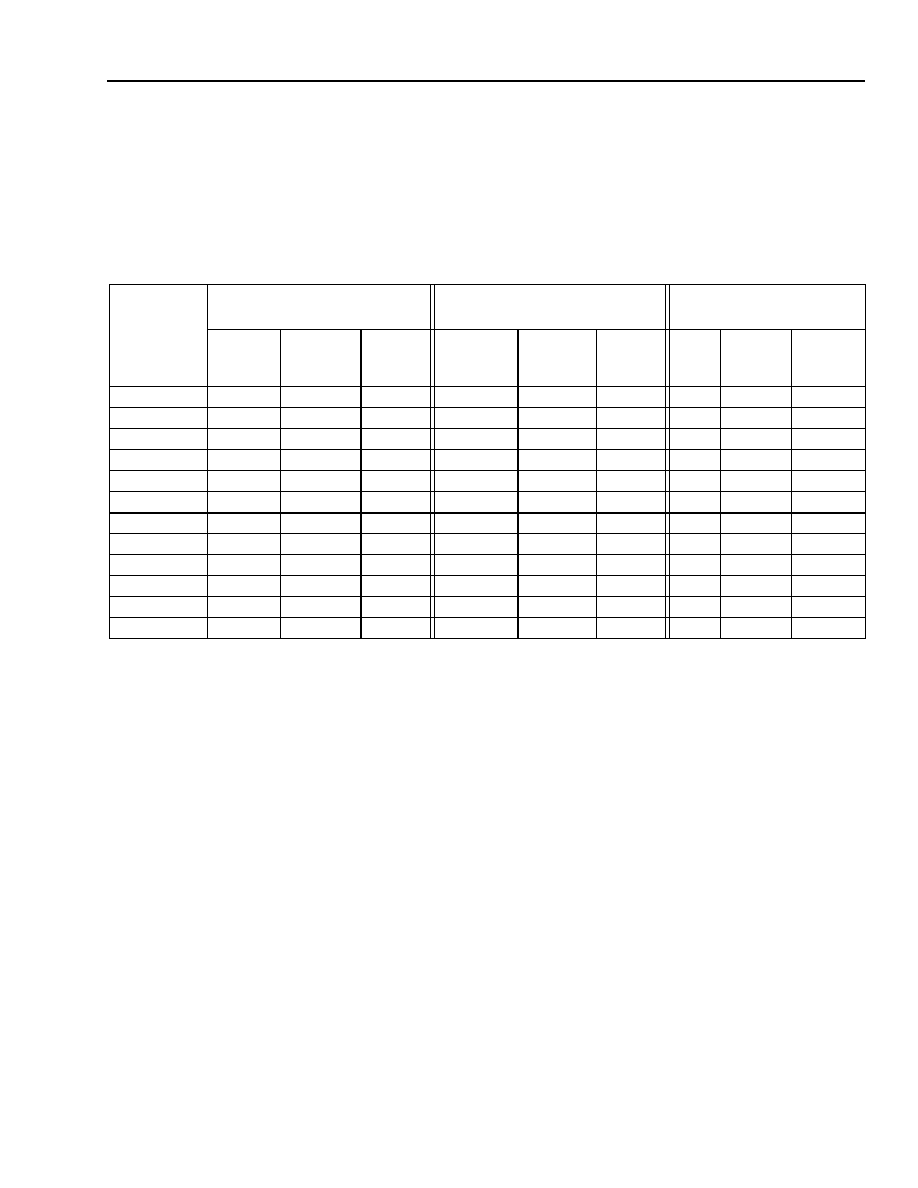

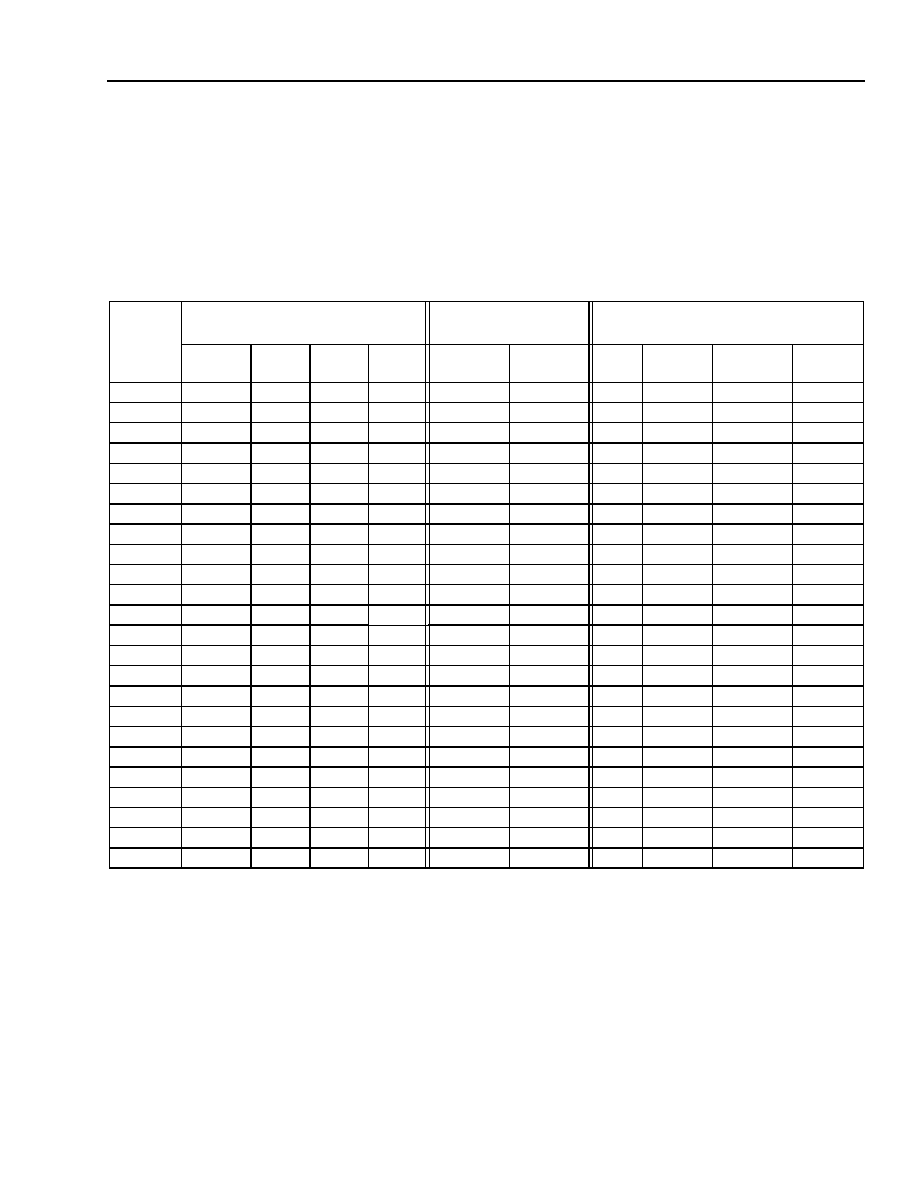

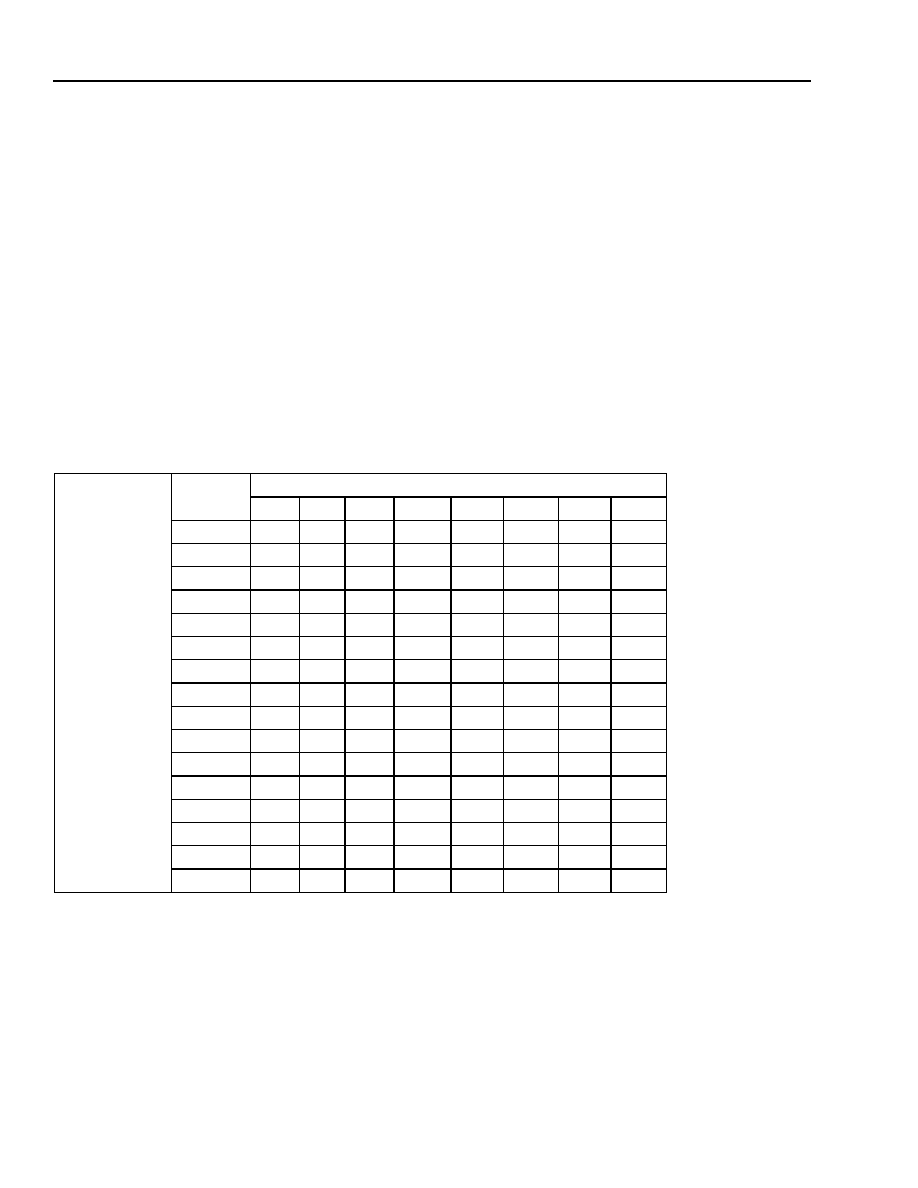

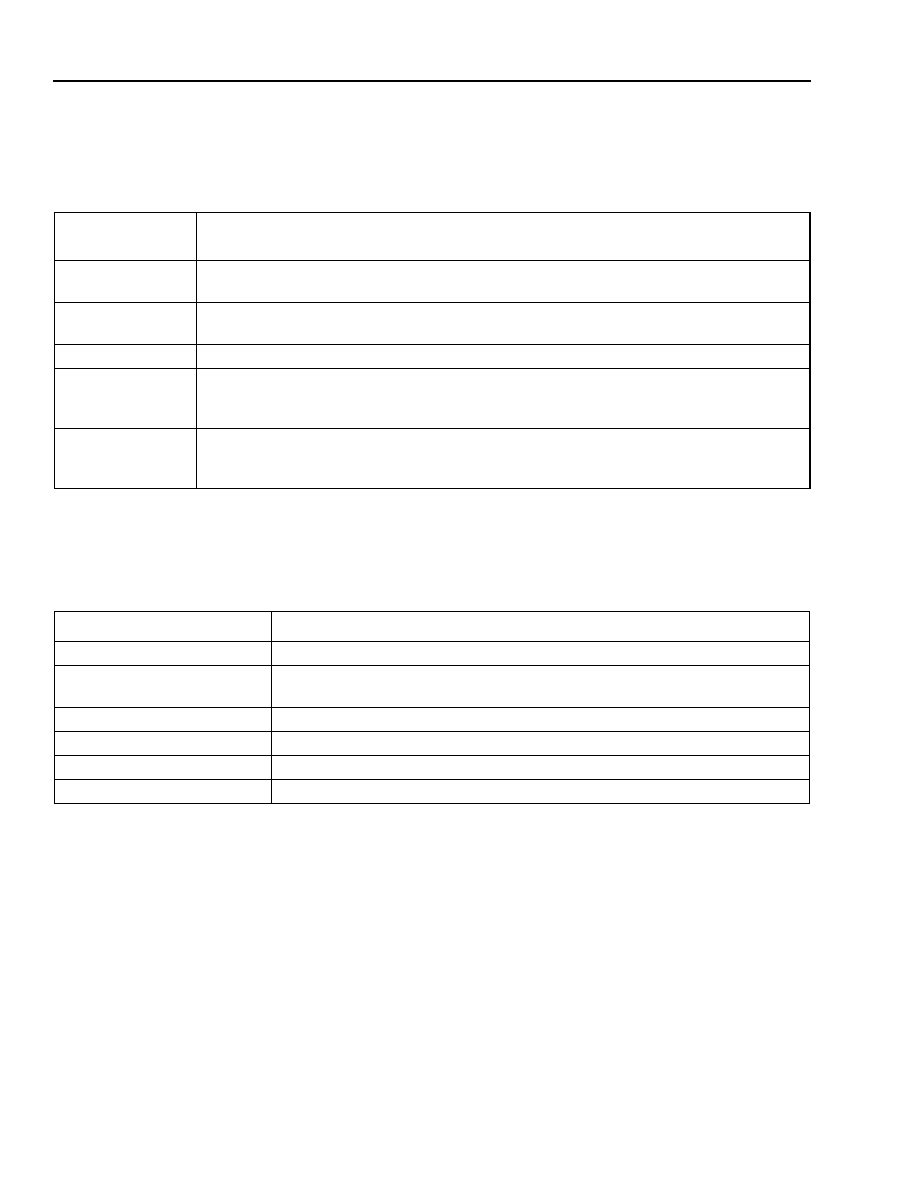

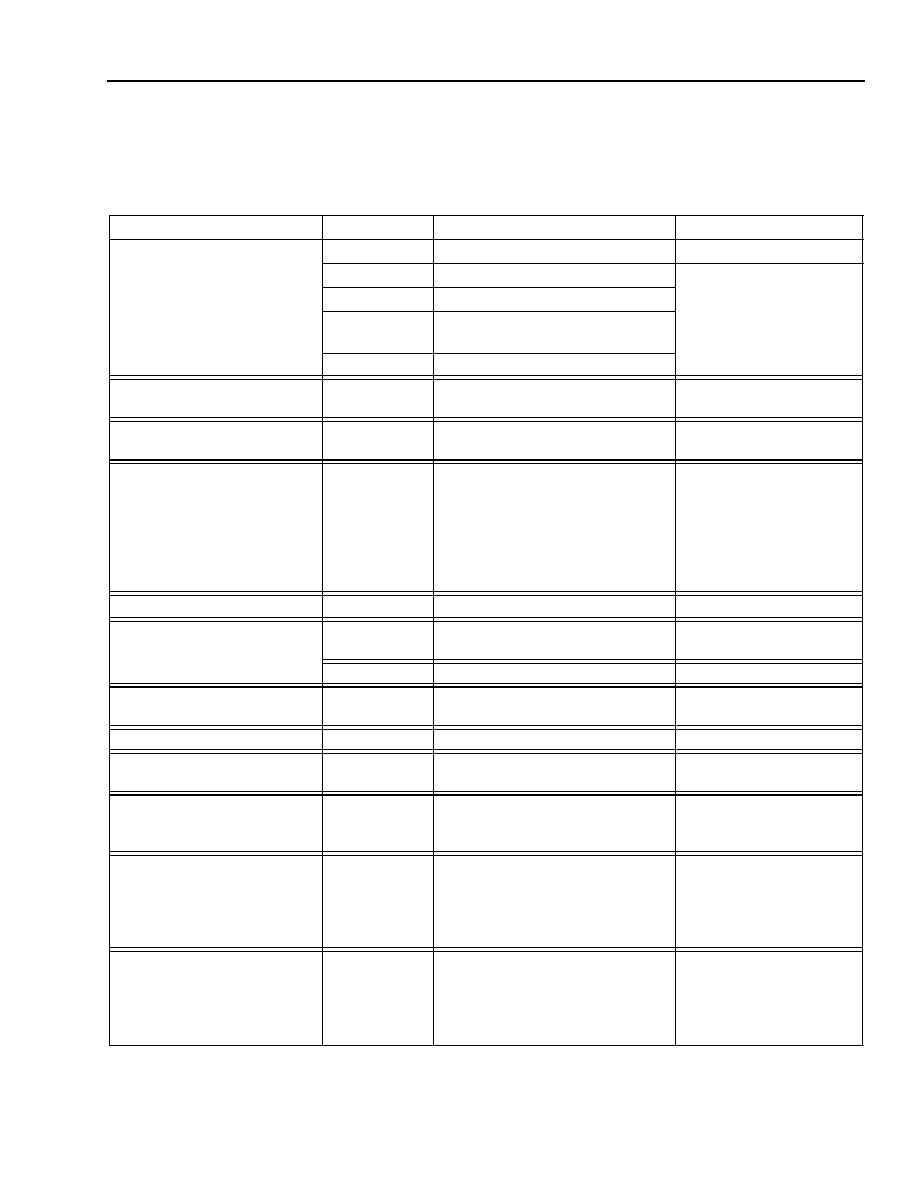

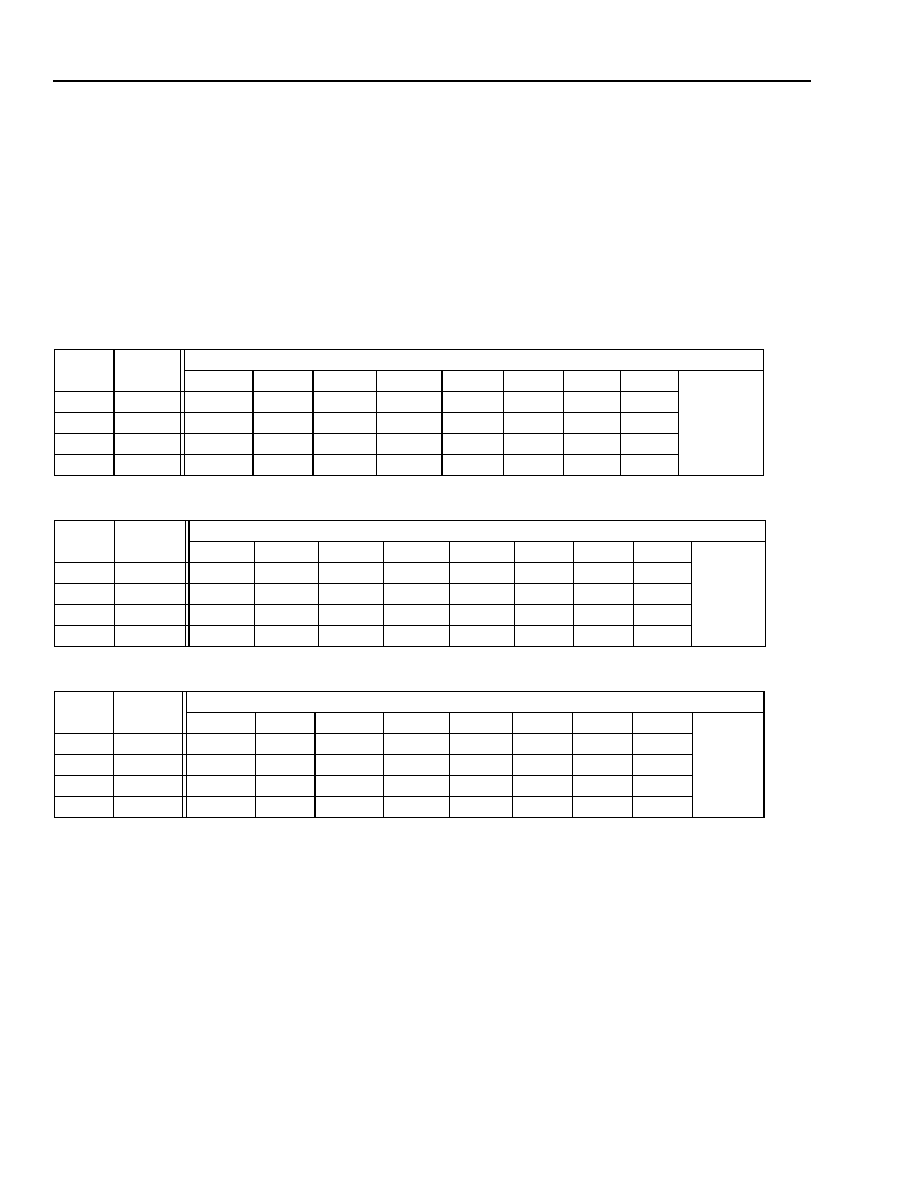

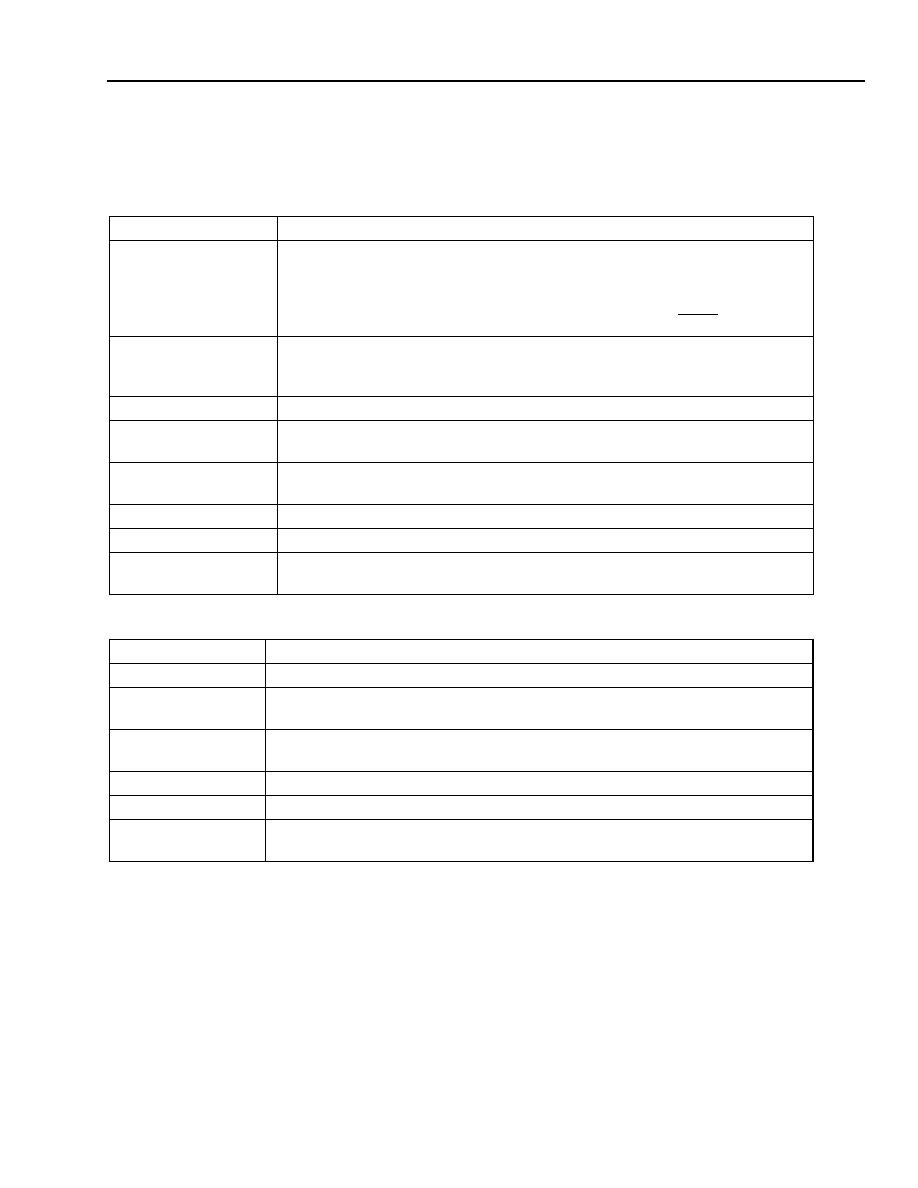

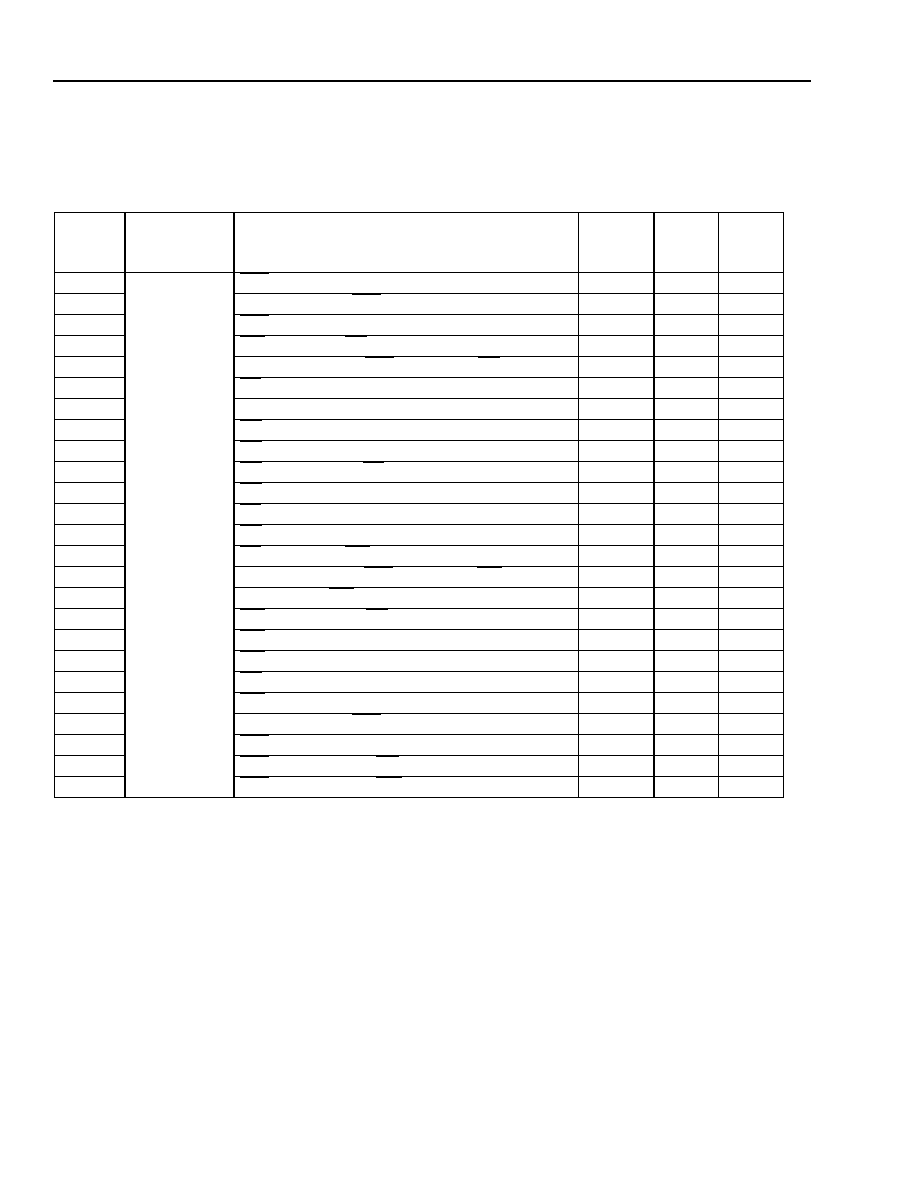

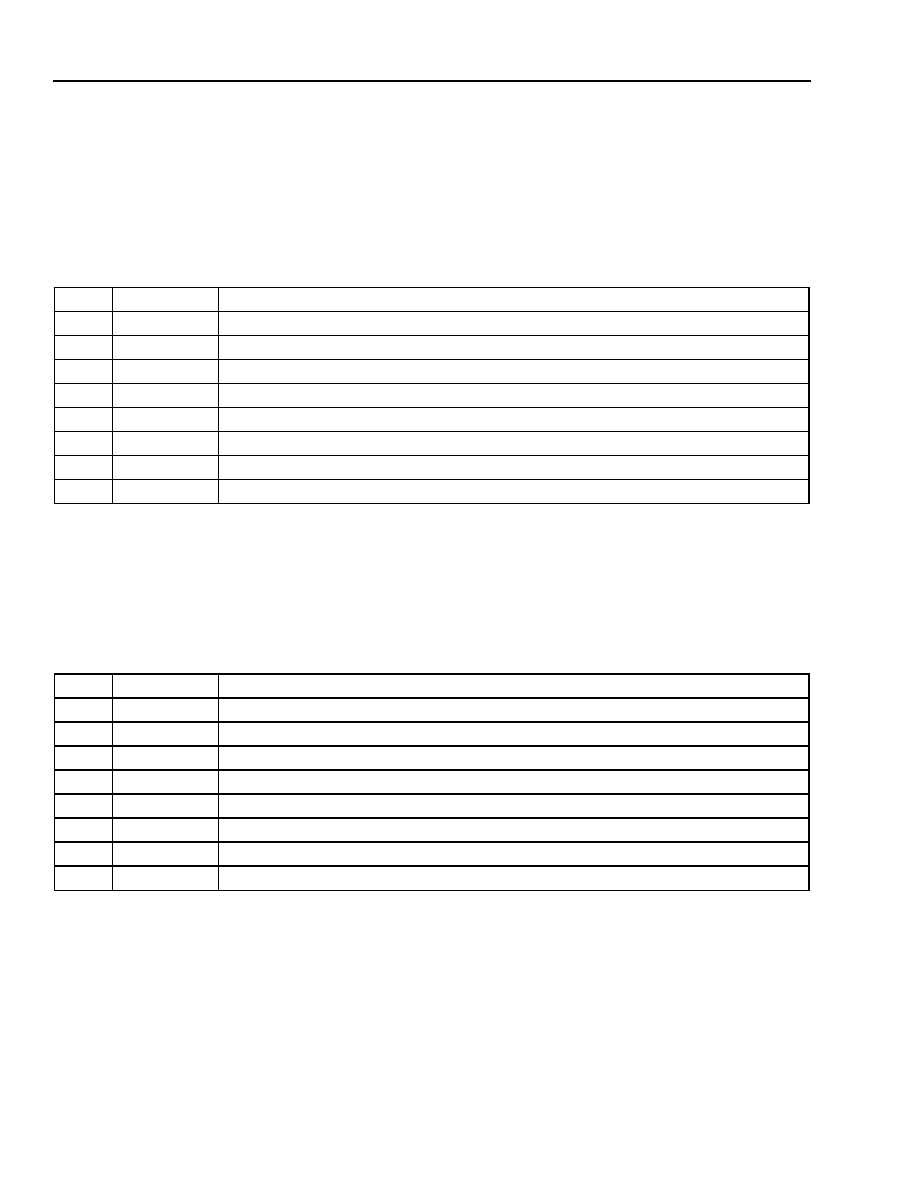

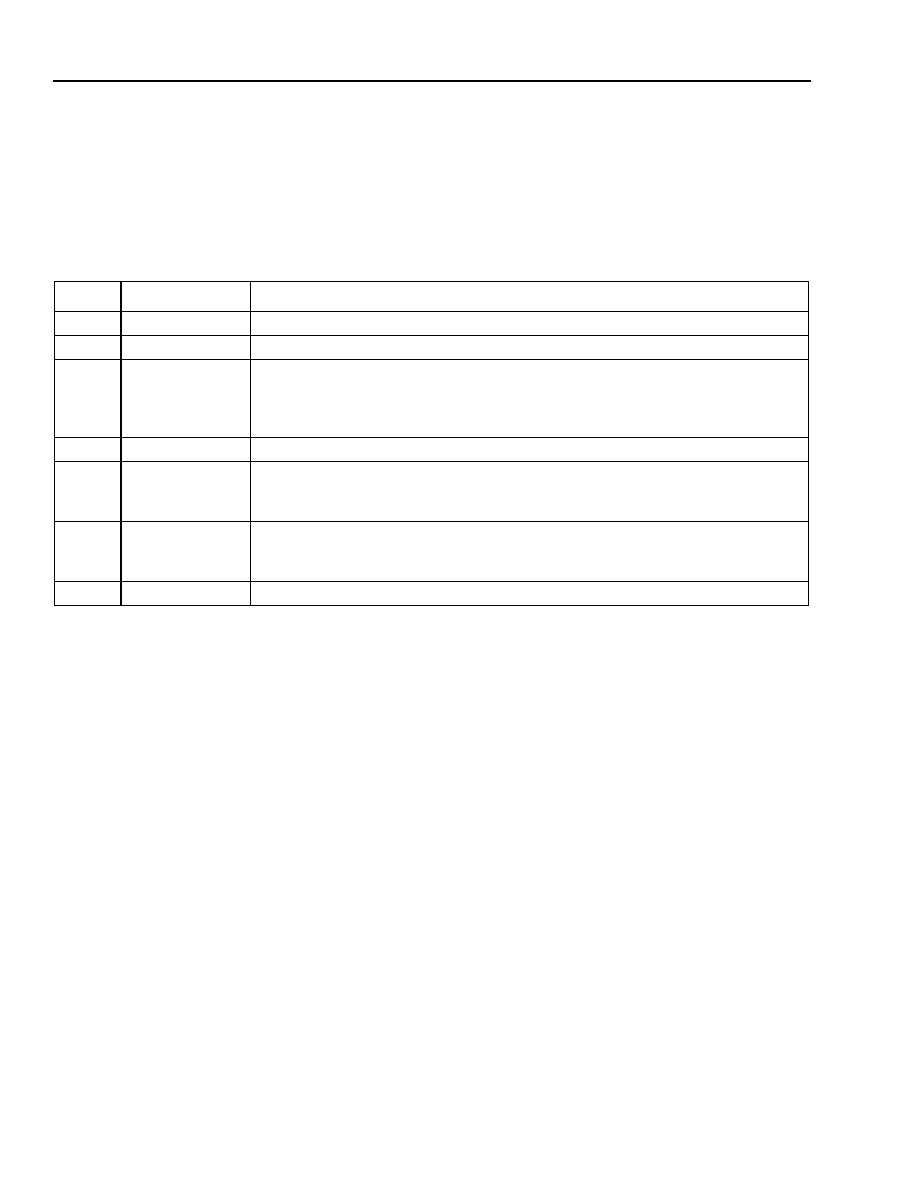

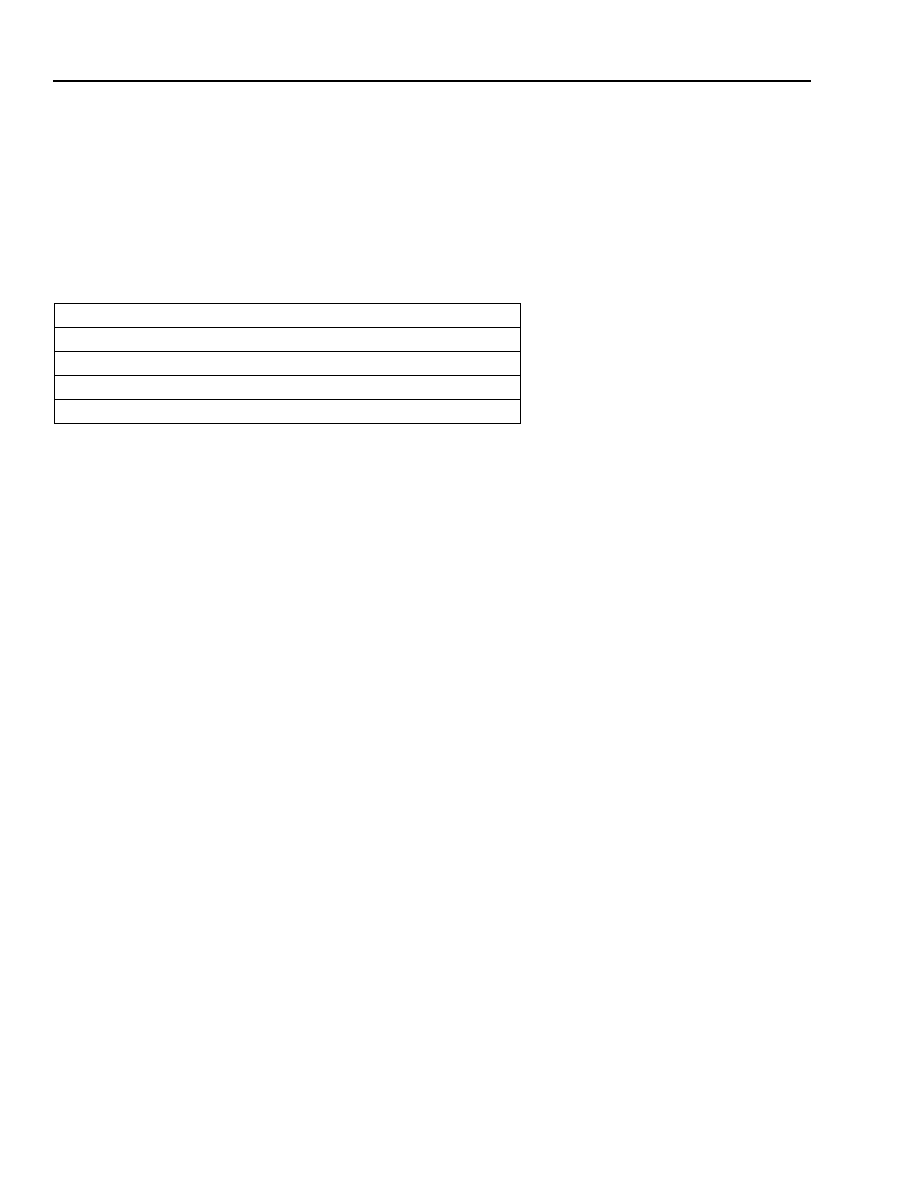

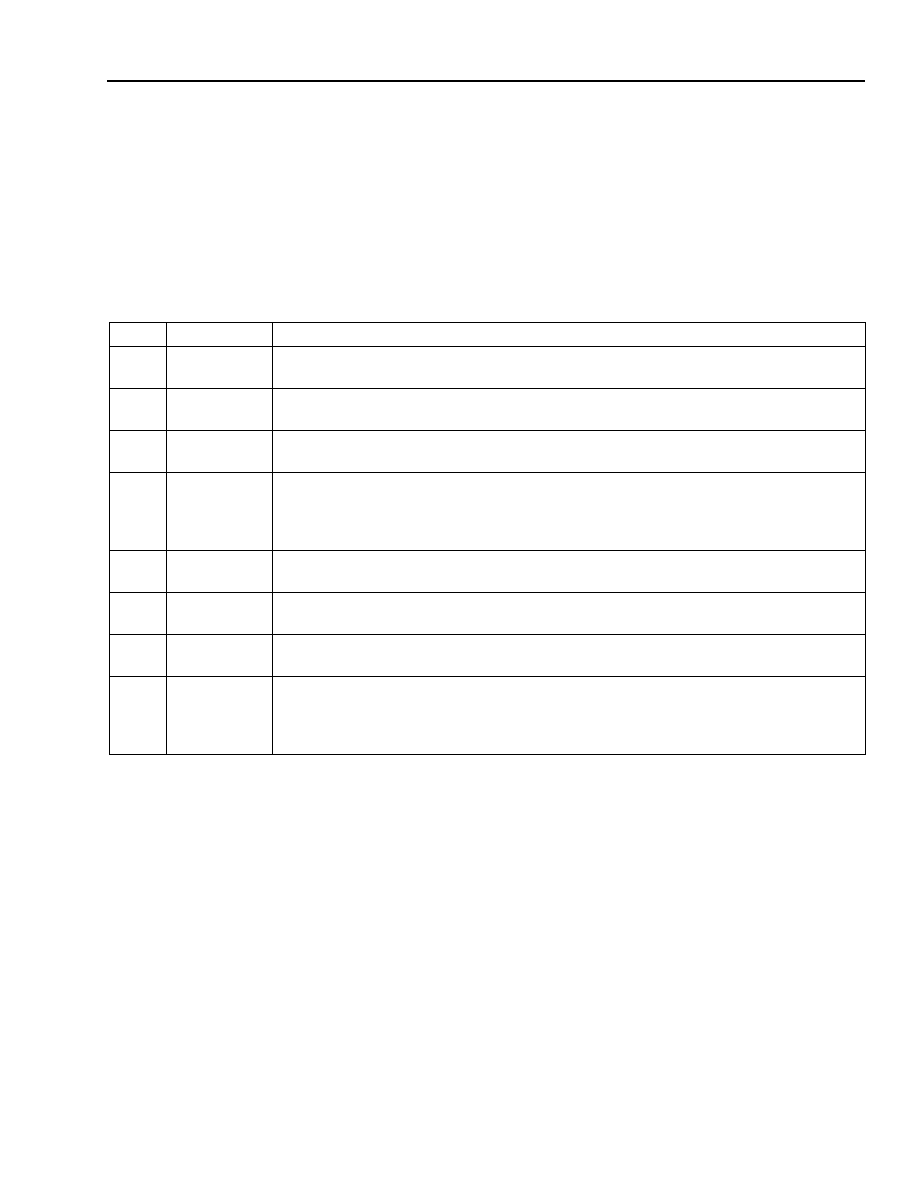

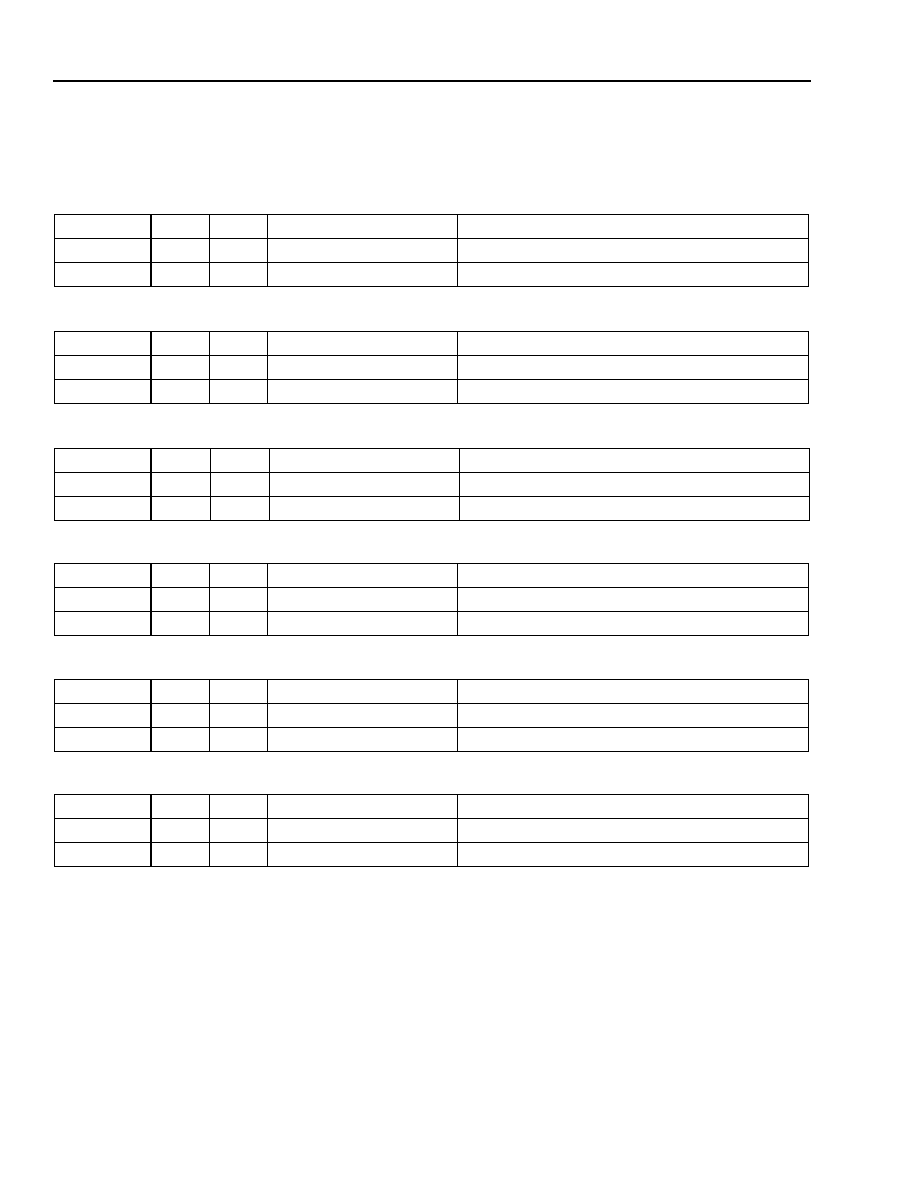

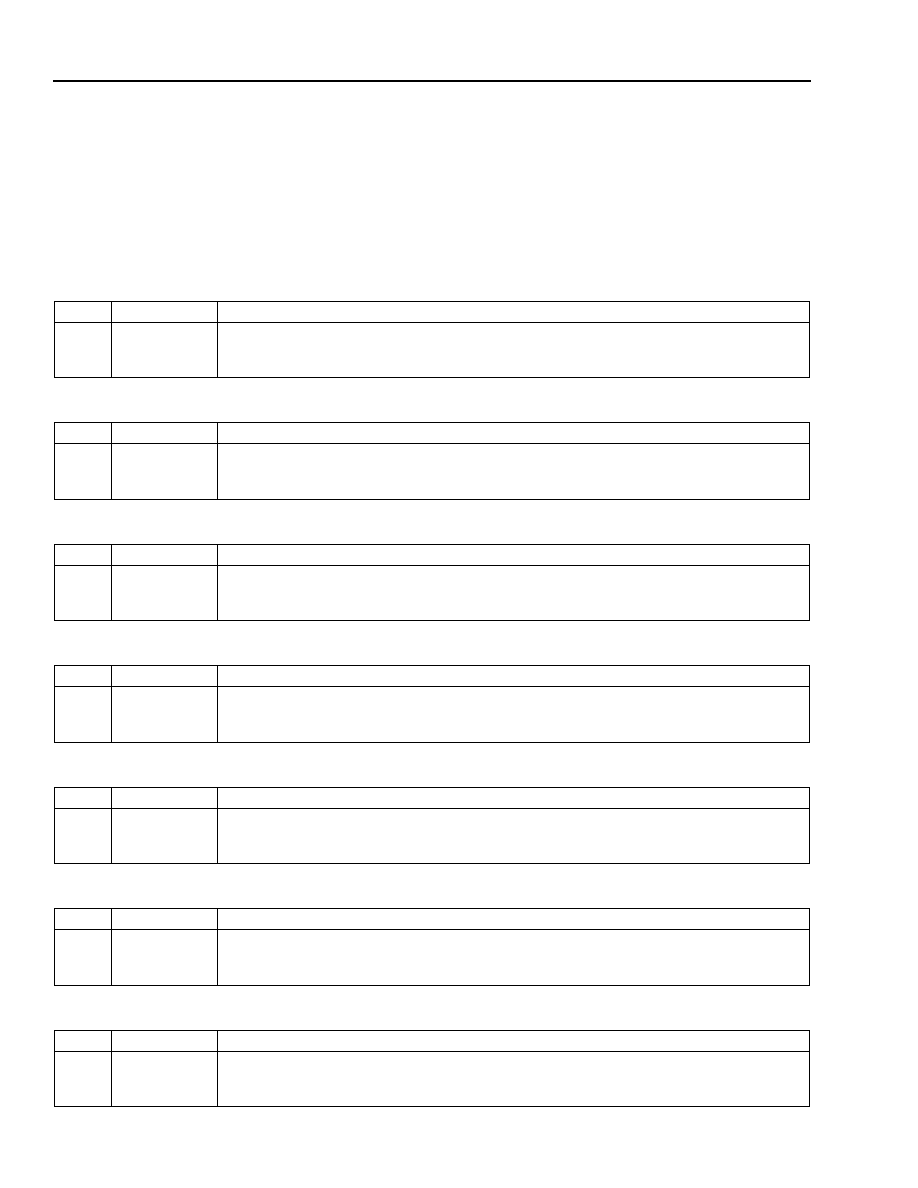

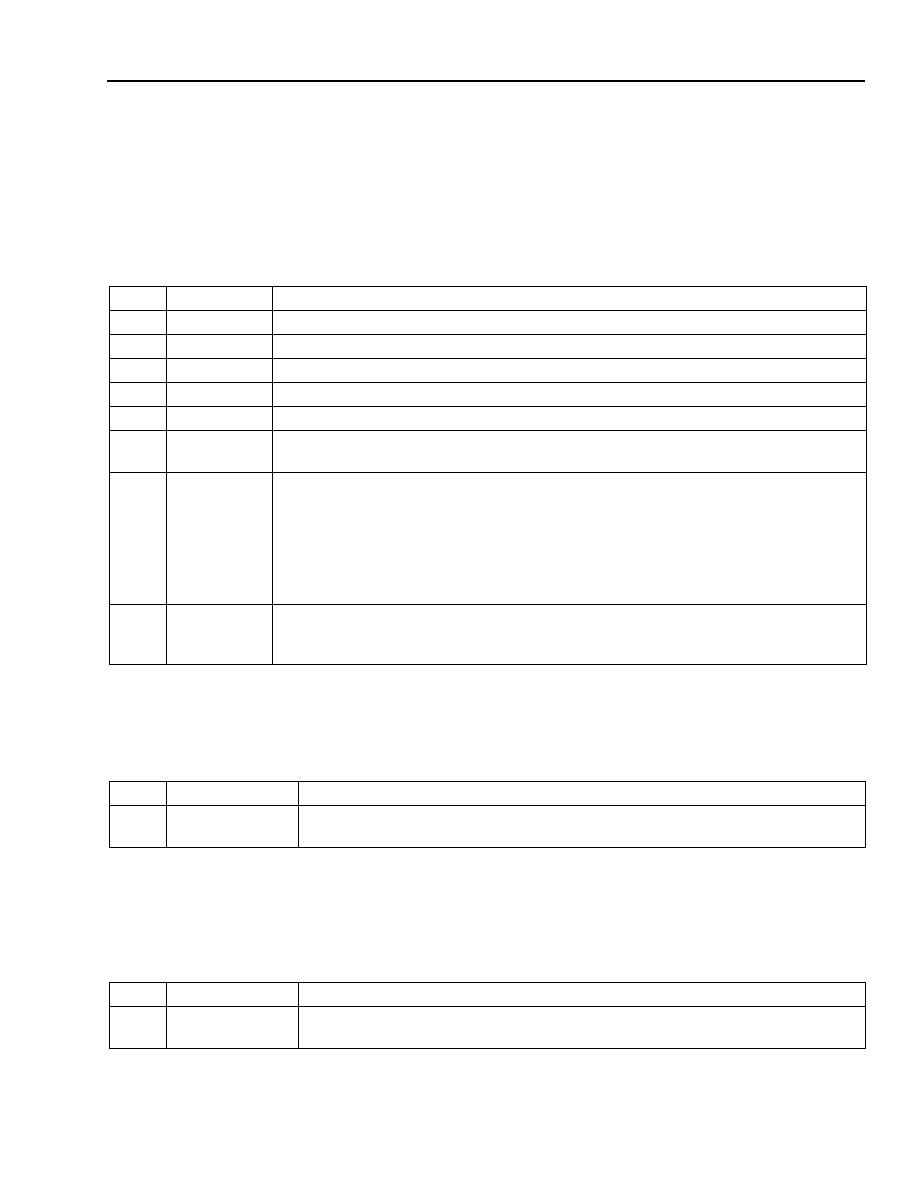

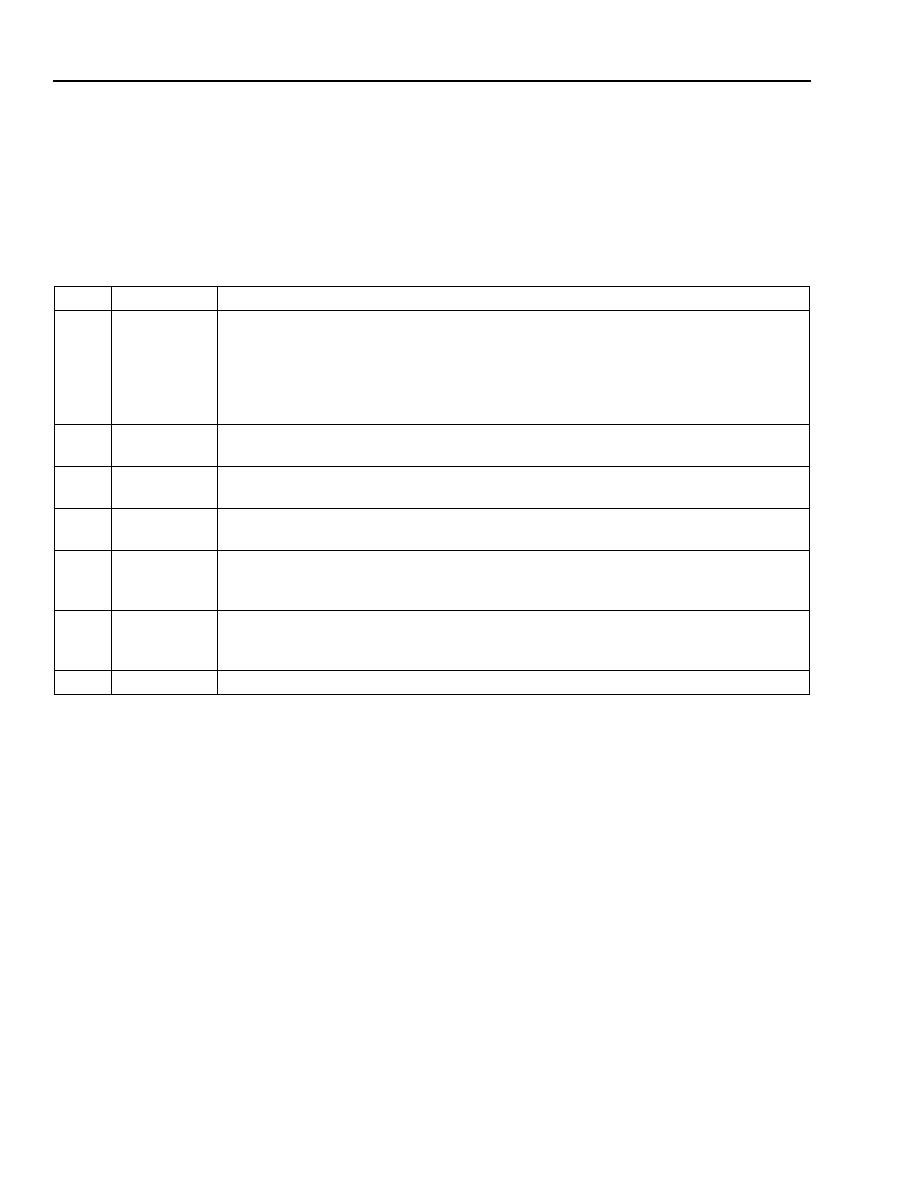

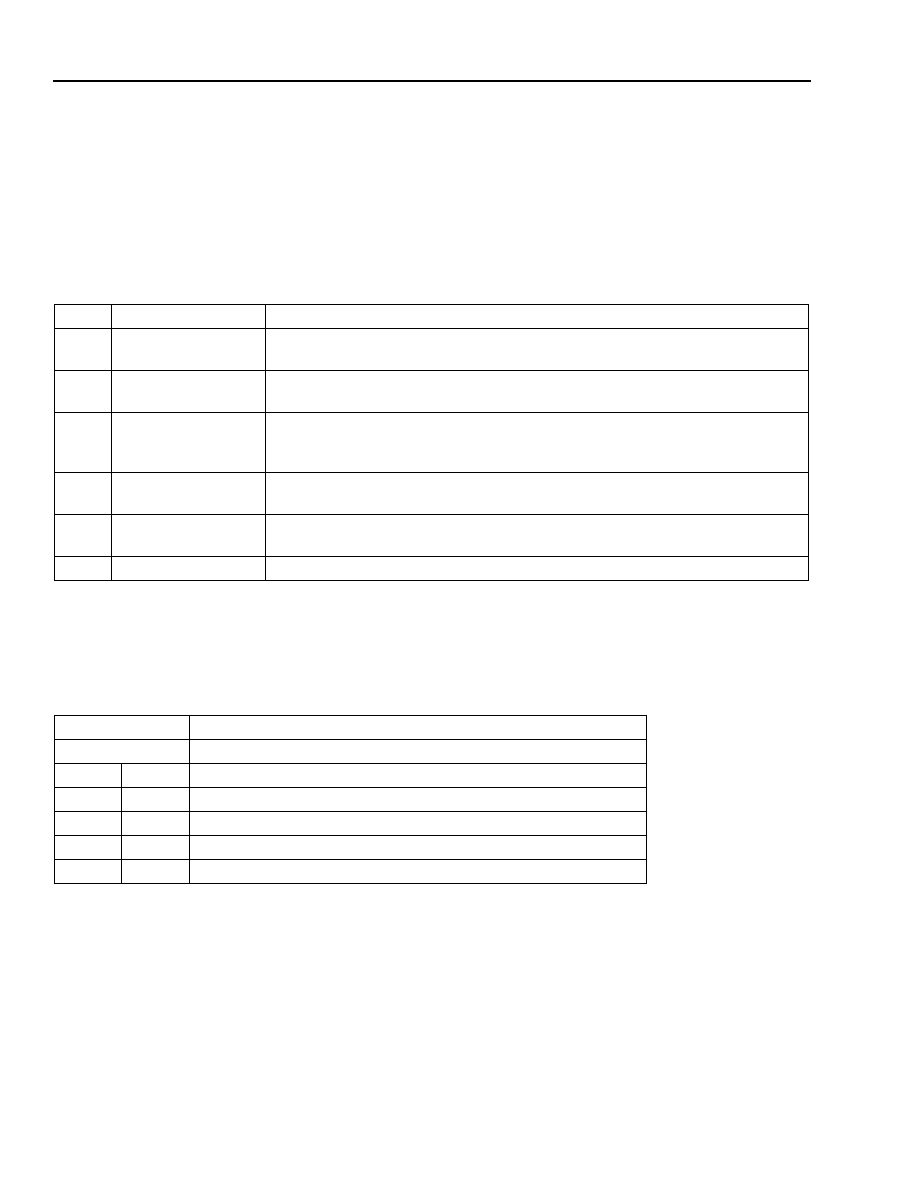

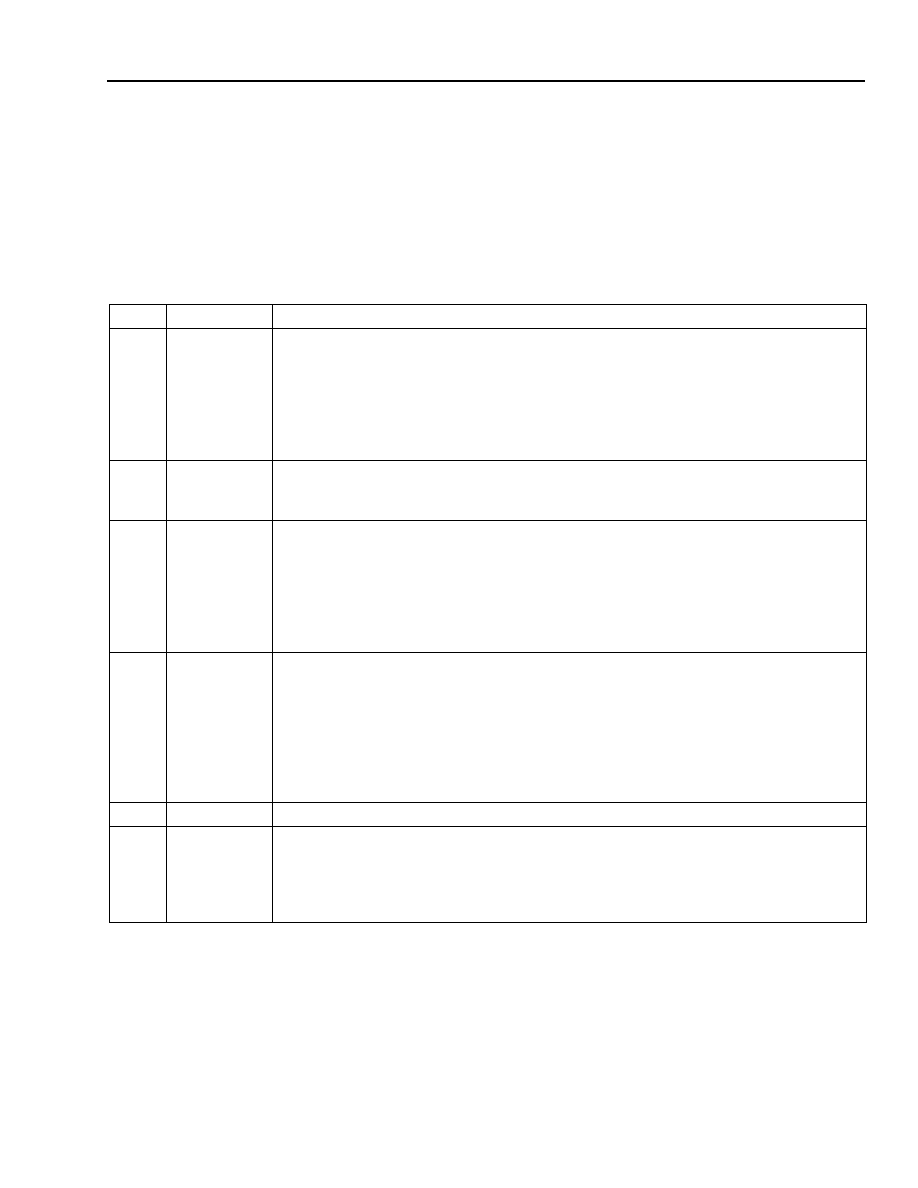

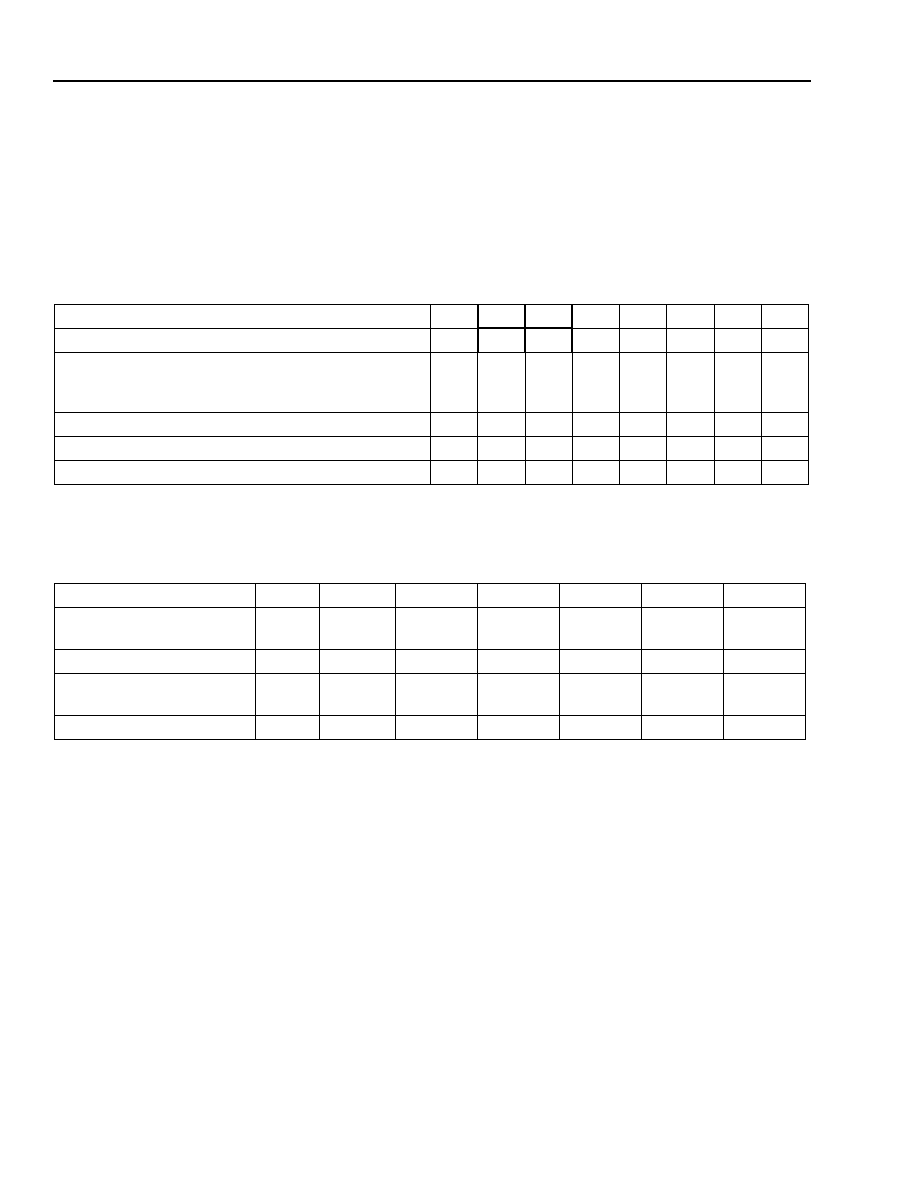

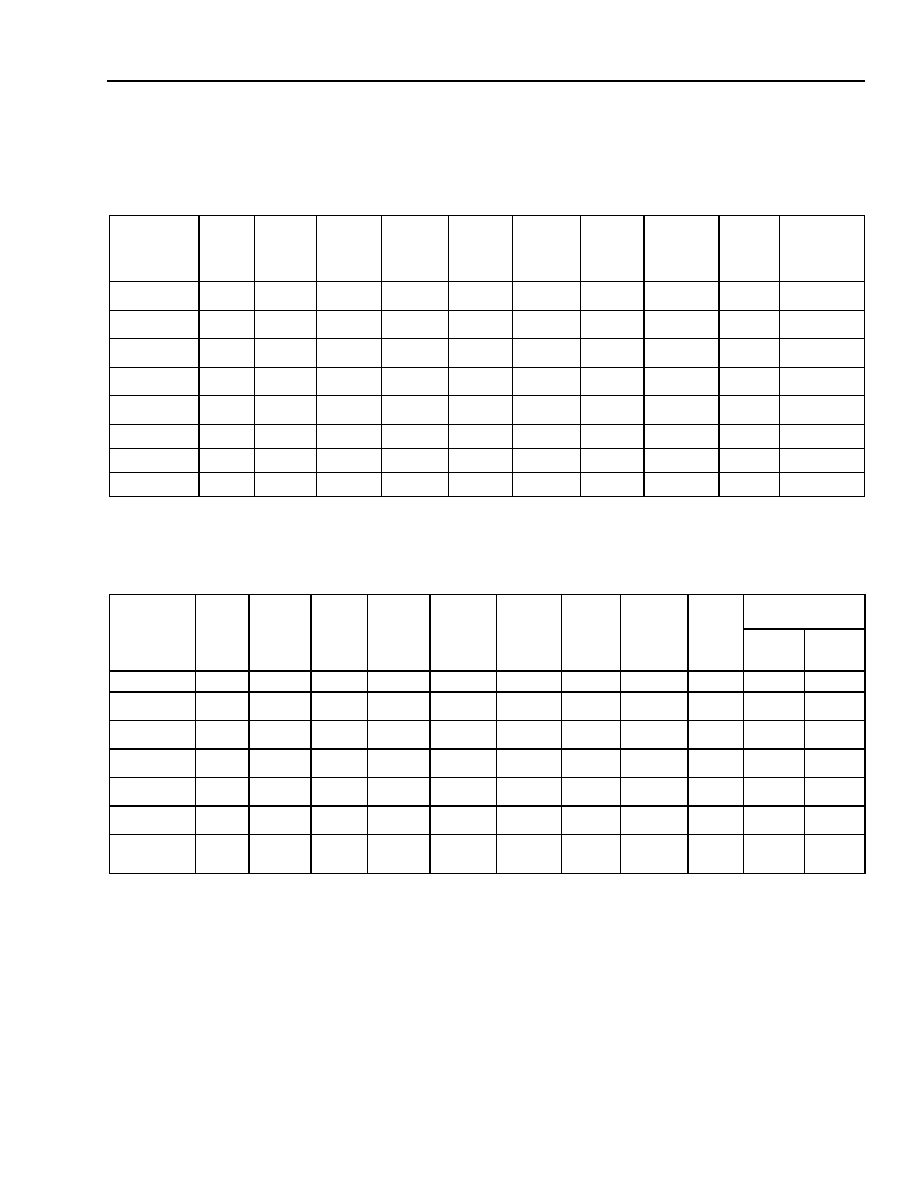

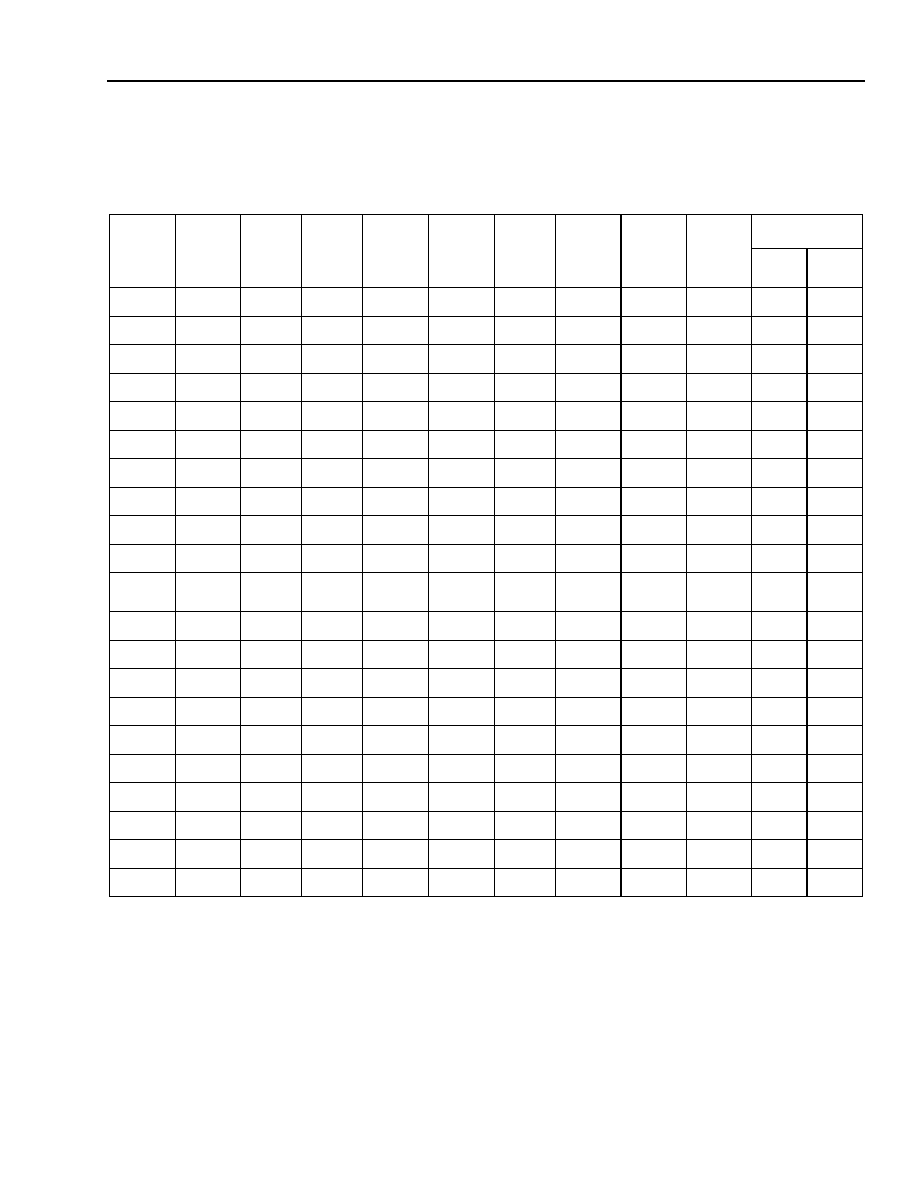

Table 1. Microprocessor Interface I/O Timing Specifications

Symbol

Configuration

Parameter

Setup

(ns)

(Min)

Hold

(ns)

(Min)

Delay

(ns)

(Max)

t1

Modes 1 & 2

AS Asserted Width

--

10

--

t2

Address Valid to AS Deasserted

10

--

--

t3

AS Deasserted to Address Invalid

--

10

--

t4

--

--

--

--

t5

R/W Valid to Both CS and DS Asserted

4

--

--

t6

Address Valid and AS Asserted to DS Asserted (Read)

0

--

--

t7

CS Asserted to DTACK Low Impedance

--

--

12

t8

DS Asserted to DTACK Asserted

--

--

15

t9

DS Asserted to AD Low Impedance (Read)

--

--

15

t10

DTACK Asserted to Data Valid

--

--

25

t11

DS Deasserted to CS Deasserted (Read)

--

*

--

t12

DS Deasserted to R/W Invalid

--

5

--

t13

DS Deasserted to DTACK Deasserted

--

--

12

t14

CS Deasserted to DTACK High Impedance

--

--

10

t15

DS Deasserted to Data Invalid (Read)

--

5

--

t16

Address Valid and AS Asserted to DS Asserted (Write)

10

--

--

t17

Data Valid to DS Asserted

10

--

--

t18

DS Deasserted to CS Deasserted (Write)

--

5

--

t19

DS Deasserted to Data Valid

--

10

--

t20

DS Asserted Width (Write)

--

10

--

t21

Address Valid to AS Falling Edge

10

--

--

t22

AS Falling Edge to Address Invalid

--

10

--

t23

AS Falling Edge to DS Asserted (Read)

0

--

--

t24

AS Falling Edge to DS Asserted (Write)

10

--

--

t25

CS Asserted to DS Asserted (Write)

10

--

--

Agere Systems Inc.

3

Device Advisory

September 1999

T7633 Device Advisory for Version 1.0 of the Device

Microprocessor Interface

(continued)

I/O Timing

(continued)

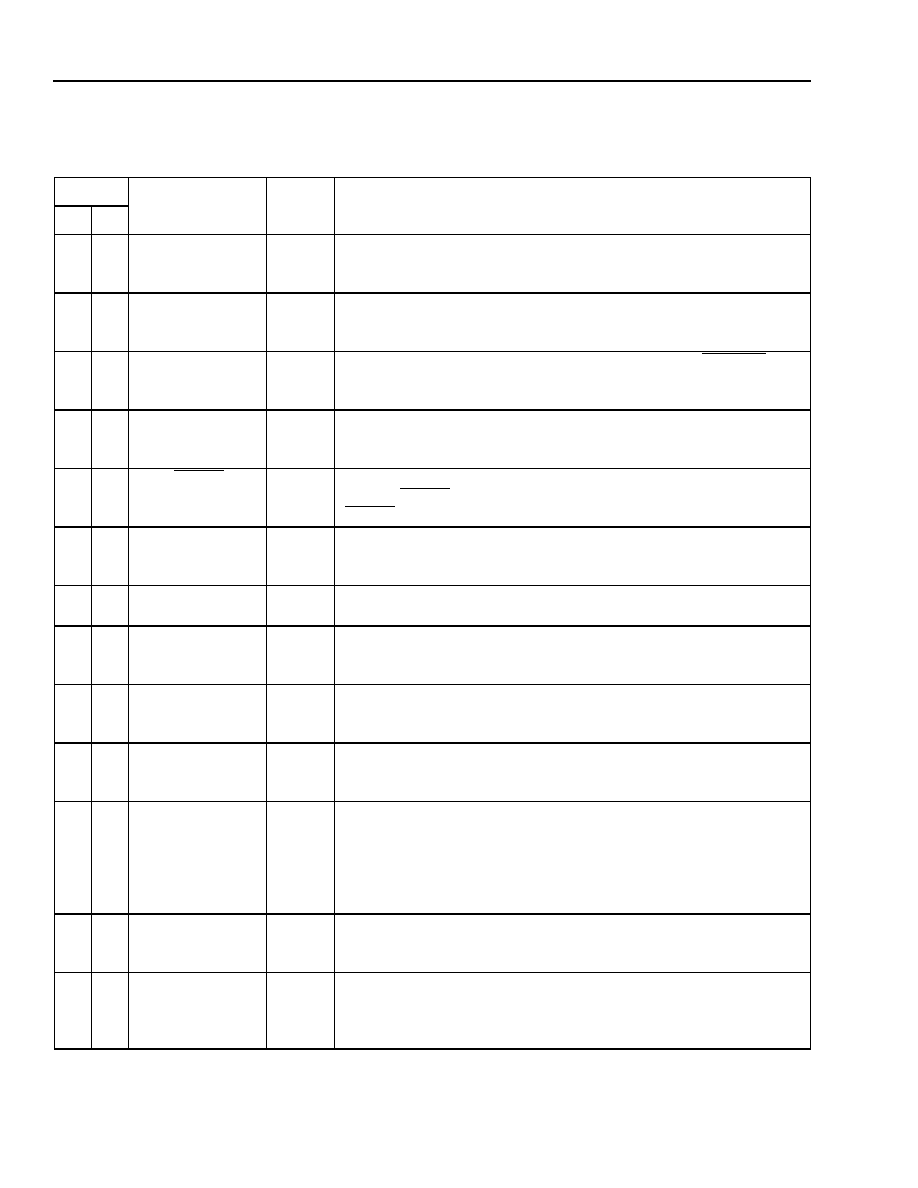

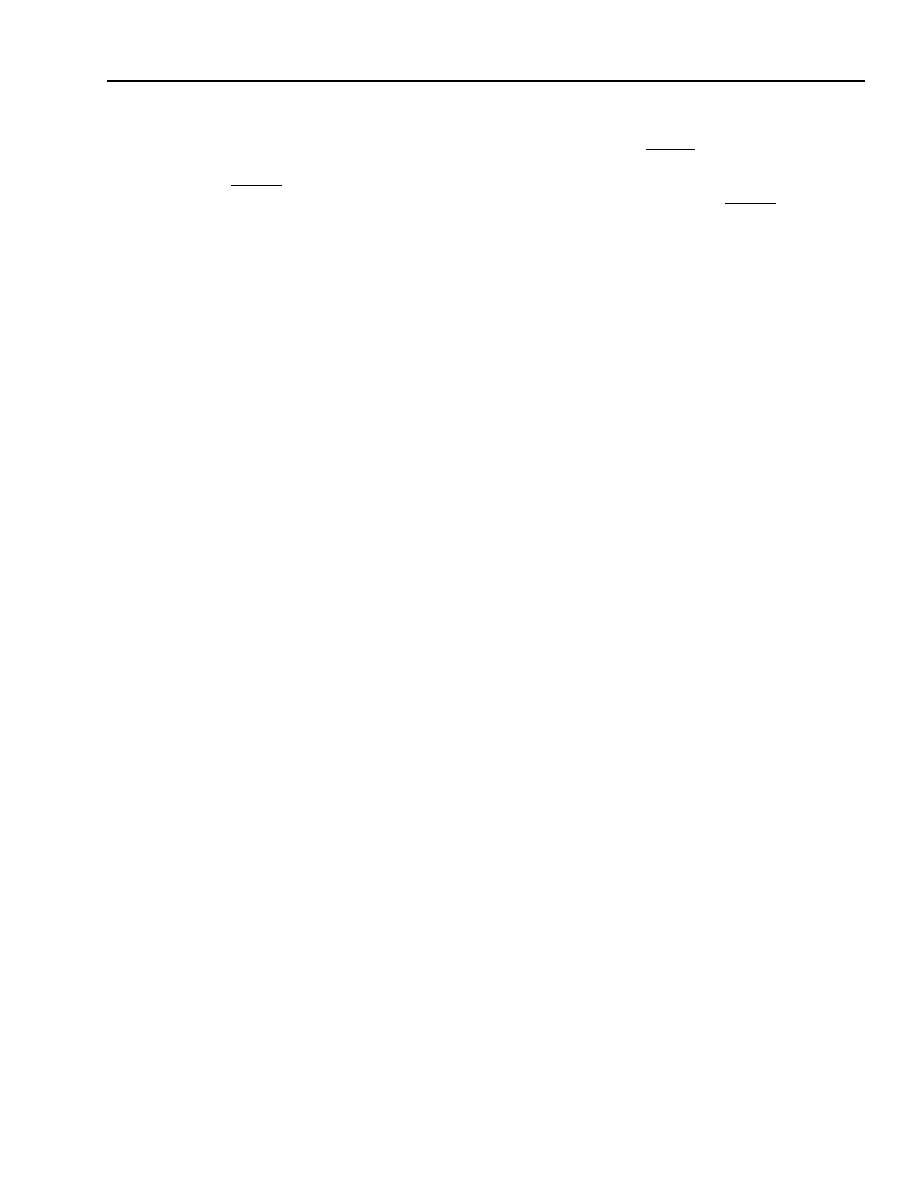

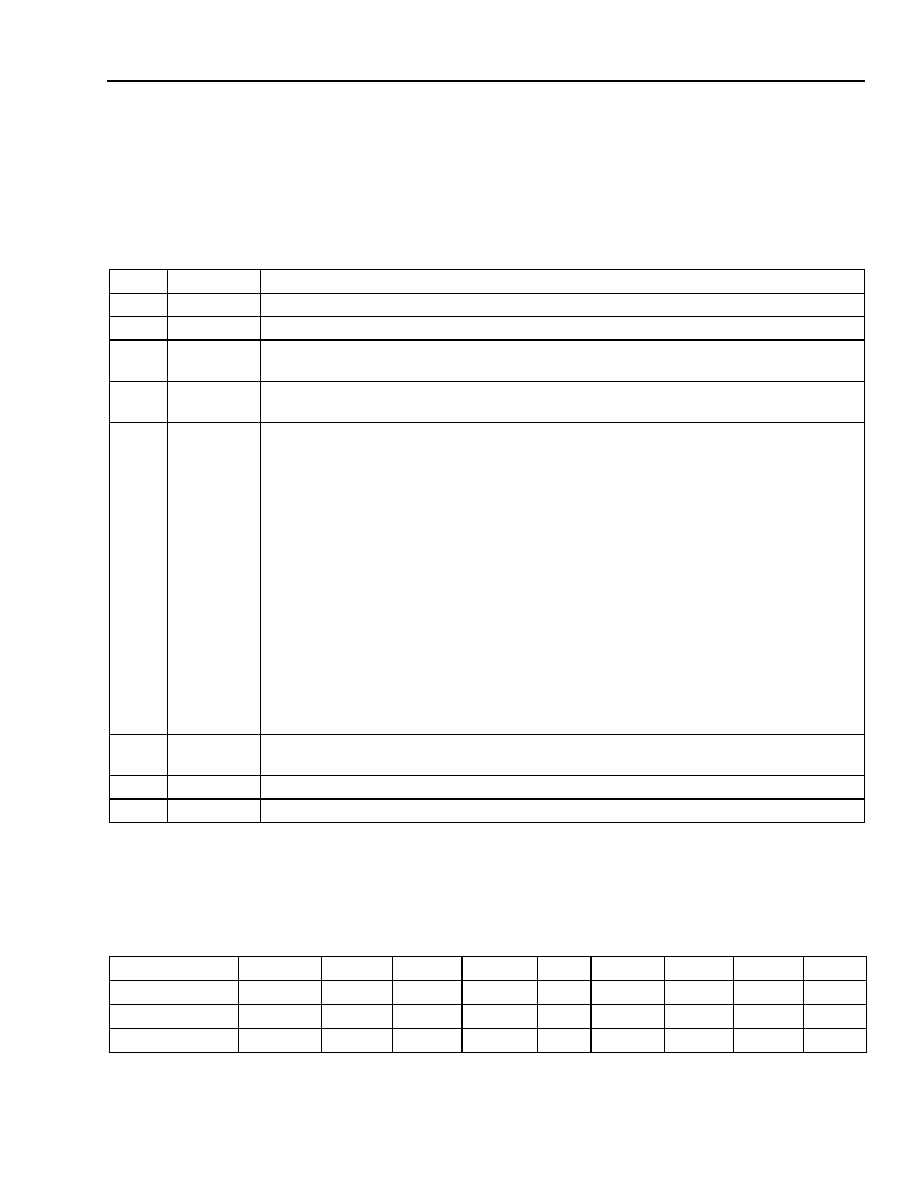

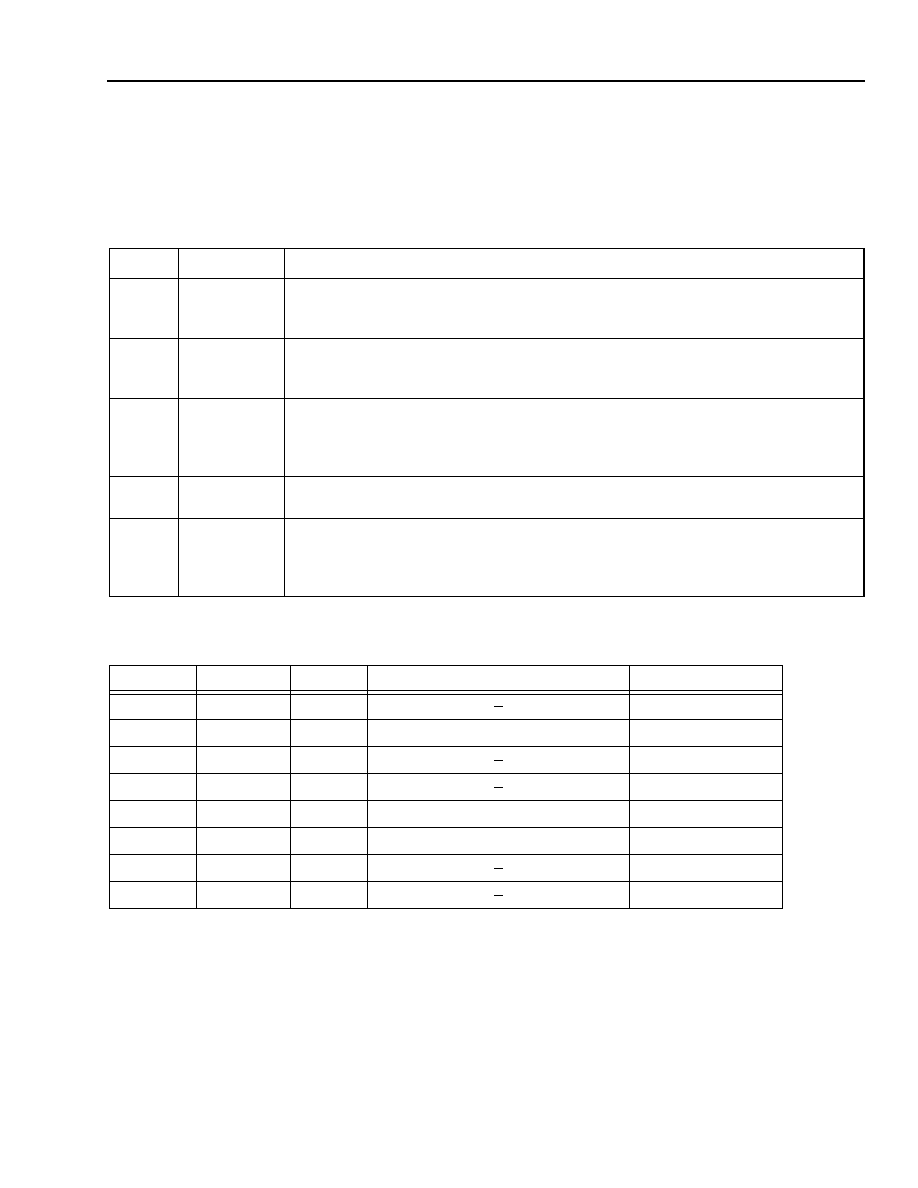

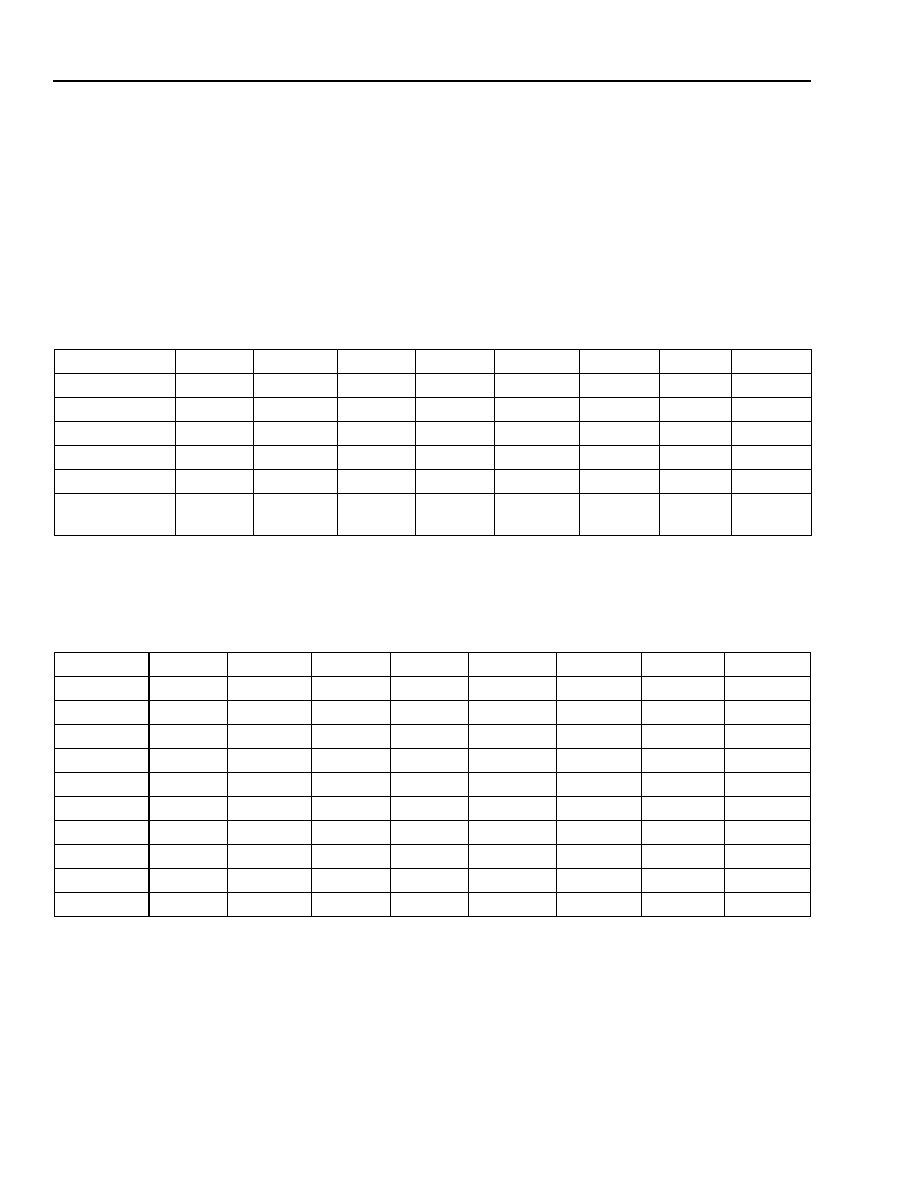

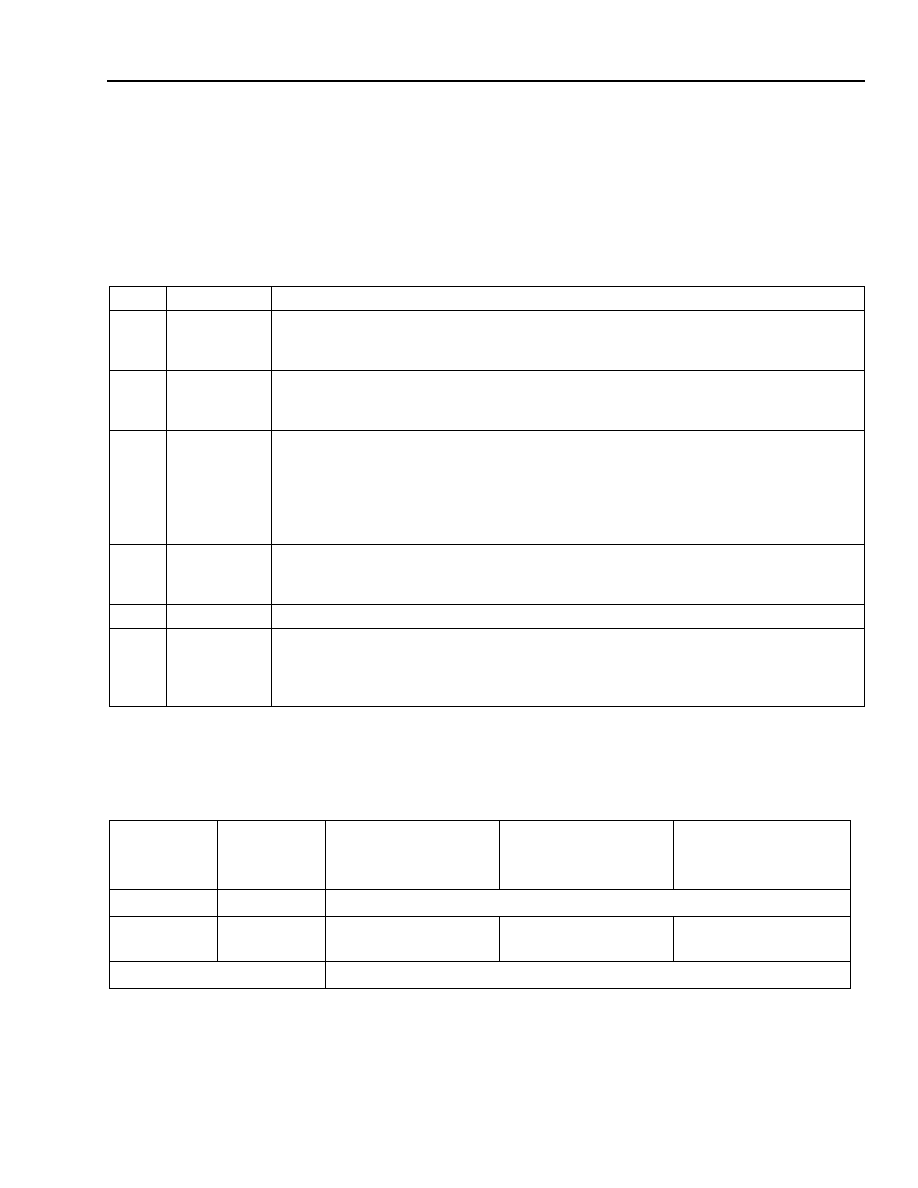

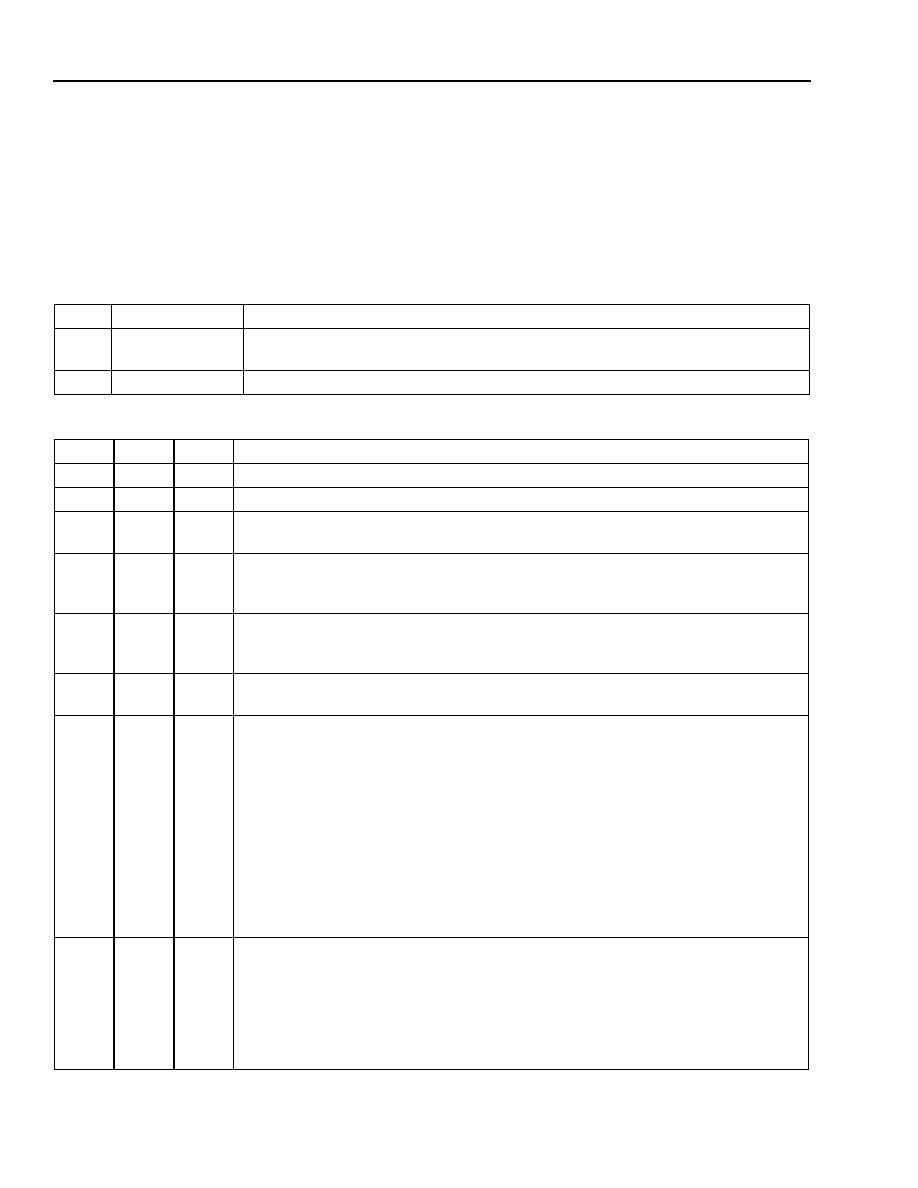

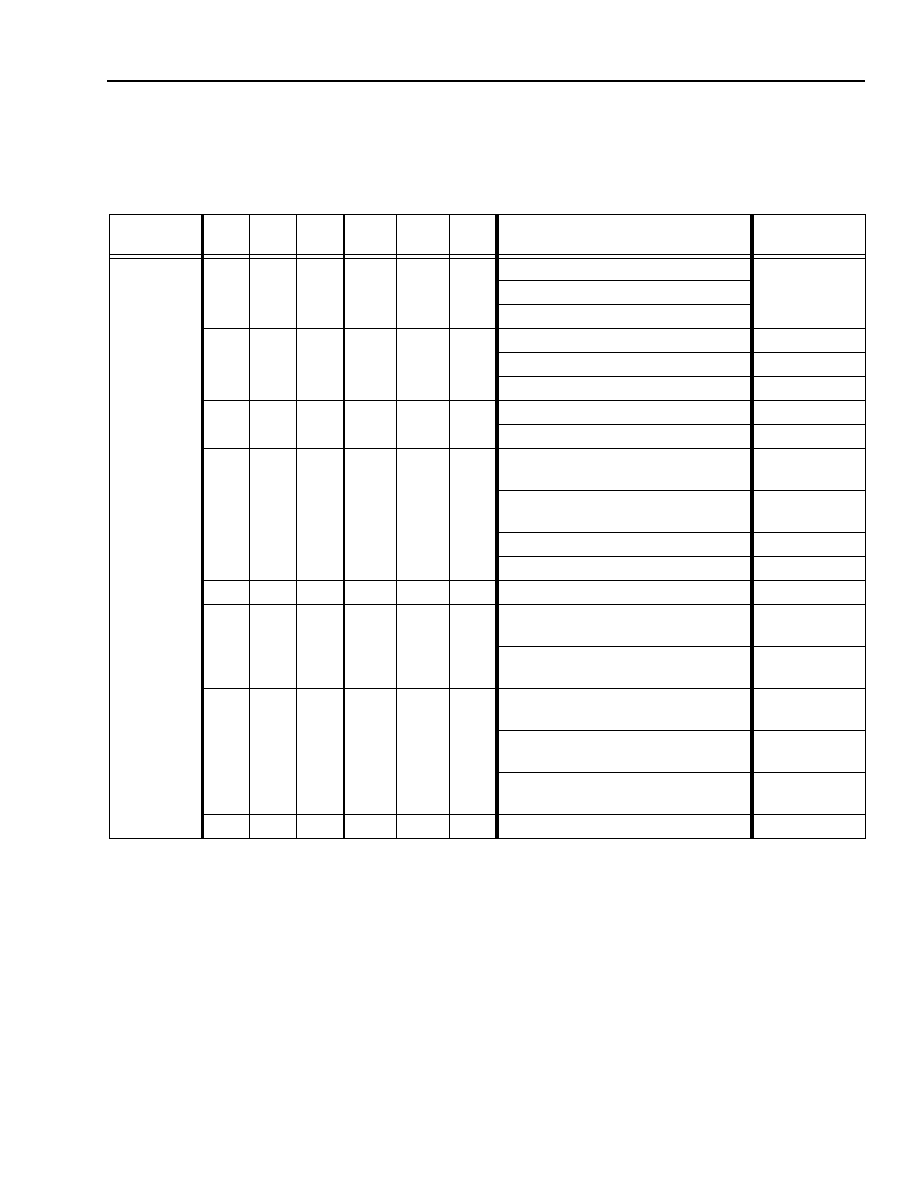

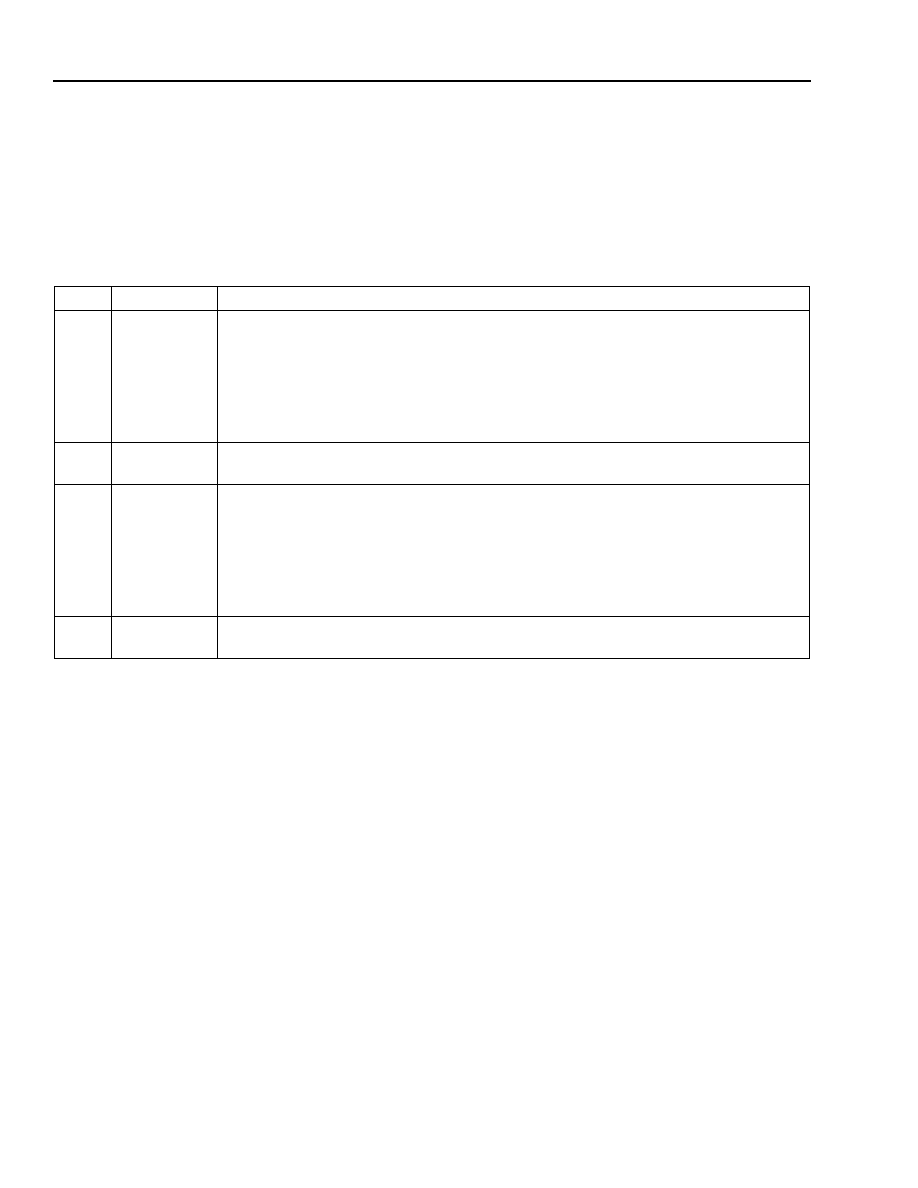

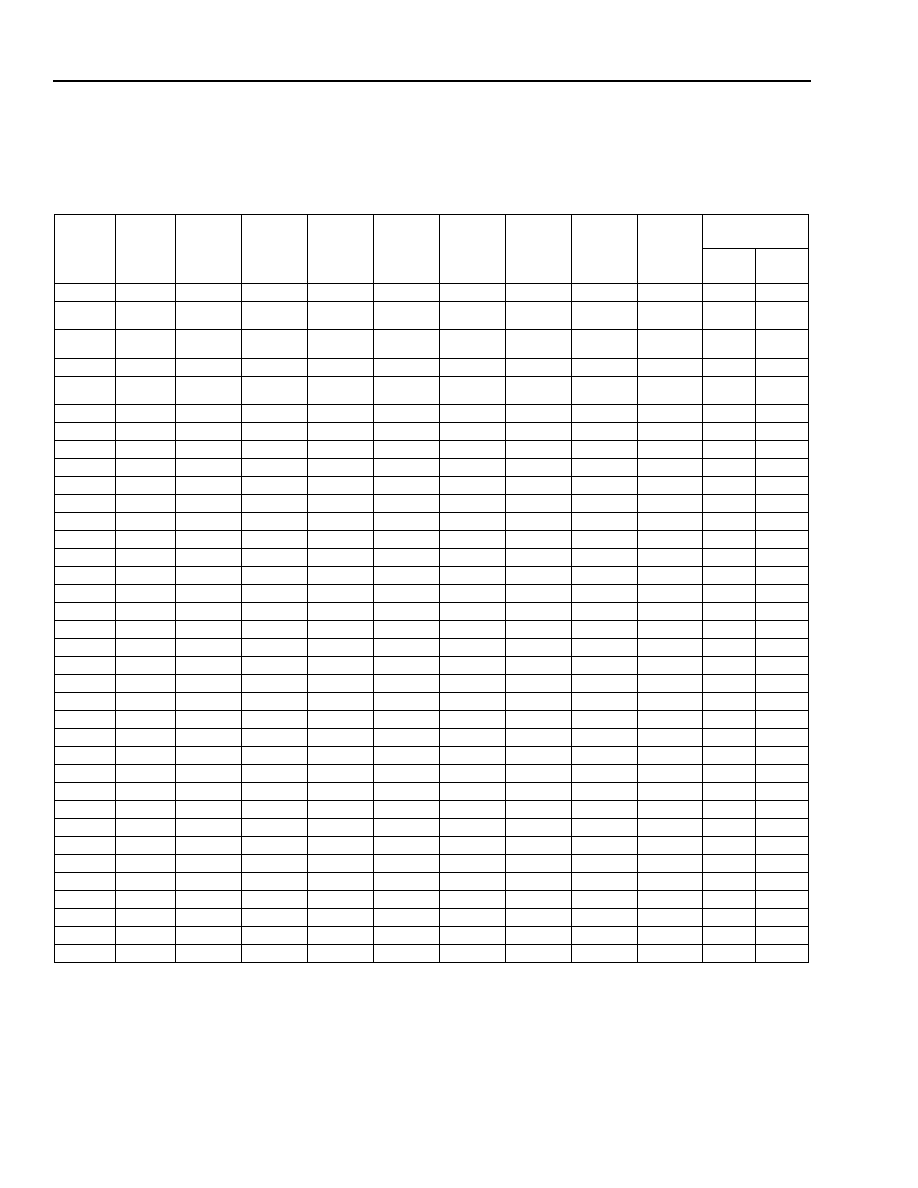

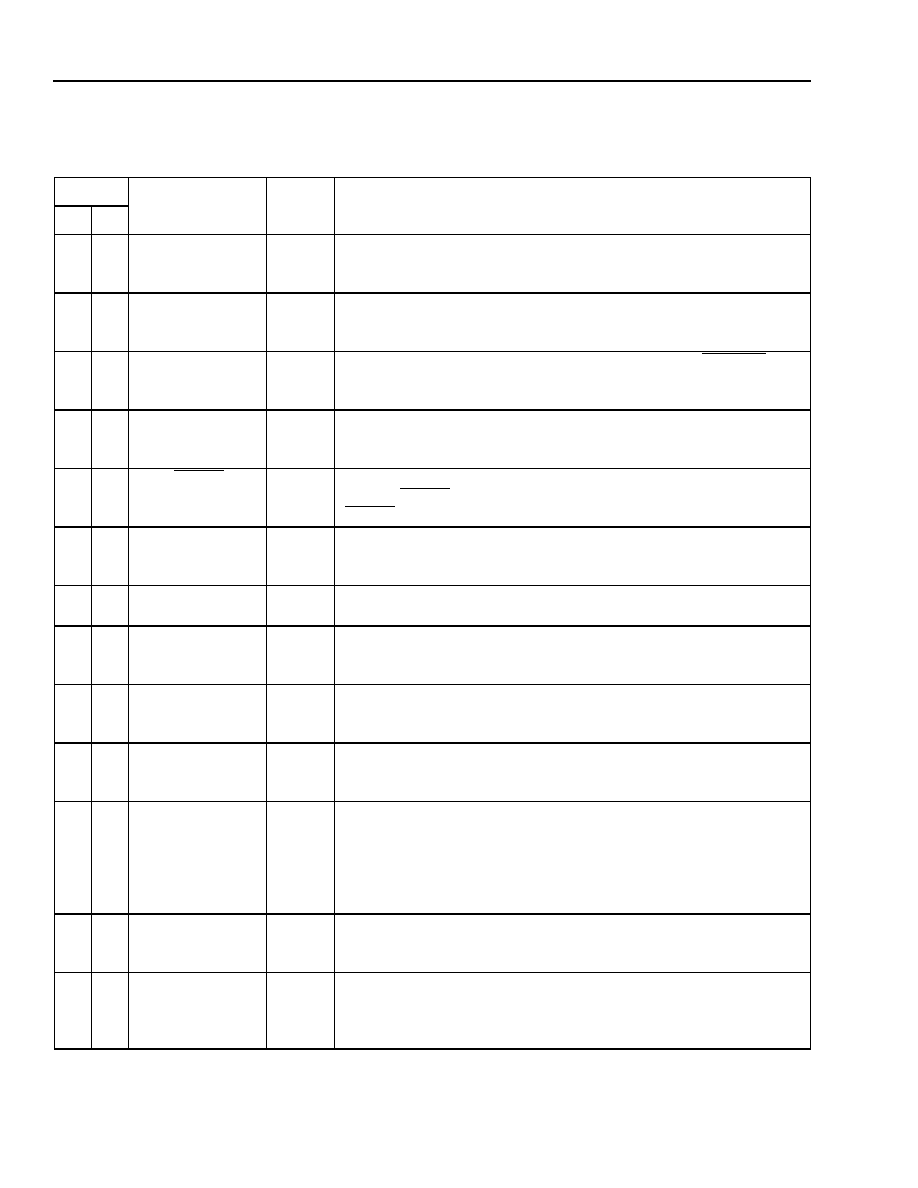

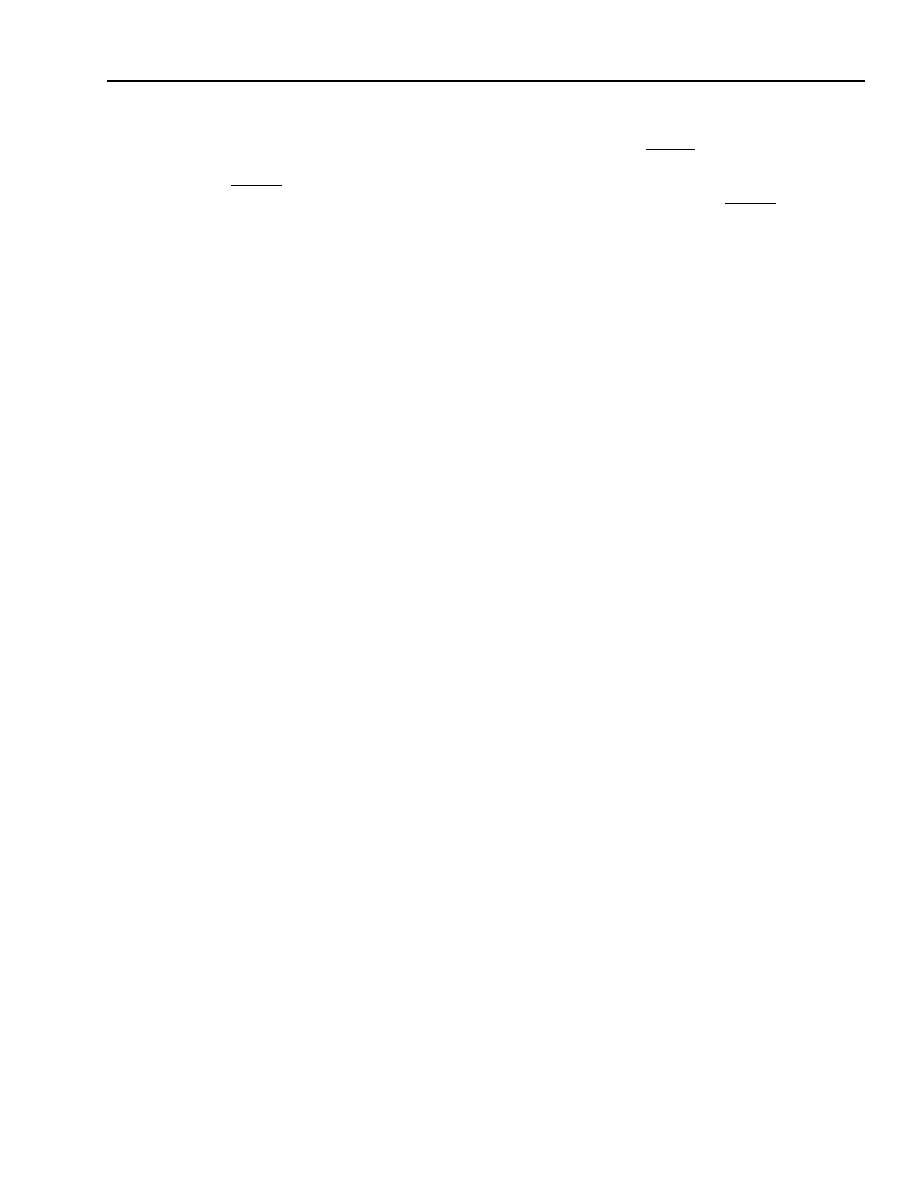

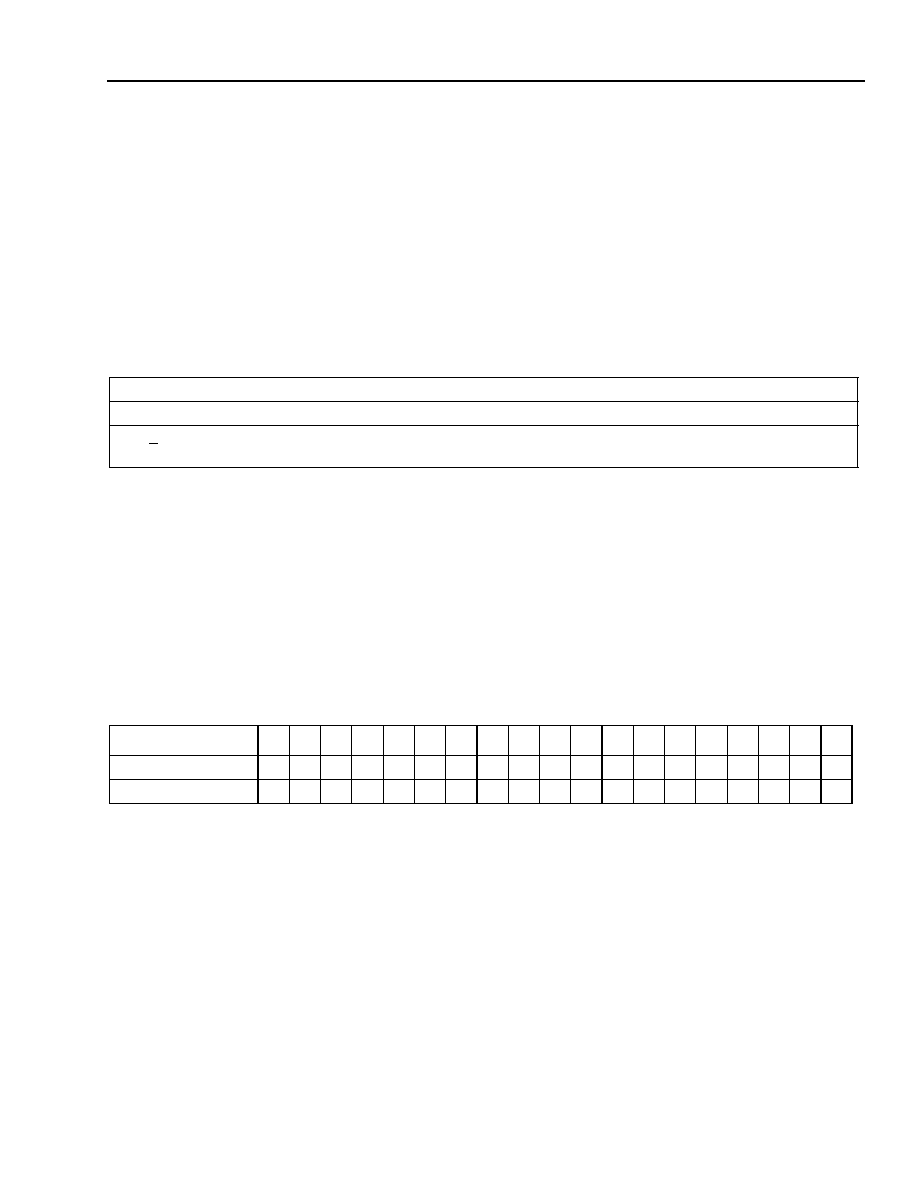

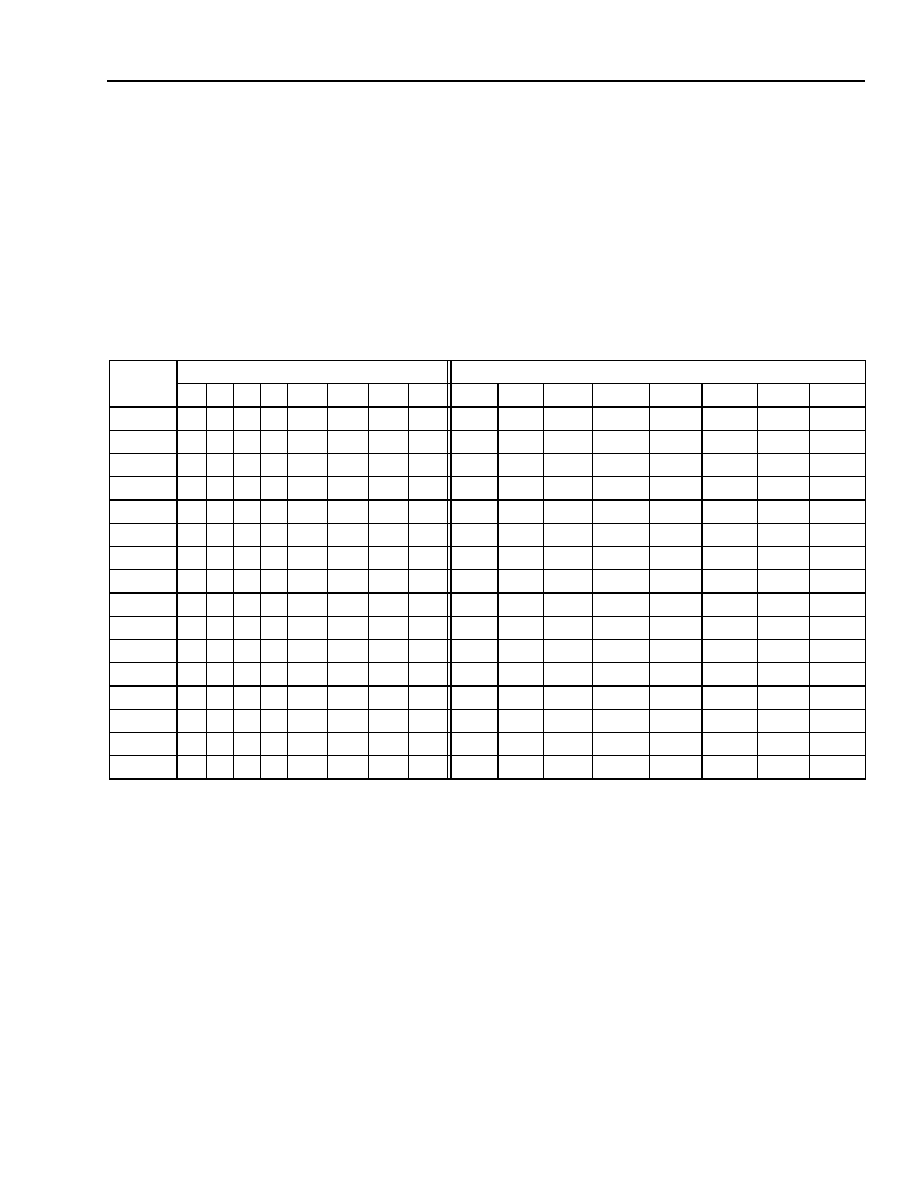

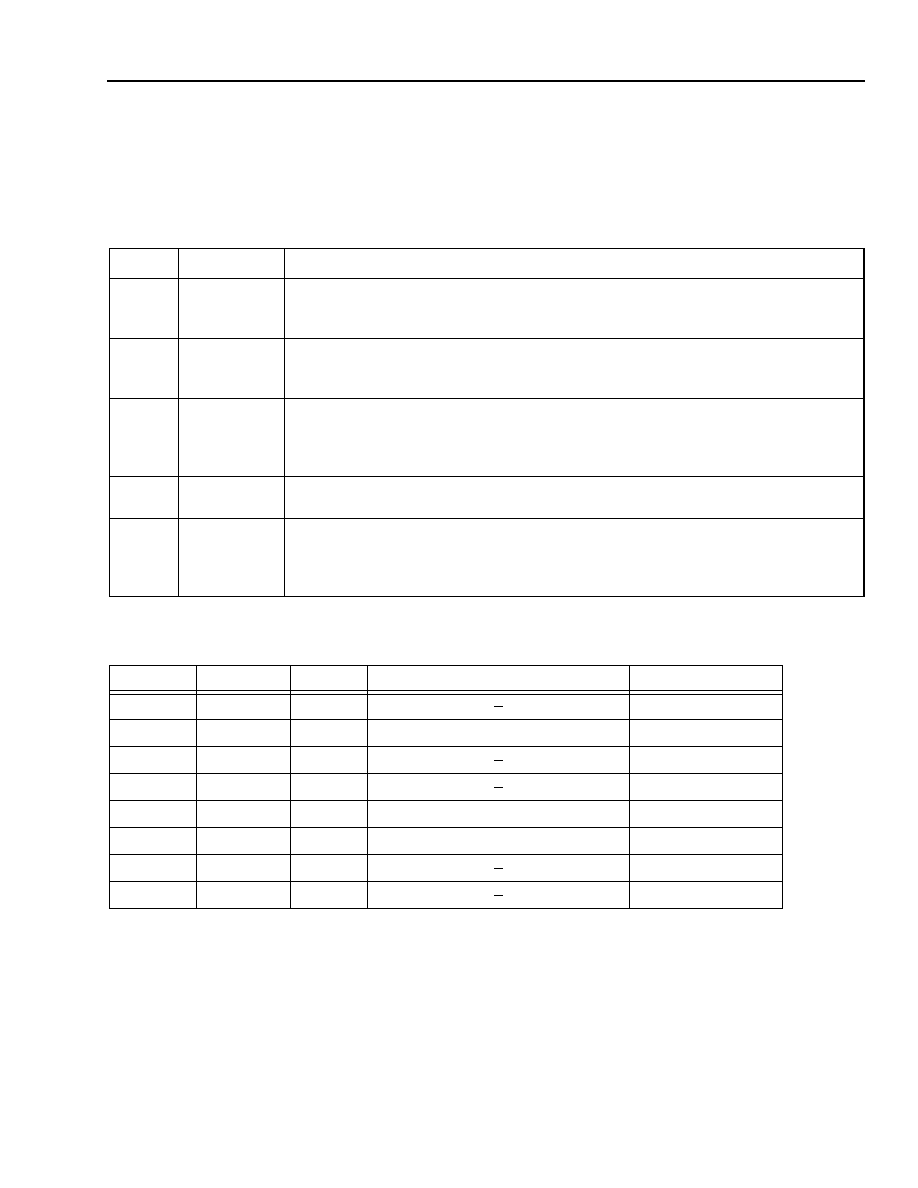

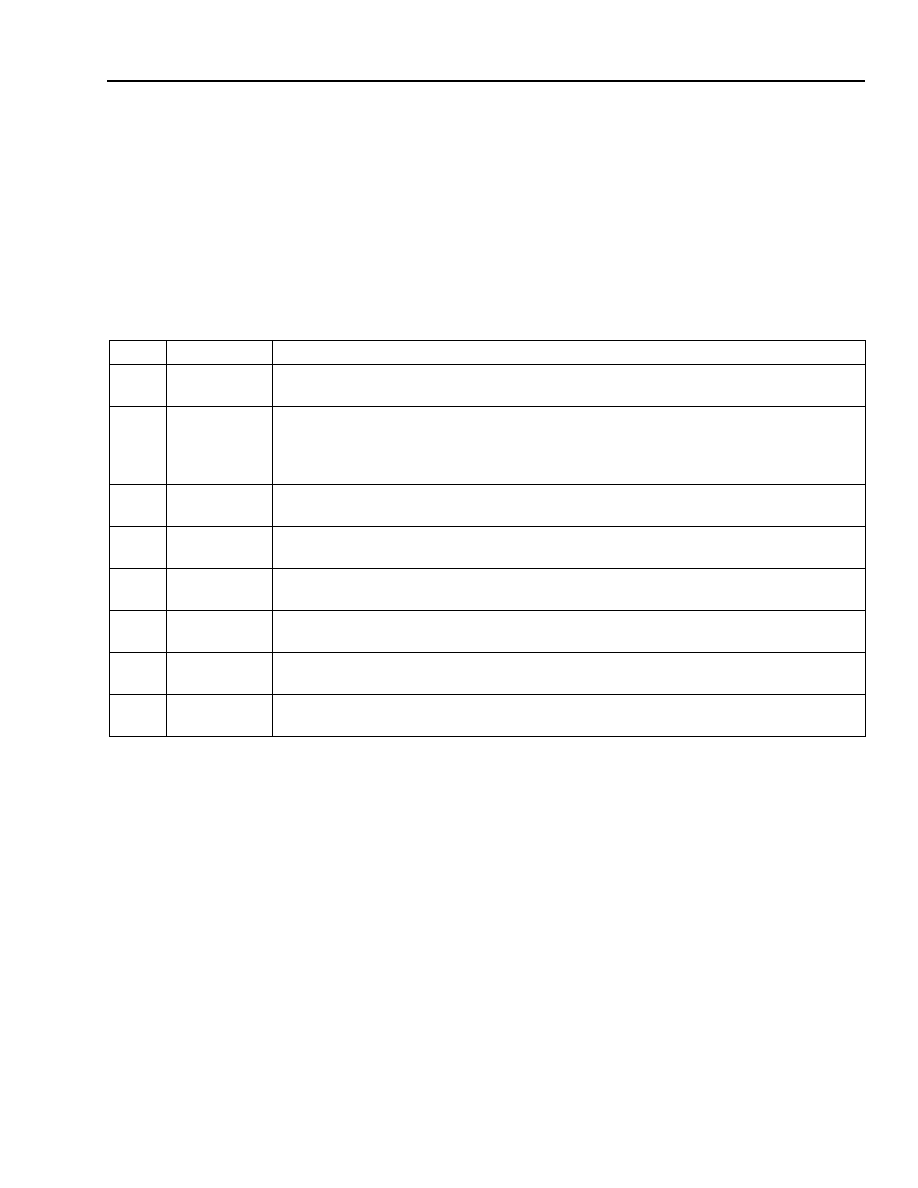

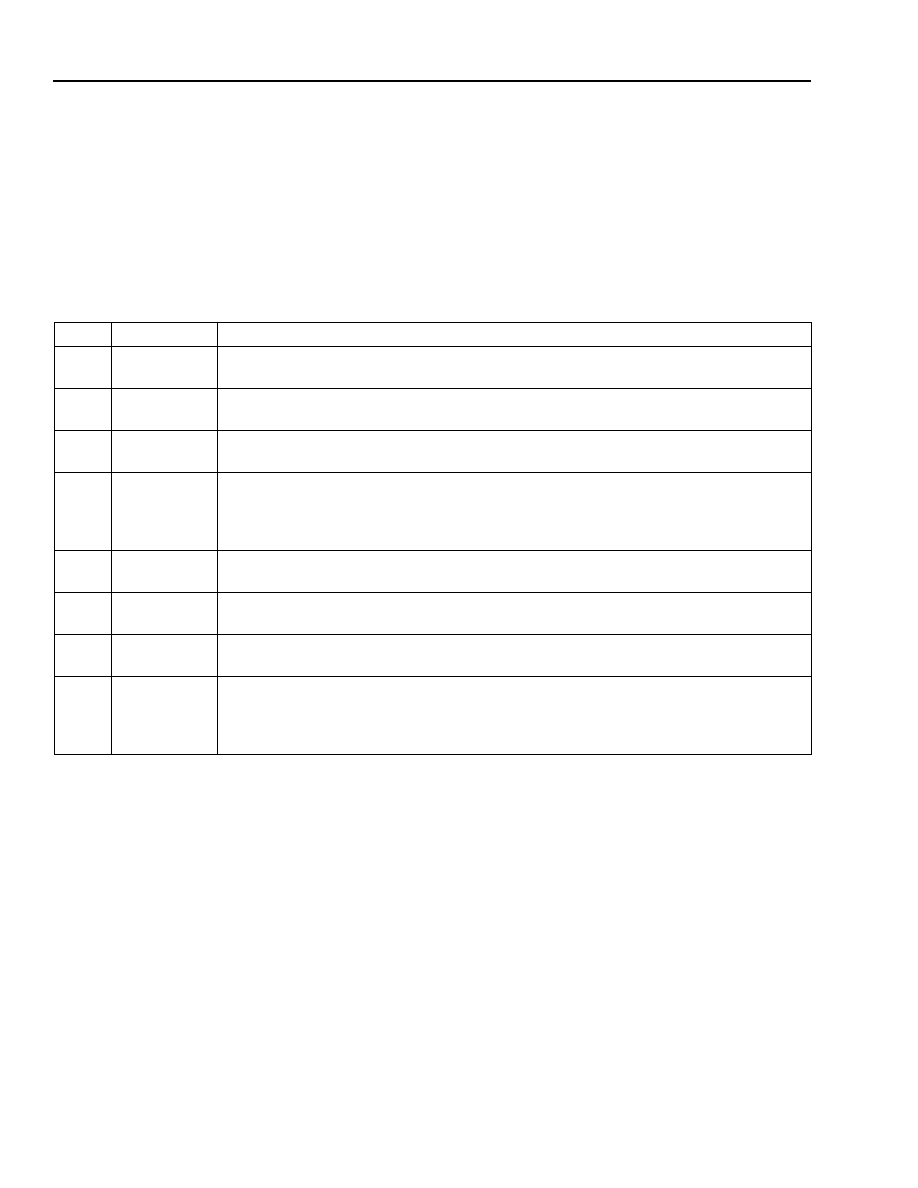

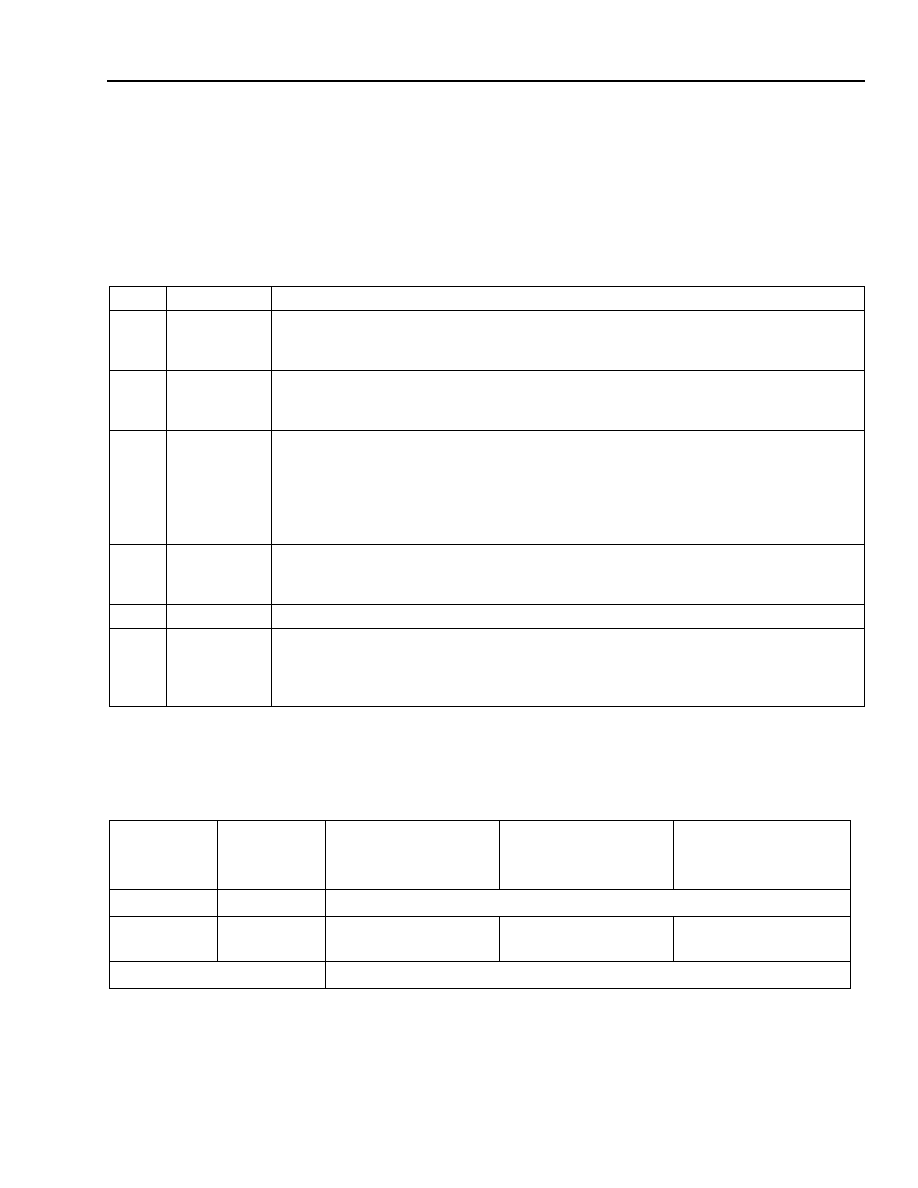

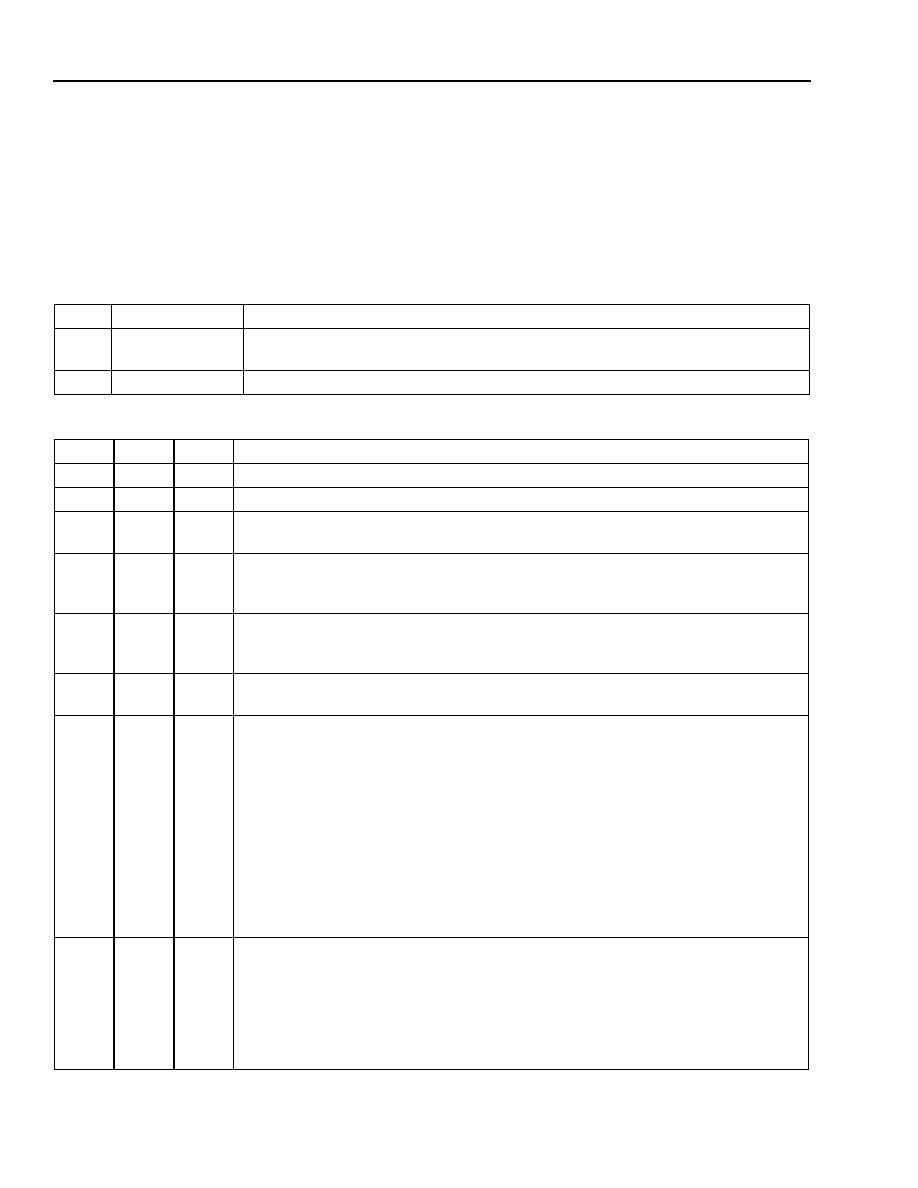

Table 1. Microprocessor Interface I/O Timing Specifications (continued)

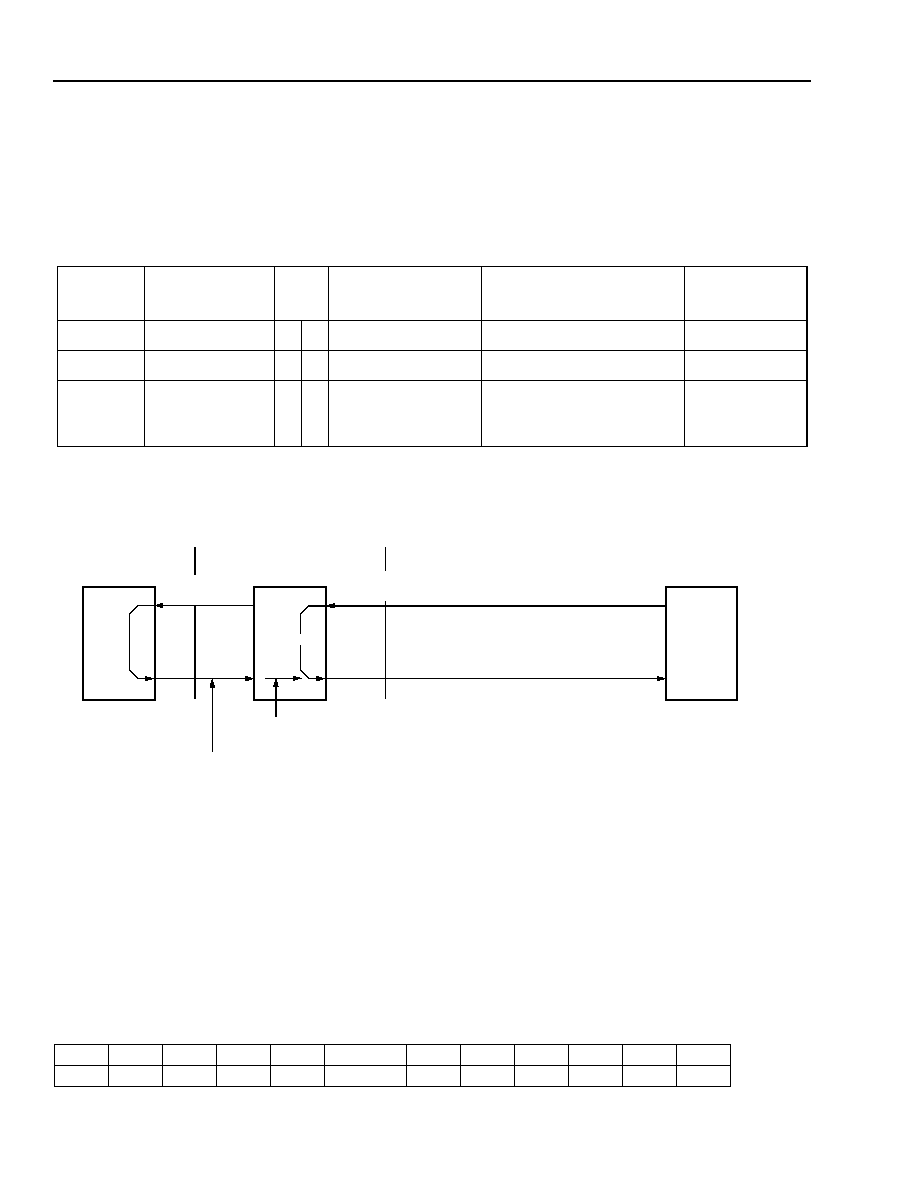

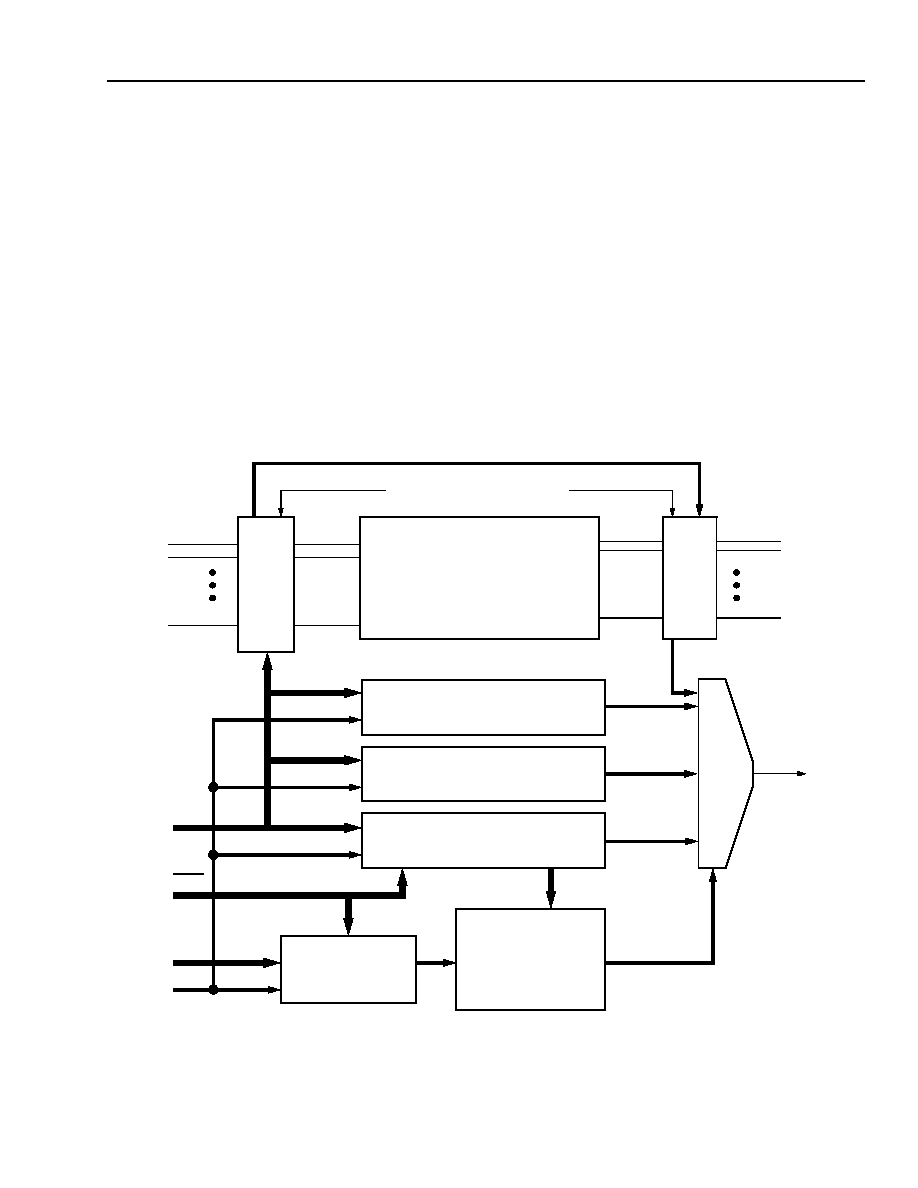

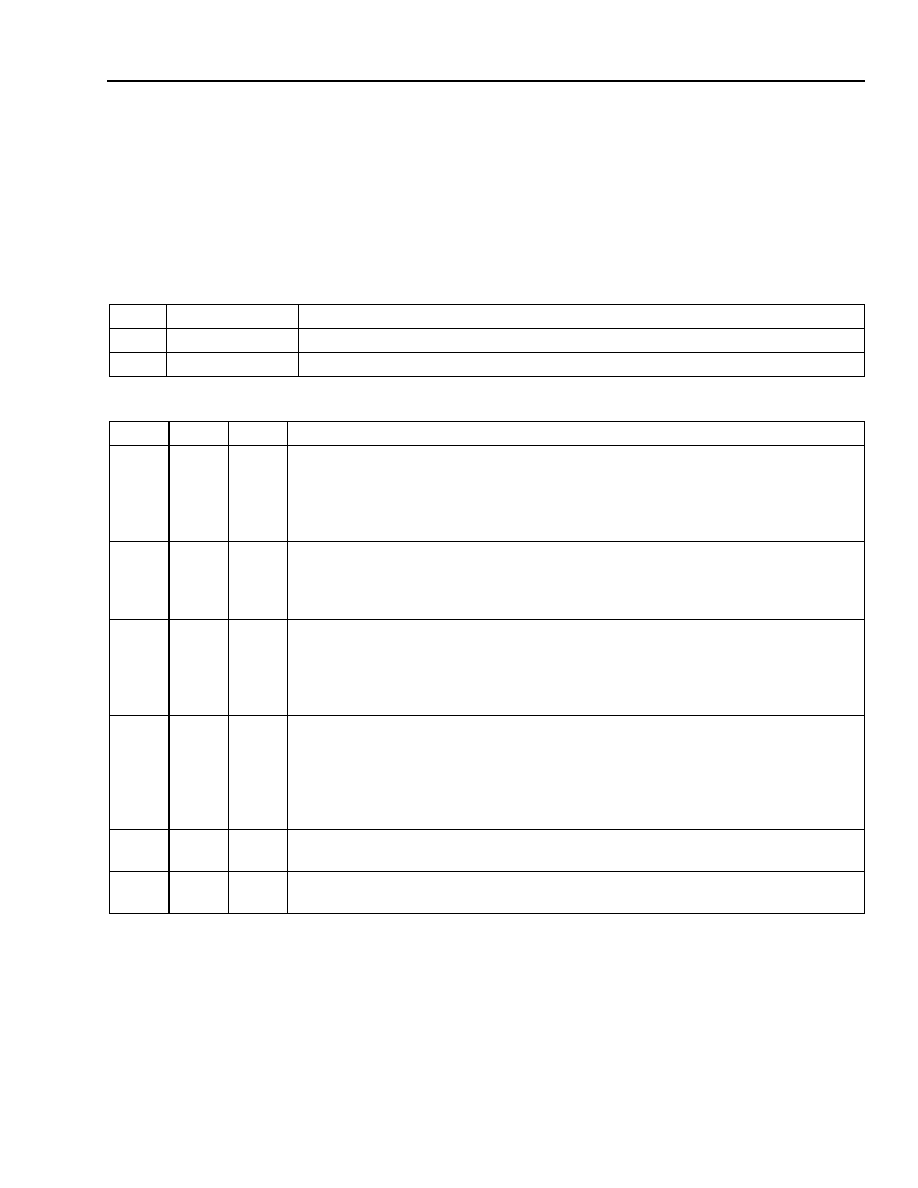

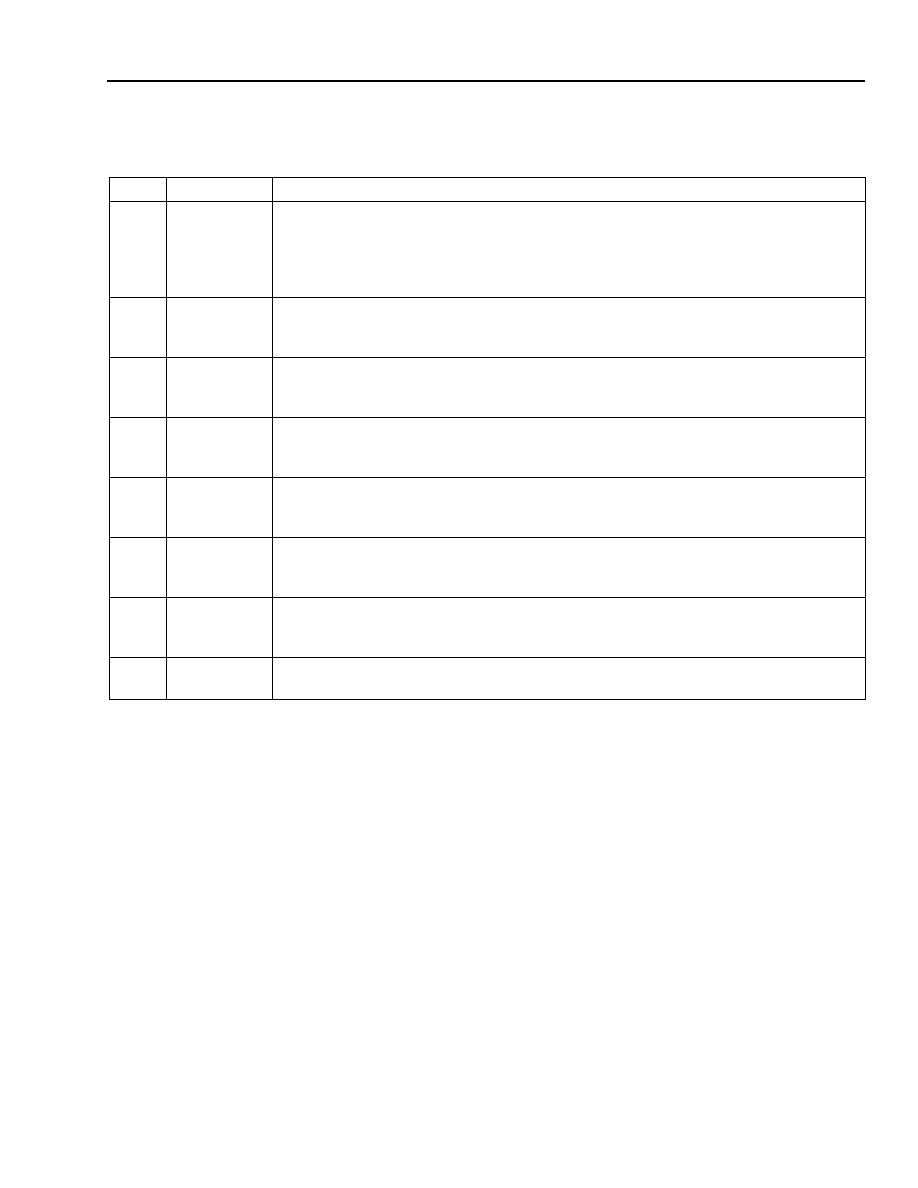

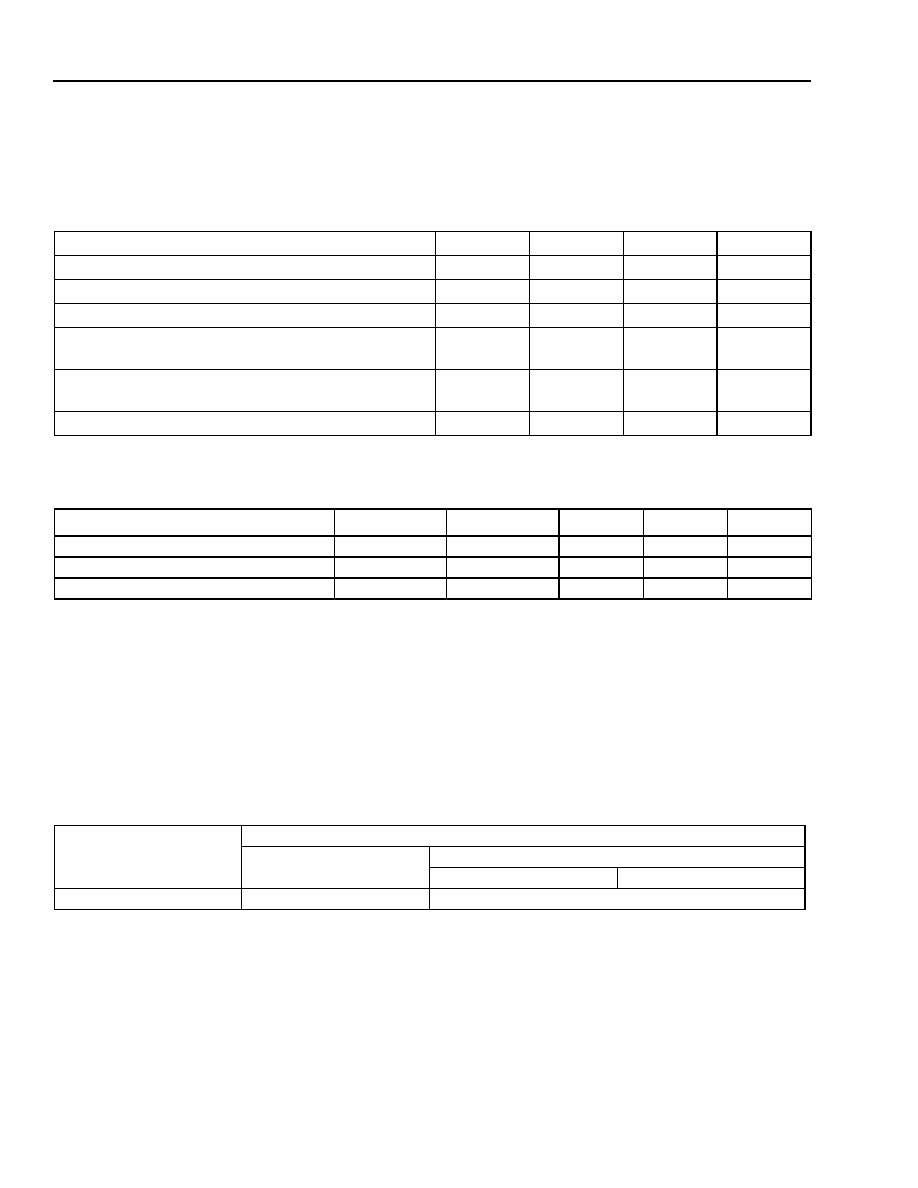

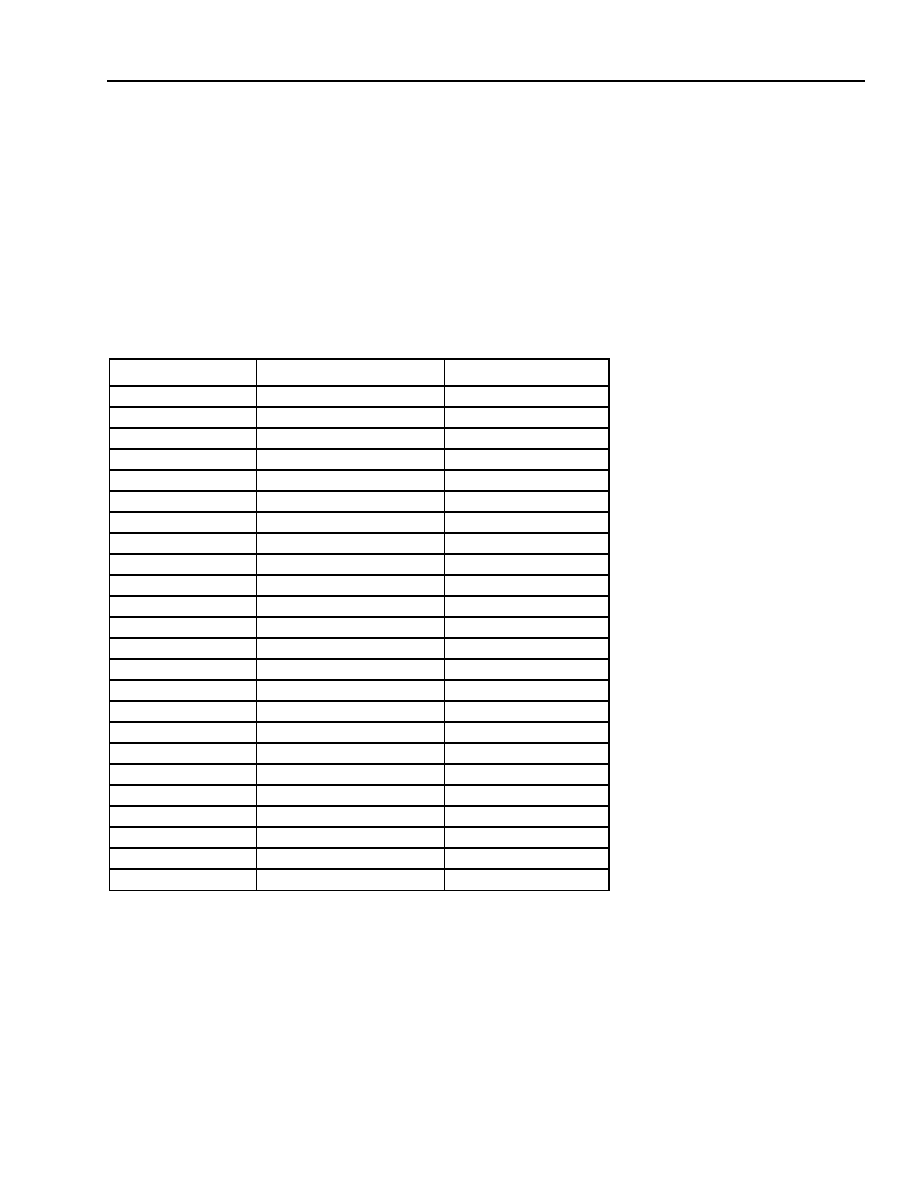

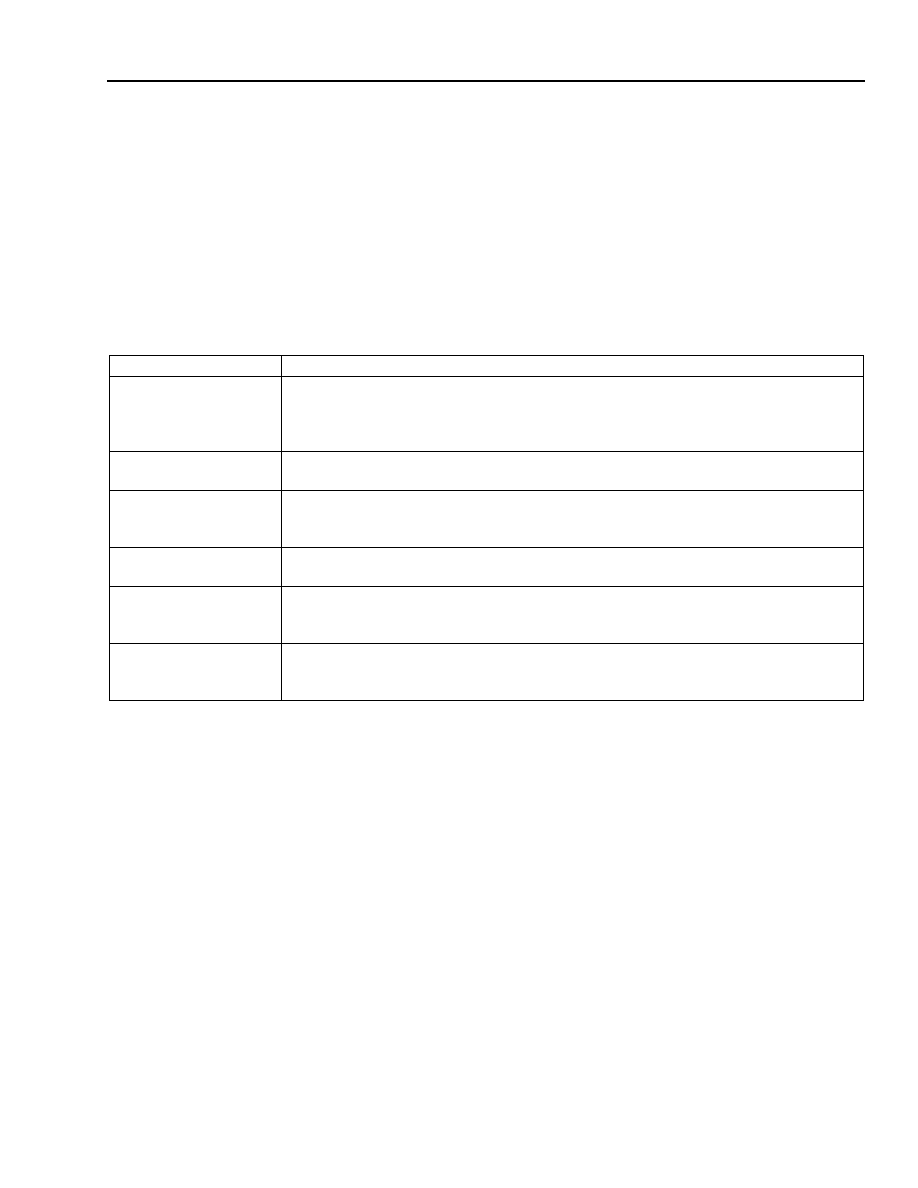

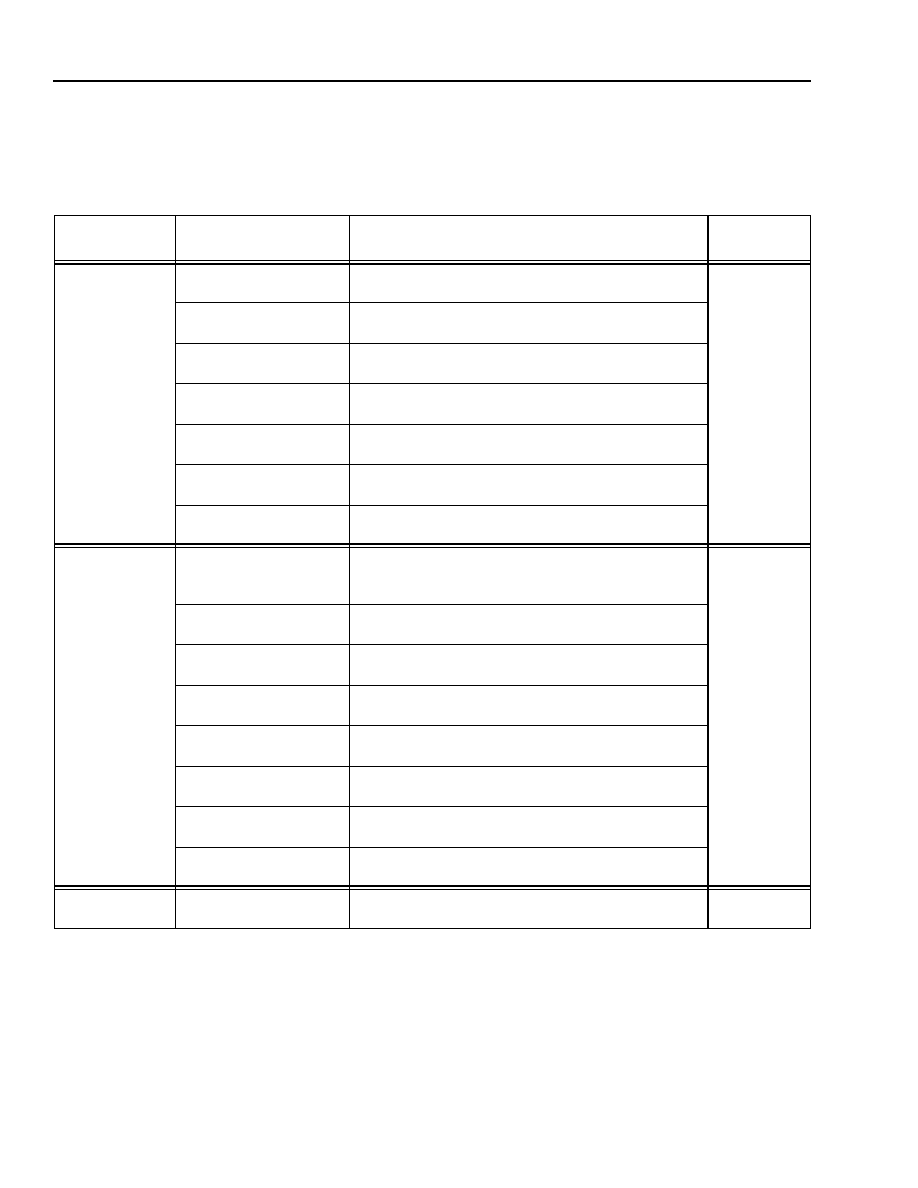

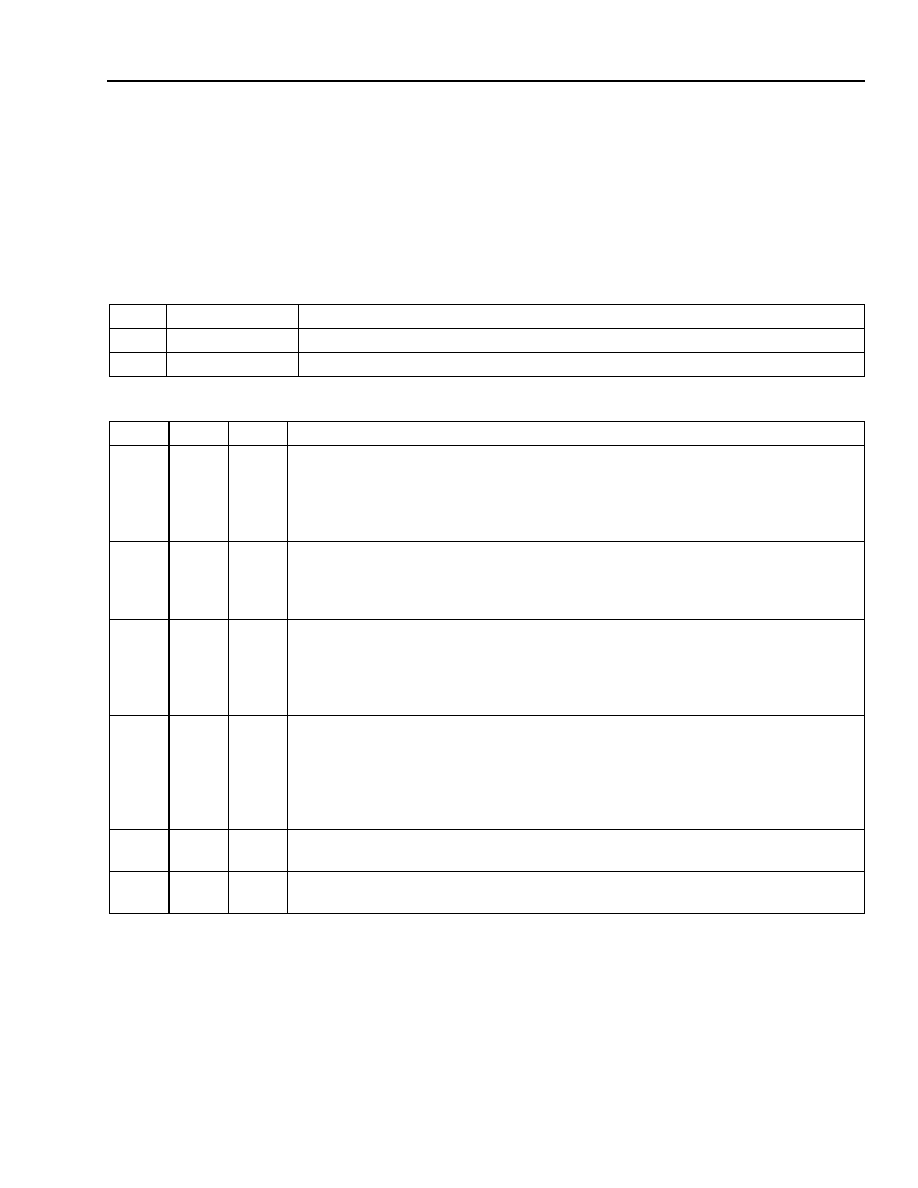

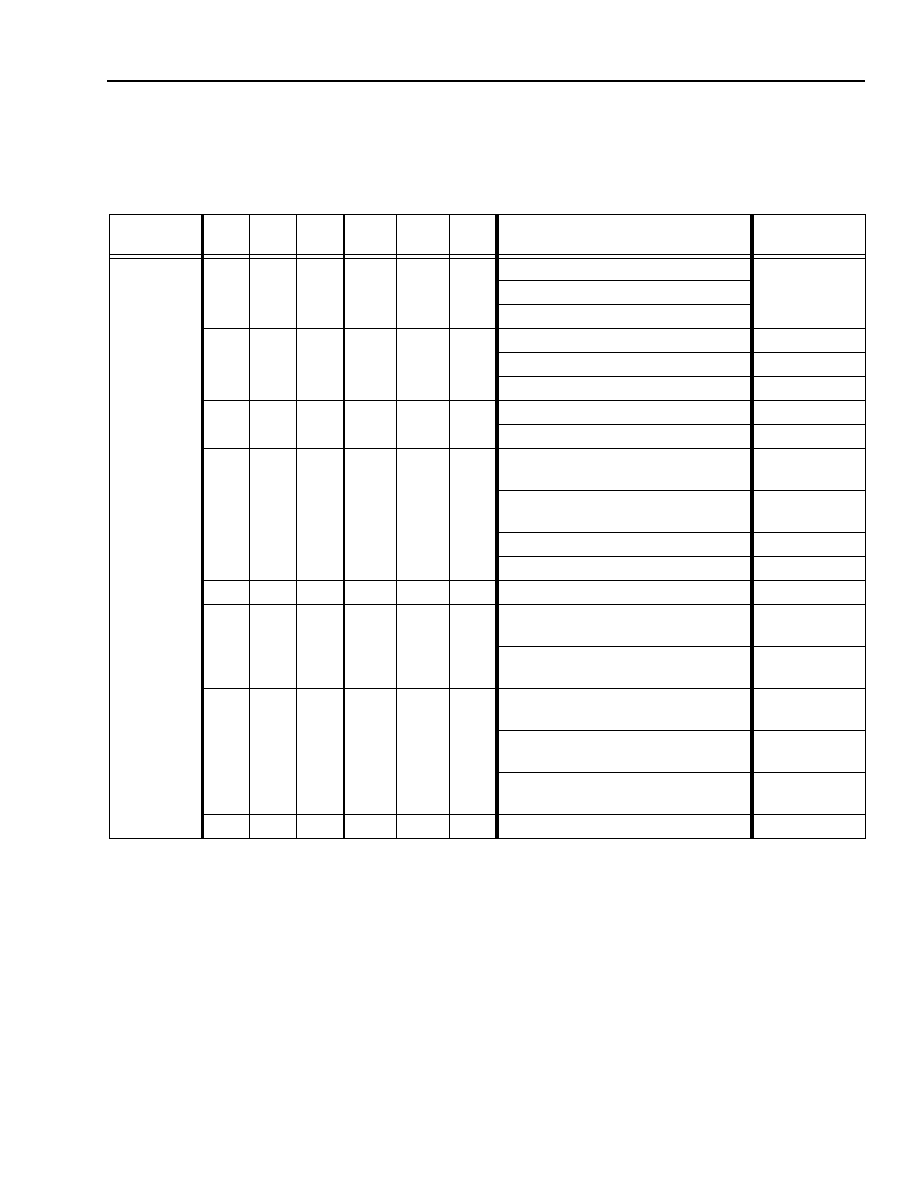

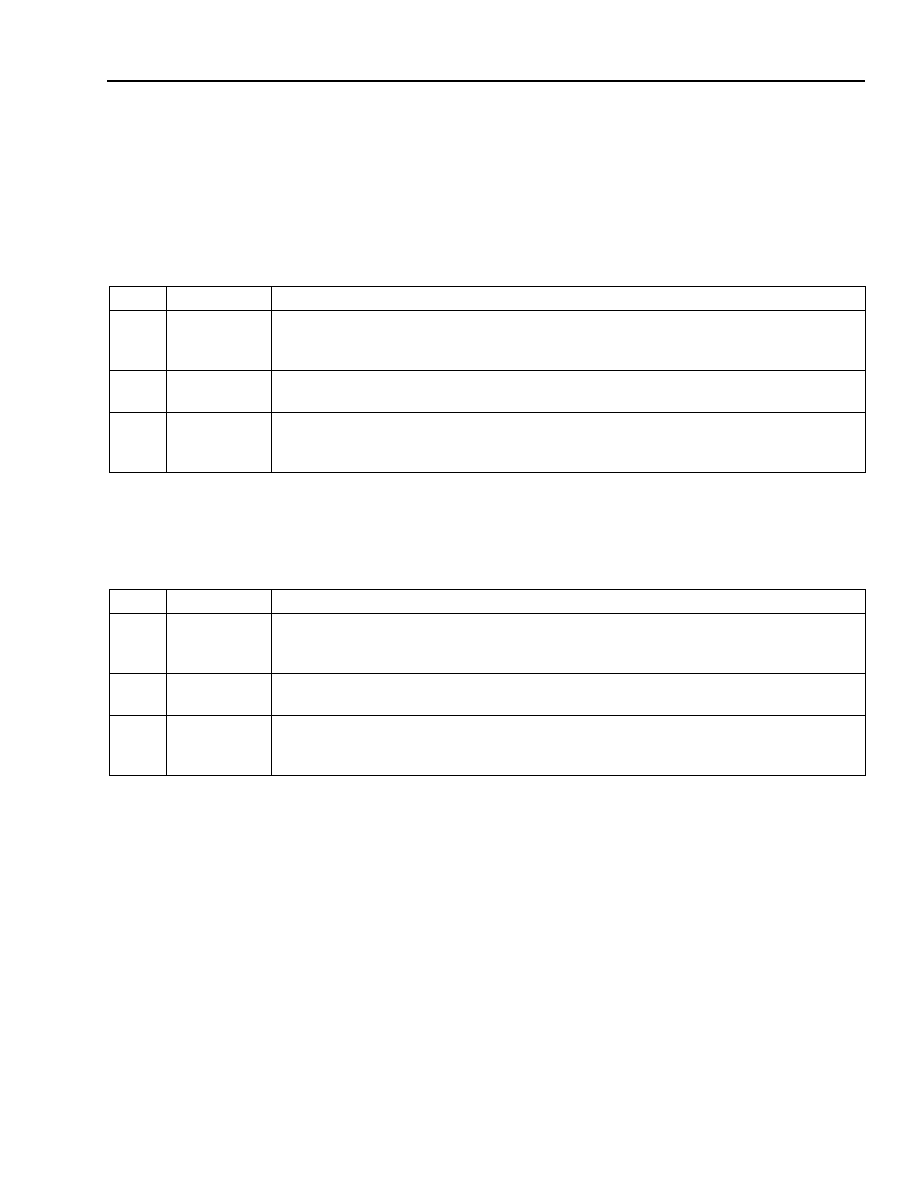

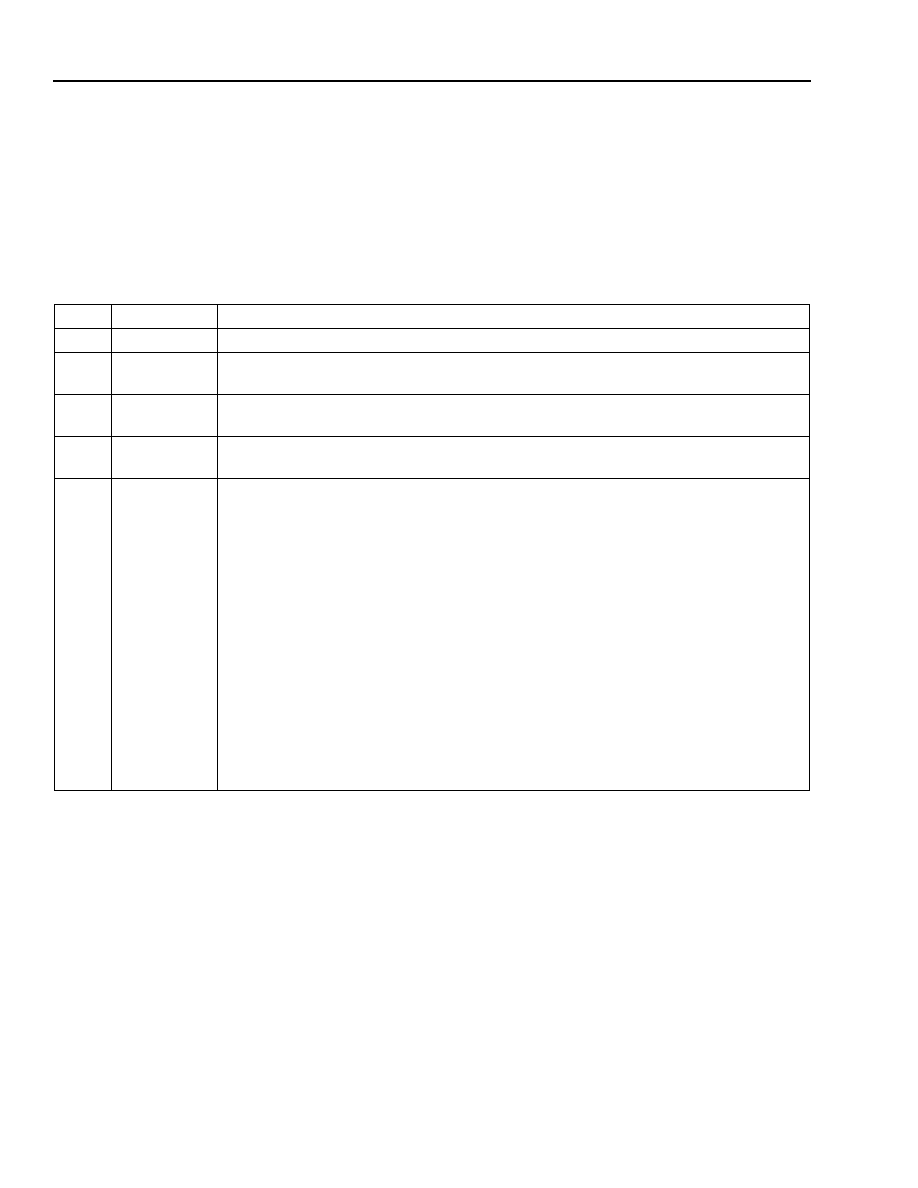

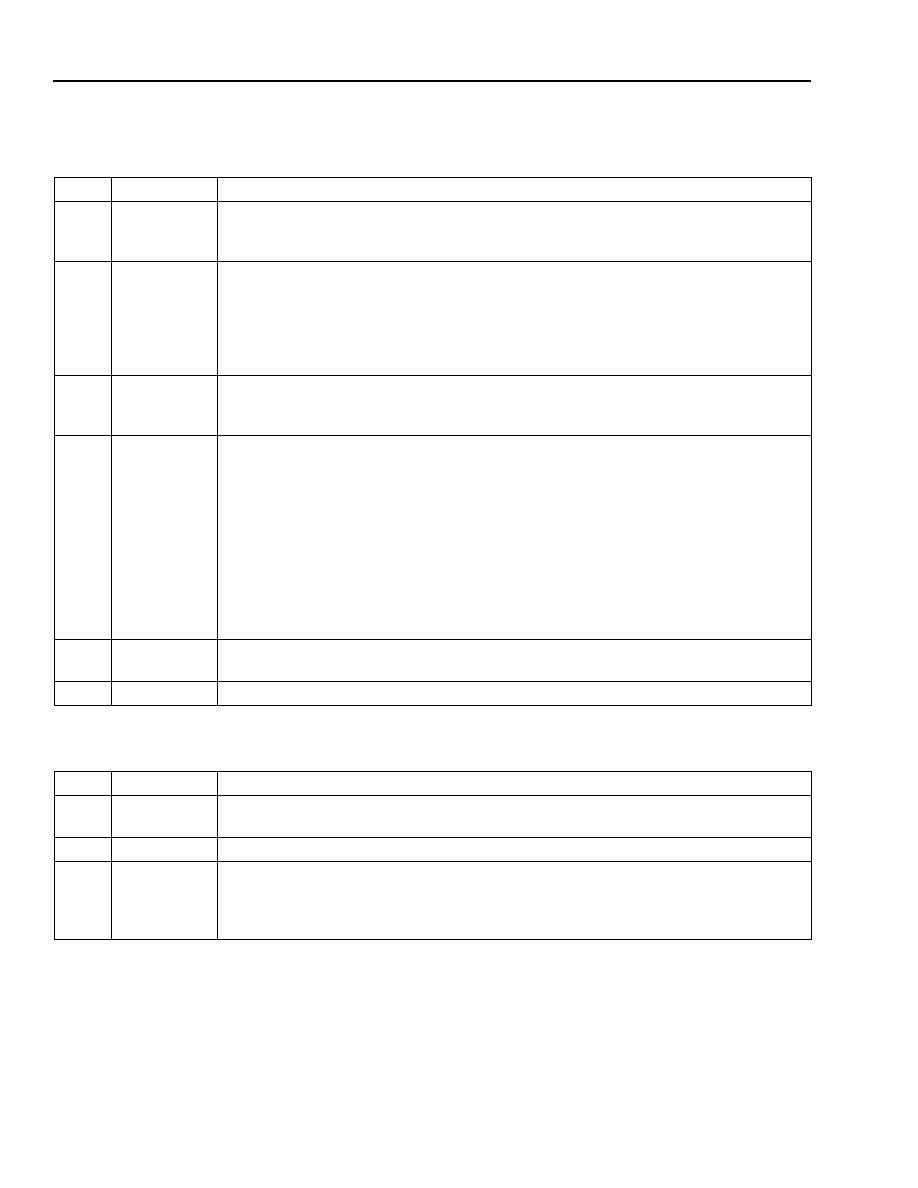

For Figure 5:

s

If ALE = 0 (ALE is not used or is inactive), then the address must be valid until CS = 1 and

-- If MPCK is used (MPCK is active), then t40 must exceed two MPCK periods,

-- If MPCK is not used (MPCK is inactive), then t40 must exceed two 16x line clock periods. A t40 of 110 ns is suggested.

s

If ALE is used ( ALE is active), then

-- If MPCK is used (MPCK is active), then t40 must exceed two MPCK periods,

-- If MPCK is not used (MPCK is inactive), then t40 must exceed two 16x line clock periods. A t40 of 110 ns is suggested.

For Figure 7:

s

If MPCK is used (MPCK is active), then t40 must exceed two MPCK periods,

s

If MPCK is not used (MPCK is inactive), then t40 must exceed two 16x line clock periods. A t40 of 110 ns is suggested.

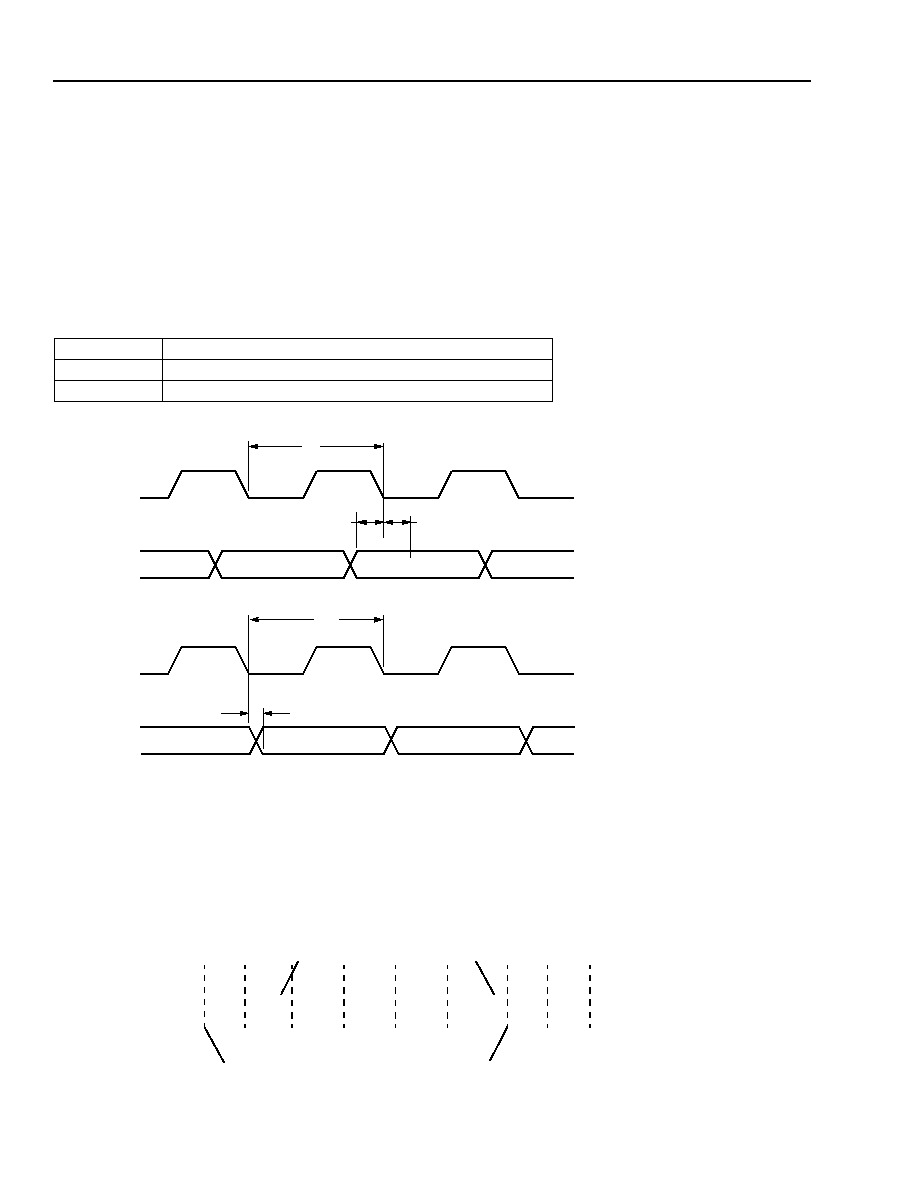

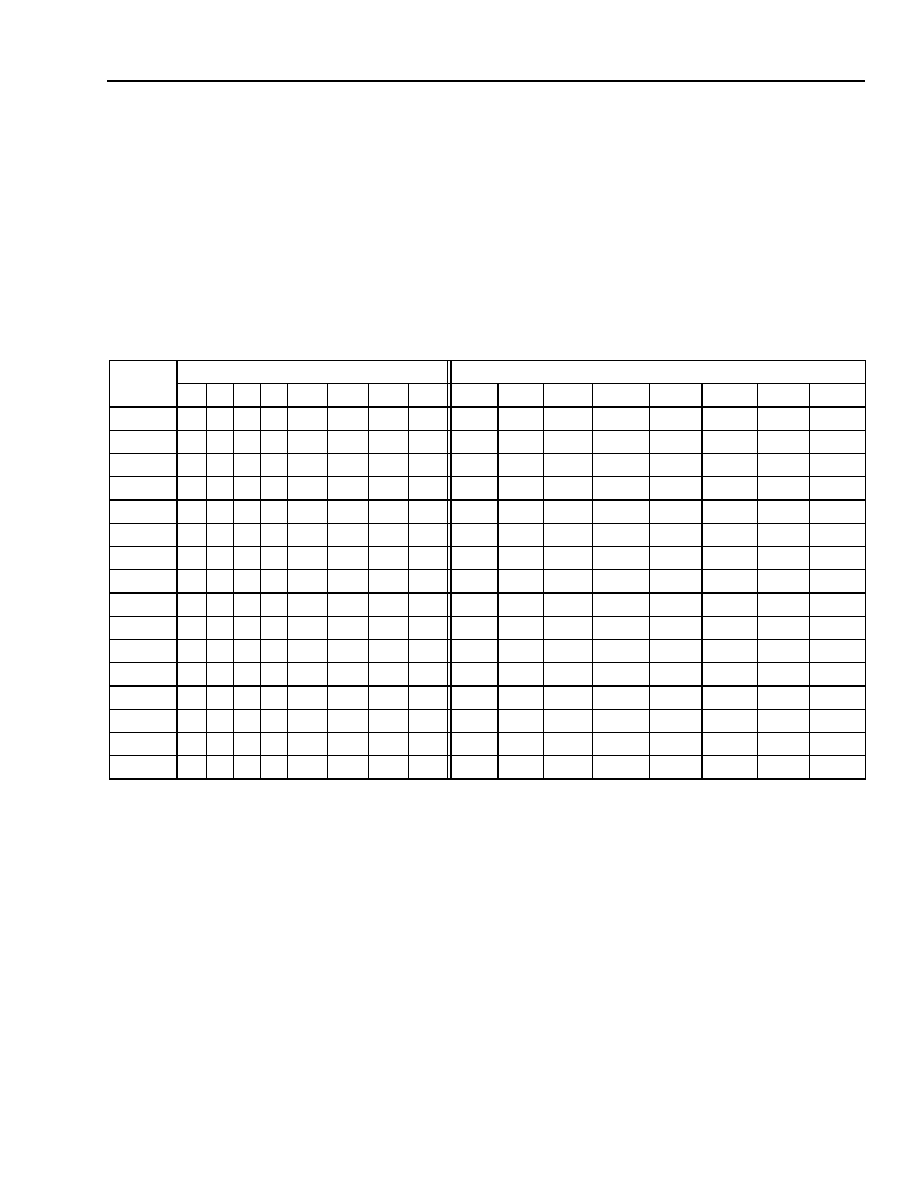

The read and write timing diagrams for all four microprocessor interface modes are shown in Figures 1--8.

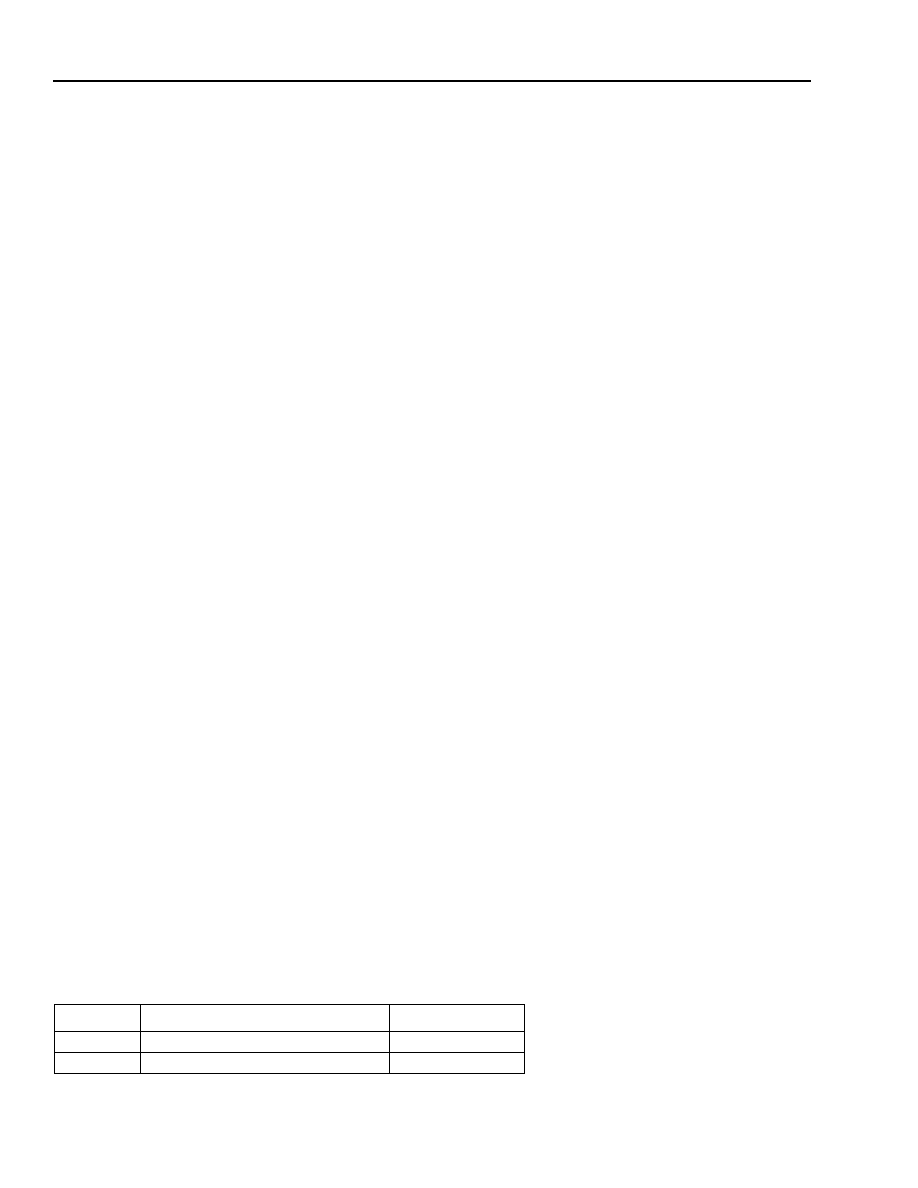

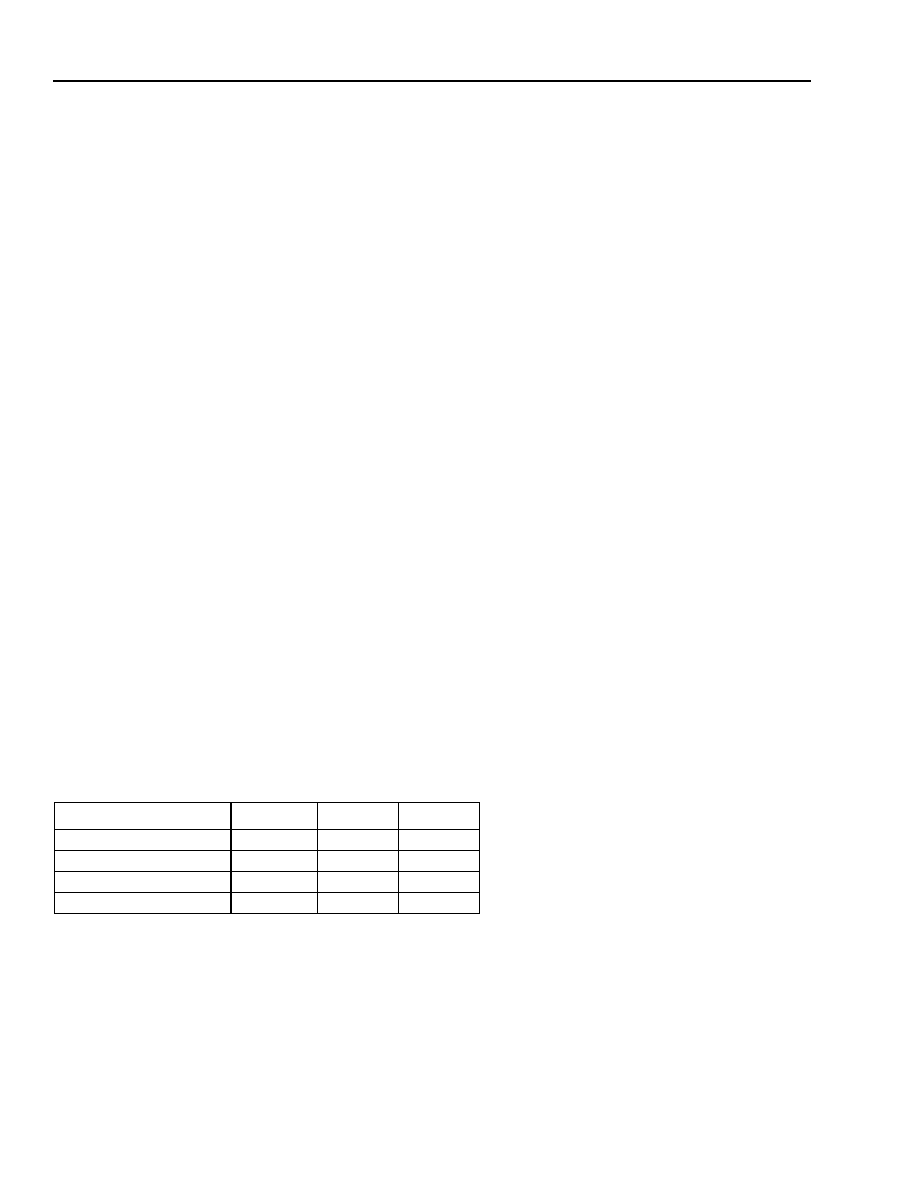

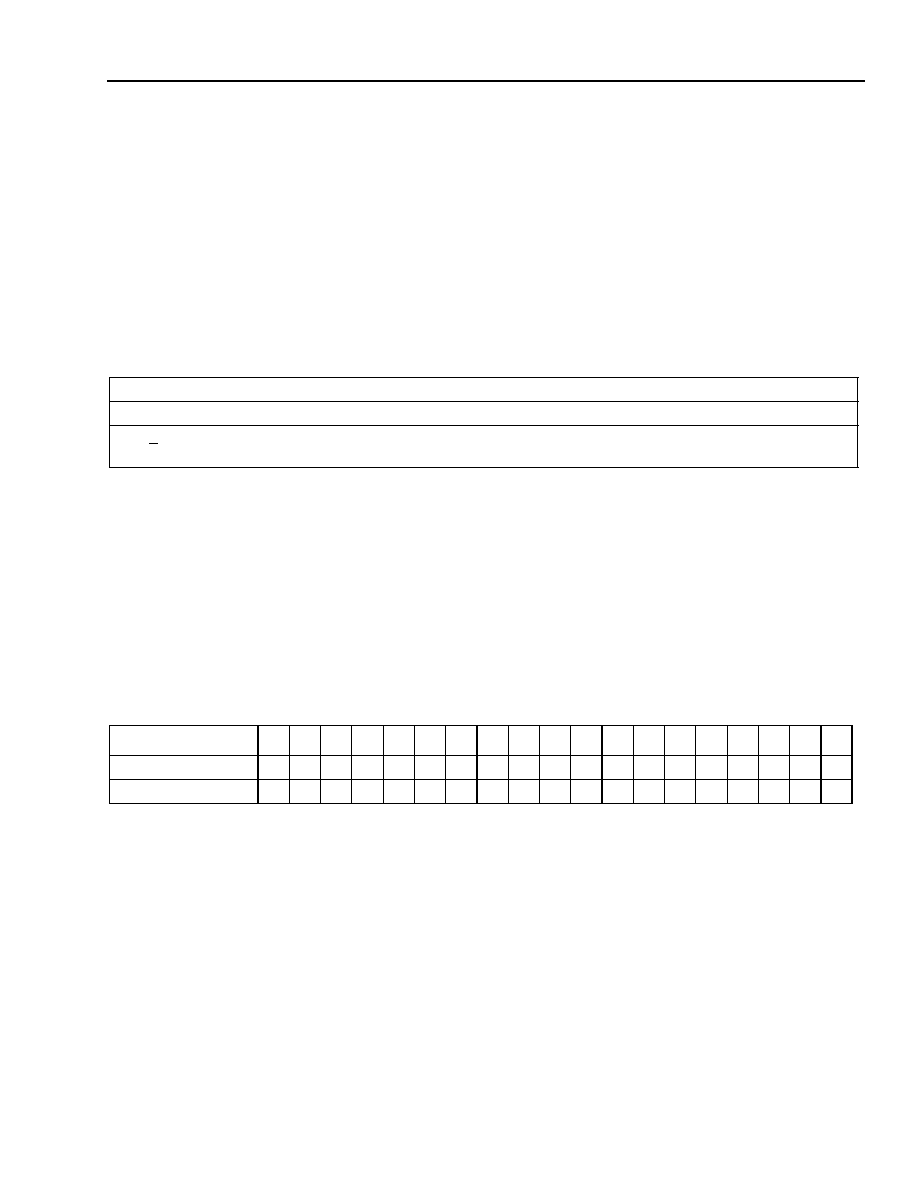

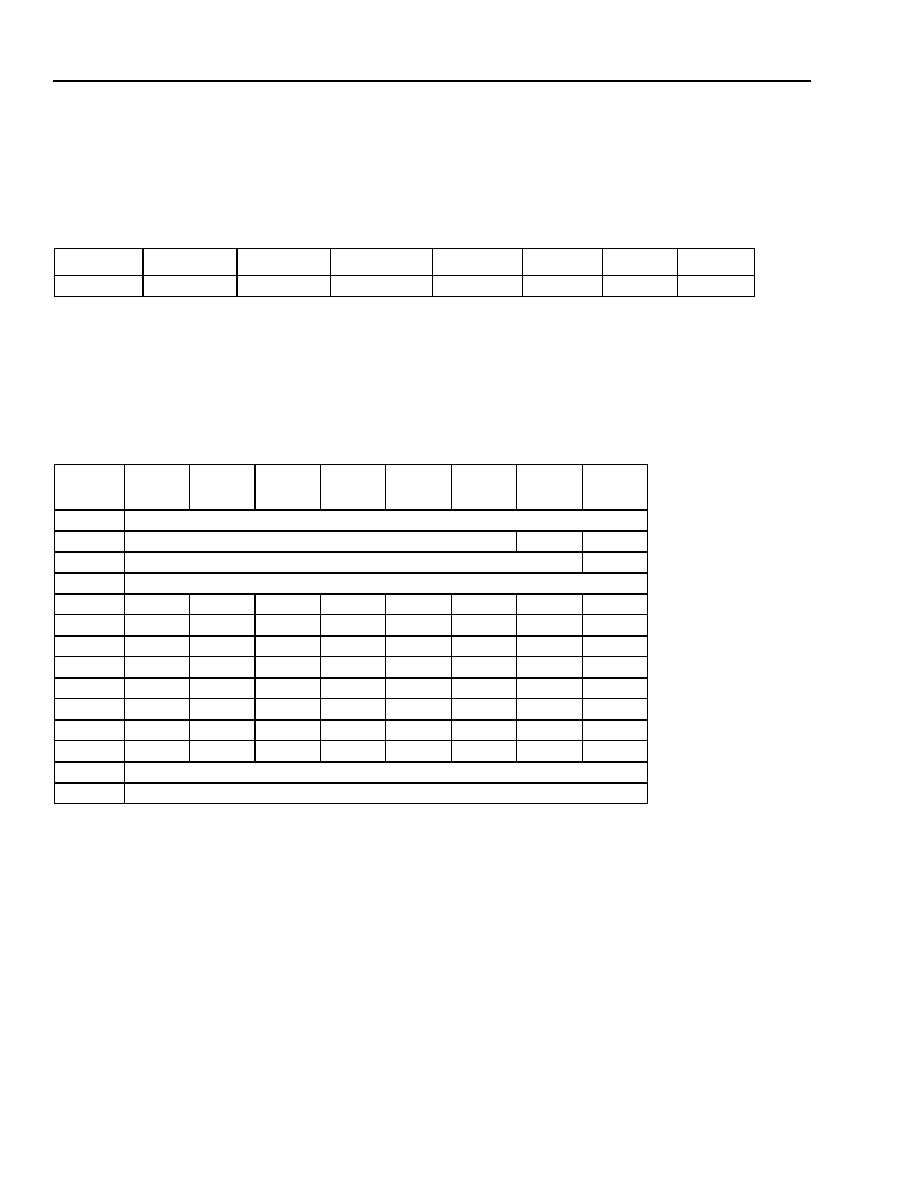

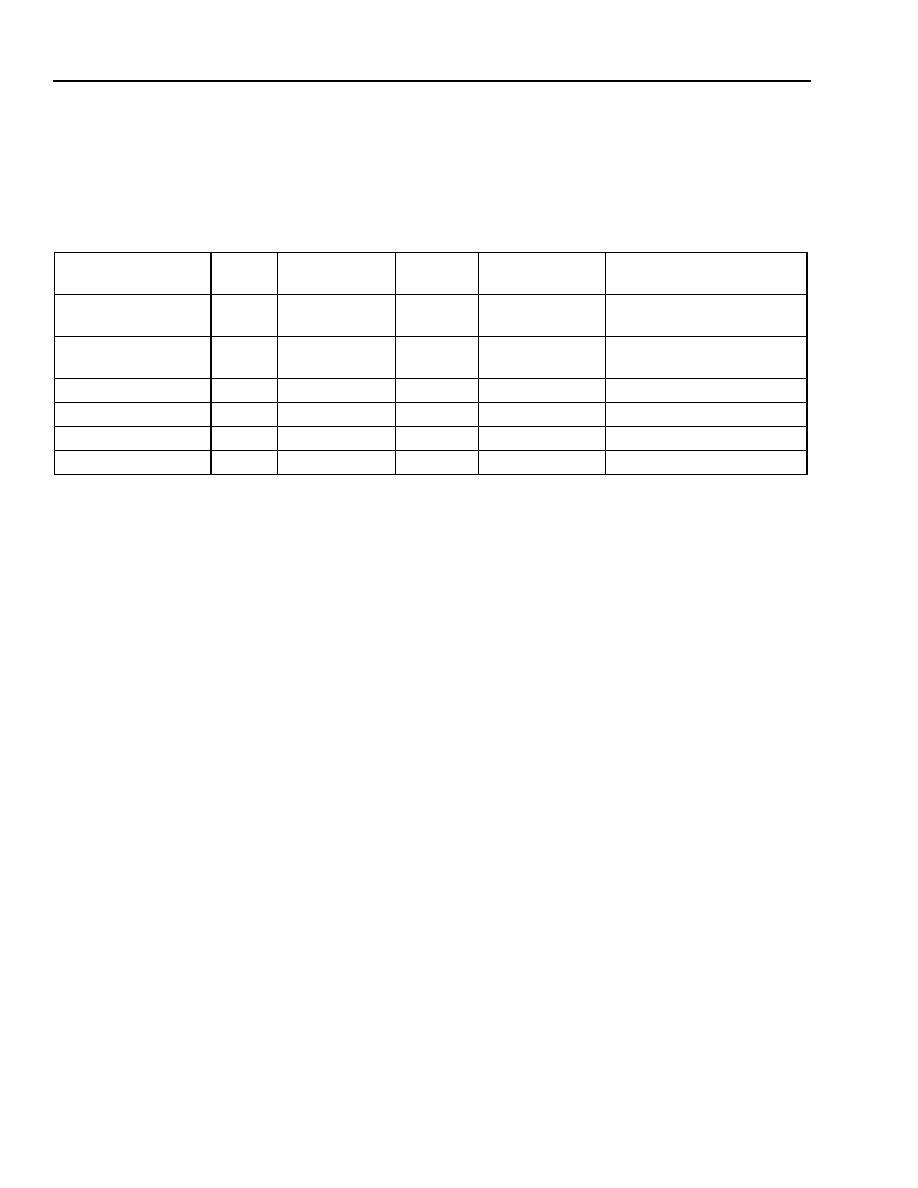

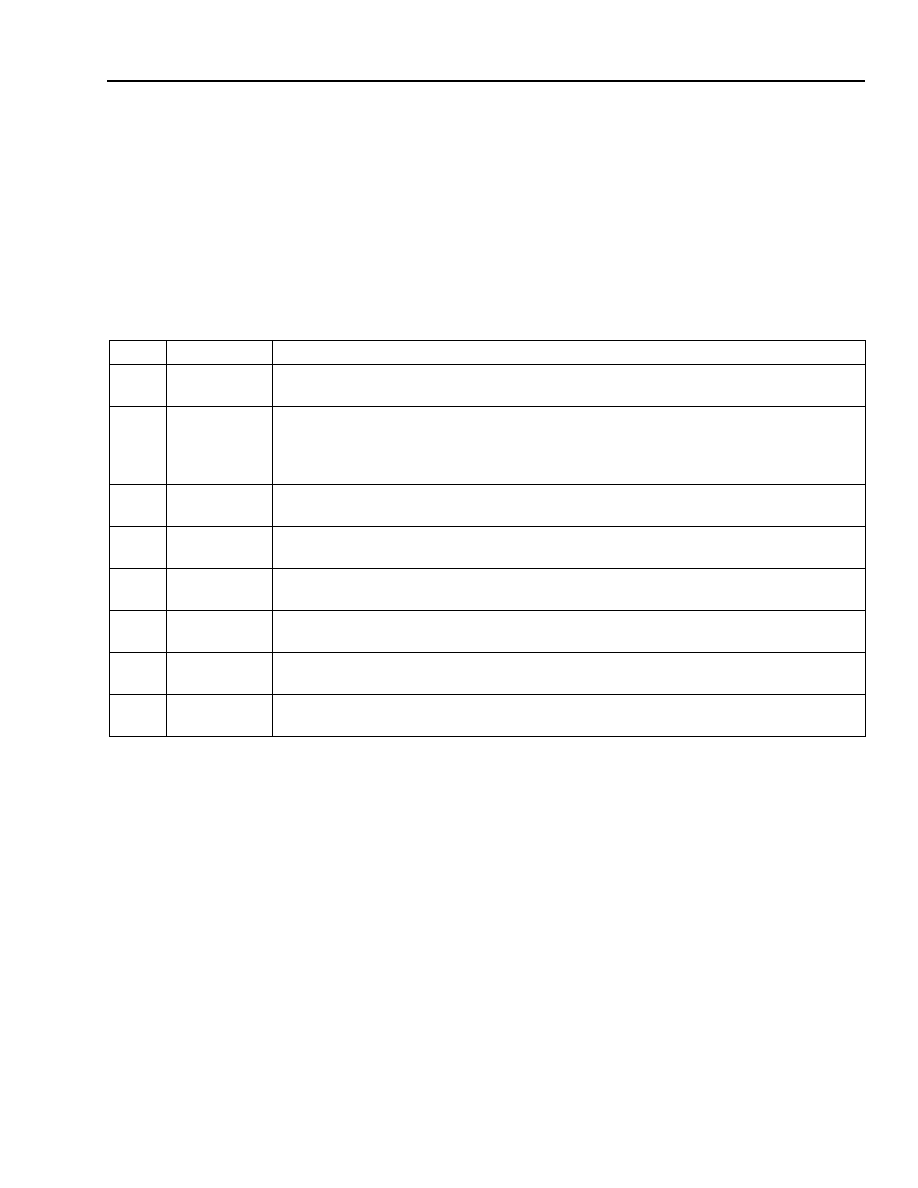

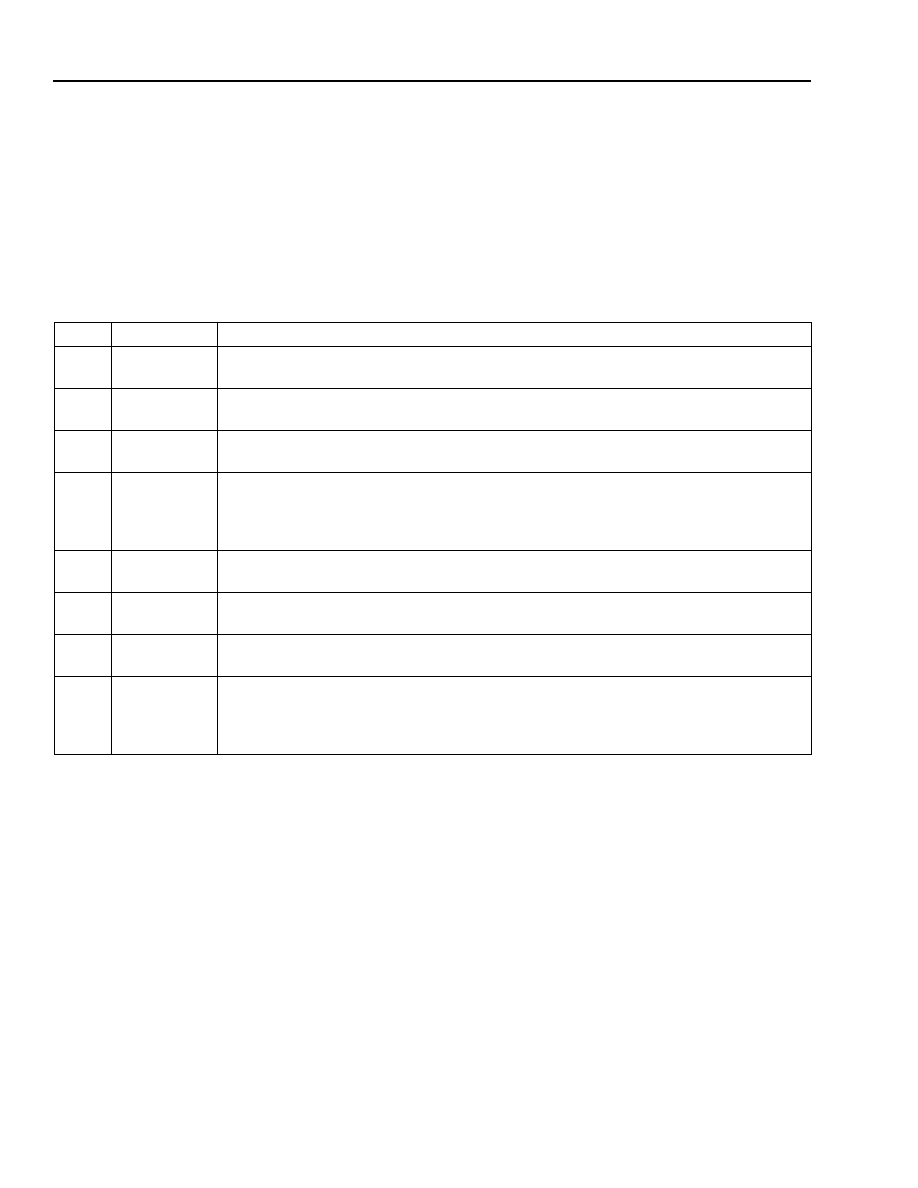

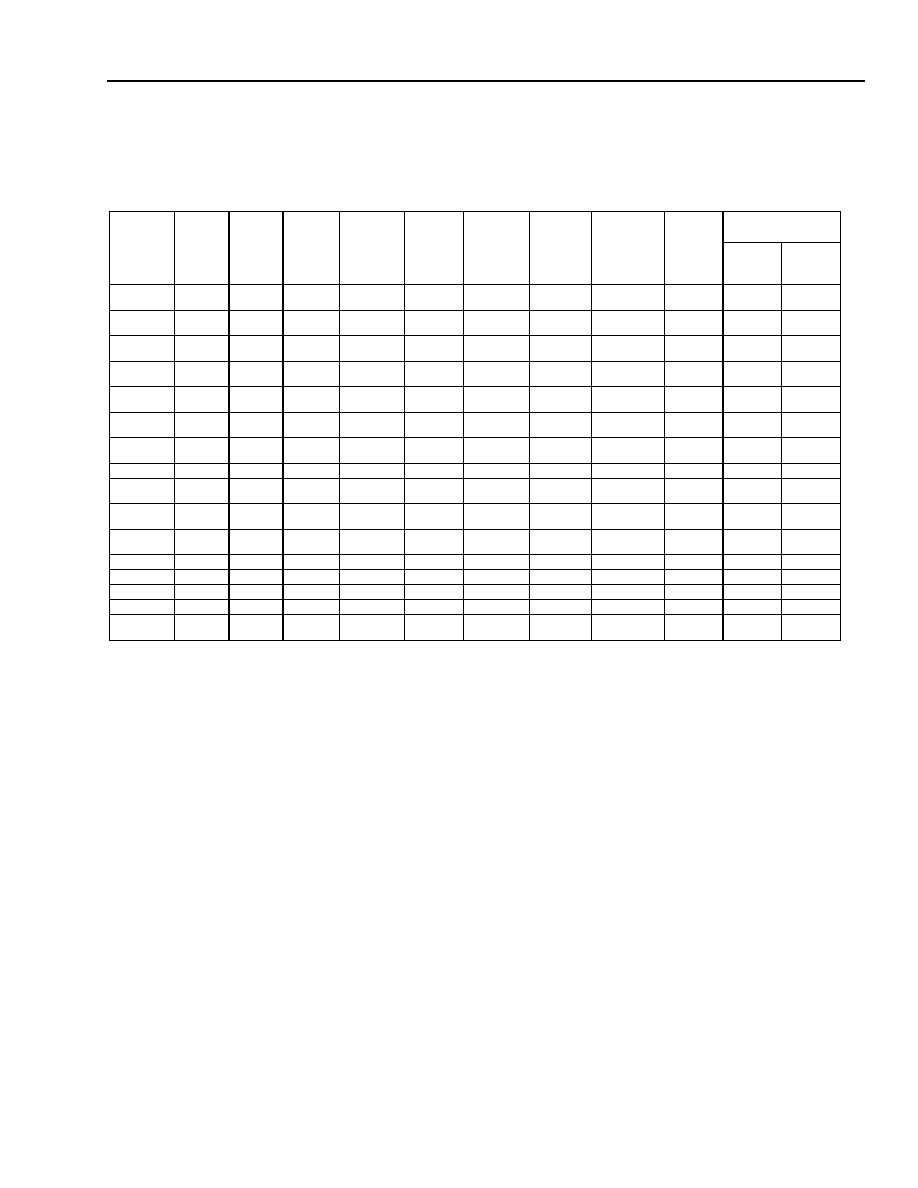

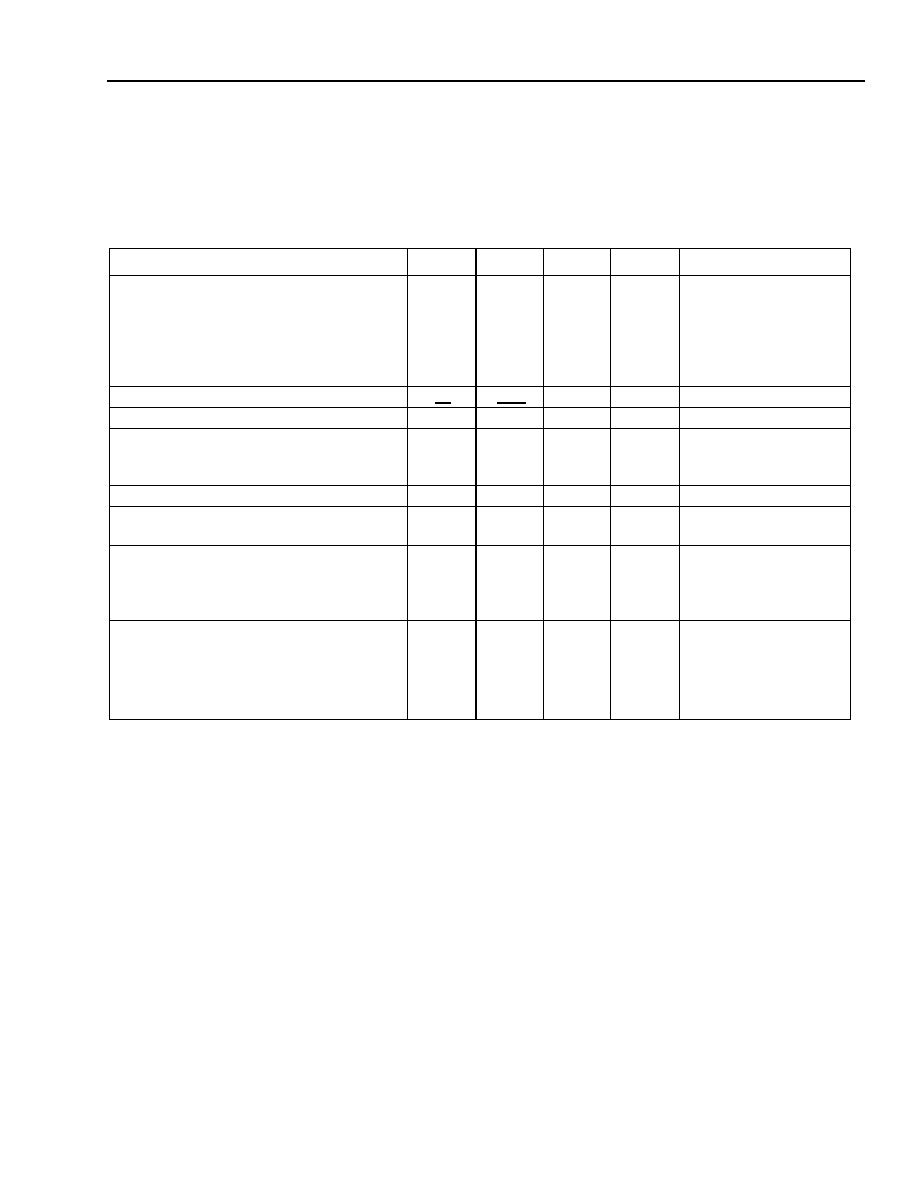

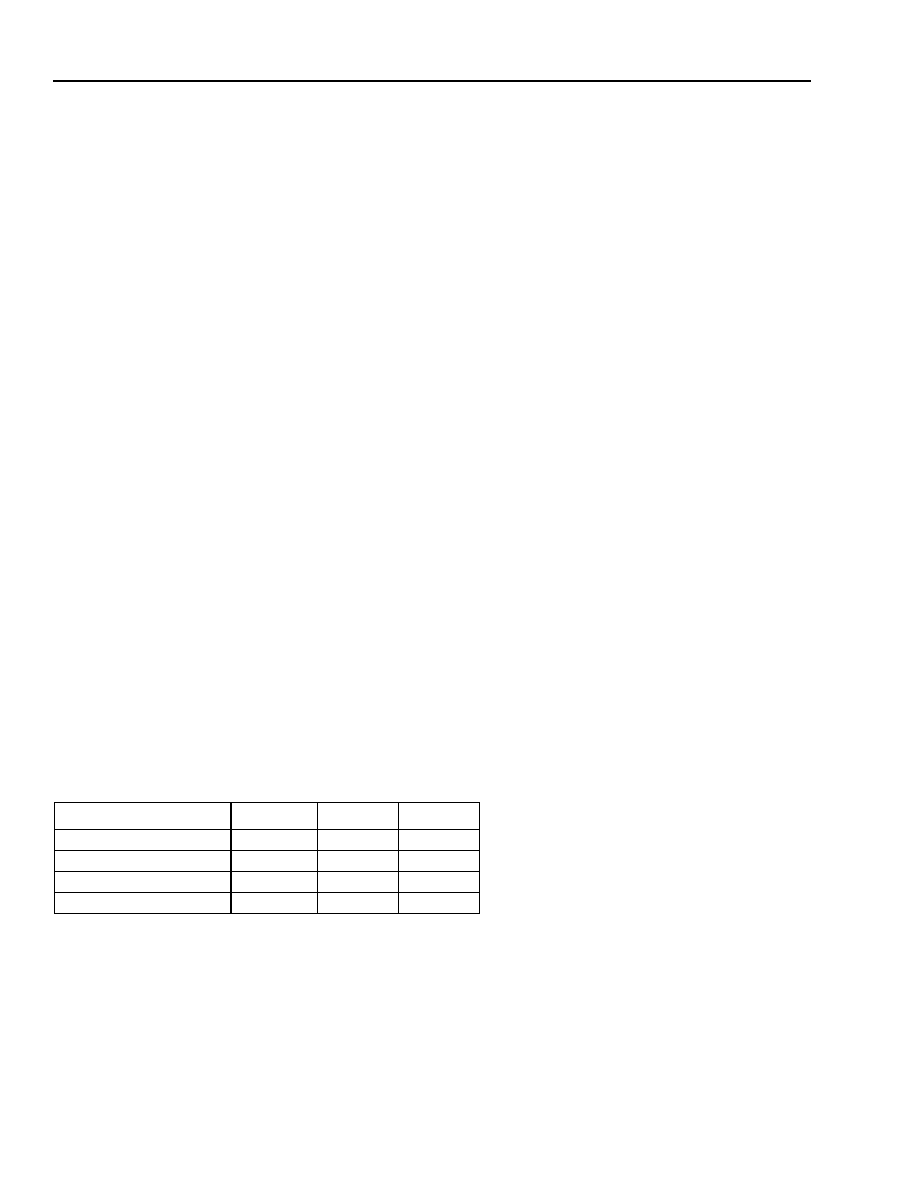

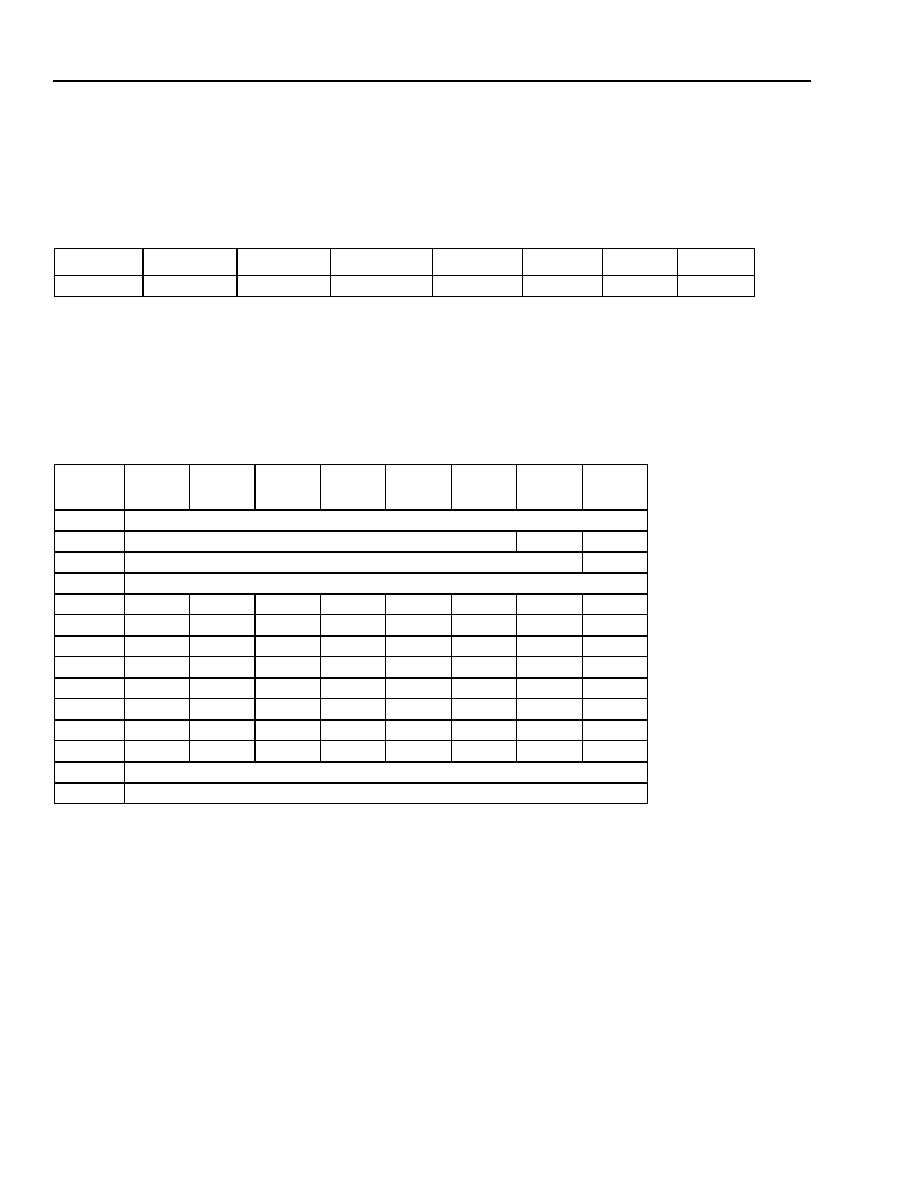

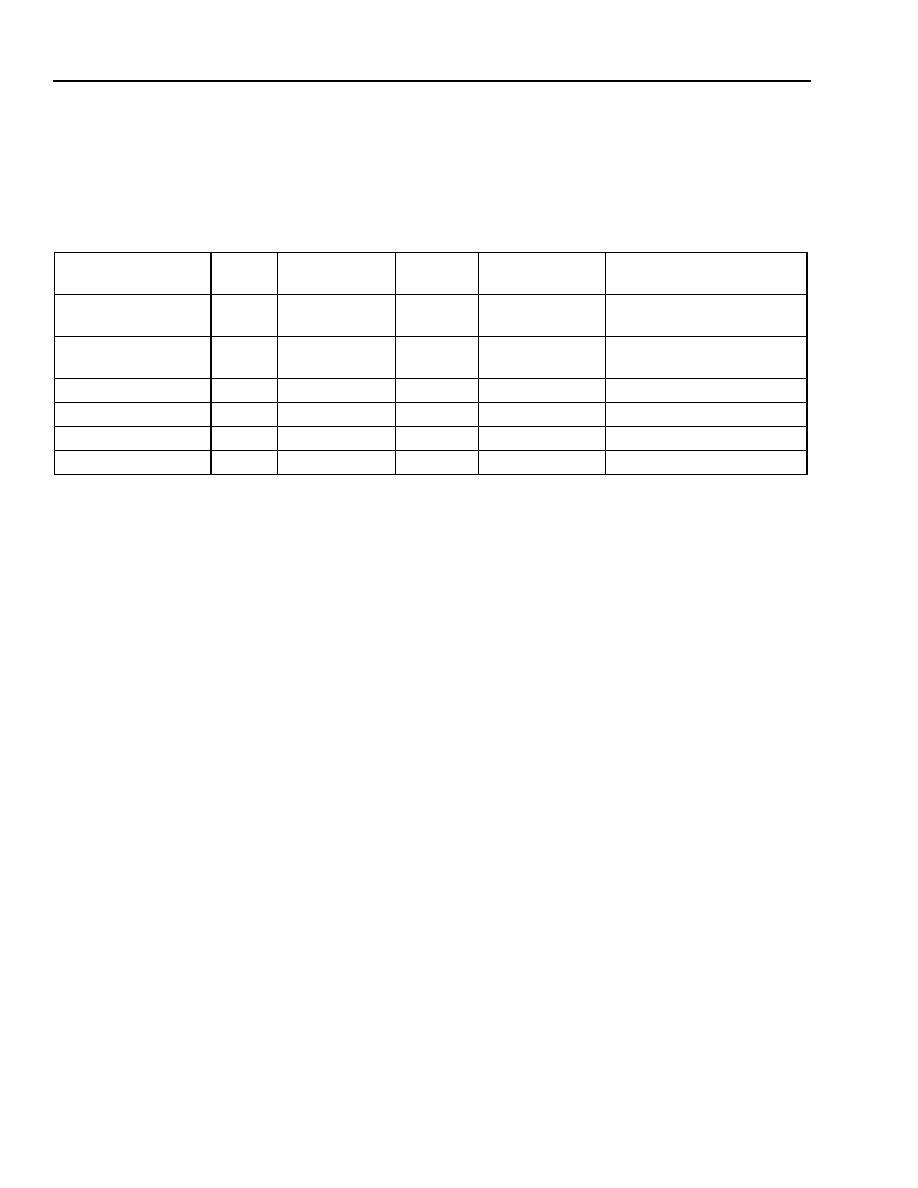

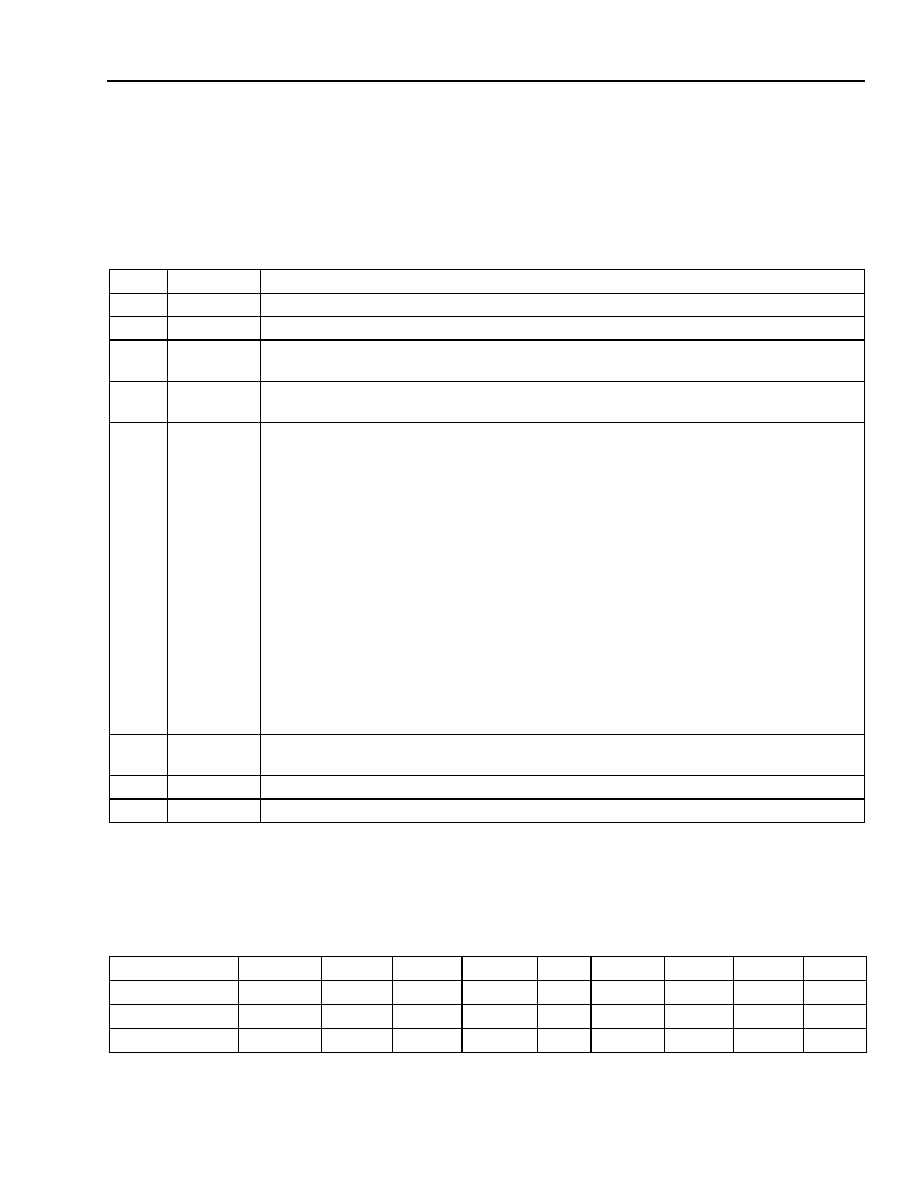

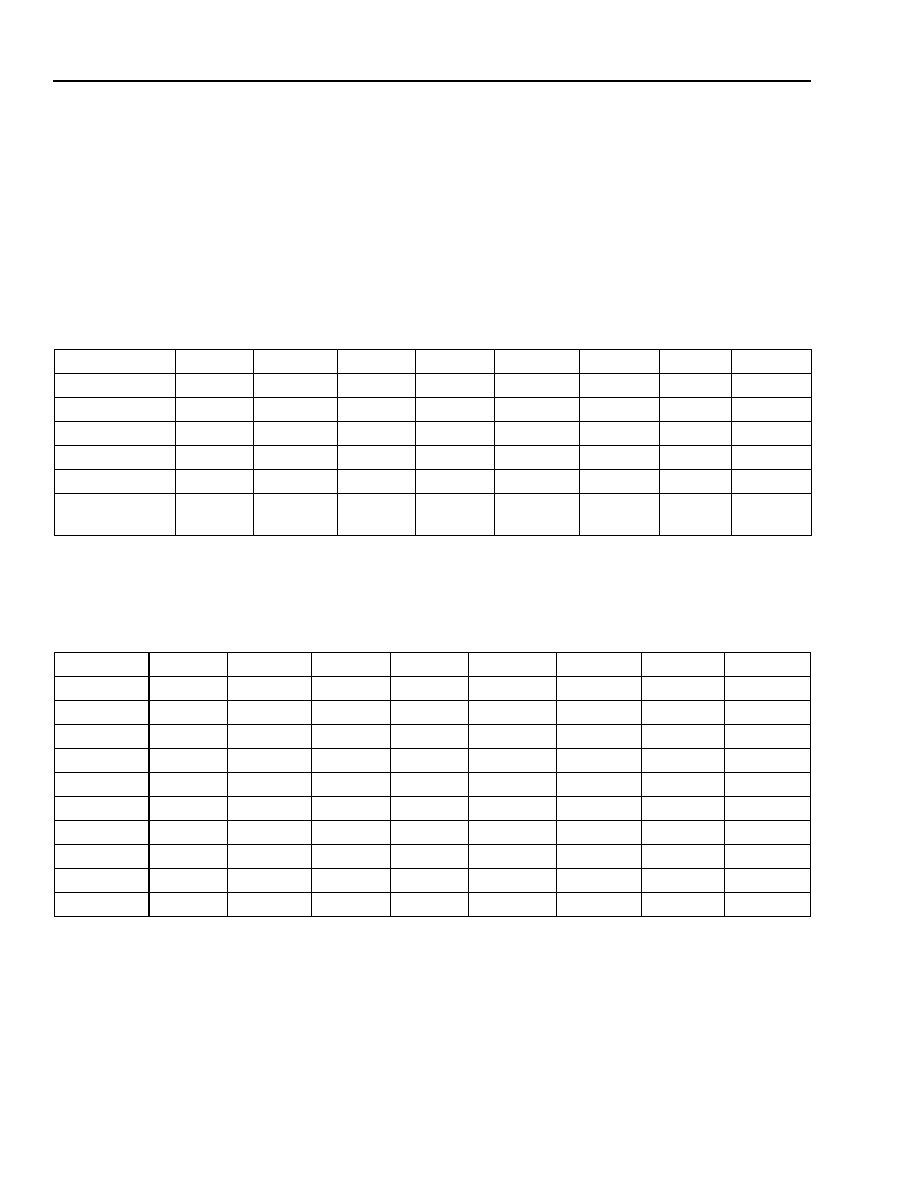

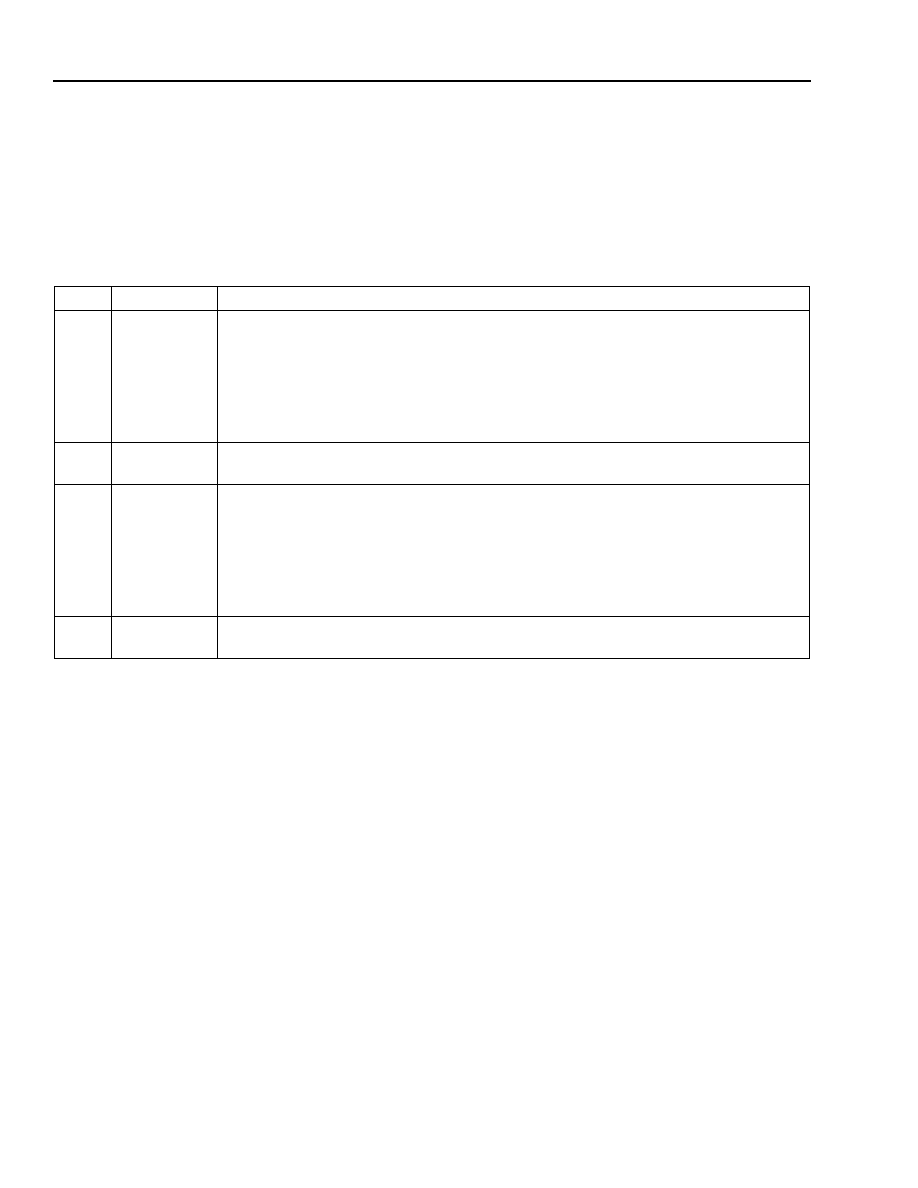

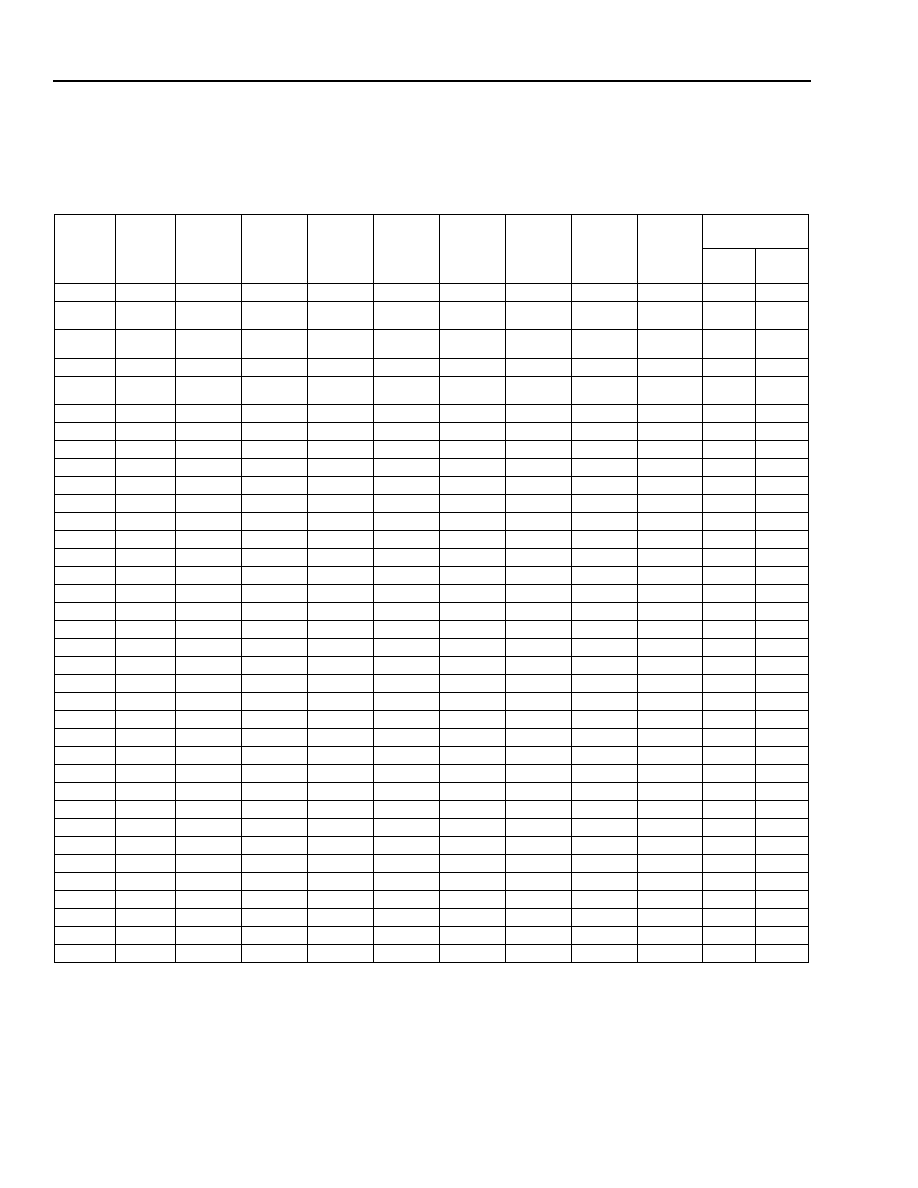

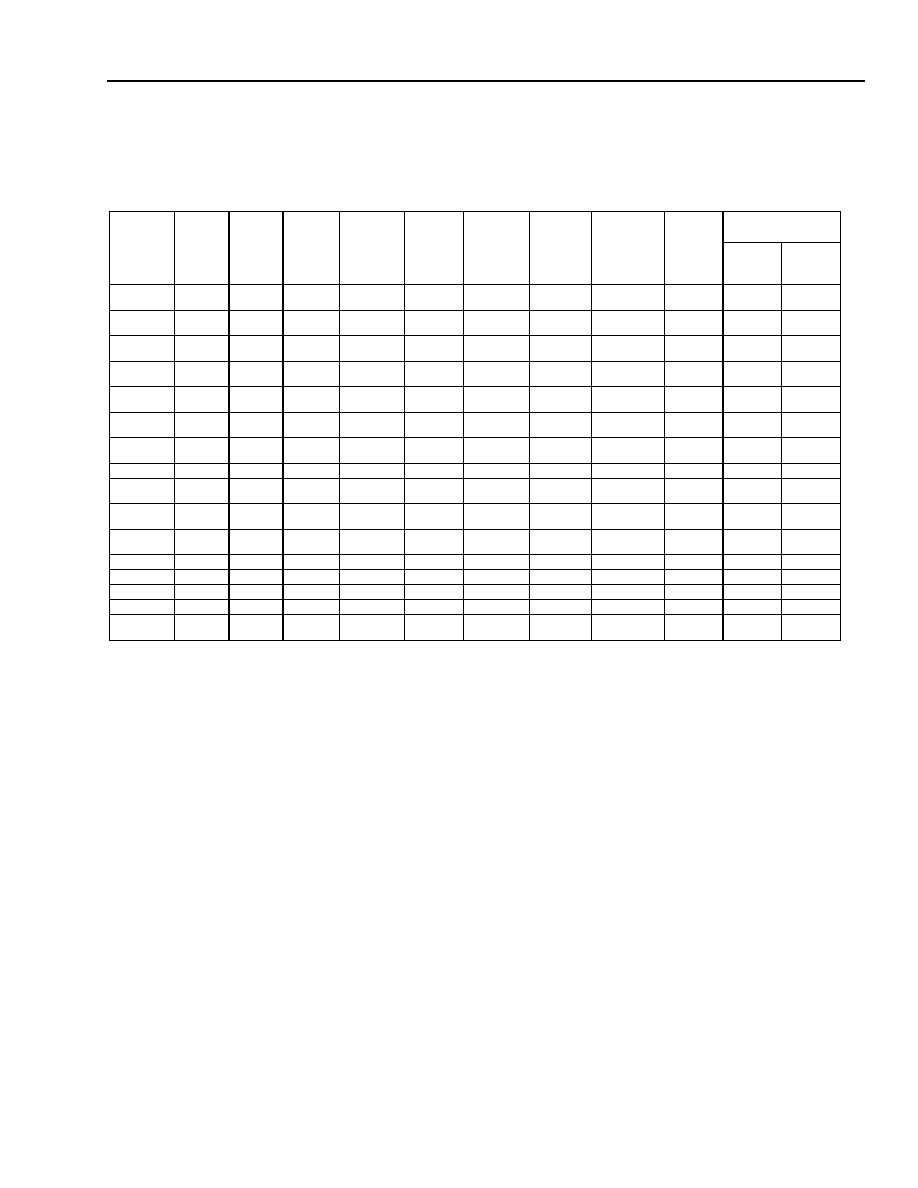

Symbol Configuration

Parameter

Setup

(ns)

(Min)

Hold

(ns)

(Min)

Delay

(ns)

(Max)

t31

Modes 3 & 4

ALE Asserted Width

--

10

--

t32

Address Valid to ALE Deasserted

10

--

--

t33

ALE Deasserted to Address Invalid

--

10

--

t34

CS Asserted to RD Asserted

0

--

--

t35

Address Valid and ALE Asserted to RD Asserted

0

--

--

t36

CS Asserted to RDY Low Impedance

--

--

12

t37

Rising Edge MPCK to RDY Asserted

--

--

15

t38

RD Asserted to AD Low Impedance

--

--

15

t39

RD Asserted to Data Valid

--

--

40

t40

RD Deasserted to CS Deasserted

--

--

t41

RD Deasserted to RDY Deasserted

--

--

15

t42

CS Deasserted to RDY High Impedance

--

--

10

t43

RD Deasserted to Data Invalid (High Impedance)

--

5

--

t44

CS Asserted to WR Asserted

0

--

--

t45

Address Valid and ALE Asserted to WR Asserted

10

--

--

t46

Data Valid to WR Asserted

10

--

--

t47

WR Deasserted to CS Deasserted

--

5

--

t48

WR Deasserted to RDY Deasserted

--

--

15

t49

WR Deasserted to Data Invalid

--

10

--

t50

RD Asserted Width

--

40

--

t51

WR Asserted Width

--

10

--

t52

Address Valid to ALE Falling Edge

10

--

--

t53

ALE Falling Edge to Address Invalid

--

10

--

t54

ALE Falling Edge to RD Asserted

0

--

--

t55

ALE Falling Edge to WR Asserted

10

--

--

4

Agere Systems Inc.

Device Advisory

September 1999

T7633 Device Advisory for Version 1.0 of the Device

Microprocessor Interface

(continued)

I/O Timing

(continued)

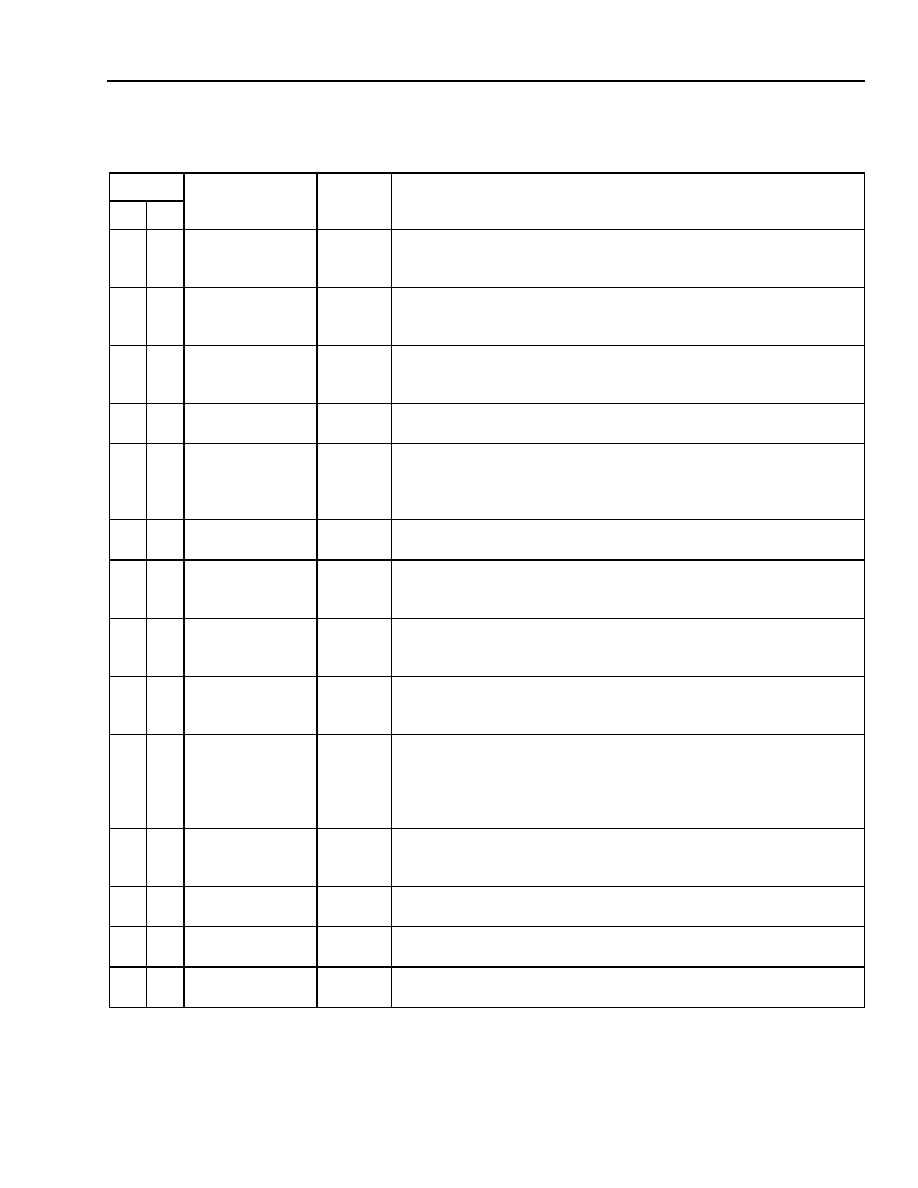

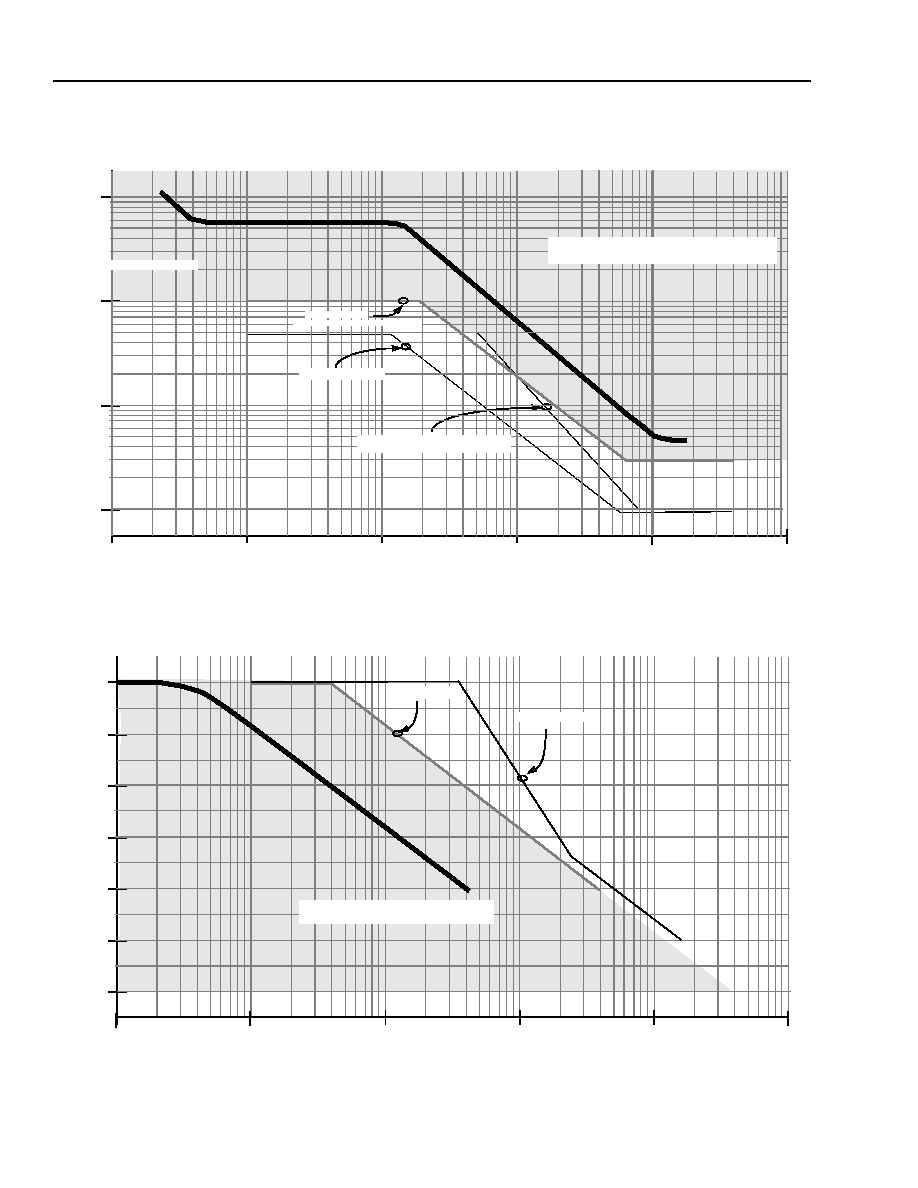

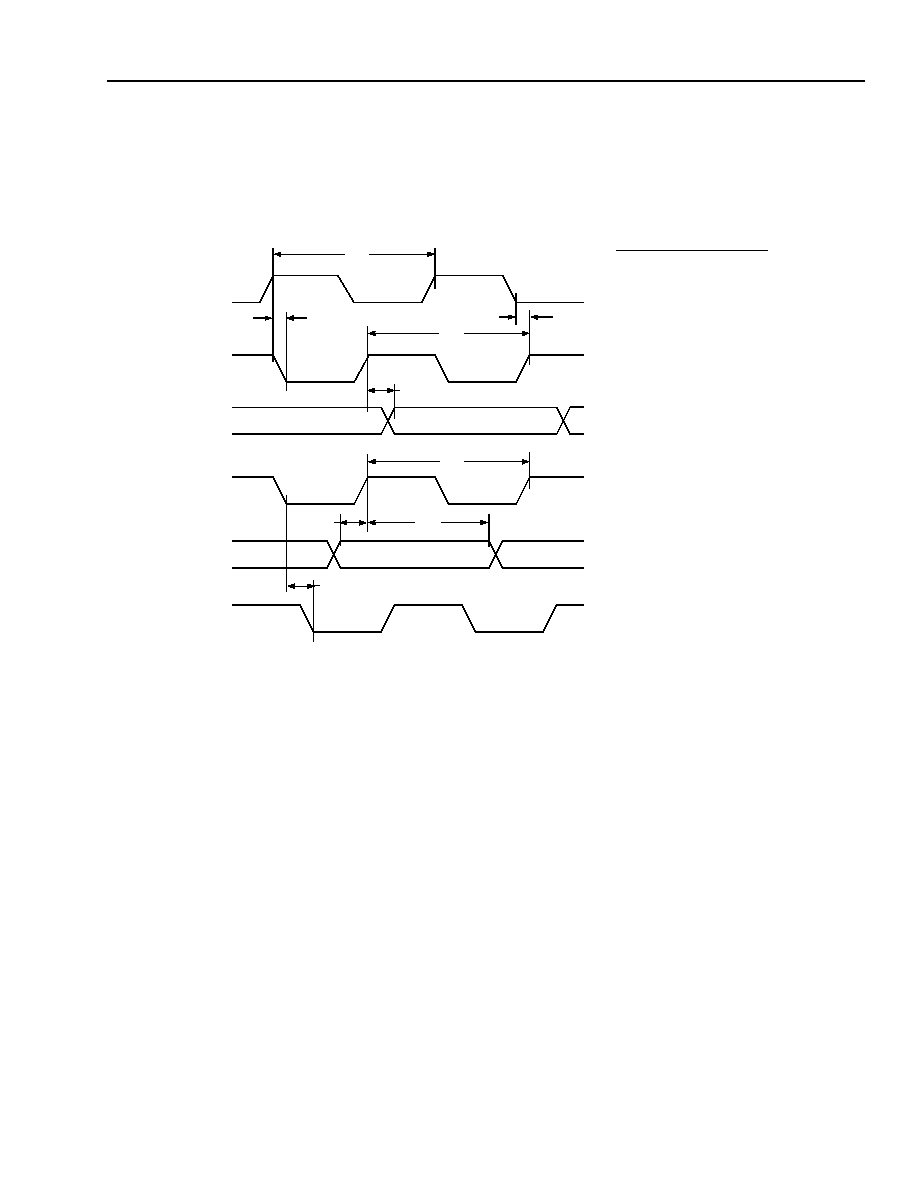

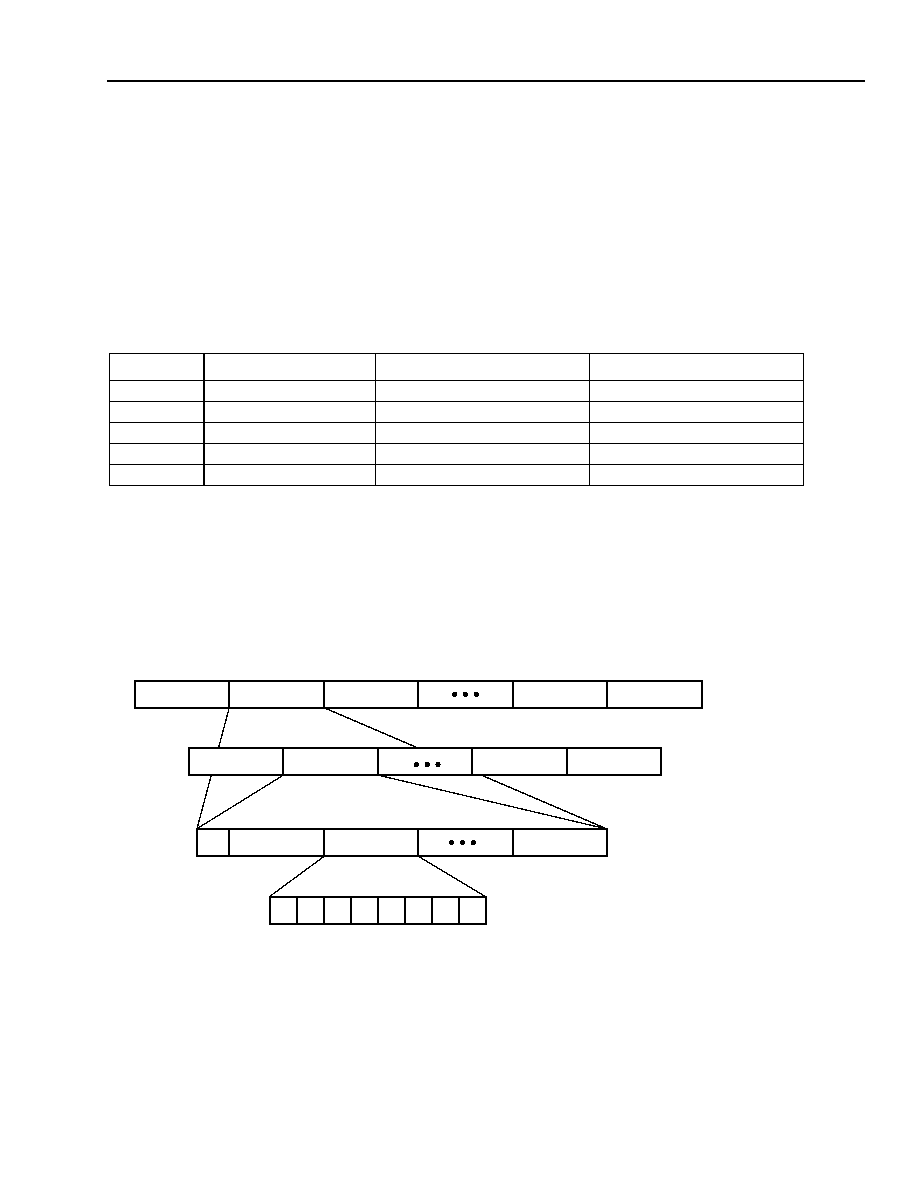

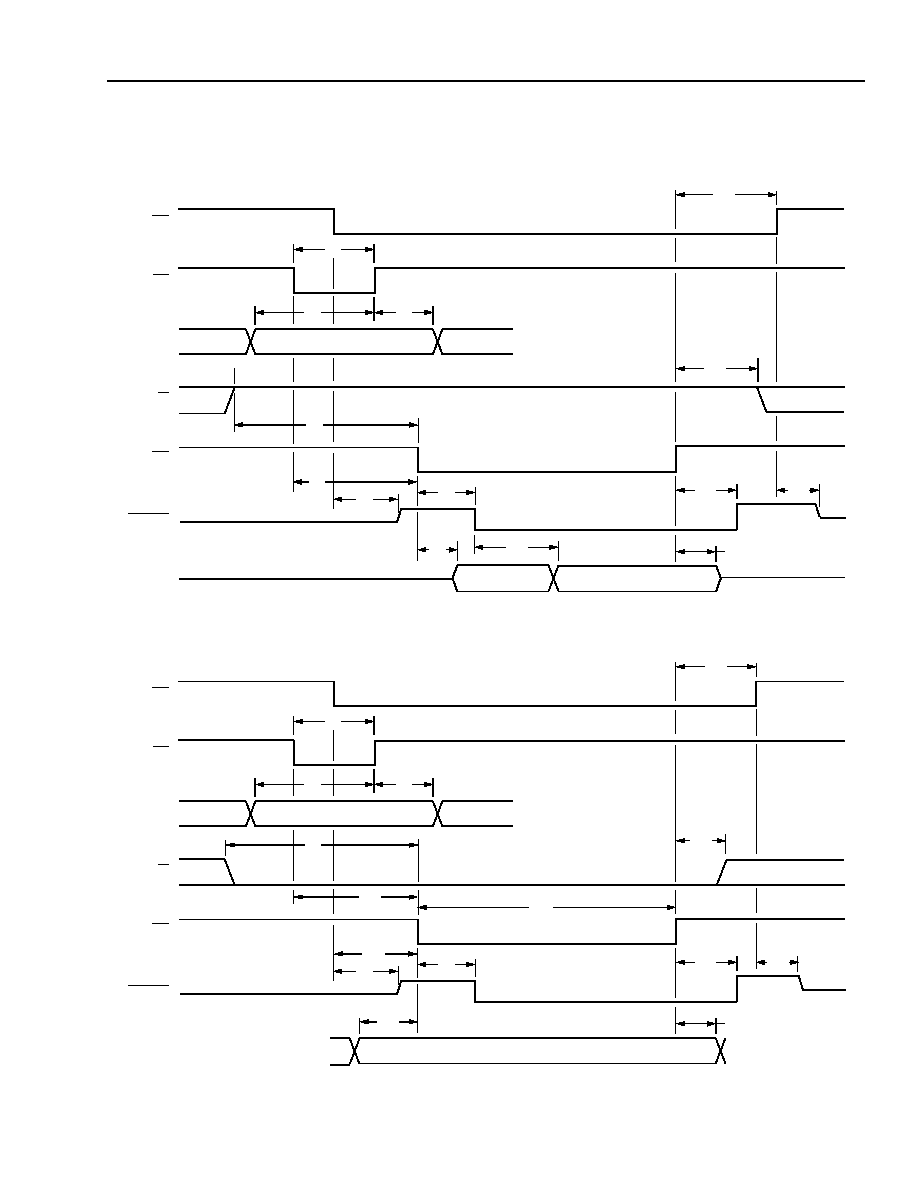

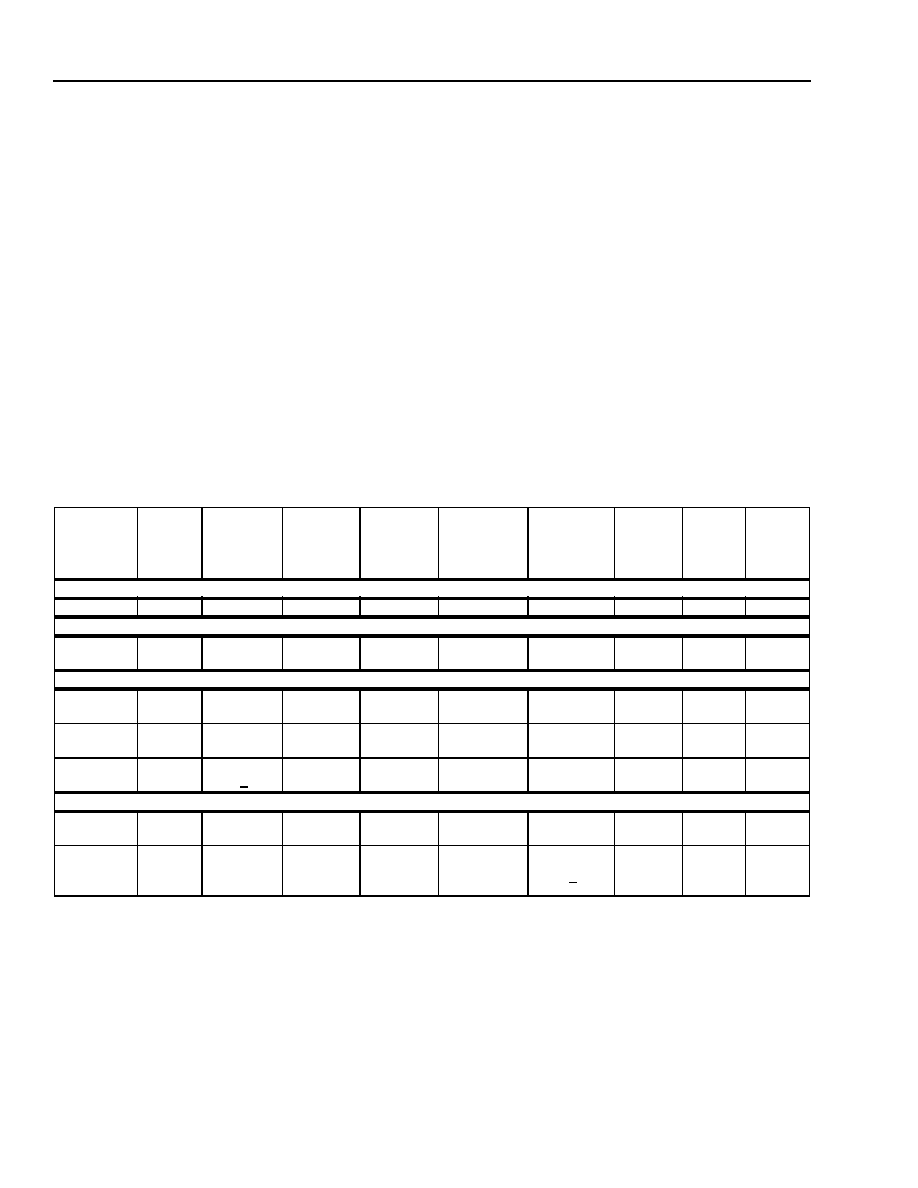

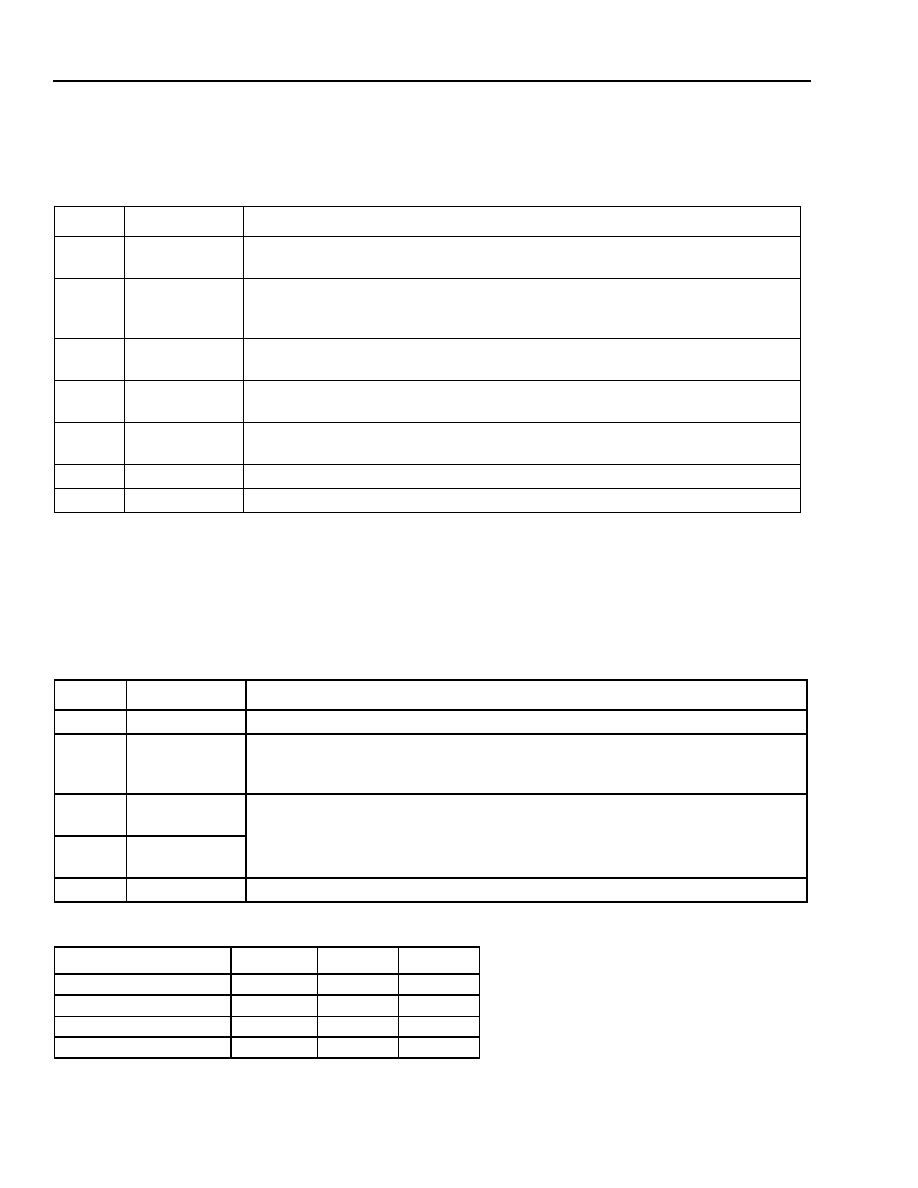

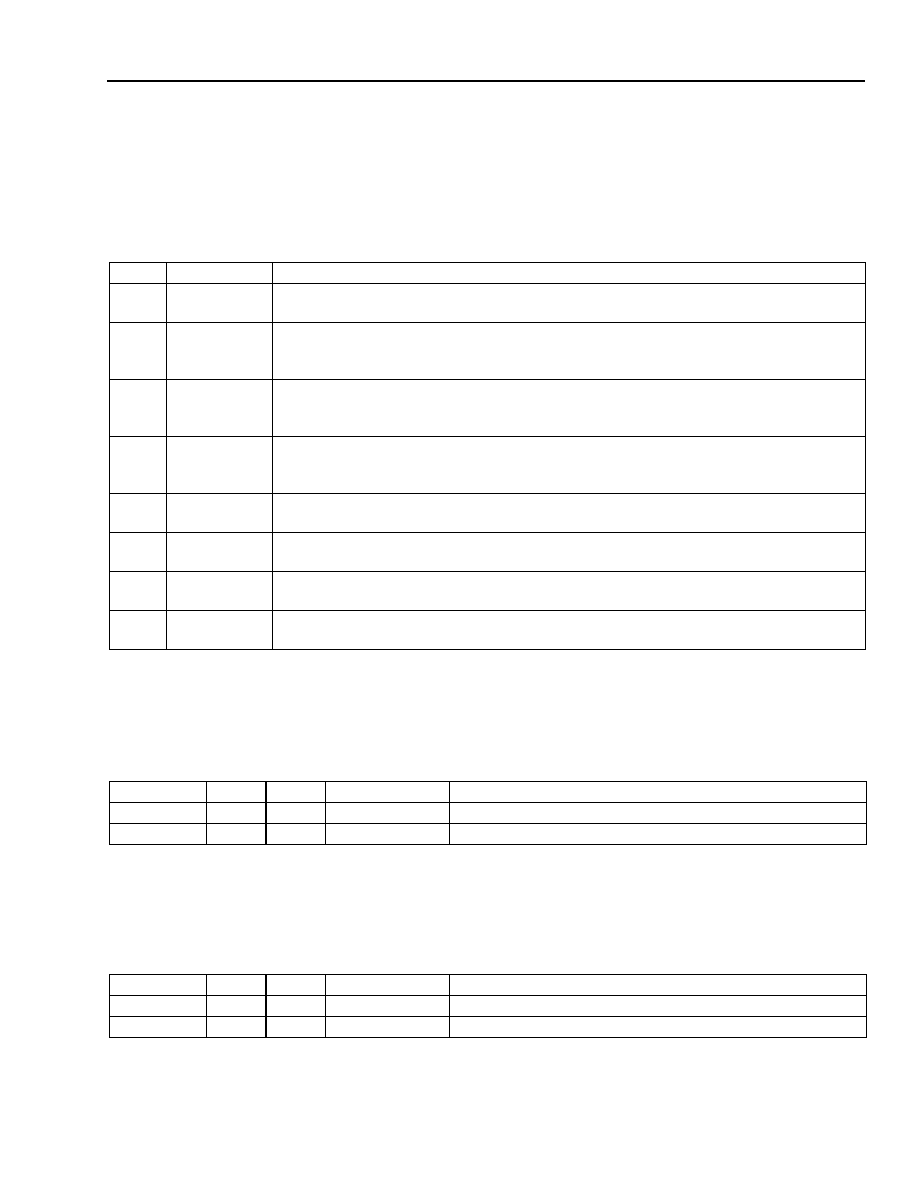

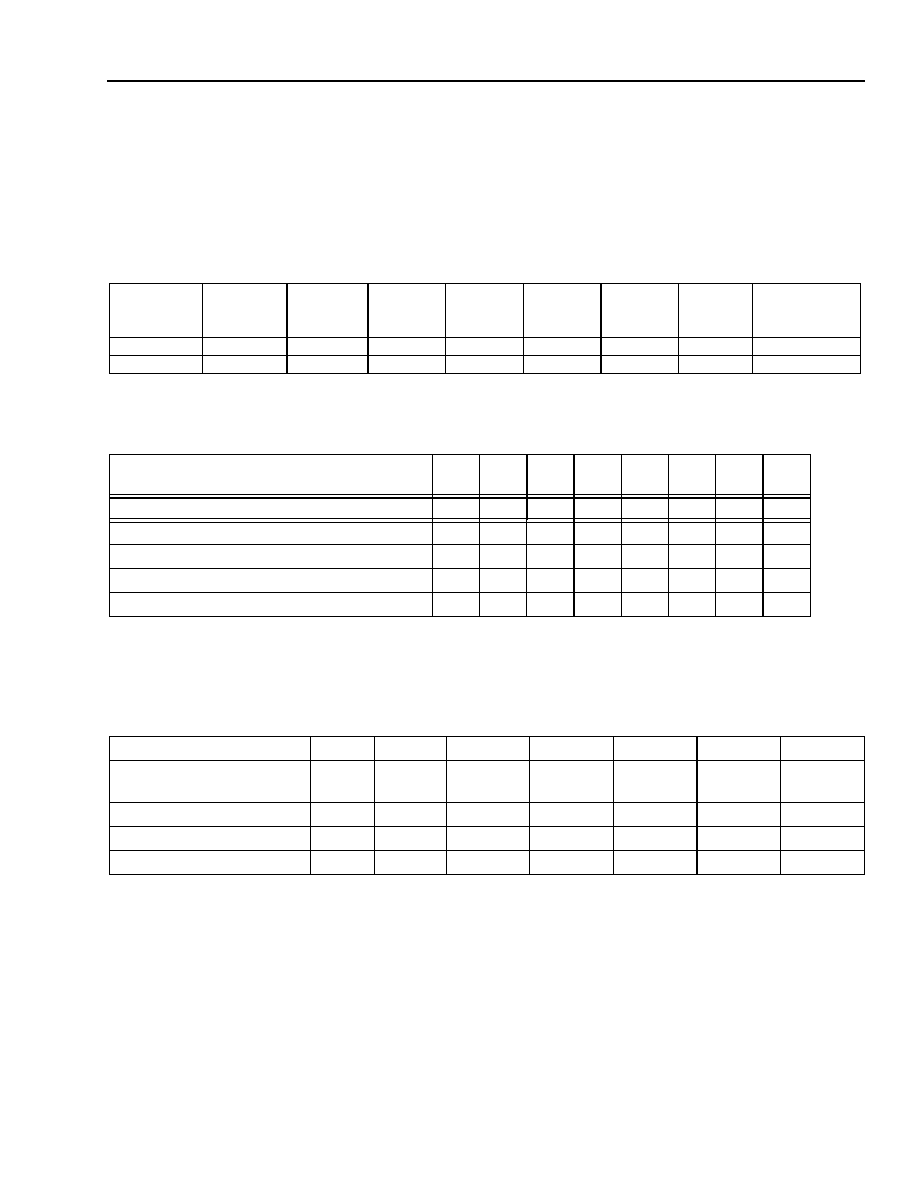

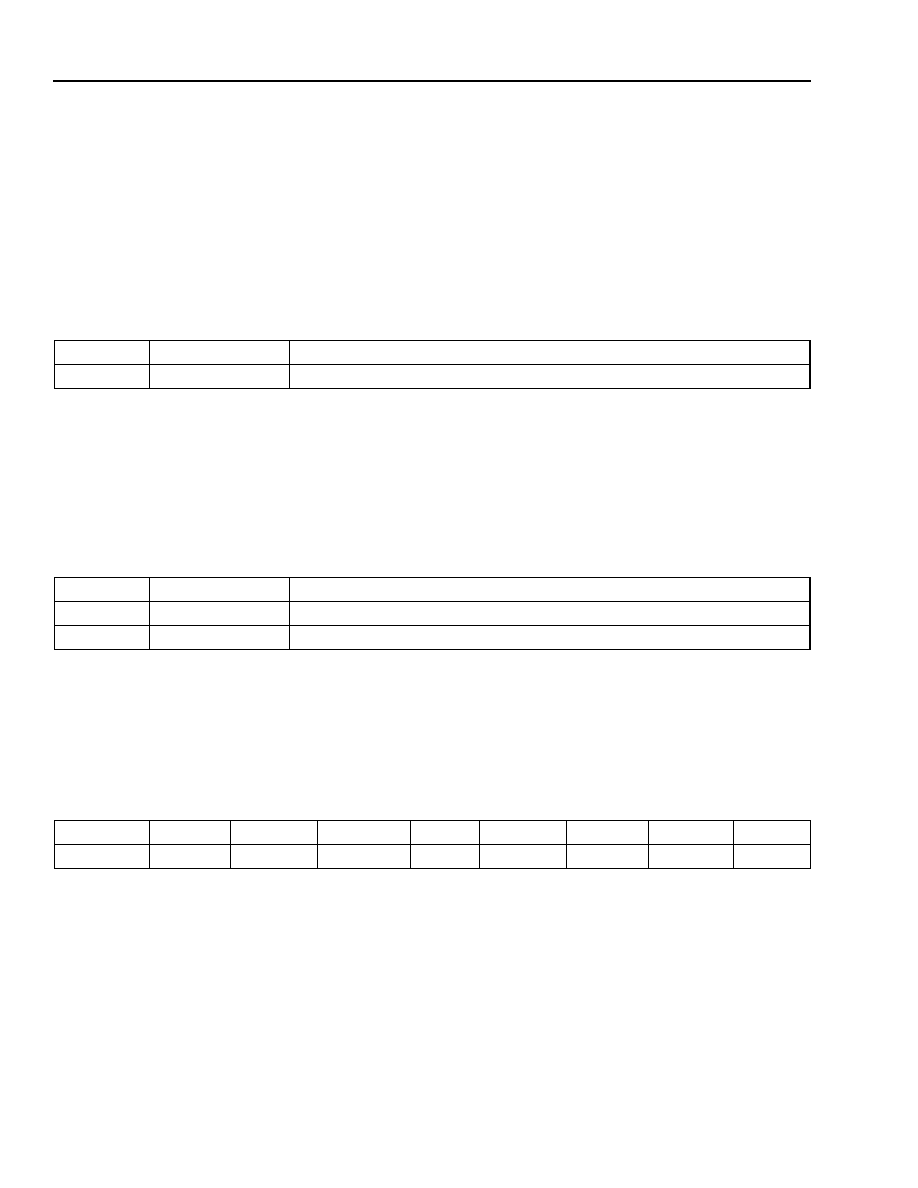

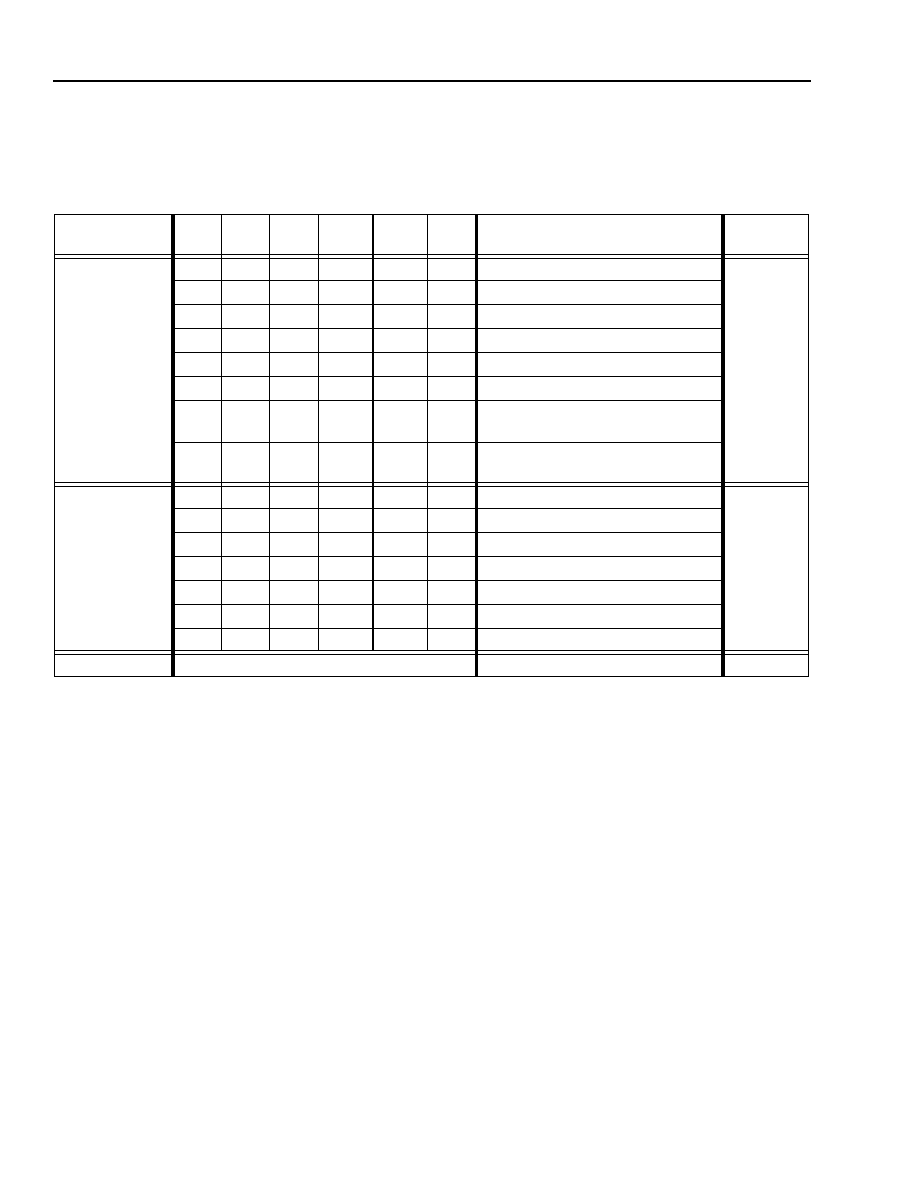

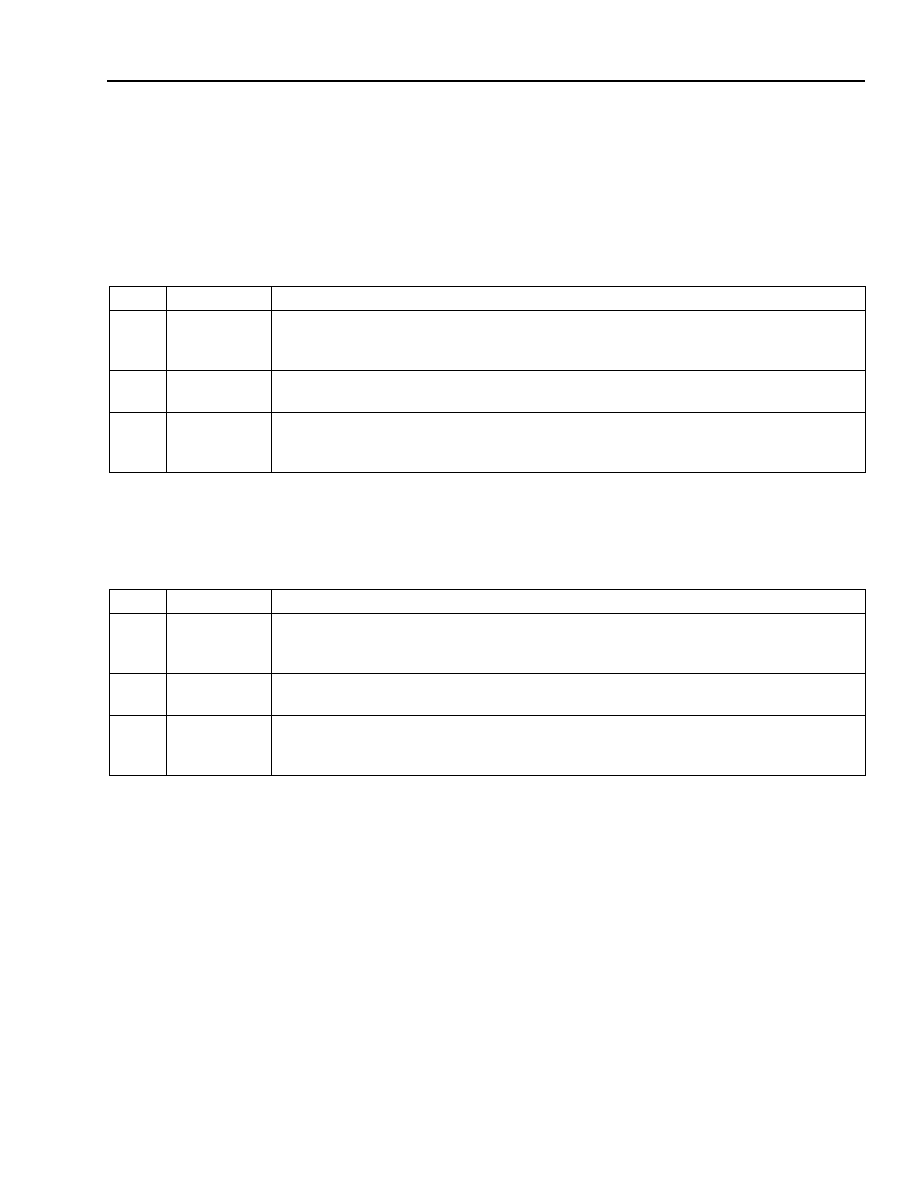

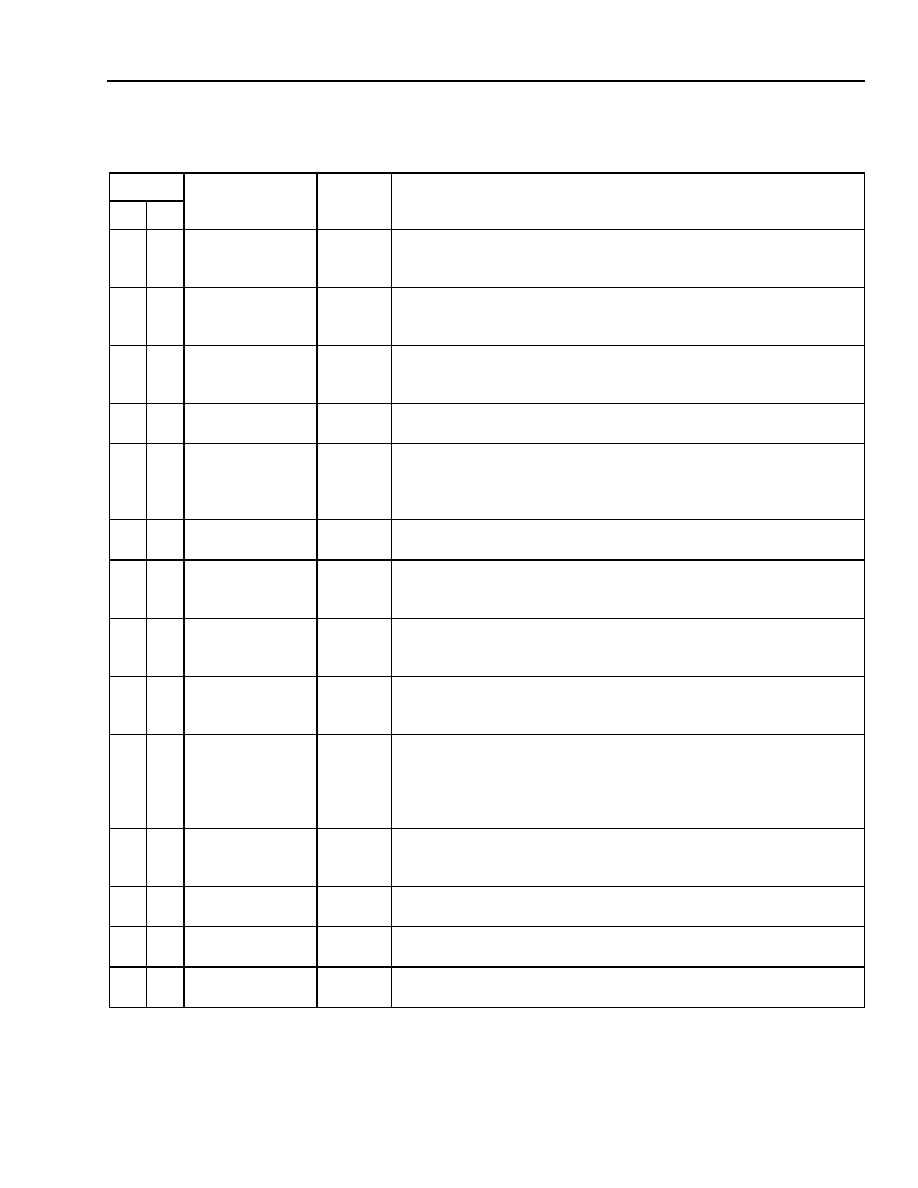

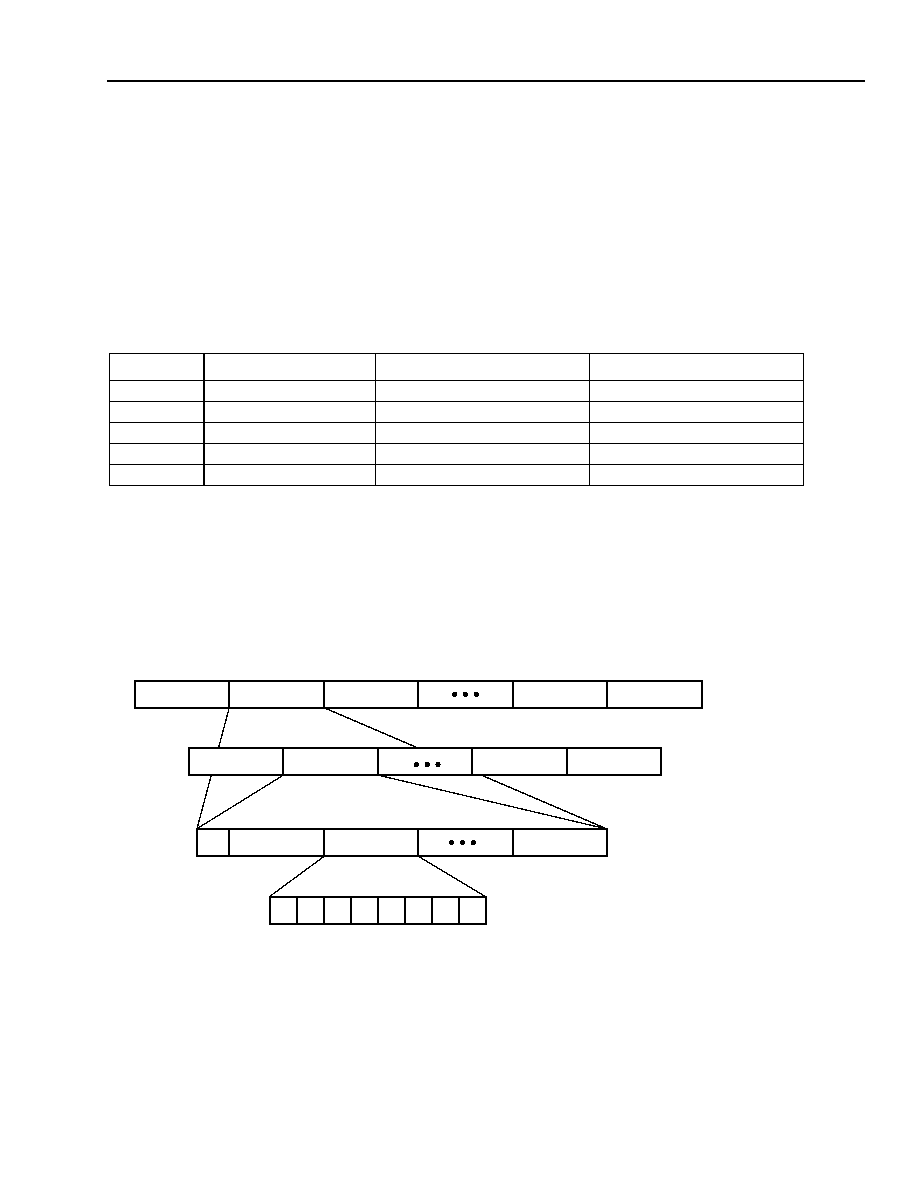

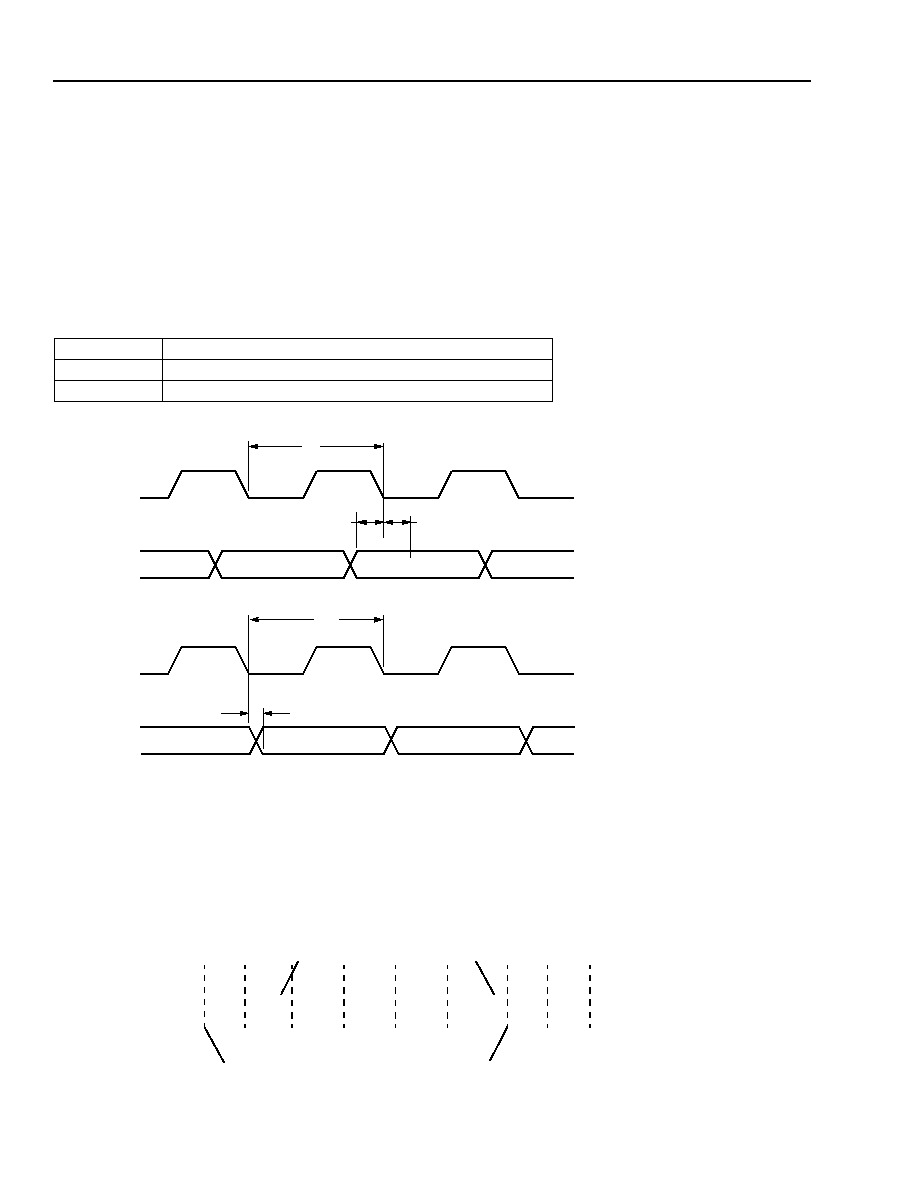

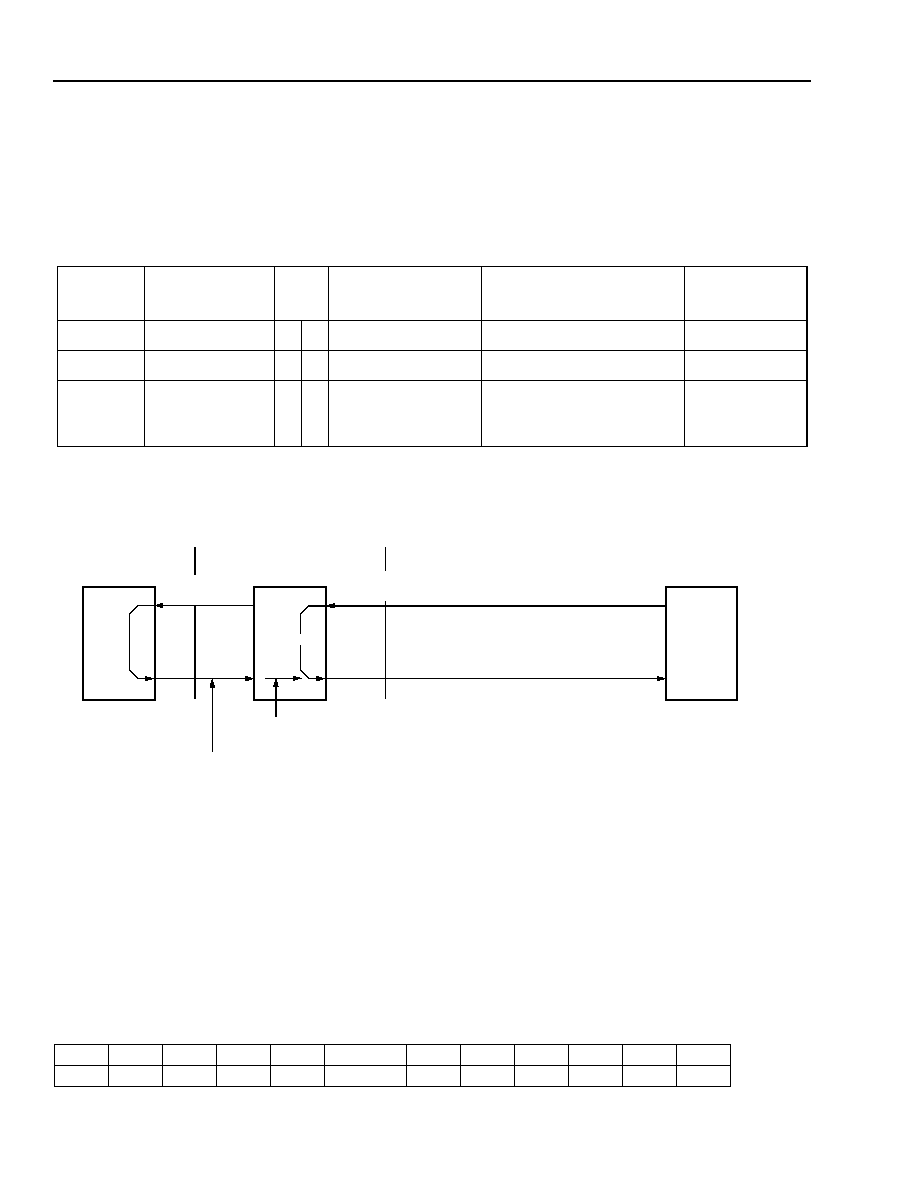

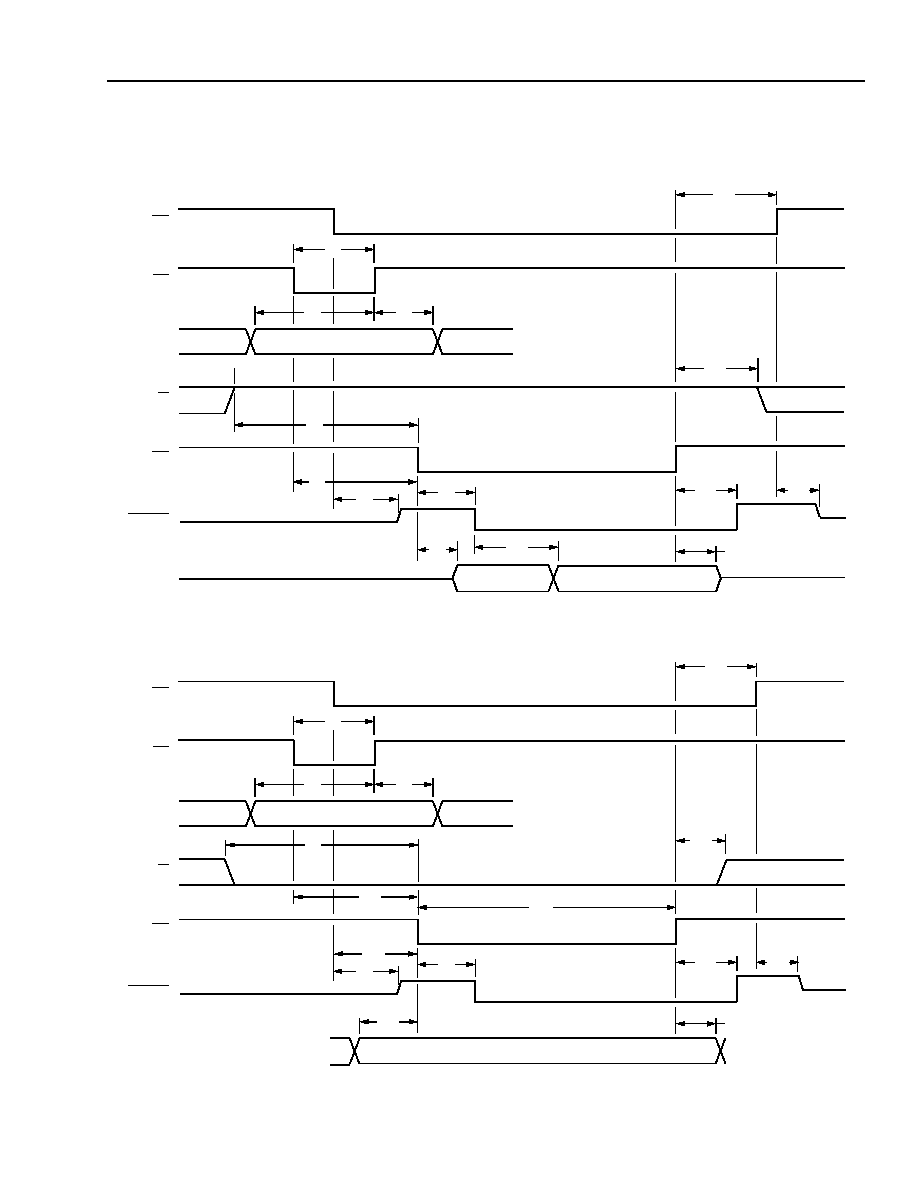

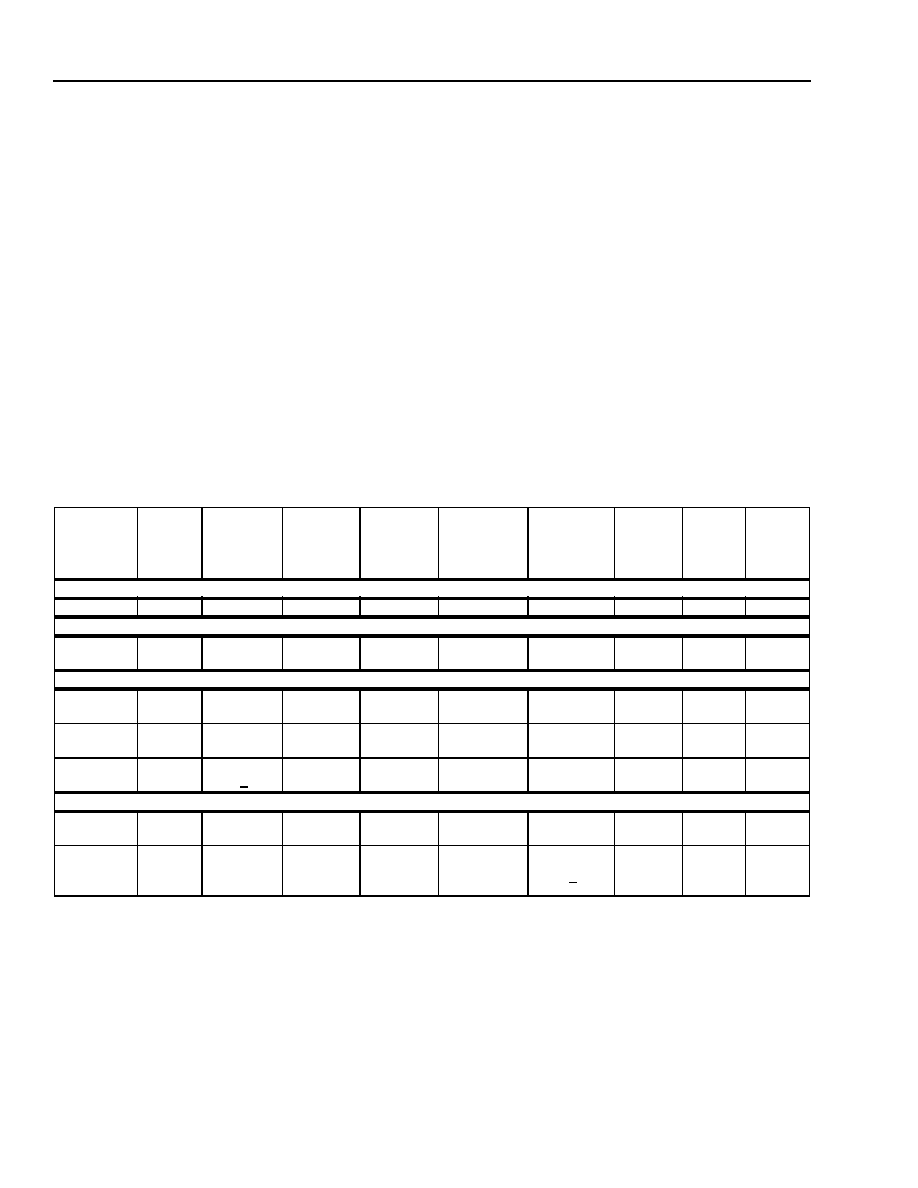

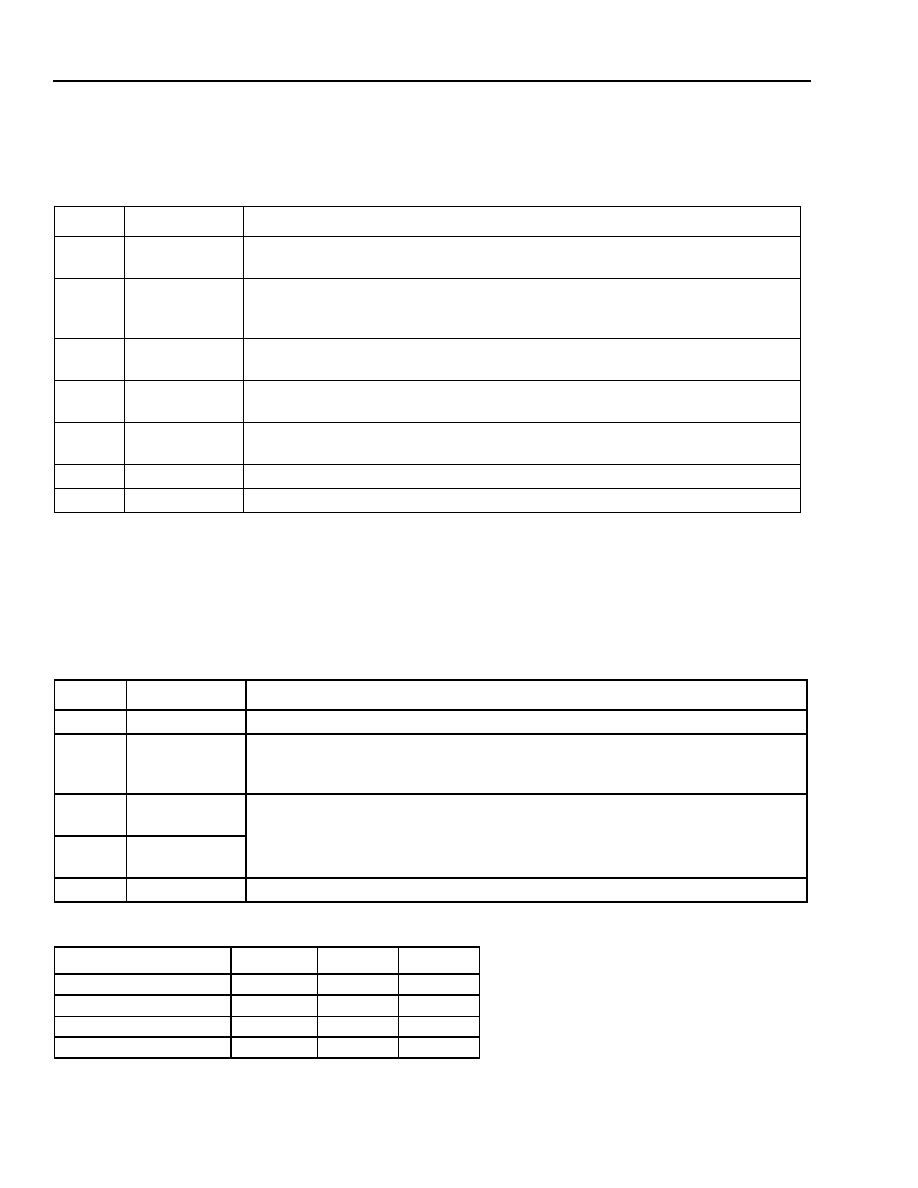

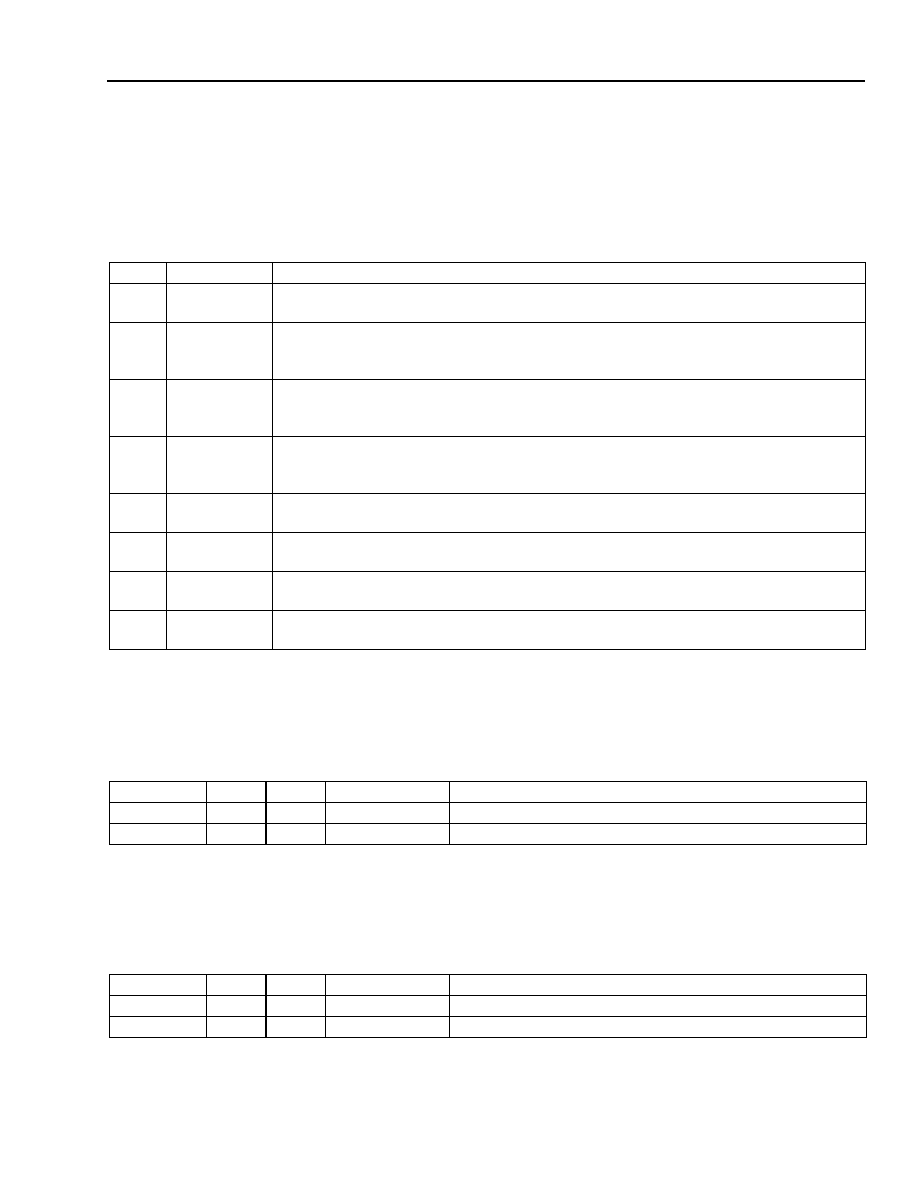

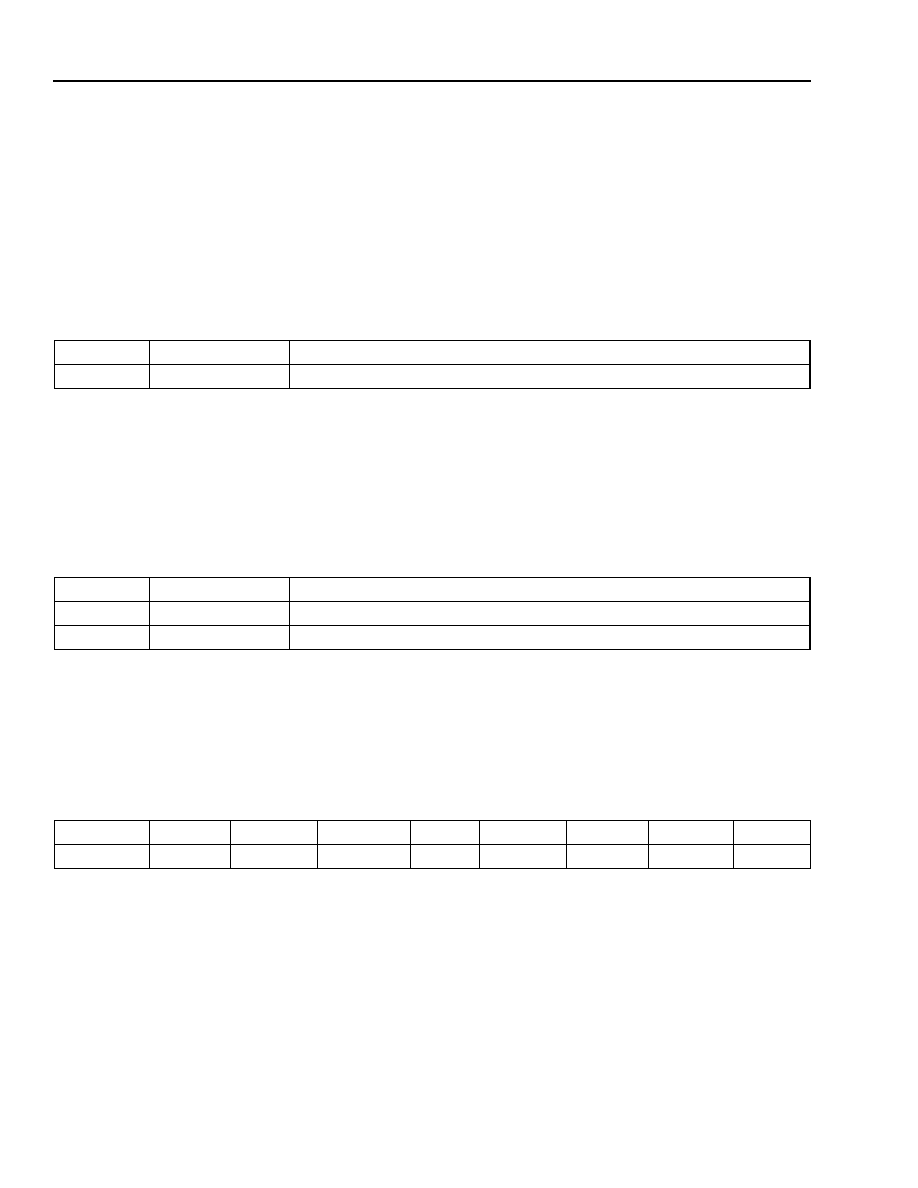

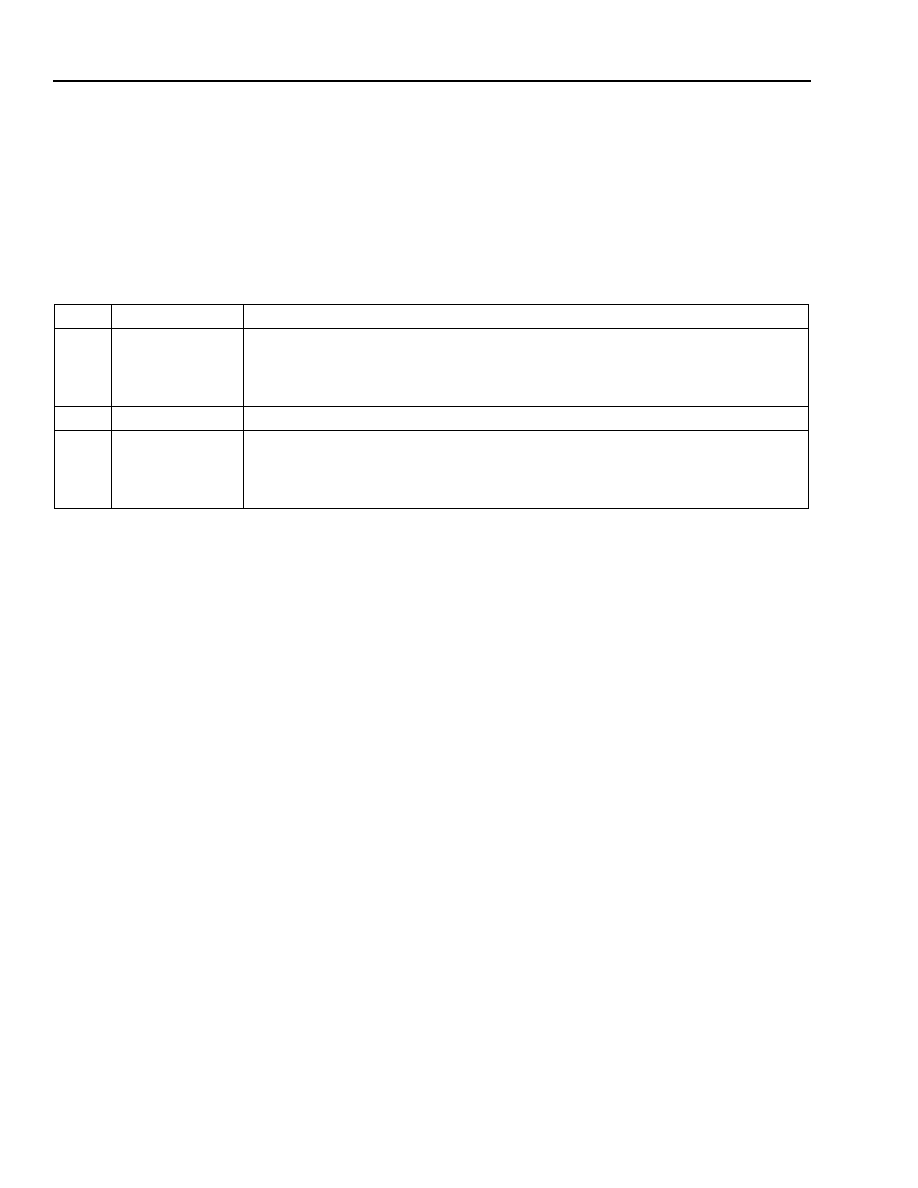

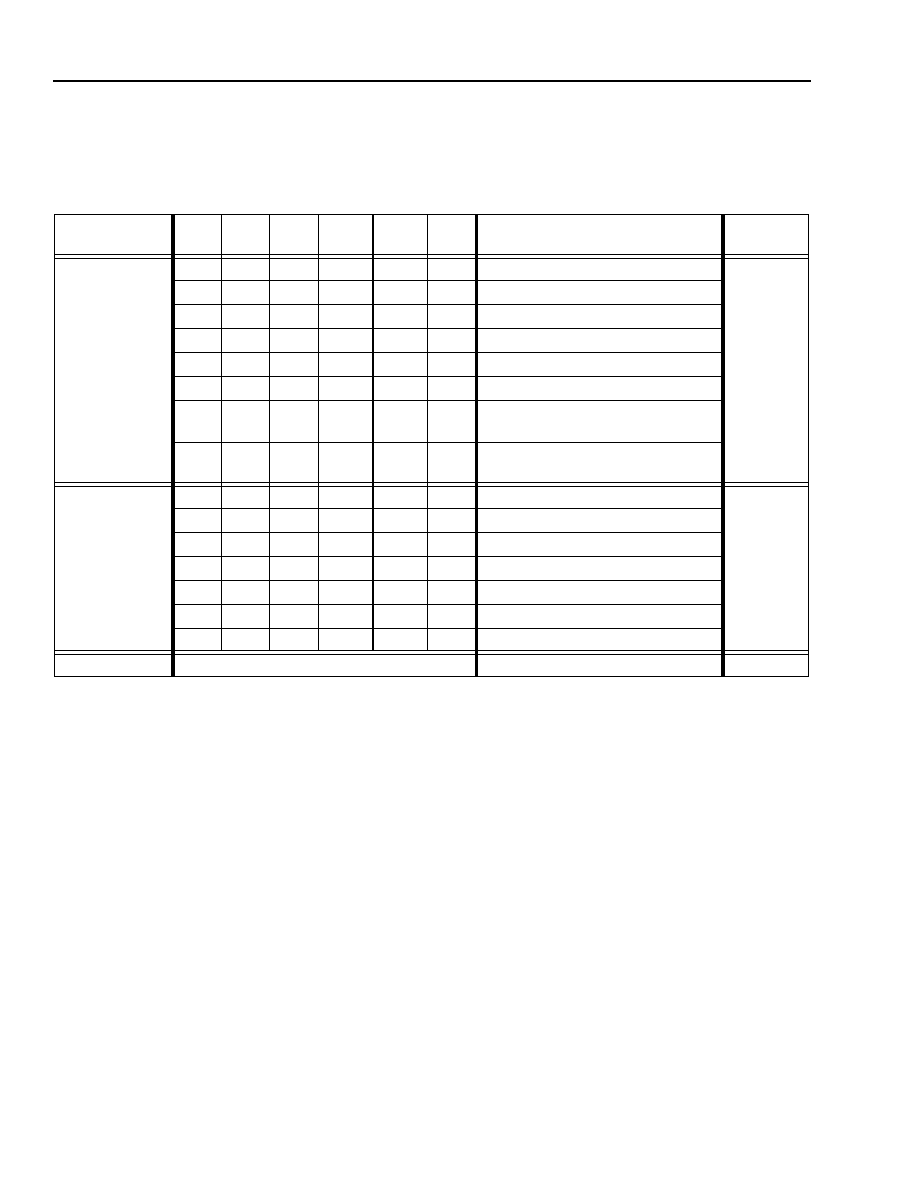

5-6422(F)r.1

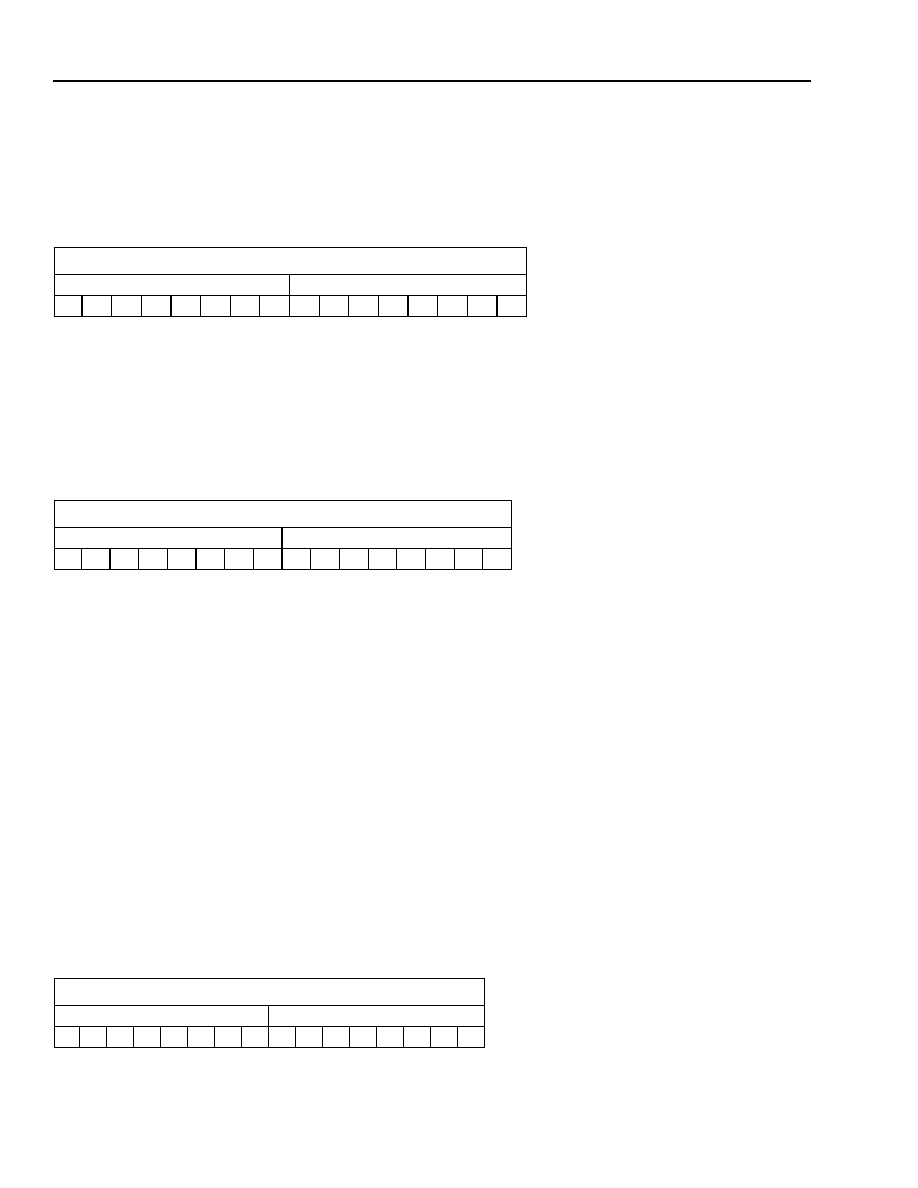

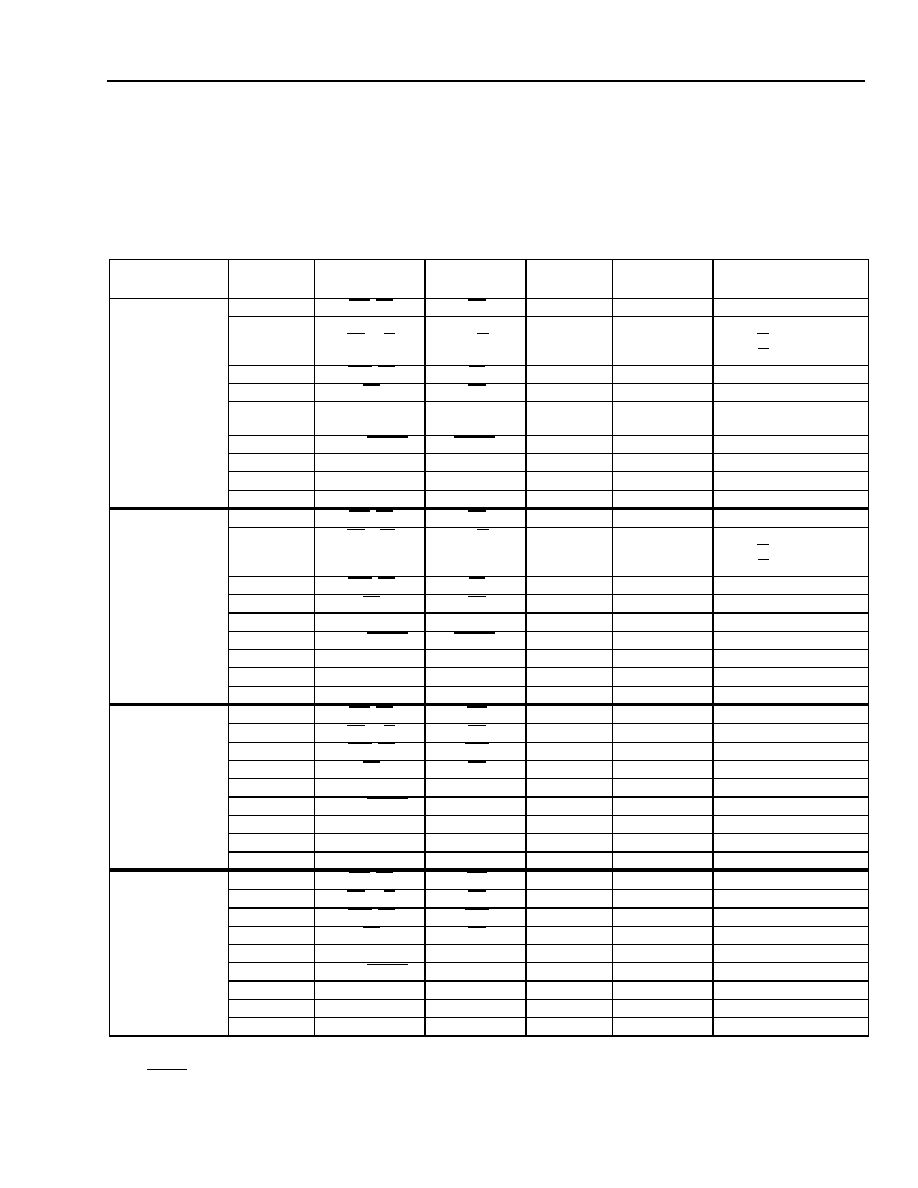

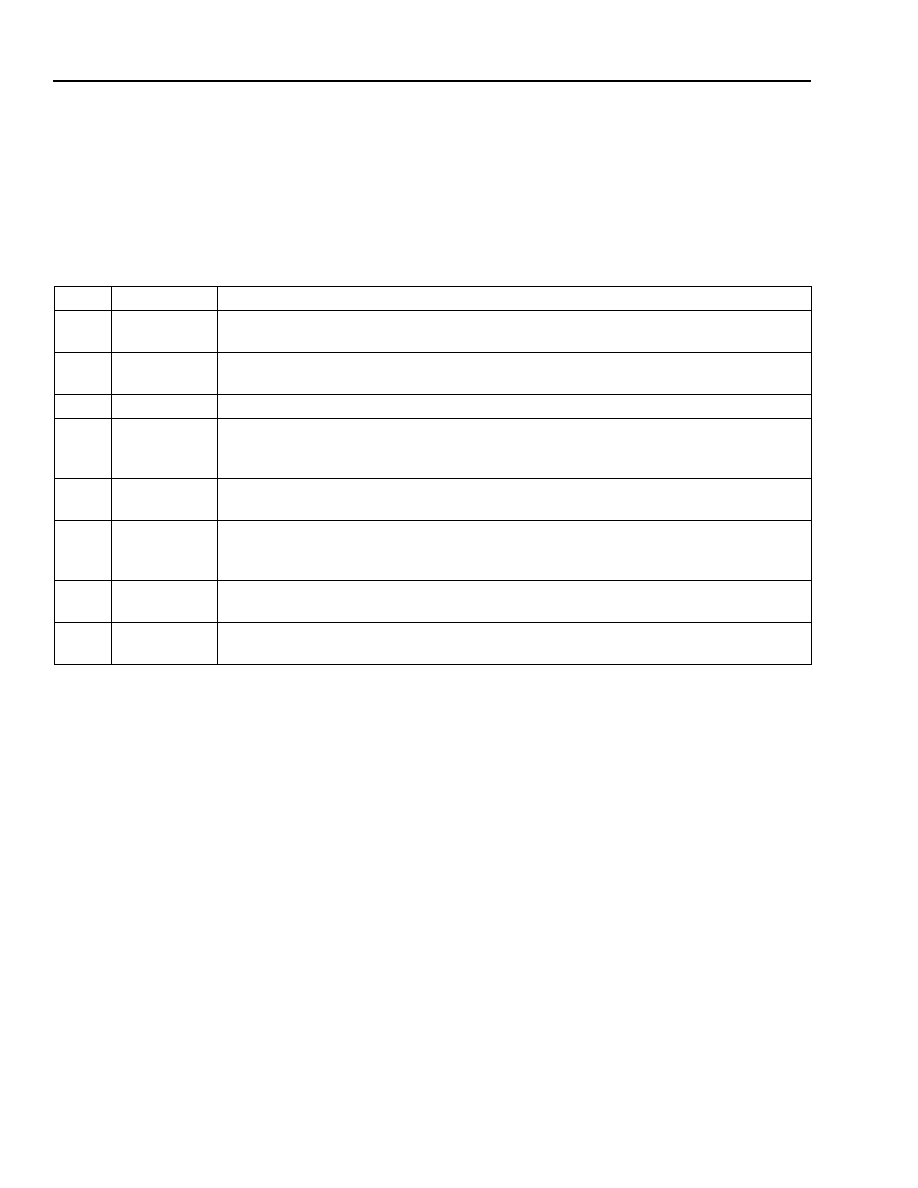

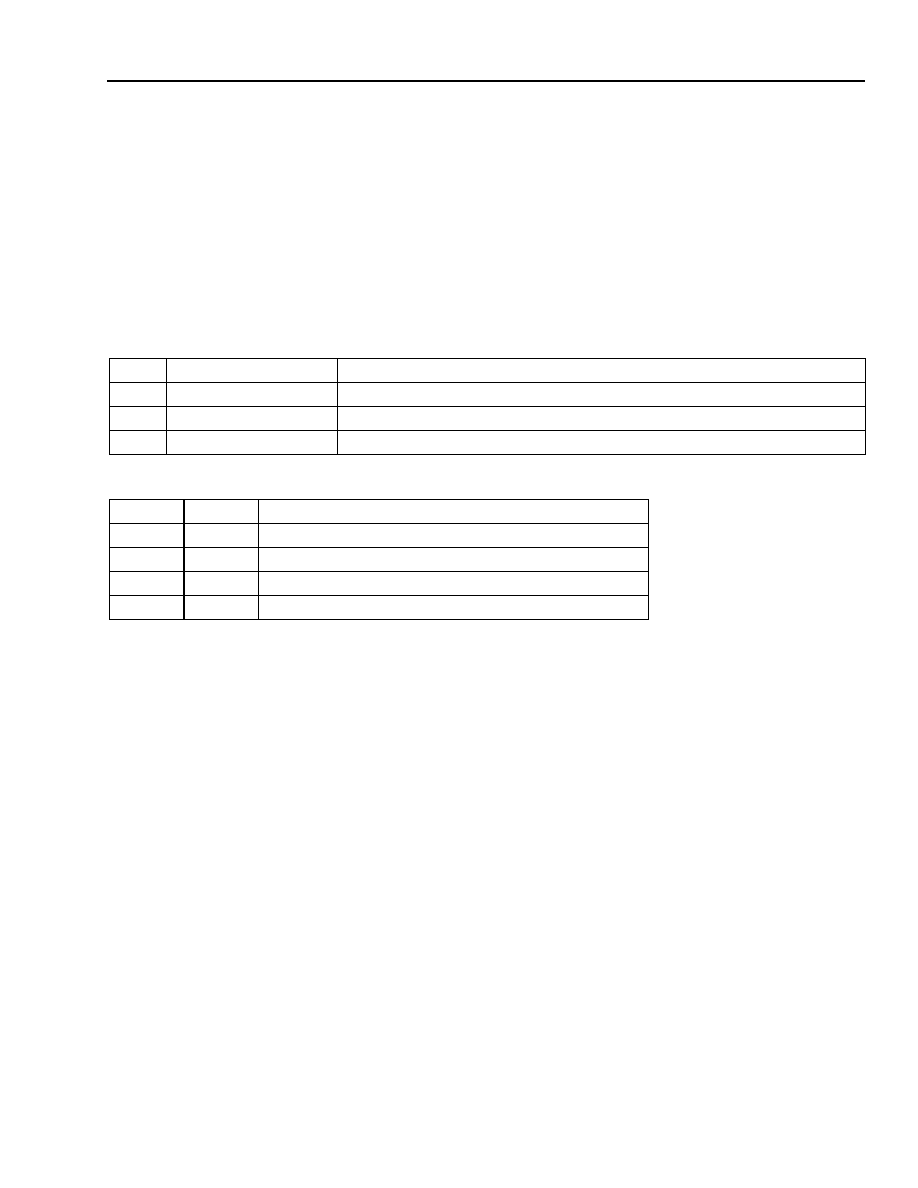

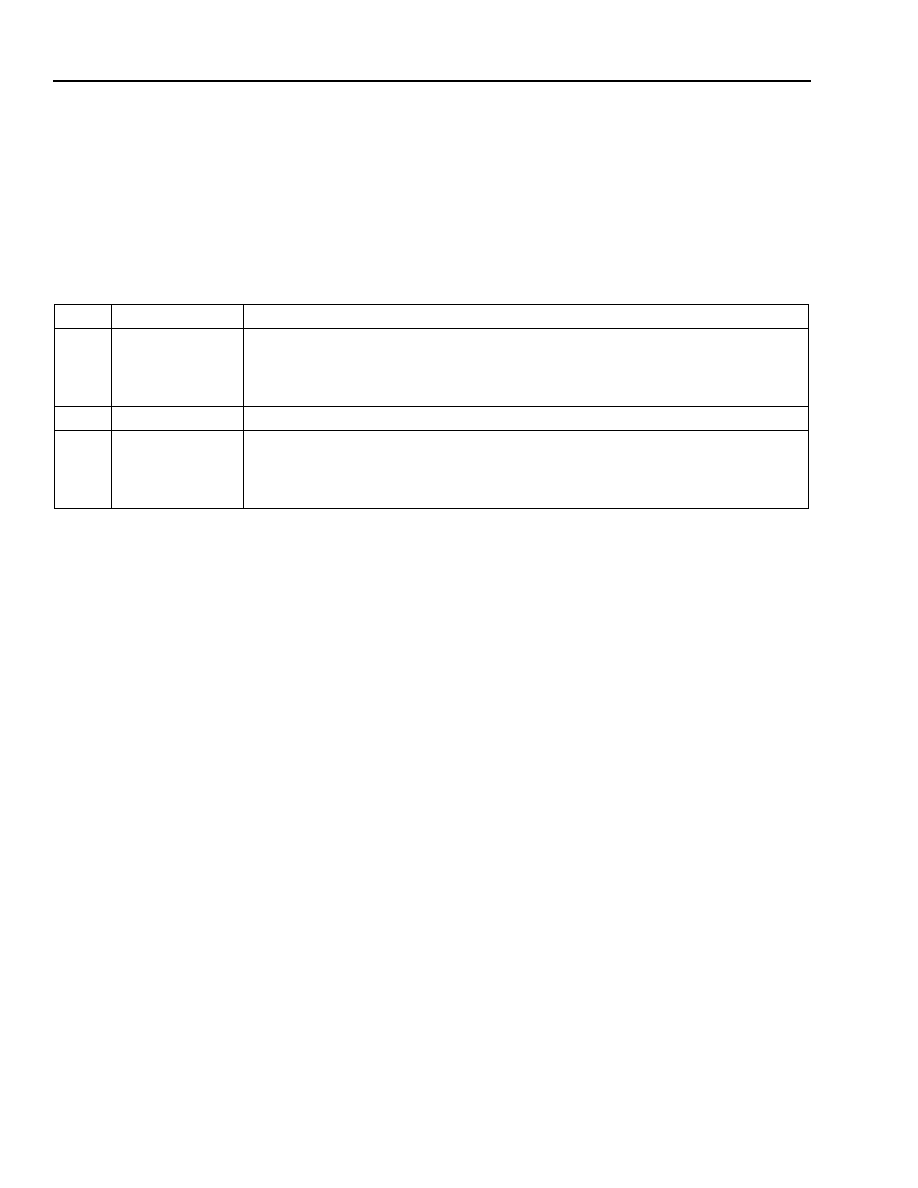

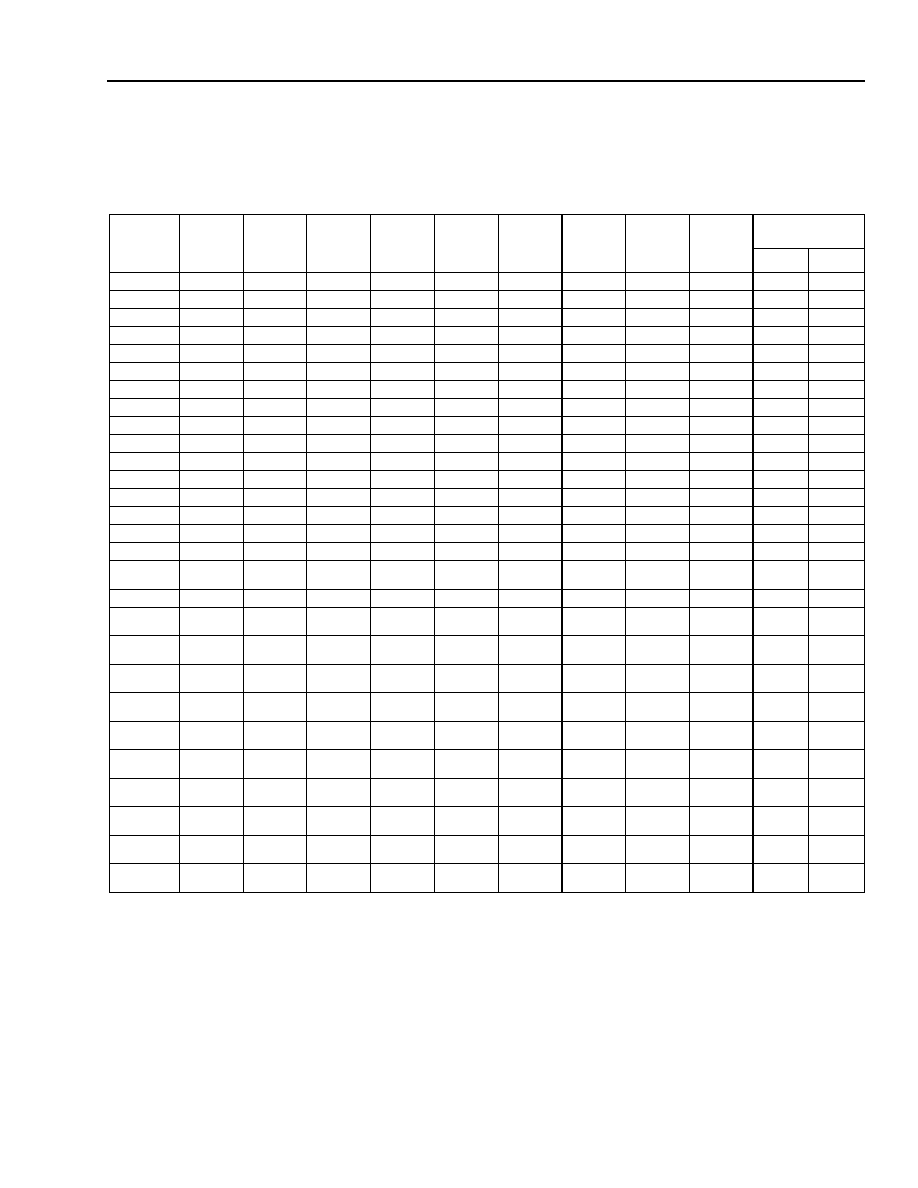

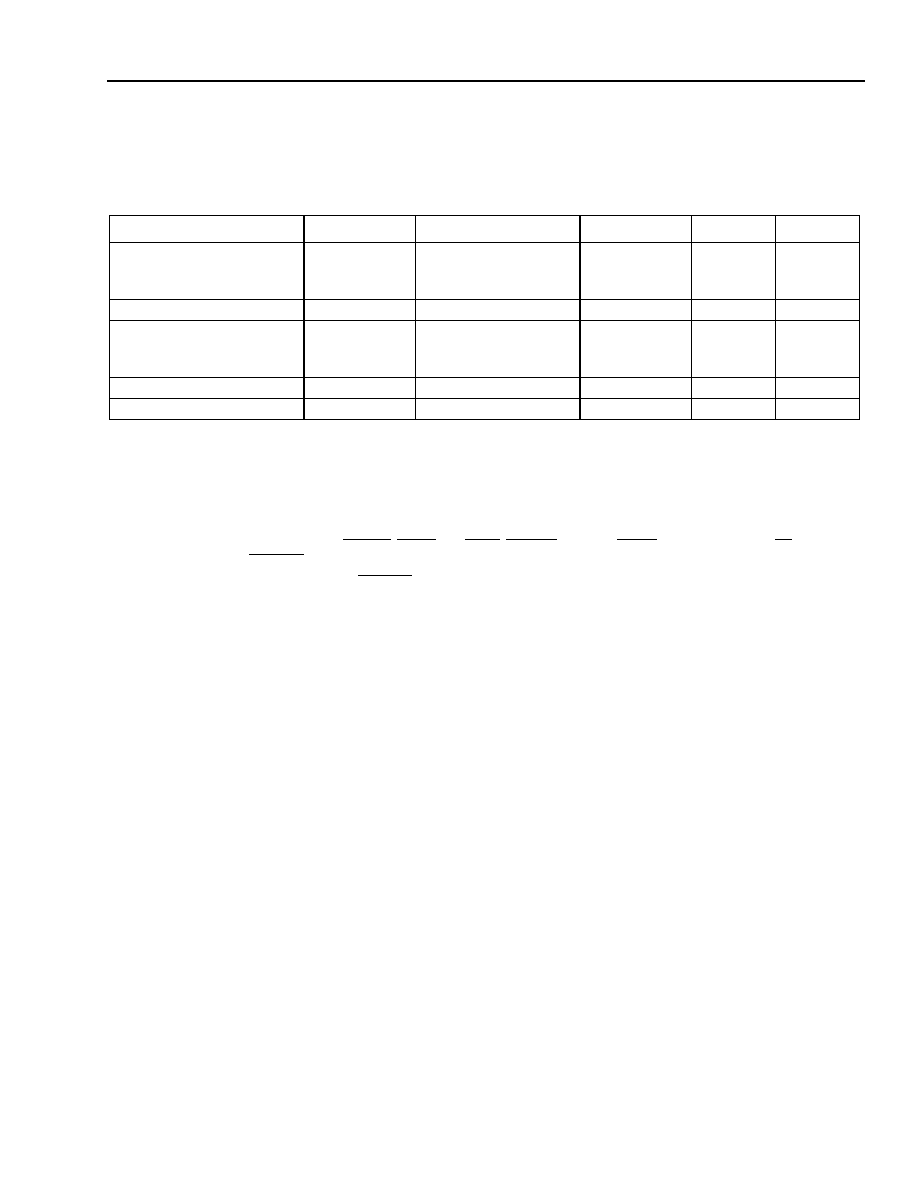

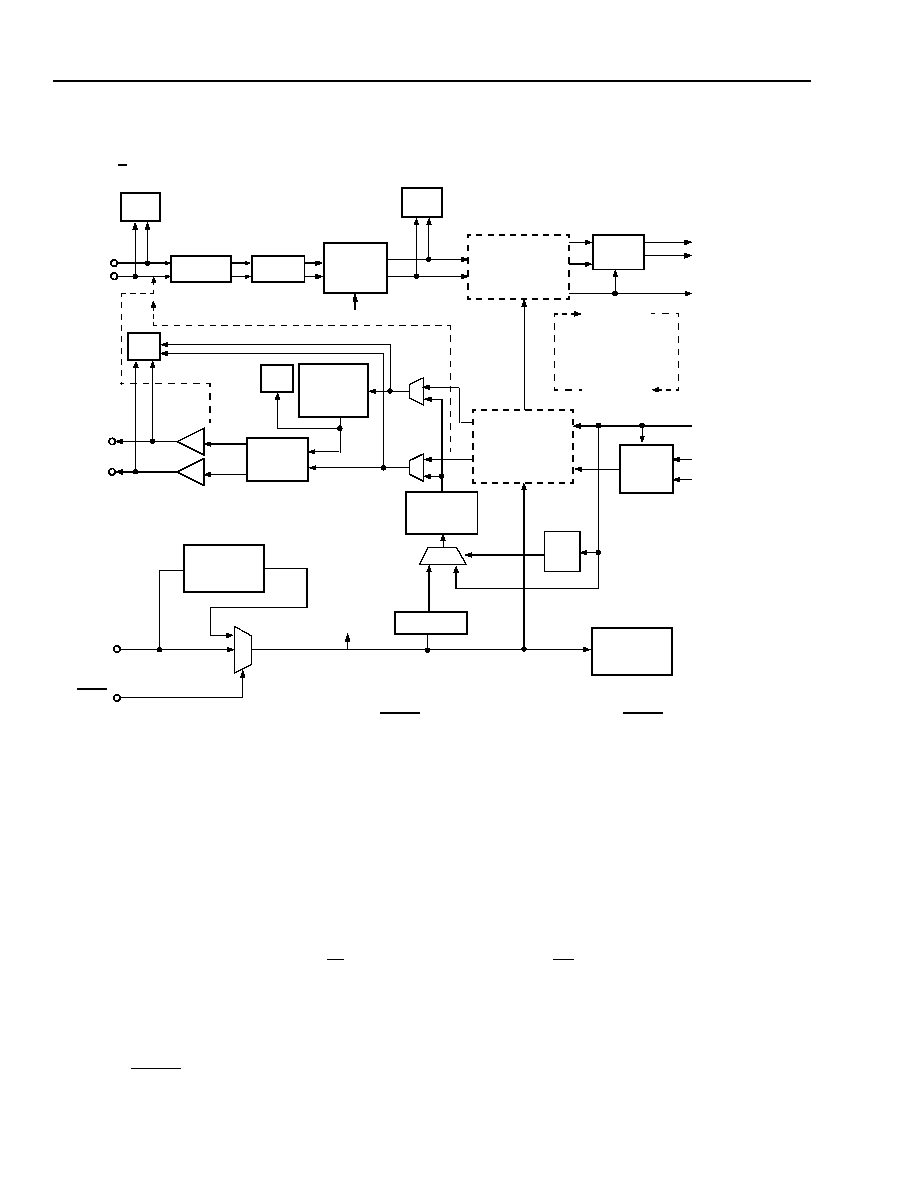

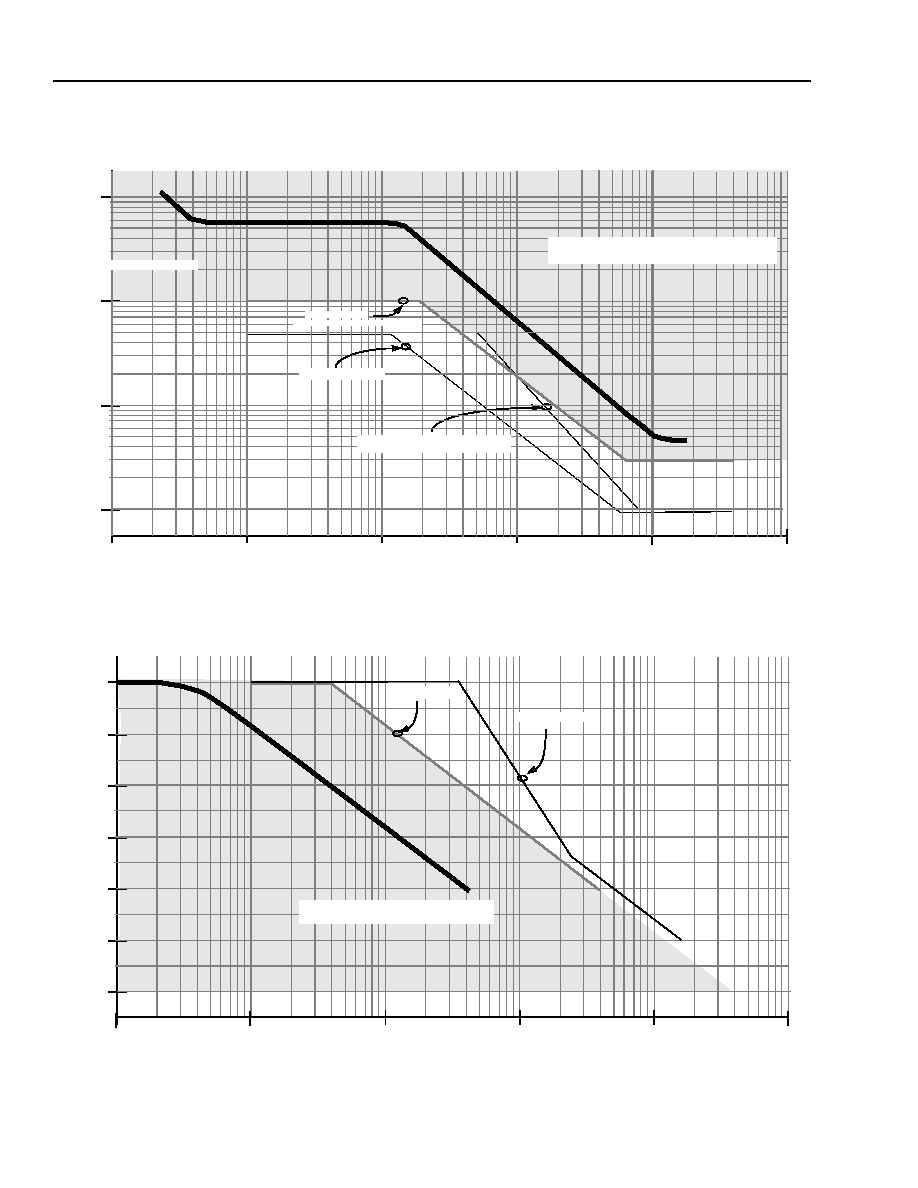

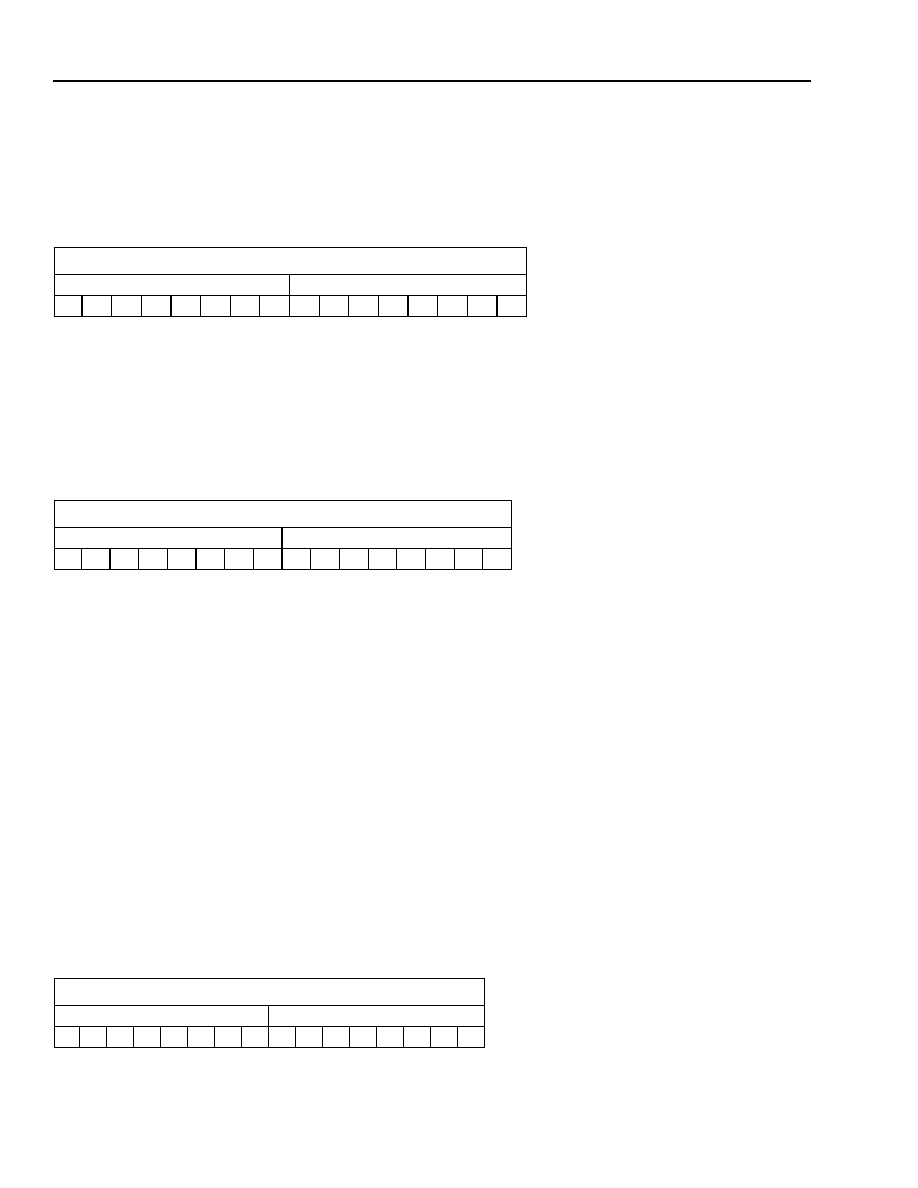

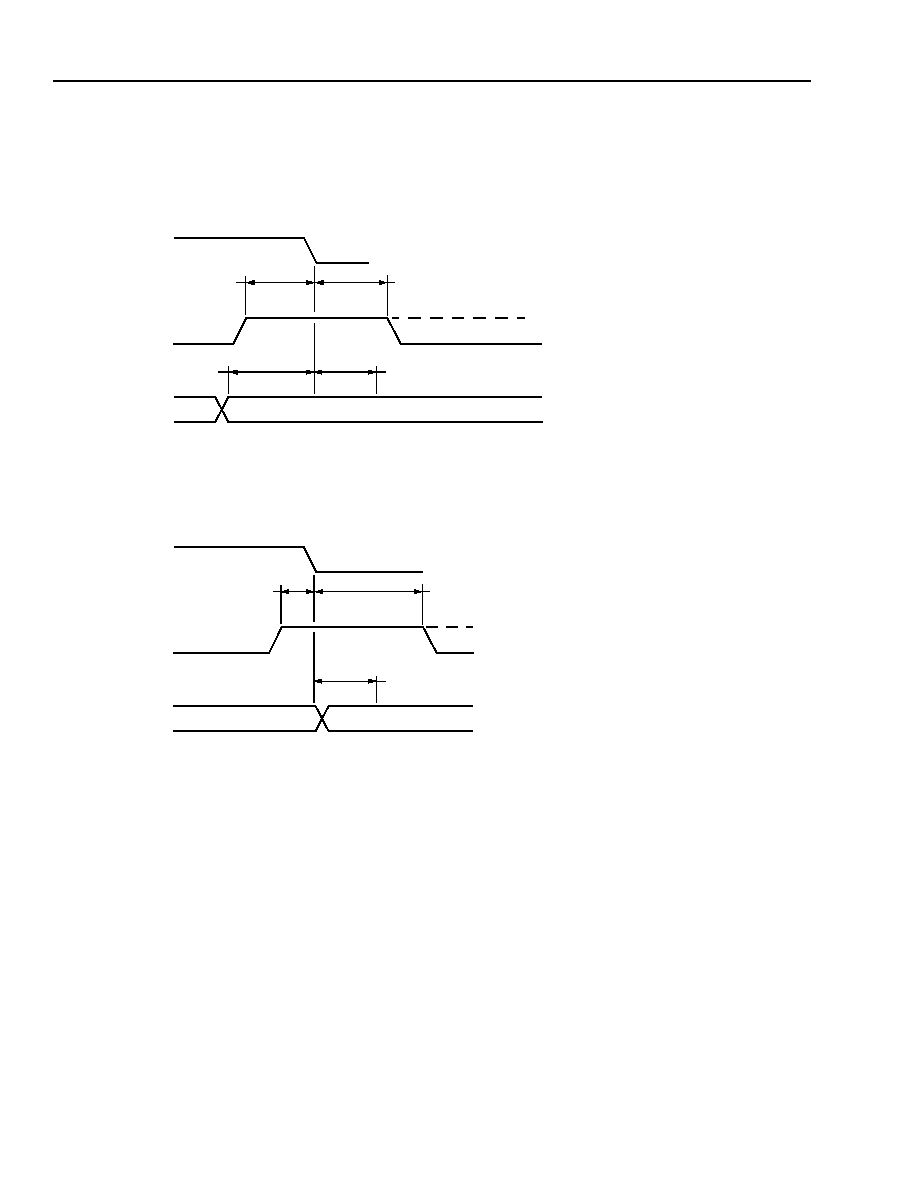

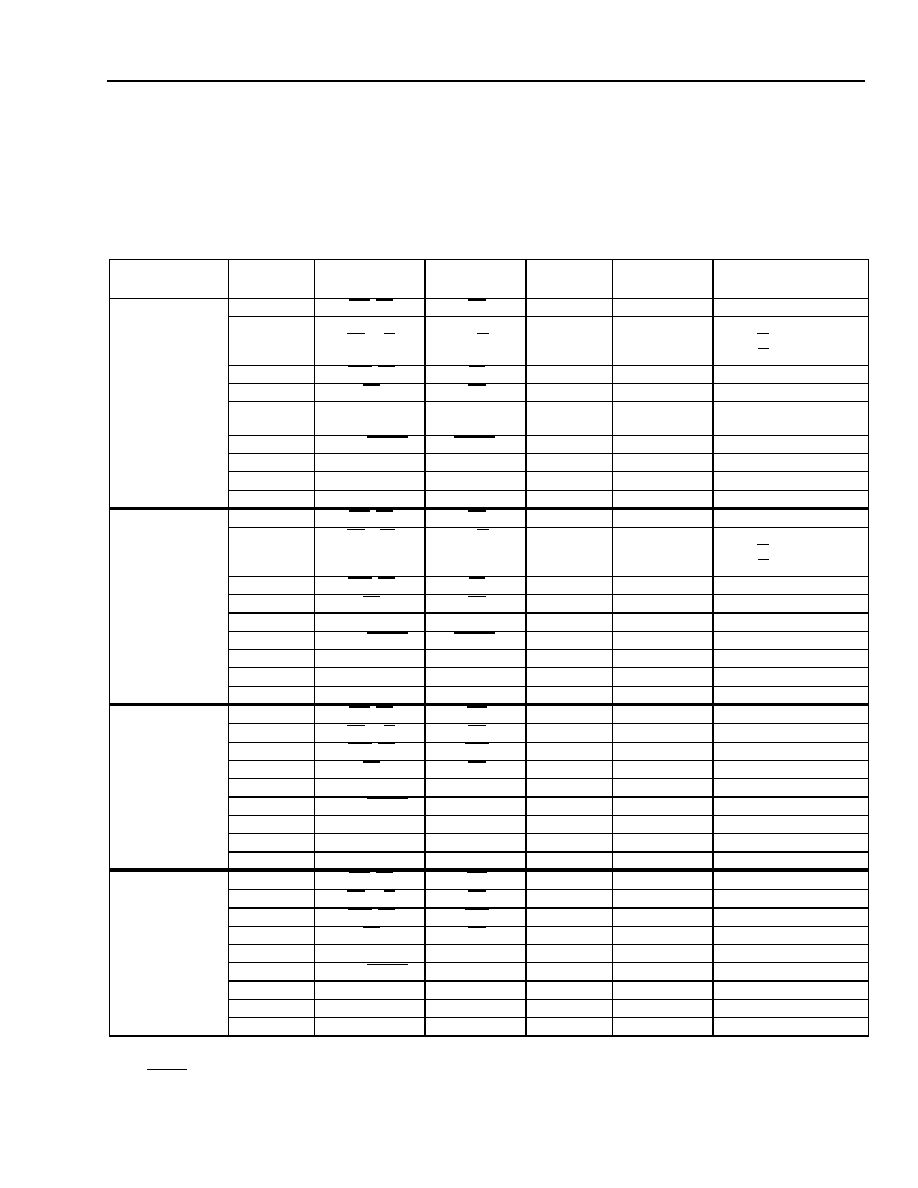

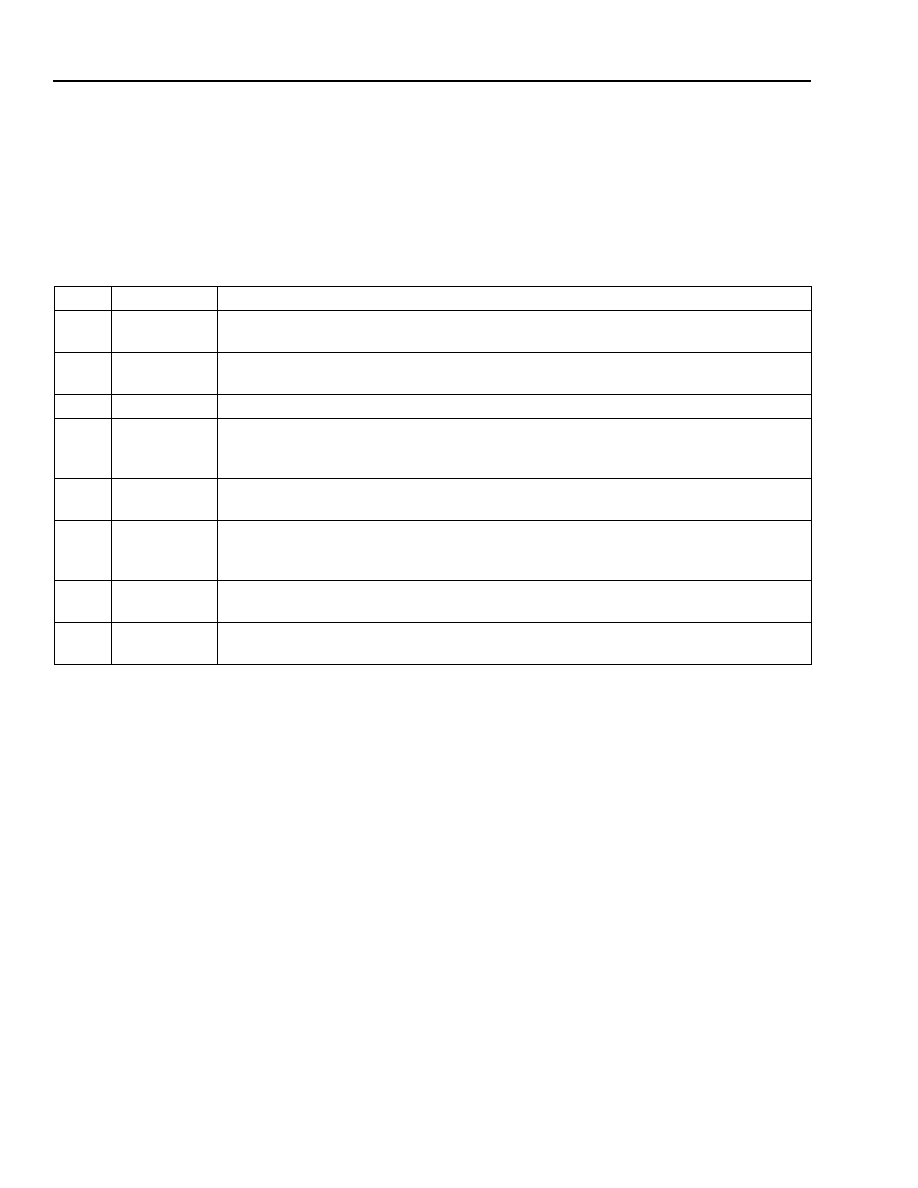

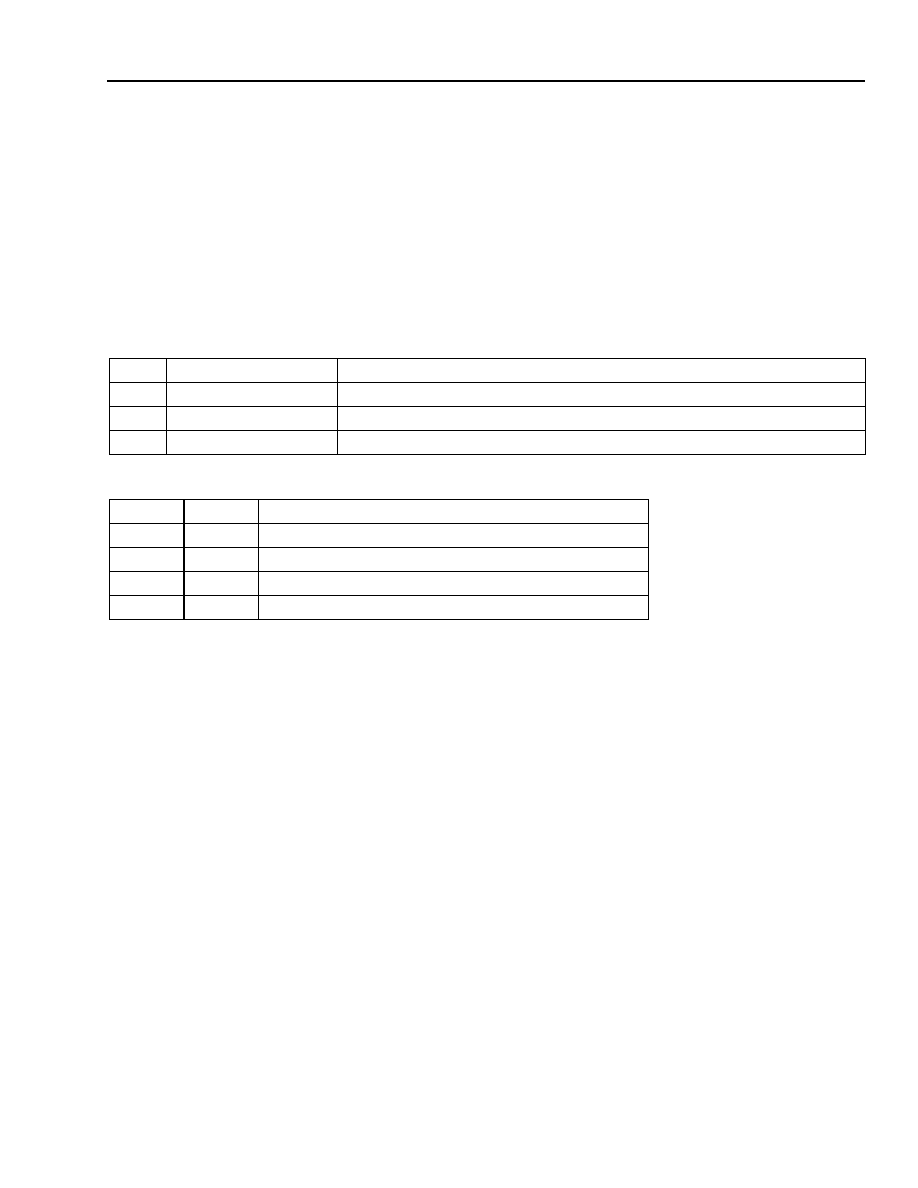

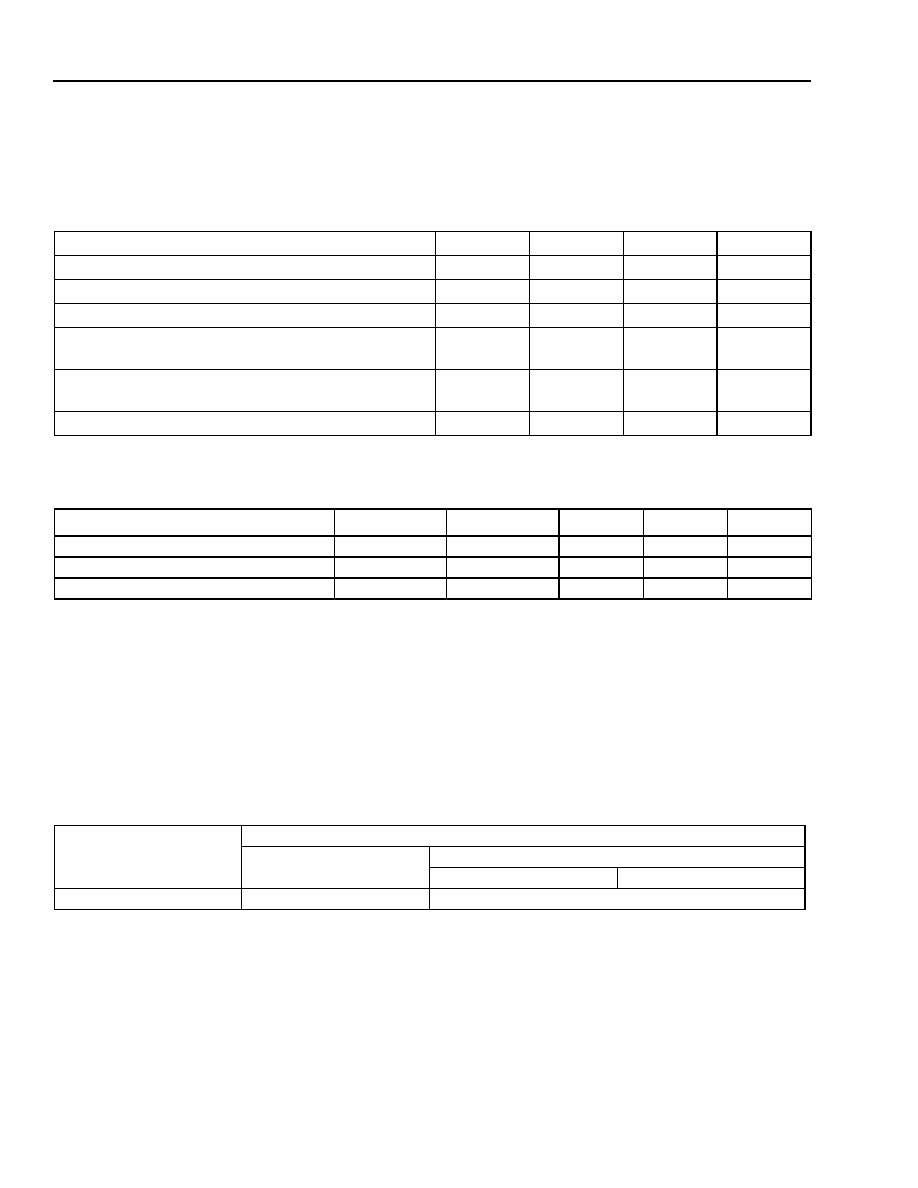

Figure 1. Mode 1--Read Cycle Timing (MPMODE = 0, MPMUX = 0)

5-6423(F)

Figure 2. Mode 1--Write Cycle Timing (MPMODE = 0, MPMUX = 0)

AD[0:7]

DTACK

DS

R/W

A[0:11]

AS

CS

t1

t2

t3

VALID ADDRESS

t5

t6

t7

t8

t10

t9

VALID DATA

t13

t15

t14

t12

t11

AD[0:7]

DTACK

DS

R/W

A[0:11]

AS

CS

t1

t2

t3

VALID ADDRESS

t16

t25

t7

t8

t17

VALID DATA

t13

t19

t14

t12

t18

t5

t20

Agere Systems Inc.

5

Device Advisory

September 1999

T7633 Device Advisory for Version 1.0 of the Device

Microprocessor Interface

(continued)

I/O Timing

(continued)

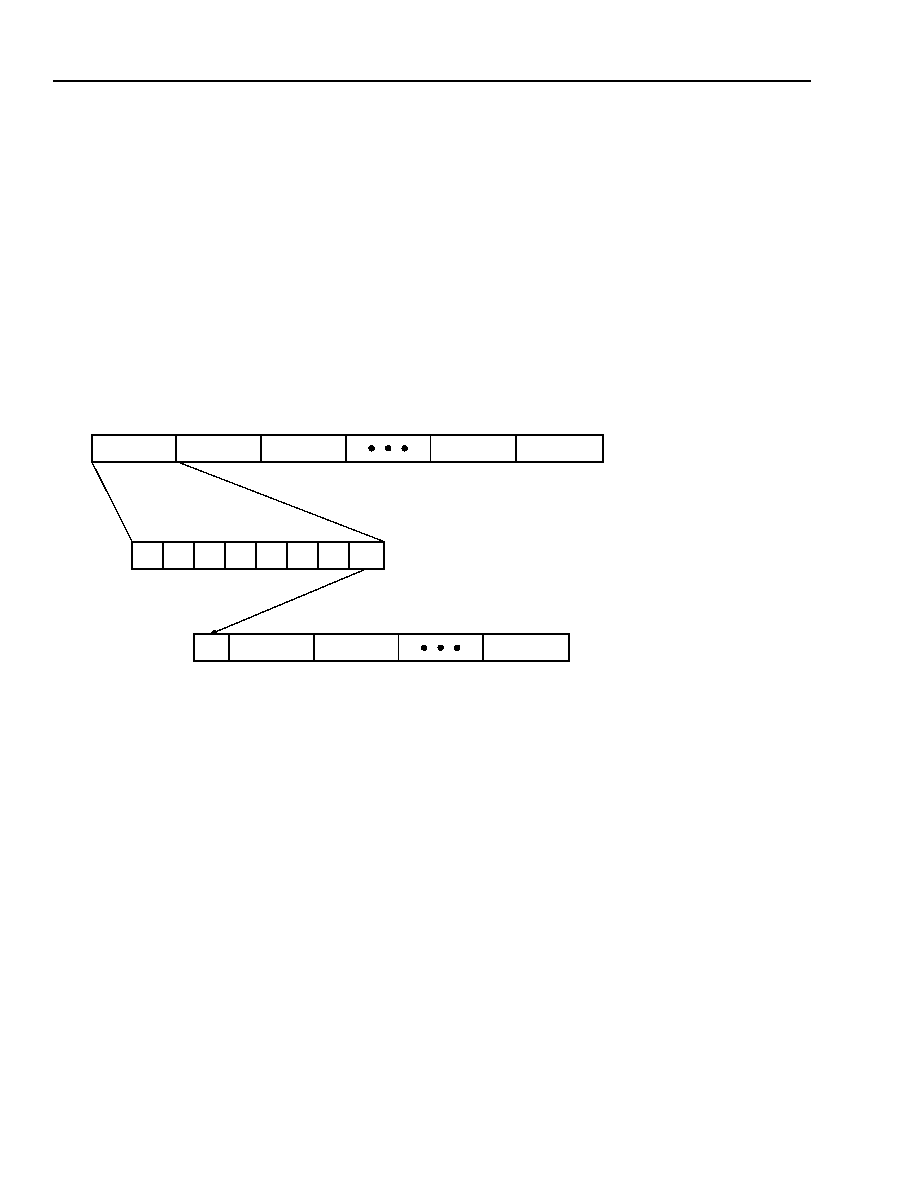

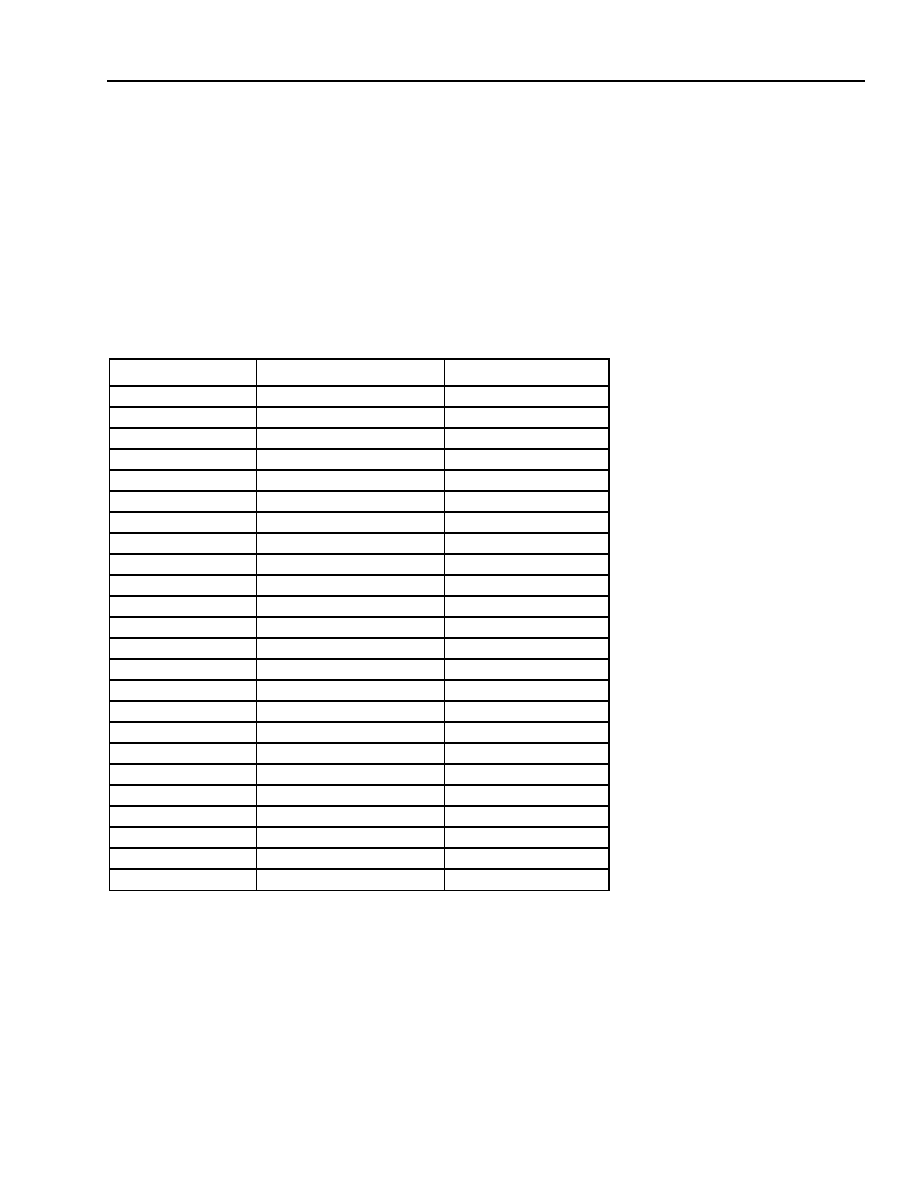

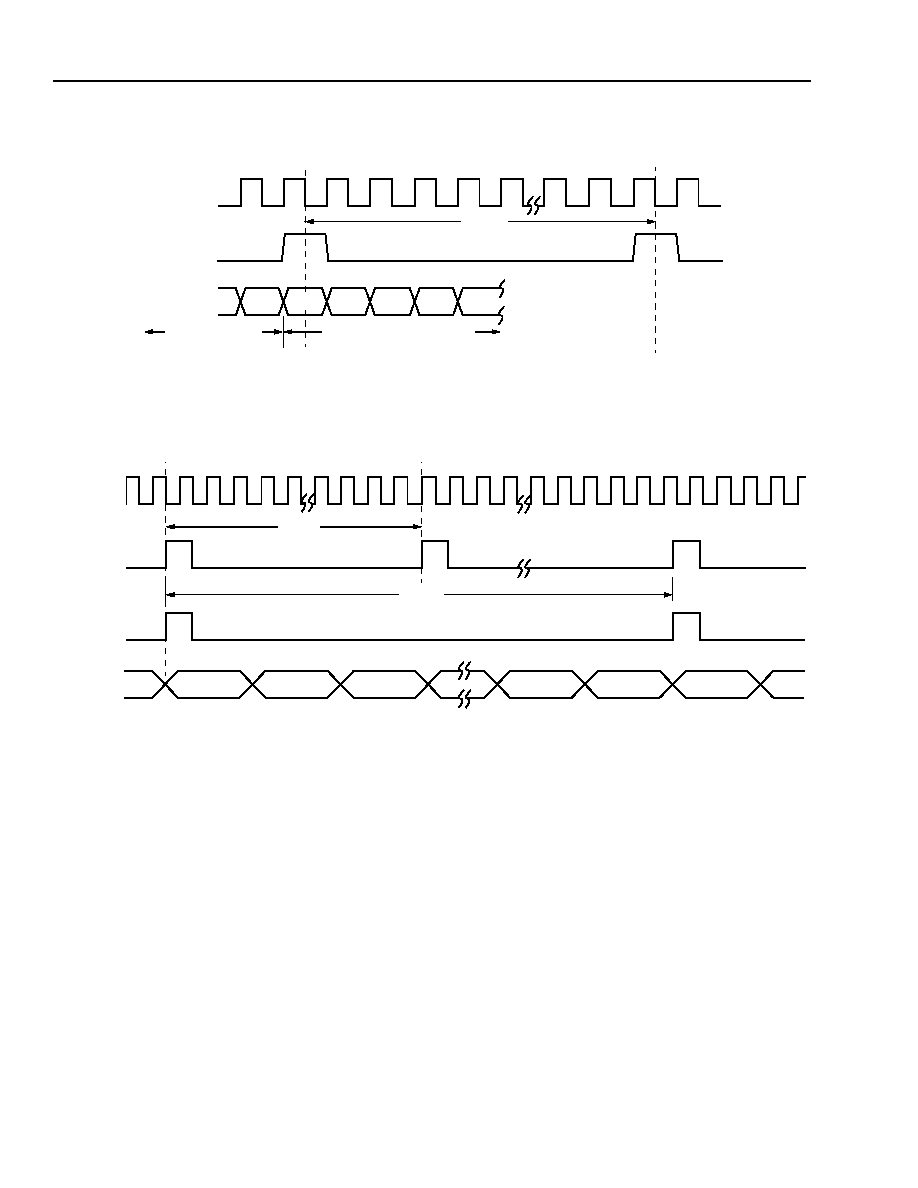

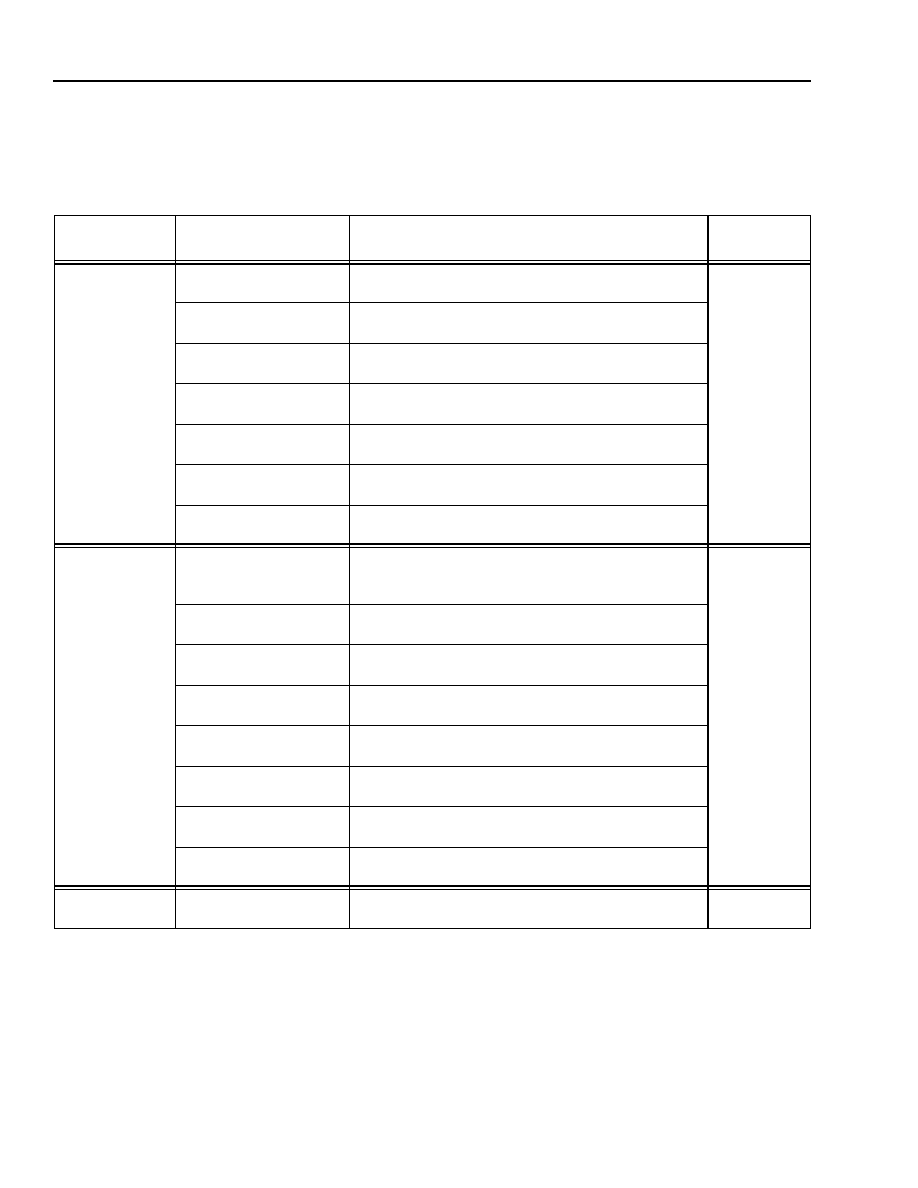

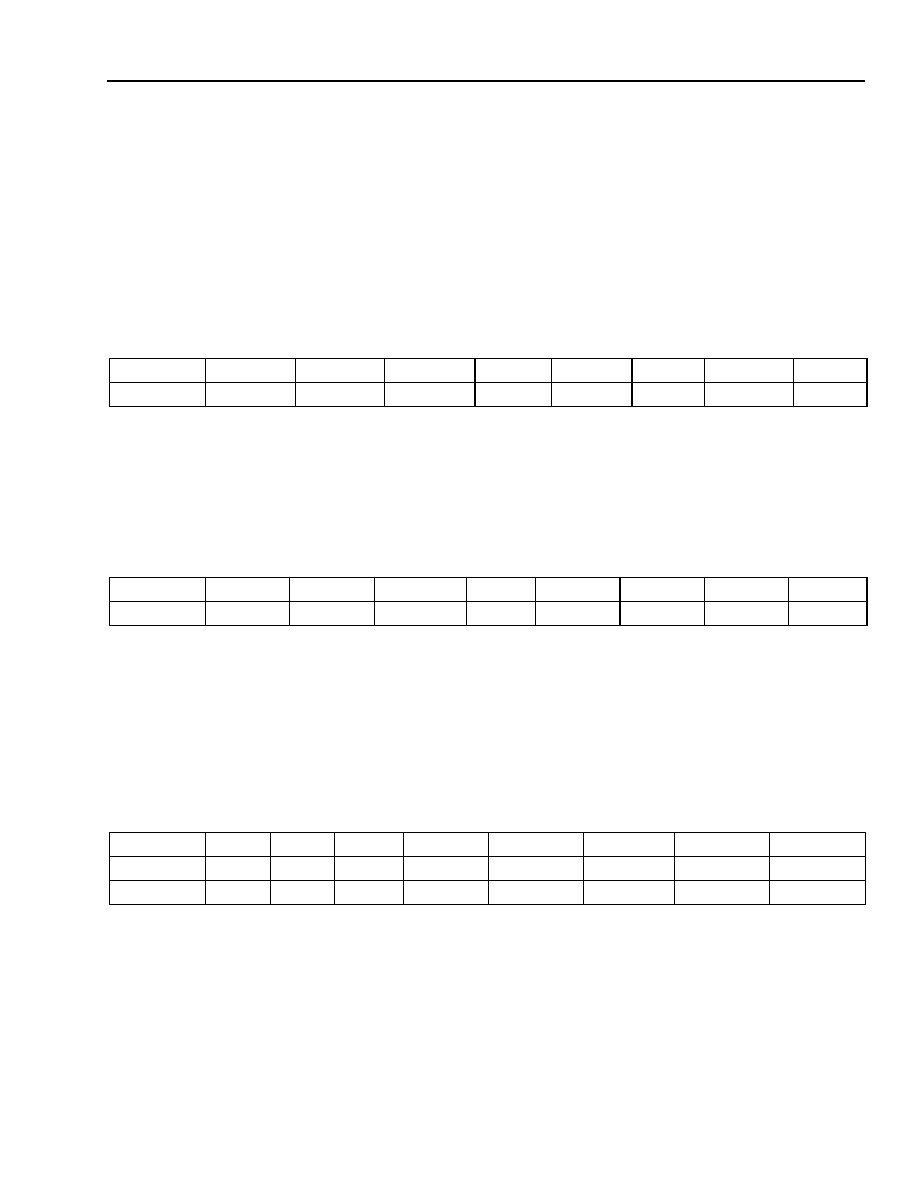

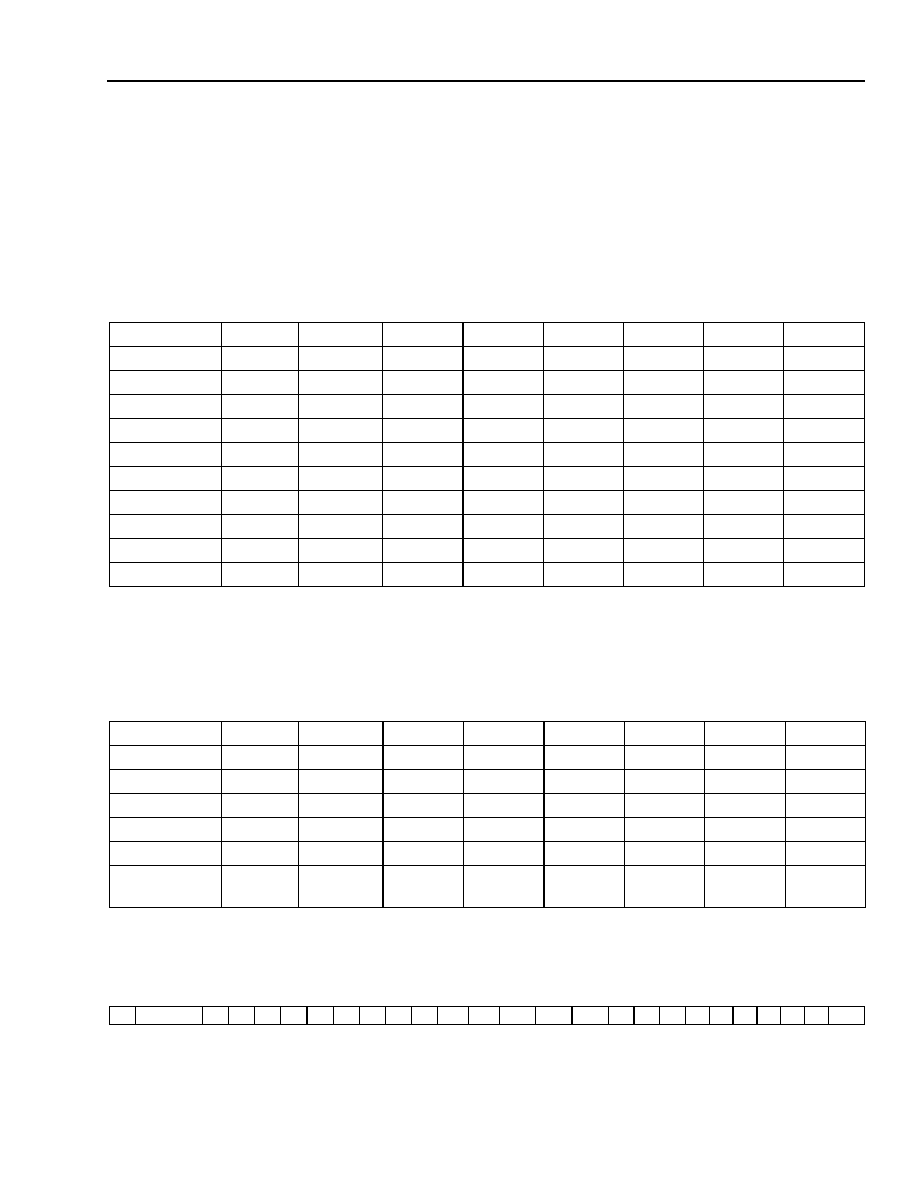

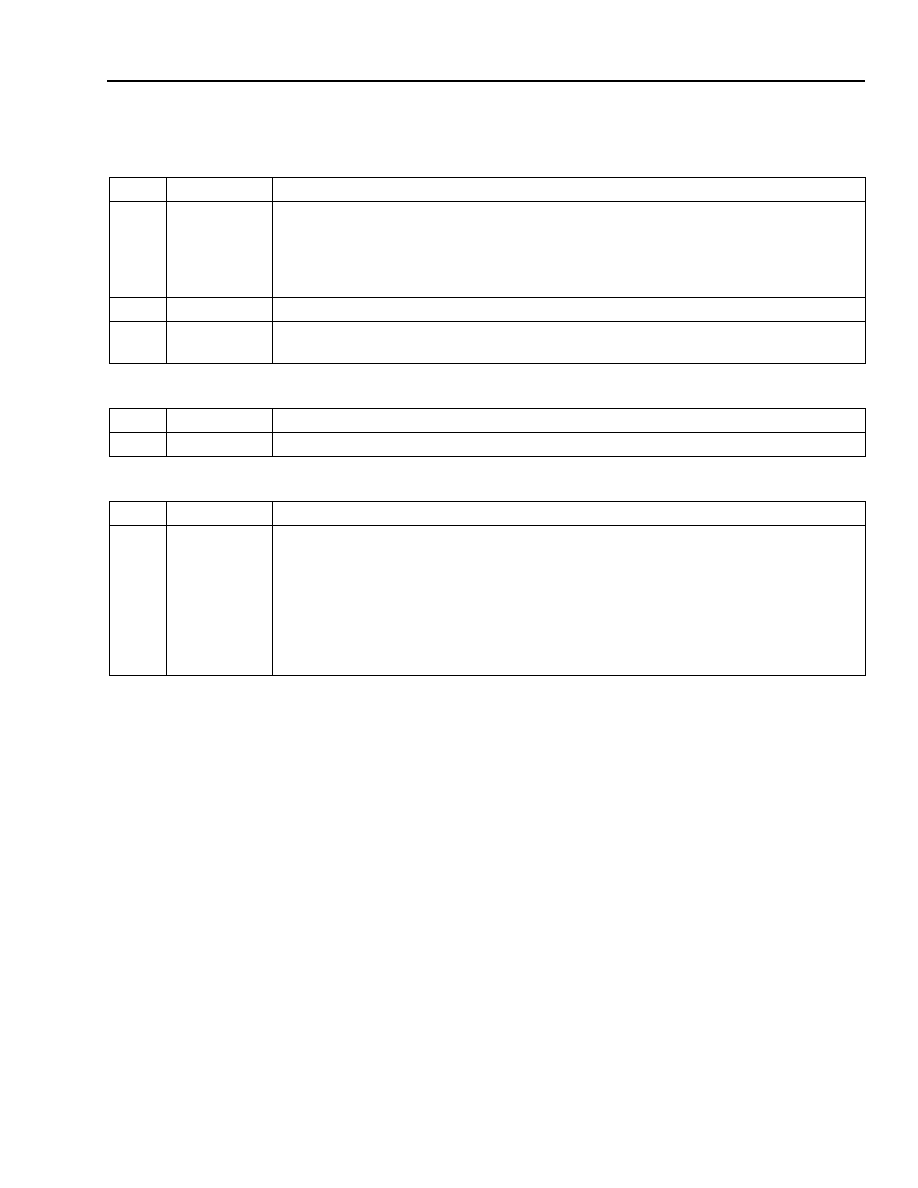

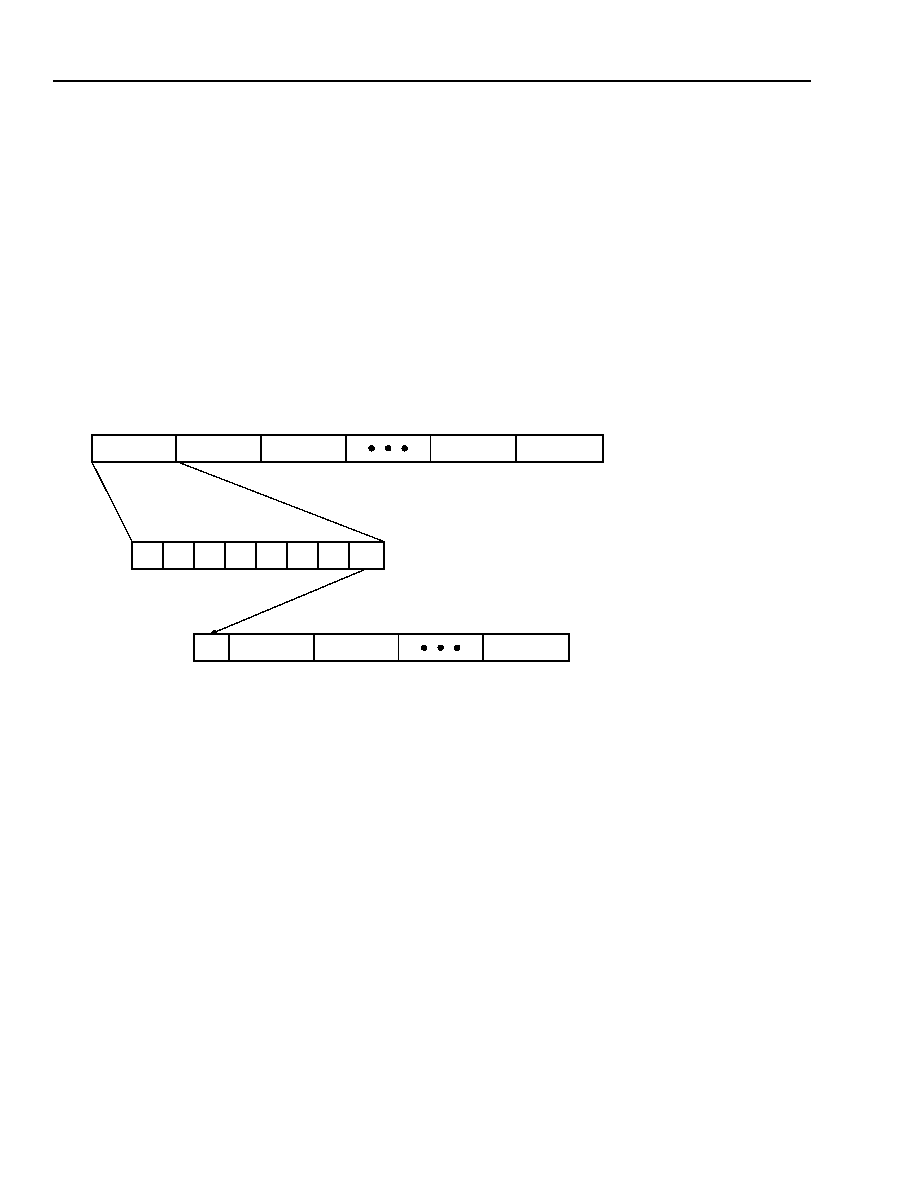

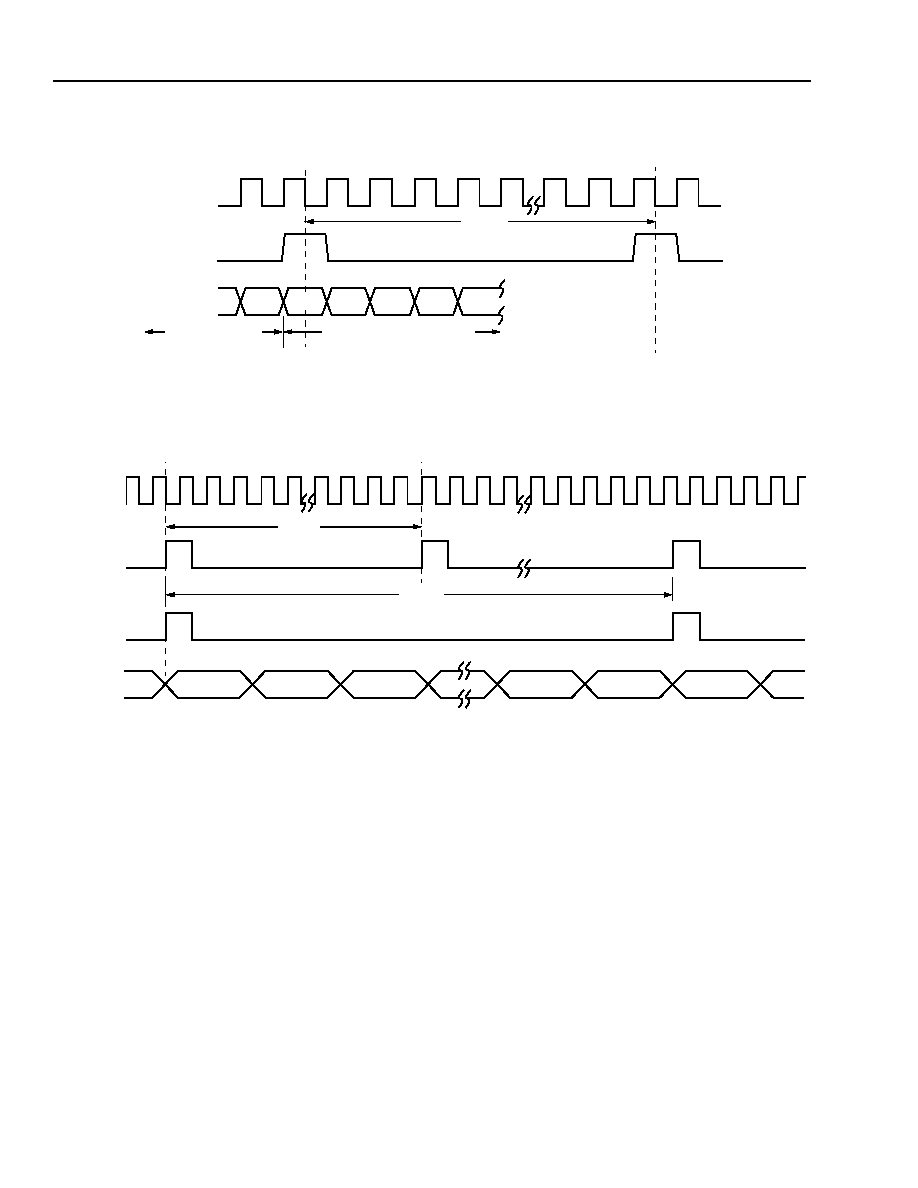

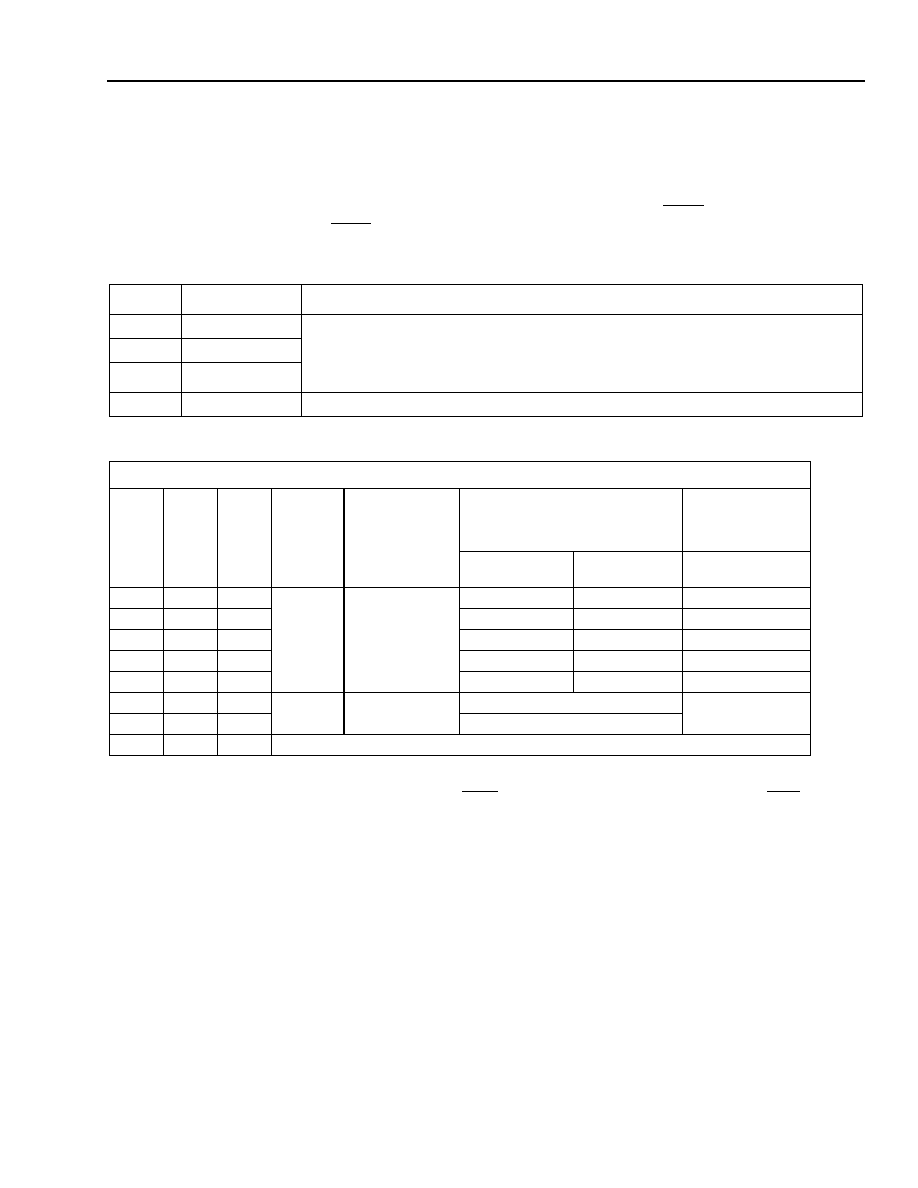

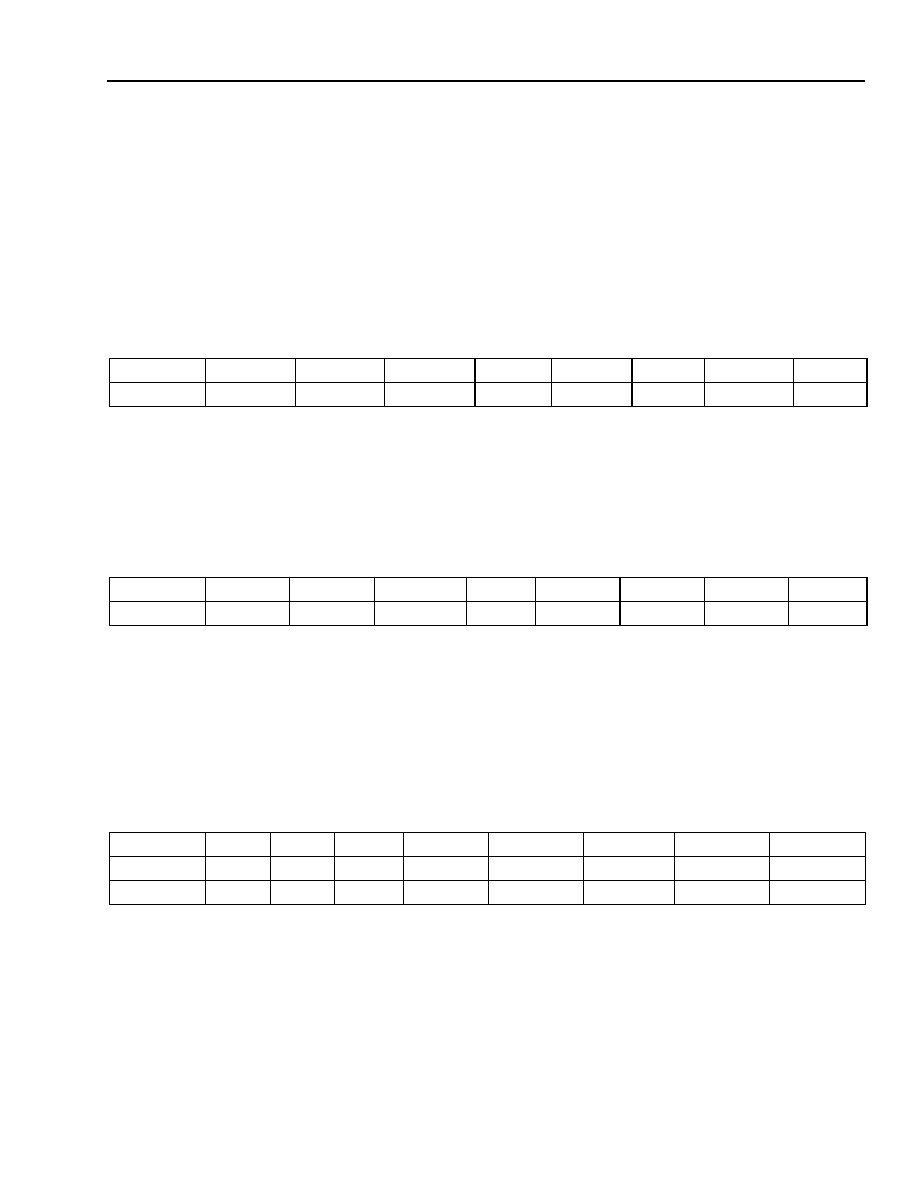

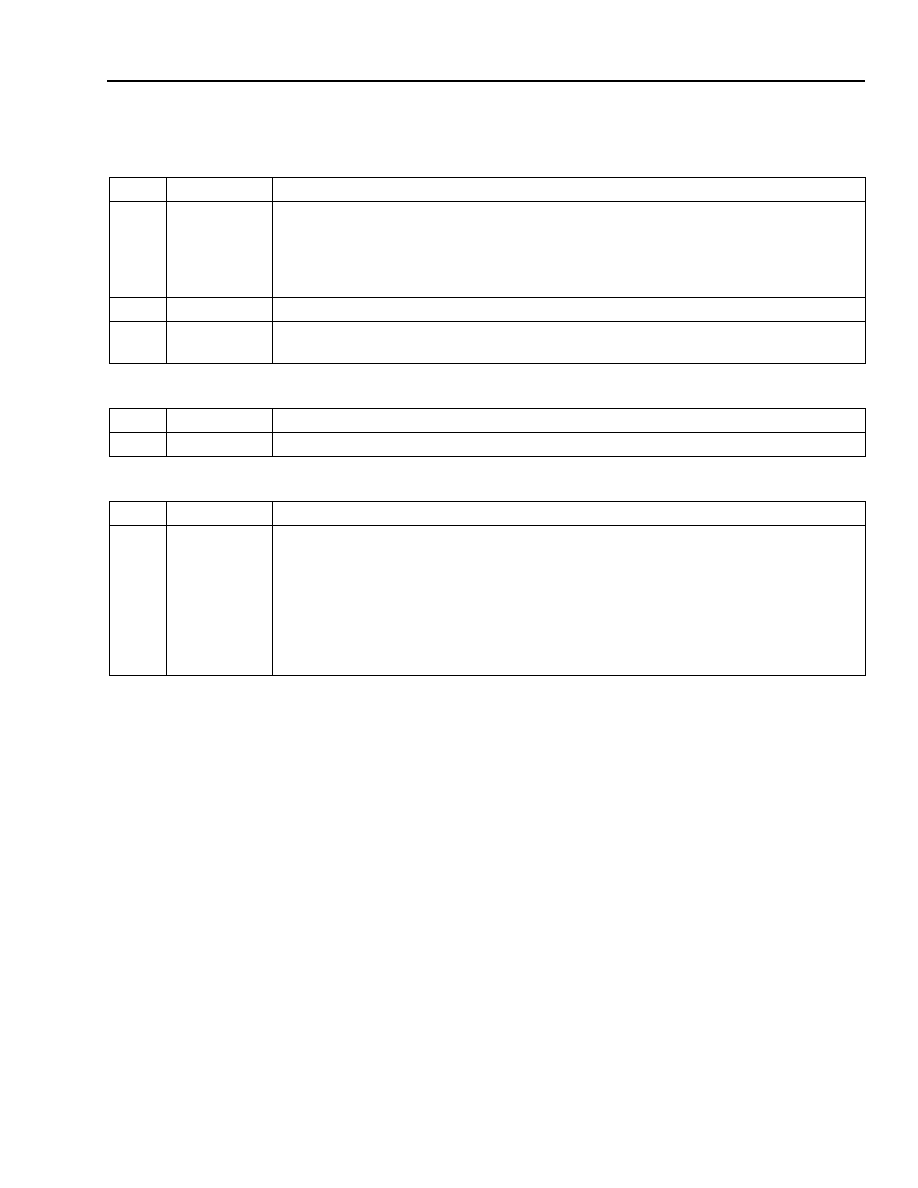

5-6424(F)

Figure 3. Mode 2--Read Cycle Timing (MPMODE = 0, MPMUX = 1)

5-6425(F)

Figure 4. Mode 2--Write Cycle Timing (MPMODE = 0, MPMUX = 1)

AD[0:7]

DTACK

DS

R/W

A[8:11]

AS

CS

t1

t21

t22

VALID ADDRESS

t5

t23

t7

t8

t10

t9

VALID DATA

t13

t15

t14

t12

t11

VALID ADDRESS

t21

t22

AD[0:7]

DTACK

DS

R/W

A[8:11]

AS

CS

t1

t21

t22

VALID ADDRESS

t5

t24

t7

t8

t17

VALID DATA

t13

t19

t14

t12

t18

VALID ADDRESS

t21

t22

t25

t20

6

Agere Systems Inc.

Device Advisory

September 1999

T7633 Device Advisory for Version 1.0 of the Device

Microprocessor Interface

(continued)

I/O Timing

(continued)

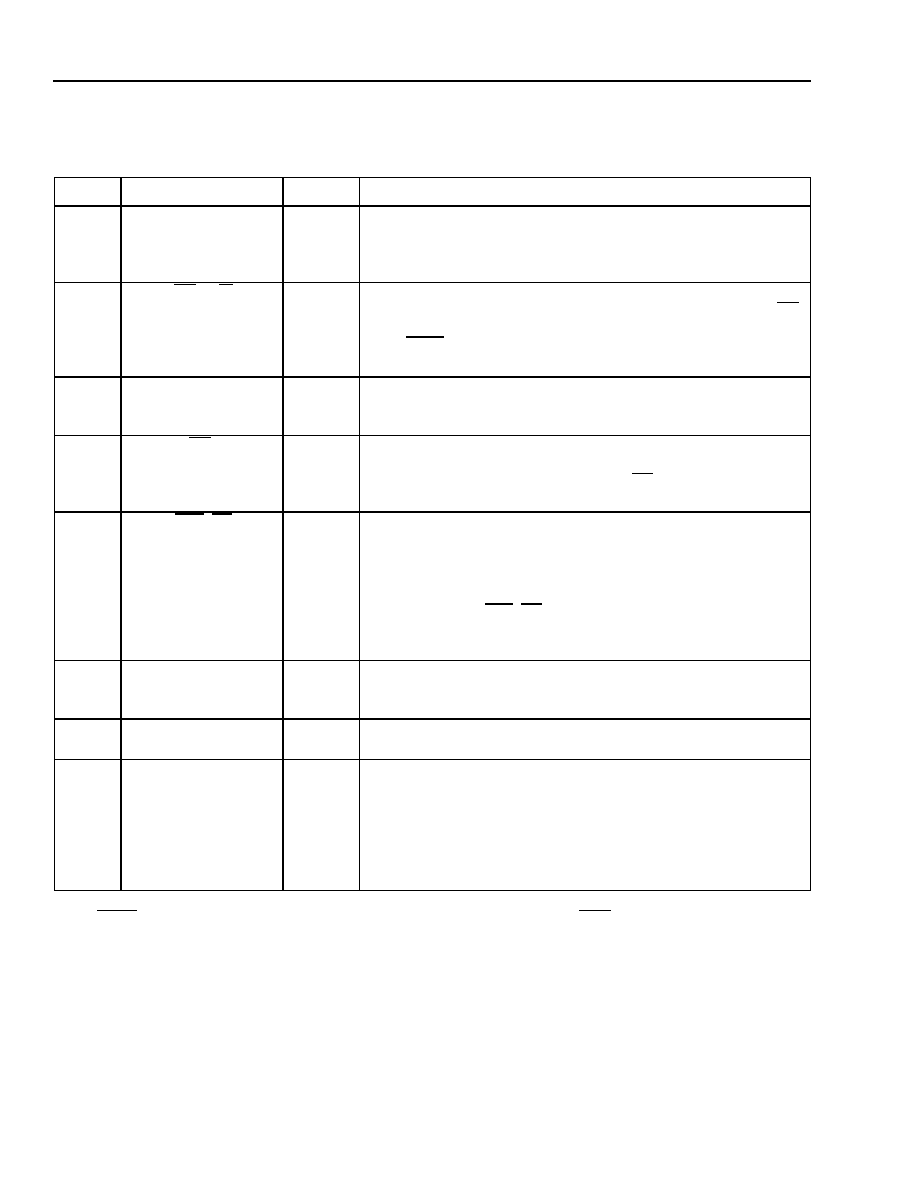

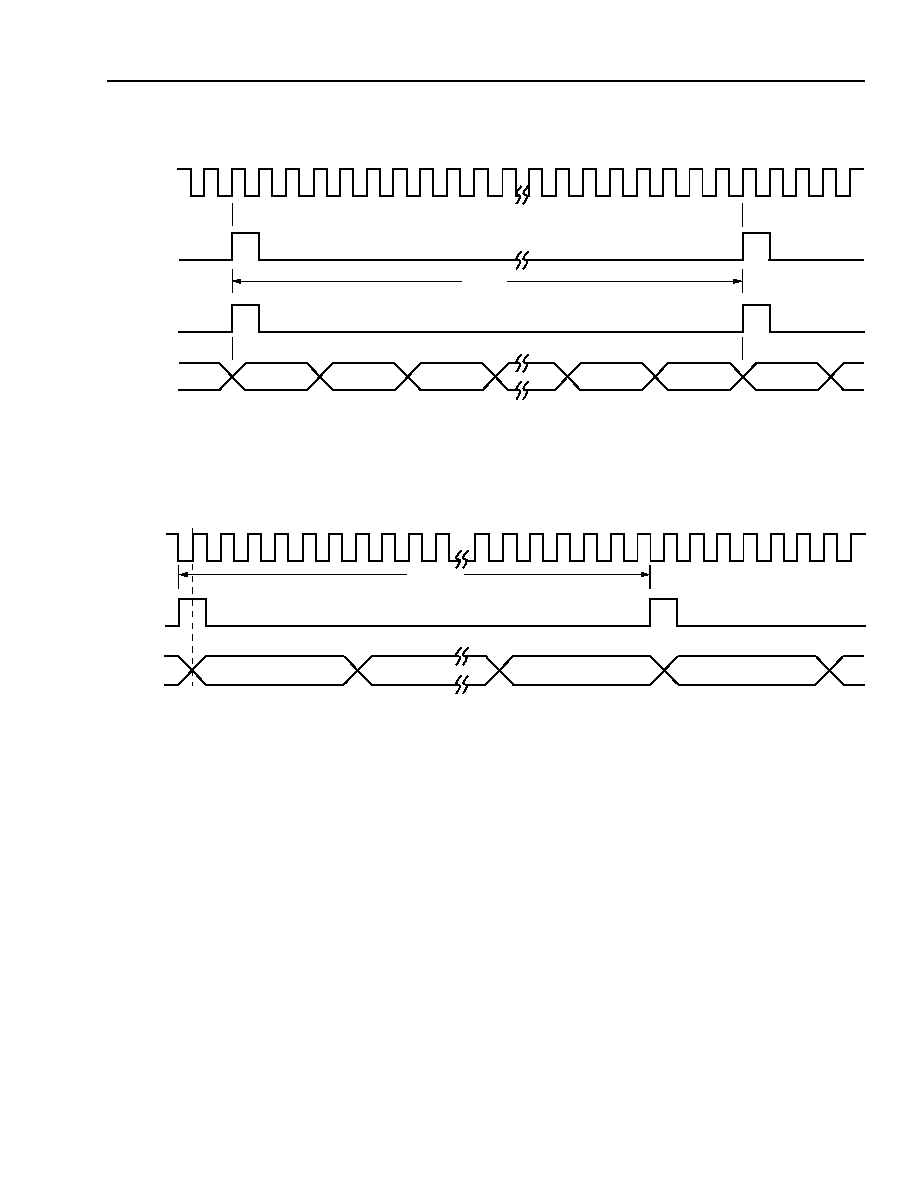

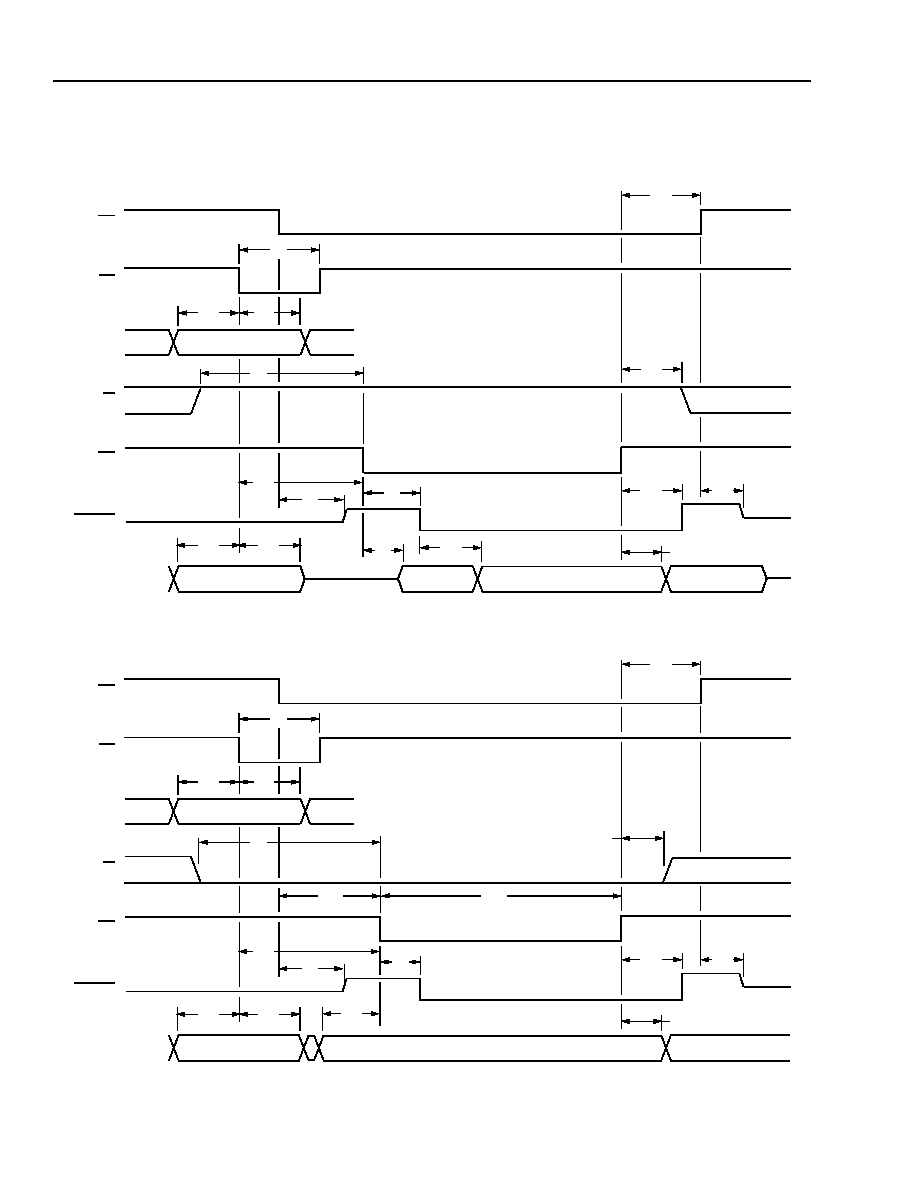

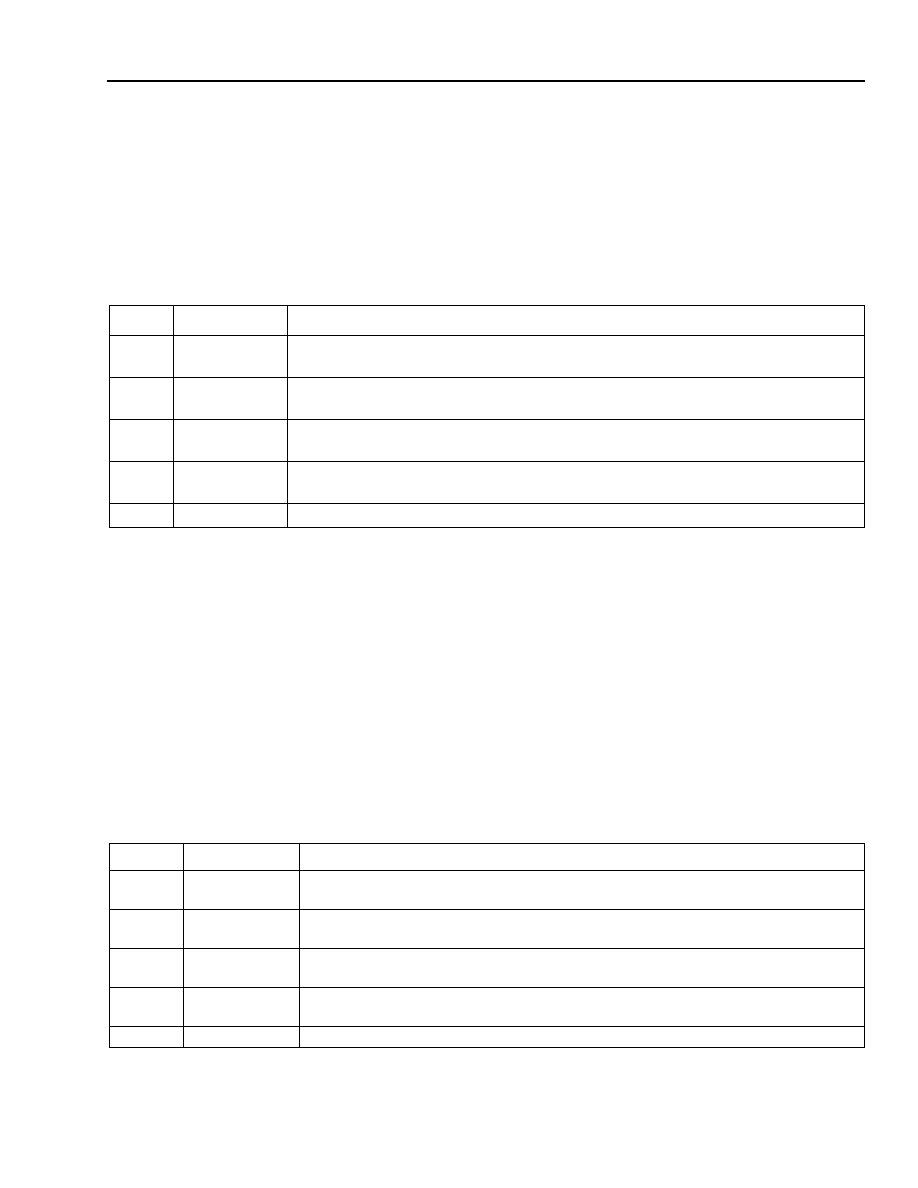

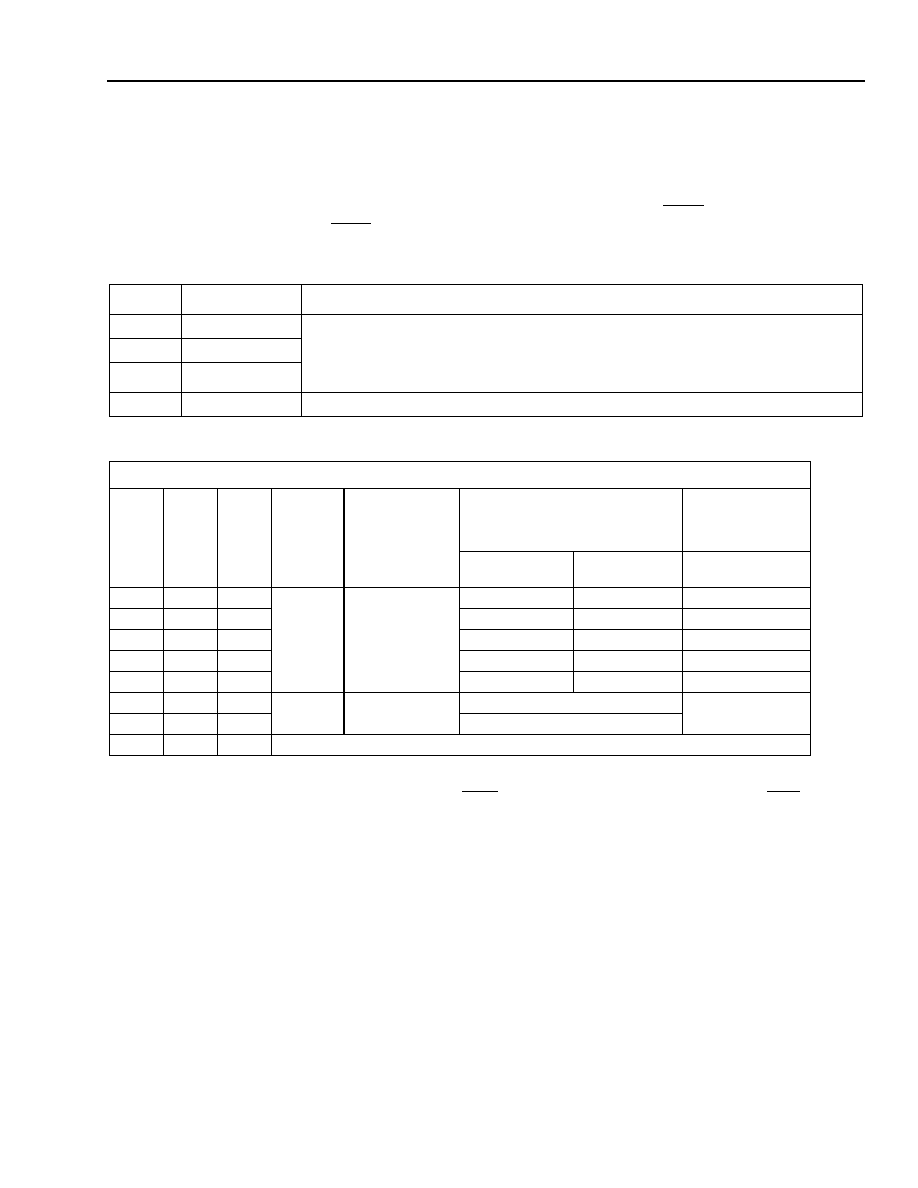

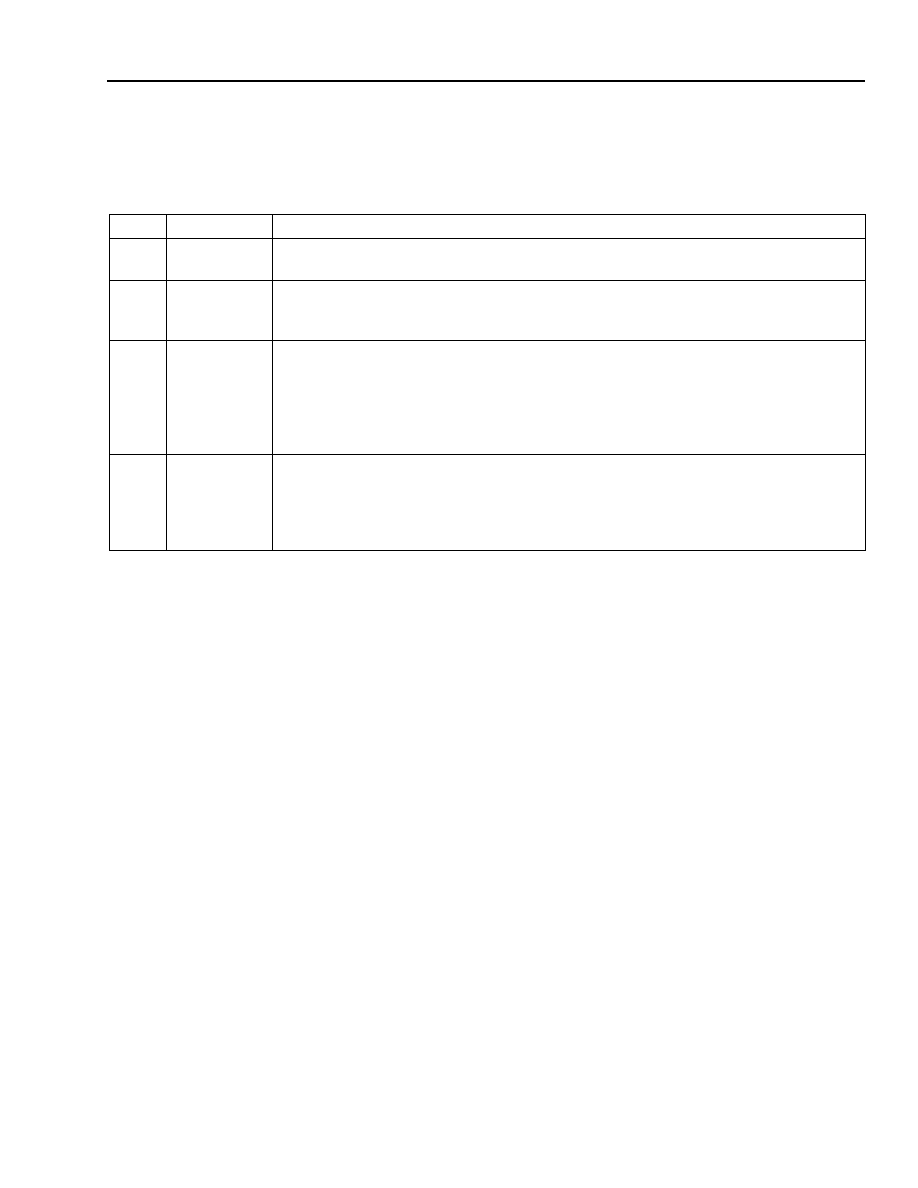

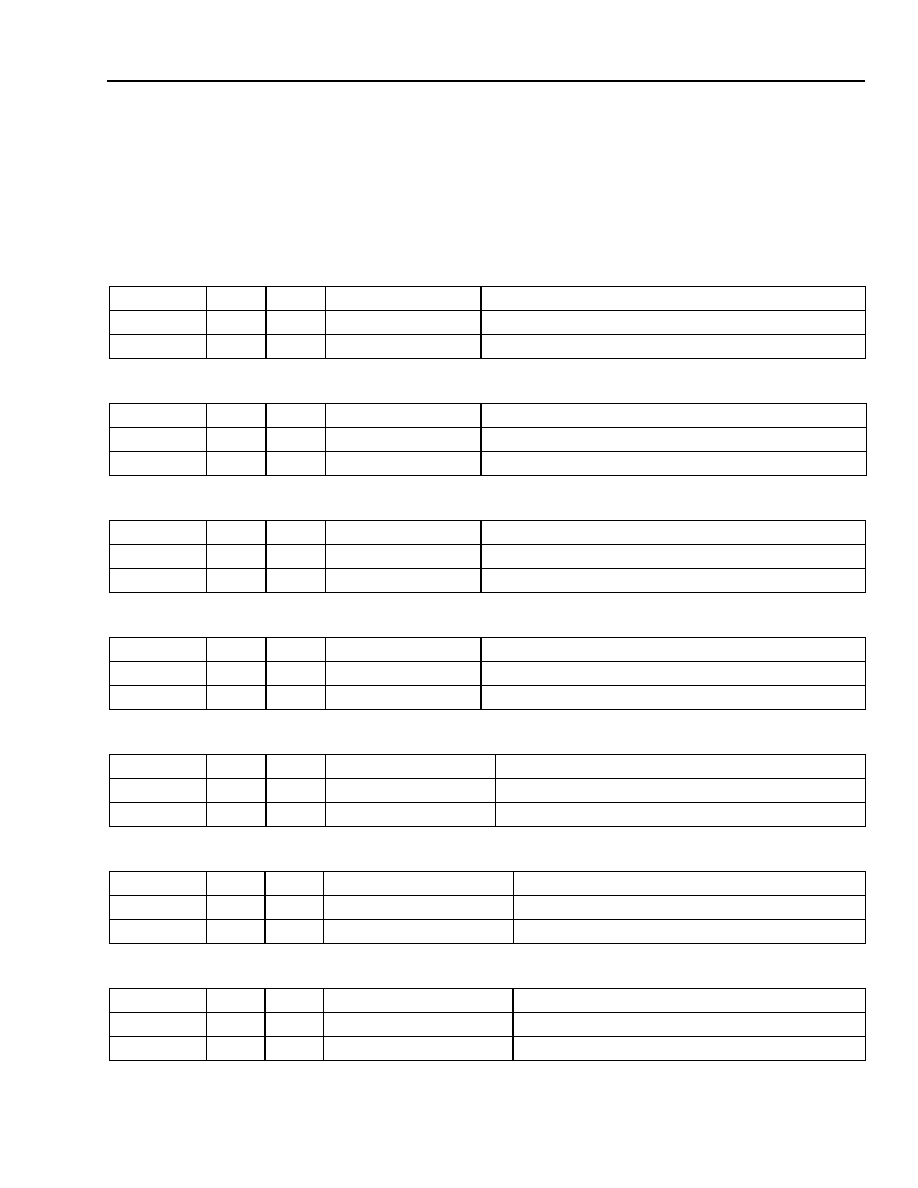

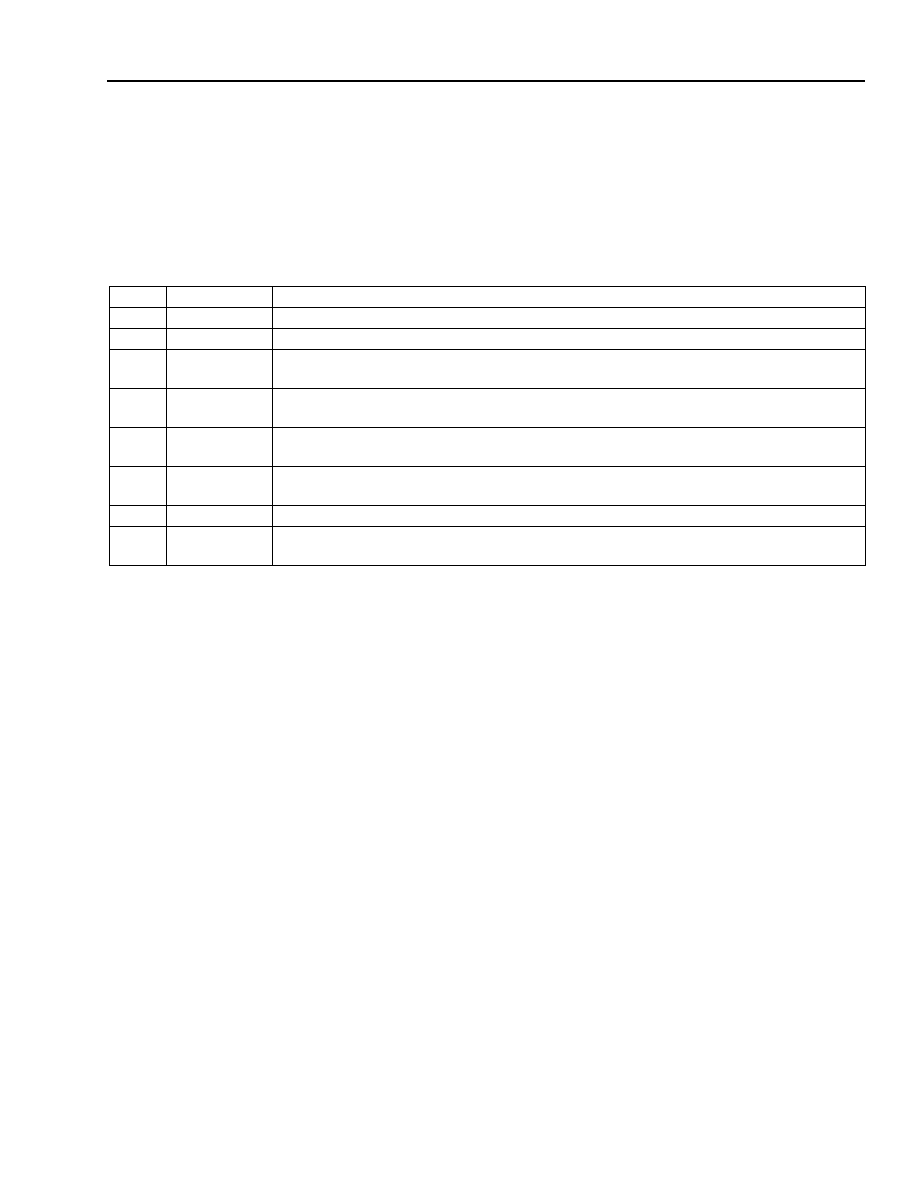

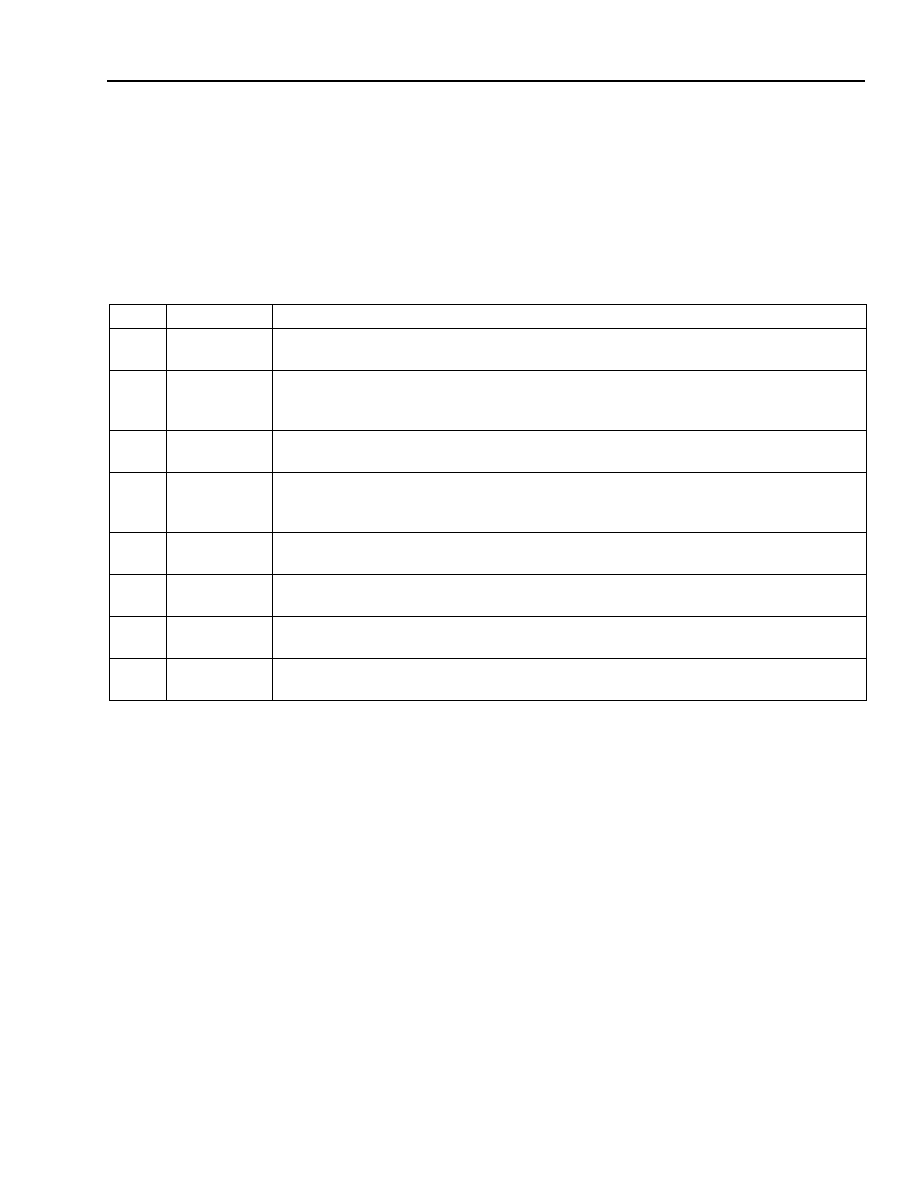

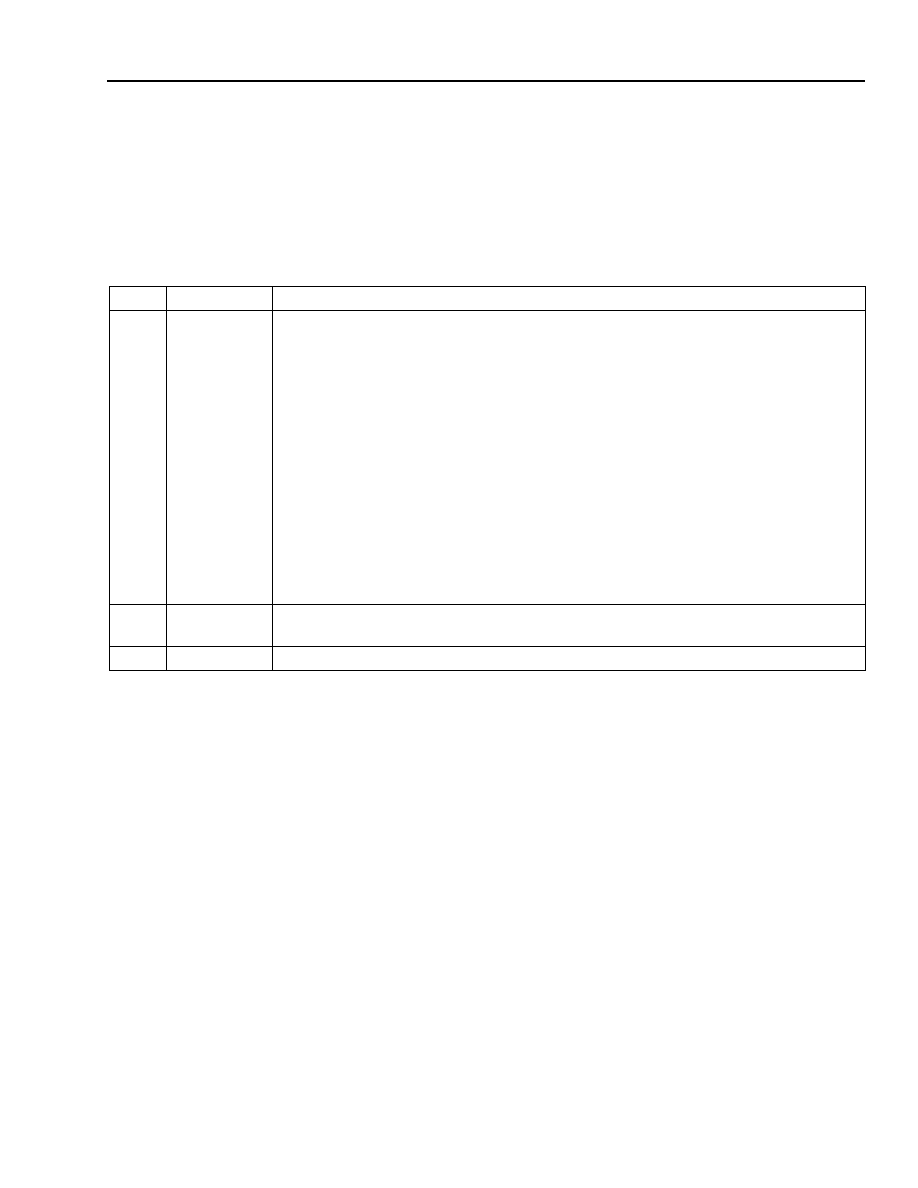

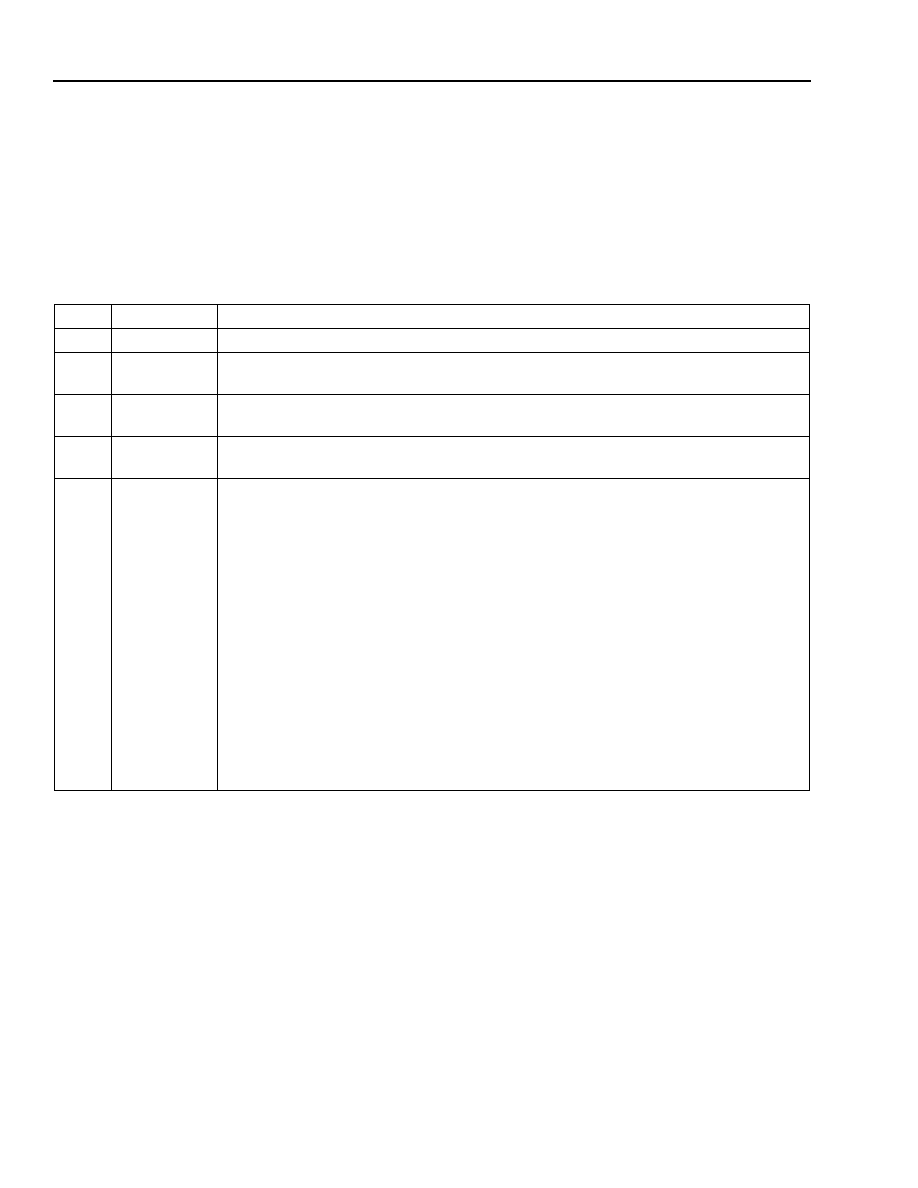

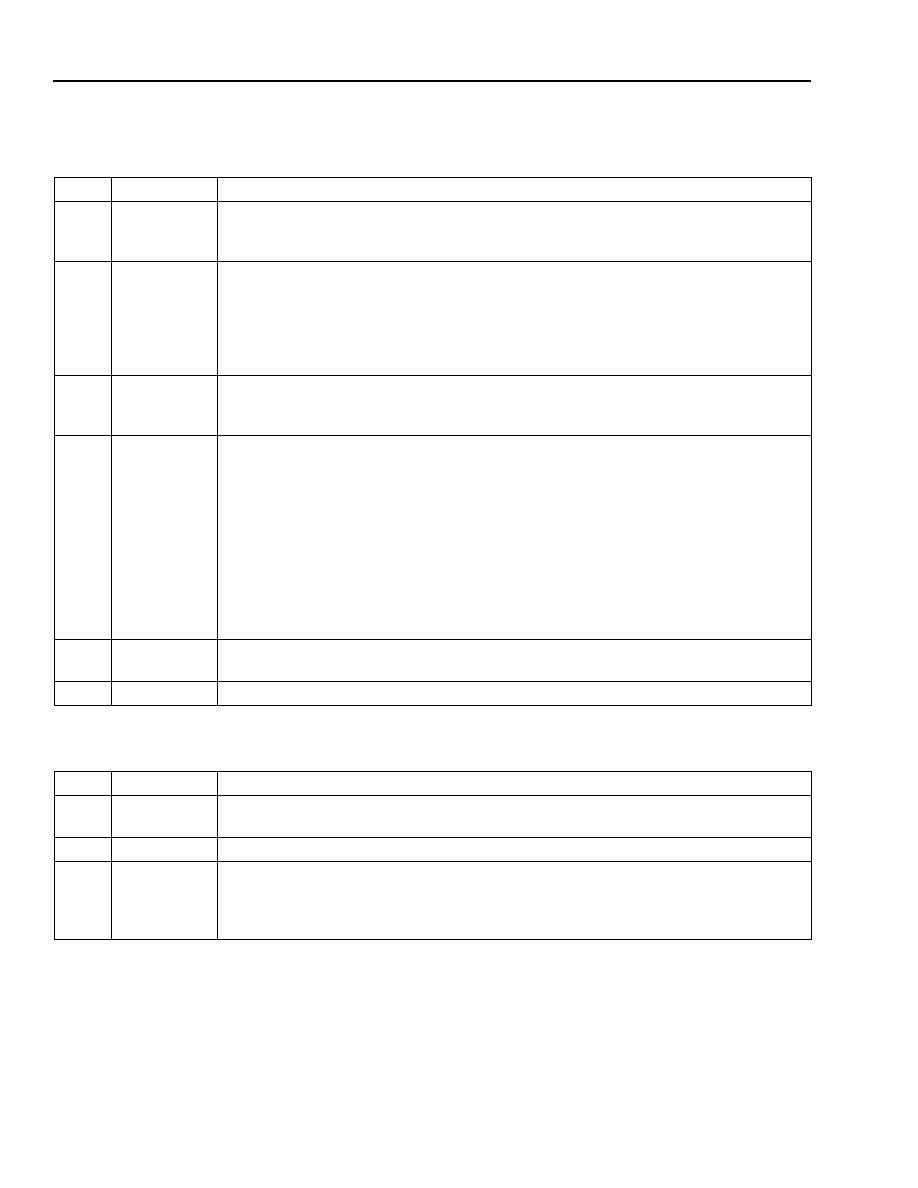

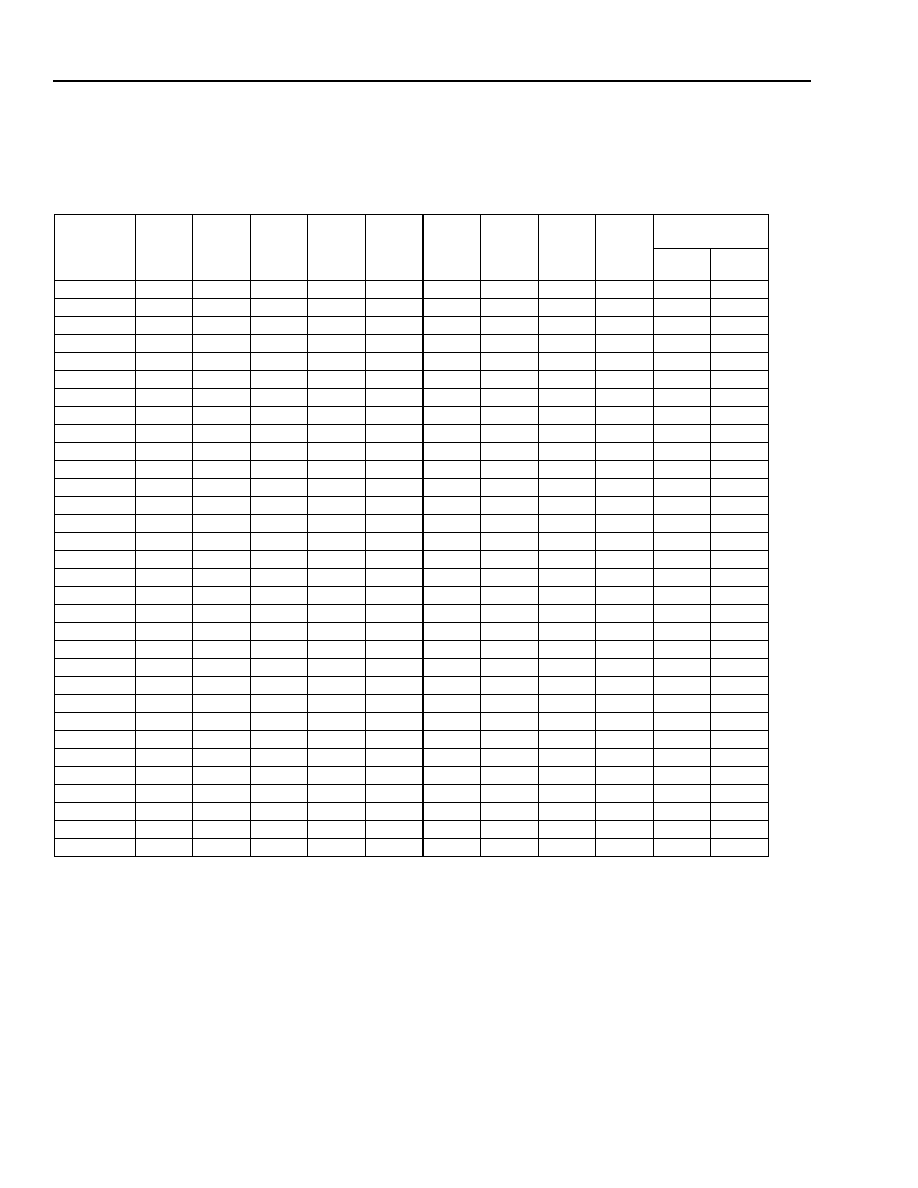

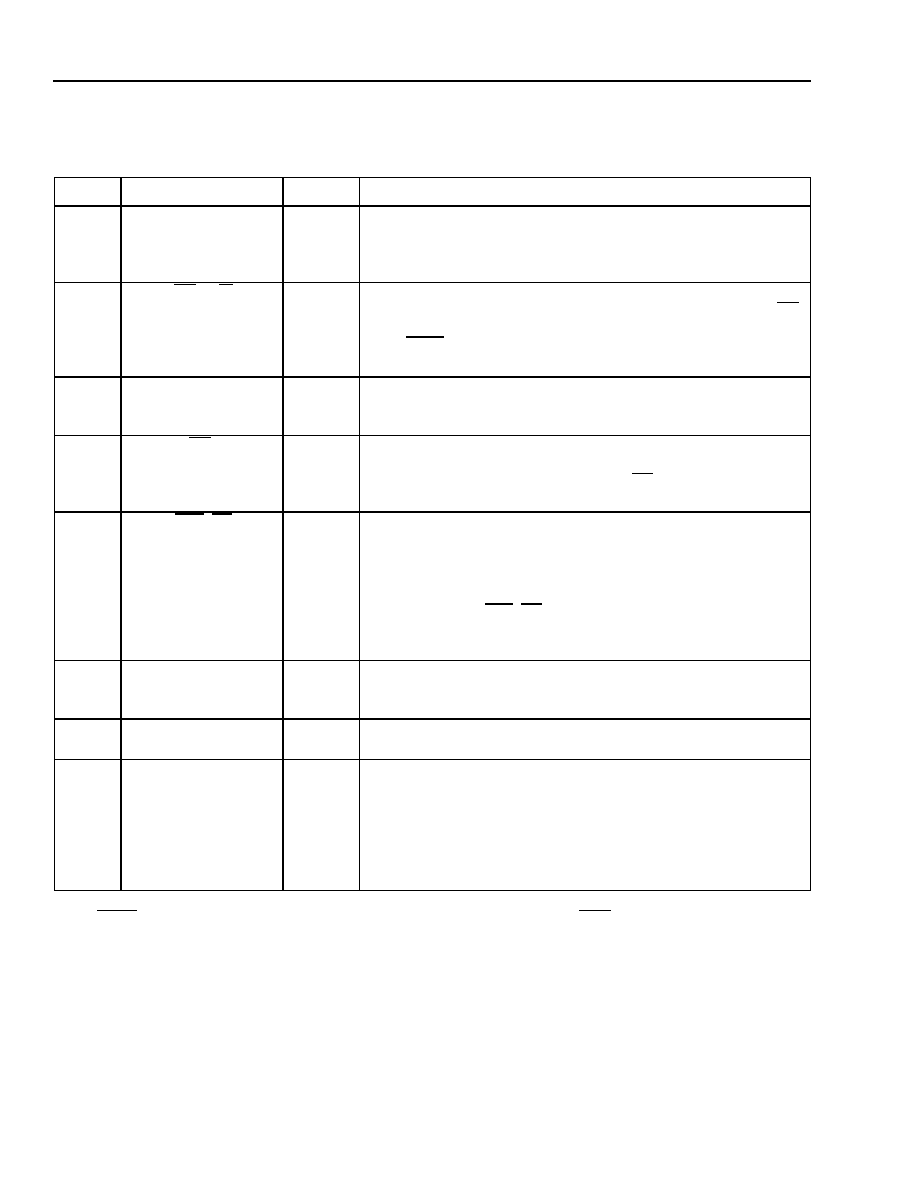

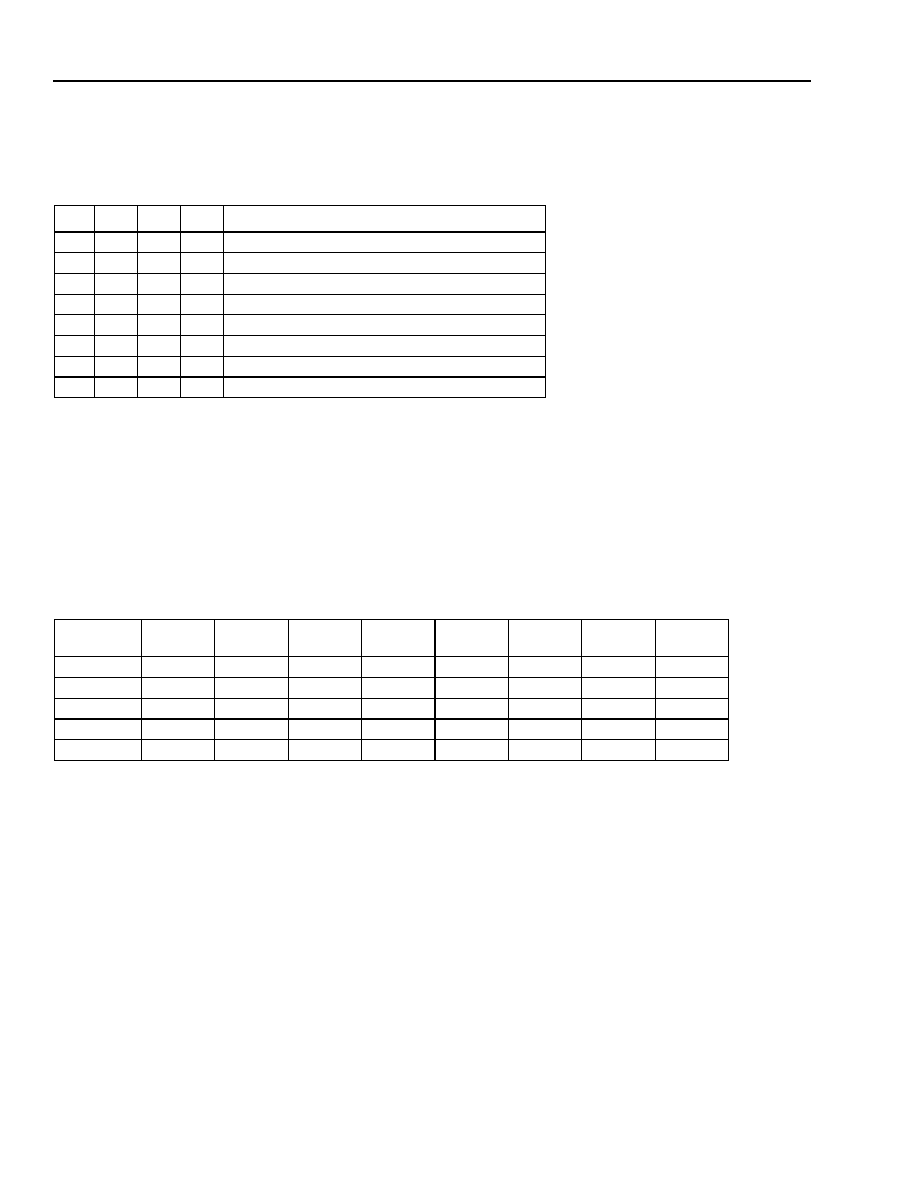

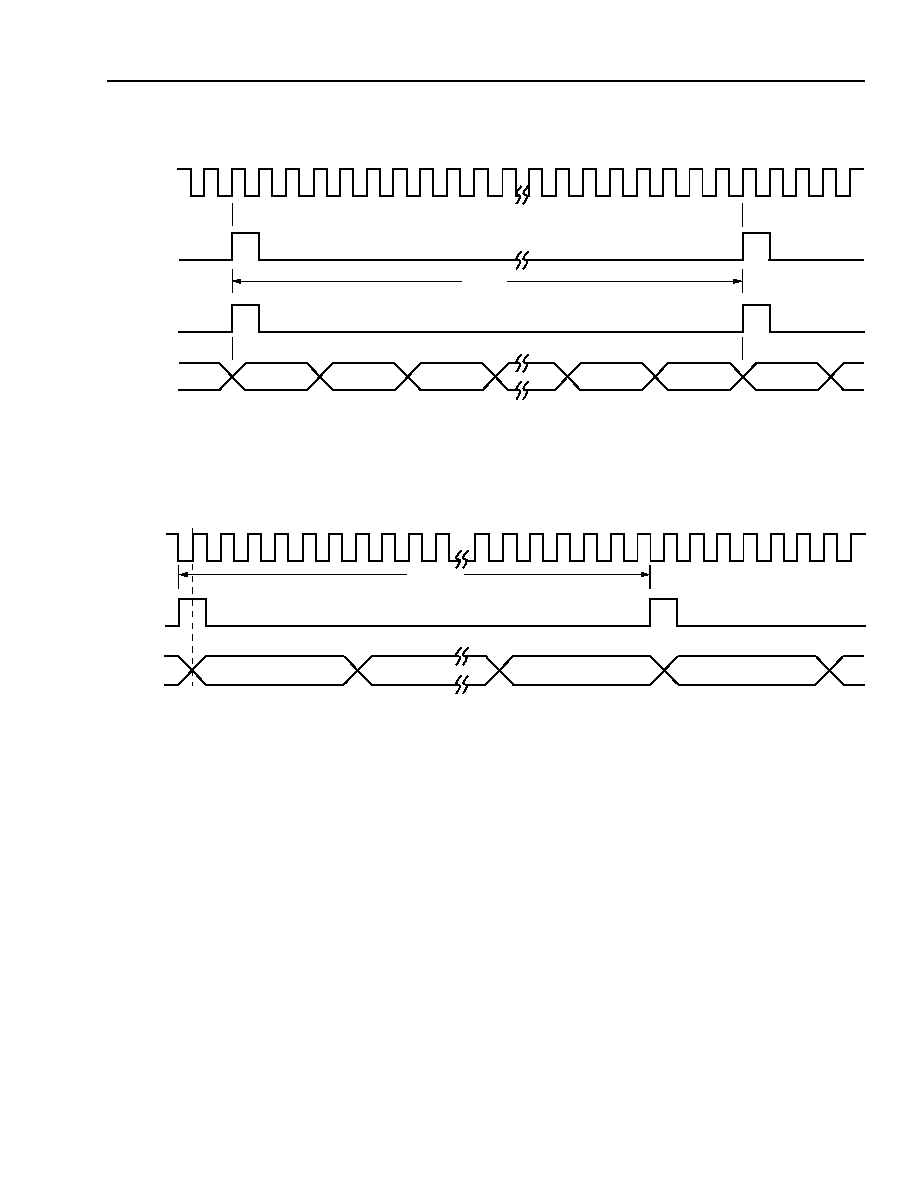

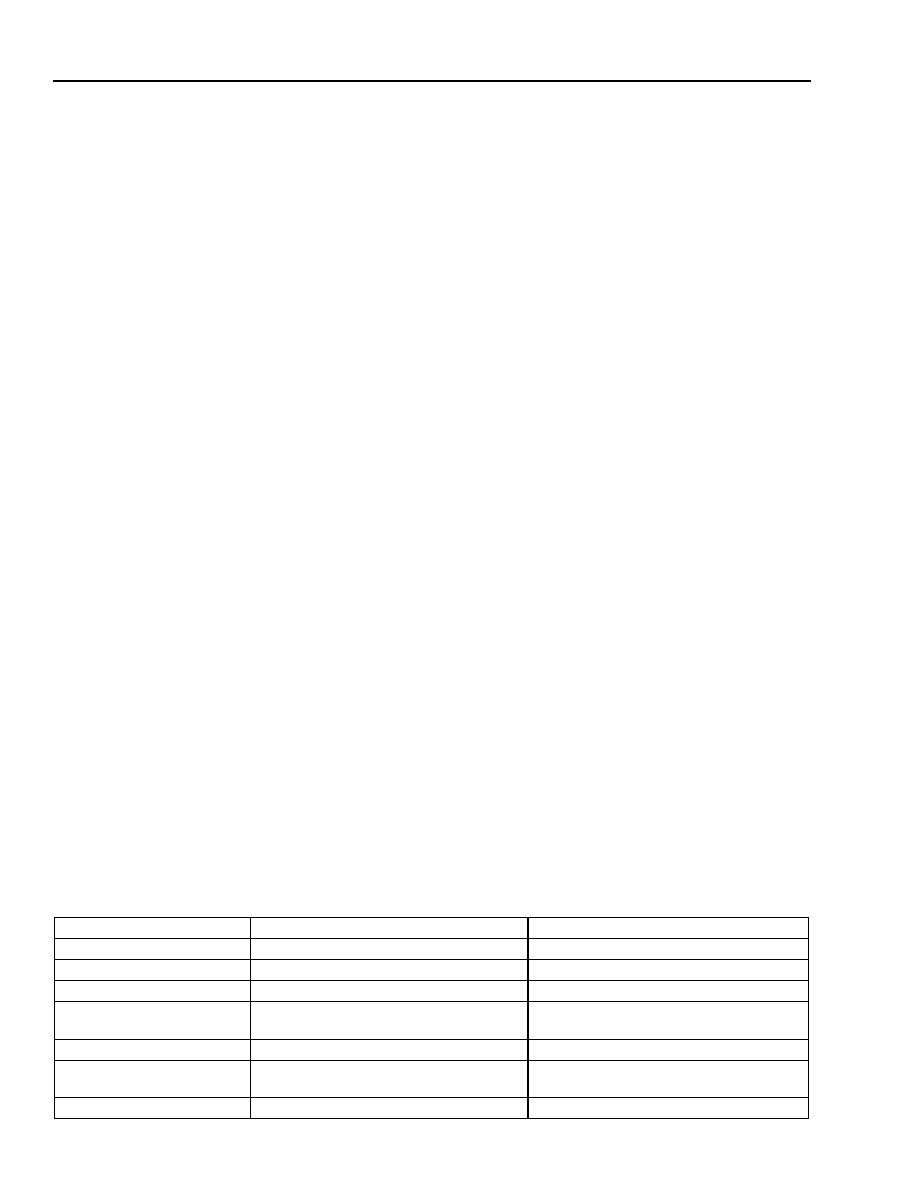

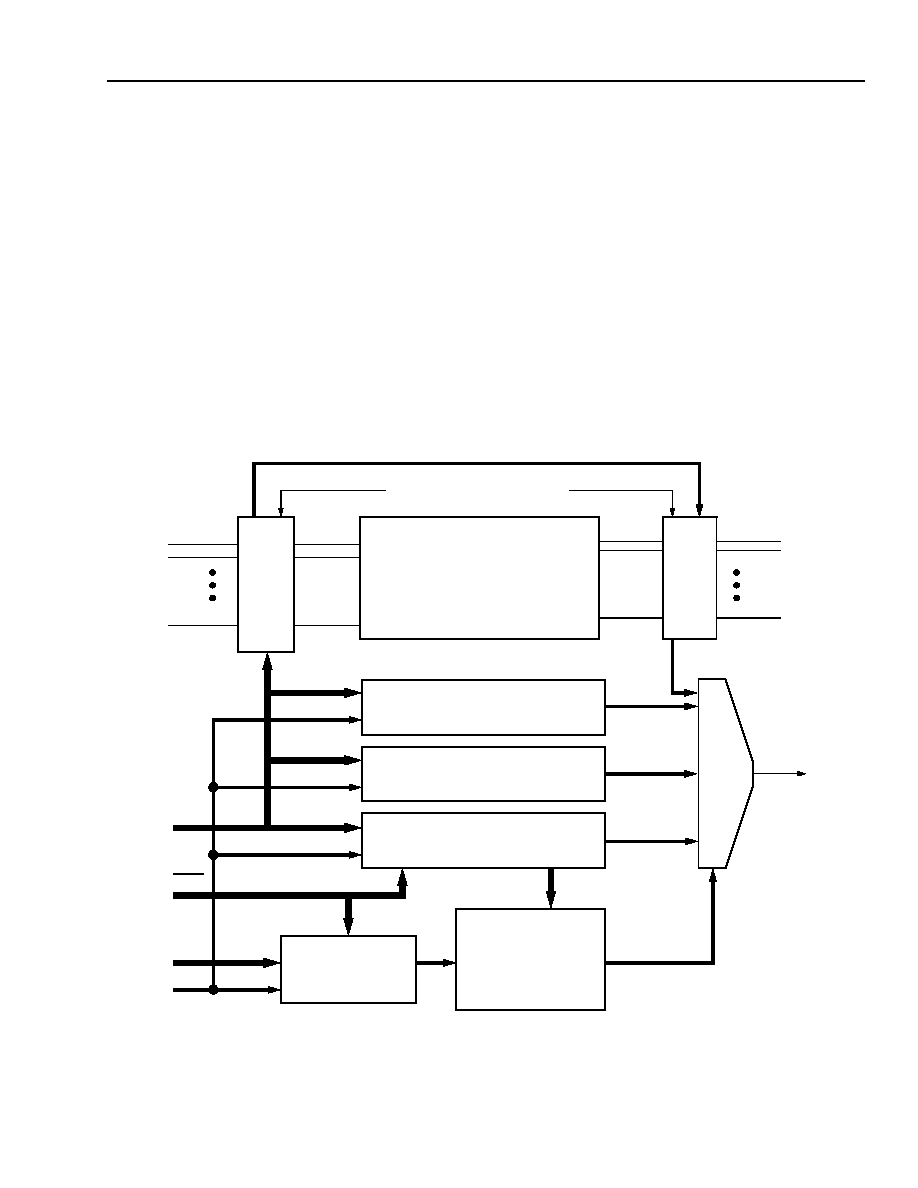

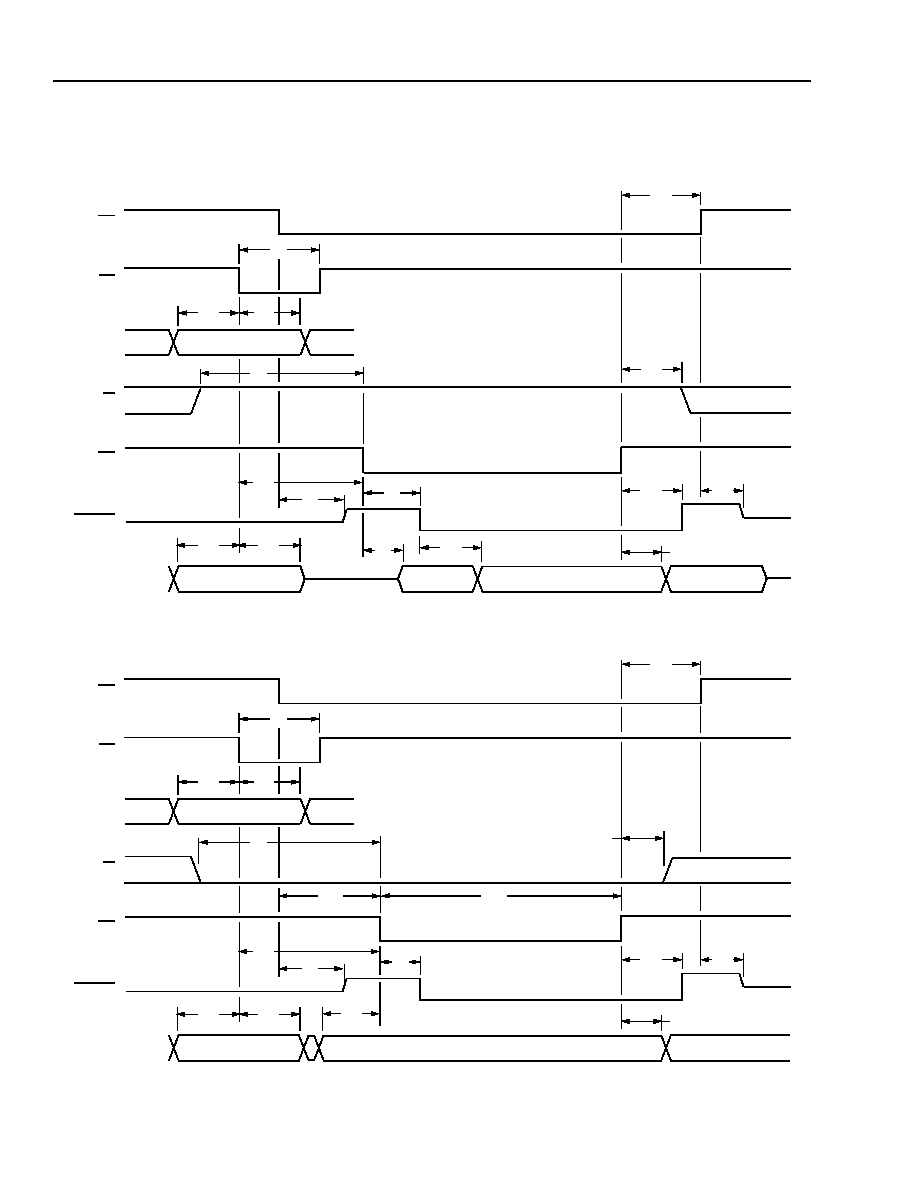

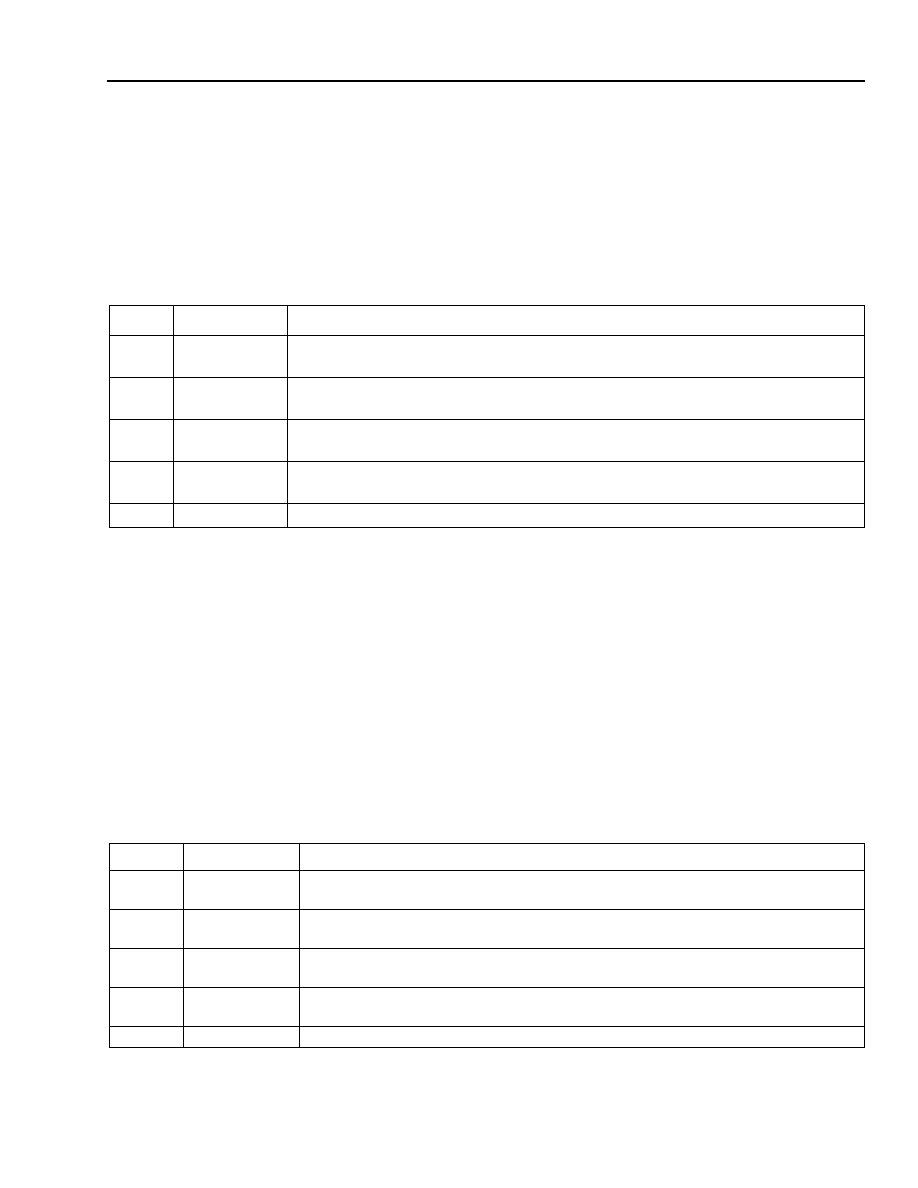

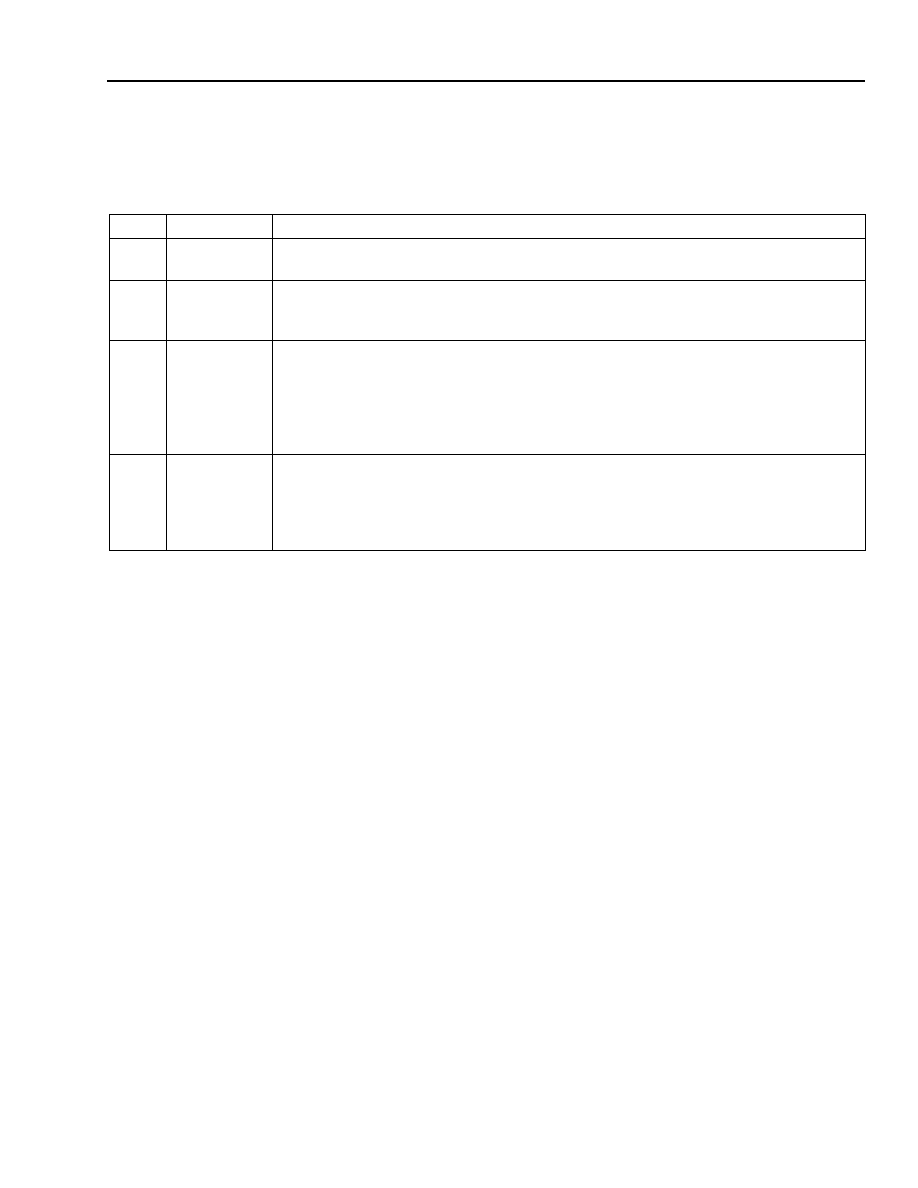

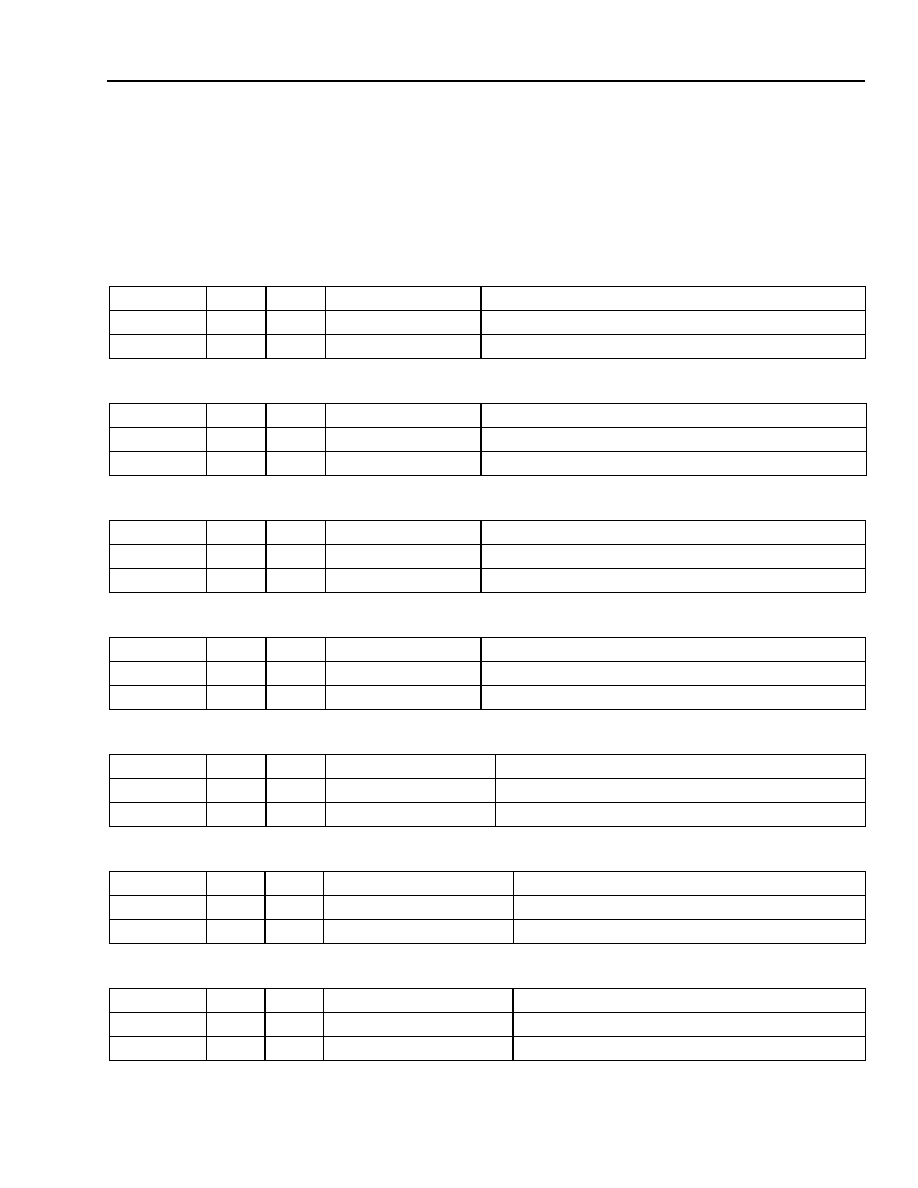

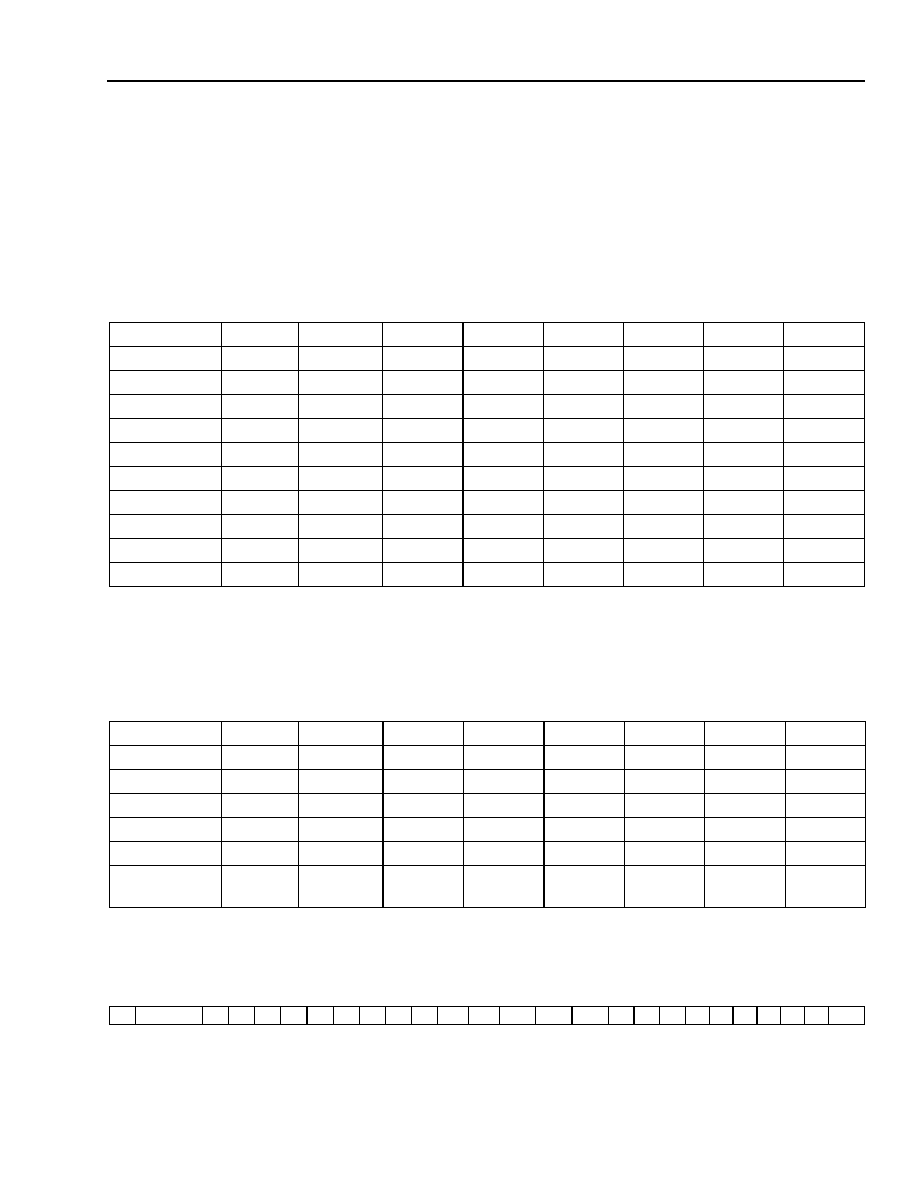

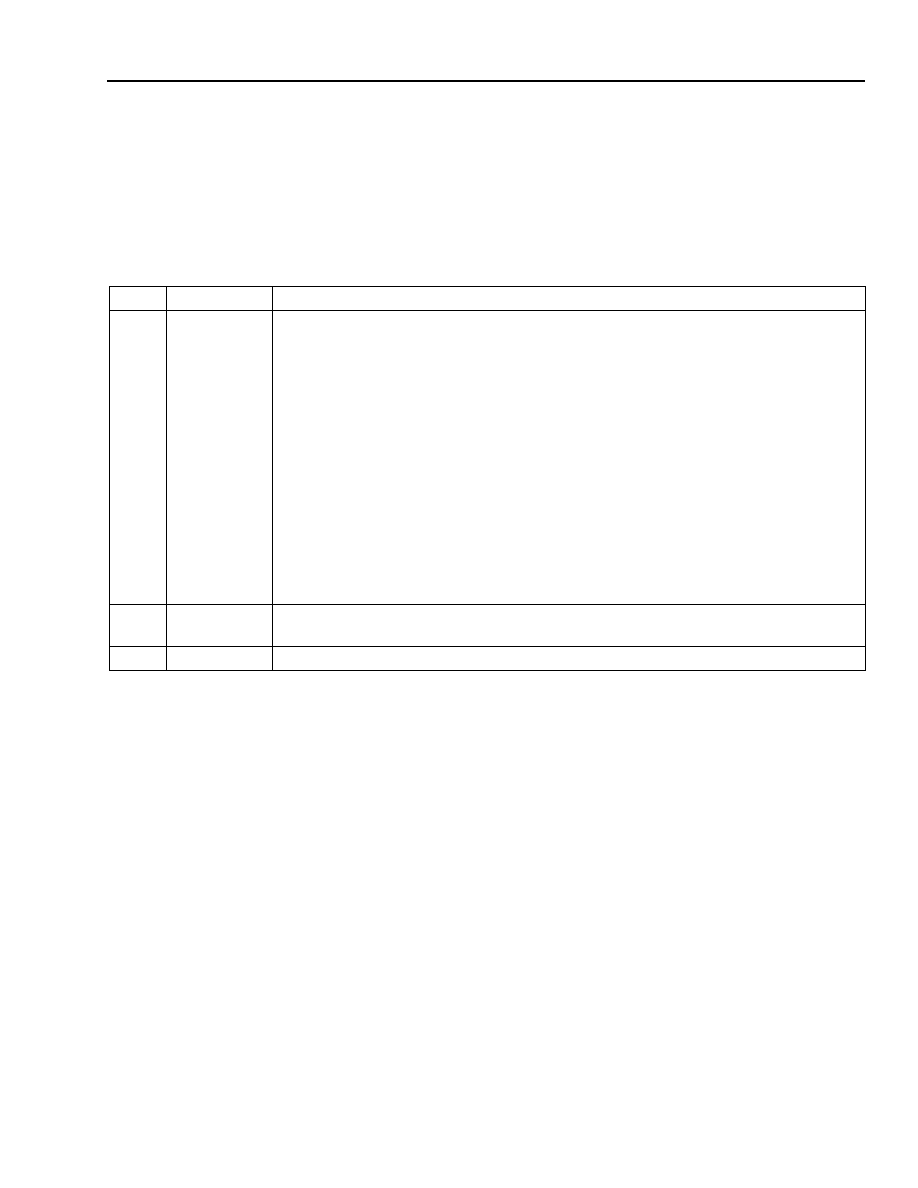

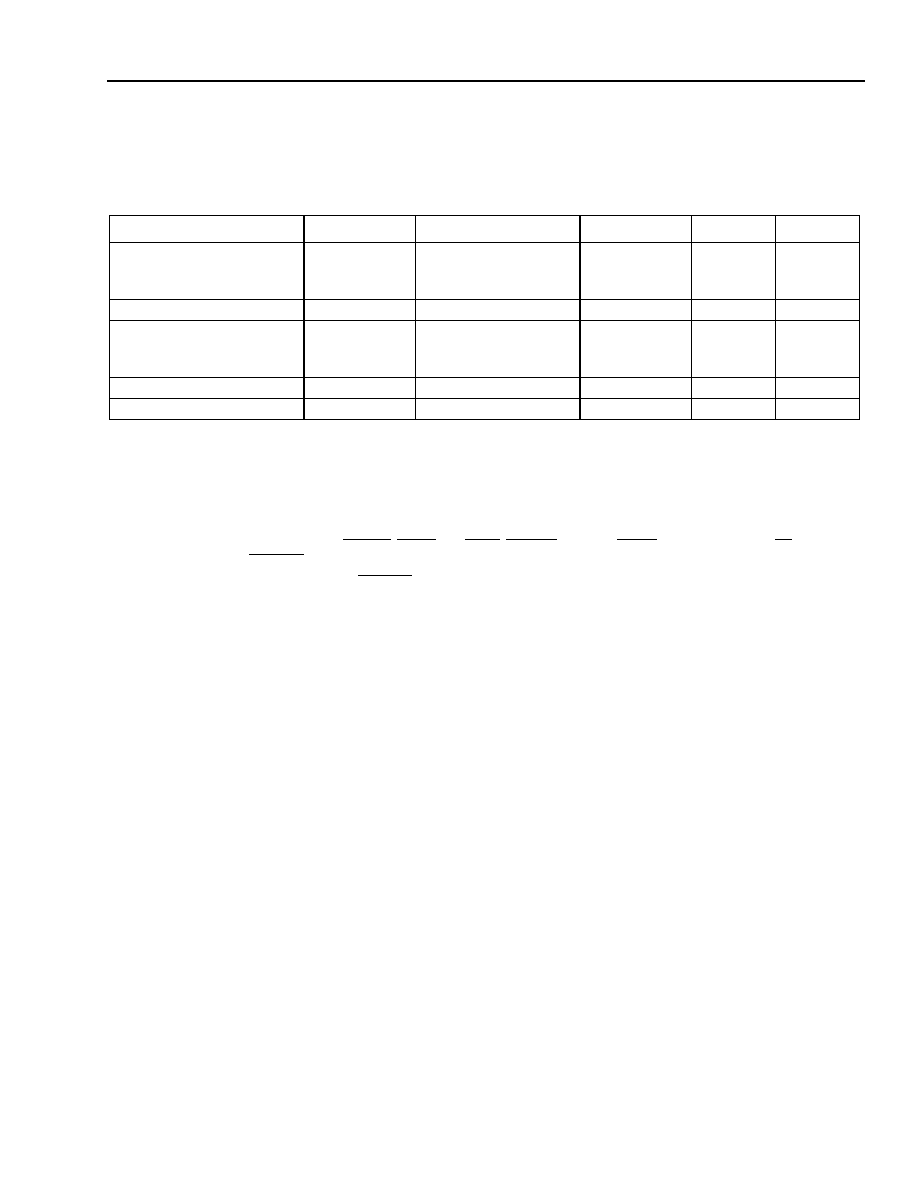

5-6426(F)r.1

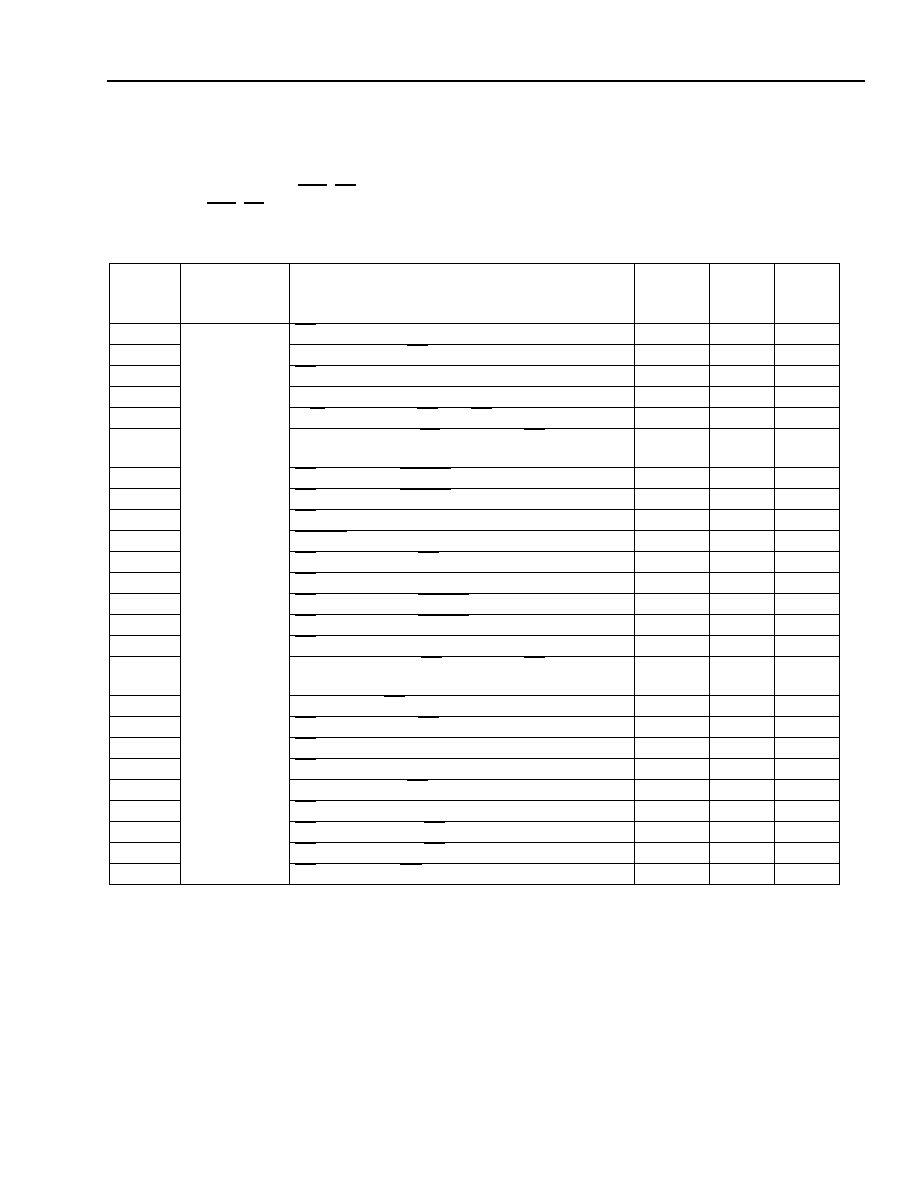

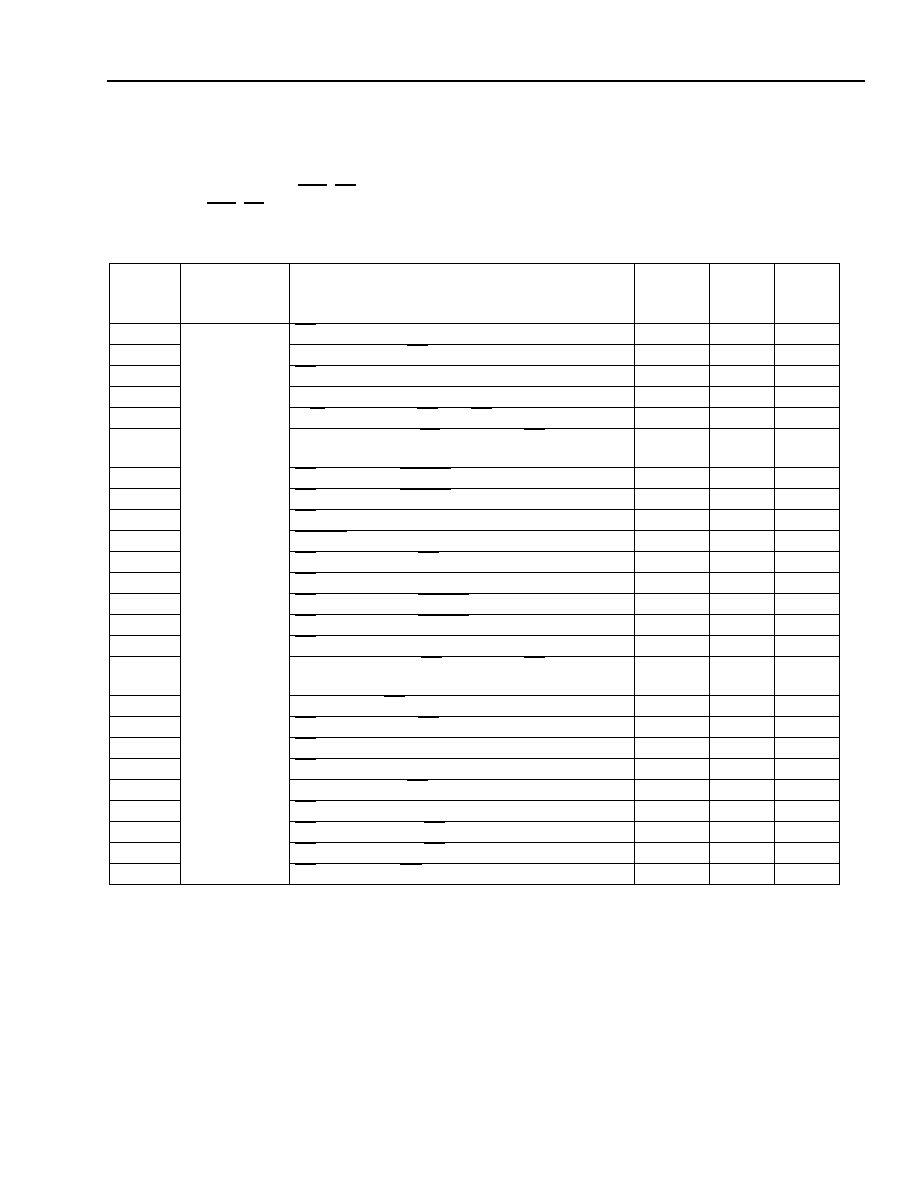

Figure 5. Mode 3--Read Cycle Timing (MPMODE = 1, MPMUX = 0)

5-6427(F)

Figure 6. Mode 3--Write Cycle Timing (MPMODE = 1, MPMUX = 0)

MPCK

AD[0:7]

RDY

RD

A[0:11]

ALE

CS

t31

t32

t33

VALID ADDRESS

t34

t50

t35

VALID DATA

t42

t41

t37

t36

t40

t39

t38

t43

MPCK

AD[0:7]

RDY

WR

A[0:11]

ALE

CS

t31

t32

t33

VALID ADDRESS

t44

t51

t45

VALID DATA

t42

t37

t36

t47

t46

t48

t49

Agere Systems Inc.

7

Device Advisory

September 1999

T7633 Device Advisory for Version 1.0 of the Device

Microprocessor Interface

(continued)

I/O Timing

(continued)

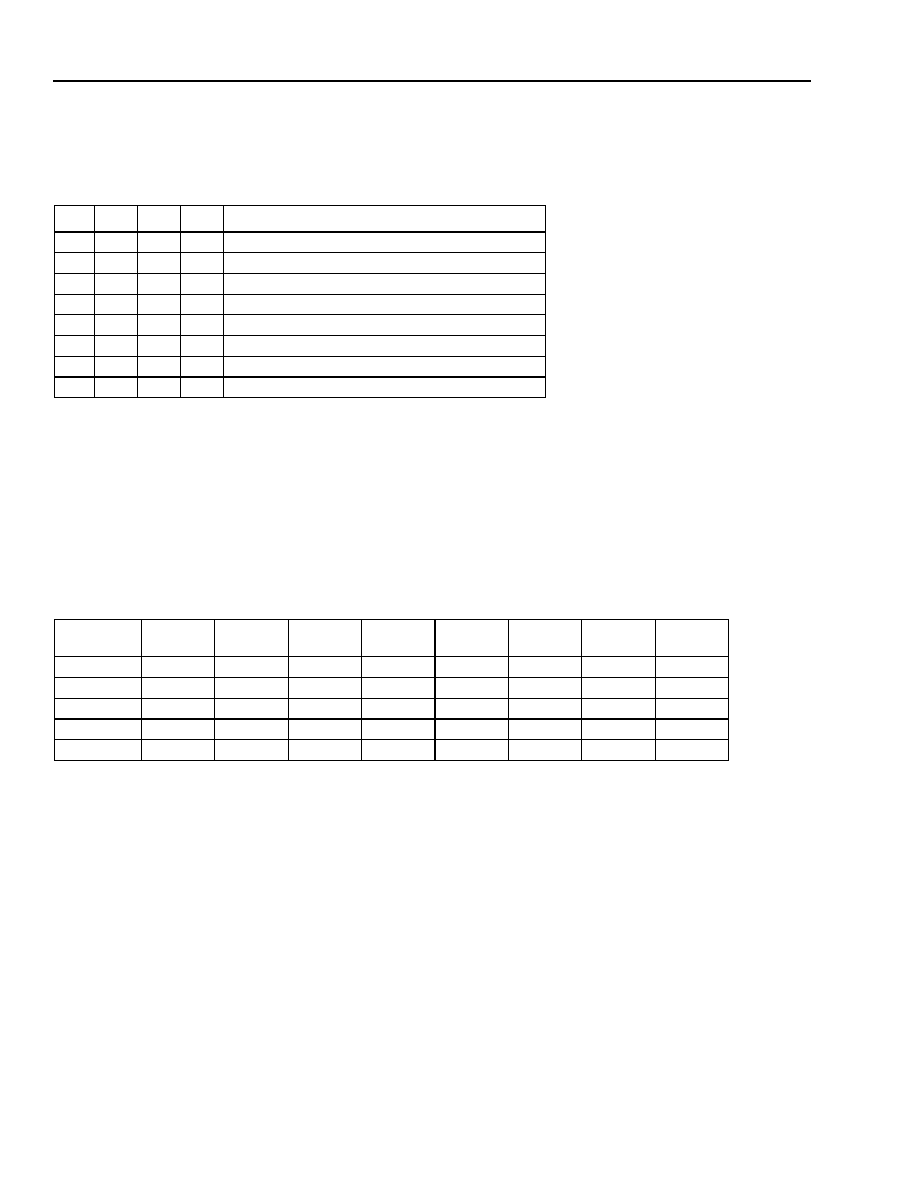

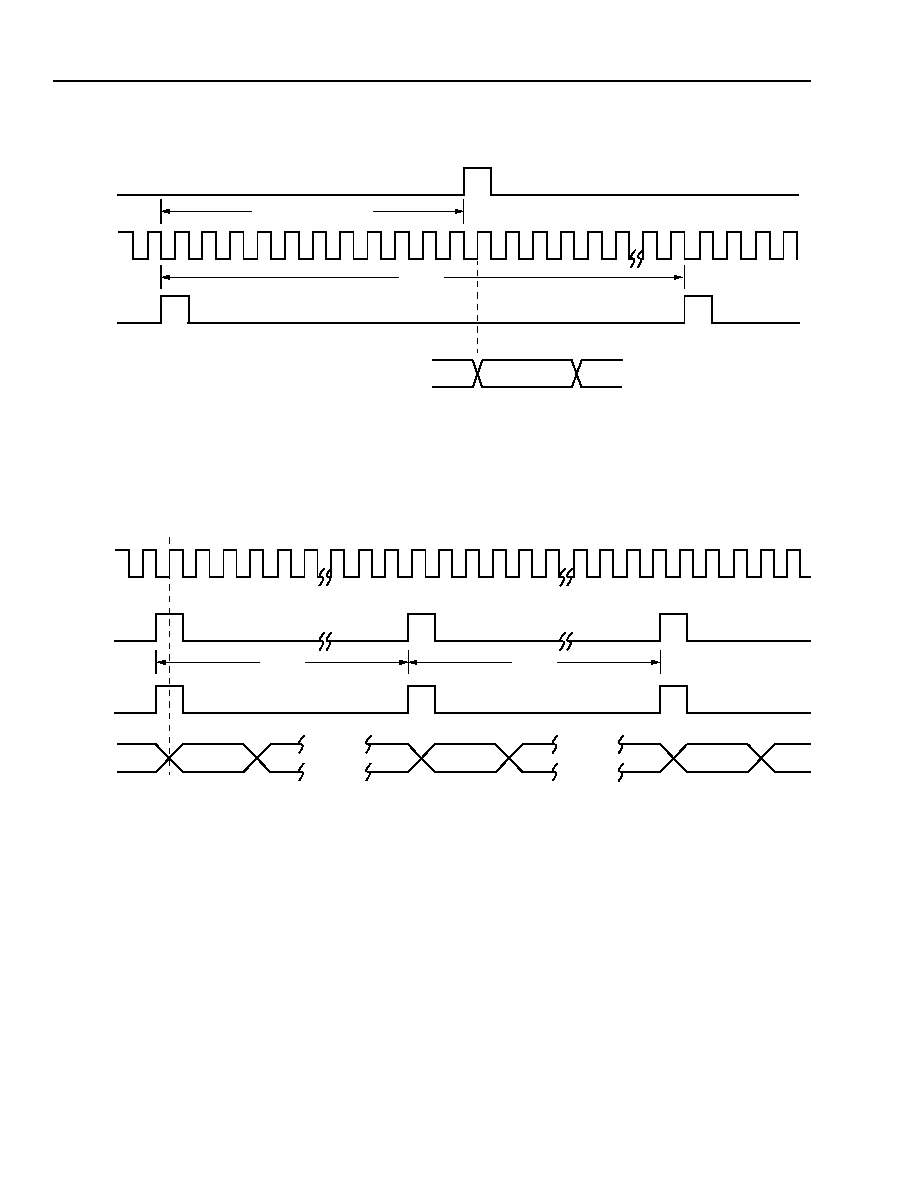

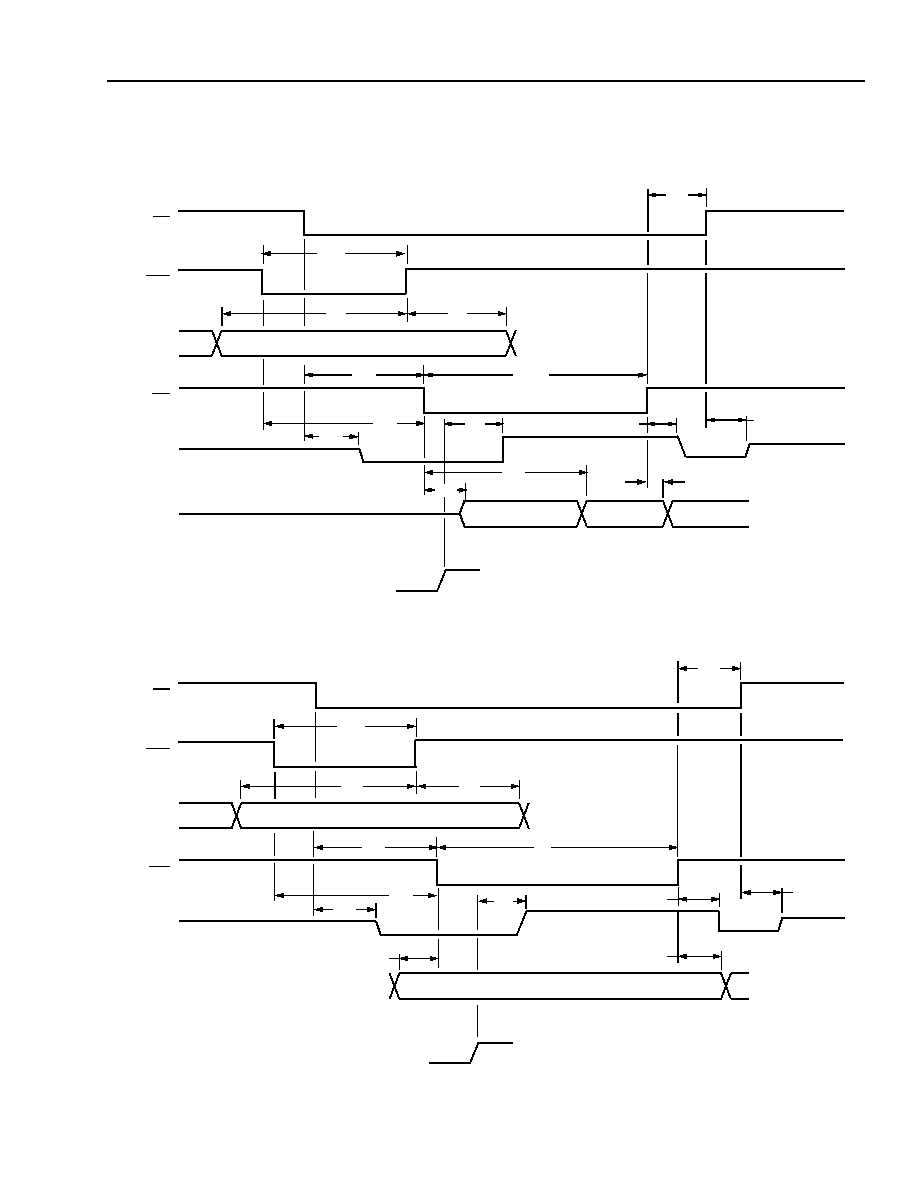

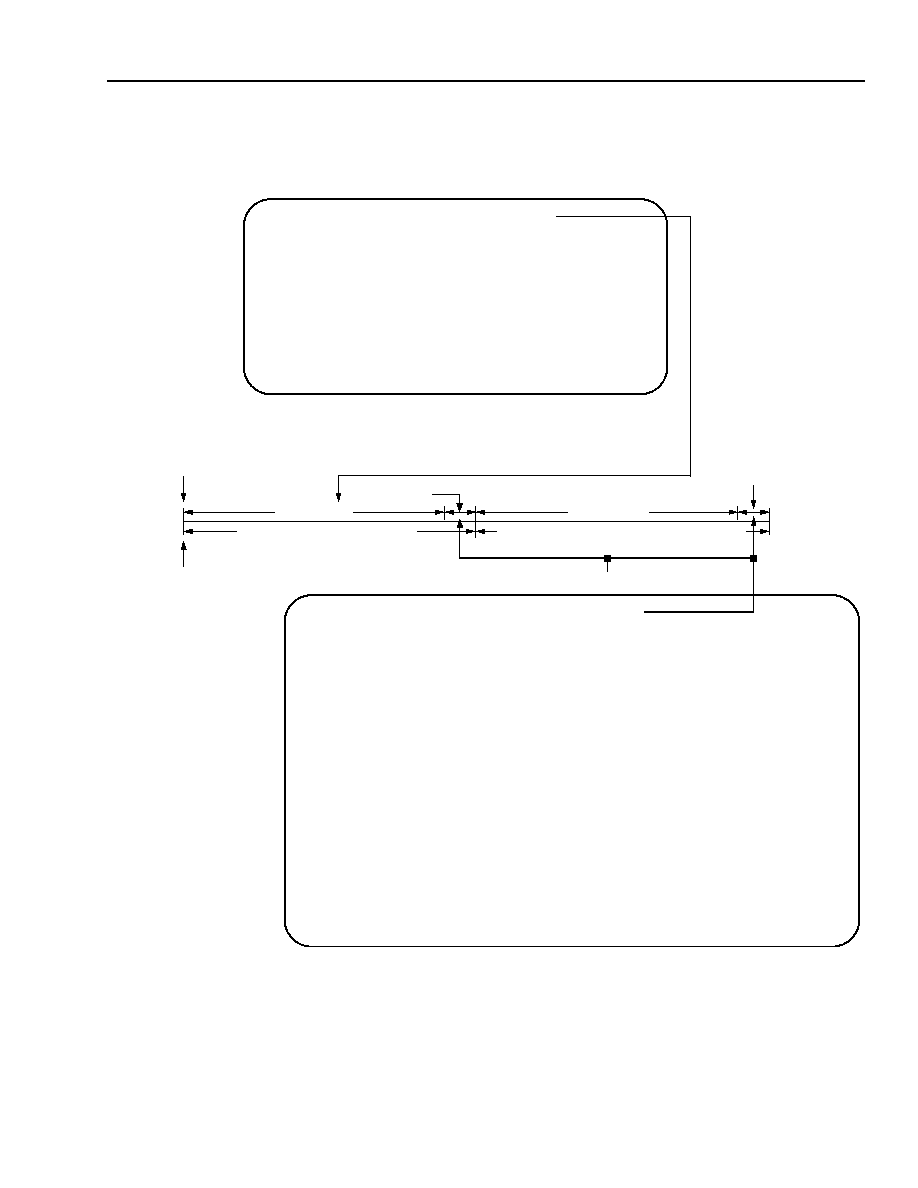

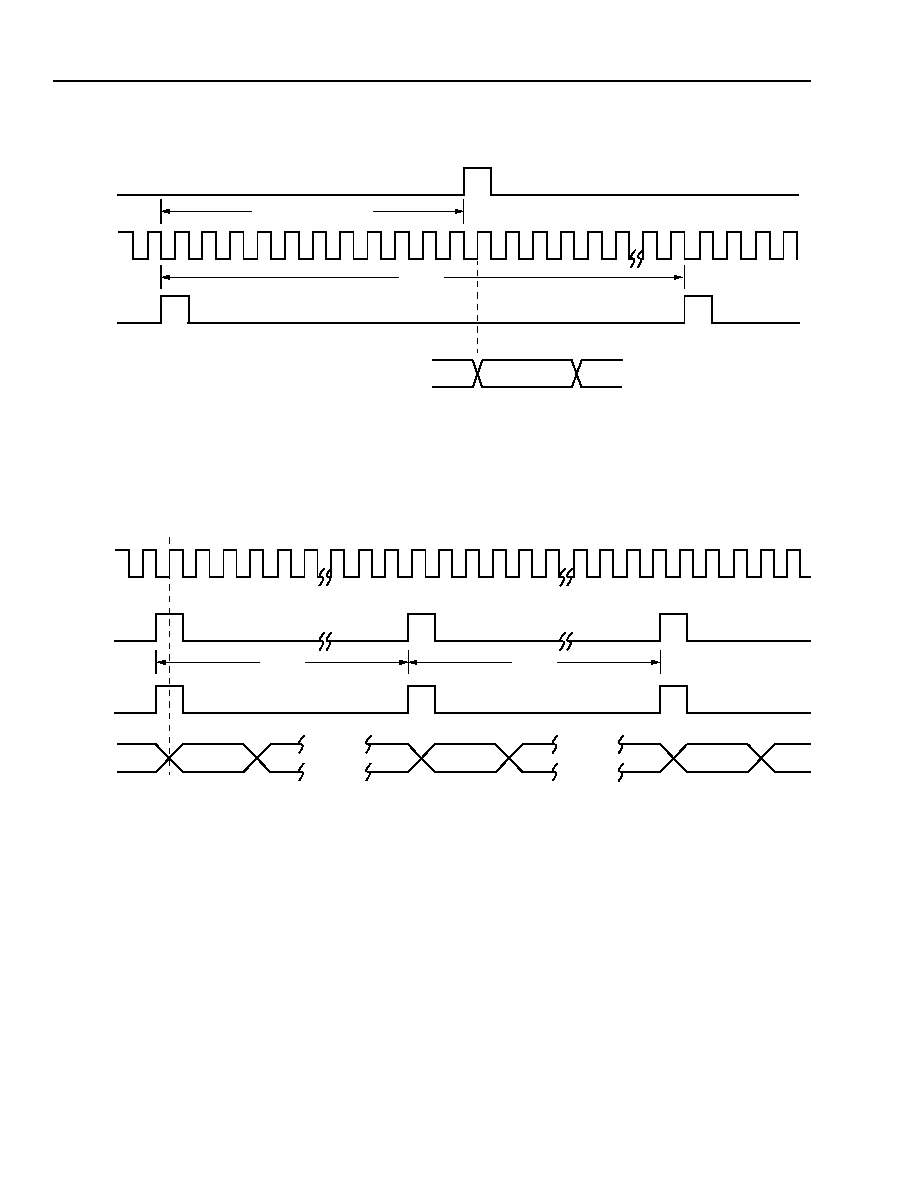

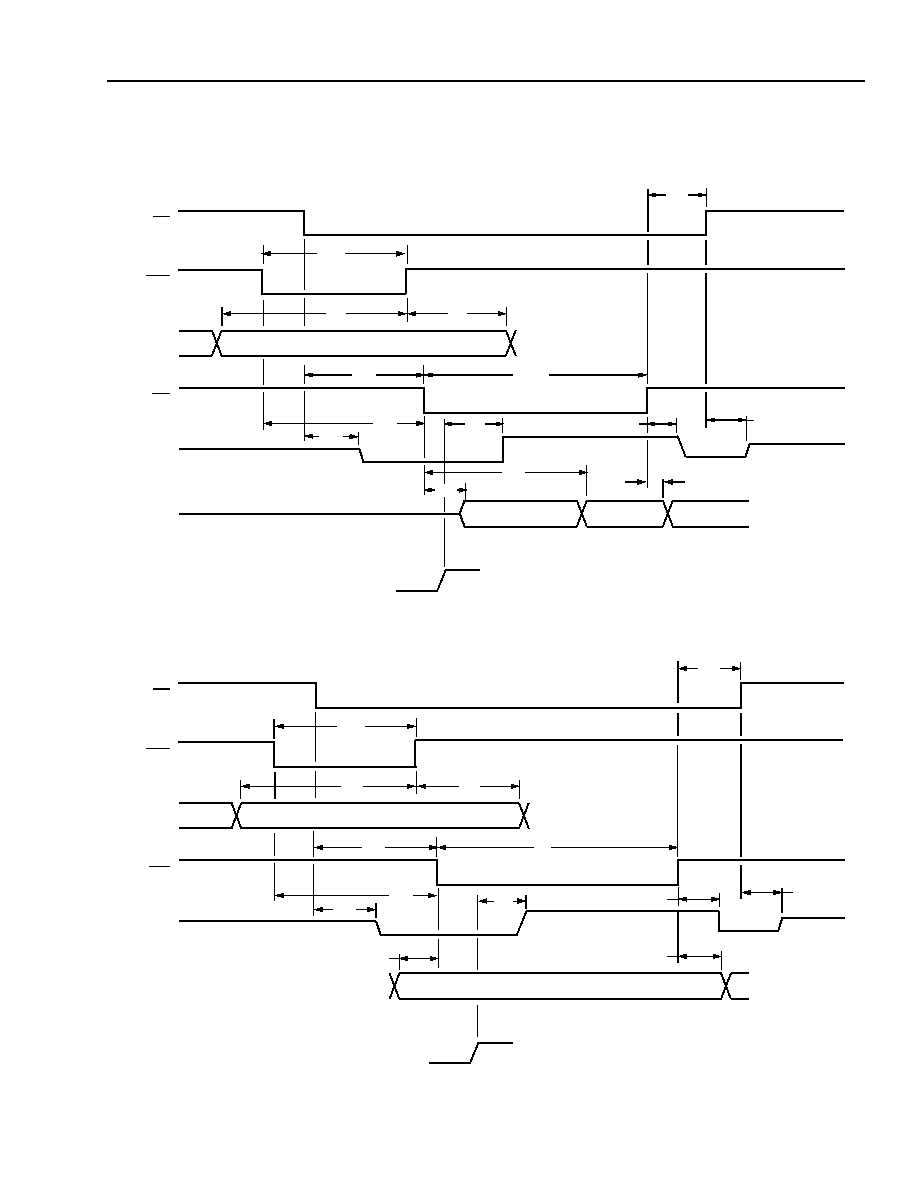

5-6428(F)r.1

Figure 7. Mode 4--Read Cycle Timing (MPMODE = 1, MPMUX = 1)

5-6429(F)r.1

Figure 8. Mode 4--Write Cycle Timing (MPMODE = 1, MPMUX = 1)

MPCK

AD

RDY

RD

A[8:11]

ALE

CS

t31

VALID ADDRESS

VALID DATA

t52

t53

t34

t54

t36

t37

t39

t38

VALID ADDRESS

t52

t53

t43

t41

t42

t40

t50

MPCK

AD

RDY

WR

A[8:11]

ALE

CS

t31

VALID ADDRESS

VALID DATA

t52

t53

t44

t55

t36

t37

VALID ADDRESS

t52

t53

t49

t48

t42

t47

t51

t46

8

Agere Systems Inc.

Device Advisory

September 1999

T7633 Device Advisory for Version 1.0 of the Device

Data Pattern Limitation for Proper Functionality of the LIU Internal Full Local

Loopback (FLLOOP)

One of the loopback modes built into the T7633 is the line interface (LIU) full local loopback (FLLOOP). This mode

connects the LIU transmit driver to the LIU line receiver circuit. This loopback mode is controlled by register

LIU_REG5 bit 2 and bit 3. The FLLOOP function is activated when LIU_REG5, bit 2 = 1 and bit 3 = 0.

Issue

In the case of a data pattern with more than 400 continuous zeros, this loopback mode could possibly be unreli-

able. The possible failure mode is the following:

1.

Latching of the data in either the one or zero state, and/or

2.

An improper period for the recovered line clock (RLCK).

The condition of an all-zero data pattern should not occur in framed T1 or E1 signals, nor should it occur in signals

that use B8ZS, HDB3, or ZCS coding. As a consequence, this possible fault in the FLLOOP function should have

minimal impact on T1 and E1 system applications of the T7633. If the case of an all-zeros data stream is used as a

special system test or diagnostic condition, these devices may be forced into the above fault condition when the

T7633 is in the FLLOOP state.

Solution

To avoid this possible fault condition, the FLLOOP loopback mode should not be used unless the data pattern is

limited to one not containing in excess of 400 contiguous zeros. Alternatively, limits on the content of the data

stream may be eliminated by using an equivalent external loopback in place of the FLLOOP loopback, or by using

an alternative internal loopback, such as DLLOOP in the LIU or BLB (board loopback) of the framer.

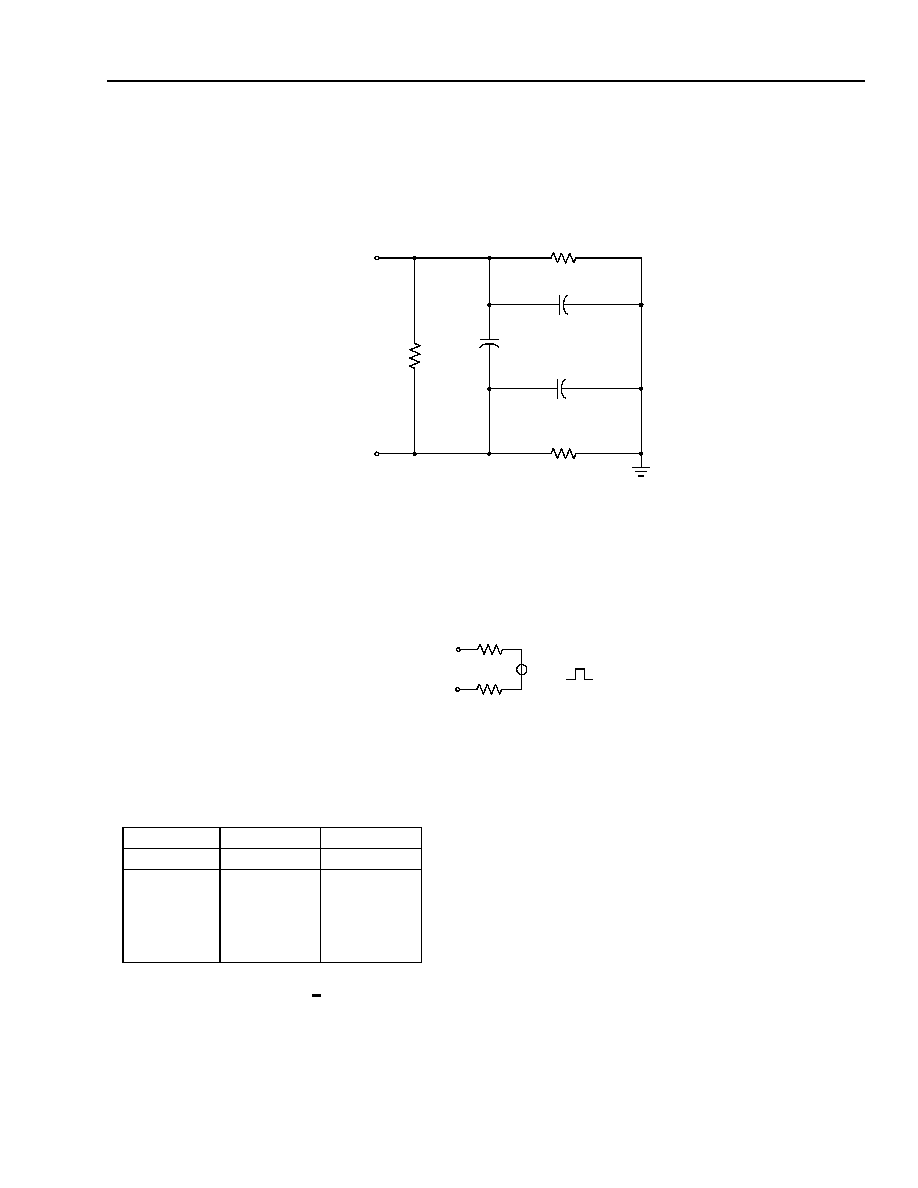

Asynchronous SYSCK and PLLCK with Jitter Attenuator in the Line Transmit Path

A feature of the T7633 Line Interface Unit (LIU) is a jitter attenuator that can be optionally included in either the line

receive or line transmit path. The jitter attenuator mode is controlled by the LIU register LIU_REG3 bits 0 and 1

(JAR and JAT). This register is located at address 403(hex) or A03(hex). Control of the jitter attenuator mode is

independent for each channel of the terminator.

Issue

In the case when the jitter attenuator is in the line transmit path and the transmit line clock, which is derived from

PLLCK, is asynchronous with SYSCK, errors may be generated in the line transmit data. These errors may appear

as pattern slips.

Solution

To avoid generation of these errors,

1.

PLLCK should be synchronous to SYSCK if the jitter attenuator is used in the transmit path,

or

2.

The jitter attenuator should not be used in the line transmit path.

Agere Systems Inc.

9

Device Advisory

September 1999

T7633 Device Advisory for Version 1.0 of the Device

AY99-010PDH Replaces AY99-007T1E1 to Incorporate the Following Updates

1.

Separate AY99-007T1E1 into two advisories: one applying to the T7630 and one applying to the T7633. This

advisory (AY99-010PDH) applies to the T7633.

2.

Page 8, added Asynchronous SYSCK and PLLCK with Jitter Attenuator in the Line Transmit Path section.

Copyright © 2002 Agere Systems Inc.

All Rights Reserved

September 1999

AY99-010PDH (Replaces AY99-007T1E1 and must accompany DS02-244BBAC)

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET: http://www.agere.com

E-MAIL: docmaster@agere.com

N. AMERICA:

Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA: Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, Kowloon

Tel. (852) 3129-2000, FAX (852) 3129-2020

CHINA: (86) 21-5047-1212 (Shanghai), (86) 10-6522-5566 (Beijing), (86) 755-695-7224 (Shenzhen)

JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 6778-8833, TAIWAN: (886) 2-2725-5858 (Taipei)

EUROPE: Tel. (44) 7000 624624, FAX (44) 1344 488 045

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Agere, Agere Systems, and the Agere logo are trademarks of Agere Systems Inc.

Device Advisory

August 1999

T7633 Device Advisory Describing Differences

Between Version 1.0 and Version 2.0 of Device

Introduction

This advisory applies only to the T7633 Dual T1/E1 3.3 V Short-Haul Terminator, and it describes the differ-

ences between the two versions of the device.

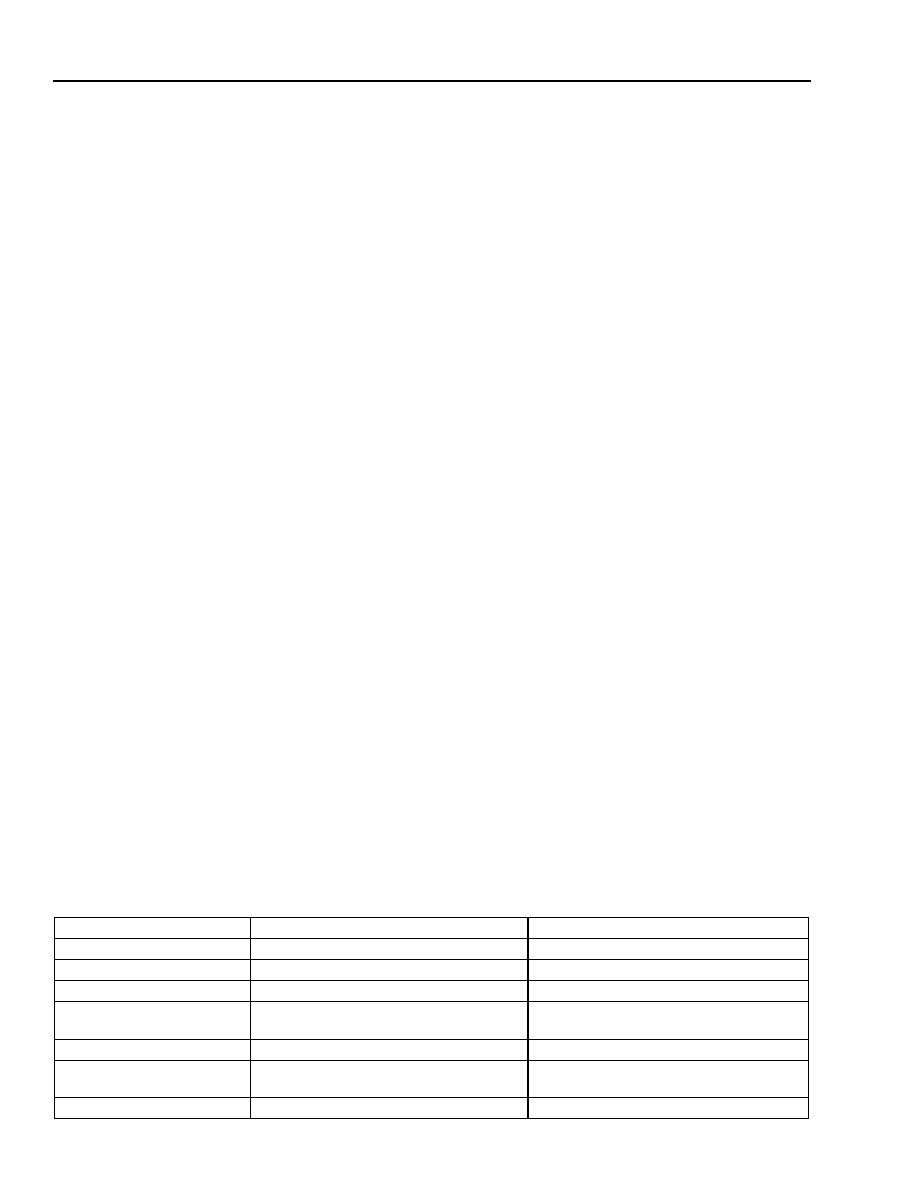

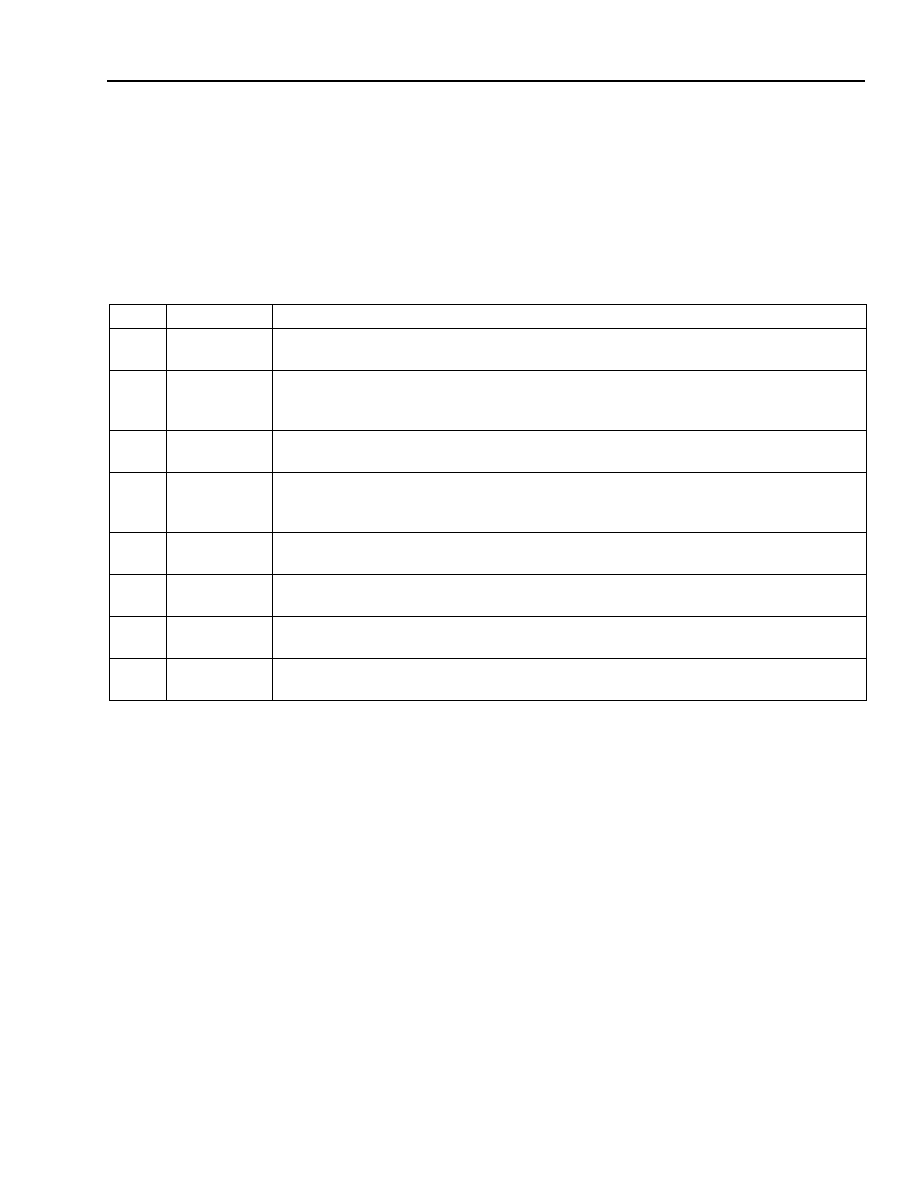

Data Sheet Changes

Table 148, Framer FDL Control Command Register (FRM_PR21) on page 189 of the May 1998

T7633 Dual

T1/E1 3.3 V Short-Haul Terminator

Advance Data Sheet (DS02-244BBAC).

s

In version 1.0 of the device, bit 0 is reserved and must be cleared (write to 0).

s

In version 2.0 of the device, bit 0 = 1 disables the receive frame sync (RFS) output when the receive framer

is in a loss of frame alignment (LFA) state; when bit 0 = 0, the device operates the same as version 1.0 of the

device.

Device Operation Updates

LIU Full Local Loopback (FLLOOP)

In version 1.0 of the device, when FLLOOP is enabled, the device occasionally drops 1s from the data pattern.

This behavior is 1s density dependent, therefore, some data sequences are more sensitive than others.

In version 2.0 of the device, the sensitivity to 1s density no longer occurs.

Microprocessor Interface Timing

In version 1.0 of the device, the LIU alarm status register (LIU_REG0) is clear-on-read (COR) and requires a

modification to the microprocesser interface timing to guarantee proper operation. The timing requirements are

described in the December 1998

T7633 Device Advisory for Version 1.0 of the Device

(AY99-007T1E1).

In version 2.0 of the device, the timing modification is no longer required.

Copyright © 2002 Agere Systems Inc.

All Rights Reserved

August 1999

AY99-033PDH (Must accompany DS02-244BBAC)

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET: http://www.agere.com

E-MAIL: docmaster@agere.com

N. AMERICA:

Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA: Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, Kowloon

Tel. (852) 3129-2000, FAX (852) 3129-2020

CHINA: (86) 21-5047-1212 (Shanghai), (86) 10-6522-5566 (Beijing), (86) 755-695-7224 (Shenzhen)

JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 6778-8833, TAIWAN: (886) 2-2725-5858 (Taipei)

EUROPE: Tel. (44) 7000 624624, FAX (44) 1344 488 045

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Agere, Agere Systems, and the Agere logo are trademarks of Agere Systems Inc.

Advance Data Sheet

May 2002

T7633 Dual T1/E1 3.3 V Short-Haul Terminator

Features

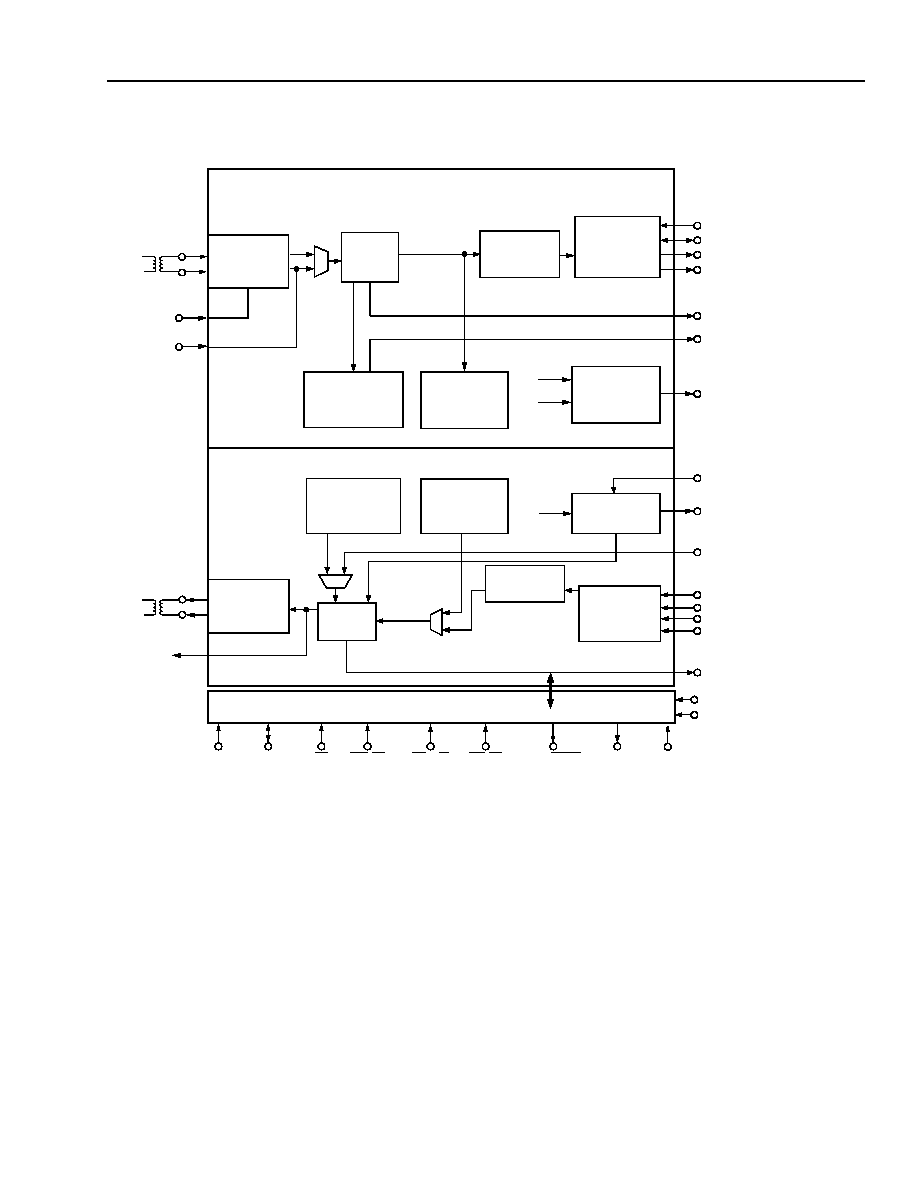

The T7633 Dual T1/E1 Terminator consists of two

independent, highly integrated, software-config-

urable, full-featured short-haul transceiver/framers.

The T7633 provides glueless interconnection from a

T1/E1 line to a digital PCM system. Minimal external

clocks are needed. Only a system clock/frame sync

and a phase-locked line rate clock are required. Sys-

tem diagnostic and performance monitoring capabil-

ity with integrated programmable test pattern

generator/detector and loopback modes is provided.

Power Requirements and Package

s

Single 3.3 V ± 5% supply.

s

Low power: 375 mW per channel maximum.

s

144-pin TQFP package.

s

Operating temperature range: ≠40 ∞C to +85 ∞C.

T1/E1 Line Interface Features

s

Full T1/E1 pulse template compliance.

s

Receiver provides equalization for up to 11 dB of

loss.

s

Digital clock and data recovery.

s

Line coding: B8ZS, HDB3, ZCS, and AMI.

s

Line interface coupling and matching networks for

T1 and E1 (120

and 75

).

T1/E1 Framer Features

s

Supports T1 framing modes ESF, D4,

SLC

Æ

-96,

T1DM DDS.

s

Supports G.704 basic and CRC-4 multiframe for-

mat E1 framing and procedures consistent with

G.706.

s

Supports unframed transmission format.

s

T1 signaling modes: transparent; ESF 2-state,

4-state, and 16-state; D4 2-state and 4-state;

SLC

-

96 2-state, 4-state, 9-state, and 16-state. E1 sig-

naling modes: transparent, CAS, CCS, and IRMS.

s

Alarm reporting and performance monitoring per

AT&T

Æ

,

ANSI

Æ

, and ITU-T standards.

s

Programmable, independent transmit and receive

system interfaces at a 2.048 MHz, 4.096 MHz, or

8.192 MHz data rate.

s

System interface master mode for generation of

system frame sync from the line source.

s

Internal phase-locked loop (with external VCXO)

for generation of system clock from the line source.

Facility Data Link Features

s

HDLC or transparent modes.

s

Automatic transmission and detection of

ANSI

T1.403 FDL performance report message and bit-

oriented codes.

s

64-byte FIFO in both transmit and receive direc-

tions.

Microprocessor Interface

s

33 MHz, 8-bit data interface, no wait-states.

s

Intel

Æ

or

Motorola

Æ

interface modes with multi-

plexed or demultiplexed buses.

s

Directly addressable control registers.

Applications

s

Customer Premises Equipment--CSU/DSU,

routers, digital PBX, channel banks (CB), base

transceiver stations (BTS-picocell), small switches,

and digital subscriber loop access multiplexers

(DSLAM).

s

Loop/Access--DLC/IDLC, DCS, BTS (microcell/

macrocell), DSLAMs, and multiplexers (terminal,

synchronous/asynchronous, add drop).

s

Central Office--Digital switches, DCS, CB,

access concentrators, remote switch modules

(RSM), and DSLAMs.

s

Test Equipment--Transmission/BERT tester.

2

Agere Systems Inc.

Advance Data Sheet

May 2002

T7633 Dual T1/E1 3.3 V Short-Haul Terminator

Table of Contents

Contents

Page

Features ................................................................................................................................................................... 1

Power Requirements and Package .................................................................................................................... 1

T1/E1 Line Interface Features............................................................................................................................ 1

T1/E1 Framer Features ...................................................................................................................................... 1

Facility Data Link Features................................................................................................................................. 1

Microprocessor Interface.................................................................................................................................... 1

Applications ........................................................................................................................................................ 1

Feature Descriptions .............................................................................................................................................. 13

T1/E1 Line Interface Features.......................................................................................................................... 13

T1/E1 Framer Features .................................................................................................................................... 13

Facility Data Link Features............................................................................................................................... 14

User-Programmable Microprocessor Interface ................................................................................................ 14

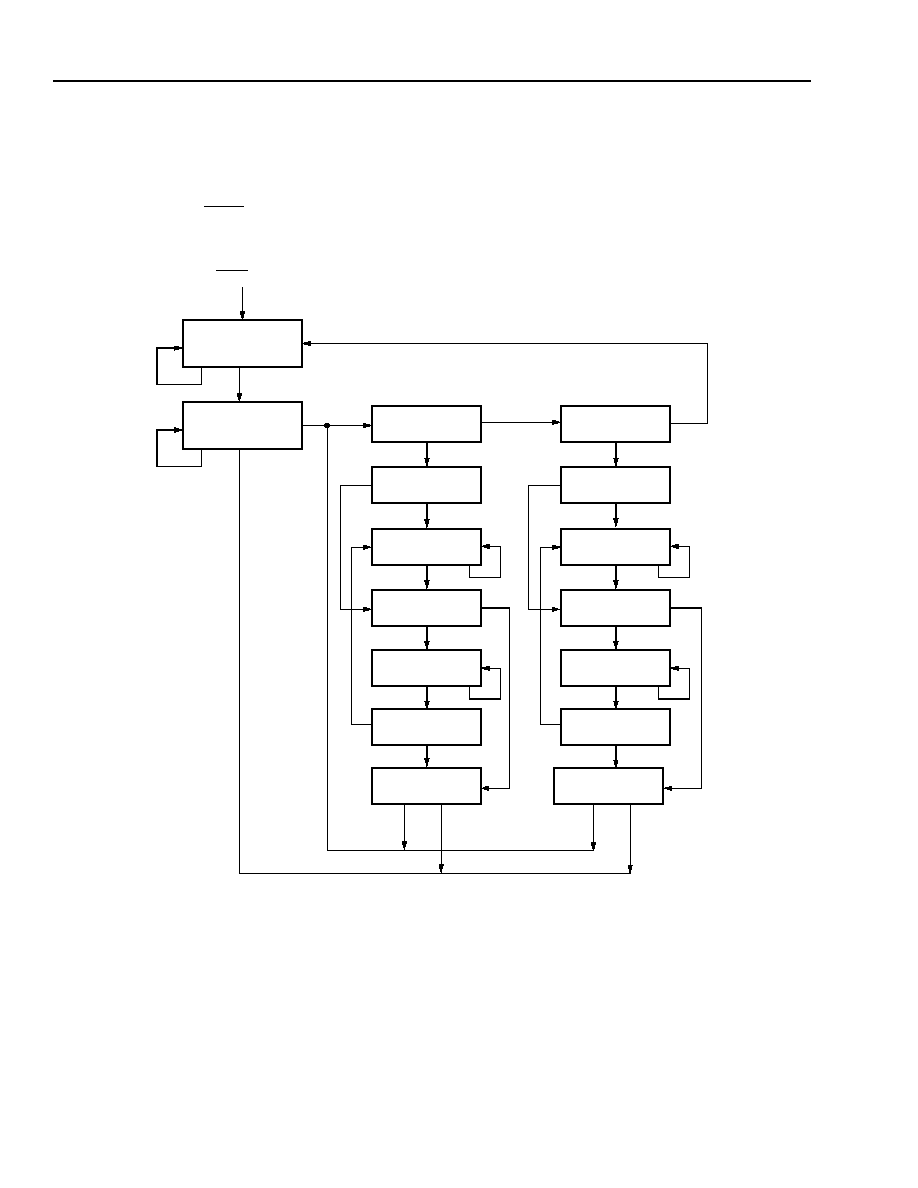

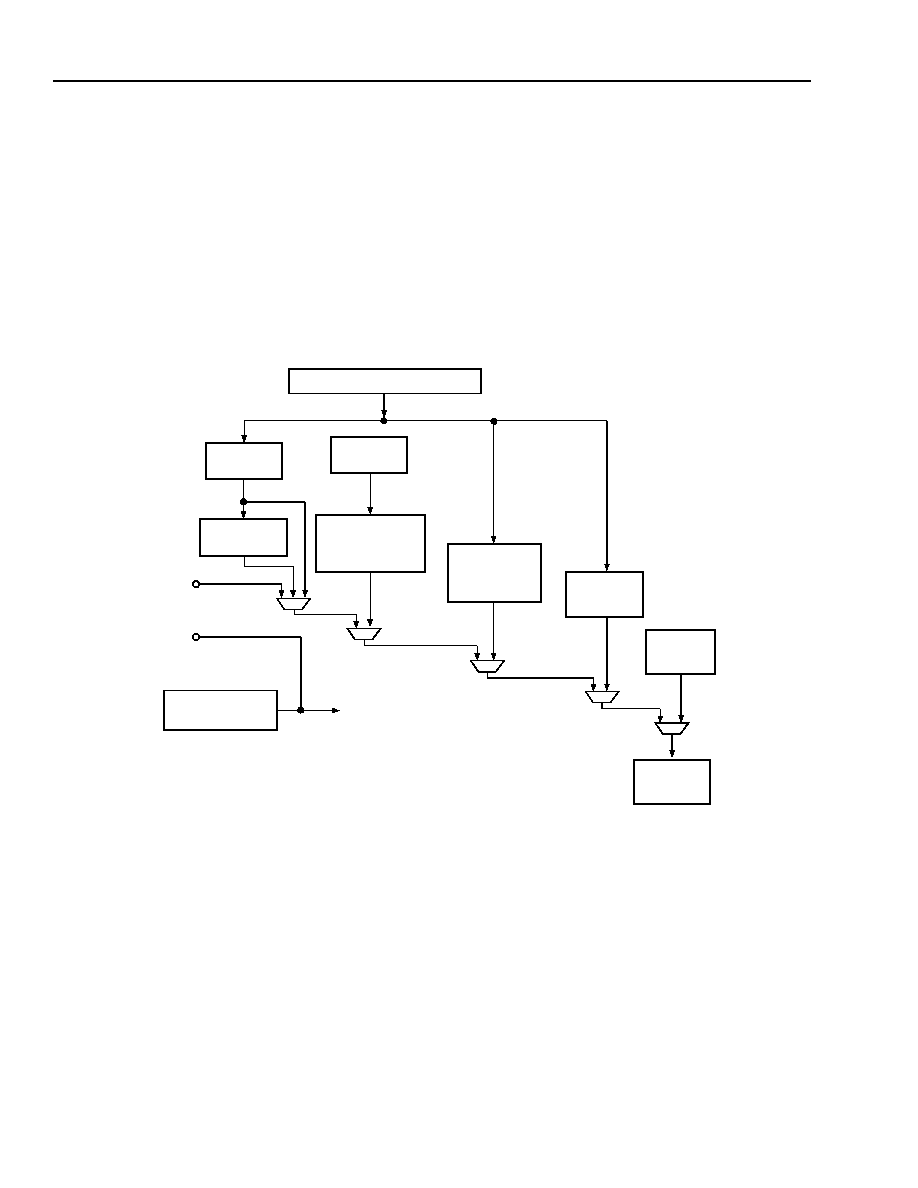

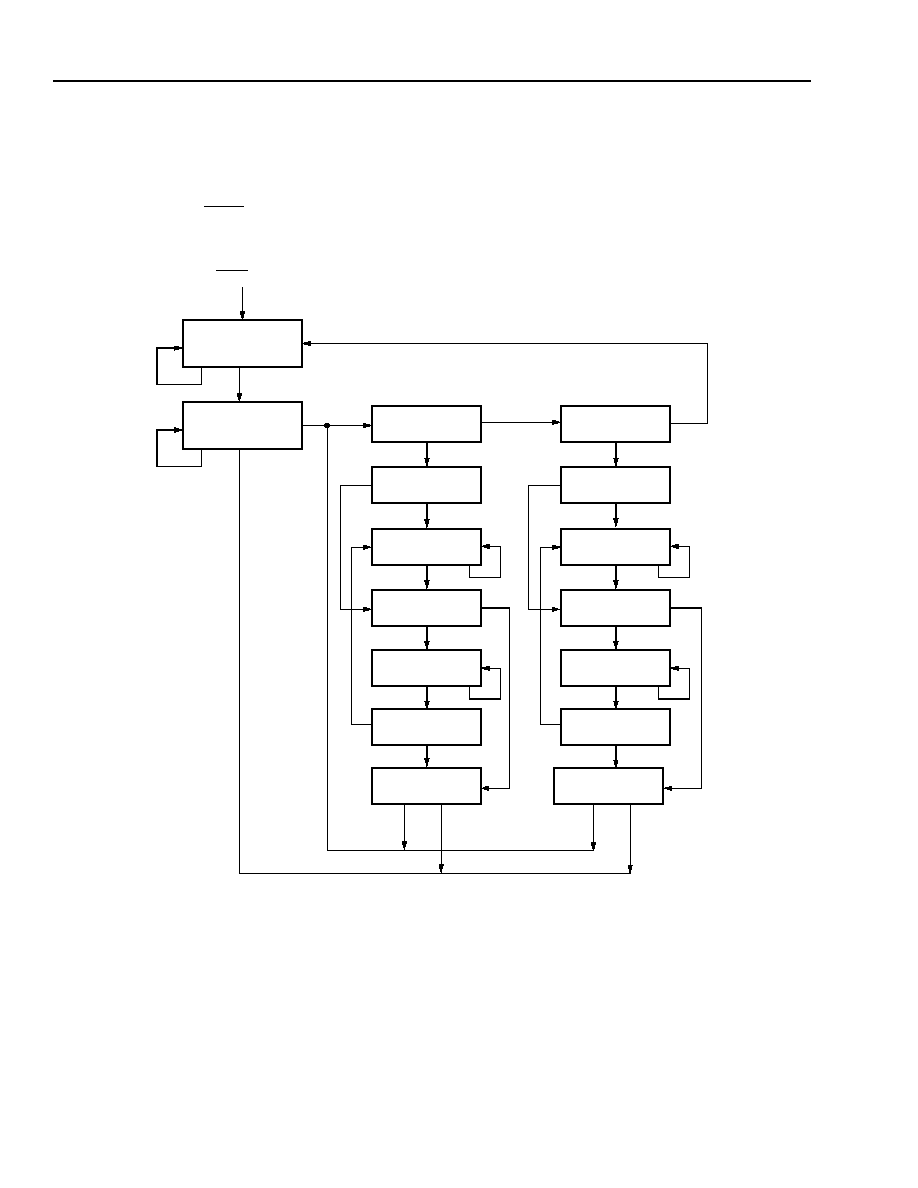

Functional Description ............................................................................................................................................ 15

Pin Information ....................................................................................................................................................... 19

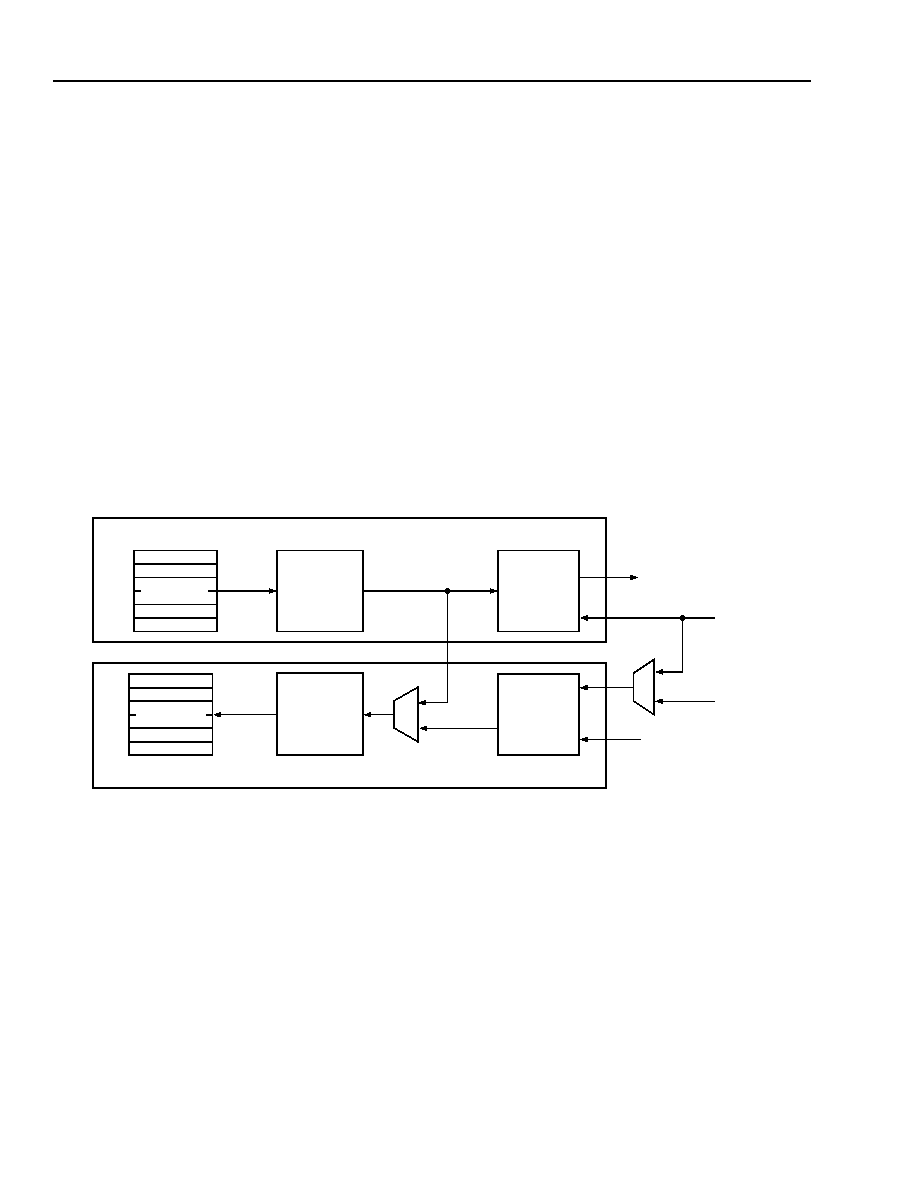

Line Interface Unit: Block Diagram ......................................................................................................................... 26

Line Interface Unit: Receive ................................................................................................................................... 26

Data Recovery.................................................................................................................................................. 26

Jitter Accommodation and Jitter Transfer Without the Jitter Attenuator ........................................................... 27

Receive Line Interface Configuration Modes ................................................................................................... 27

T1/DS1 LIU Receiver Specifications ................................................................................................................ 30

CEPT LIU Receiver Specifications ................................................................................................................... 31

Line Interface Unit: Transmit .................................................................................................................................. 34

Output Pulse Generation.................................................................................................................................. 34

LIU Transmitter Configuration Modes .............................................................................................................. 35

LIU Transmitter Alarms .................................................................................................................................... 35

DSX-1 Transmitter Pulse Template and Specifications ................................................................................... 37

CEPT Transmitter Pulse Template and Specifications .................................................................................... 38

Line Interface Unit: Jitter Attenuator ....................................................................................................................... 40

Generated (Intrinsic) Jitter................................................................................................................................ 40

Jitter Transfer Function .................................................................................................................................... 40

Jitter Accommodation....................................................................................................................................... 41

Jitter Attenuator Enable (Transmit or Receive Path) ........................................................................................ 41

Line Interface Unit: Loopbacks ............................................................................................................................... 44

Full Local Loopback (FLLOOP)........................................................................................................................ 44

Remote Loopback (RLOOP) ............................................................................................................................ 44

Digital Local Loopback (DLLOOP) ................................................................................................................... 44

Line Interface Unit: Other Features ........................................................................................................................ 45

LIU Powerdown (PWRDN) ............................................................................................................................... 45

Loss of Framer Receive Line Clock (LOFRMRLCK Pin).................................................................................. 45

In-Circuit Testing and Driver High-Impedance State (3-STATE)...................................................................... 45

LIU Delay Values.............................................................................................................................................. 45

SYSCK Reference Clock........................................................................................................................................ 46

Line Interface Unit: Line Interface Networks........................................................................................................... 48

LIU-Framer Interface .............................................................................................................................................. 50

LIU-Framer Physical Interface.......................................................................................................................... 50

Interface Mode and Line Encoding................................................................................................................... 52

DS1: Zero Code Suppression (ZCS)................................................................................................................ 53

CEPT: High-Density Bipolar of Order 3 (HDB3)............................................................................................... 54

Agere Systems Inc.

3

Advance Data Sheet

May 2002

T7633 Dual T1/E1 3.3 V Short-Haul Terminator

Table of Contents

(continued)

Contents

Page

Frame Formats........................................................................................................................................................55

T1 Framing Structures ......................................................................................................................................55

T1 Loss of Frame Alignment (LFA) ...................................................................................................................62

T1 Frame Recovery Alignment Algorithms .......................................................................................................63

T1 Robbed-Bit Signaling ...................................................................................................................................64

CEPT 2.048 Basic Frame, CRC-4 Time Slot 0, and Signaling Time Slot 16 Multiframe Structures .................66

CEPT 2.048 Basic Frame Structure..................................................................................................................67

CEPT Loss of Basic Frame Alignment (LFA)....................................................................................................69

CEPT Loss of Frame Alignment Recovery Algorithm .......................................................................................69

CEPT Time Slot 0 CRC-4 Multiframe Structure ................................................................................................70

CEPT Loss of CRC-4 Multiframe Alignment (LTS0MFA)..................................................................................71

CEPT Loss of CRC-4 Multiframe Alignment Recovery Algorithms ...................................................................72

CEPT Time Slot 16 Multiframe Structure ..........................................................................................................76

CEPT Loss of Time Slot 16 Multiframe Alignment (LTS16MFA) ......................................................................78

CEPT Loss of Time Slot 16 Multiframe Alignment Recovery Algorithm............................................................78

CEPT Time Slot 0 FAS/NOT FAS Control Bits .......................................................................................................79

FAS/NOT FAS Si- and E-Bit Source .................................................................................................................79

NOT FAS A-Bit (CEPT Remote Frame Alarm) Sources ...................................................................................80

NOT FAS Sa-Bit Sources..................................................................................................................................80

Sa Facility Data Link Access.............................................................................................................................81

NOT FAS Sa Stack Source and Destination.....................................................................................................82

CEPT Time Slot 16 X0--X2 Control Bits ..........................................................................................................84

Signaling Access.....................................................................................................................................................85

Transparent Signaling .......................................................................................................................................85

DS1: Robbed-Bit Signaling ...............................................................................................................................85

CEPT: Time Slot 16 Signaling...........................................................................................................................86

Auxiliary Framer I/O Timing ....................................................................................................................................87

Alarms and Performance Monitoring.......................................................................................................................91

Interrupt Generation ..........................................................................................................................................91

Alarm Definition.................................................................................................................................................91

Event Counters Definition .................................................................................................................................97

Loopback and Transmission Modes .................................................................................................................99

Line Test Patterns ...........................................................................................................................................102

Automatic and On-Demand Commands .........................................................................................................106

Facility Data Link (FDL).........................................................................................................................................108

Receive Facility Data Link Interface................................................................................................................108

Transmit Facility Data Link Interface...............................................................................................................114

HDLC Operation..............................................................................................................................................115

Transparent Mode...........................................................................................................................................118

Diagnostic Modes............................................................................................................................................120

Phase-Lock Loop Circuit .......................................................................................................................................122

Framer-System (CHI) Interface .............................................................................................................................124

DS1 Modes .....................................................................................................................................................124

CEPT Modes...................................................................................................................................................124

Receive Elastic Store ......................................................................................................................................124

Transmit Elastic Store .....................................................................................................................................124

Concentration Highway Interface (CHI) ................................................................................................................125

CHI Parameters ..............................................................................................................................................126

CHI Frame Timing...........................................................................................................................................129

CHI Offset Programming.................................................................................................................................132

4

Agere Systems Inc.

Advance Data Sheet

May 2002

T7633 Dual T1/E1 3.3 V Short-Haul Terminator

Table of Contents

(continued)

Contents

Page

JTAG Boundary-Scan Specification ..................................................................................................................... 135

Principle of the Boundary Scan ...................................................................................................................... 135

Test Access Port Controller............................................................................................................................ 136

Instruction Register ........................................................................................................................................ 138

Boundary-Scan Register ................................................................................................................................ 139

BYPASS Register........................................................................................................................................... 139

IDCODE Register ........................................................................................................................................... 139

3-State Procedures ........................................................................................................................................ 139

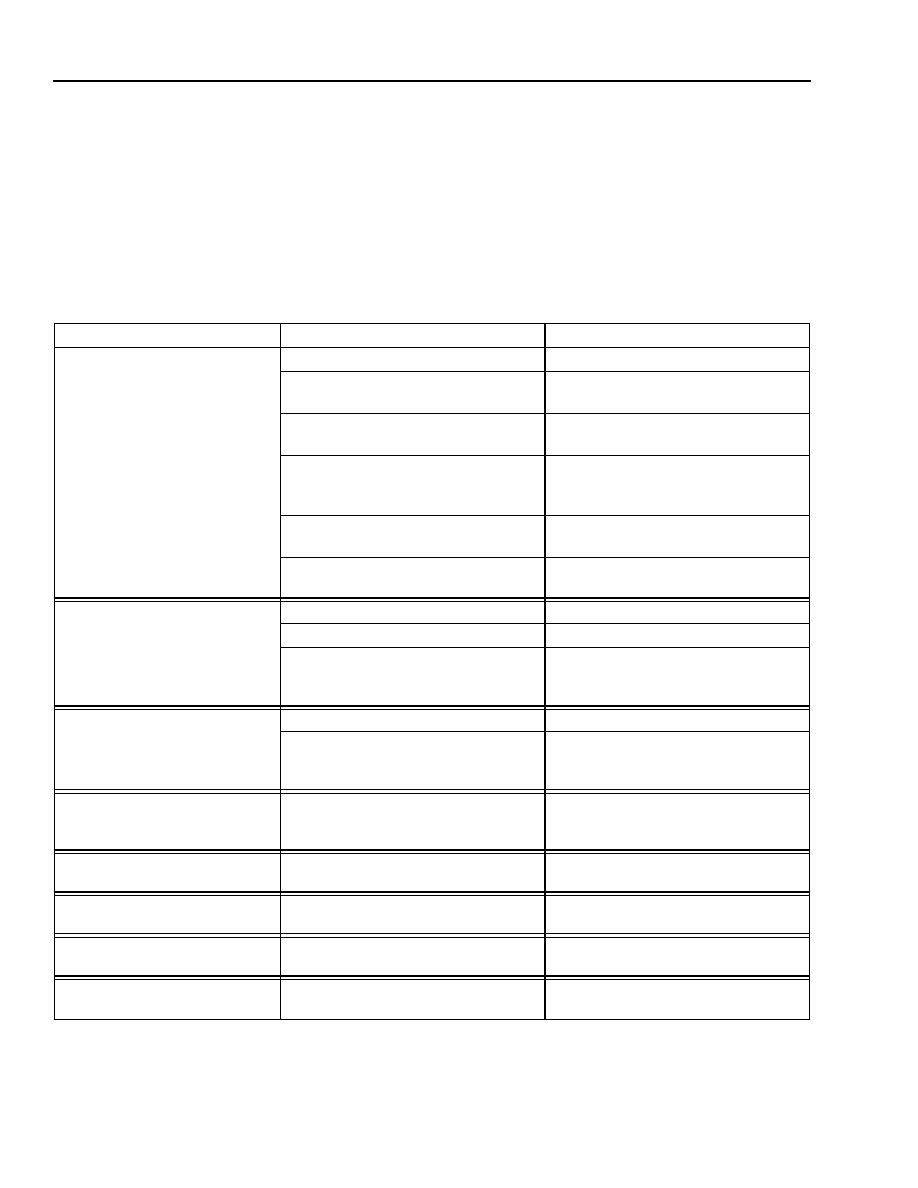

Microprocessor Interface ...................................................................................................................................... 140

Overview ........................................................................................................................................................ 140

Microprocessor Configuration Modes............................................................................................................. 140

Microprocessor Interface Pinout Definitions ................................................................................................... 141

Microprocessor Clock (MPCLK) Specifications.............................................................................................. 142

Microprocessor Interface Register Address Map ........................................................................................... 142

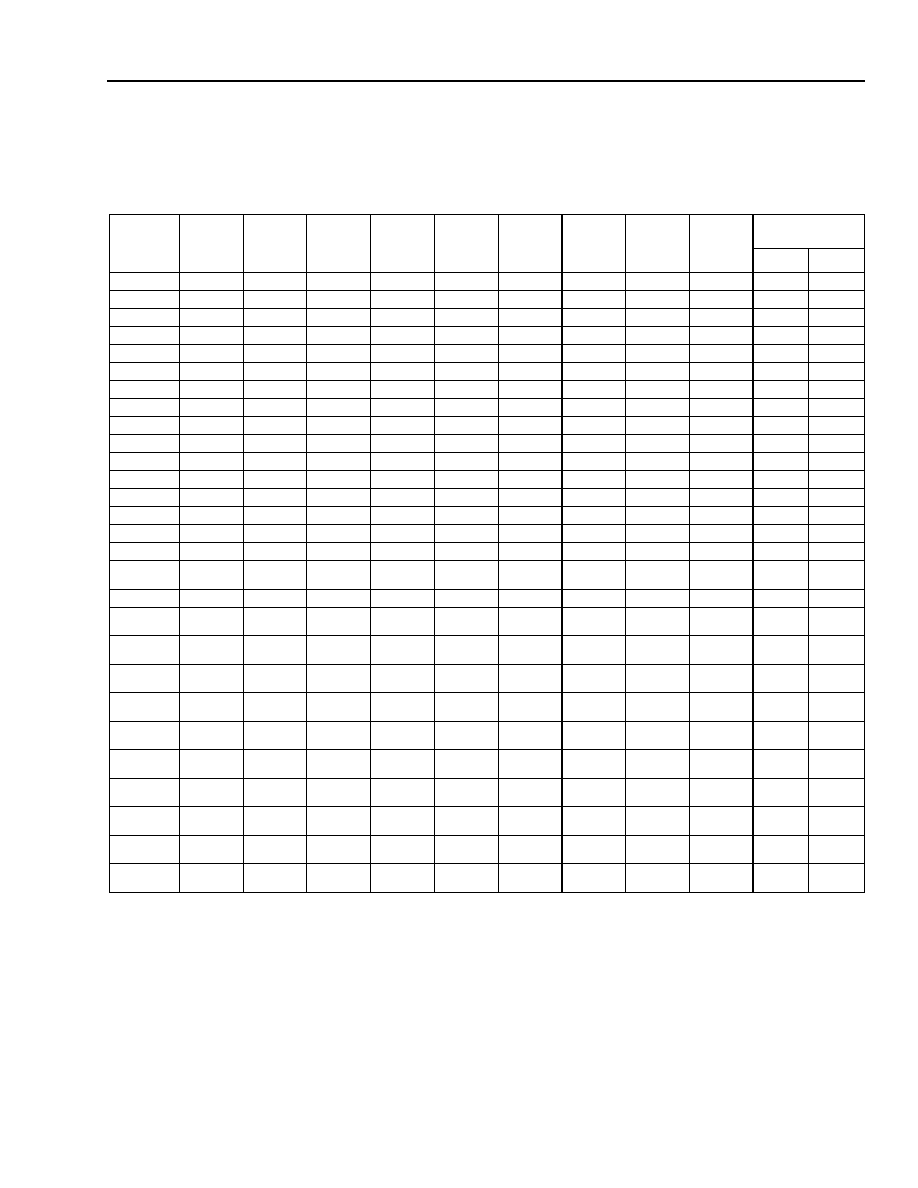

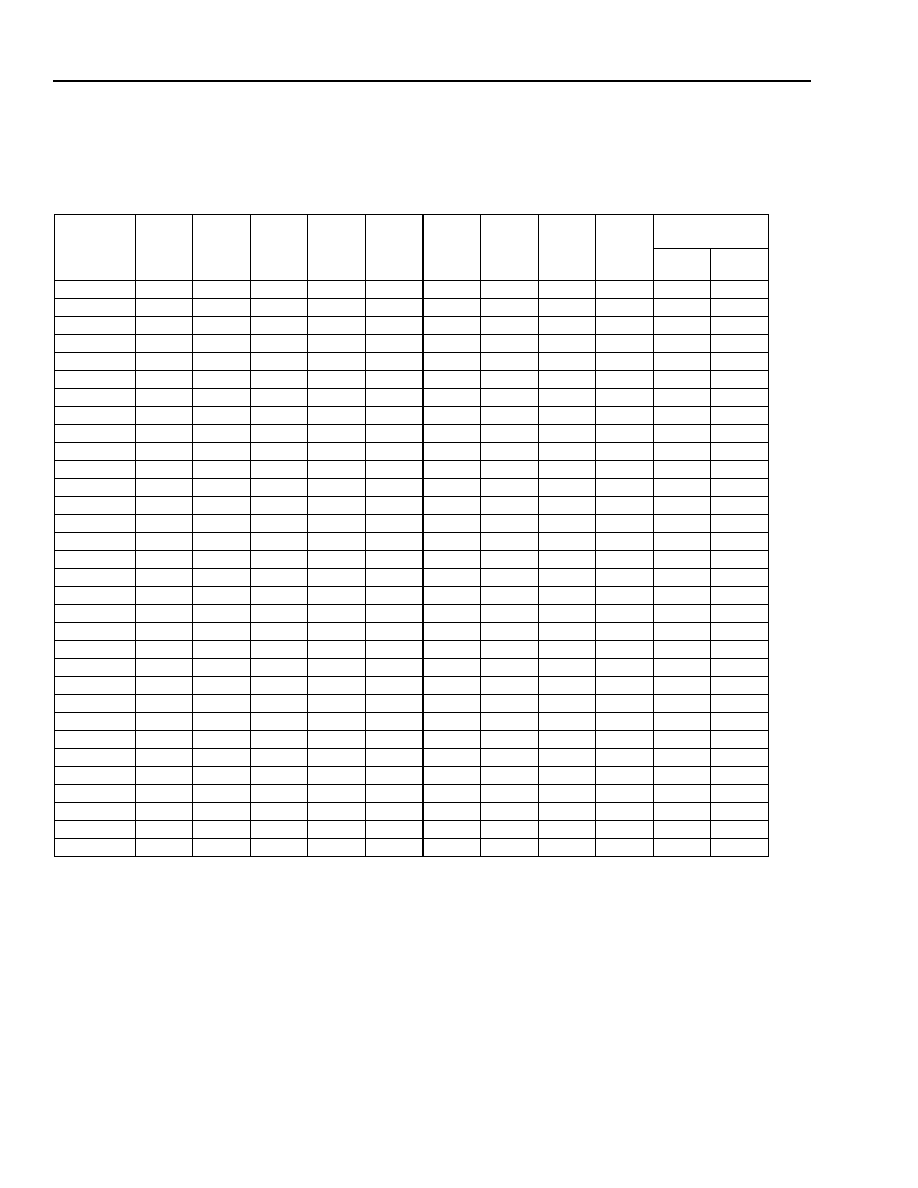

I/O Timing....................................................................................................................................................... 142

Reset .................................................................................................................................................................... 149

Hardware Reset (Pin 43/139)......................................................................................................................... 149

Software Reset/Software Restart ................................................................................................................... 149

Interrupt Generation ............................................................................................................................................. 149

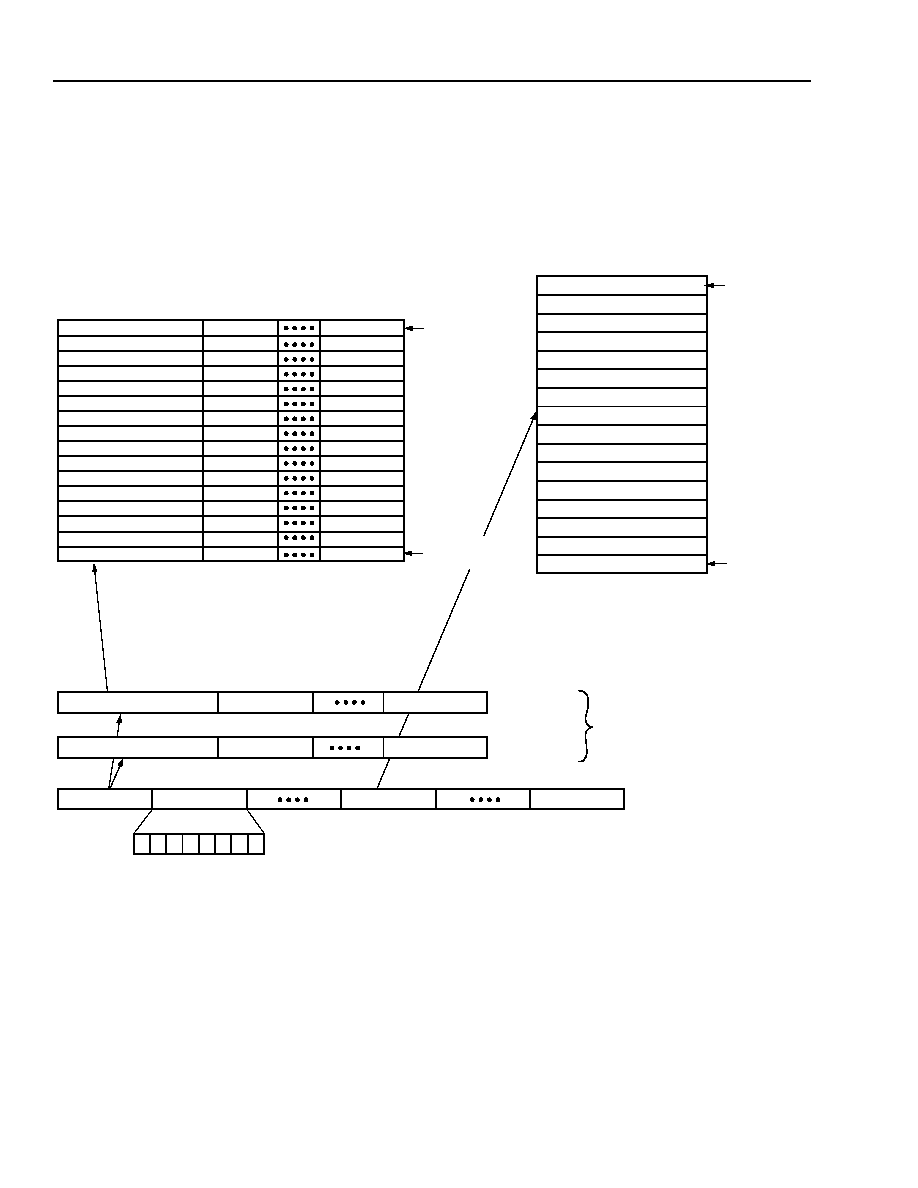

Register Architecture ............................................................................................................................................ 150

Global Register Architecture................................................................................................................................. 154

Global Register Structure ..................................................................................................................................... 155

Primary Block Interrupt Status Register (GREG0) ......................................................................................... 155

Primary Block Interrupt Enable Register (GREG1) ........................................................................................ 155

Global Loopback Control Register (GREG2) ................................................................................................. 156

Global Loopback Control Register (GREG3) ................................................................................................. 156

Global Control Register (GREG4) .................................................................................................................. 157

Device ID and Version Registers (GREG5--GREG7) ................................................................................... 157

Line Interface Unit (LIU) Register Architecture..................................................................................................... 158

Line Interface Alarm Register ............................................................................................................................... 159

Alarm Status Register (LIU_REG0)................................................................................................................ 159

Line Interface Alarm Interrupt Enable Register .................................................................................................... 159

Alarm Interrupt Enable Register (LIU_REG1) ................................................................................................ 159

Line Interface Control Registers ........................................................................................................................... 160

LIU Control Register (LIU_REG2) .................................................................................................................. 160

LIU Control Register (LIU_REG3) .................................................................................................................. 161

LIU Control Register (LIU_REG4) .................................................................................................................. 162

LIU Configuration Register (LIU_REG5) ........................................................................................................ 162

LIU Configuration Register (LIU_REG6) ........................................................................................................ 163

Framer Register Architecture ............................................................................................................................... 164

Framer Status/Counter Registers................................................................................................................... 165

Framer Parameter/Control Registers ............................................................................................................. 180

FDL Register Architecture .................................................................................................................................... 211

FDL Parameter/Control Registers (800--80E; E00--E0E) .................................................................................. 212

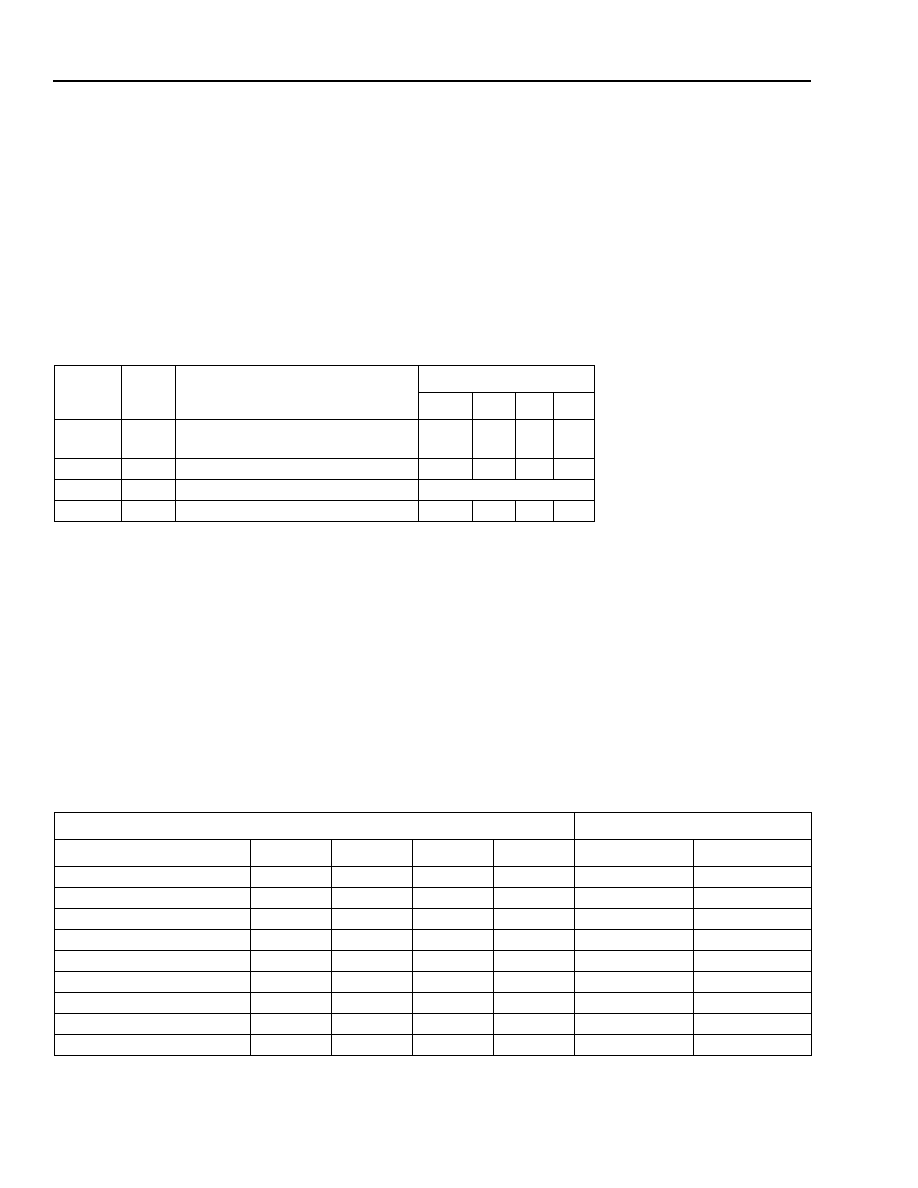

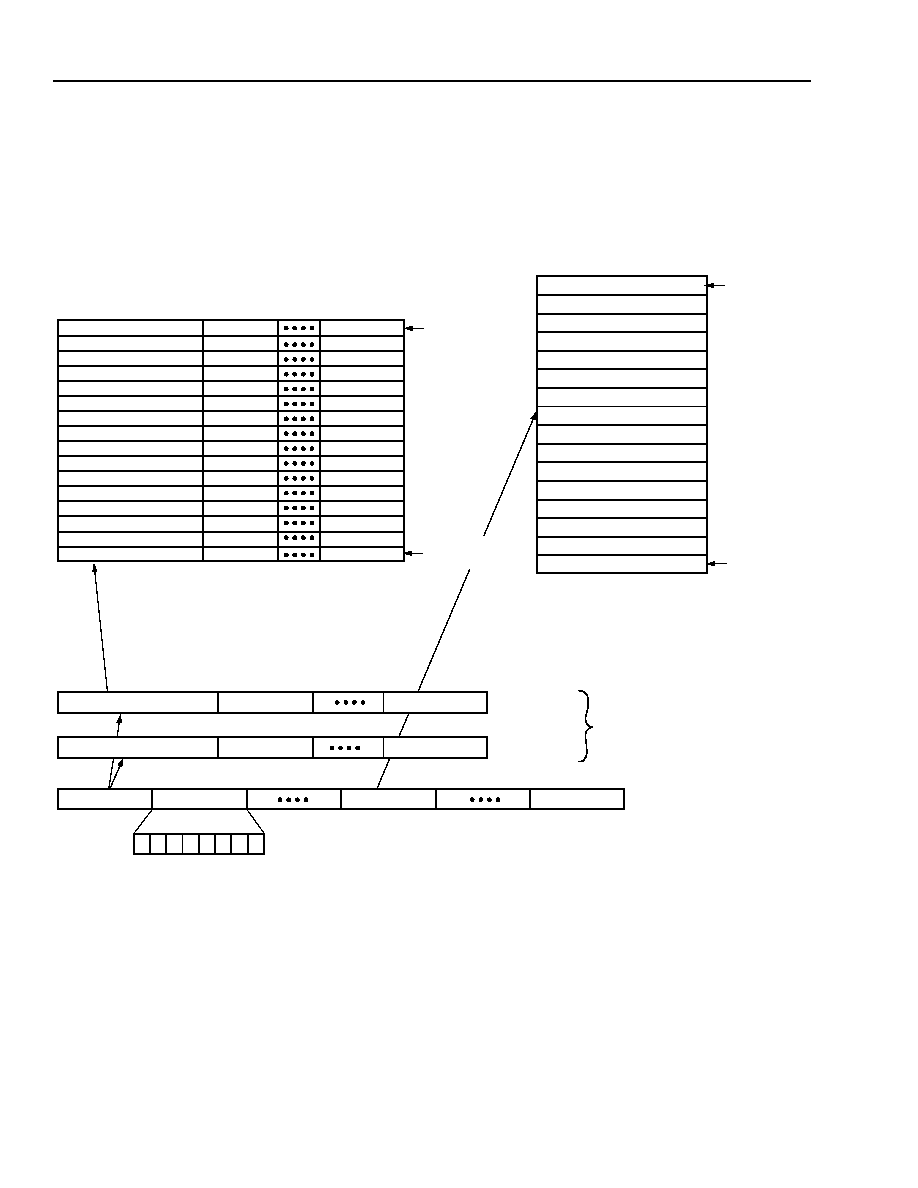

Register Maps ...................................................................................................................................................... 219

Global Registers............................................................................................................................................. 219

Line Interface Unit Parameter/Control and Status Registers ......................................................................... 219

Framer Parameter/Control Registers (READ-WRITE) ................................................................................... 220

Receive Framer Signaling Registers (READ-ONLY) ..................................................................................... 222

Framer Unit Parameter Register Map ............................................................................................................ 223

Transmit Signaling Registers (READ/WRITE) ............................................................................................... 226

Facility Data Link Parameter/Control and Status Registers (READ-WRITE) ................................................. 227

Agere Systems Inc.

5

Advance Data Sheet

May 2002

T7633 Dual T1/E1 3.3 V Short-Haul Terminator

Table of Contents

(continued)

Contents

Page

Absolute Maximum Ratings ..................................................................................................................................228

Operating Conditions ............................................................................................................................................228

Handling Precautions ............................................................................................................................................228

Electrical Characteristics .......................................................................................................................................229

Logic Interface Characteristics........................................................................................................................229

Power Supply Bypassing ......................................................................................................................................229

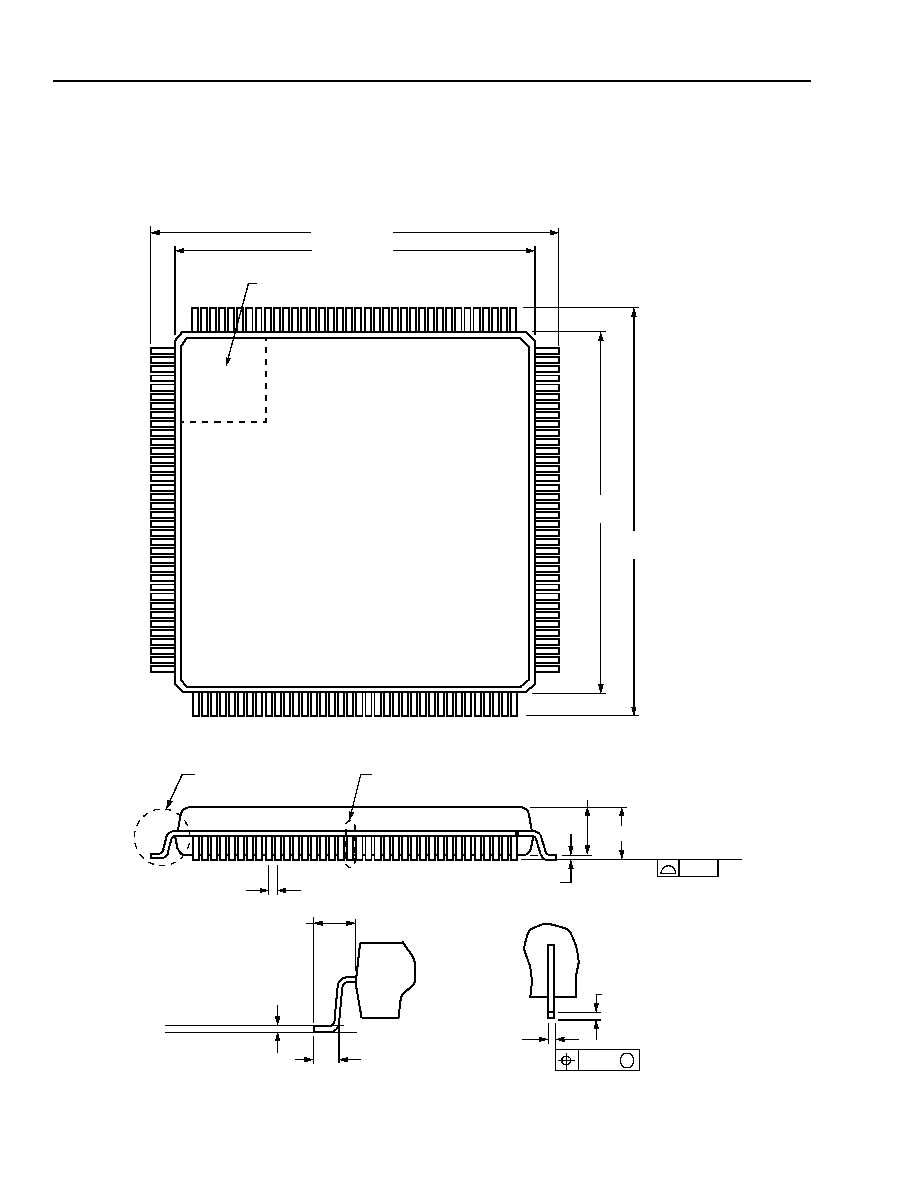

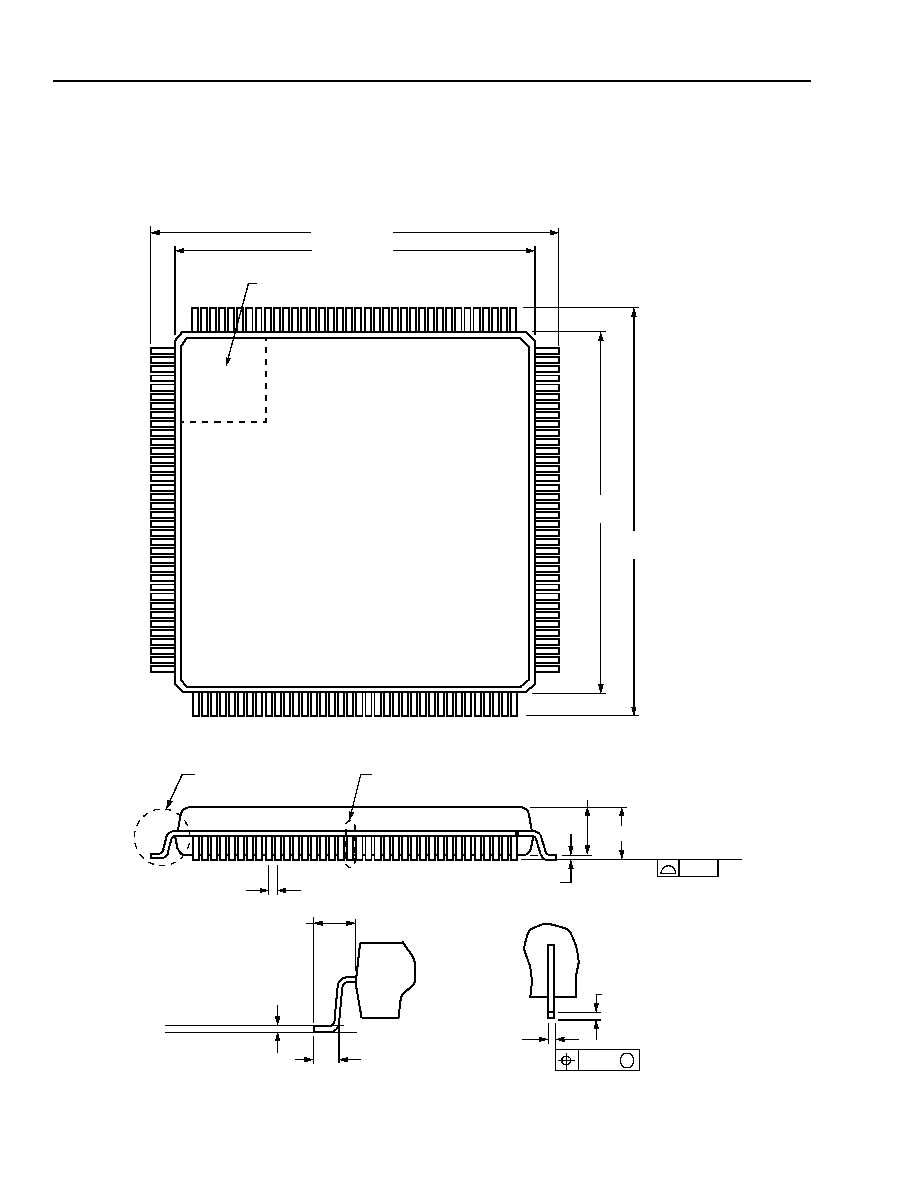

Outline Diagram ....................................................................................................................................................230

144-Pin TQFP .................................................................................................................................................230

Ordering Information .............................................................................................................................................231

Index .....................................................................................................................................................................232

6

Agere Systems Inc.

Advance Data Sheet

May 2002

T7633 Dual T1/E1 3.3 V Short-Haul Terminator

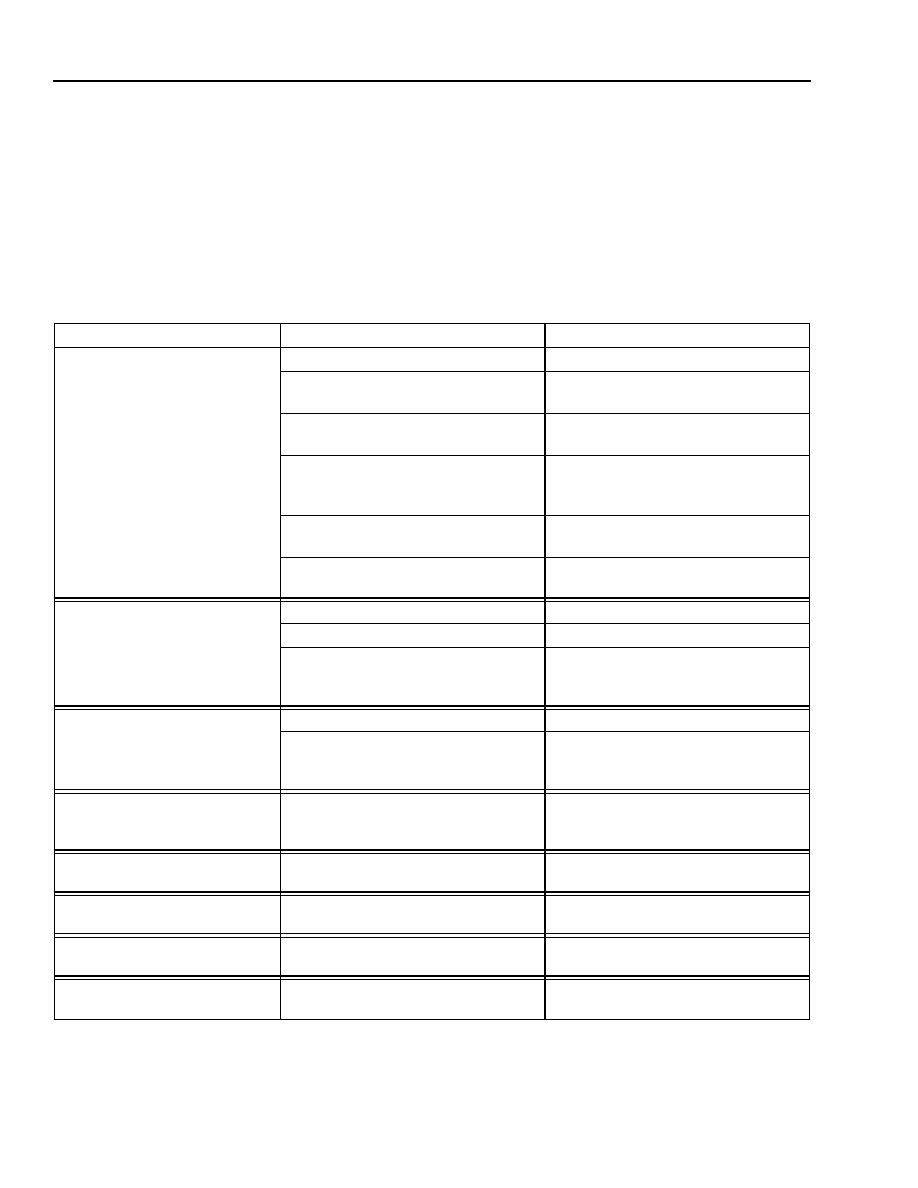

List of Figures

Figure

Page

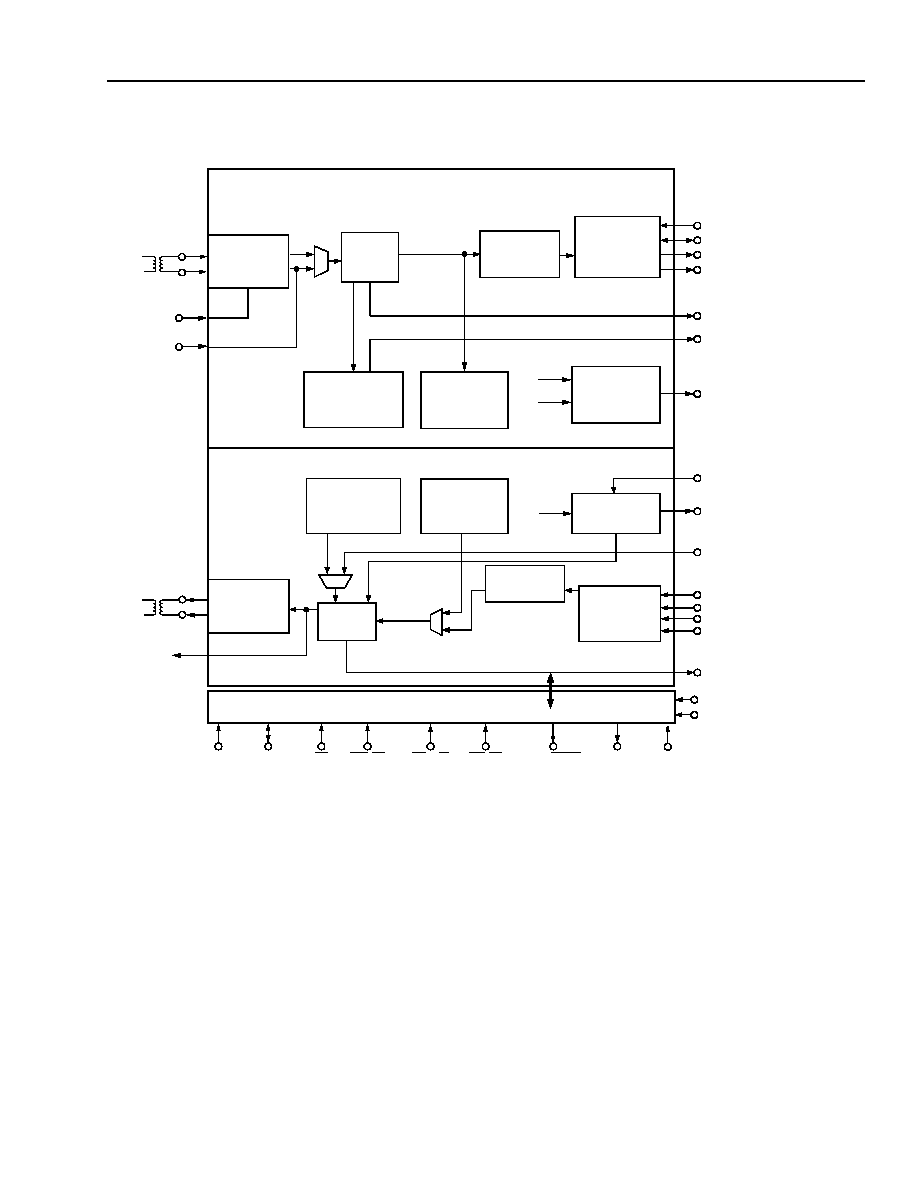

Figure 1. T7633 Block Diagram (One of Two Channels)........................................................................................ 15

Figure 2. T7633 Block Diagram: Receive Section (One of Two Channels)............................................................ 17

Figure 3. T7633 Block Diagram: Transmit Section (One of Two Channels)........................................................... 18

Figure 4. Pin Assignment ....................................................................................................................................... 19

Figure 5. Block Diagram of Line Interface Unit: Single Channel ............................................................................ 26

Figure 6. T1/DS1 Receiver Jitter Accommodation Without Jitter Attenuator.......................................................... 32

Figure 7. T1/DS1 Receiver Jitter Transfer Without Jitter Attenuator ...................................................................... 32

Figure 8. CEPT/E1 Receiver Jitter Accommodation Without Jitter Attenuator ....................................................... 33

Figure 9. CEPT/E1 Receiver Jitter Transfer Without Jitter Attenuator ................................................................... 33

Figure 10. DSX-1 Isolated Pulse Template ............................................................................................................ 37

Figure 11. ITU-T G.703 Pulse Template ................................................................................................................ 38

Figure 12. T1/DS1 Receiver Jitter Accommodation with Jitter Attenuator.............................................................. 42

Figure 13. T1/DS1 Jitter Transfer of the Jitter Attenuator....................................................................................... 42

Figure 14. CEPT/E1 Receiver Jitter Accommodation with Jitter Attenuator........................................................... 43

Figure 15. CEPT/E1 Jitter Transfer of the Jitter Attenuator.................................................................................... 43

Figure 16. Line Termination Circuitry ..................................................................................................................... 48

Figure 17. T7633 Line Interface Unit Approximate Equivalent Analog I/O Circuits ................................................ 49

Figure 18. Block Diagram of Framer Line Interface................................................................................................ 50

Figure 19. Transmit Framer TLCK to TND, TPD and Receive Framer RND, RPD to RLCK Timing...................... 51

Figure 20. T1 Frame Structure ............................................................................................................................... 55

Figure 21. T1 Transparent Frame Structure........................................................................................................... 56

Figure 22. T7633 Facility Data Link Access Timing of the Transmit and Receive Framer Sections ...................... 58

Figure 23. ITU 2.048 Basic Frame, CRC-4 Multiframe, and Channel Associated Signaling Multiframe

Structures............................................................................................................................................... 66

Figure 24. CEPT Transparent Frame Structure ..................................................................................................... 68

Figure 25. Receive CRC-4 Multiframe Search Algorithm Using the 100 ms Internal Timer................................... 73

Figure 26. Receive CRC-4 Multiframe Search Algorithm for Automatic, CRC-4/Non-CRC-4 Equipment

Interworking as Defined by ITU (From ITU Rec. G.706, Annex B.2.2 - 1991) ...................................... 75

Figure 27. Facility Data Link Access Timing of the Transmit and Receive Framer Sections in the CEPT Mode ... 81

Figure 28. Transmit and Receive Sa Stack Accessing Protocol ............................................................................ 83

Figure 29. Timing Specification for RFRMCK, RFRMDATA, and RFS in DS1 Mode............................................. 87

Figure 30. Timing Specification for TFS, TLCK, and TPD in DS1 Mode ................................................................ 87

Figure 31. Timing Specification for RFRMCK, RFRMDATA, and RFS in CEPT Mode .......................................... 88

Figure 32. Timing Specification for RFRMCK, RFRMDATA, RFS, and RSSFS in CEPT Mode ............................ 88

Figure 33. Timing Specification for RCRCMFS in CEPT Mode.............................................................................. 89

Figure 34. Timing Specification for TFS, TLCK, and TPD in CEPT Mode ............................................................. 89

Figure 35. Timing Specification for TFS, TLCK, TPD, and TSSFS in CEPT Mode ................................................ 90

Figure 36. Timing Specification for TFS, TLCK, TPD, and TCRCMFS in CEPT Mode .......................................... 90

Figure 37. Relation Between RLCK1 and Interrupt (Pin 99)................................................................................... 91

Figure 38. Timing for Generation of LOPLLCK (Pin 39/143).................................................................................. 93

Figure 39. The T and V Reference Points for a Typical CEPT E1 Application....................................................... 96

Figure 40. Loopback and Test Transmission Modes............................................................................................ 101

Figure 41. 20-Stage Shift Register Used to Generate the Quasi-Random Signal................................................ 102

Figure 42. 15-Stage Shift Register Used to Generate the Pseudorandom Signal ............................................... 103

Figure 43. T7633 Facility Data Link Access Timing of the Transmit and Receive Framer Sections .................... 108

Figure 44. Block Diagram for the Receive Facility Data Link Interface ................................................................ 109

Figure 45. Block Diagram for the Transmit Facility Data Link Interface ............................................................... 114