| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: T-8110L | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Data Sheet

February 2004

Ambassador

Æ

T8110L H.100/H.110 Switch

1 Introduction

The T8110L is the newest addition to the Ambassa-

dor series of TDM switching and backlane intercon-

nect standard products. The T8110L can switch 4096

simultaneous time slots with 32 bidirectional local

streams and 32 bidirectional H.100/H.110 streams.

The T8110L has all the features of the T810X

devices. Additionally, the T8110L has more robust

clocking fallback abilities and is pin compatible with

the T8110. (The full version of the T8110 has a PCI

and minbridge interface.)

1.1 Features

!

4,096-connection unified switch

!

Full H.100/H.110 support (32 data lines, all clock

modes)

!

32 local I/O lines (2, 4, 8, or 16 Mbits/s)

!

Microprocessor interface: Motorola

Æ

/Intel

Æ

modes

!

Interrupt controller with external inputs

!

Eight independent general-purpose I/O lines

!

Eight independently programmed framing signals

!

Four local clocks

!

T1/E1 rate adaptation

!

Two clock-fallback modes

!

Stratum 4/4E and AT&T

Æ

62411 MTIE compliant

!

Incorporates 38 H.100 and 34 H.110 termination

resistors

!

Subrate switching of 4 bits, 2 bits, or 1 bit

!

Backward compatible to all T810x devices

!

Pin compatible with T8110

!

JTAG/boundary-scan testing support

!

BSDL files available

!

Assists H.110 hot swap

!

Single 3.3 V supply with 5 V tolerant inputs and

TTL compatible outputs

!

272 PBGA package

!

Evaluation boards available

Table of Contents

Contents

Page

2

Agere Systems Inc.

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

1

Introduction ......................................................................................................................................................... 1

1.1

Features.................................................................................................................................................... 1

2

Pin Description ..................................................................................................................................................10

2.1

Interface Signals .....................................................................................................................................10

2.2

T8110L Pinout Information ..................................................................................................................... 12

2.3

Special Buffer Requirements .................................................................................................................. 20

2.3.1

H1x0 Bus Signal Internal Pull-Up/Pull-Down .............................................................................. 20

2.3.2

Local Bus Signal Internal Pull-Up ...............................................................................................20

3

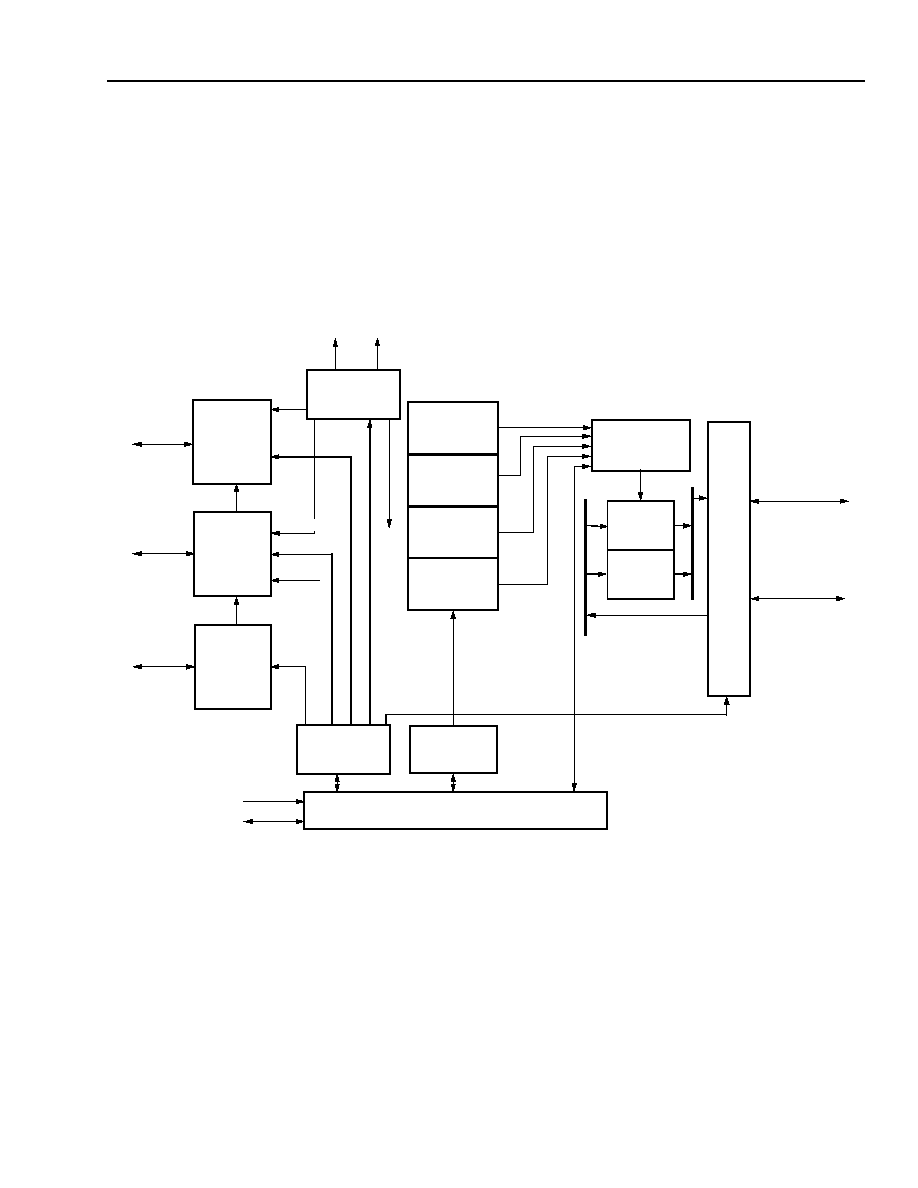

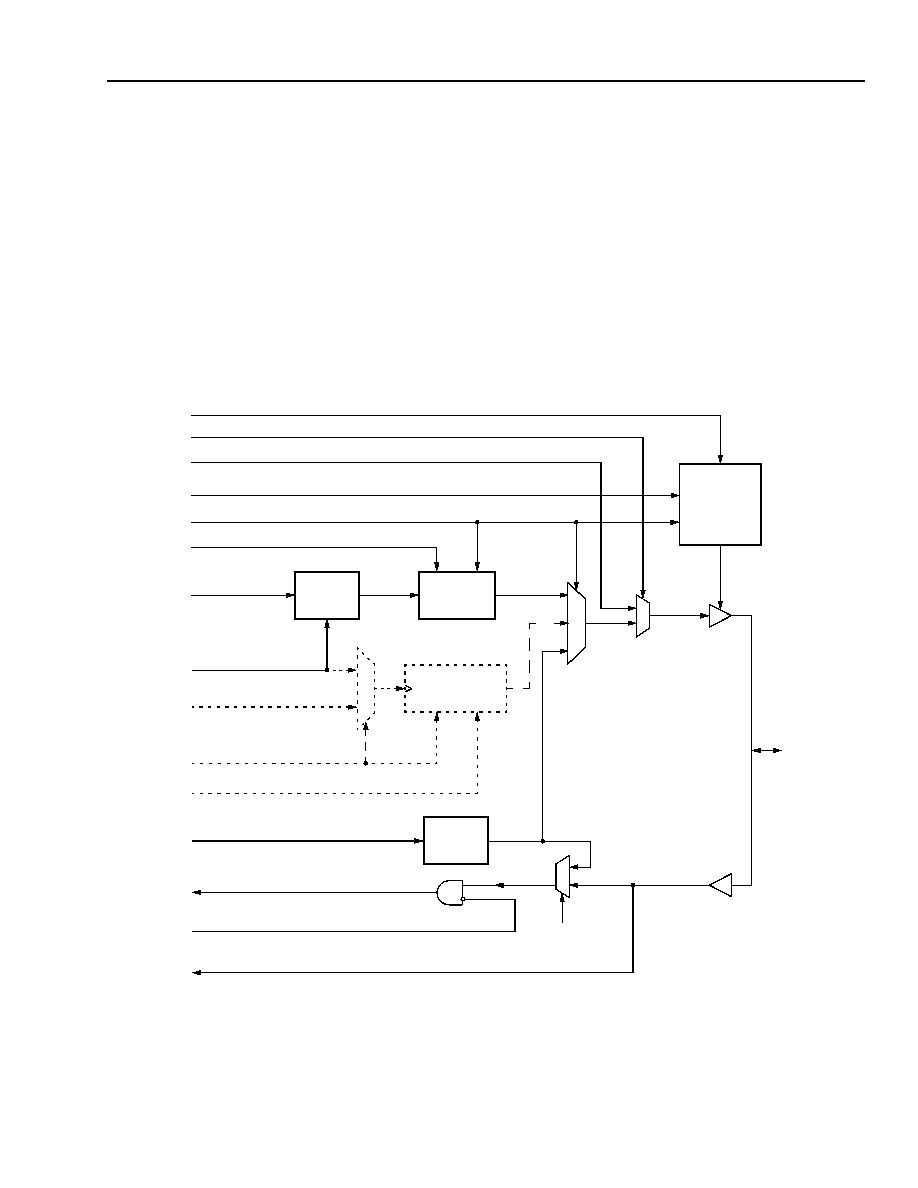

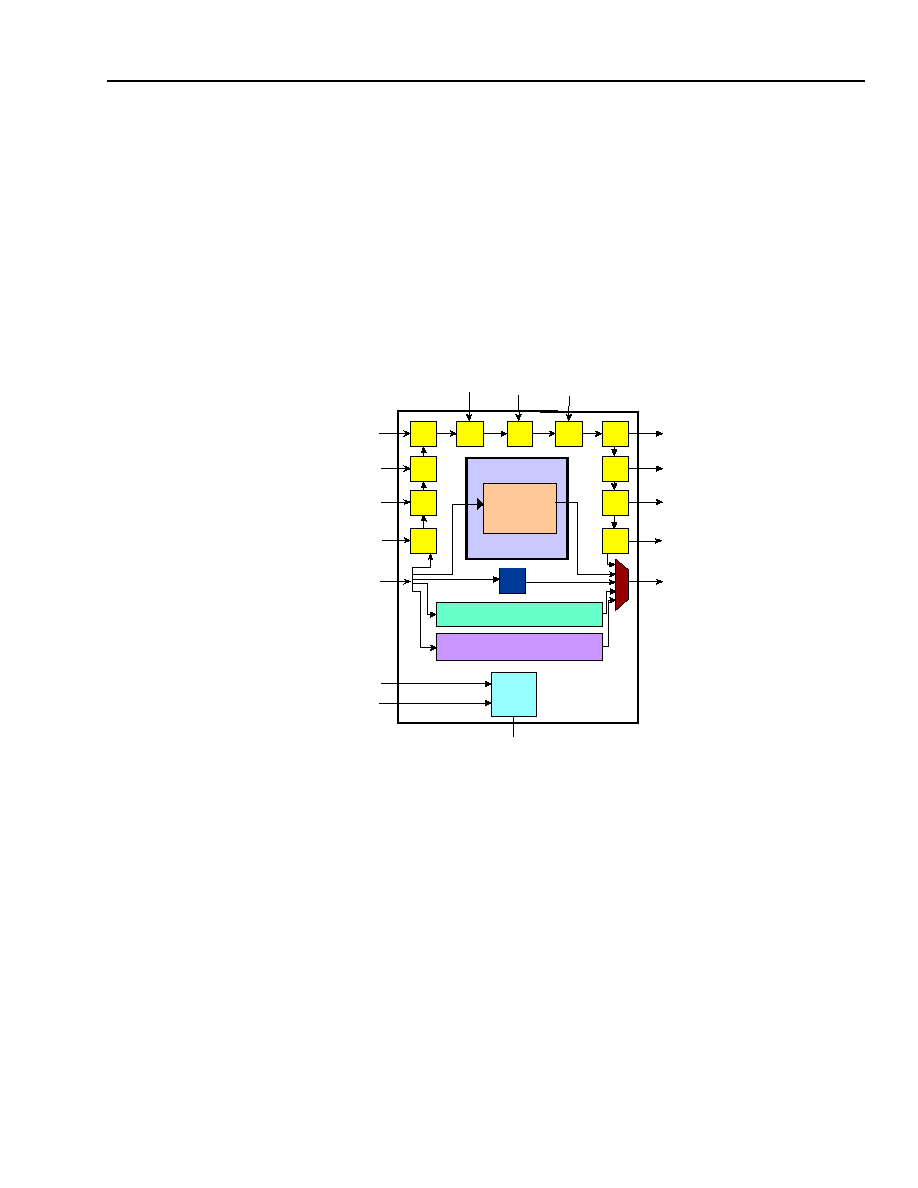

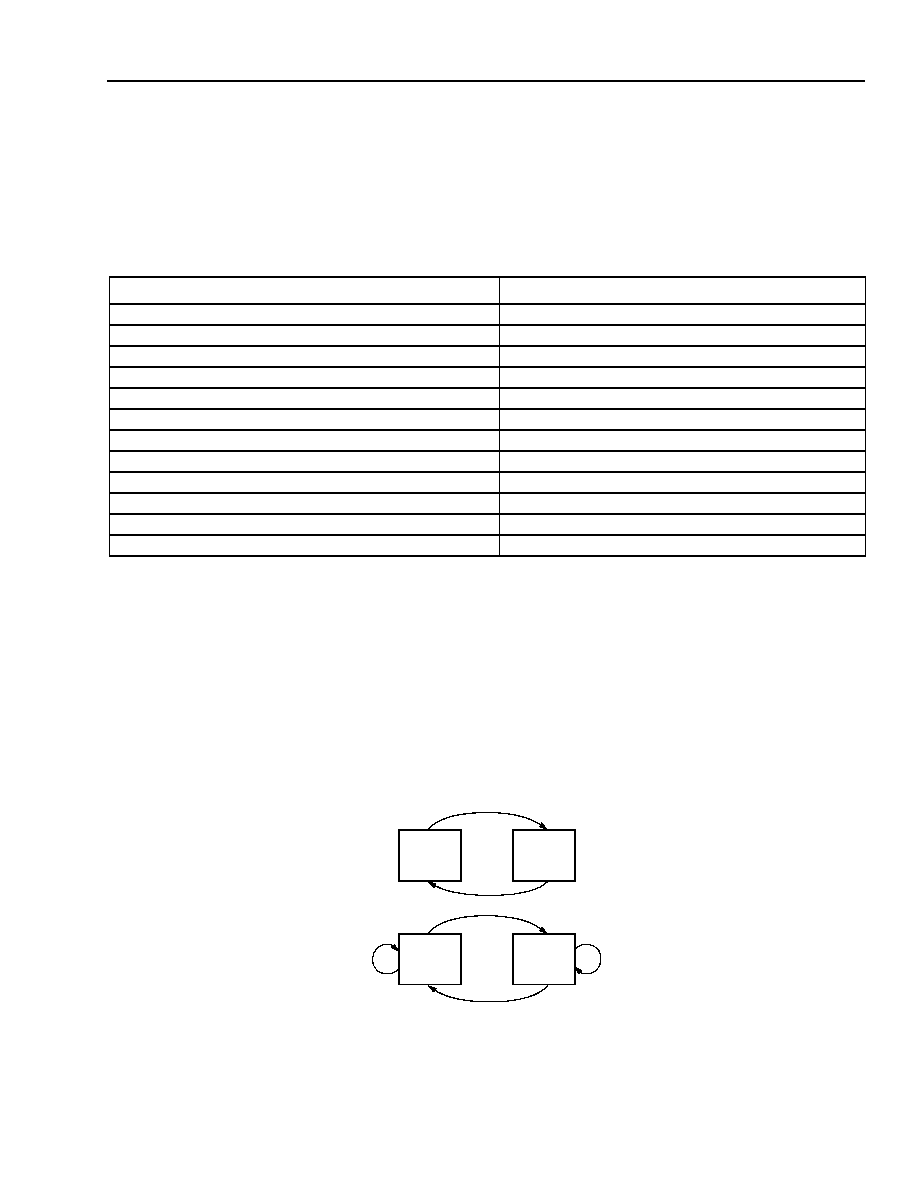

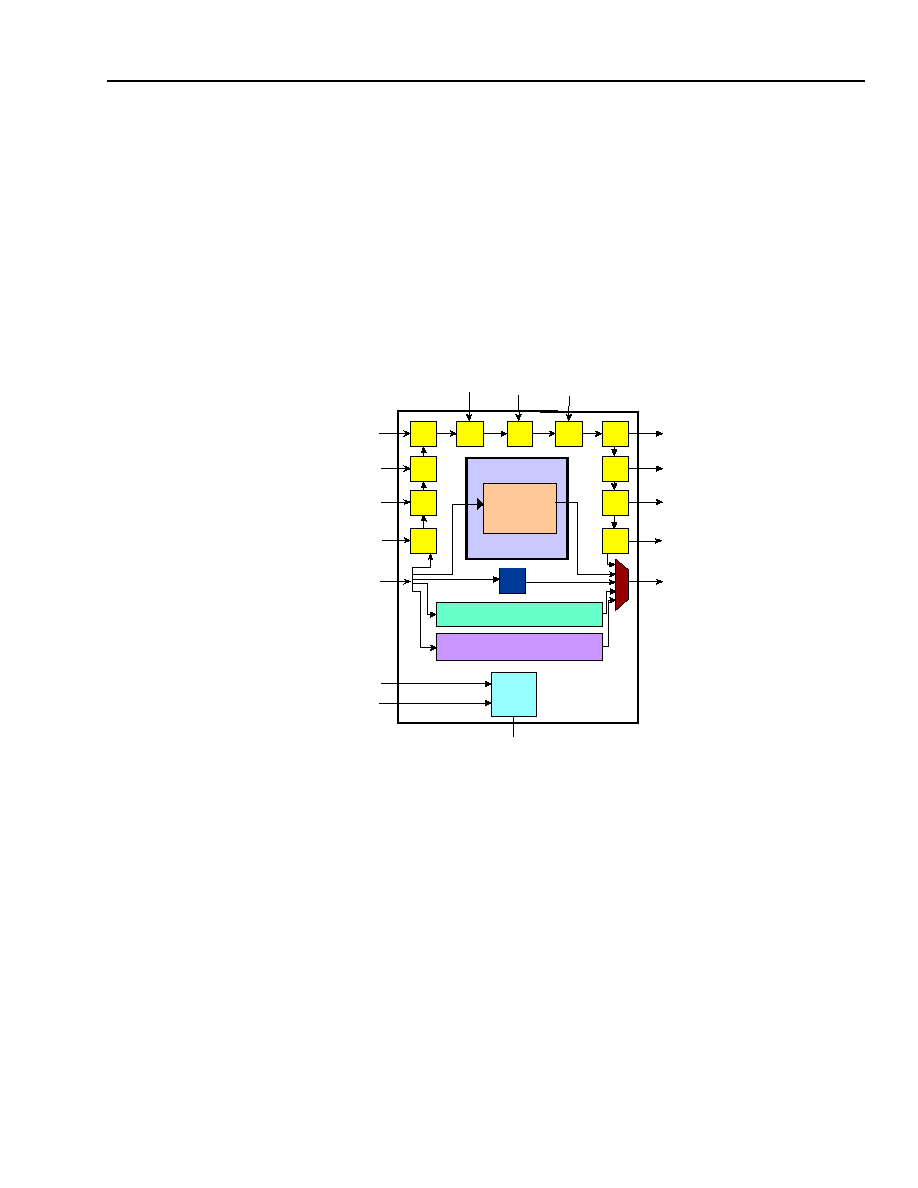

Main Architectural Features .............................................................................................................................. 21

3.1

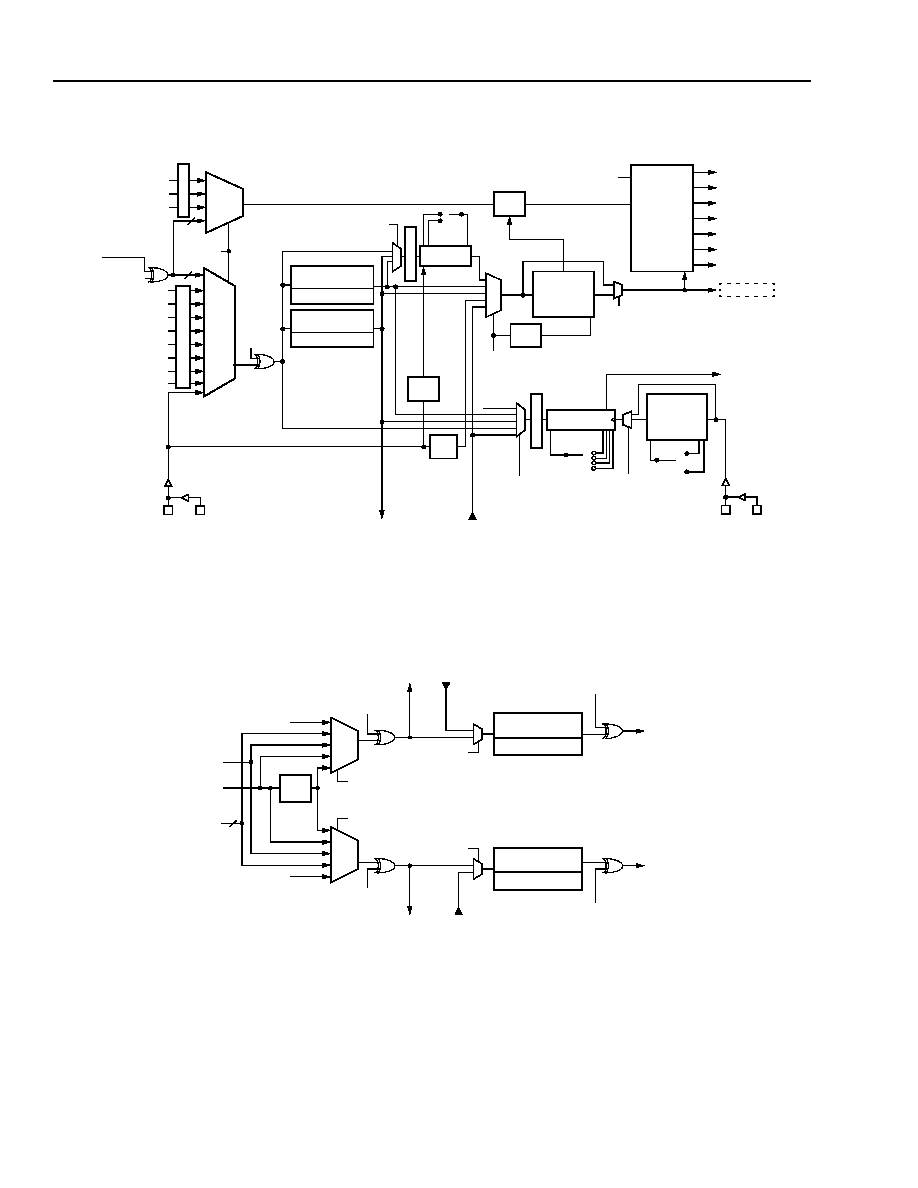

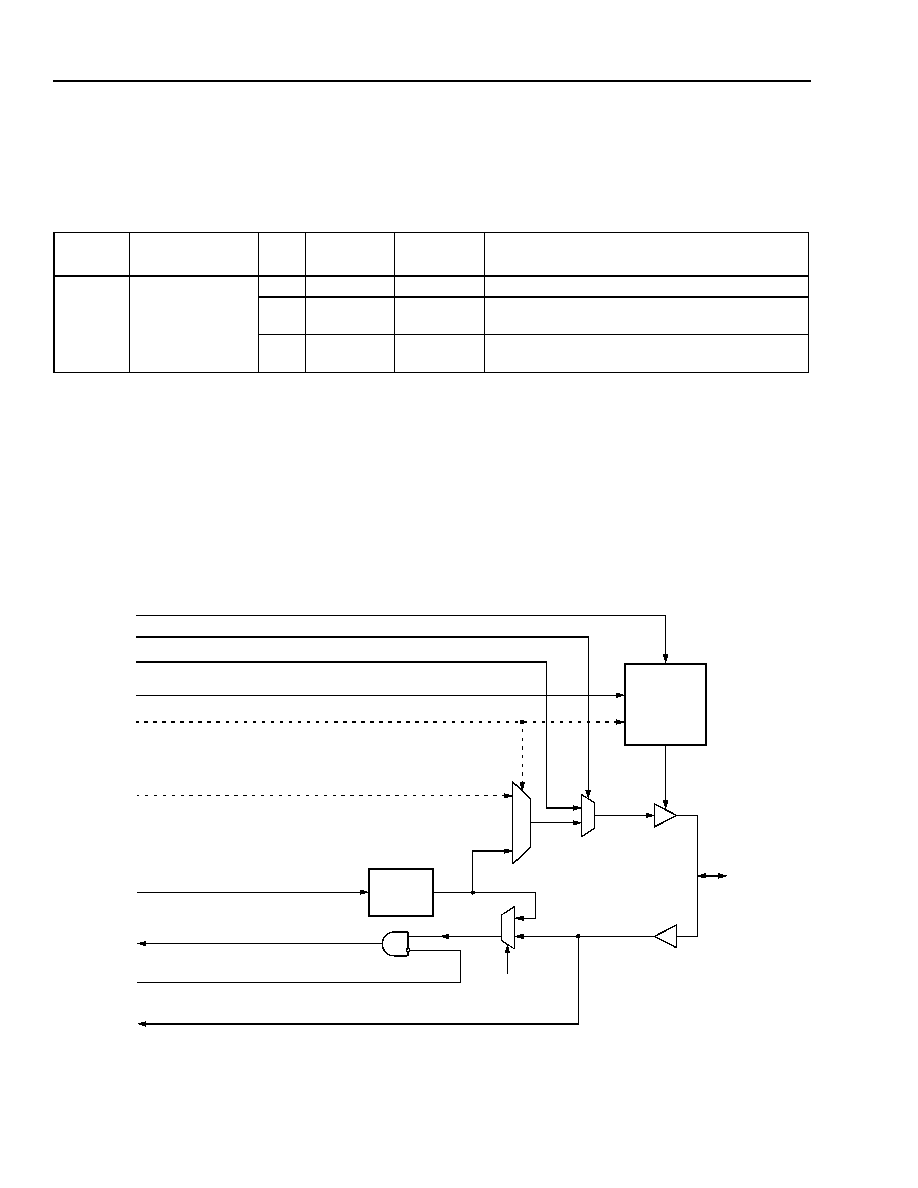

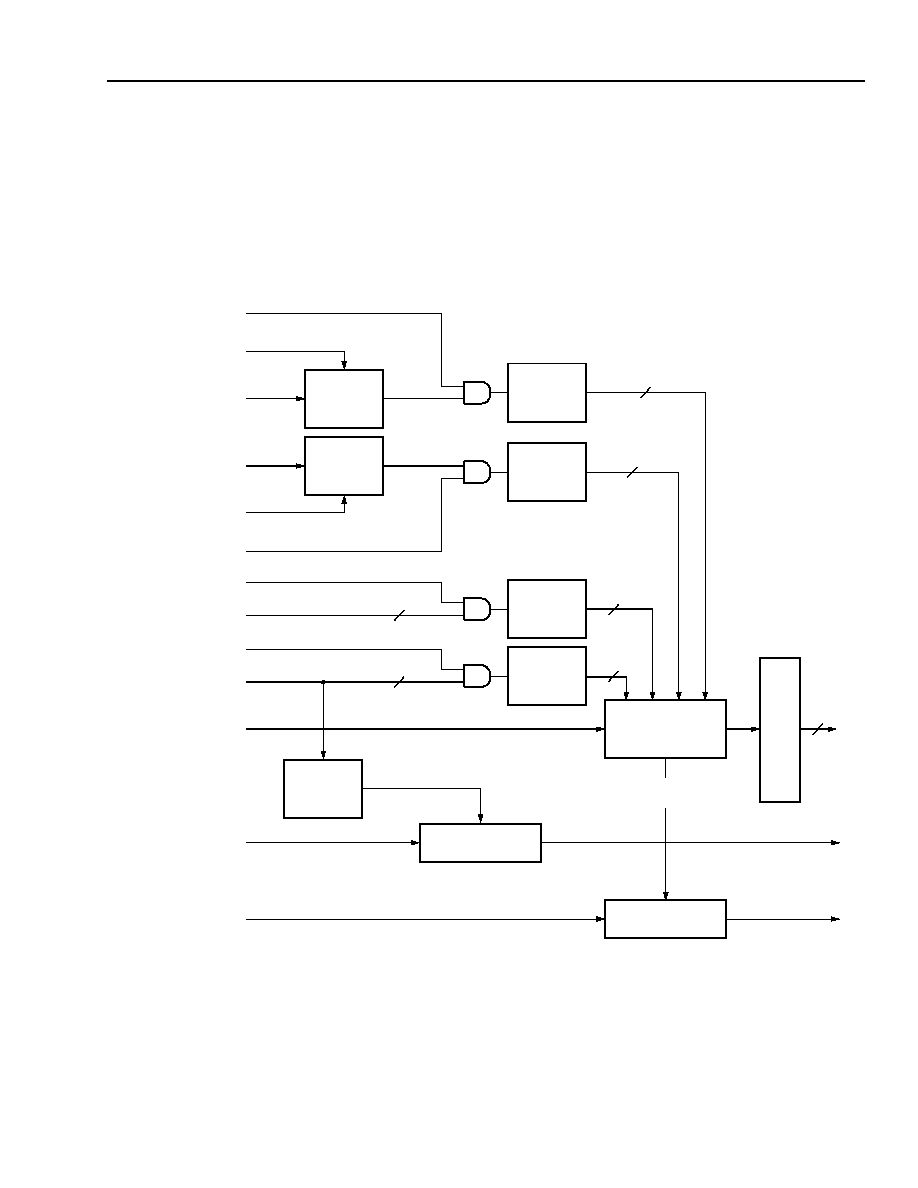

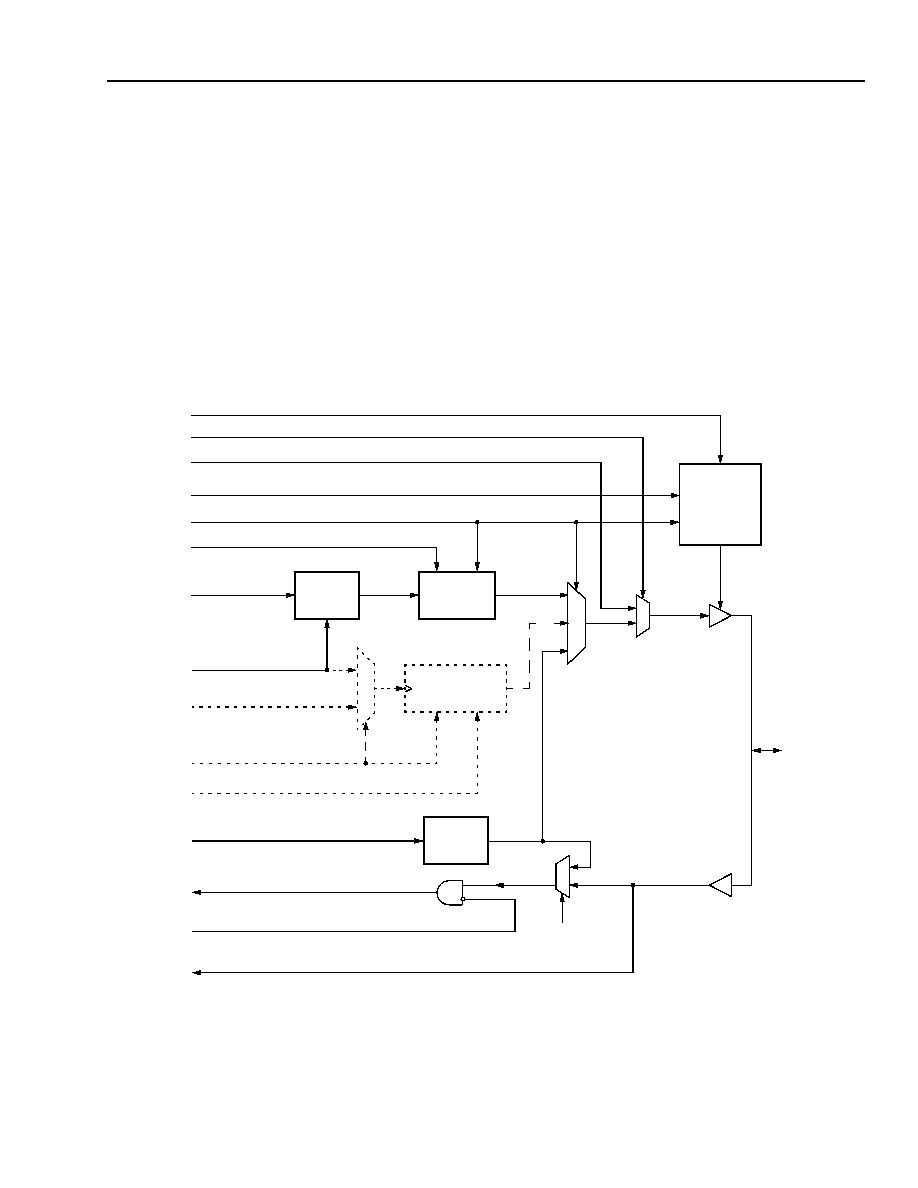

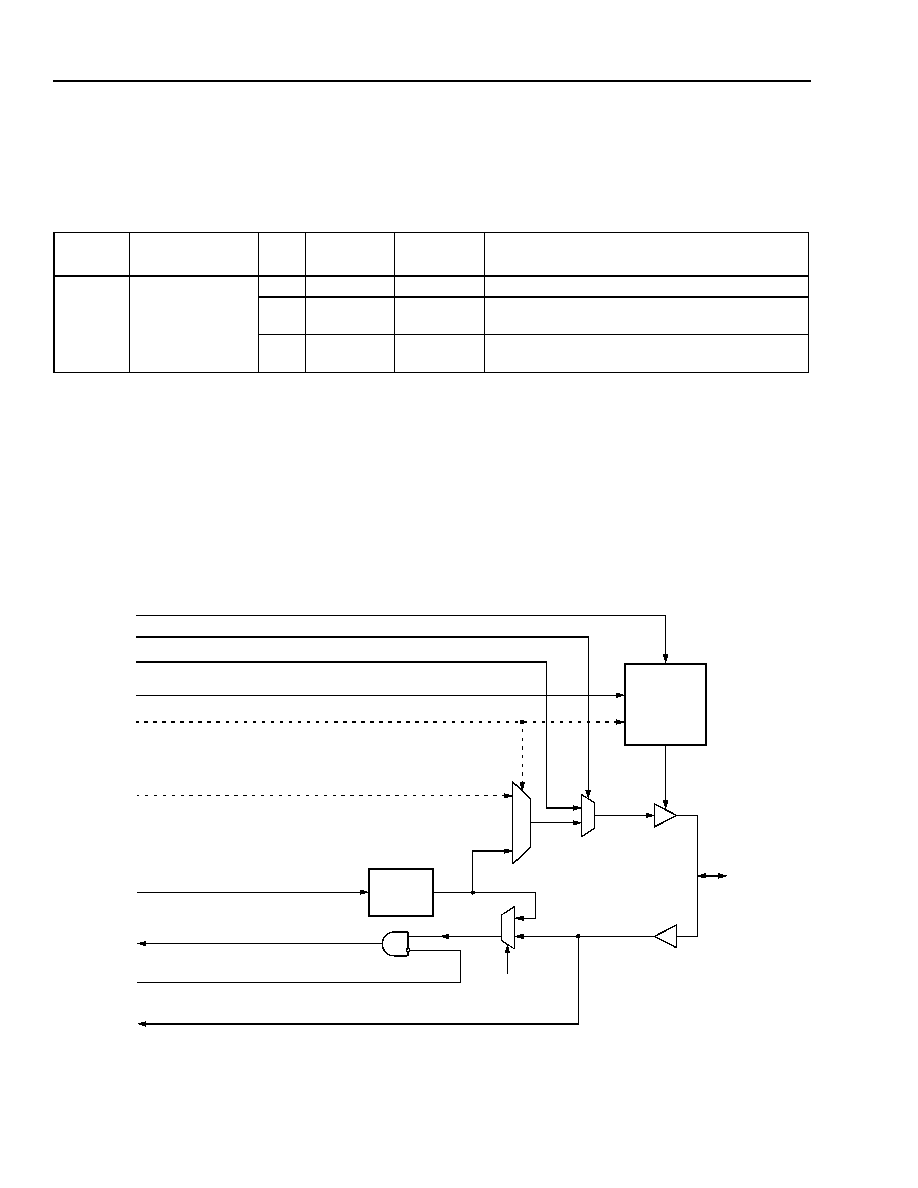

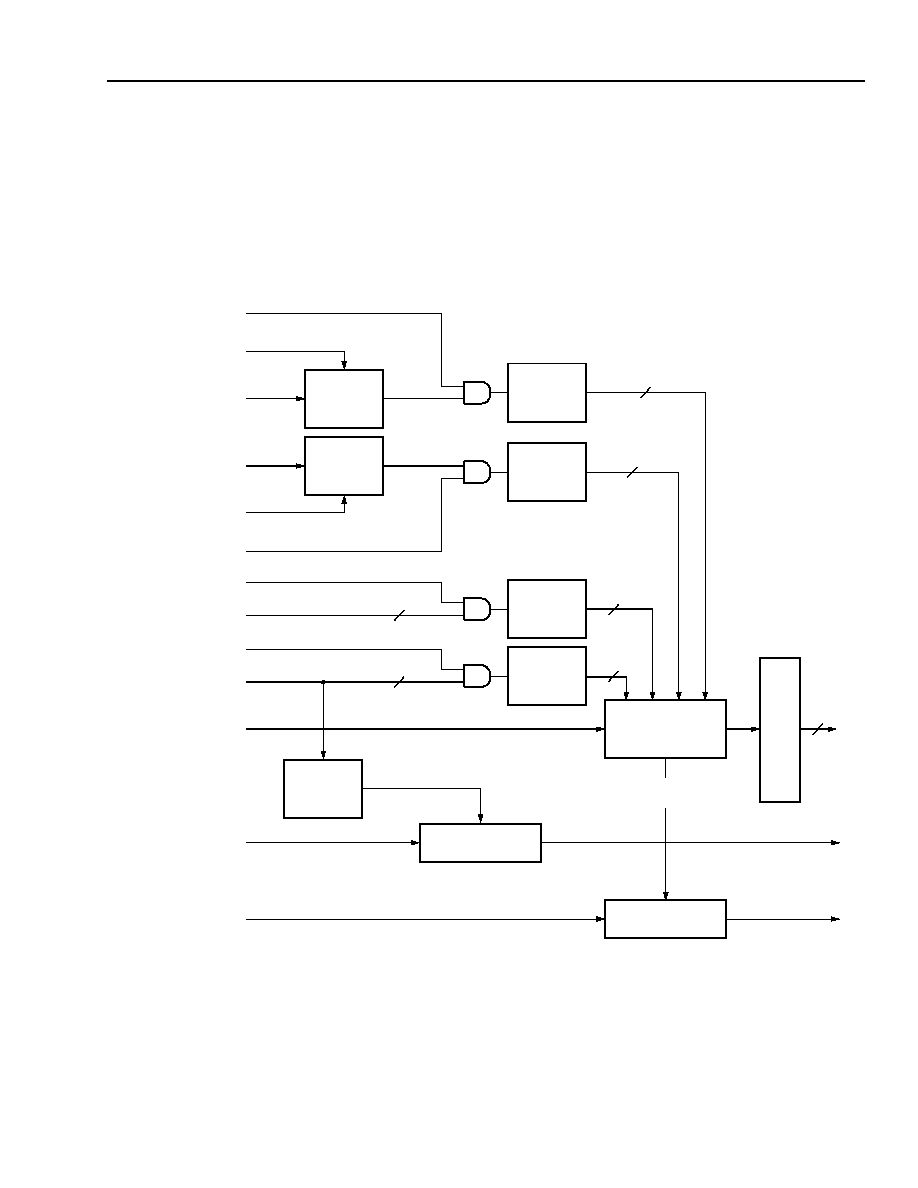

T8110L Architecture ............................................................................................................................... 21

4

Microprocessor Interface .................................................................................................................................. 22

4.1

Intel/Motorola Protocol Selector.............................................................................................................. 22

4.2

Word/Byte Addressing Selector.............................................................................................................. 22

4.3

Access Via the Microprocessor Bus ....................................................................................................... 23

4.3.1

Microprocessor Interface Register Map ...................................................................................... 24

4.3.2

Register Space Access ............................................................................................................... 28

4.3.3

Connection Memory Space Access ............................................................................................ 28

4.3.4

Data Memory Space Access....................................................................................................... 29

5

Operating Control and Status ........................................................................................................................... 30

5.1

Control Registers .................................................................................................................................... 30

5.1.1

Reset Registers .......................................................................................................................... 30

5.1.2

Master Output Enable Register................................................................................................... 31

5.1.3

Connection Control--Data Memory Selector Register ...............................................................32

5.1.4

General Clock Control (Phase Alignment, Fallback, Watchdogs) Register ................................ 33

5.1.5

Phase Alignment Select Register ...............................................................................................33

5.1.6

Fallback Control Register............................................................................................................33

5.1.7

Fallback Type Select Register .................................................................................................... 34

5.1.8

Fallback Trigger Registers .......................................................................................................... 35

5.1.9

Watchdog Select, C8, and NETREF Registers........................................................................... 36

5.1.10 Watchdog EN Register ............................................................................................................... 37

5.1.11 Failsafe Control Registers........................................................................................................... 38

5.2

Error and Status Registers ..................................................................................................................... 39

5.2.1

Clock Errors ................................................................................................................................ 40

5.2.1.1

Transient Clock Errors Registers................................................................................. 40

5.2.1.2

Latched Clock Error Register ...................................................................................... 41

5.2.2

System Status ............................................................................................................................. 42

5.2.2.1

Clock Fallback Status Register.................................................................................... 42

5.2.2.2

Device Identification Registers .................................................................................... 43

5.2.2.3

System Device Errors.................................................................................................. 43

6

Clock Architecture ............................................................................................................................................. 44

6.1

Clock Input Control Registers ................................................................................................................. 45

6.1.1

Main Input Selector Register....................................................................................................... 45

6.1.2

Main Divider Register.................................................................................................................. 46

6.1.3

Analog PLL1 (APLL1) Input Selector Register............................................................................46

6.1.4

APLL1 Rate Register .................................................................................................................. 47

6.1.5

Main Inversion Select Register ................................................................................................... 47

6.1.6

Resource Divider Register .......................................................................................................... 48

6.1.7

Analog PLL2 (APLL2) Rate Register .......................................................................................... 48

6.1.8

LREF Input Select Registers....................................................................................................... 49

6.1.9

DPLL1 Input Selector .................................................................................................................. 50

Table of Contents

(continued)

Contents

Page

Agere Systems Inc.

3

February 2004

Ambassador T8110L H.100/H.110 Switch

Data Sheet

6.1.9.1

DPLL1 Rate Register...................................................................................................50

6.1.10 DPLL2 Input Selector ..................................................................................................................50

6.1.10.1 DPLL2 Rate Register...................................................................................................51

6.1.11 NETREF1 Registers....................................................................................................................51

6.1.12 NETREF2 Registers....................................................................................................................52

6.2

Clock Output Control Registers ..............................................................................................................53

6.2.1

Master Output Enables Register .................................................................................................53

6.2.2

Clock Output Format Registers...................................................................................................54

6.2.3

TCLK and L_SCx Select Registers .............................................................................................55

6.3

Clock Register Access............................................................................................................................57

6.4

Clock Circuit Operation--APLL1 ............................................................................................................57

6.4.1

Main Clock Selection, Bit Clock, and Frame ...............................................................................57

6.4.1.1

Watchdog Timers ........................................................................................................58

6.4.1.2

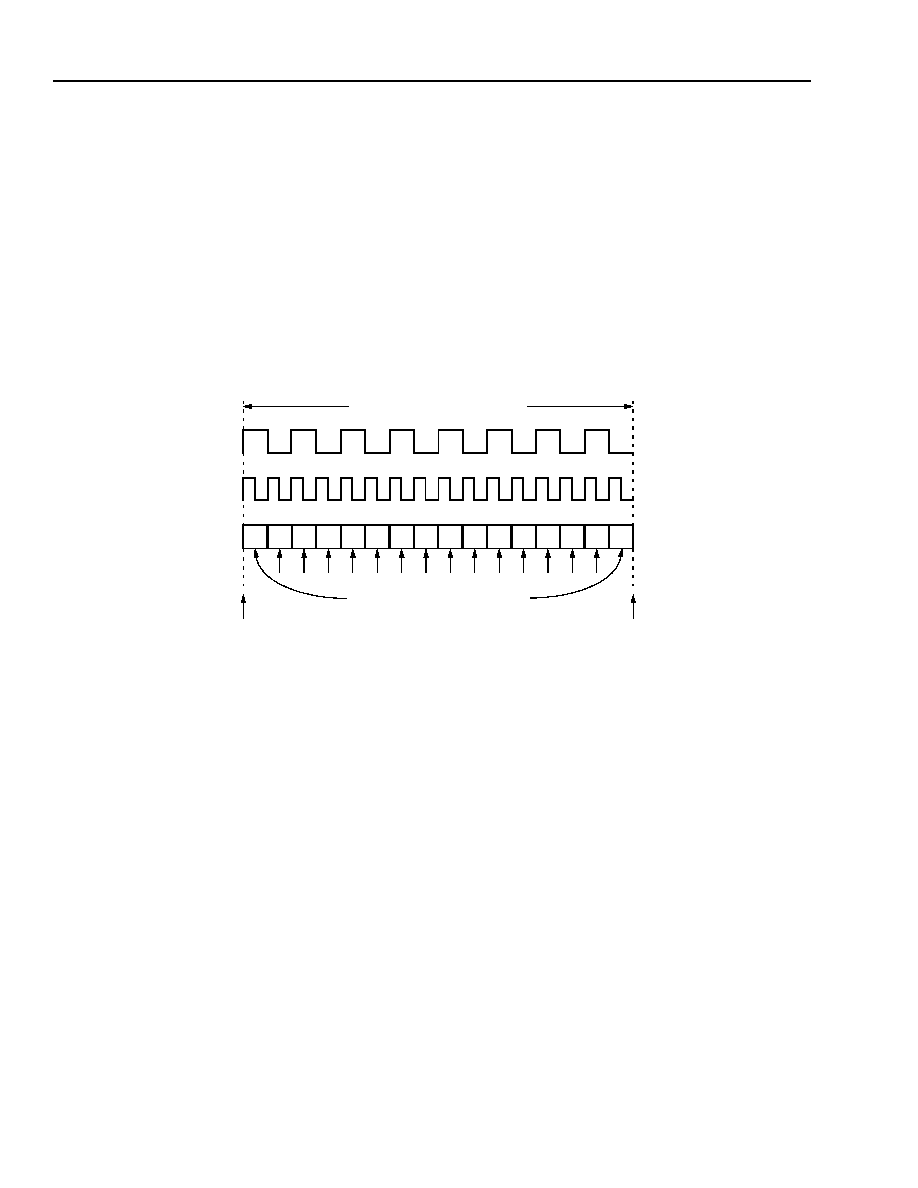

Frame Center Sampling ..............................................................................................59

6.4.1.3

LREF Pair Polarity Configuration.................................................................................60

6.4.2

Main and Resource Dividers .......................................................................................................61

6.4.3

DPLL1 .........................................................................................................................................61

6.4.4

Reference Selector .....................................................................................................................61

6.4.5

Internal Clock Generation ...........................................................................................................61

6.4.5.1

Phase Alignment .........................................................................................................62

6.5

Clock Circuit Operation, APLL2 ..............................................................................................................63

6.5.1

DPLL2 .........................................................................................................................................63

6.6

Clock Circuit Operation, CT_NETREF Generation.................................................................................63

6.6.1

NETREF Source Select ..............................................................................................................63

6.6.2

NETREF Divider..........................................................................................................................63

6.7

Clock Circuit Operation--Fallback and Failsafe .....................................................................................64

6.7.1

Clock Fallback.............................................................................................................................64

6.7.1.1

Fallback Events ...........................................................................................................64

6.7.1.2

Fallback Scenarios--Fixed vs. Rotating Secondary....................................................65

6.7.1.3

H-Bus Clock Enable/Disable on Fallback ....................................................................68

6.7.2

Clock Failsafe .............................................................................................................................70

6.7.2.1

Failsafe Events ............................................................................................................70

7

Frame Group and FG I/O ..................................................................................................................................72

7.1

Frame Group Control Registers..............................................................................................................72

7.1.1

FGx Lower and Upper Start Registers ........................................................................................72

7.1.2

FGx Width Registers ...................................................................................................................73

7.1.3

FGx Rate Registers ....................................................................................................................73

7.2

FG7 Timer Option ...................................................................................................................................74

7.2.1

FG7 Counter (Low and High Byte) Registers..............................................................................74

7.3

FGIO Control Registers ..........................................................................................................................75

7.3.1

FGIO Data Register ....................................................................................................................75

7.3.2

FGIO Read Mask Register..........................................................................................................75

7.3.3

FGIO R/W Register .....................................................................................................................76

7.4

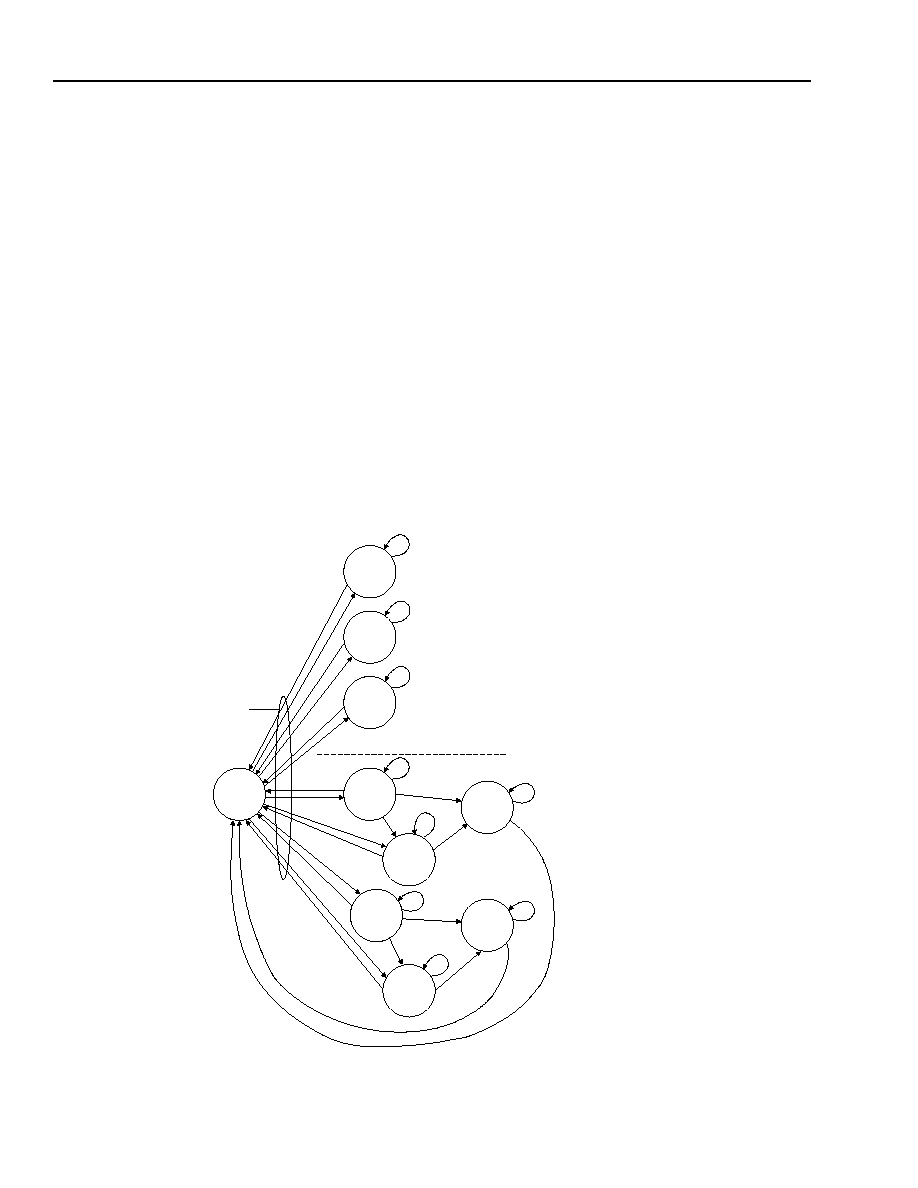

FG Circuit Operation...............................................................................................................................77

7.4.1

Frame Group 8 kHz Reference Generation ................................................................................78

7.4.2

FGIO General-Purpose Bits ........................................................................................................79

7.4.3

Programmable Timer (FG7 Only)................................................................................................79

7.4.4

FG External Interrupts.................................................................................................................79

7.4.5

FG Diagnostic Test Point Observation........................................................................................79

8

General-Purpose I/O .........................................................................................................................................80

8.1

GPIO Control Registers ..........................................................................................................................80

Table of Contents

(continued)

Contents

Page

4

Agere Systems Inc.

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

8.1.1

GPIO Data Register .................................................................................................................... 80

8.1.2

GPIO Read Mask Register ......................................................................................................... 81

8.1.3

GPIO R/W Register..................................................................................................................... 81

8.1.4

GPIO Override Register .............................................................................................................. 82

8.2

GP Circuit Operation............................................................................................................................... 82

8.2.1

GPIO General-Purpose Bits........................................................................................................ 83

8.2.2

GP Dual-Purpose Bits GPIO (Override)...................................................................................... 83

8.2.2.1

GP H.110 Clock Master Indicators (GP0, GP1 Only) ..................................................83

8.2.3

GP External Interrupts ................................................................................................................ 83

8.2.4

GP Diagnostic Test Point Observation ....................................................................................... 83

9

Stream Rate Control ......................................................................................................................................... 84

9.1

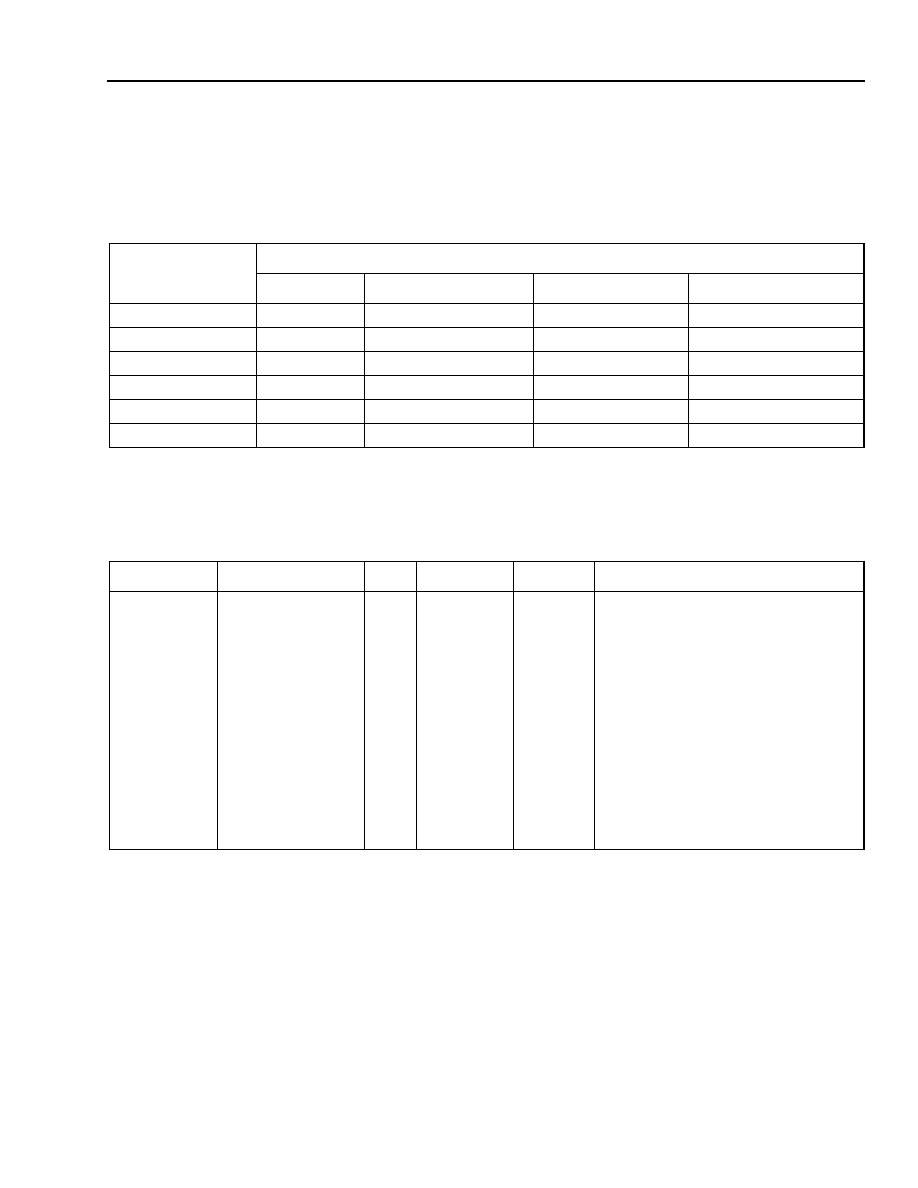

H-Bus Stream Rate Control Registers.................................................................................................... 85

9.1.1

H-Bus Rate Registers ................................................................................................................. 85

9.2

L-Bus Stream Rate Control Registers .................................................................................................... 85

9.2.1

L-Bus Rate Registers .................................................................................................................. 85

9.2.2

L-Bus 16.384 Mbits/s Operation ................................................................................................. 86

9.2.3

16.384 Mbits/s Local I/O Superrate ............................................................................................ 88

9.2.4

16.384 Mbits/s Local I/O Superrate ............................................................................................ 89

10 Error Reporting and Interrupt Control ............................................................................................................... 90

10.1

Interrupt Control Registers...................................................................................................................... 90

10.1.1 Interrupts Via External FG[7:0] Registers ................................................................................... 90

10.1.1.1 FGIO Interrupt Pending Register................................................................................. 90

10.1.2 Interrupts Via External GP[7:0] ................................................................................................... 92

10.1.2.1 GPIO Interrupt Pending Register................................................................................. 92

10.1.2.2 GPIO Edge/Level and GPIO Polarity Registers .......................................................... 93

10.1.3 Interrupts Via Internal System Errors .......................................................................................... 93

10.1.4 System Interrupt Pending High/Low Registers ........................................................................... 94

10.1.5 System Interrupt Enable High/Low Registers ............................................................................. 95

10.1.6 Interrupts Via Internal Clock Errors ............................................................................................. 96

10.1.7 Clock Interrupt Pending High/Low Registers .............................................................................. 97

10.1.8 Clock Interrupt Enable High/Low Registers ................................................................................ 98

10.1.9 Interrupt Servicing Registers....................................................................................................... 99

10.1.9.1 Arbitration Control Register .........................................................................................99

10.1.9.2 SYSERR and CLKERR Output Select Register .......................................................... 99

10.1.9.3 Interrupt In-Service Registers.................................................................................... 101

10.2

Error Reporting and Interrupt Controller Circuit Operation ...................................................................103

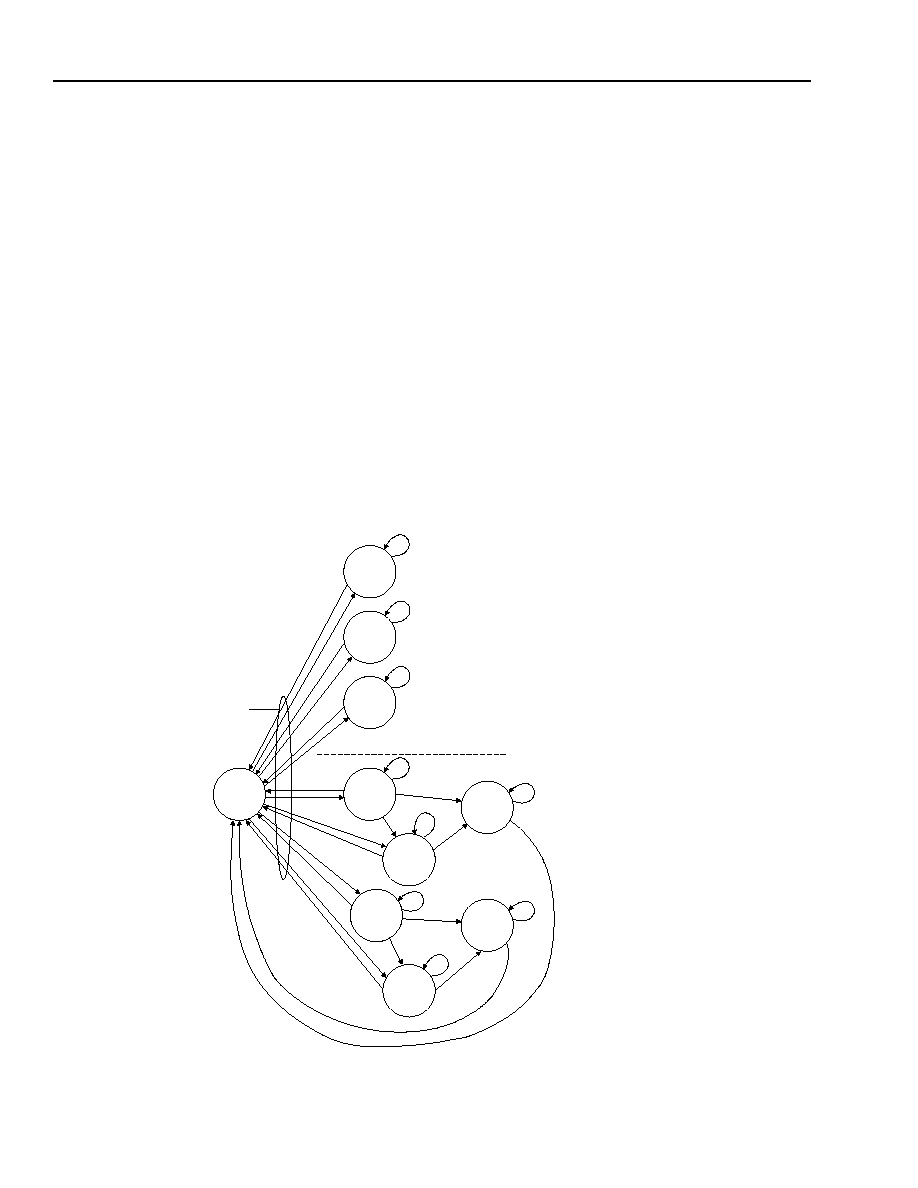

10.2.1 Externally Sourced Interrupts Via FG[7:0], GP[7:0] .................................................................. 104

10.2.2 Internally Sourced System Error Interrupts ............................................................................... 104

10.2.3 Internally Sourced Clock Error Interrupts .................................................................................. 104

10.2.4 Arbitration of Pending Interrupts ............................................................................................... 104

10.2.4.1 Arbitration Off ............................................................................................................ 104

10.2.4.2 Flat Arbitration ........................................................................................................... 104

10.2.4.3 Tier Arbitration ........................................................................................................... 104

10.2.4.4 Pre-Empting Disabled................................................................................................ 105

10.2.4.5 Pre-Empting Enabled ................................................................................................ 105

10.2.5 CLKERR Output........................................................................................................................ 105

10.2.6 SYSERR Output .......................................................................................................................105

10.2.7 System Handling of Interrupts................................................................................................... 105

11 Test and Diagnostics ...................................................................................................................................... 106

11.1

Diagnostics Control Registers .............................................................................................................. 106

11.1.1 FG Testpoint Enable Register................................................................................................... 106

Table of Contents

(continued)

Contents

Page

Agere Systems Inc.

5

February 2004

Ambassador T8110L H.100/H.110 Switch

Data Sheet

11.1.2 GP Testpoint Enable Register ..................................................................................................108

11.1.3 State Counter Modes Registers ................................................................................................110

11.1.4 Miscellaneous Diagnostics Low Register..................................................................................110

11.1.5 Miscellaneous Diagnostic Registers .........................................................................................111

11.2

Diagnostic Circuit Operation .................................................................................................................112

12 Connection Control .........................................................................................................................................113

12.1

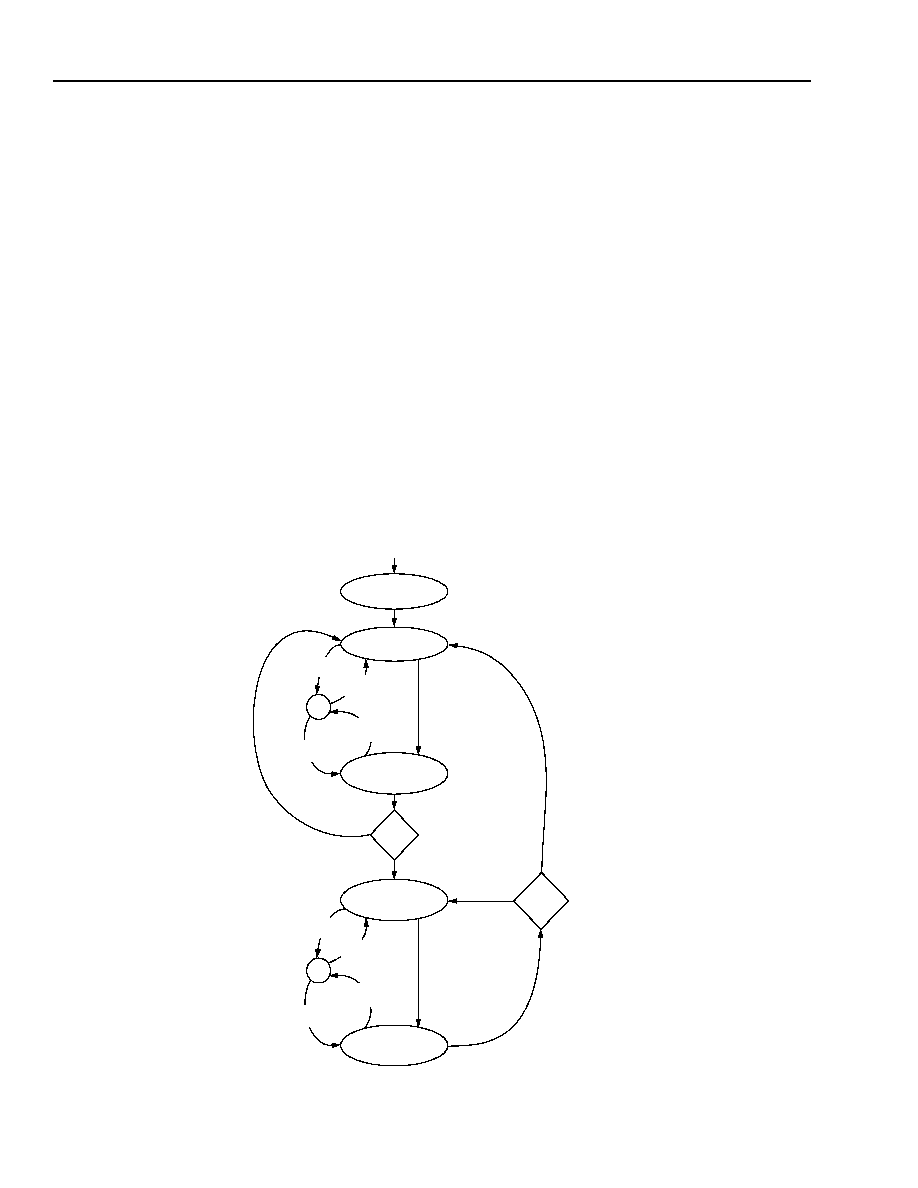

Programming Interface .........................................................................................................................113

12.1.1 Connection Memory Programming ...........................................................................................113

12.2

Switching Operation..............................................................................................................................115

12.2.1 Memory Architecture and Configuration....................................................................................115

12.2.1.1 Connection Memory ..................................................................................................115

12.2.1.2 Data Memory .............................................................................................................116

12.2.2 Standard Switching ...................................................................................................................117

12.2.2.1 Constant Delay and Minimum Delay Connections ....................................................117

12.2.2.2 Pattern Mode .............................................................................................................117

12.2.2.3 Subrate ......................................................................................................................117

13 Electrical Characteristics.................................................................................................................................124

13.1

Absolute Maximum Ratings ..................................................................................................................124

13.1.1 Handling Precautions ................................................................................................................124

13.2

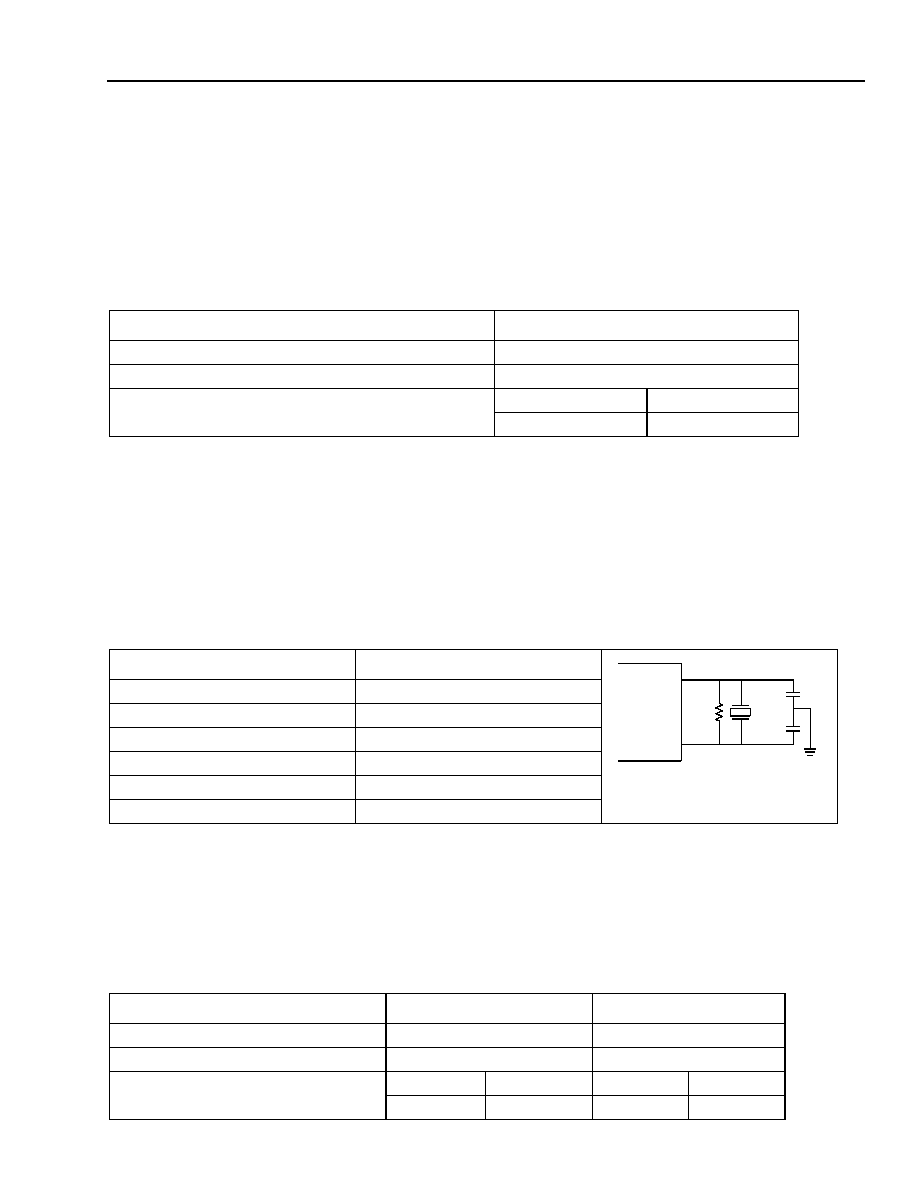

Crystal Specifications ...........................................................................................................................124

13.2.1 XTAL1 Crystal ...........................................................................................................................124

13.2.2 XTAL2 Crystal ...........................................................................................................................125

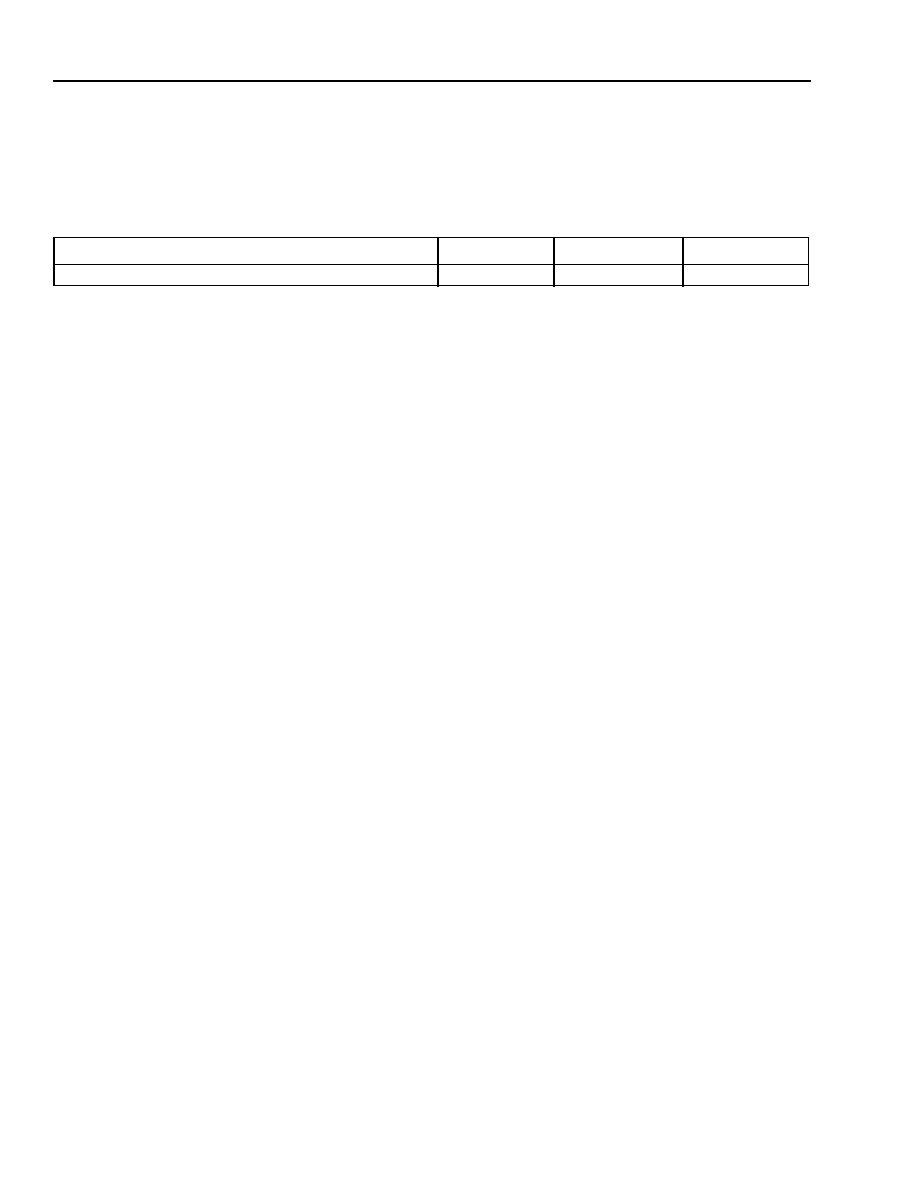

13.2.3 Reset Pulse...............................................................................................................................126

13.3

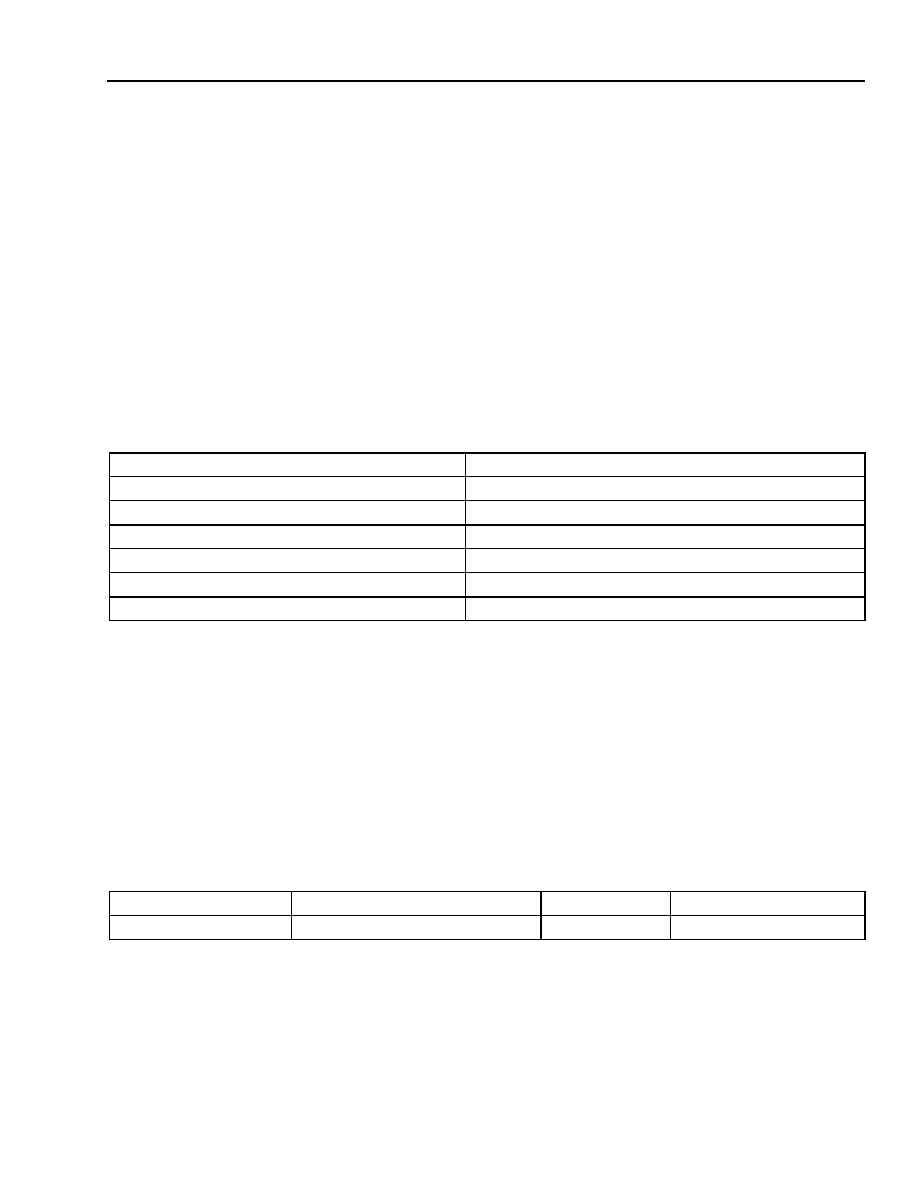

Thermal Parameters (Definitions and Values)......................................................................................126

13.4

Reliability ..............................................................................................................................................127

13.5

dc Electrical Characteristics..................................................................................................................128

13.5.1 Electrical Drive Specifications, CT_C8 and /CT_FRAME .........................................................128

13.5.2 All Other Pins ............................................................................................................................129

13.6

H-Bus Timing ........................................................................................................................................129

13.6.1 Timing Diagrams .......................................................................................................................129

13.7

ac Electrical Characteristics..................................................................................................................130

13.7.1 Skew Timing, H-Bus..................................................................................................................130

13.8

Hot Swap ..............................................................................................................................................131

13.8.1 LPUE (Local Pull-Up Enable)....................................................................................................131

13.9

Decoupling............................................................................................................................................131

13.10 APLL V

DD

Filter ....................................................................................................................................132

13.11 PC Board PBGA Considerations ..........................................................................................................133

13.12 Unused Pins .........................................................................................................................................133

13.13 External Pull-Up Pins............................................................................................................................133

13.14 T8110L Evaluation Kits.........................................................................................................................133

13.15 T8110L Ordering Information................................................................................................................133

14 JTAG/Boundary Scan .....................................................................................................................................137

14.1

The Principle of Boundary-Scan Architecture.......................................................................................137

14.1.1 Instruction Register ...................................................................................................................138

14.2

Boundary-Scan Register.......................................................................................................................138

A

Constant and Minimum Delay Connections ....................................................................................................139

A.1

Connection Definitions..........................................................................................................................139

A.2

Delay Type Definitions..........................................................................................................................139

B

Register Bit Field Mnemonic Summary...........................................................................................................142

Significant Changes Between the June 2003 and November 2003 Release ........................................................163

List of Figures

Figure

Page

6

Agere Systems Inc.

Ambassador T8110L H.100/H.110 Switch

February 2004

Data Sheet

Figure 1.

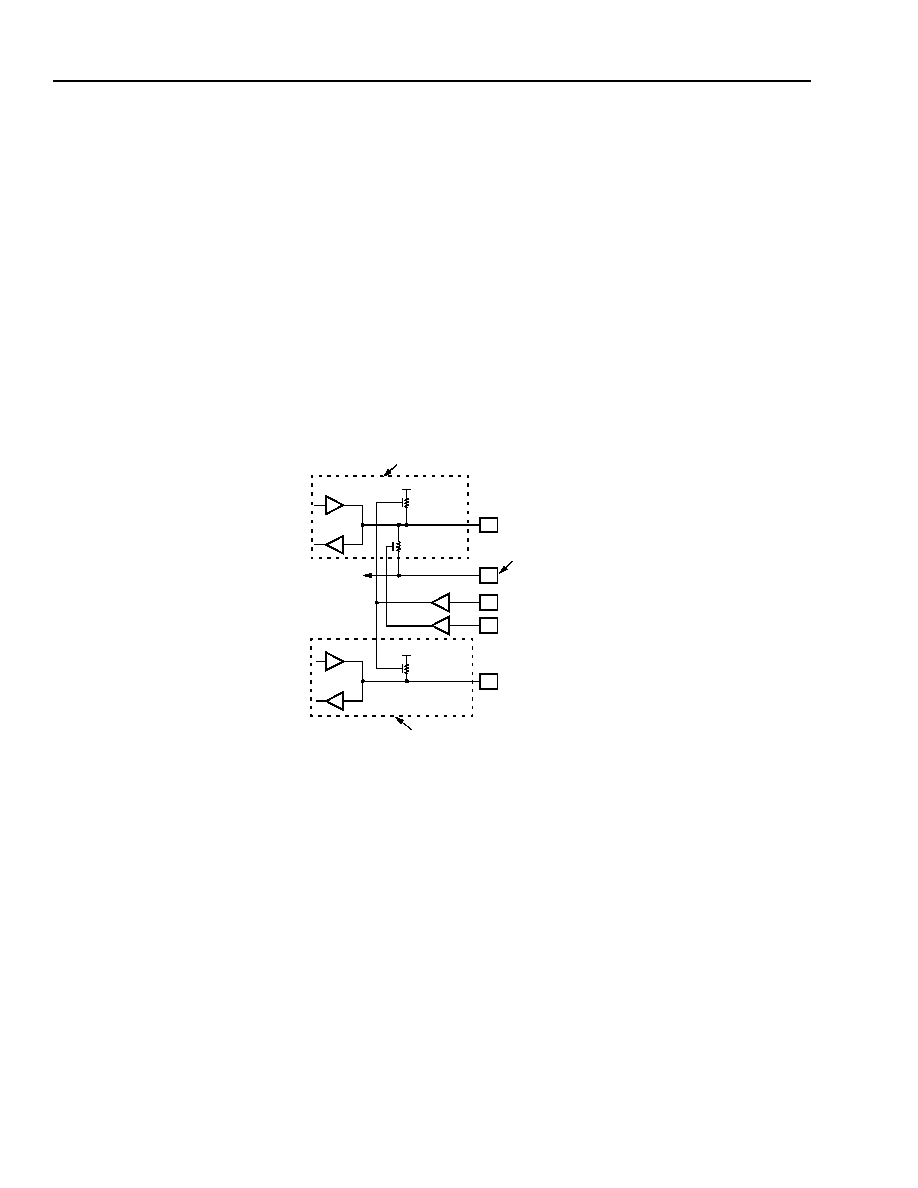

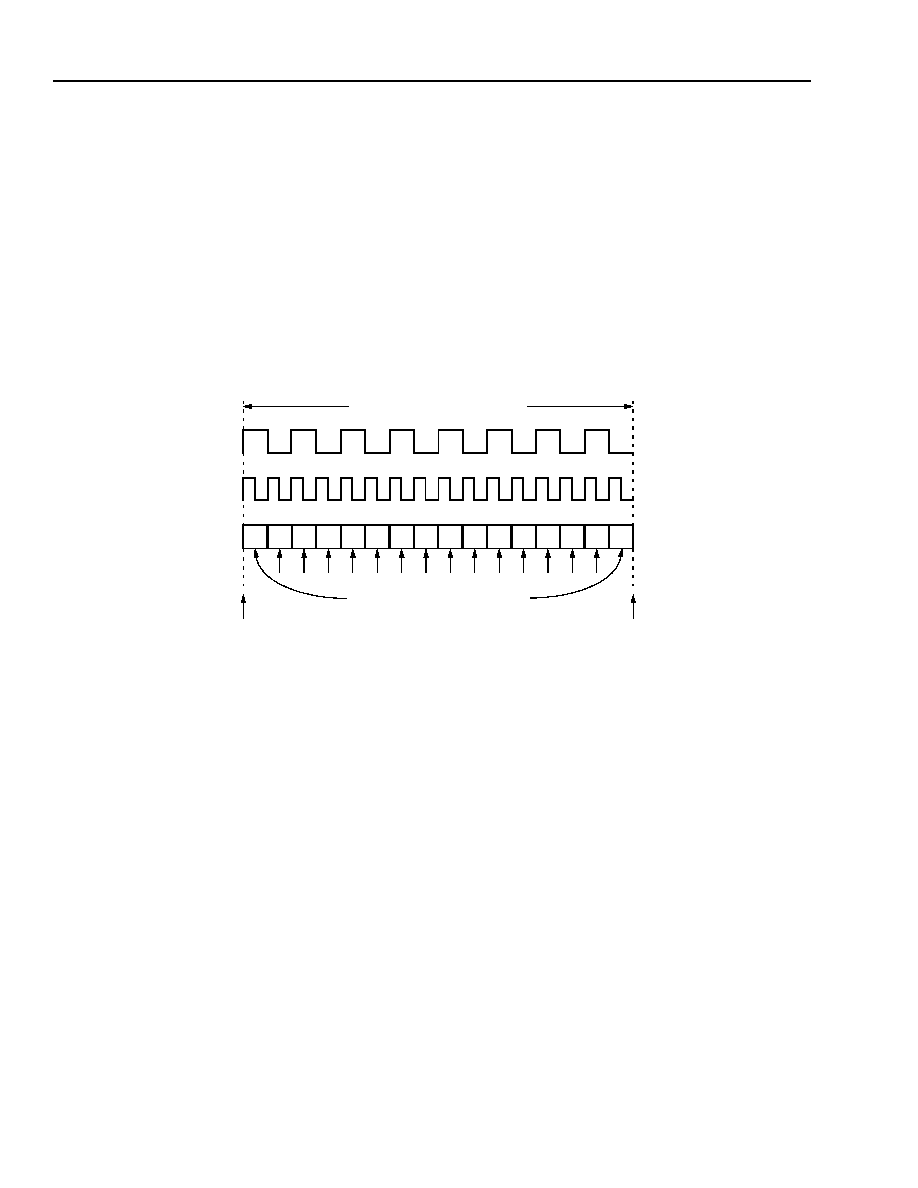

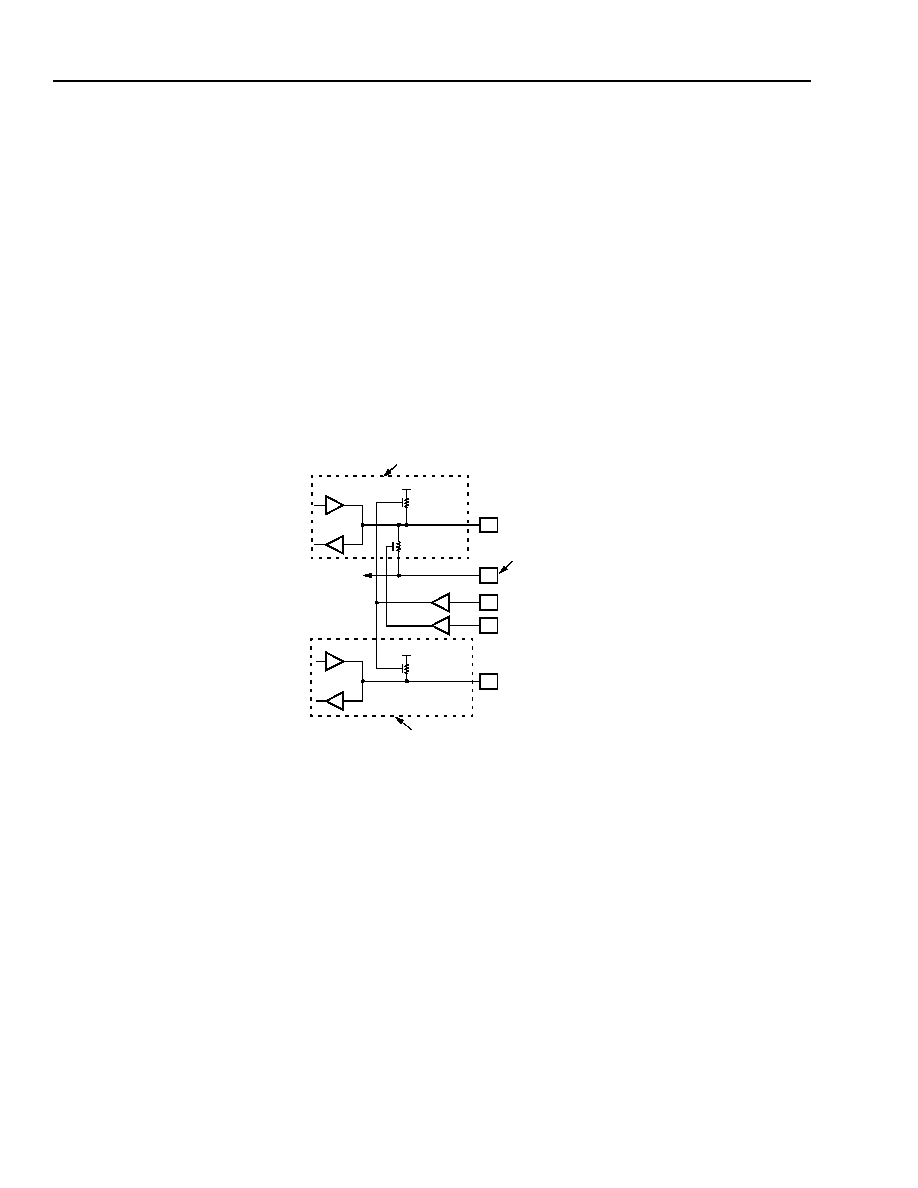

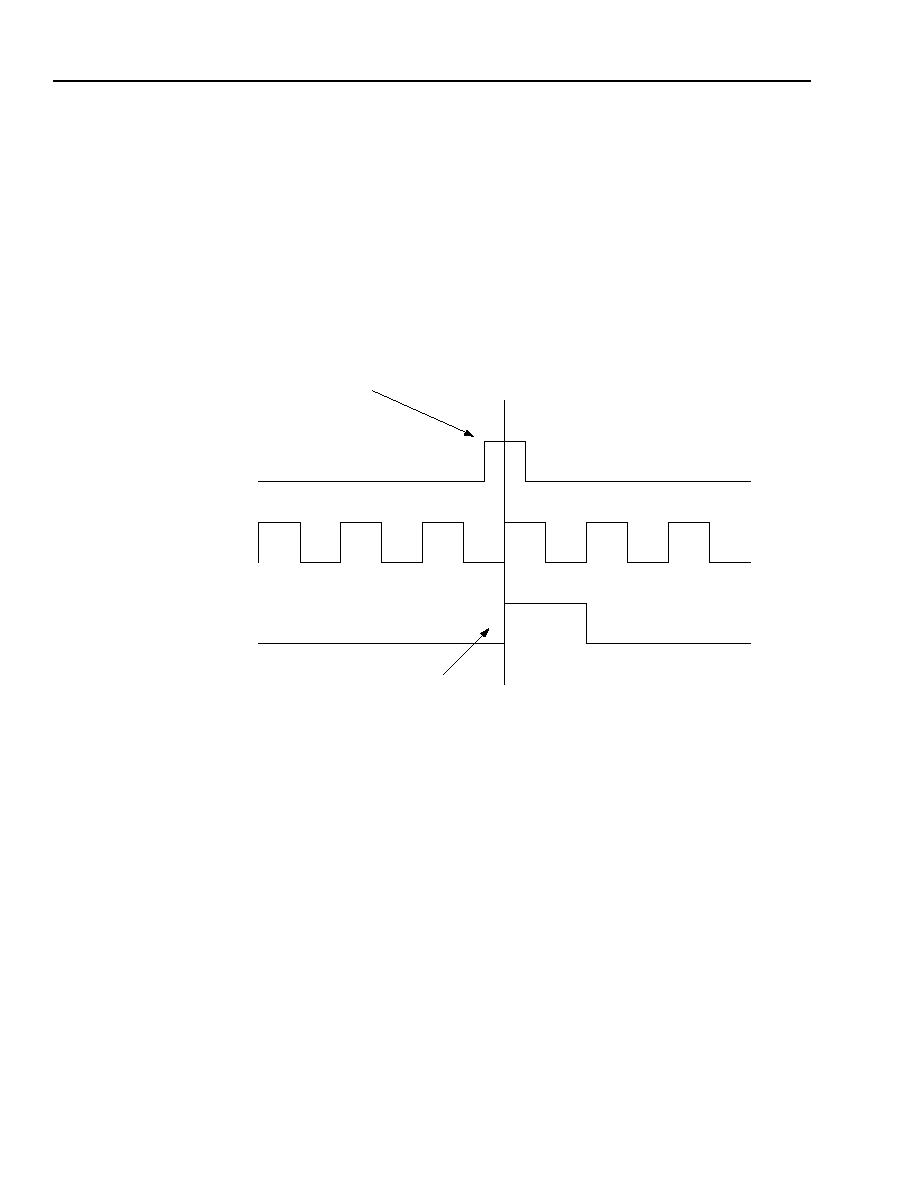

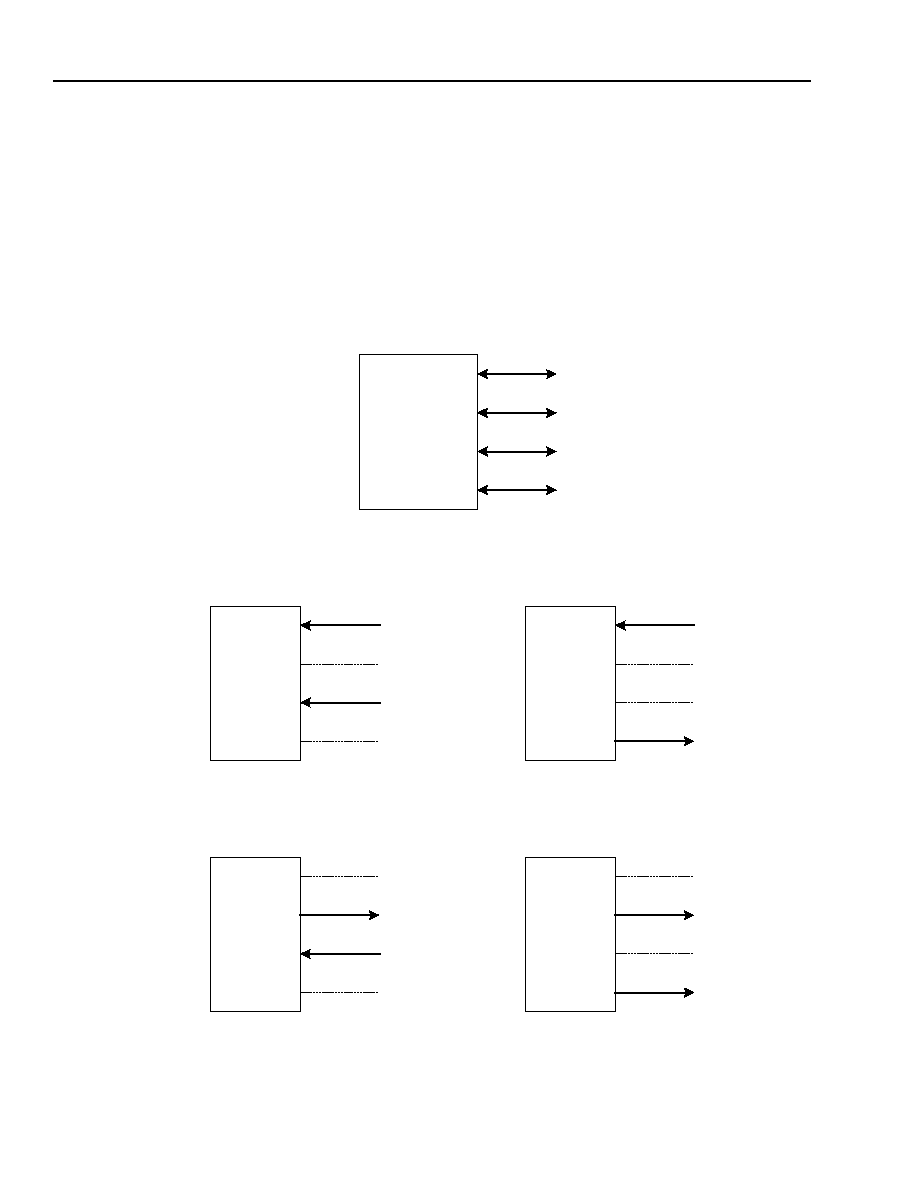

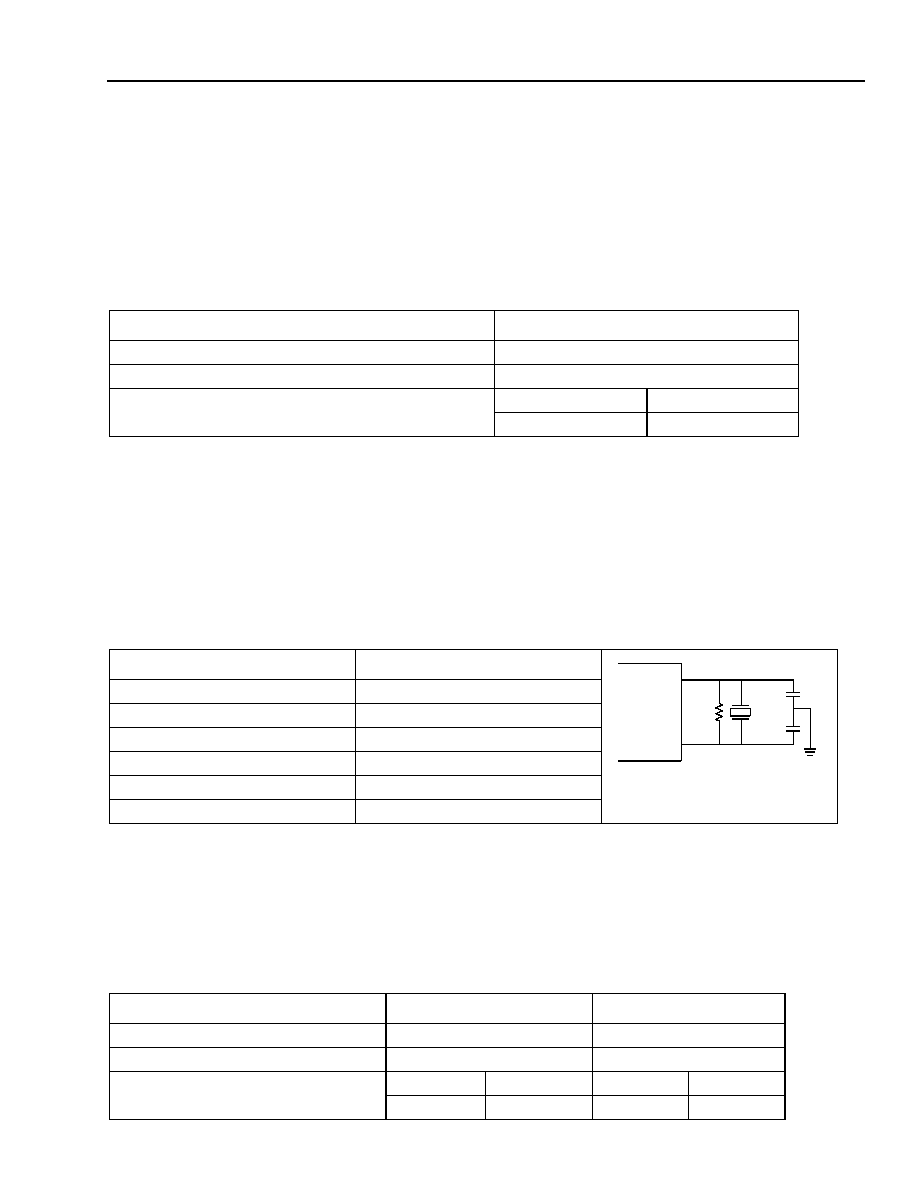

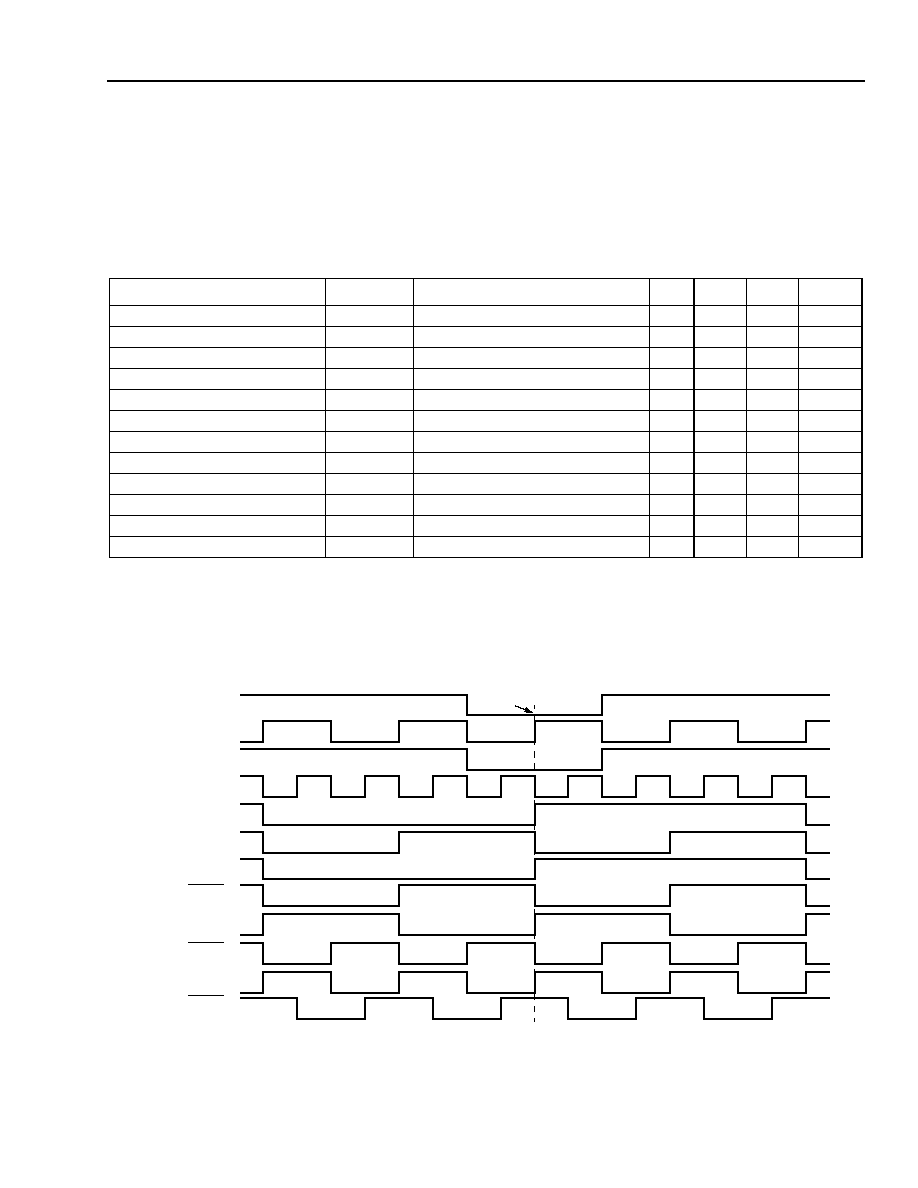

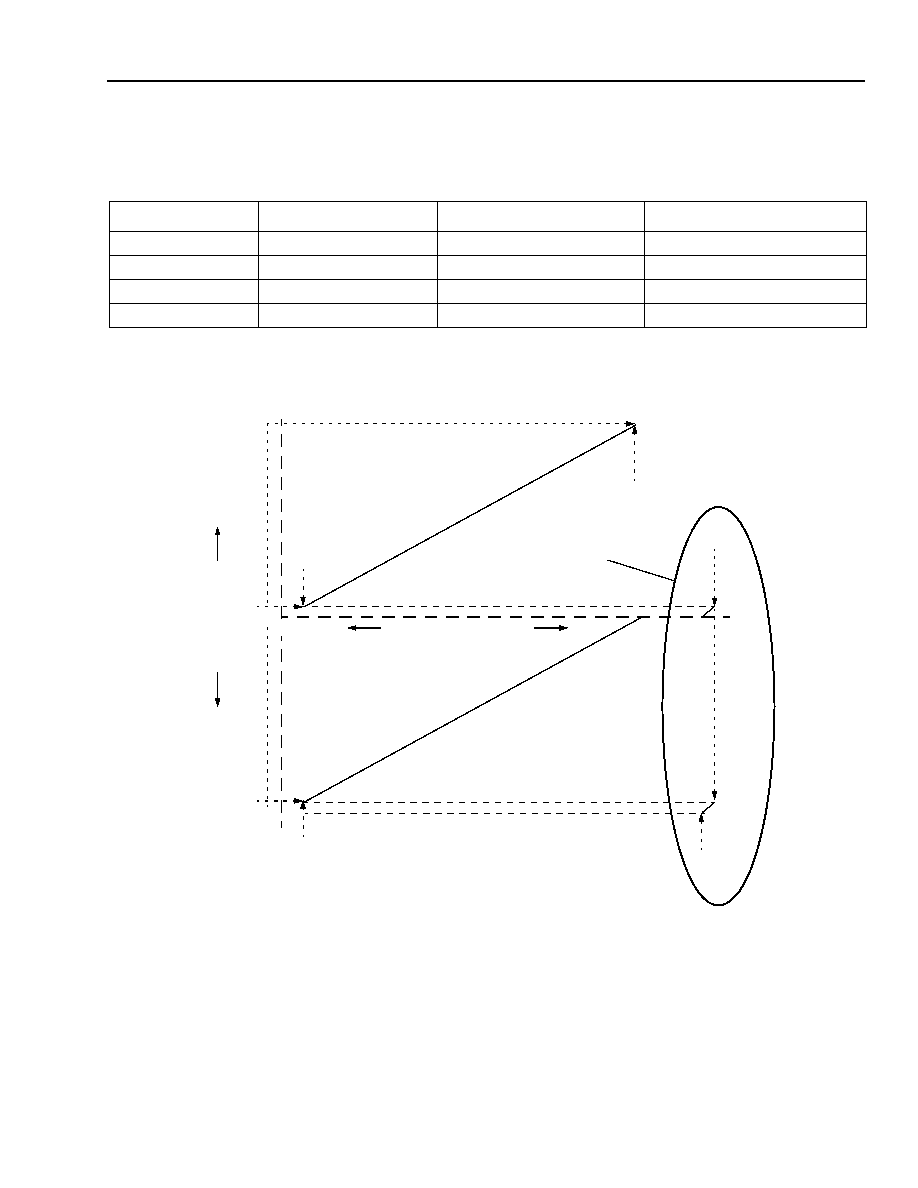

T8110L Pull-Up/Pull-Down Arrangement for H1x0 Pins ....................................................................... 20

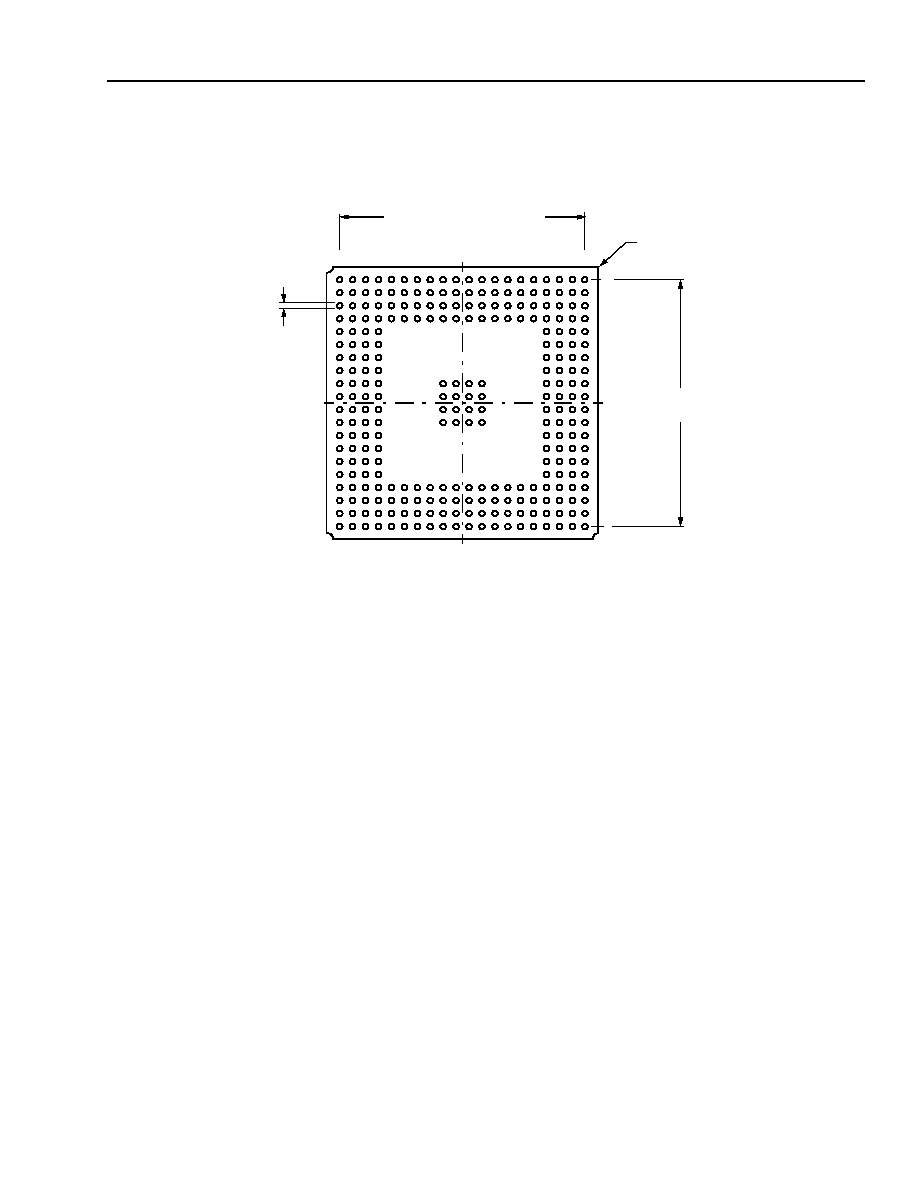

Figure 2.

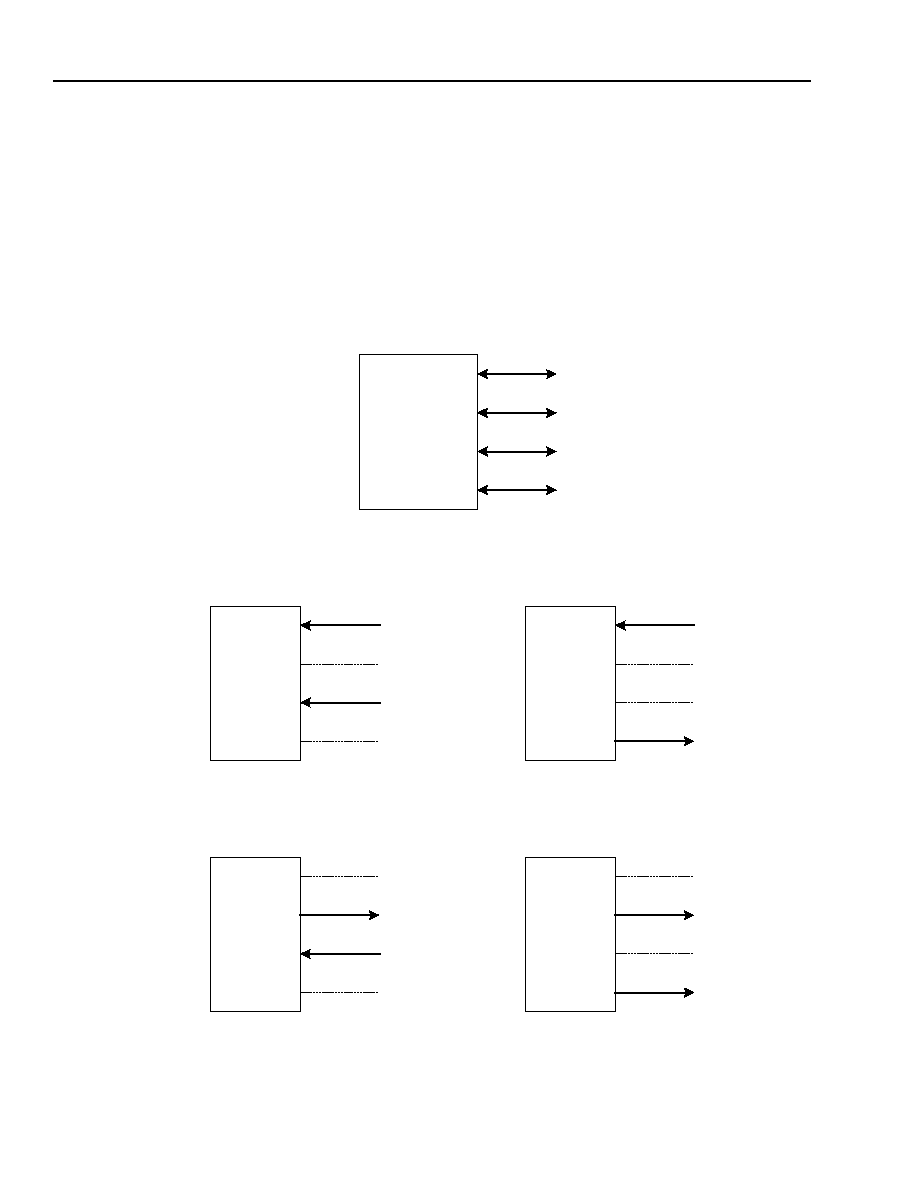

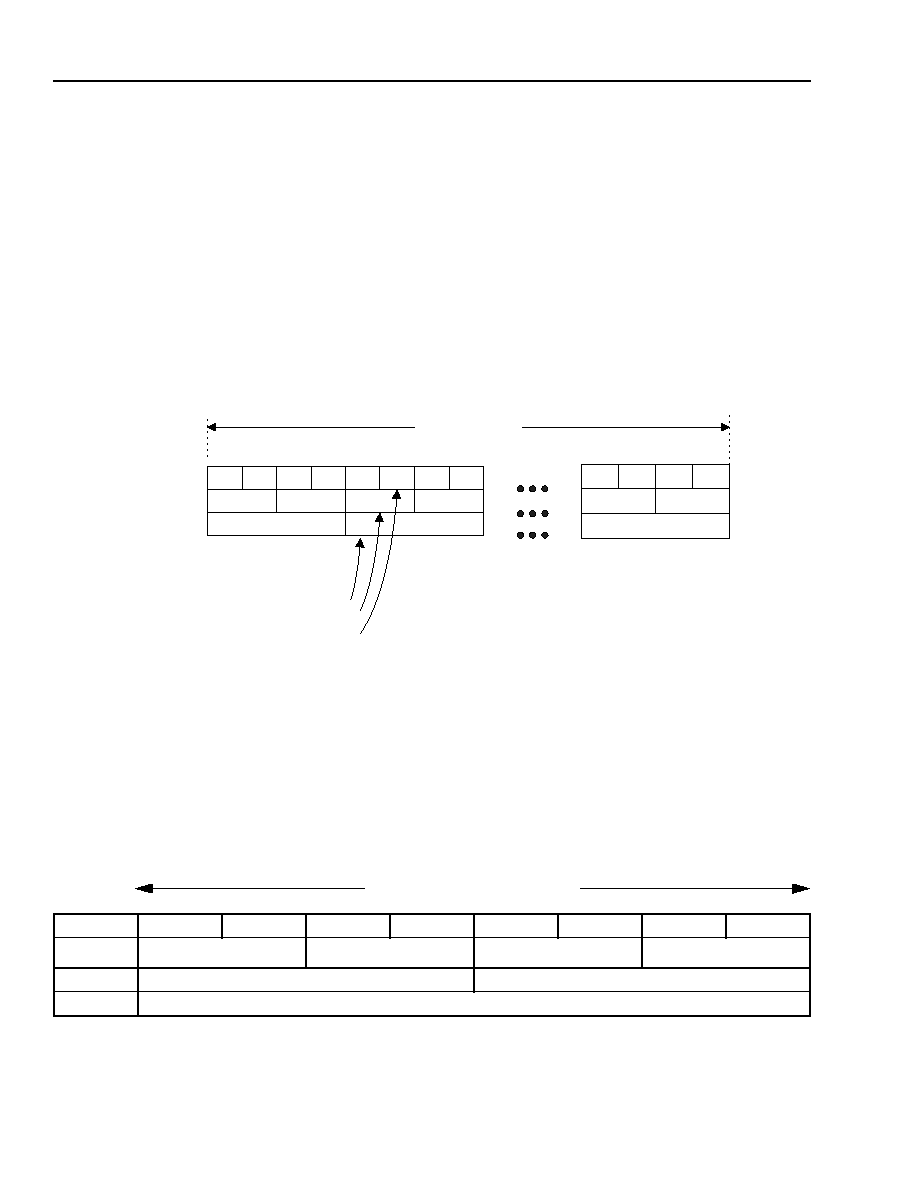

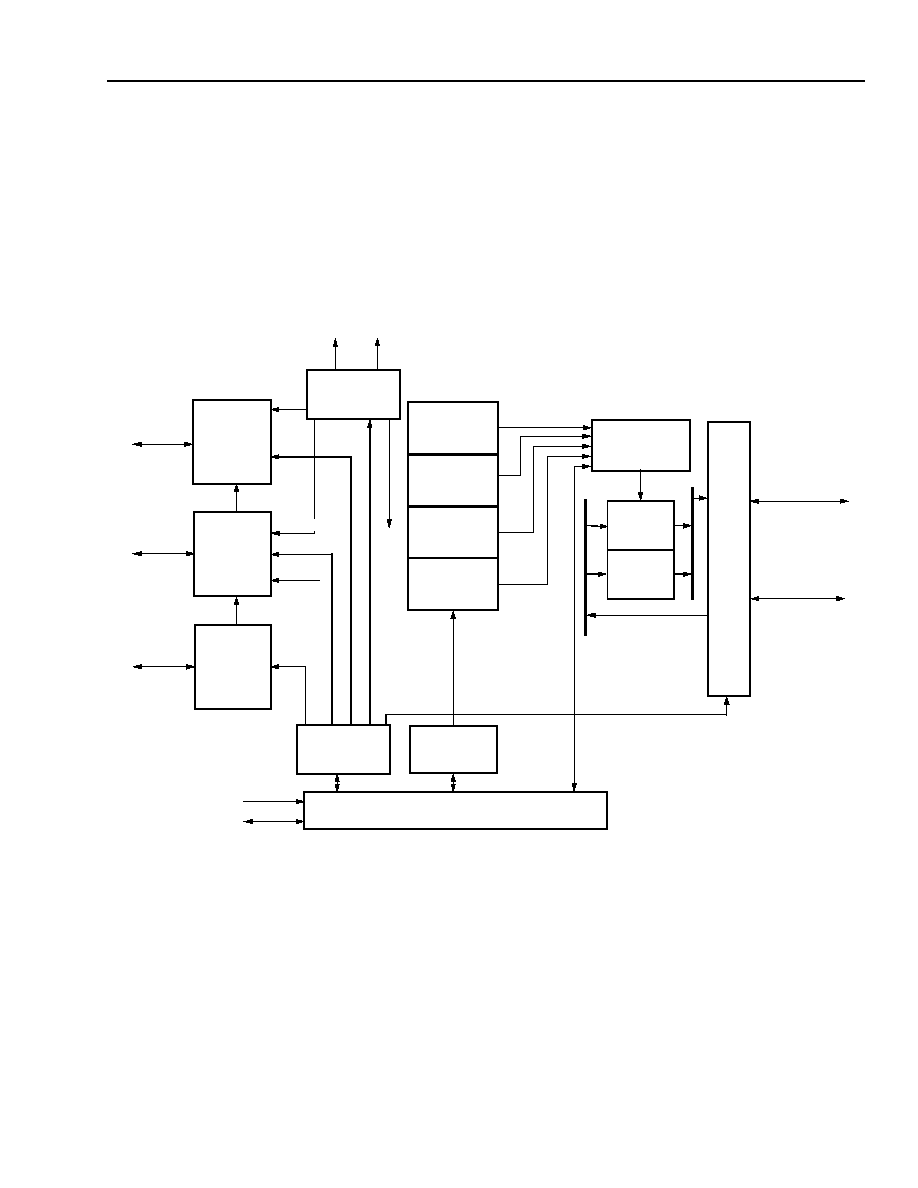

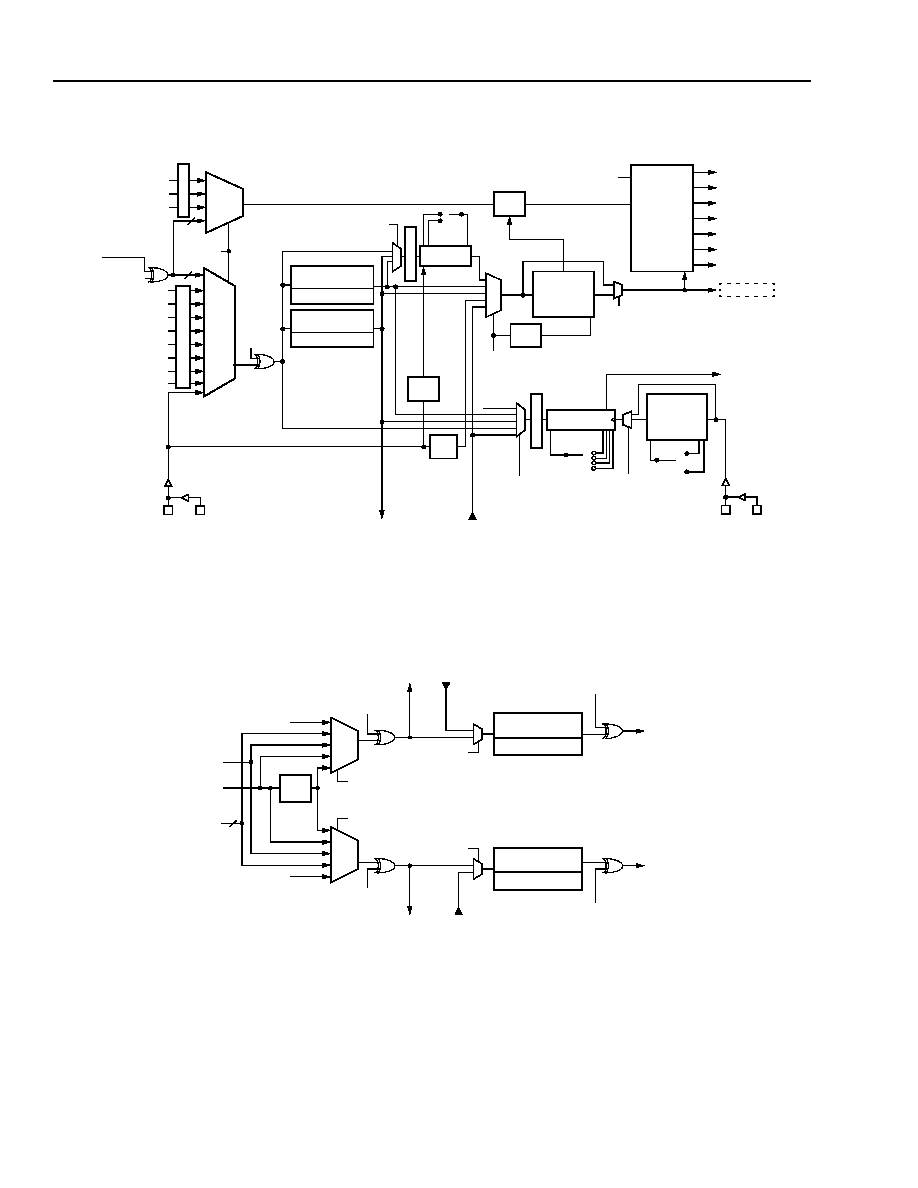

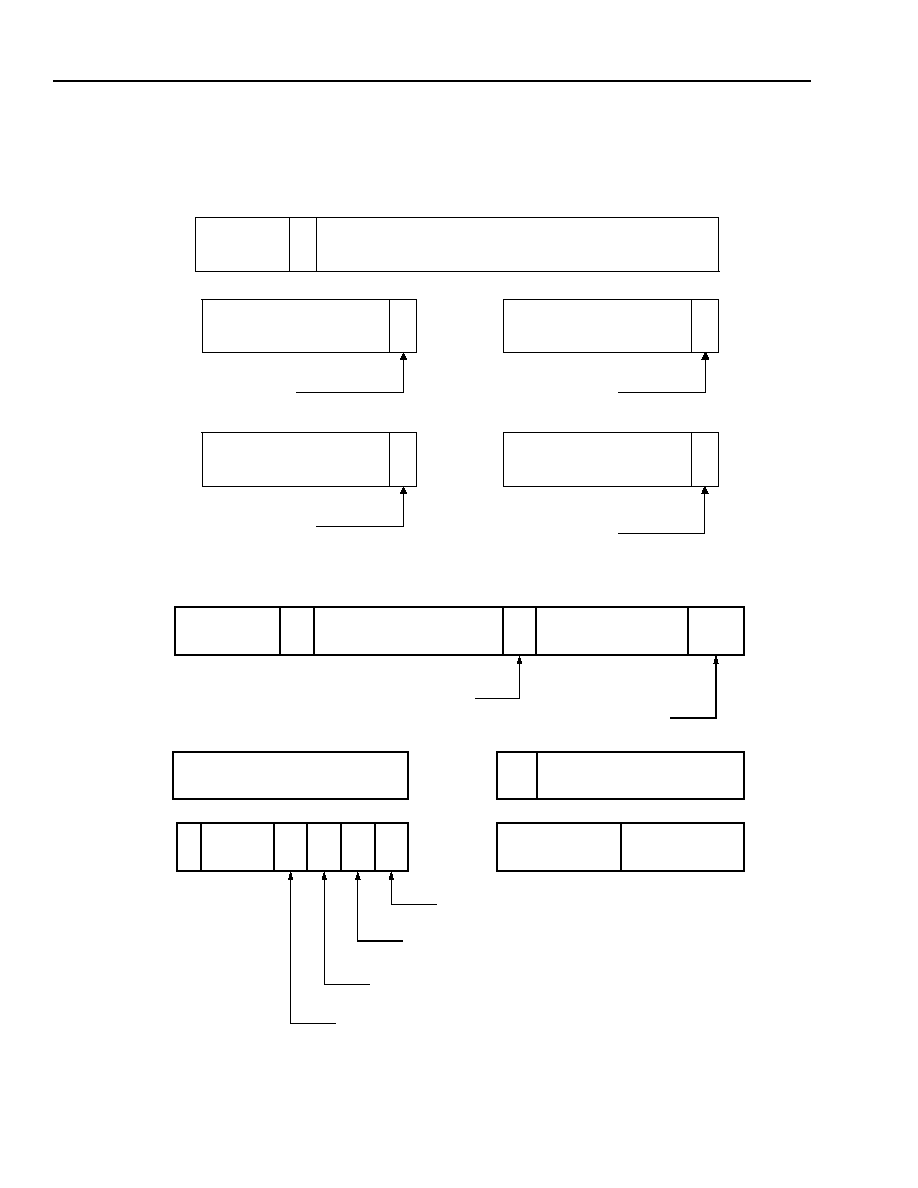

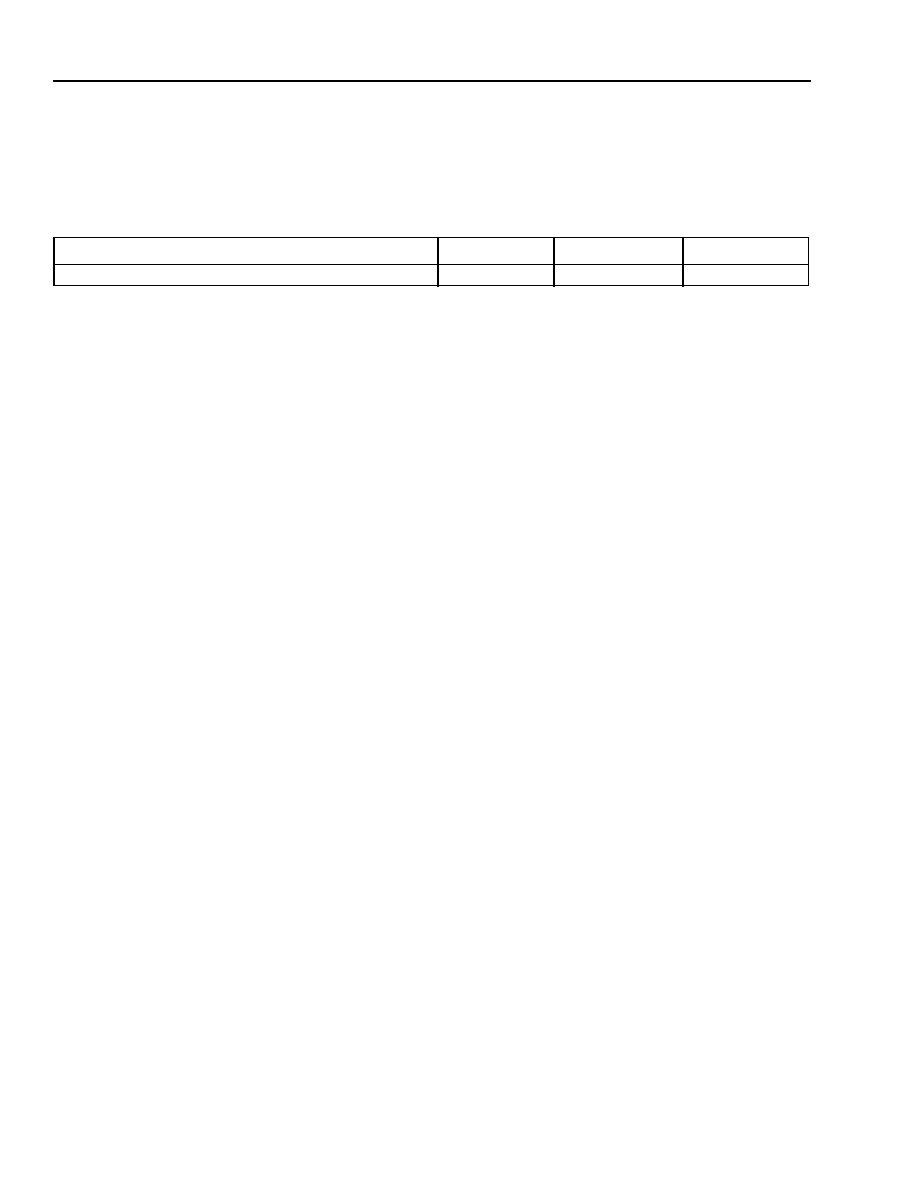

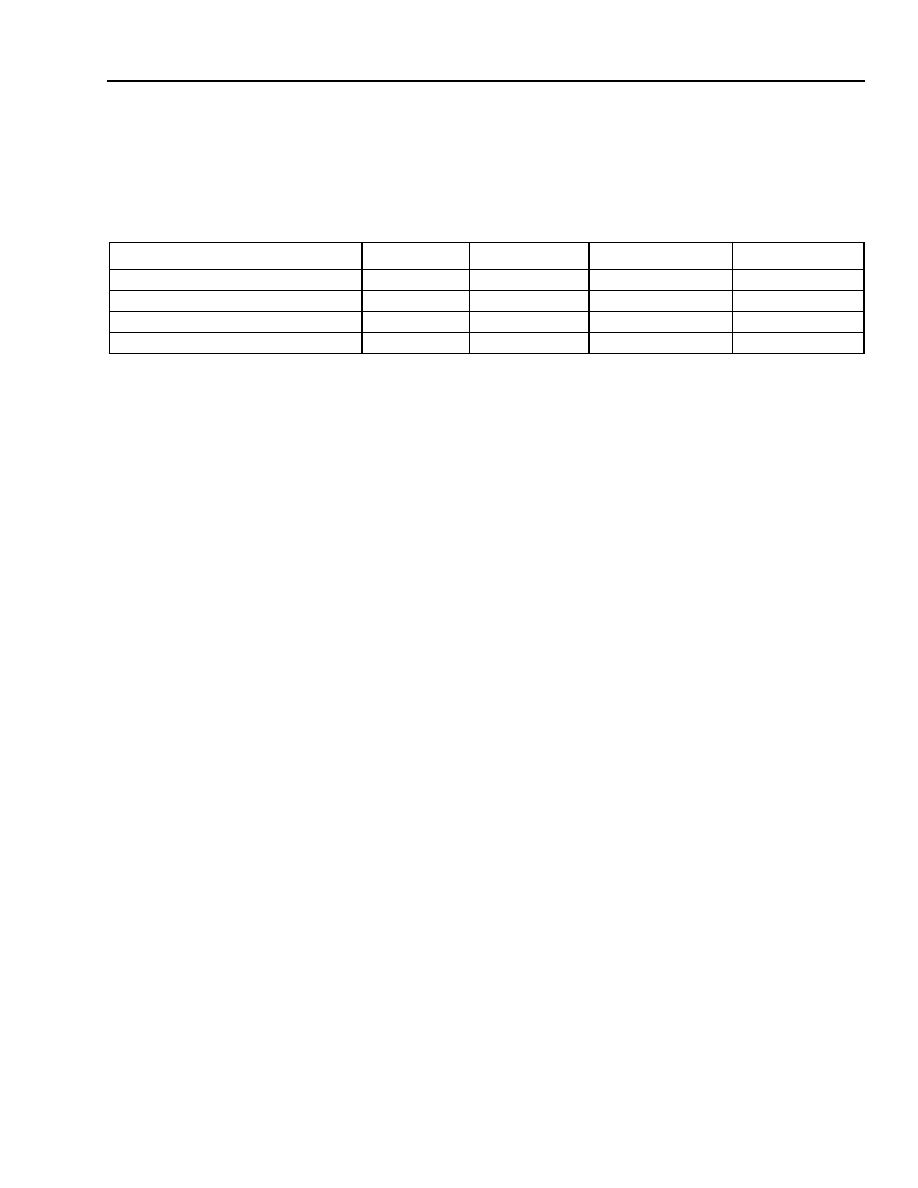

T8110L Architecture Block Diagram ..................................................................................................... 21

Figure 3.

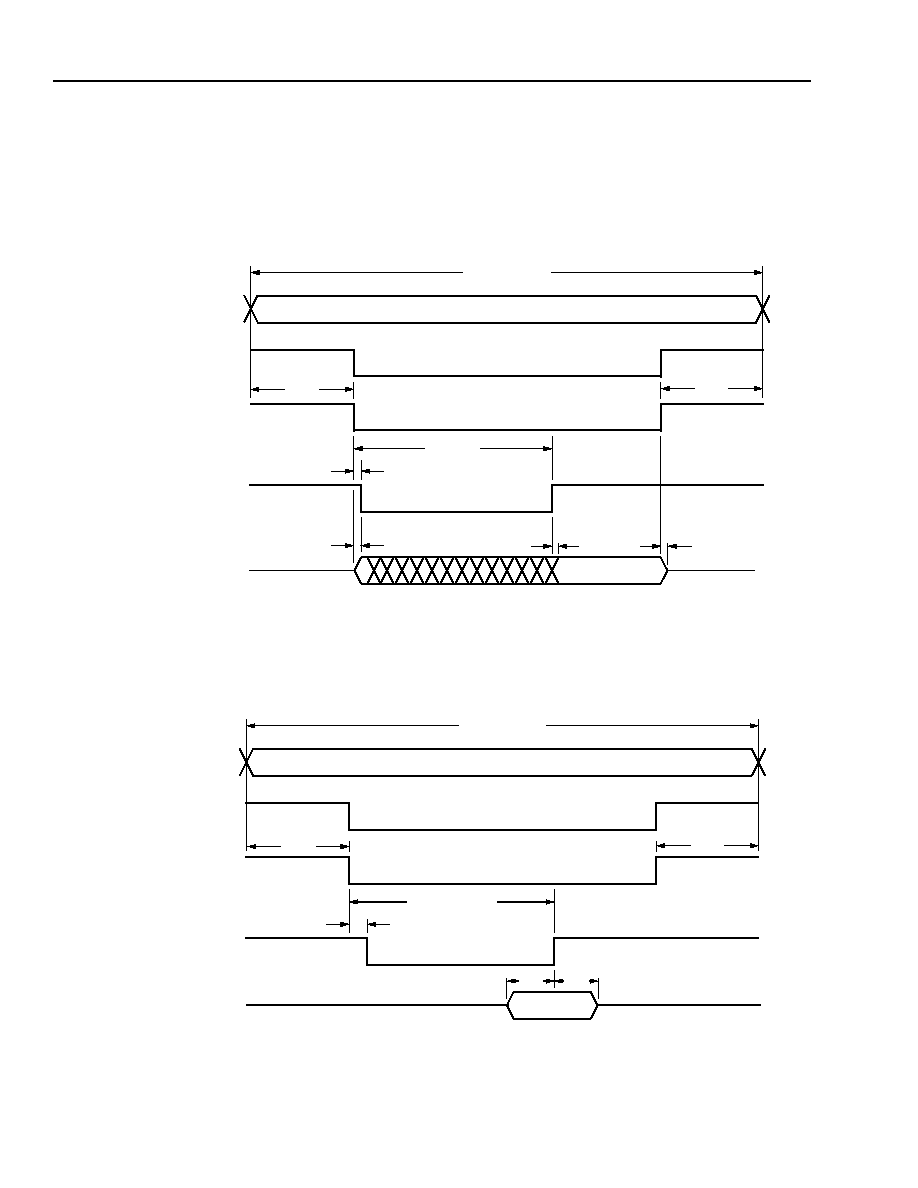

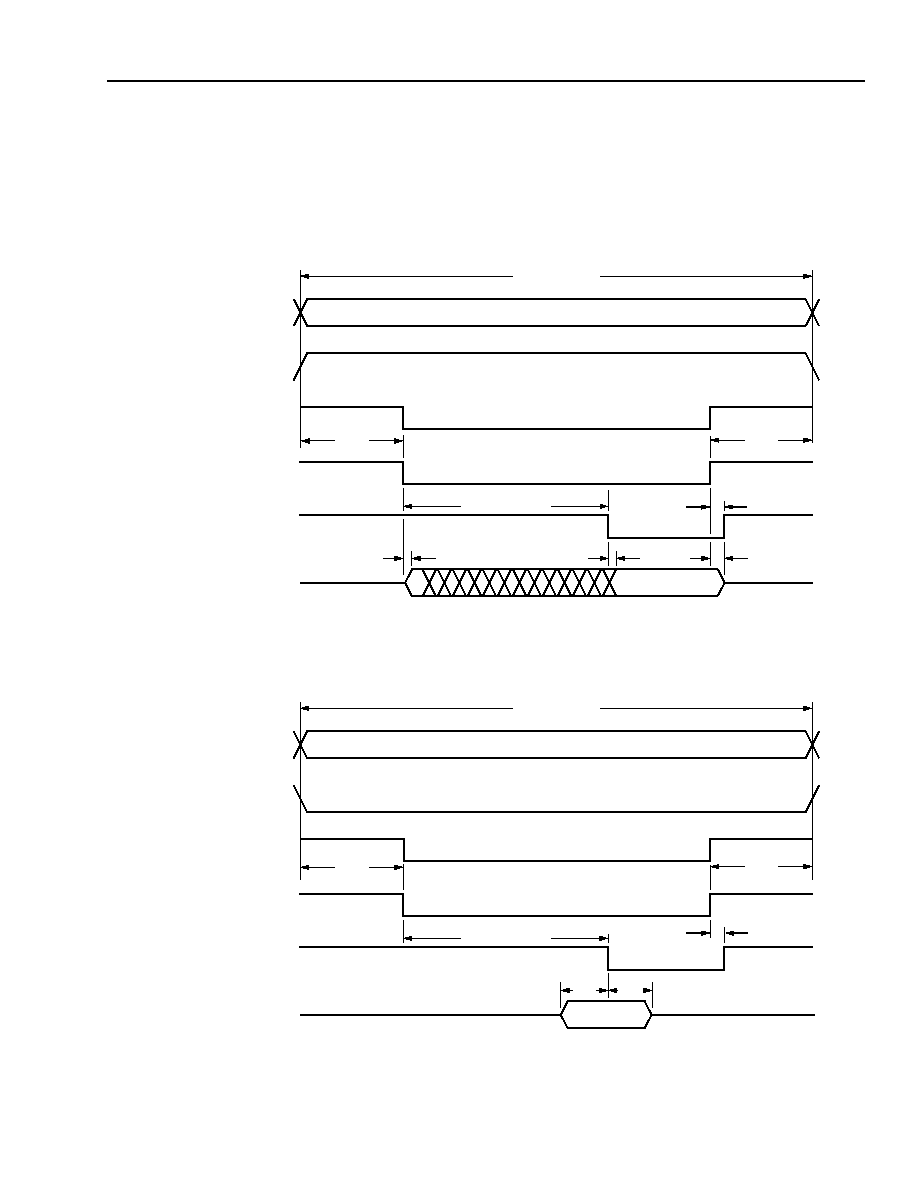

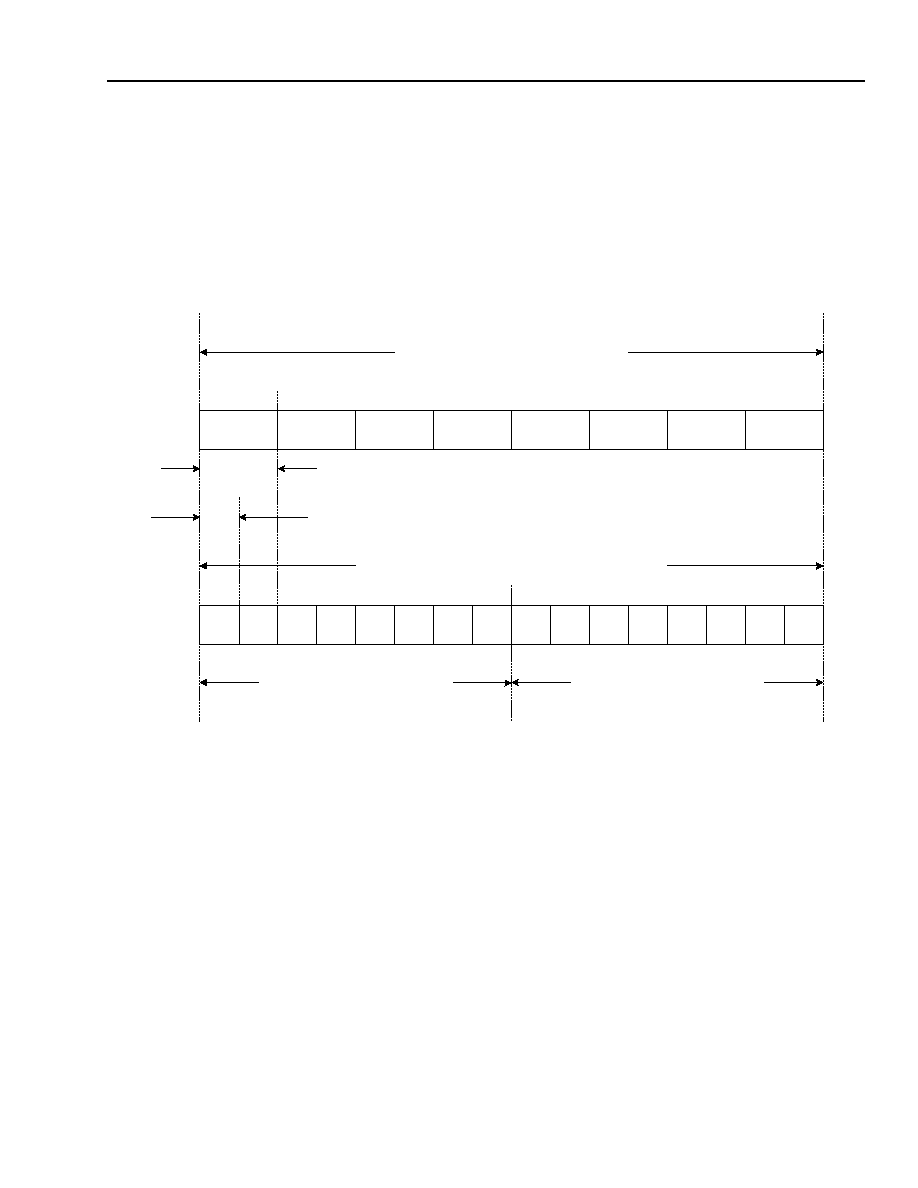

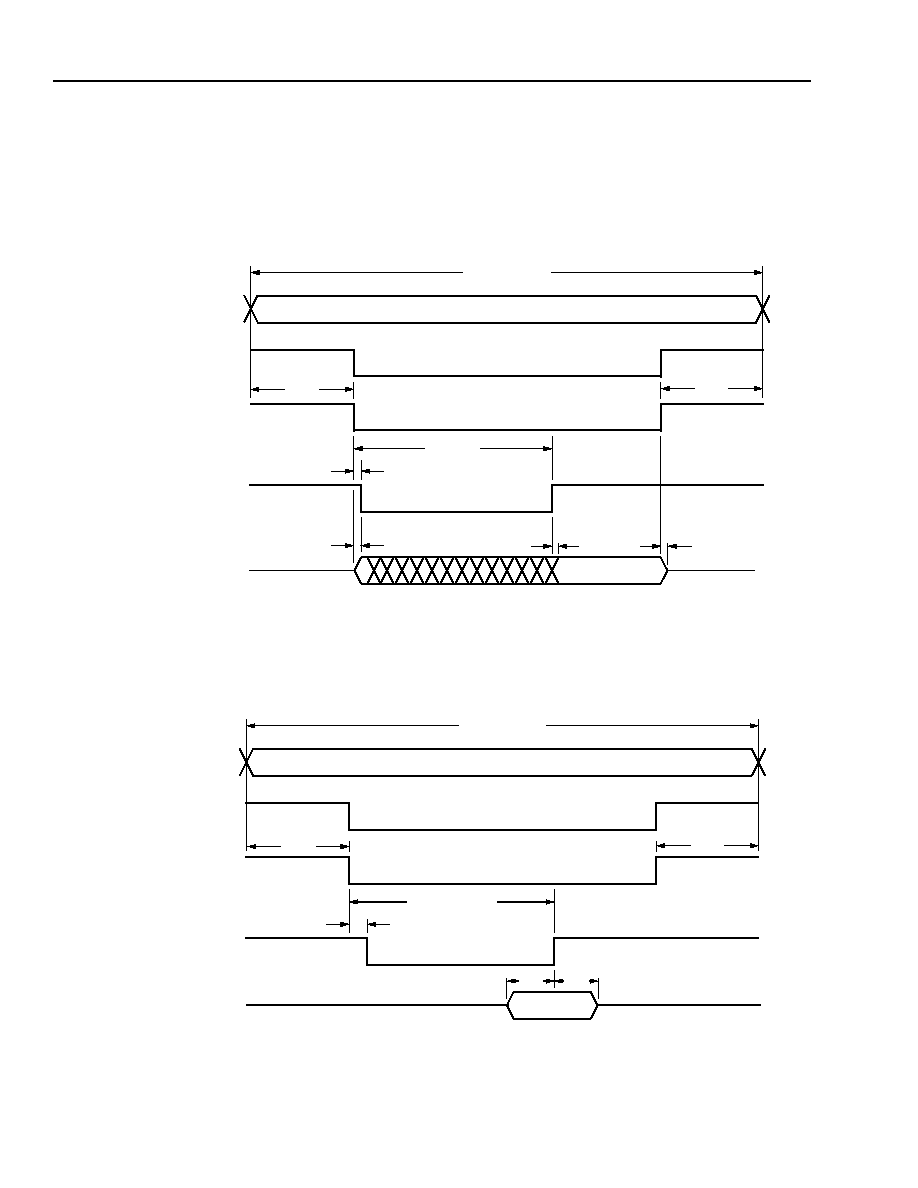

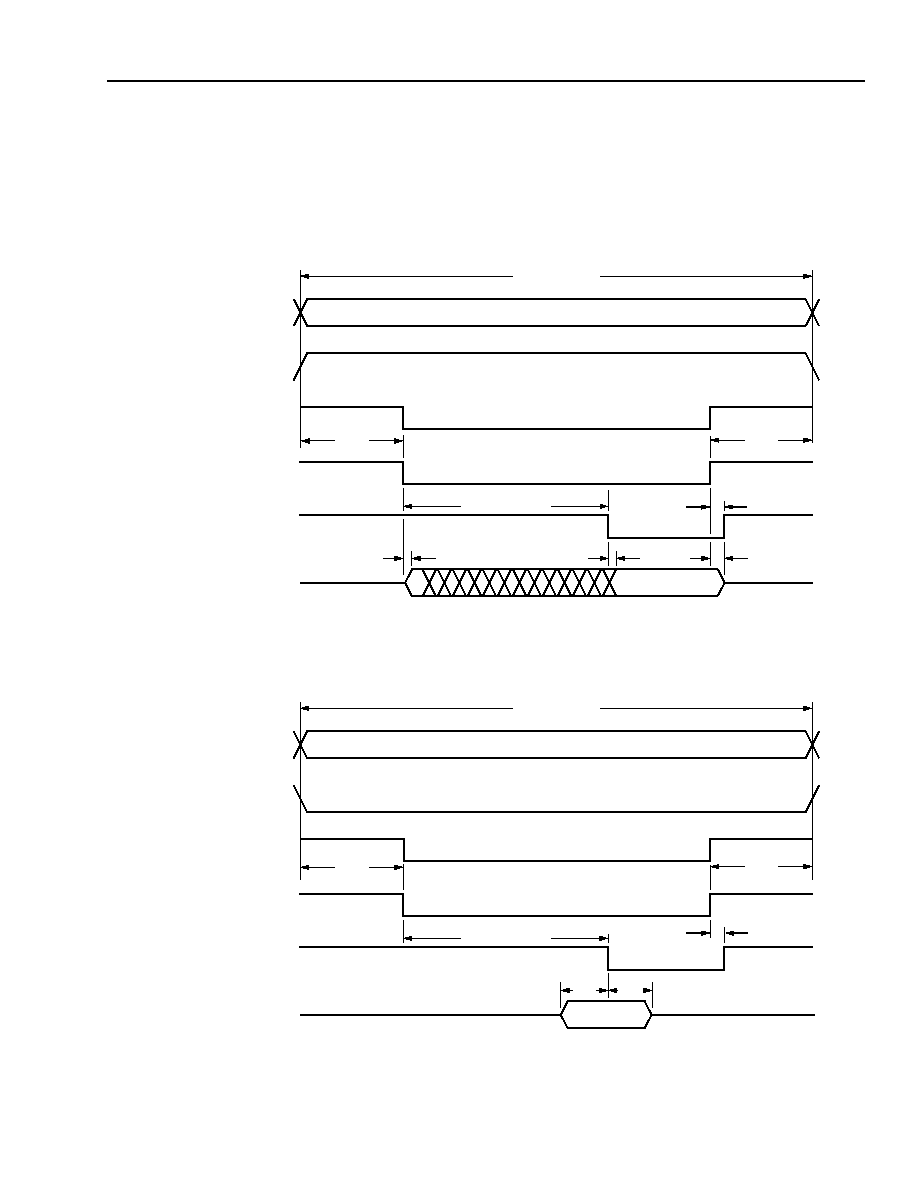

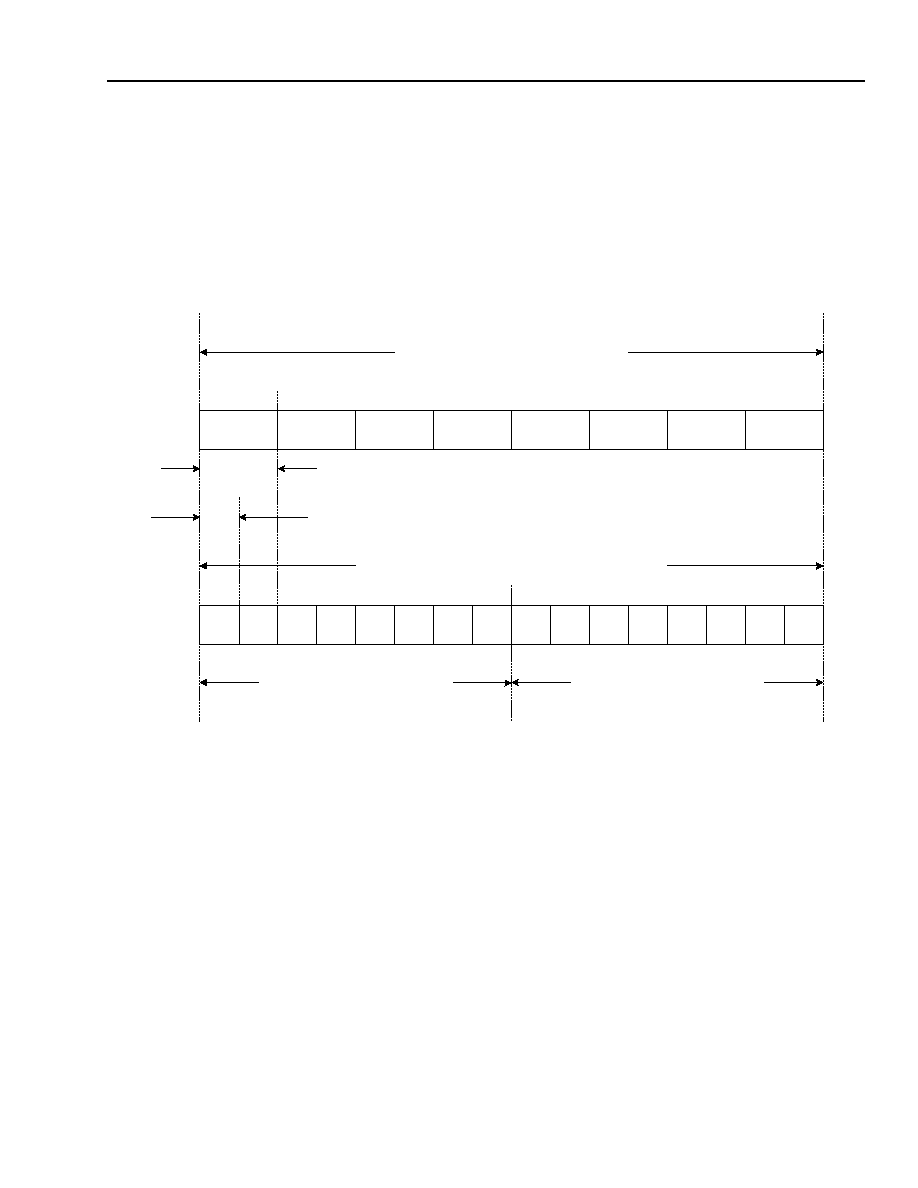

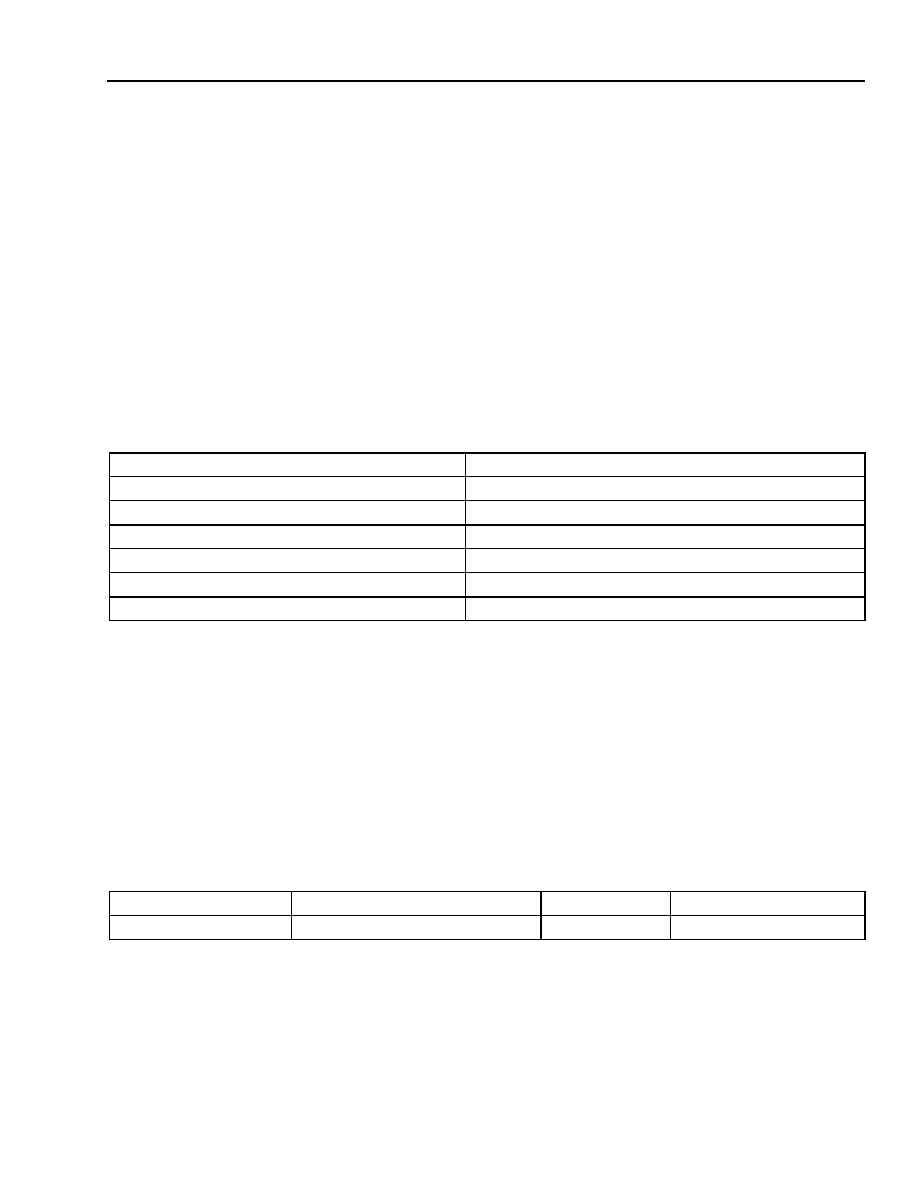

Microprocessor Access Timing, Intel Protocol ...................................................................................... 26

Figure 4.

Microprocessor Access Timing, Motorola Protocol ............................................................................... 27

Figure 5.

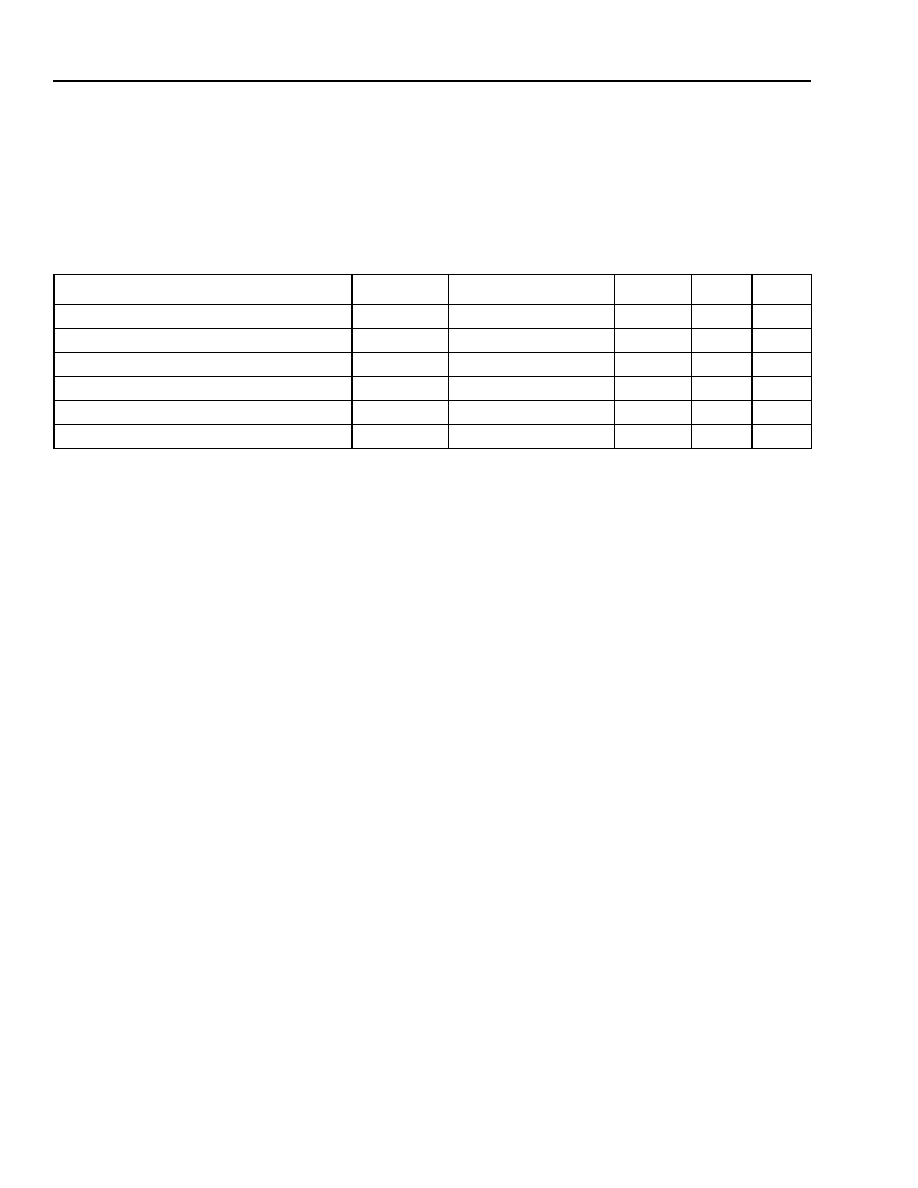

T8110L Main Clocking Paths ................................................................................................................ 44

Figure 6.

T8110L NETREF Paths ........................................................................................................................ 44

Figure 7.

T8110L Required Frame Pulse and Bit Clock with Polarities ............................................................... 60

Figure 8.

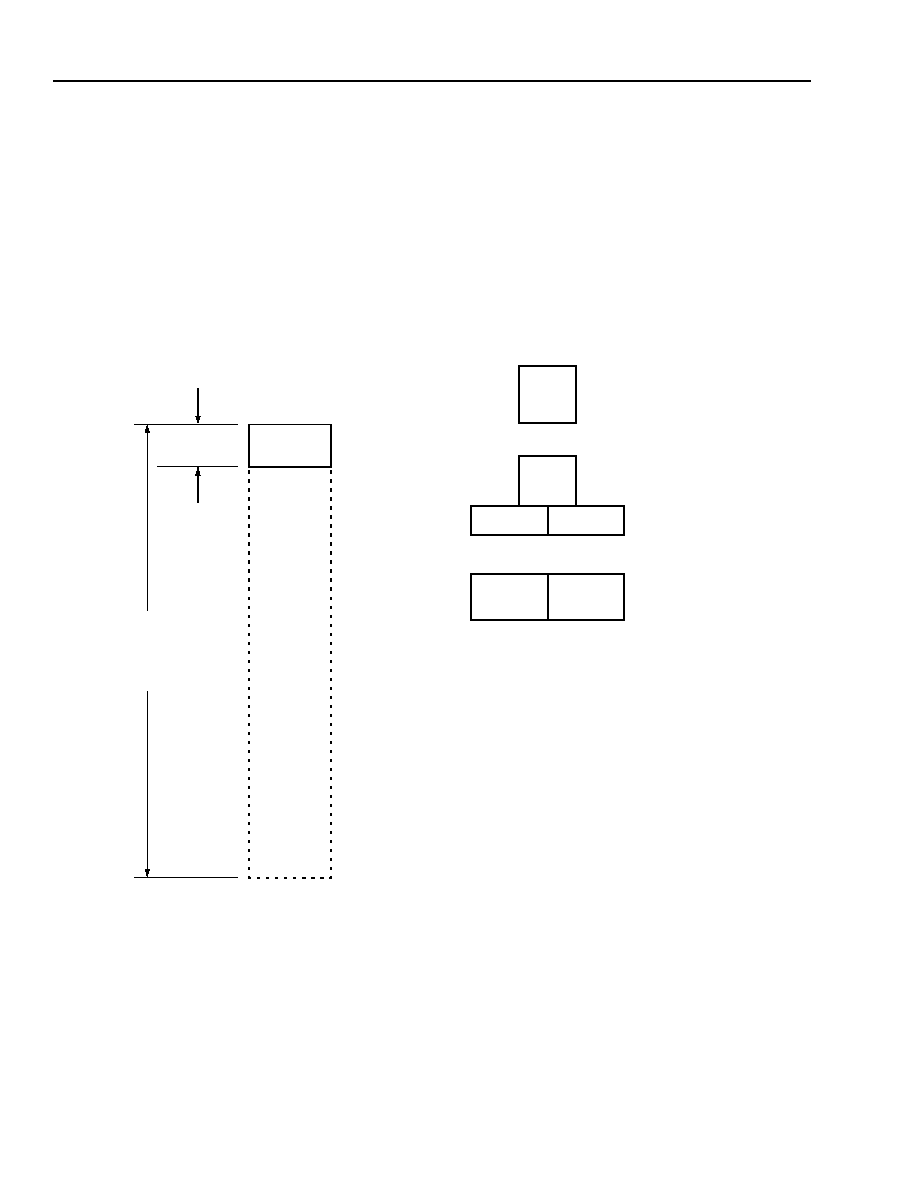

T8110L Phase Alignment, SNAP and SLIDE ....................................................................................... 62

Figure 9.

Fallback--Fixed vs. Rotating Secondary .............................................................................................. 65

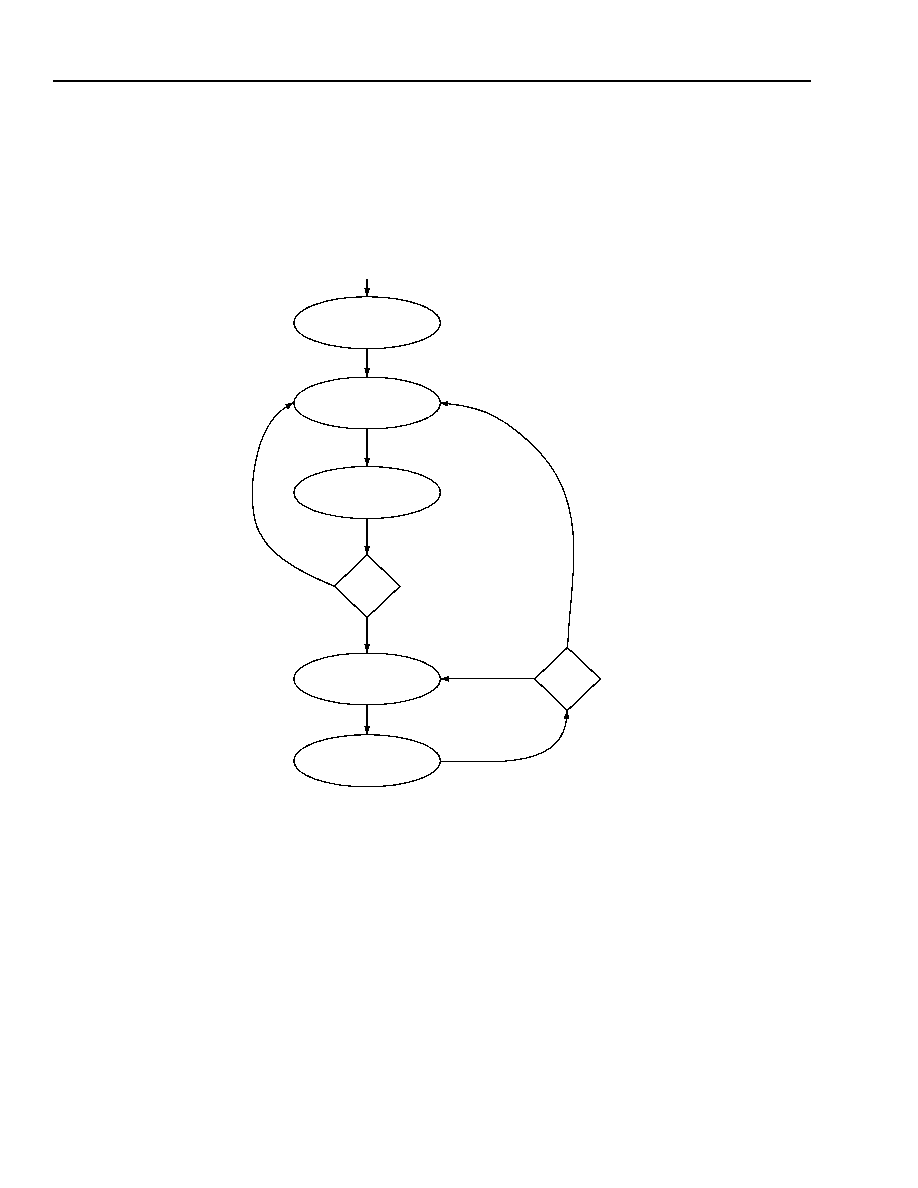

Figure 10. T8110L Clock Fallback States .............................................................................................................. 66

Figure 11. T8110L H-Bus Clock Enable States ..................................................................................................... 68

Figure 12. T8110L Clock Failsafe States ............................................................................................................... 70

Figure 13. FG[7:0] Functional Paths ...................................................................................................................... 77

Figure 14. Frame Group 8 kHz Reference Timing ................................................................................................. 78

Figure 15. GP[7:0] Functional Paths ...................................................................................................................... 82

Figure 16. Local Stream 16.384 Mbits/s Timing..................................................................................................... 86

Figure 17. Local Stream 16.384 Mbits/s Circuit ..................................................................................................... 87

Figure 18. Superrate I/O Configuration .................................................................................................................. 88

Figure 19. Relationship Between 8.192 Mbits/s and 16.384 Mbits/s Time Slots ................................................... 89

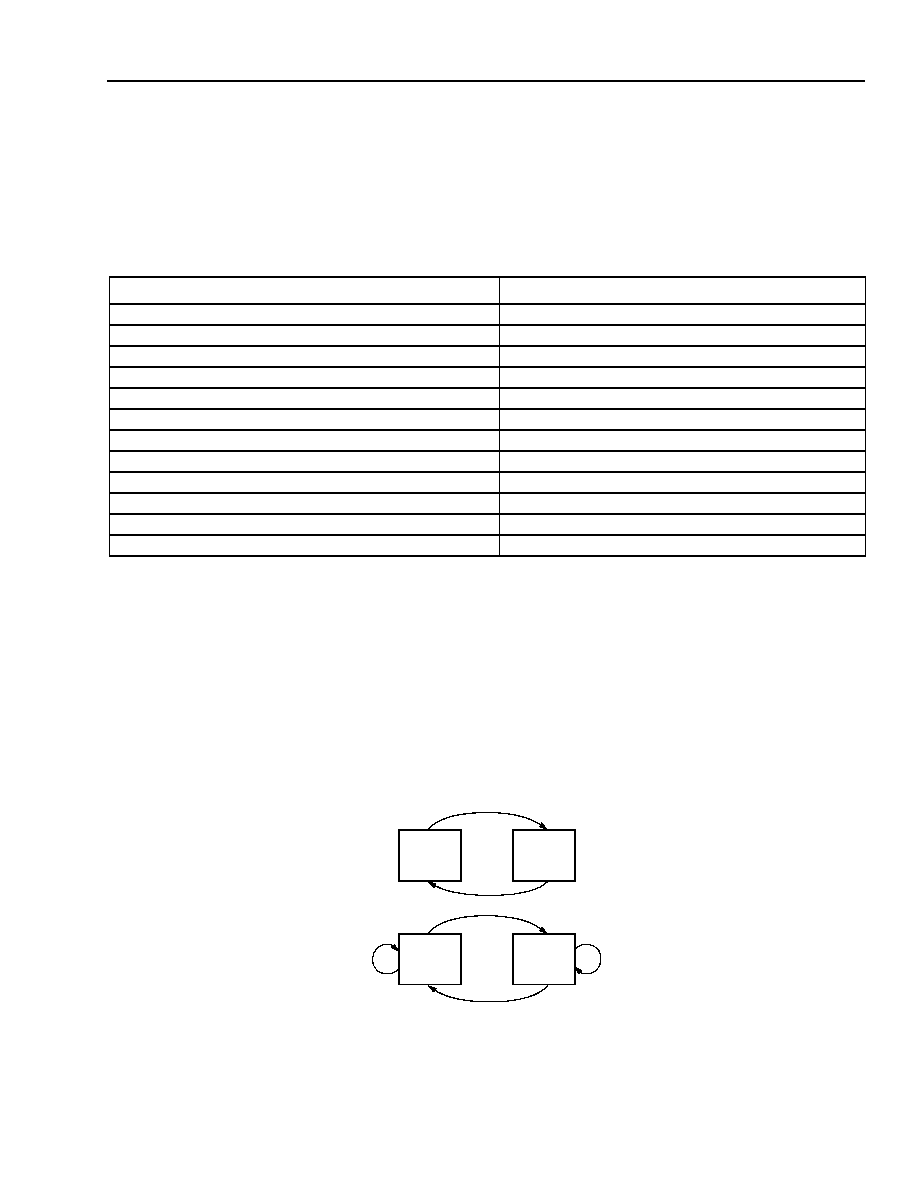

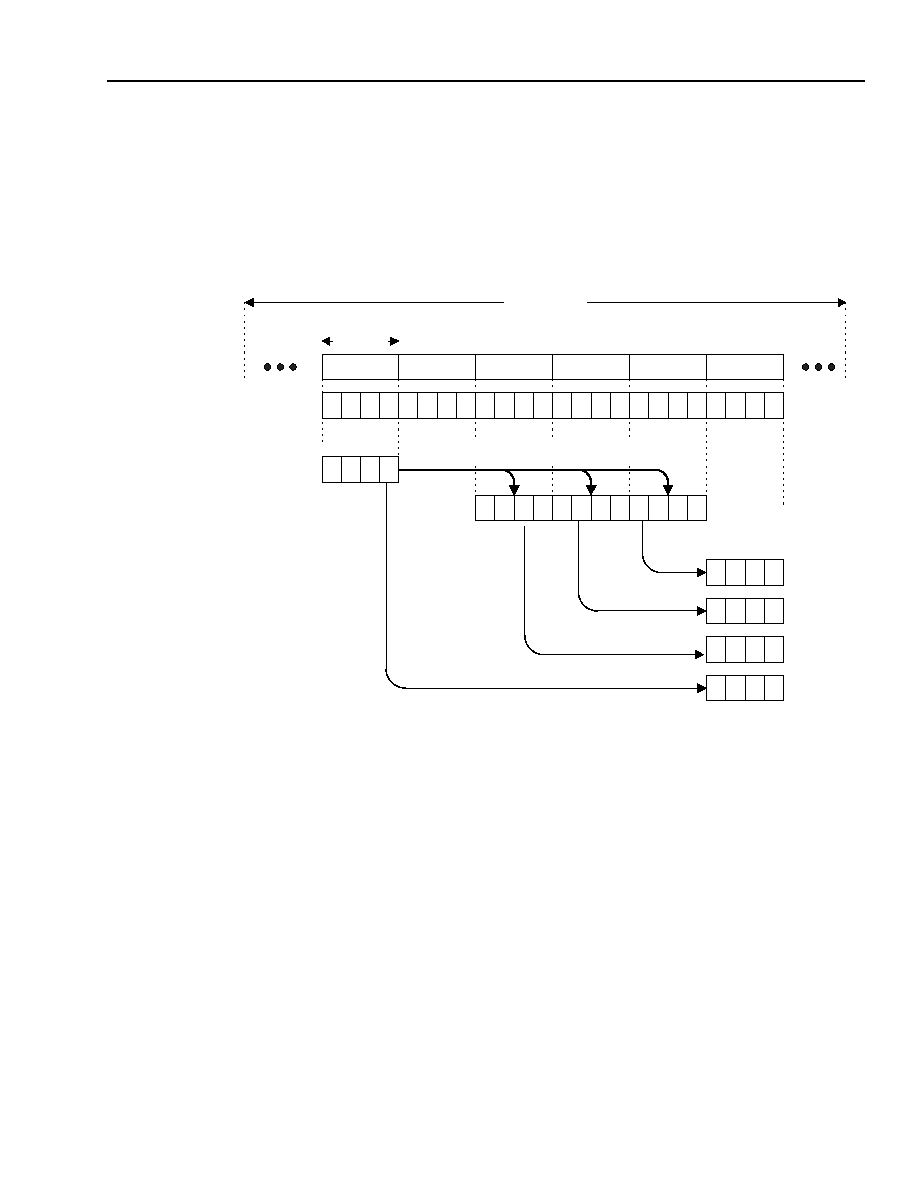

Figure 20. Interrupt Controller .............................................................................................................................. 103

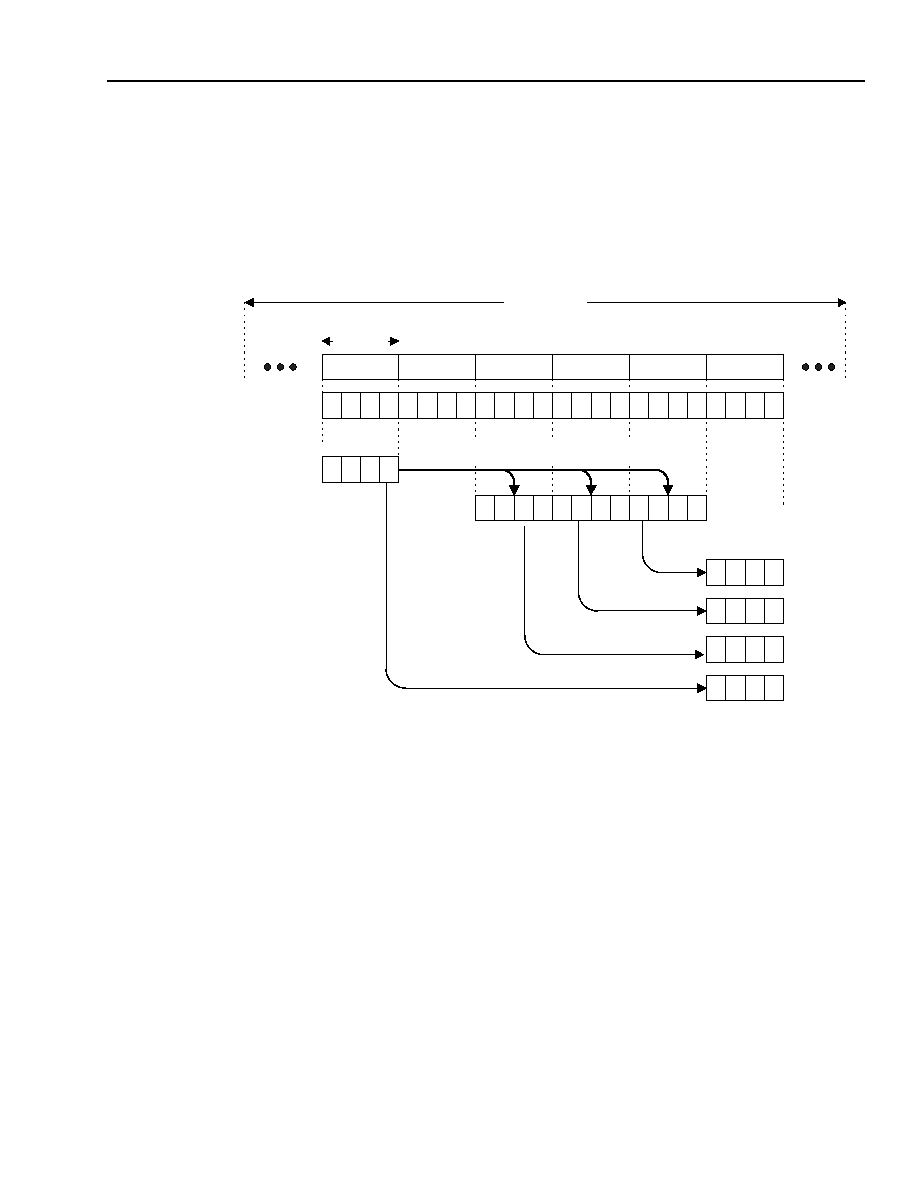

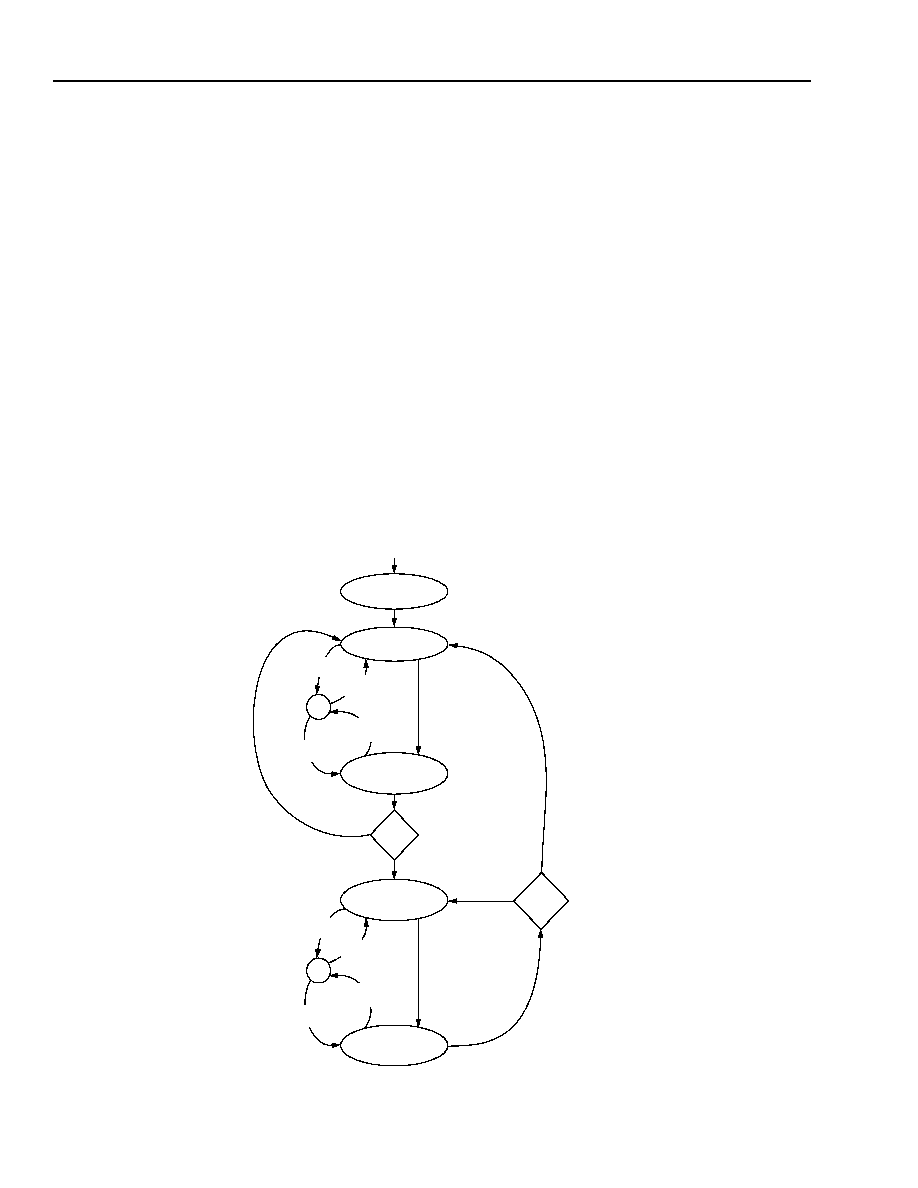

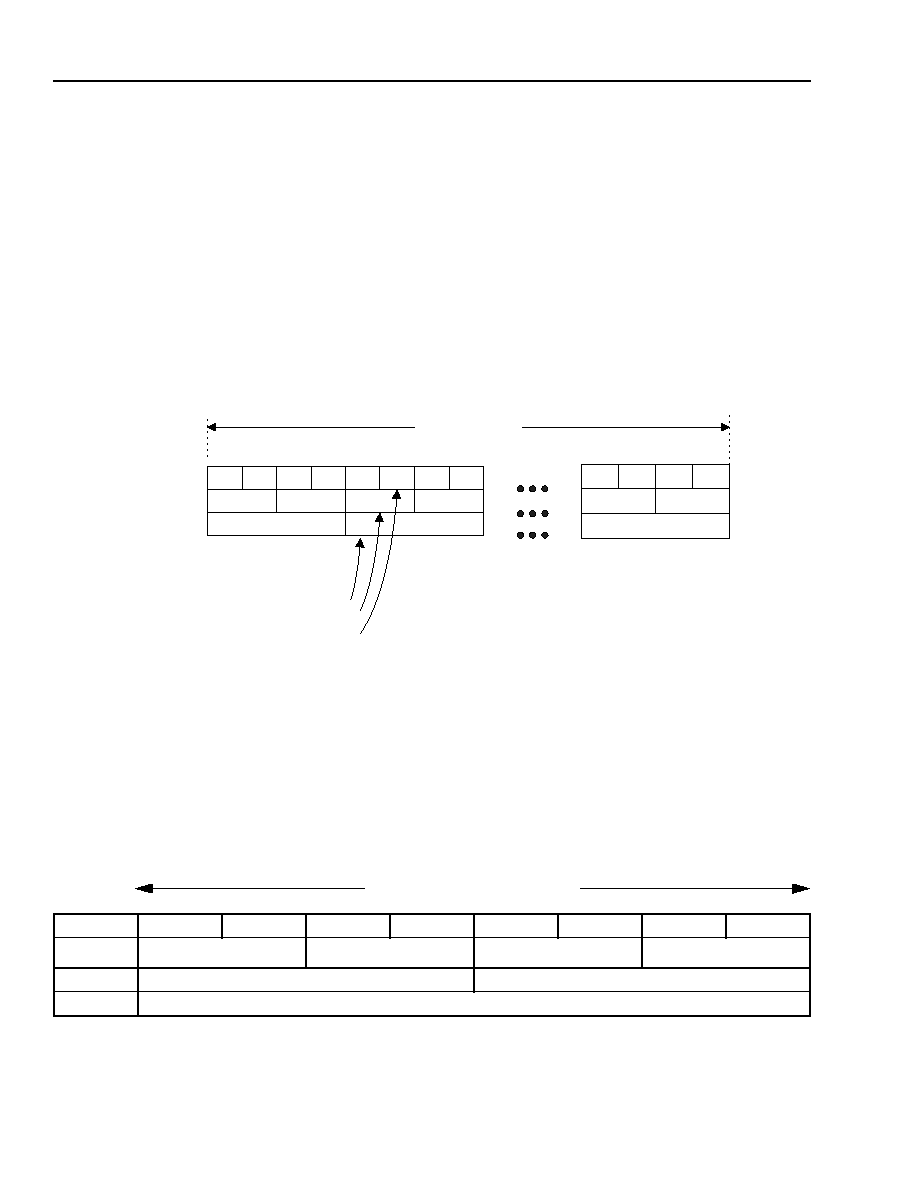

Figure 21. Microprocessor Programming--Reset Page Command ..................................................................... 114

Figure 22. Microprocessor Programming--Make/Break/Query Telephony Connections..................................... 114

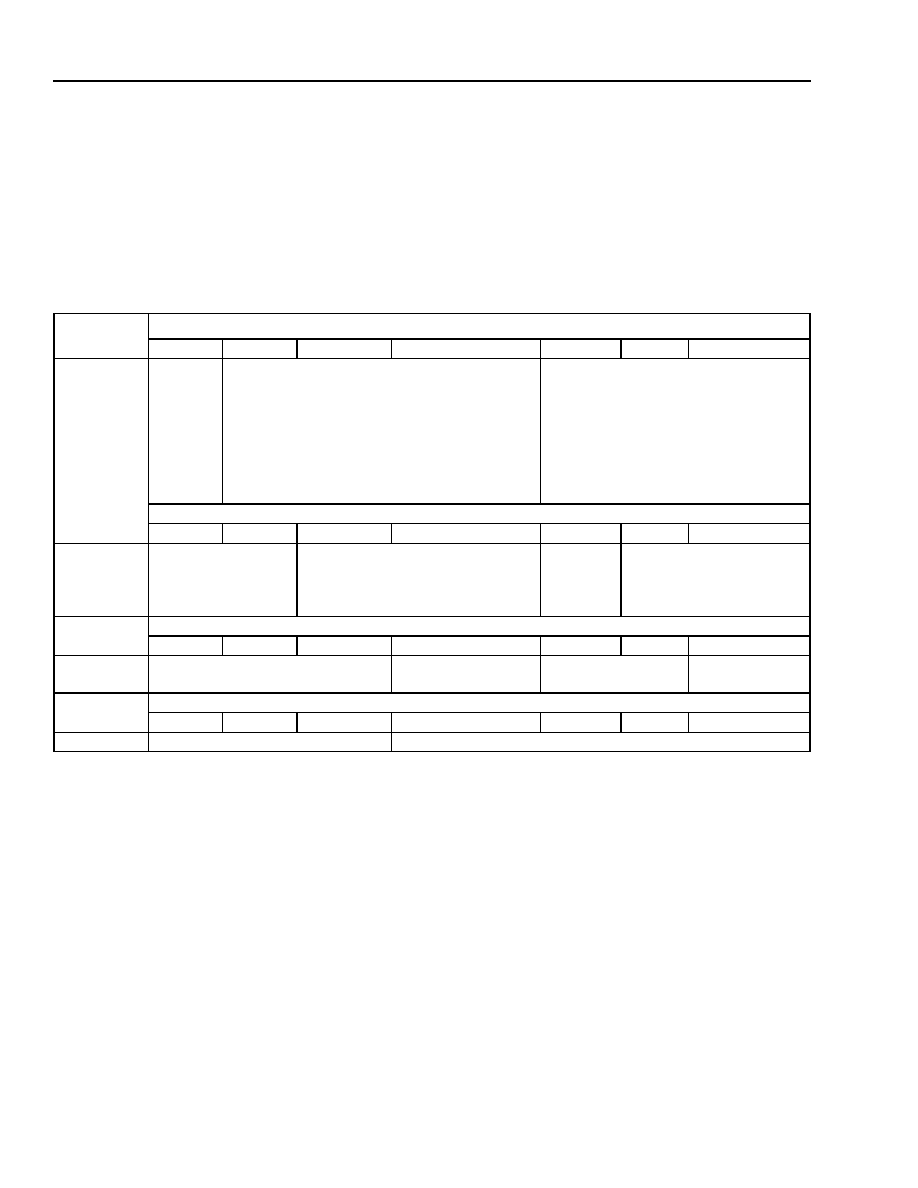

Figure 23. T8110L Data Memory Map and Configurations .................................................................................. 116

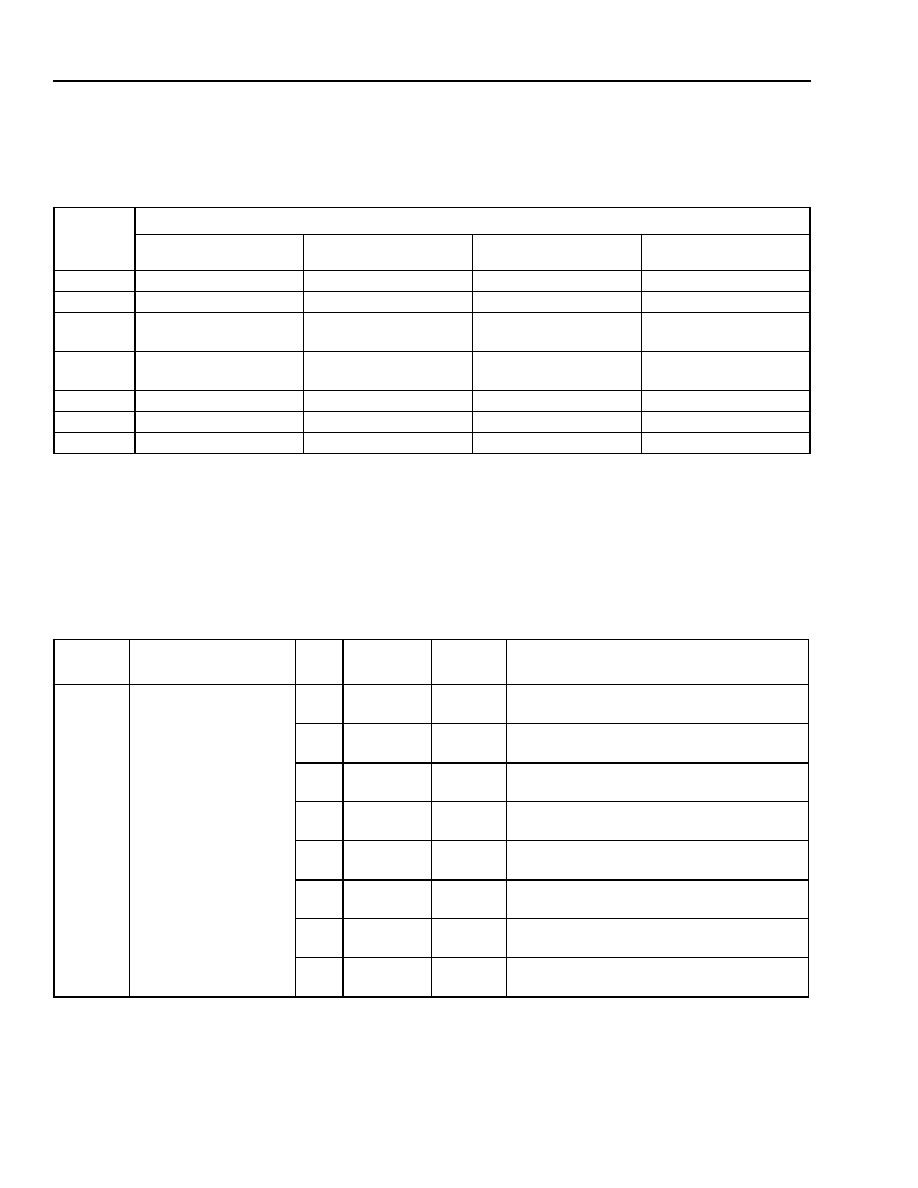

Figure 24. TDM Data Stream Bit Rates ............................................................................................................... 118

Figure 25. Subrate Switching Example, Byte Packing ......................................................................................... 121

Figure 26. Subrate Switching Example, Byte Unpacking ..................................................................................... 123

Figure 27. Clock Alignment .................................................................................................................................. 129

Figure 28. Frame Timing Diagram ....................................................................................................................... 130

Figure 29. Detailed Clock Skew Timing Diagram................................................................................................. 130

Figure 30. APLL V

DD

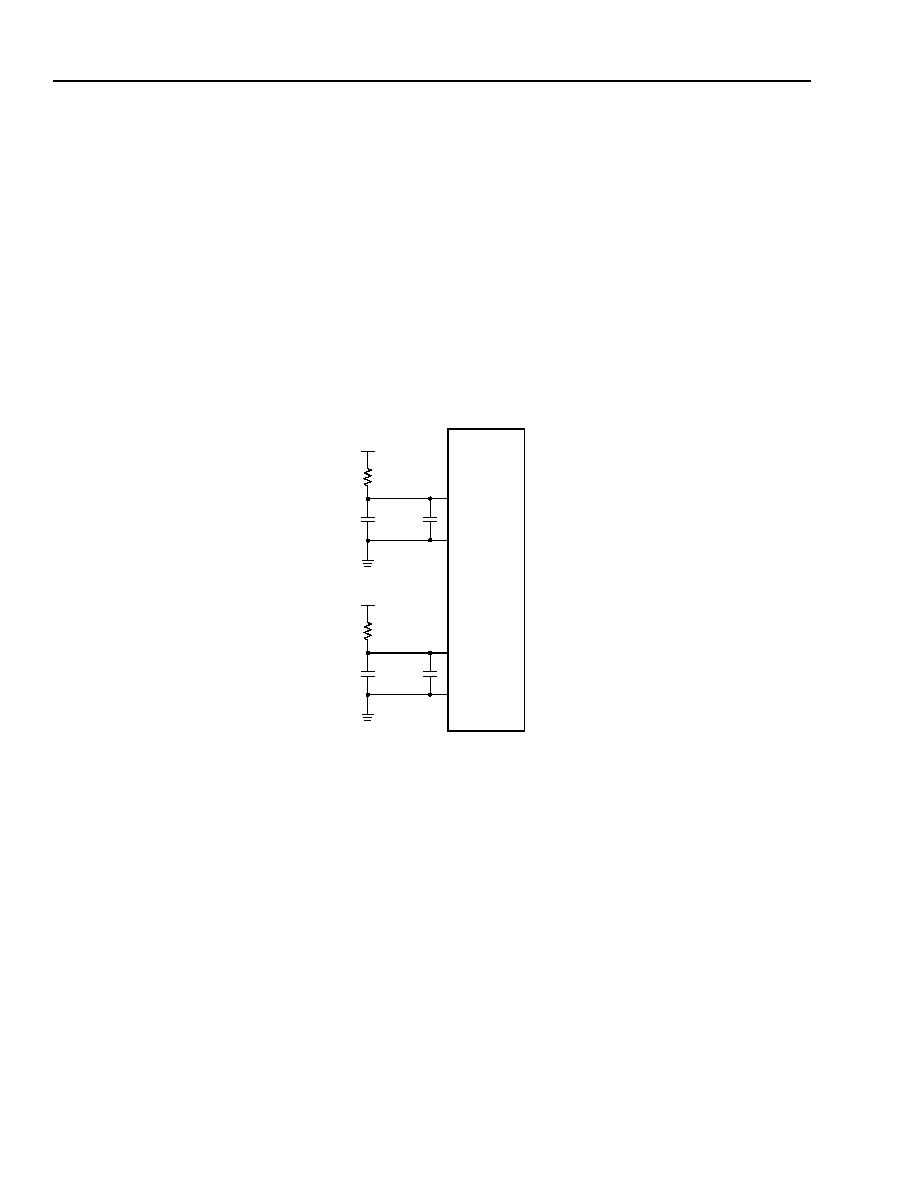

Filtering .............................................................................................................................. 132

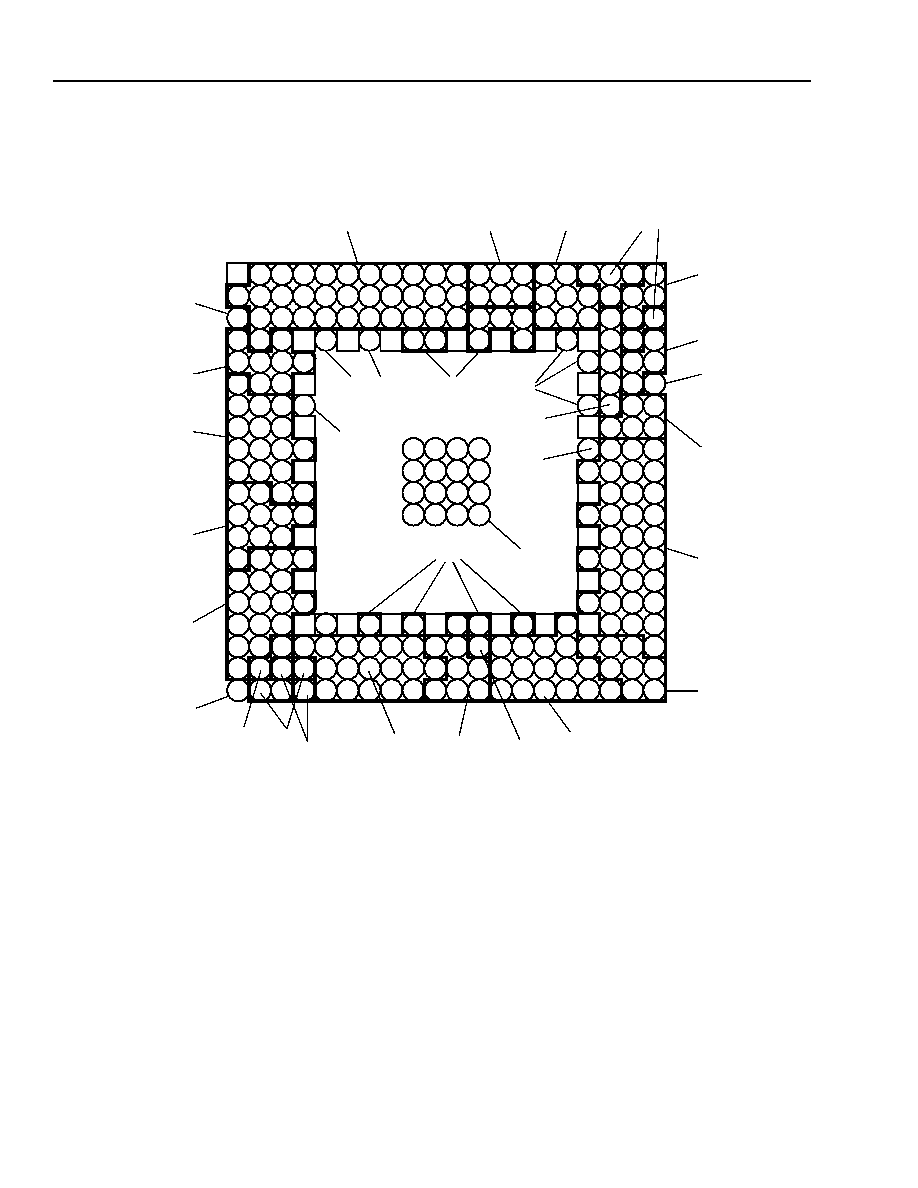

Figure 31. T8110L Pins by Functional Group ...................................................................................................... 134

Figure 32. IEEE

Æ

1149.1 Boundary-Scan Architecture ........................................................................................ 137

Figure 33. Constant Delay Connection Latency................................................................................................... 140

Figure 34. Minimum Delay Connection Latency .................................................................................................. 141

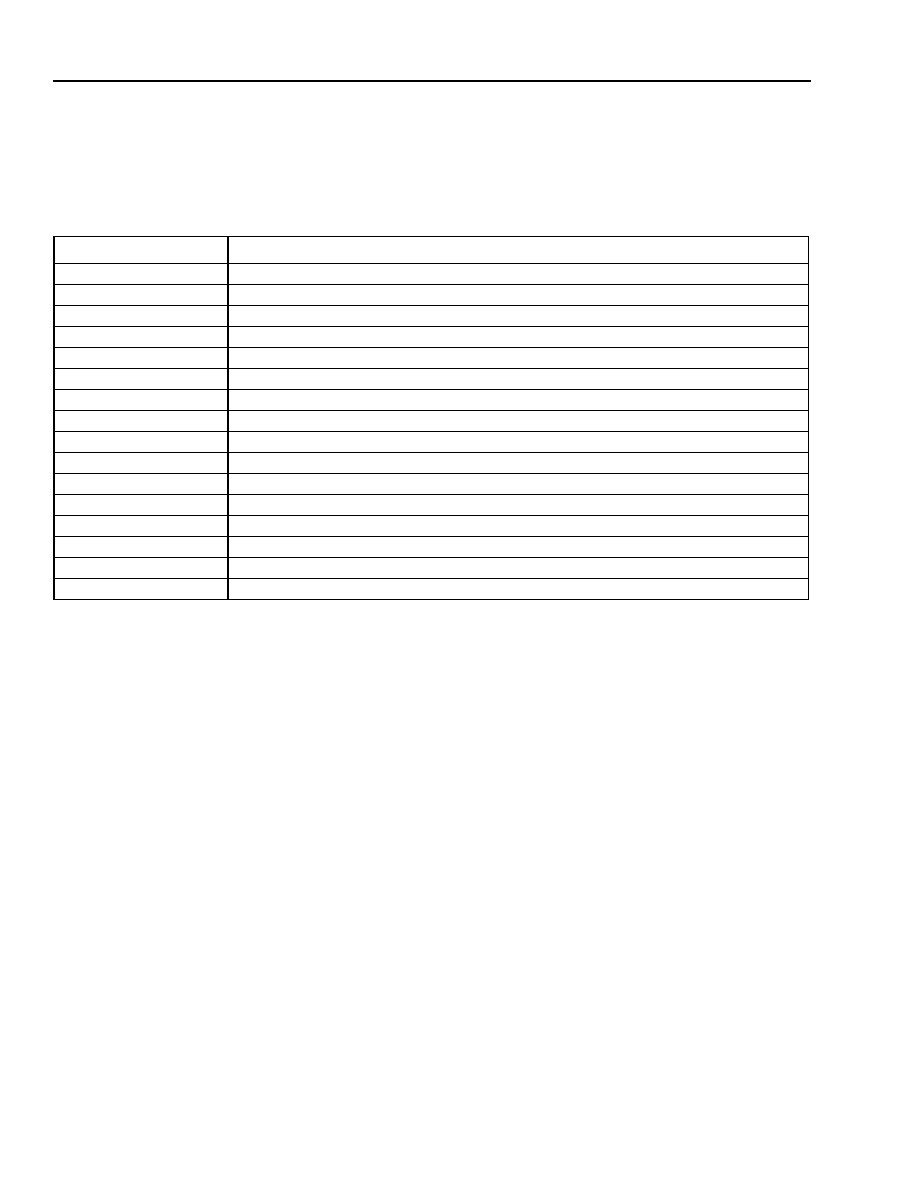

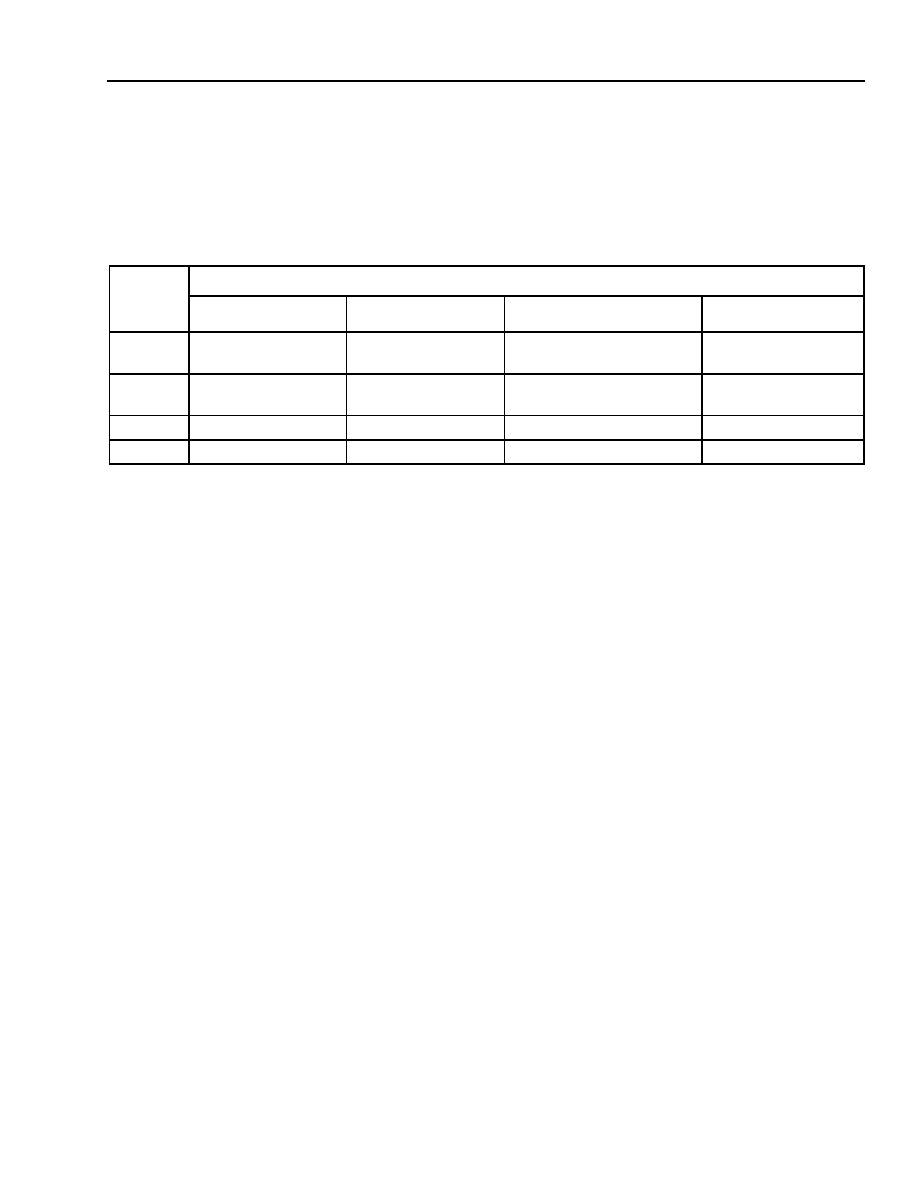

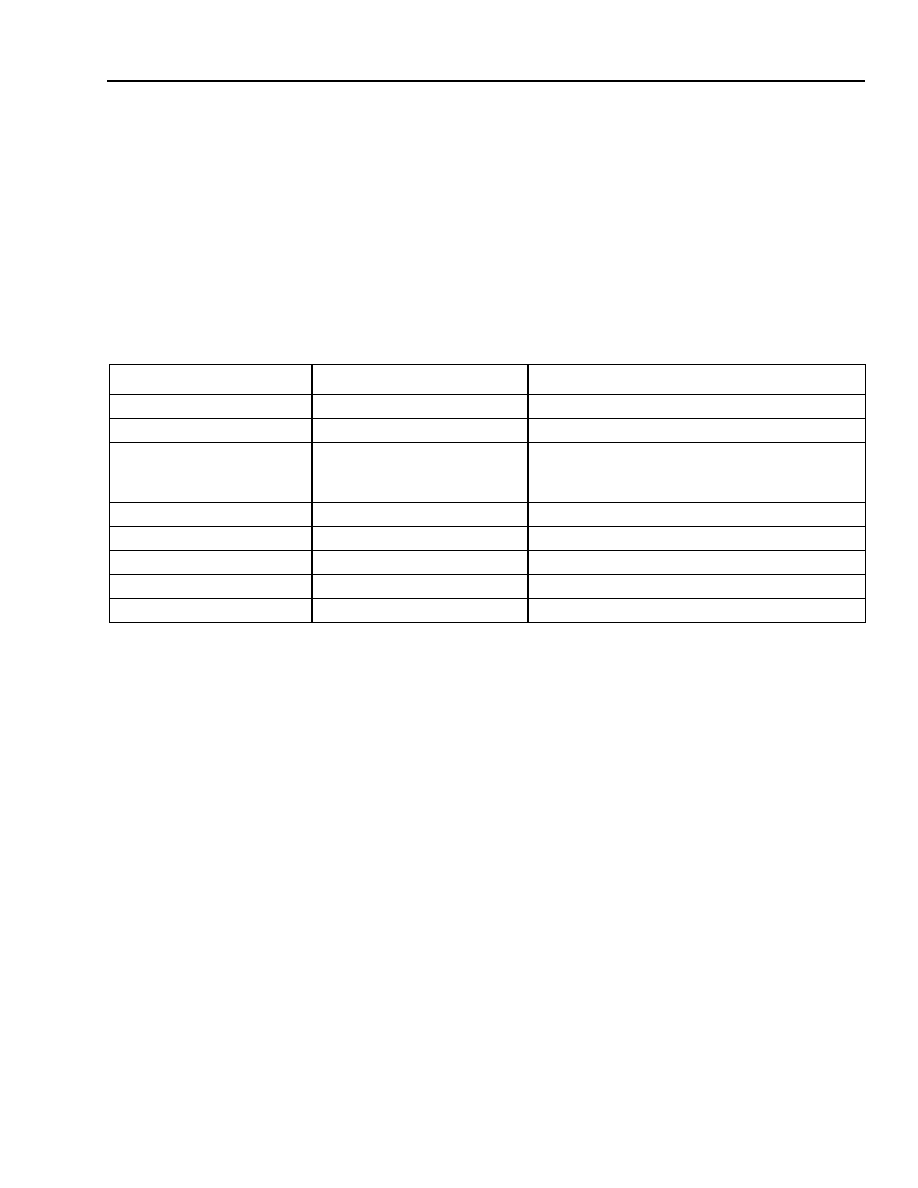

List of Tables

Table

Page

Agere Systems Inc.

7

February 2004

Ambassador T8110L H.100/H.110 Switch

Data Sheet

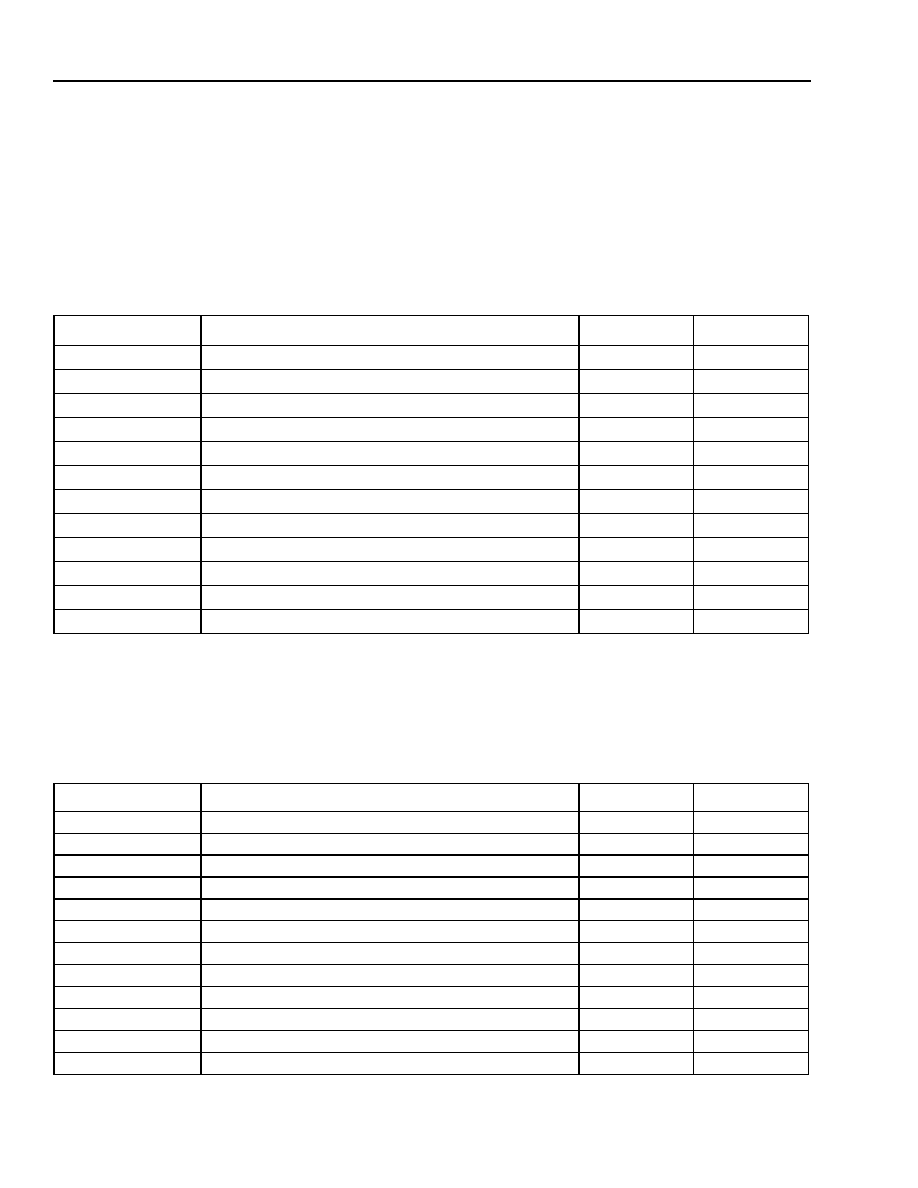

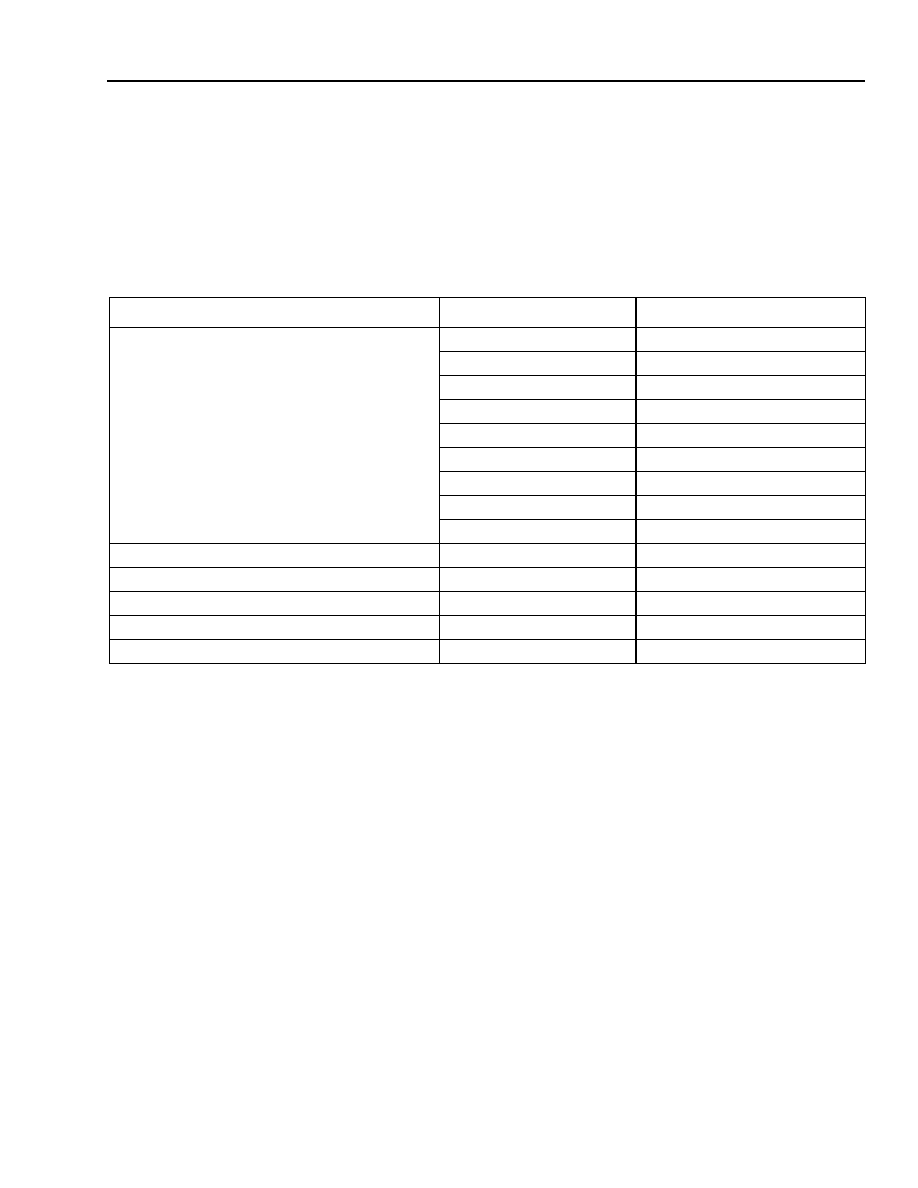

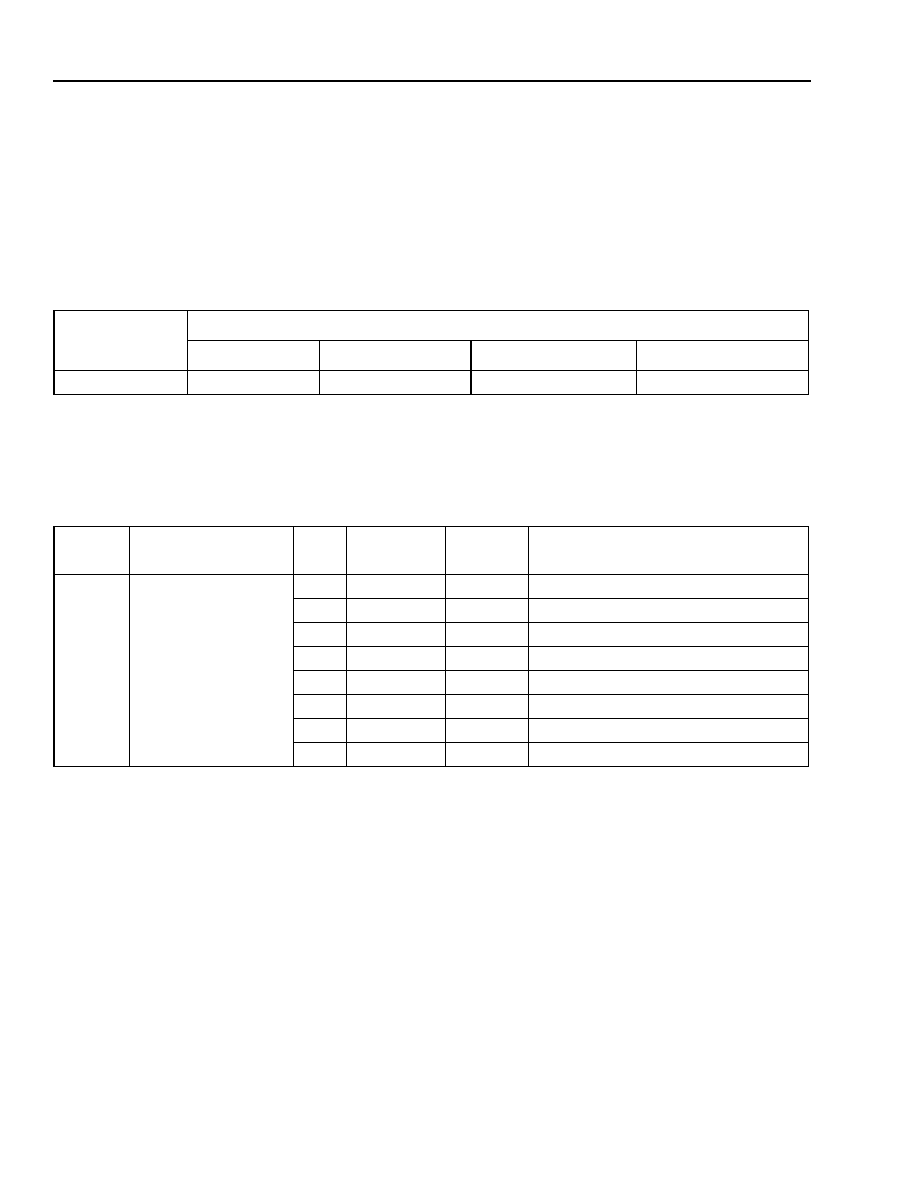

Table 1.

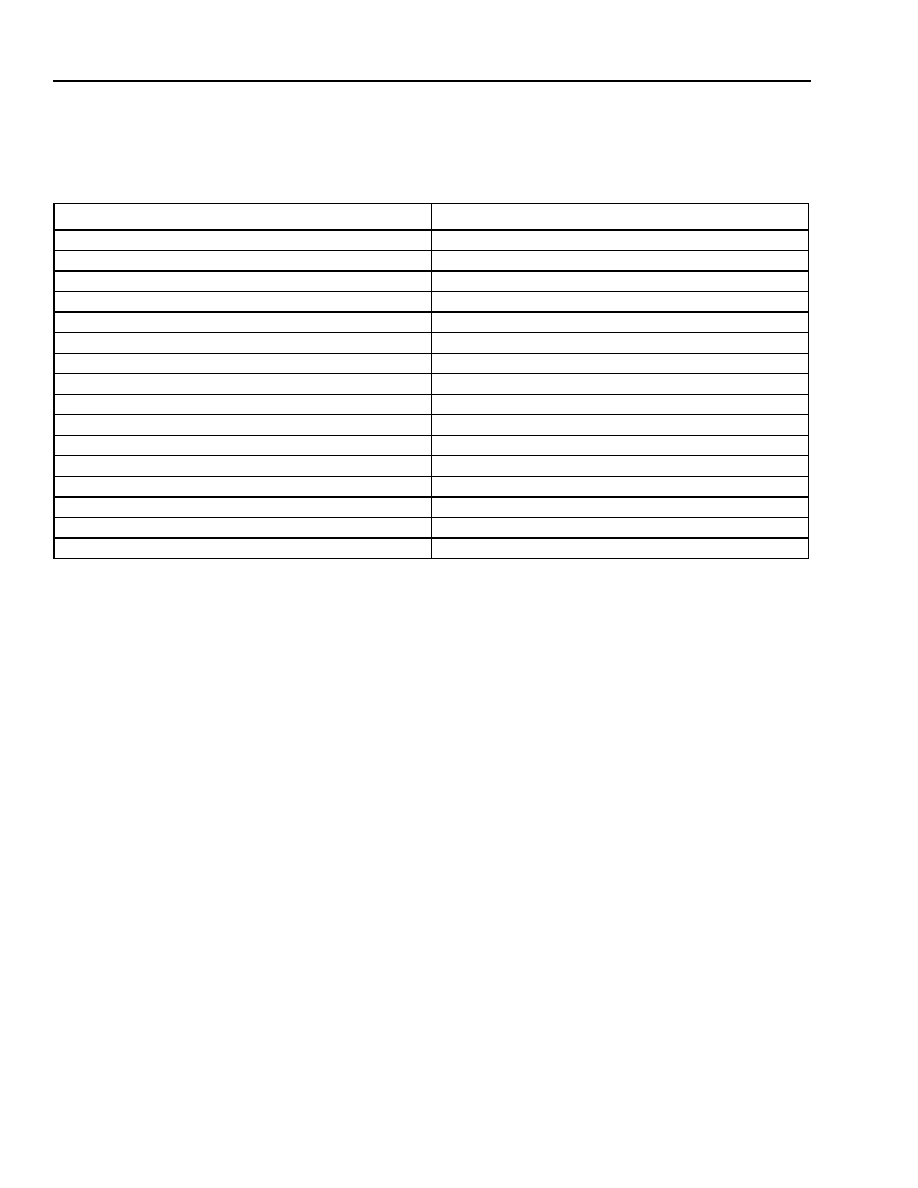

Microprocessor Interface Signals ..........................................................................................................10

Table 2.

H-Bus (H.100/H.110 Interface) Signals .................................................................................................10

Table 3.

L-Bus (Local) Interface Signals .............................................................................................................10

Table 4.

Clock Circuit Interface Signals ..............................................................................................................11

Table 5.

GPIO Interface Signals..........................................................................................................................11

Table 6.

Miscellaneous Interface Signals ............................................................................................................11

Table 7.

JTAG Signals ........................................................................................................................................11

Table 8.

T8110L Pinouts .....................................................................................................................................13

Table 9.

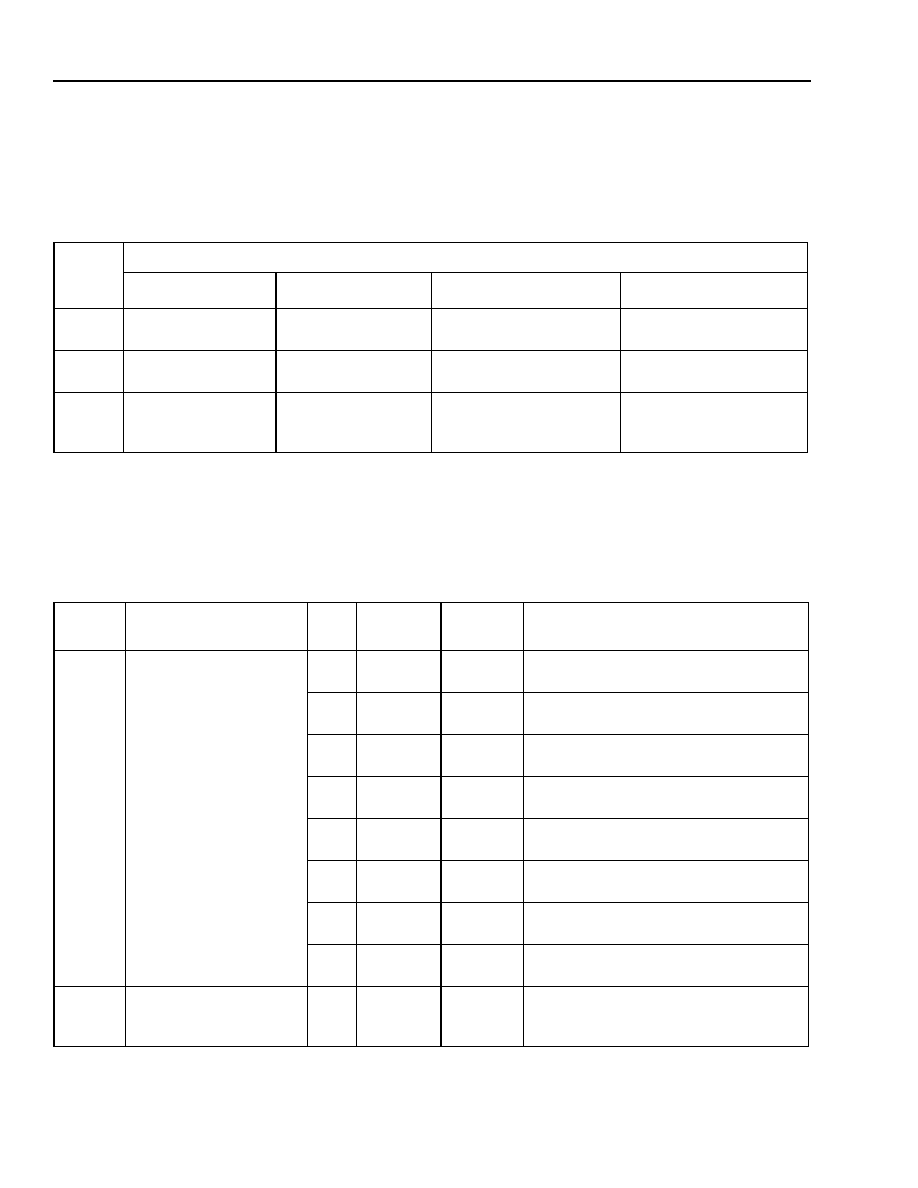

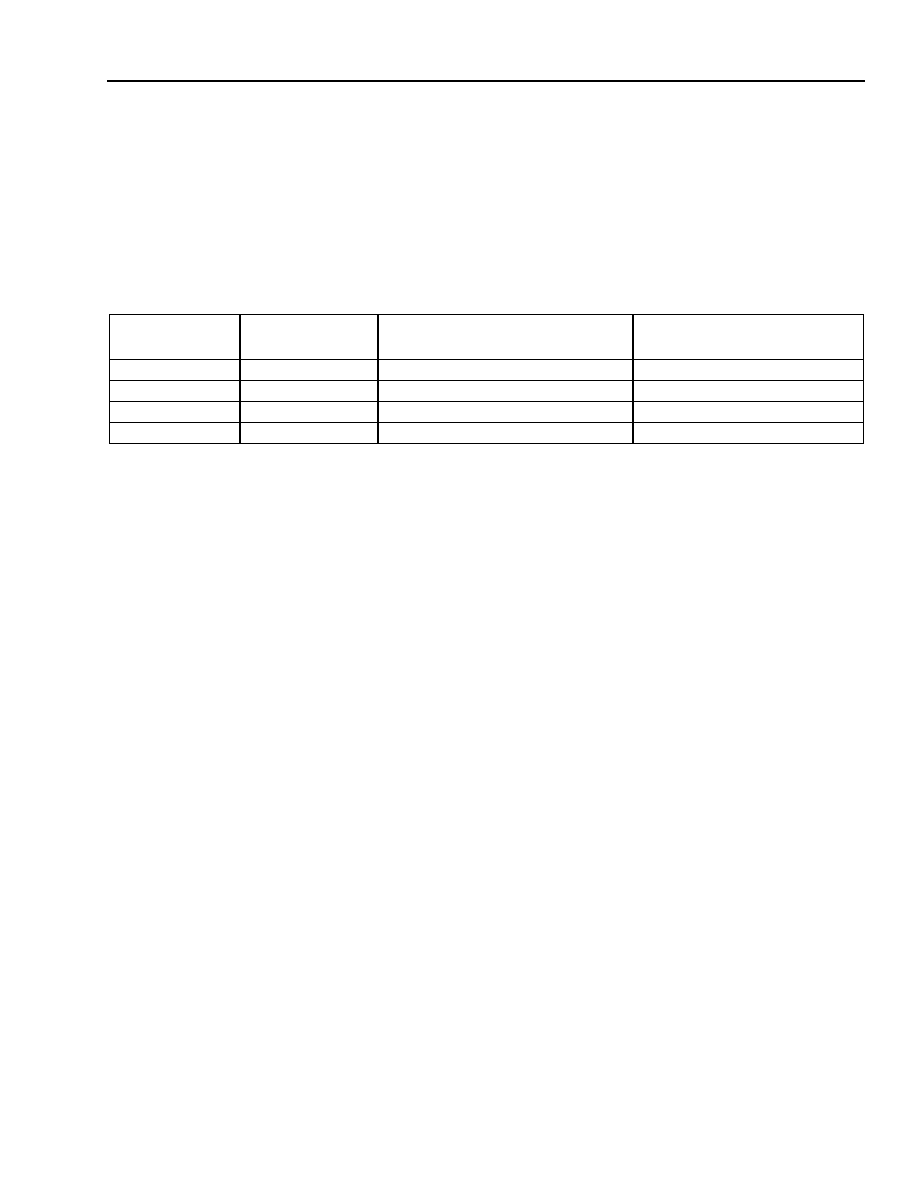

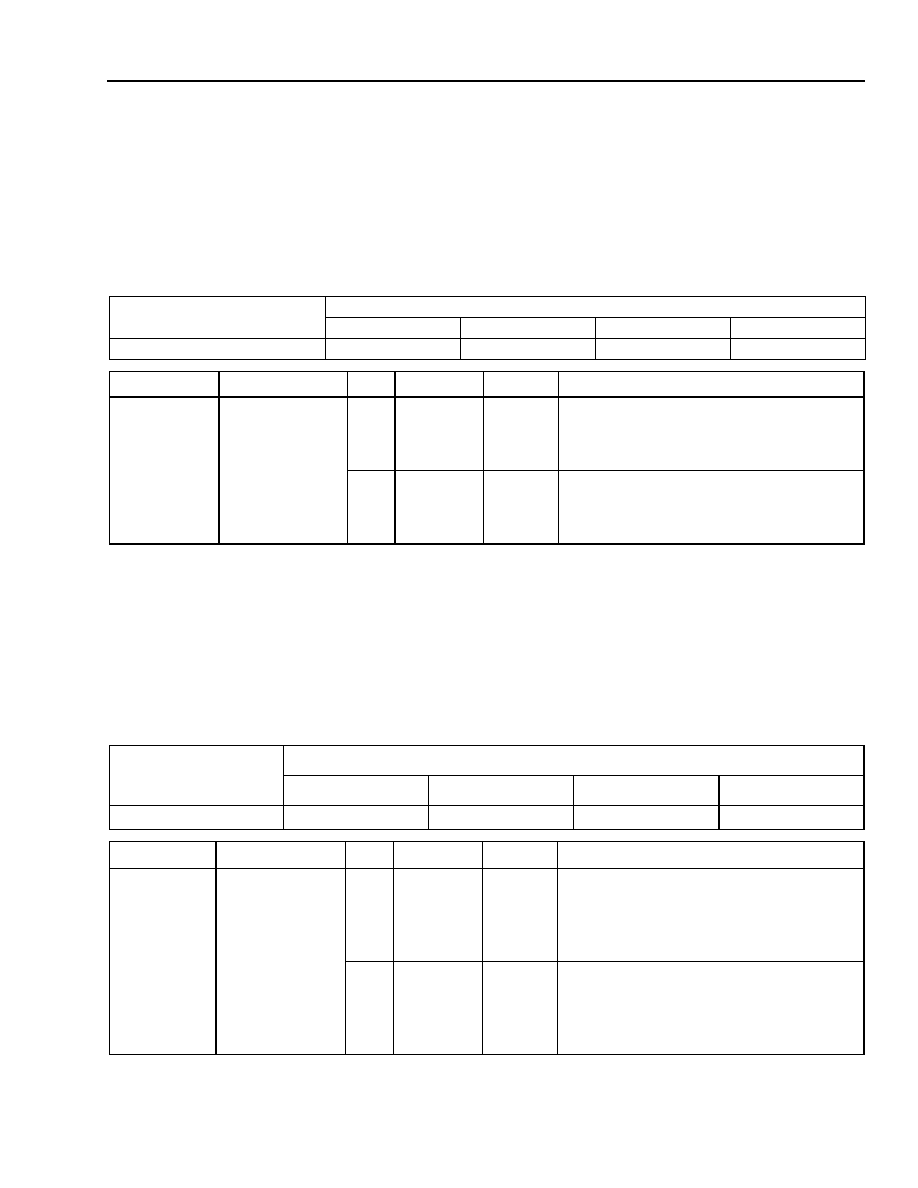

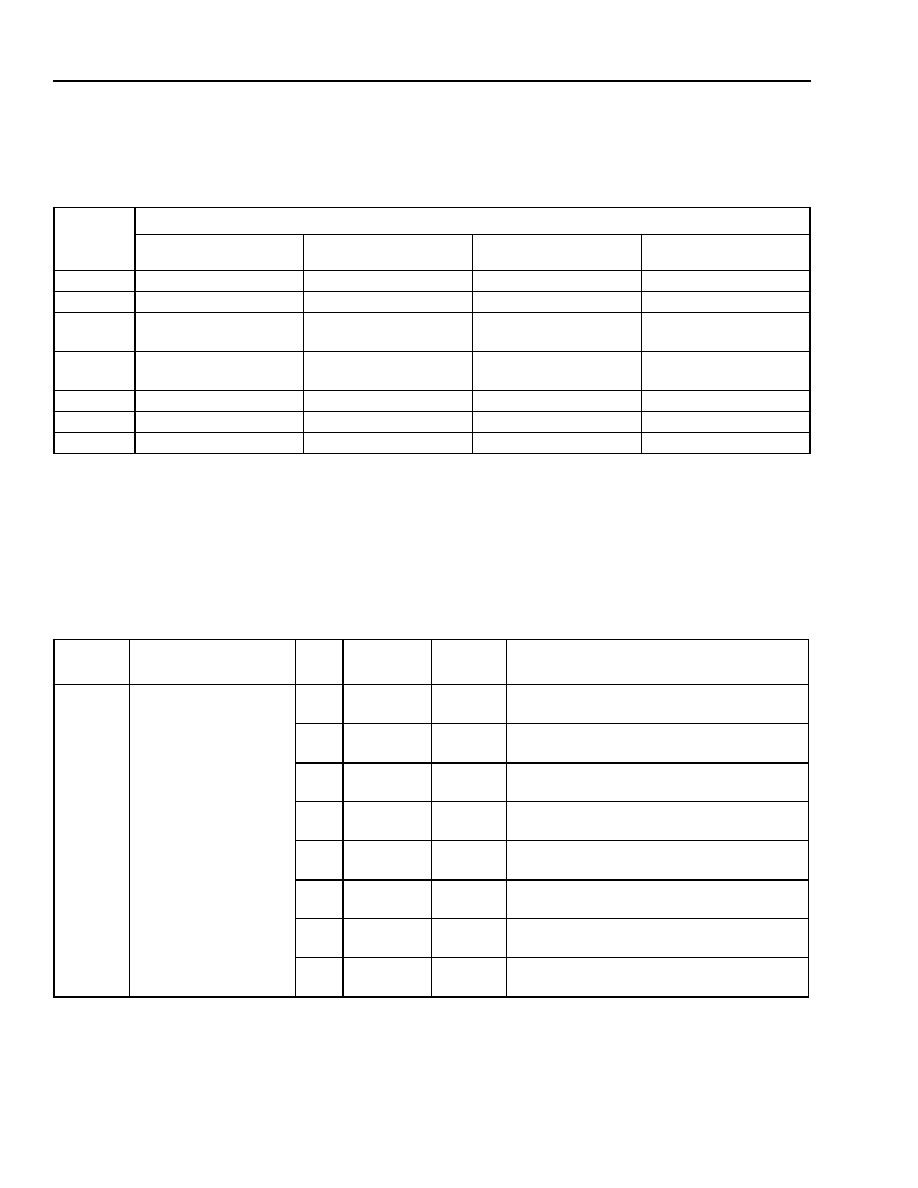

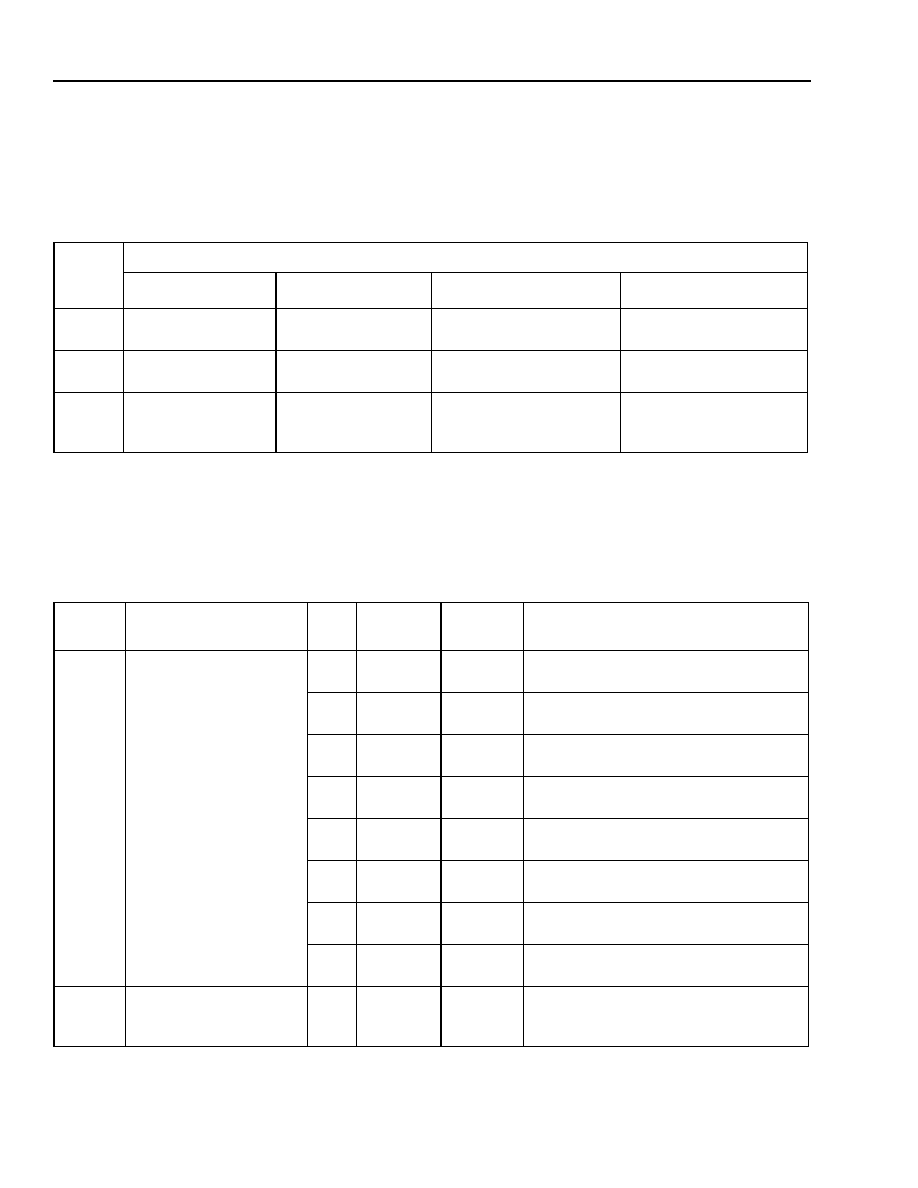

Intel/Motorola Protocol Selector ............................................................................................................22

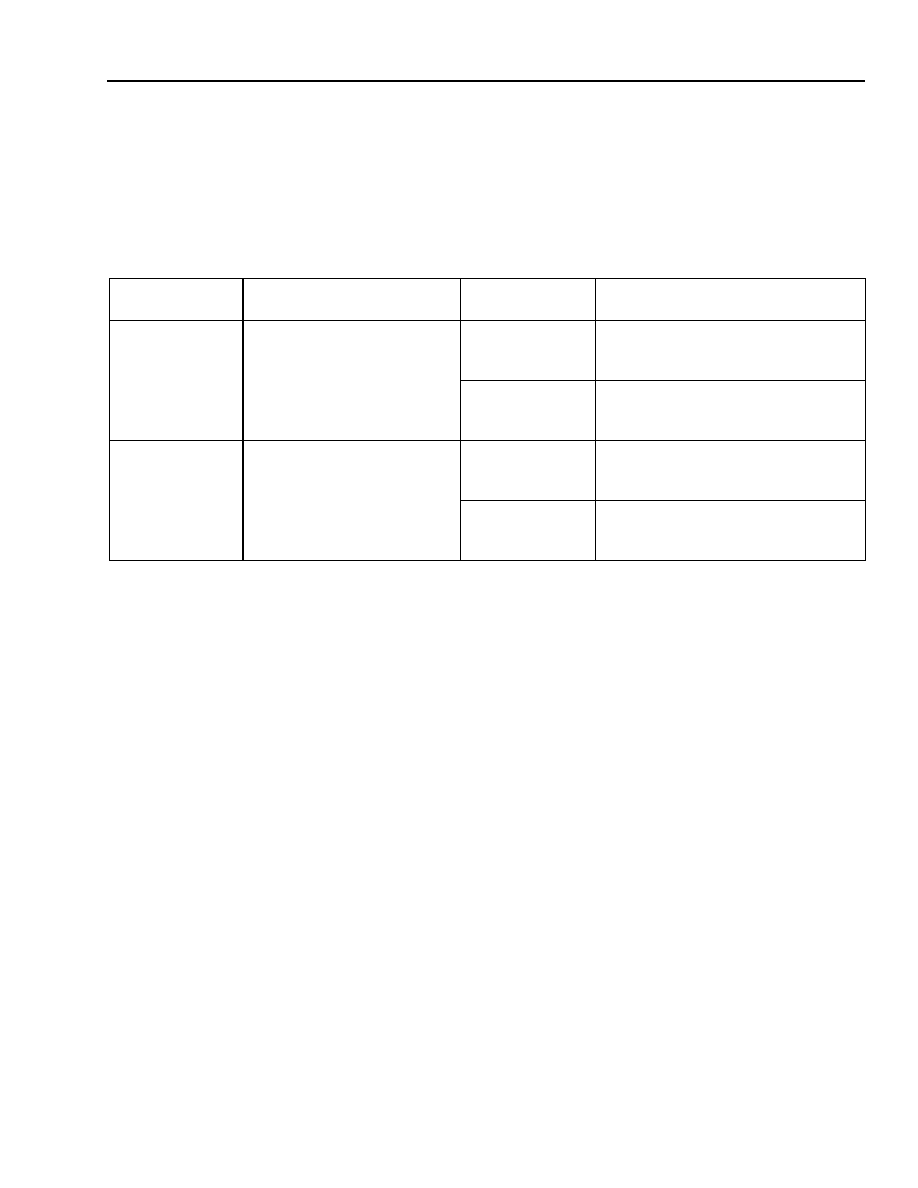

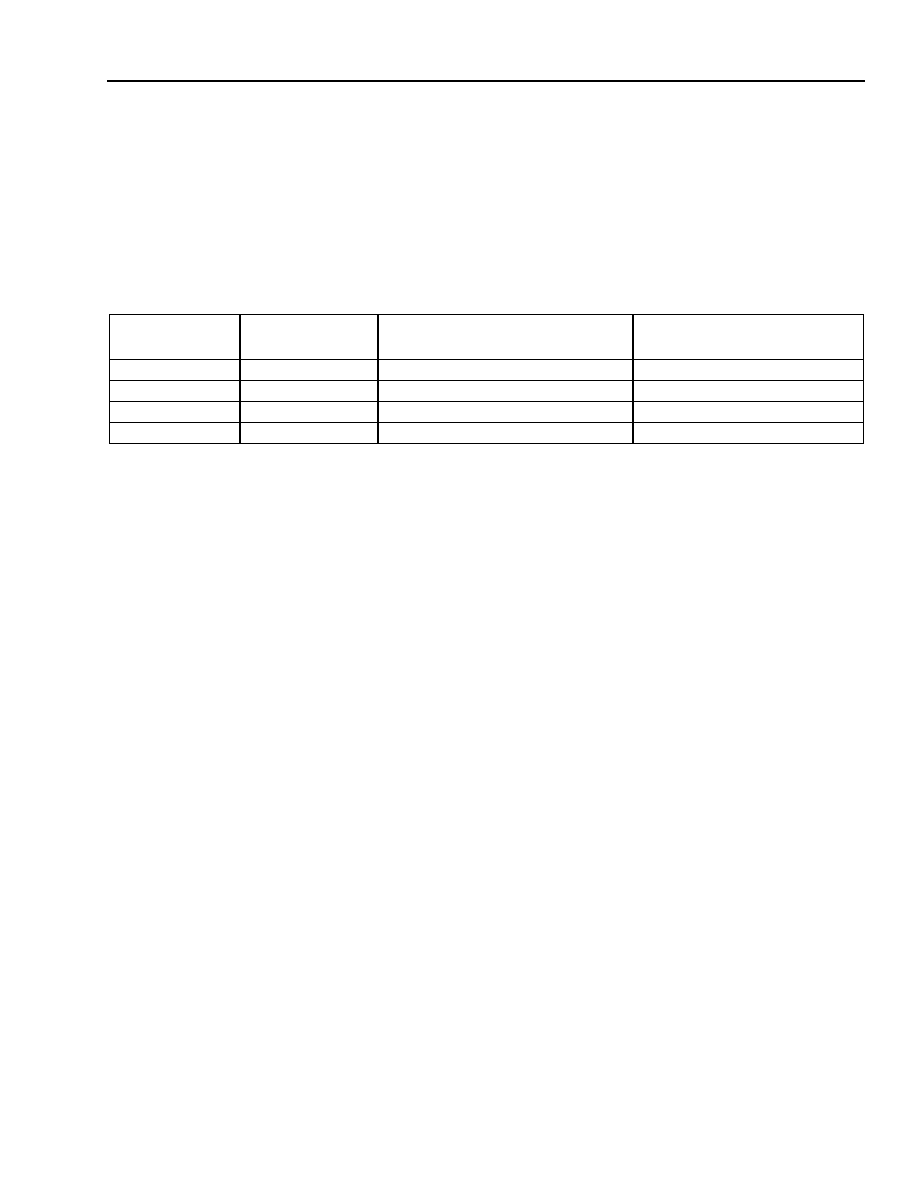

Table 10. T8110L Memory Mapping to Microprocessor Space.............................................................................23

Table 11. Microprocessor Interface Register Map ................................................................................................24

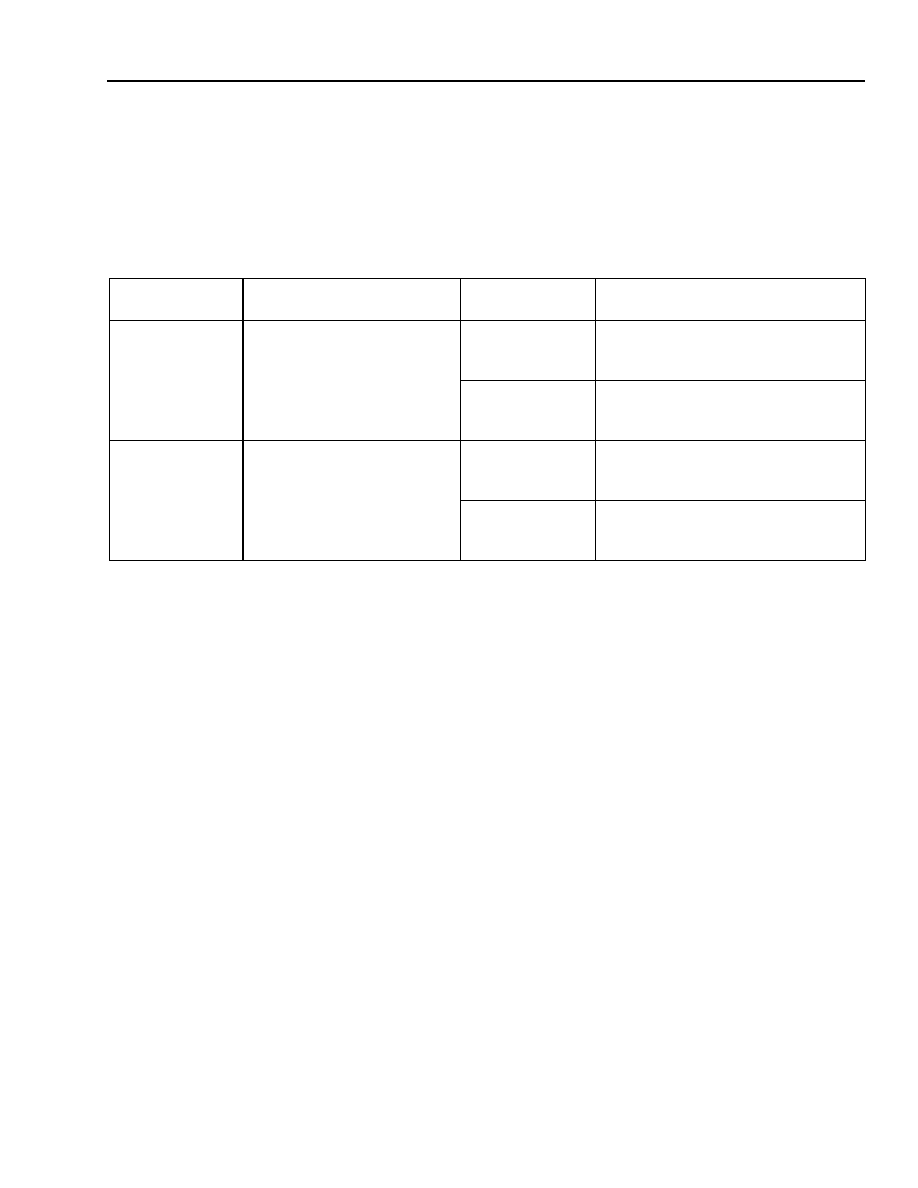

Table 12. Register Space Access Timing .............................................................................................................28

Table 13. Connection Memory Space Access Timing...........................................................................................28

Table 14. Data Memory Space Access Timing .....................................................................................................29

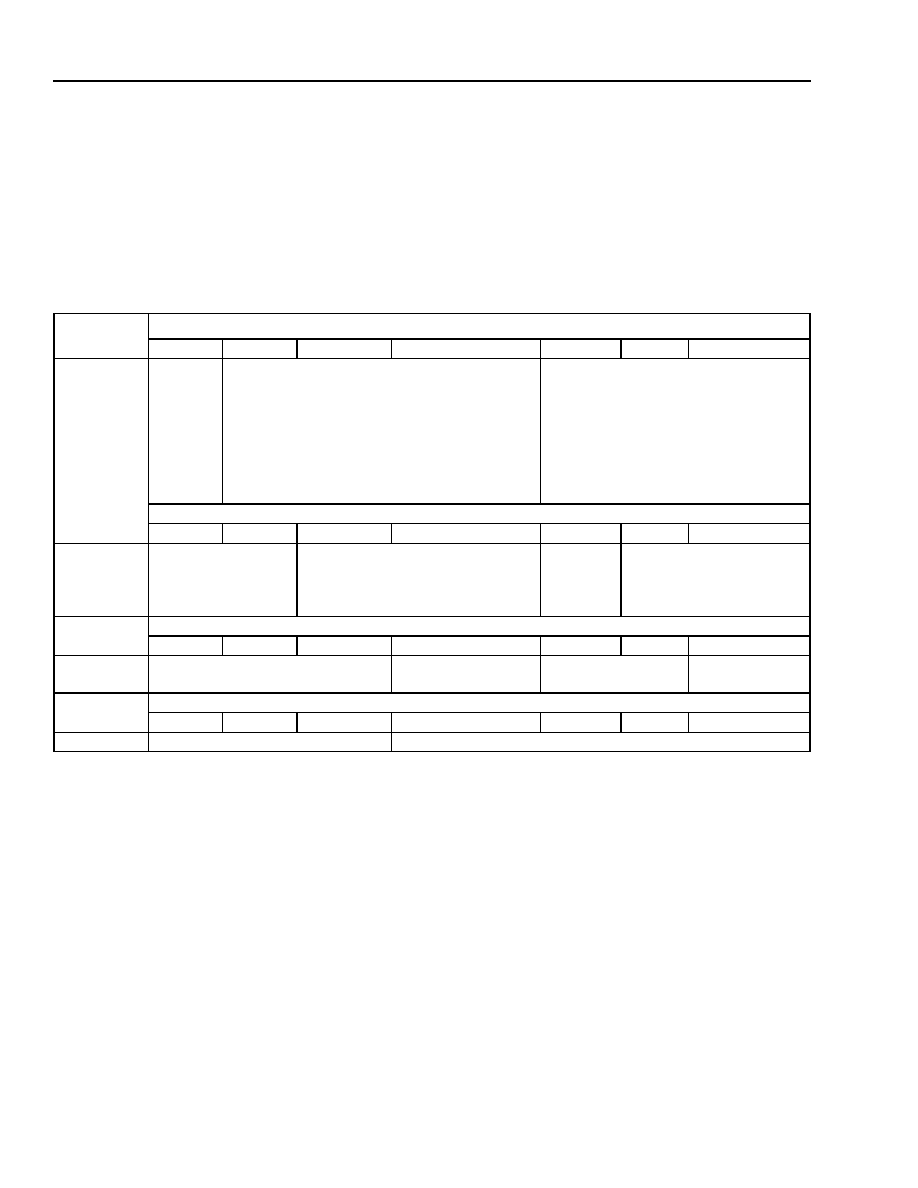

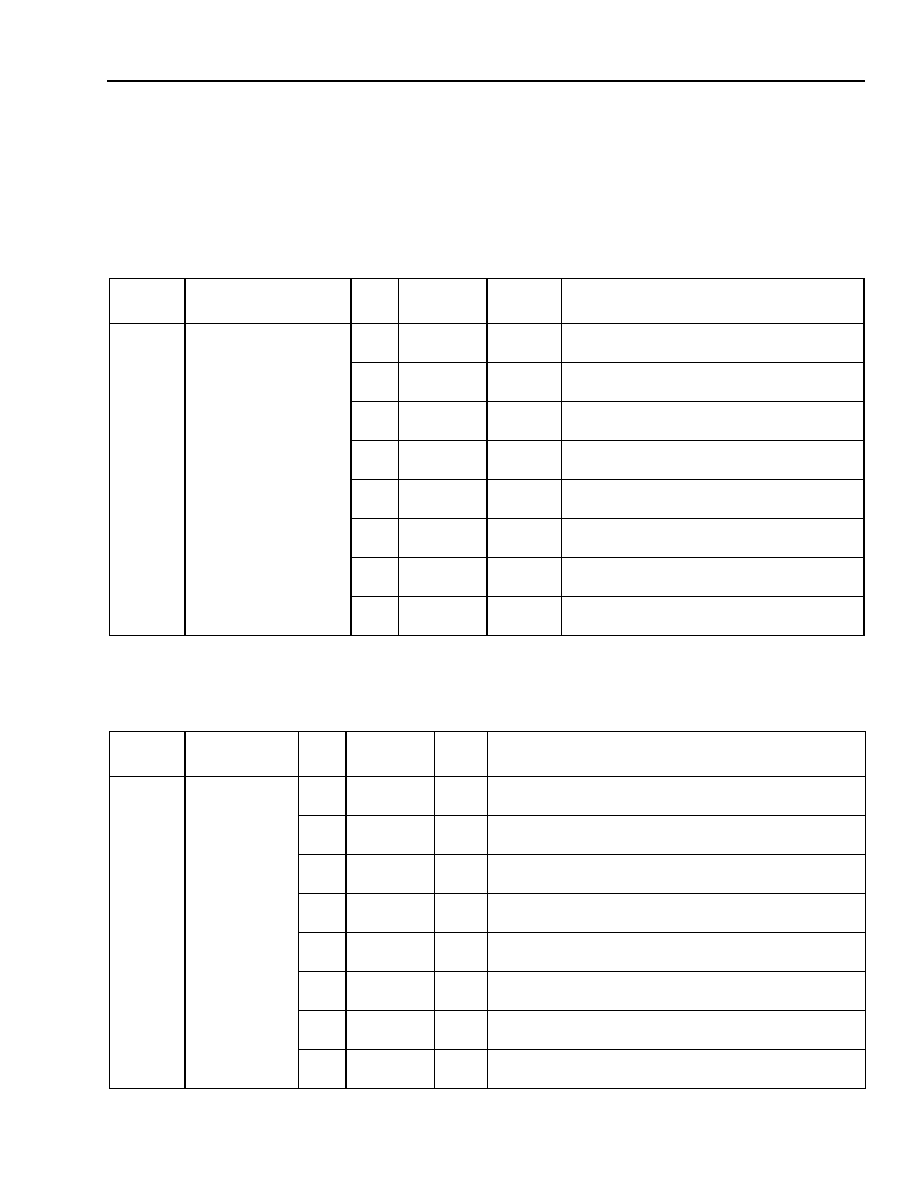

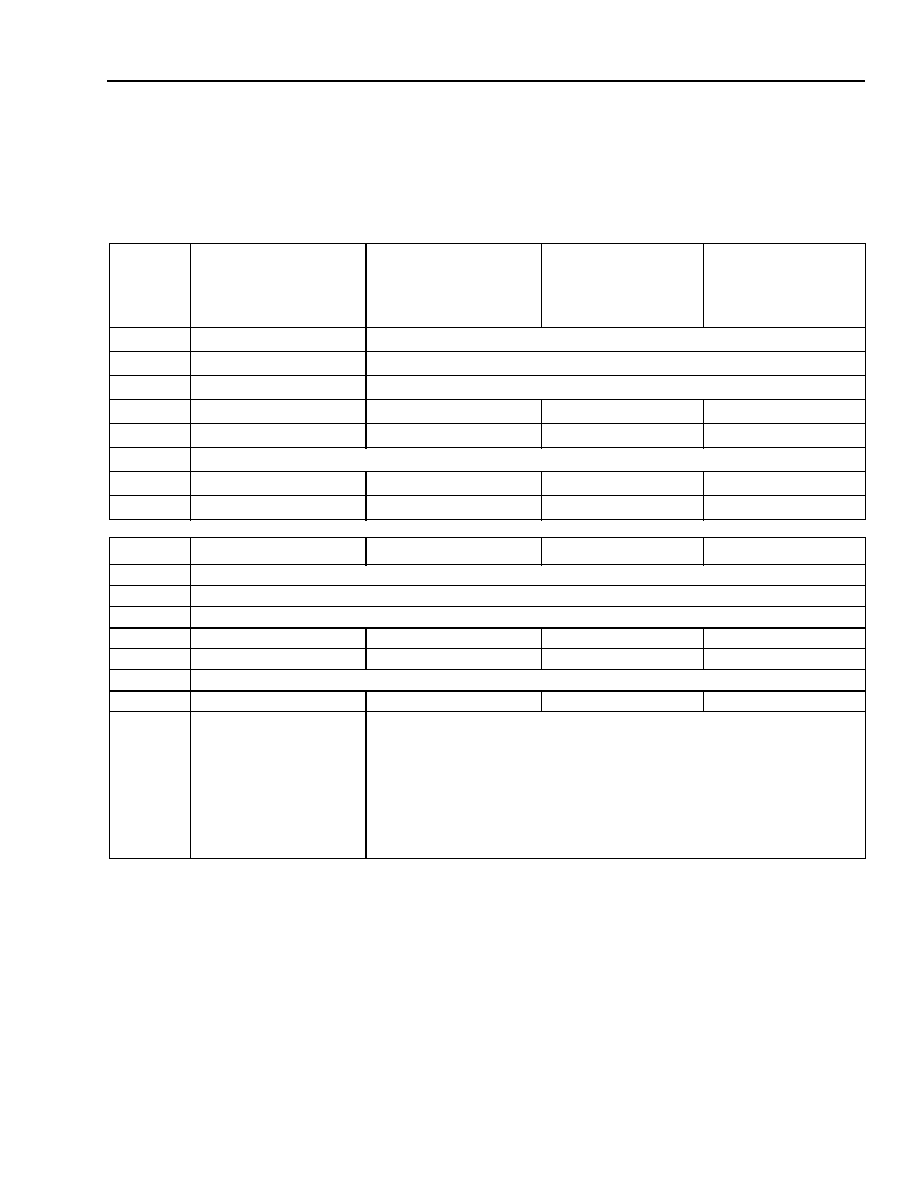

Table 15. Control Register Map ............................................................................................................................30

Table 16. Reset Registers .....................................................................................................................................31

Table 17. Master Output Enable Register .............................................................................................................32

Table 18. Data Memory Mode Select Register .....................................................................................................32

Table 19. Clock Register Access Select Register .................................................................................................33

Table 20. Phase Alignment Select Register ..........................................................................................................33

Table 21. Fallback Control Register ......................................................................................................................34

Table 22. Fallback Type Select Register...............................................................................................................35

Table 23. Fallback Trigger Registers ....................................................................................................................35

Table 24. Watchdog Select, C8, NETREF Registers ............................................................................................36

Table 25. Watchdog EN Registers ........................................................................................................................37

Table 26. Failsafe Control Register .......................................................................................................................38

Table 27. Error and Status Register Map ..............................................................................................................39

Table 28. Clock Error Registers ............................................................................................................................40

Table 29. Latched Clock Error Registers ..............................................................................................................41

Table 30. Fallback and Failsafe Status Register ...................................................................................................42

Table 31. System Errors Registers .......................................................................................................................43

Table 32. Device Identification Registers ..............................................................................................................43

Table 33. Clock Input Control Register Map .........................................................................................................45

Table 34. Main Input Selector Register .................................................................................................................45

Table 35. Main Divider Register ............................................................................................................................46

Table 36. APLL1 Input Selector Register ..............................................................................................................46

Table 37. APLL1 Rate Register.............................................................................................................................47

Table 38. Main Inversion Select Register..............................................................................................................47

Table 39. Resource Divider Register ....................................................................................................................48

Table 40. APLL2 Rate Register.............................................................................................................................48

Table 41. LREF Input/Inversion Select Registers .................................................................................................49

Table 42. DPLL1 Input Selector Registers ............................................................................................................50

Table 43. DPLL2 Register .....................................................................................................................................51

Table 44. NETREF1 Registers ..............................................................................................................................51

Table 45. NETREF2 Registers ..............................................................................................................................52

Table 46. Clock Output Control Register Map.......................................................................................................53

Table 47. Master Output Enables Registers .........................................................................................................54

Table 48. Clock Output Format Registers .............................................................................................................55

Table 49. TCLK Select and L_SCx Select Registers ............................................................................................56

Table 50. Bit Clock and Frame ..............................................................................................................................57

List of Tables

(continued)

Table

Page

8

Agere Systems Inc.

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

Table 51. Watchdog Timer Description ................................................................................................................. 58

Table 52. Frame Center Sampling ........................................................................................................................ 59

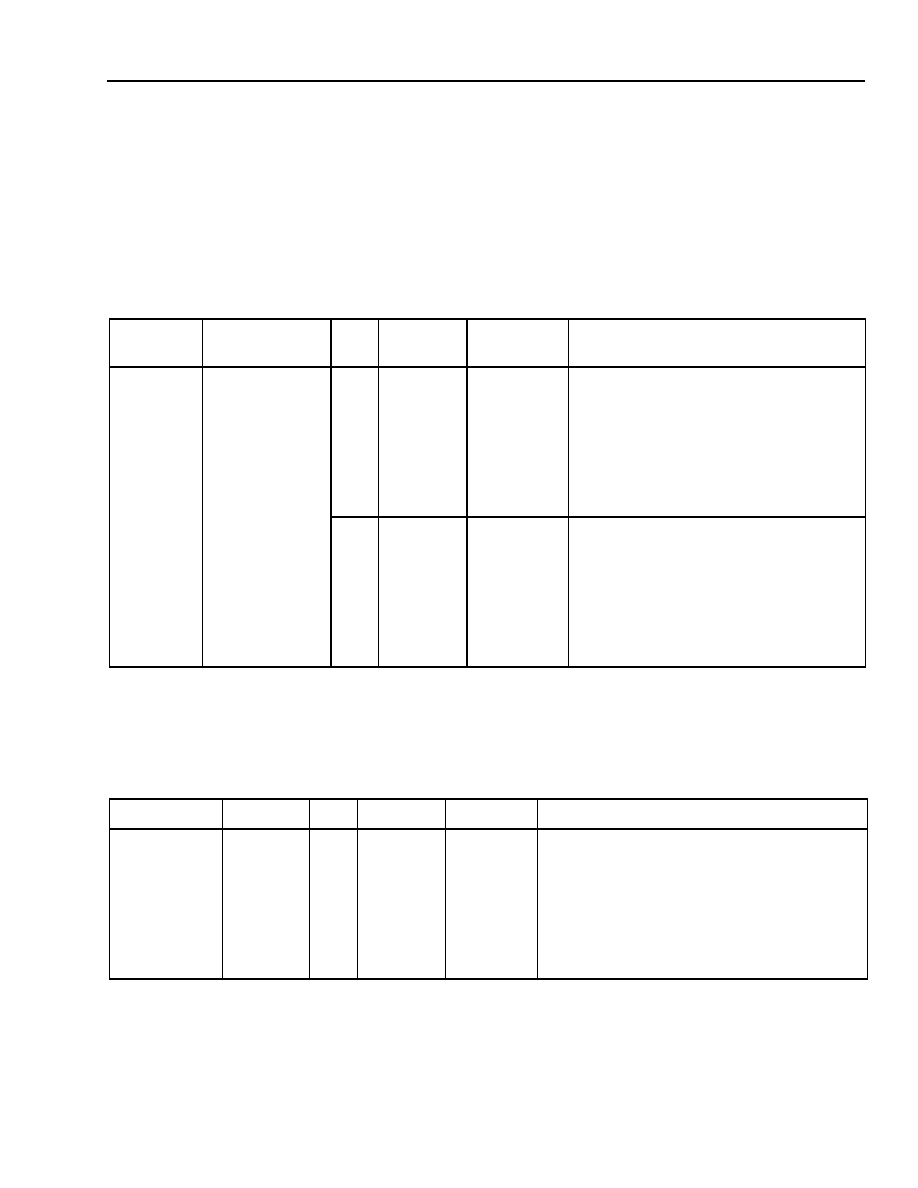

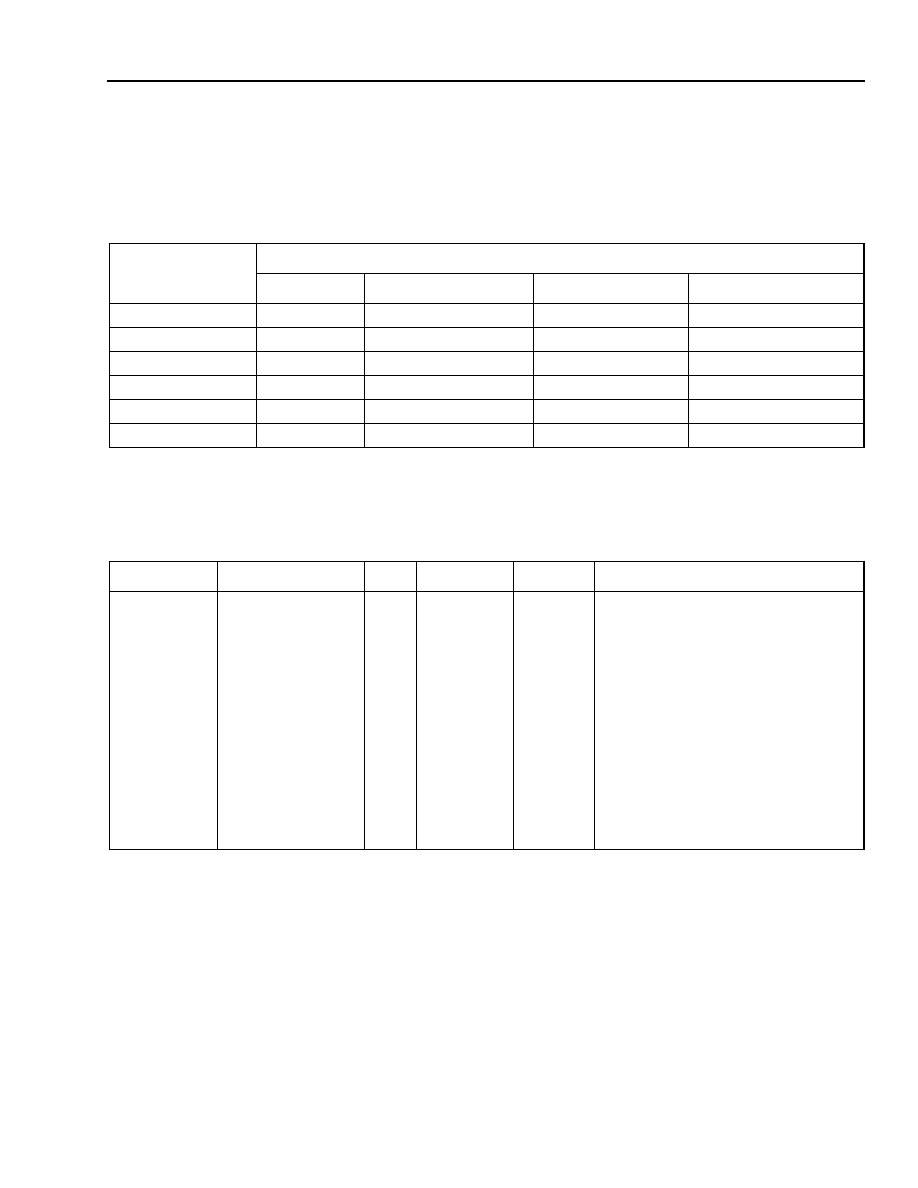

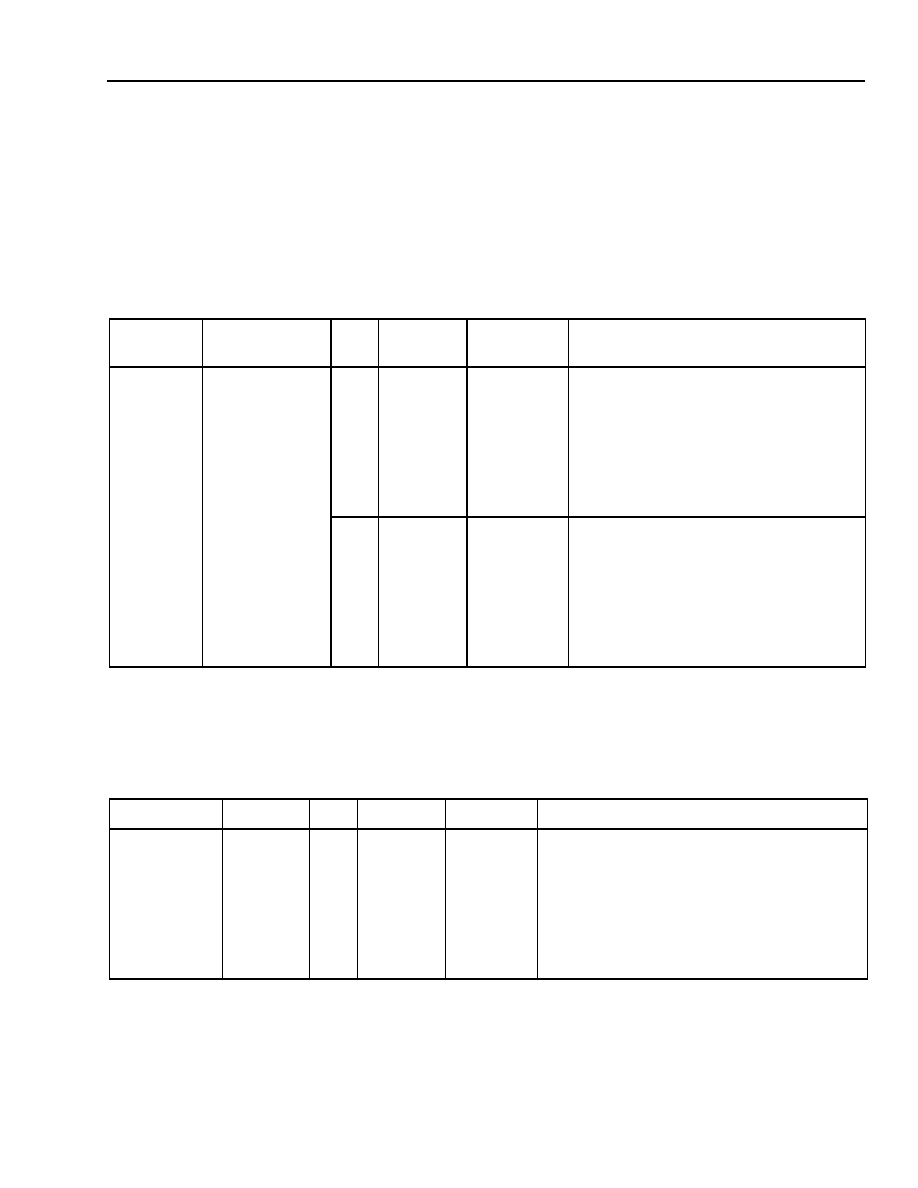

Table 53. Legacy Mode Fallback Event Triggers .................................................................................................. 65

Table 54. Clock Fallback State Description........................................................................................................... 67

Table 55. H-Bus Clock Enable State Description .................................................................................................. 69

Table 56. Clock Failsafe State Descriptions.......................................................................................................... 71

Table 57. Frame Group and FG I/O Register Map ................................................................................................ 72

Table 58. FGx Lower and Upper Start Registers .................................................................................................. 72

Table 59. FGx Width Registers ............................................................................................................................. 73

Table 60. FGx Rate Registers ............................................................................................................................... 73

Table 61. FG7 Counter (Low and High Byte) Registers ........................................................................................ 74

Table 62. FGIO Data Register............................................................................................................................... 75

Table 63. FGIO Read Mask Register .................................................................................................................... 75

Table 64. FGIO R/W Register ............................................................................................................................... 76

Table 65. GPIO Register ....................................................................................................................................... 80

Table 66. GPIO Data Register .............................................................................................................................. 80

Table 67. GPIO Read Mask Register.................................................................................................................... 81

Table 68. GPIO R/W Register ............................................................................................................................... 81

Table 69. GPIO Override Register ........................................................................................................................ 82

Table 70. T8110L Serial Stream Groupings.......................................................................................................... 84

Table 71. H-Bus Rate Registers............................................................................................................................ 85

Table 72. L-Bus Rate Registers ............................................................................................................................ 85

Table 73. Interrupt Control Register Map .............................................................................................................. 90

Table 74. FGIO Interrupt Pending Registers......................................................................................................... 90

Table 75. FGIO Edge/Level and Polarity Registers .............................................................................................. 91

Table 76. GPIO Interrupt Pending Register .......................................................................................................... 92

Table 77. GPIO Edge/Level and GPIO Polarity Registers .................................................................................... 93

Table 78. System Error Interrupt Assignments ..................................................................................................... 93

Table 79. System Interrupt Pending High/Low Registers...................................................................................... 94

Table 80. System Interrupt Enable High/Low Registers........................................................................................ 95

Table 81. Clock Error Interrupt Assignments ........................................................................................................ 96

Table 82. Clock Interrupt Pending High/Low Registers.........................................................................................97

Table 83. Clock Interrupt Enable High/Low Registers........................................................................................... 98

Table 84. Arbitration Control Register ...................................................................................................................99

Table 85. SYSERR Output Select Registers....................................................................................................... 100

Table 86. Interrupt In-Service Register ............................................................................................................... 101

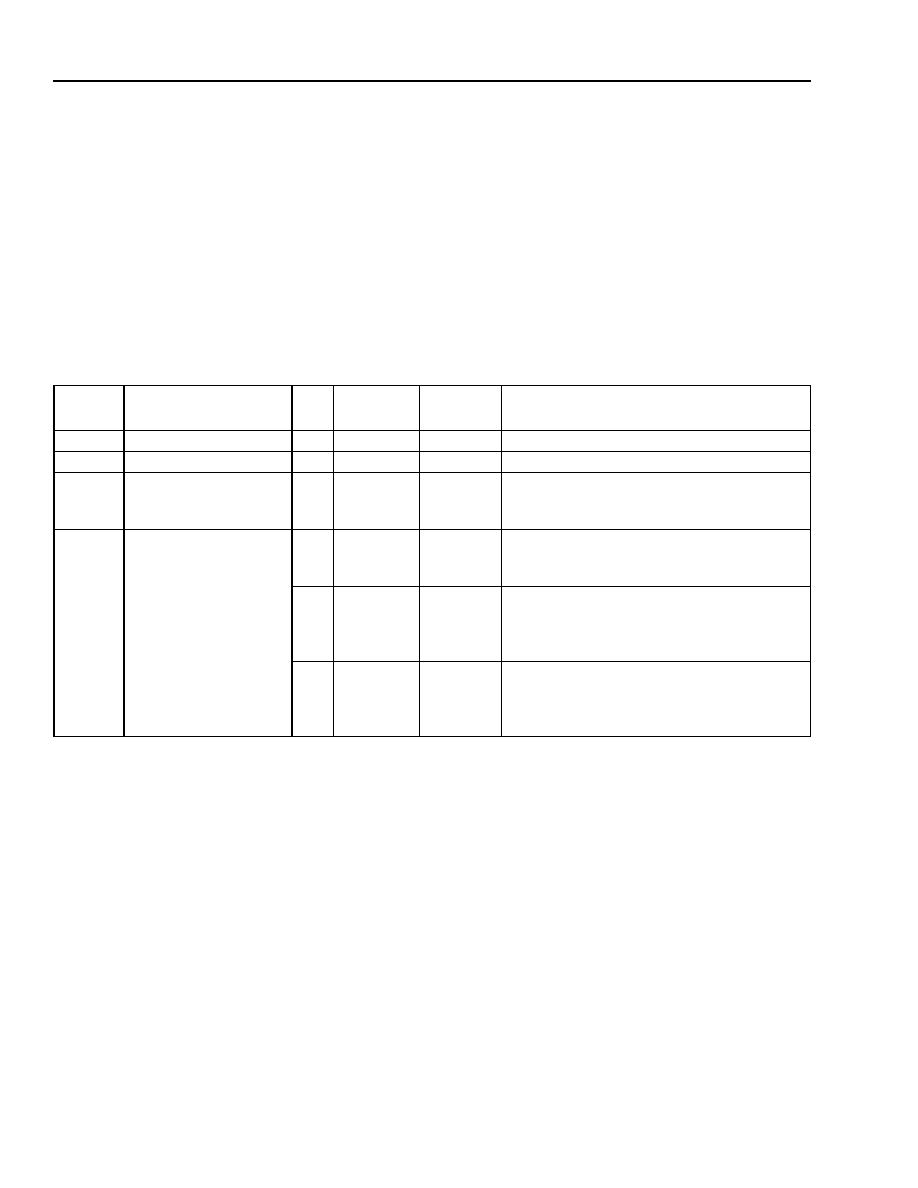

Table 87. Diagnostics Control Register Map ....................................................................................................... 106

Table 88. FG Testpoint Enable Registers ........................................................................................................... 106

Table 89. FG[7:0] Internal Testpoint Assignments .............................................................................................. 107

Table 90. Testpoint Enable Registers .................................................................................................................108

Table 91. GP[7:0] Internal Testpoint Assignments.............................................................................................. 109

Table 92. State Counter Modes Registers ..........................................................................................................110

Table 93. Miscellaneous Diagnostics Low Register ............................................................................................ 110

Table 94. Miscellaneous Diagnostic Registers....................................................................................................111

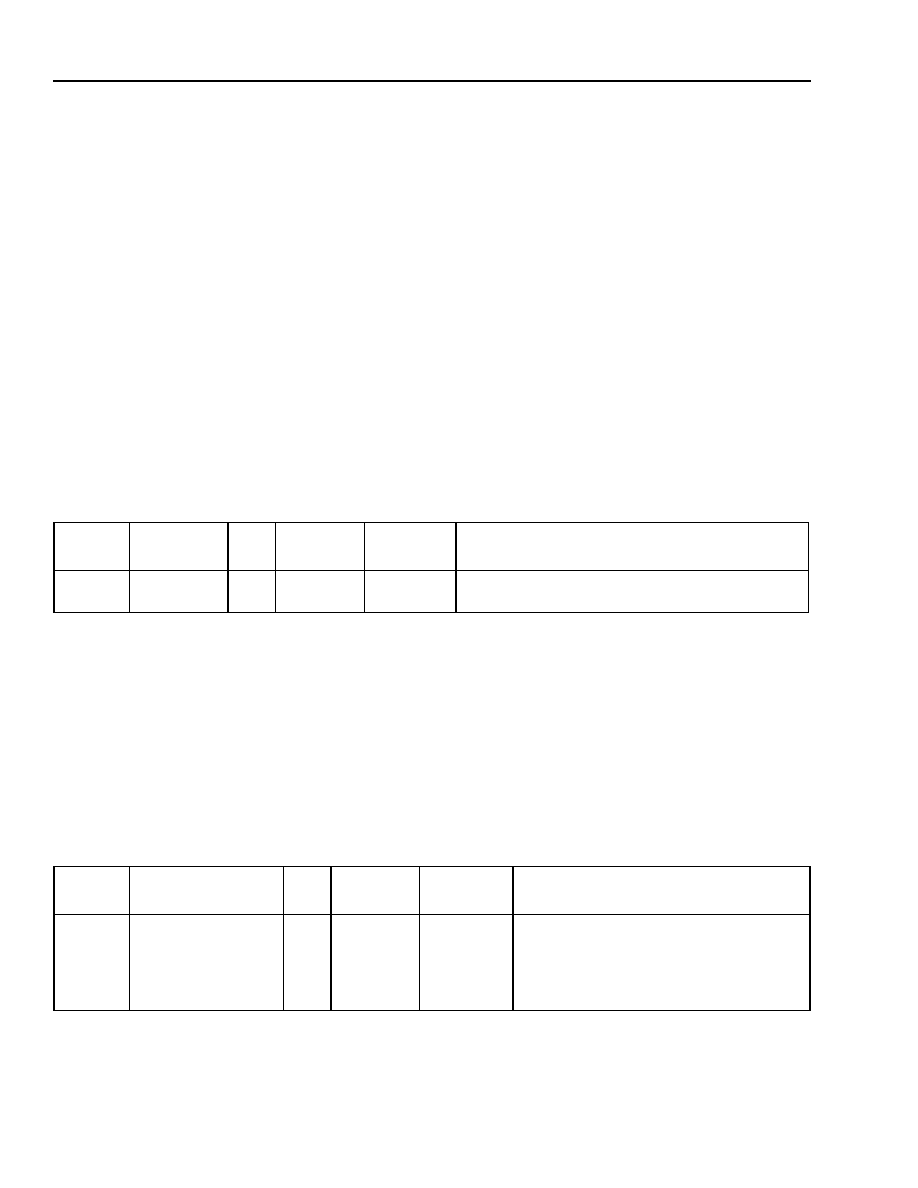

Table 95. Microprocessor Programming, Connection Memory Access .............................................................. 113

Table 96. TDM Data Stream ............................................................................................................................... 118

Table 97. Subrate Switching, Data Propagation Rate vs. Channel Capacity ...................................................... 119

Table 98. Subrate Switching, Connection Memory Programming Setup ............................................................ 120

Table 99. Absolute Maximum Ratings.................................................................................................................124

Table 100. XTAL1 Specifications .......................................................................................................................... 124

List of Tables

(continued)

Table

Page

Agere Systems Inc.

9

February 2004

Ambassador T8110L H.100/H.110 Switch

Data Sheet

Table 101. 16.384 MHz Oscillator Requirements..................................................................................................125

Table 102. XTAL2 Specifications ..........................................................................................................................125

Table 103. 6.176 MHz/12.352 MHz Oscillator Requirements ...............................................................................125

Table 104. Reset Pulse .........................................................................................................................................126

Table 105. Thermal Parameter Values..................................................................................................................127

Table 106. Reliability Data.....................................................................................................................................127

Table 107. Electrical Drive Specifications, CT_C8 and /CT_FRAME....................................................................128

Table 108. dc Electrical Characteristics, All Other Pins ........................................................................................129

Table 109. Skew Timing, H-Bus ............................................................................................................................130

Table 110. L_SC[3:0] and Frame Group Rise and Fall Time ................................................................................131

Table 111. T8110L Ordering Information ..............................................................................................................133

Table 112. Instruction Register..............................................................................................................................138

Table 113. Special Cases (Exceptions).................................................................................................................141

Table 114. Mnemonic Summary, Sorted by Name................................................................................................143

Table 115. Mnemonic Summary, Sorted by Register............................................................................................153

Table 116. Changes ..............................................................................................................................................163

10

10

Agere Systems Inc.

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

2 Pin Description

2.1 Interface Signals

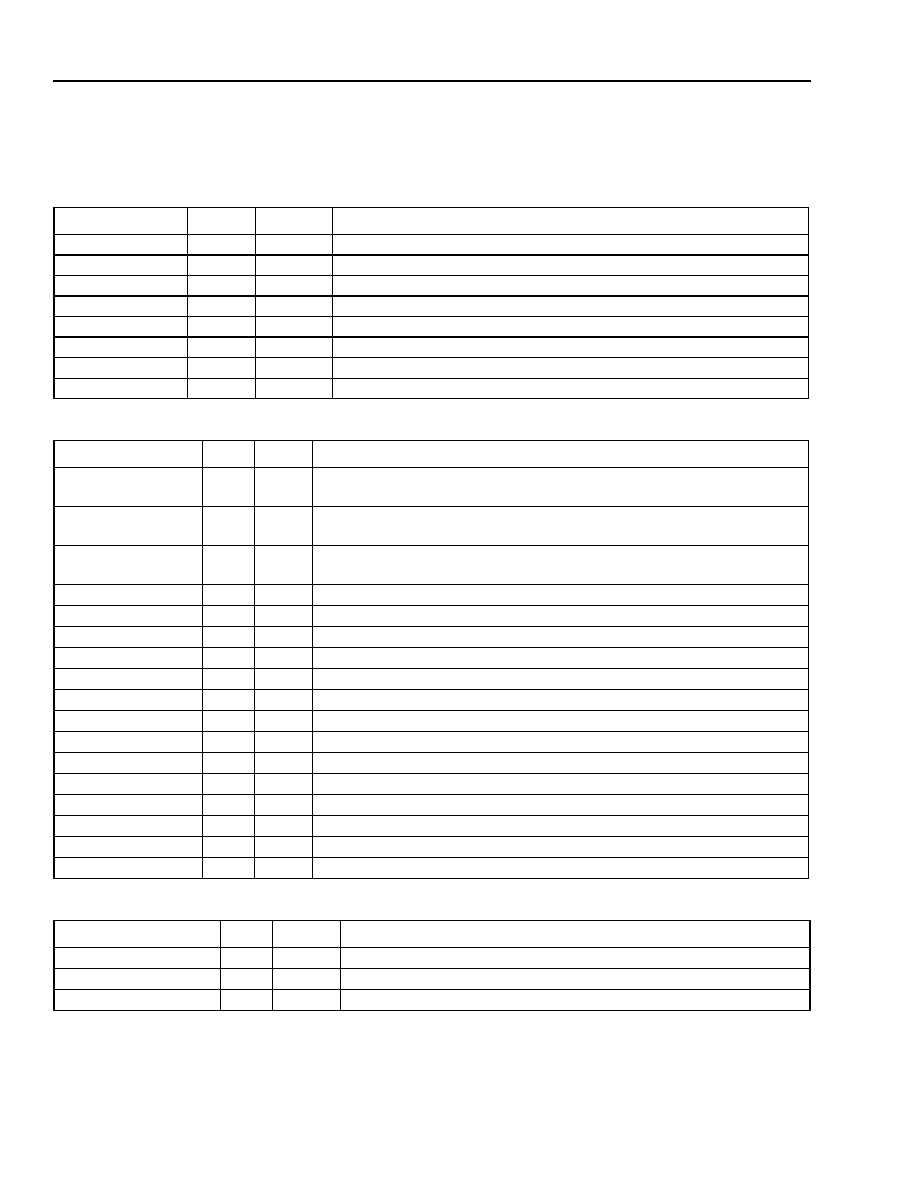

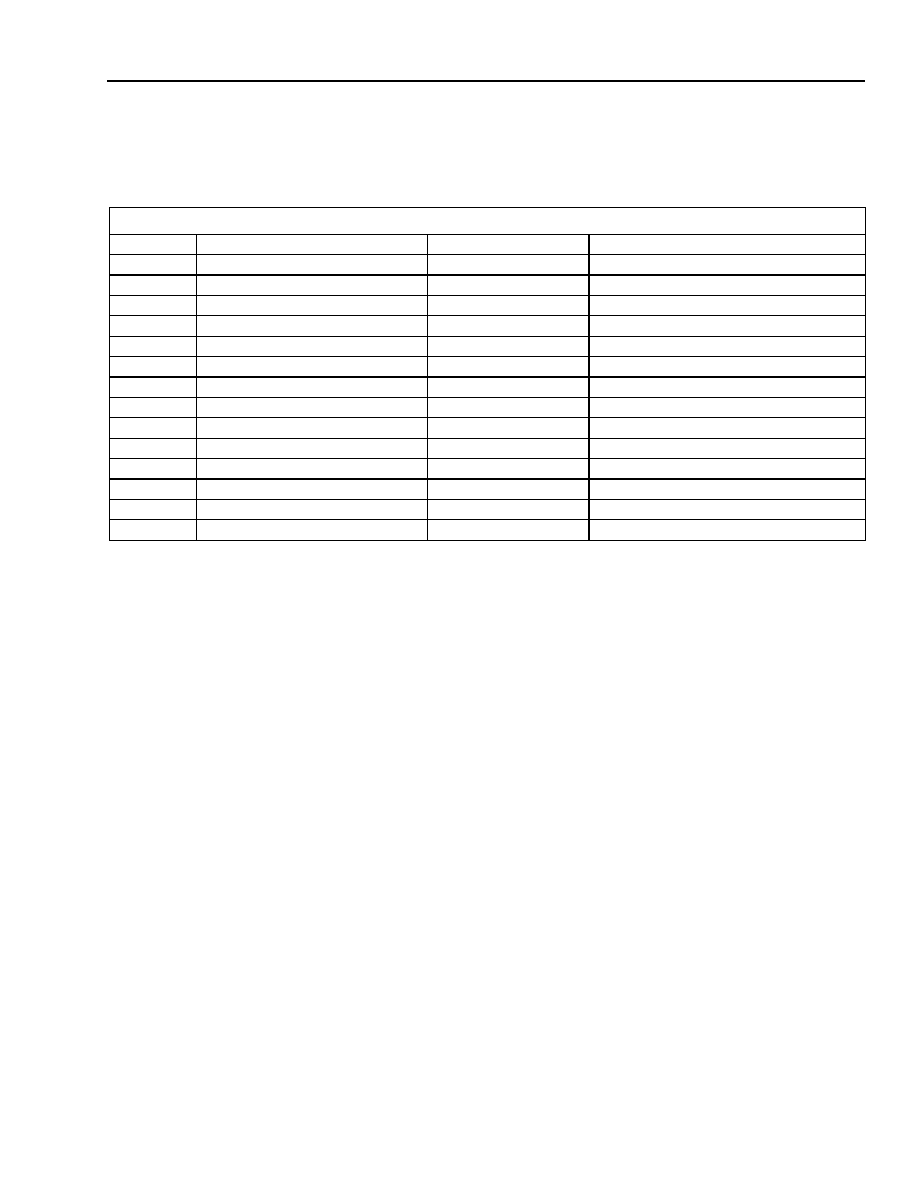

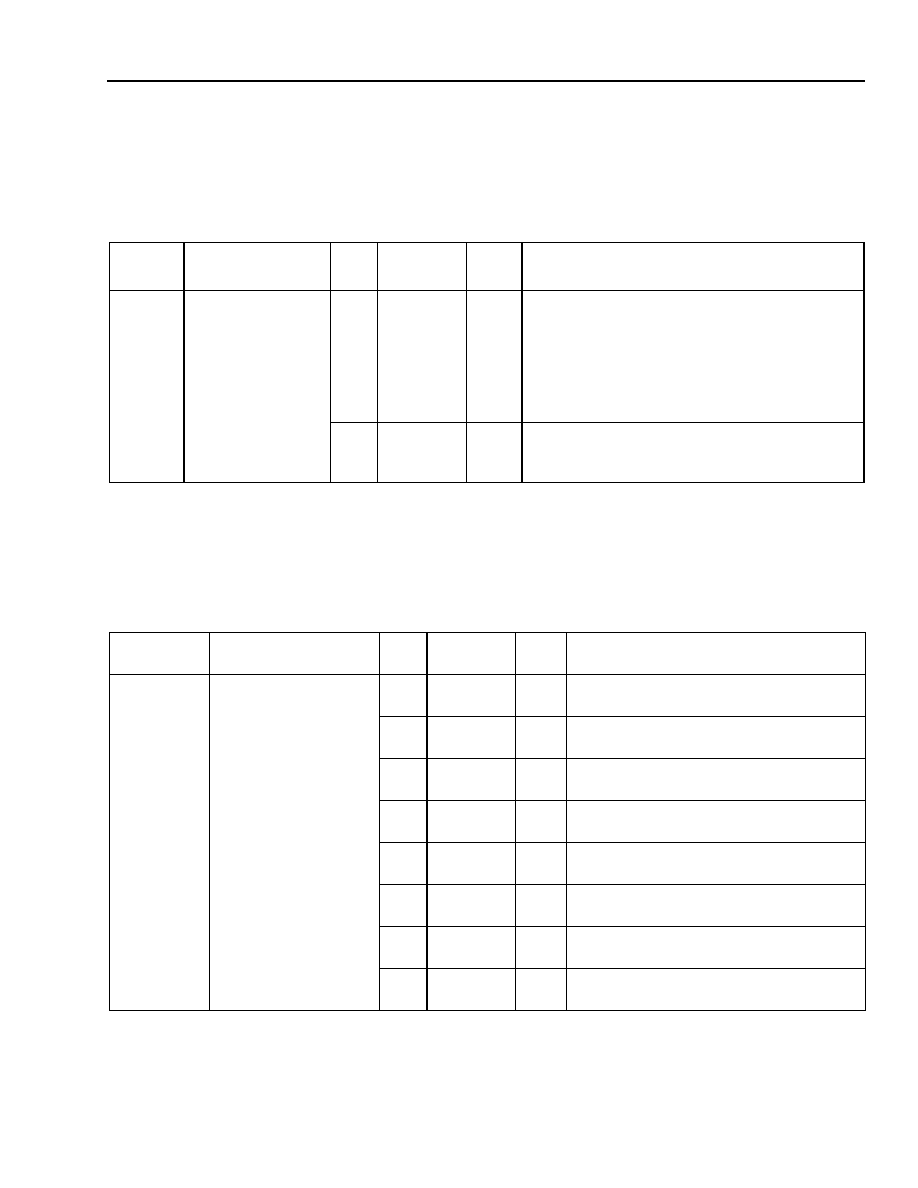

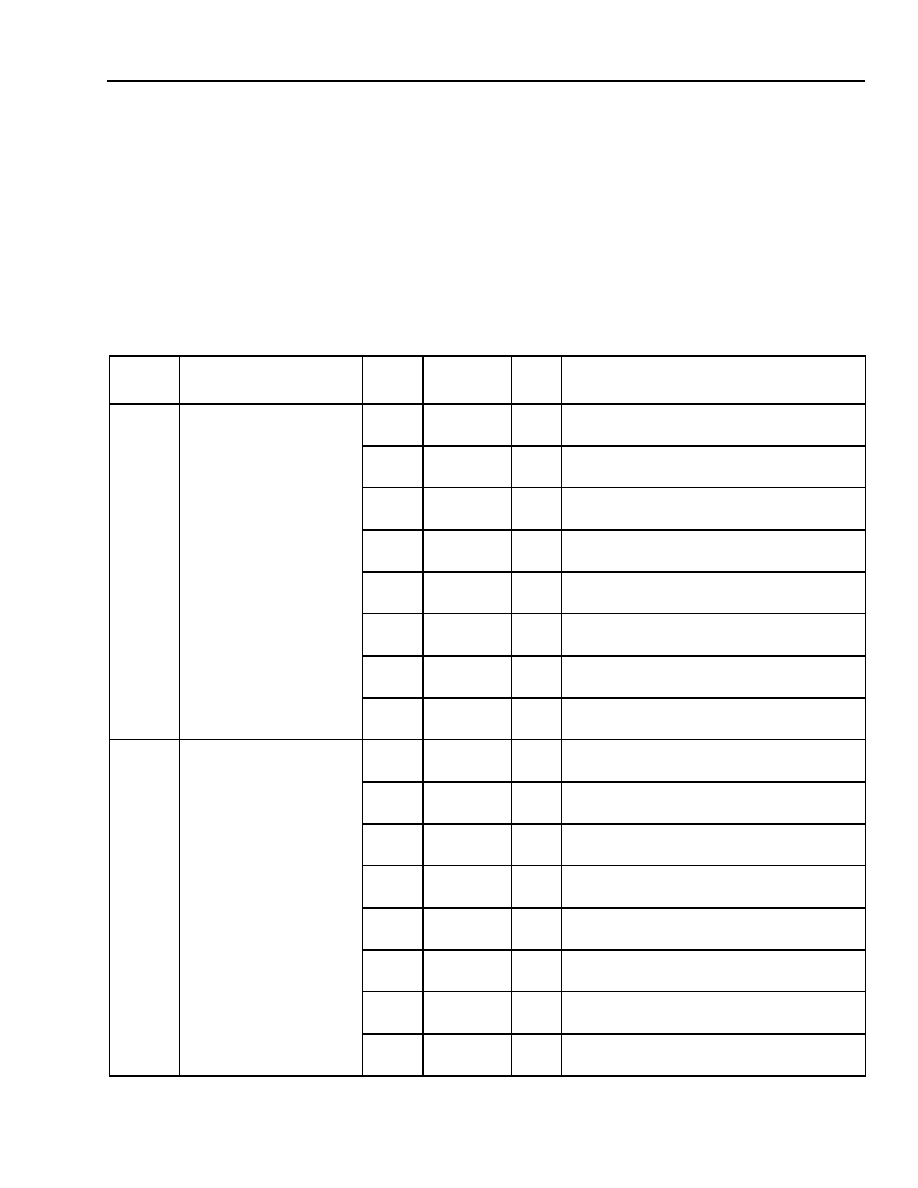

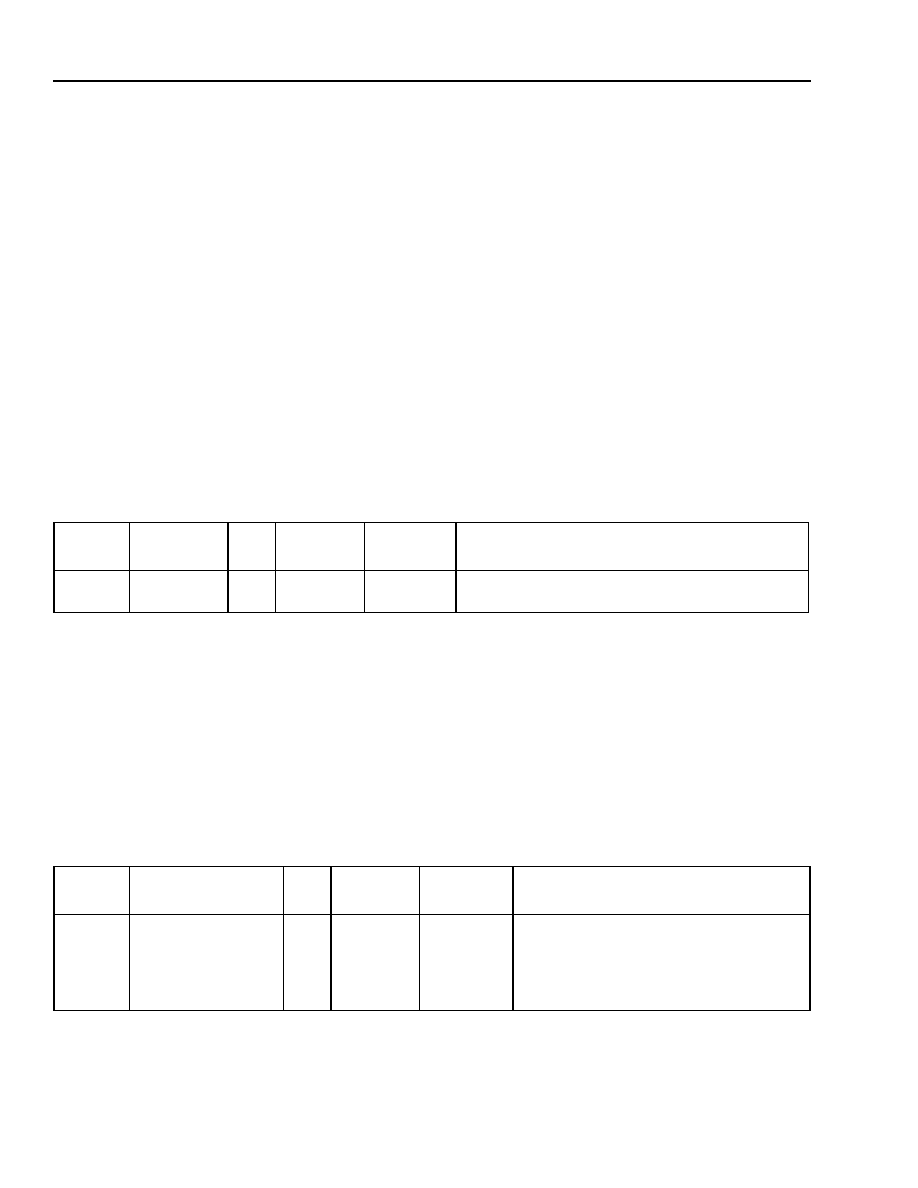

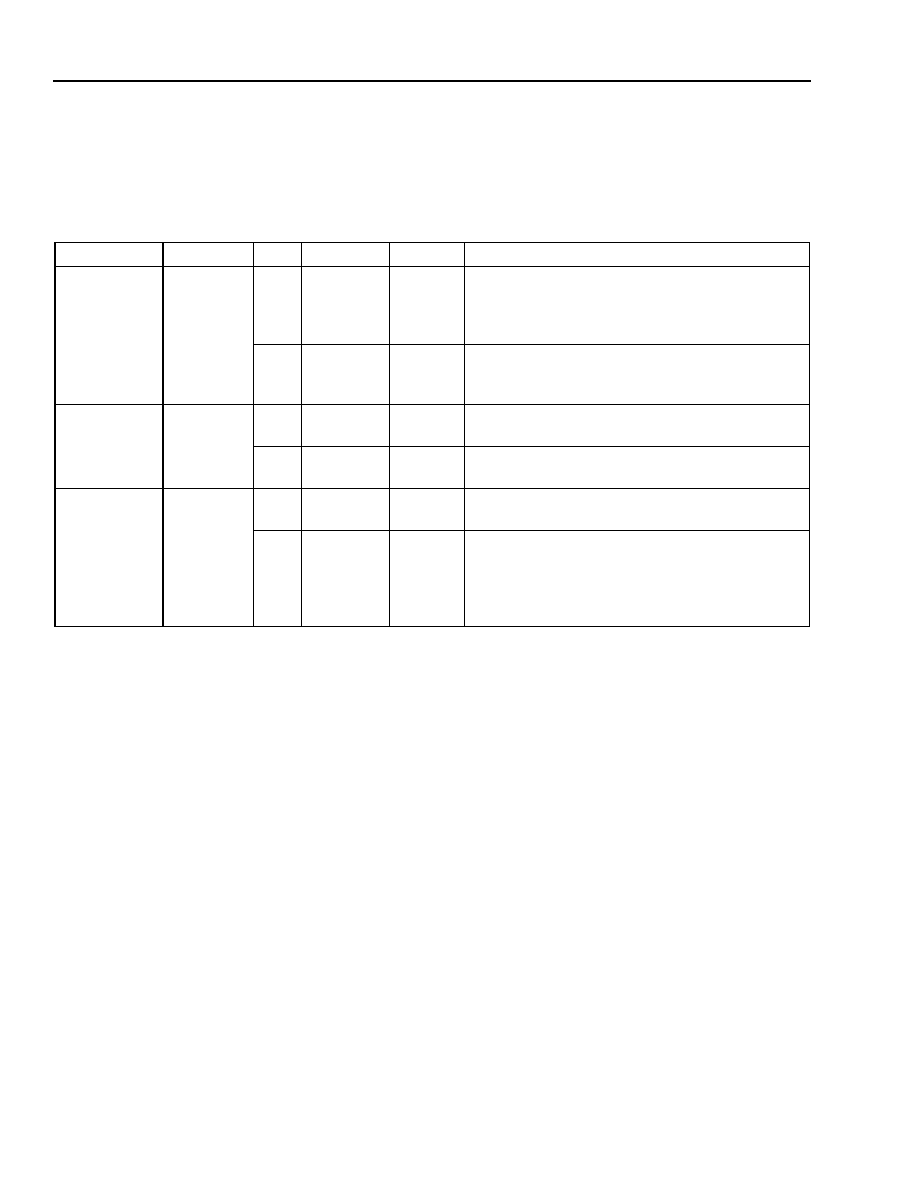

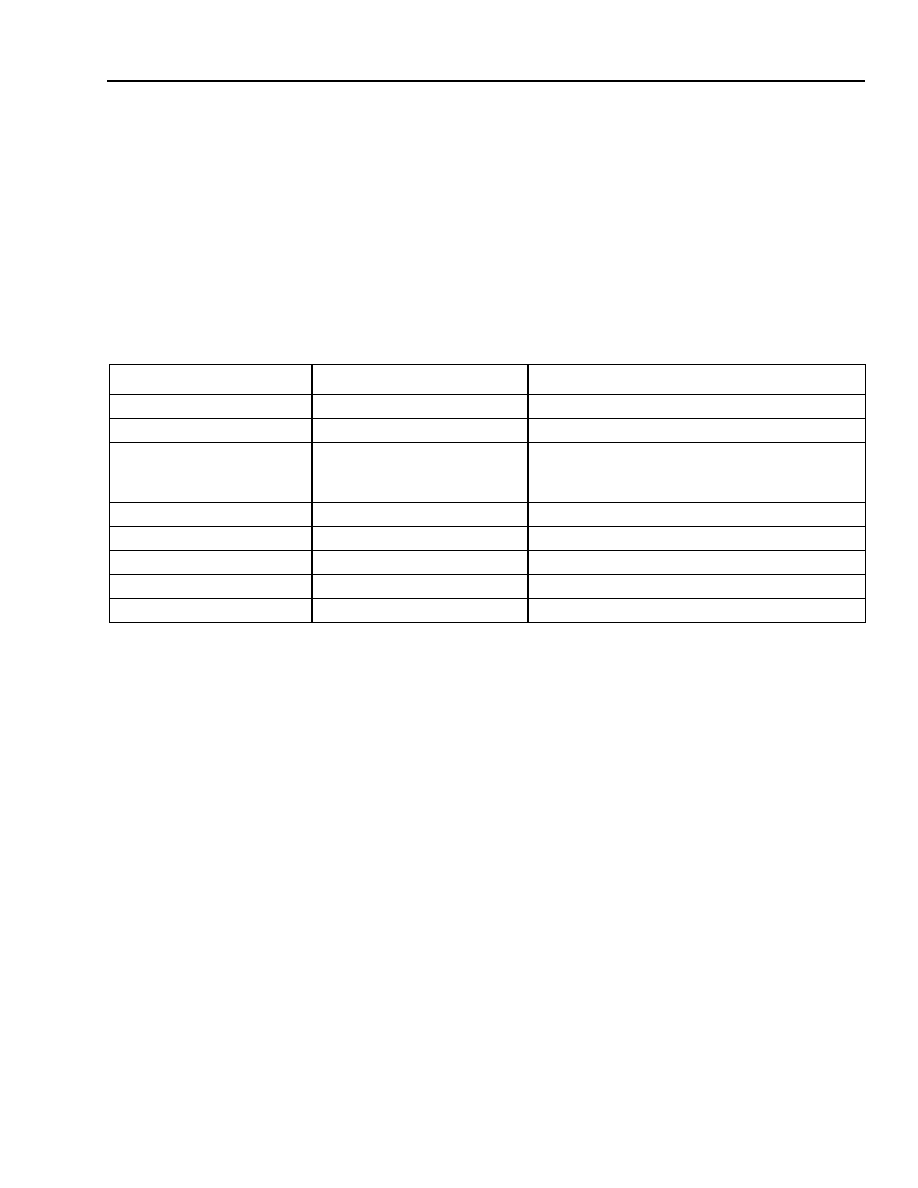

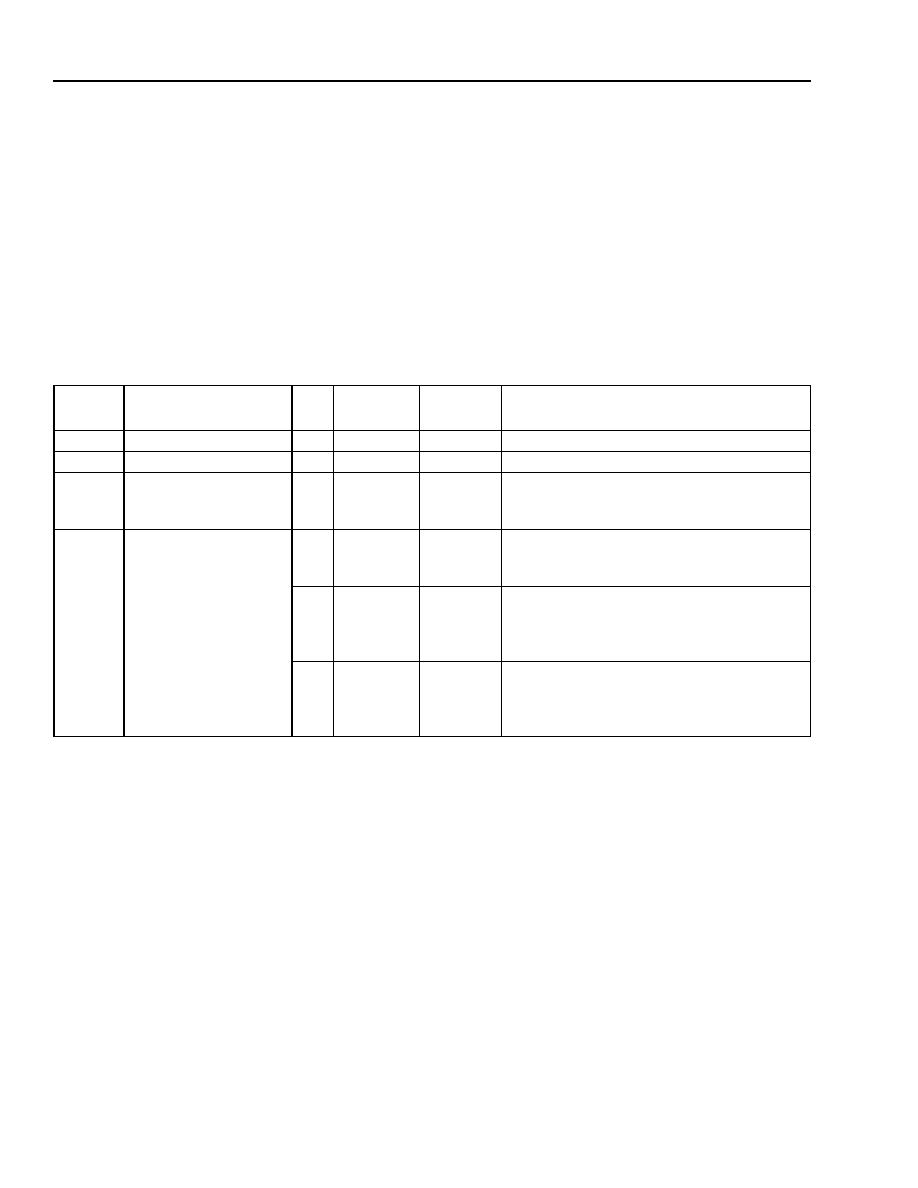

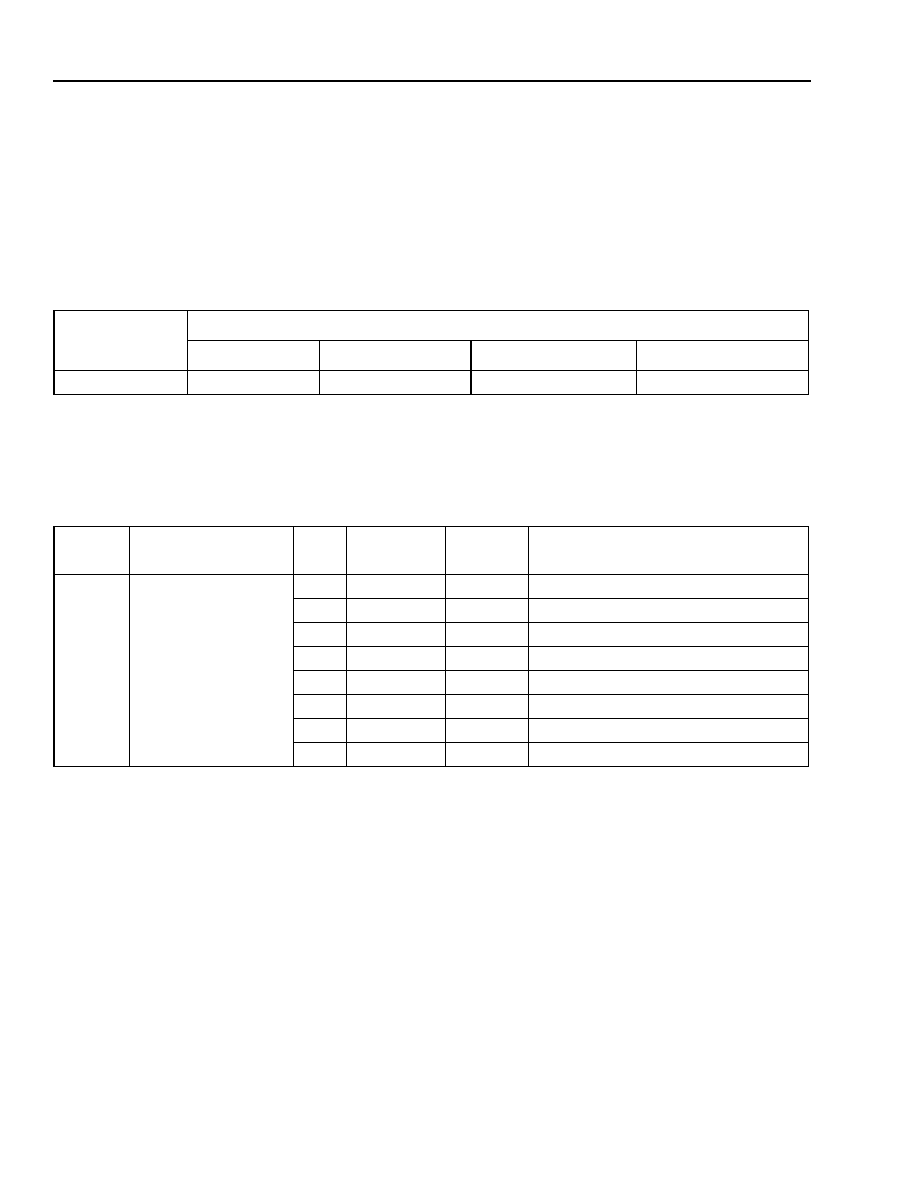

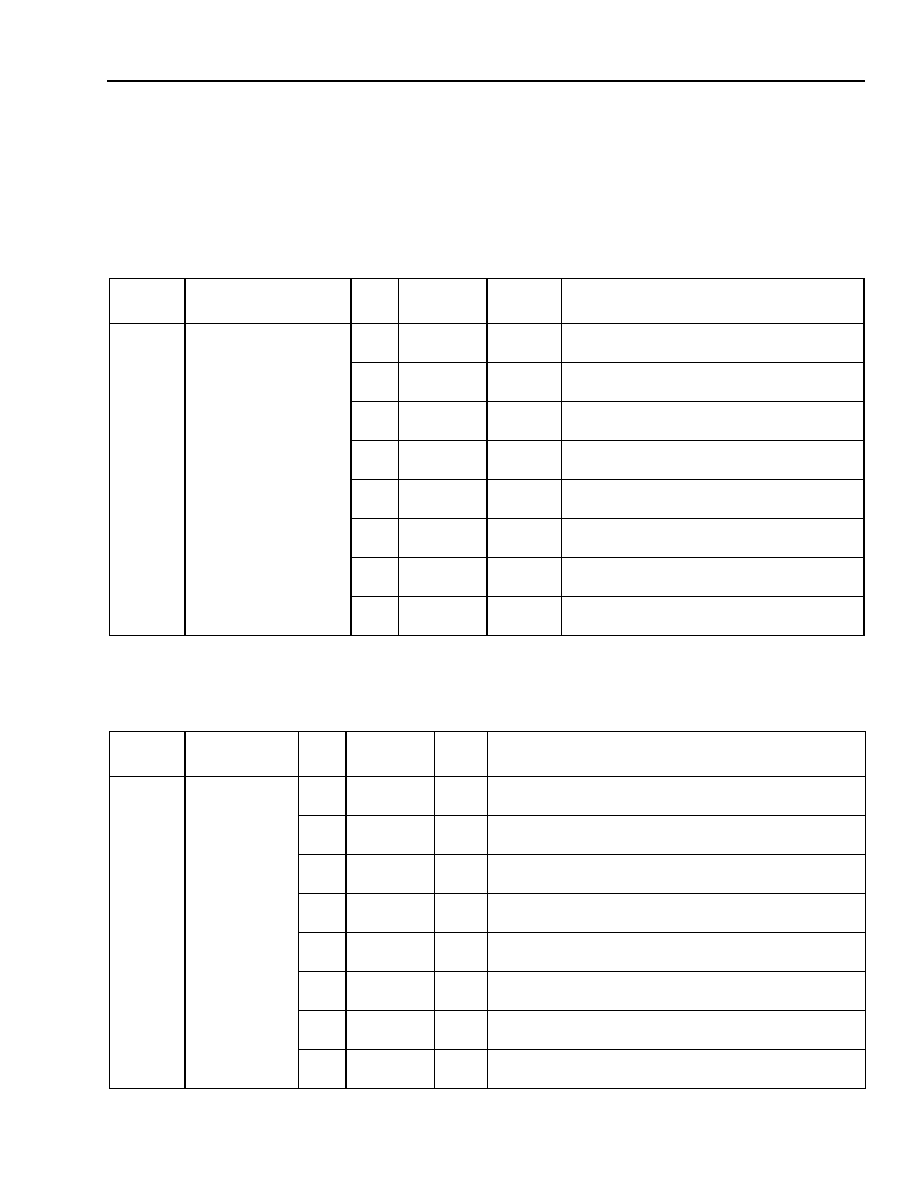

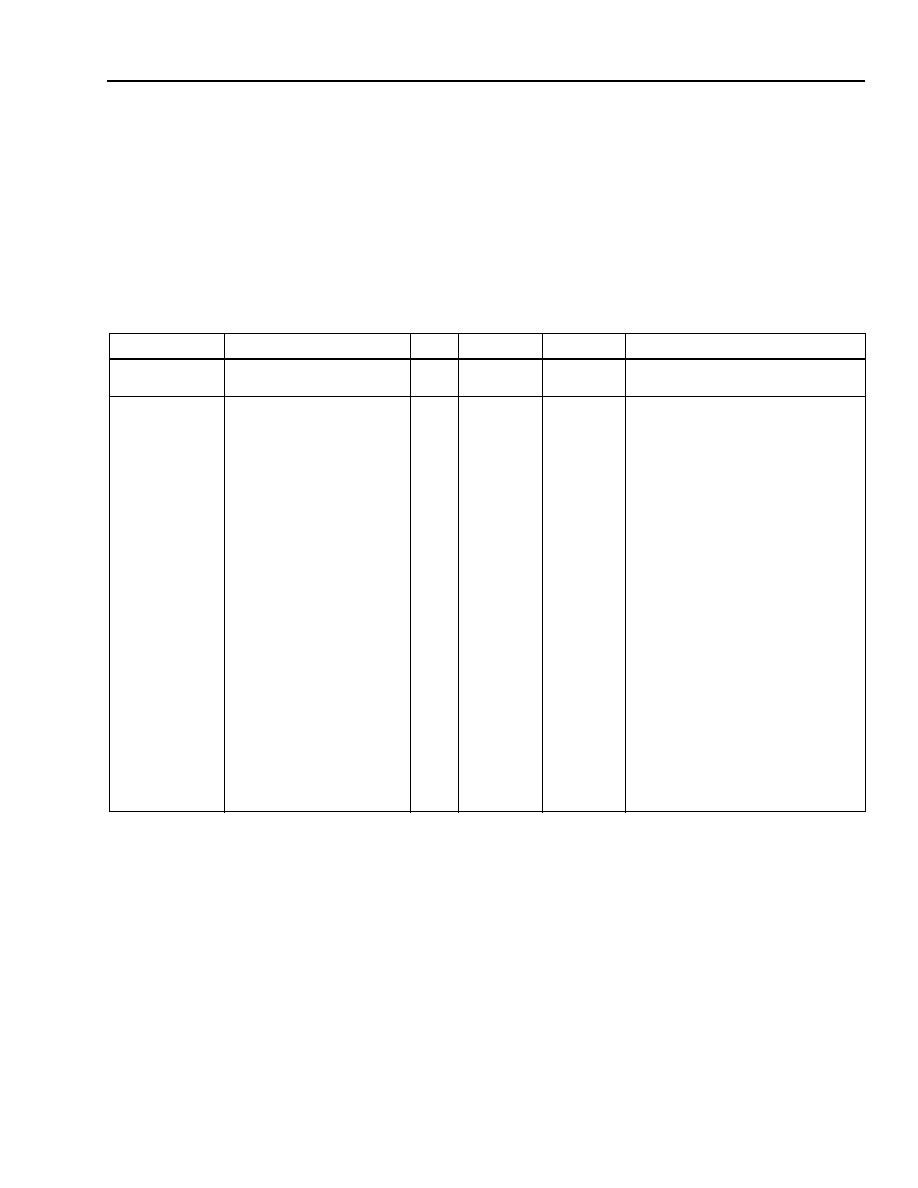

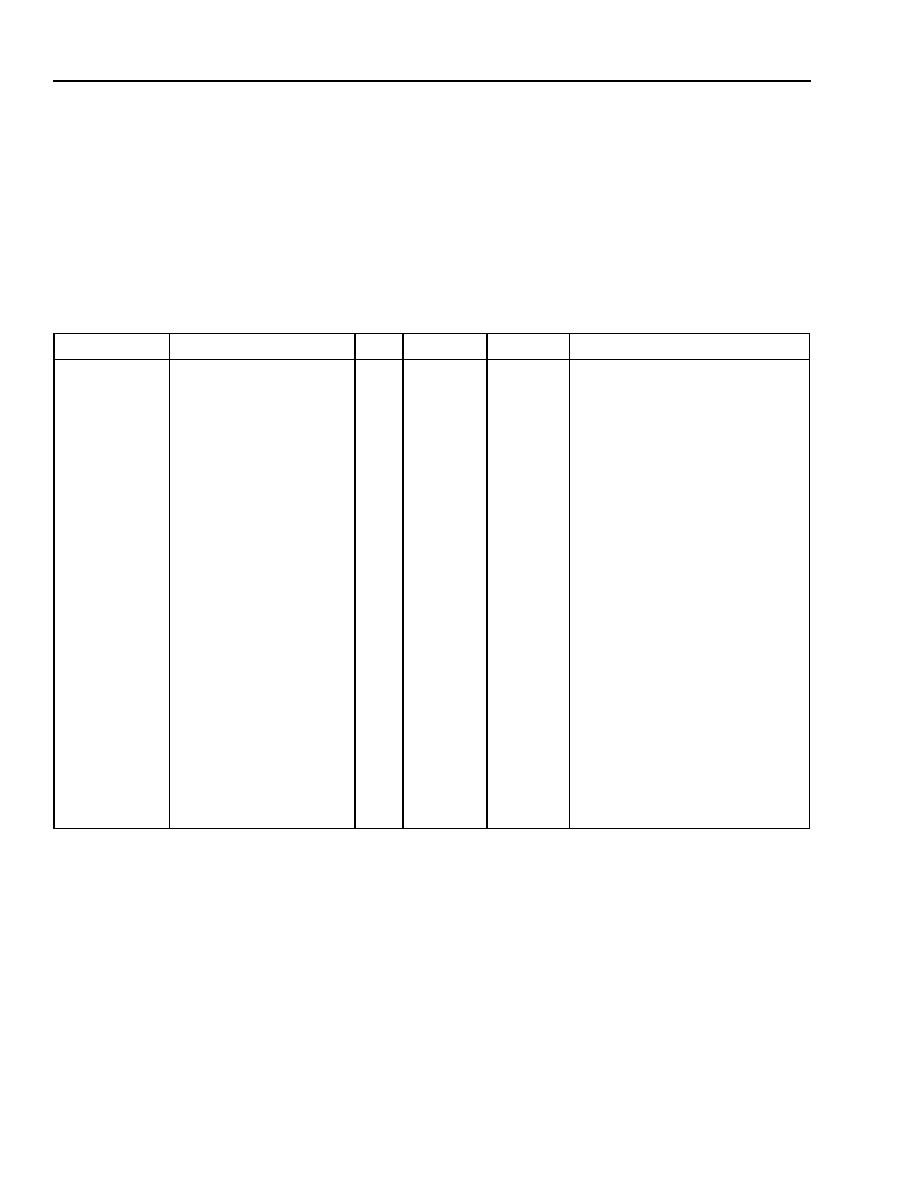

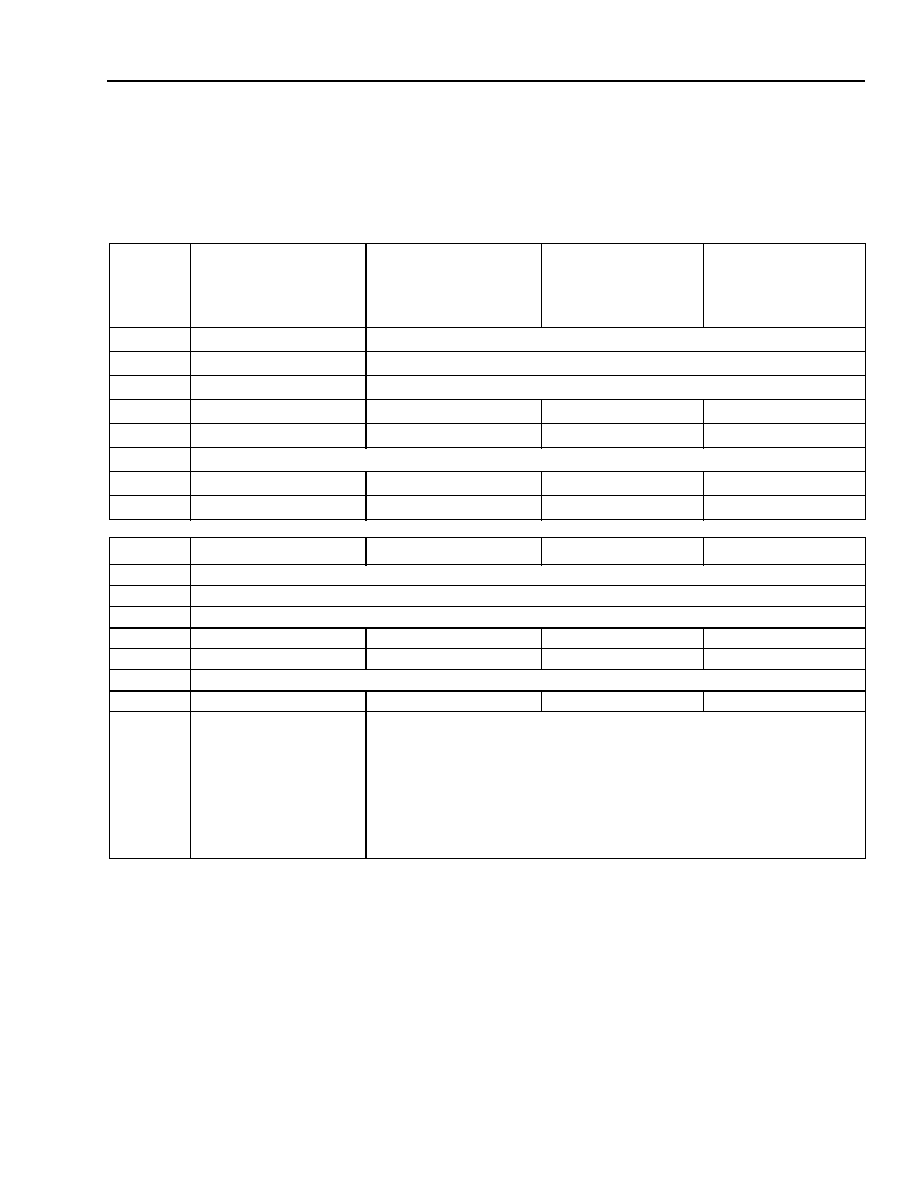

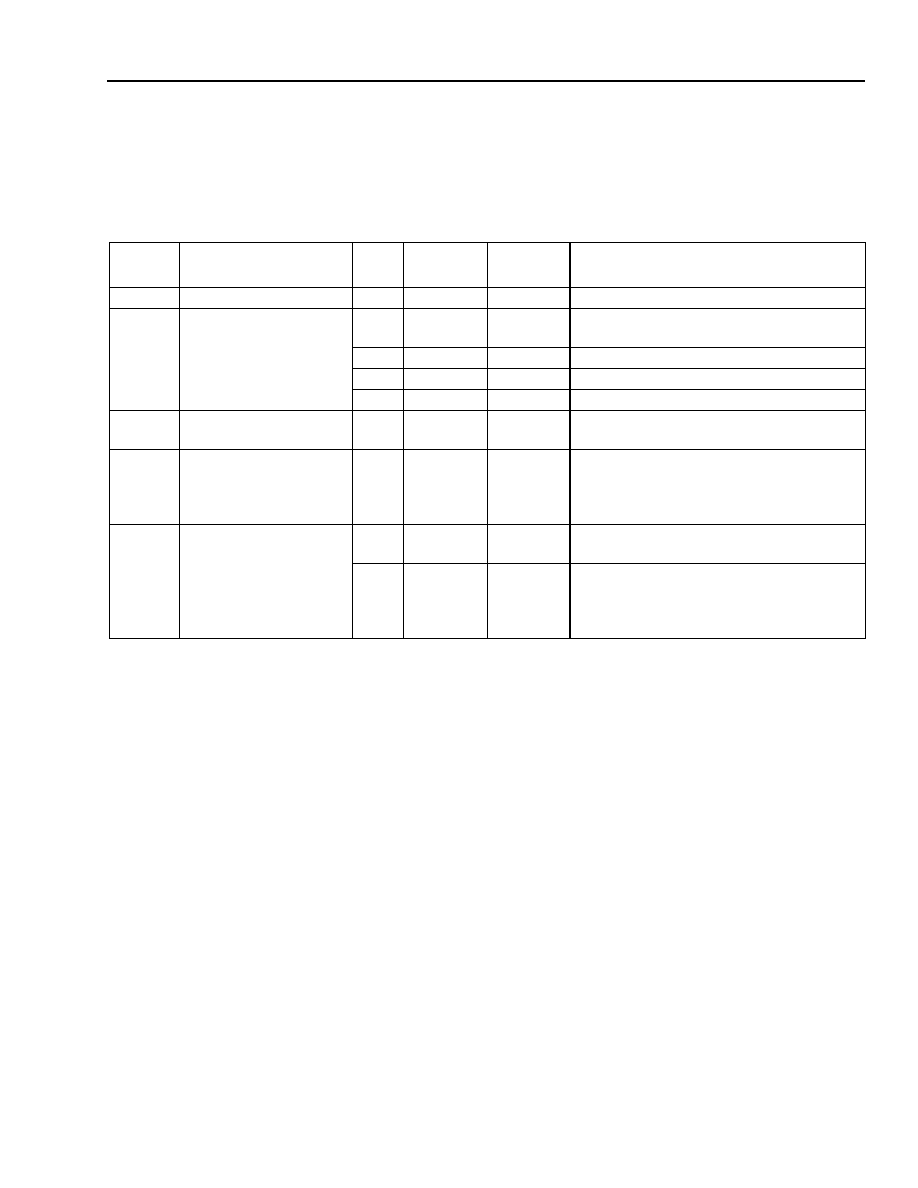

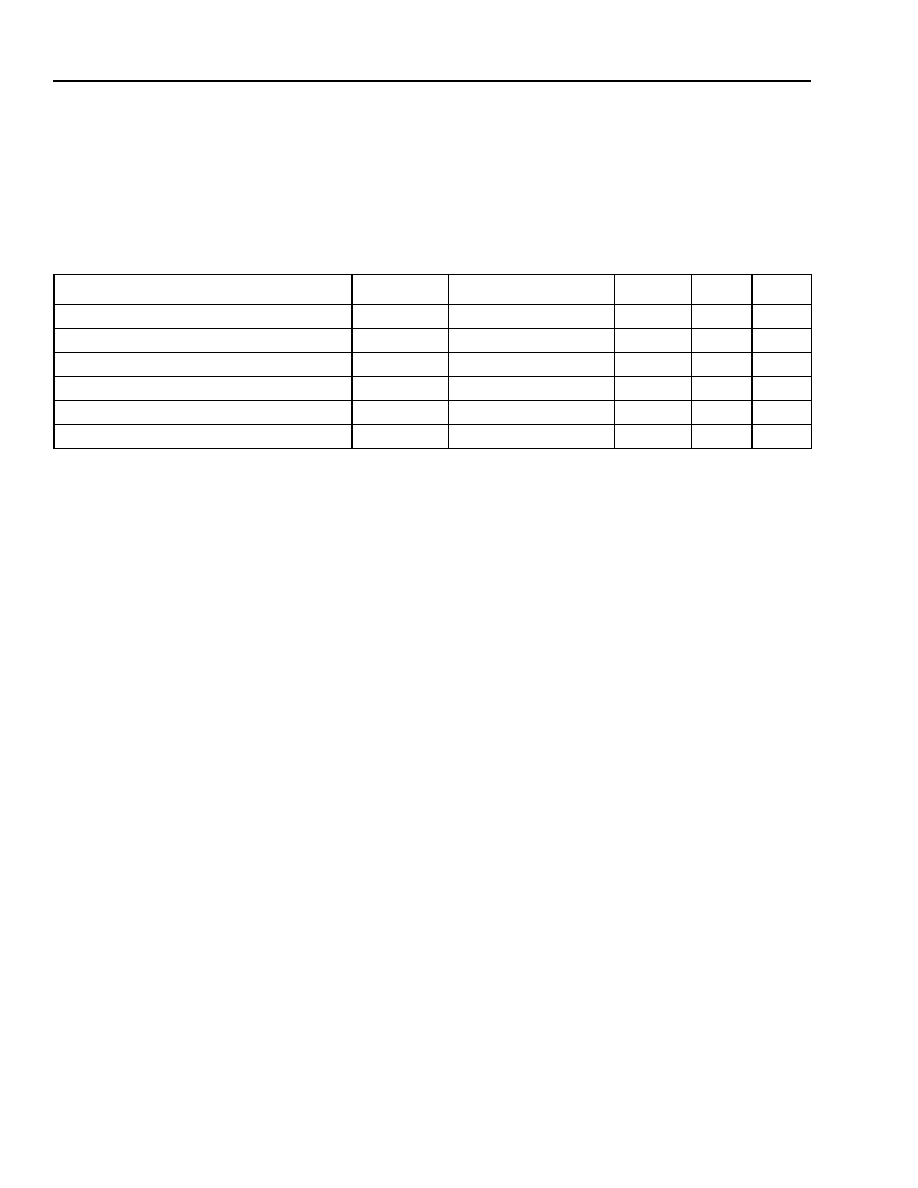

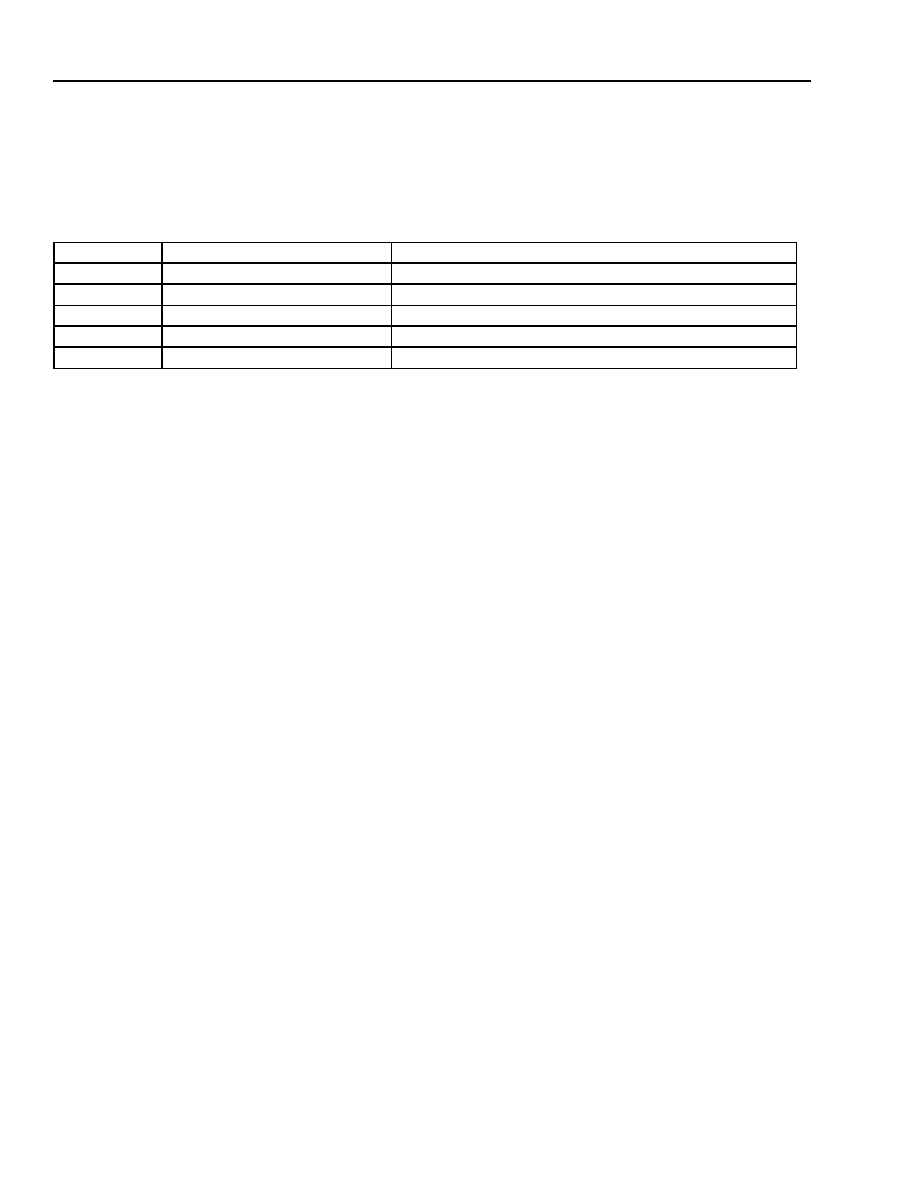

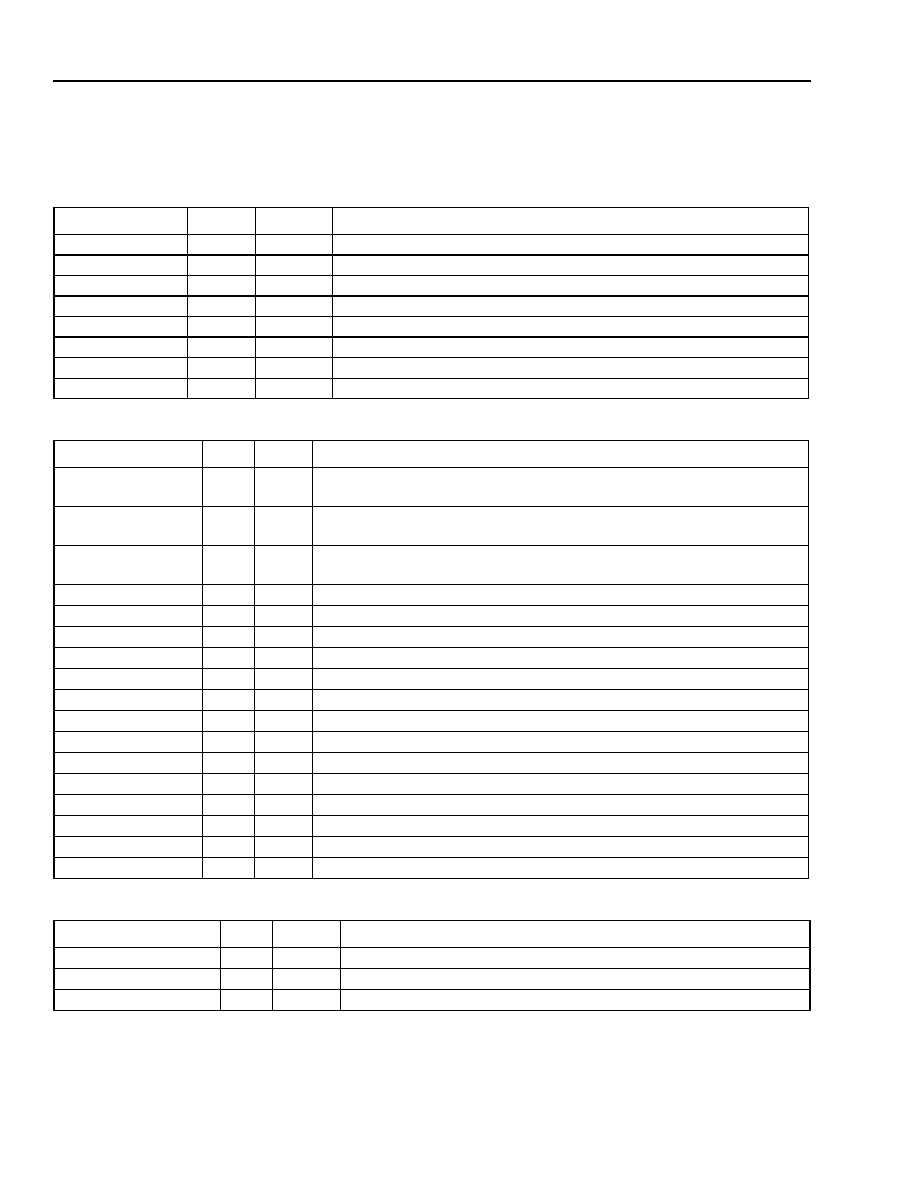

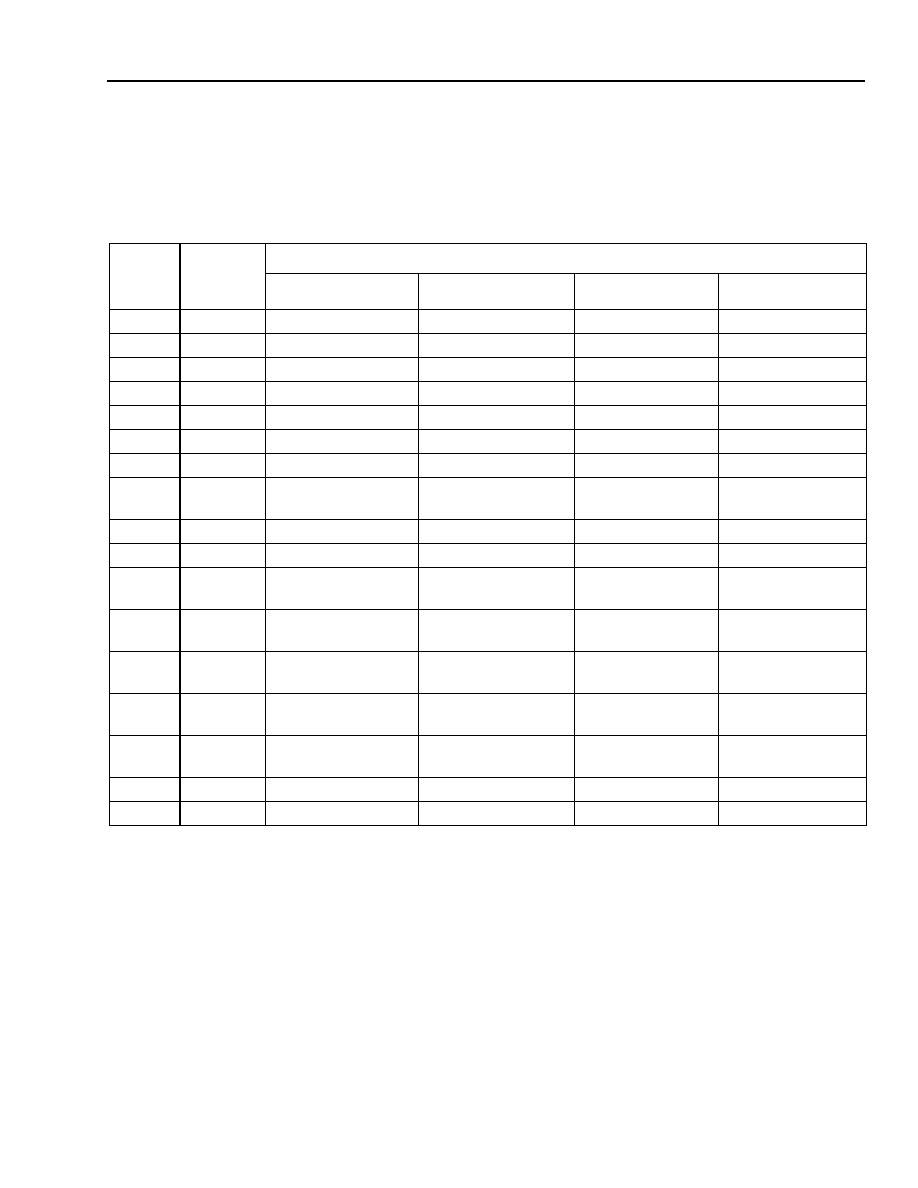

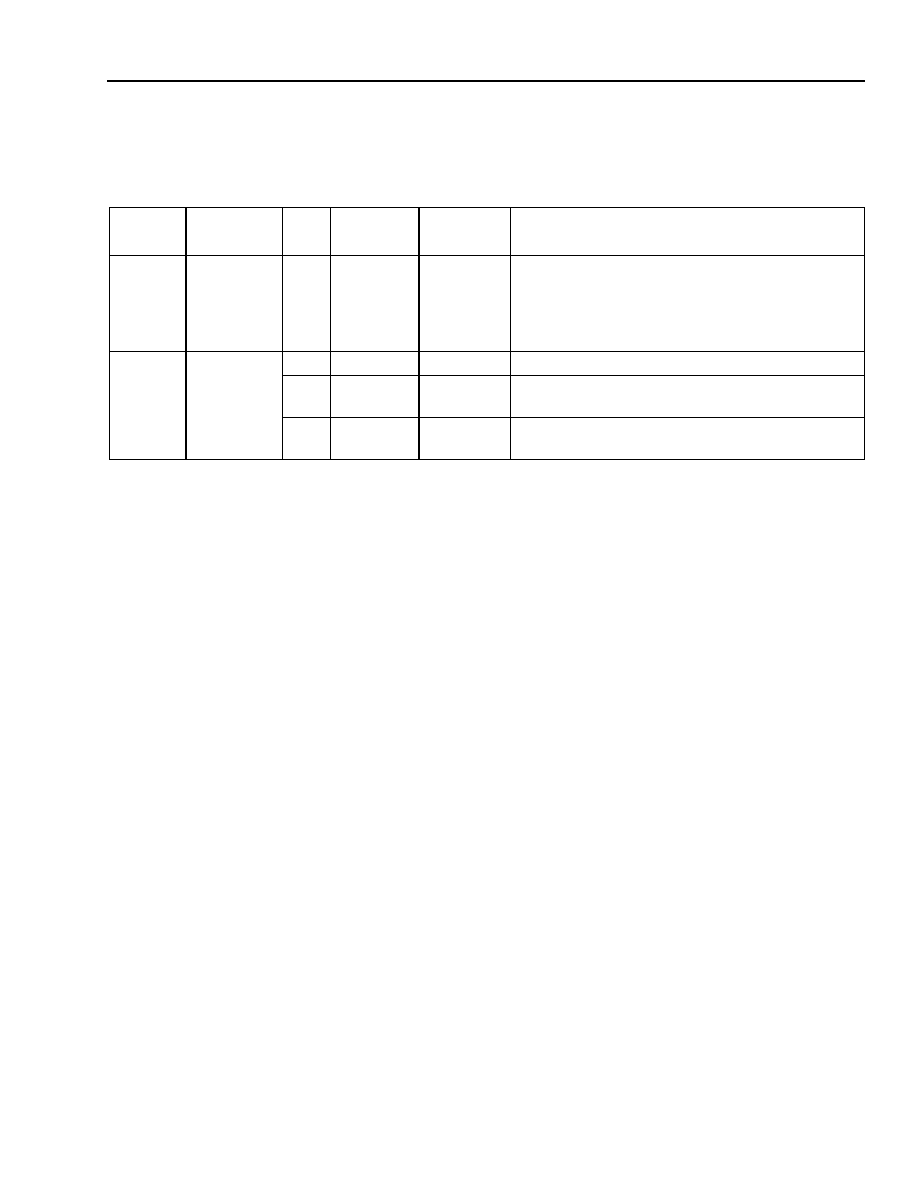

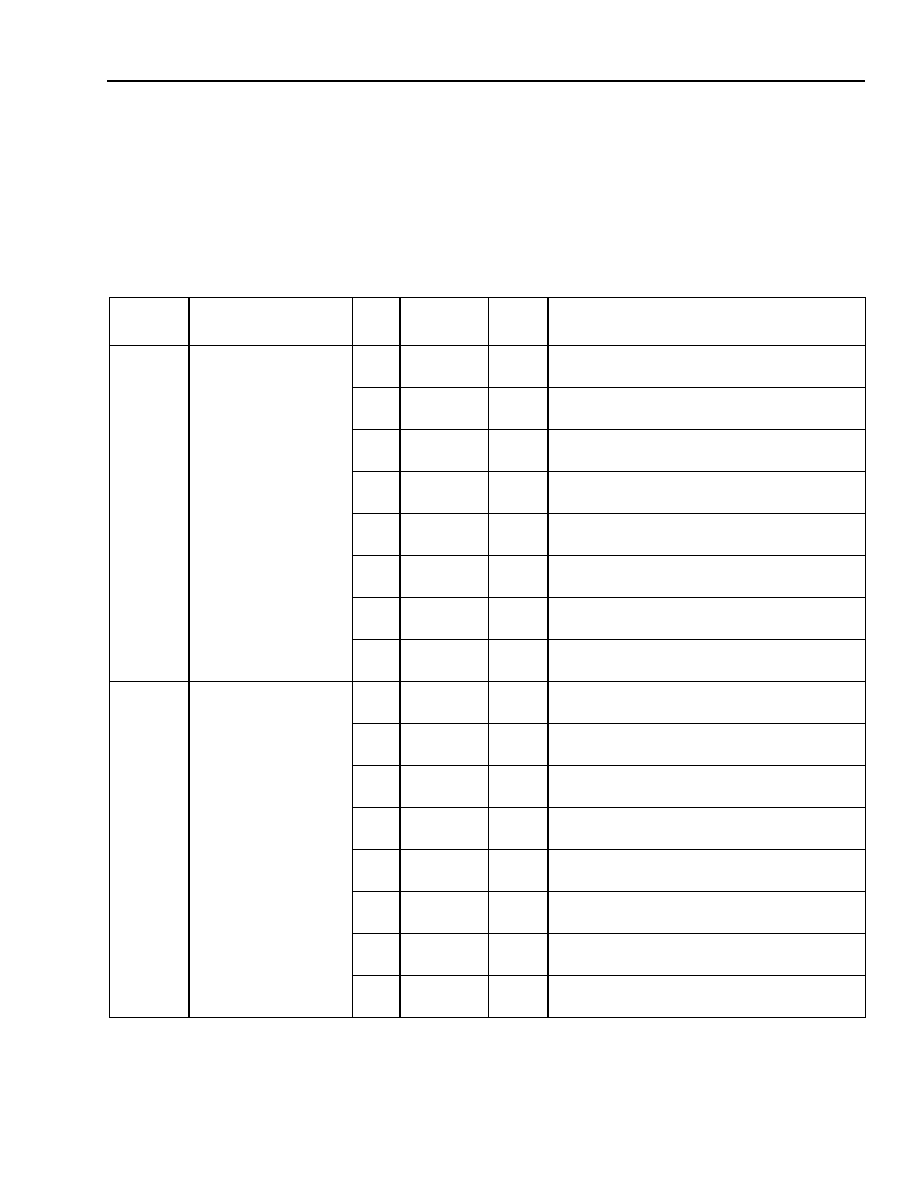

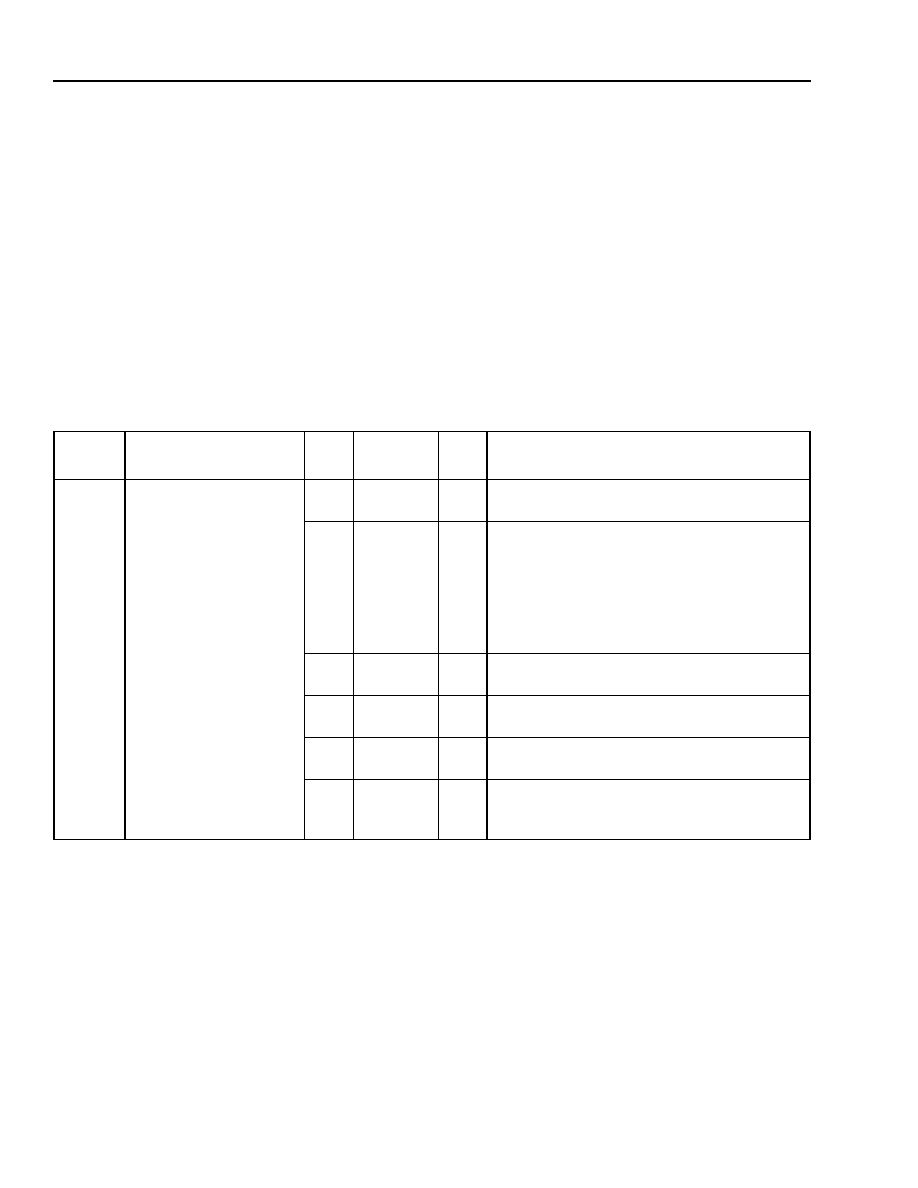

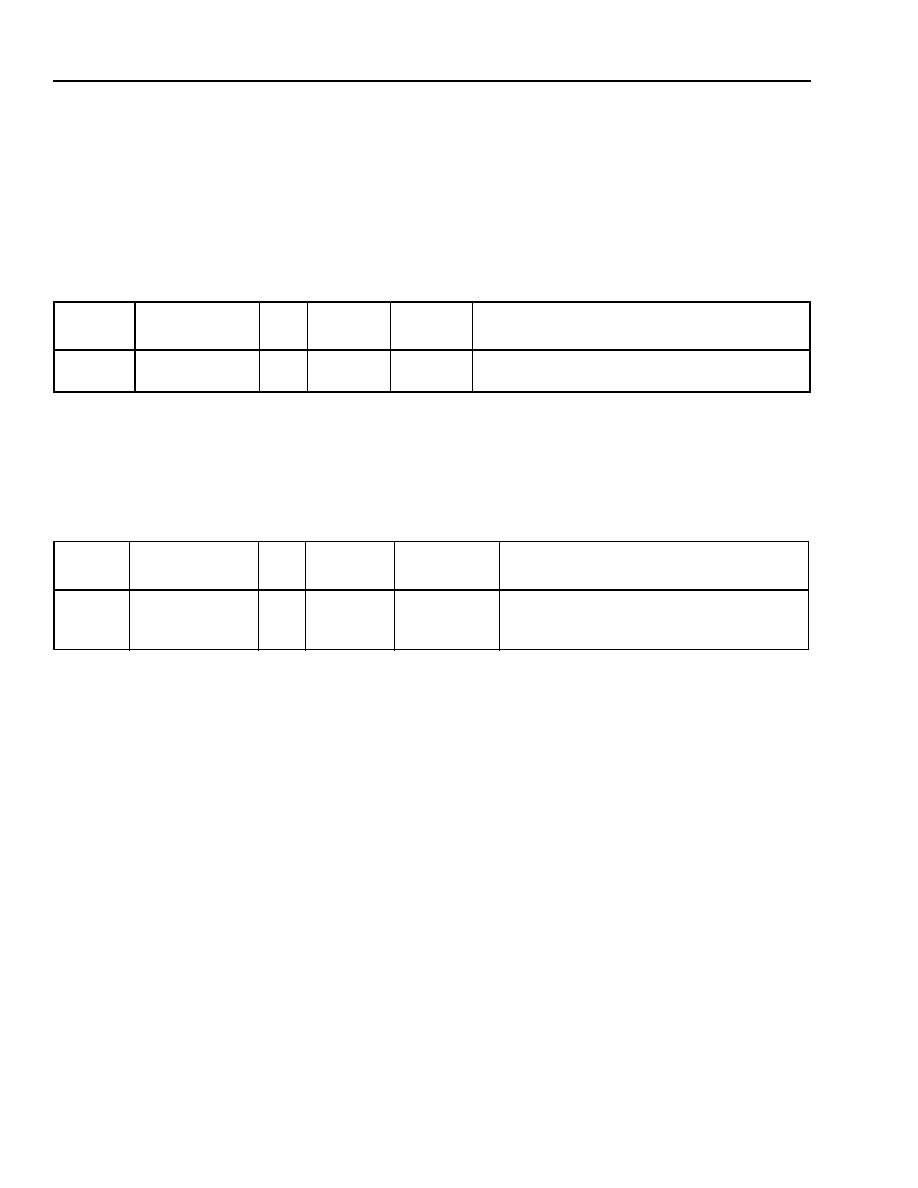

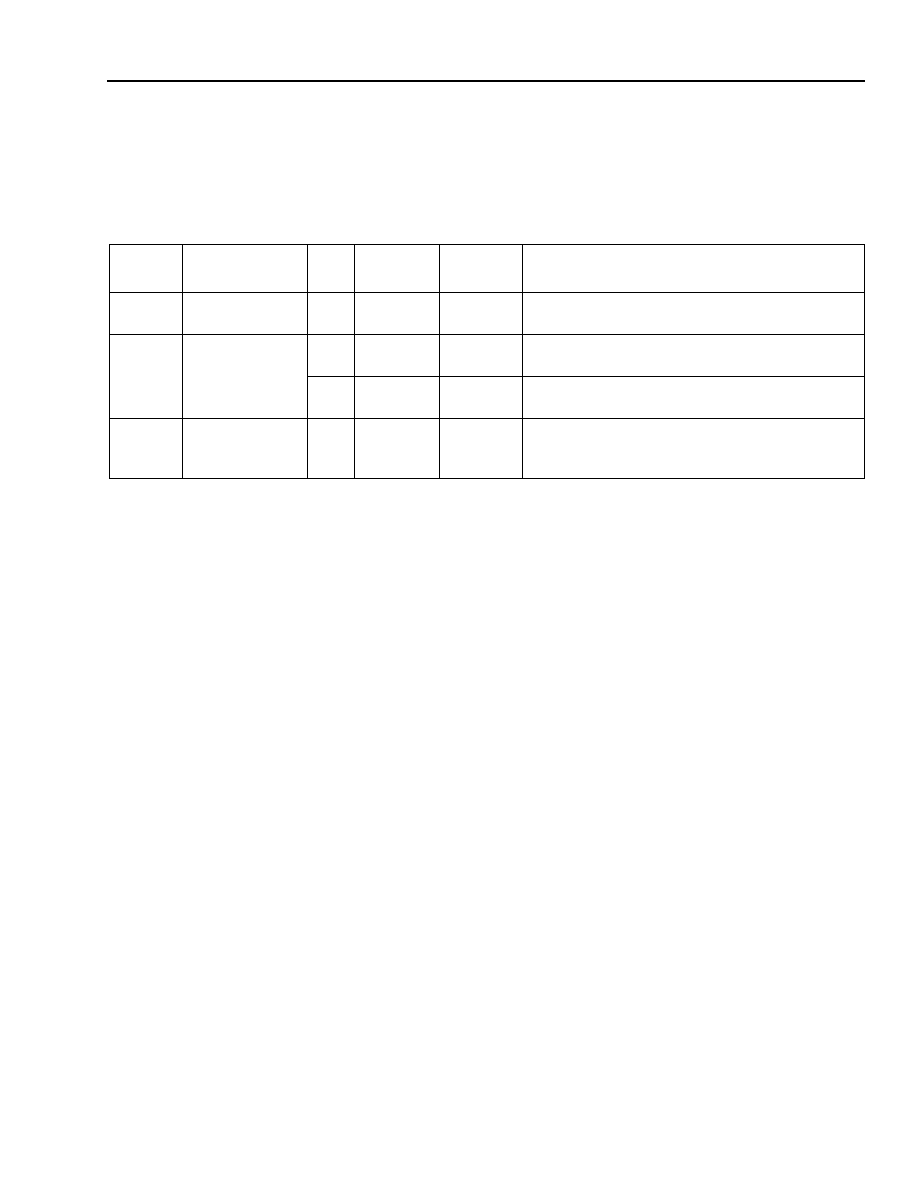

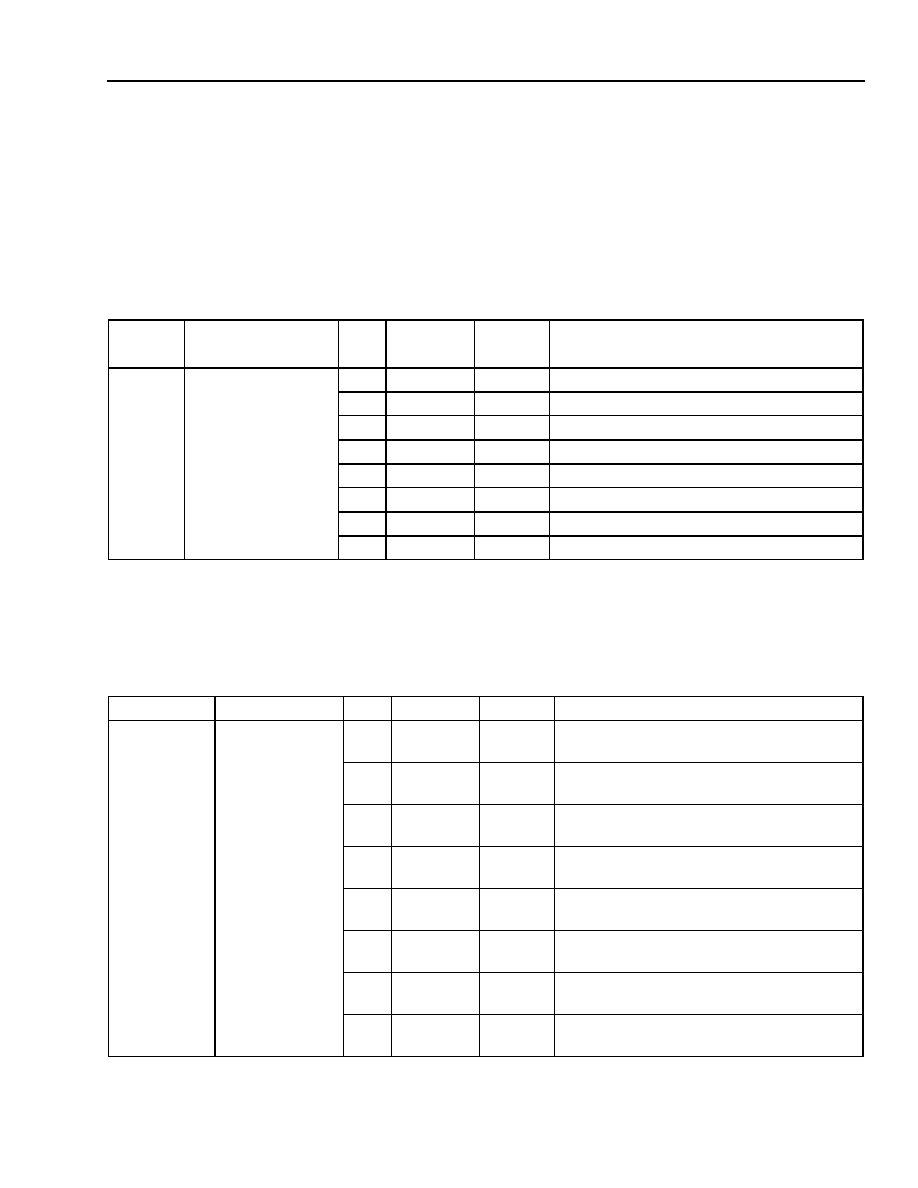

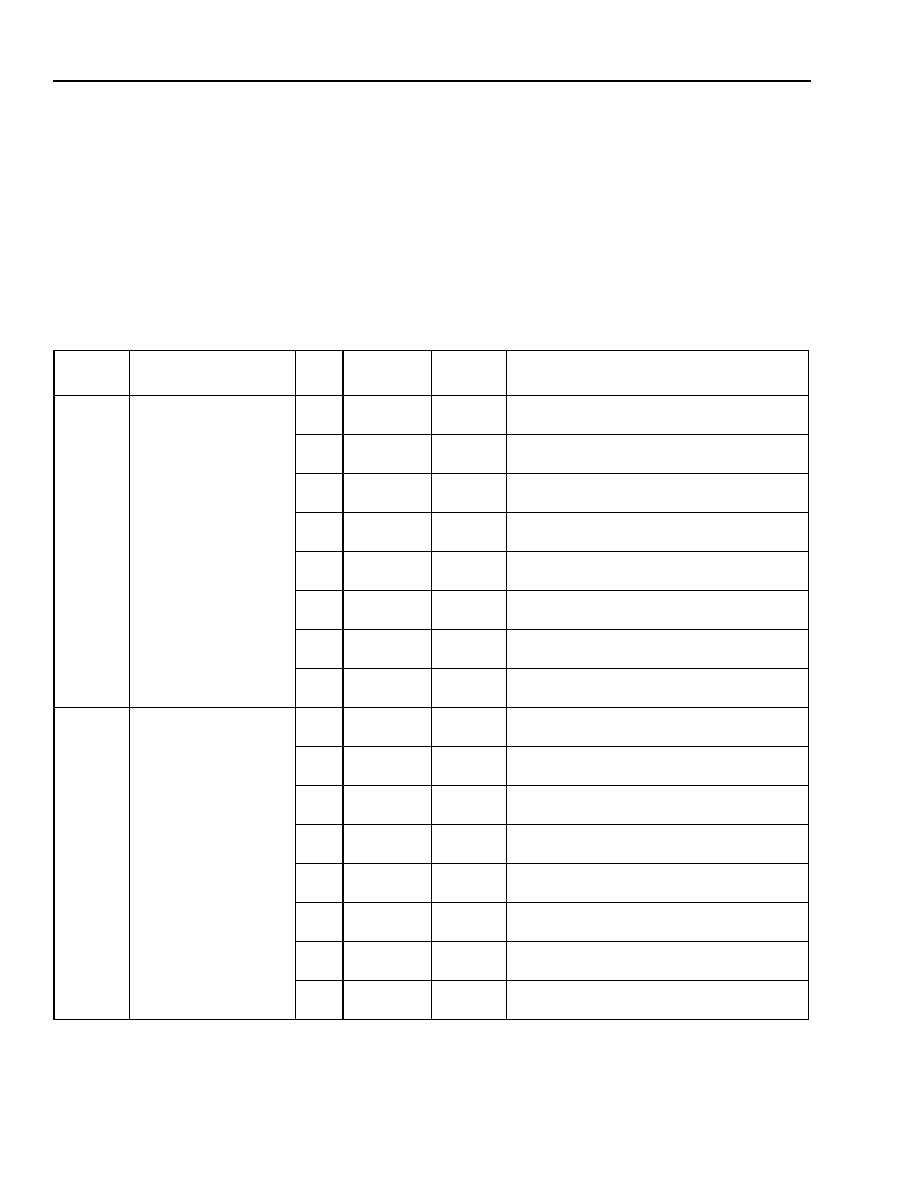

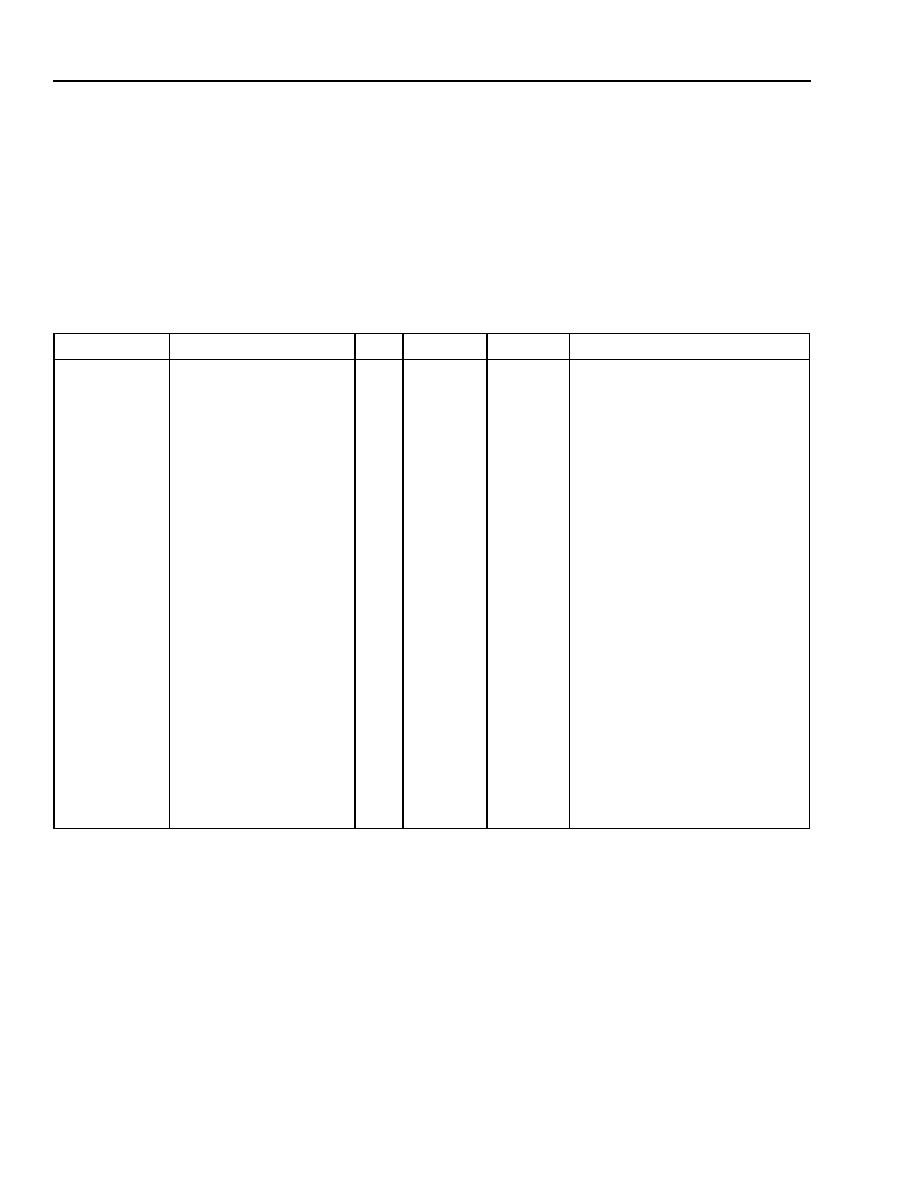

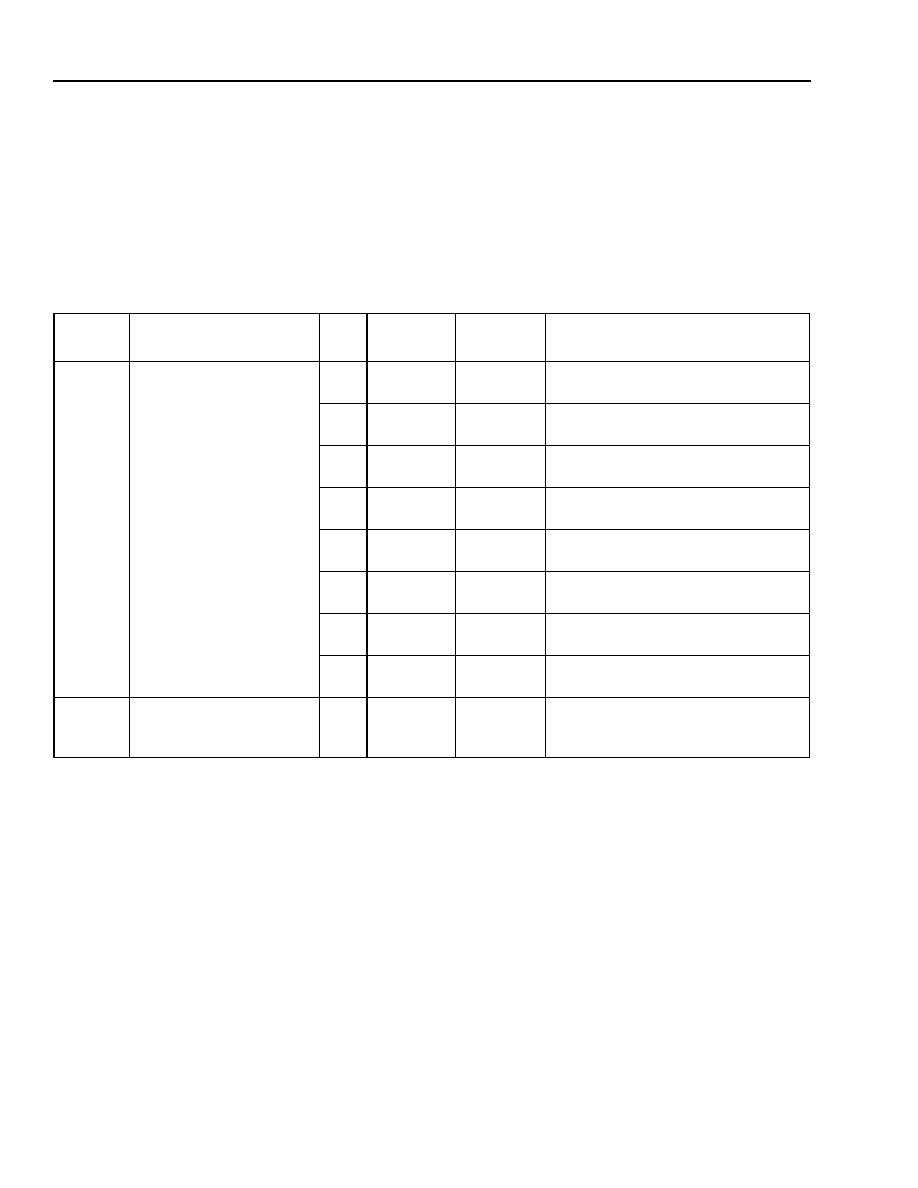

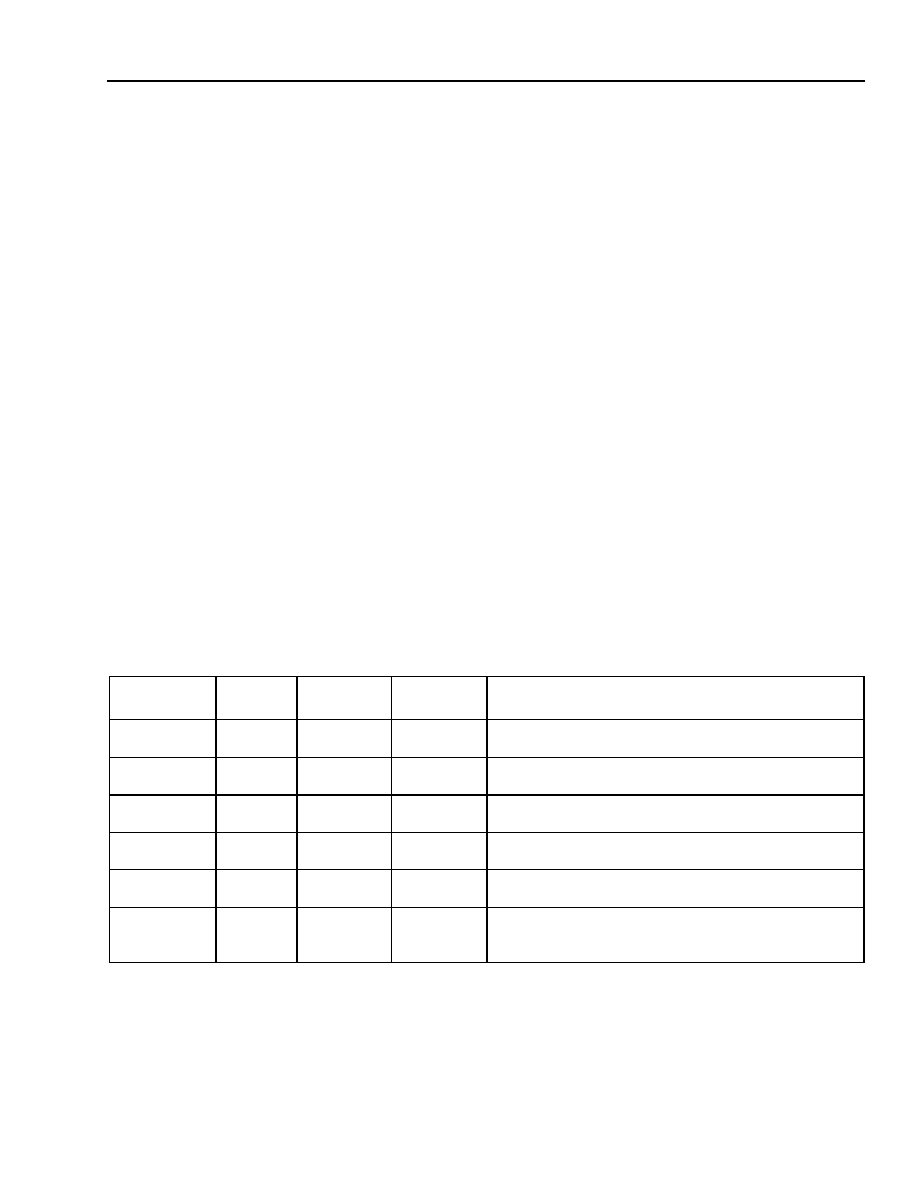

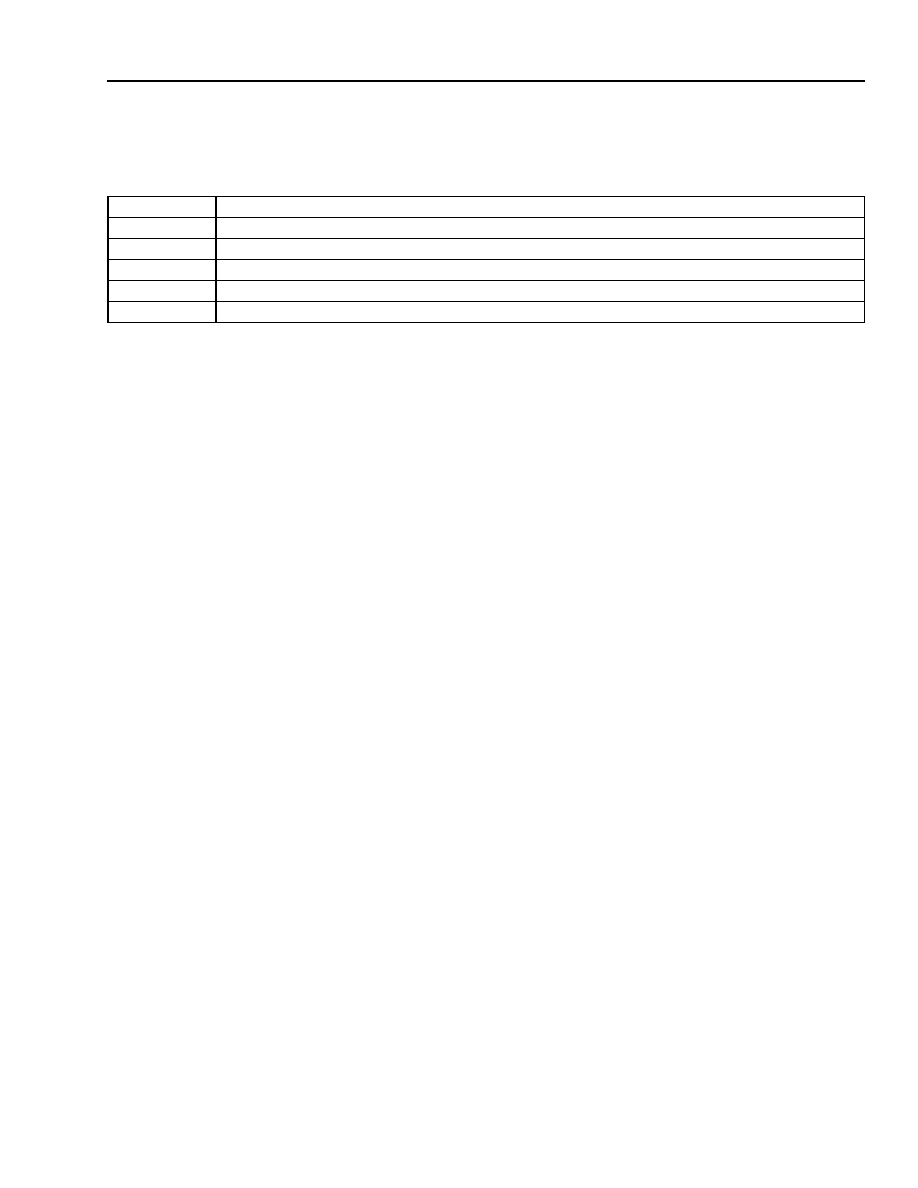

Table 1. Microprocessor Interface Signals

Signal

I/O

Width

Microprocessor Interface Function

A

I

20

Address[19:0] in.

D

I/O

16

Data bus in/out.

RD# (DS#)

I

1

RDn(DSn) in.

WR# (R/W#)

I

1

WRn(R/Wn) in.

CSN

I

1

CSn in.

WB_SEL

I

1

Word/byte select in.

RDY (DTACK#)

Out

1

RDY(DTACKn) out.

IM_SEL

I

1

Intel/Motorola select in.

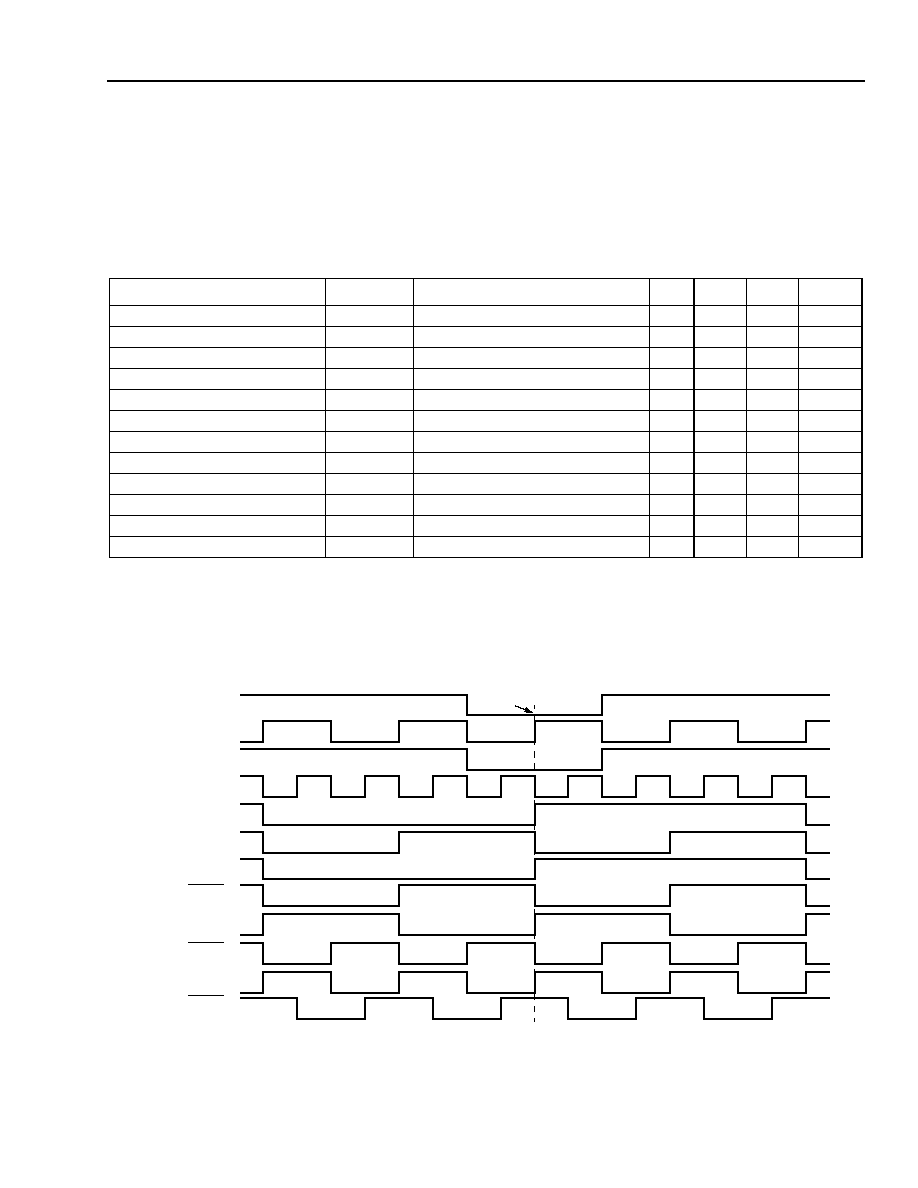

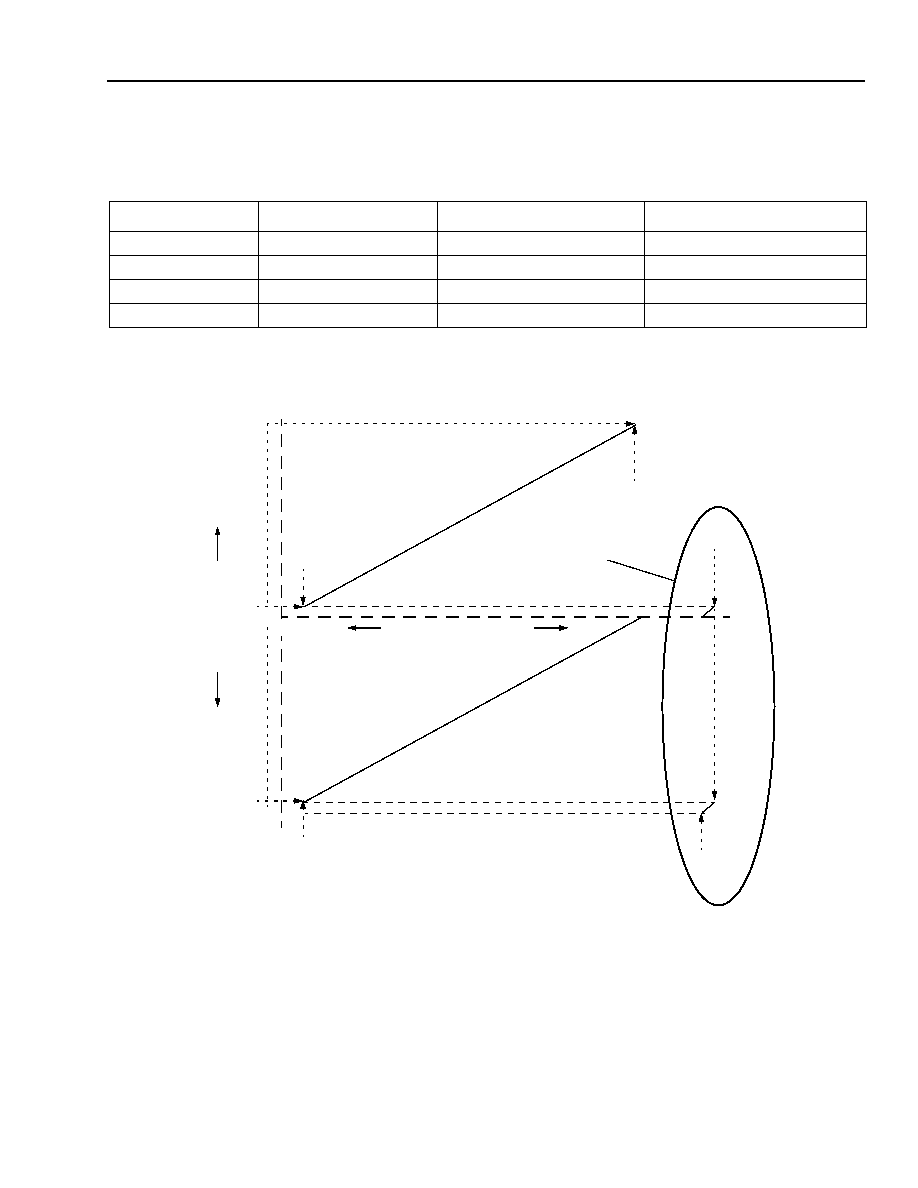

Table 2. H-Bus (H.100/H.110 Interface) Signals

Signal

I/O

Width

Function

VPRECHARGE

In

1

Precharge voltage for pull-downs, H.110 bus signals:

CT_D, CT_NETREF1, CT_NETREF2.

H110_ENABLE

In

1

Pull-down enable for H.110 bus signals: CT_D, CT_NETREF1,

CT_NETREF2.

H100_ENABLE

In

1

Pull-up enable for H.100 bus signals: CT_D, CT_NETREF1,

CT_NETREF2, CT_C8_A, CT_C8_B, /CT_FRAME_A, /CT_FRAME_B.

CT_D

I/O

32

H.100/H.110 bus data.

CT_C8_A

I/O

1

H.100/H.110 bit clock A.

/CT_FRAME_A

I/O

1

H.100/H.110 frame reference A.

CT_C8_B

I/O

1

H.100/H.110 bit clock B.

/CT_FRAME_B

I/O

1

H.100/H.110 frame reference B.

CT_NETREF1

I/O

1

H.100/H.110 network reference 1.

CT_NETREF2

I/O

1

H.100/H.110 network reference 2.

/C16+

I/O

1

H-MVIPTM compatibility clock (16.384 MHz, differential).

/C16≠

I/O

1

H-MVIP compatibility clock (16.384 MHz, differential).

/C4

I/O

1

MVIP compatibility clock (4.096 MHz).

C2

I/O

1

MVIP compatibility clock (2.048 MHz).

SCLK

I/O

1

SC-bus compatibility clock.

/SCLKx2

I/O

1

SC-bus compatibility clock.

/FR_COMP

I/O

1

Compatibility frame reference.

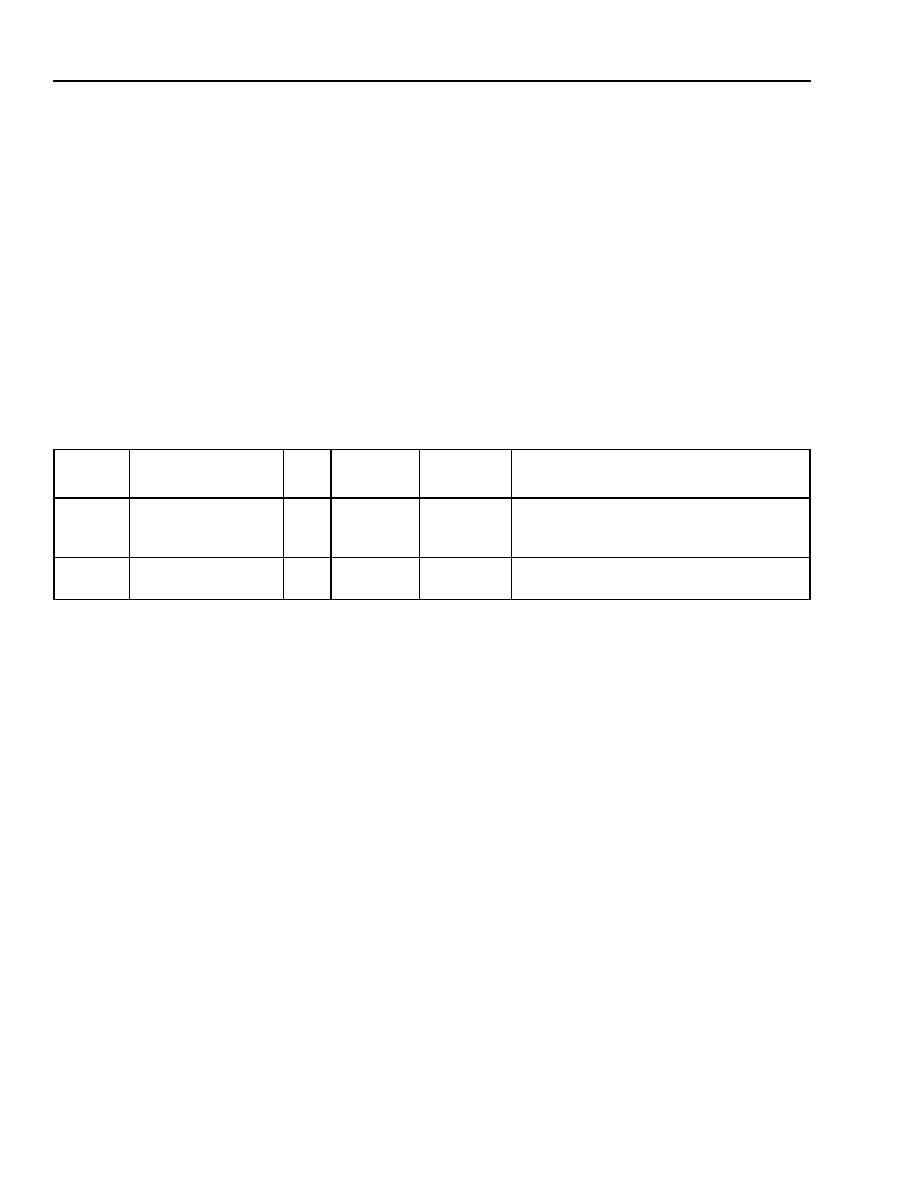

Table 3. L-Bus (Local) Interface Signals

Signal

I/O

Width

Function

L_D

I/O

32

Local bus data.

L_SC

Out

4

Local bus clock outputs.

FG

I/O

8

Local frame groups.

Agere Systems Inc.

11

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

2 Pin Description

(continued)

2.1 Interface Signals

(continued)

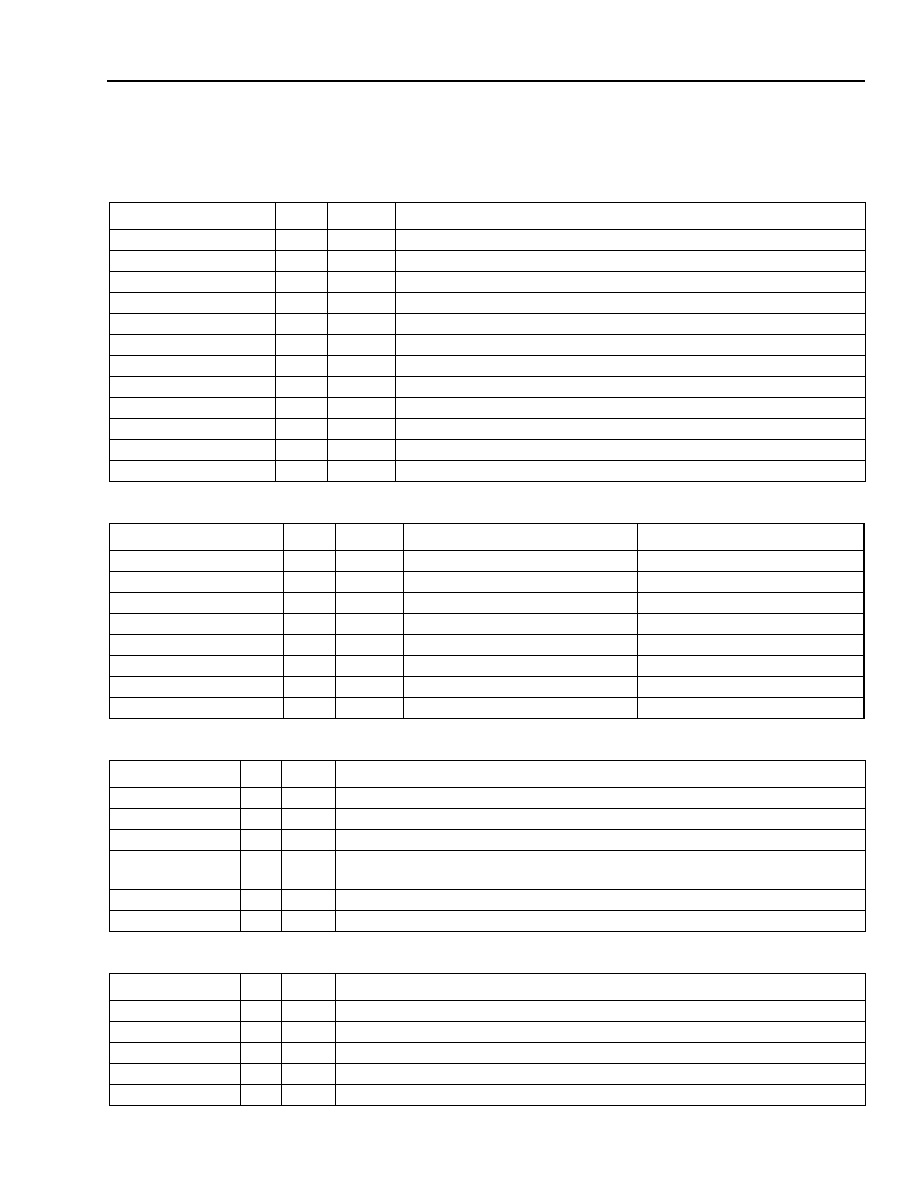

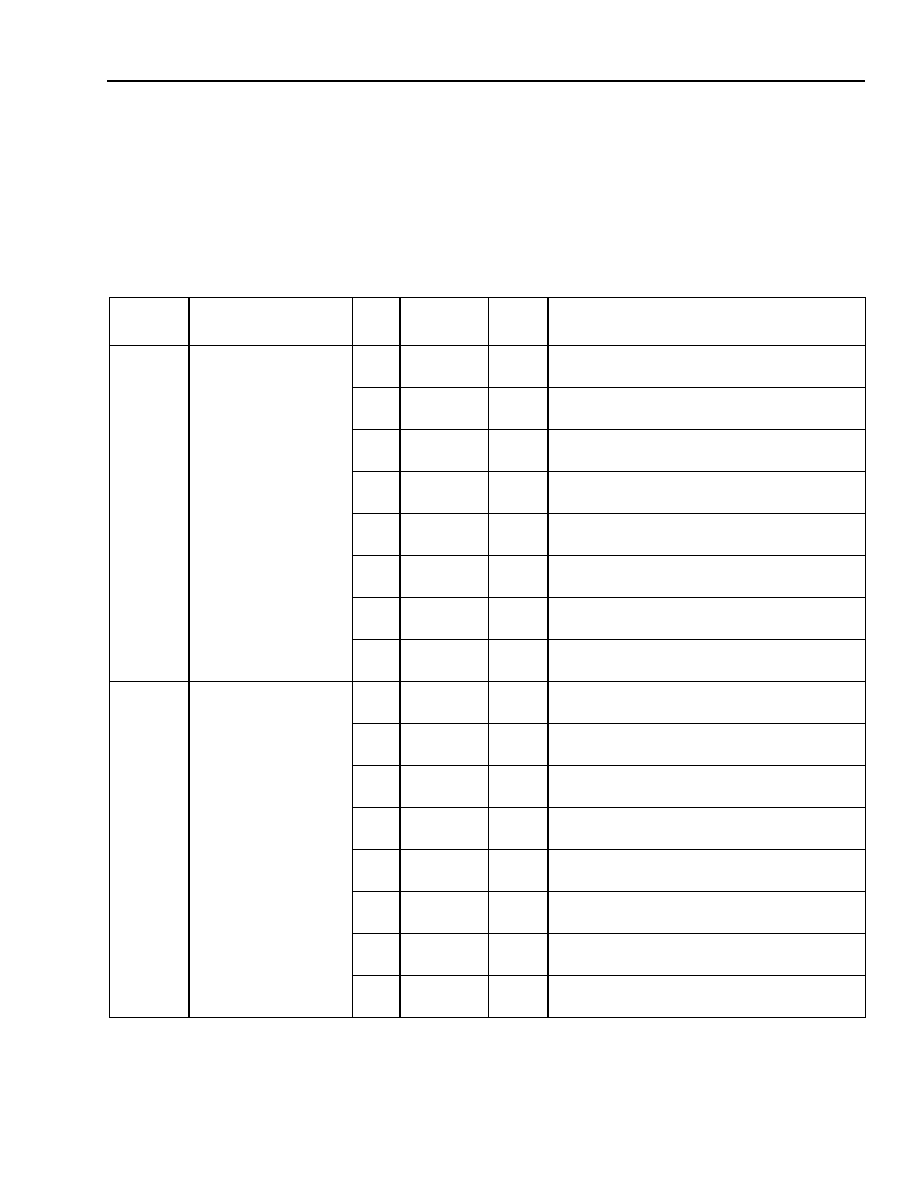

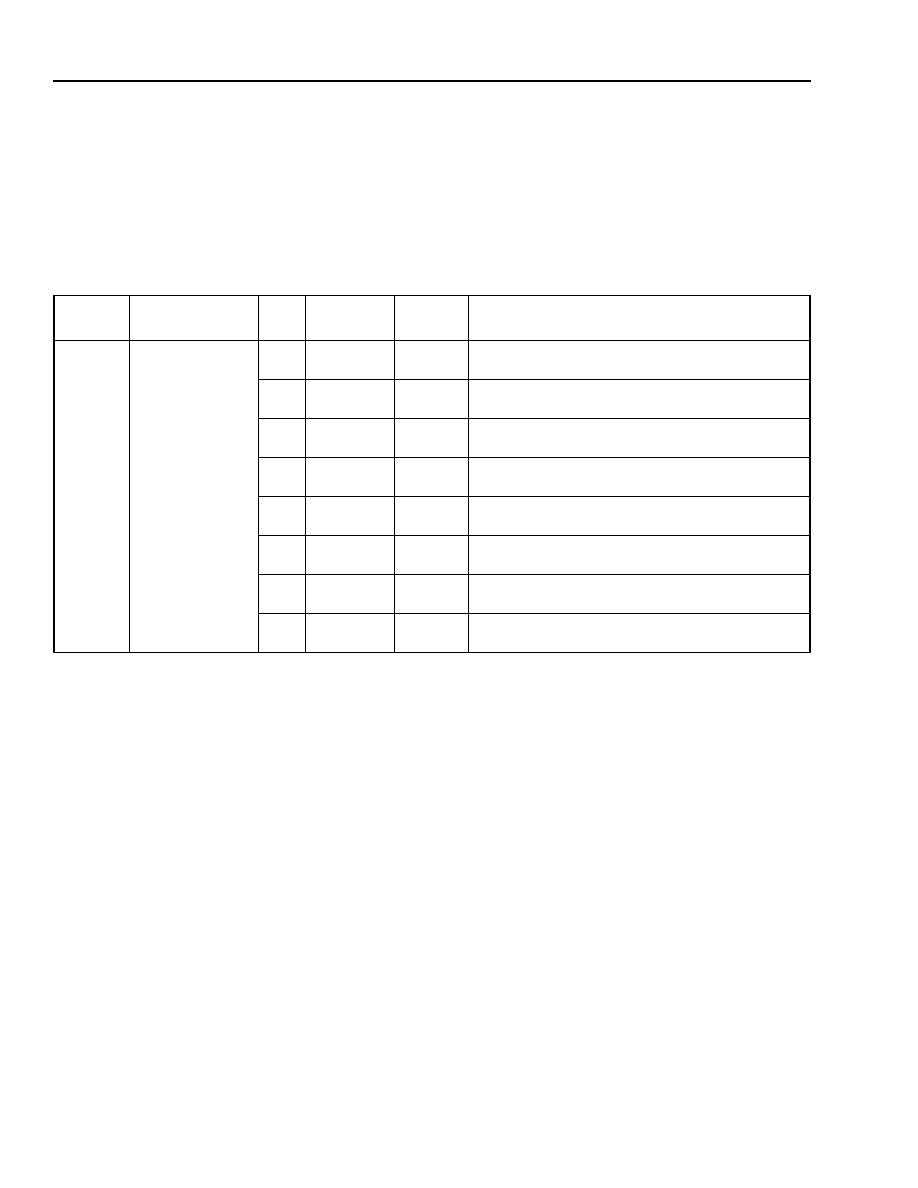

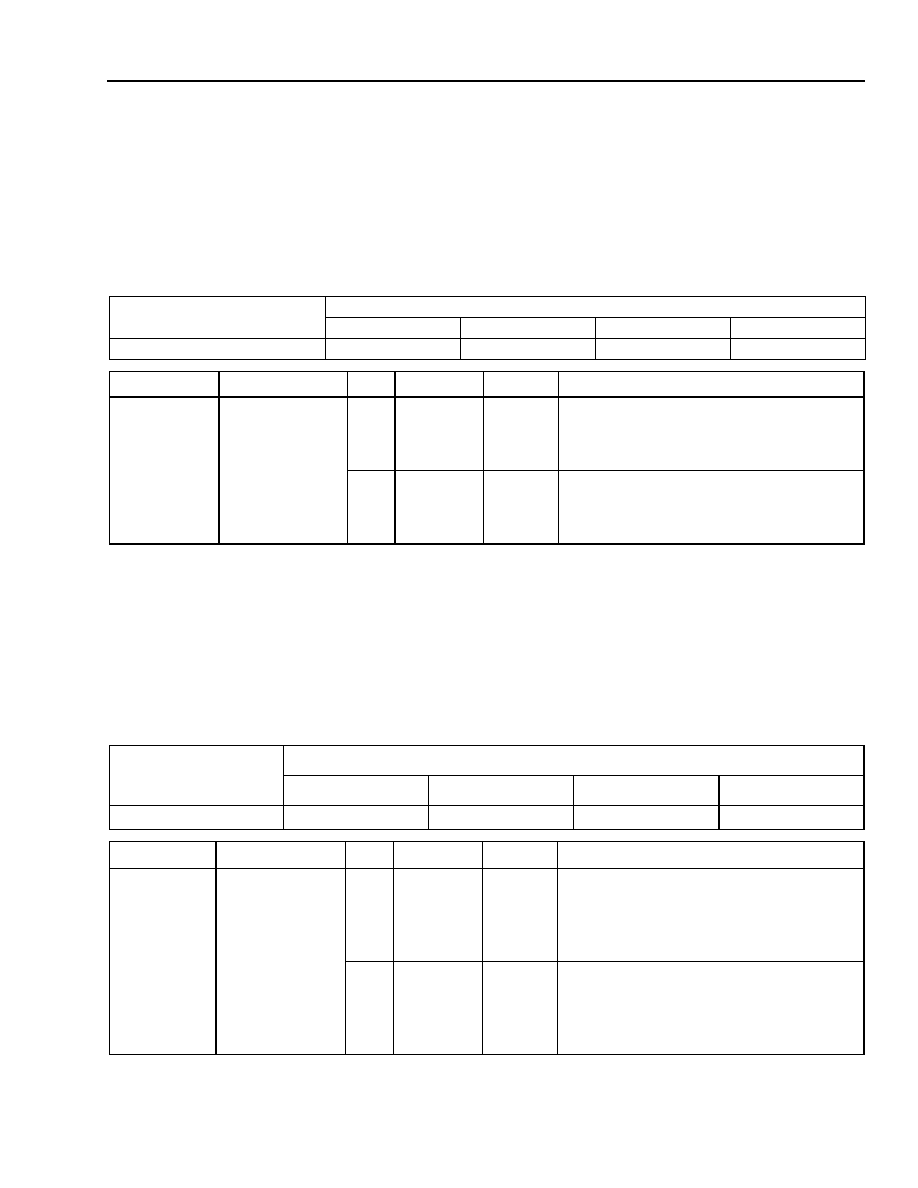

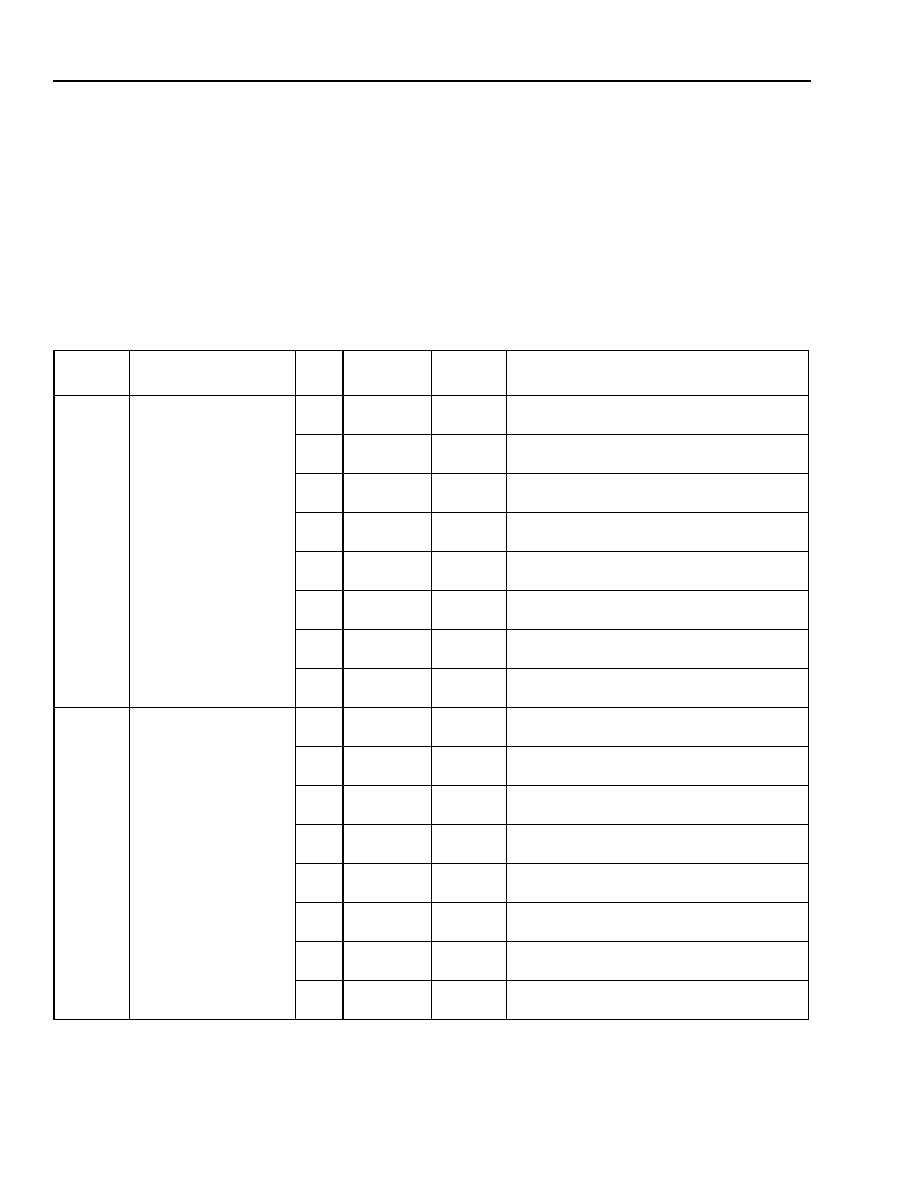

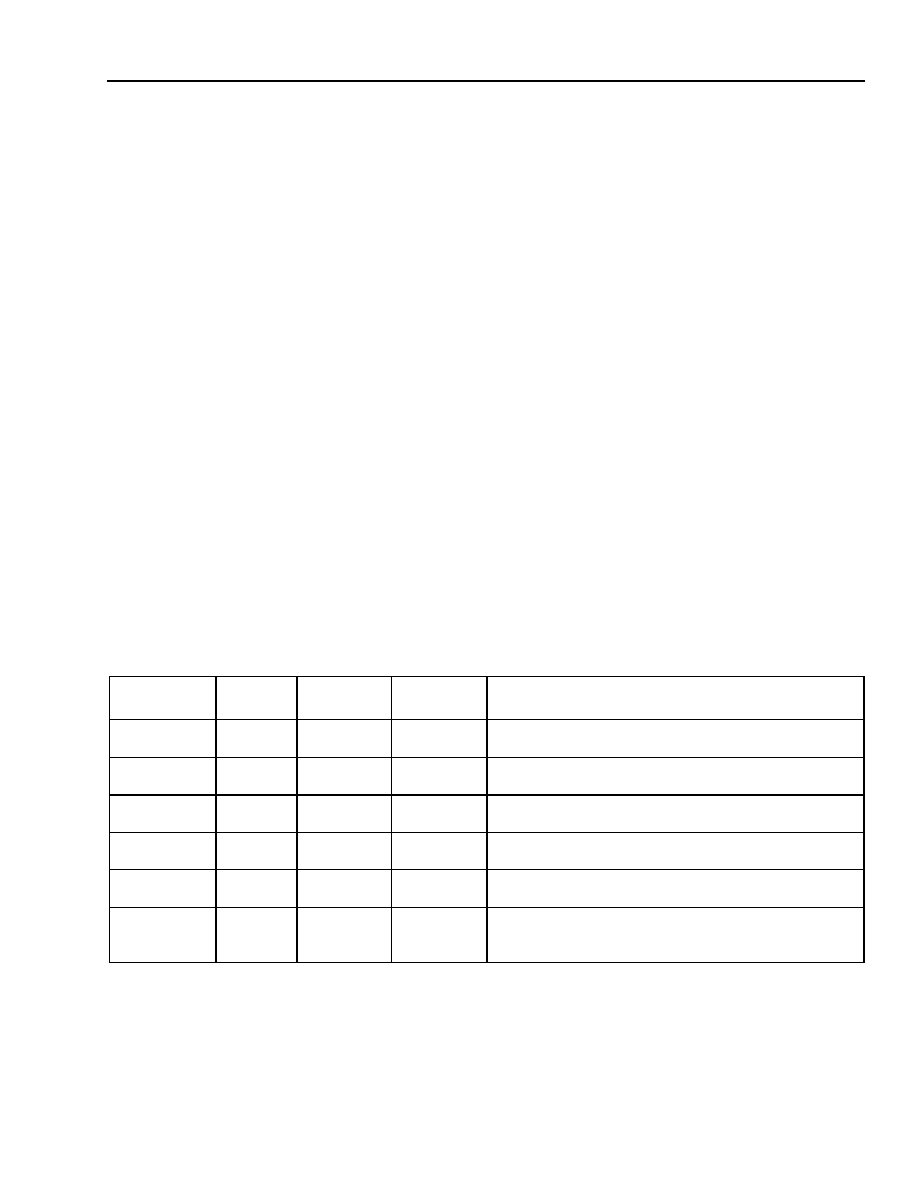

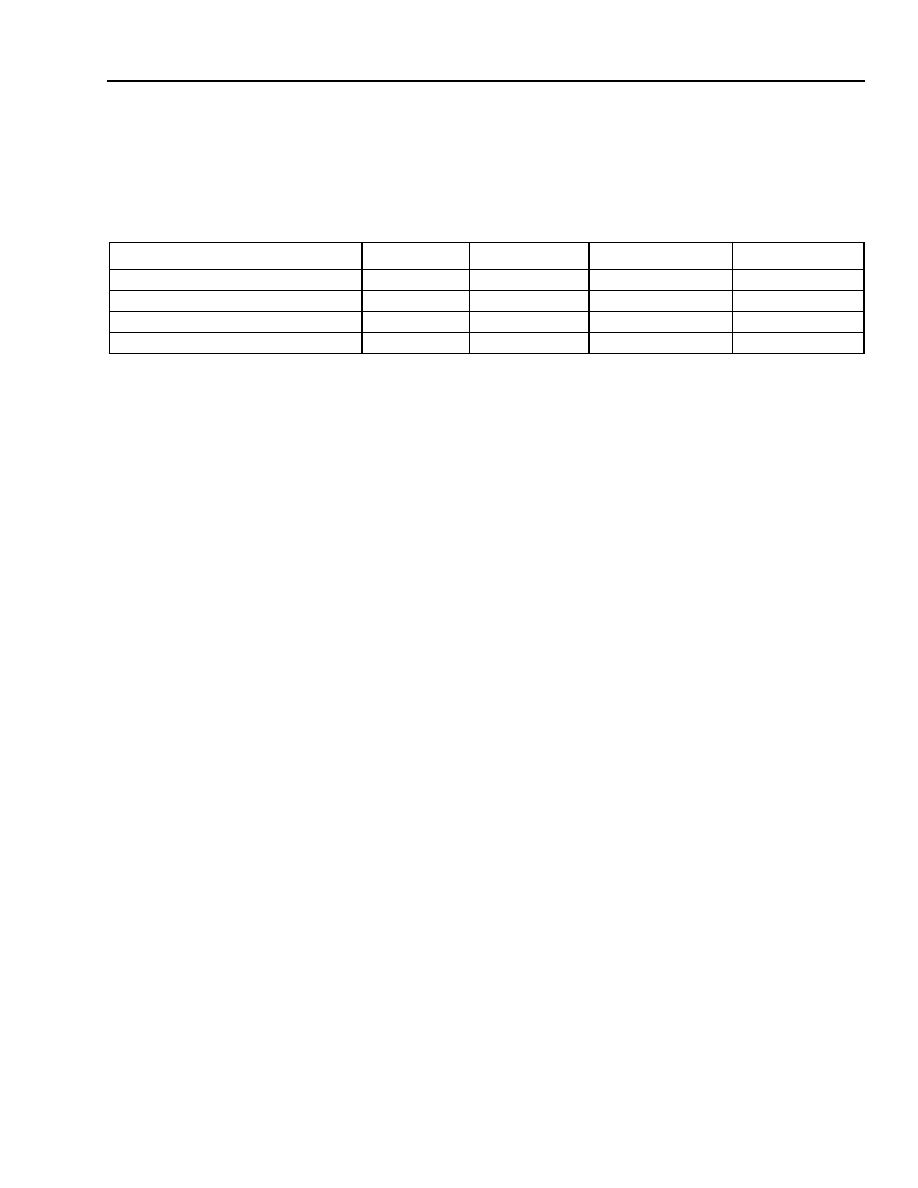

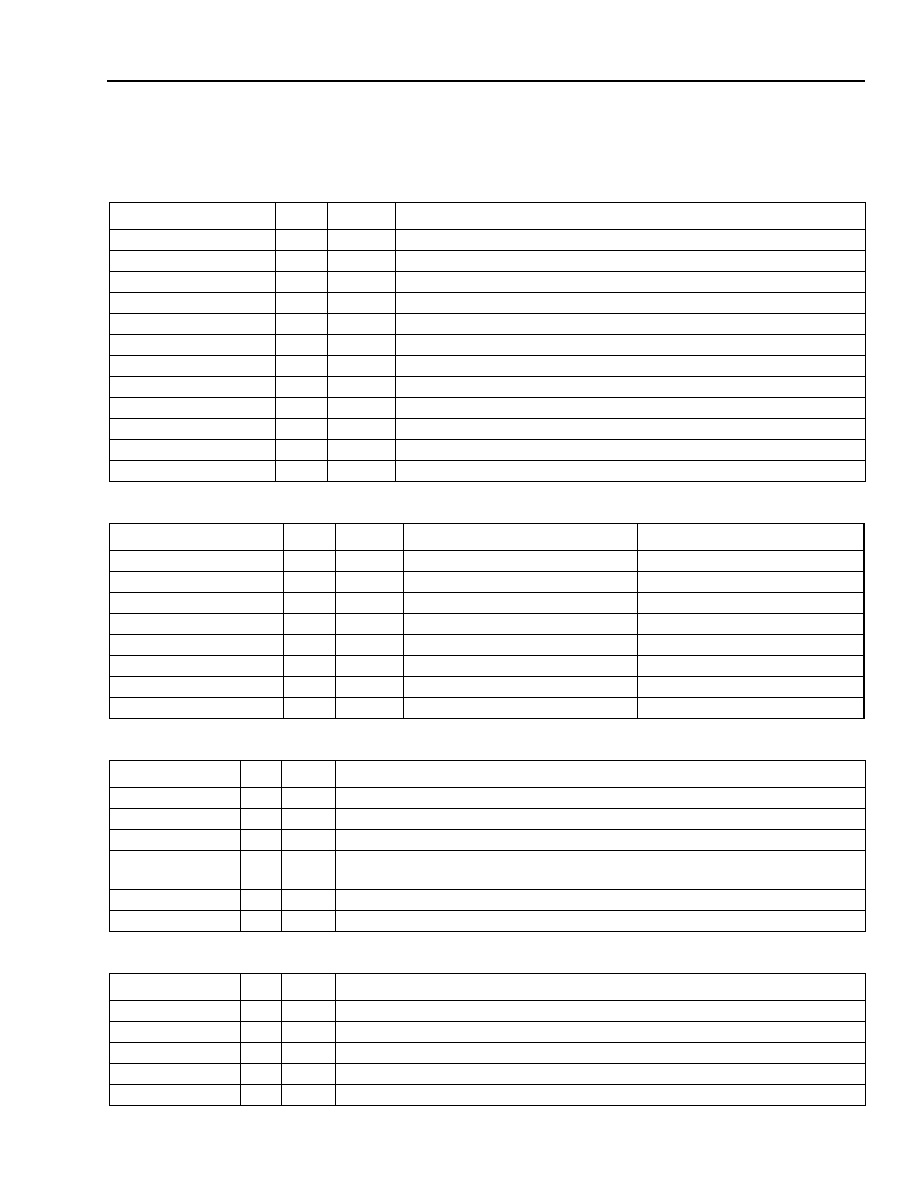

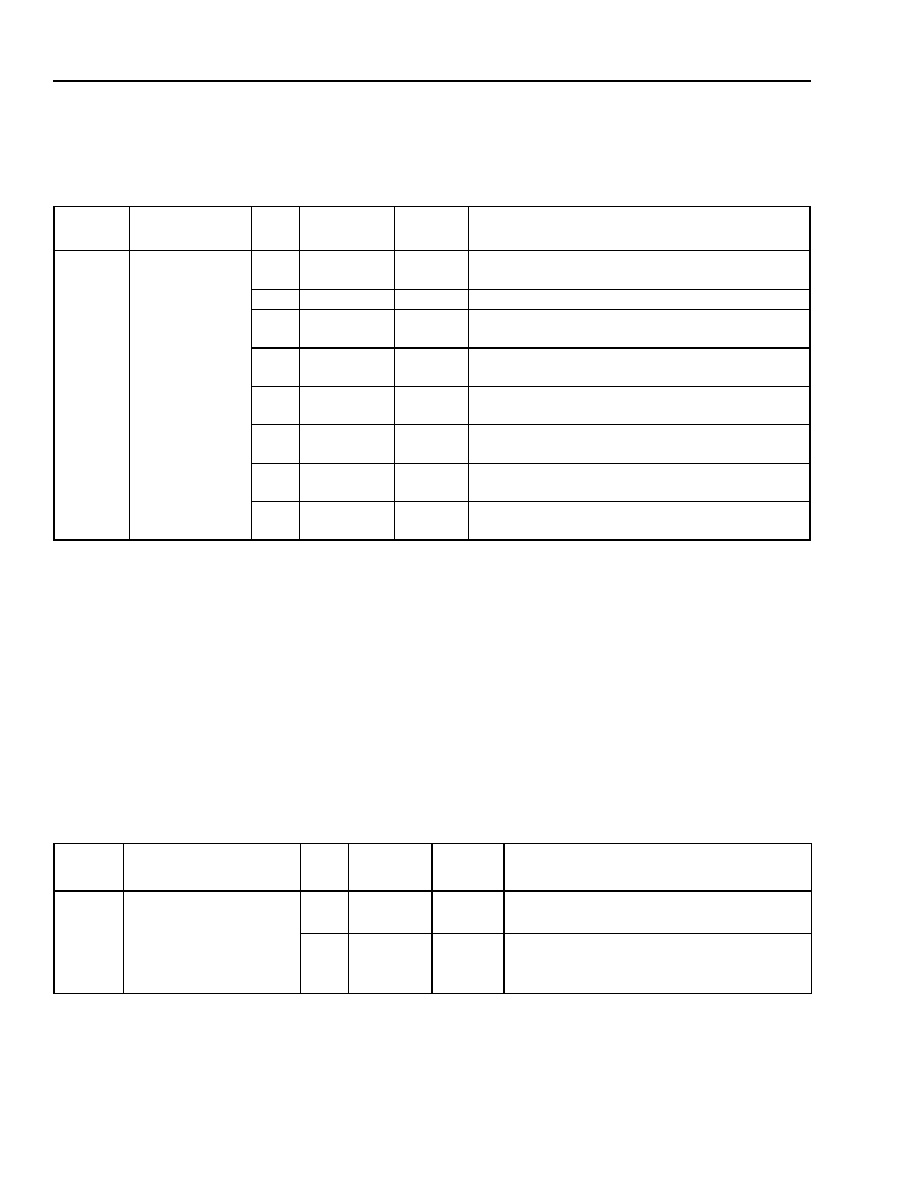

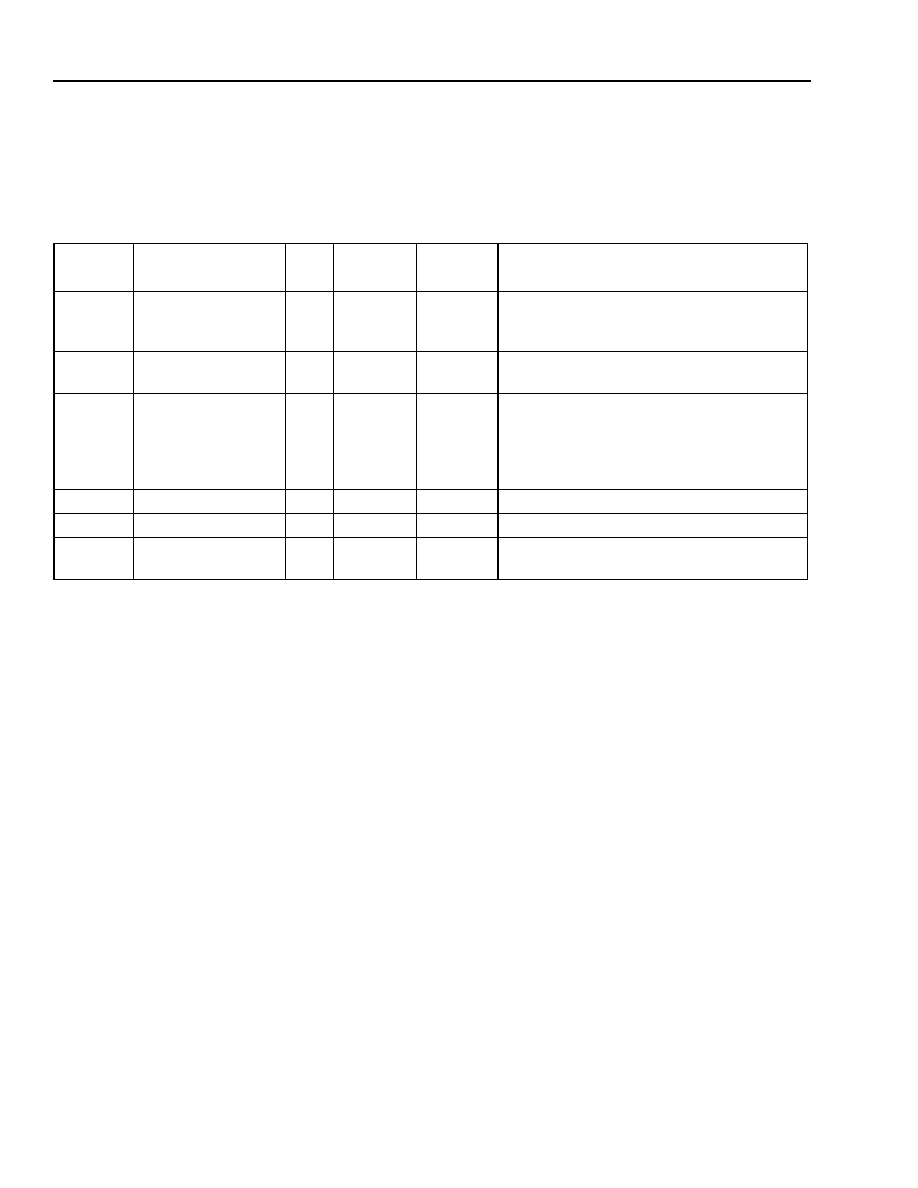

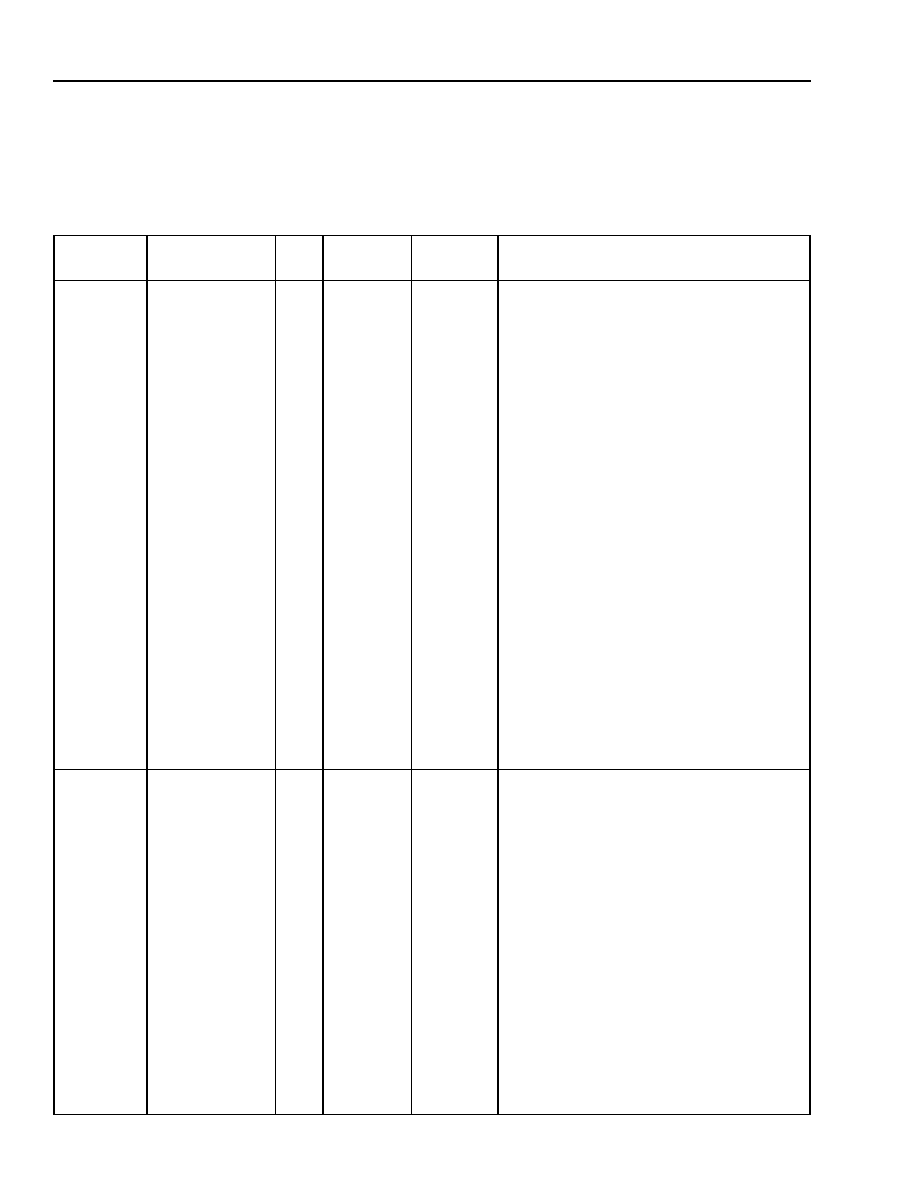

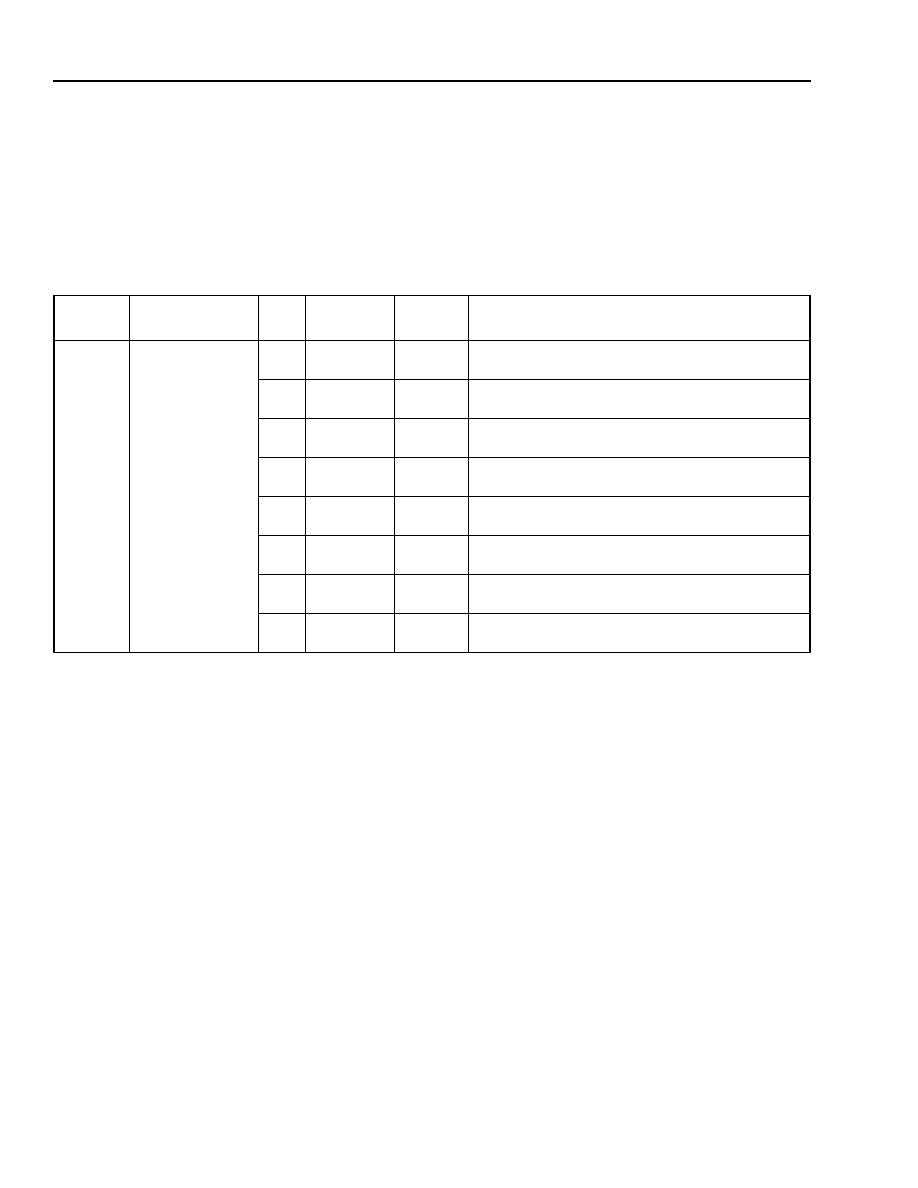

Table 4. Clock Circuit Interface Signals

Signal

I/O

Width

Function

XTAL1_IN

In

1

Crystal oscillator #1 input (16.384 MHz).

XTAL1_OUT

Out

1

Crystal oscillator #1 feedback.

XTAL2_IN

In

1

Crystal oscillator #2 input (6.176 MHz or 12.352 MHz).

XTAL2_OUT

Out

1

Crystal oscillator #2 feedback.

LREF

In

8

Local clock reference inputs.

TCLK_OUT

Out

1

Internal chip clock output.

PRI_REF_OUT

Out

1

Main divider reference out for CLAD/DJAT.

PRI_REF_IN

In

1

CLAD/DJAT reference in for APLL1.

NR1_SEL_OUT

Out

1

CT_NETREF1 selection out for CLAD/DJAT.

NR1_DIV_IN

In

1

CLAD/DJAT reference in for CT_NETREF1 divider.

NR2_SEL_OUT

Out

1

CT_NETREF2 selection out for CLAD/DJAT.

NR2_DIV_IN

In

1

CLAD/DJAT reference in for CT_NETREF2 divider.

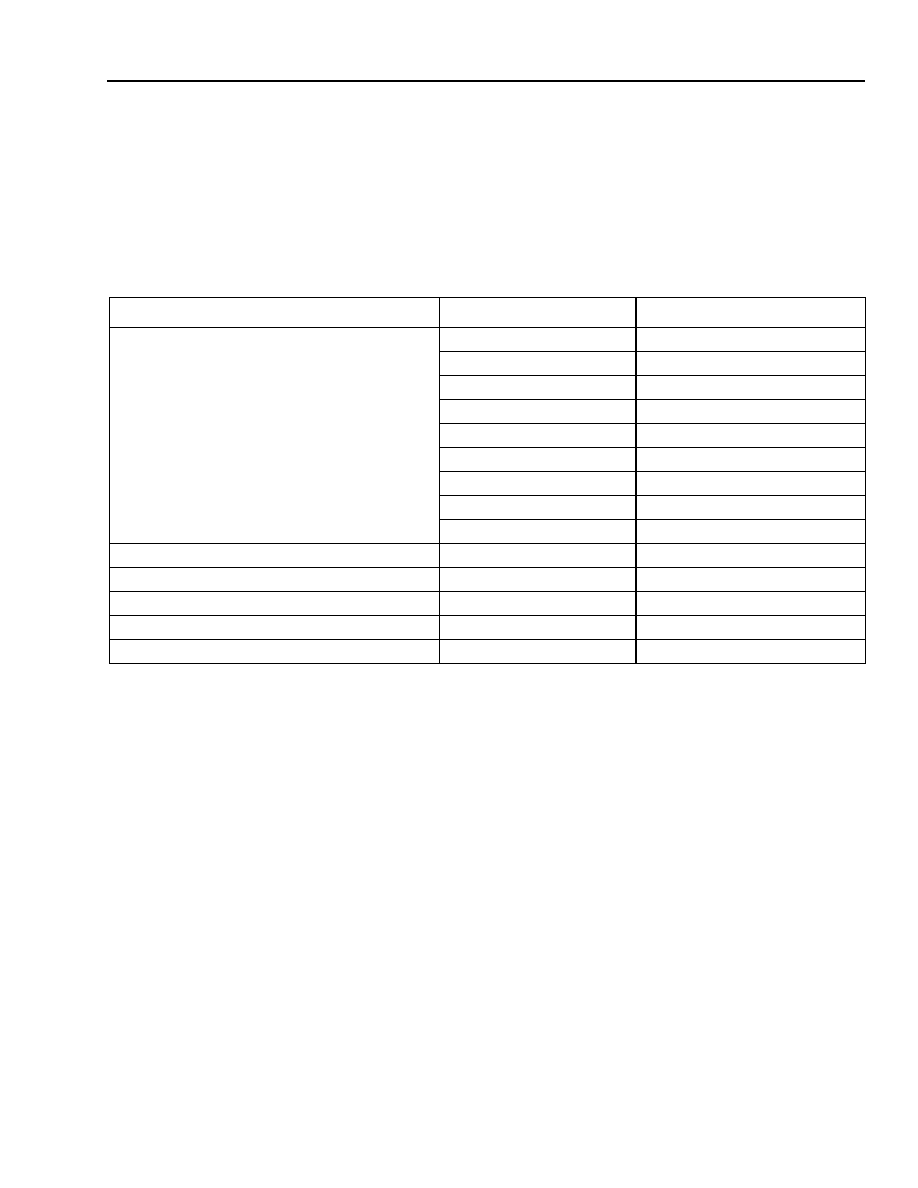

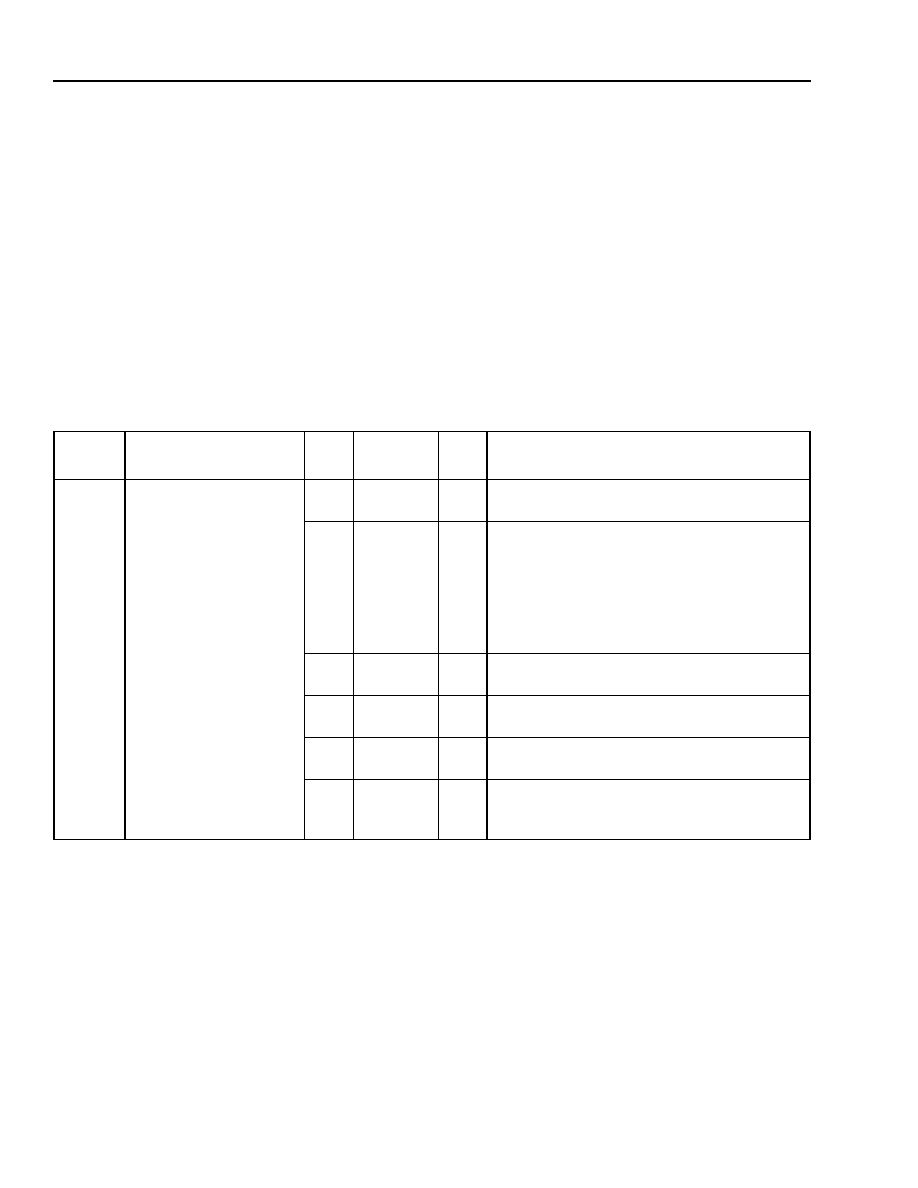

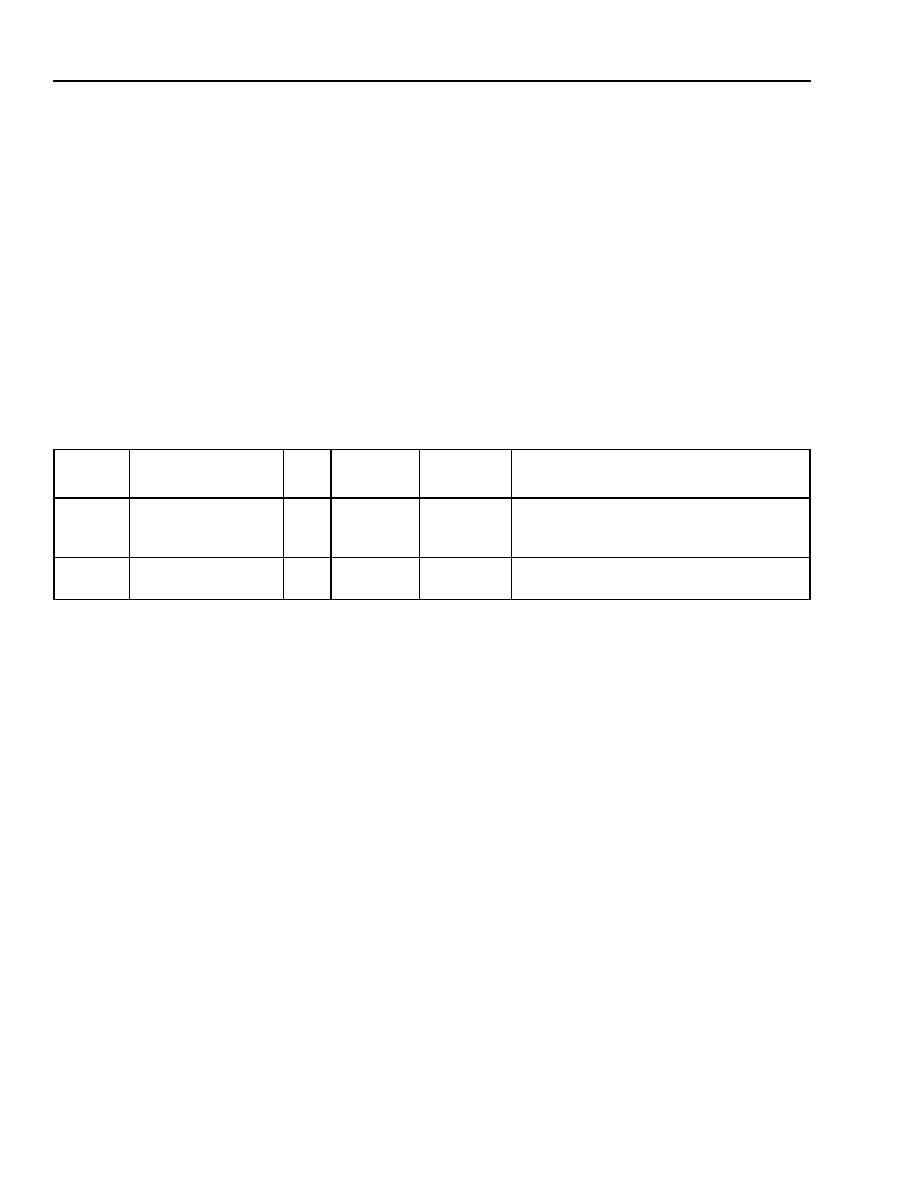

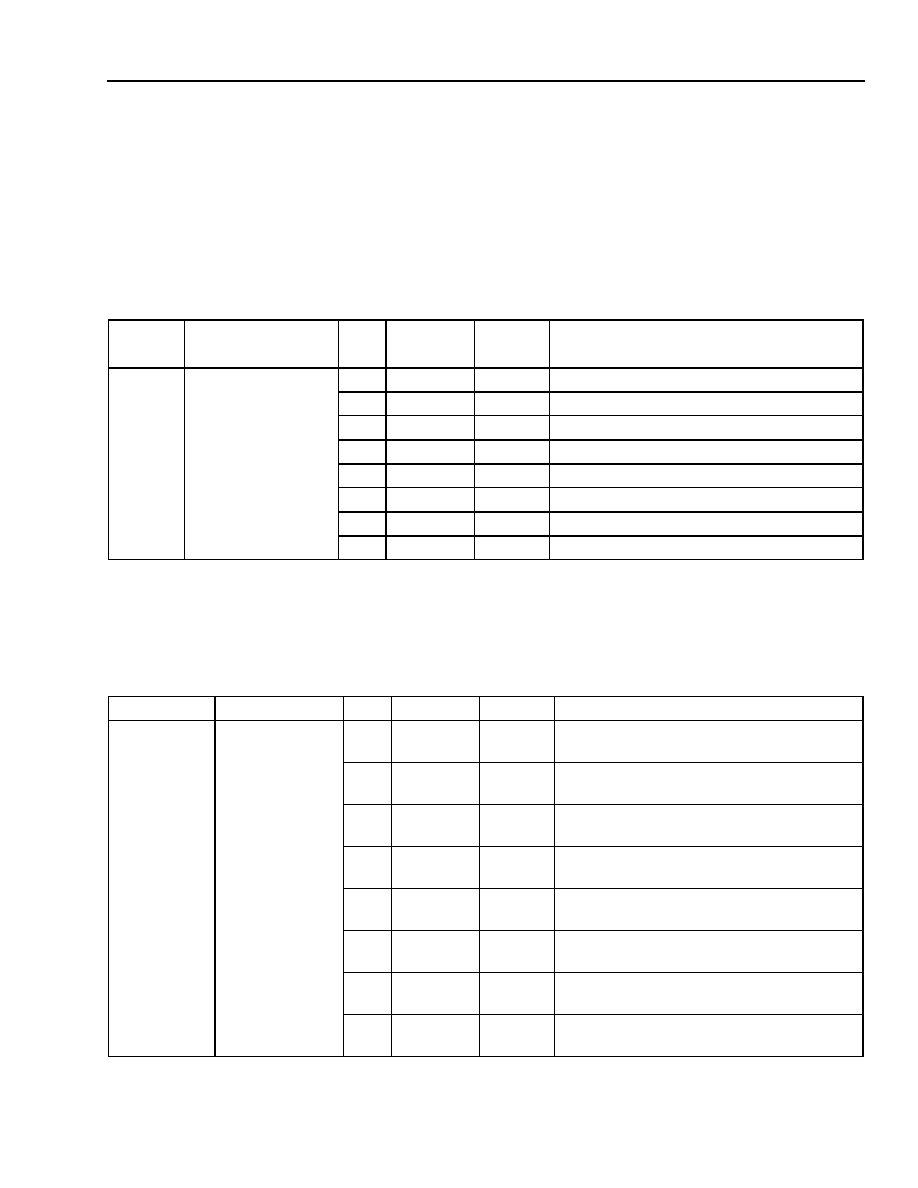

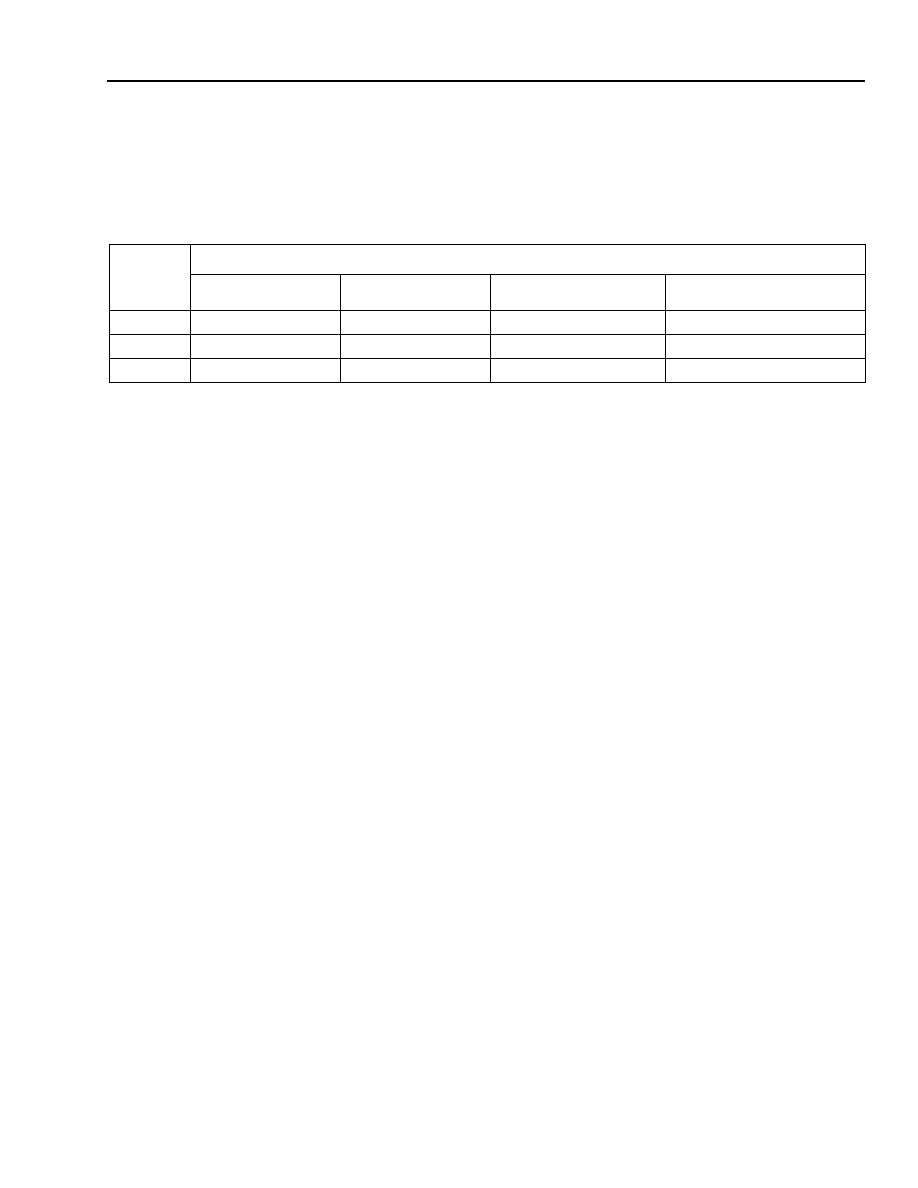

Table 5. GPIO Interface Signals

Signal

I/O

Width

GPIO Function

Alternate Function

GP0

I/O

1

GPIO bit 0 I/O

A-master indicator out.

GP1

I/O

1

GPIO bit 1 I/O

B-master indicator out.

GP2

I/O

1

GPIO bit 2 I/O

--

GP3

I/O

1

GPIO bit 3 I/O

--

GP4

I/O

1

GPIO bit 4 I/O

--

GP5

I/O

1

GPIO bit 5 I/O

--

GP6

I/O

1

GPIO bit 6 I/O

--

GP7

I/O

1

GPIO bit 7 I/O

--

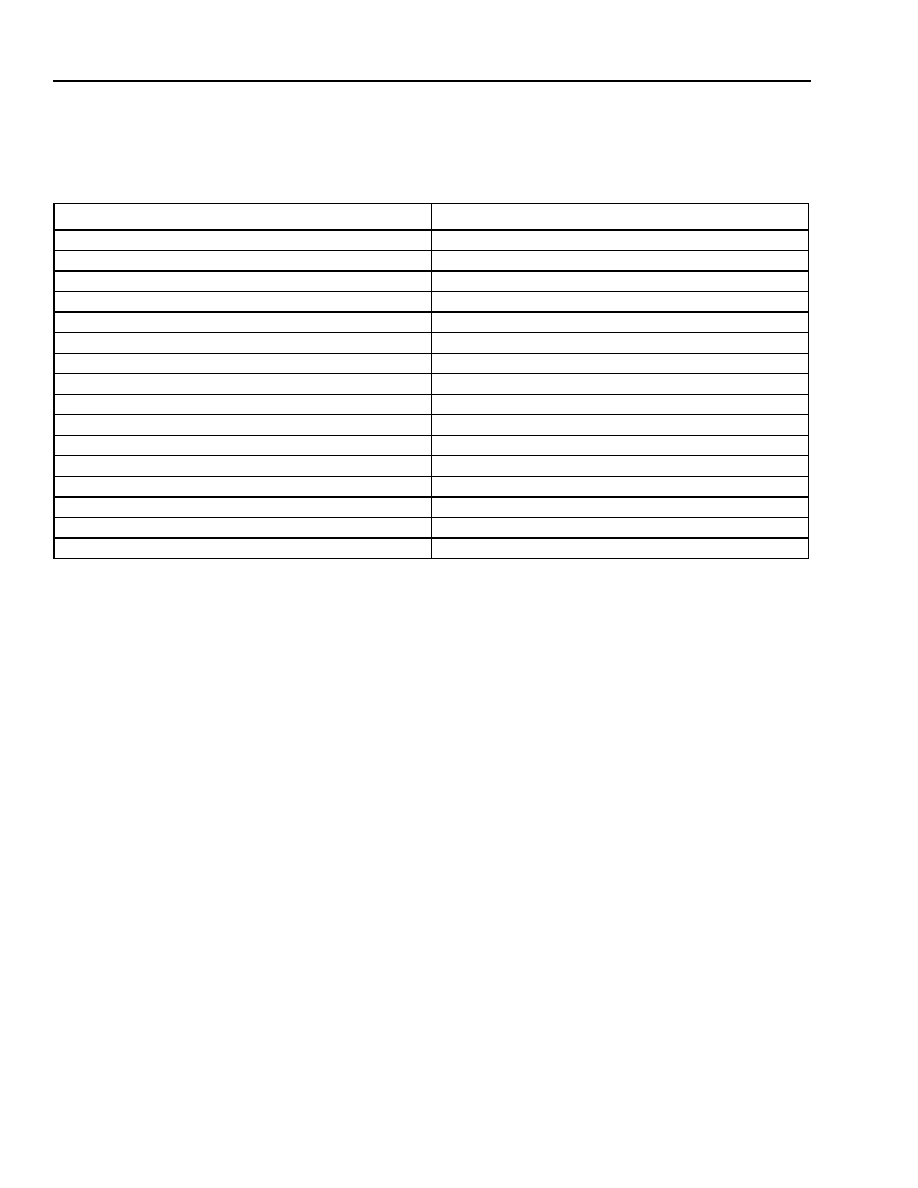

Table 6. Miscellaneous Interface Signals

Signal

I/O

Width

Function

RESET#

In

1

Chip reset.

SYSERR

Out

1

System error indicator.

CLKERR

Out

1

Clocking error indicator.

LPUE

In

1

Pull-up enable for signals: FG, GP, L_D, LREF, D, NR1_DIV_IN, NR2_DIV_IN,

PRI_REF_IN.

PEN

In

1

Reserved. Must be left unconnected.

TESTMODE

In

1

Reserved. Must be left unconnected.

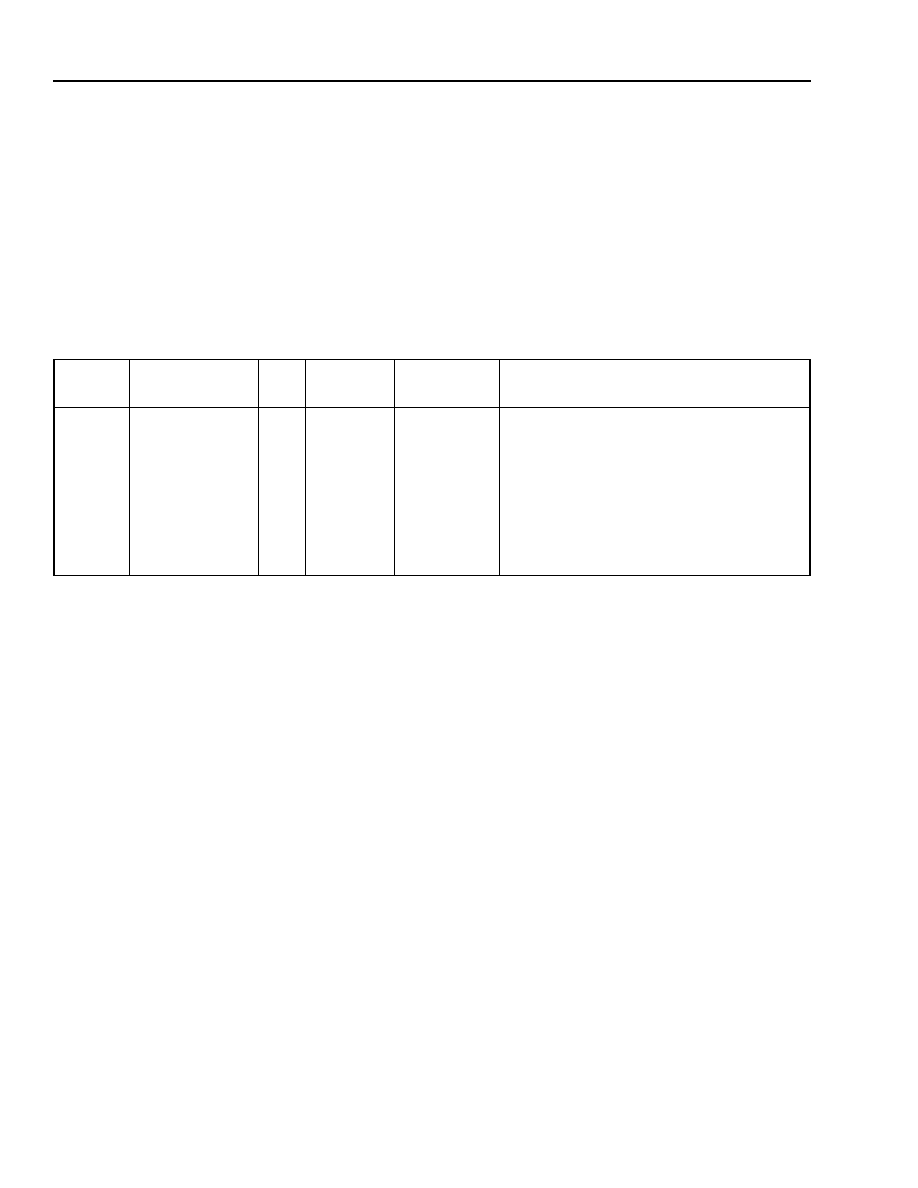

Table 7. JTAG Signals

Signal

I/O

Width

Function

TRST#

In

1

JTAG reset.

TCK

In

1

JTAG clock.

TMS

In

1

JTAG mode select.

TDI

In

1

JTAG data in.

TDO

Out

1

JTAG data out.

12

Agere Systems Inc.

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

2 Pin Description

(continued)

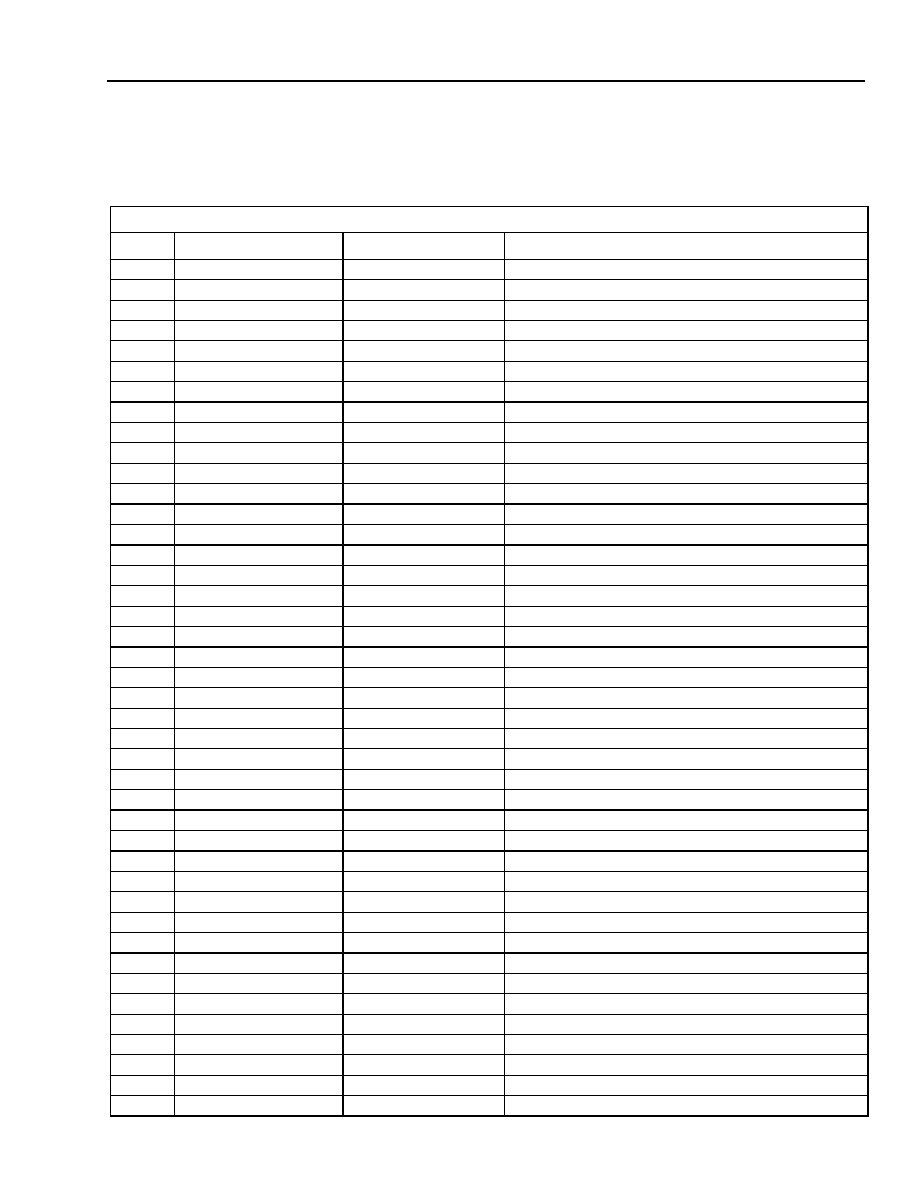

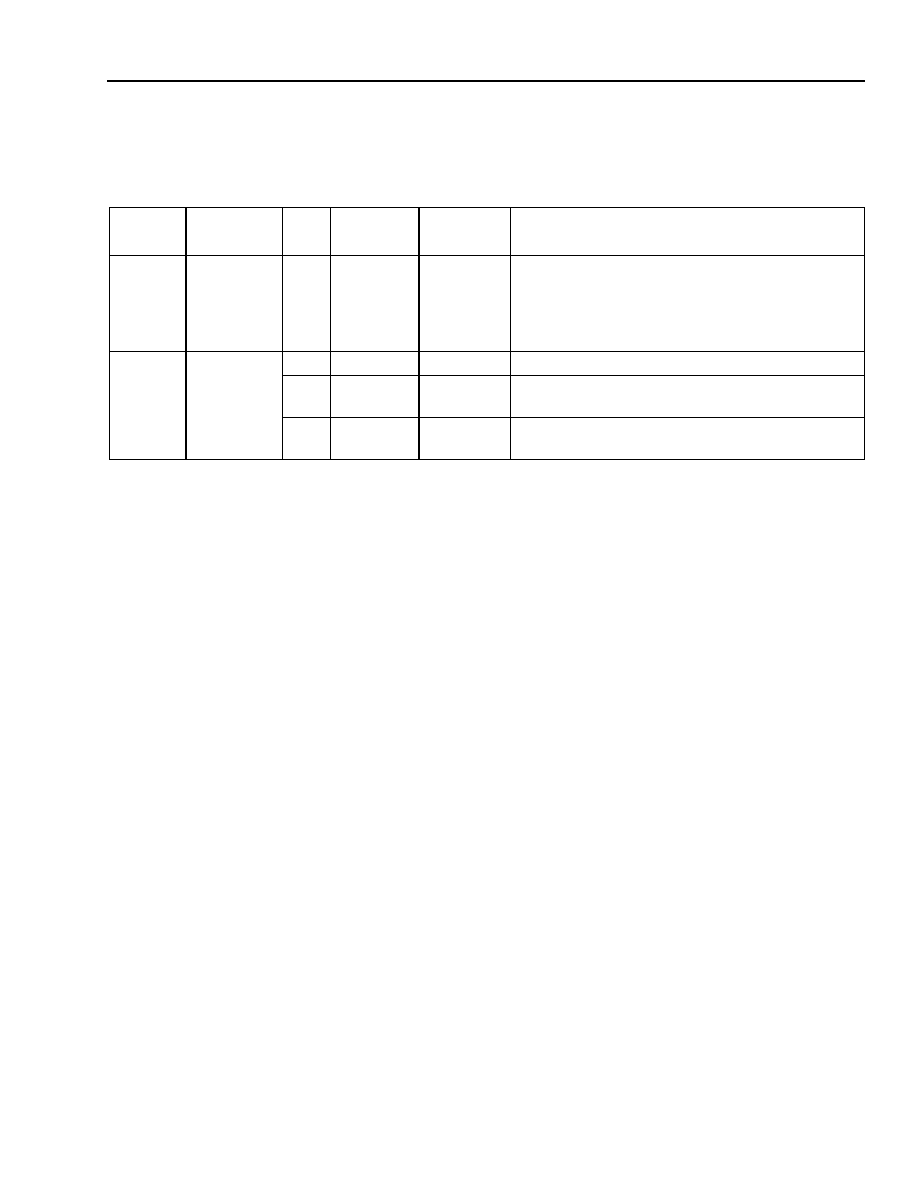

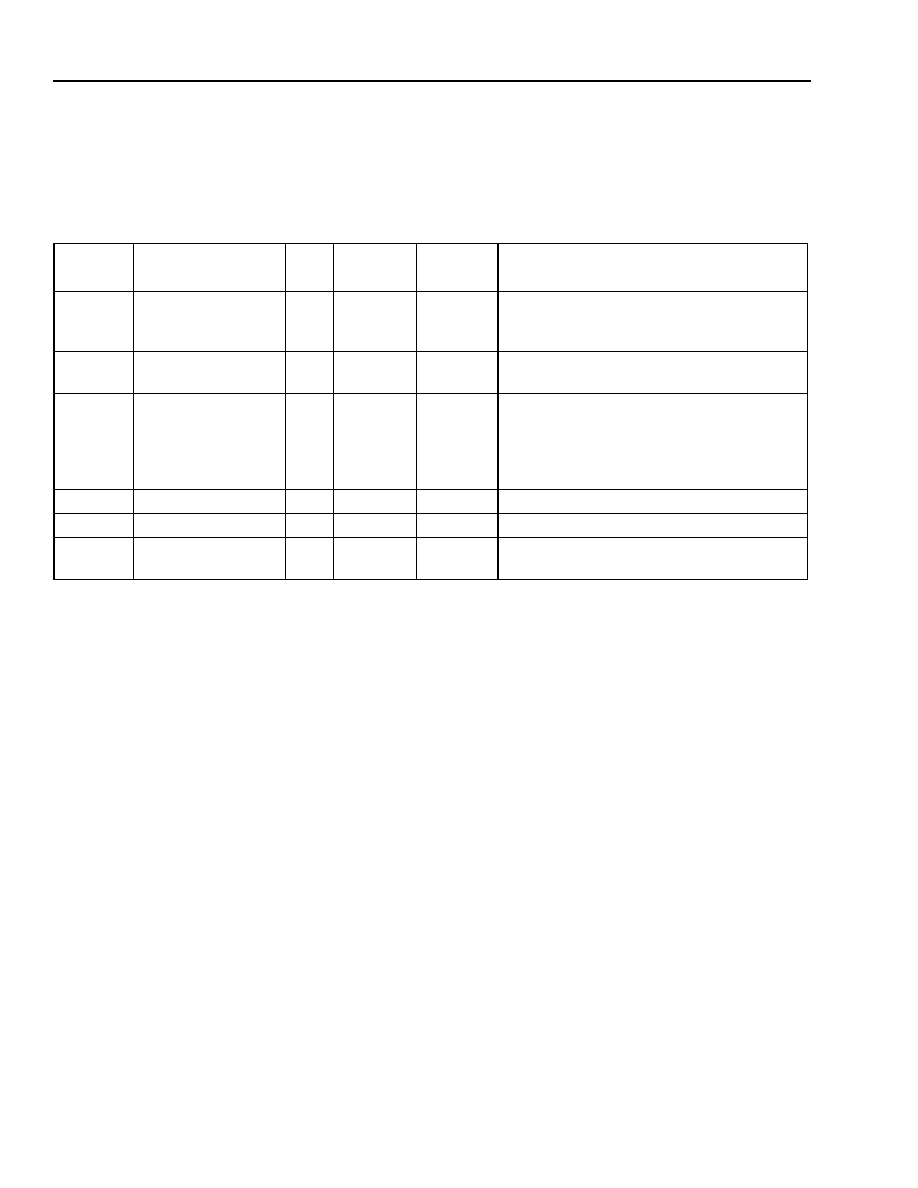

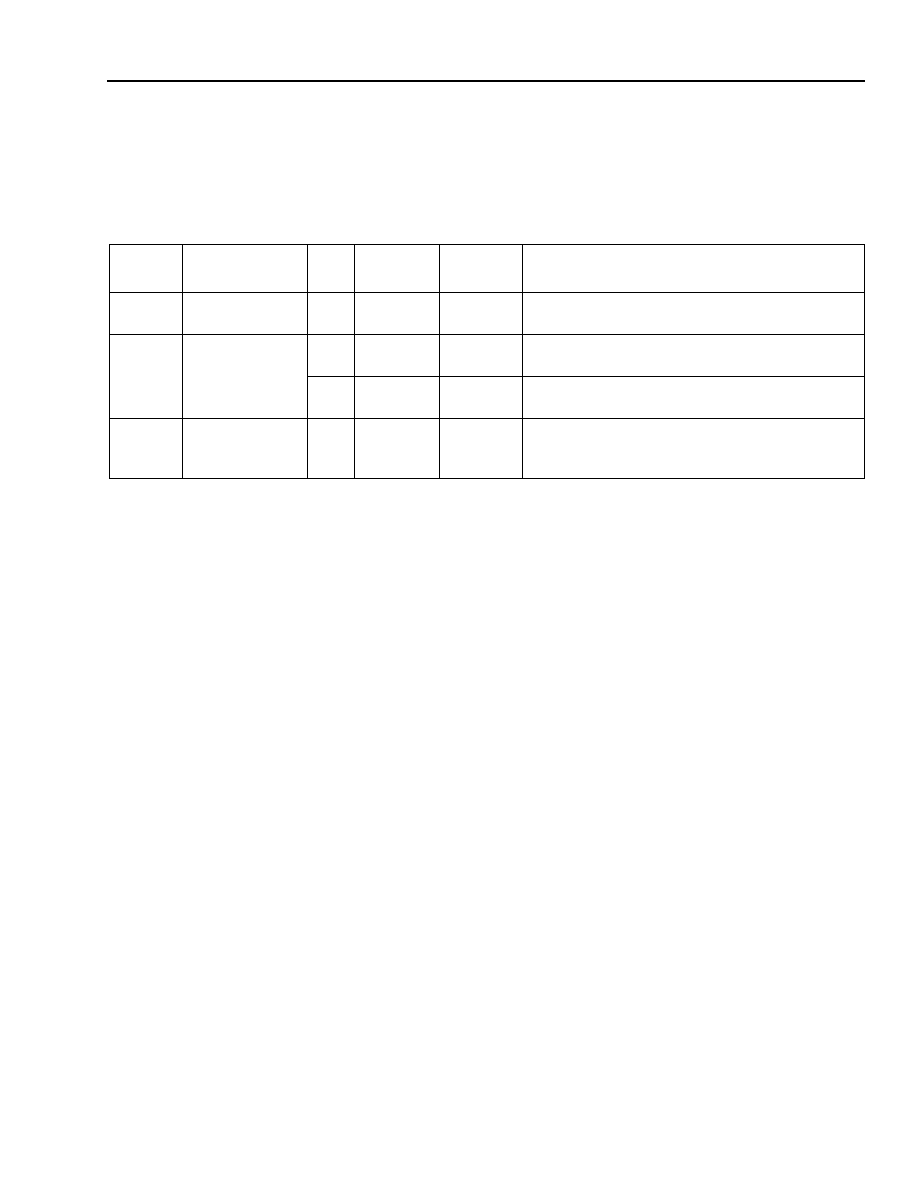

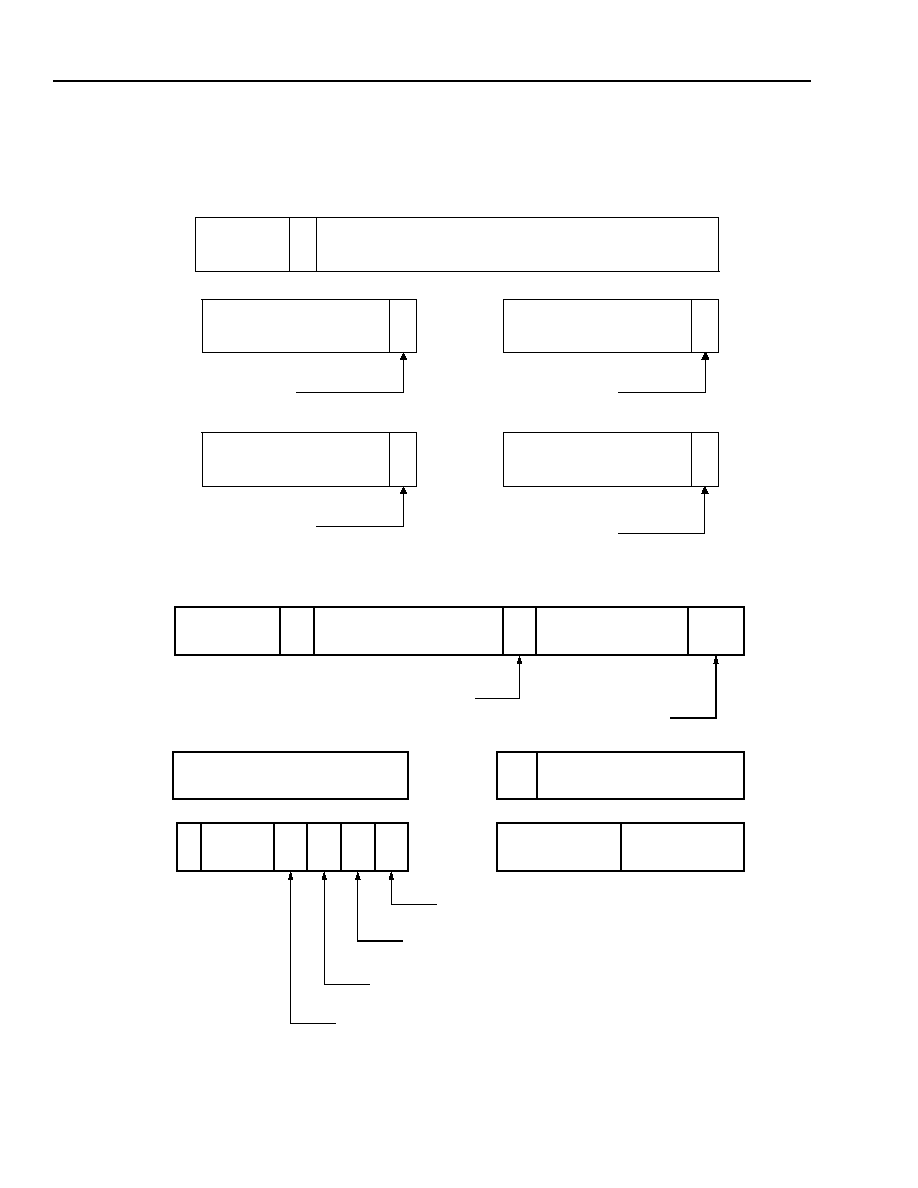

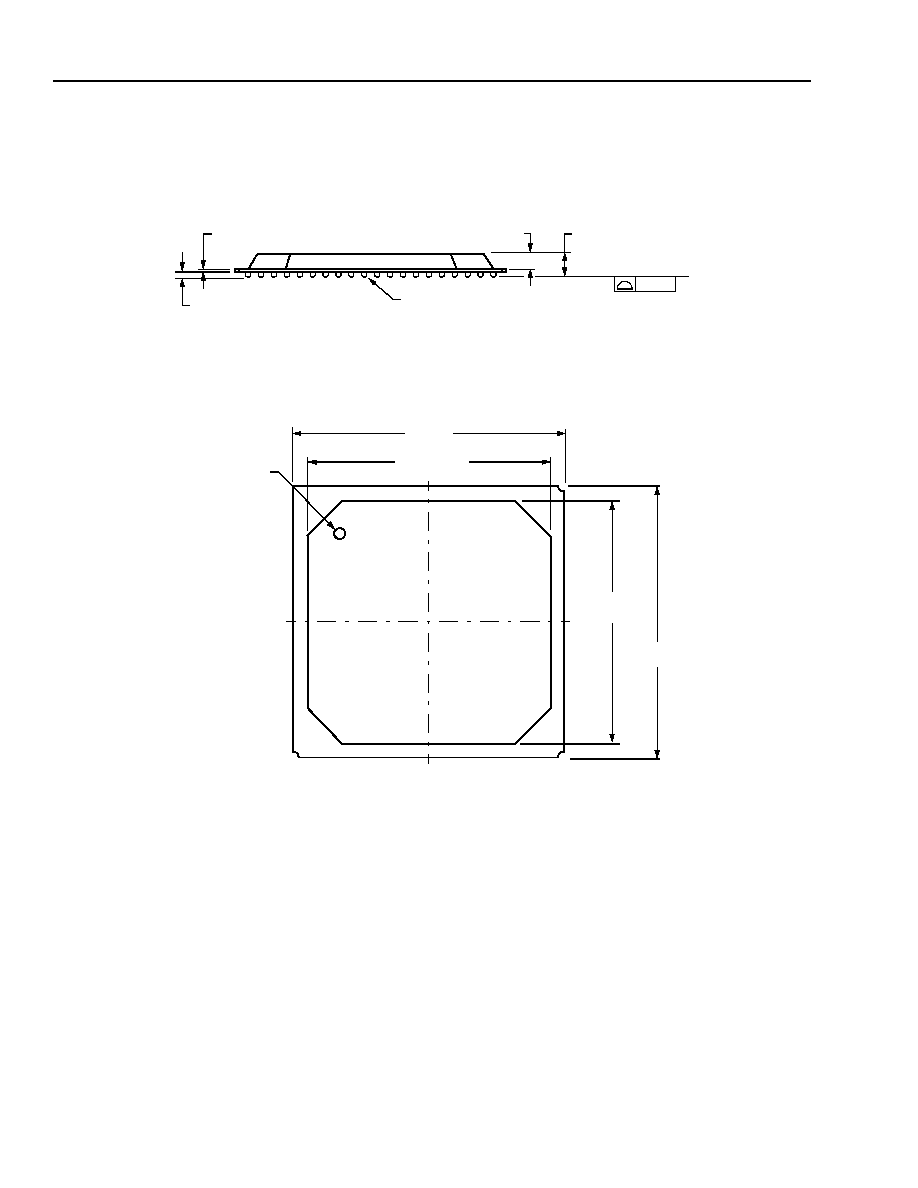

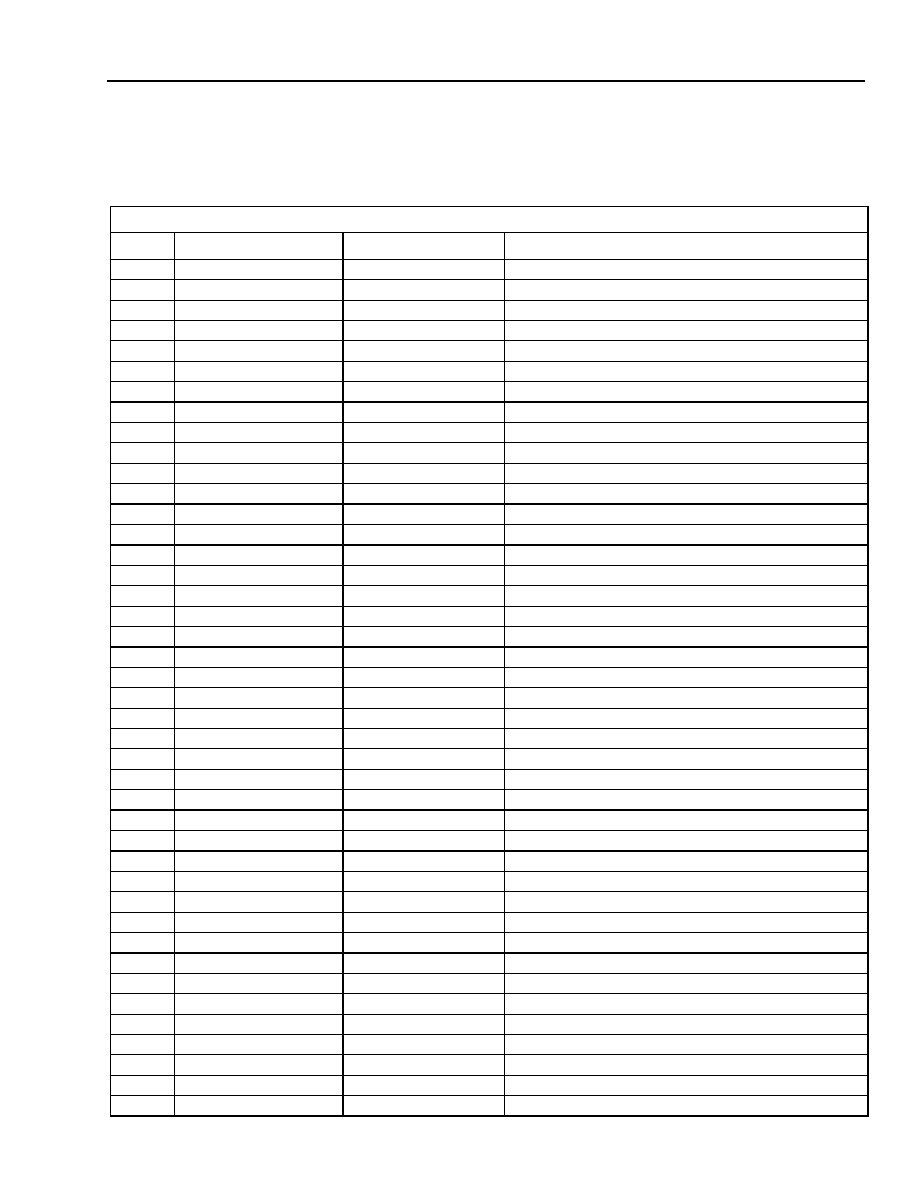

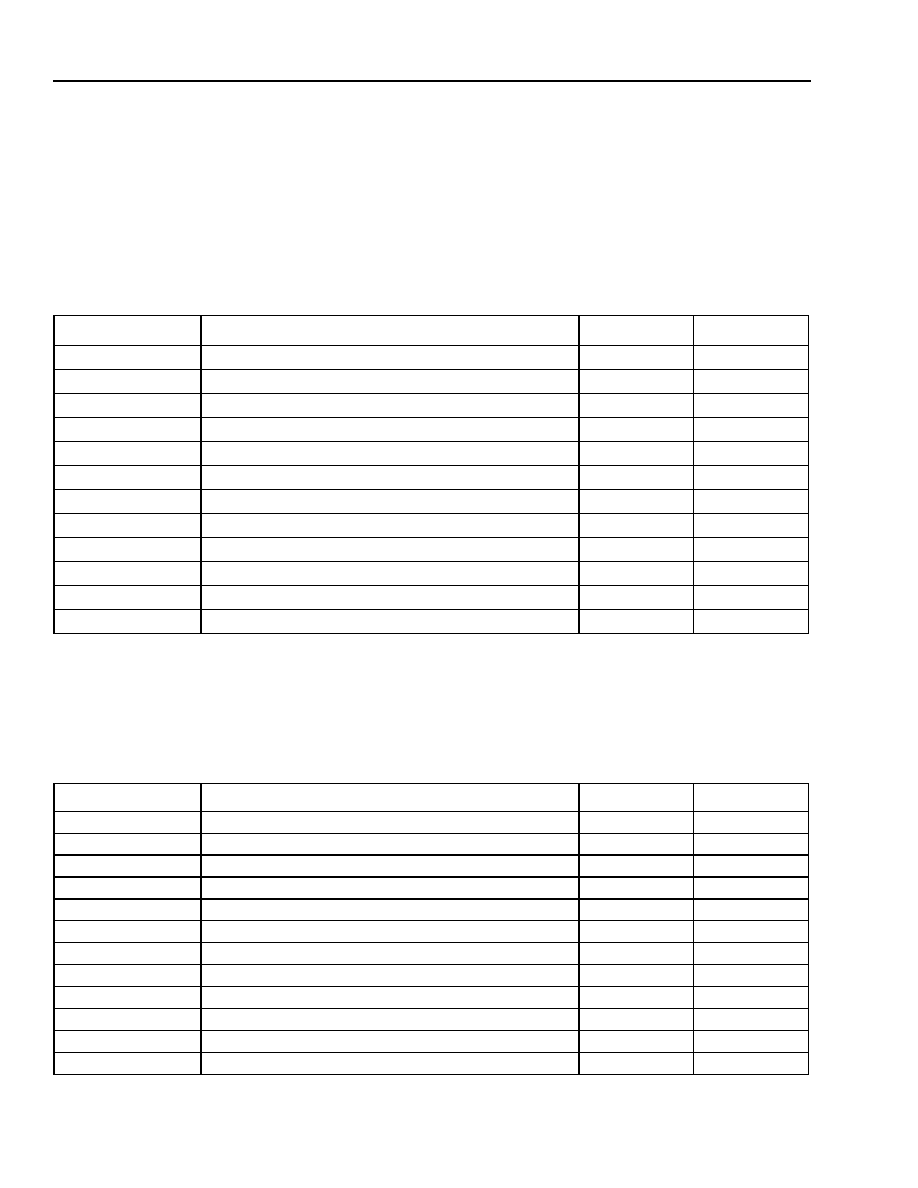

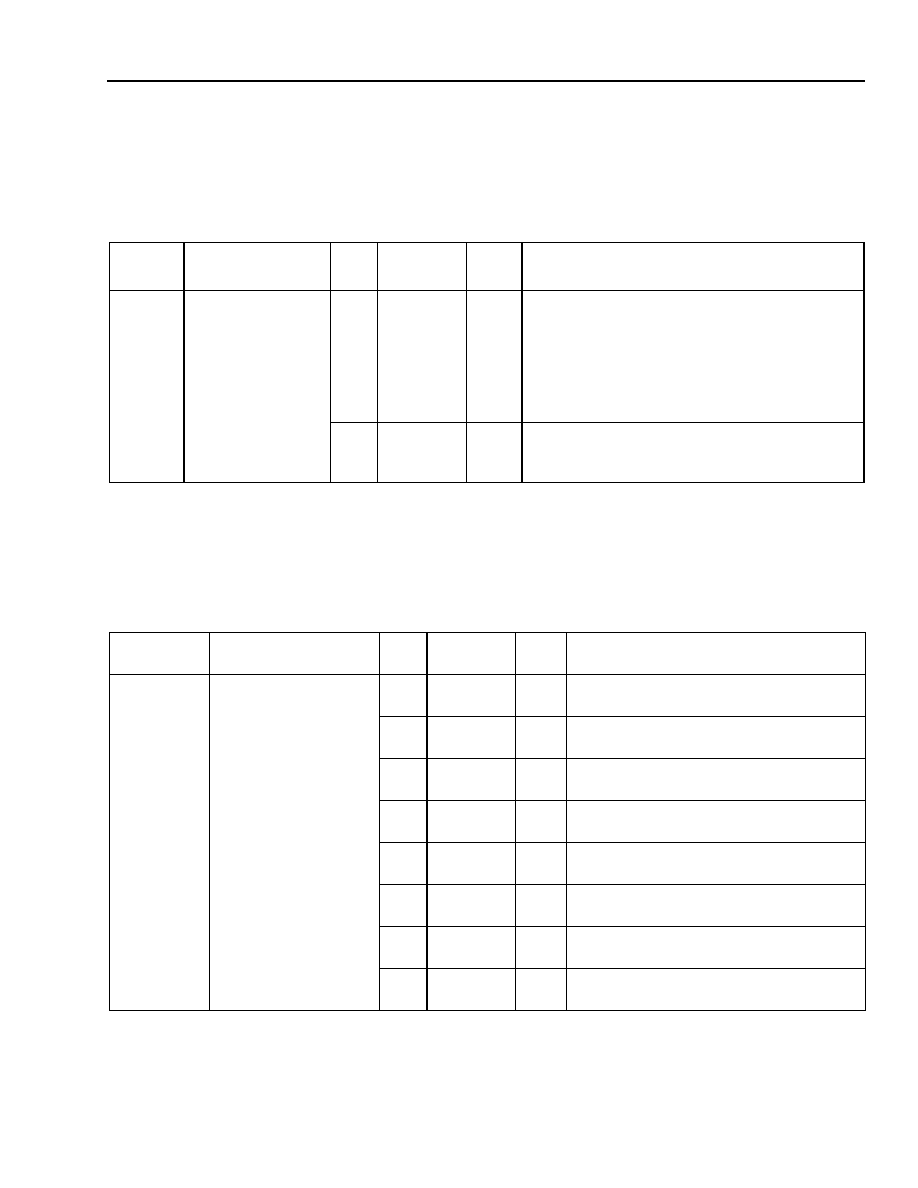

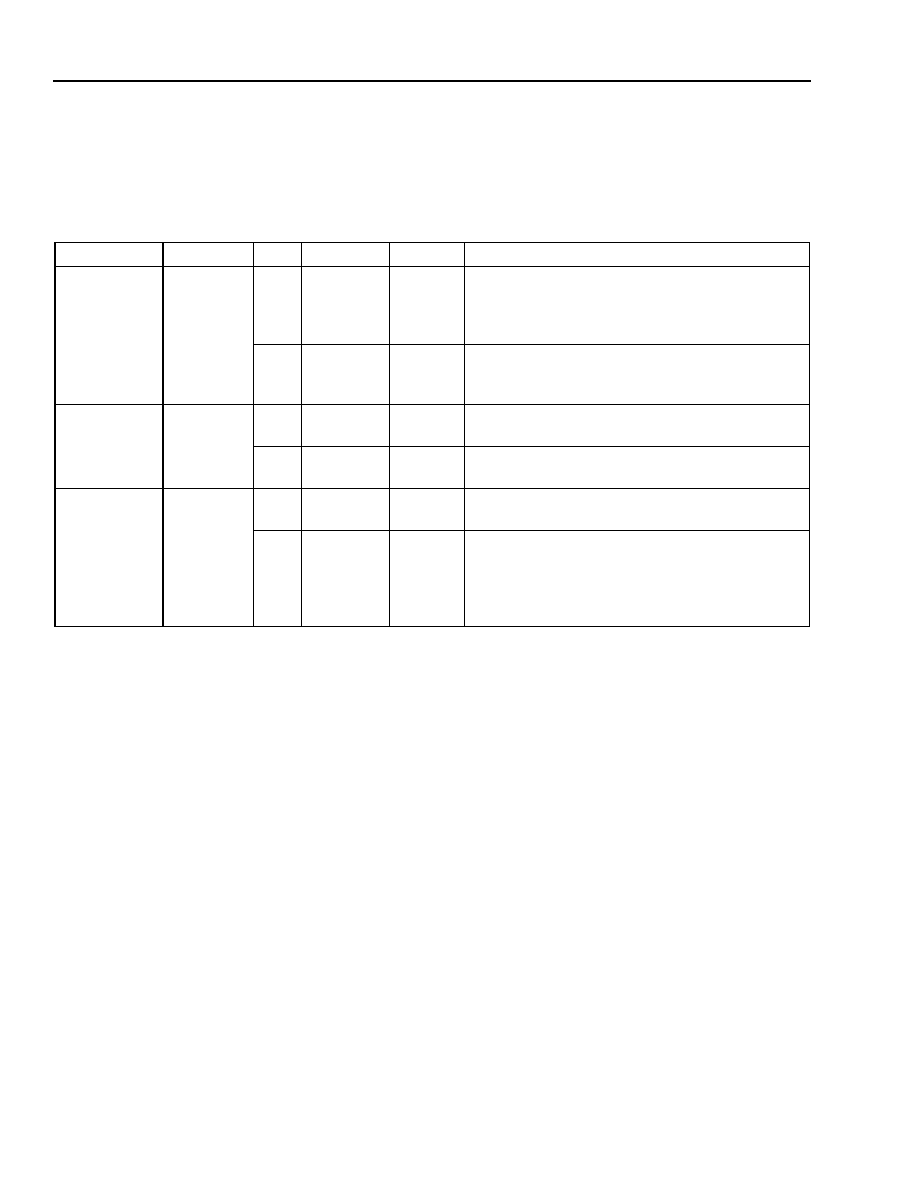

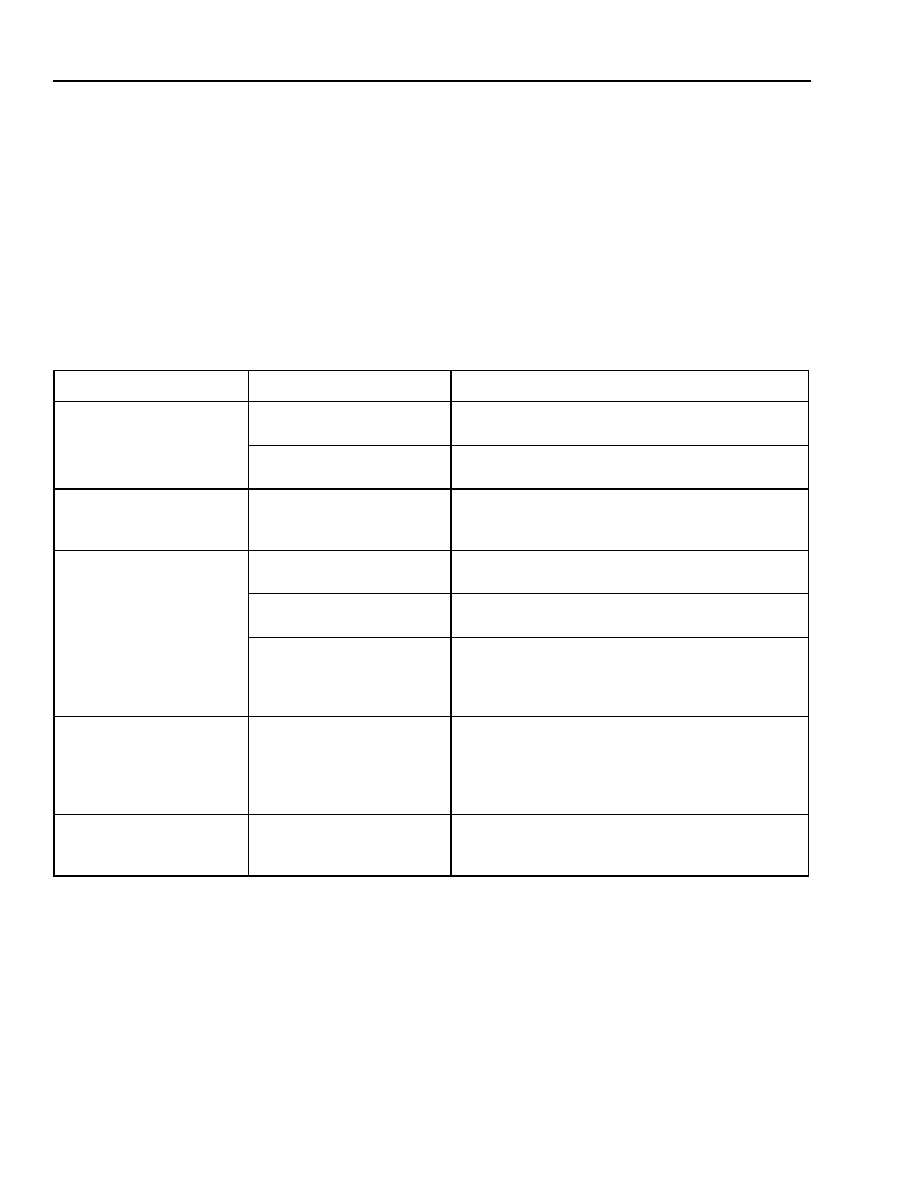

2.2 T8110L Pinout Information

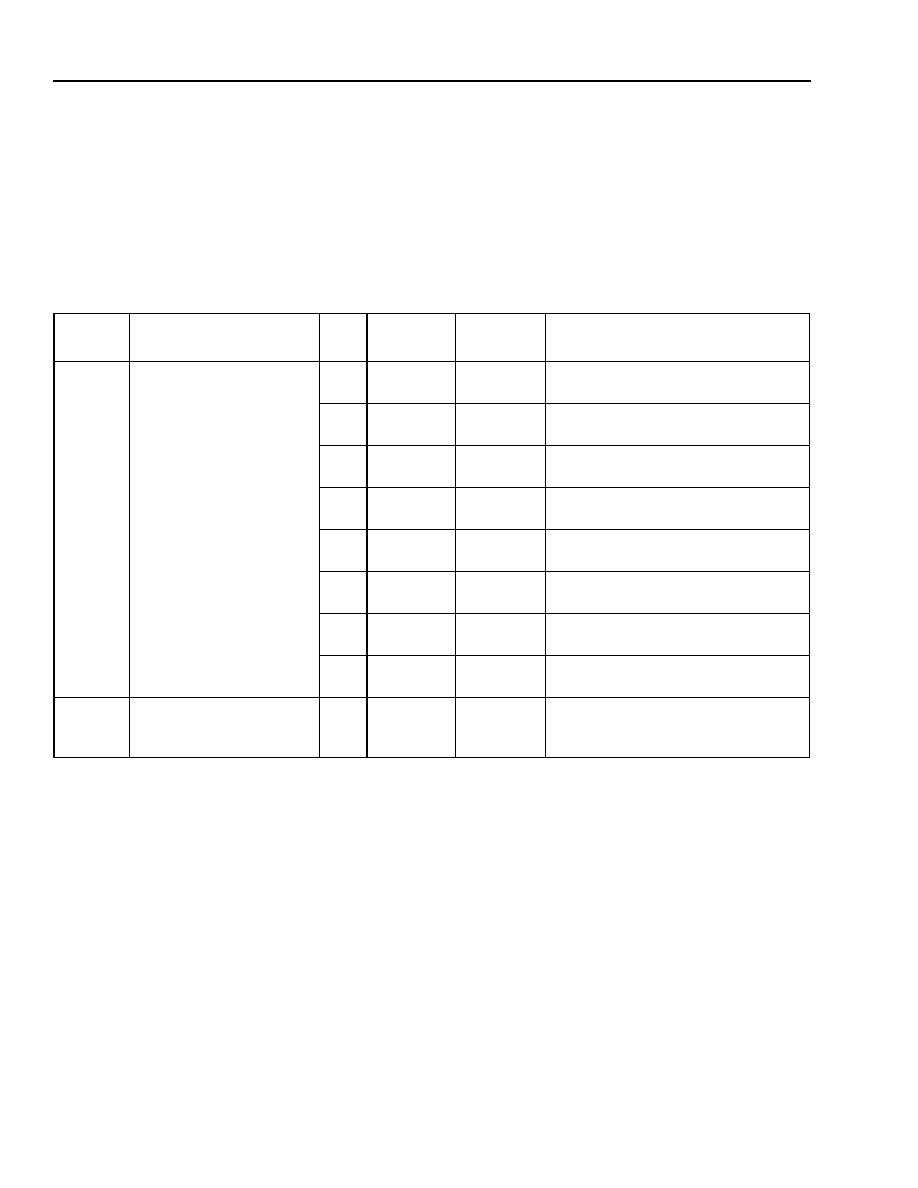

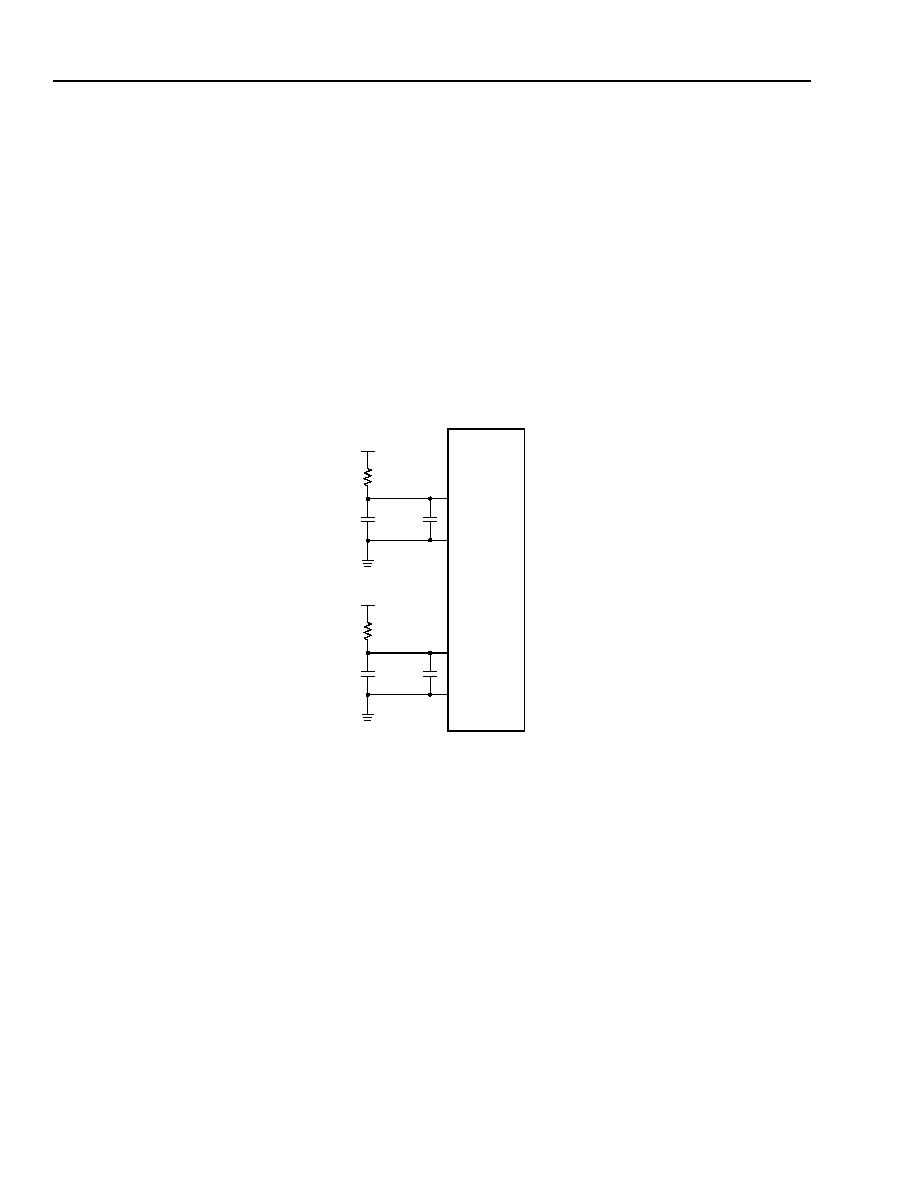

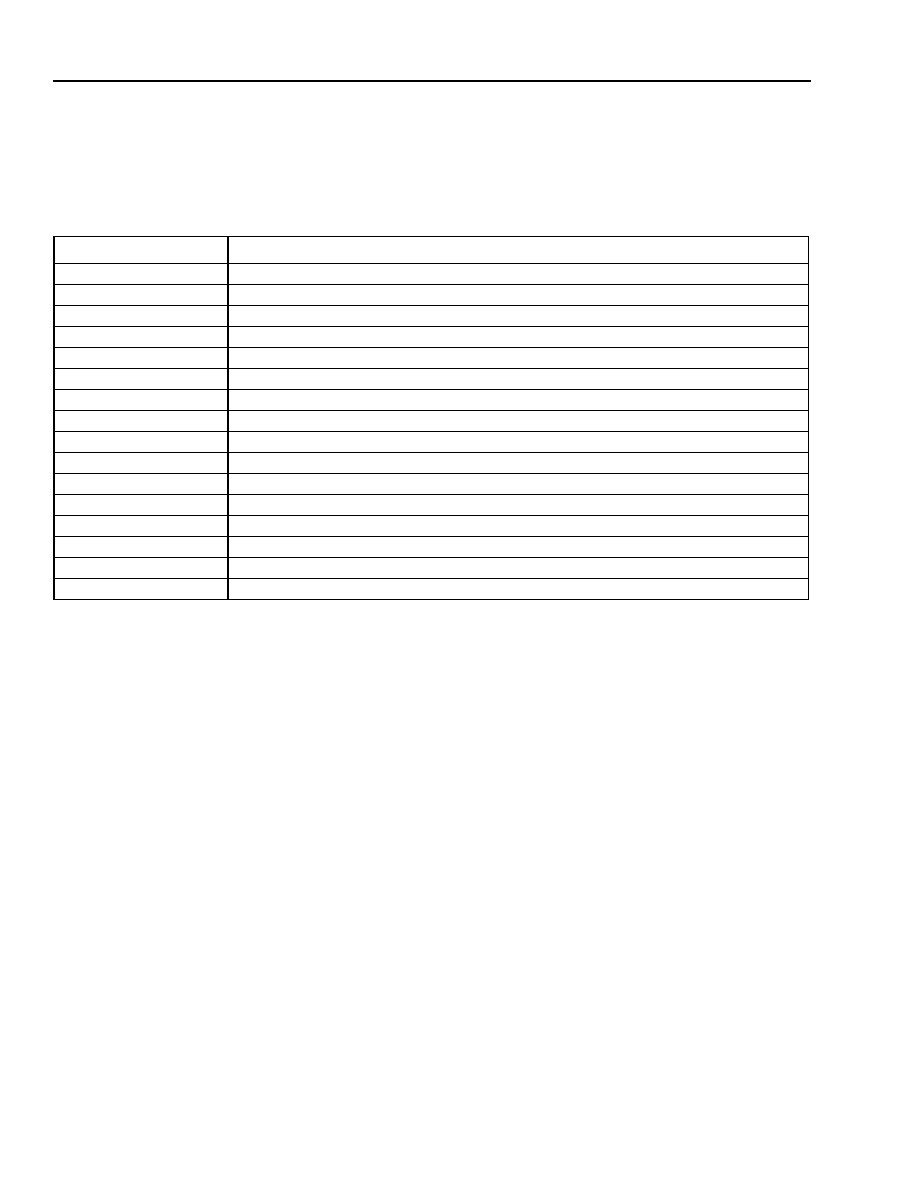

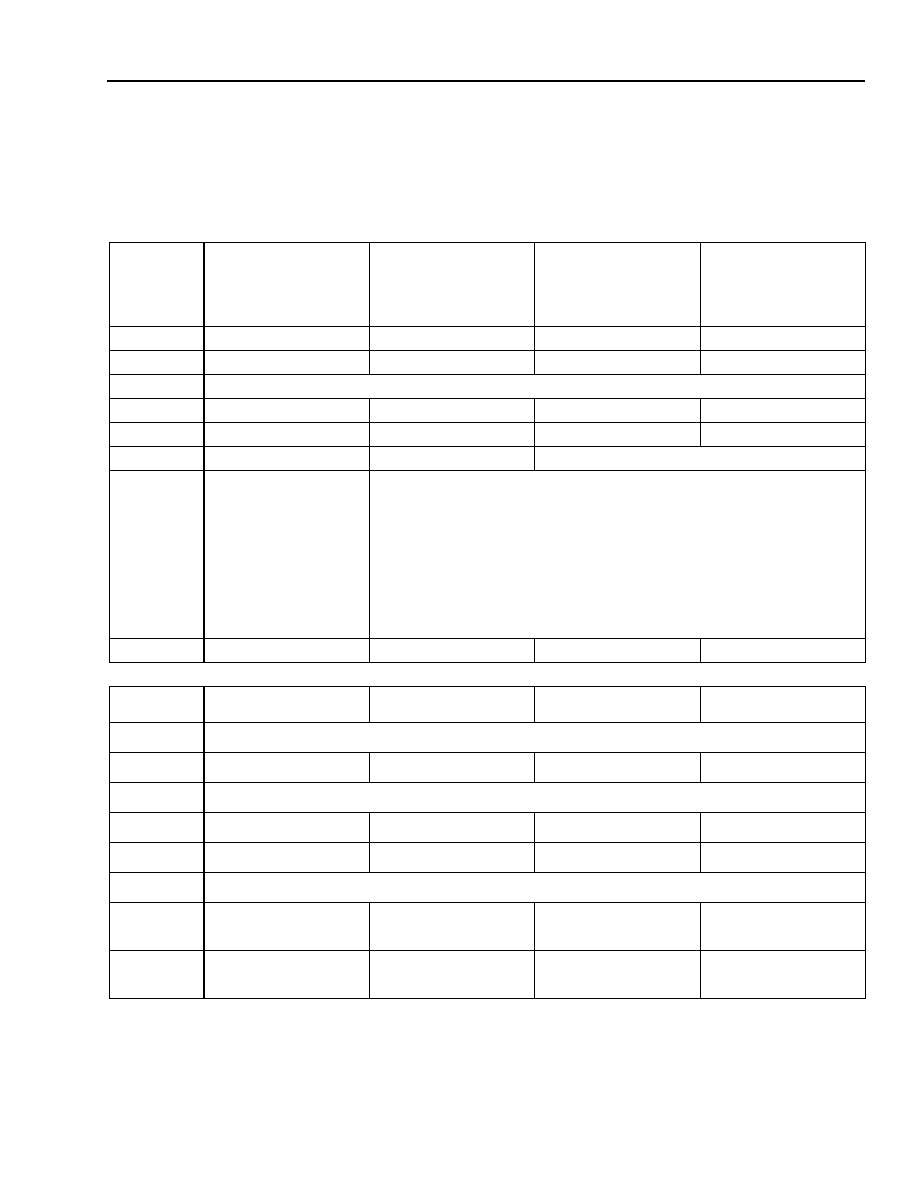

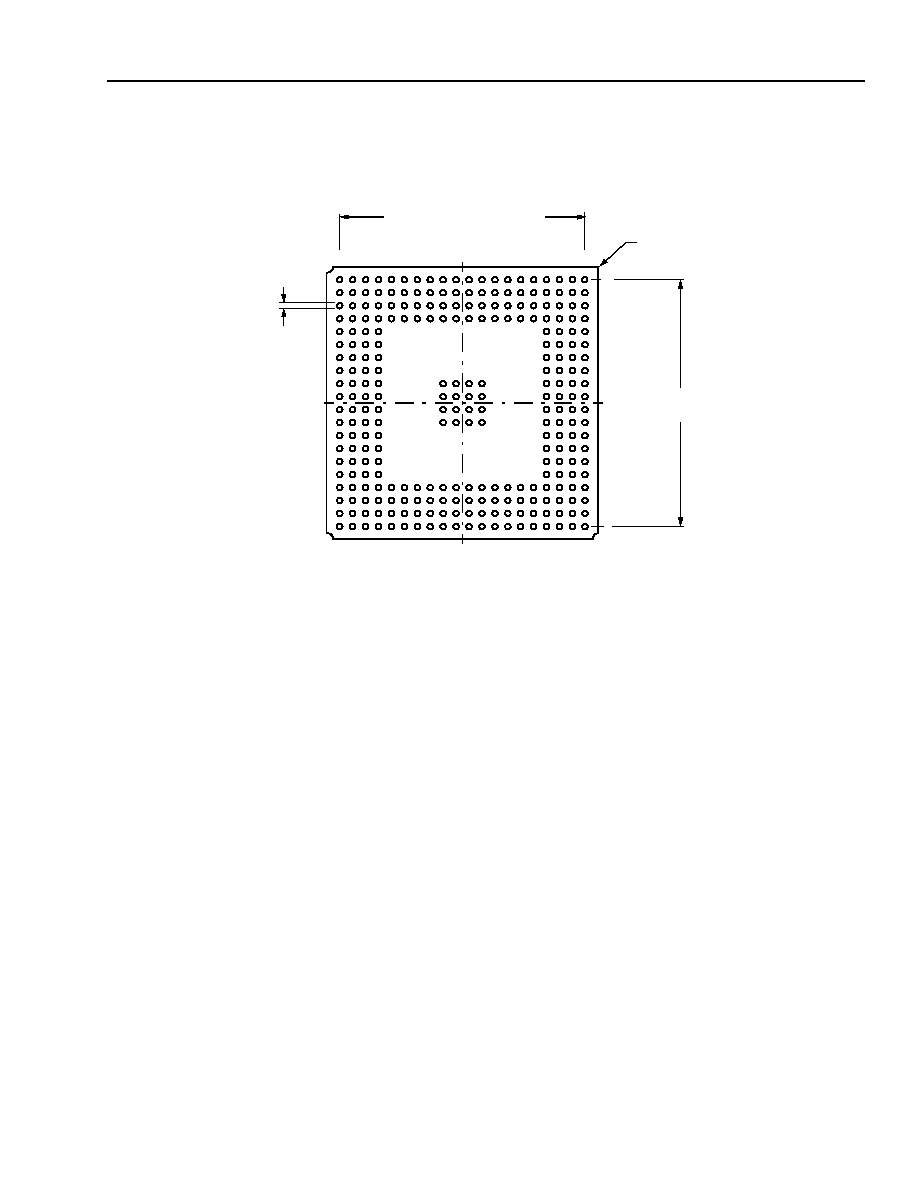

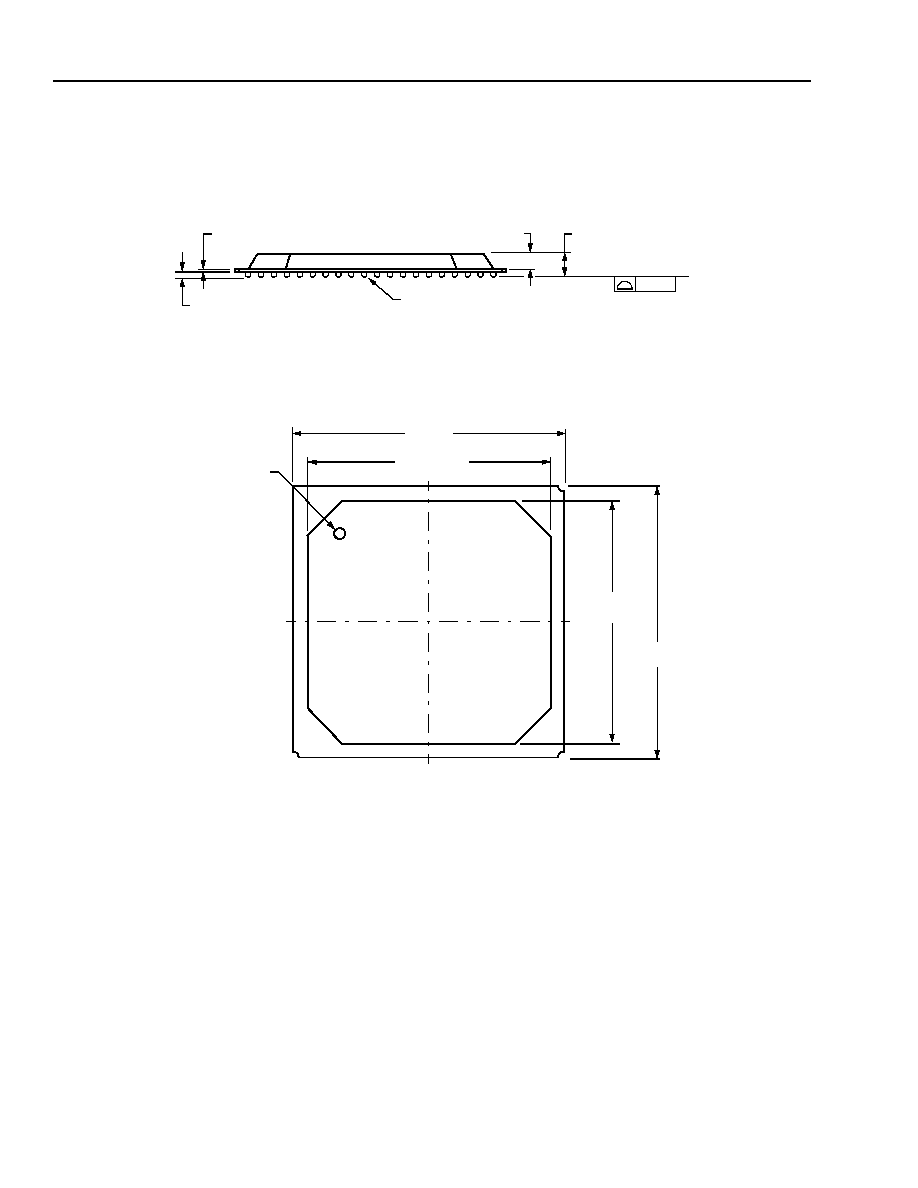

The T8110L package is a 272-pin PBGA ball grid array. Refer to the table below for ball assignment, buffer type,

and pull-up/pull-down information.

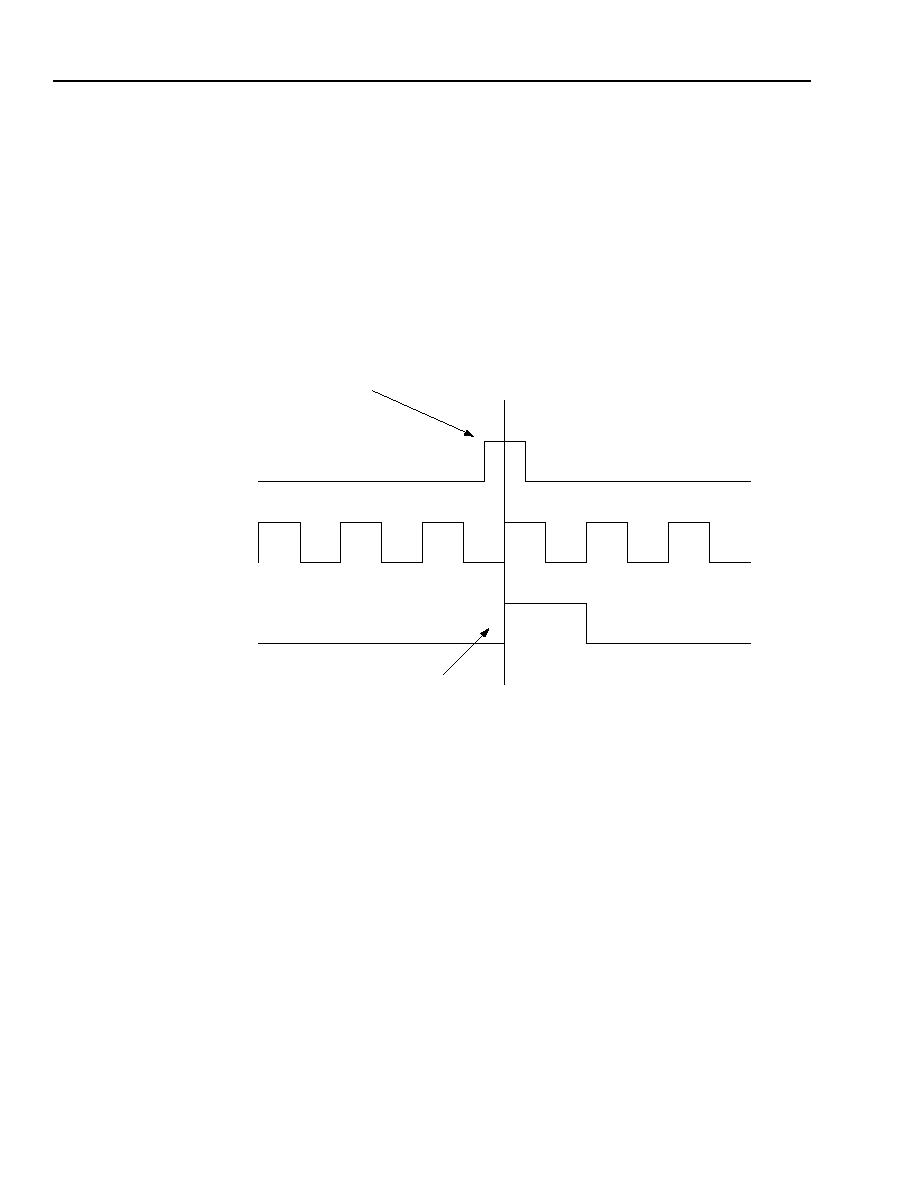

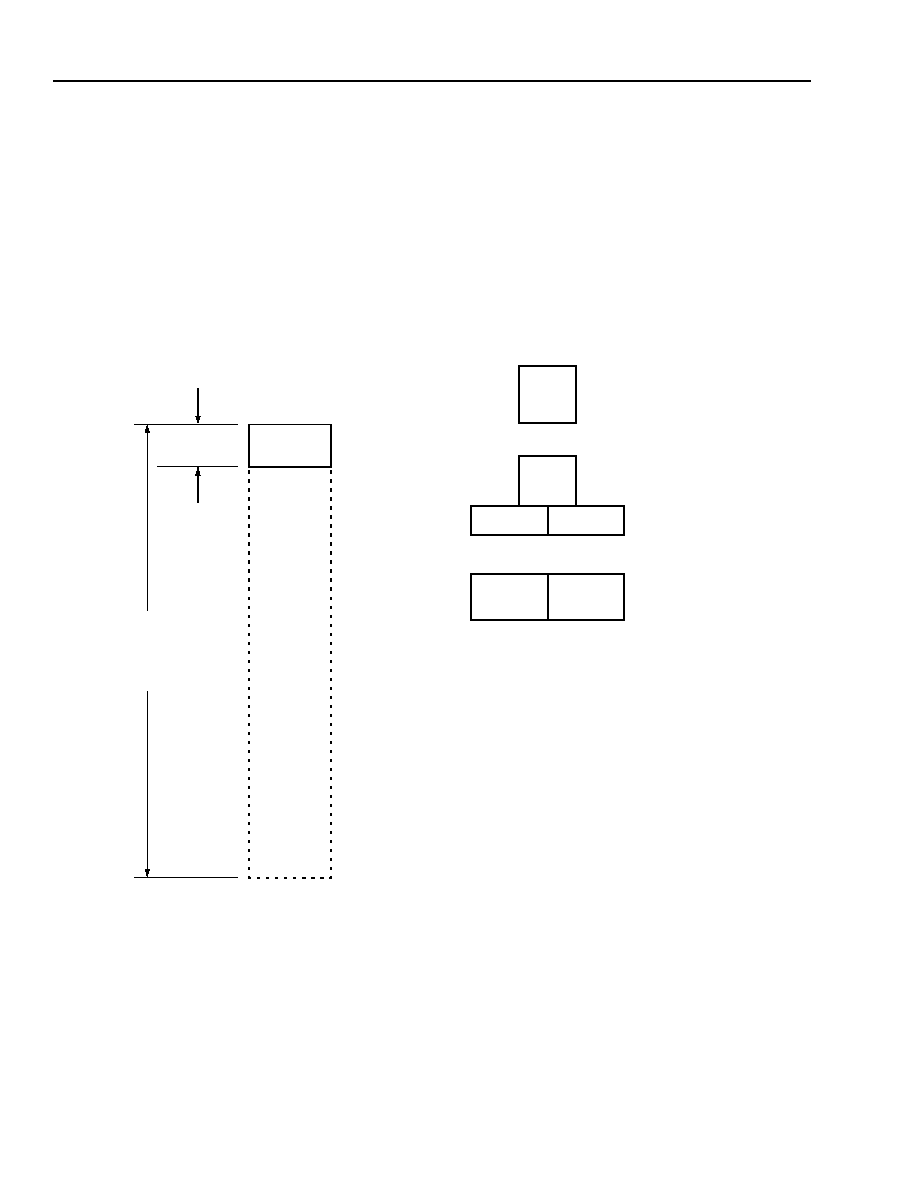

Note: The pull-up/down column in the following table is defined as follows:

!

20 k

down--20 k

pull-down resistor is always in-circuit.

!

50 k

up--50 k

pull-up resistor is always in-circuit.

!

LPUE: 50 k

up--when LPUE = 1, a 50 k

pull-up resistor is in-circuit.

!

Enabled: 50 k

up/20 k

Vpre--when H100_ENABLE = 1, a 50 k

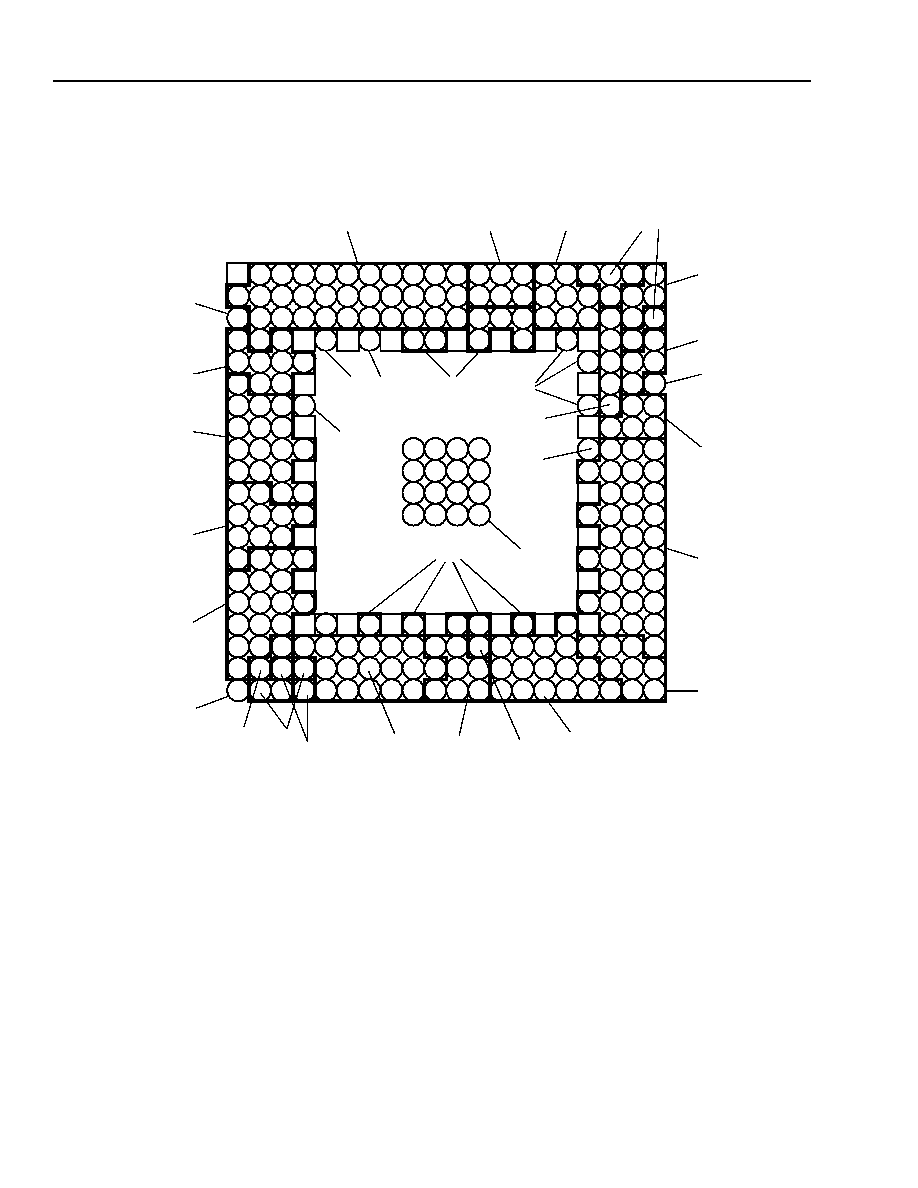

pull-up resistor is in-circuit (see Figure 1 on

page 20). When H110_ENABLE = 1, a 20 k

pull-down resistor from the VPRECHARGE input to this signal is in-

circuit.

Agere Systems Inc.

13

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

2 Pin Description

(continued)

2.2 T8110L Pinout Information

(continued)

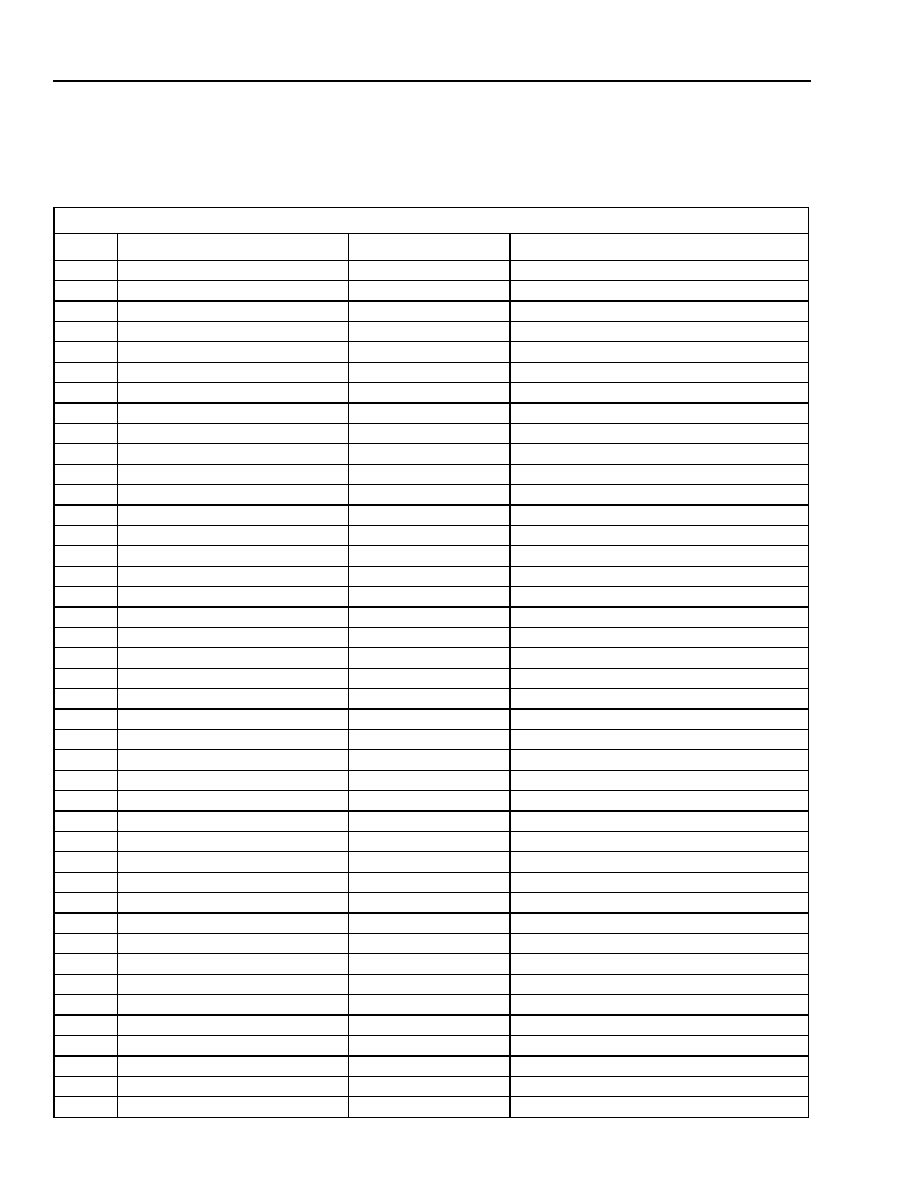

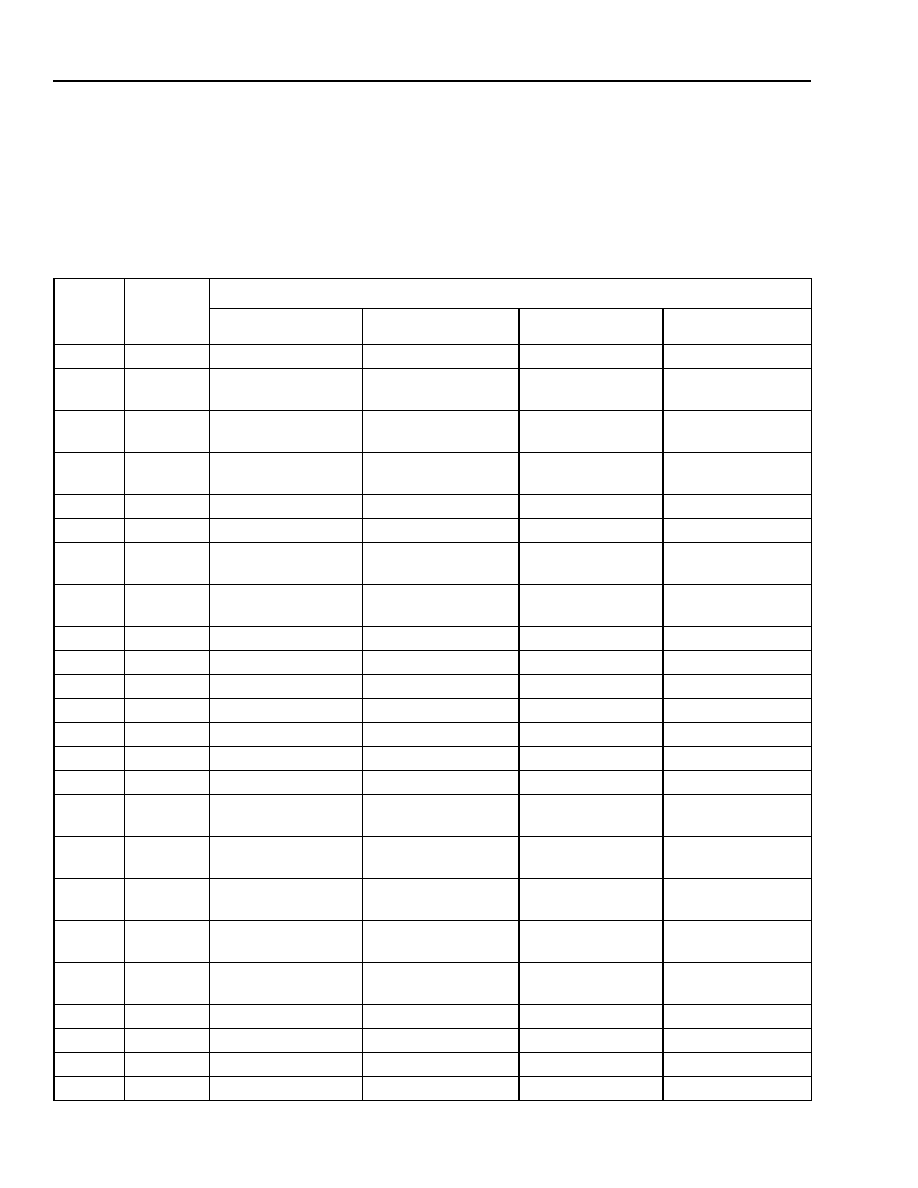

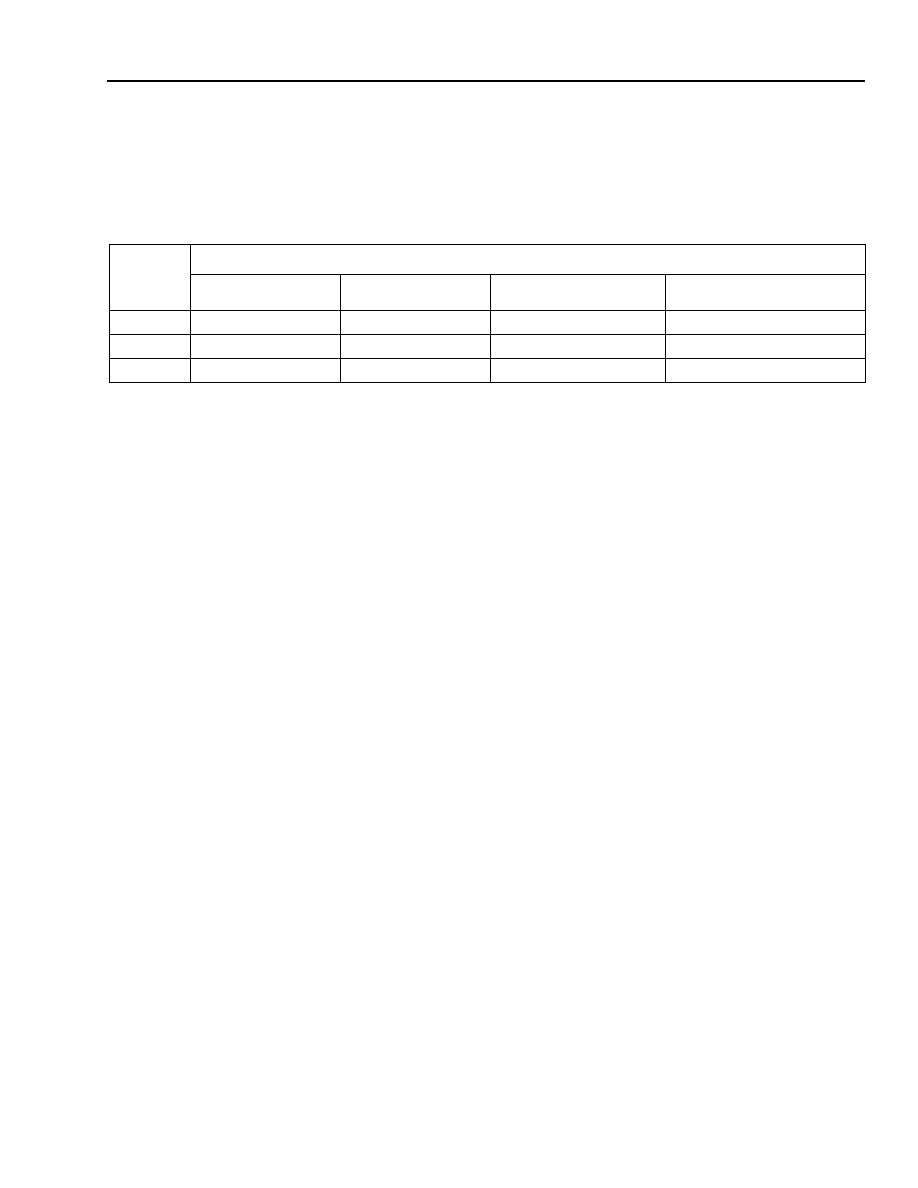

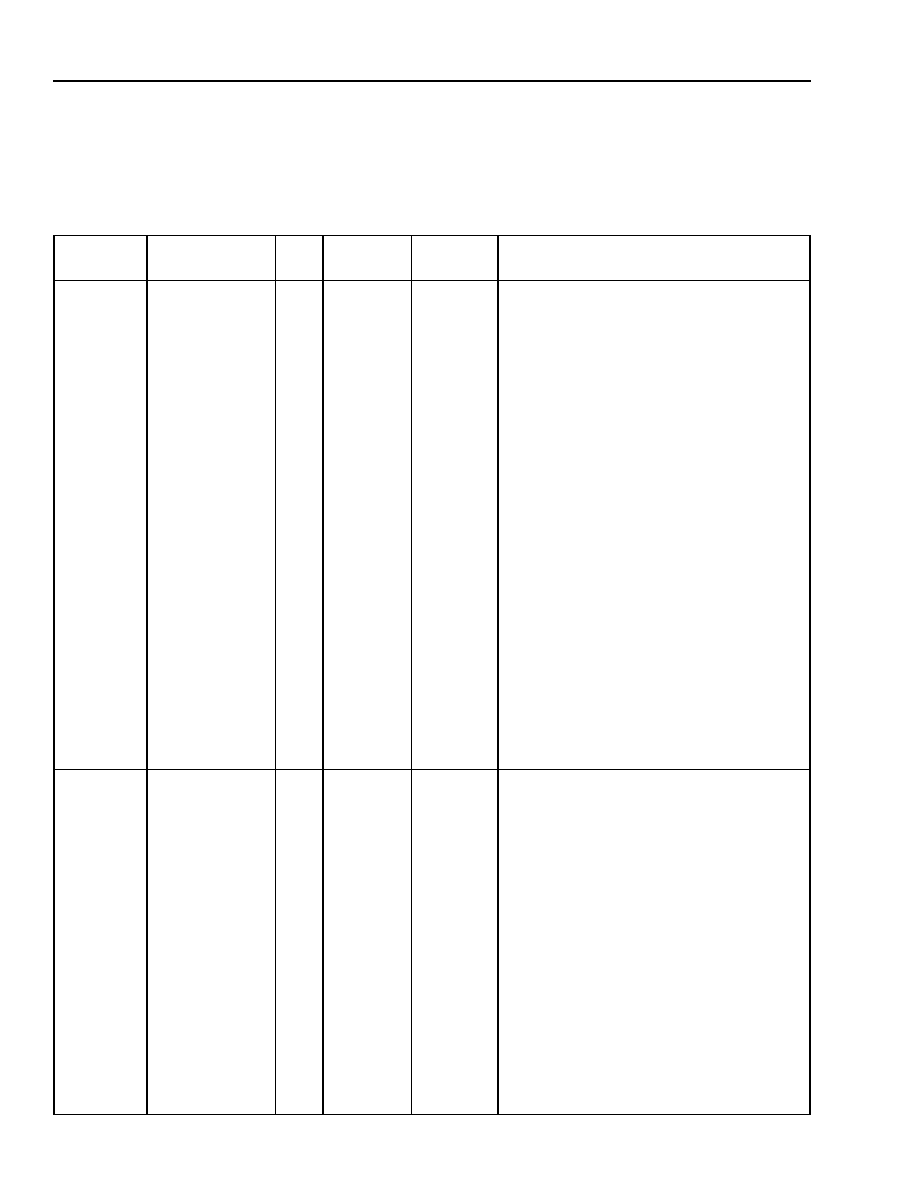

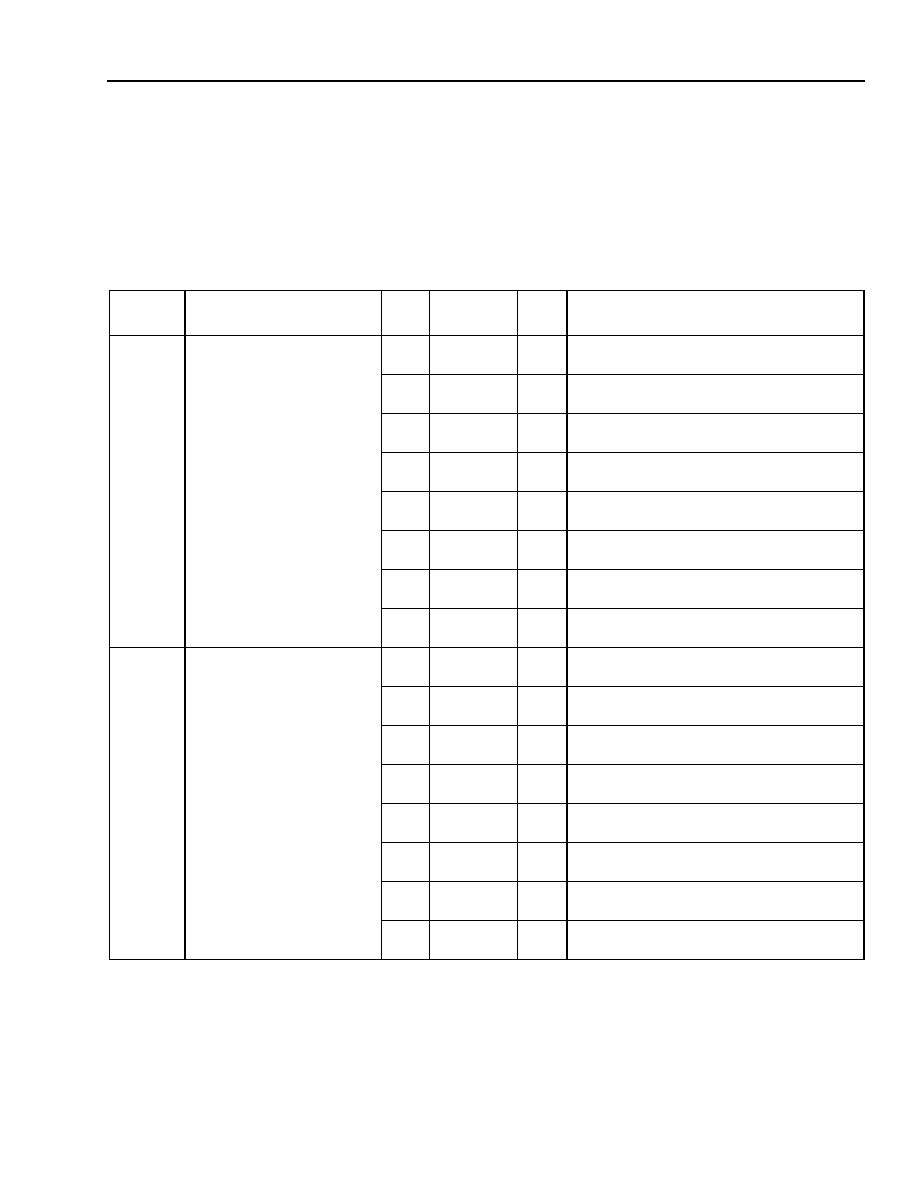

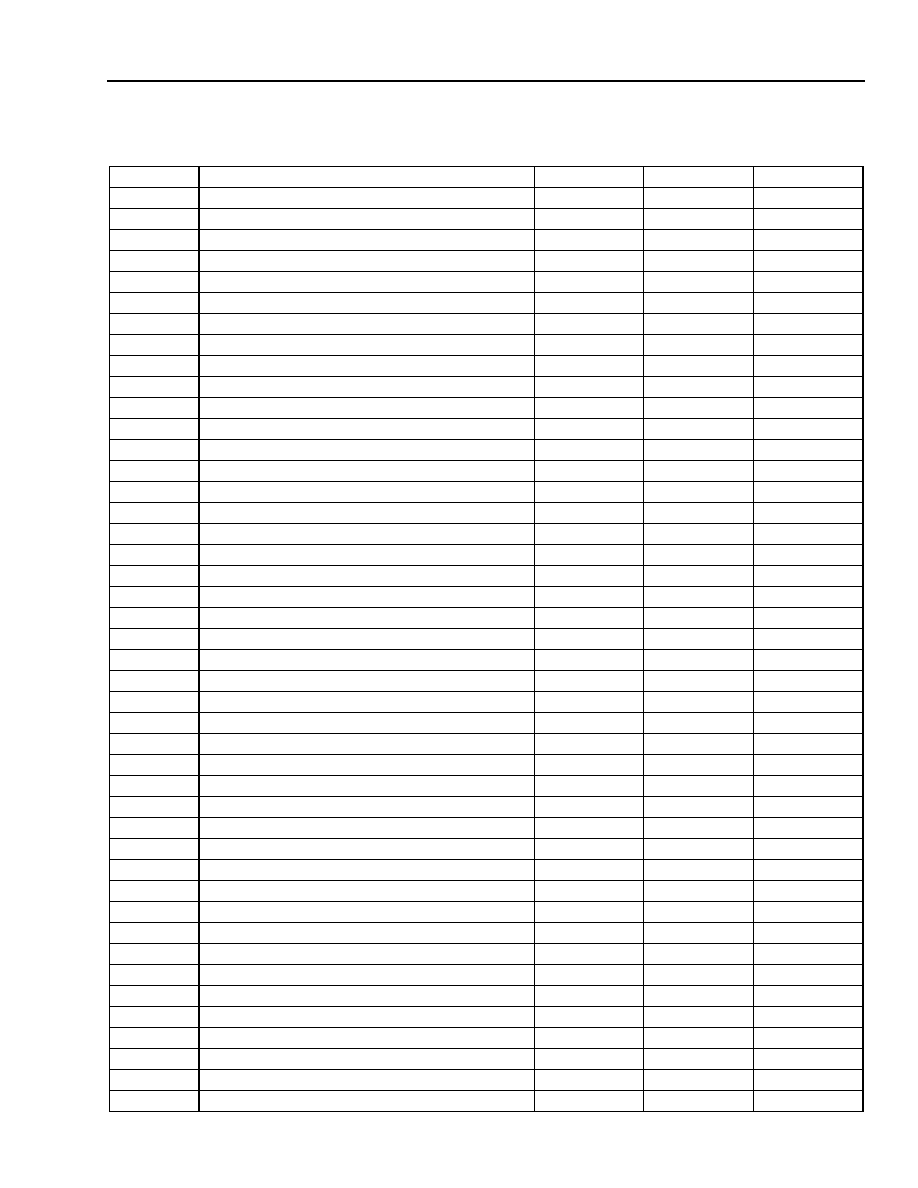

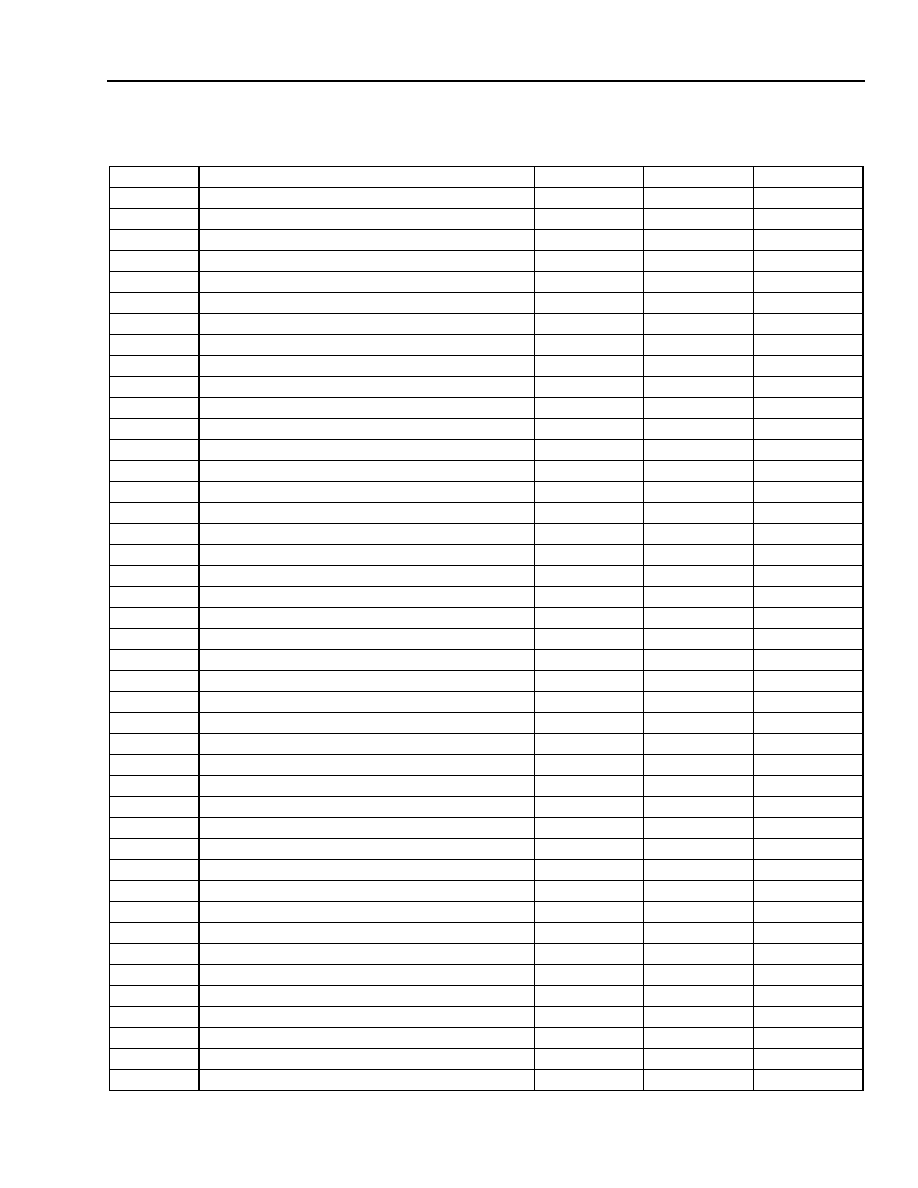

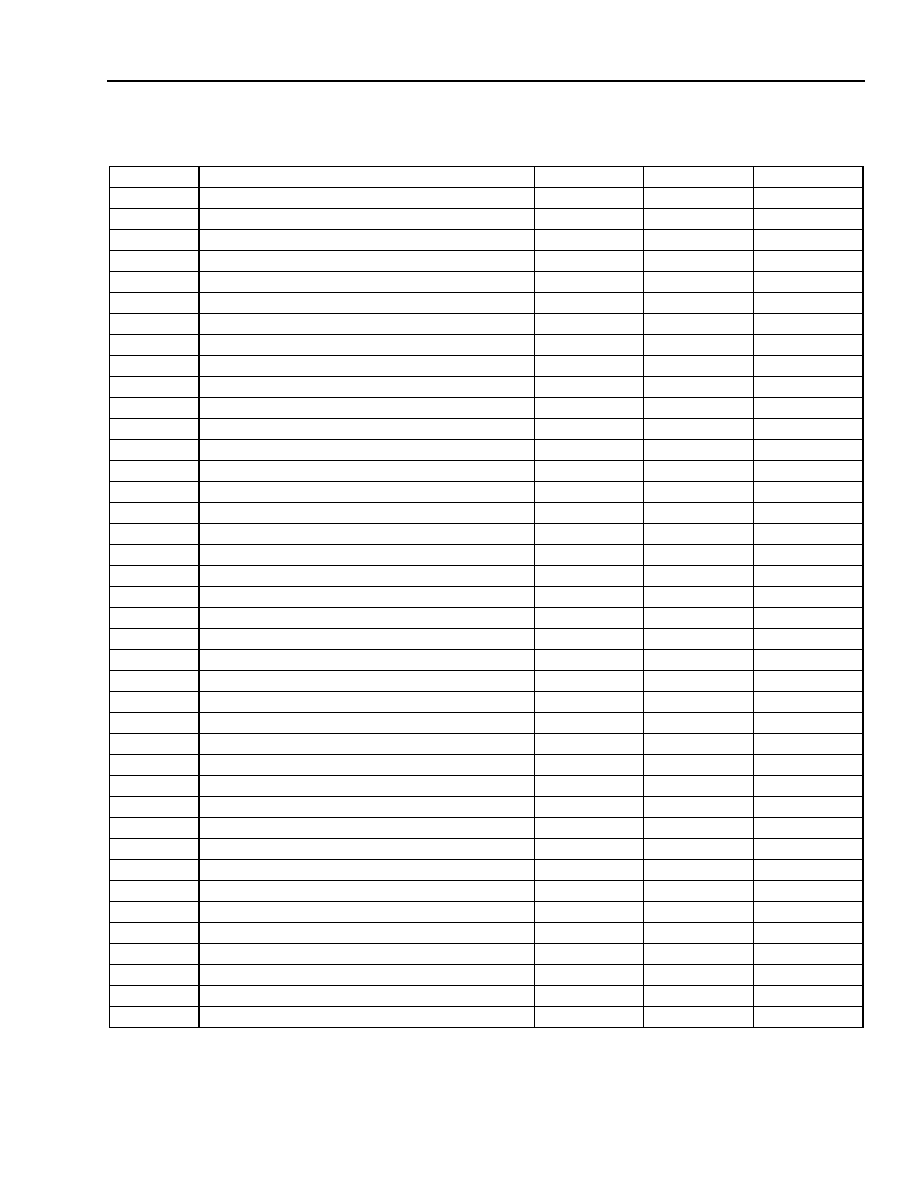

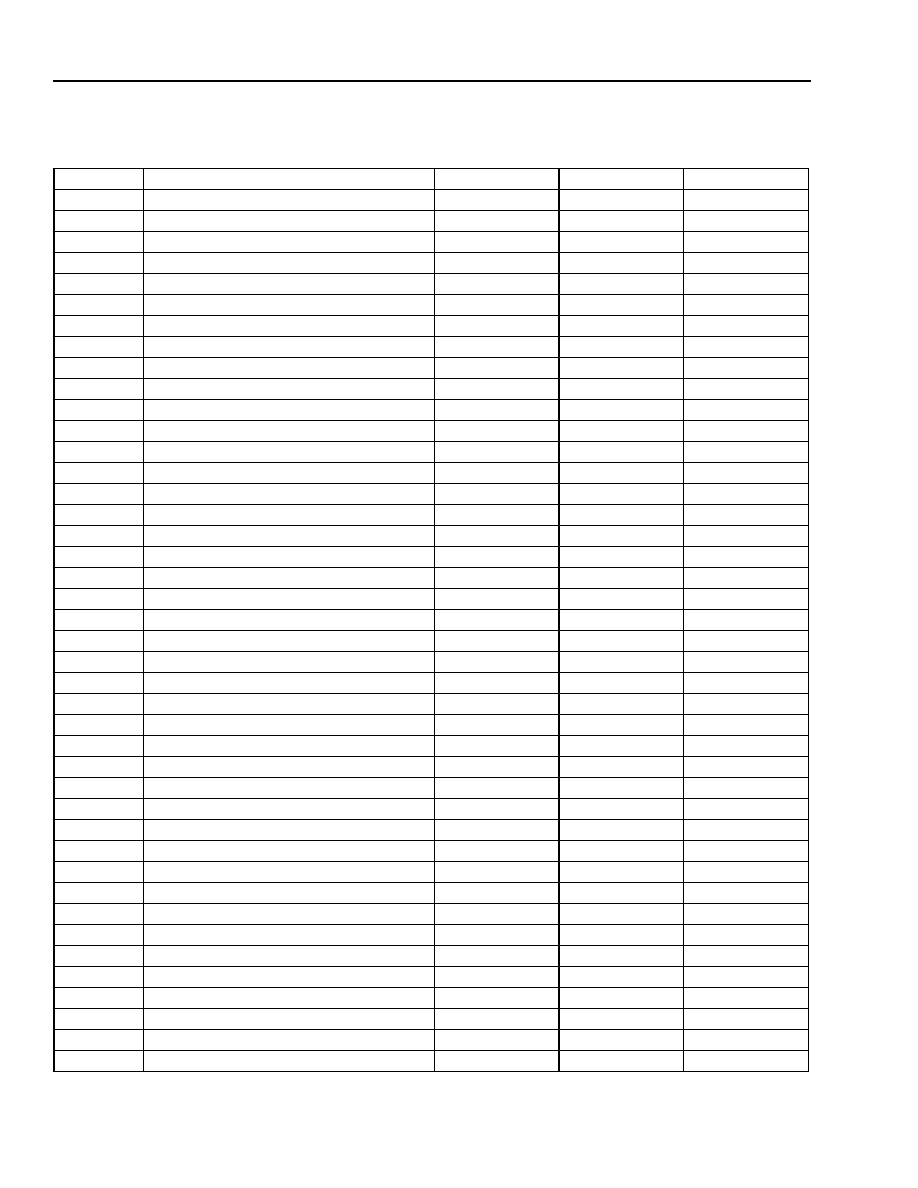

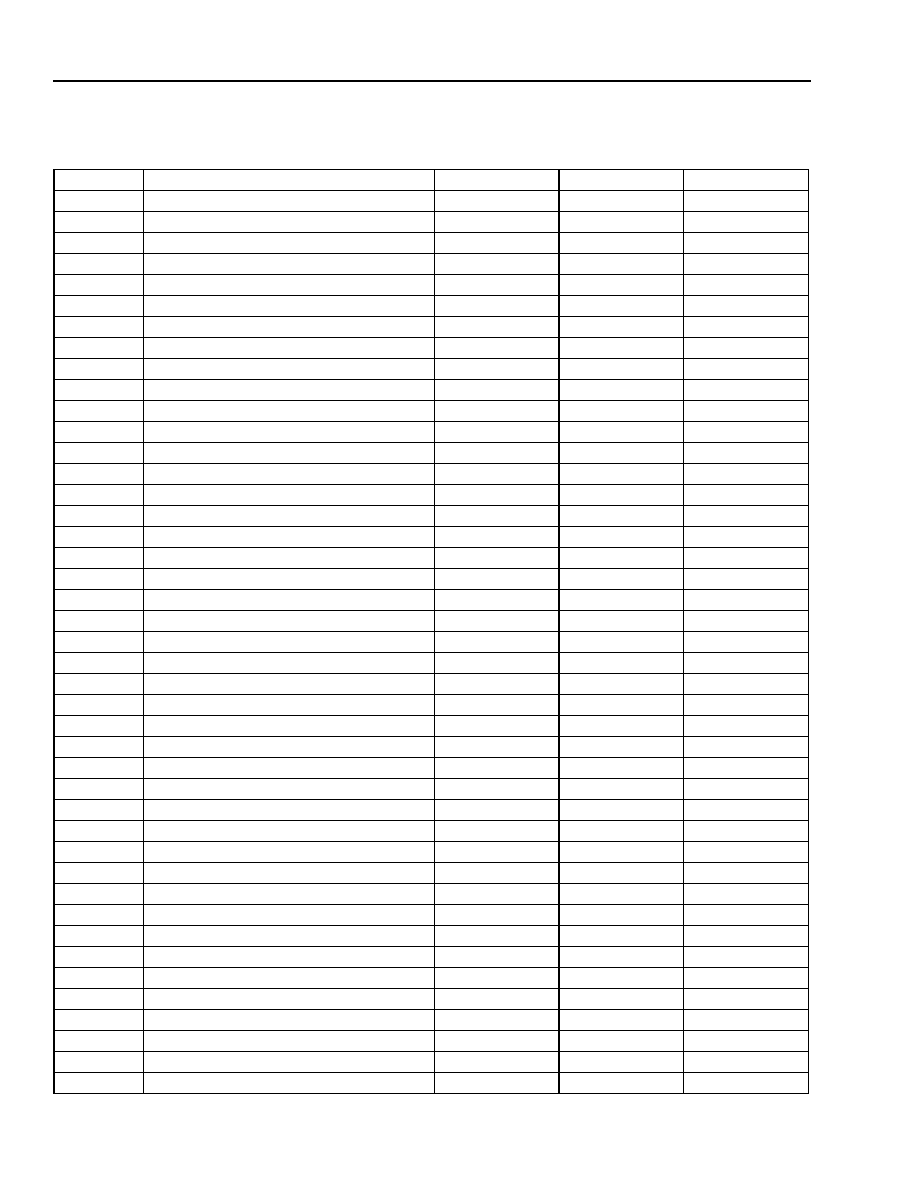

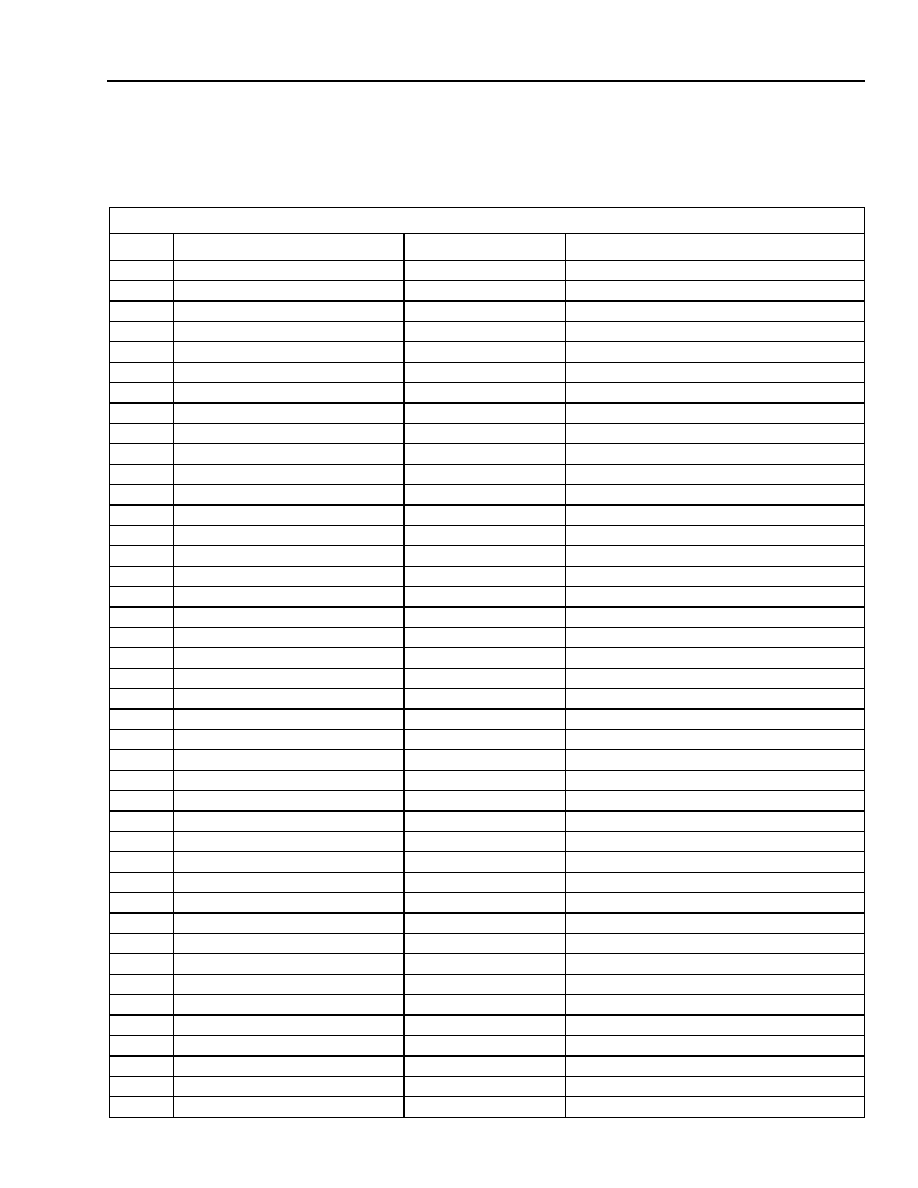

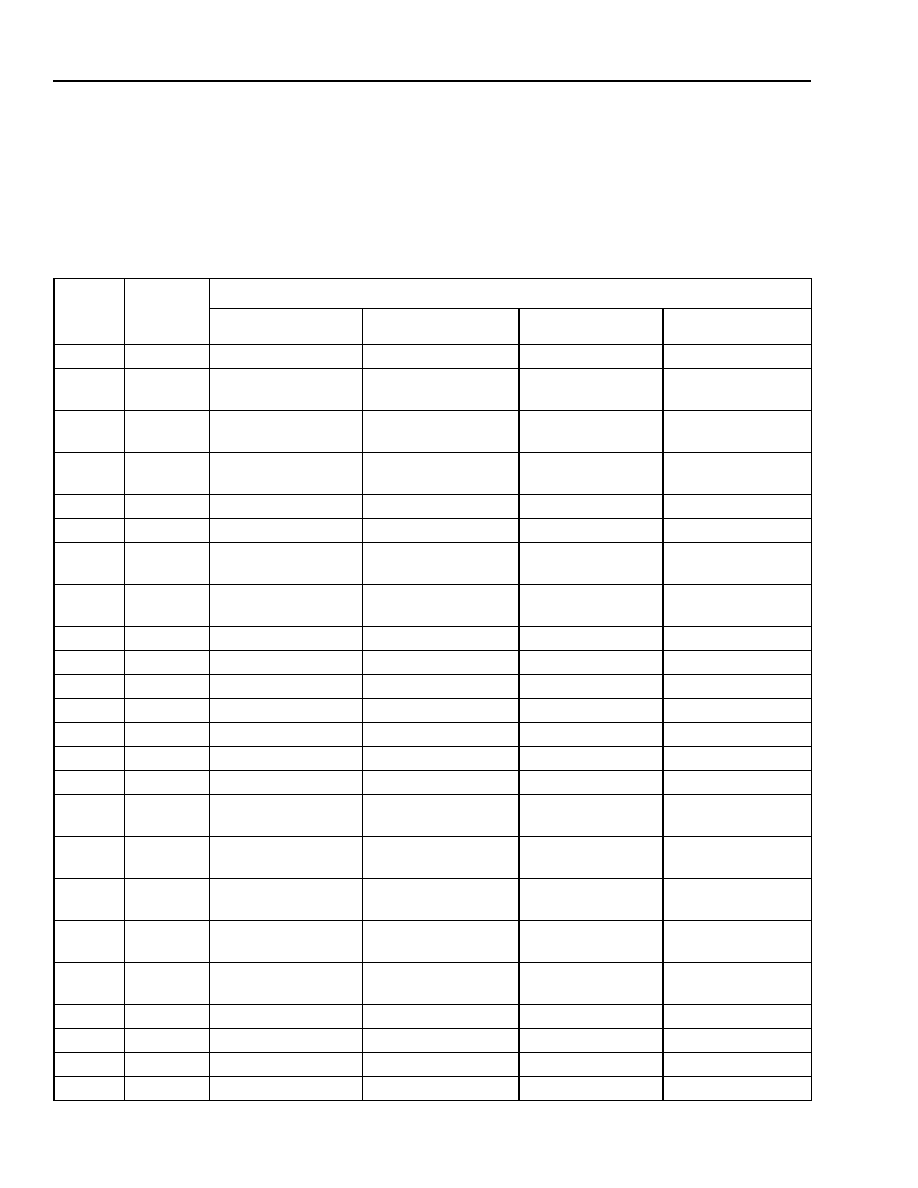

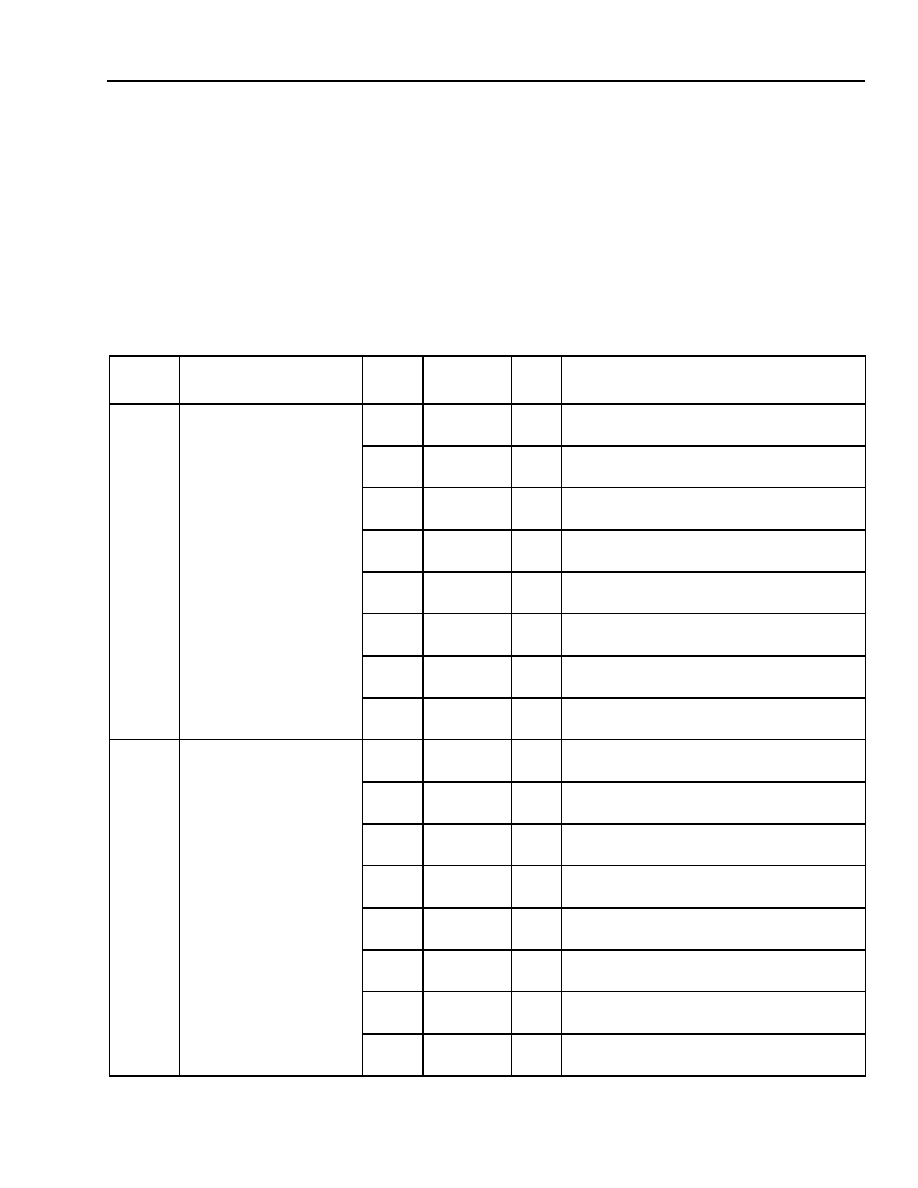

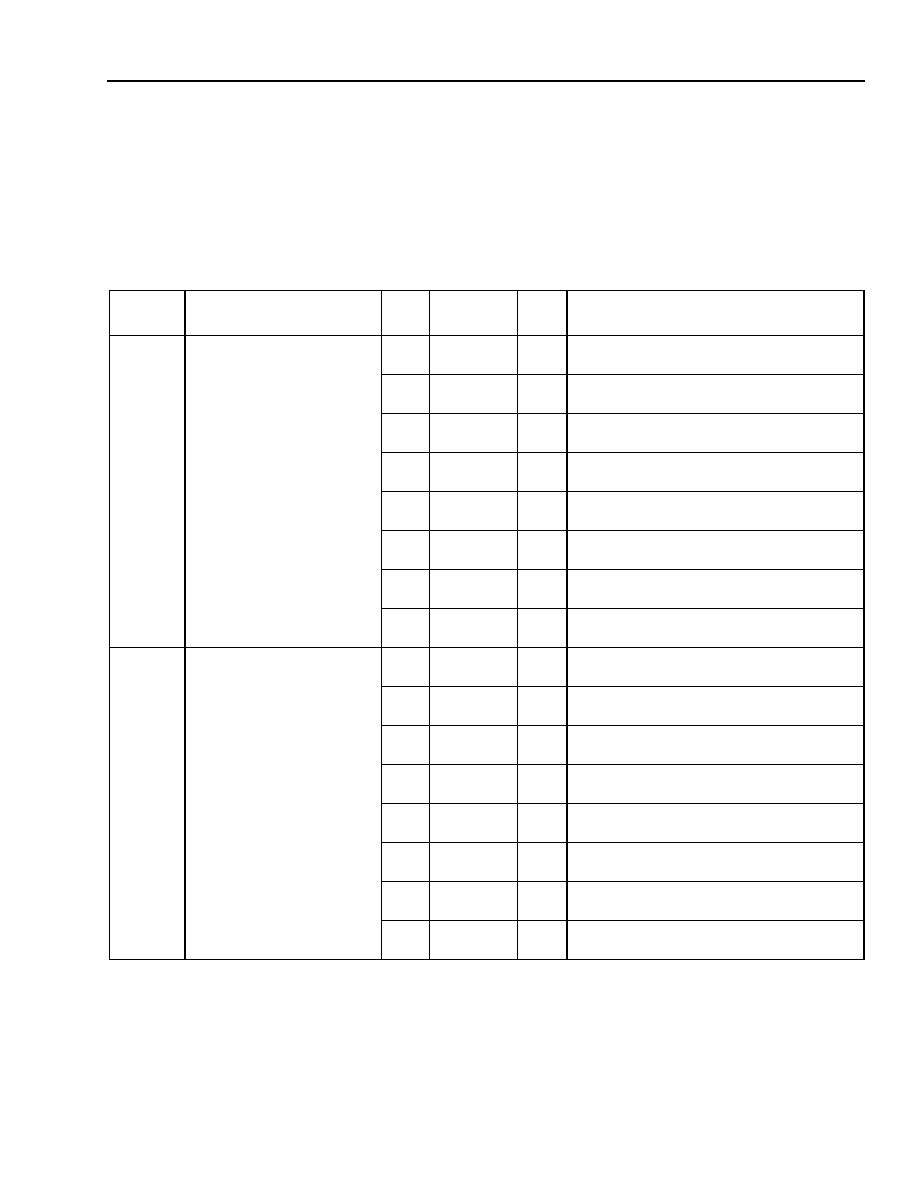

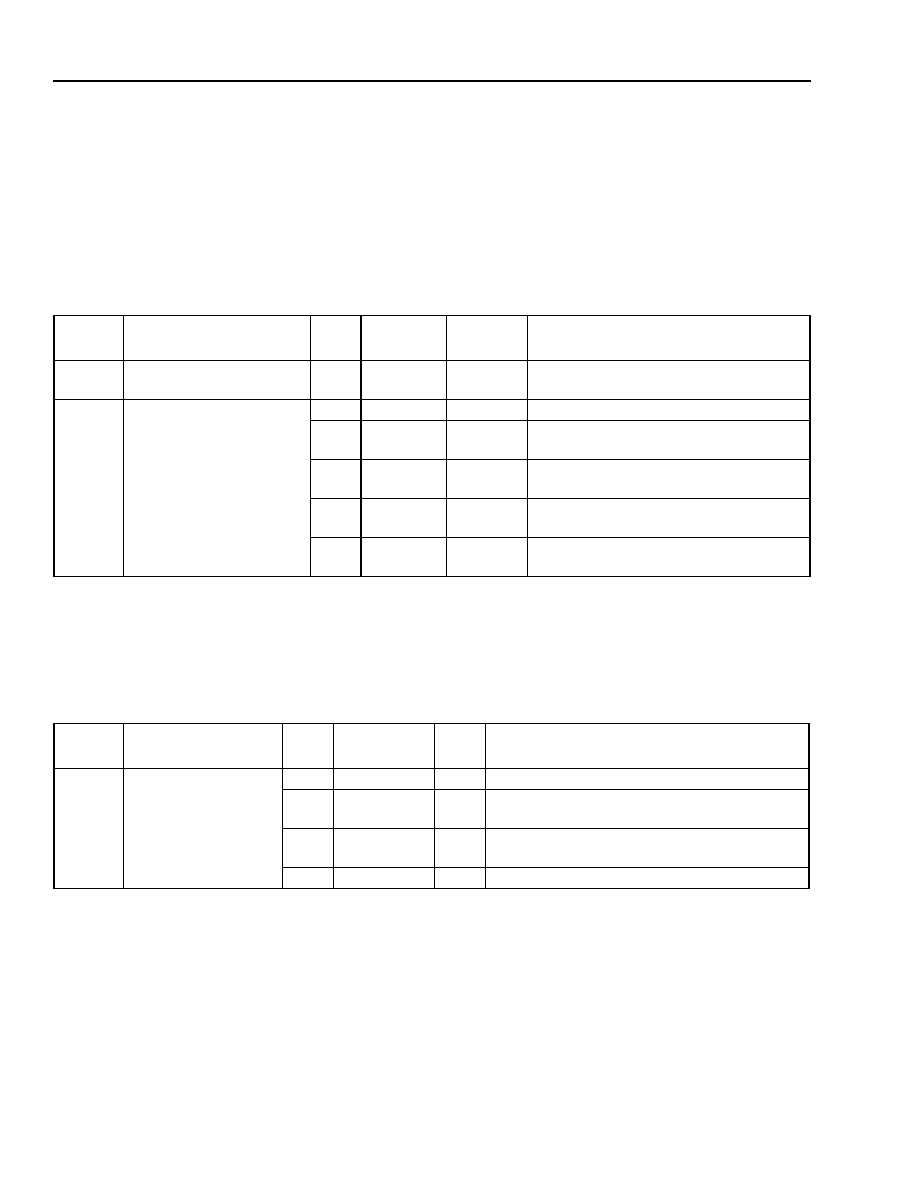

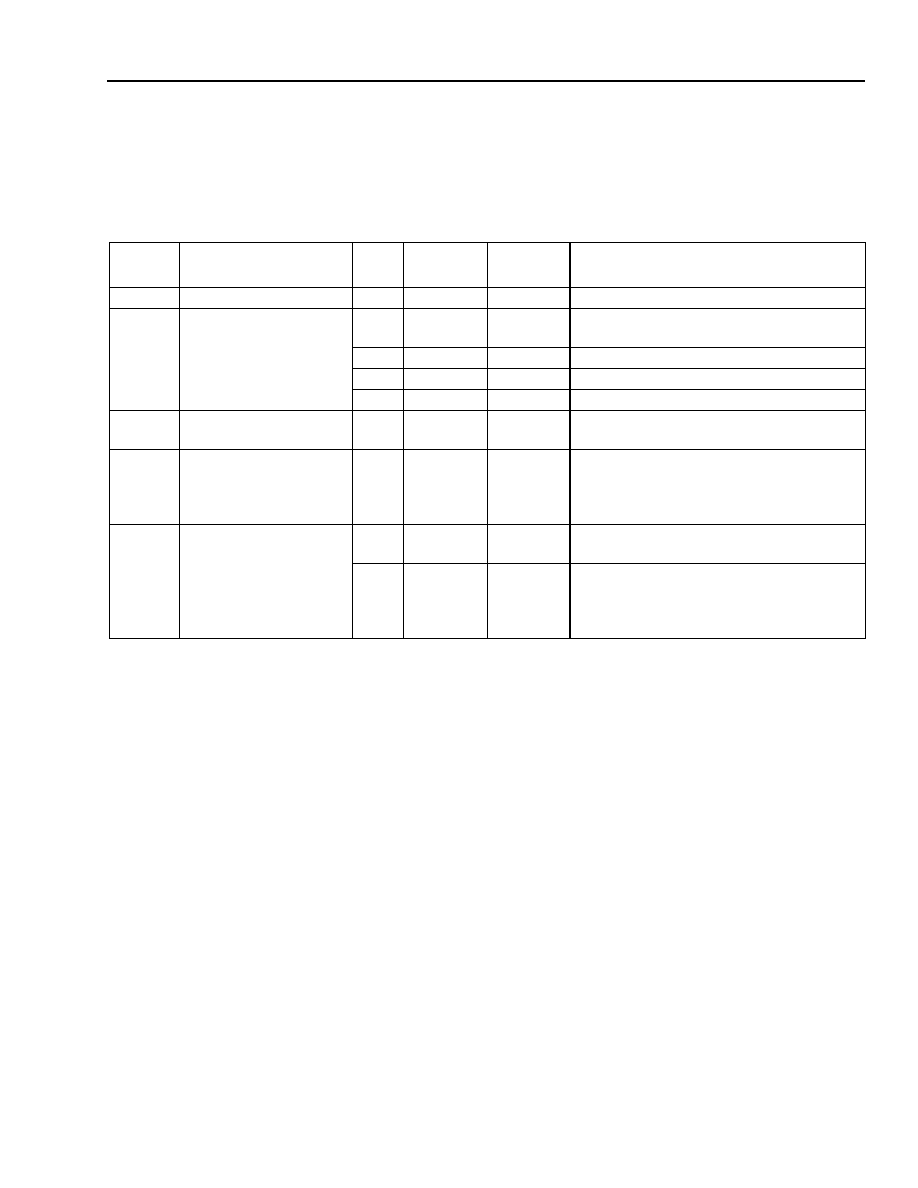

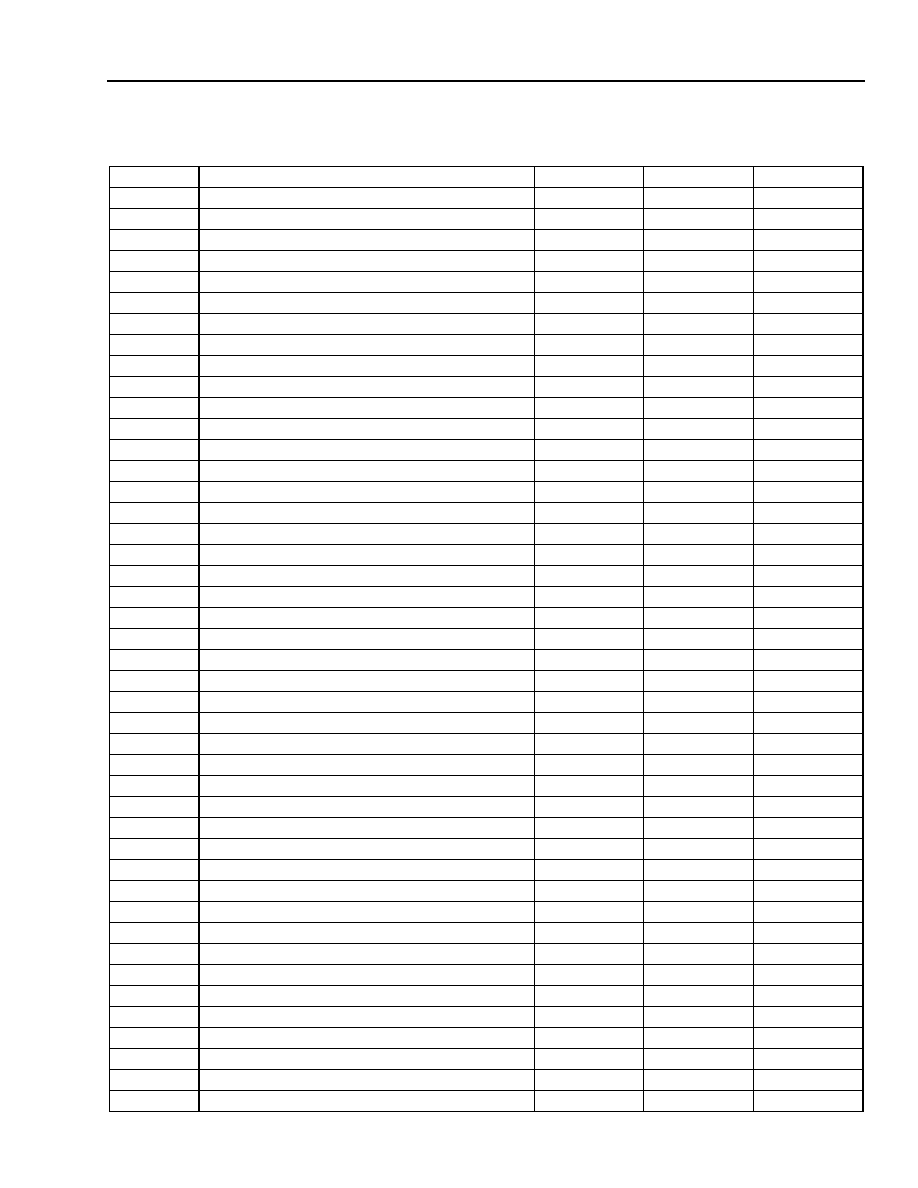

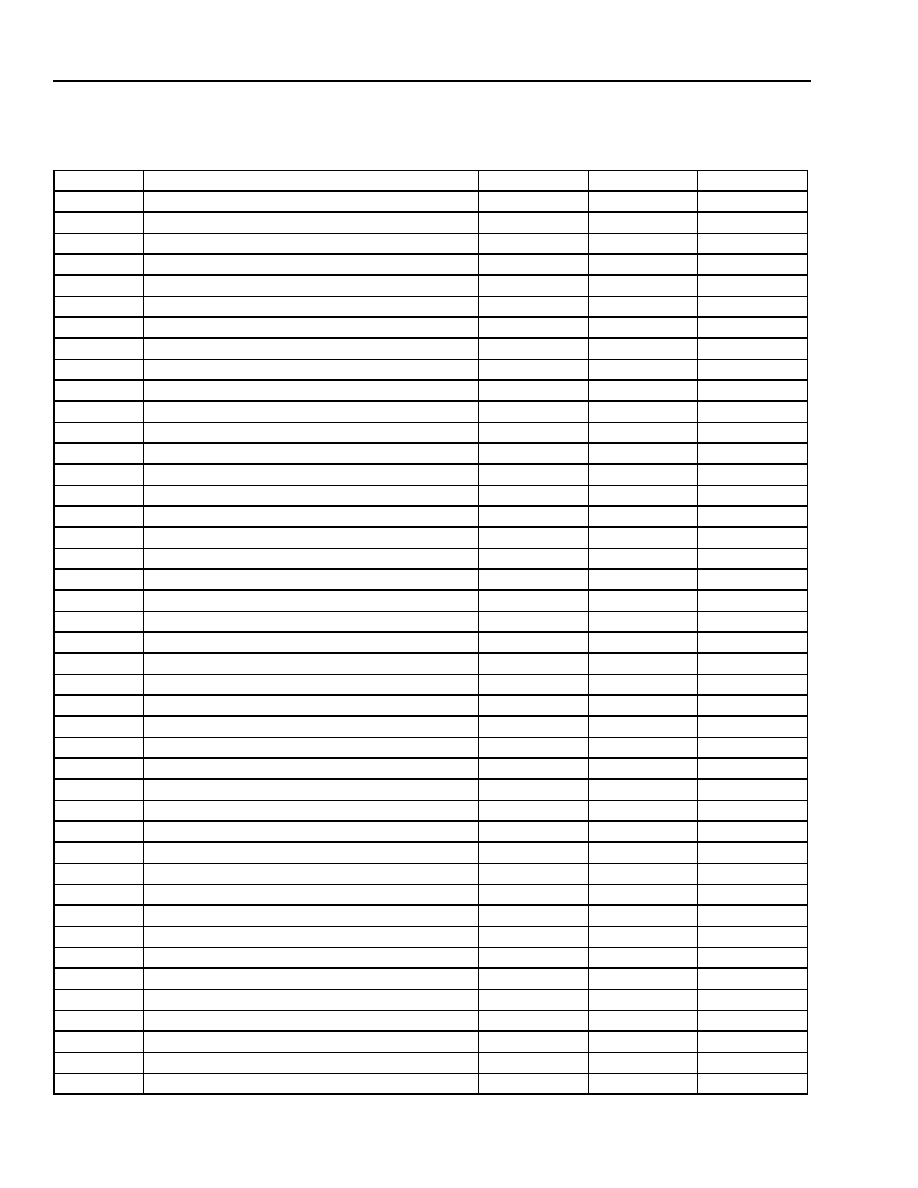

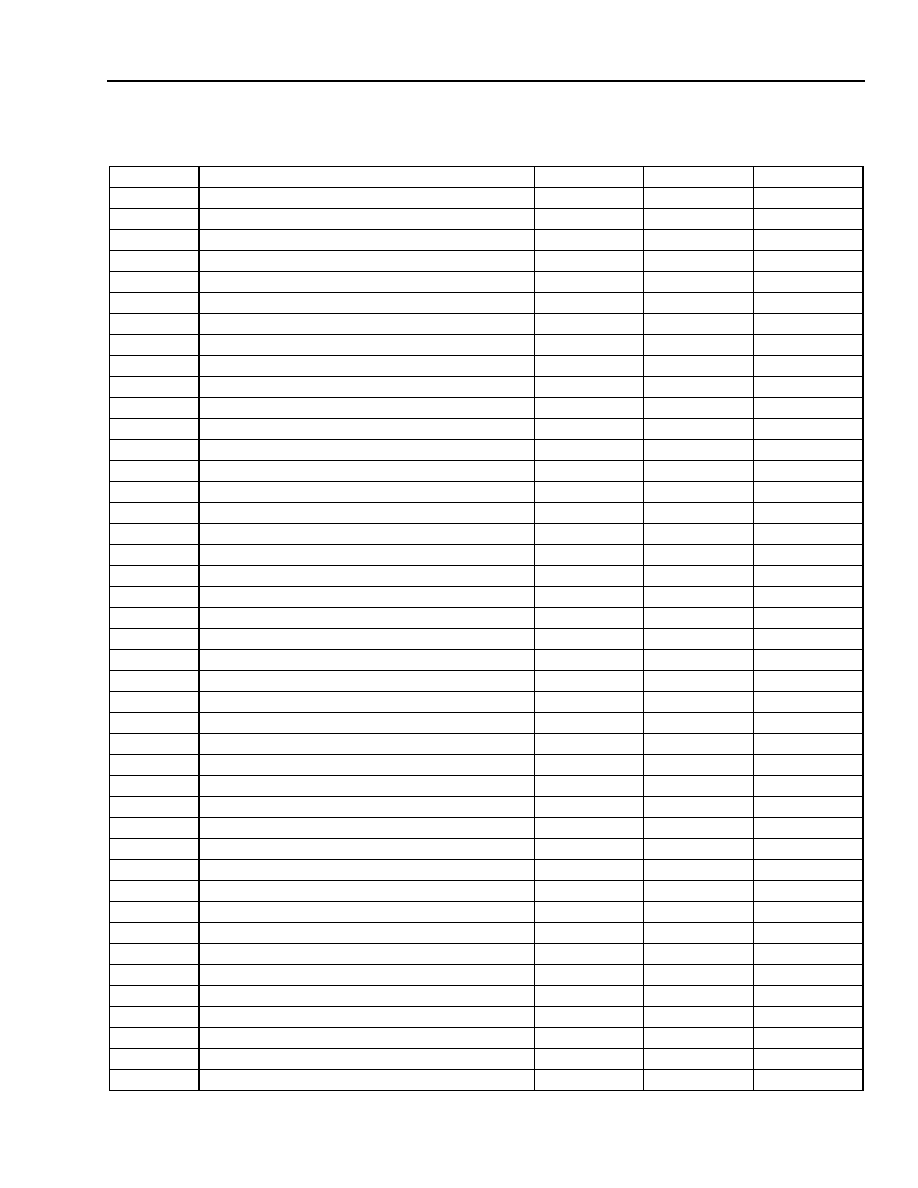

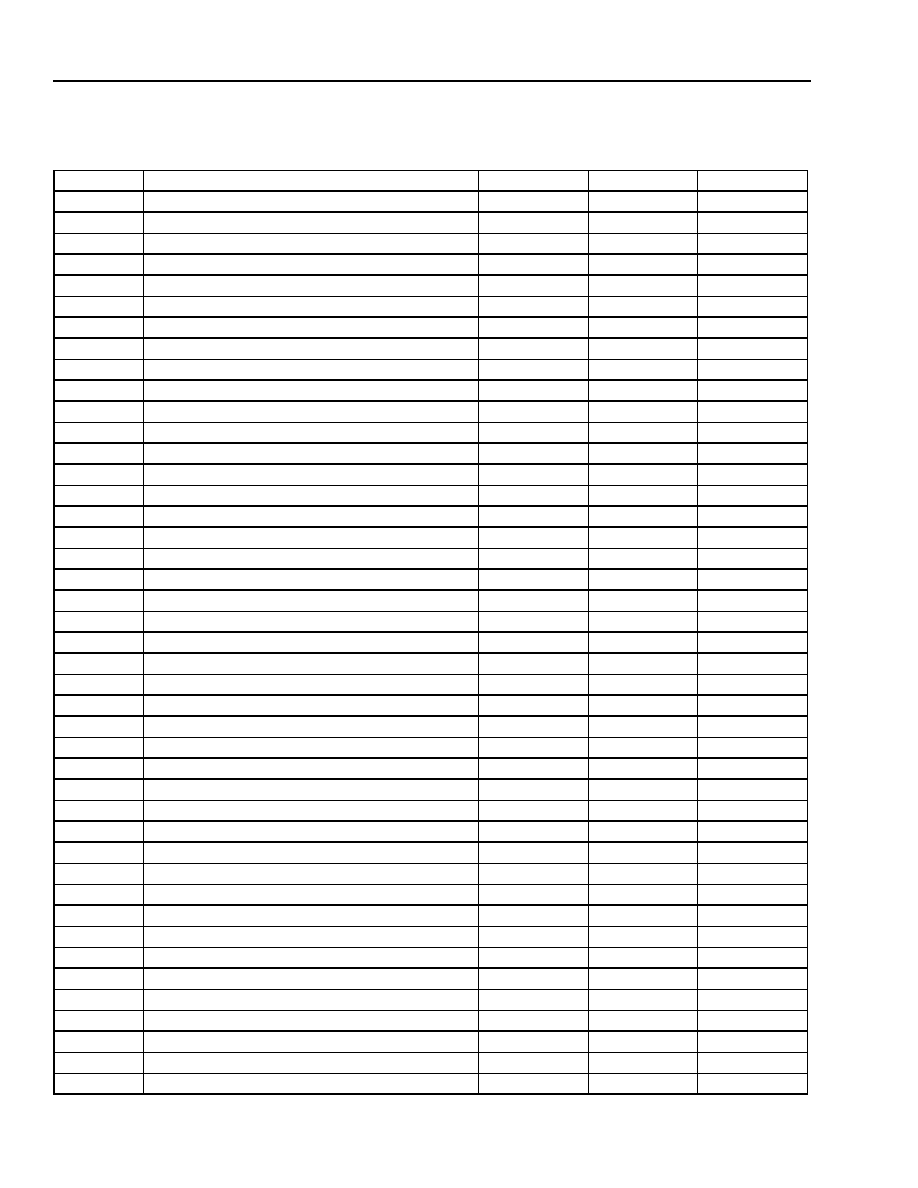

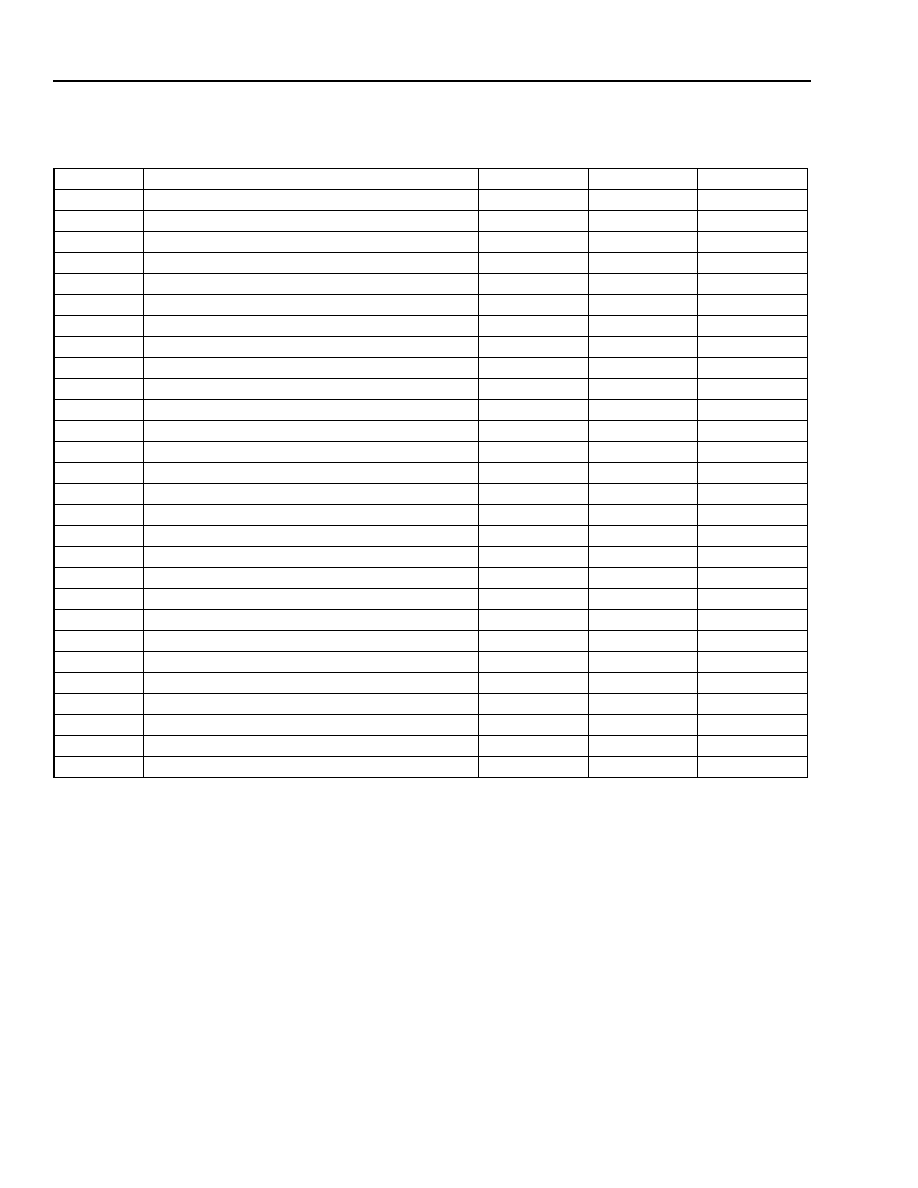

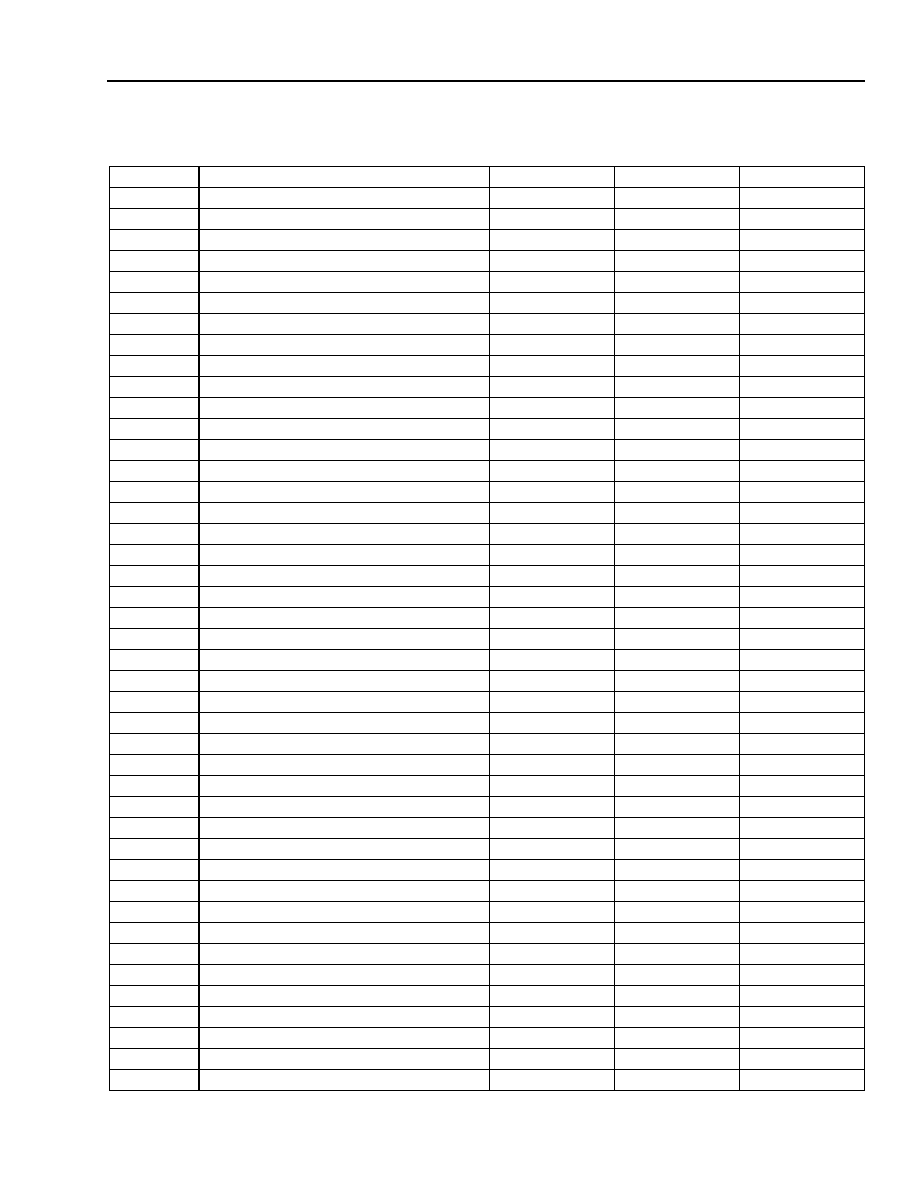

Table 8. T8110L Pinouts

Microprocessor Interface

Ball

Pin Name

Buffer Type

Pull-Up/Down (see note on page 12)

F1

A0

8 mA I/O-Schmitt

20 k

down

G1

A1

8 mA I/O-Schmitt

20 k

down

K3

A10

8 mA I/O-Schmitt

20 k

down

J3

A11

8 mA I/O-Schmitt

20 k

down

K1

A12

8 mA I/O-Schmitt

20 k

down

K2

A13

8 mA I/O-Schmitt

20 k

down

L3

A14

8 mA I/O-Schmitt

20 k

down

L4

A15

8 mA I/O-Schmitt

20 k

down

G2

A2

8 mA I/O-Schmitt

20 k

down

G3

A3

8 mA I/O-Schmitt

20 k

down

H1

A4

8 mA I/O-Schmitt

20 k

down

H2

A5

8 mA I/O-Schmitt

20 k

down

H3

A6

8 mA I/O-Schmitt

20 k

down

J4

A7

8 mA I/O-Schmitt

20 k

down

J1

A8

8 mA I/O-Schmitt

20 k

down

J2

A9

8 mA I/O-Schmitt

20 k

down

W1

D0

8 mA I/O-Schmitt

LPUE: 50 k

up

V1

D1

8 mA I/O-Schmitt

LPUE: 50 k

up

V2

D2

8 mA I/O-Schmitt

LPUE: 50 k

up

U3

D3

8 mA I/O-Schmitt

LPUE: 50 k

up

U1

D4

8 mA I/O-Schmitt

LPUE: 50 k

up

U2

D5

8 mA I/O-Schmitt

LPUE: 50 k

up

T3

D6

8 mA I/O-Schmitt

LPUE: 50 k

up

T4

D7

8 mA I/O-Schmitt

LPUE: 50 k

up

T1

D8

8 mA I/O-Schmitt

LPUE: 50 k

up

T2

D9

8 mA I/O-Schmitt

LPUE: 50 k

up

R3

D10

8 mA I/O-Schmitt

LPUE: 50 k

up

P4

D11

8 mA I/O-Schmitt

LPUE: 50 k

up

R1

D12

8 mA I/O-Schmitt

LPUE: 50 k

up

R2

D13

8 mA I/O-Schmitt

LPUE: 50 k

up

P2

D14

8 mA I/O-Schmitt

LPUE: 50 k

up

P3

D15

8 mA I/O-Schmitt

LPUE: 50 k

up

N1

RD#(DS#)

8 mA I/O-Schmitt

LPUE: 50 k

up

P1

WR#(R/W#)

8 mA I/O-Schmitt

LPUE: 50 k

up

L1

A16

8 mA I/O-Schmitt

20 k

down

L2

A17

8 mA I/O-Schmitt

20 k

down

M1

A18

8 mA I/O-Schmitt

20 k

down

M2

A19

8 mA I/O-Schmitt

20 k

down

M3

CSN

8 mA I/O-Schmitt

LPUE: 50 k

up

M4

WB_SEL

8 mA I/O-Schmitt

LPUE: 50 k

up

N2

RDY(DTACK#)

8 mA 3-state

External pull-up required

N3

IM_SEL

8 mA I/O-Schmitt

LPUE: 50 k

up

14

Agere Systems Inc.

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

2 Pin Description

(continued)

2.2 T8110L Pinout Information

(continued)

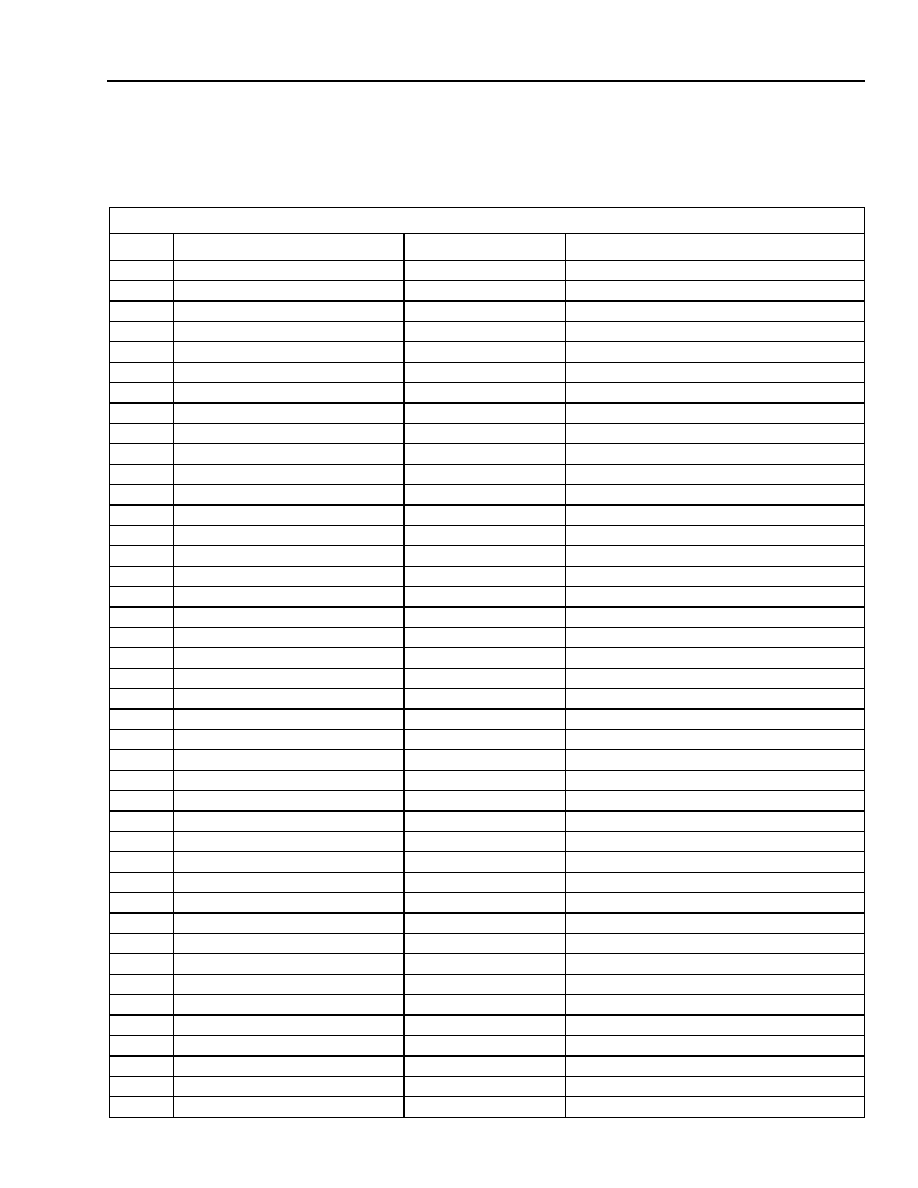

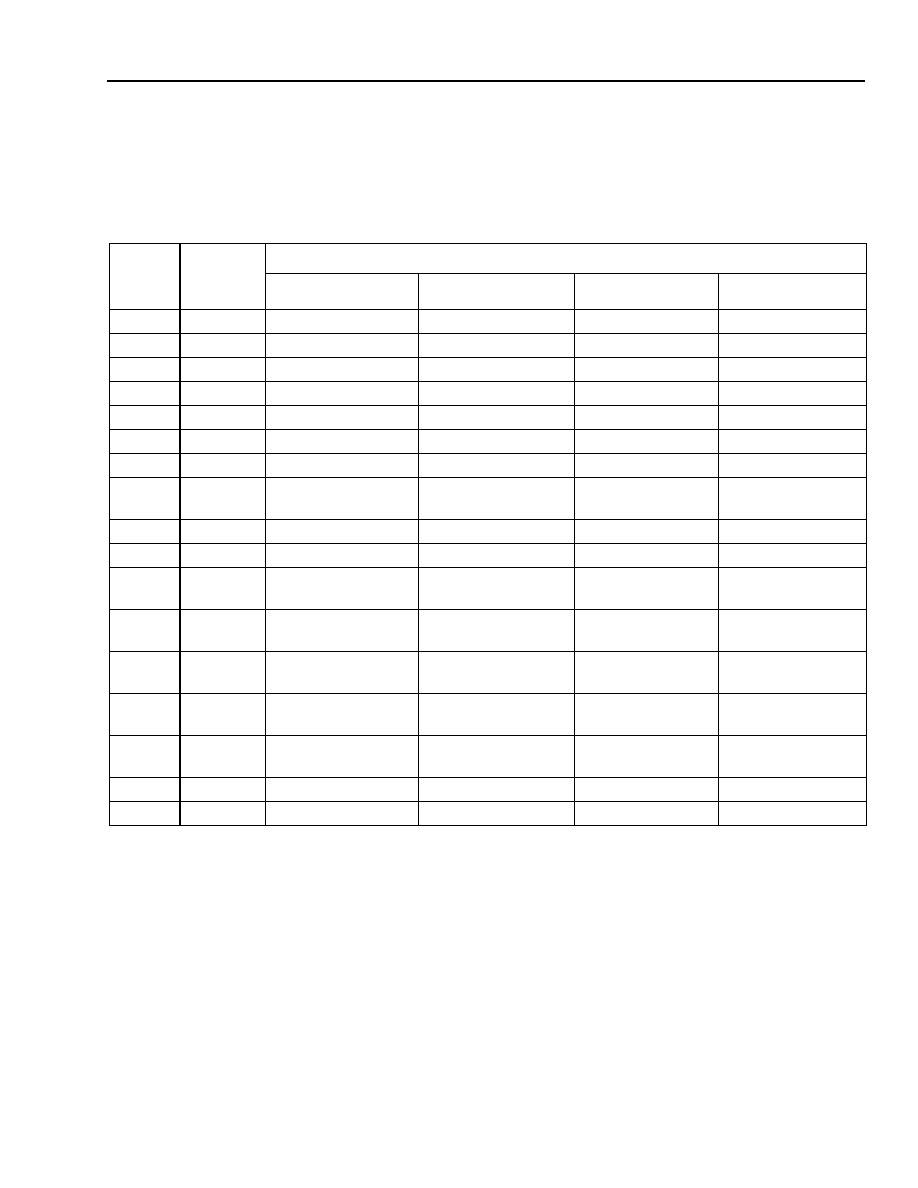

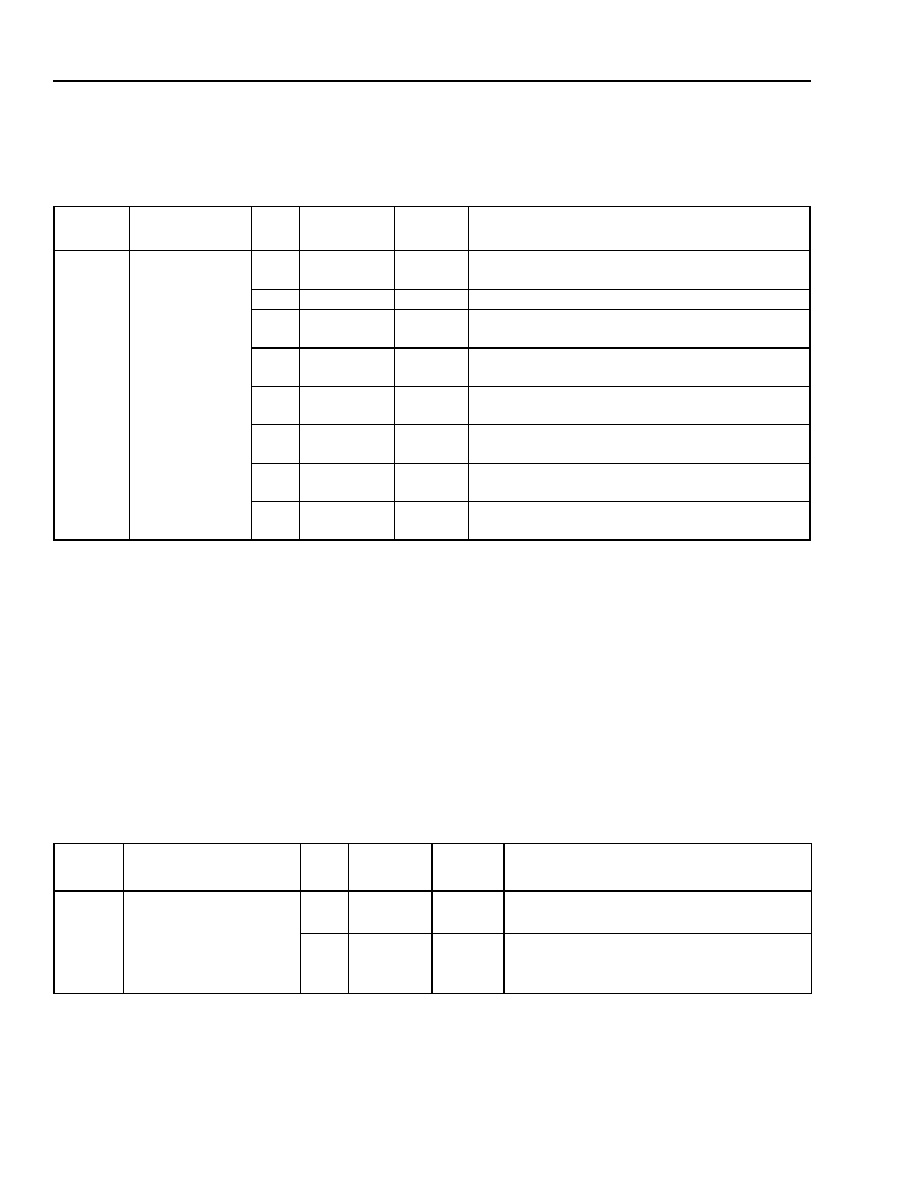

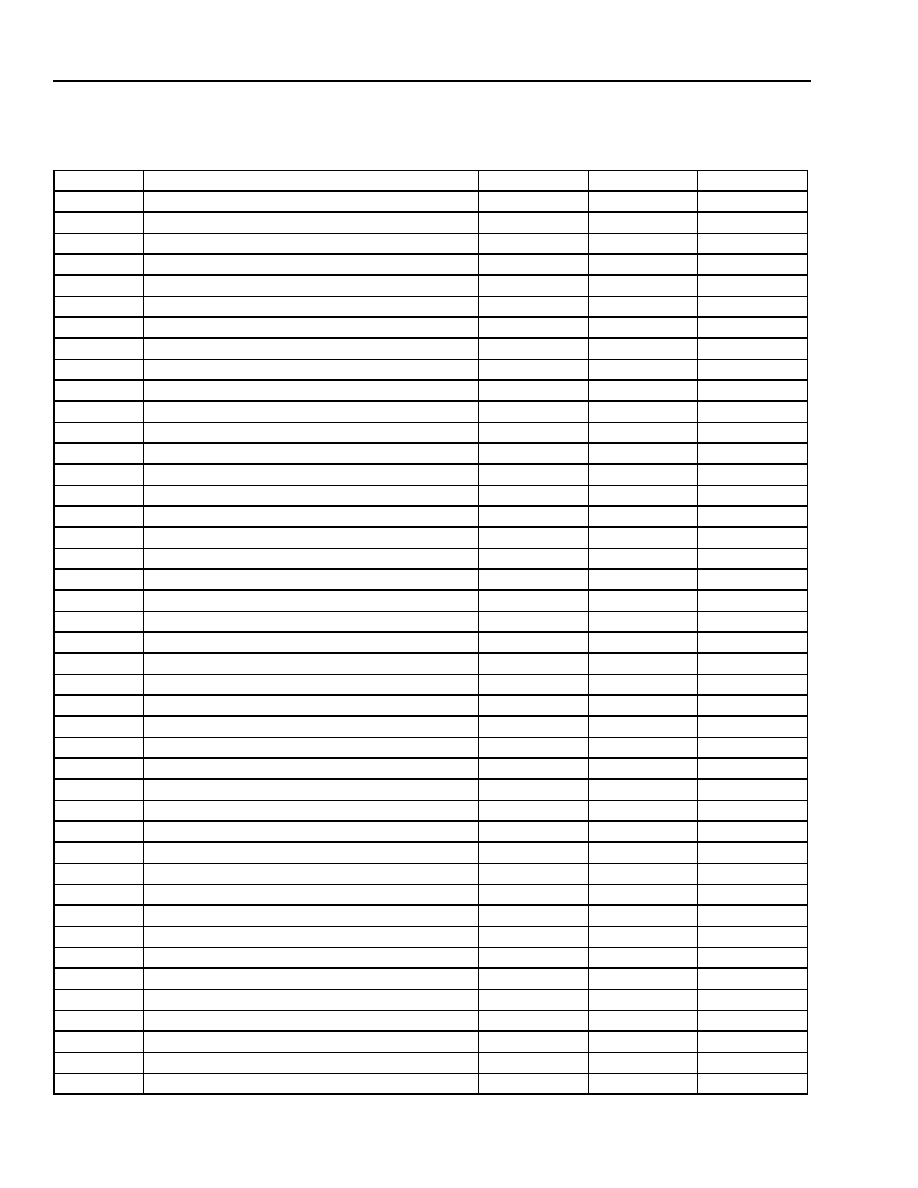

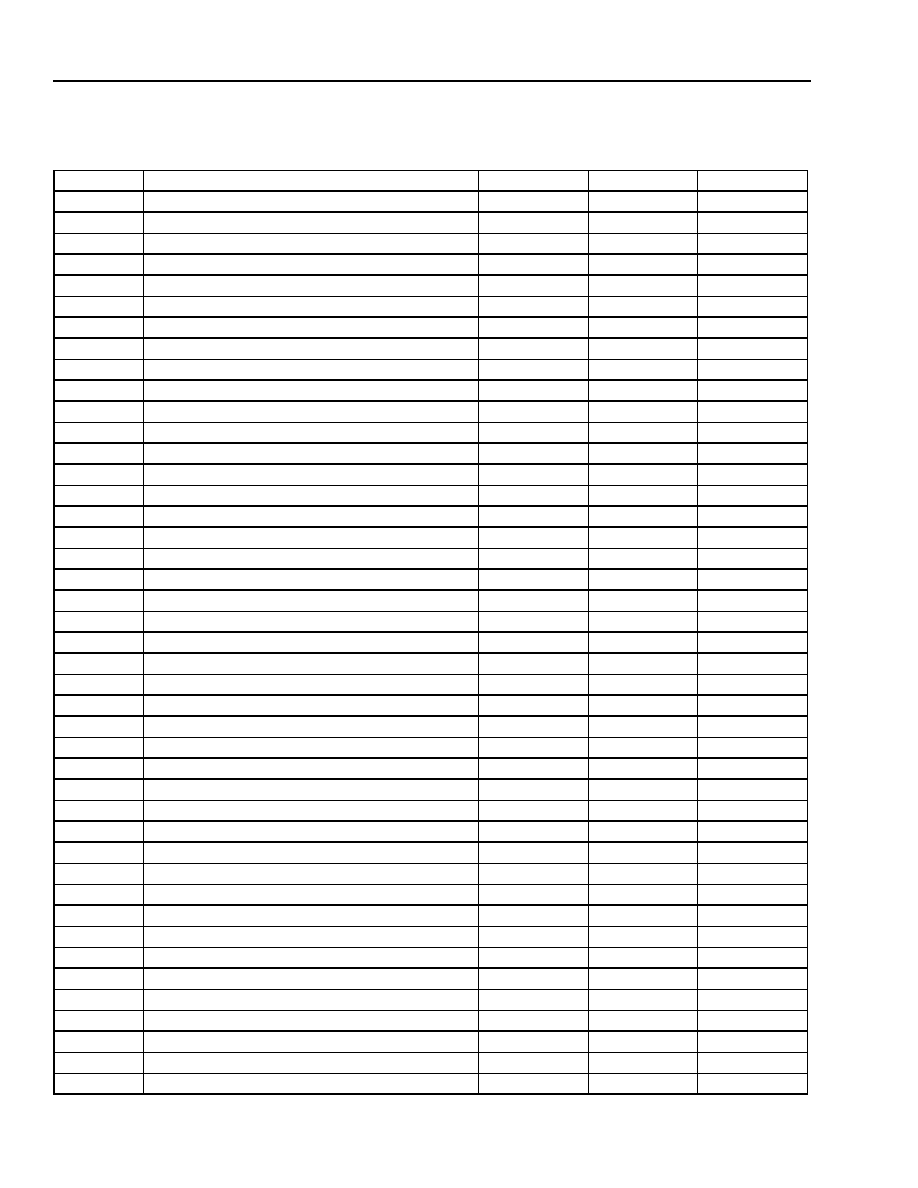

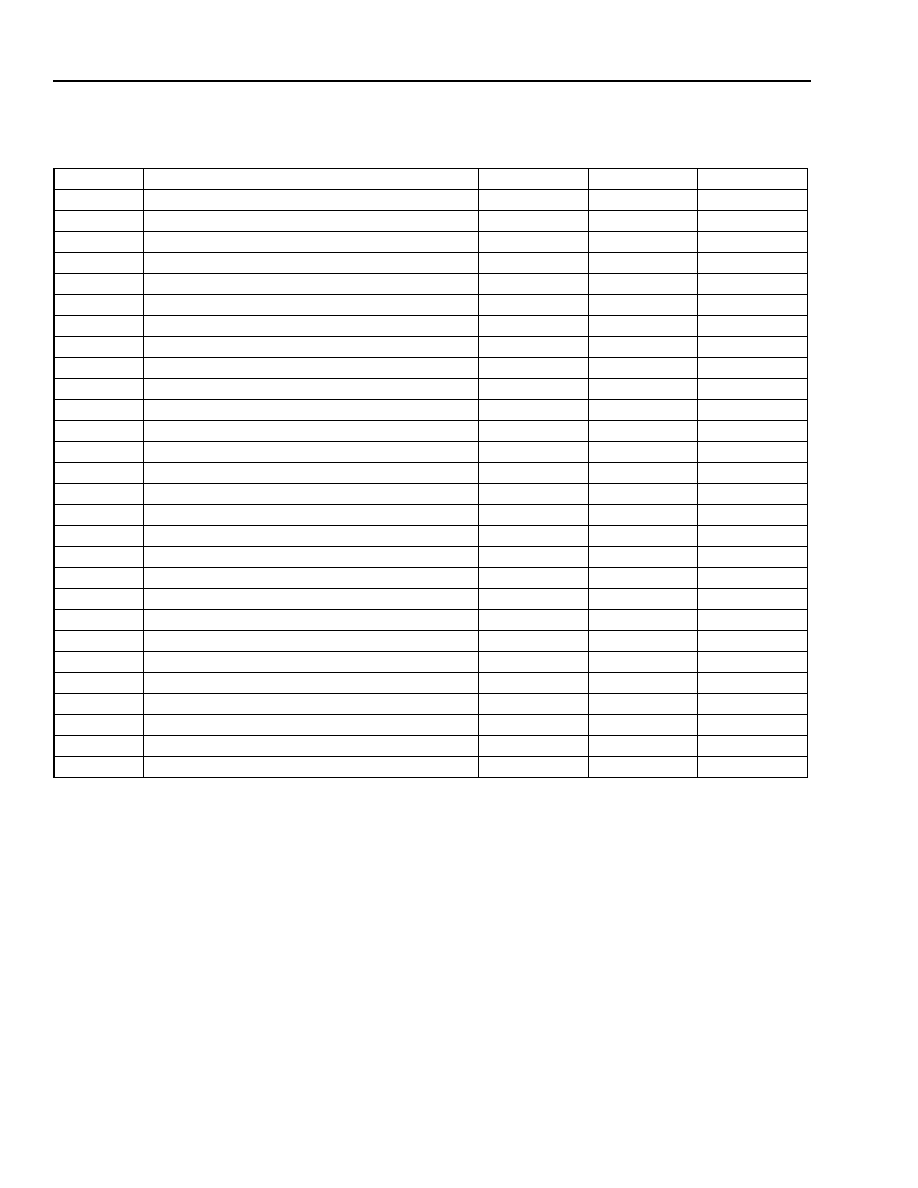

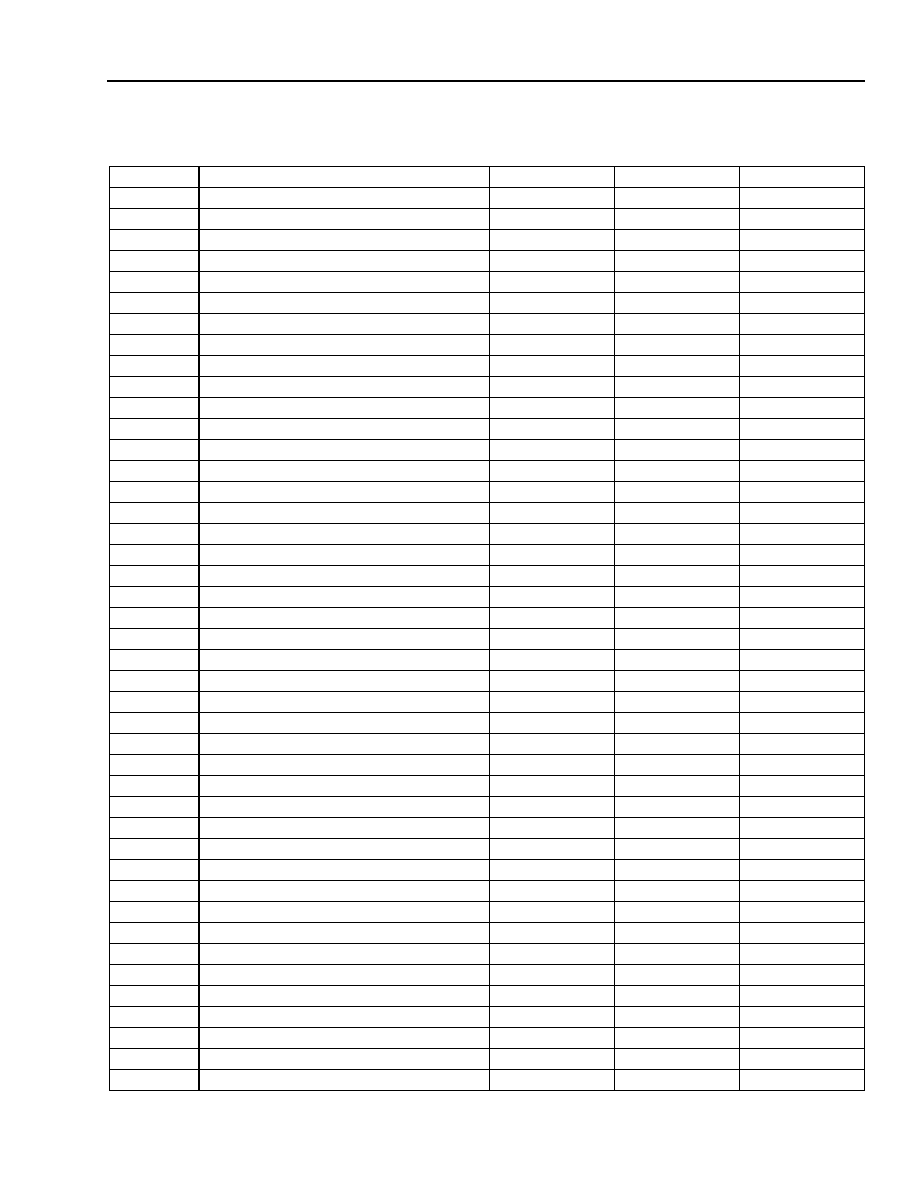

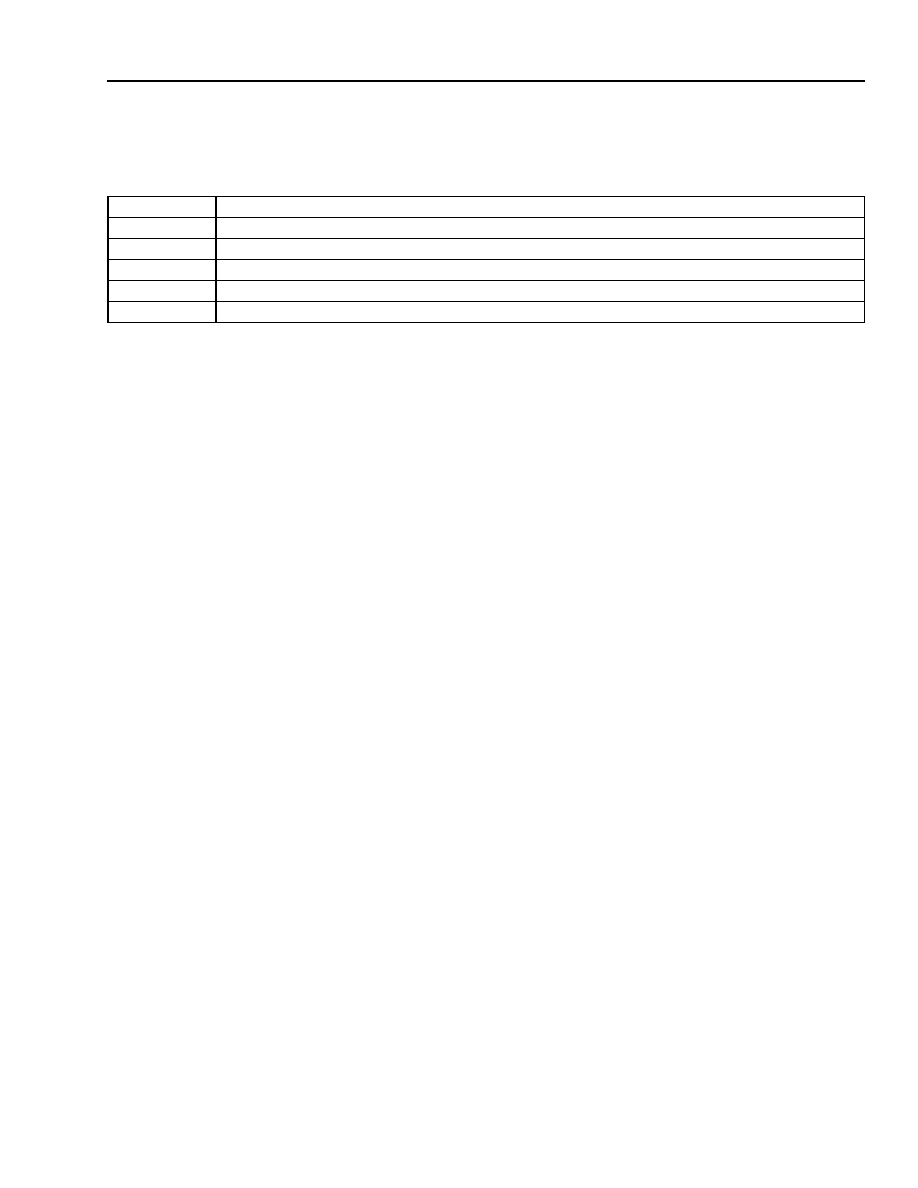

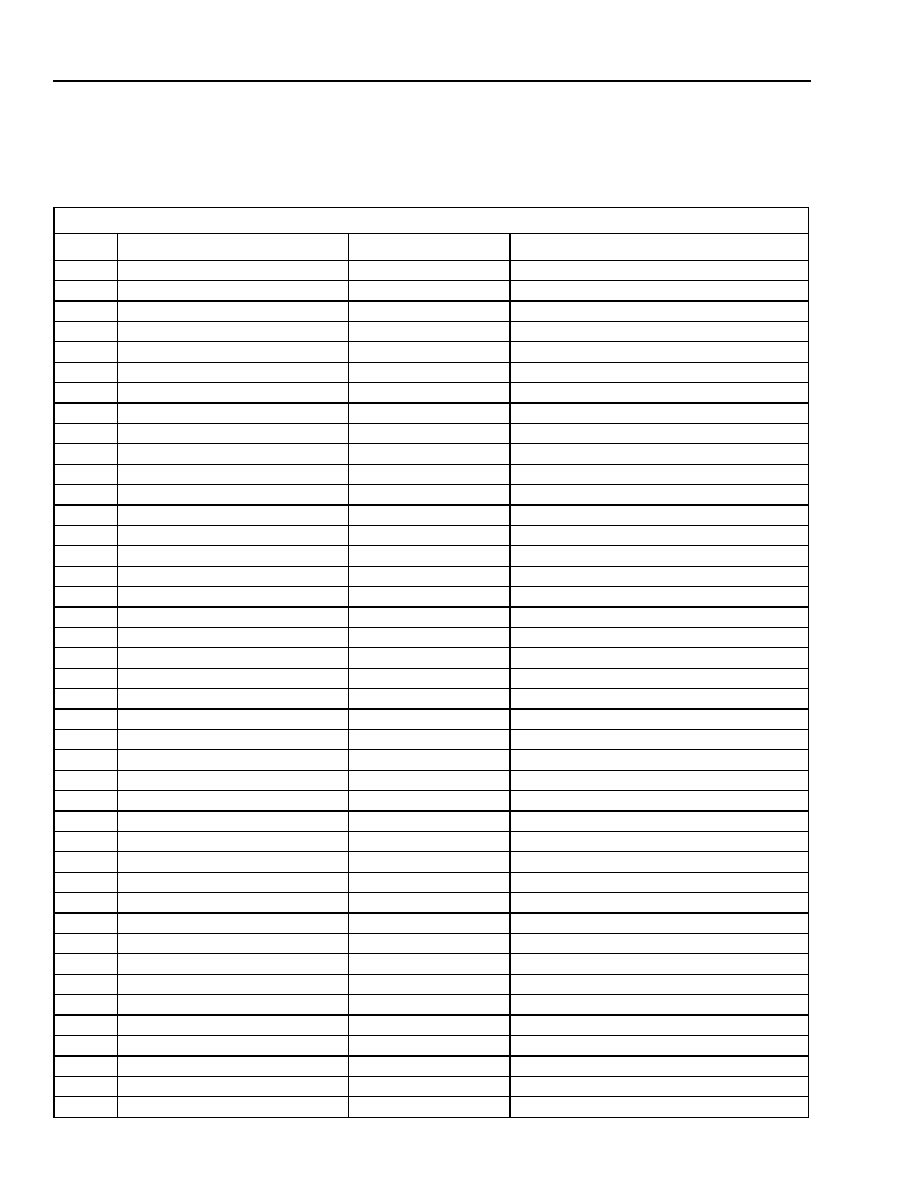

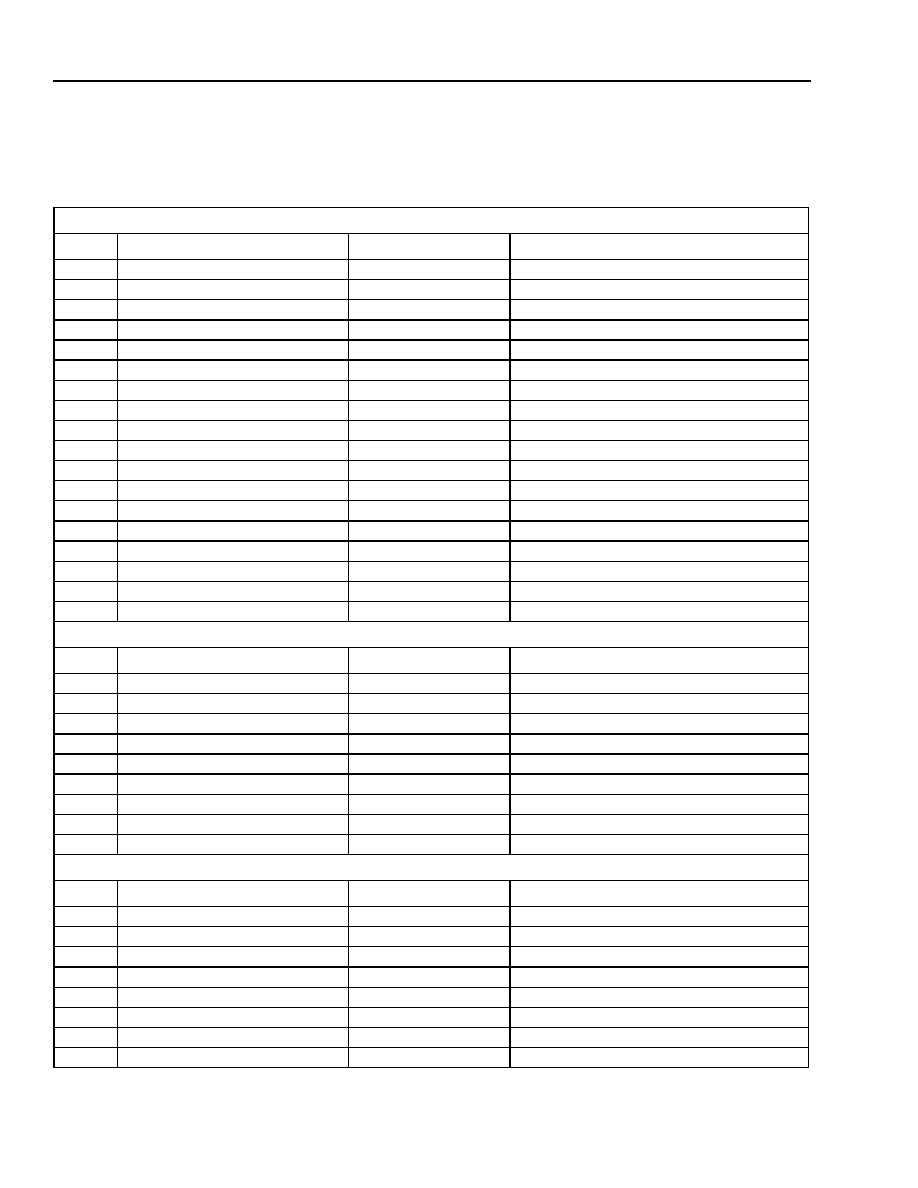

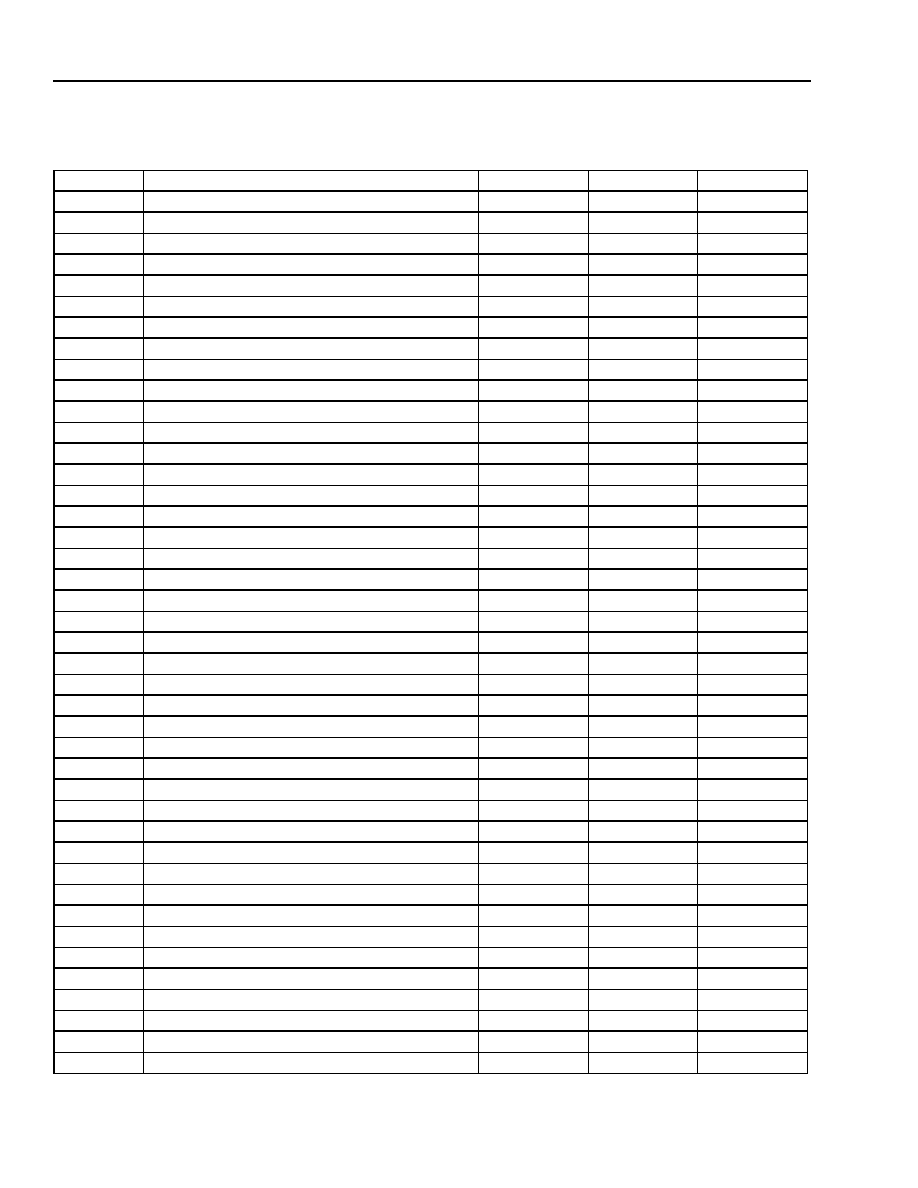

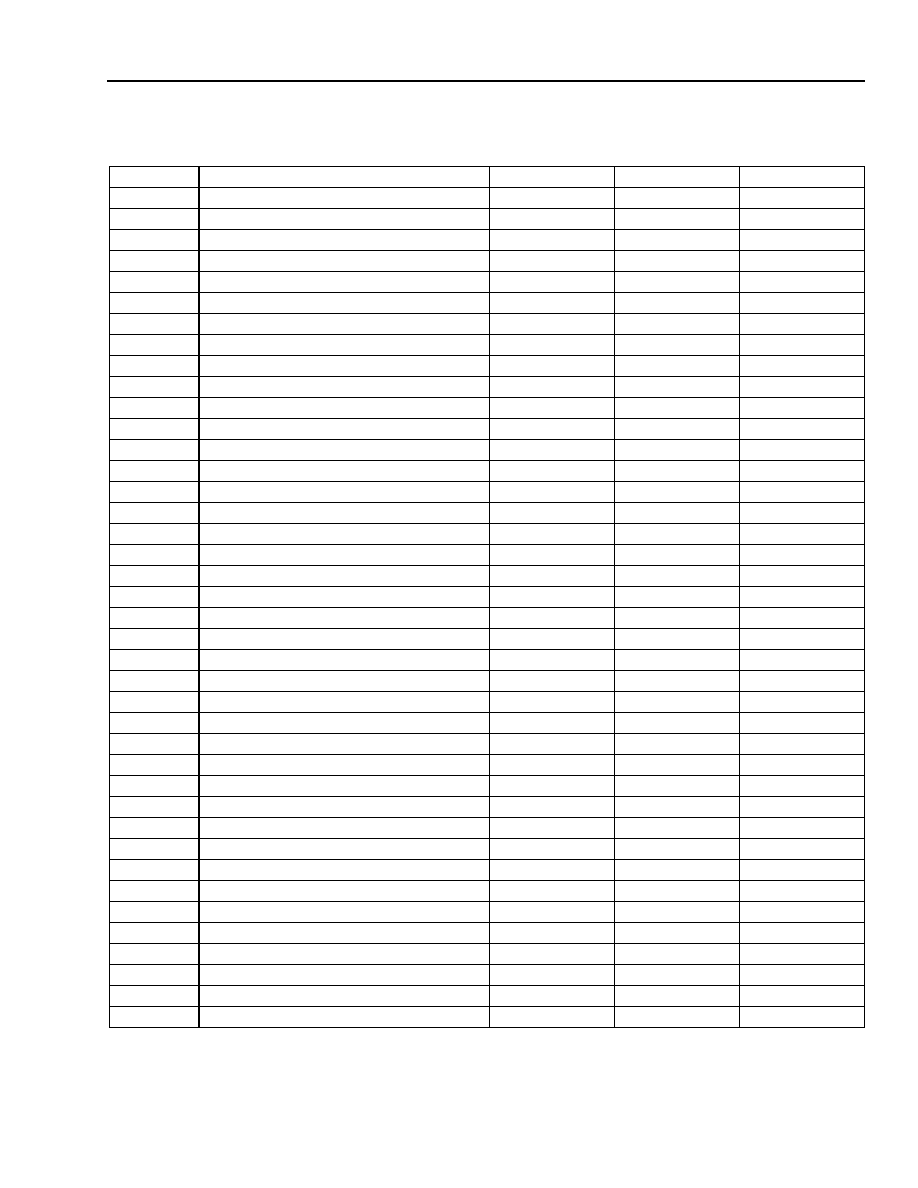

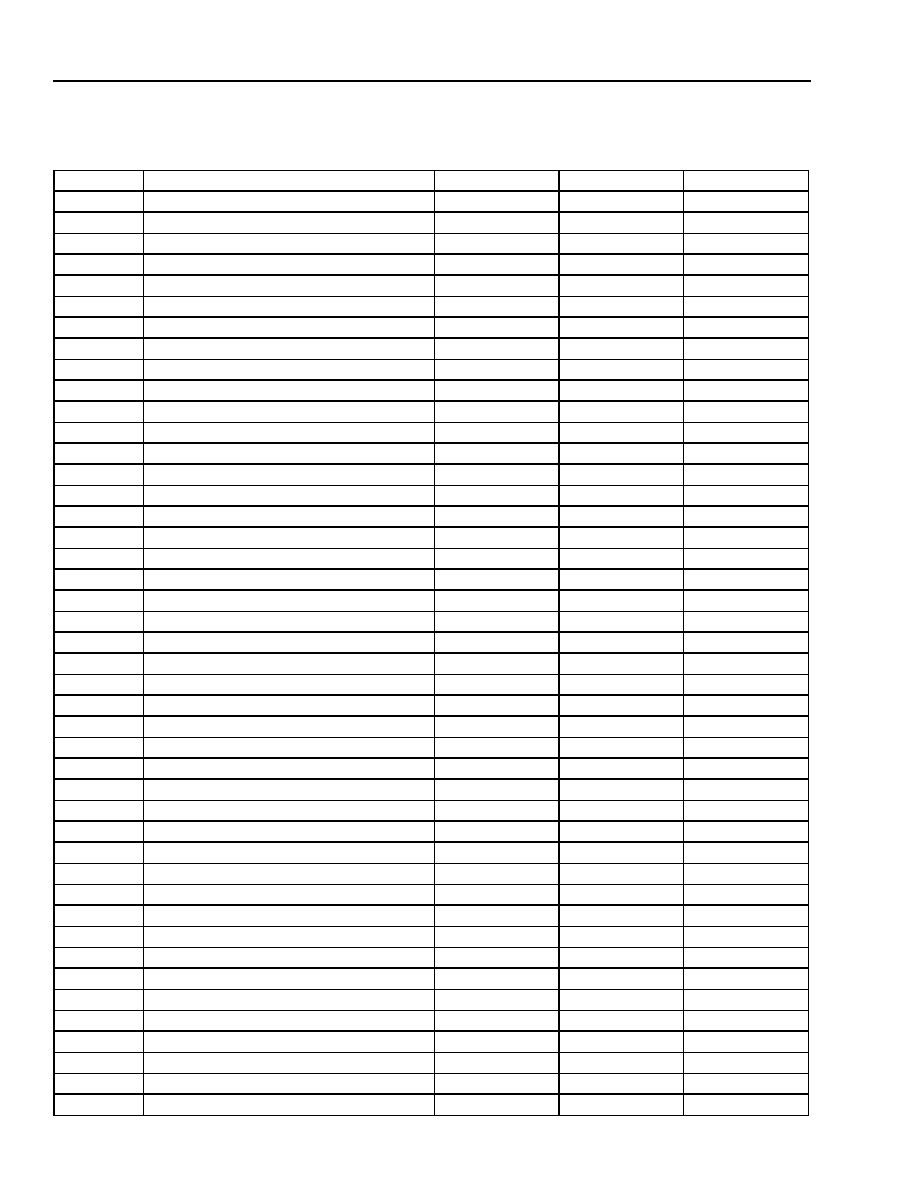

Table 8. T8110L Pinouts (continued)

H-Bus Interface

Ball

Pin Name

Buffer Type

Pull-Up/Down (see note on page 12)

C1

VPRECHARGE

Op amp noninvert

--

D5

H110_ENABLE

Input

20 k

down

D7

H100_ENABLE

Input

20 k

down

A11

CT_D0

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B11

CT_D1

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C10

CT_D2

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C11

CT_D3

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A10

CT_D4

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B10

CT_D5

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B9

CT_D6

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C9

CT_D7

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A9

CT_D8

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B8

CT_D9

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C8

CT_D10

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A8

CT_D11

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C7

CT_D12

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A7

CT_D13

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B7

CT_D14

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C6

CT_D15

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A6

CT_D16

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B6

CT_D17

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C5

CT_D18

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A5

CT_D19

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B5

CT_D20

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A4

CT_D21

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B4

CT_D22

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C4

CT_D23

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A3

CT_D24

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B3

CT_D25

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C3

CT_D26

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A2

CT_D27

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B2

CT_D28

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B1

CT_D29

PCI I/O

Enabled: 50 k

up/20 k

Vpre

C2

CT_D30

PCI I/O

Enabled: 50 k

up/20 k

Vpre

D2

CT_D31

PCI I/O

Enabled: 50 k

up/20 k

Vpre

A13

CT_C8_A

24 mA I/O-Schmitt

Enabled: 50 k

up

A12

/CT_FRAME_A

24 mA I/O-Schmitt

Enabled: 50 k

up

B13

CT_C8_B

24 mA I/O-Schmitt

Enabled: 50 k

up

B12

/CT_FRAME_B

24 mA I/O-Schmitt

Enabled: 50 k

up

A14

CT_NETREF1

PCI I/O

Enabled: 50 k

up/20 k

Vpre

B14

CT_NETREF2

PCI I/O

Enabled: 50 k

up/20 k

Vpre

D9

/C16+

24 mA I/O-Schmitt

50 k

up

Agere Systems Inc.

15

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

2 Pin Description

(continued)

2.2 T8110L Pinout Information

(continued)

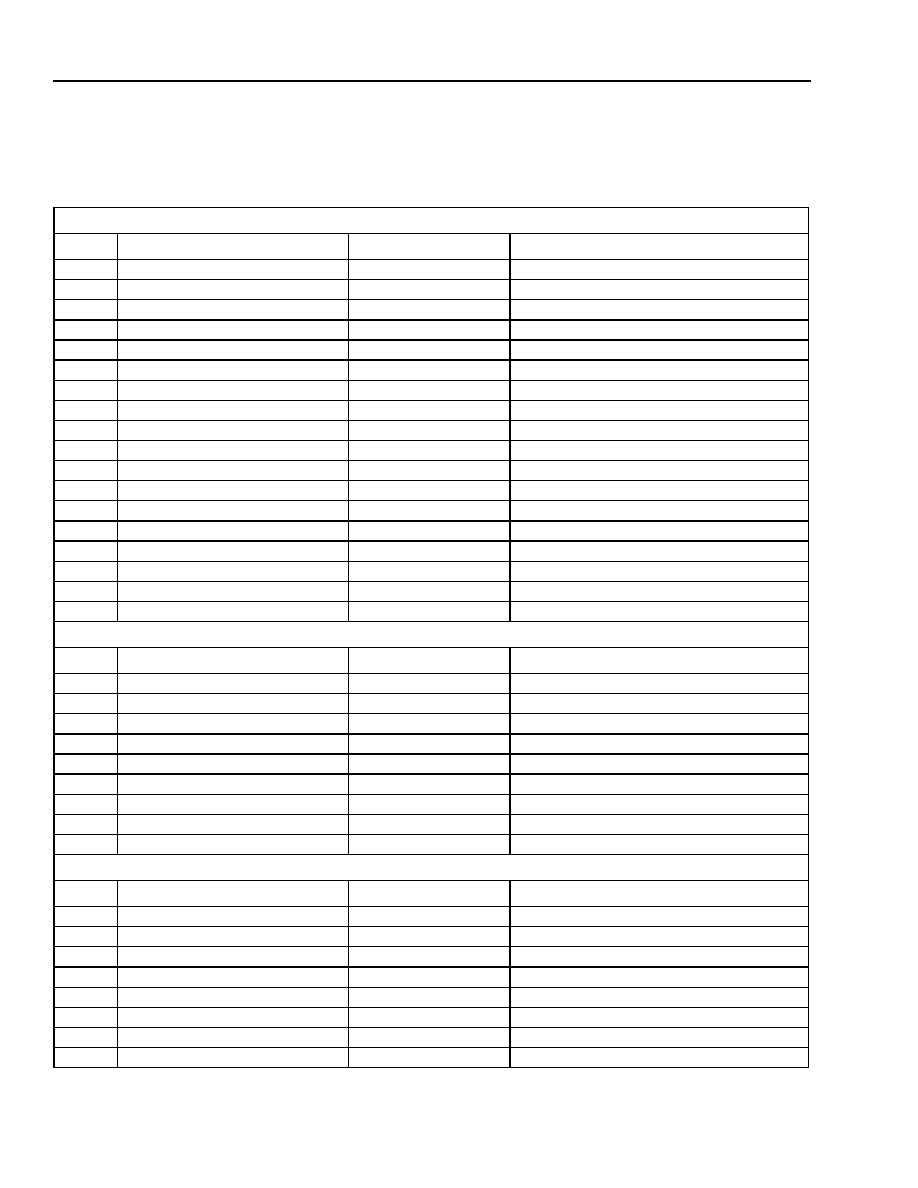

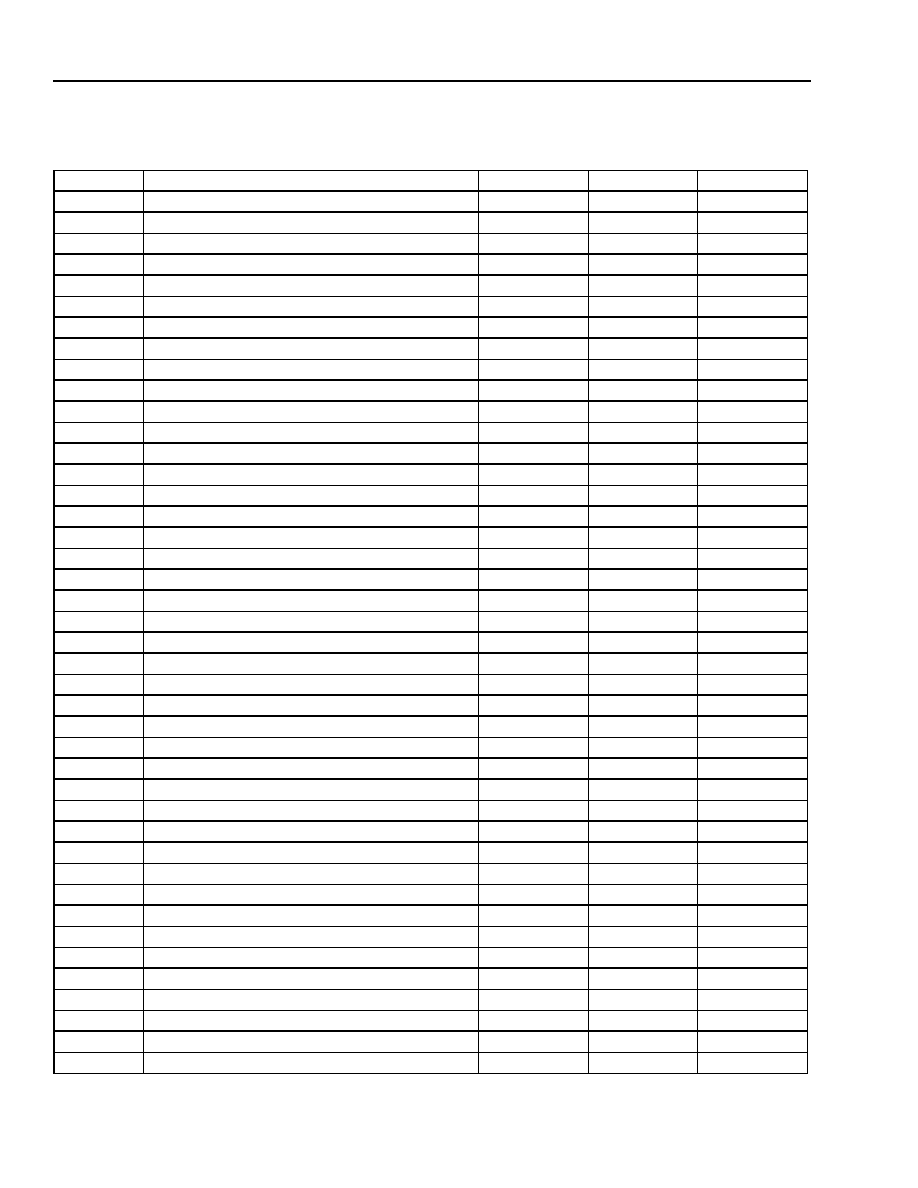

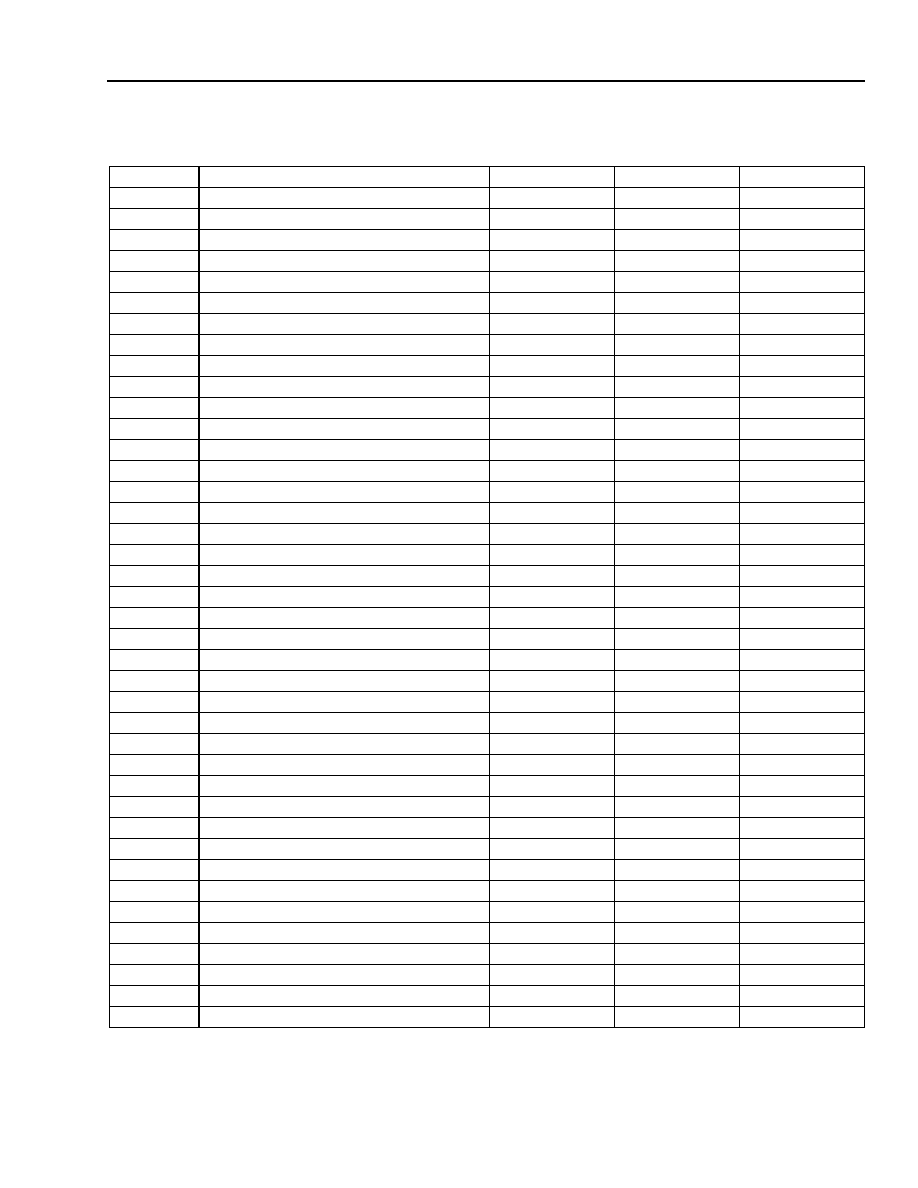

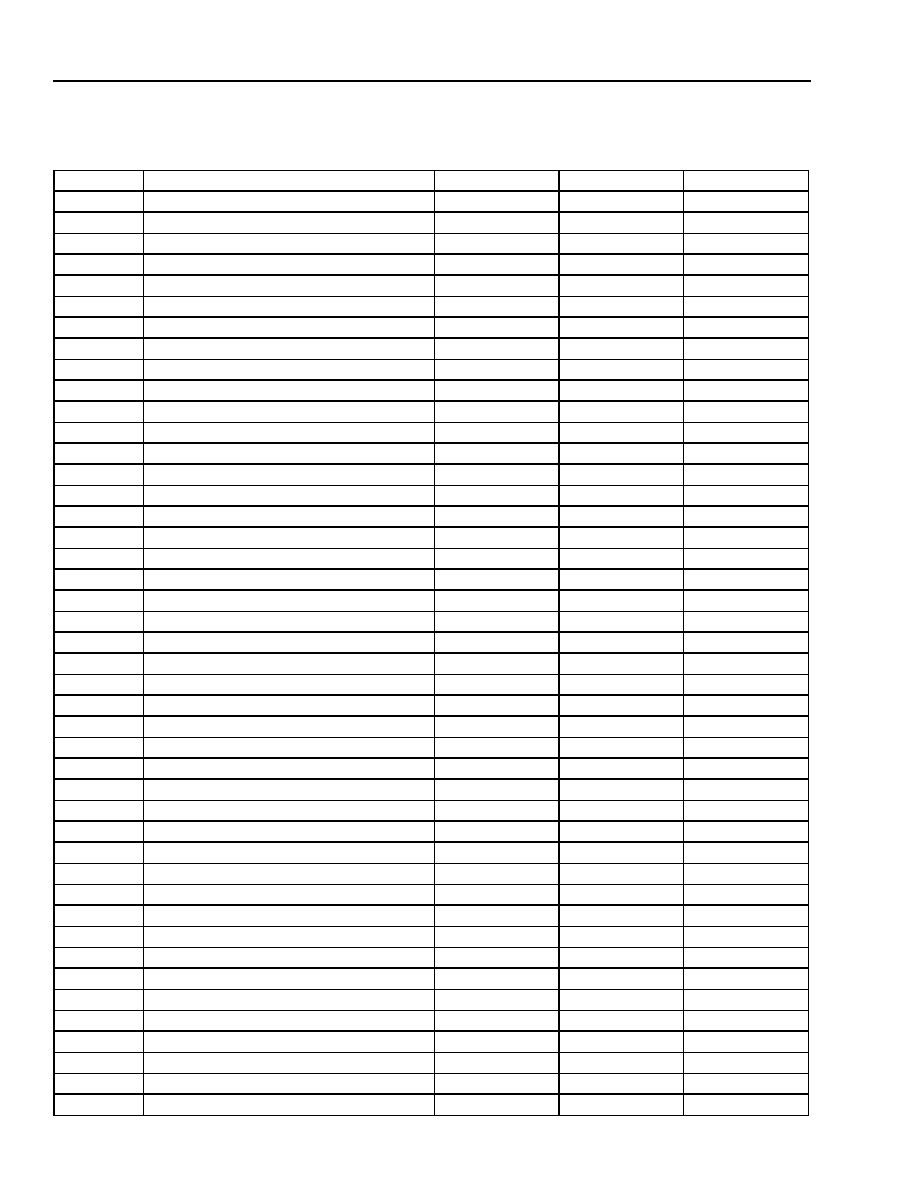

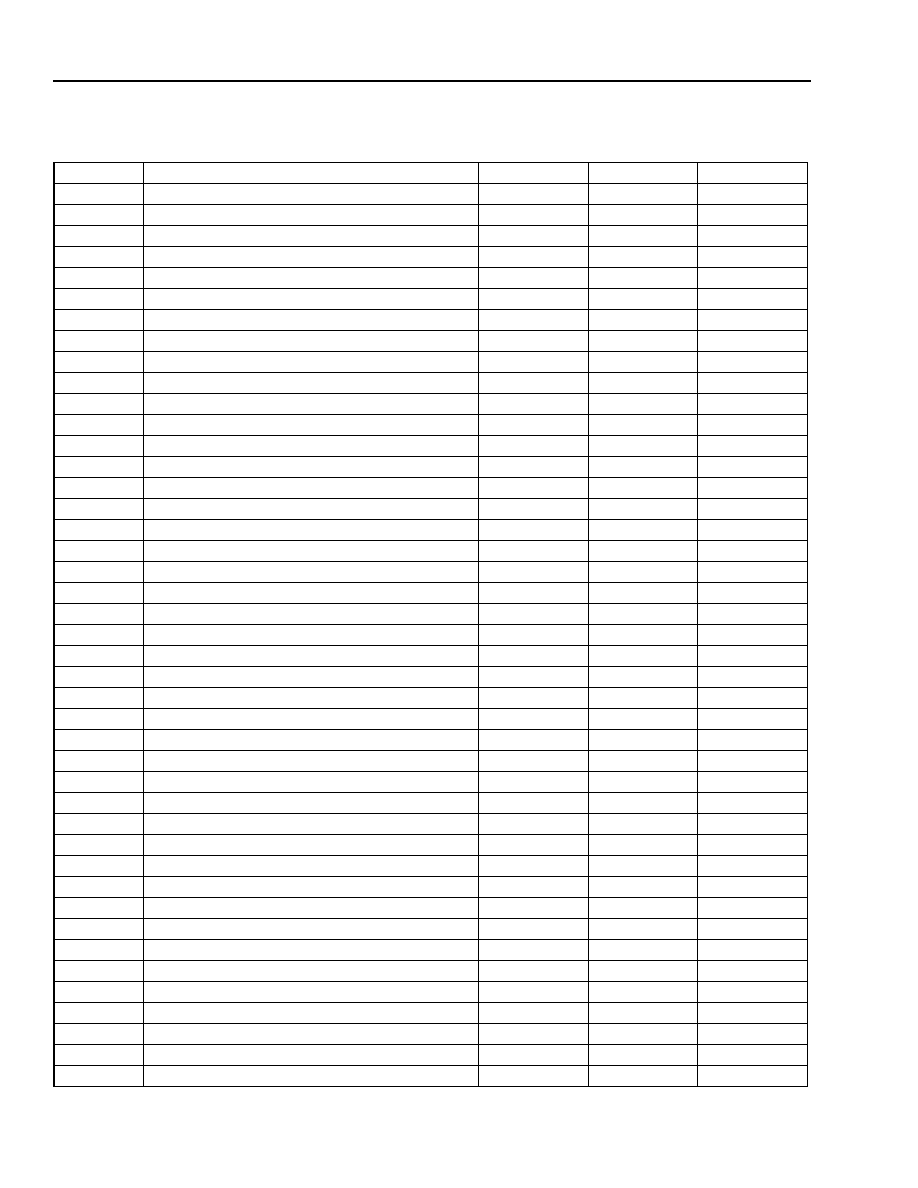

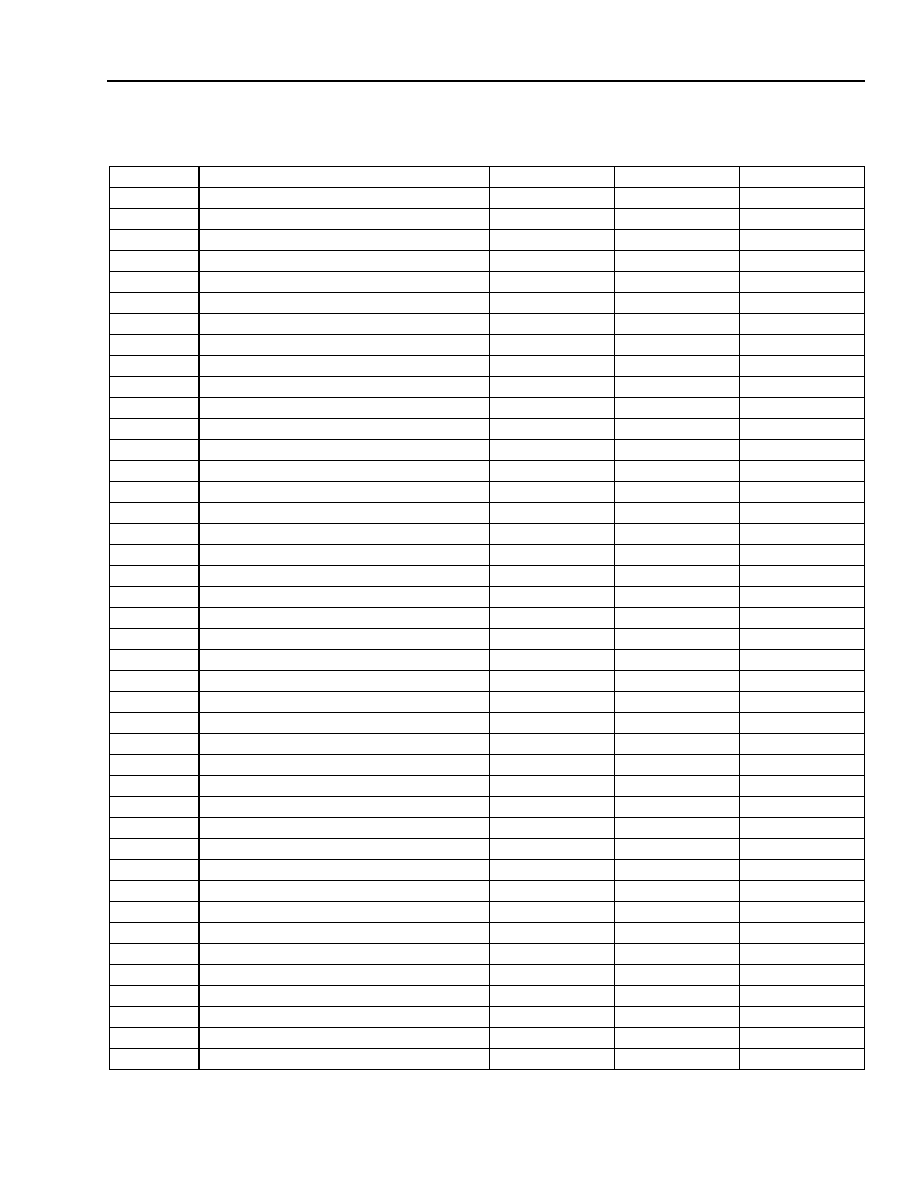

Table 8. T8110L Pinouts (continued)

H-Bus Interface (continued)

Ball

Pin Name

Buffer Type

Pull-Up/Down (see note on page 12)

D10

/C16≠

24 mA I/O-Schmitt

50 k

up

D12

/C4

8 mA I/O-Schmitt

50 k

up

D14

C2

8 mA I/O-Schmitt

50 k

up

C14

SCLK

24 mA I/O-Schmitt

50 k

up

C13

/SCLKX2

24 mA I/O-Schmitt

50 k

up

C12

/FR_COMP

24 mA I/O-Schmitt

50 k

up

J20

LD0

8 mA I/O-Schmitt

LPUE: 50 k

up

J19

LD1

8 mA I/O-Schmitt

LPUE: 50 k

up

J18

LD2

8 mA I/O-Schmitt

LPUE: 50 k

up

K17

LD3

8 mA I/O-Schmitt

LPUE: 50 k

up

K20

LD4

8 mA I/O-Schmitt

LPUE: 50 k

up

K19

LD5

8 mA I/O-Schmitt

LPUE: 50 k

up

K18

LD6

8 mA I/O-Schmitt

LPUE: 50 k

up

L18

LD7

8 mA I/O-Schmitt

LPUE: 50 k

up

L20

LD8

8 mA I/O-Schmitt

LPUE: 50 k

up

L19

LD9

8 mA I/O-Schmitt

LPUE: 50 k

up

M18

LD10

8 mA I/O-Schmitt

LPUE: 50 k

up

M17

LD11

8 mA I/O-Schmitt

LPUE: 50 k

up

M20

LD12

8 mA I/O-Schmitt

LPUE: 50 k

up

M19

LD13

8 mA I/O-Schmitt

LPUE: 50 k

up

N19

LD14

8 mA I/O-Schmitt

LPUE: 50 k

up

N18

LD15

8 mA I/O-Schmitt

LPUE: 50 k

up

N20

LD16

8 mA I/O-Schmitt

LPUE: 50 k

up

P20

LD17

8 mA I/O-Schmitt

LPUE: 50 k

up

P19

LD18

8 mA I/O-Schmitt

LPUE: 50 k

up

P18

LD19

8 mA I/O-Schmitt

LPUE: 50 k

up

R20

LD20

8 mA I/O-Schmitt

LPUE: 50 k

up

R19

LD21

8 mA I/O-Schmitt

LPUE: 50 k

up

R18

LD22

8 mA I/O-Schmitt

LPUE: 50 k

up

P17

LD23

8 mA I/O-Schmitt

LPUE: 50 k

up

T20

LD24

8 mA I/O-Schmitt

LPUE: 50 k

up

T19

LD25

8 mA I/O-Schmitt

LPUE: 50 k

up

T18

LD26

8 mA I/O-Schmitt

LPUE: 50 k

up

U20

LD27

8 mA I/O-Schmitt

LPUE: 50 k

up

V20

LD28

8 mA I/O-Schmitt

LPUE: 50 k

up

U19

LD29

8 mA I/O-Schmitt

LPUE: 50 k

up

U18

LD30

8 mA I/O-Schmitt

LPUE: 50 k

up

T17

LD31

8 mA I/O-Schmitt

LPUE: 50 k

up

H20

L_SC0

8 mA 3-state

--

H19

L_SC1

8 mA 3-state

--

H18

L_SC2

8 mA 3-state

--

G19

L_SC3

8 mA 3-state

--

16

Agere Systems Inc.

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

2 Pin Description

(continued)

2.2 T8110L Pinout Information

(continued)

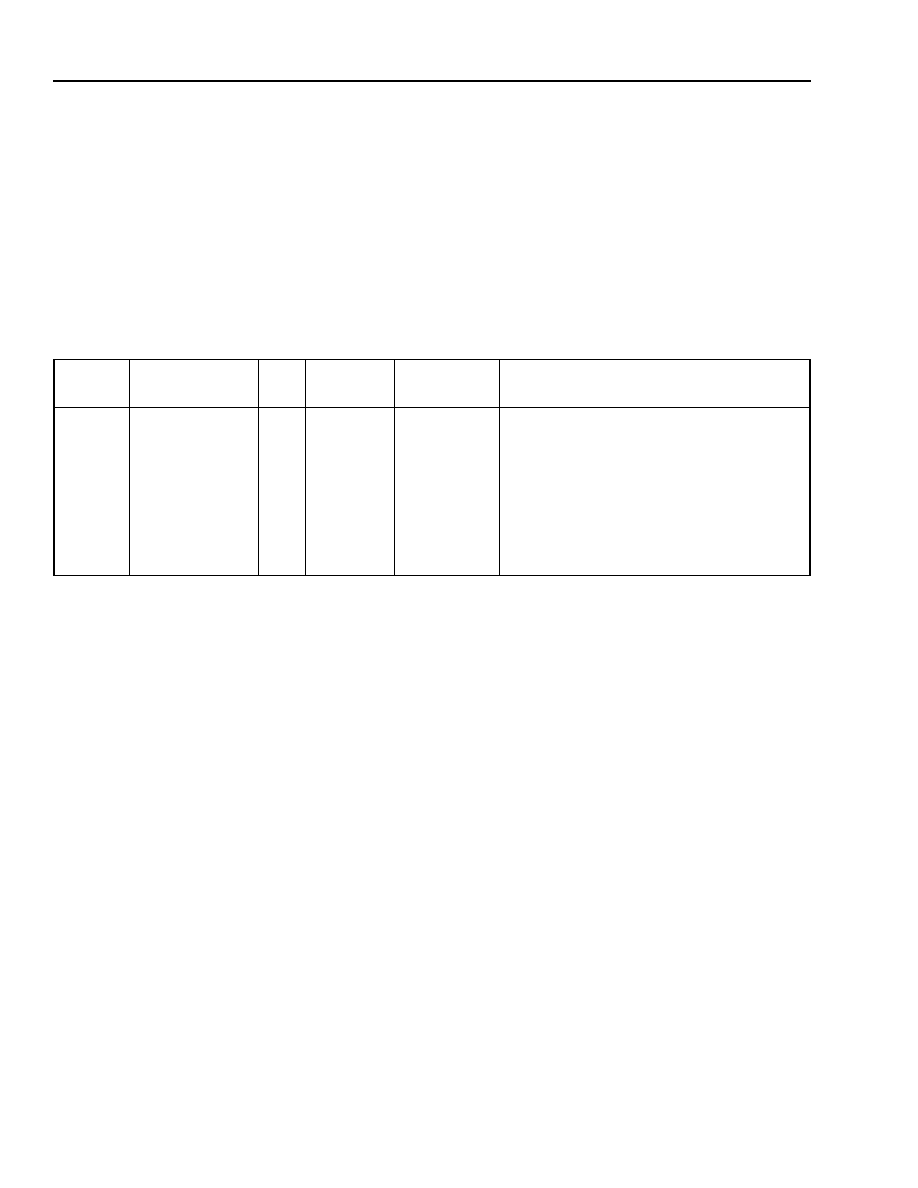

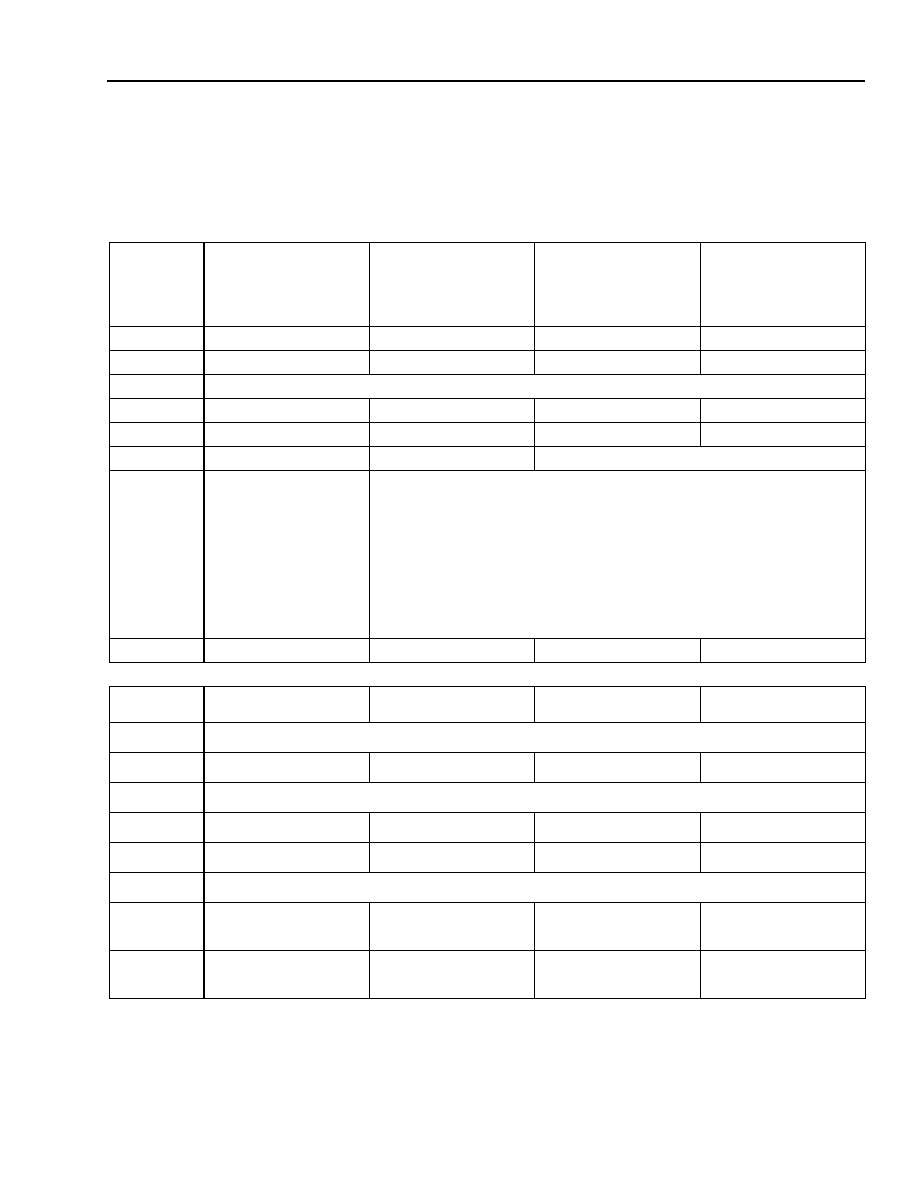

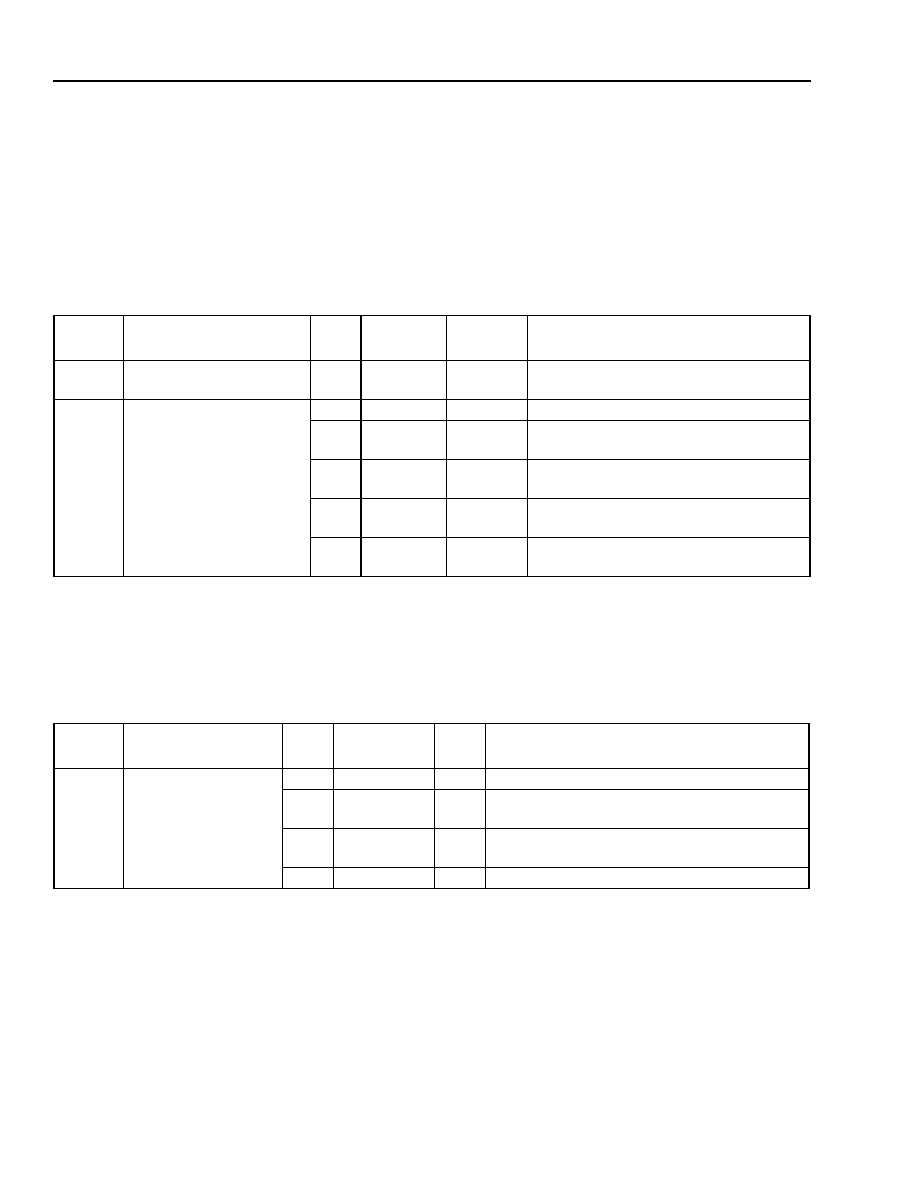

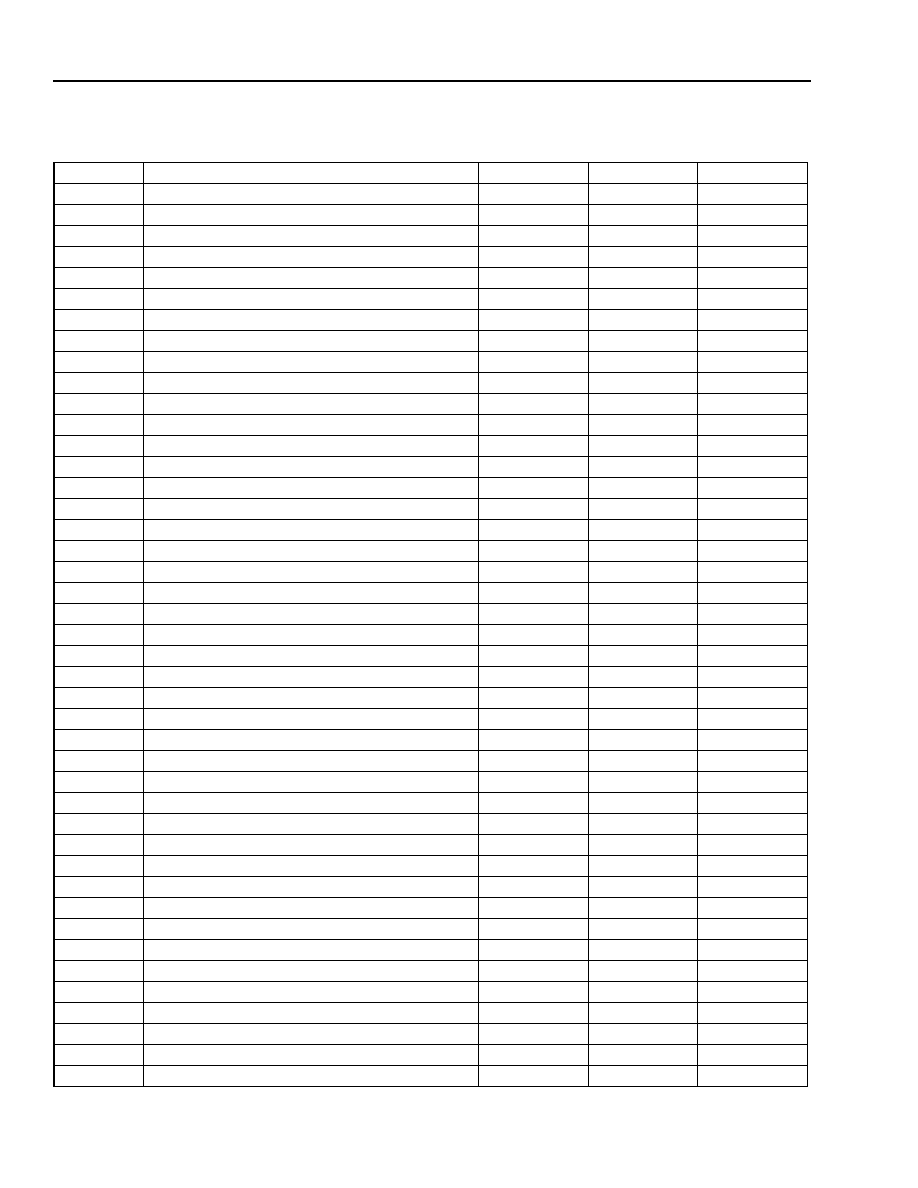

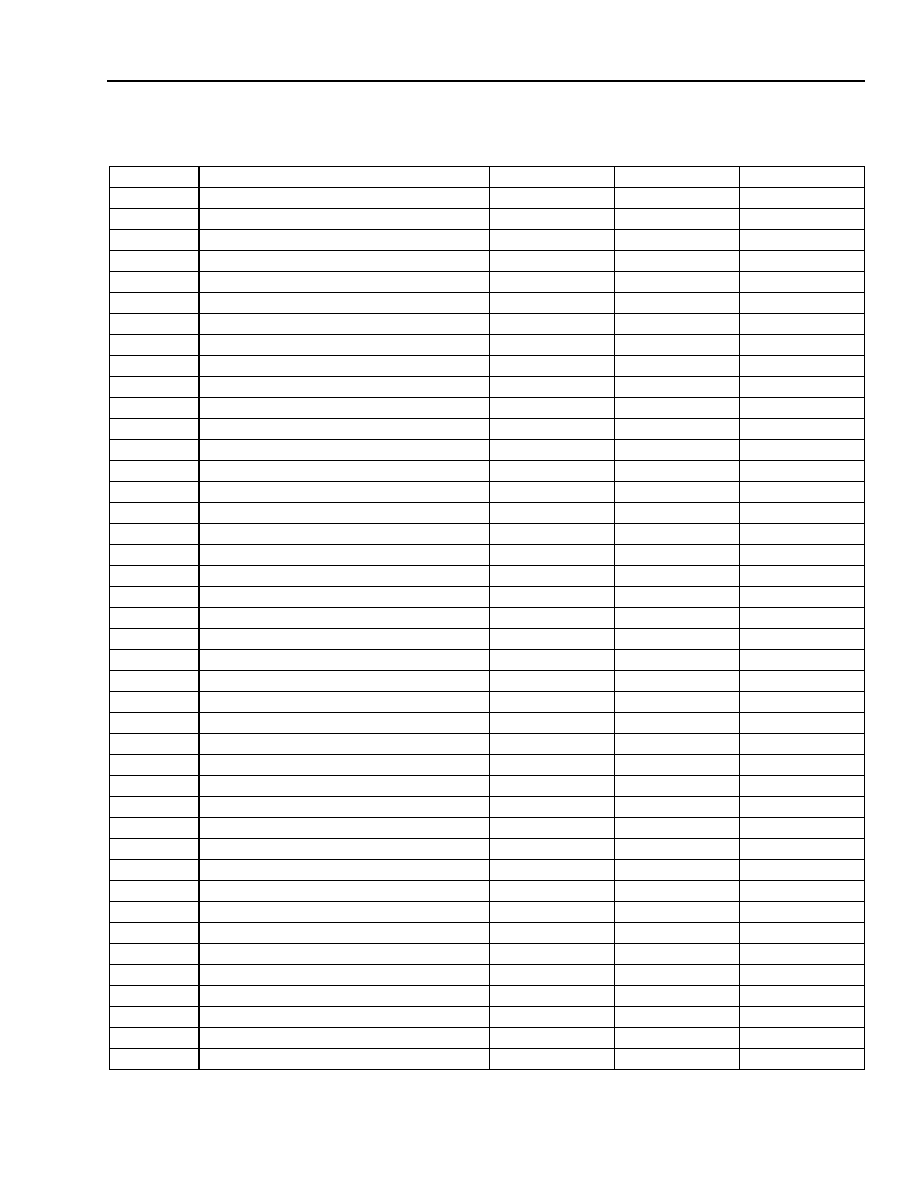

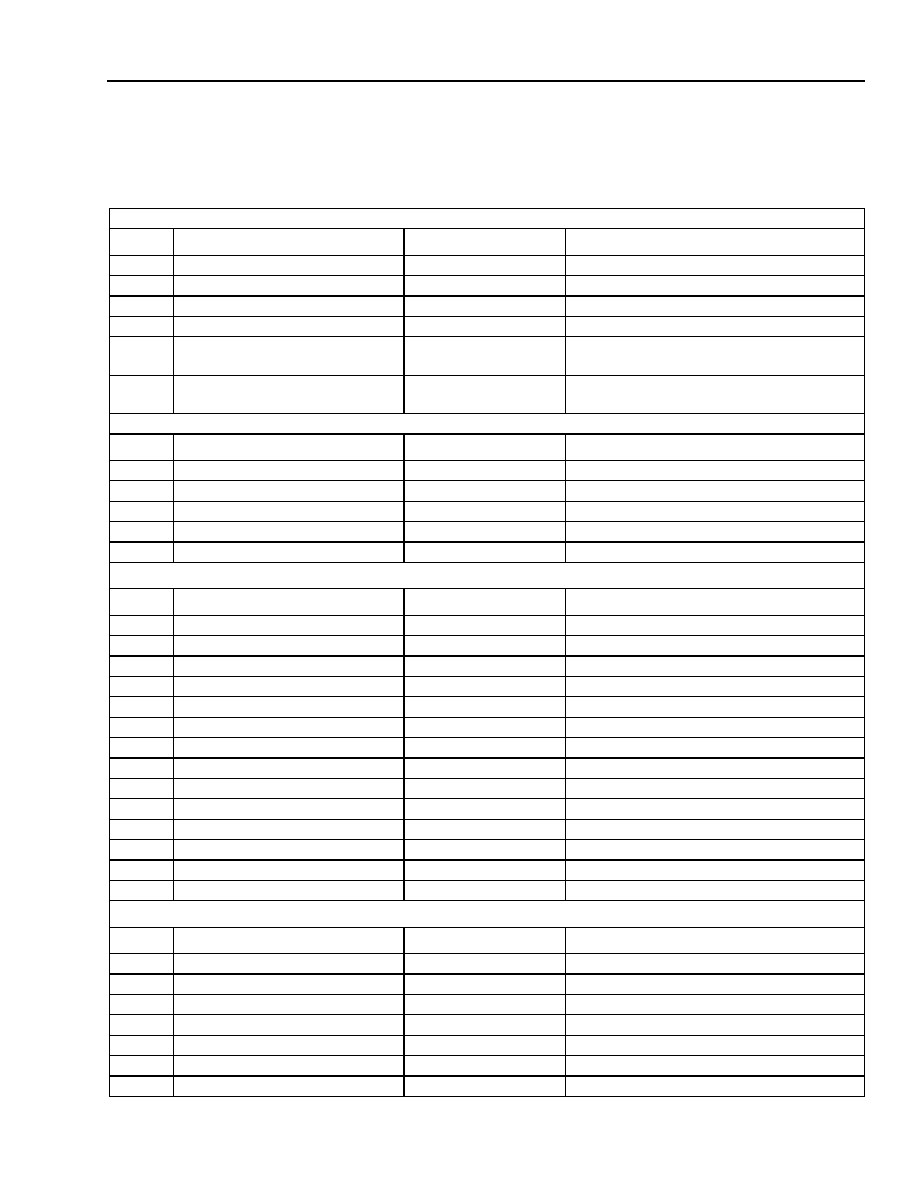

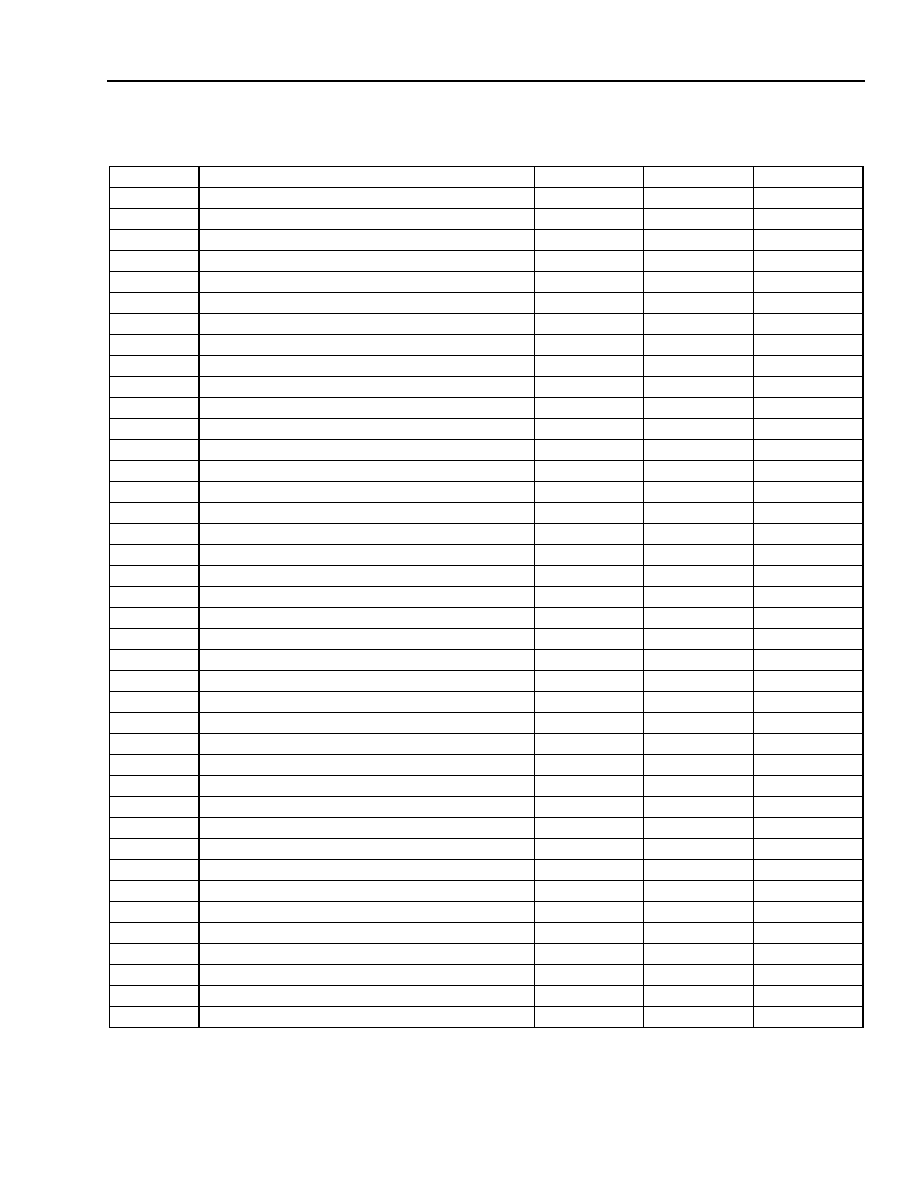

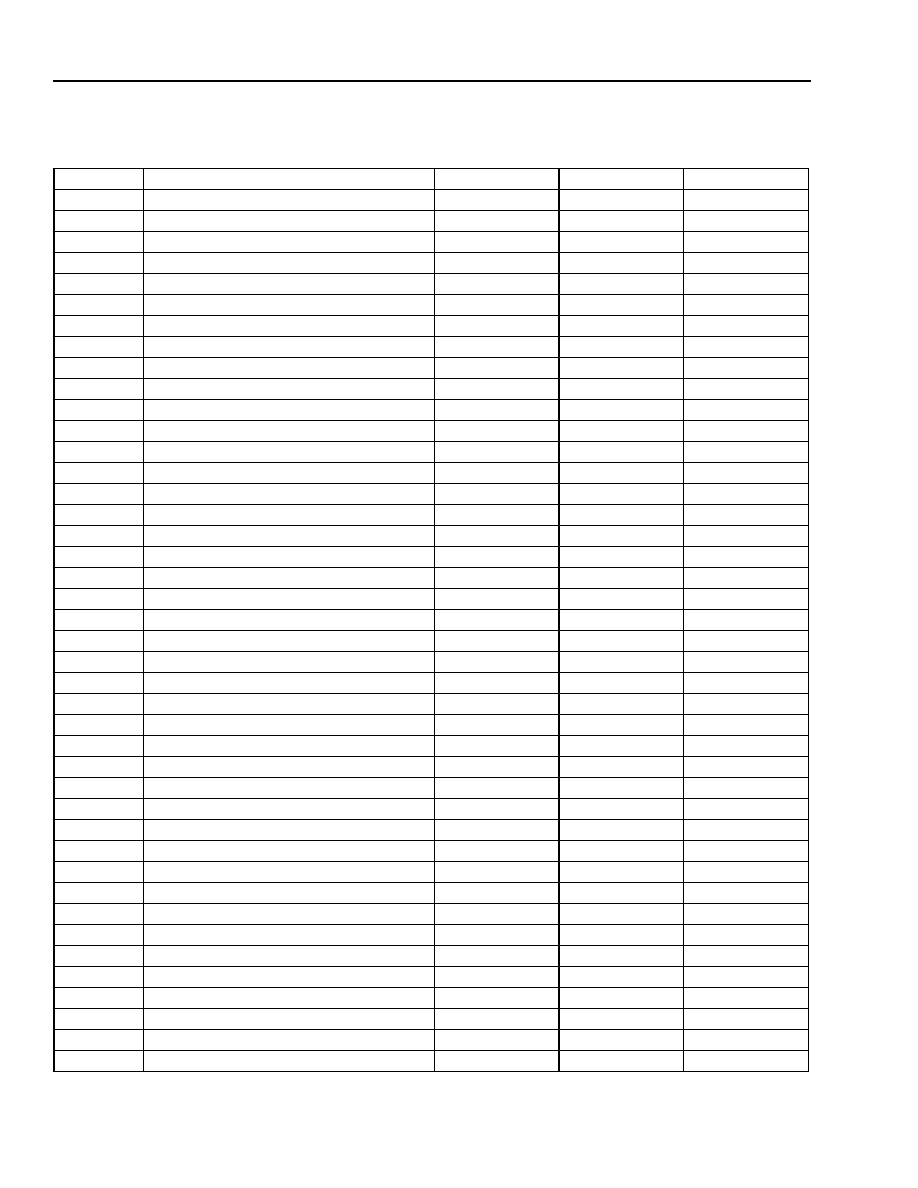

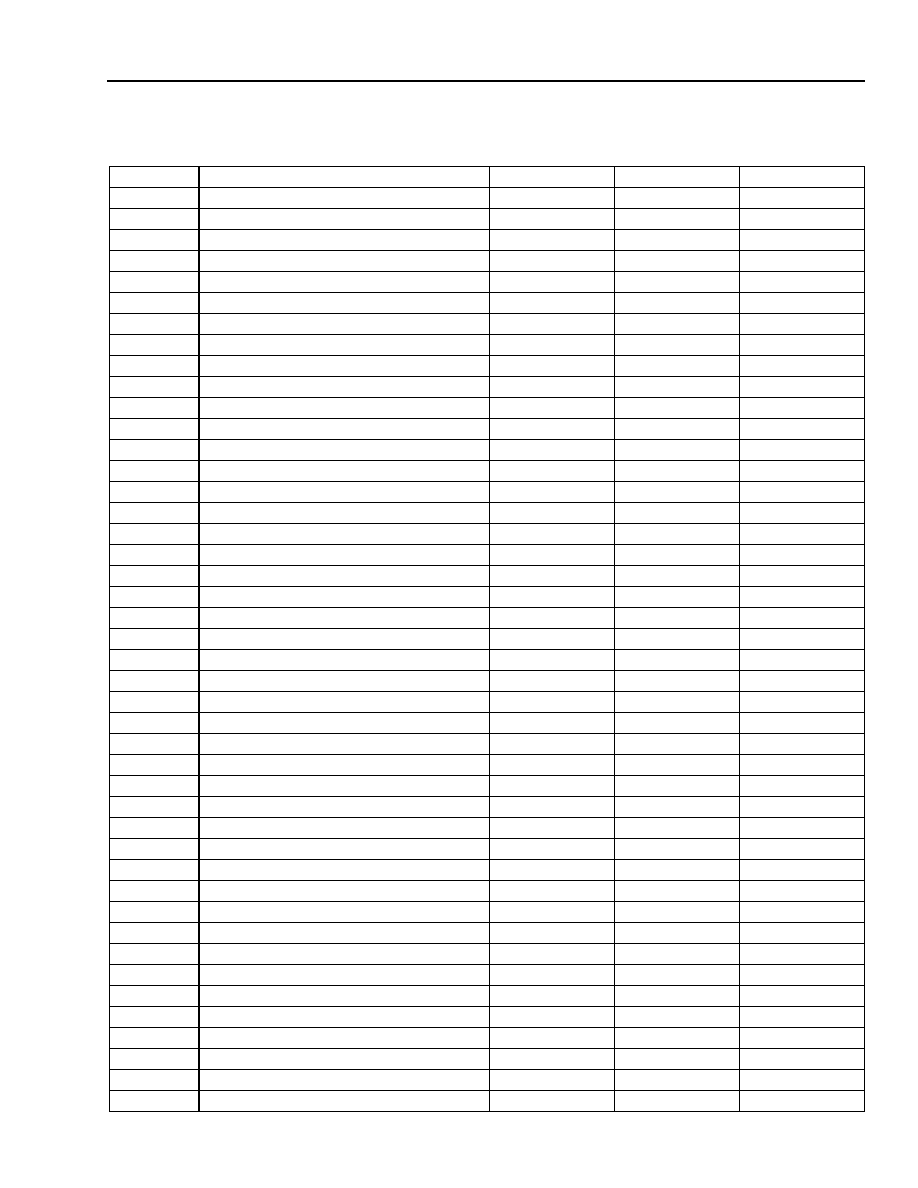

Table 8. T8110L Pinouts (continued)

L-Bus Interface

Ball

Pin Name

Buffer Type

Pull Up/Down (see note on page 12)

Y20

FG0

8 mA I/O-Schmitt

LPUE: 50 k

up

Y19

FG1

8 mA I/O-Schmitt

LPUE: 50 k

up

W20

FG2

8 mA I/O-Schmitt

LPUE: 50 k

up

W19

FG3

8 mA I/O-Schmitt

LPUE: 50 k

up

W18

FG4

8 mA I/O-Schmitt

LPUE: 50 k

up

V19

FG5

8 mA I/O-Schmitt

LPUE: 50 k

up

V18

FG6

8 mA I/O-Schmitt

LPUE: 50 k

up

V17

FG7

8 mA I/O-Schmitt

LPUE: 50 k

up

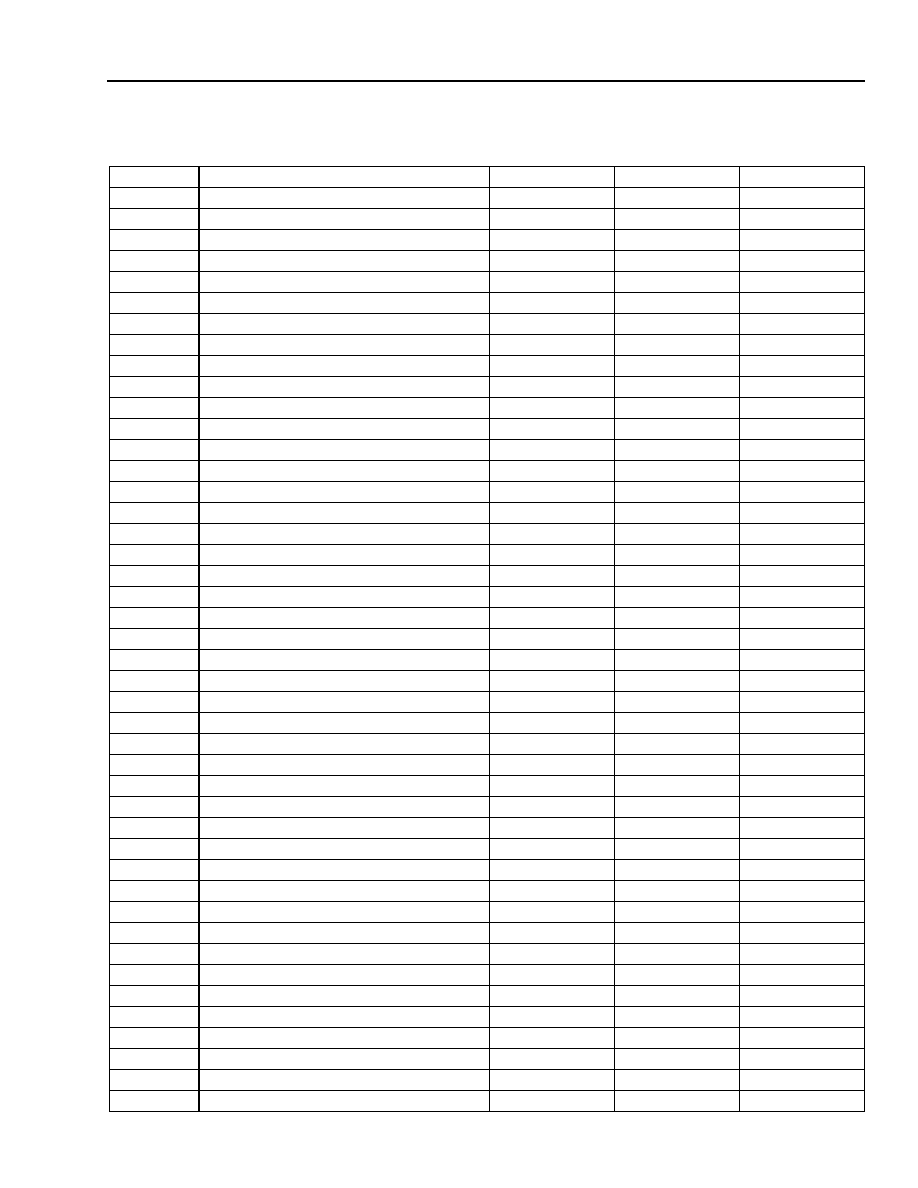

B20

XTAL1_IN

Input

--

C19

XTAL1_OUT

Crystal feedback

--

E20

XTAL2_IN

Input

--

F19

XTAL2_OUT

Crystal feedback

--

A15

LREF0

Input-Schmitt

LPUE: 50 k

up

B15

LREF1

Input-Schmitt

LPUE: 50 k

up

C15

LREF2

Input-Schmitt

LPUE: 50 k

up

C16

LREF3

Input-Schmitt

LPUE: 50 k

up

A16

LREF4

Input-Schmitt

LPUE: 50 k

up

B16

LREF5

Input-Schmitt

LPUE: 50 k

up

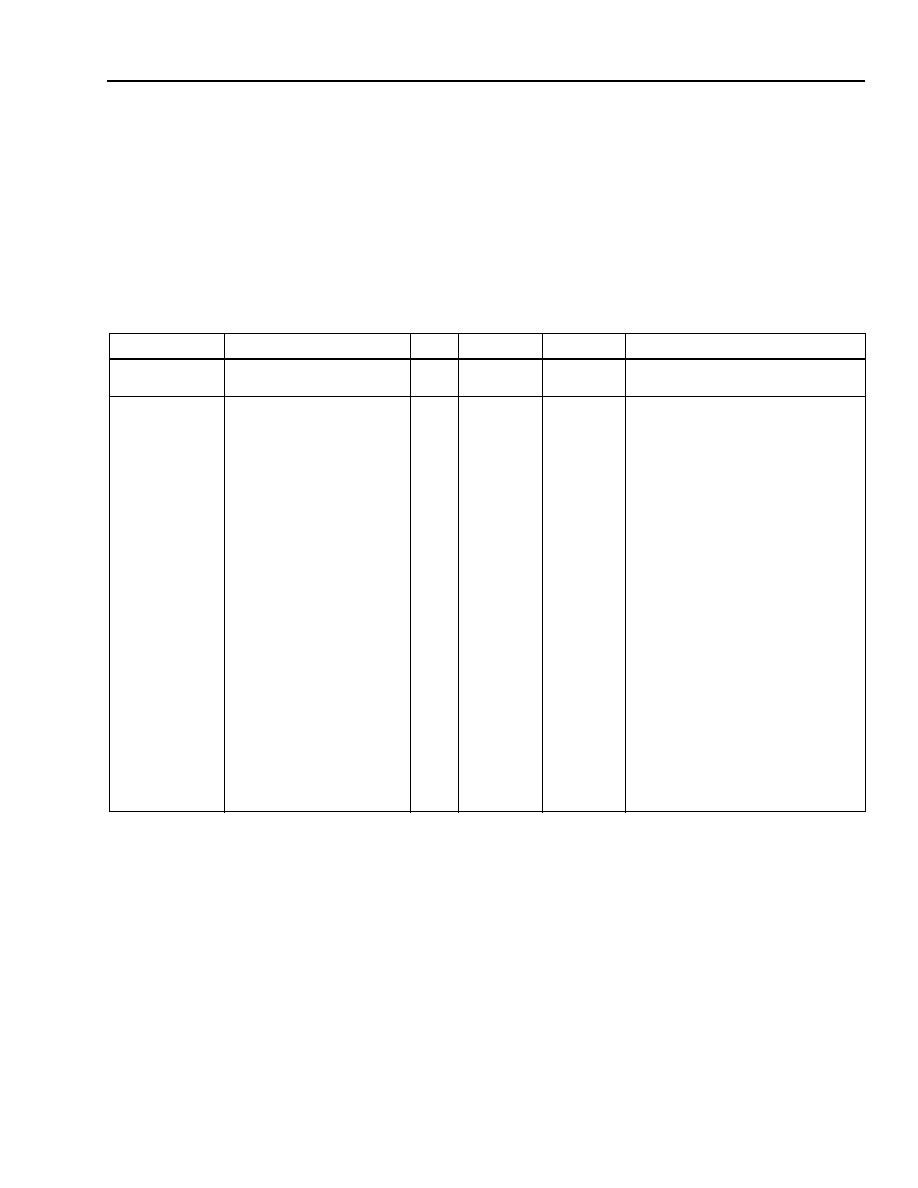

Clock Circuit Interface

Ball

Pin Name

Buffer Type

Pull Up/Down (see note on page 12)

B17

LREF6

Input-Schmitt

LPUE: 50 k

up

C17

LREF7

Input-Schmitt

LPUE: 50 k

up

G20

TCLK_OUT

8 mA 3-state

--

A17

PRI_REF_OUT

8 mA 3-state

--

A18

PRI_REF_IN

Input-Schmitt

LPUE: 50 k

up

B18

NR1_SEL_OUT

8 mA 3-state

--

A19

NR1_DIV_IN

Input-Schmitt

LPUE: 50 k

up

D19

NR2_SEL_OUT

8 mA 3-state

--

C20

NR2_DIV_IN

Input-Schmitt

LPUE: 50 k

up

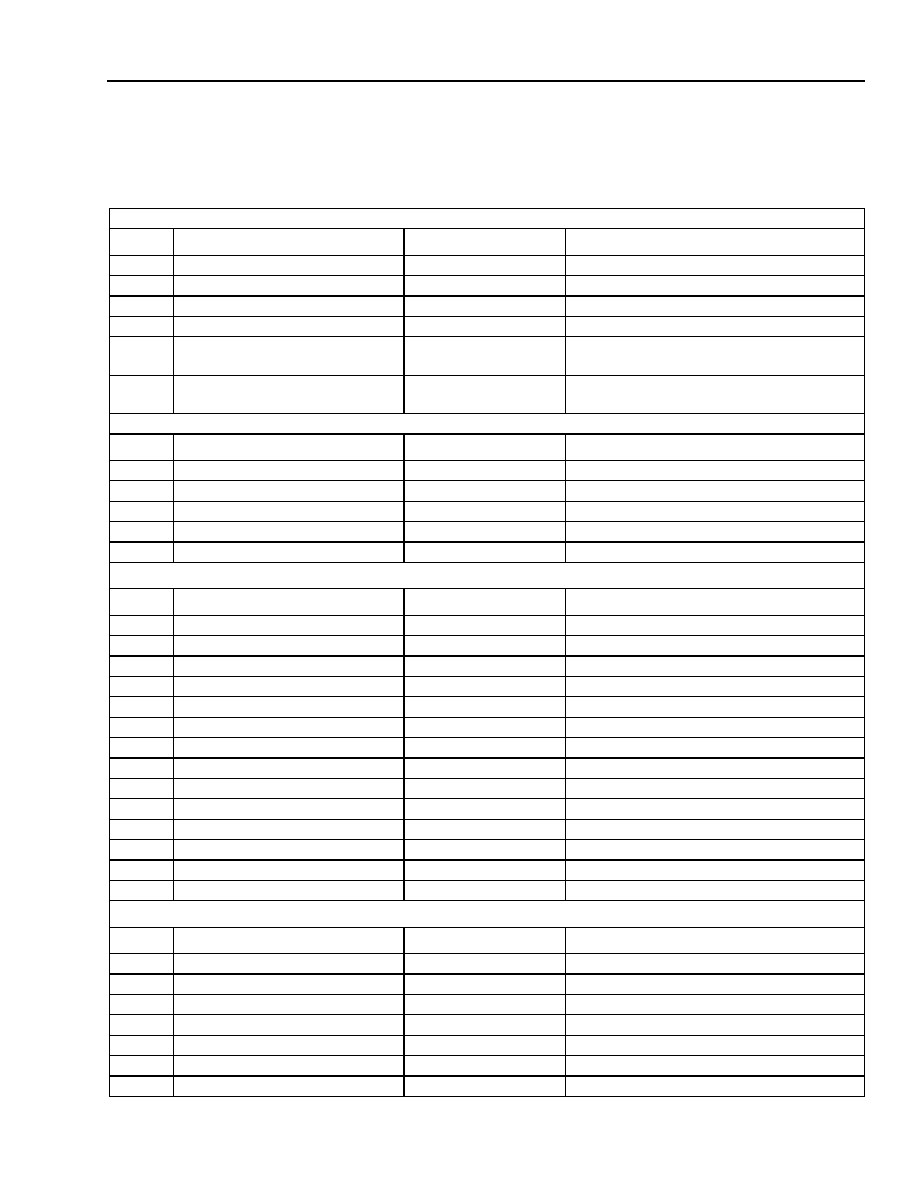

GPIO Interface

Ball

Pin Name

Buffer Type

Pull Up/Down (see note on page 12)

D1

GP0/AMASTER

8 mA I/O-Schmitt

LPUE: 50 k

up

E1

GP1/BMASTER

8 mA I/O-Schmitt

LPUE: 50 k

up

E2

GP2

8 mA I/O-Schmitt

LPUE: 50 k

up

F2

GP3

8 mA I/O-Schmitt

LPUE: 50 k

up

D3

GP4

8 mA I/O-Schmitt

LPUE: 50 k

up

F3

GP5

8 mA I/O-Schmitt

LPUE: 50 k

up

E3

GP6

8 mA I/O-Schmitt

LPUE: 50 k

up

E4

GP7

8 mA I/O-Schmitt

LPUE: 50 k

up

Agere Systems Inc.

17

Data Sheet

February 2004

Ambassador T8110L H.100/H.110 Switch

2 Pin Description

(continued)

2.2 T8110L Pinout Information

(continued)

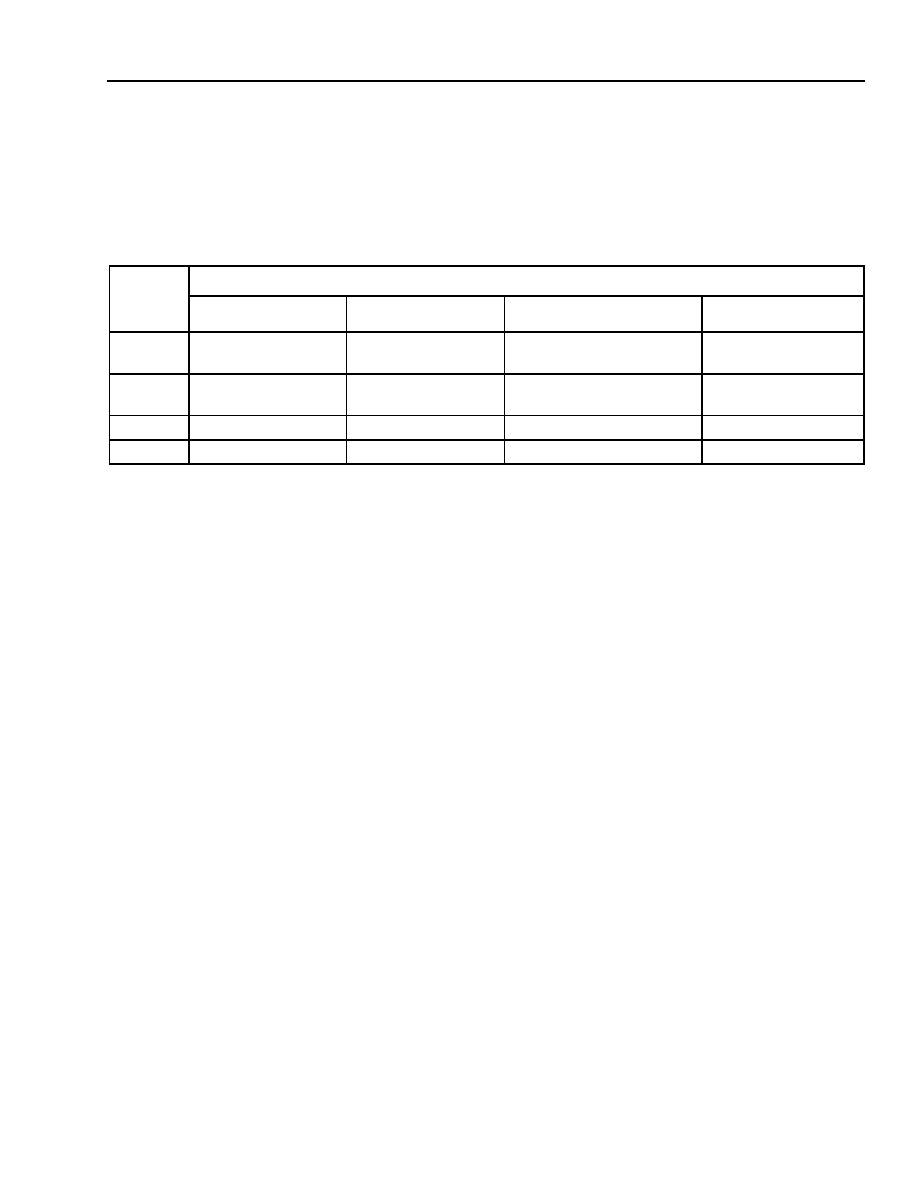

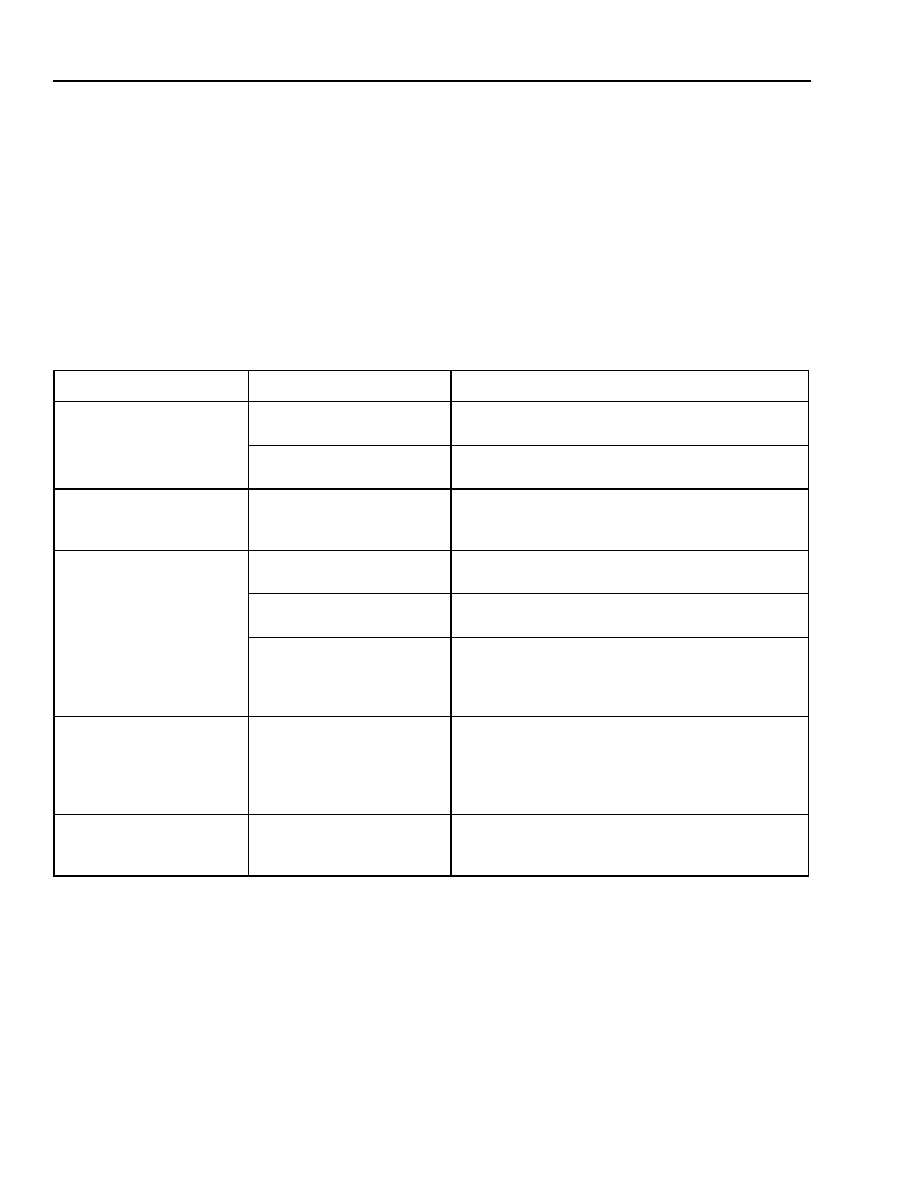

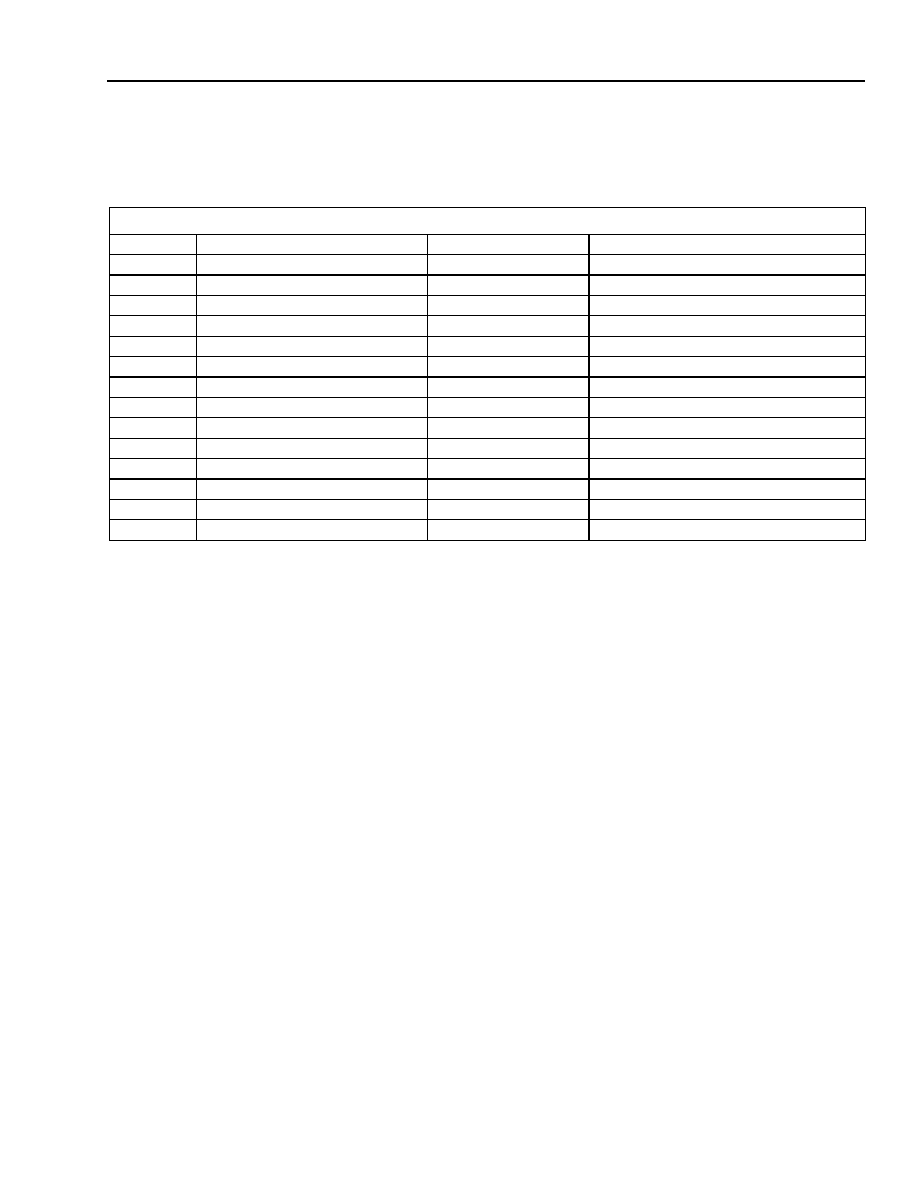

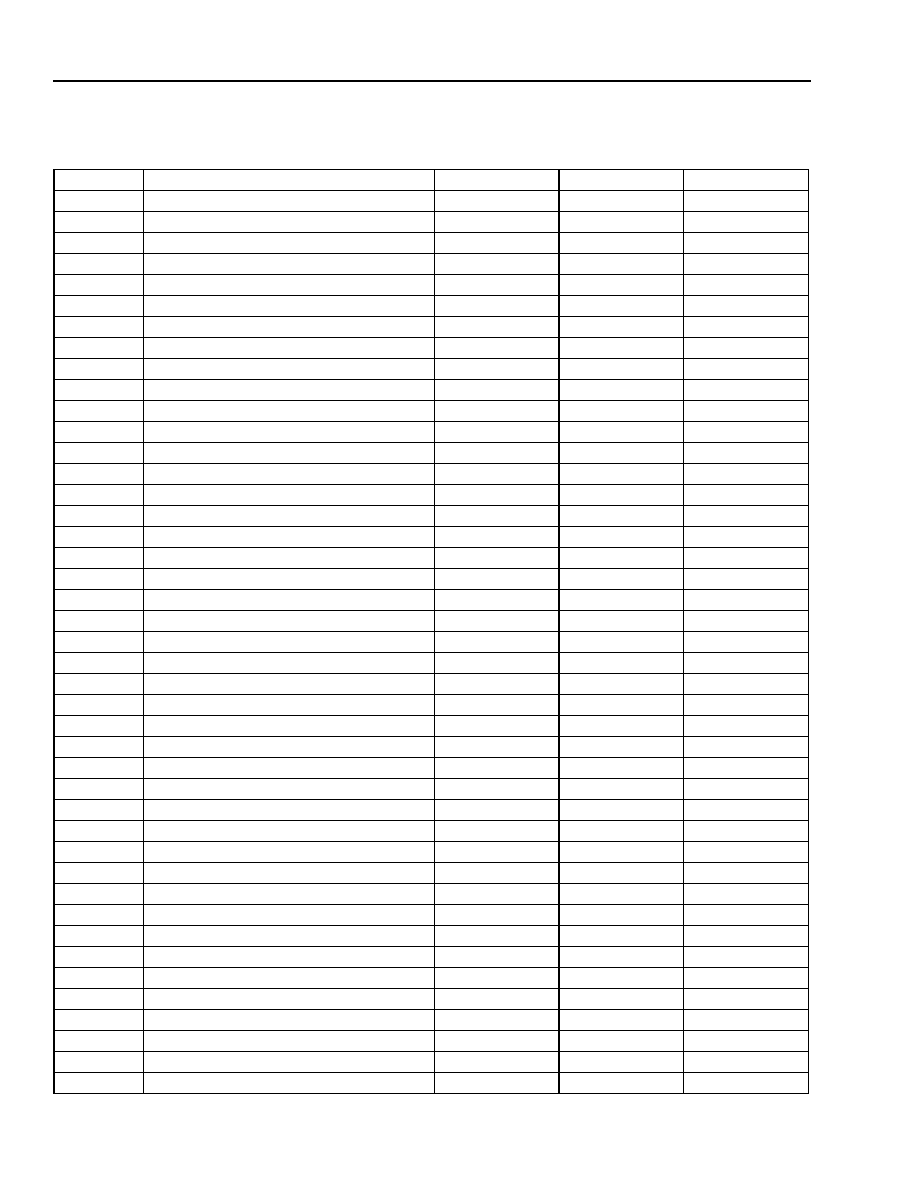

Table 8. T8110L Pinouts (continued)

Miscellaneous Interfaces

Ball

Pin Name

Buffer Type

Pull Up/Down (see note on page 12)

Y1

RESET#

Input-Schmitt

50 k

up

V3

SYSERR

8 mA 3-state

--

W2

CLKERR

8 mA 3-state

--

J17

LPUE

Input

50 k

up

A20

PEN

Input

50 k

up. This pin is unused and must be

left unconnected.

F20

TESTMODE

Input

20 k

up. This pin is unused and must be

left unconnected.

JTAG Interface

Ball

Pin Name

Buffer Type

Pull Up/Down (see note on page 12)

C18

TRST#

Input-Schmitt

50 k

up

E18

TCK

Input-Schmitt

50 k

up

D18

TMS

Input-Schmitt

50 k

up

F18

TDI

Input-Schmitt

50 k

up

G18

TDO

4 mA 3-state

--

Power

Ball

Pin Name

Buffer Type

Pull Up/Down

B19

APLL1V

DD

Analog V

DD

--

E19

APLL2V

DD

Analog V

DD

--

D6

V

DD

--

--

D11

V

DD

--

--

D15

V

DD

--

--

F4

V

DD

--

--

F17

V

DD

--

--

K4

V

DD

--

--

L17

V

DD

--

--

R4

V

DD

--

--

R17

V

DD

--

--

U6

V

DD

--

--

U10

V

DD

--

--

U15

V

DD

--

--

Ground

Ball

Pin Name

Buffer Type

Pull Up/Down

A1

V

SS

--

--

D4

V

SS

--

--

D8

V

SS

--

--

D13

V

SS

--

--

D17

V

SS

--

--

H4

V

SS

--

--

H17

V

SS

--

--

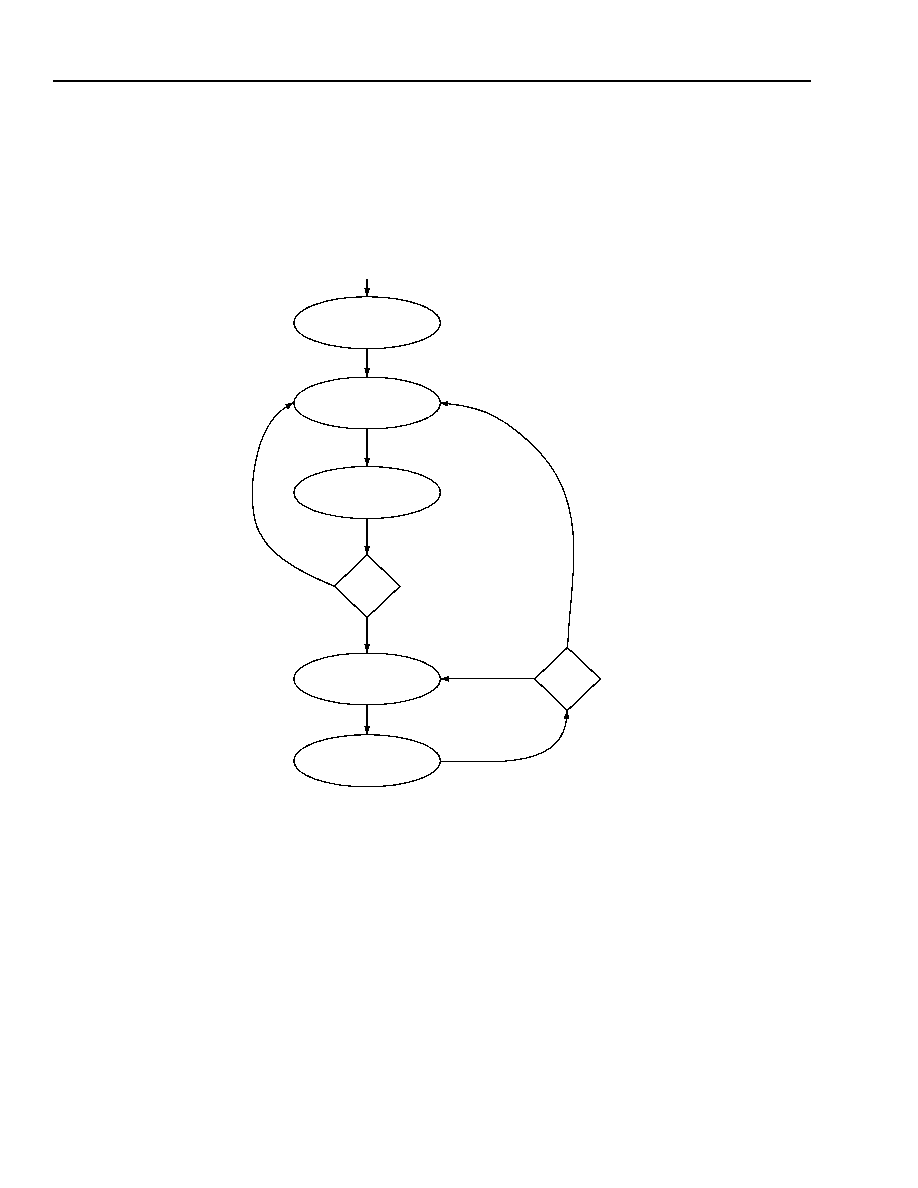

18