| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TAAD08JU2 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Preliminary Data Sheet

August 18, 2003

TAAD08JU2

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

1 Features

s

System-on-a-chip integrated circuit supports low-

speed ATM access for next-generation wireless

base transmission station (BTS), base station con-

troller (BSC), node-B, radio network controller

(RNC), and remote access concentrator (RAC)

applications.

s

IC provides an integrated octal framer that sup-

ports T1/E1/J1 formats.

s

Supports inverse multiplexing for ATM (IMA) over

selected group and link mappings ranging from

four two-link groups up to one eight-link group per

ATM Forum AF-PHY-0086.001.

s

Integrates an ATM adaptation layer 2 (AAL2) seg-

mentation and reassembly (SAR) function for sup-

port of low-speed data or voice traffic per ITU

I.363.2.

s

Provides AAL5 SAR functionality per ITU I.363.5.

s

Provides quality of service (QoS) connection iden-

tifier (CID) multiplexing per ITU I.366.1.

s

Enables ATM layer user network interface (UNI) or

IMA mode, selectable on a per-link basis for flexi-

ble transport of delay critical voice and data traffic.

s

Guarantees QoS for a variety of traffic types

(including delay-sensitive voice, real-time data,

non-real-time data, and signaling information)

through an advanced hierarchical three-level prior-

ity scheduler and per-VC queueing.

s

Supports 2032 bidirectional AAL2 CIDs.

s

Supports 2032 bidirectional high-speed data con-

nections or virtual circuits (VCs) via embedded

context memory; filters control cells and accepts

control cells via a host microprocessor interface.

s

On-board memory is used for connection manage-

ment and queue data storage. No external memory

is needed.

s

Software package includes the following:

-- Device manager source code (C-based device

manager ready-to-use with host RTOS).

-- Setup file utility to provision TAAD08JU2.

-- Firmware for embedded controller (executable

binary).

-- API reference manual available for device man-

ager software.

s

Designed in 0.16 µm, low-power CMOS

technology.

2 Physical

s

3.3 V digital I/O compatibility; 1.5 V core power

s

520 enhanced ball-grid array (EBGA) package

s

≠40

o

C to +85

o

C temperature range

3 Standards

ITU I.363.2, ITU I.363.5, ITU I.366.1, ITU I.366.2,

ITU I.432, ITU I.361, ITU I.371, ITU G.703, ITU

G.704, ITU G.804, ITU G.732, ITU G.706, ITU I.610,

ITU G.775, ITU G.733, ITU G.735, ITU G.965,

ITU O.162, ANSI

Æ

T1.403, ANSI T1.231,

ATM Forum AF-PHY-0086.001

ATM Forum AF-PHY-0039.000

ATM Forum AF-TM-0121.000

ETS 300.417-1-1

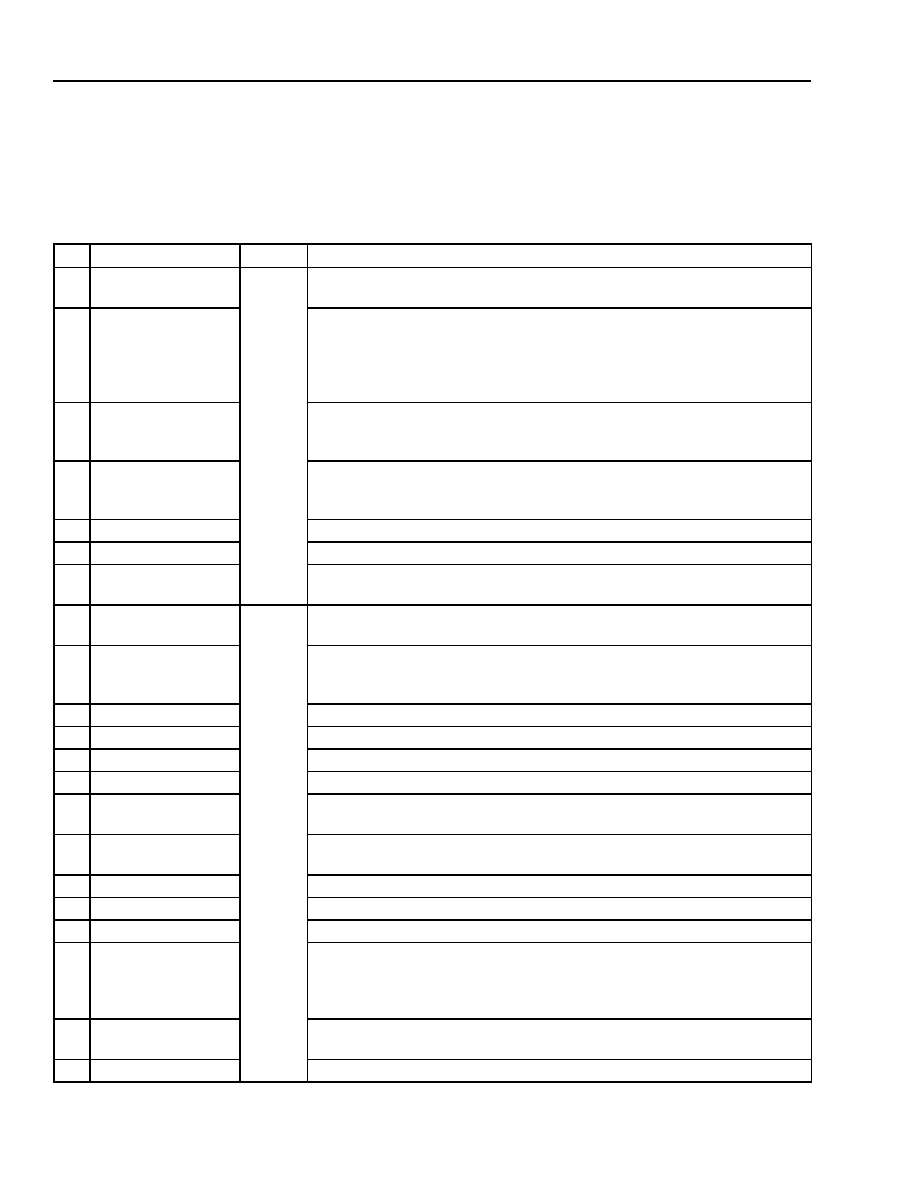

Table of Contents

2

Agere Systems - Proprietary

Agere Systems Inc.

Preliminary Data Sheet

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

TAAD08JU2

Contents

Page

1

Features .............................................................................................................................................................1

2

Physical ..............................................................................................................................................................1

3

Standards ...........................................................................................................................................................1

4

Description ....................................................................................................................................................... 11

5

Pin Definitions ..................................................................................................................................................12

6

Pin Description .................................................................................................................................................12

7

Package Pin Layout .........................................................................................................................................21

8

Block Diagram ..................................................................................................................................................27

9

Software Components ......................................................................................................................................28

9.1

Firmware.................................................................................................................................................29

9.2

Device Manager......................................................................................................................................29

9.3

Setup File Utility (SFU) ...........................................................................................................................30

9.4

TAAD08JU2 Application Code................................................................................................................31

9.5

System Software.....................................................................................................................................32

9.6

Software Development Environment ......................................................................................................32

9.7

Notes ......................................................................................................................................................33

10 Functional Overview.........................................................................................................................................34

10.1 Receive Direction Data Flow ..................................................................................................................34

10.1.1

PHY Layer ................................................................................................................................34

10.1.2

Low-Speed PHY Links ..............................................................................................................34

10.1.3

High-Speed PHY Links .............................................................................................................35

10.1.4

TC and IMA Layers...................................................................................................................35

10.1.5

ATM Layer ................................................................................................................................36

10.1.6

AAL Engine...............................................................................................................................36

10.1.7

Embedded Device Controller....................................................................................................37

10.2 Transmit Direction Data Flow..................................................................................................................37

10.2.1

SSCS/AAL Layer Interaction ....................................................................................................37

10.2.2

ATM Layer ................................................................................................................................37

10.2.3

IMA/TC Layer............................................................................................................................38

10.2.4

PHY Layer ................................................................................................................................38

11 Modes of Operation..........................................................................................................................................39

11.1 Interface Modes ......................................................................................................................................39

11.1.1

UTOPIA-2 Expansion Port Multiplexing Modes ........................................................................39

11.1.2

System Interface Port Multiplexing Modes ...............................................................................39

11.1.3

Line-Interface Modes ................................................................................................................40

11.2 Device Operating Modes ........................................................................................................................40

11.2.1

Operating Mode 1: Internal PHY Mode.....................................................................................40

11.2.2

Operating Mode 2: External PHY Mode ...................................................................................42

11.2.3

Operating Mode 3: SAR-Only Mode .........................................................................................43

11.2.4

Operating Mode Summary........................................................................................................43

12 Applications ......................................................................................................................................................44

12.1 BTS Network Interface Termination ........................................................................................................44

12.2 VToA Trunking Application......................................................................................................................46

12.3 Low-Speed ATM Access.........................................................................................................................47

12.4 AAL2 Cross Connect ..............................................................................................................................47

13 Embedded Device Controller (EDC) ................................................................................................................48

13.1 Introduction.............................................................................................................................................48

13.2 Features..................................................................................................................................................48

13.3 EDC Functional Description....................................................................................................................48

13.4 Host Interface .........................................................................................................................................48

13.5 Host Interface Signals and Timing..........................................................................................................49

Table of Contents

(continued)

Contents

Page

Data Sheet

TAAD08JU2

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

Agere Systems Inc.

Agere Systems - Proprietary

3

Use pursuant to Company instructions

13.6 Host Interactions.....................................................................................................................................49

14 Framer Block ....................................................................................................................................................53

14.1 Introduction .............................................................................................................................................53

14.2 Features..................................................................................................................................................53

14.3 Framer-to-Line Interface Unit Physical Interface ....................................................................................54

14.3.1

Line Interface References/Standards .......................................................................................54

14.3.2

Clocking Modes ........................................................................................................................54

14.3.3

Frame Formats .........................................................................................................................55

14.3.4

Transmit Framer Functions.......................................................................................................55

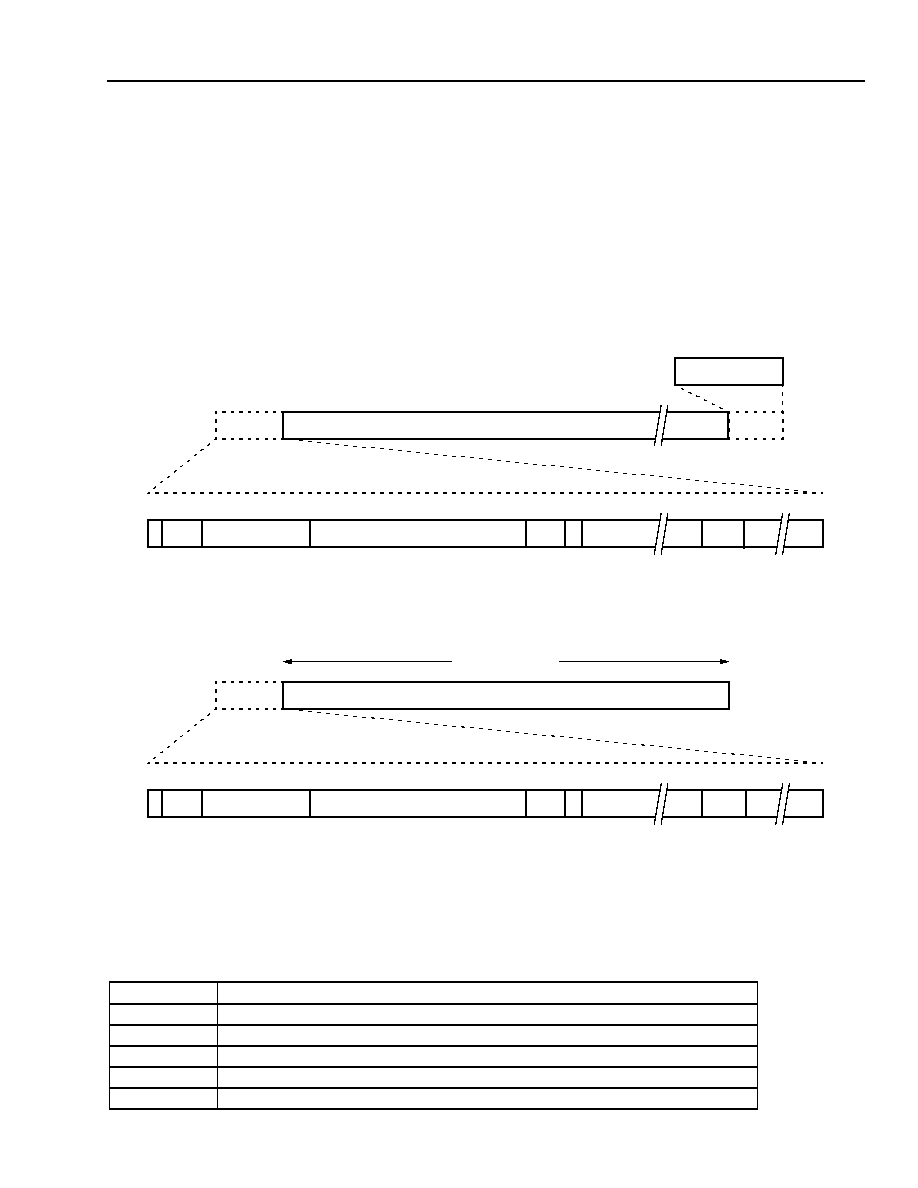

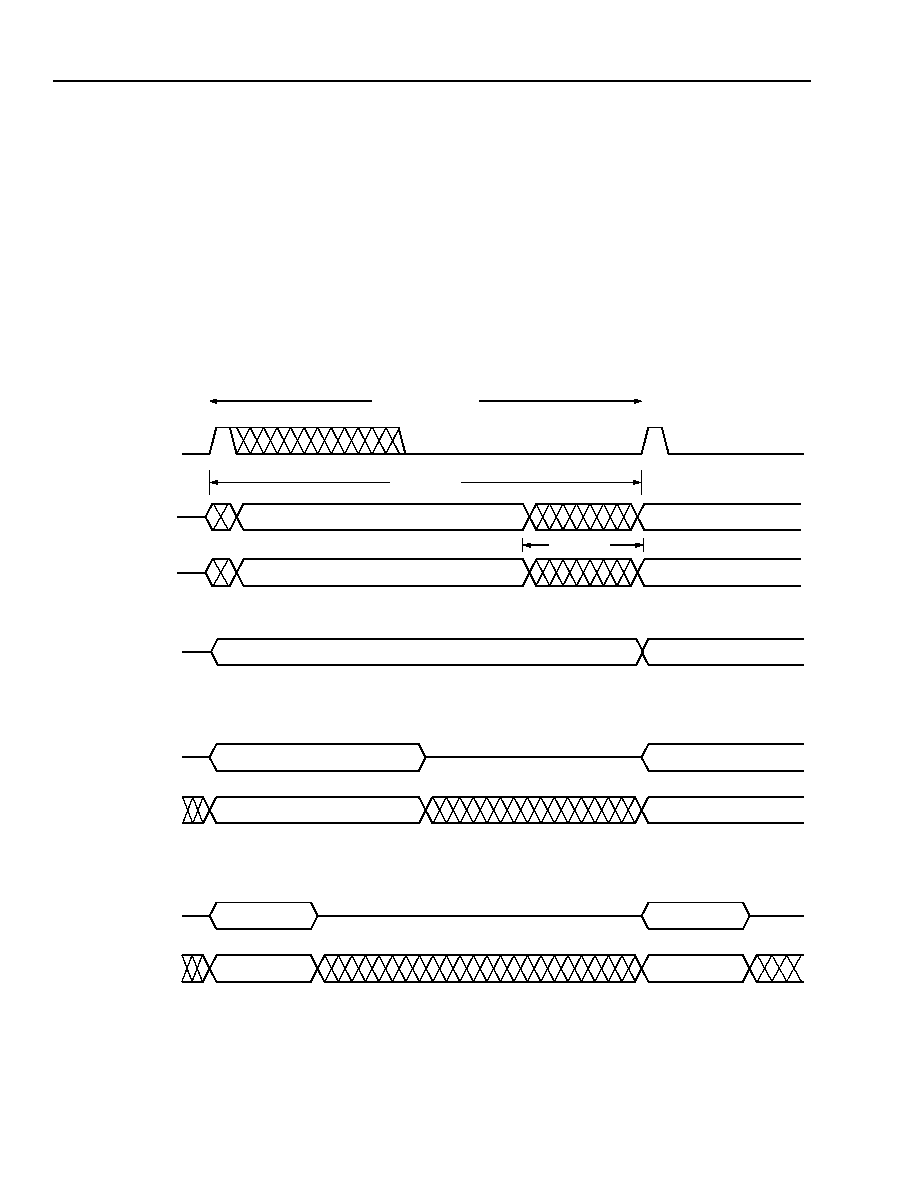

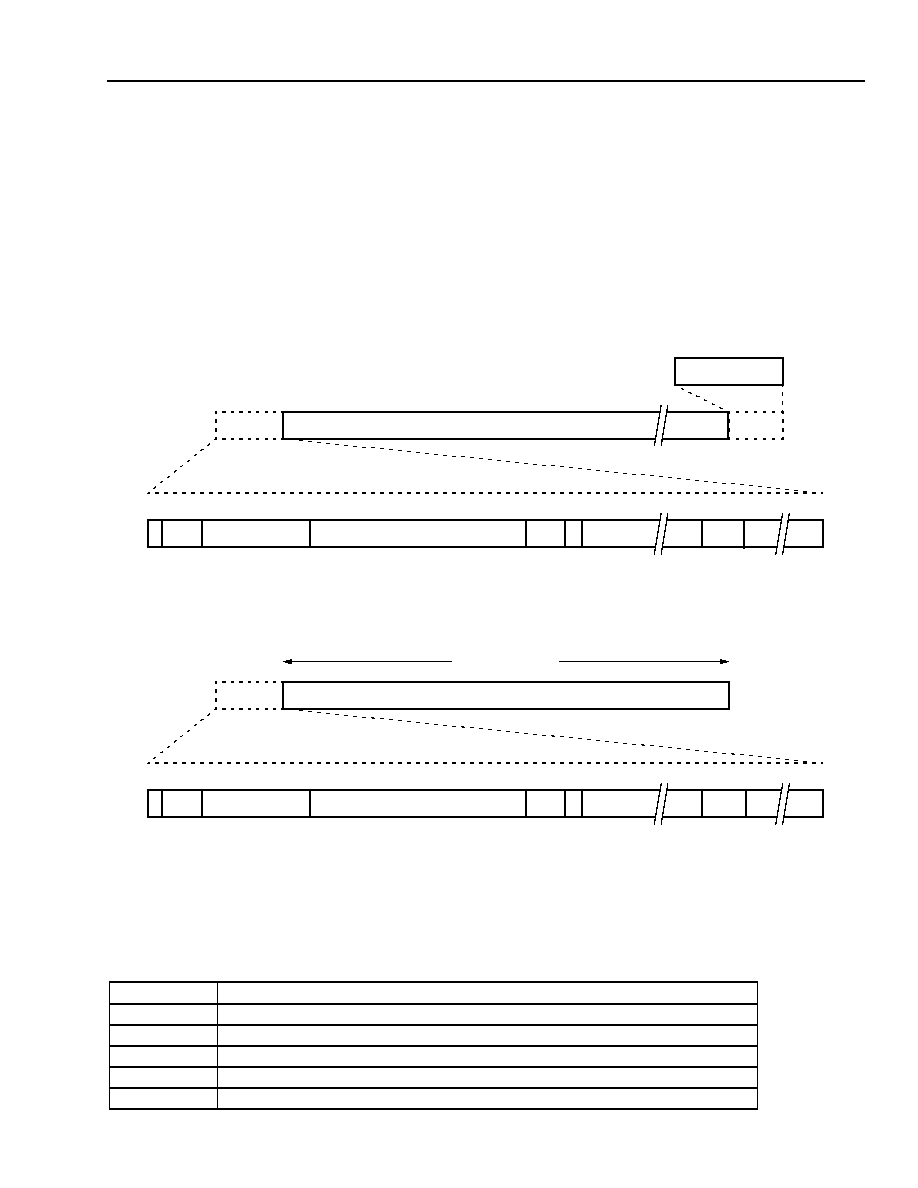

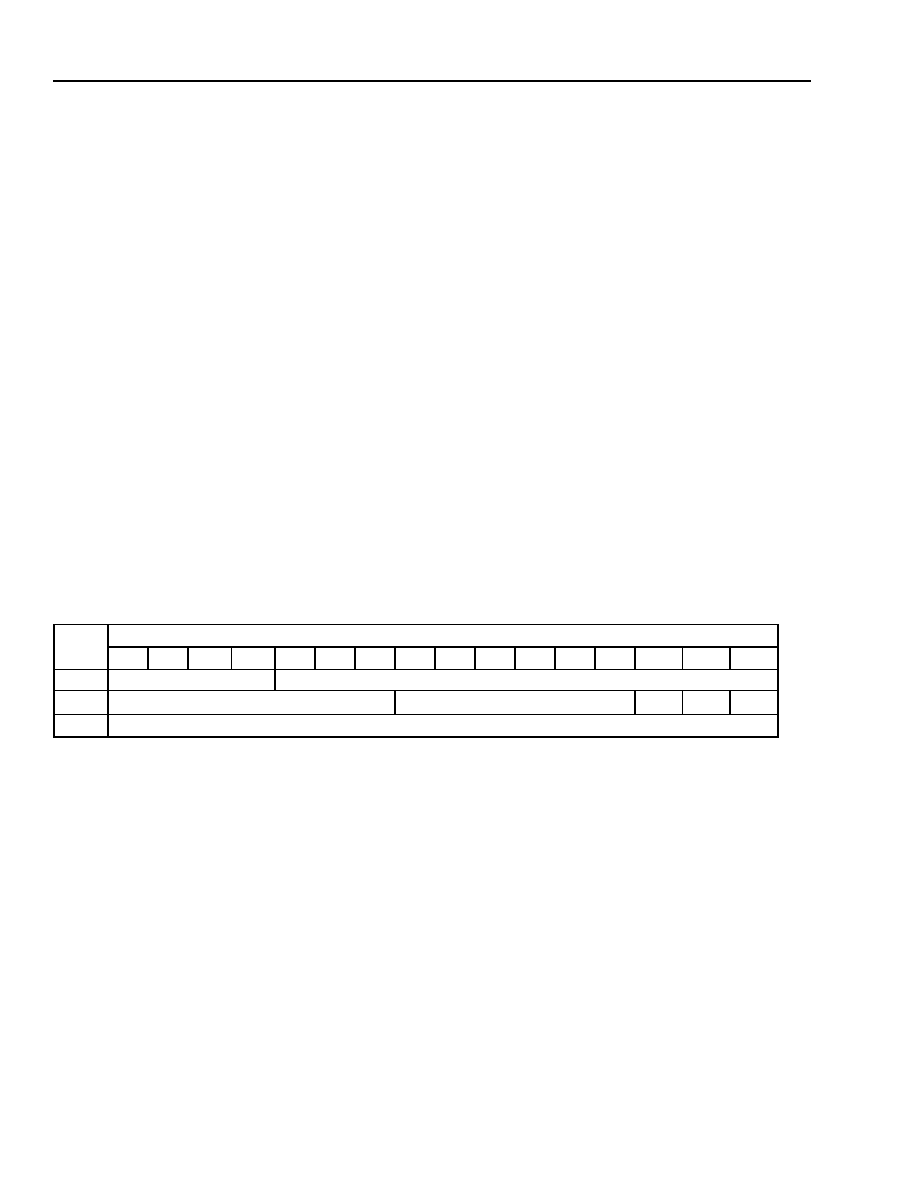

14.4 DS1 Transparent Framing Format ..........................................................................................................55

14.5 CEPT 2.048 Basic Frame Structure Transparent Framing Format.........................................................56

14.6 Receive Framer Nonalignment Mode (DS1/E1) .....................................................................................57

14.6.1

Loss of Frame Alignment Criteria .............................................................................................57

14.6.1.1 Frame Bit Errors.........................................................................................................57

14.6.1.2 CRC Errors.................................................................................................................57

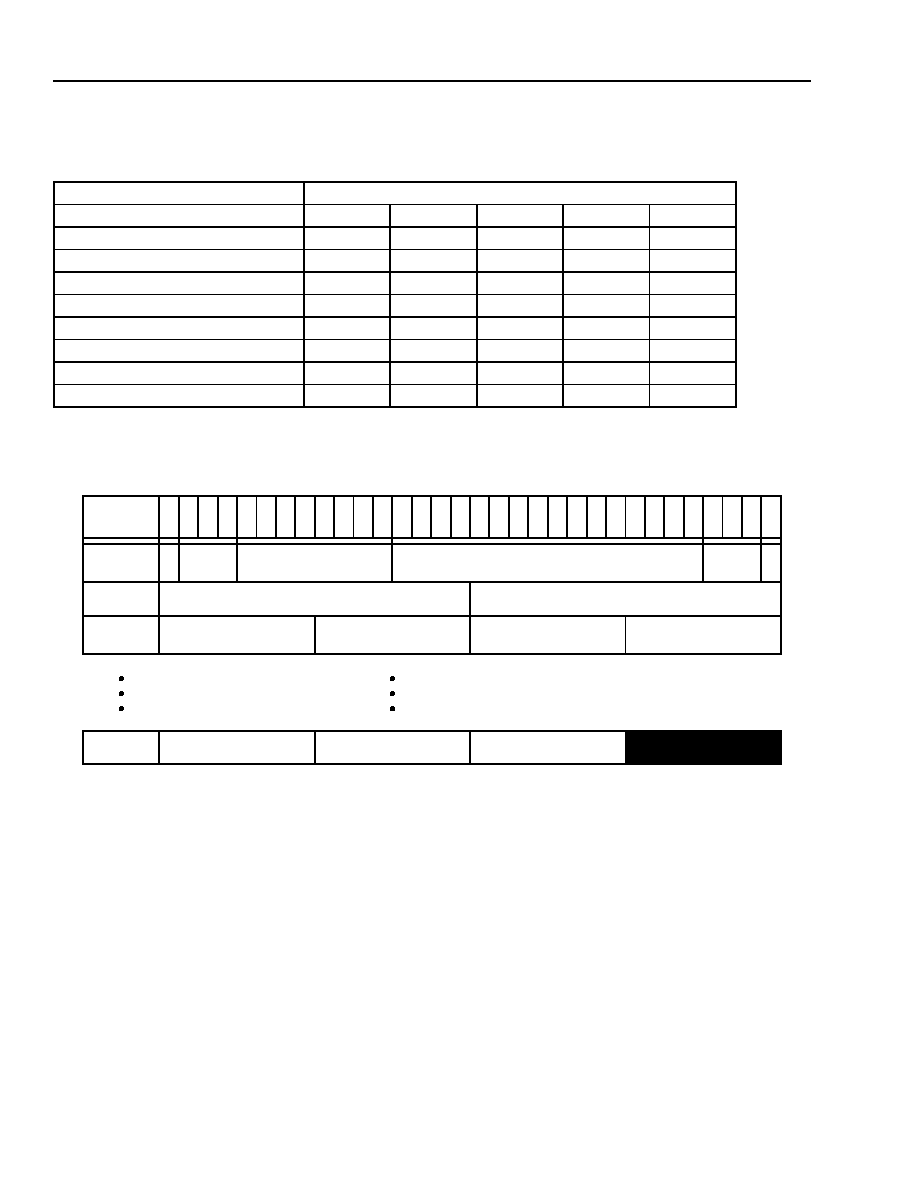

14.7 Frame Alignment Criteria........................................................................................................................57

14.8 Performance-Monitoring Functional Integration Into Framer ..................................................................58

14.9 Performance Report Message................................................................................................................61

14.10 ESF Data Link.........................................................................................................................................62

14.11 Facility Data Link ....................................................................................................................................62

14.11.1 Facility Data Link References/Standards ..................................................................................62

14.11.2 Receive Data Link Functional Description ................................................................................63

14.11.3 SLC-96 Superframe Receive Data Link....................................................................................63

14.11.4 DDS Receive Data Link Stack ..................................................................................................63

14.11.5 CEPT; CEPT CRC-4 (100 ms); CEPT CRC-4 (400 ms) Multiframe Sa Bits Receive Stack .....63

14.11.6 Receive Data Link Stack Idle Modes ........................................................................................64

14.11.7 Transmit Facility Data Link Functional Description ...................................................................64

14.11.8 SLC-96 Superframe Transmit Data Link...................................................................................64

14.11.9 DDS Transmit Data Link Stack .................................................................................................64

14.11.10 Transmit ESF Data Link Bit-Oriented Messages ......................................................................64

14.11.11 CEPT, CEPT Multiframe Transmit Data Link Sa Bits Stack ......................................................65

14.11.12 Transmit Data Link Stack Idle Modes .......................................................................................66

14.11.13 SLC-96, DDS, or CEPT ESF Frame Alignment ........................................................................66

14.12 Concentration Highway Interface (CHI) ..................................................................................................66

14.12.1 CHI References/Standards .......................................................................................................66

14.12.2 Transmit/Receive CHI Features................................................................................................66

14.12.3 Double NOTFAS System Time-Slot Mode................................................................................67

14.12.4 Transparent Mode.....................................................................................................................67

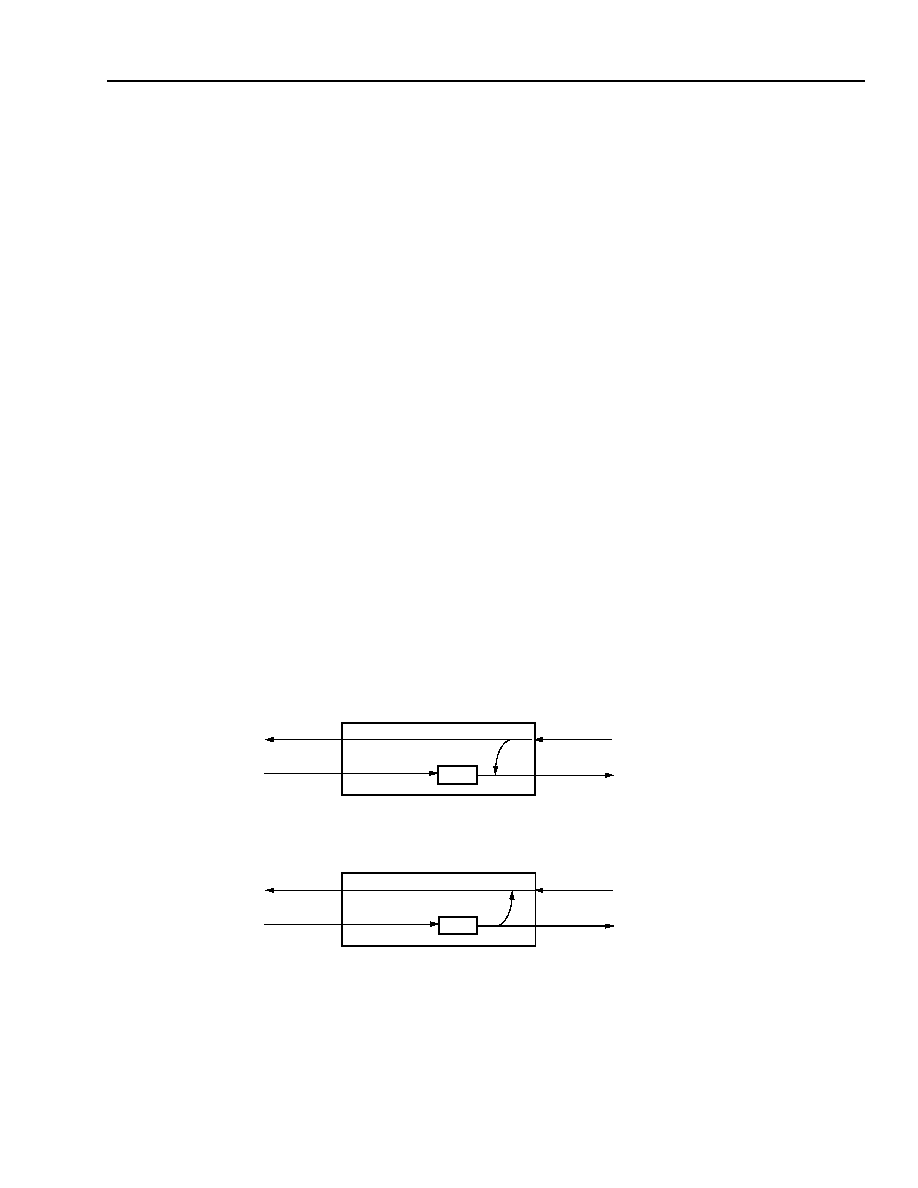

14.12.5 Loopbacks ................................................................................................................................67

14.12.6 Nominal CHI Timing..................................................................................................................68

14.12.7 CHI Timing with CHI Double Time-Slot Timing (CHIDTS) Mode Enabled ................................69

14.12.8 Clocking Scheme......................................................................................................................69

15 Transmission Convergence (TC) Block............................................................................................................70

15.1 Introduction .............................................................................................................................................70

15.2 Features..................................................................................................................................................70

15.3 TC--Receive Direction ...........................................................................................................................71

15.4 TC--Transmit Direction ..........................................................................................................................71

15.4.1

HEC Generation/Checking .......................................................................................................72

15.5 Cell Delineation.......................................................................................................................................72

15.6 Cell Payload Scrambling/Descrambling..................................................................................................72

15.7 Cell Mapping...........................................................................................................................................72

15.8 Facility Maintenance ...............................................................................................................................72

Table of Contents

(continued)

Contents

Page

TAAD08JU2 Data

Sheet

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

August 18, 2003

4

Agere Systems - Proprietary

Agere Systems Inc.

Use pursuant to Company instructions

15.9 Cell Rate Decoupling ..............................................................................................................................73

15.10 Functionality............................................................................................................................................73

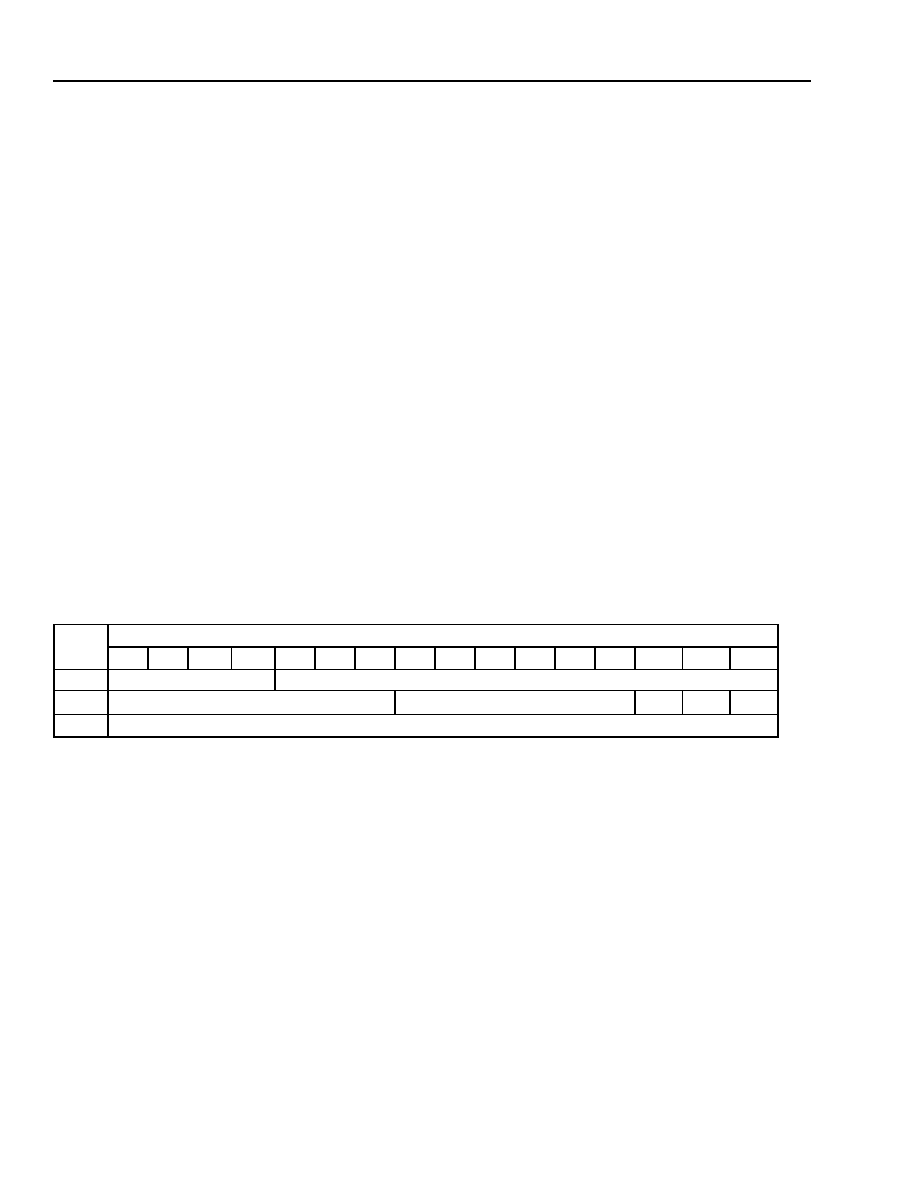

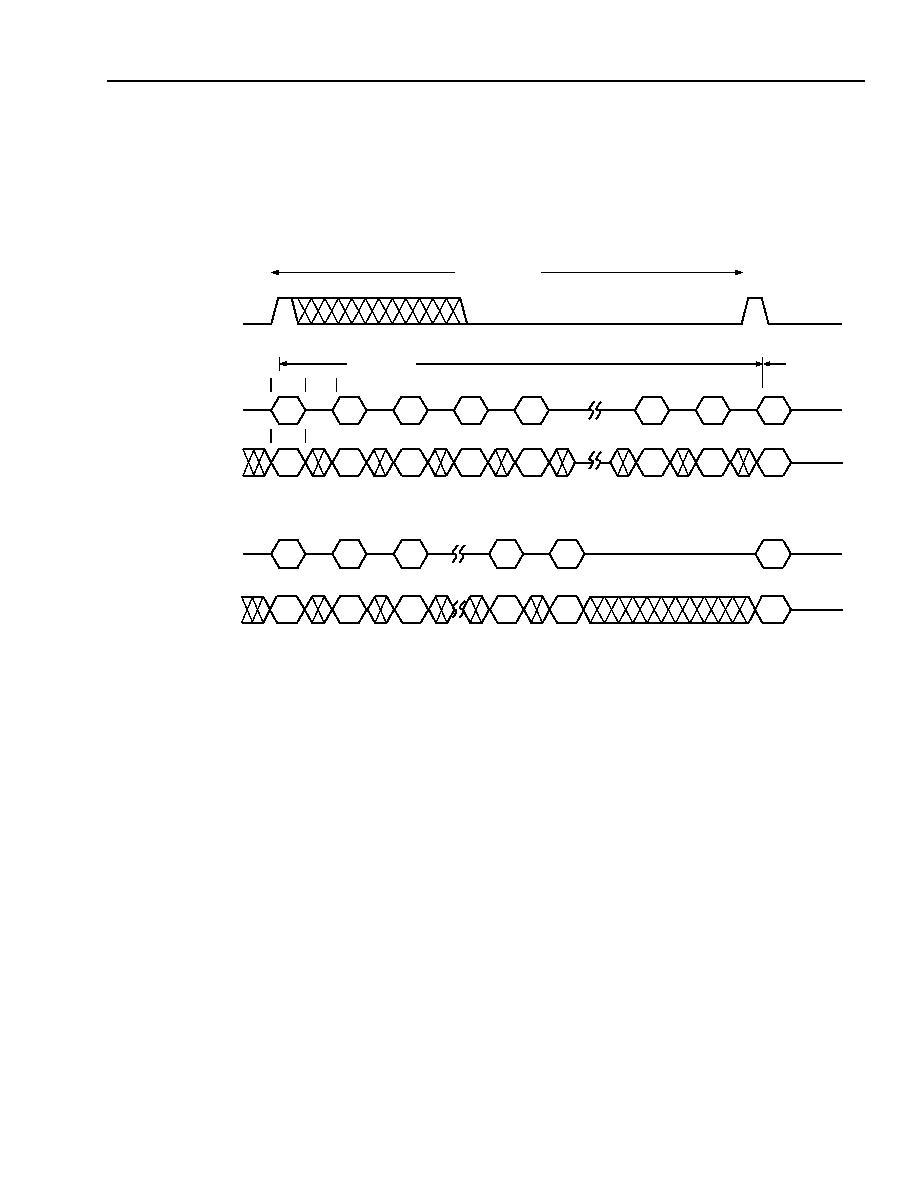

16 Inverse Multiplexing for ATM (IMA) Block.........................................................................................................74

16.1 Introduction.............................................................................................................................................74

16.2 Features..................................................................................................................................................75

16.3 Multi-PHY UTOPIA Slave Interface ........................................................................................................76

16.4 Link Processor ........................................................................................................................................76

16.5 Group Processor.....................................................................................................................................77

16.6 Delay Compensation Buffer (DCB).........................................................................................................78

16.7 Programming the DCB............................................................................................................................85

16.7.1

Link Start-Up Guardband Field .................................................................................................85

16.7.2

Link Maximum Operational Delay.............................................................................................85

16.8 Features Not Supported in IMA ..............................................................................................................85

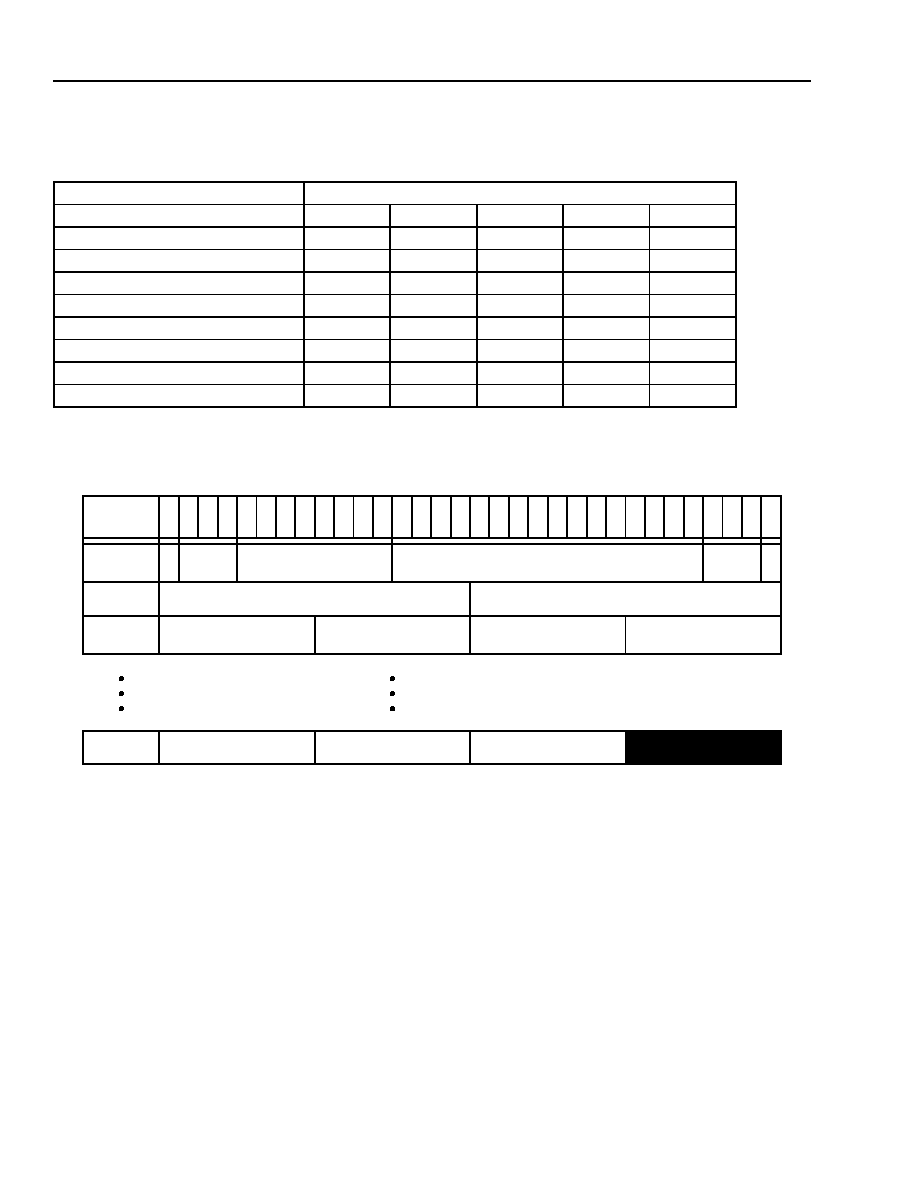

17 ATM Port Controller (APC) Block .....................................................................................................................87

17.1 Introduction.............................................................................................................................................87

17.2 Architecture.............................................................................................................................................88

17.3 Features..................................................................................................................................................89

17.4 Summary of Commands .........................................................................................................................90

17.5 Buffer Management ................................................................................................................................90

17.6 Scheduling..............................................................................................................................................92

17.6.1

Ingress Scheduling ...................................................................................................................92

17.6.2

Fabric Backpressure.................................................................................................................93

17.6.3

Egress Scheduling....................................................................................................................93

17.7 ABR Flow Control ...................................................................................................................................93

17.8 Control Plane Functions .........................................................................................................................94

17.8.1

APC Support for Control Plane Functions ................................................................................94

17.9 Management Plane Functions ................................................................................................................94

17.9.1

Operation Administration and Maintenance (OAM) ..................................................................94

17.10 Statistics Counters ..................................................................................................................................95

17.11 Ingress Enqueue Operations ..................................................................................................................95

17.11.1 Connection Look-Up .................................................................................................................96

17.11.2 OAM Processing.......................................................................................................................97

17.11.3 Policing .....................................................................................................................................98

17.11.4 Buffer Thresholding ..................................................................................................................98

17.11.5 Egress--APC VC Queueing Structure......................................................................................98

17.12 Connection Management........................................................................................................................99

17.12.1 Connection Admission Control .................................................................................................99

17.12.1.1 CBR............................................................................................................................99

17.12.1.2 rt-VBR ........................................................................................................................99

17.12.1.3 nrt-VBR ......................................................................................................................99

17.12.1.4 ABR............................................................................................................................99

17.12.1.5 UBR............................................................................................................................99

18 ATM Adaptation Layer (AAL) Block ................................................................................................................100

18.1 Introduction...........................................................................................................................................100

18.2 Features................................................................................................................................................100

18.3 Definitions .............................................................................................................................................101

18.4 Architecture...........................................................................................................................................102

18.4.1

Datapath Flows .......................................................................................................................102

18.4.2

Subblock Architecture.............................................................................................................105

18.4.3

Subblock Definition .................................................................................................................106

18.4.4

Subblock Flows.......................................................................................................................107

18.4.5

Address Translation ................................................................................................................108

Table of Contents

(continued)

Contents

Page

Data Sheet

TAAD08JU2

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

Agere Systems Inc.

Agere Systems - Proprietary

5

Use pursuant to Company instructions

18.4.6

Queueing and Scheduling ......................................................................................................109

18.4.7

Modes .....................................................................................................................................109

18.4.8

User Data Types (UDT) and AAL Types................................................................................. 110

18.4.9

UDT: ATM Cell ........................................................................................................................ 111

18.4.10 AAL Type: AAL0 ..................................................................................................................... 111

18.4.11 AAL Type: AAL2 ..................................................................................................................... 111

18.4.12 AAL2 Subtype: SPAAL2 (Single-Packet AAL2) ...................................................................... 112

18.4.13 CPS-AAL0 .............................................................................................................................. 113

18.4.14 AAL Type: AAL5 ..................................................................................................................... 113

18.4.15 UDT: Packet ATM (PATM)....................................................................................................... 114

18.4.16 UDT: HPF................................................................................................................................ 115

18.4.17 AAL Type: NPAAL (No Particular AAL)................................................................................... 116

18.4.18 Nonuser Data Types: ESI Messages ...................................................................................... 116

18.4.18.1 ESI Message Format ............................................................................................... 116

18.4.18.2 ESI Violation Code ................................................................................................... 117

18.4.18.3 ESI Packet Length ................................................................................................... 117

18.4.19 Service Types ......................................................................................................................... 117

18.4.20 CPS_SERVICE....................................................................................................................... 118

18.4.21 SEG_AAL2_SSSAR_SERVICE ............................................................................................. 119

18.4.22 SEG_AAL2_SSTED_SERVICE.............................................................................................. 119

18.4.23 SEG_AAL5_SERVICE............................................................................................................ 119

18.4.24 TRANSPARENT_SERVICE....................................................................................................120

18.4.25 REASS_AAL2_SSSAR_SERVICE .........................................................................................120

18.4.26 REASS_AAL2_SSTED_SERVICE .........................................................................................120

18.4.27 REASS_AAL5_SERVICE .......................................................................................................120

18.5 Provisioning ..........................................................................................................................................122

18.5.1

Some Notes on Terminology and Command Referencing......................................................122

18.5.2

System Interface.....................................................................................................................122

18.5.3

Port Table................................................................................................................................123

18.5.4

MEMI Shared Memory............................................................................................................124

18.5.4.1 MEMI-SM Provisioning Constraints..........................................................................125

18.5.4.2 VC Table...................................................................................................................125

18.5.4.3 AAL2 VC Table.........................................................................................................126

18.5.4.4 Connection Table .....................................................................................................127

18.5.4.5 Level 0 Queue Descriptor ........................................................................................129

18.5.4.6 ICID Table ................................................................................................................129

18.5.5

SQASE Shared Memory.........................................................................................................129

18.6 Configuration ........................................................................................................................................130

18.6.1

Connection and Channel Setup..............................................................................................130

18.6.1.1 AAL2 Data Flow (CPS/SSSAR/SSTED) ..................................................................133

18.6.1.2 CPS-AAL0 Data Flow...............................................................................................133

18.6.1.3 AAL0/AAL5 Data Flow..............................................................................................133

18.6.1.4 HPF Data Flow .........................................................................................................133

18.6.2

Configuration for QoS .............................................................................................................134

18.6.2.1 Packet Scheduling ...................................................................................................134

18.6.2.2 IL1Q Scheduler Algorithm ........................................................................................134

18.6.2.3 IL2Q Scheduler Algorithm ........................................................................................134

18.6.2.4 Latency Policing .......................................................................................................136

18.6.2.5 Latency-Sensitive Data Discard ...............................................................................136

18.6.2.6 Internal Queue Housekeeping .................................................................................136

18.6.2.7 Reference Clock Generation....................................................................................136

18.6.2.8 Latency Timer Enable/Disable Functions.................................................................137

Table of Contents

(continued)

Contents

Page

TAAD08JU2 Data

Sheet

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

August 18, 2003

6

Agere Systems - Proprietary

Agere Systems Inc.

Use pursuant to Company instructions

18.6.2.9 Queue Length Policing.............................................................................................137

18.6.2.10 Connection Queue Length Policing..........................................................................138

18.6.2.11 IL1Q and L1Q Length Policing .................................................................................139

18.6.2.12 IL2Q Length Policing................................................................................................140

18.6.3

Configuration for Exceptions...................................................................................................140

18.7 Interface Timing Diagrams....................................................................................................................143

18.7.1

SIF UT2/UT2+ Interface .........................................................................................................143

18.7.2

Polling Algorithms for UTOPIA 2 and UT2+ Modes................................................................152

18.7.2.1 Receive Interface Polling .........................................................................................152

18.7.2.2 Transmit Interface Polling.........................................................................................153

18.7.3

NIF ..........................................................................................................................................153

18.7.4

ESI ..........................................................................................................................................153

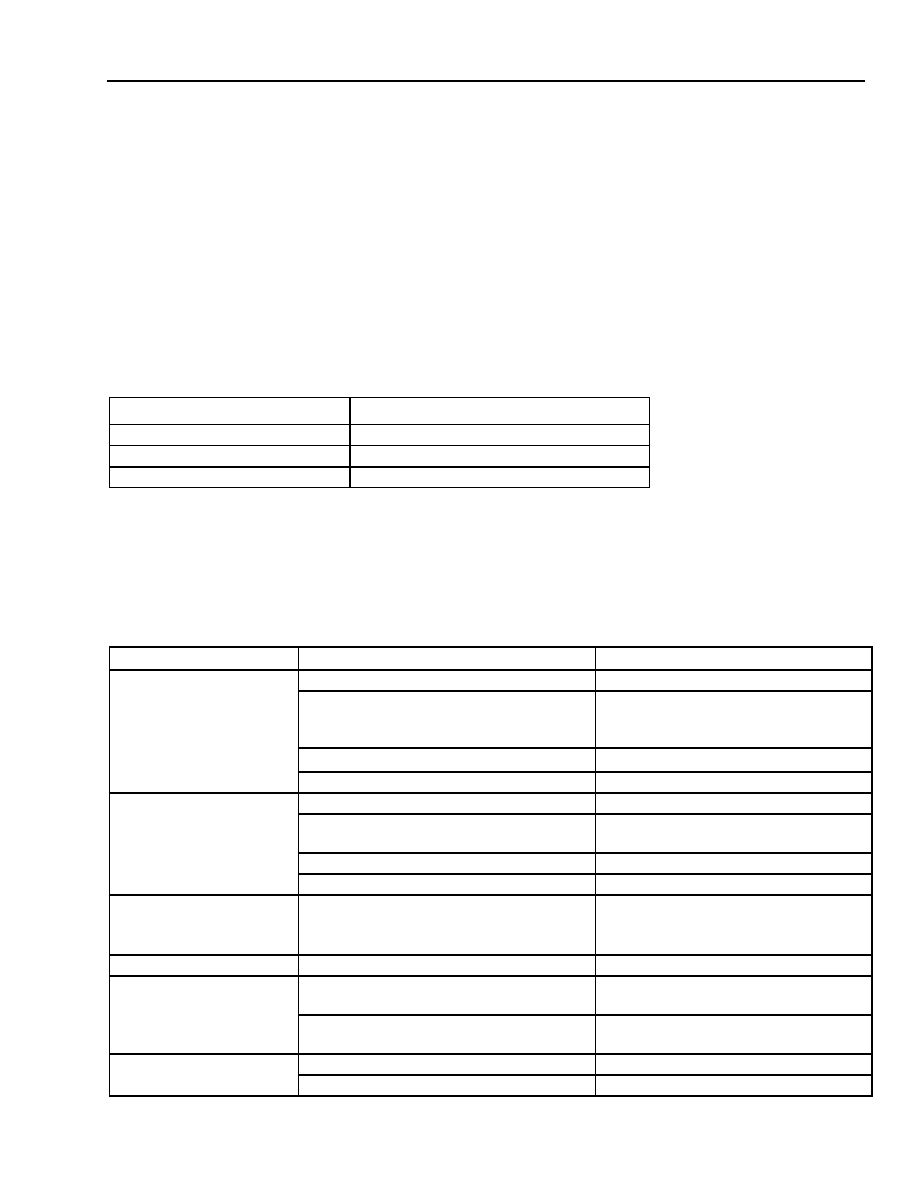

19 Absolute Maximum Ratings............................................................................................................................154

20 Power Requirements......................................................................................................................................154

21 Handling Precautions .....................................................................................................................................155

22 Electrical Characteristics ................................................................................................................................155

22.1 Logical Interface Electrical Characteristics, Version 2.1 .......................................................................155

22.2 Logical Interface Electrical Characteristics, Version 3.1 .......................................................................156

23 Timing Characteristics ....................................................................................................................................157

23.1 Input Clocks, Versions 2.1 and 3.1 .......................................................................................................157

23.2 Host Interface Timing............................................................................................................................158

23.3 Reset Timing.........................................................................................................................................160

23.4 Concentration Highway (CHI) Timing, Versions 2.1 and 3.1 ................................................................161

23.5 Fabric Interface--Ports A and B, Versions 2.1 and 3.1 ........................................................................162

23.6 Expansion UTOPIA2 Interface..............................................................................................................164

23.6.1

Receive Interface Timing ........................................................................................................164

23.6.2

Transmit Interface Timing .......................................................................................................164

23.7 Enhanced Services Interface (ESI), Versions 2.1 and 3.1....................................................................164

23.8 JTAG.....................................................................................................................................................165

23.9 System Interface, Version 2.1...............................................................................................................165

23.9.1

Receive Interface Timing, Version 2.1 ....................................................................................165

23.9.2

Transmit Interface Timing, Version 2.1 ...................................................................................165

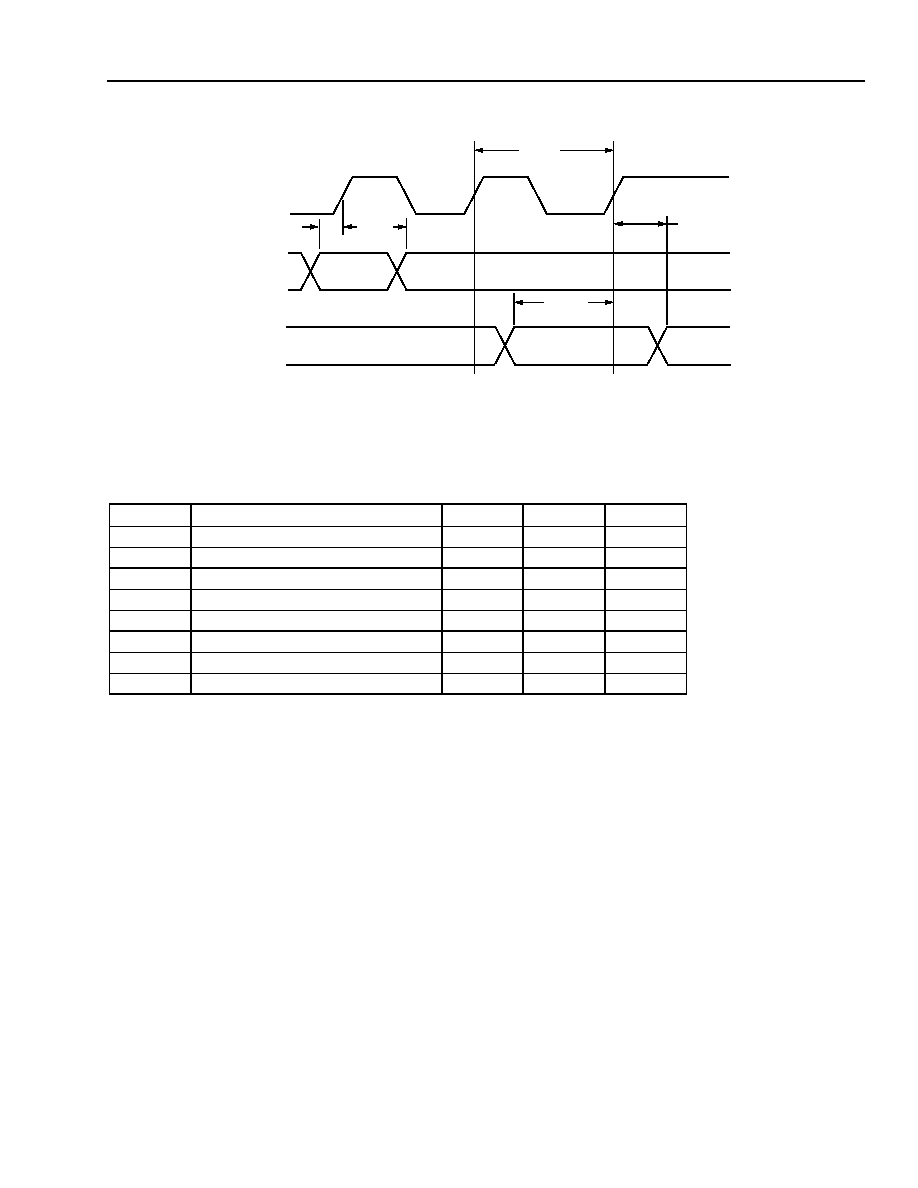

23.10 System Interface, Version 3.1...............................................................................................................166

23.10.1 Receive Interface Timing, Version 3.1 (SUCLK Is an Input.) ..................................................166

23.10.2 Transmit Interface Timing, Version 3.1 (SUCLK Is an Input.) .................................................166

24 Referenced Documents..................................................................................................................................167

25 Glossary .........................................................................................................................................................169

Appendix A. Revision History ................................................................................................................................172

List of Figures

Figure

Page

Data Sheet

TAAD08JU2

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

Agere Systems Inc.

Agere Systems - Proprietary

7

Use pursuant to Company instructions

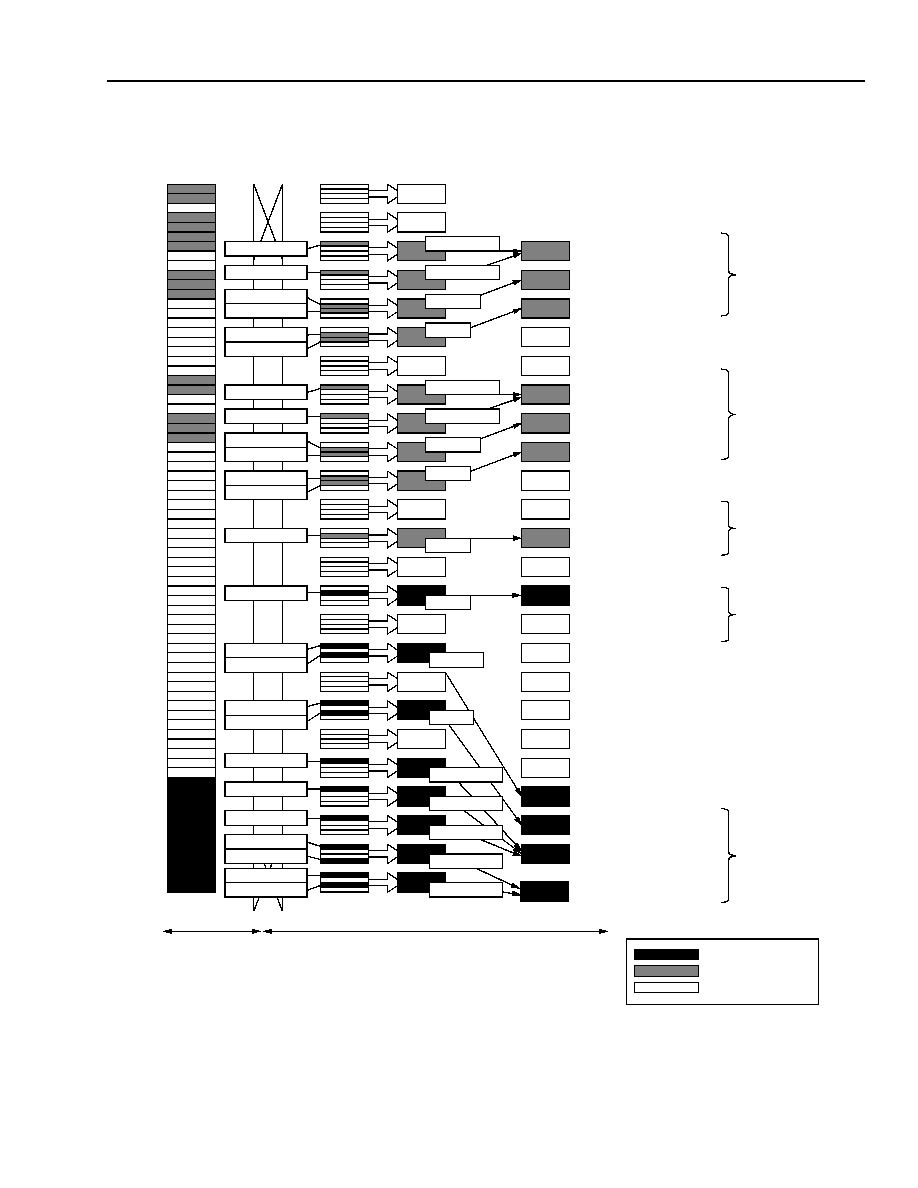

Figure 1.

Pin Configuration Diagram ................................................................................................................21

Figure 2.

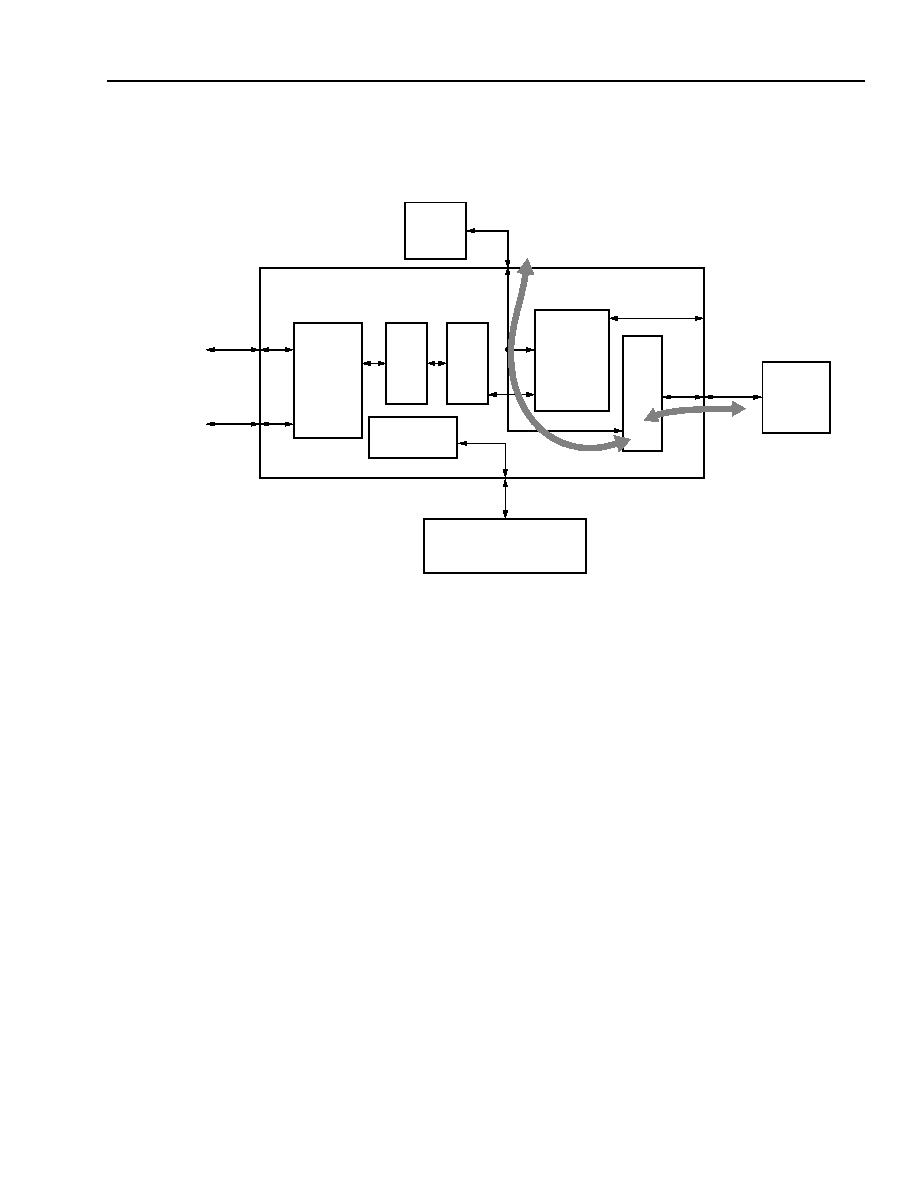

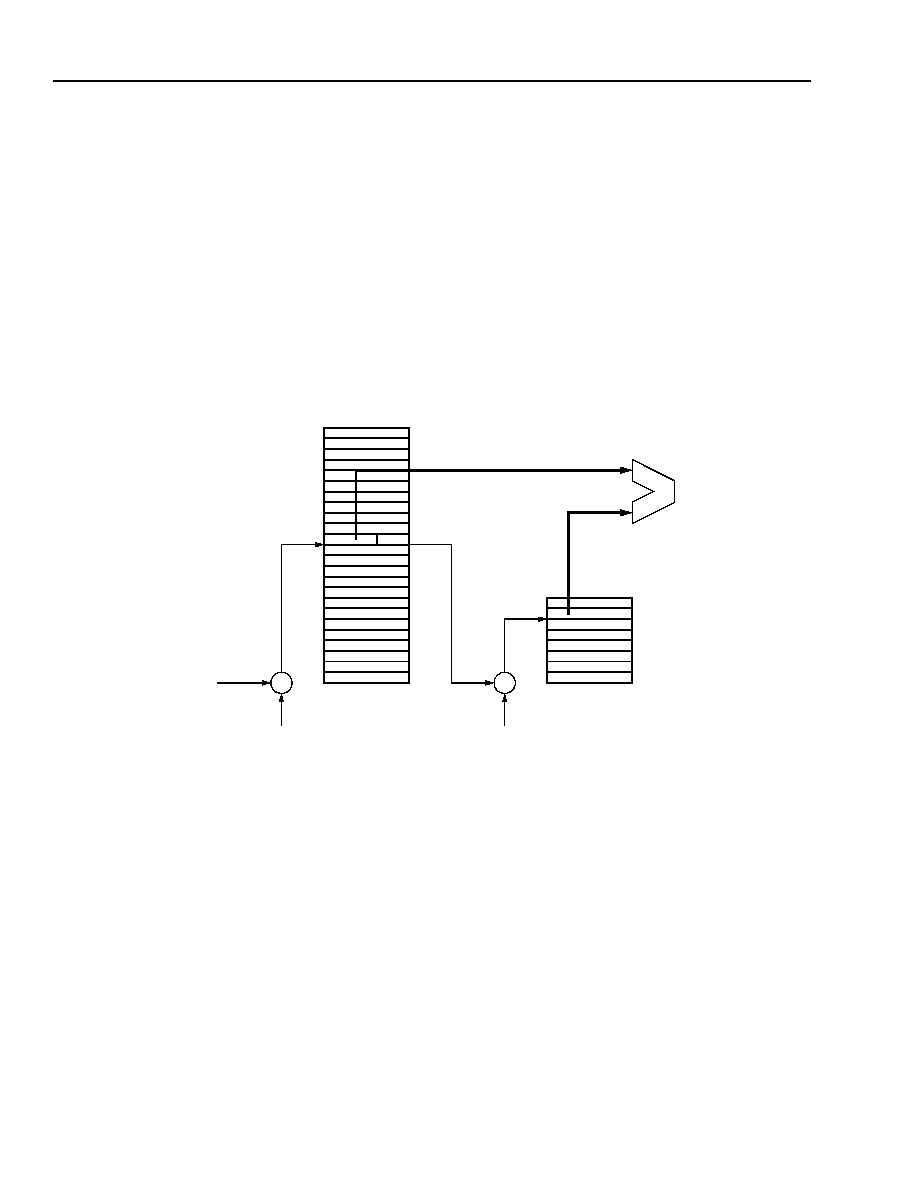

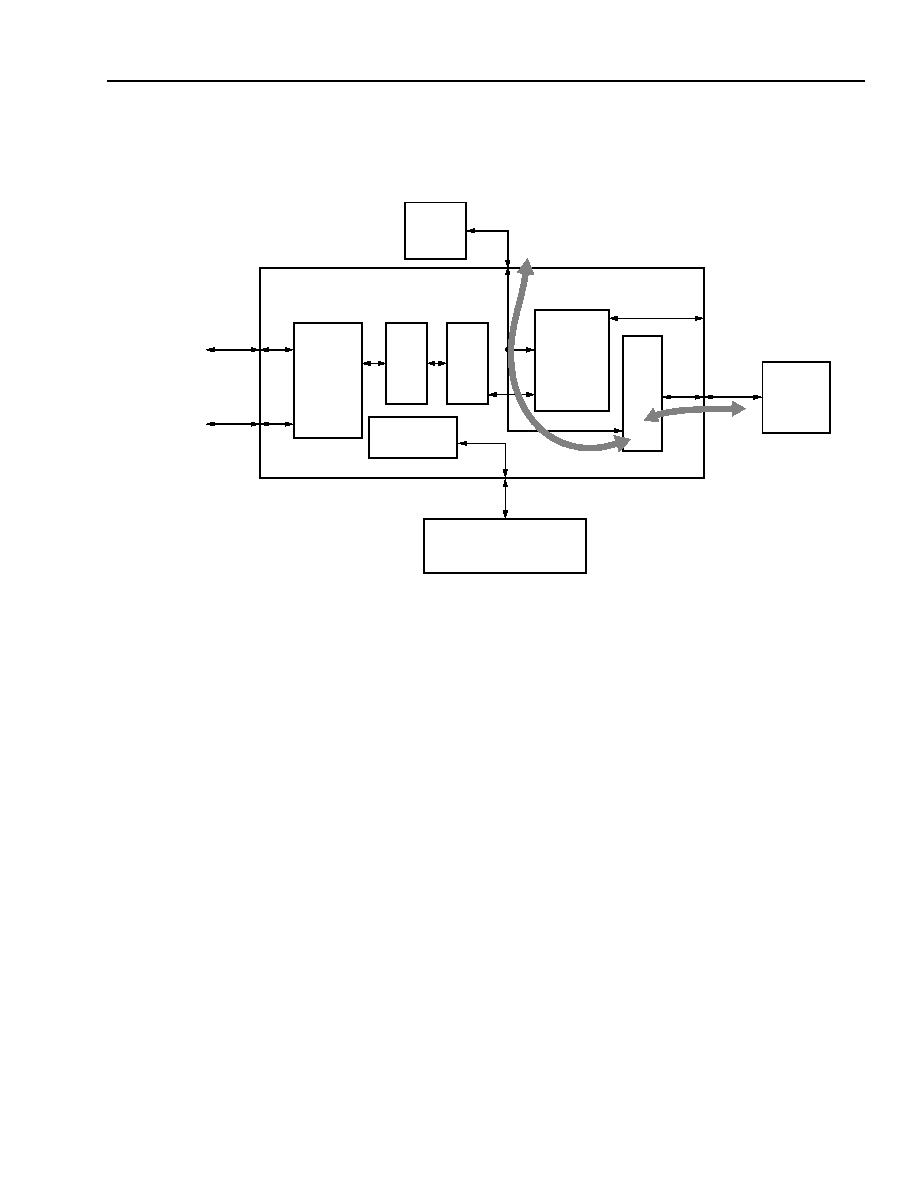

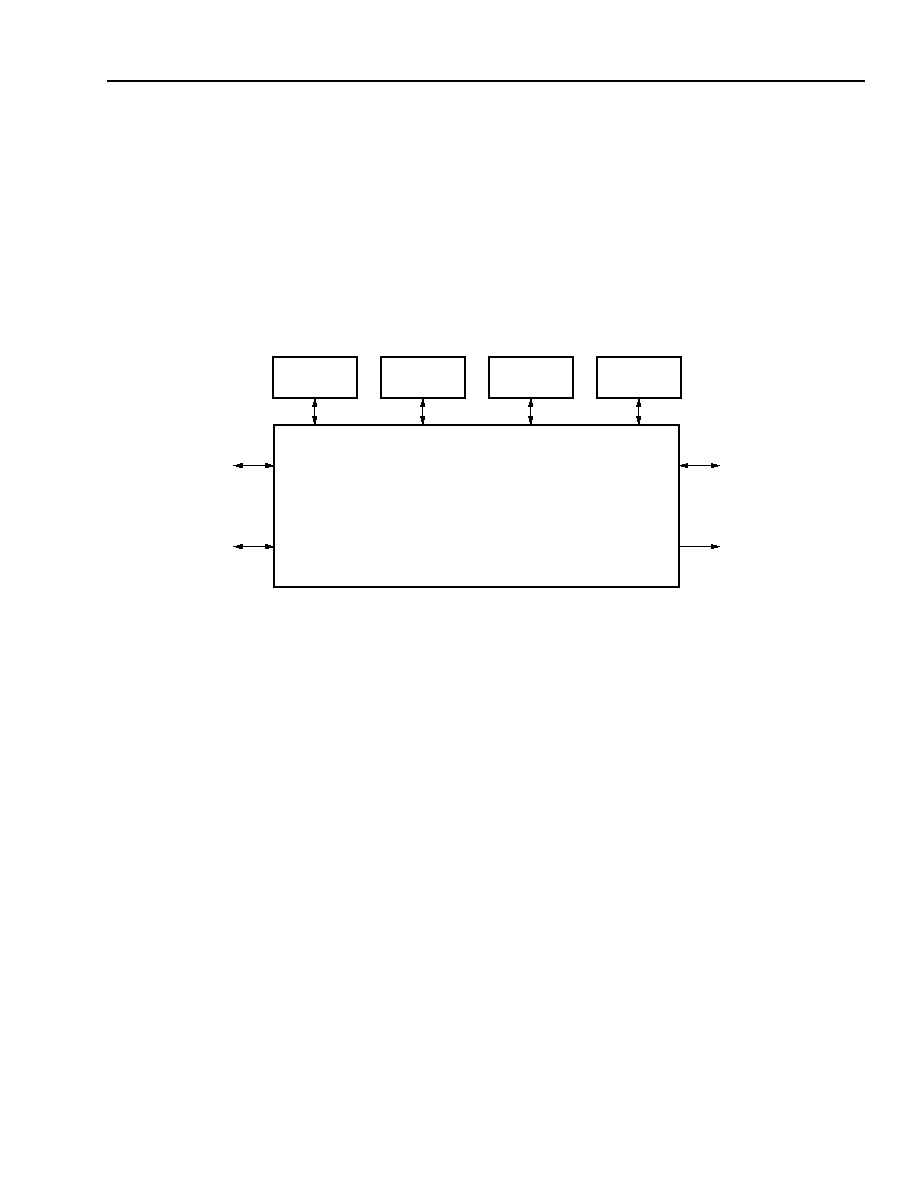

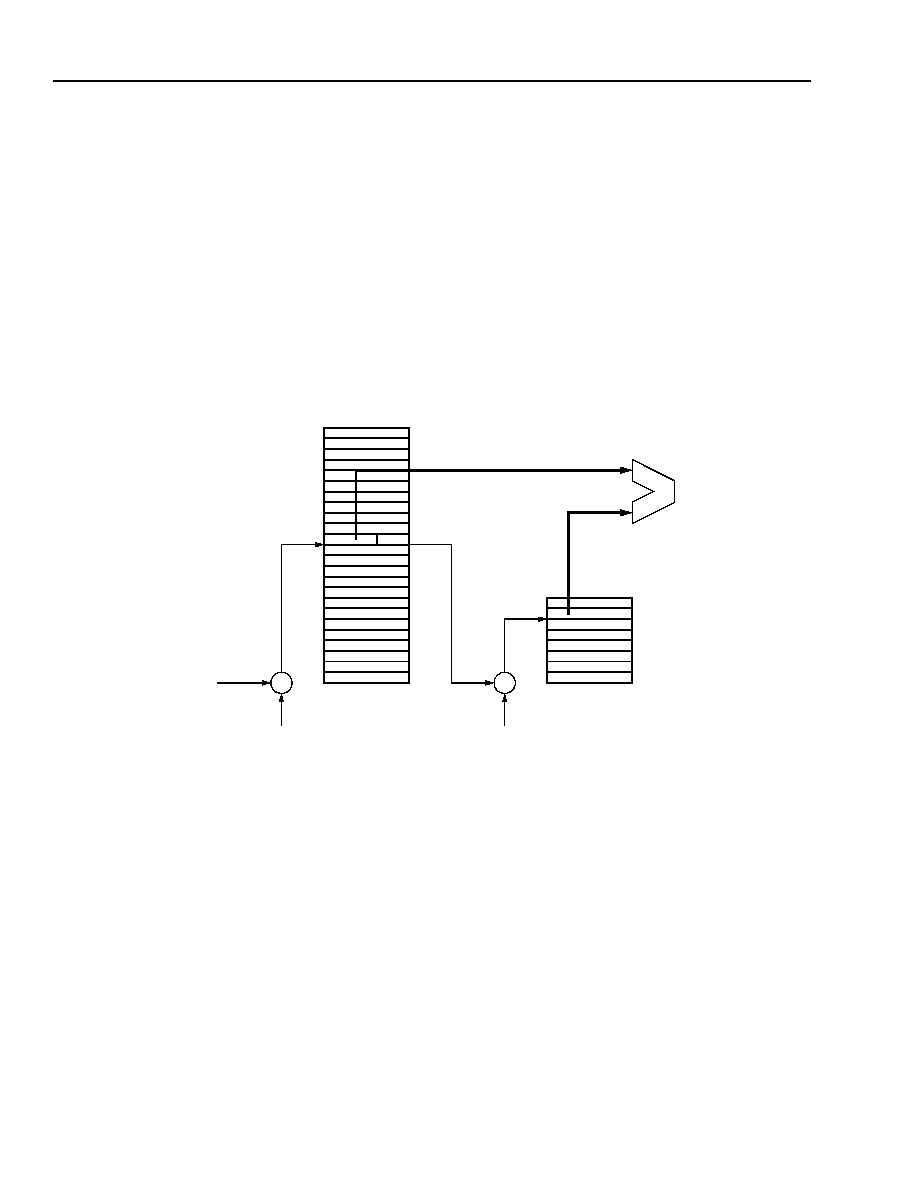

Architecture of the TAAD08JU2 Device ............................................................................................27

Figure 3.

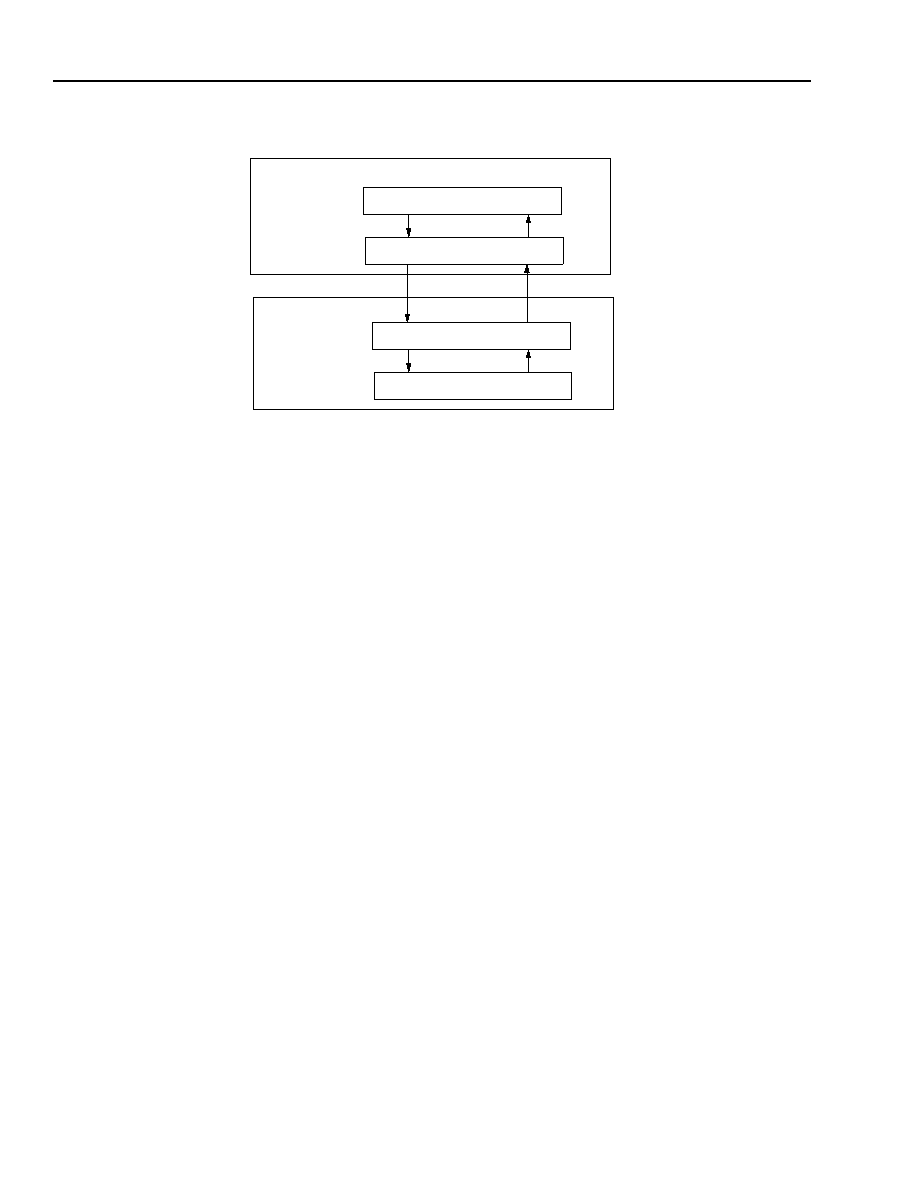

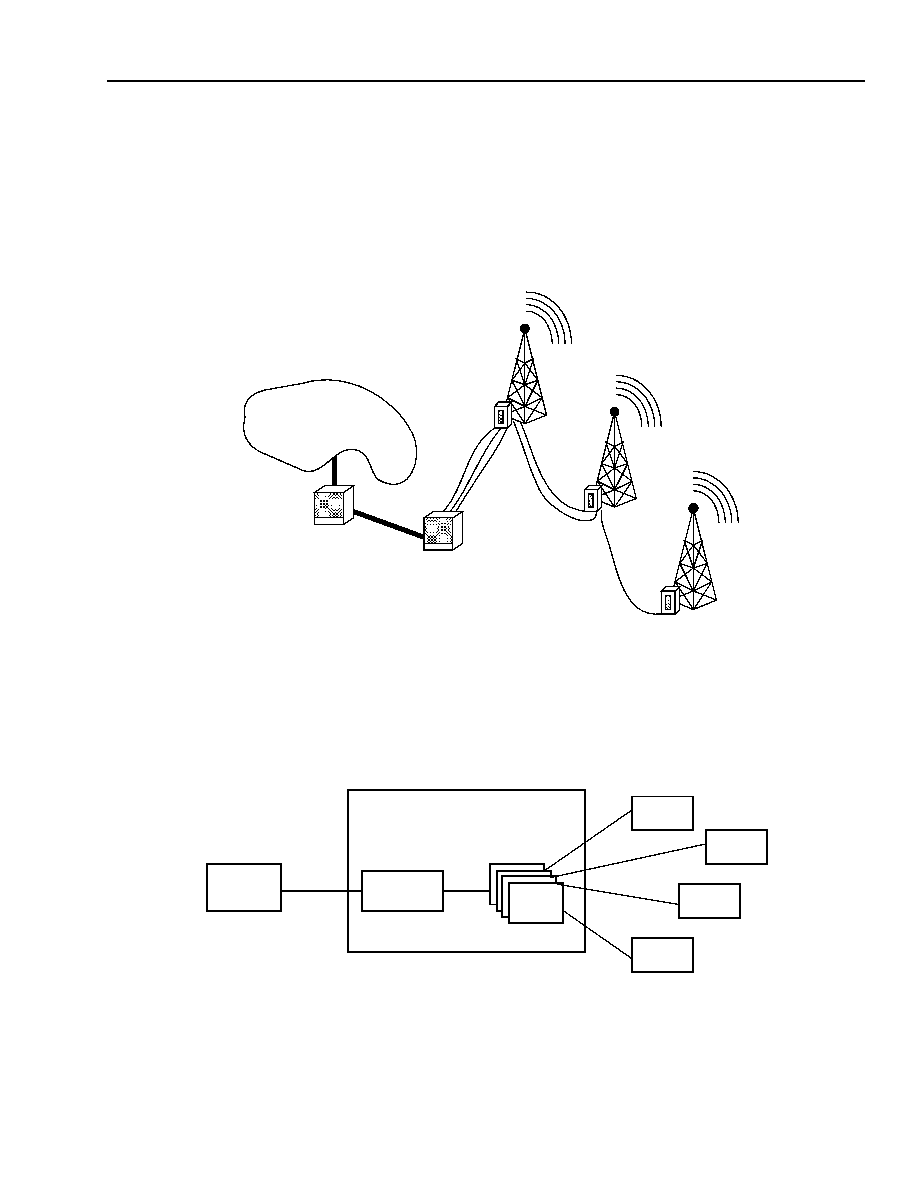

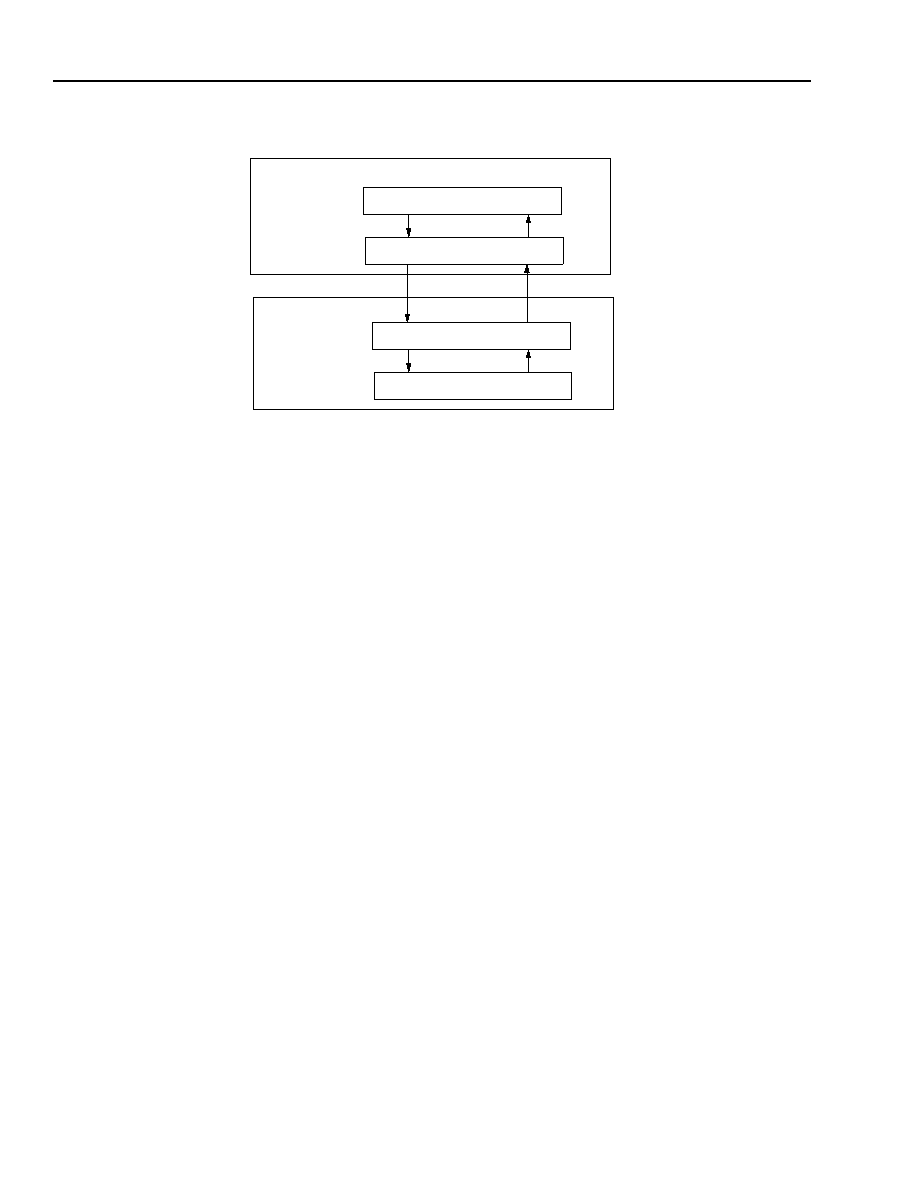

Software Components .......................................................................................................................28

Figure 4.

Device Manager APIs and TAAD08JU2 Communications ................................................................30

Figure 5.

TAAD08JU2 Software Development Environment ............................................................................32

Figure 6.

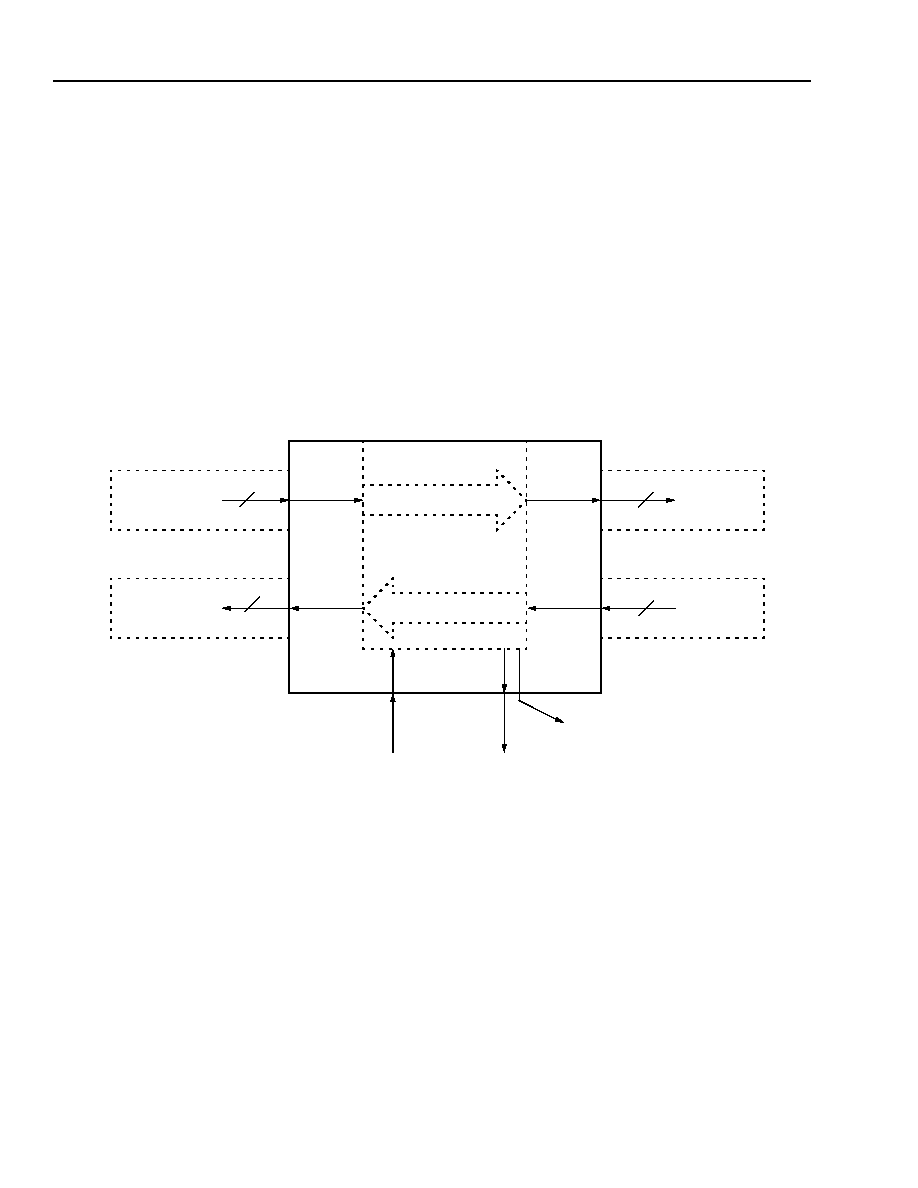

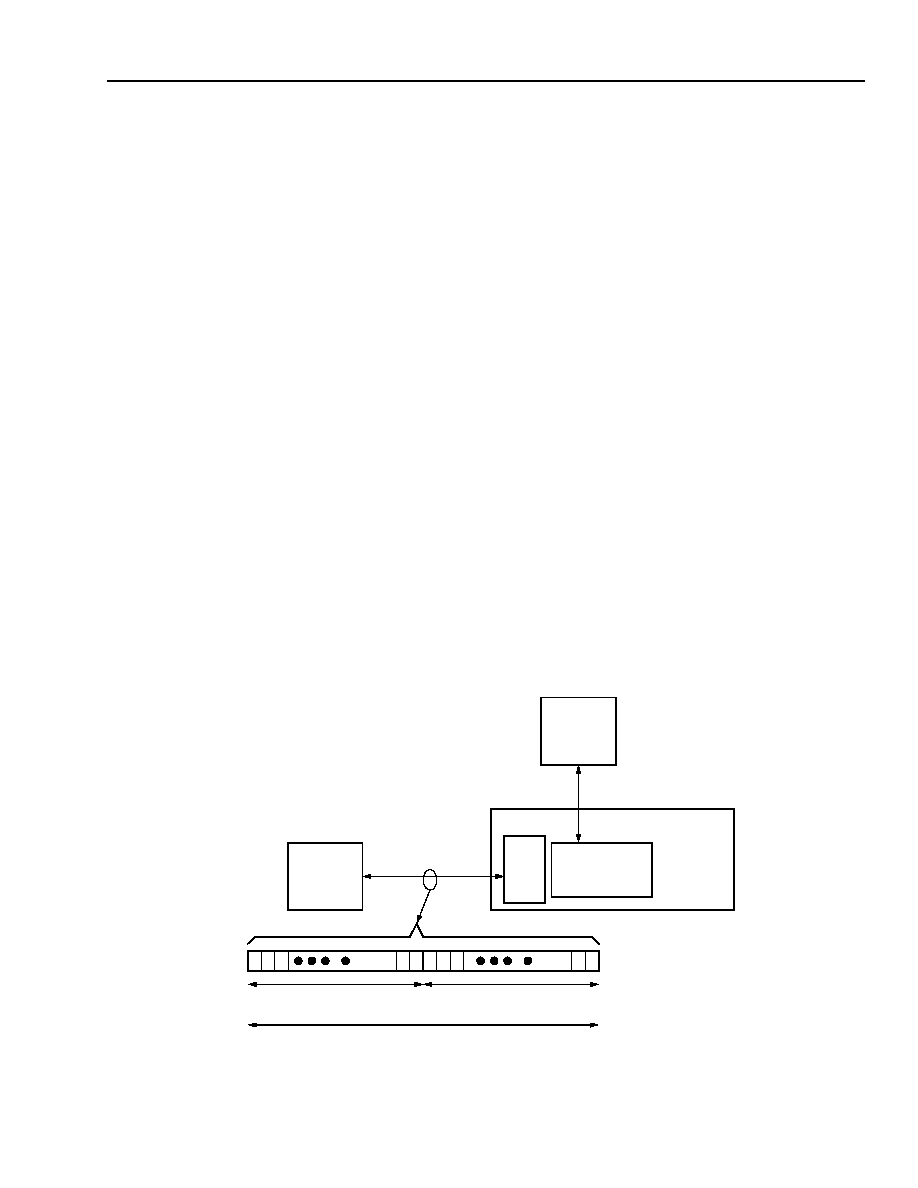

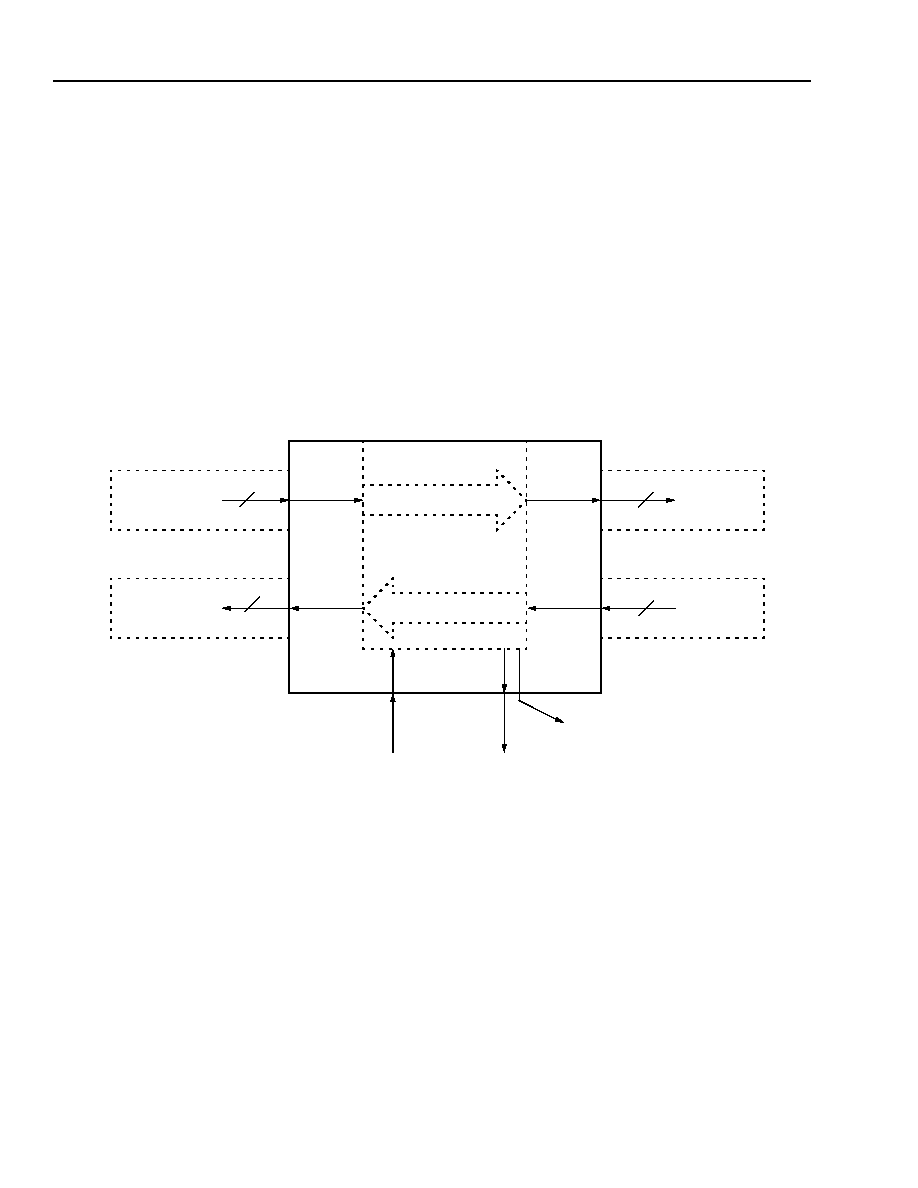

TAAD08JU2 Interfaces......................................................................................................................39

Figure 7.

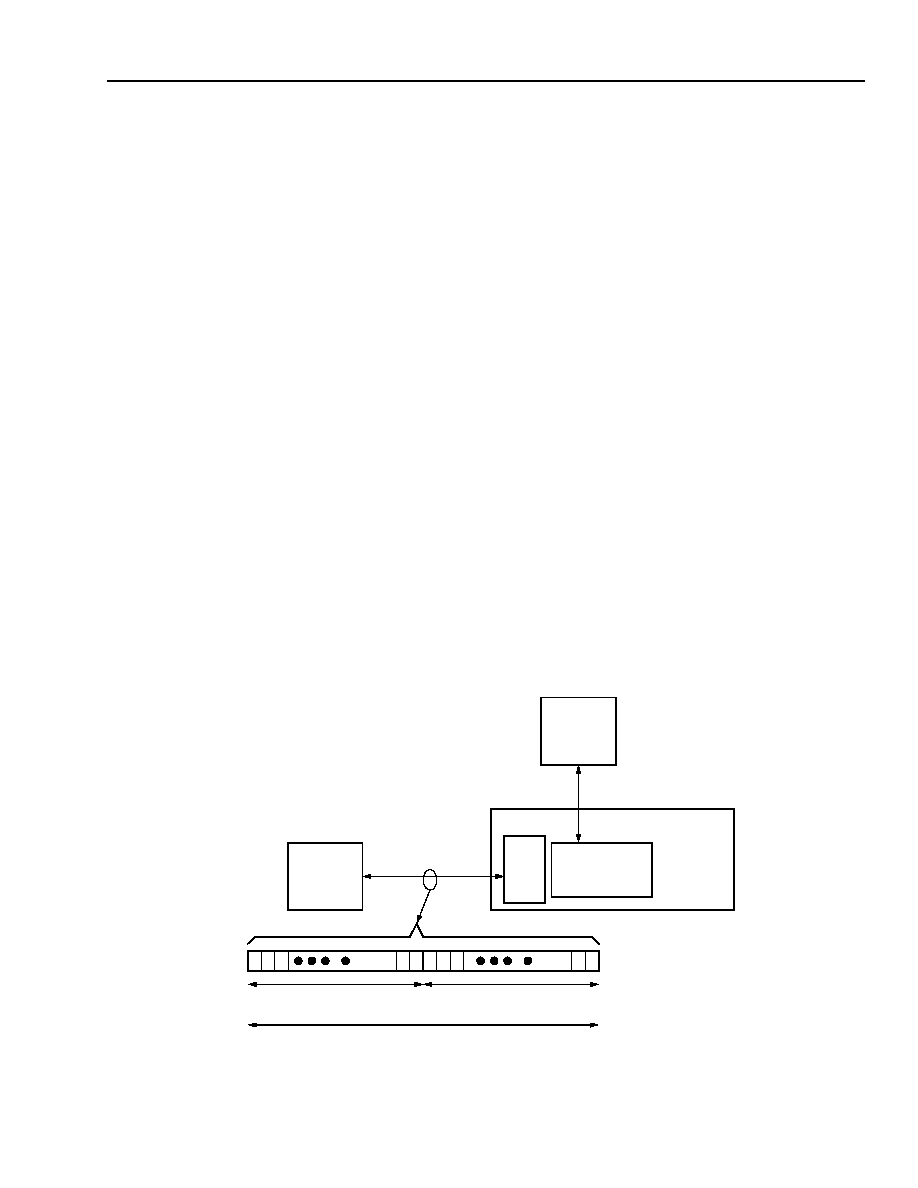

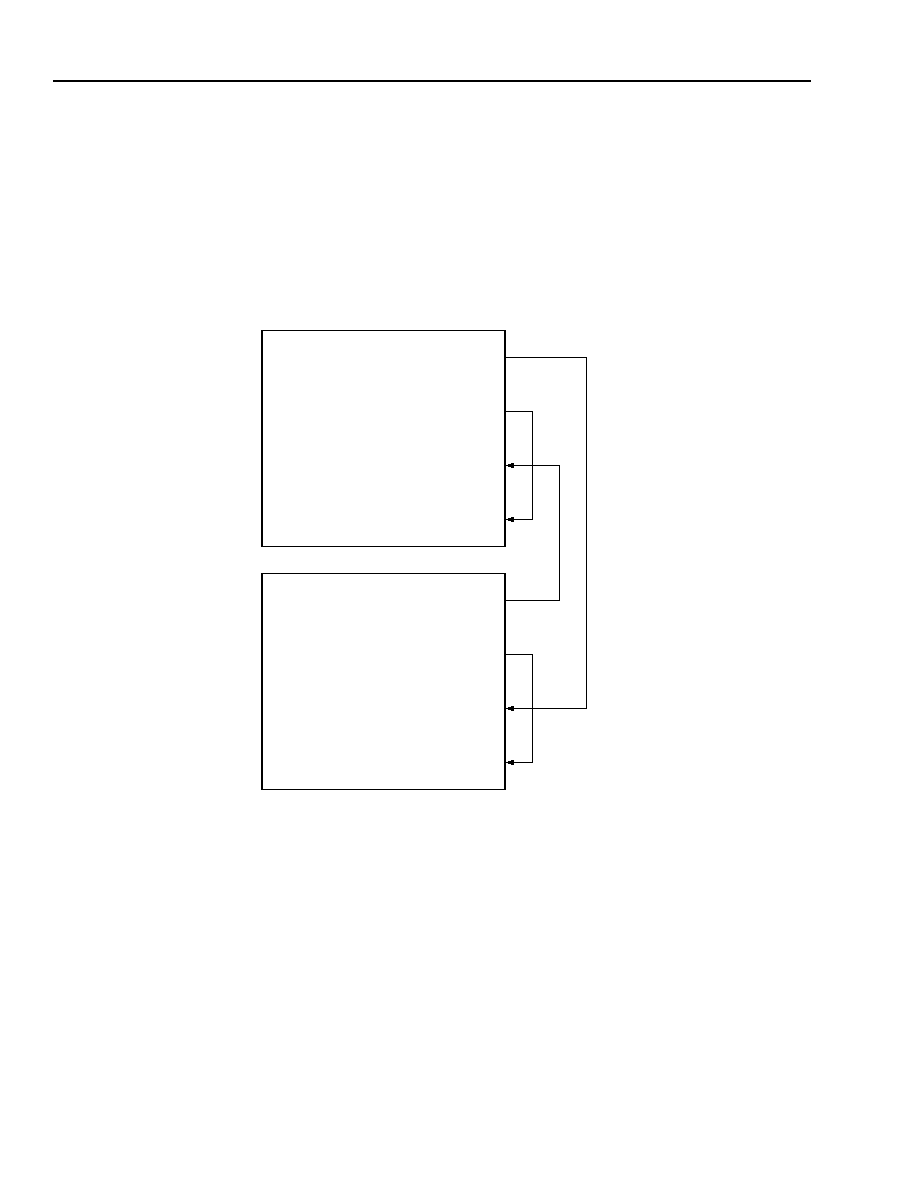

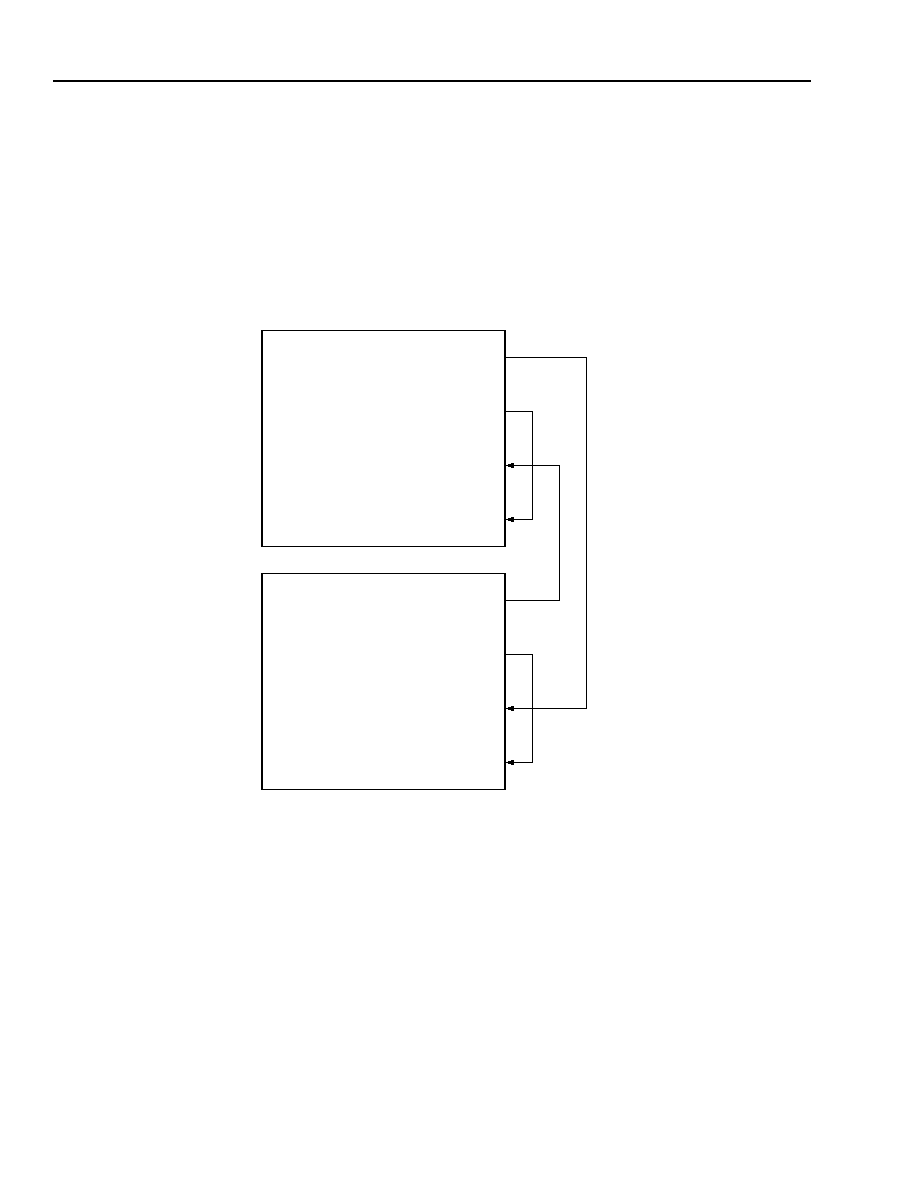

Mode 1: Internal PHY Mode Operation .............................................................................................40

Figure 8.

Example of Sharing Span Line with TDM and ATM Data..................................................................41

Figure 9.

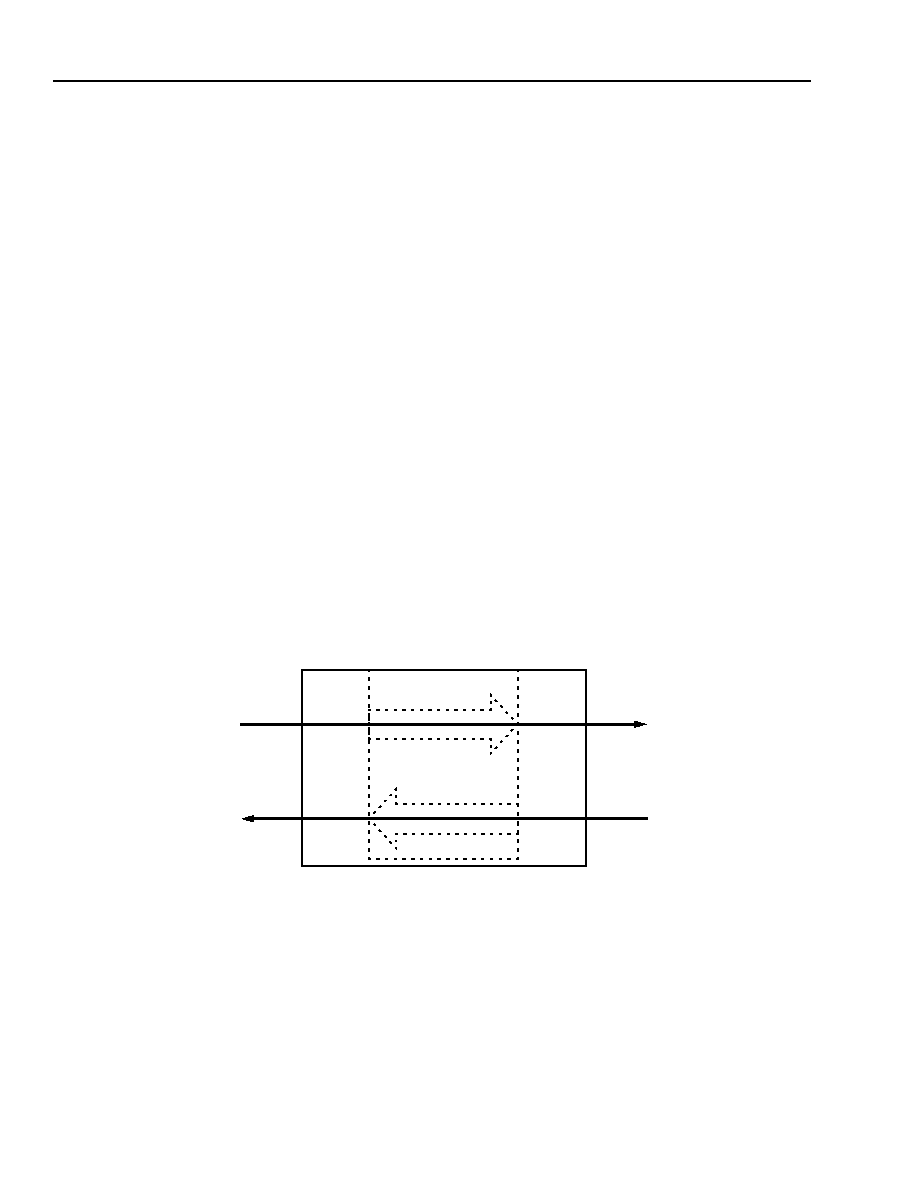

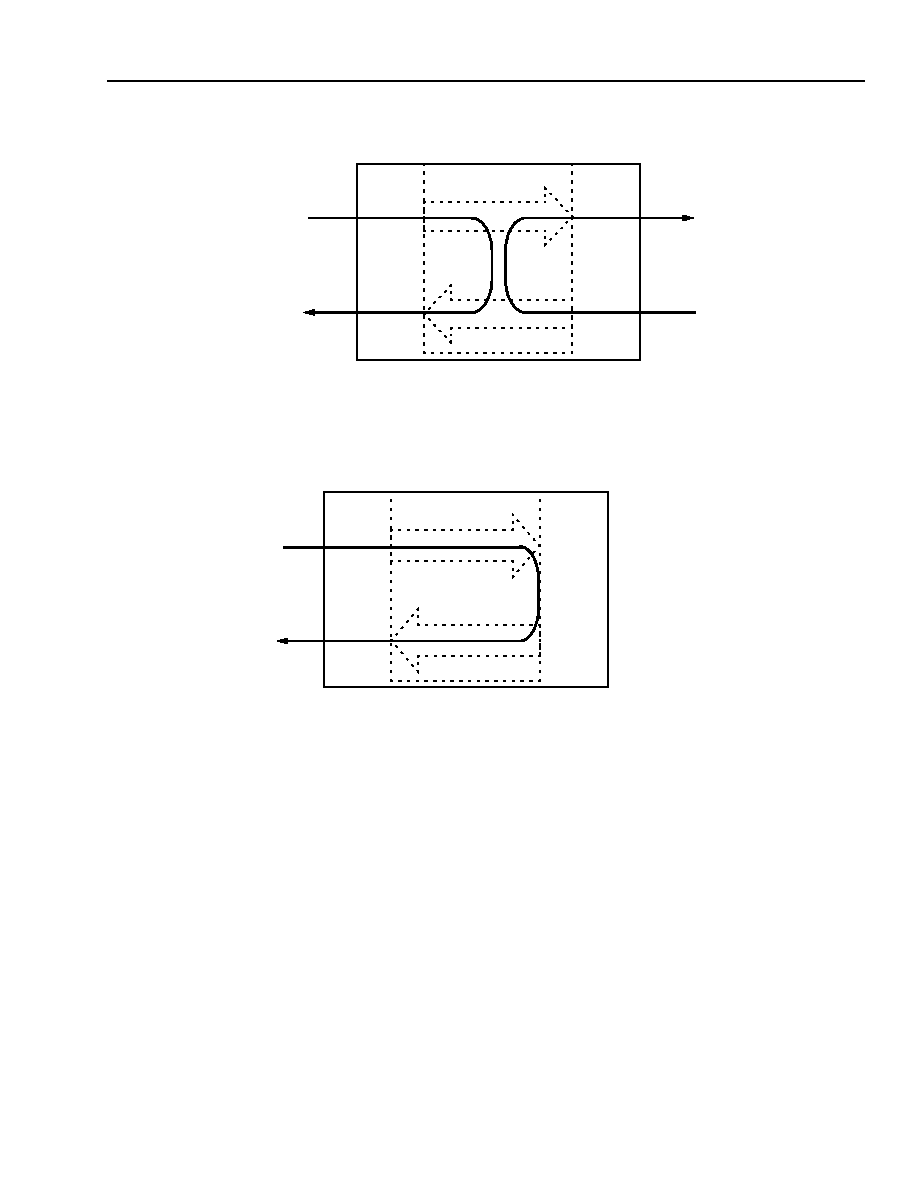

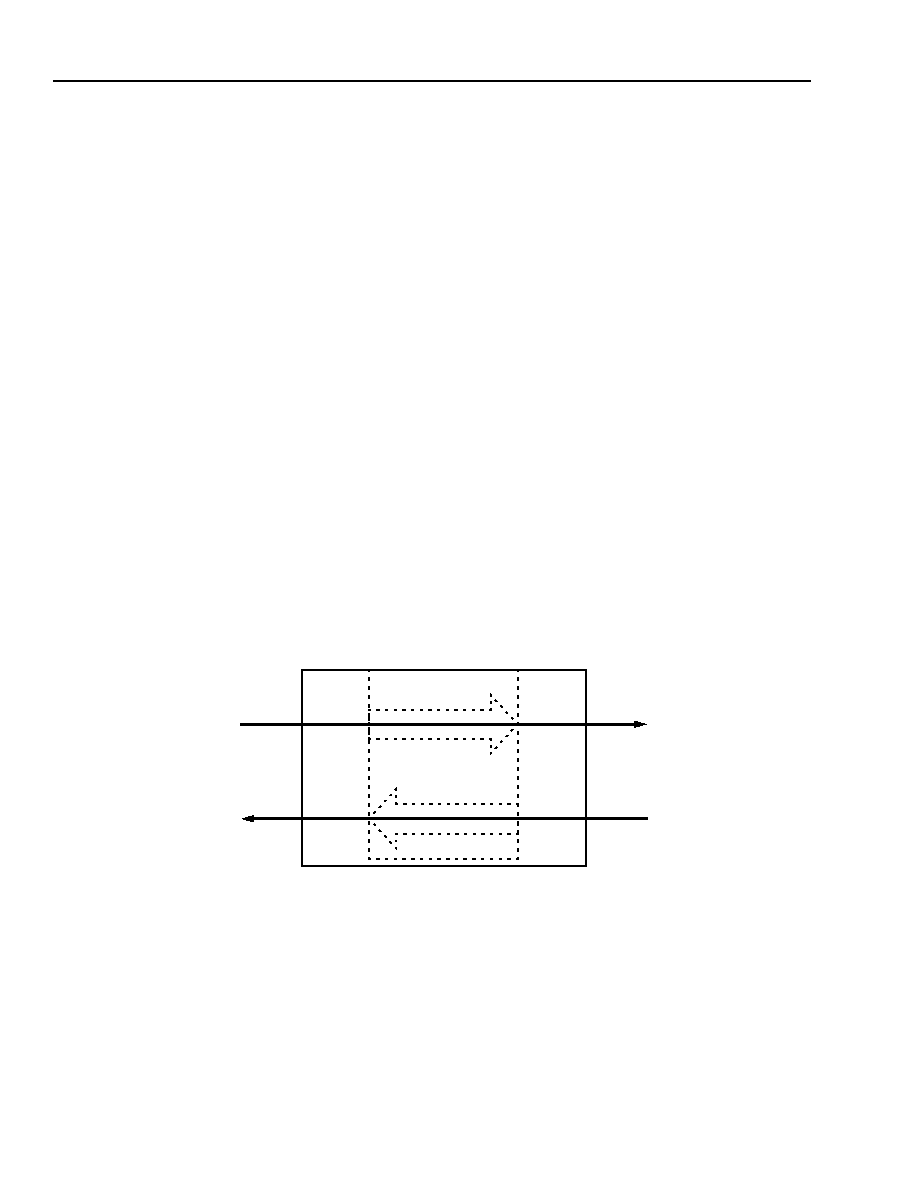

Mode 2: External PHY Mode .............................................................................................................42

Figure 10.

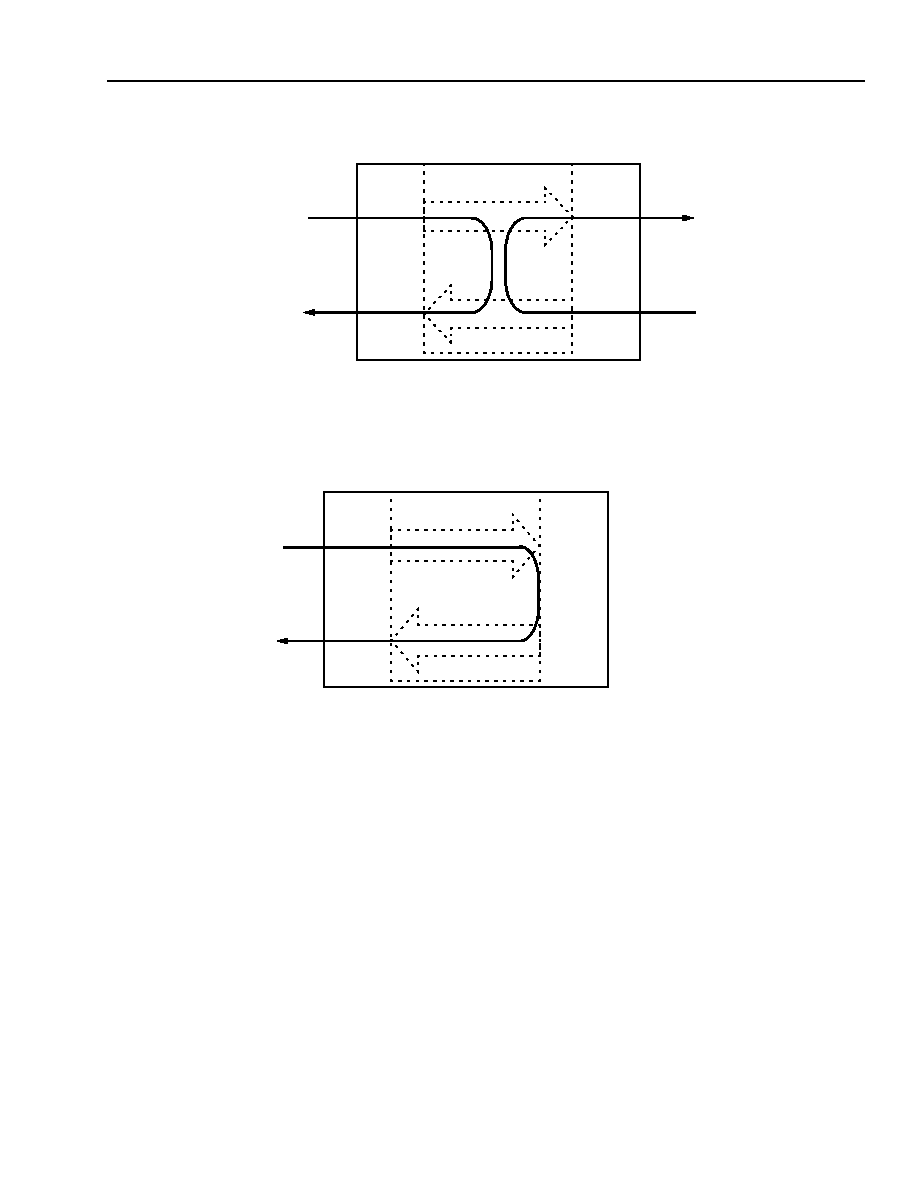

Mode 3: SAR-Only Mode...................................................................................................................43

Figure 11.

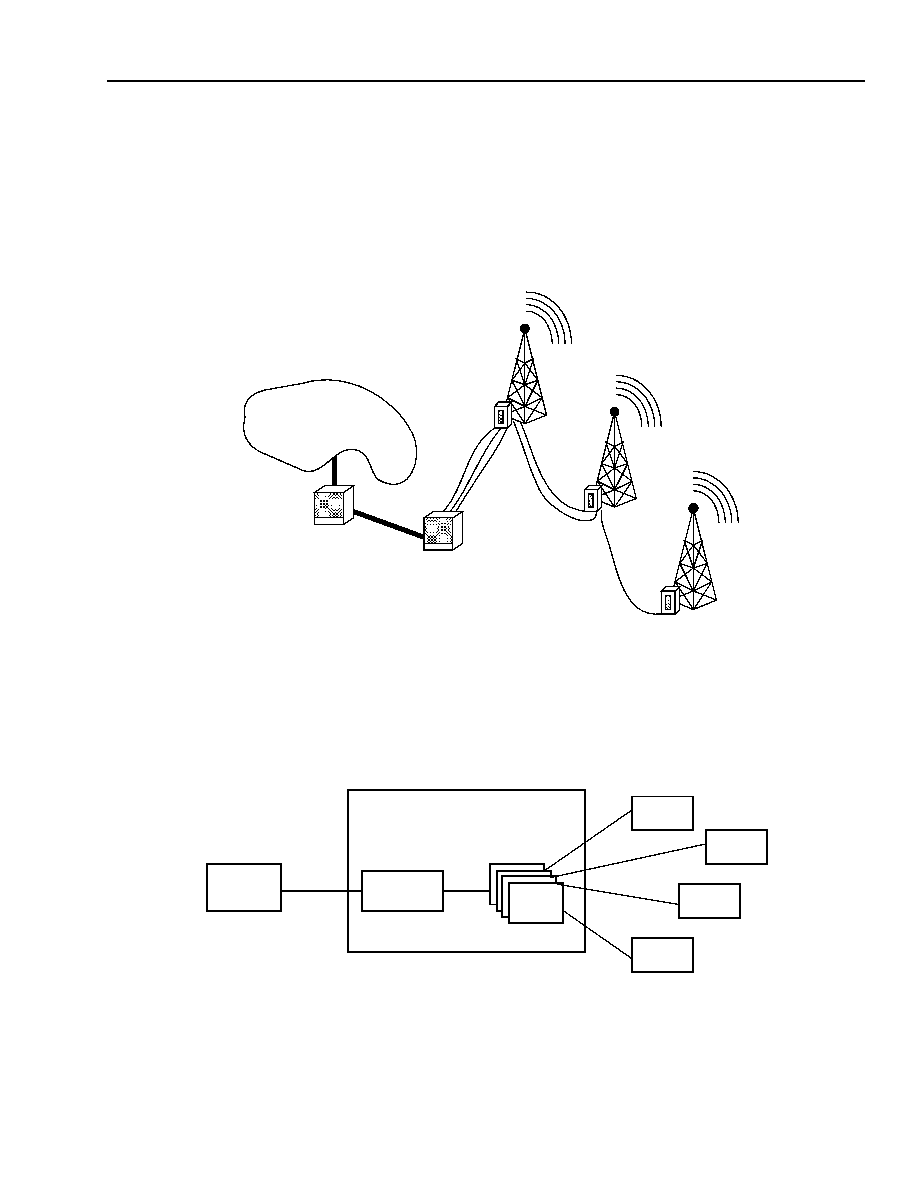

BTS Application .................................................................................................................................44

Figure 12.

BTSs Require ADM Functions...........................................................................................................45

Figure 13.

Gateway Controller............................................................................................................................45

Figure 14.

Remote Access Concentrator Application .........................................................................................46

Figure 15.

Edge/Access Switch Application .......................................................................................................46

Figure 16.

AAL2 Cross Connect .........................................................................................................................47

Figure 17.

Stand-Alone AAL2 Cross Connect ....................................................................................................47

Figure 18.

Standard Host Interface Timing.........................................................................................................49

Figure 19.

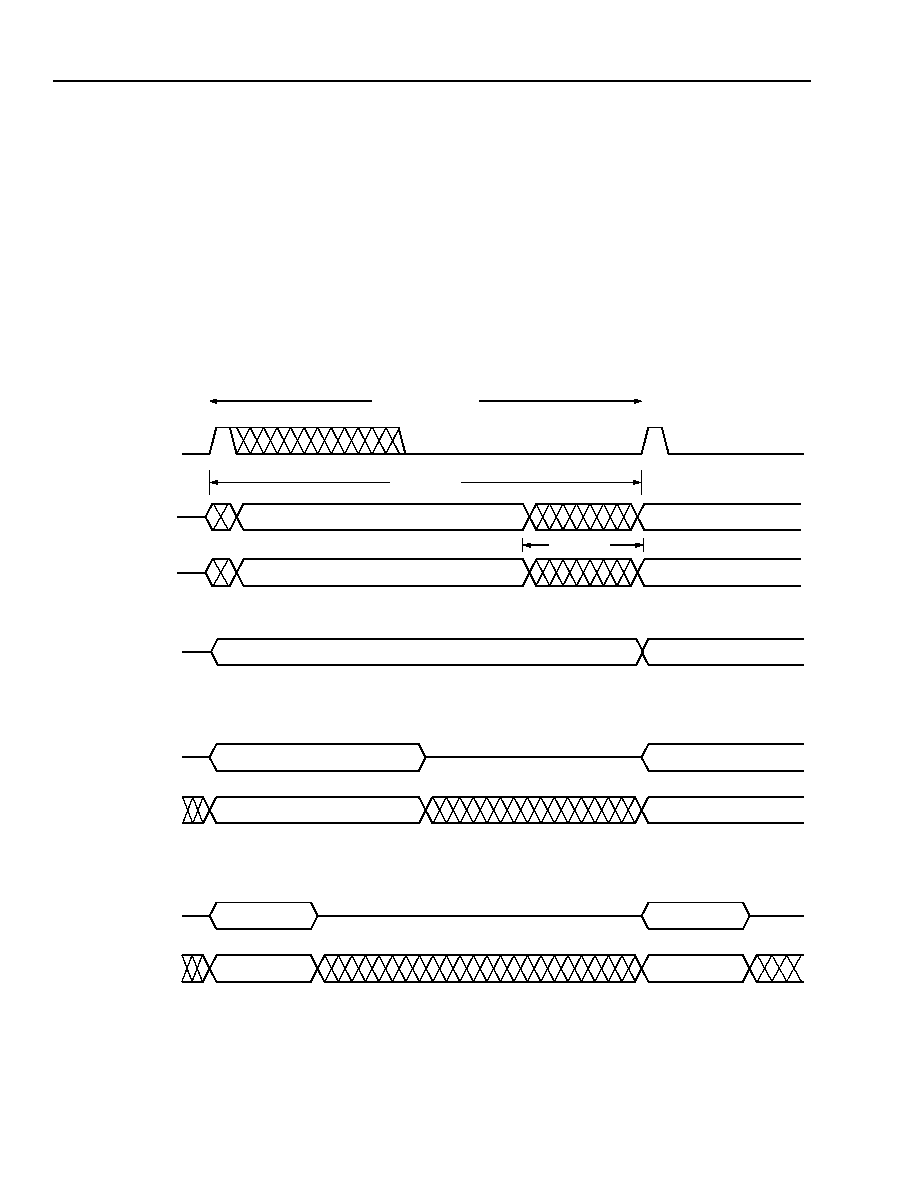

DS1 Transparent Frame Structure ....................................................................................................56

Figure 20.

CEPT Transparent Frame Structure..................................................................................................56

Figure 21.

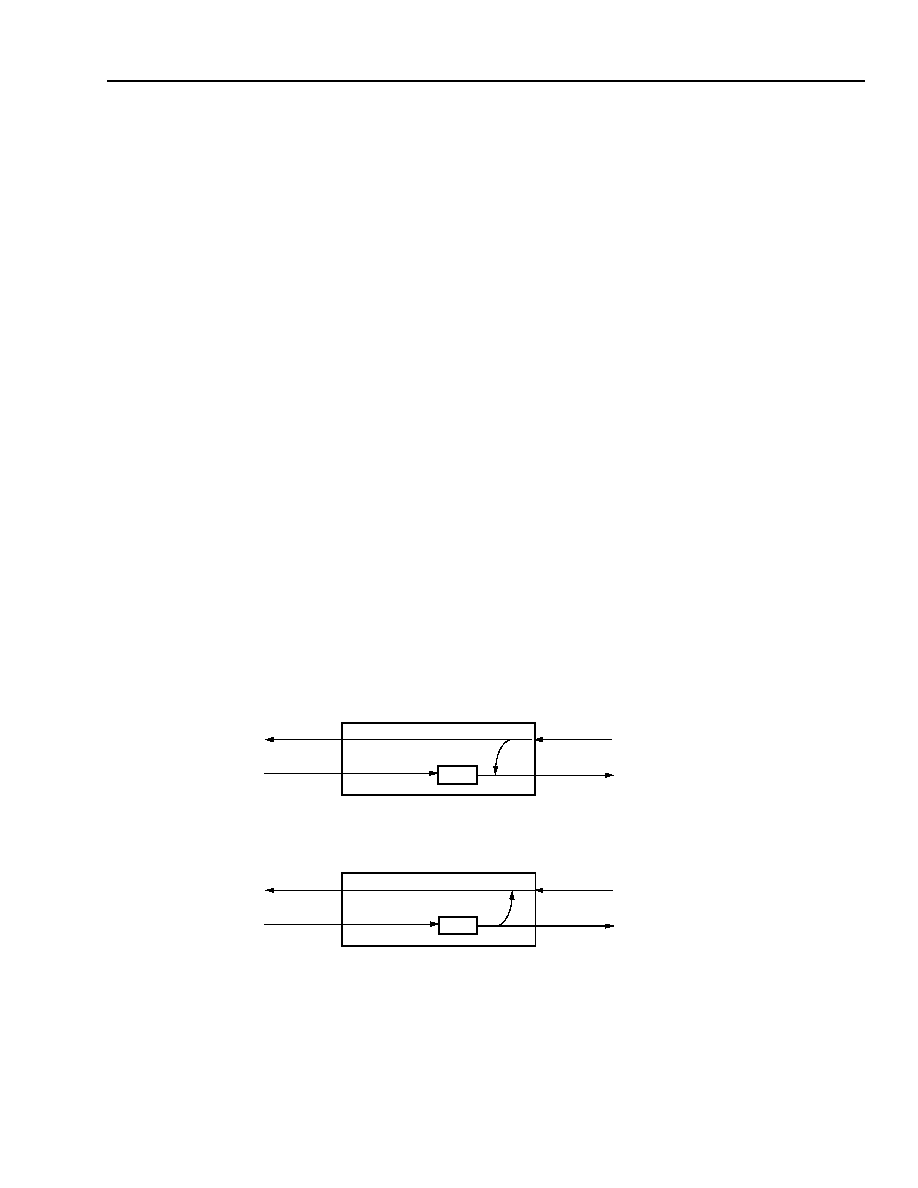

System Loopbacks ............................................................................................................................67

Figure 22.

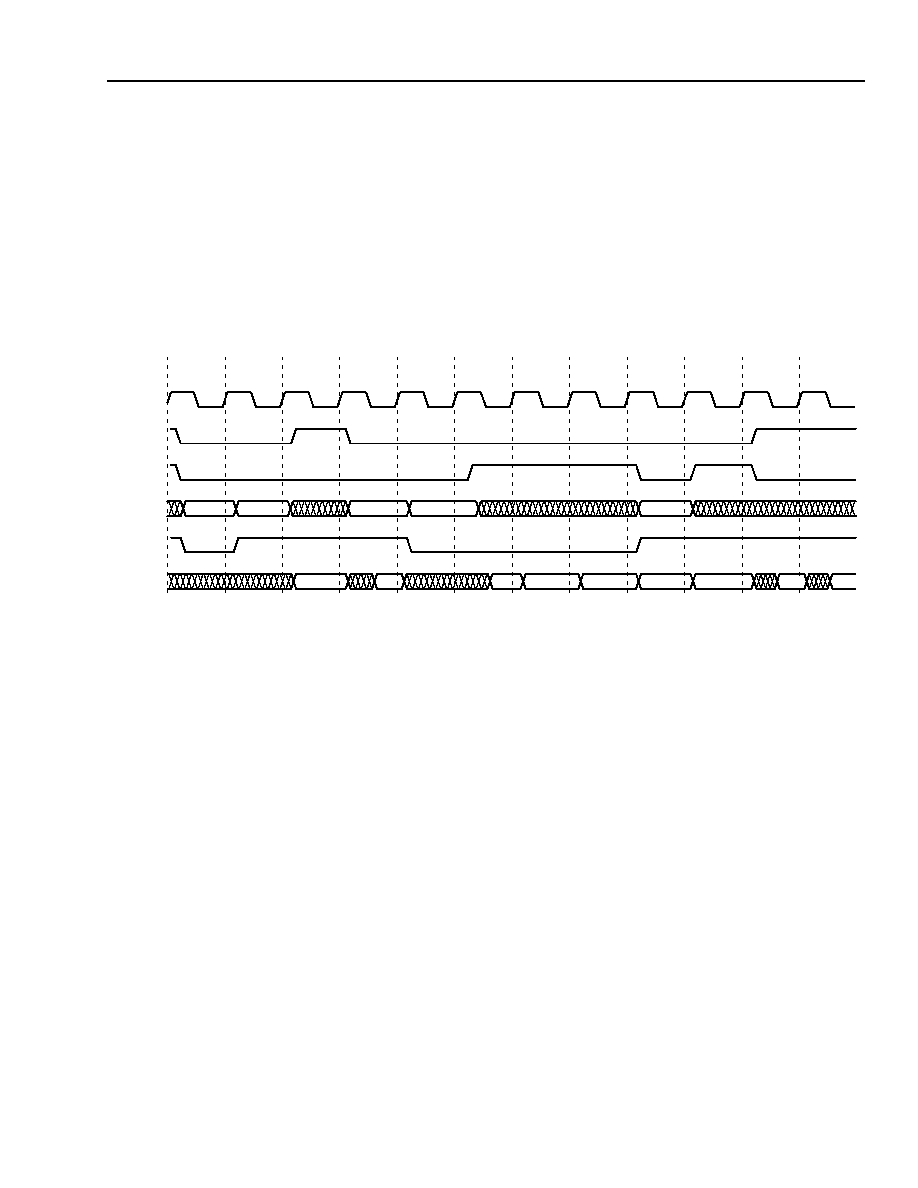

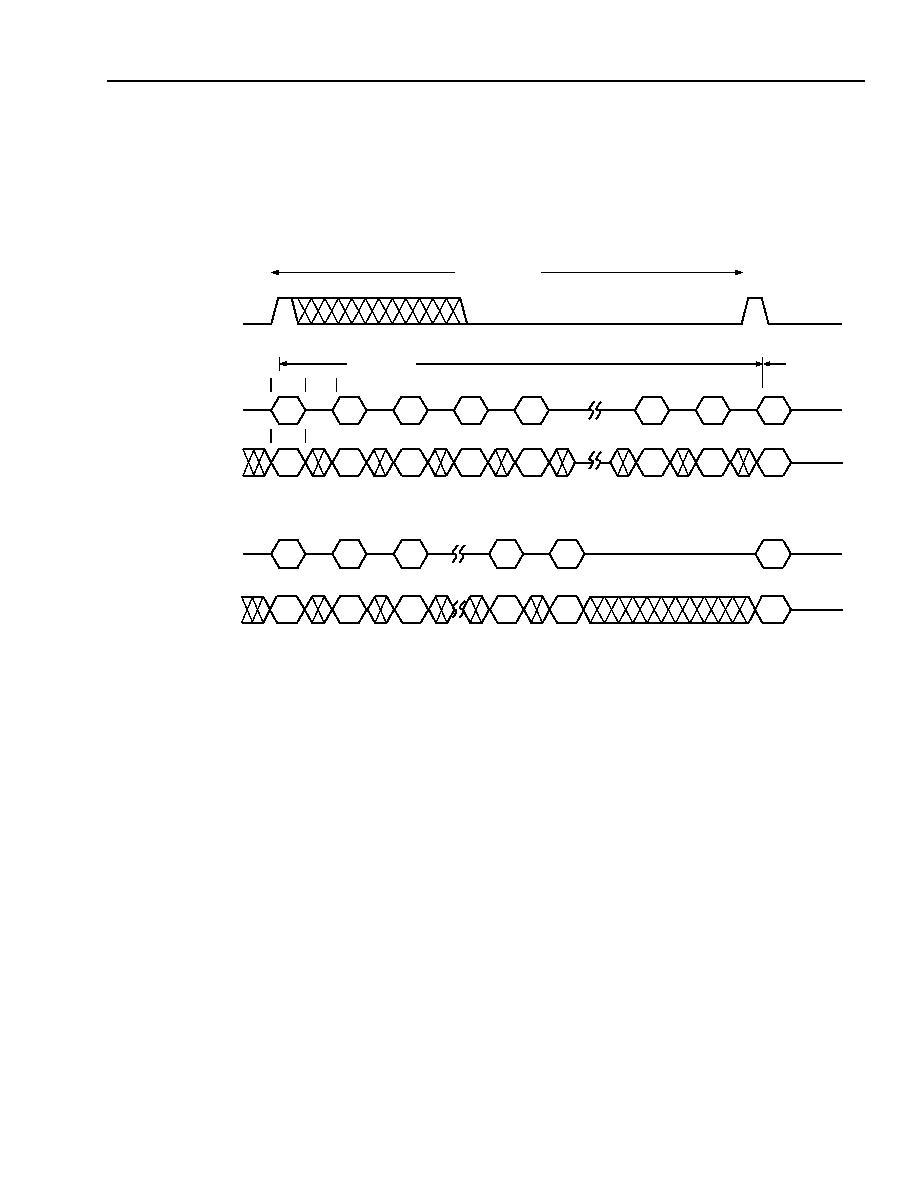

Nominal Concentration Highway Interface Timing ............................................................................68

Figure 23.

CHIDTS Mode Concentration Highway Interface Timing ..................................................................69

Figure 24.

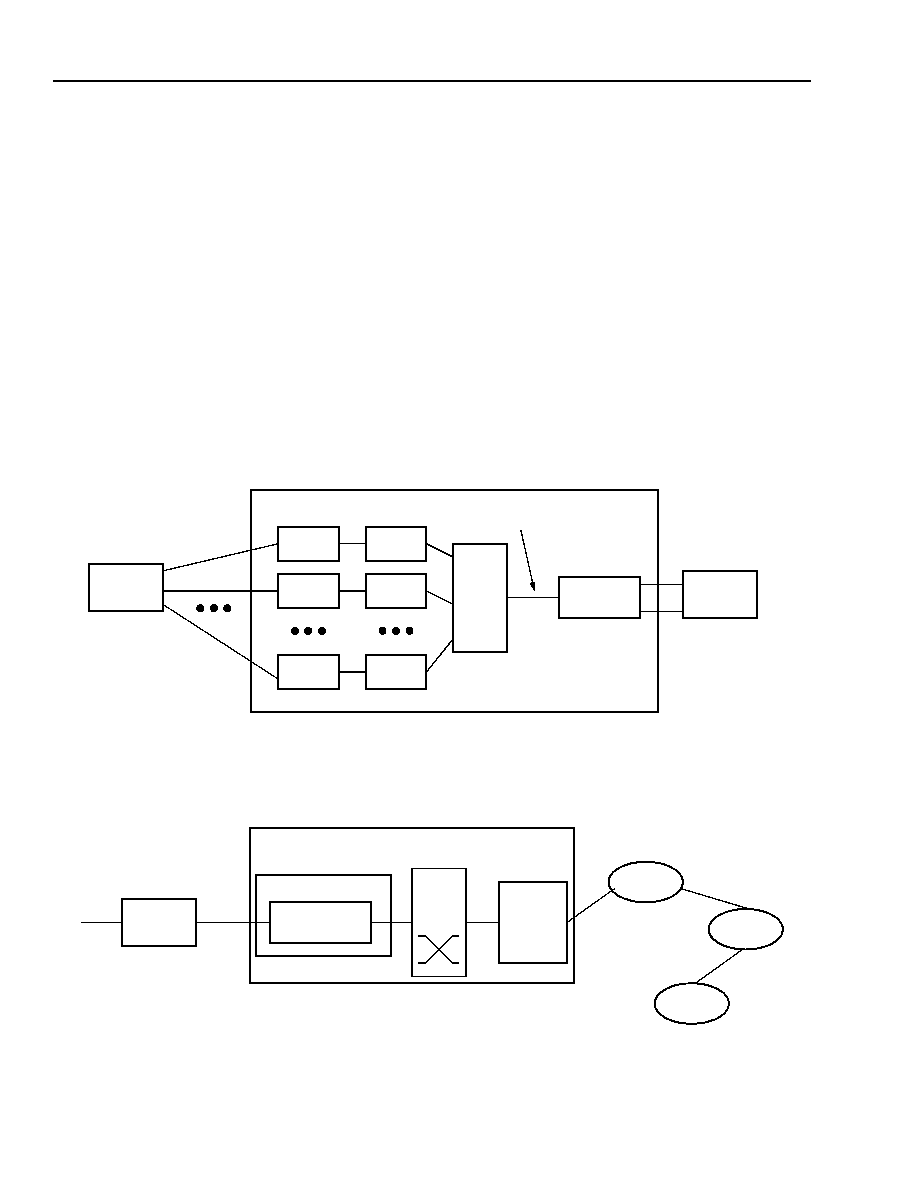

IMA Application..................................................................................................................................74

Figure 25.

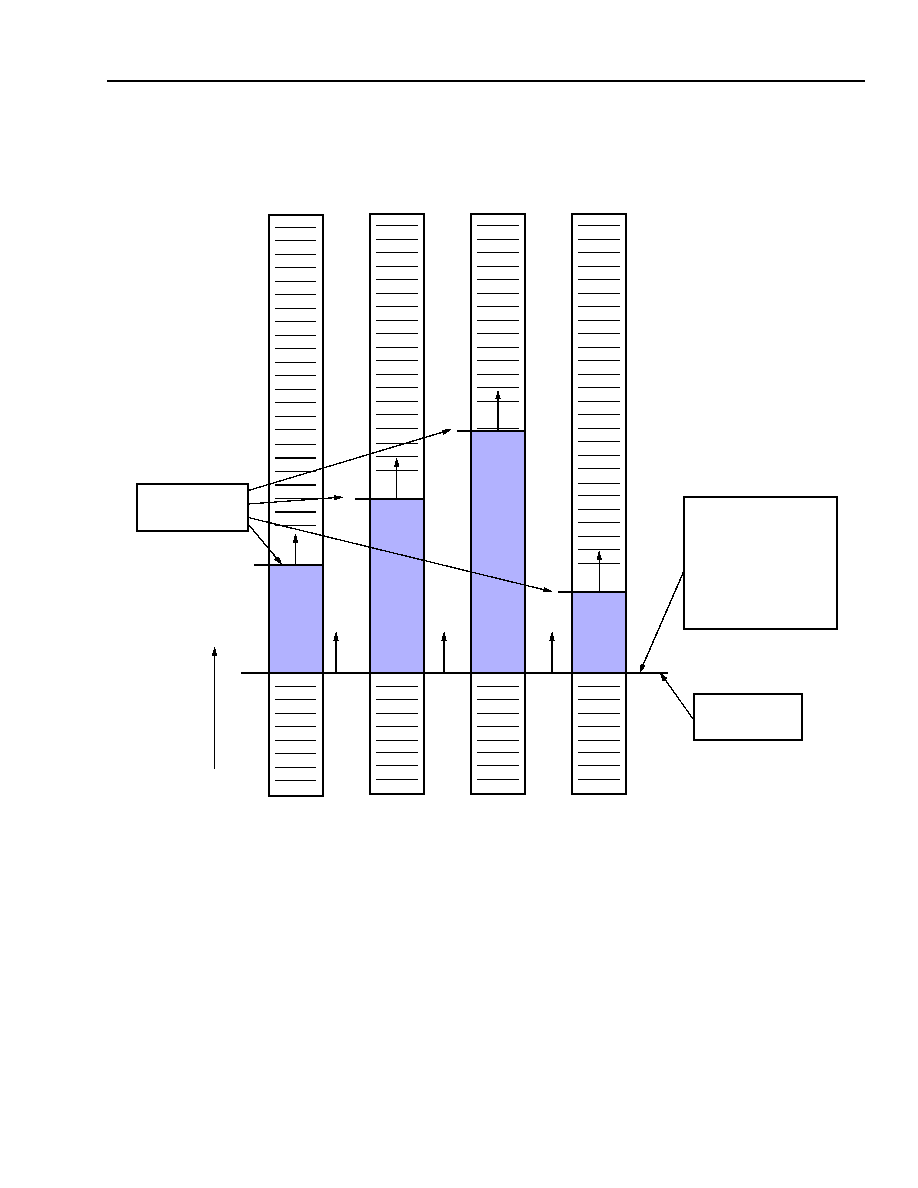

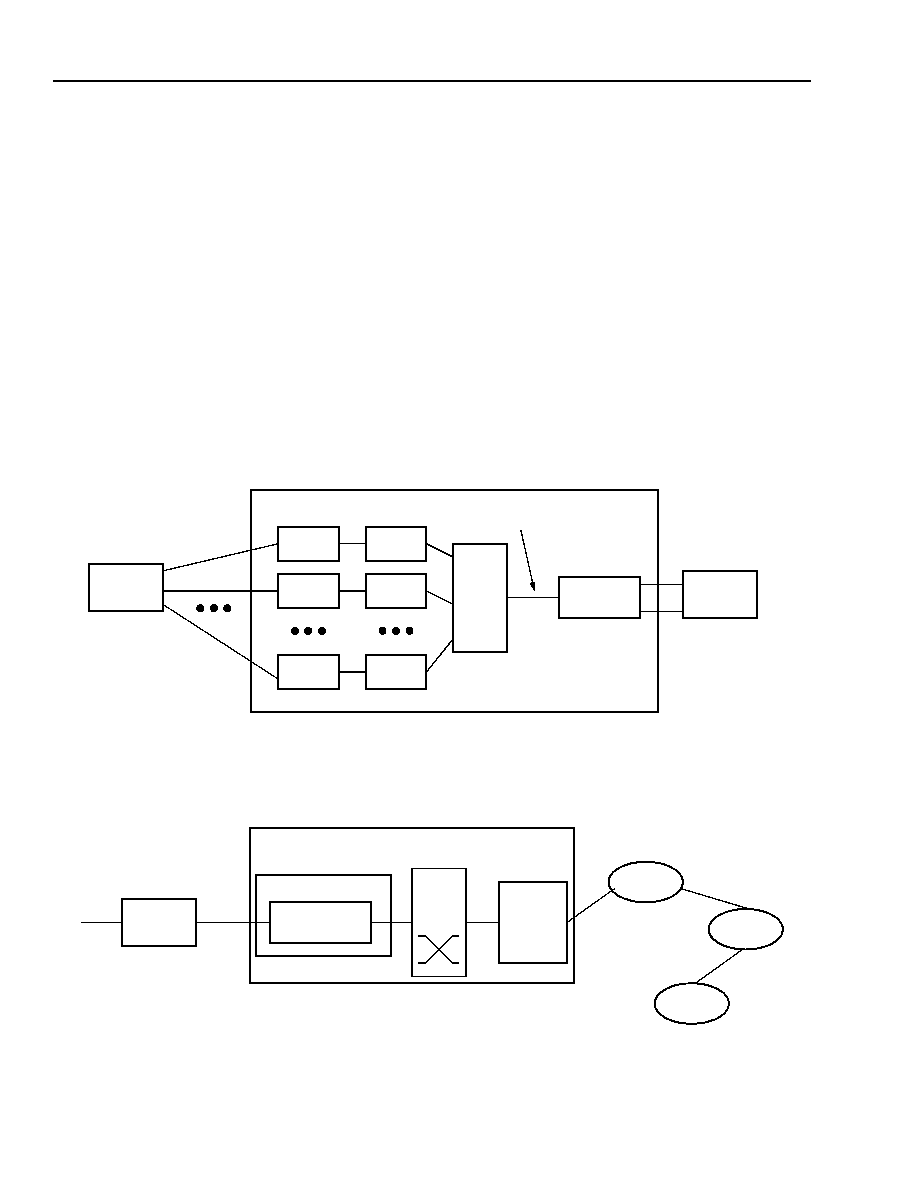

IMA High-Level Interconnect Block Diagram.....................................................................................75

Figure 26.

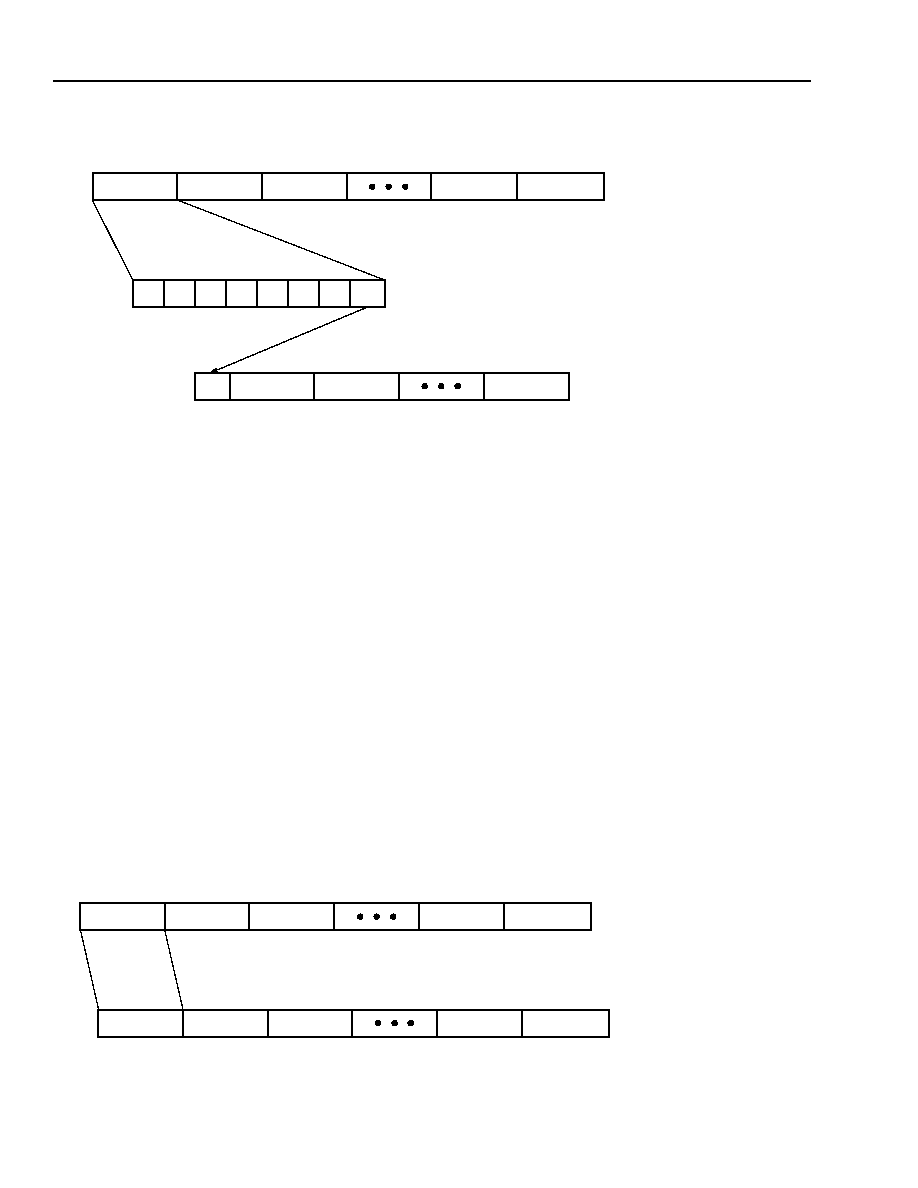

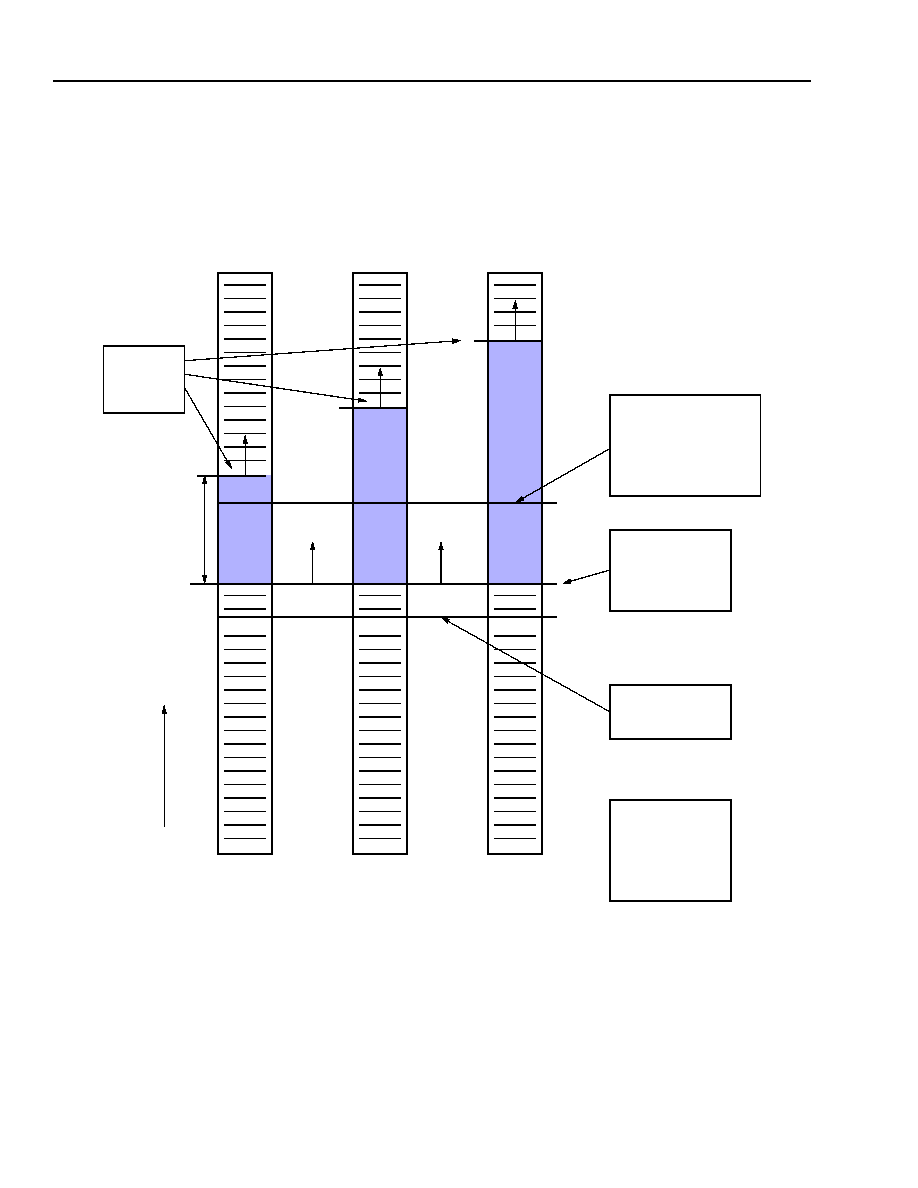

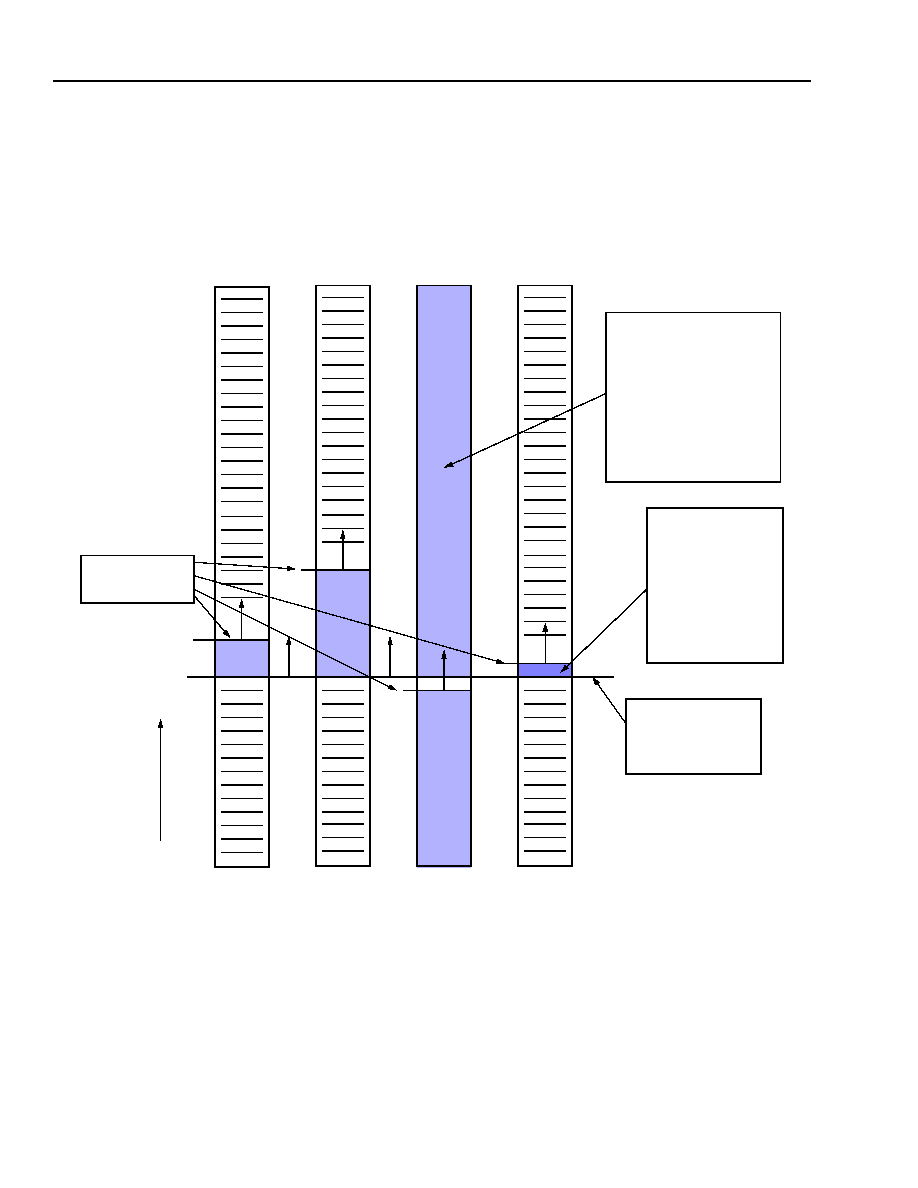

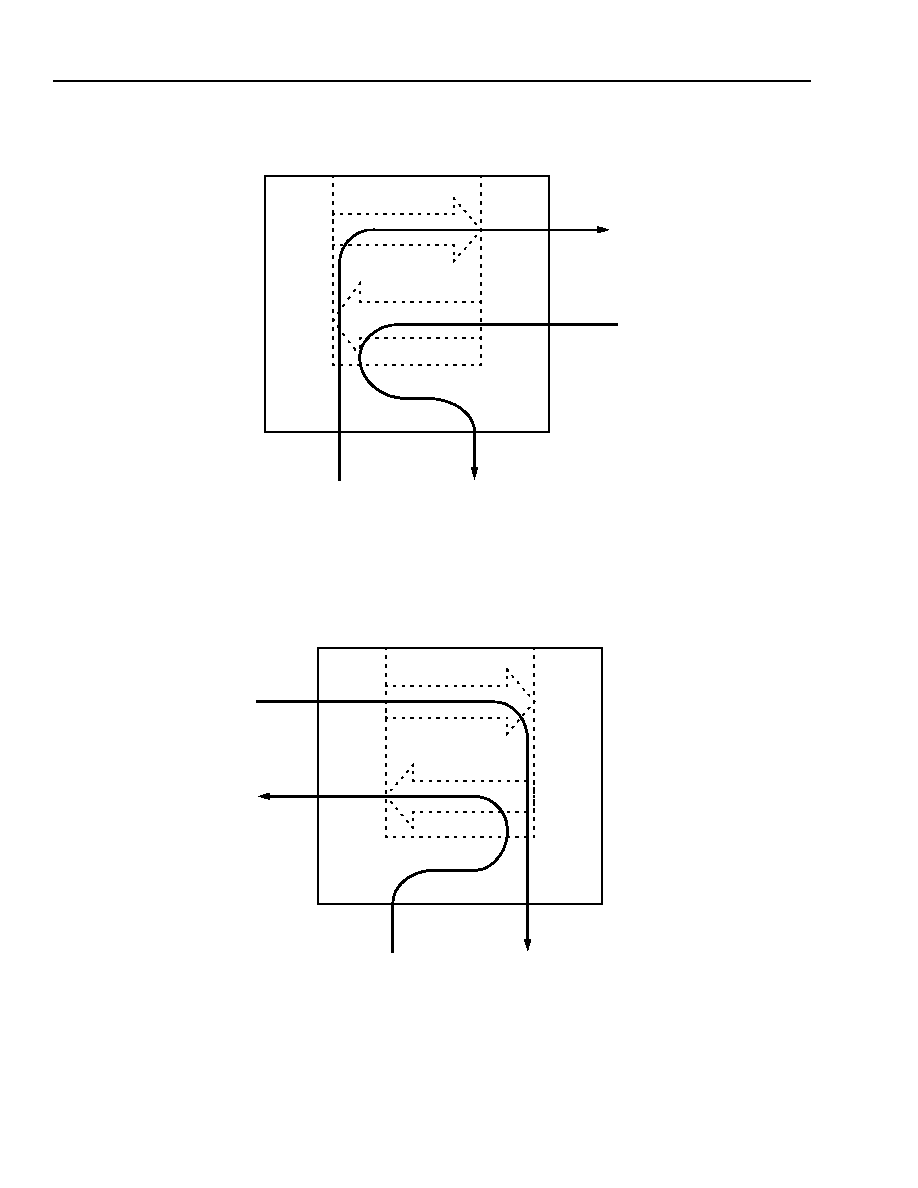

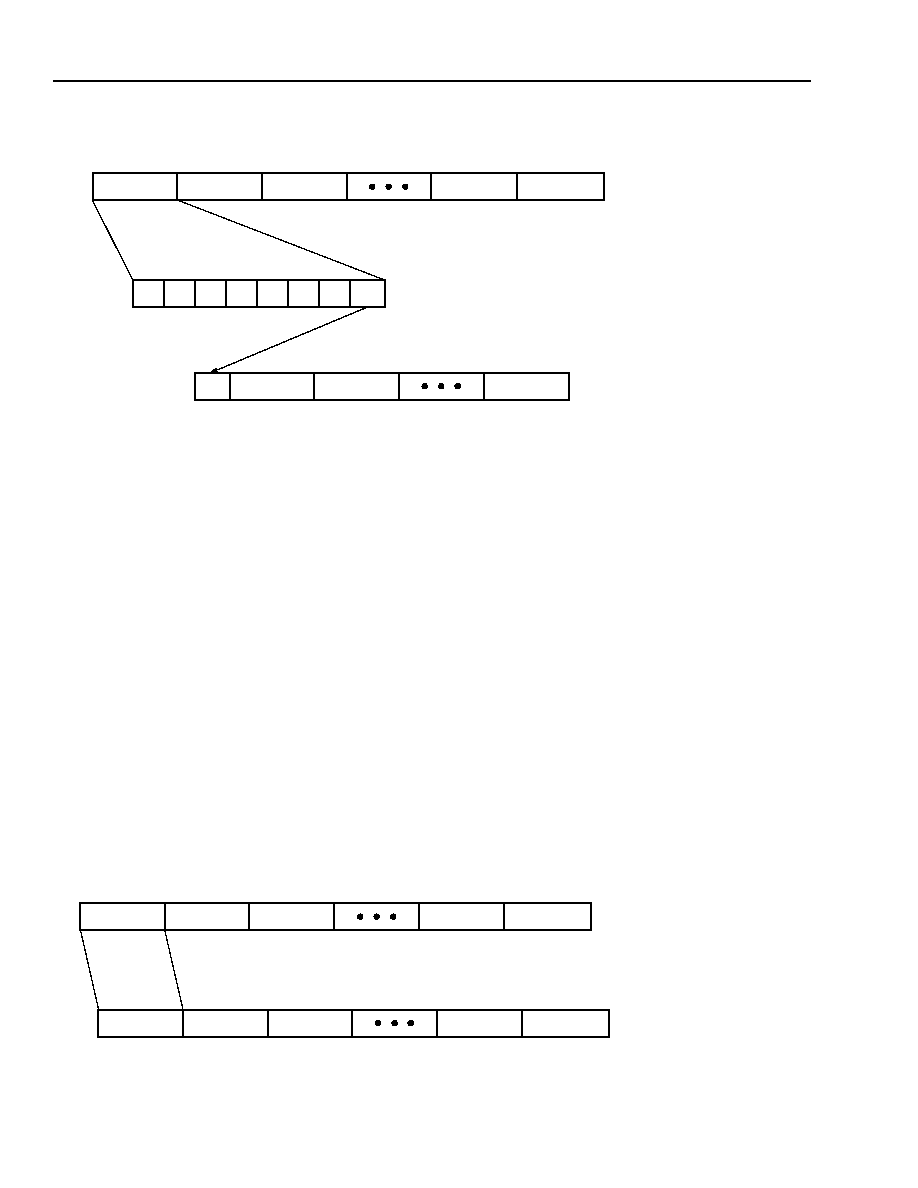

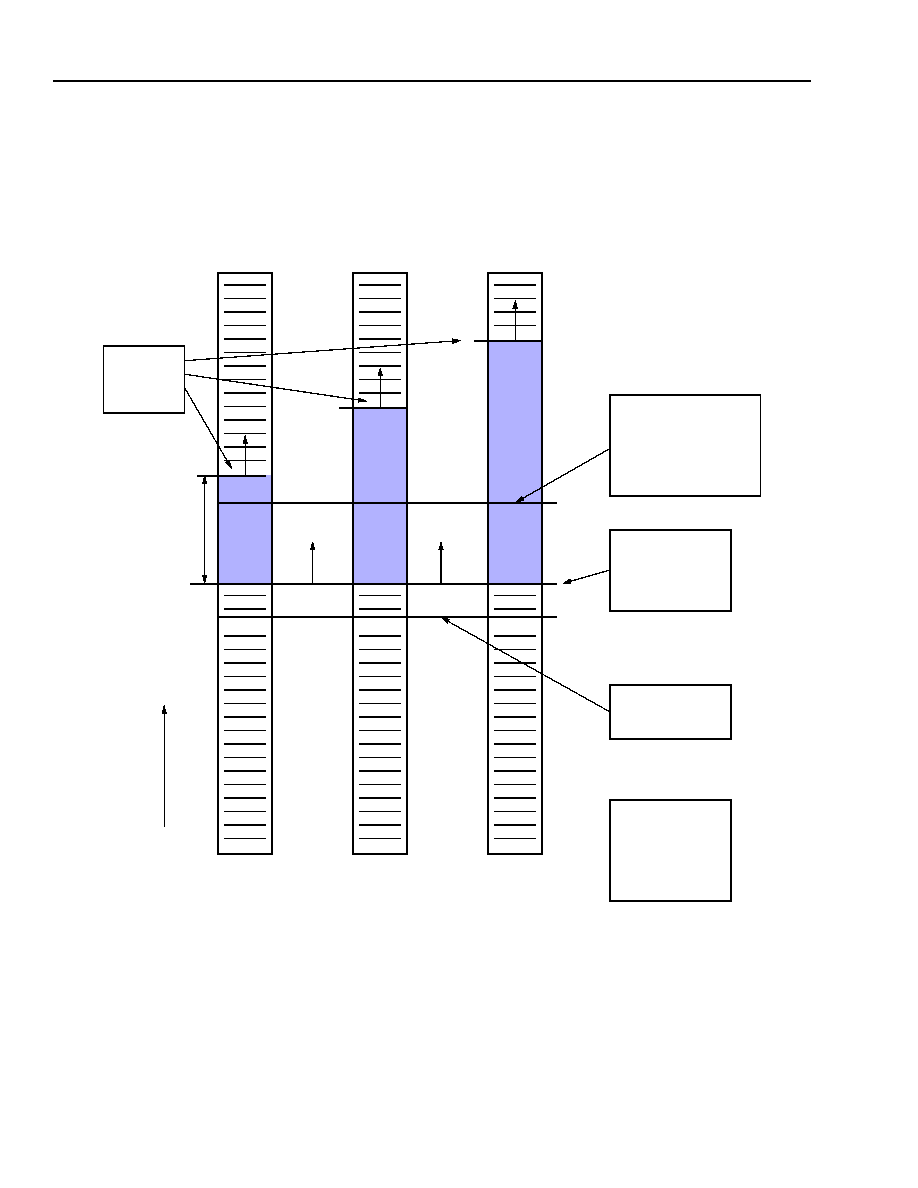

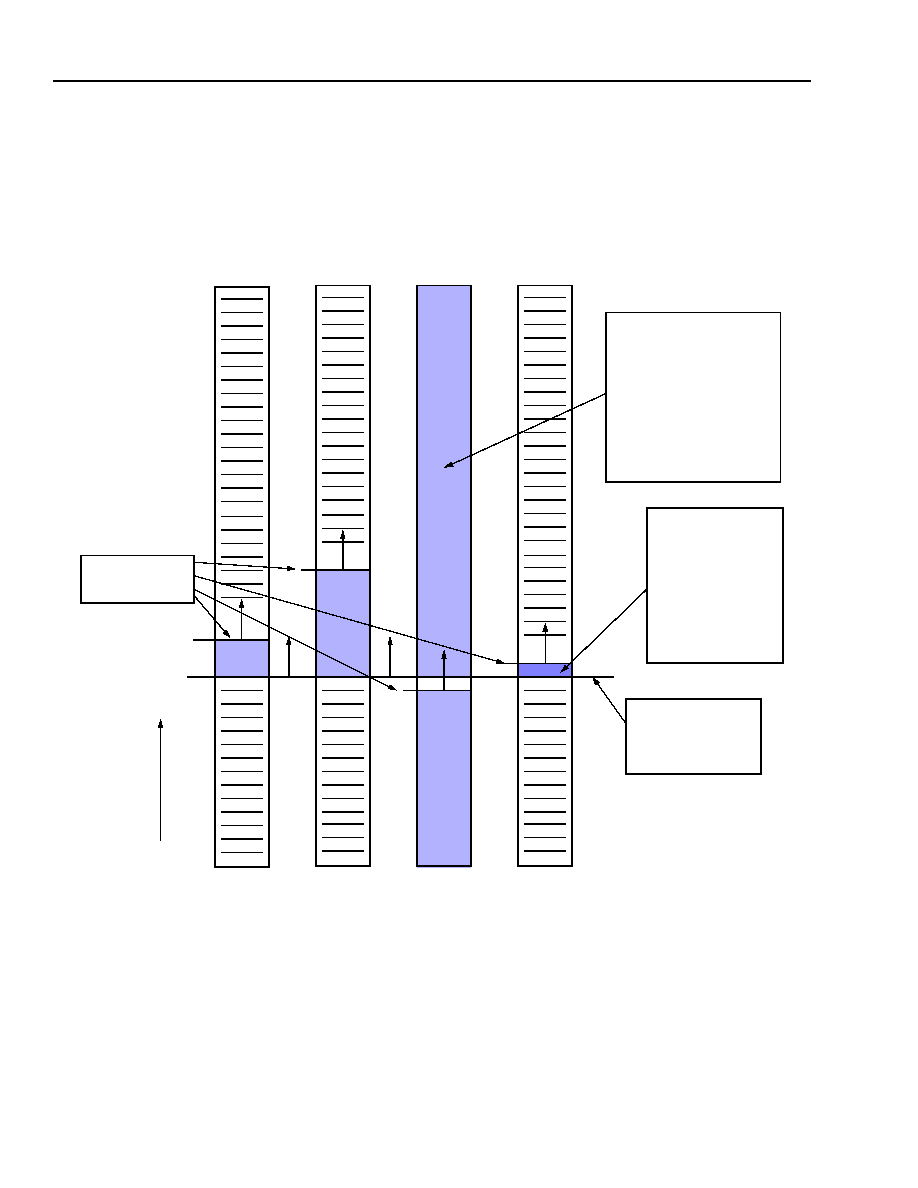

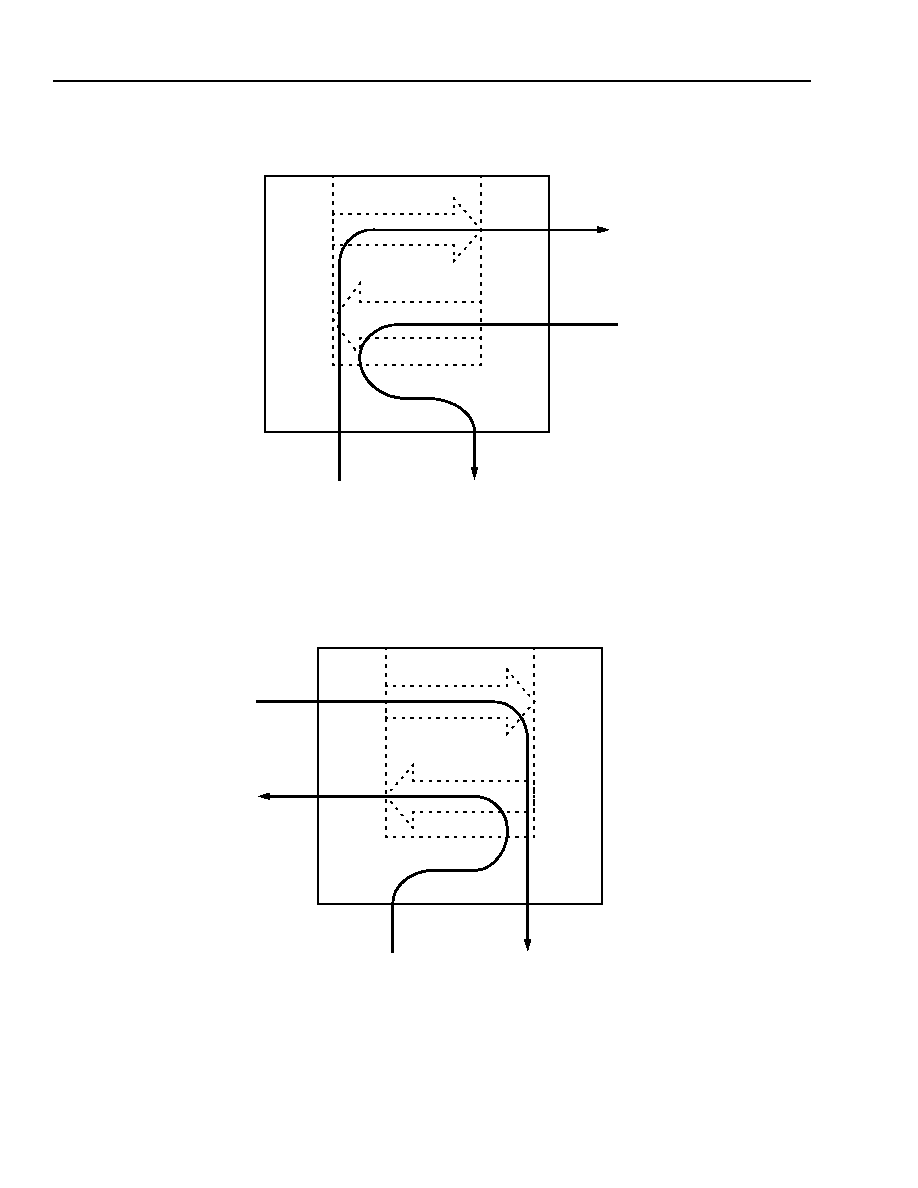

Logical View of Three-Link Group's DCB Shortly After Starting to Receive Data from the Line .......78

Figure 27.

Logical View of Three-Link Group's DCB When It Starts Reading DCB ...........................................79

Figure 28.

Logical View of Three-Link Group's DCB After It Starts Reading DCB .............................................80

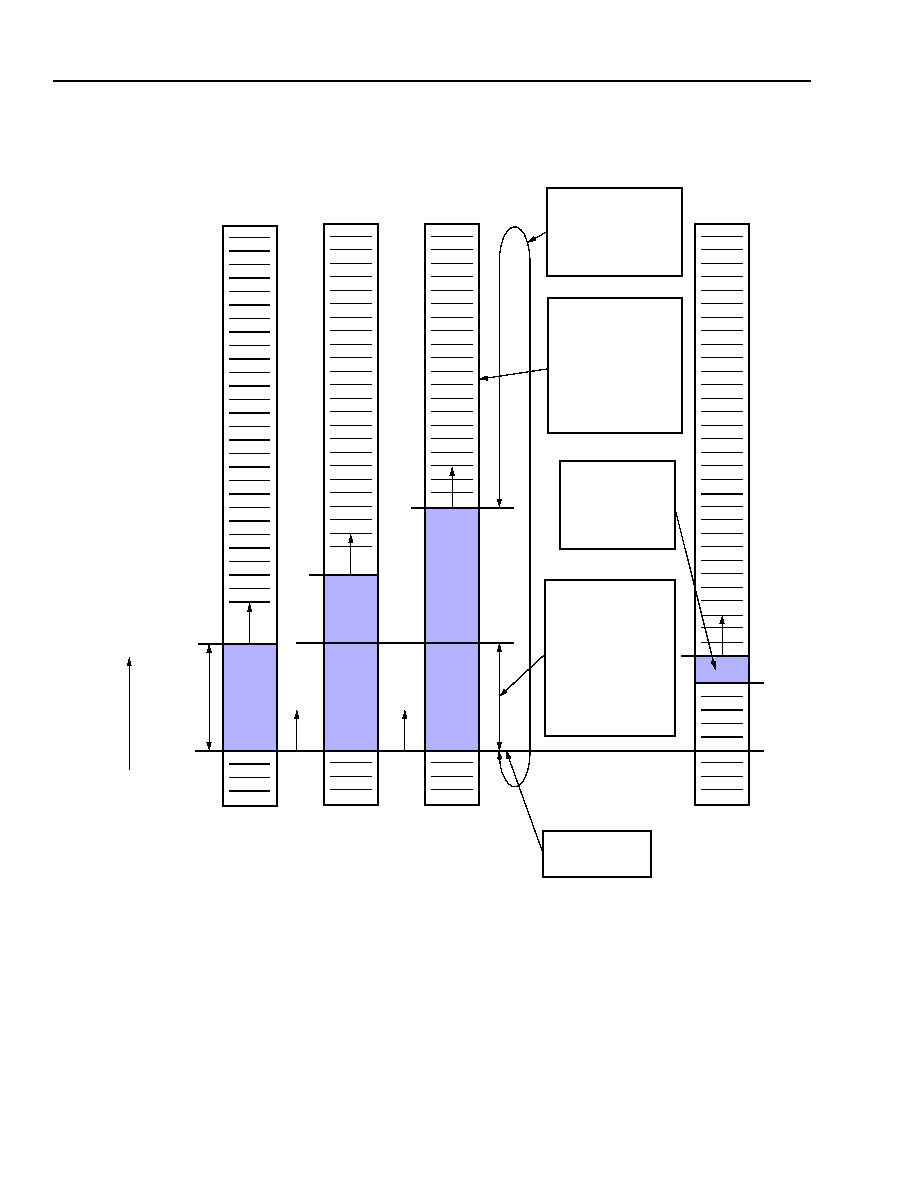

Figure 29.

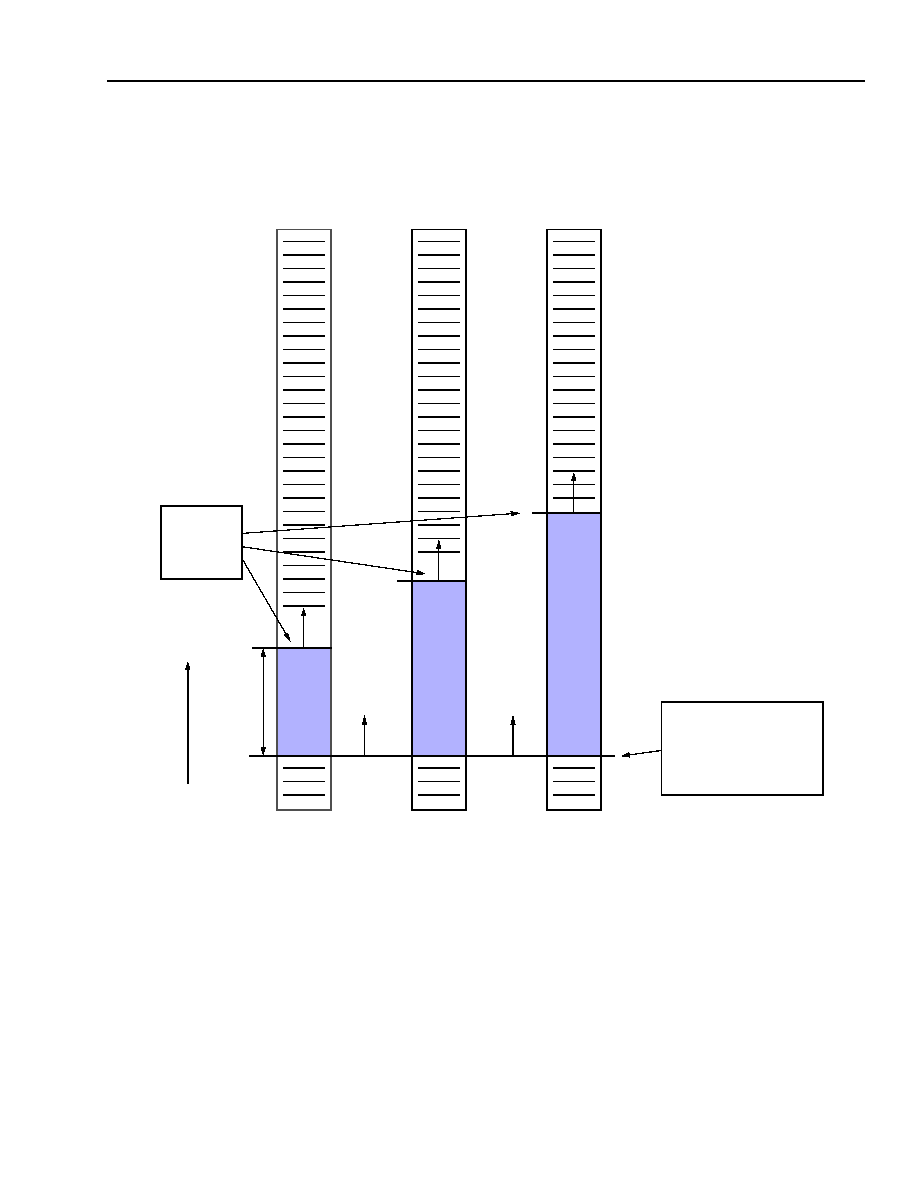

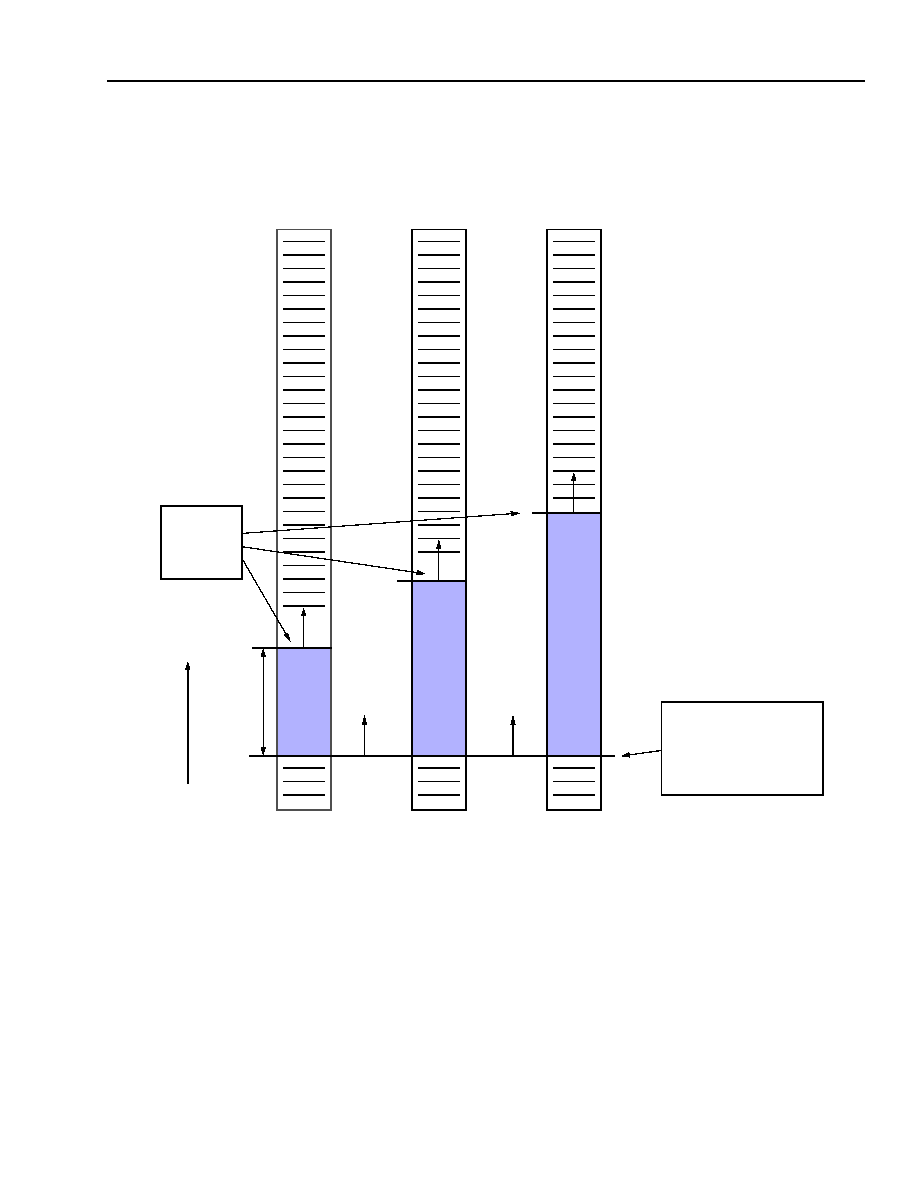

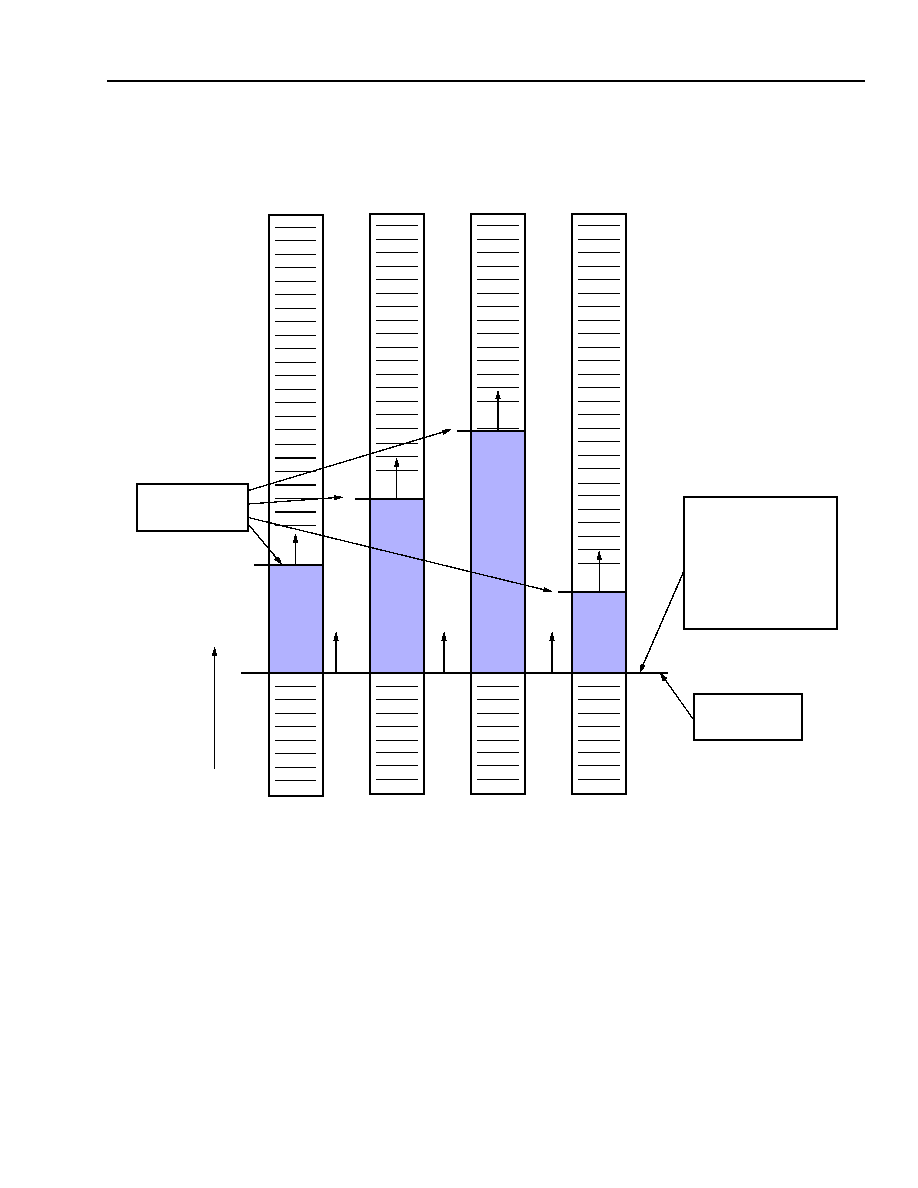

DCB During Normal Operation ..........................................................................................................81

Figure 30.

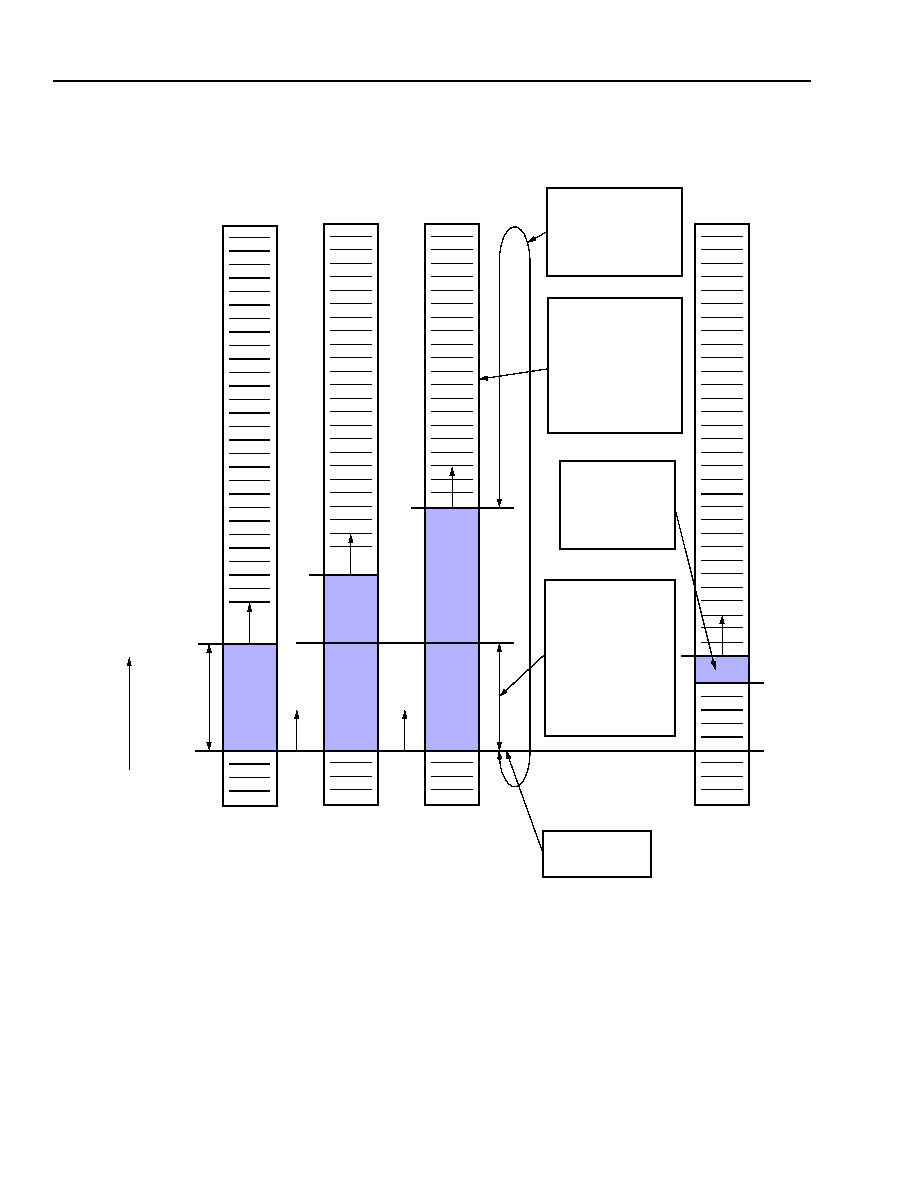

Starting to Add a Link to a Group ......................................................................................................82

Figure 31.

Link Now Being Read ........................................................................................................................83

Figure 32.

Effects of Link #3 and Link #4 Faults.................................................................................................84

Figure 33.

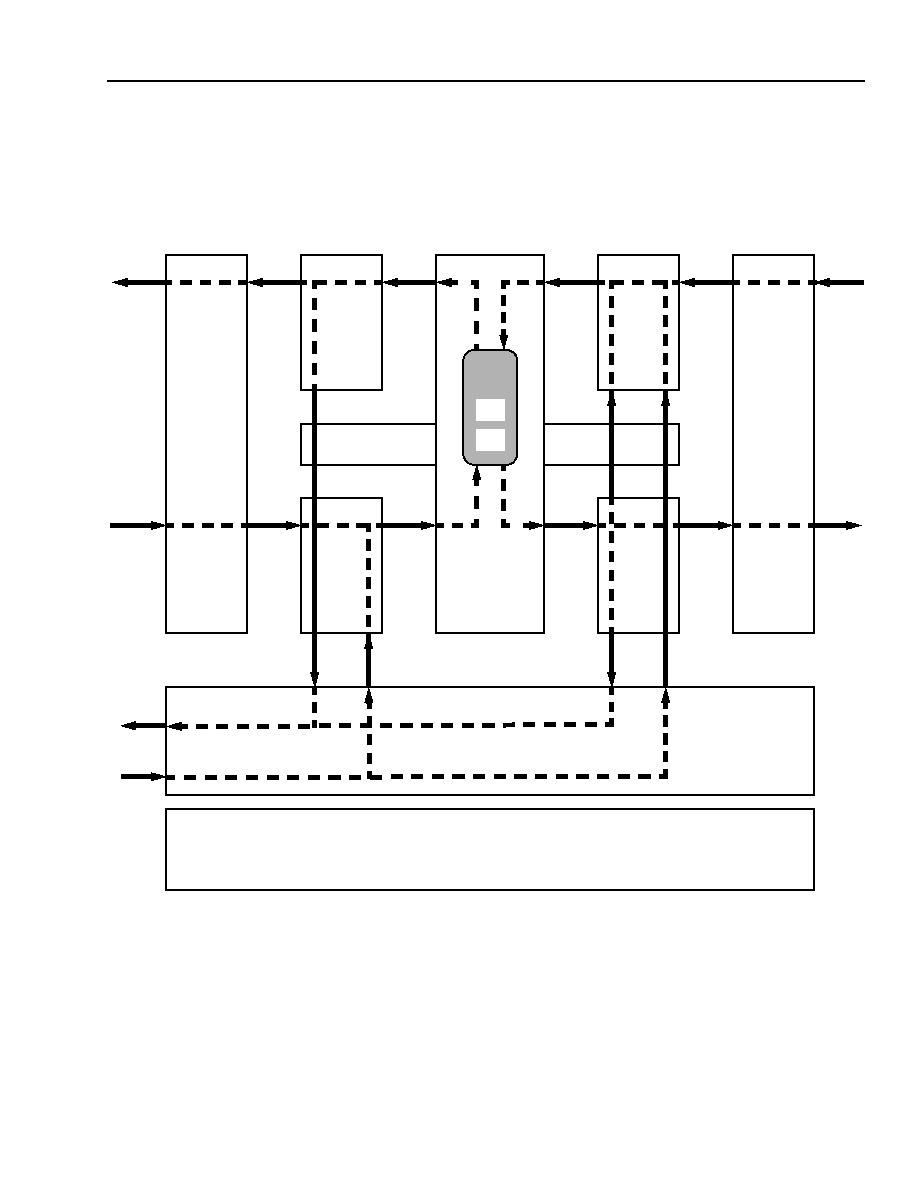

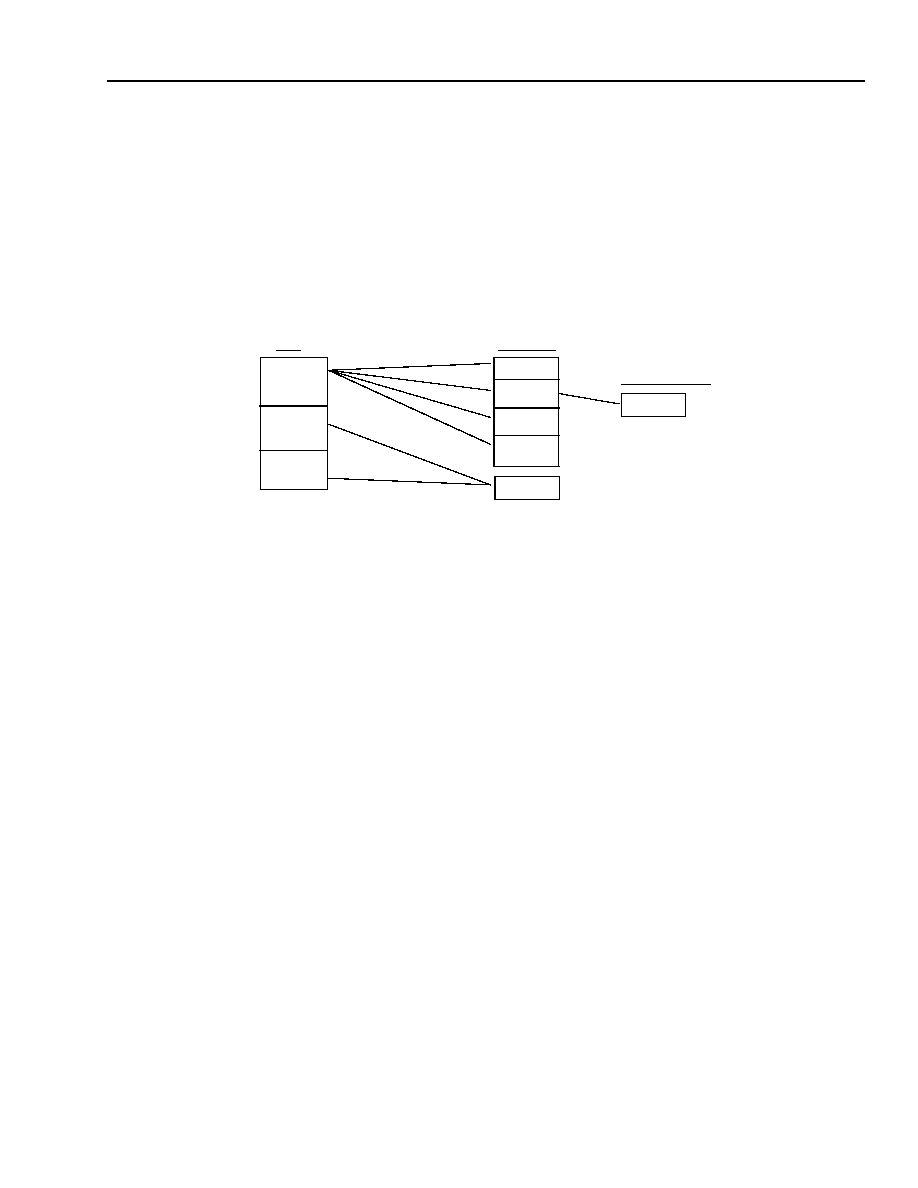

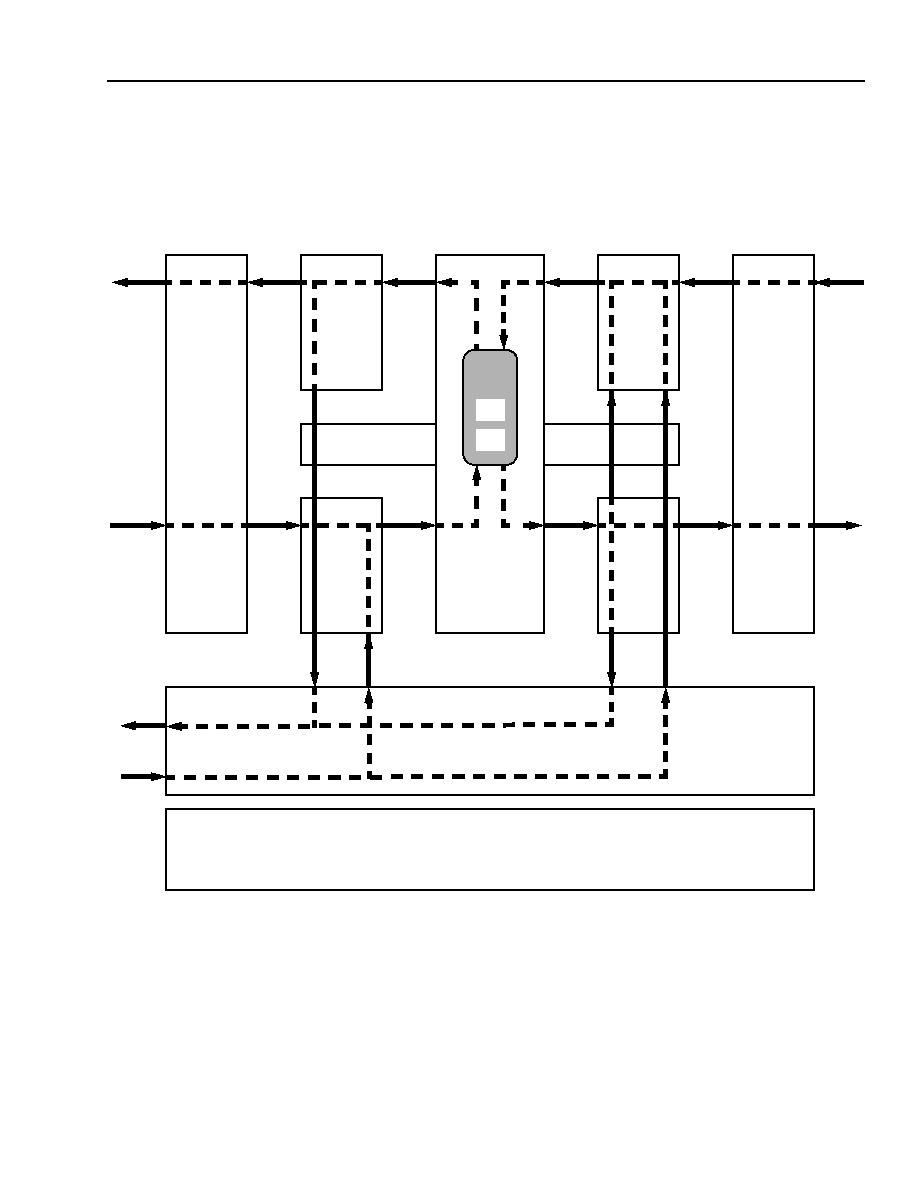

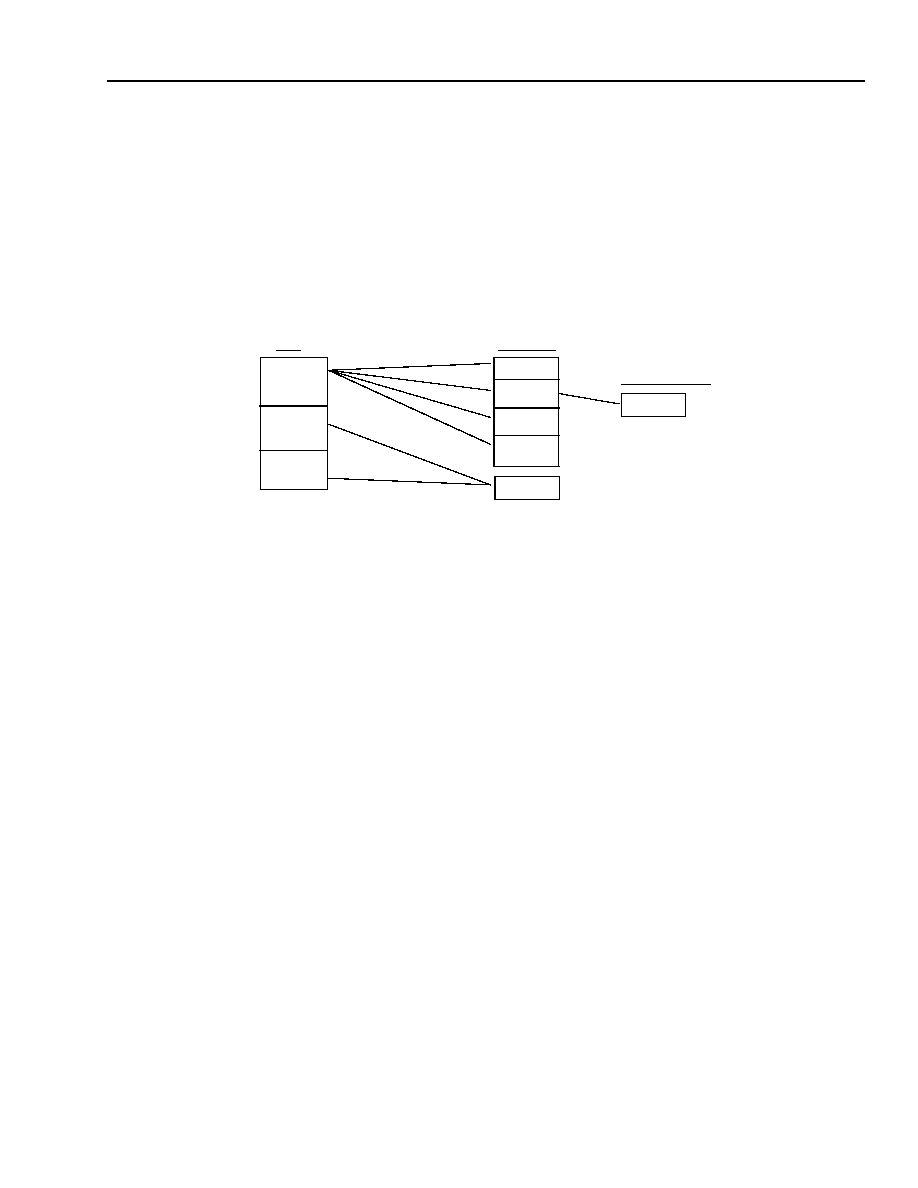

APC Block Integrated Memory Configuration....................................................................................87

Figure 34.

Switch Fabric Connections for Dual TAAD08JU2 Switch Mode........................................................88

Figure 35.

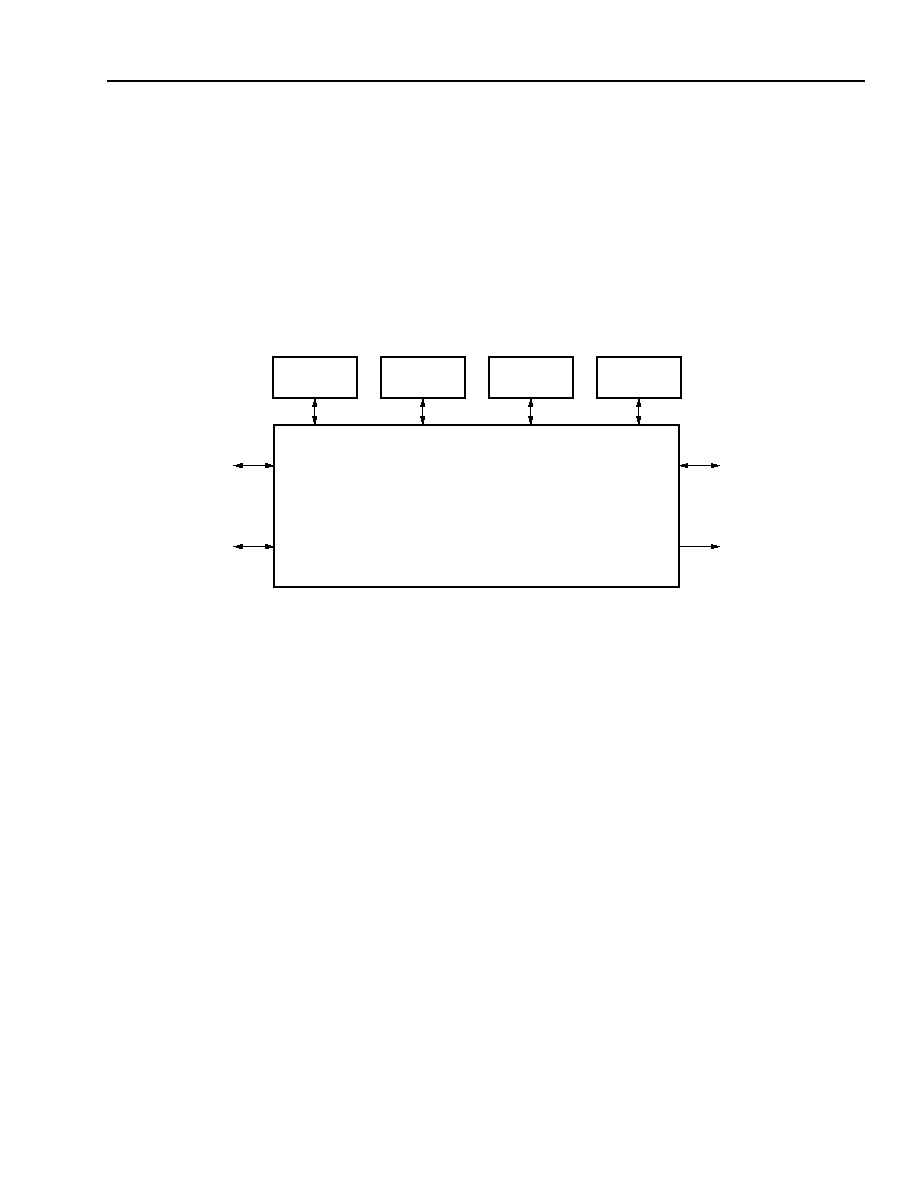

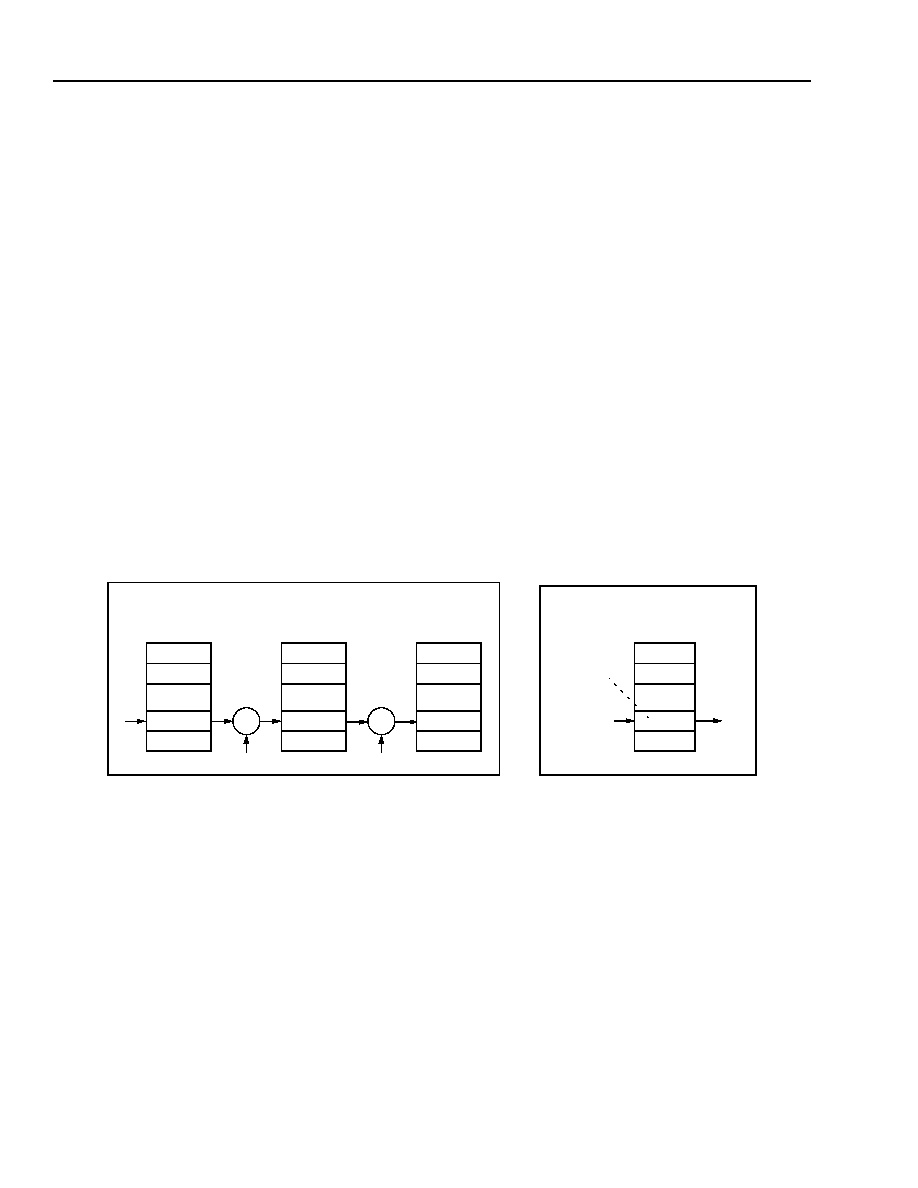

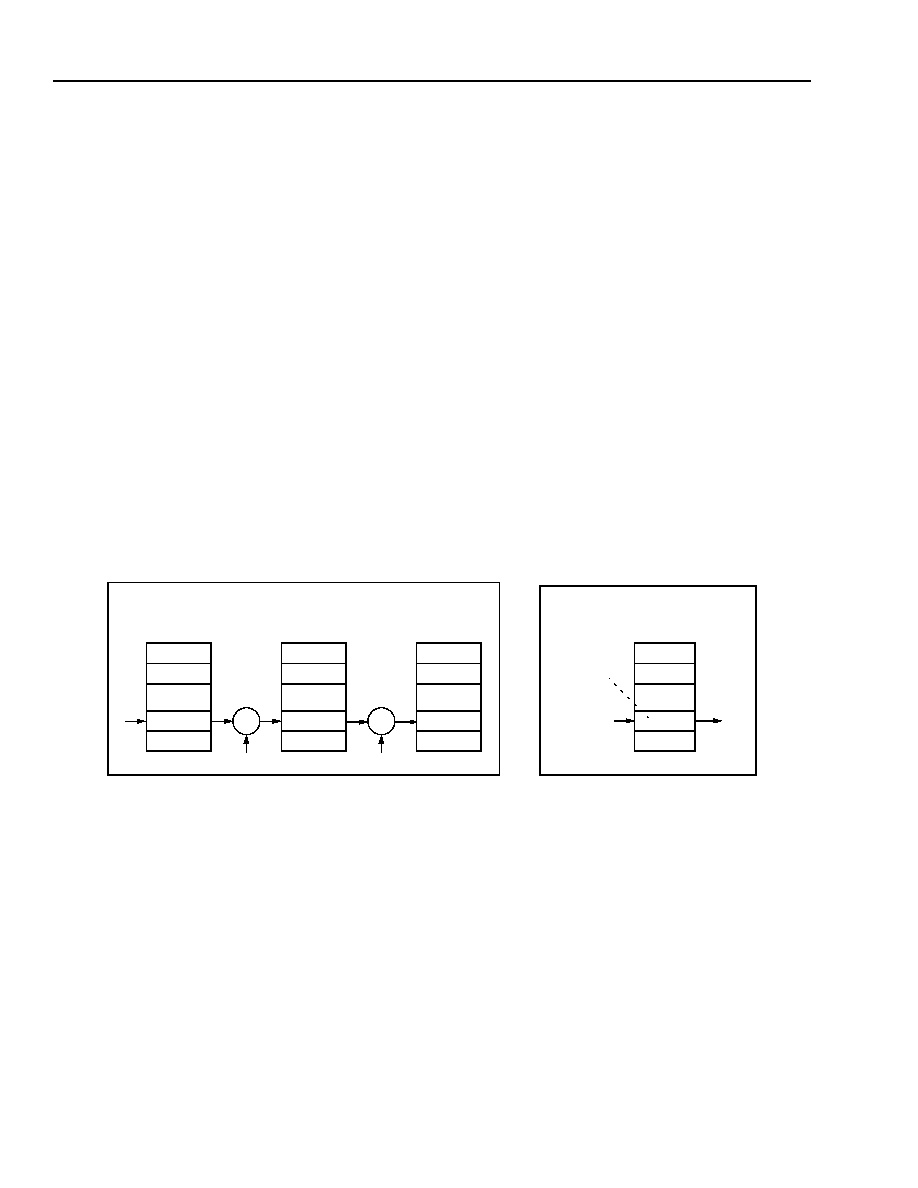

AAL Engine Block Diagram .............................................................................................................100

Figure 36.

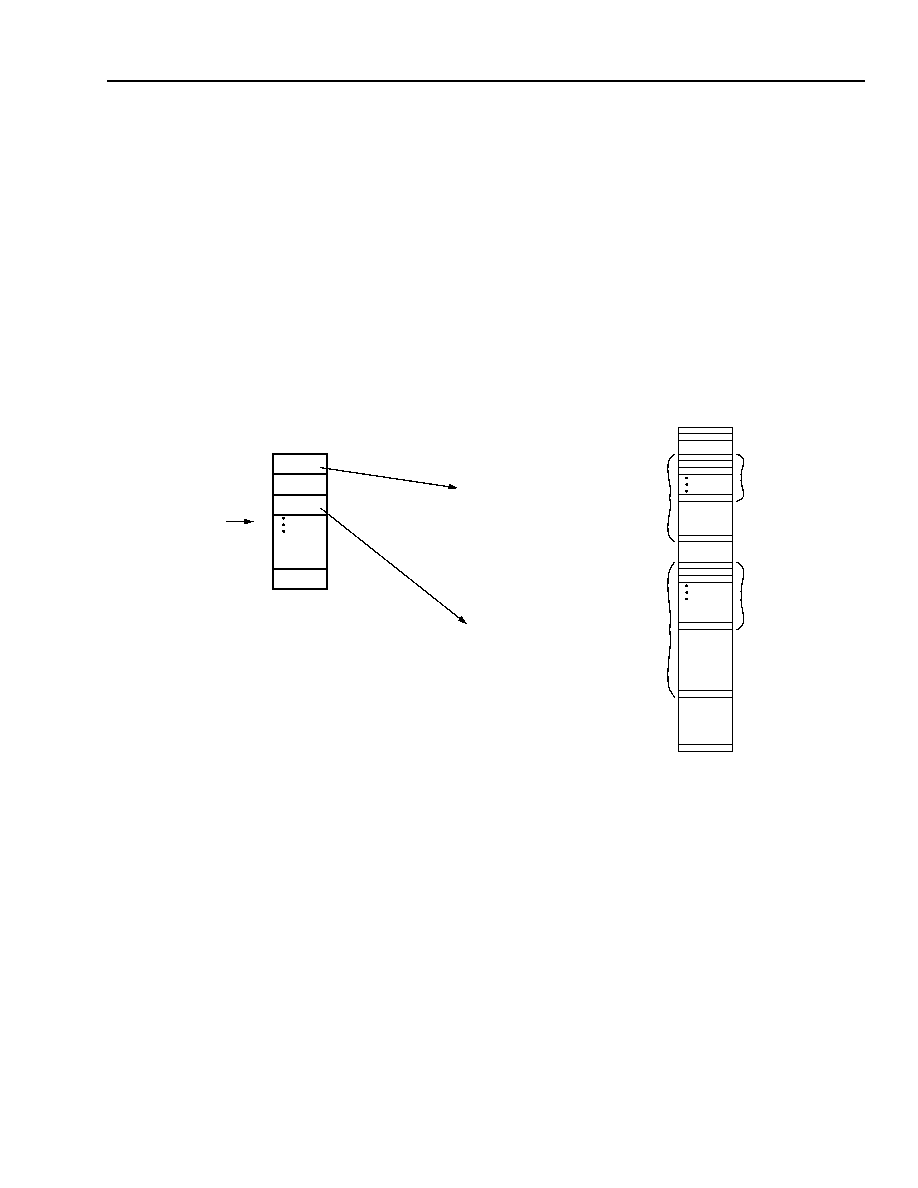

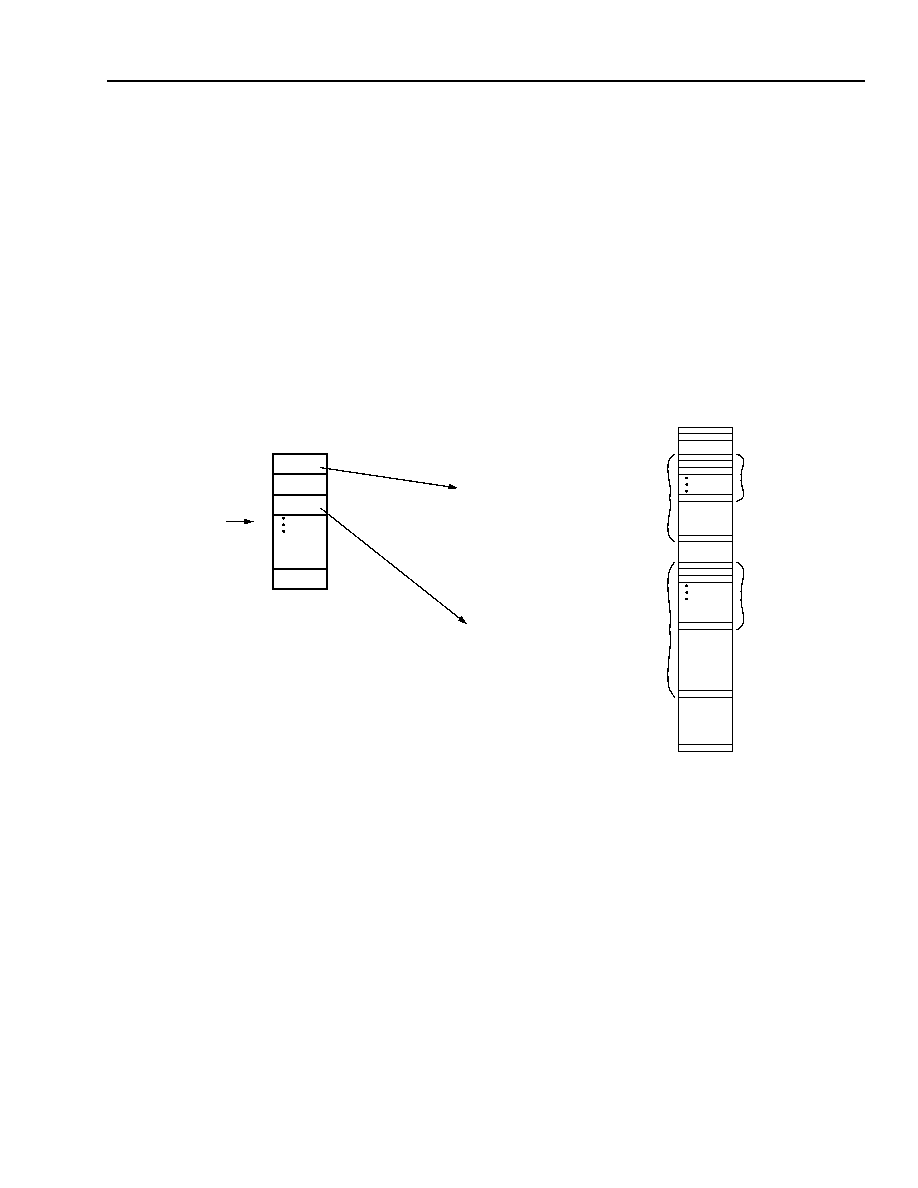

SIF-to-NIF, NIF-to-SIF .....................................................................................................................102

Figure 37.

SIF Loopback, NIF Loopback ..........................................................................................................103

Figure 38.

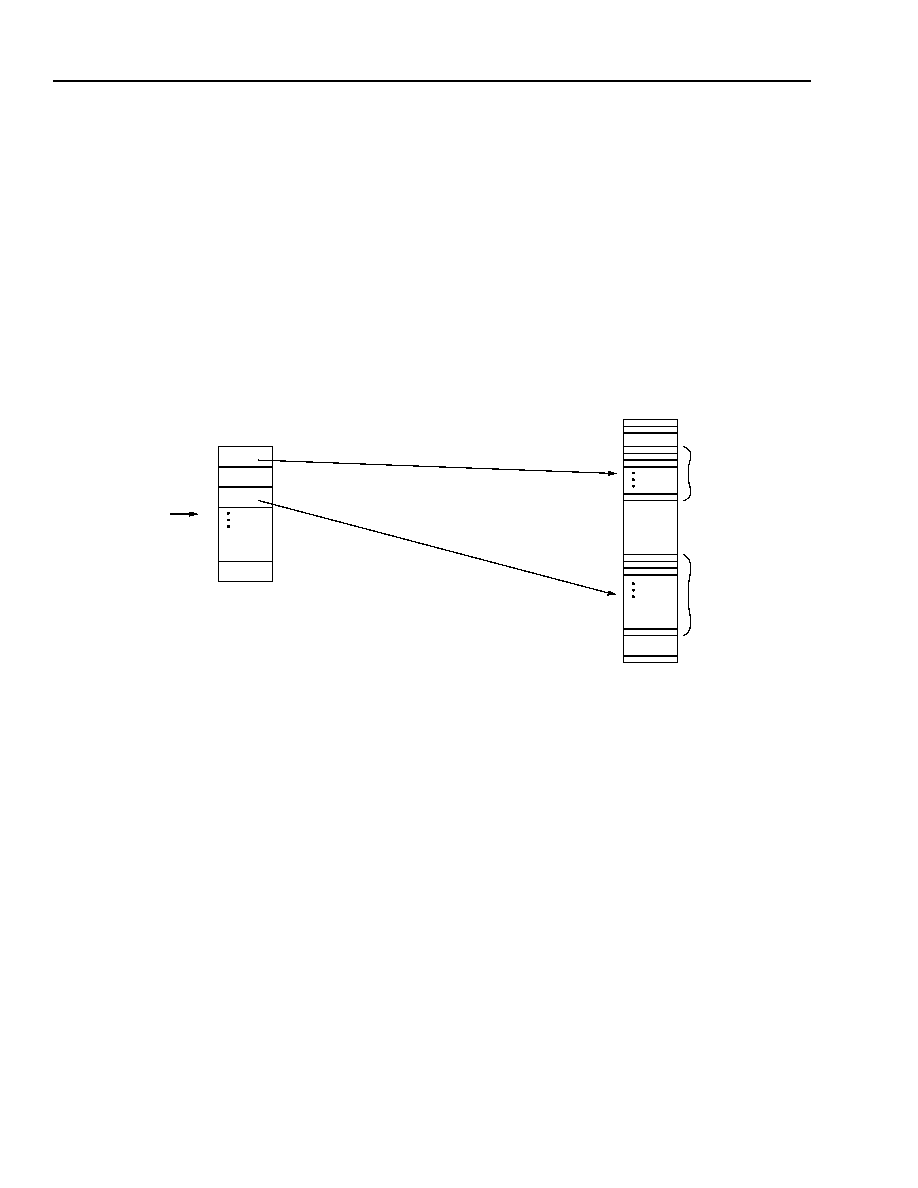

NIF Adaptation Loopback ................................................................................................................103

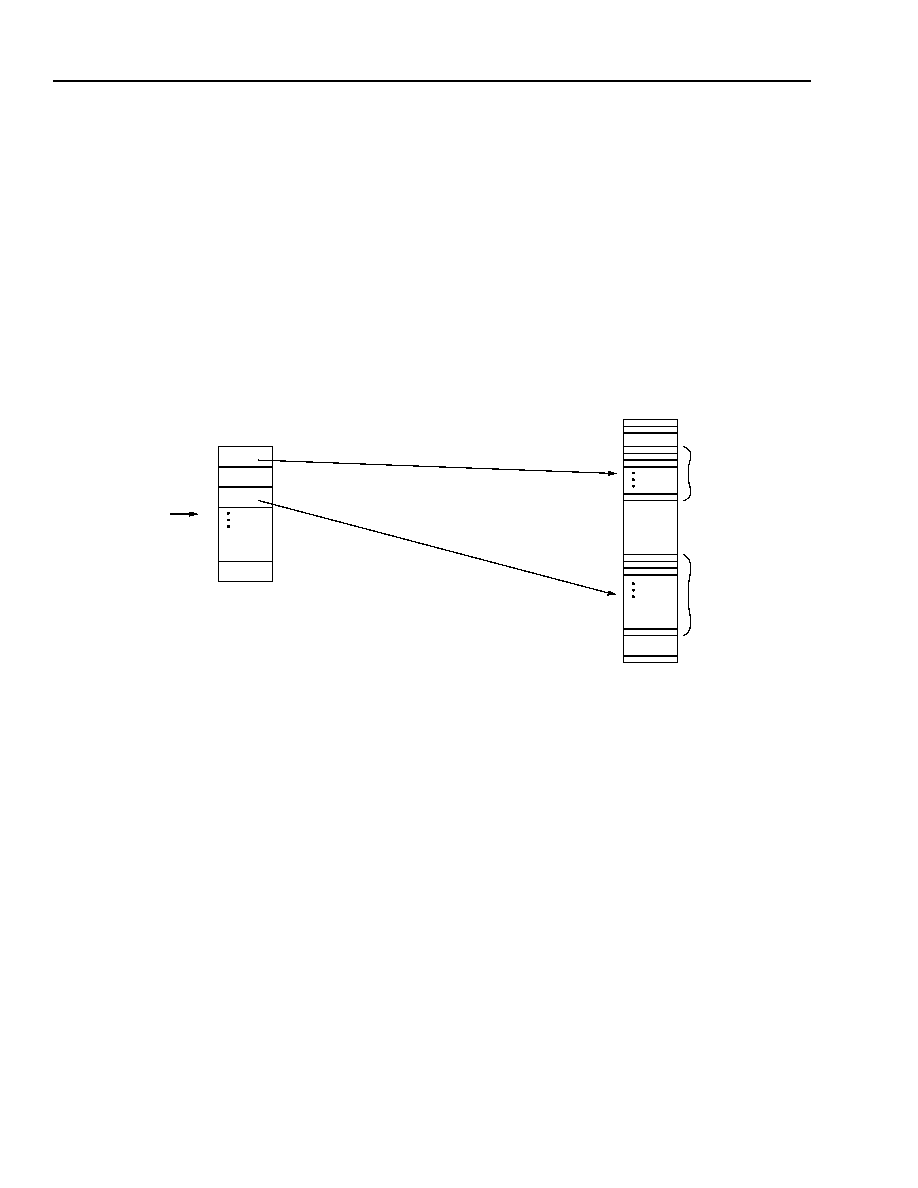

Figure 39.

Host-to-SIF, SIF-to-Host..................................................................................................................104

Figure 40.

Host-to-NIF, NIF-to-Host .................................................................................................................104

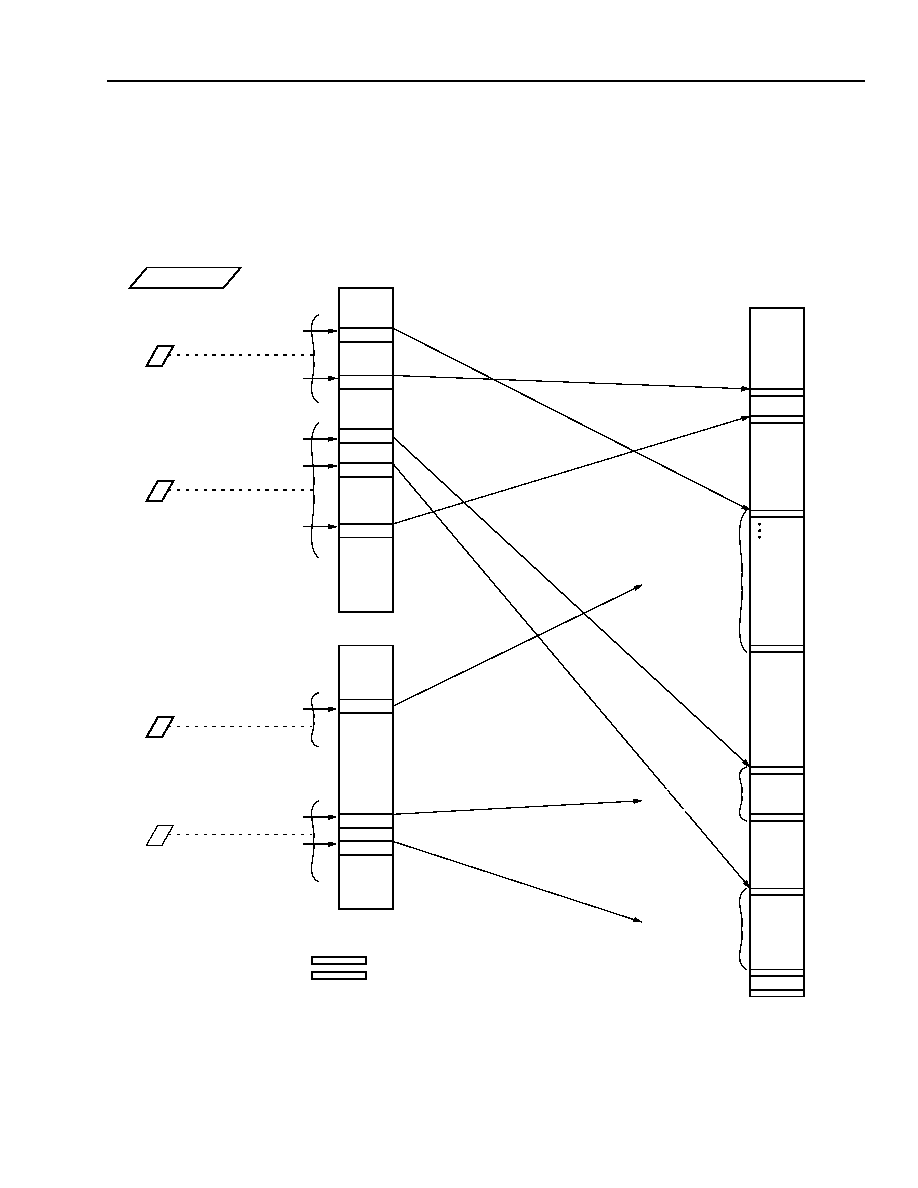

Figure 41.

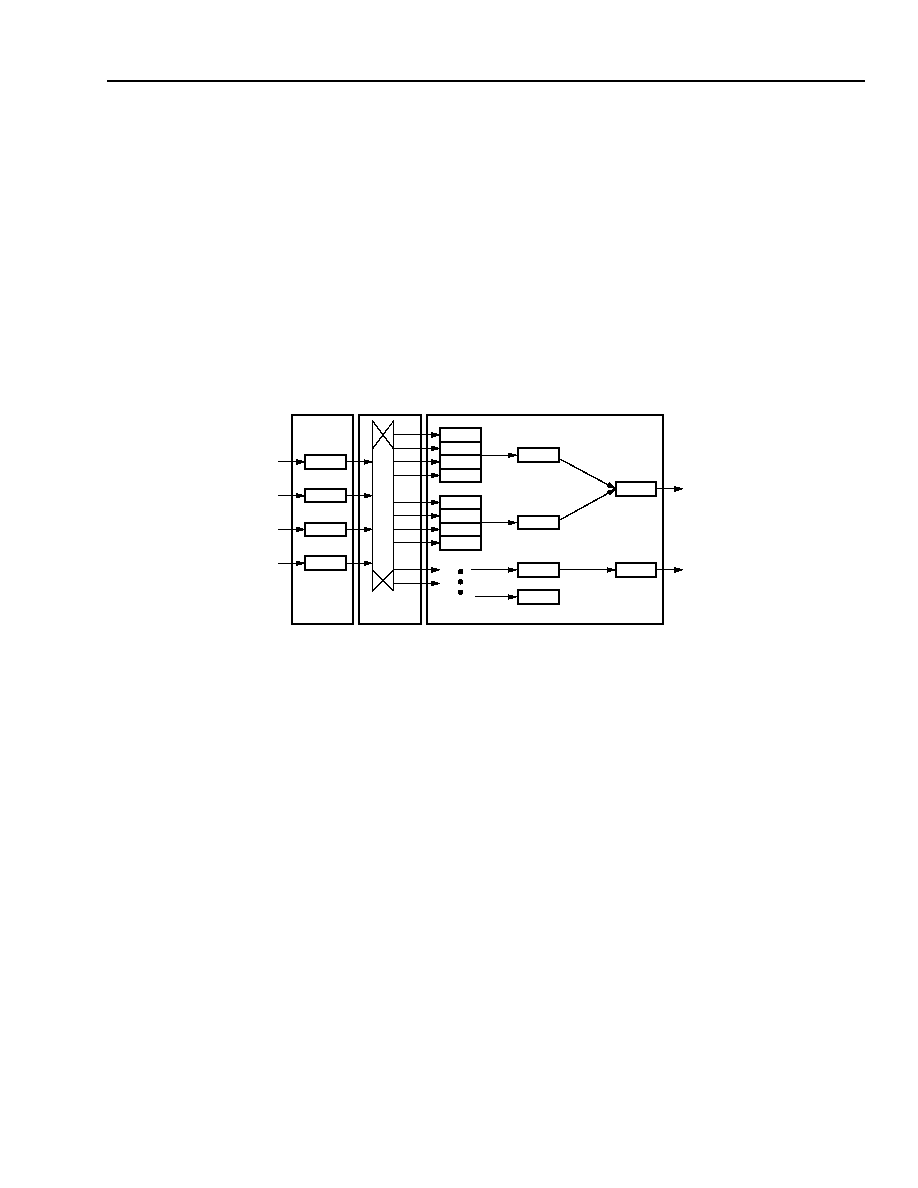

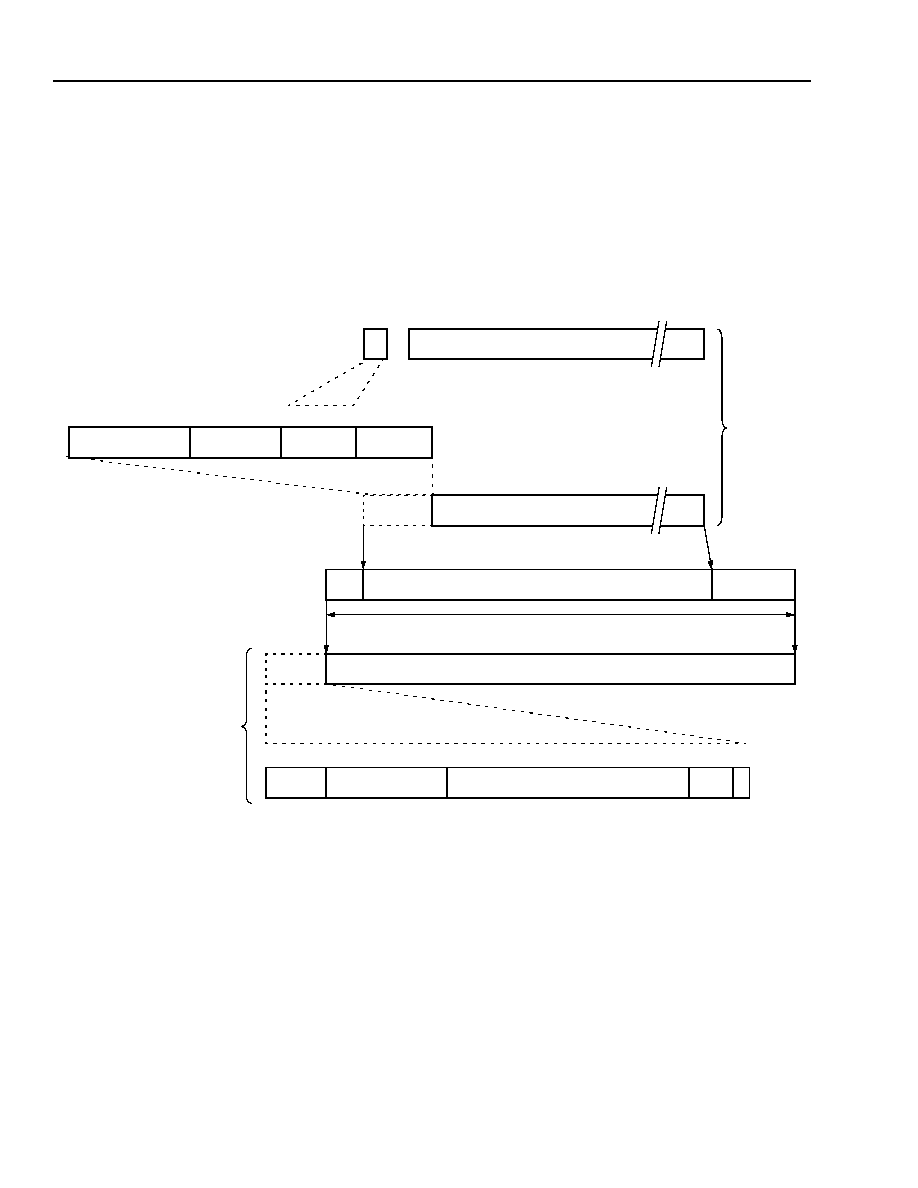

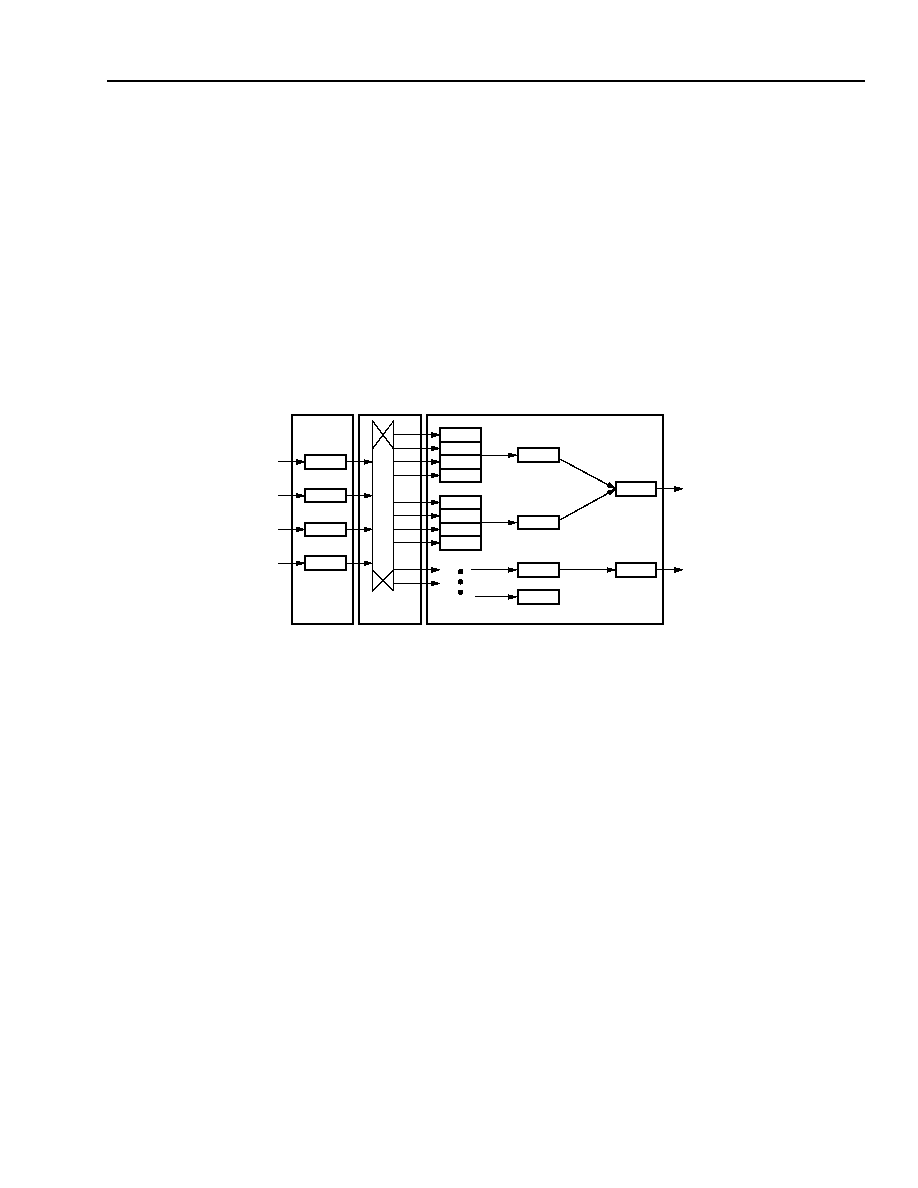

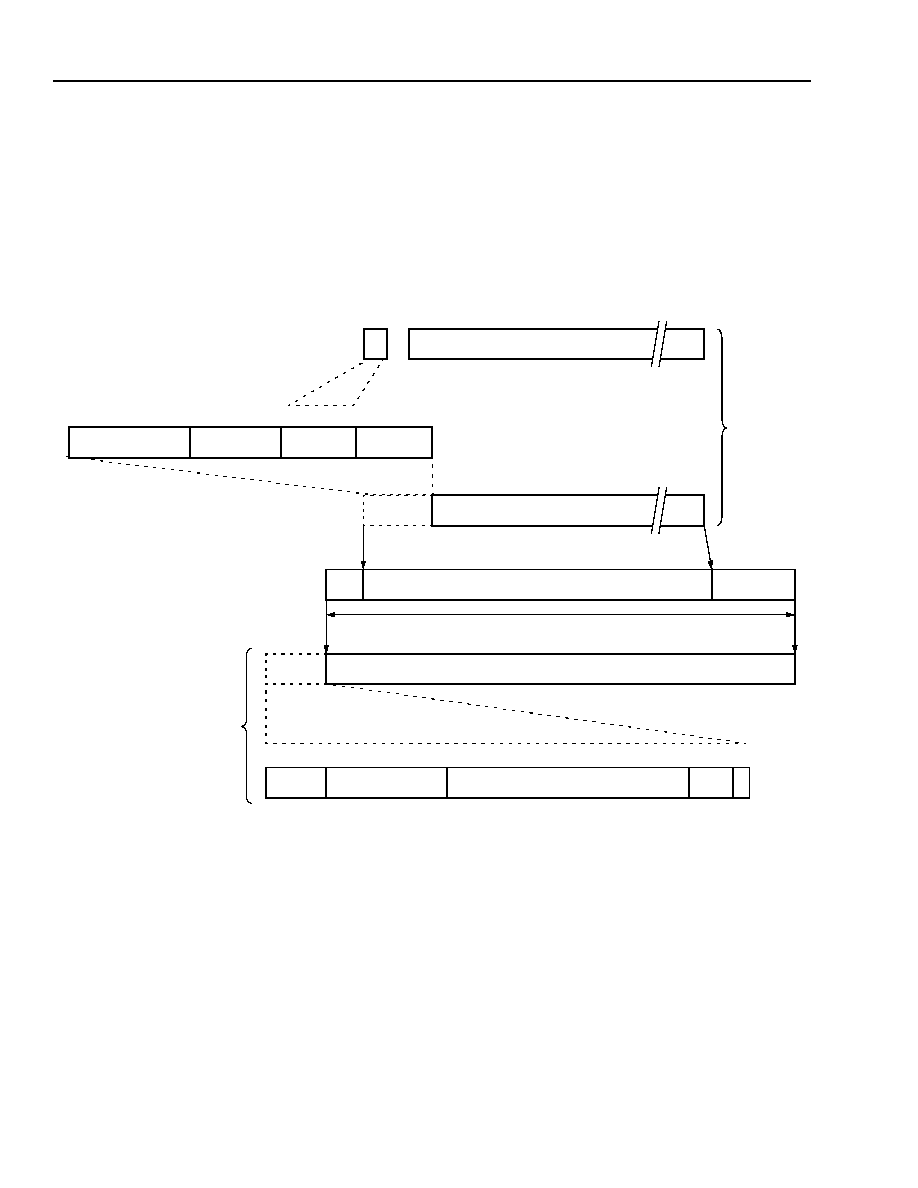

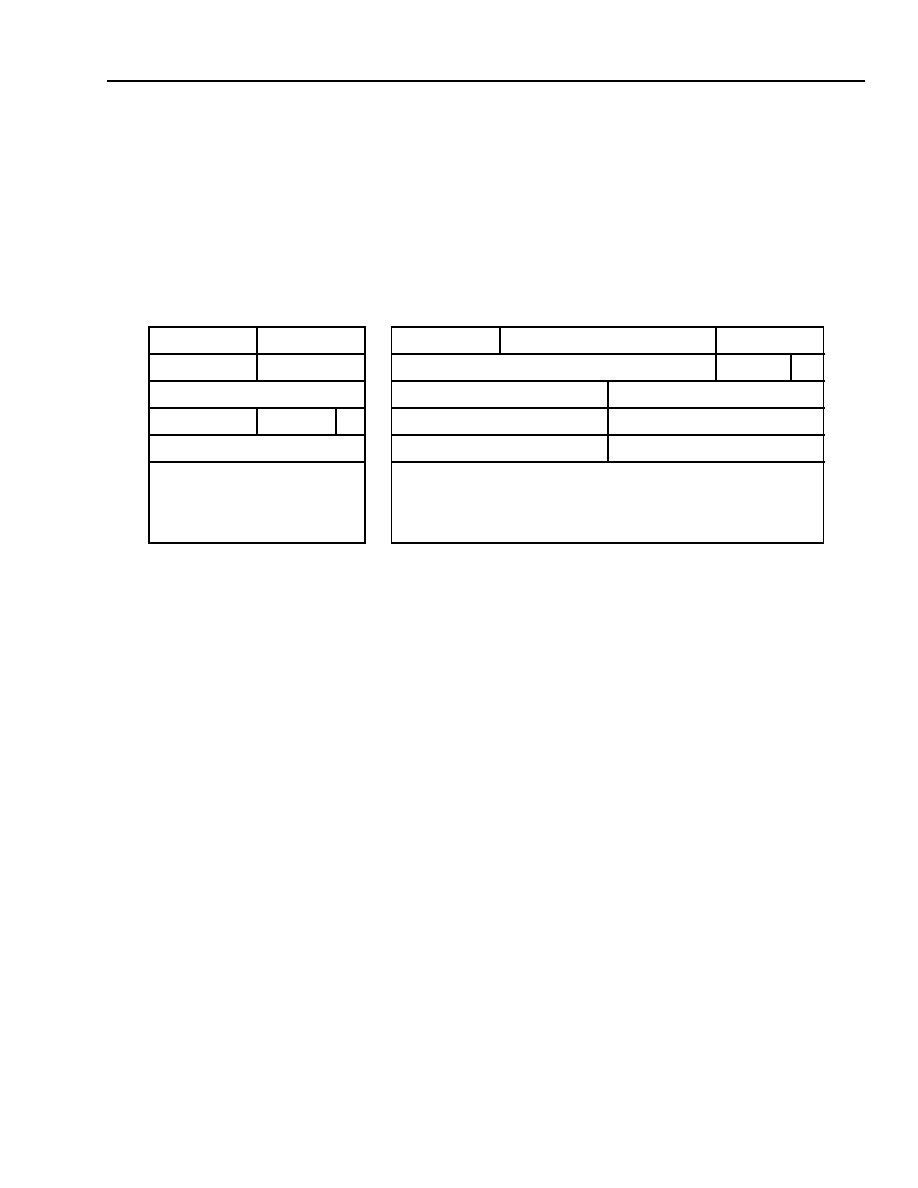

SAR Subblock Diagram...................................................................................................................105

Figure 42.

Logical View of the Enqueue (Left) and Dequeue (Right) Address Translation Procedure.............108

Figure 43.

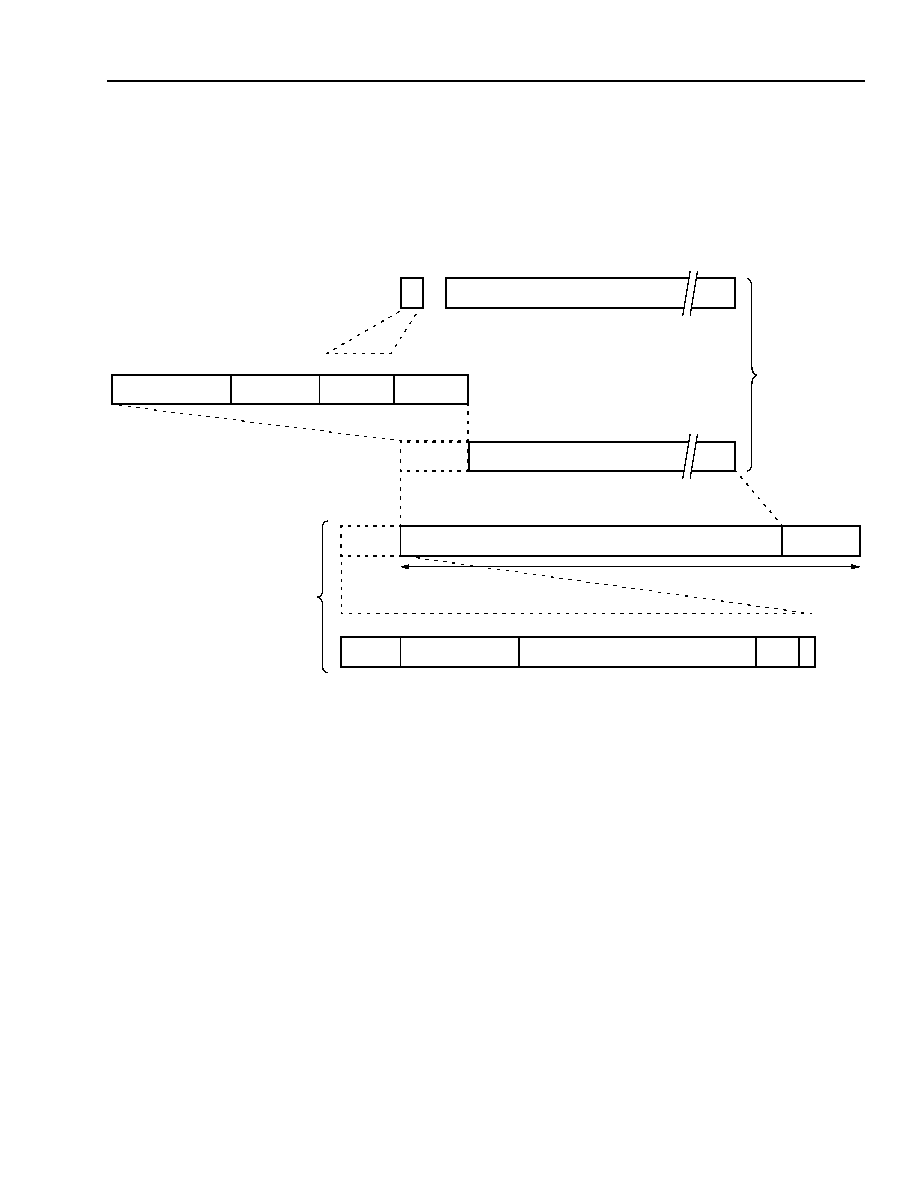

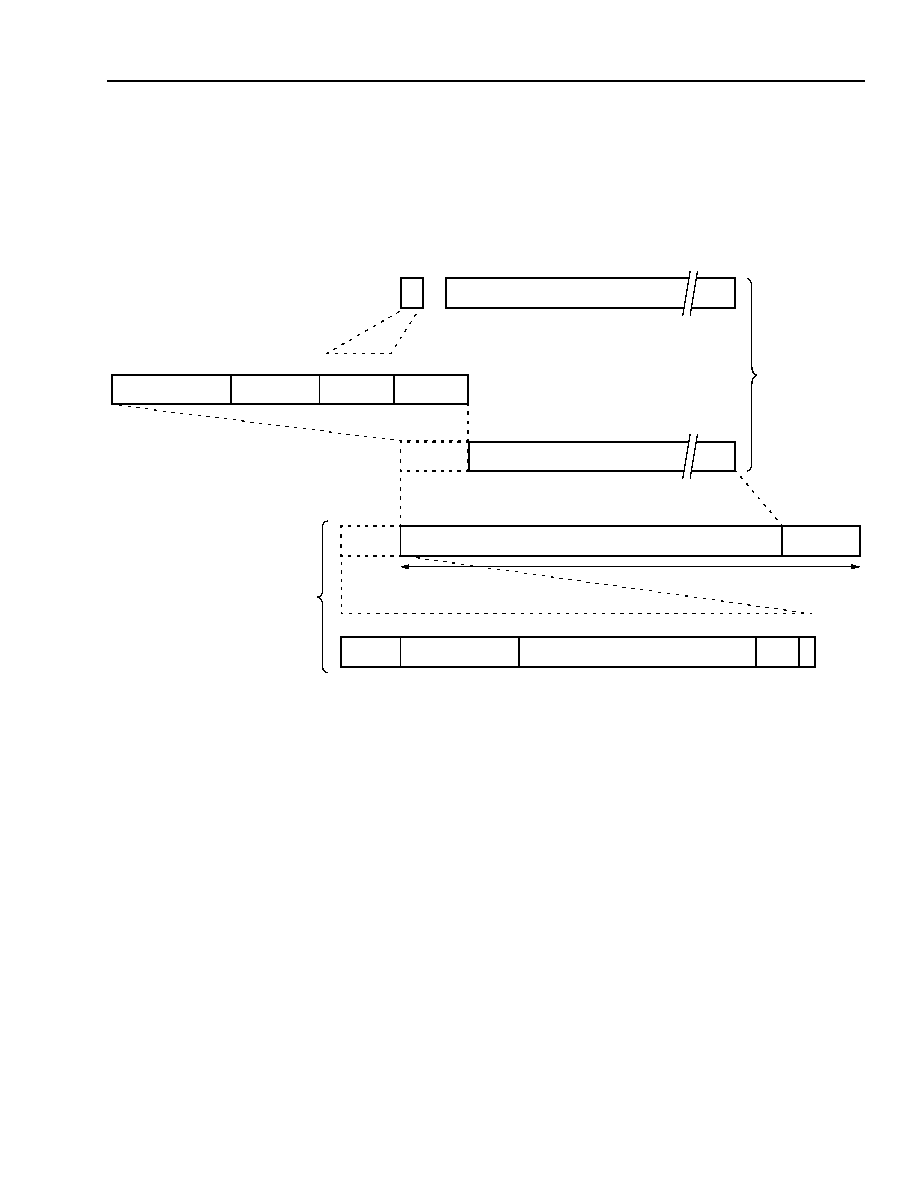

Simplified Diagram of SQASE Queueing Structure.........................................................................109

Figure 44.

User Data Types and AAL Types at the Interfaces .........................................................................110

Figure 45.

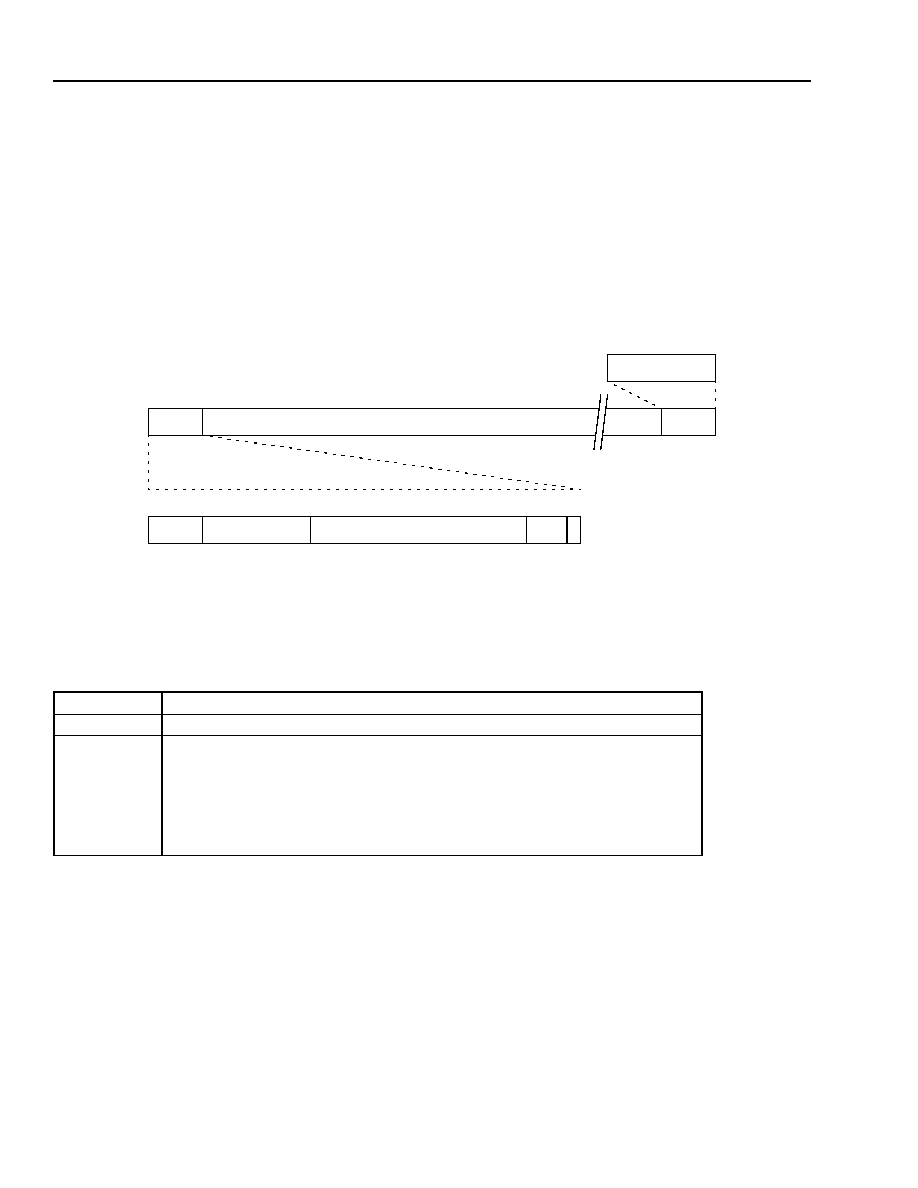

User Data Type (UDT) vs. AAL Type Mapping ...............................................................................111

Figure 46.

SPAAL2 Data Format ......................................................................................................................112

Figure 47.

CPS-AAL0 Data Format ..................................................................................................................113

Figure 48.

PATM Format ..................................................................................................................................114

Figure 49.

HPF Format .....................................................................................................................................115

Figure 50.

Transferring an HPF Packet over the Host Interface Example........................................................118

Figure 51.

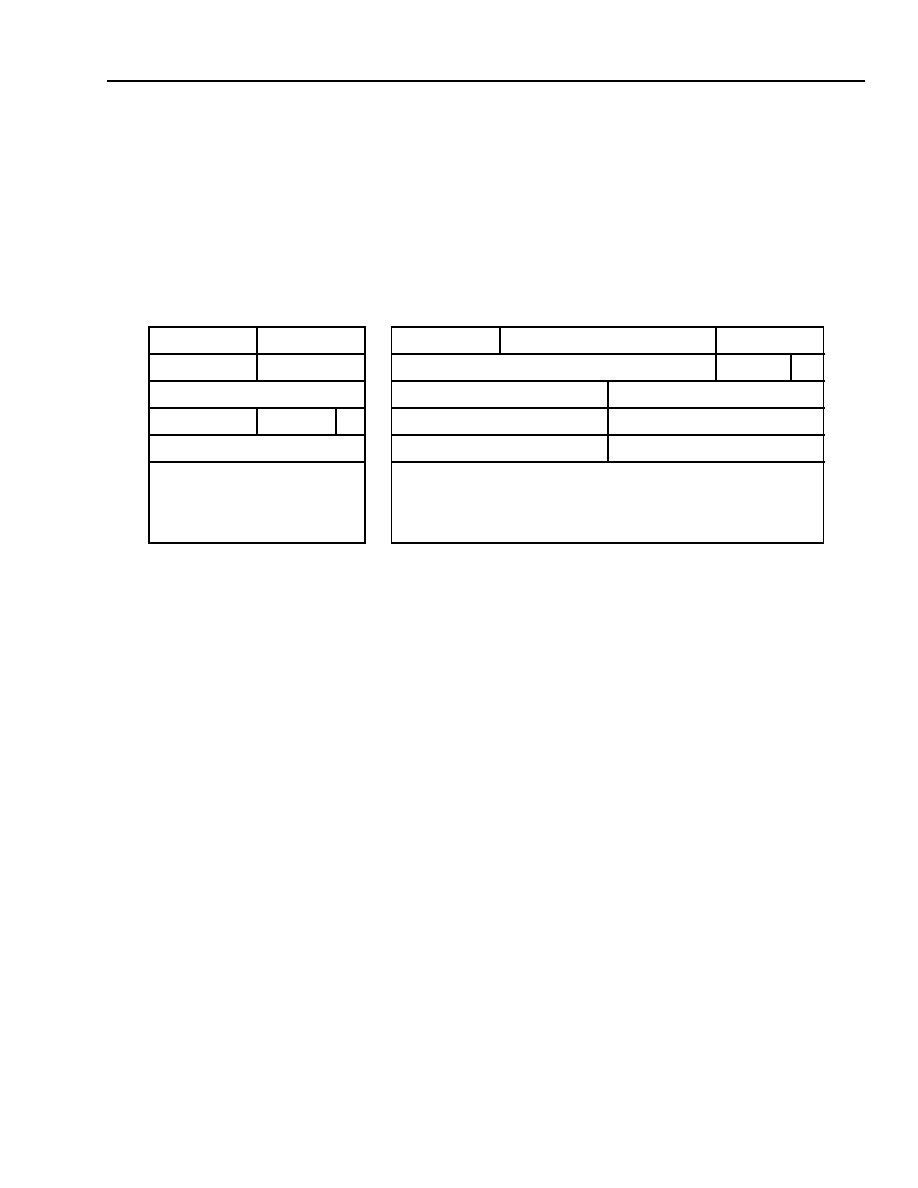

Port Table ........................................................................................................................................123

Figure 52.

VC Table..........................................................................................................................................125

List of Figures

(continued)

TAAD08JU2 Data

Sheet

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

August 18, 2003

Figures

Page

8

Agere Systems - Proprietary

Agere Systems Inc.

Use pursuant to Company instructions

Figure 53.

AAL2 VC Table................................................................................................................................126

Figure 54.

Connection Table ............................................................................................................................127

Figure 55.

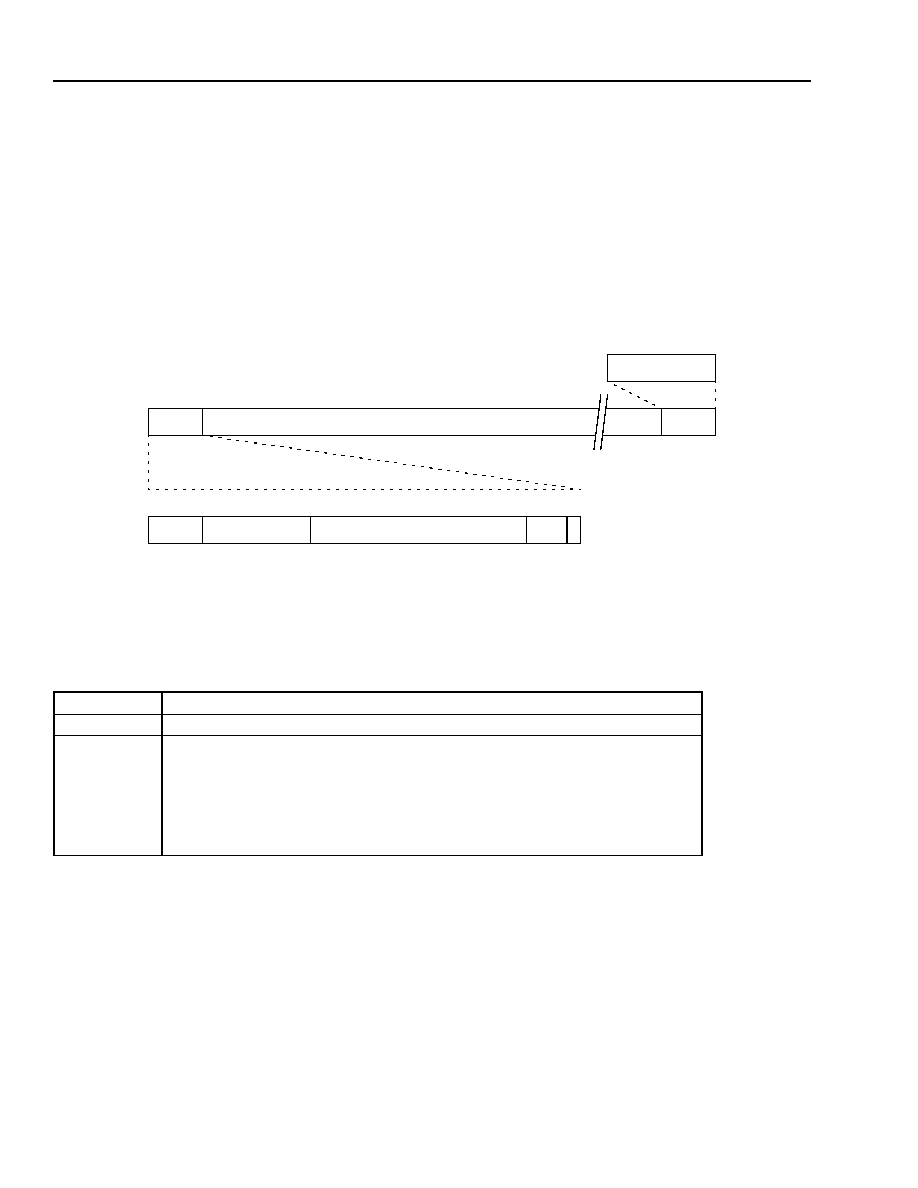

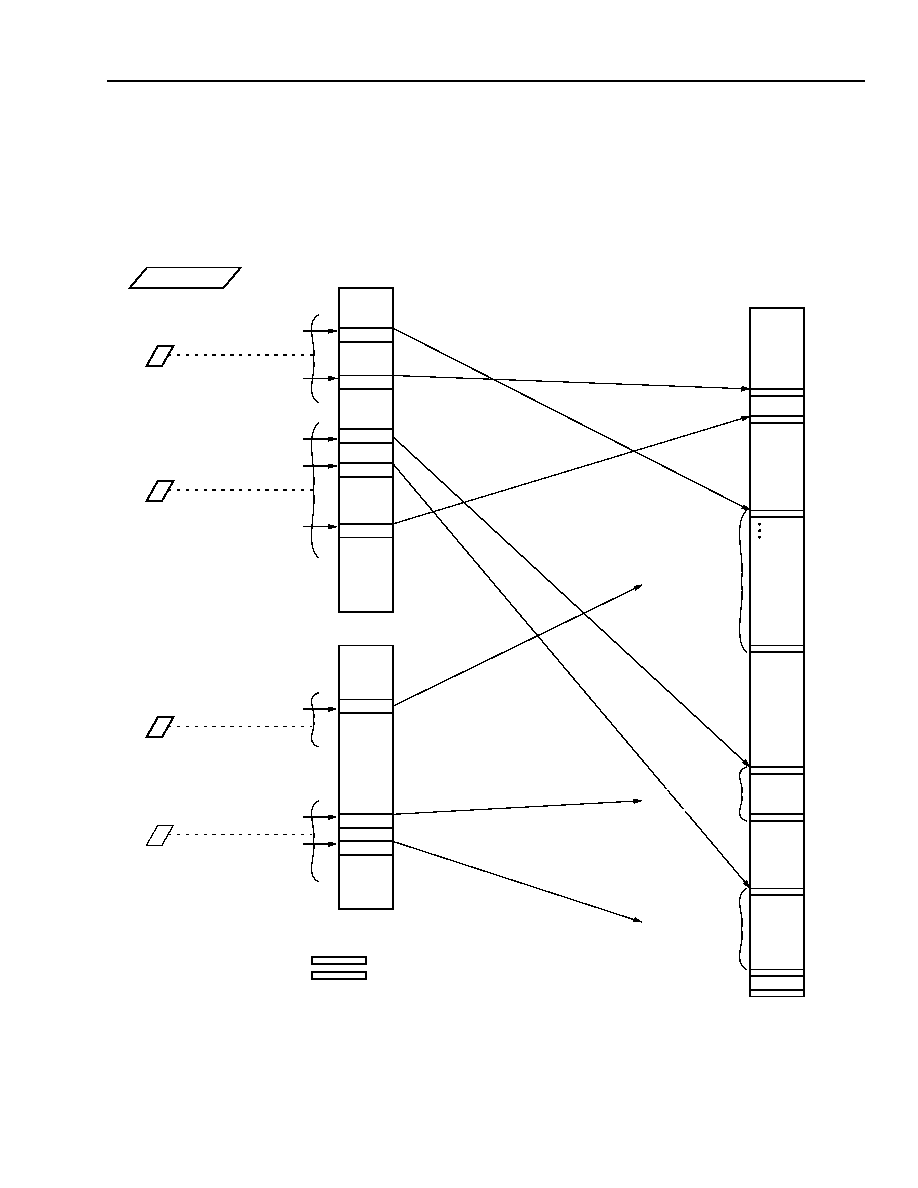

SQASE Queueing Structure ............................................................................................................131

Figure 56.

Connection Queue Length Policing .................................................................................................138

Figure 57.

IL1Q/L1Q Length Policing ...............................................................................................................139

Figure 58.

IL2Q Length Policing .......................................................................................................................140

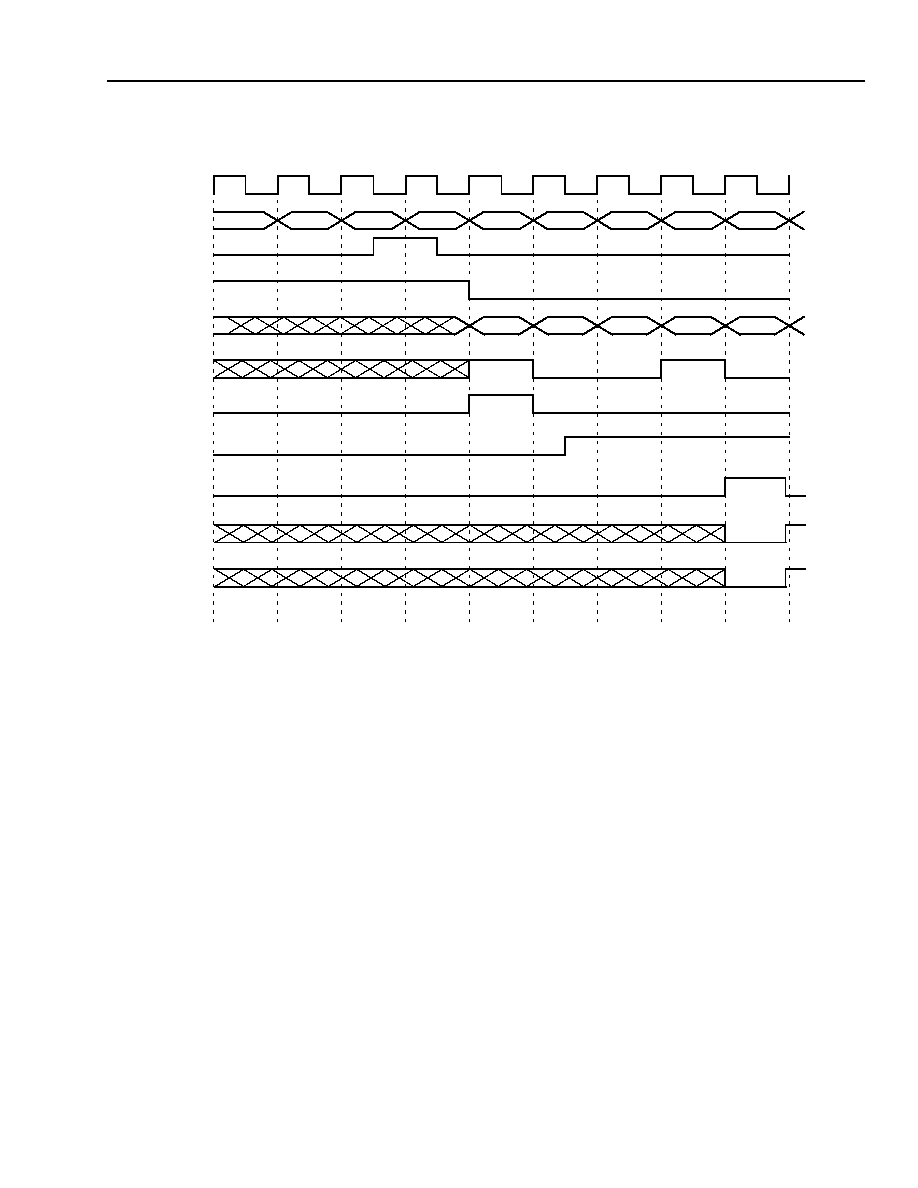

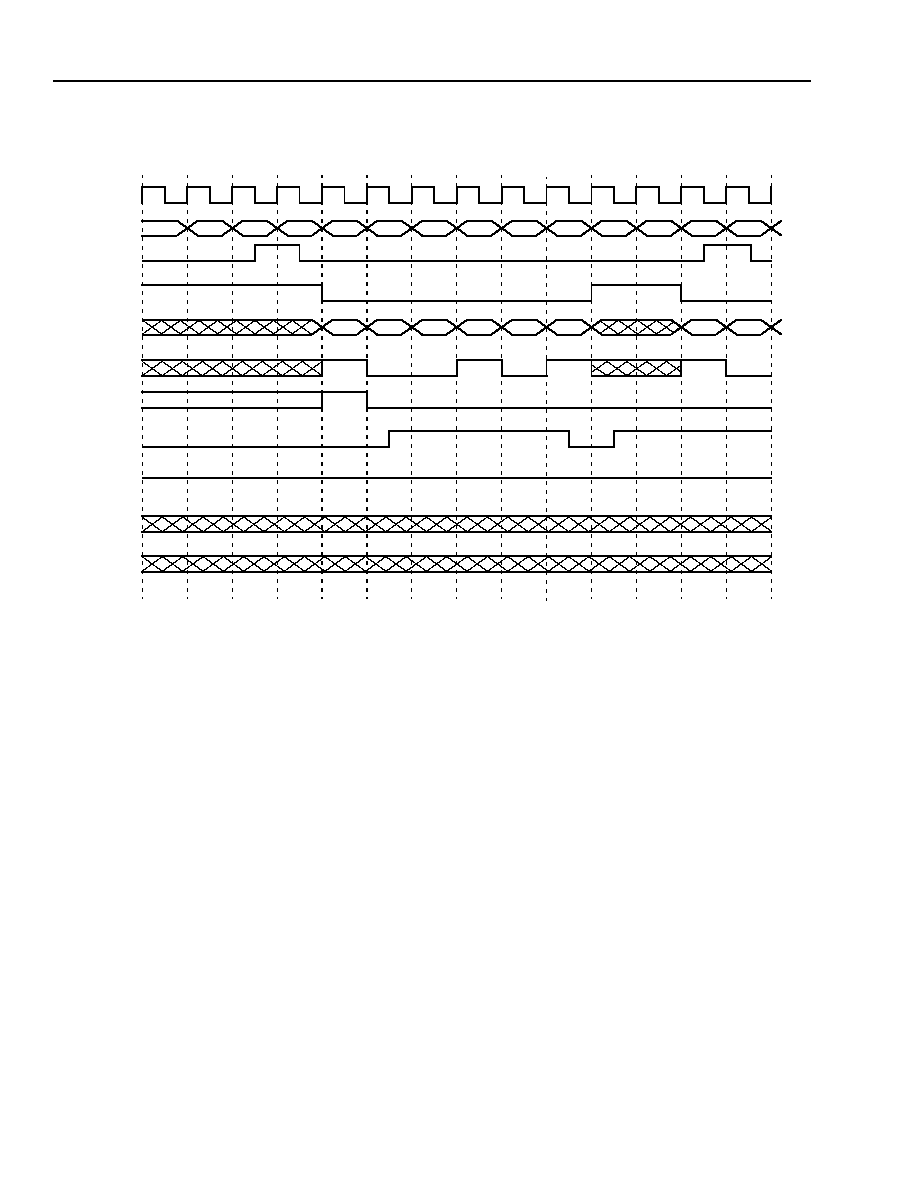

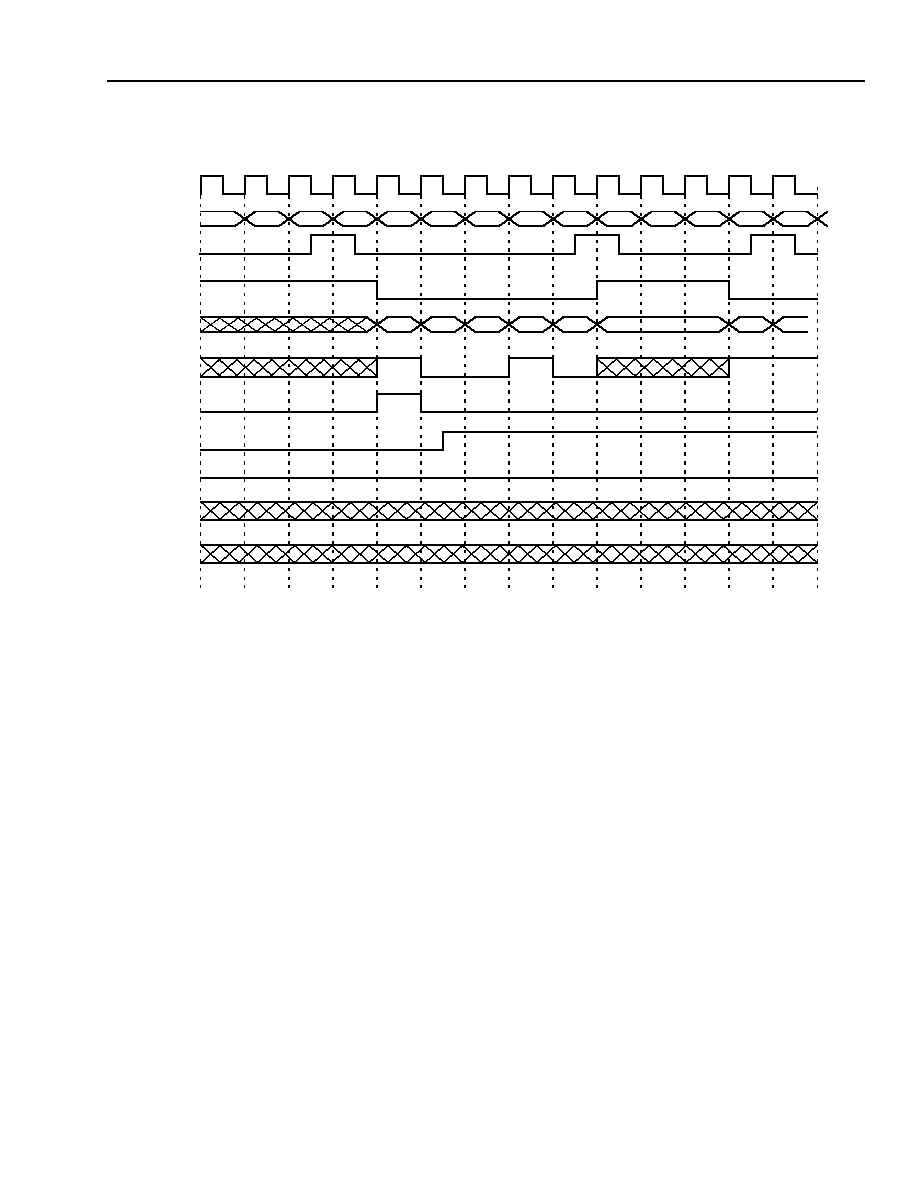

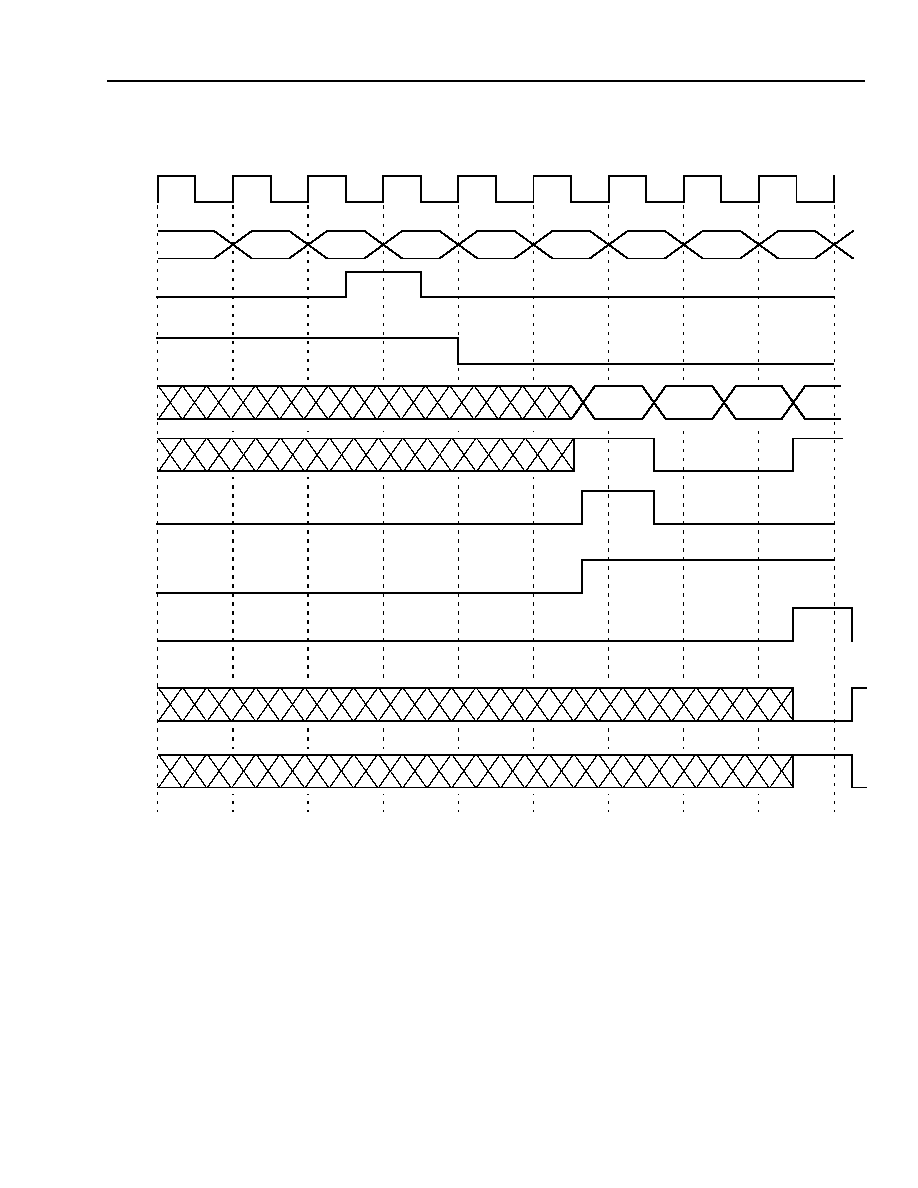

Figure 59.

UT2/UT2+ Header at the SIF Interface ...........................................................................................143

Figure 60.

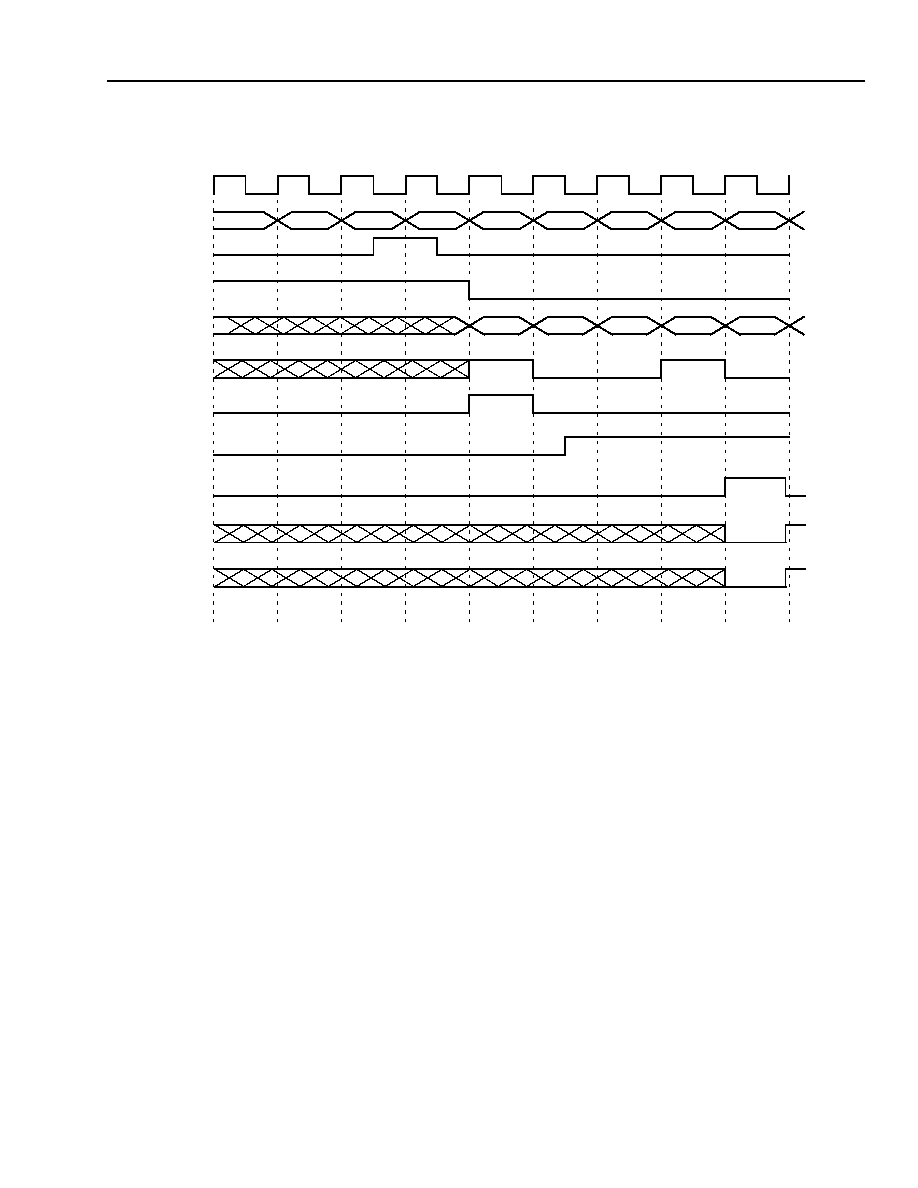

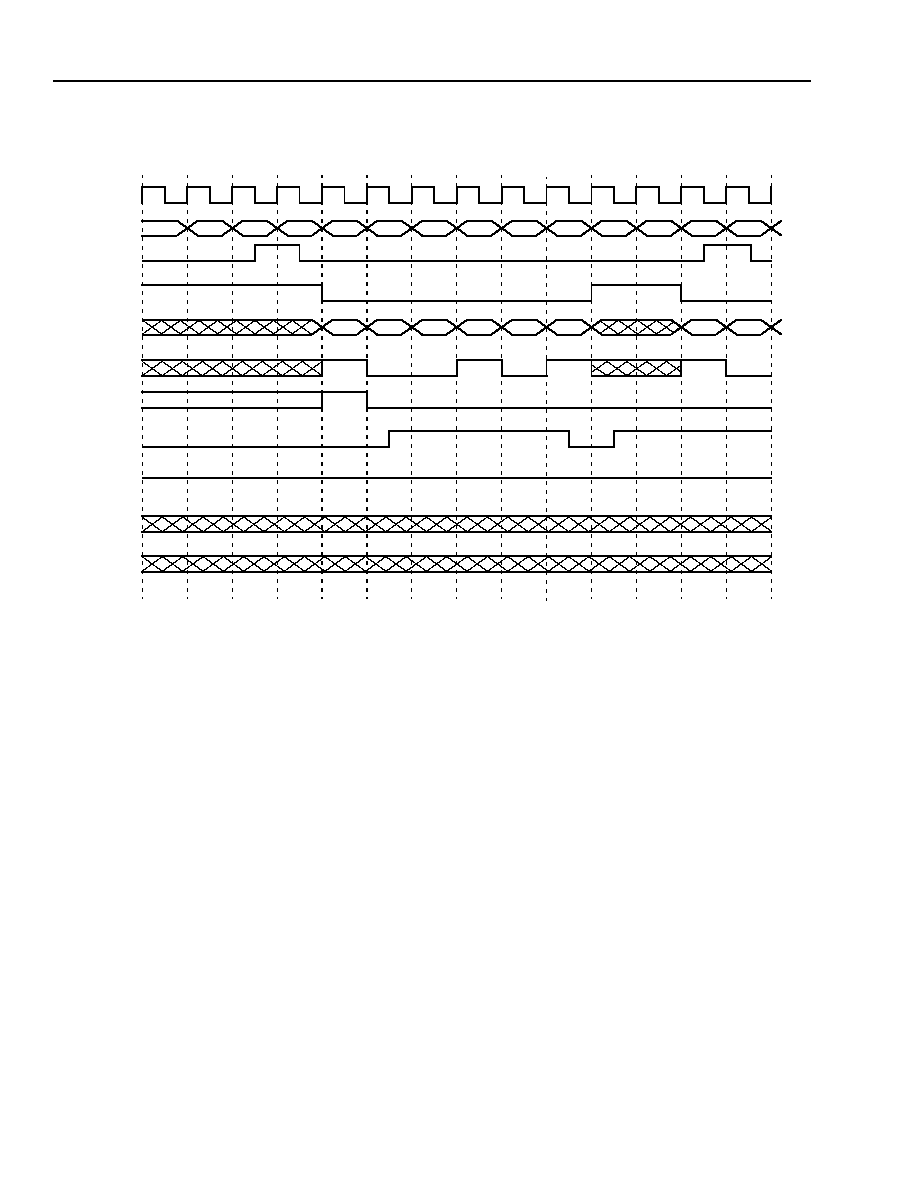

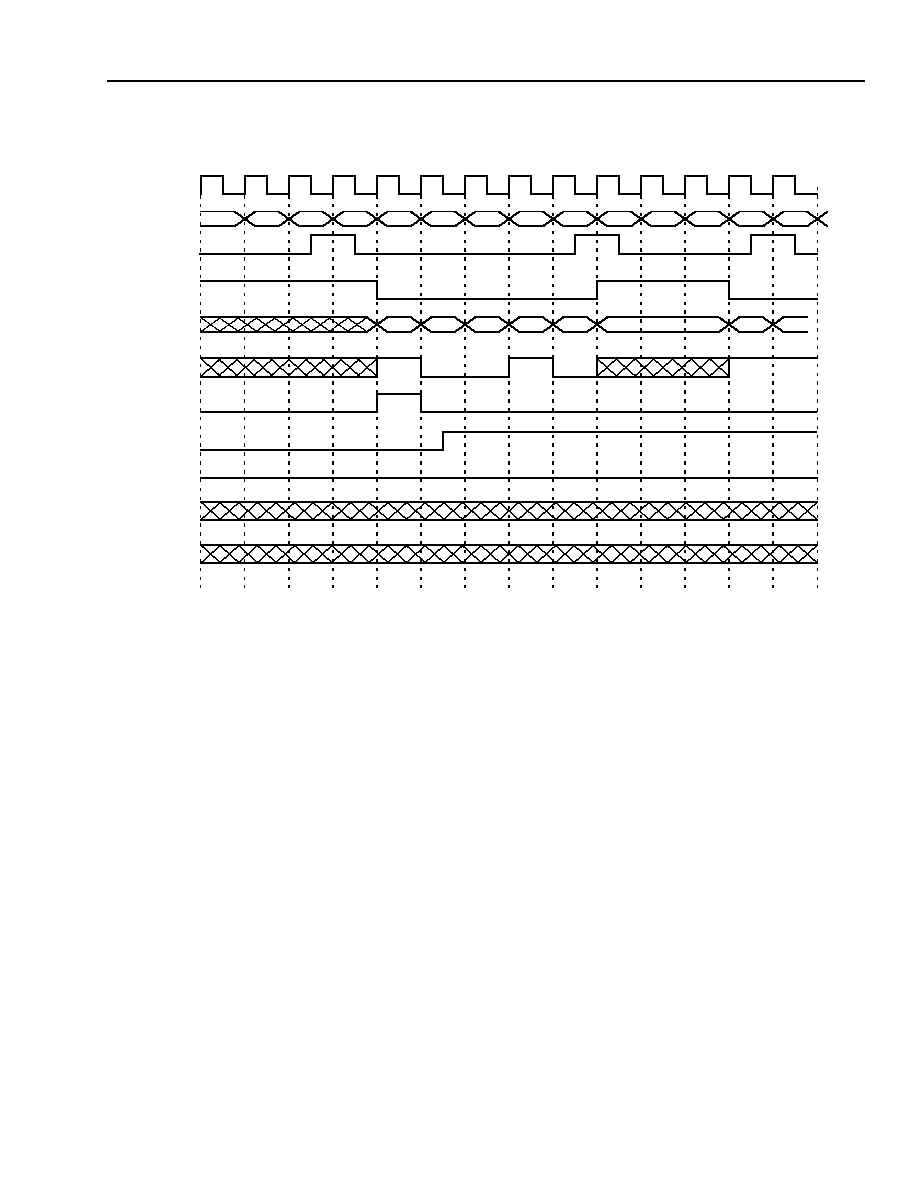

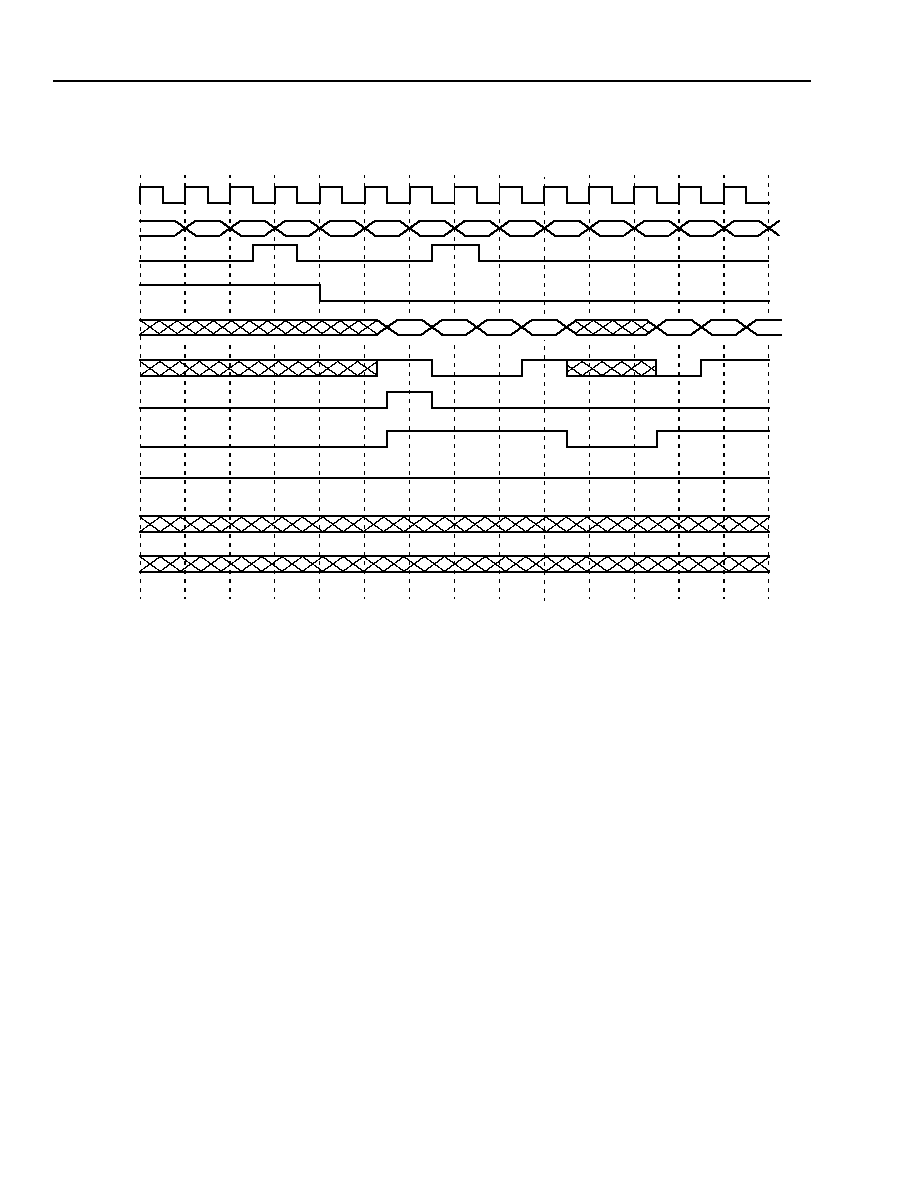

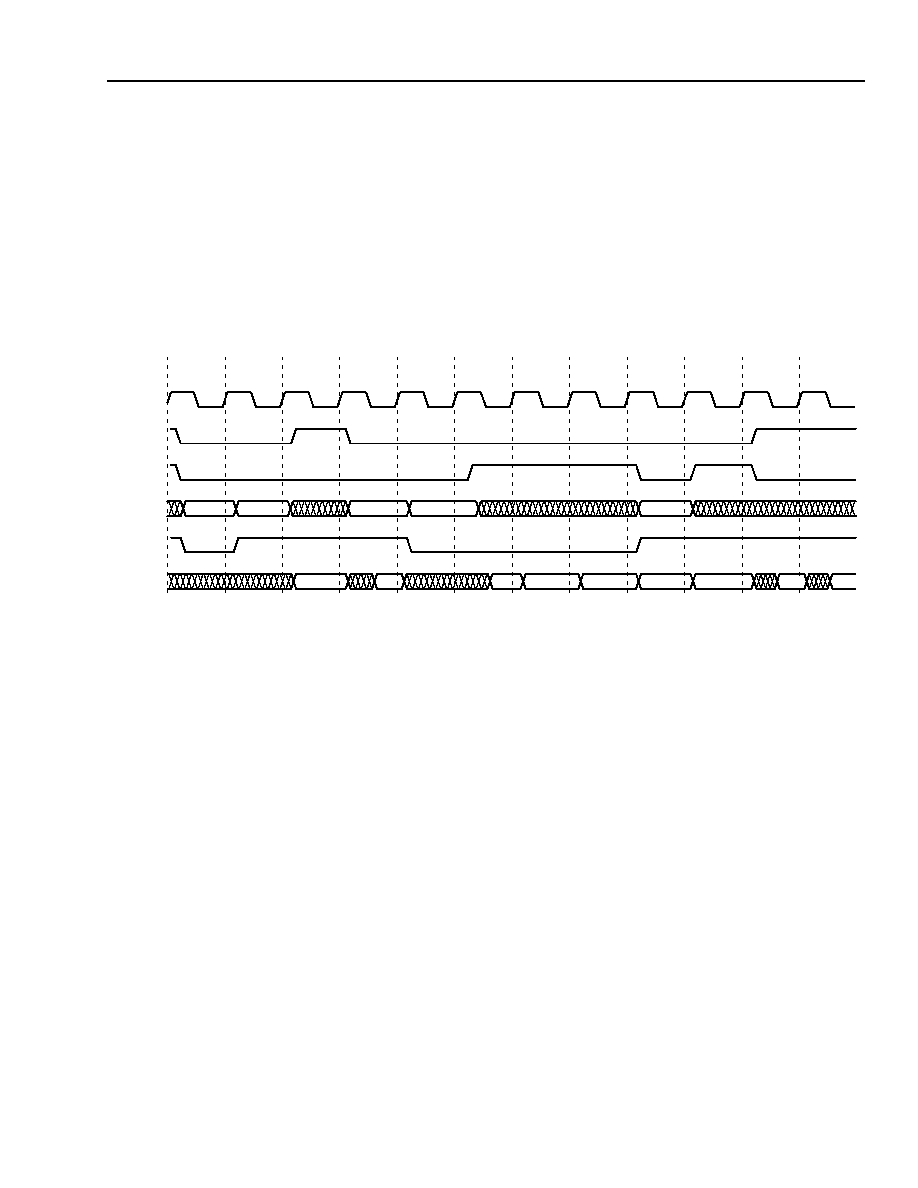

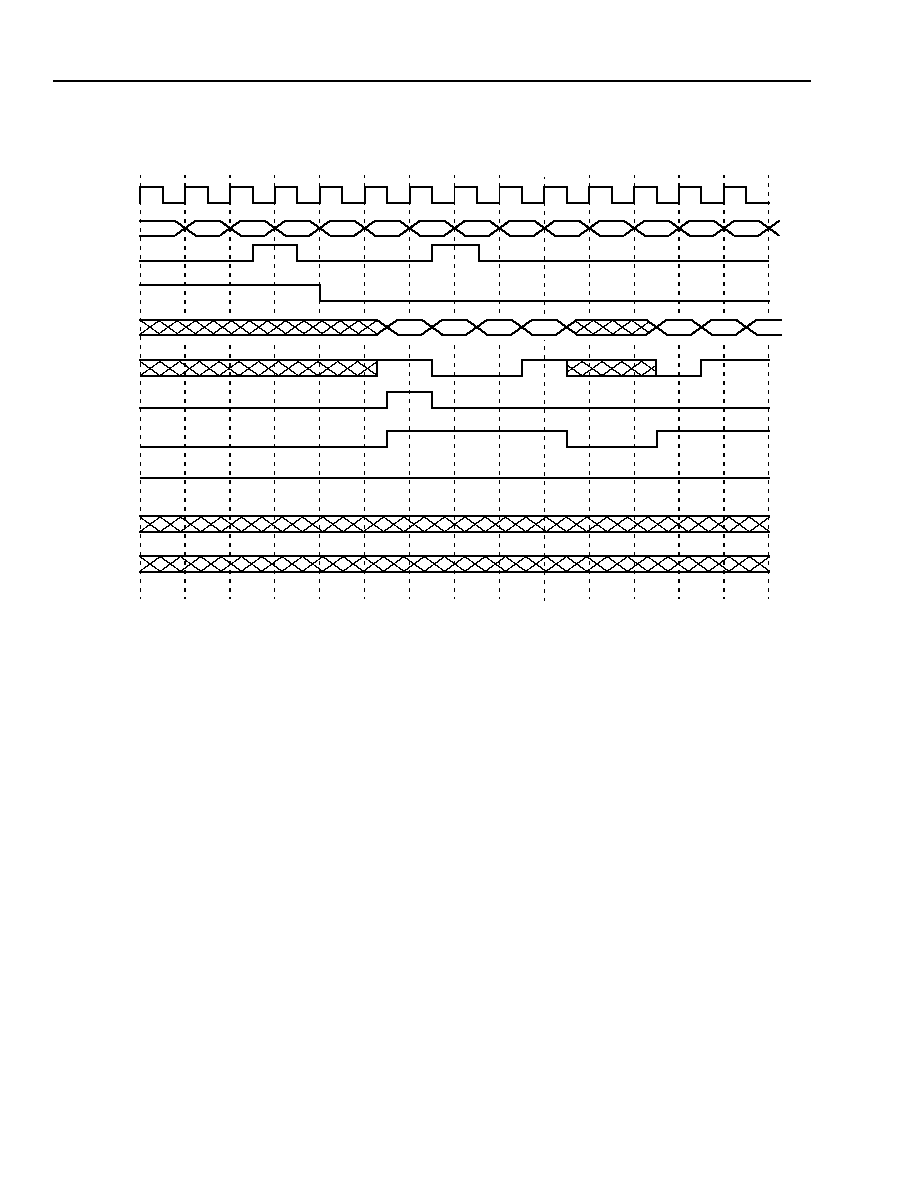

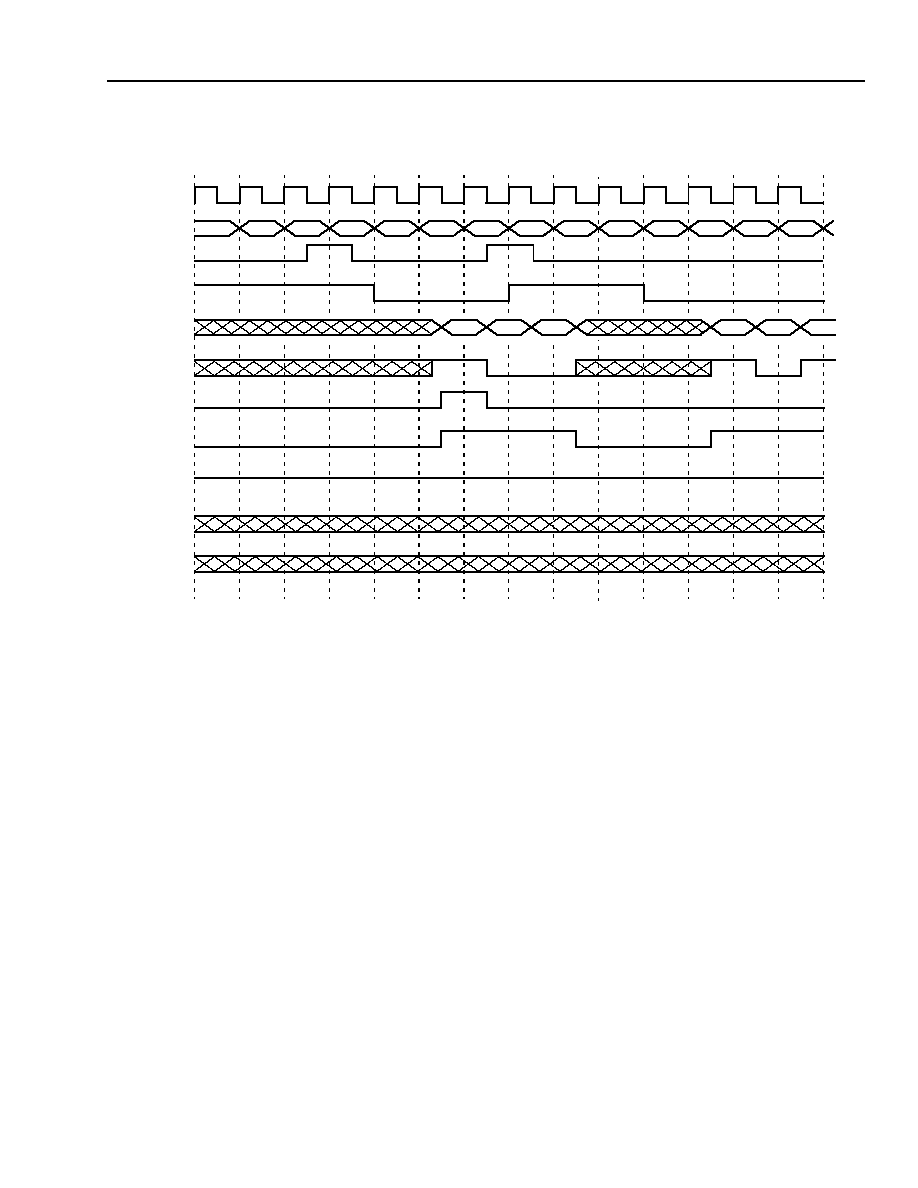

Cell Transmission on the SIF Interface ...........................................................................................144

Figure 61.

Packet Transmission on the SIF Interface with No Stalls................................................................145

Figure 62.

Packet Transmission on the SIF Interface with the PHY Stalling ....................................................146

Figure 63.

Packet Transmission on the SIF Interface with the Master Stalling ................................................147

Figure 64.

Reception of a Cell on the SIF Interface..........................................................................................148

Figure 65.

Reception of a Packet on the SIF Interface with No Stalls ..............................................................149

Figure 66.

Reception of a Packet on the SIF Interface with the PHY Stalling ..................................................150

Figure 67.

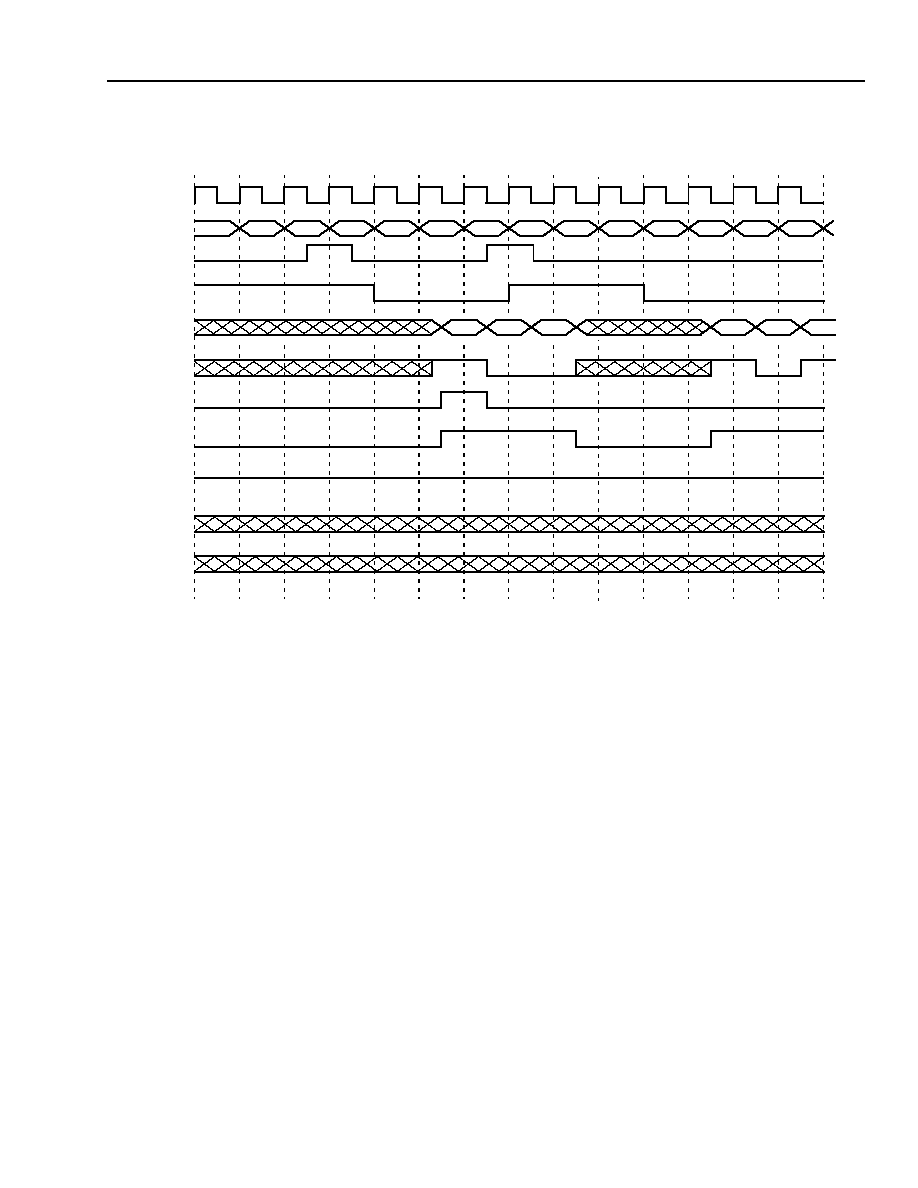

Reception of a Packet on the SIF Interface with the Master Stalling...............................................151

Figure 68.

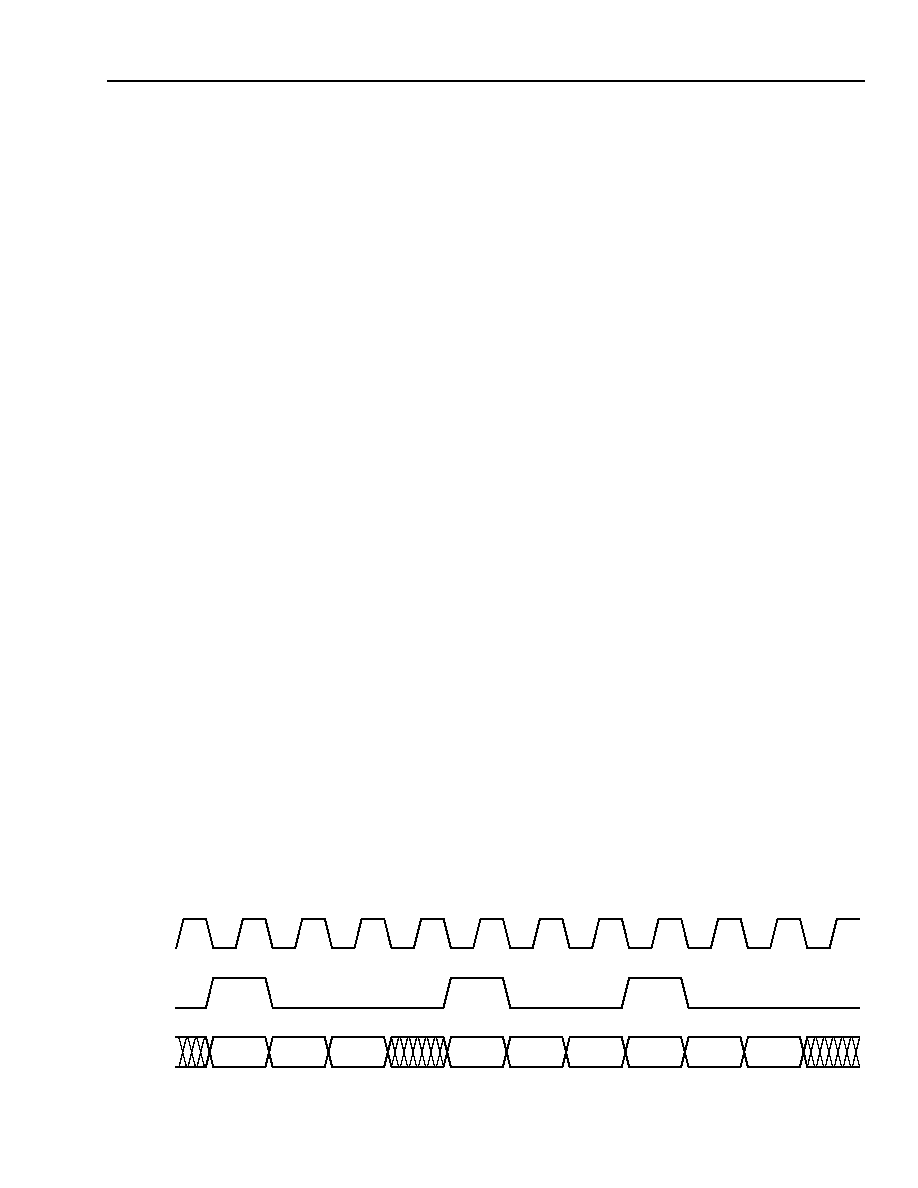

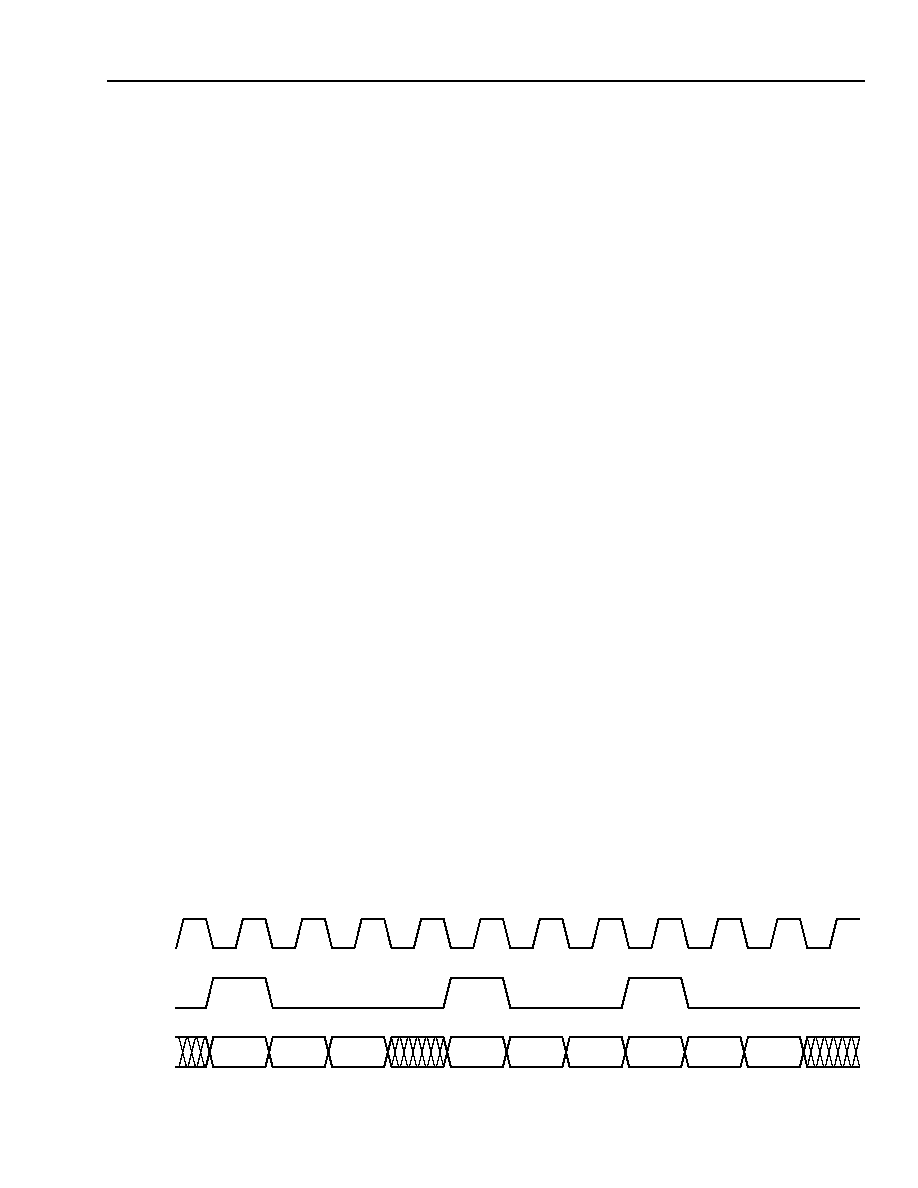

ESI Functional Timing Diagram.......................................................................................................153

Figure 69.

Data Read from TAAD08JU21 ........................................................................................................158

Figure 70.

Data Written to TAAD08JU2............................................................................................................159

Figure 71.

Power-On Reset ..............................................................................................................................160

Figure 72.

Stable Reset ....................................................................................................................................160

Figure 73.

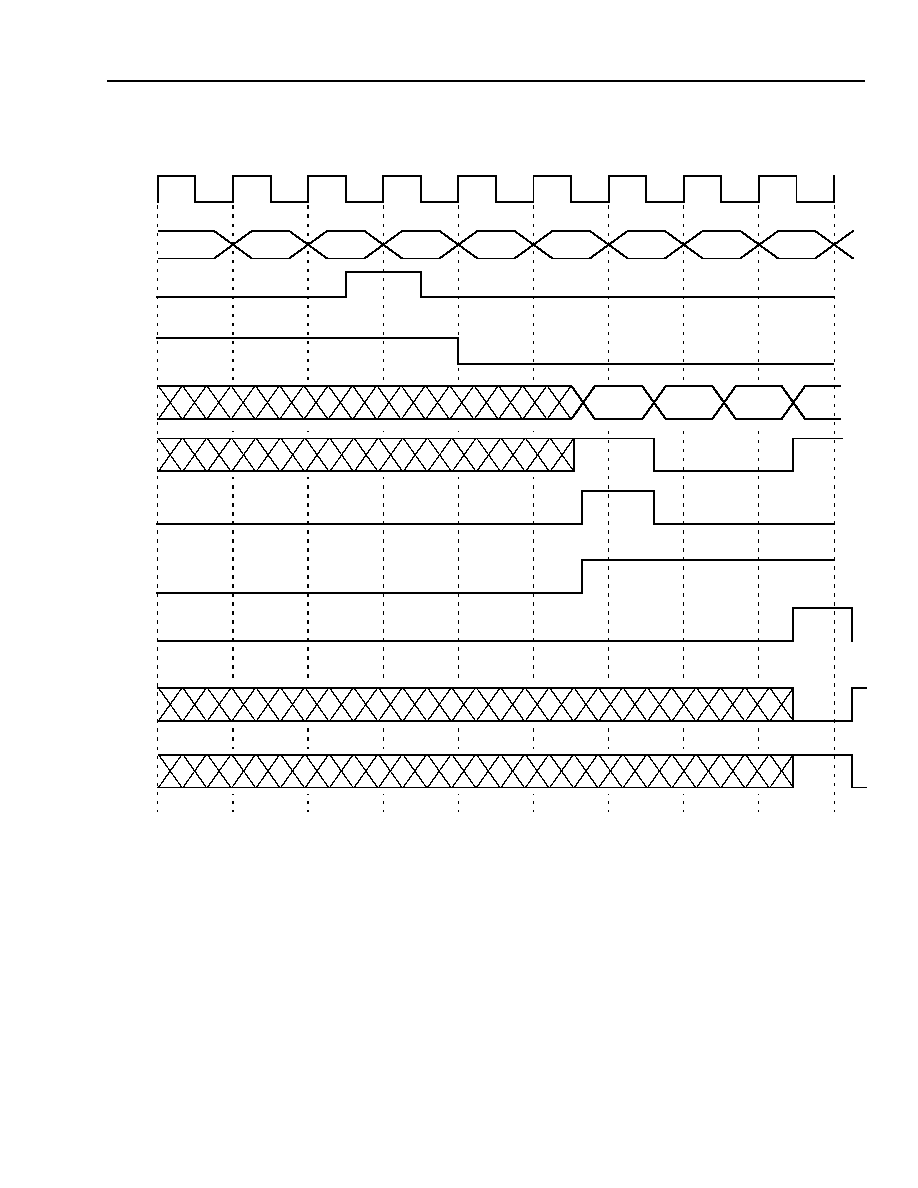

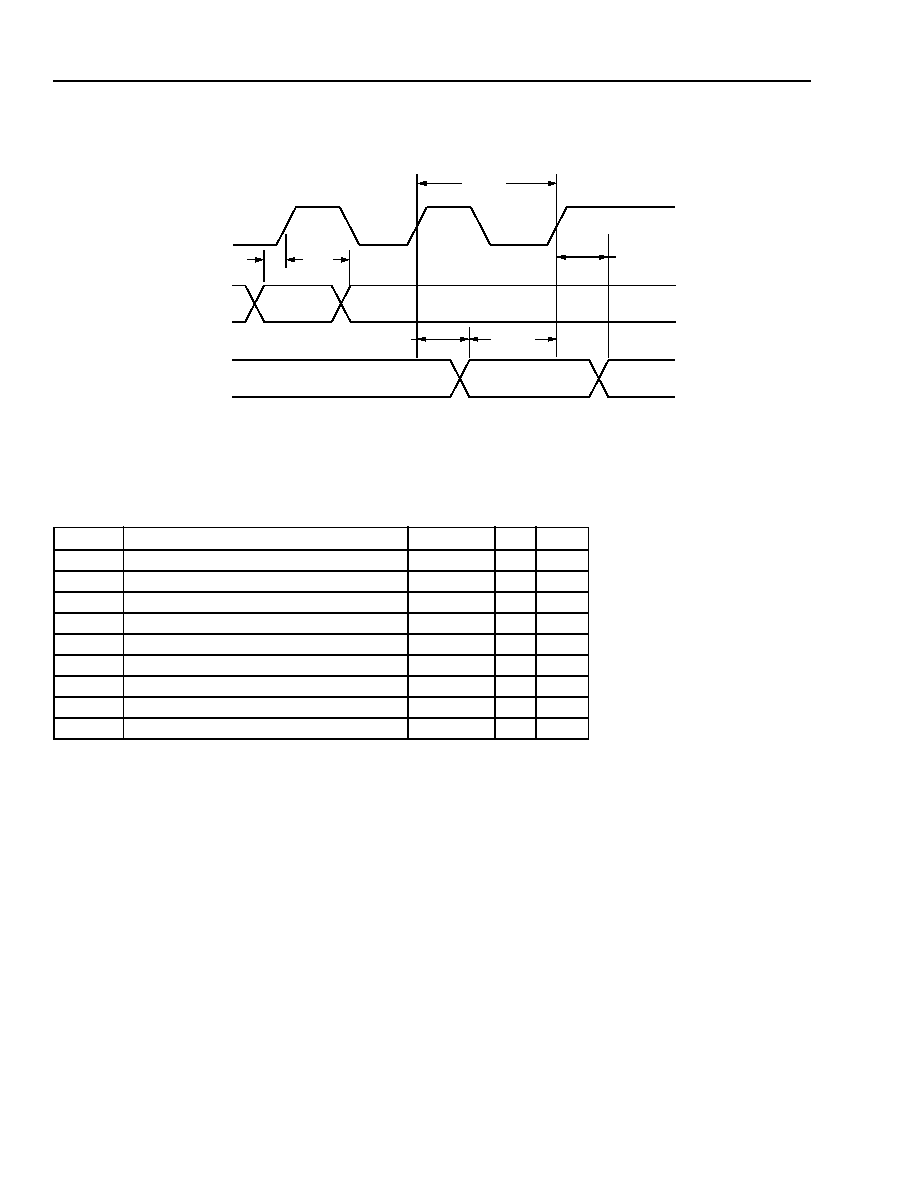

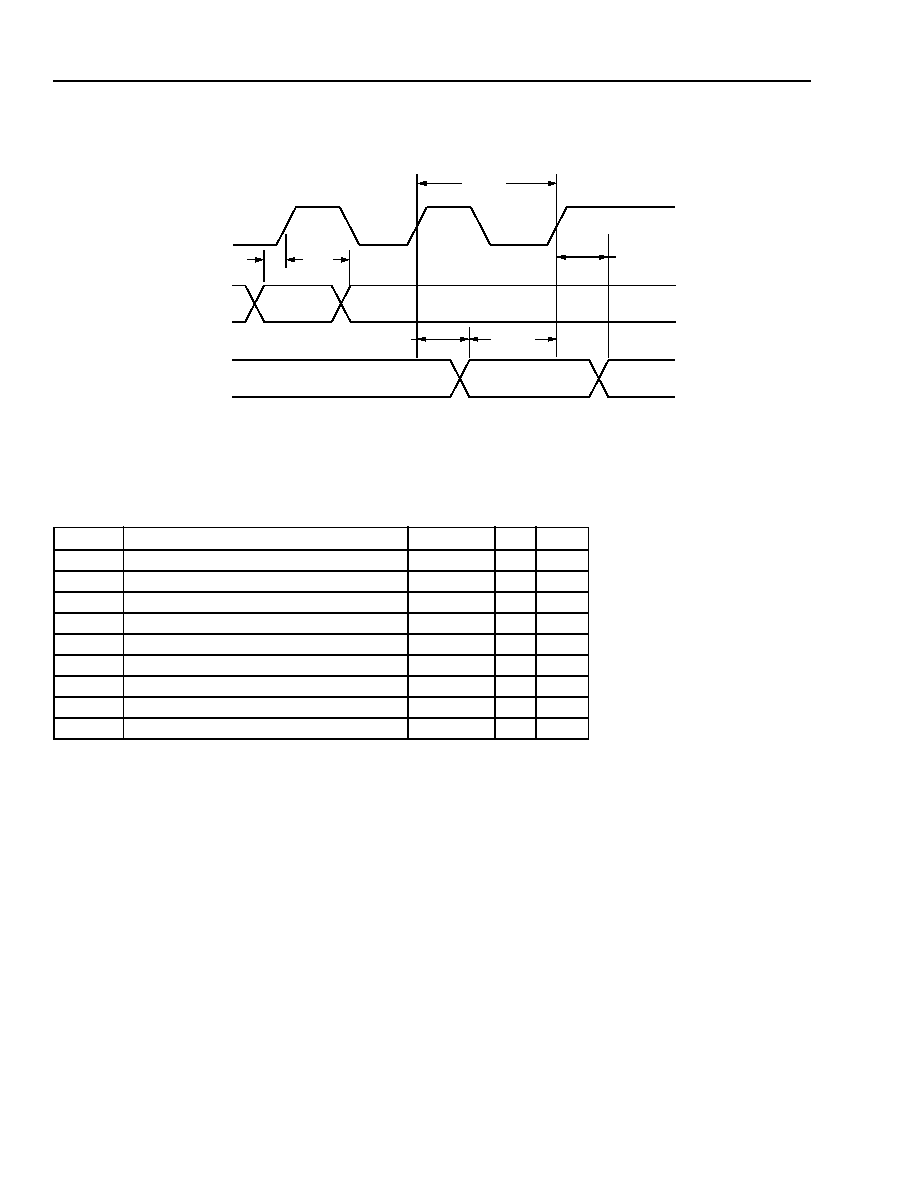

CHI Transmit I/O Timing..................................................................................................................161

Figure 74.

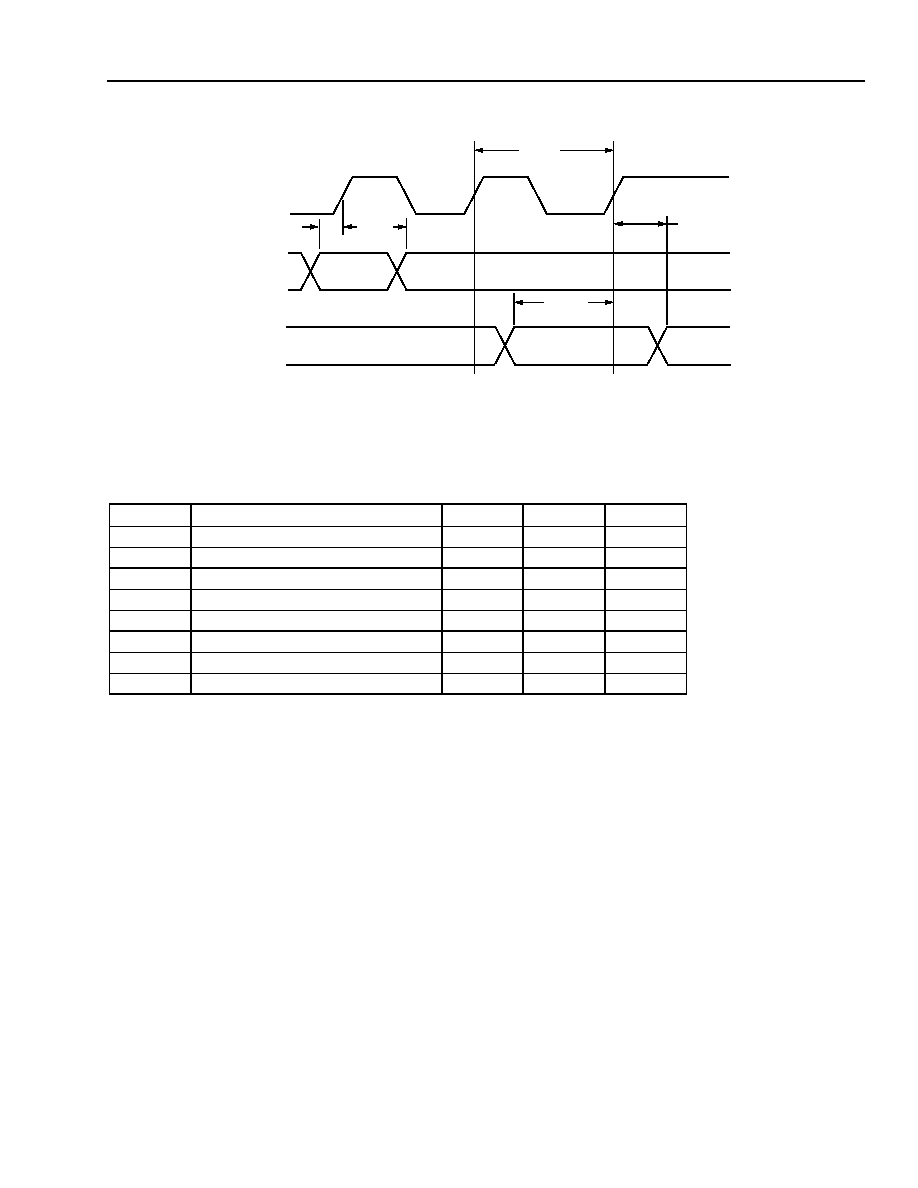

CHI Receive I/O Timing...................................................................................................................162

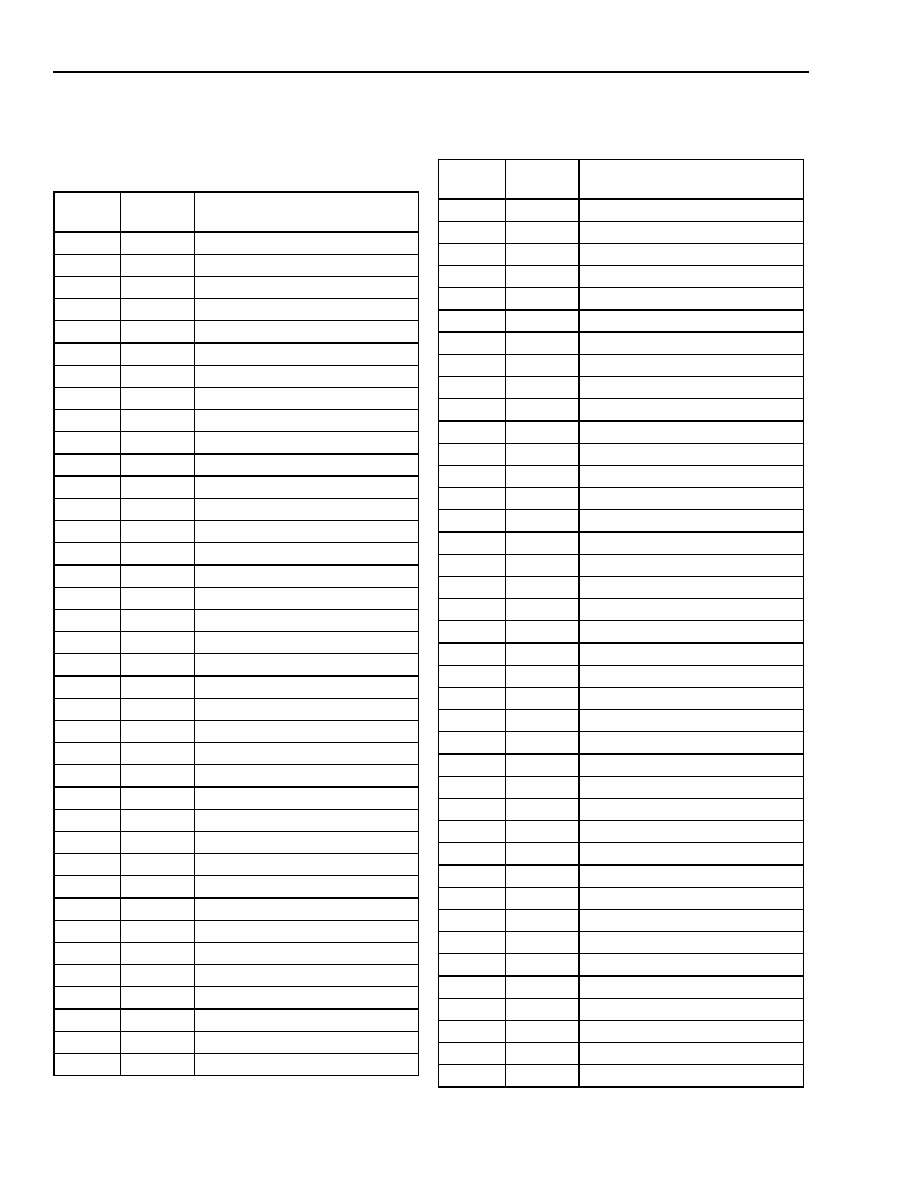

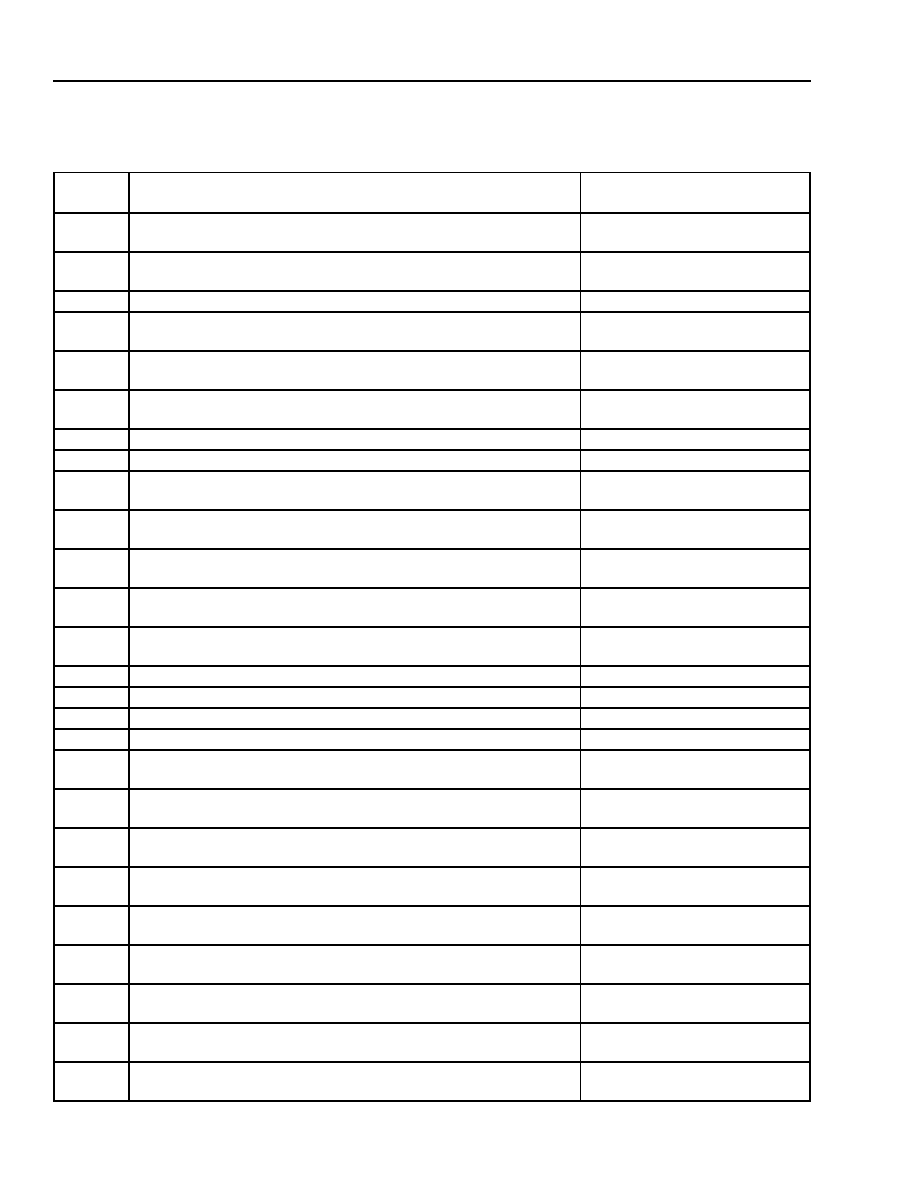

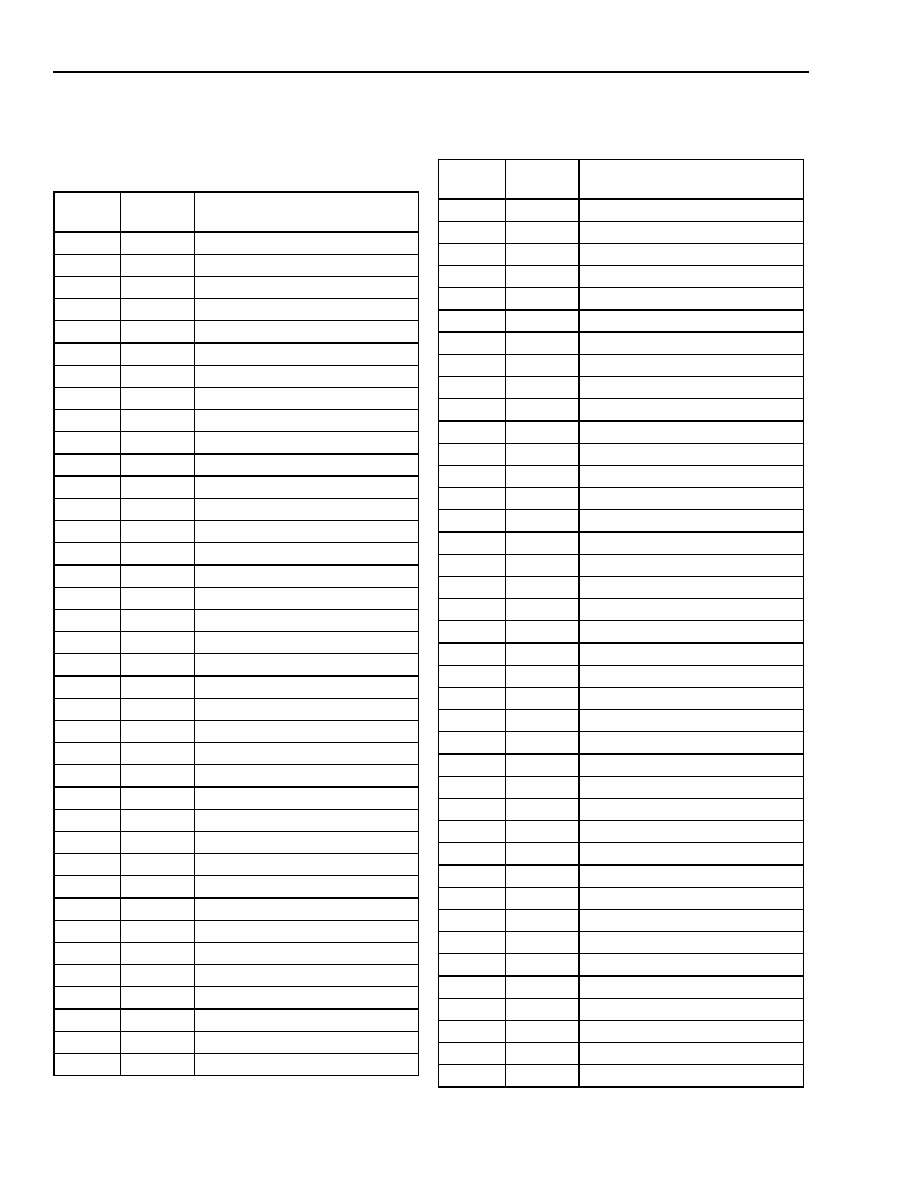

List of Tables

Table

Page

Agere Systems Inc.

Agere Systems - Proprietary

9

Use pursuant to Company instructions

Data Sheet

TAAD08JU2

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

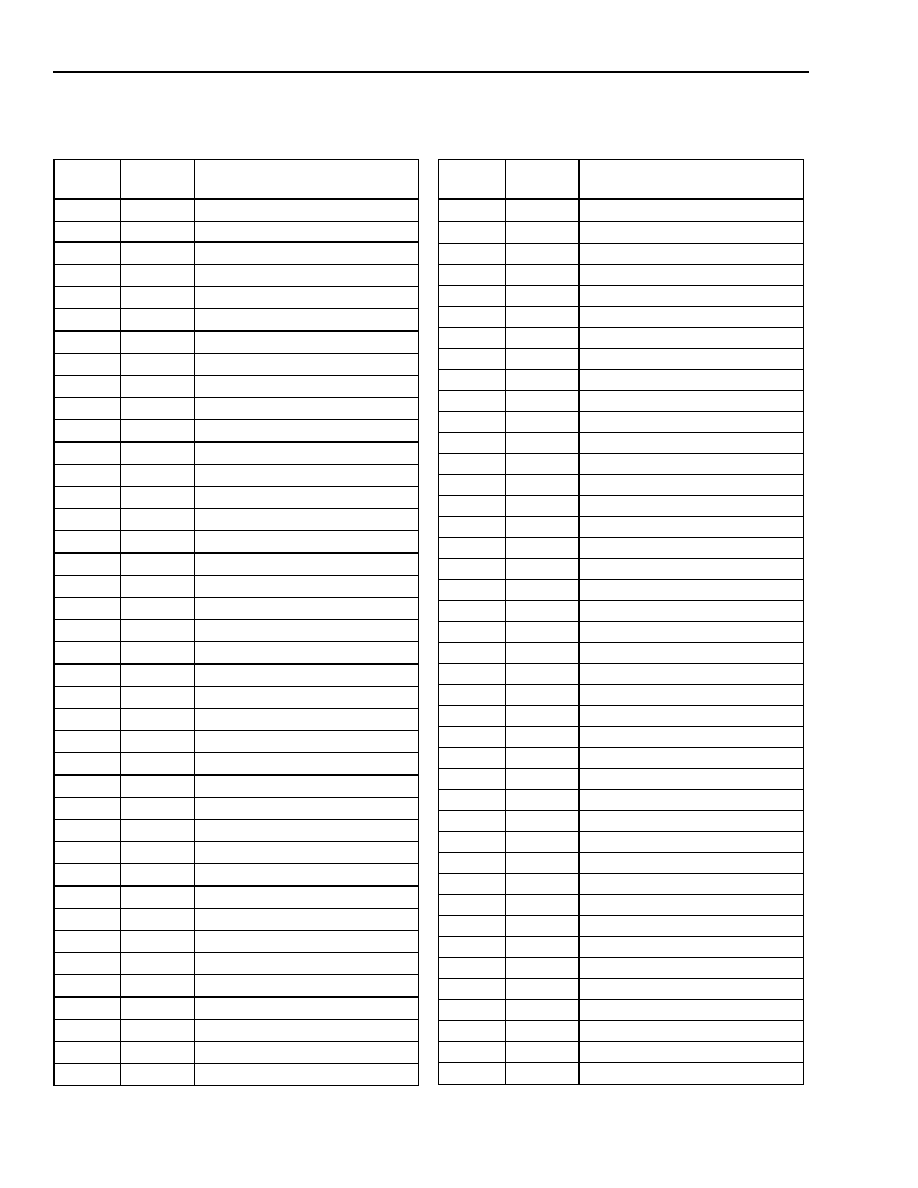

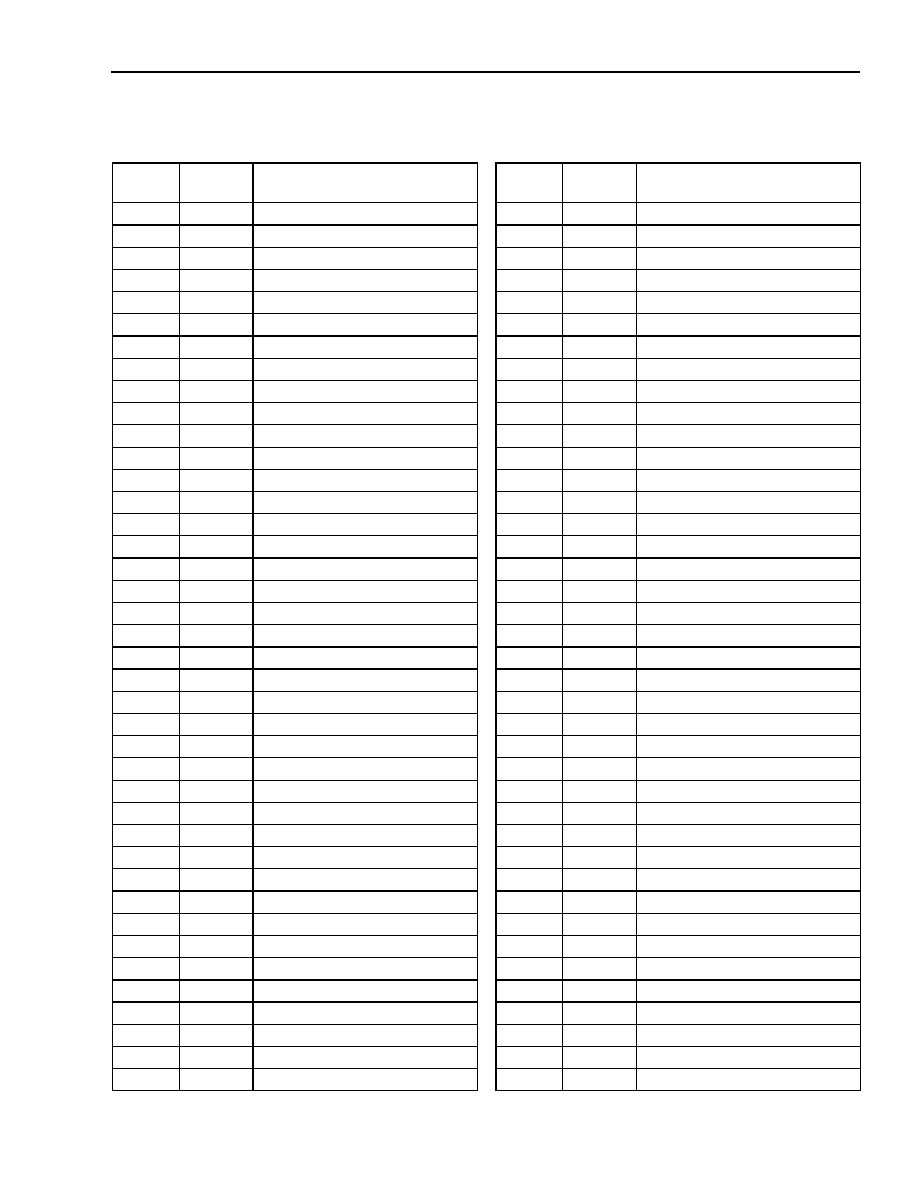

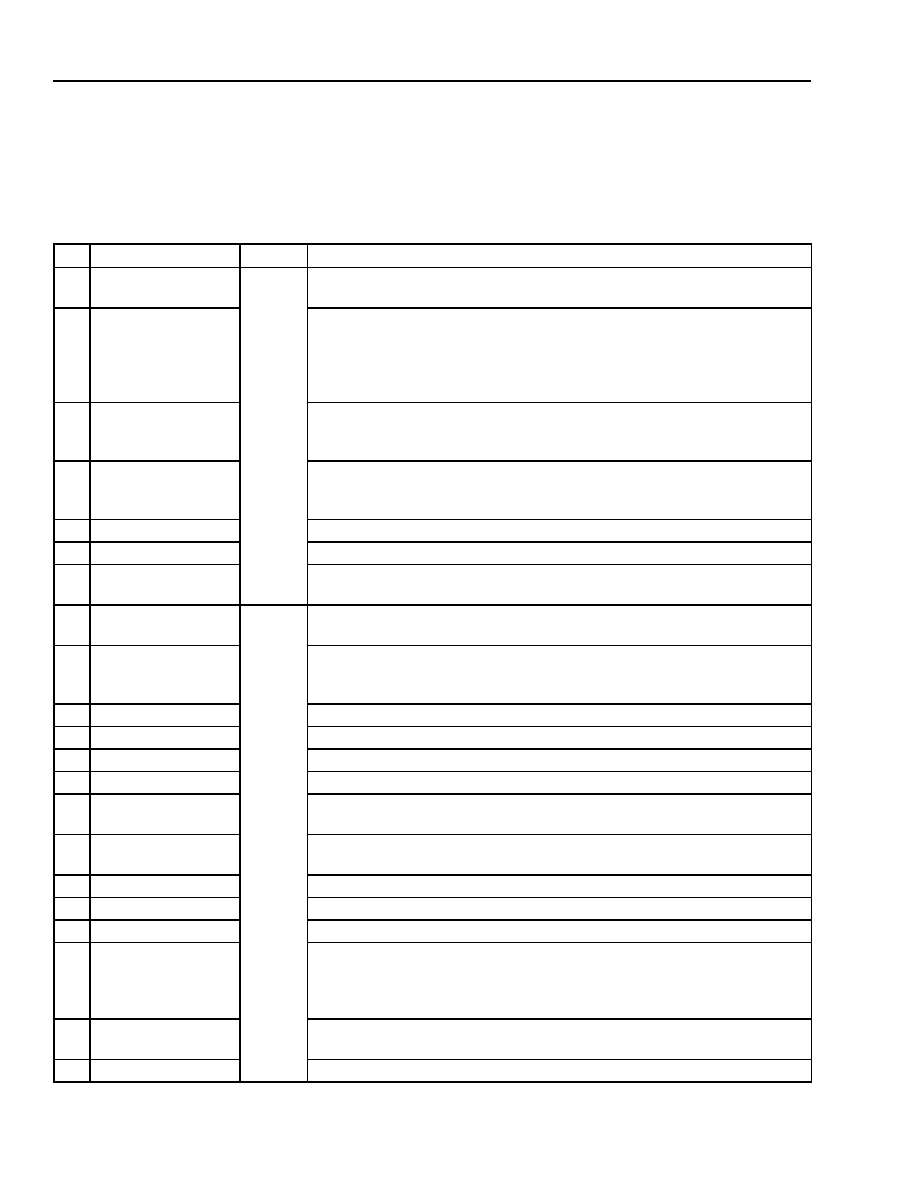

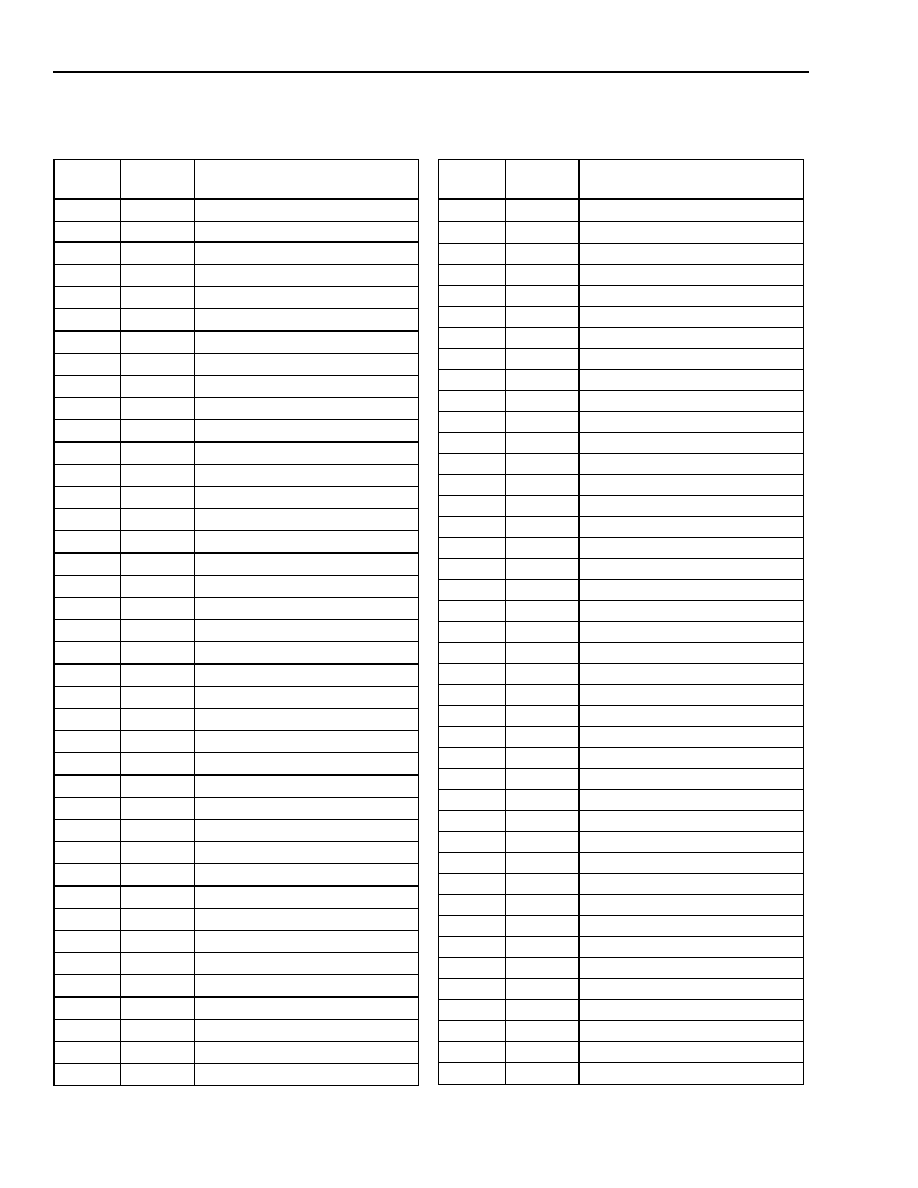

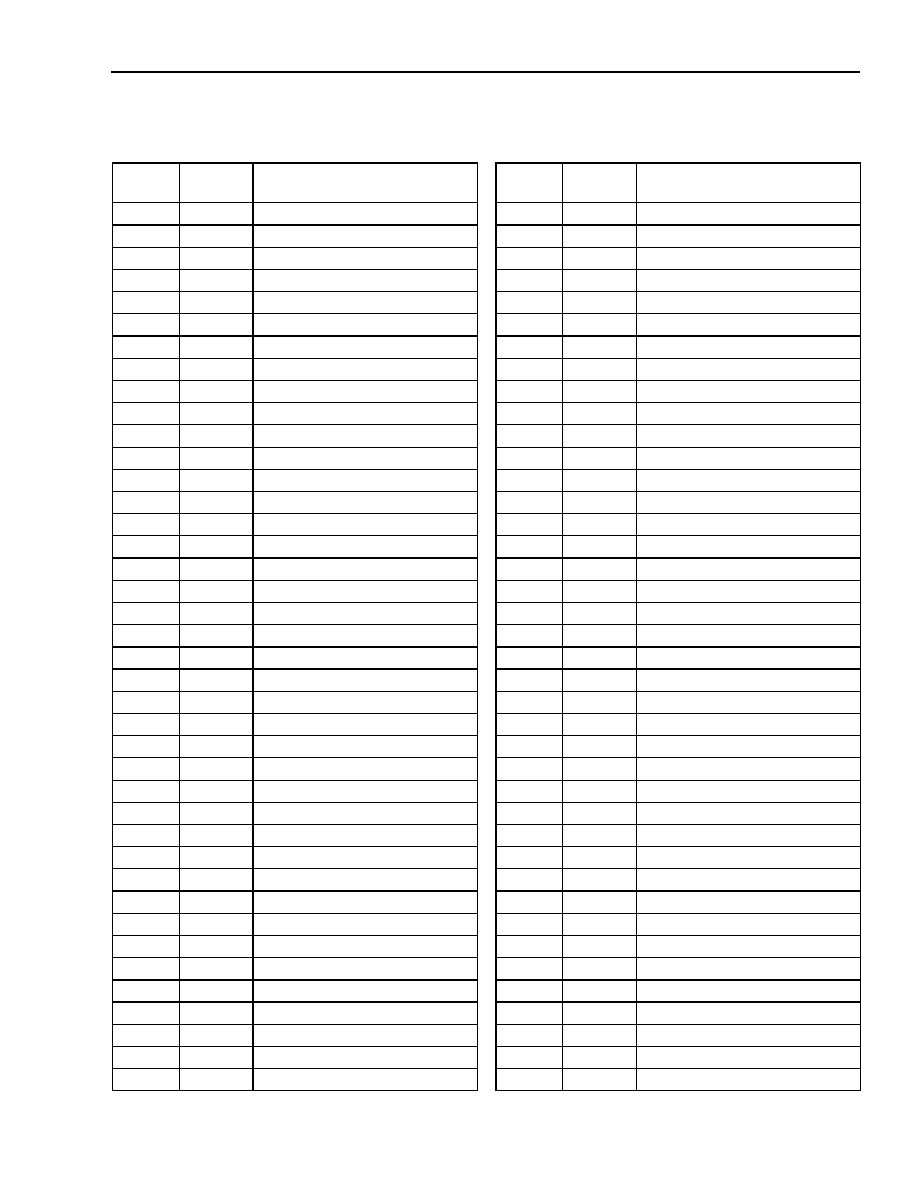

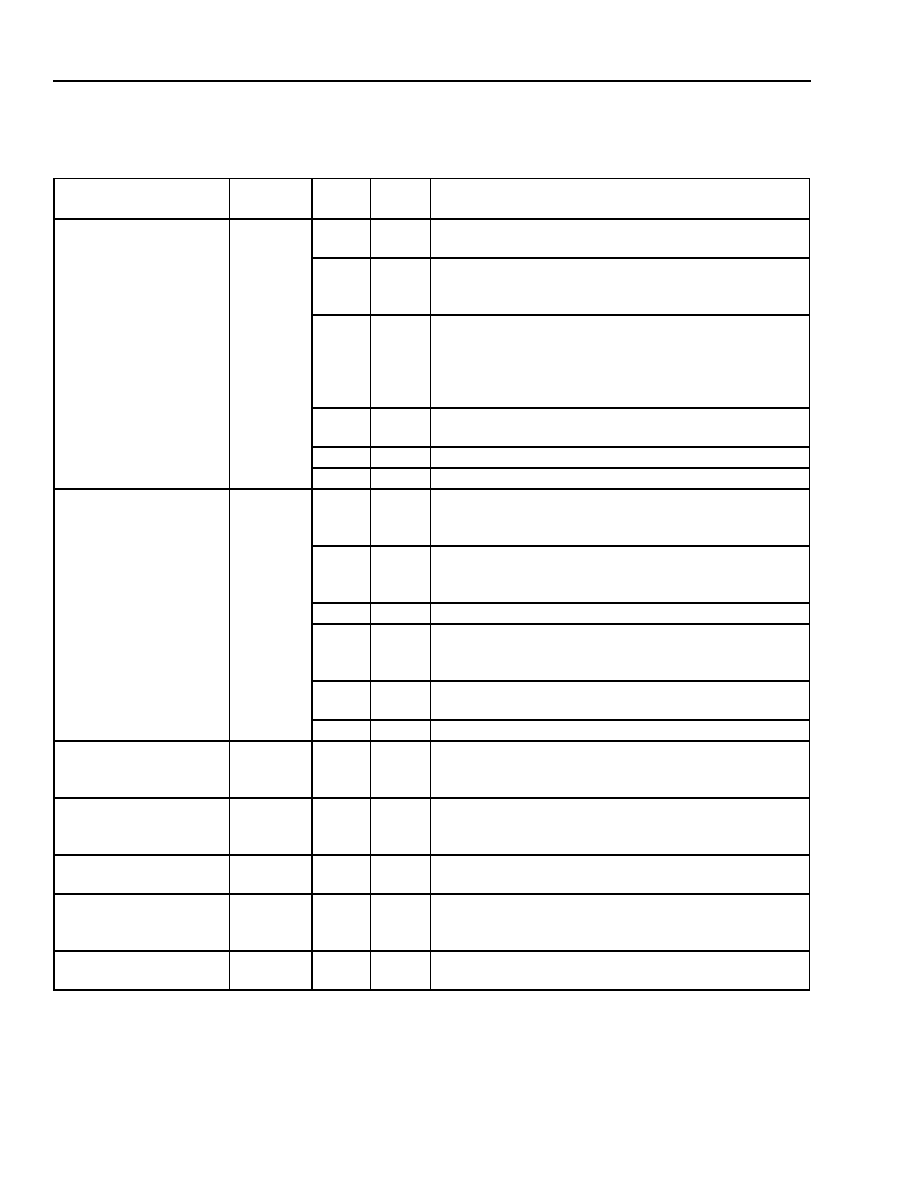

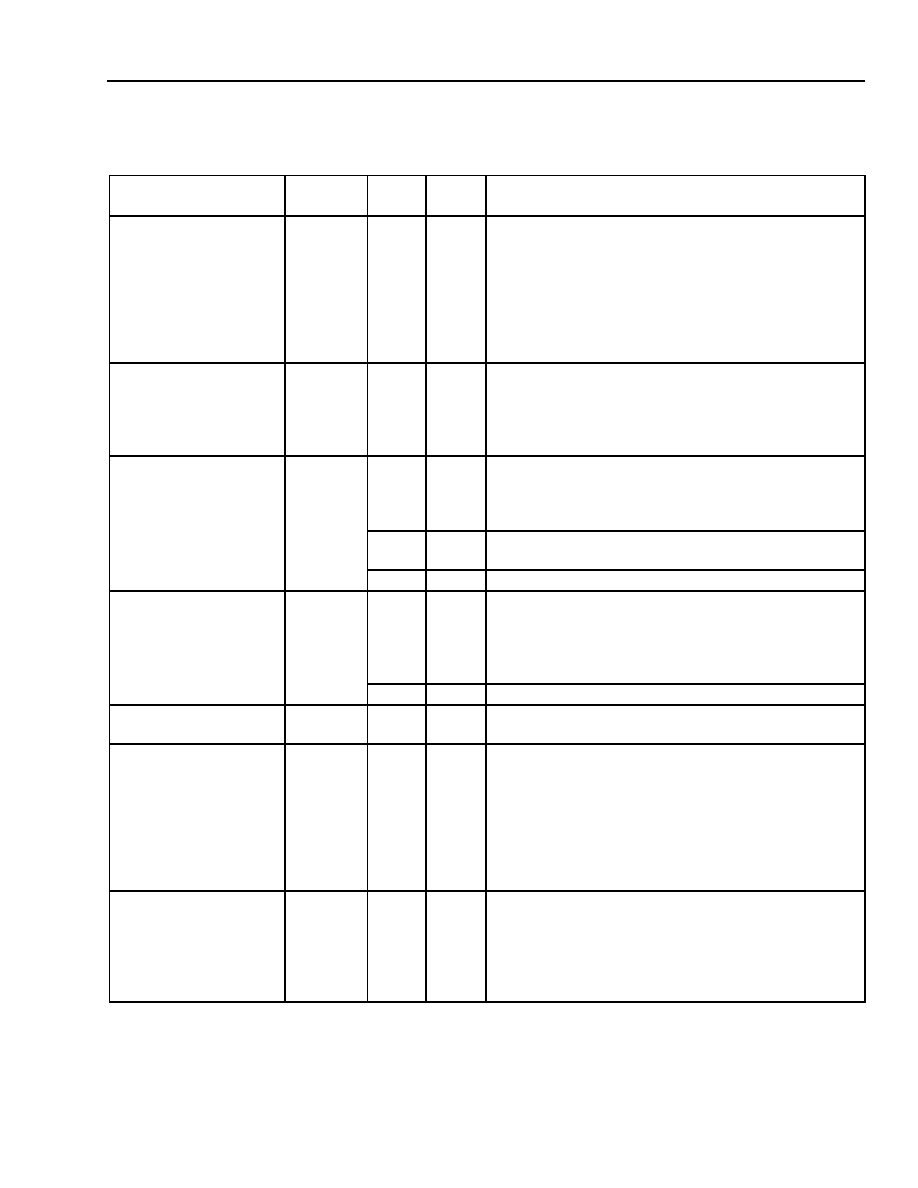

Table 1.

Pin Definitions................................................................................................................................... 12

Table 2.

Transmission Line Interface Signals (48 Signals) ............................................................................ 13

Table 3.

CHI Interface Signals (20 Signals) ................................................................................................... 14

Table 4.

UTOPIA 2 Expansion Interface Signals (52 Signals) ....................................................................... 14

Table 5.

System Interface Signals (62 Signals).............................................................................................. 15

Table 6.

Switch Fabric Interface Signals (50 Pins)......................................................................................... 17

Table 7.

APC External Statistics Interface Signals (18 Signals) .................................................................... 18

Table 8.

SAR External Statistics Interface Signals (18 Signals)..................................................................... 18

Table 9.

Host Interface Signals (49 Signals) .................................................................................................. 19

Table 10.

JTAG Interface Pins (6 Signals) ...................................................................................................... 19

Table 11.

Global/Miscellaneous Signal Pins (10 Signals) ................................................................................ 19

Table 12.

Power Supply Pins (4 Analog Power Pins, 120 Digital Power Pins) ............................................... 20

Table 13.

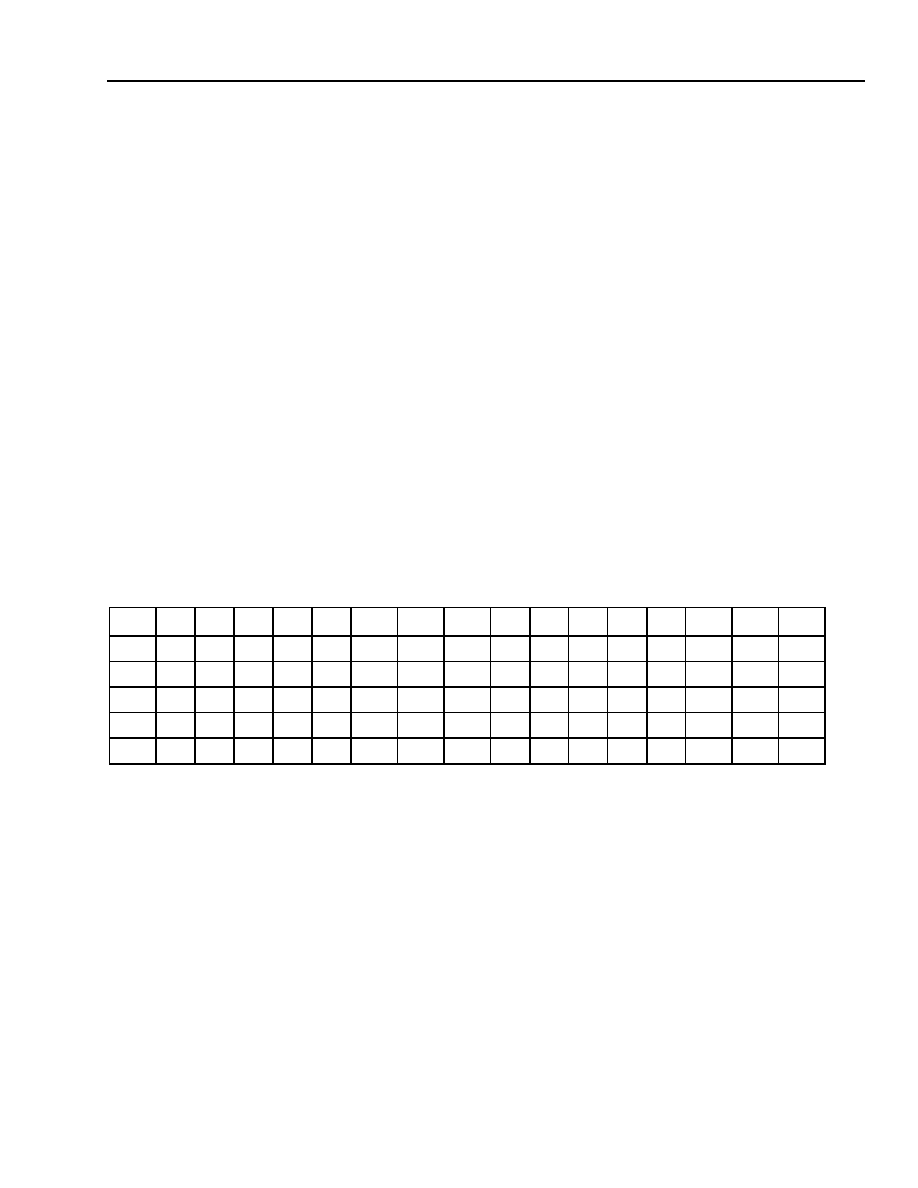

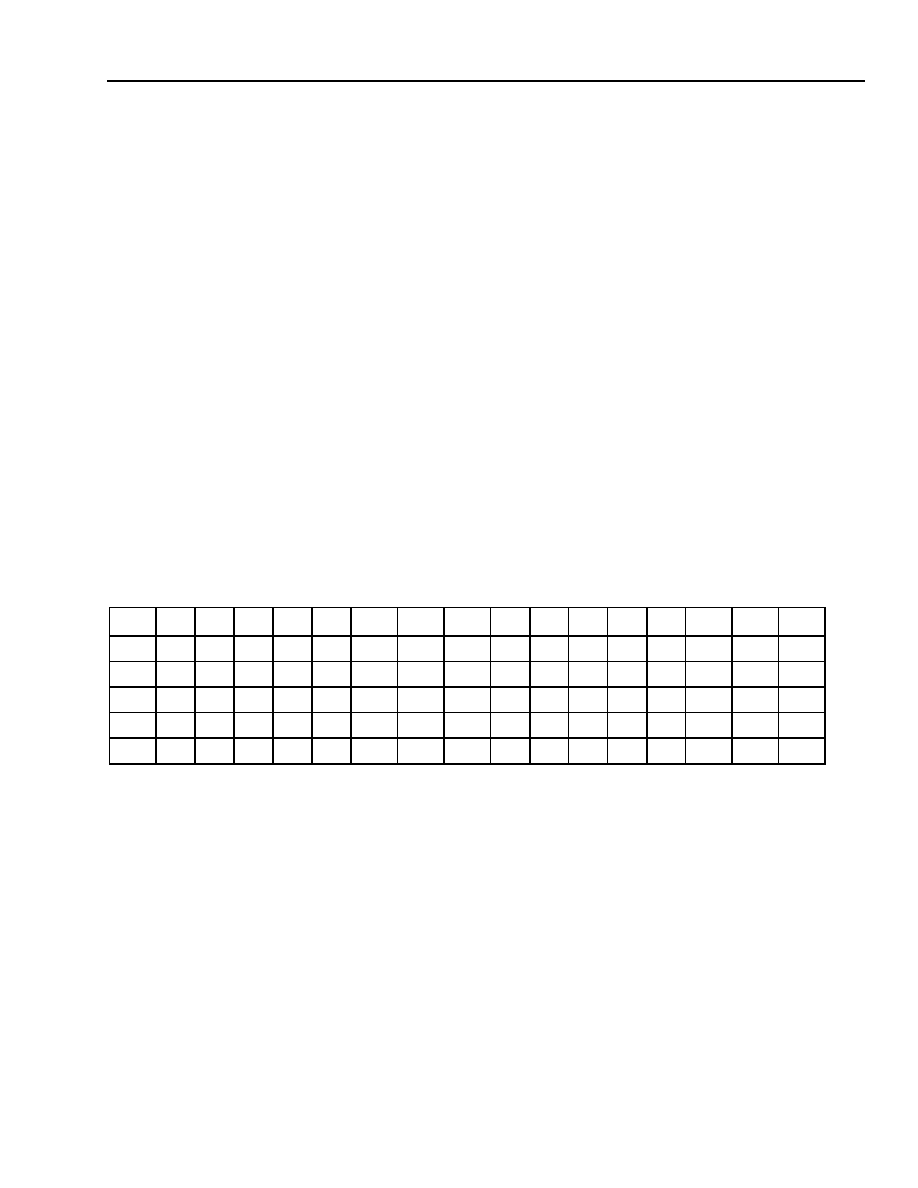

Signal-to-Ball Mapping ..................................................................................................................... 22

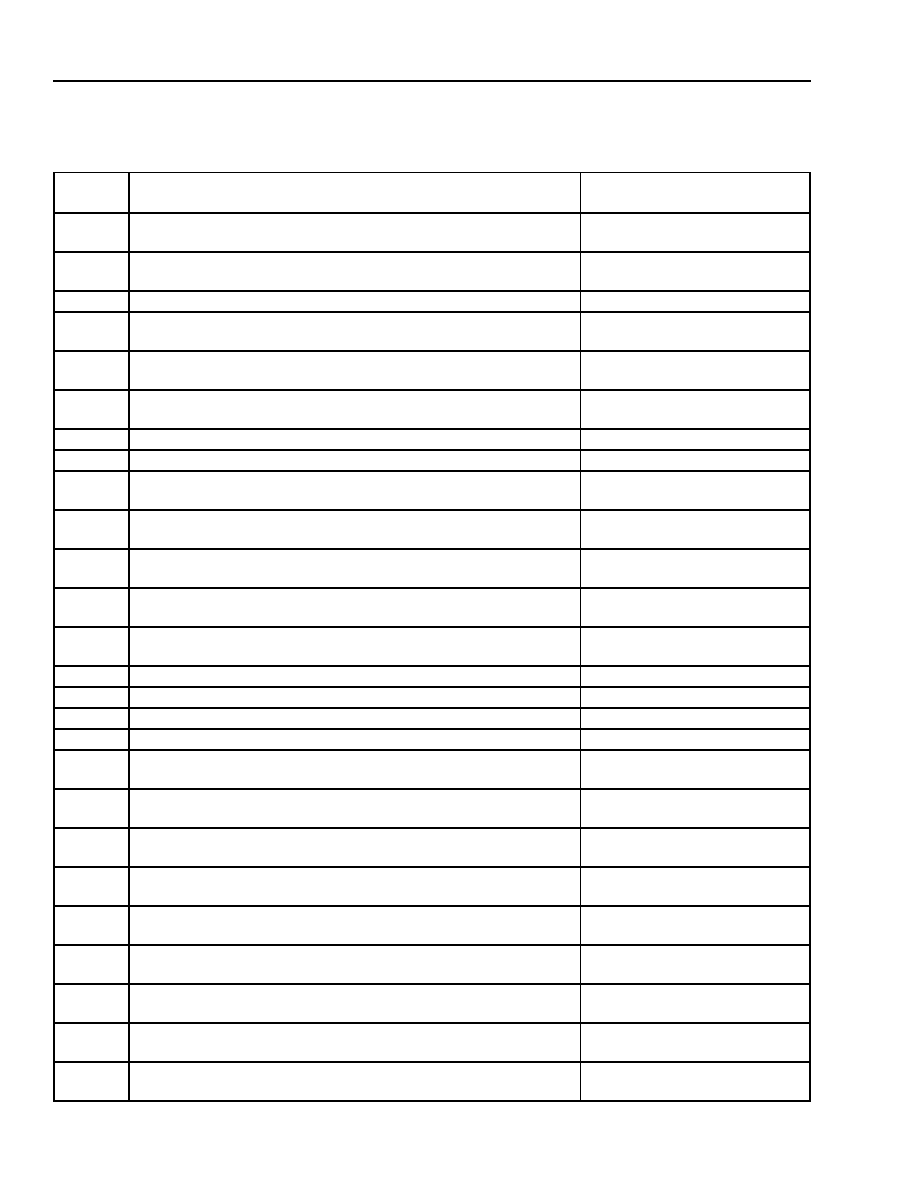

Table 14.

Host Registers .................................................................................................................................. 50

Table 15.

Frame Alignment Criteria.................................................................................................................. 58

Table 16.

Performance Monitor Functional Descriptions.................................................................................. 59

Table 17.

Performance Report Message Format ............................................................................................. 61

Table 18.

Performance Report Message Field Definition................................................................................. 62

Table 19.

Shared Tx Stack Format for CEPT Frame ....................................................................................... 65

Table 20.

Cell Headers of Idle, Unassigned, and Invalid Cells......................................................................... 73

Table 21.

TC Functionality................................................................................................................................ 73

Table 22.

TAAD08JU2 Exceptions to the IMA PICS Proforma ........................................................................ 85

Table 23.

PATM Fields ................................................................................................................................... 114

Table 24.

HPF Fields...................................................................................................................................... 115

Table 25.

ESI Message Format (AALXDATA[15:0])....................................................................................... 116

Table 26.

ESI Violation Codings..................................................................................................................... 117

Table 27.

AAL Type vs. Service Type Compatibility....................................................................................... 118

Table 28.

Transport of Congestion Indication and Loss Priority..................................................................... 121

Table 29.

PortIndex to Enqueue Block Port Mapping..................................................................................... 123

Table 30.

MEMI-SM Resources ..................................................................................................................... 124

Table 31.

SQASE-SM Resources .................................................................................................................. 130

Table 32.

L1Q and IL2Q Scheduling .............................................................................................................. 135

Table 33.

Example Stage-Two Divider Settings ............................................................................................. 137

Table 34.

Exceptions ...................................................................................................................................... 141

Table 35.

Absolute Maximum Ratings............................................................................................................ 154

Table 36.

Power Requirements ...................................................................................................................... 154

Table 37.

Operating Conditions...................................................................................................................... 154

Table 38.

Handling Precautions ..................................................................................................................... 155

Table 39.

Version 2.1 Logic Interface Characteristics .................................................................................... 155

Table 40.

Version 3.1 Logic Interface Characteristics .................................................................................... 156

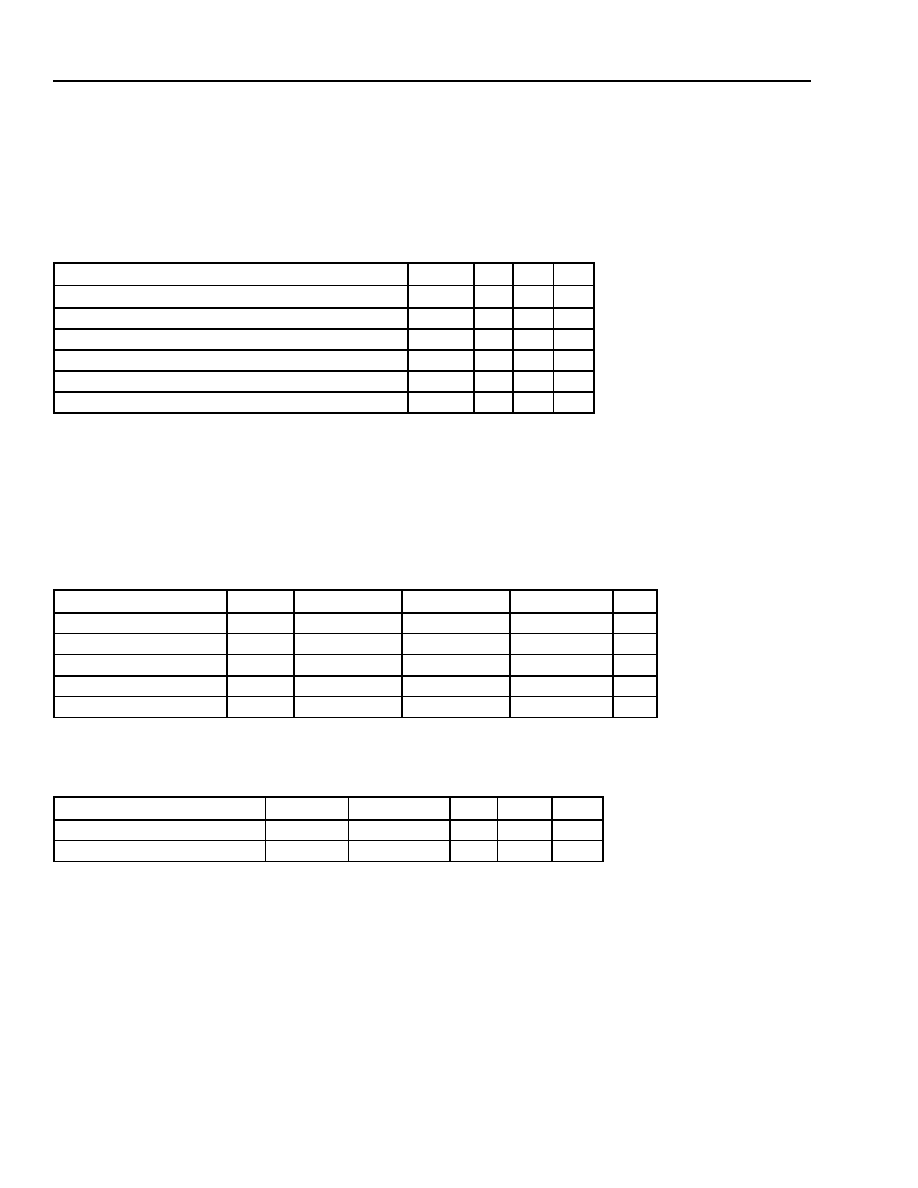

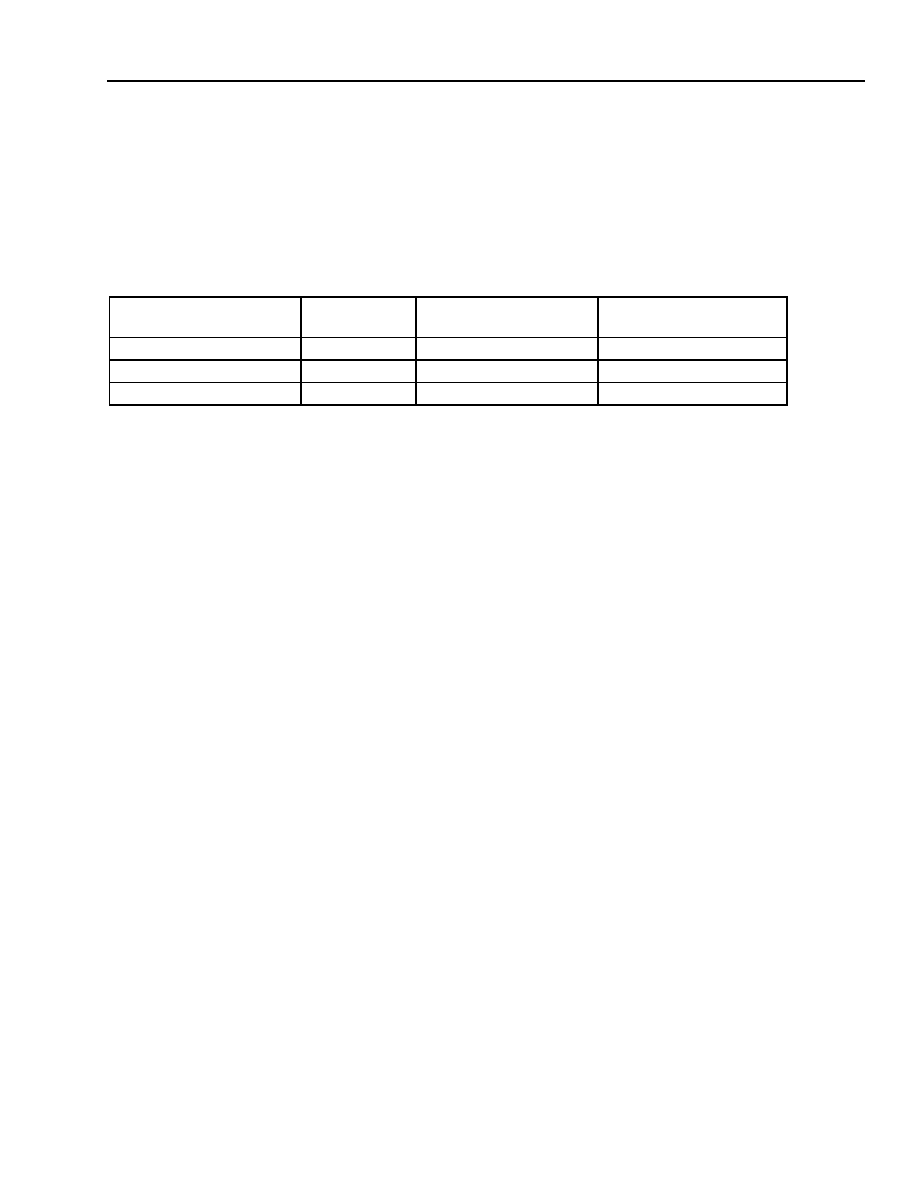

Table 41.

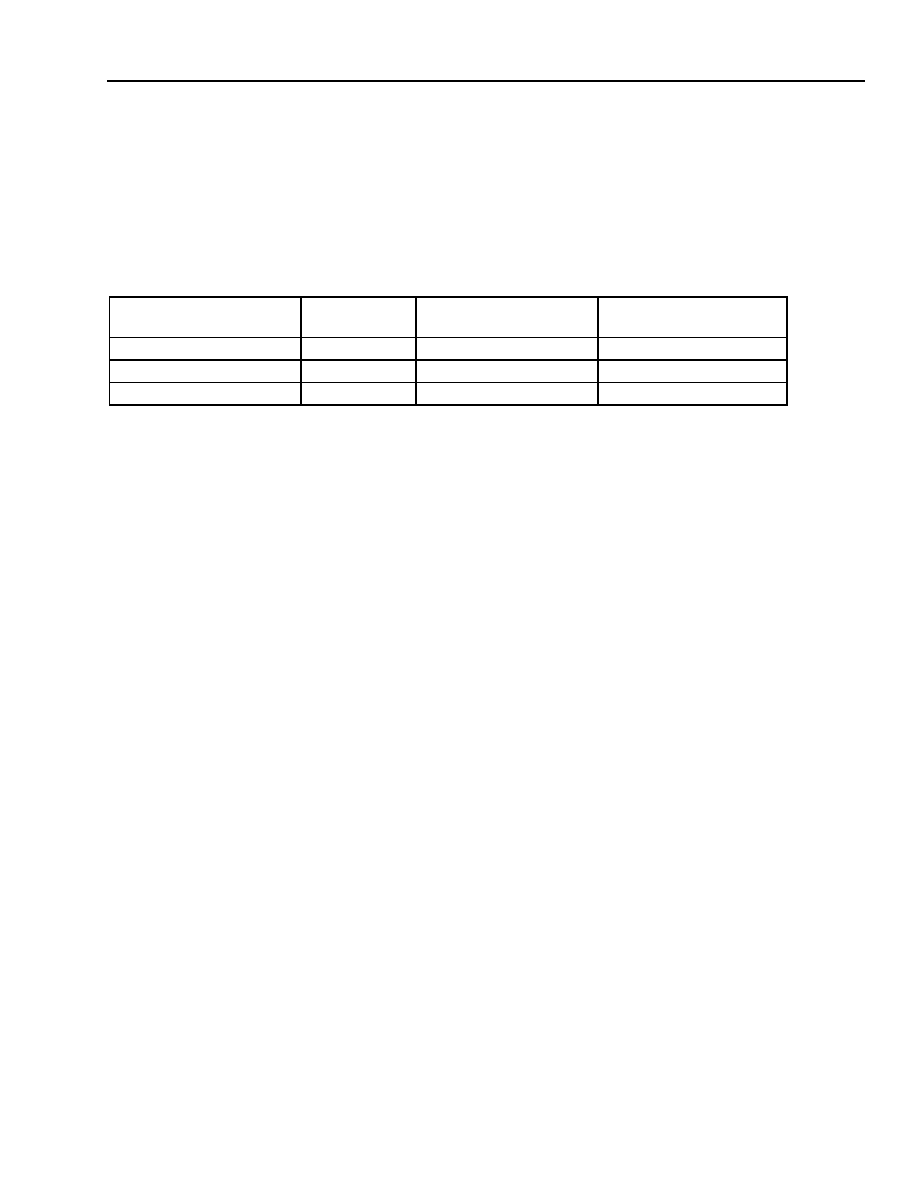

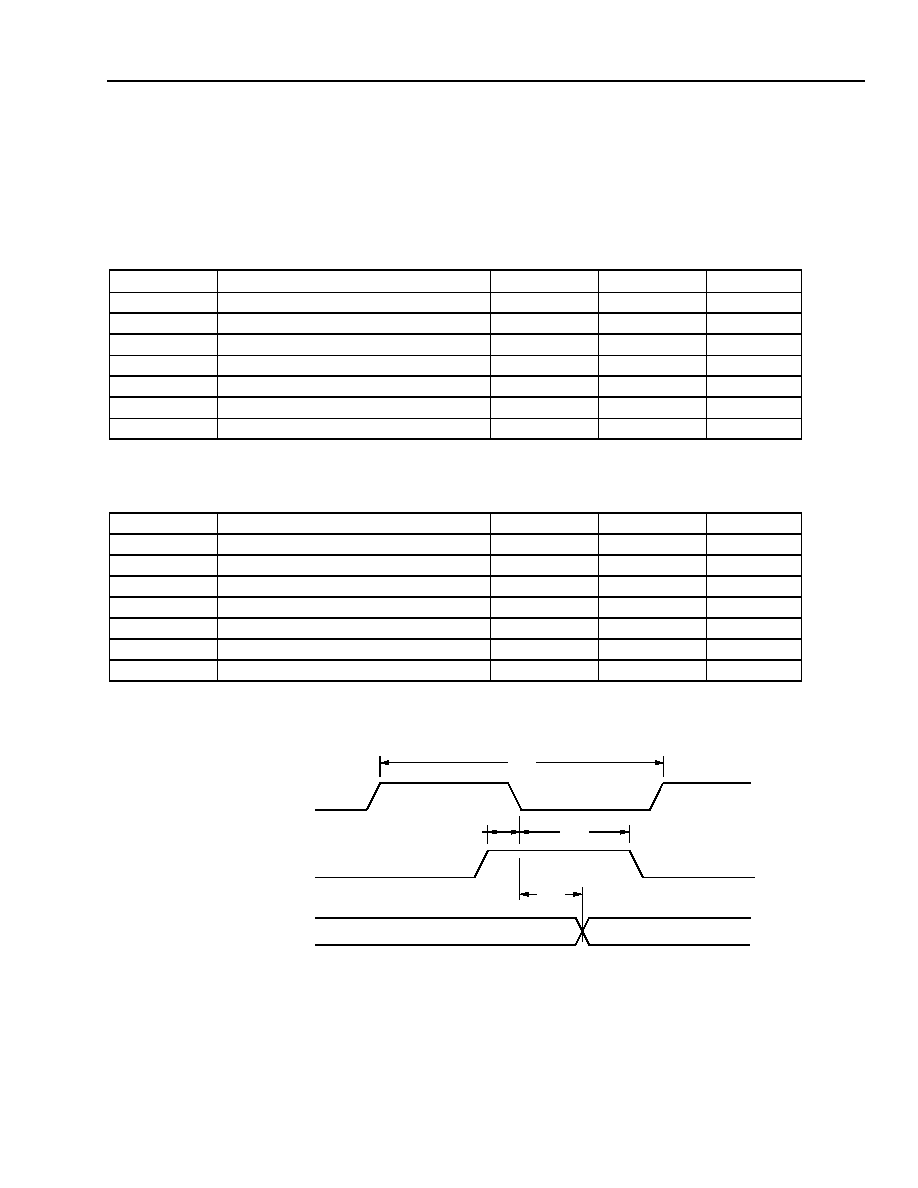

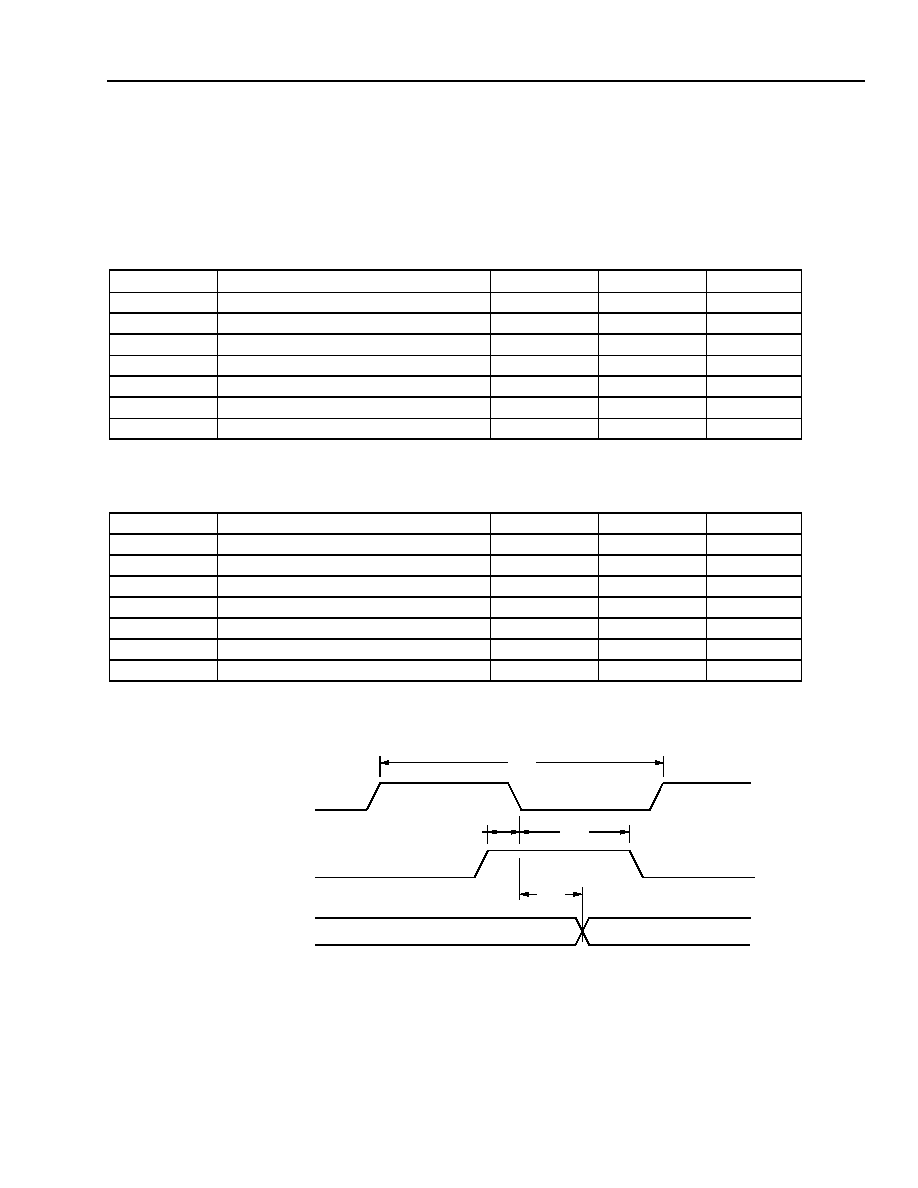

Versions 2.1 and 3.1 Main System Clock (GCLK) Timing Specifications....................................... 157

Table 42.

Version 2.1 UTOPIA Input Clocks (UCLK) Timing Specifications .................................................. 157

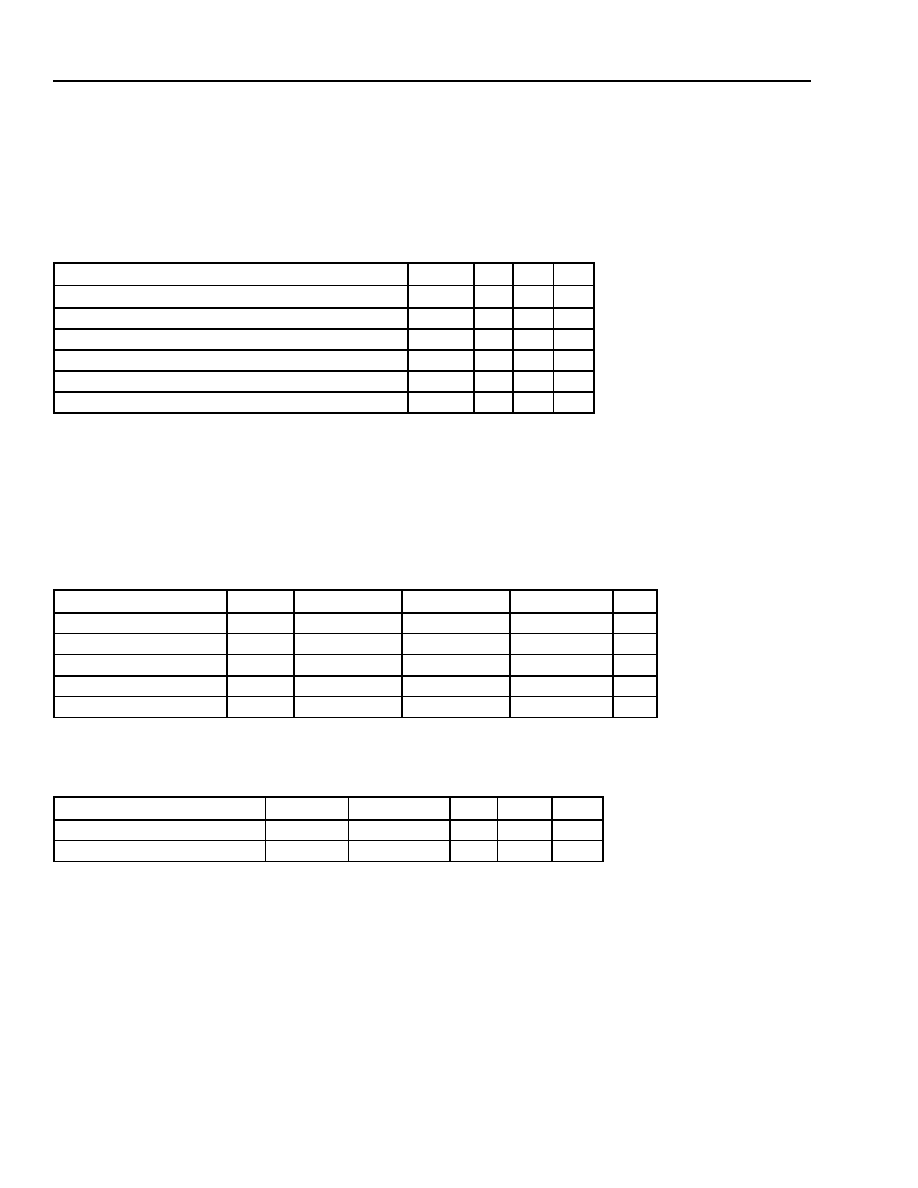

Table 43.

Version 3.1 UTOPIA Input Clocks (UCLK_A[B]) Timing Specifications ......................................... 157

Table 44.

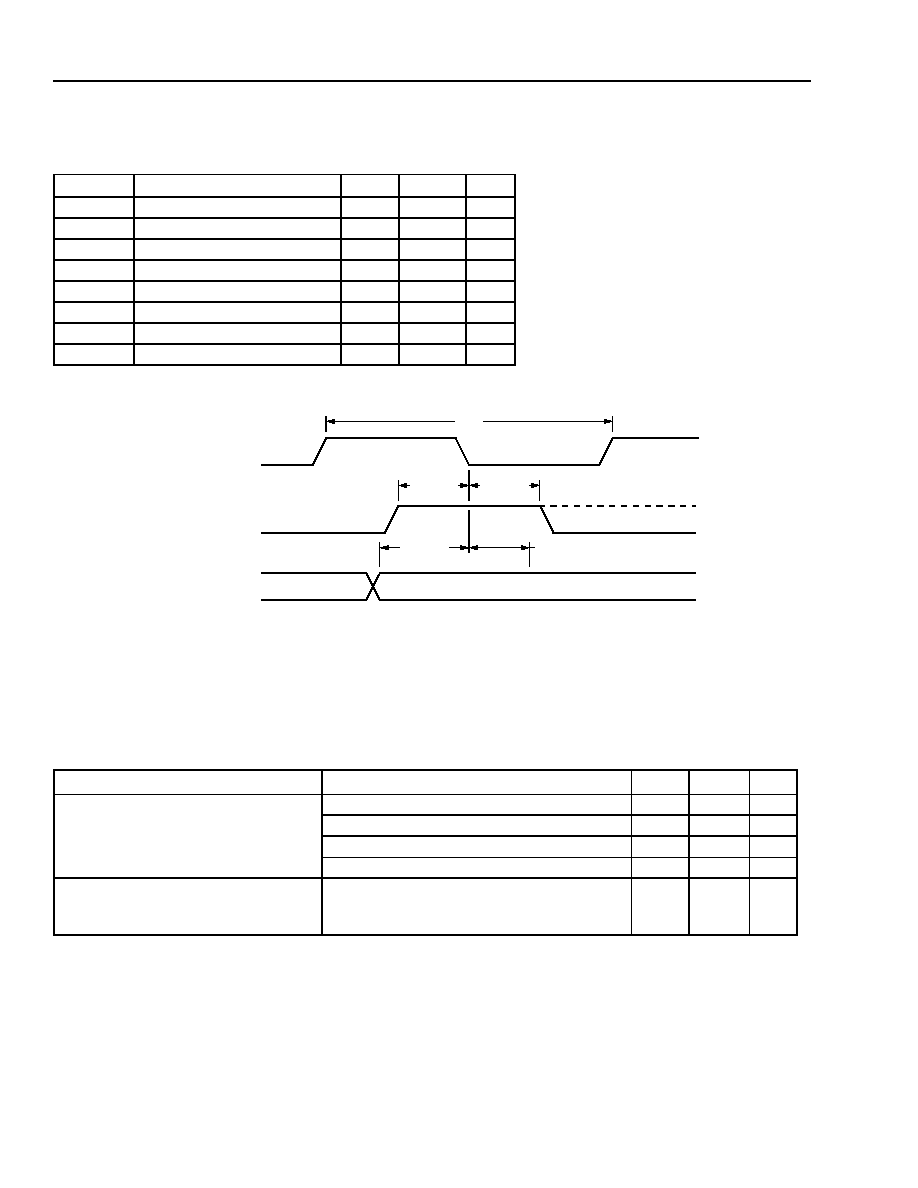

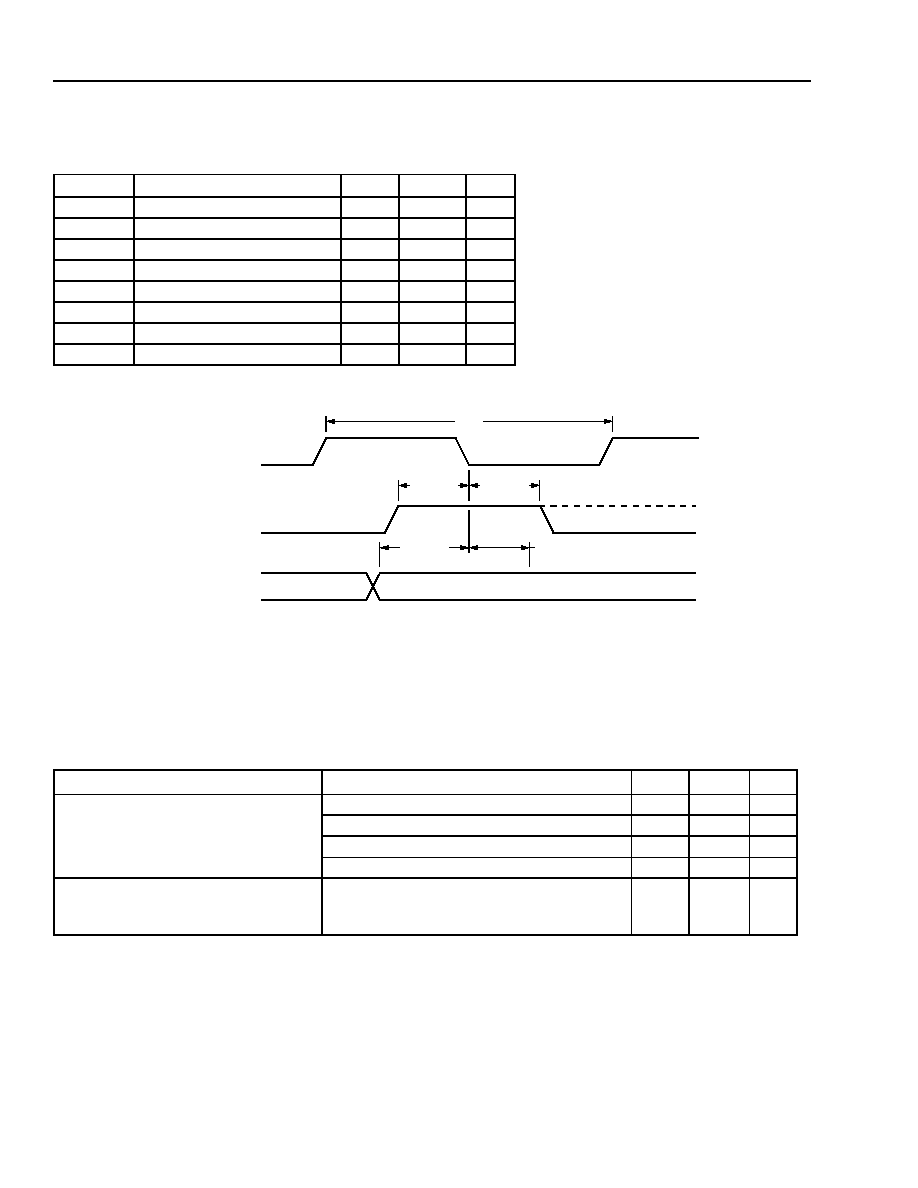

Host Read Timing Characteristics .................................................................................................. 158

Table 45.

Host Write Timing Characteristics .................................................................................................. 159

Table 46.

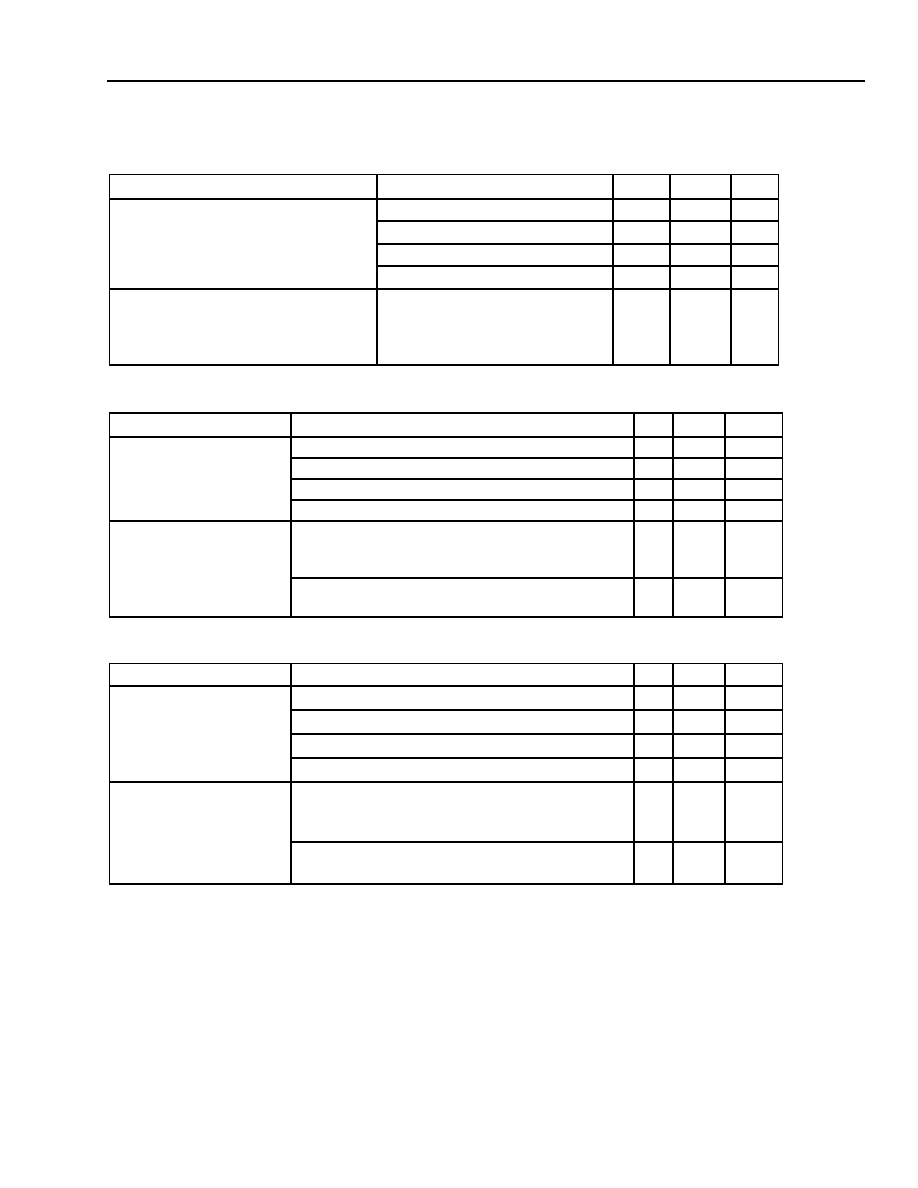

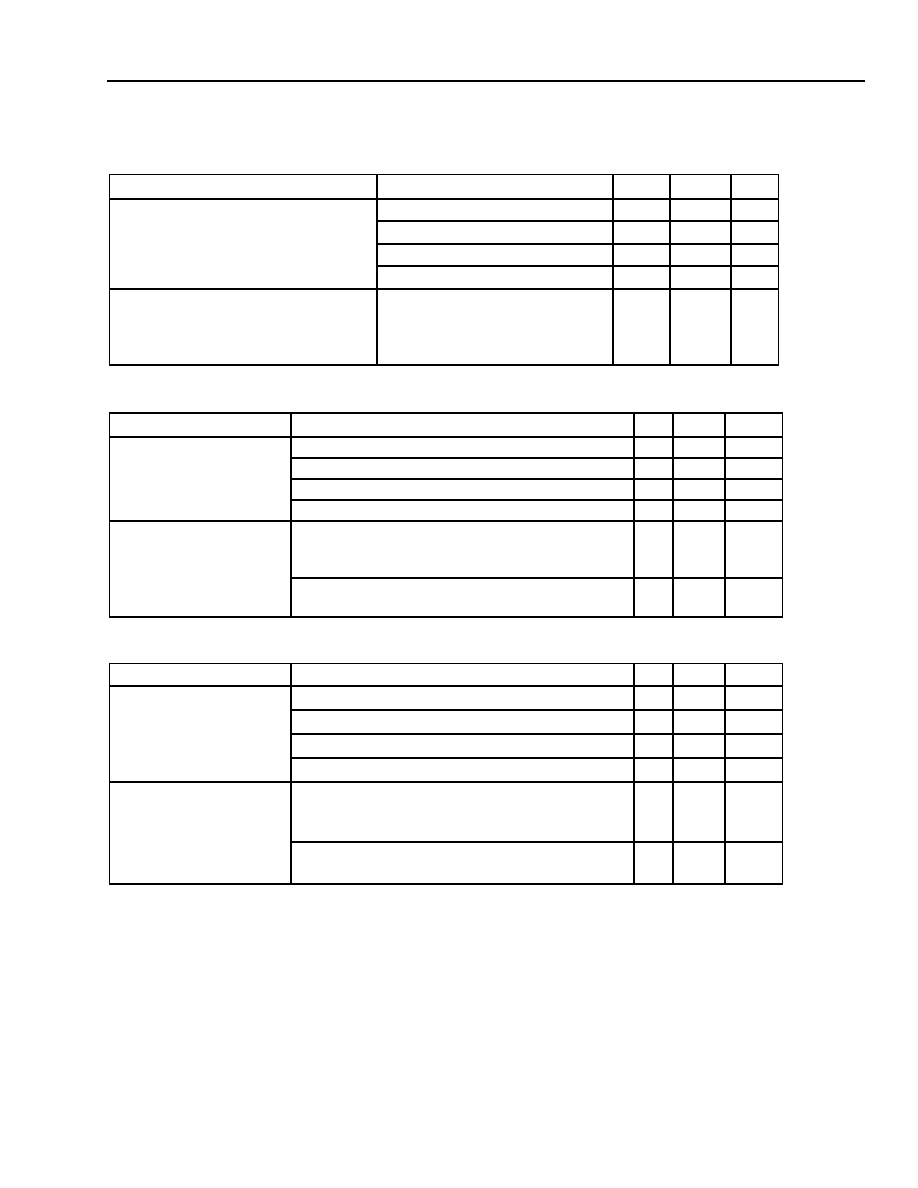

Version 2.1 CHI Transmit Timing Characteristics........................................................................... 161

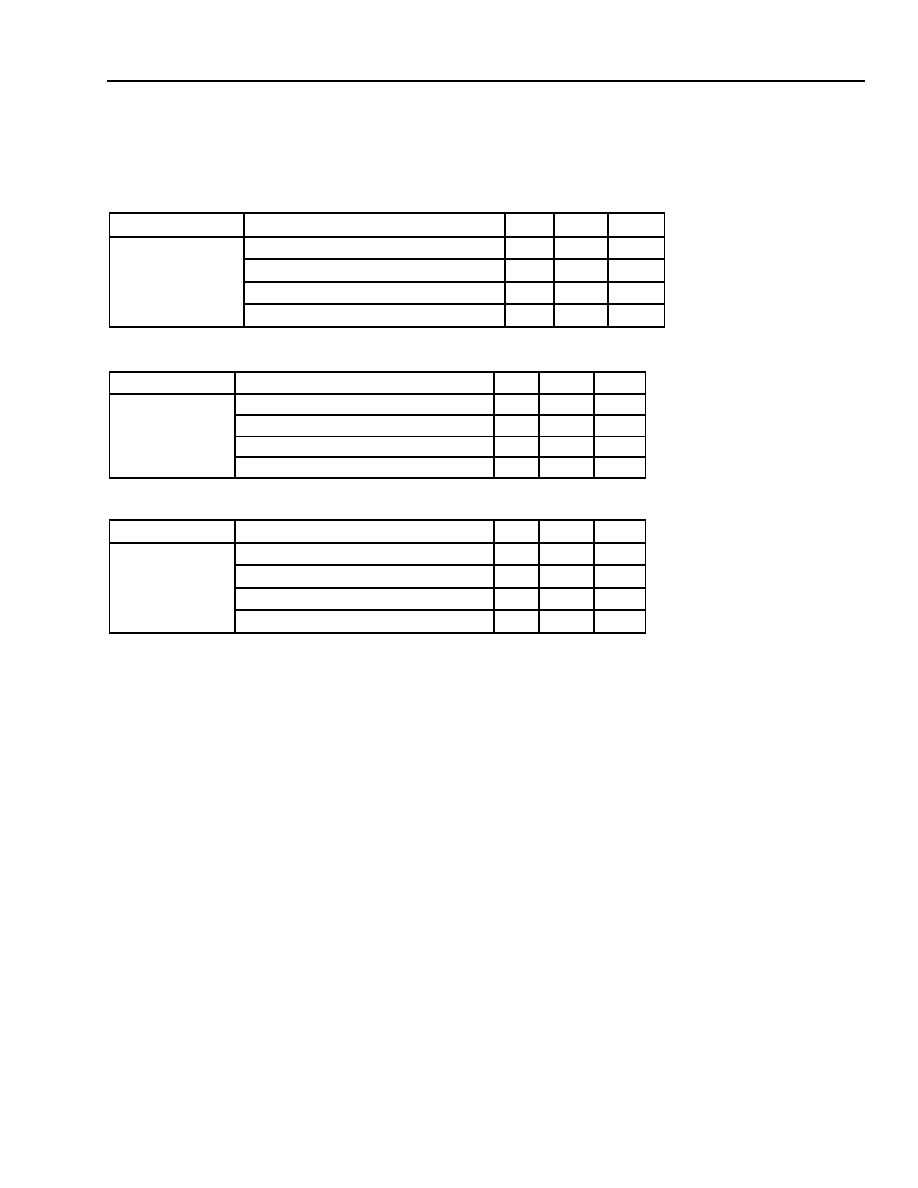

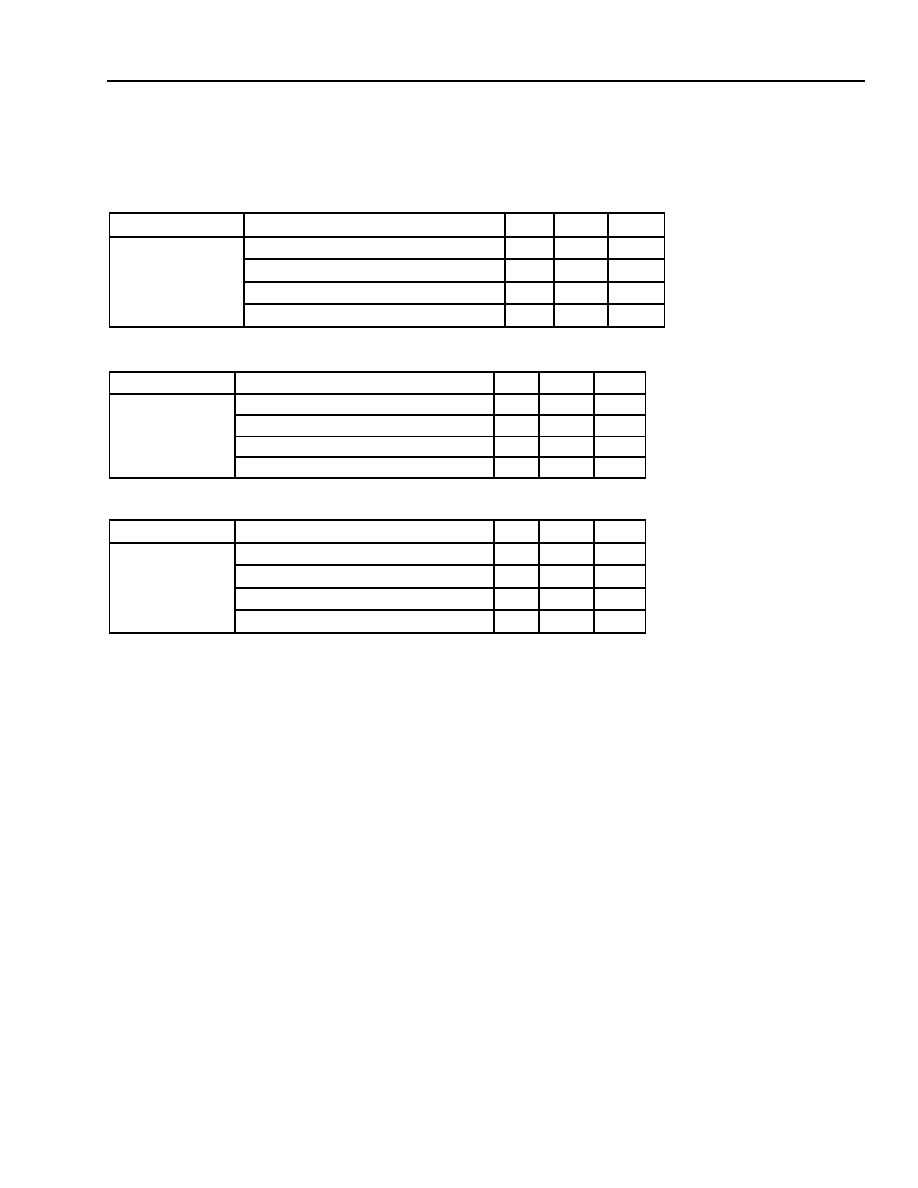

Table 47.

Version 3.1 CHI Transmit Timing Characteristics........................................................................... 161

Table 48.

CHI Receive Timing Characteristics............................................................................................... 162

Table 49.

Version 2.1 Fabric Interface Timing Specifications (Transmit Interface) ........................................ 162

Table 50.

Version 3.1 Fabric Interface Timing Specifications (Transmit Interface) ........................................ 163

Table 51.

Version 2.1 Fabric Interface Timing Specifications (Receive Interface) ......................................... 163

Table 52.

Version 3.1 Fabric Interface Timing Specifications (Receive Interface) ......................................... 163

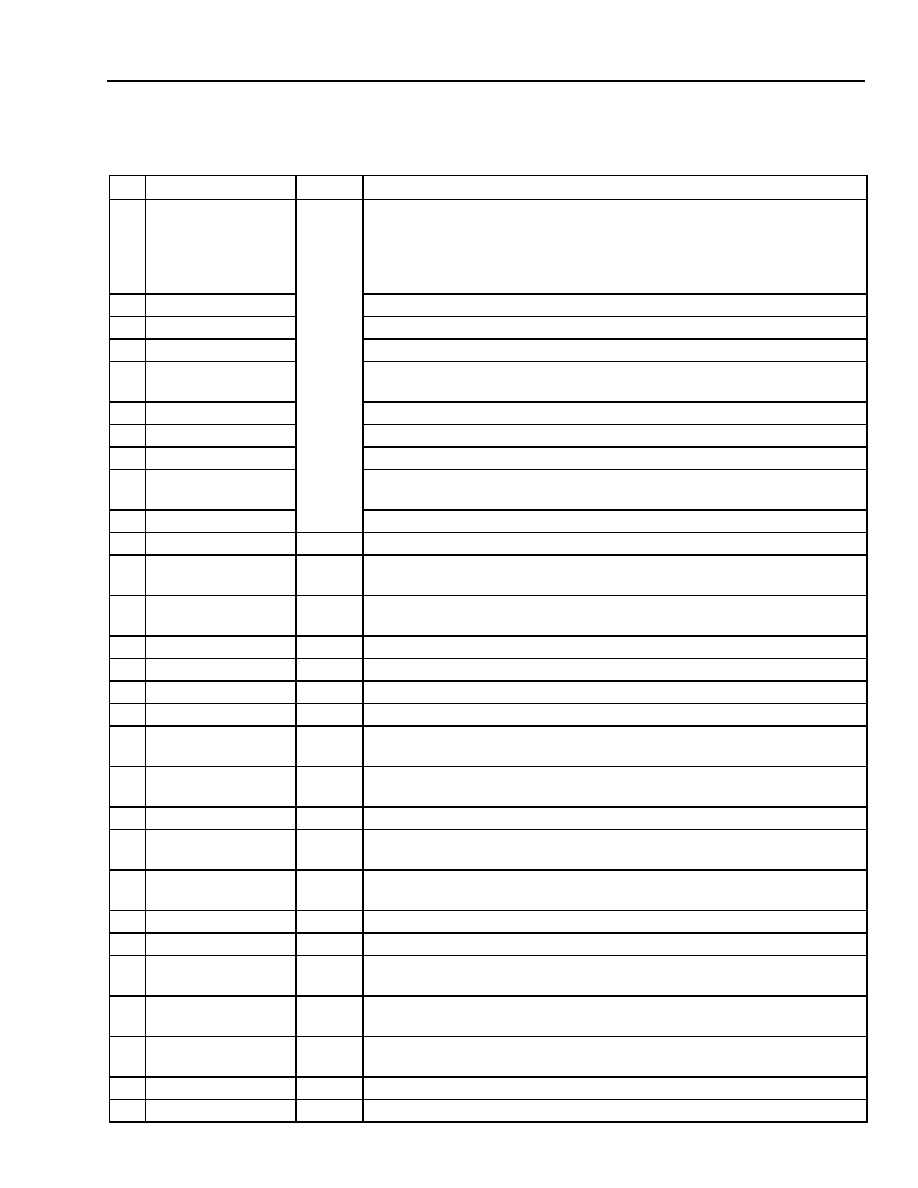

List of Tables

(continued)

Table

Page

TAAD08JU2 Data

Sheet

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

August 18, 2003

10

Agere Systems - Proprietary

Agere Systems Inc.

Use pursuant to Company instructions

Table 53.

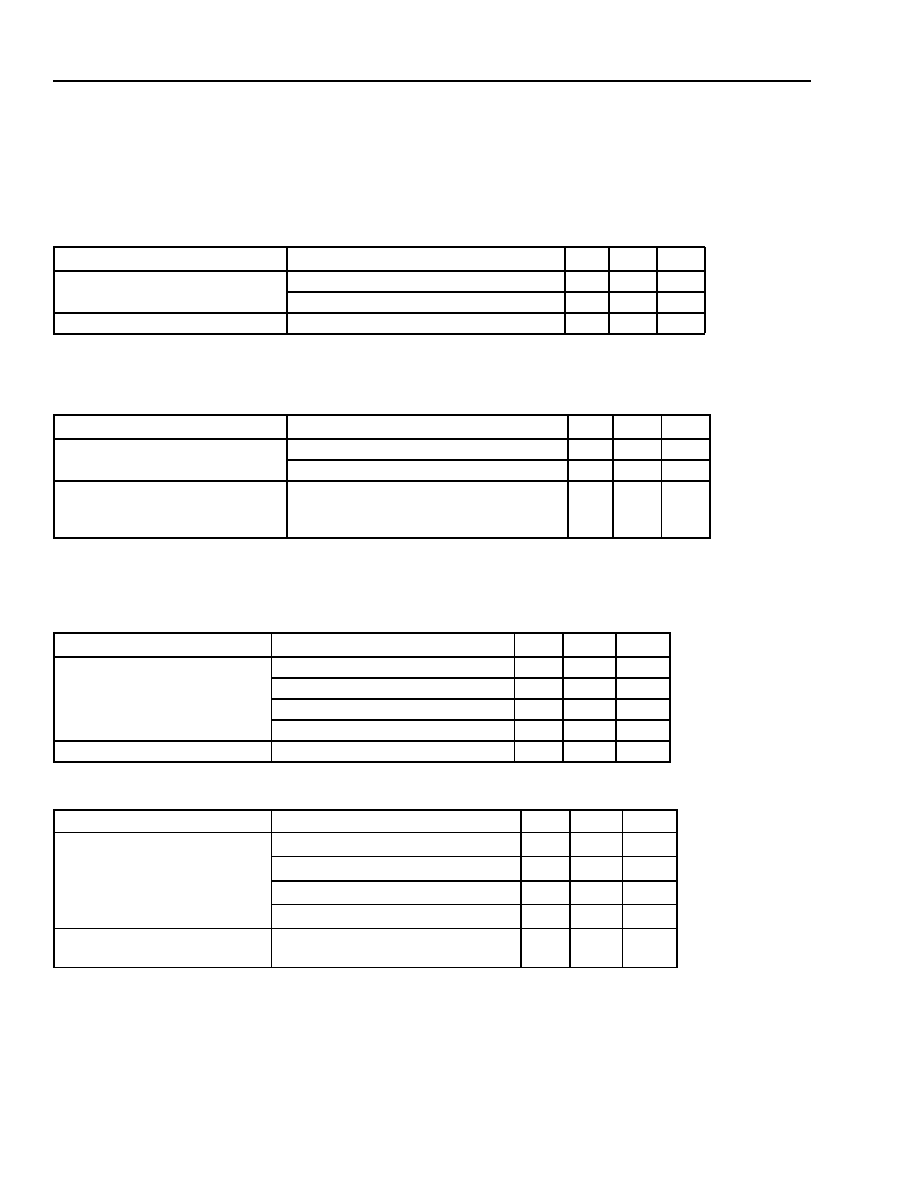

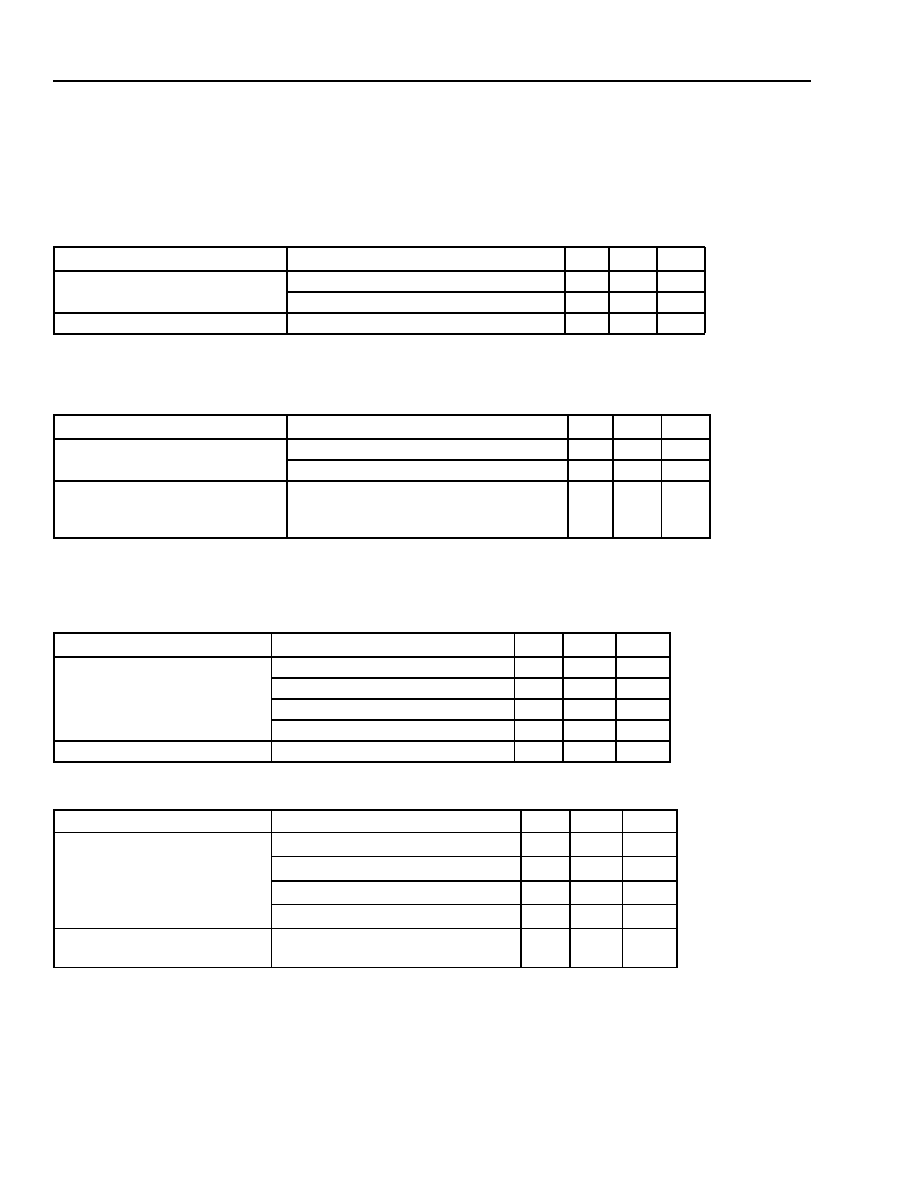

Expansion UTOPIA2 Receive Interface Timing Specifications: 50 MHz ........................................ 164

Table 54.

UTOPIA2 Transmit Interface Timing Specifications: 50 MHz......................................................... 164

Table 55.

Version 2.1 ESI Interface Timing Specifications............................................................................. 164

Table 56.

Version 3.1 ESI Interface Timing Specifications (SAR and APC) .................................................. 164

Table 57.

JTAG Timing Specifications ........................................................................................................... 165

Table 58.

Version 2.1 Receive Interface Timing............................................................................................. 165

Table 59.

Version 2.1 Transmit Interface Timing............................................................................................ 165

Table 60.

Version 3.1 Receive Interface Timing (SUCLK Input) .................................................................... 166

Table 61.

Version 3.1 Transmit Interface Timing (SUCLK Input) ................................................................... 166

Table A-1.

Revision History.............................................................................................................................. 172

Data Sheet

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

TAAD08JU2

Agere Systems Inc.

Agere Systems - Proprietary

11

4 Description

TAAD08JU2 provides a flexible network-interface solution for next-generation applications in which efficient trans-

port of narrowband voice and broadband data information is critical to guaranteeing network QoS for the user and

transmission efficiency for the network operator. Constructed using Agere's 0.16 µm CMOS technology, the chip

has an integrated octal framer, IMA processor, cell scheduler and router, and AAL2/5 SAR functions.

TAAD08JU2 operates in either UNI or IMA mode (selectable on a per-span line basis). The complete AF-PHY-

0086.001 management information base (MIB) is supported. Flexible provisioning of link and group combinations

enables a mix of IMA and UNI mappings to various AAL services.

Support for AAL2 is provided via an AAL/CPS function that maps/demaps variable-sized CPS packets to/from

ATM-SDU. A total of 2032 bidirectional CIDs are supported. These CIDs can be transported within a programma-

ble number of VCs per direction. TAAD08JU2 supports up to 124 AAL2 VCs, which may be allocated between

ingress and egress traffic.

Support for high-speed data switching is provided whereby AAL5 VCs are routed through to the system interface

toward their destinations. TAAD08JU2 provides support for up to 2032 bidirectional AAL5 VCs via an internal con-

text memory.

TAAD08JU2 provides the following:

!

Integrated policing

!

F4/F5 operations, administration, and maintenance (OAM)

!

Cell processing

!

Statistics collection for performance monitoring

Communication with TAAD08JU2 is accomplished through a 32-bit microprocessor interface. The system interface

is through two choices: a UTOPIA 2 interface with support for both 8-bit and 16-bit data bus width and a UTOPIA-

derived packet interface with support for both 8-bit and 16-bit data bus widths.

TAAD08JU2 provides a complete ATM access function from AAL/CPS mapping functions (for AAL2 and 5) through

ATM/TC/PHY layers. The highly integrated, flexible architecture results in unified OAM features, simpler operation,

and best-in-class operation with respect to area, power, and function.

12

Agere Systems - Proprietary

Agere Systems Inc.

Data Sheet

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

TAAD08JU2

5 Pin Definitions

6 Pin Description

Many of the pins of the TAAD08JU2 device are multiplexed for different functions. In these cases, both functions

are shown in the same row of Table 2.

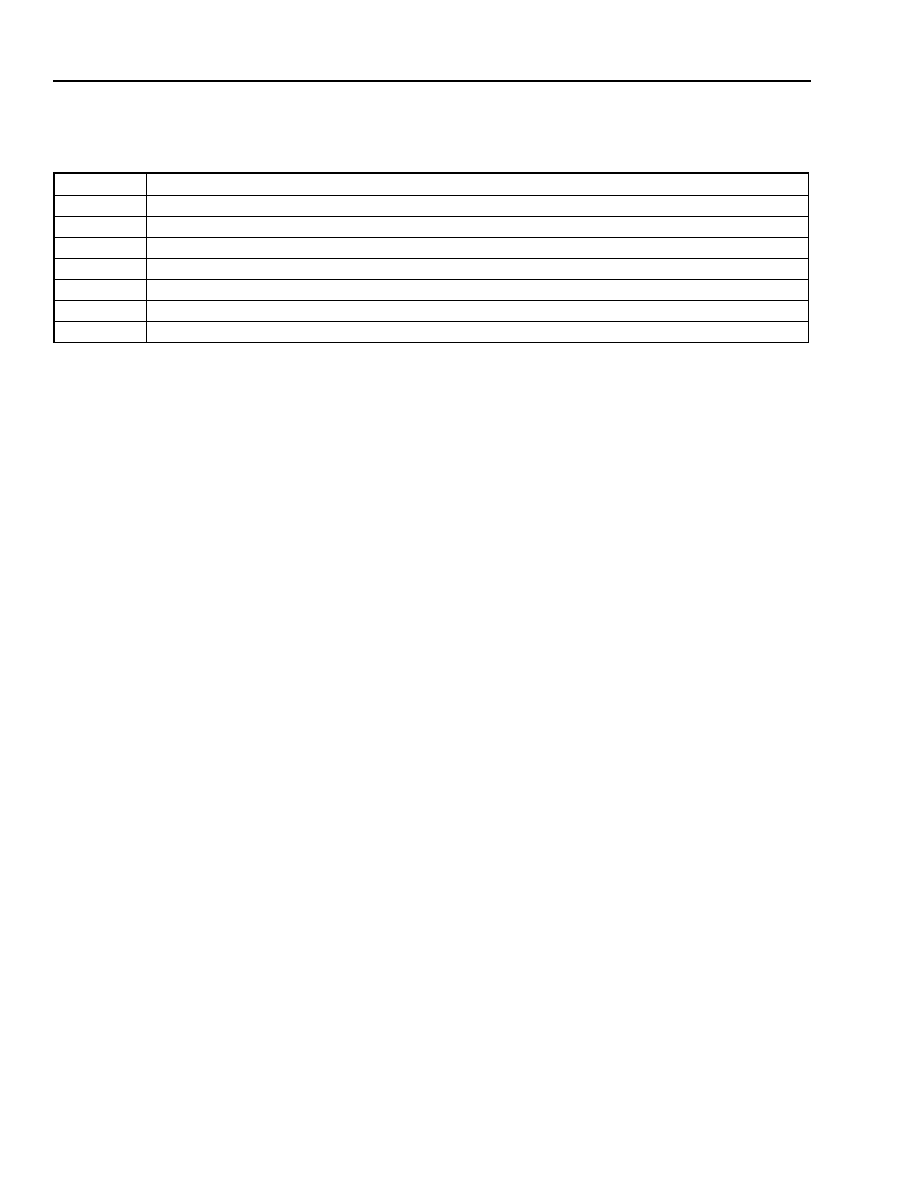

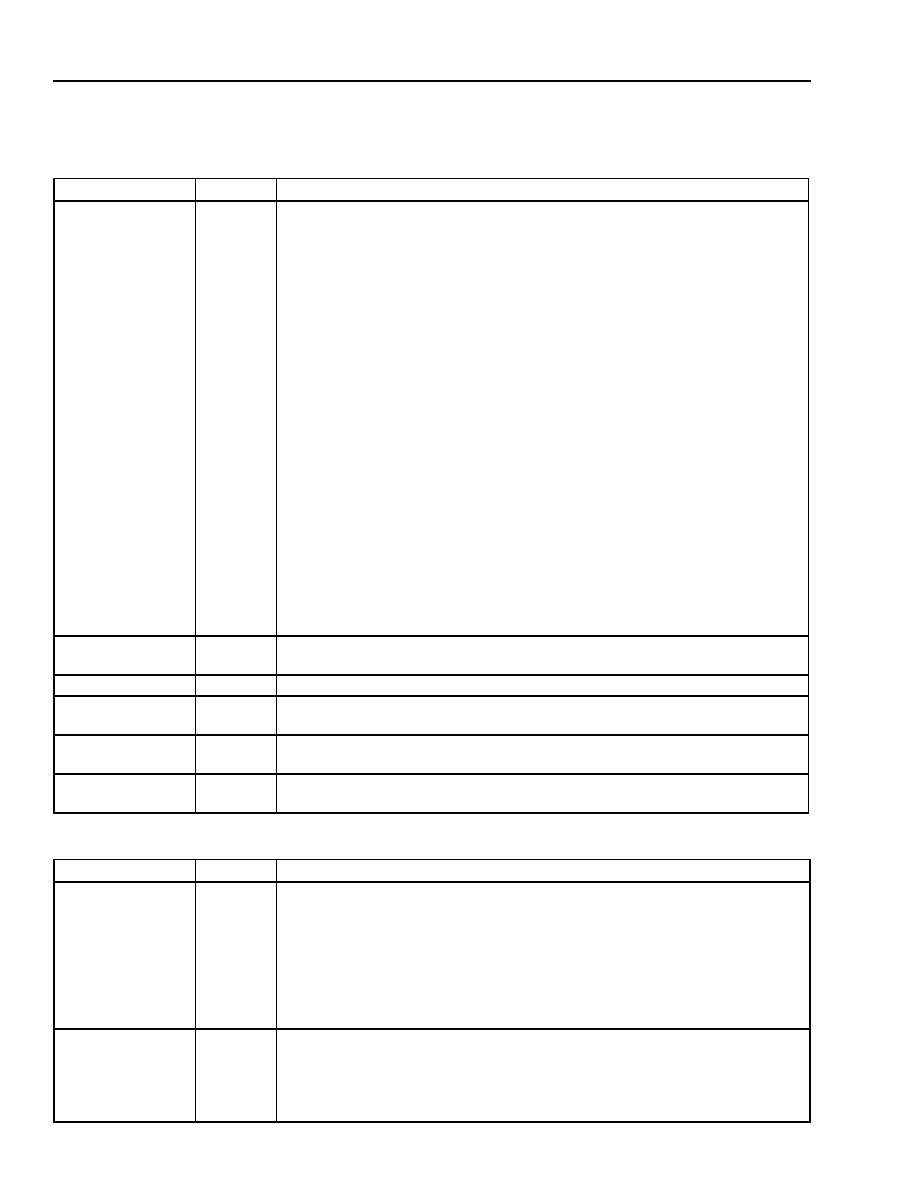

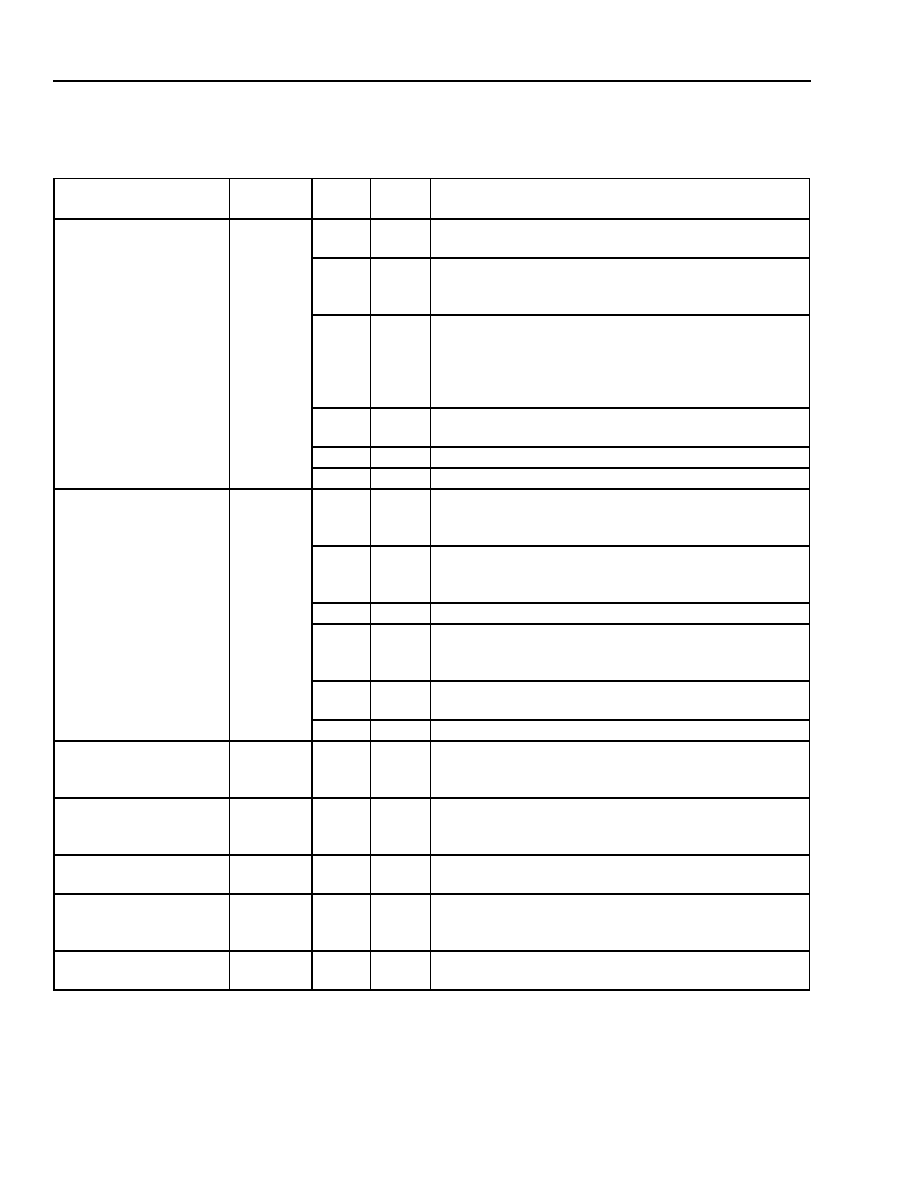

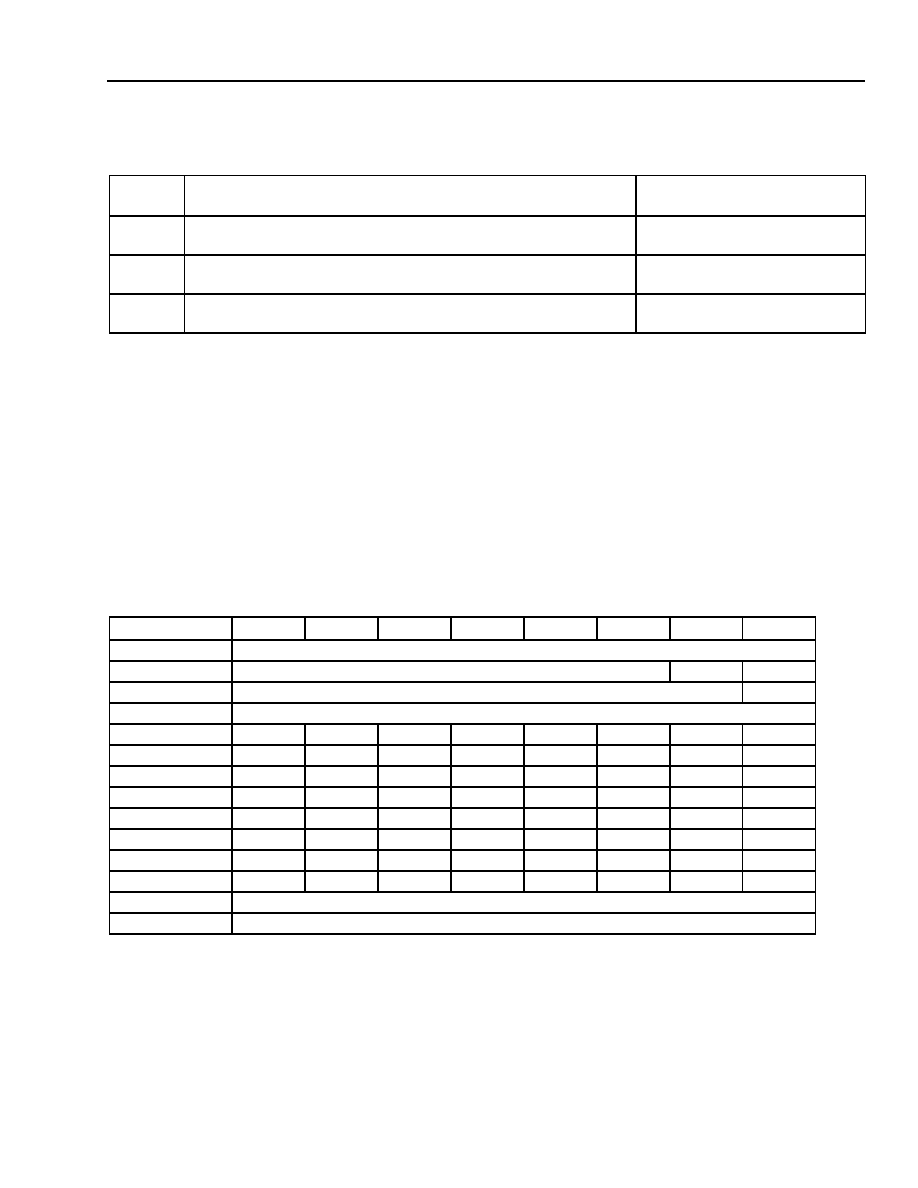

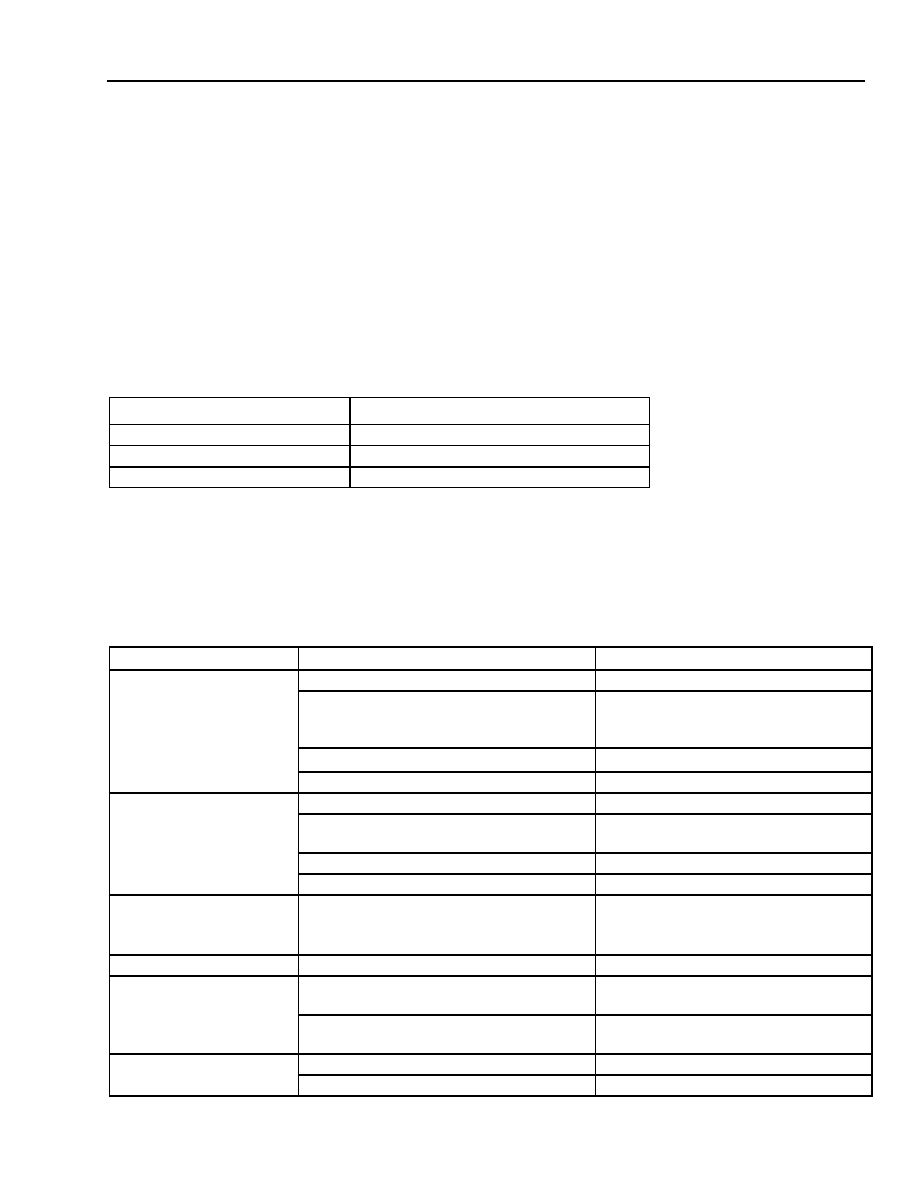

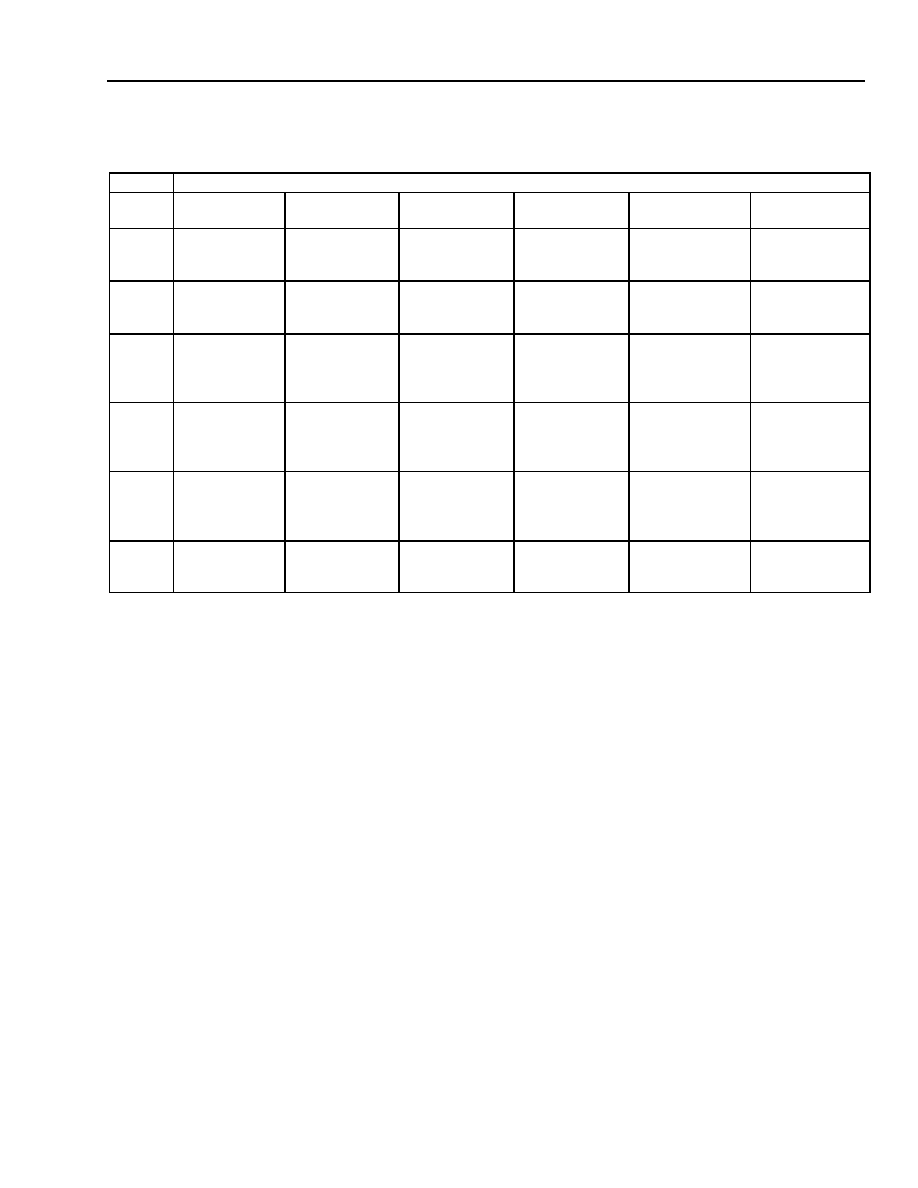

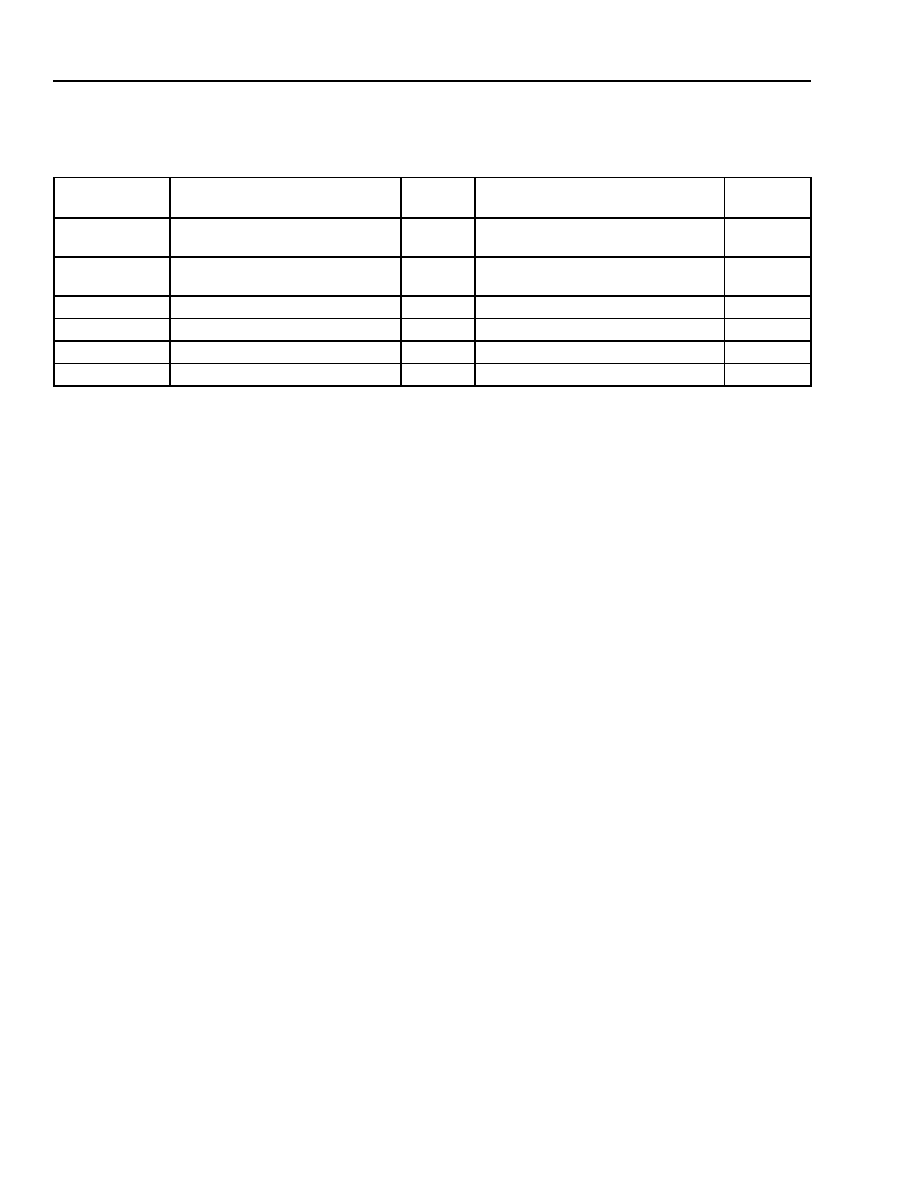

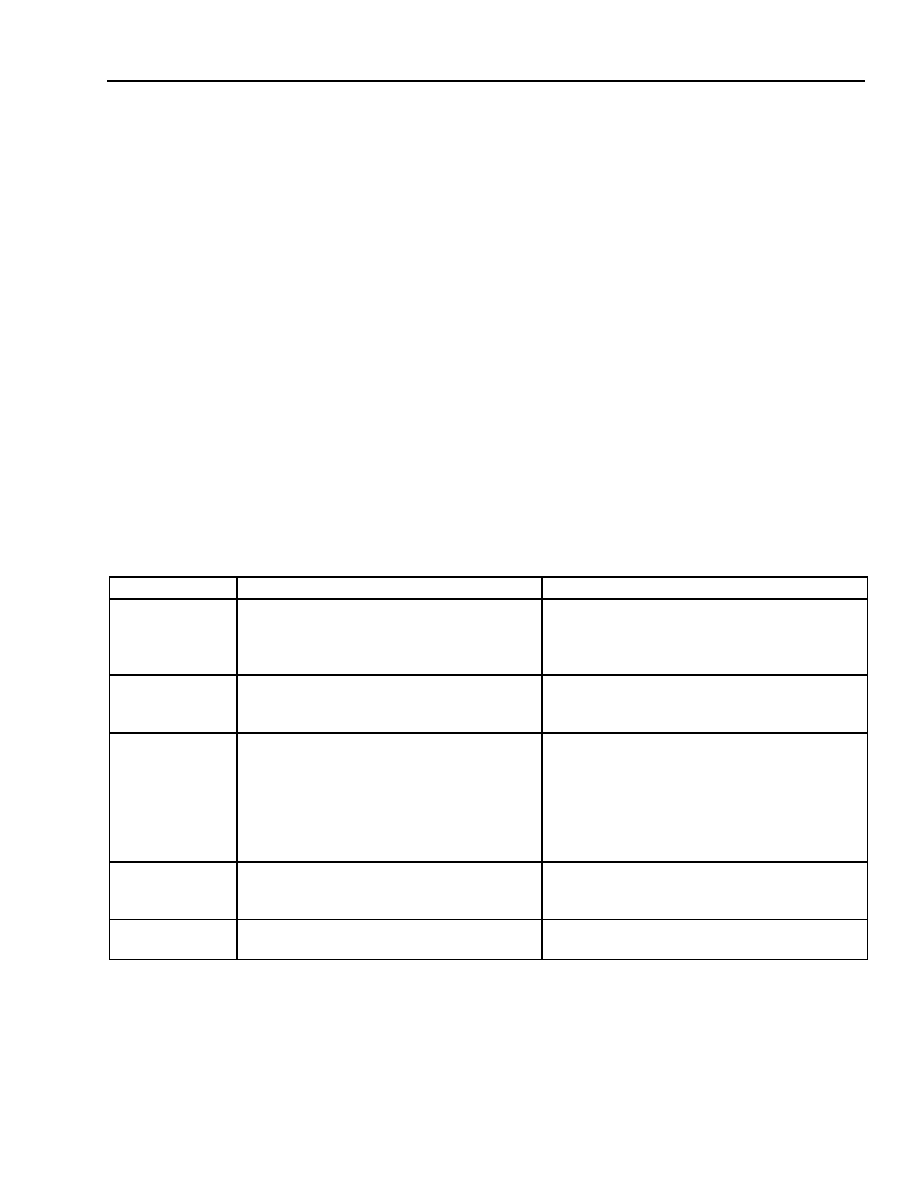

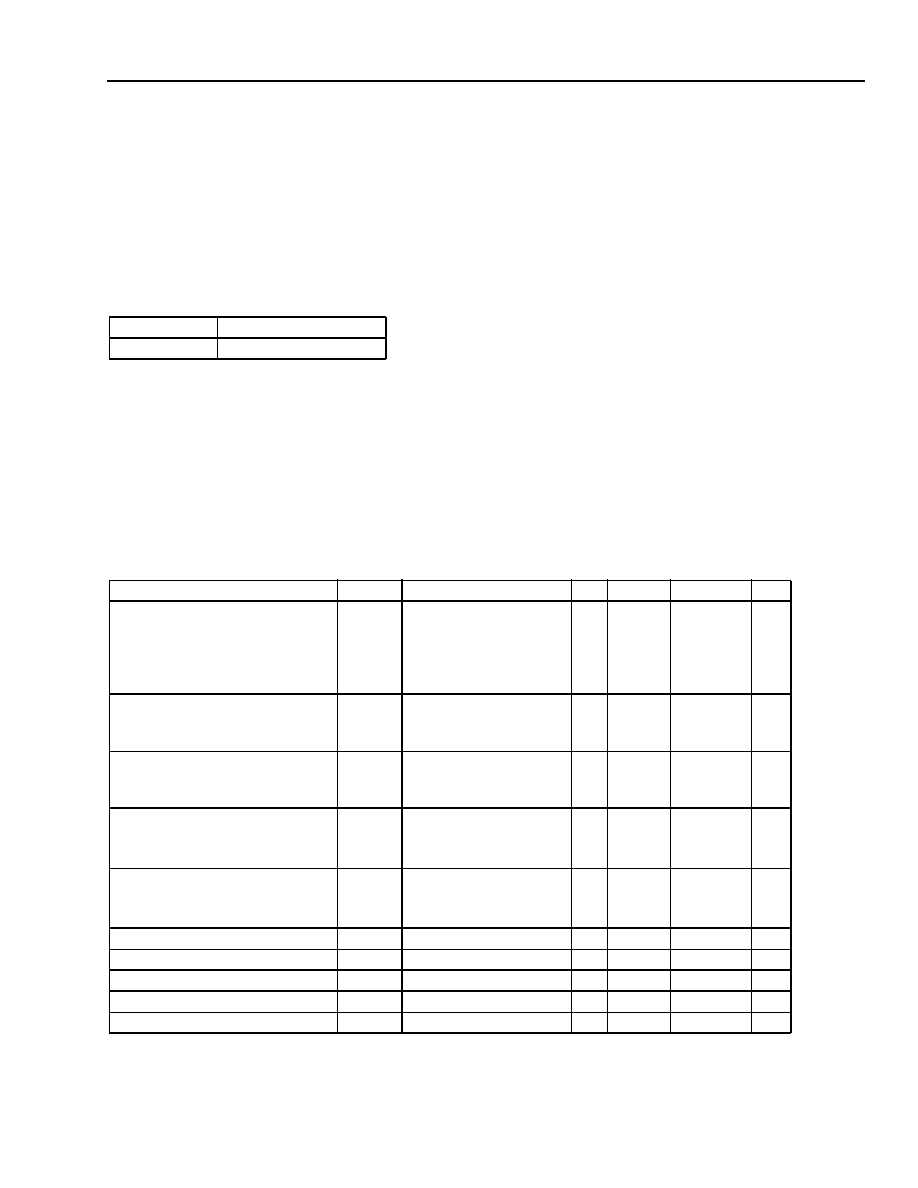

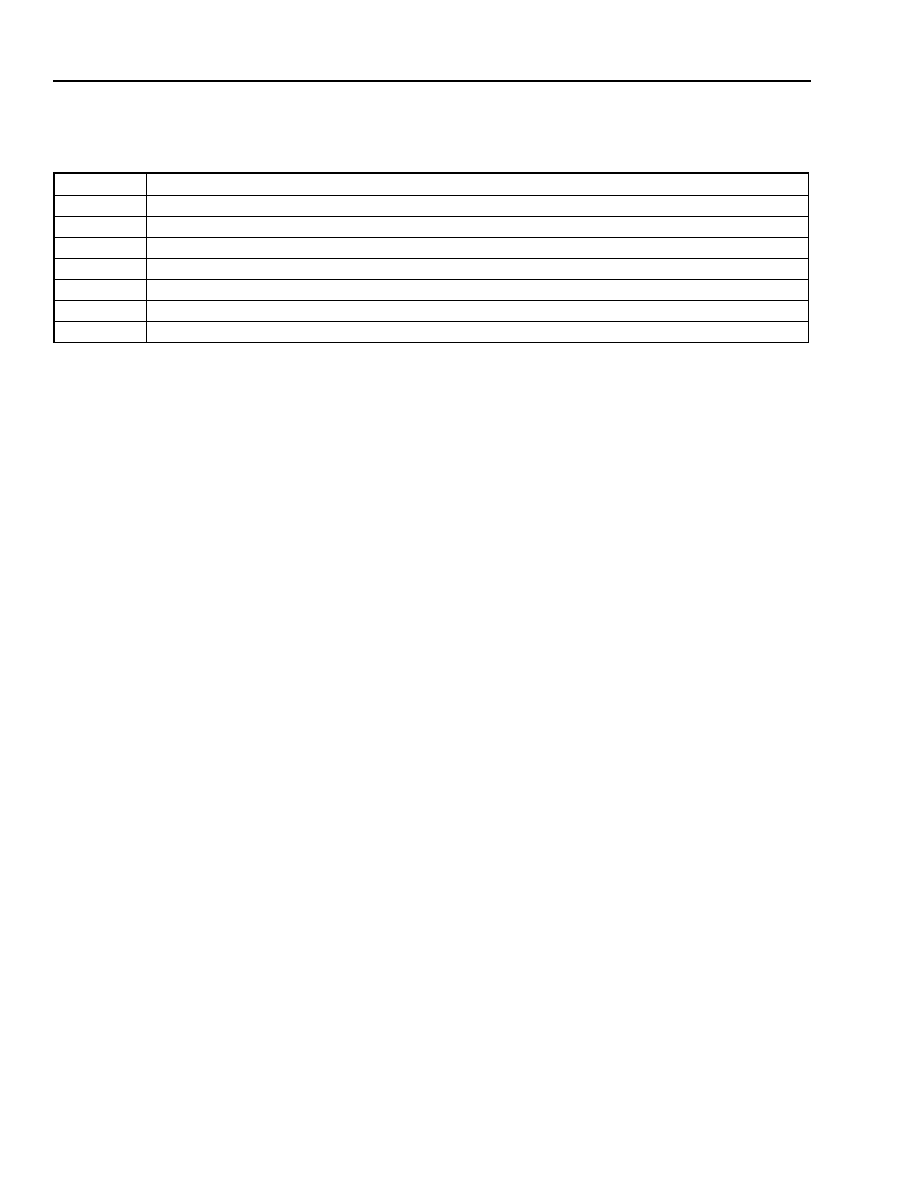

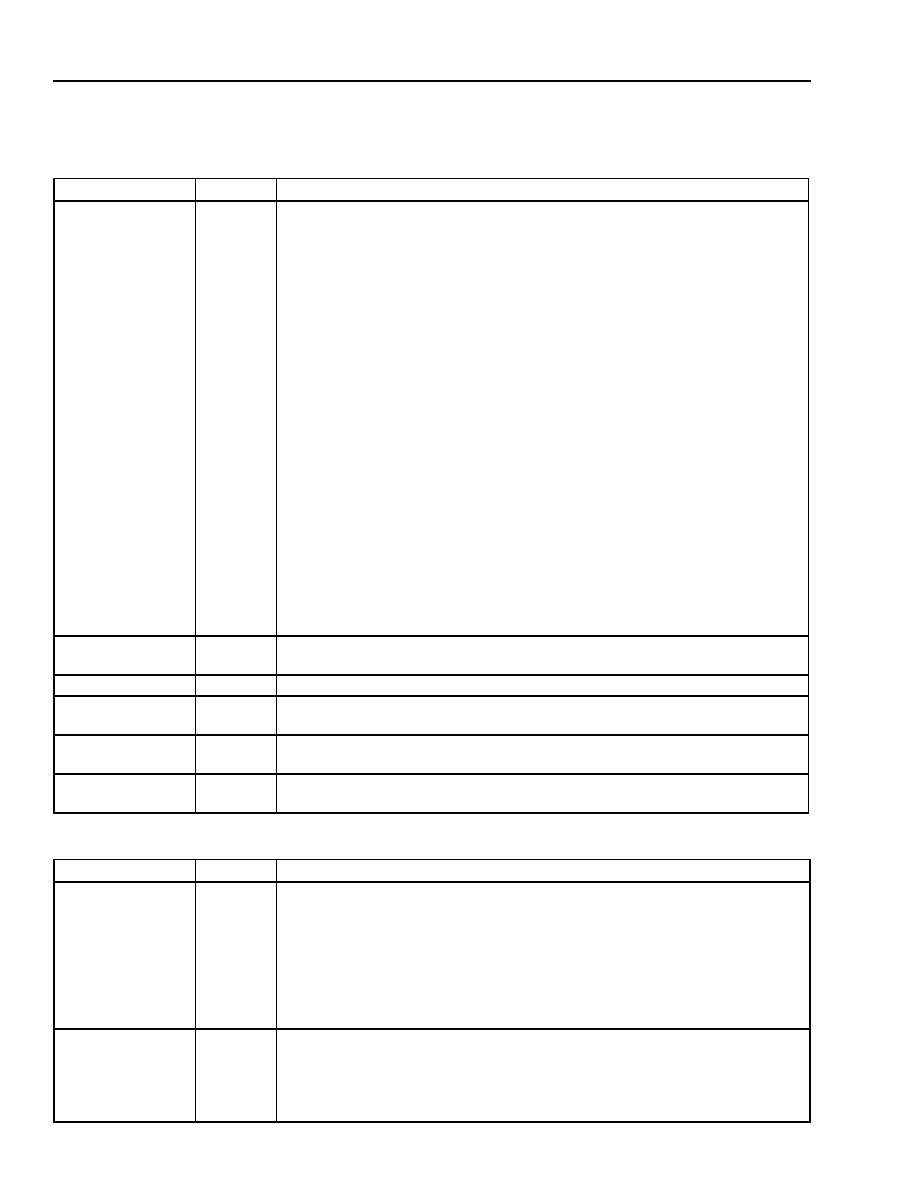

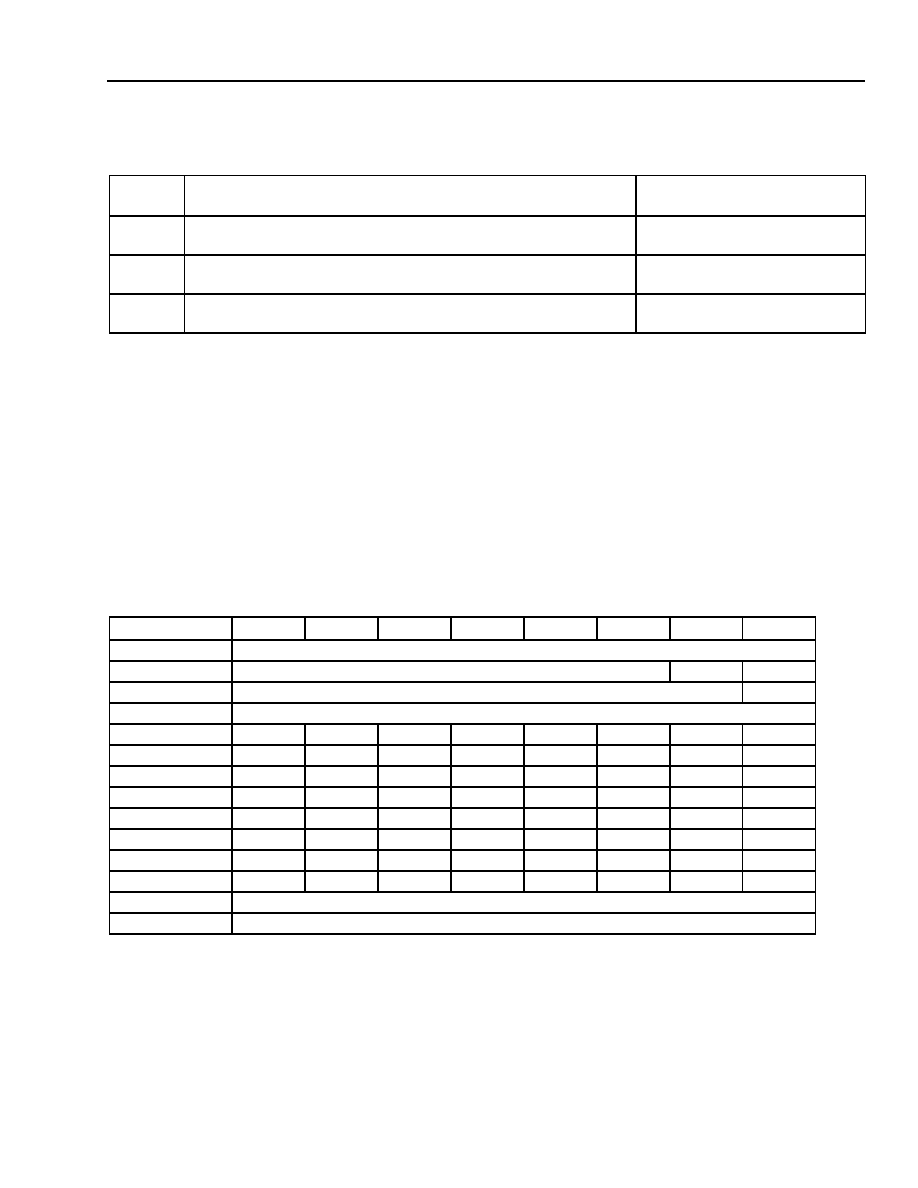

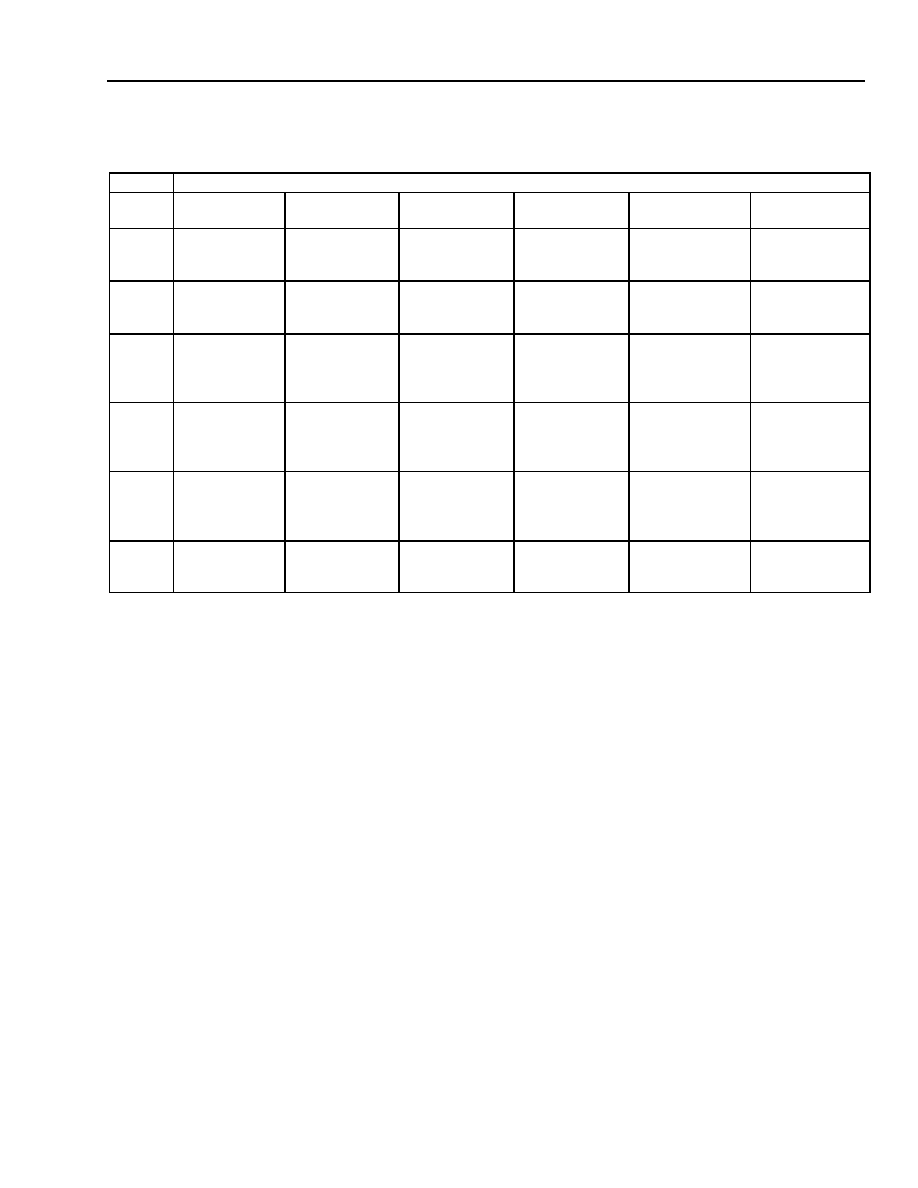

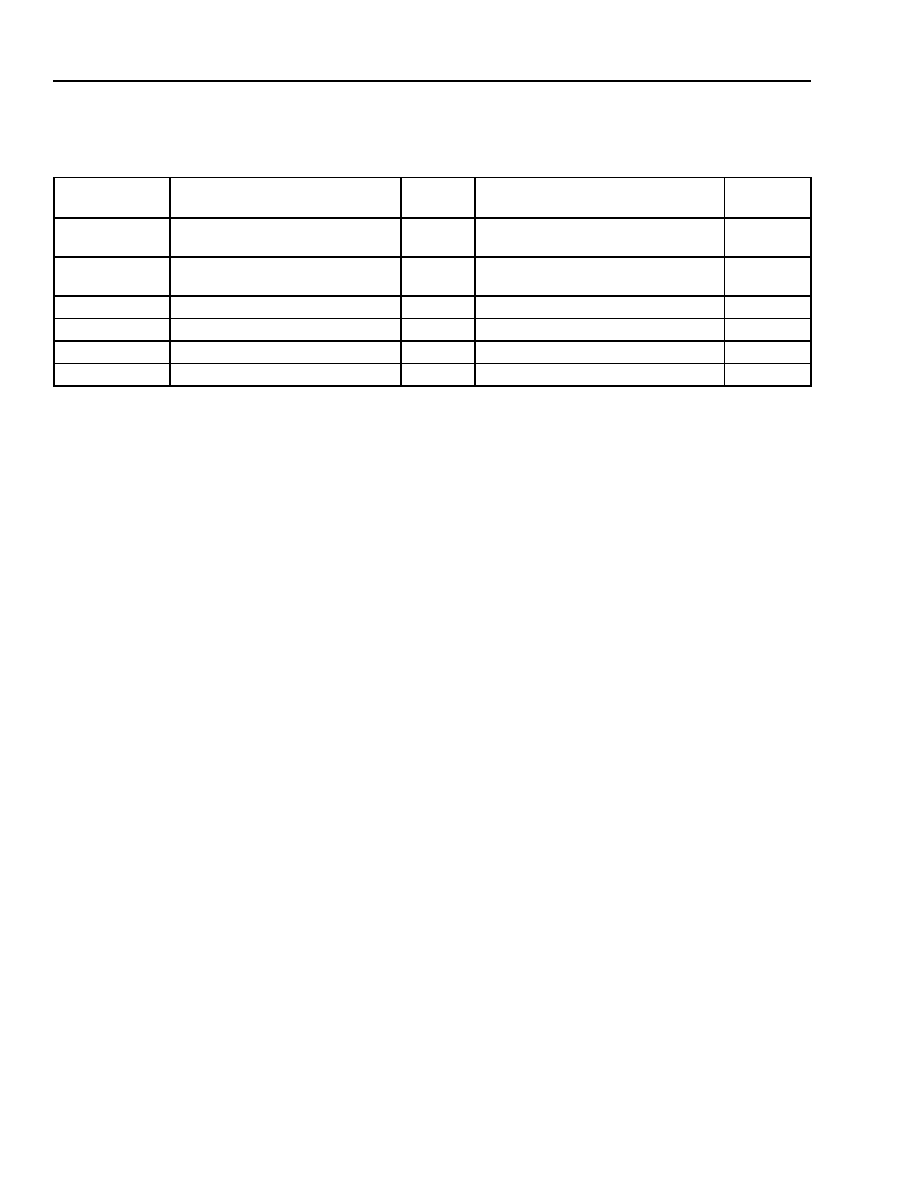

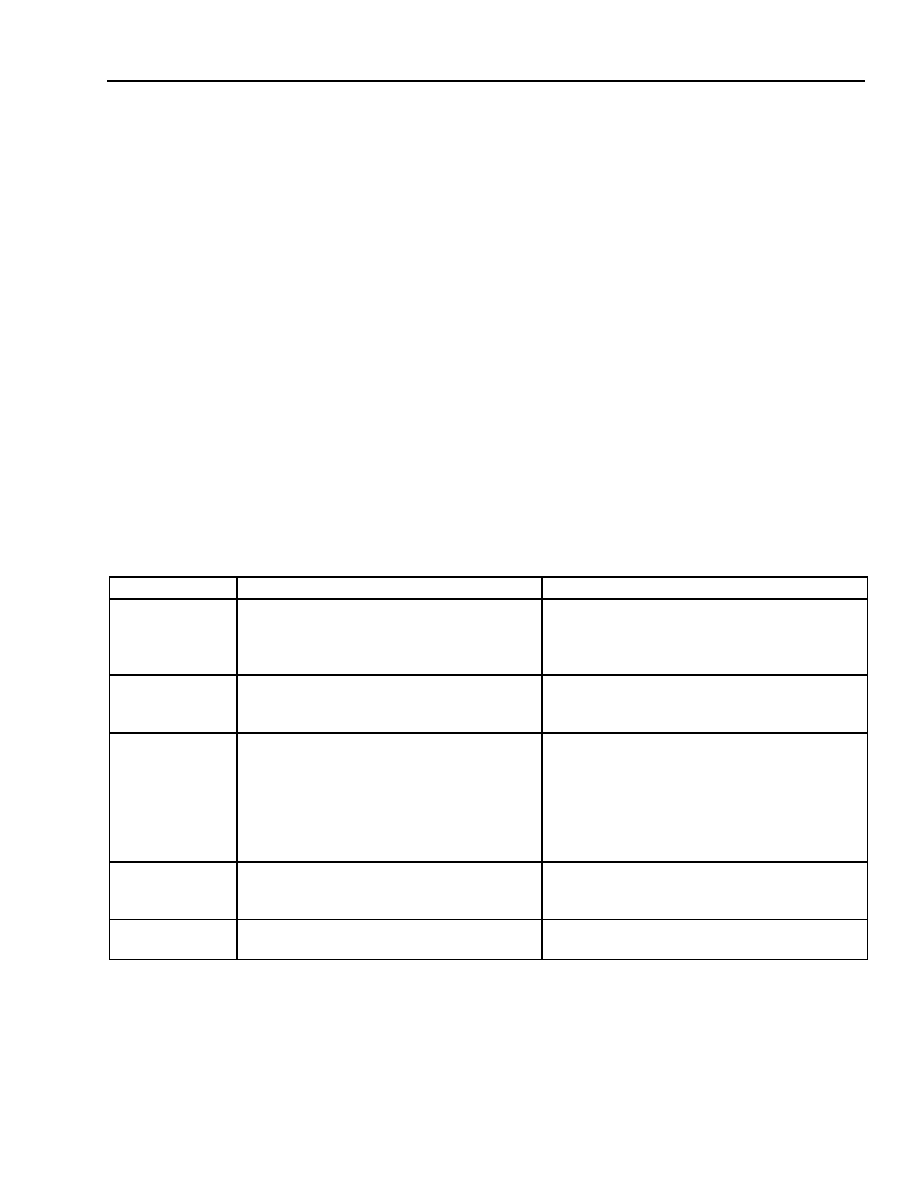

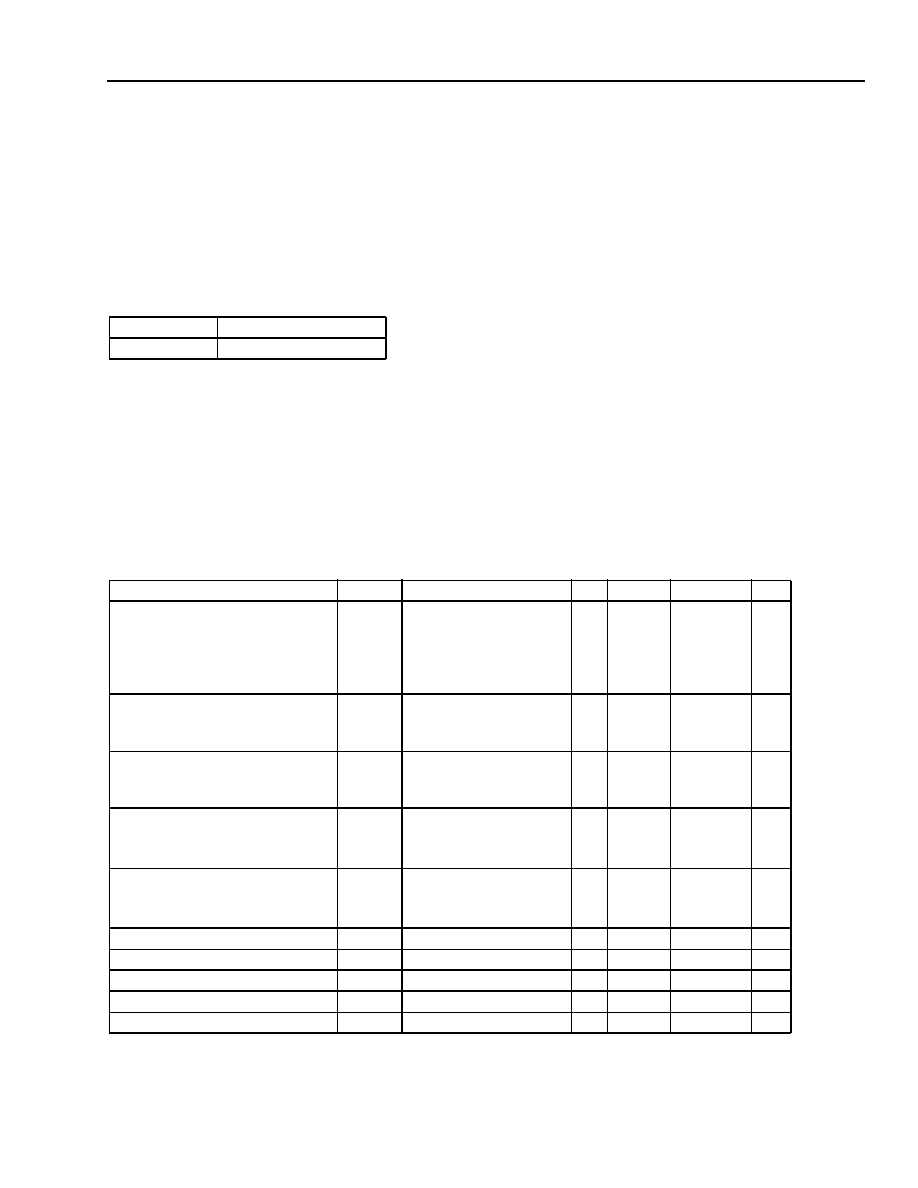

Table 1. Pin Definitions

Type

Description

I

Input only. All 3.3 V inputs are designed to be TTL compatible.

I

u

Input with high-value pull-up resistor internal to TAAD08JU2.

I

d

Input with high-value pull-down resistor internal to TAAD08JU2.

O

Output only. These outputs have I

OL

/I

OH

= 10 mA.

O-6

Output only. These outputs have I

OL

/I

OH

= 6 mA.

I/O

Bidirectional input and output.

P

Power or ground.

Agere Systems Inc.

Agere Systems - Proprietary

13

Data Sheet

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

TAAD08JU2

6 Pin Description

(continued)

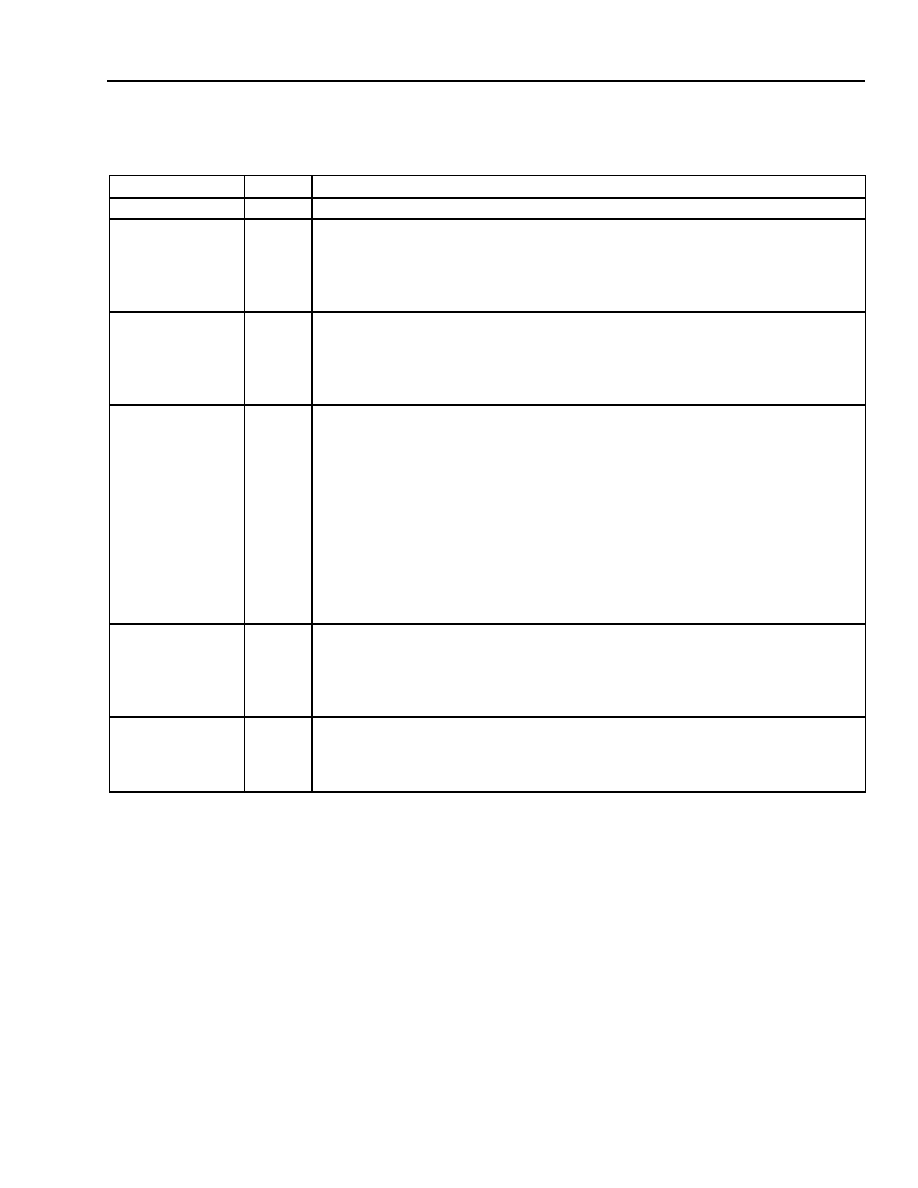

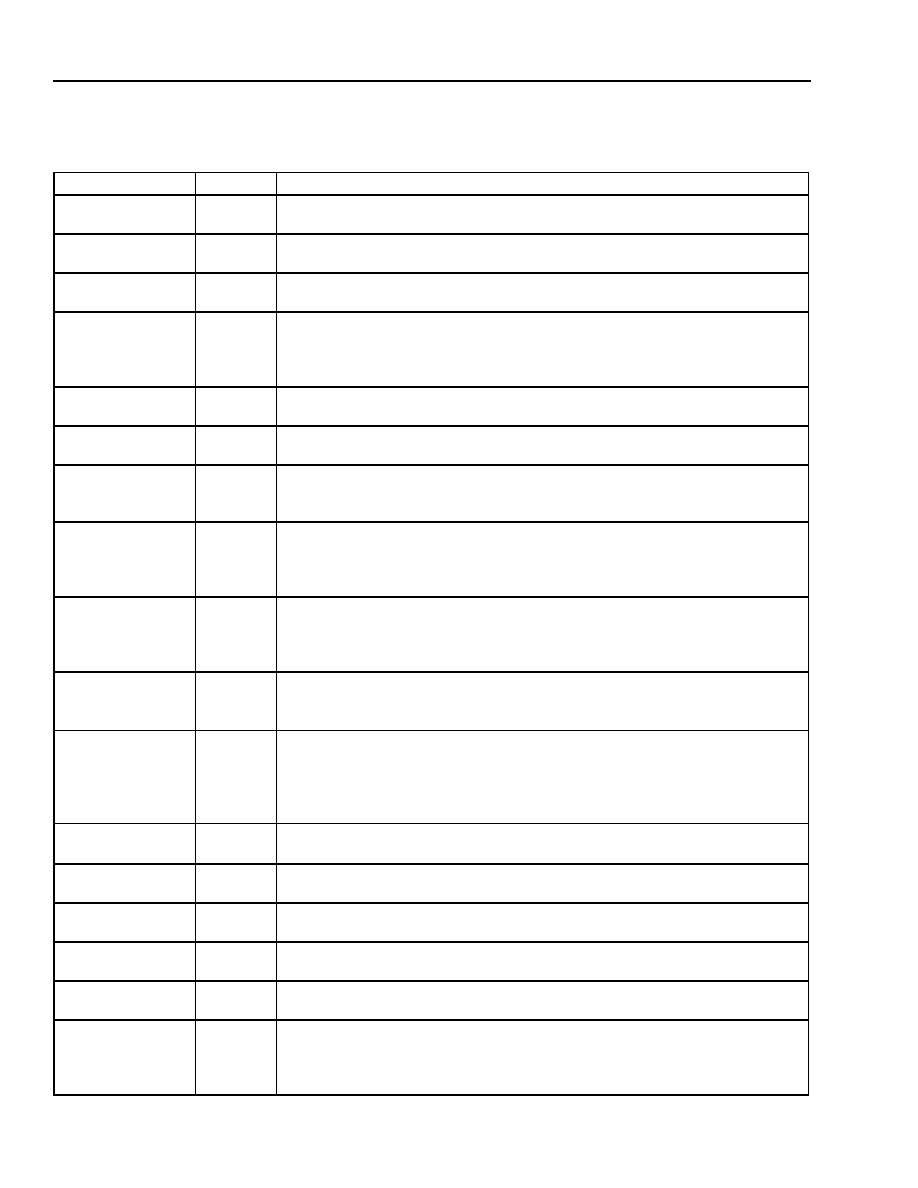

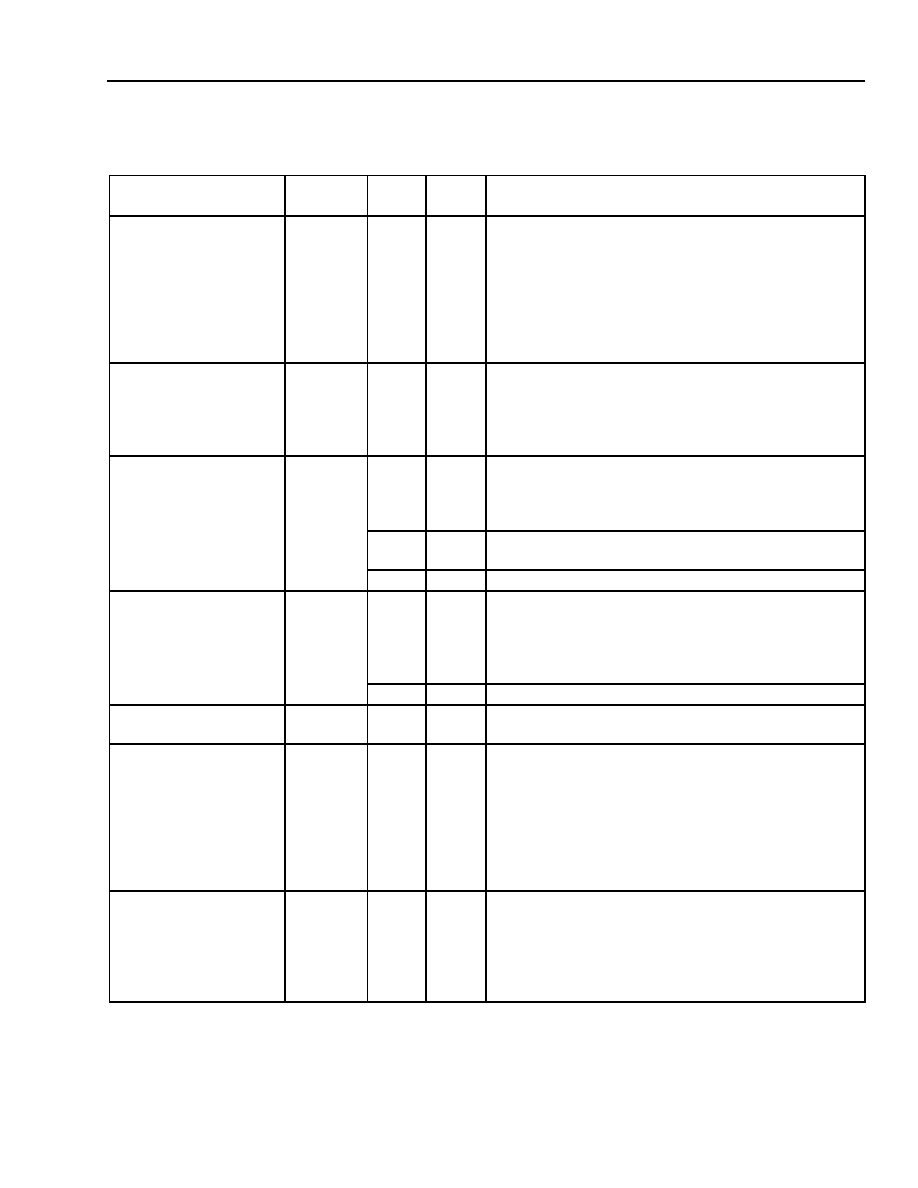

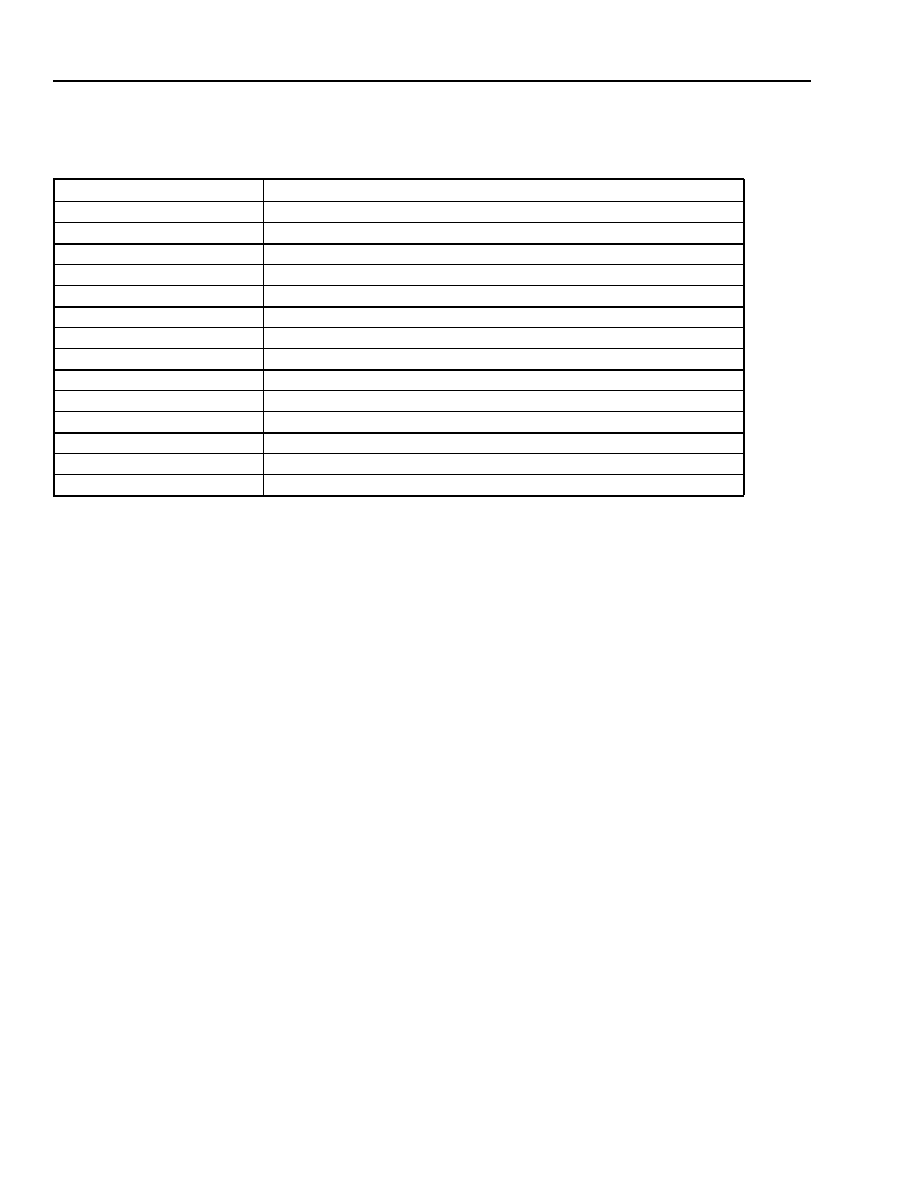

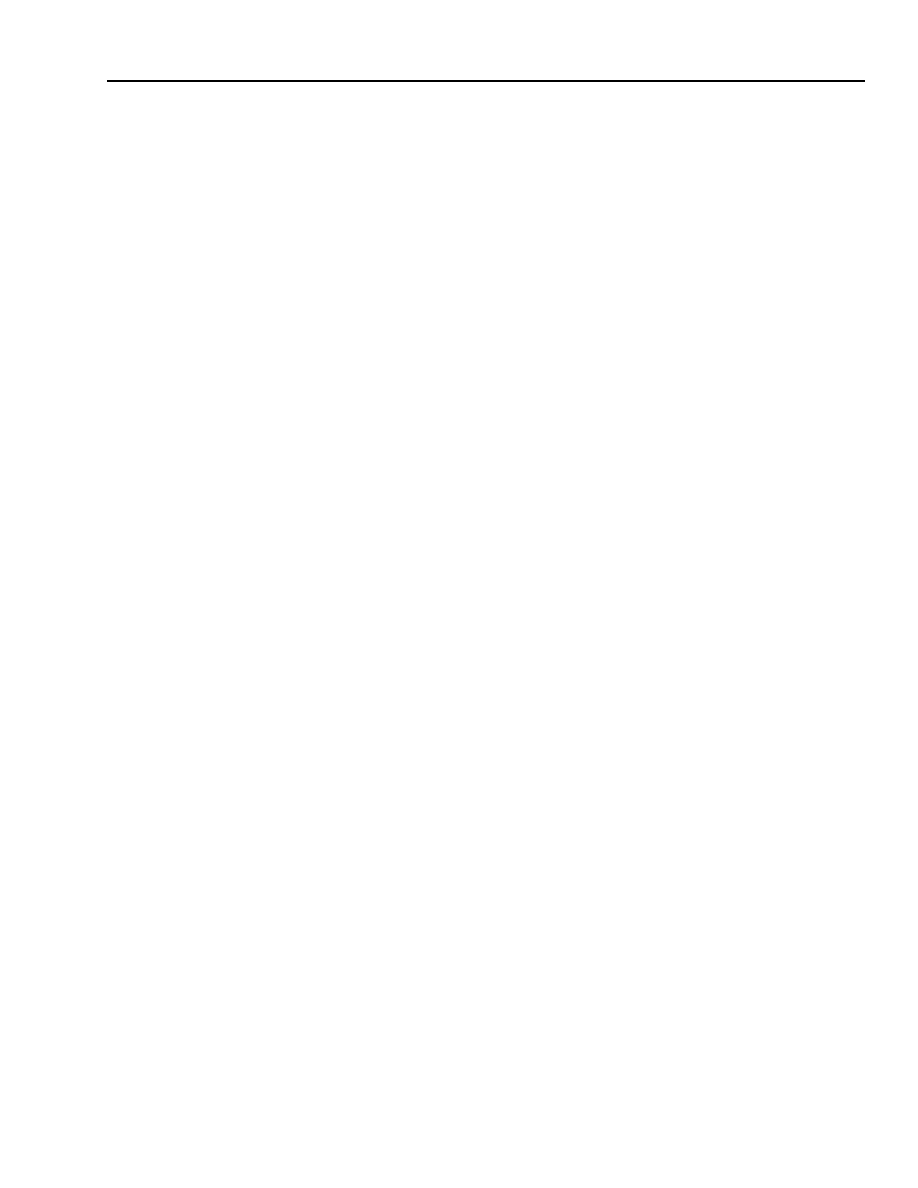

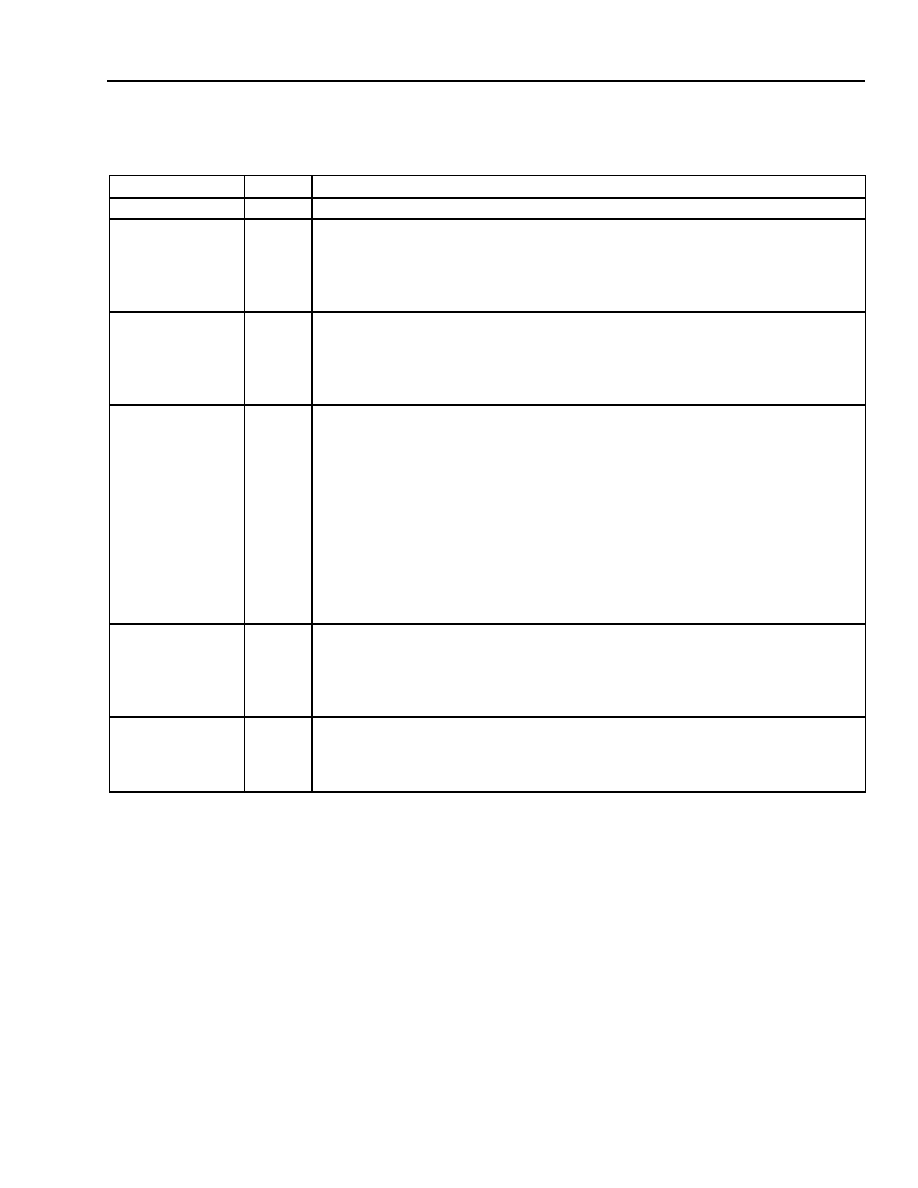

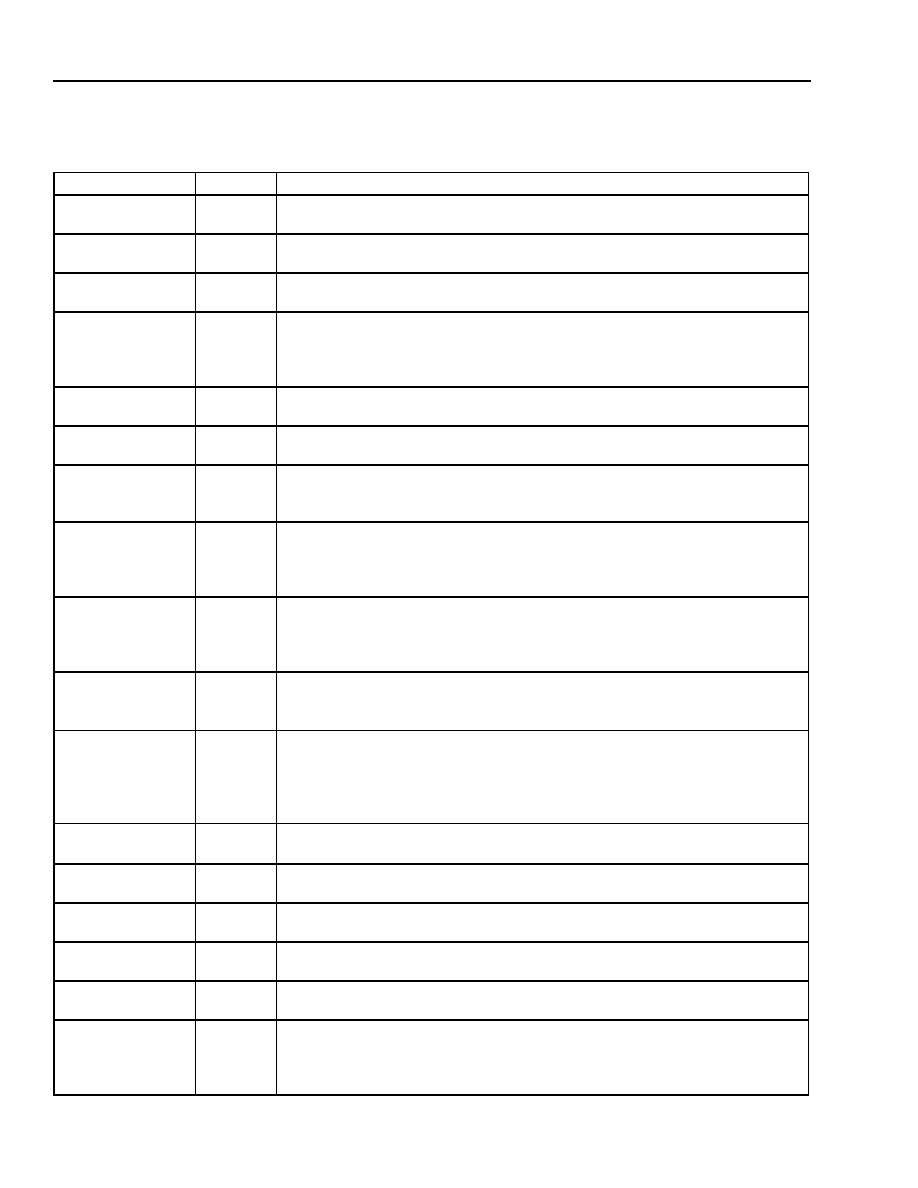

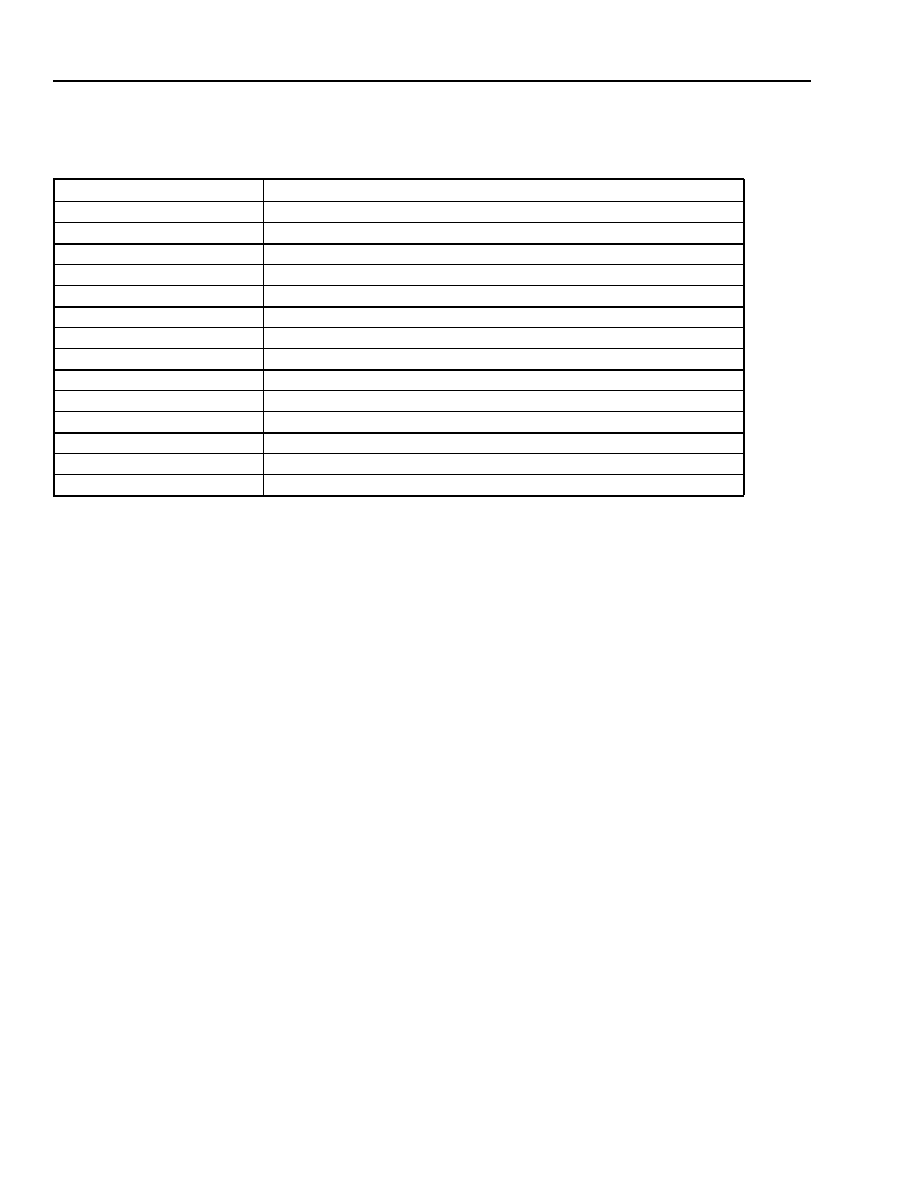

Table 2. Transmission Line Interface Signals (48 Signals)

Signal

Type

Description

LRXCLK(0:7)

I

d

Line Interface Receive Clocks. Receive path clock from the LIU.

LRXPDATA(0:7)/

LRXDATA(0:7)

I

d

Line Interface Receive Positive Rail Data/Line Interface Receive Data. When

the TAAD08JU2 device is configured to operate in a dual-rail line interface mode,

this pin is the positive receive data from the external LIU. When the TAAD08JU2

device is configured to operate in a single-rail line interface mode, this pin is the

receive data from the external LIU.

LRXNDATA(0:7)/

LRXBPV(0:7)

I

d

Line Interface Receive Negative Rail Data/Line Interface Receive Bipolar Vio-

lations. When the TAAD08JU2 device is configured to operate in a dual-rail line

interface mode, this pin is the negative receive data from the external LIU. When

the TAAD08JU2 device is configured to operate in a single-rail line interface mode,

this pin is the receive bipolar violations signal from the external LIU.

LTXCLK(0:7)

I

d

/O

Line Interface Transmit Clock. These pins can be individually programmed as

either a clock input or output in one of three modes:

1. Global clock mode. All the LTXCLK signals are outputs derived from a global

clock input signal (see CHI interface CRXCLK in Table 3).

2. All of the LTXCLK signals are outputs of the corresponding LRXCLK signals

looped back internally.

3. Independent transmit clock mode. Each LTXCLK pin is an input from the line

interface.

The clock rates, when used as either inputs or outputs, are 1.544 MHz or

2.048 MHz. When the CHI interface is active, these pins must be configured in the

global clock mode.

LTXPDATA(0:7)/

LTXDATA(0:7)

O

Line Interface Transmit Positive Rail Data/Line Interface Transmit Data. When

the TAAD08JU2 device operates in a dual-rail line interface mode, this pin is the

positive transmit data sent to the external LIU. When the TAAD08JU2 device oper-

ates in a single-rail line interface mode, this pin is the transmit data sent to the

external LIU.

LTXNDATA(0:7)

O

Line Interface Transmit Negative Rail Data. When the TAAD08JU2 device oper-

ates in a dual-rail line interface mode, this pin is the negative transmit data sent to

external LIU. When the TAAD08JU2 device operates in a single-rail line interface

mode, this pin outputs an 8 kHz frame sync pulse.

14

Agere Systems - Proprietary

Agere Systems Inc.

Data Sheet

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

TAAD08JU2

6 Pin Description

(continued)

Table 3. CHI Interface Signals (20 Signals)

Signal

Type

Description

CRXCLK

I

CHI Receive Clock. This signal is used to perform two basic functions: 1) this

pin is used to clock the CHI receive interface; 2) depending on transmit line

clock mode, the clock on this pin can be used to drive the Tx line clock (of

which there are several suboptions). These suboptions are as follows:

!

When the receive CHI interface is used, then 2.048 MHz, 4.096 MHz,

8.192 MHz, or 16.384 MHz can be supplied. Internally, TAAD08JU2 will

derive 1.544 MHz and 2.048 MHz to support T1, E1, or a mix of T1 and E1

lines.

!

If the CHI is not used, this pin can be used to drive the line clocks in two sub-

modes, as follows:

-- This pin would directly drive the Tx interface. In this mode, 1.544 MHz (T1)

or 2.048 MHz (E1) is applied to CRXCLK, and all eights links run at this

line rate.

-- A 2.048 MHz reference is applied to CRXCLK and TAAD08JU2 internally

derives 1.544 MHz and 2.048 MHz to support either T1, E1, or a mix of

T1/E1 transmit lines. This mode is essentially a subset of option 1 above,

except the CHI is not used.

!

This pin is not used when the TAAD08JU2 is programmed into independent

transmit clock mode or receive loop timing mode.

!

The CRXCLK pin does not require a clock to be connected if that pin is not

being used for any framer or CHI clocking modes. However, if a clock is

required, this can be easily accommodated by connecting GCLK to this pin.

CRXDATA(0:7)

I

CHI Receive Data. These are the received CHI data inputs at 2.048 Mbits/s,

4.096 Mbits/s, or 8.192 Mbits/s.

CRXFS

I

CHI Receive Frame Sync. Global 8 kHz frame sync for the receive CHI ports.

CTXCLK

I

CHI Transmit Clock. Global system clock for transmit defined as a 2.048 MHz,

4.096 MHz, 8.192 MHz, or 16.384 MHz global input clock.

CTXDATA(0:7)

O

CHI Transmit Data. These are the transmitted CHI data outputs clocked by the

CTXCLK at 2.048 Mbits/s, 4.096 Mbits/s, or 8.192 Mbits/s.

CTXFS

I

CHI Transmit Frame Sync. Input global 8 kHz frame sync for the transmit sys-

tem.

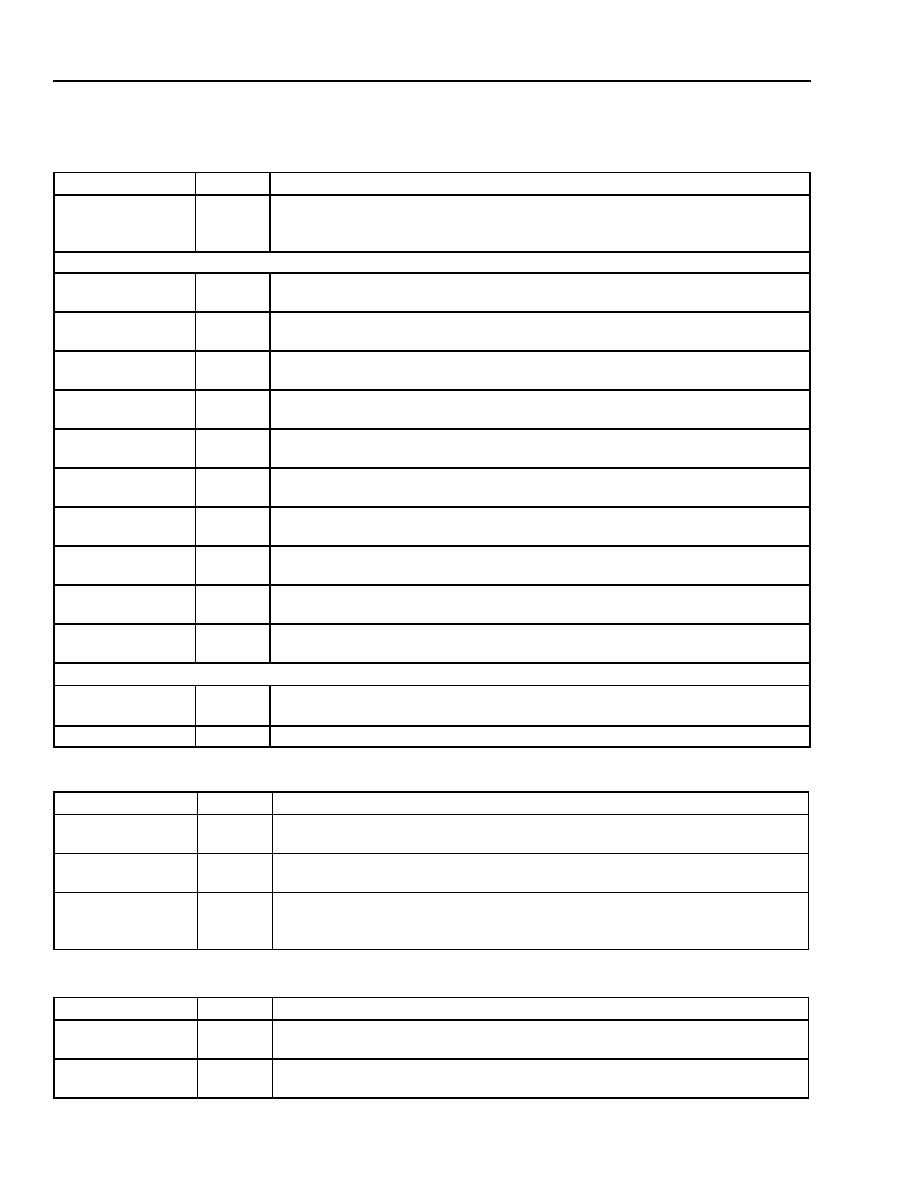

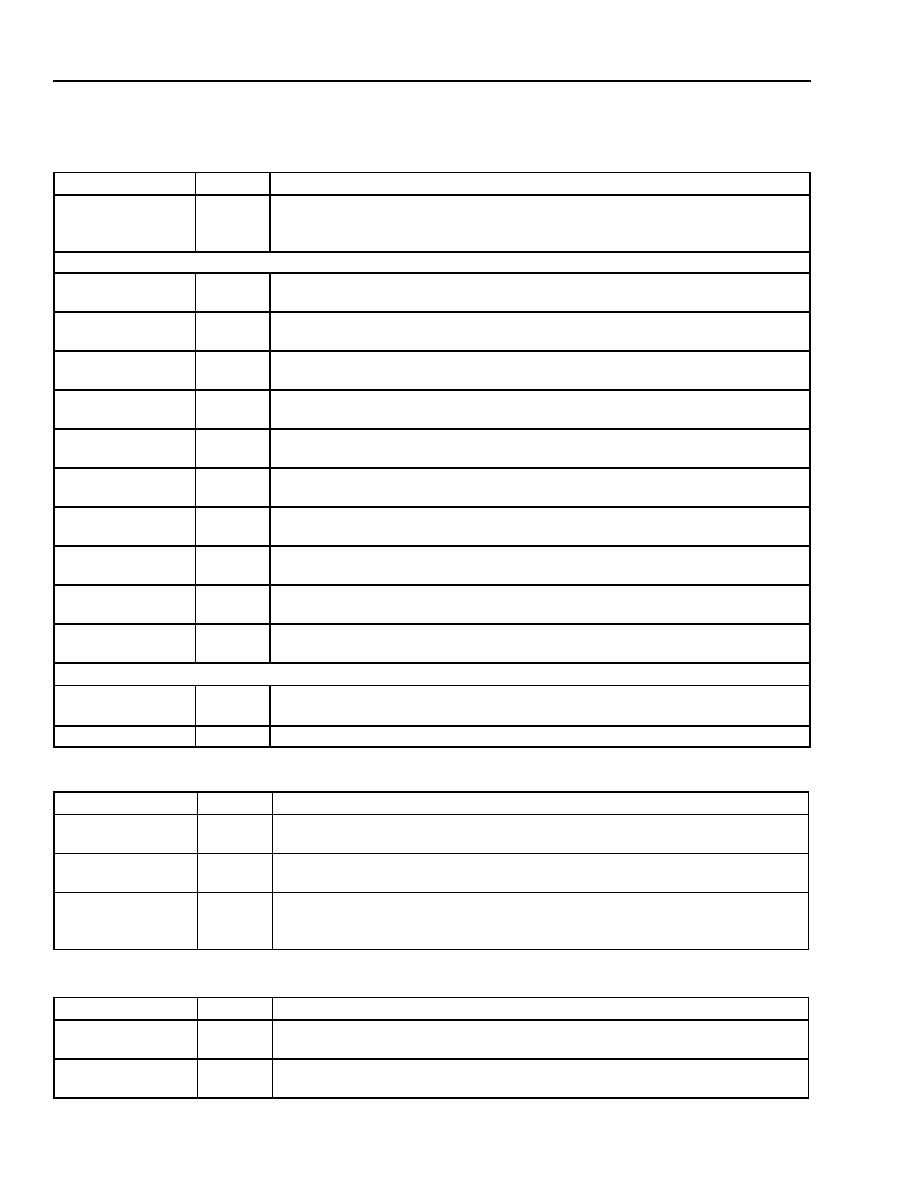

Table 4. UTOPIA 2 Expansion Interface Signals (52 Signals)

Signal

Type

Description

UMODE

I

UTOPIA Expansion Interface Mode. This pin sets the mode of operation for

this interface. The modes are described below:

0: Master Mode: This signal is set low when TAAD08JU2 is programmed to

operate in either internal or external PHY mode. In this case, the internal

APC block controls the expansion interface pins as a UTOPIA master.

1: Slave Mode: This is set high when the TAAD08JU2 is programmed into

SAR-only mode. In this mode, this interface connects to the SAR block as a

UTOPIA slave.

UCLK

I

UTOPIA Expansion Clock. This is the UTOPIA clock input for both the trans-

mit and receive UTOPIA. The clock frequency applied to this pin should be less

than or equal to GCLK. A clock must be supplied on this pin at all times. Even if

this interface is not otherwise used, a clock must still be provided. Typically, this

can be easily accommodated by connecting GCLK to this pin.

Agere Systems Inc.

Agere Systems - Proprietary

15

Data Sheet

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

TAAD08JU2

6 Pin Description

(continued)

URXDATA[15:0]

Master: I

d

Slave: O

UTOPIA Expansion Receive Data. In master mode, these signals are the par-

allel 16-bit data input bus from an external PHY device. In slave mode, these

signals are a data output bus to an external PHY device. These signals are

clocked in/out on the rising edge of UCLK. Bit URXDATA[15] is the MSB.

URXPRTY

Master: I

d

Slave: O

UTOPIA Expansion Receive Data Parity. This signal either receives (master

mode) or sends (slave mode) the receive data parity signal. When a master,

TAAD08JU2's APC block can be configured to check for odd parity or can be

disabled. When a slave, this can be configured to odd, even, or no parity.

URXSOC Master:

I

d

Slave: O

UTOPIA Expansion Receive Start of Cell. Active-high signal asserted when

U

RXDATA

contains the first word of a cell.

URXENB Master:

O

Slave: I

u

UTOPIA Expansion Receive Enable. Active-low signal asserted by the ATM

layer to signal that a transfer will occur at the next rising edge of

UCLK.

URXADDR[4:0]

Master: O

Slave: I

d

UTOPIA Expansion Receive Address. 5-bit address used by the UTOPIA

master to select the UTOPIA slave for the receive signal path. Bit 4 is the MSB.

URXCLAV

Master: I

Slave: O

UTOPIA Expansion Receive Cell Available. Active-high signal asserted when

a complete cell is available in the FIFO of the device selected by U

RXADDR

.

UTXDATA[15:0]

Master: O

Slave: I

d

UTOPIA Expansion Transmit Data. In master mode, these signals are a paral-

lel 16-bit data output bus to an external PHY device. In slave mode, these sig-

nals are a parallel 16-bit data input bus from an external PHY device. Data is

clocked out/in on the rising edge of UCLK. Bit UTXDATA[15] is the MSB.

UTXPRTY

Master: O

Slave: I

d

UTOPIA Expansion Transmit Data Parity. This signal either sends (master

mode) or receives (slave mode) the transmit data parity signal. In slave mode,

this can be configured to odd, even, or no parity on UTXDATA bus. In master

mode, transmit parity can be either odd or disabled. The default is odd.

UTXSOC Master:

O

Slave: I

d

UTOPIA Expansion Transmit Start of Cell. Active-high signal asserted when

U

TXDATA

contains the first word of a cell.

UTXENB Master:

O

Slave: I

u

UTOPIA Expansion Transmit Enable. Active-low signal asserted by the ATM

layer to signal that U

TXDATA

and U

TXSOC

contain valid data.

UTXADDR[4:0]

Master: O

Slave: I

d

UTOPIA Expansion Transmit Address. 5-bit address used by the master to

select the UTOPIA slave for the transmit signal path. Bit 4 is the MSB.

UTXCLAV

Master: I

d

Slave: O

UTOPIA Expansion Transmit Cell Available. Active-high signal asserted

when the polled slave is ready to receive complete cell can be stored in the

FIFO of the device selected by U

TXADDR

.

Table 5. System Interface Signals (62 Signals)

Signal

Type

Description

SMODE[2:0]

I

d

System Interface Mode. The two LSBs (SMODE[1:0]) determine the operating

mode of the interface, while SMODE[2] determines the clock mode in UTOPIA

cell and packet modes.

SMODE[1:0] Description

00: UTOPIA mode

01: Packet (UT2+) mode

10: Unused

11: Unused

SMODE[2] sets the clock mode for the system interface. A low on this pin

causes TAAD08JU2 to input SUCLK, and a high sets TAAD08JU2 to generate

SUCLK.

Table 4. UTOPIA 2 Expansion Interface Signals (52 Signals) (continued)

Signal

Type

Description

16

Agere Systems - Proprietary

Agere Systems Inc.

Data Sheet

August 18, 2003

T1/E1/J1 ATM Processor, Versions 2.1 and 3.1

TAAD08JU2

6 Pin Description

(continued)

SUCLK

I

d

/O

System Interface Clock. Pin programmable to be an input or output. The clock

frequency applied to this pin should be less than or equal to GCLK.

STXDATA[15:0]

O

System Interface Transmit Data. Parallel data bus to the ATM layer clocked

out on the rising edge of SUCLK. Bit 15 is the MSB.

STXADDR[4:0]

O

System Transmit Address. 5-bit address used to select the external UTOPIA

slave for the transmit signal path.

STXSOC/STXSOP

O

System Transmit Start of Cell/Packet. In cell or packet mode, when STXSOC

is high, the first word of the packet is present on the STXDATA bus. STXSOC is

considered valid only when STXENB is asserted and is updated on the rising

edge of SUCLK.

STXPRTY

O

System Transmit Data Parity. This signal sends the parity bits for the STX-

DATA bus.

STXENB

O

System Transmit Enable. Active-low signal asserted by the ATM layer to sig-

nal that STXDATA contains valid data.

STXEOP

O

System UT2+ Transmit End of Packet. This signal is high when the last word

of a packet is on the STXDATA bus. STXEOP is valid only when STXENB is

asserted and is updated on the rising edge of SUCLK (UT2+ mode only).

STXSIZ

O

System UT2+ Transmit Size. This signal indicates the size of the current word

on STXDATA. STXSIZ is valid only when STXEOP is asserted. If the last word

contains two valid bytes, STXSIZ is high while that word is on the STXDATA

bus (16-bit UT2+ mode only).

STXERR

I

d

System UT2+ Transmit Error. SRXERR is an active-high signal that indicates

when the current packet is to be aborted and discarded, if possible. STXERR is