Product Brief

October 1999

TADM042G5 SONET/SDH

155/622/2488 Mbits/s Interface

Features

s

Transmission convergence and SONET/SDH ter-

minal/ADM functionality for linear and ring net-

works.

s

Versatile IC supports 155/622/2488 Mbits/s

SONET/SDH interface solutions for packet over

SONET (POS), frame relay (FR), or asynchronous

transfer mode (ATM) applications.

s

Low-power 2.5 V/3.3 V operation.

s

≠40 ∞C to +85 ∞C temperature range.

SONET/SDH Interface

s

Termination of quad STS-3/STM-1,

quad STS-12/STM-4, or single STS-48/STM-16.

s

Supports overhead processing for transport and

path overhead bytes.

s

Optional insertion and extraction of overhead bytes

via serial overhead interface.

s

STS pointer processing to align the receive frame

to the system frame.

s

STS-1 granularity cross connect between receive,

mate, STM, and data payloads.

s

Support for 1+1 and 1:1 linear networks; UPSR

and BLSR ring networks.

s

Full path termination and SPE extraction/insertion.

s

SONET/SDH compliant condition and alarm

reporting.

s

Handles all concatenation levels of STS-3c to

STS-48c (in multiples of 3: e.g., 3c, 6c, 9c, etc.).

s

Built-in diagnostic loopback modes.

s

Compliant with Bellcore,

ANSI

*, and ITU stan-

dards.

Data Processing

s

Provisionable data engine supports payload inser-

tion/extraction for PPP, ATM, or HDLC streams.

s

Extraction and insertion of DS3 frames containing

HDLC or ATM data streams for up to 16 channels.

s

Integrated UTOPIA Level 2 and Level 3 compatible

physical layer interface for packets or ATM cells.

*

ANSI

is a registered trademark of American National Standards

Institute, Inc.

s

Insertion and extraction of up to 16 separate data

channels.

s

Maintains counts for cell/packet traffic (e.g., total

number of cells, number of discarded cells).

s

Direct cell/packet over fiber interface device.

s

Compliant with ATM forum, ITU standards, and

IETF standards.

Interfaces

s

Enhanced UTOPIA interface for cell and packet

transfer (PLATO).

s

Built-in redundant STS/STM backplane interface

using 622 MHz LVDS technology.

s

Mate-to-mate backplane interface using 622 MHz

LVDS technology for 1+1, 1:1, BLSR, and UPSR

network support.

s

Optional 78 MHz bus (32-bit) for STS/STM inter-

face.

Microprocessor Interface

s

Up to 66 MHz synchronous.

s

16-bit address and 16-bit data interface.

s

Synchronous or asynchronous modes available.

Description

The TADM042G5 SONET/SDH interface device pro-

vides a versatile solution for quad OC-3, quad OC-

12, and for single OC-48 linear and ring datacom/

telecom applications. Constructed using Agere's

state-of-the-art CMOS technology, this device incor-

porates integrated SONET/SDH framing, section/

line/path termination, pointer processing, cross con-

nect, and data engine blocks.

The device provides complete encapsulation and de-

encapsulation for packet and ATM streams into and

out of SONET/SDH payloads.

Communication with the TADM device is accom-

plished through a generic microprocessor interface.

The device supports separate address and data

buses.

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Copyright © 2001 Agere Systems Inc.

All Rights Reserved

October 1999

PN00-010SONT (Replaces PN99-173SONT)

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET:

http://www.agere.com

E-MAIL:

docmaster@agere.com

N. AMERICA:

Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA:

Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, Kowloon

Tel. (852) 3129-2000, FAX (852) 3129-2020

CHINA: (86) 21-5047-1212 (Shanghai), (86) 10-6522-5566 (Beijing), (86) 755-695-7224 (Shenzhen)

JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 778-8833, TAIWAN: (886) 2-2725-5858 (Taipei)

EUROPE:

Tel. (44) 7000 624624, FAX (44) 1344 488 045

Product Brief

October 1999

TADM042G5 SONET/SDH

155/622/2488 Mbits/s Interface

Description

(continued)

With the TADM device, construction of all types of interfaces for OC-3/OC-12/OC-48 data equipment is simplified

and cost reduced allowing extremely competitive solutions to be constructed.

This device integrates the SONET/SDH network termination functions with a generic cell/packet delineation circuit.

It supports STS-48/STM-16, quad STS-12/STM-4 and quad STS-3/STM-1 interface rates. Up to 16 data channels

transported within an STS-N payload are processed and handed off over an enhanced UTOPIA interface. The con-

catenation levels supported by this device are STS-1, STS-3c, STS-6c, STS-9c, STS12c, STS-15c, . . . , STS45c,

STS-48c. The data formats processed by this device are ATM cells or HDLC framed packets such as PPP or SDL

(SDL is planned for future releases of the device) framed packets. Future plans for the TADM042G5 also call for a

virtual concatenation feature allowing all non-traditional concatenation modes like STS-5c, STS-7c, etc. Enabling

service providers flexibility to adjust their bandwidth on demand.

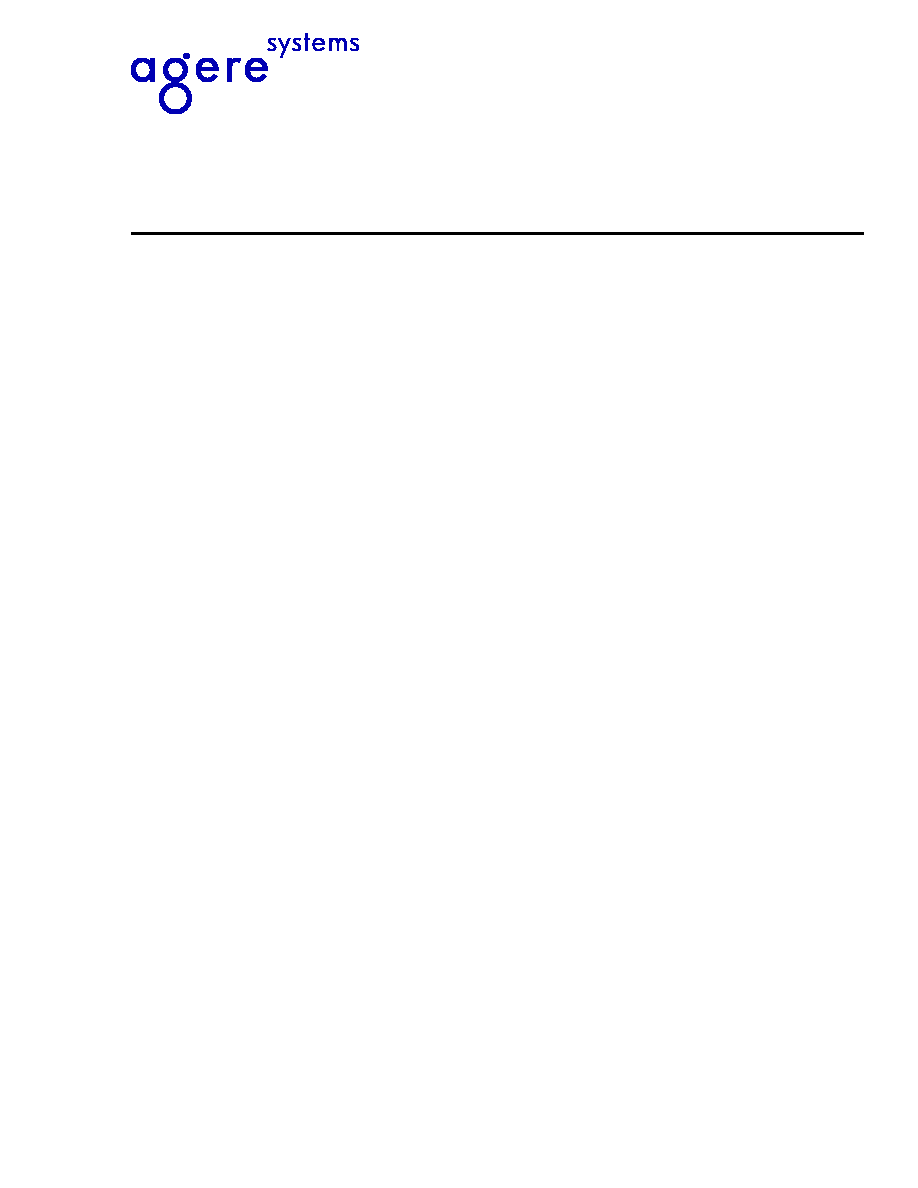

5-7393(F)r.3

Figure 1. Block Diagram

PACKET/CELL

OVERHEAD

PROCESSOR:

∑DELINEATION

∑DESCRAMBLING

∑DECAPSULATION

PROCESSOR

MONITOR

OVERHEAD

PROCESSOR

INSERT

TRANSPORT

OVERHEAD

INT

E

RF

A

C

E

B

L

O

CK

PO

I

N

T

E

R

PR

O

C

ES

S

O

R

CONNECTION

MEMORY

PTR

INTER

AND

DS3

MPR

PACKET/CELL

FIFOs

CONTROL

DS3

MPR

AND

SPE

MPR

PACKET/CELL

PROCESSOR:

∑ENCAPSULATION

∑SCRAMBLING

PAYLOAD

TERMINATION

TSI

STM INTERFACE

MATE

INTERFACE

SWITCHING

UTOPIA

INTERFACE

STM_B

STM_A

MPU INTERFACE

DIRECT CELL/PACKET OVER FIBER

SINGLE

STM-16/STS-48

OR QUAD

STM-4/STS-12

OR QUAD

STM-1/STS-3

SINGLE

STM-16/STS-48

OR QUAD

STM-4/STS-12

OR QUAD

STM-1/STS-3

MISCELLANEOUS

GPIO/STMDCC

TOAC INTERFACE

TERMINATION

TXCLK

PATH

SWITCH

LINE

SWITCH

DIRECT CELL/PACKET OVER FIBER