Product Brief

October 1999

TDAT042G5 SONET/SDH

155/622/2488 Mbits/s Data Interface

Features

s

Point-to-point path termination device for interface

termination.

s

Versatile IC supports 155/622/2488 Mbits/s

SONET/SDH interface solutions for packet over

SONET (POS), asynchronous transfer mode

(ATM), or simplified data link (SDL) for data over

fiber applications.

s

Supports point-to-point and multi-PHY UTOPIA.

s

Low-power 3.3 V operation, CMOS technology.

s

High-speed I/O is LVPECL. All other logic has 5 V

tolerant TTL-level inputs.

s

≠40 ∞C to +85 ∞C temperature range.

s

600 LBGA package.

SONET/SDH Interface

s

Termination of quad STS-3/STM-1,

quad STS-12/STM-4, or single STS-48/STM-16.

s

Supports overhead processing for transport and

path overhead bytes.

s

Optional insertion and extraction of overhead bytes

via serial overhead interface.

s

Full path termination and SPE extraction/insertion.

s

SONET/SDH compliant condition and alarm

reporting.

s

Handles all concatenation levels of STS-3c

through STS-48c (in multiples of 3; i.e., 3c, 6c, 9c,

etc.), STM-1 through STM-16.

s

Built-in diagnostic loopback modes.

s

Compliant with the following Bellcore,

ANSI

*, and

ITU standards:

-- GR-253 CORE: SONET Transport Systems:

Common Generic Criteria.

*

ANSI

is a registered trademark of American National Standards

Institute, Inc.

-- ITU-T G.707: Network Node Interface for the

Synchronous Digital Hierarchy.

-- ITU-T G.803: Architecture of Transport Net-

works Based on the Synchronous Digital

Hierarchy.

-- T1.105: SONET-Basic Description including

Multiplex Structure, Rates and Formats.

-- T1.105.02 SONET-Payload Mappings.

-- T1.105.03 SONET-Jitter at Network Interfaces.

-- T1.105.06 SONET Physical Layer

Specifications.

-- T1.105.07 SONET-Sub-STS-1 Interface Rates

and Formats Specification.

-- ITU-T I.432: B-ISDN User-Network Interface-

Physical Layer Specification.

-- IETF RFC 1619: PPP over SONET/SDH.

-- IETF RFC 1661: The Point-to-Point Protocol

(PPP).

-- IETF RFC 1662: PPP in HDLC-like Framing.

Data Processing

s

Provisionable data engine supports payload inser-

tion/extraction and CRC-16/-32 generation/verifi-

cation for ATM cell or PPP, SDL, or HDLC streams.

s

Maintains counts for cell/packet traffic (e.g., total

number of cells, number of discarded cells).

s

Integrated UTOPIA Level 2- and UTOPIA Level 3-

compatible ATM physical layer interface with

packet extensions for all test and operations.

s

Insertion and extraction of up to four separate data

channels.

s

Compliant with 1998: ATM Forum, ITU standards,

and IETF standards.

Microprocessor Interface

s

16-bit address and 16-bit data interface with up to

66 MHz read and write access.

s

Compatible with most industry-standard proces-

sors.

TDAT042G5 SONET/SDH

Product Brief

155/622/2488 Mbits/s Data Interface

October 1999

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Copyright © 2001 Agere Systems Inc.

All Rights Reserved

October 1999

PN00-002SONT (Replaces PN98-130TIC)

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET:

http://www.agere.com

E-MAIL:

docmaster@agere.com

N. AMERICA:

Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA:

Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, Kowloon

Tel. (852) 3129-2000, FAX (852) 3129-2020

CHINA: (86) 21-5047-1212 (Shanghai), (86) 10-6522-5566 (Beijing), (86) 755-695-7224 (Shenzhen)

JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 778-8833, TAIWAN: (886) 2-2725-5858 (Taipei)

EUROPE:

Tel. (44) 7000 624624, FAX (44) 1344 488 045

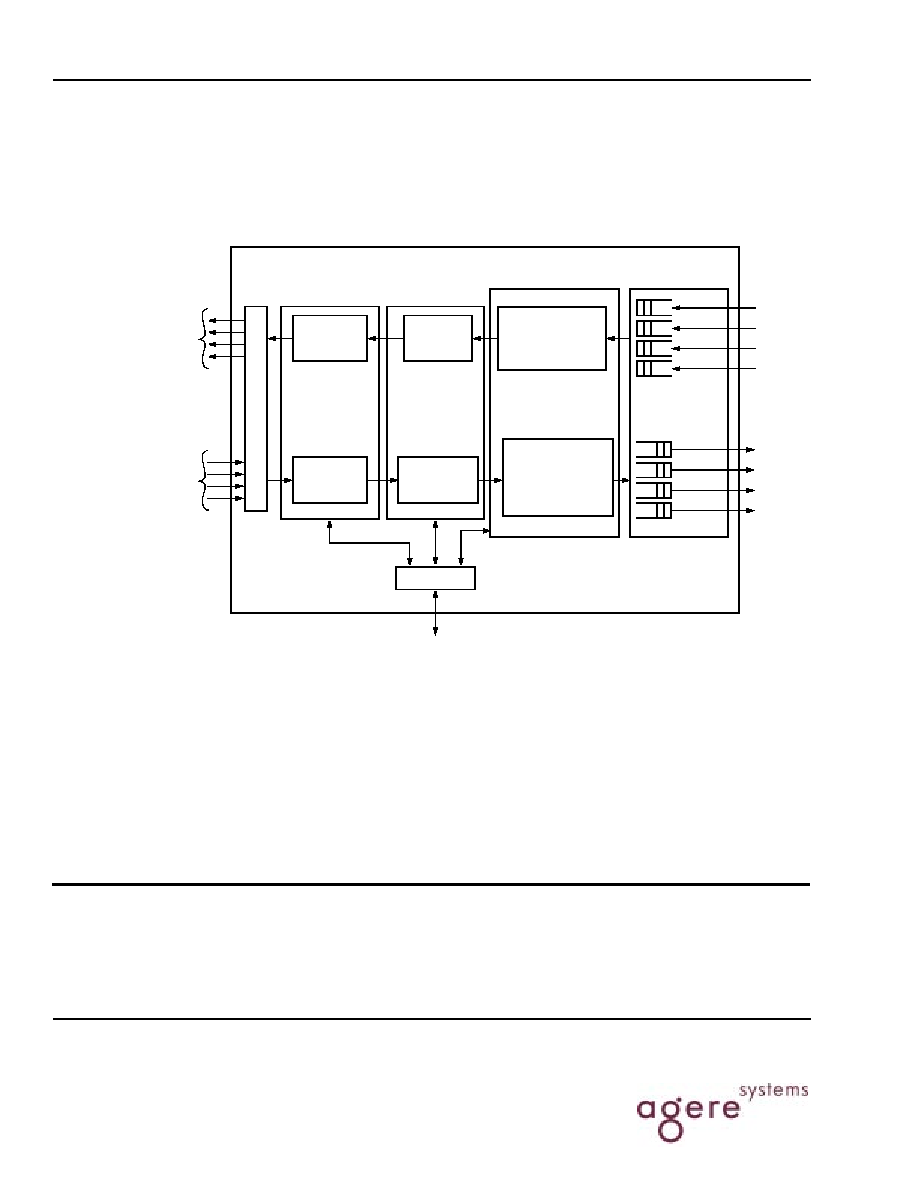

Description

The TDAT042G5 SONET/SDH interface device provides a versatile solution for quad STS-3/STM-1, quad STS-12/

STM-4, and for single STS-48/STM-16 point-to-point datacom/telecom applications. Constructed using Lucent

Technologies Microelectronics Group's state-of-the-art CMOS technology, this device incorporates integrated

SONET/SDH framing, section and line overhead insertion and extraction, path termination, and generation.

5-6680(F).ar.15

Figure 1. Overview Block Diagram

OVERHEAD

PROCESSOR

OVERHEAD

PROCESSOR

SPE

MAPPER

POINTER

INTERPRETER

L

I

NE

INT

E

RF

A

C

E

B

L

O

CK

LINE

TERMINATION

PATH

TERMINATION

PAYLOAD

TERMINATION

PACKET/CELL

PROCESSOR

-DELINEATION

-DECAPSULATION

-UNSCRAMBLING

SINGLE STM-16/STS-48

OR QUAD STM-4/STS-12

ENHANCED

OR QUAD STM-1/STS-3

SINGLE STM-16/STS-48

OR QUAD STM-4/STS-12

OR QUAD STM-1/STS-3

CONTROL

µ

P INTERFACE

UTOPIA

INSERT

MONITOR

-CRC VERIFICATION

ENHANCED

UTOPIA

COMPATIBLE

INTERFACE

PACKET/CELL

PROCESSOR

-ENCAPSULATION

-SCRAMBLING

-CRC GENERATION

L

I

NE

INT

E

RF

A

C

E

(U2, U2+, U3, U3+)

INTERFACE