| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TDAT04622 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- DA01-010SONT.pdf

- Introduction

- TDAT04622

- TDAT021G2

- TDAT042G5

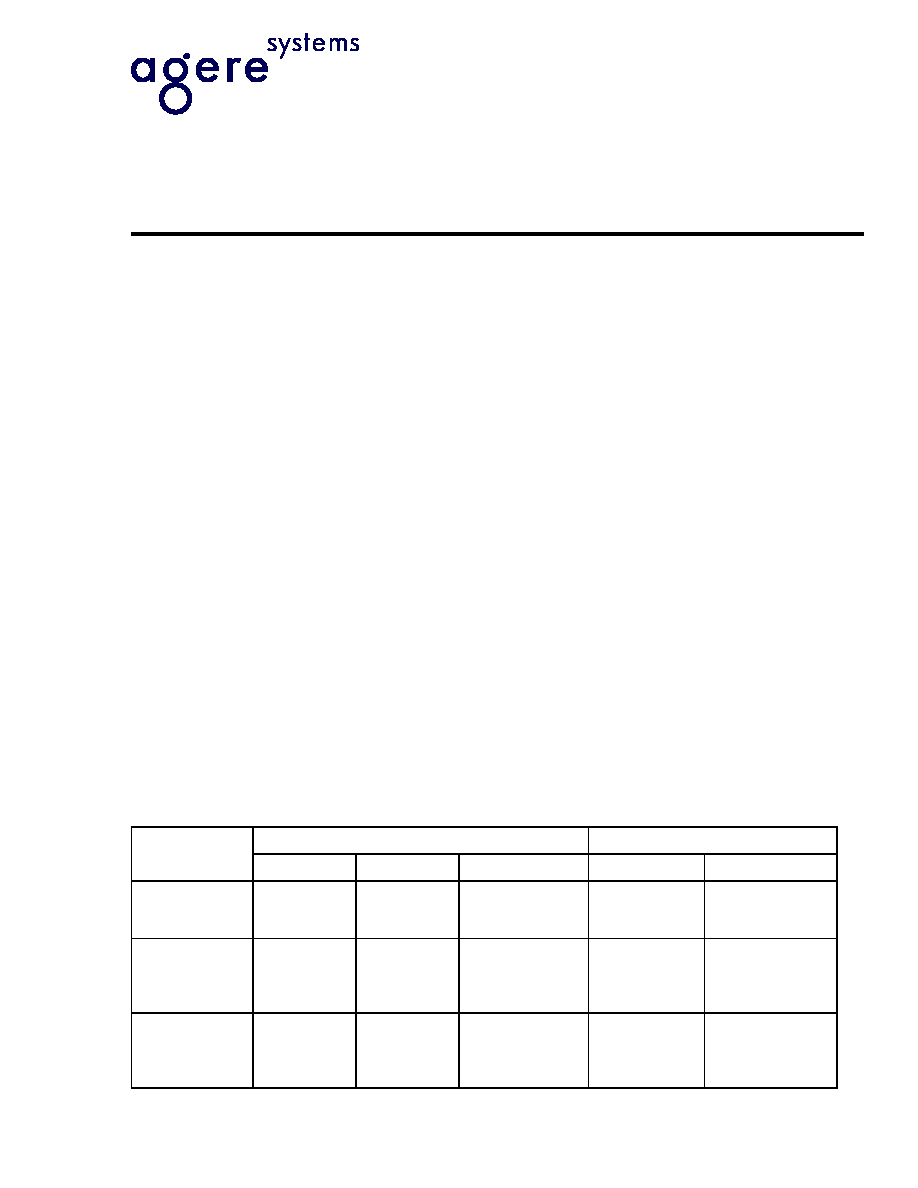

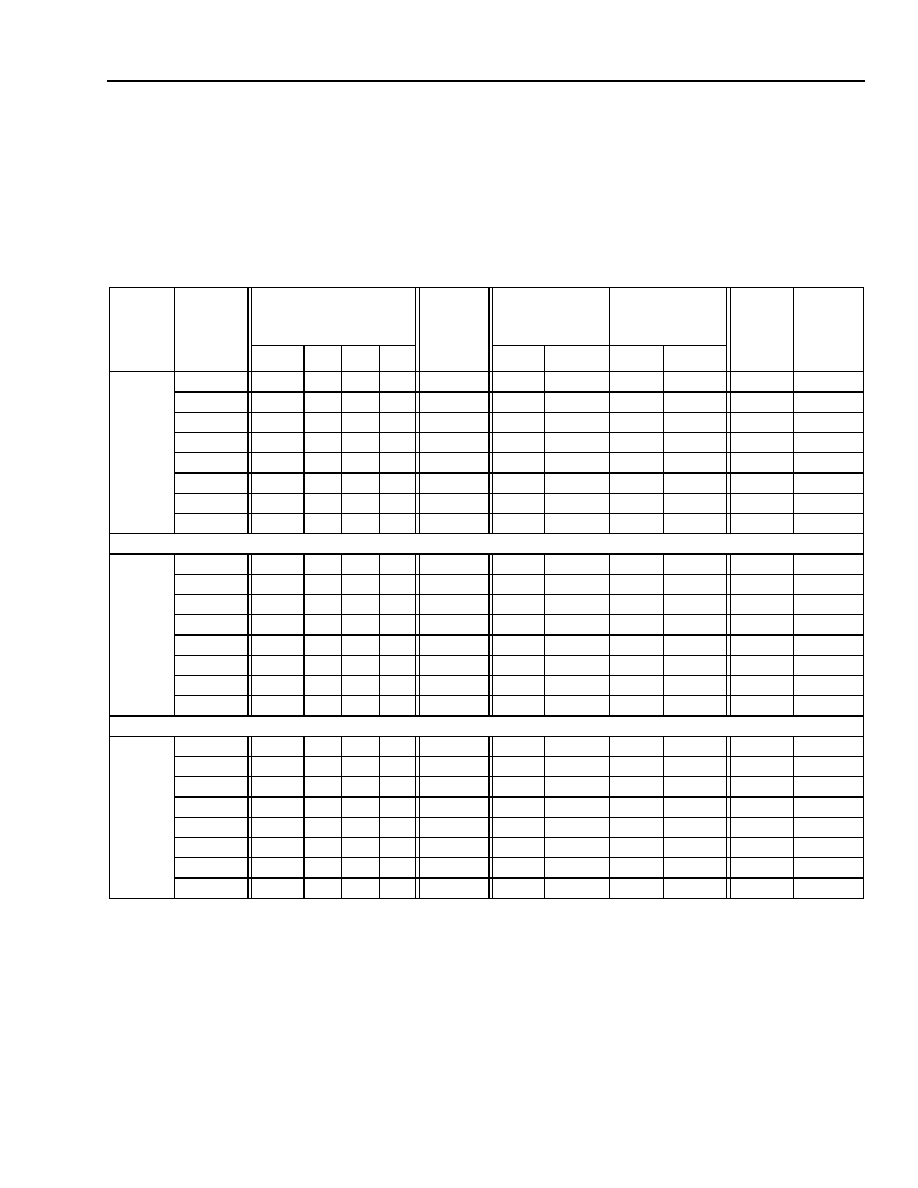

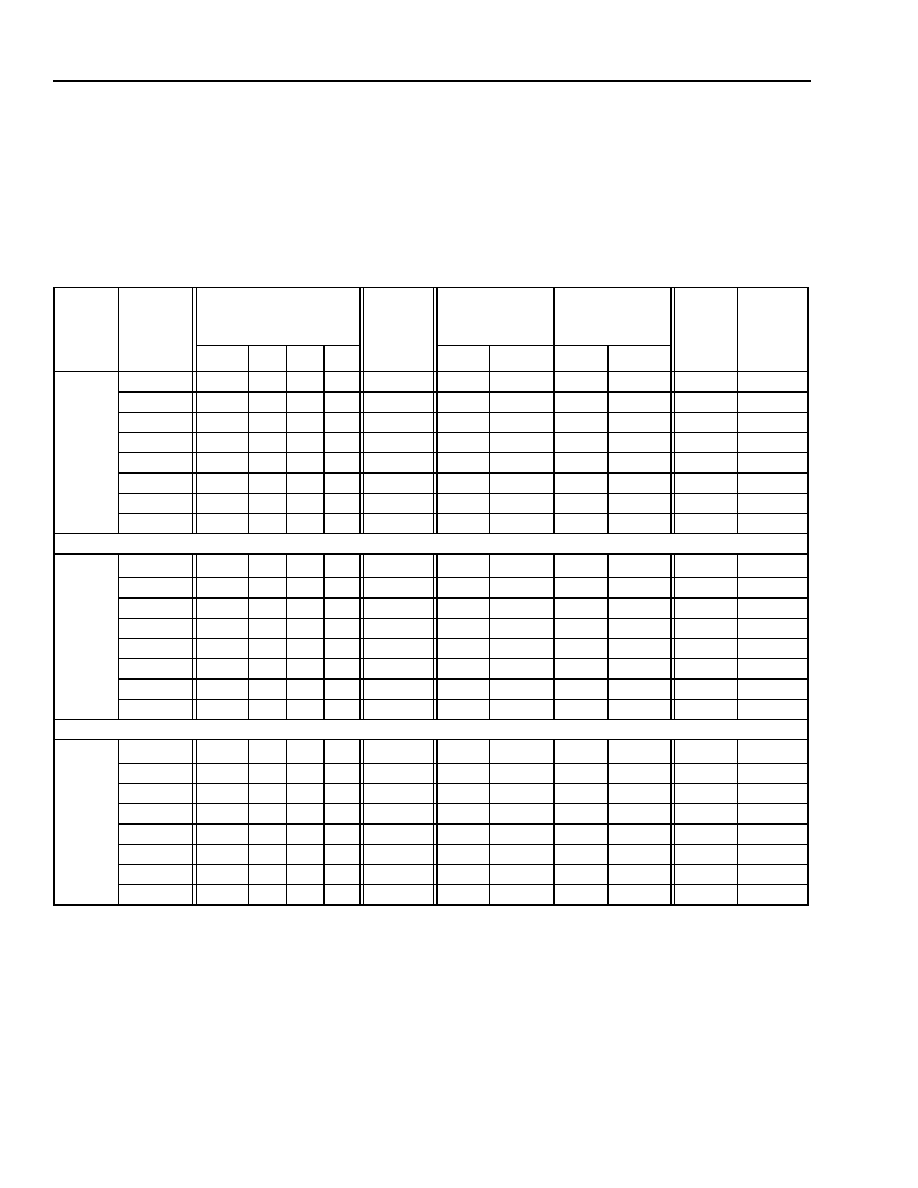

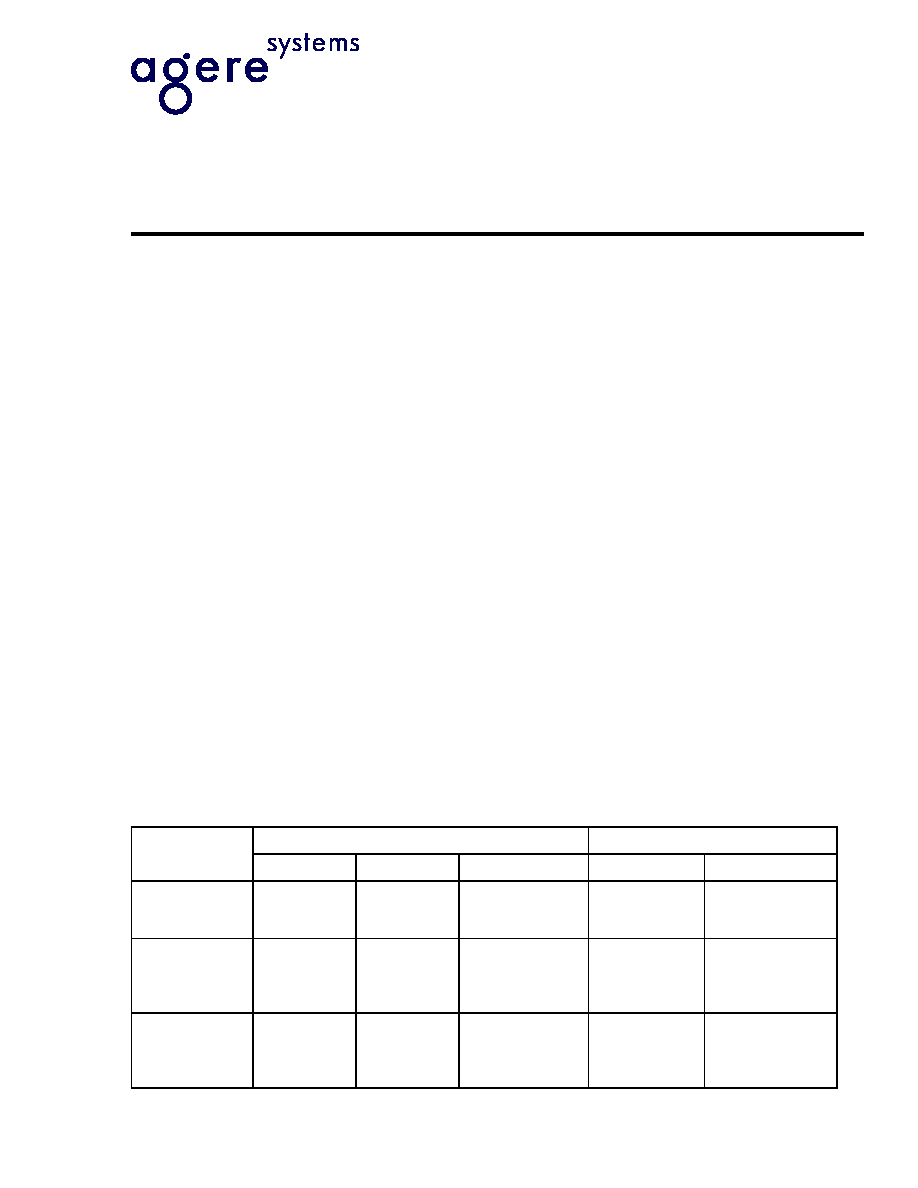

- Table 1. TDAT Device Product Line

- Contact Us

- AY01015.pdf

- System Programming (SP)

- SP1. Required Provisioning Sequence and Clocks

- SP2. Behavior During Loss of Receive Line Clock

- SP3. PT Register Addressing

- Microprocessor Interface (MPU)

- MPU1. Interface to Motorola* MC68360 Processor Is Not Glueless

- MPU2. Synchronous Microprocessor Interface Mode Is Nonfunctional

- Core Registers (CR)

- CR1. Clear on Read/Clear on Write Behavior

- Line Interface (LI)

- LI1. STS-48/STM-16 Mode Lacks Facility Loopback

- Path Terminator (PT)

- PT1. Signal Degrade (SD) and Signal Fail (SF) Bit Behavior

- PT2. Clear-After-Write Behavior of Signal Degrade Clear Bits

- PT3. Remote Defect Indicator (RDI) Behavior

- PT4. SS Pointer Interpretation Algorithm

- PT5. Delta/Event Registers in COR Mode

- Data Engine (DE)

- DE1. SDL ModeÑHeader Error Correction in LSB

- DE2. Incorrect ATM Loss of Cell Delineation (LCD) Implementation

- DE3. ATM Transmit Count of Idle Cells

- DE4. Channel Provisioning

- DE5. Packet Behavior in POS/SDL ModeÑDry Mode

- DE6. Incorrect ATM Out of Cell Delineation (OCD) Implementation

- DE7. Incorrect Frame State of ATM Data Streams

- DE8. Clearing DE Interrupt Register (0x1002)

- DE9. Single Packet Transmission in HDLC-CRC, SDL-CRC, and PPP Modes

- DE10. Excessive HDLC Flag Characters

- UTOPIA (UT)

- UT1. Polling in Multidevice MPHY Mode

- UT2. UTOPIA Clock Limitations

- UT3. PMRST Register Value Invalid After Reset

- UT4. FIFO Overflow and Error Reporting

- UT5. Timing Difference Between Direct and Polled Status Modes

- UT6. UTOPIA Interface D Nonfunctional in Some Mixed MPHY and Point-to-Point Configurations

- UT7. Response to 0x1F MPHY Address

- UT8. Far-End Loopback Bandwidth Limitations

- UT9. Clock Requirements for MPHY Modes

- UT10. Egress Packet Mode Overflows

- UT11. Clearing UT Interrupt Register

- UT12. Incorrect Implementation of POS Multi-PHY Mode

- UT13. Invalid Extra Cycle Between EOP and SOP in CRC-16/32 Mode

- UT14. Nonfunctional RxPA Signal for Channels B and D in Packet Direct Status MPHY Mode

- Overhead Processor (OHP)

- OHP1. Maximum BER Count

- OHP2. RDI-L Reporting

- OHP3. M1 Error Counter in STS-48/STM-16 Mode

- Packaging and Pinouts (P)

- P1. Pin F5 (Previously JTEST) Is No Connect (NC)

- P2. Modified Pinout and Power Supply ConfigurationÑFuture Versions

- P3. Change to TDAT042G5 Version 1 Pinout

- P4. Power Dissipation

- Data Addenda

- DA1. Incorrect PT Control Register Mapping

- DA2. Variable Change

- AY99-013SONT-2 Replaces AY99-013SONT to Incorporate the Following Updates

- AY99-013SONT-3 Replaces AY99-013SONT-2 to Incorporate the Following Updates

- AY99-013SONT-4 Replaces AY99-013SONT-3 to Incorporate the Following Updates

- AY01-015SONT (Replaces AY99-013SONT-4 and Must Accompany DS98-193SONT-4) Replaces AY99-013SONT-4 ...

- Change List

- 1/25/01

- 1/29/01

- 2/13/01

- 3/1/01

- List of Figures

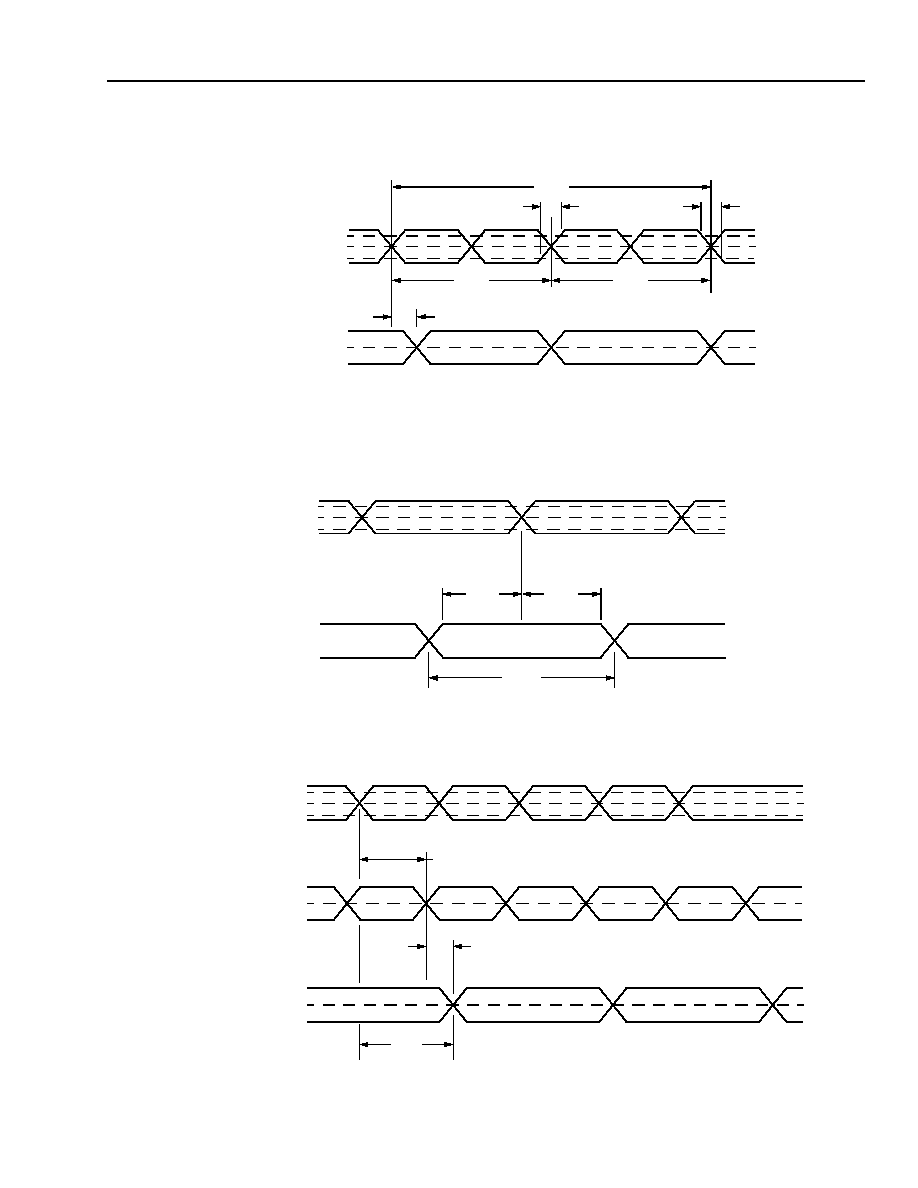

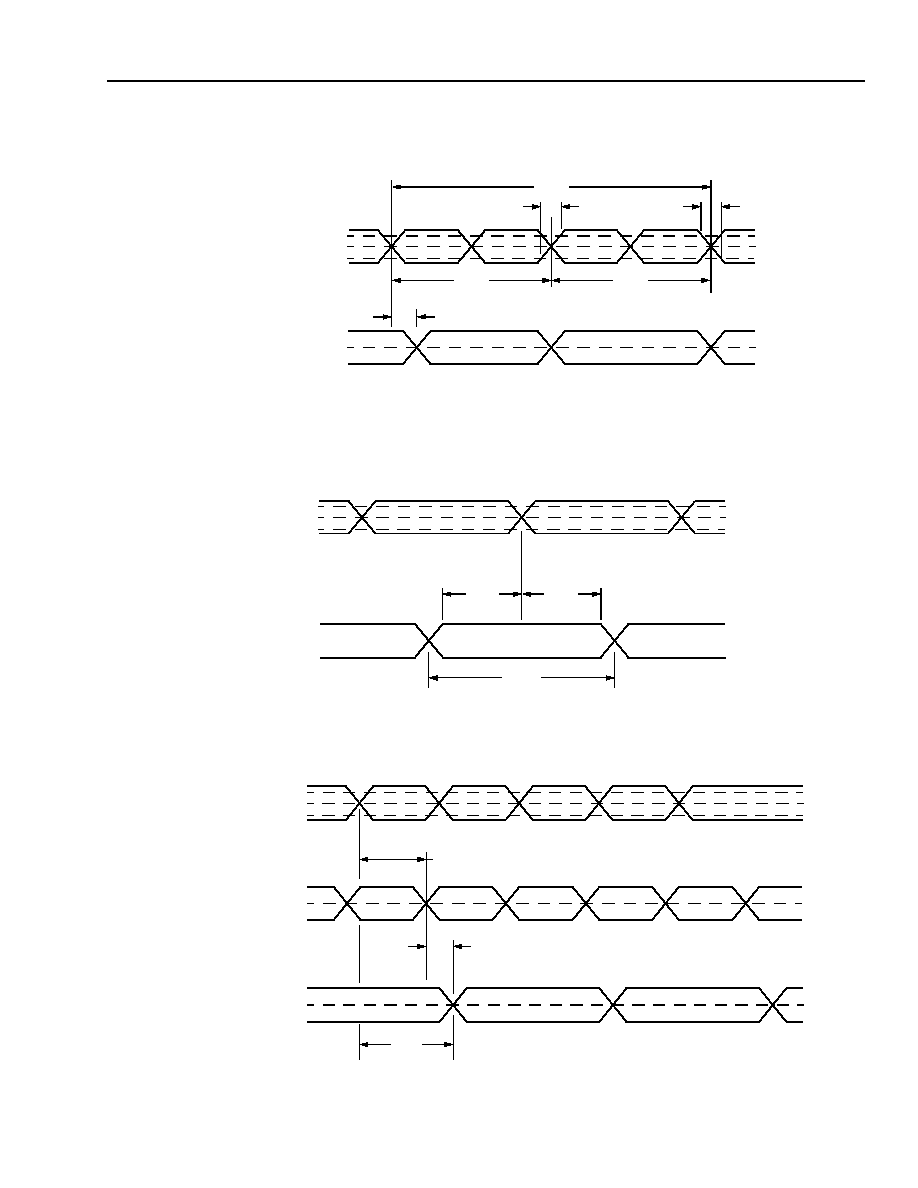

- Figure 1. Receive-Side UTOPIA Interface and Channel FIFOs

- Figure 2. Master Control Flow Chart

- List of Tables

- Table 1. COR/W Settings of Register 0x0010, Bit 6

- Table 2. Transmit DE Egress and Sequencer Cell State Registers

- Table 3. Required UTOPIA Clock (TxCLK) Rates

- Table 4. Register 0x1002: DE Interrupt (COR/W)

- Table 5. Cell/Packet Corruption Rates

- Table 6. Settings at Which Overflows Reported in Error

- Table 7. Settings to Prevent Overflows Reported in Error

- Table 8. Signal Degrade and Signal Fail Algorithm OHP Registers [6:3]

- Table 9. Power Dissipation and Relative Package Thermal Characteristics

- Contact Us

- Features

- Description

- Pin Information

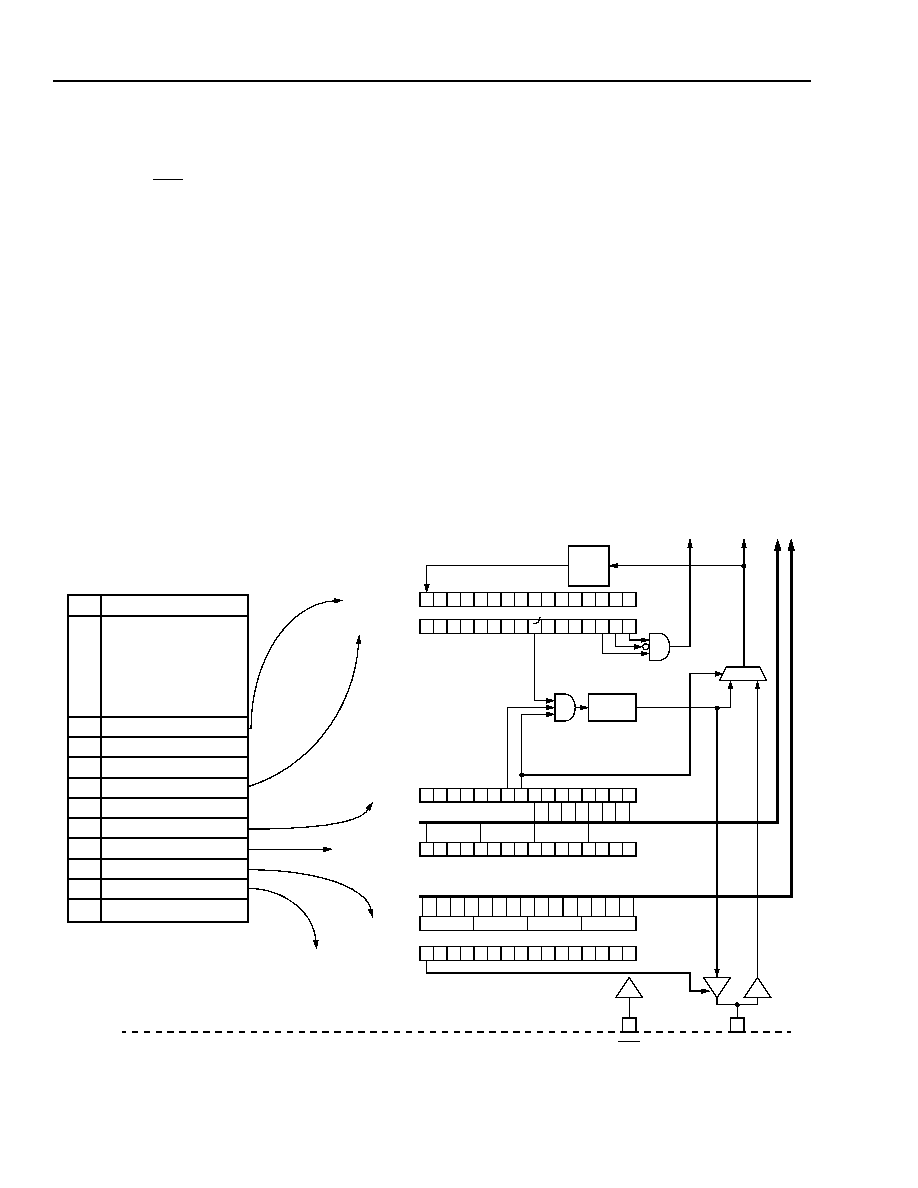

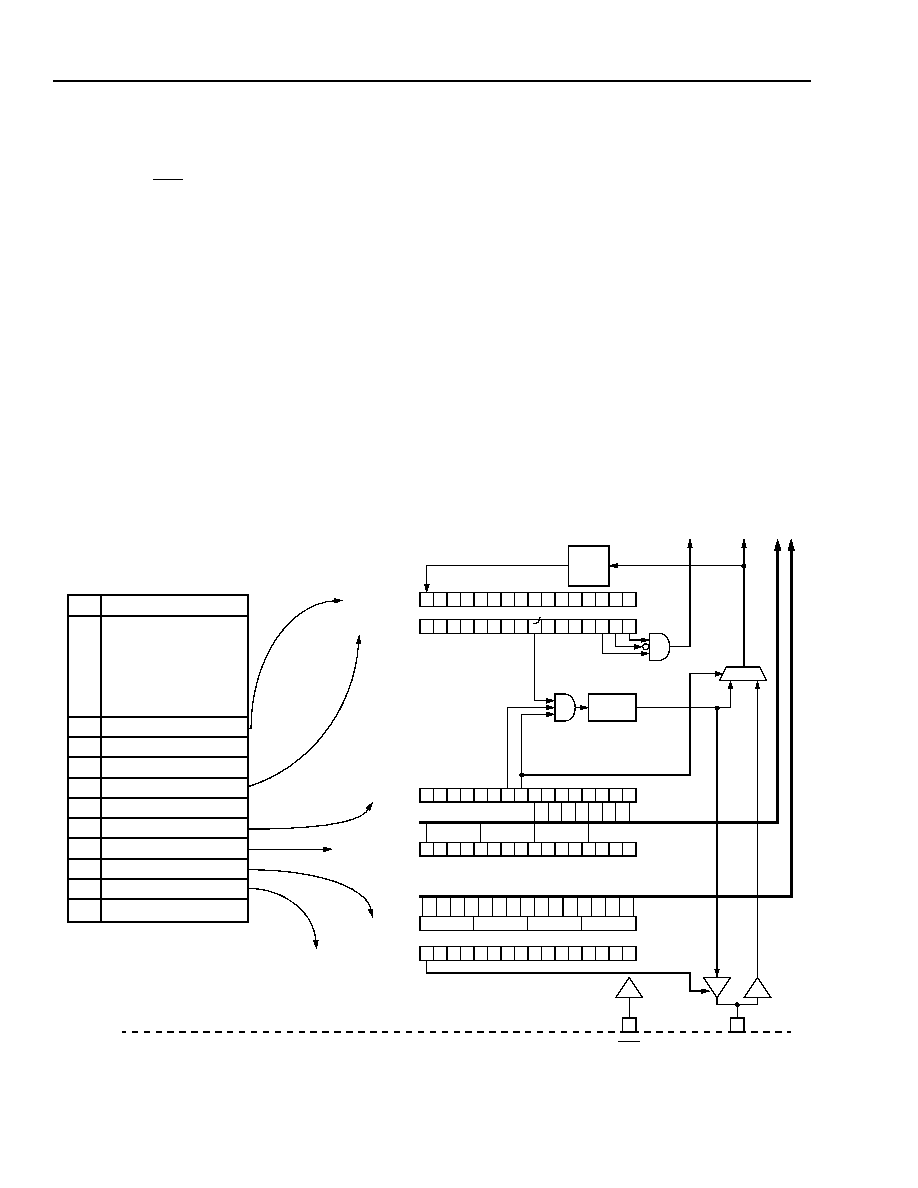

- Overview

- Functional Description

- Line Interface

- Interface Description

- Register Access Description

- Register Maps

- Register Descriptions

- Absolute Maximum Ratings

- Handling Precautions

- Operating Conditions

- Electrical Characteristics

- Interface Timing Specifications

- Reference of SONET/SDH Terms and Comparisons

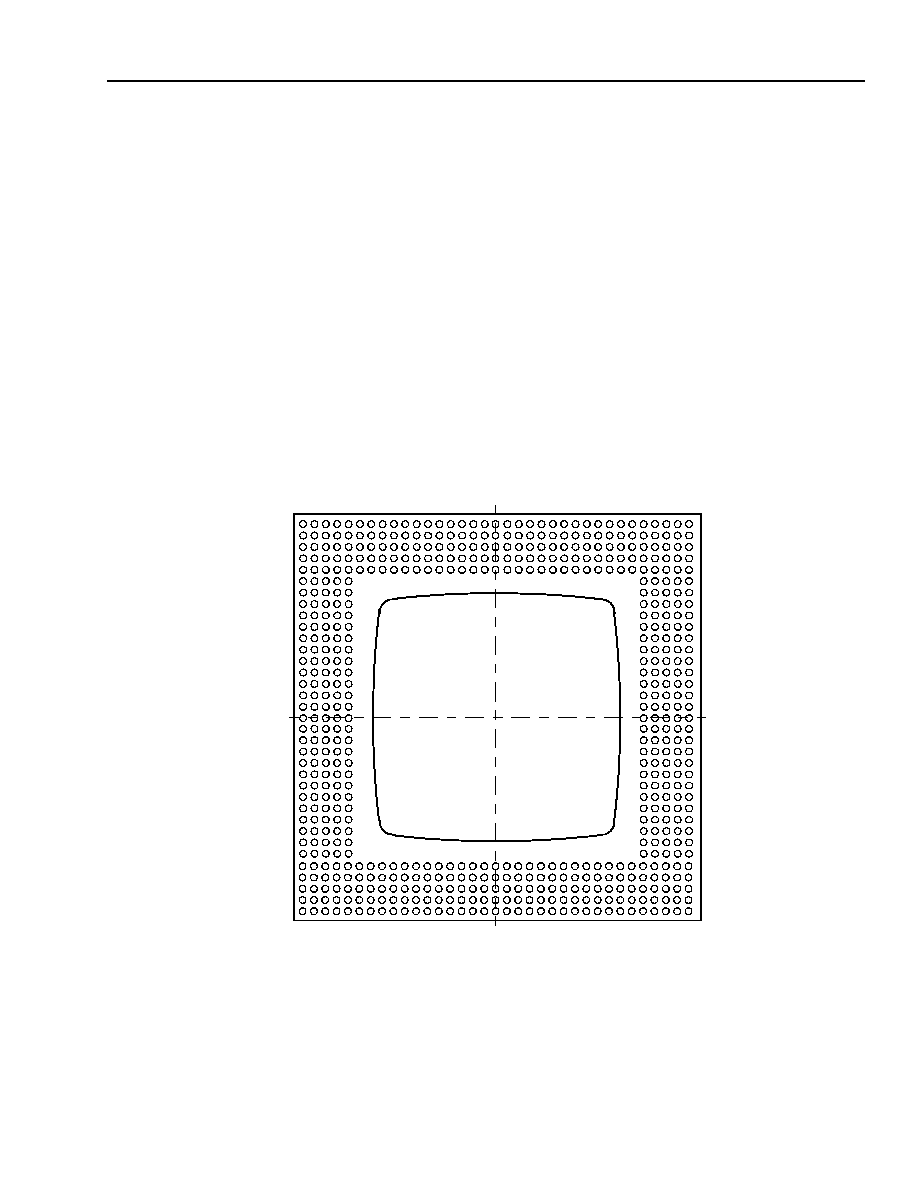

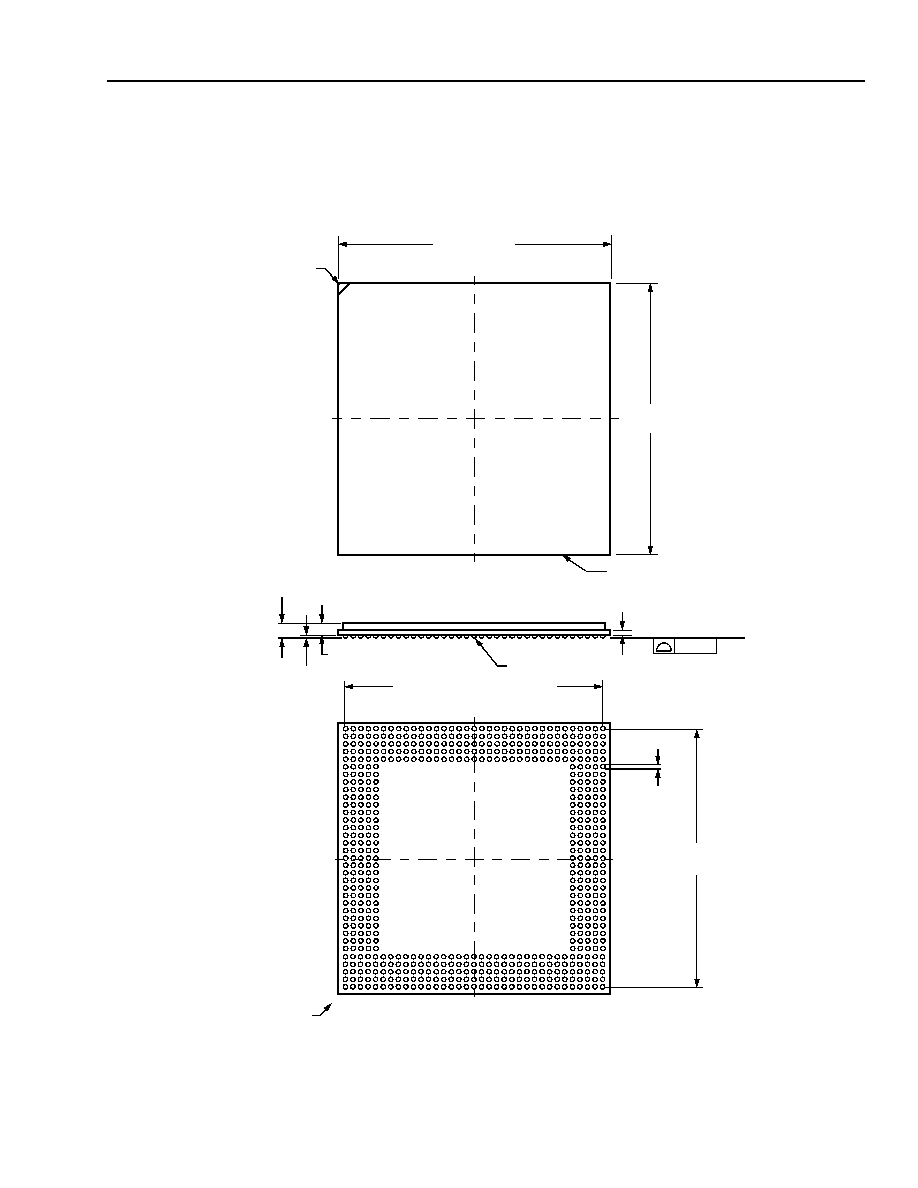

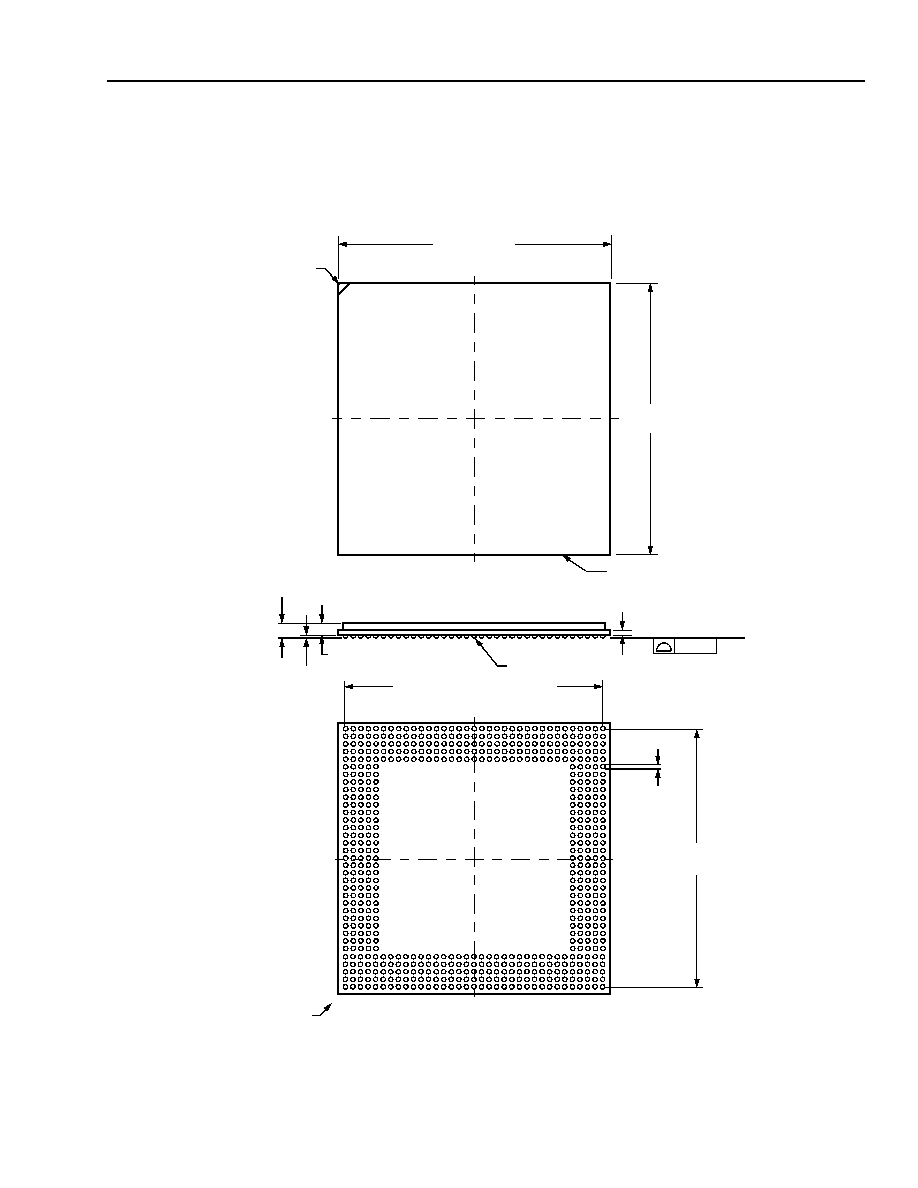

- Outline Diagram

- Ordering Information

- DS98-193SONT-4 Replaces DS98-193SONT-3 to Incorporate the Following Updates

- List of Figures

- List of Tables

- Table 1. Pin Assignments for 600-Pin LBGA by Pin Number Order

- Table 2. Pin Assignments for 600-Pin LBGA by Signal Name

- Table 3. Pin DescriptionsÑLine Interface Signals

- Table 4. Pin DescriptionsÑTOH Interface Signals

- Table 5. Pin DescriptionsÑEnhanced UTOPIA Interface Signals

- Table 6. Pin DescriptionsÑMicroprocessor Interface Signals

- Table 7. Pin DescriptionsÑGeneral-Purpose I/O Signals: Interface Signals

- Table 8. Pin DescriptionsÑJTAG Interface Signals

- Table 9. Pin DescriptionsÑPower Signals

- Table 10. Pin DescriptionsÑNo Connect Pins

- Table 11. Optional Offset Field

- Table 12. Line Interface Modes

- Table 13. Clock Settings for CLKDIV Pin

- Table 14. R/T TOH Interface Rates

- Table 15. TOAC Byte Insertion: An STS-3/STM-1 Example

- Table 16. Ns, L, M, and B Values to Set the BER Indicator

- Table 17. Ns, L, M, and B Values to Clear the BER Indicator

- Table 18. TOAC Channel I/O vs. STS Number/Time Slot

- Table 19. Types of Signal Labels

- Table 20. 1-bit Mode

- Table 21. 3-bit Mode (Enhanced RDI)

- Table 22. Valid Concatenation Starting Locations: STS-Mc into an STS-48c

- Table 23. Packet Length Field

- Table 24. UTOPIA Traffic Types

- Table 25. Standard 53-byte ATM Cell Structure

- Table 26. Bus Format for 16-bit Interface

- Table 27. Bus Format for 8-bit Interface

- Table 28. Bus Format for 32-bit Interface

- Table 29. Egress High Watermark Thresholds

- Table 30. Nominal dc Power for Suggested Terminations

- Table 31. MPU Modes

- Table 32. PMRST Provisioning

- Table 33. Quad ATM UTOPIA 3 Interface

- Table 34. Quad POS UTOPIA 3 Interface

- Table 35. Register Address Space

- Table 36. Map of Core Registers

- Table 37. Map of UT Registers

- Table 38. Map of OHP Registers

- Table 39. Map of Path Terminator Registers

- Table 40. Map of DE Registers

- Table 41. Register 0x0000: Device Version (RO)

- Table 42. Registers 0x0001Ñ0x0005: Device Name (RO)

- Table 43. Register 0x0008: Composite Interrupts (RO or COR/W)

- Table 44. Register 0x000A: GPIO Input (RO)

- Table 45. Register 0x000C: Block Interrupt Masks (R/W)

- Table 46. Register 0x000E: Core Resets (WO)

- Table 47. Register 0x000F: GPIO Output (R/W)

- Table 48. Register 0x0010: Line Provisioning/Mode (R/W)

- Table 49. Register 0x0011: Channel (AÑD) Control (R/W)

- Table 50. Register 0x0012: Loopback Control (R/W)

- Table 51. Register 0x0013: GPIO Mode (R/W)

- Table 52. Registers 0x0014, 0x0015: GPIO Output Configuration

- Table 53. Register 0x001F: Scratch (R/W)

- Table 54. Register 0x0200: UT Macrocell Version Number (RO)

- Table 55. Register 0x0201: UT Interrupt (RO)

- Table 56. Registers 0x0202, 0x0203, 0x0204, 0x0205: Channel [AÑD] (COR)

- Table 57. Register 0x0206: Interrupt Mask (R/W)

- Table 58. Registers 0x0207, 0x0208, 0x0209, 0x020A: Interrupt MaskÑChannel [AÑD] (R/W)

- Table 59. Register 0x020B: Channel [AÑD] Error Count in PMRST Mode (RO)

- Table 60. Fields of the Provisioning Registers

- Table 61. Registers 0x020F, 0x0213, 0x0217, 0x021B: Channel [AÑD] Receive Provisioning Register (...

- Table 62. Registers 0x0210, 0x0214, 0x0218, 0x021C: Channel [AÑD] Transmit Provisioning Register ...

- Table 63. Registers 0x0211, 0x0215, 0x0219, 0x021D: Channel [AÑD] Ingress Provisioning Register (...

- Table 64. Registers 0x0212, 0x0216, 0x021A, 0x021E: Channel [AÑD] Egress Provisioning Register (R/W)

- Table 65. Register 0x021F: Reset Register (R/W)

- Table 66. Register 0x0220: Channel [AÑD] Error Count (RO)

- Table 67. Register 0x0224: UT_Scratch Register (R/W)

- Table 68. Register 0x0225: PA Response Register (R/W)

- Table 69. Register 0x0226: Size Mode Register (R/W)

- Table 70. Register 0x0400: OHP Macrocell Version Number (RO)

- Table 71. Register 0x0401: OHP Interrupt (RO)

- Table 72. Registers 0x0402Ñ0x0409: Delta/Event (COR/W)

- Table 73. Registers 0x040AÑ0x040D: Receive/Transmit State (RO)

- Table 74. Registers 0x040E, 0x0410, 0x0412, 0x0414: Mask Bits (R/W)

- Table 75. Registers 0x040F, 0x0411, 0x0413, 0x0415: Mask Bits (R/W)

- Table 76. Registers 0x0416Ñ0x0419: Toggles (R/W)

- Table 77. Registers 0x041A, 0x041C, 0x041E, 0x0420: Continuous N Times Detect (CNTD) Values (R/W)

- Table 78. Registers 0x041B, 0x041D, 0x041F, 0x0421: Continuous N Times Detect (CNTD) Values (R/W)

- Table 79. Registers 0x0422Ñ0x042D: Receive Control (R/W)

- Table 80. Registers 0x042E: Transmit Control Port A (R/W)

- Table 81. Registers 0x042F, 0x0431, 0x0433, 0x0435: Transmit Control (R/W)

- Table 82. Registers 0x0430, 0x0432, 0x0434: Transmit Control Port [BÑD] (R/W)

- Table 83. Registers 0x0436Ñ0x0439: Transmit Control (R/W)

- Table 84. Registers 0x043AÑ0x0451: OHP Signal Degrade BER Algorithm Parameters (R/W)

- Table 85. Registers 0x0452Ñ0x0469: OHP Signal Fail BER Algorithm Parameters (R/W)

- Table 86. Ns, L, M, and B Values to Set the BER Indicator

- Table 87. Ns, L, M, and B Values to Clear the BER Indicator

- Table 88. Registers 0x046AÑ0x047D: B1, B2, M1 Error Count (RO)

- Table 89. Registers 0x047EÑ0x0485: Transmit F1, S1, K2, K1 OH Insert Value (R/W)

- Table 90. Registers 0x0486Ñ0x0491: Receive F1, S1, K2, K1 Monitor Value (RO)

- Table 91. Registers 0x0492Ñ0x04F9: Receive J0 Monitor Value (RO)

- Table 92. Registers 0x0512Ñ0x0579: Transmit J0 Insert Value (R/W)

- Table 93. Registers 0x05AAÑ0x05C1: Transmit Z0 Insert Value (R/W)

- Table 94. Register 0x05C2: Scratch Register (R/W)

- Table 95. Register 0x0800: PT Macrocell Version Number (RO)

- Table 96. Register 0x0801: PT Interrupt (RO)

- Table 97. Registers 0x0802, 0x080F, 0x081C, 0x0829 and 0x0803, 0x0810, 0x081D, 0x082A: PT Delta/E...

- Table 98. Registers 0x0836Ñ0x083B, 0x0868Ñ0x0887, 0x0888Ñ0x088D, 0x08BAÑ0x08D9, 0x08DAÑ0x08DF, 0x...

- Table 99. Register 0x097E: PT Interrupt Mask Control (R/W)

- Table 100. Registers 0x097FÑ0x0980, 0x098CÑ0x098D, 0x0999Ñ0x099A, 0x09A6Ñ0x09A7: PT Interrupt Mas...

- Table 101. Registers (0x09B3, 0x09BF, 0x09CB, 0x09D7, 0x09E3), (0x09EF, 0x09FB, 0x0A07, 0x0A14, 0...

- Table 102. Register 0x0AA4: PT One-Shot Control Parameters (WO)

- Table 103. Registers 0x0AA6Ñ0x0AAD, 0x0AAE, 0x0AB5, 0x0AB6Ñ0x0ABD, 0x0ABEÑ0x0AC5: PT Control Para...

- Table 104. Registers 0x0AC6Ñ0x0AF7: PT Provisioning (R/W)

- Table 105. Registers 0x0ACCÑ0x0AD1: PT Signal Fail BER Algorithm Parameters (R/W)

- Table 106. Registers 0x0AD2Ñ0x0AD7: PT Signal Degrade BER Algorithm Parameters (R/W)

- Table 107. Ns, L, M, and B Values to Set the BER Indicator

- Table 108. Ns, L, M, and B Values to Clear the BER Indicator

- Table 109. Registers 0x0AD8Ñ0x0AF7: Transmit J1 Data Insert (R/W)

- Table 110. Register 0x0AF8: Scratch Register (R/W)

- Table 111. Register 0x1000: DE Macrocell Version Number (RO)

- Table 112. Register 0x1001, 0x1002: DE Interrupts (0x1001 is RO, 0x1002 is RO and COR/W)

- Table 113. Register 0x1004: Dry Escape Marker (R/W)

- Table 114. Registers 0x1010Ñ0x1015: Sequencer Provisioning Registers (R/W) (continued)

- Table 115. Registers 0x1016Ñ0x1021: Egress Configuration (R/W)

- Table 116. Registers 0x1022Ñ0x102D: Ingress Configuration (R/W)

- Table 117. Registers 0x102EÑ0x1031: Over-Fiber Mode (Packet-Over-Fiber or POF) Control (R/W)

- Table 118. Registers 0x1032Ñ0x1036: Sequencer Cell State Registers (R/W)

- Table 119. Registers 0x1040Ñ0x1043: Ingress Payload Type and Mode Control (R/W)

- Table 120. Receive Type and Mode Control Summary Table (Registers 0x1040Ñ0x1043)

- Table 121. Registers 0x1080Ñ0x1087: ATM Framer Idle Cell Match Mask (R/W)

- Table 122. Registers 0x1088Ñ0x108F: ATM Idle Cell Registers (R/W)

- Table 123. Registers 0x1090Ñ0x1097: ATM Unassigned Cell Match Mask (R/W)

- Table 124. Registers 0x1098Ñ0x109F: ATM Unassigned Cell Registers (R/W)

- Table 125. Registers 0x10A0Ñ0x10A3: ATM Framer State Registers (RO)

- Table 126. Register 0x10A4: ATM X43 Frame Control (R/W)

- Table 127. Register 0x10A5: ATM X31 Frame Control (R/W)

- Table 128. Register 0x10A6: ATM X31 V/W Values (R/W)

- Table 129. Register 0x10A7: ATM X31 X/Y Values (R/W)

- Table 130. Register 0x10A8: ATM X31 Z Value (R/W)

- Table 131. Register 0x10A9: Frame State Interrupt Mask (R/W)

- Table 132. Register 0x10AA: Scrambler State Interrupt Mask (R/W)

- Table 133. Register 0x10AB: ATM Receive Debug Register (R/W)

- Table 134. Registers 0x10B0Ñ0x10B3: PPP Attach (R/W)

- Table 135. Registers 0x10E0Ñ0x10E3: Egress Payload Type and Mode Control (R/W)

- Table 136. Transmit Type and Mode Control Summary Table (Registers 0x10E0Ñ0x10E3)

- Table 137. Registers 0x10F0Ñ10FB: PPP Header Value Detach (R/W)

- Table 138. Registers 0x10FCÑ0x10FF: PPP Header Detach Search (R/W)

- Table 139. Registers 0x1100Ñ0x1107: ATM/HDLC/SDL FramerÑCondition Counter 1 (PMRST Update) (RO)

- Table 140. Registers 0x1108Ñ0x110F: ATM/HDLC/SDL FramerÑCondition Counter 2 (PMRST Update) (RO)

- Table 141. Registers 0x1110Ñ0x1117: CRC CheckerÑBad Packet Counter (PMRST Update) (RO)

- Table 142. Registers 0x1118Ñ0x111F: PPP DetachÑMismatched Header Counter (PMRST Update) (RO)

- Table 143. Registers 0x1120Ñ0x1127: Receive Good Packet/Cell Counter (PMRST Update) (RO)

- Table 144. Registers 0x1128Ñ0x112F: Transmit Good Packet/Cell Counter (PMRST Update) (RO)

- Table 145. Registers 0x1180Ñ0x1186: Interrupt Masks for Packet Counters (R/W)

- Table 146. Registers 0x1181Ñ0x1187: Interrupts for Packet Counters (COR/W)

- Table 147. Registers 0x1200Ñ0x1213, 0x12F0: ATM Transmit Registers (R/W)

- Table 148. Registers 0x1400Ñ0x1403: SDL State Registers (RO)

- Table 149. Registers 0x1470Ñ0x1473: A Message Mailbox Registers (RO)

- Table 150. Registers 0x1480Ñ0x1483: A Message Mailbox Registers (RO)

- Table 151. Registers 0x1490Ñ0x1493: A Message Mailbox Registers (RO)

- Table 152. Registers 0x14A0Ñ0x14A3: B Message Mailbox Registers (RO)

- Table 153. Registers 0x14B0Ñ0x14B3: B Message Mailbox Registers (RO)

- Table 154. Registers 0x14C0Ñ0x14C3: B Message Mailbox Registers (RO)

- Table 155. Registers 0x14D0Ñ0x14D3: SDL Interrupt Masks (R/W)

- Table 156. Registers 0x14E0Ñ0x14E3: SDL Interrupts (COR/W)

- Table 157. Register 0x14F0: SDL Receive Configuration Registers (R/W)

- Table 158. Registers 0x1600Ñ0x1607: SDL Transmit Registers (R/W)

- Table 159. Recommended Operating Conditions

- Table 160. 3.3 V Logic Interface Characteristics

- Table 161. LVPECL Interface Characteristics

- Table 162. LVPECL 3.3 V Logic Interface Characteristics

- Table 163. Microprocessor Interface Synchronous Write Cycle Specifications

- Table 164. Microprocessor Interface Synchronous Read Cycle Specifications

- Table 165. Microprocessor Interface Asynchronous Write Cycle Specifications

- Table 166. Microprocessor Interface Asynchronous Read Cycle Specifications

- Table 167. Receive Line-Side Timing Specifications

- Table 168. Transmit Line-Side Timing Specifications

- Table 169. Transmit UTOPIA Interface Timing Specifications

- Table 170. Receive UTOPIA Interface Timing Specifications

- Table 171. UTOPIA Interface Clock Specifications

- Table 172. Transmit TOAC Interface Timing Specifications

- Table 173. Receive TOAC Interface Timing Specifications

- Table 174. SONET/SDH Comparisons

- Table 175. SONET/SDH New Terminology

- Contact Us

Data Addendum

May 2001

TDAT SONET/SDH

155/622/2488 Mbits/s Data Interfaces

Introduction

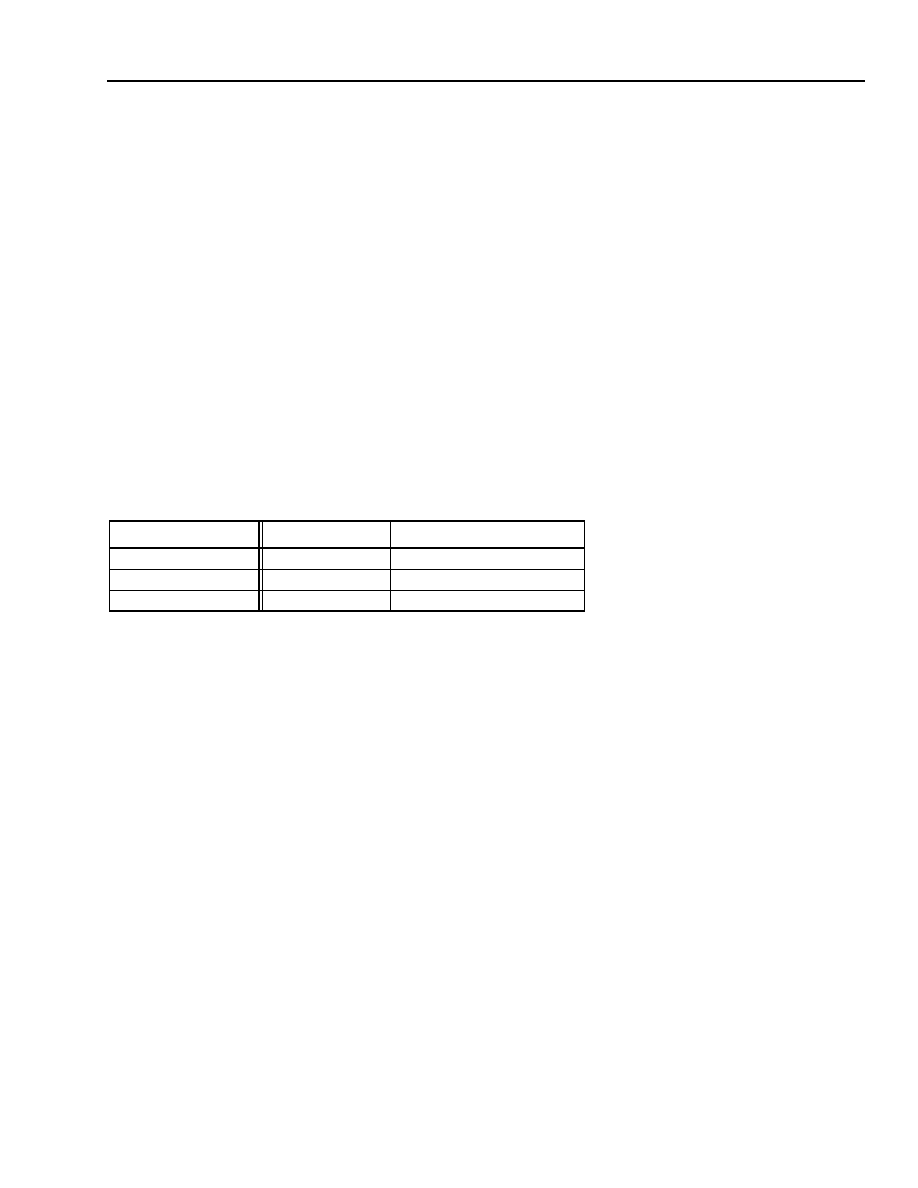

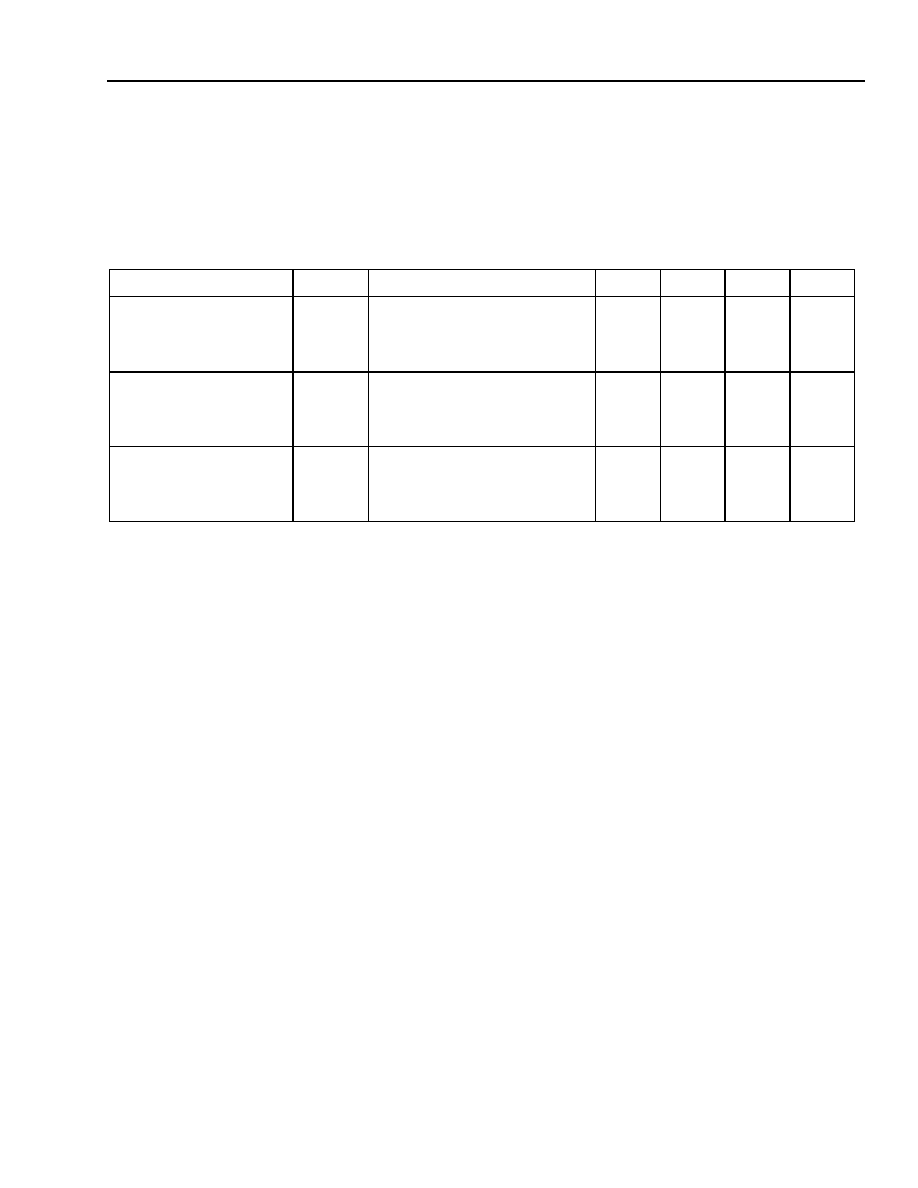

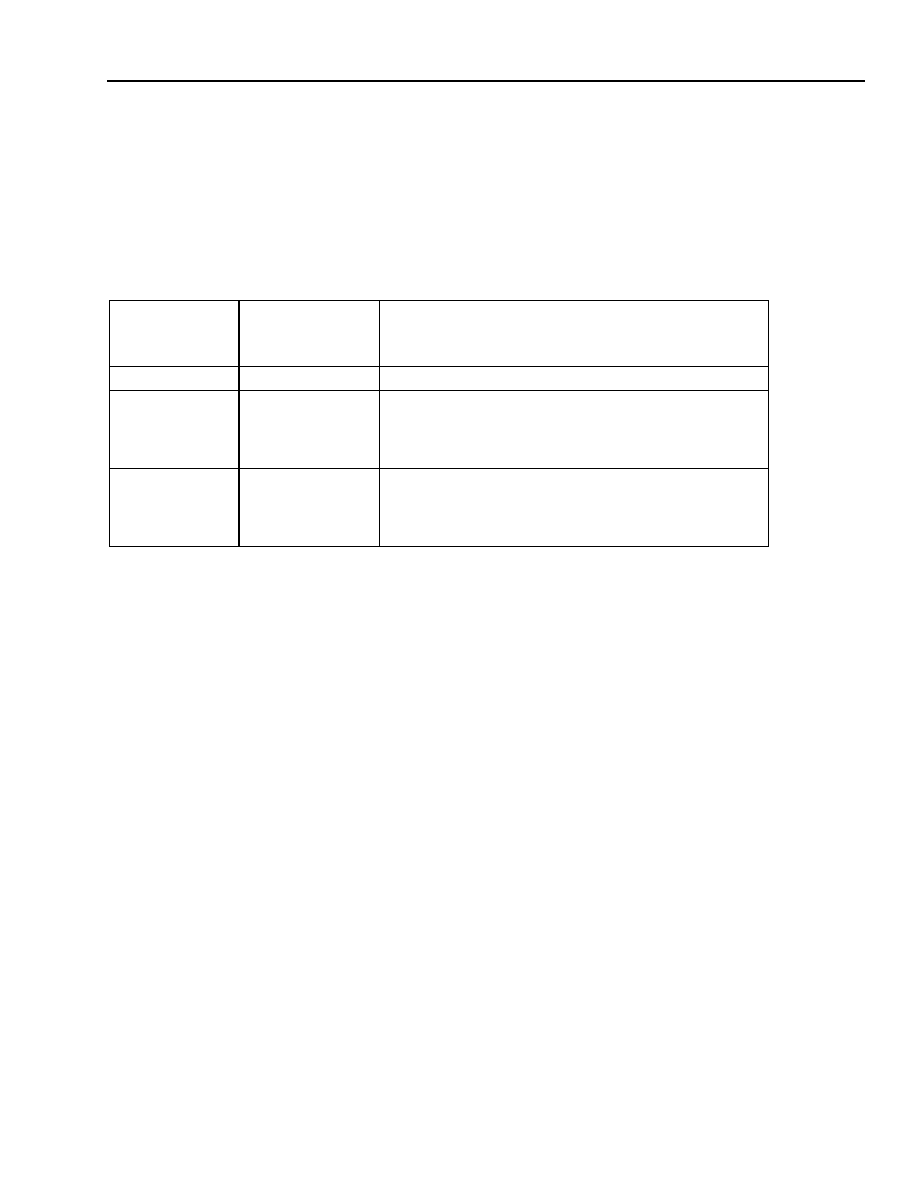

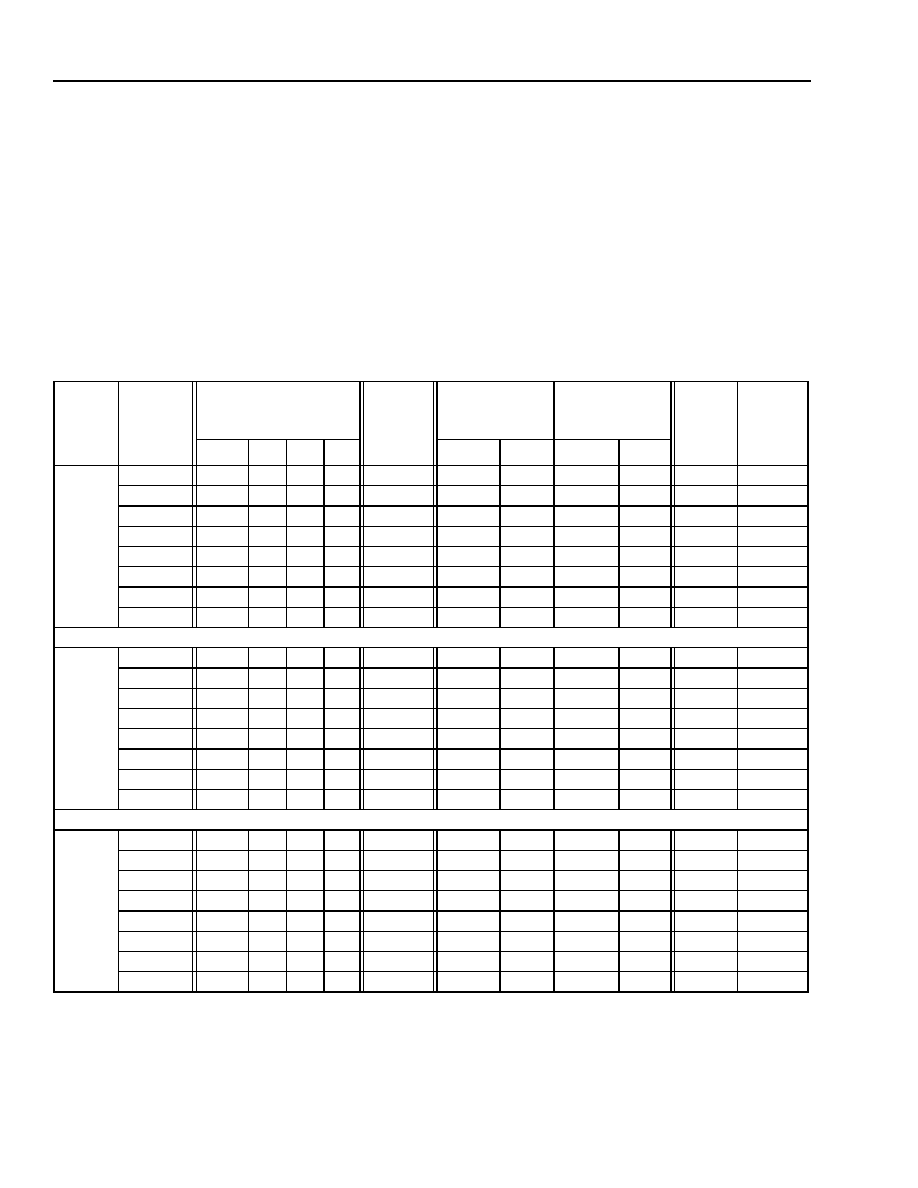

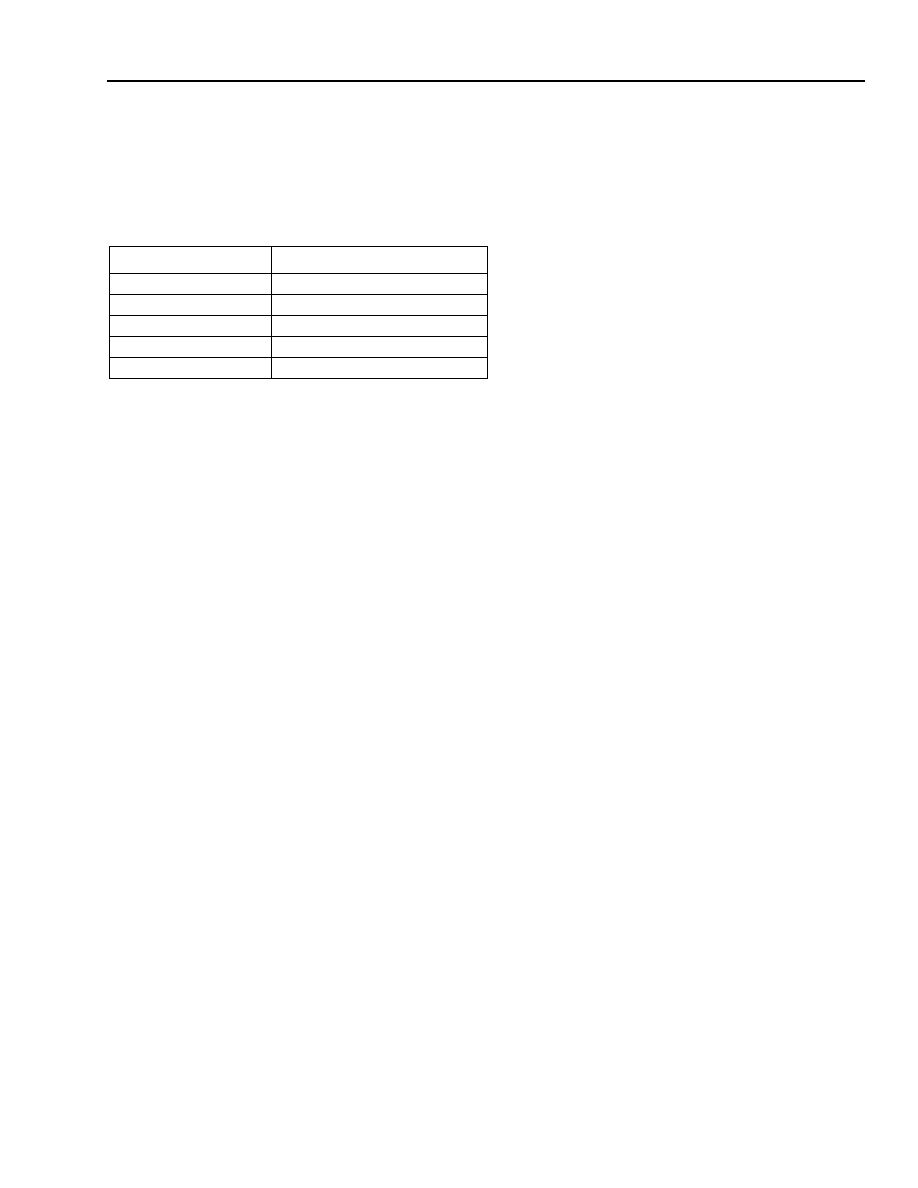

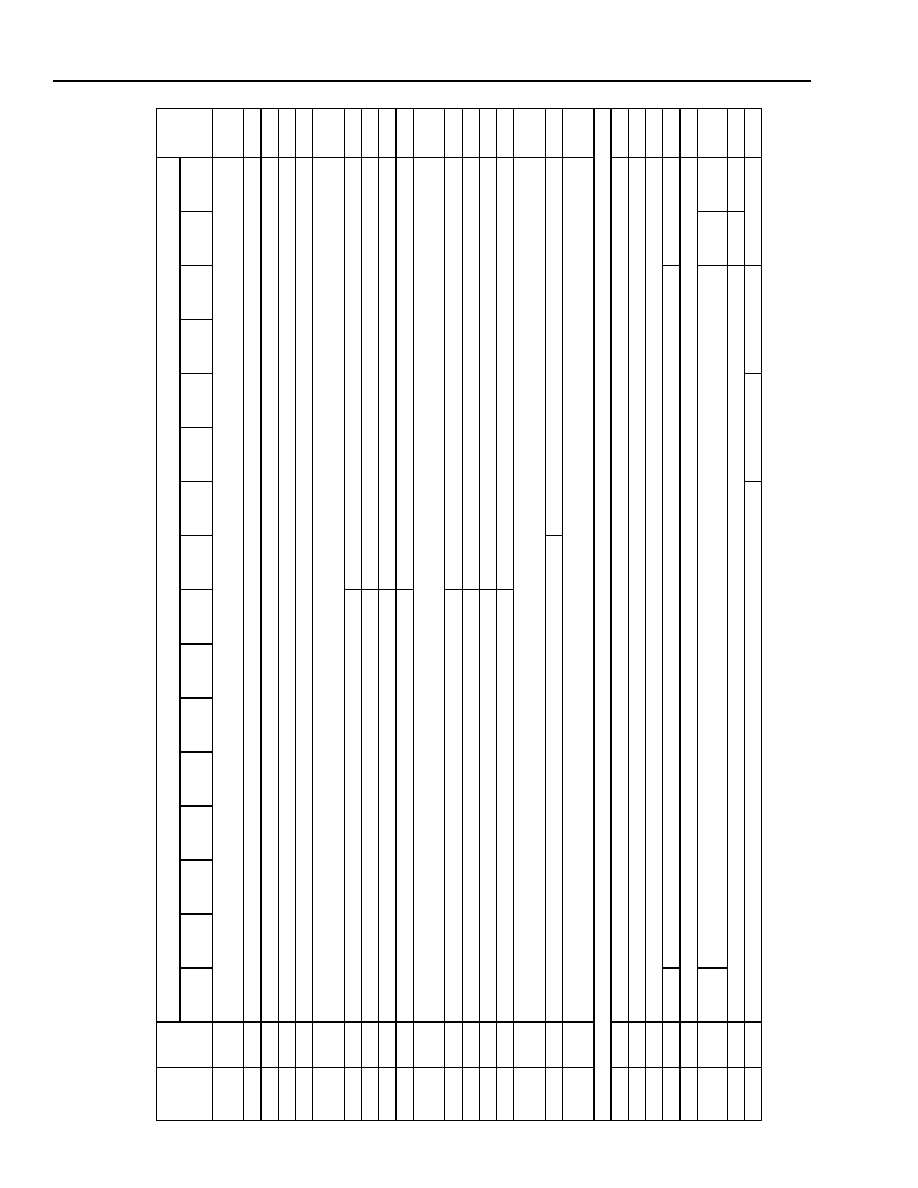

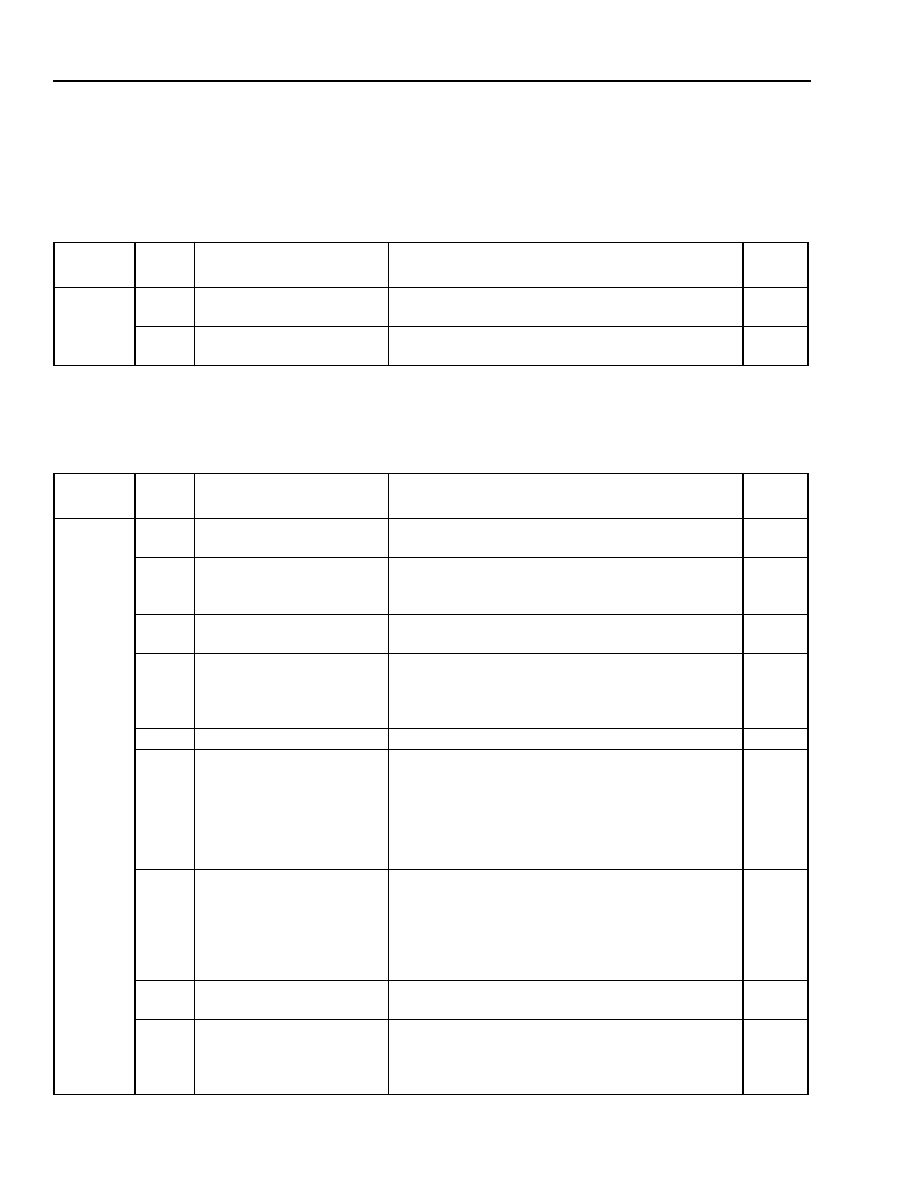

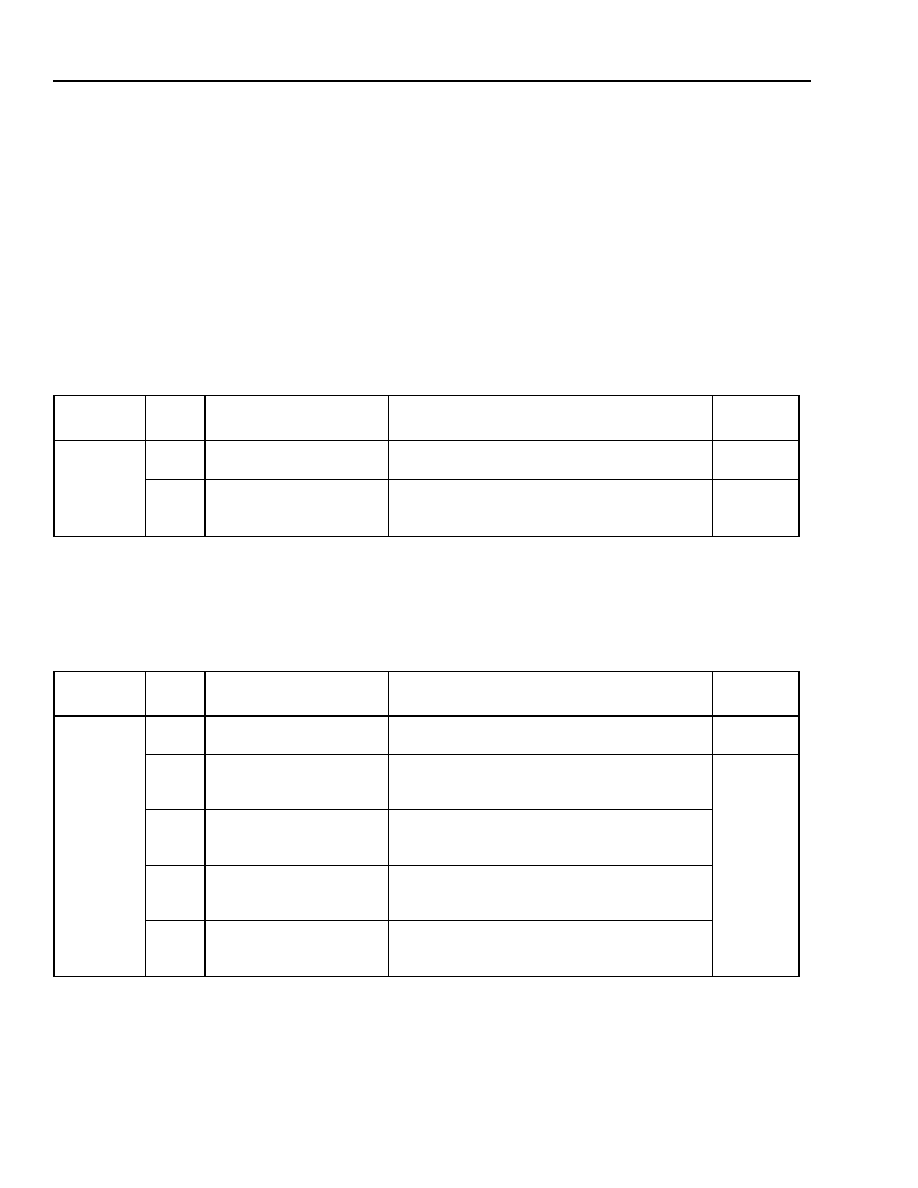

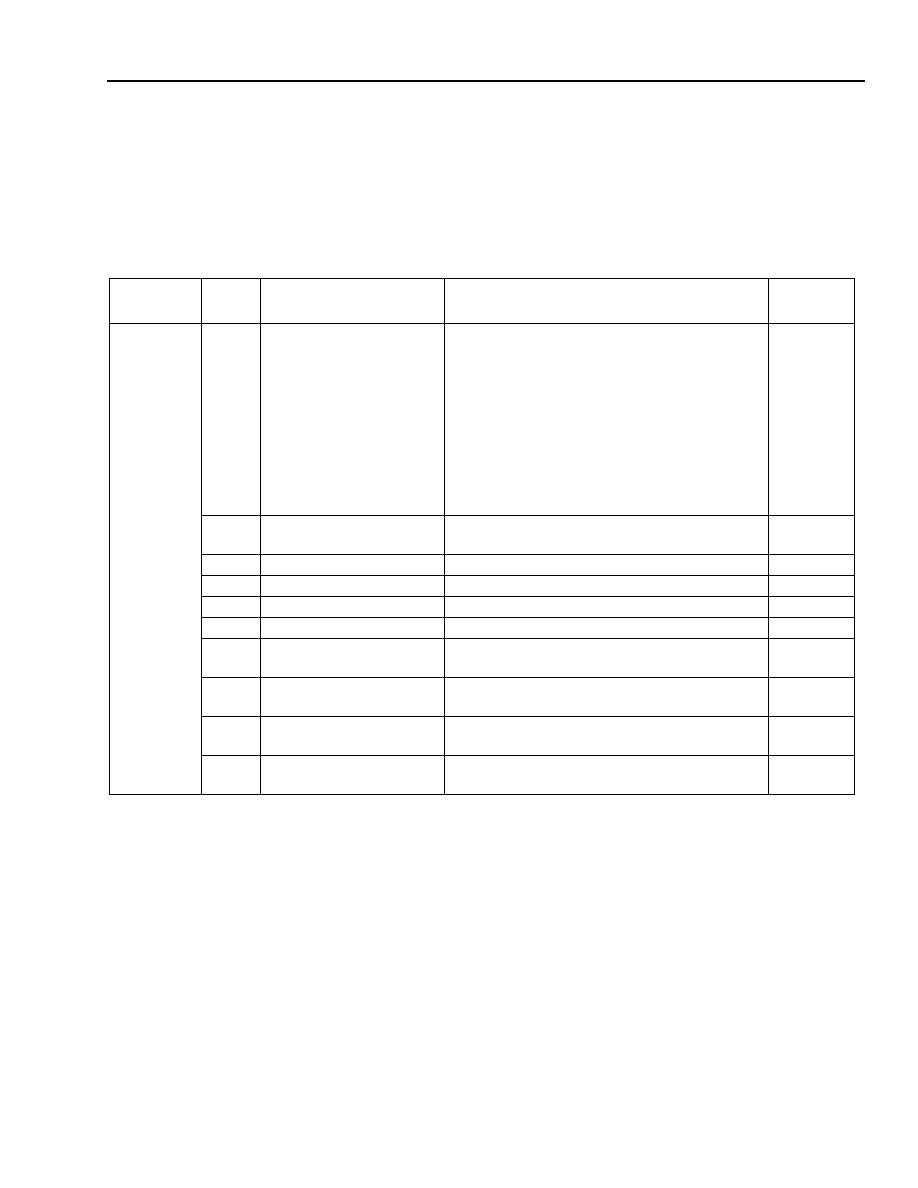

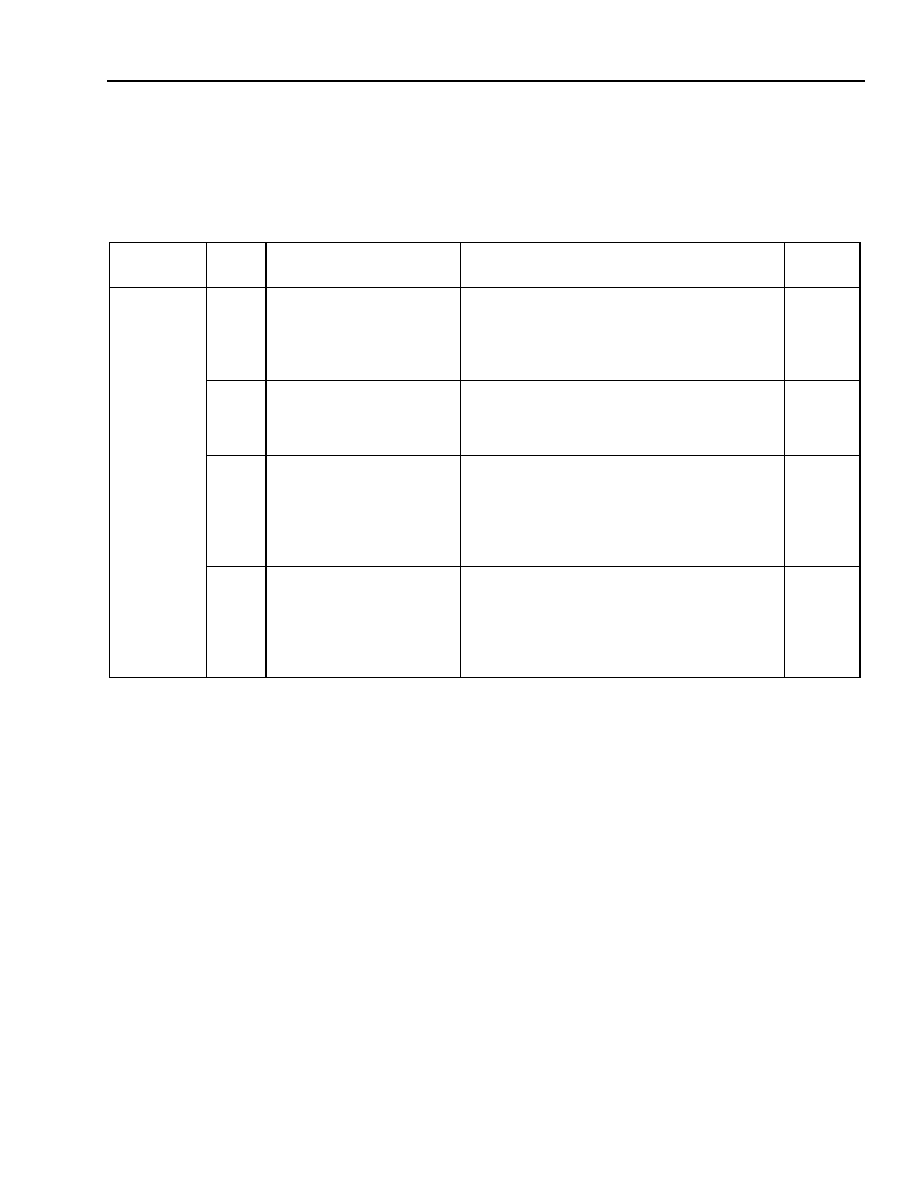

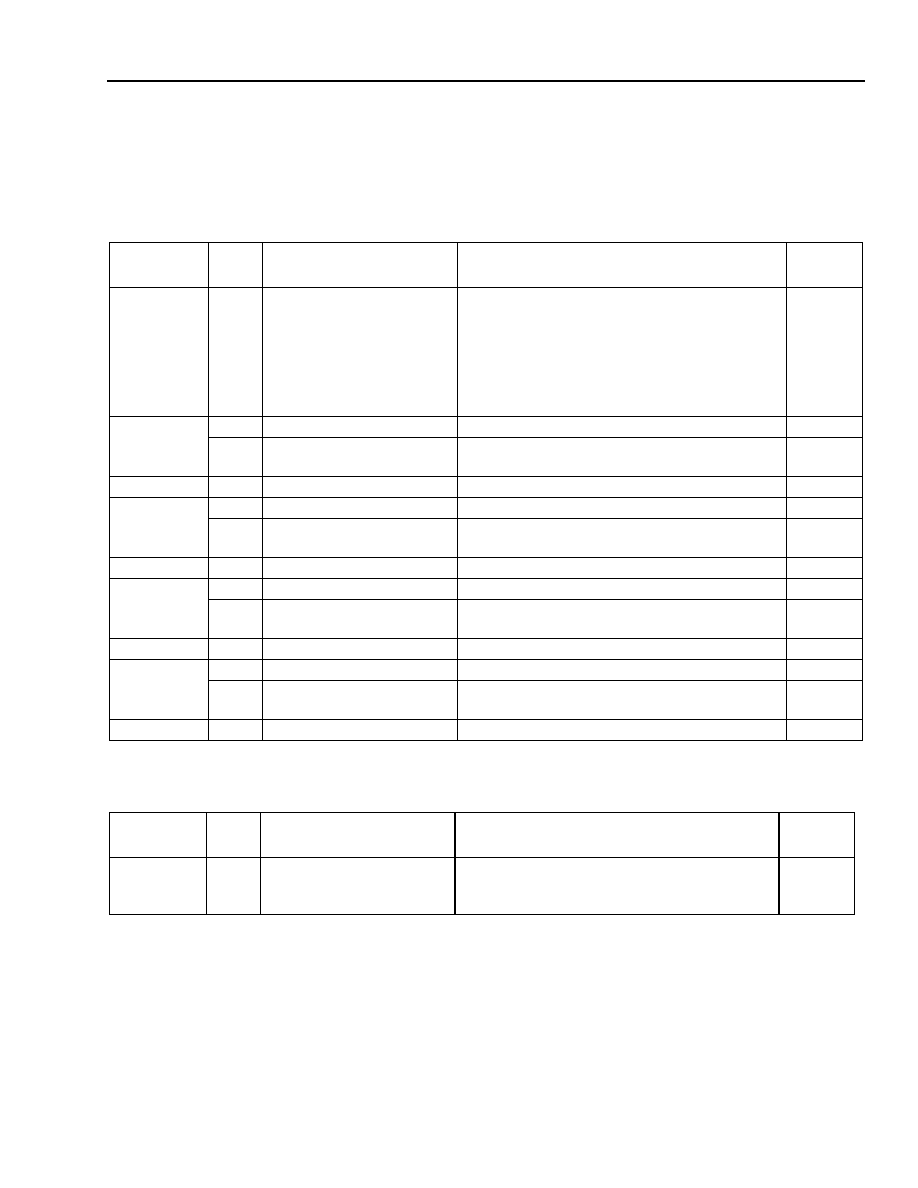

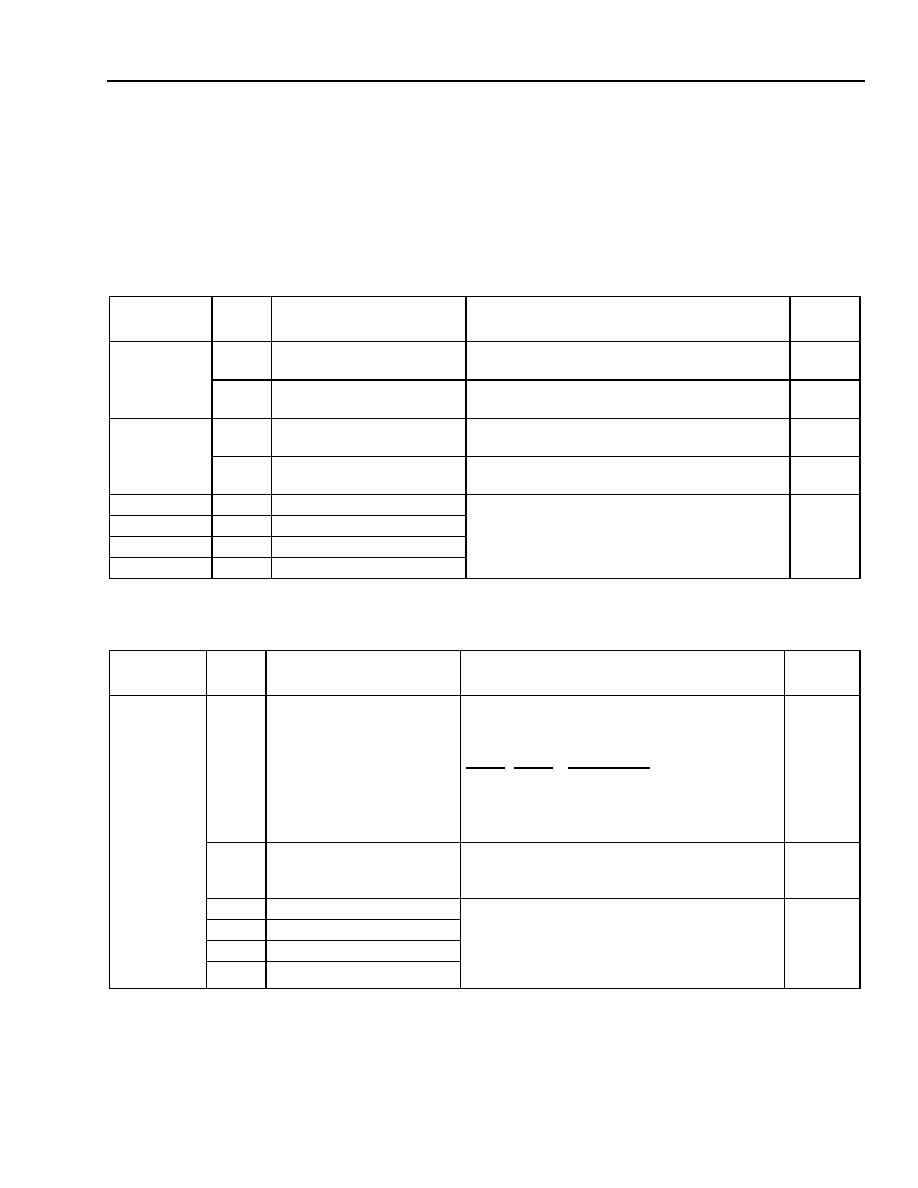

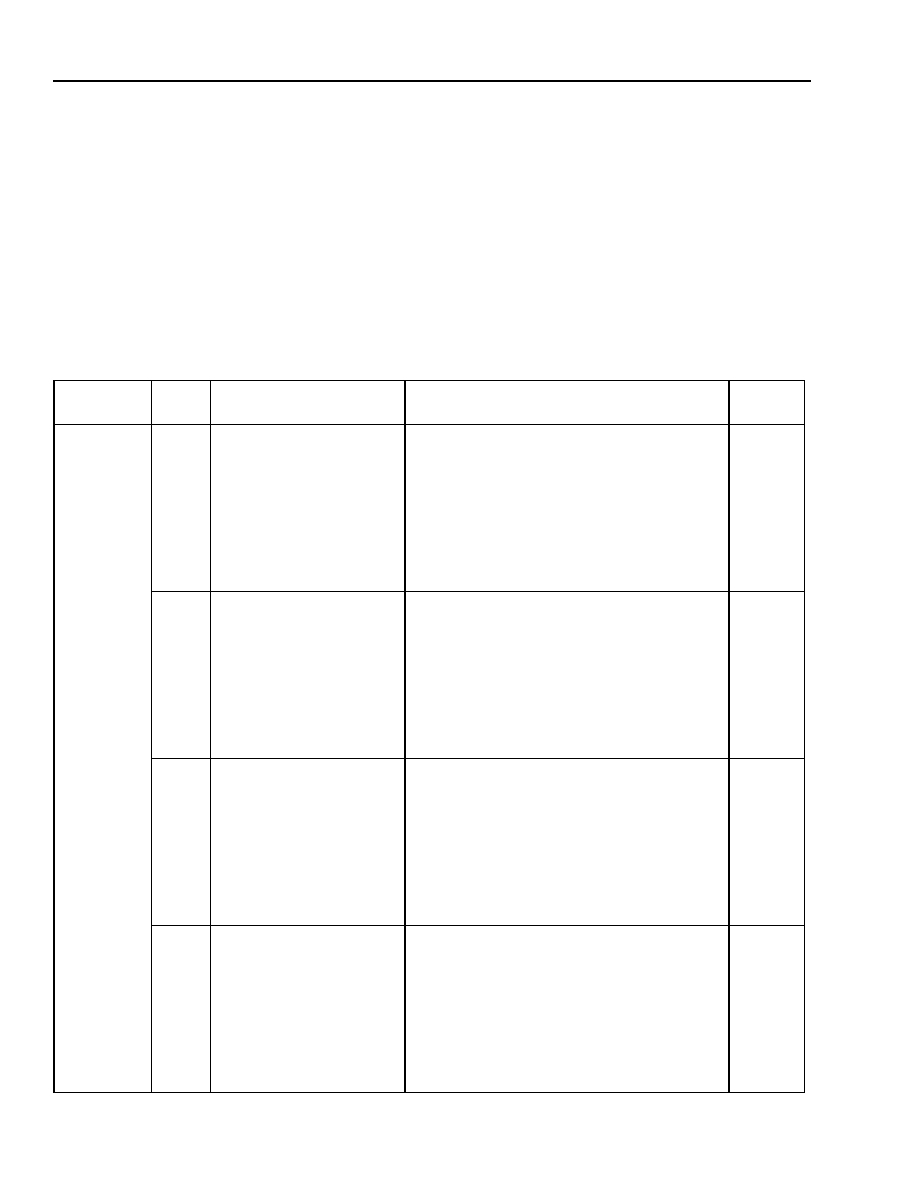

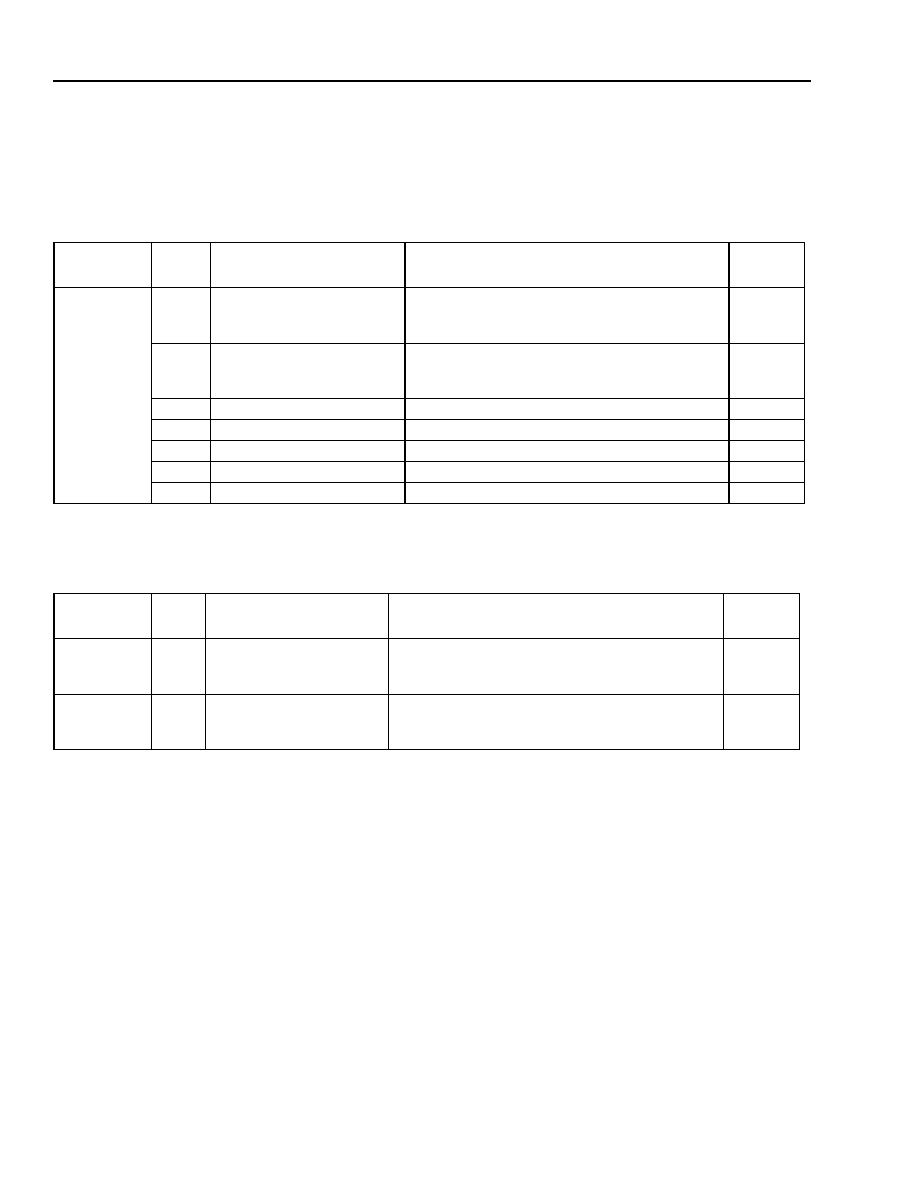

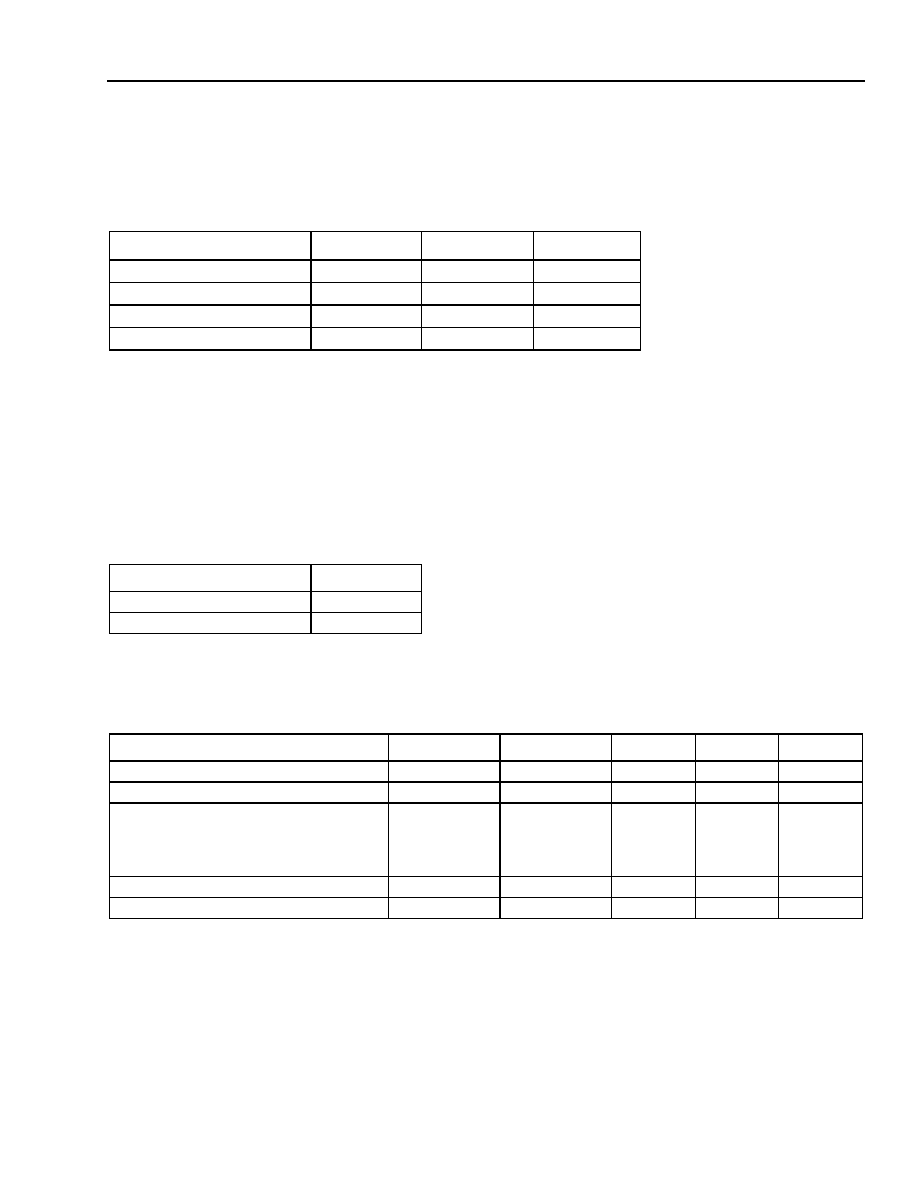

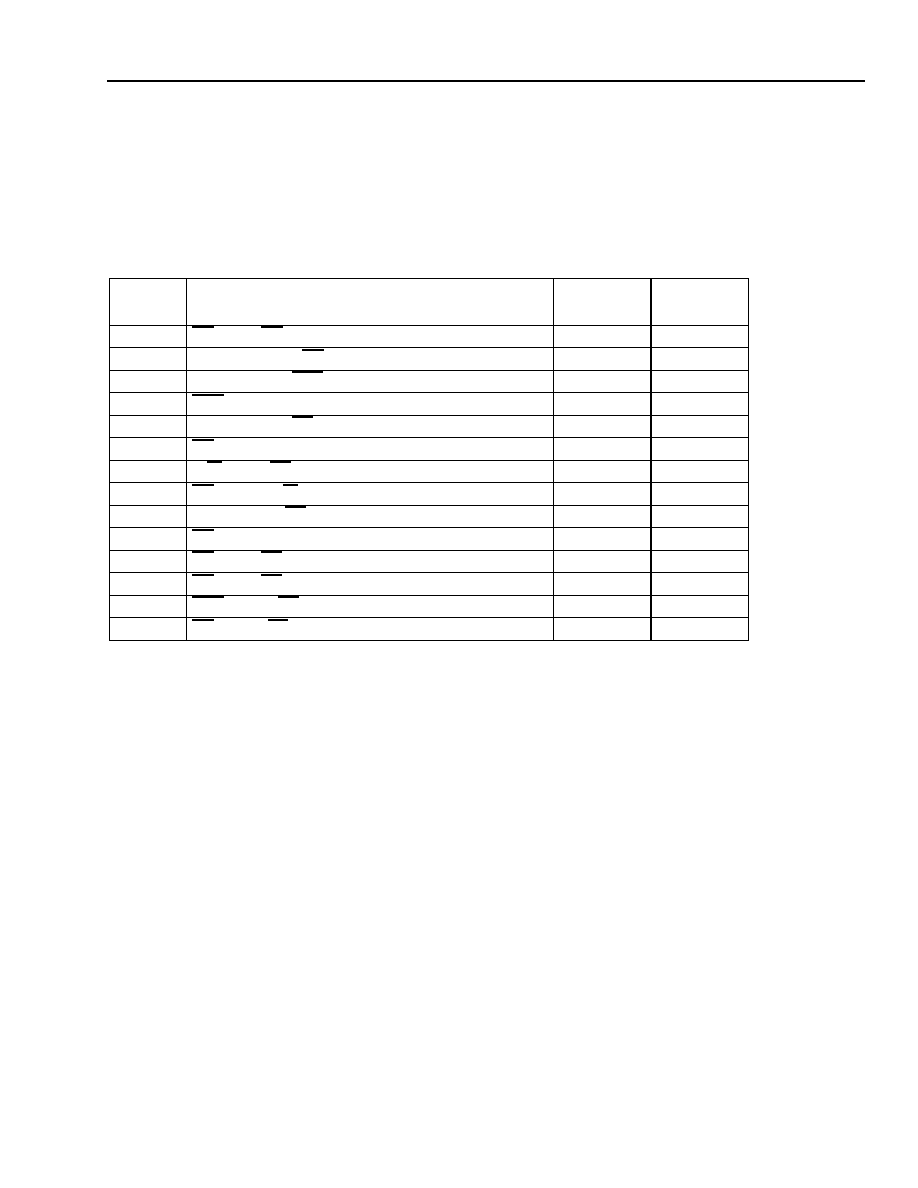

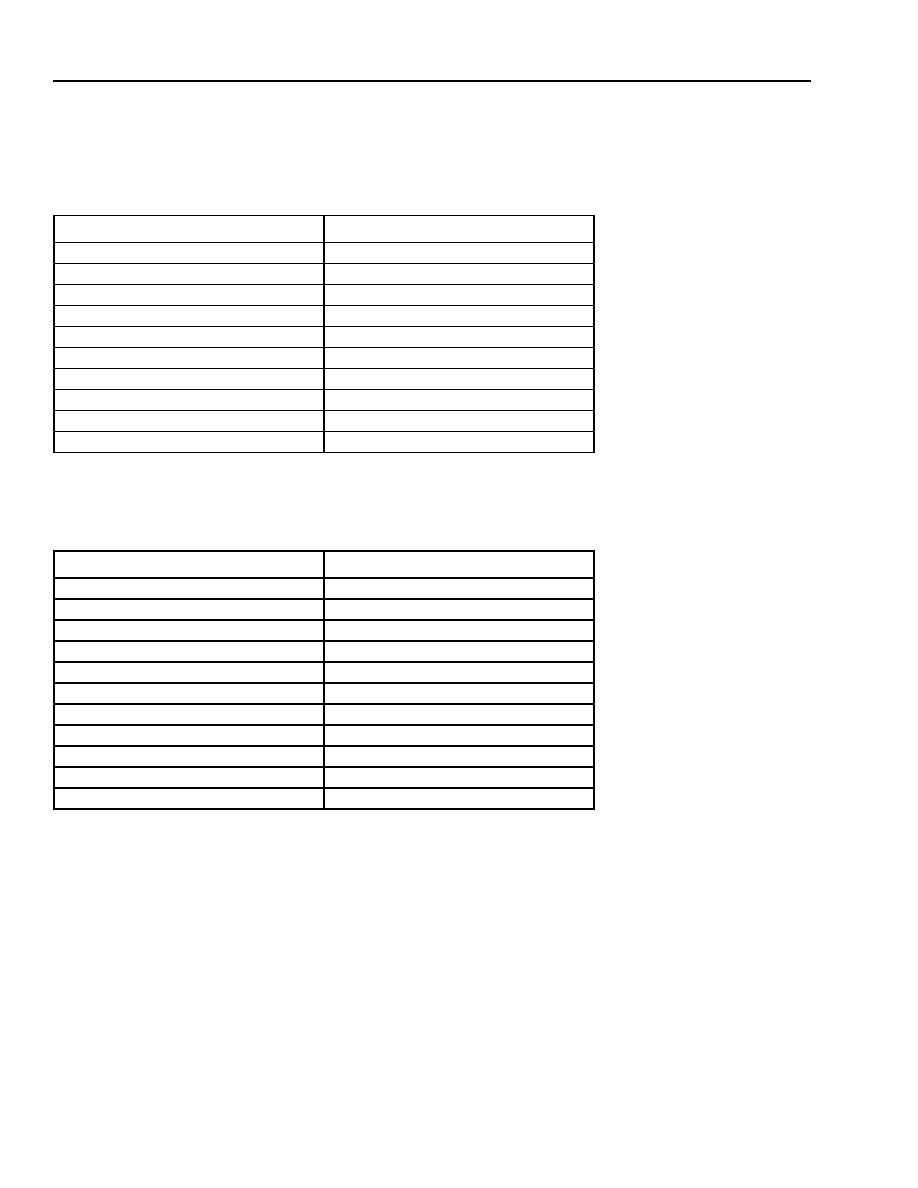

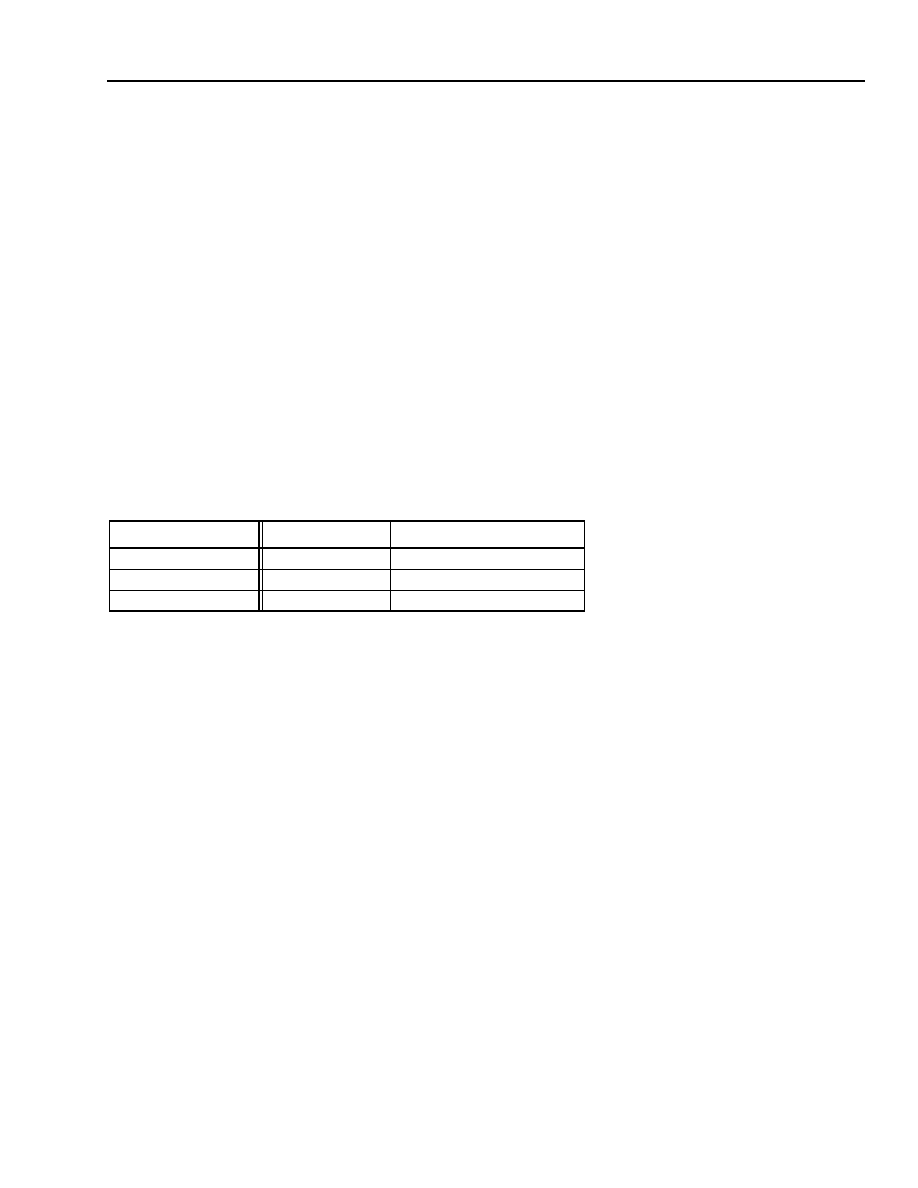

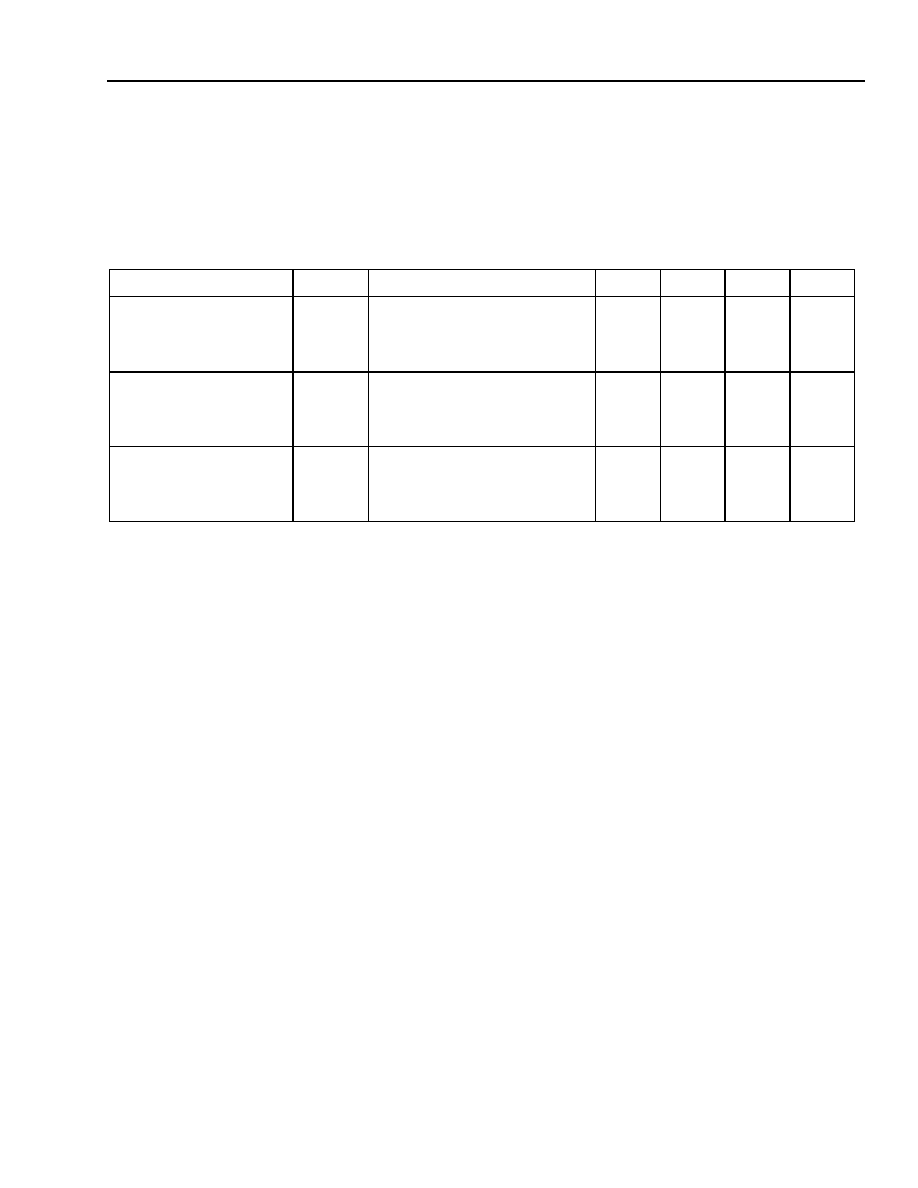

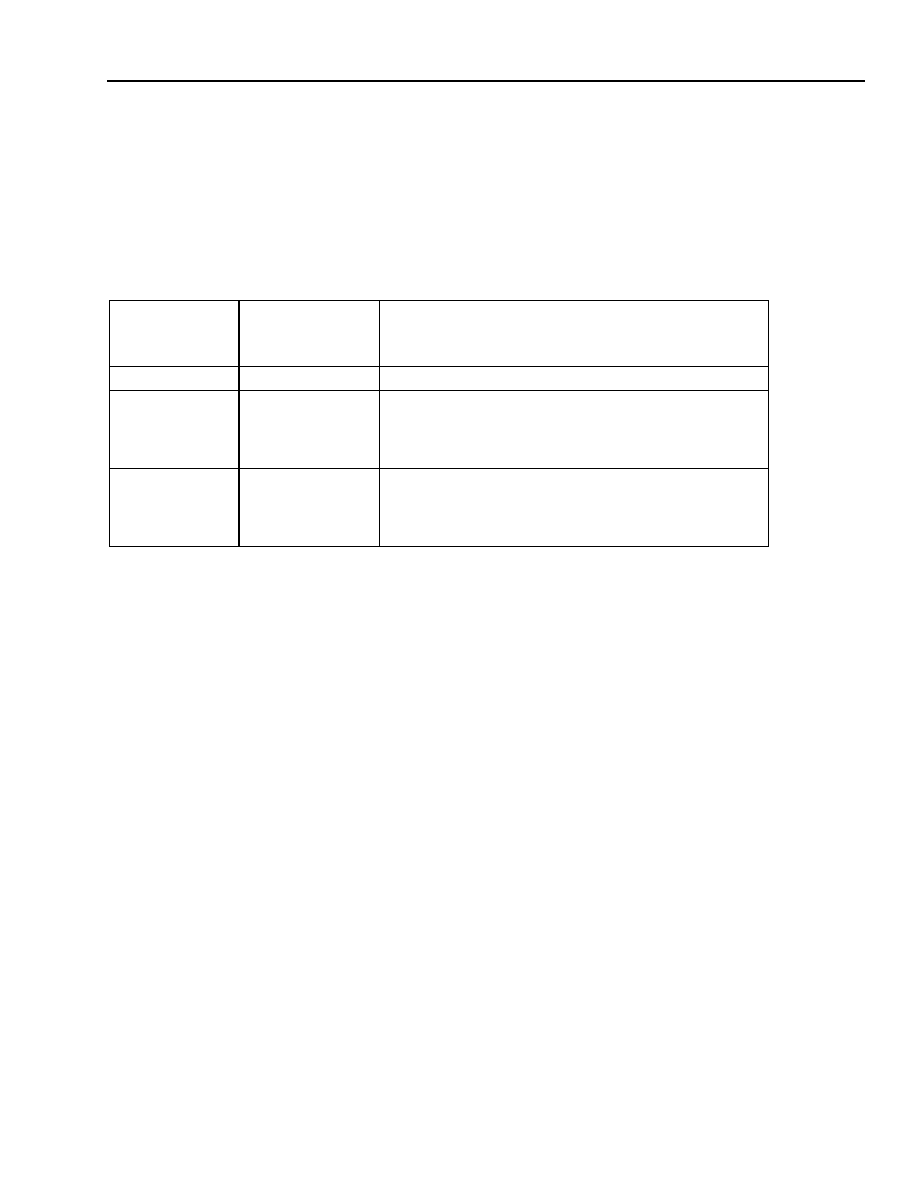

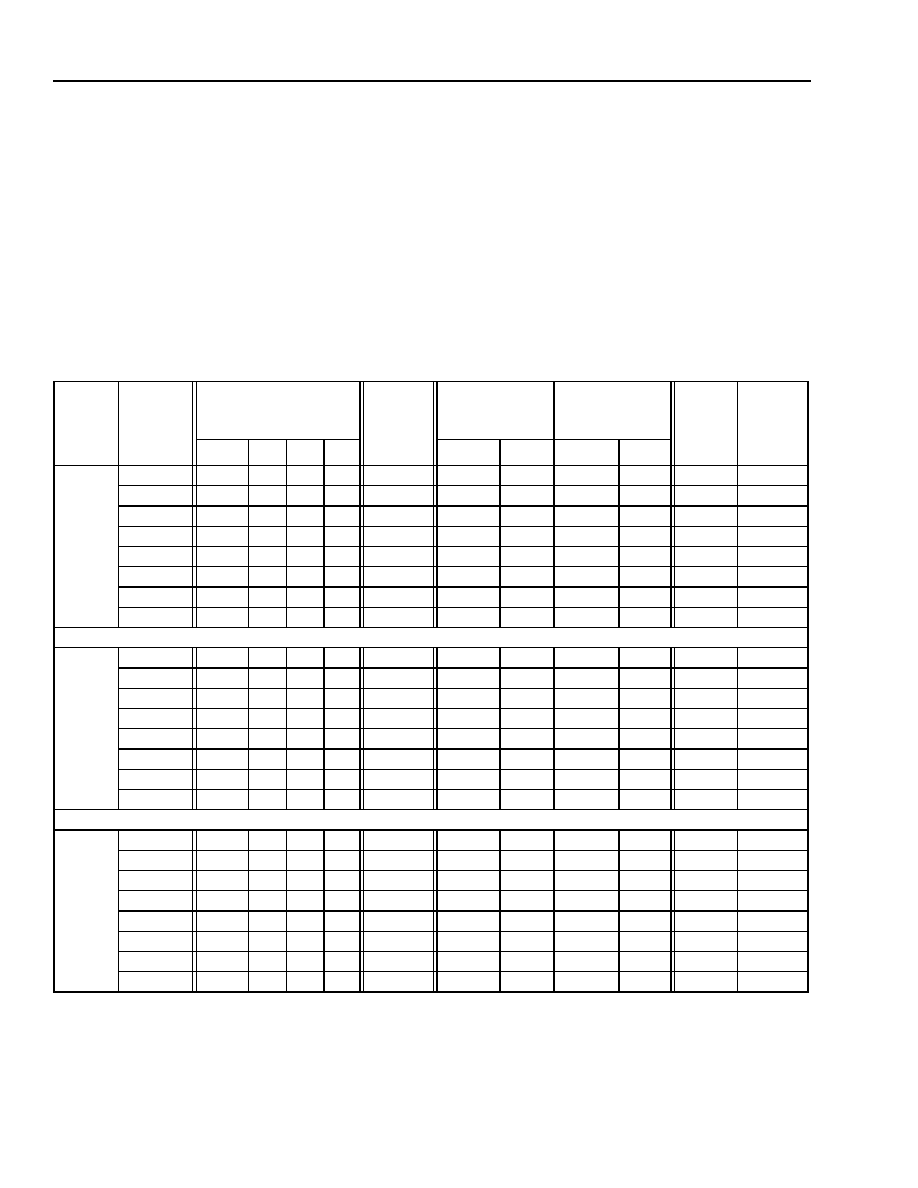

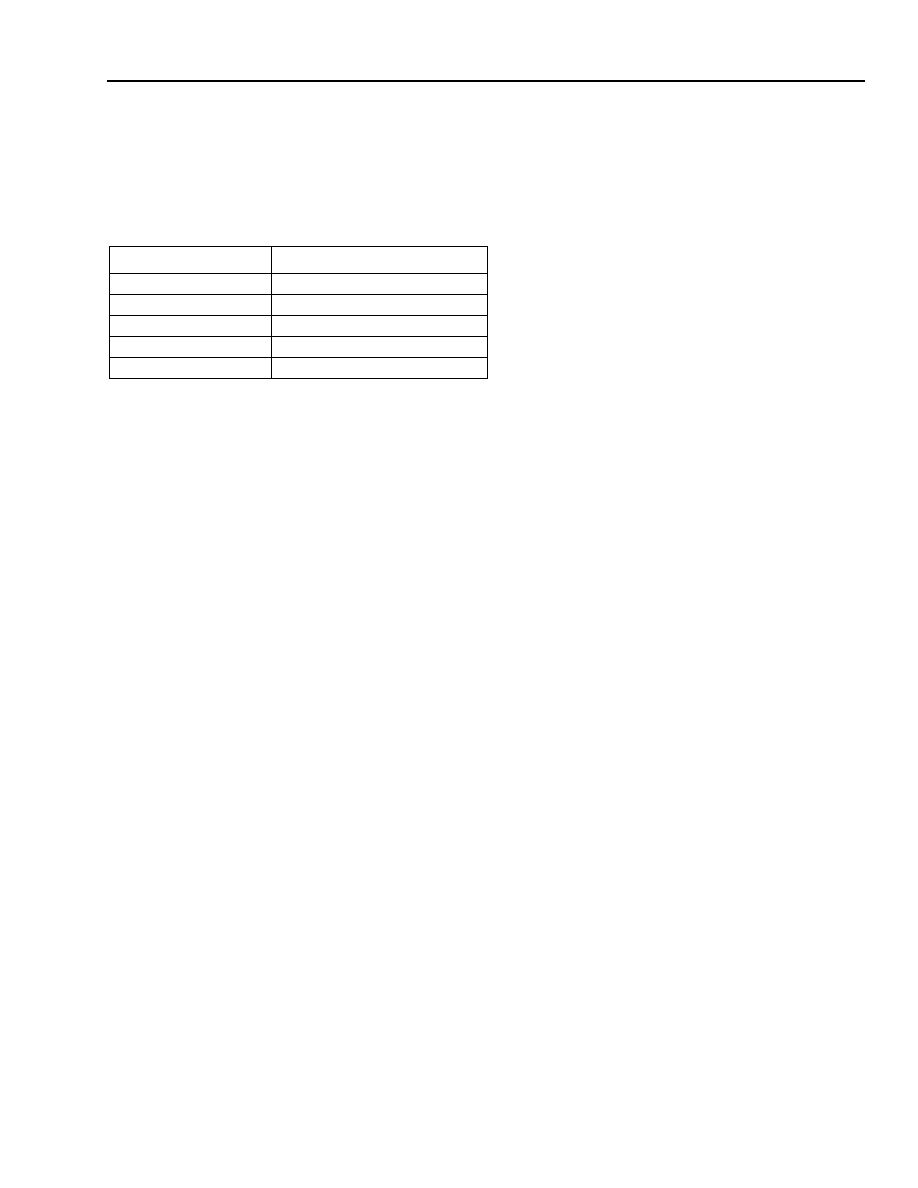

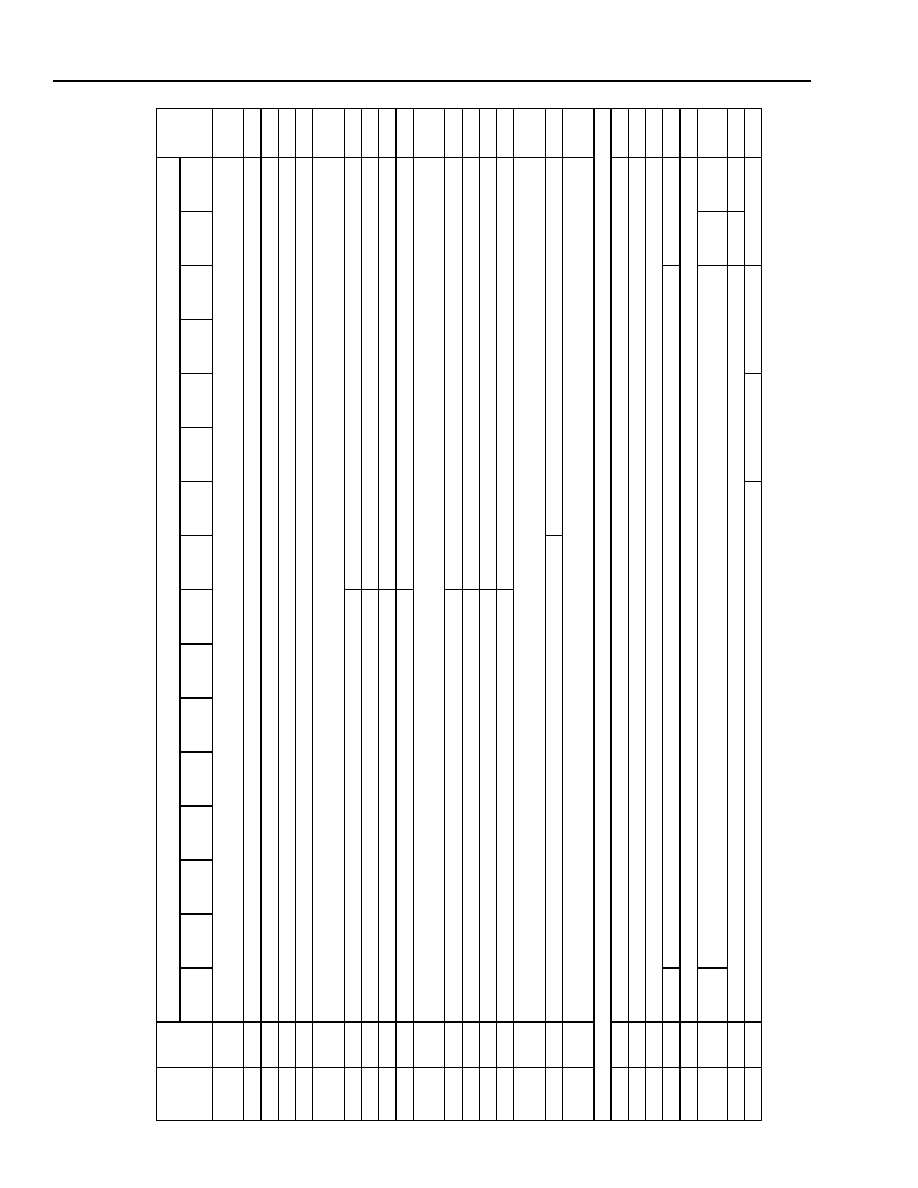

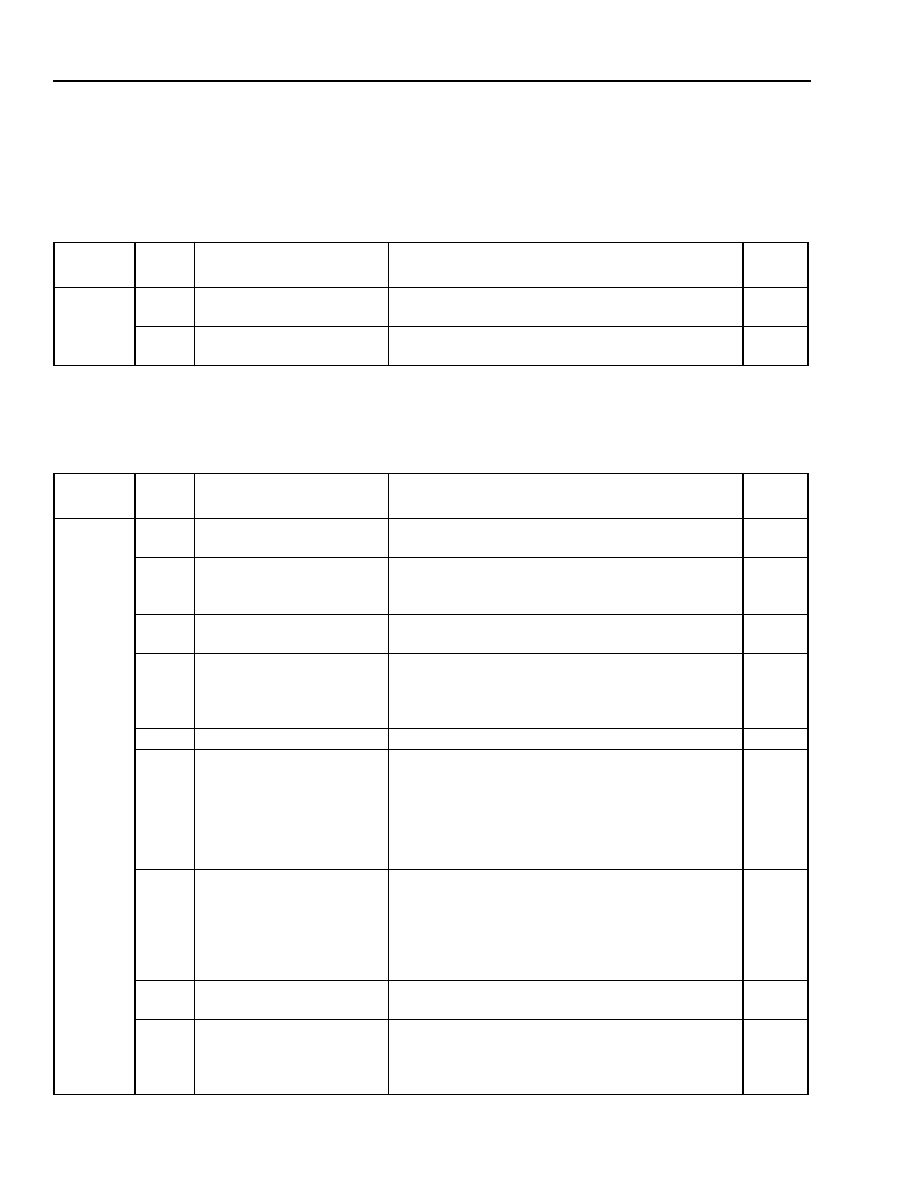

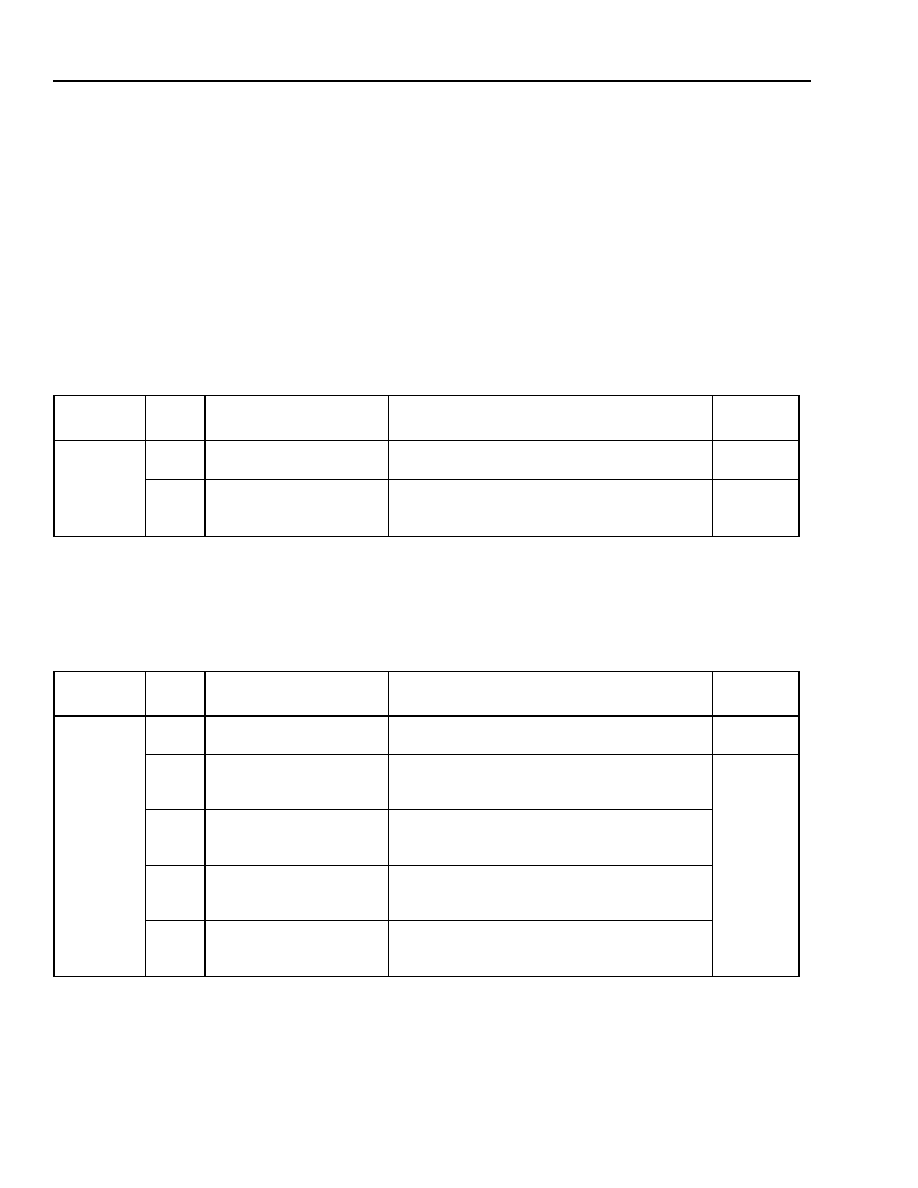

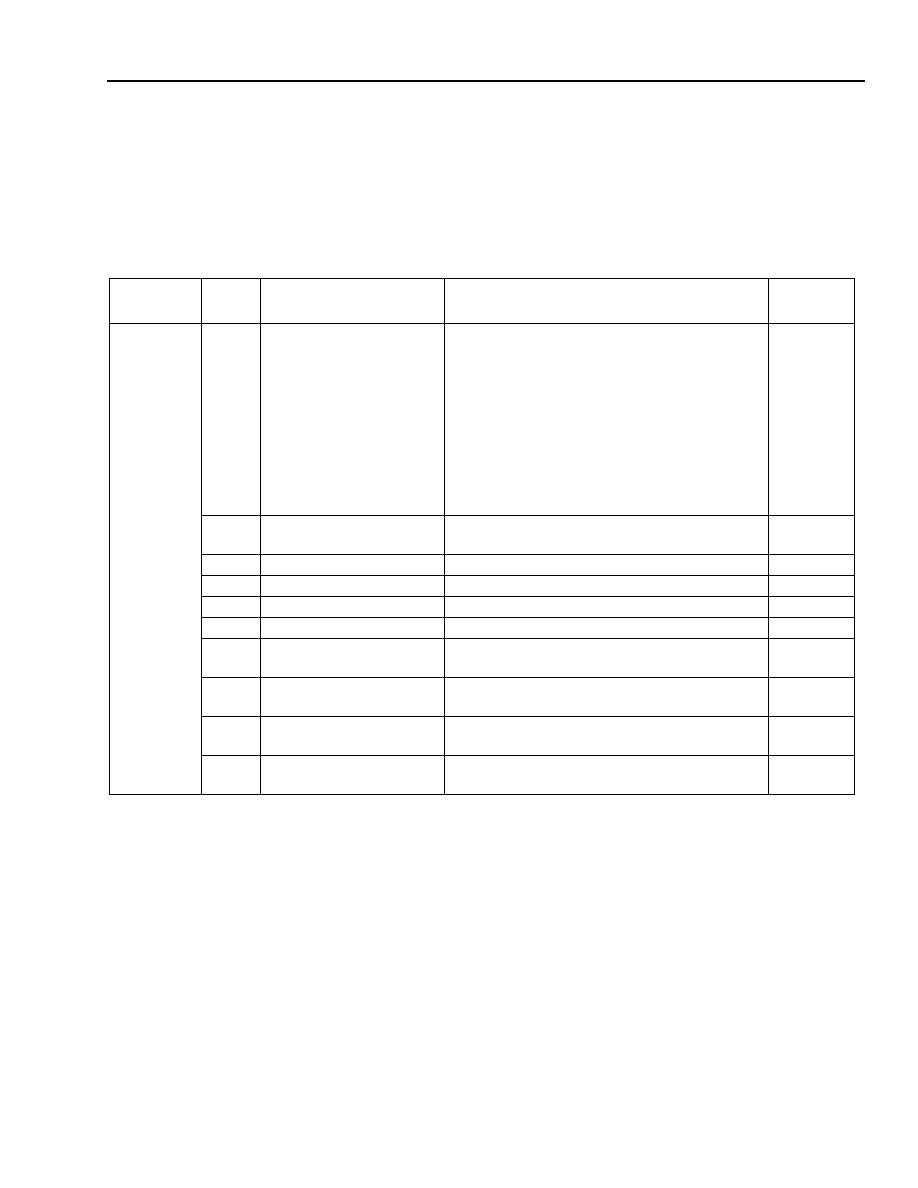

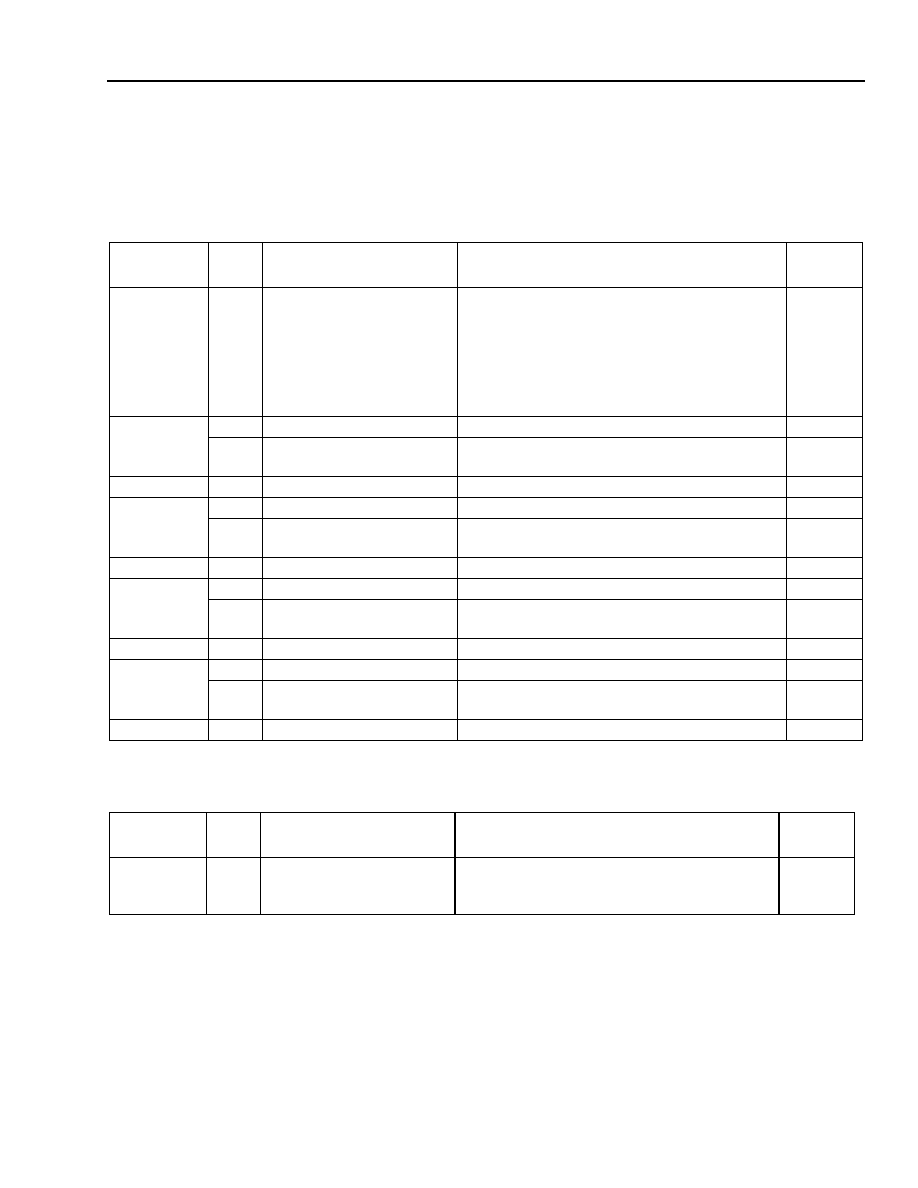

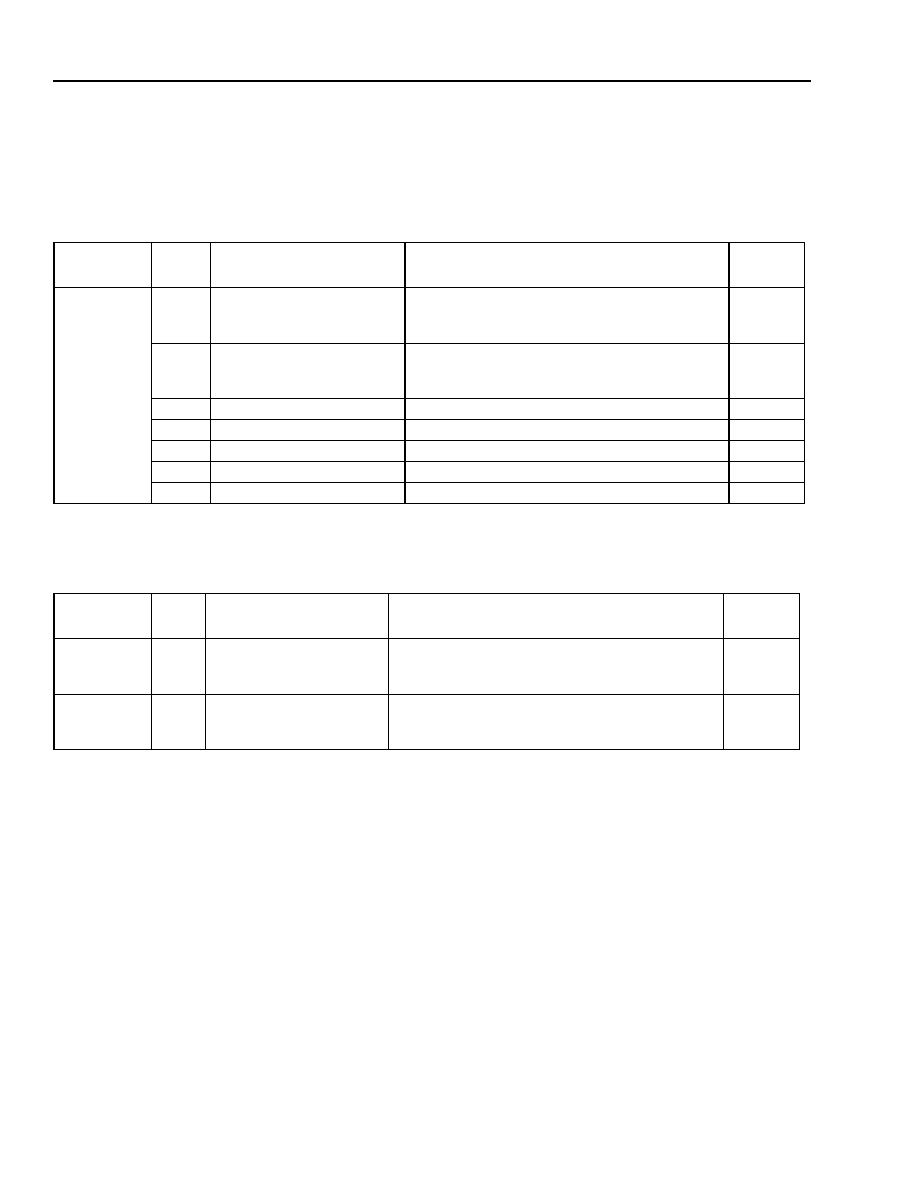

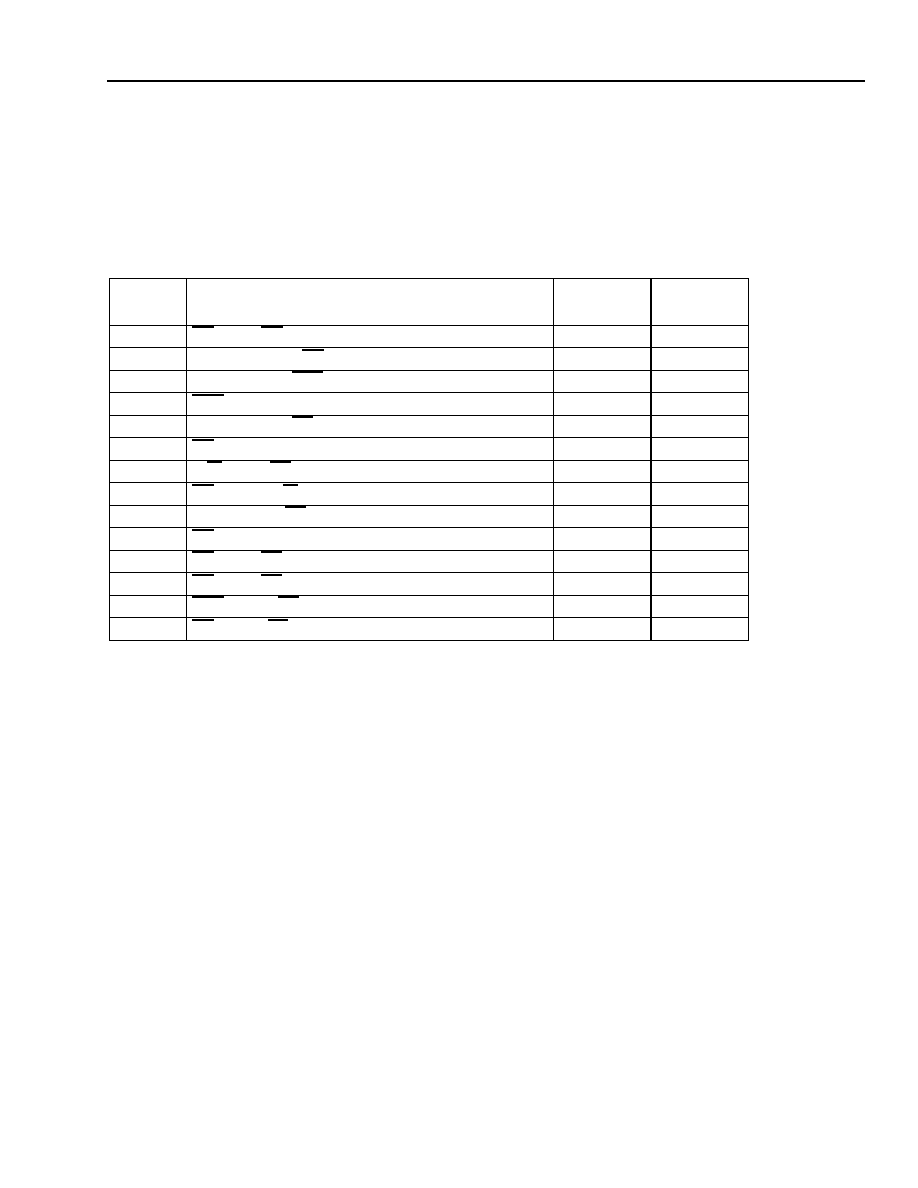

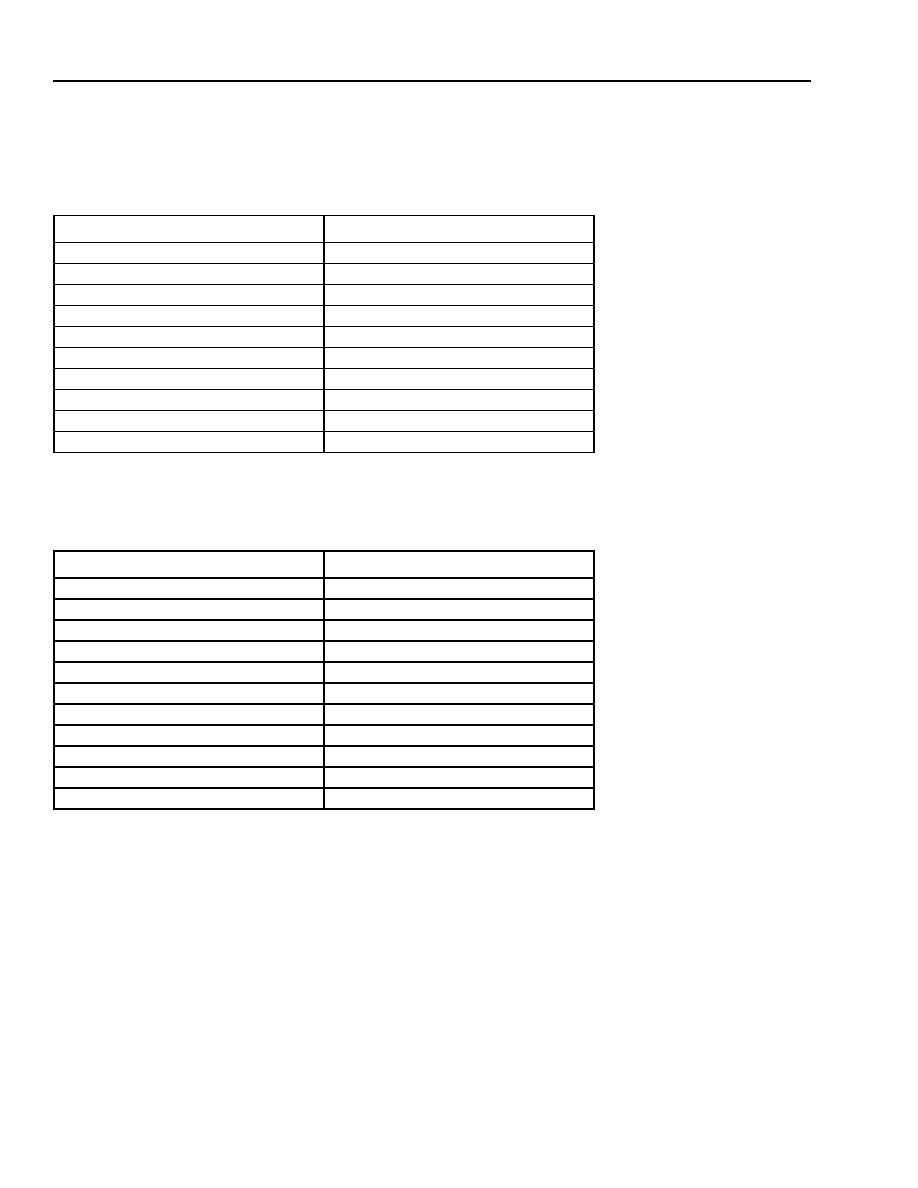

The TDAT data interface is available in three different configurations as summarized in Table 1.

TDAT04622

The TDAT04622 device contains a subset of the TDAT042G5 device. The TDAT04622 device functions as

described in the TDAT042G5 SONET/SDH 155/622/2488 Mbits/s Data Interface Data Sheet

(DS98-193SONT-4) with the following limitations:

s

Quad OC-3 operation only or single OC-12 operation only.

s

Single UTOPIA port.

TDAT021G2

The TDAT021G2 device contains a subset of the TDAT042G5 device. The TDAT021G2 device functions as

described in the TDAT042G5 SONET/SDH 155/622/2488 Mbits/s Data Interface Data Sheet

(DS98-193SONT-4) with the following limitations:

s

Quad OC-3 operation only or dual OC-12 operation only.

s

Two UTOPIA ports.

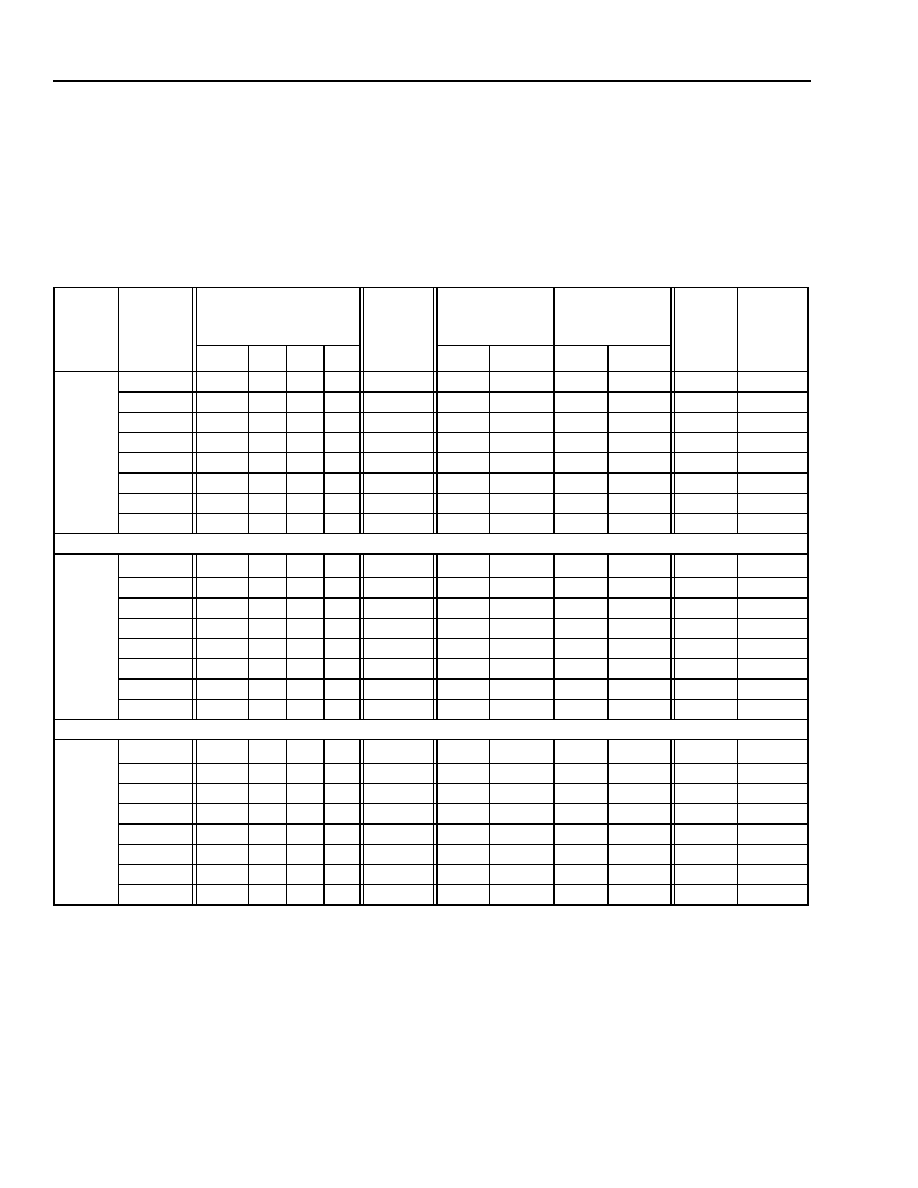

TDAT042G5

The TDAT042G5 device contains all functionality as described in the TDAT042G5 SONET/SDH 155/622/2488

Mbits/s Data Interface Data Sheet (DS98-193SONT-4).

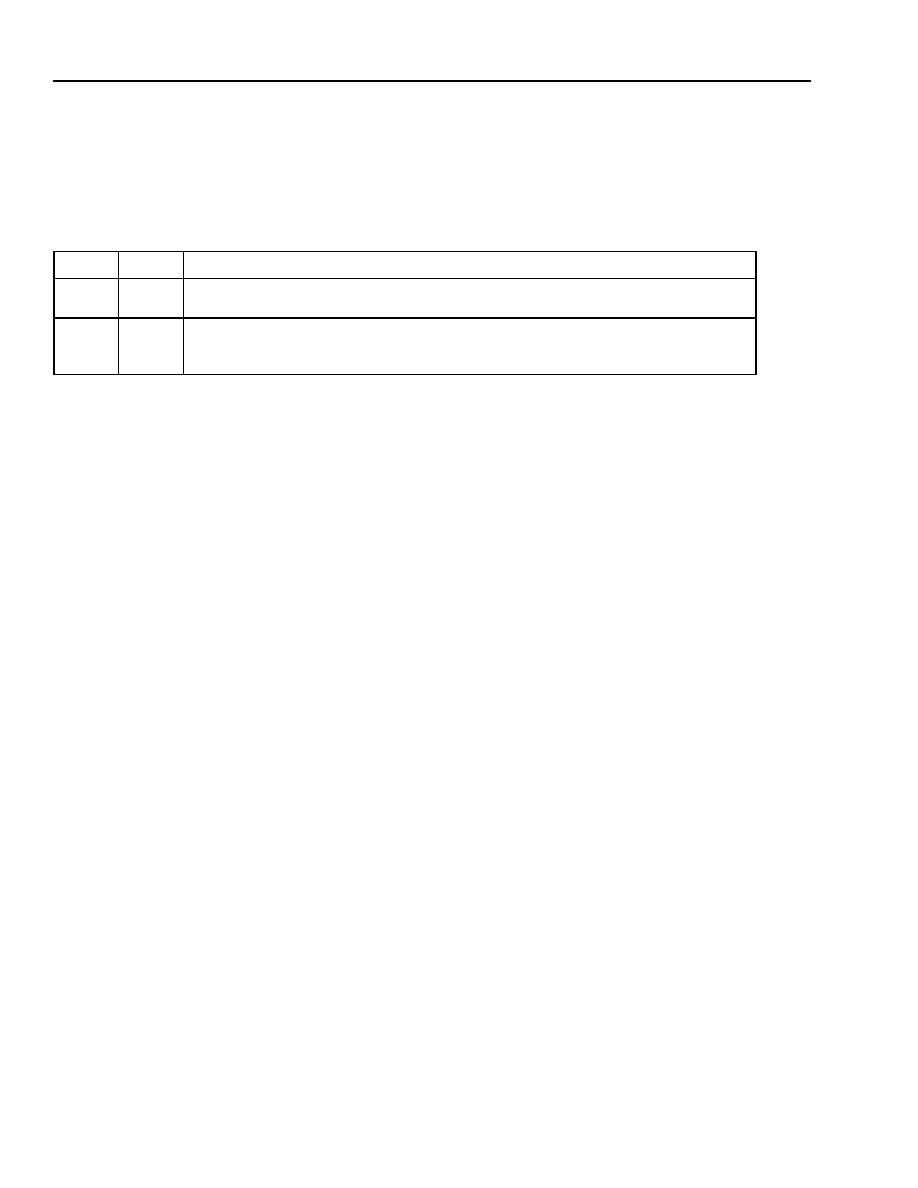

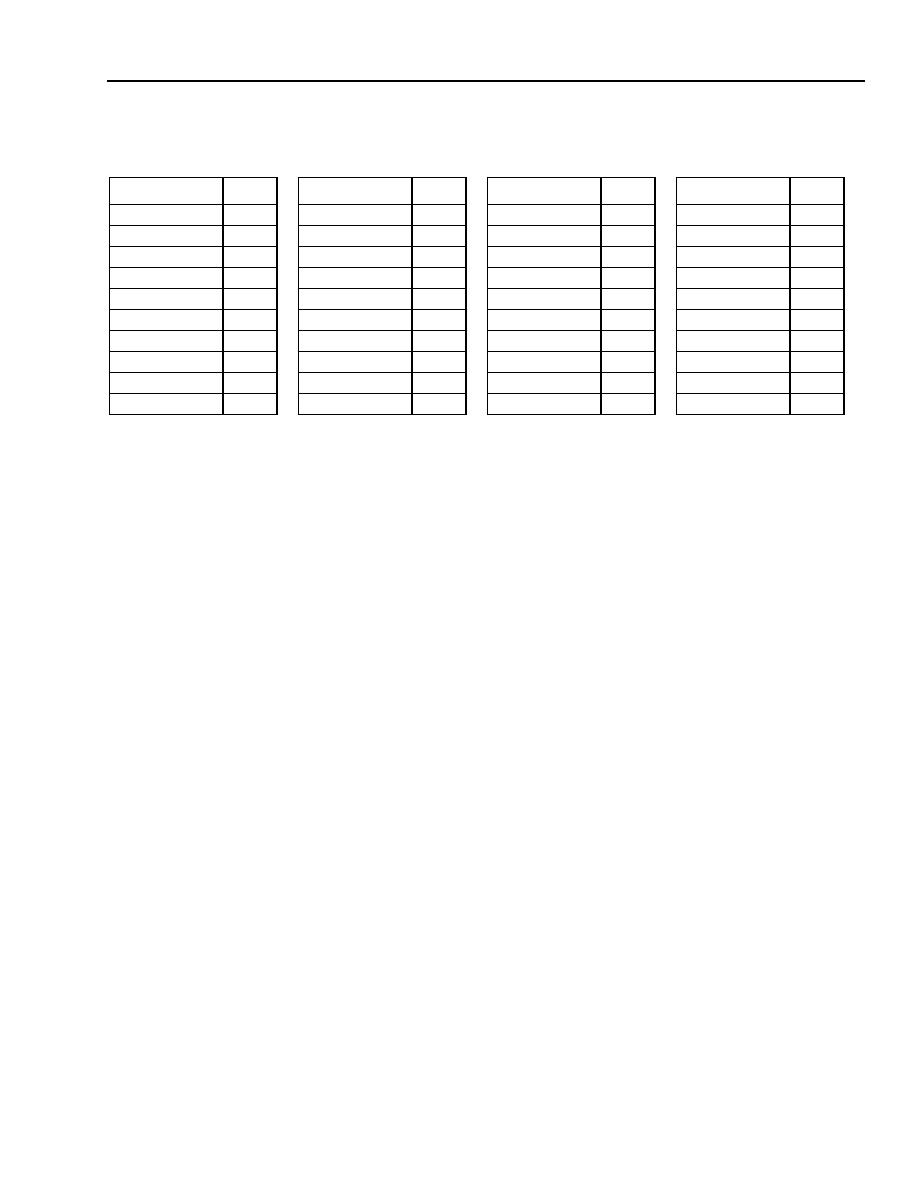

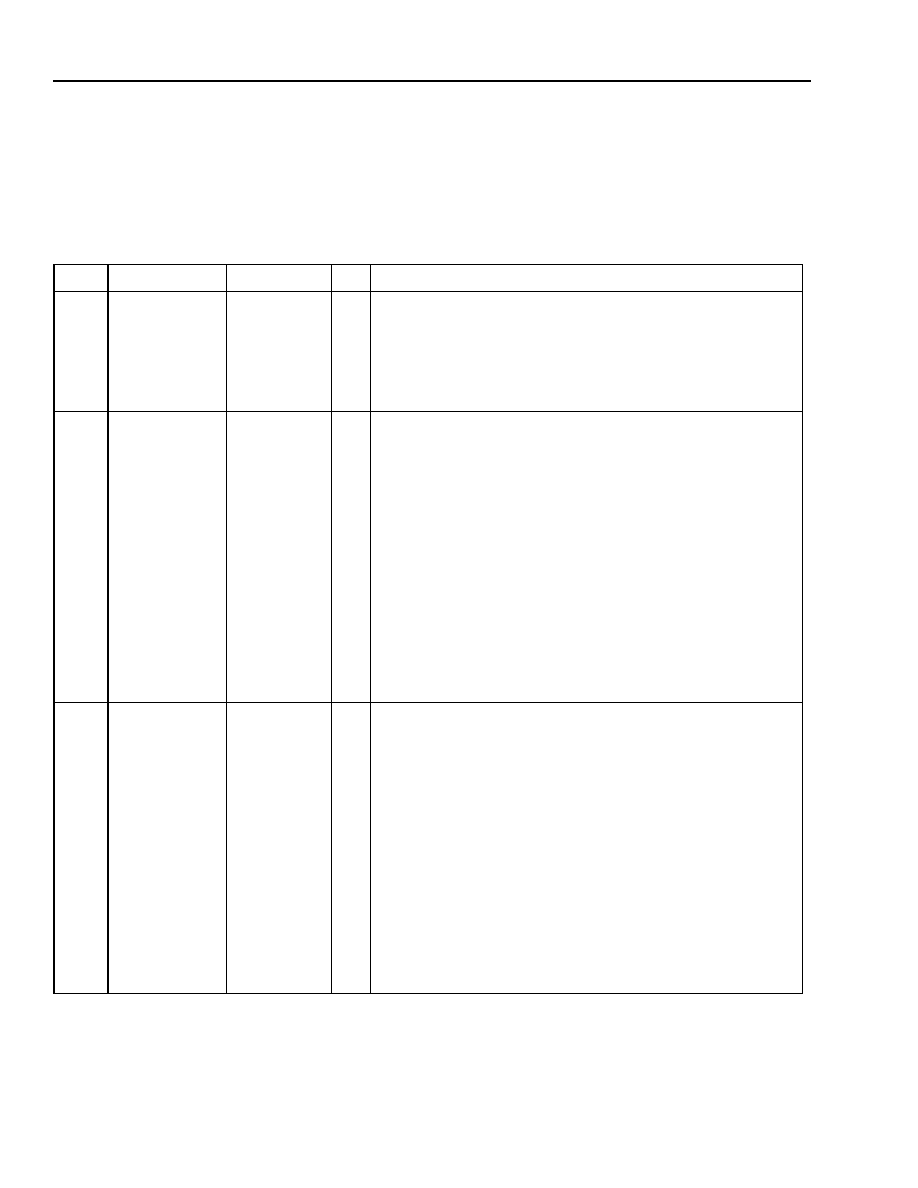

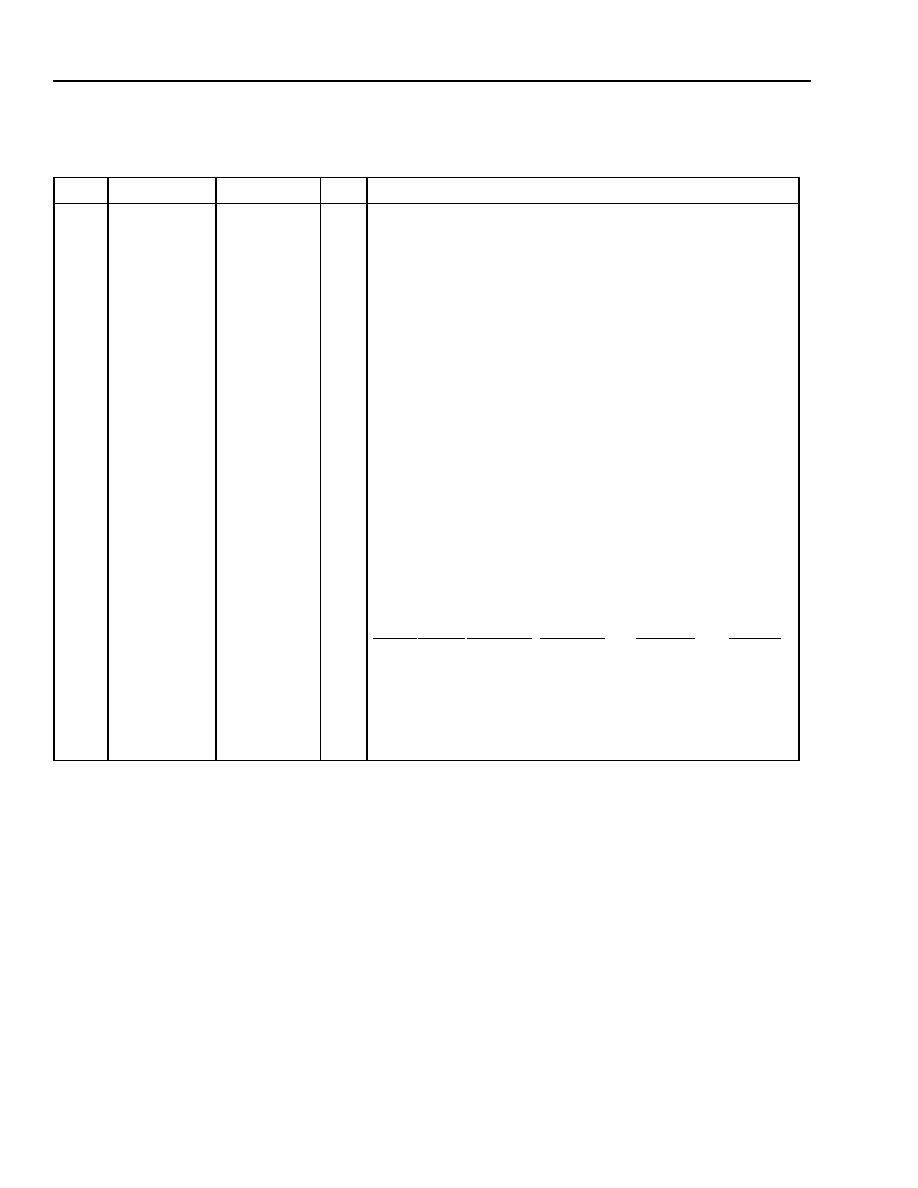

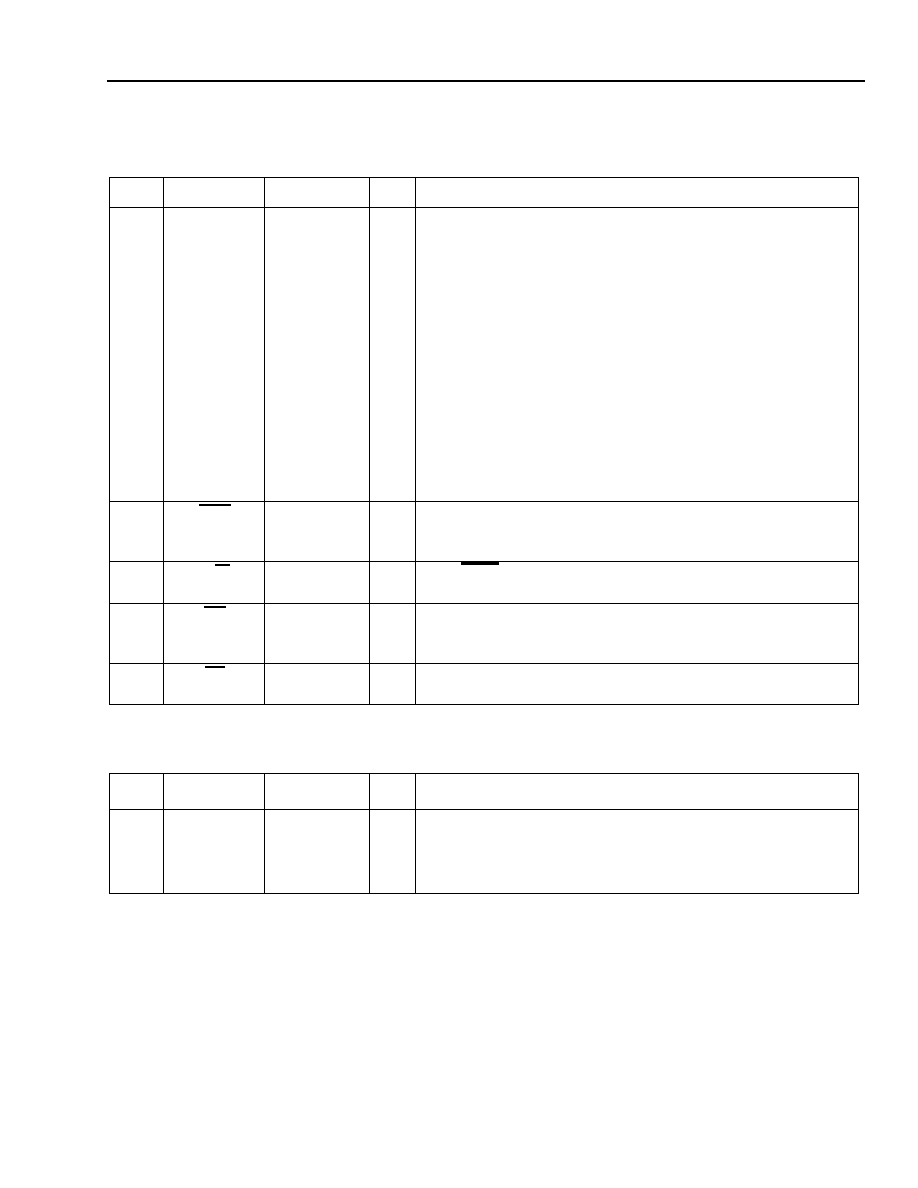

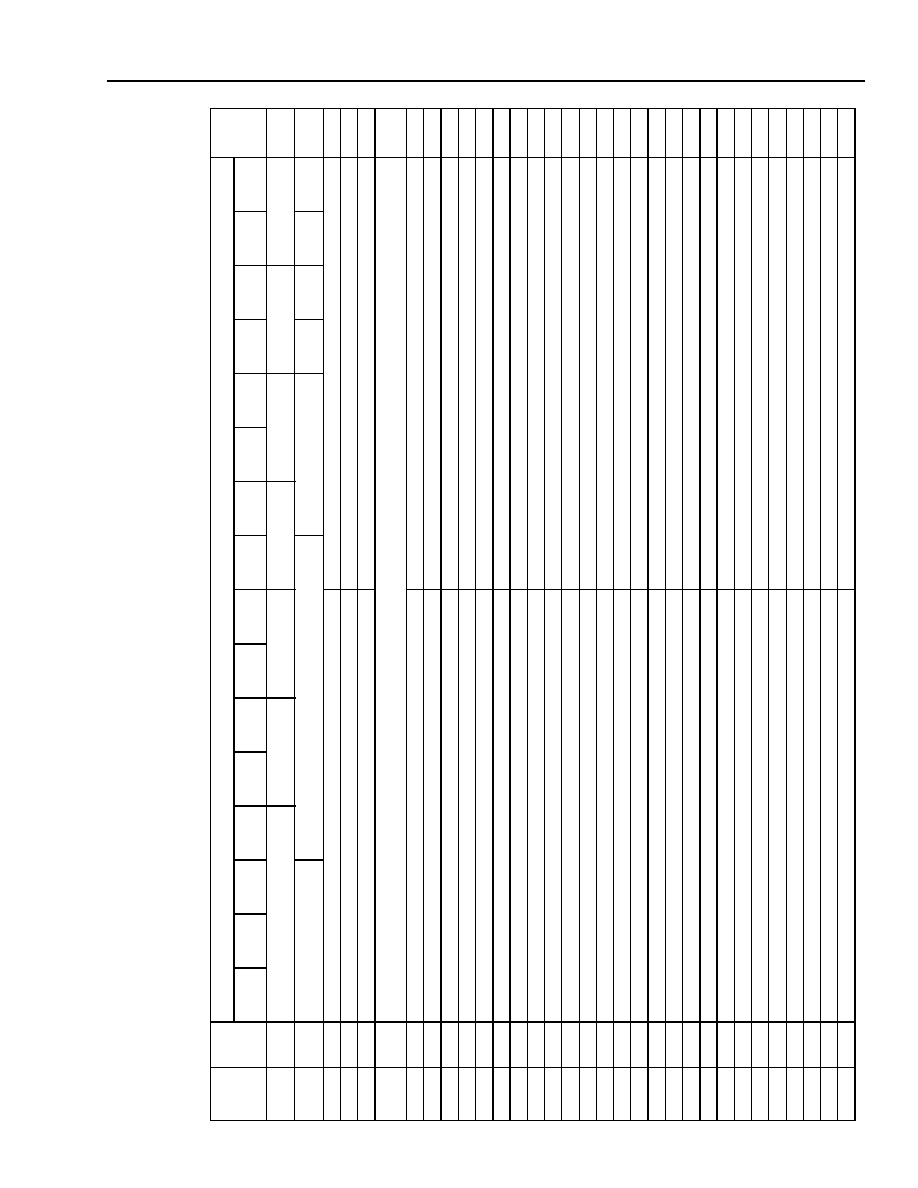

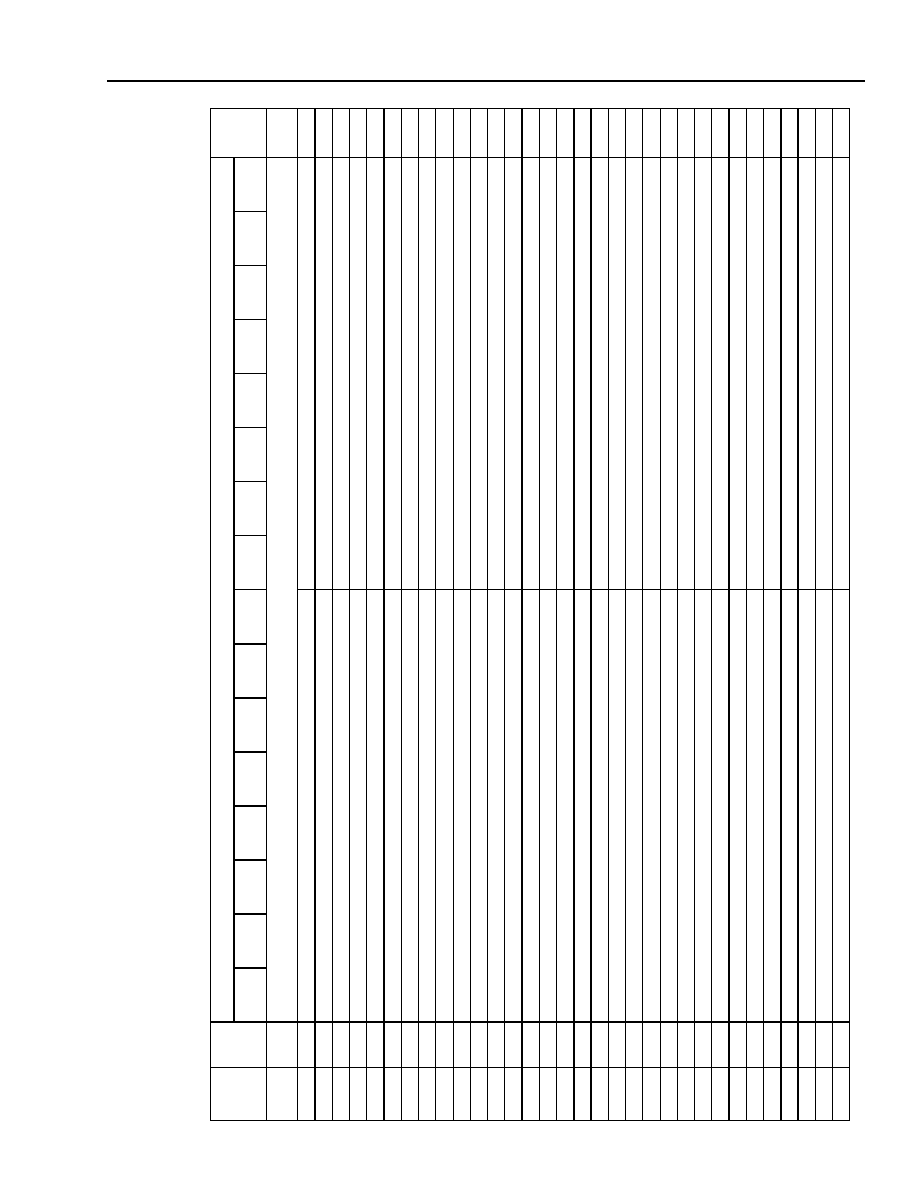

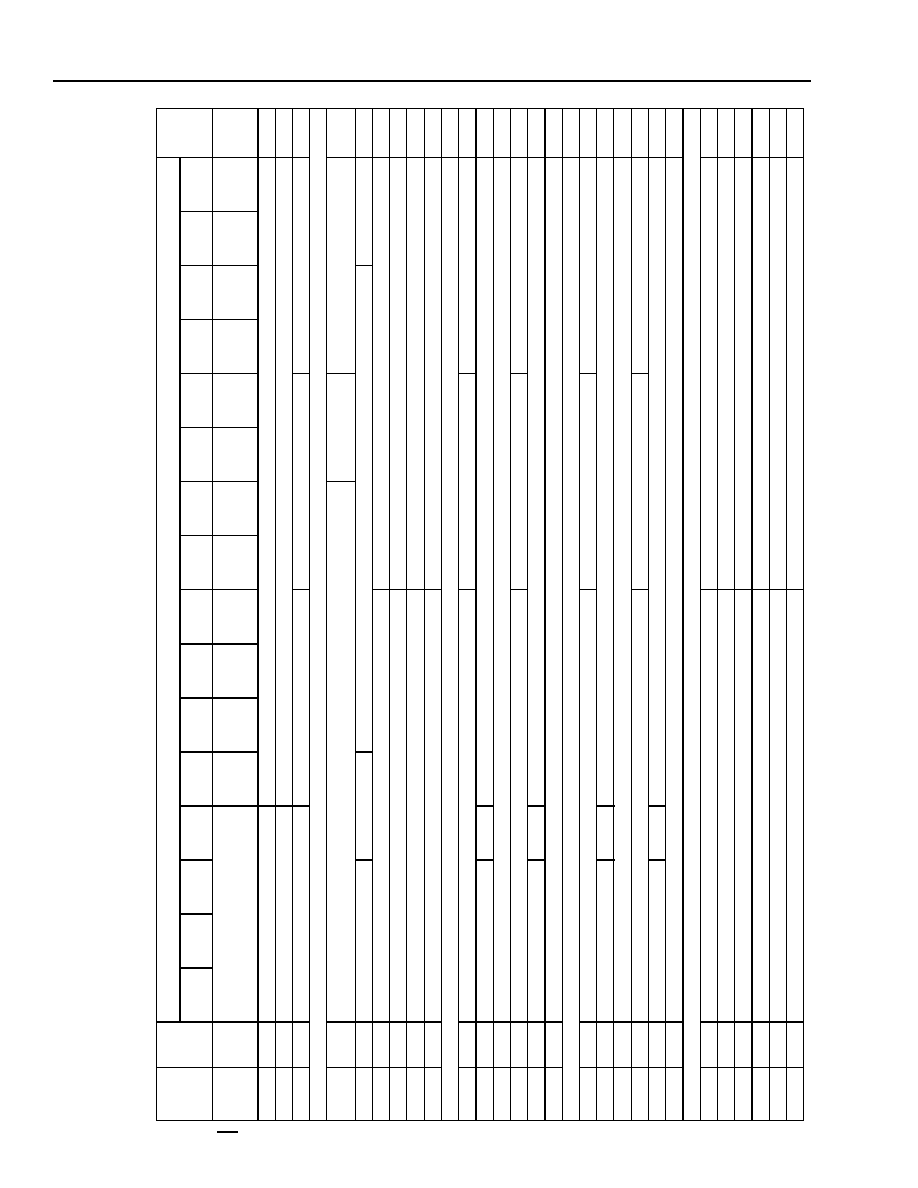

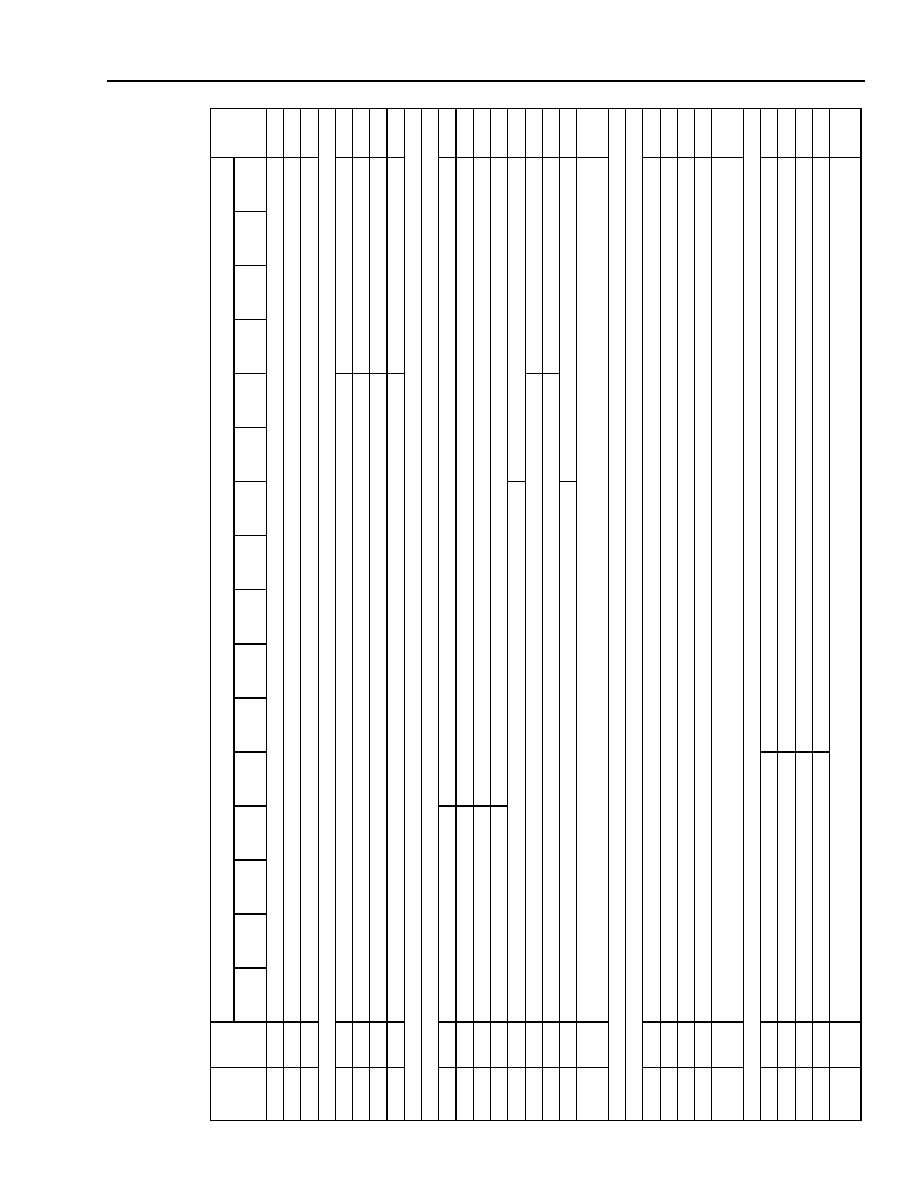

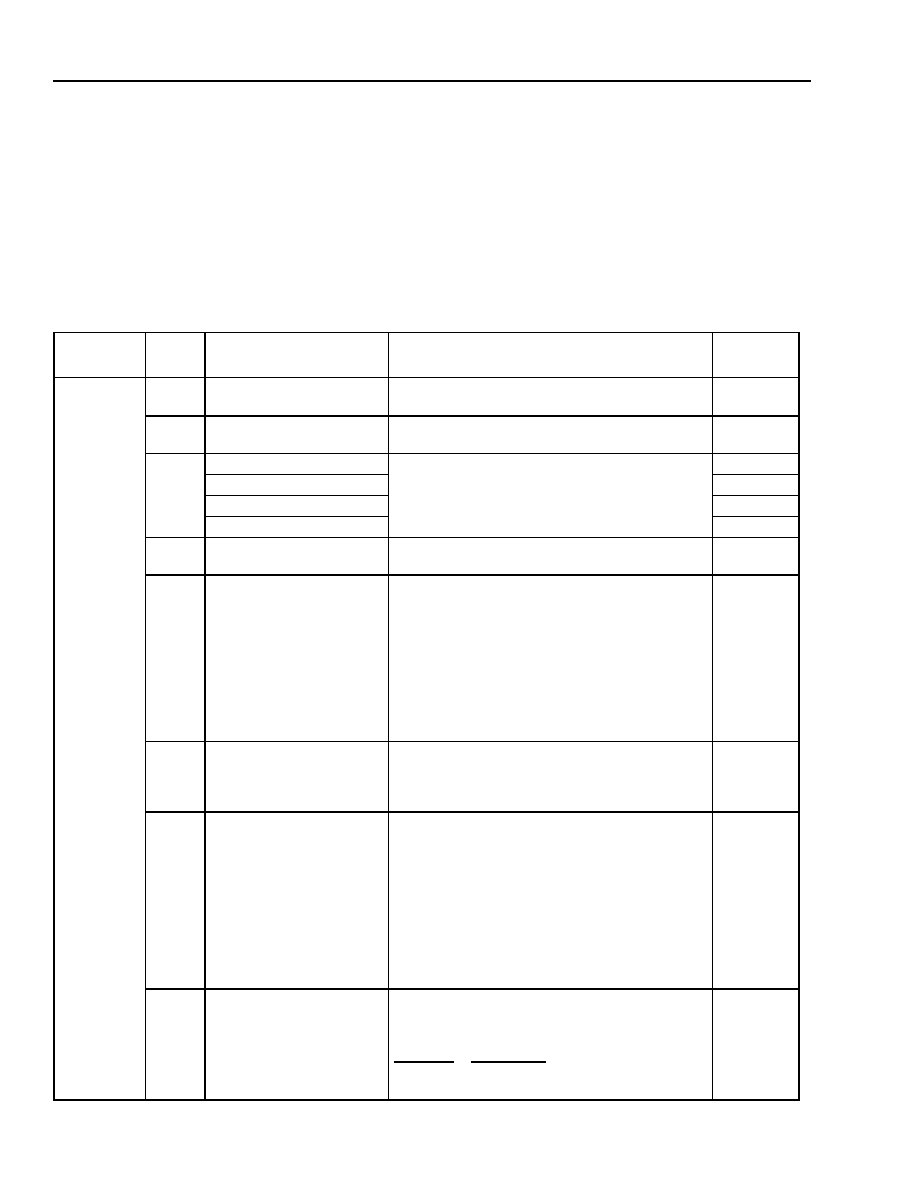

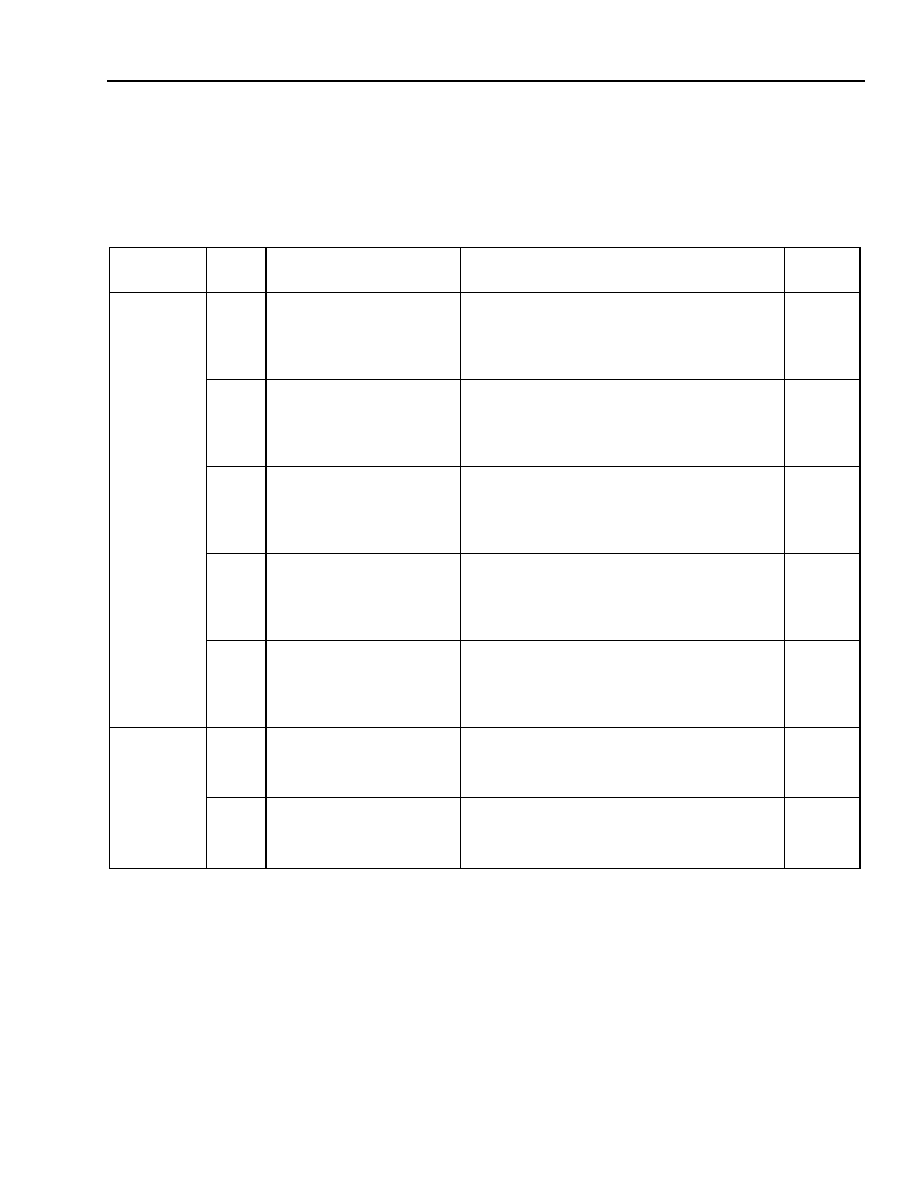

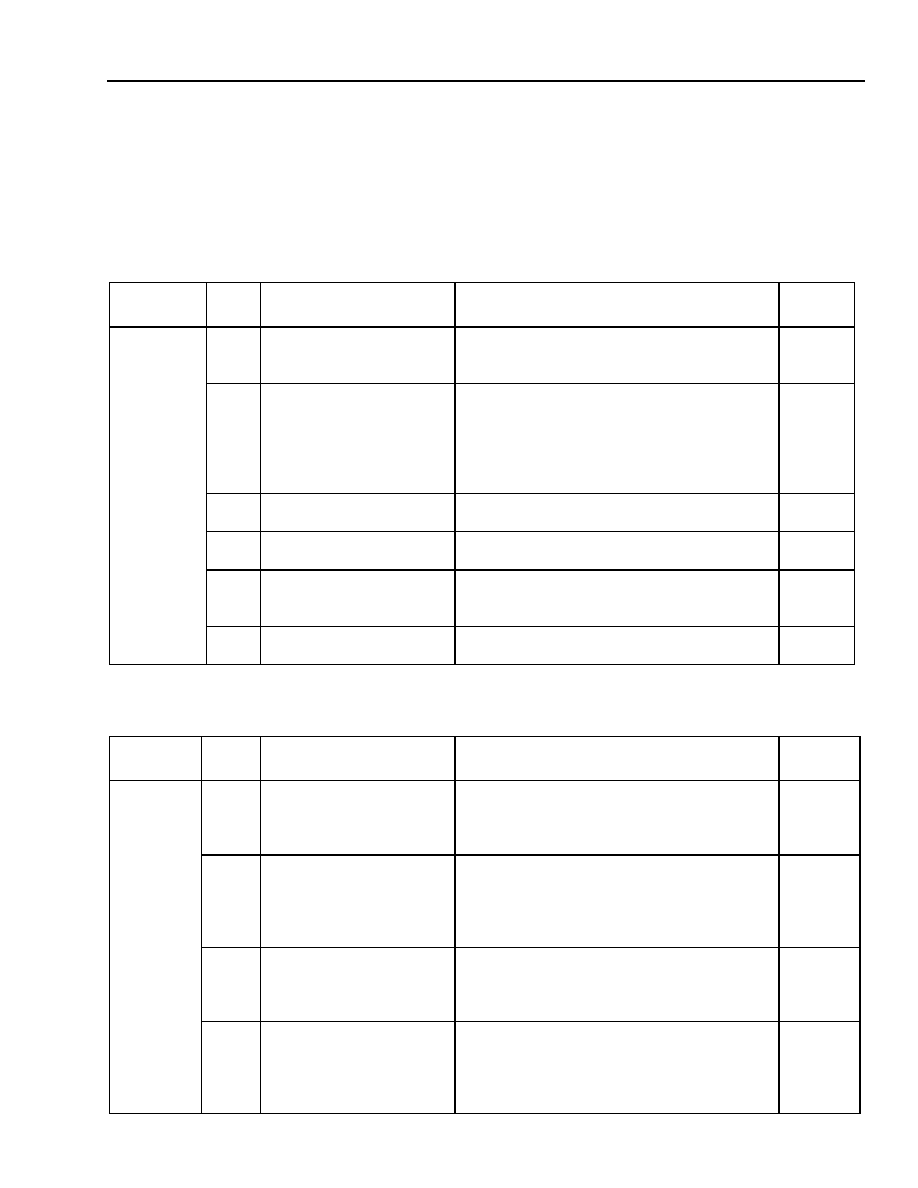

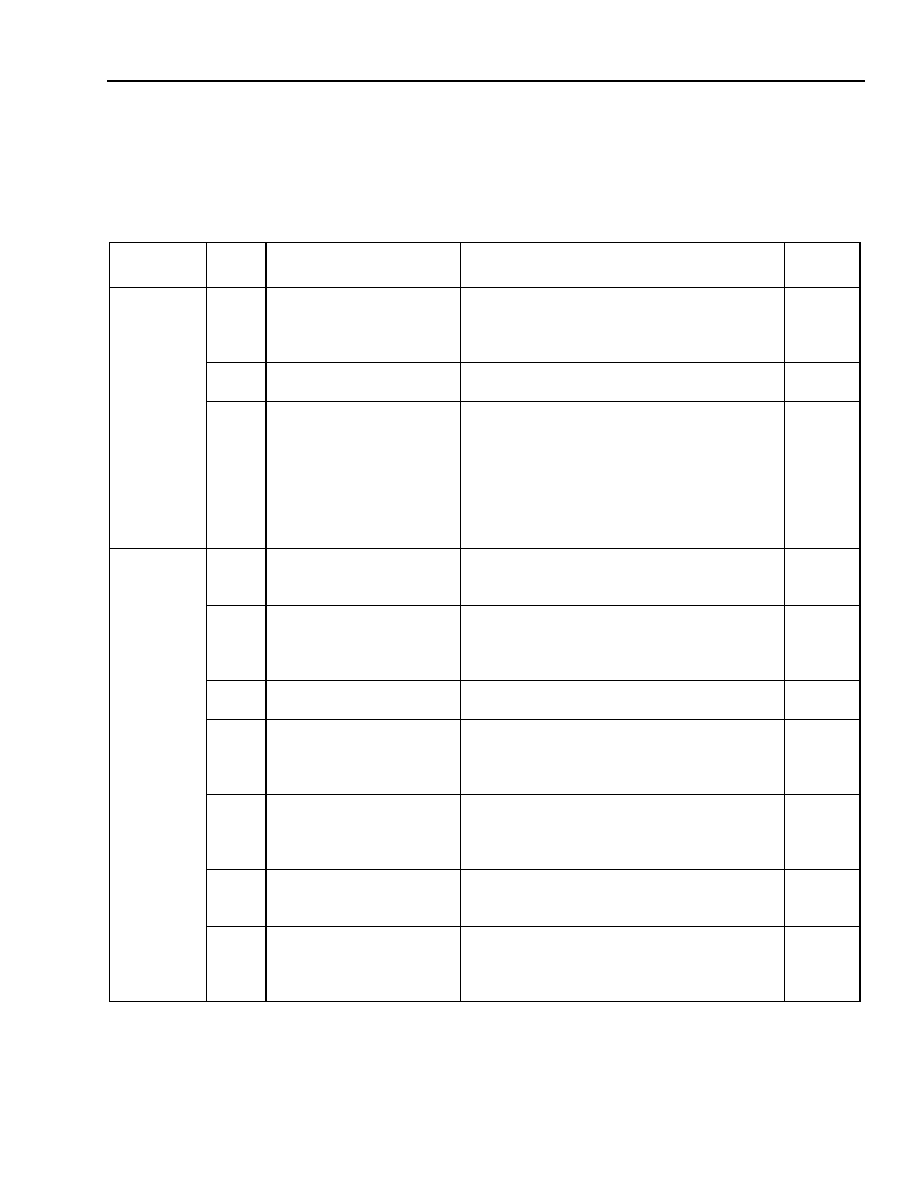

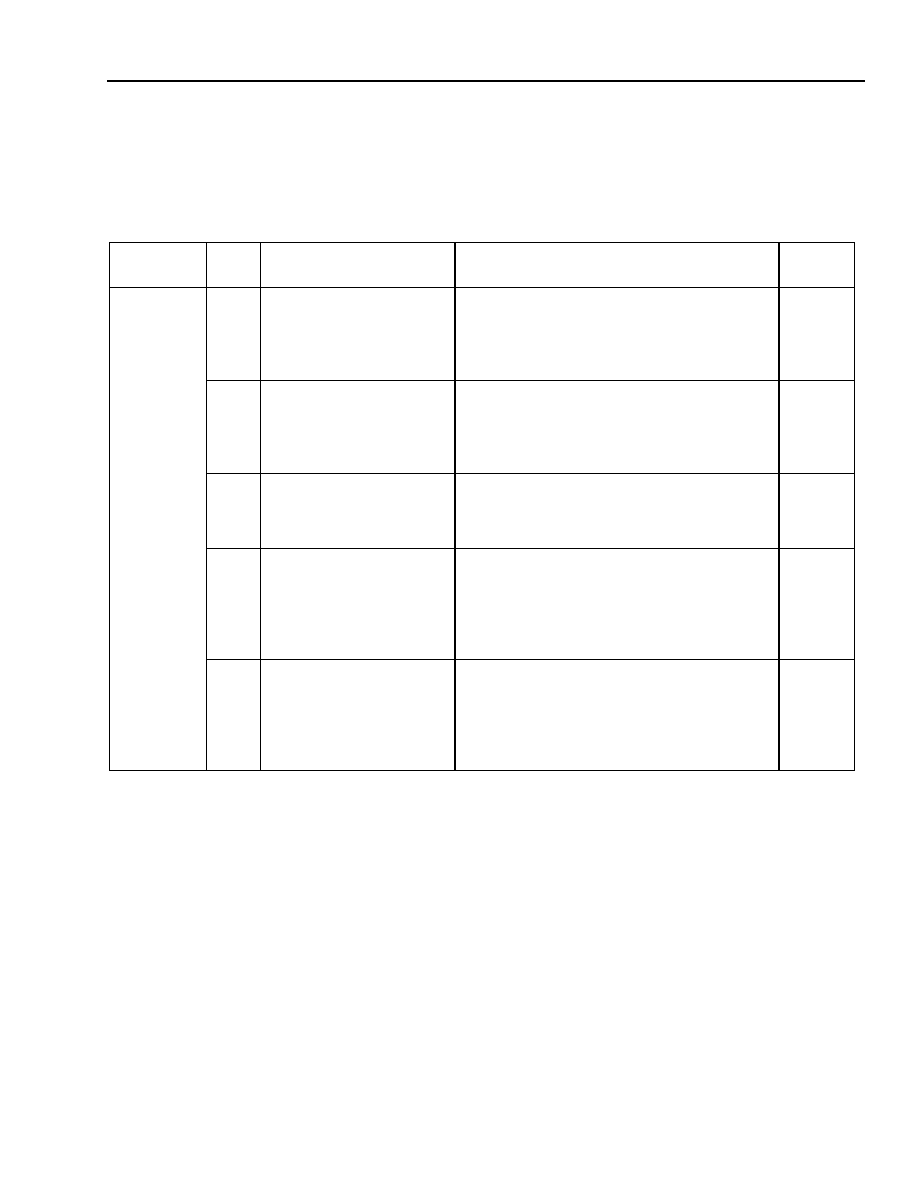

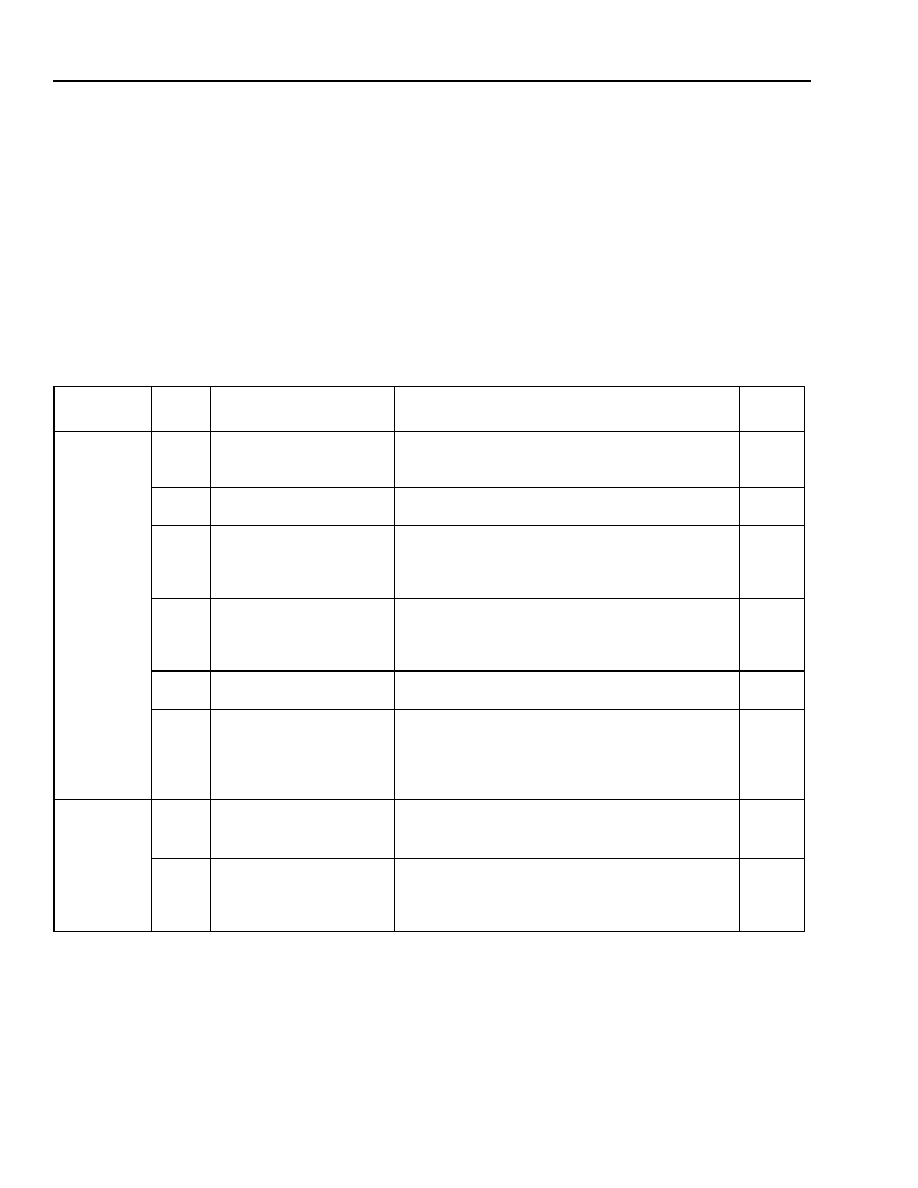

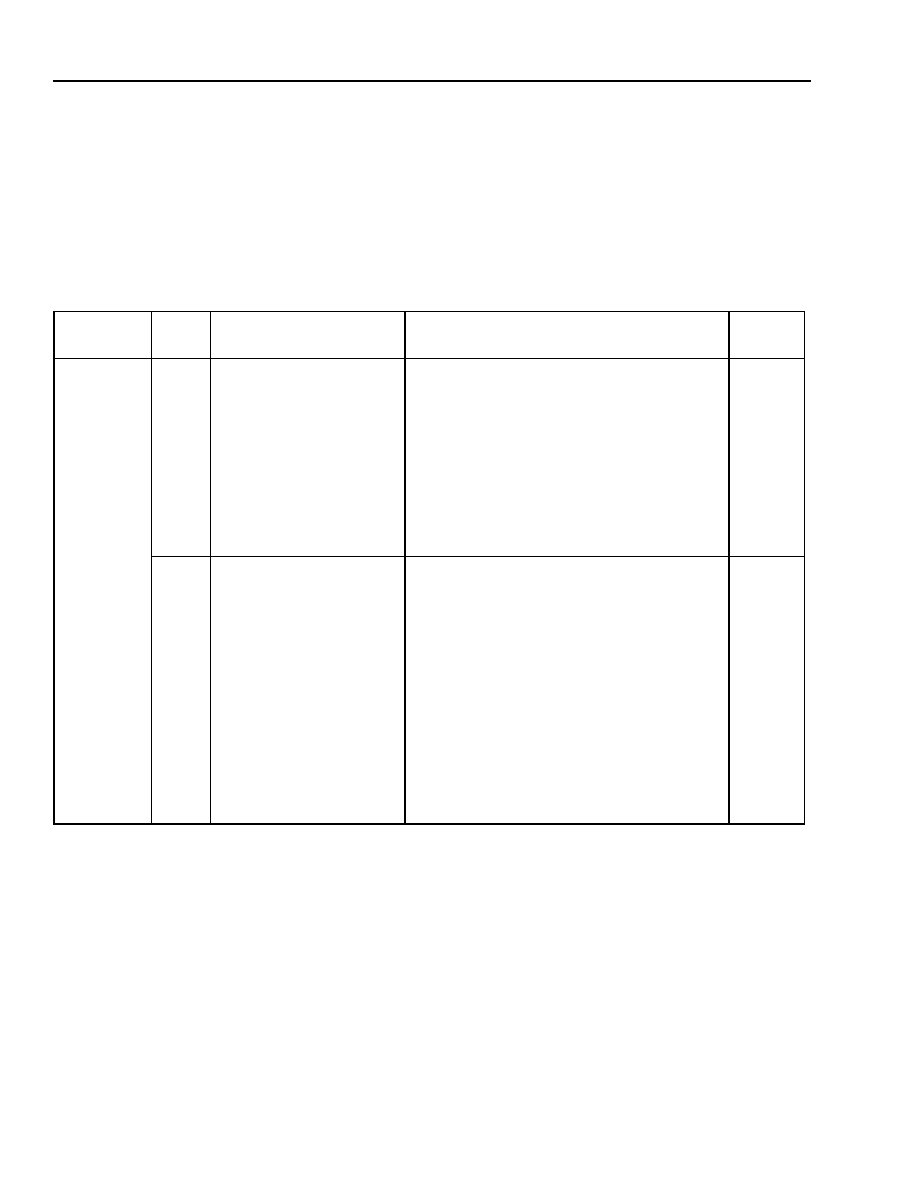

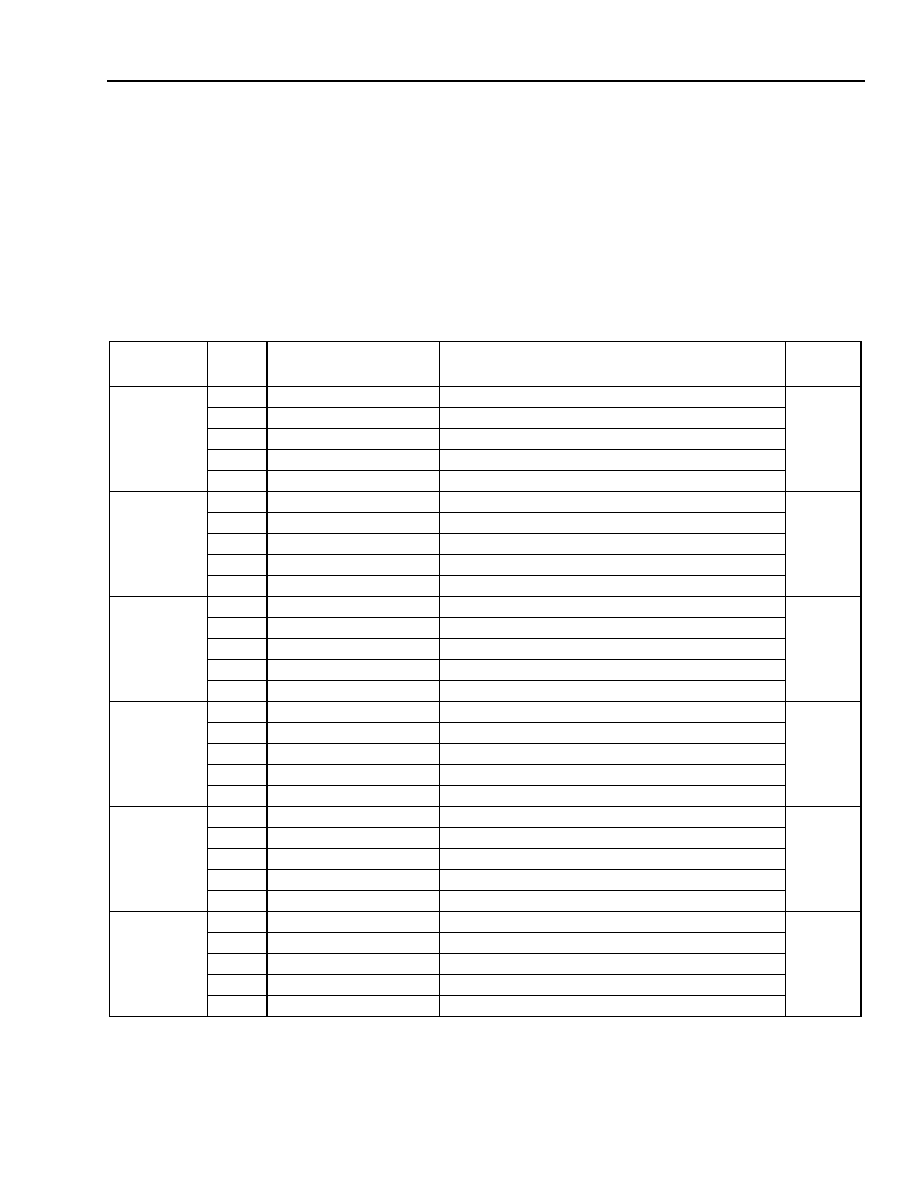

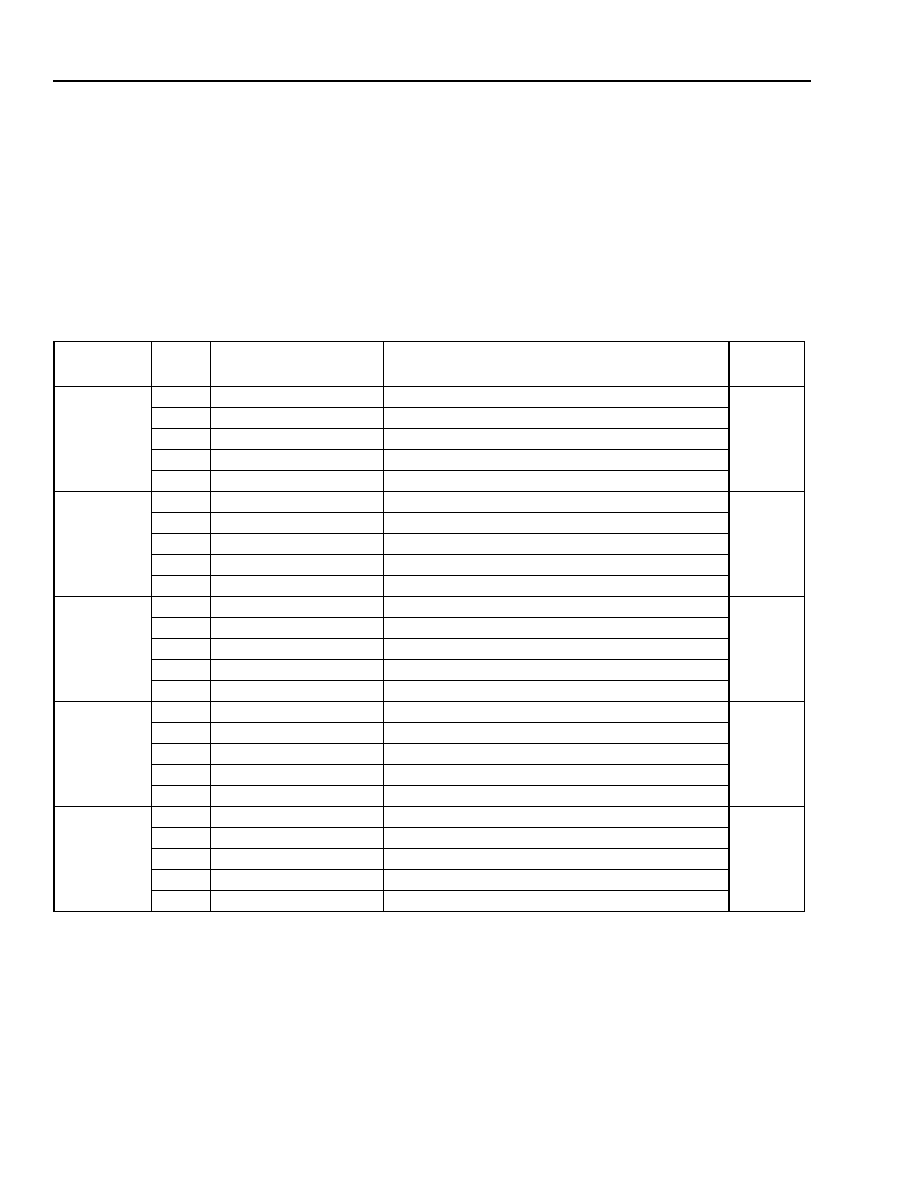

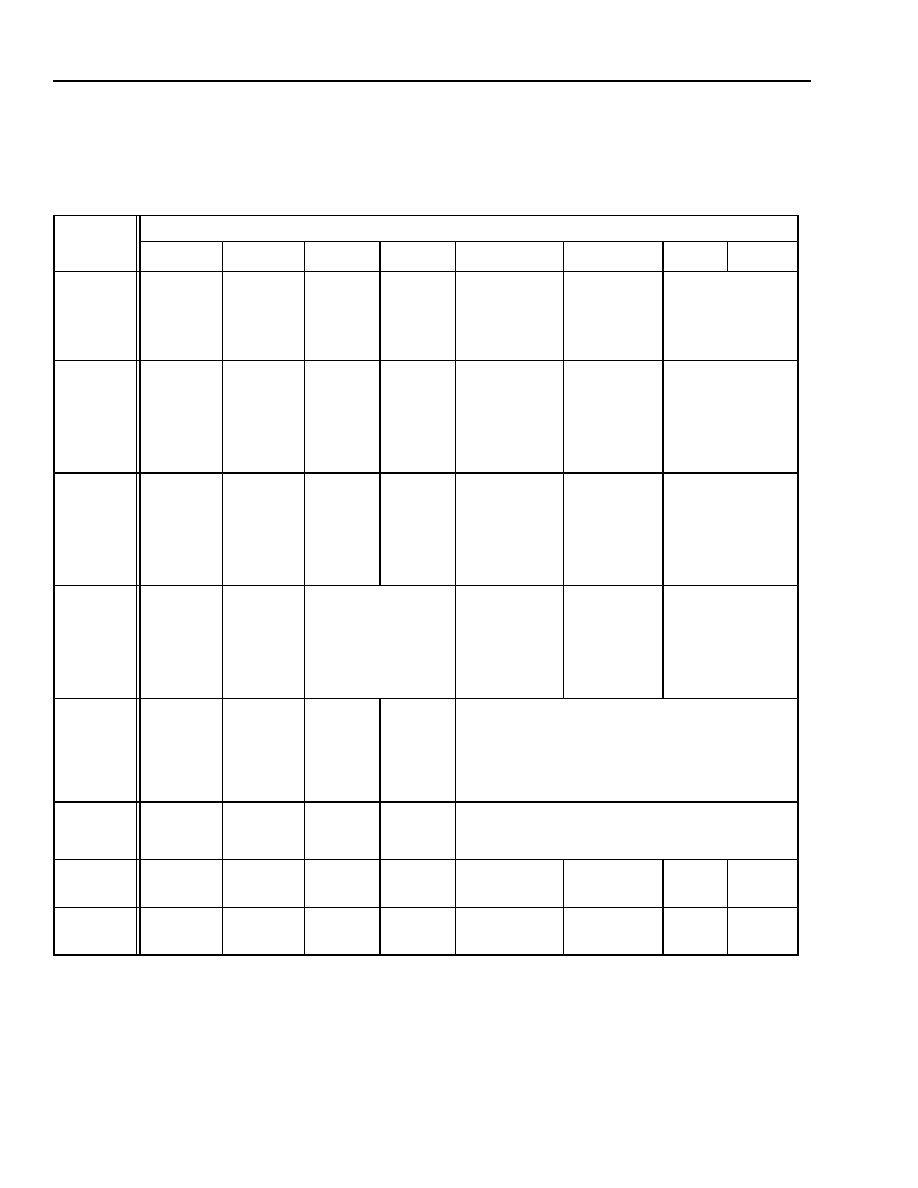

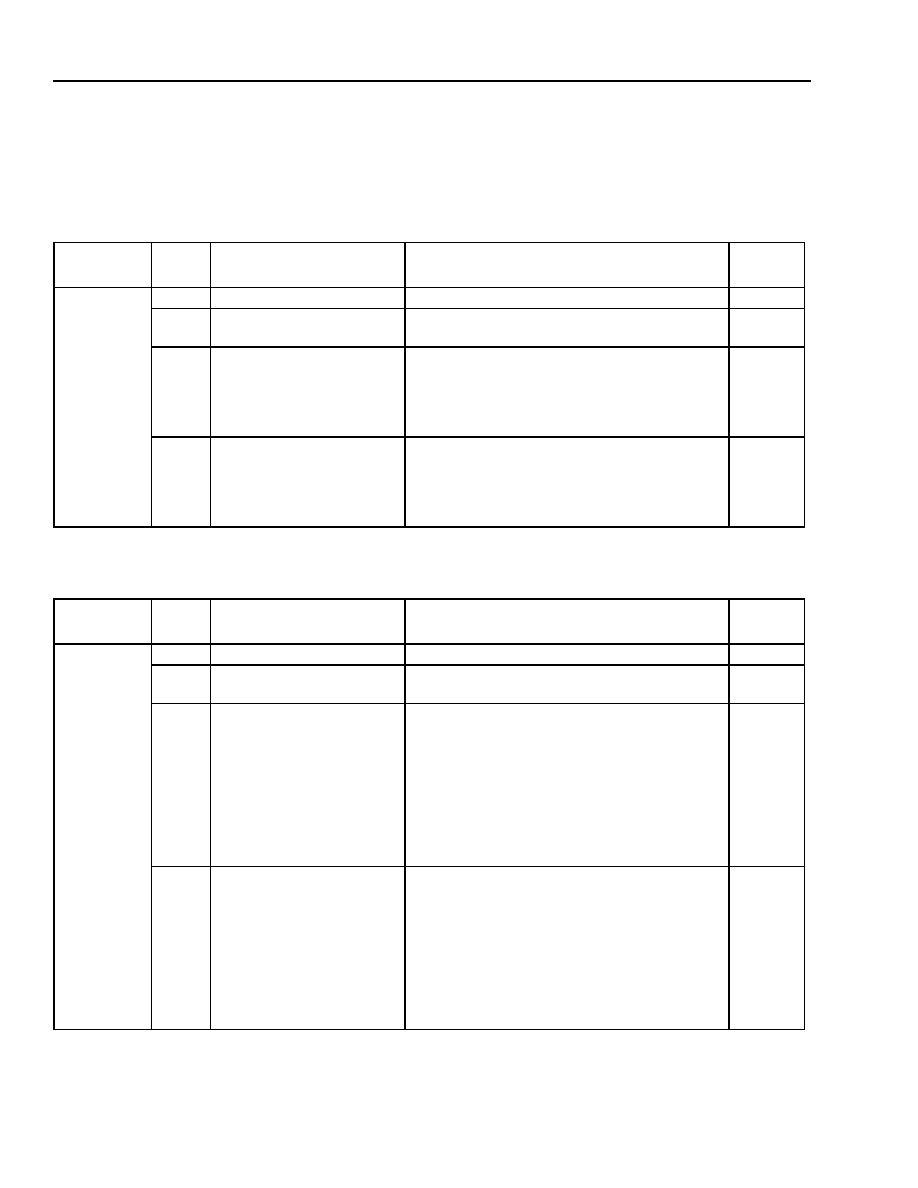

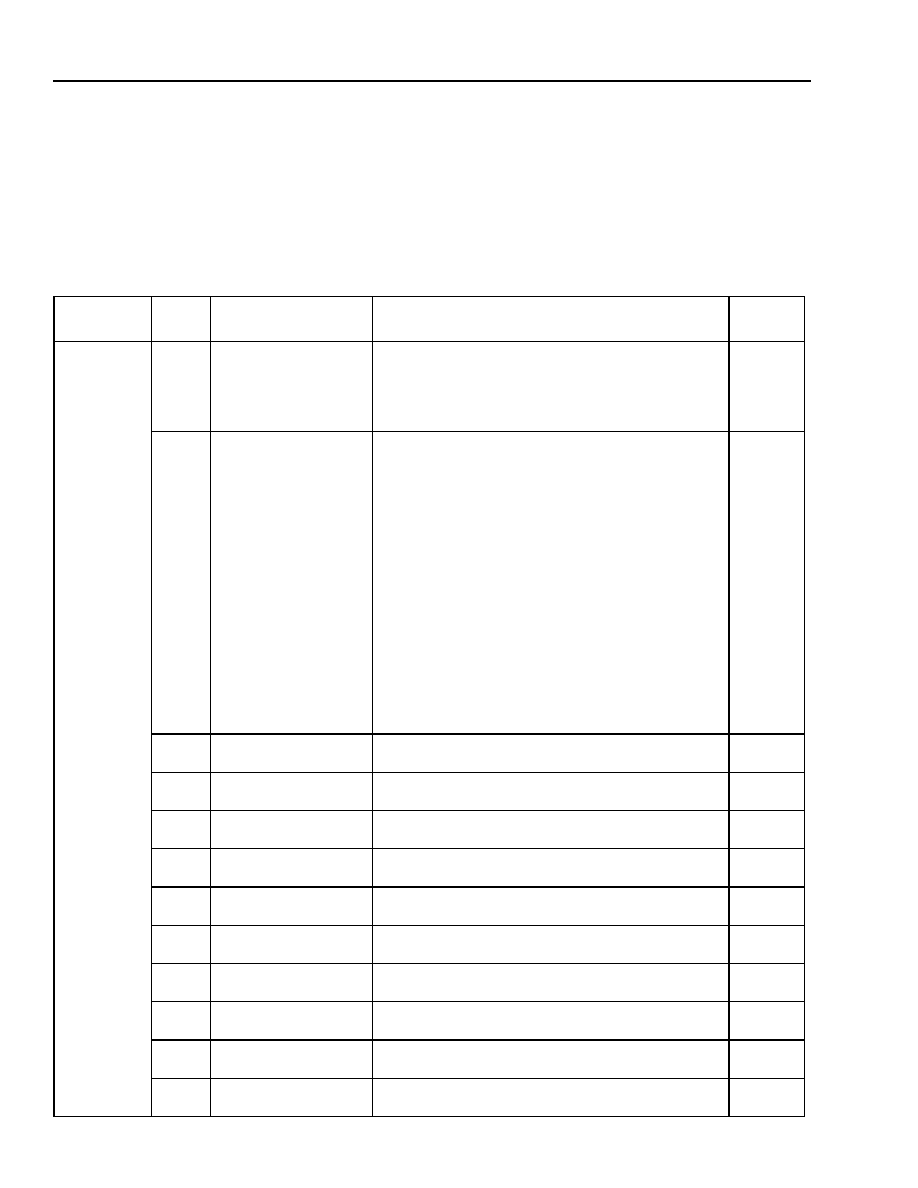

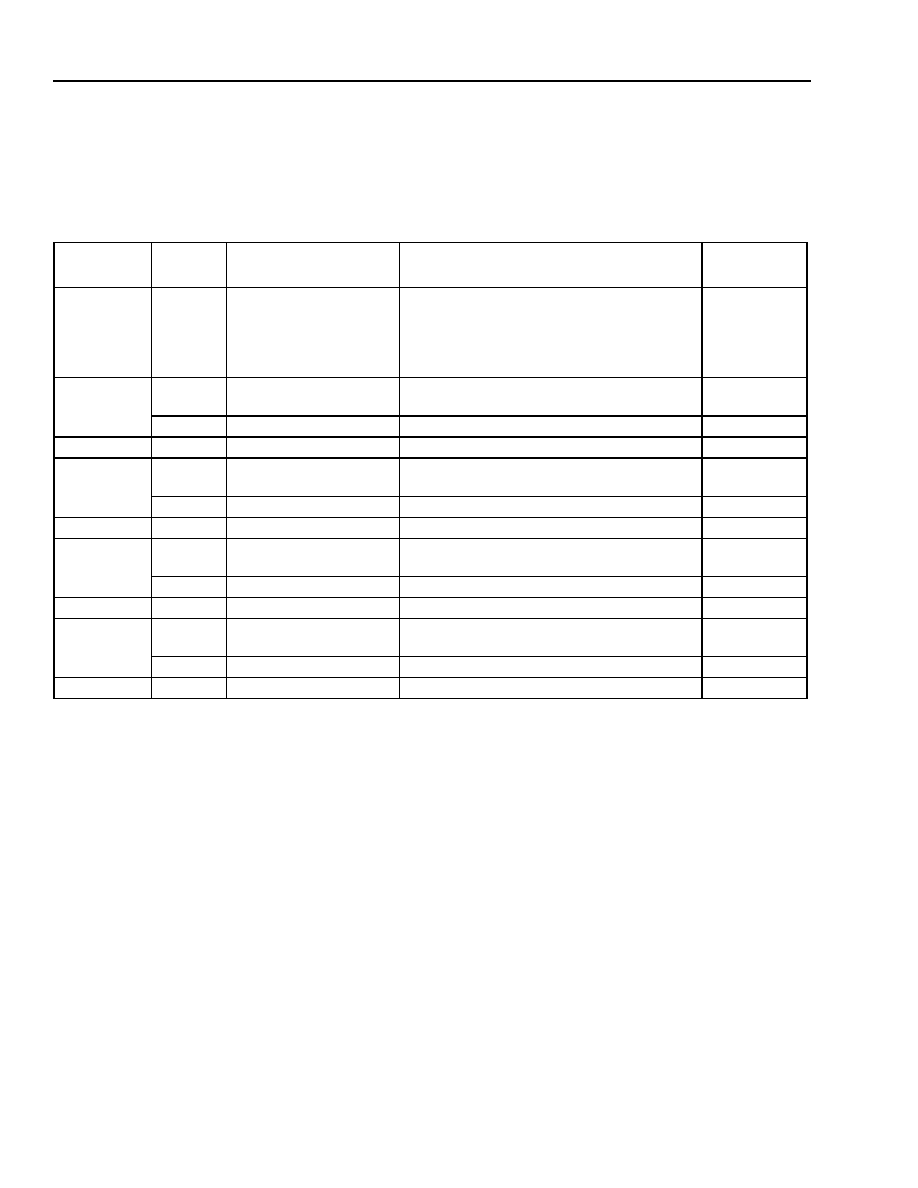

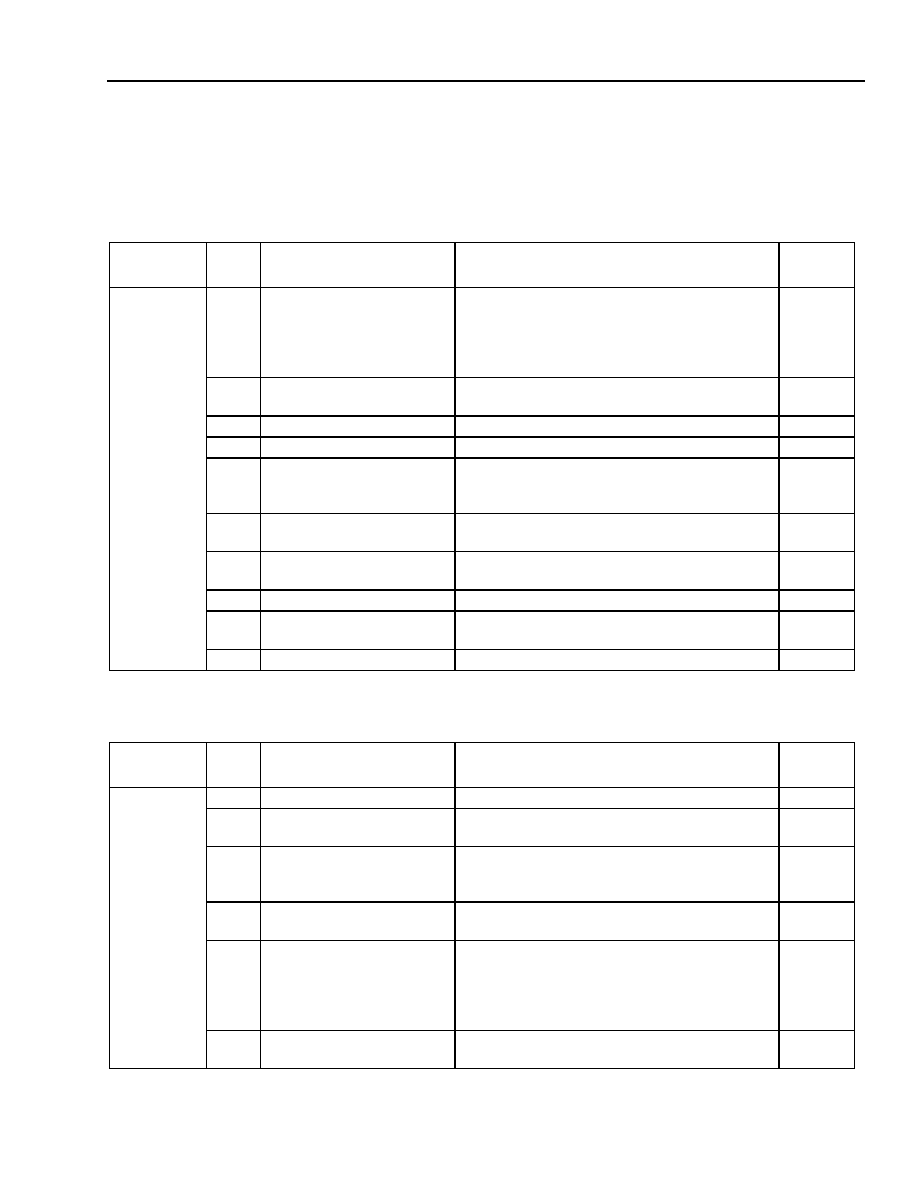

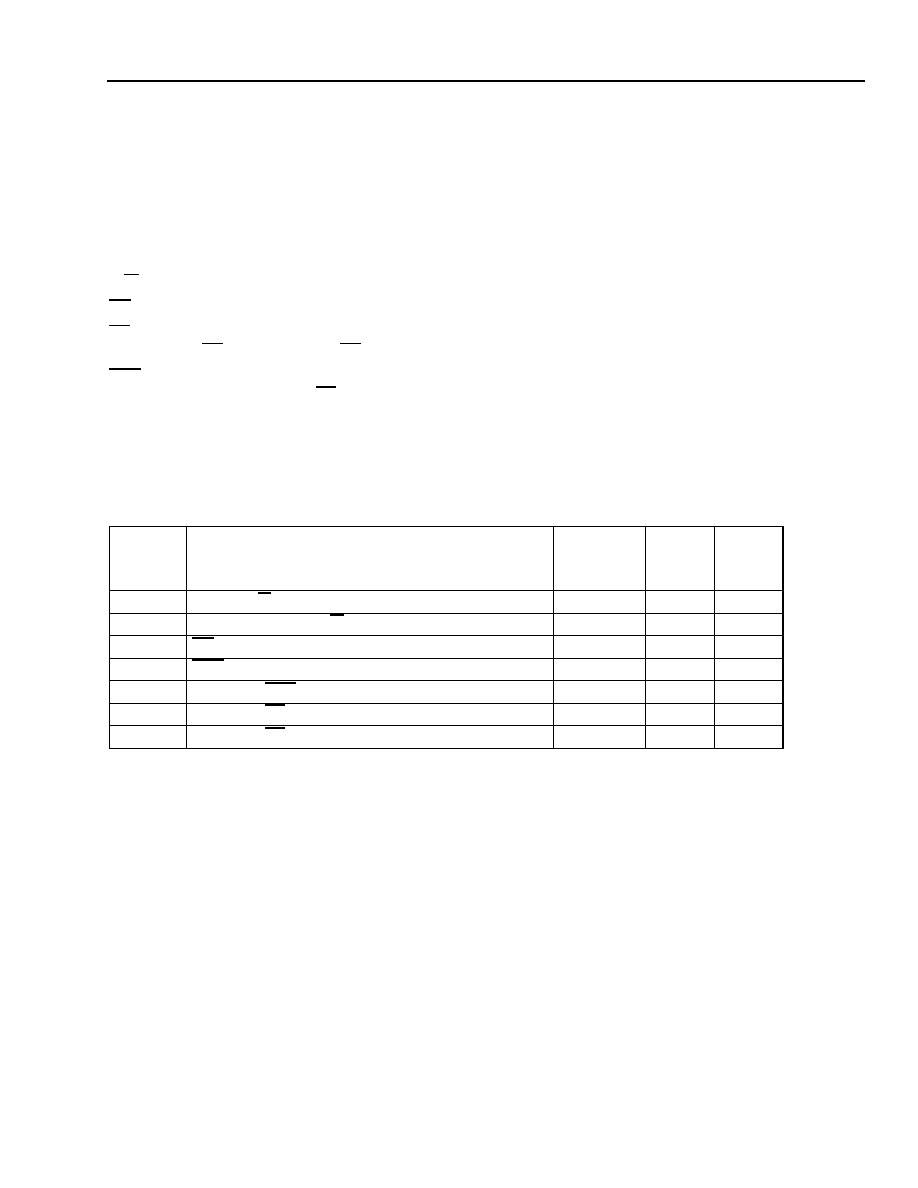

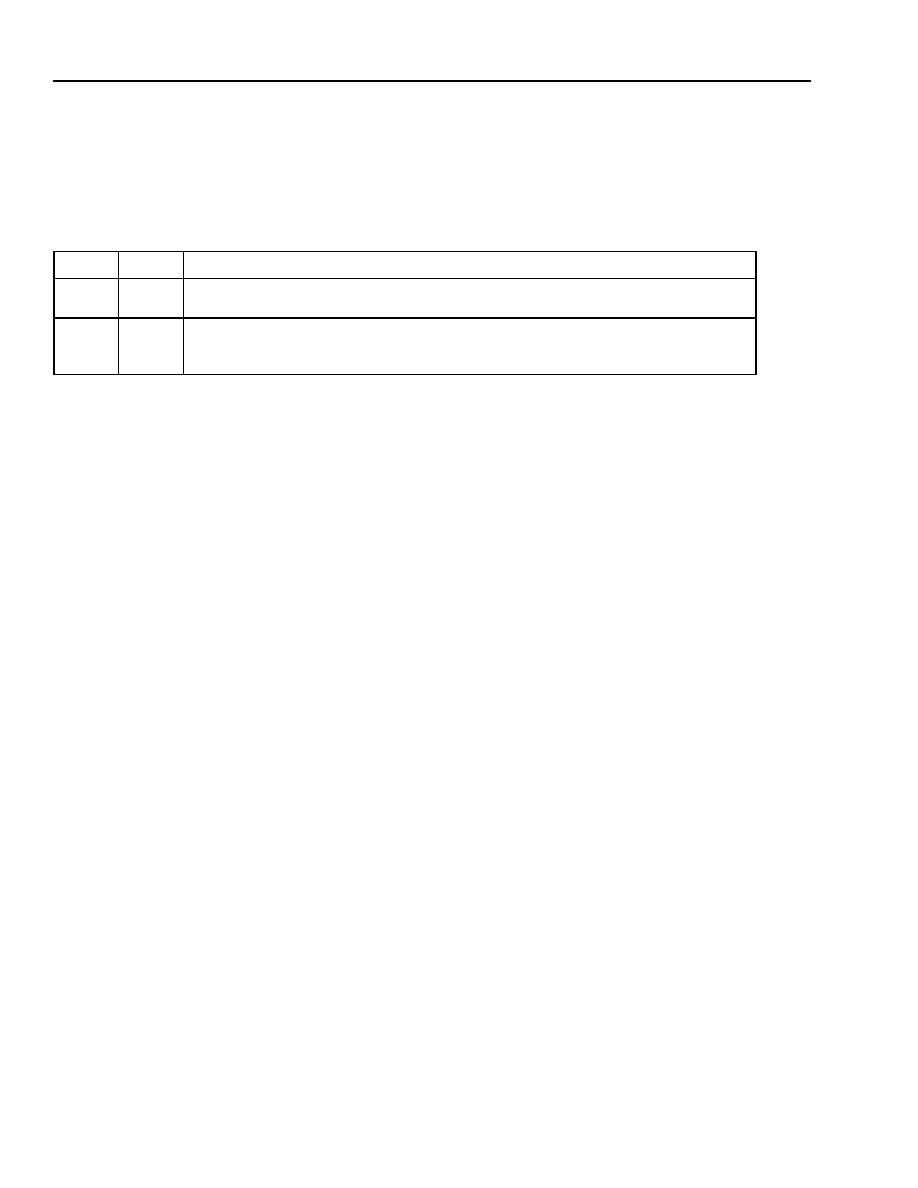

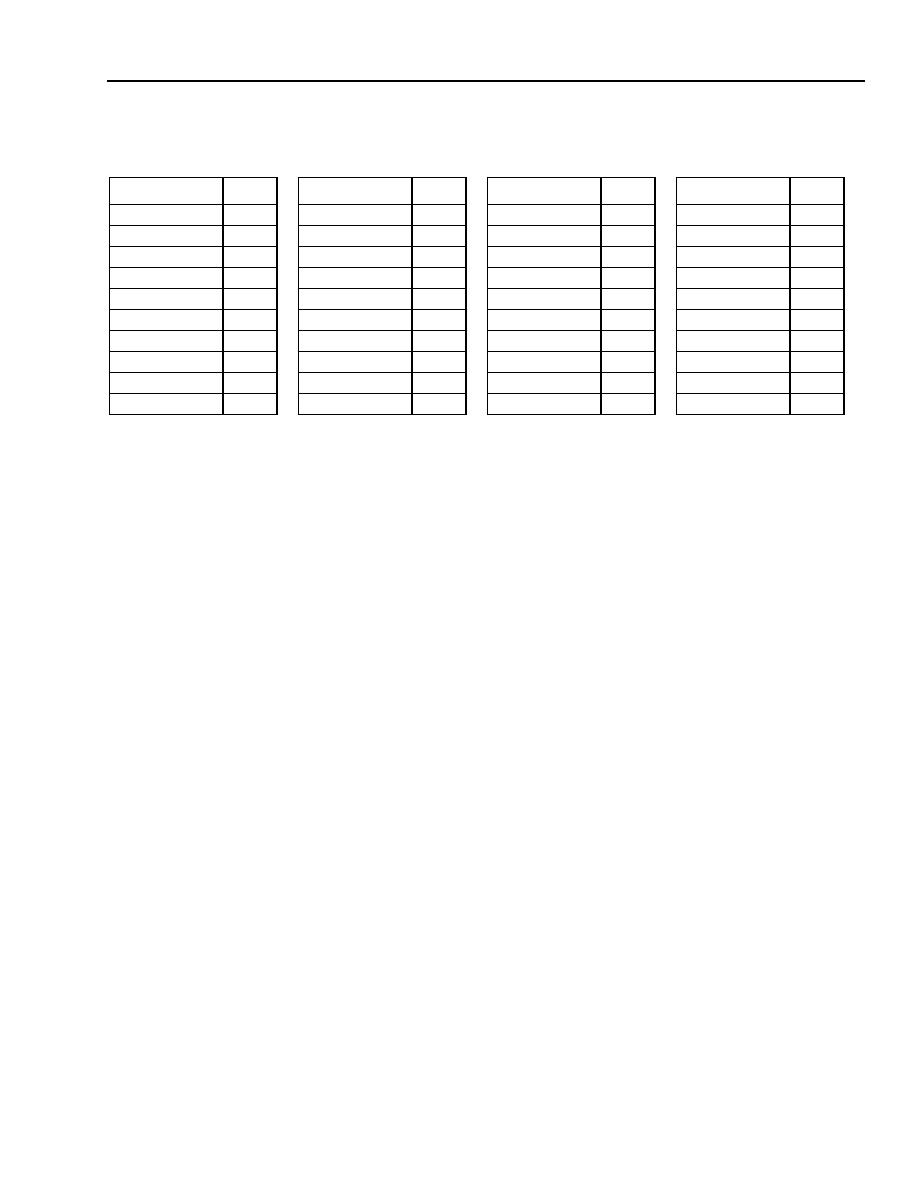

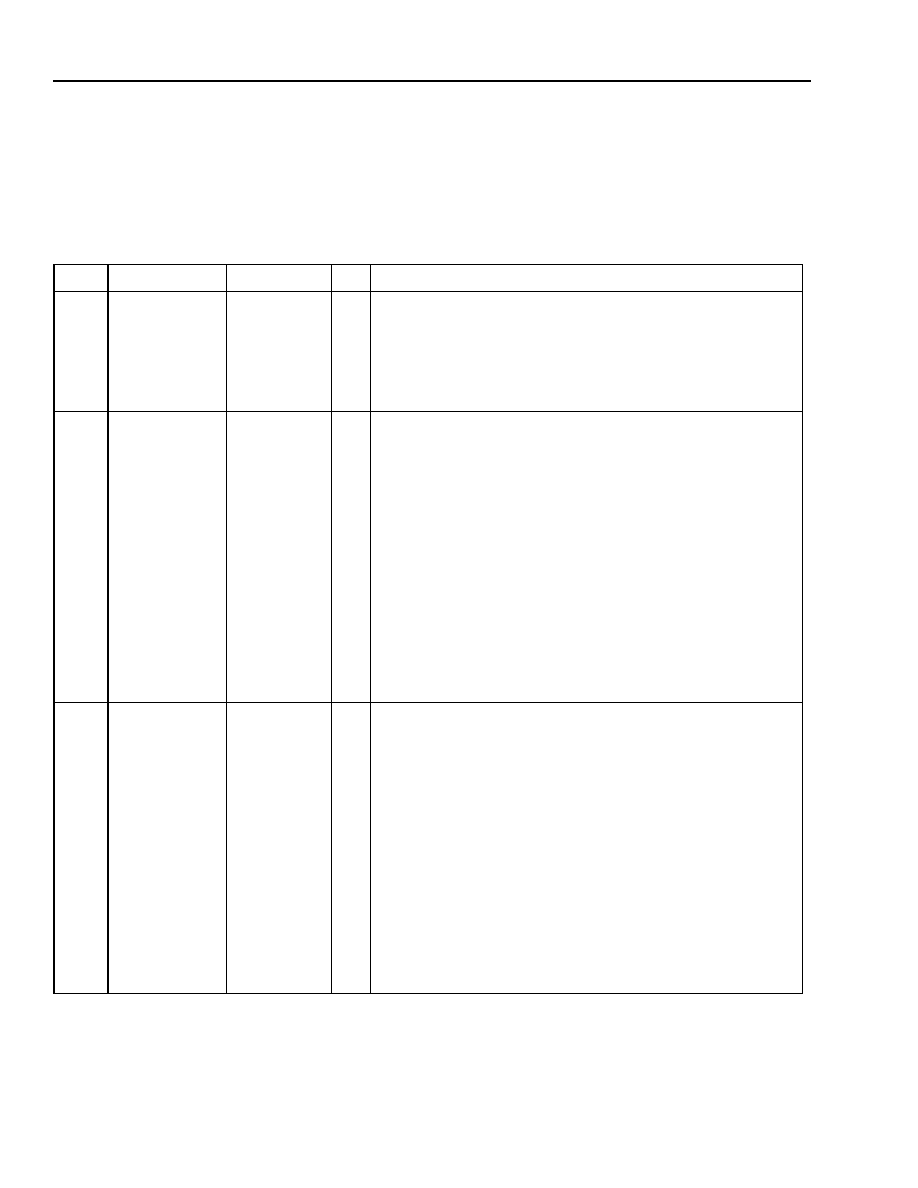

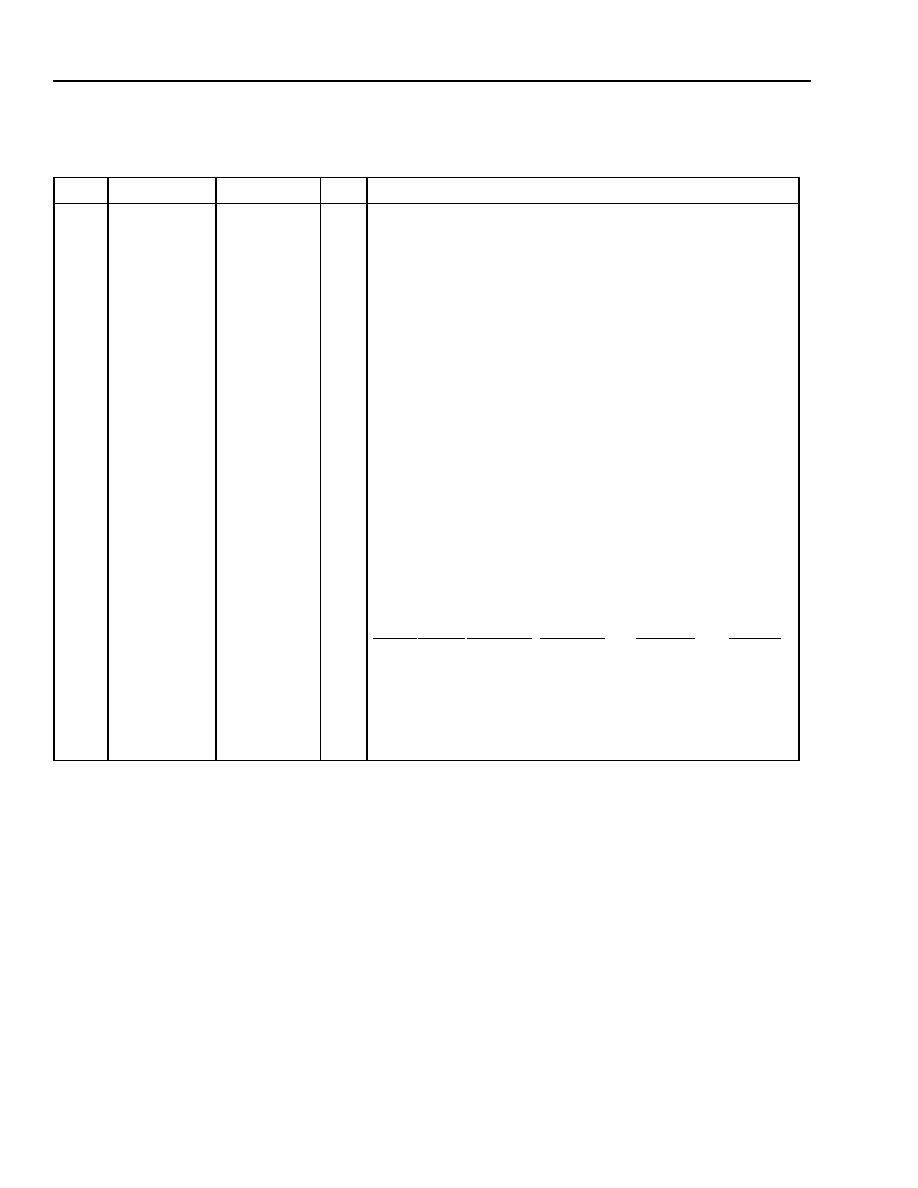

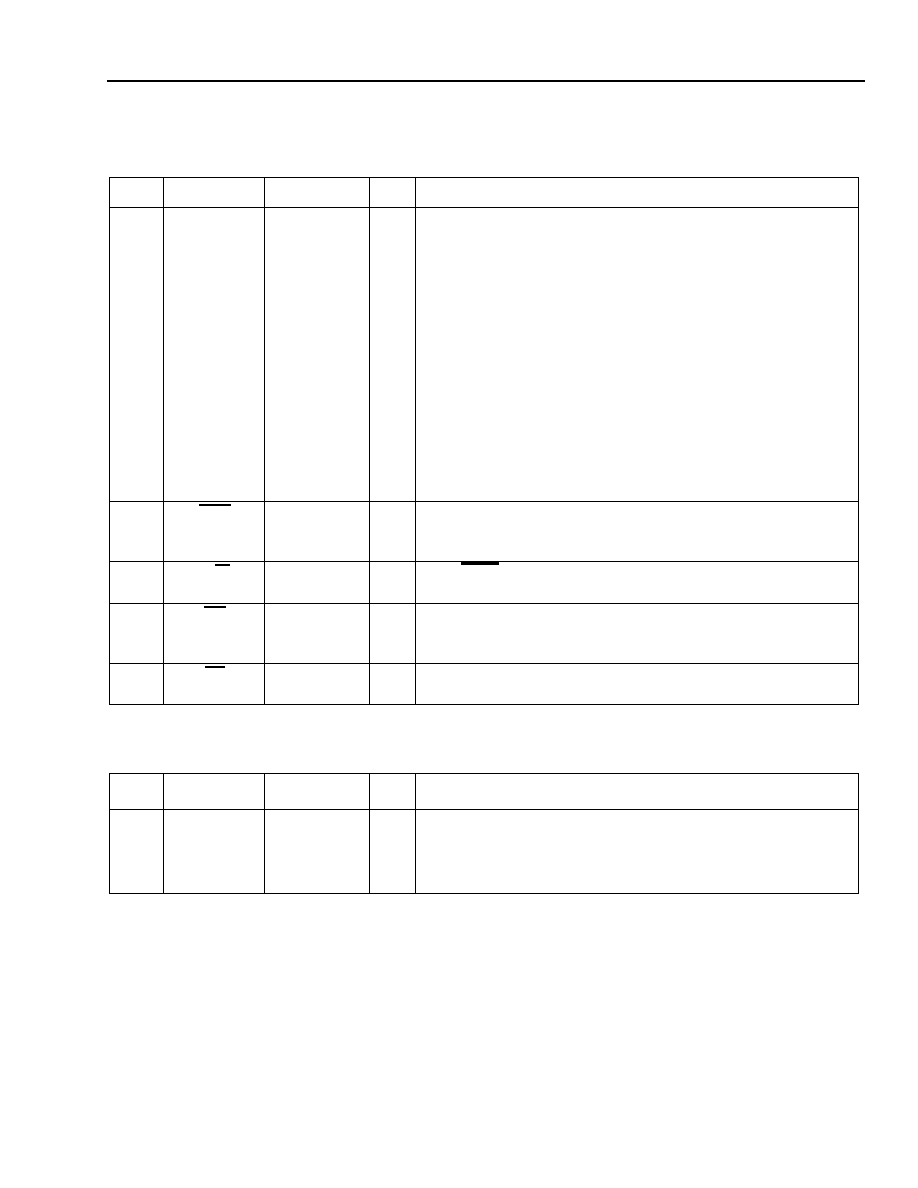

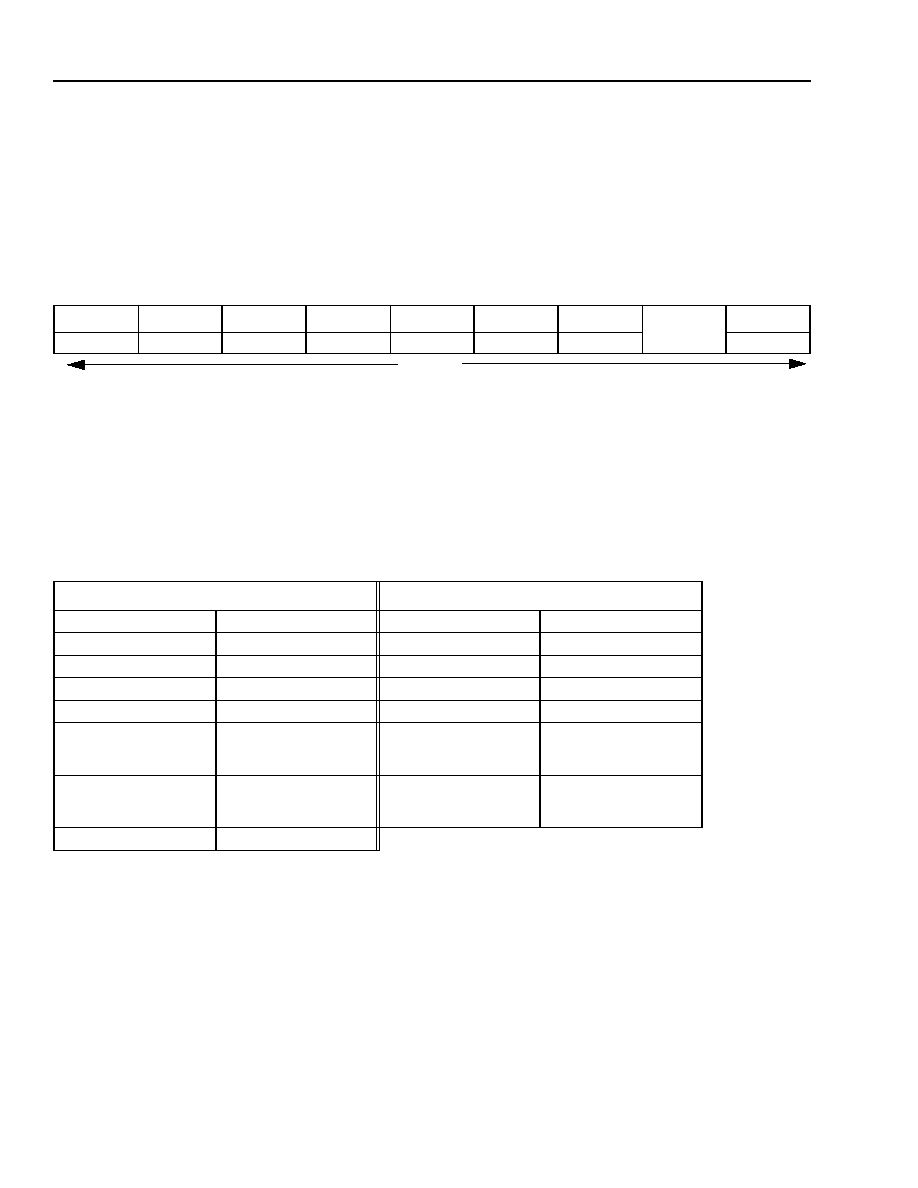

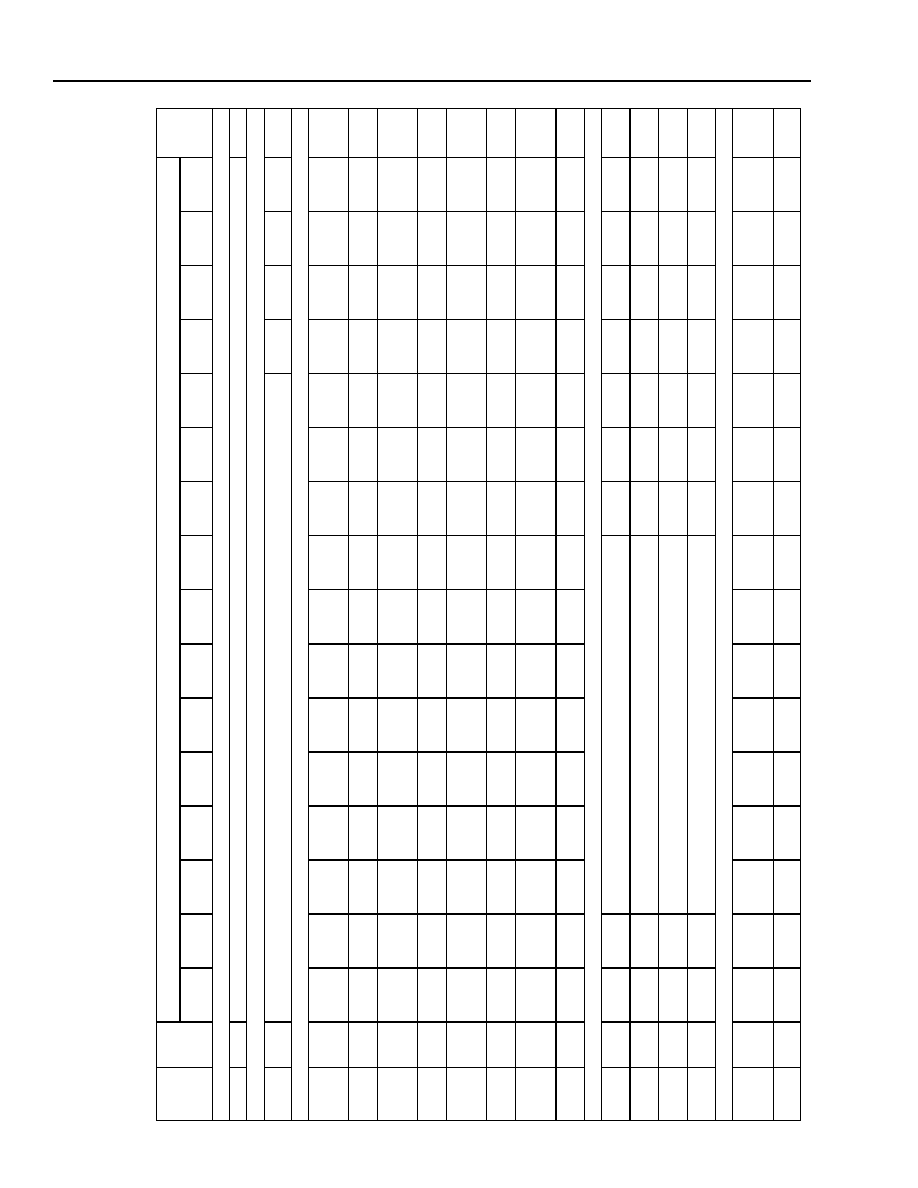

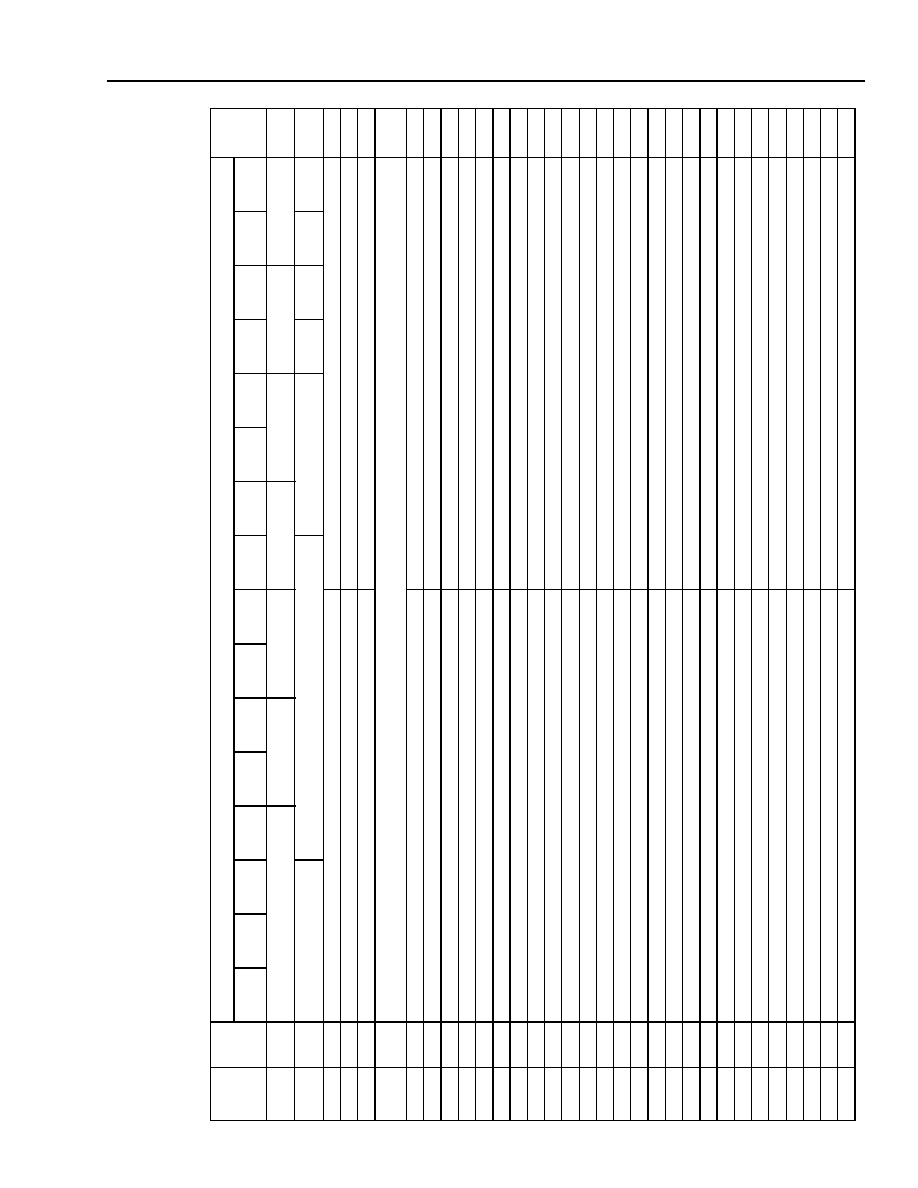

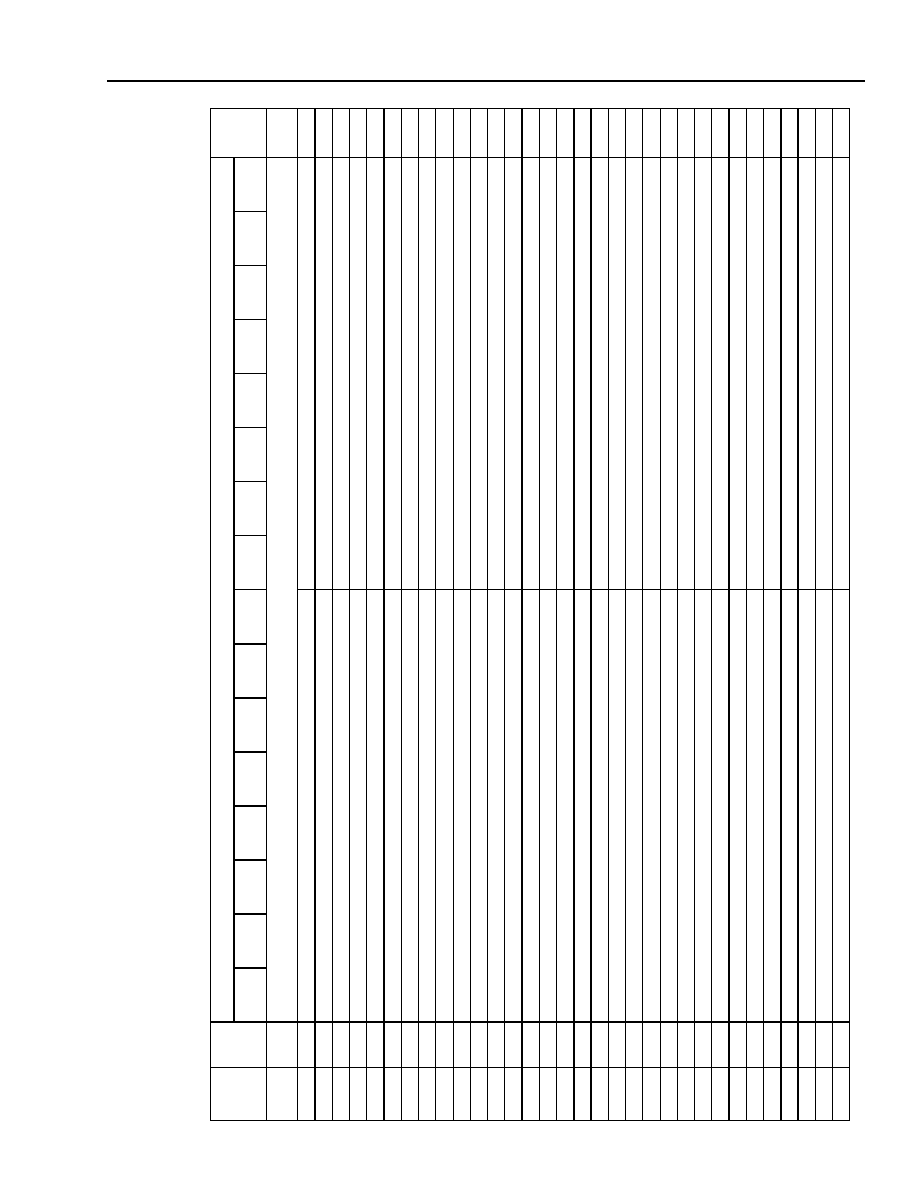

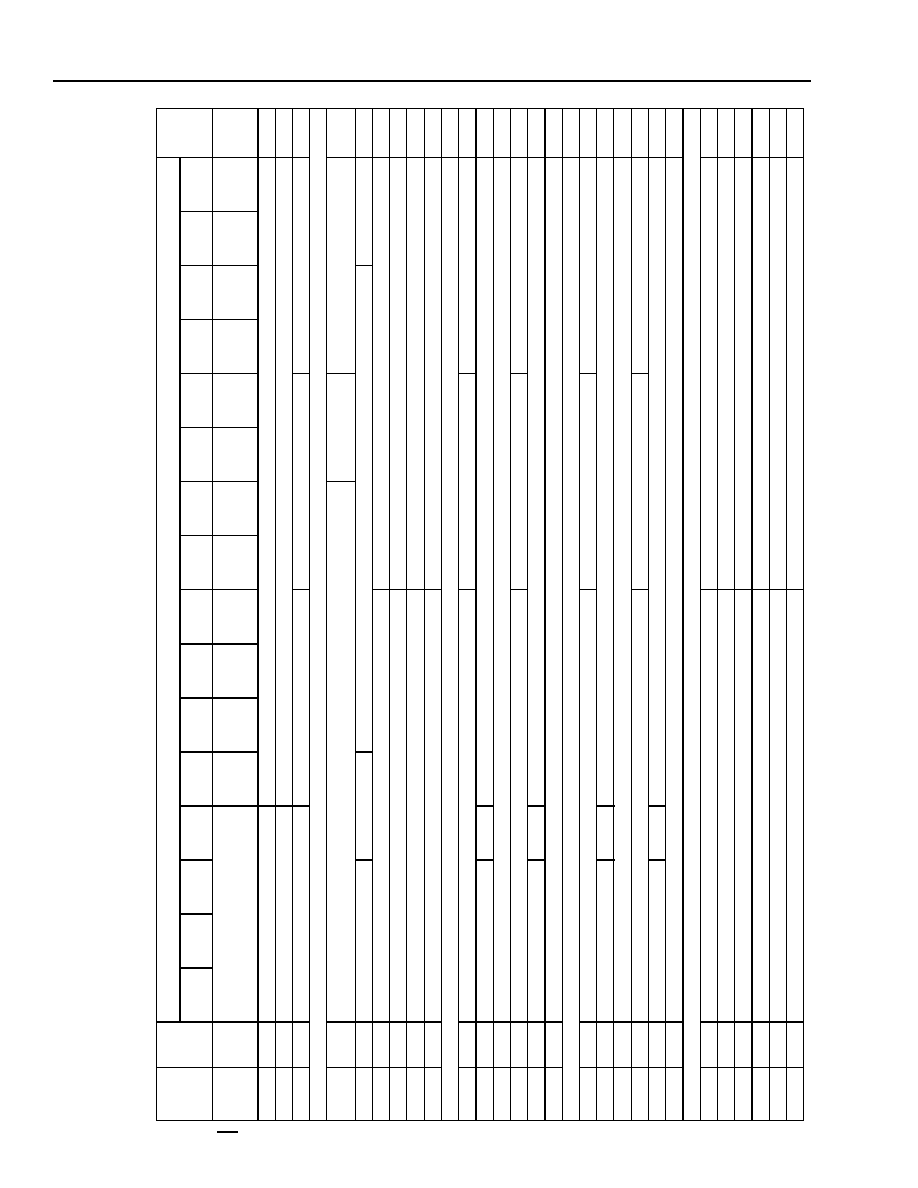

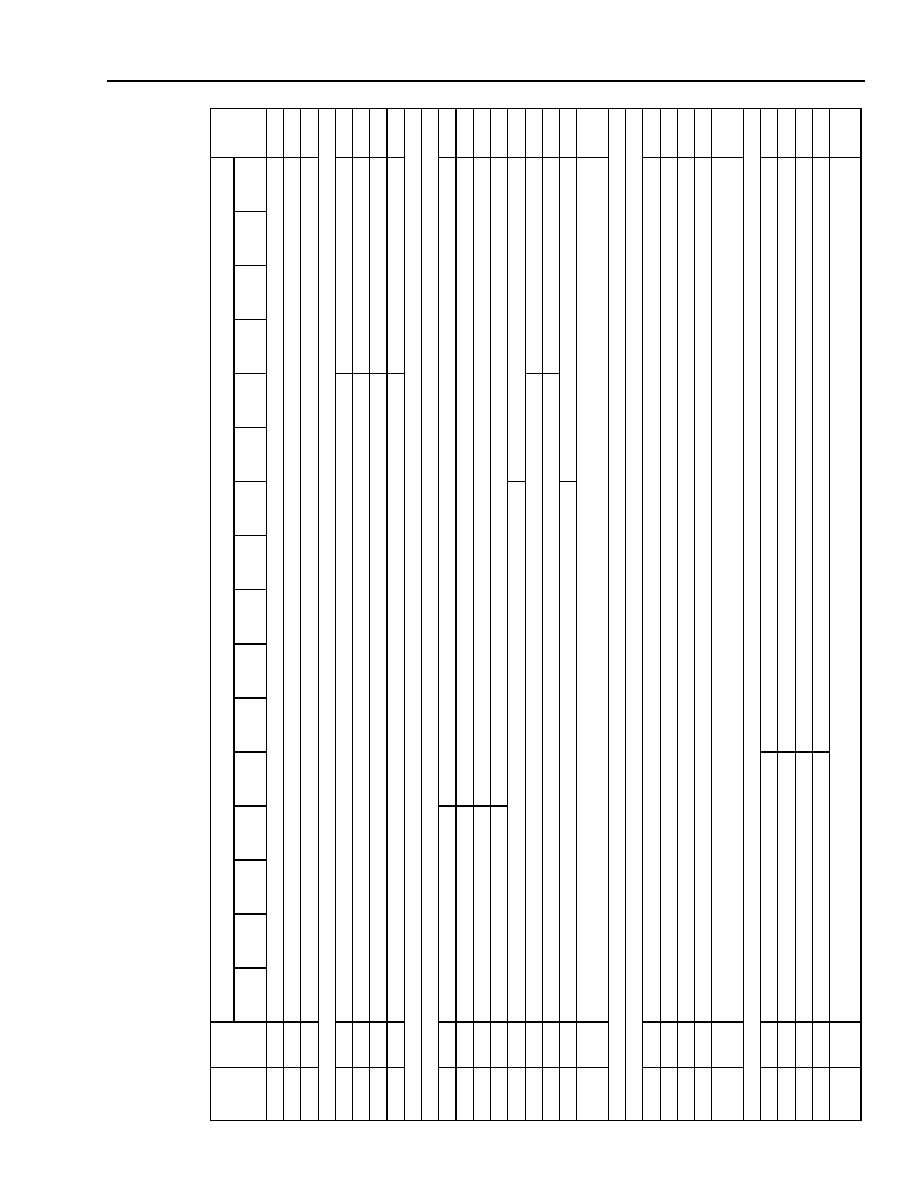

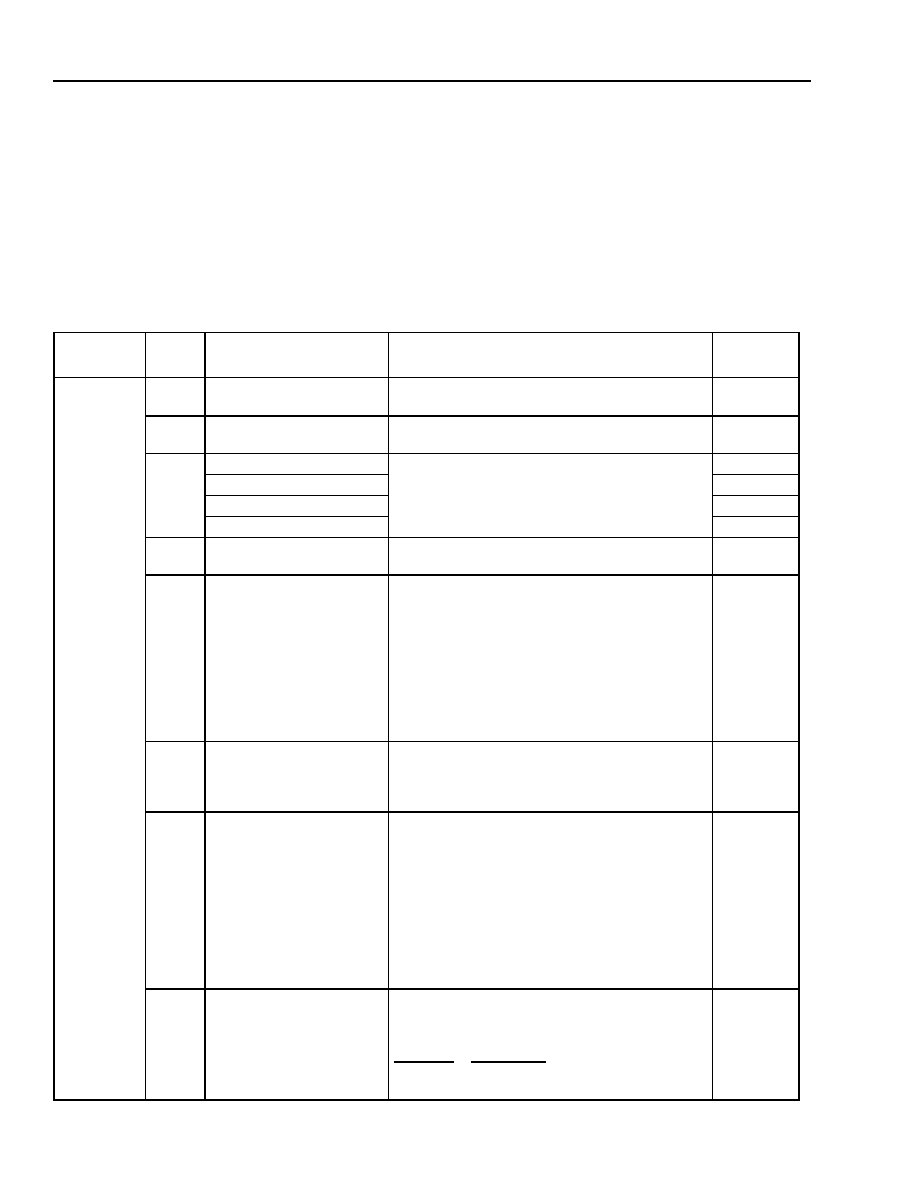

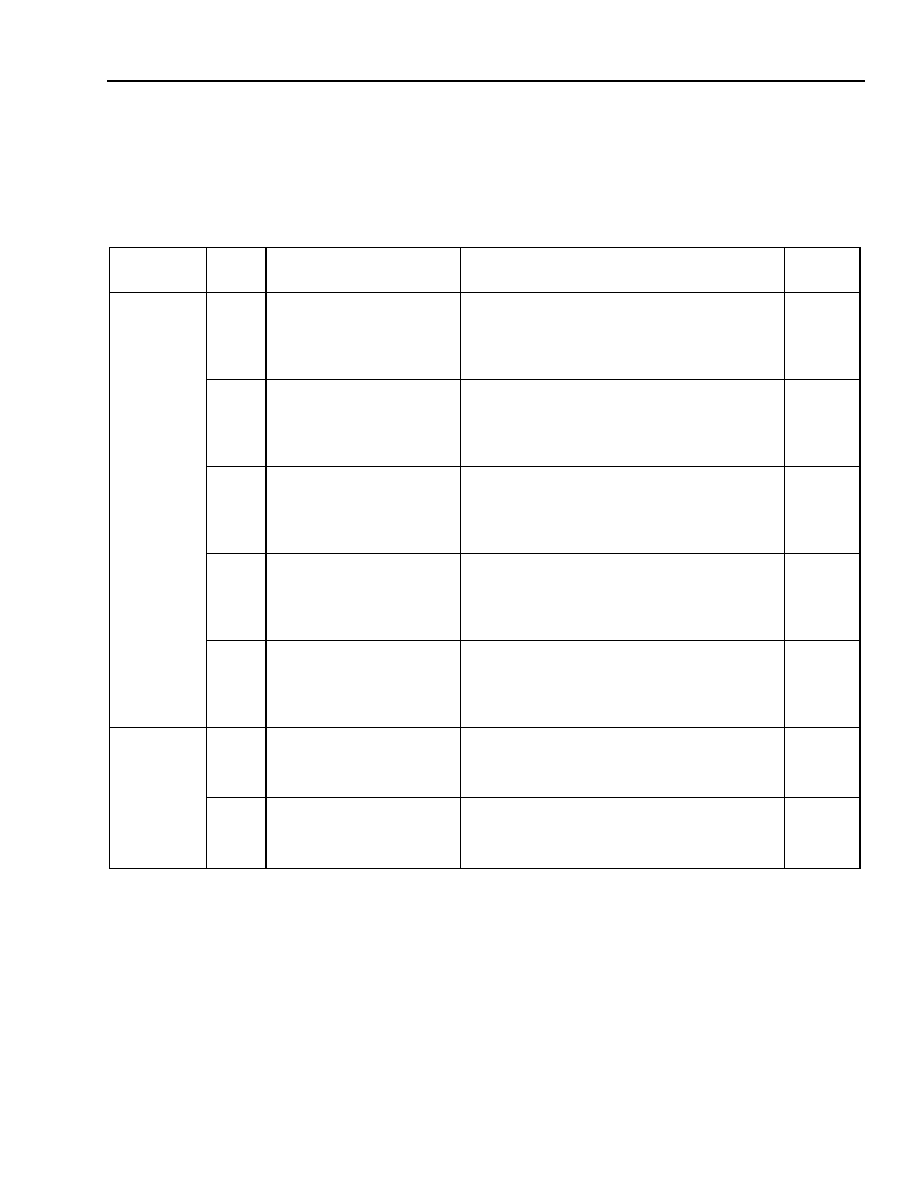

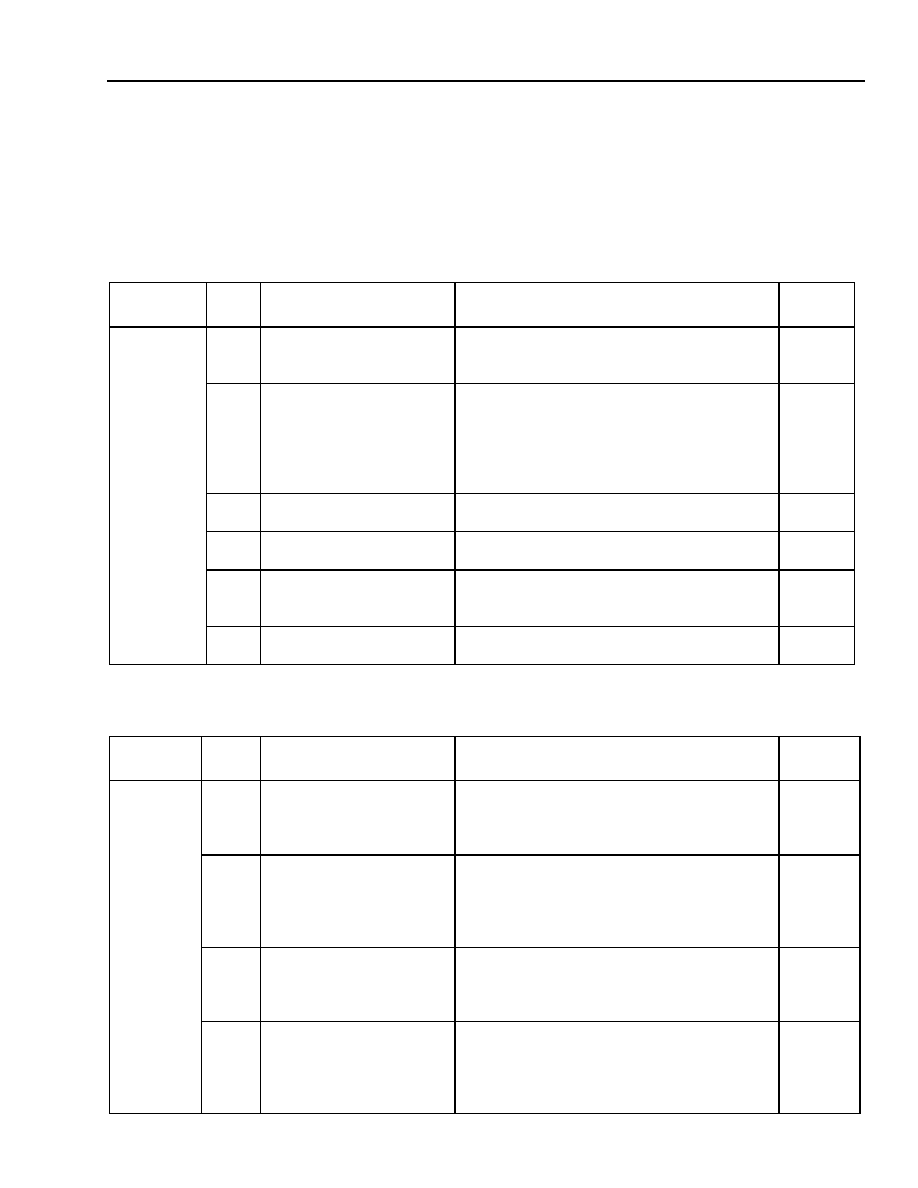

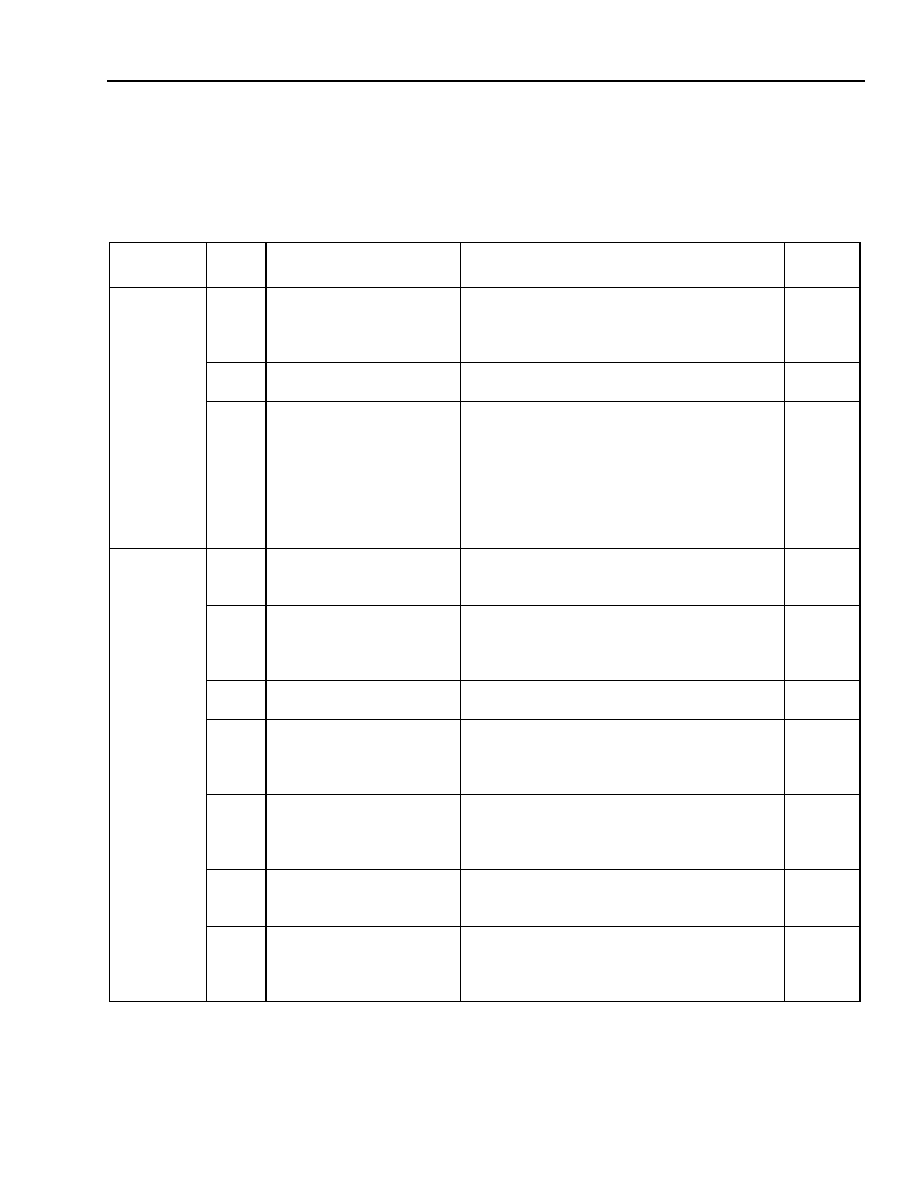

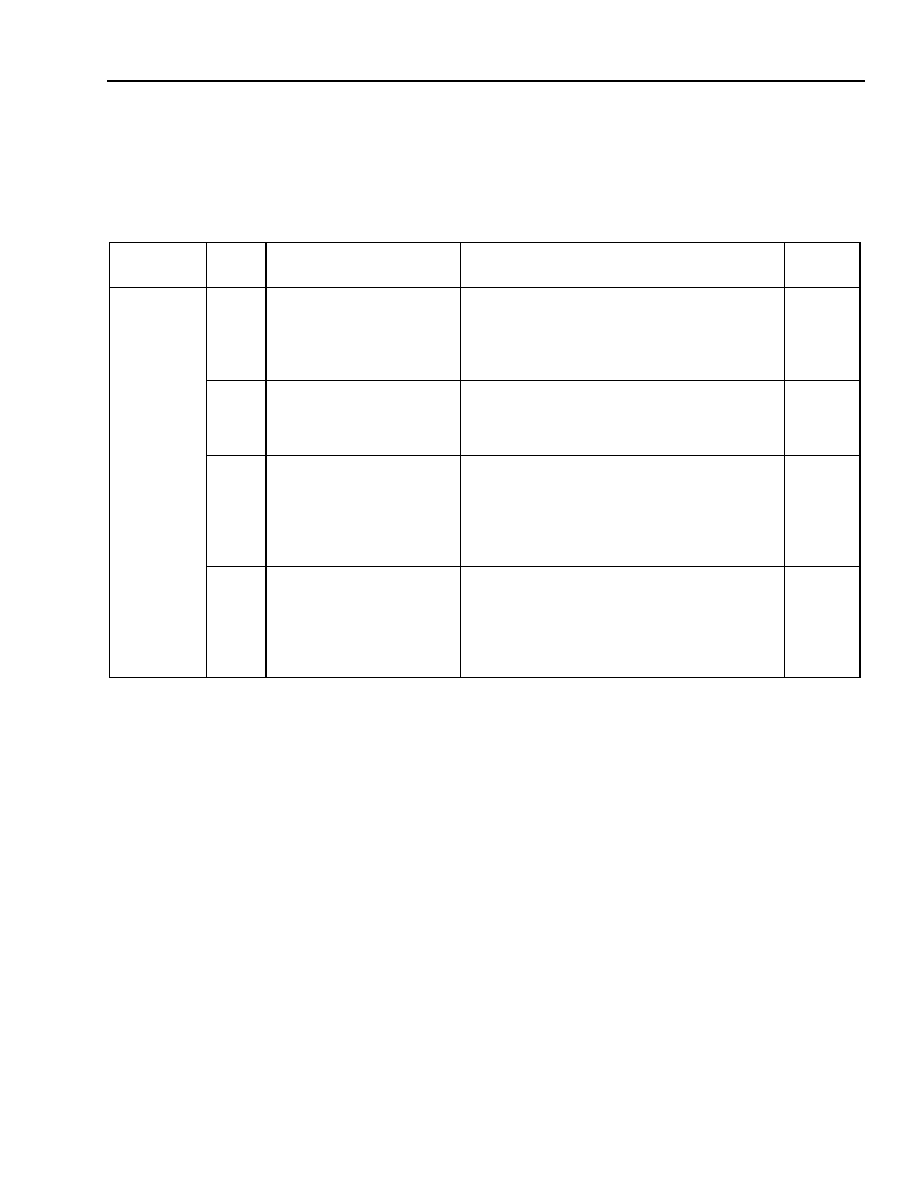

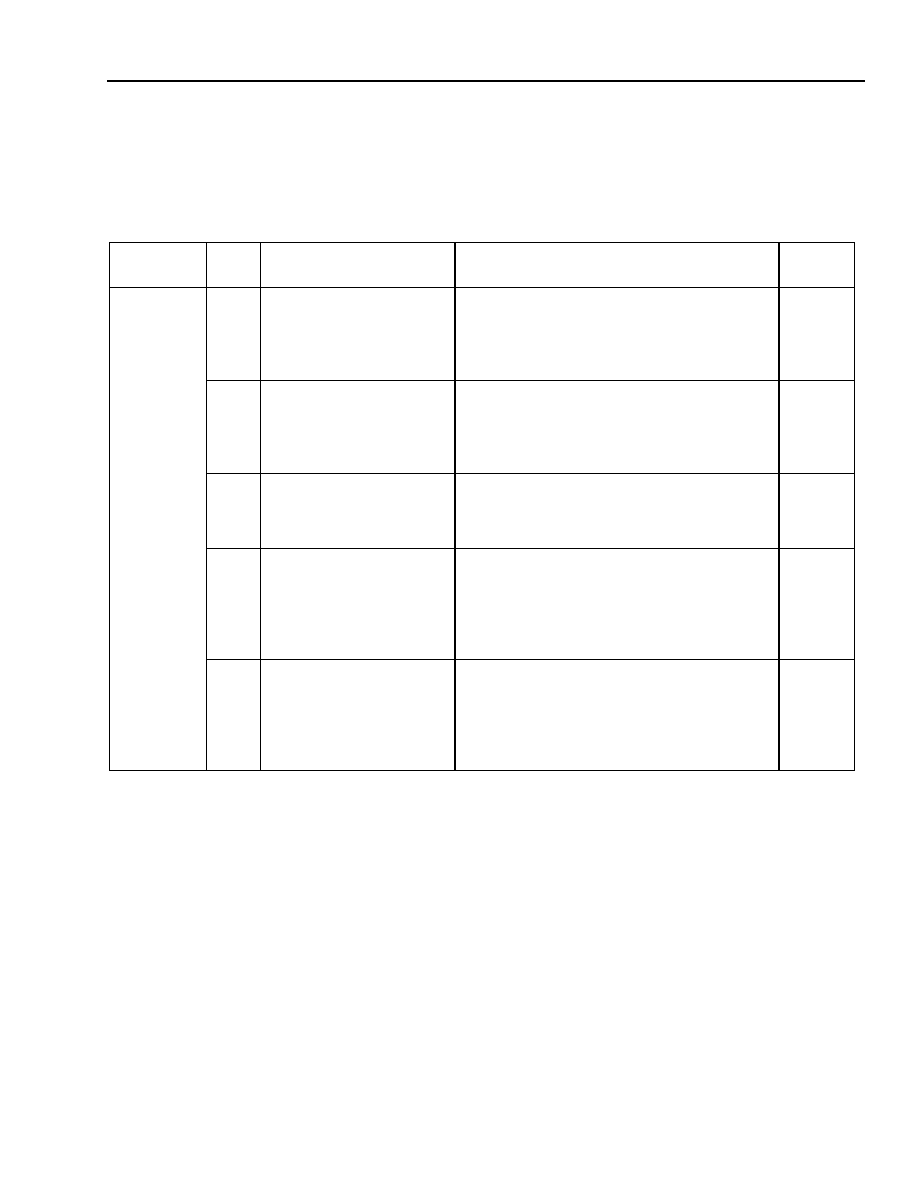

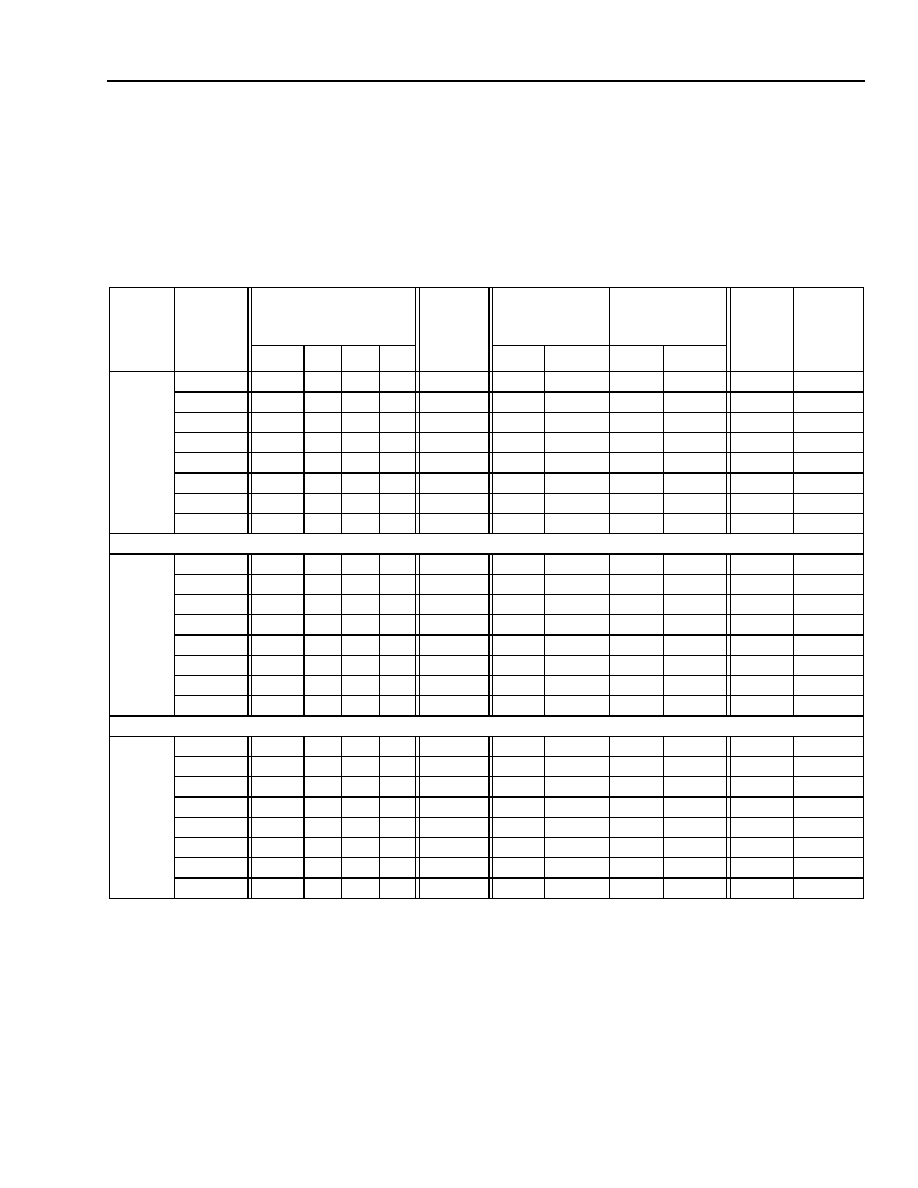

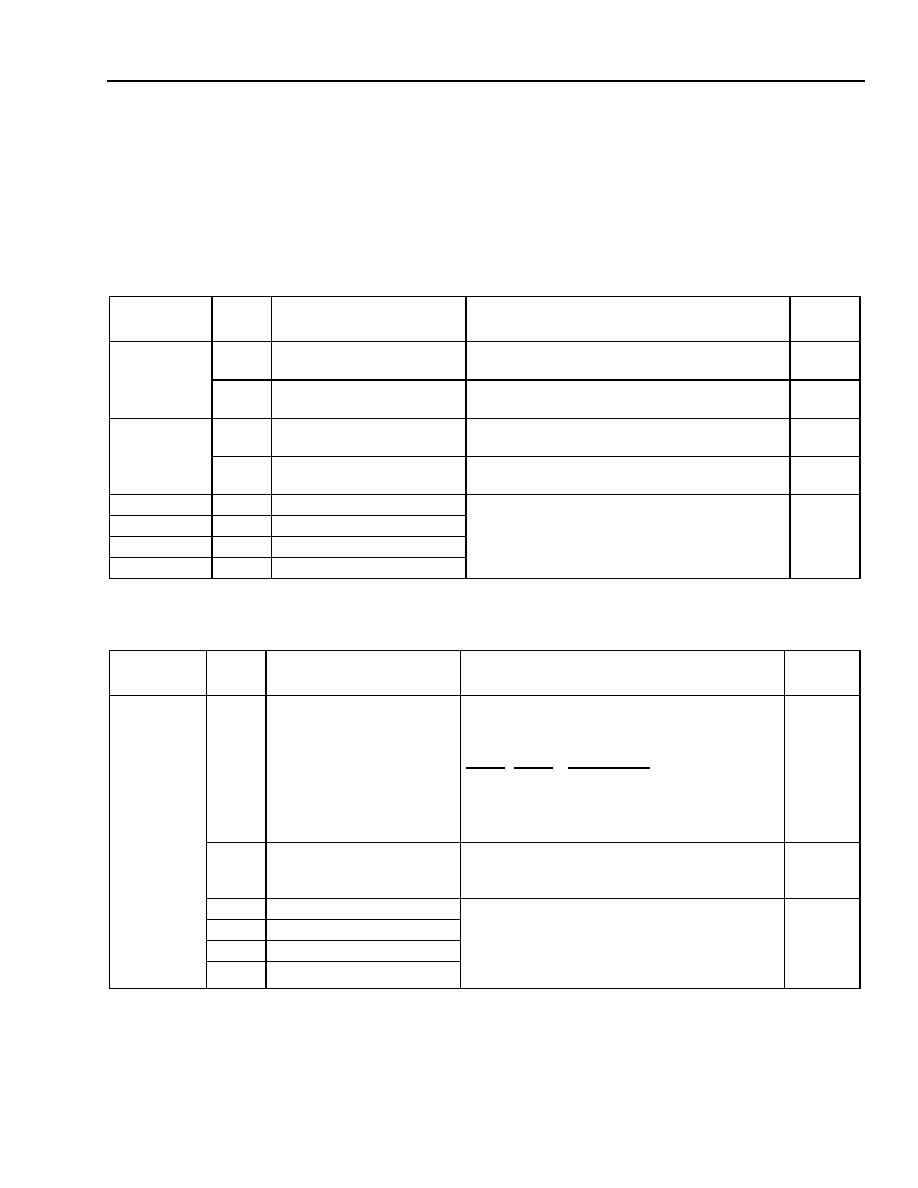

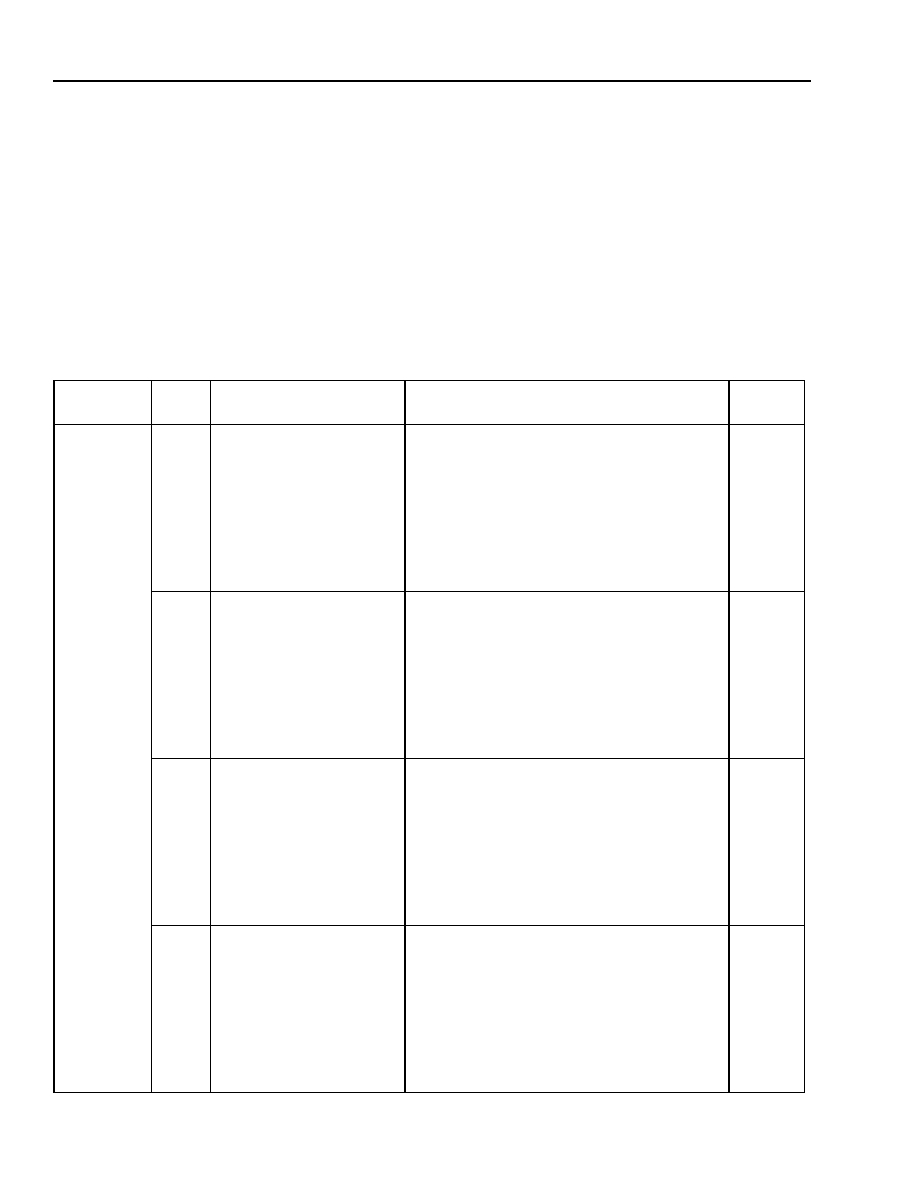

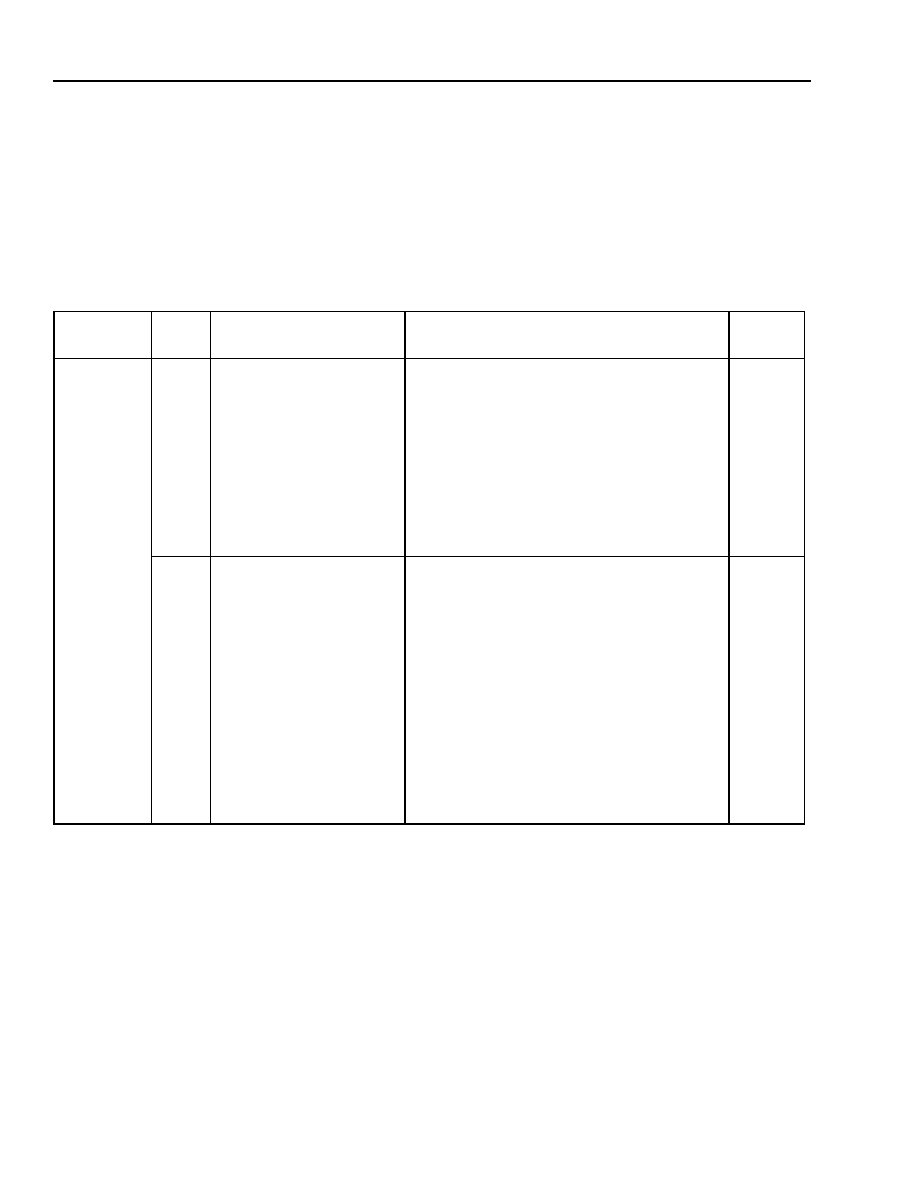

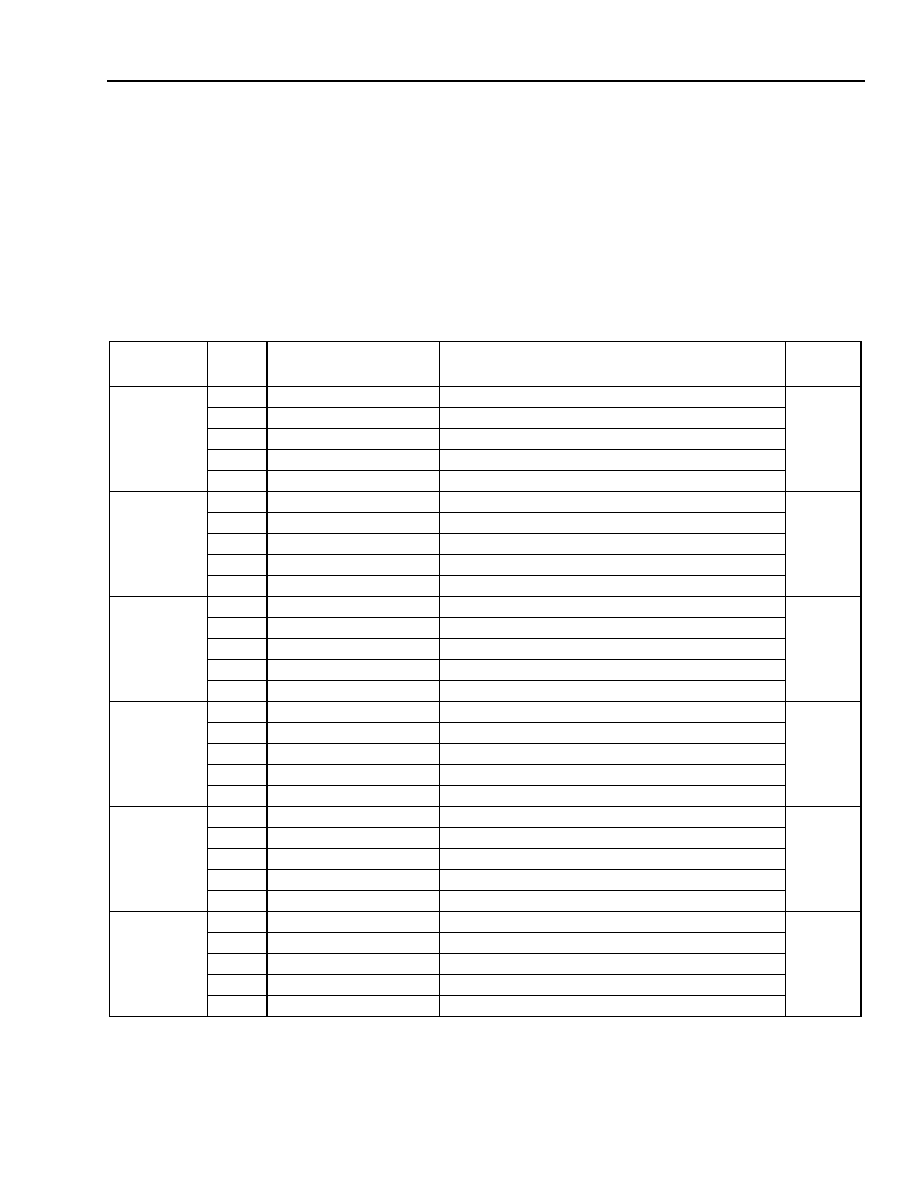

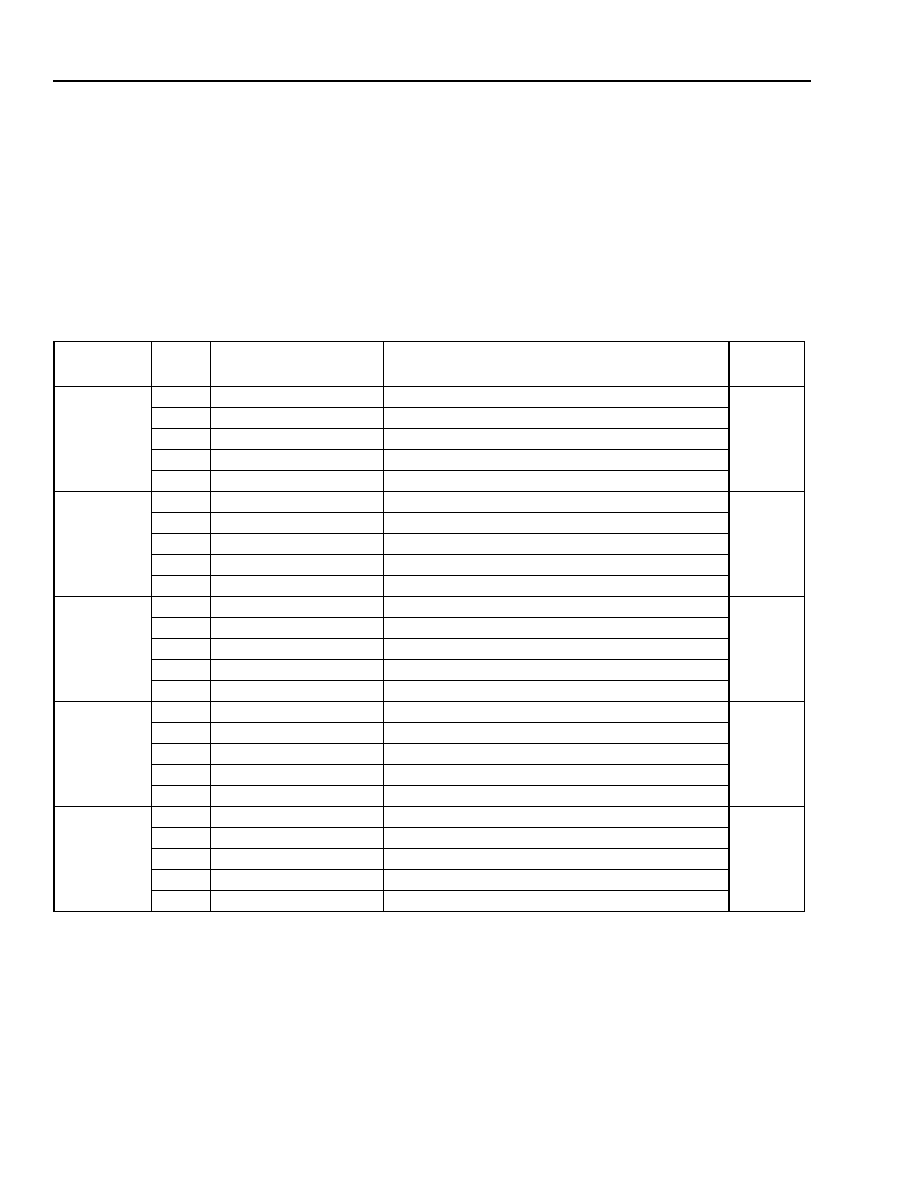

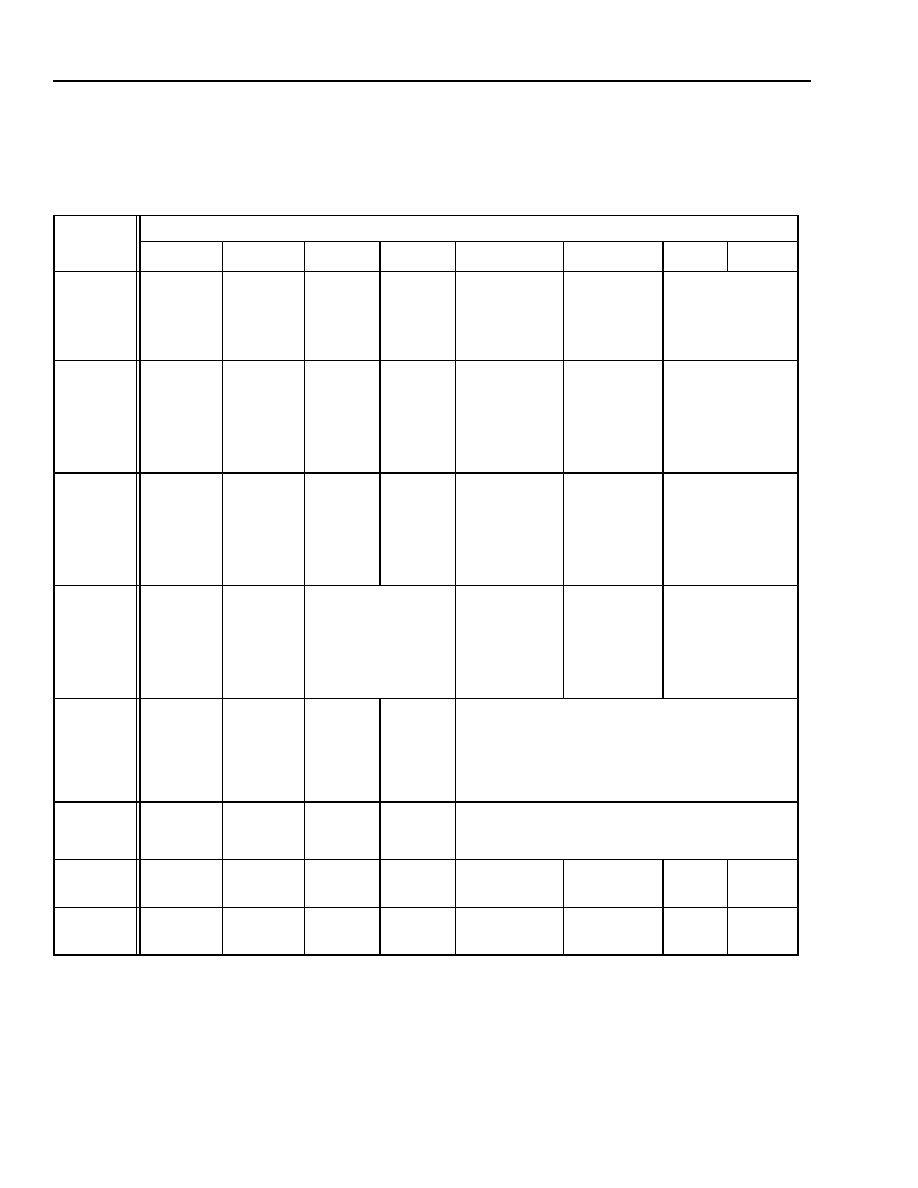

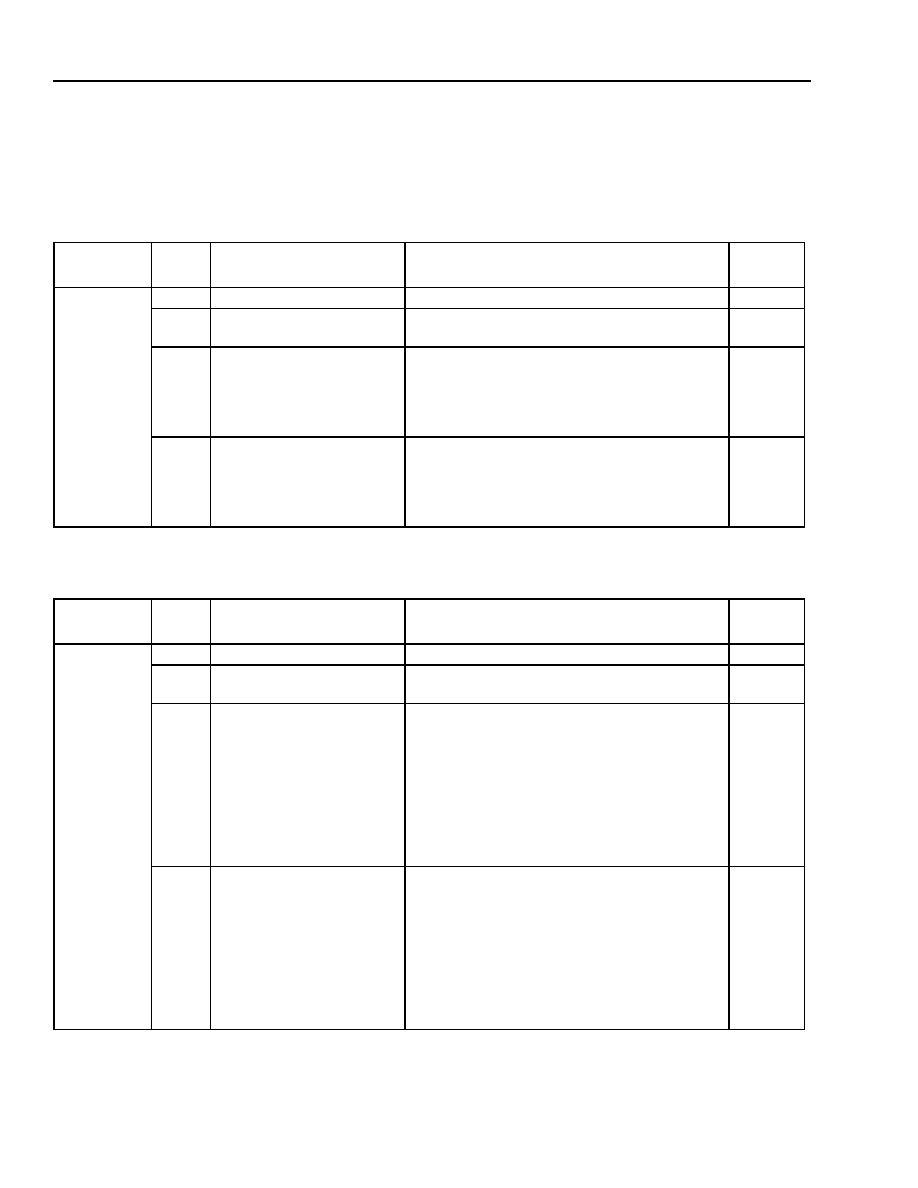

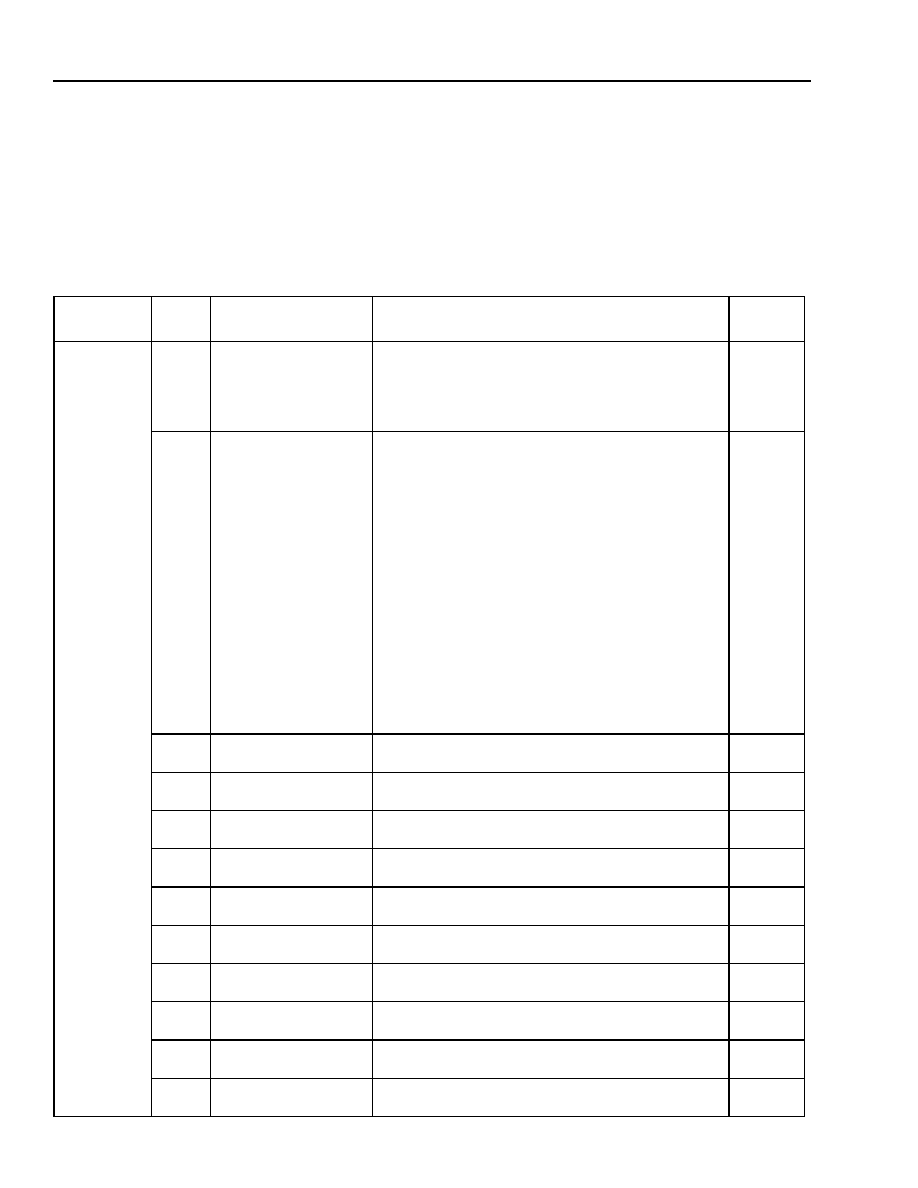

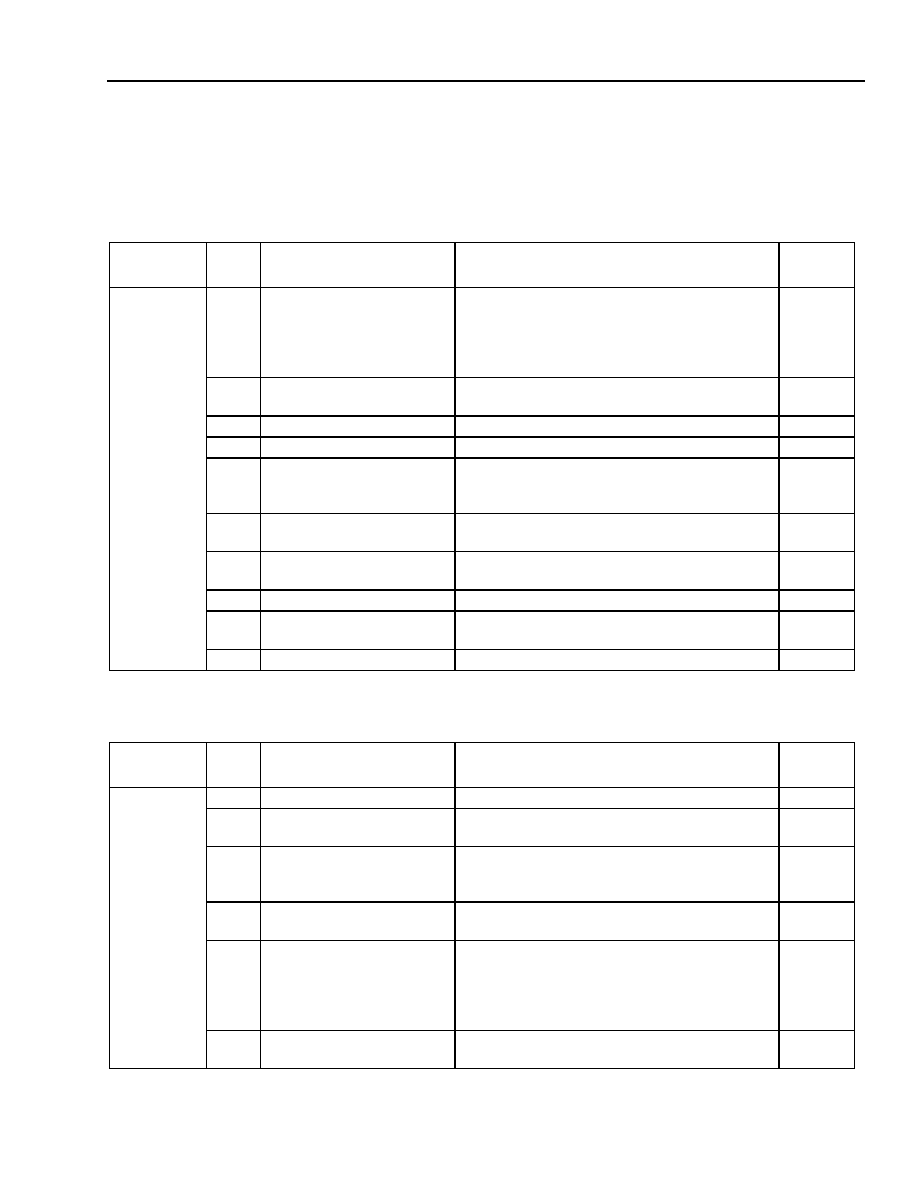

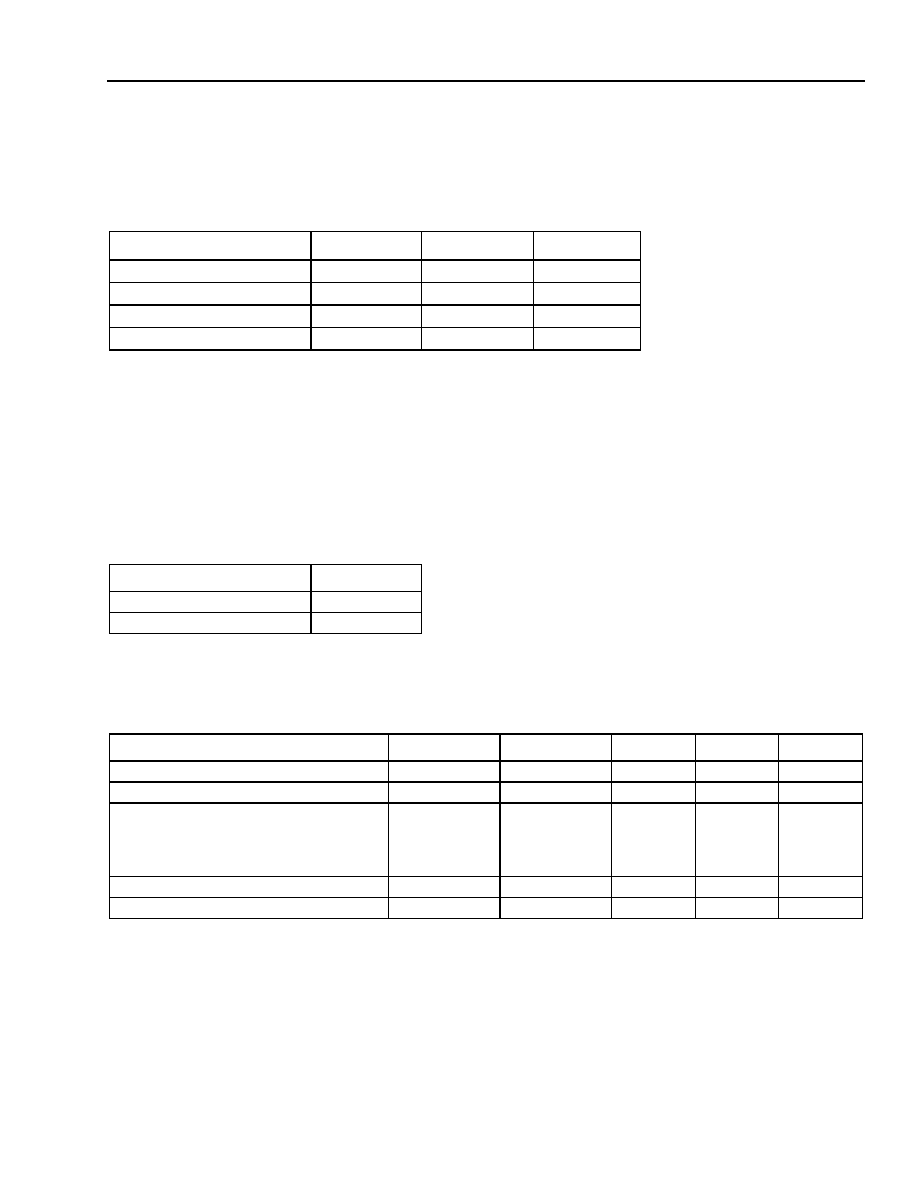

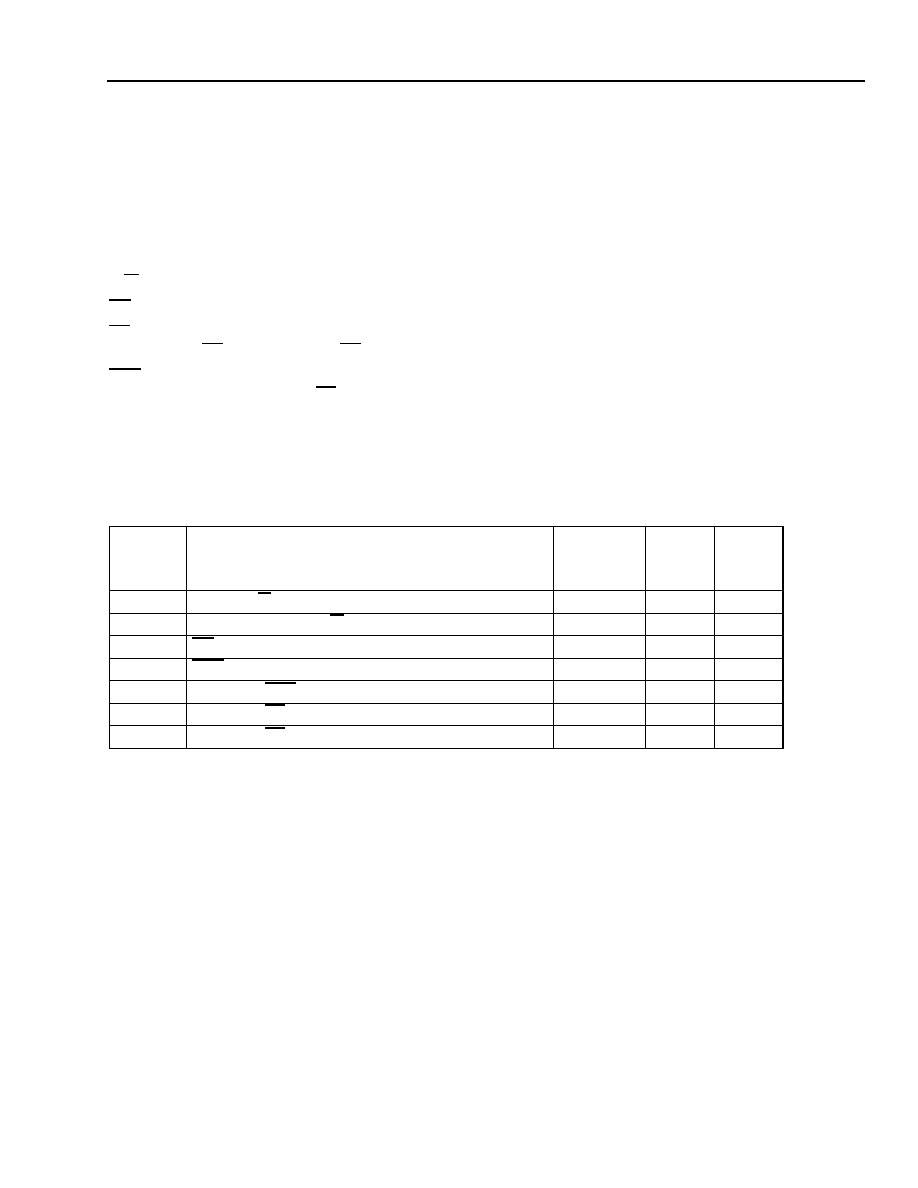

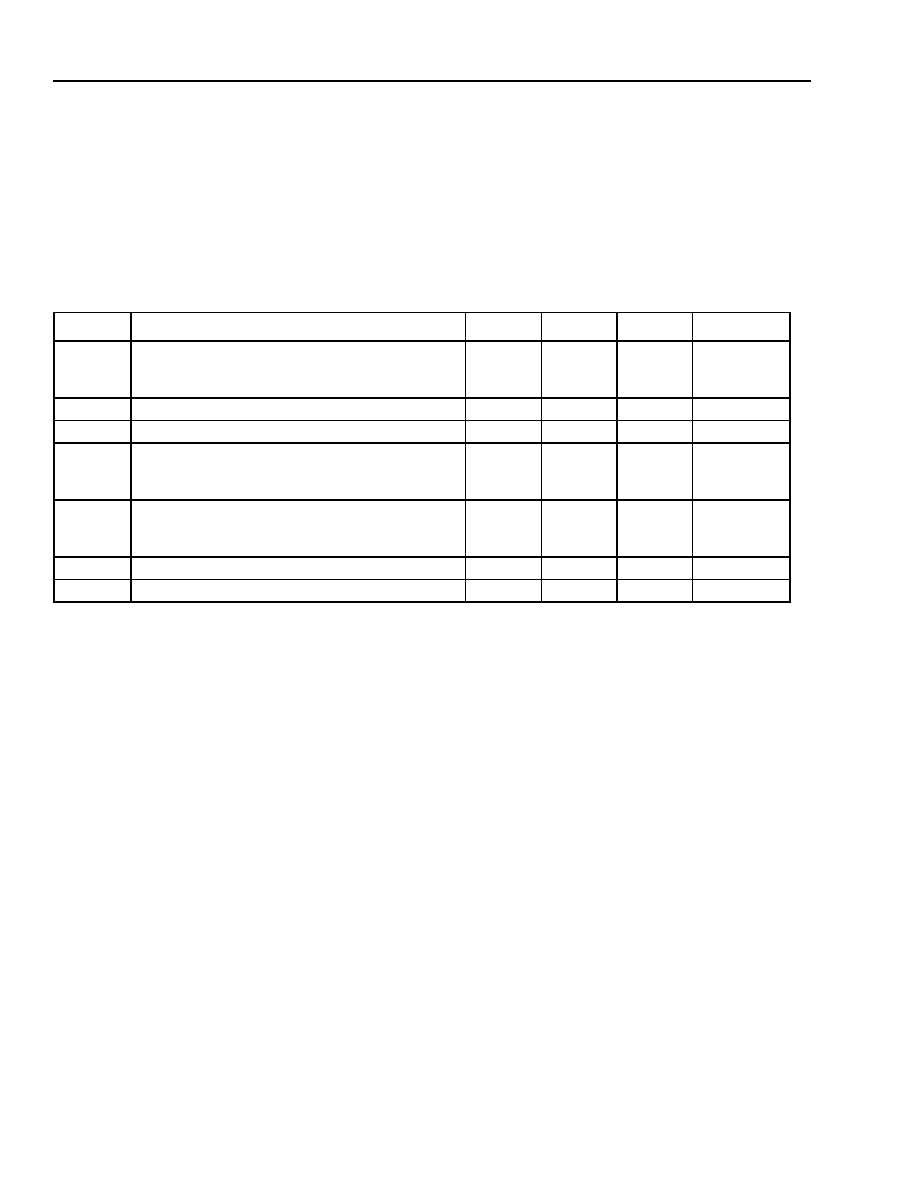

Table 1. TDAT Device Product Line

Device

Line Ports

UTOPIA Ports

OC-3

OC-12

OC-48

Ports Present

Modes

TDAT04622

4

(A, B, C, D)

1

(A)

NA

1

(A)

U2, U2+, U3, U3+

s

8-bit

s

16-bit

TDAT021G2

4

(A, B, C, D)

2

(A, B)

NA

2

(A, B)

U2, U2+, U3, U3+

s

8-bit

s

16-bit

s

32-bit

TDAT042G5

4

(A, B, C, D)

4

(A, B, C, D)

1

(16-bit parallel

multiplexed/

demultiplexed)

4

(A, B, C, D)

U2, U2+, U3, U3+

s

8-bit

s

16-bit

s

32-bit

Data Addendum

May 2001

155/622/2488 Mbits/s Data Interfaces

TDAT SONET/SDH

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Copyright © 2001 Agere Systems Inc.

All Rights Reserved

Printed in U.S.A.

May 2001

DA01-010SONT (Replaces DA00-001SONT and must accompany DS98-193SONT-4)

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET:

http://www.agere.com

E-MAIL:

docmaster@micro.lucent.com

N. AMERICA: Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA PACIFIC: Agere Systems Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

CHINA:

Agere Systems (Shanghai) Co., Ltd., 33/F Jin Mao Tower, 88 Century Boulevard Pudong, Shanghai 200121 PRC

Tel. (86) 21 50471212, FAX (86) 21 50472266

JAPAN:

Agere Systems Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700

EUROPE:

Data Requests: DATALINE: Tel. (44) 7000 582 368, FAX (44) 1189 328 148

Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot),

FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 3507670 (Helsinki),

ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Advisory

May 2001

TDAT042G5 Device Advisory

for Version 1 and 1A of the Device

System Programming (SP)

SP1. Required Provisioning Sequence and Clocks

The core registers must be written prior to provisioning any other registers (1) to establish the internal clock

rates for the device, and (2) because writing to certain core registers resets the remainder of the device. Cer-

tain clocks must be present to read/write registers prior to provisioning the device.

One of the following clocks must be present prior to provisioning to enable register access:

I

TxCKP and TxCKN

I

MPU clock (microprocessor interface synchronous mode only)

Provisioning must be implemented in the following sequence:

I

Core register 0x0010 (mode) must be provisioned first

I

Core register 0x0011 (channel [A--D] control) second

I

Remainder of the core registers must then be provisioned (order does not matter)

It is recommended, but not required, that the remainder of the device be provisioned in the following order:

I

OHP, PT, and DE blocks (order does not matter)

I

UT block to turn on the data source to the master and slave

Workaround

Provisioning must be implemented in the following sequence:

I

Apply either TxCKP and TxCKN or MPU clock.

I

Provision core:

-- Mode, register 0x0010

-- Channel [A--D] control, register 0x0011

-- Remainder of the core

Corrective Action

Not applicable. Use above procedure in provisioning the device.

2

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

System Programming (SP)

(continued)

SP2. Behavior During Loss of Receive Line Clock

All state and counter values will be held at their current values when Rx line clock has been lost. The device will not

automatically multiplex in the Tx line clock when the Rx line clock is lost.

Workaround

System software should monitor loss of line clock bits in the receive/transmit state register (addresses 0x040A--

0x040D) and ignore all other alarms. This condition must be serviced as a major failure event.

Corrective Action

This is informational only. No corrective action is required for this condition.

SP3. PT Register Addressing

Addresses for the PT error counter registers are as follows:

I

Channel A: 0x09B3 to 0x09E3

I

Channel B: 0x09EF to 0x0A20

I

Channel C: 0x0A2C to 0x0A5C

I

Channel D: 0x0A68 to 0x0A98

Note: The reserved address space between the error counter registers is not symmetric. (The reserved space

between channels B and C is 0x003D, and the reserved space between channels A and B and channels

C and D is 0x003C.)

Workaround

This is informational only. No workaround is available for this condition.

Corrective Action

No corrective action is required for this condition.

Agere Systems Inc.

3

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Microprocessor Interface (MPU)

MPU1. Interface to Motorola* MC68360 Processor Is Not Glueless

The interface between the Motorola MC68360 processor and TDAT042G5 requires intervening logic because of

the following incompatibilities in the specifications of these two devices. For a 33 MHz microprocessor clock rate,

the Motorola MC68360 series processors can be interfaced to TDAT042G5 without intervening glue logic, if used

without DT and if programmed for six wait-states. If a user wishes not to use the wait-states, then the chip select

applied to TDAT042G5 must be held low until the address changes. Details are given below.

Chip Select Timing

The TDAT042G5 CS input signal requirements are not compatible with the Motorola MC68360 series processor

CSx output signals. TDAT042G5 timing does not allow simultaneous deassertion of CS and ADS signals. Chip

select applied to TDAT042G5 must be held low for at least 5 ns after the MC68360 deasserts ADS.

Workaround: Use external glue logic to decode the address to generate CS, or provide microprocessor interface

signals meeting the requirements of TDAT042G5.

DT Timing

If the Motorola MC68360 processor CSx signal is used to drive the TDAT042G5 CS, then TDAT042G5 DT output

does not satisfy the MC68360 processor DSACK timing requirement. DT is not pulled to 1 before it is placed in a

high-impedance state. This causes the next MPU cycle to be terminated early.

Workaround: Place a 1 k

resistor from DT to V

DDD

.

Corrective Action

Corrective action for MPU1 has not been determined.

MPU2. Synchronous Microprocessor Interface Mode Is Nonfunctional

The synchronous microprocessor interface mode, MPMODE = 1 (pin D8), functions as described in the advance

data sheet, but causes data errors. Placing TDAT042G5 in the synchronous mode and placing a clock on MPCLK

(pin C8) will cause the data passing through the device to be corrupted. Data errors are generated at a rate of 1%

or less of corrupted packets.

Workaround

Use the TDAT042G5 in the asynchronous microprocessor mode, MPMODE = 0, with no clock applied to MPCLK.

Corrective Action

This condition will be resolved in version 1A of the device.

* Motorola is a registered trademark of Motorola, Inc.

4

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Core Registers (CR)

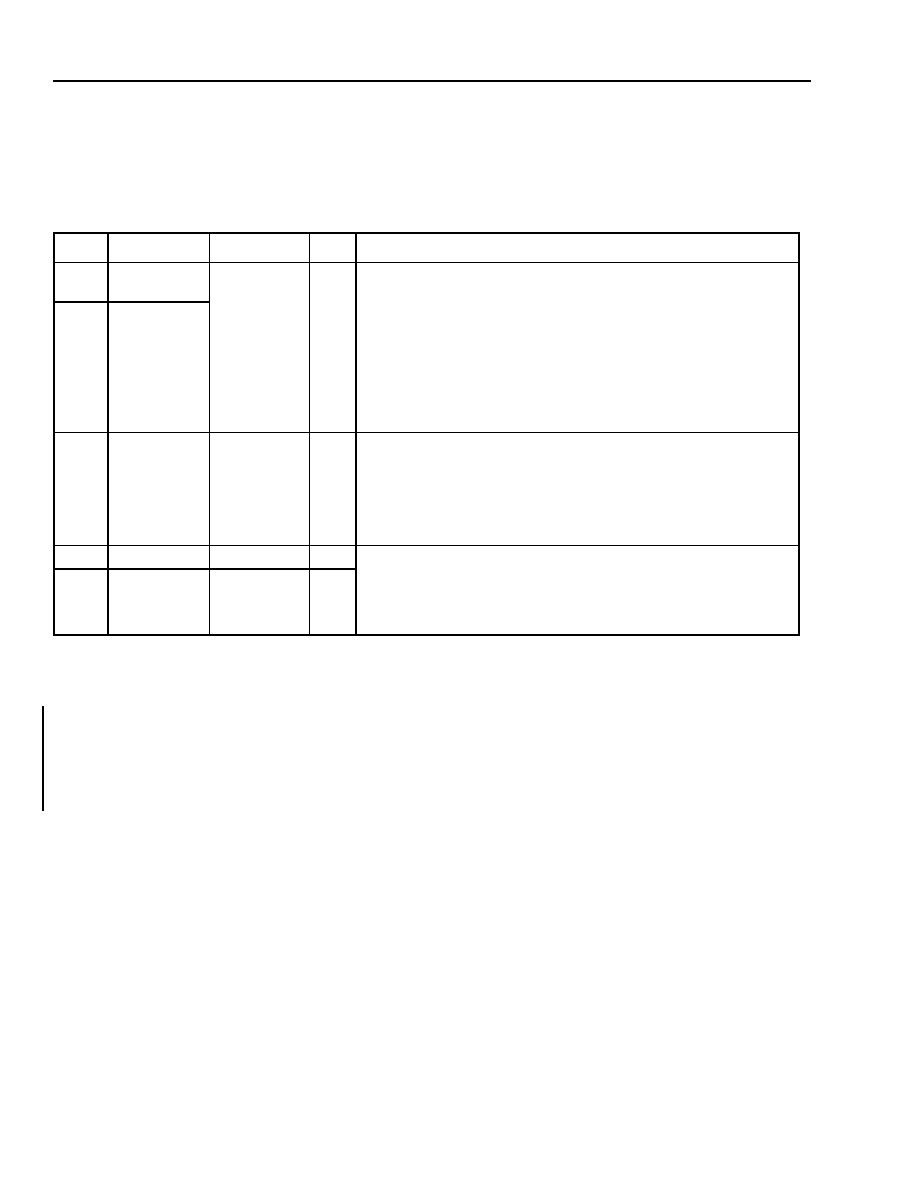

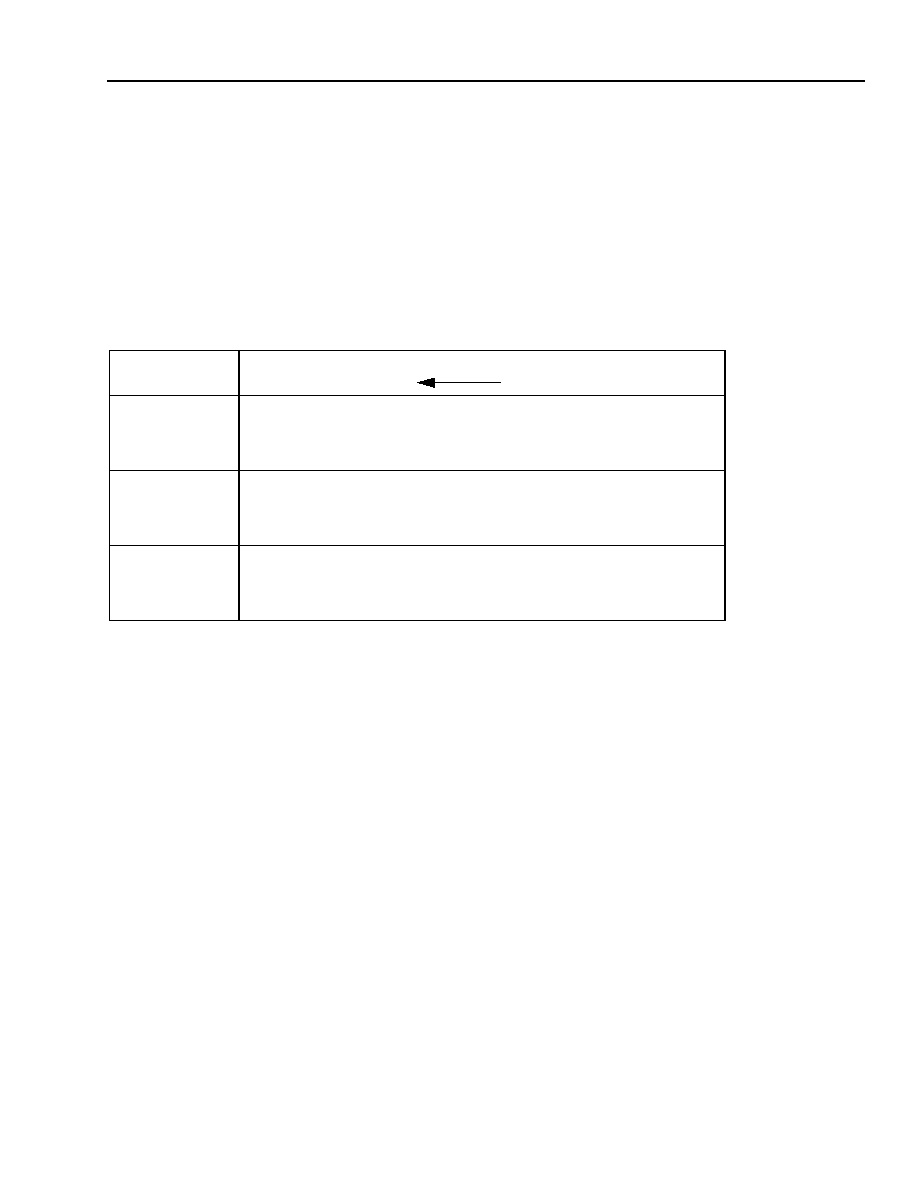

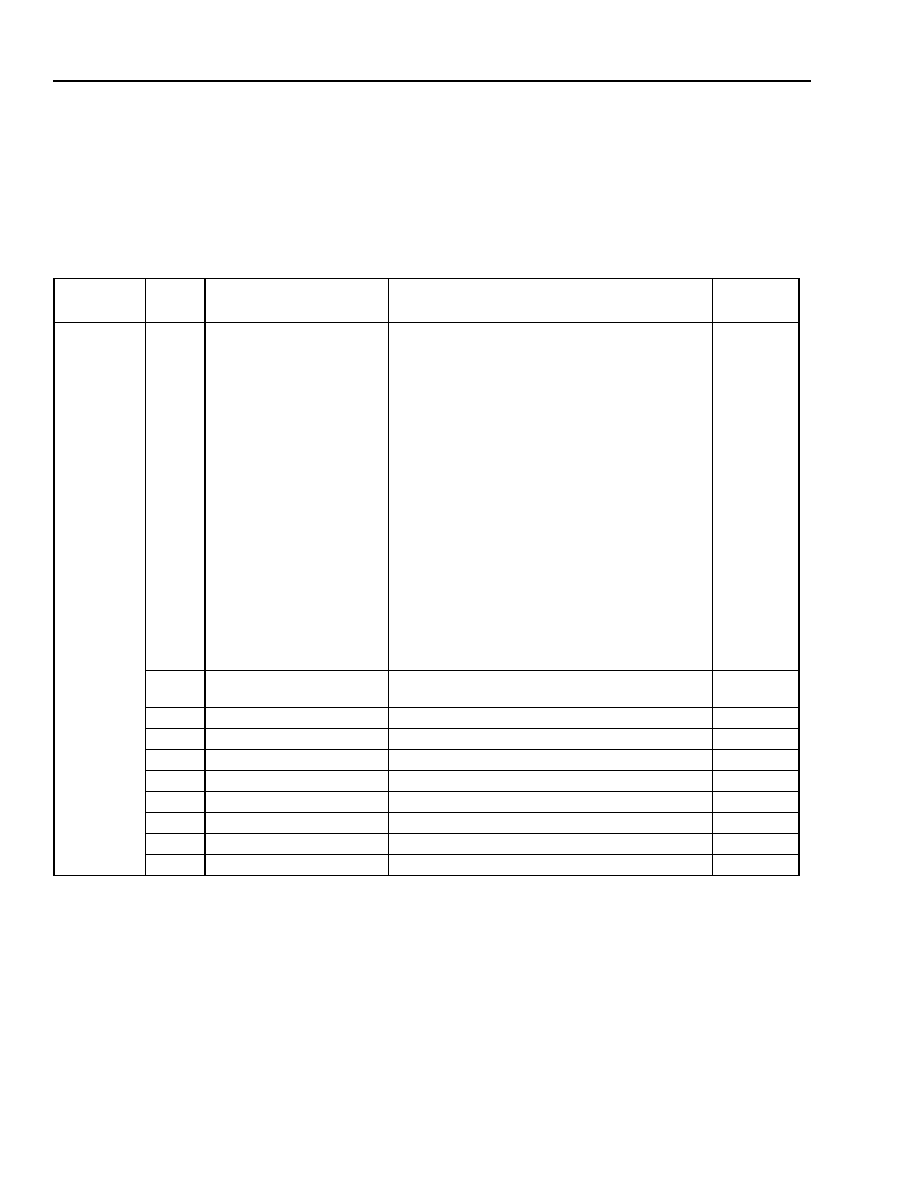

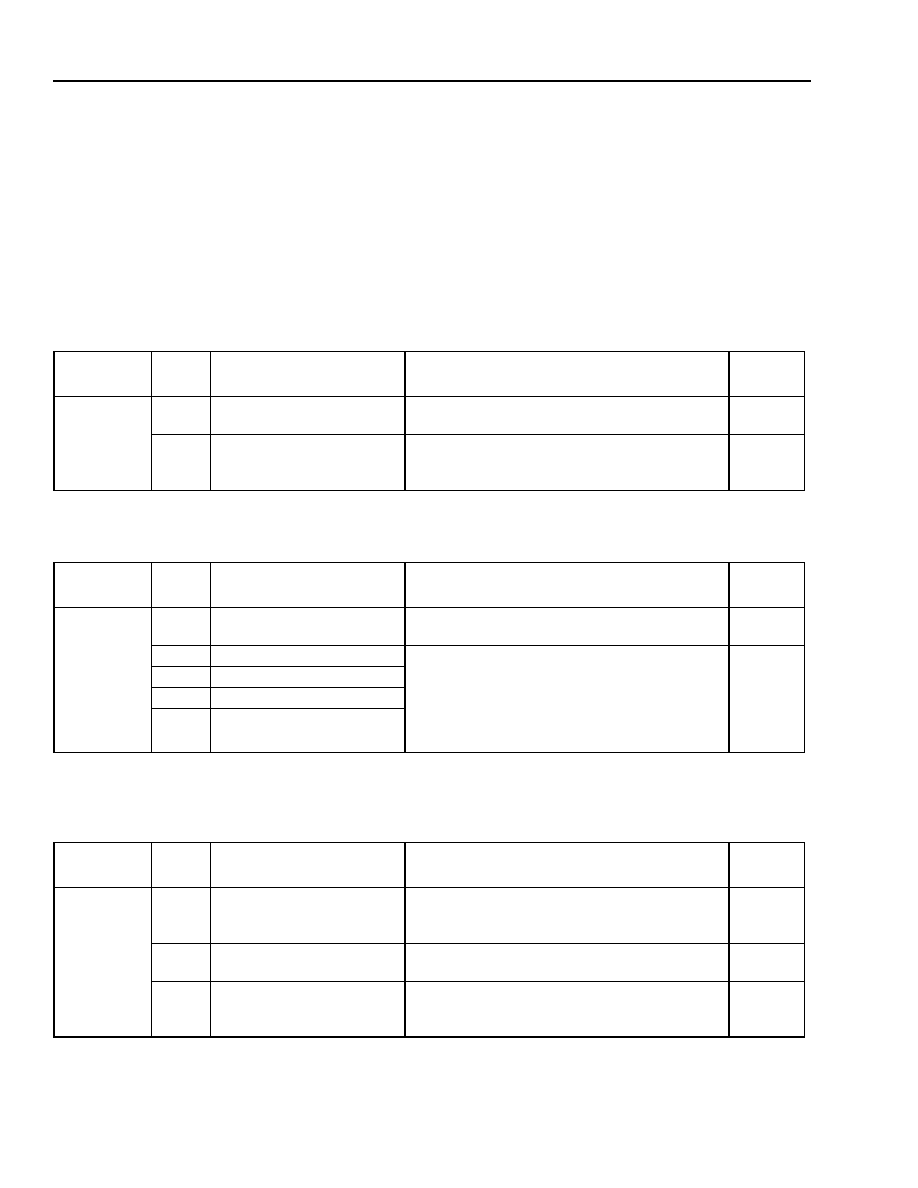

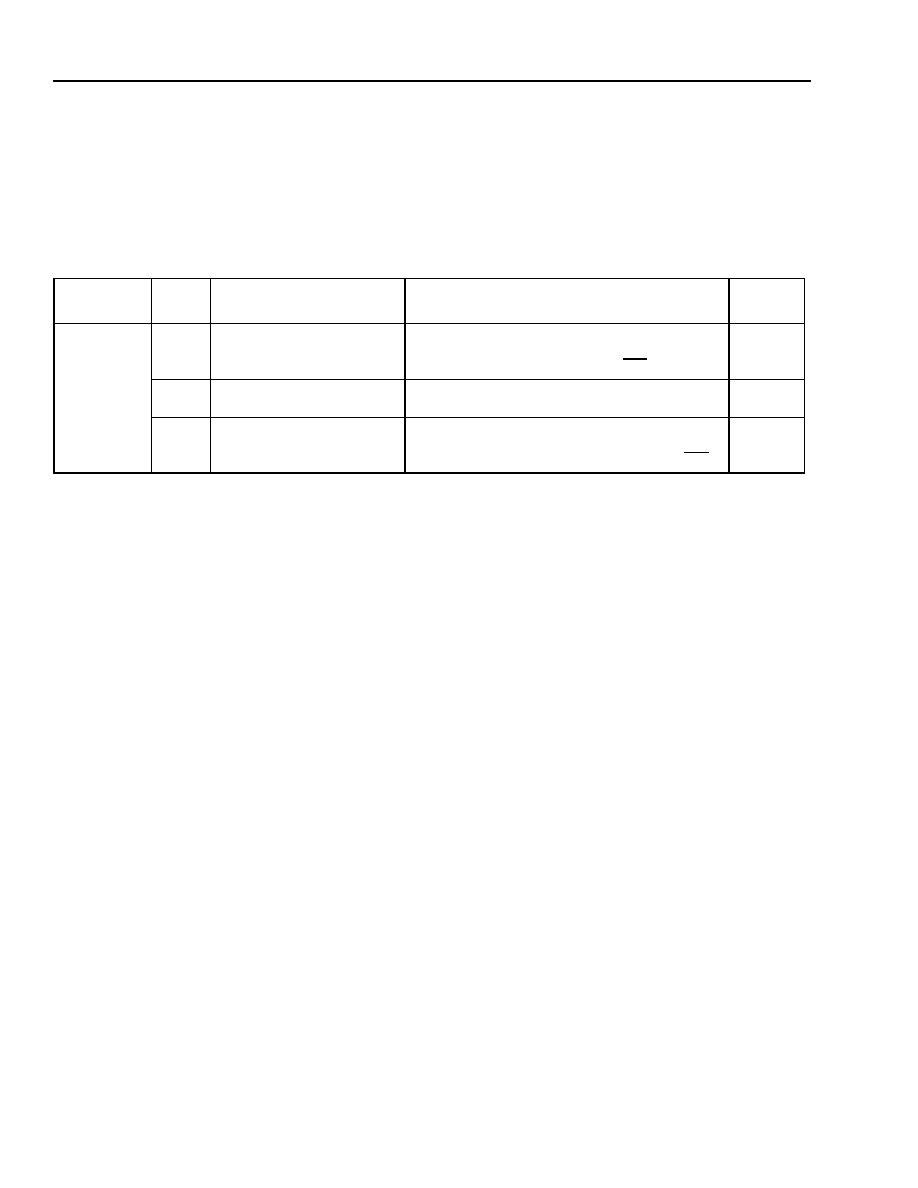

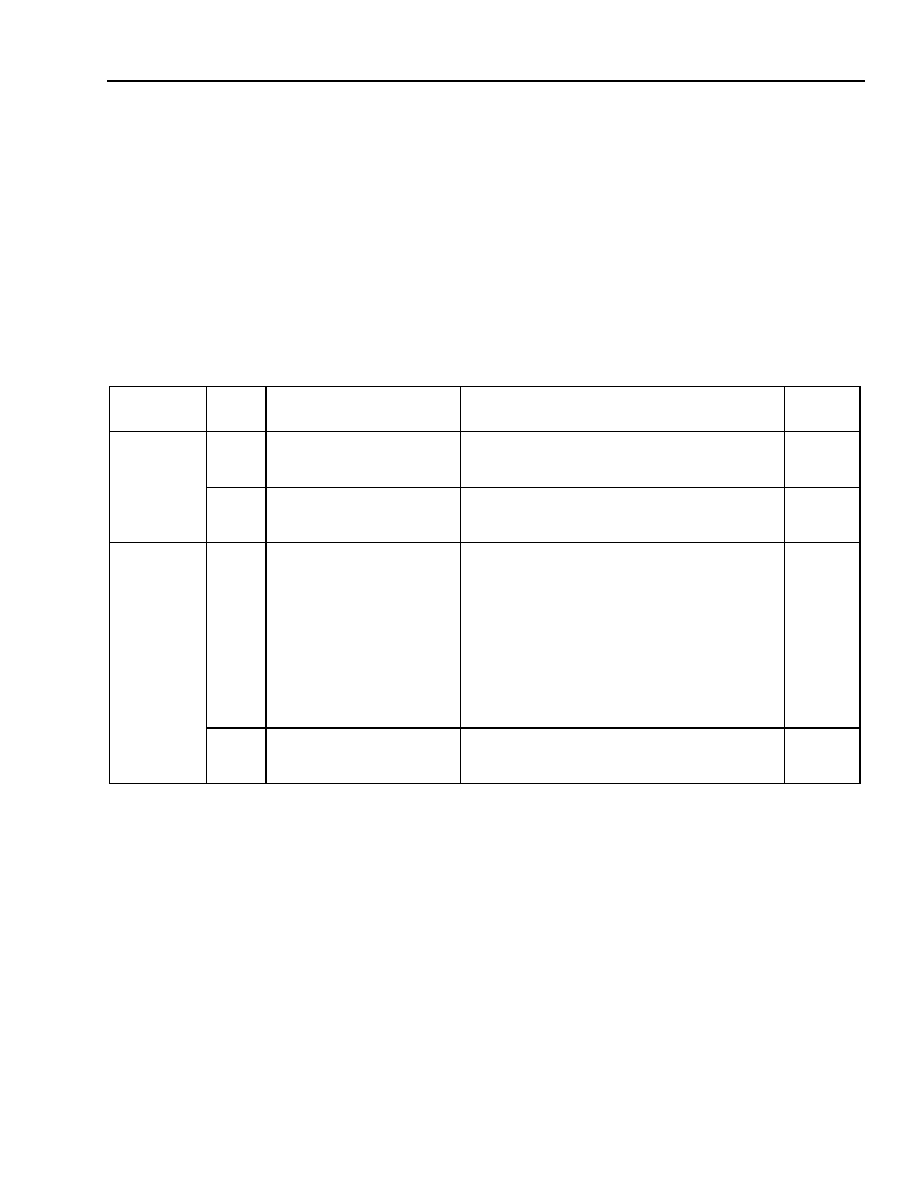

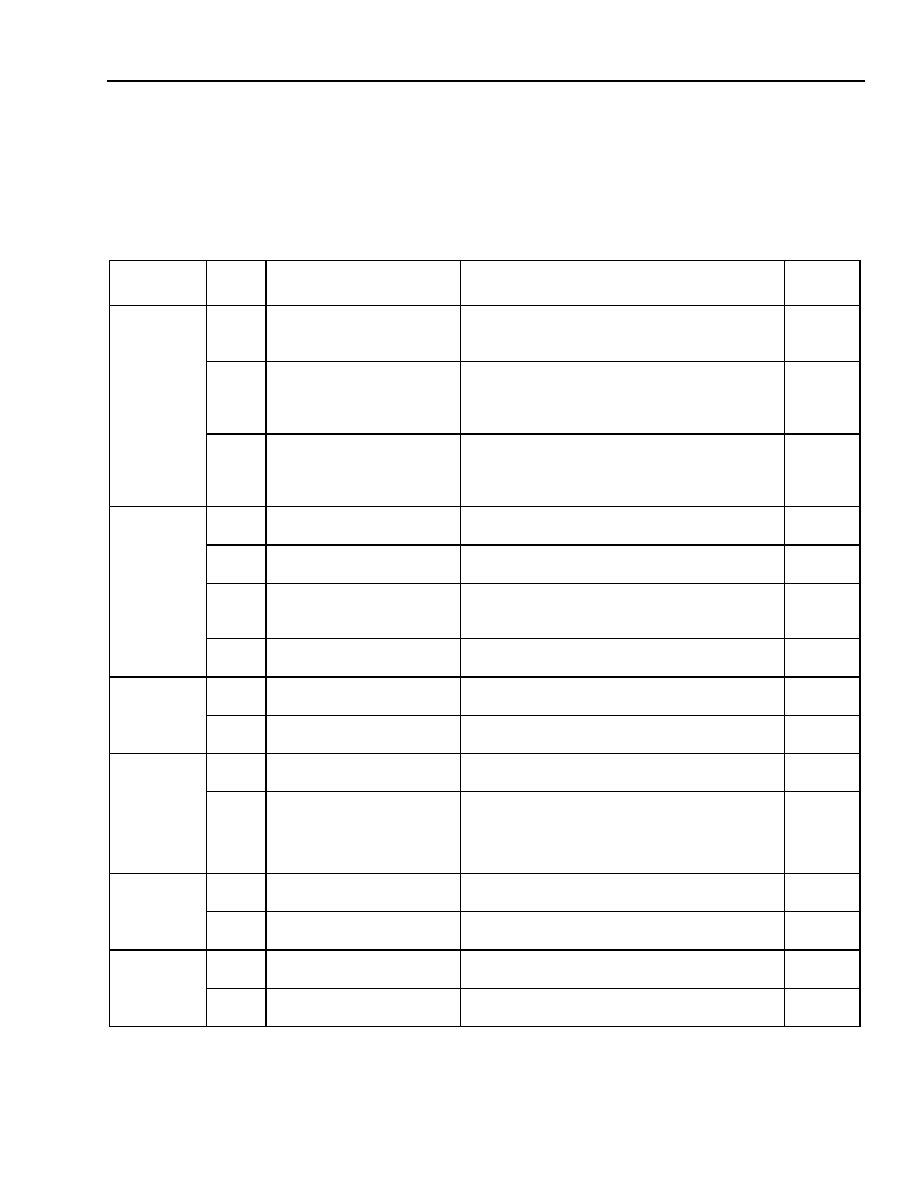

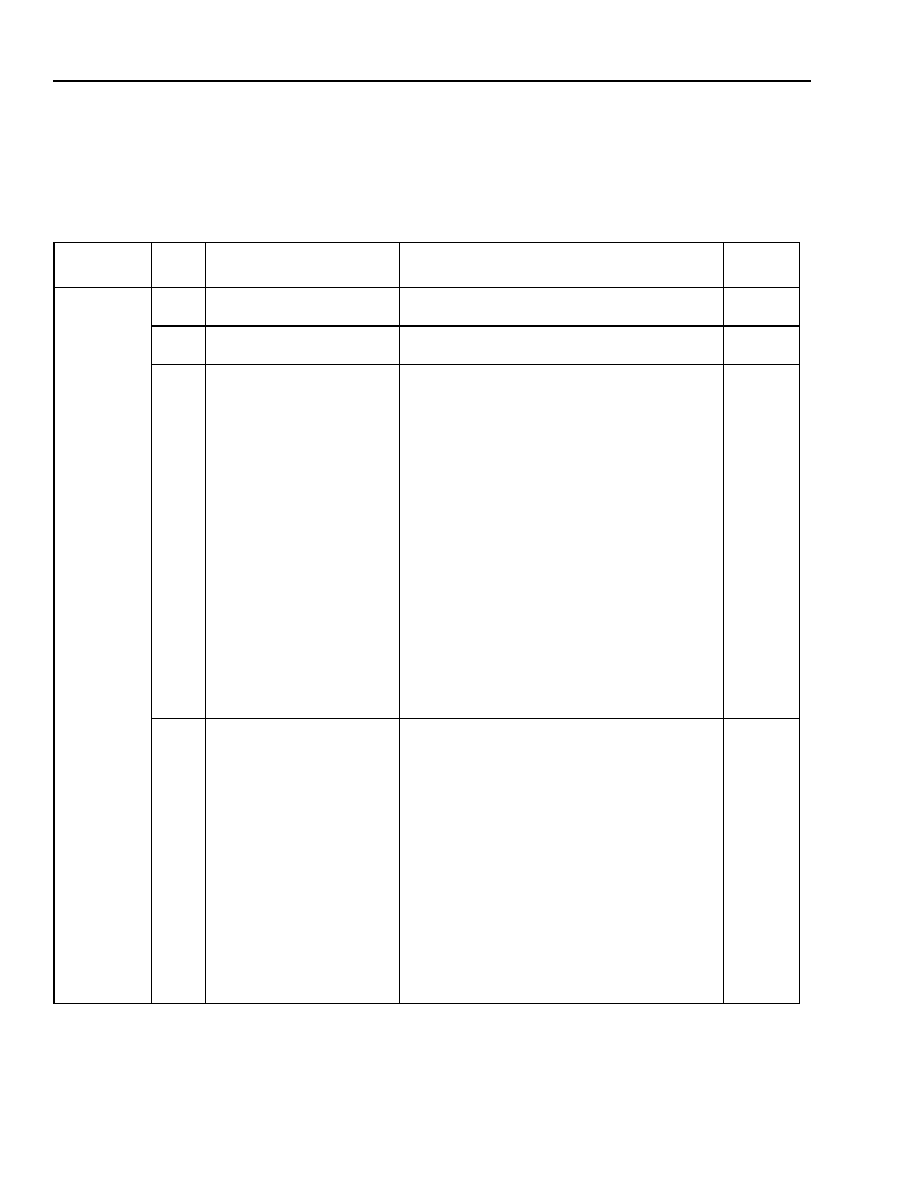

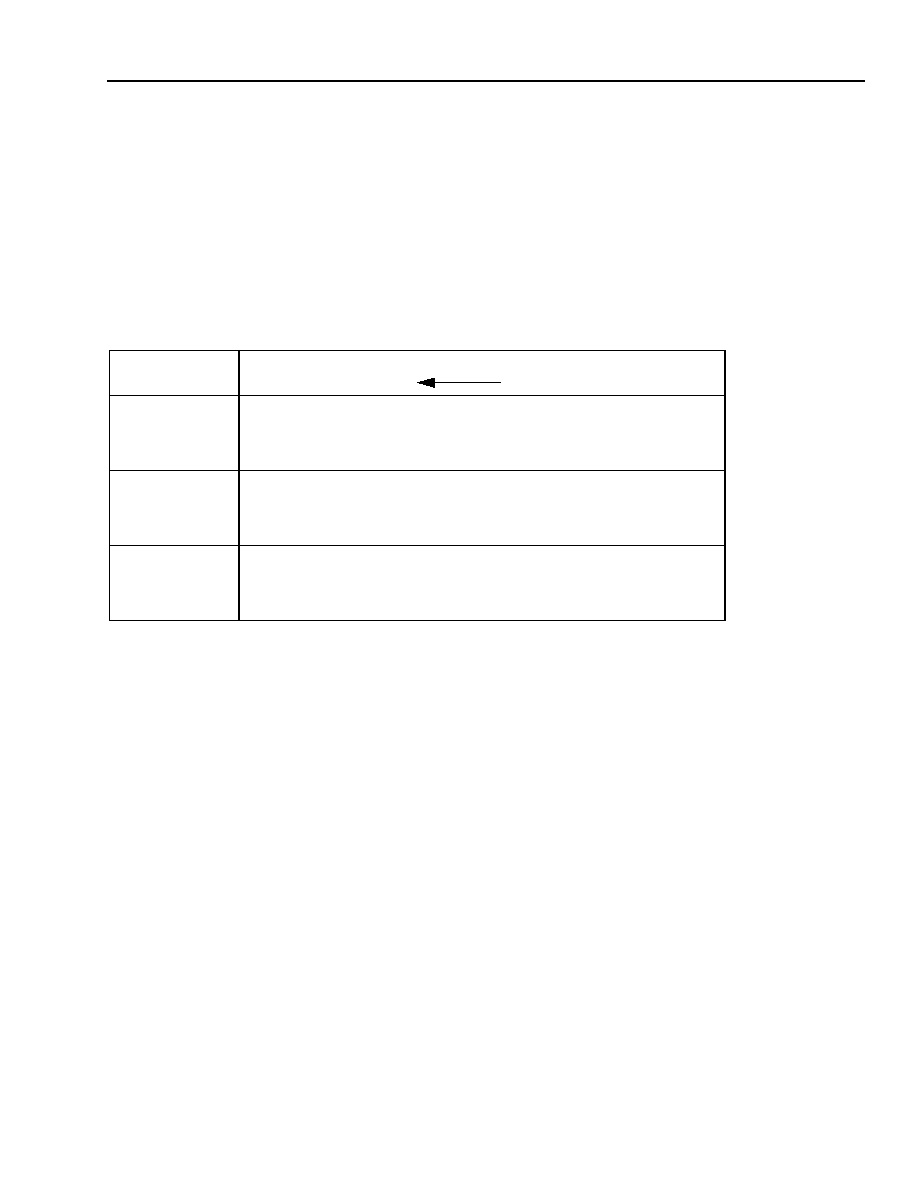

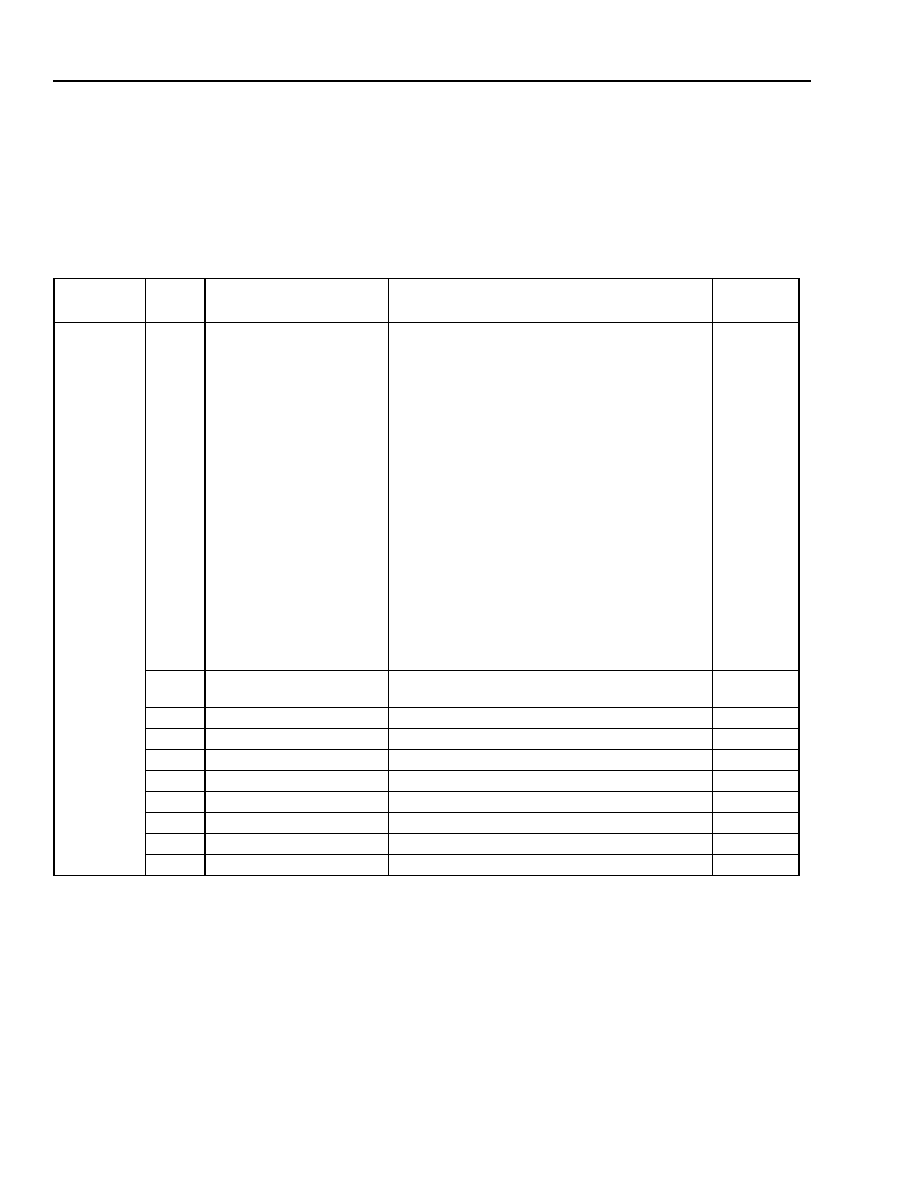

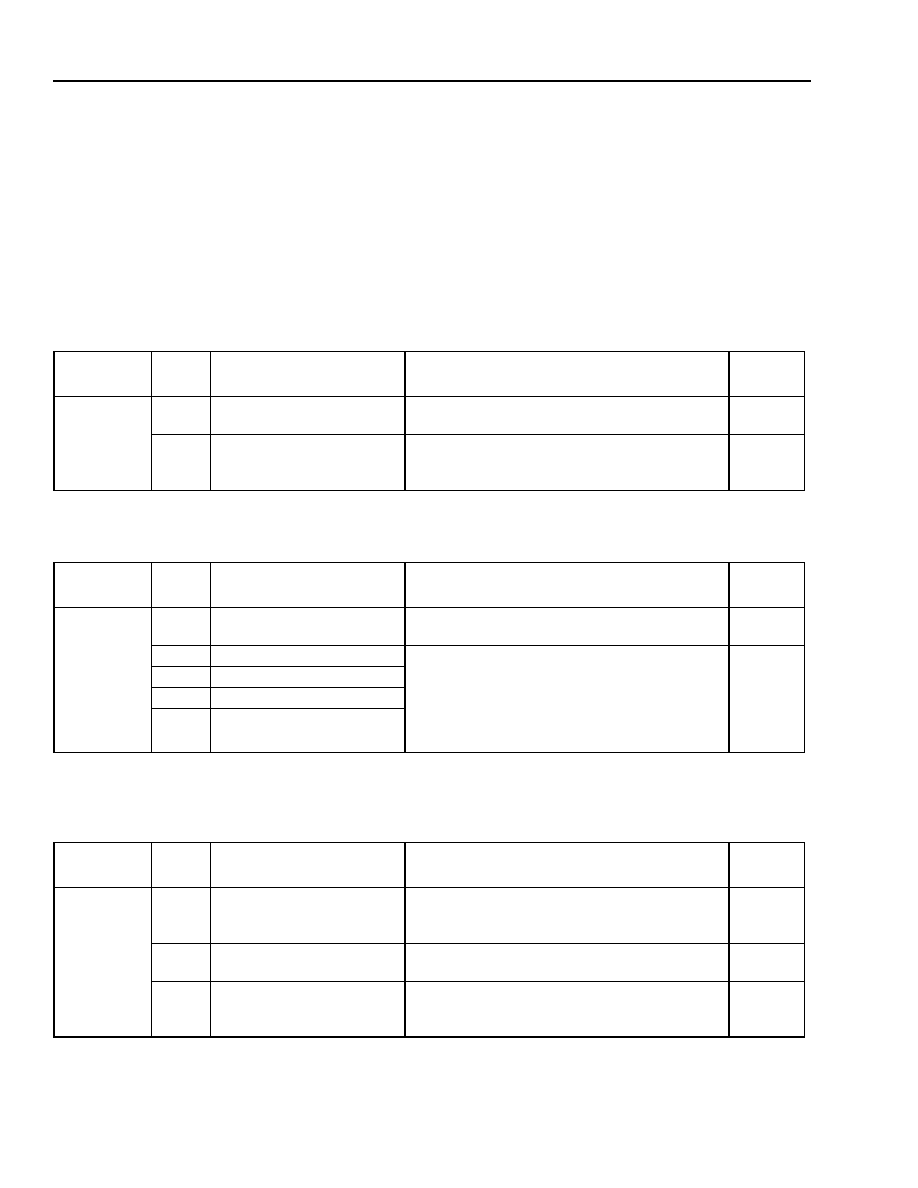

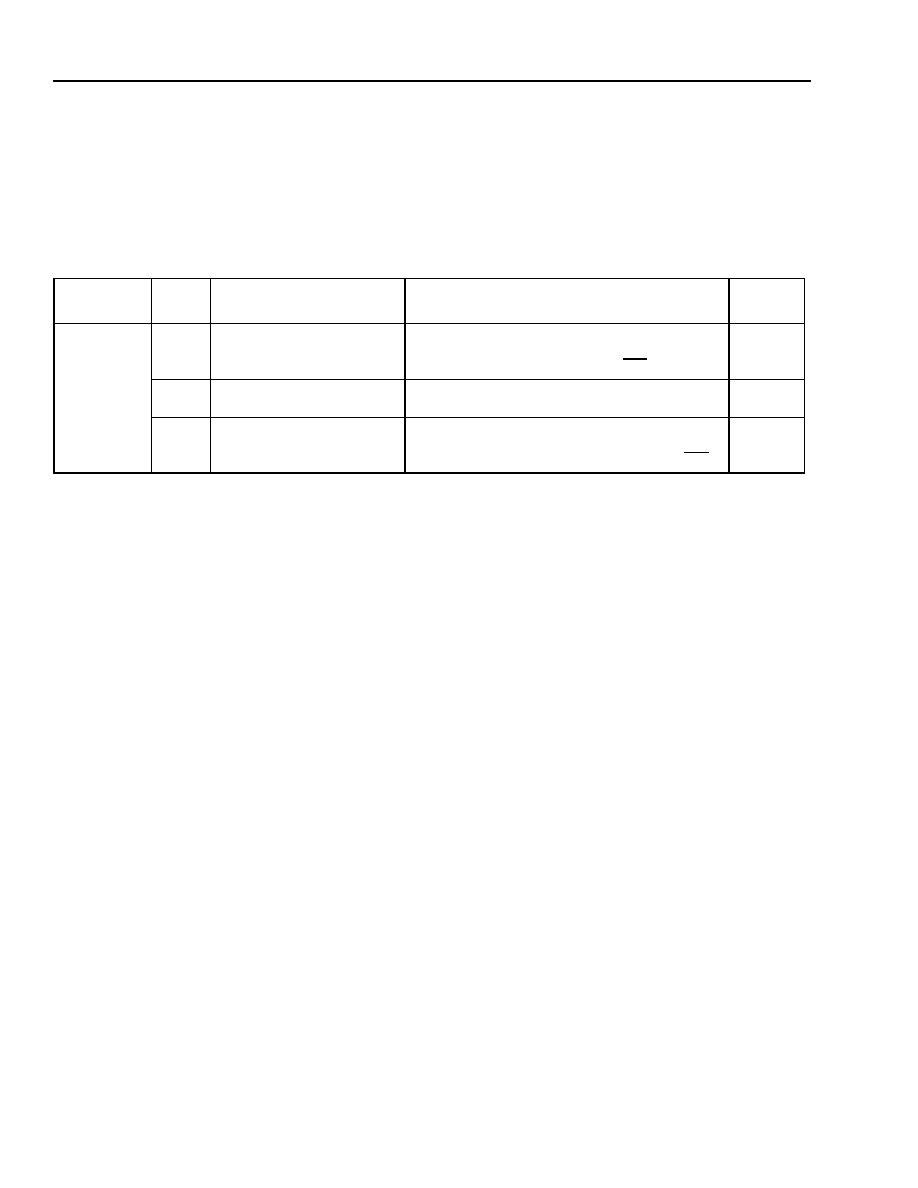

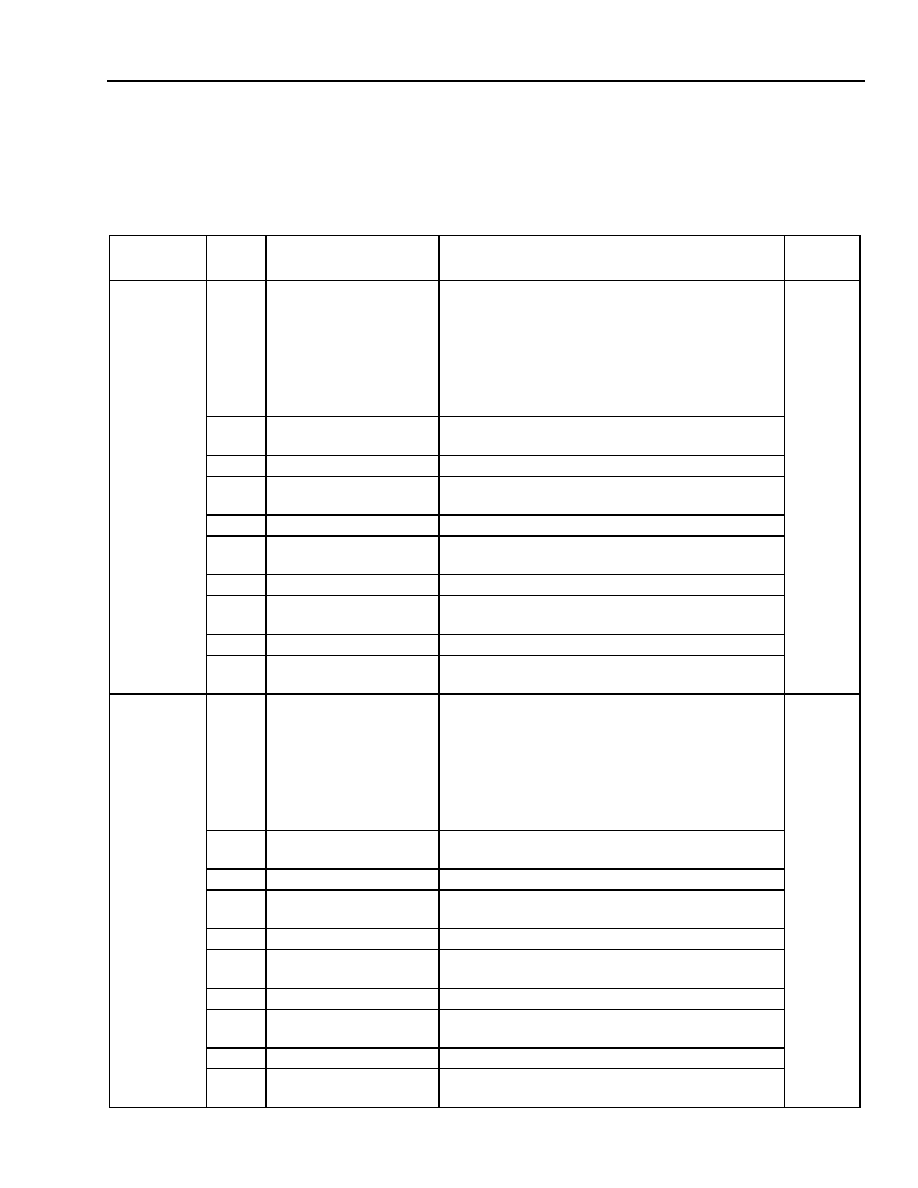

CR1. Clear on Read/Clear on Write Behavior

Bit 6 of line provisioning register 0x0010 sets the functionality of the COR/W registers.

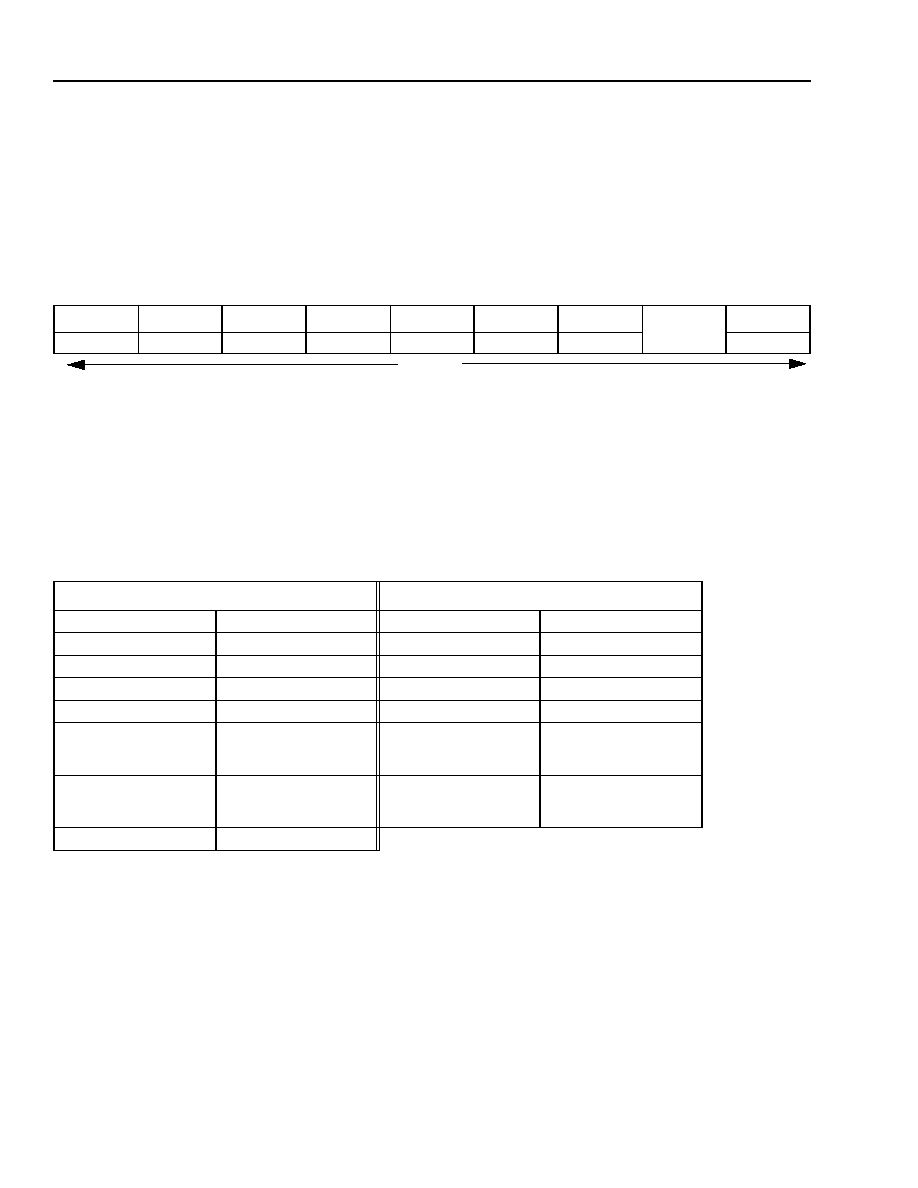

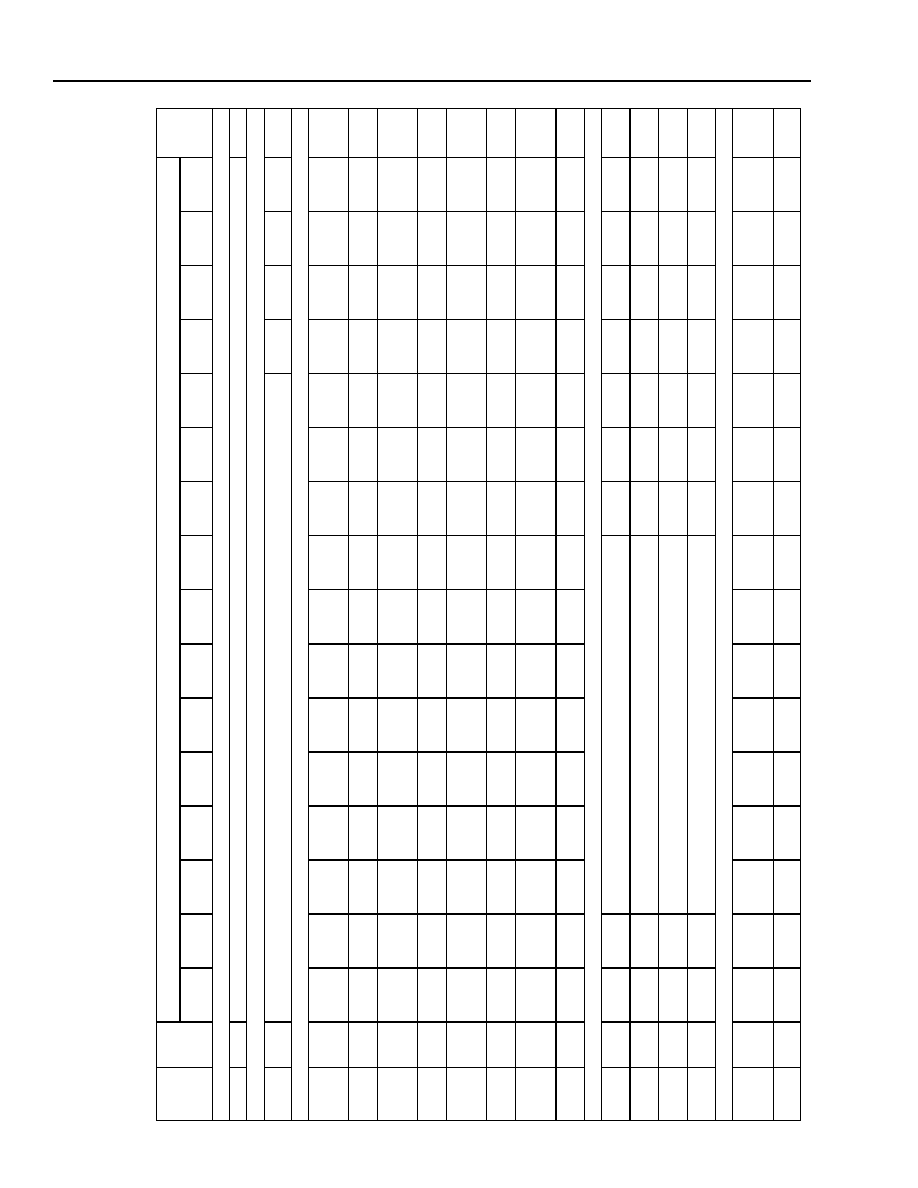

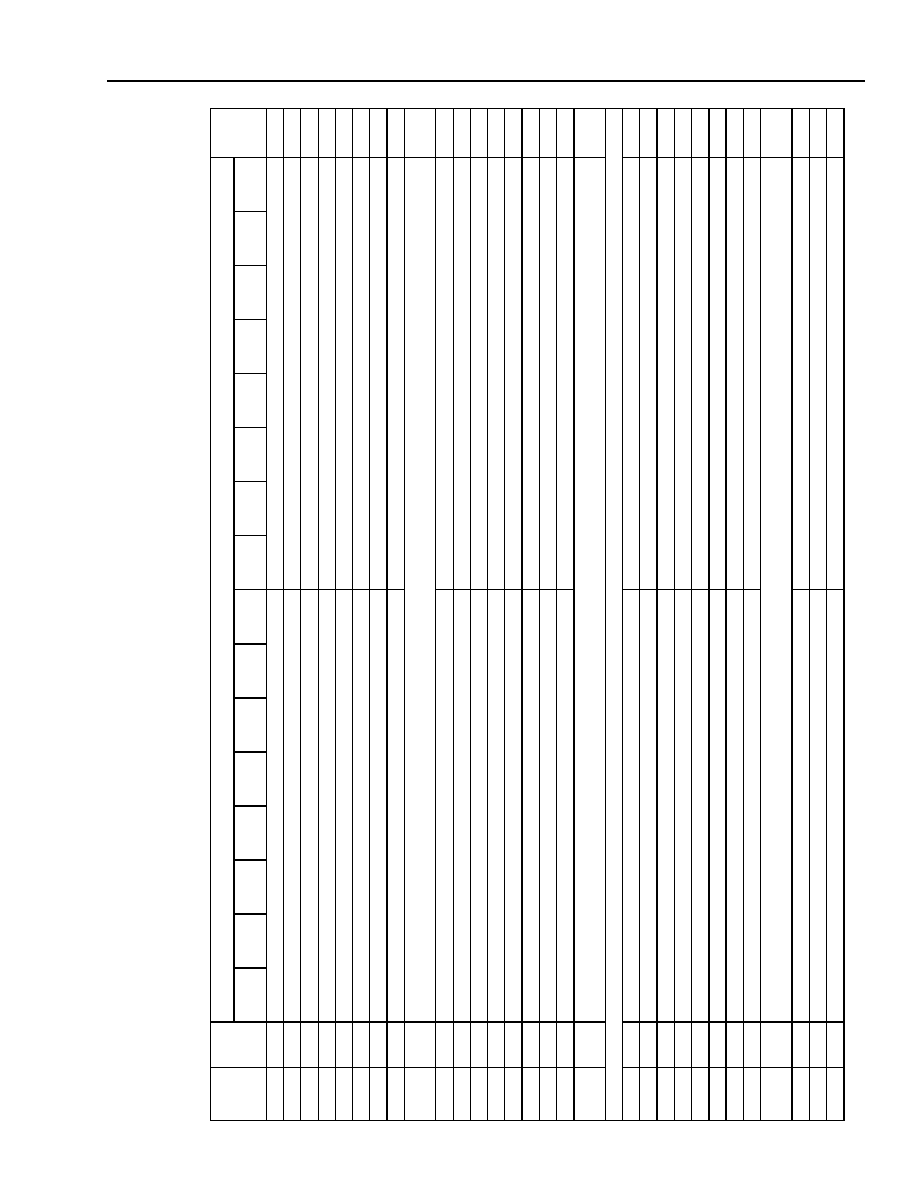

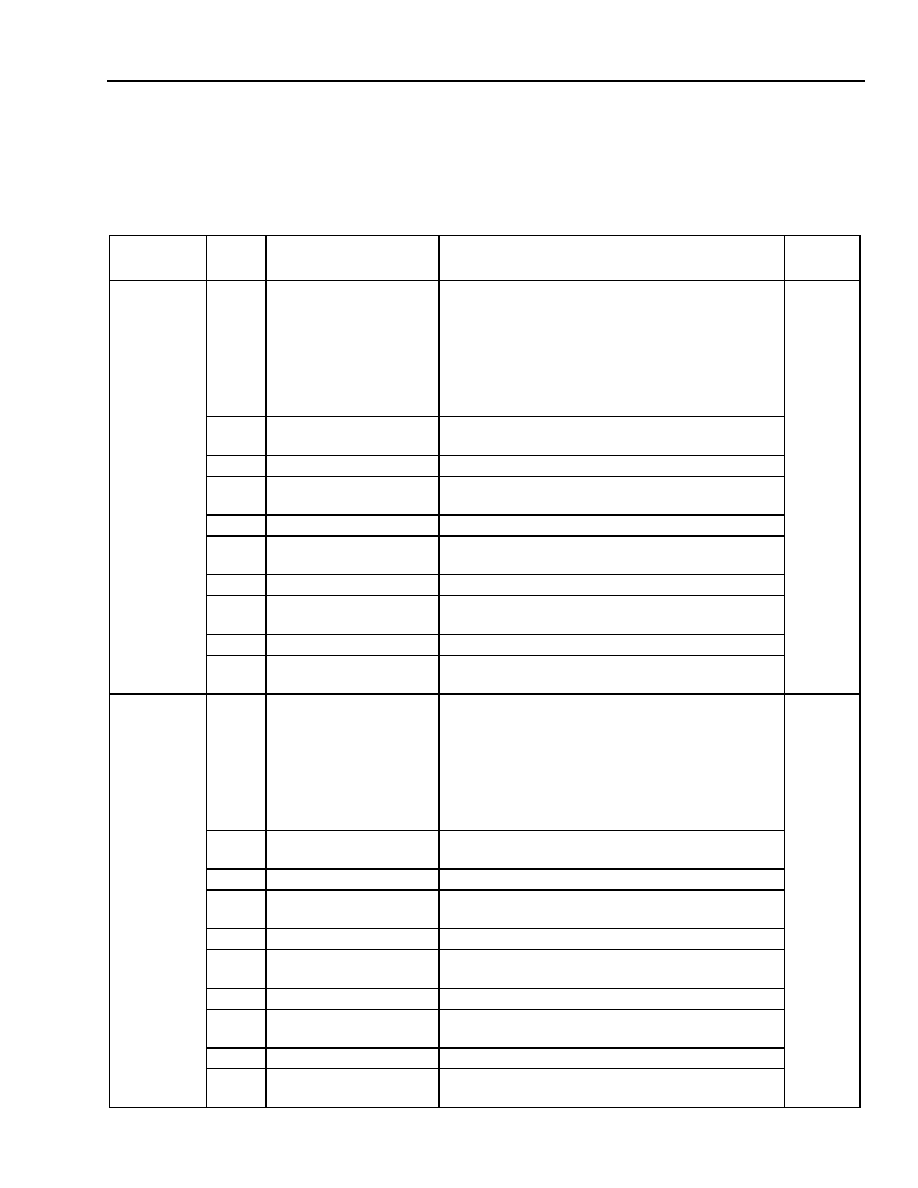

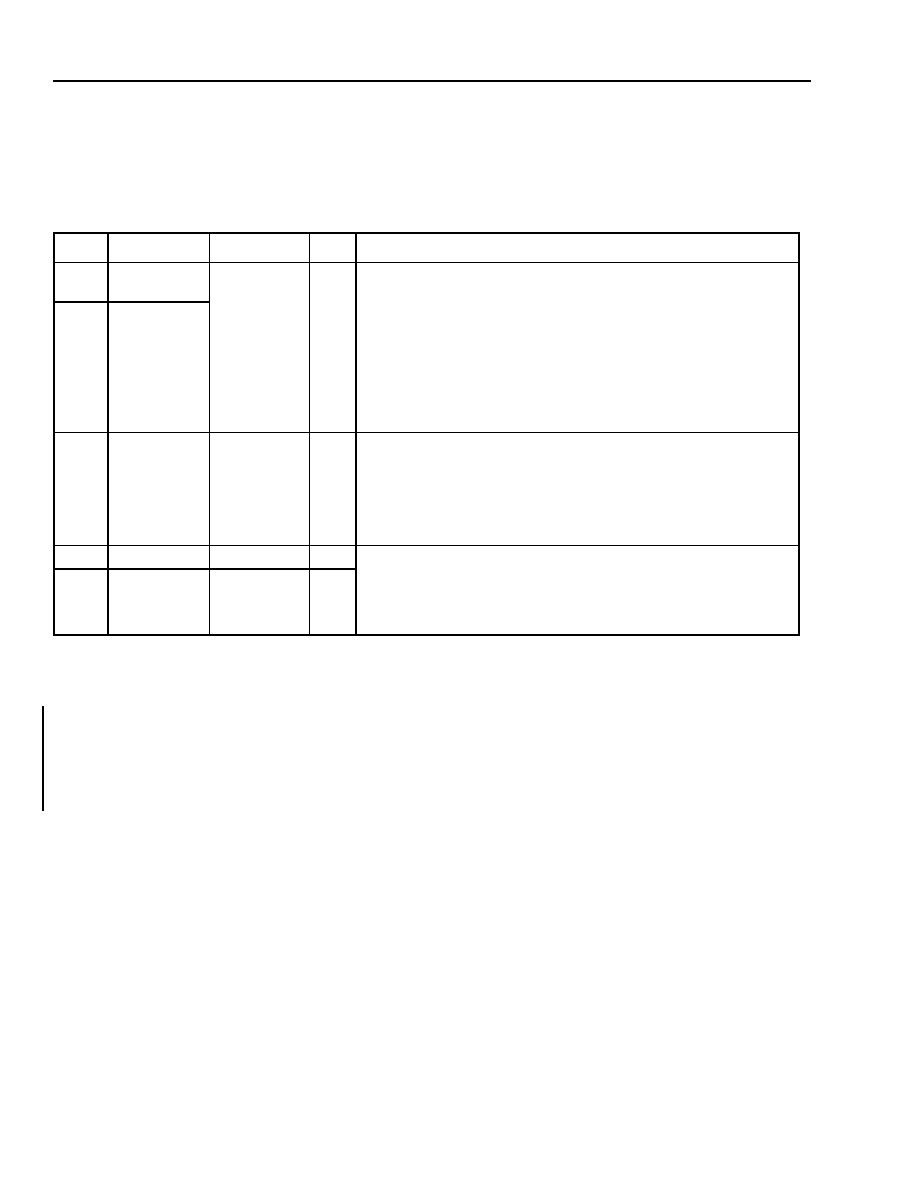

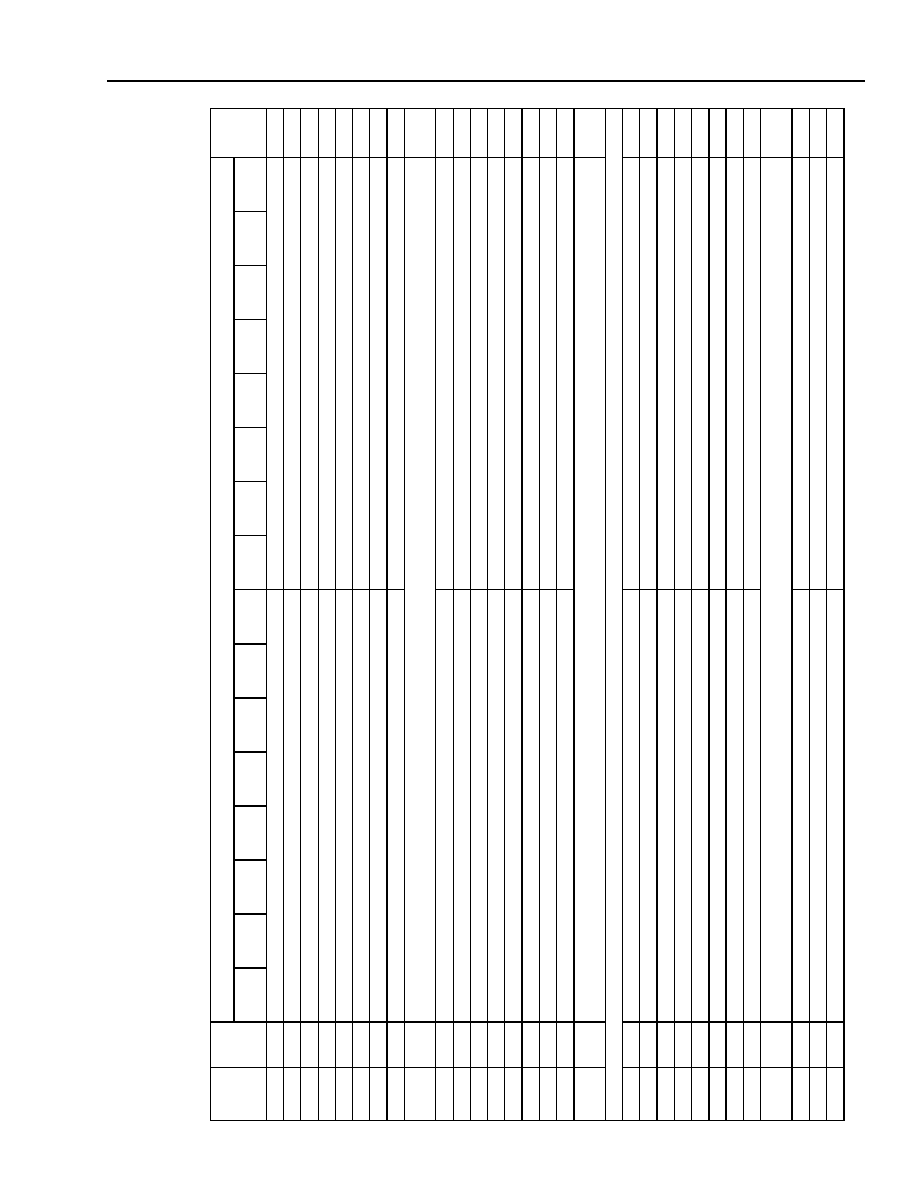

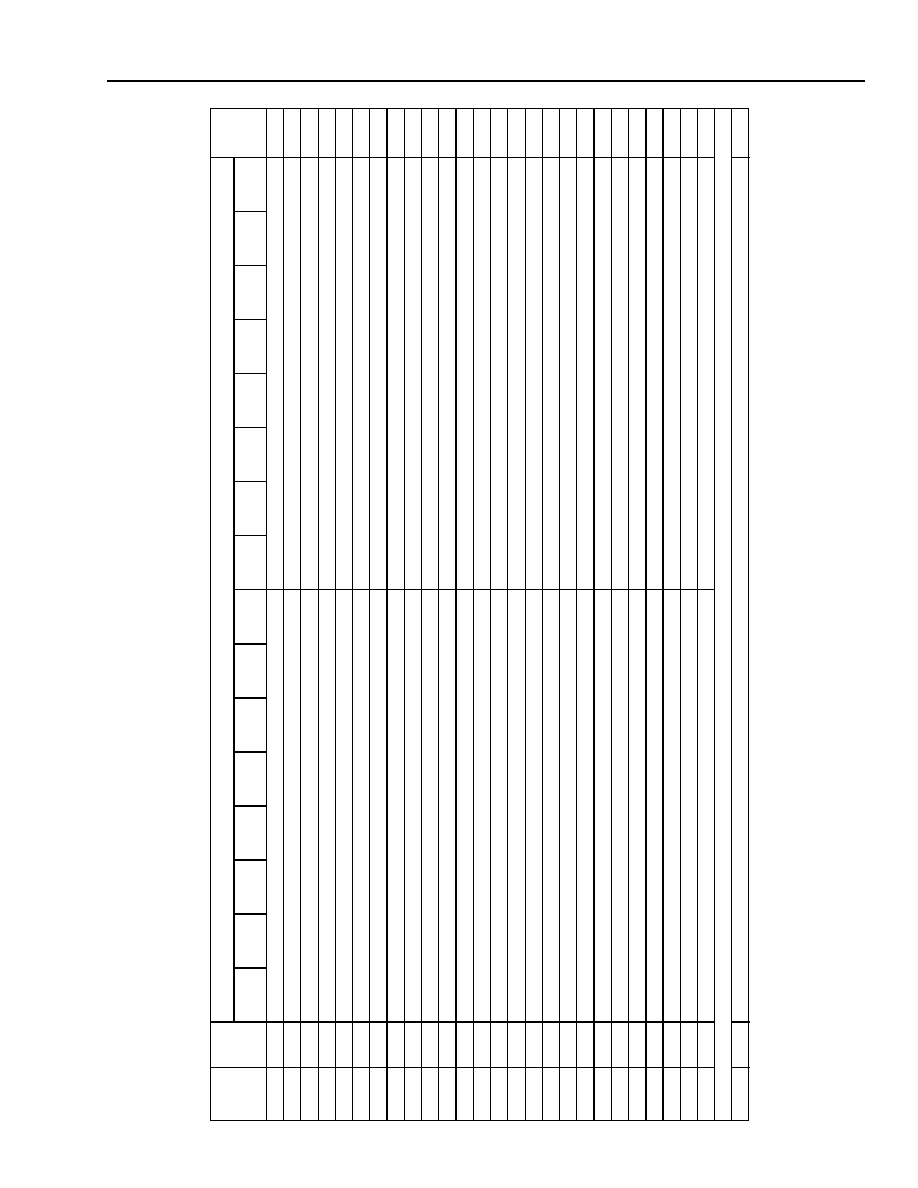

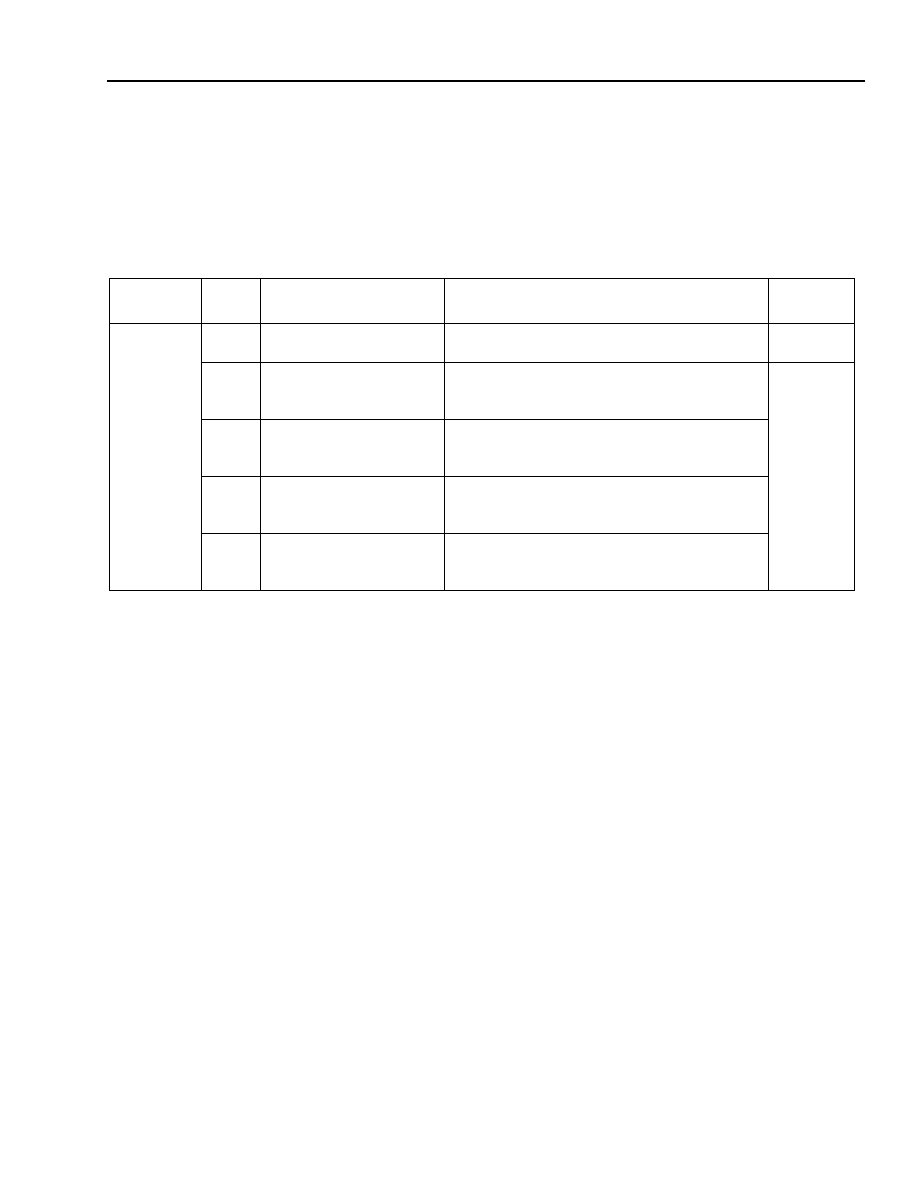

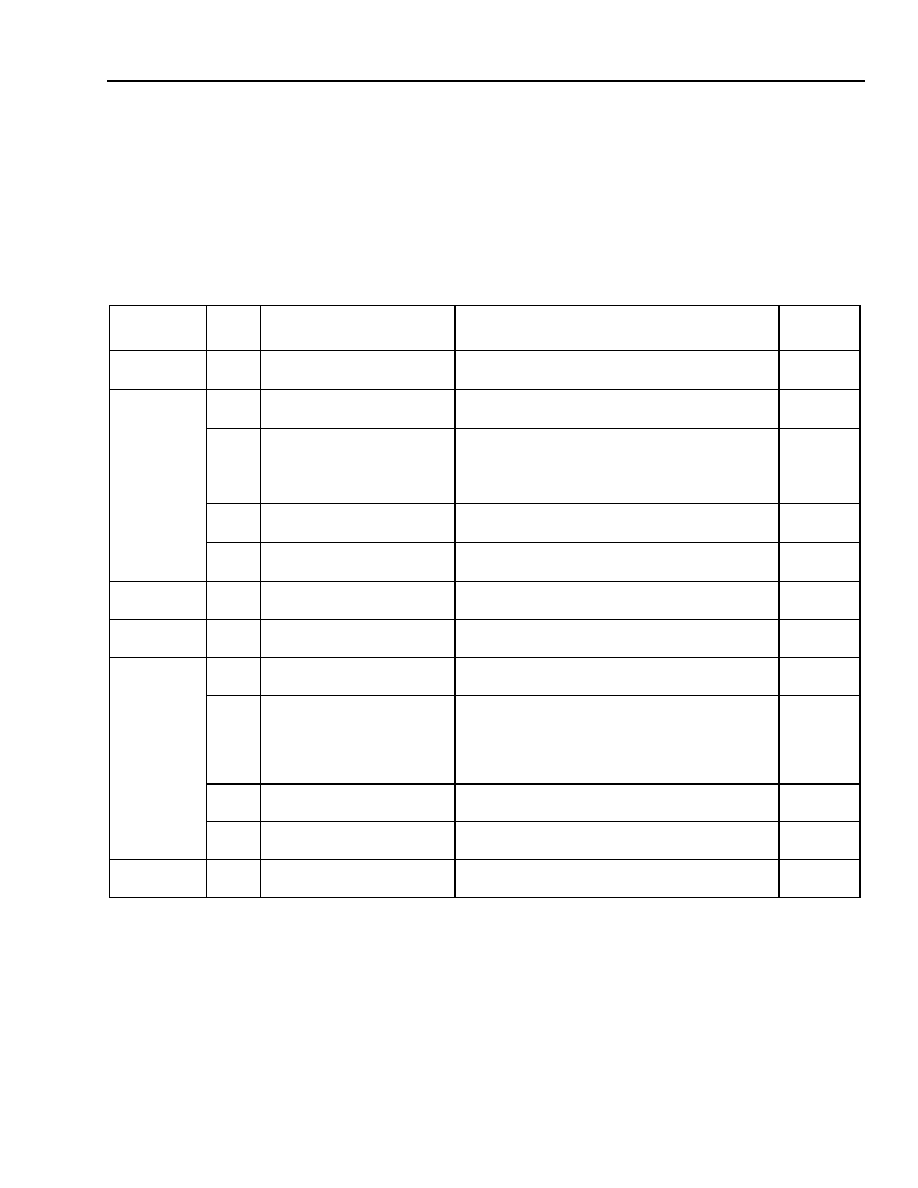

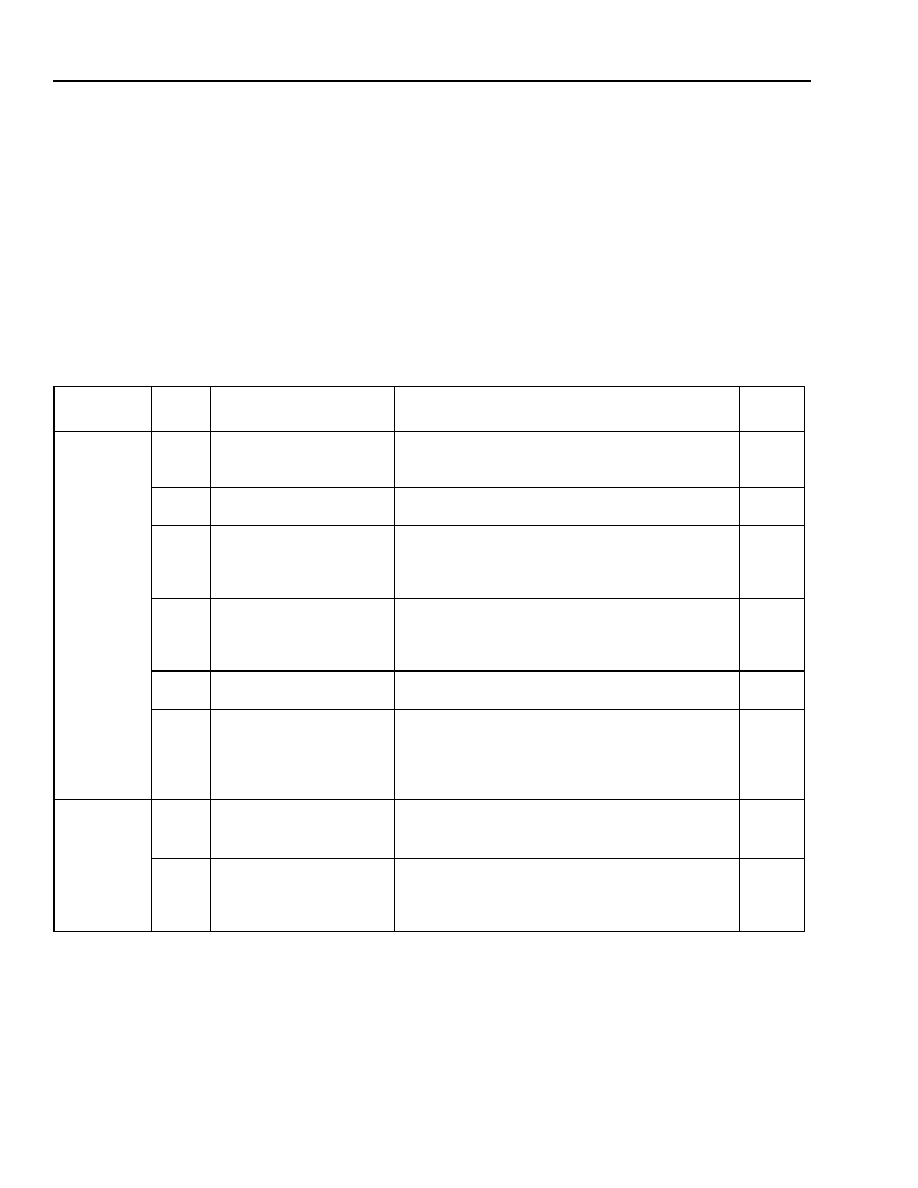

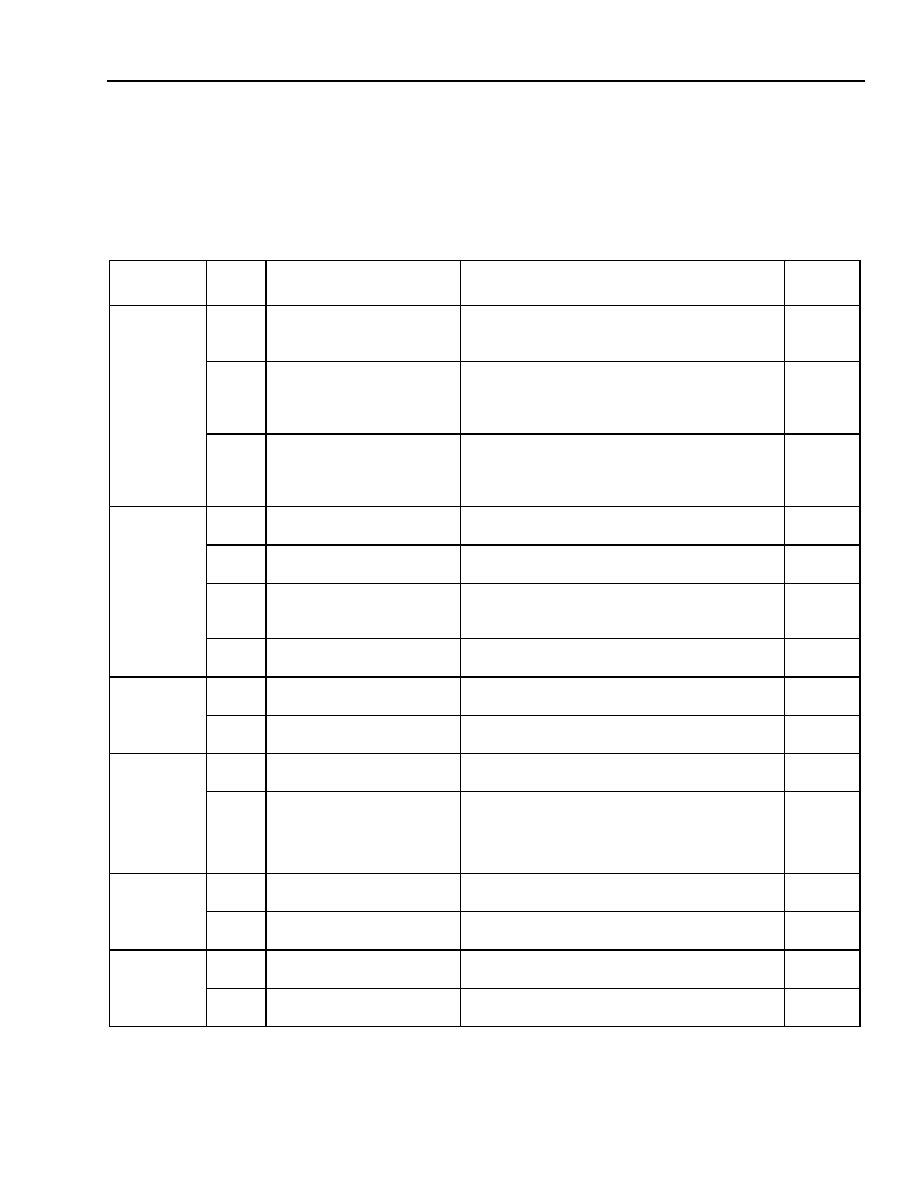

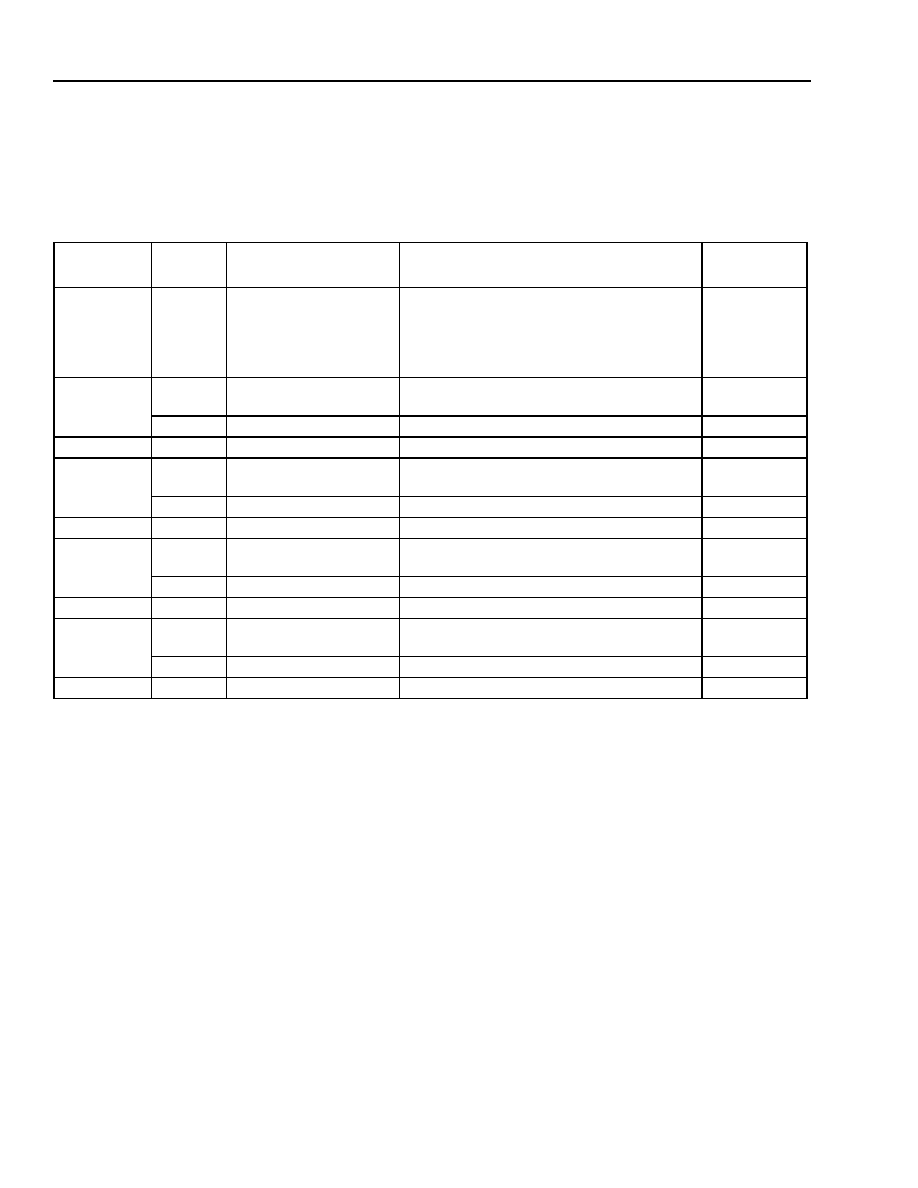

Table 1. COR/W Settings of Register 0x0010, Bit 6

Workaround

This is informational only. No workaround is available for this condition.

Corrective Action

This condition will be described in revision 4 of the advance data sheet.

Line Interface (LI)

LI1. STS-48/STM-16 Mode Lacks Facility Loopback

There is no facility loopback function (line input to line output) available in STS-48/STM-16 mode. Facility loopback

is available only in STS-12/STM-4 and STS-3/STM-1 modes as described in the advance data sheet.

Workaround

This function is not a feature of TDAT042G5.

Corrective Action

No corrective action is required for this condition.

Bit 6

Mode

Bit Clear Behavior of Accessed Registers

1

COR

After COR has been set (address 0x0010, bit 6 = 1), all registers that are accessed

are cleared when read.

0

COW

After COW has been set (address 0x0010, bit 6 = 0), a 1 must be written to a given bit

in a given register to clear that bit. Writing a 0 to a bit in a given register does not clear

that bit.

Agere Systems Inc.

5

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Path Terminator (PT)

PT1. Signal Degrade (SD) and Signal Fail (SF) Bit Behavior

Receive signal degrade and receive signal fail bits in the PT state registers (addresses 0x0838, 0x088A, 0x08DC,

and 0x092E, bits [1:0]) do not function as described. Until the signal degrade (SD) and signal fail (SF) thresholds

are programmed, the SD and SF bits will toggle on a frame-by-frame basis.

Workaround

Program thresholds during system software initialization.

Corrective Action

This functionality will be retained in its current state in future versions of the device. The advance data sheet will be

corrected to reflect the actual function of the registers.

PT2. Clear-After-Write Behavior of Signal Degrade Clear Bits

Signal degrade clear (bits 15--12) of the PT one-shot control parameters register (address 0x0AA4) are described

as one-shot, clear-after-write bits. Writing these bits should automatically set and then clear the bits. This one-shot

behavior is not observed.

Workaround

The bits must be set to 1 and then explicitly set to 0 to clear these signal degrade bits.

Corrective Action

This functionality will be retained in its current state in future versions of the device. The advance data sheet will be

corrected to reflect the actual function of the registers.

6

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Path Terminator (PT)

(continued)

PT3. Remote Defect Indicator (RDI) Behavior

The SONET standards require that when an RDI changes value, it should hold the value for a minimum of

20 frames. This applies to a no error state, which should be maintained for at least 20 consecutive frames.

However, it is also intended by the SONET standard that the occurrence of an error state should be reported

immediately.

TDAT042G5 responds to error conditions within 100 ms (ANSI

*

T1.105 which states only that RDI-L must be gen-

erated or removed within 100 ms of detecting or terminating an incoming defect), in which case the two require-

ments become functionally the same.

Single-bit and enhanced RDI behave differently under the following conditions:

I

Transition from error state to no error state.

I

While in the error state, a subsequent error occurs.

The single-bit error RDI does not hold the no error state for 20 frames. However, the enhanced RDI does hold the

no error state for 20 consecutive frames.

Workaround

No workaround is available for this condition.

Corrective Action

The enhanced RDI indicator in future versions of the device will behave the same as the single-bit error indicator.

PT4. SS Pointer Interpretation Algorithm

The SDH standards do not require that the SS bits are set to binary 10 for SDH equipment. The SS bit values are

not used in determining a valid pointer value. Because of this, the SS pointer interpretation algorithm is not imple-

mented in the device. Bit 5 (RSSPTRNORM[A--D]) of PT control registers 0x0AA6, 0xAAE, 0x0AB6, and 0x0ABE

is not used. Bits 1 and 0 (RSSEXP[1:0]) of PT provisioning register 0x0AC7 are not used.

Workaround

No workaround is available for this condition.

Corrective Action

These bits will be removed from the PT registers in future revisions of the advance data sheet.

* ANSI is a registered trademark of American National Standards Institute, Inc.

Agere Systems Inc.

7

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Path Terminator (PT)

(continued)

PT5. Delta/Event Registers in COR Mode

Because there is a one-cycle delay before the PT delta event registers (0x802, 0x080F, 0x081C, 0x0829) are

cleared after being read in COR mode, new interrupts may be lost.

Workaround

No workaround is available for this condition.

Corrective Action

This condition will be addressed in future versions of the device.

Data Engine (DE)

DE1. SDL Mode--Header Error Correction in LSB

In SDL mode, the header error correction process is susceptible to single-bit errors in the least significant bit (LSB)

of the special payload.

Workaround

No workaround is available for this condition.

Corrective Action

This condition will be addressed in future versions of the device.

DE2. Incorrect ATM Loss of Cell Delineation (LCD) Implementation

Currently, the LCD is implemented in the same way that out of cell delineation (OCD) is implemented. This is not in

accordance with the ITU-TI.432-2 February 1999 standard.

Workaround

No workaround is available for this condition.

Corrective Action

A software workaround will be available with version 1A of the device.

8

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Data Engine (DE)

(continued)

DE3. ATM Transmit Count of Idle Cells

For ATM mode in the transmit direction, all cells are currently counted, including the idle cells. Only the cells con-

taining data should be counted.

Workaround

No workaround is available for this condition.

Corrective Action

This condition will be addressed in version 1A of the device.

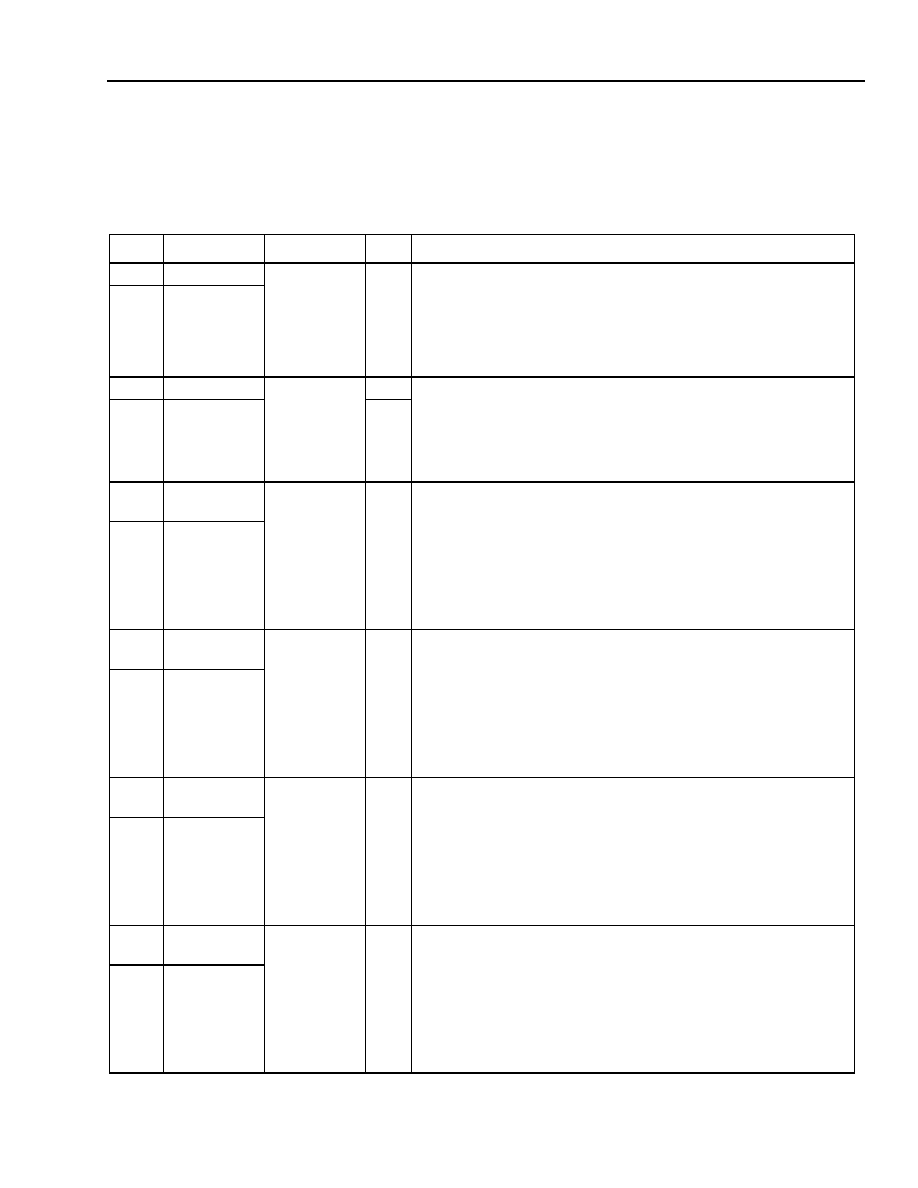

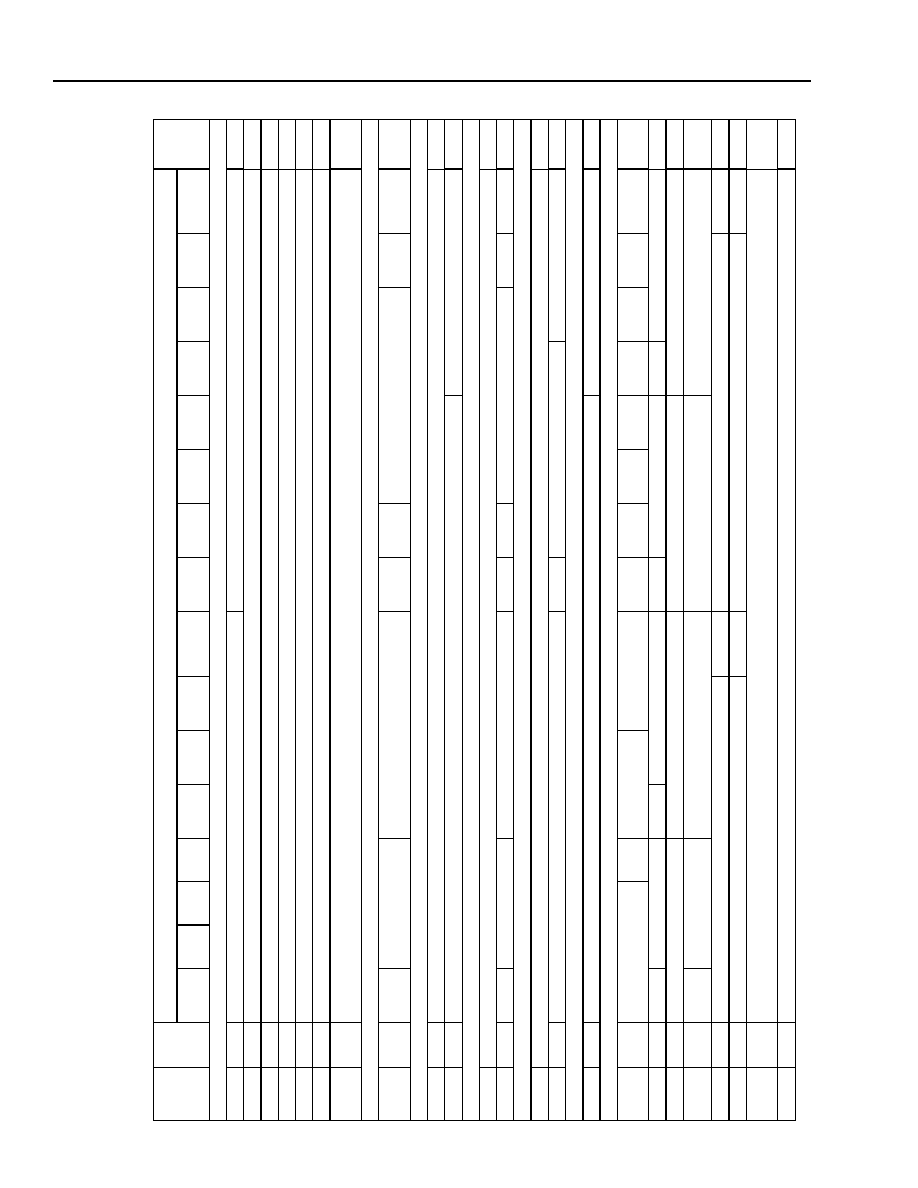

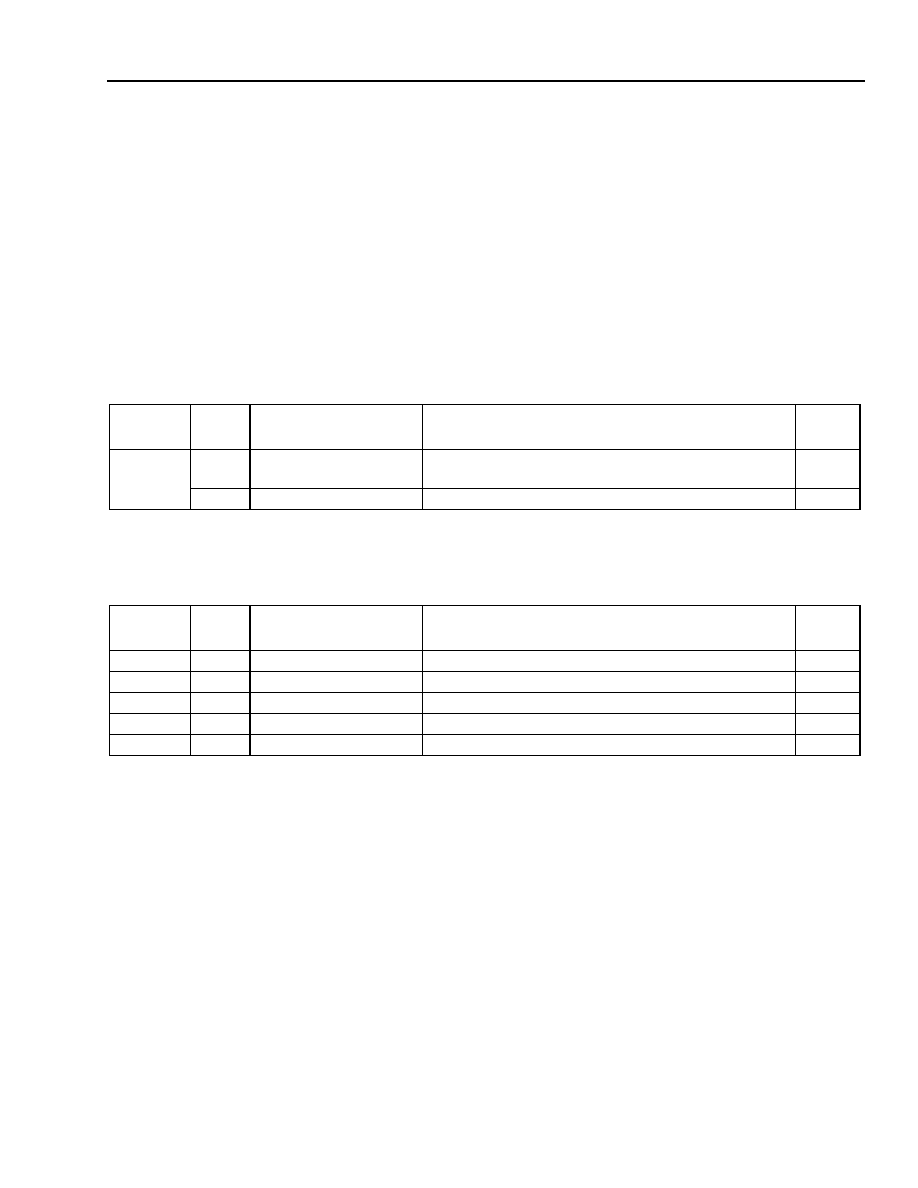

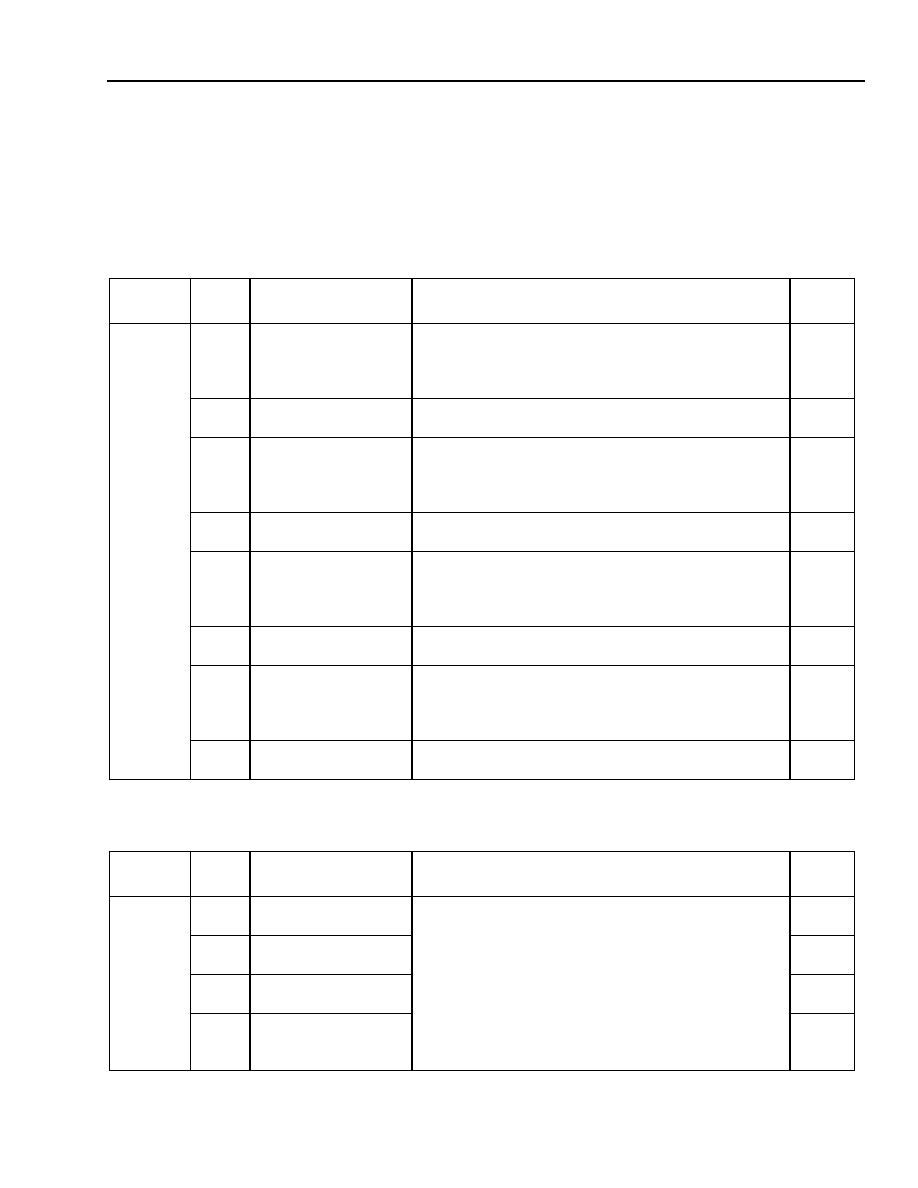

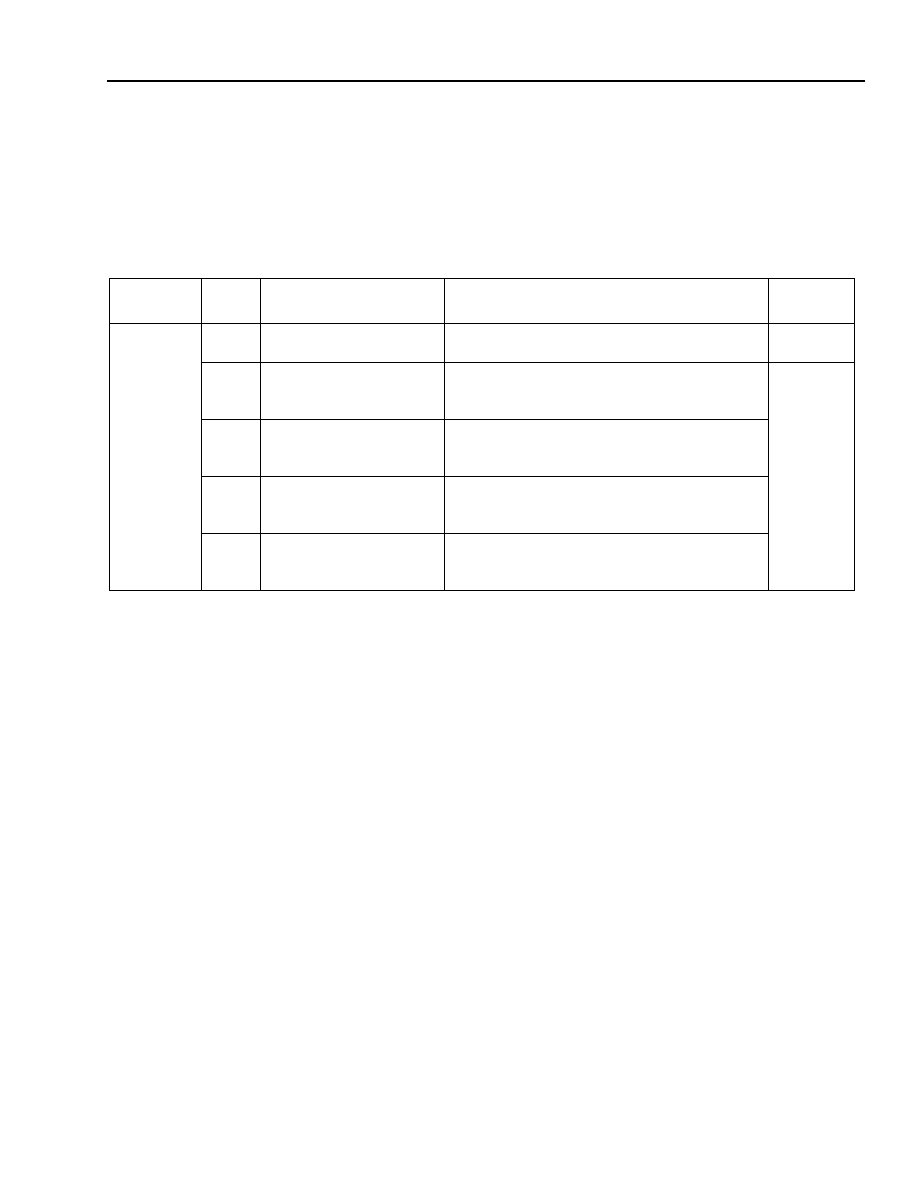

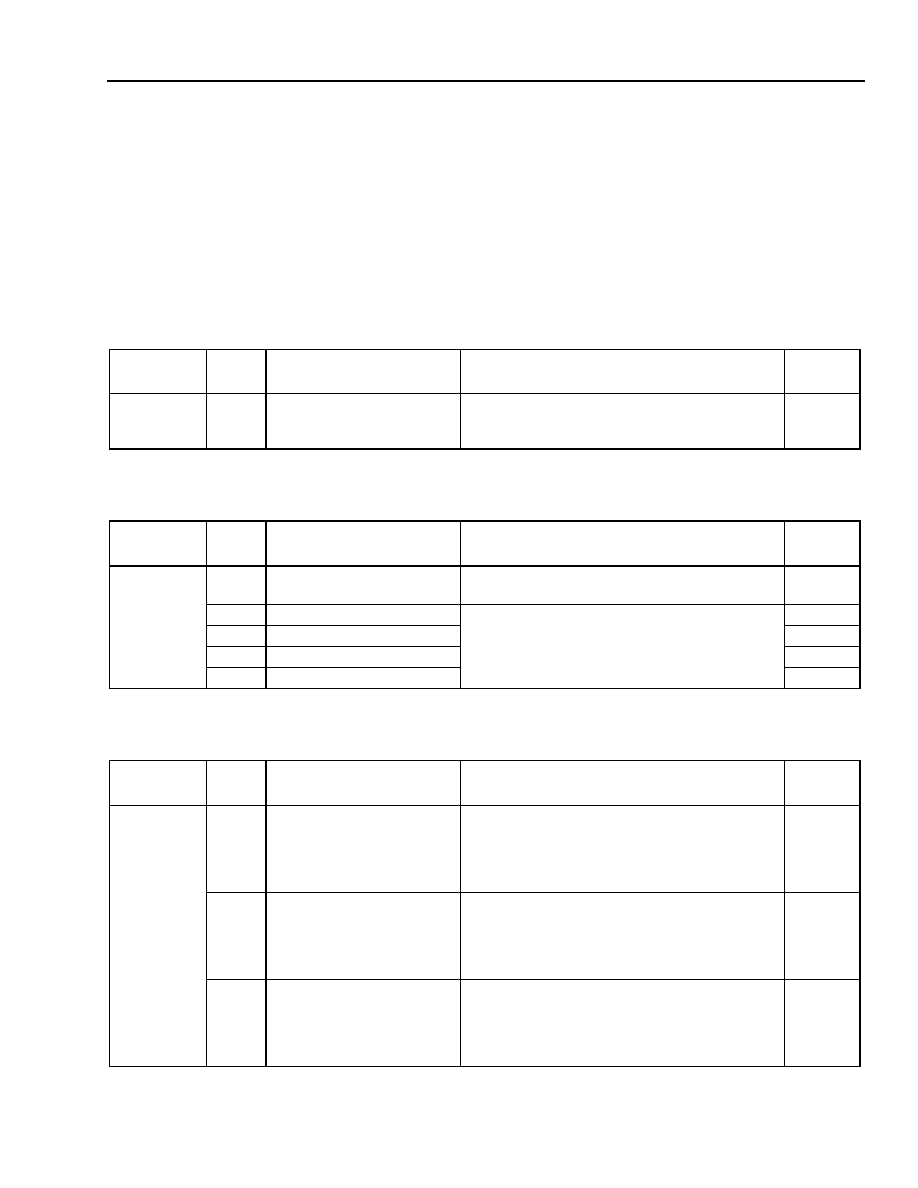

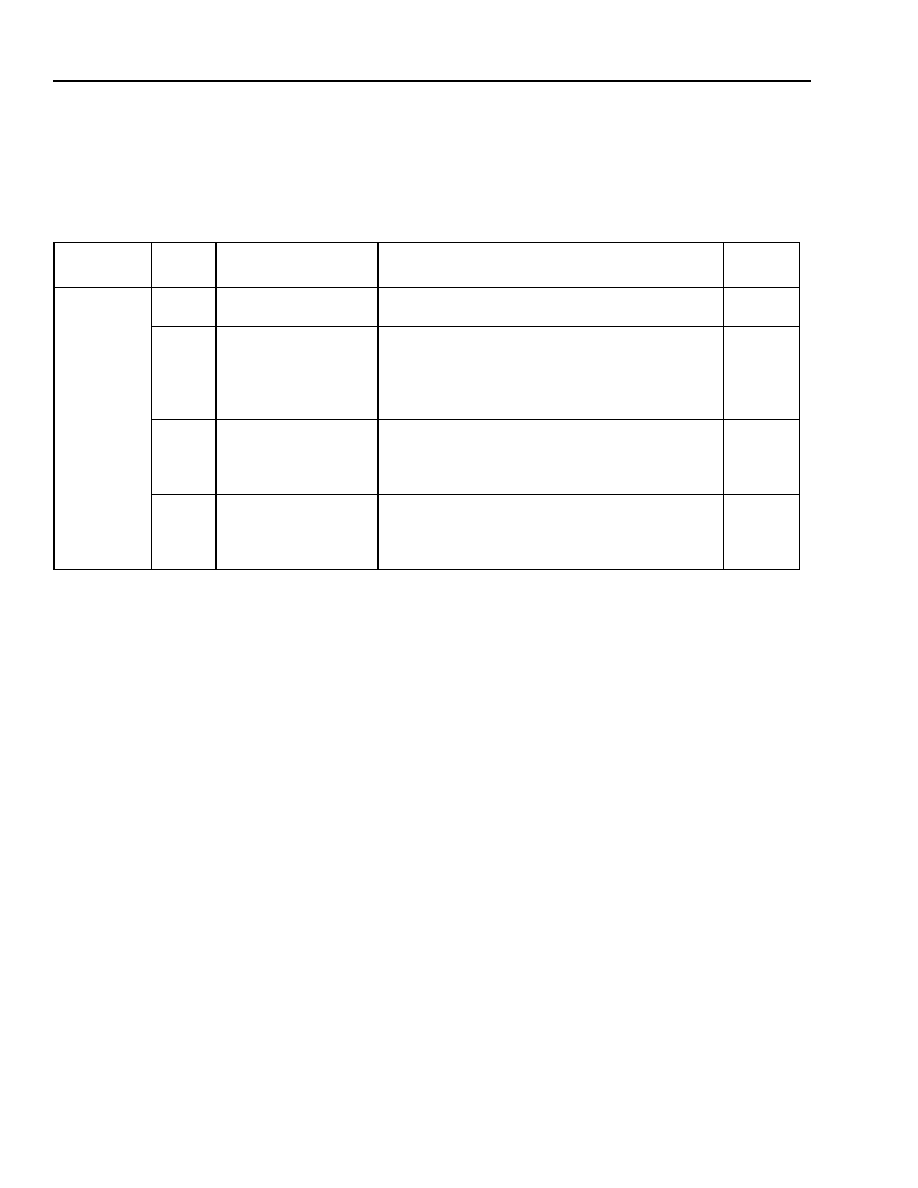

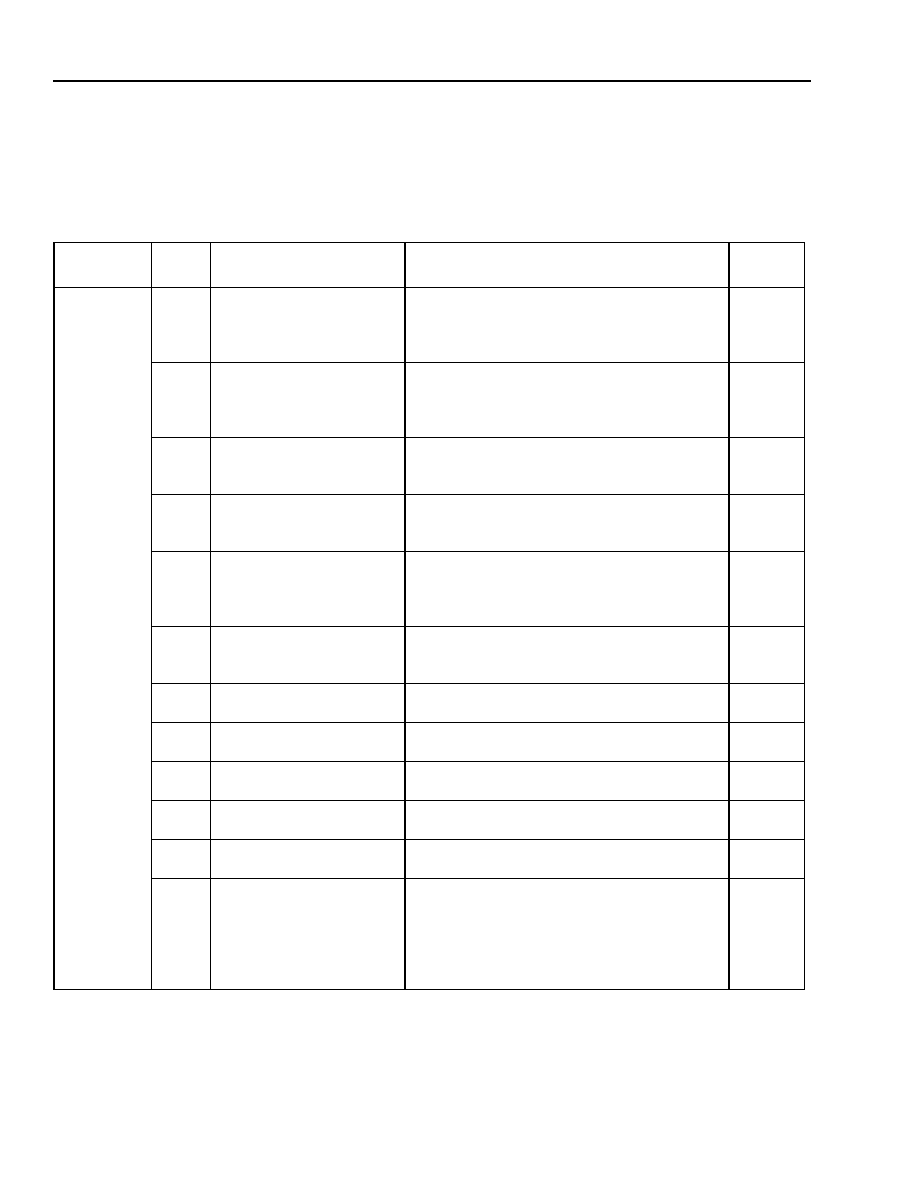

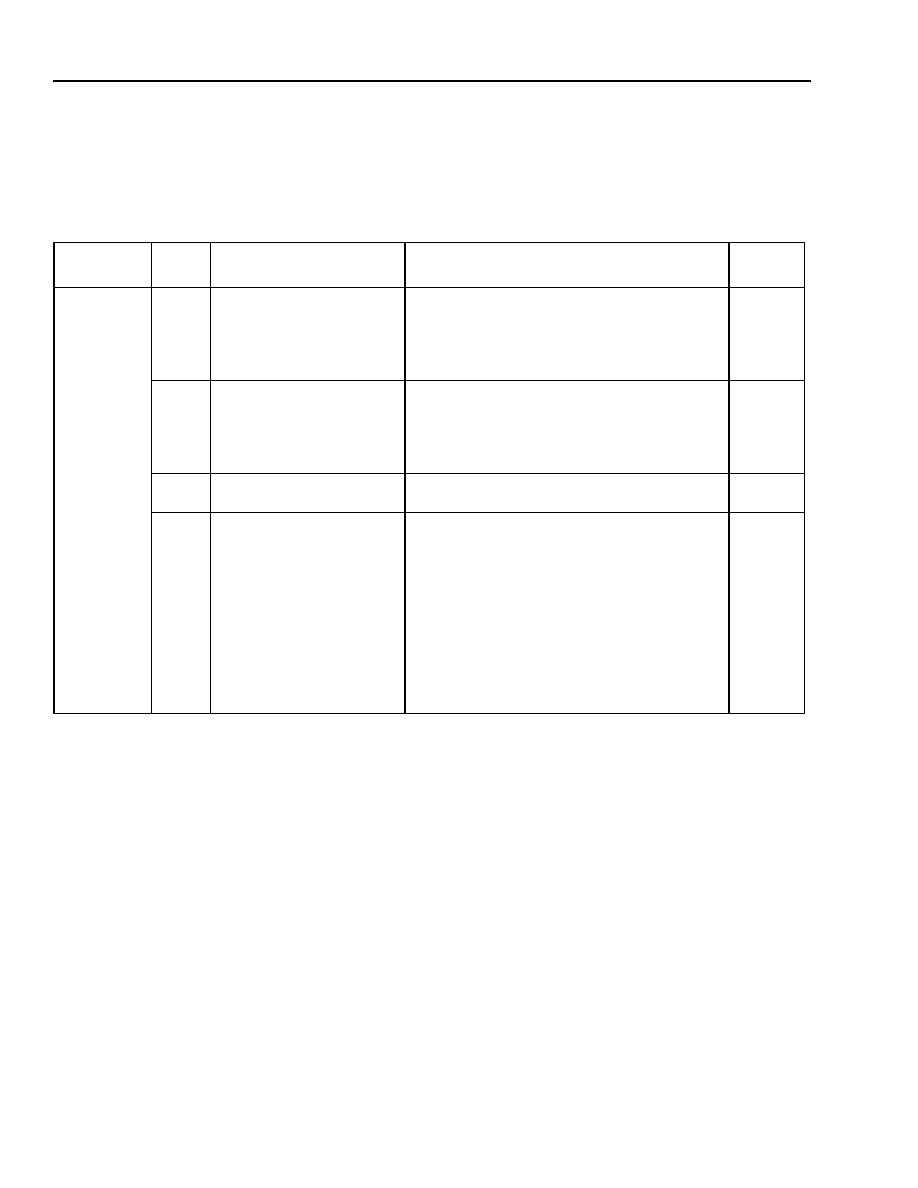

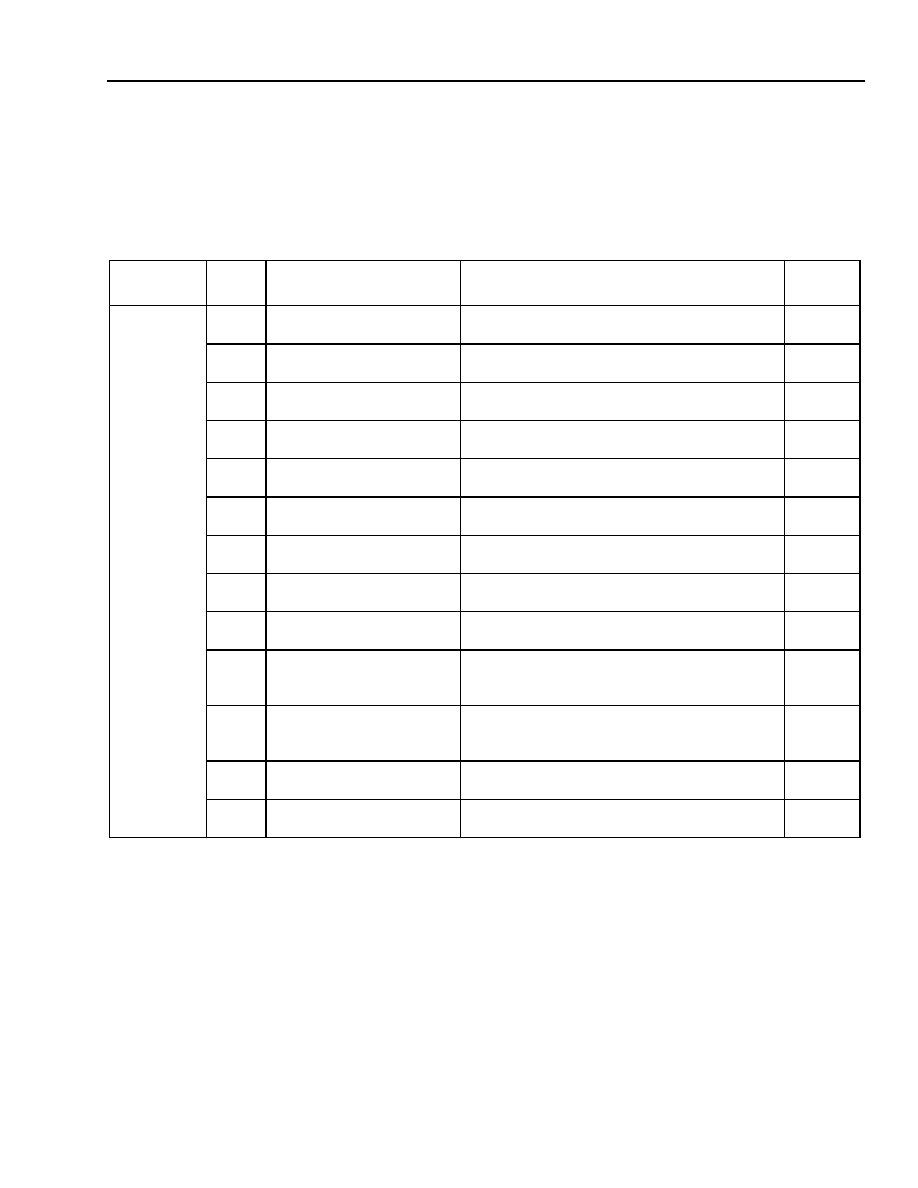

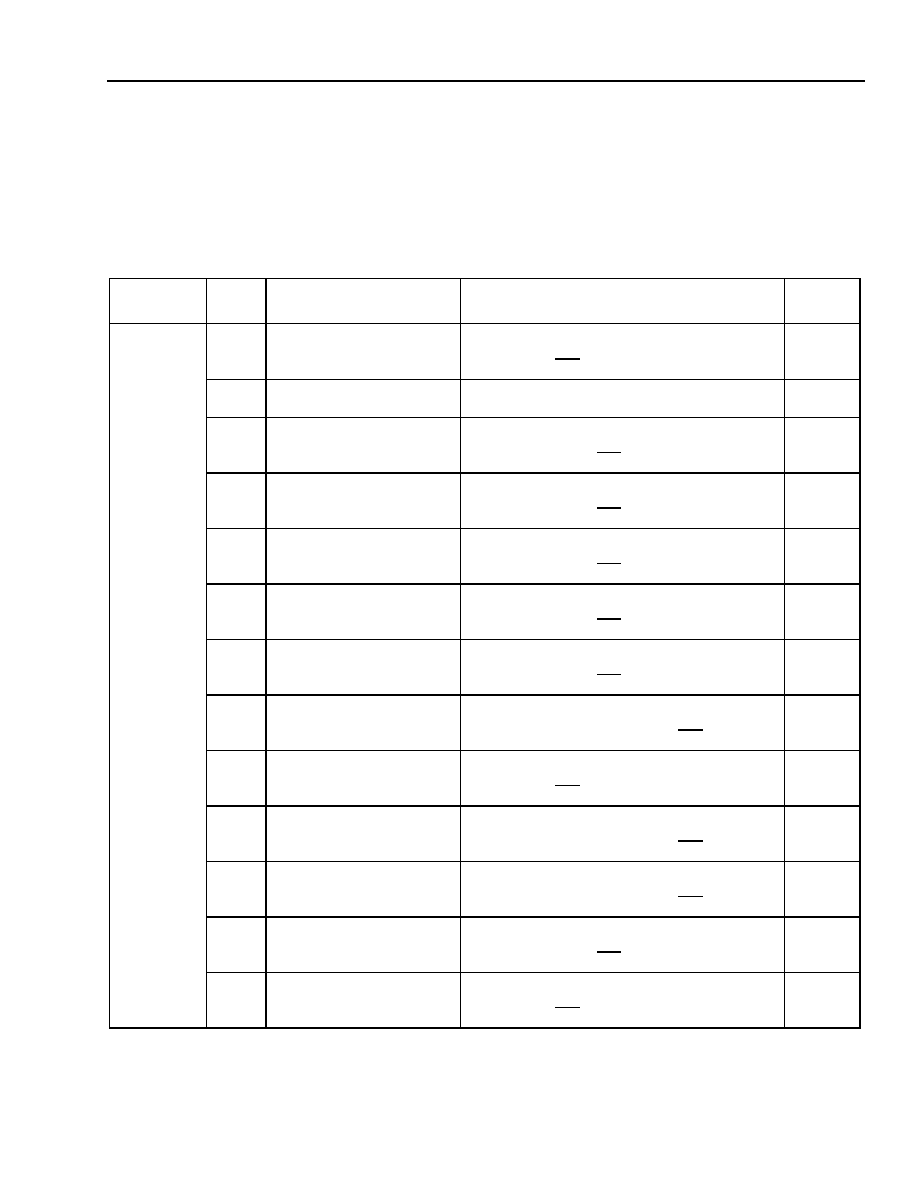

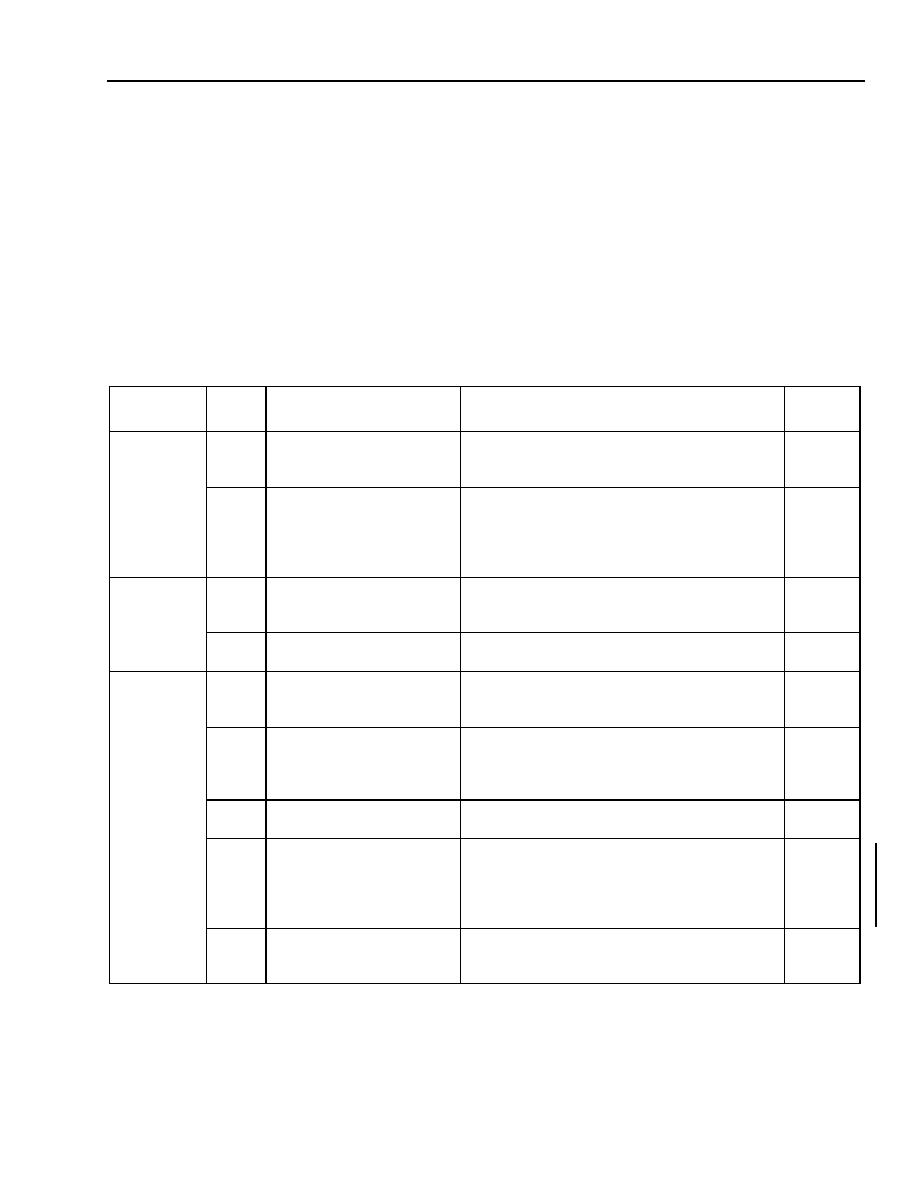

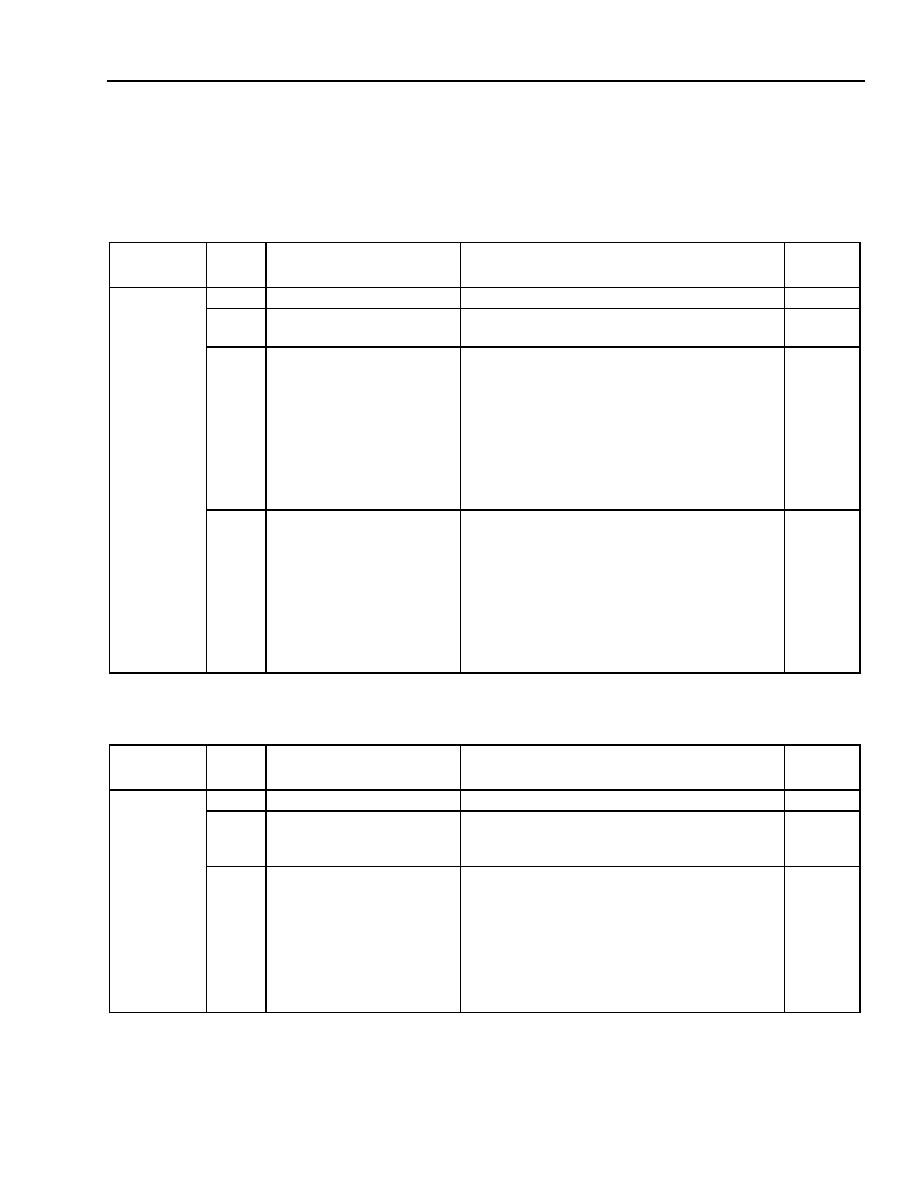

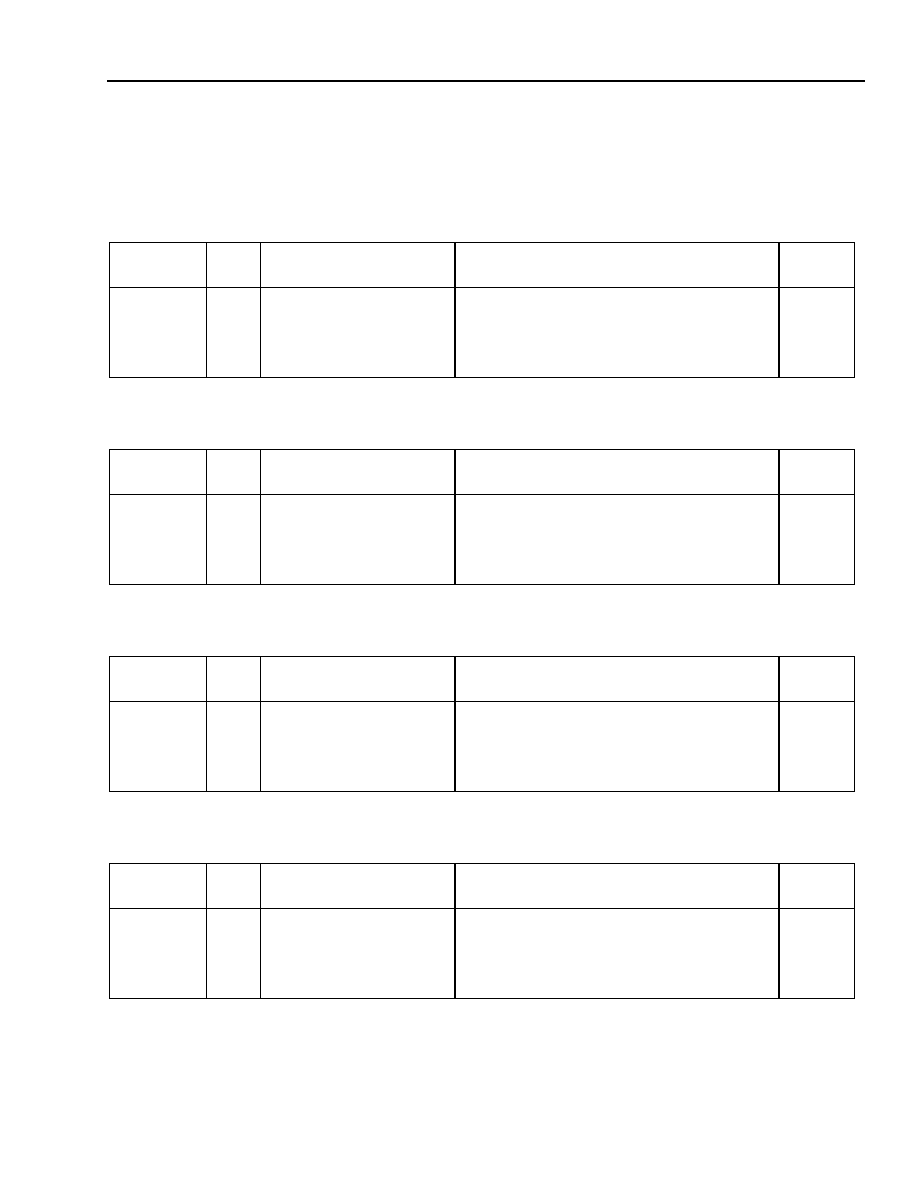

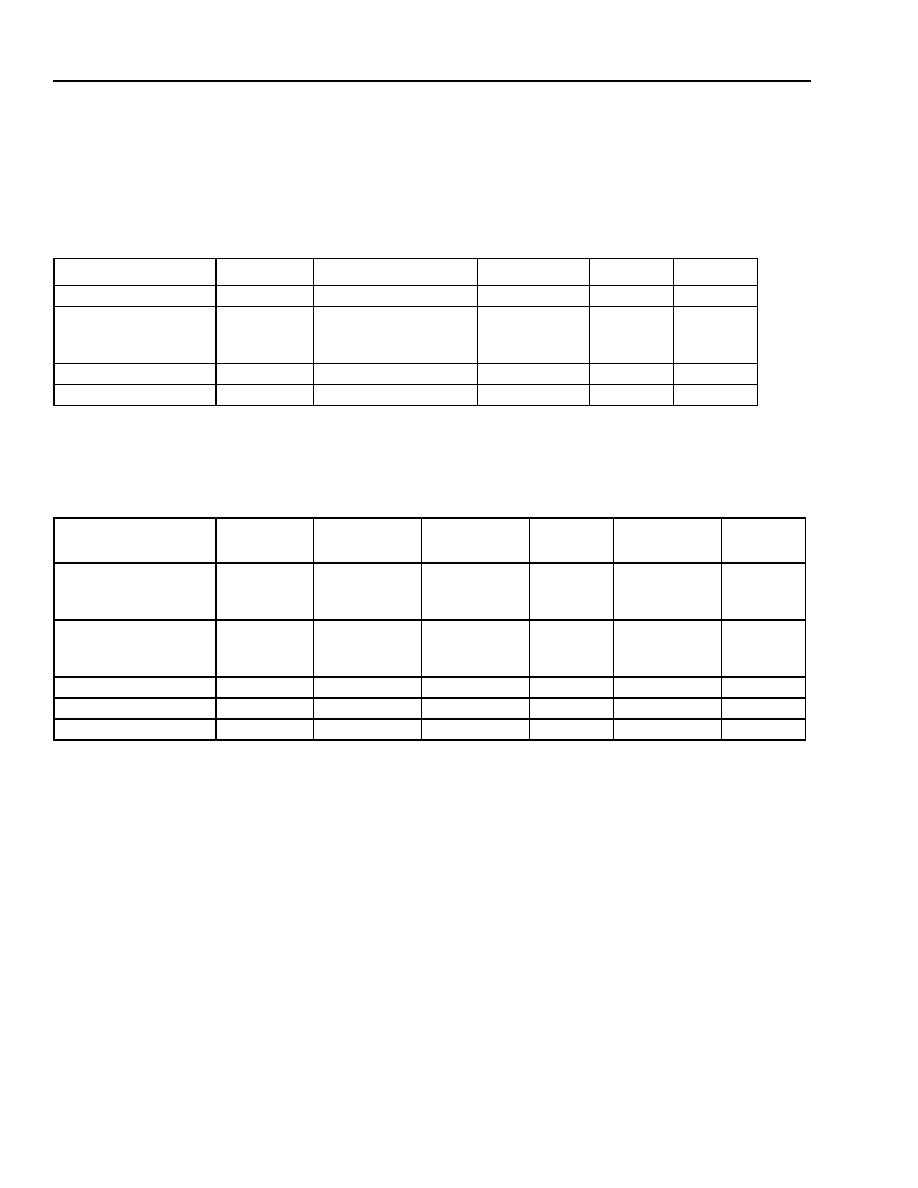

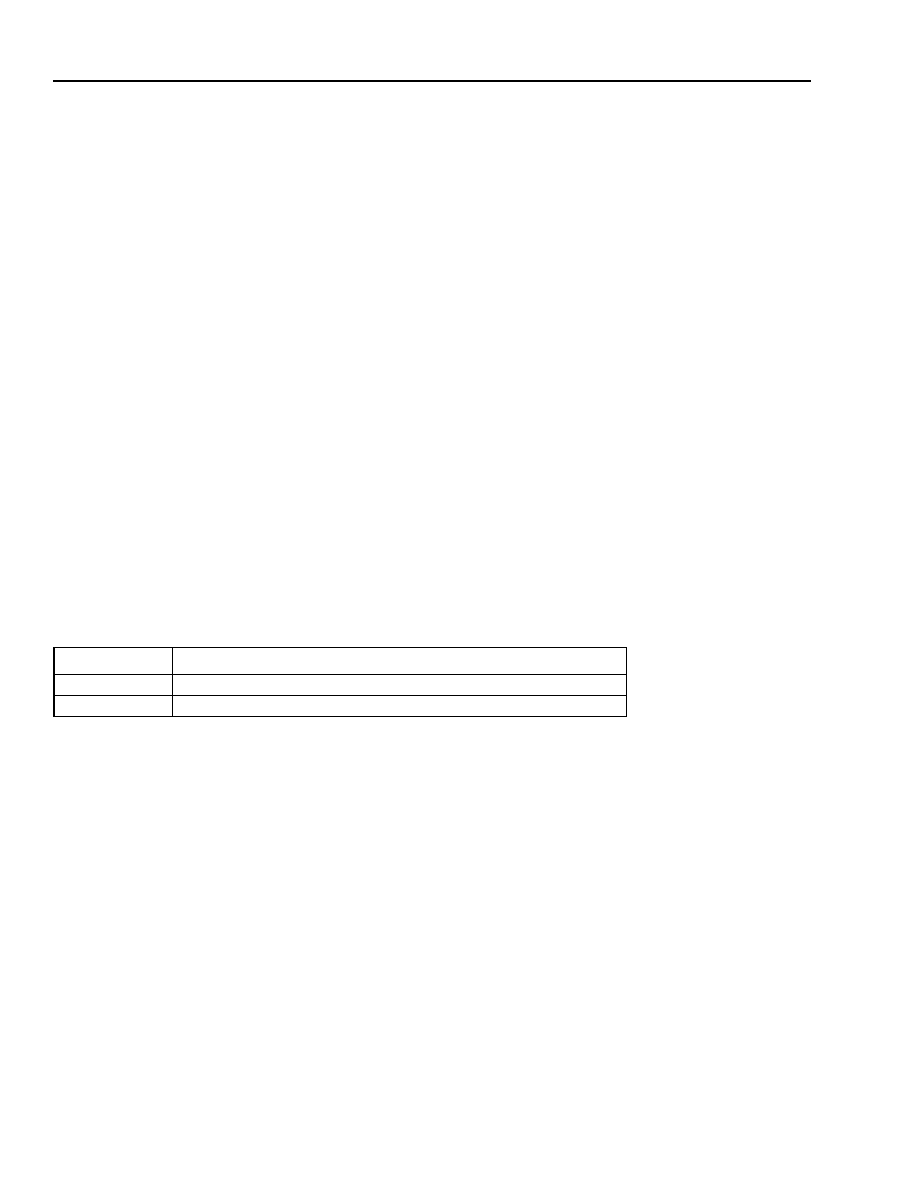

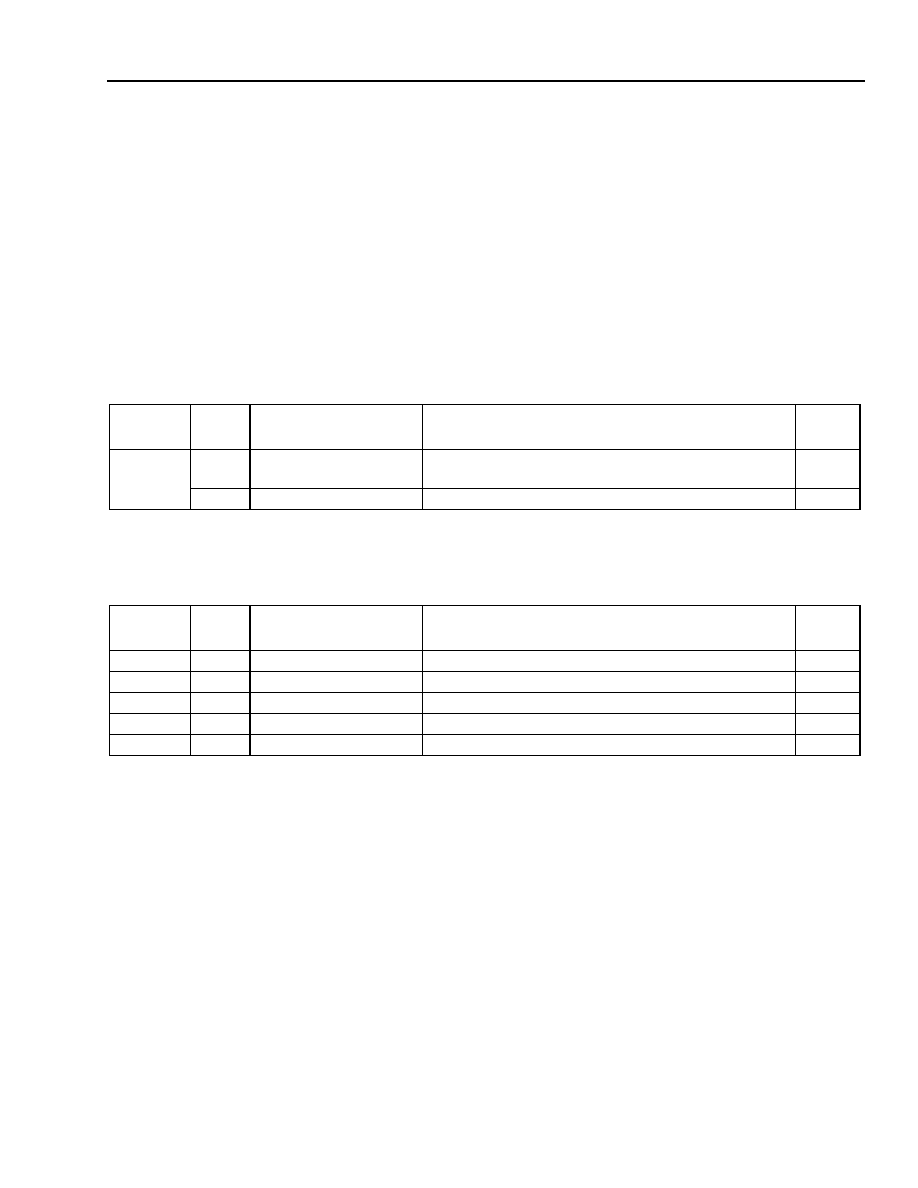

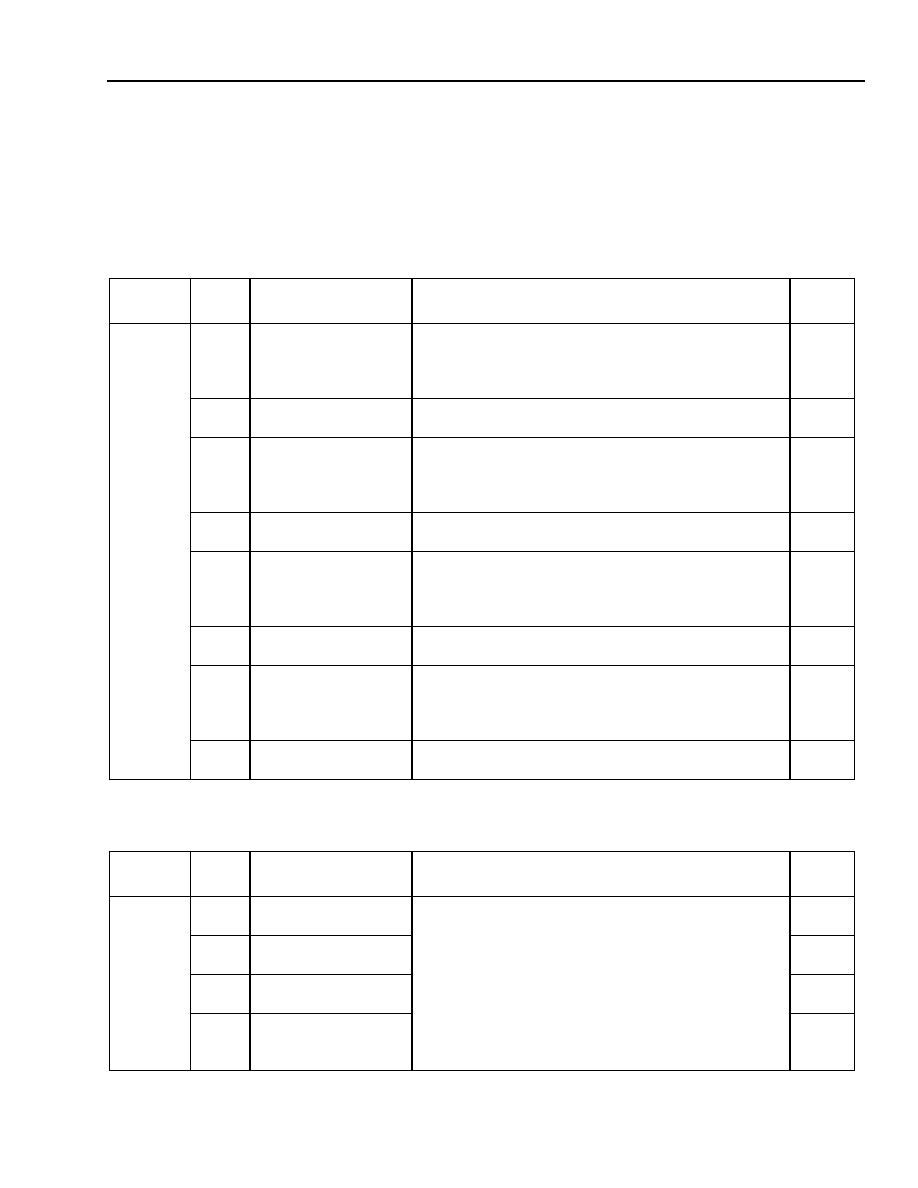

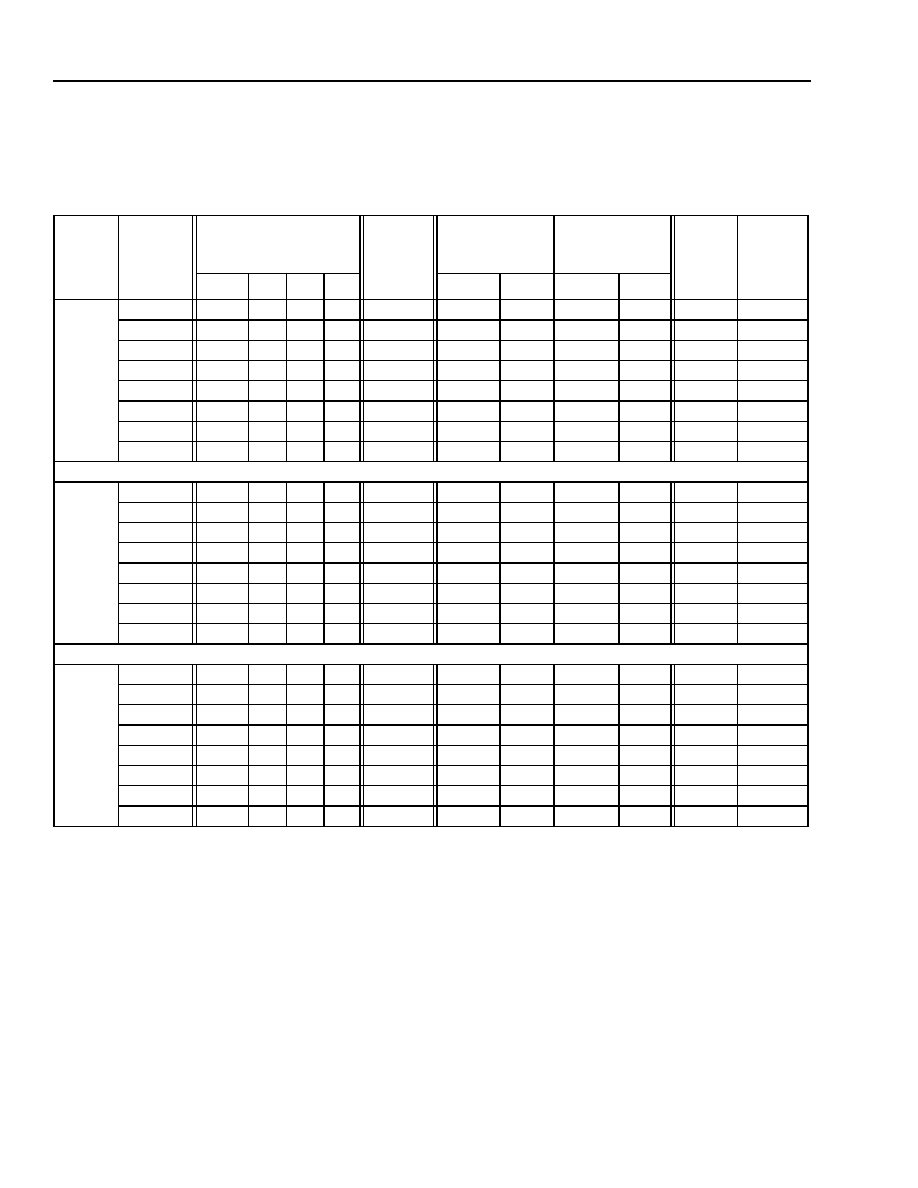

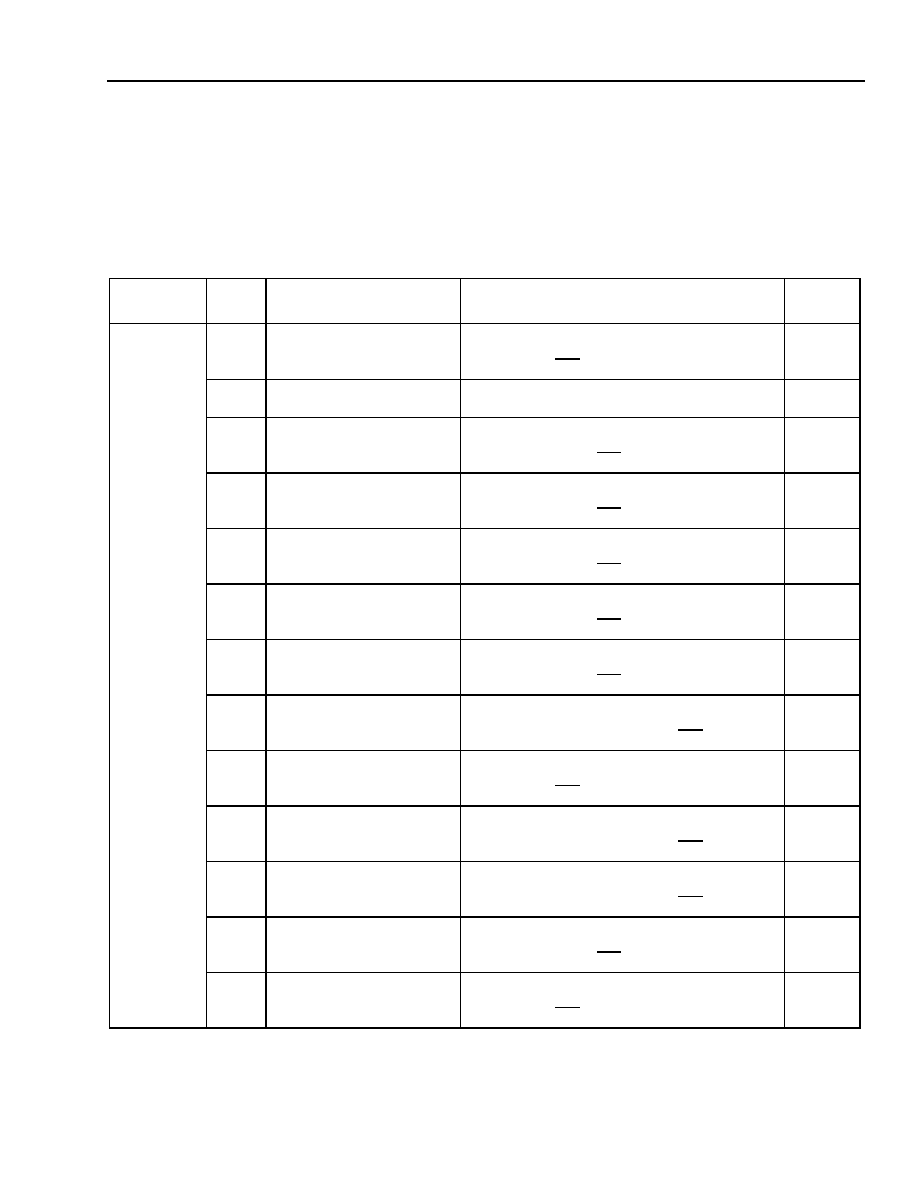

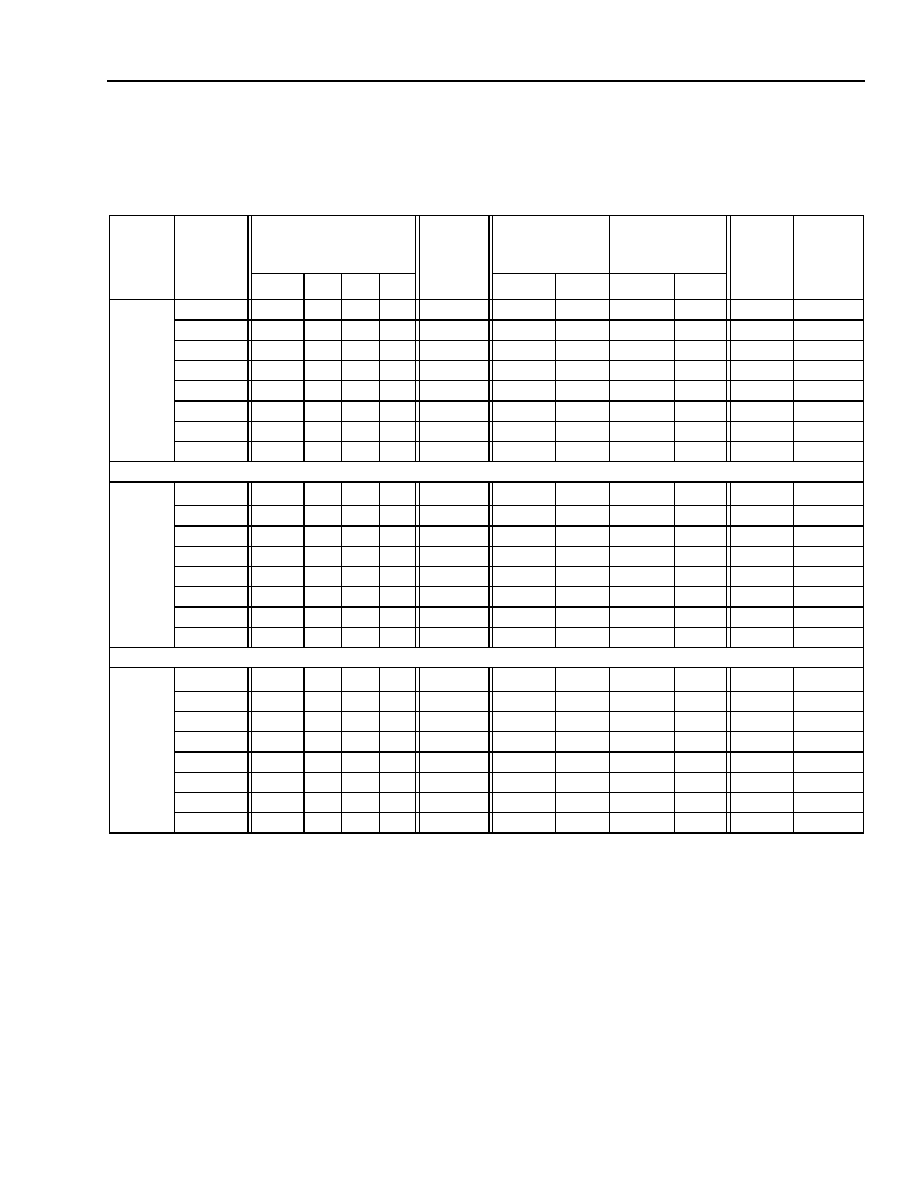

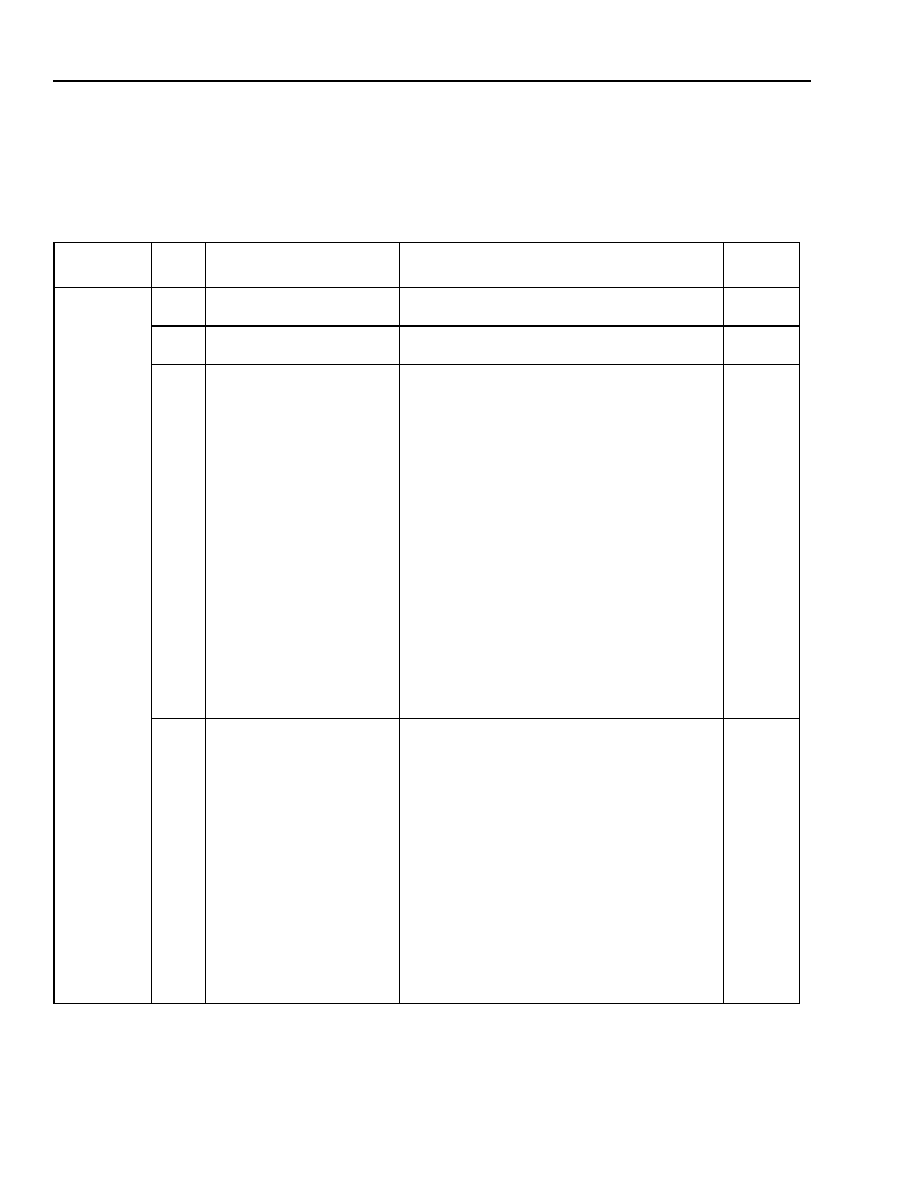

DE4. Channel Provisioning

When using the device in STS-3/STM-1 and STS-12/STM-4 modes with either PPP, CRC, or HDLC, egress config-

uration registers 0x1016, 0x1017, 0x1018, and sequencer cell state register 0x1036 of all four channels must be

provisioned, even if a channel is not being used.

Workaround

Provision all four transmit DE channels. Set DE egress configuration registers and the sequencer cell state register

as shown in Table 2.

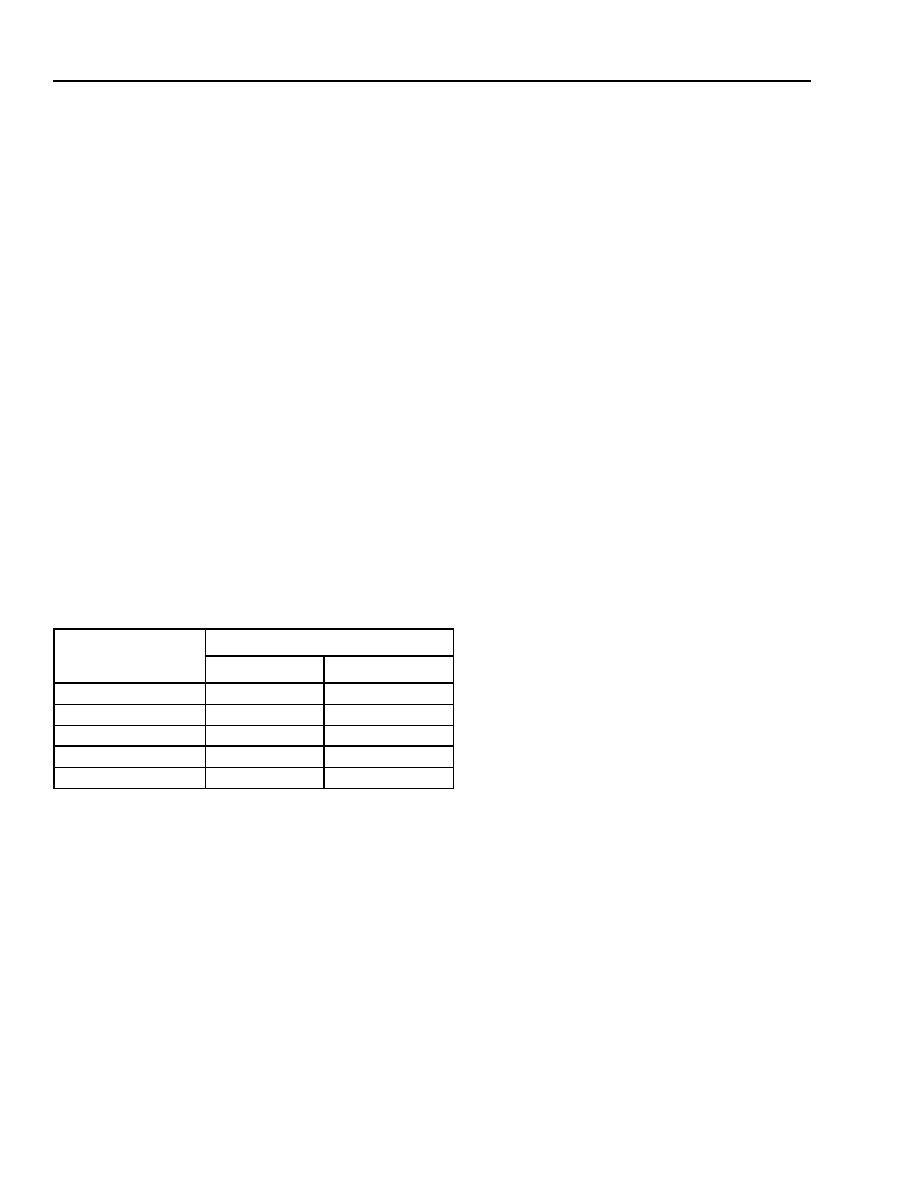

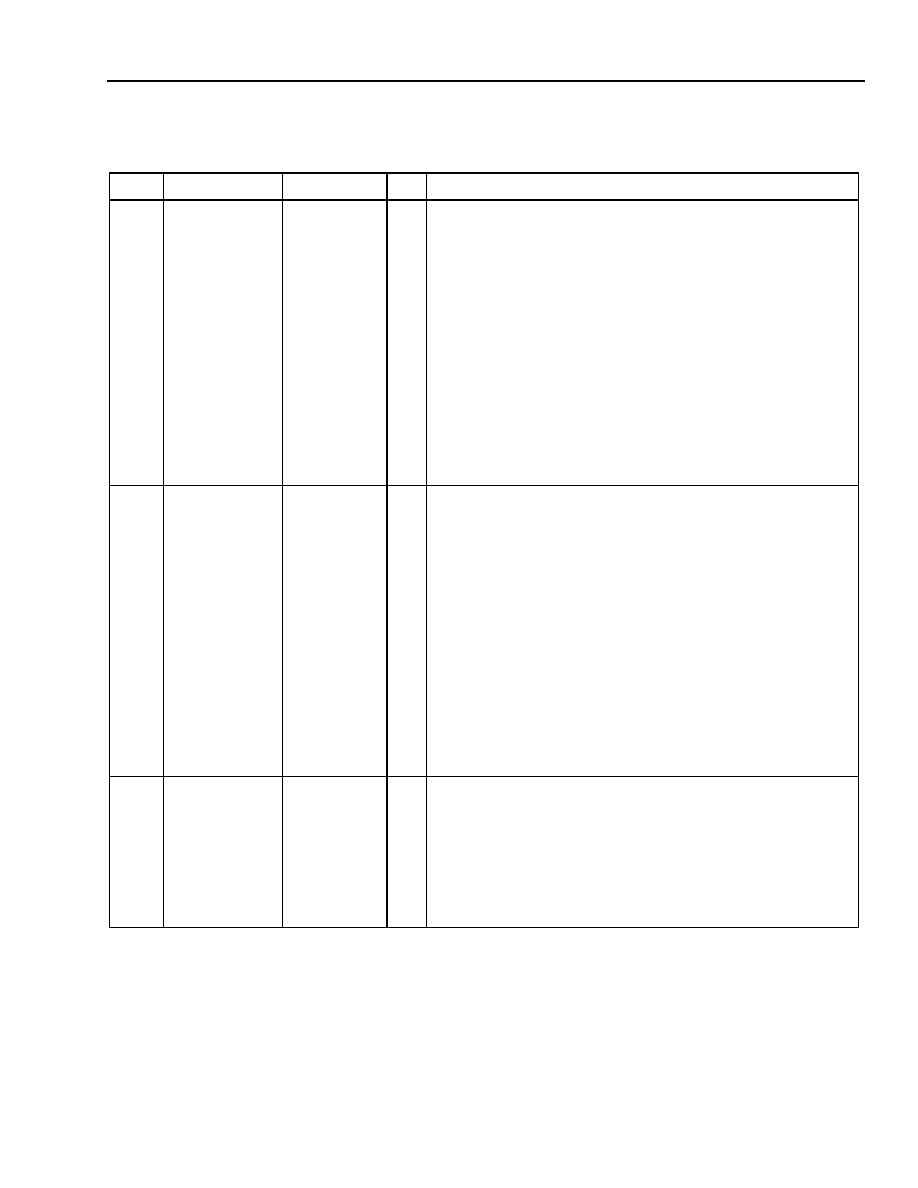

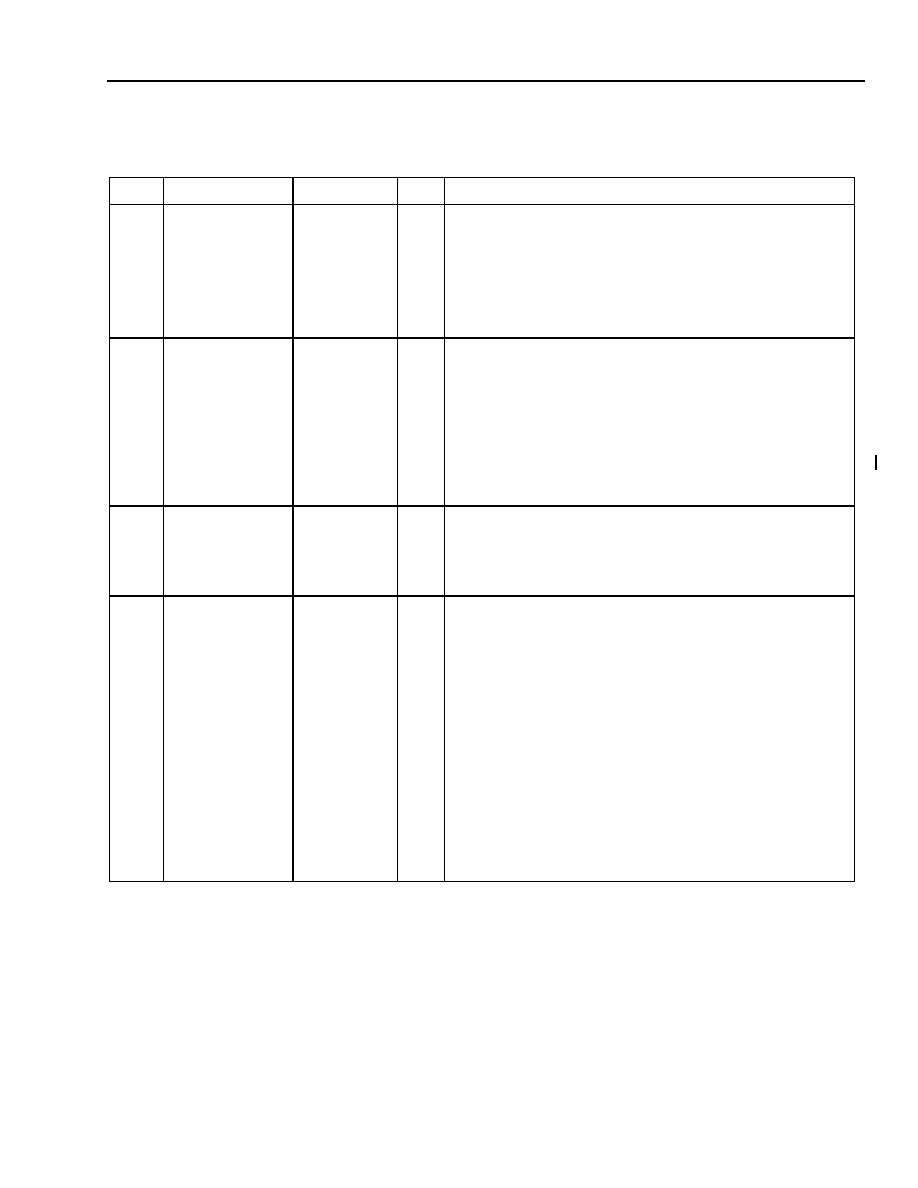

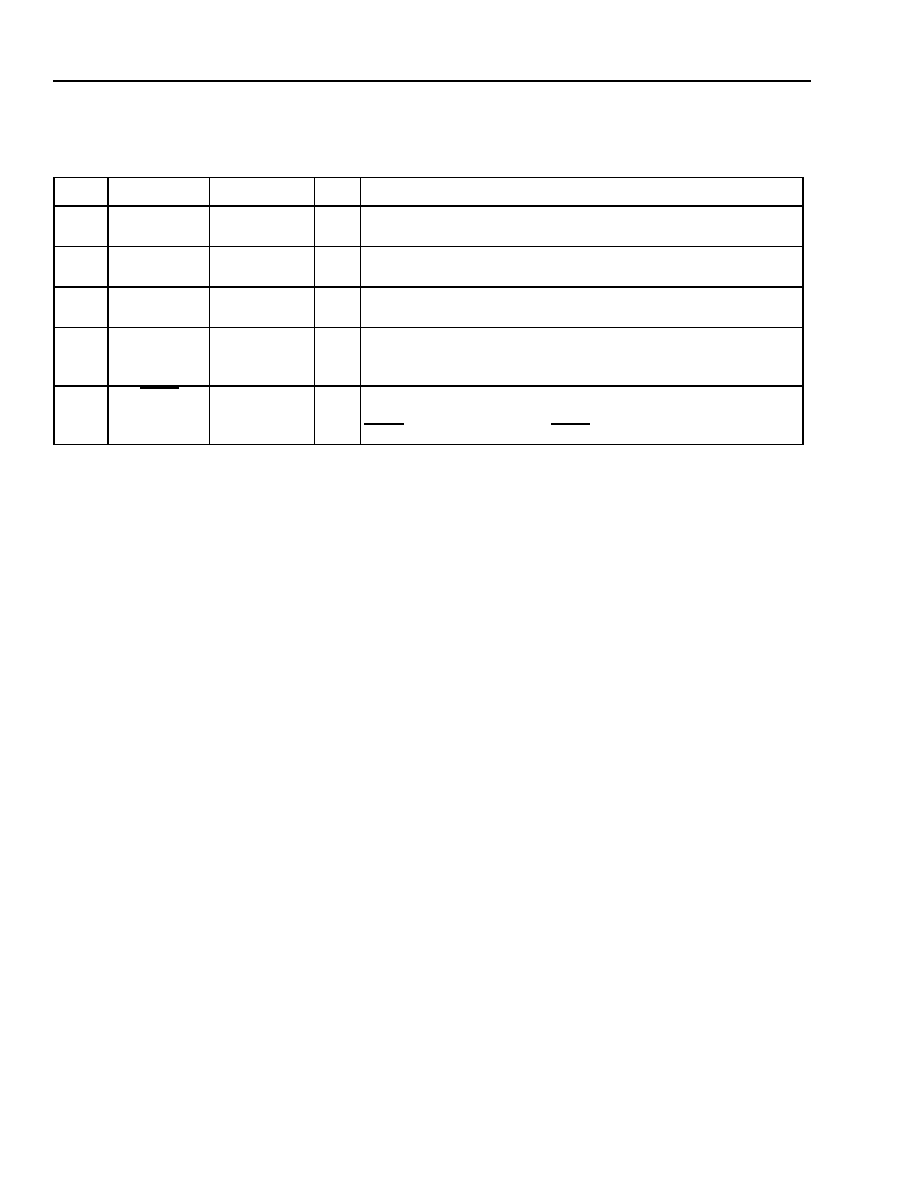

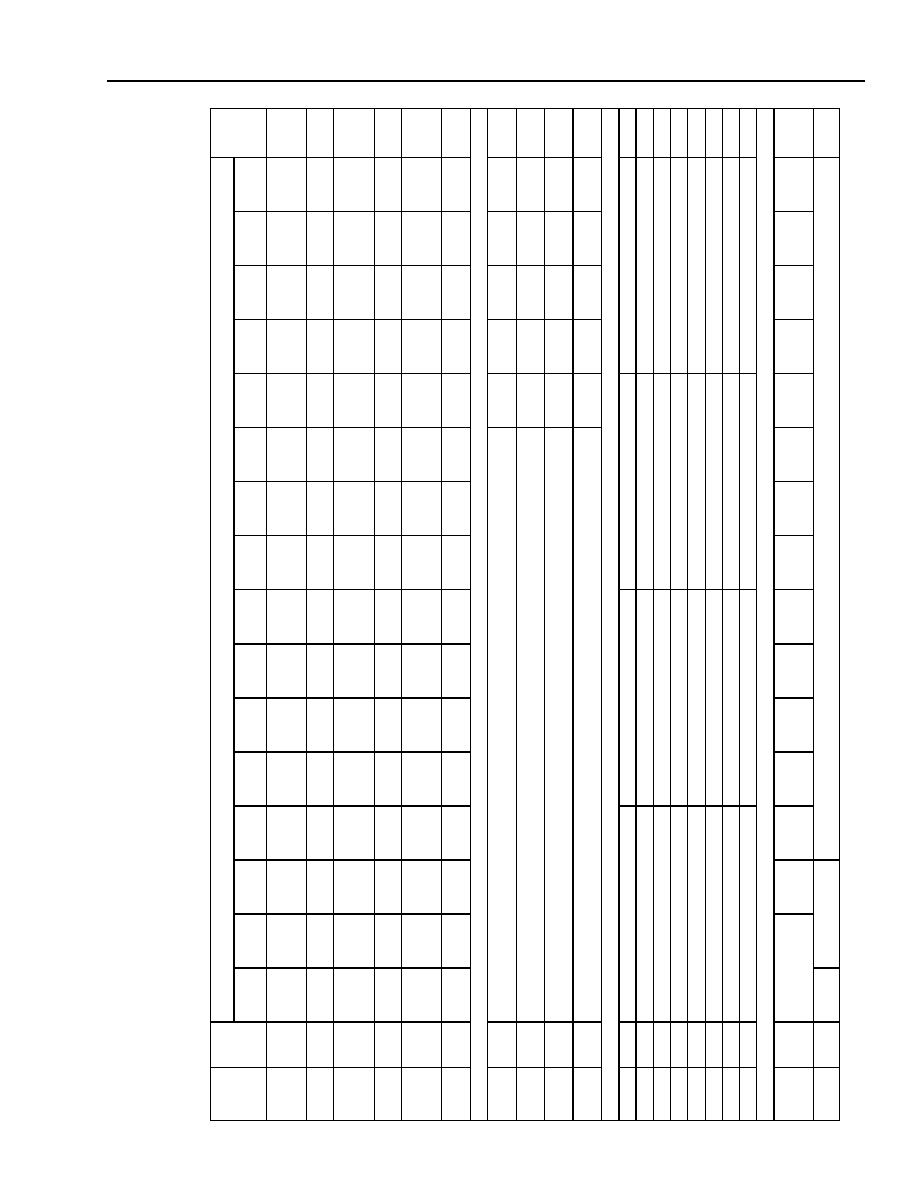

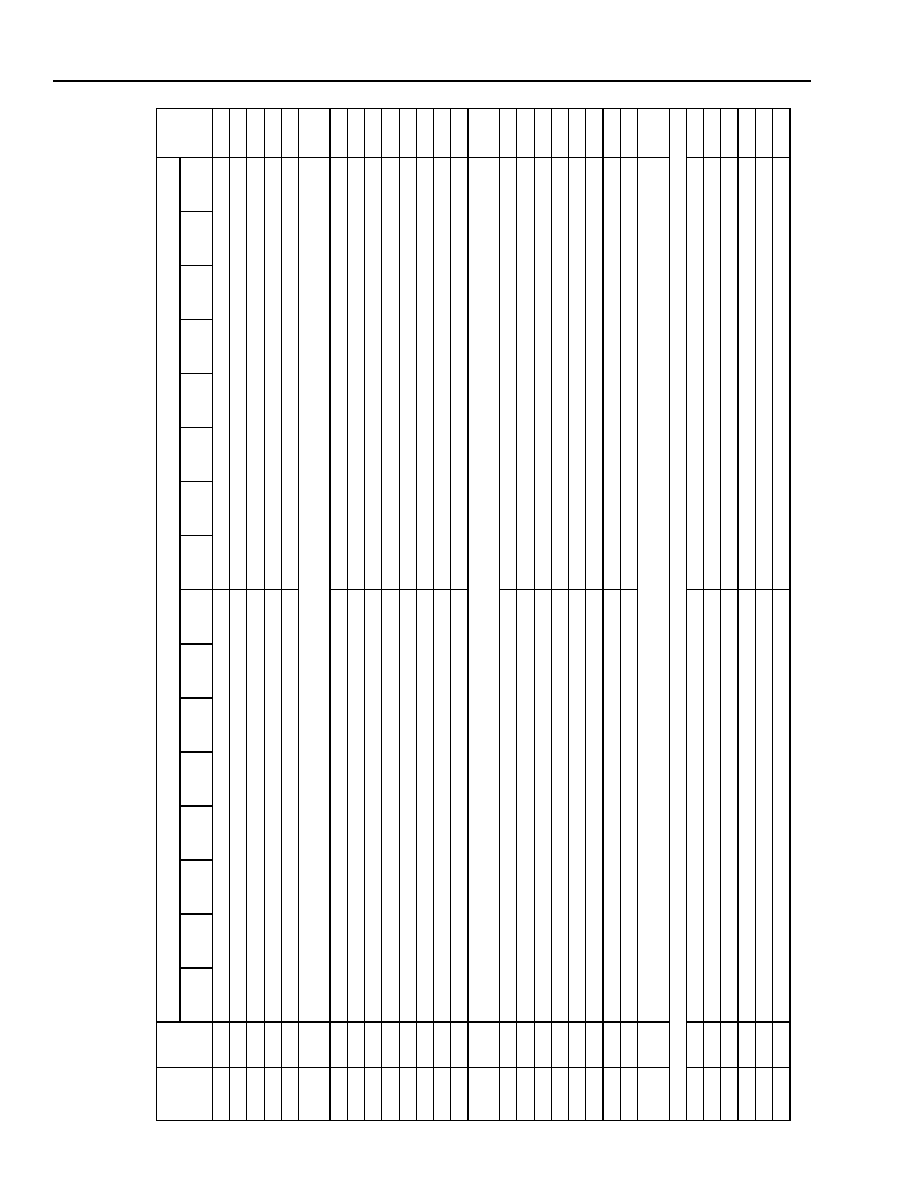

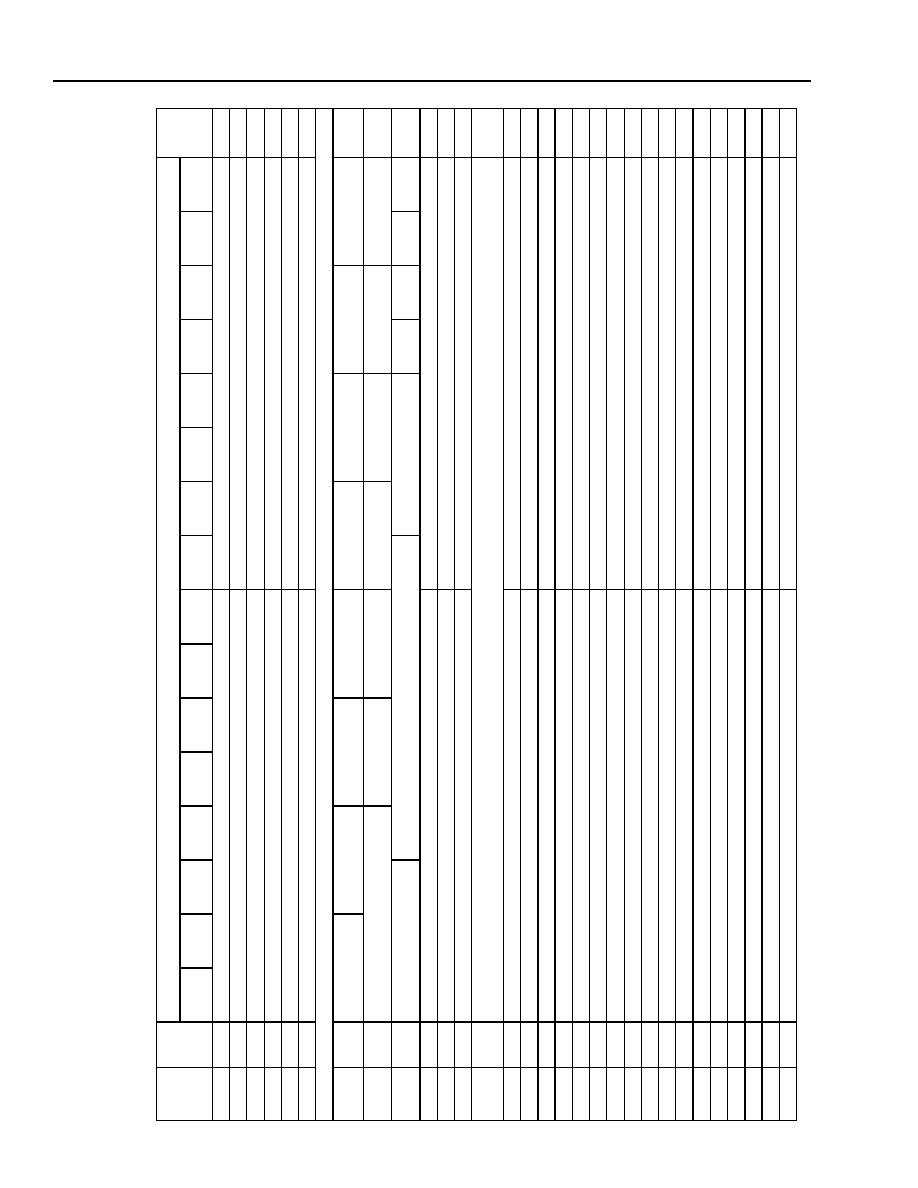

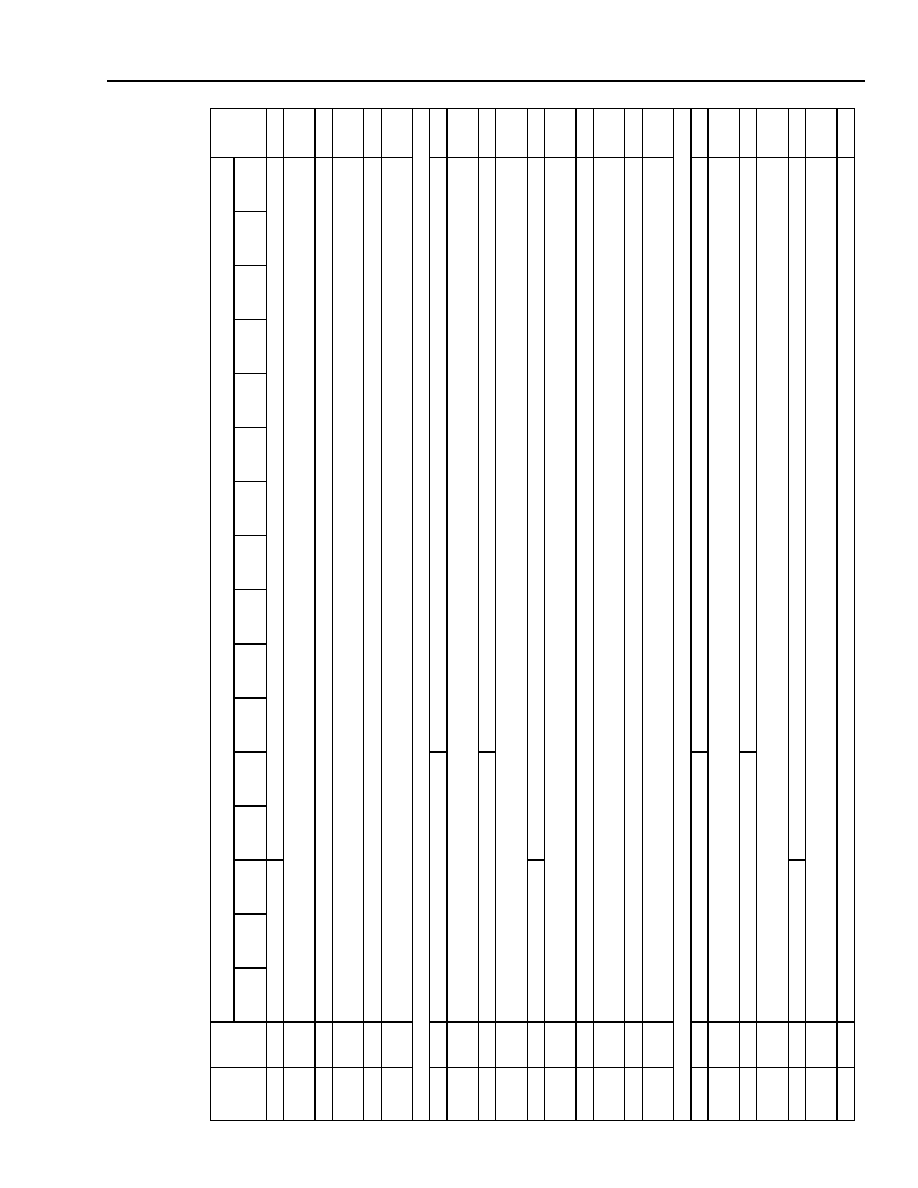

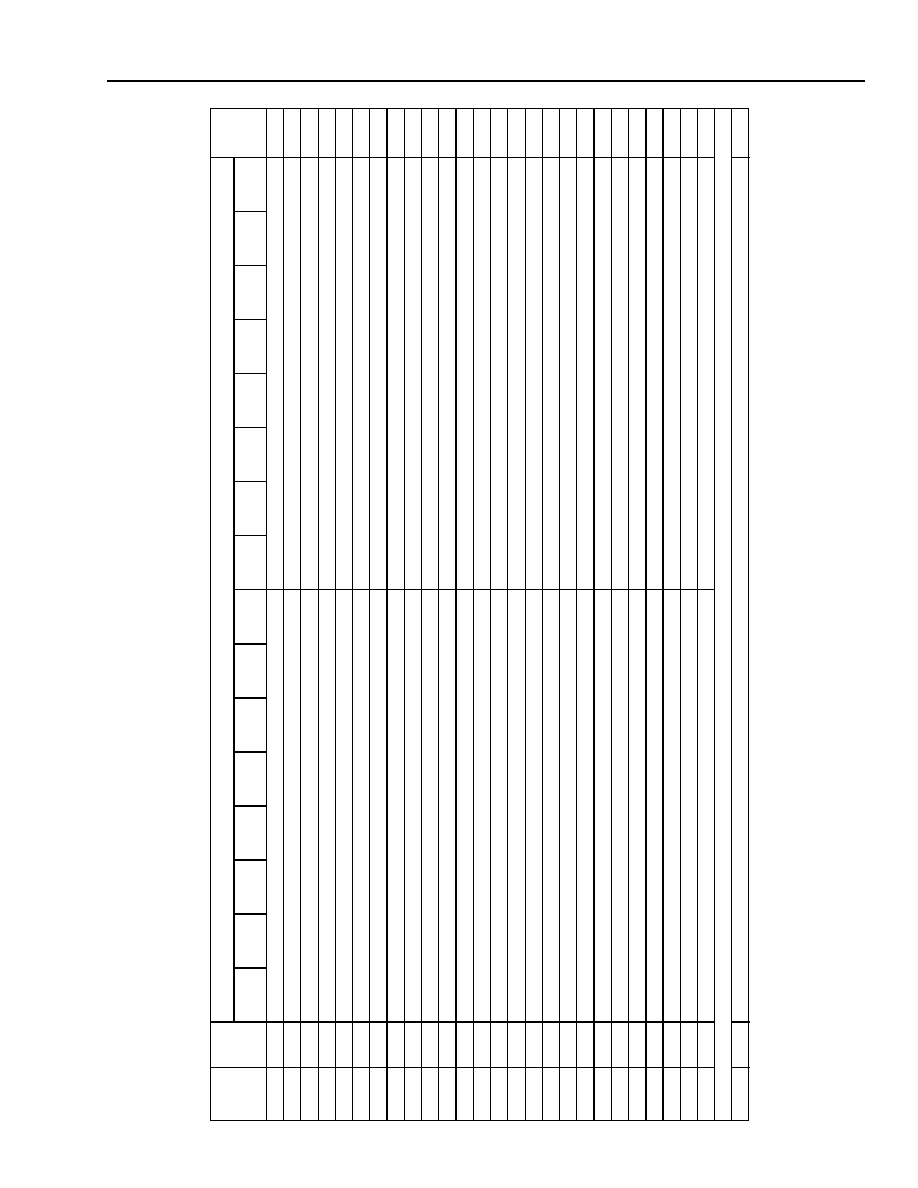

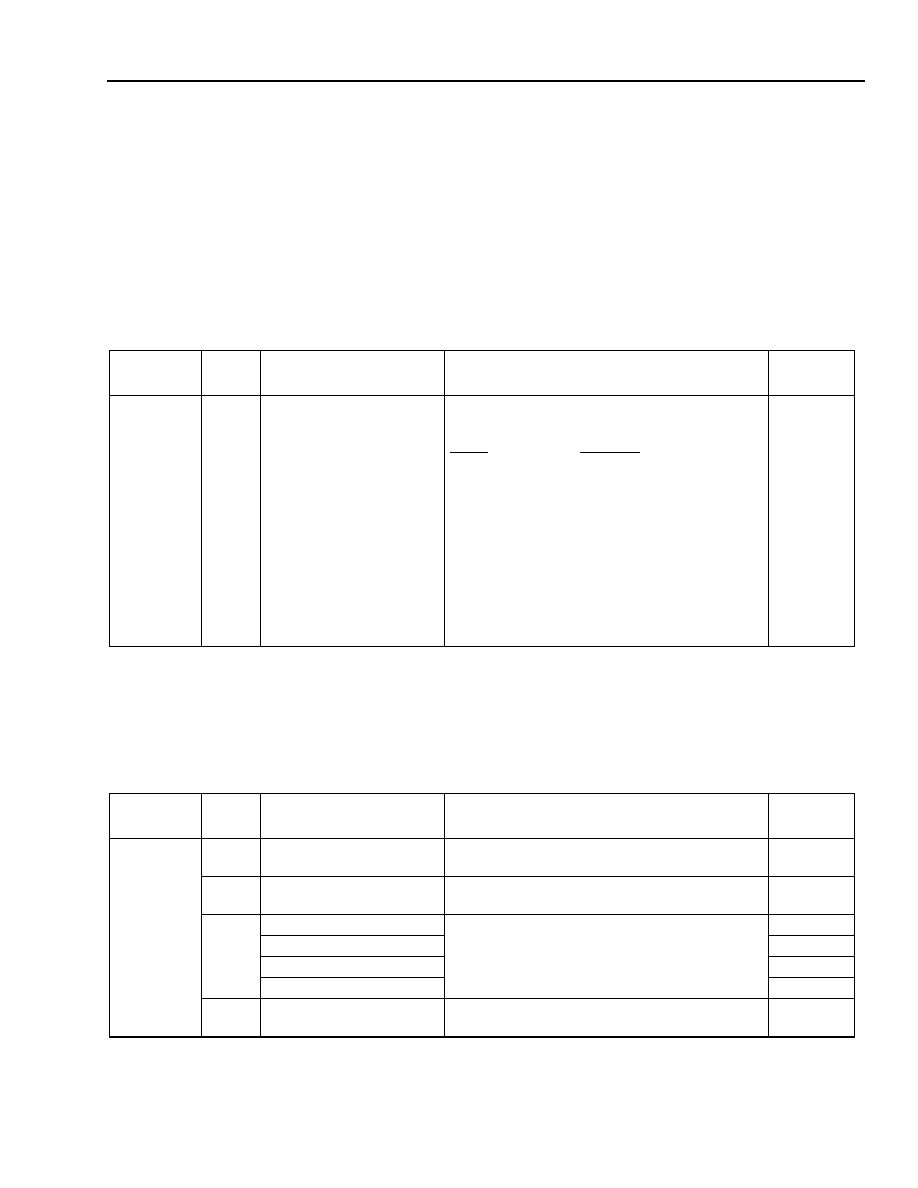

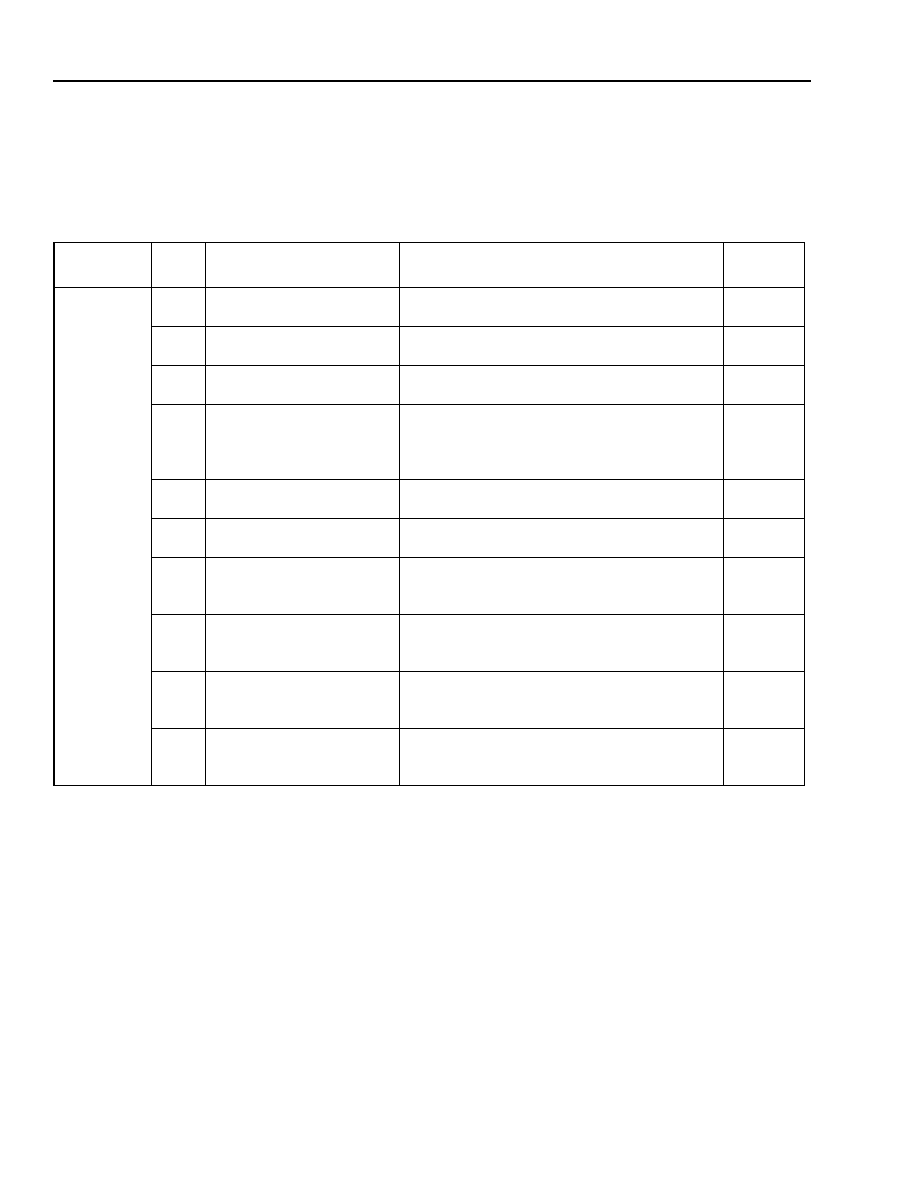

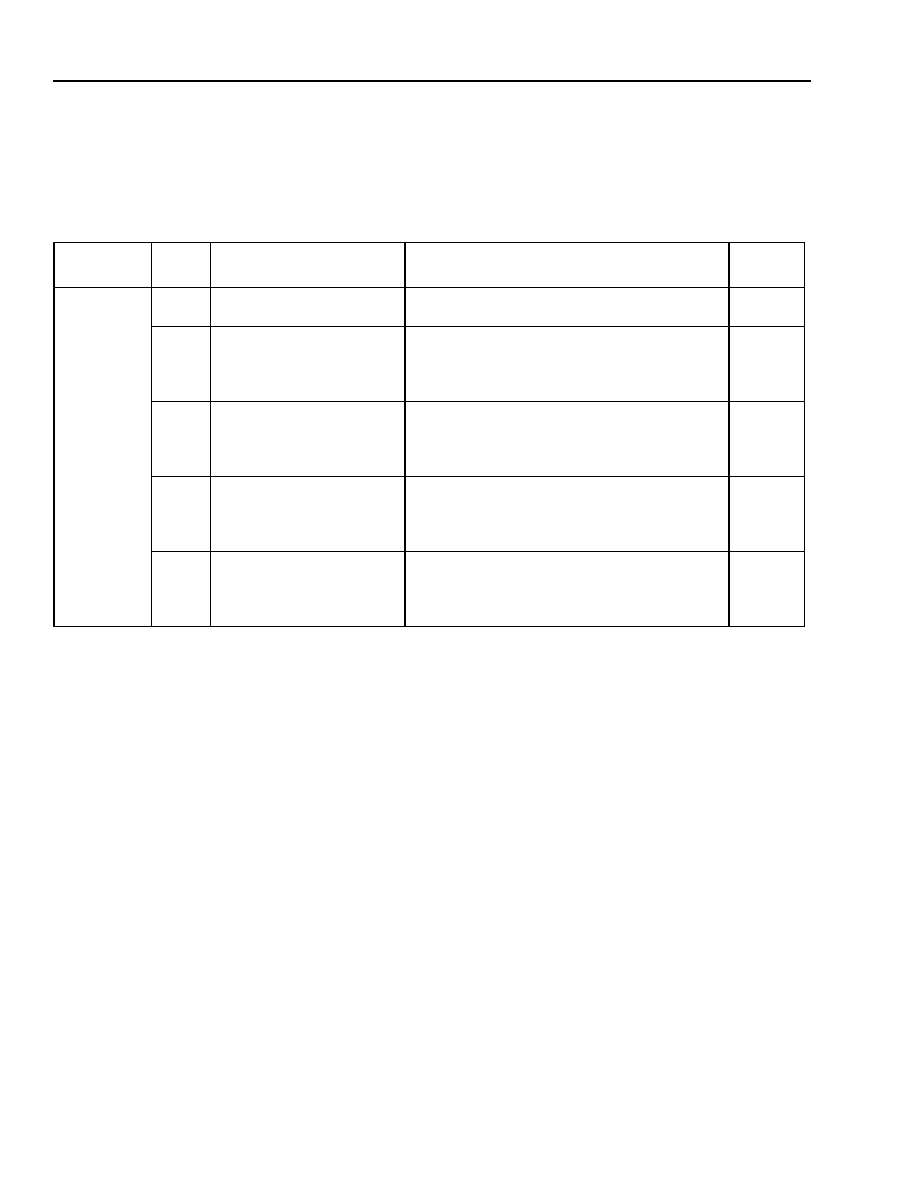

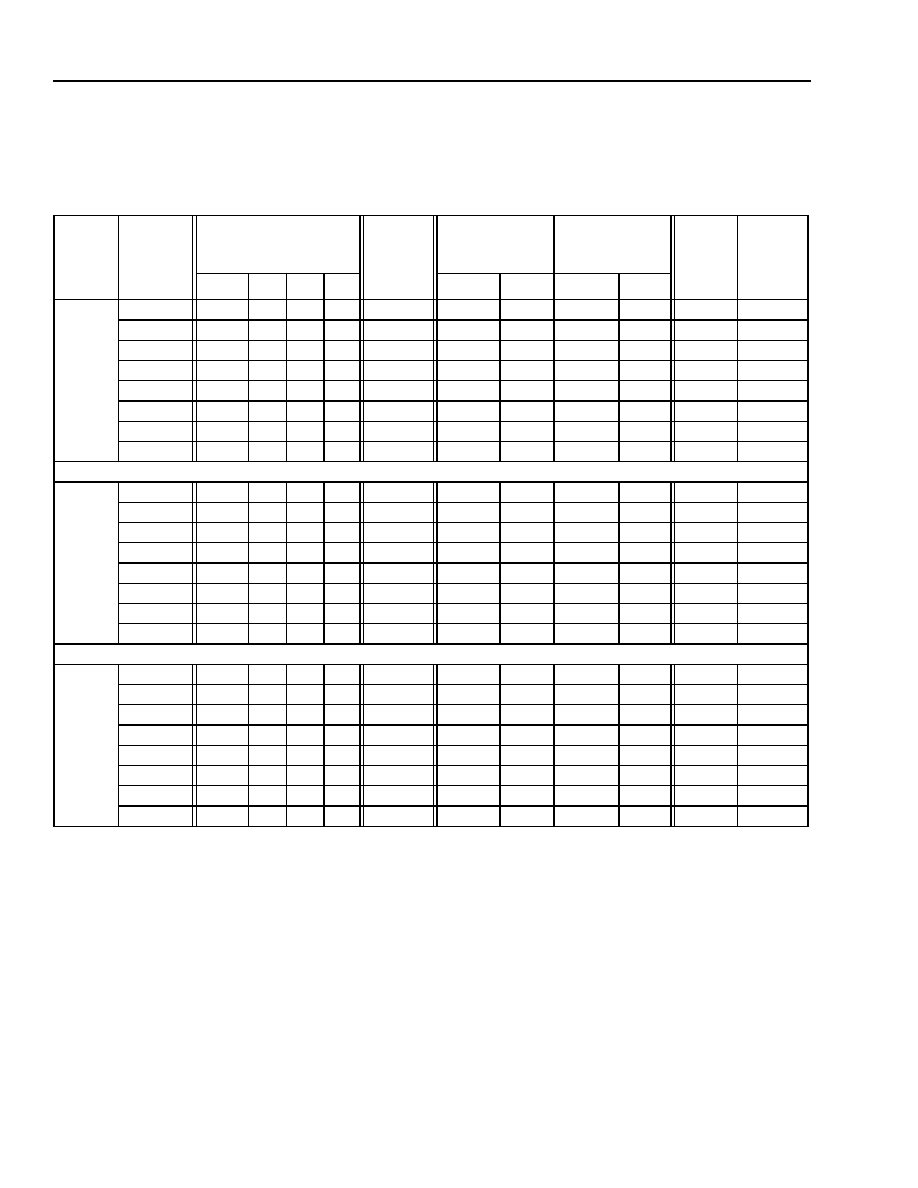

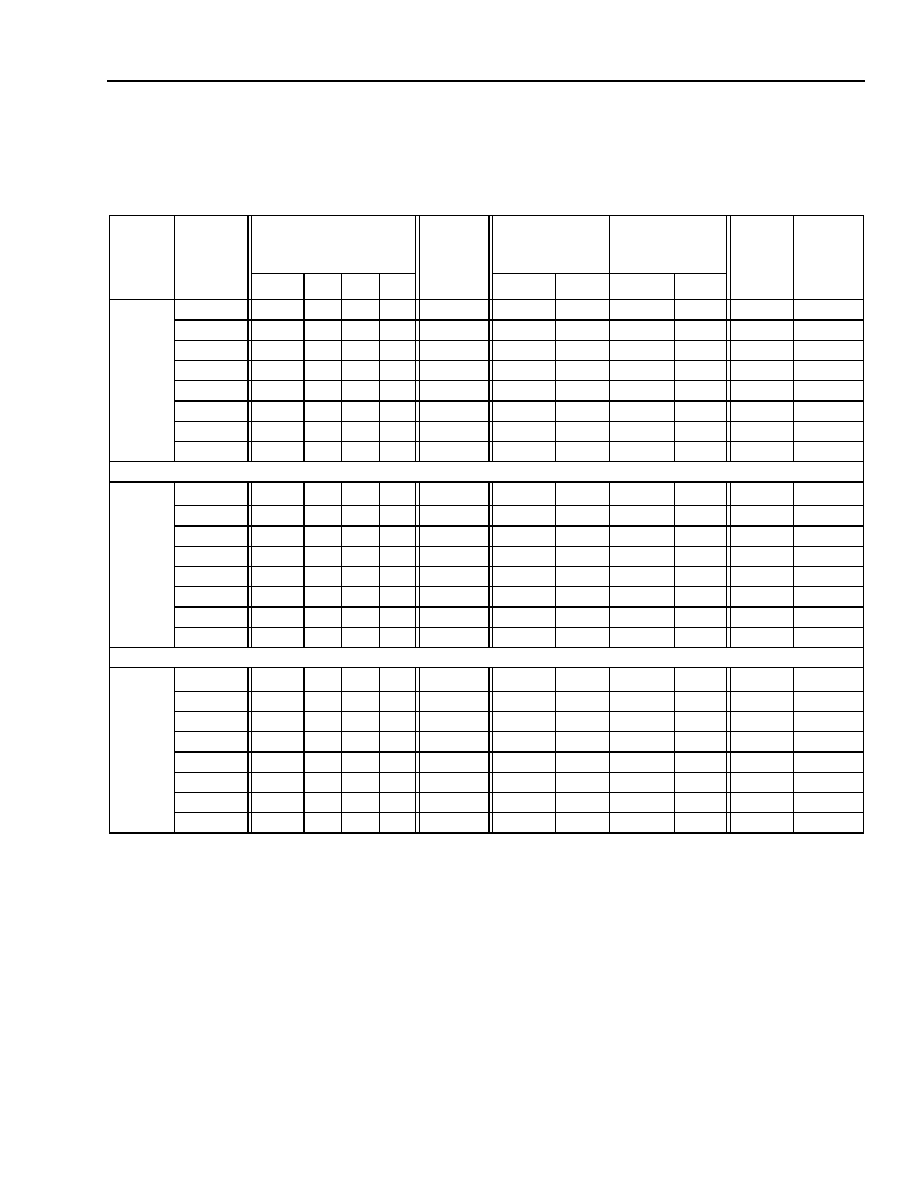

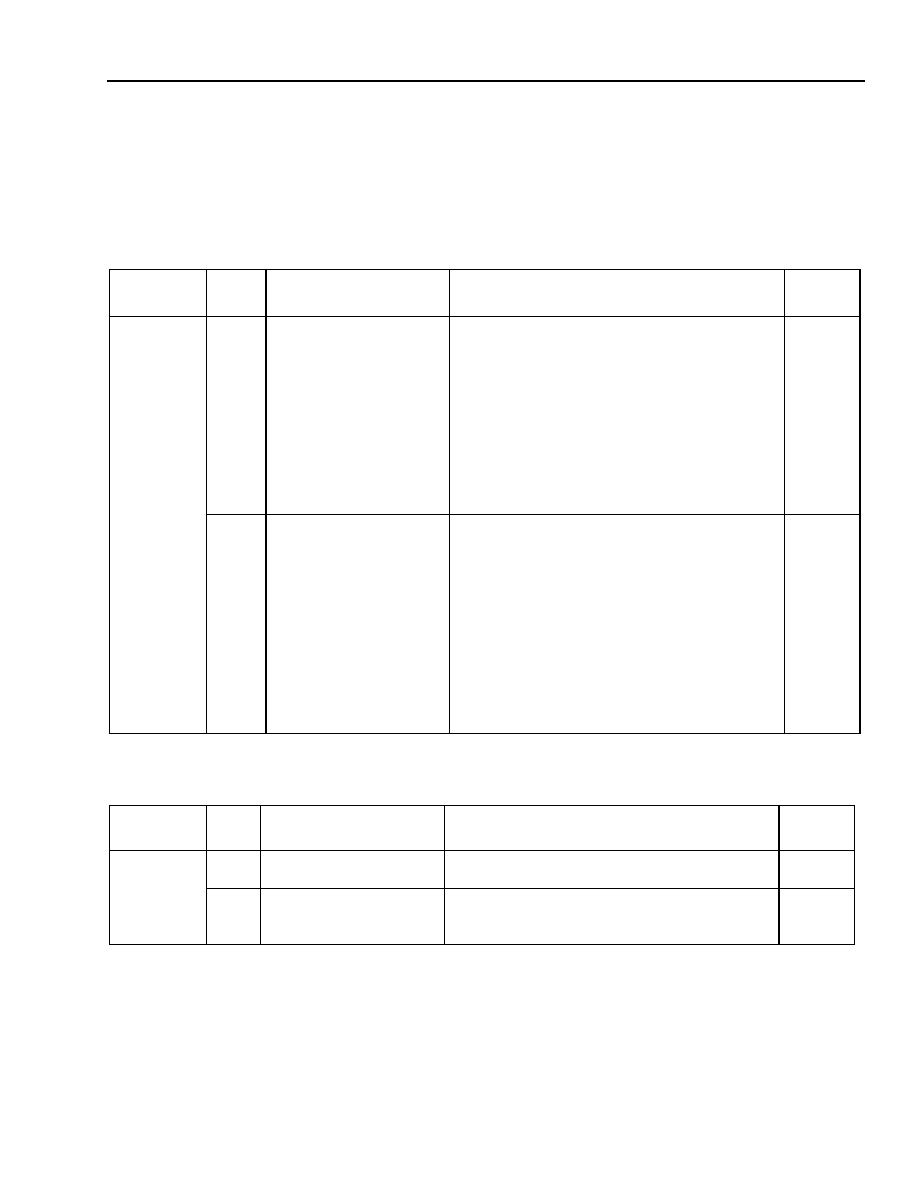

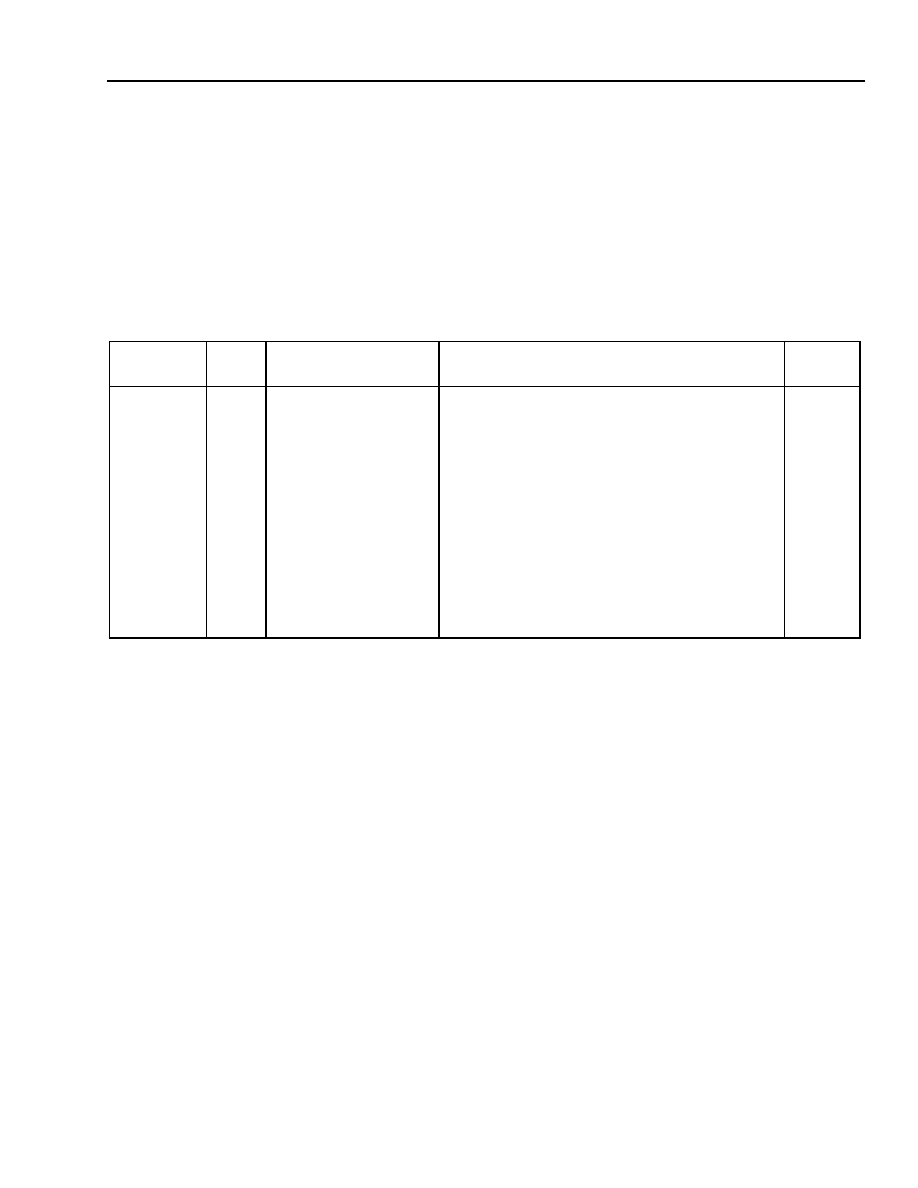

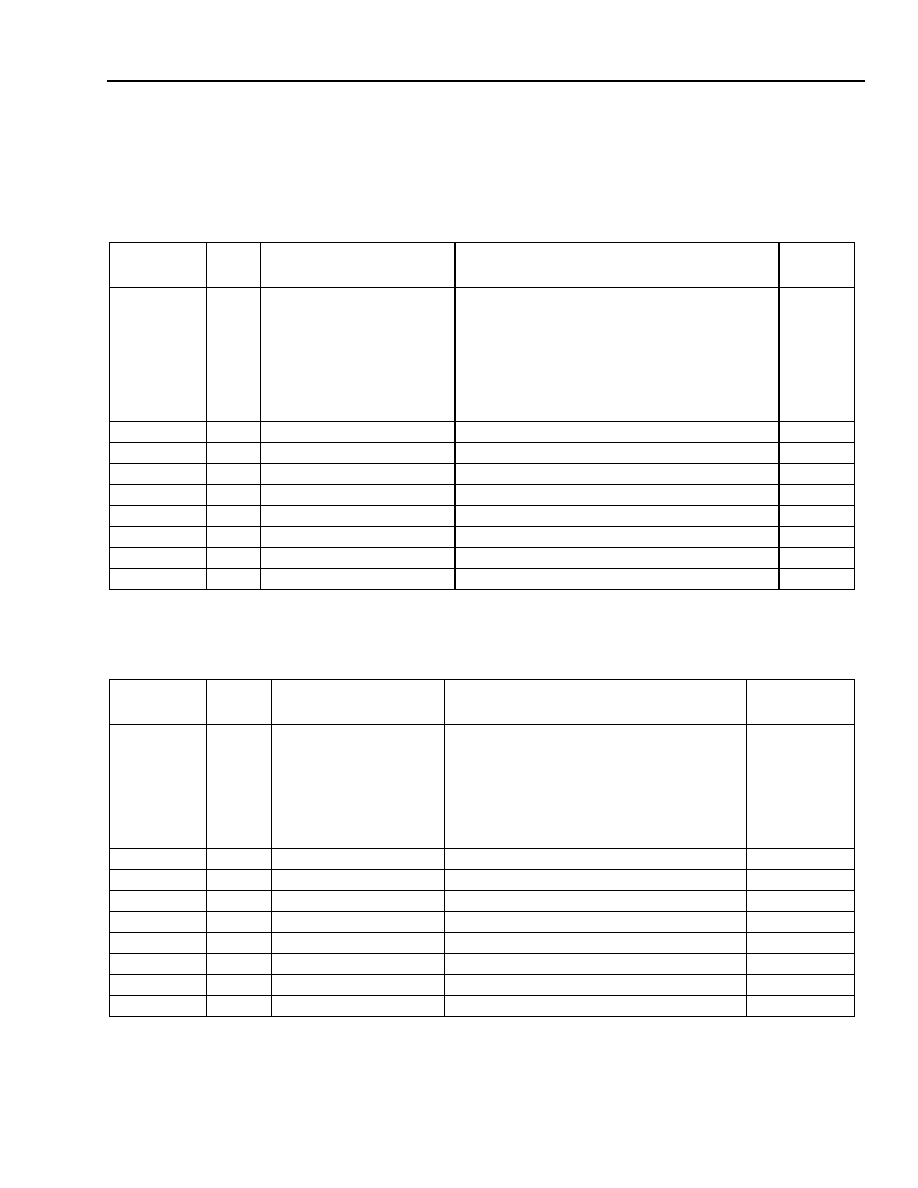

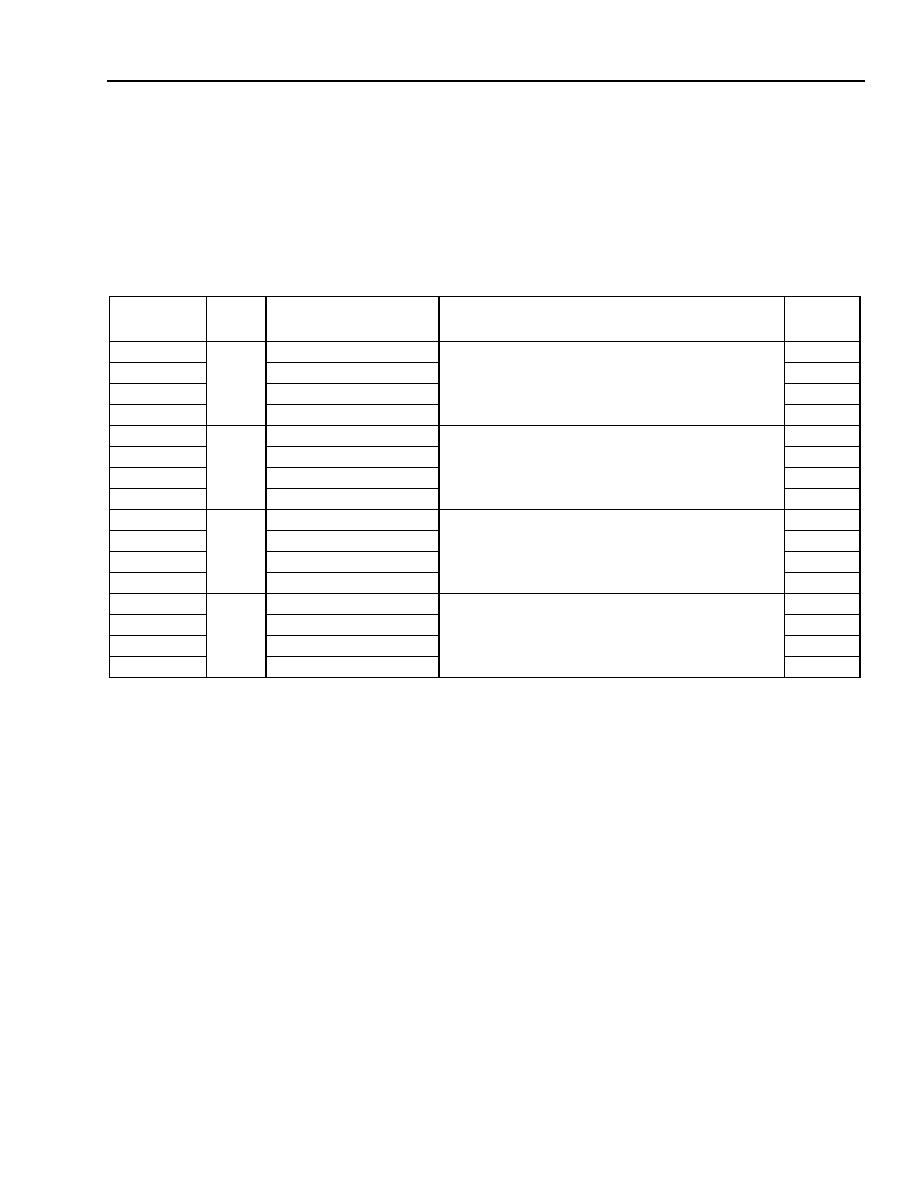

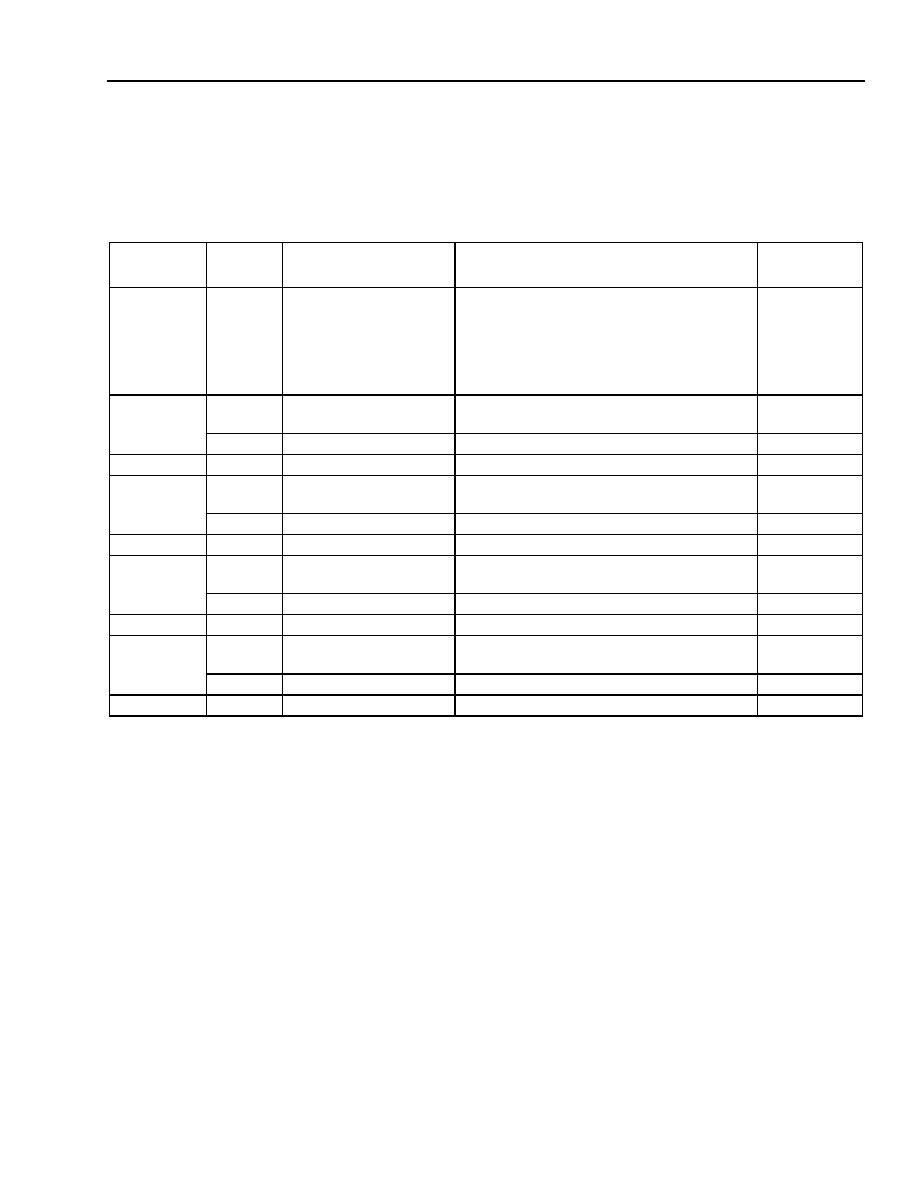

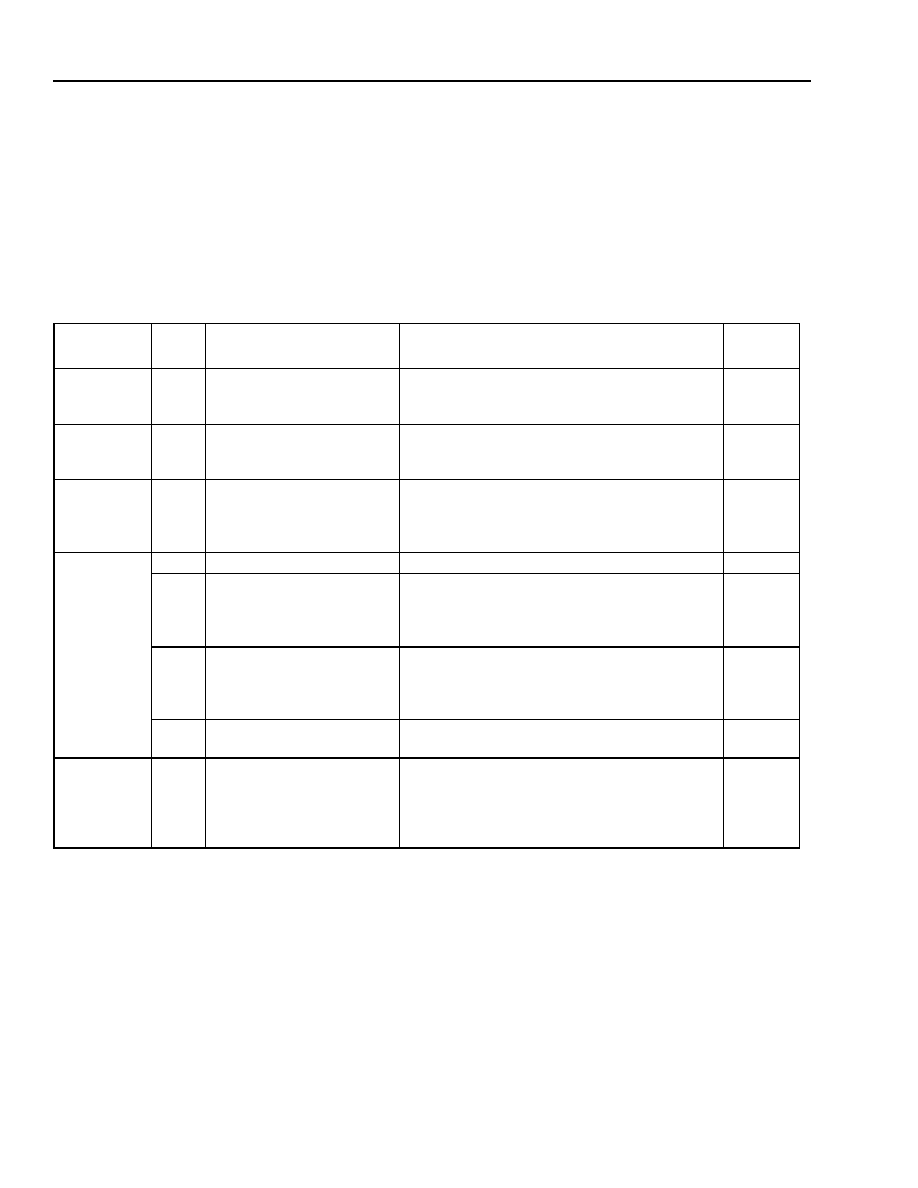

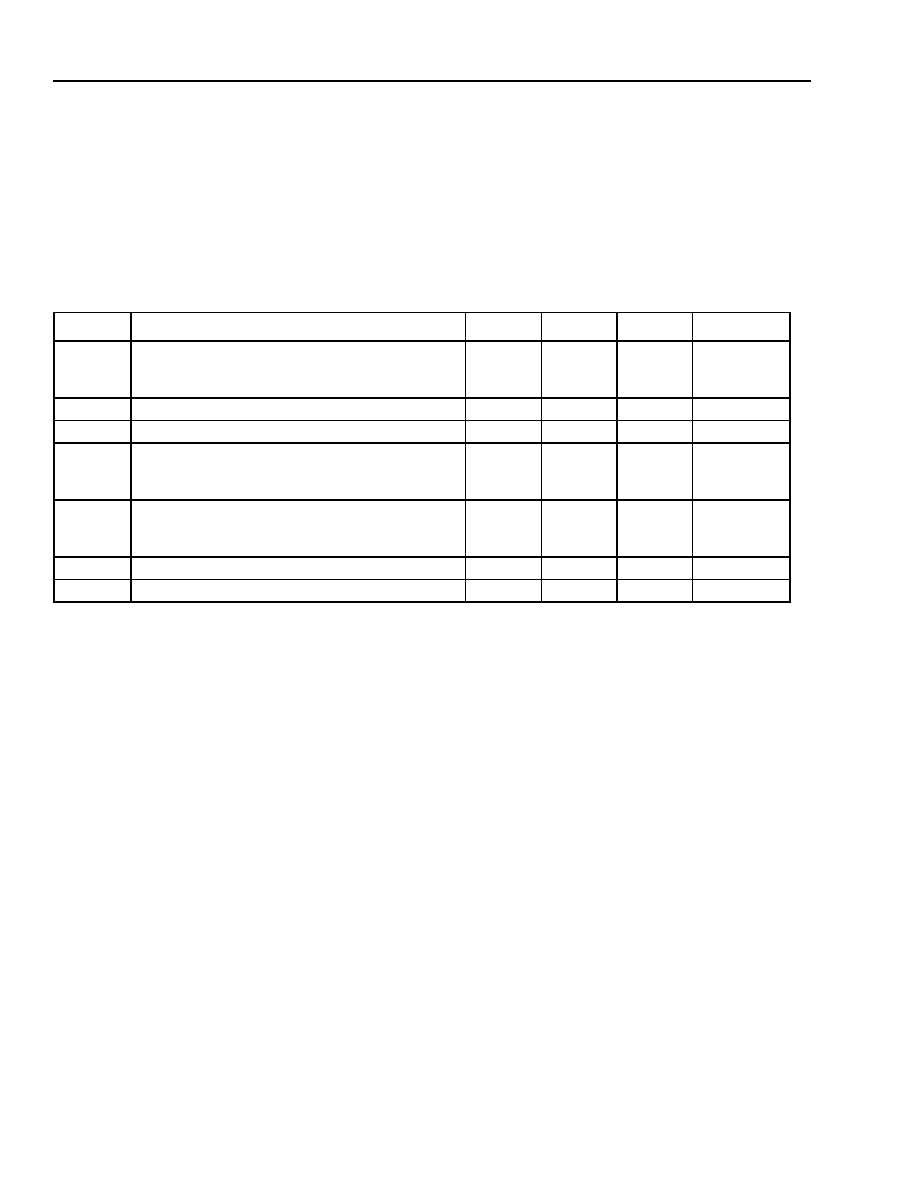

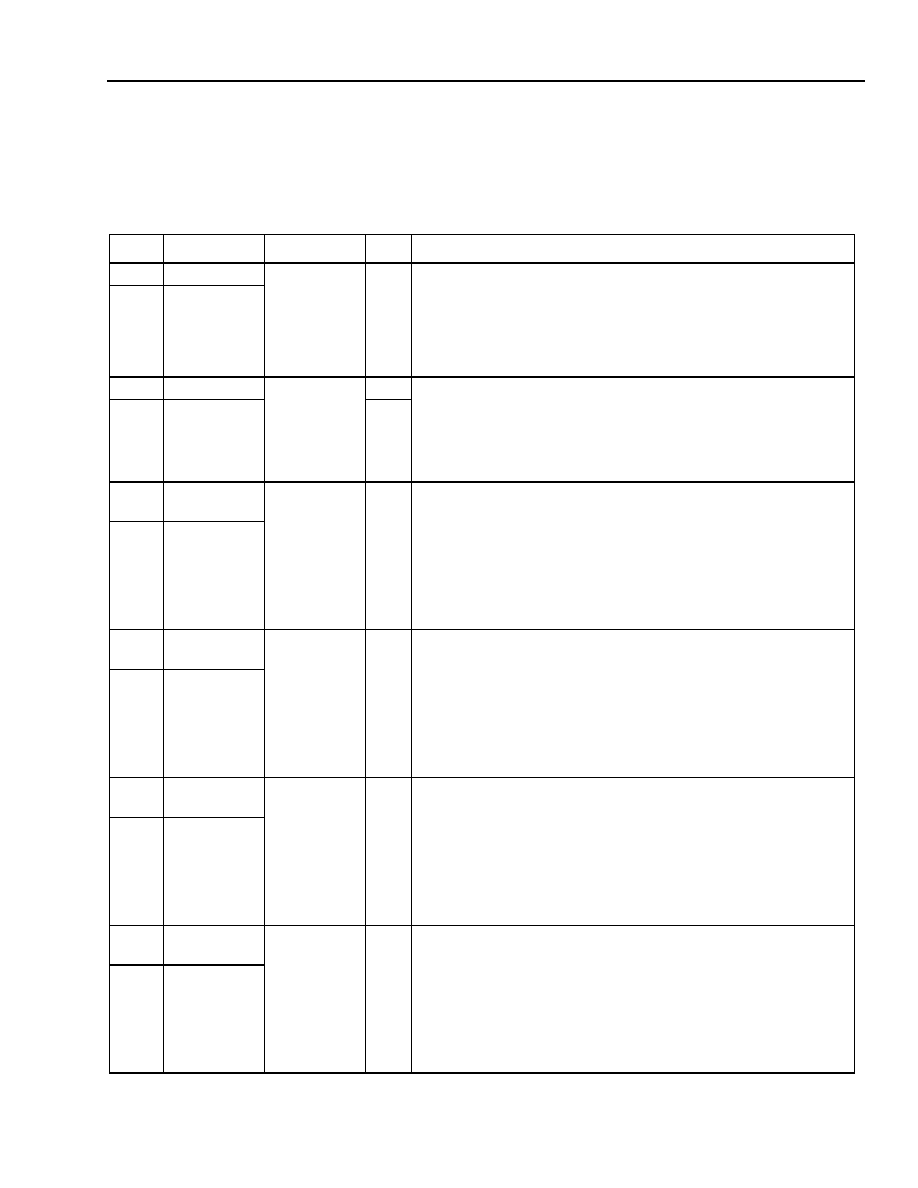

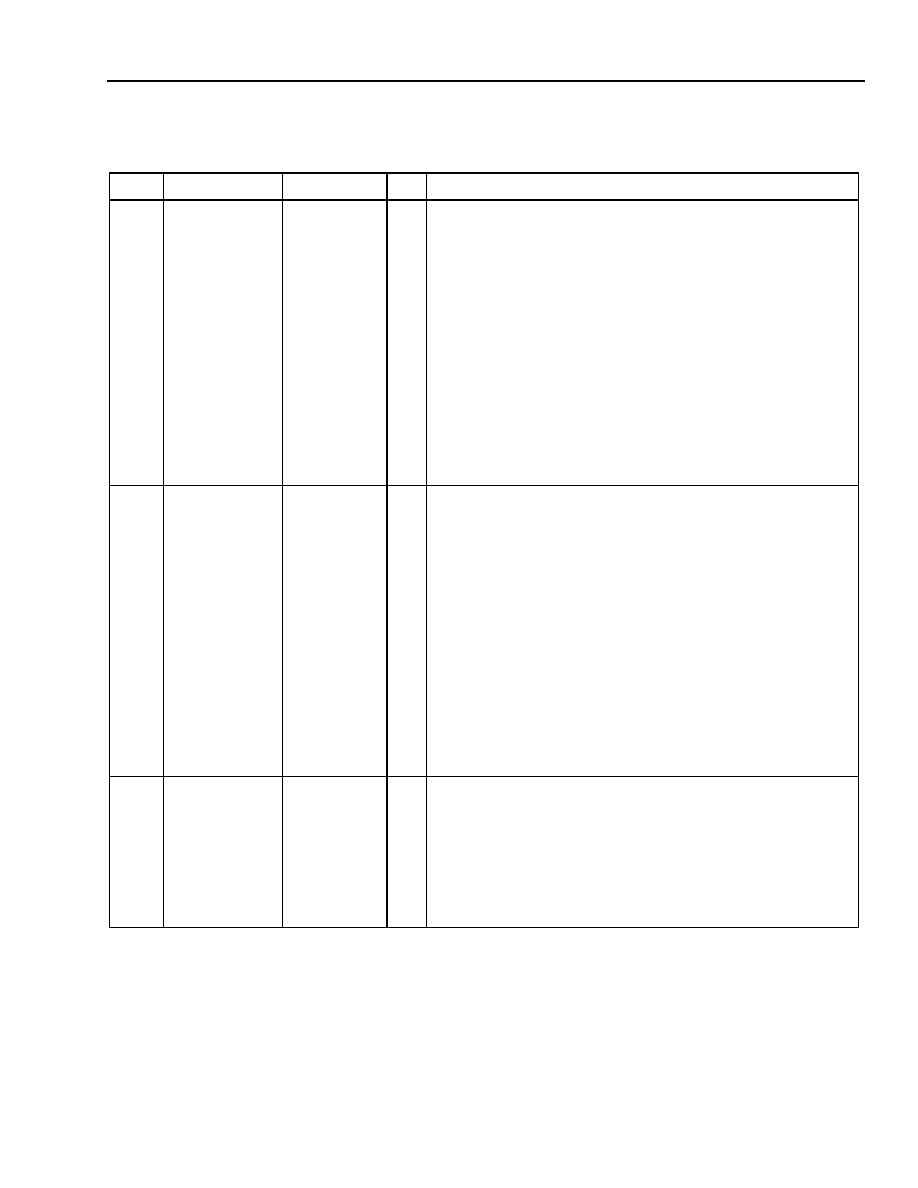

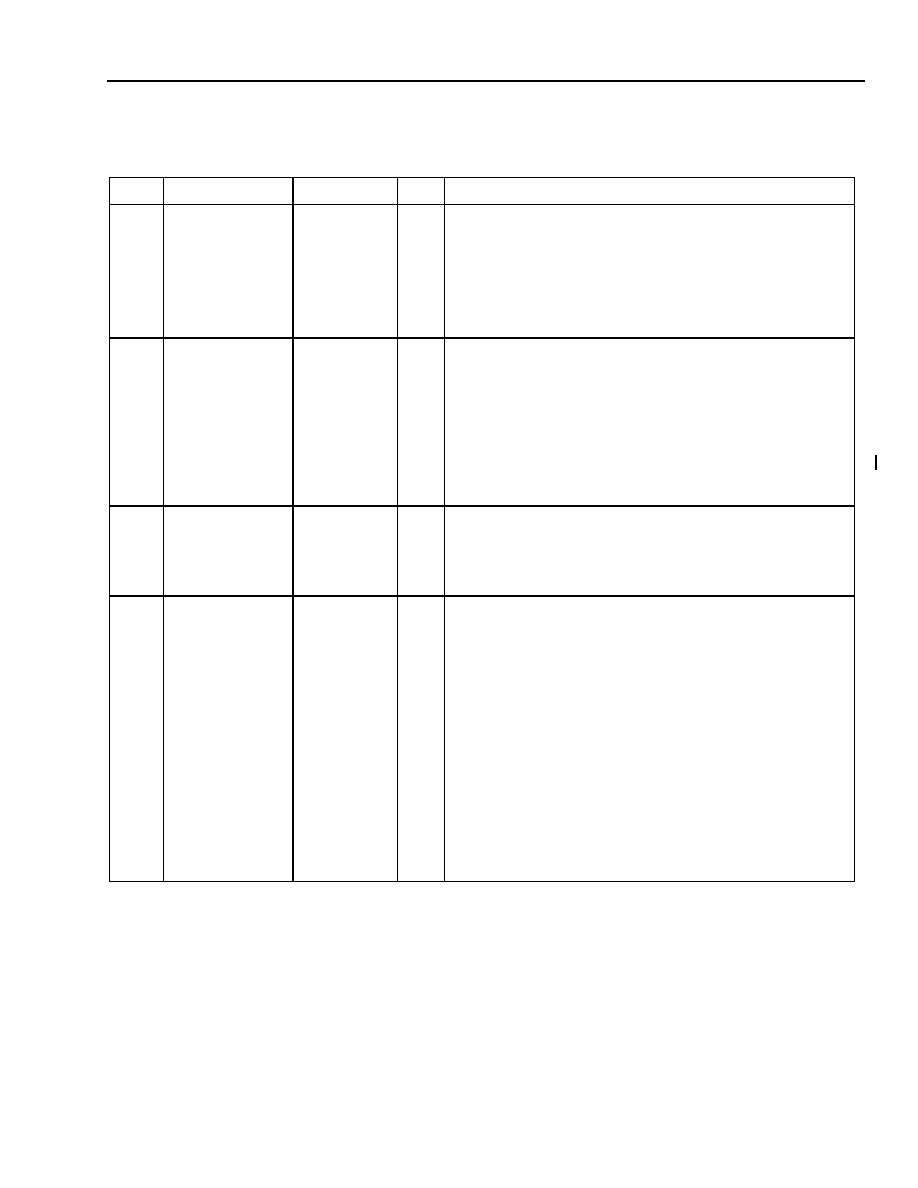

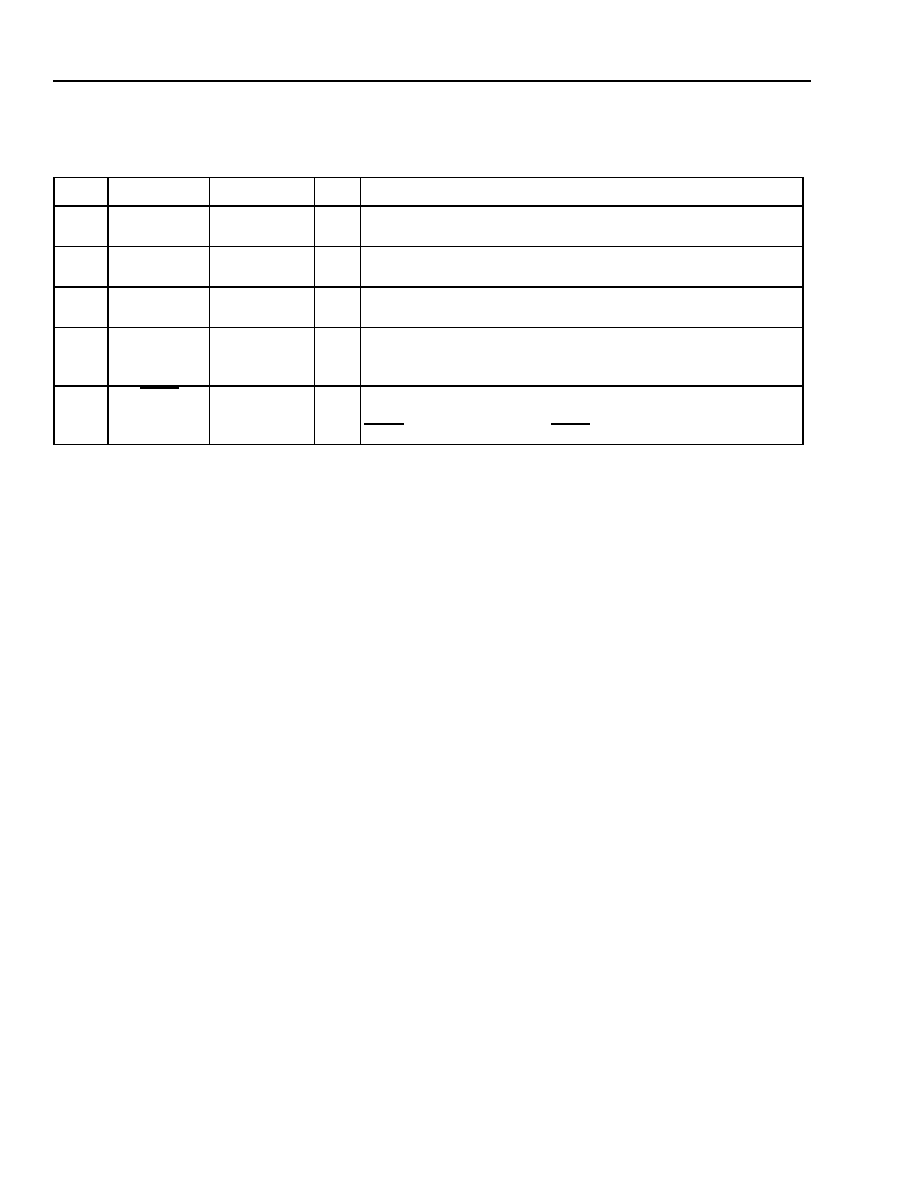

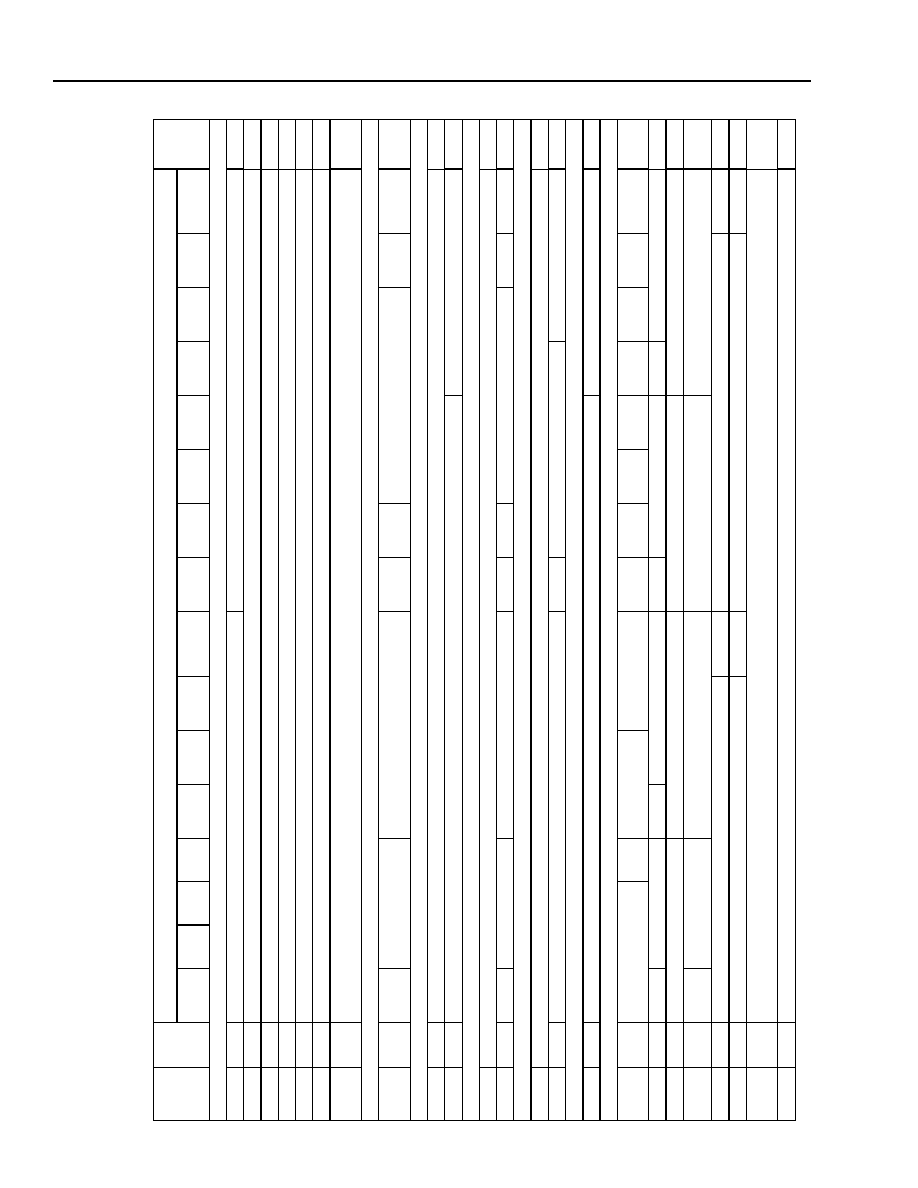

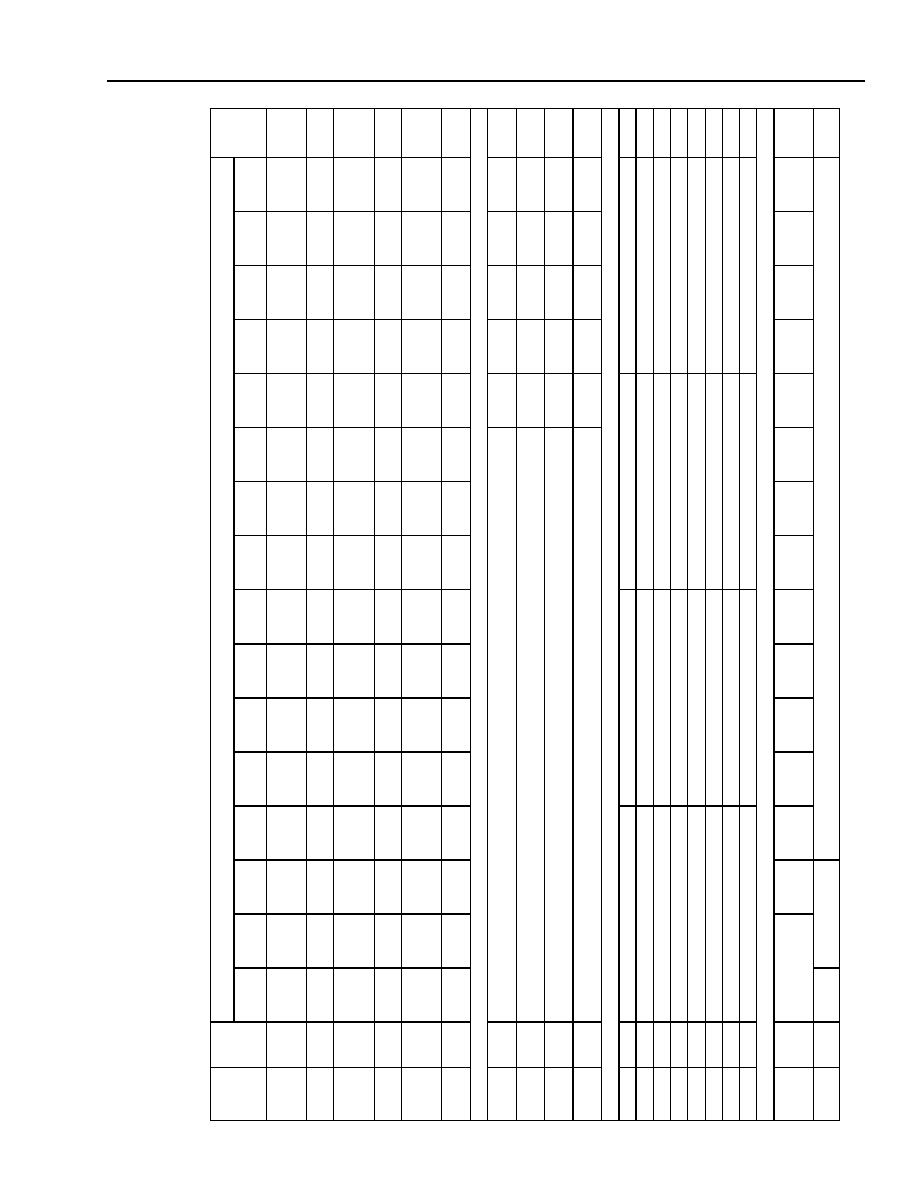

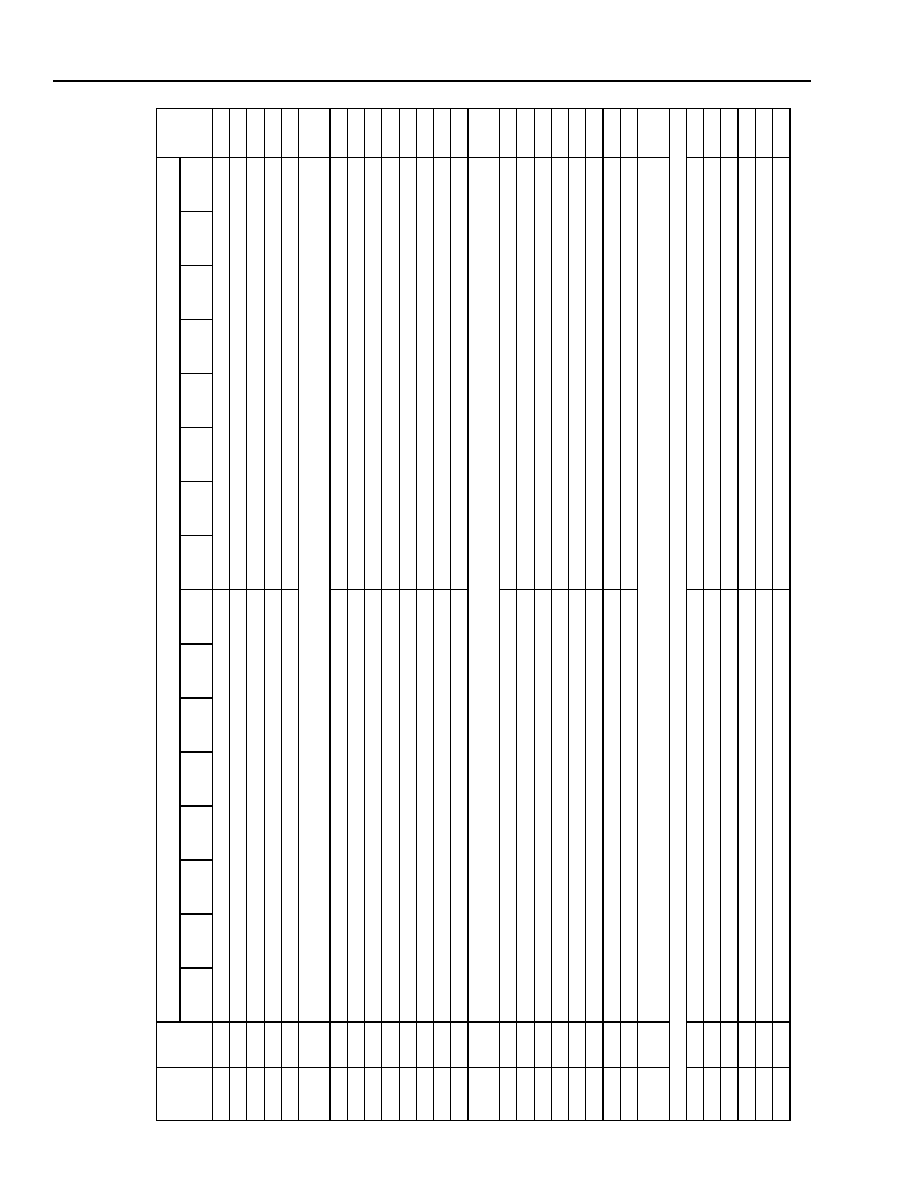

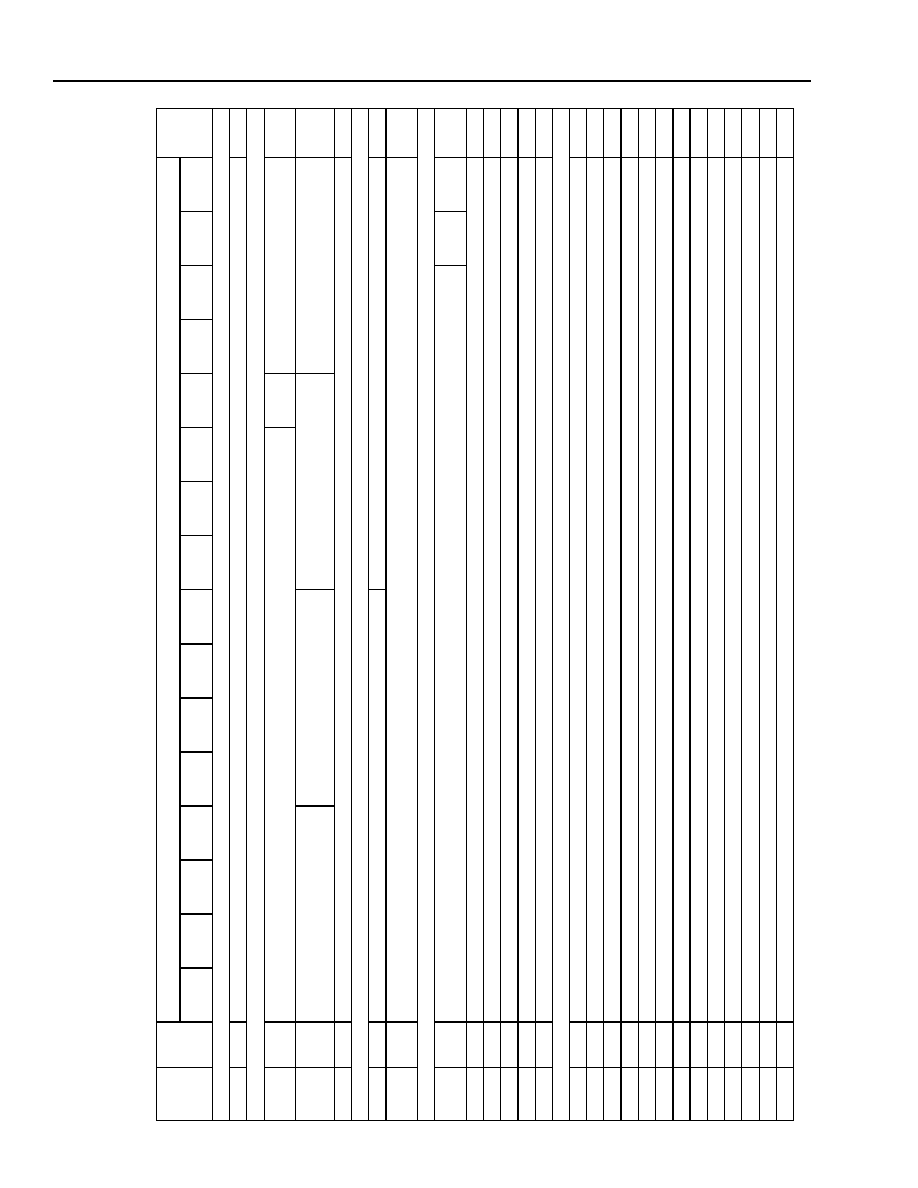

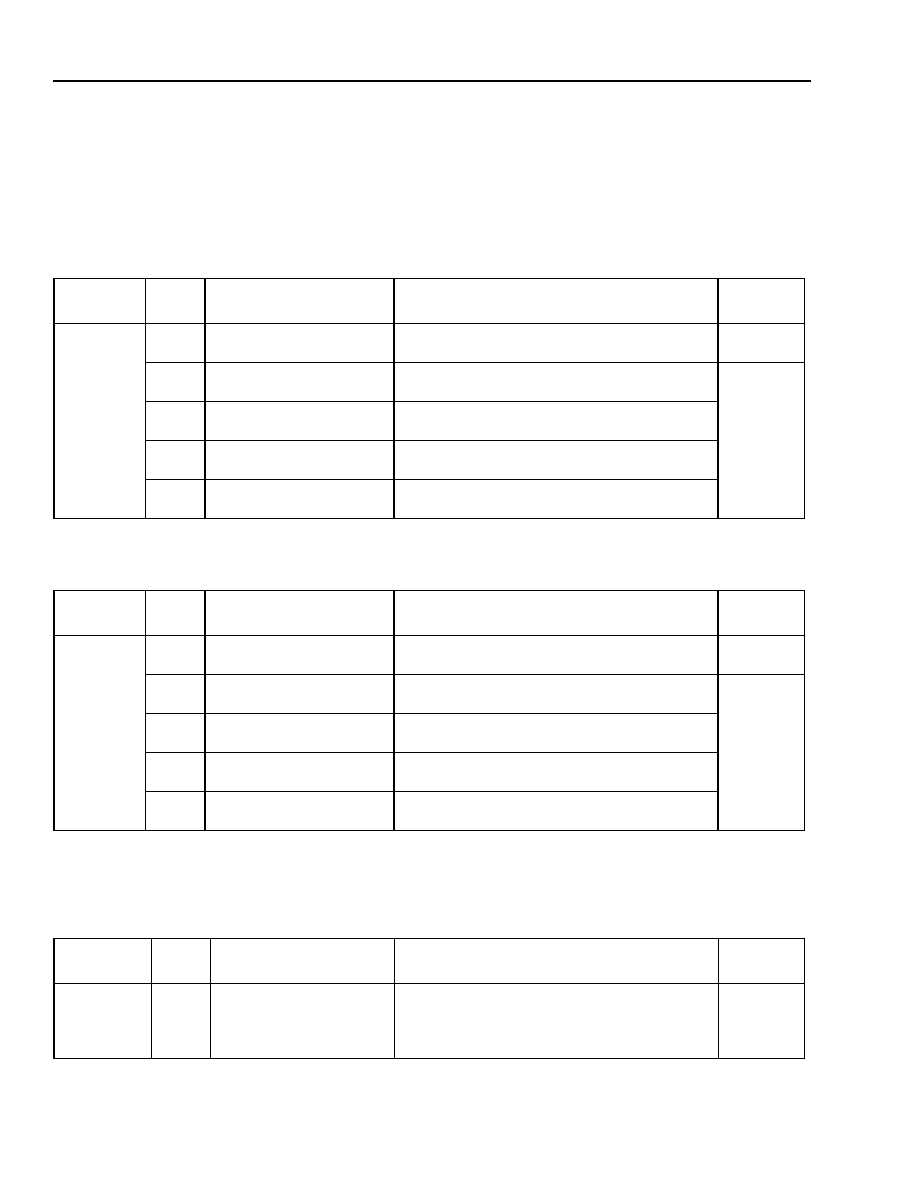

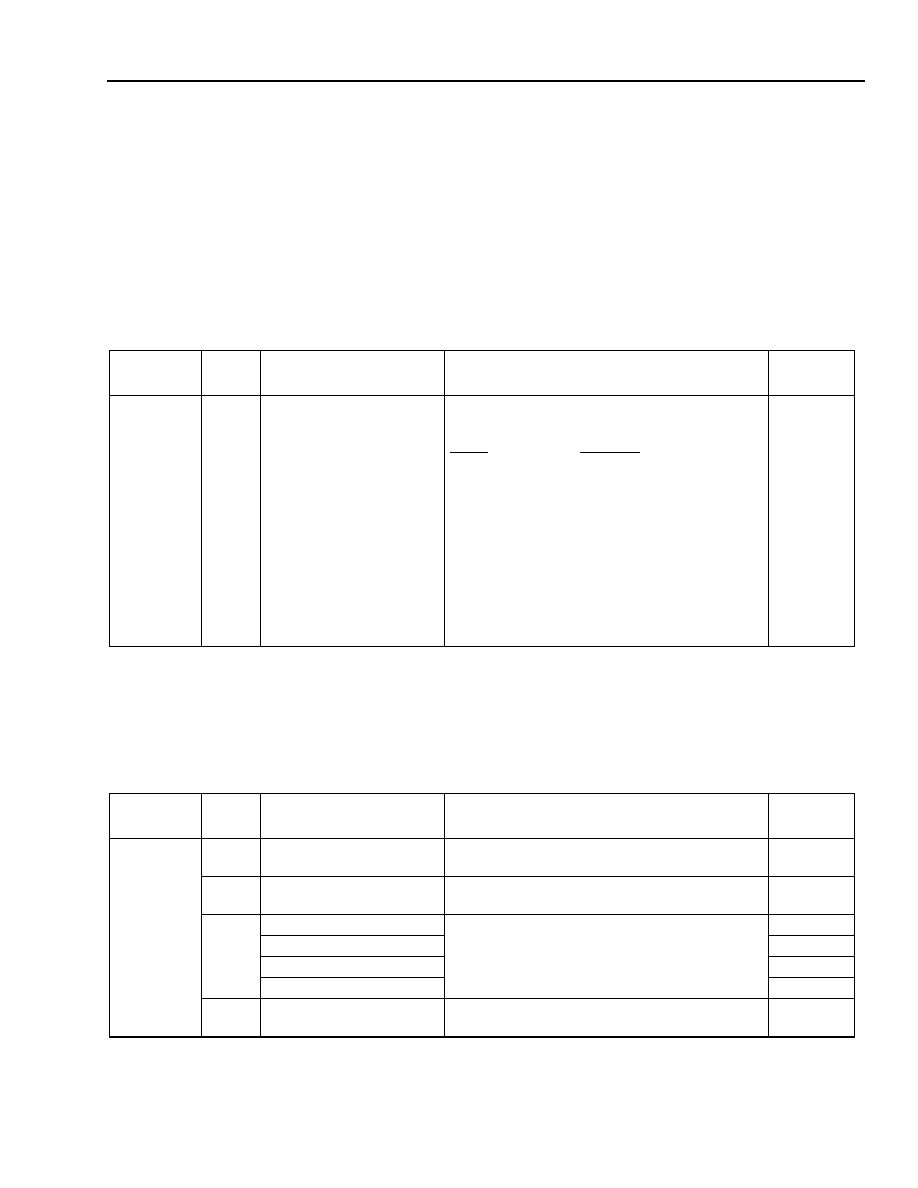

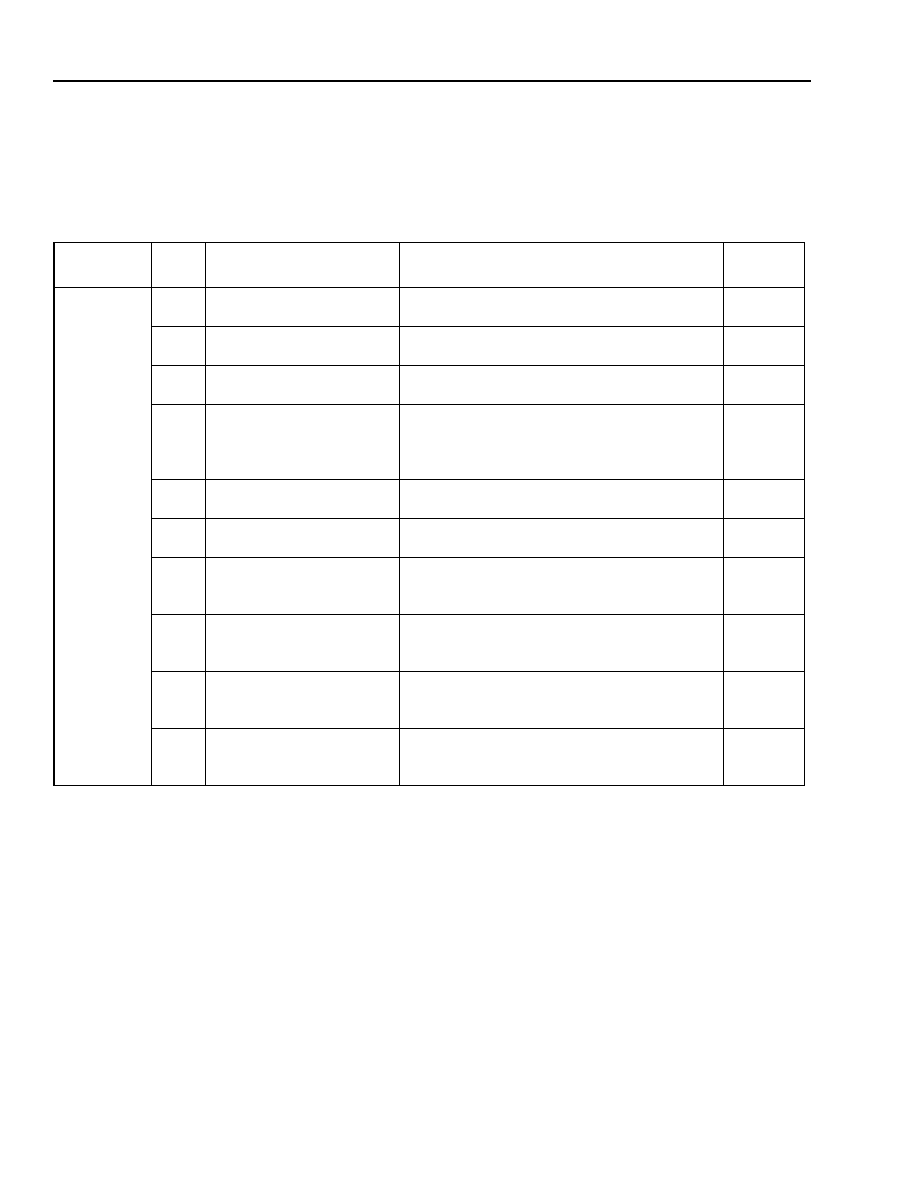

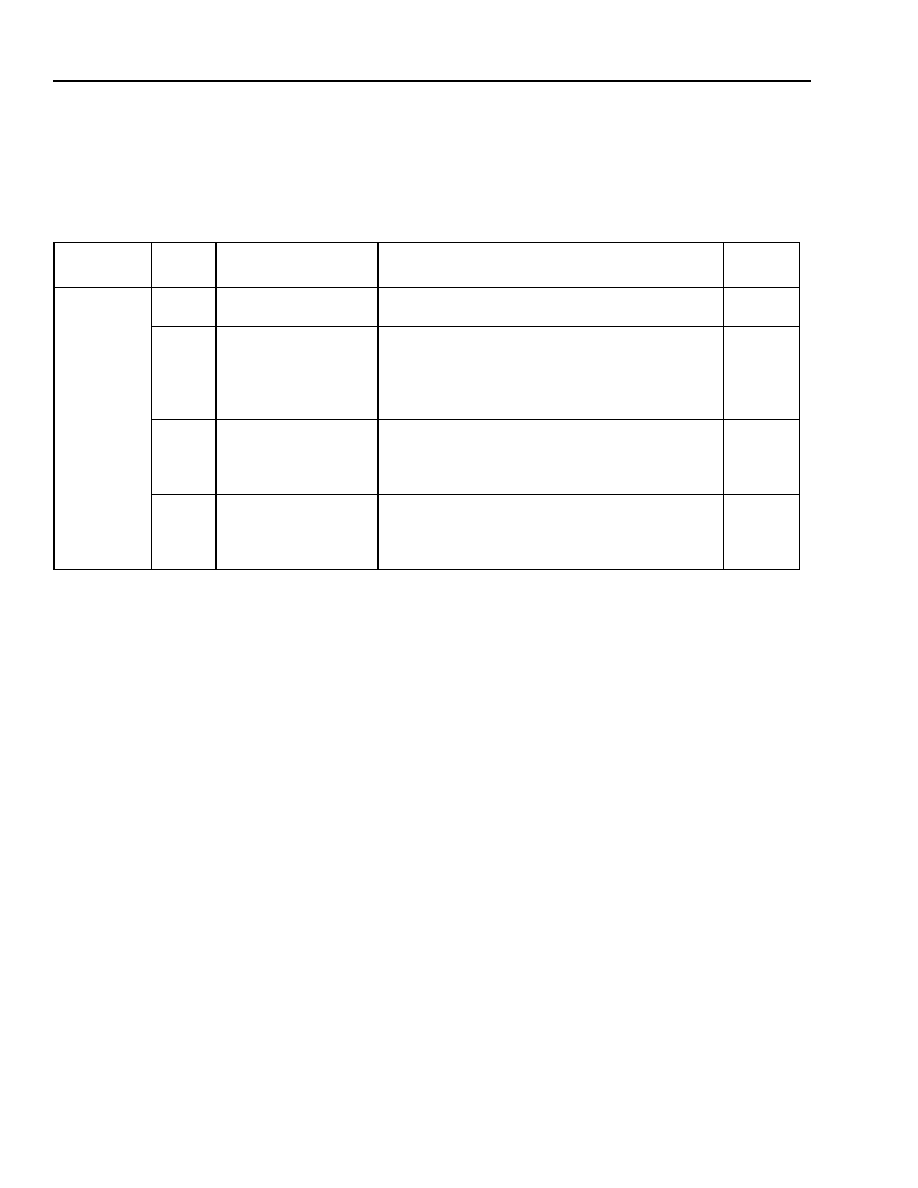

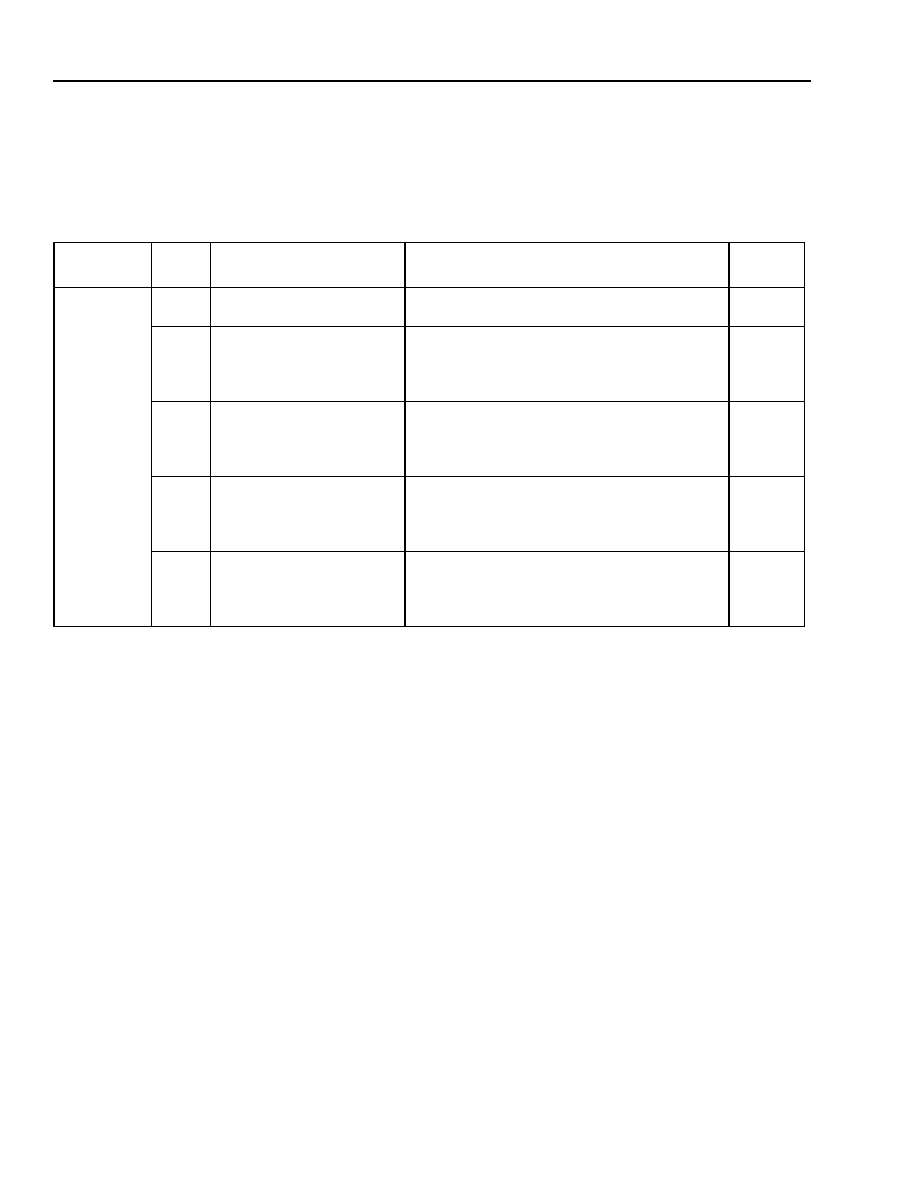

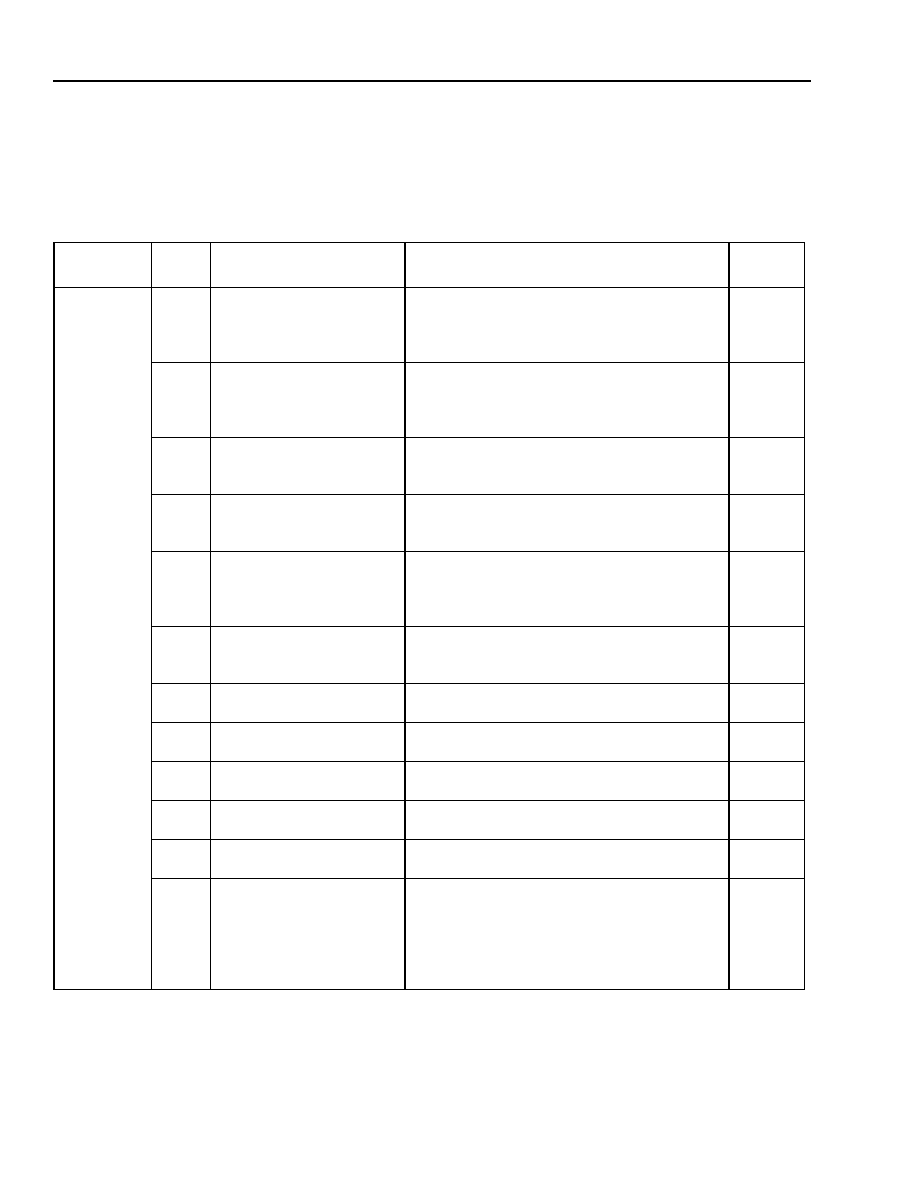

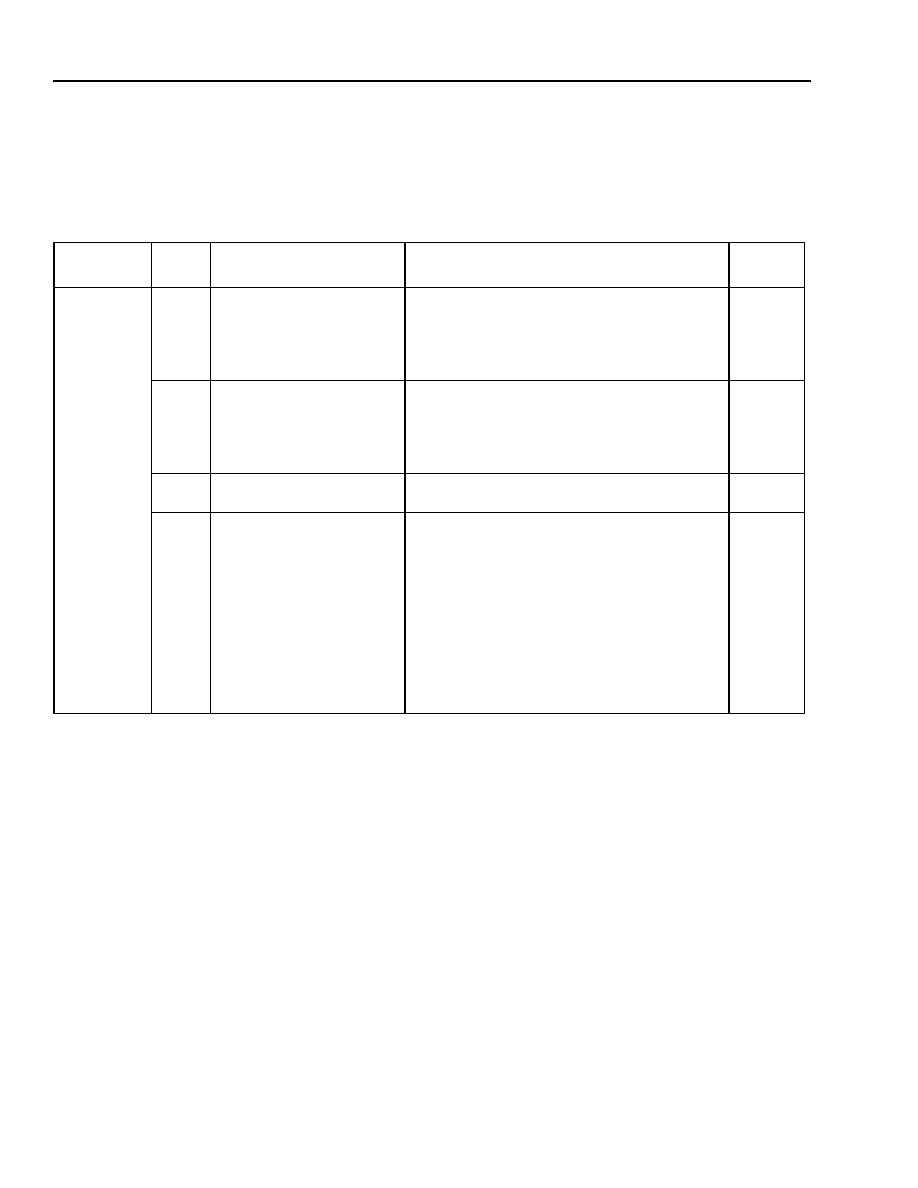

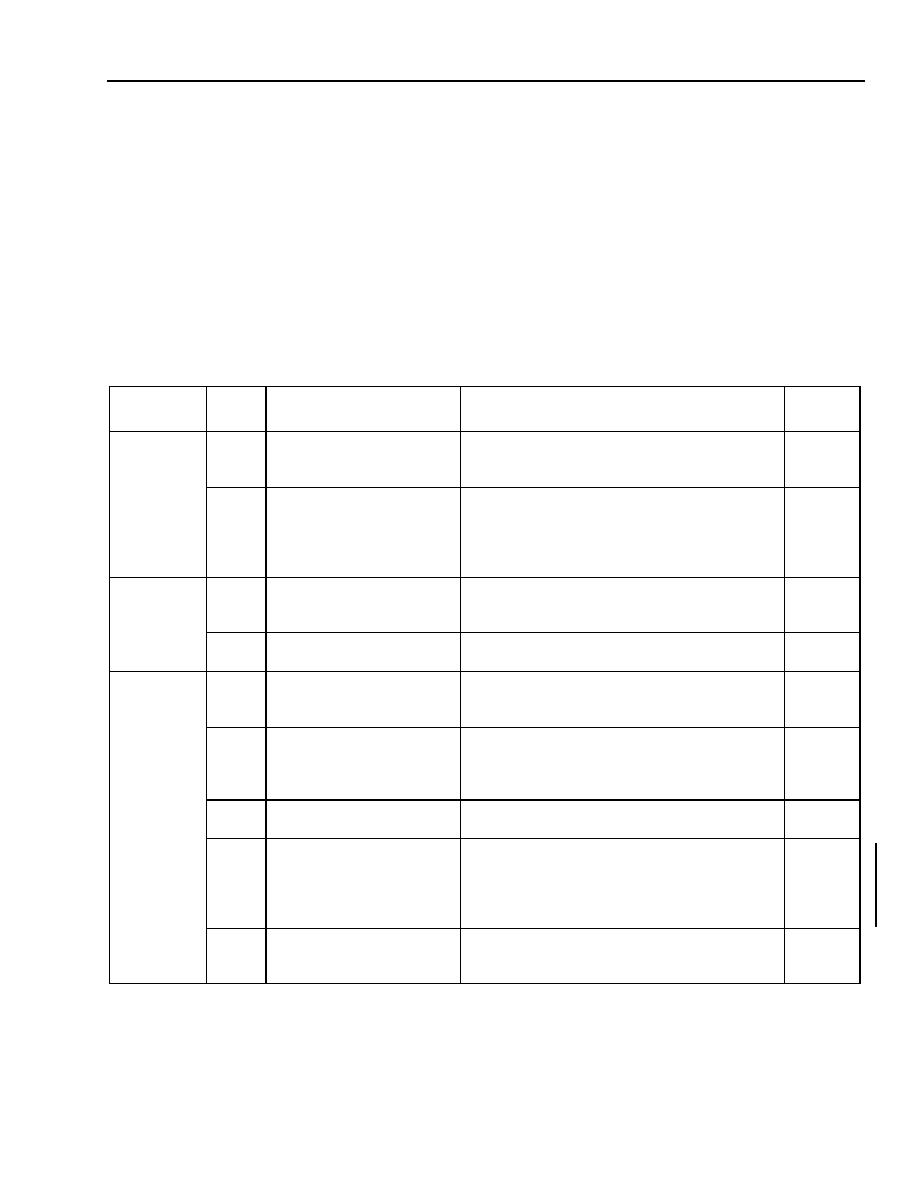

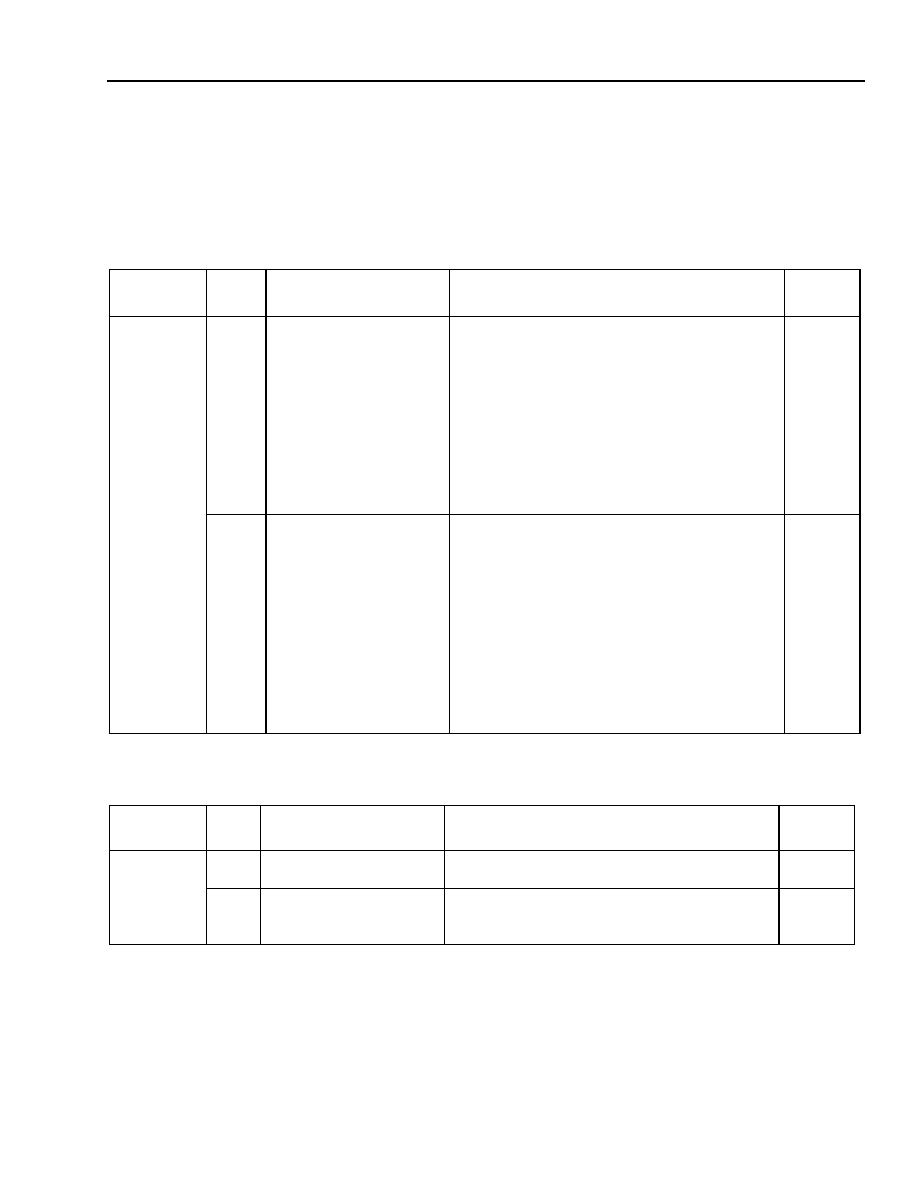

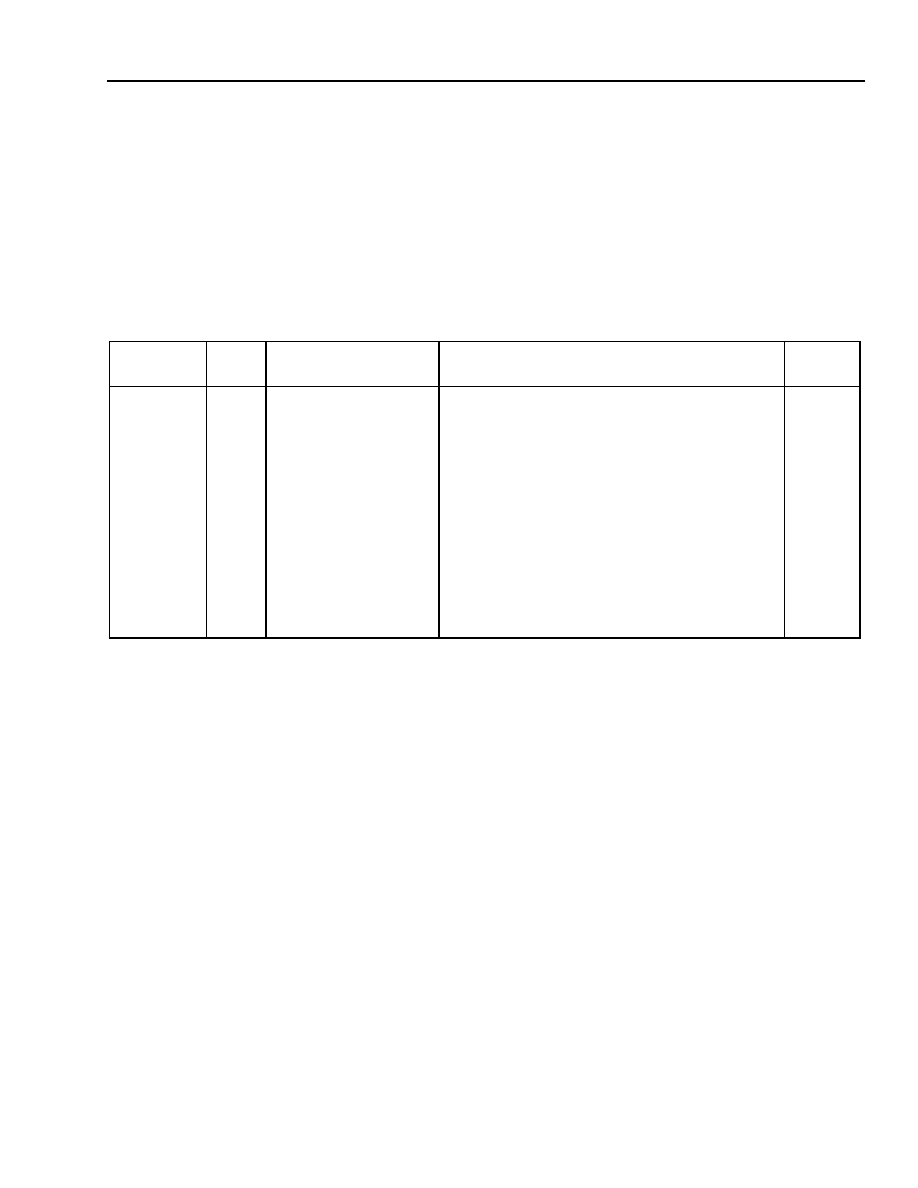

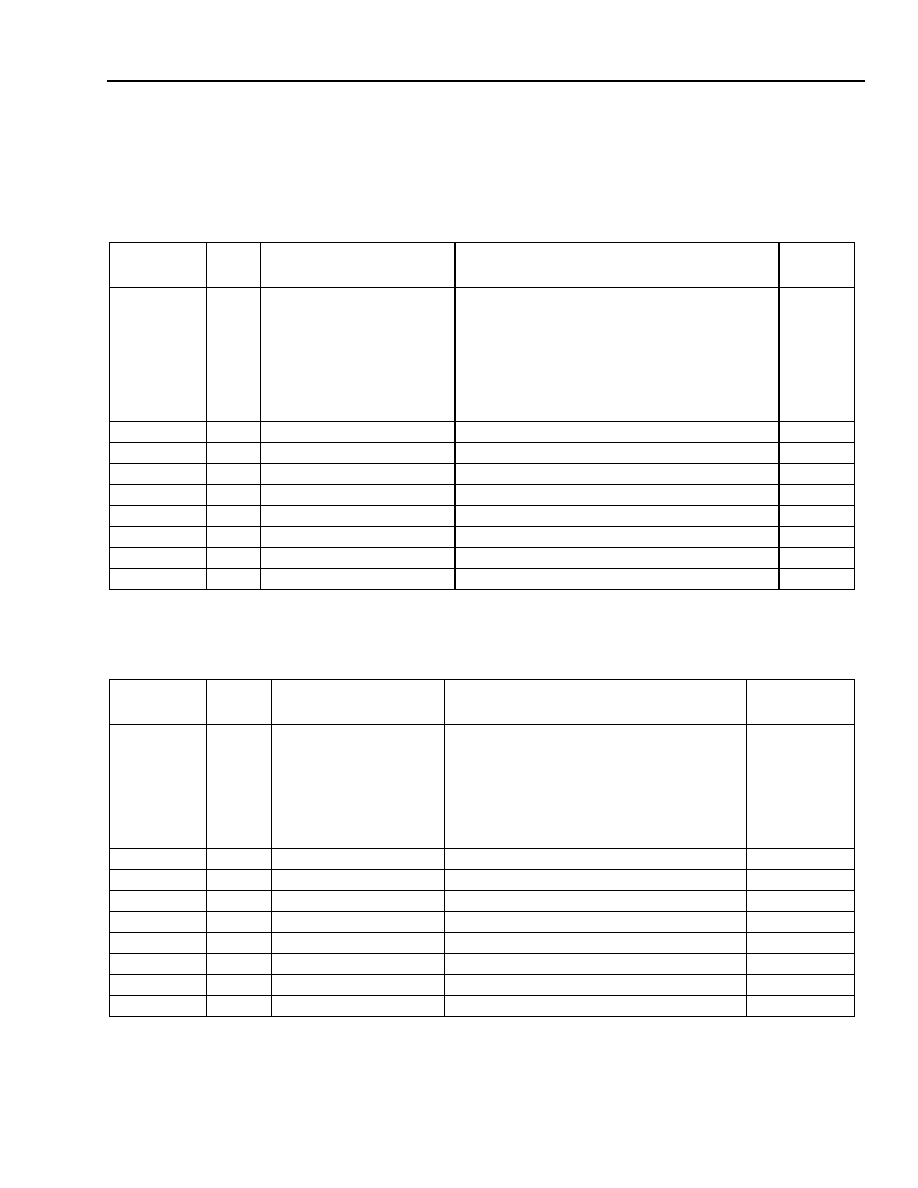

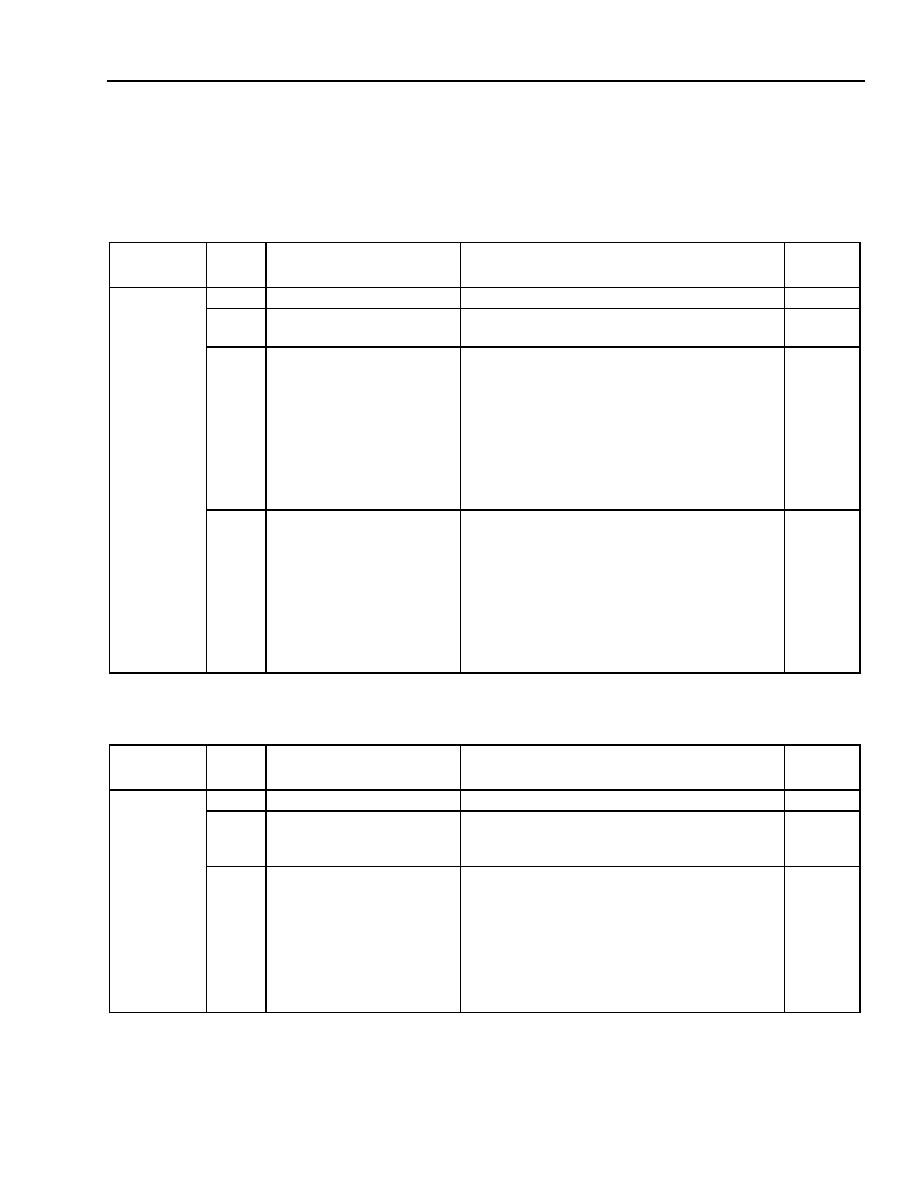

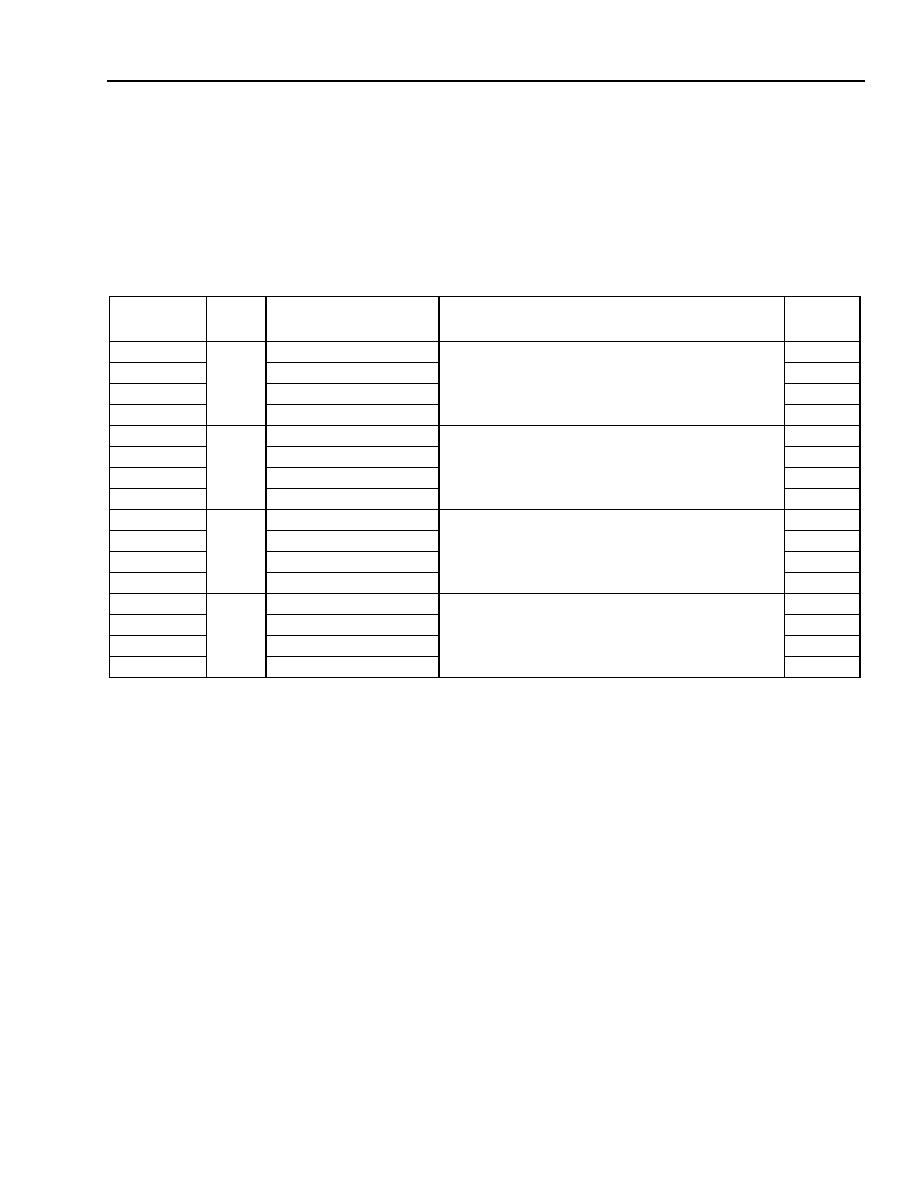

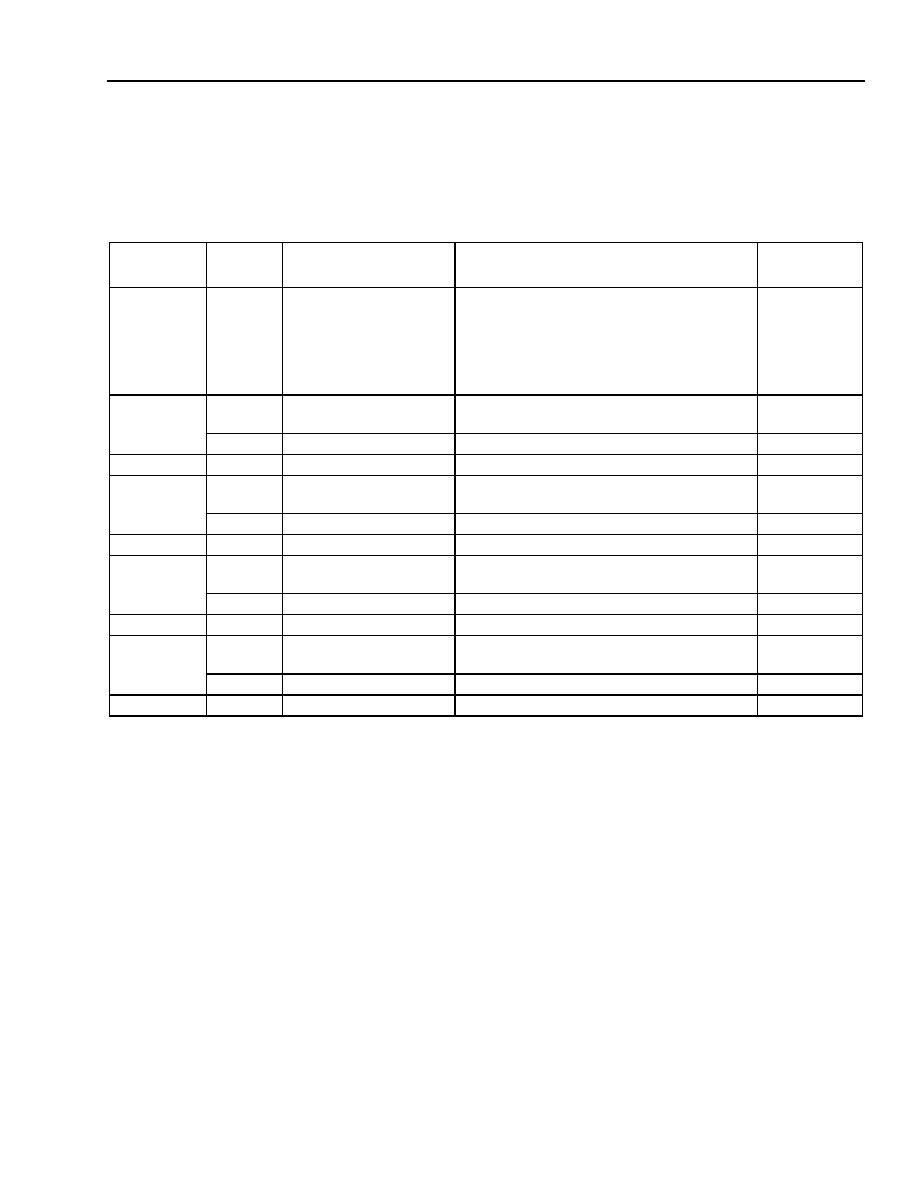

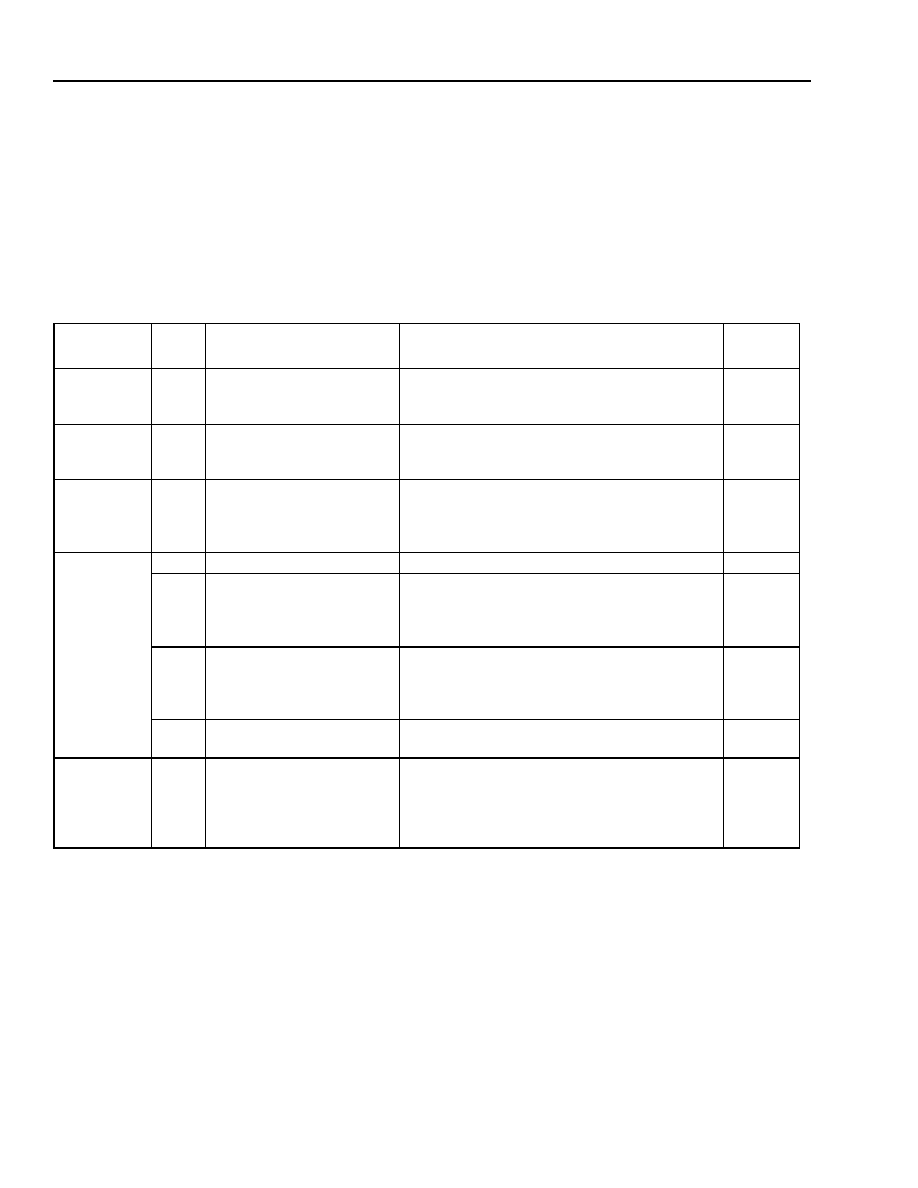

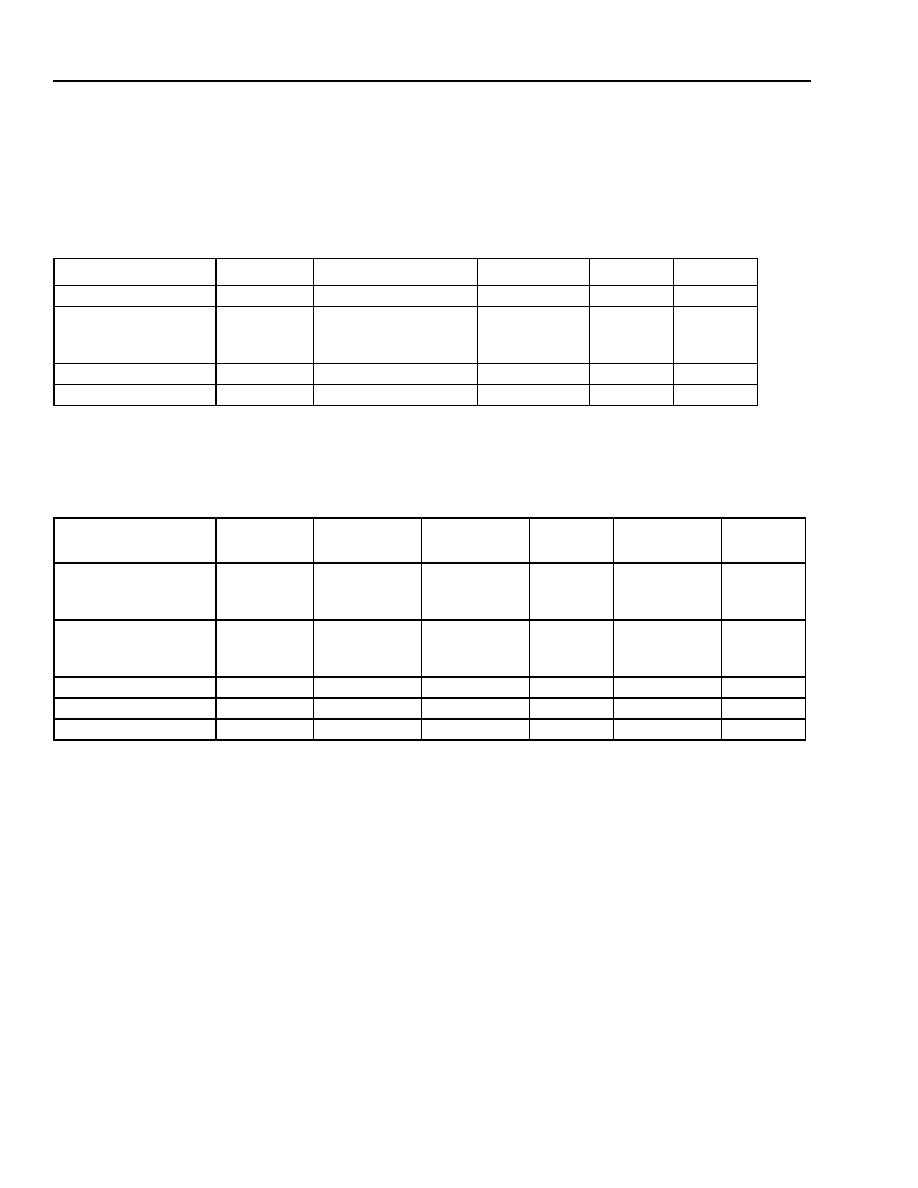

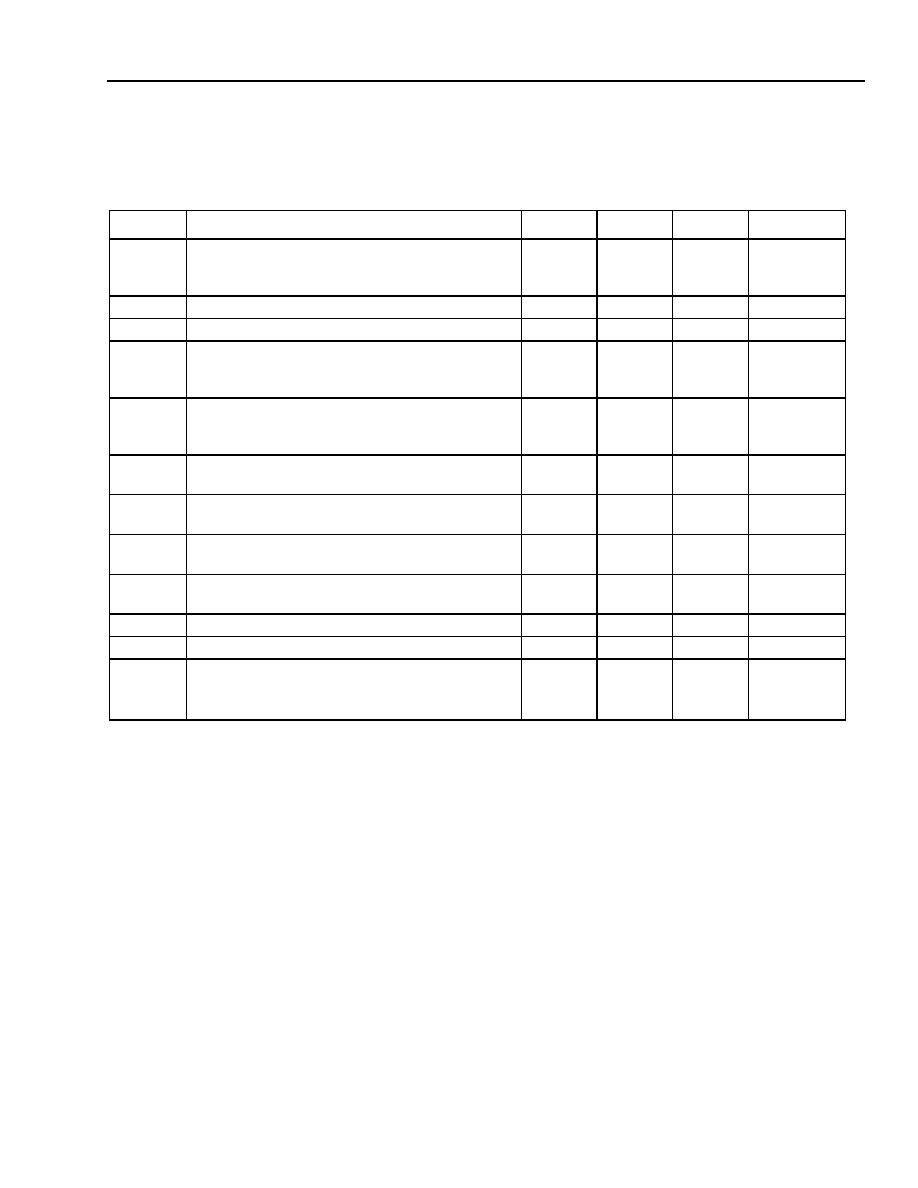

Table 2. Transmit DE Egress and Sequencer Cell State Registers

Corrective Action

This condition will be addressed in future versions of the device.

Address

Value

STS-3/STM-1

STS-12/STM-4

0x1016

0x4567

0x4567

0x1017 0x4567

0x4567

0x1018

0x4567

0x4567

0x1019--0x1021

--

0x4567

0x1036 0x0000

0x0000

Agere Systems Inc.

9

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Data Engine (DE)

(continued)

DE5. Packet Behavior in POS/SDL Mode--Dry Mode

When the device is configured in POS mode with dry mode enabled, the following conditions may persist:

I

PPP mode; STS-48/STS-12/STS-3.

When running in PPP mode, the PPP header--0xFF03 0x0021 (provisionable)--may be incorrectly inserted at

any point in a packet within the outgoing data stream when the FIFO runs dry, thereby corrupting the packet.

Packets being sent are corrupted if the FIFO runs dry.

I

PPP and CRC modes; STS-48/STS-12/STS-3.

CRC, PPP, and HDLC modes; STS-48/STS-12/STS-3.

In PPP, CRC, and HDLC dry modes, some of the packet data may be corrupted when the packet length is above

a certain size where size is dependent upon UT clock rate and low watermark setting. Either sections of the

packet may be lost or additional packets may be inserted.

Workaround

Several workarounds are possible:

I

Do not provision dry mode for this device.

I

If dry mode is provisioned:

-- Do not allow the FIFO to be emptied.

-- Run the UTOPIA clock fast enough, as shown in Table 3, so that the FIFO is never empty.

-- Use a larger external FIFO to buffer the data.

-- Do not allow the packet size to exceed the low watermark.

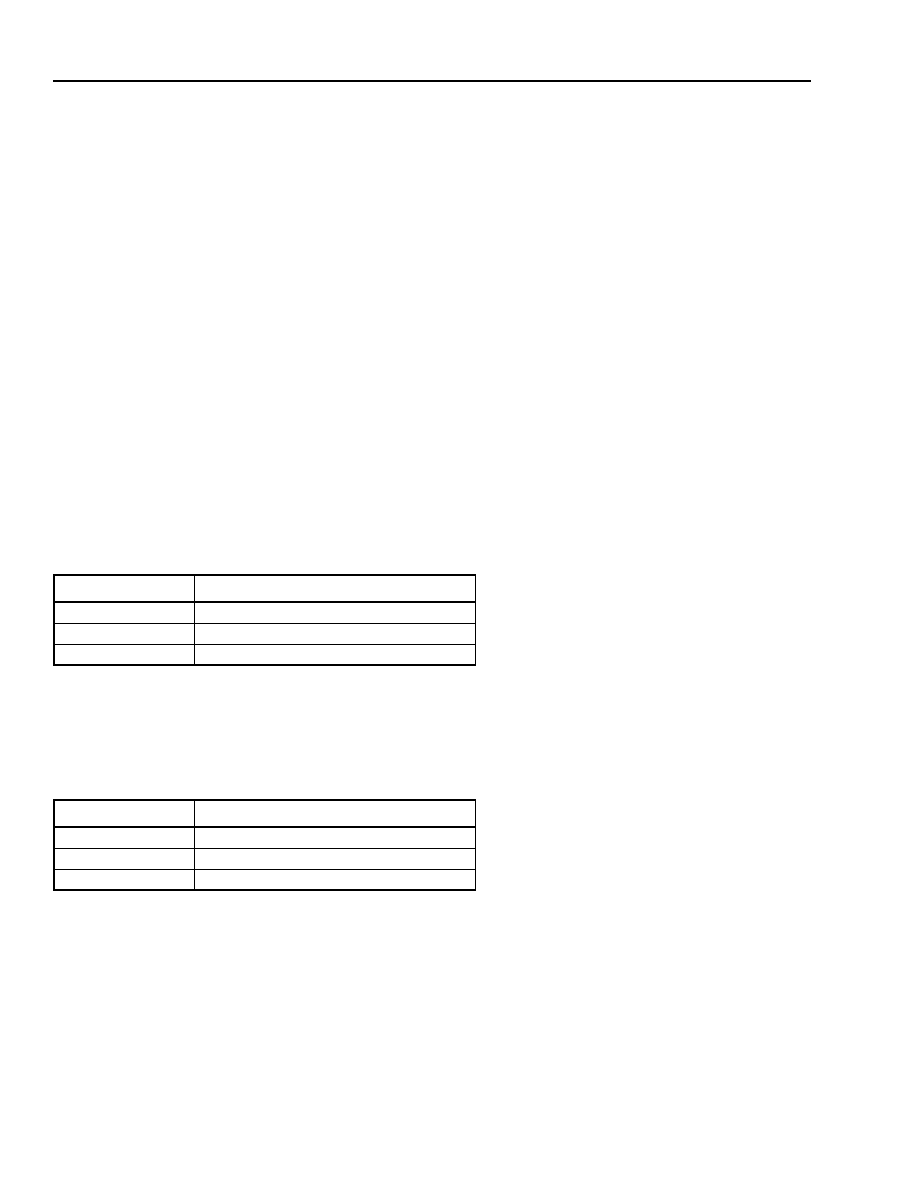

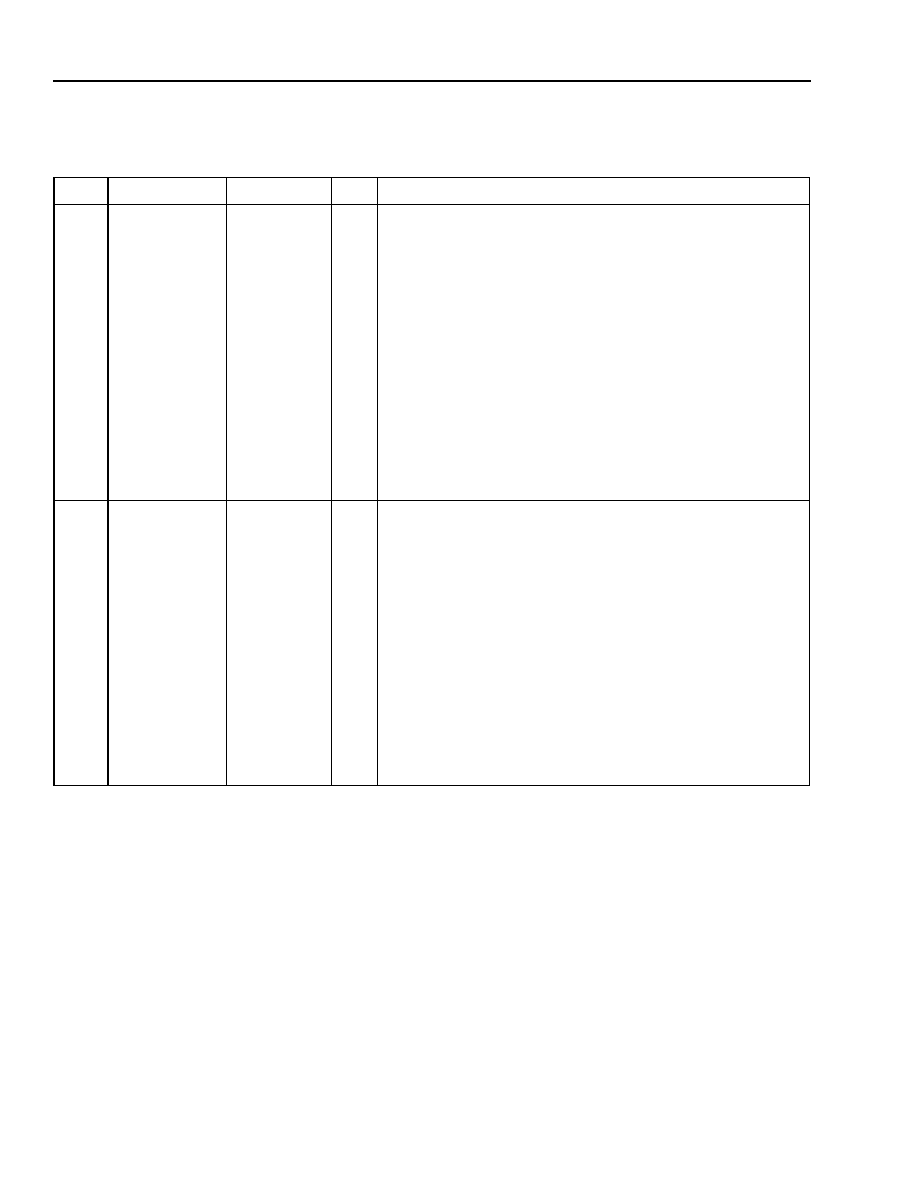

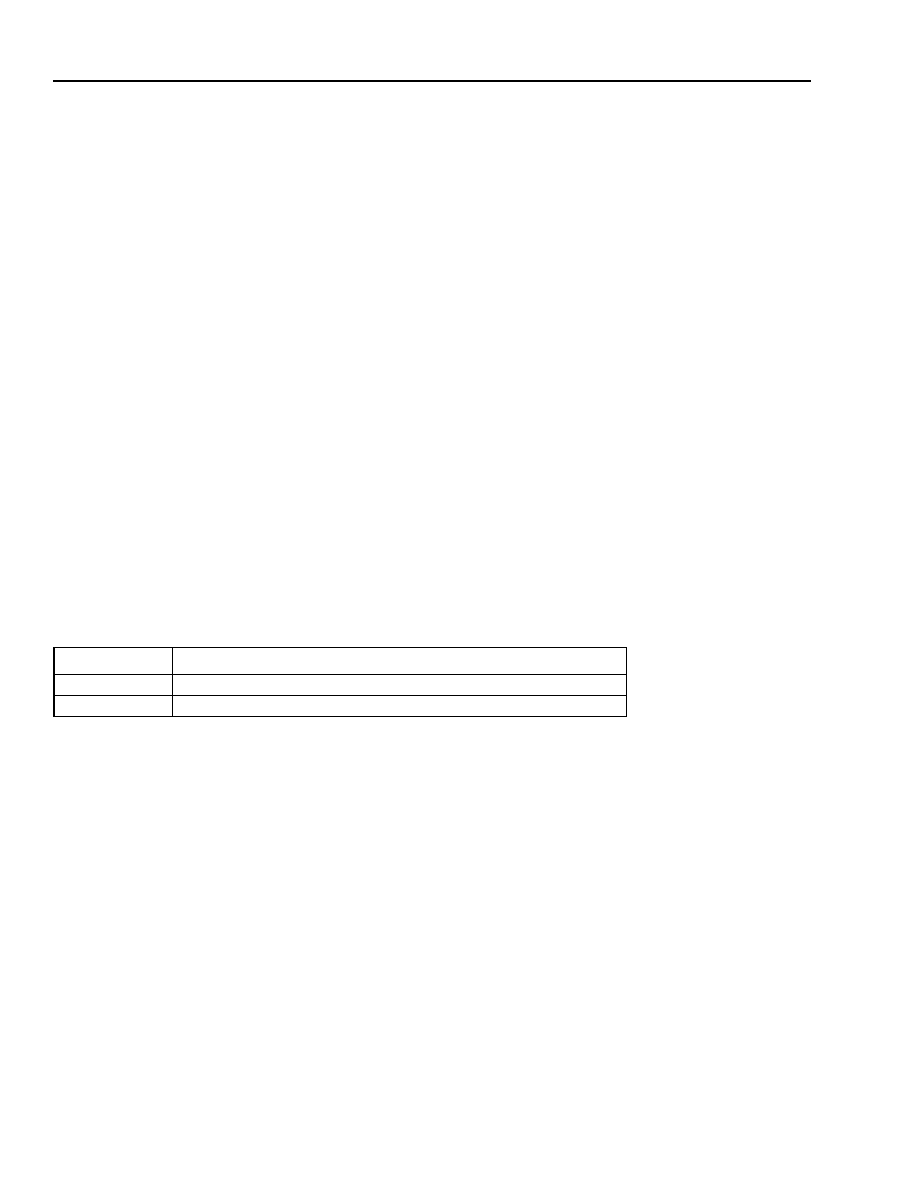

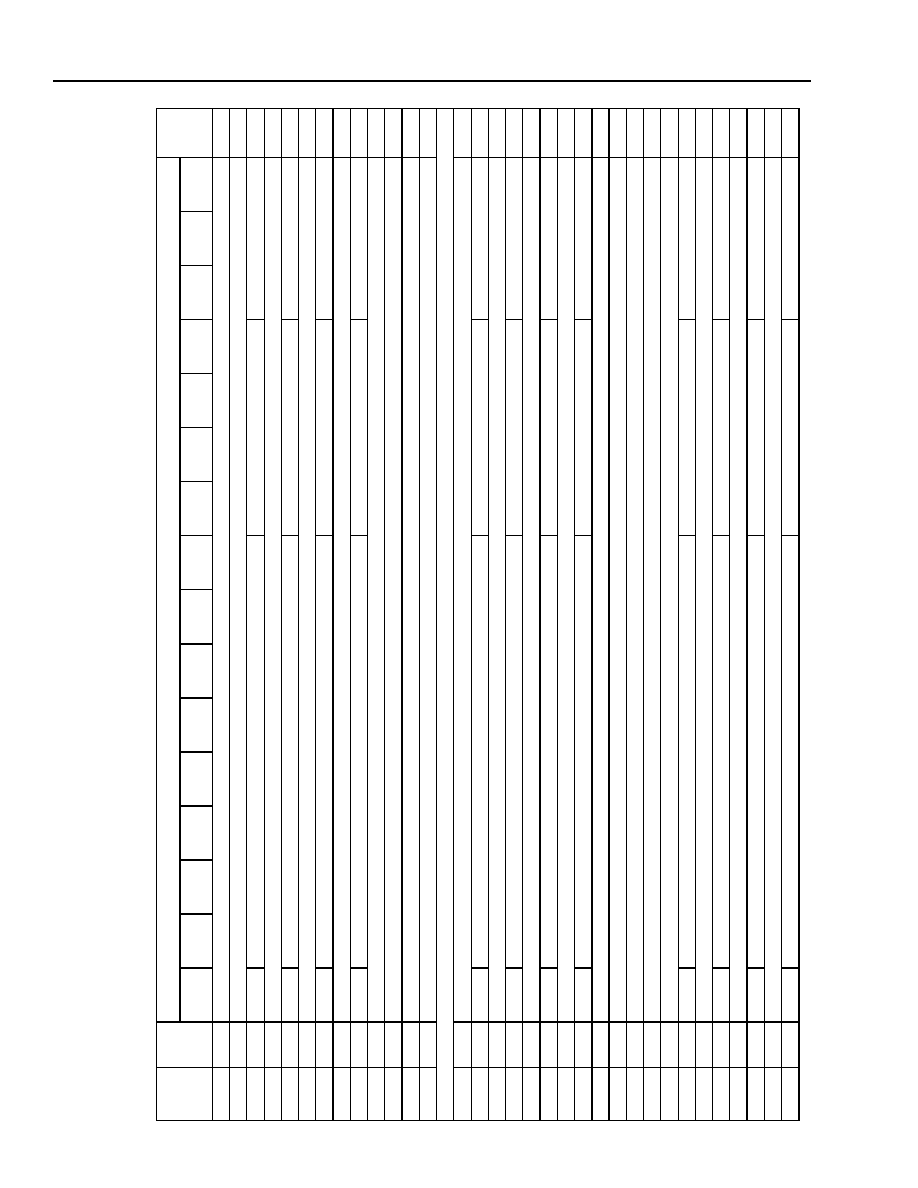

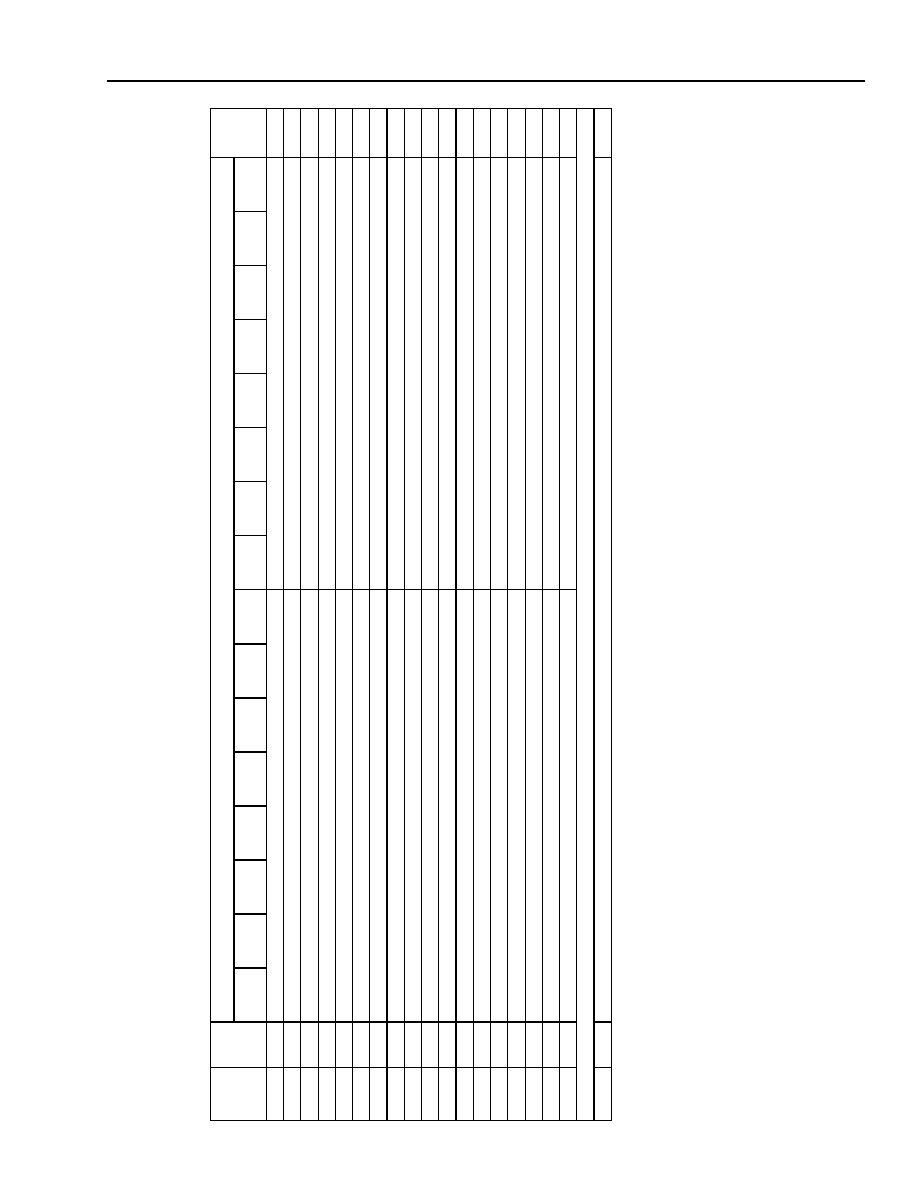

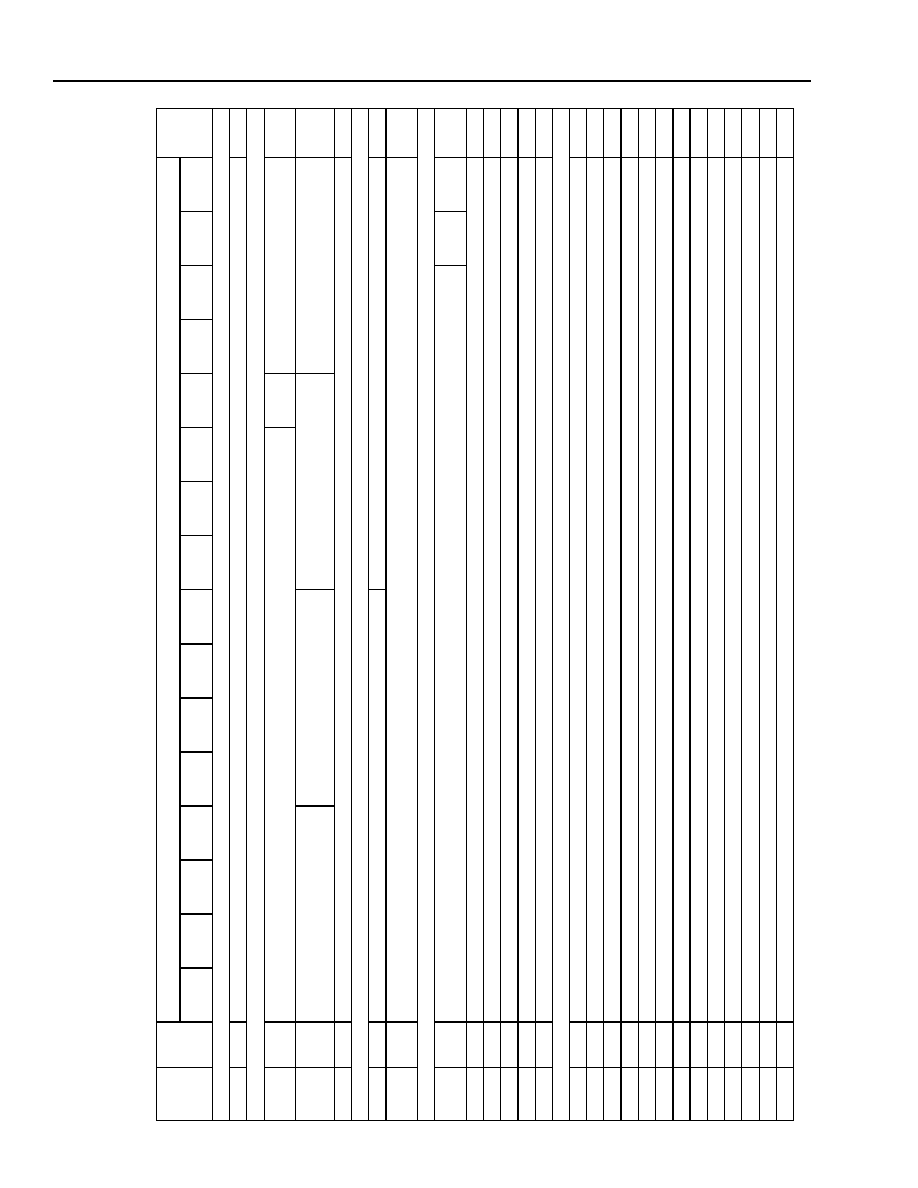

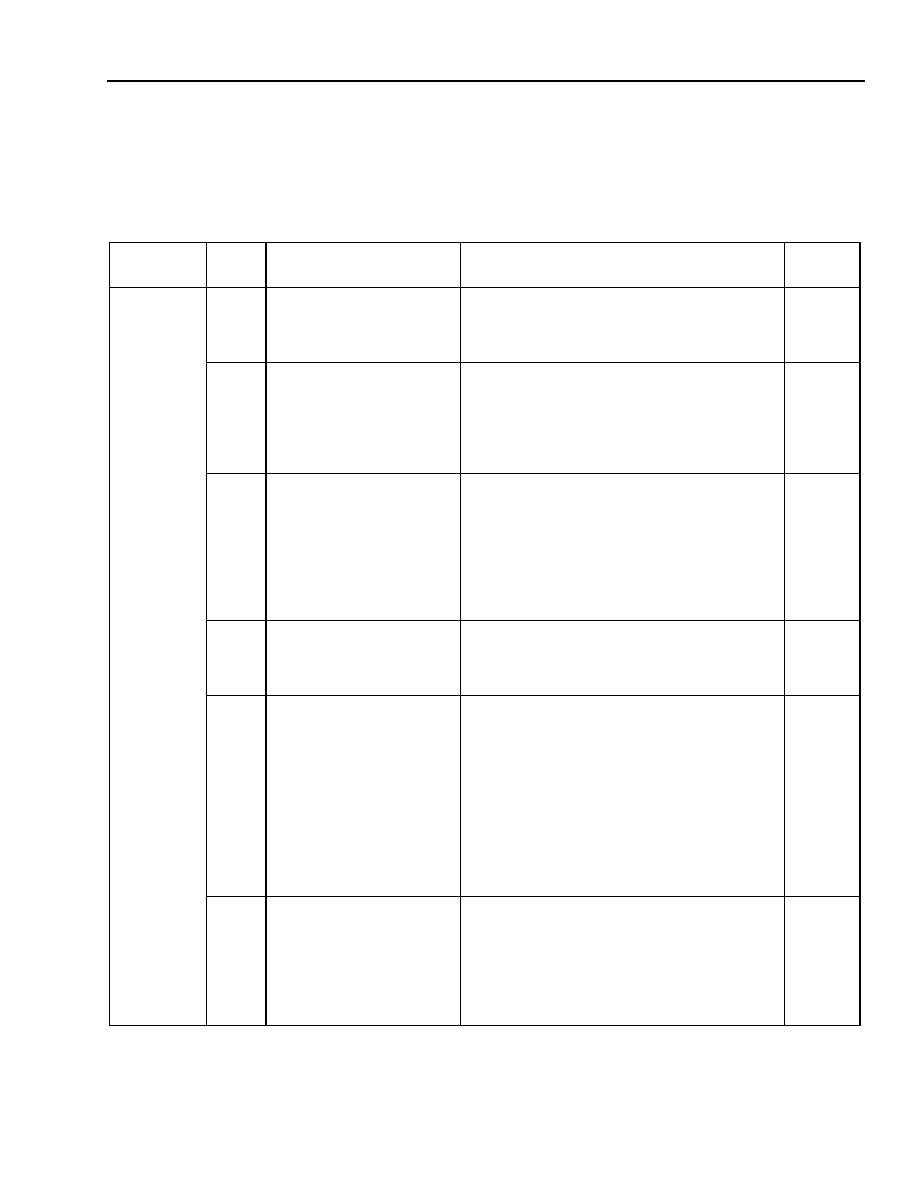

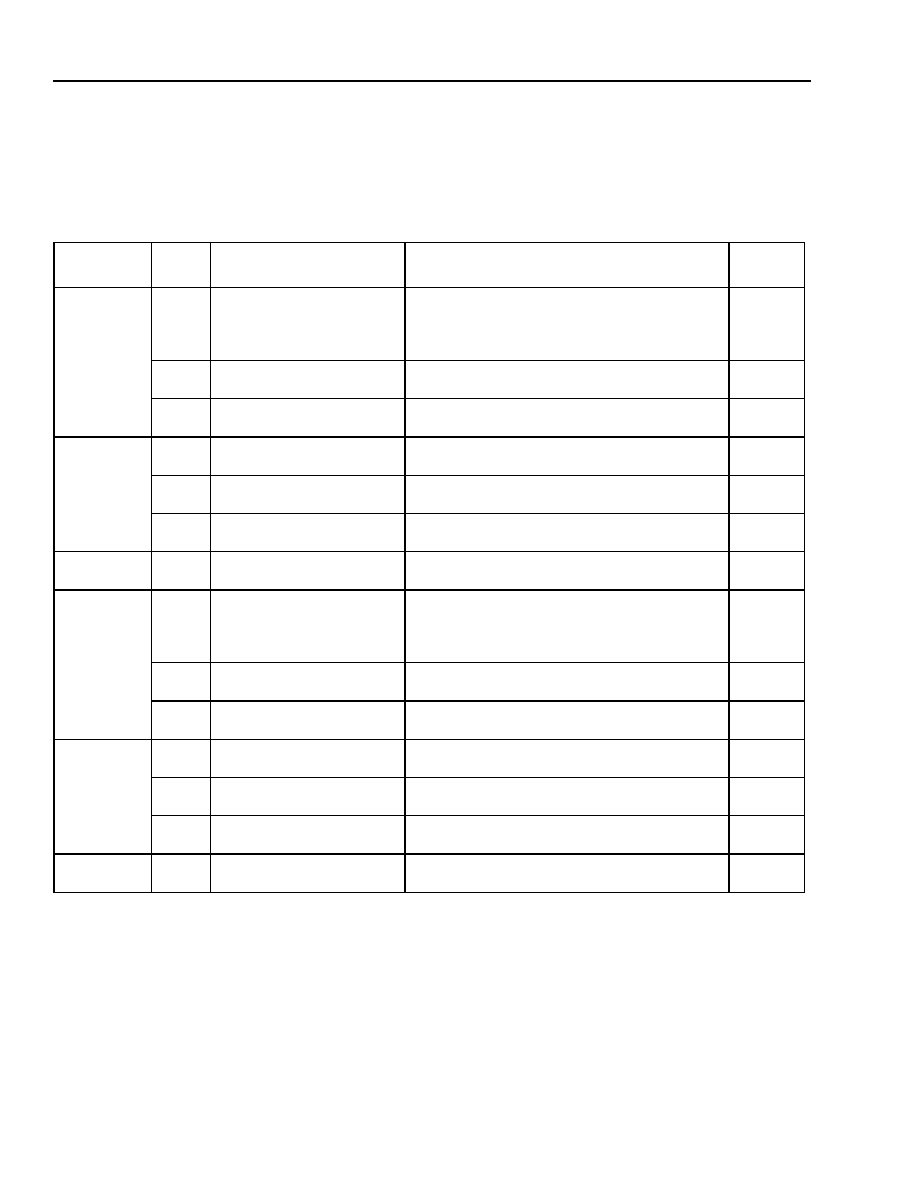

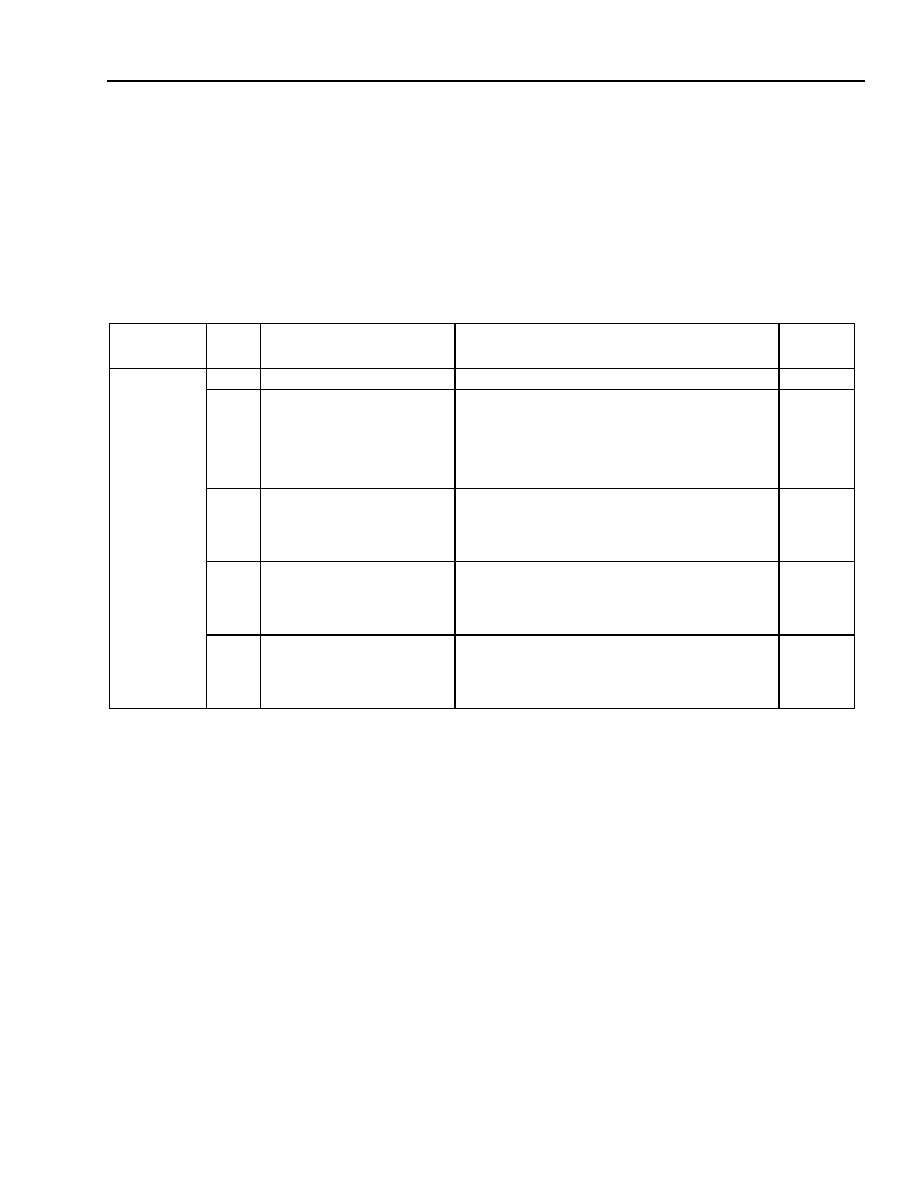

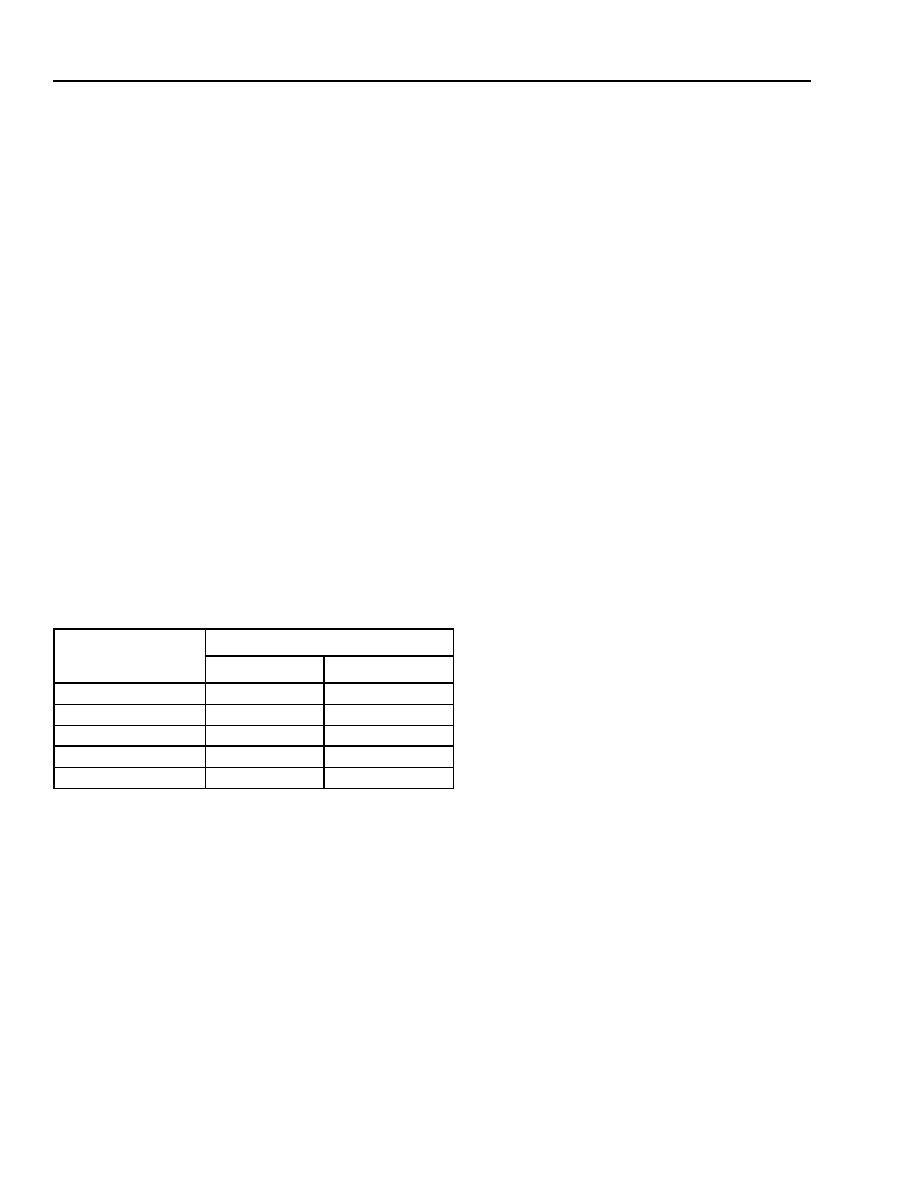

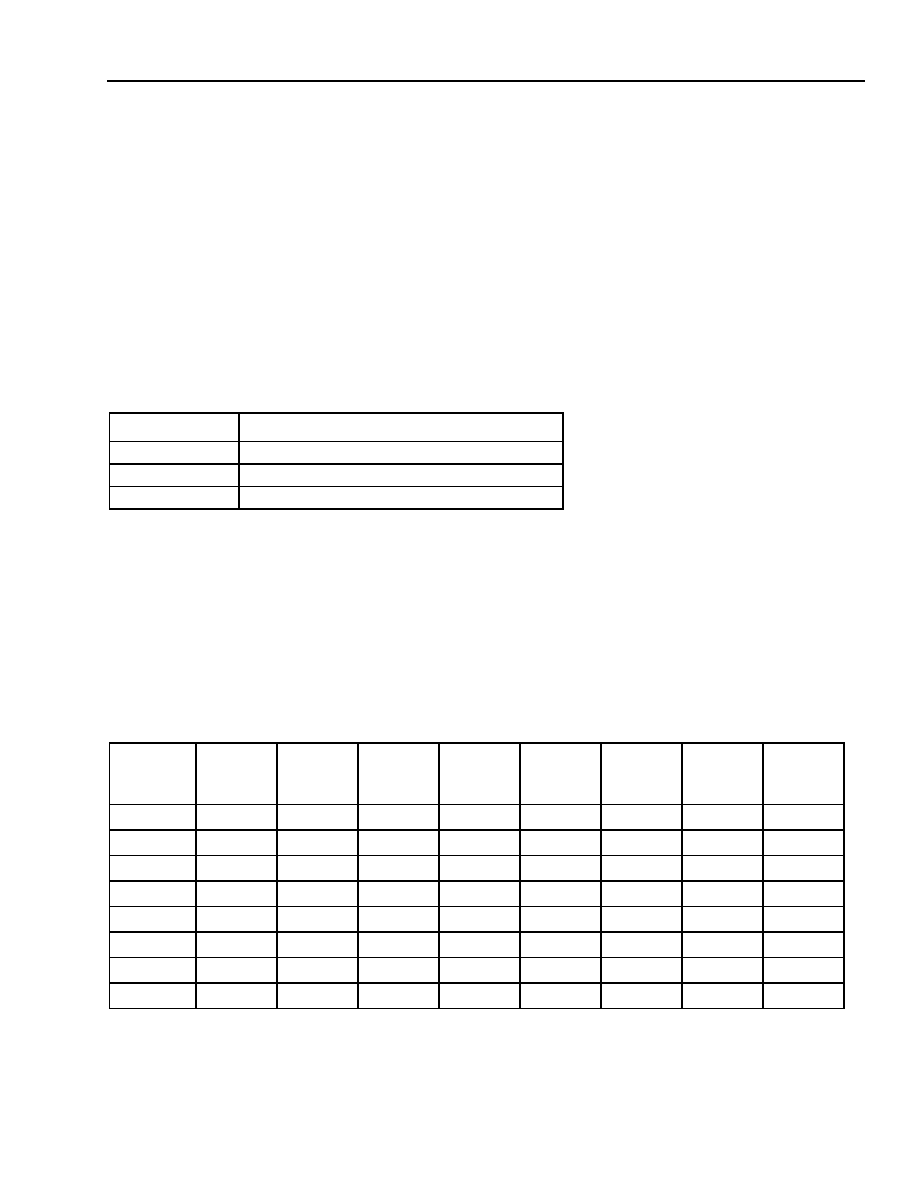

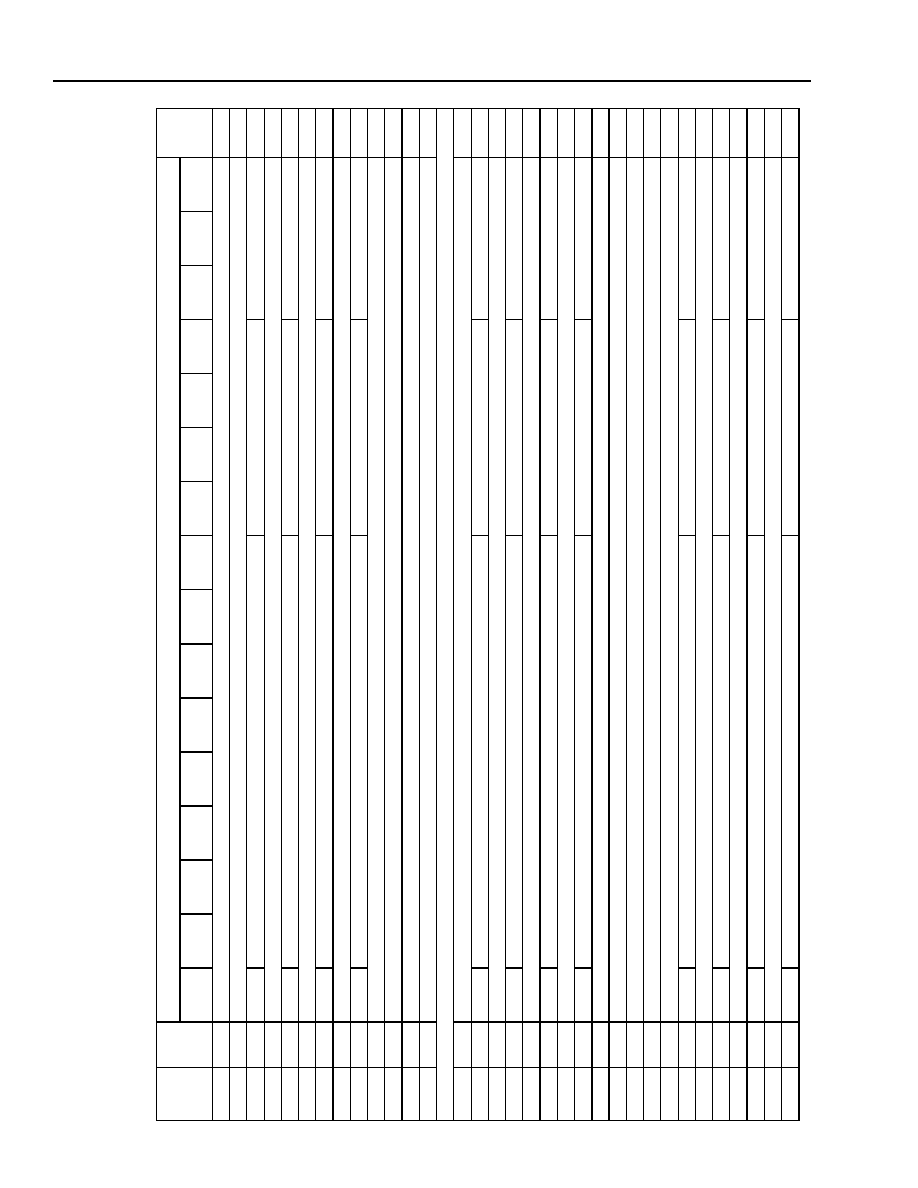

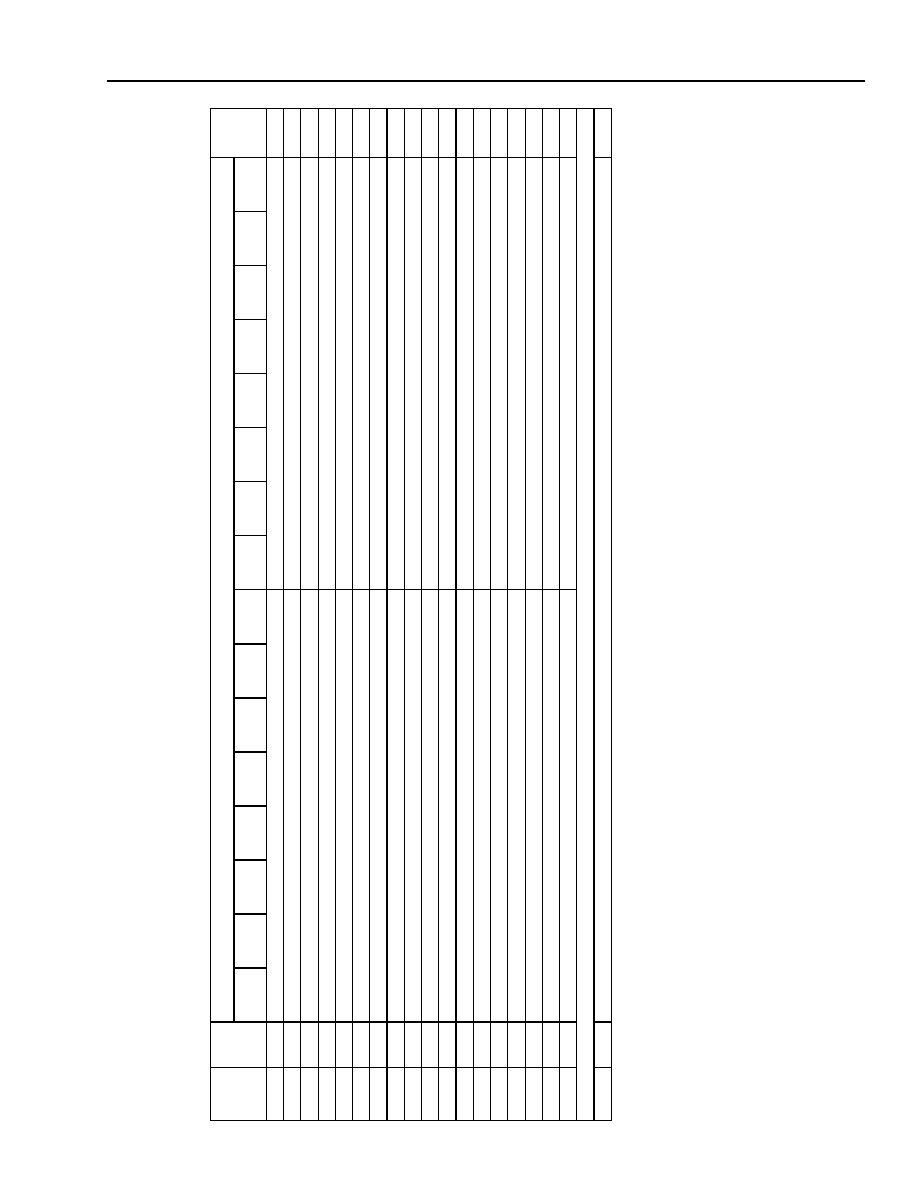

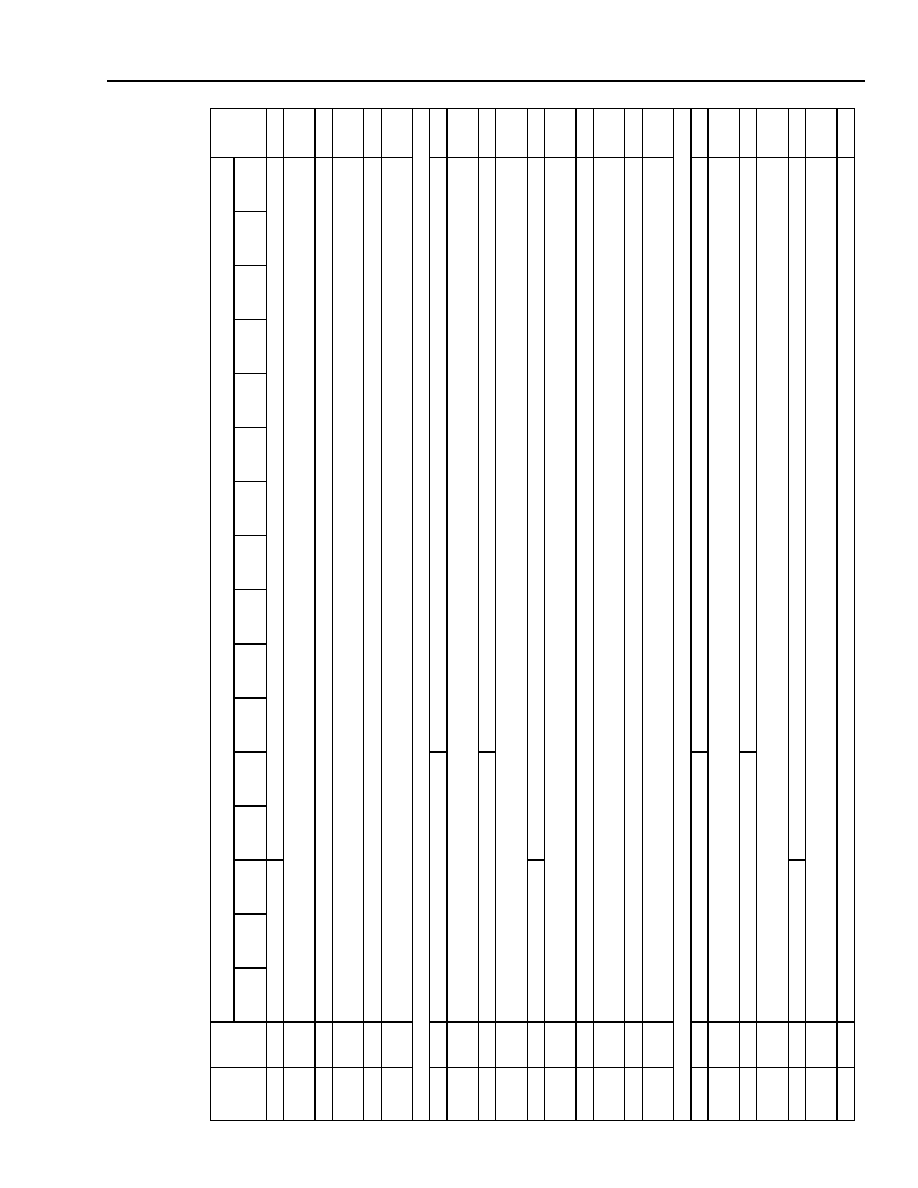

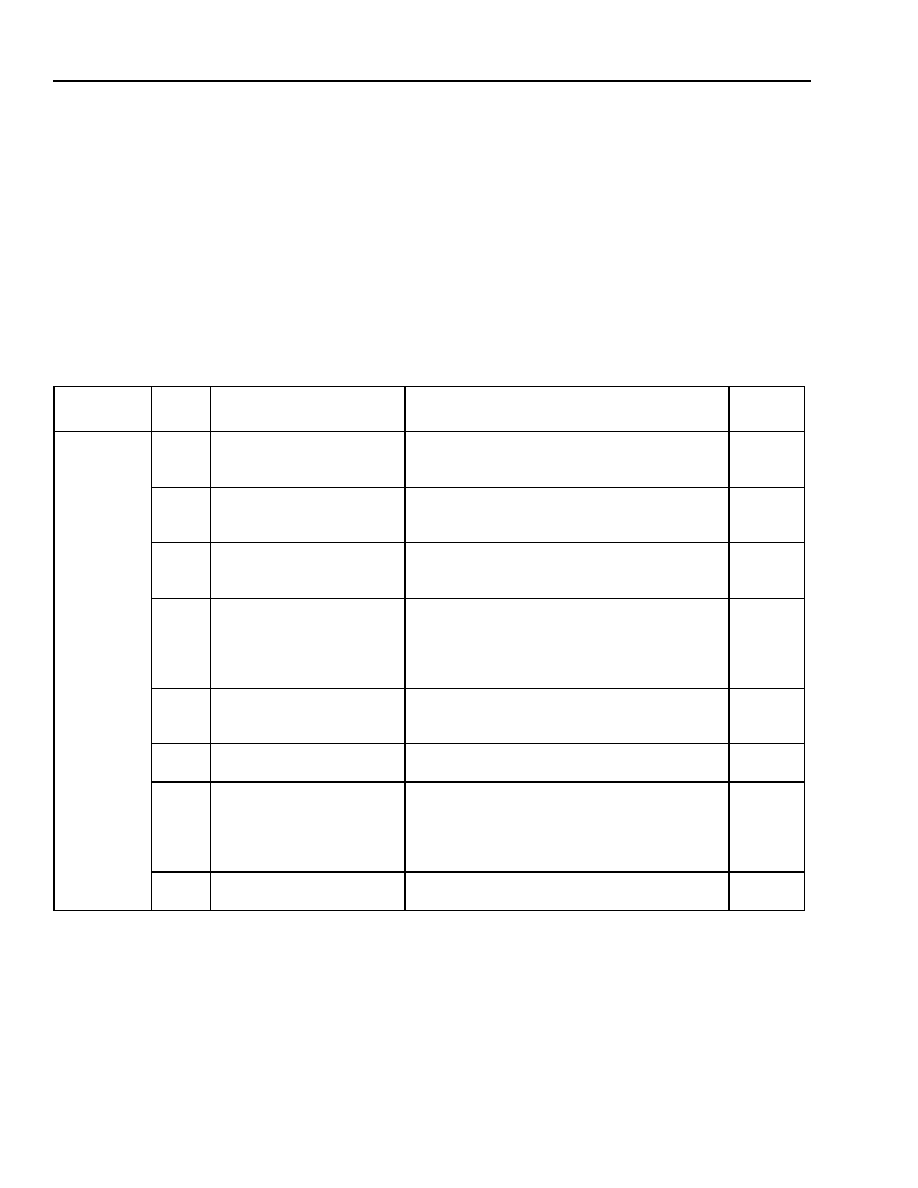

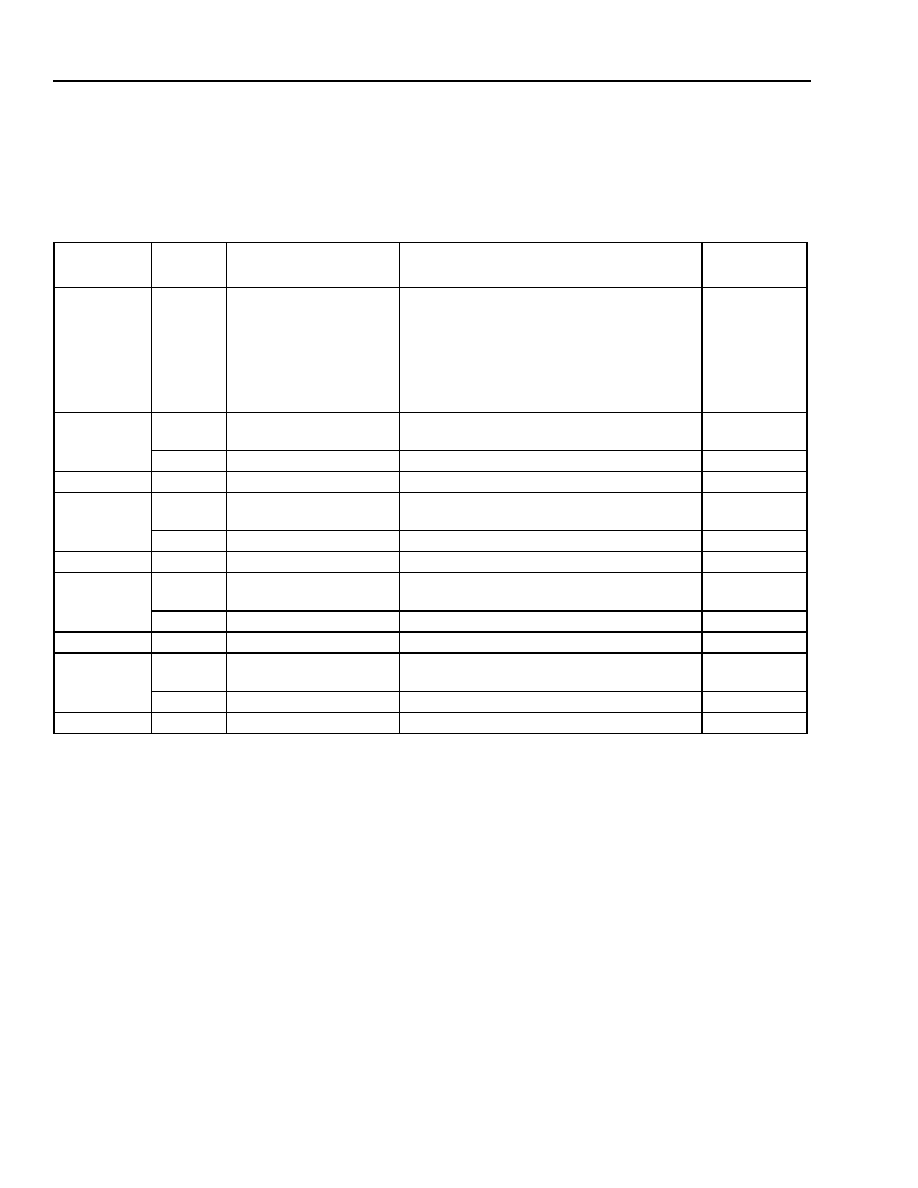

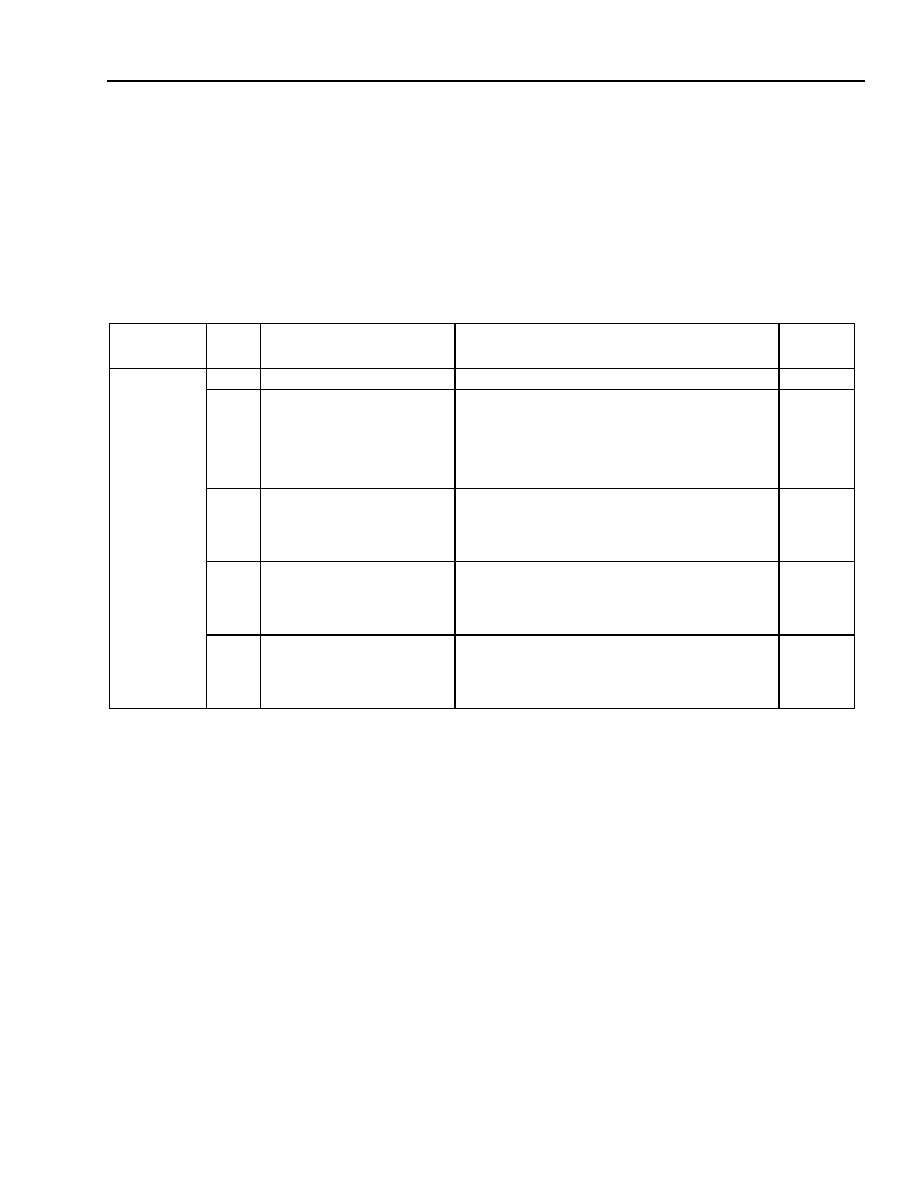

Table 3. Required UTOPIA Clock (TxCLK) Rates

Corrective Action

This condition will be corrected in version 1A of the device.

Mode

TxCLK and Rate

STS-48/STM-16

TxCLK > 77 MHz (U3+, 32-bit mode)

STS-12/STM-4

TxCLK > 40 MHz

STS-3/STM-1

TxCLK > 10 MHz

10

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Data Engine (DE)

(continued)

DE6. Incorrect ATM Out of Cell Delineation (OCD) Implementation

In ATM mode, the OCD reporting for channels B, C, and D is incorrect. The OCD state of channel A is reported for

channels B, C, and D. The OCD reporting is correct for channel A.

Workaround

No workaround is available for this condition.

Corrective Action

This condition will be corrected in version 1A of the device.

DE7. Incorrect Frame State of ATM Data Streams

When sending a single ATM data stream to channel A, the frame states of channels B, C, and D are incorrectly set

to sync mode. This prevents LCD errors from being reported on channel A as well. In addition, when sending a sin-

gle ATM data stream to channels B, C, or D, the frame states always remain in hunt mode. This results in LCD

errors on those channels.

Workaround

No workaround is available for this condition.

Corrective Action

A software workaround will be available with version 1A of the device.

Agere Systems Inc.

11

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Data Engine (DE)

(continued)

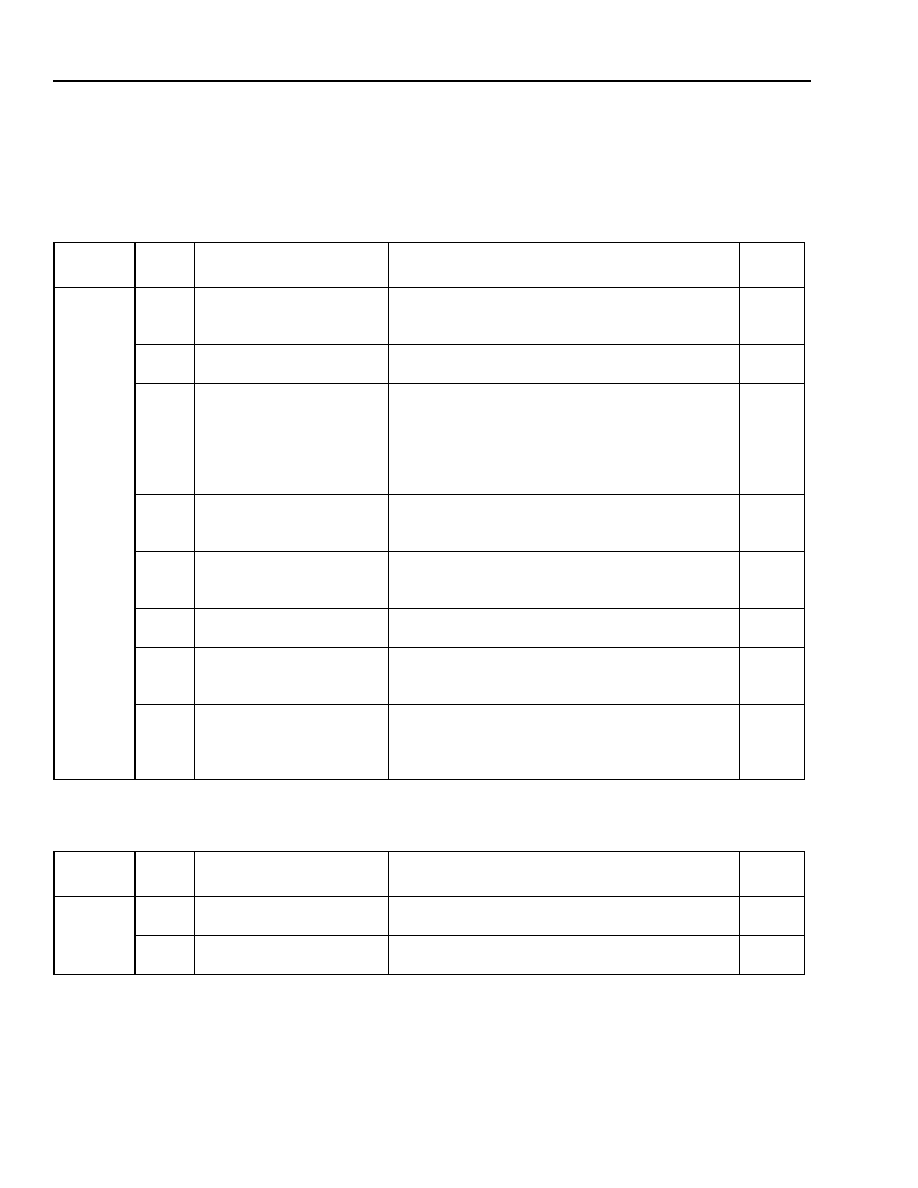

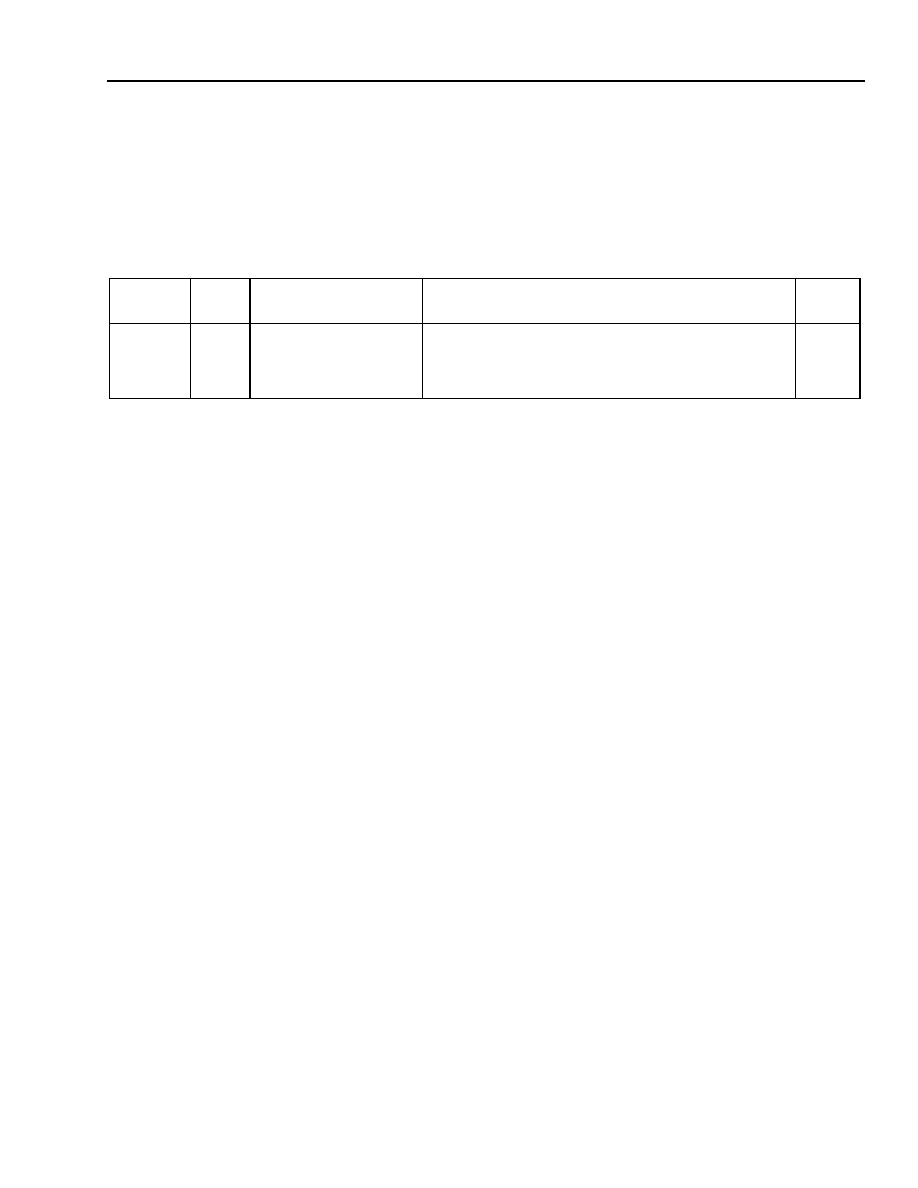

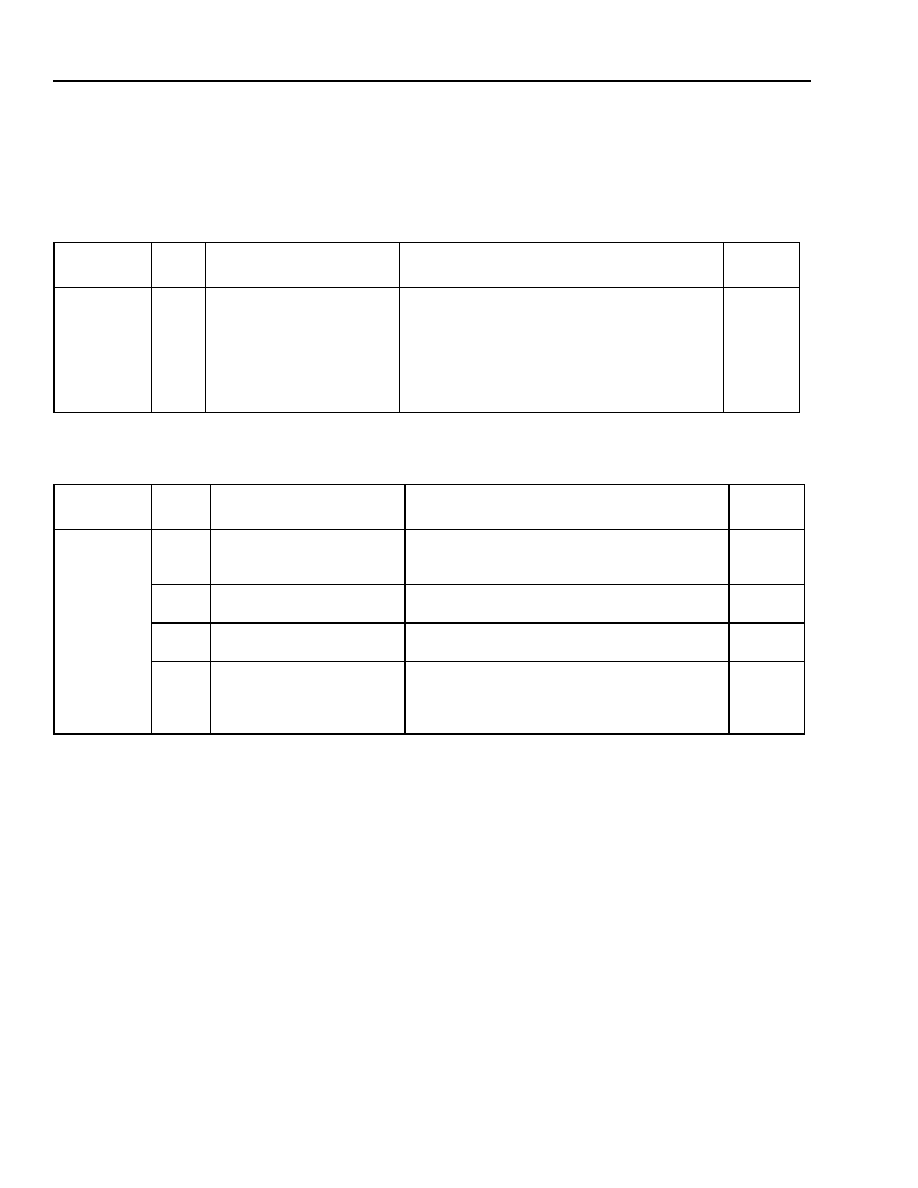

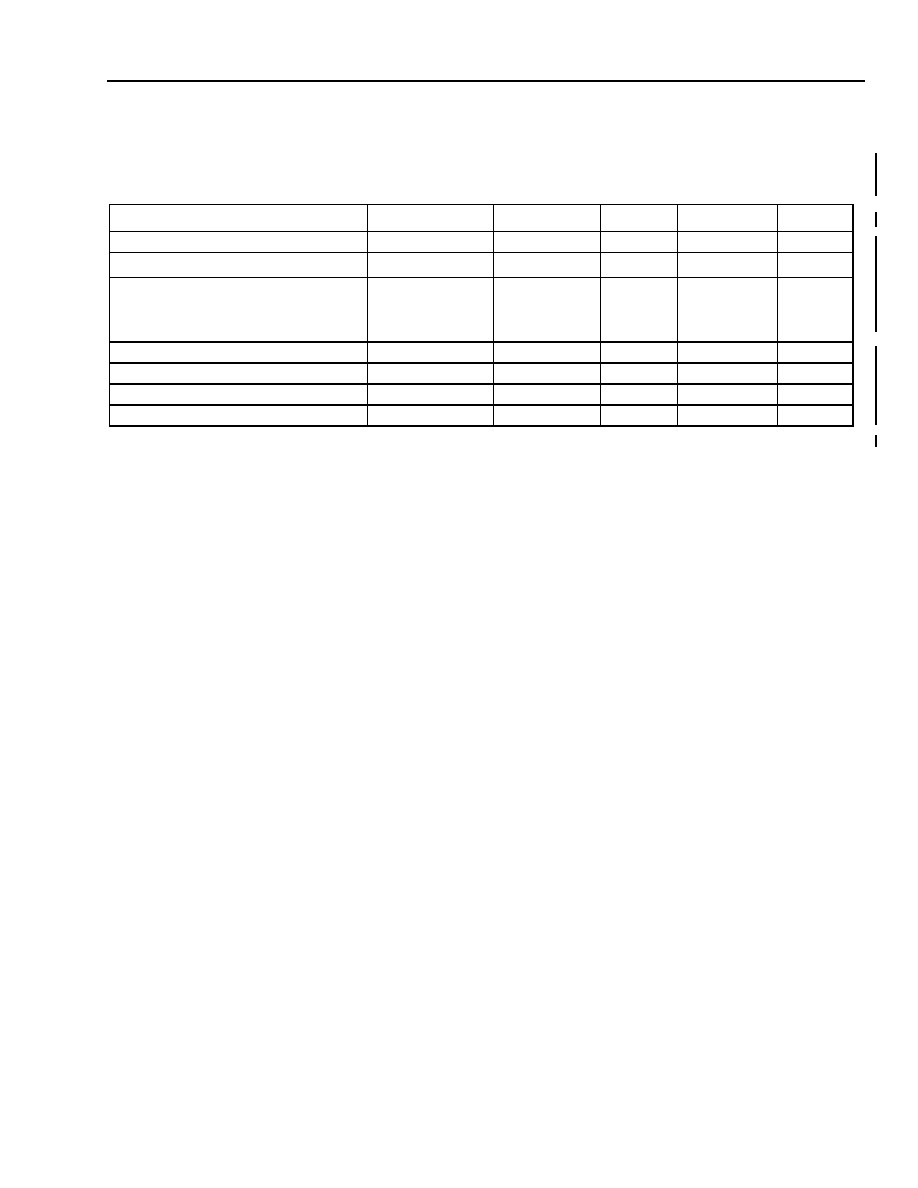

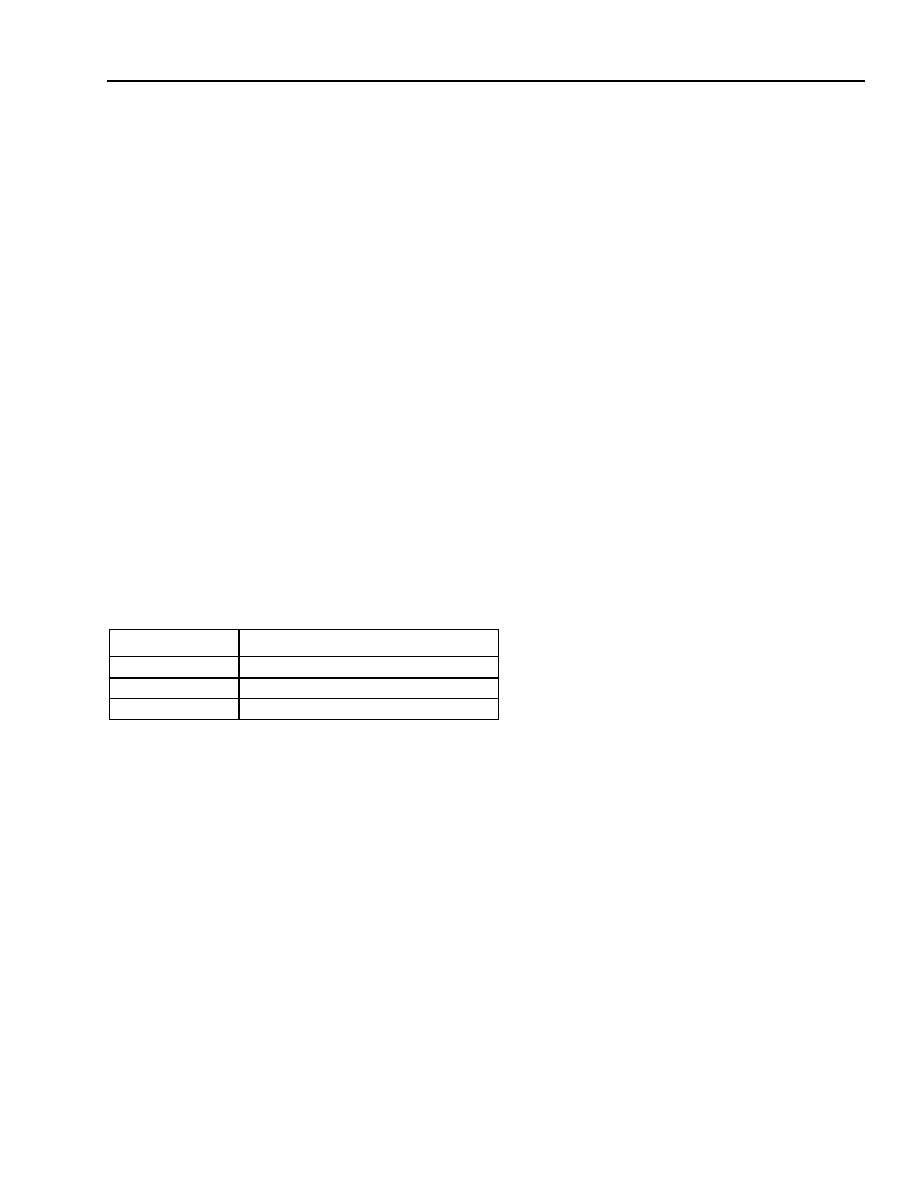

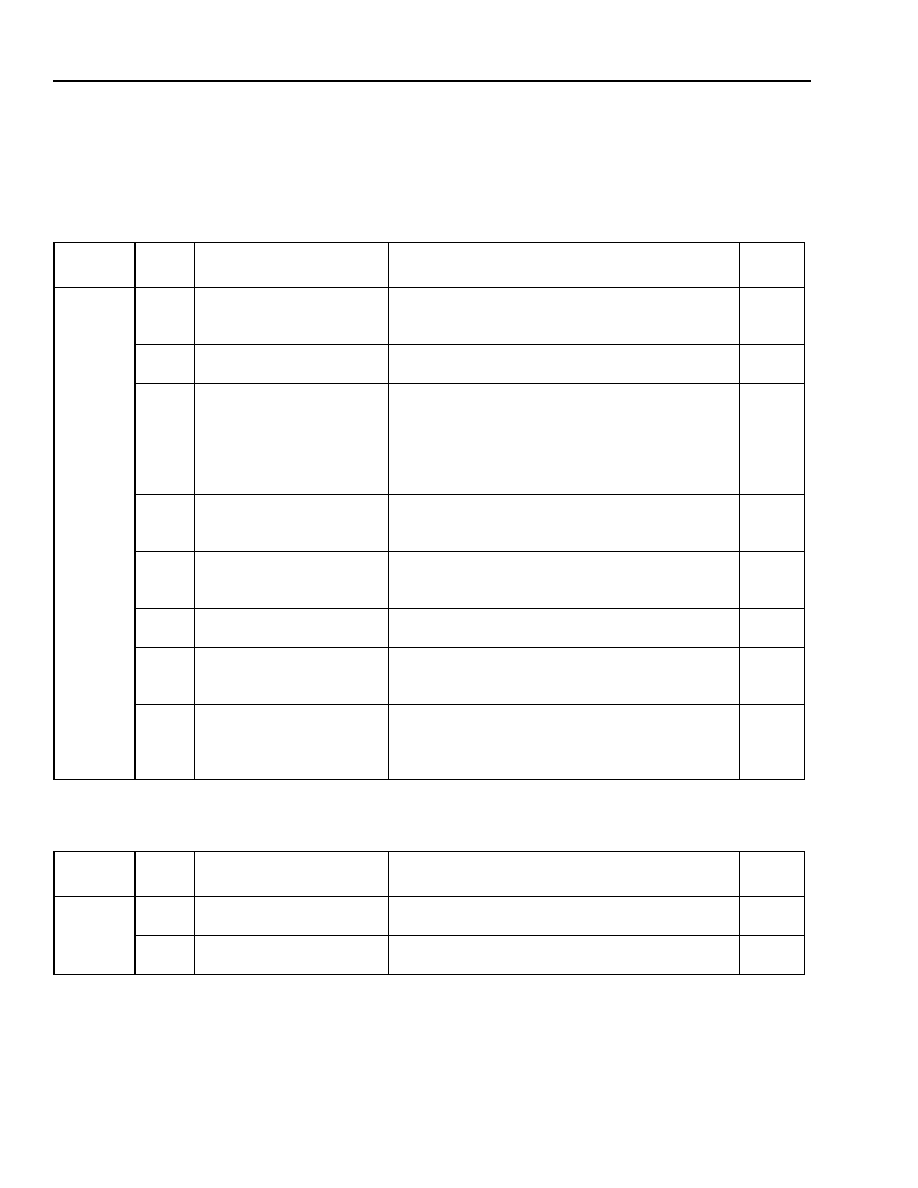

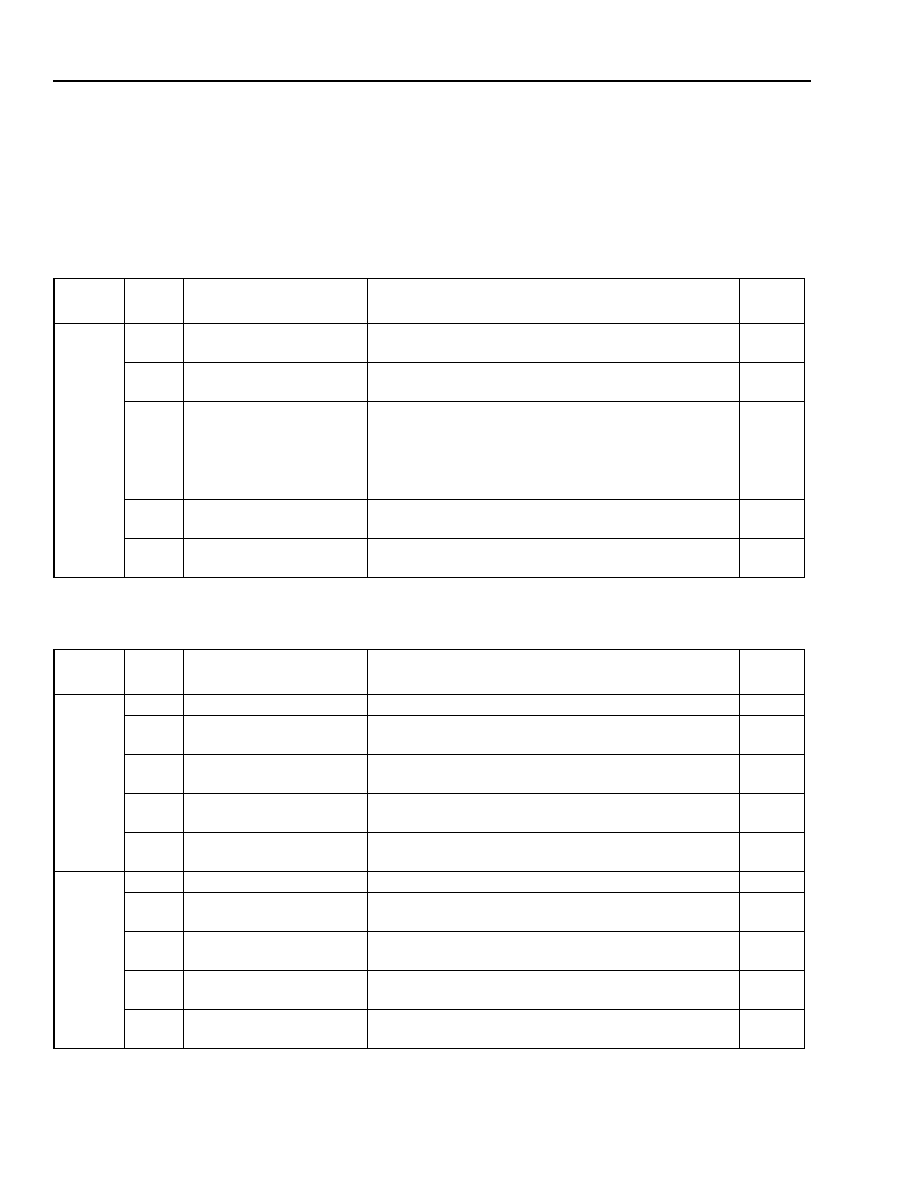

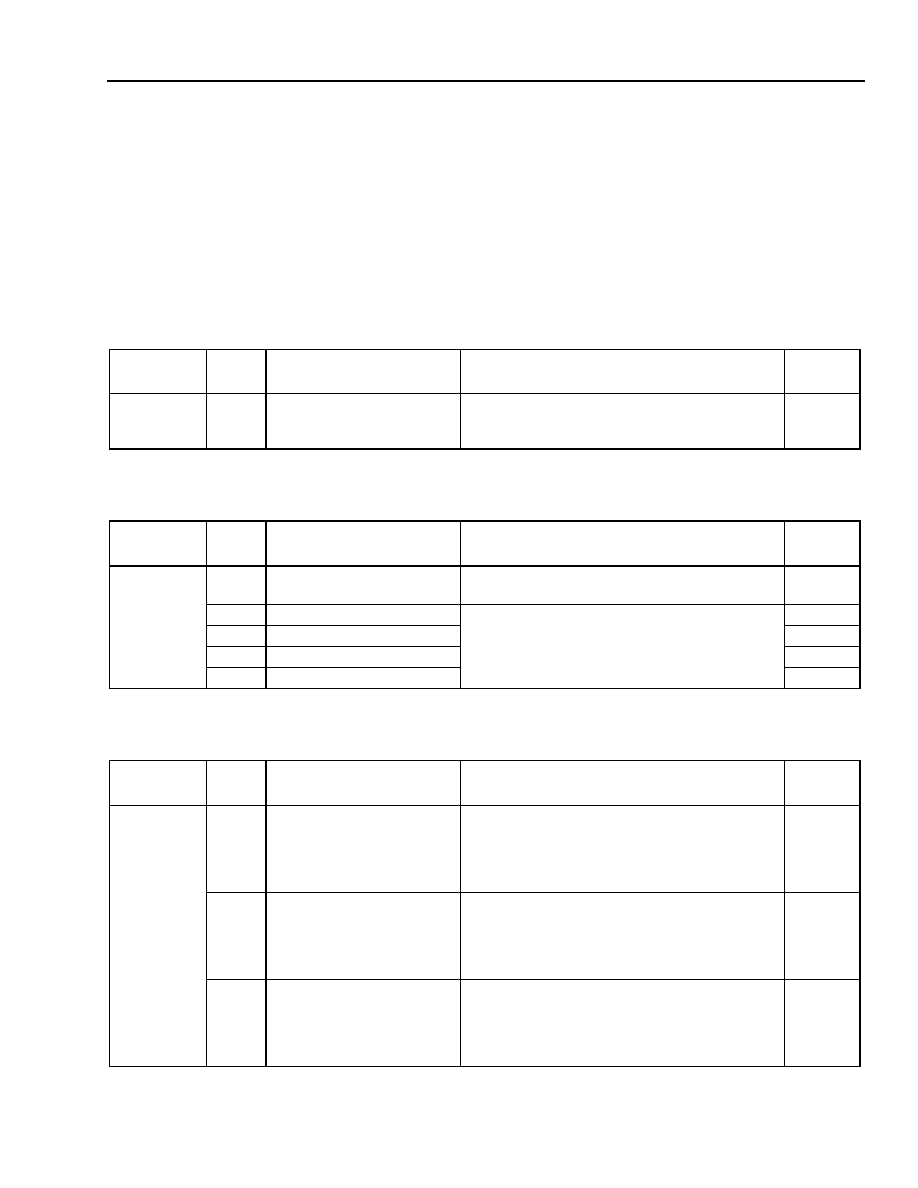

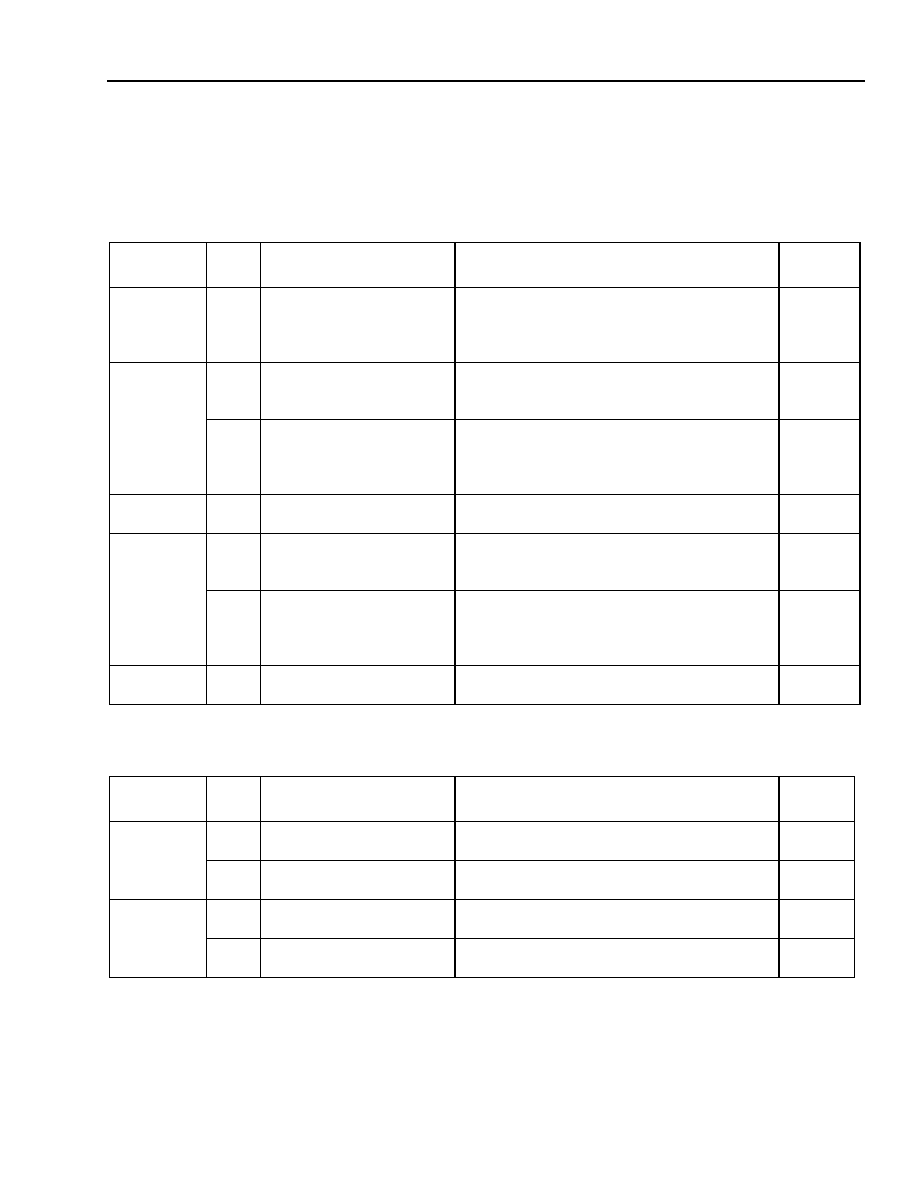

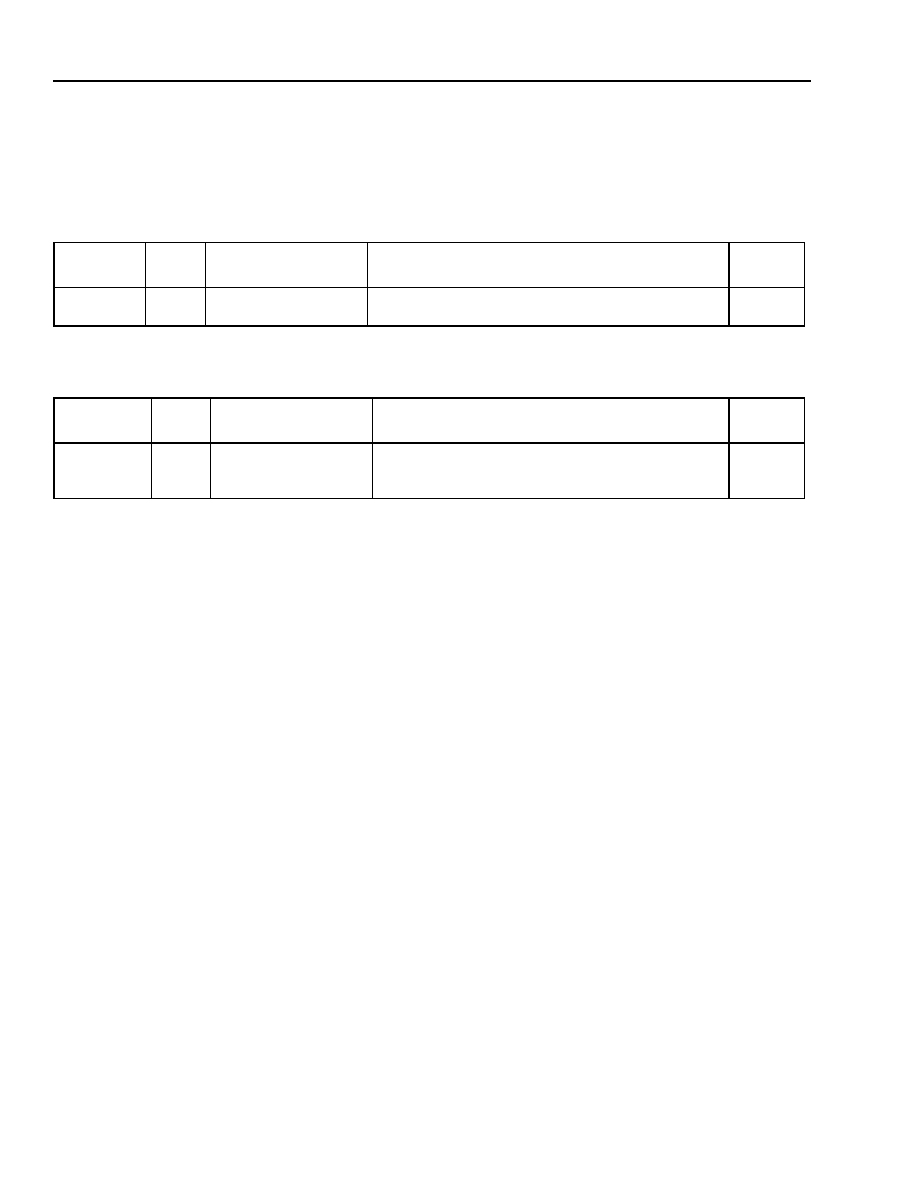

DE8. Clearing DE Interrupt Register (0x1002)

DE interrupt register 0x1002 is incorrectly defined in the revision 3 of the data sheet as RO. DE interrupt register

0x1002 is correctly defined as a COR/W register. However, register 0x1002 must be used in the COR mode (regis-

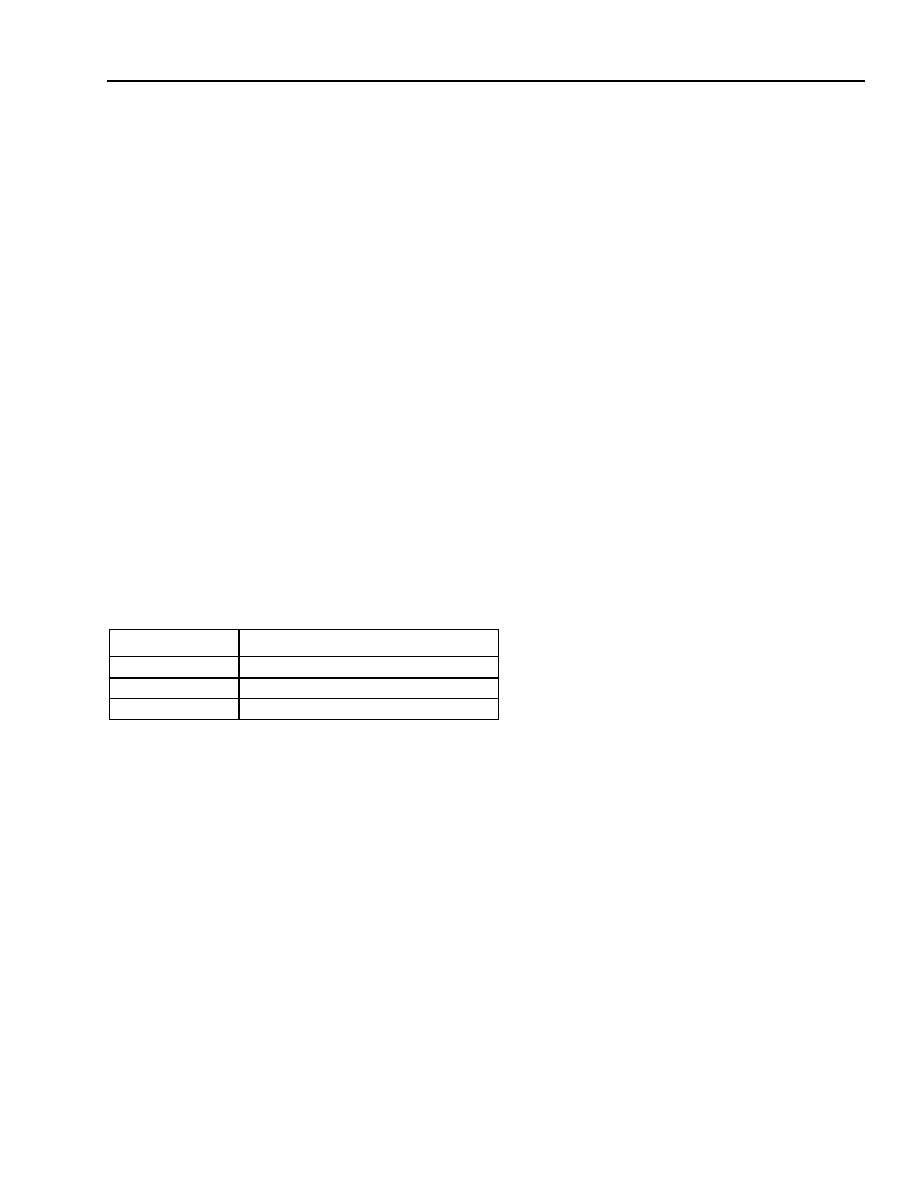

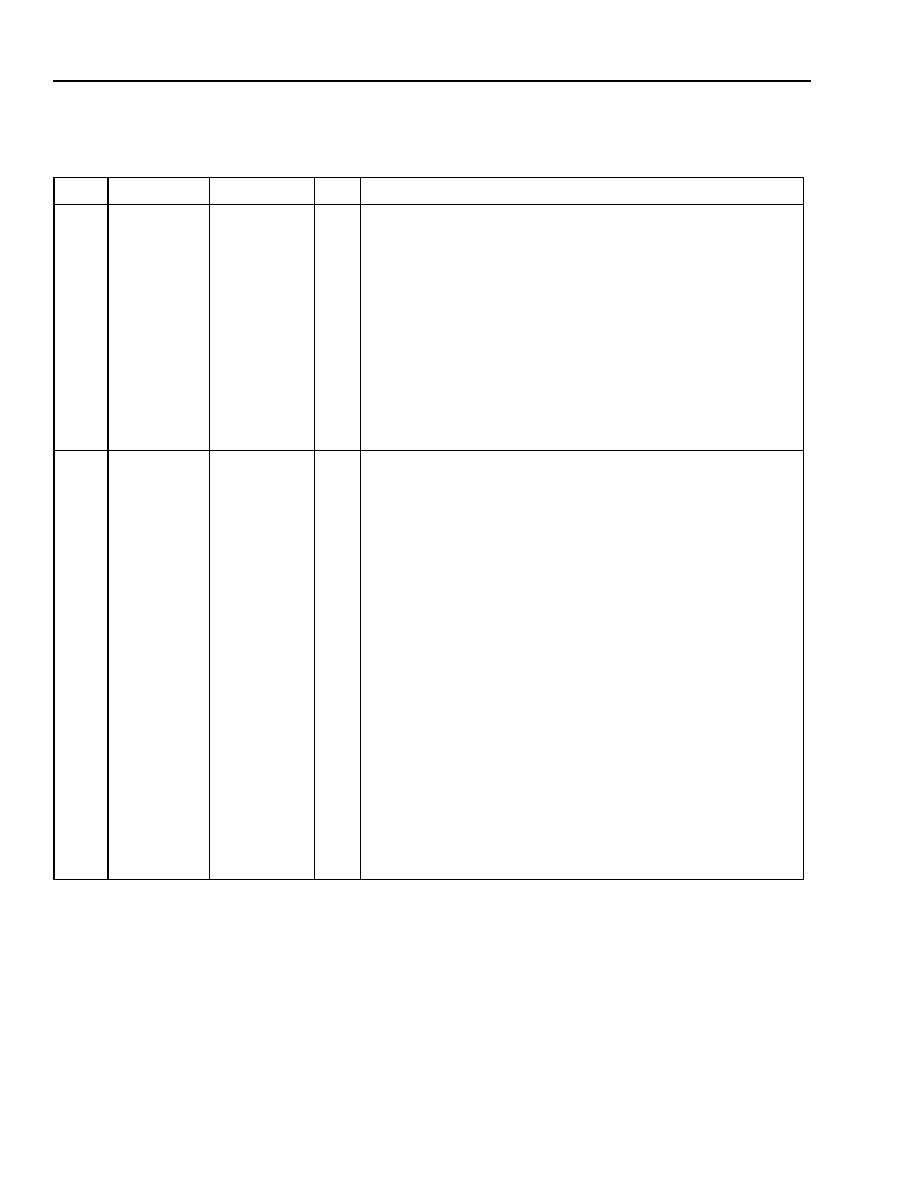

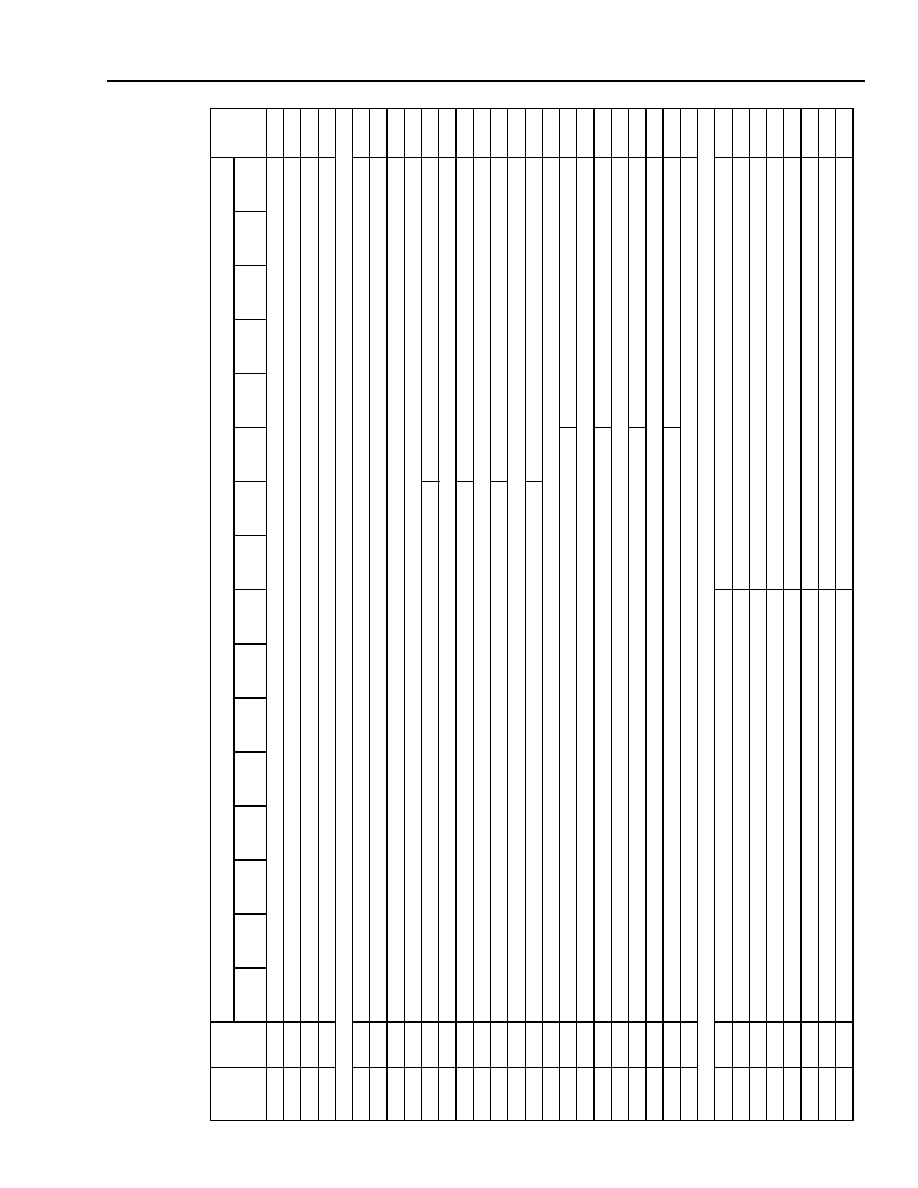

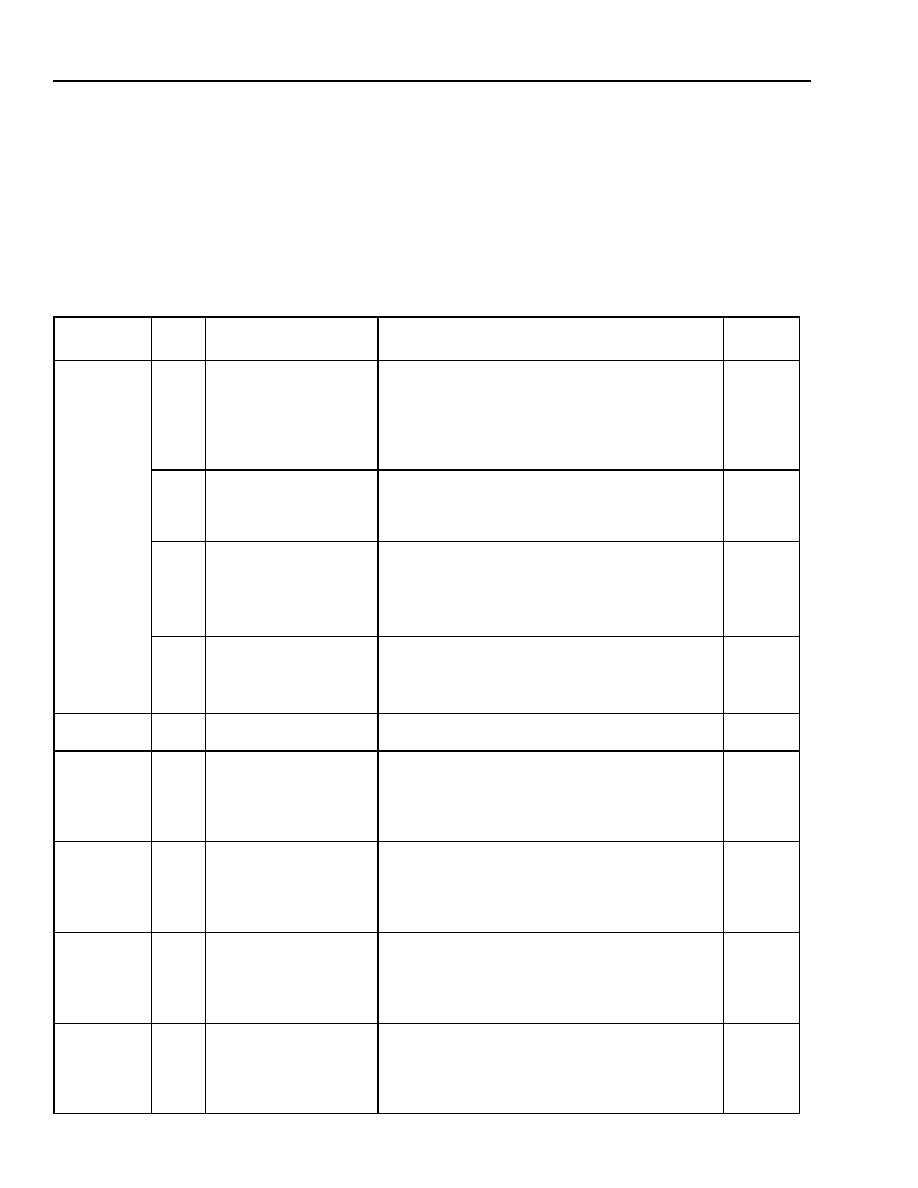

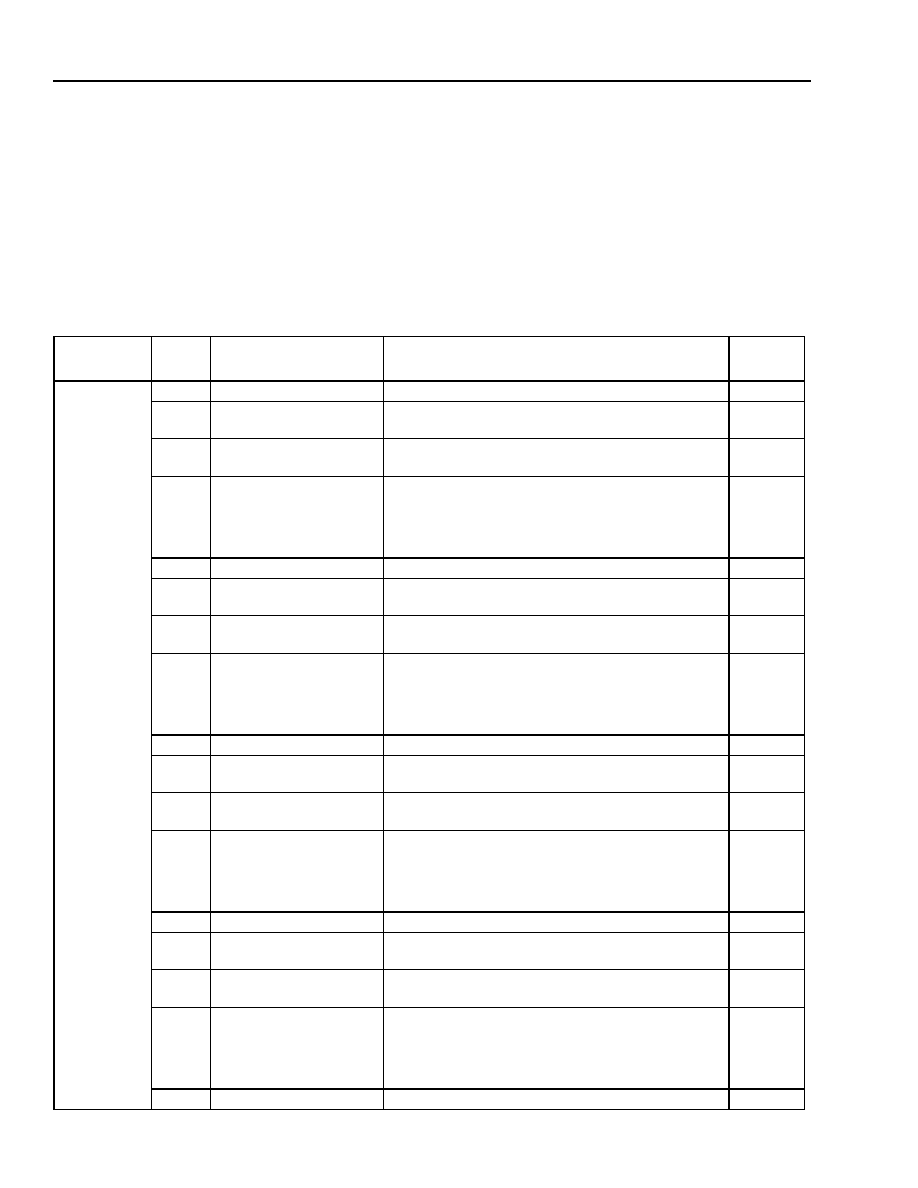

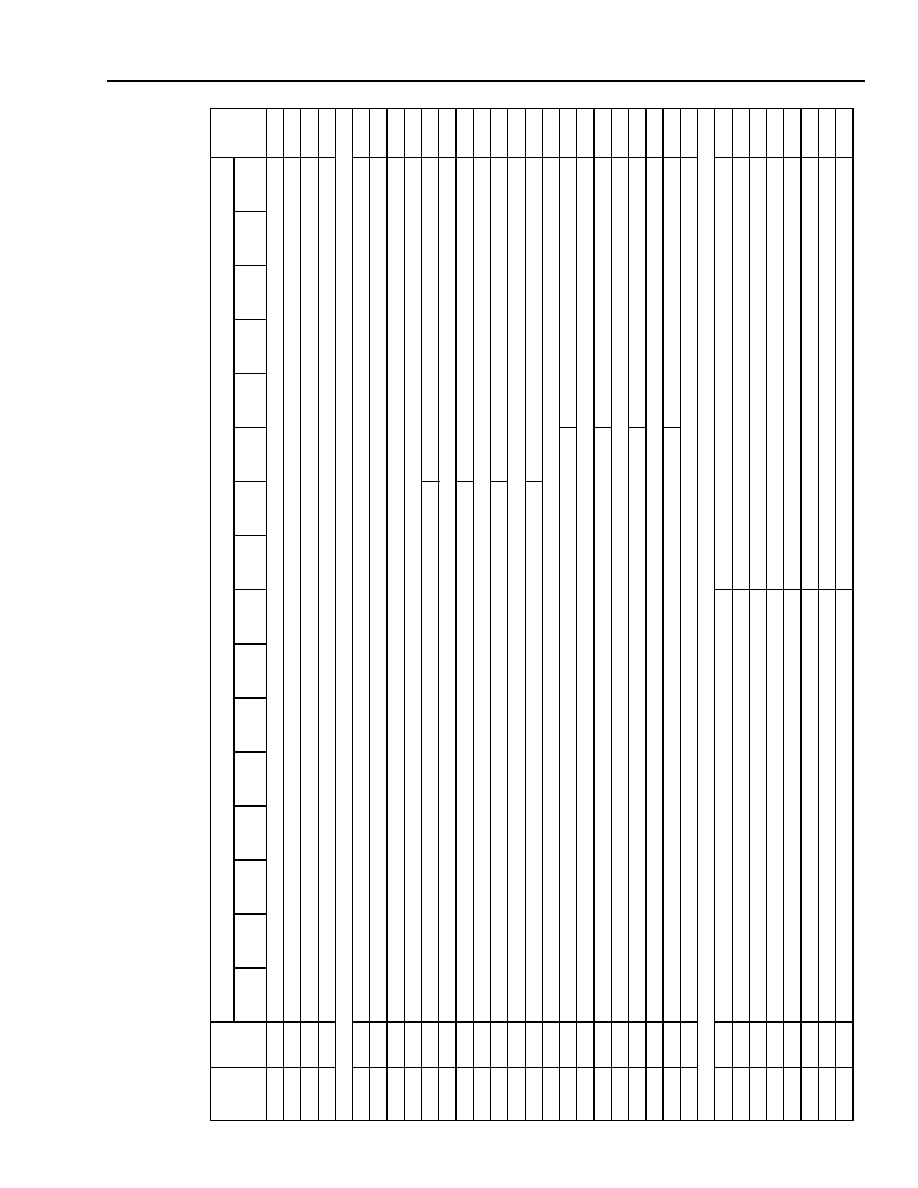

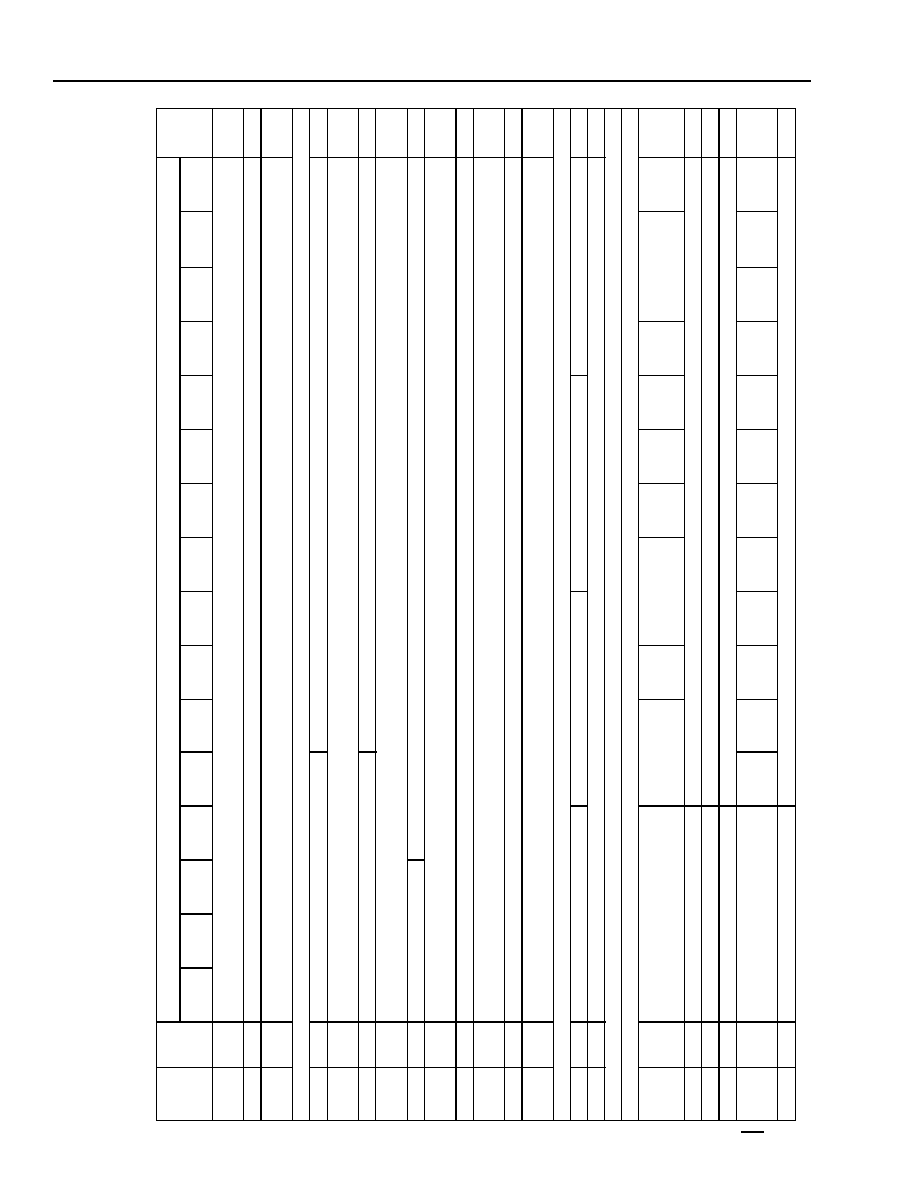

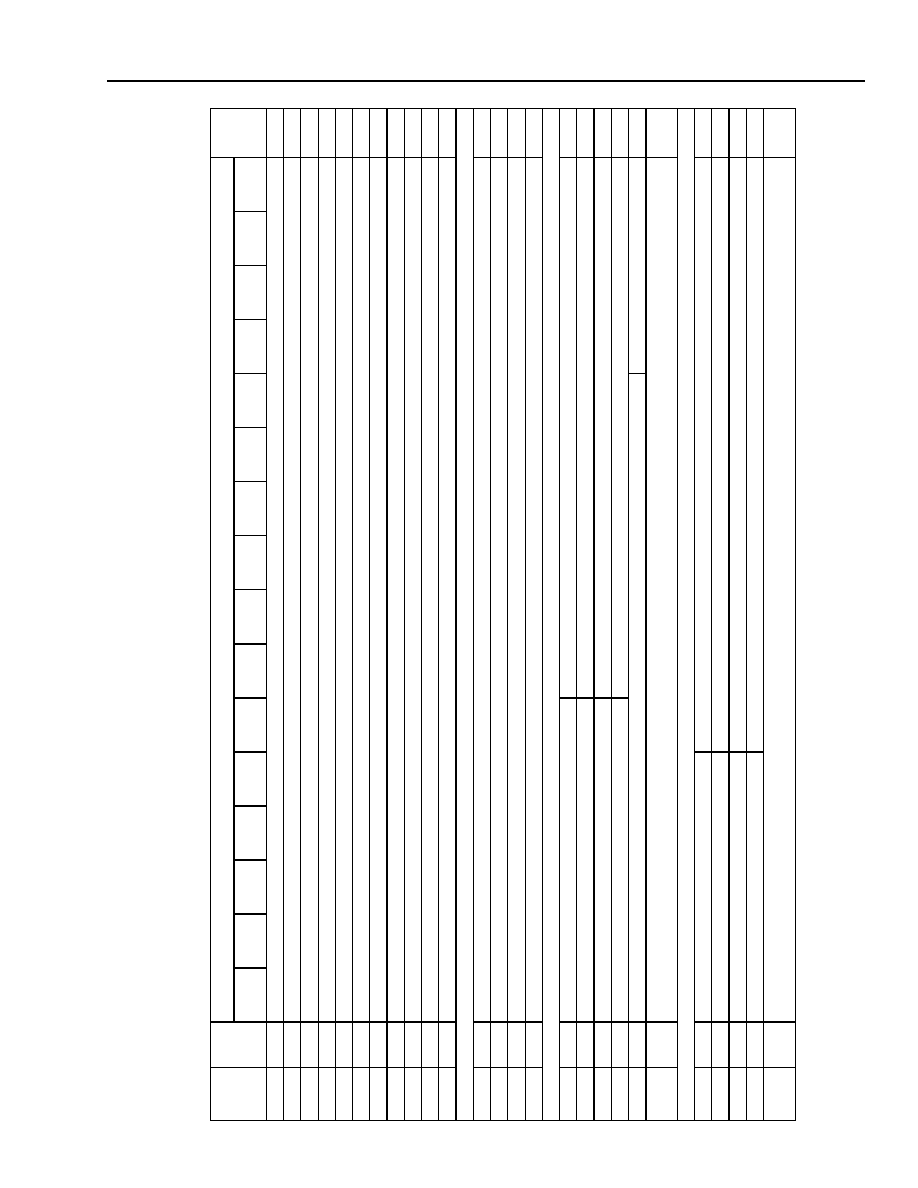

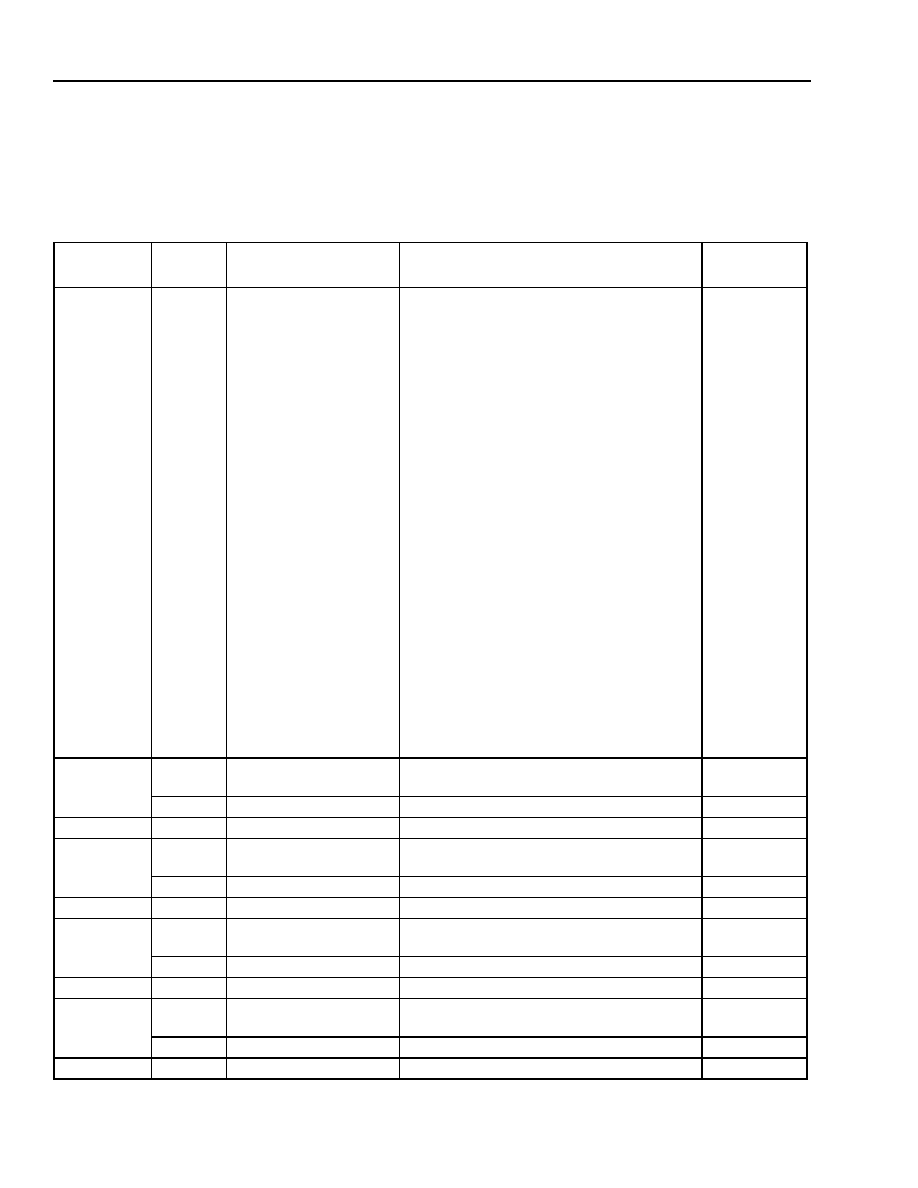

ter 0x0010 bit 6 set to 1). The bits of register 0x1002 are explained in detail in Table 4.

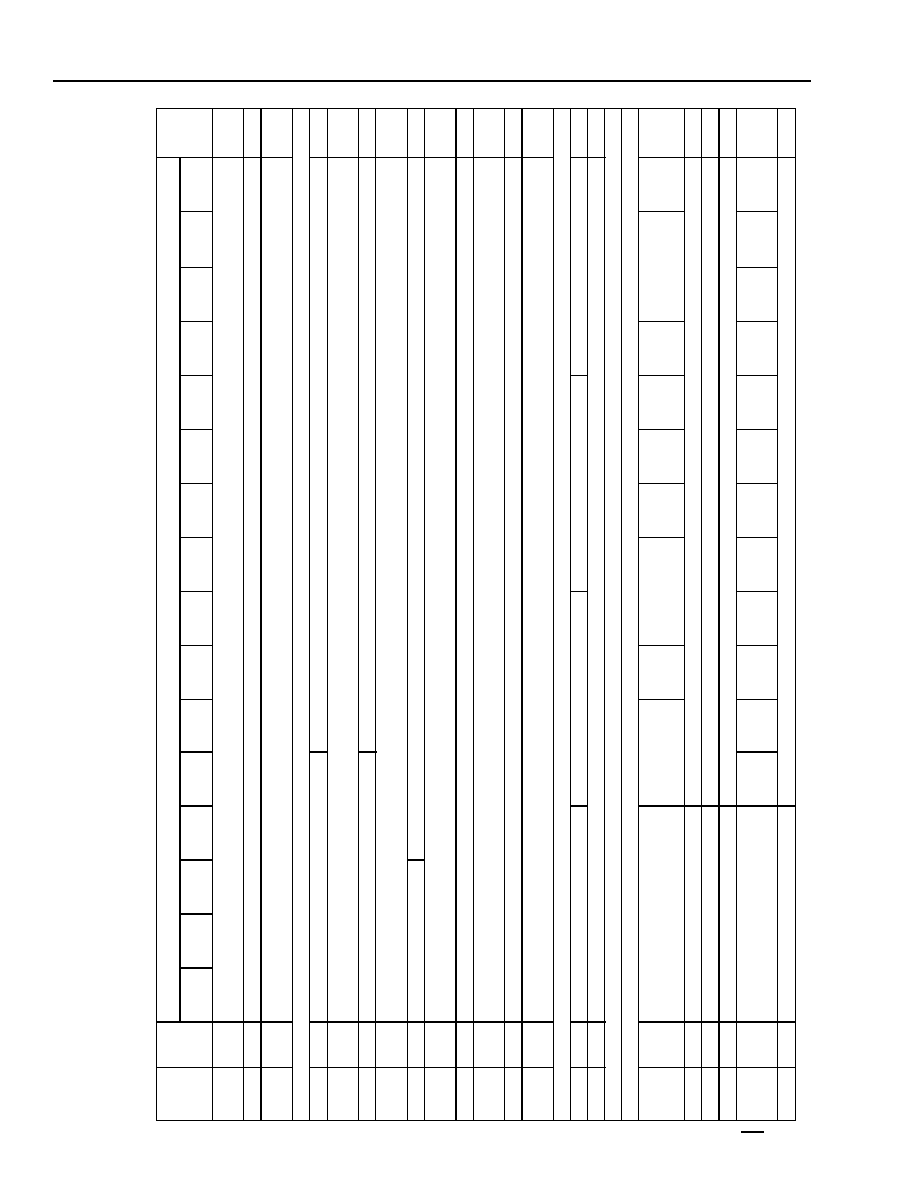

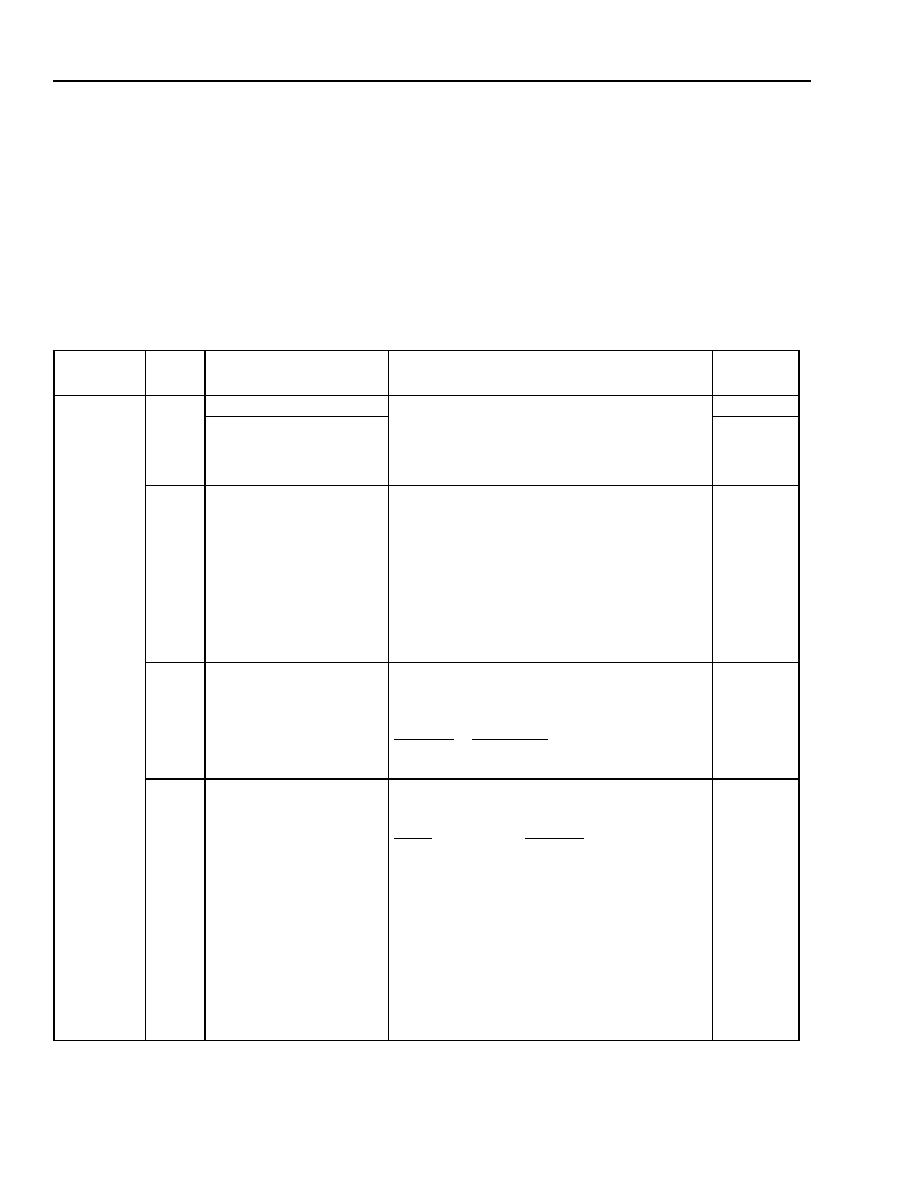

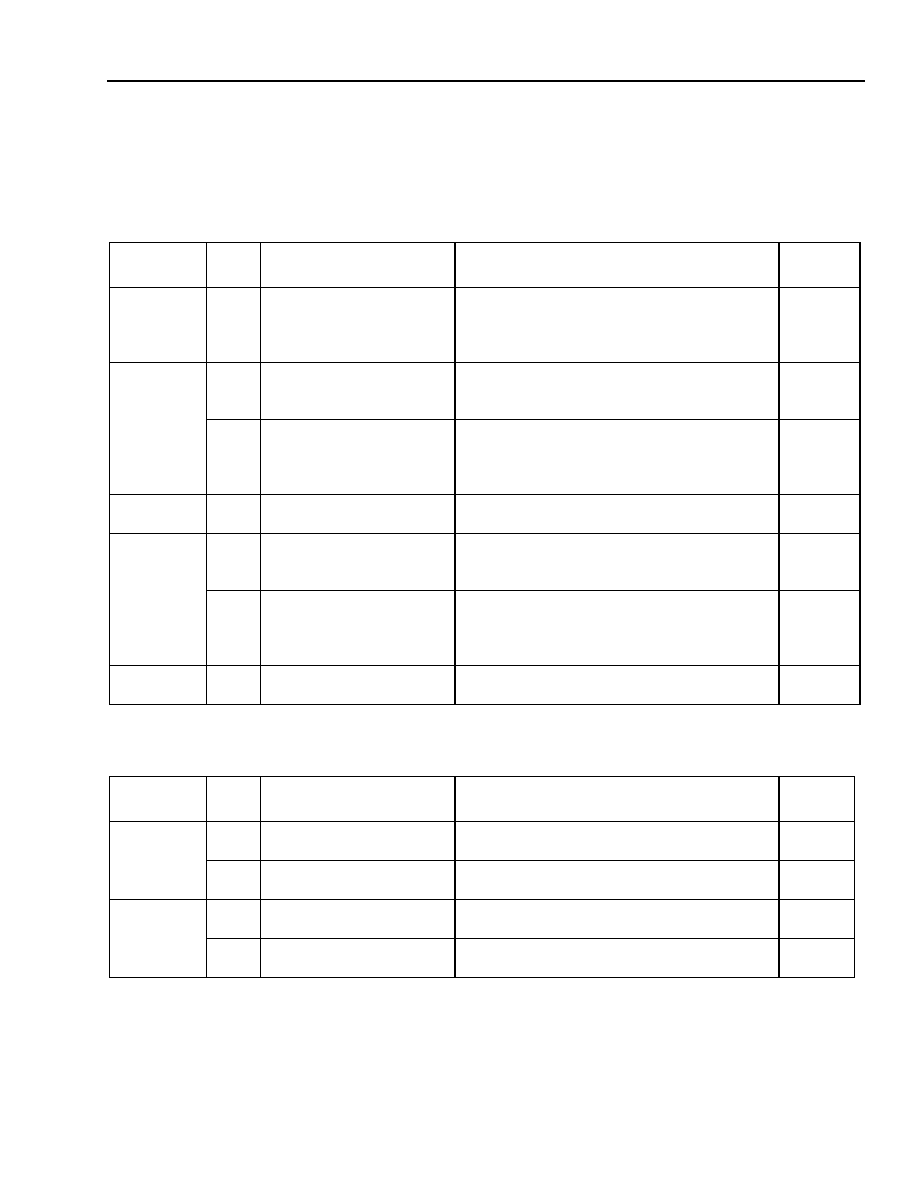

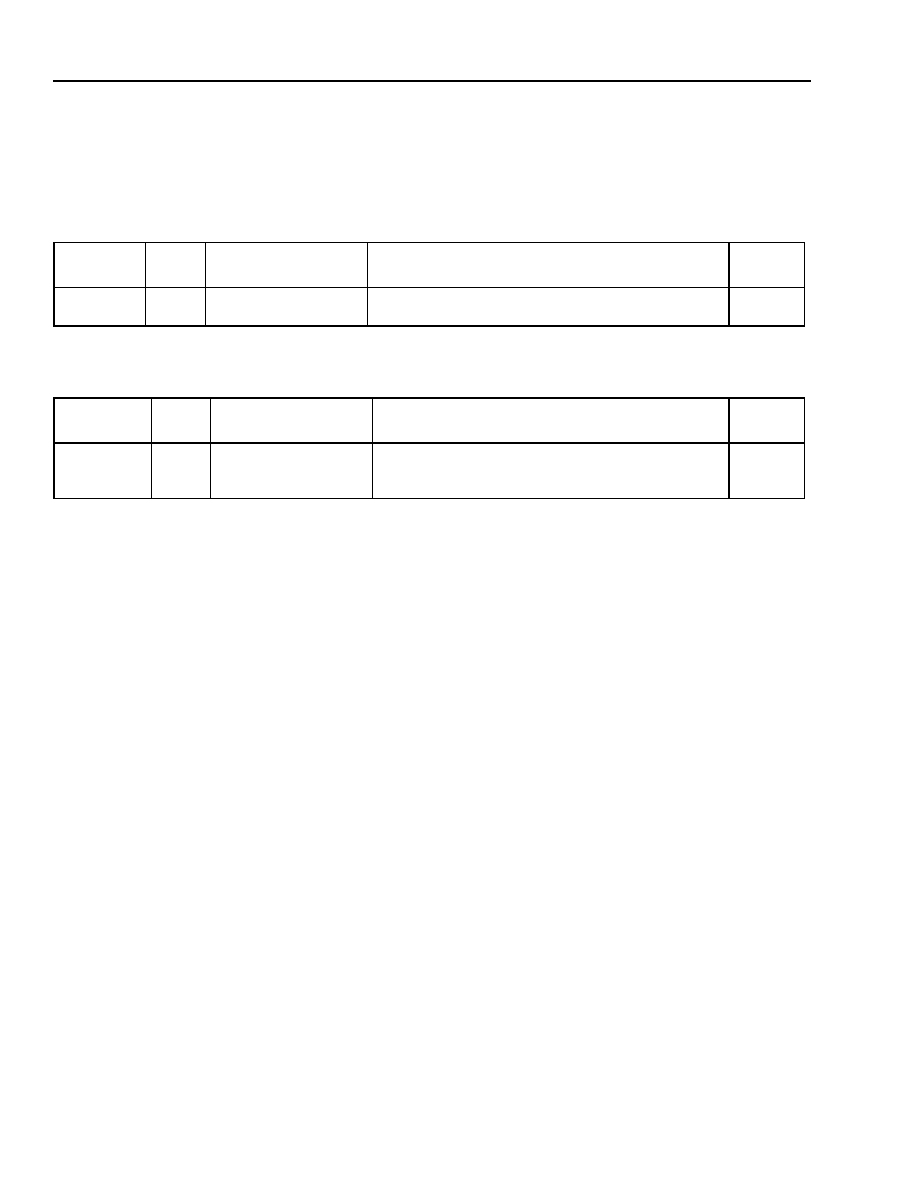

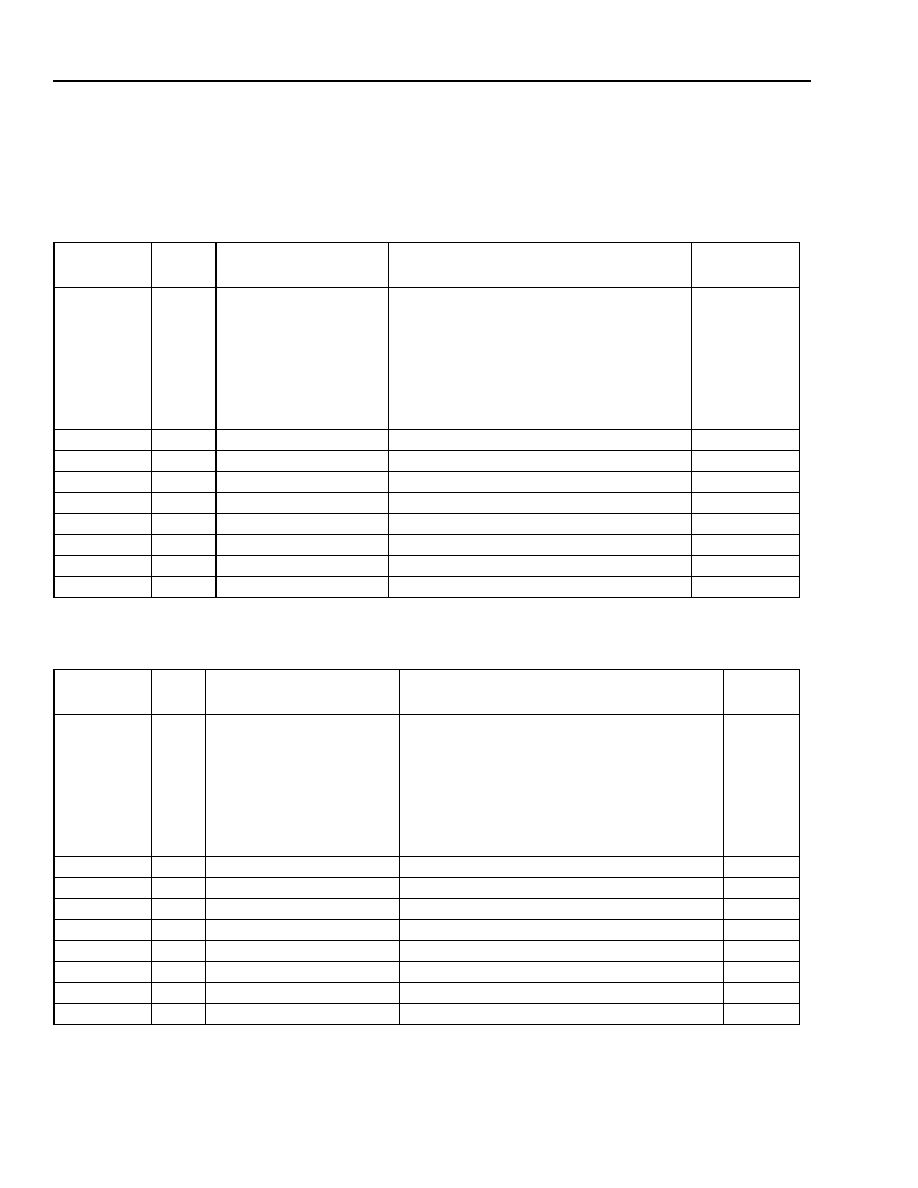

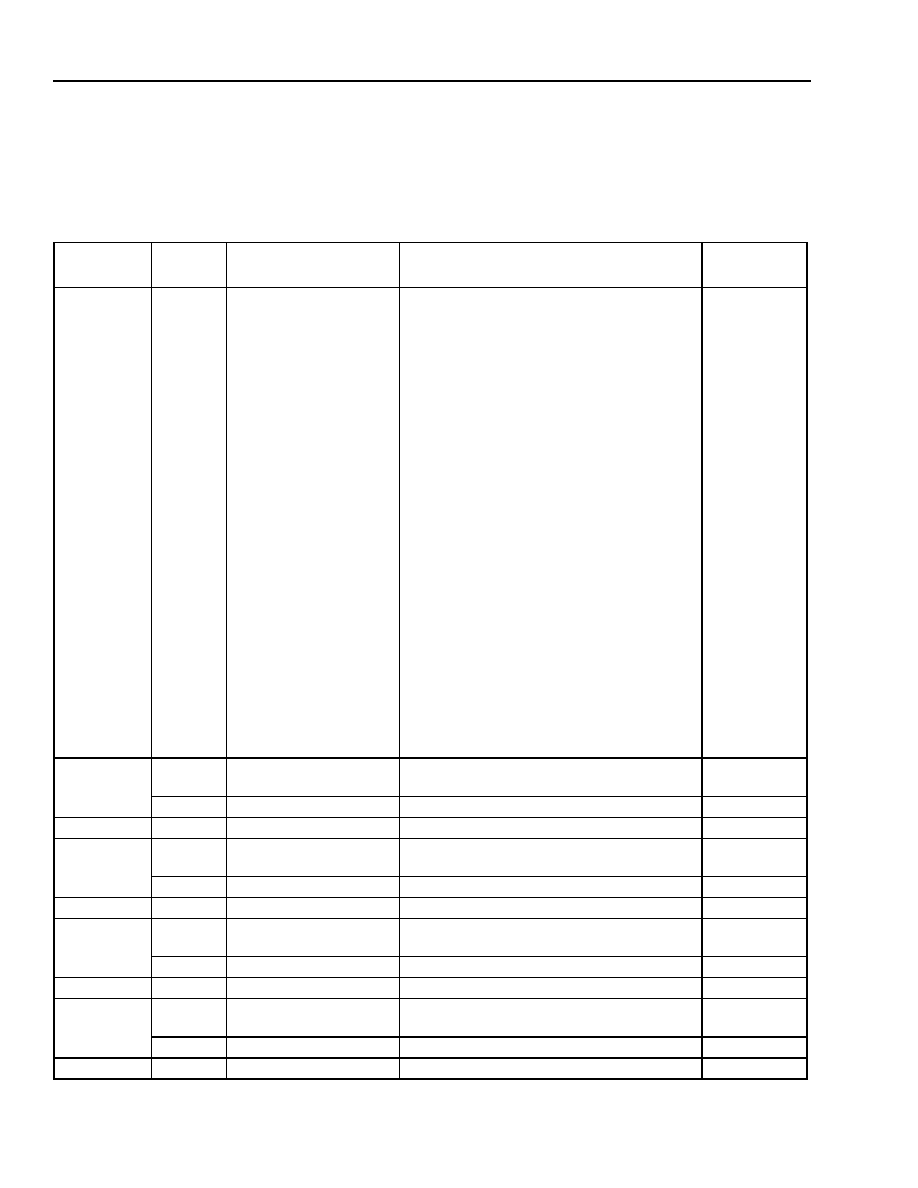

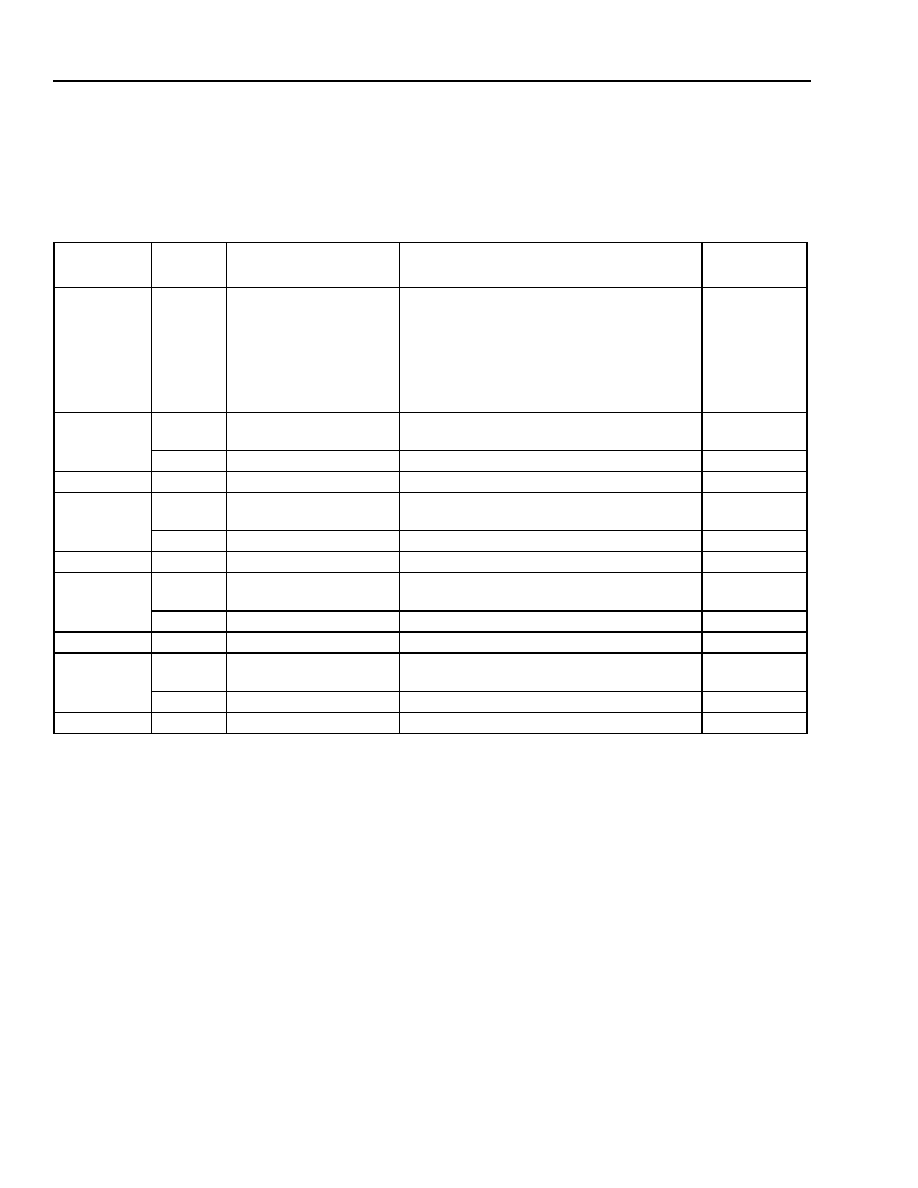

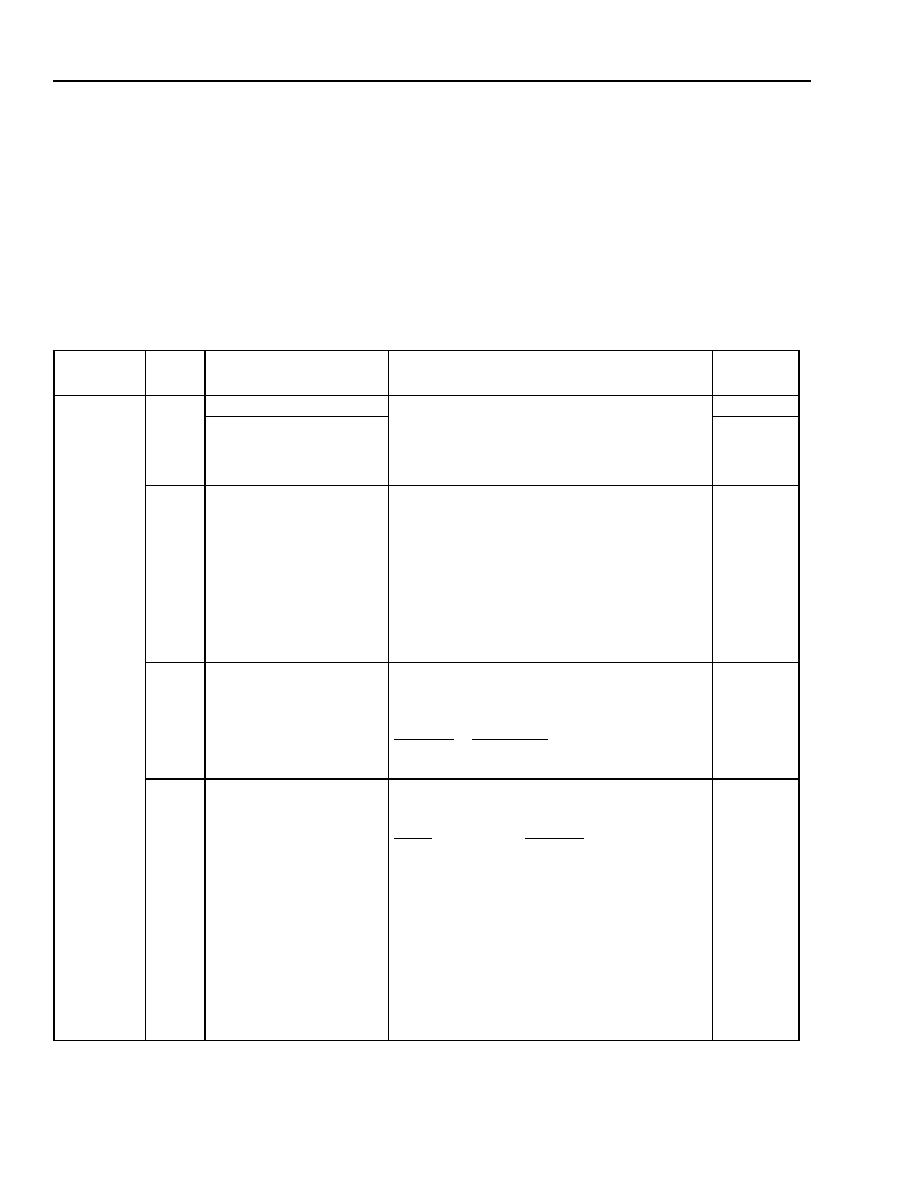

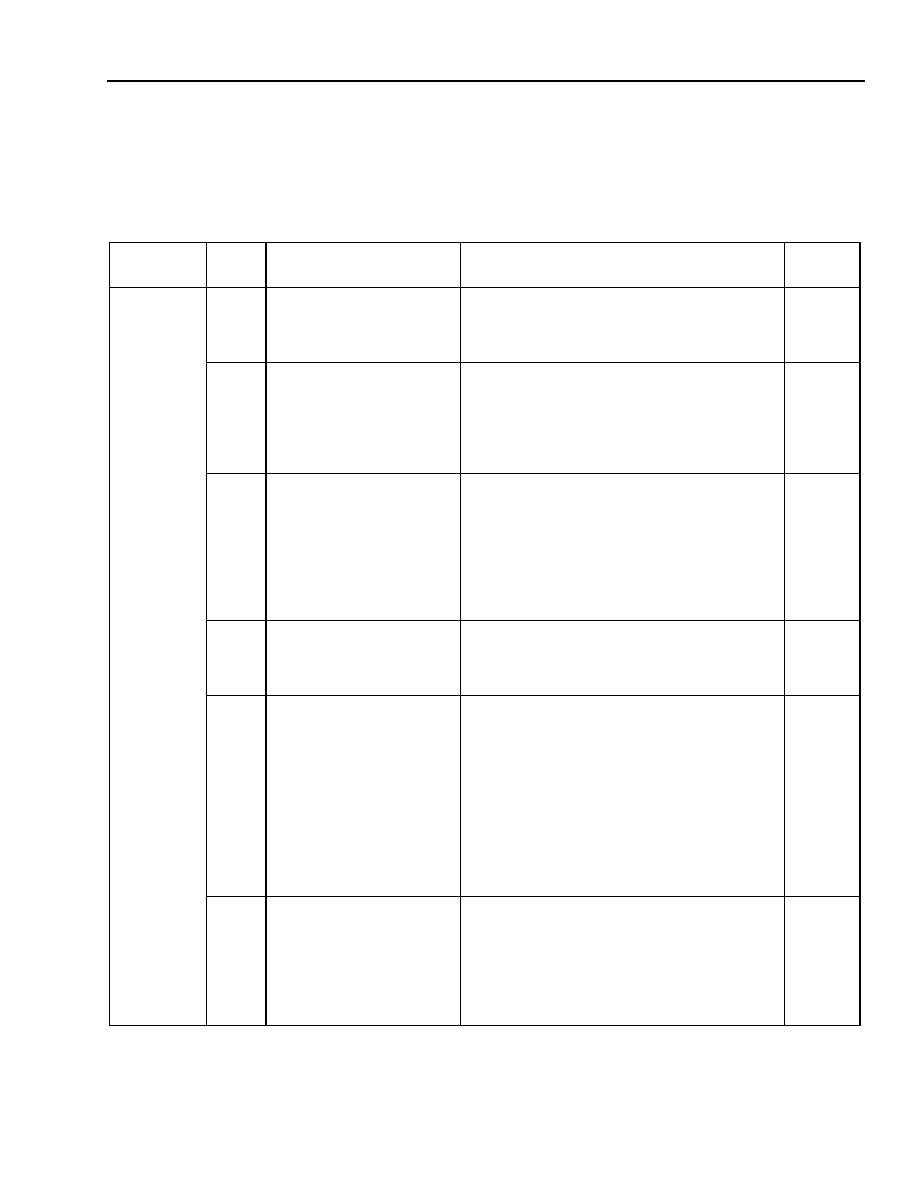

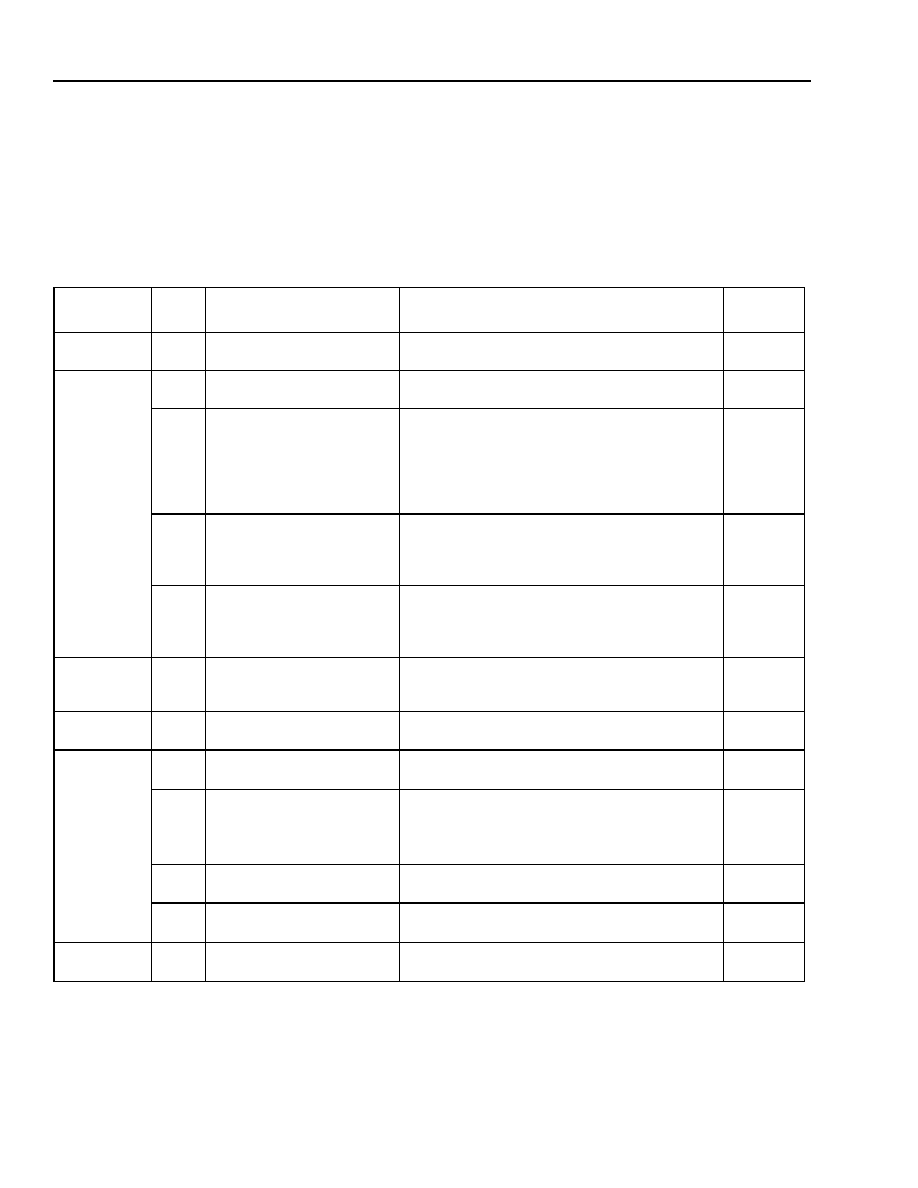

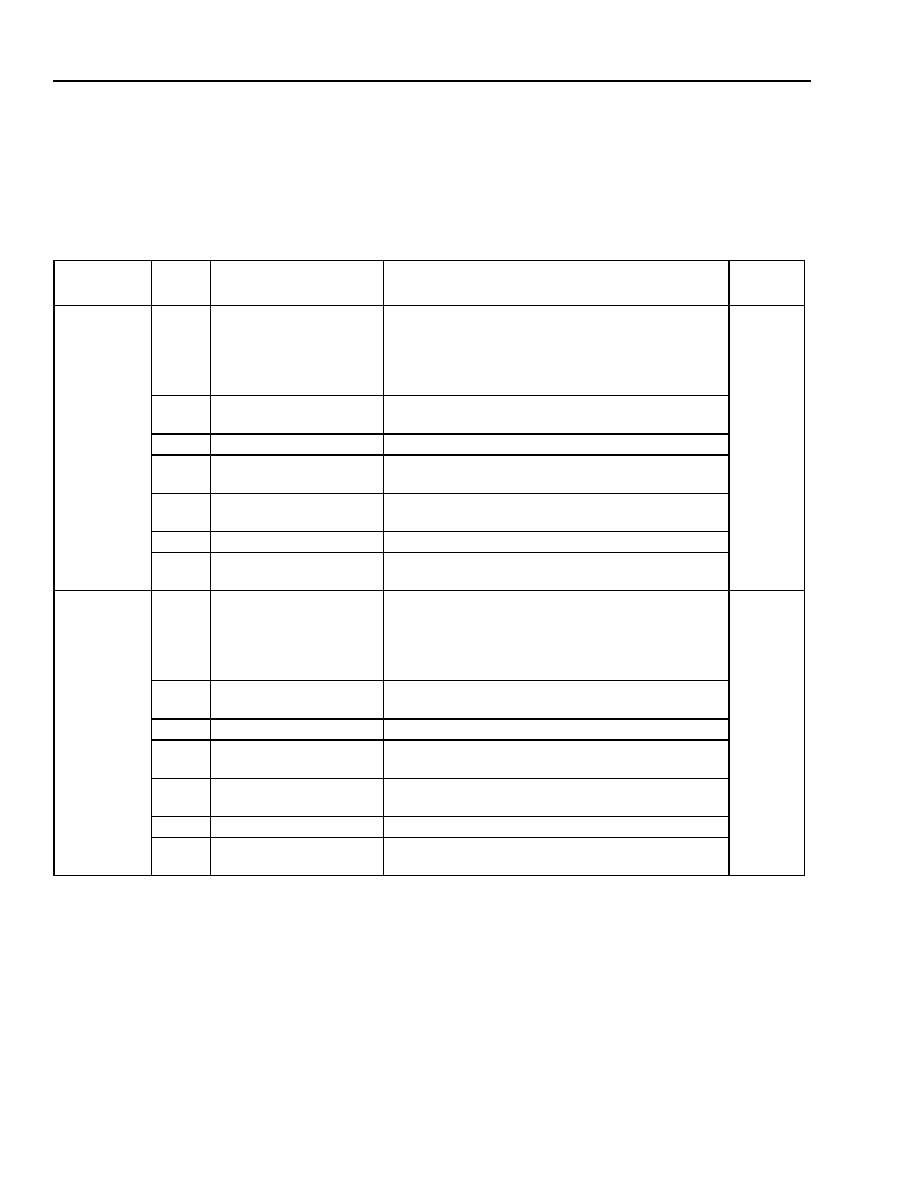

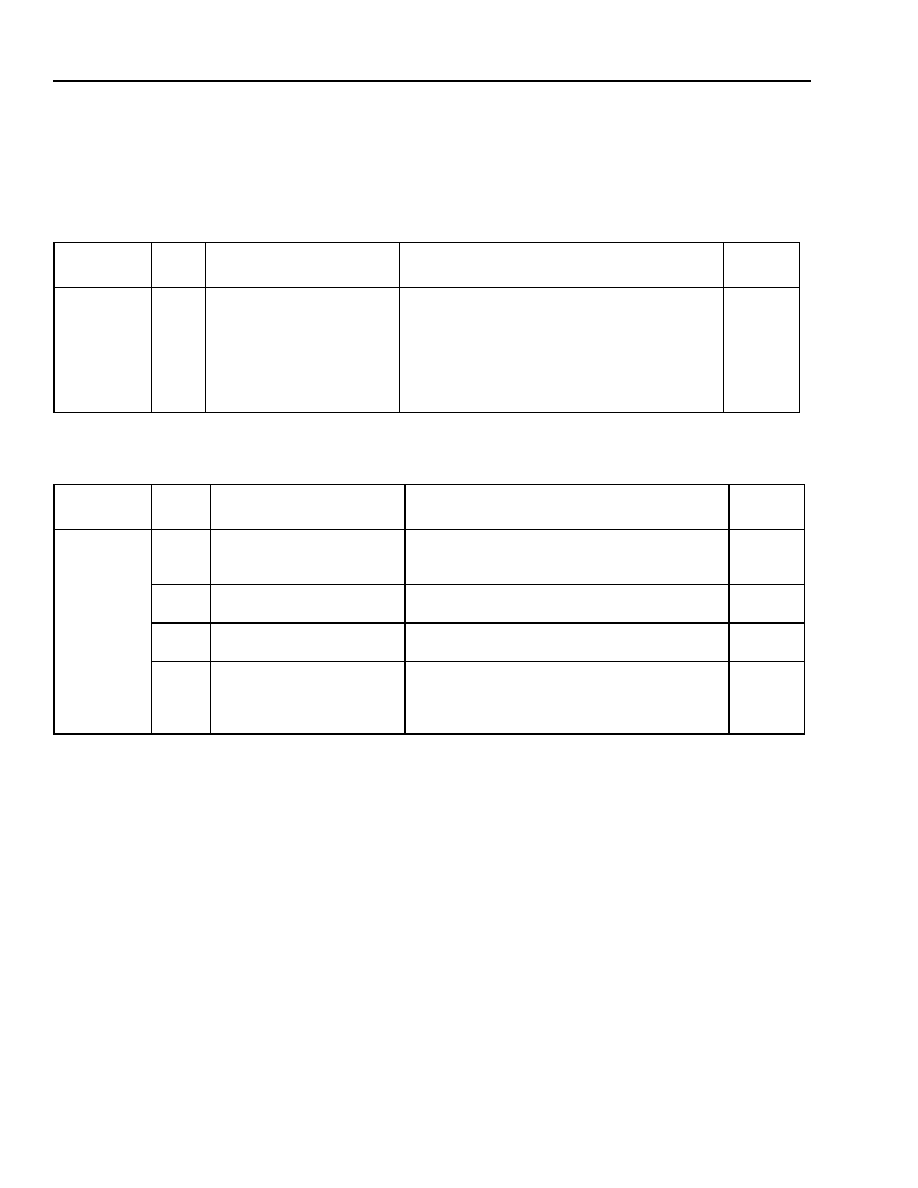

Table 4. Register 0x1002: DE Interrupt (COR/W)

Workaround

This is informational only. No workaround is available for this condition.

Corrective Action

This behavior will be described in future revisions of the advance data sheet.

DE9. Single Packet Transmission in HDLC-CRC, SDL-CRC, and PPP Modes

When receiving in either PPP or CRC mode, a single packet may not pass through the device. This occurs when

the end of packet (which contains the CRC) never reaches the UT FIFO. The ingress channel suspends transfer to

the UT when there is no end of packet in the FIFO. These bytes are transferred to the UT when the next packet is

received. This problem will affect HDLC-CRC, SDL-CRC, and PPP modes.

Workaround

There are two possible workarounds:

I

Set ingress payload type and mode control registers (0x1040--0x1043) to CRC strip mode. However, in CRC-16

mode, single packets may still get stuck if CRC ends on bytes A or B.

I

Send a minimum 4-byte dummy packet after each packet.

Corrective Action

This condition will be addressed in future versions of the device.

Bits

Mode

Clear Behavior of Register 0x1002

15--12

RO

To clear these SDL Rx frame state interrupt bits, read and

clear their associated interrupt source registers

(addresses 0x14E0--0x14E3).

11--0

COR or COW

(address 0x0010, bit 6)

To properly clear these bits, device must be in COR mode

(address 0x0010, bit 6 = 1).

12

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Data Engine (DE)

(continued)

DE10. Excessive HDLC Flag Characters

The following three issues refer to HDLC flag character (0x7E) problems in the data engine:

I

An excessive number of HDLC flag characters (0x7Es) may be inserted between packets on the transmit side if

the UTOPIA low watermark value is set above 2. This will have the effect of reducing the bandwidth of the device.

I

The data engine operates on 32-bit boundaries. Egress packets that are not multiples of four will be filled with

0x7Es.

I

Egress packets consisting of all 0x7Es as data will be corrupted.

Workaround

Set the UTOPIA egress low watermark value in the UTOPIA egress provisioning registers (0x0212, 0x0216,

0x021A, 0x021E) to either 1 or 2 to prevent excessive 0x7Es from being inserted between packets.

Corrective Action

This condition will be addressed in future versions of the device.

UTOPIA (UT)

UT1. Polling in Multidevice MPHY Mode

When the TDAT042G5 is polled and responds, the data bus becomes enabled. In a multidevice MPHY configura-

tion, if the data bus is active from a different PHY device, response to a poll from the device will corrupt a data

transfer already in progress. TDAT042G5 MPHY always functions without data corruption in a single-device

(slave), multiple-channel configuration (point-to-point).

Workaround

No workaround is available for this condition.

Corrective Action

This condition will be addressed in future versions of the device.

Agere Systems Inc.

13

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

UTOPIA (UT)

(continued)

UT2. UTOPIA Clock Limitations

The maximum speed of the UTOPIA interface is 104 MHz. When operating at clock speeds greater than 52 MHz,

RxCLK[D:A] must be placed in source mode and will use the same external clock as the corresponding

TxCLK[D:A] clock. RxCLK[D:A] source mode is set by provisioning bit 6 (CLOCK_MODE_Rx) for channel A of the

UTOPIA receive provisioning registers (address 0x020F).

When operating at speeds less than 52 MHz, separate external clocks for RxCLK[D:A] and TxCLK[D:A] may be

used.

Workaround

This is informational only. No workaround is available for this condition.

Corrective Action

This condition will be addressed in future versions of the device. Design modifications will be directed towards

allowing a maximum interface speed of 104 MHz in all cases. Note that UTOPIA Level 3 clock architecture has

changed in the ATM Forum's UTOPIA Level 3 specification as of the July 1998 version.

UT3. PMRST Register Value Invalid After Reset

The value in PMRST_PECTx[A--D] (addresses 0x020B through 0x020E) is invalid after reset until the second

PMRST clock period is completed. After the second PMRST, the register value is valid.

Workaround

Always have the system software execute a read of PMRST_PECTx as part of the system initialization following a

reset.

Corrective Action

This condition will be addressed in future versions of the device.

14

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

UTOPIA (UT)

(continued)

UT4. FIFO Overflow and Error Reporting

If the RxFIFO overflows, RxEOP is not asserted as expected. Therefore, when errors occur, two packets will be

corrupted instead of one because two start of packets (SOPs) occurred without an end of packet (EOP). RxERR is

not asserted when the above overflow condition occurs. No effect is noticeable in the ATM mode. Channel A works

as expected; this problem occurs in channels B, C, and D.

Workaround

This error is detectable in the status registers. No workaround is available for this condition.

Corrective Action

This condition will be addressed in future versions of the device.

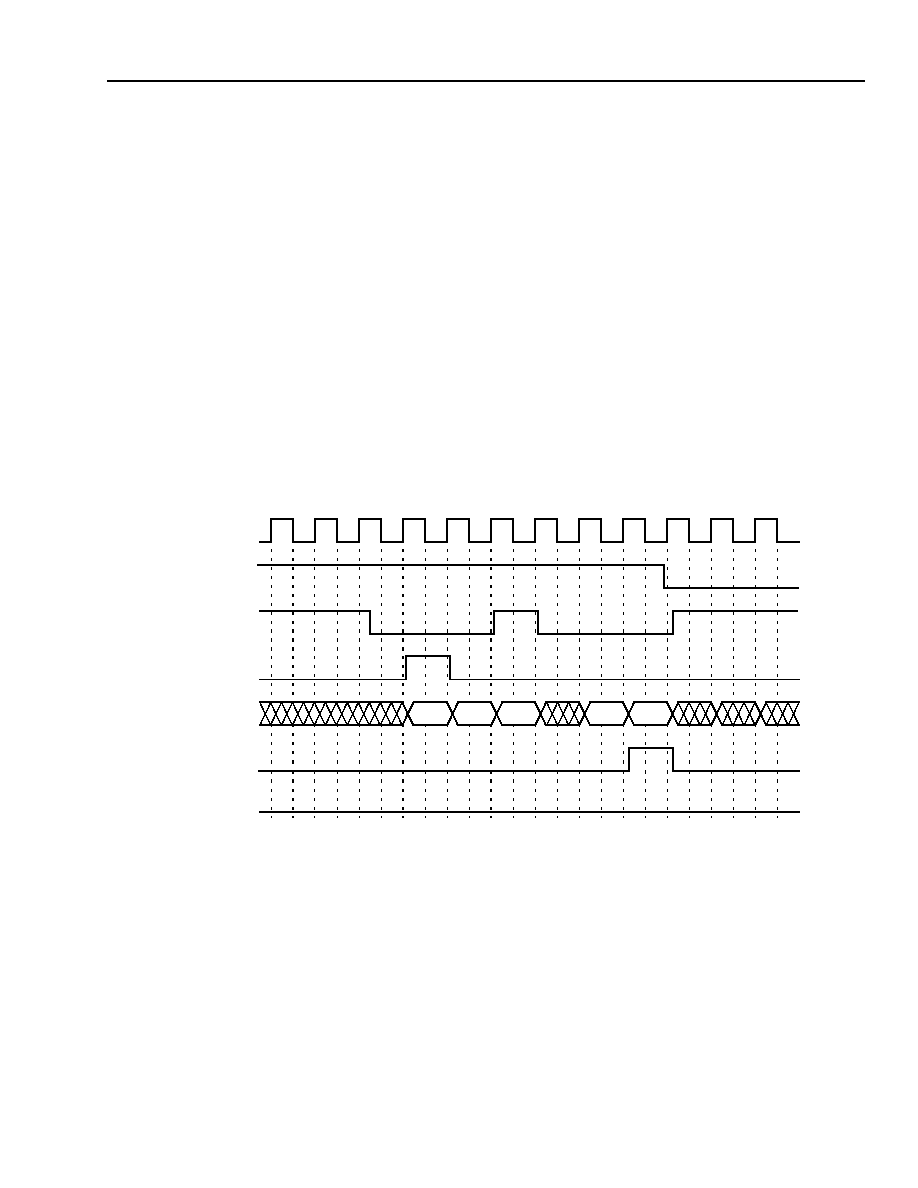

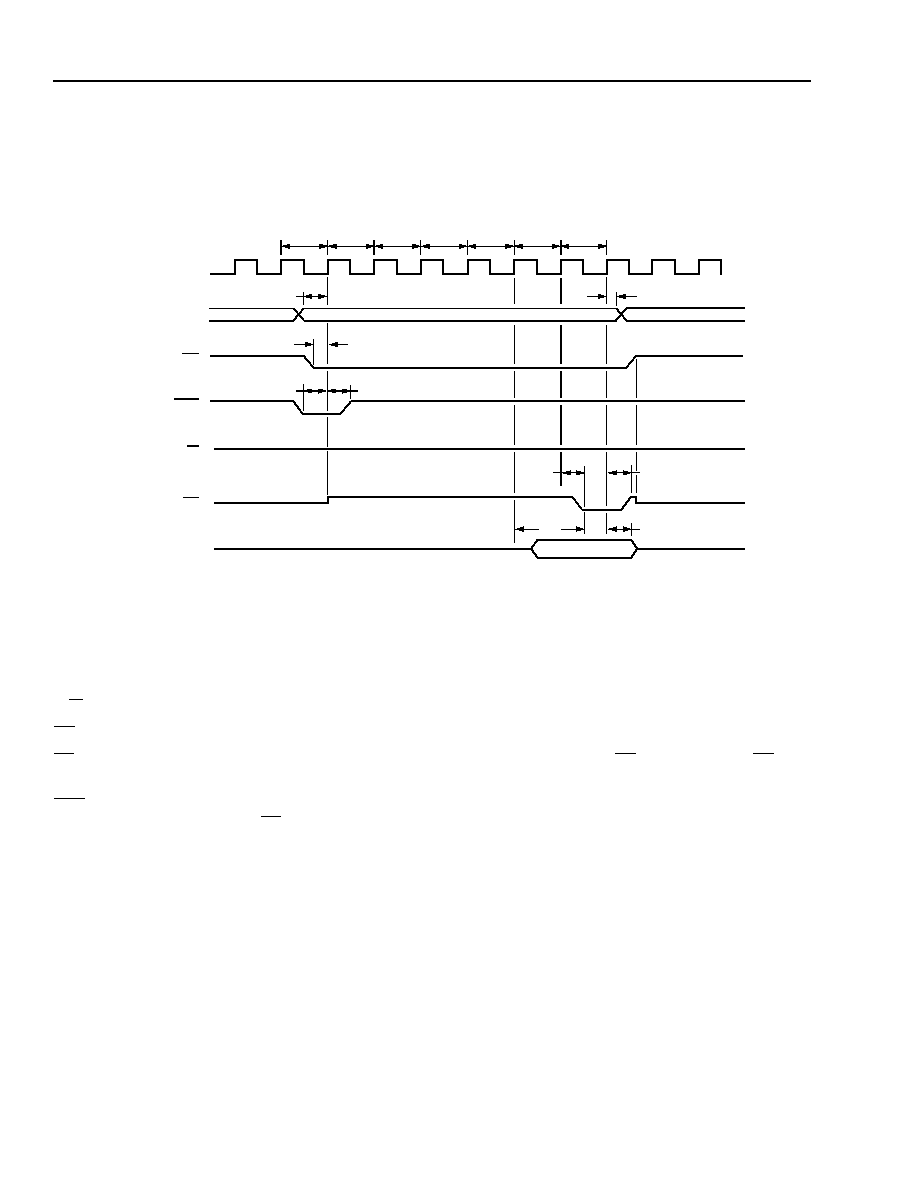

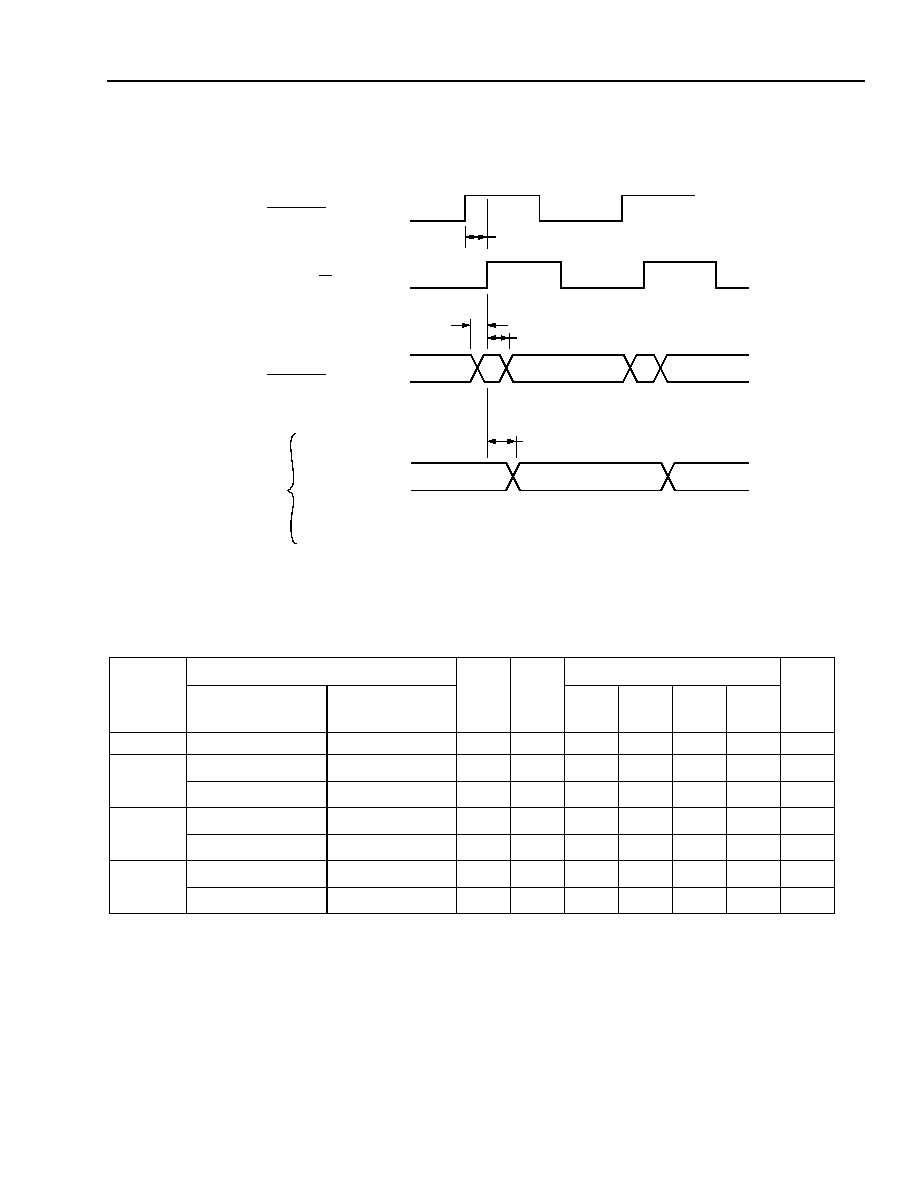

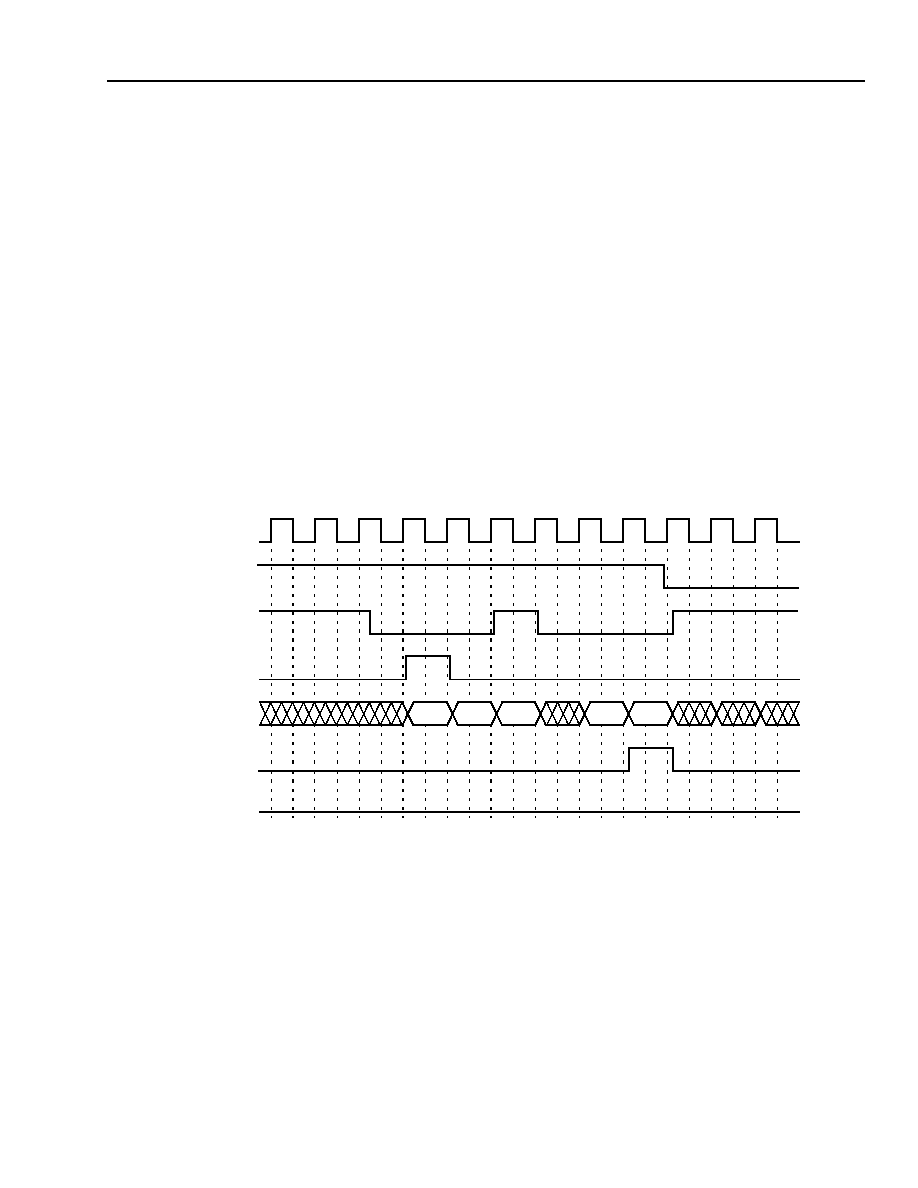

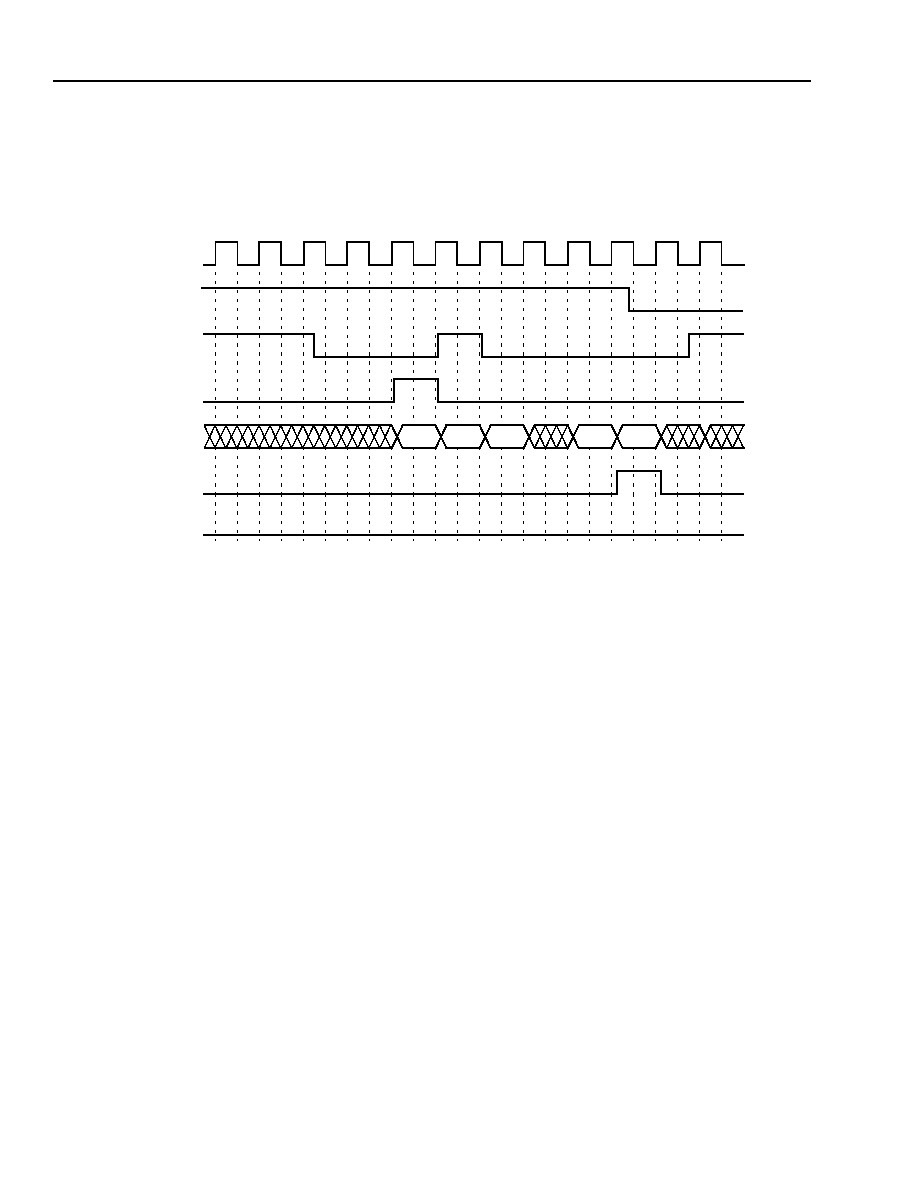

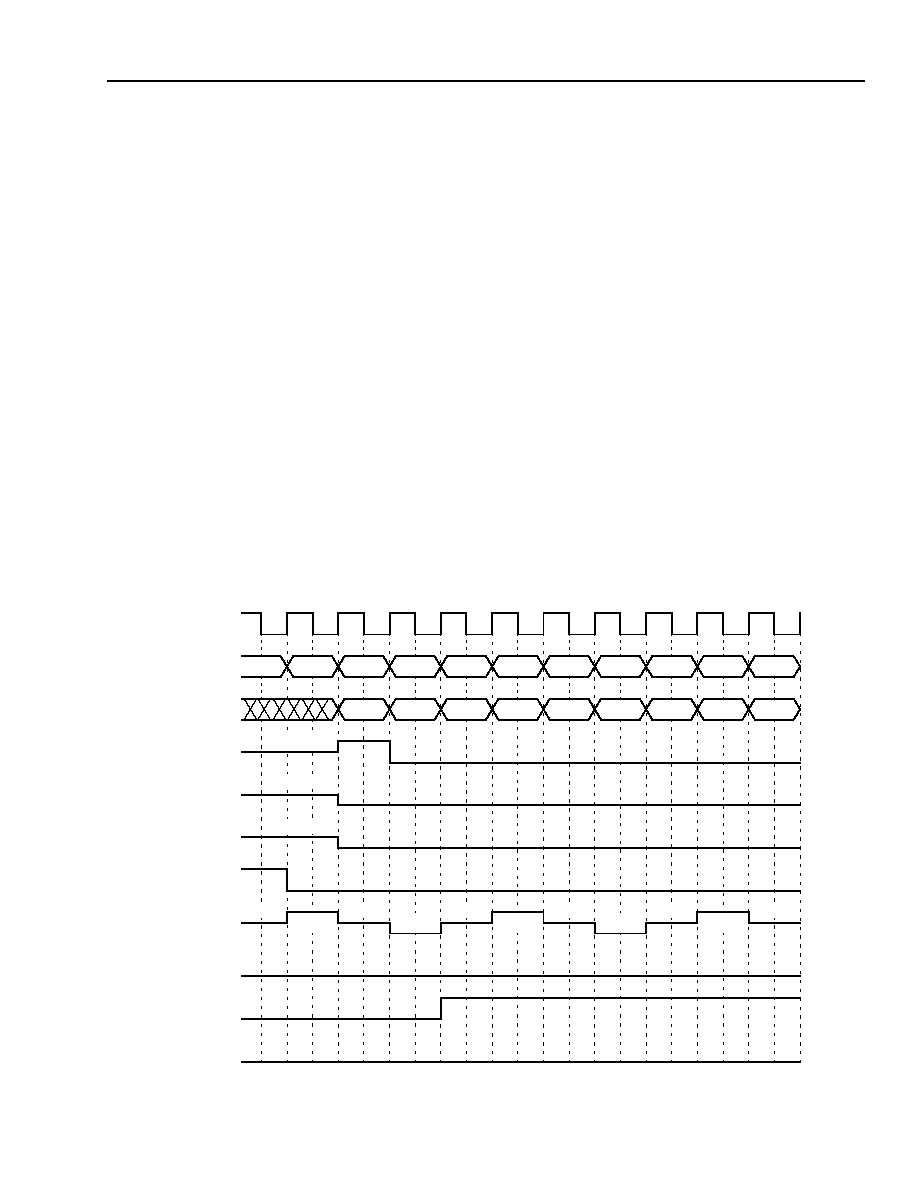

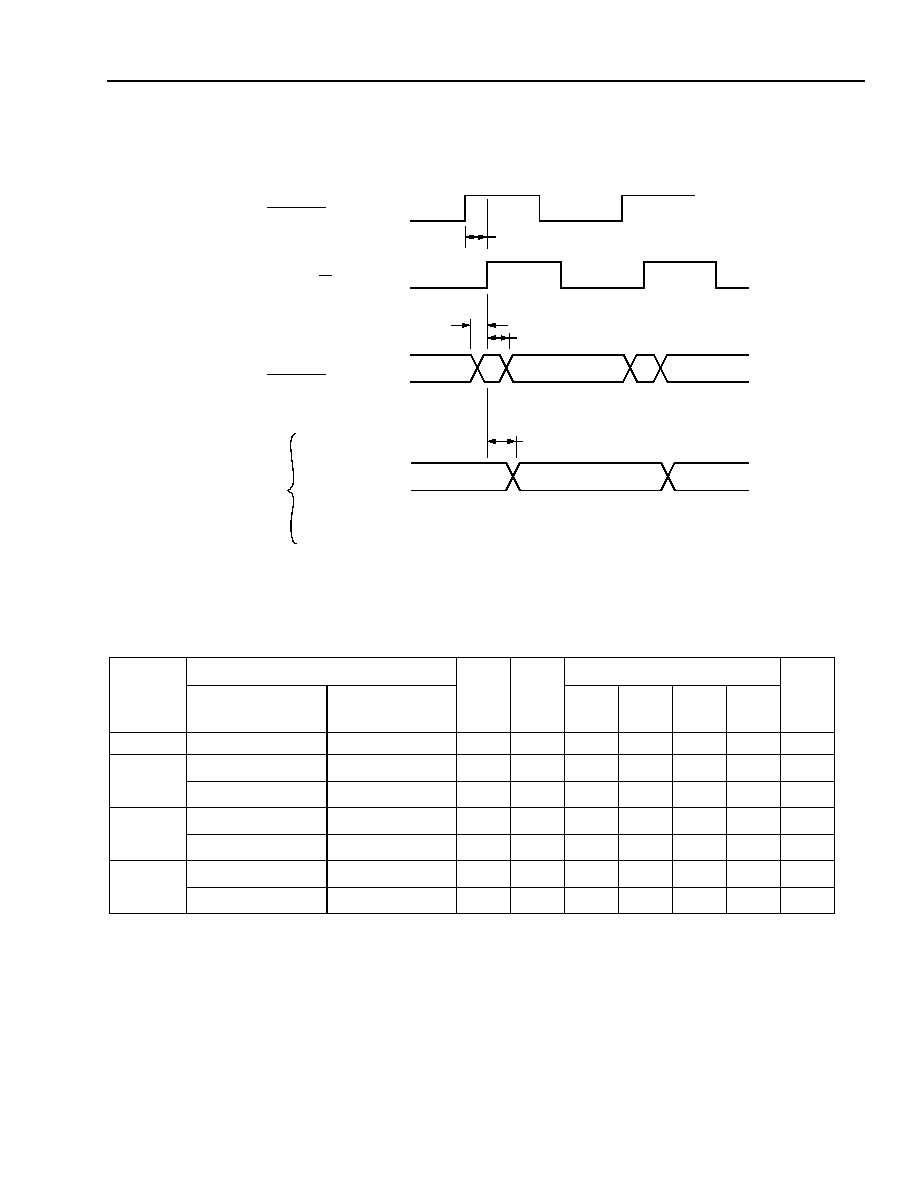

UT5. Timing Difference Between Direct and Polled Status Modes

In the receive direction of the MPHY mode, RxPA[A] shows the polled packet (or ATM) available status for all four

slices, while the RxPA[B], RxPA[C], and RxPA[D] show the direct status states of their respective FIFOs. In some

cases, the status of RxPA[A] does not agree with the status of RxPA[D:B]. The direct status indication has one

additional cycle of pipeline delay from that of the polled status.

Workaround

This is informational only. No workaround is available for this condition.

Corrective Action

No corrective action is required for this condition.

UT6. UTOPIA Interface D Nonfunctional in Some Mixed MPHY and Point-to-Point

Configurations

When TDAT042G5 is configured with slice D in a point-to-point mode, slice D is nonfunctional in one special case.

If UTOPIA interfaces A and B are configured for 32-bit MPHY operation with slice C as part of the polled channels,

interface D will be nonfunctional and cannot be independently configured in a UTOPIA Level 2 point-to-point mode.

This condition does not occur in 16-bit MPHY operation.

Workaround

For mixed MPHY and point-to-point configuration, use UTOPIA slice D for MPHY mode instead of slice C.

UTOPIA slice C will then be available for normal point-to point mode.

Corrective Action

This condition will be addressed in future versions of the device.

Agere Systems Inc.

15

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

UTOPIA (UT)

(continued)

UT7. Response to 0x1F MPHY Address

TDAT042G5 MPHY currently generates a polled status response to the address 0x1F (the null address), which is

not compliant with the UTOPIA Level 2 standard. The address 0x1F is valid for UTOPIA Level 3 operation.

Workaround

No workaround is available for this condition.

Corrective Action

This condition will be addressed in future versions of the device.

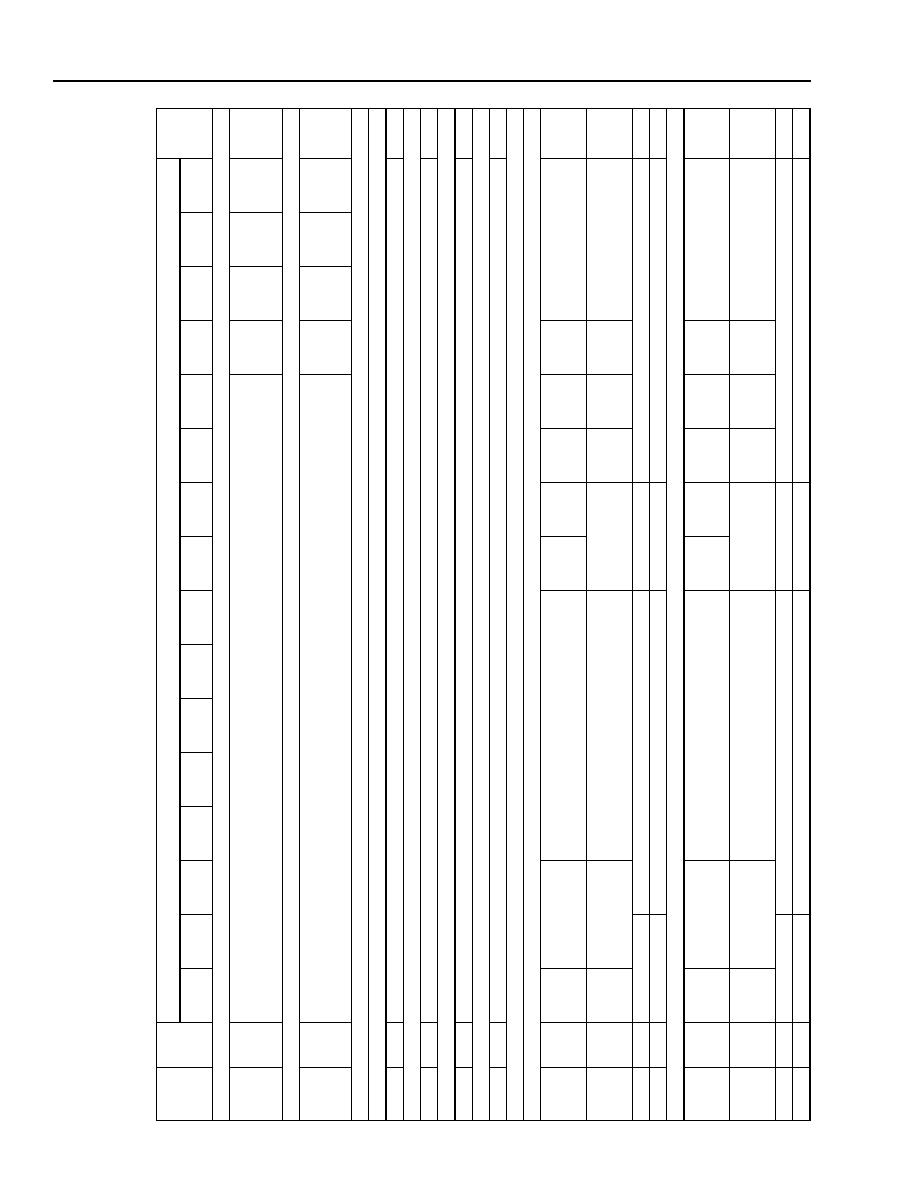

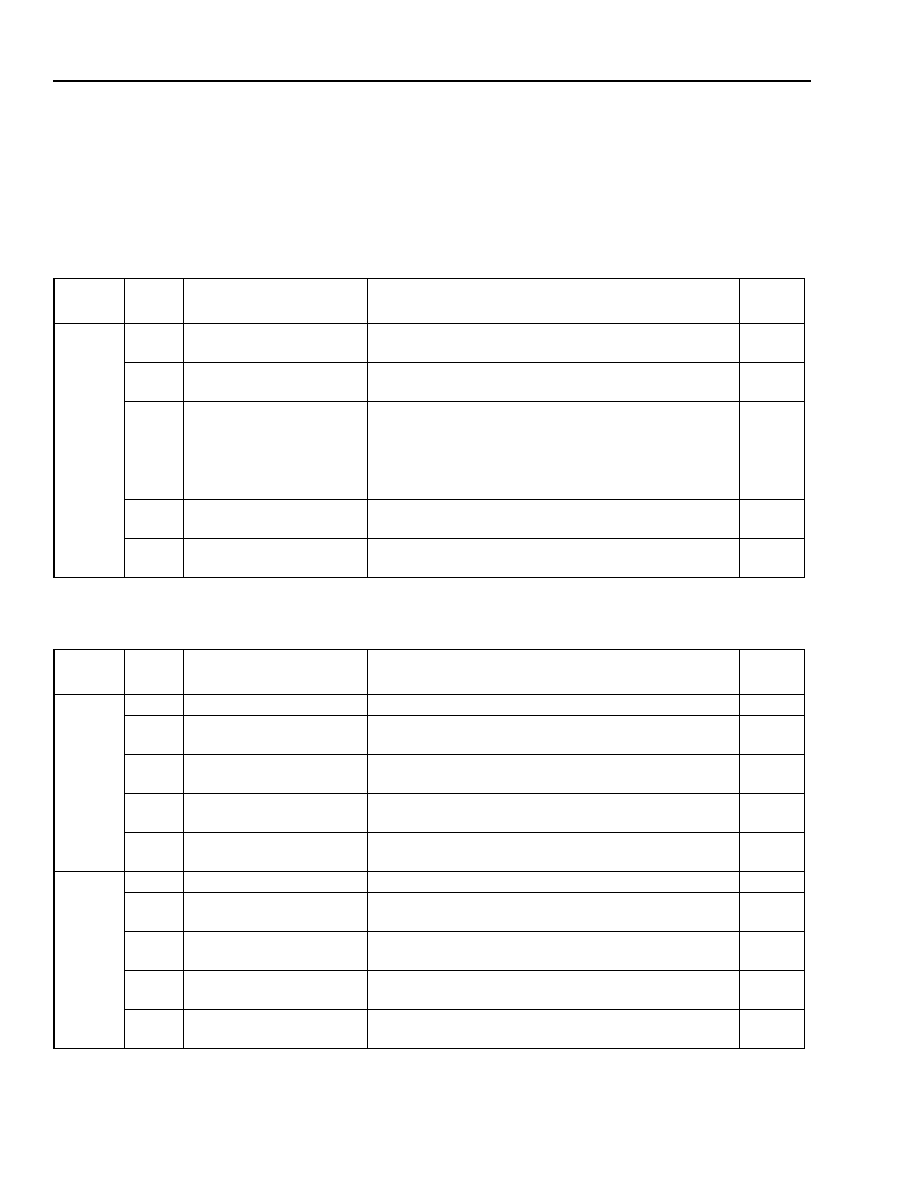

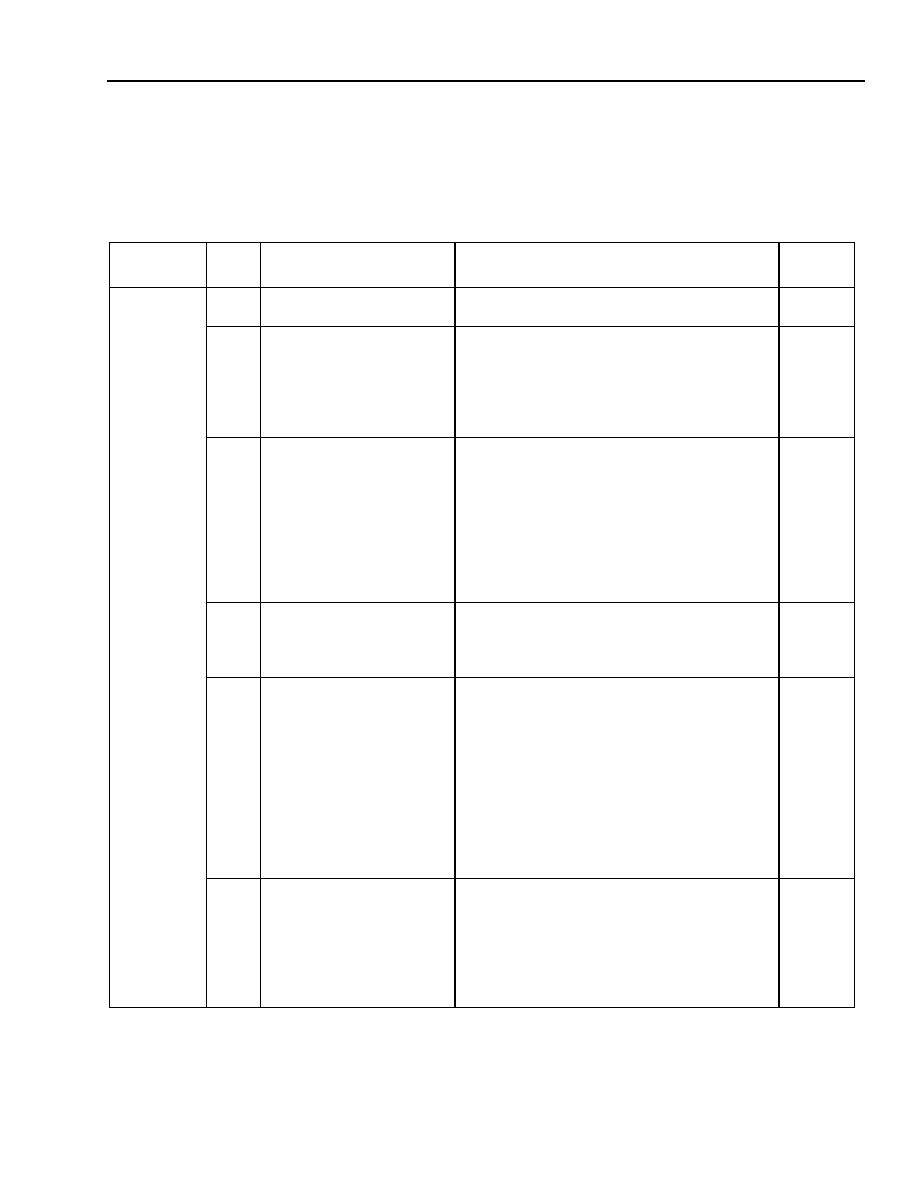

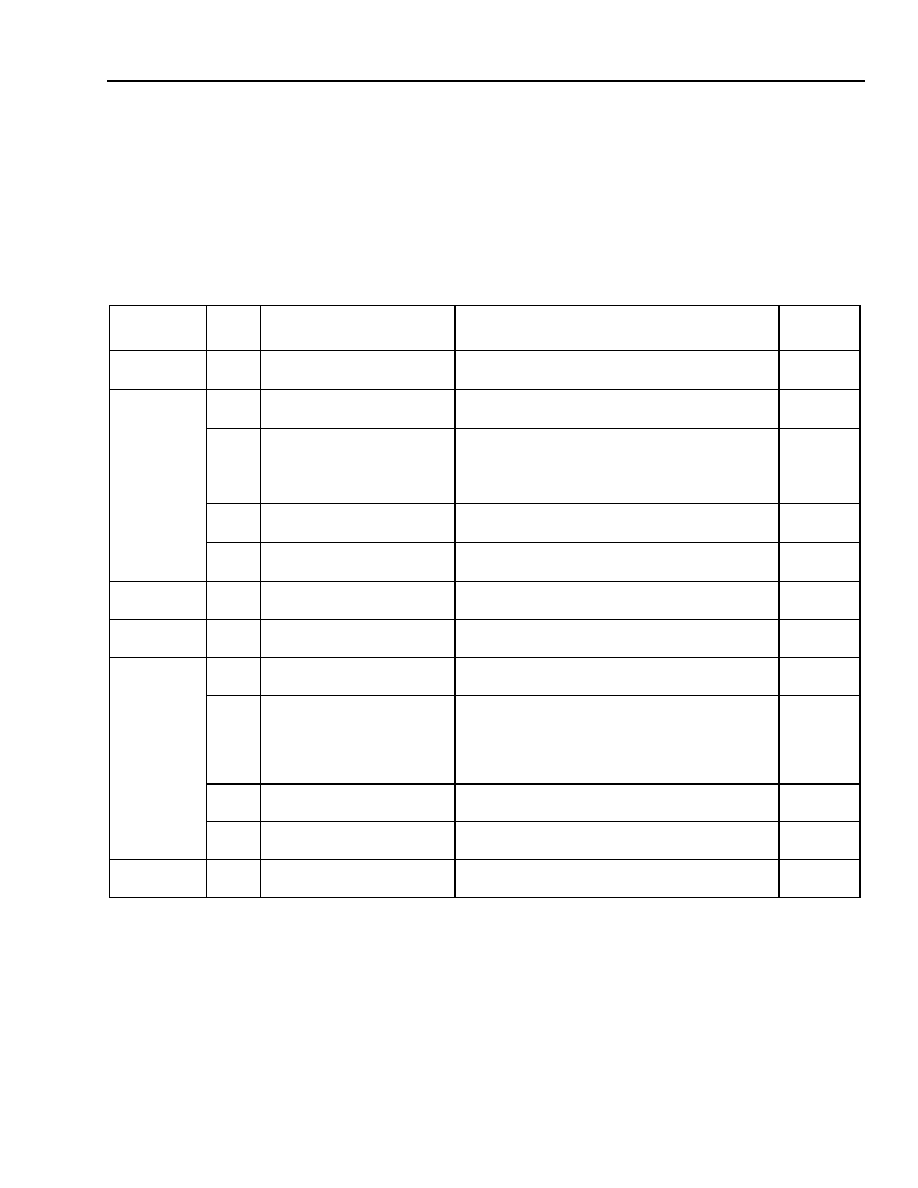

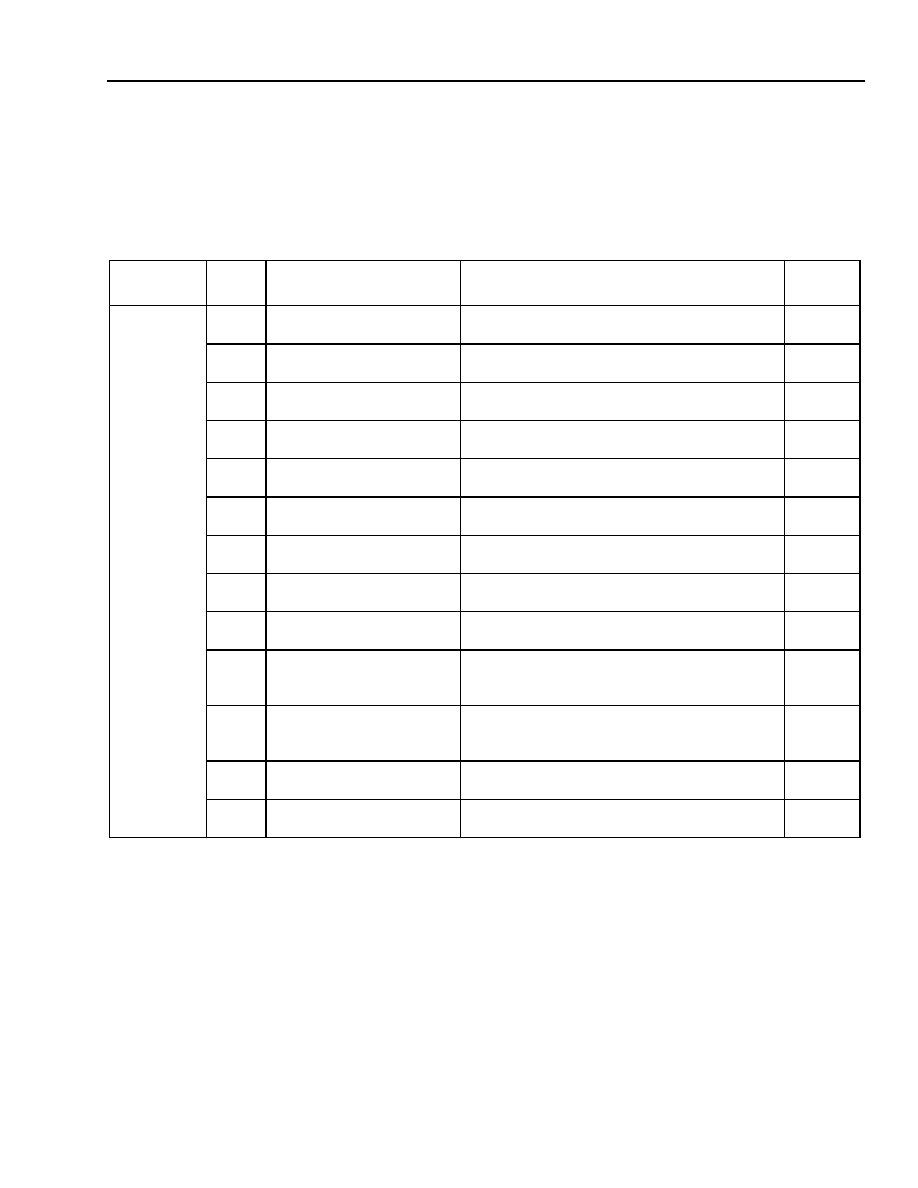

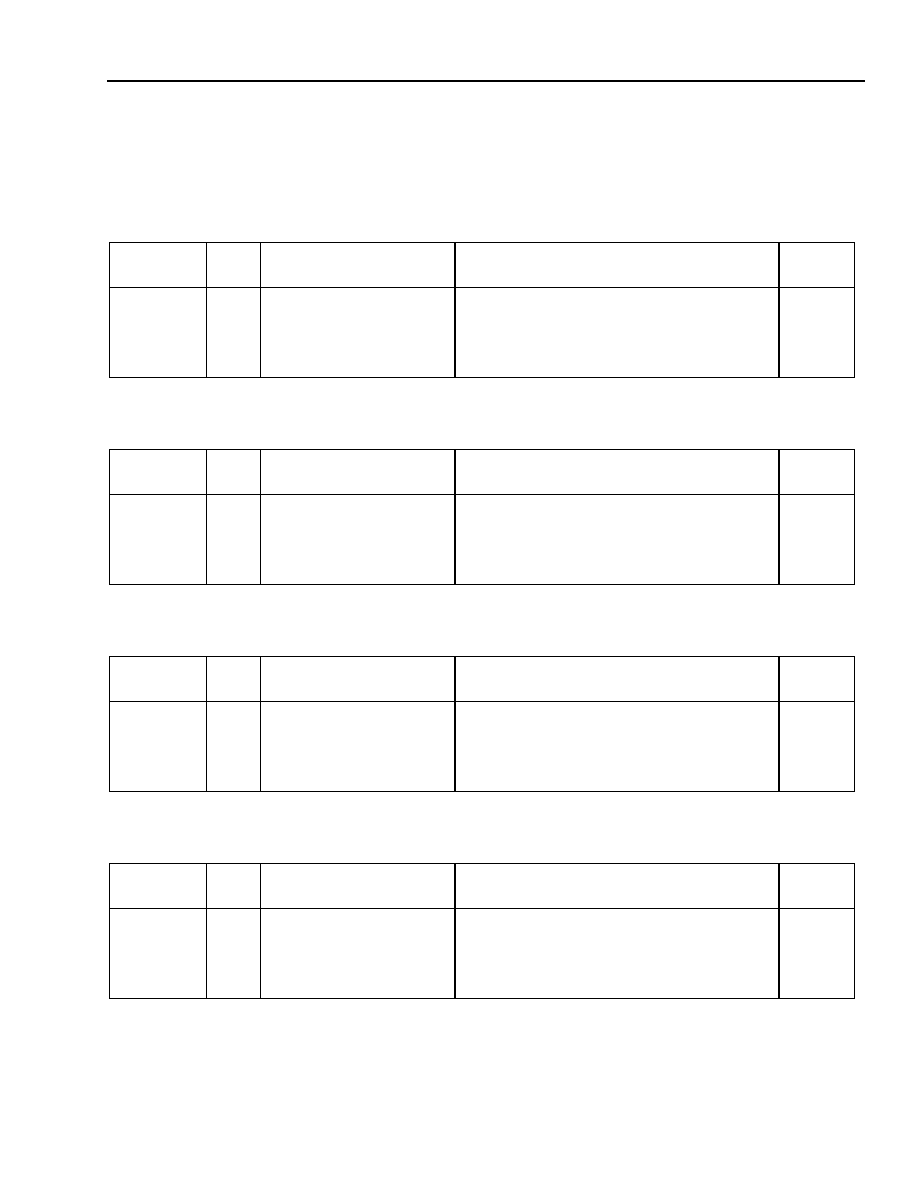

UT8. Far-End Loopback Bandwidth Limitations

In the STS-48/STM-16 mode (U3, U3+), looping back data at the far end (UTOPIA interface) can only be accom-

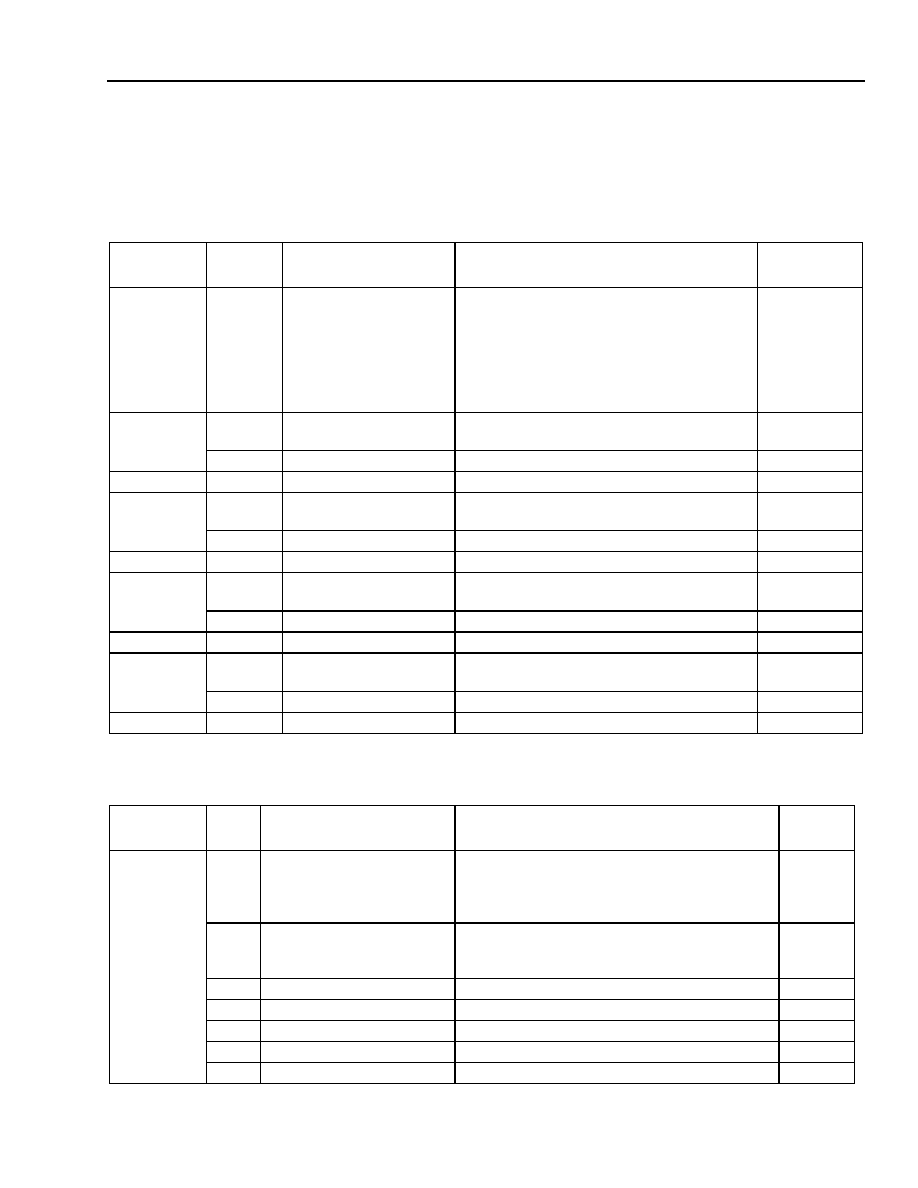

plished without cell/packet corruption at rates below the following, as shown in Table 5.

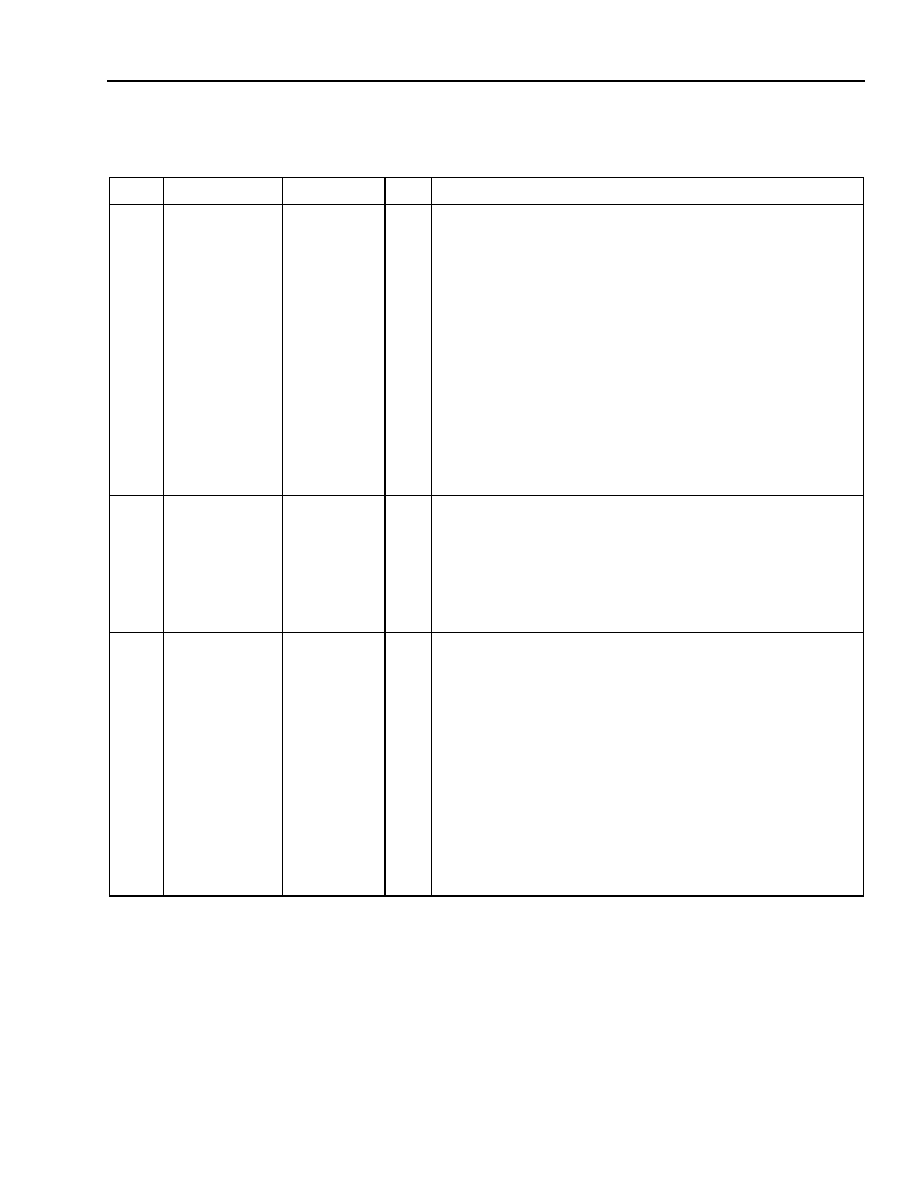

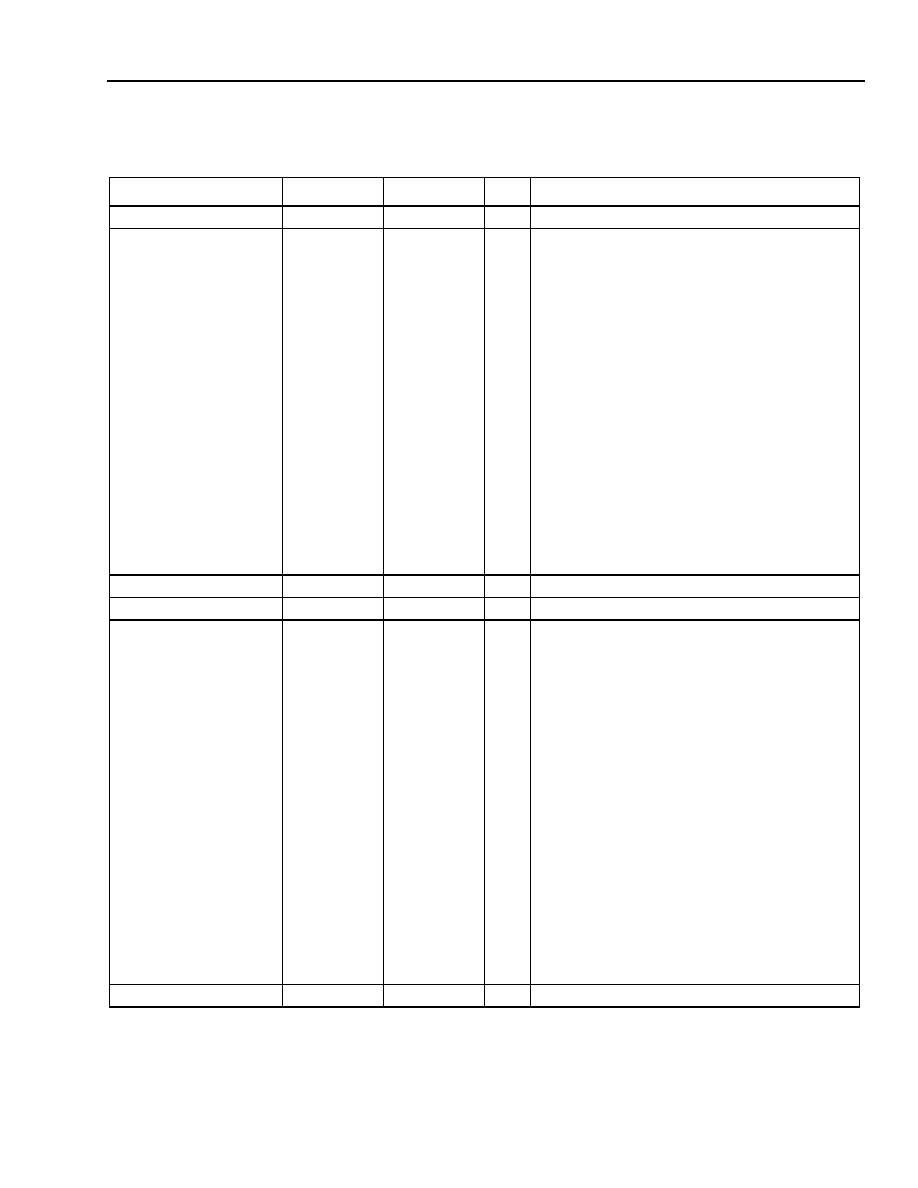

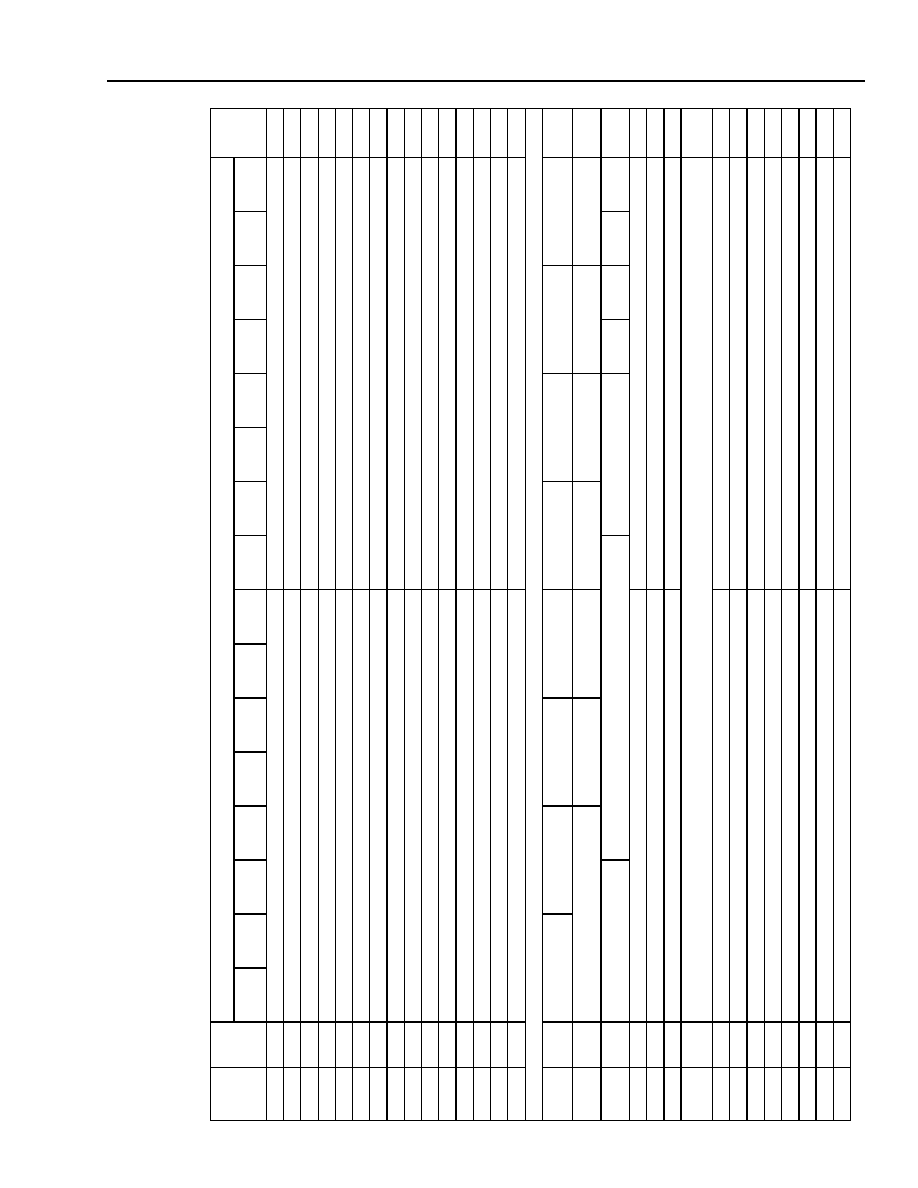

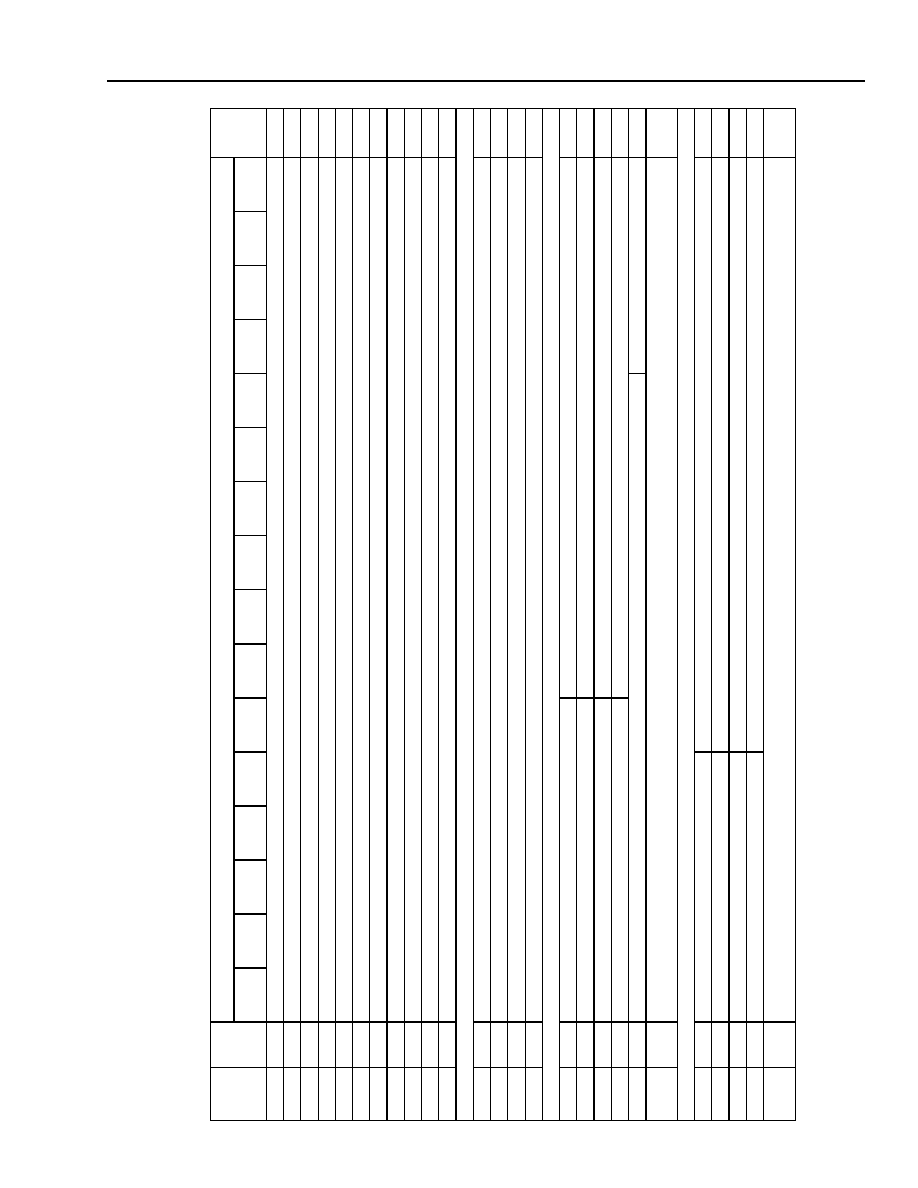

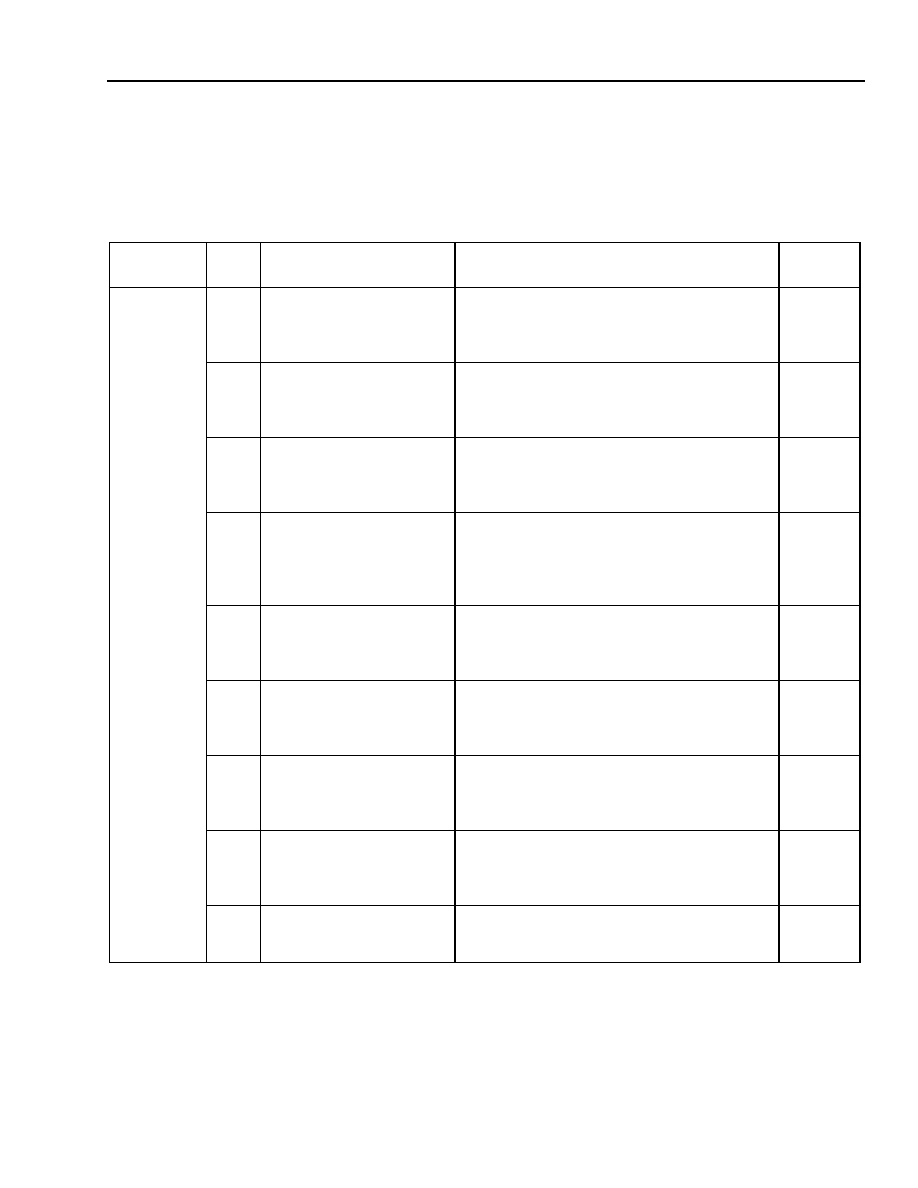

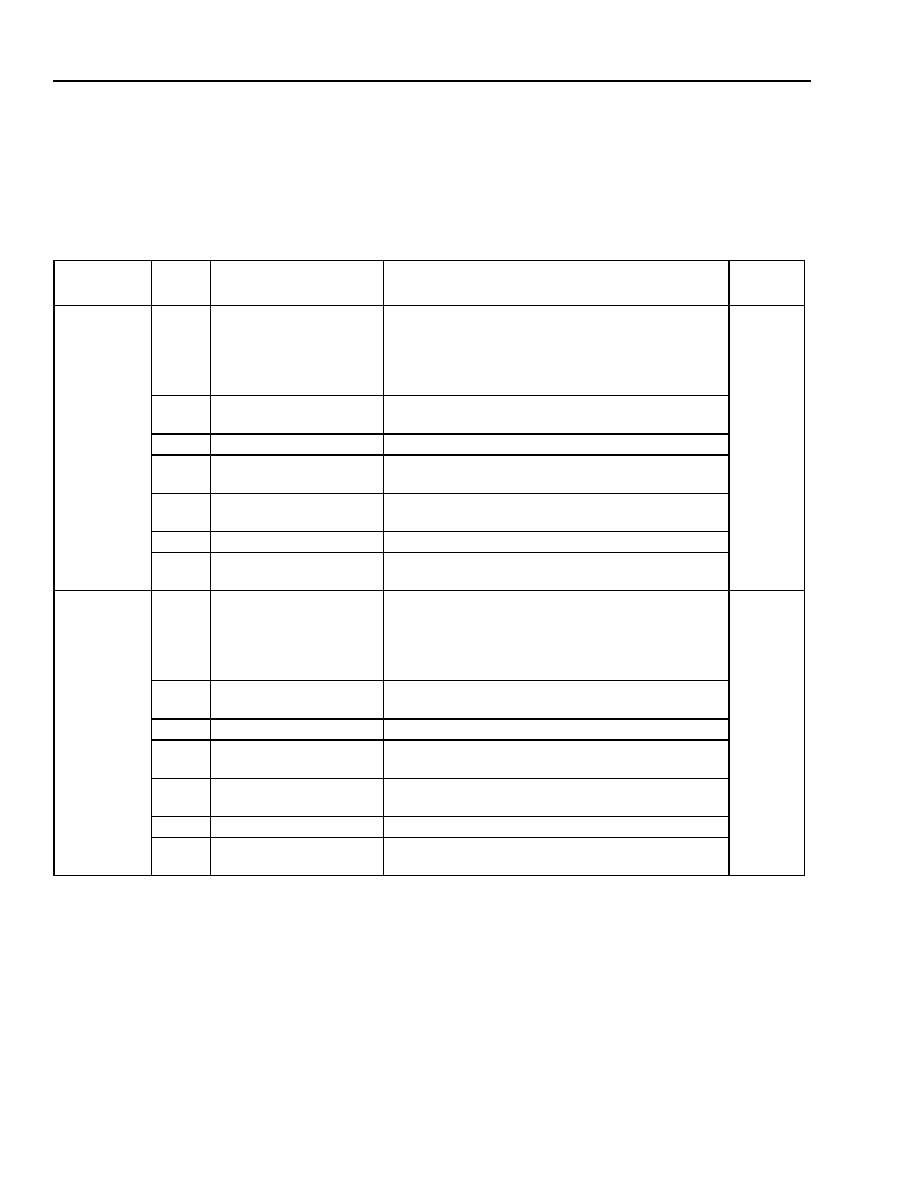

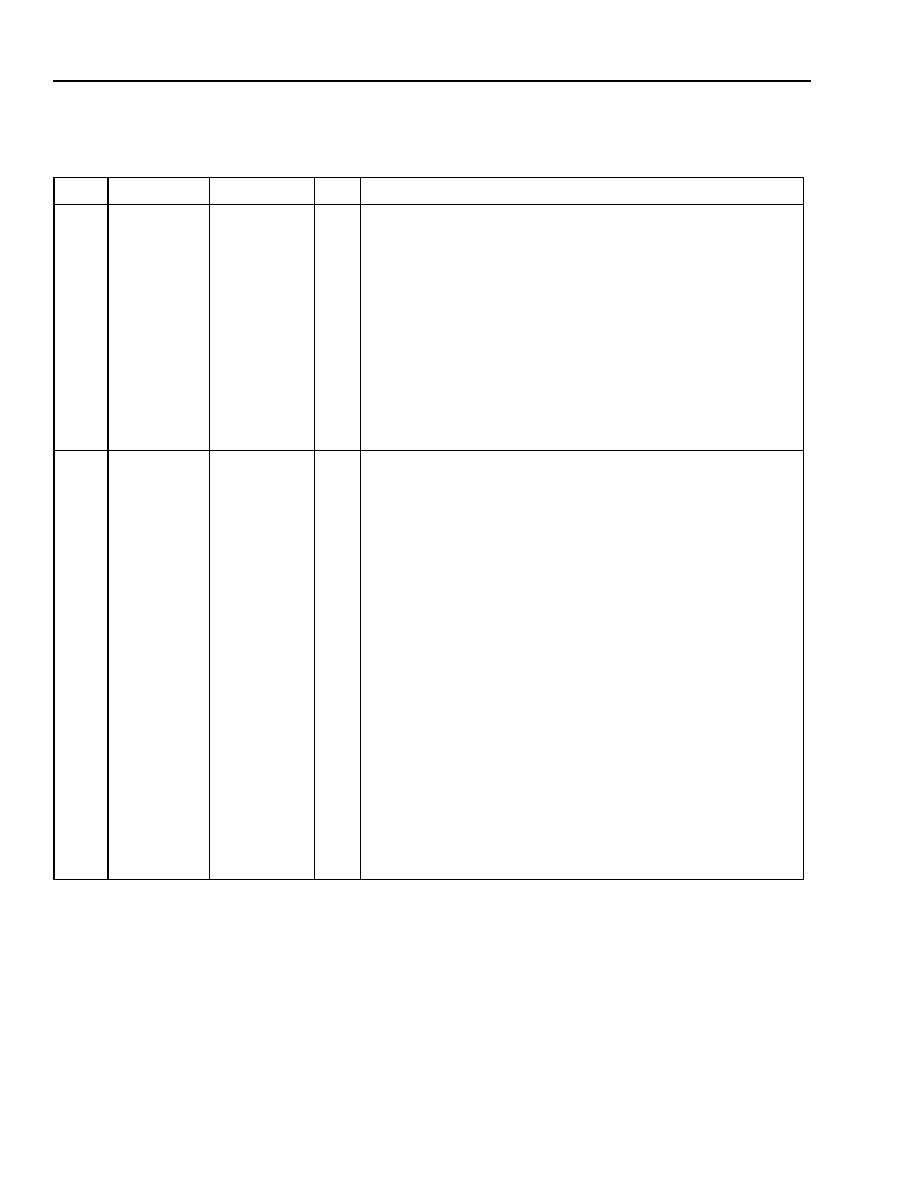

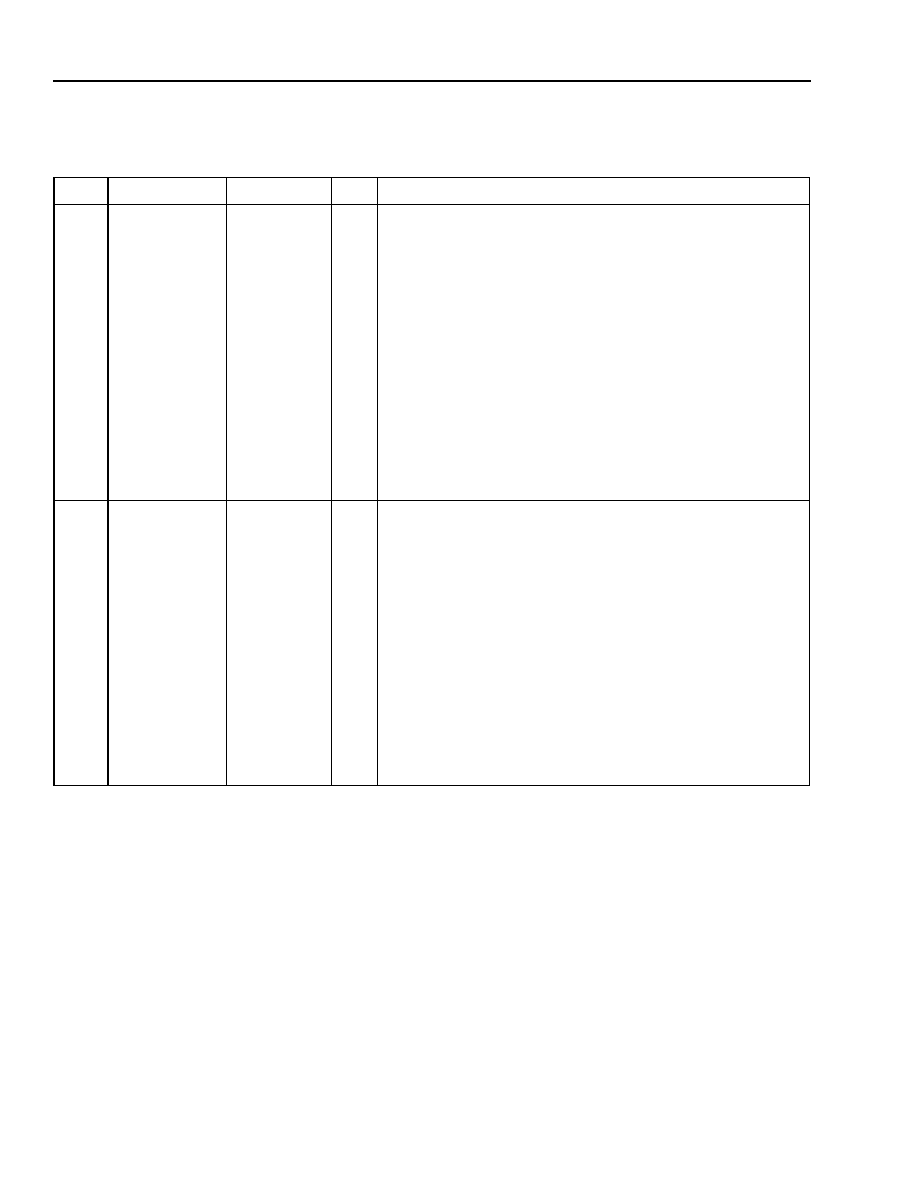

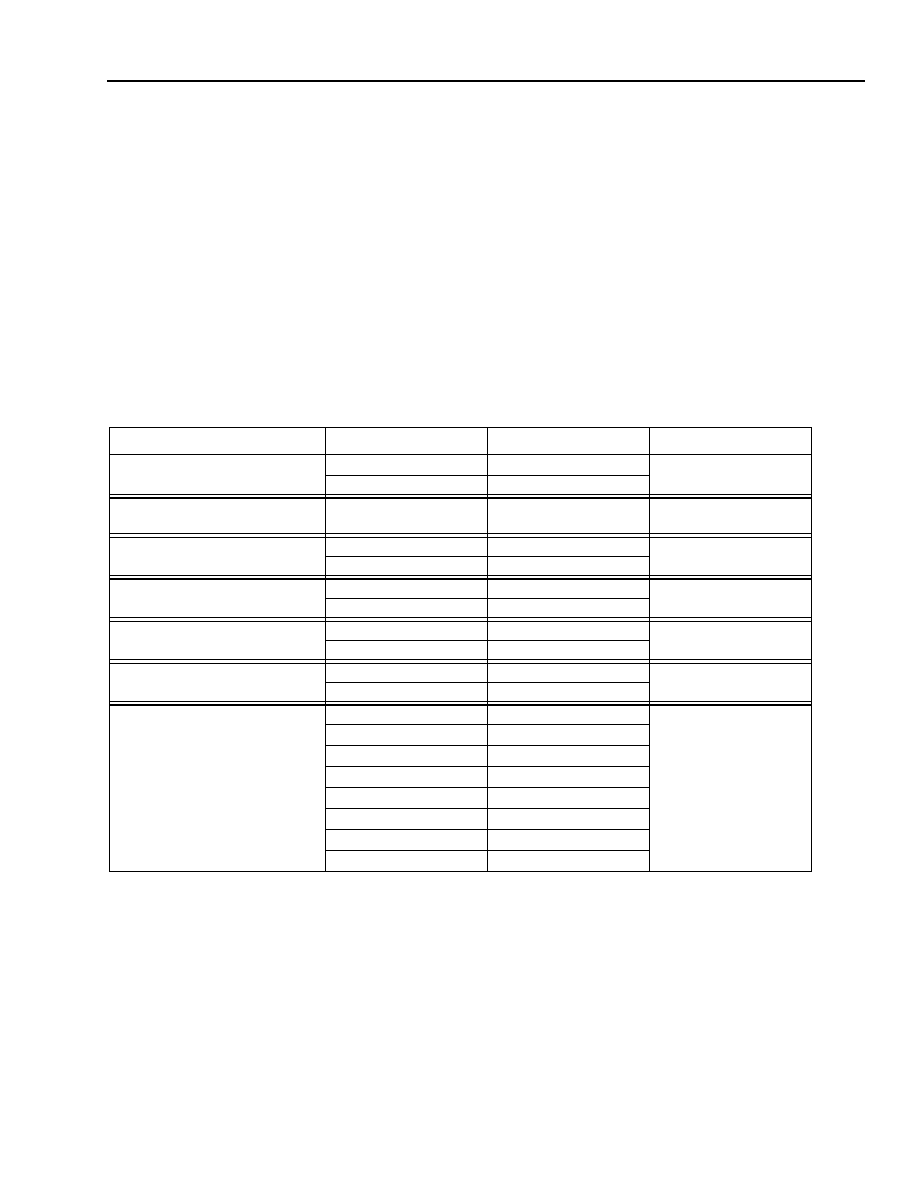

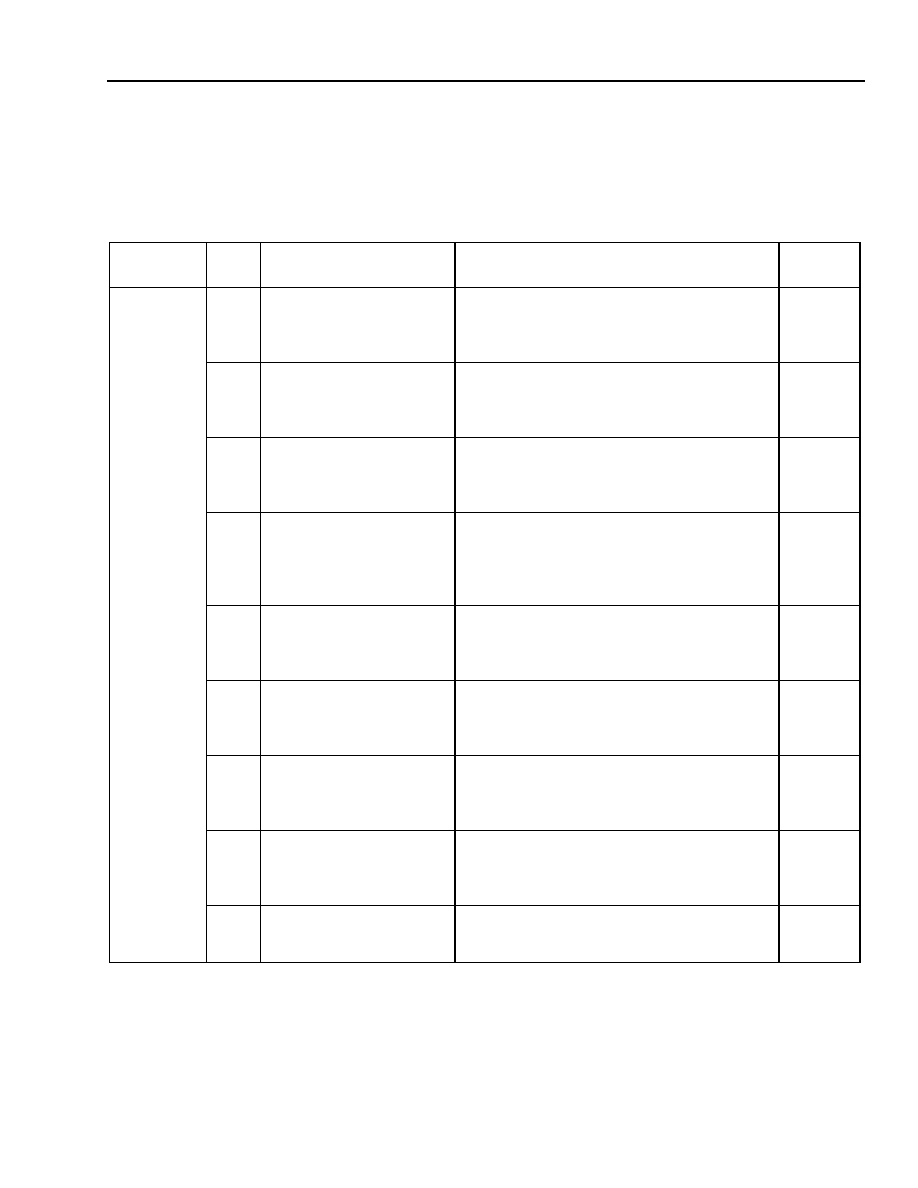

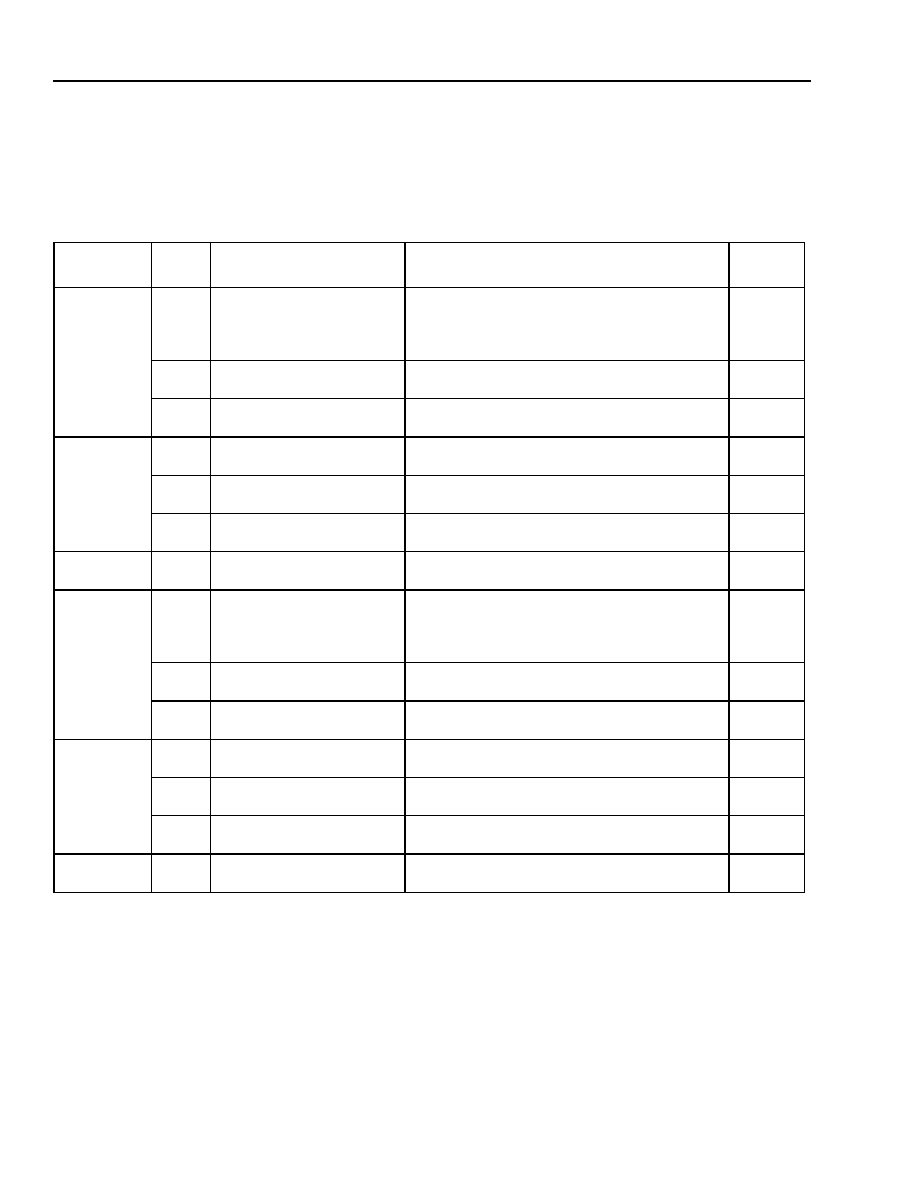

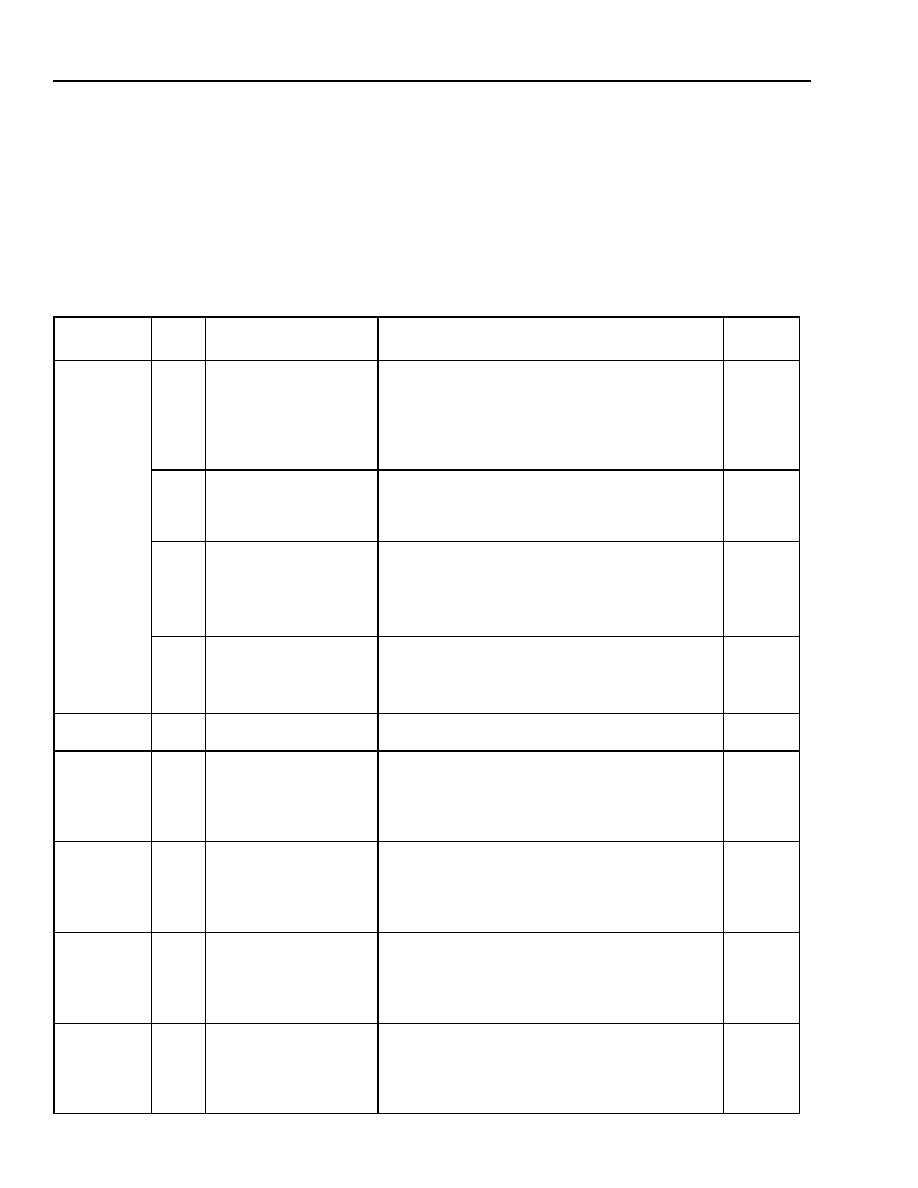

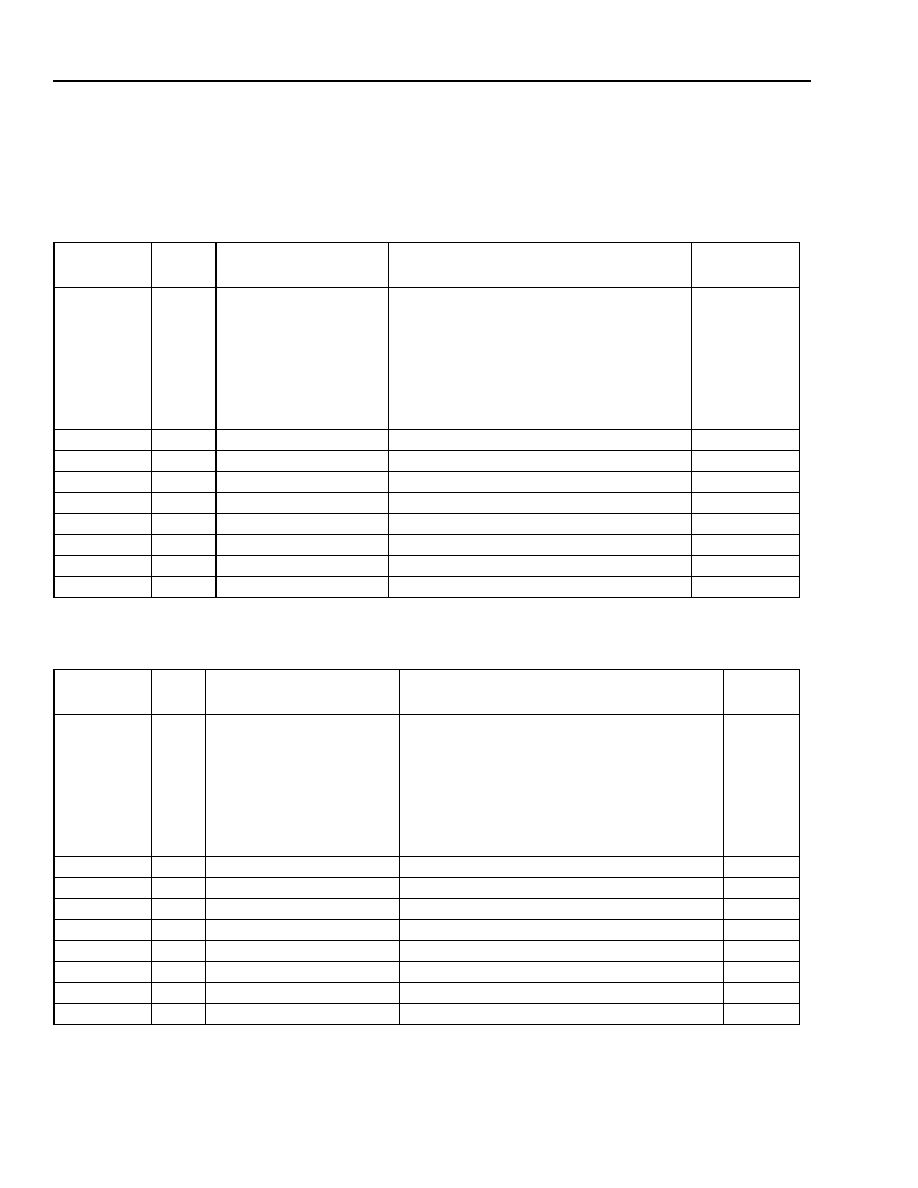

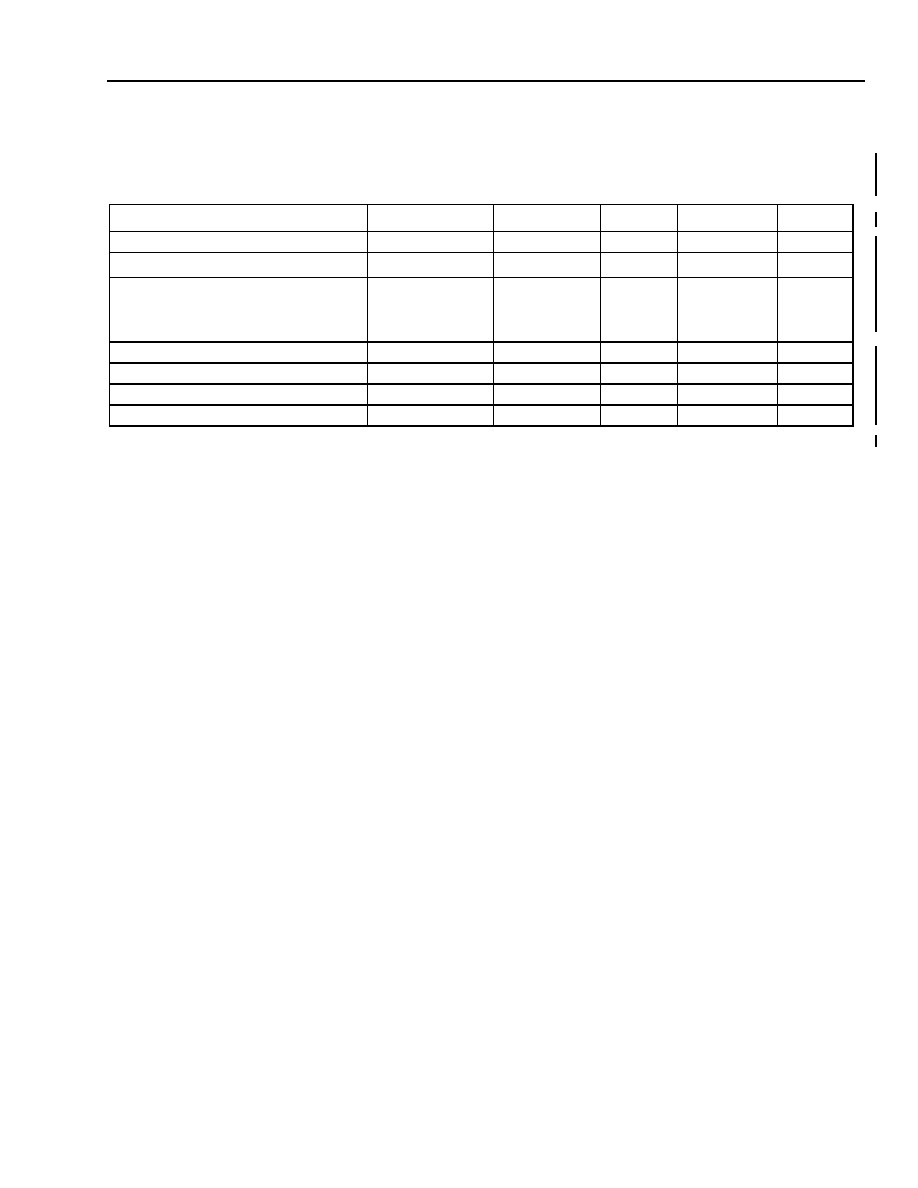

Table 5. Cell/Packet Corruption Rates

When cell/packet corruption occurs, the device reports transmit FIFO underflow.

Workaround

No workaround is available for this condition.

Corrective Action

This condition will be addressed in future versions of the device.

Mode

ATM

Packet

STS-48/STM-16

300 Mbits/s

Rate not yet determined

STS-12/STM-4

70 Mbits/s

Rate not yet determined

STS-3/STM-1

30 Mbits/s

Rate not yet determined

16

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

UTOPIA (UT)

(continued)

UT9. Clock Requirements for MPHY Modes

When using the TDAT042G5 in MPHY mode, receive and transmit clocks must be provided for all channels (A, B,

C, and D). Also, the packet available (PA) signal for each channel must be provided on each channel's associated

PA pin.

Workaround

It is possible to place RxCLK[D:A] into source mode by provisioning bit 6 (CLOCK_MODE_Rx) of the UTOPIA

receive provisioning registers (addresses 0x020F, 0x0213, 0x0217, 0x021B). This will eliminate the need to supply

separate receive and transmit clocks.

Corrective Action

This is informational only. No corrective action is required for this condition.

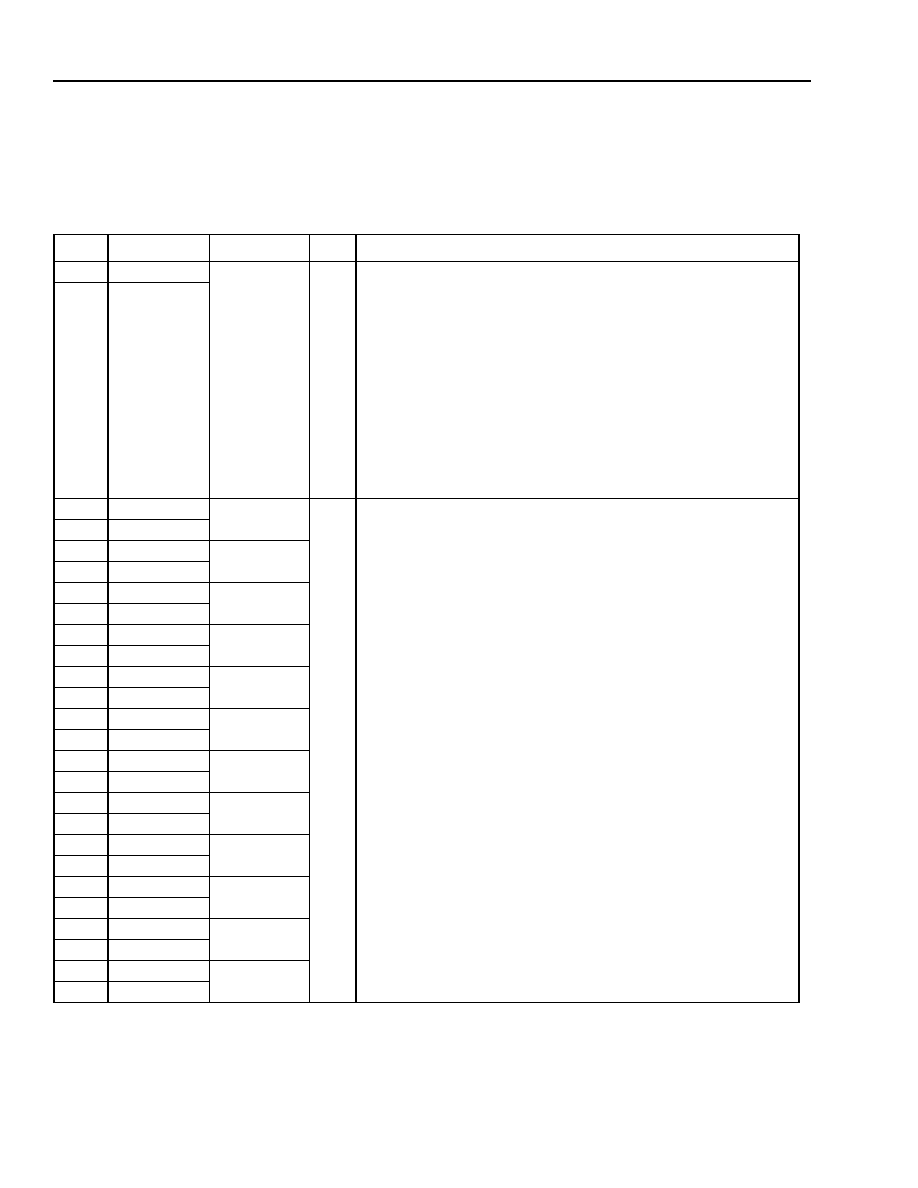

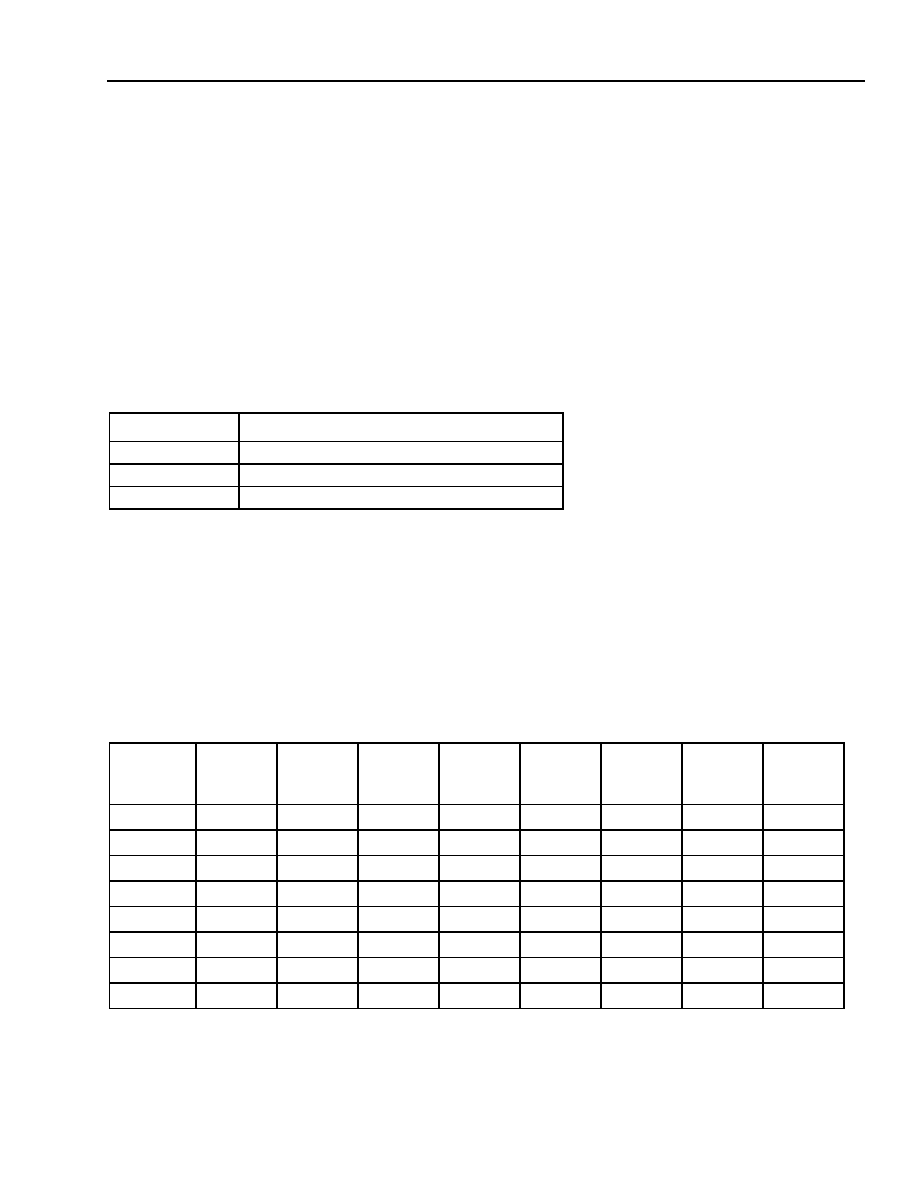

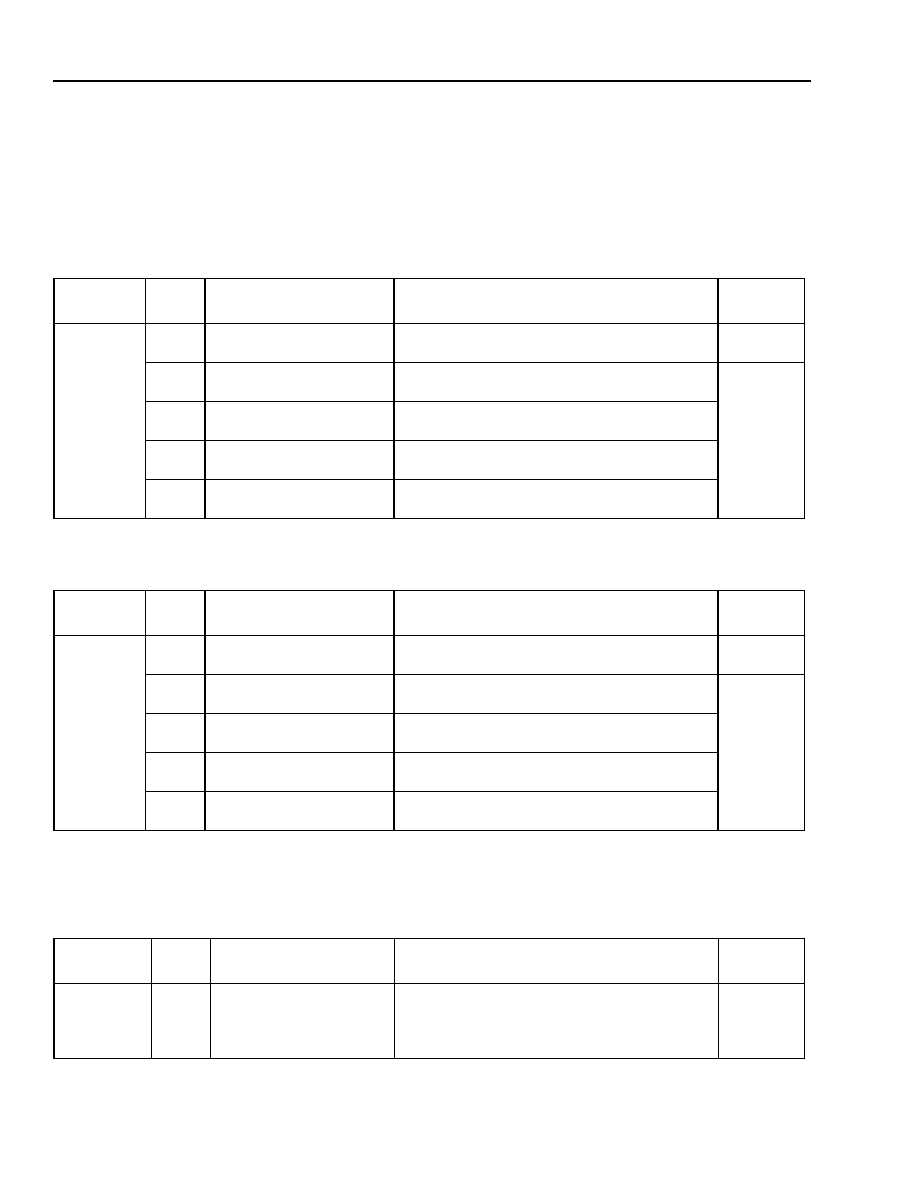

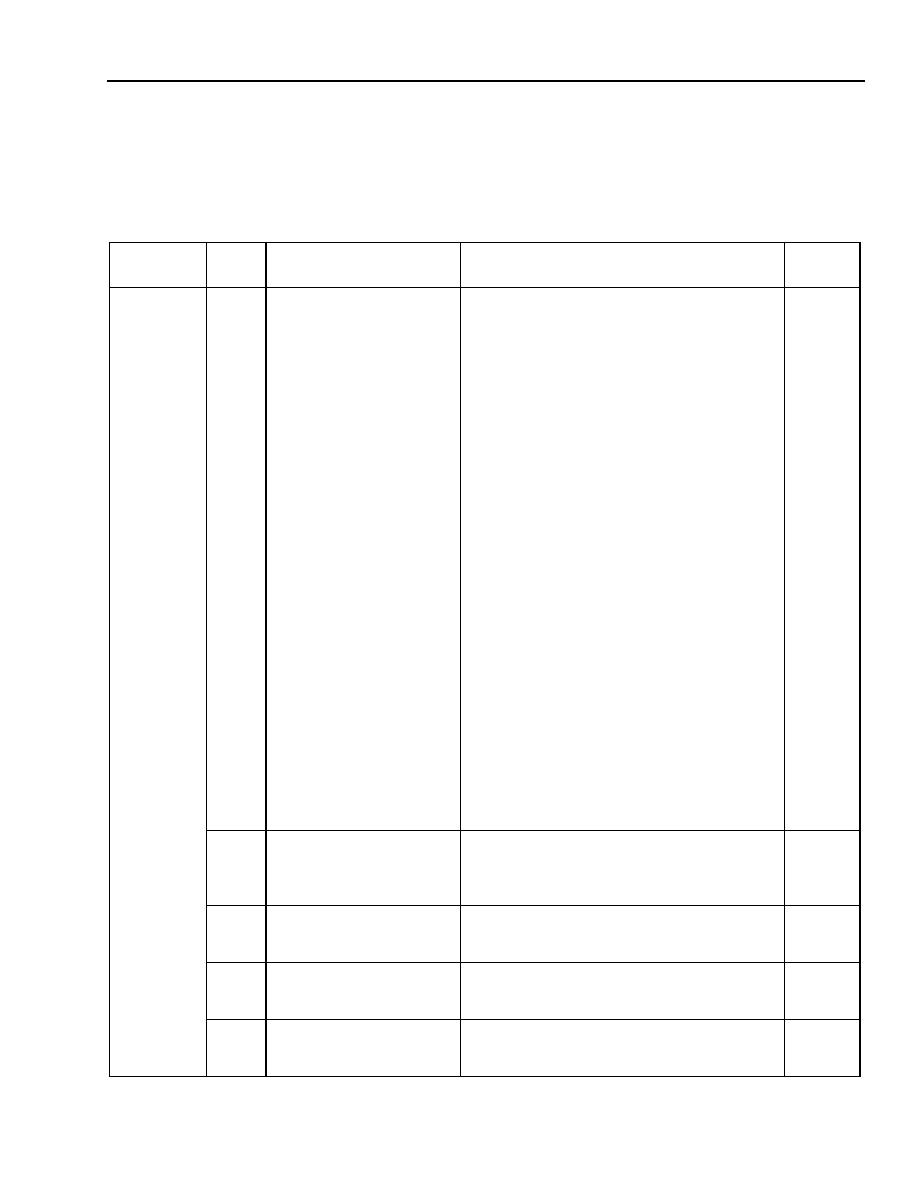

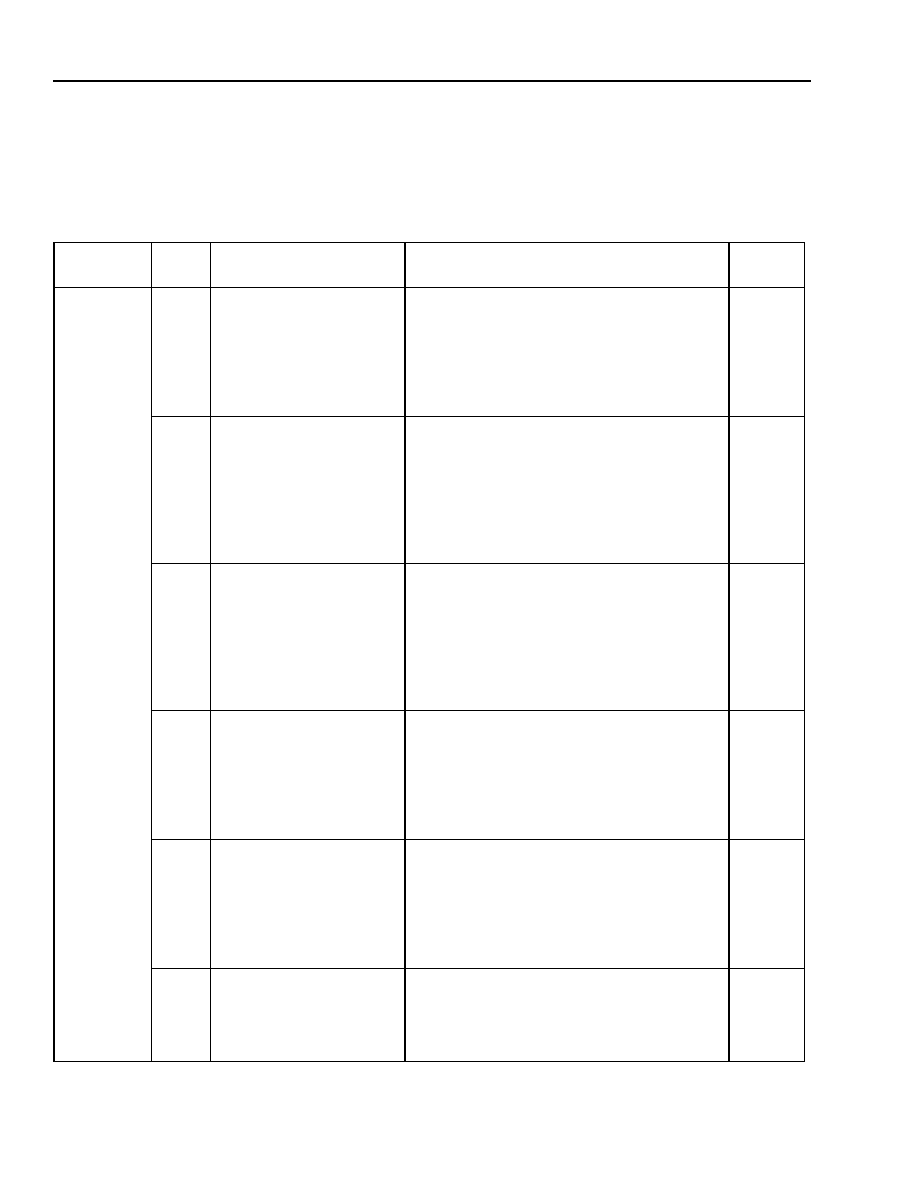

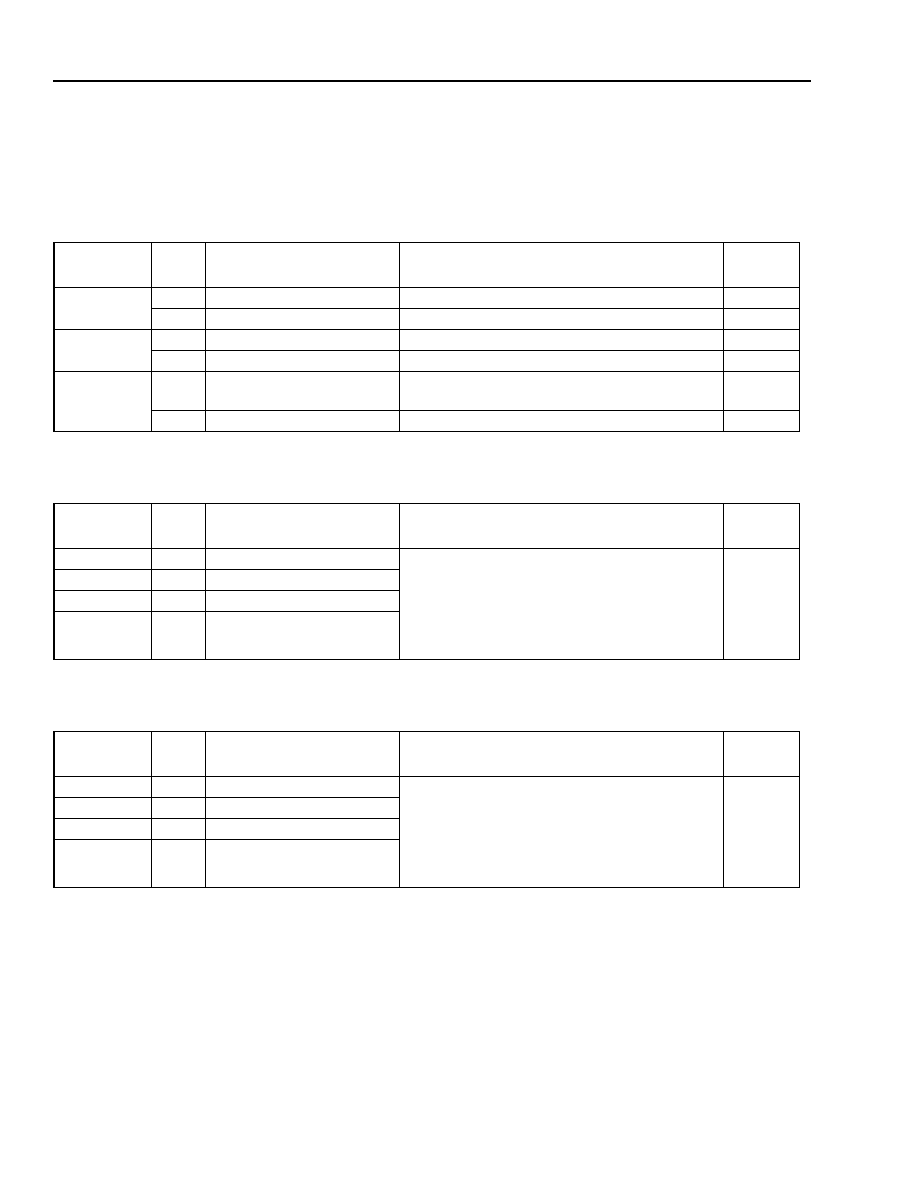

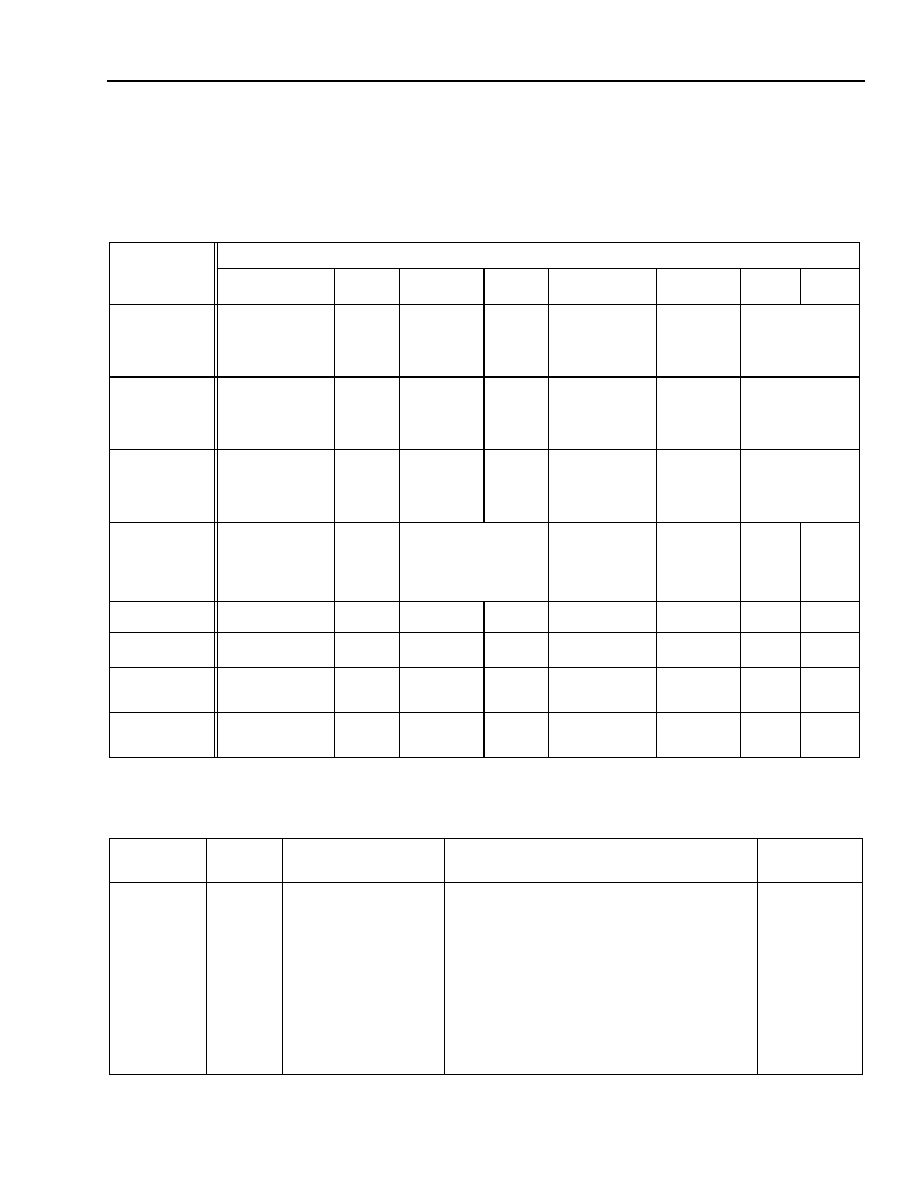

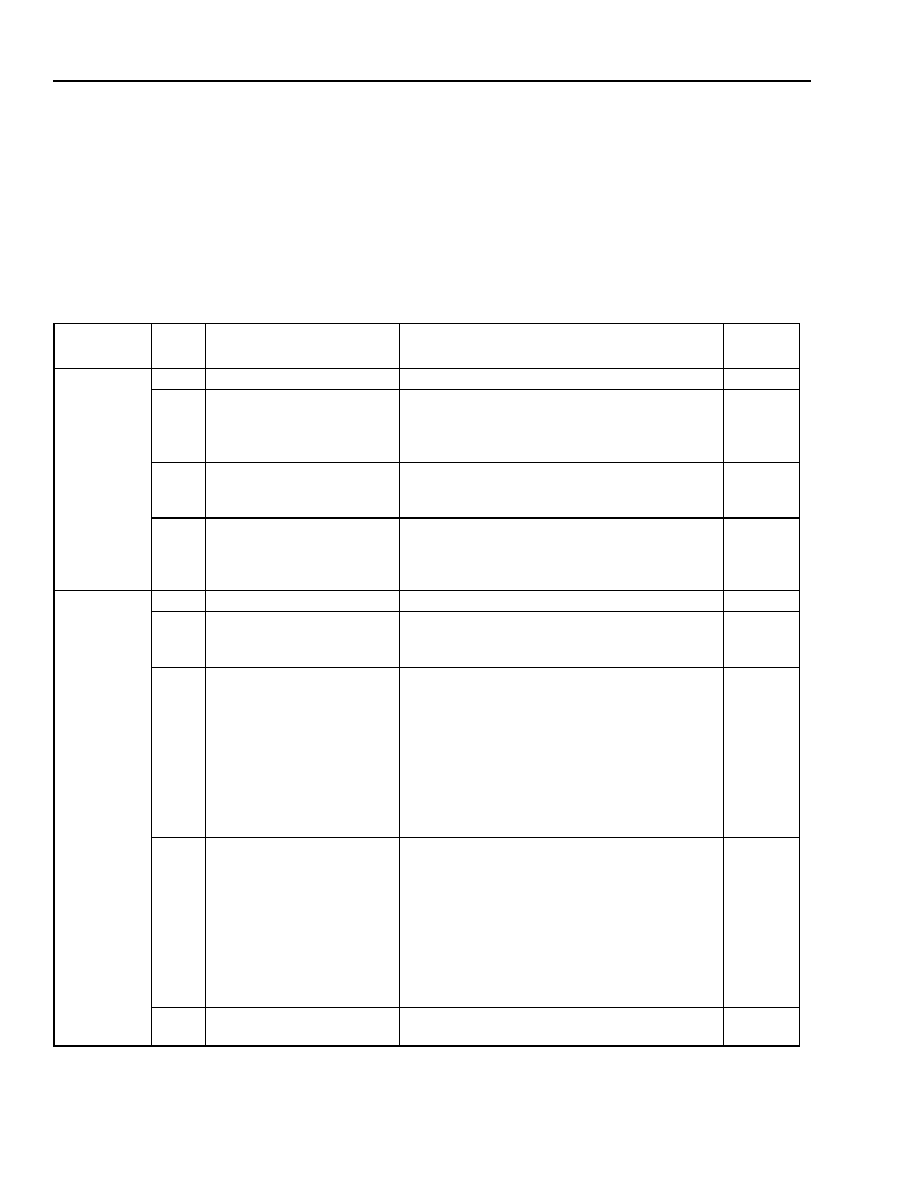

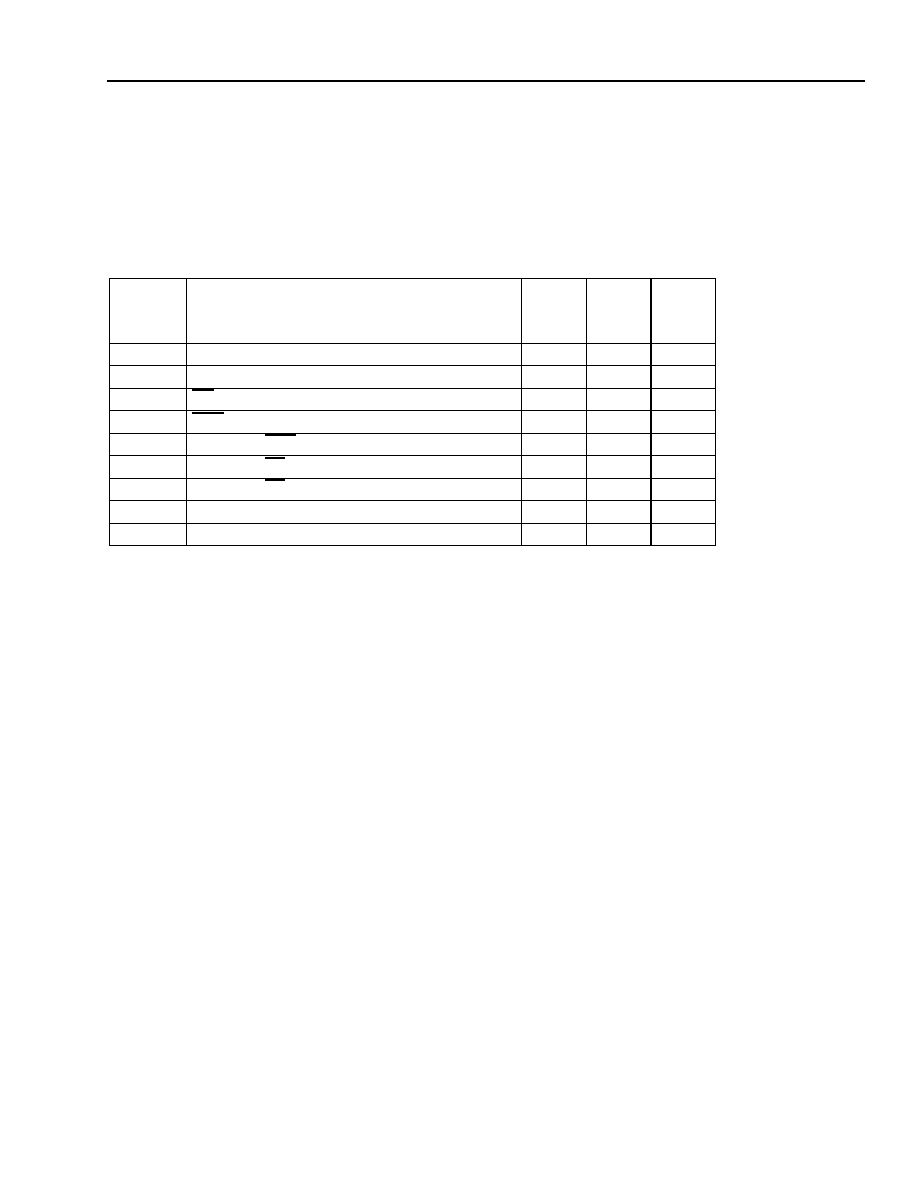

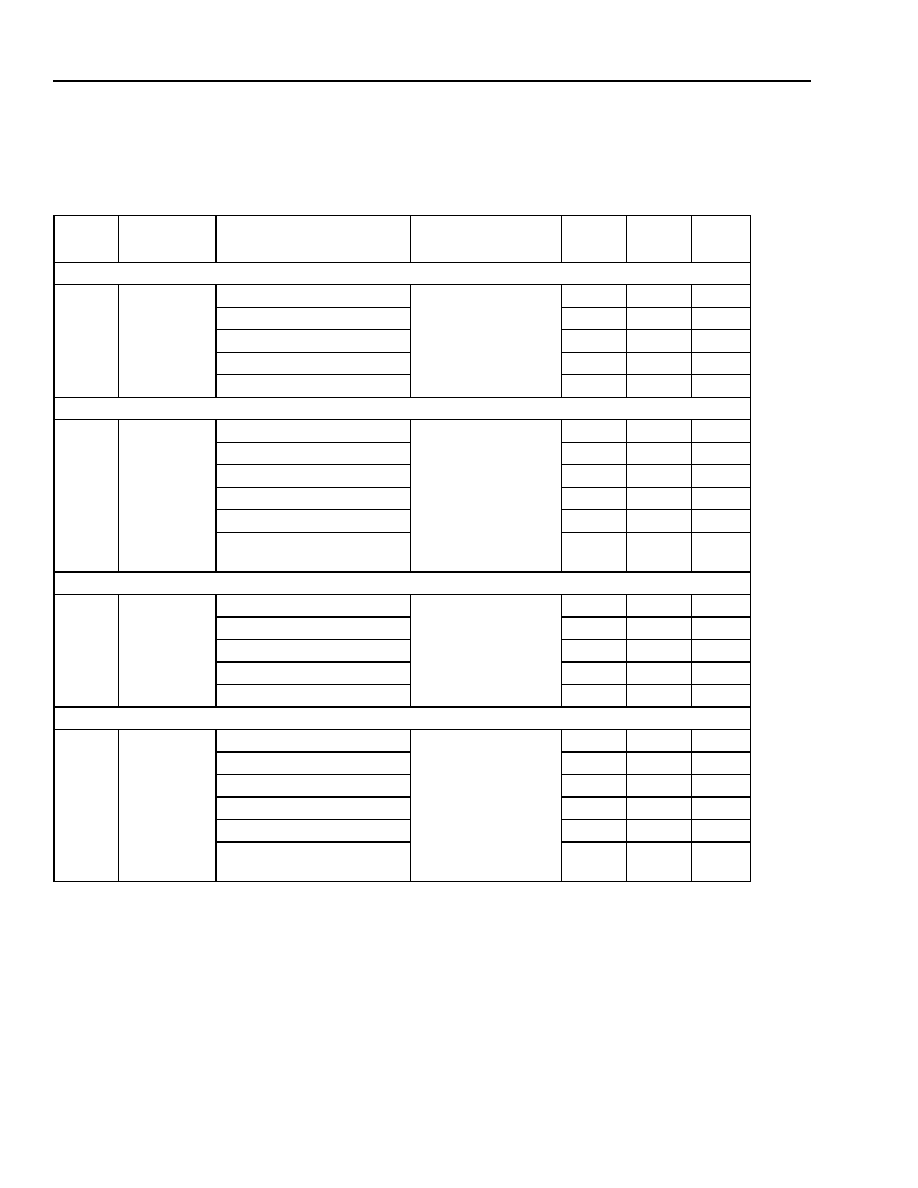

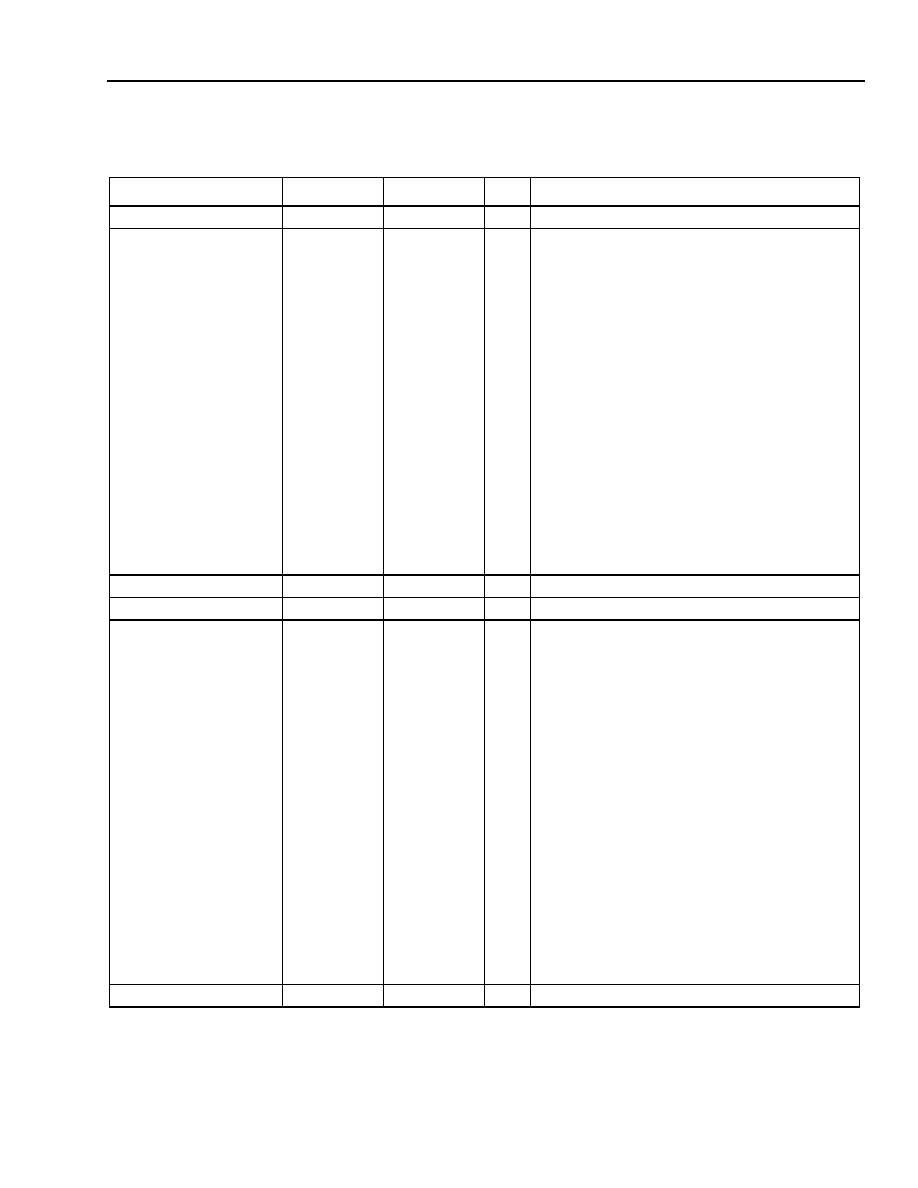

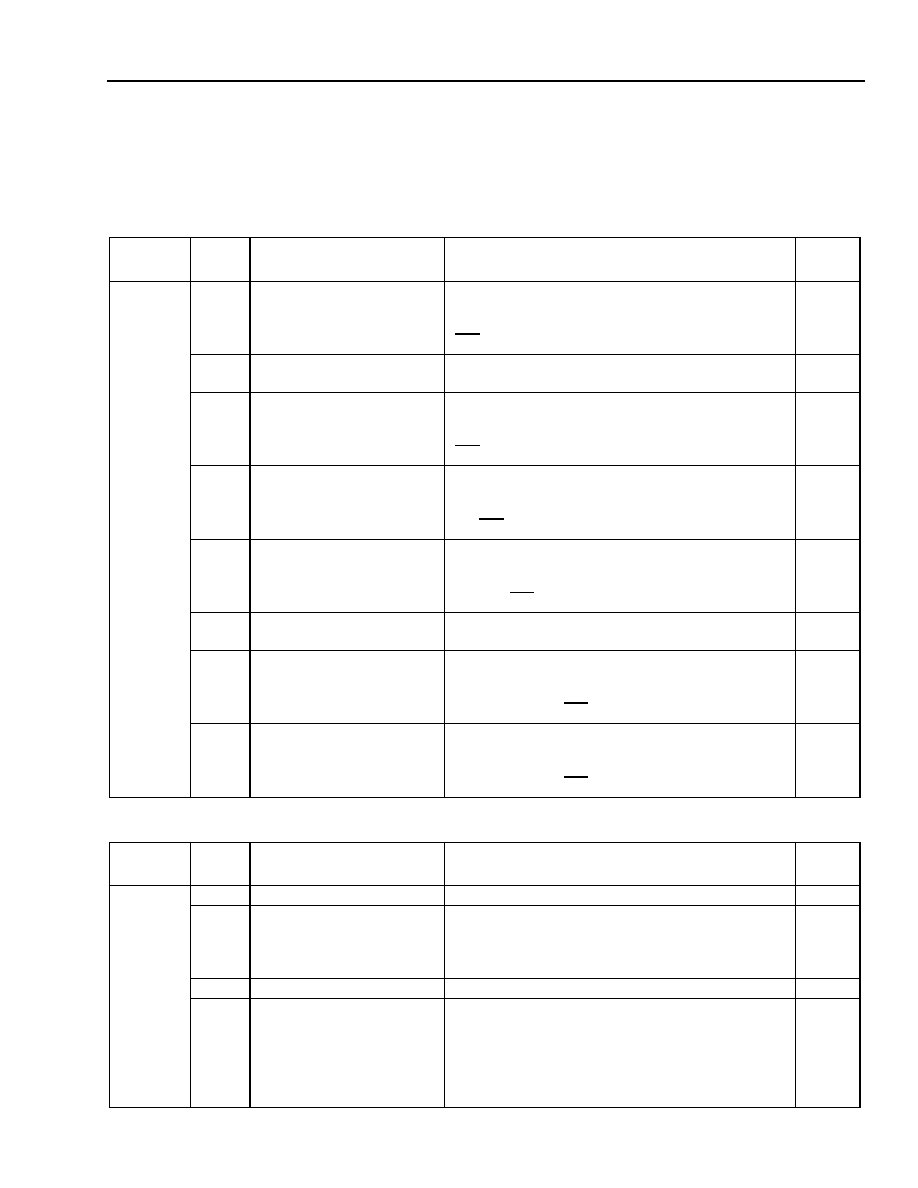

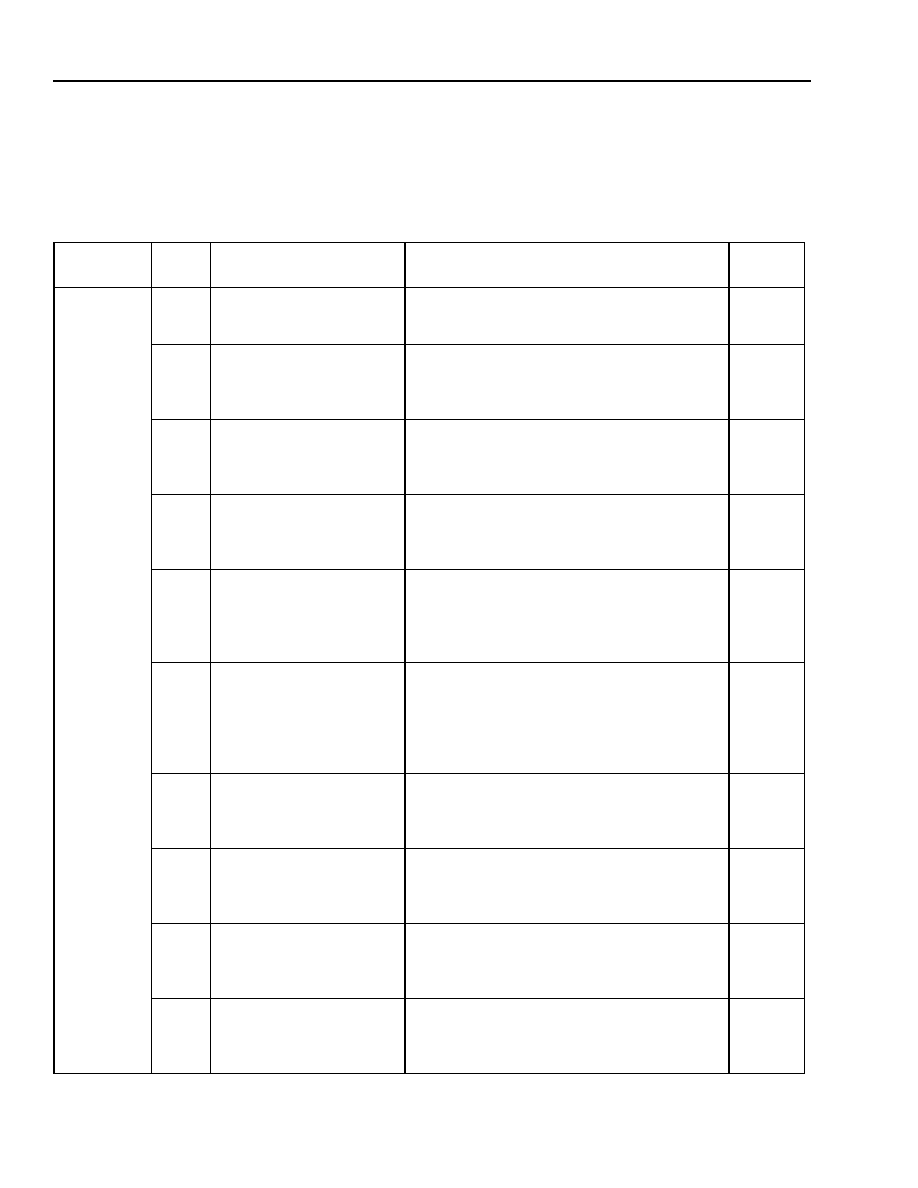

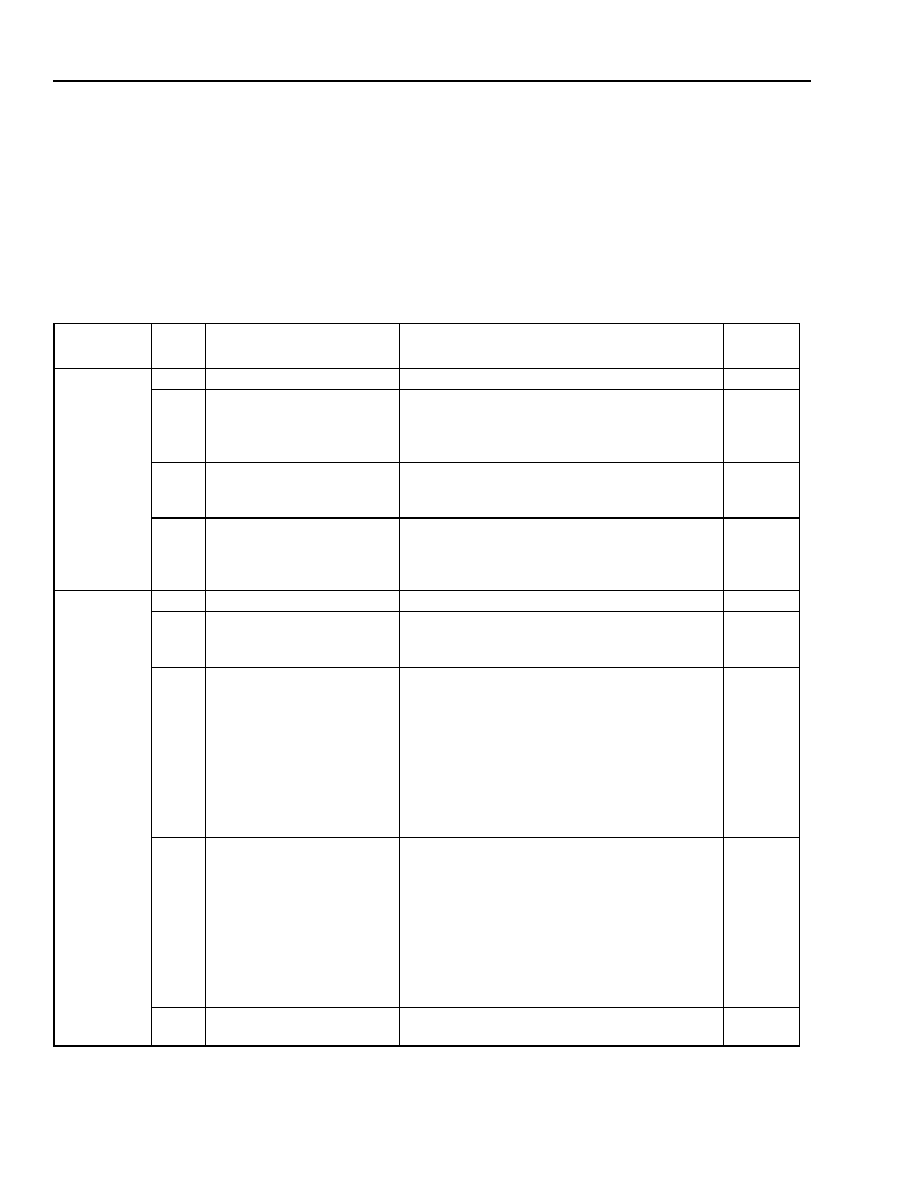

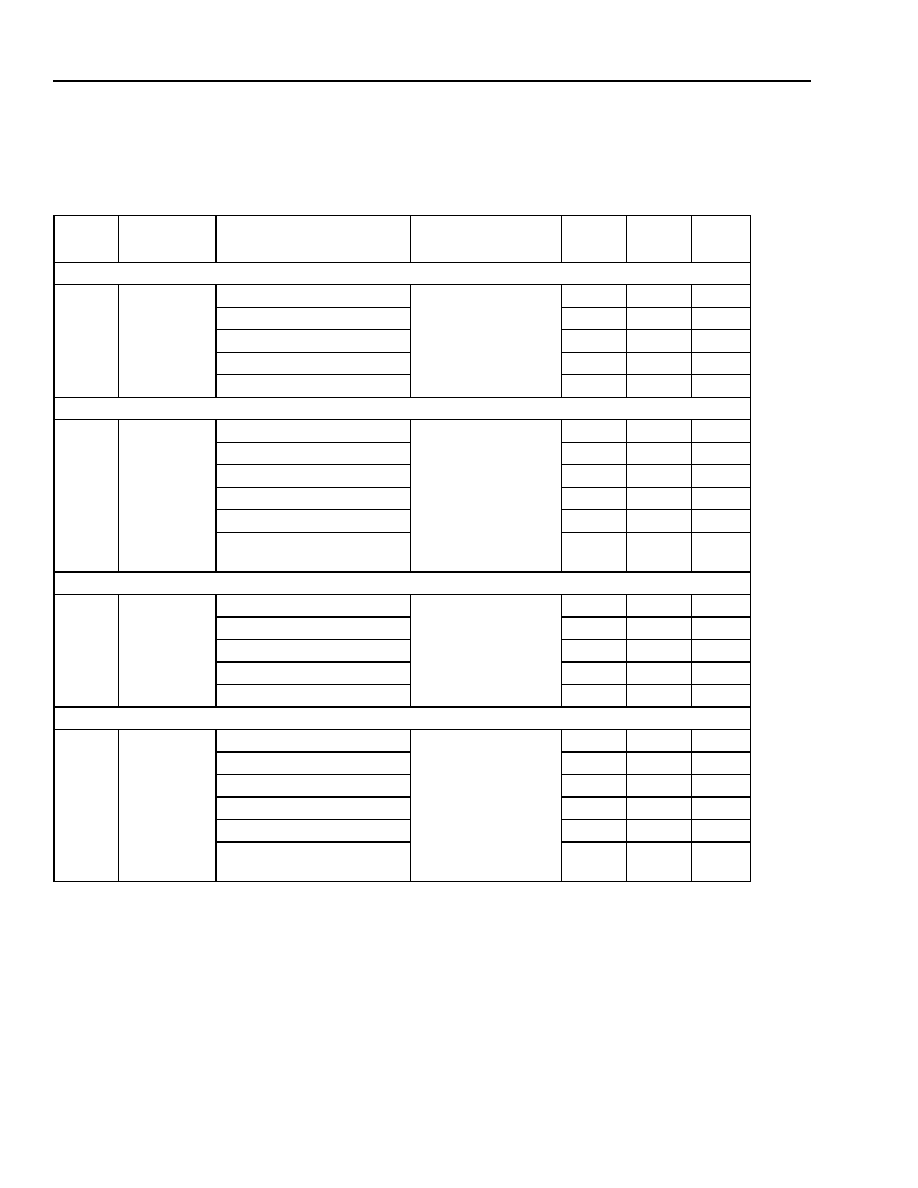

UT10. Egress Packet Mode Overflows

In the UTOPIA modes listed below, the device will report transmit packet overflow errors when no overflows have

occurred. This occurs when the egress high watermark is set for the UTOPIA modes as shown in Table 6.

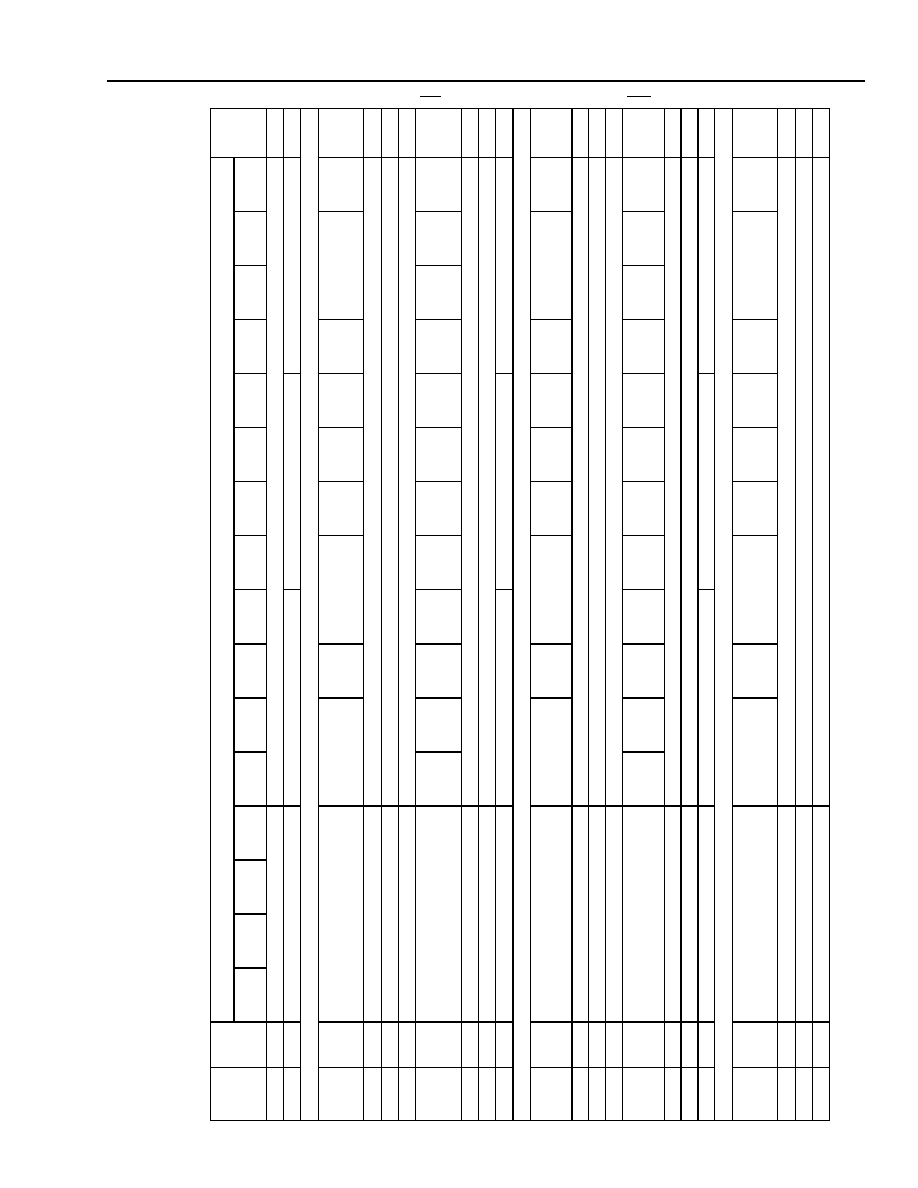

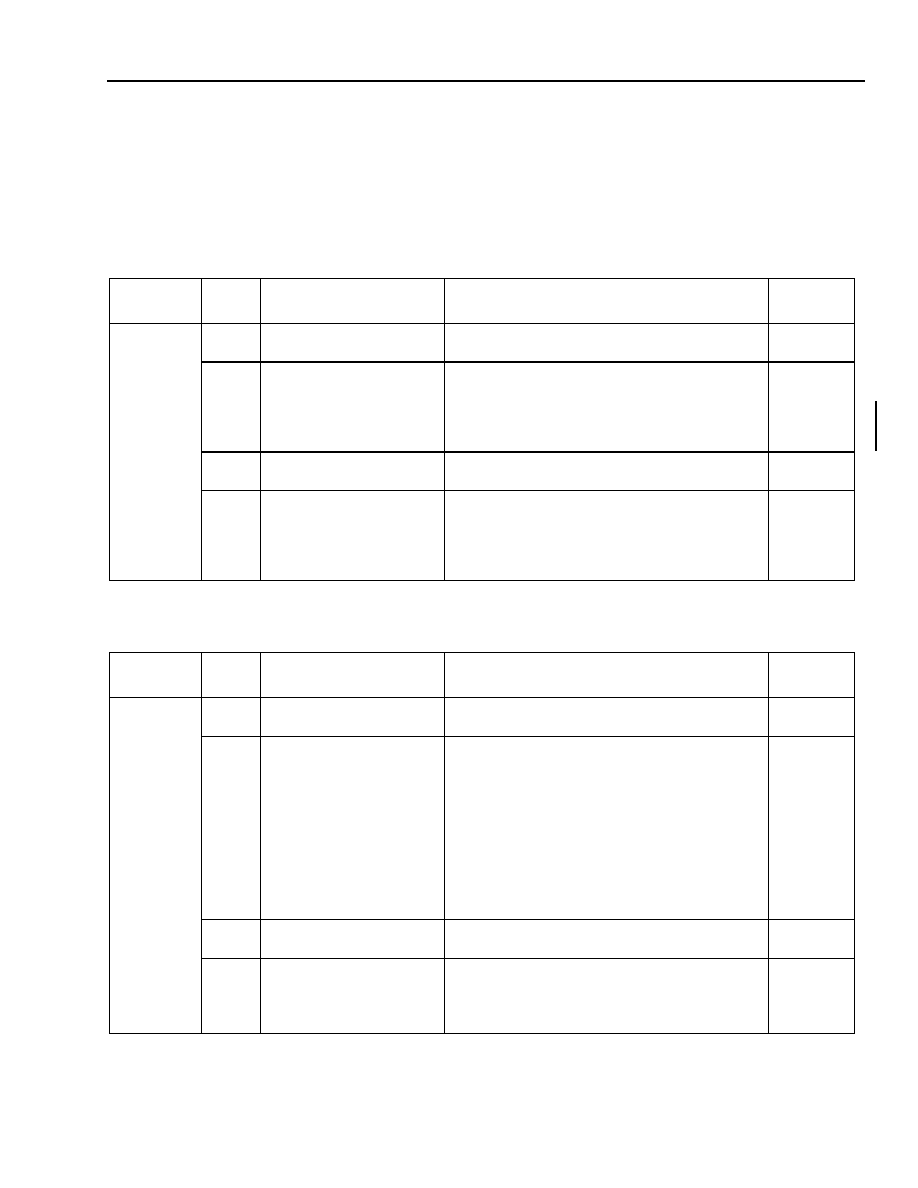

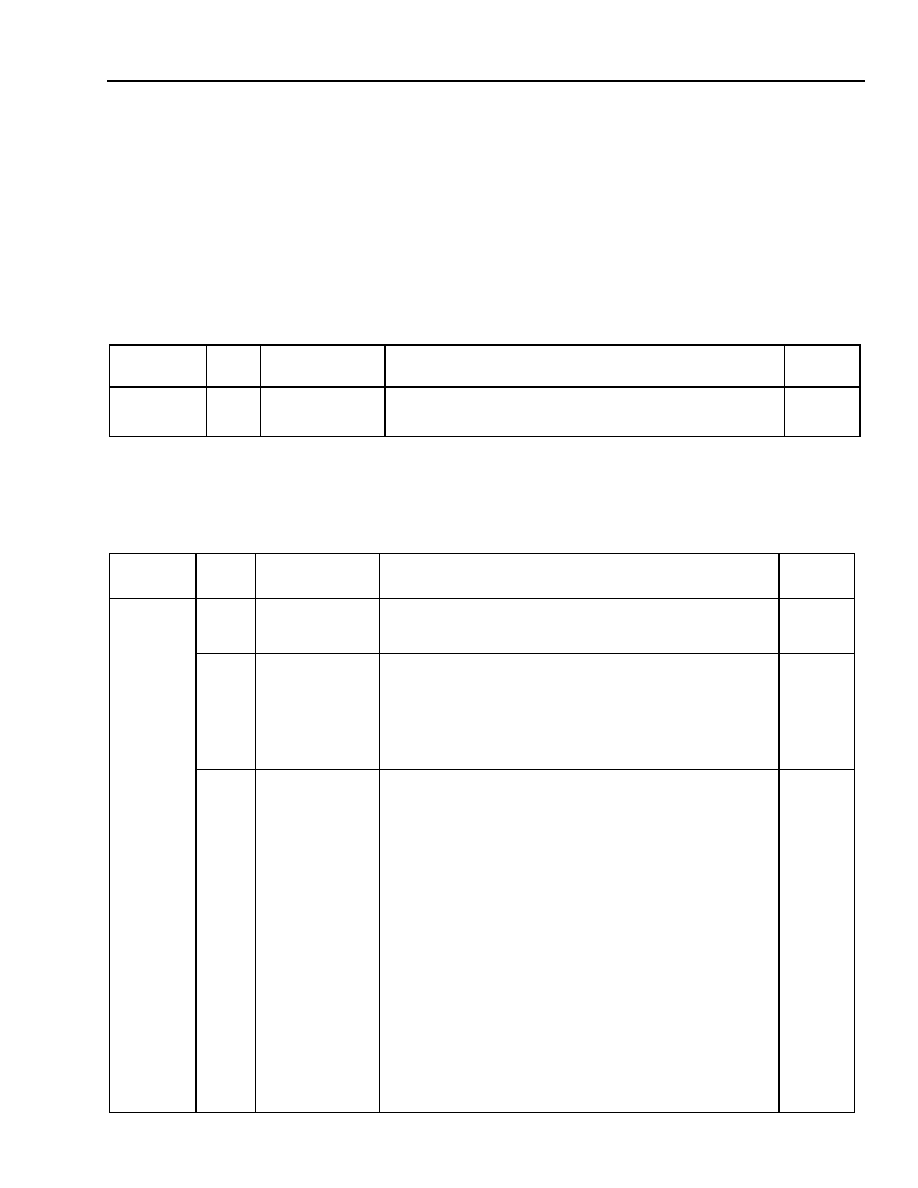

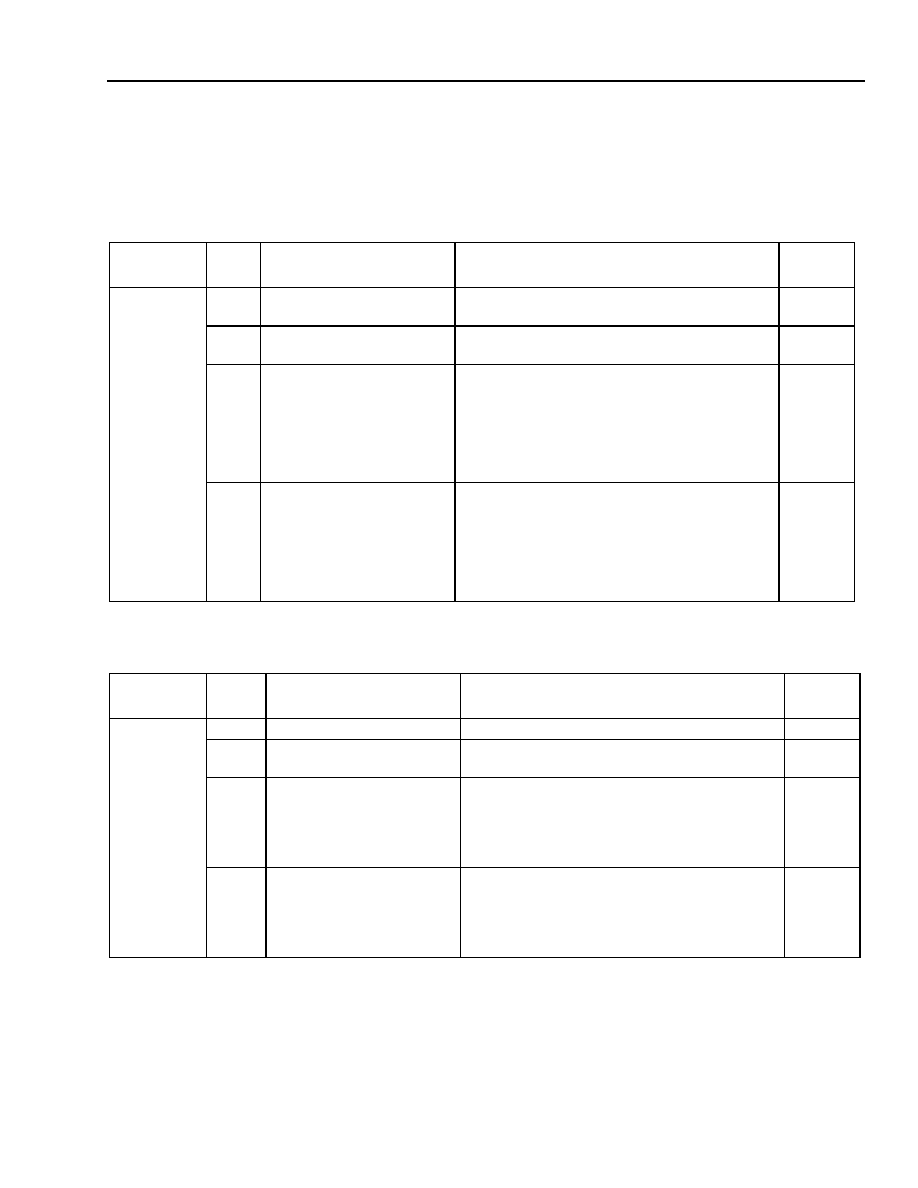

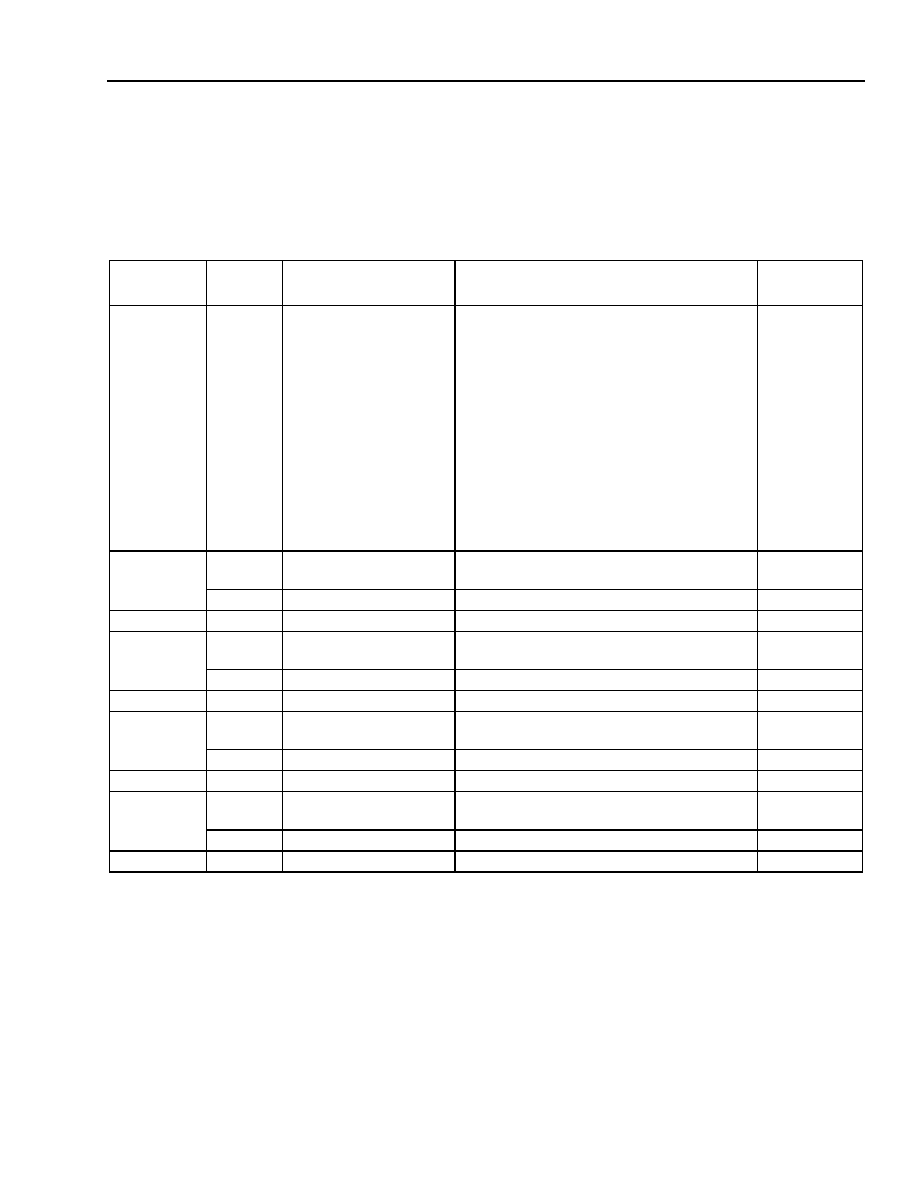

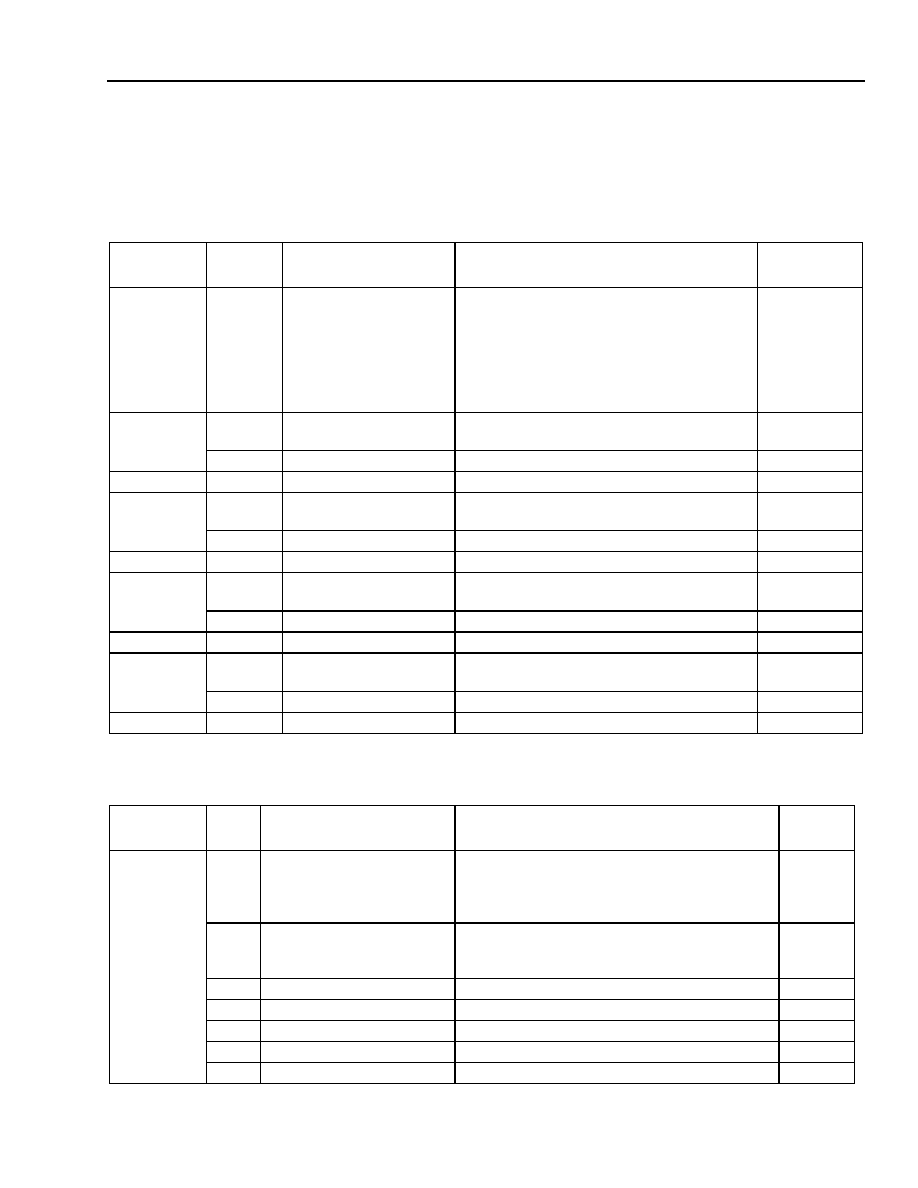

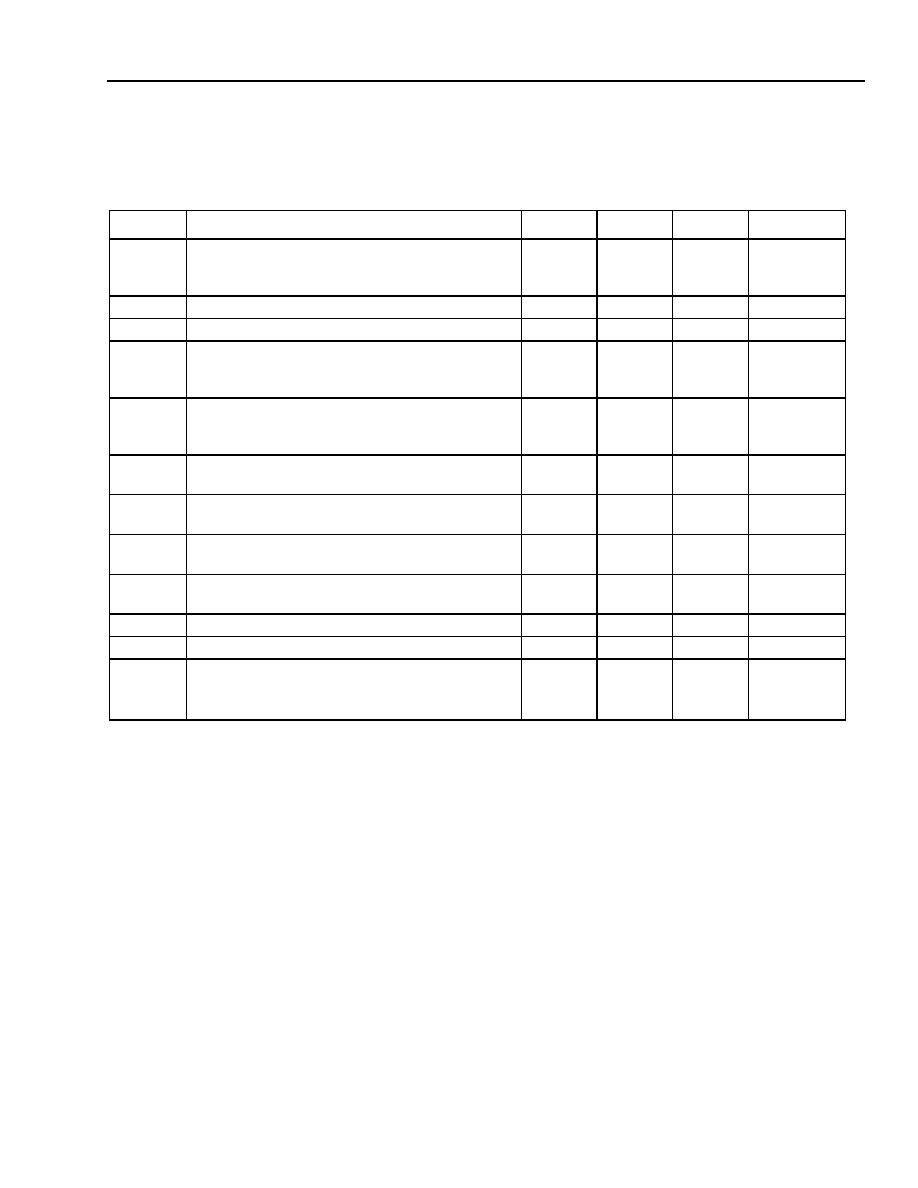

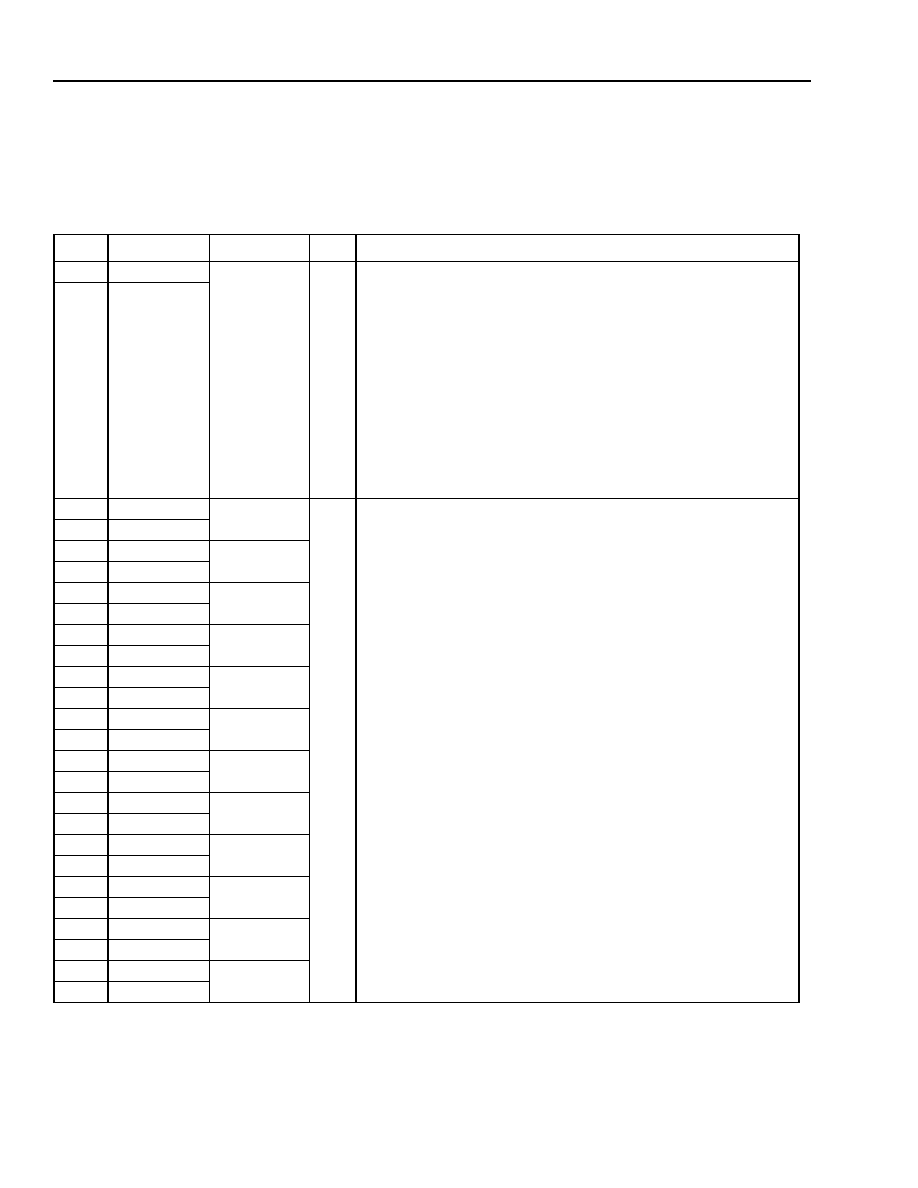

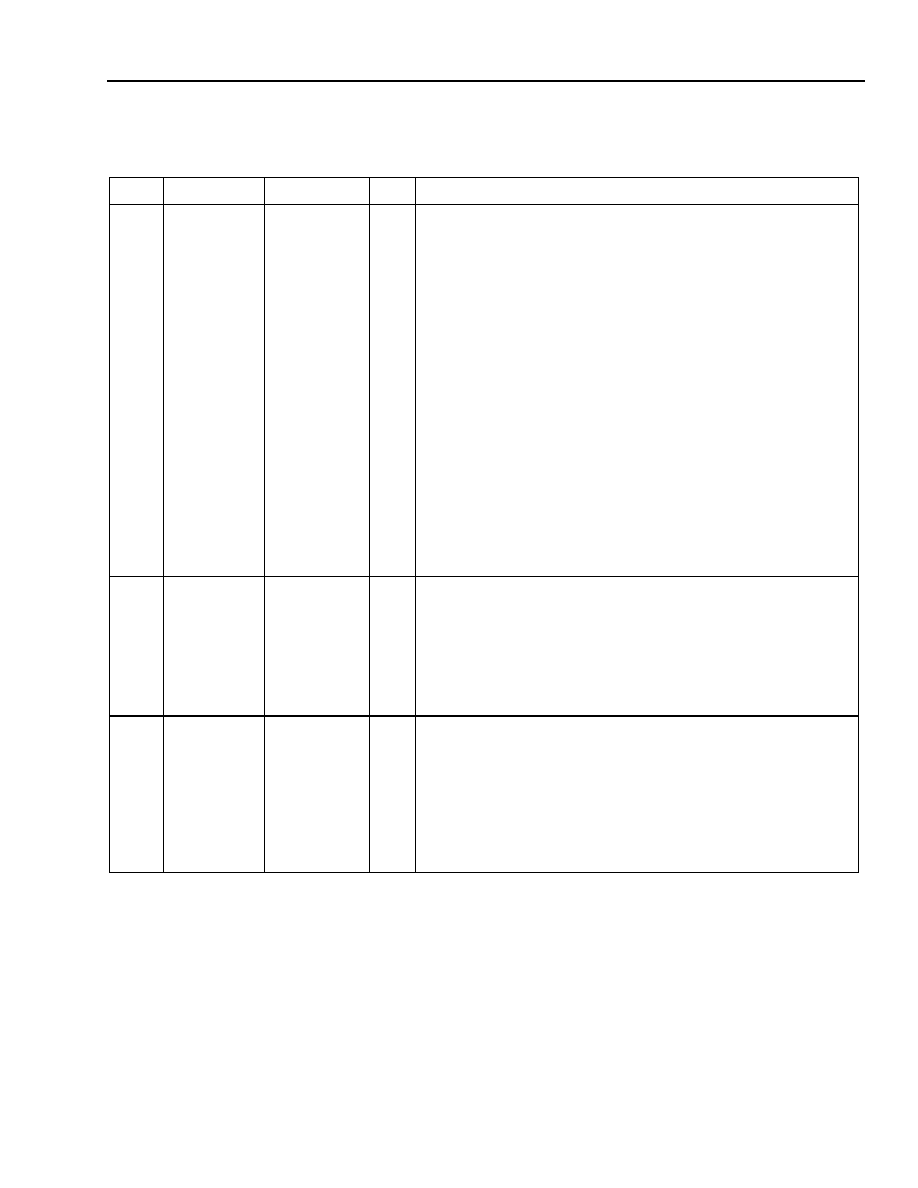

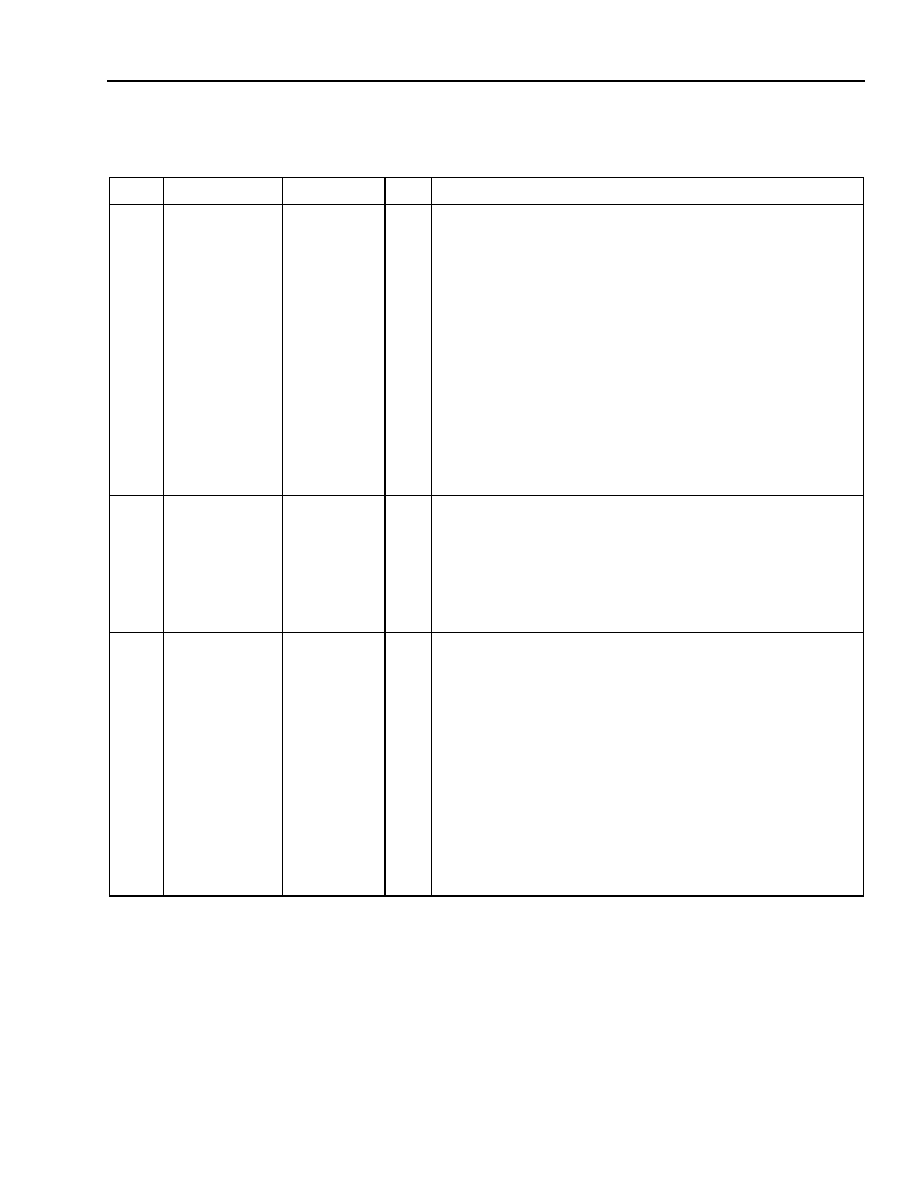

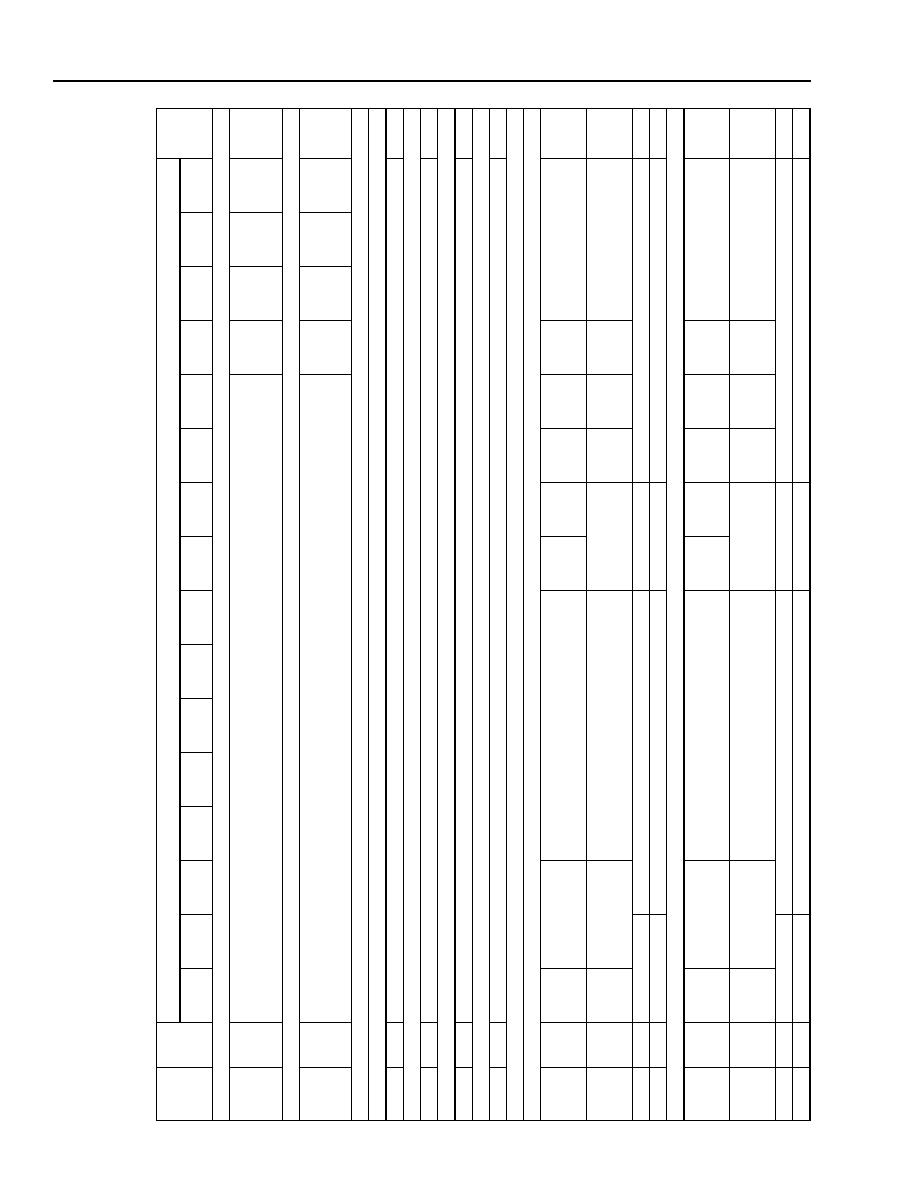

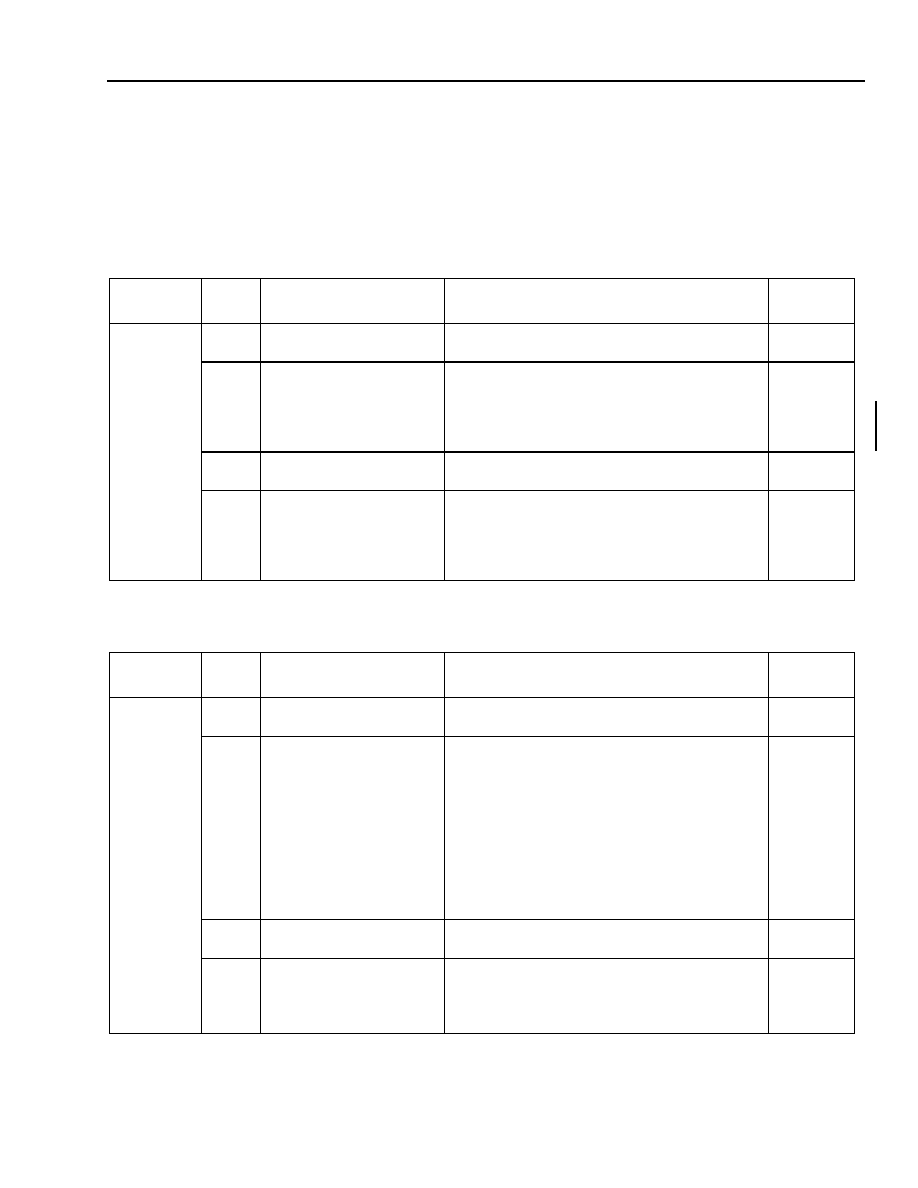

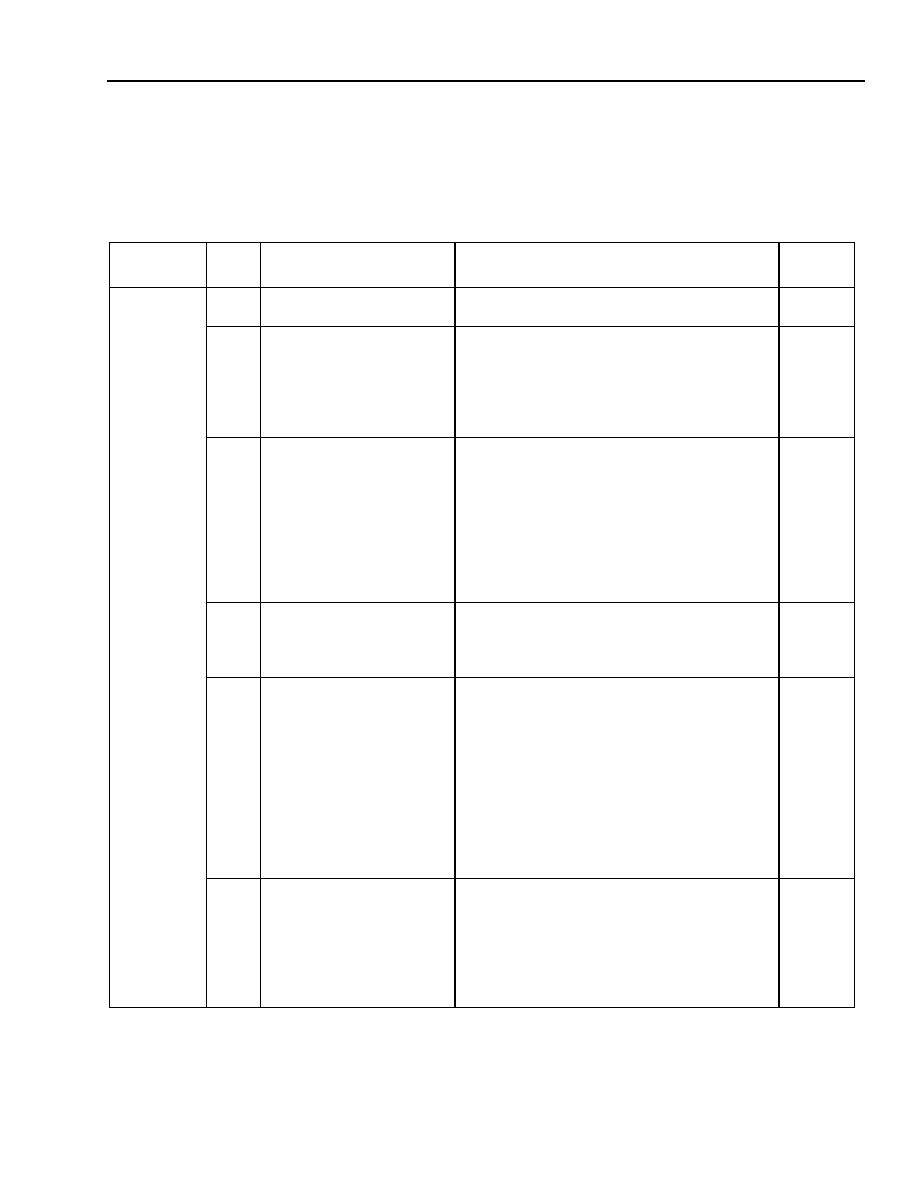

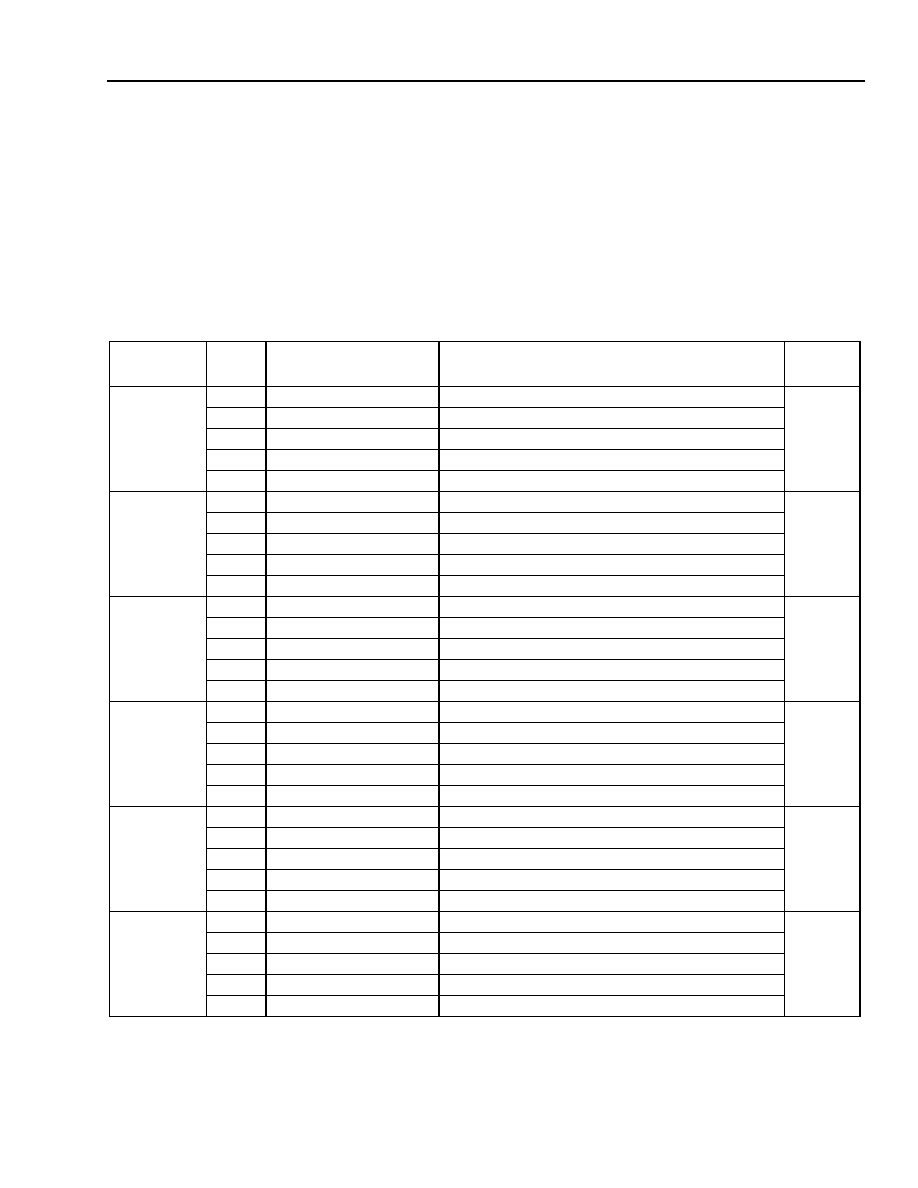

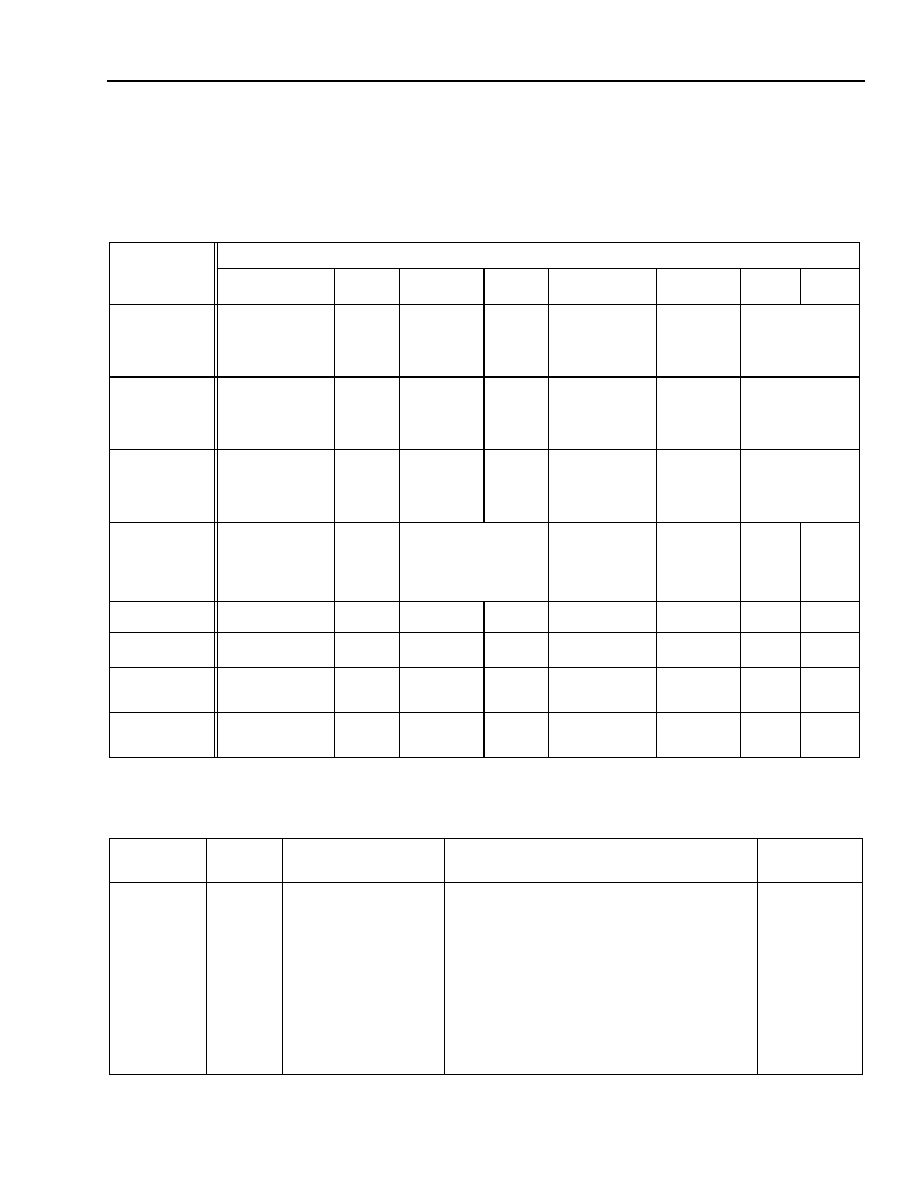

Table 6. Settings at Which Overflows Reported in Error

Workaround

Set the egress high watermark threshold as shown in Table 7. If there is a delay between TxPA deassertion and

TxENB deassertion, the additional cycles should also be accounted for when setting the threshold.

Table 7. Settings to Prevent Overflows Reported in Error

Corrective Action

This condition will be addressed in future versions of the device.

UTOPIA Modes

Egress High Watermark Thresholds

8-bit, U3+

0x3D

16-bit, U2+

0x3B

32-bit, U3+

0x37

UTOPIA Modes

Egress High Watermark Thresholds

8-bit, U3+

<

0x3D

16-bit, U2+

<

0x3B

32-bit, U3+

<

0x37

Agere Systems Inc.

17

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

UTOPIA (UT)

(continued)

UT11. Clearing UT Interrupt Register

When a UT interrupt event occurs and COW mode is enabled, writing to UT interrupt register 0x0201 does not

clear the register (this register is read-only). The interrupt is cleared by writing to the UT delta and event registers

(addresses 0x0202--0x0205).

Workaround

This is informational only. No workaround is available for this condition.

Corrective Action

No corrective action is required for this condition.

UT12. Incorrect Implementation of POS Multi-PHY Mode

Because the TDAT042G5 lacks a selected PA signal (SPA), the status of a channel that is transmitting data in POS

MPHY mode is not known during polling. Therefore, the PA signal cannot be used as a data valid signal. If the

channel transmitting data runs dry, the master side may receive invalid data.

Workaround

Use direct status polling mode only and ensure that the address of channel A is applied to the address bus at all

times, except during the clock cycle when another channel is being selected.

Corrective Action

No corrective action is required for this condition.

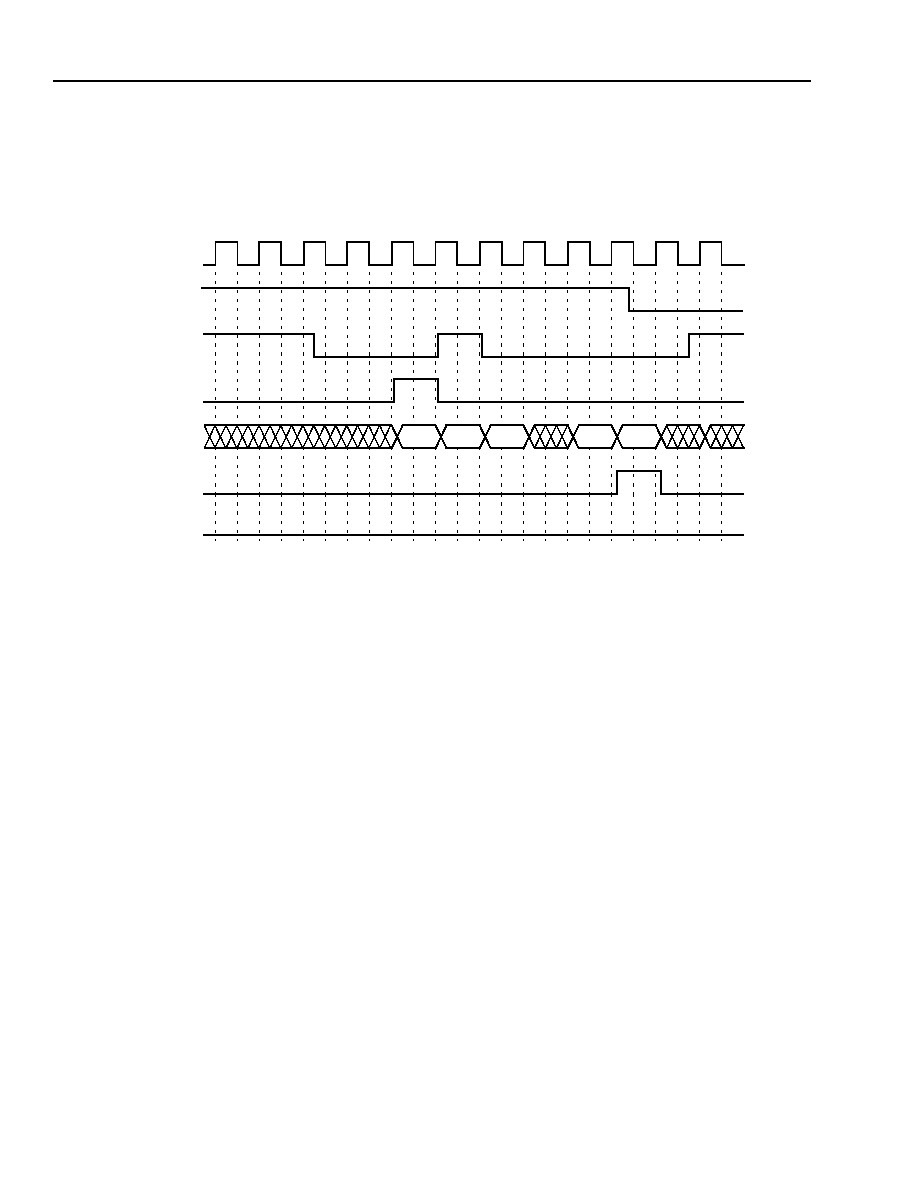

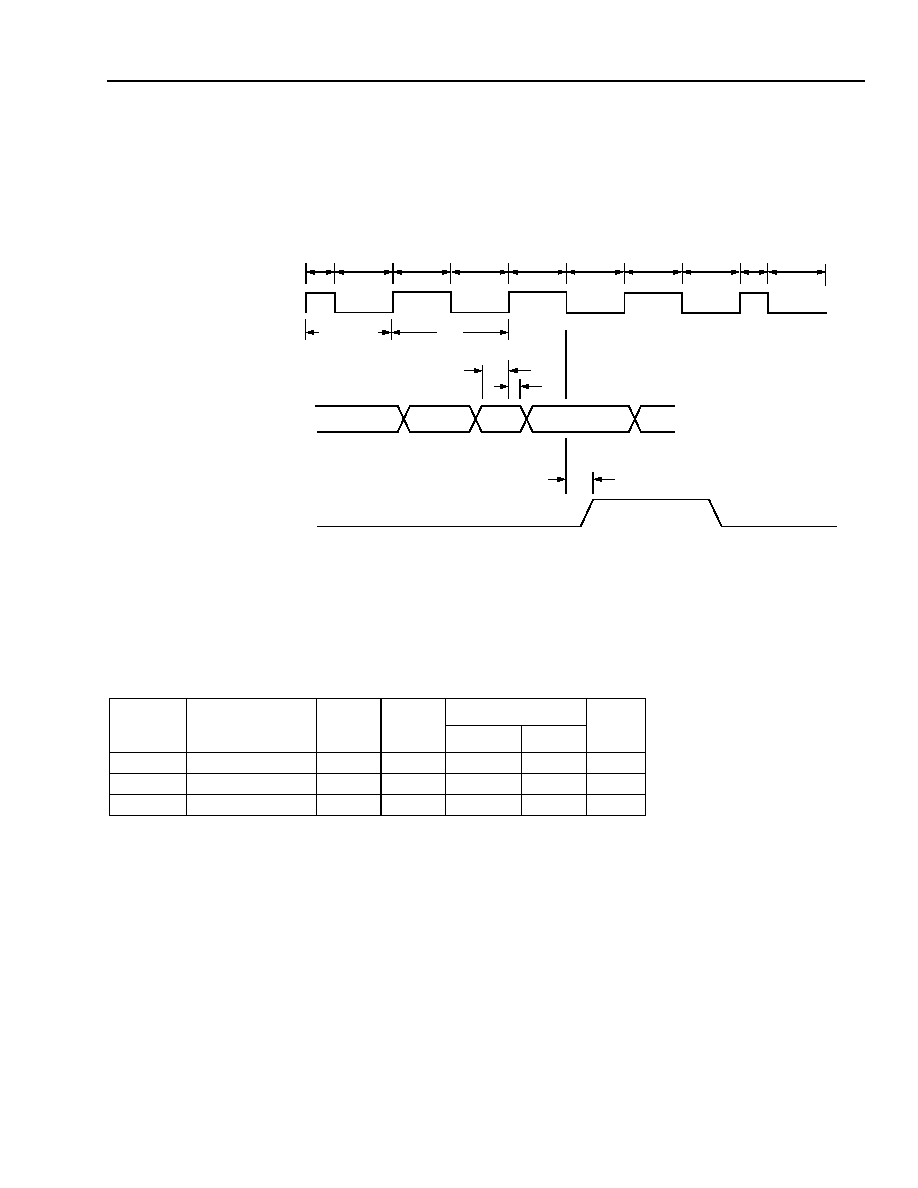

UT13. Invalid Extra Cycle Between EOP and SOP in CRC-16/32 Mode

When using the device in CRC-16 or CRC-32 mode, there is always an extra cycle between the end of packet

(EOP) of the previous packet and the start of packet (SOP) of the following packet.

Workaround

This is informational only. No workaround is available for this condition.

Corrective Action

This is condition will be addressed in the future version of the device.

18

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

UTOPIA (UT)

(continued)

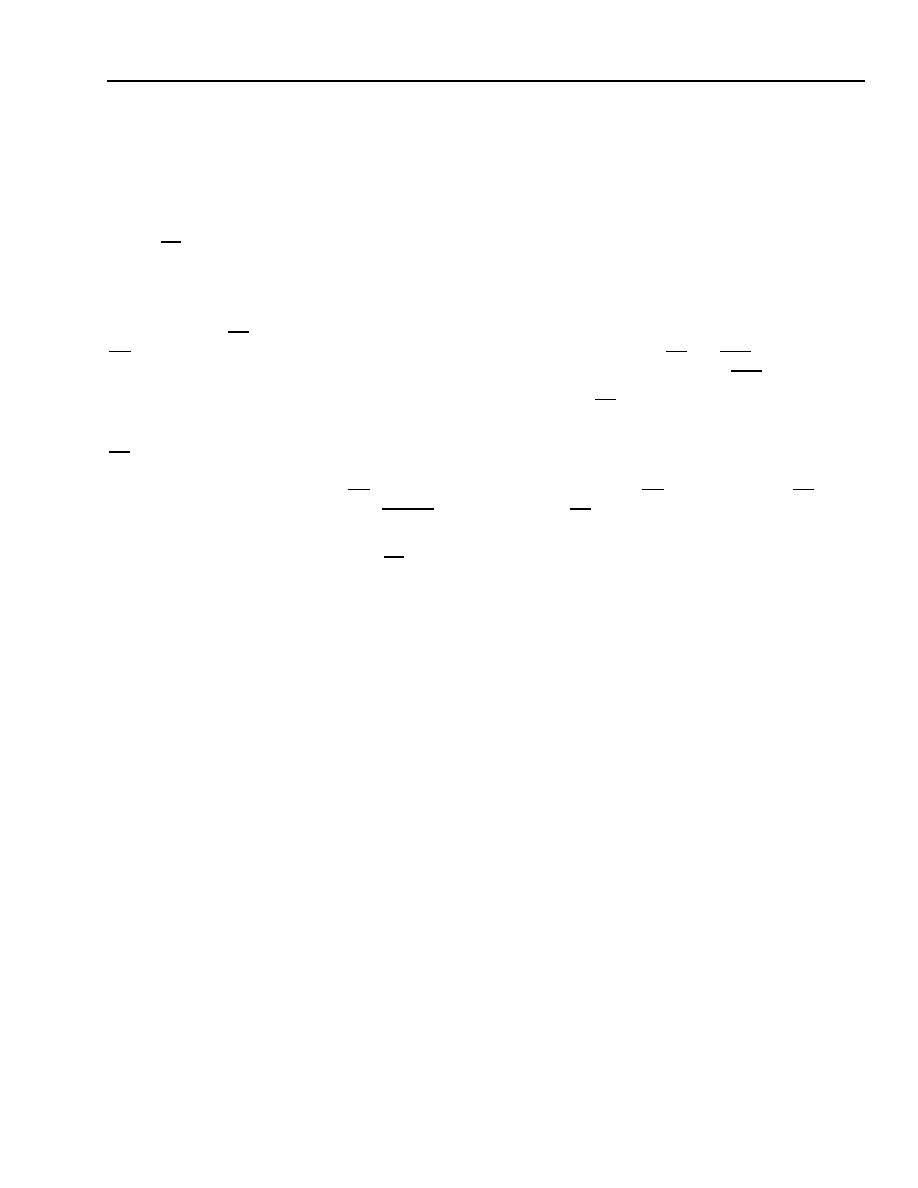

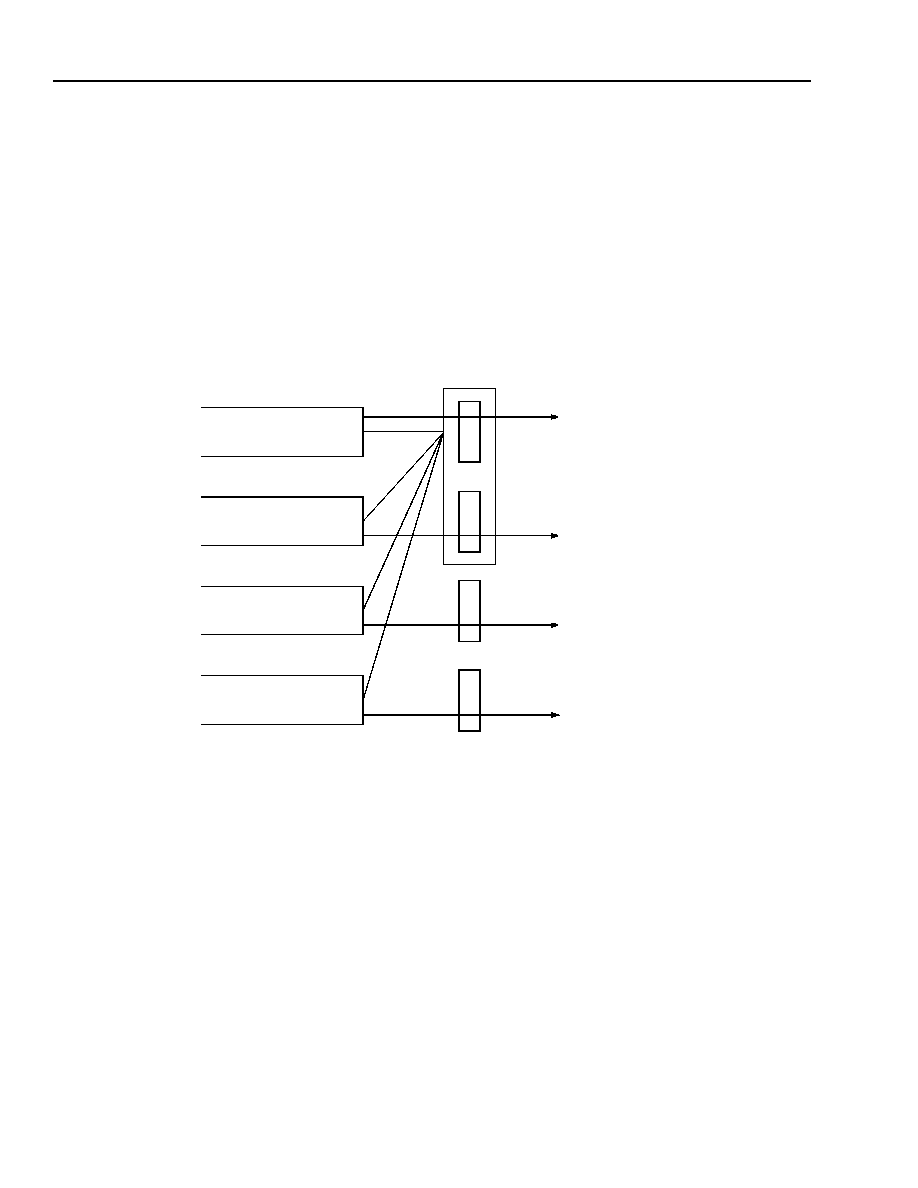

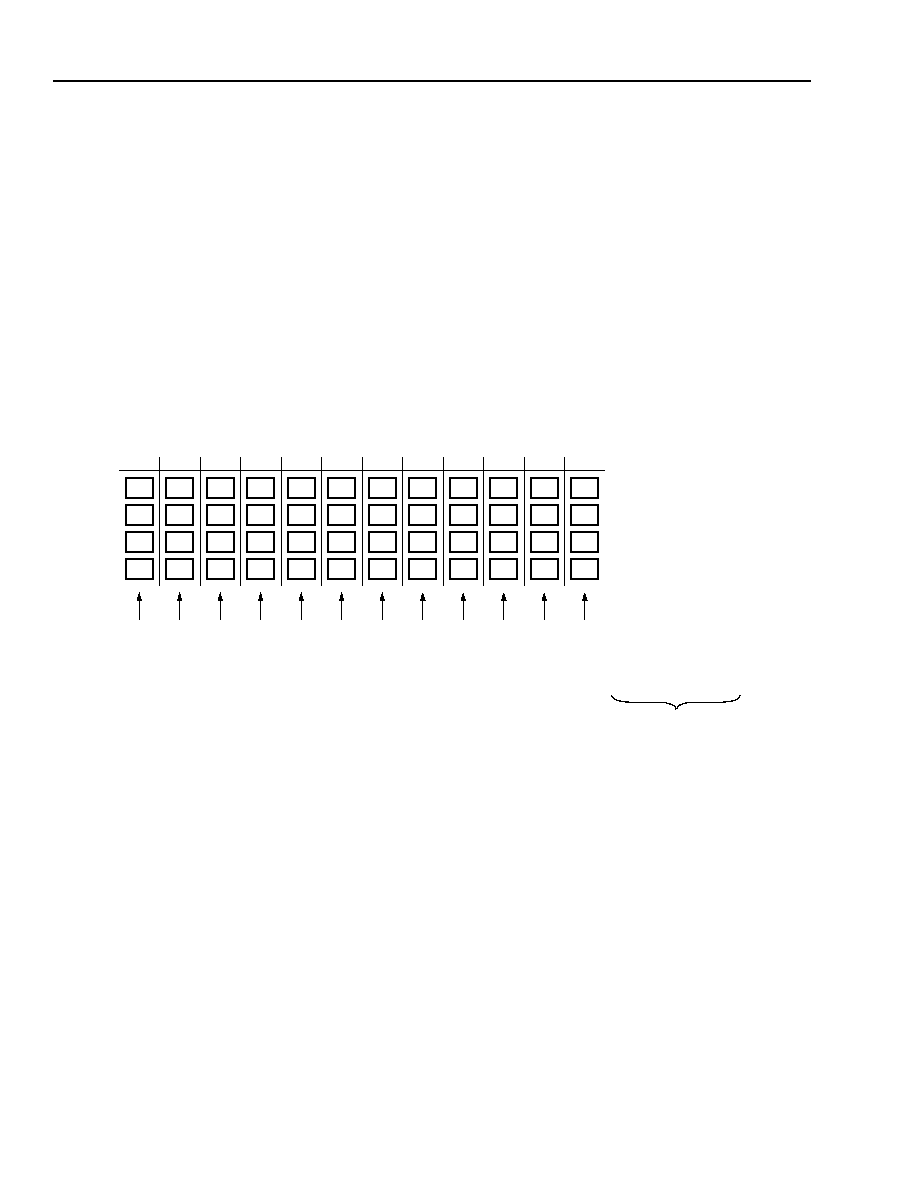

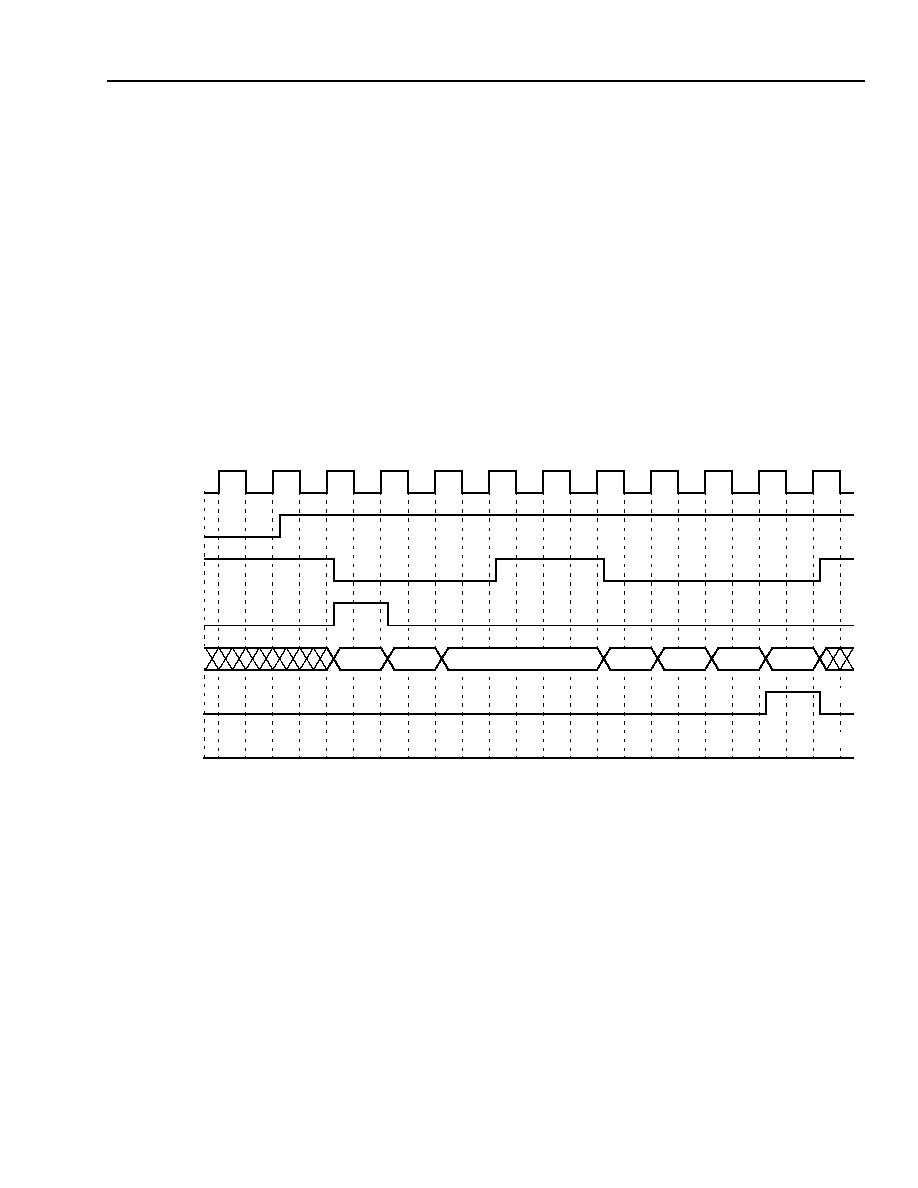

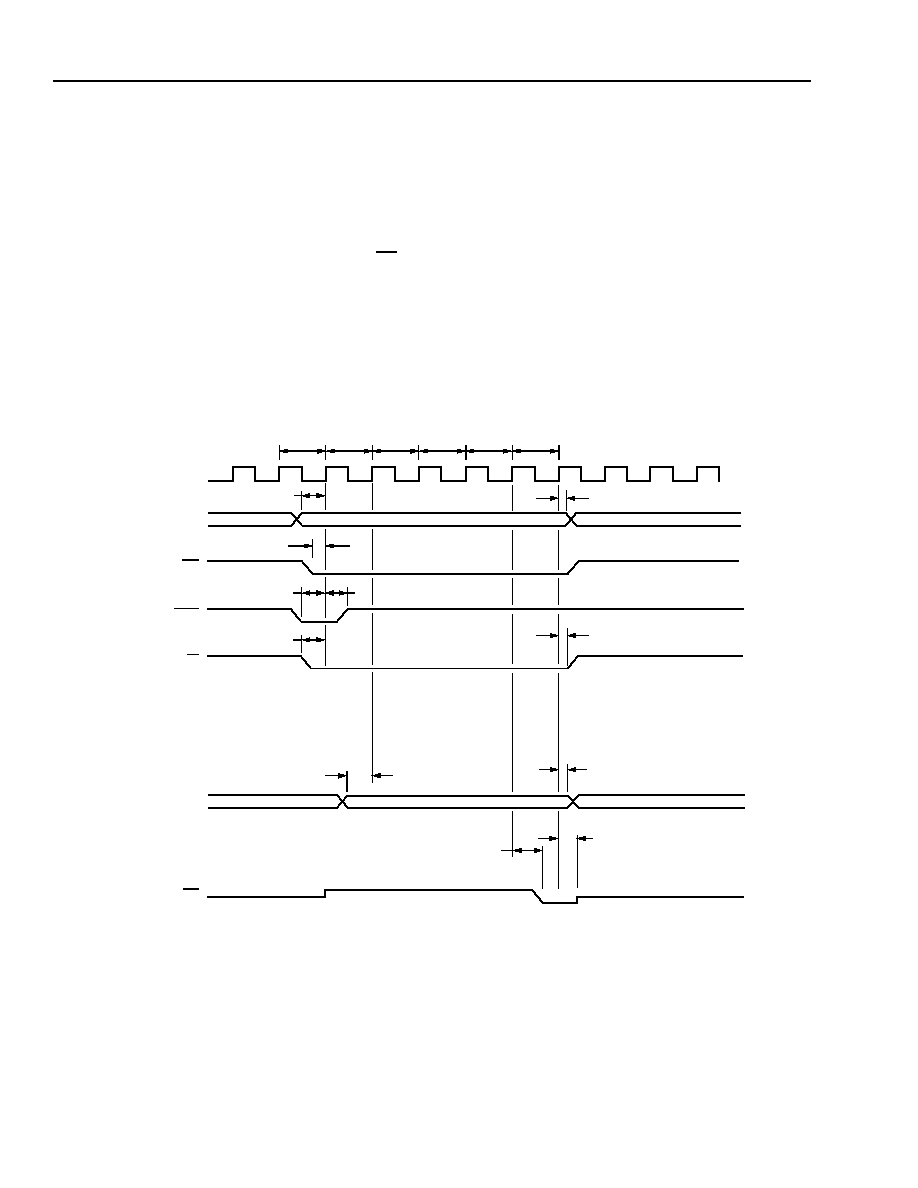

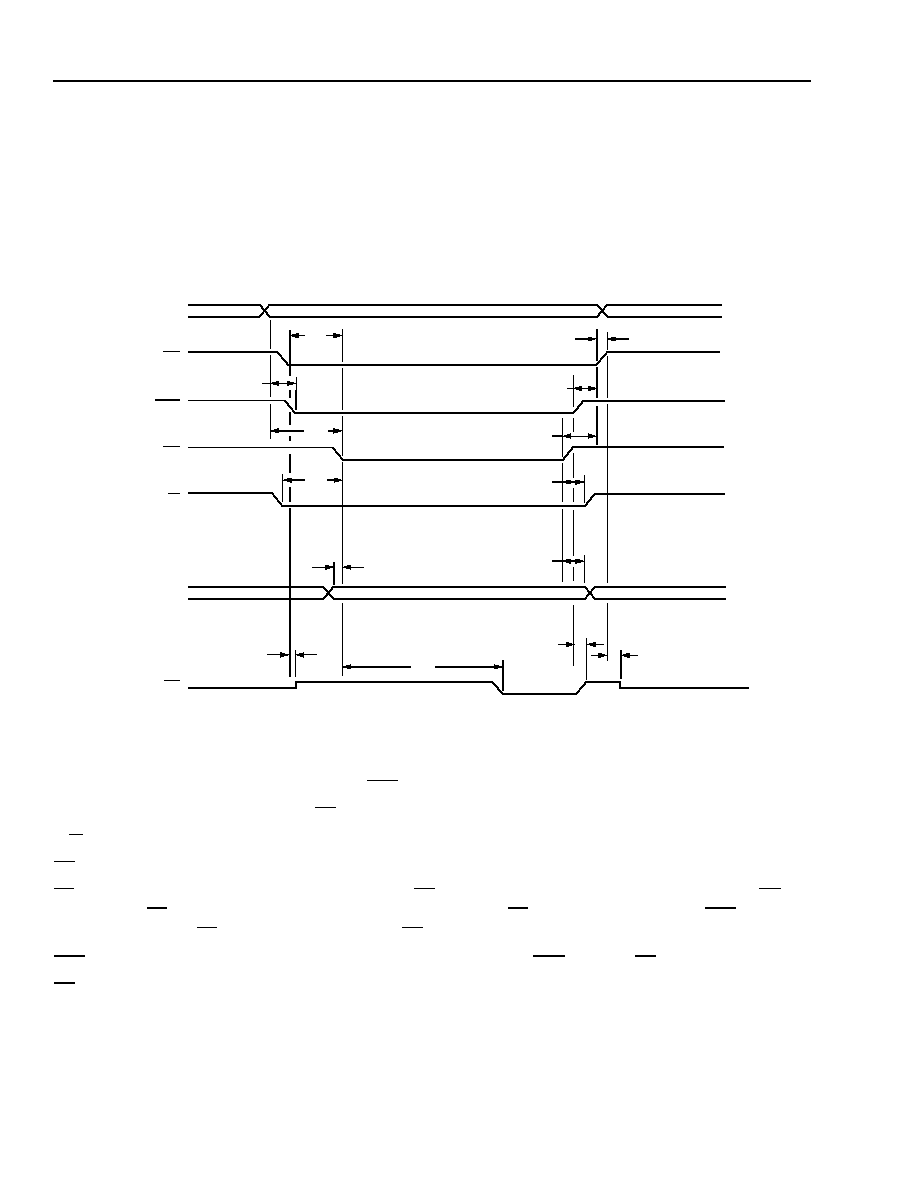

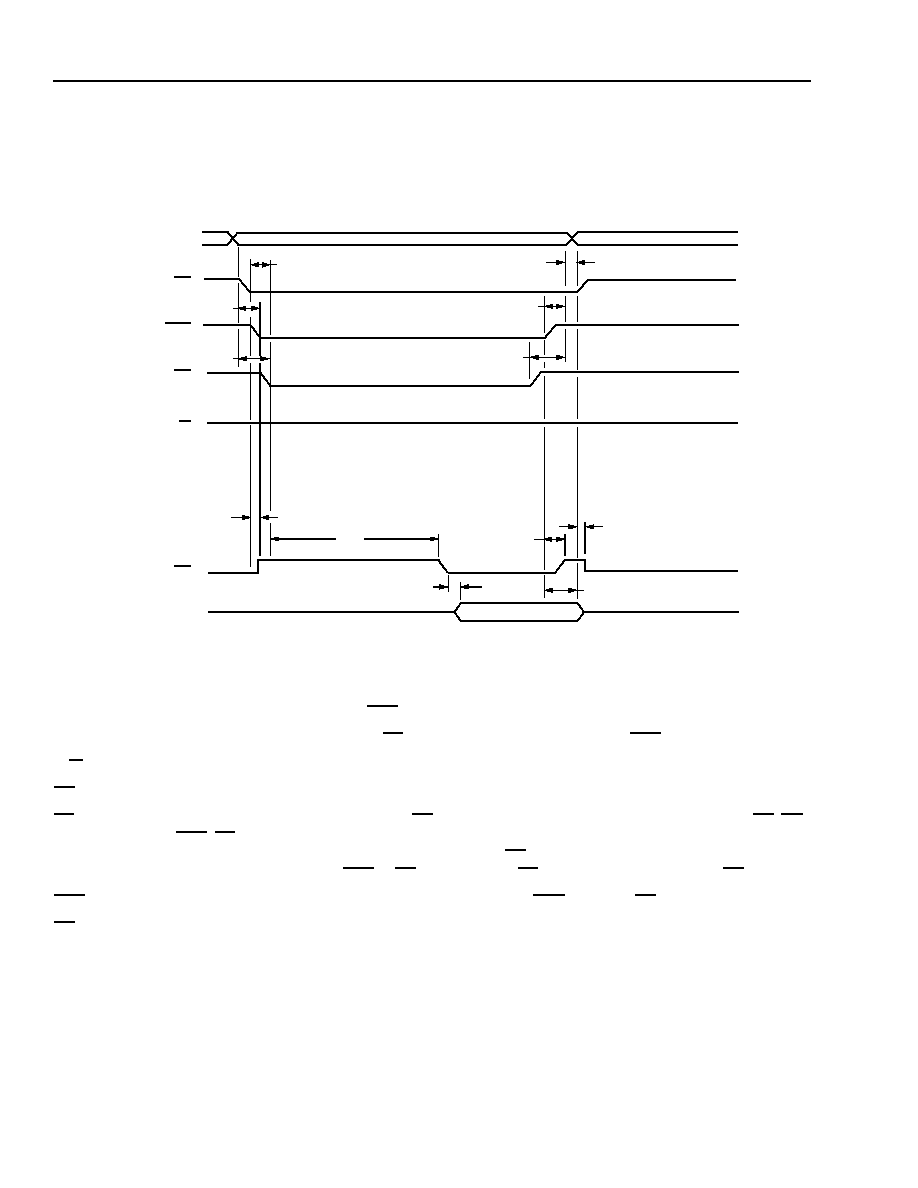

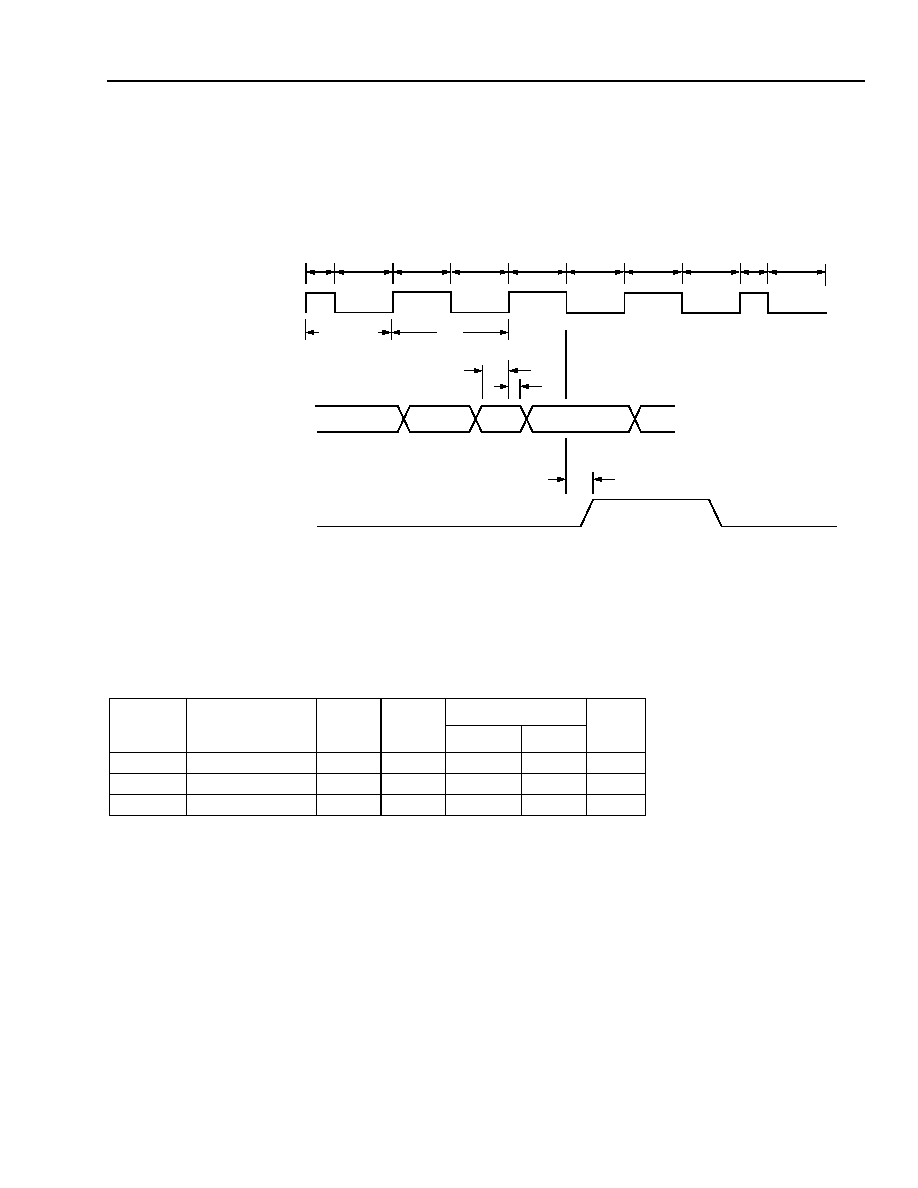

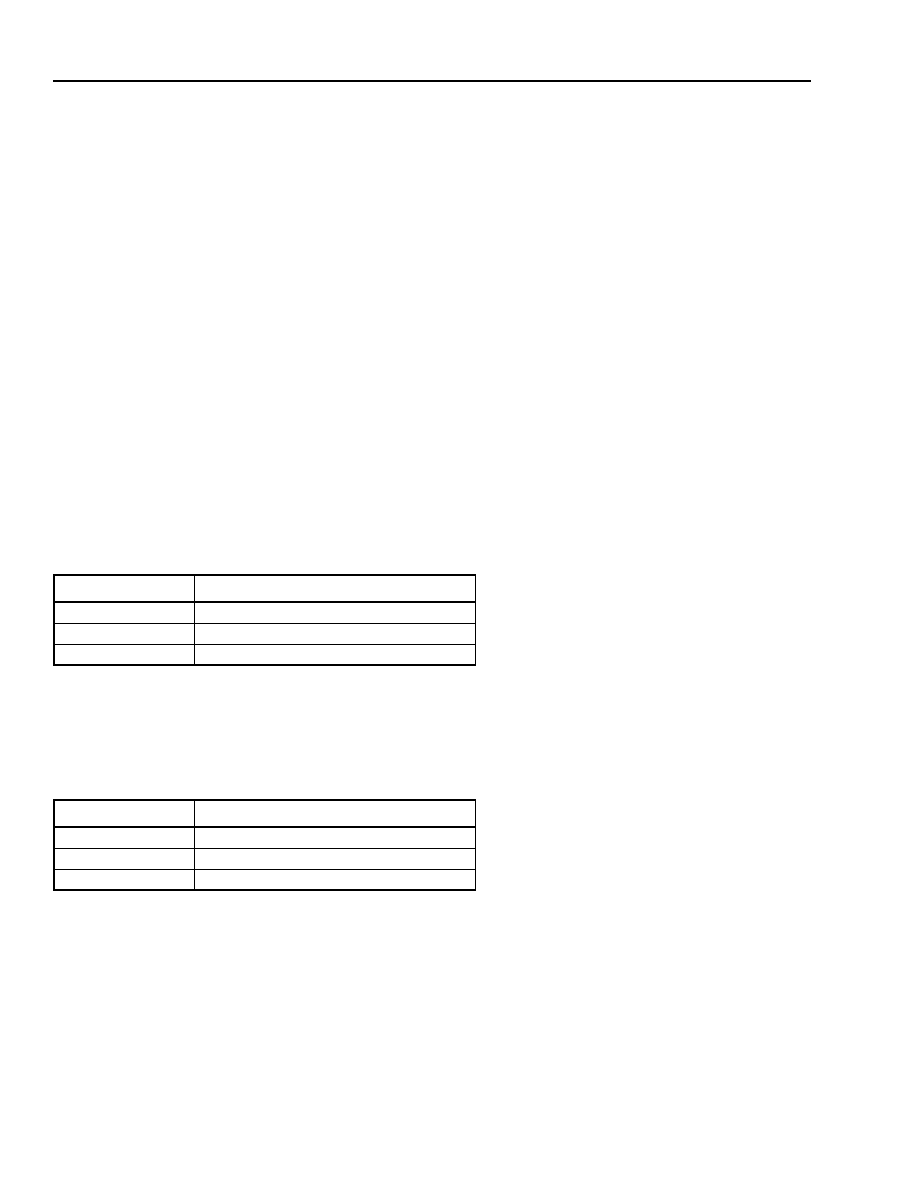

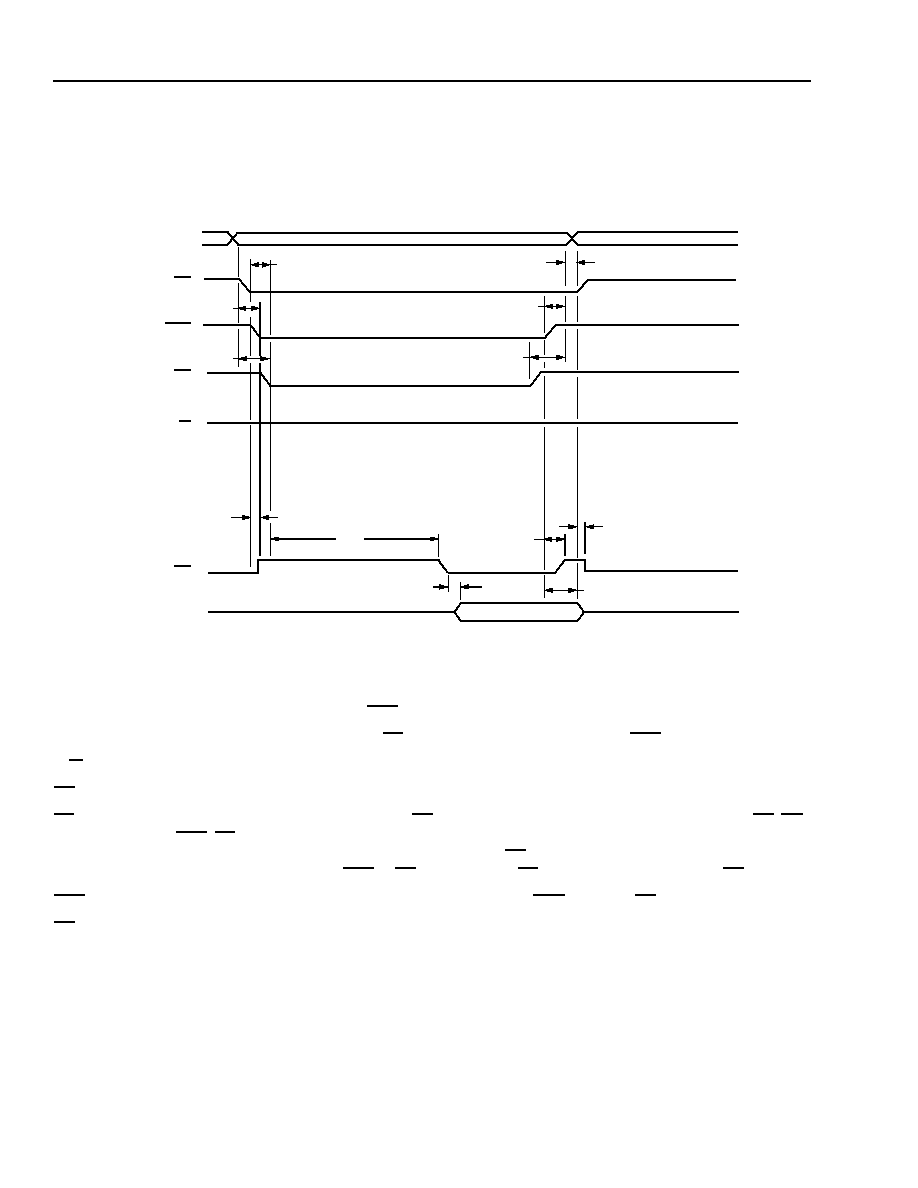

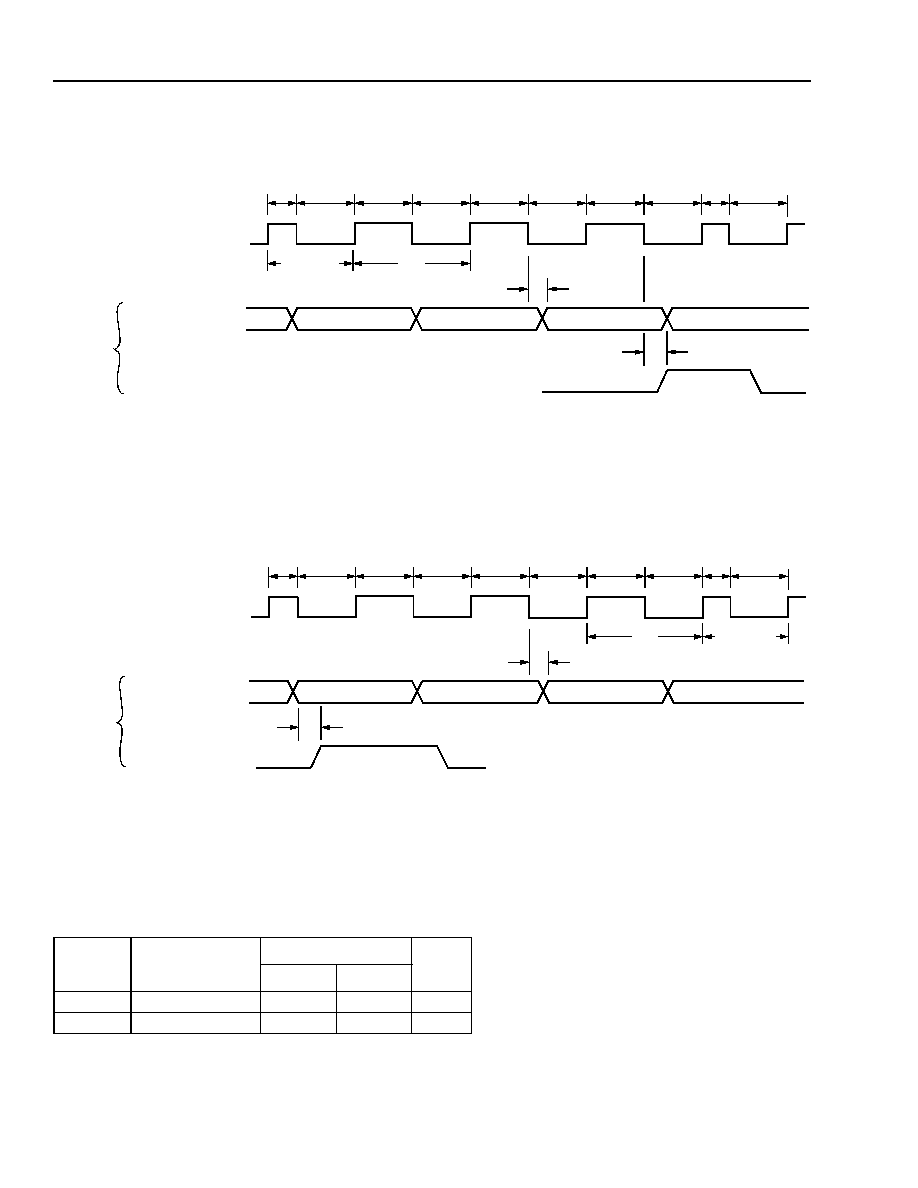

UT14. Nonfunctional RxPA Signal for Channels B and D in Packet Direct Status MPHY Mode

When using MPHY direct status for all operational modes (8-bit, 16-bit, and 32-bit), the RxPA signal for channels B

and D is not functional. The RxPA signal is functional only for channels A and C.

Workaround

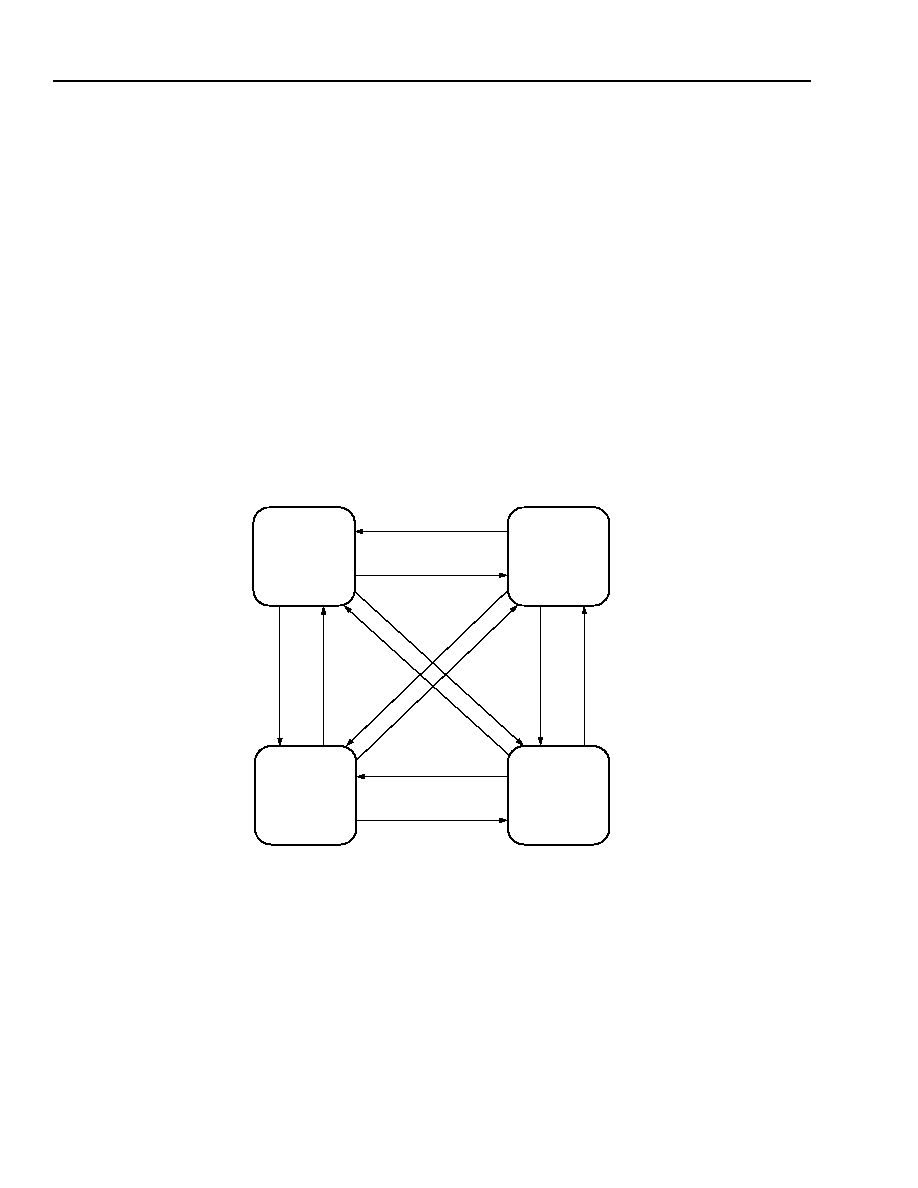

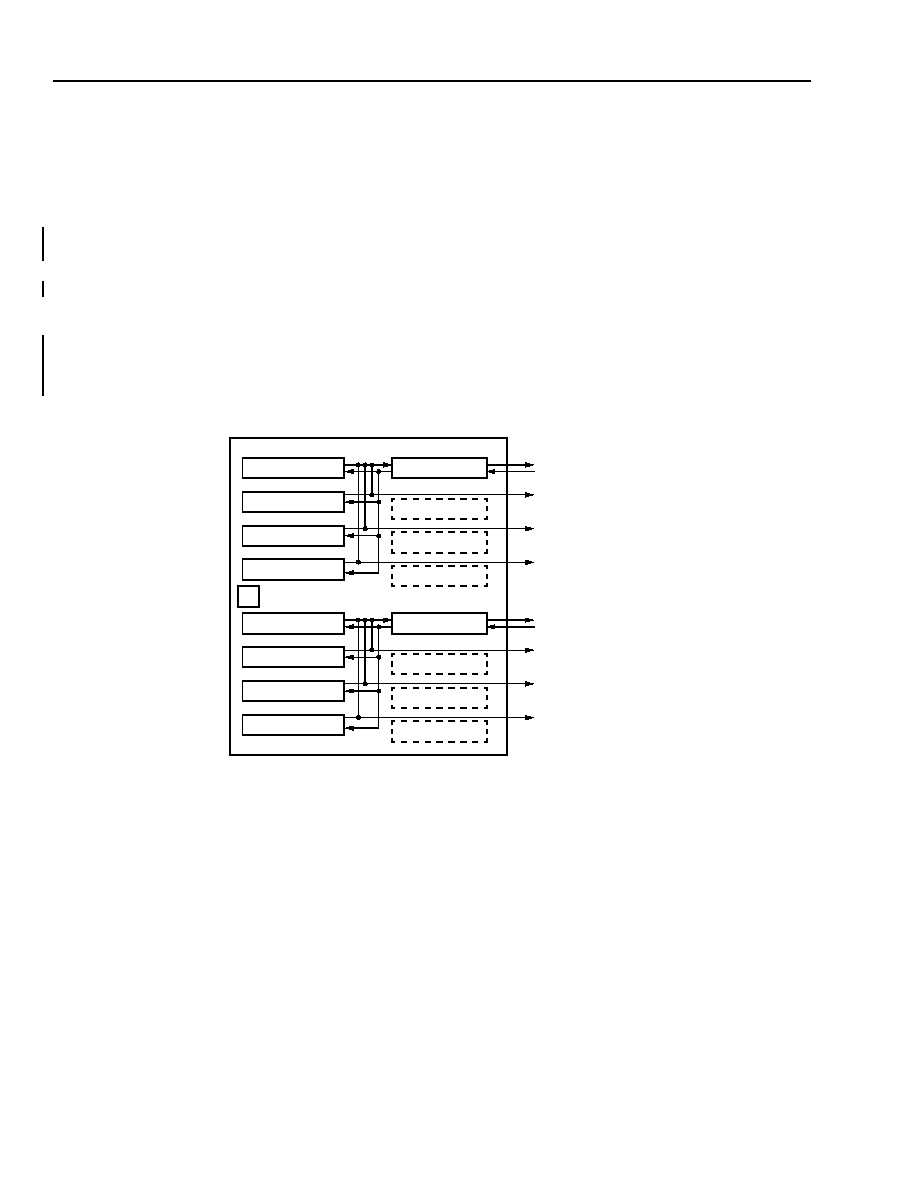

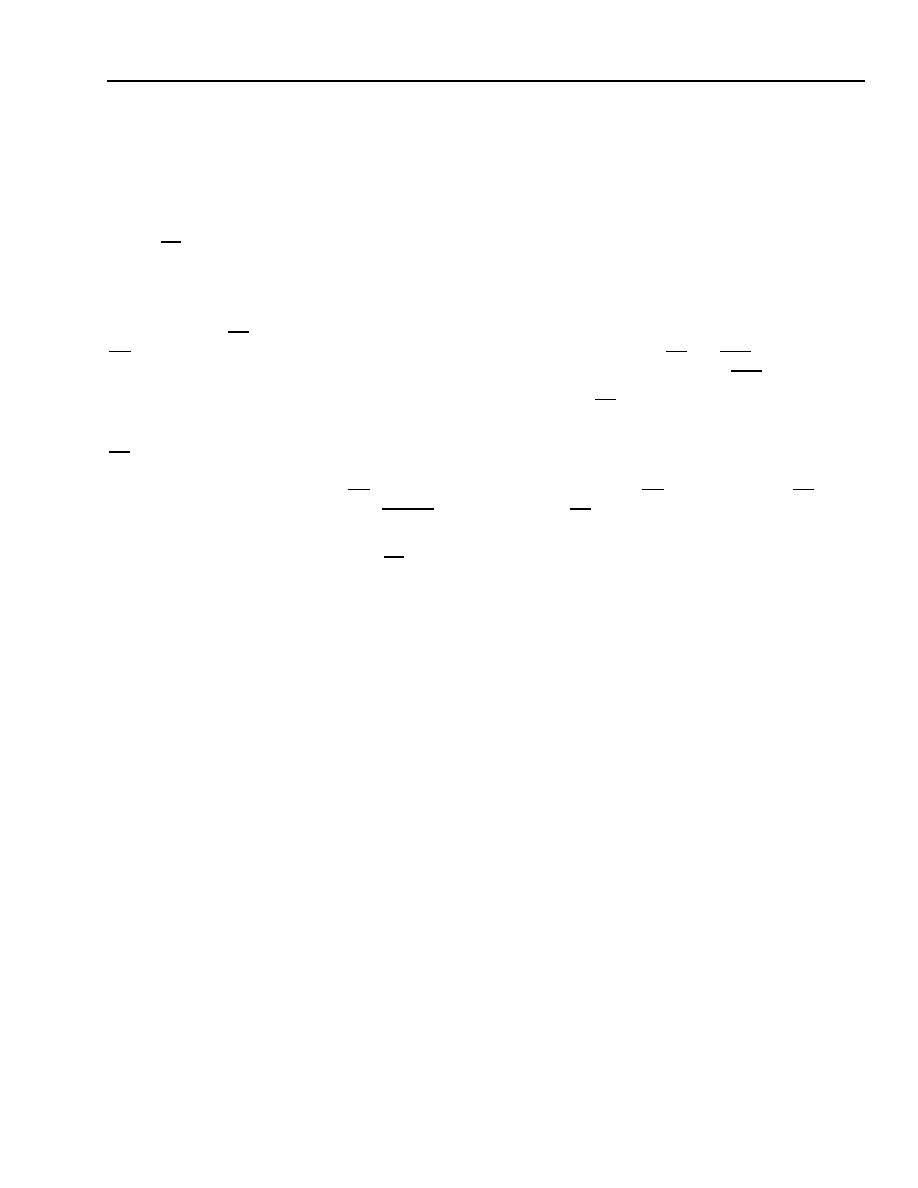

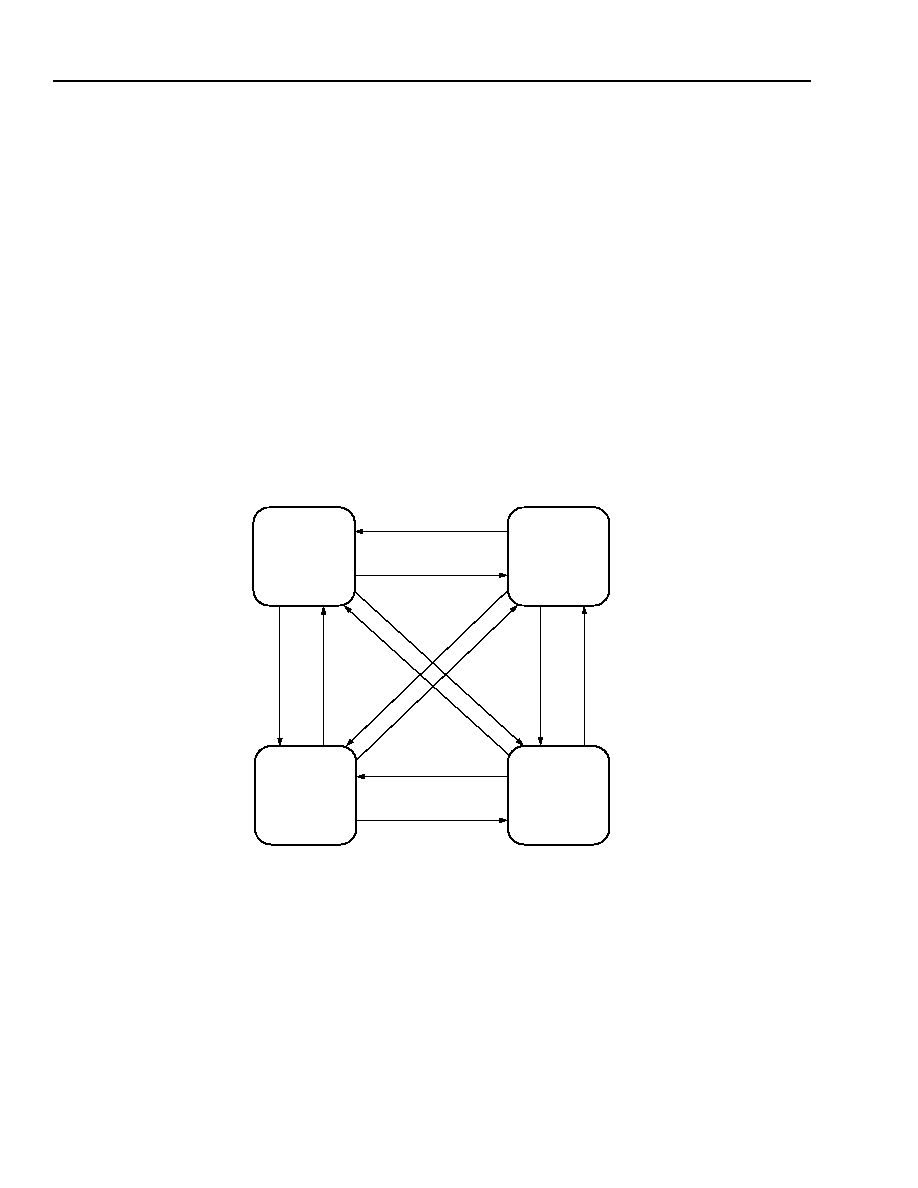

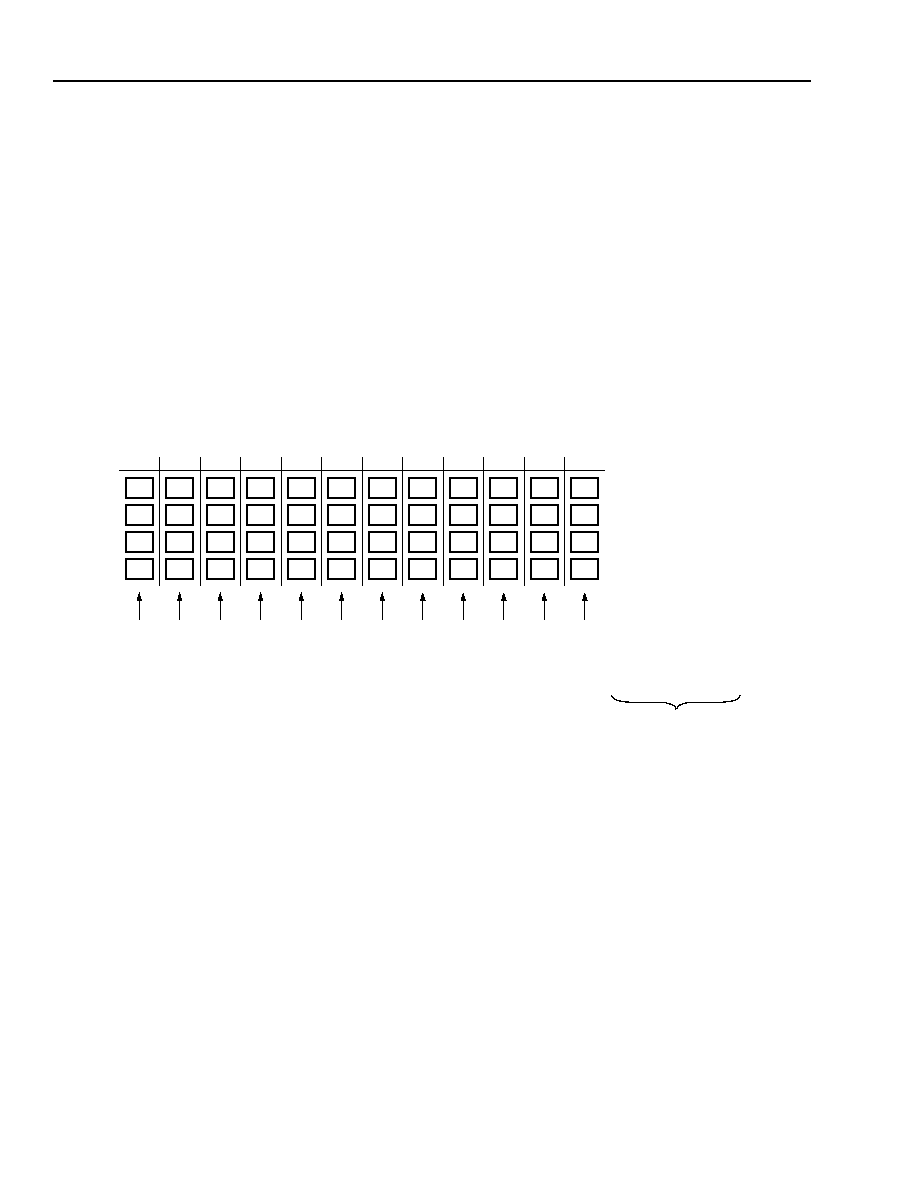

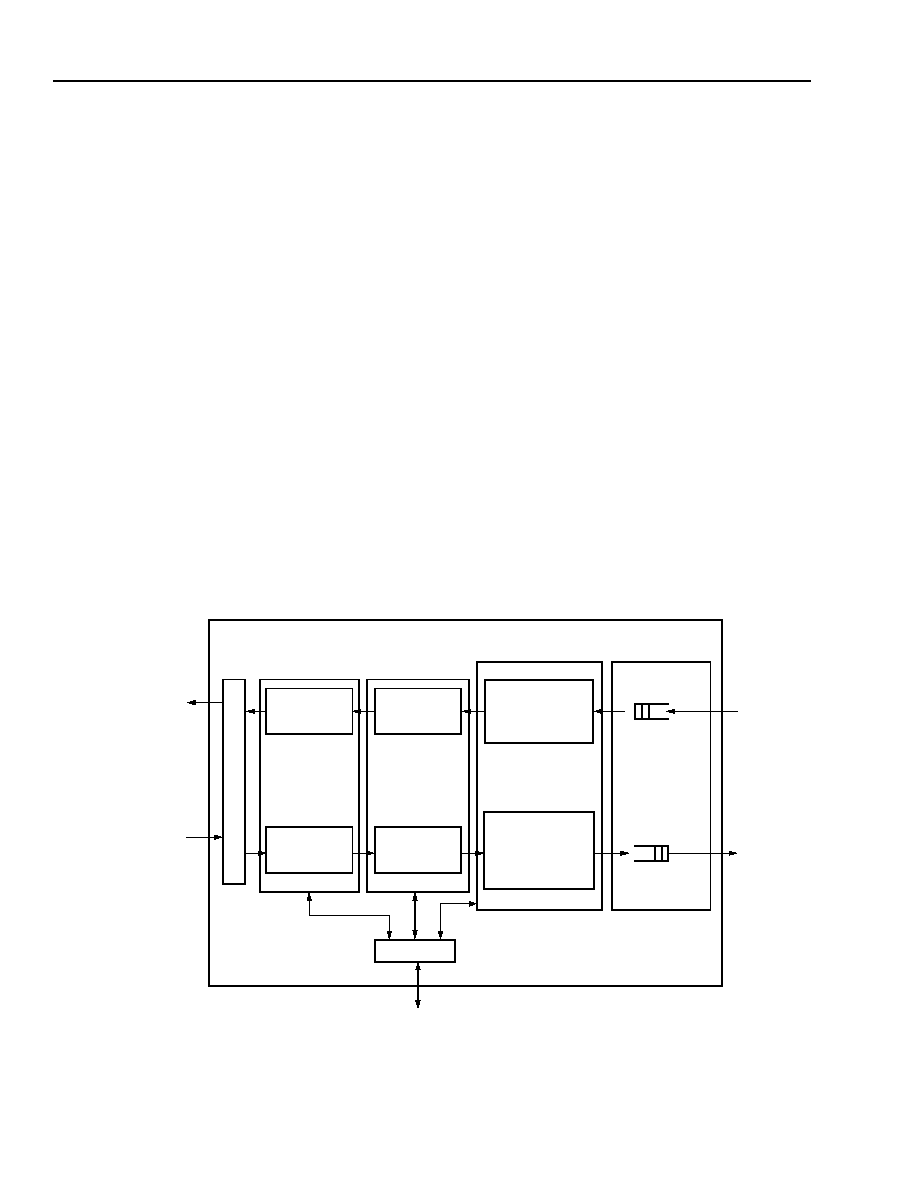

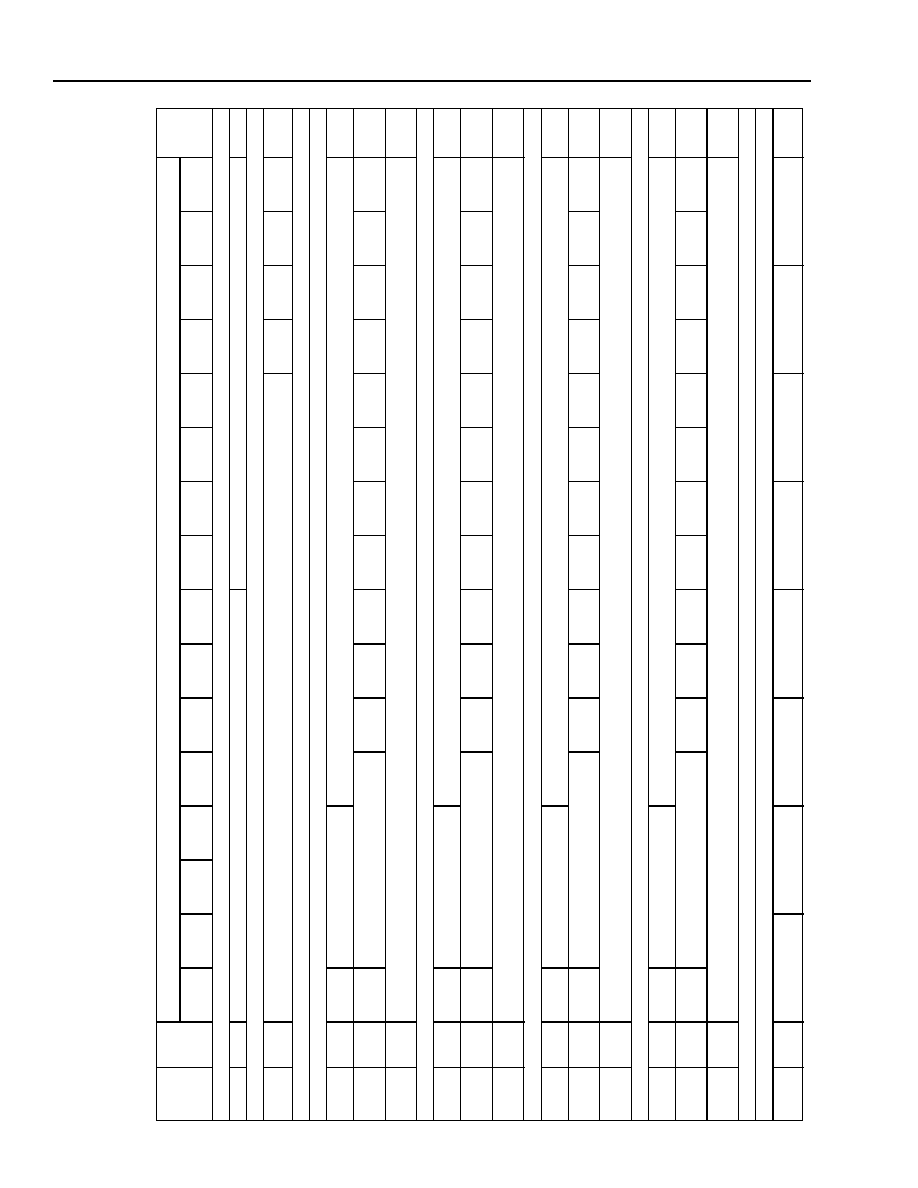

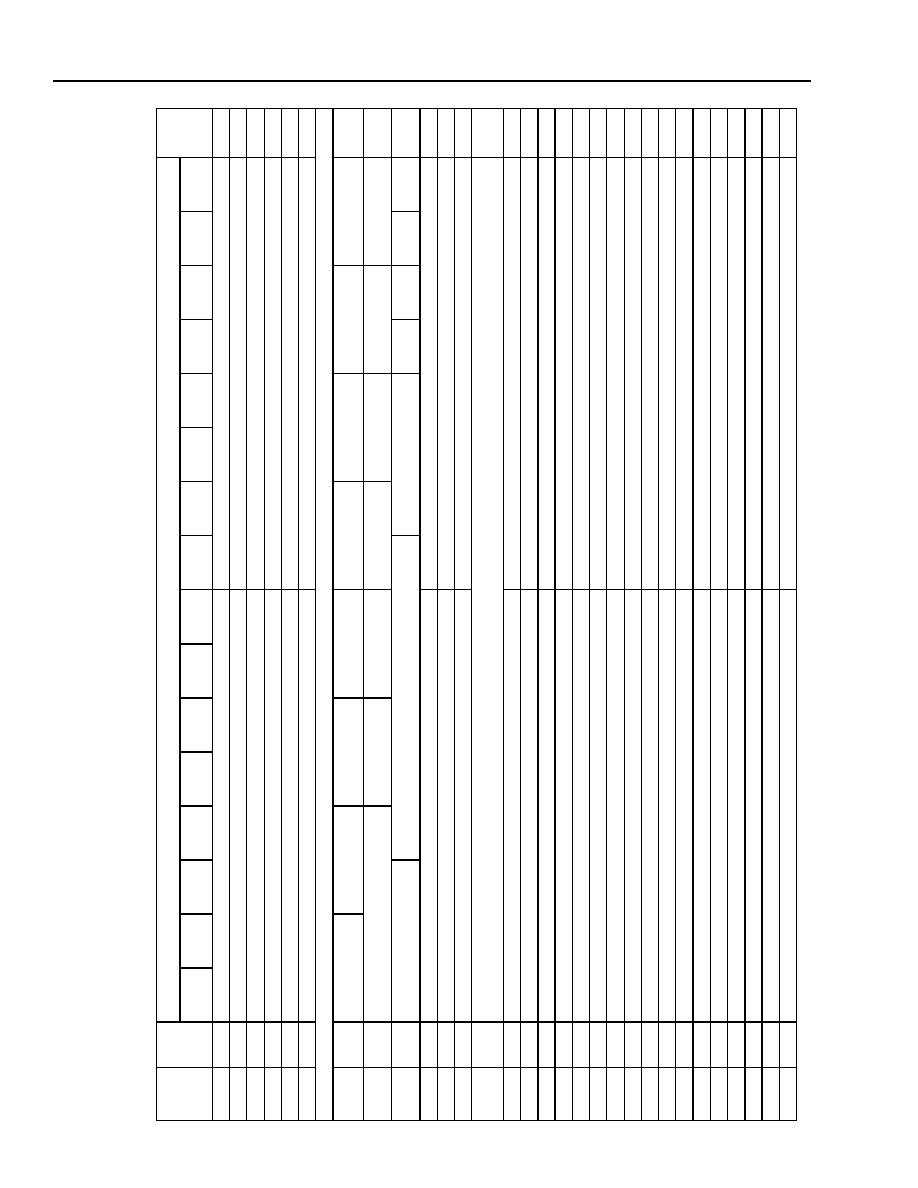

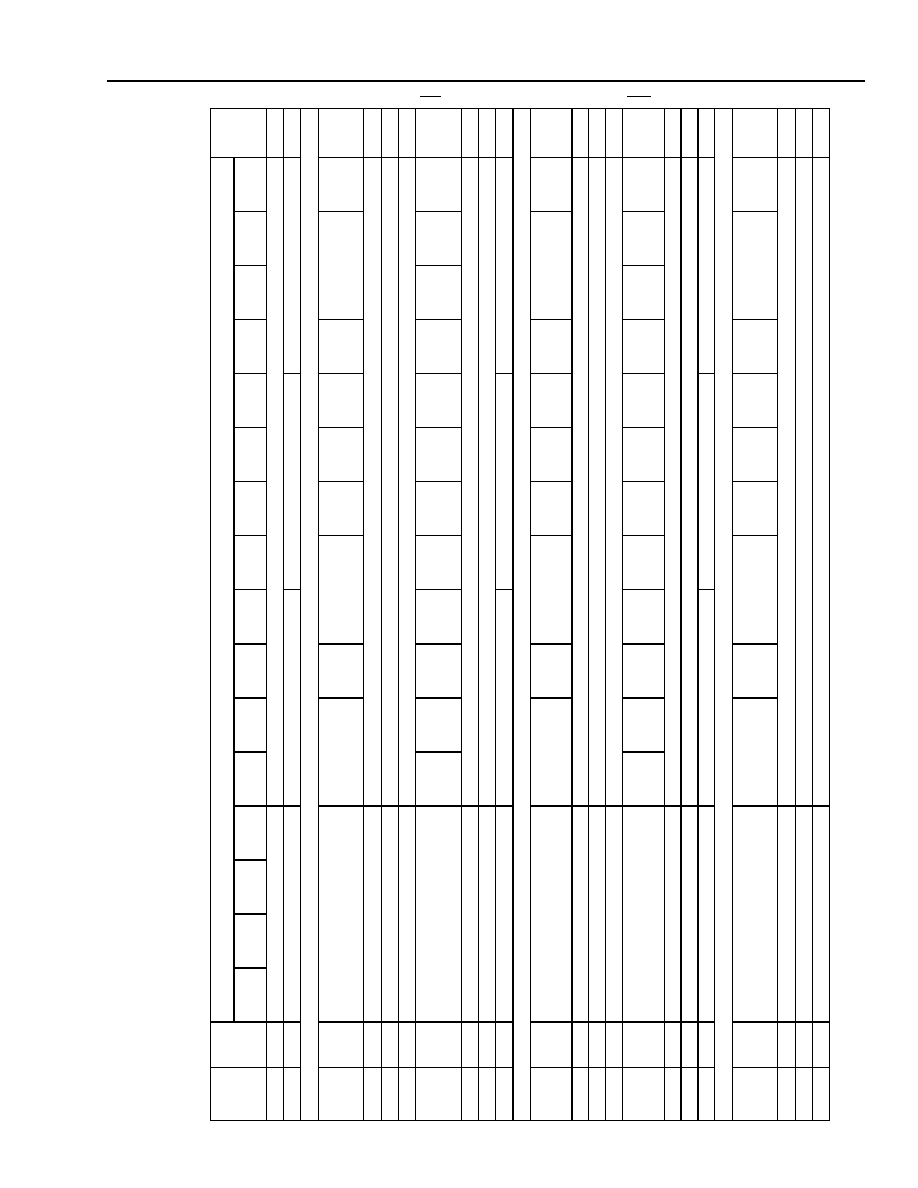

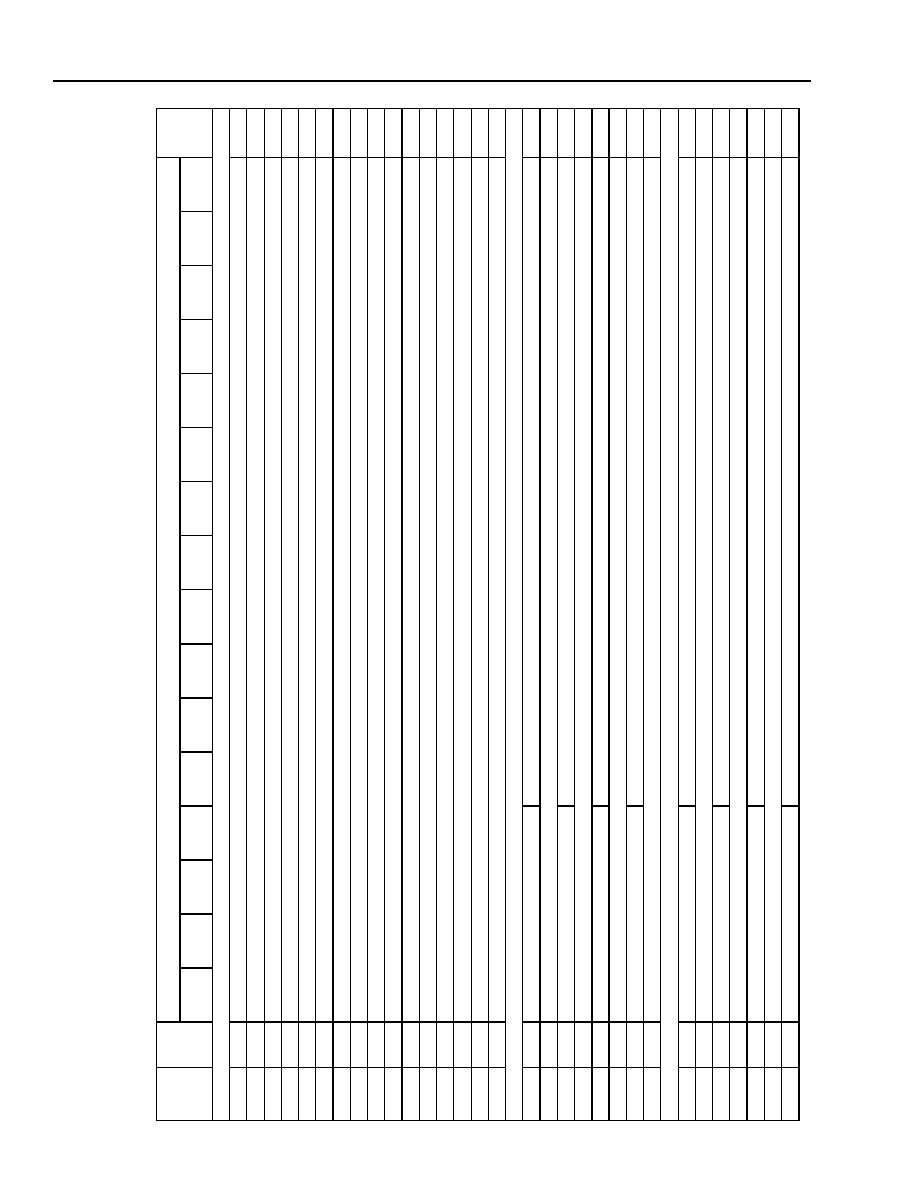

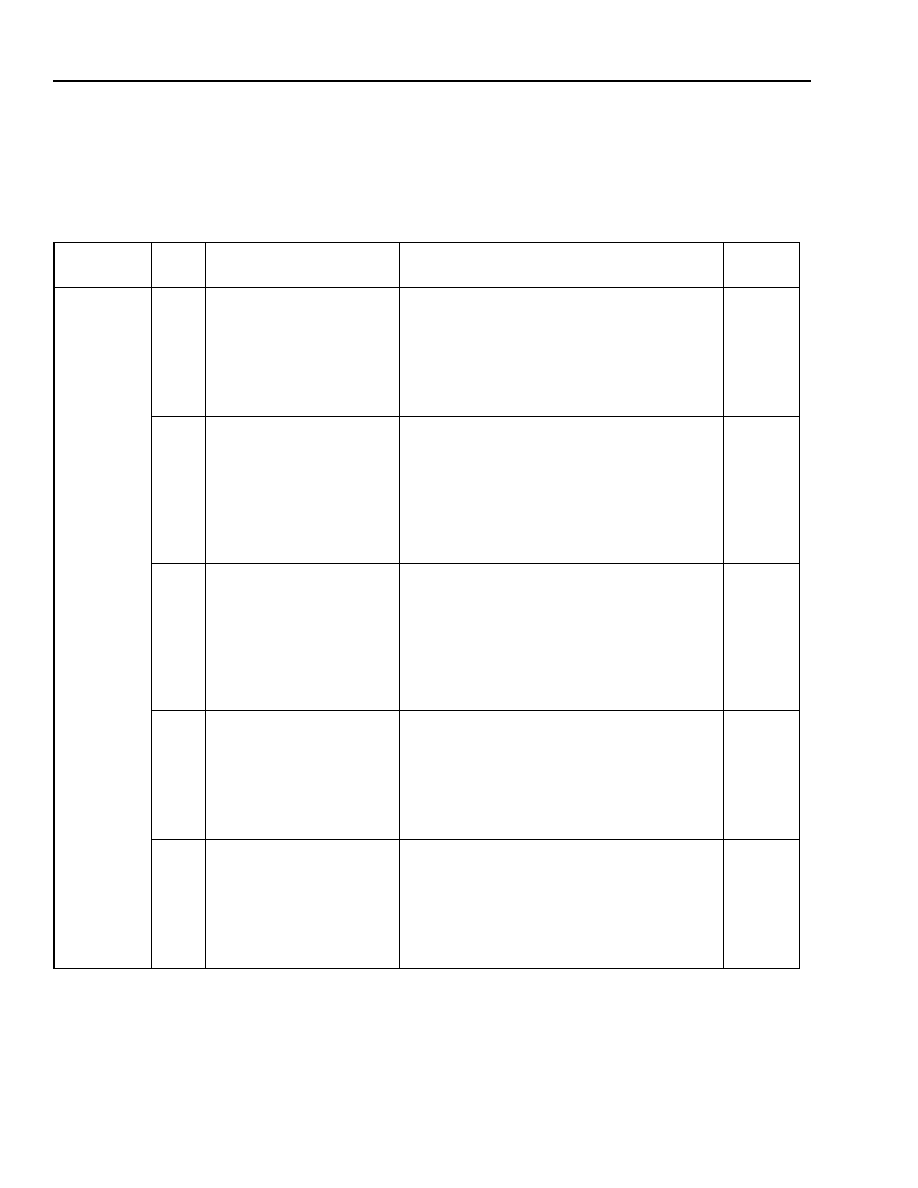

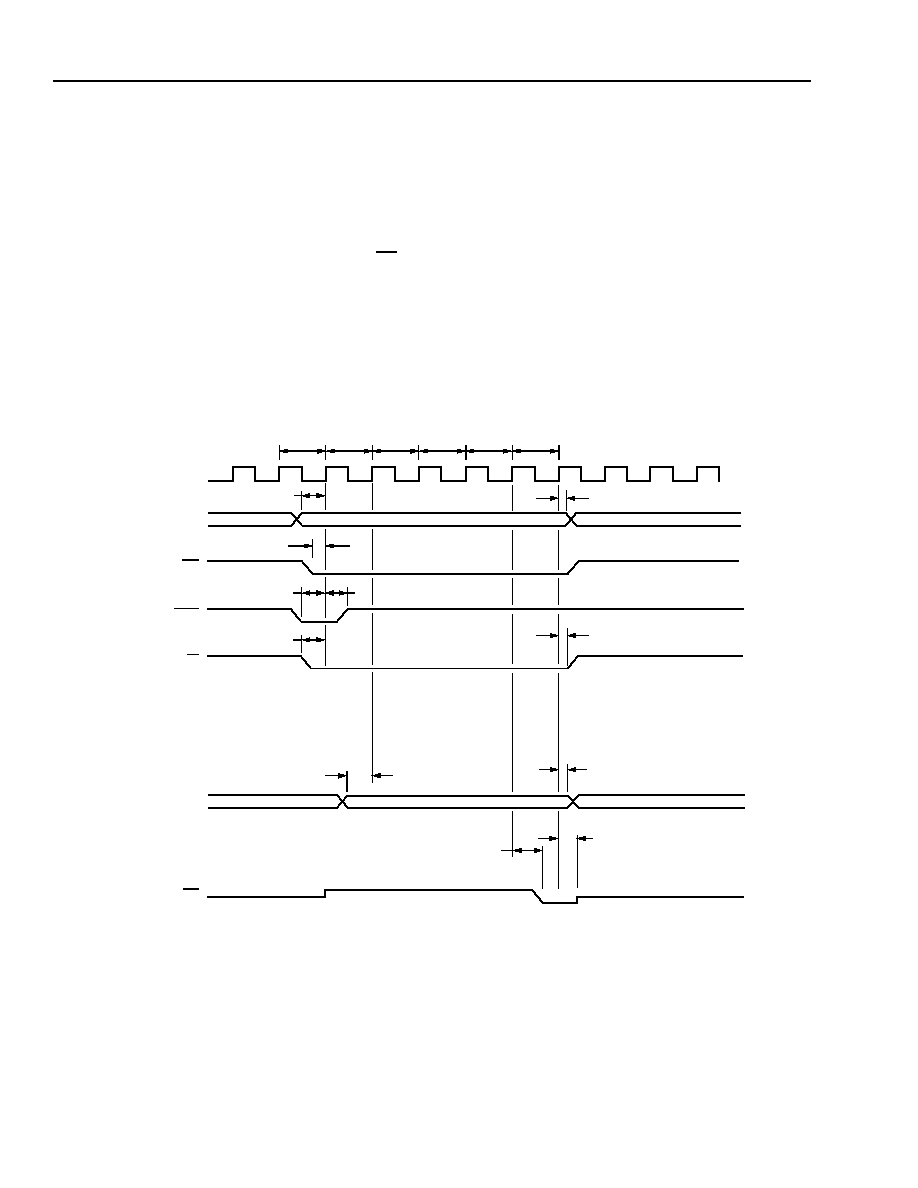

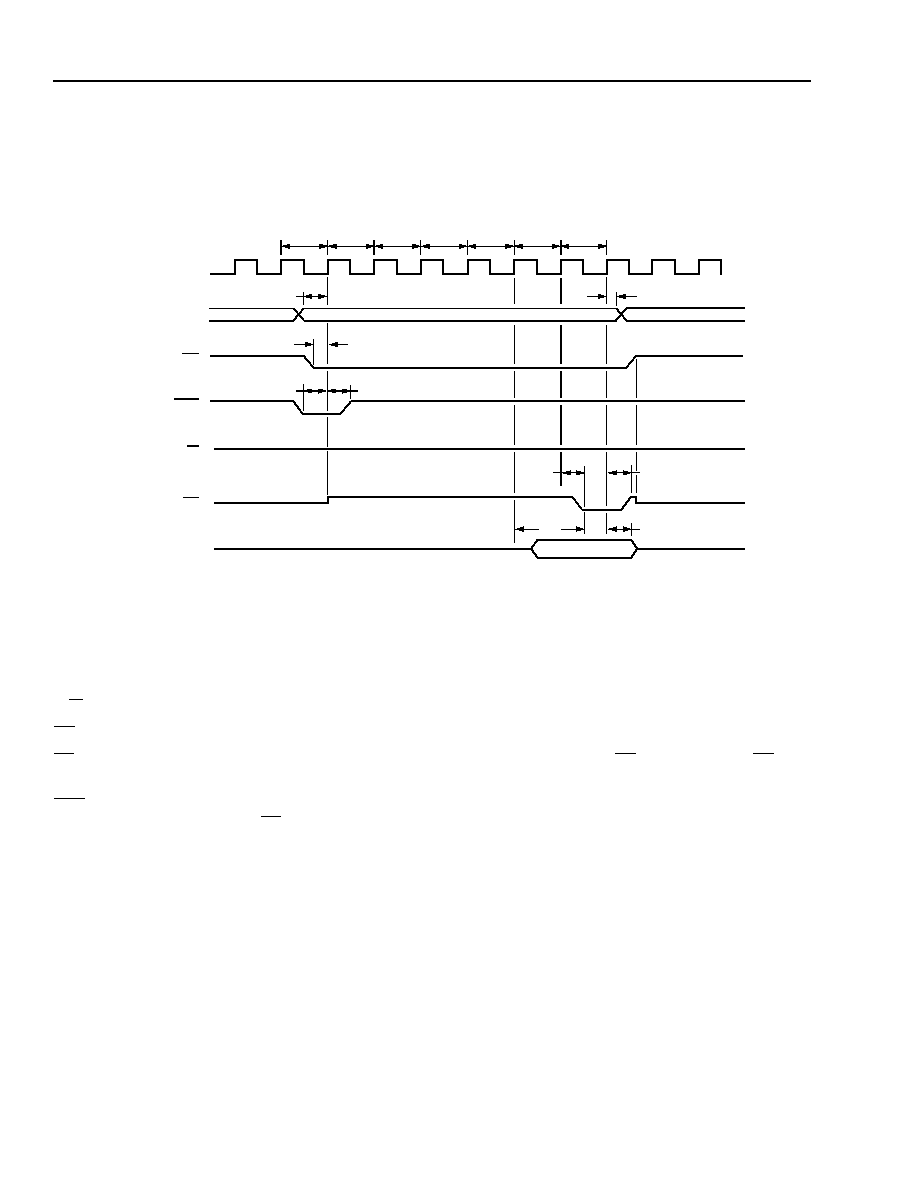

The TDAT UTOPIA interface currently has nonfunctioning RxPAB and RxPAD output signals when used in four-

channel Multi-PHY mode as shown in Figure 1. The result of this problem is the unavailability of direct status polling

on the receive-side UTOPIA interface. To work around this problem, the following analysis is done to aid the user in

doing a round-robin data extraction procedure.

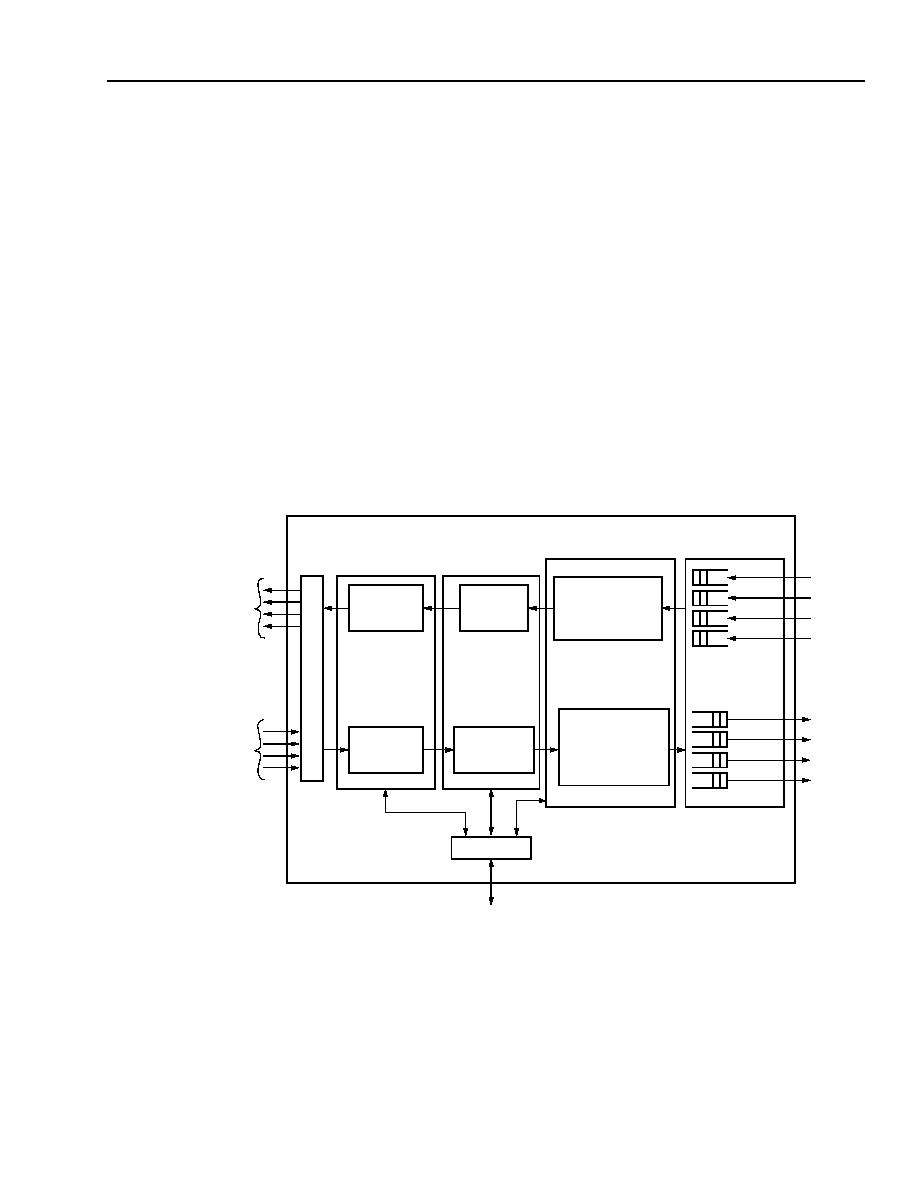

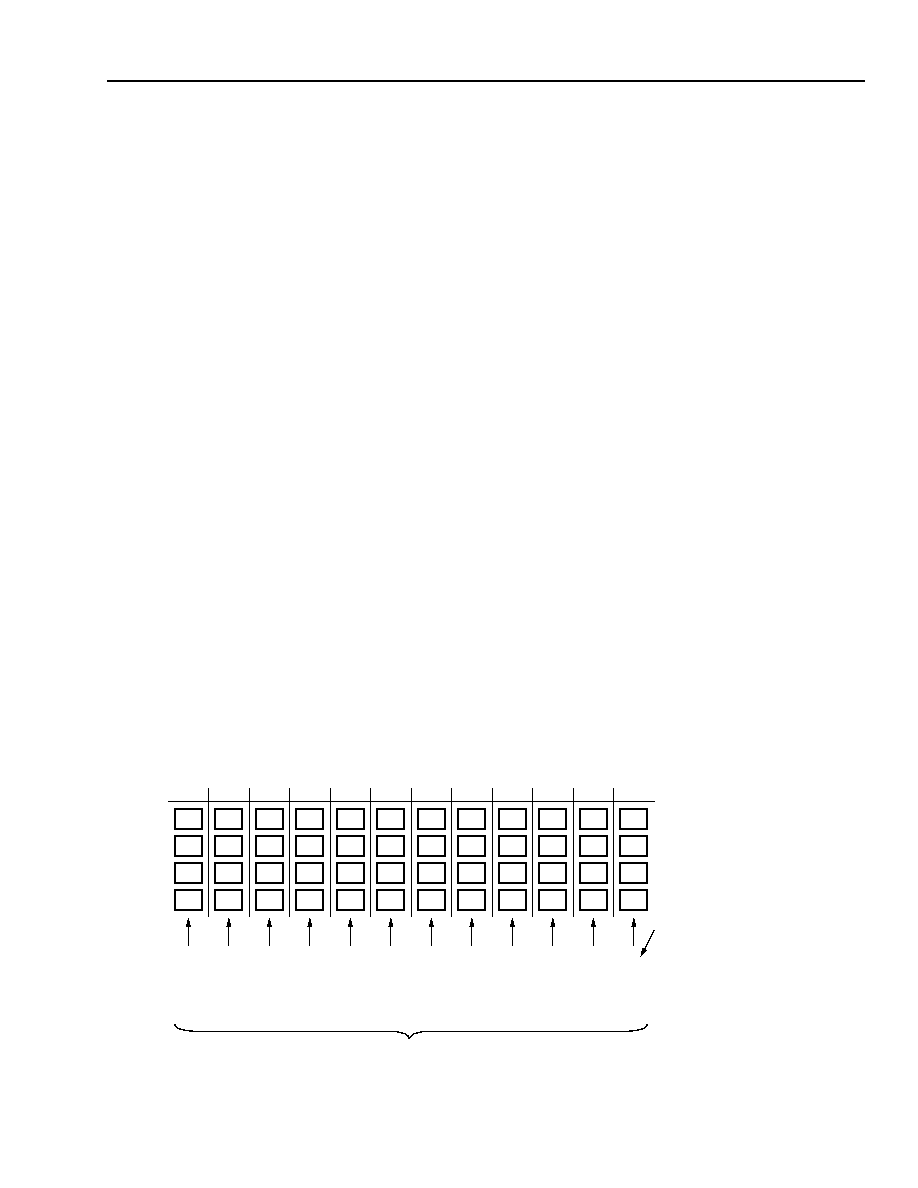

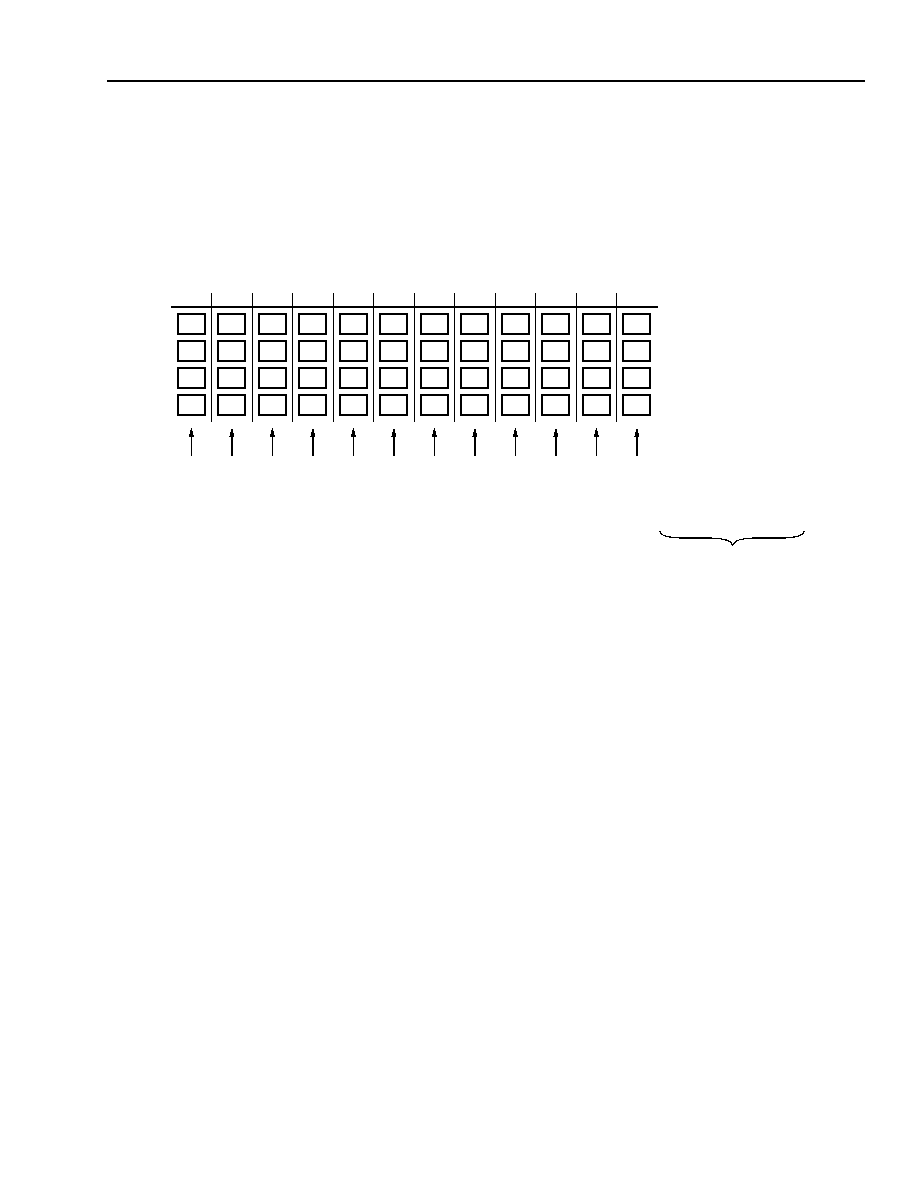

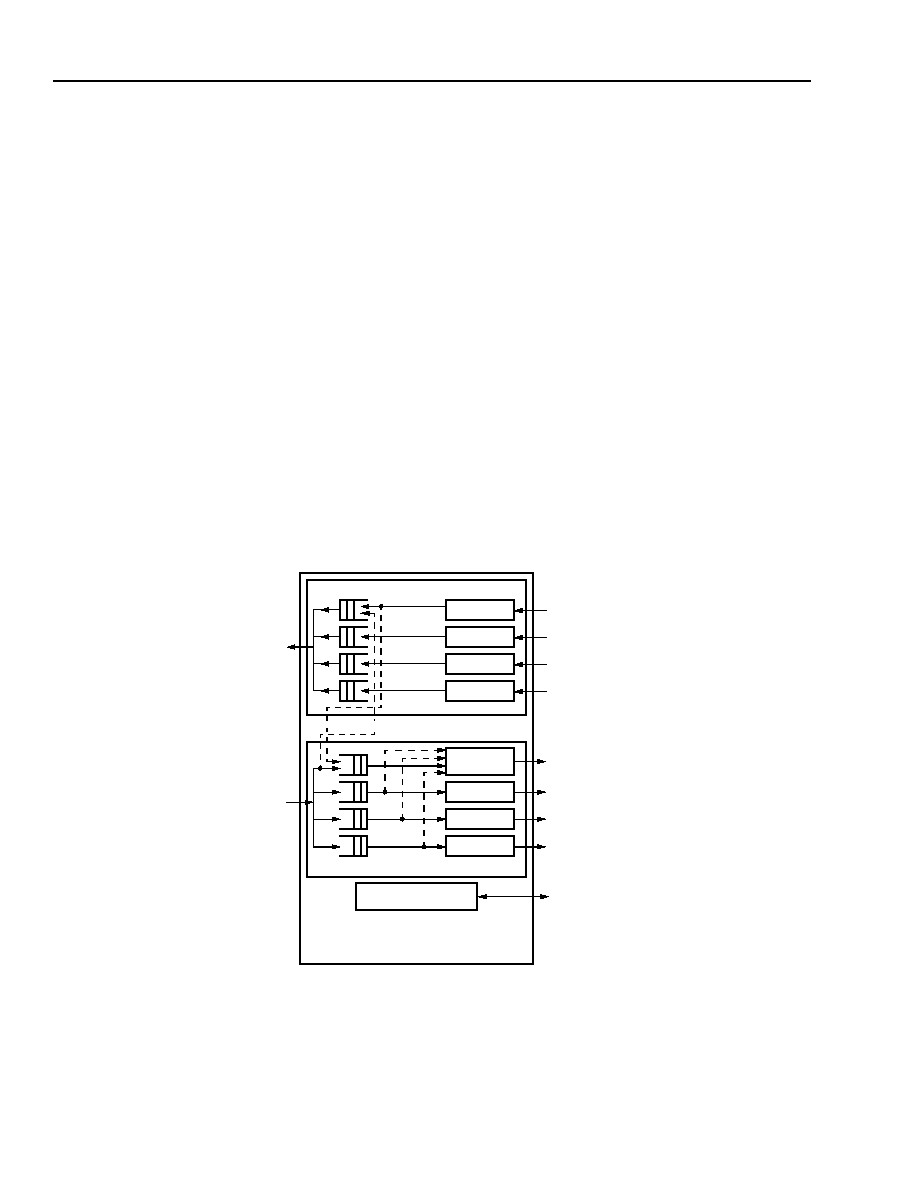

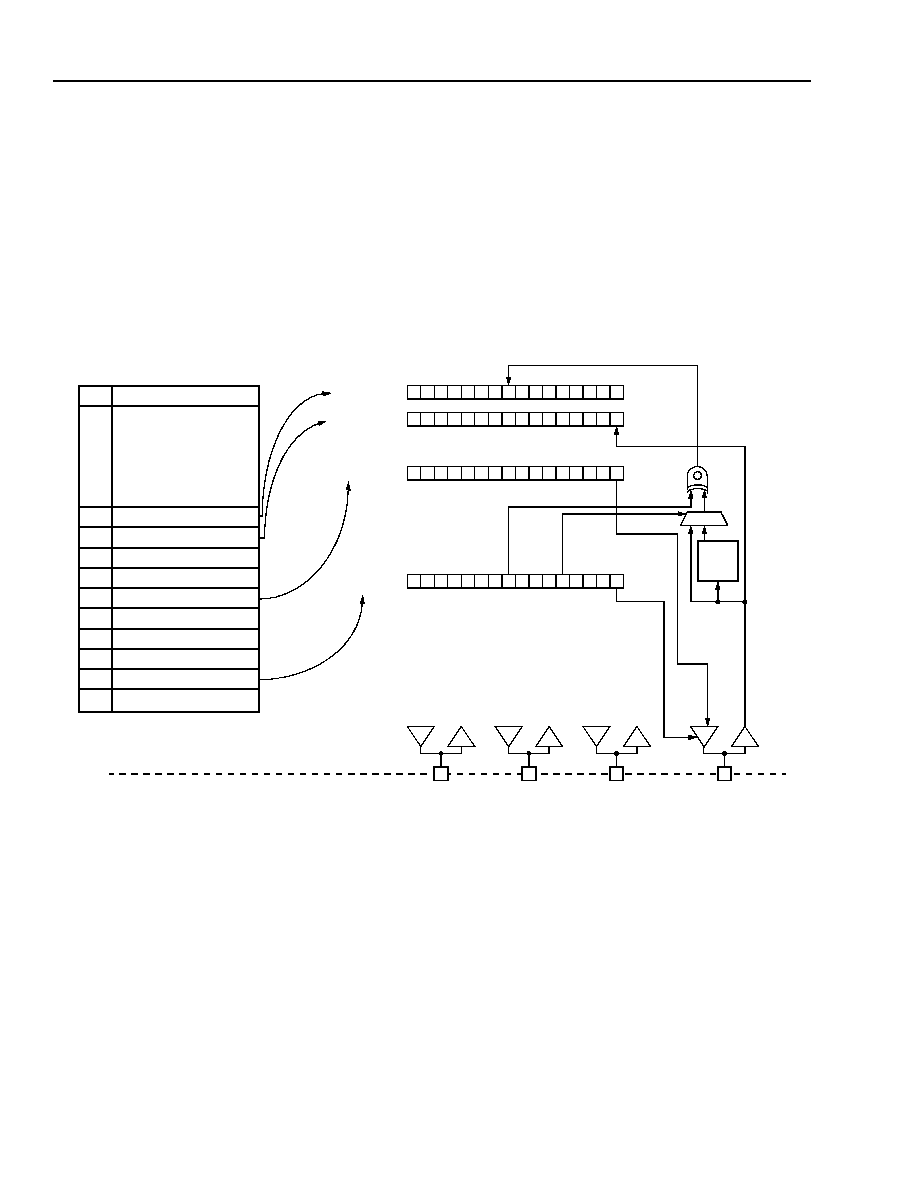

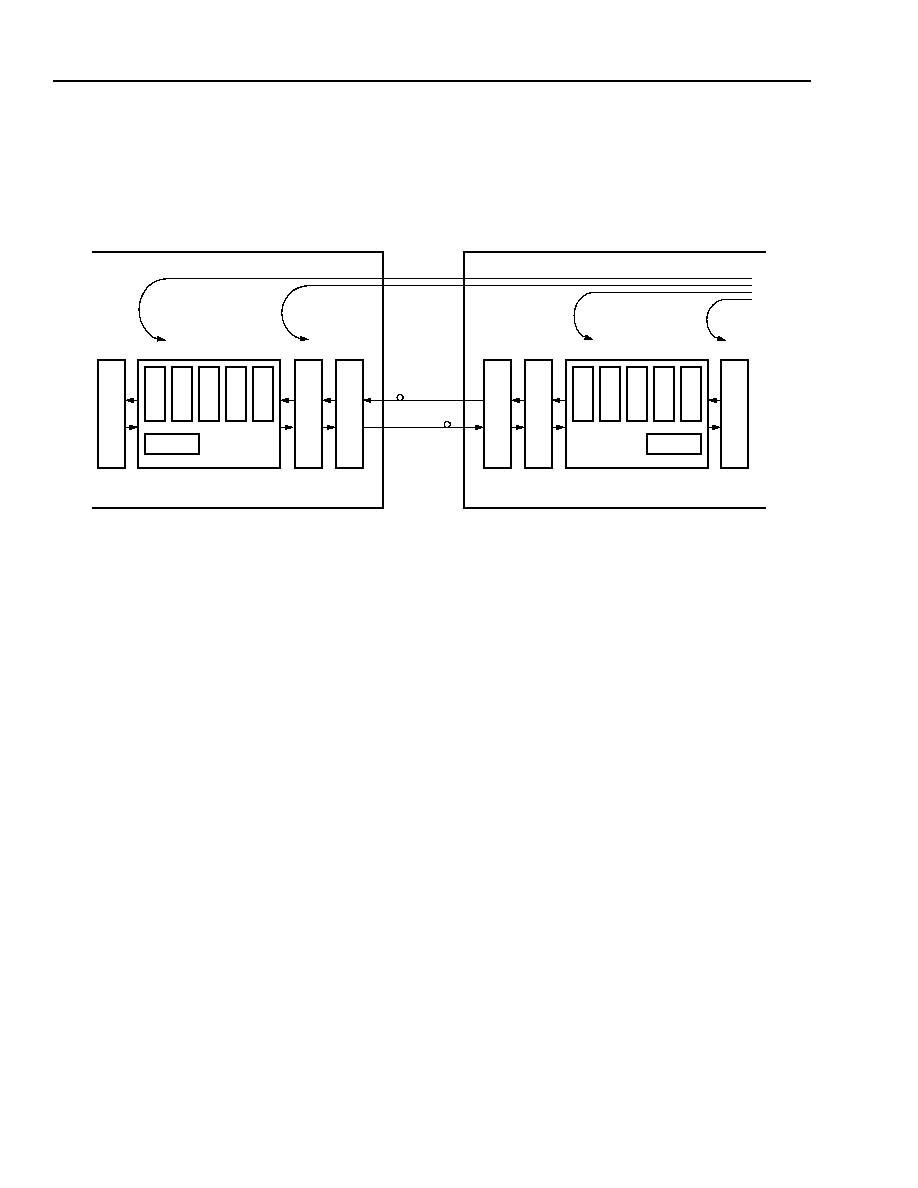

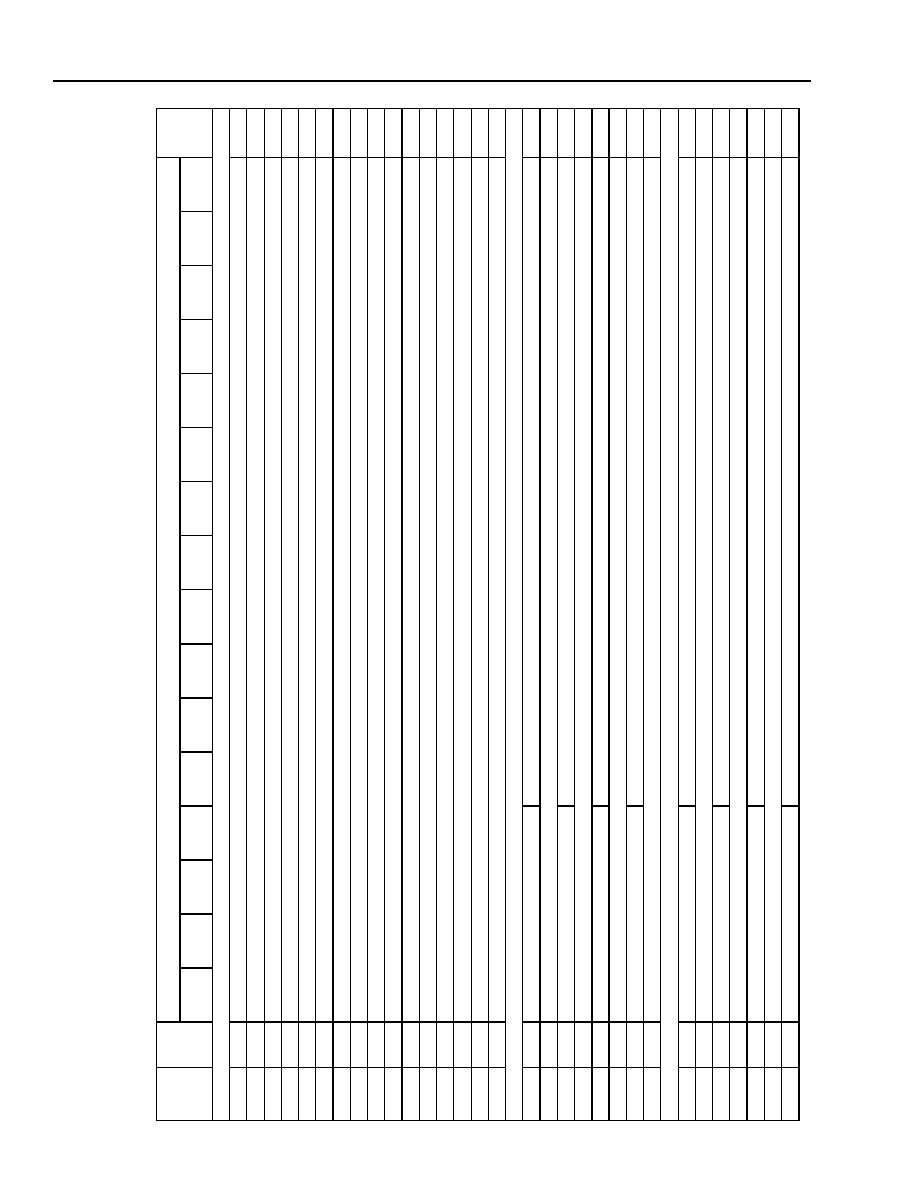

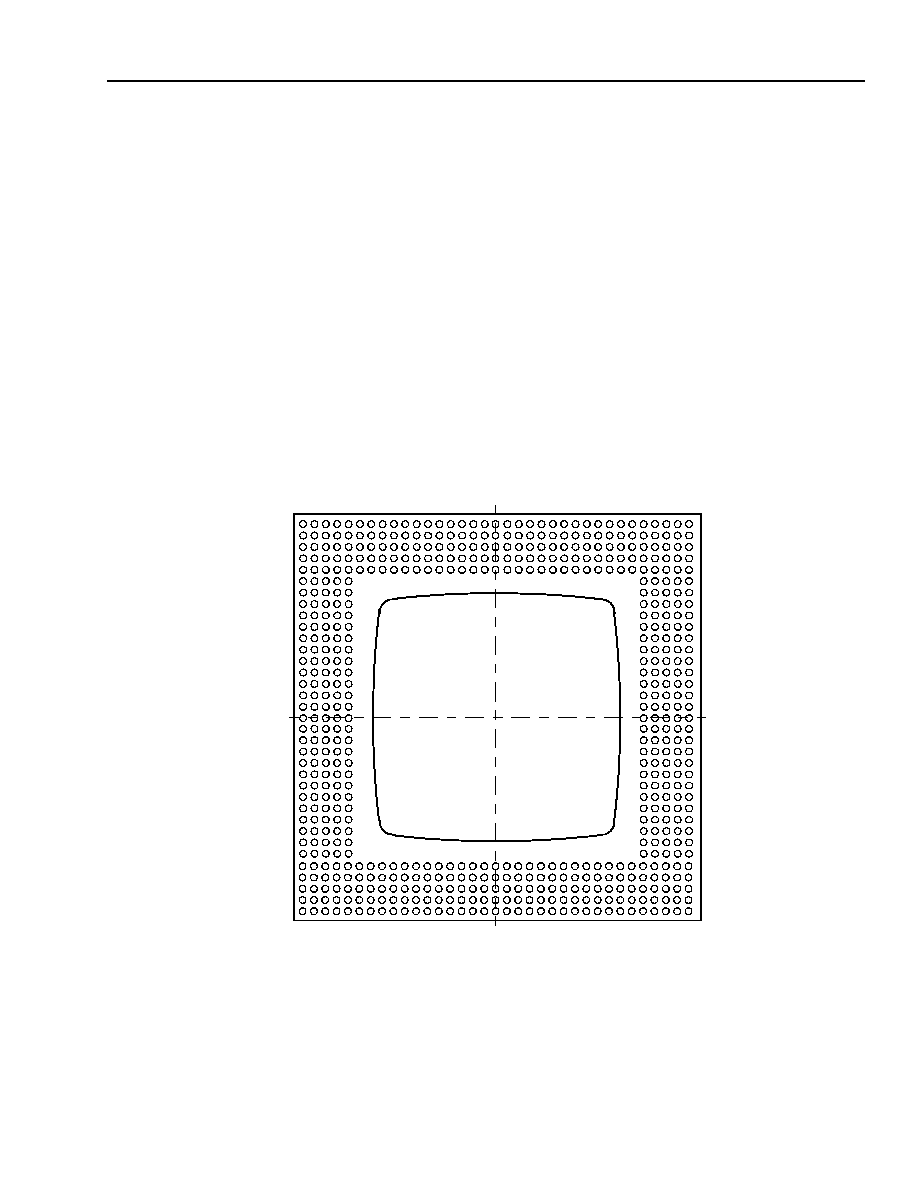

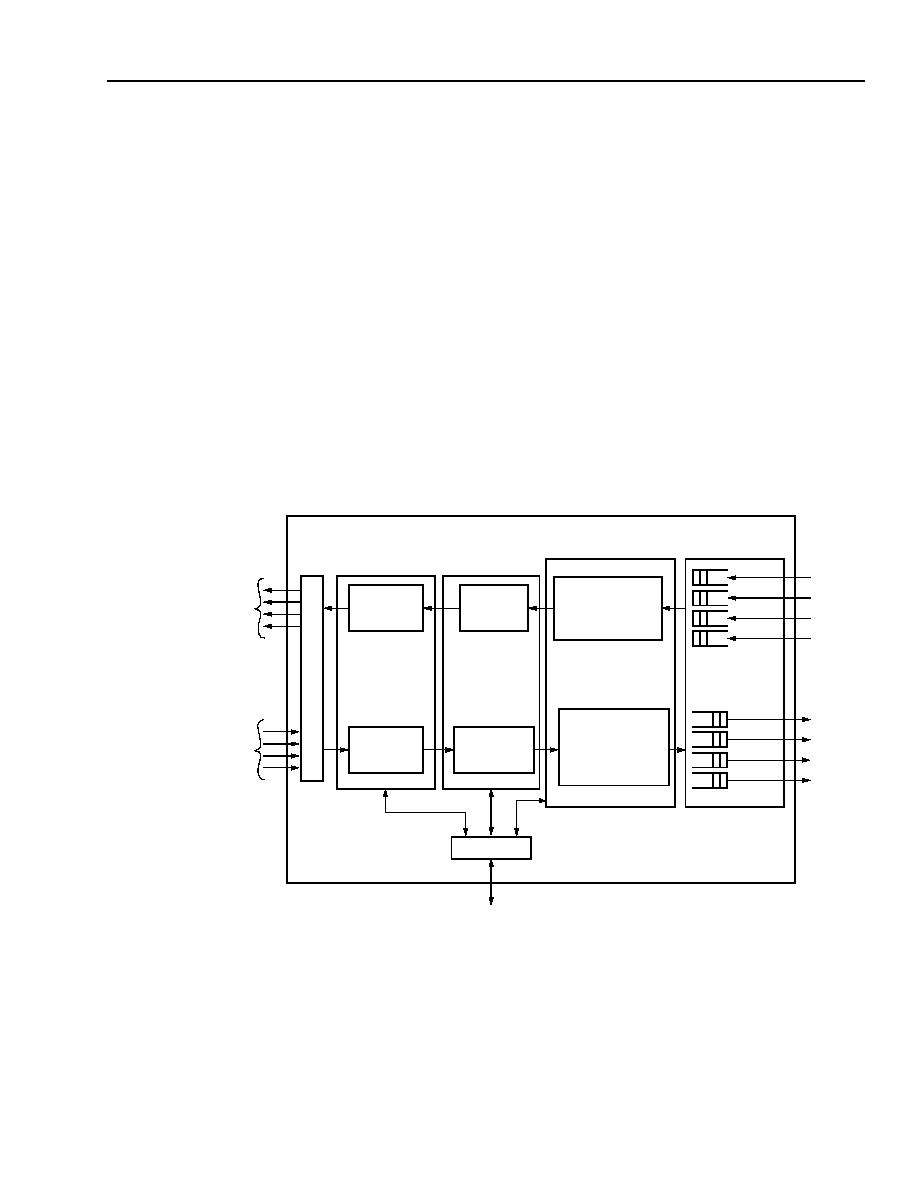

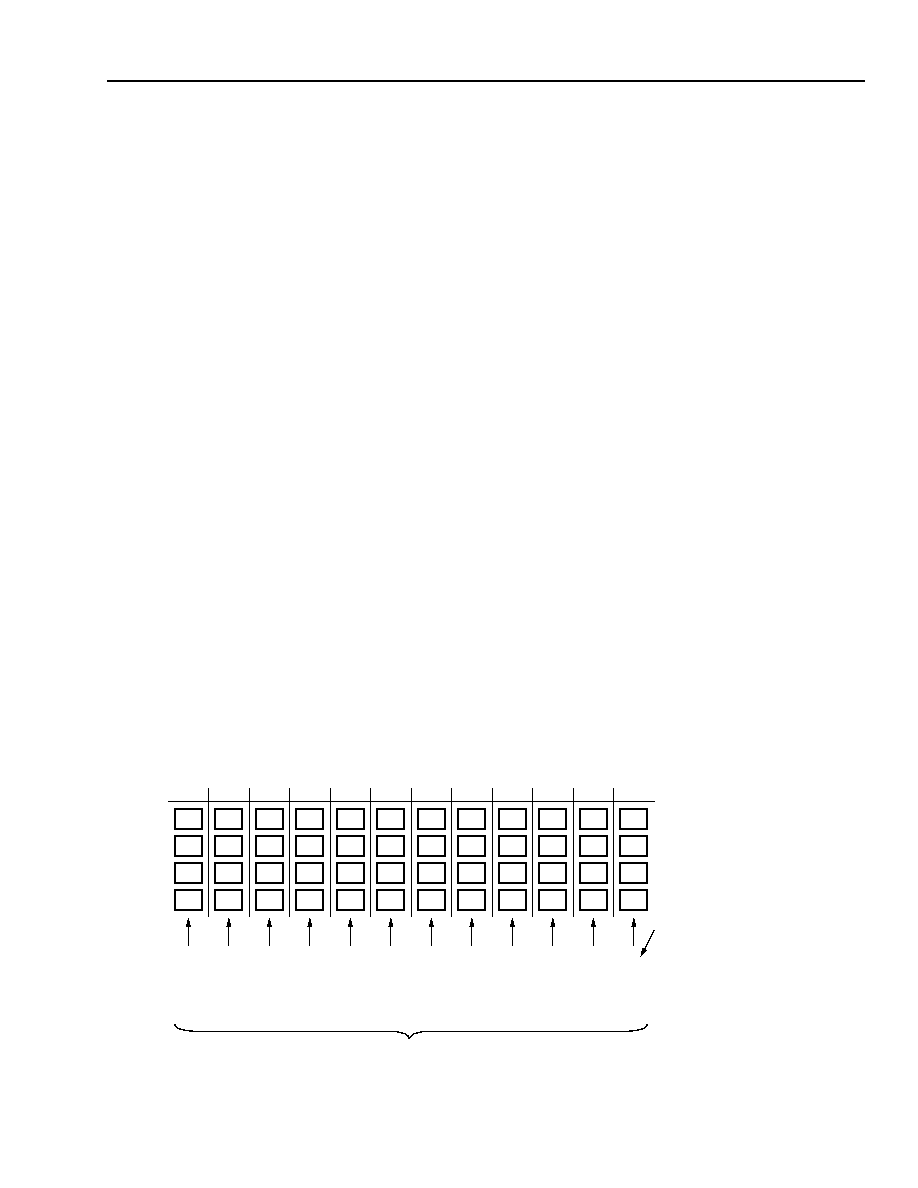

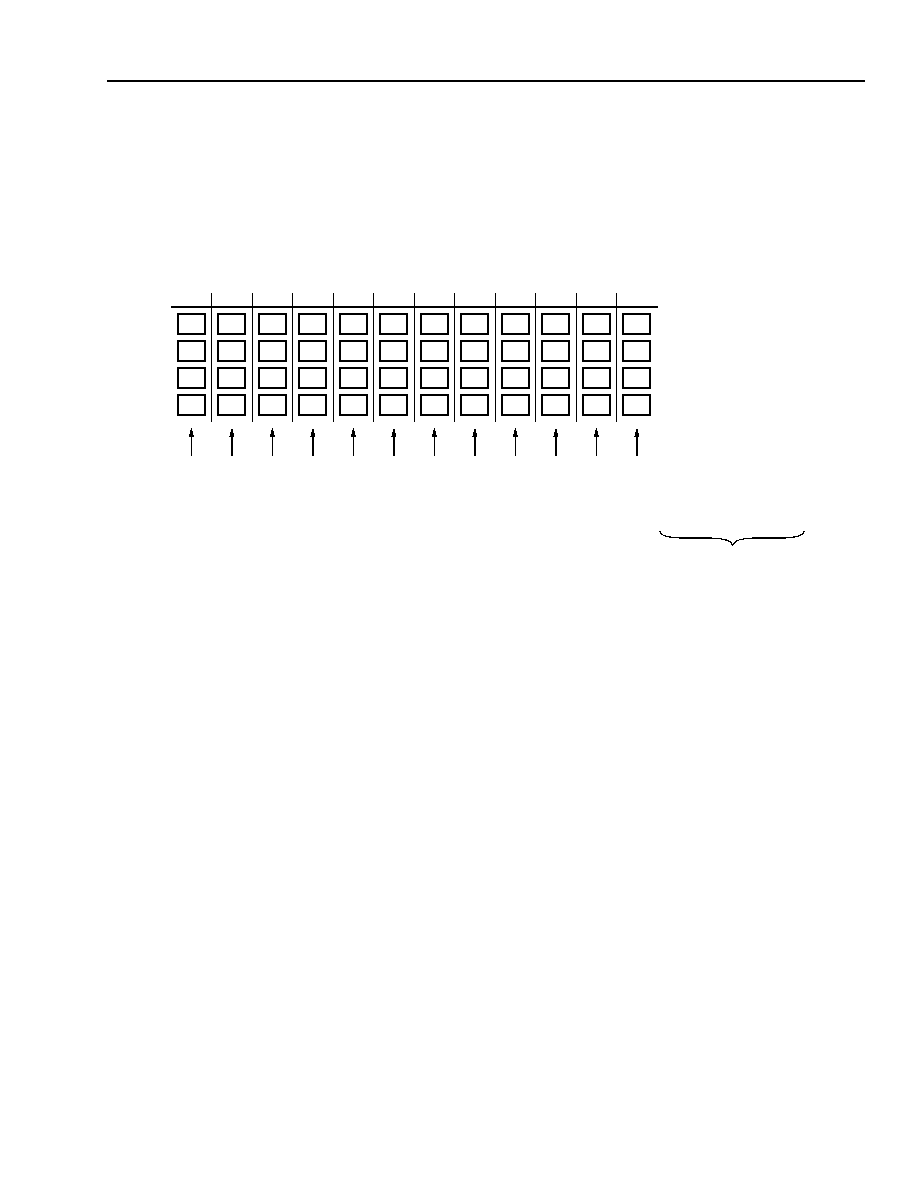

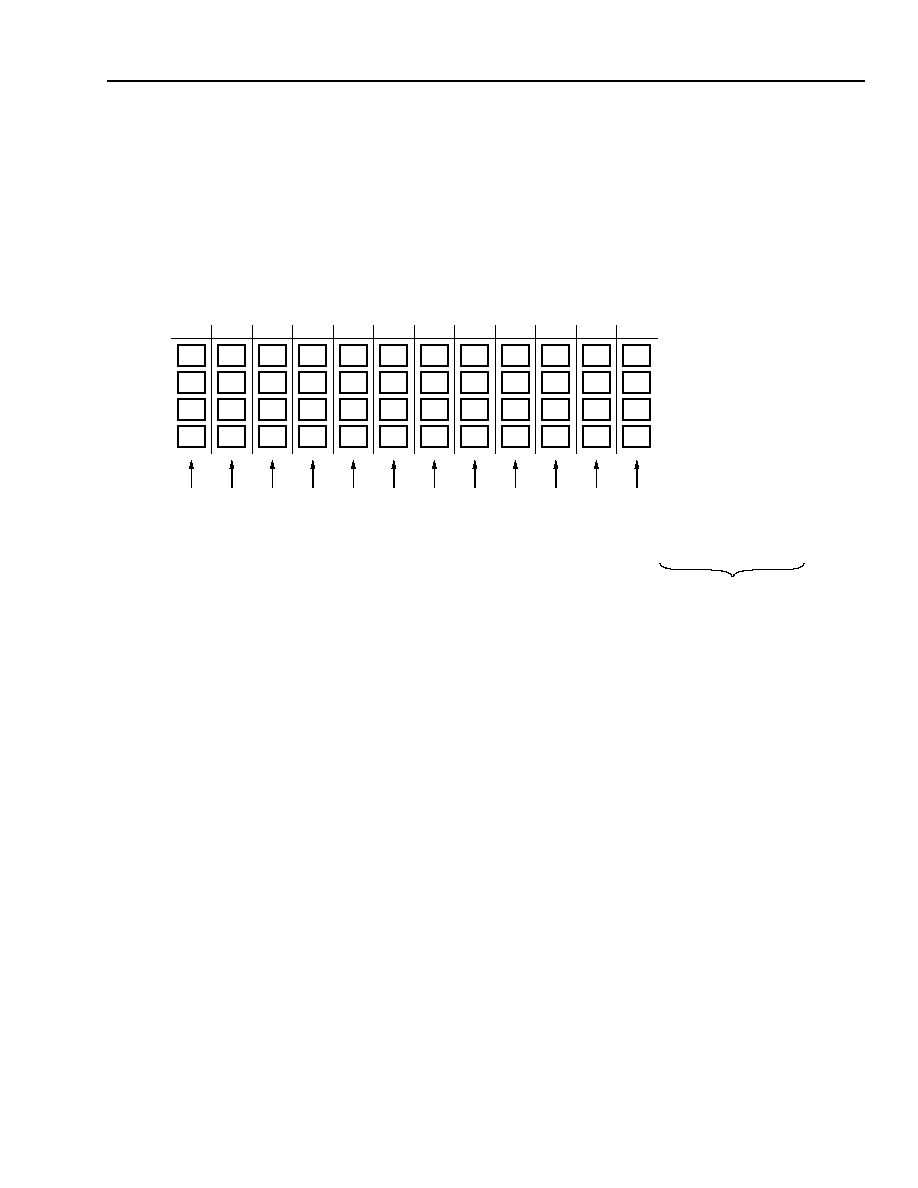

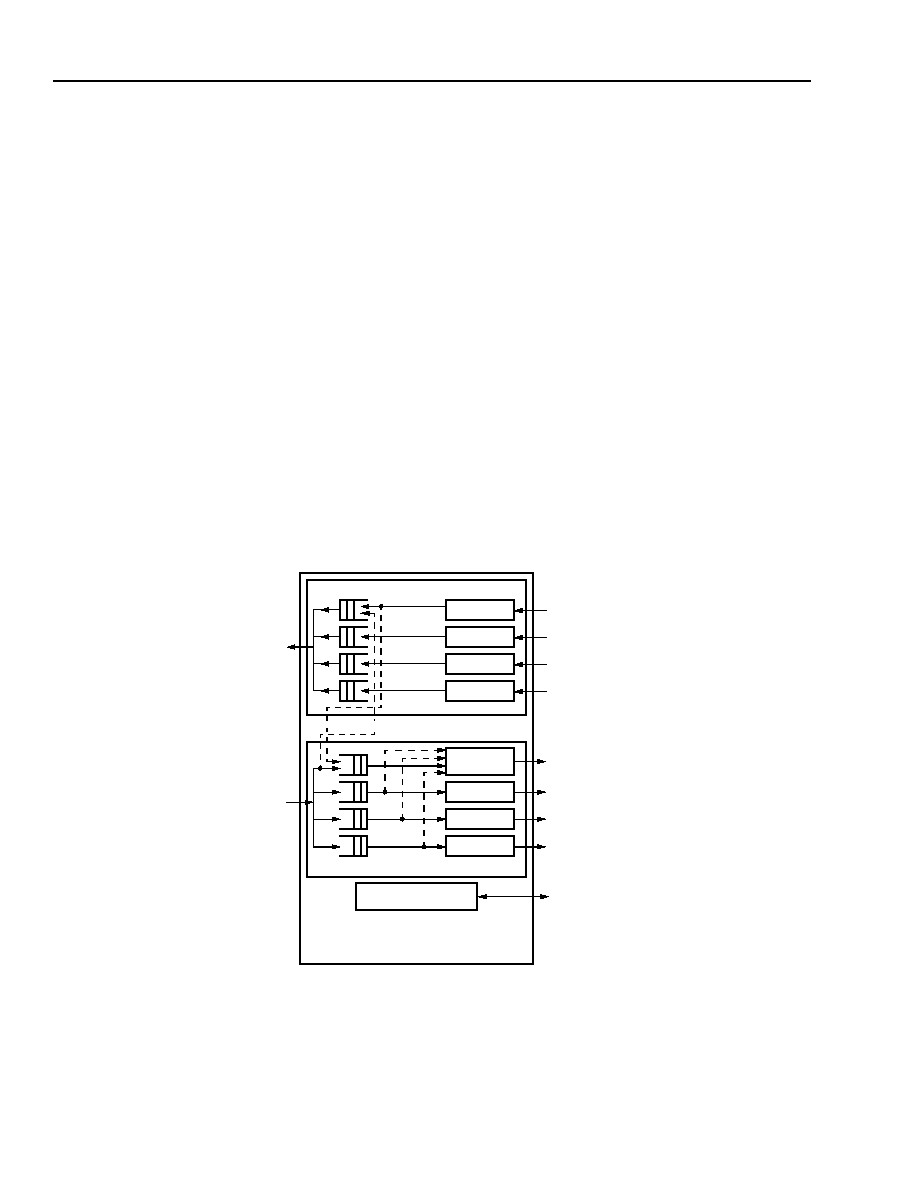

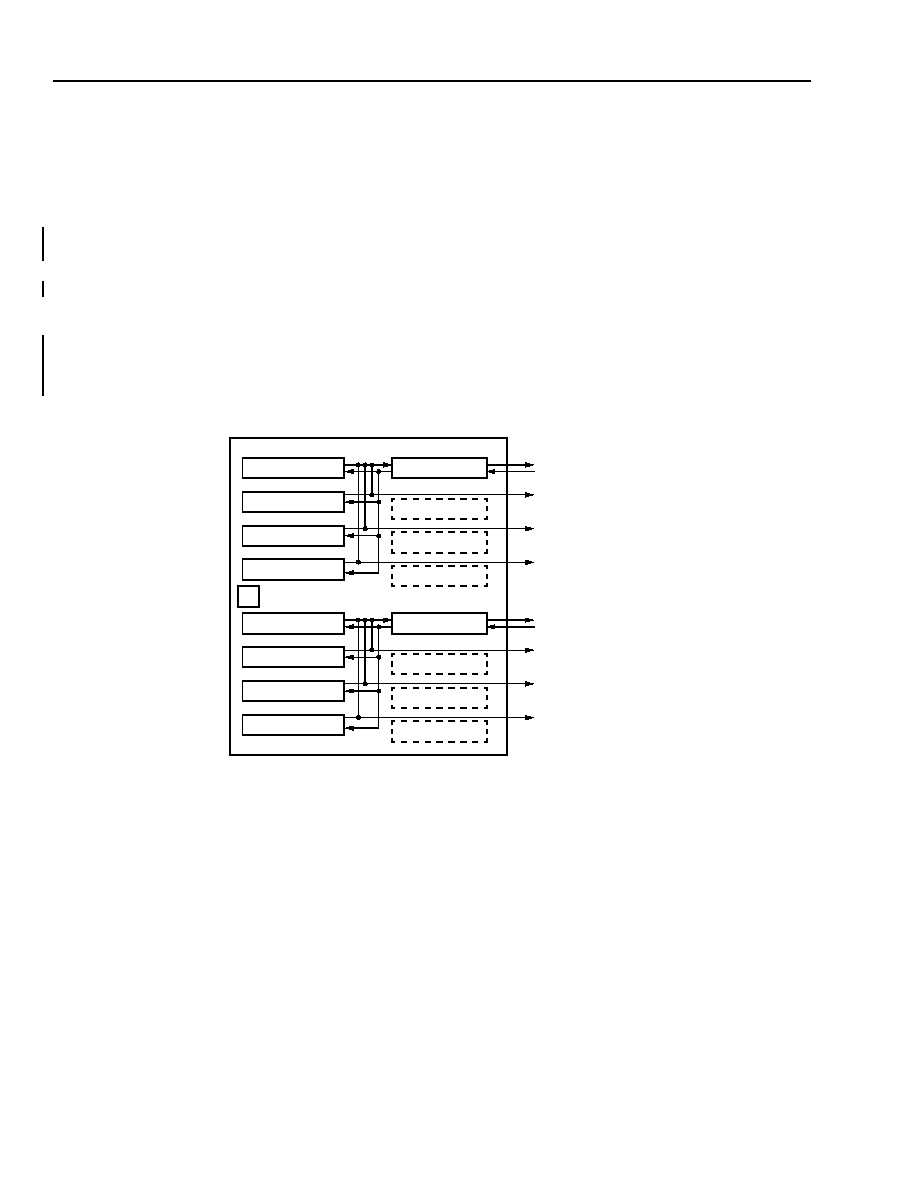

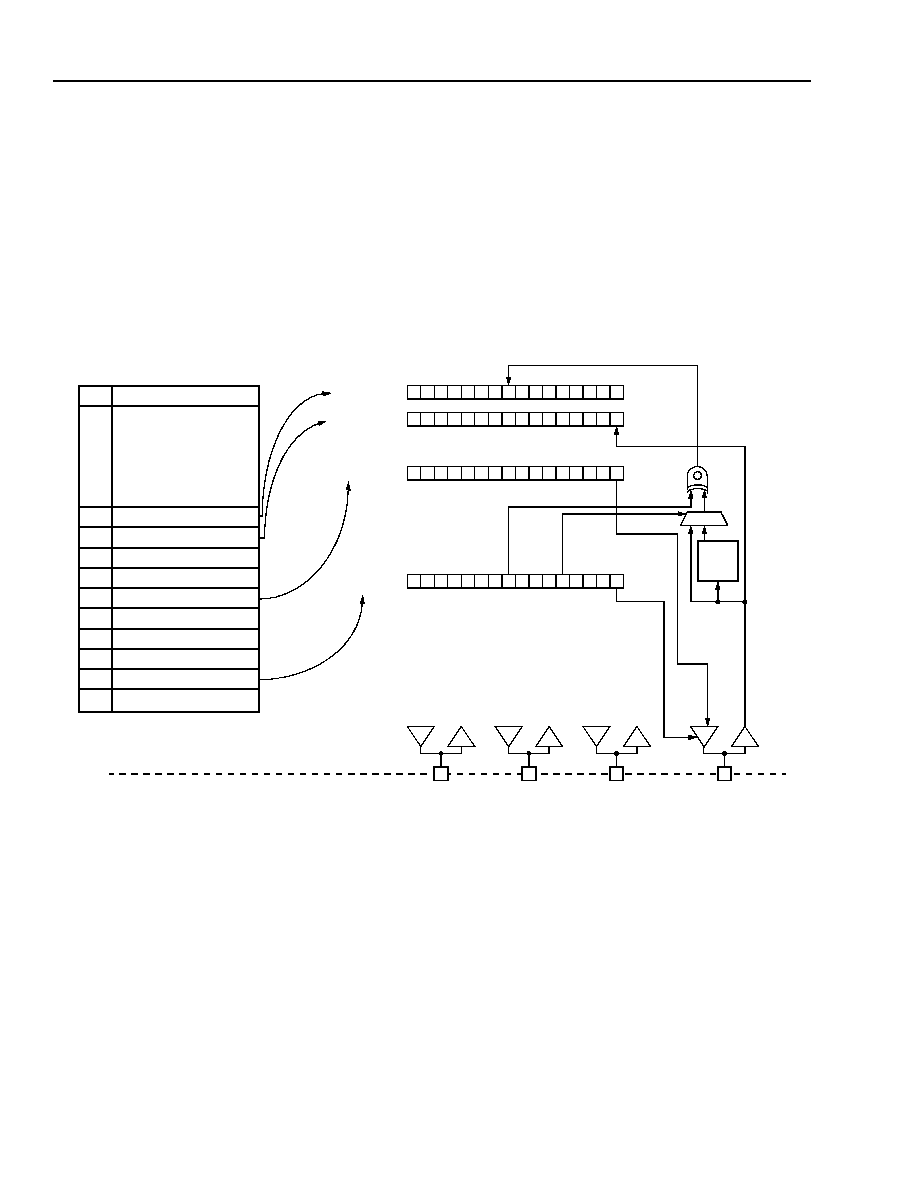

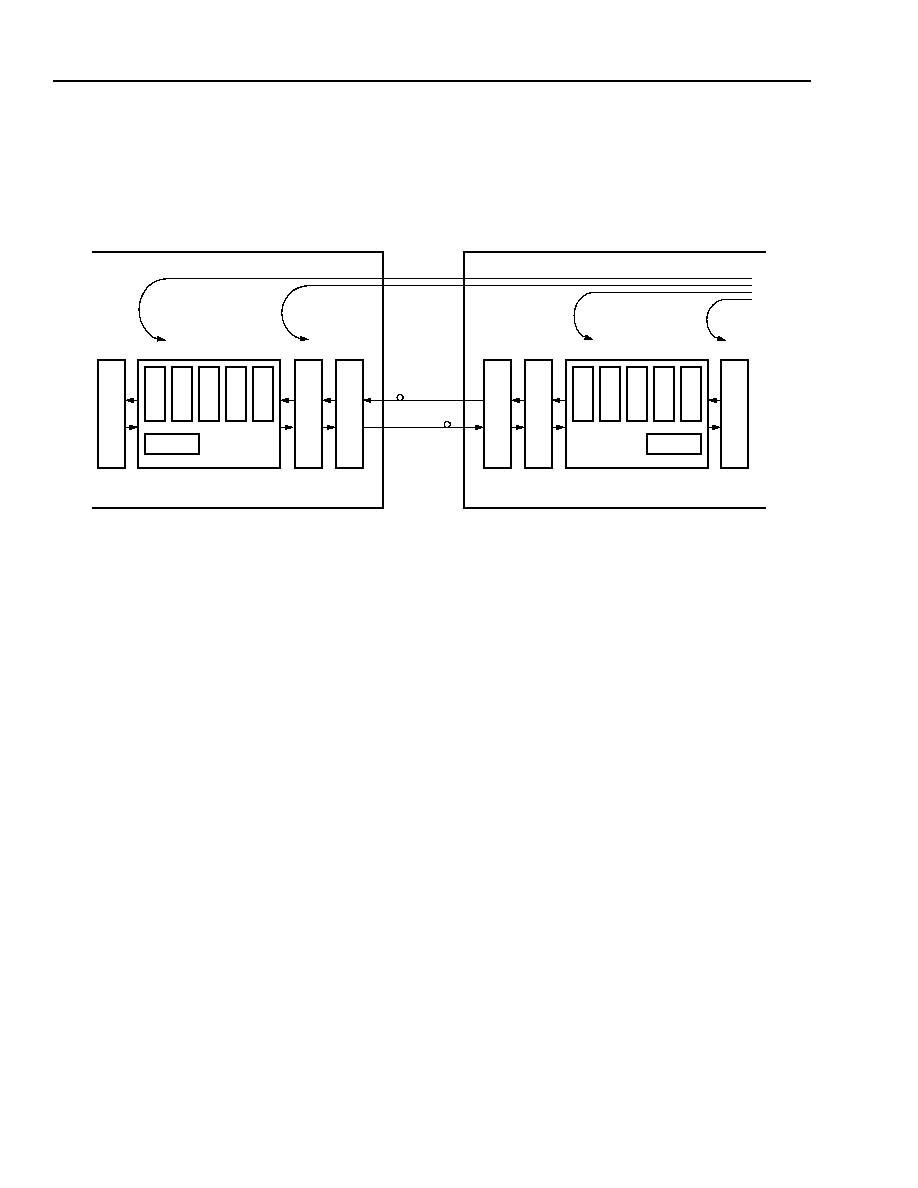

1664 (F)

Figure 1. Receive-Side UTOPIA Interface and Channel FIFOs

The rate at which data fills and drains the receive-side UTOPIA FIFOs is calculated as follows:

I

The data enters each UTOPIA FIFO from the data engine bytewise running on a 77.76 MHz system clock.

I

If we assume each channel (worst case) is filled with an STS-12c rate signal, then the amount of data (excluding

SONET overhead, both section/line, path, and three stuff columns) per second is

(87 x12 x 9 x 8000) ≠ (4 x 9 x 8000) = 74.88 Mbytes/STS-12c/s or 599.040 Mbits/STS-12c/s.

I

Since each FIFO contains a maximum of 256 bytes/FIFO, it takes on average

(256/74,880,000) = 3.4188

µ

s to fill a FIFO, and with a clock cycle of 77.76 MHz, it requires as a worst case,

3.2922

µ

s to fill the FIFO.

I

Since there are four FIFOs all receiving data at 74.88 Mbytes/s, then the total bandwidth requirements of all four

channels combined is (4 x 74,880,000) = 299.52 Mbytes/s.

I

The servicing rate on each FIFO is based on the UTOPIA interface width and frequency. If we assume a

32-bit A/B UTOPIA interface operating at 100 MHz, then the service rate is 400 Mbytes/s to service all the

channels.

INGRESS CHANNEL A FIFO

256 bytes DEEP

INGRESS CHANNEL B FIFO

256 bytes DEEP

INGRESS CHANNEL C FIFO

256 bytes DEEP

A

B

R

X

PAA

32-bit INTERFACE (A AND B)

R

X

PAB

C

R

X

PAC

INGRESS CHANNEL D FIFO

256 bytes DEEP

D

R

X

PAD

X

X

Agere Systems Inc.

19

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

UTOPIA (UT)

(continued)

I

The interface can drain an entire FIFO at a rate of 400 Mbytes/s. To drain 256 bytes, it requires a maximum of

(256 / 400,000,000) = 0.64

µ

s to drain a FIFO that is completely full. To drain all four FIFOs, it requires

(0.64 x 4) = 2.56

µ

s total

.

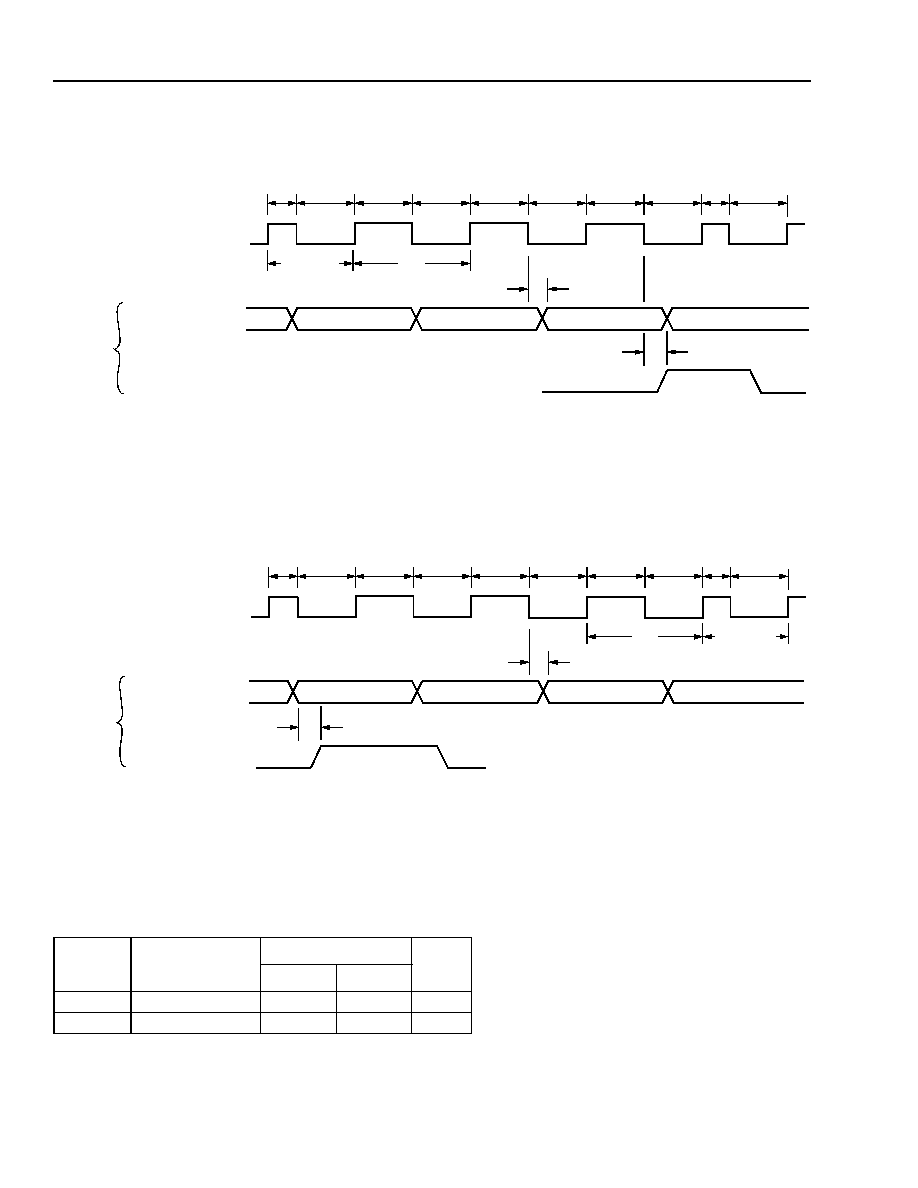

For data to be efficiently removed from each of the Rx FIFOs, a round-robin extraction method must be employed

since the RxPAB and RxPAD signals are not available for direct status polling. Since it requires a worst case total of

3.2922

µ

s to fill a FIFO, the master must service all FIFOs in a manner such that it does not allow any particular

FIFO to fill and hence overflow. Assuming equal servicing of each FIFO, the master must therefore not service any

particular FIFO for longer than (3.2922 / 4) = 0.8231

µ

s. This also must account for any dead cycles in a cycling

between channels and any dead cycles on a particular channel (single dead cycle between EOP and SOP).

When servicing four FIFOs, there is a maximum clock cycle penalty for switching between channels. For two-cycle

mode, this penalty is a maximum of four UTOPIA master clock cycles; so to switch between all four channels, a

total of up to sixteen master clock cycles may be required to perform all the switching. The value of four is worst

case, and in some cases this can be as low as one cycle. The value of four results from the case where the FIFO

drains while servicing that channel, which will be common when draining at the 100 MHz frequency. In that case,

the master must first see that the FIFO has drained by observing that RxPAA is invalid on the last cycle while drain-

ing the FIFO (best case is one cycle lost). It must then deactivate RxENB and place a new channel address on the

address bus on the following cycle (best case is one cycle lost). It must then activate RxENB for the new channel

on the following cycle and have TDAT sample RxENB low (best case is one cycle lost). The TDAT will then output

data two cycles later when using a PA response mode of two cycles (one cycle lost with data output on second

cycle). Any additional delays by the master must be added to these to calculate a worst-case condition. The best-

case condition occurs when the master stops the data flow when there are still more than two data items contained

within the FIFO. In this case, the master deactivates RxENB at some predetermined maximum 32-bit word drain

value, where the PA response on the cycle prior to deactivation had valid data. For two-cycle mode, two additional

data items will be output from the FIFO for that particular channel, if available. The master deactivates RxENB,

places the new channel address on the FIFO, and activates RxENB. On the cycle where RxENB is activated, the

last valid data item from the previous channel may be output (best case), and one dead cycle will follow this before

data for the following selected channel is output.

Given the information above, assume the worst case of four cycles between channel switching. Also assume the

FIFOs are filling at a worst-case rate, 3.2922

µ

s/FIFO. Assume the master is draining each FIFO using the 32-bit,

100 MHz, A/B, UTOPIA interface. Assume the master extracts a maximum of thirty 32-bit words (120 bytes) from

each FIFO before switching to an alternate channel. This requires (30 x 10) = 300 ns/FIFO, and assume that it

takes the worst-case four clock cycles to switch to alternate channels. Therefore, the total servicing time per FIFO

is (300 + 4 x 10) = 340 ns/channel, and the total servicing time per four channels is (4 x 340) = 1.36

µ

s per round

robin servicing of all four channels. At this round-robin rate, a maximum of 120 bytes are serviced per channel per

1.360

µ

s interval; so to service the total bytes per channel (74.88 Mbytes/s), it requires a total of 0.849 seconds,

which is sufficient bandwidth to service all channels.

Since the FIFOs fill at the maximum rate of 1 byte/13.355 ns, each FIFO will fill to a depth of 102 bytes in the

1.360

µ

s interval between channel servicing. This is well below the overflow threshold, which is set by the user to a

value near the top of the FIFO (high watermark, 0x36 (216 bytes) default) and is below the number of bytes ser-

viced by the master per channel per round-robin servicing (120 bytes). Each customer's servicing characteristics

will depend on the master's behavior and how fast it performs the channel switching. If it cannot switch in the worst-

case, four-cycle manner described above, performance will degrade.

One item not accounted for in the above analysis is the fact that TDAT may place a dead cycle between packets (in

CRC and PPP modes, not in HDLC mode). In this case, there can be a maximum of three dead cycles per FIFO

(assuming 40-byte packets worst case and 102 bytes in FIFO between round-robin cycle). This will be taken up by

the slack provided above, where (102 bytes + 4 bytes/dead cycle x 3 dead cycles) = 114 bytes, which still falls

below the servicing rate of 120 bytes per round-robin servicing.

20

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

UTOPIA (UT)

(continued)

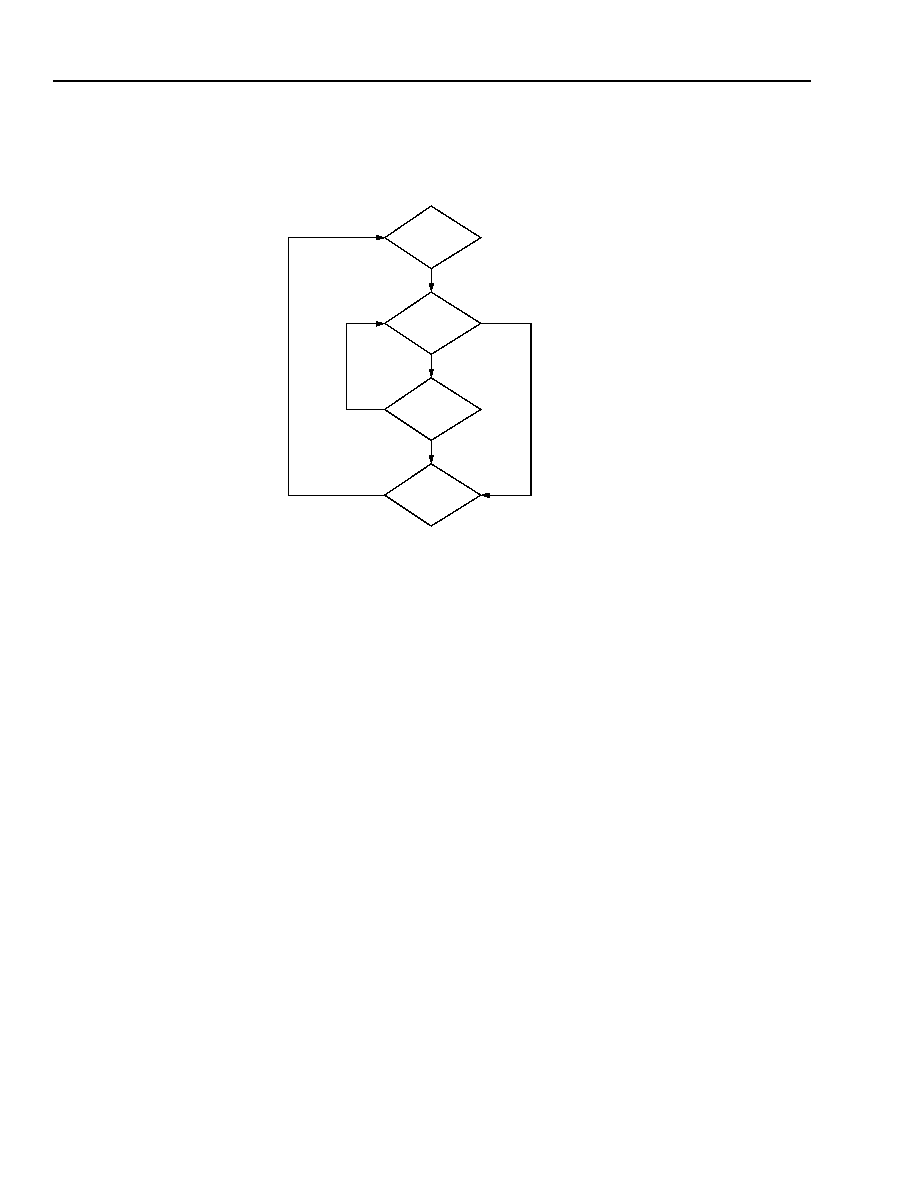

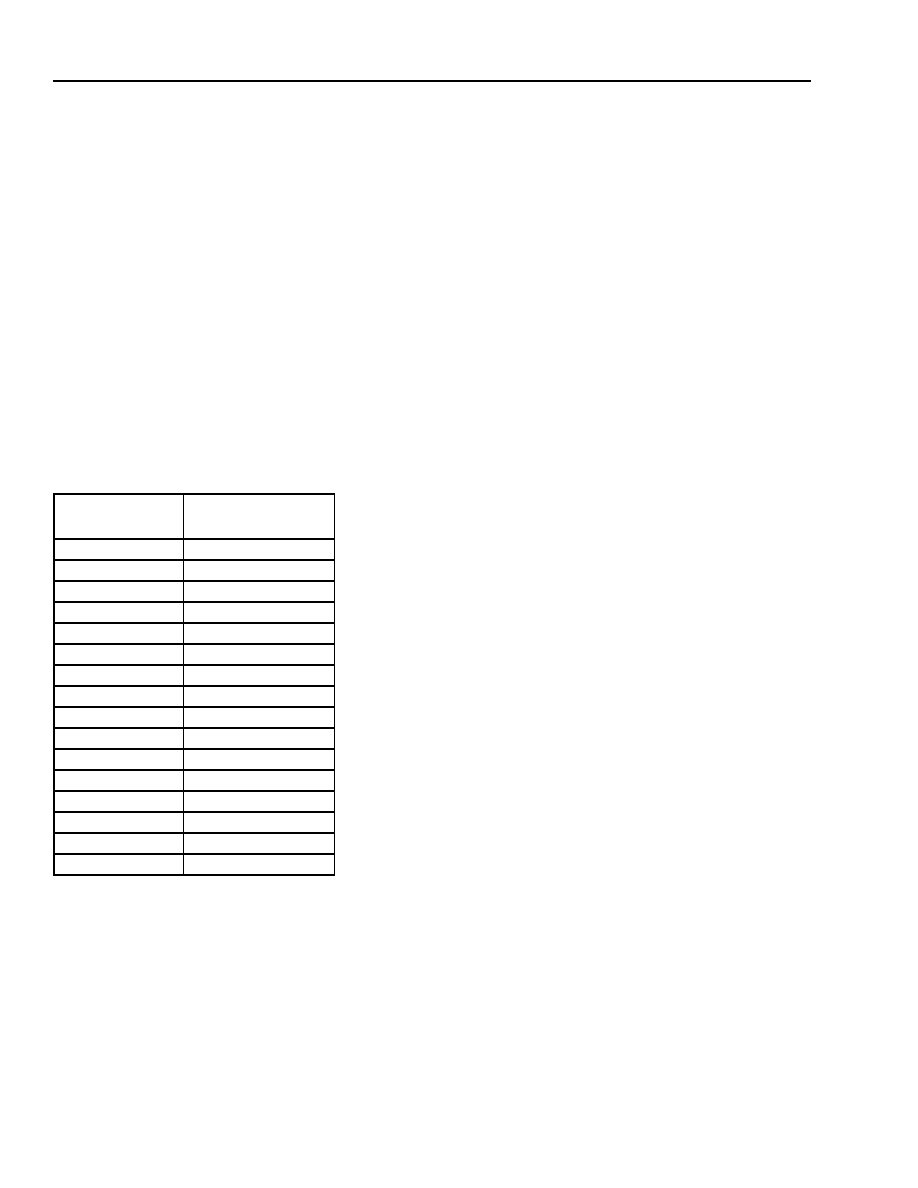

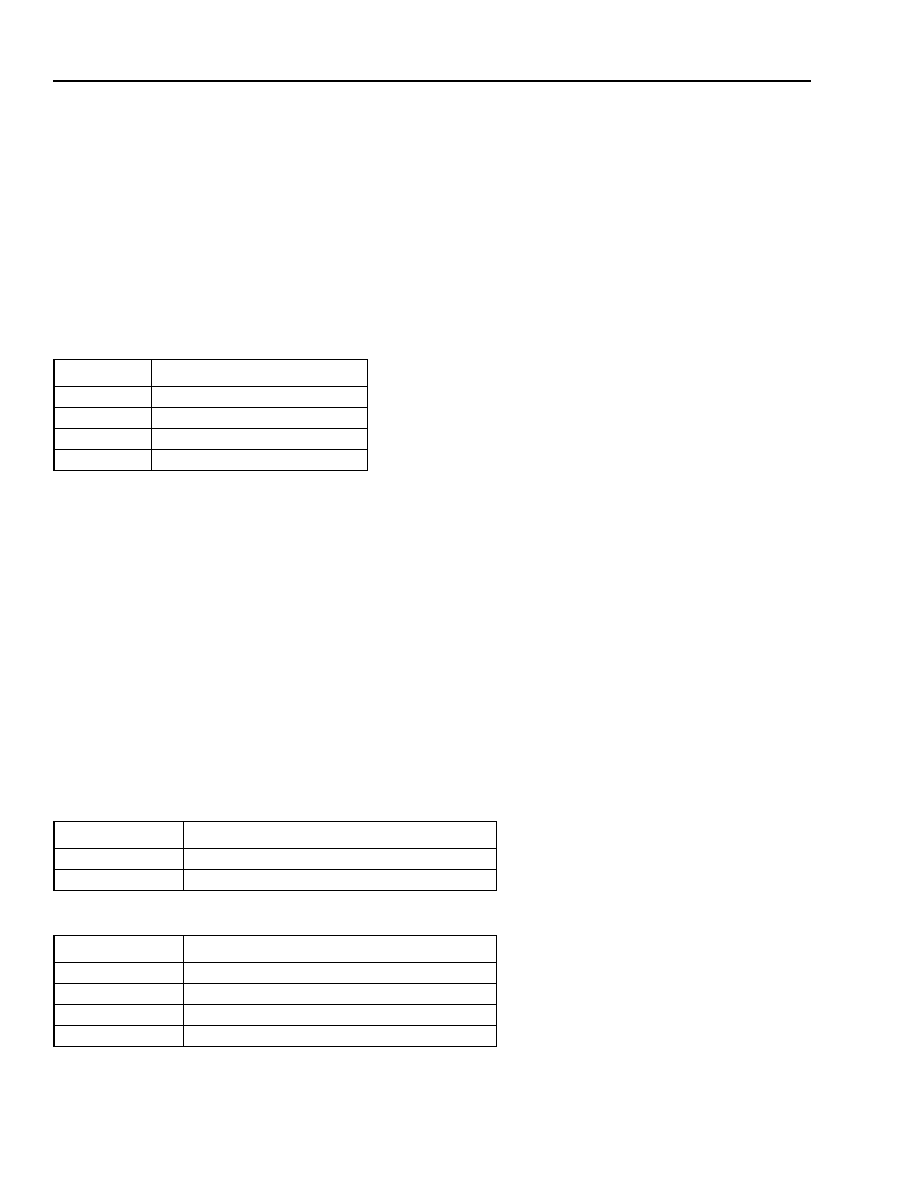

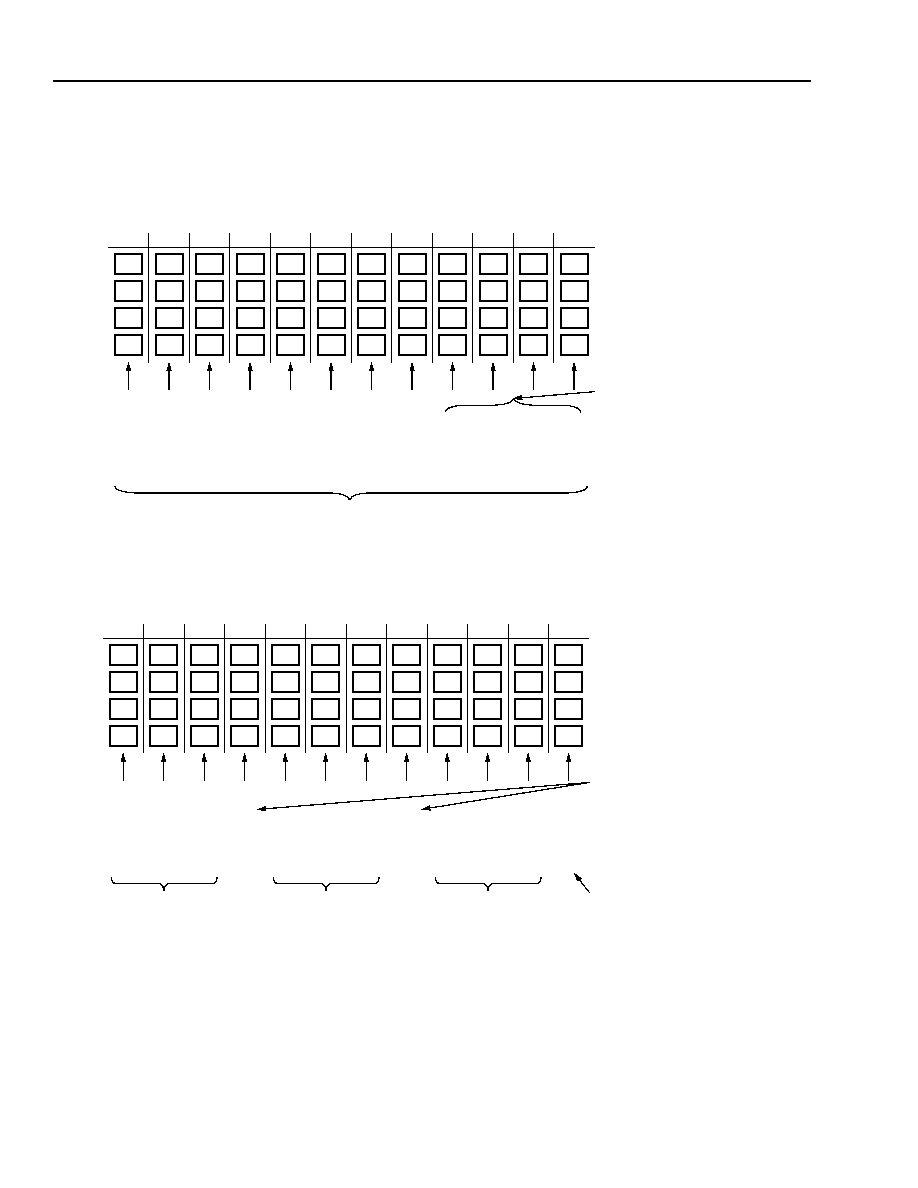

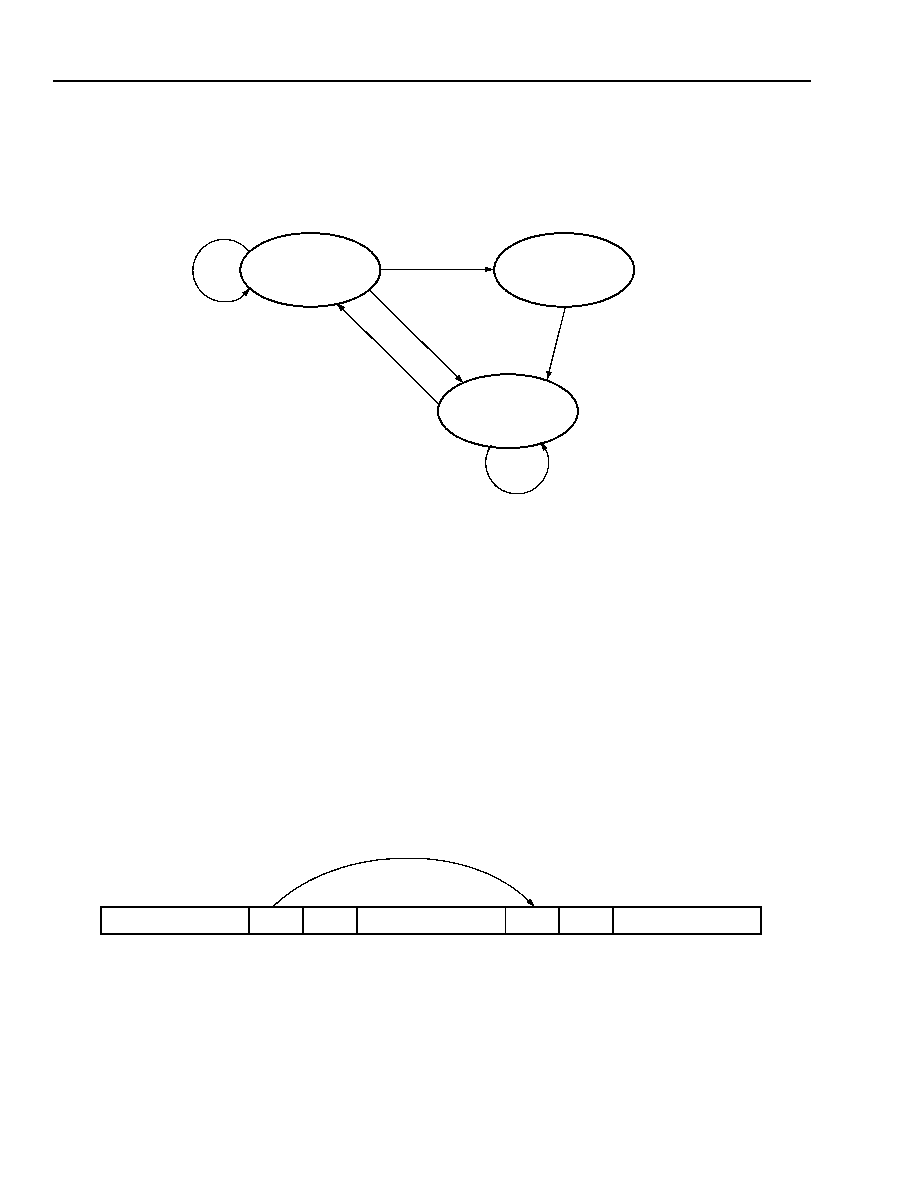

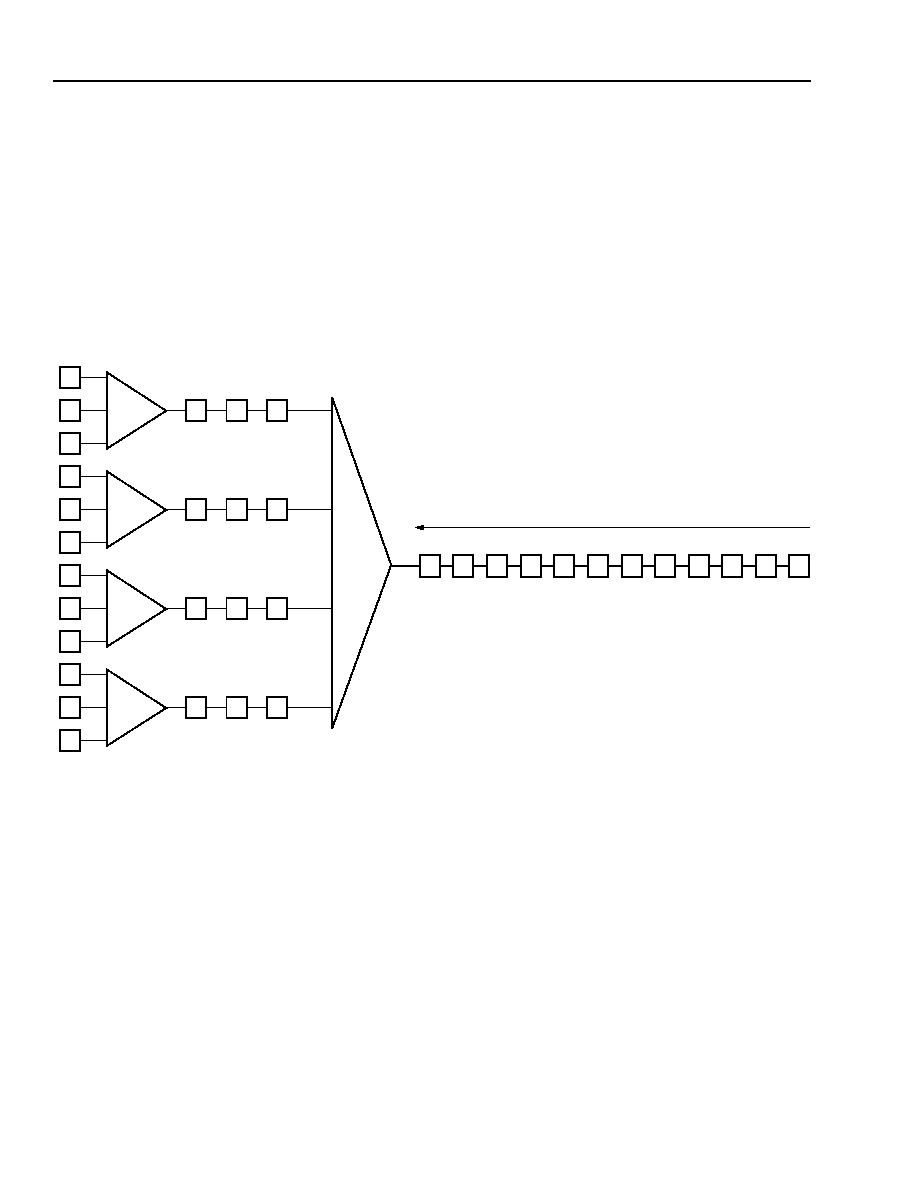

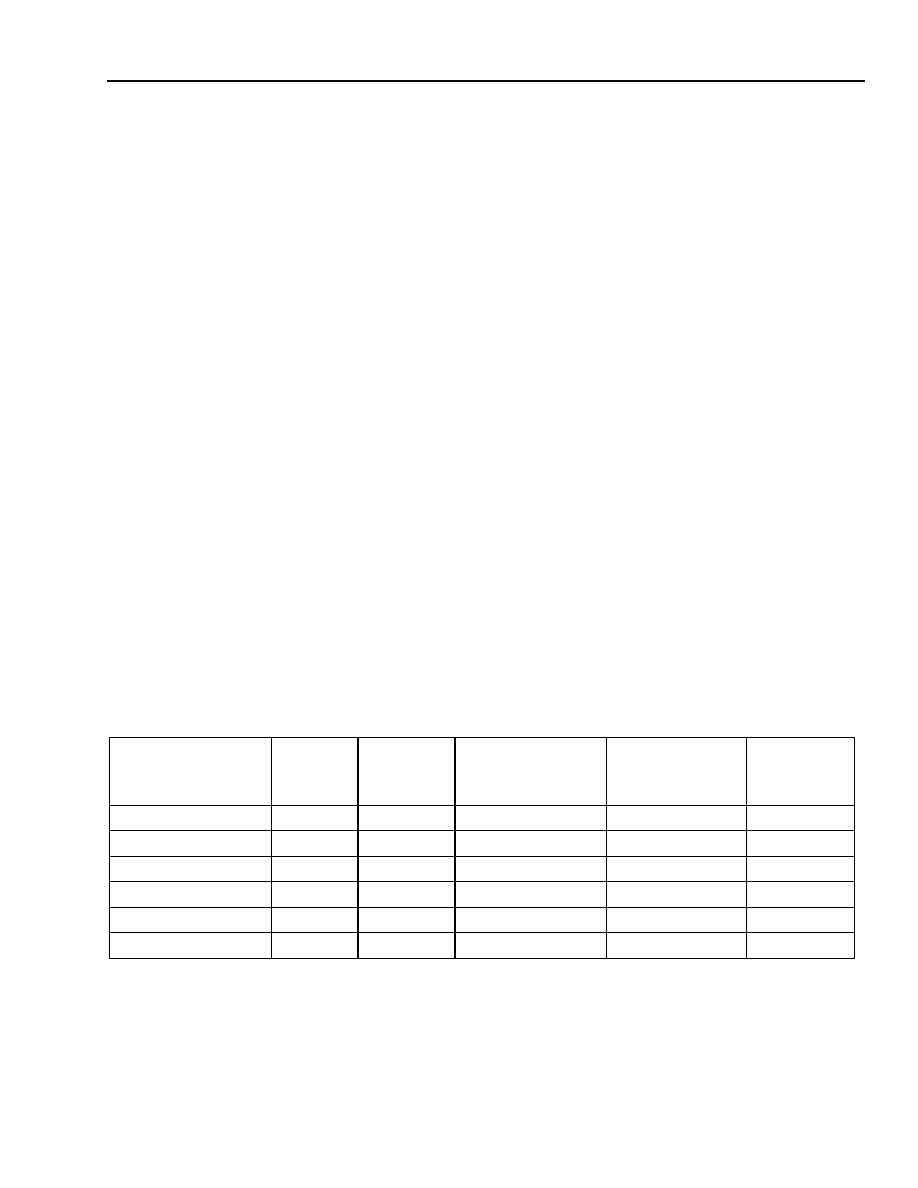

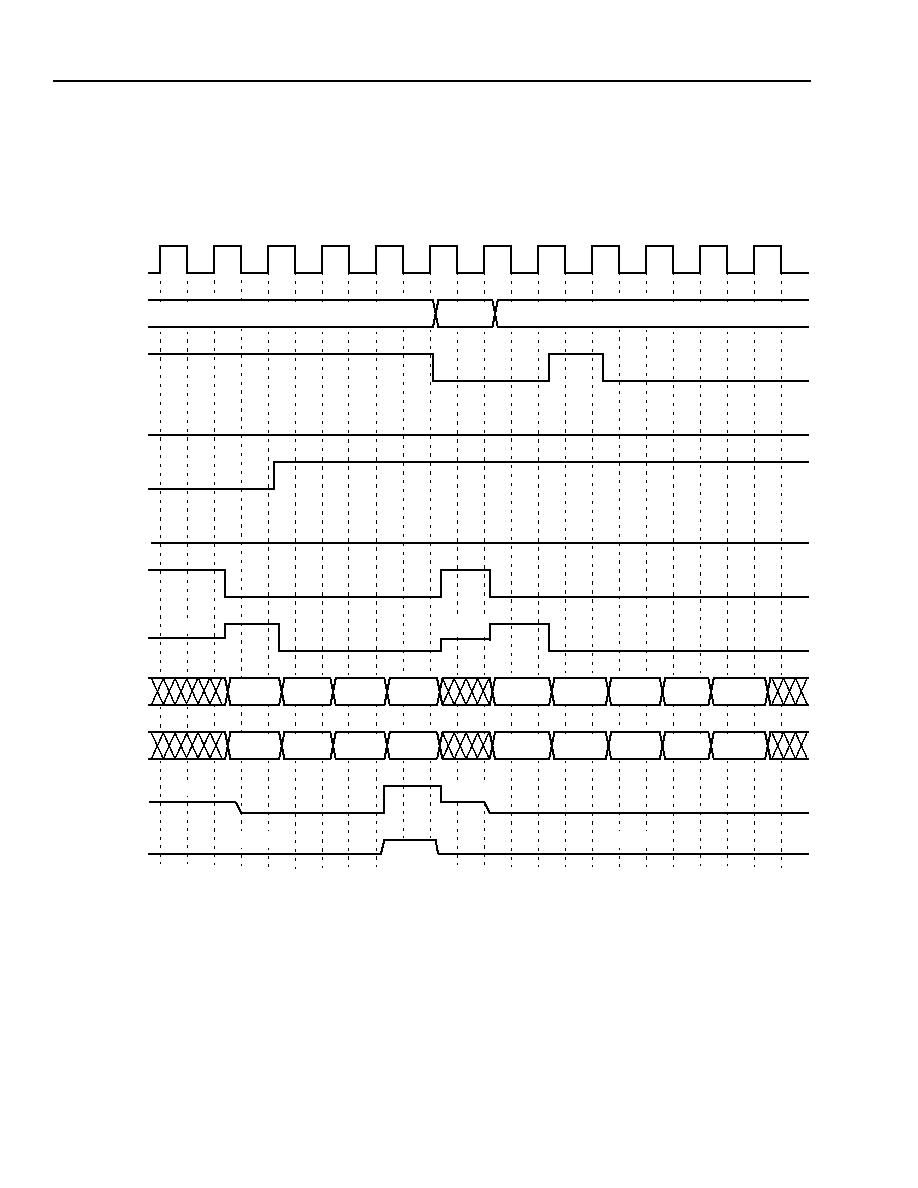

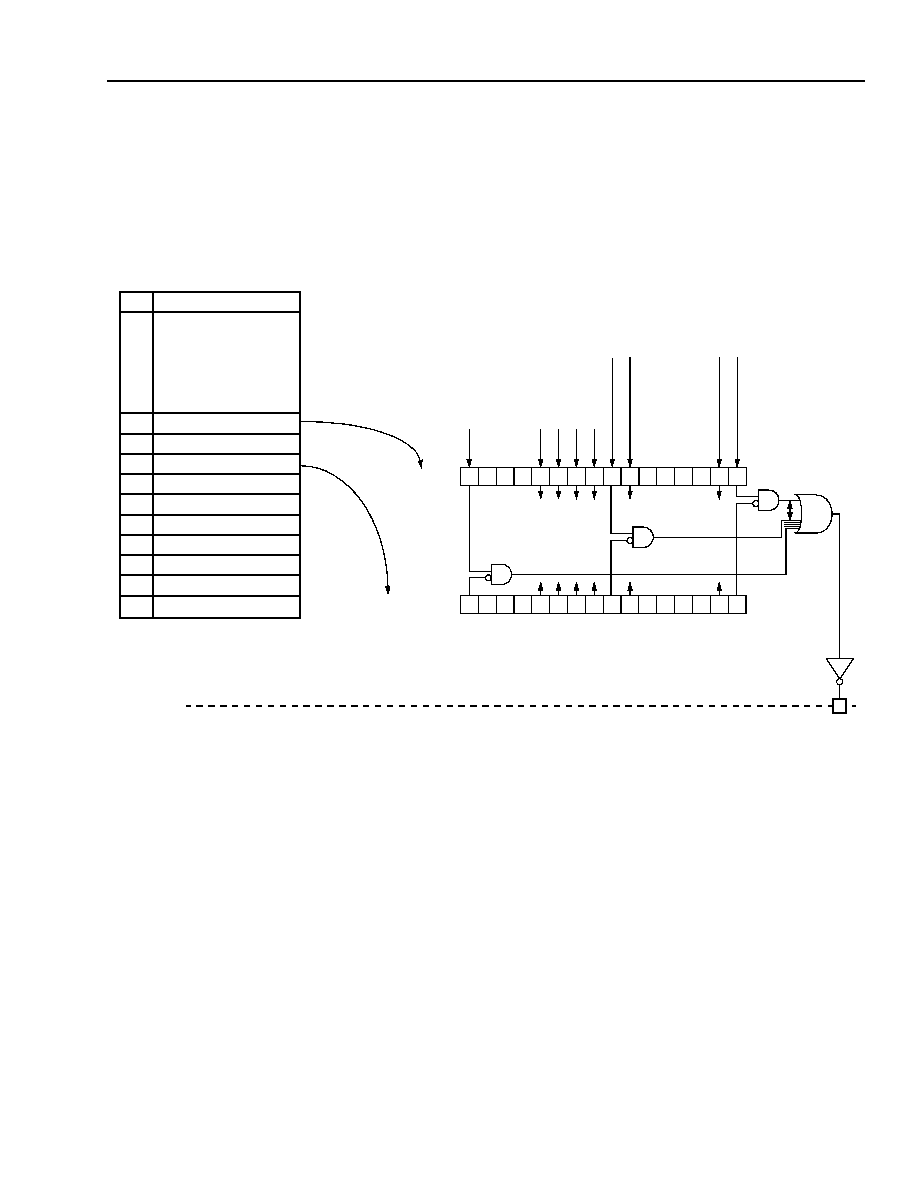

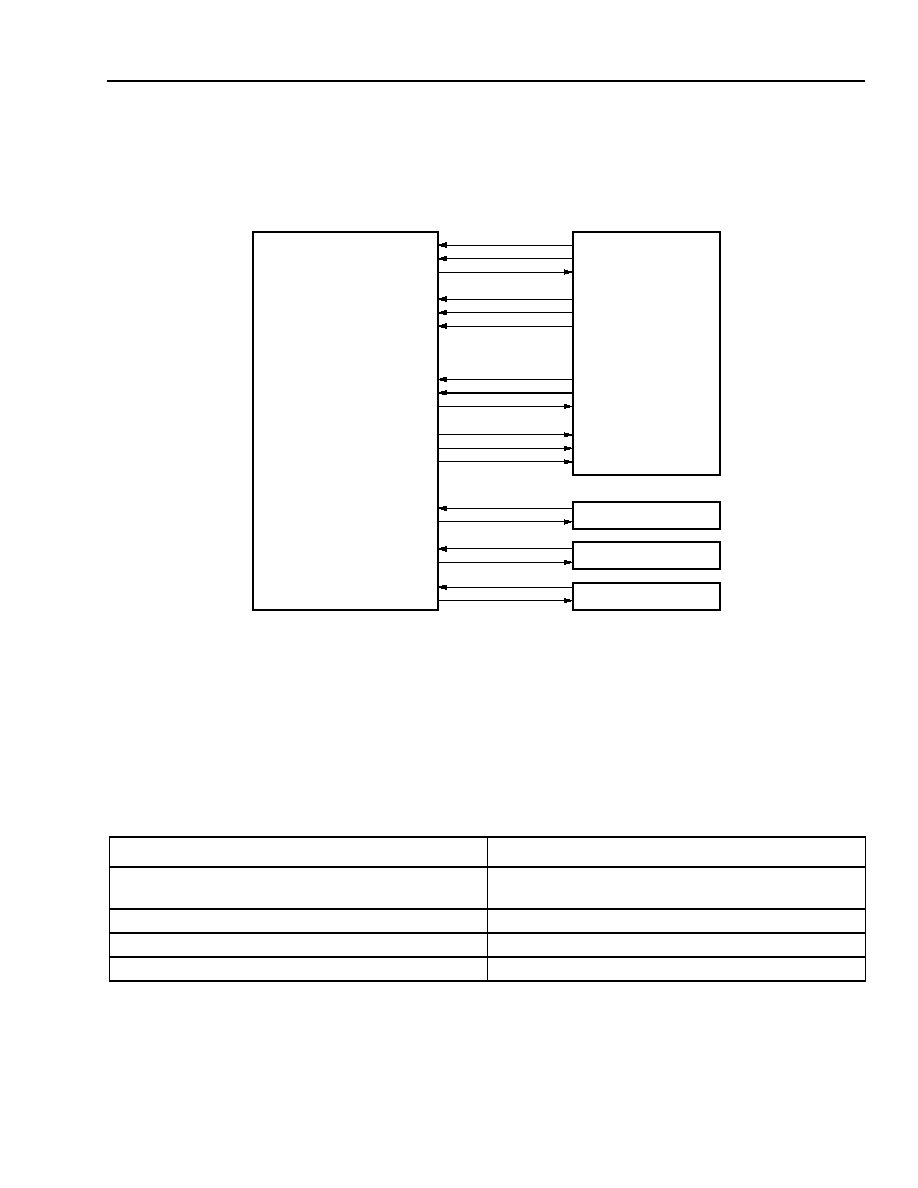

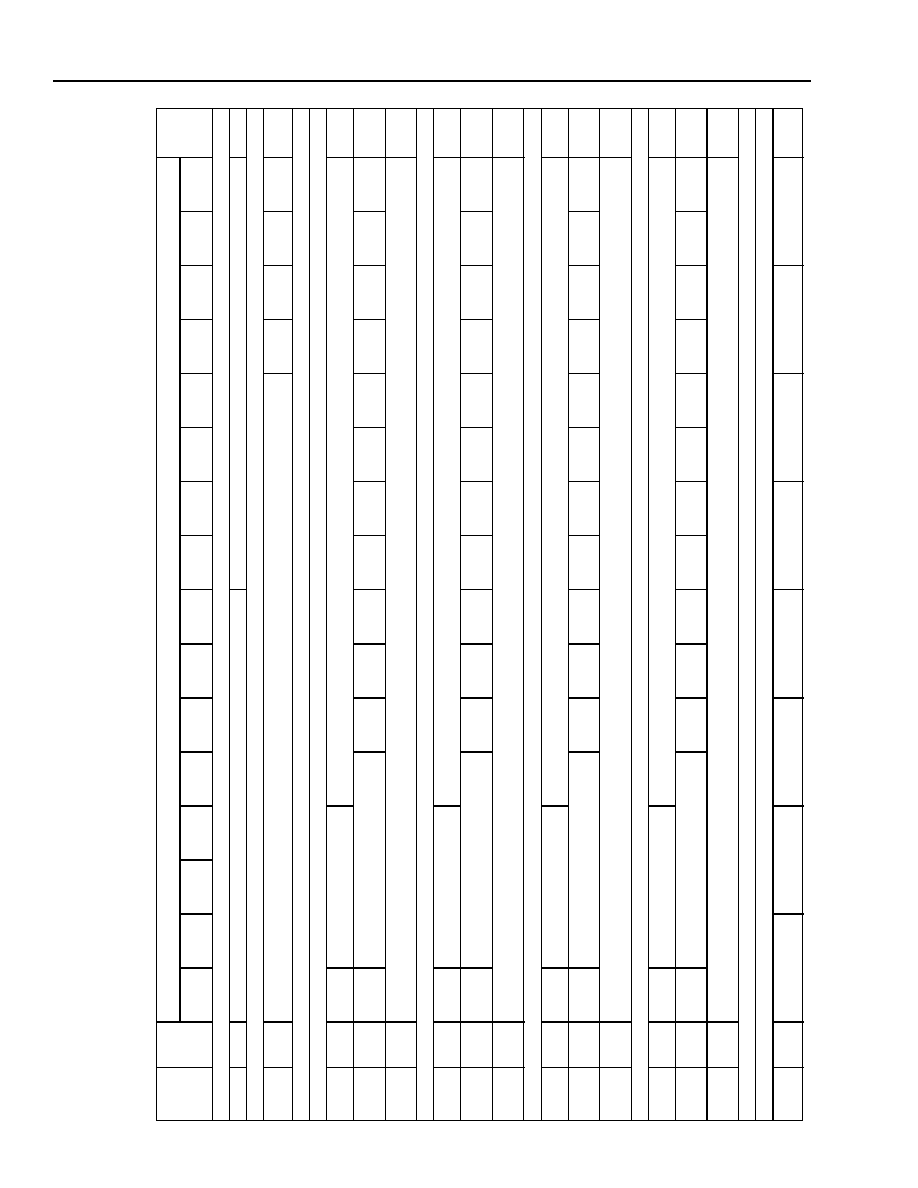

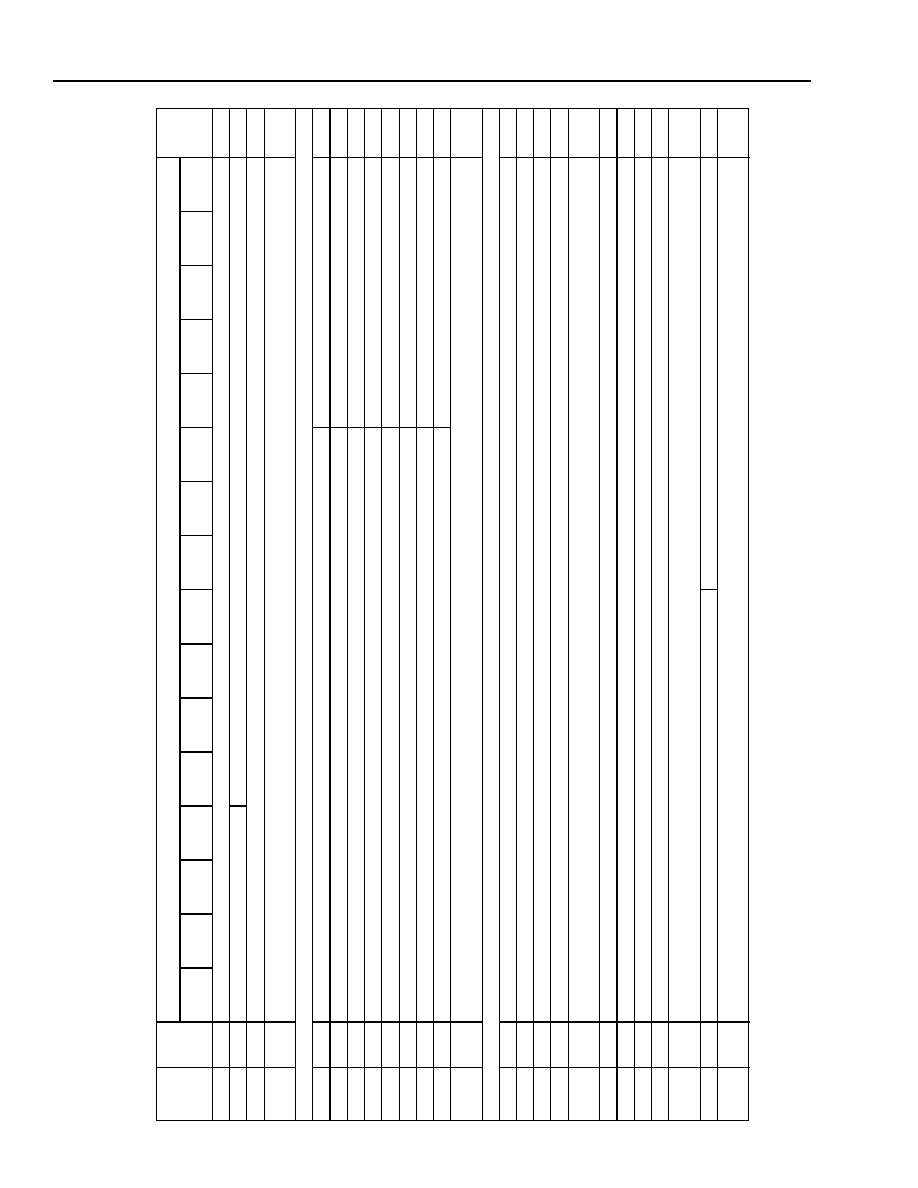

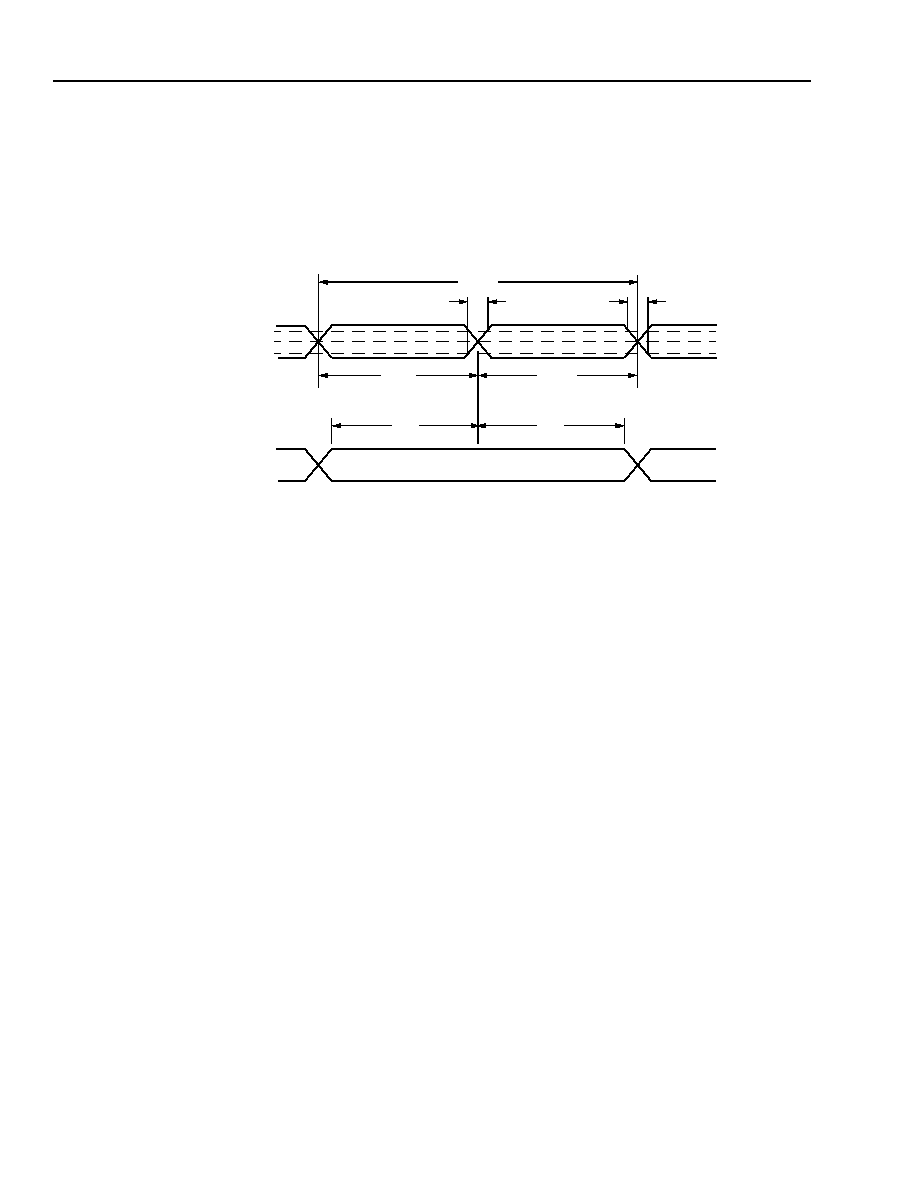

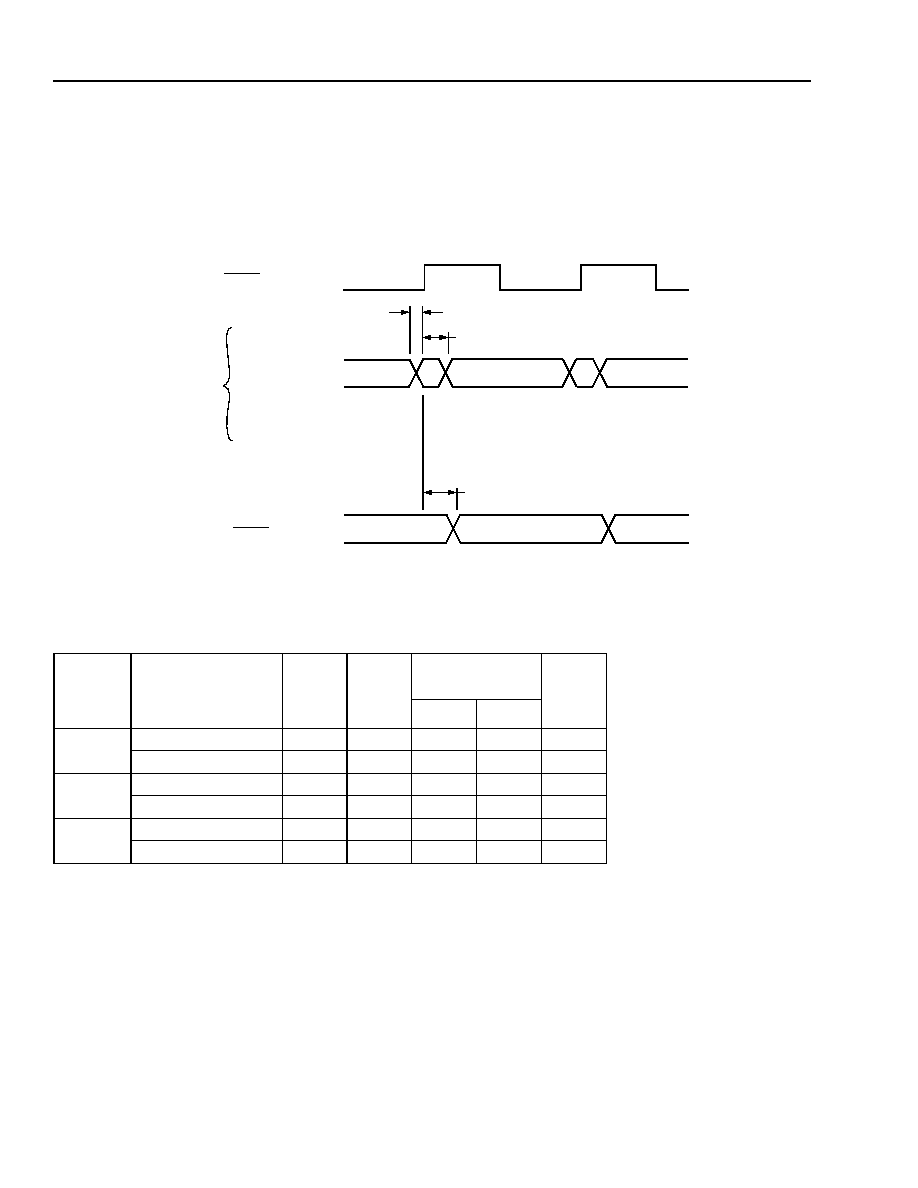

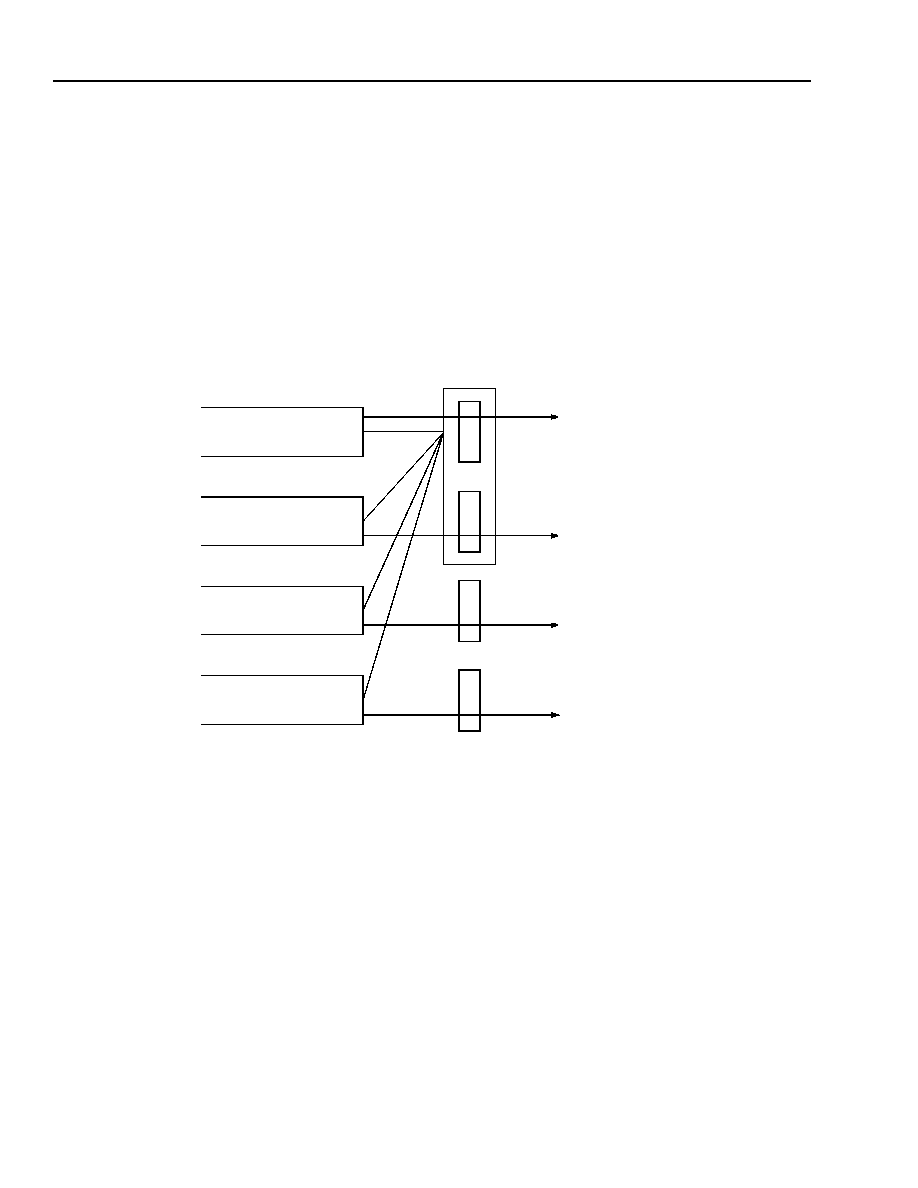

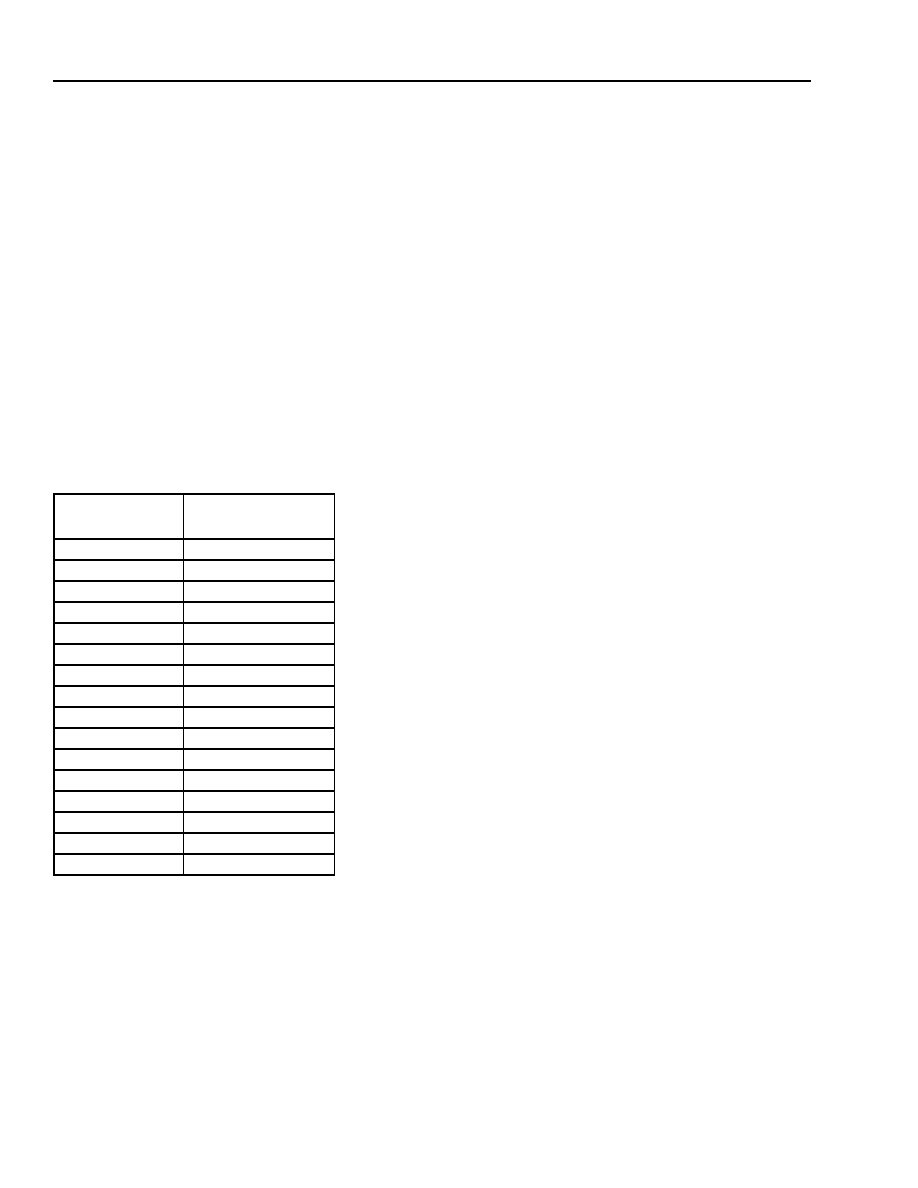

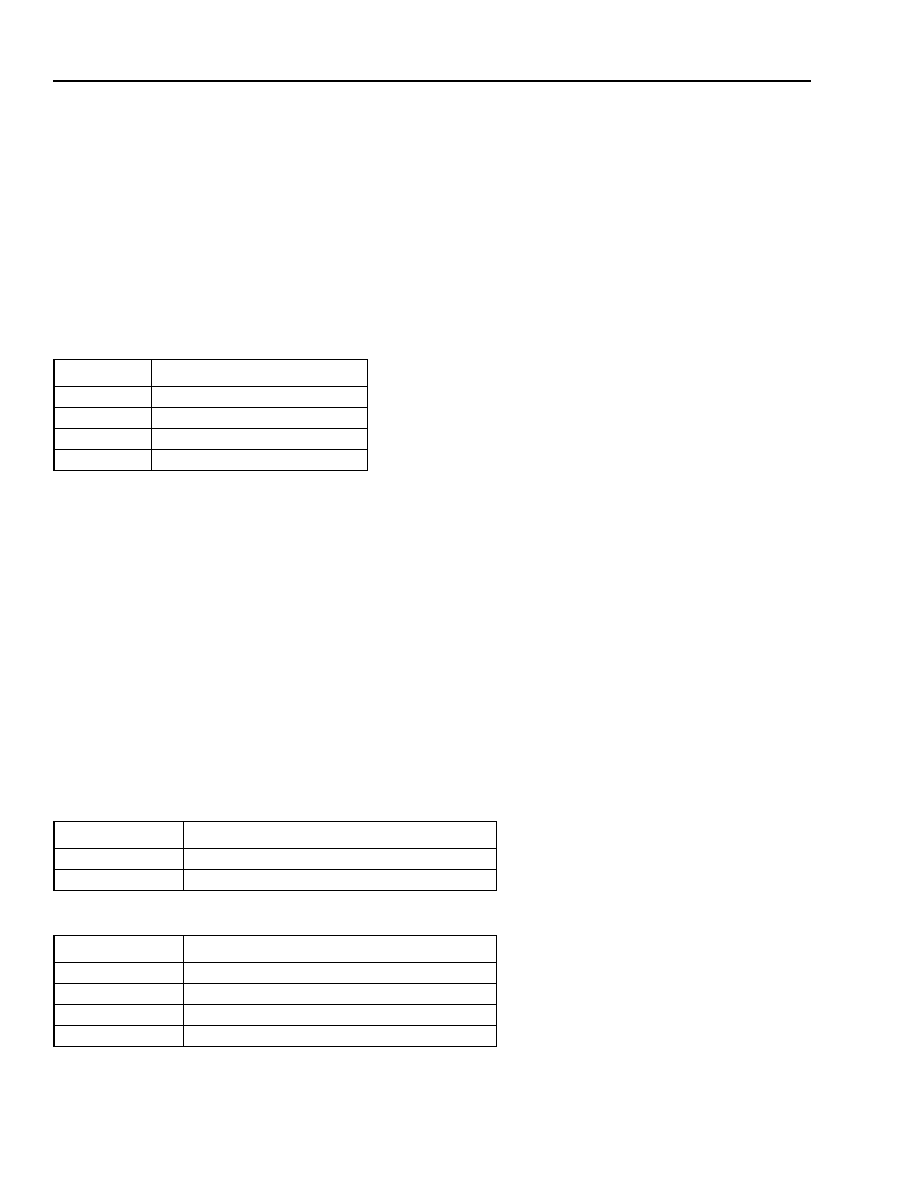

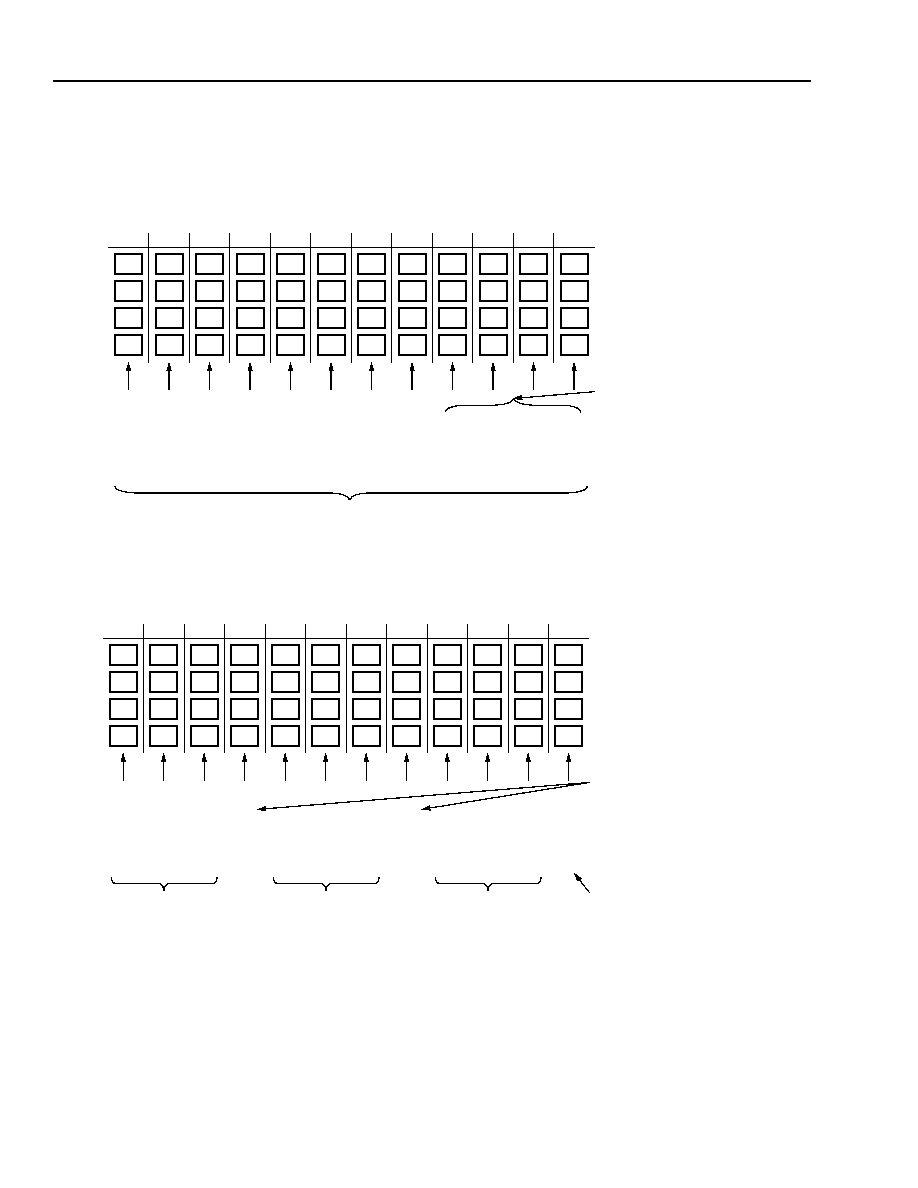

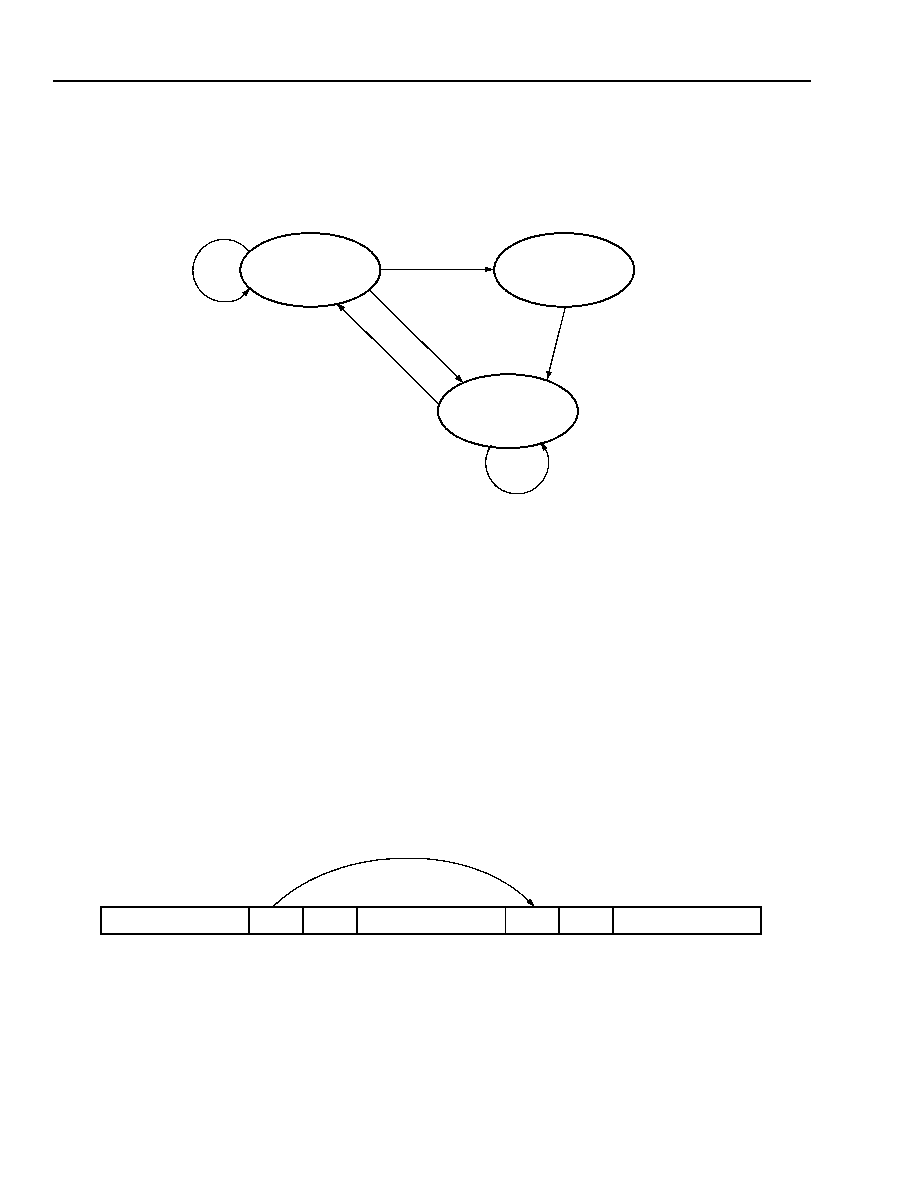

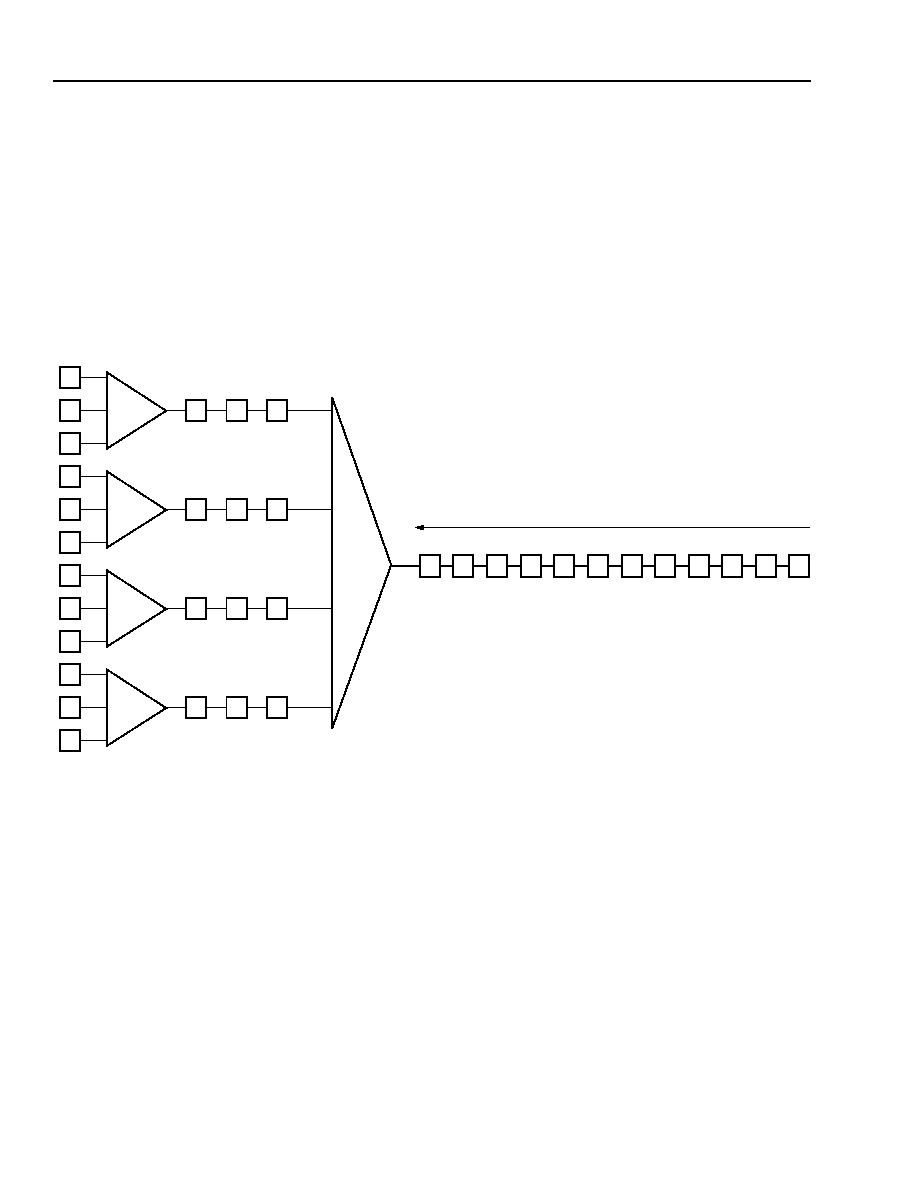

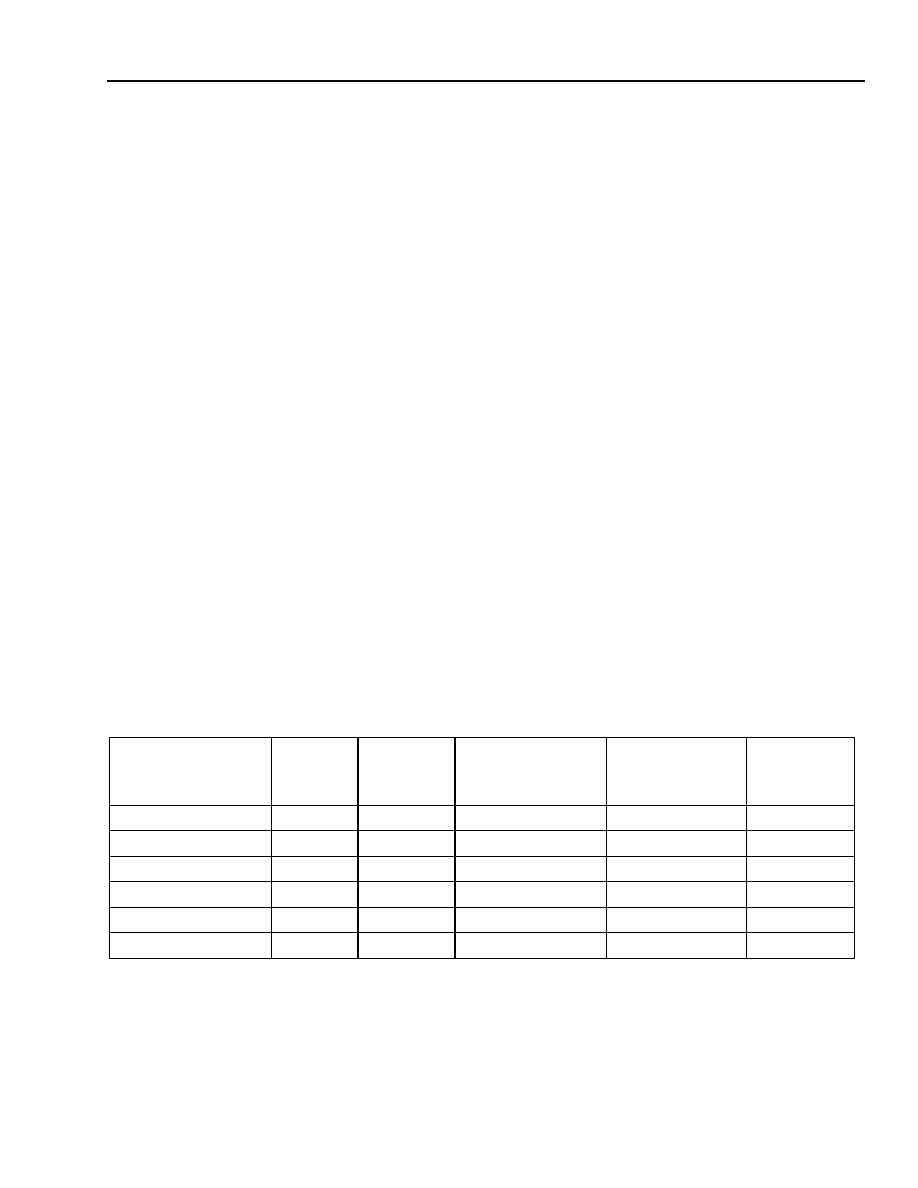

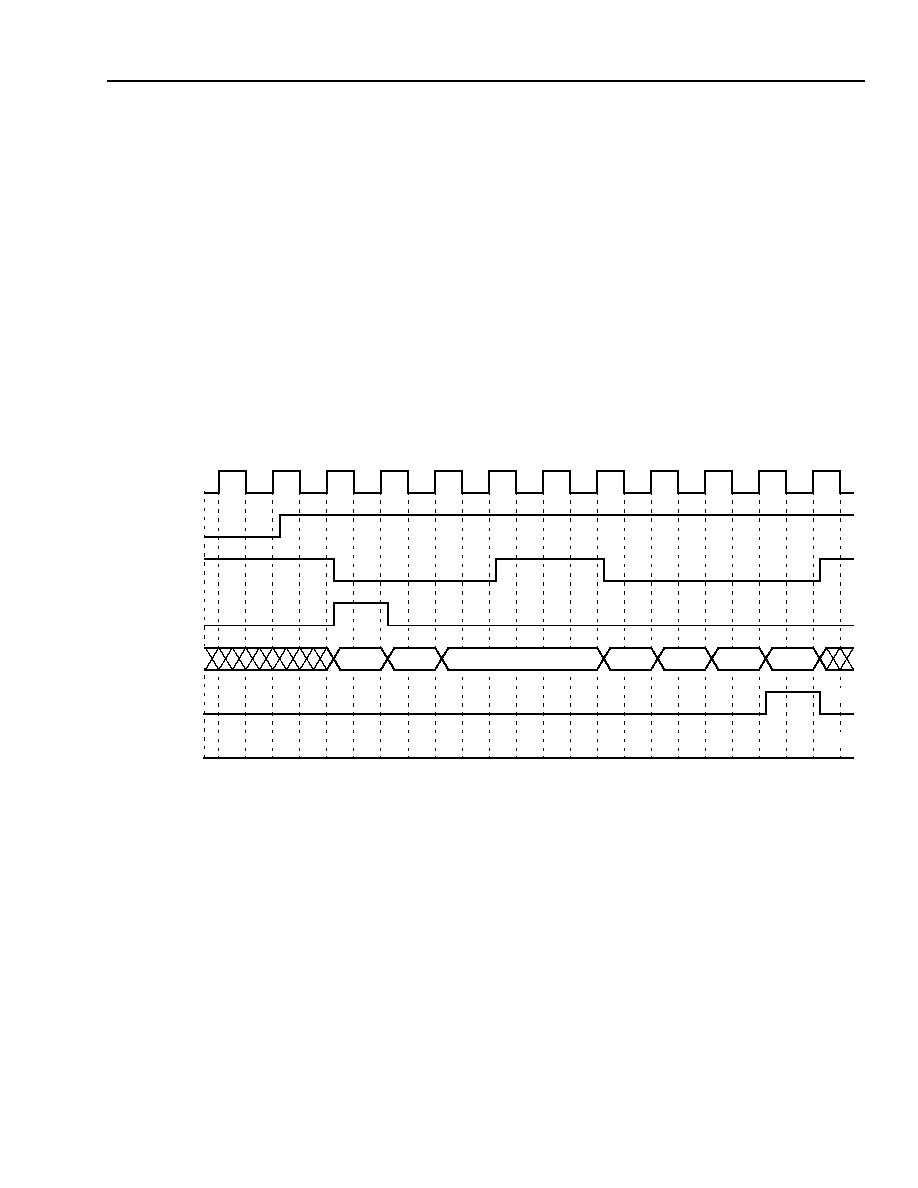

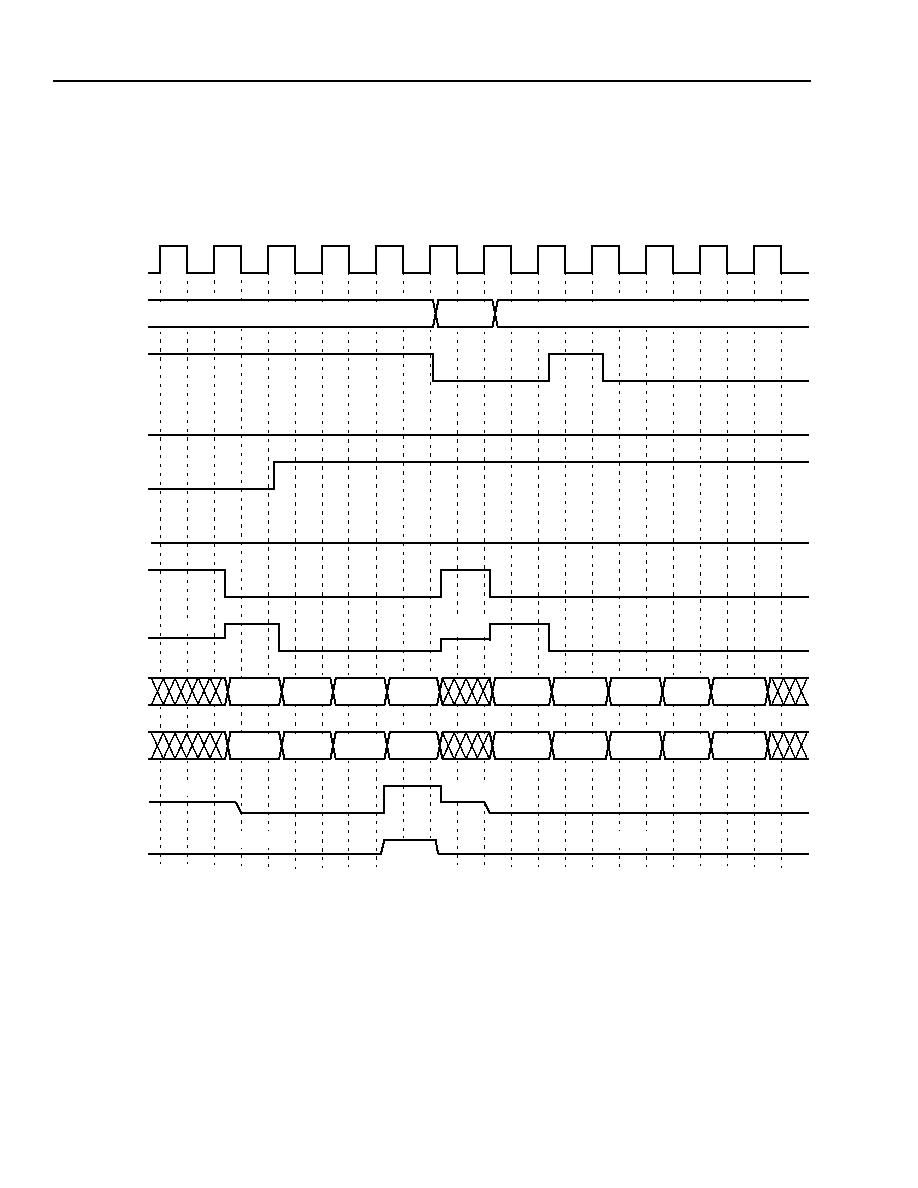

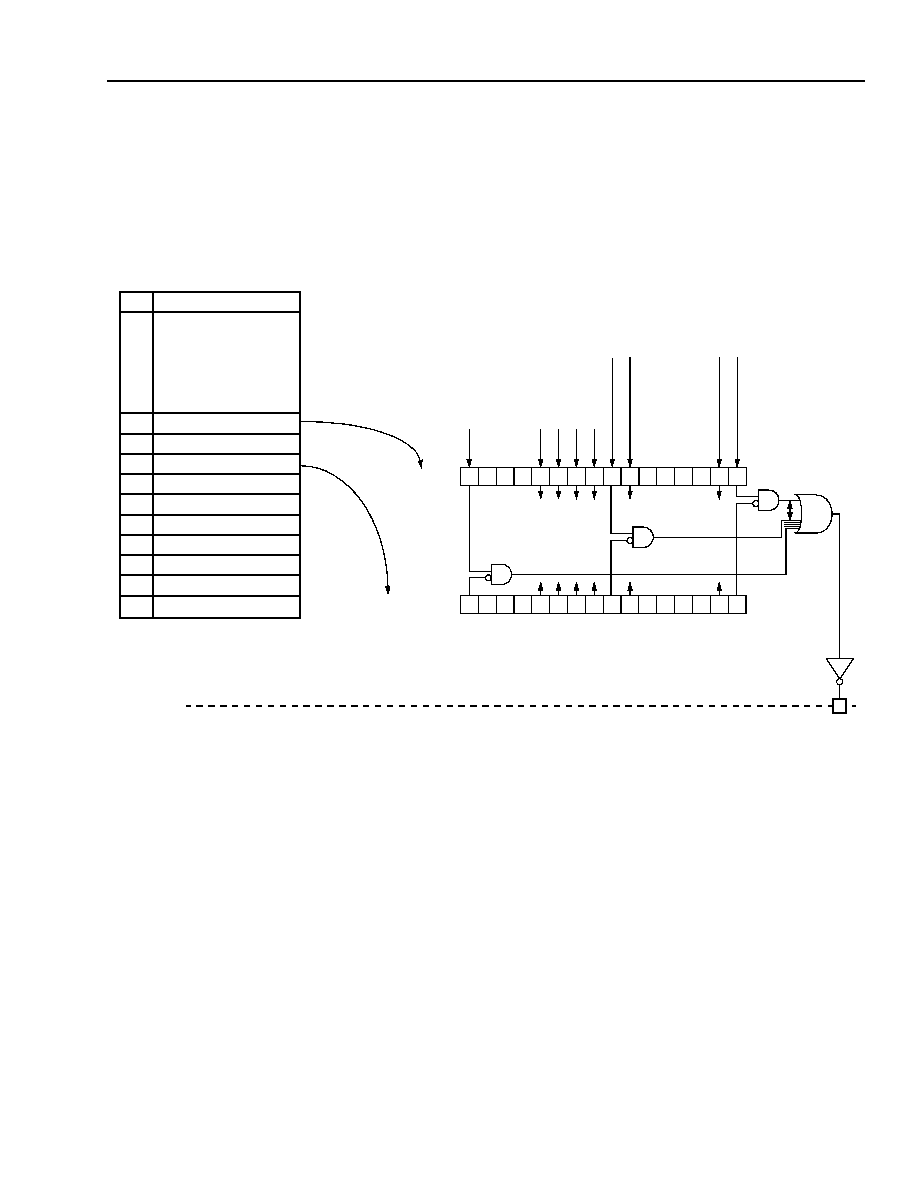

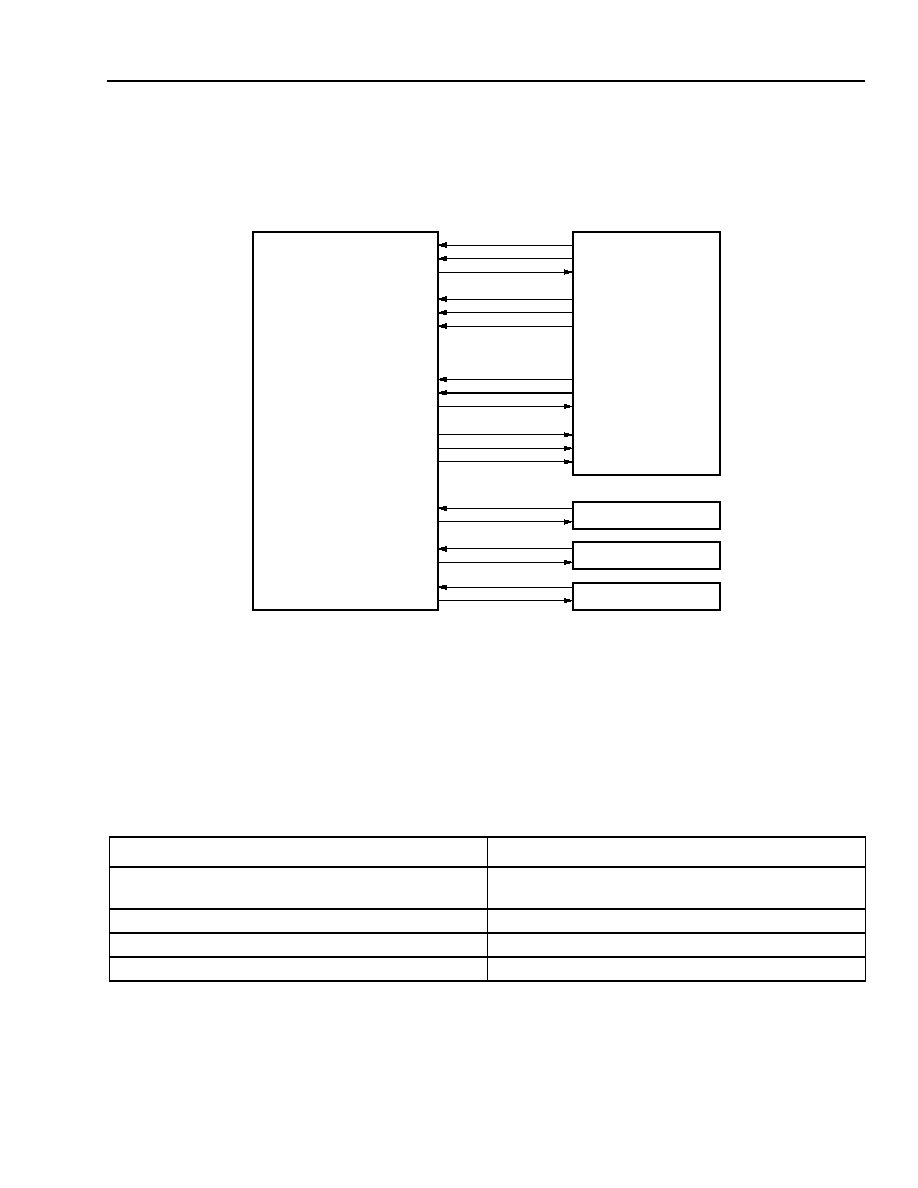

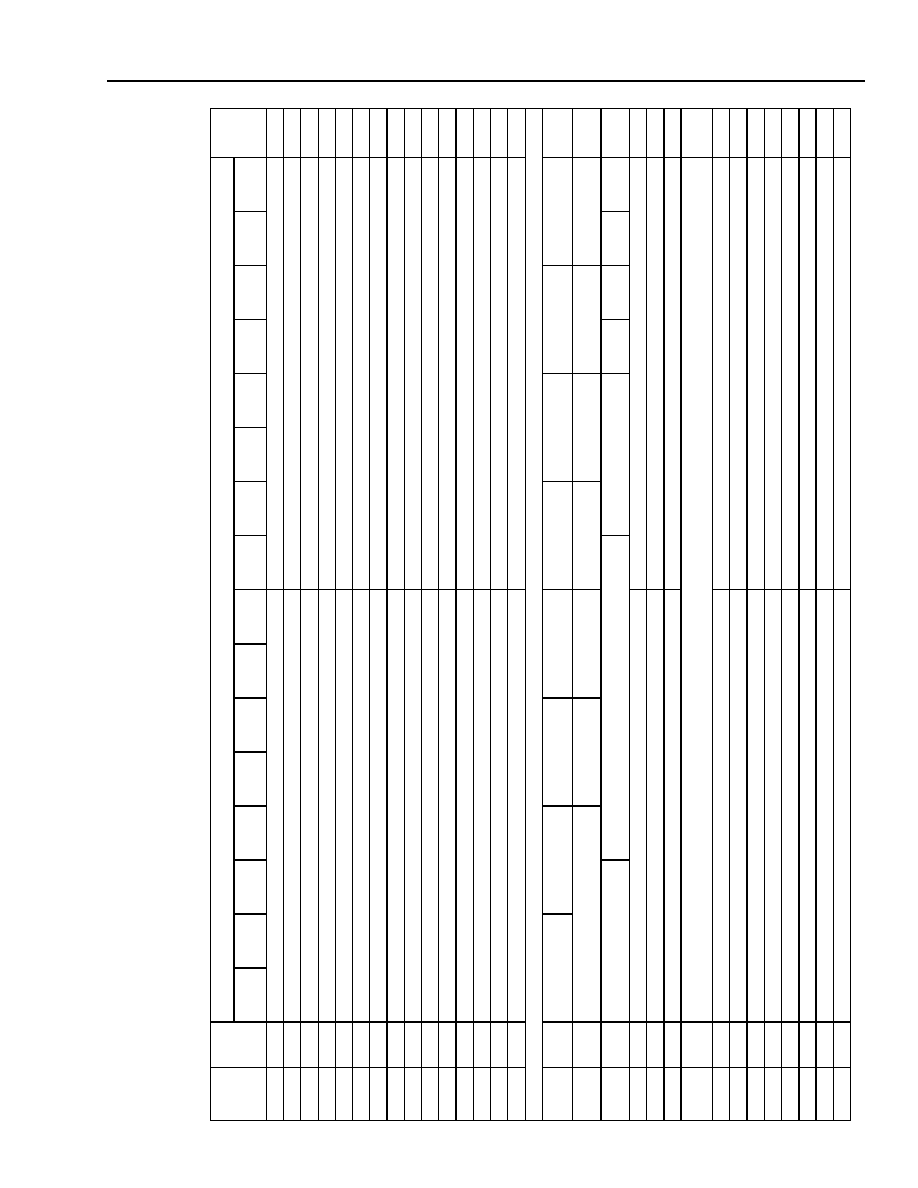

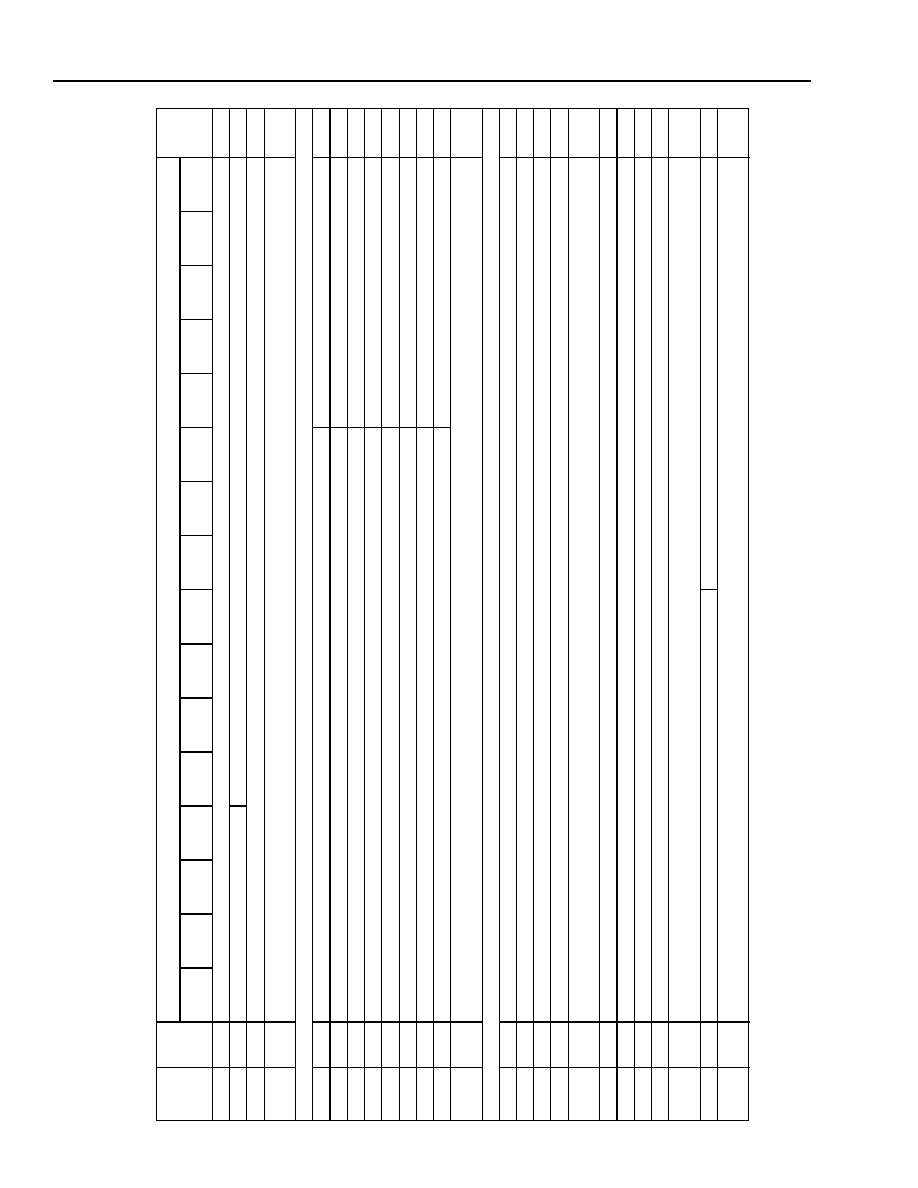

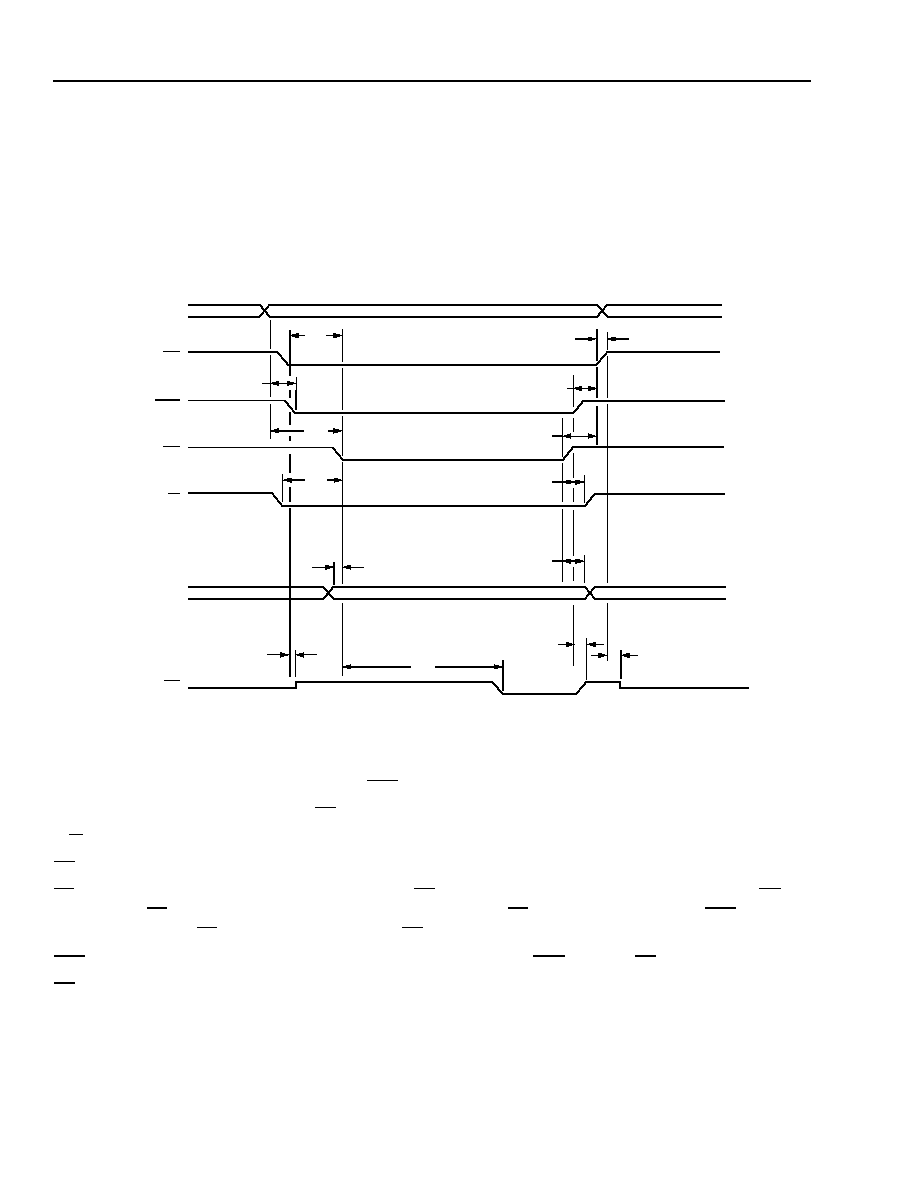

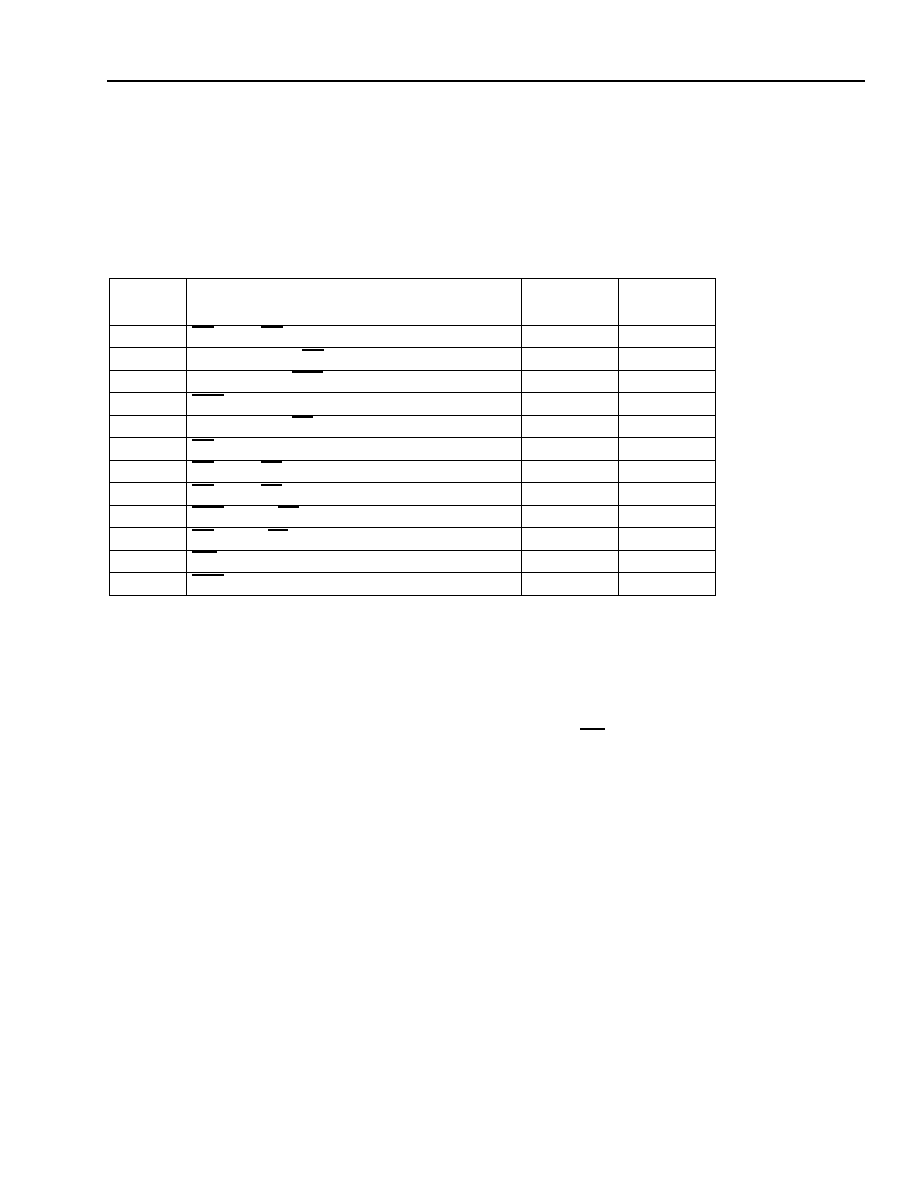

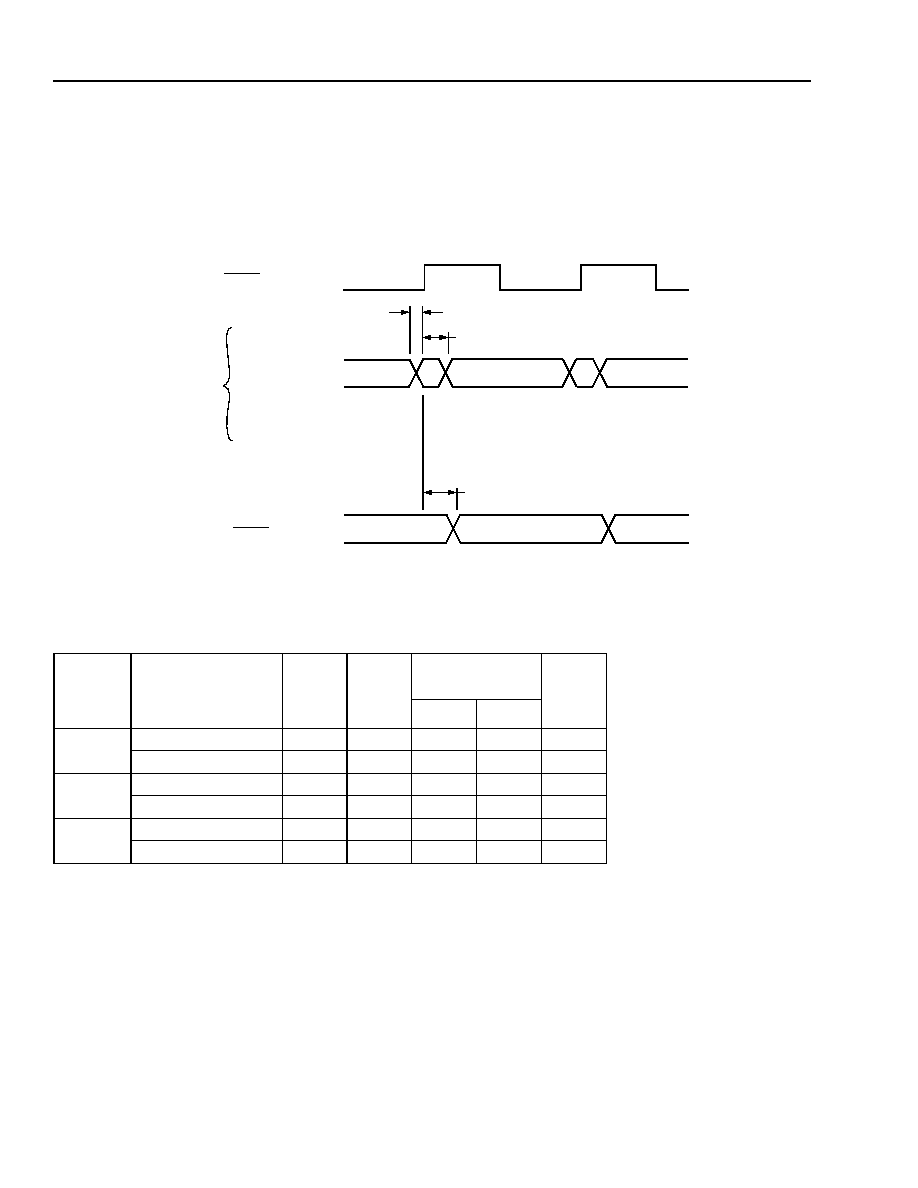

The logical flow of the above procedure is shown in Figure 2 below:

1665 (F)

Figure 2. Master Control Flow Chart

Select channel

If PA = 1 continue

If count = 30 words, then deactivate RxENB and switch to new channel

Else continue with current channel

Else deactivate RxENB and switch to next channel

Return to selection of new channel

Corrective Action

This is condition will be addressed in the future version of the device.

SELECT NEXT

PA = 1

CHANNEL

COUNT

<

30

DEACTIVATE

R

X

ENB

YES

NO

YES

HOLD ADDRESS OF SELECTED

CHANNEL ON ADDRESS BUS

NO

Agere Systems Inc.

21

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Overhead Processor (OHP)

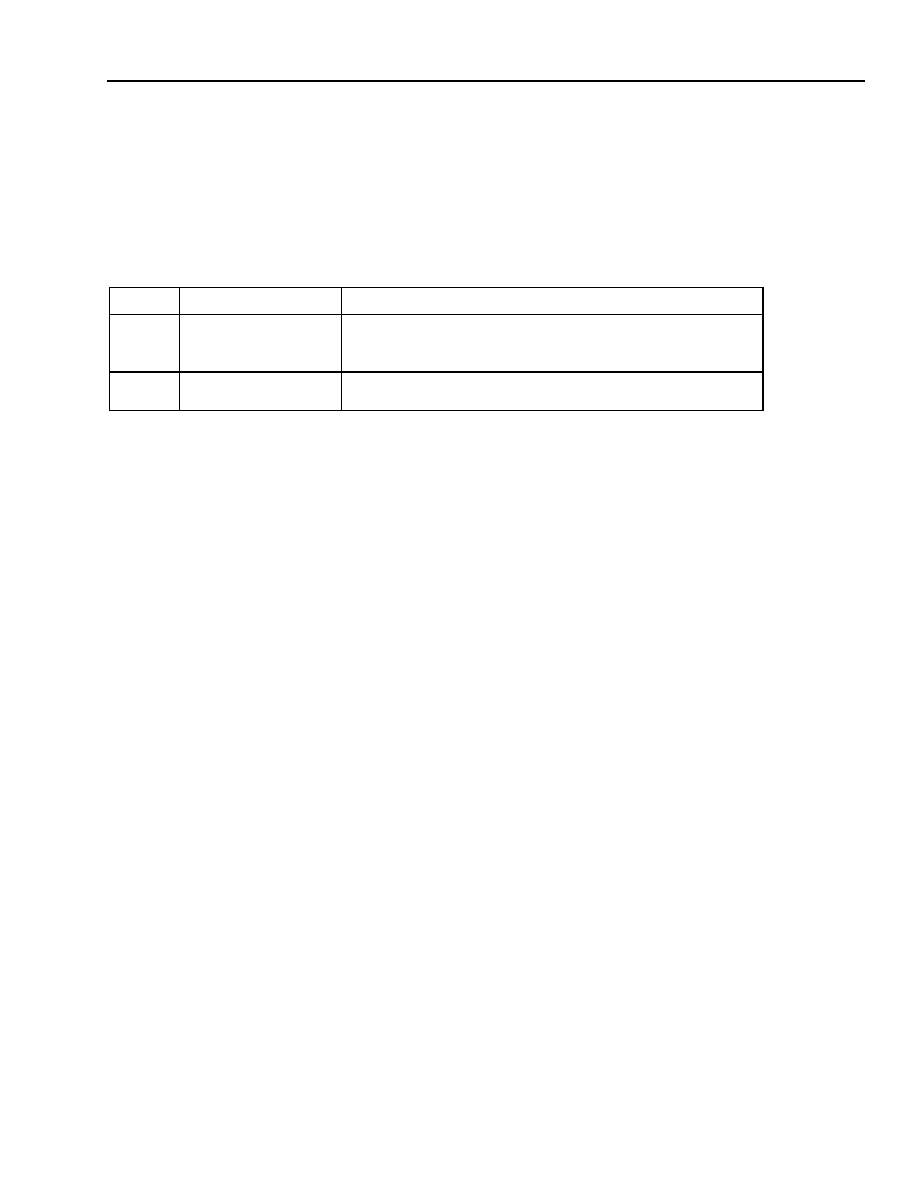

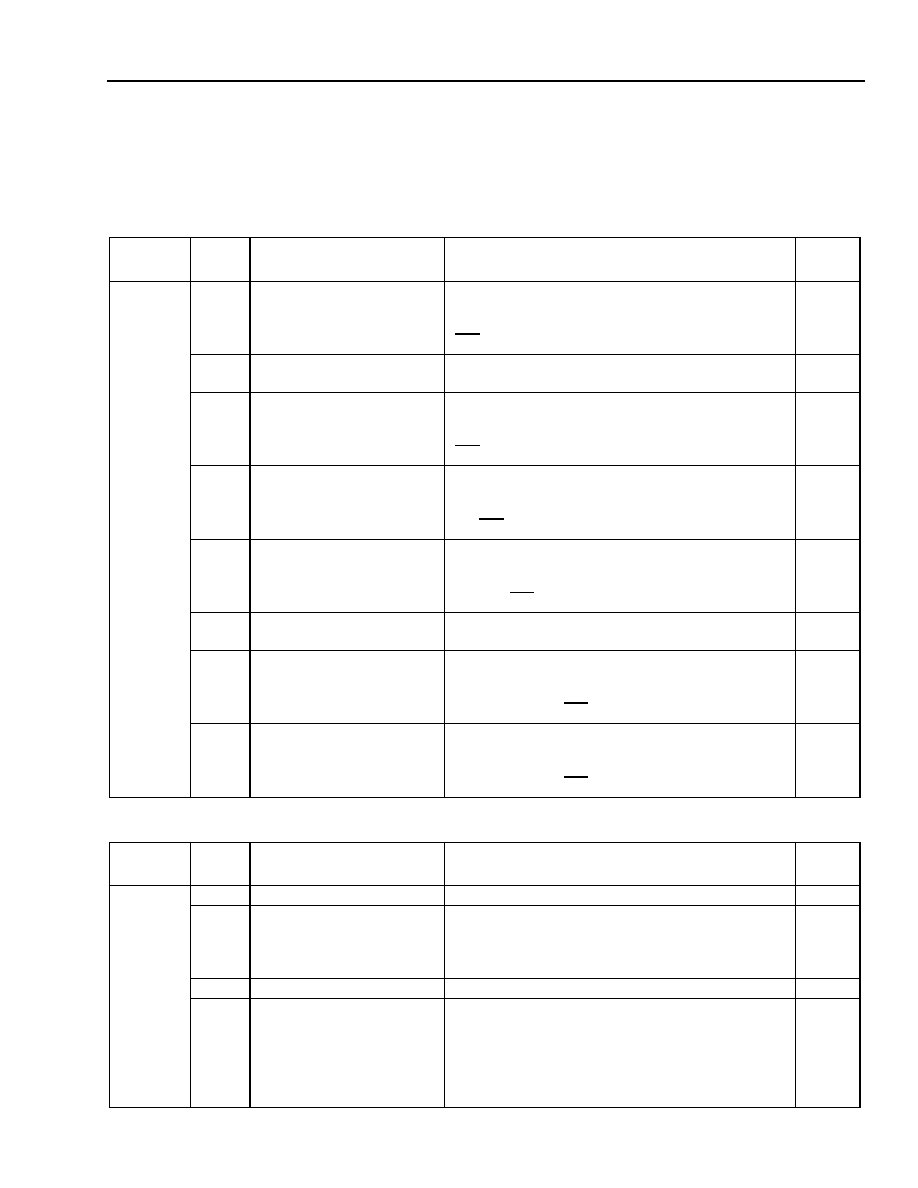

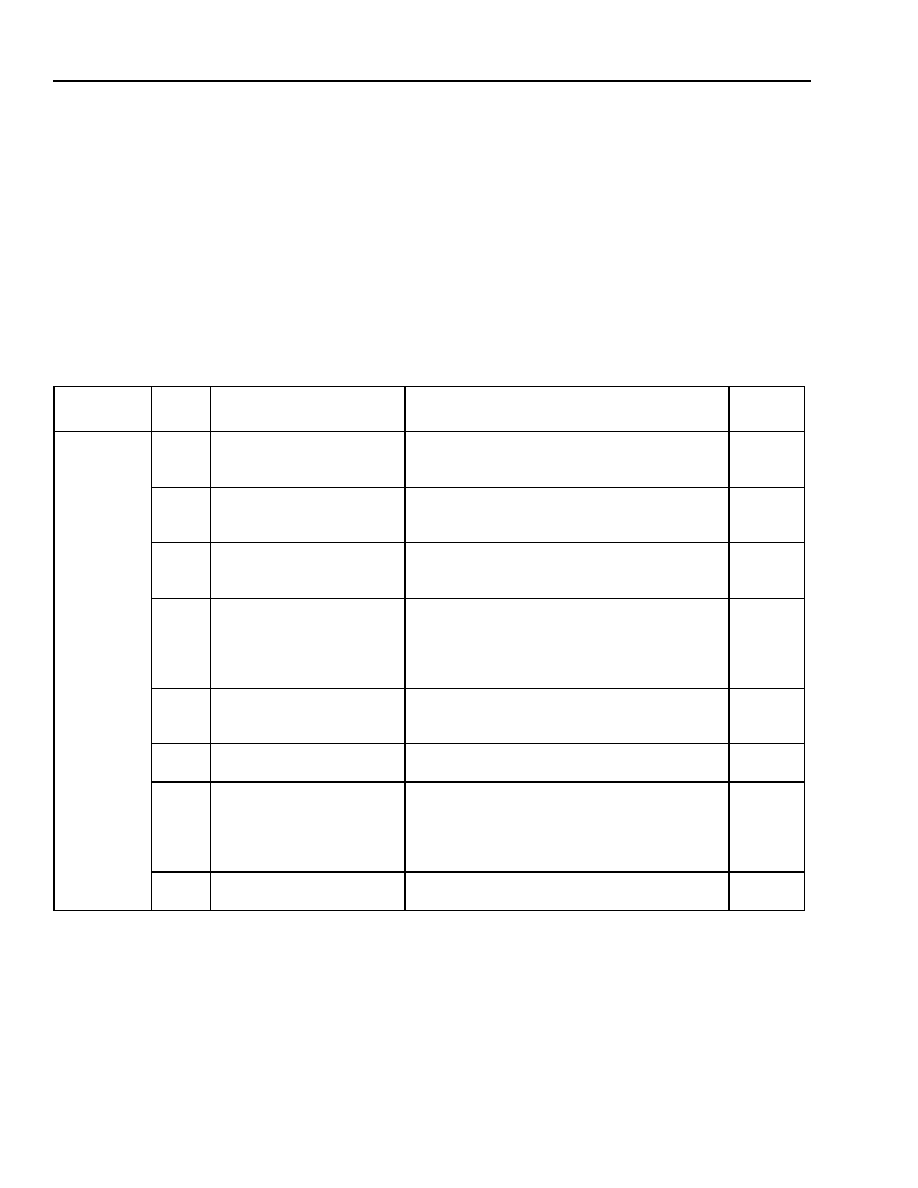

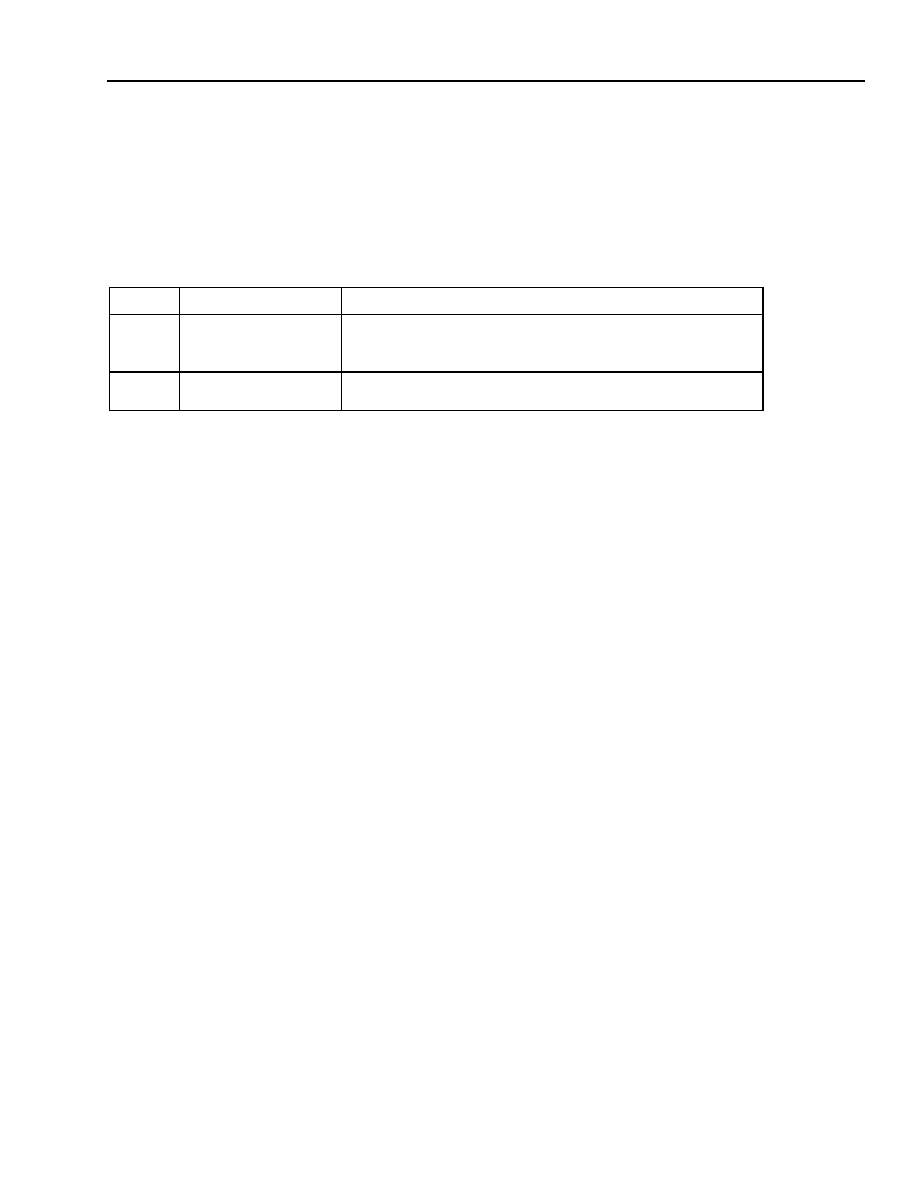

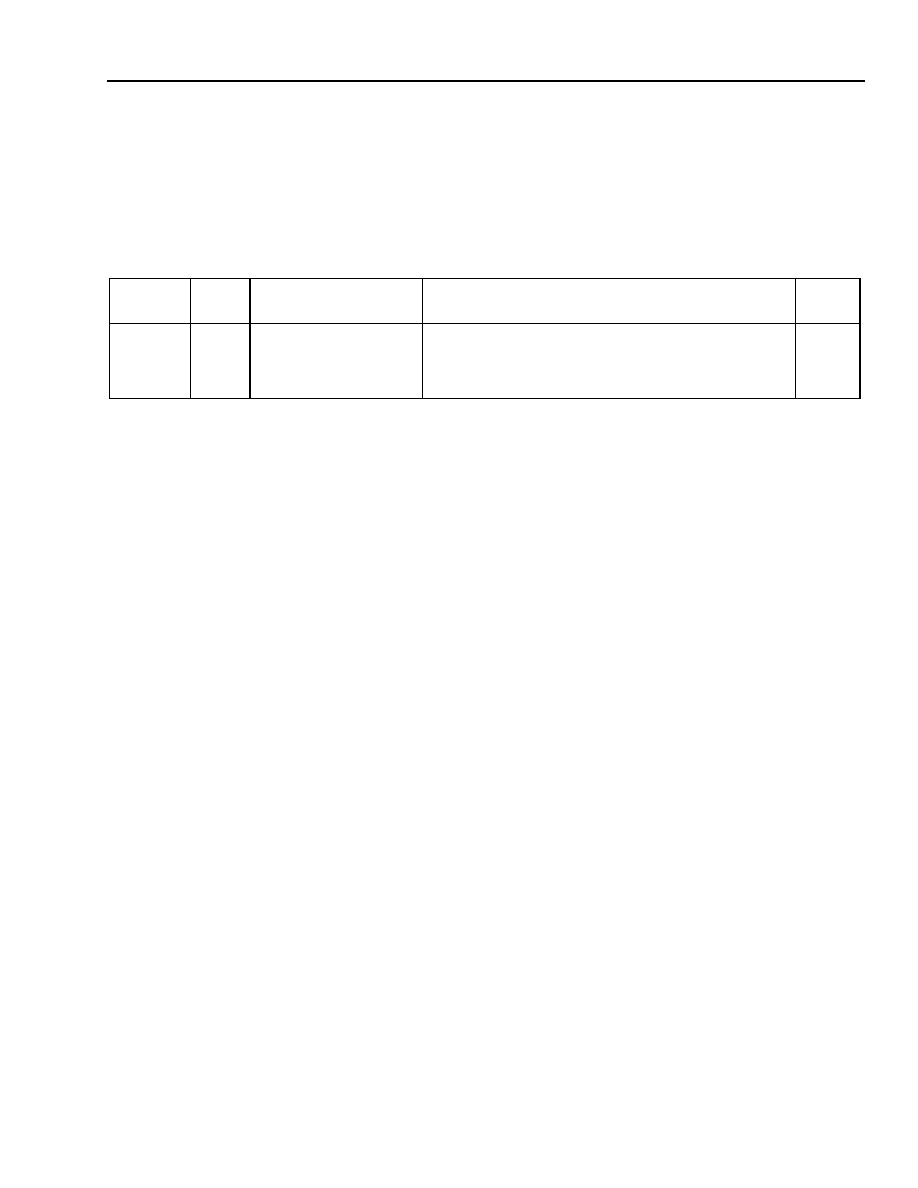

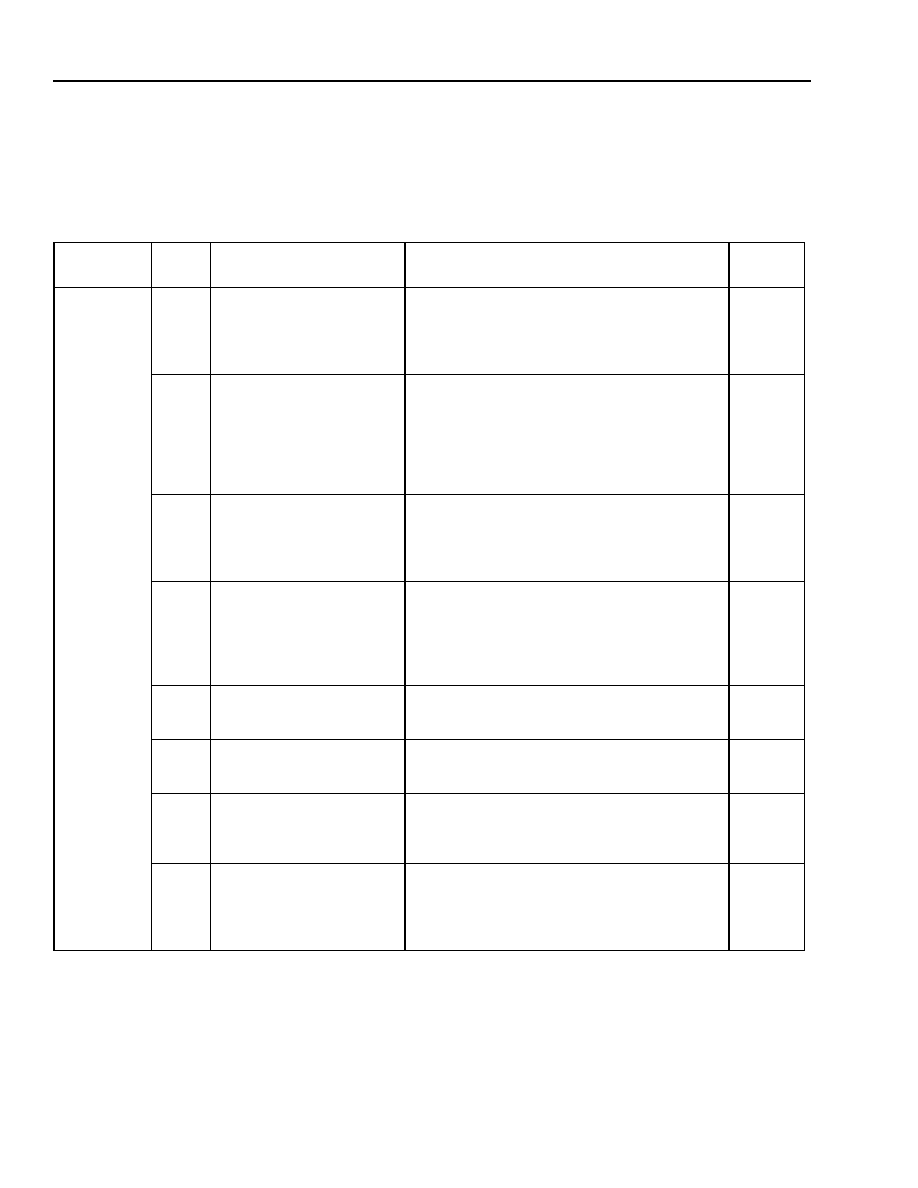

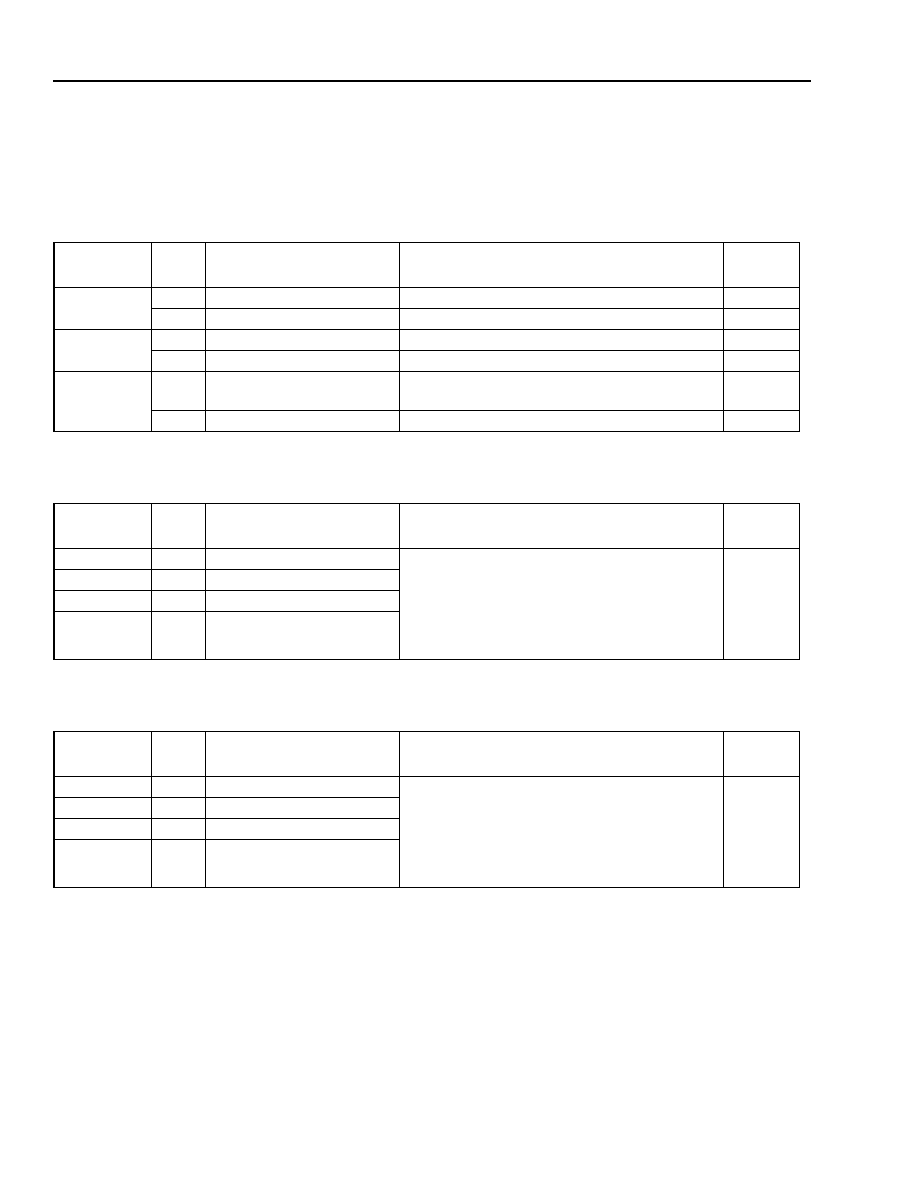

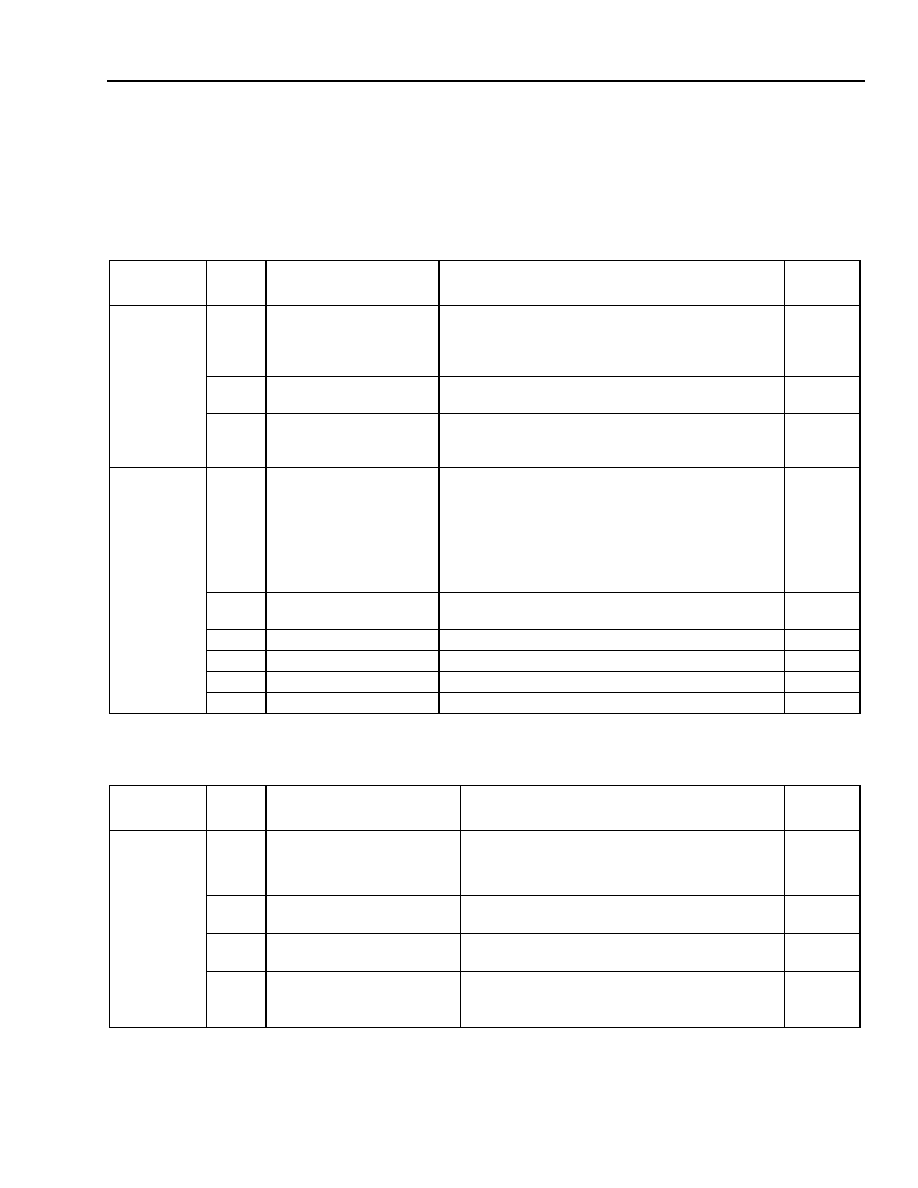

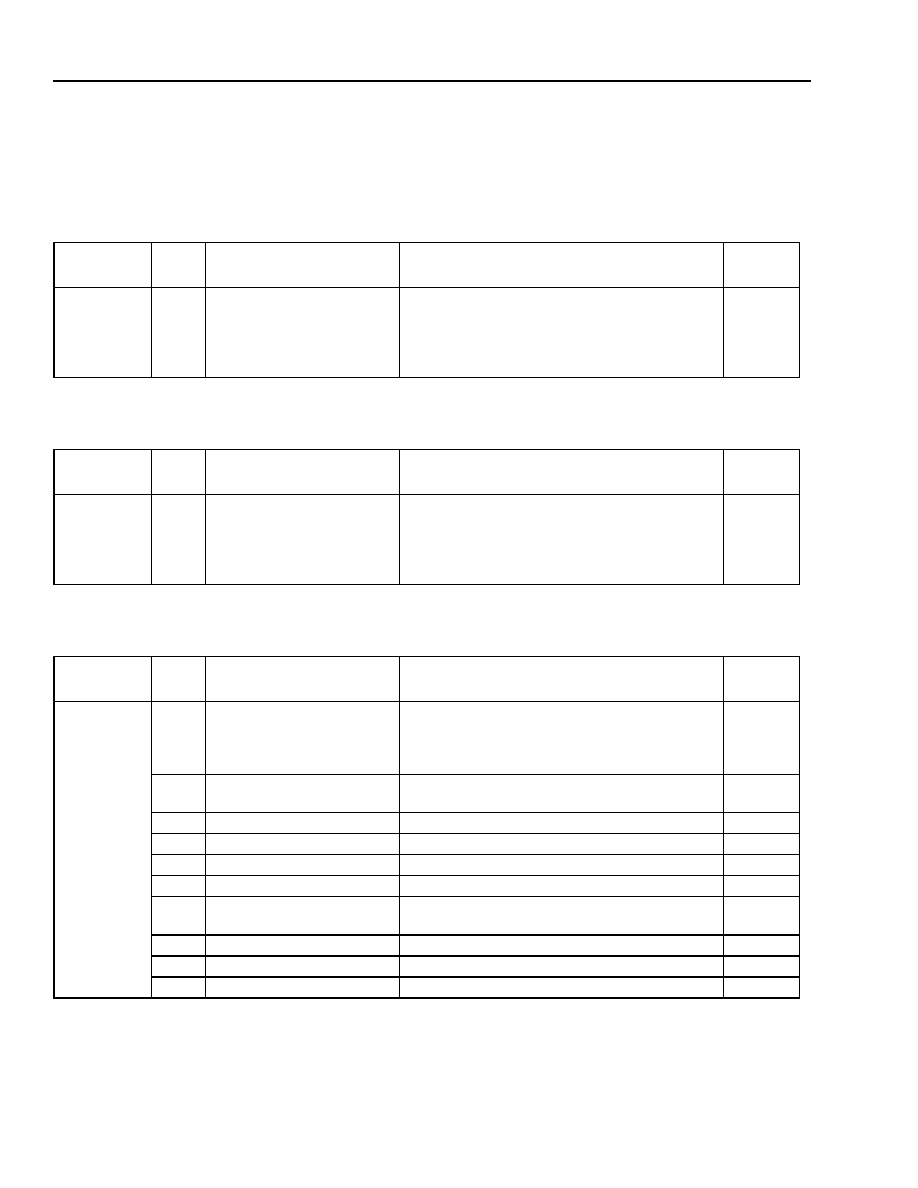

OHP1. Maximum BER Count

The maximum number of errors the device can report is limited to 5.00E-04 in STS-12/STM-4 mode and 1.00E-04

in STS-48/STM-16 mode. This applies to the SDLSET, SDLCLEAR, SFLSET, and SFLCLEAR bits of the signal

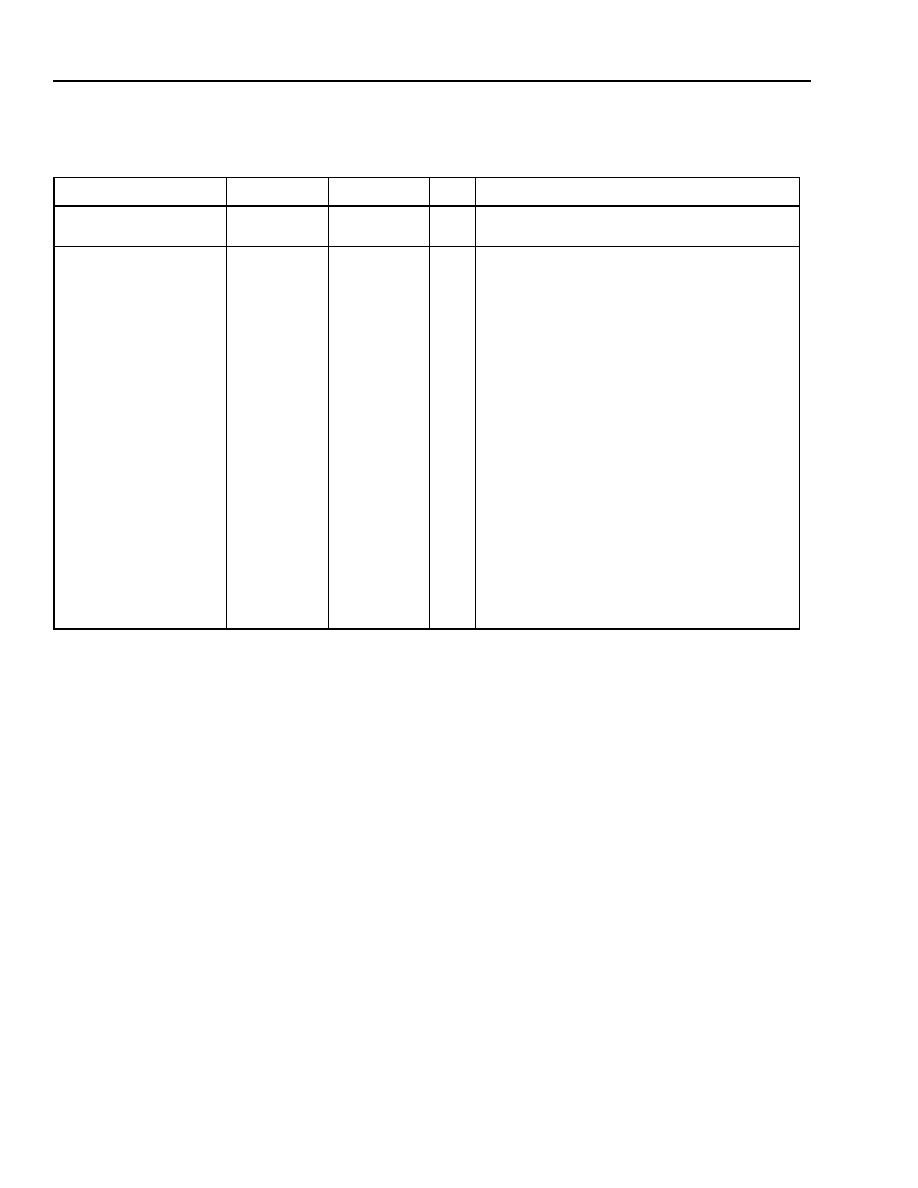

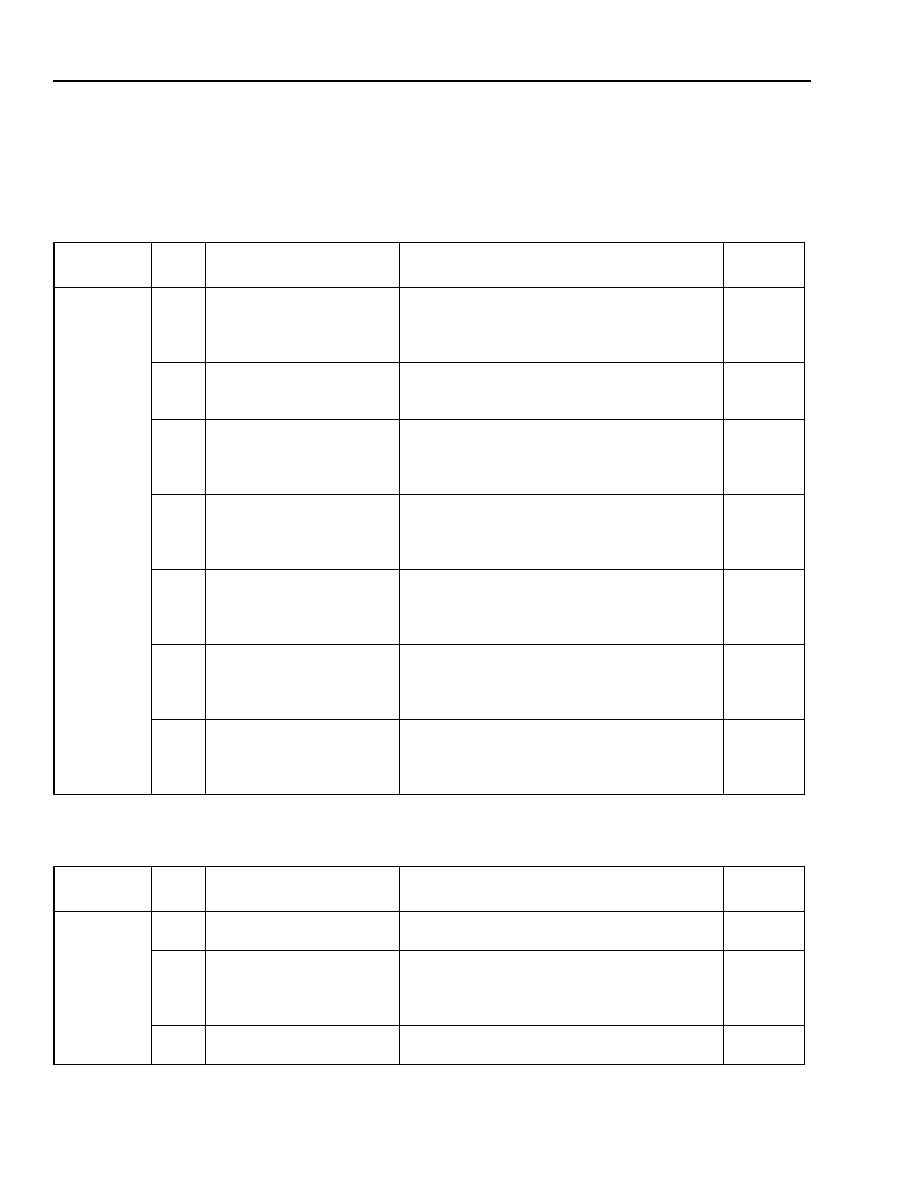

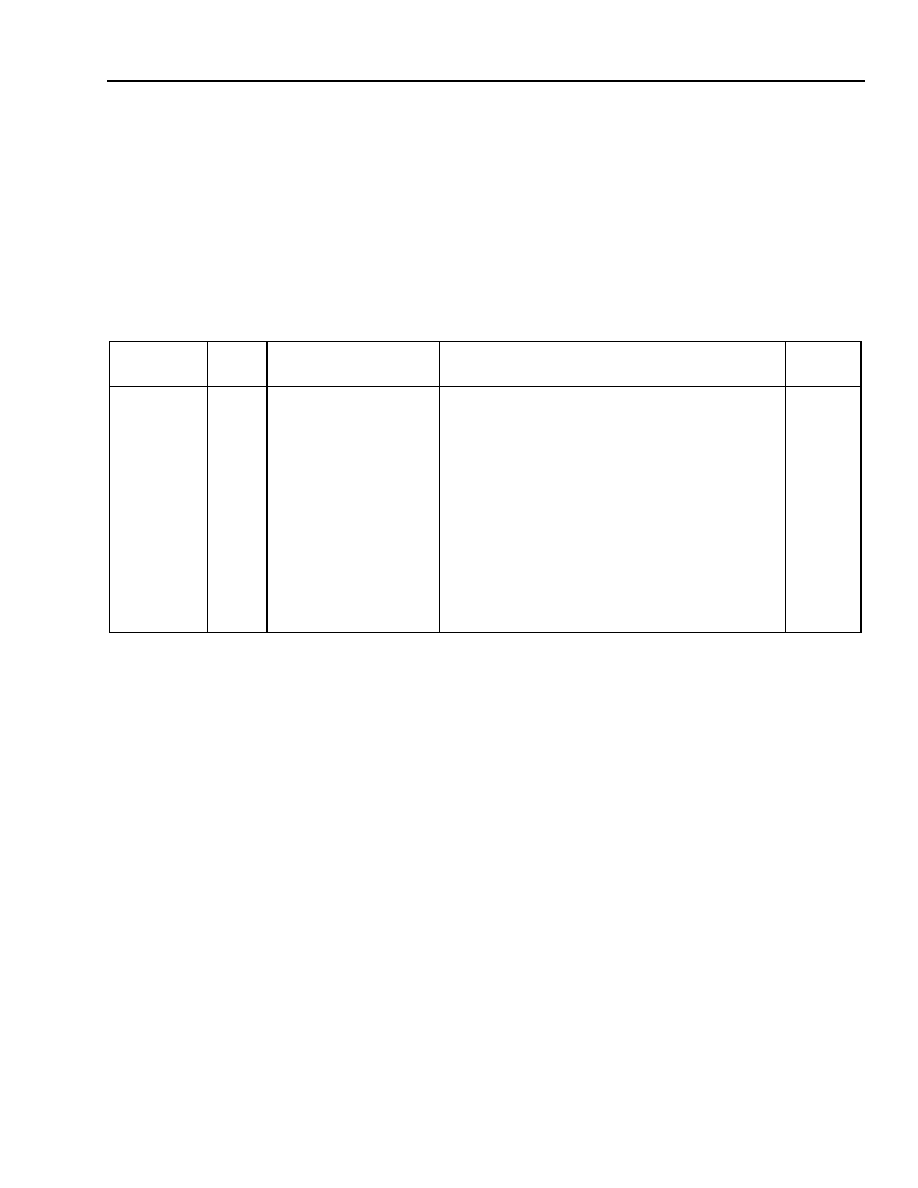

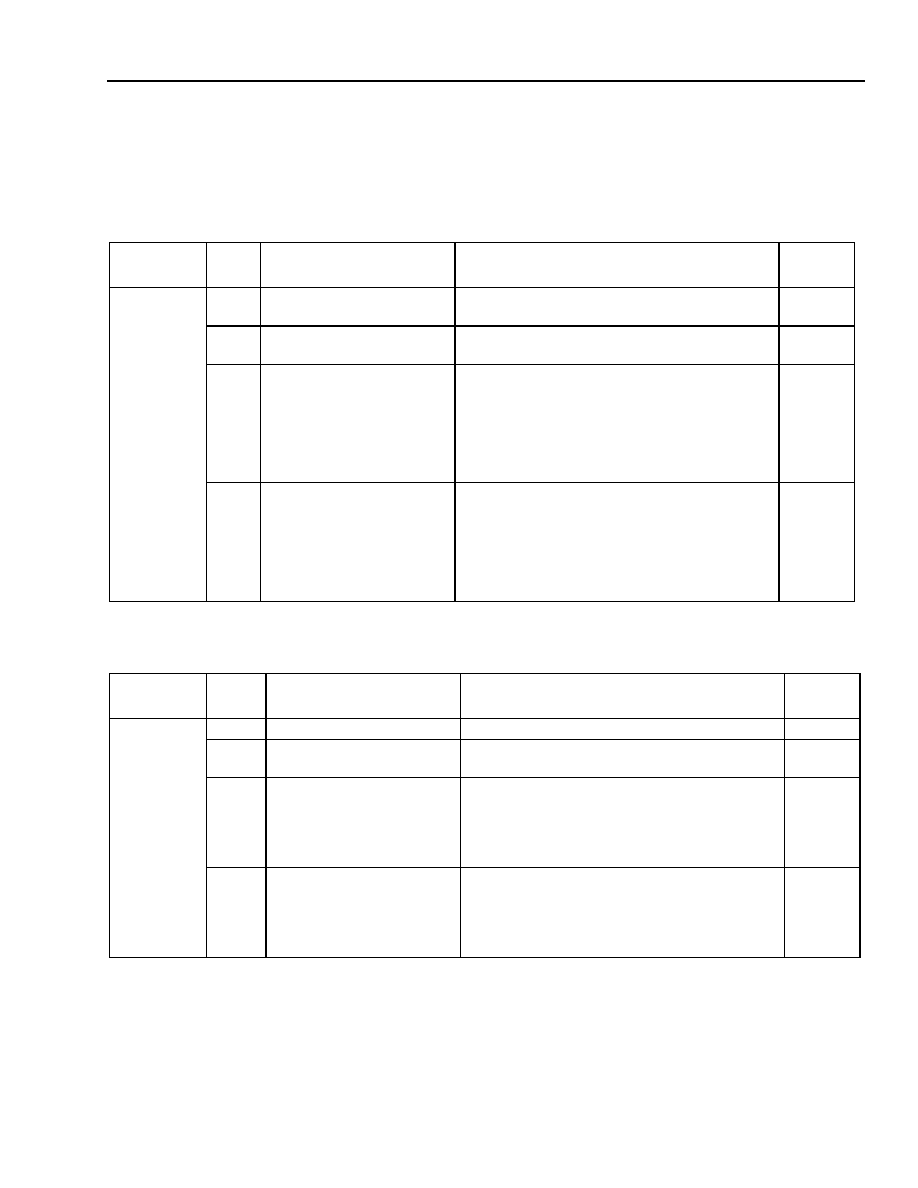

degrade and signal fail BER algorithm OHP registers. These bits are shown in Table 8.

Table 8. Signal Degrade and Signal Fail Algorithm OHP Registers [6:3]

* The OHP prefix shown here will be added to the current bit names in revision 4 of the advance data

sheet.

Workaround

This is informational only. No workaround is available for this condition.

Corrective Action

No corrective action is required for this condition.

OHP2. RDI-L Reporting

When the device is initially powered up, it defaults to STS-48/STM-16 mode. This locks a counter value into trans-

mit control registers for channels B, C, and D. When the device is configured for STS-3/STM-1 mode, the counter

does not automatically clear.

Workaround

During STS-3/STM-1 OHP configuration in the system code, manually clear transmit control registers 0x0431,

0x0433, and 0x0435 for channels B, C, and D. In order to clear these transmit control registers, the bits must be

toggled. The following pseudocode shows how to clear the bits on channels B, C, and D:

Set address 0x0431 to 0x007F # set bits on channel B

Set address 0x0431 to 0x0000 # clear bits on channel B

Set address 0x0433 to 0x007F # set bits on channel C

Set address 0x0433 to 0x0000 # clear bits on channel C

Set address 0x0435 to 0x007F # set bits on channel D

Set address 0x0435 to 0x0000 # clear bits on channel D

Corrective Action

This is informational only. No corrective action is required for this condition.

OHP Bits*

Addresses

OHP_SDLSET[A--D][3:0]

0x043B, 0x043D, 0x043F, 0x0441

OHP_SDLCLEAR[A--D][3:0]

0x0447, 0x0449, 0x044B, 0x044D

OHP_SFLSET[A--D][3:0]

0x0453, 0x0455, 0x0457, 0x0459

OHP_SFLCLEAR[A--D][3:0]

0x045F, 0x0461, 0x0463, 0x0465

22

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Overhead Processor (OHP)

(continued)

OHP3. M1 Error Counter in STS-48/STM-16 Mode

When the device receives REI-L errors in the STS-48/STM-16 mode, no M1 errors are reported.

Workaround

There are several workarounds for this problem:

I

Pass the B2 error count value to the far end through system software.

I

Process the M1 byte from the receive TOAC with an external FPGA.

I

Pass the B2 error count from the receive to the transmit direction using transmit TOAC capability. The error count

must be inserted into the eleventh Z2 byte in an STS-48/STM-16 transmit signal. The transmit TOAC signal is

driven by an external device with software insert capability.

I

Pass the B2 error count from the receive to the transmit direction in the section overhead byte. The device has F1

and S1 monitor capability; the protocol for sending the error message to the far end with F1 or S1 bytes is user-

defined.

Corrective Action

This condition will be addressed in future versions of the device.

Packaging and Pinouts (P)

P1. Pin F5 (Previously JTEST) Is No Connect (NC)

Item deleted. Corrected in the advance data sheet.

P2. Modified Pinout and Power Supply Configuration--Future Versions

Item deleted. No modifications to the power supply configuration will be made.

P3. Change to TDAT042G5 Version 1 Pinout

Item deleted. All devices conform to power pin assignments as listed in the advance data sheet.

Agere Systems Inc.

23

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Packaging and Pinouts (P)

(continued)

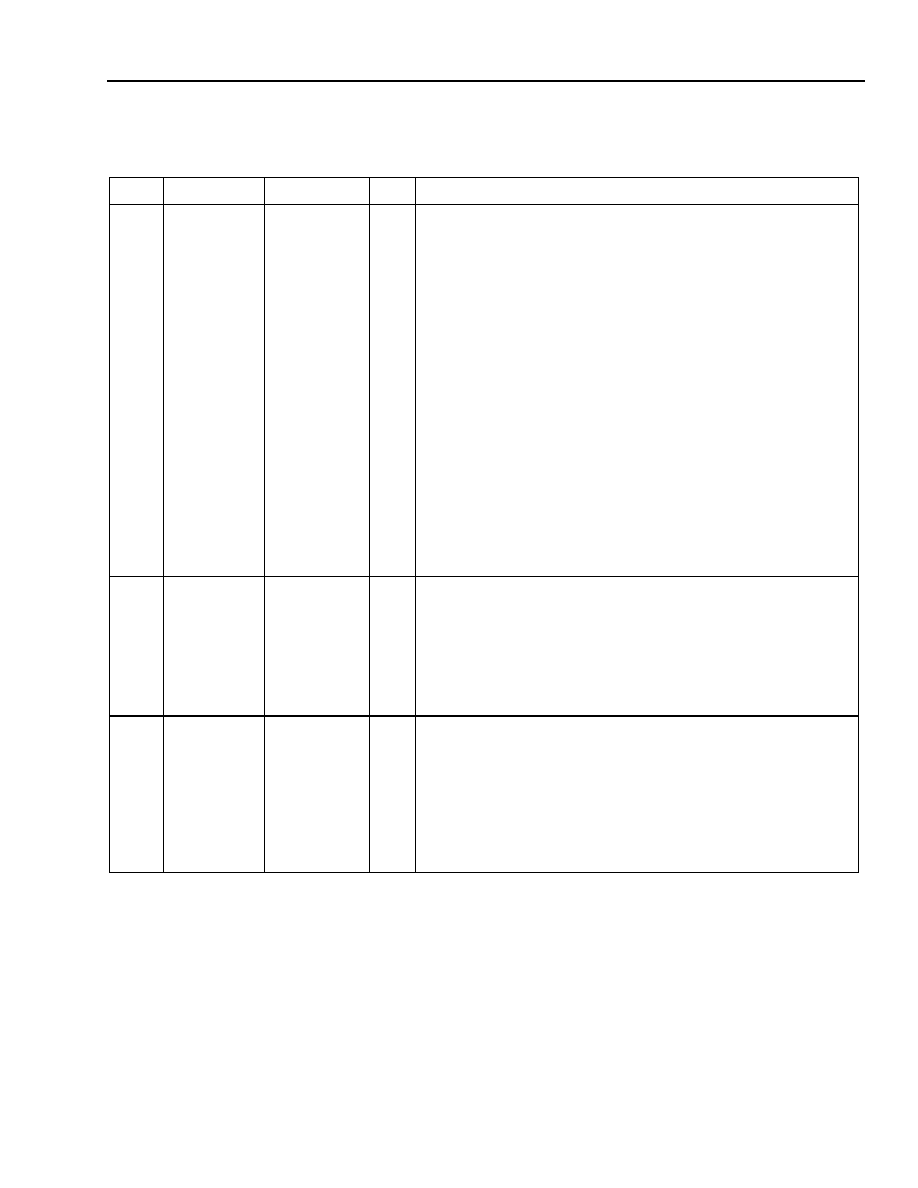

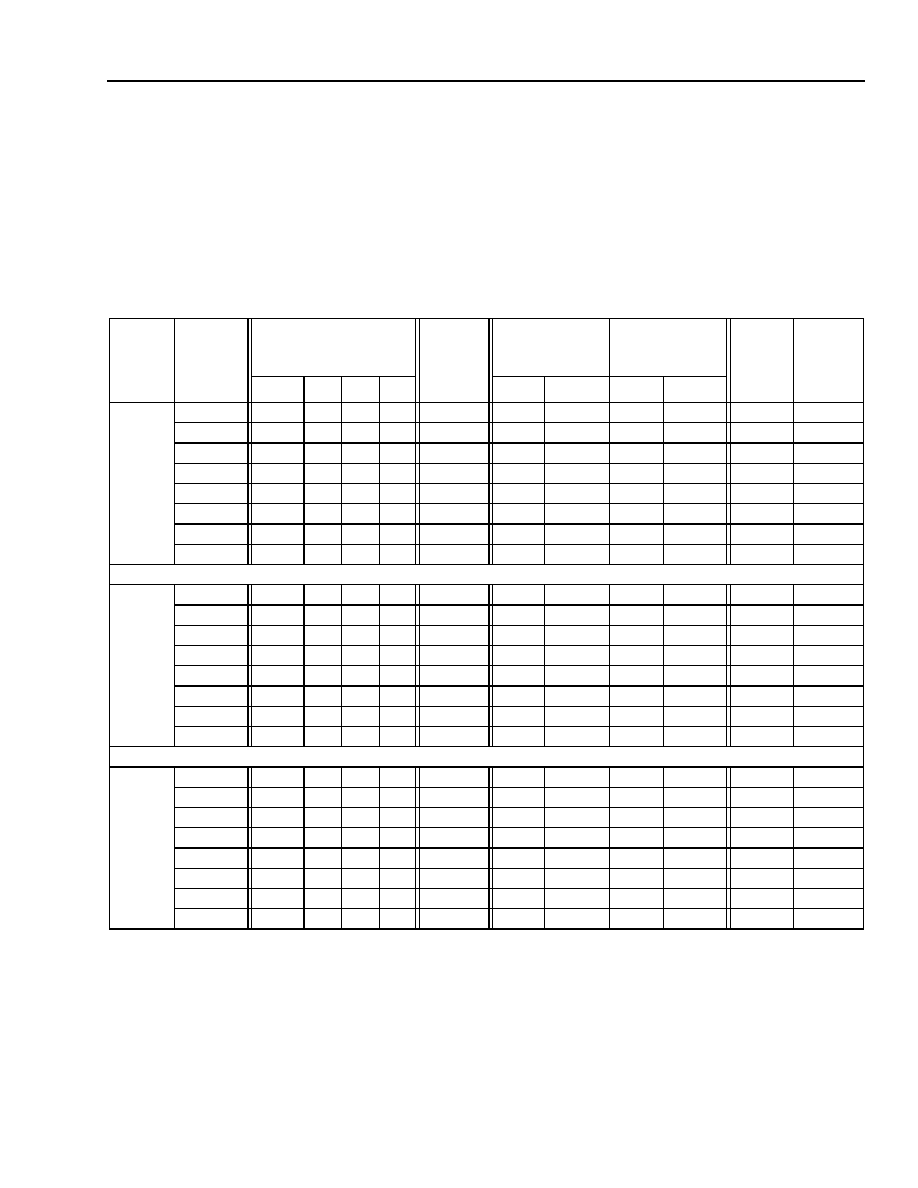

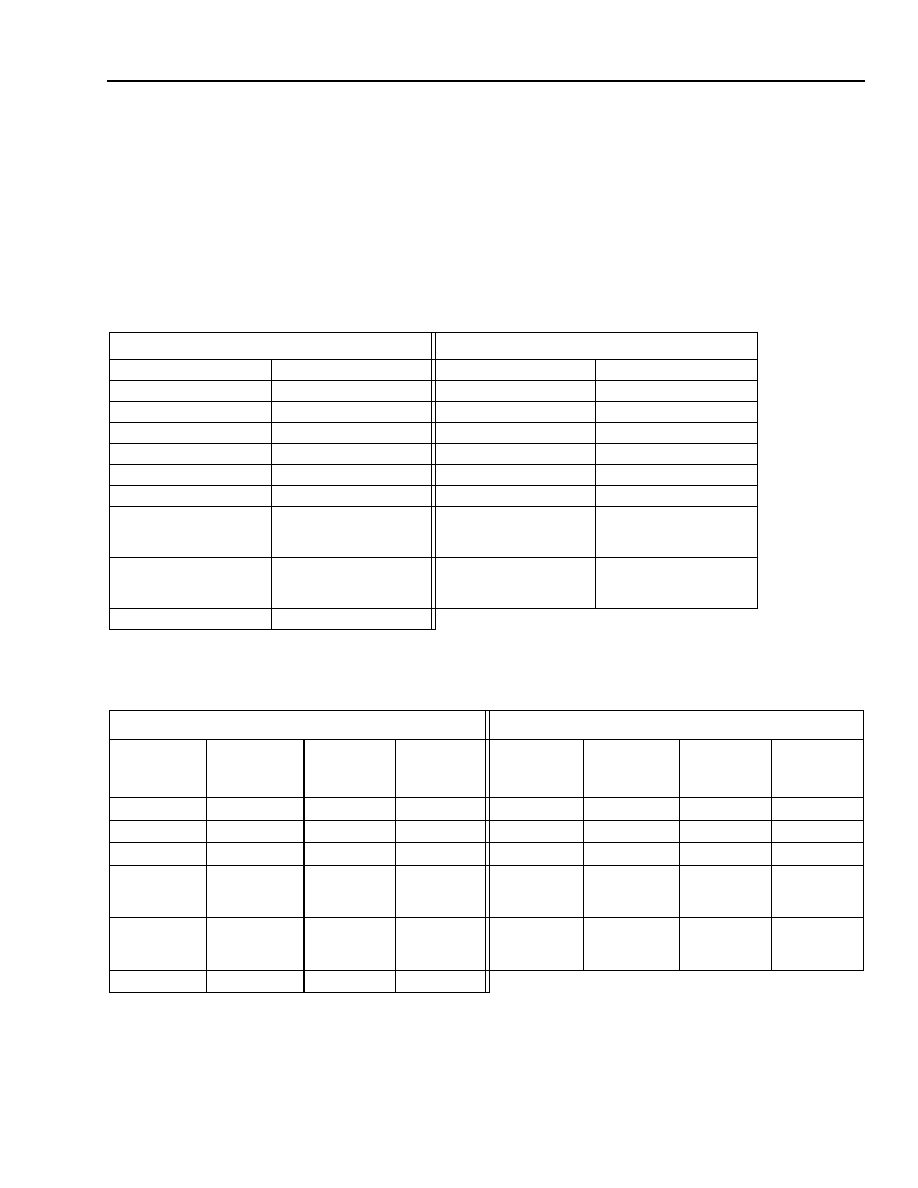

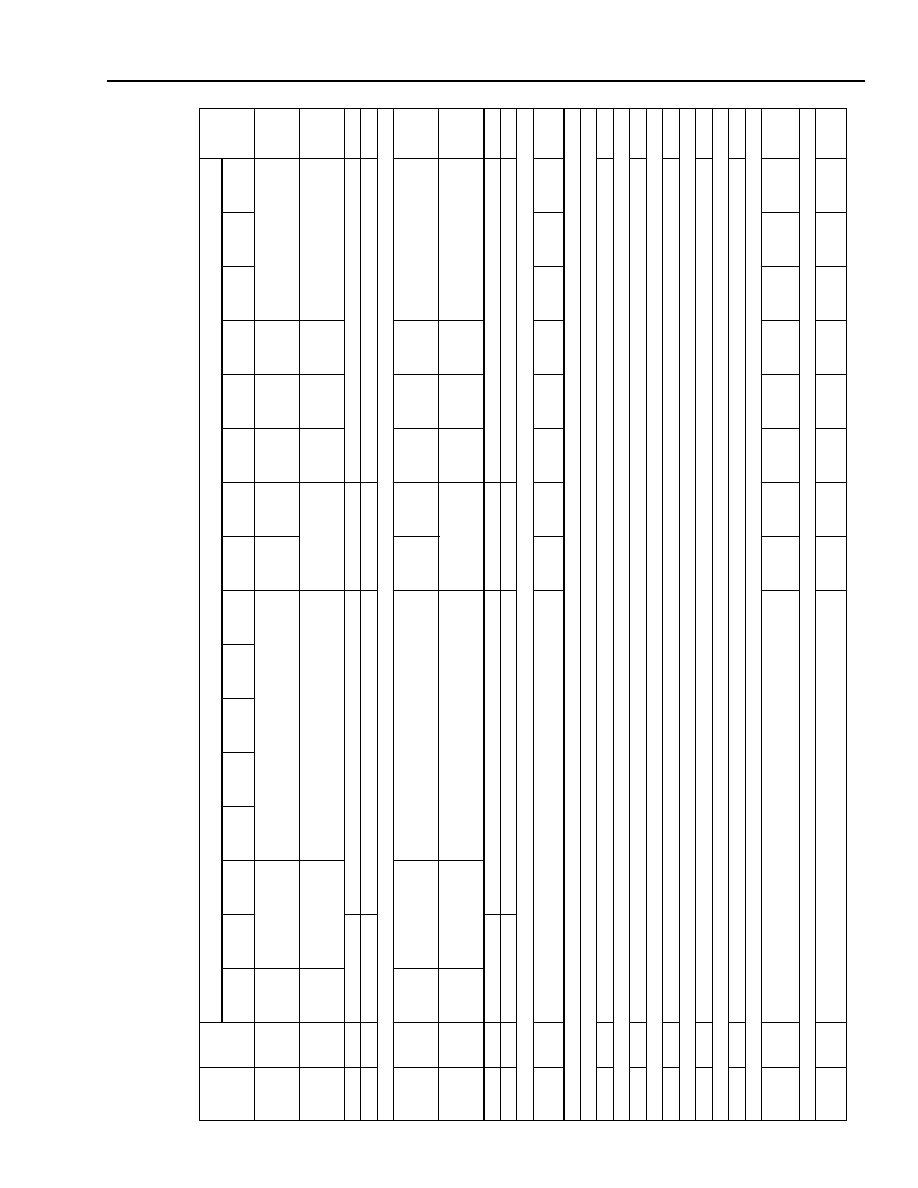

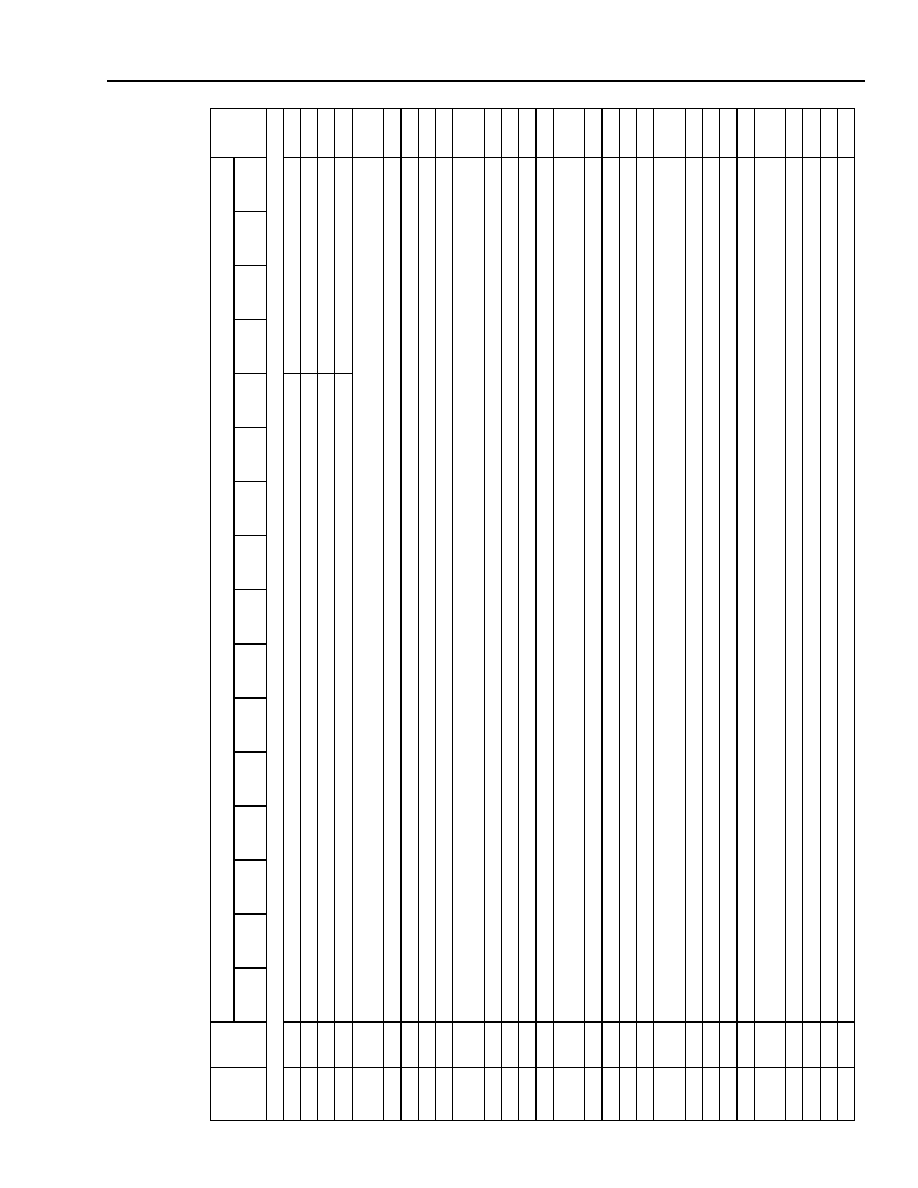

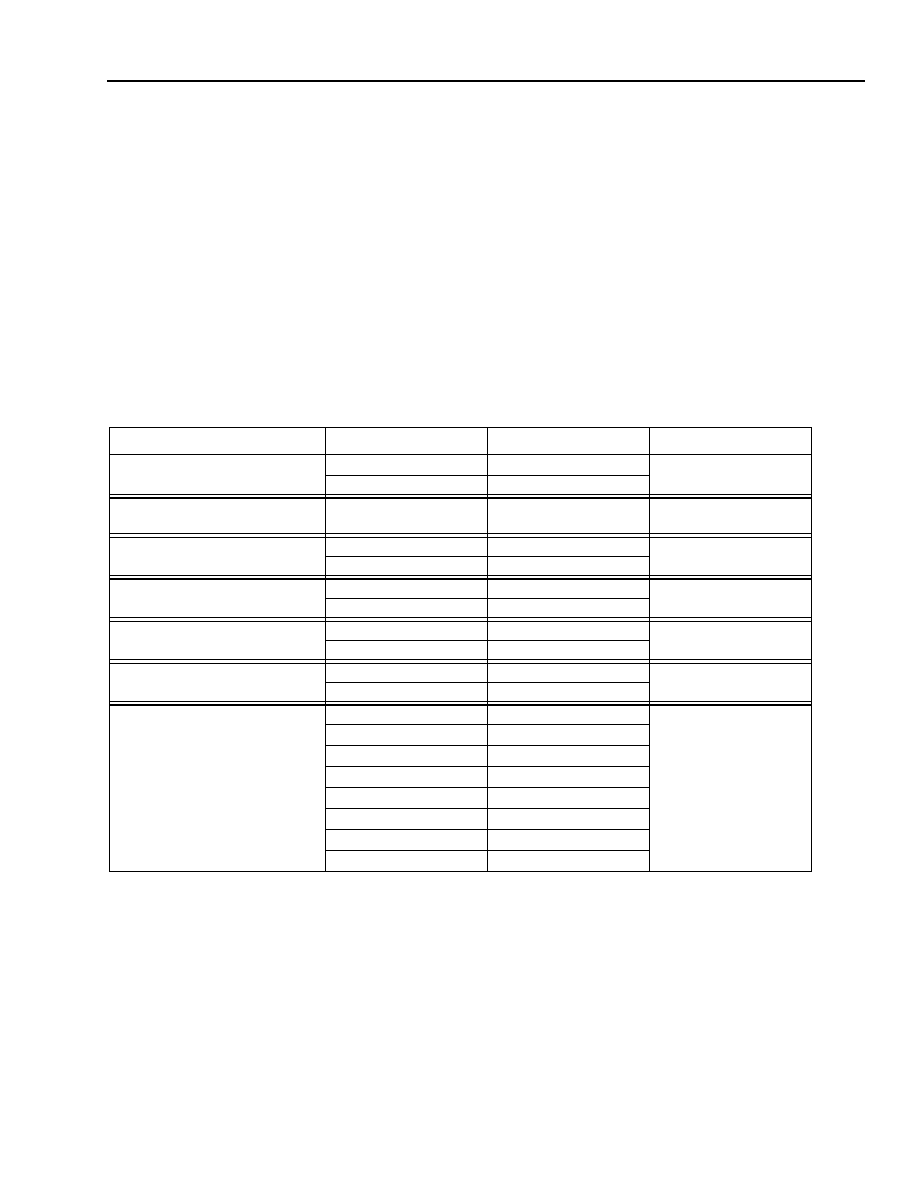

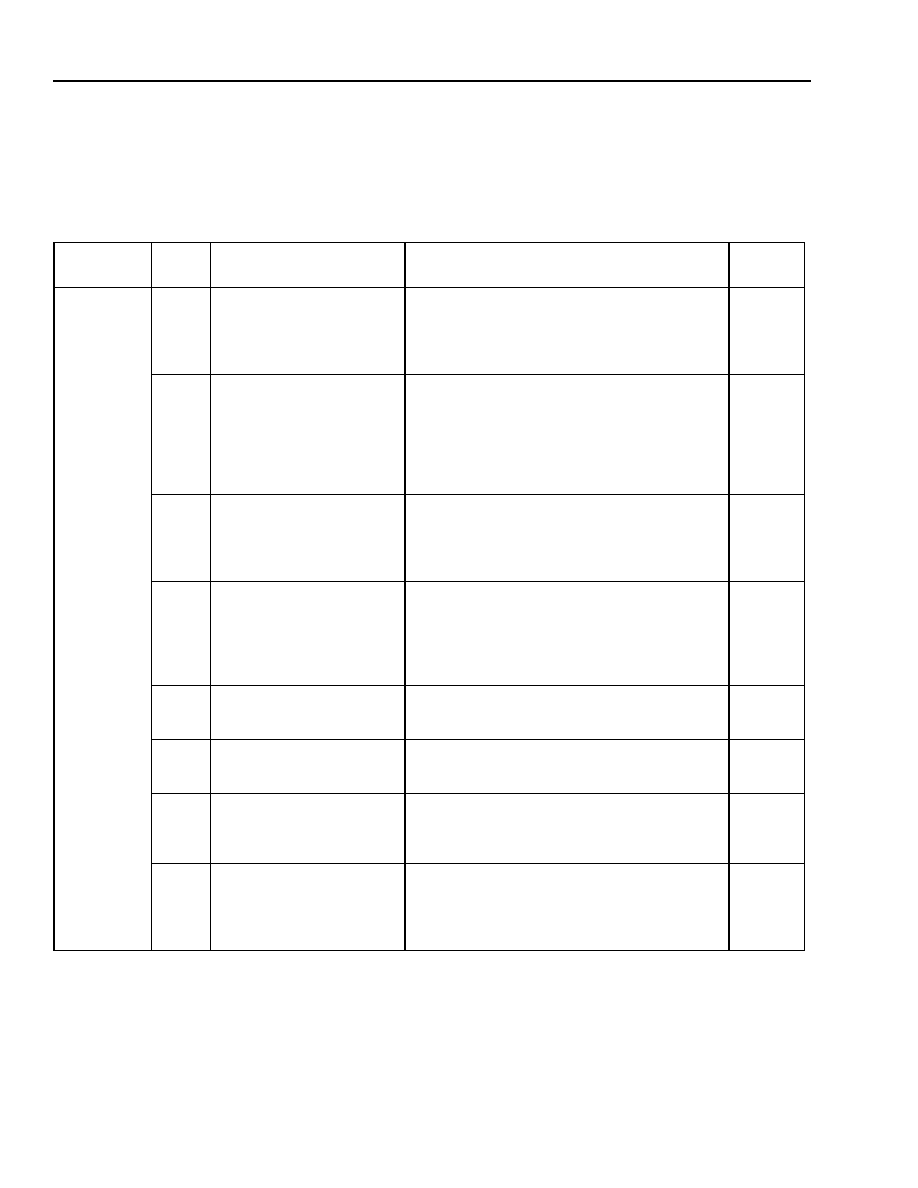

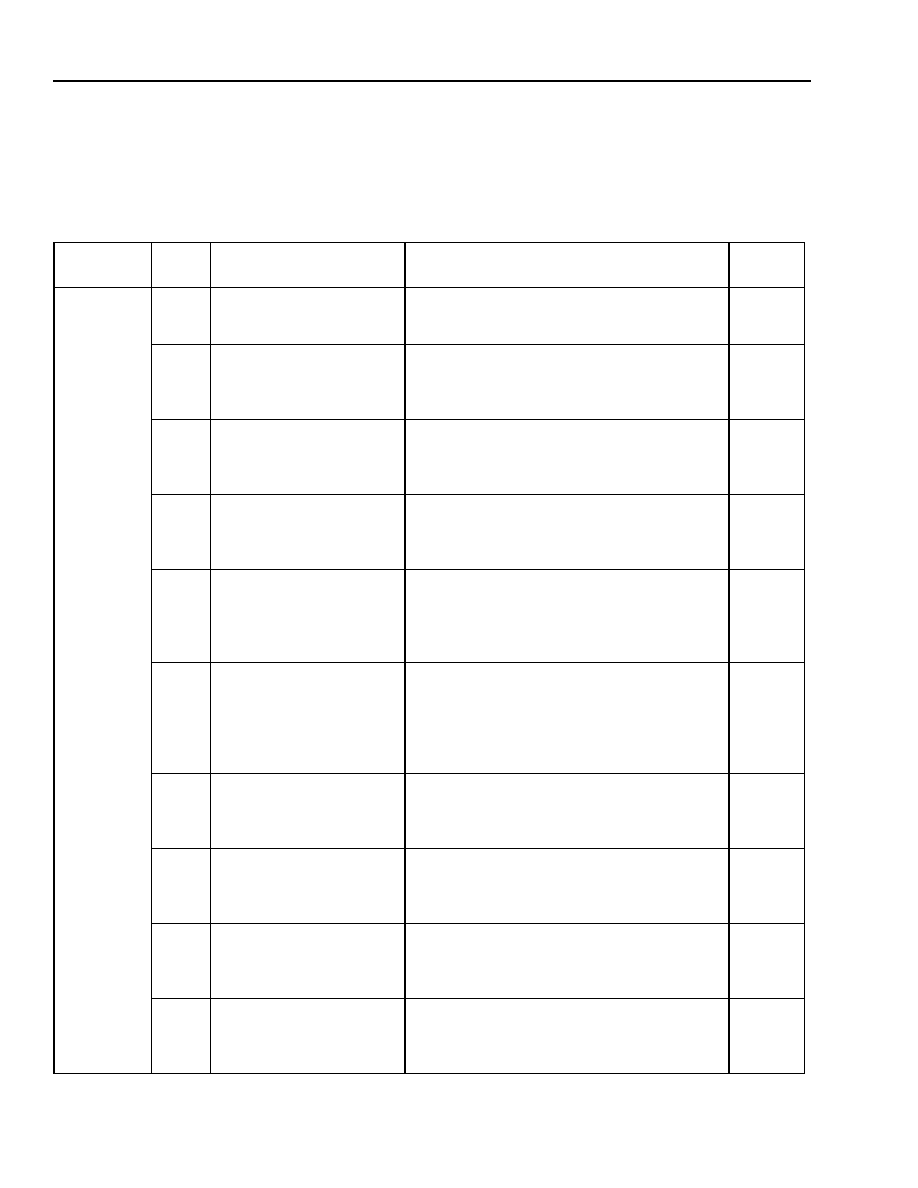

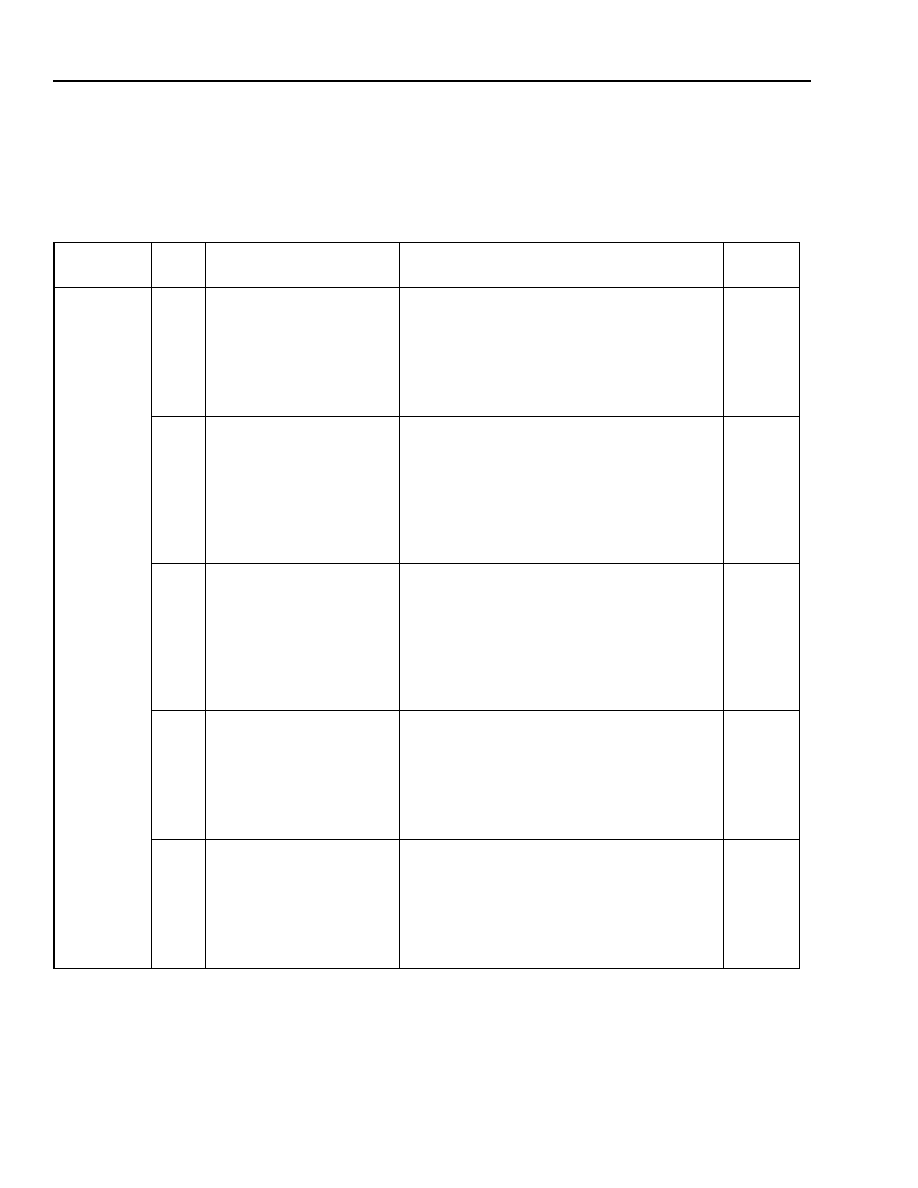

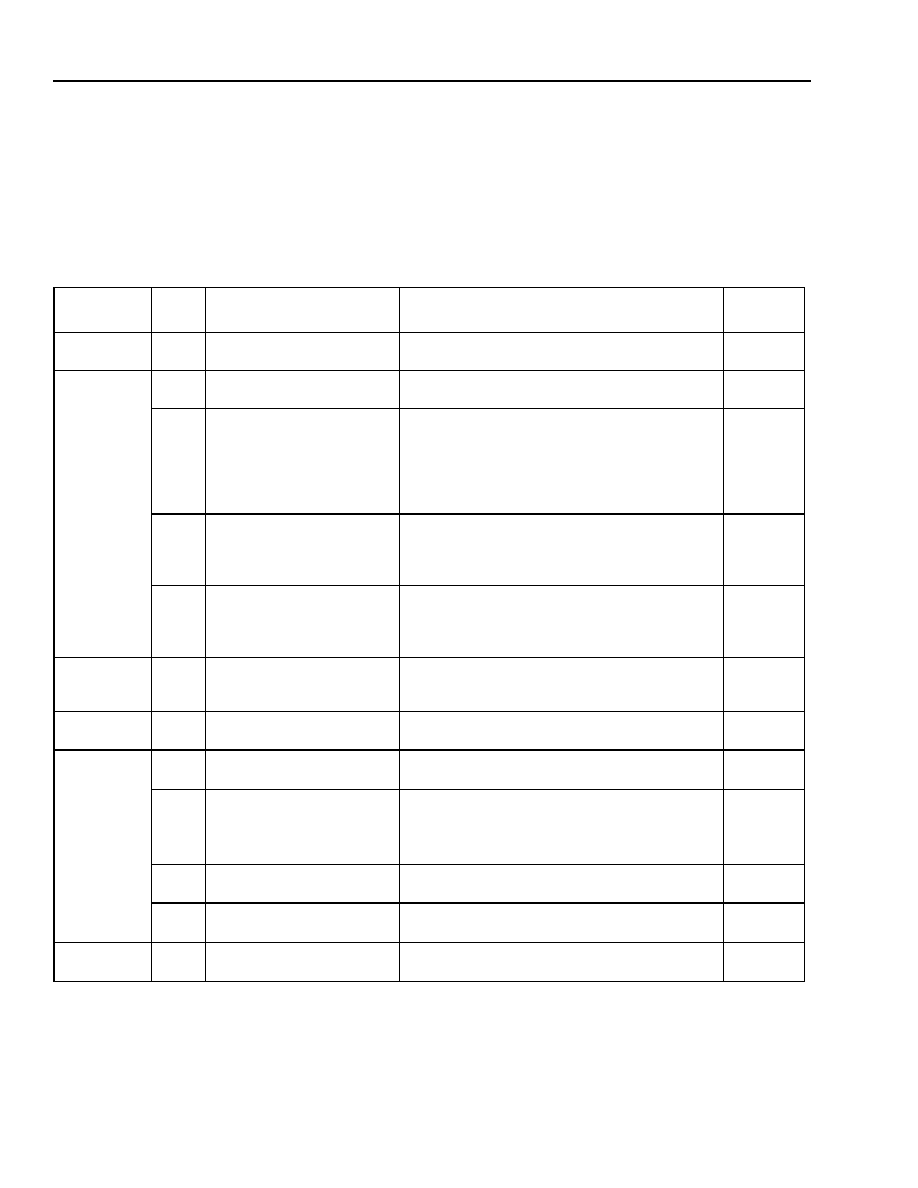

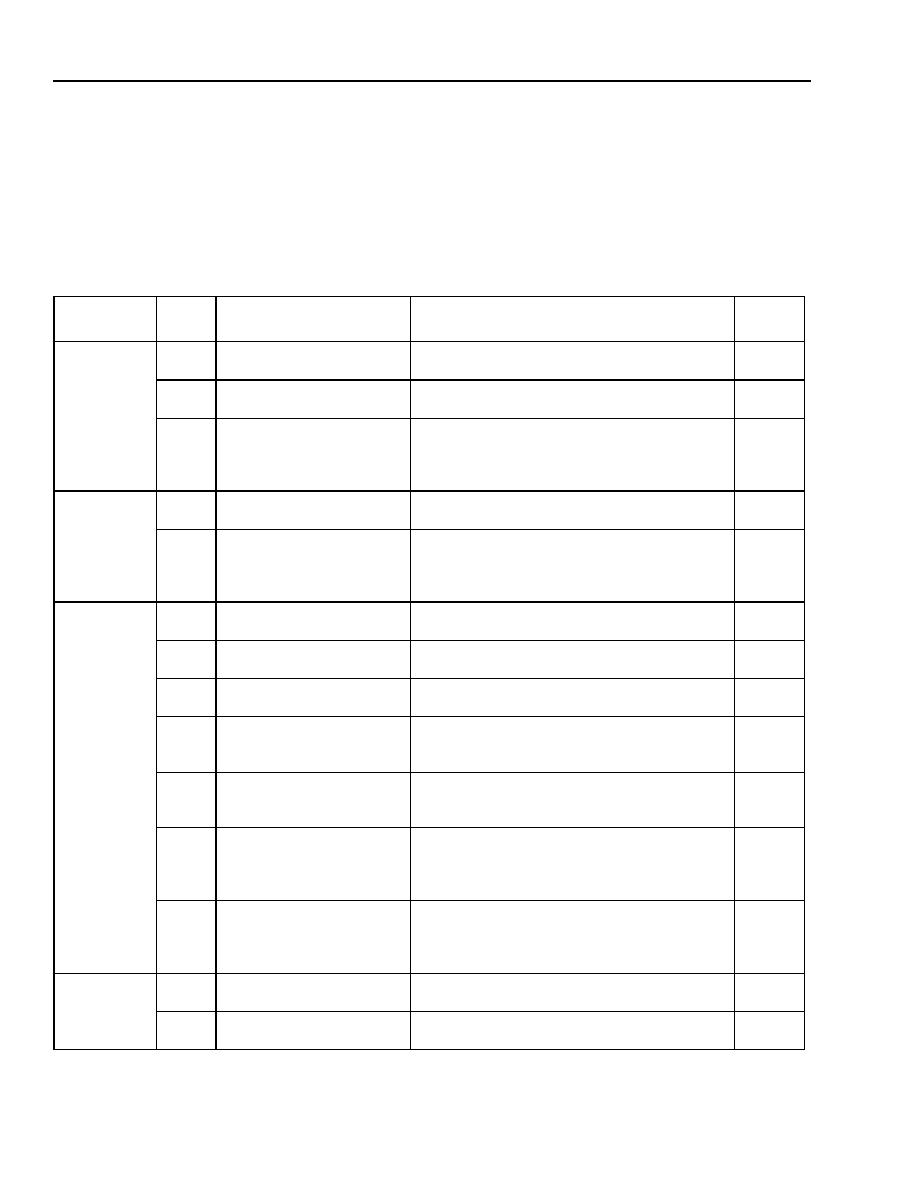

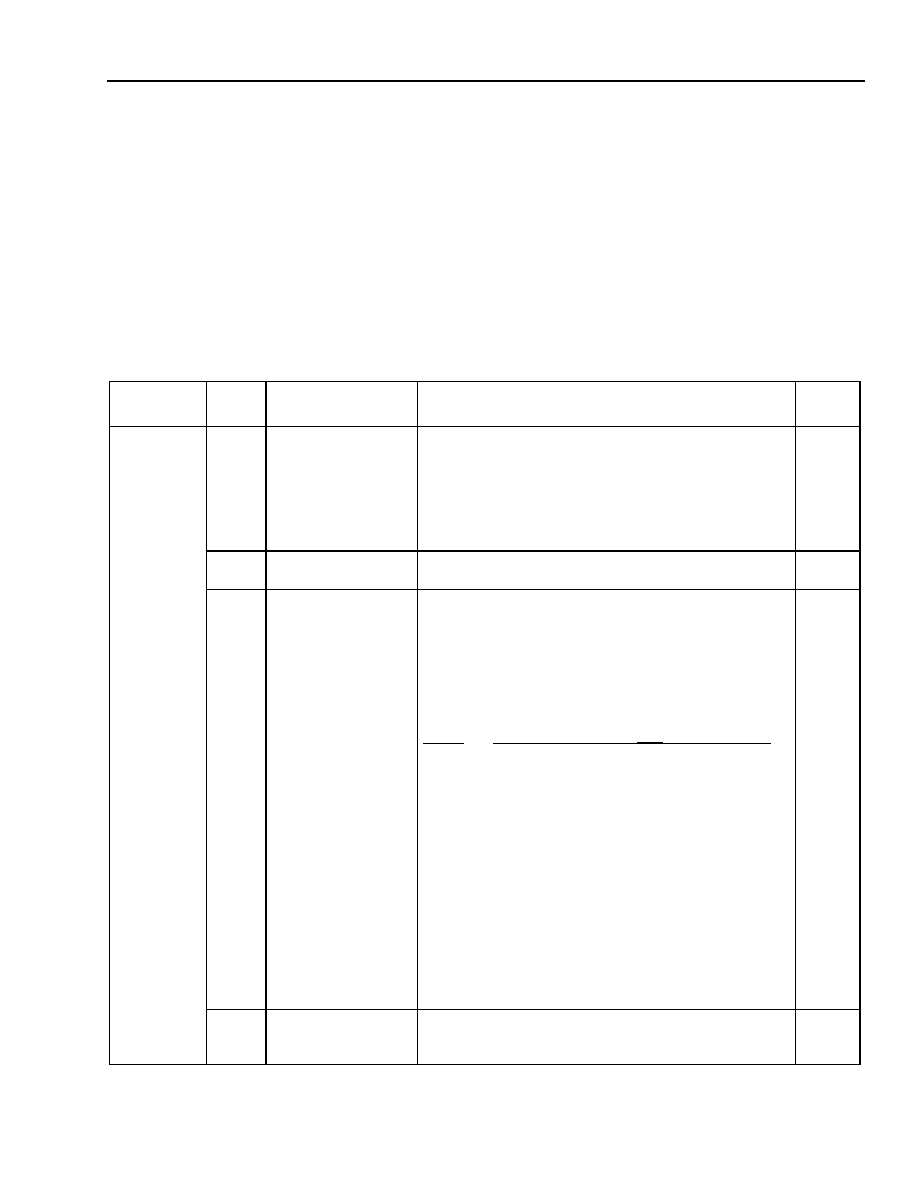

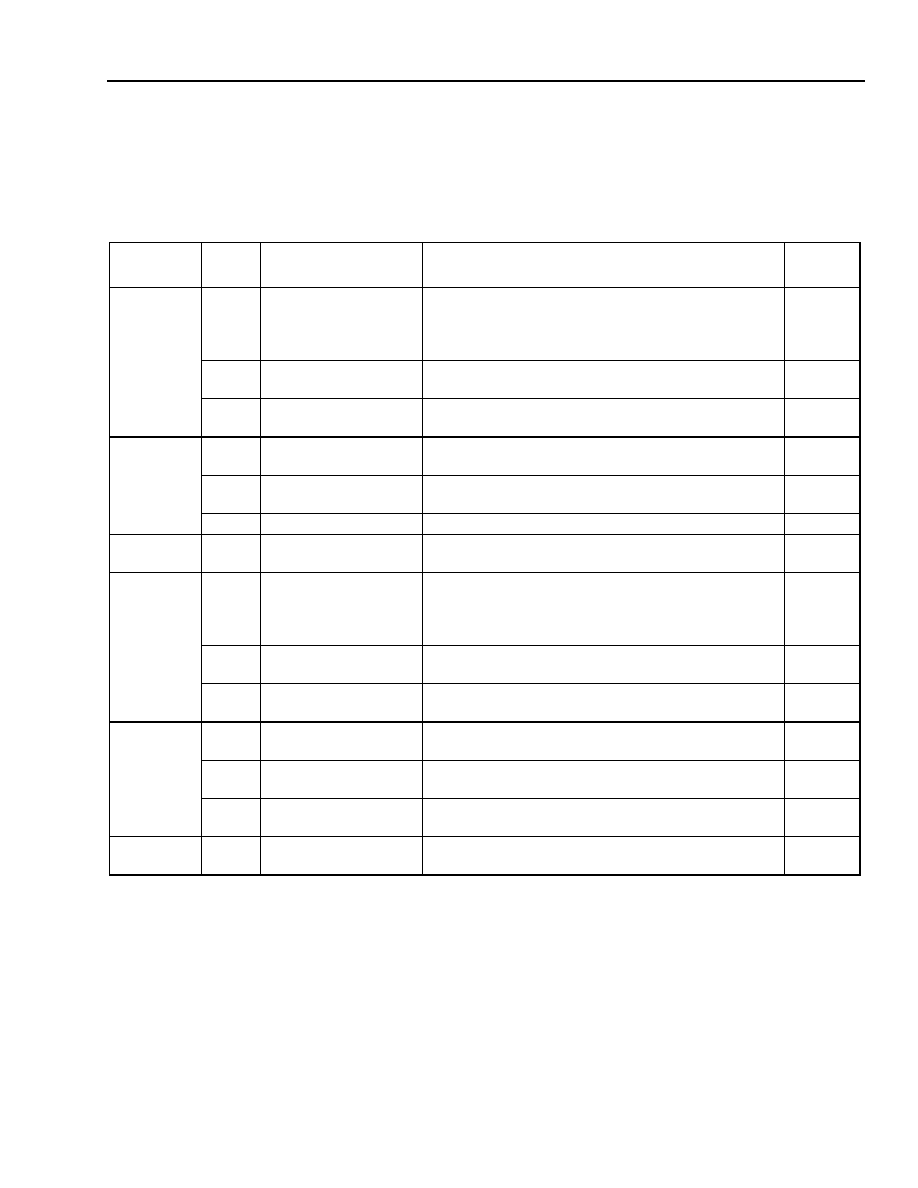

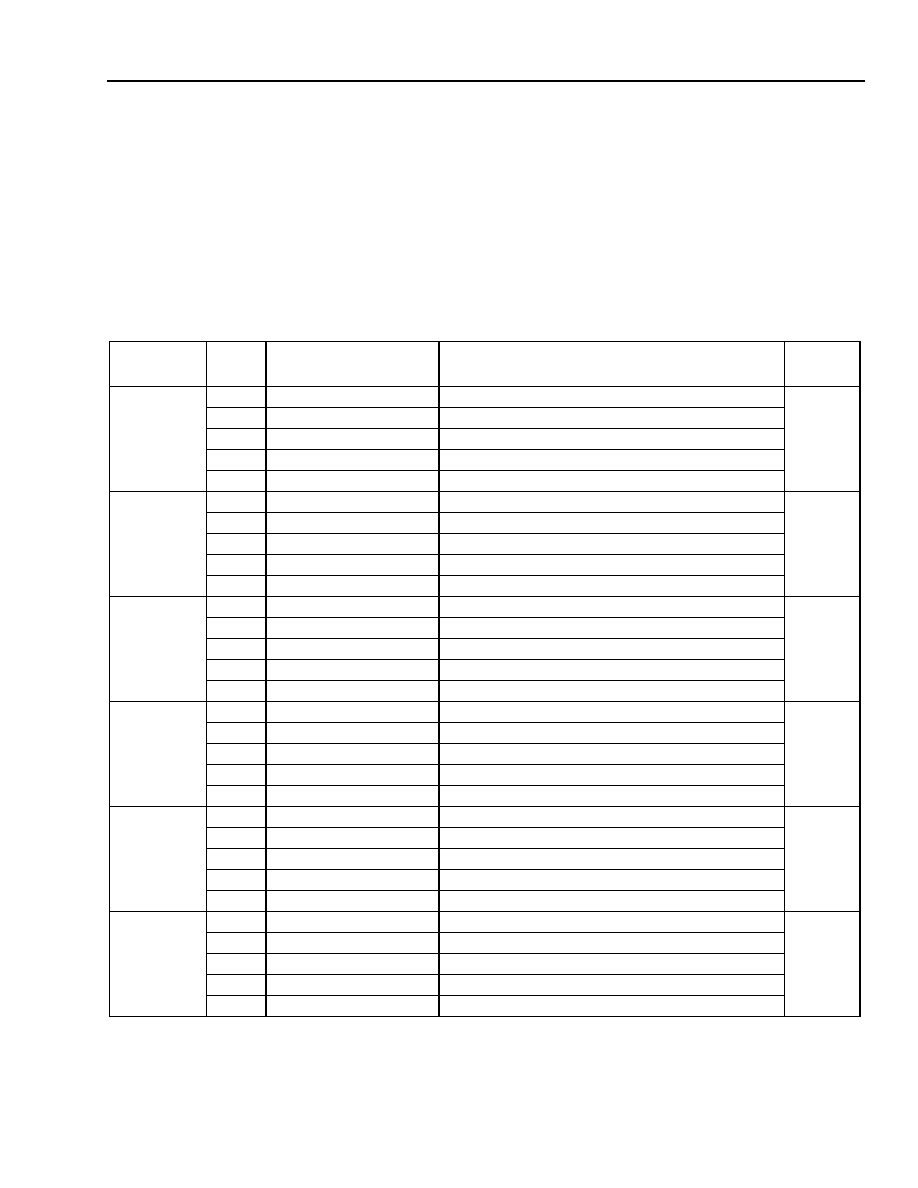

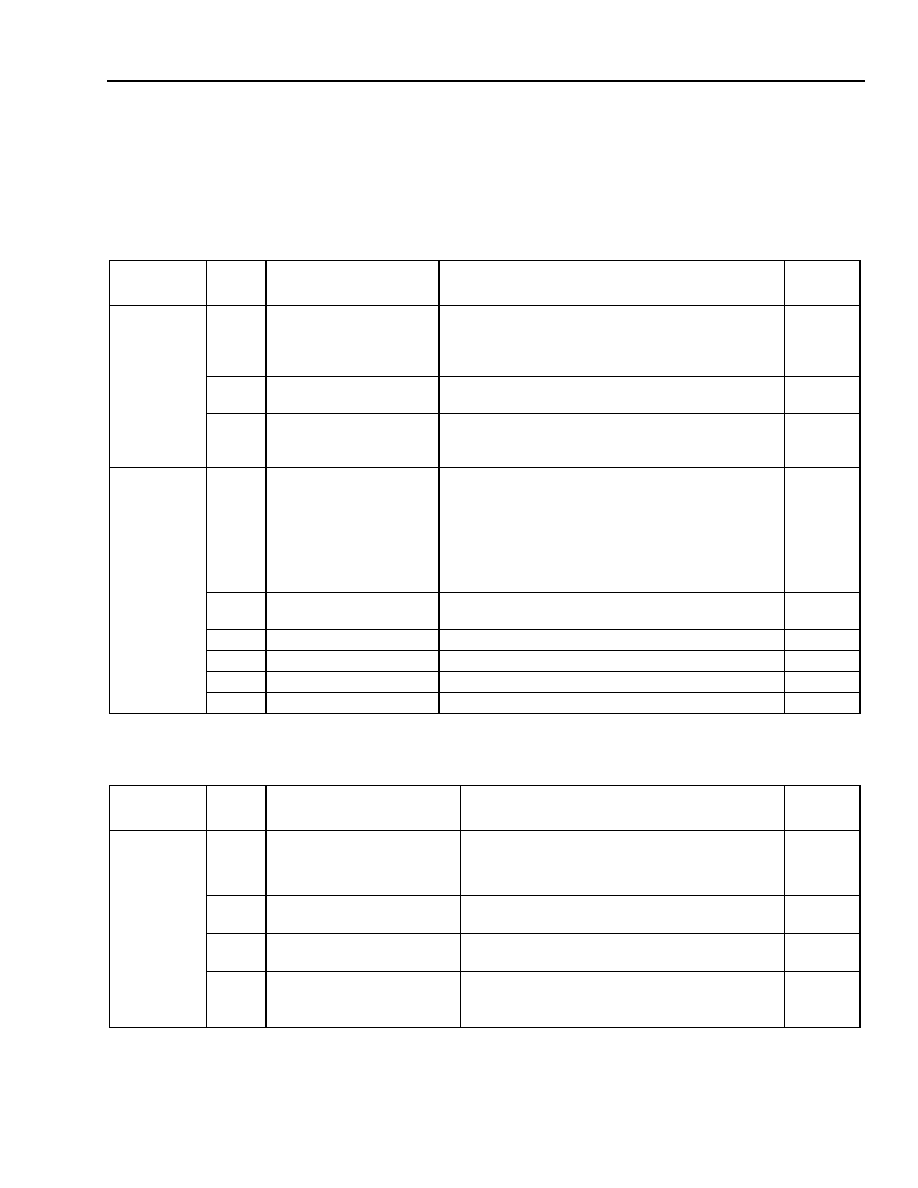

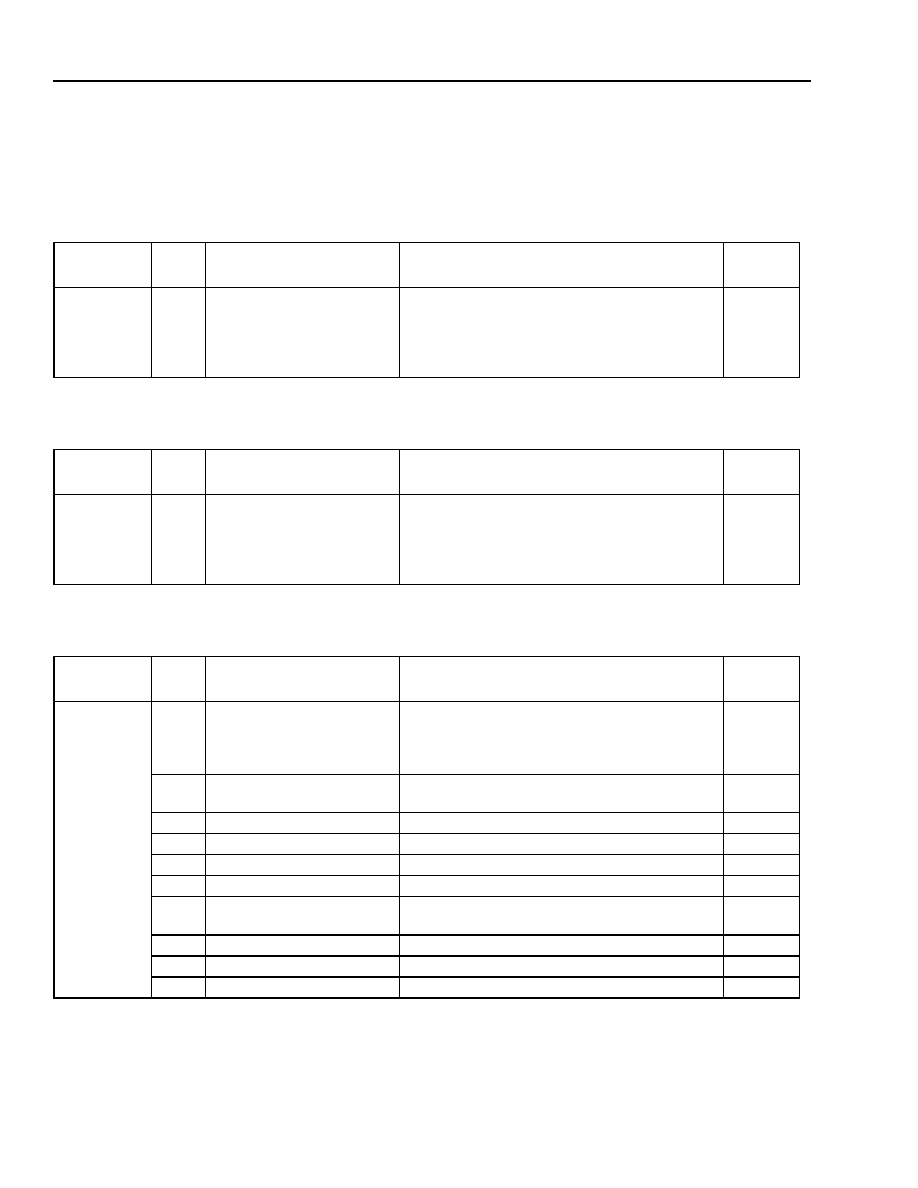

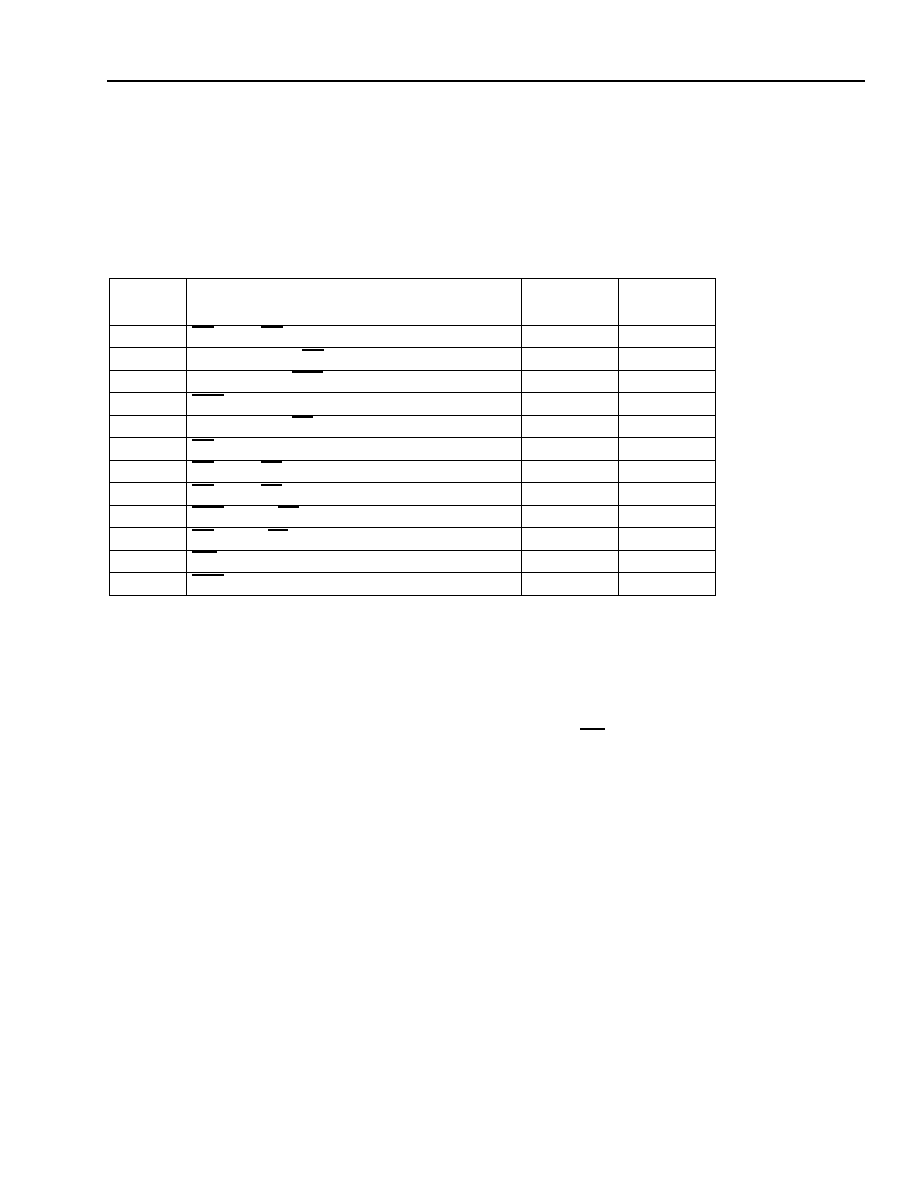

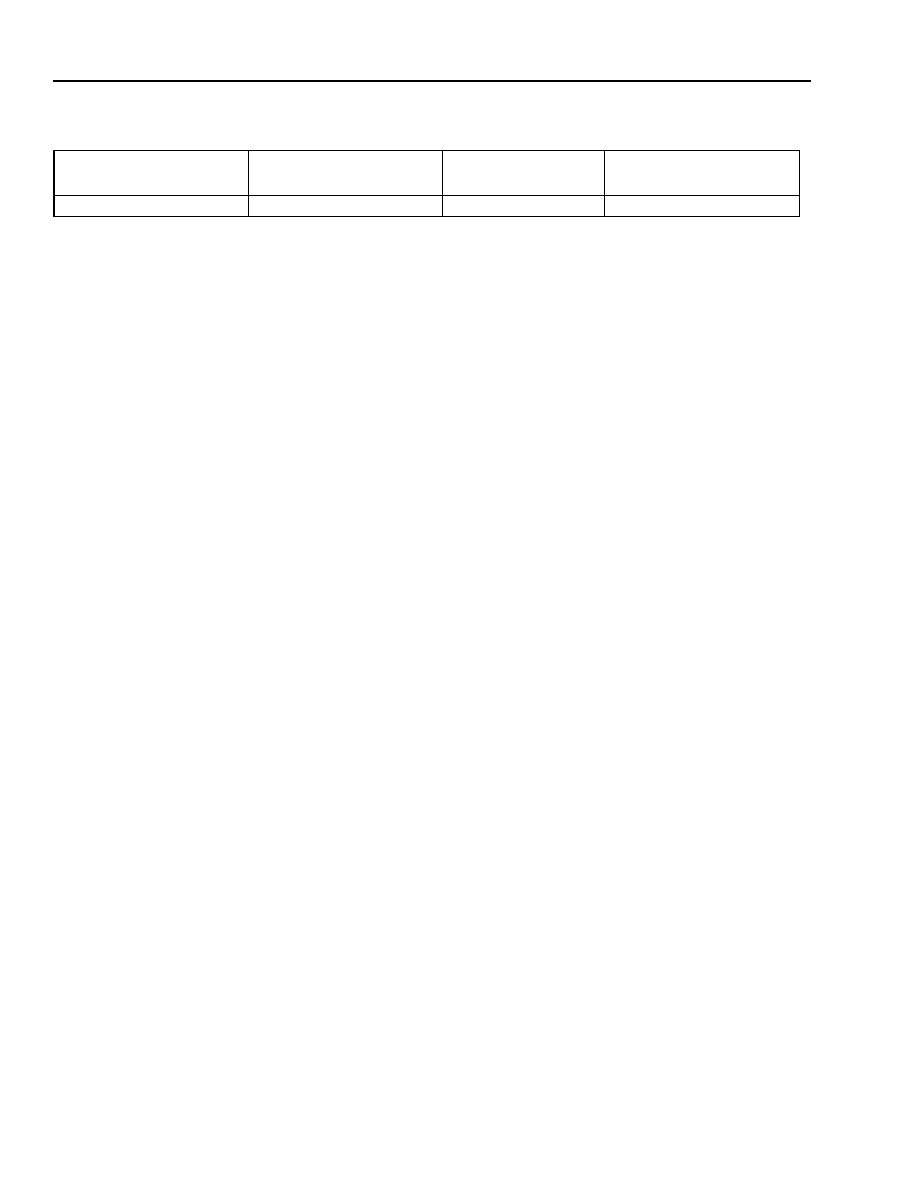

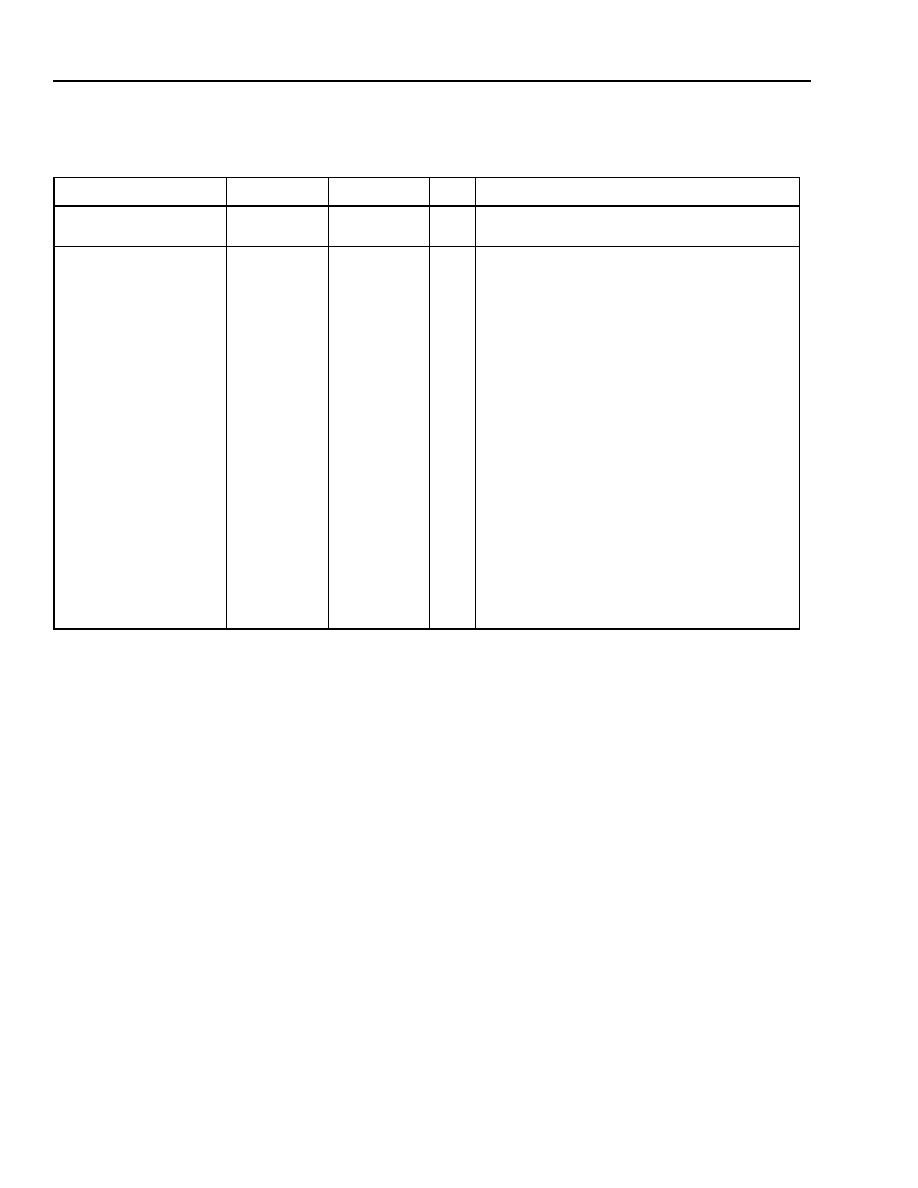

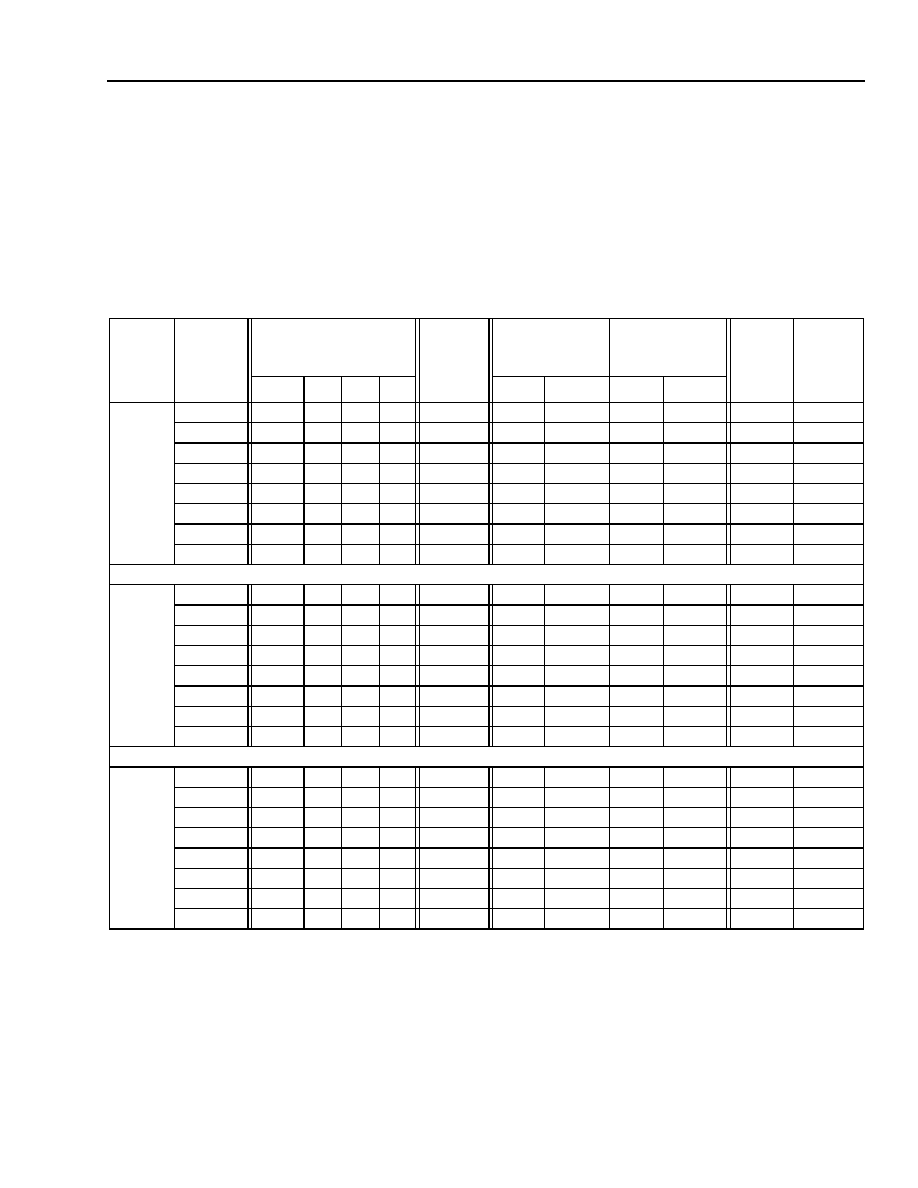

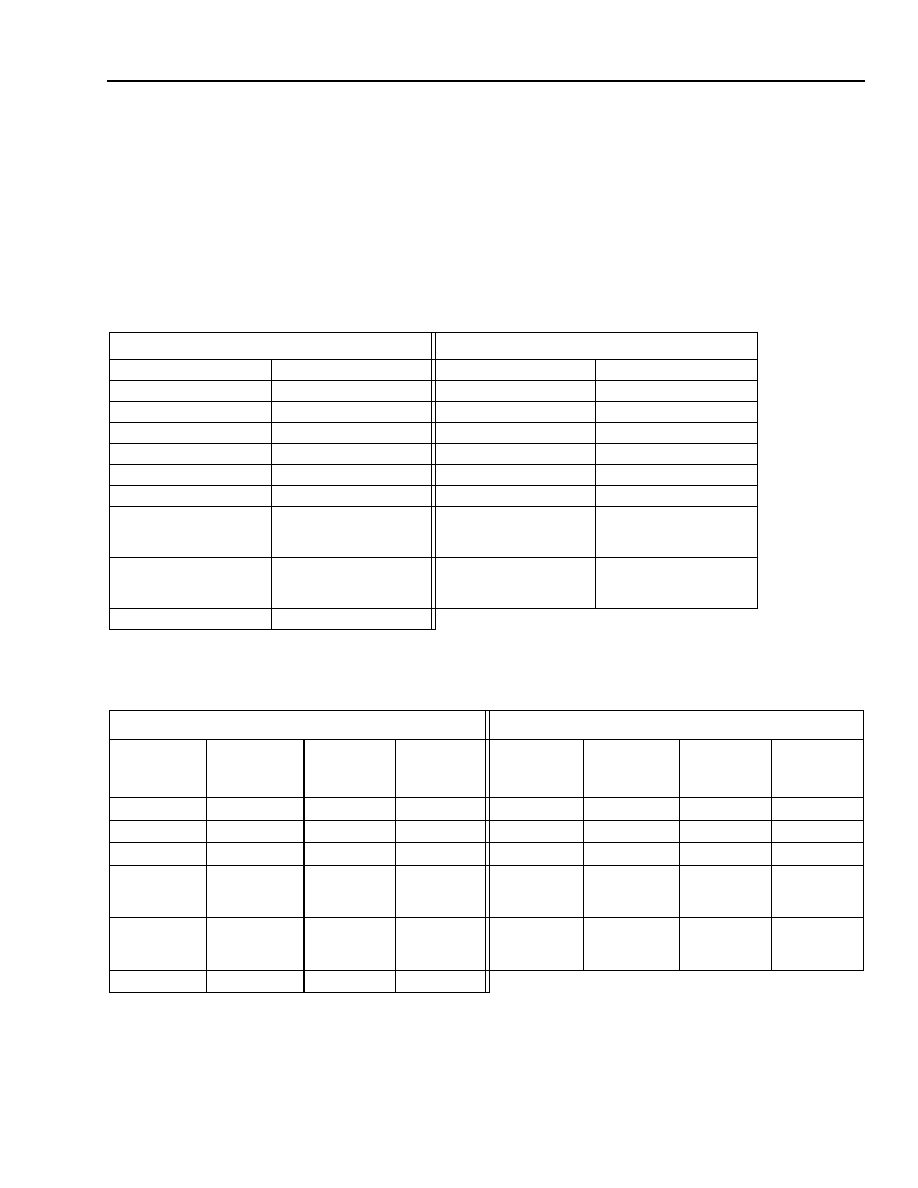

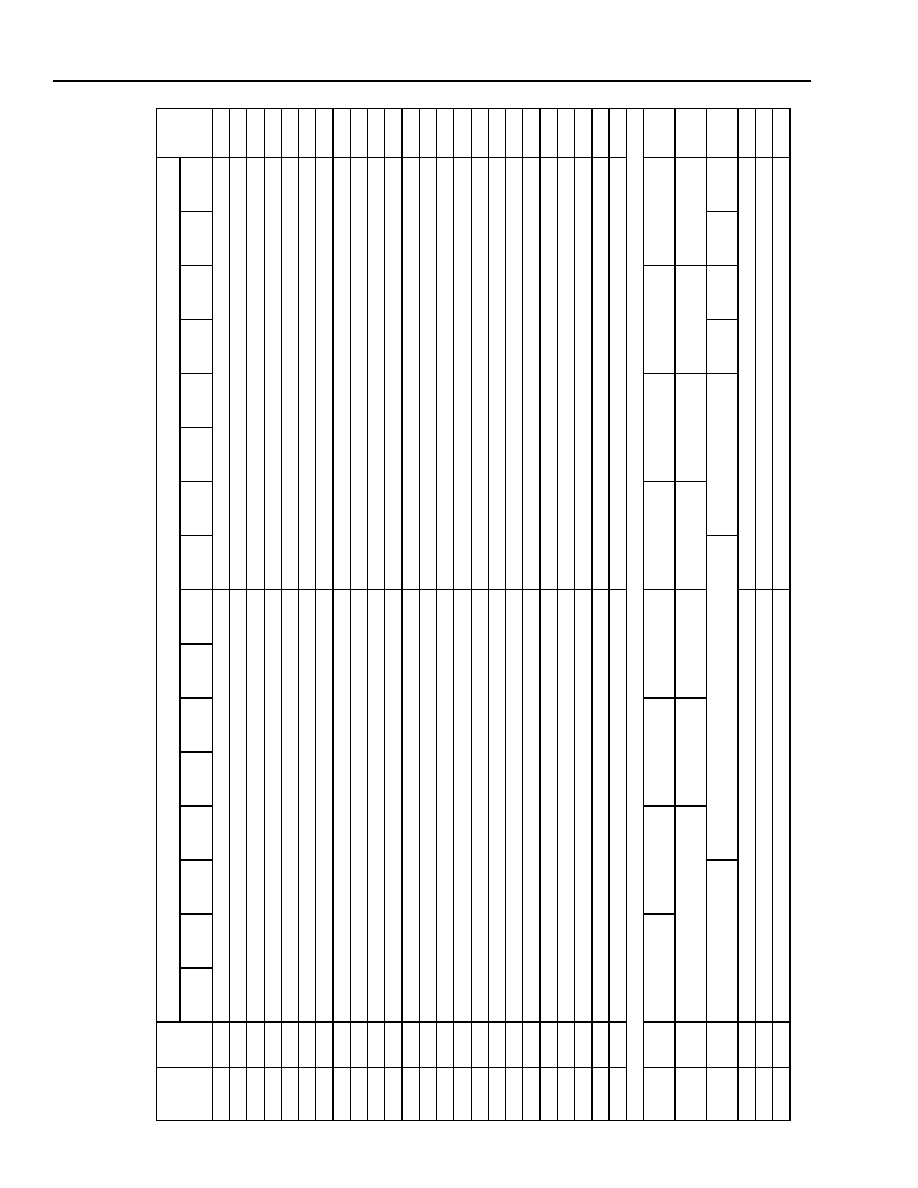

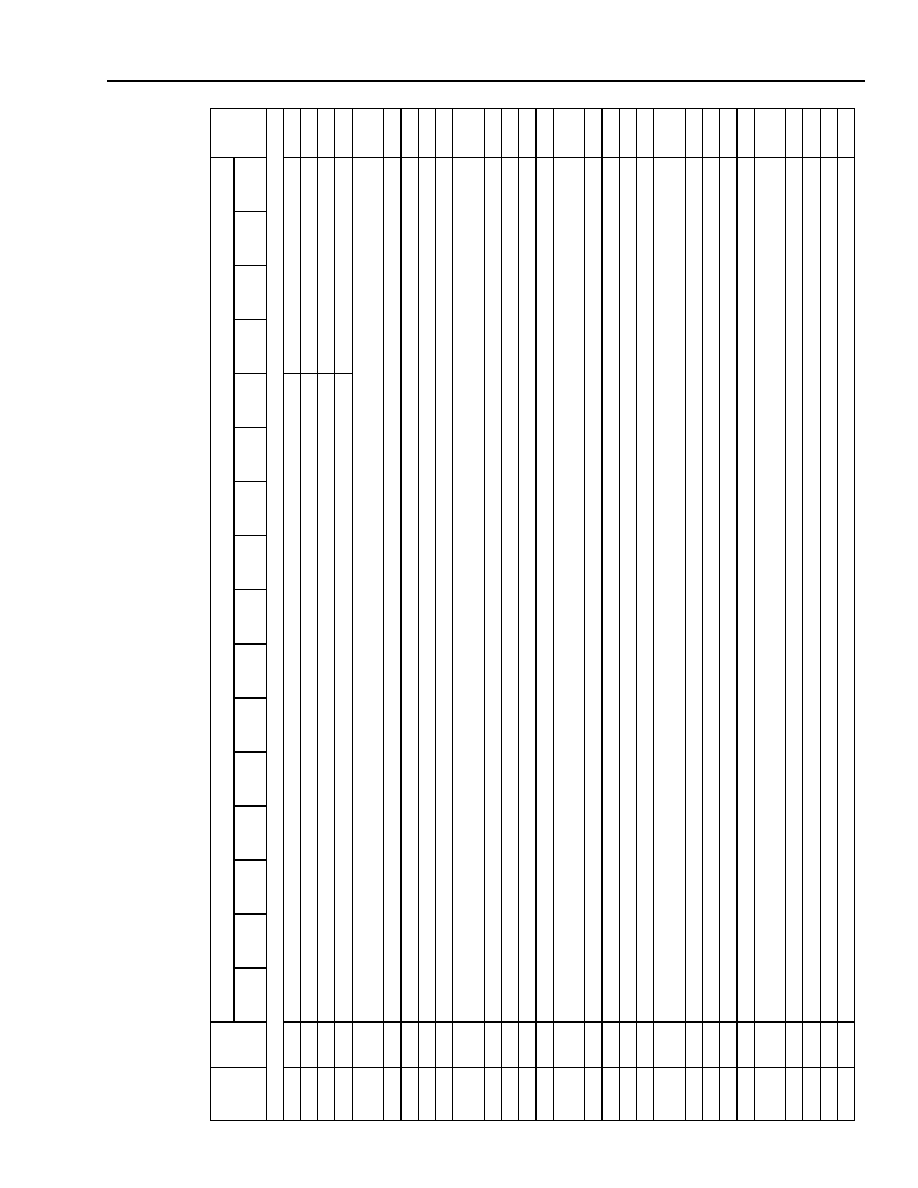

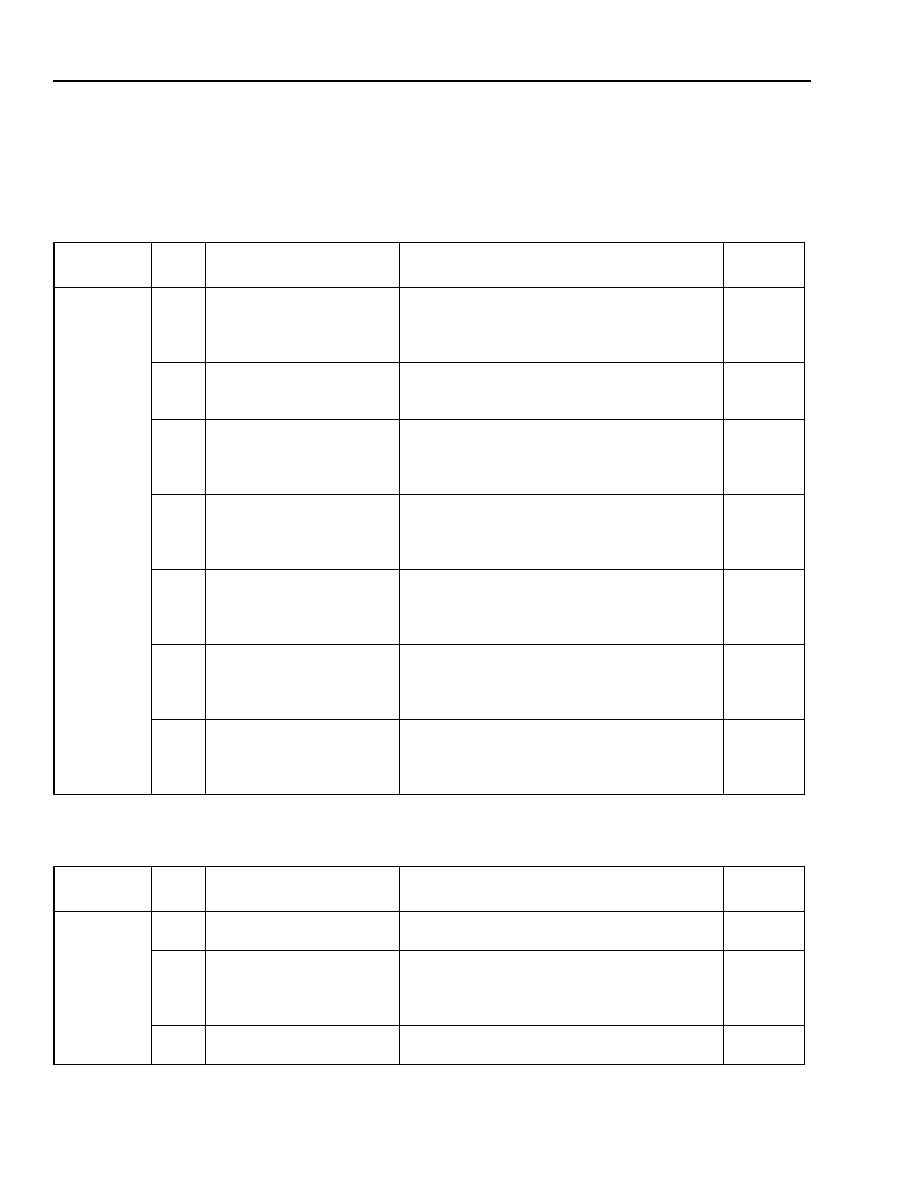

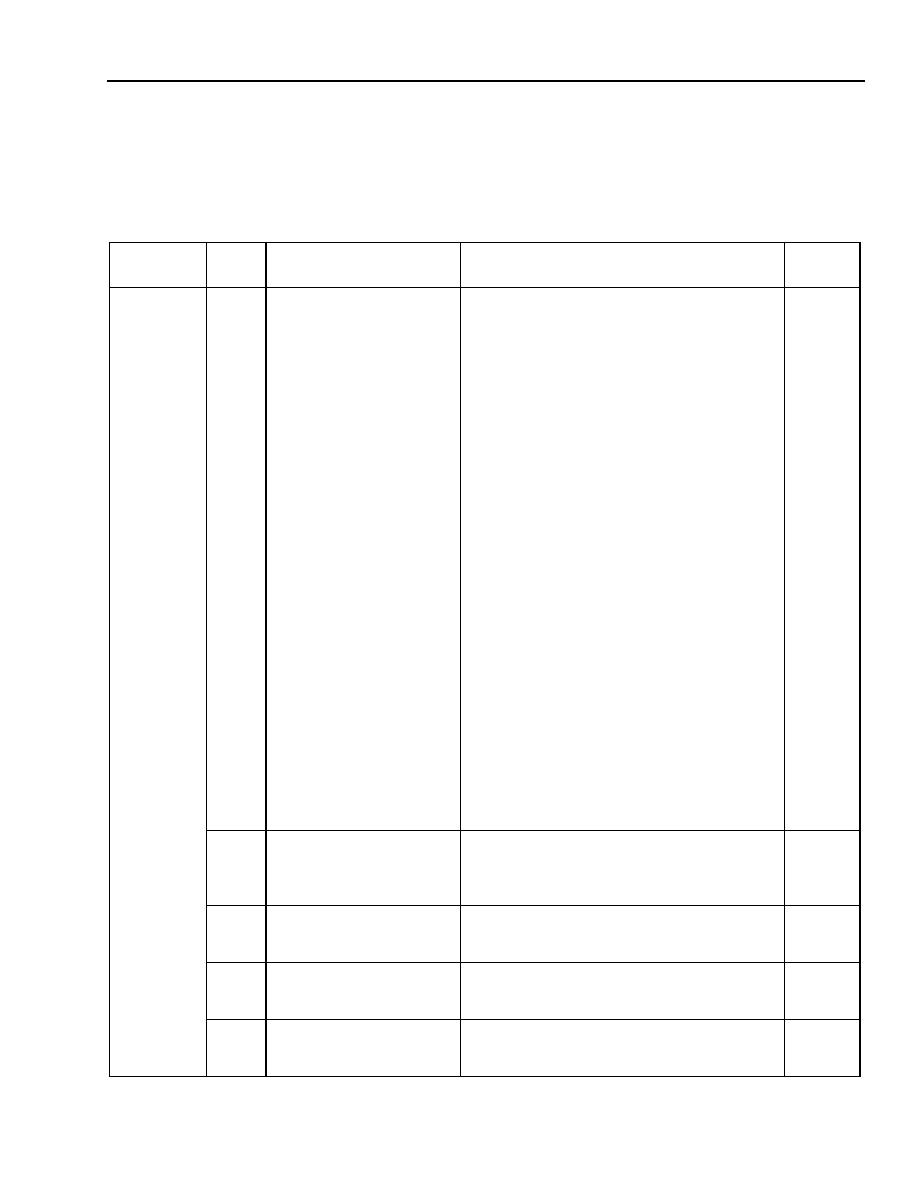

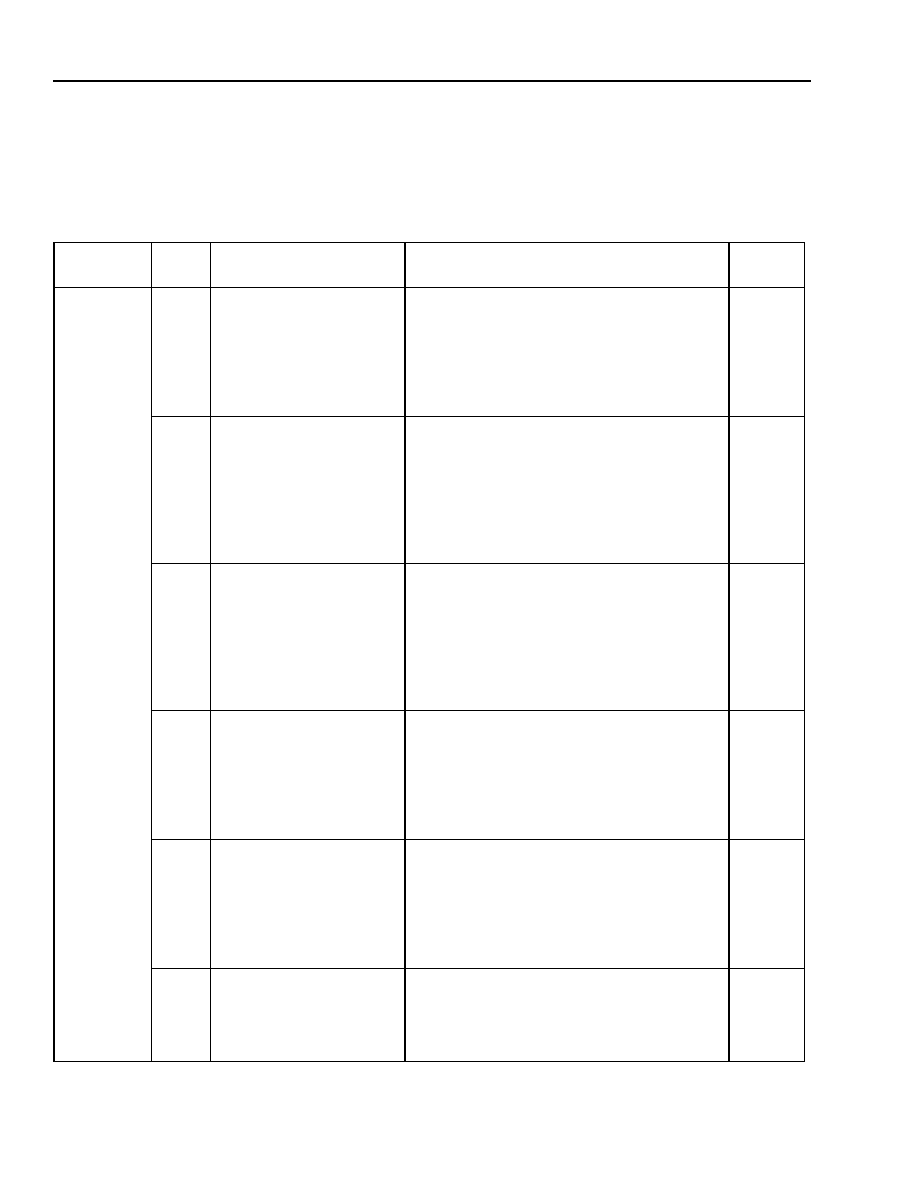

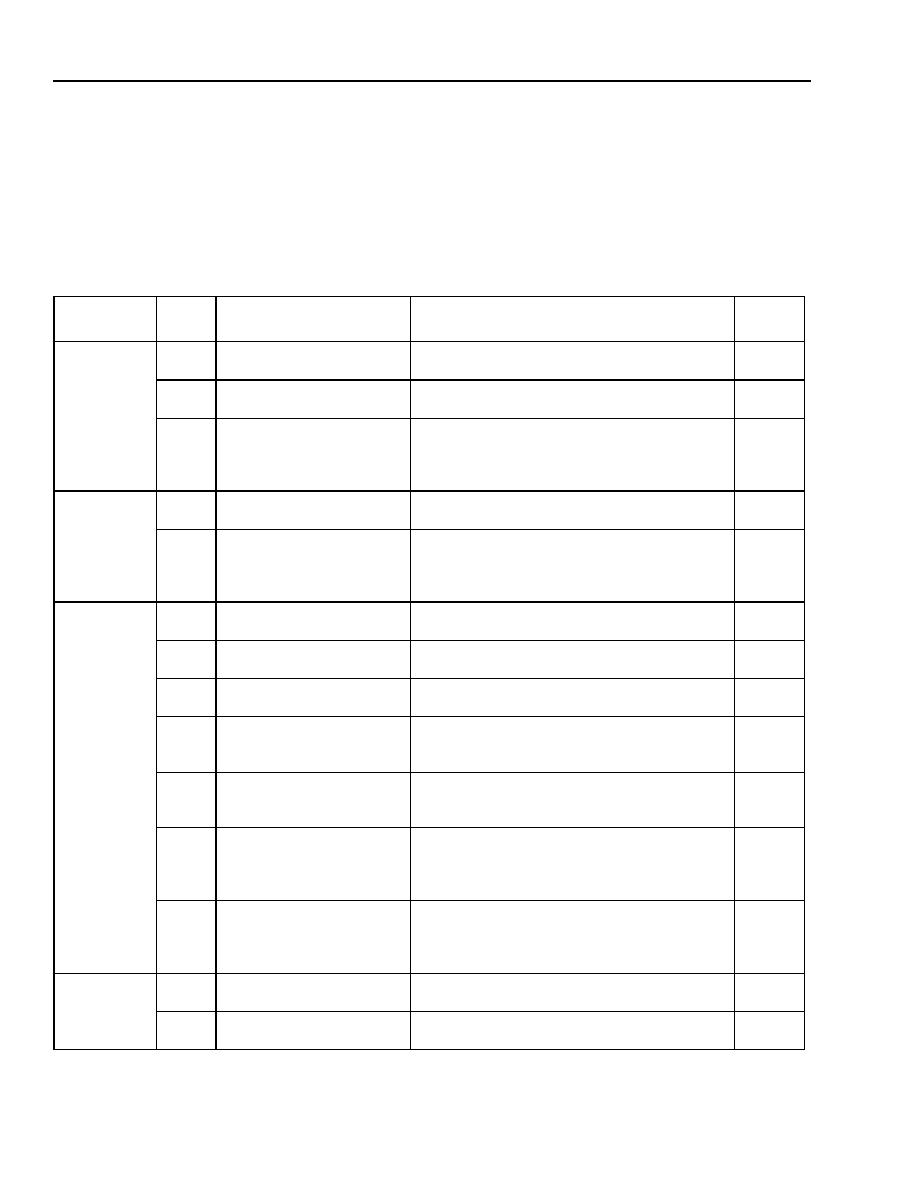

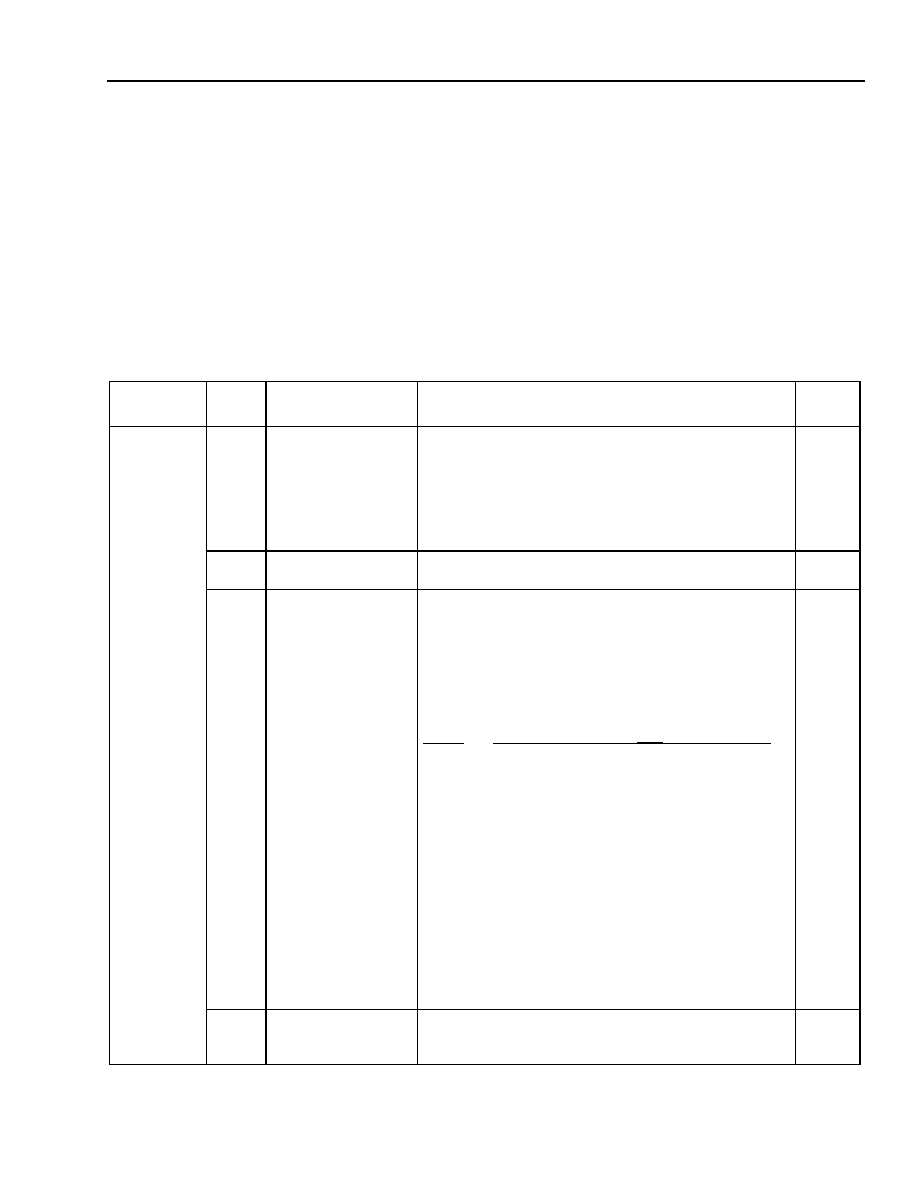

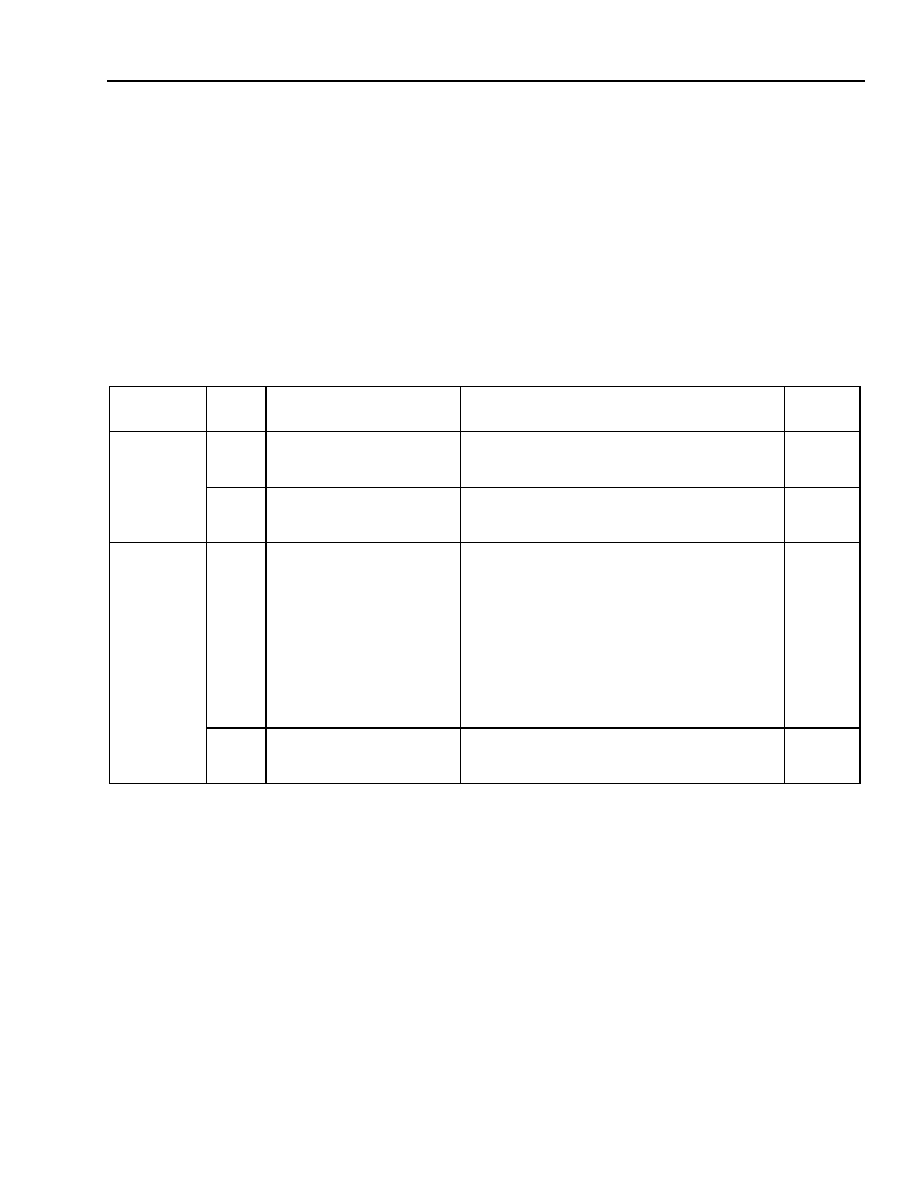

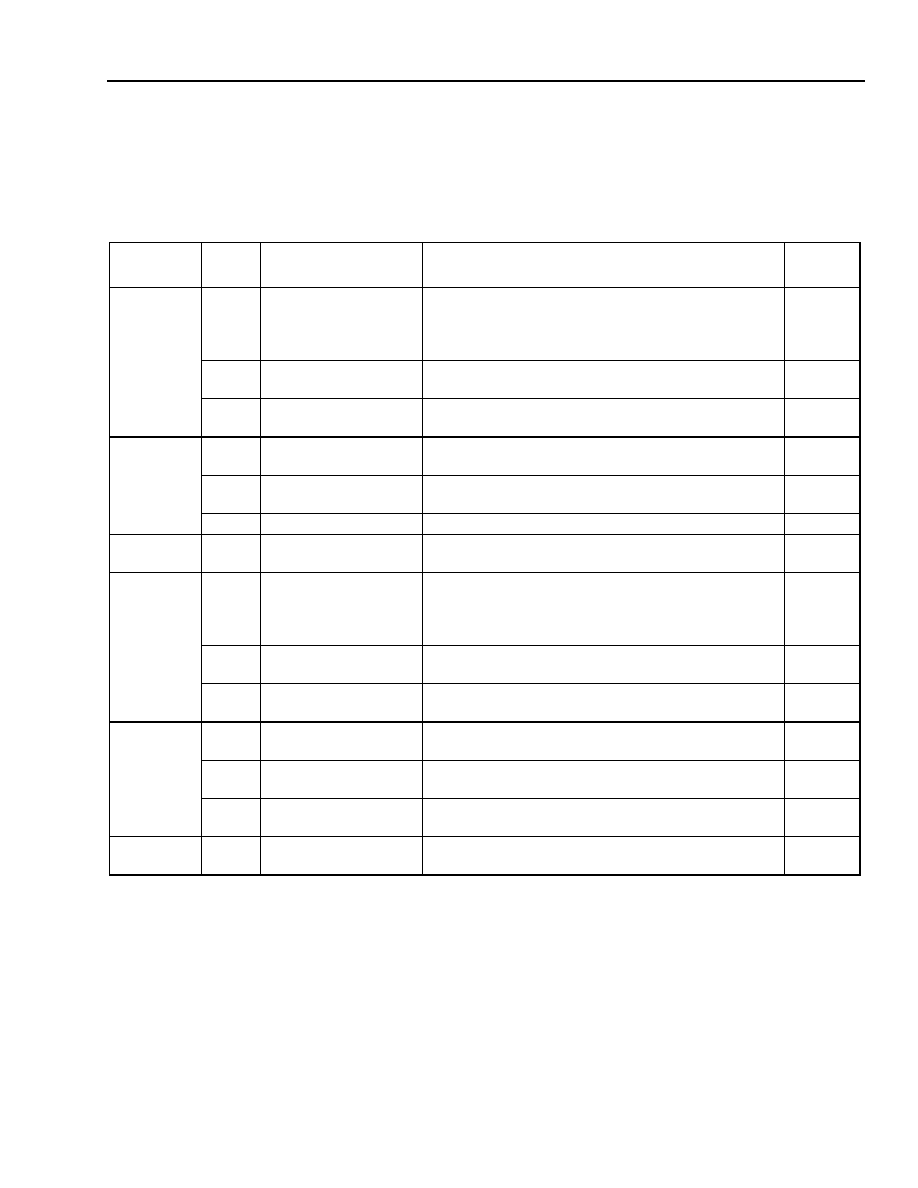

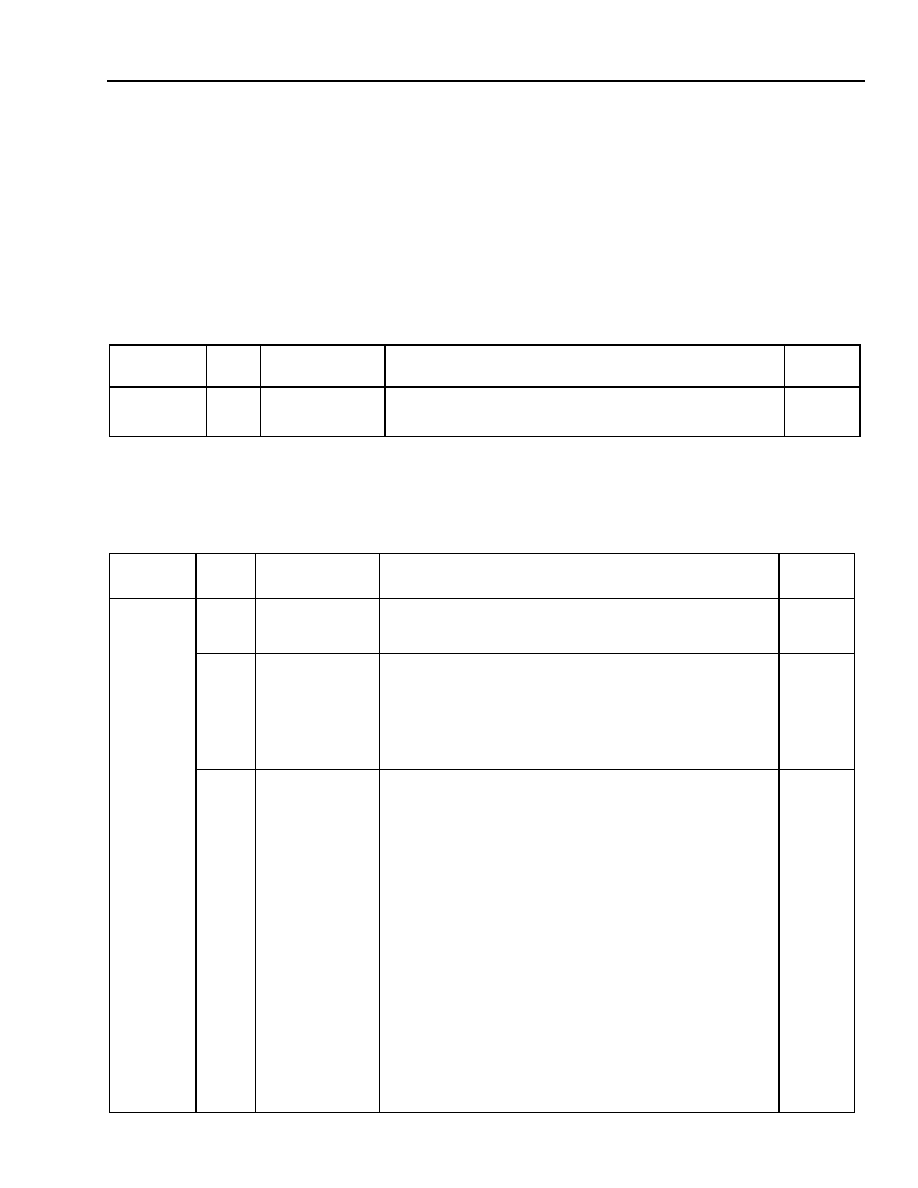

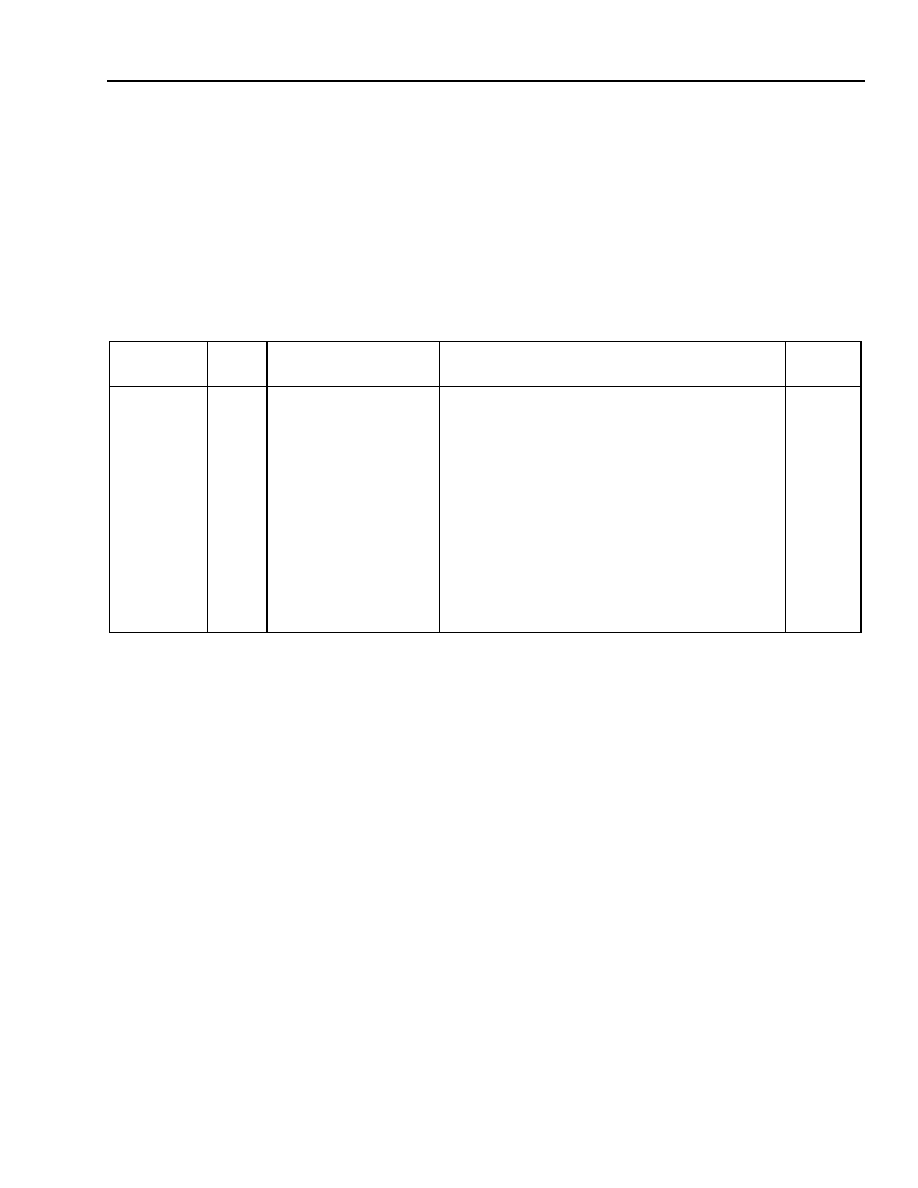

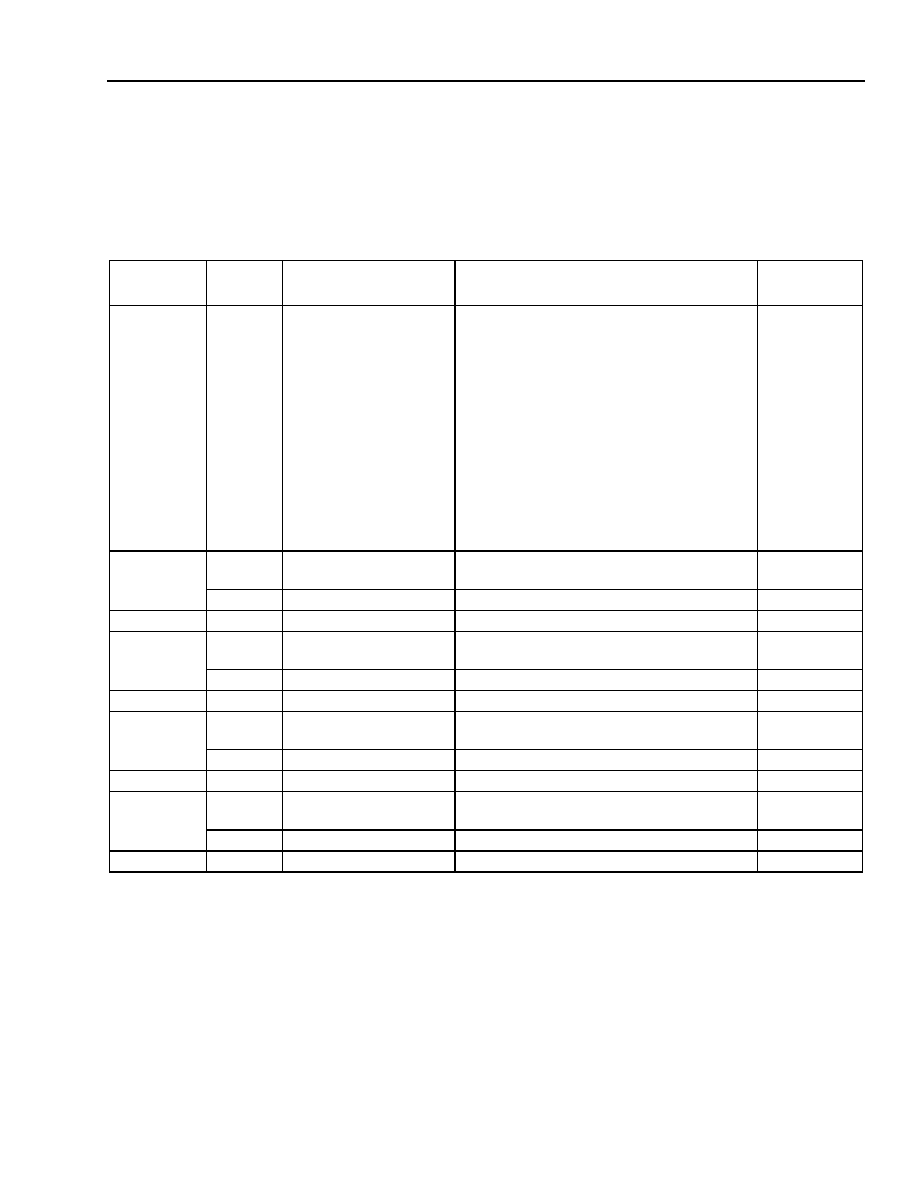

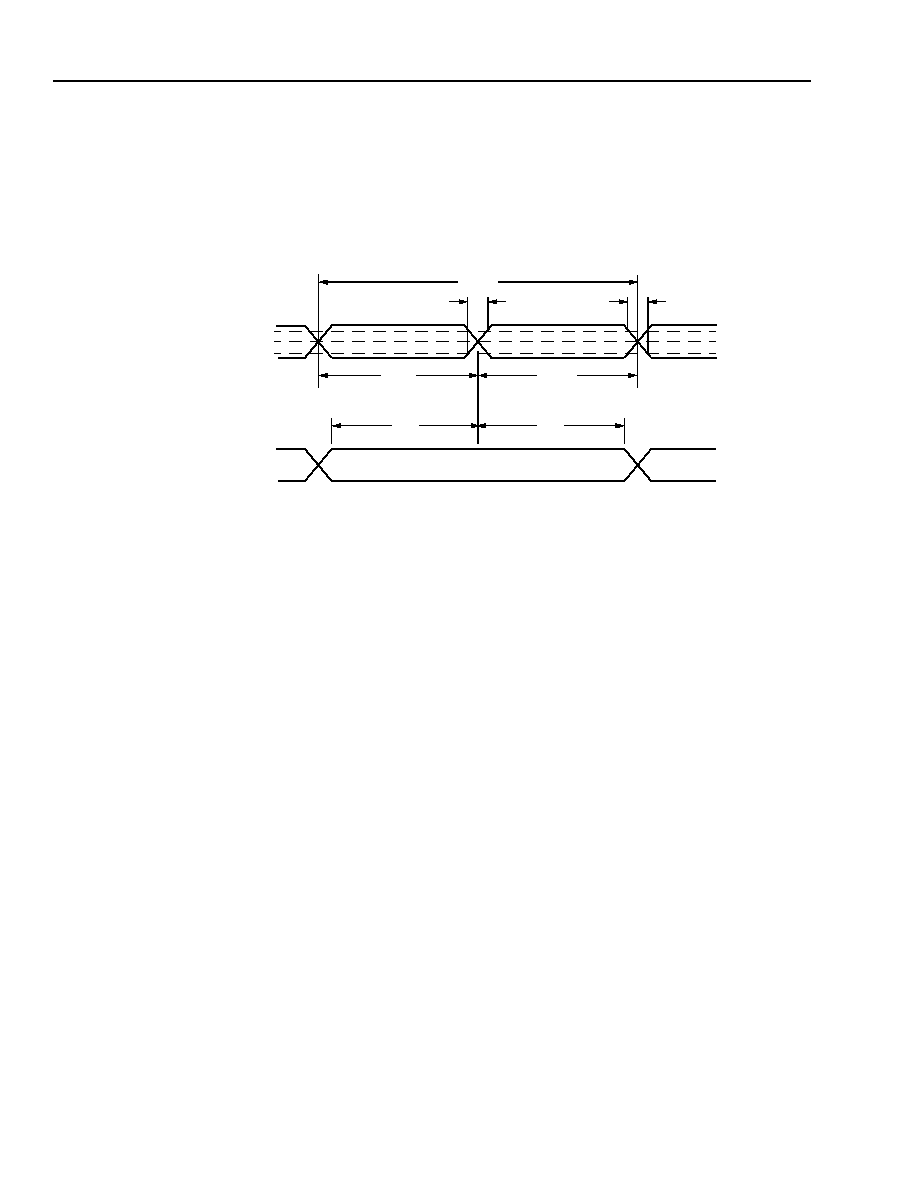

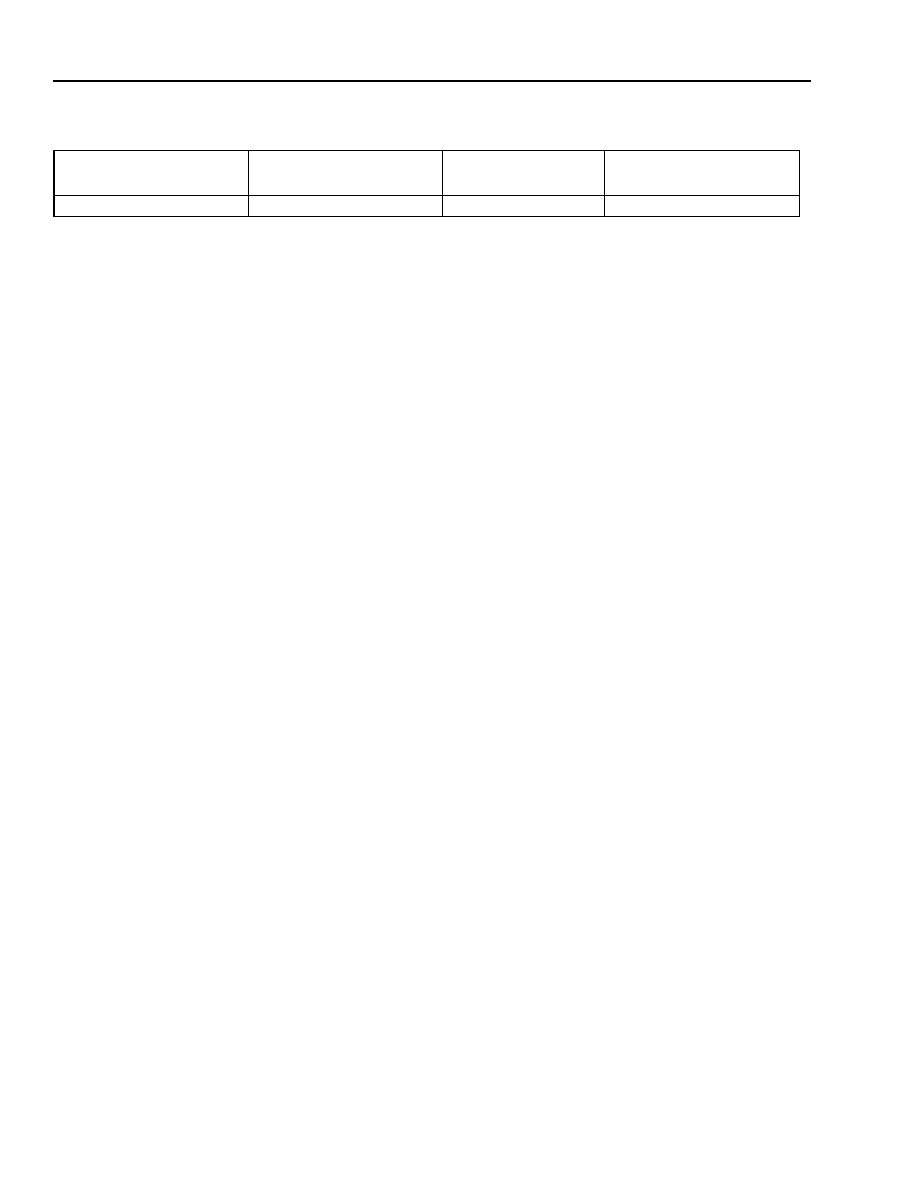

P4. Power Dissipation

The worst-case power dissipation of TDAT042G5 is currently estimated to be 7.5 W. The minimum and maximum

power dissipation is listed in Table 9, as well as the relative package thermal characteristics.

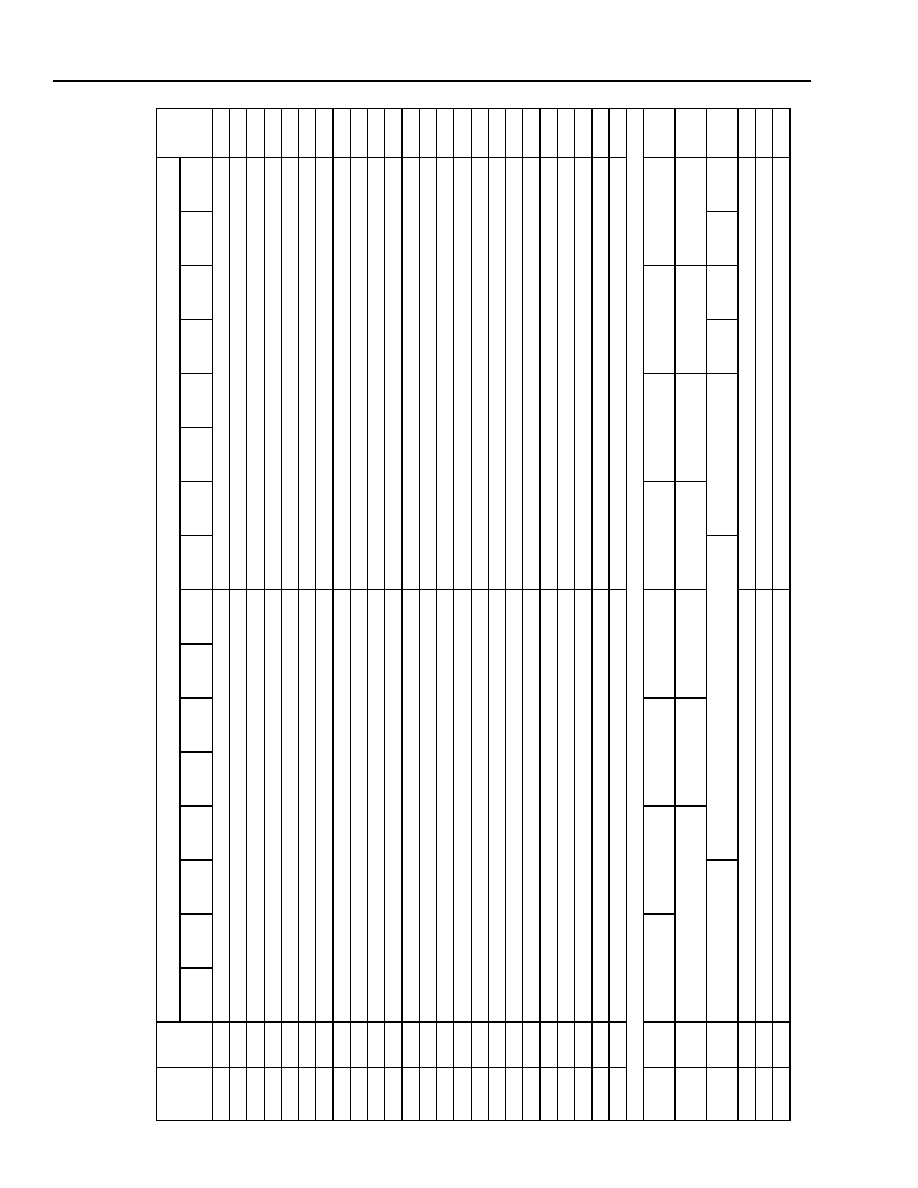

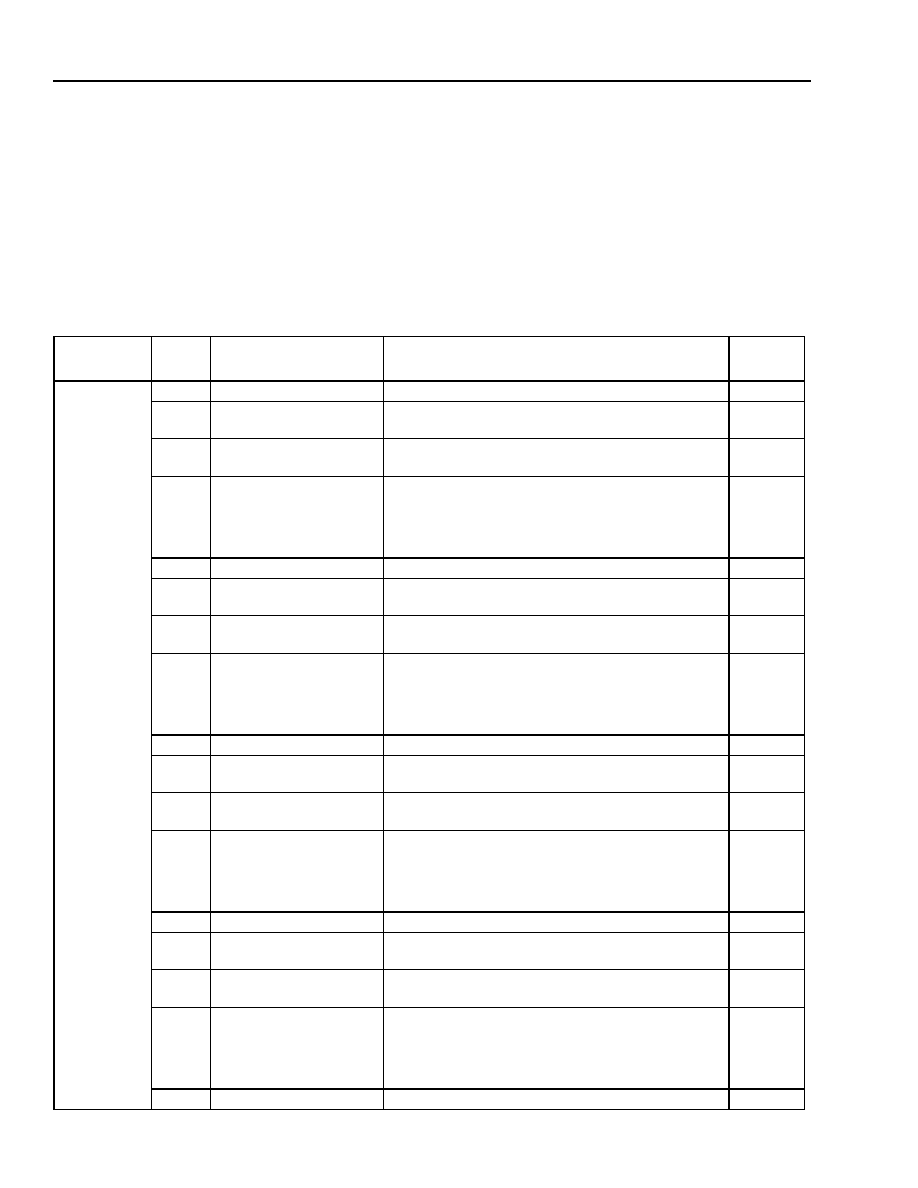

Table 9. Power Dissipation and Relative Package Thermal Characteristics

*

JA

= (T

J

≠ T

A

)/P

D

: T

J

= junction temperature, T

A

= ambient temperature of medium surrounding the package, P

D

= electrical power dissipated

by the device.

JC

= (T

J

≠ T

C

)/P

D

: T

J

= junction temperature, T

C

= package temperature (top, dead-center), P

D

= electrical power dissipated by the device.

Maximum junction temperature of TDAT042G5 is 125 ∞C. Therefore, maximum case temperature under natural

convection conditions must be less than approximately 50 ∞C, and in this case, an external heat sink is required.

References

Jeff Weiss, 600 LBGA Thermal Test Report, February 25, 1999.

HL250C 3.3 Volt 0.25

µ

m CMOS Standard-Cell Library (MN98-060ASIC-02), pages 2-2 and 2-3.

Workaround

An external heat sink is required.

Corrective Action

Power consumption will be addressed in future versions of the device.

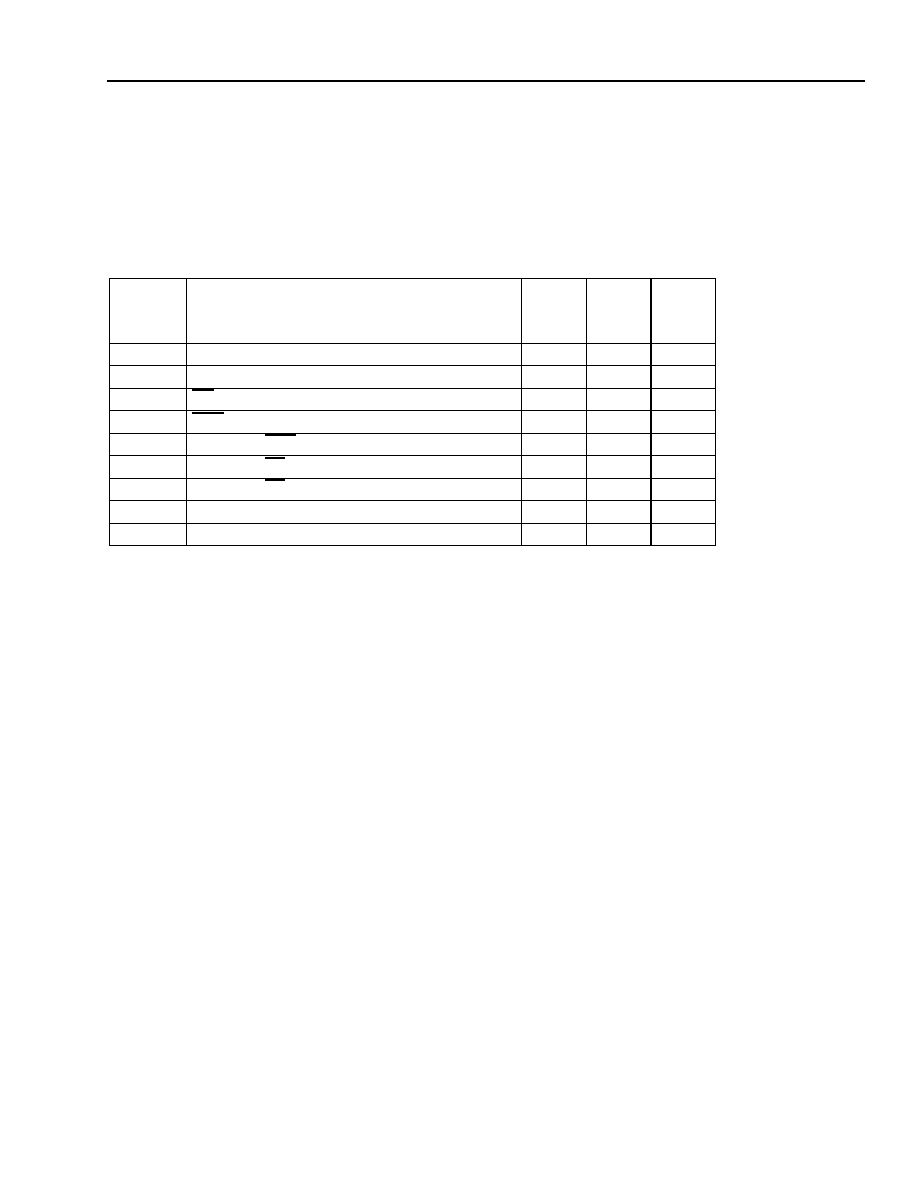

Parameter

Symbol

Test Conditions

Min

Typ

Max

Unit

Power Dissipation:

Minimum

Maximum

P

D

STS-3/STM-1 line rate

STS-12/STM-4 and STS-48/

STM-16 line rates

--

--

3

6

--

--

W

W

Thermal Performance

(JEDEC standard

conditions)*

JA

Standard JEDEC 4-layer PWB:

I

Standard natural convection

I

200 LFPM airflow

I

800 LFPM airflow

--

--

--

9

6.5

5

--

--

--

∞C/W

∞C/W

∞C/W

Correlation Factor

Between Die and Case

Temperatures

JC

Standard JEDEC 4-layer PWB:

I

Standard natural convection

I

200 LFPM airflow

I

800 LFPM airflow

--

--

--

0.3

0.4

0.5

--

--

--

∞C/W

∞C/W

∞C/W

24

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Data Addenda

DA1. Incorrect PT Control Register Mapping

TDAT042G5 SONET/SDH 155/622/2488 Mbits/s Data Interface Advance Data Sheet, Rev. 3 lists the following bit

mapping for PT control registers 0x0AAA, 0x0AB2, 0x0ABA, and 0x0AC2:

bit #9 TRDIP_PLMPINH[A--D]

bit #8 TRDIP_UNEQUIPINH[A--D]

bit #7 TRDIP_LCDINH[A--D]

The correct bit mapping is the following:

bit #9 TRDIP_LCDINH[A--D]

bit #8 TRDIP_PLMPINH[A--D]

bit #7 TRDIP_UNEQUIPINH[A--D]

Workaround

No workaround is available for this condition.

Corrective Action

This correct bit mapping will be included in July 2000 of the advance data sheet.

DA2. Variable Change

TDAT042G5 SONET/SDH 155/622/2488 Mbits/s Data Interface Advance Data Sheet, Rev. 3 lists the variable

TRD_LCDINH[A--D], which has been changed to TRD_LCD[A--D] in the January 2001 revision.

Workaround

No workaround is available for this condition.

Corrective Action

This correction will be included in January 2001 of the advance data sheet.

Agere Systems Inc.

25

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

AY99-013SONT-2 Replaces AY99-013SONT to Incorporate the Following Updates

1. Page 1, SP1. Required Provisioning Sequence and Clocks, added new issue.

2. Page 8, DE4. Channel Provisioning, added new issue.

3. Page 9, DE5. Packet Behavior in POS/SDL Mode--Dry Mode, added new issue.

4. Page 15, UT8. Far-End Loopback Bandwidth Limitations, added new issue.

5. Page 16, advance data sheet document number corrected.

AY99-013SONT-3 Replaces AY99-013SONT-2 to Incorporate the Following Updates

1. Page 1, notice that the advisory issues still apply to the advance data sheet which has just been updated.

AY99-013SONT-4 Replaces AY99-013SONT-3 to Incorporate the Following Updates

1. Replaced OC- designation with STS- and STM- throughout advisory.

2. Page 2, SP2. Behavior During Loss of Receive Line Clock, added new issue.

3. Page 2, SP3. PT Register Addressing, added new issue.

4. Page 4, CR1. Clear on Read/Clear on Write Behavior, added new issue.

5. Page 5, PT2. Clear-After-Write Behavior of Signal Degrade Clear Bits, corrected description.

6. Page 6, PT4. SS Pointer Interpretation Algorithm, added new issue.

7. Page 7, PT5. Delta/Event Registers in COR Mode, added new issue.

8. Page 7, DE2. Incorrect ATM Loss of Cell Delineation (LCD) Implementation, identified the specific ITU stan-

dard with which the LCD implementation does not comply.

9. Page 8, DE4. Channel Provisioning, Table Transmit DE Egress and Sequencer Cell State Registers, corrected

register 0x102D to 0x1021.

10. Page 9, DE5. Packet Behavior in POS/SDL Mode--Dry Mode, identified dry mode issues.

11. Page 10, DE6. Incorrect ATM Out of Cell Delineation (OCD) Implementation, added new issue.

12. Page 10, DE7. Incorrect Frame State of ATM Data Streams, added new issue.

13. Page 11, DE8. Clearing DE Interrupt Register (0x1002), added new issue.

14. Page 11, DE9. Single Packet Transmission in HDLC-CRC, SDL-CRC, and PPP Modes, added new issue.

15. Page 12, DE10. Excessive HDLC Flag Characters, added new issue.

16. Page 13, UT2. UTOPIA Clock Limitations, clarified wording.

17. Page 14, UT4. FIFO Overflow and Error Reporting, clarified wording.

18. Page 16, UT9. Clock Requirements for MPHY Modes, added new issue.

19. Page 16, UT10. Egress Packet Mode Overflows, added new issue.

20. Page 17, UT11. Clearing UT Interrupt Register, added new issue.

21. Page 17, UT12. Incorrect Implementation of POS Multi-PHY Mode, added new issue.

22. Page 21, OHP1. Maximum BER Count, added new issue. In addition, differentiated OHP bits from PT bits with

the same name; the names will be corrected in revision 4 of the advance data sheet.

26

Agere Systems Inc.

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

AY99-013SONT-4 Replaces AY99-013SONT-3 to Incorporate the Following Updates

(continued)

23. Page 21, OHP2. RDI-L Reporting, added new issue.

24. Page 22, OHP3. M1 Error Counter in STS-48/STM-16 Mode, added new issue.

25. Page 22, removed issue P1. Pin 5 (Previously JTEST) Is No Connect (NC). Pin F5 was corrected to NC in the

accompanying advance data sheet, DS98-193SONT-3.

26. Page 22, removed issue P2. Modified Pinout and Power Supply Configuration--Future Versions. Plans for 2.5 V

power ring implementation considered, but no schedule available at this time.

27. Page 22, removed issue P3. Change to TDAT042G5 Version 1 Pinout. Listed pins have been corrected to NC in

the accompanying advance data sheet, DS98-193SONT-3.

28. Page 24, DA1. Incorrect PT Control Register Mapping, added new issue.

AY01-015SONT (Replaces AY99-013SONT-4 and Must Accompany

DS98-193SONT-4) Replaces AY99-013SONT-4 to Incorporate the Following

Updates

Change List

This change list summarizes changes across the various versions of this document starting with the version dated

1/25/01.

1/25/01

1. Page 6, PT3. Remote Defect Indicator (RDI) Behavior, clarified wording.

2. Page 12, DE 11. ATM Header Error Correction (HEC) Behavior, added entire section to document.

1/29/01

1. Page 24, DA1. Incorrect PT Control Register Mapping, changed corrective action description to include the July

2000 date.

2. Page 24, DA2. Variable Change, added entire section to document.

2/13/01

1. Page 12, updated issue on DE 11. ATM Header Error Correction (HEC) Behavior, to include more information.

2. Page 17, added issue UT13. Invalid Extra Cycle Between EOP and SOP in CRC-16/32 Mode.

3. Page 18, added issue UT14. Nonfunctional RxPA Signal for Channels B and D in Packet Direct Status MPHY

Mode.

3/1/01

1. Page 12, removed DE 11 from document.

2. Page 18, UT14. Nonfunctional RxPA Signal for Channels B and D in Packet Direct Status MPHY Mode, added

workaround to document.

Agere Systems Inc.

27

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Notes

Advisory

May 2001

for Version 1 and 1A of the Device

TDAT042G5 Device Advisory

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Copyright © 2001 Agere Systems Inc.

All Rights Reserved

Printed in U.S.A.

May 2001

AY01-015SONT (Replaces AY99-013SONT-4 and Must Accompany DS98-193SONT-4)

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET:

http://www.agere.com

E-MAIL:

docmaster@micro.lucent.com

N. AMERICA:

Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA PACIFIC: Agere Systems Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

CHINA:

Agere Systems (Shanghai) Co., Ltd., 33/F Jin Mao Tower, 88 Century Boulevard Pudong, Shanghai 200121 PRC

Tel. (86) 21 50471212, FAX (86) 21 50472266

JAPAN:

Agere Systems Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700

EUROPE:

Data Requests: DATALINE: Tel. (44) 7000 582 368, FAX (44) 1189 328 148

Technical Inquiries:GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot),

FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 3507670 (Helsinki),

ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Data Sheet

May 2001

TDAT042G5 SONET/SDH

155/622/2488 Mbits/s Data Interface

Features

I

Point-to-point path termination device for interface

termination.

I

Versatile IC supports 155/622/2488 Mbits/s

SONET/SDH interface solutions for packet over

SONET (POS), asynchronous transfer mode

(ATM), or simplified data link (SDL) for data over

fiber applications.

I

Supports point-to-point and multi-PHY UTOPIA.

I

Low-power 3.3 V operation, CMOS technology.

I

High-speed I/O is LVPECL. All other logic has 5 V

tolerant TTL-level inputs.

I

≠40 ∞C to +85 ∞C temperature range.

I

600 LBGA package.

SONET/SDH Interface

I

Termination of quad STS-3/STM-1, quad STS-12/

STM-4, or single STS-48/STM-16.

I

Supports overhead processing for transport and

path overhead bytes.

I

Optional insertion and extraction of overhead bytes

via serial overhead interface.

I

Full path termination and SPE extraction/insertion.

I

SONET/SDH compliant condition and alarm

reporting.

I

Handles all concatenation levels of STS-3c

through STS-48c (in multiples of 3; i.e., 3c, 6c, 9c,

etc.), STM-1 through STM-16.

I

Built-in diagnostic loopback modes.

I

Compliant with the following Telcordia

(Bellcore),

ANSI*, and ITU standards:

-- GR-253 CORE: SONET Transport Systems:

Common Generic Criteria.

*ANSI is a registered trademark of American National Standards

Institute, Inc.

Telcordia is a registered trademark of Bell Communications

Research, Inc.

-- ITU-T G.707: Network Node Interface for the

Synchronous Digital Hierarchy.

-- ITU-T G.803: Architecture of Transport Net-

works Based on the Synchronous Digital Hier-

archy.

-- T1.105: SONET-Basic Description including

Multiplex Structure, Rates, and Formats.

-- T1.105.02 SONET-Payload Mappings.

-- T1.105.03 SONET-Jitter at Network Interfaces.

-- T1.105.06 SONET Physical Layer Specifica-

tions.

-- T1.105.07 SONET-Sub-STS-1 Interface Rates

and Formats Specification.

-- ITU-T I.432: B-ISDN User-Network Interface-

Physical Layer Specification.

-- IETF RFC 2615 (June 1999): PPP over

SONET/SDH.

-- IETF RFC 1661: The Point-to-Point Protocol

(PPP).

-- IETF RFC 1662: PPP in HDLC-like Framing.

Data Processing

I

Provisionable data engine supports payload inser-

tion/extraction and CRC-16/-32 generation/verifica-

tion for ATM cell or PPP, SDL, or HDLC streams.

I

Maintains counts for cell/packet traffic (e.g., total

number of cells, number of discarded cells).

I

Integrated UTOPIA Level 2- and UTOPIA Level 3-

compatible ATM physical layer interface with

packet extensions for all test and operations.

I

Insertion and extraction of up to four separate data

channels.

I

Compliant with 1998: ATM Forum, ITU standards,

and IETF standards.

Microprocessor Interface

I

16-bit address and 16-bit data interface with up to

66 MHz read and write access.

I

Compatible with most industry-standard proces-

sors.

Please see the Description section, page 11, for

details.

Table of Contents

Contents

Page

4

Agere Systems Inc.

Data Sheet

May 2001

155/622/2488 Mbits/s Data Interface

TDAT042G5 SONET/SDH

Features ................................................................................................................................................................... 3

SONET/SDH Interface ........................................................................................................................................... 3

Data Processing ..................................................................................................................................................... 3

Microprocessor Interface ....................................................................................................................................... 3

Description .............................................................................................................................................................. 11

Pin Information ....................................................................................................................................................... 11

Overview ................................................................................................................................................................. 45

ATM/HDLC/HDLC-CRC/PPP Support ................................................................................................................. 47