Document Outline

- Features

- Description

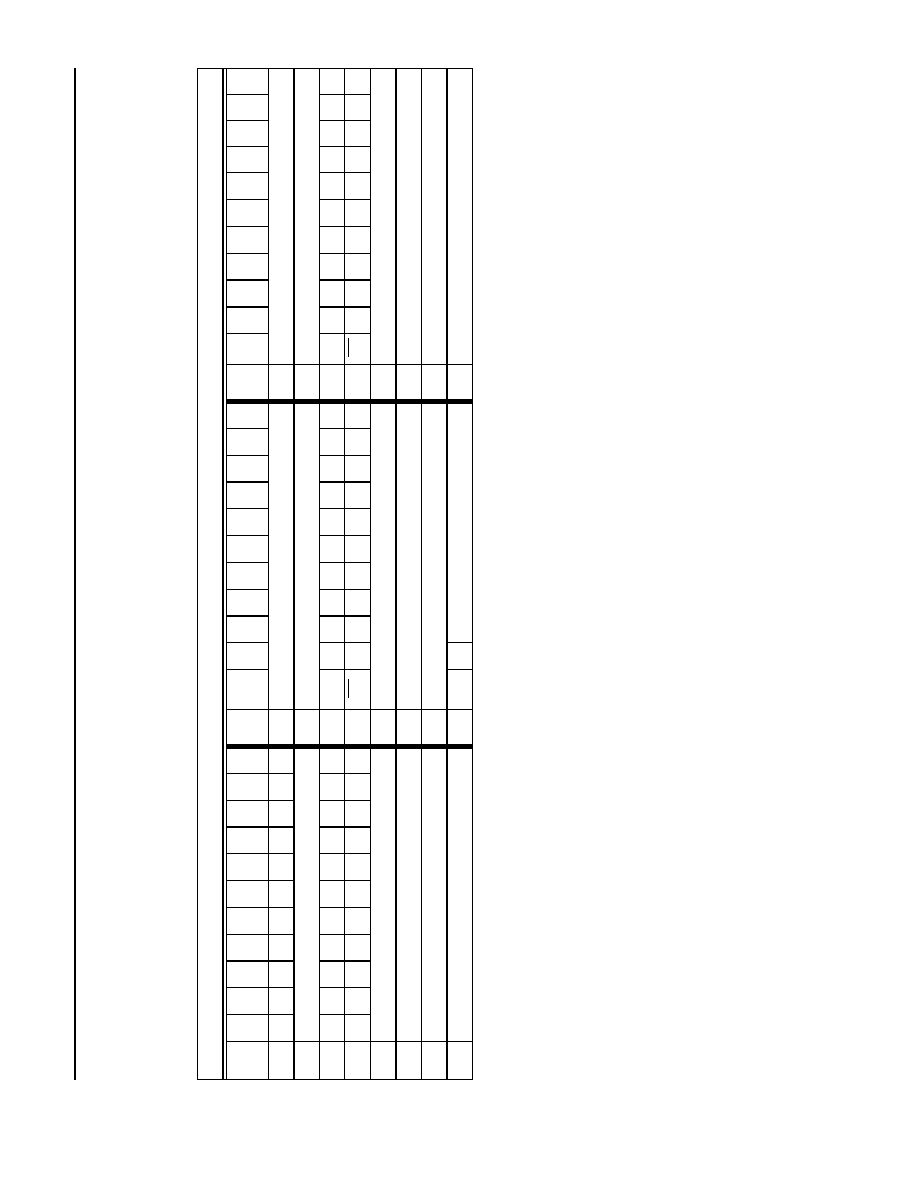

- Target Applications Supported

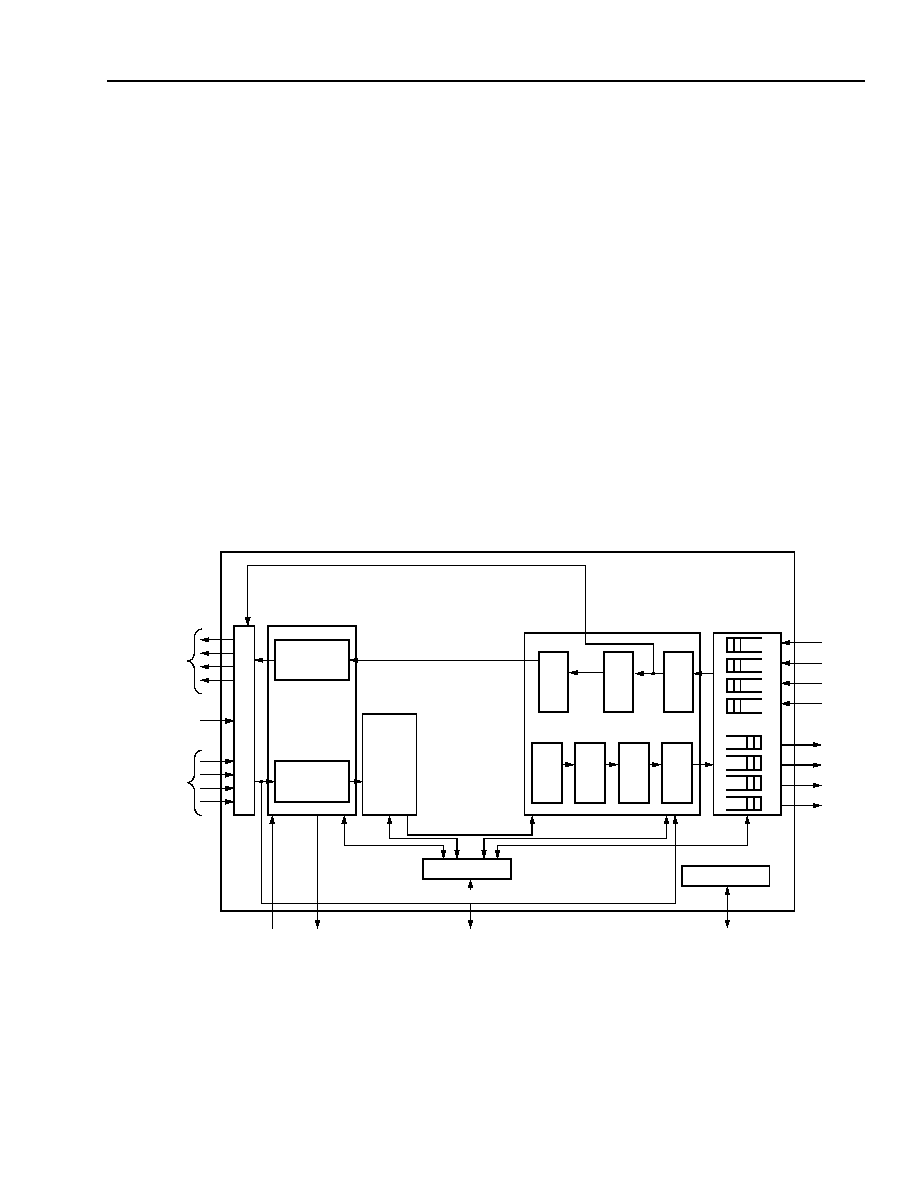

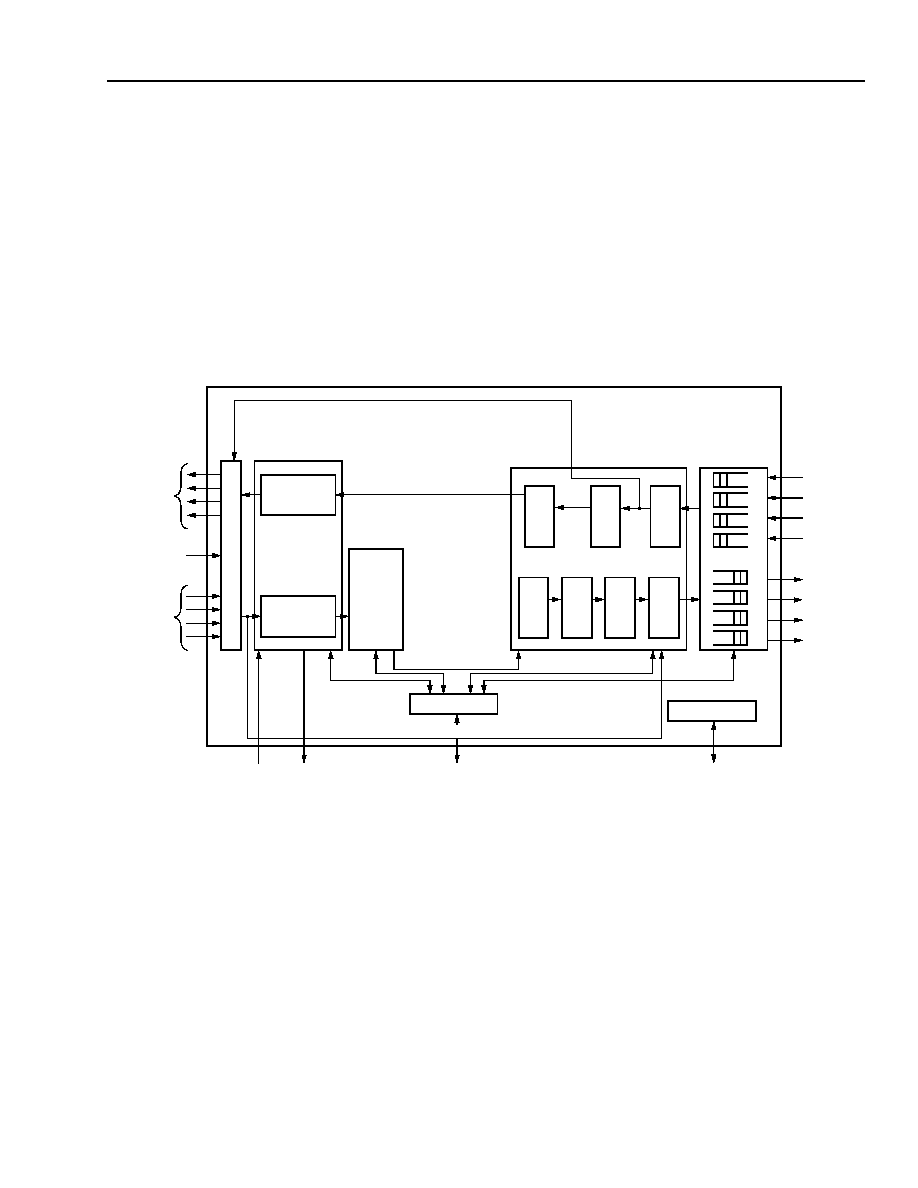

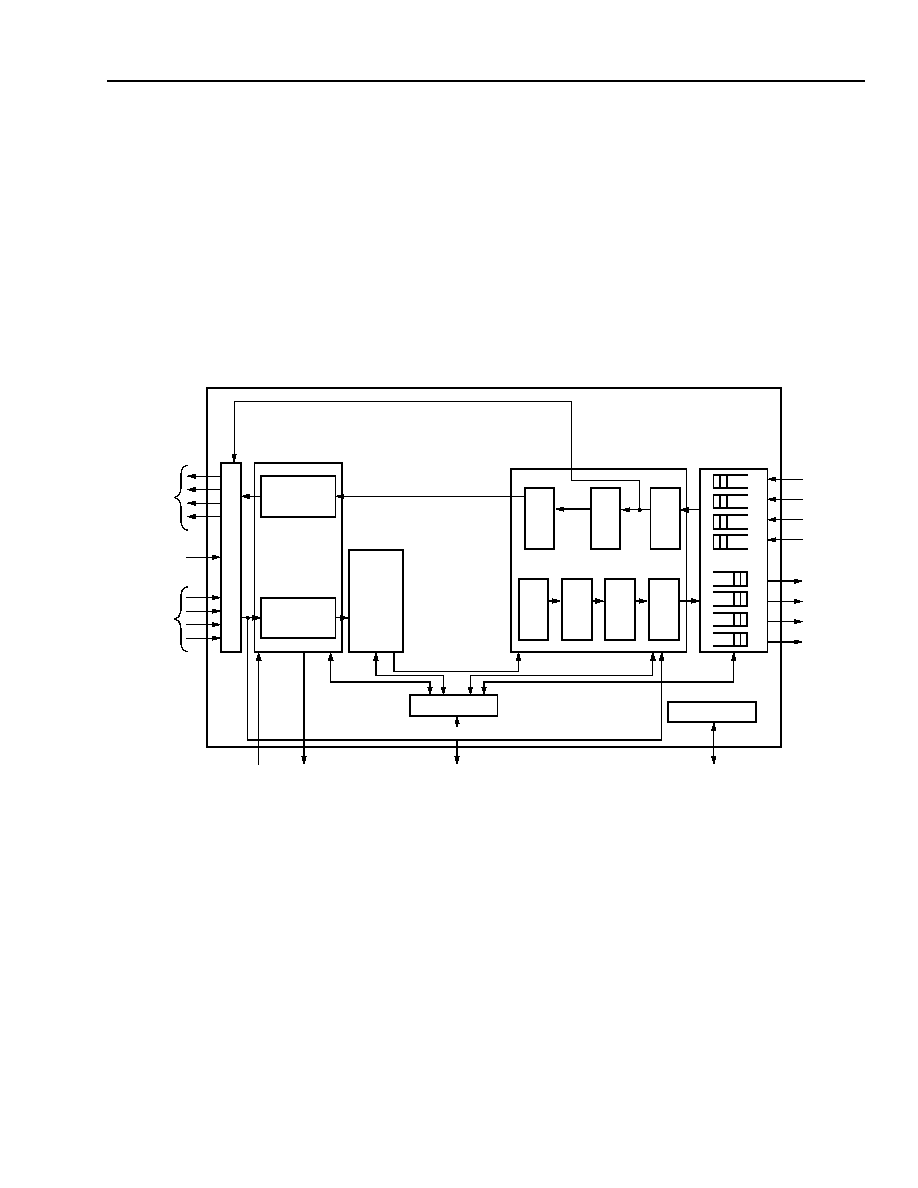

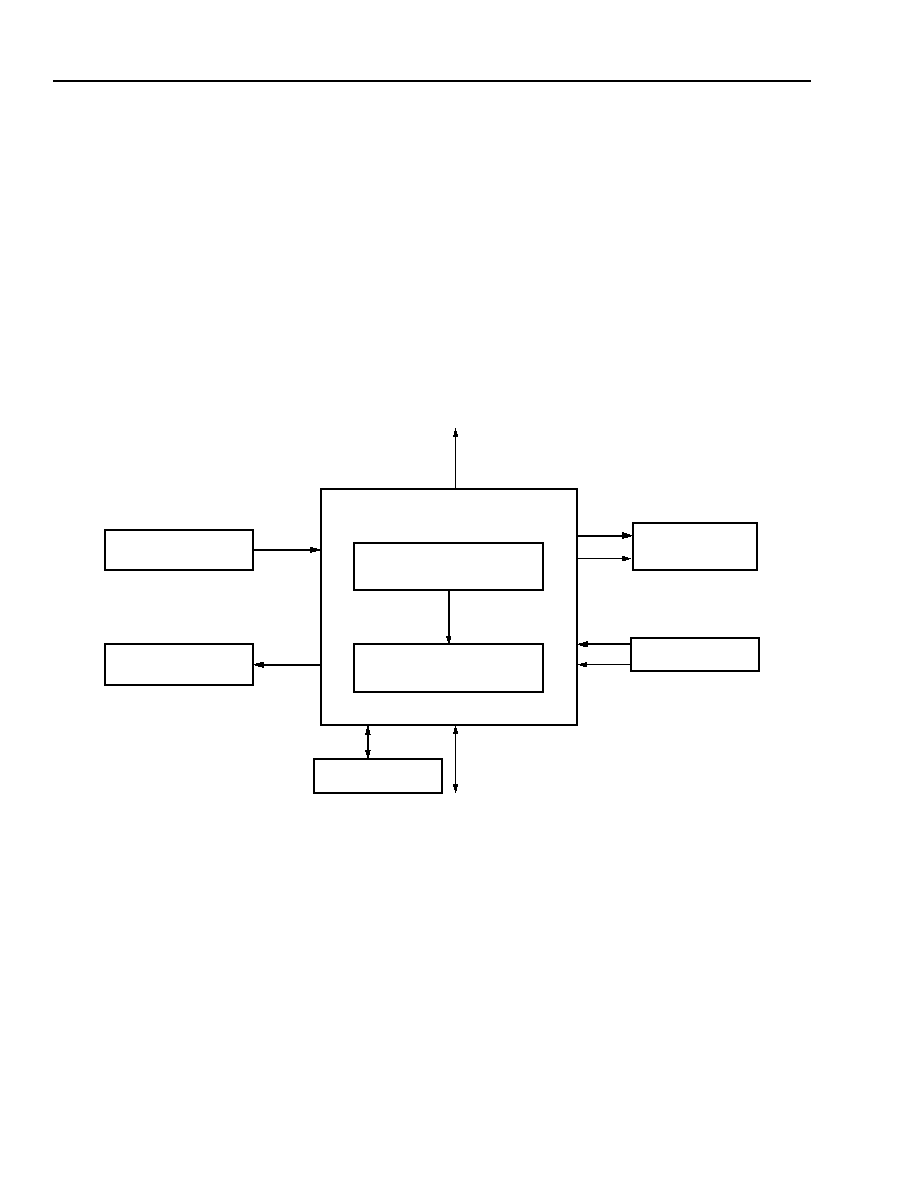

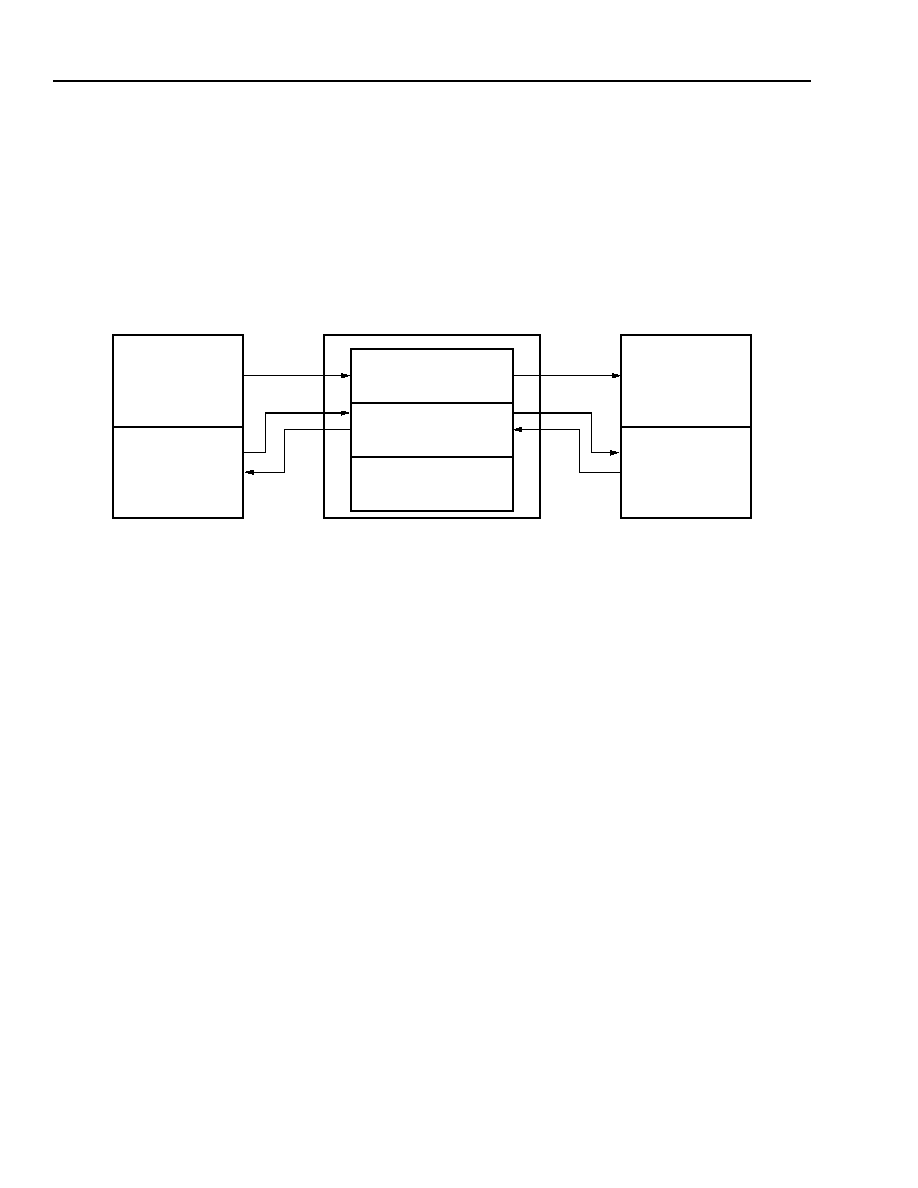

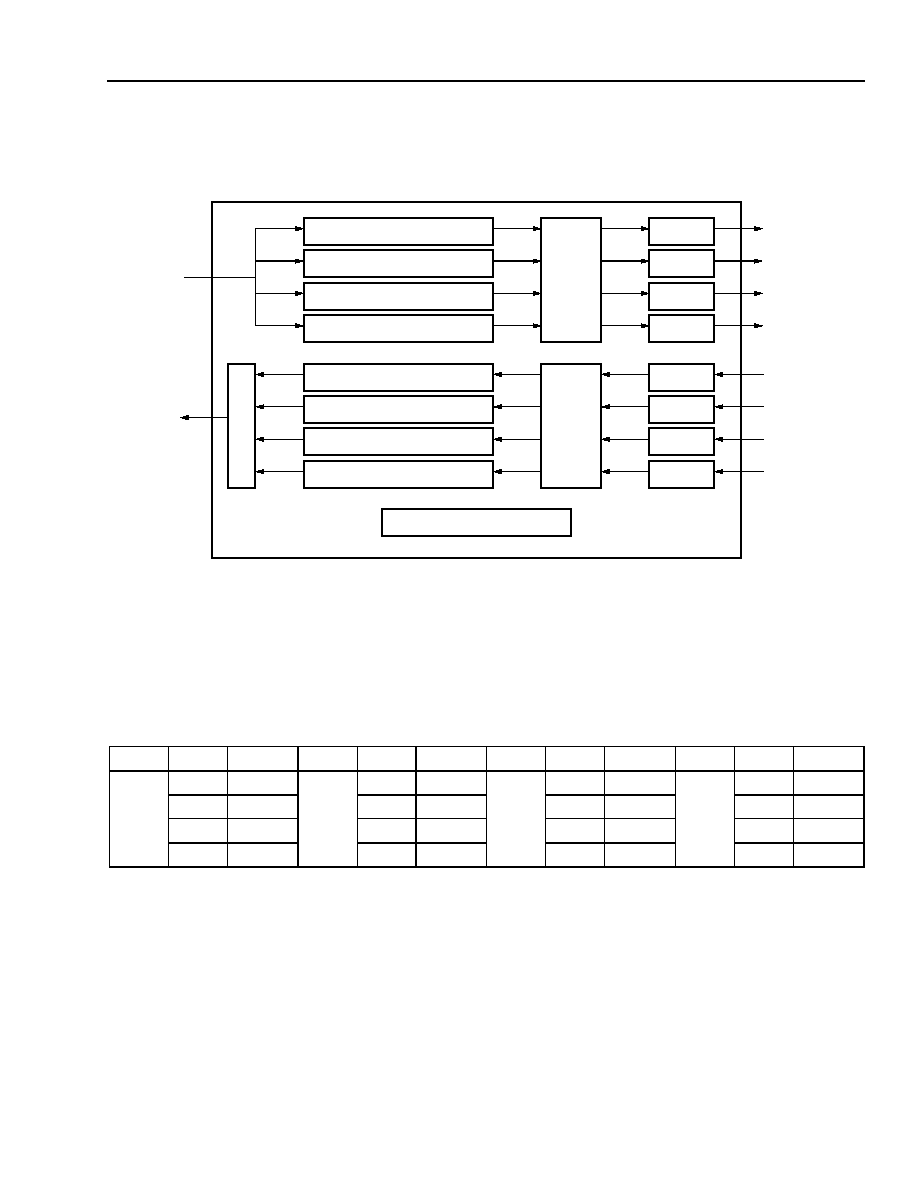

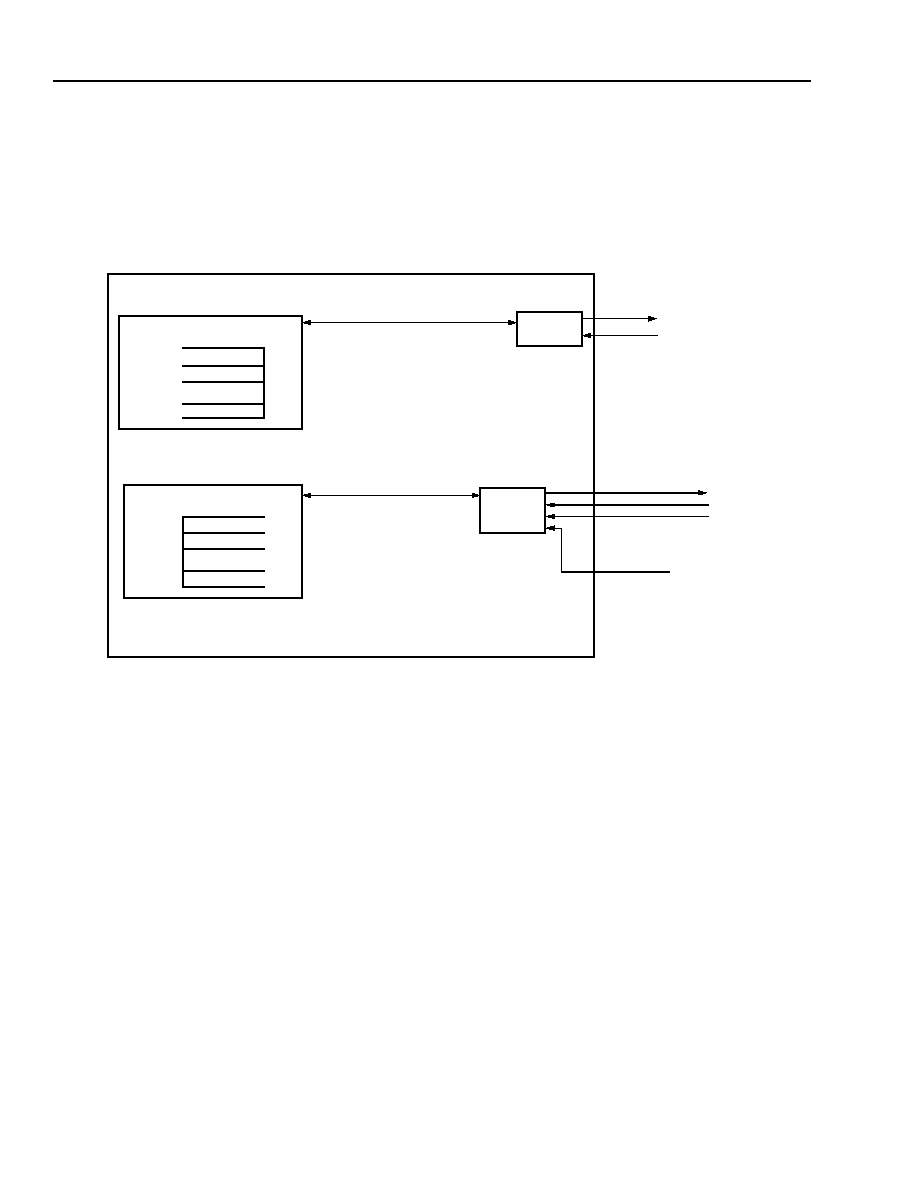

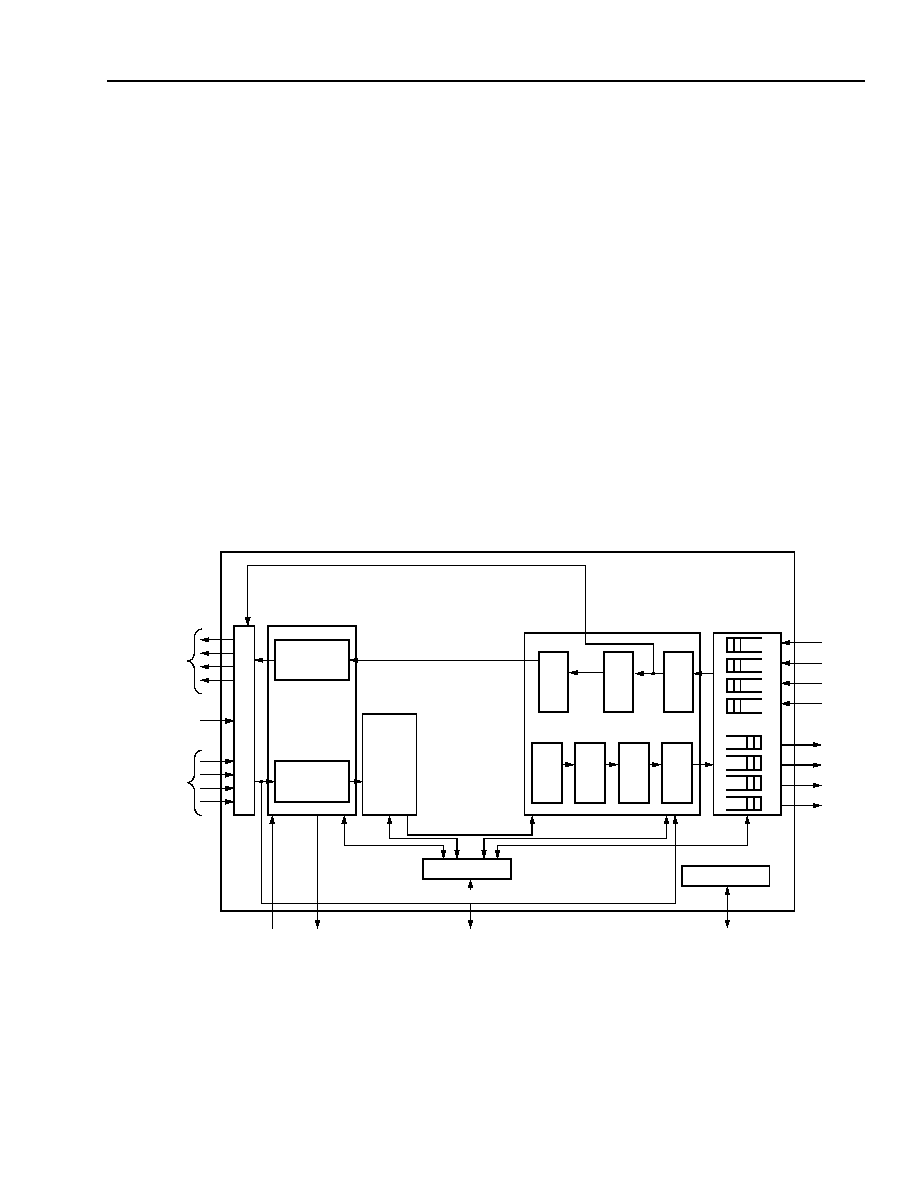

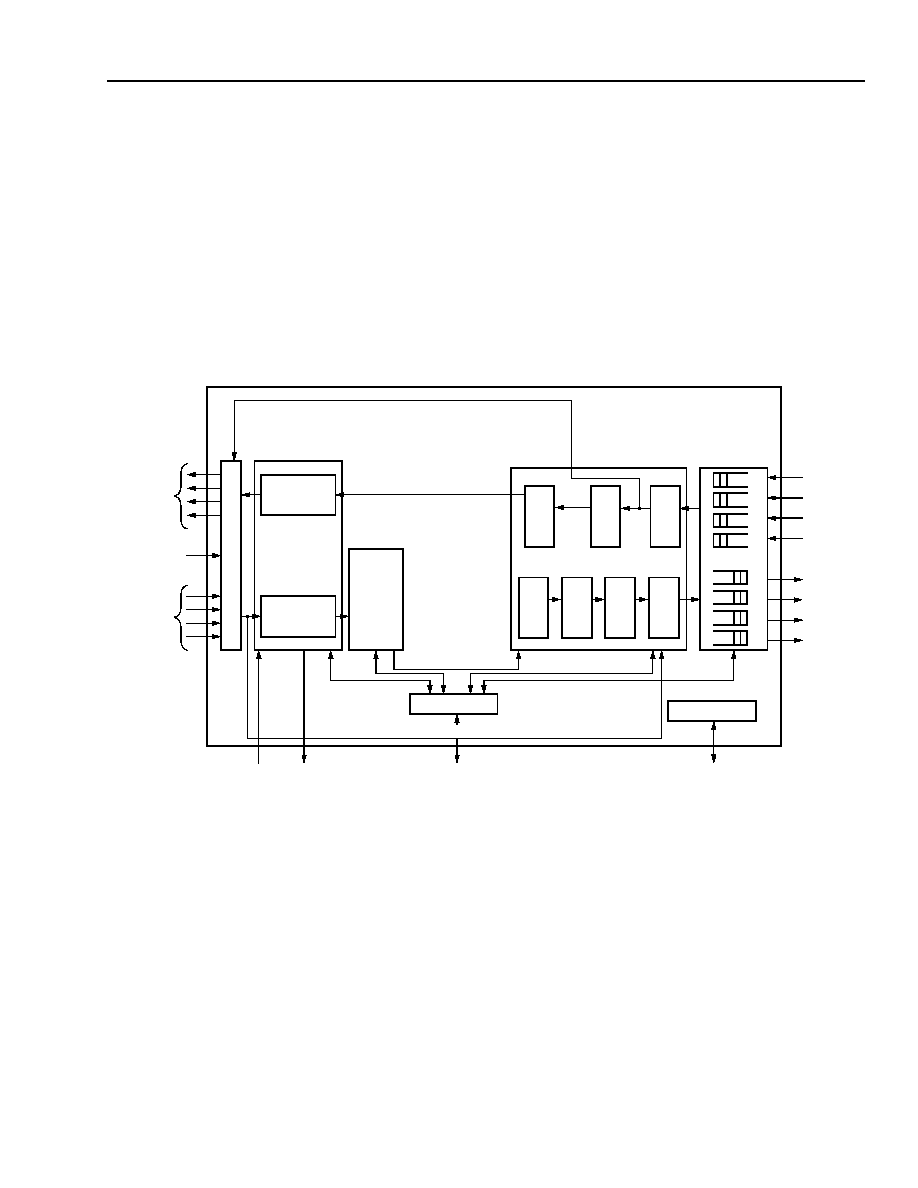

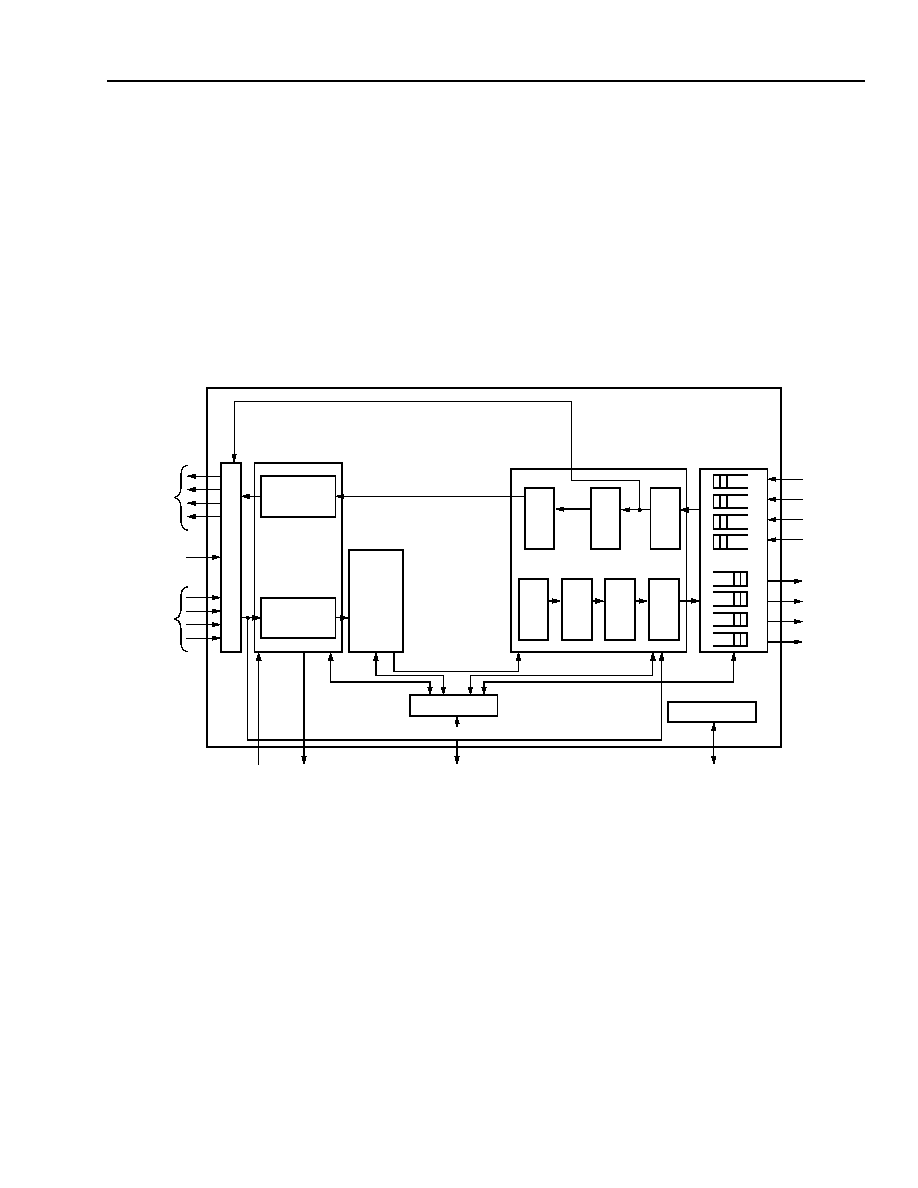

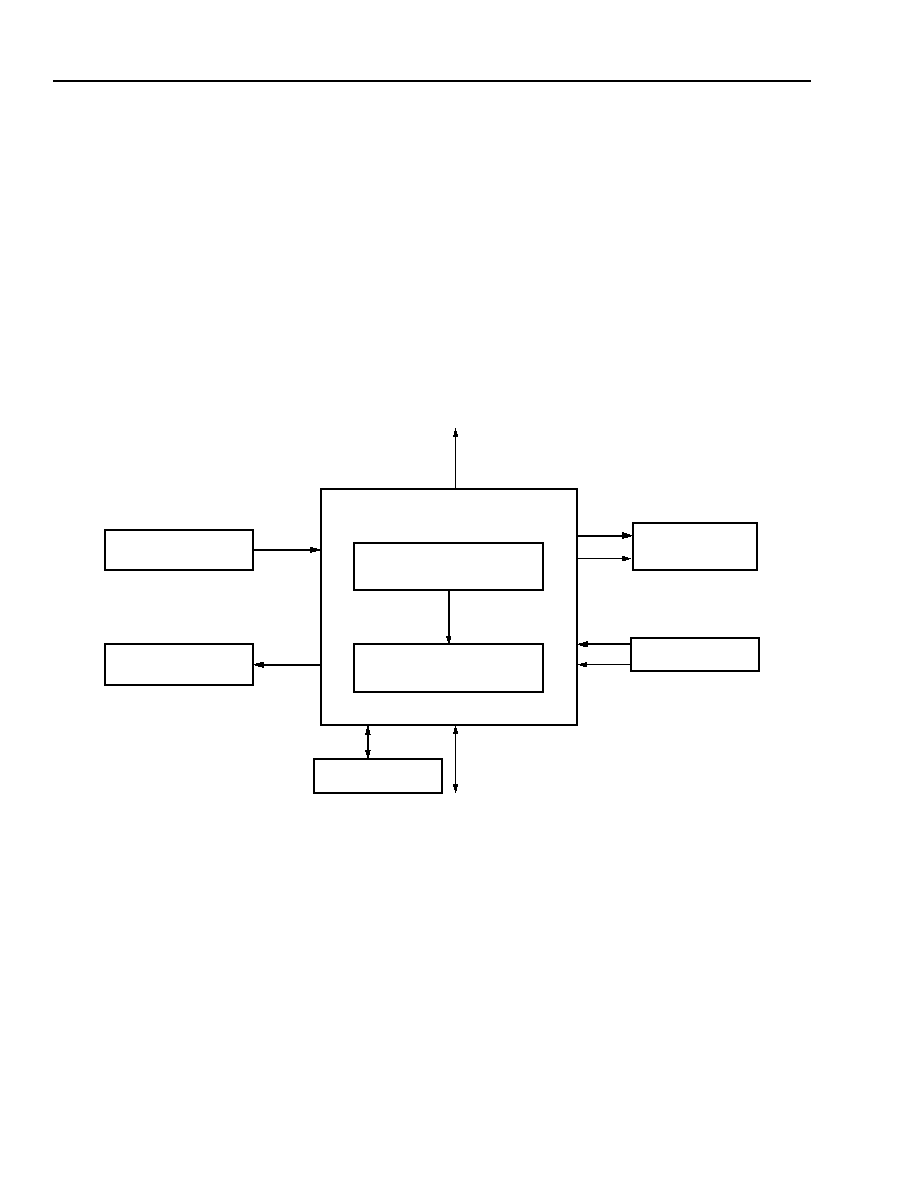

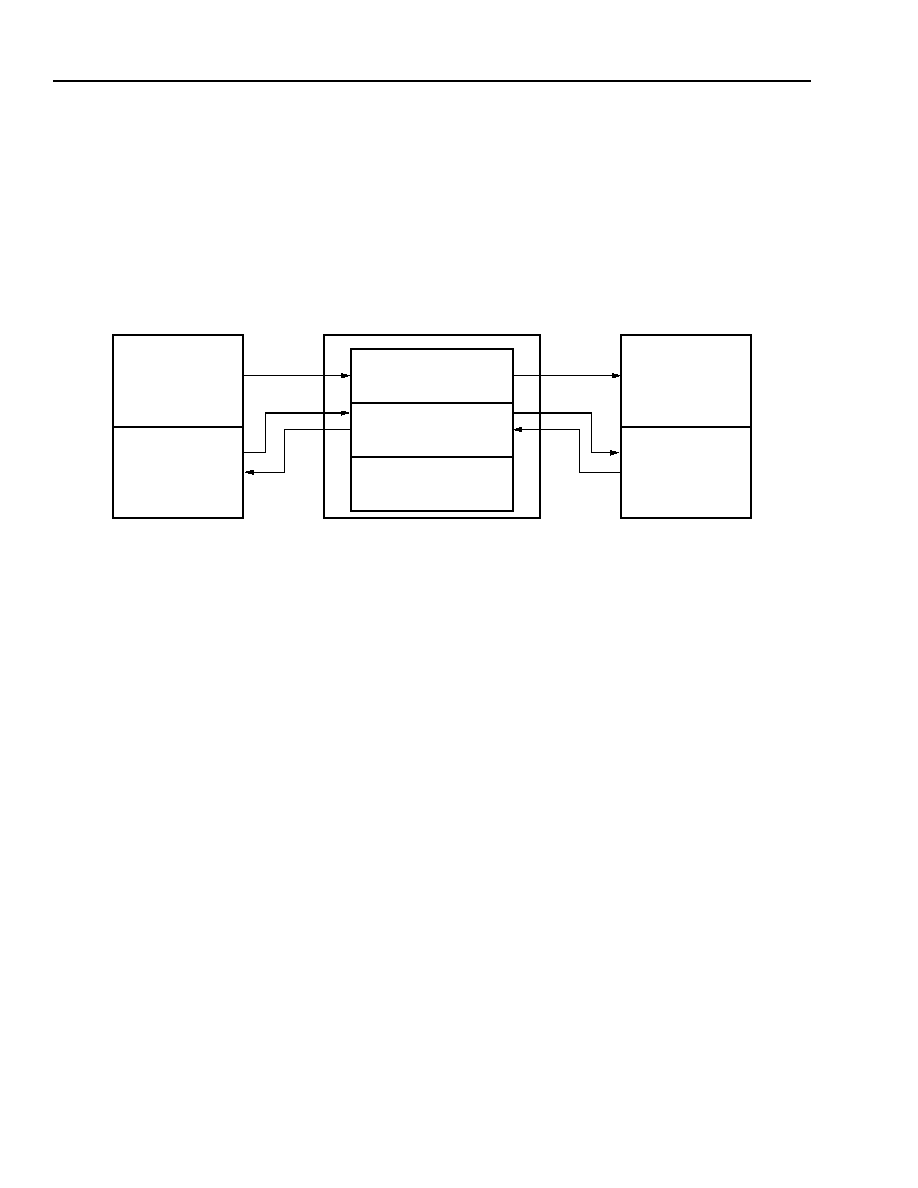

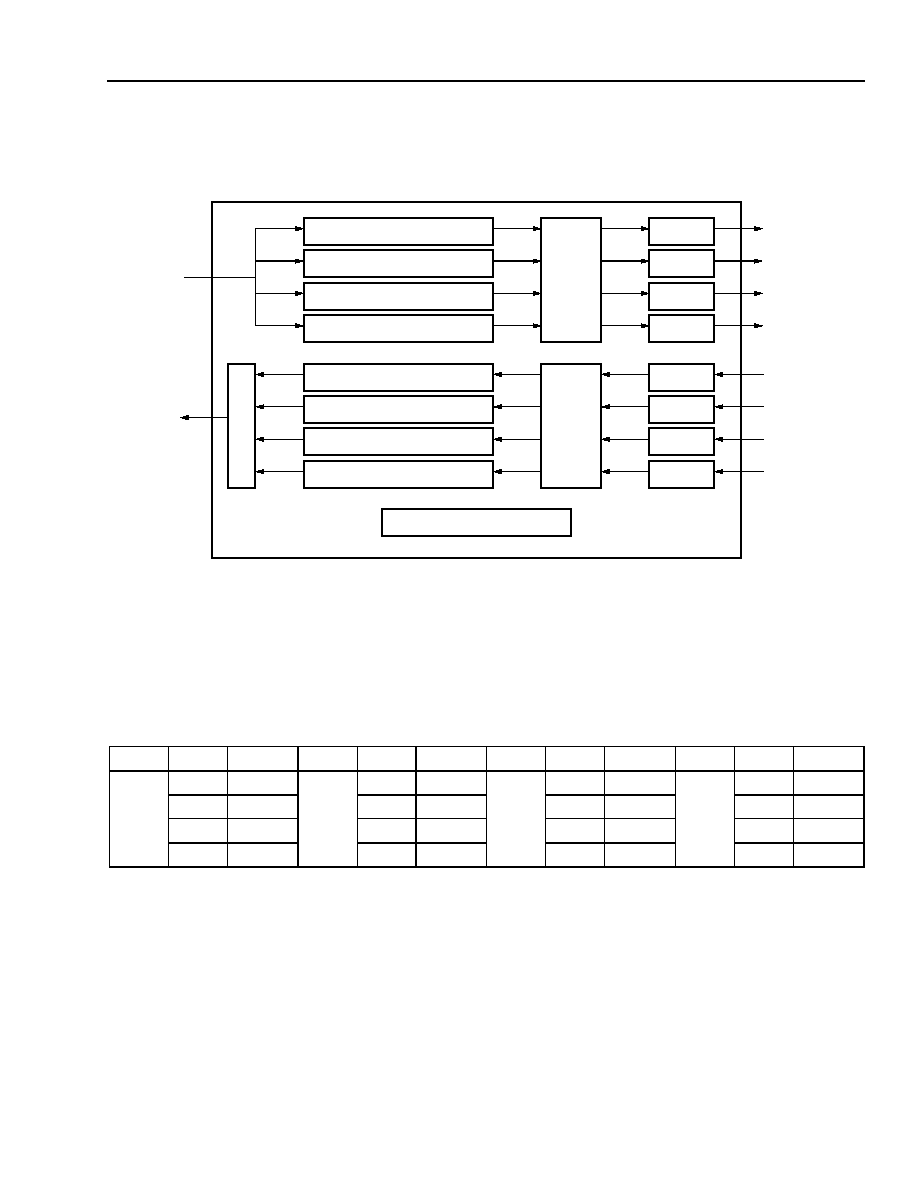

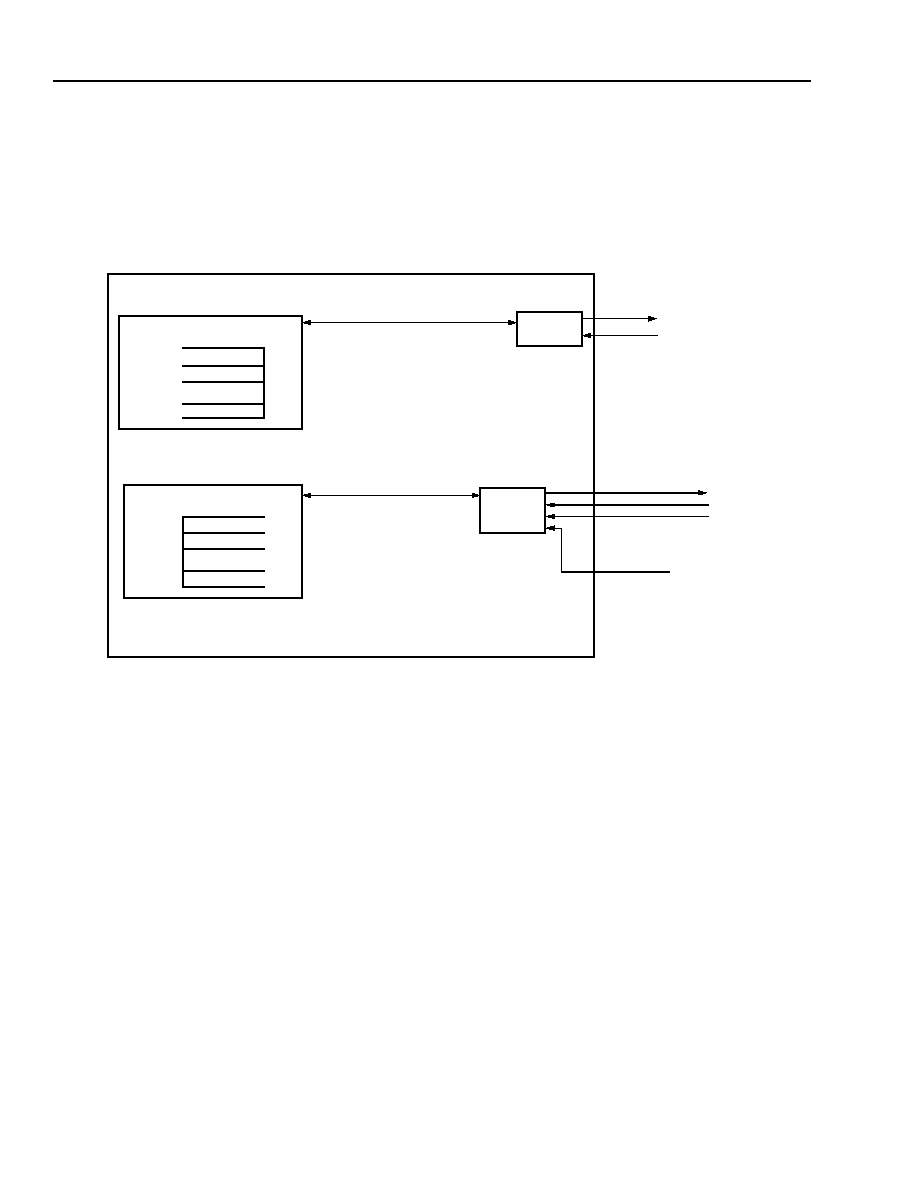

- Overview

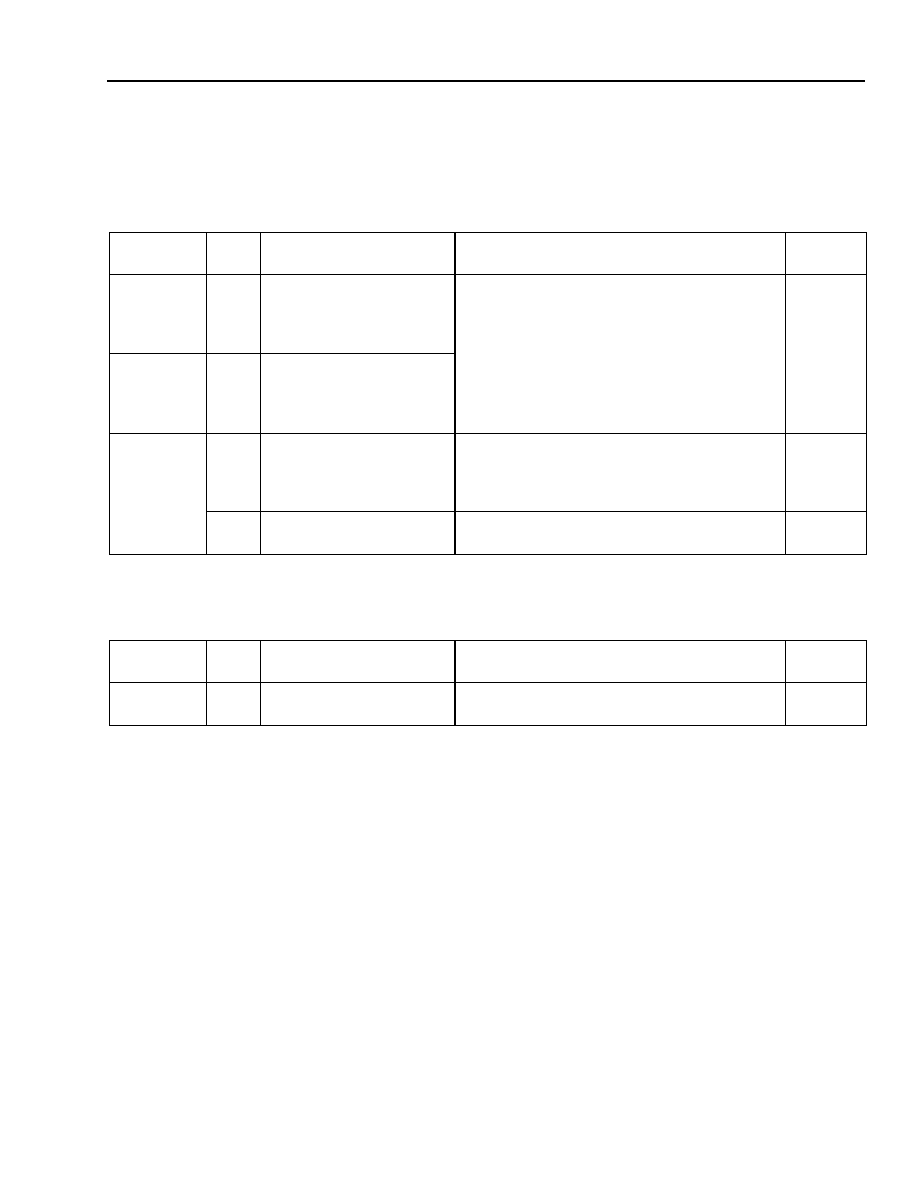

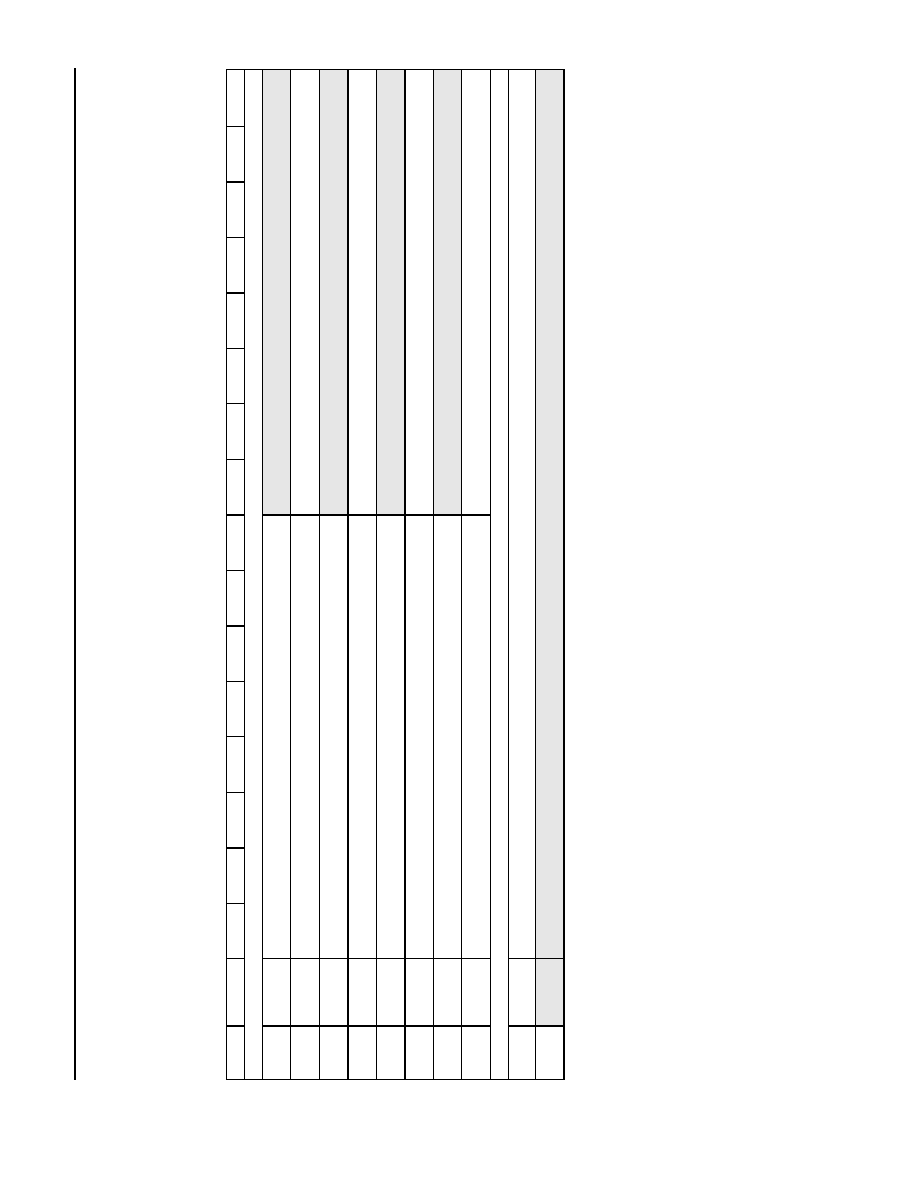

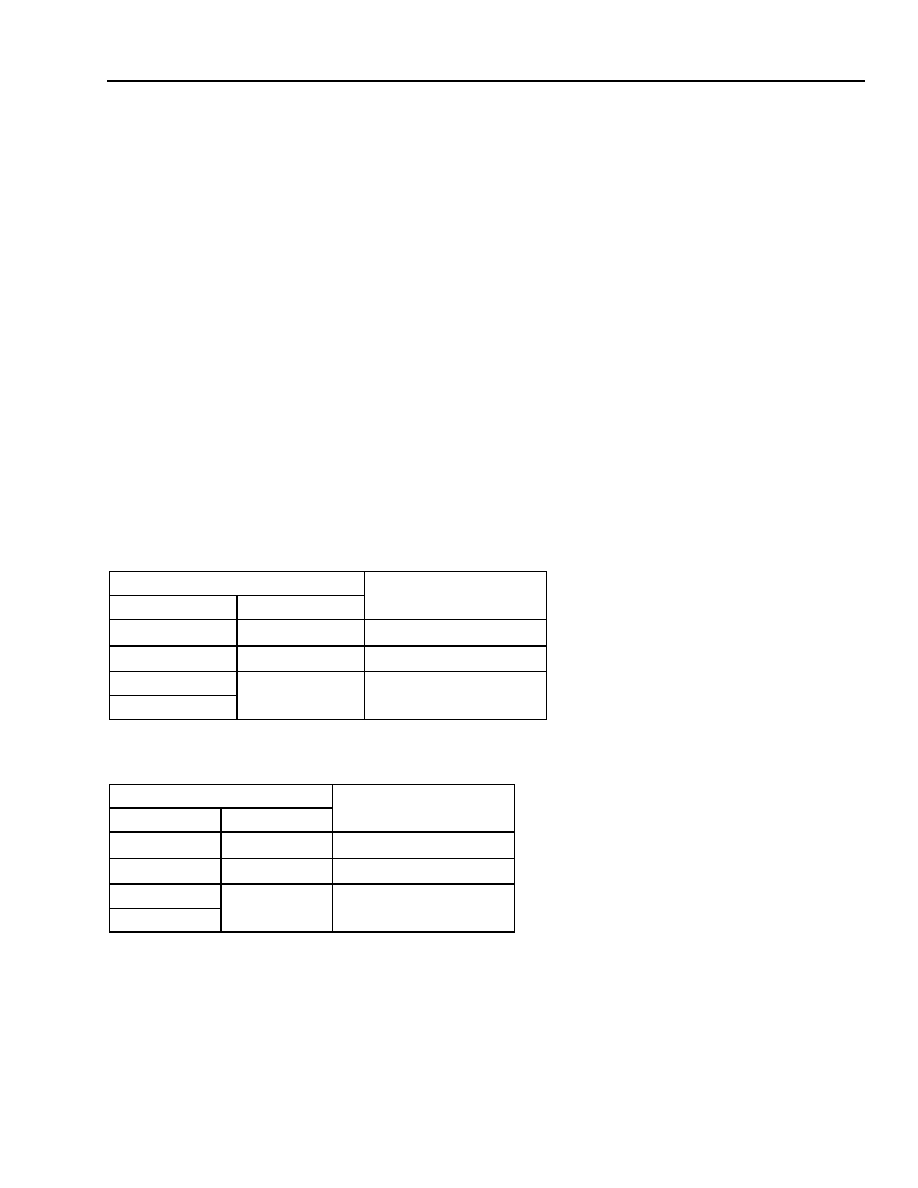

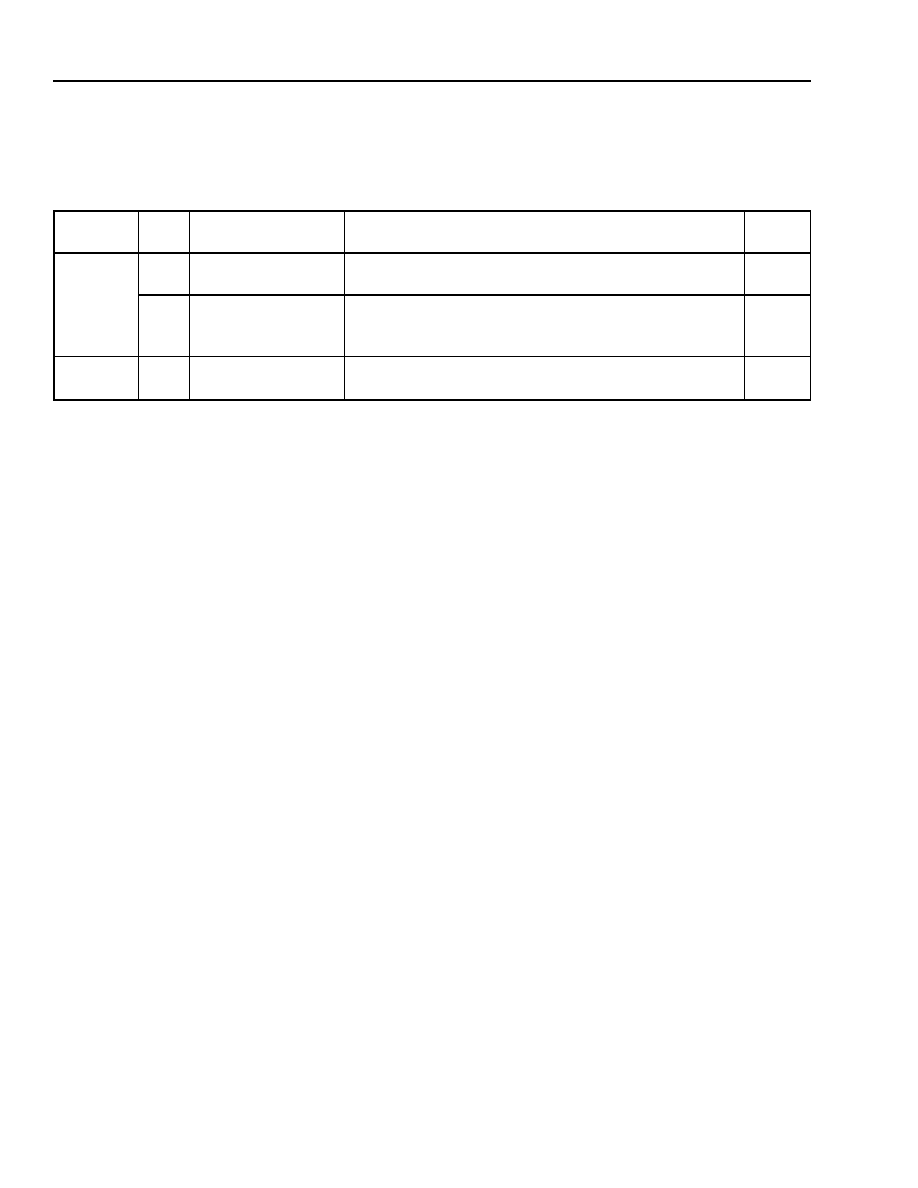

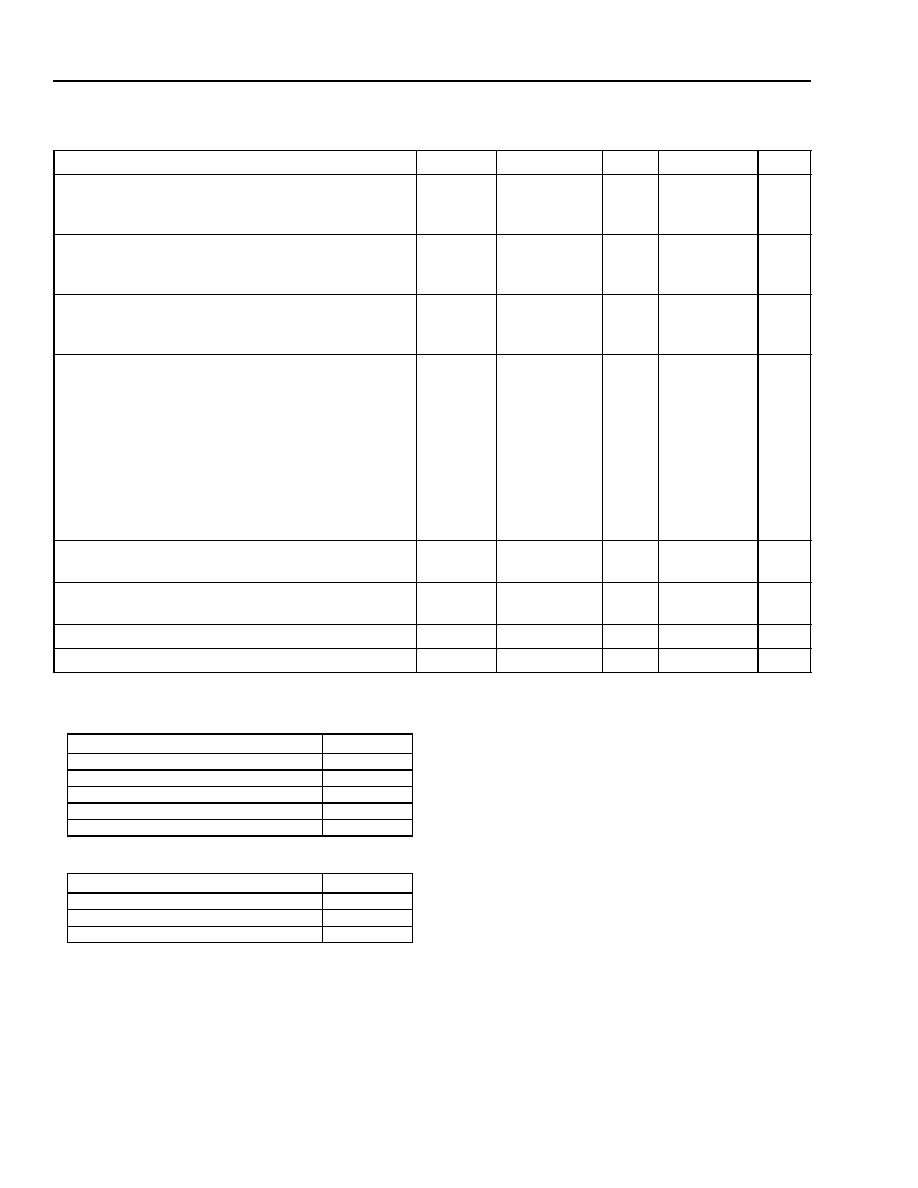

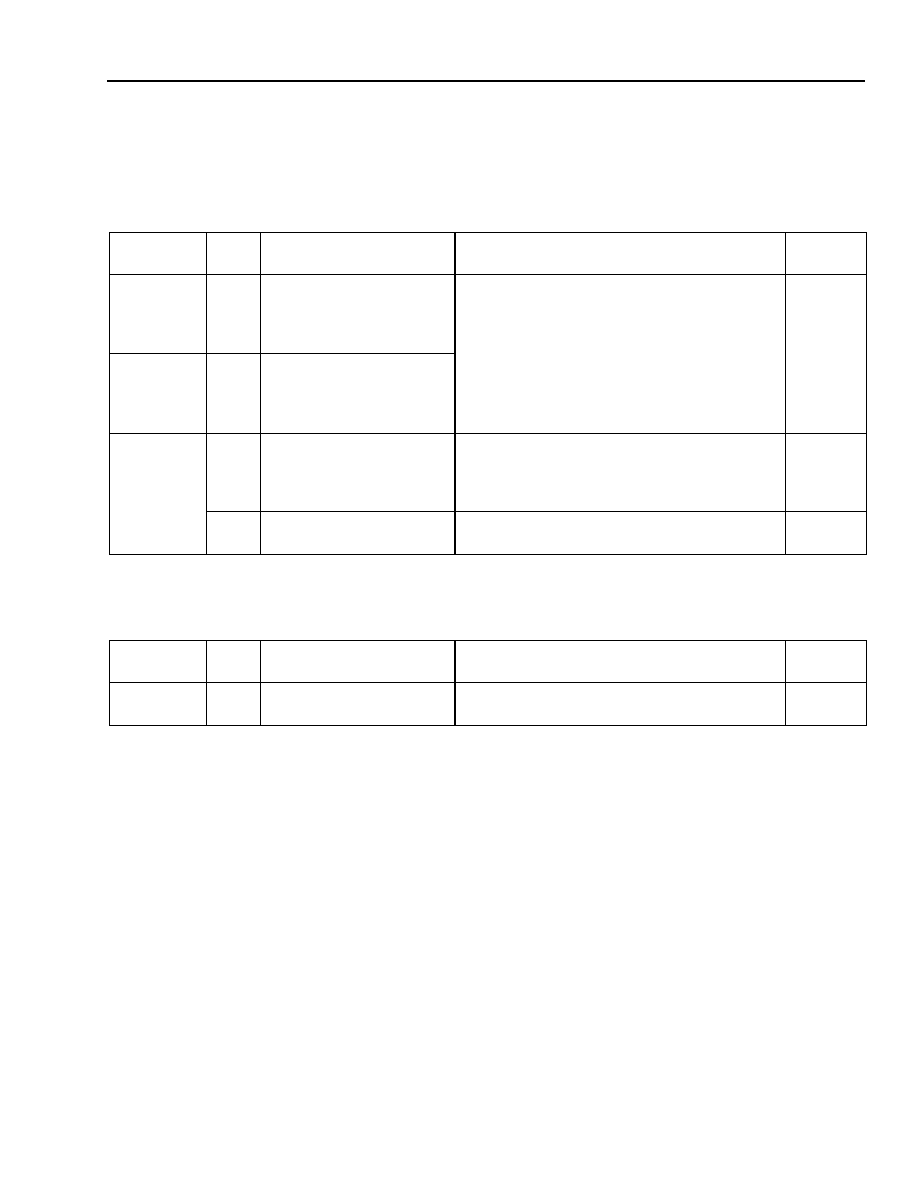

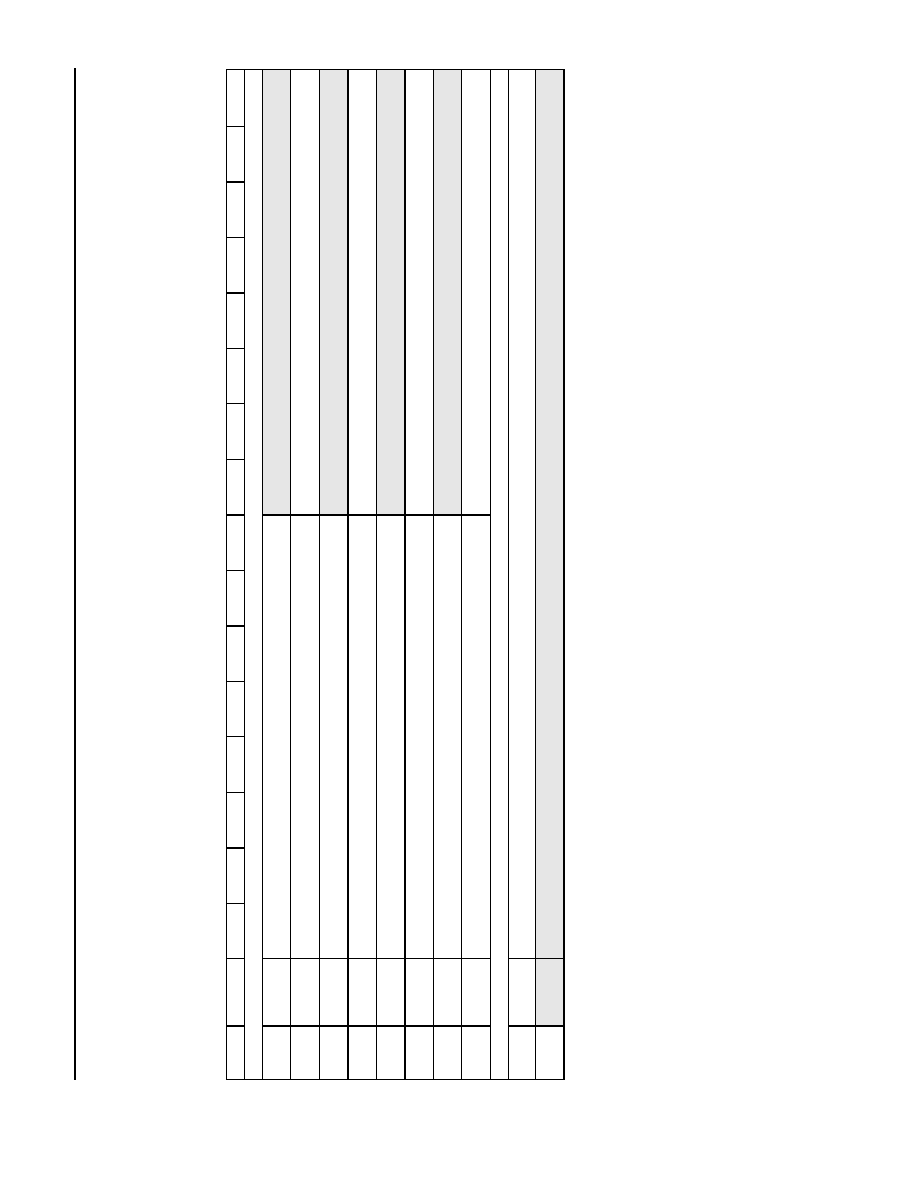

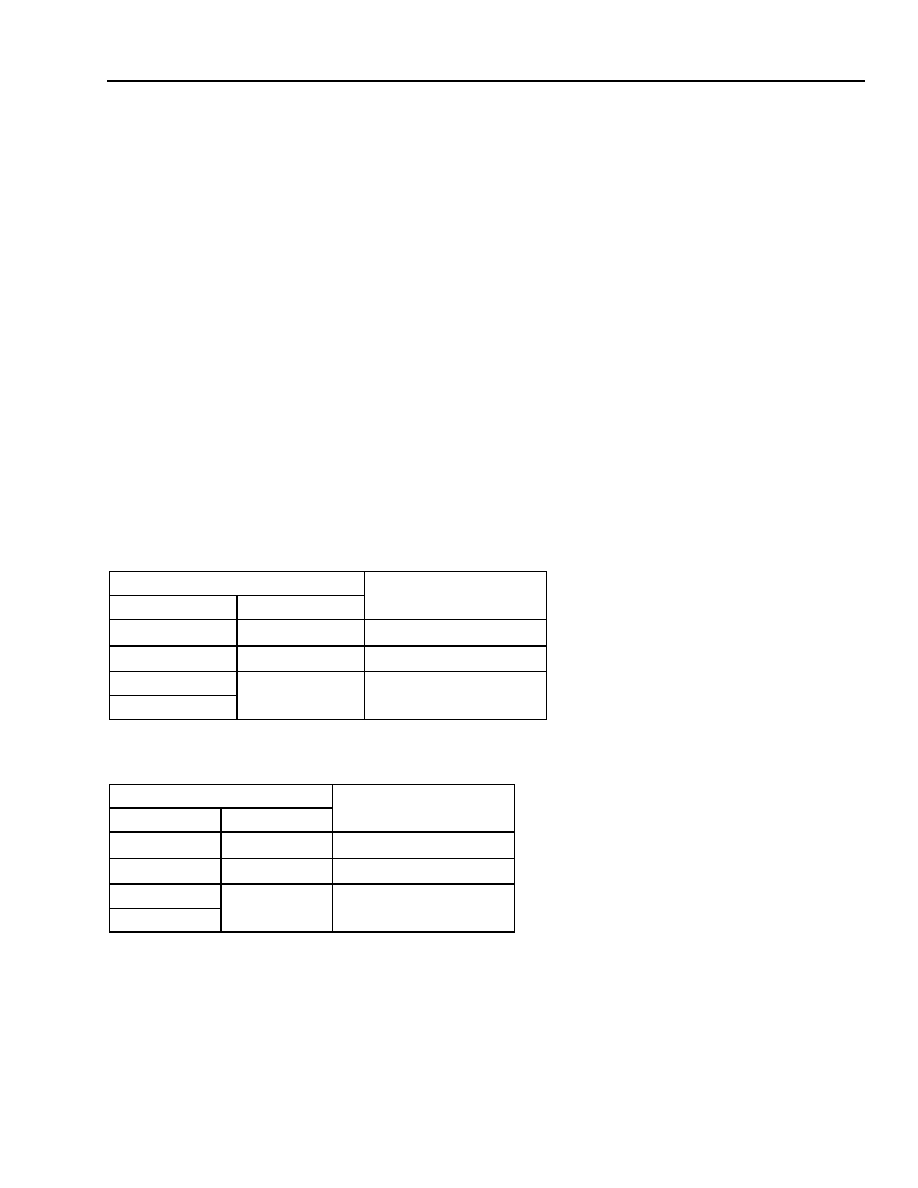

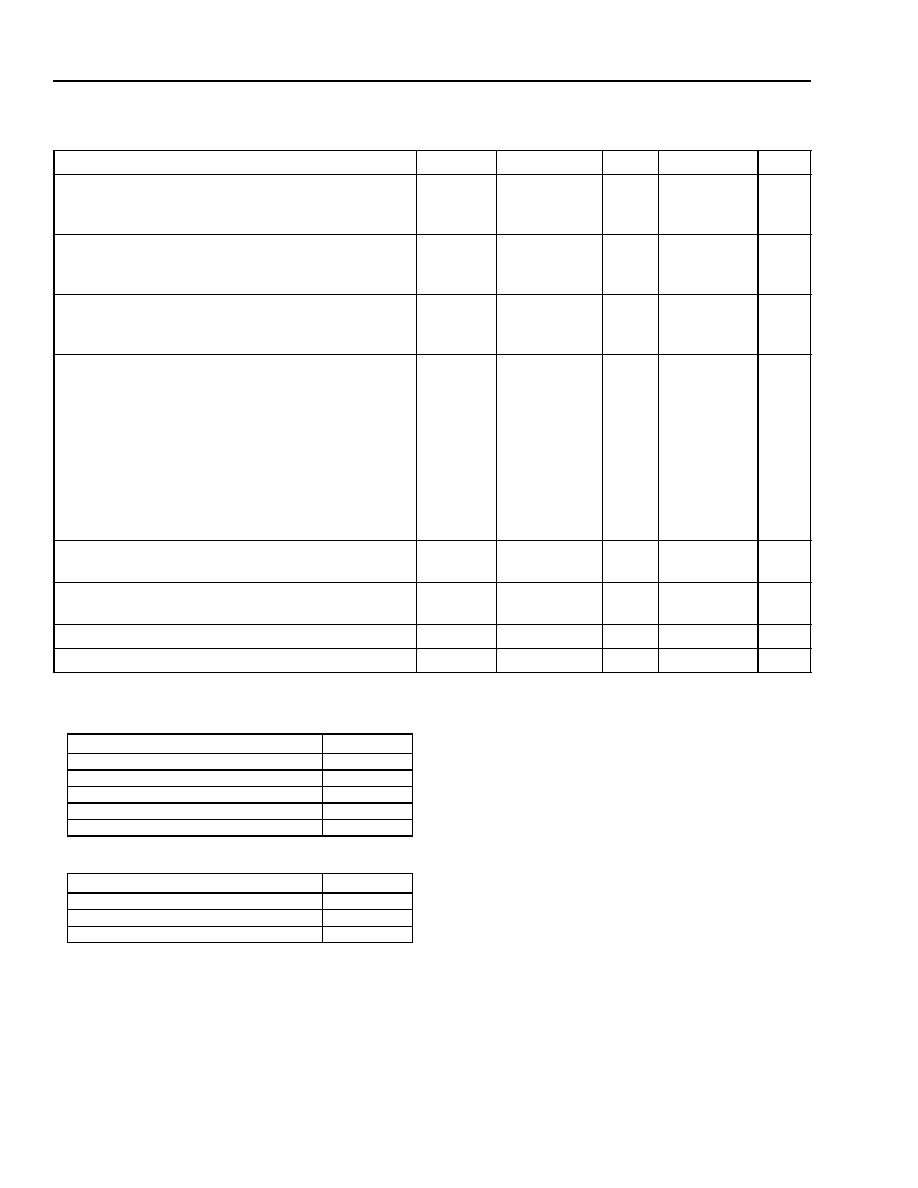

- MARS2G5 P-Pro (792-Pin PBGA) Low-Speed Devices Available

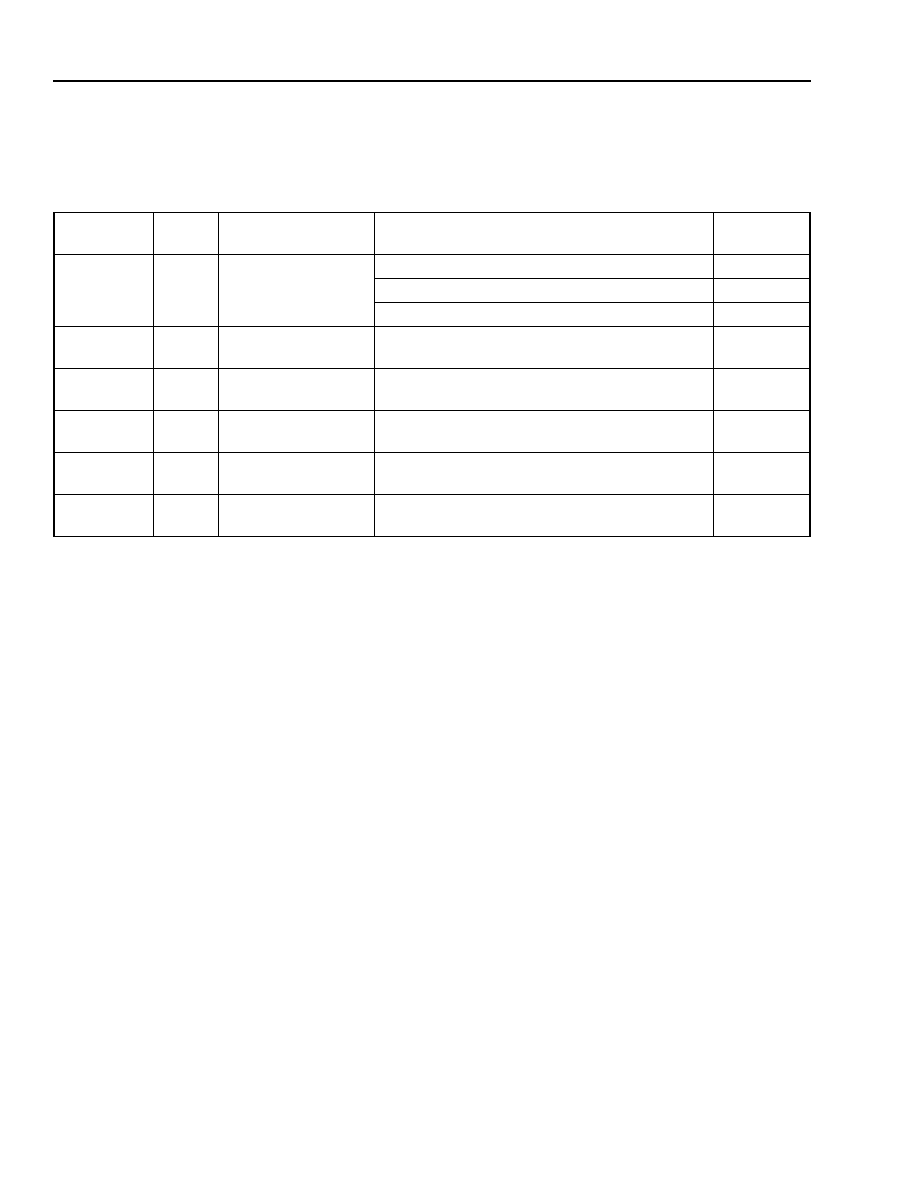

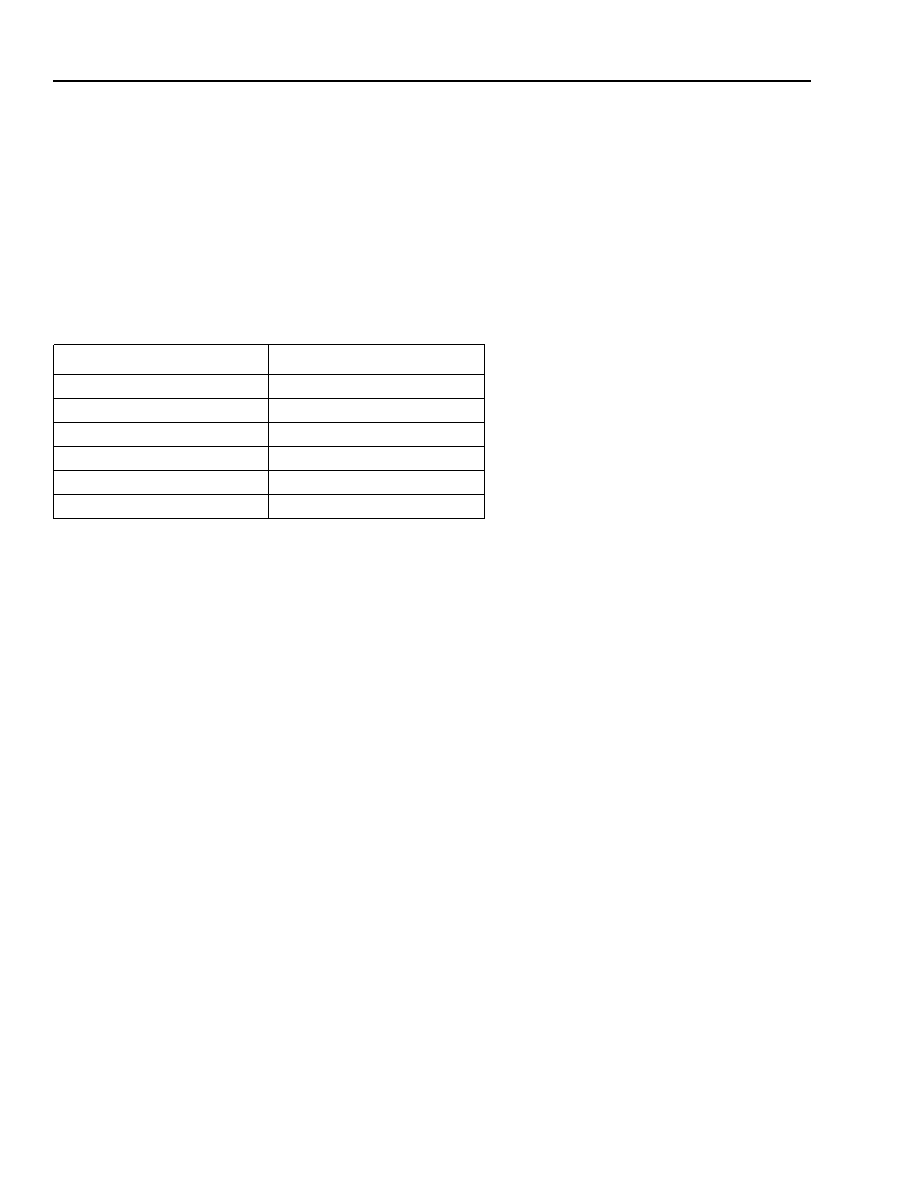

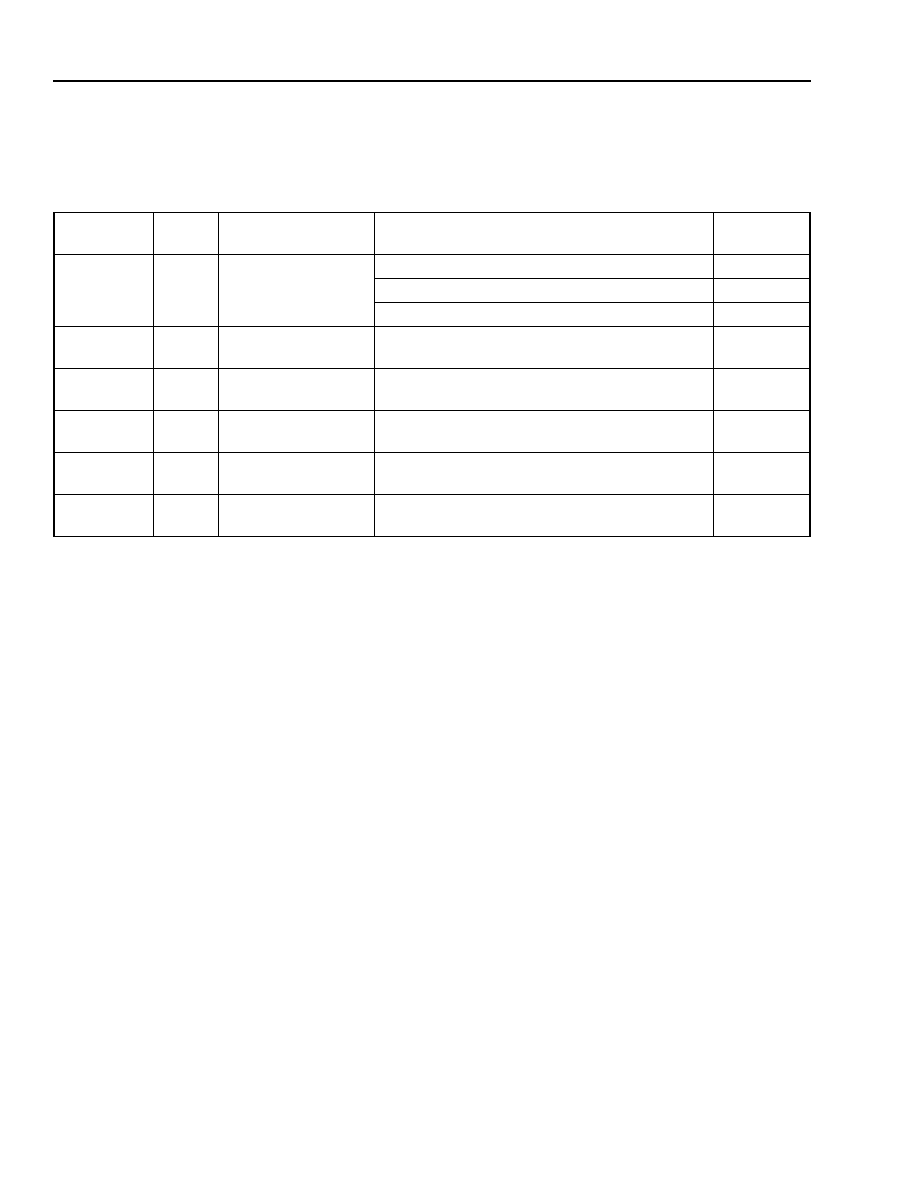

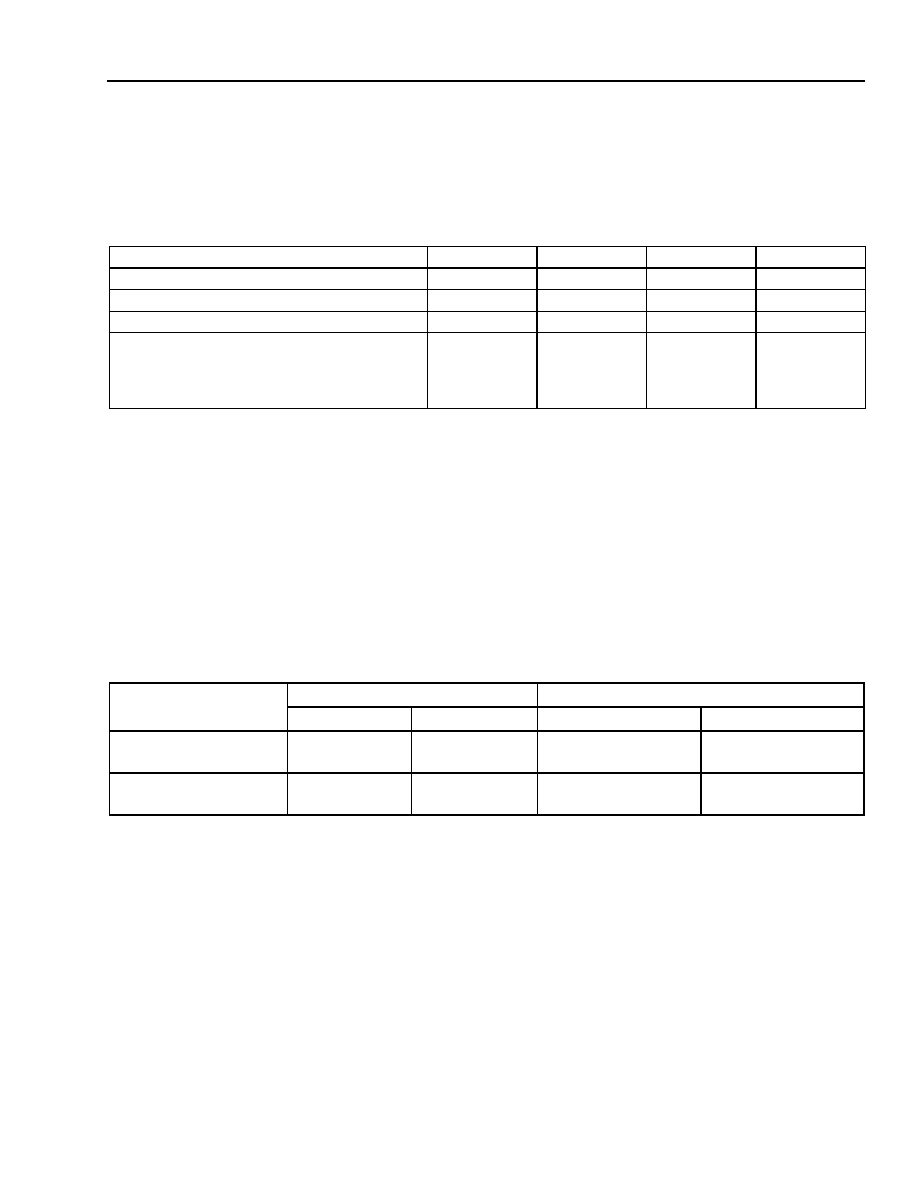

- MARS2G5 P-Pro Device Product Line Table Summaries

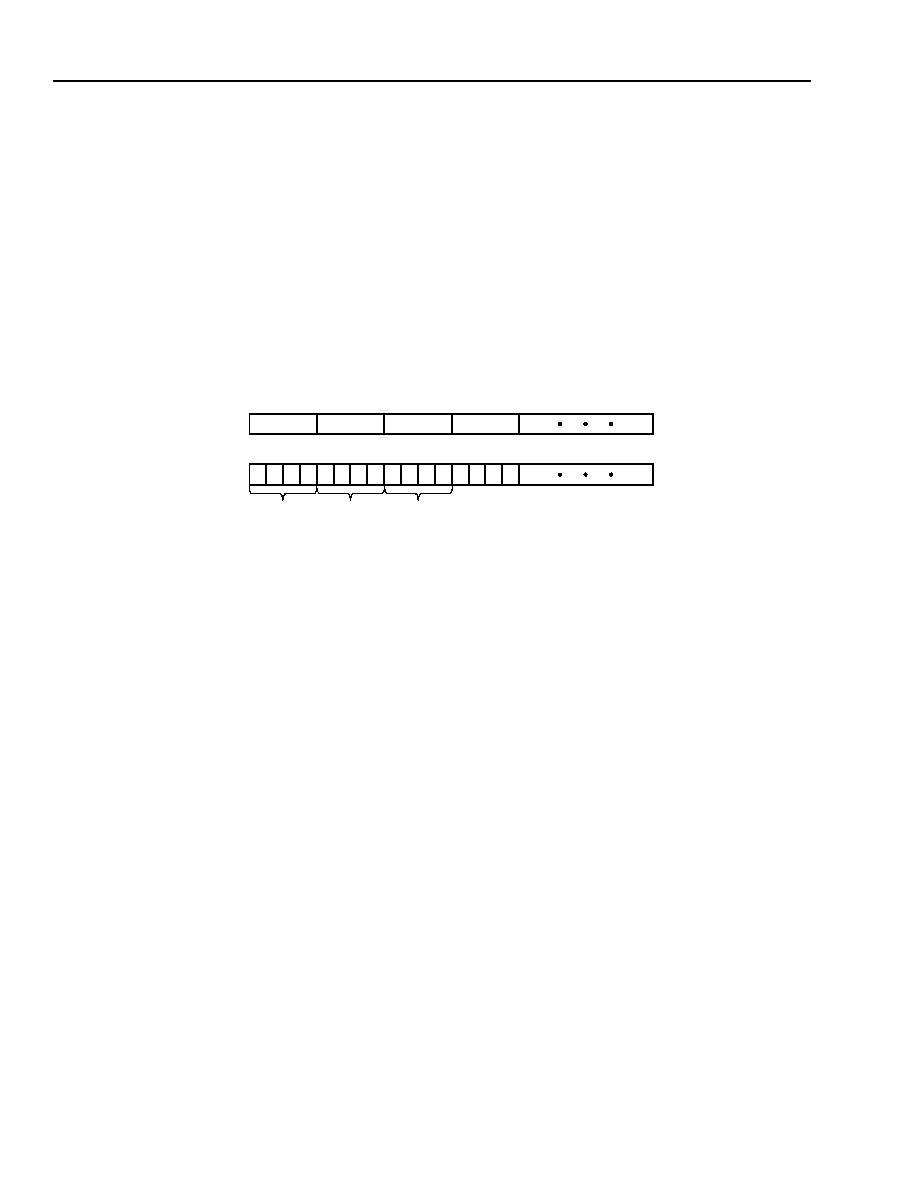

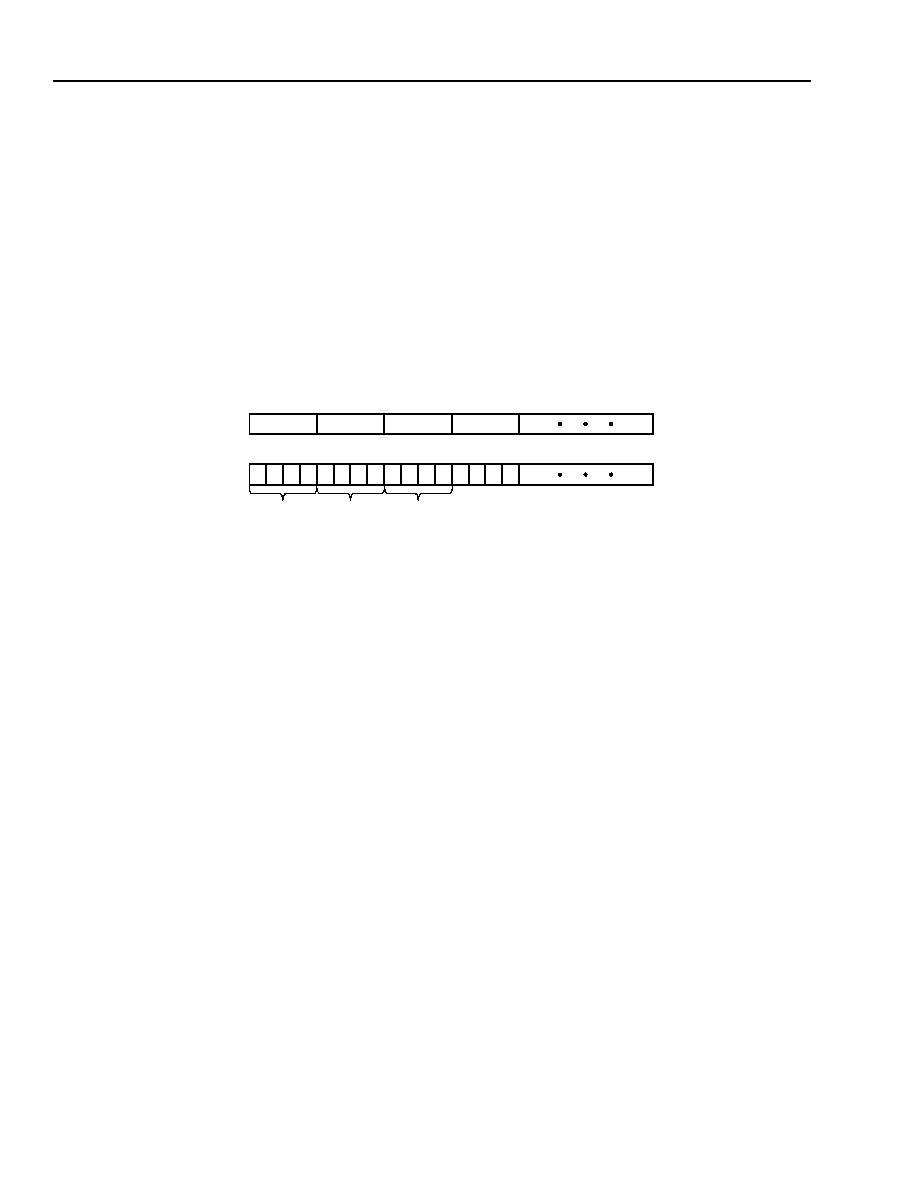

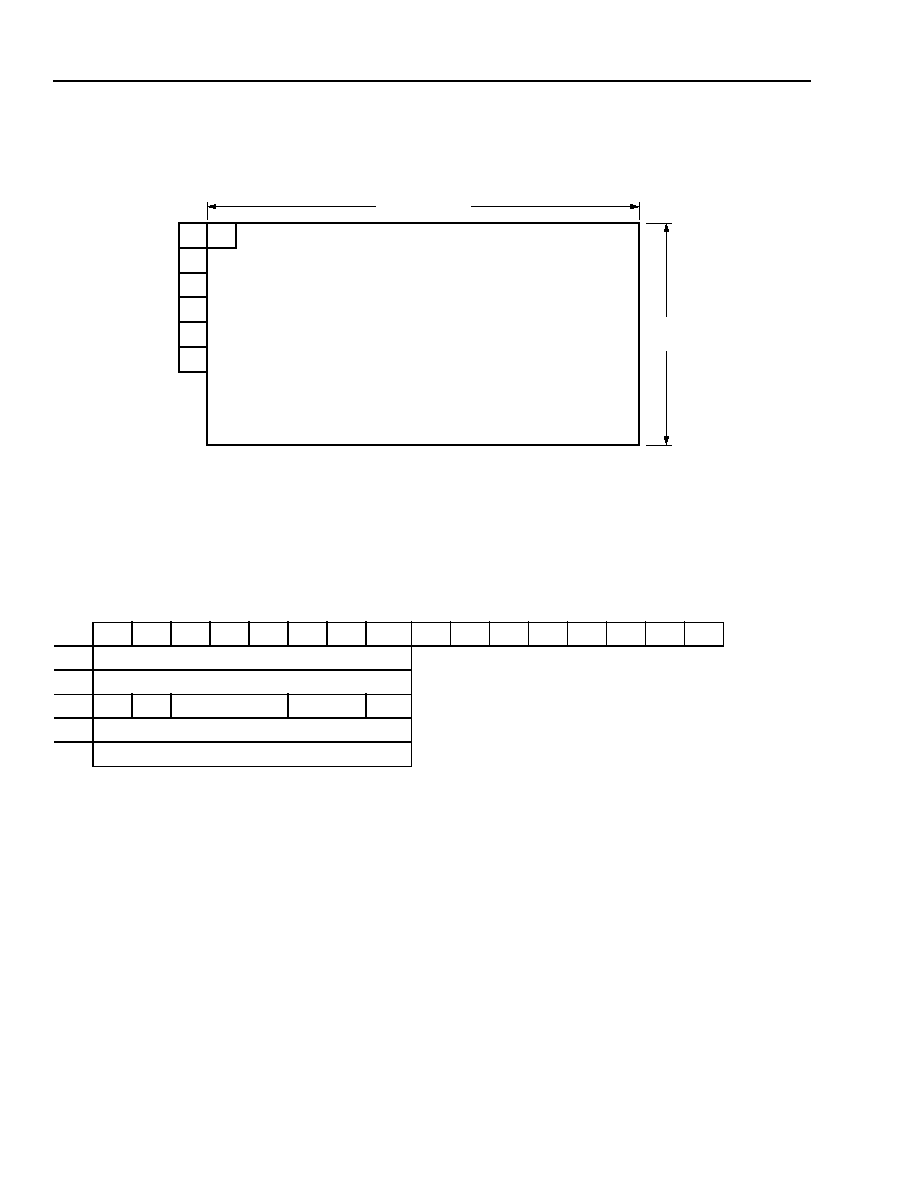

- Pin Information

- Pin Descriptions

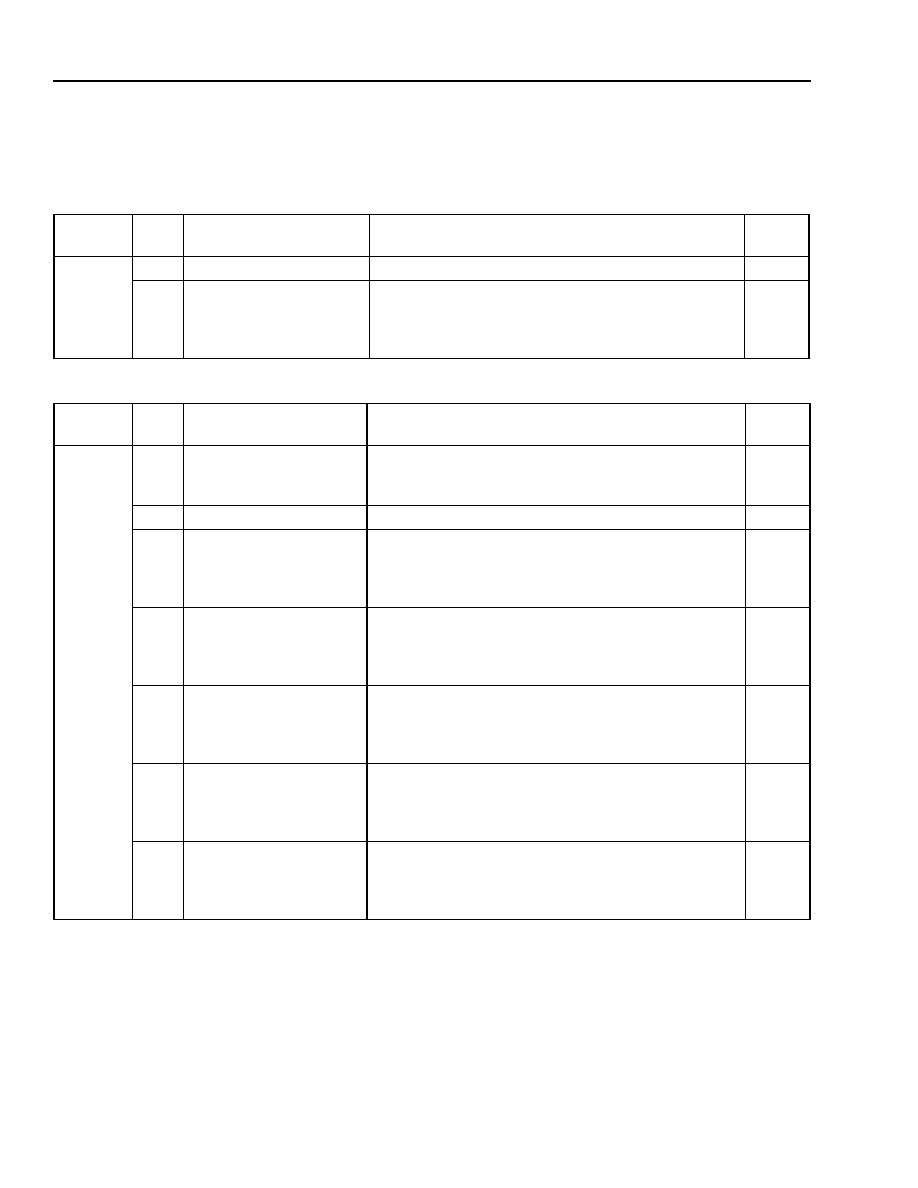

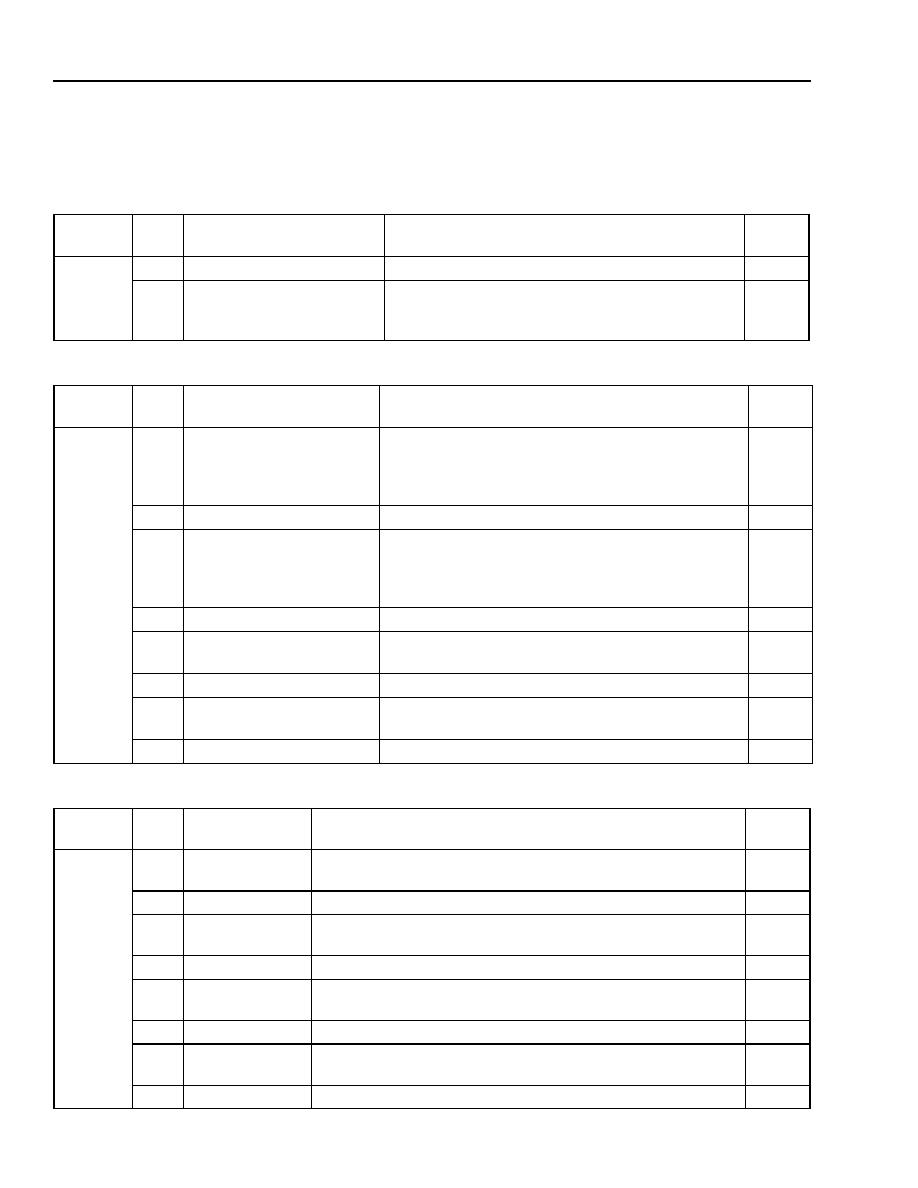

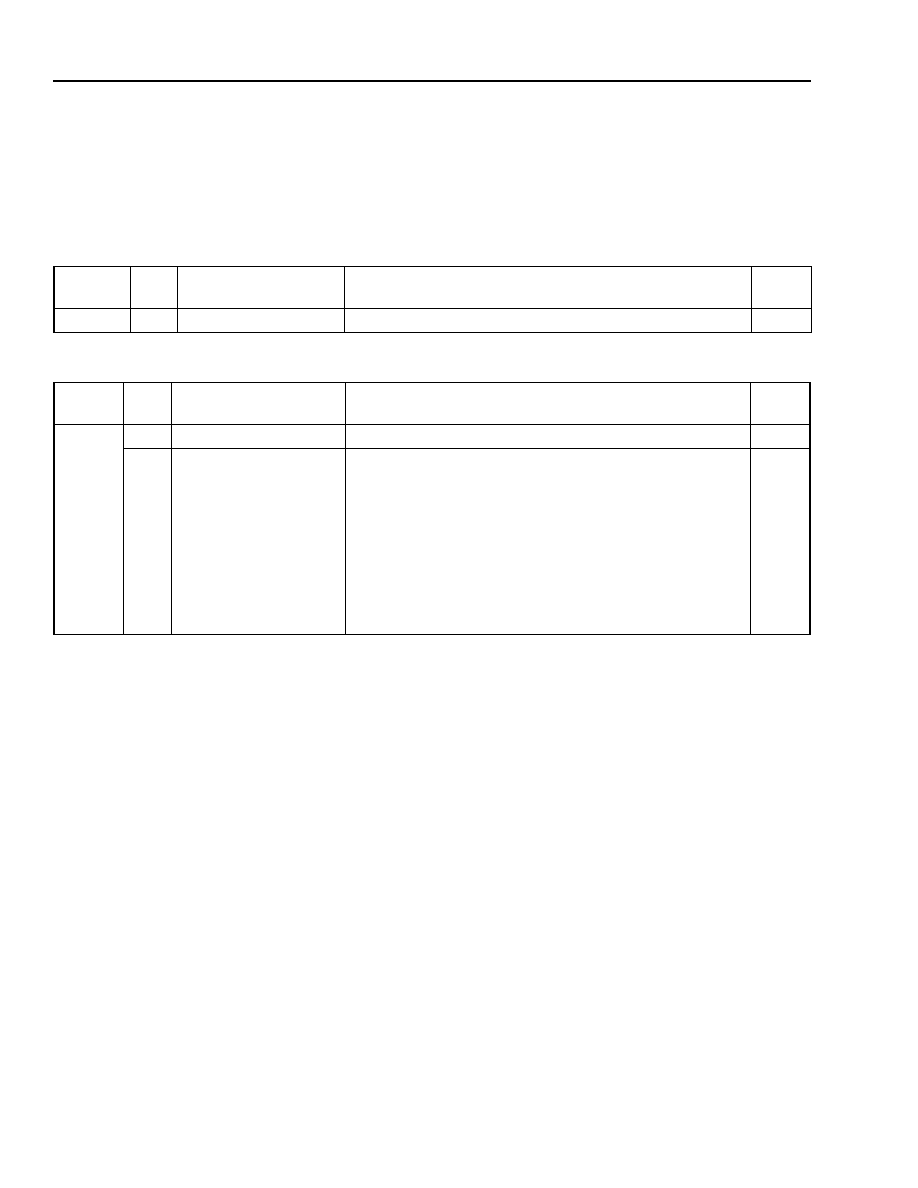

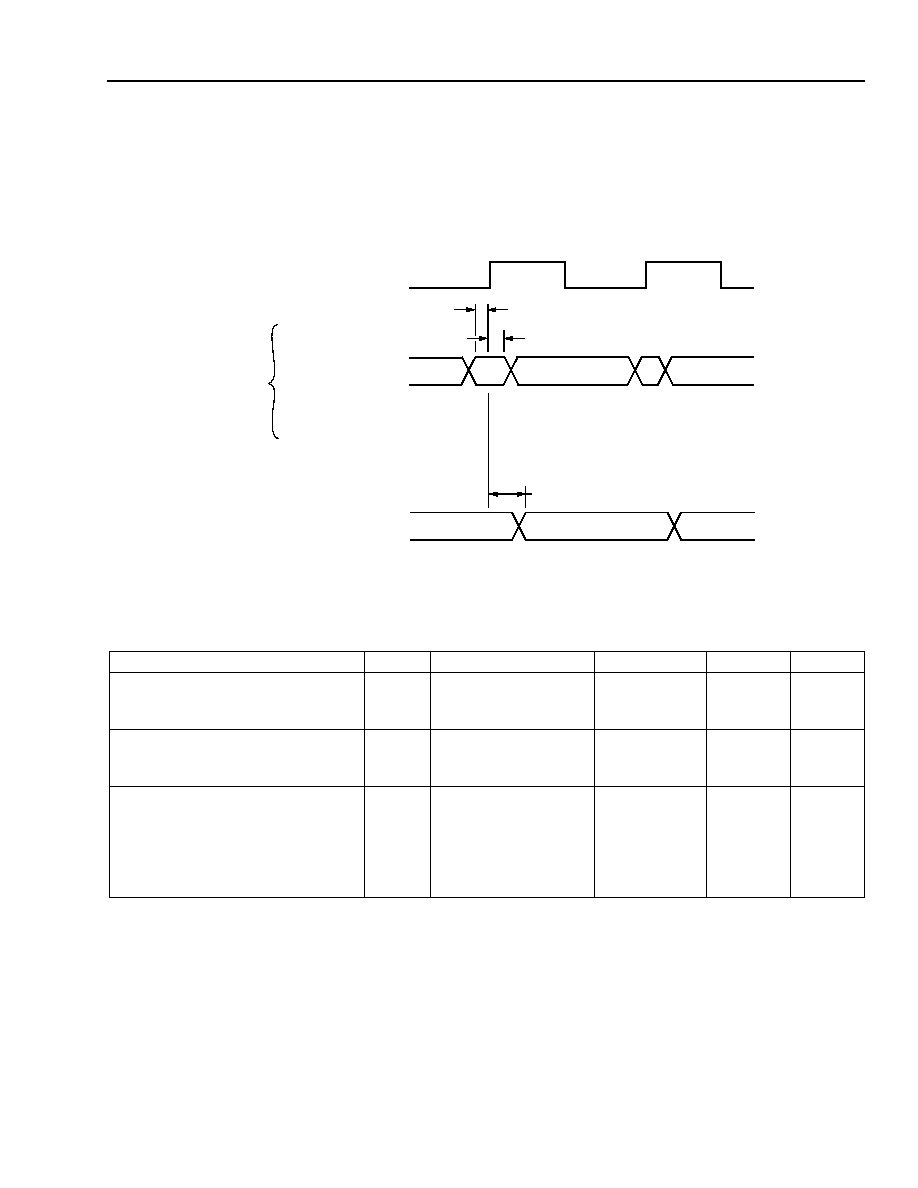

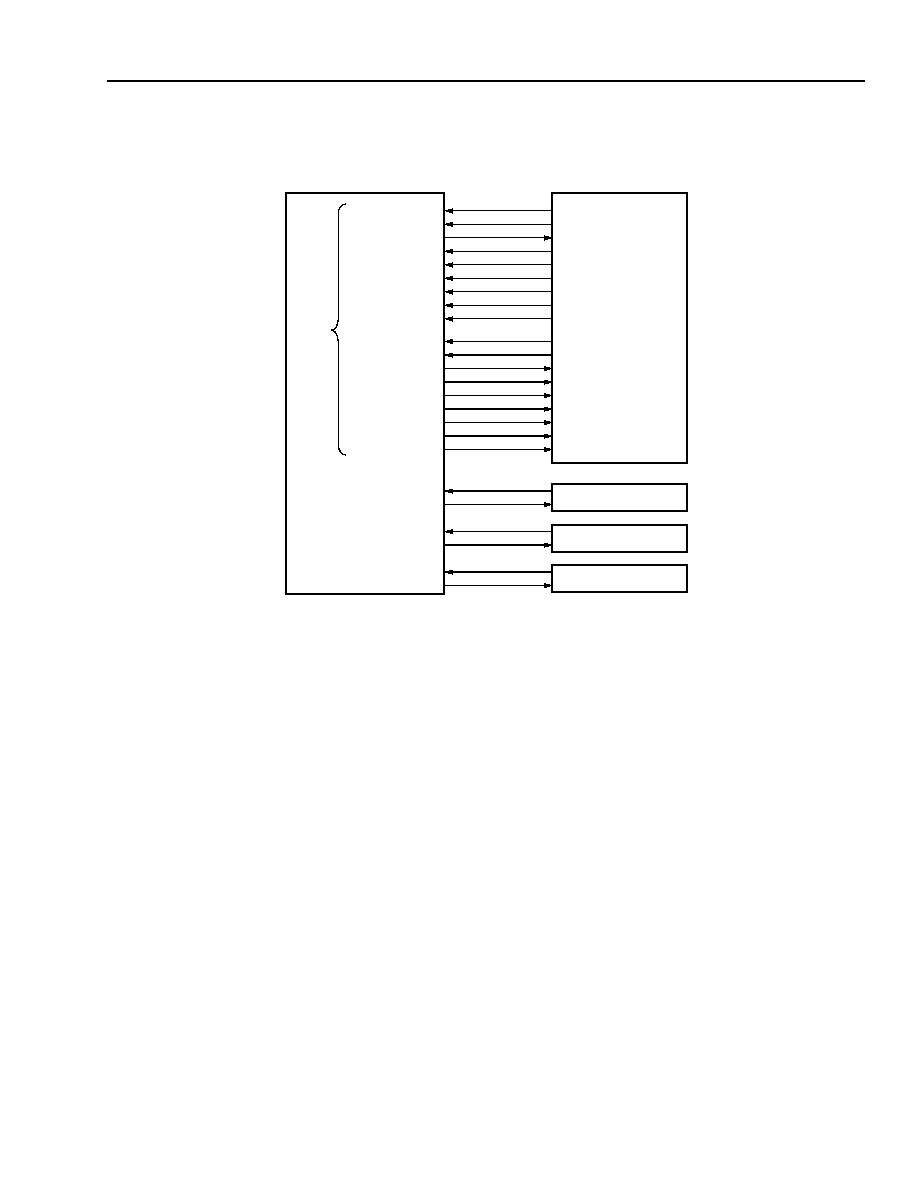

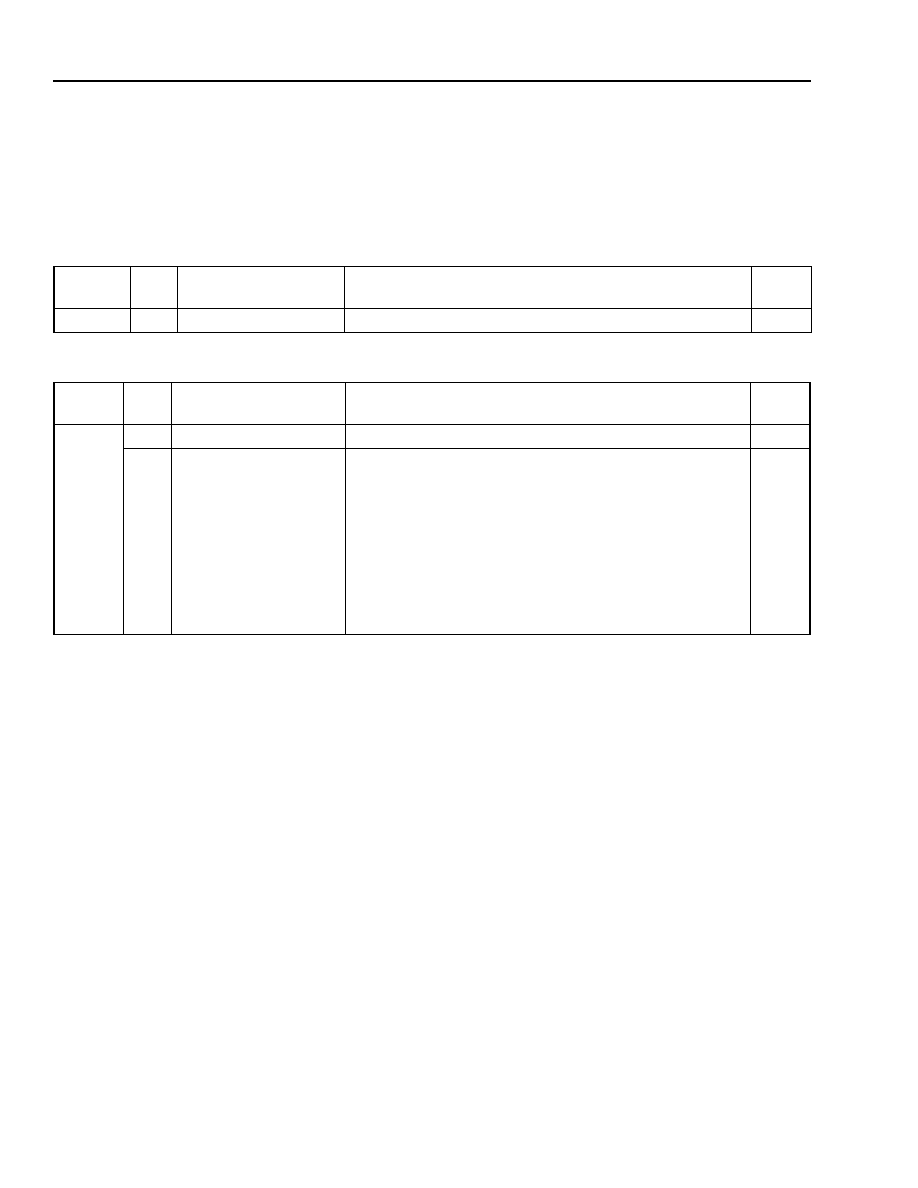

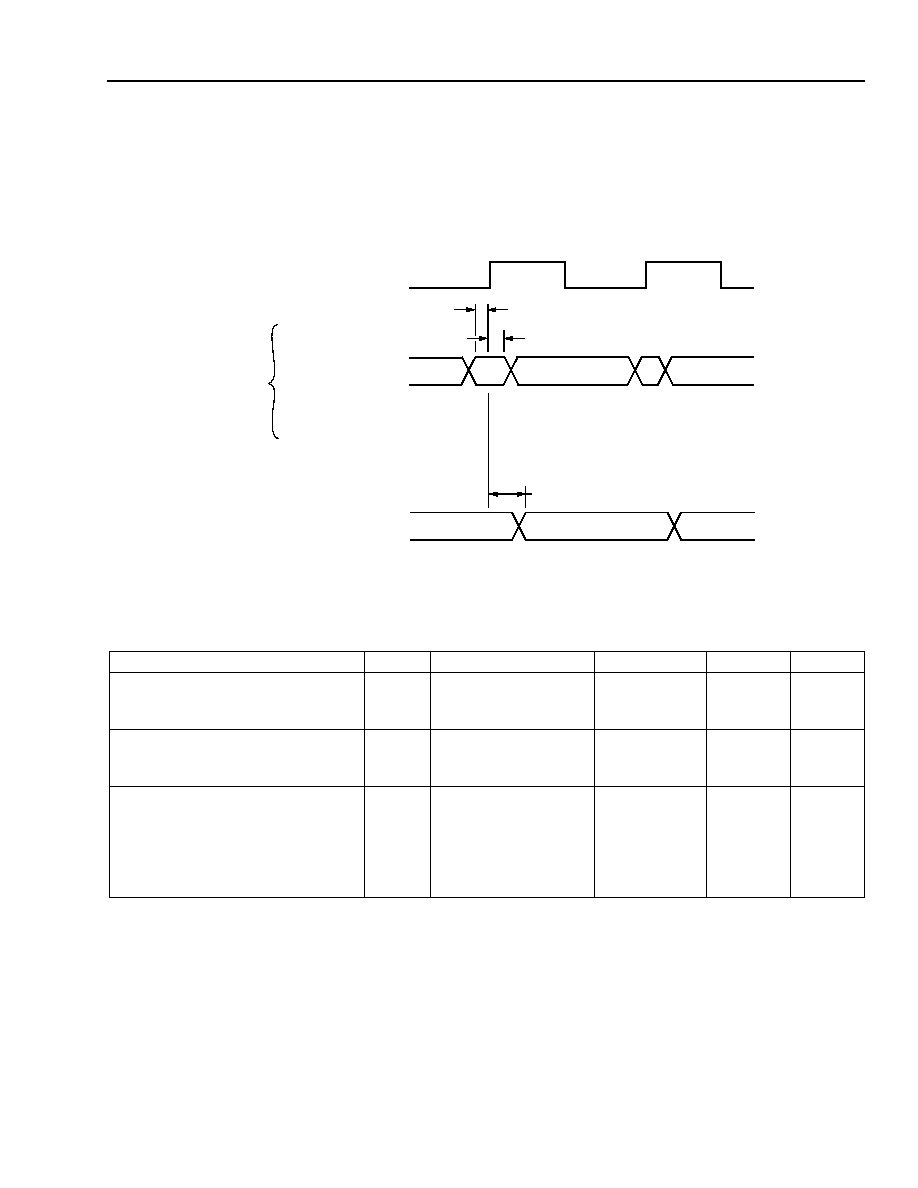

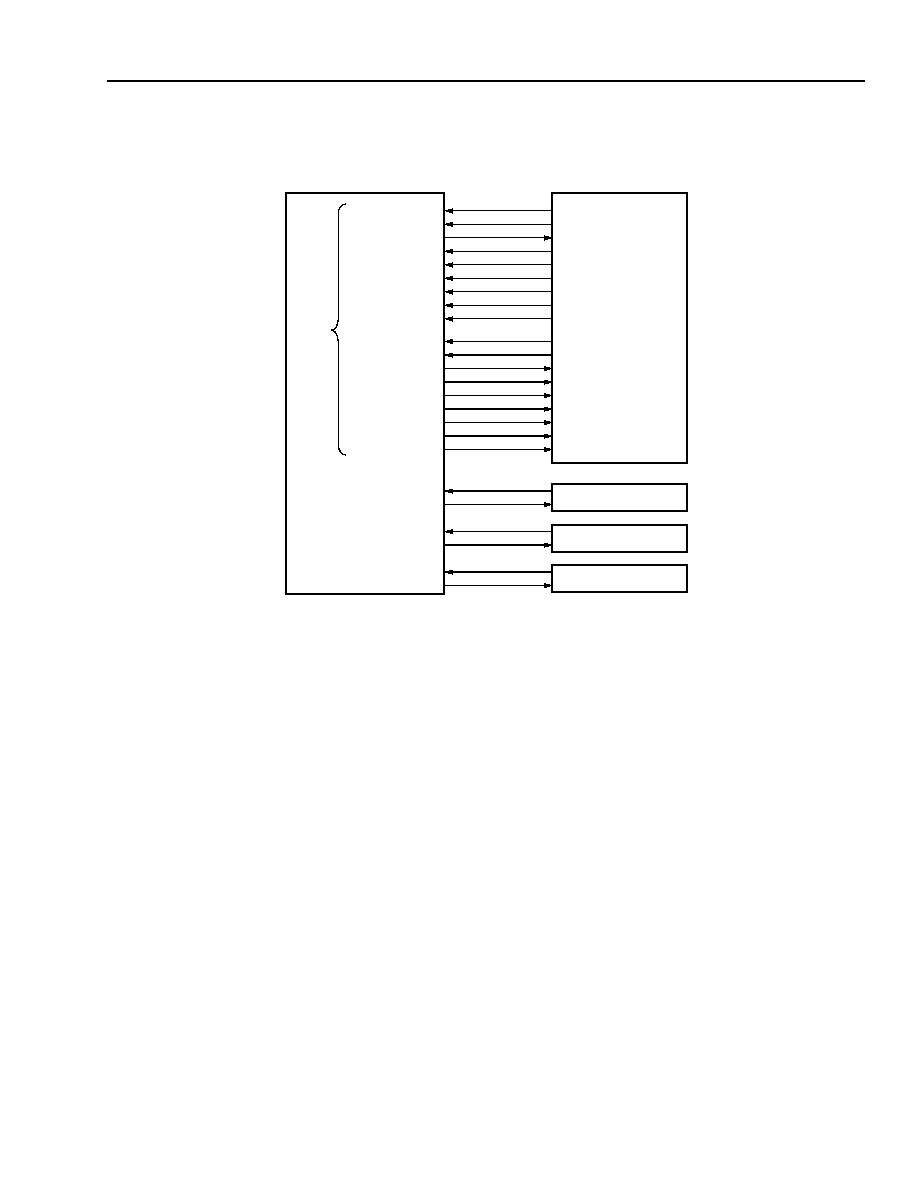

- Microprocessor (MPU) Interface

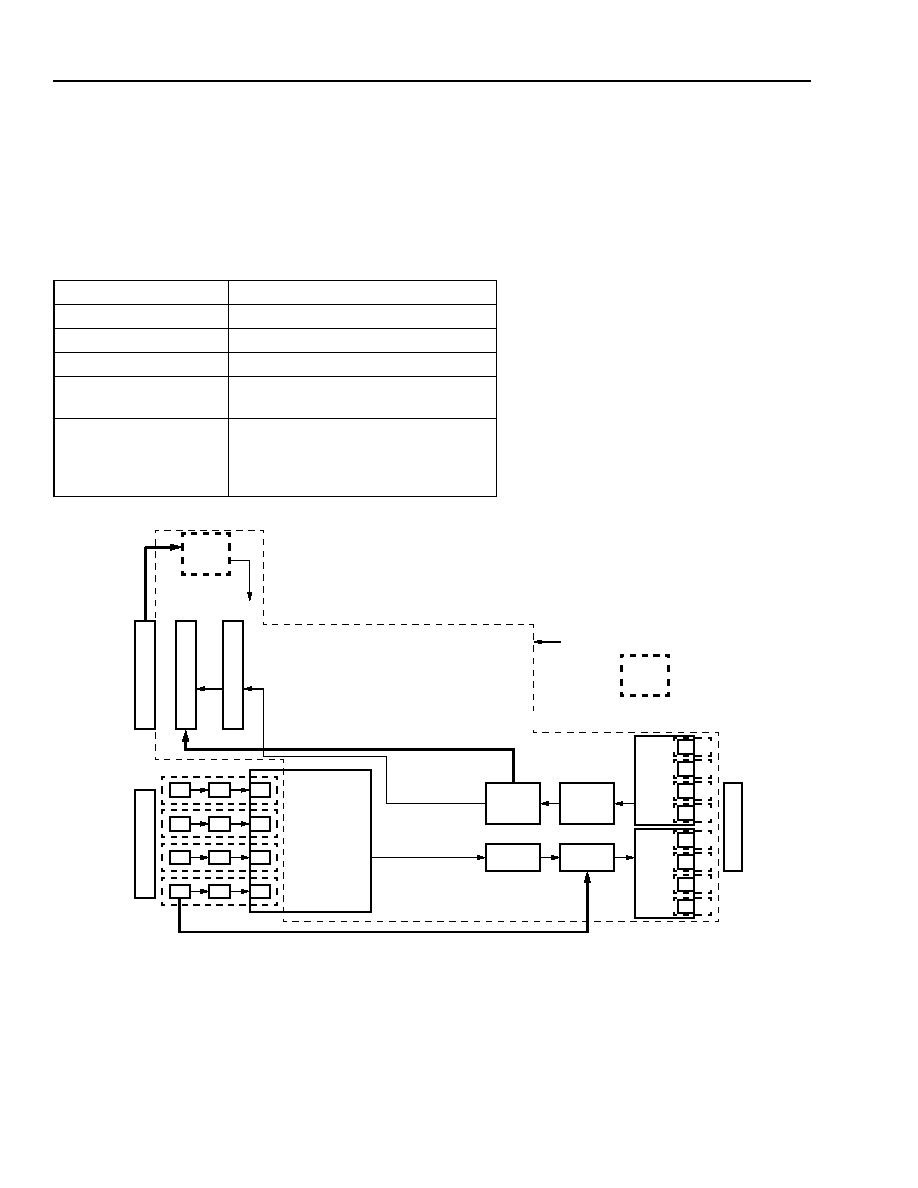

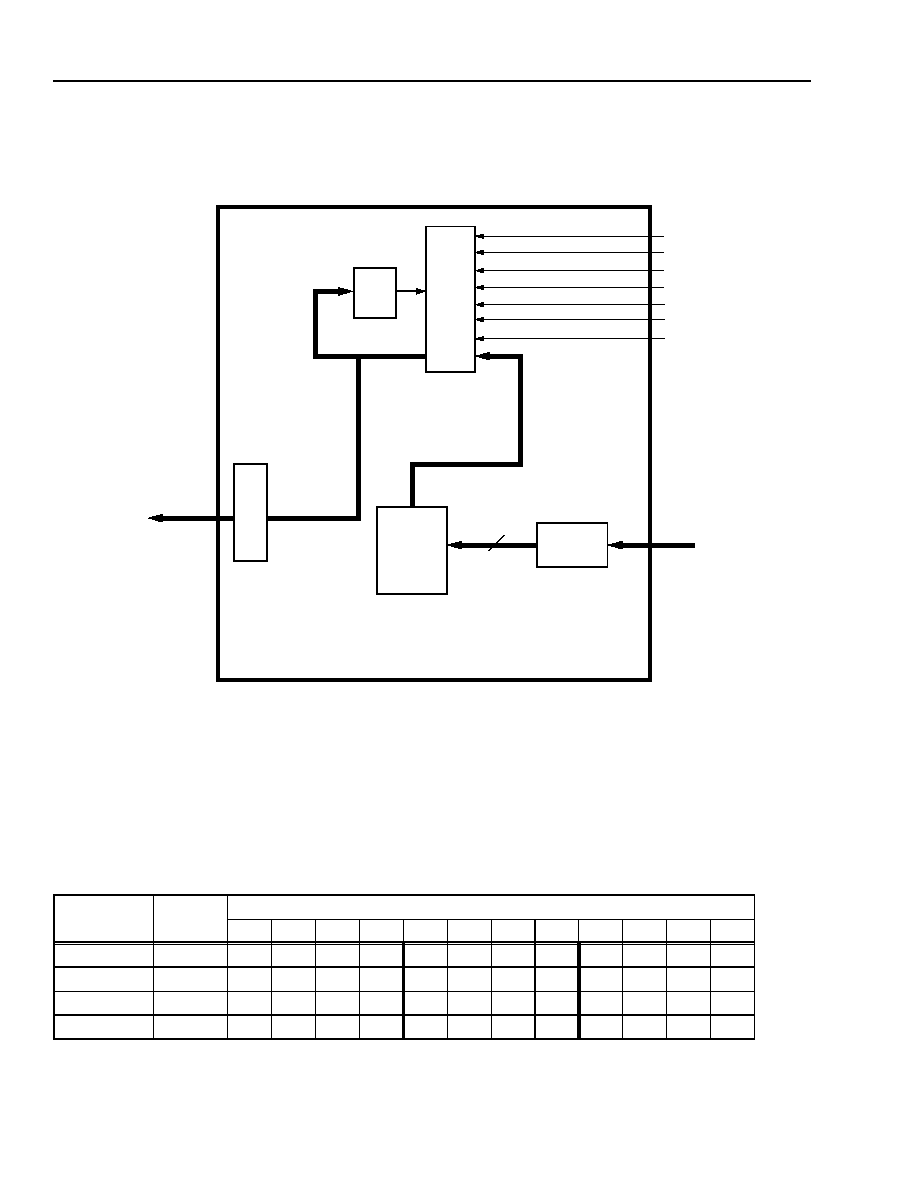

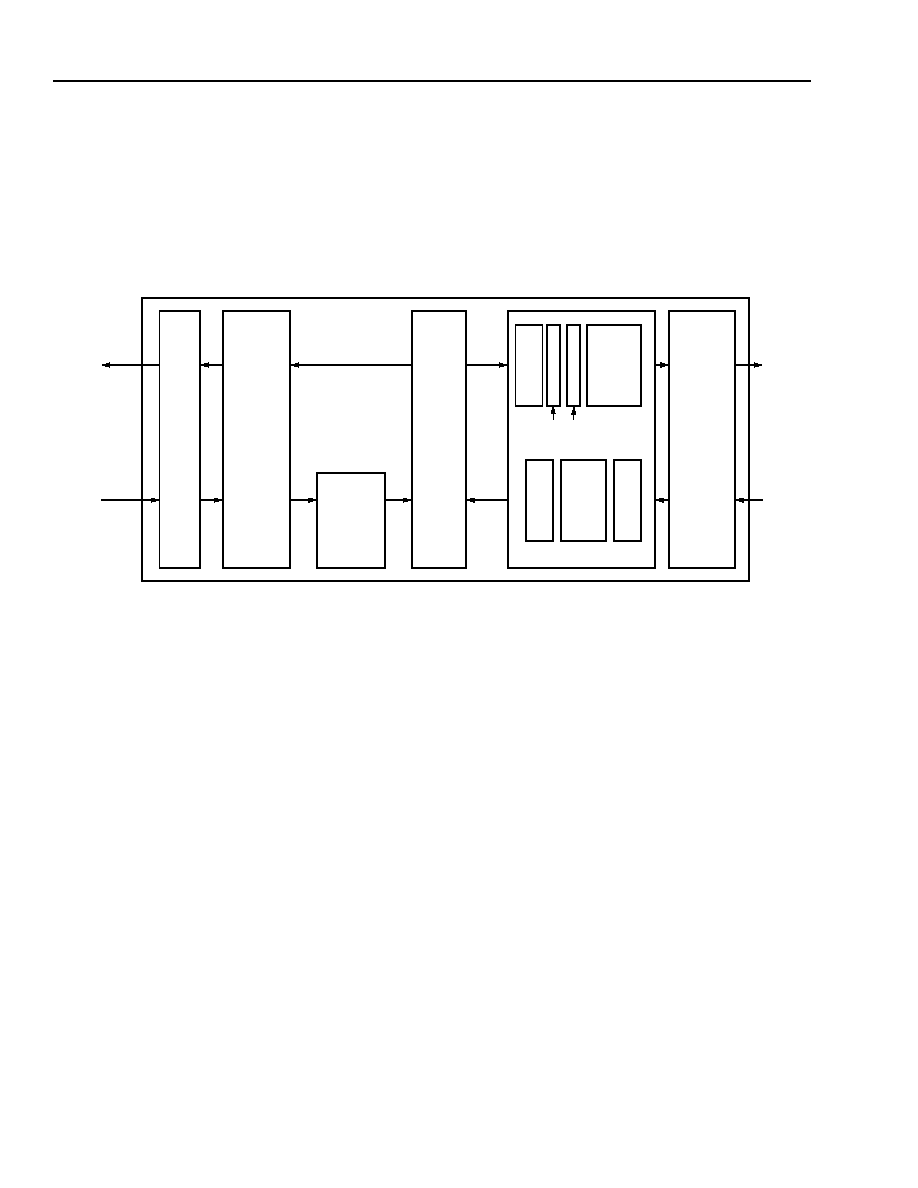

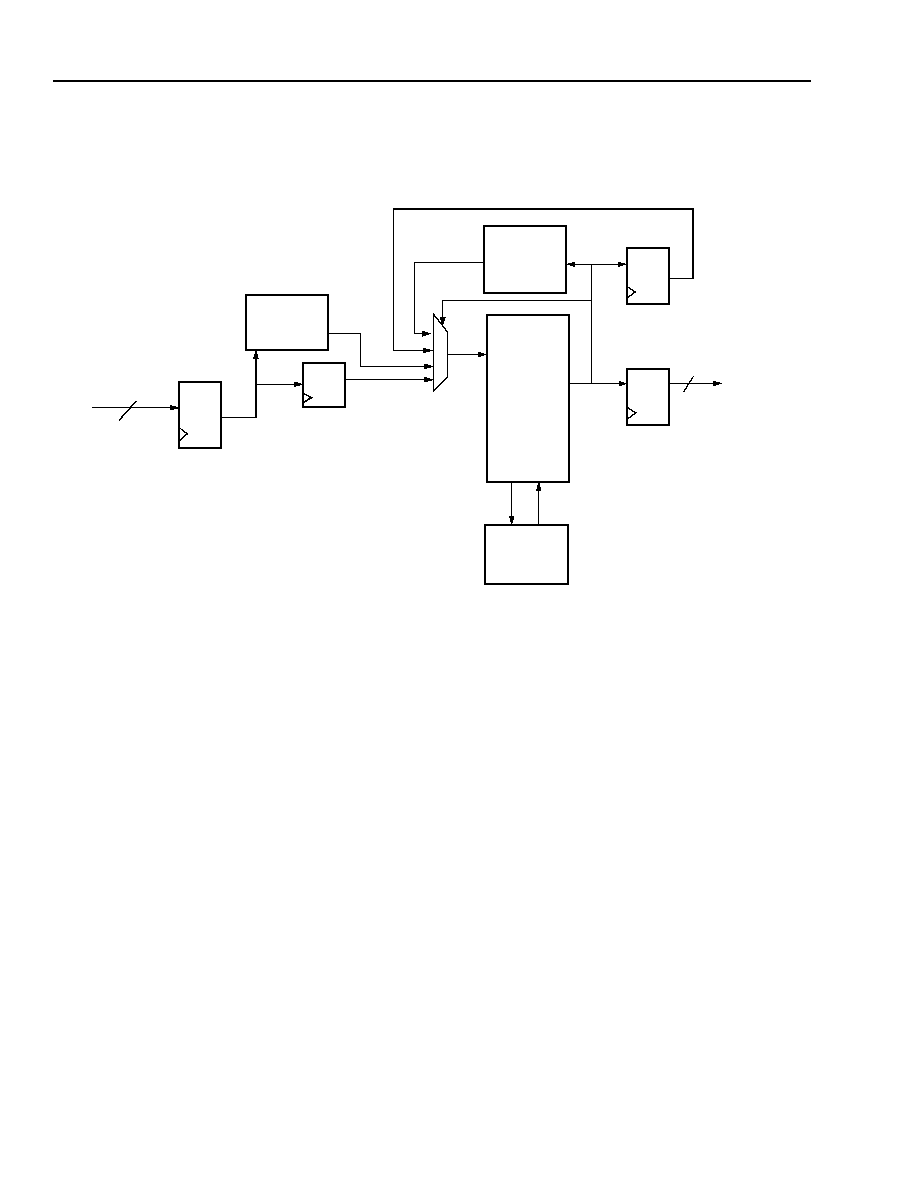

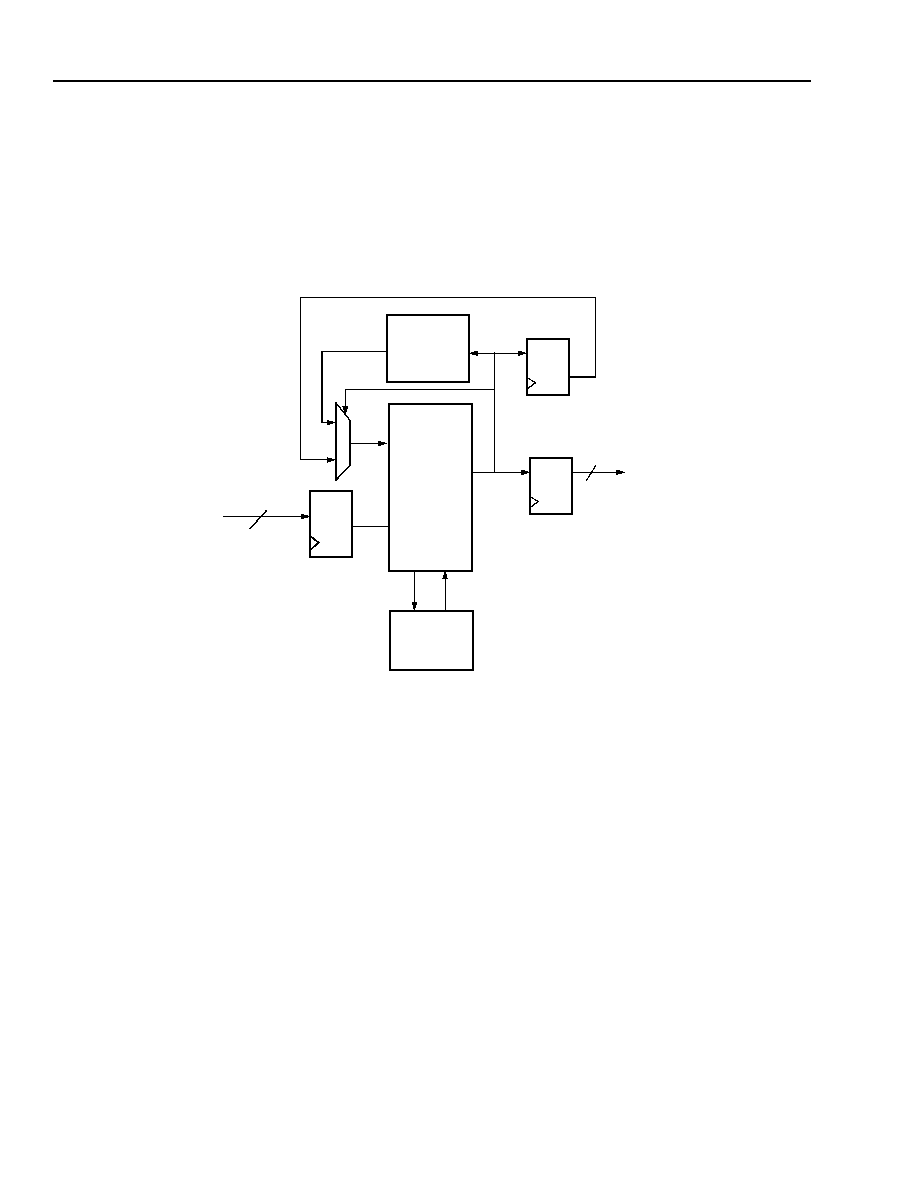

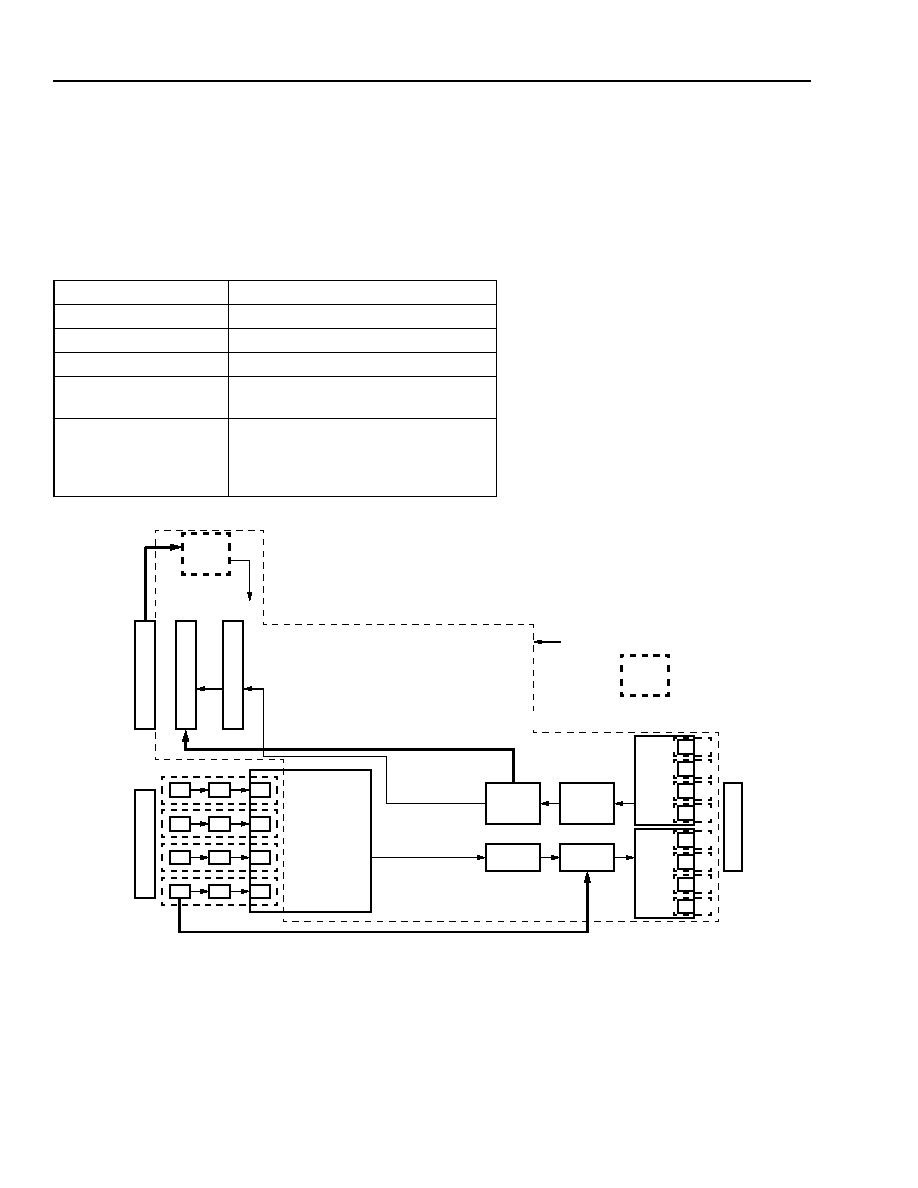

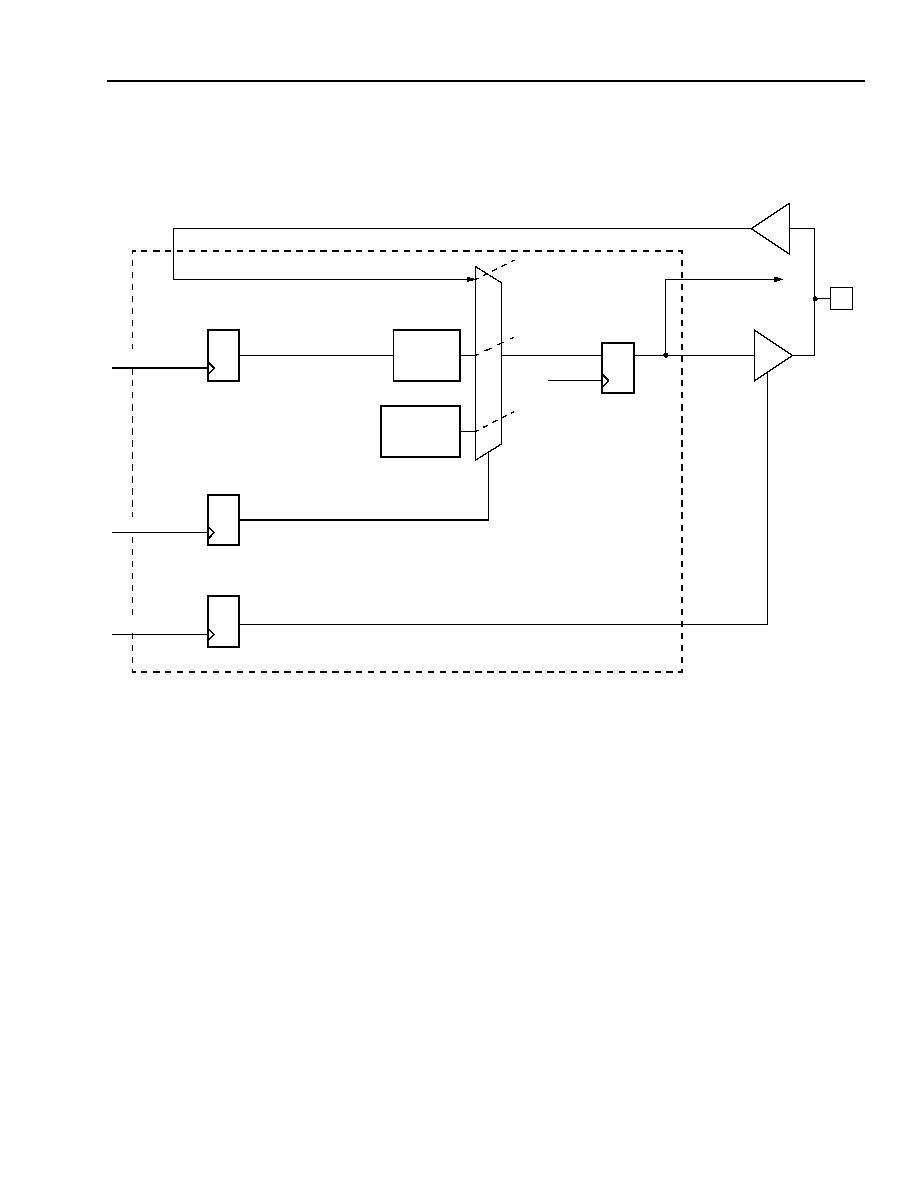

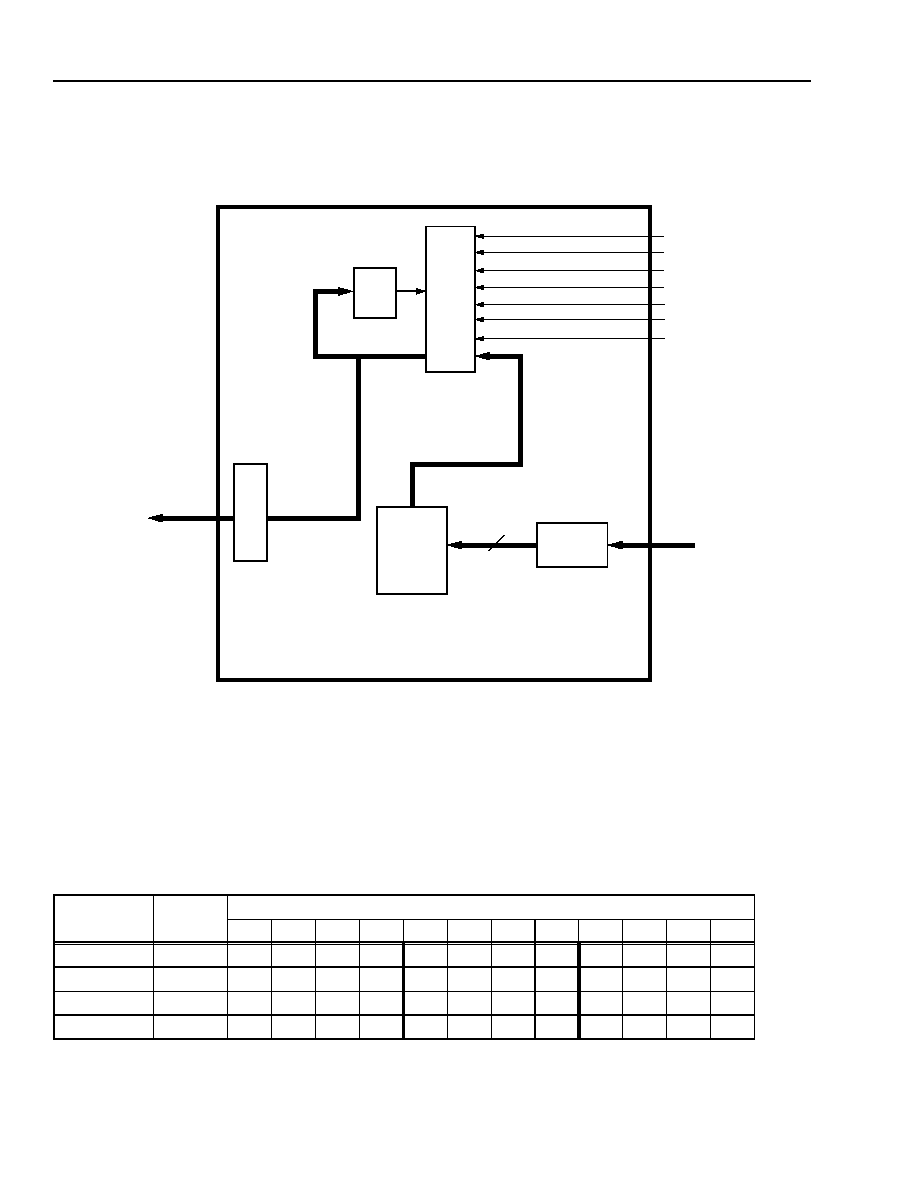

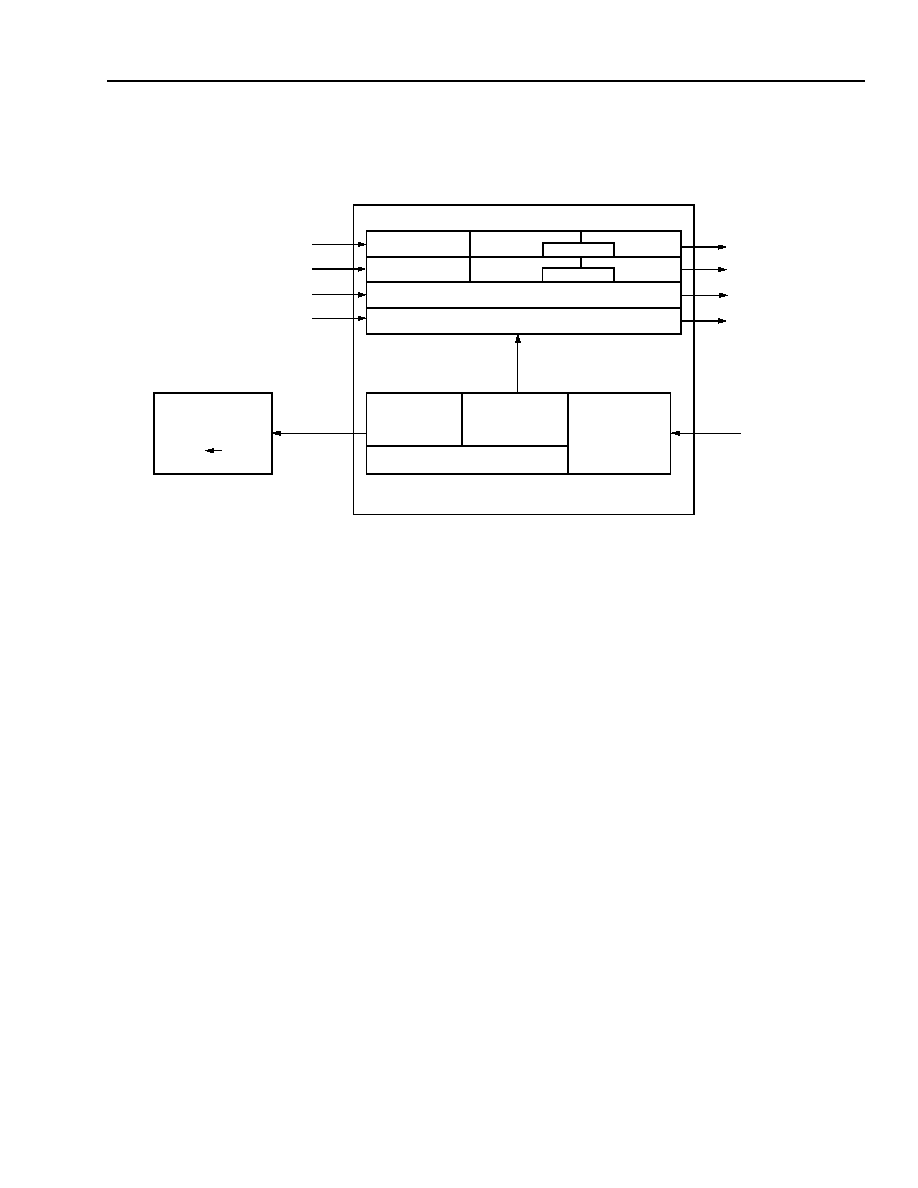

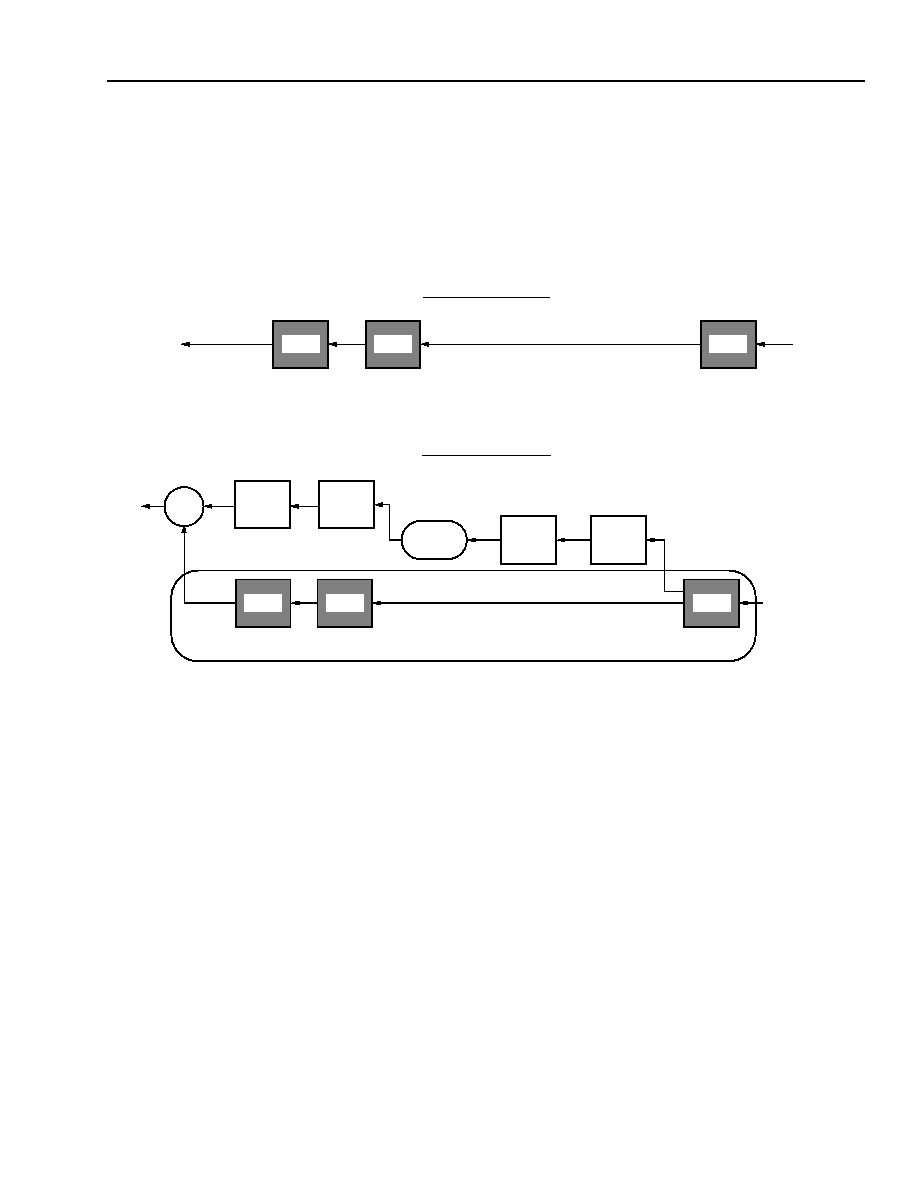

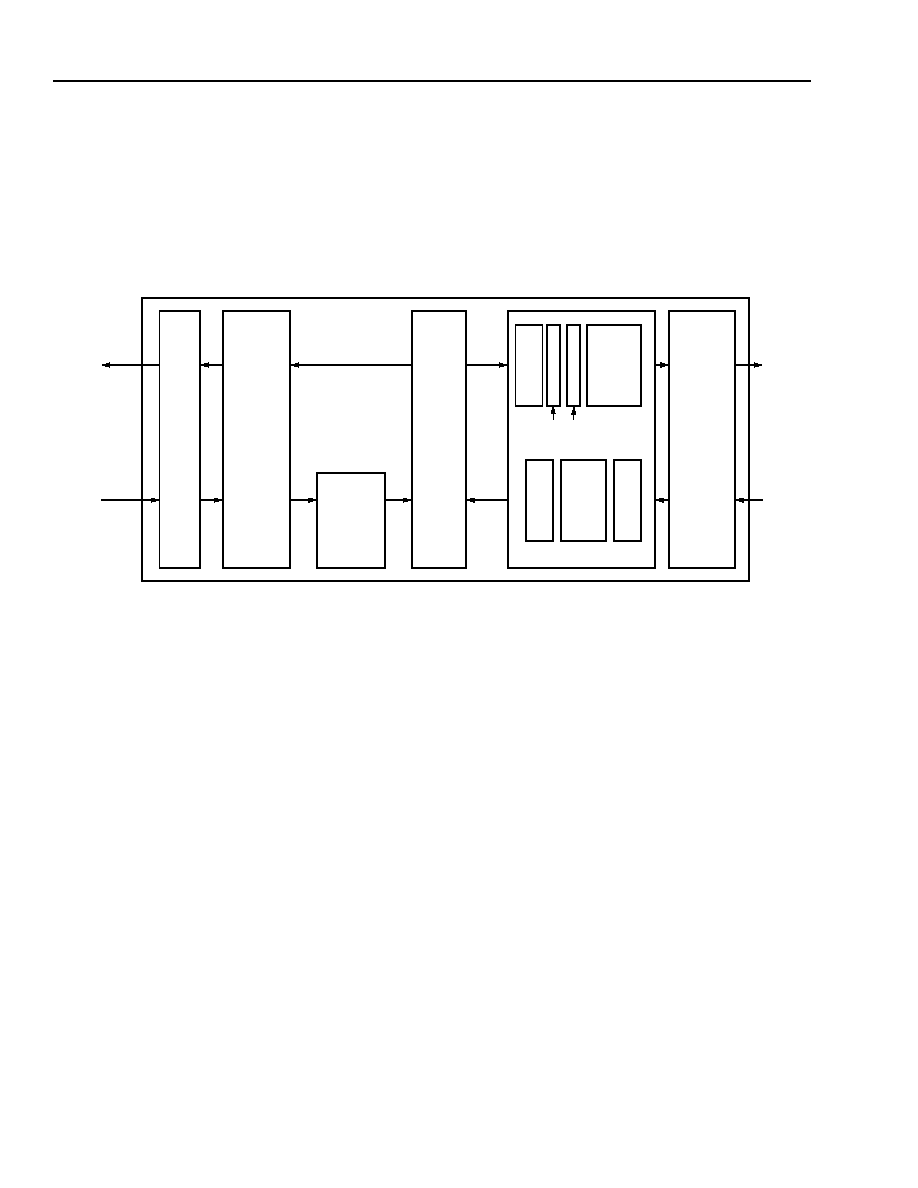

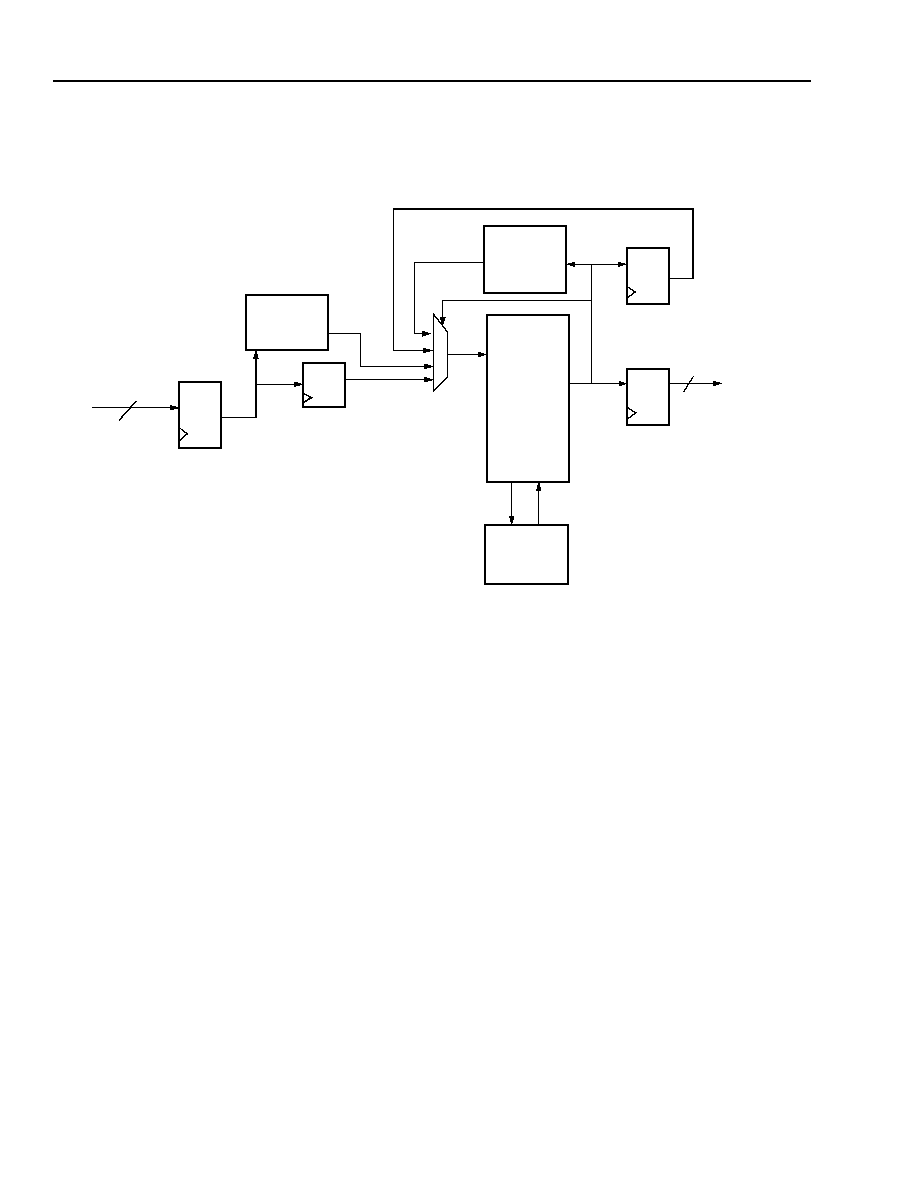

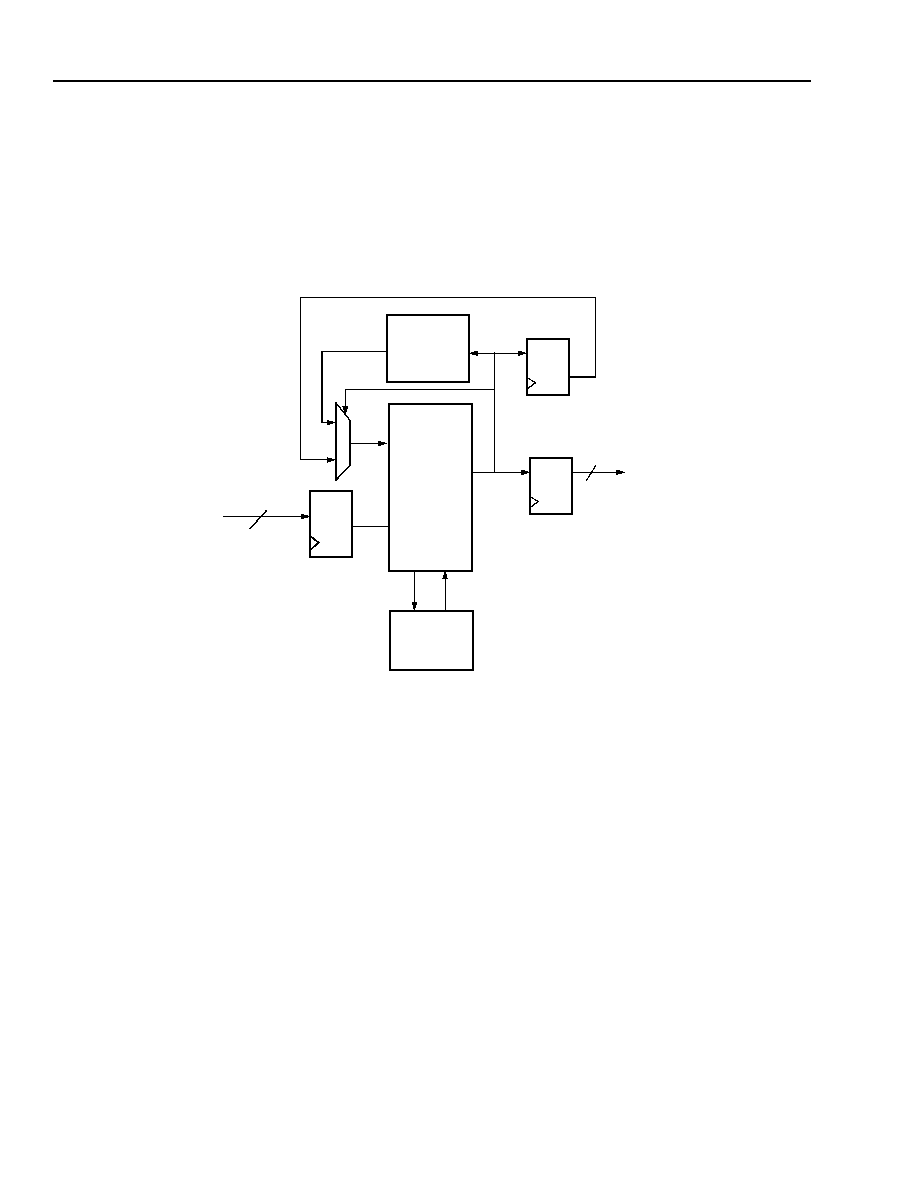

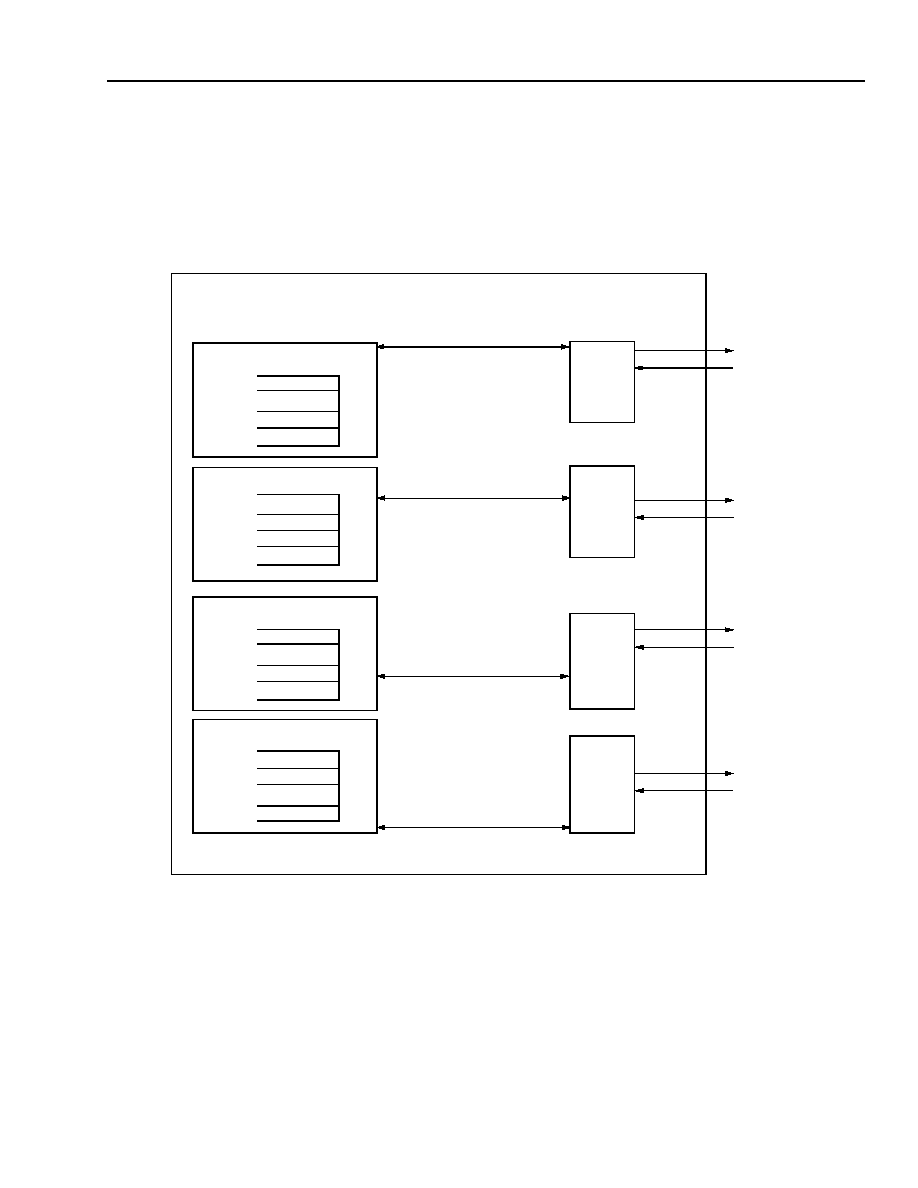

- Functional Description

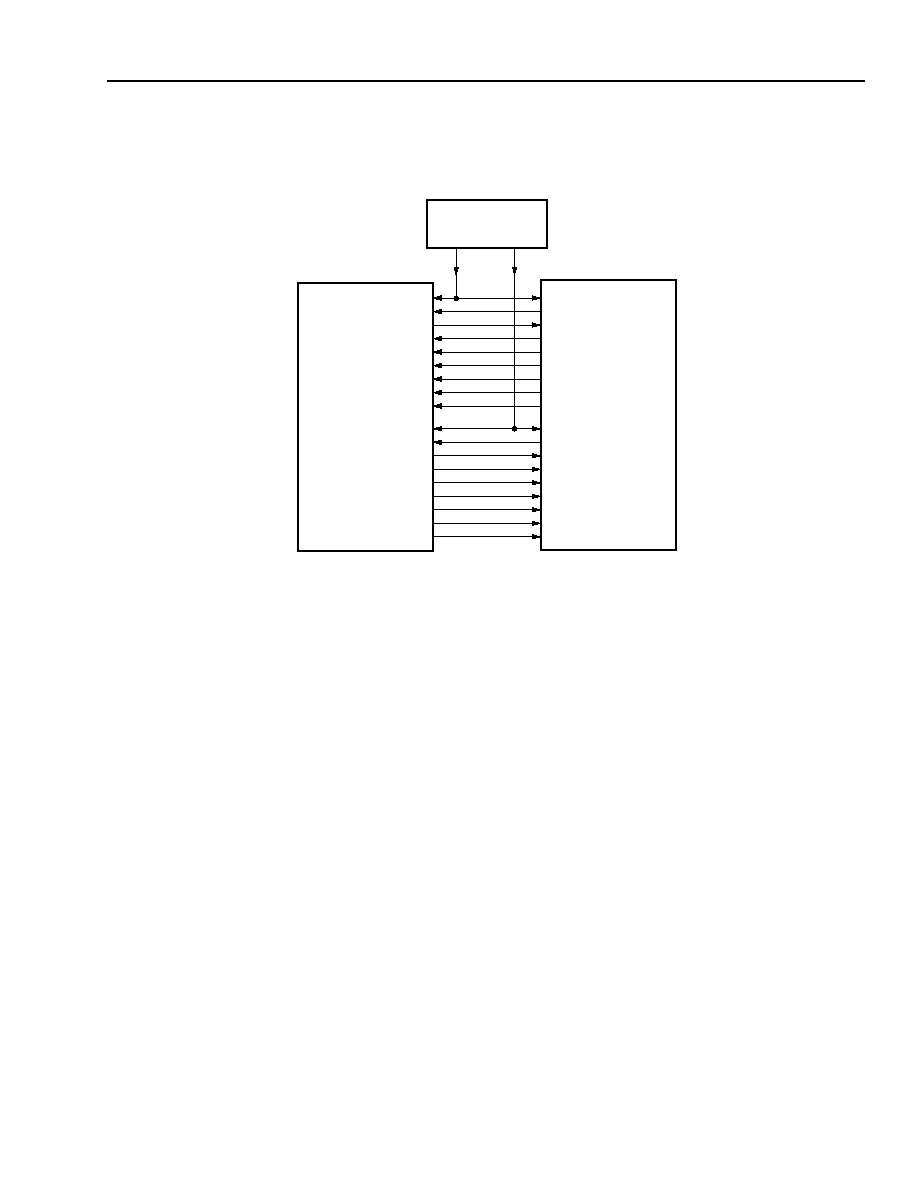

- Line Interface

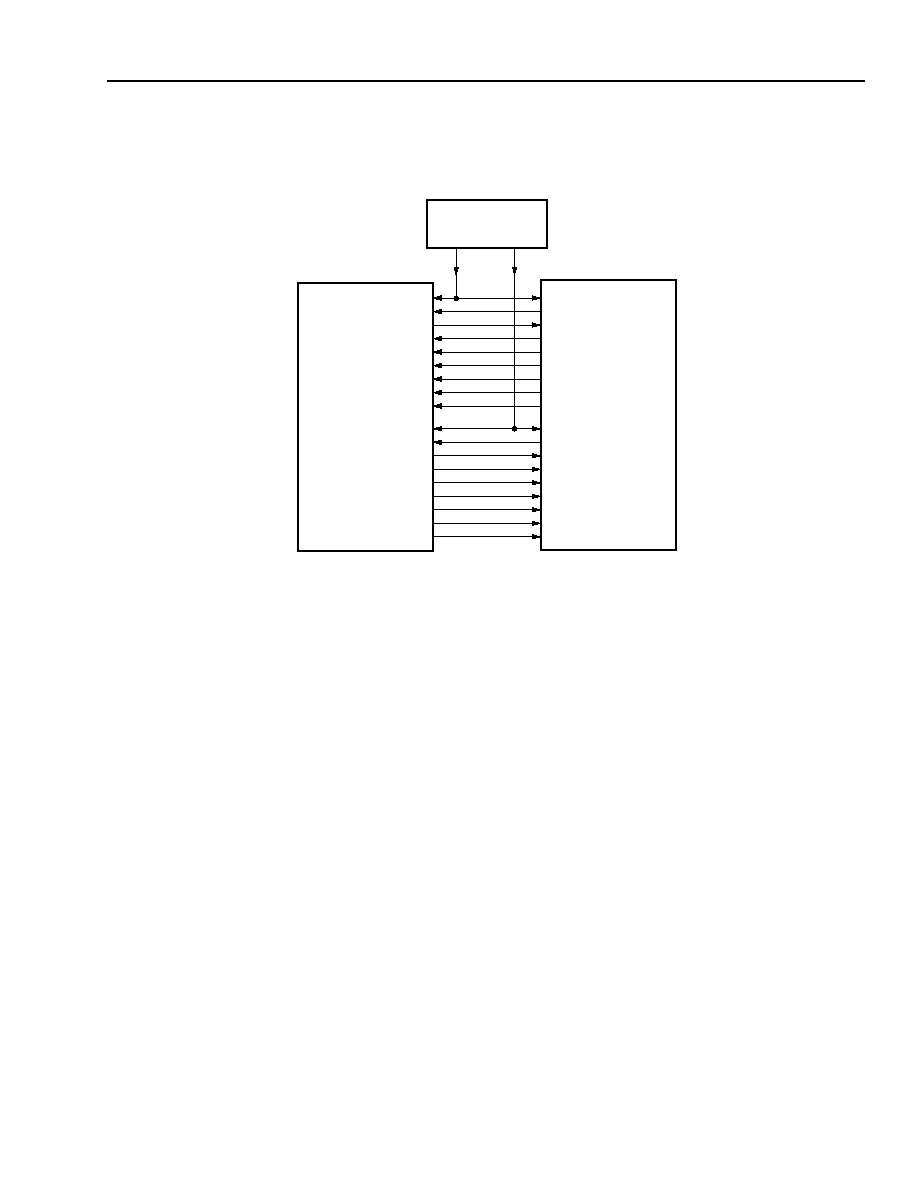

- Transport Overhead Processor (TOHP-48) Block

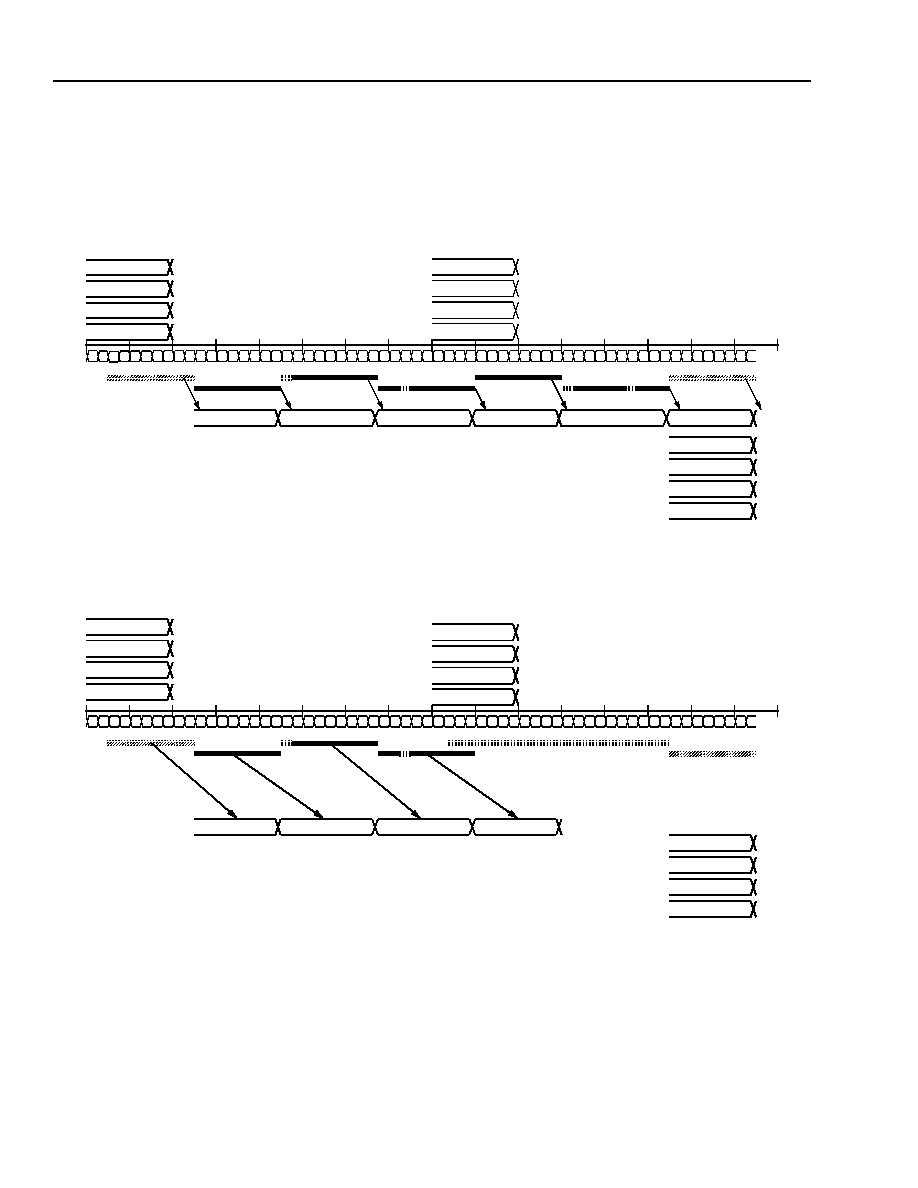

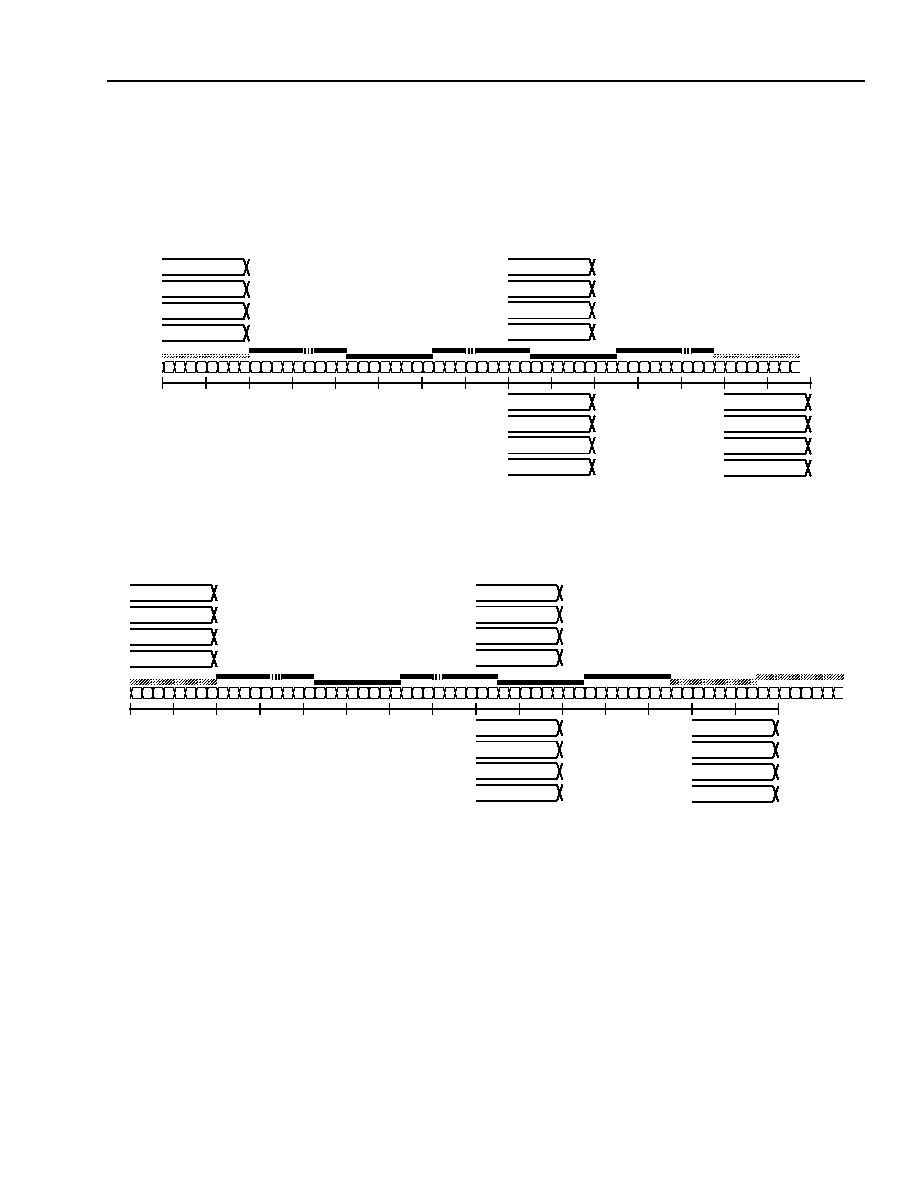

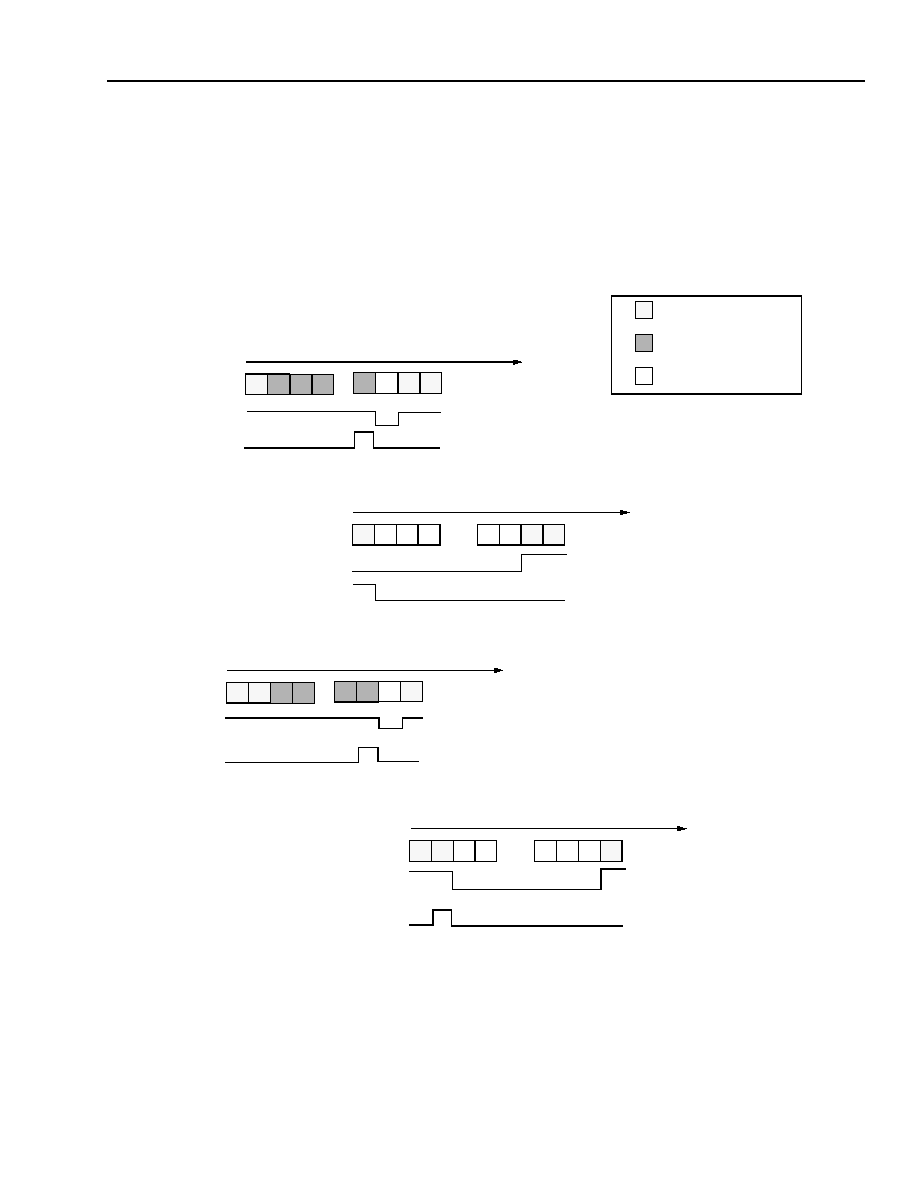

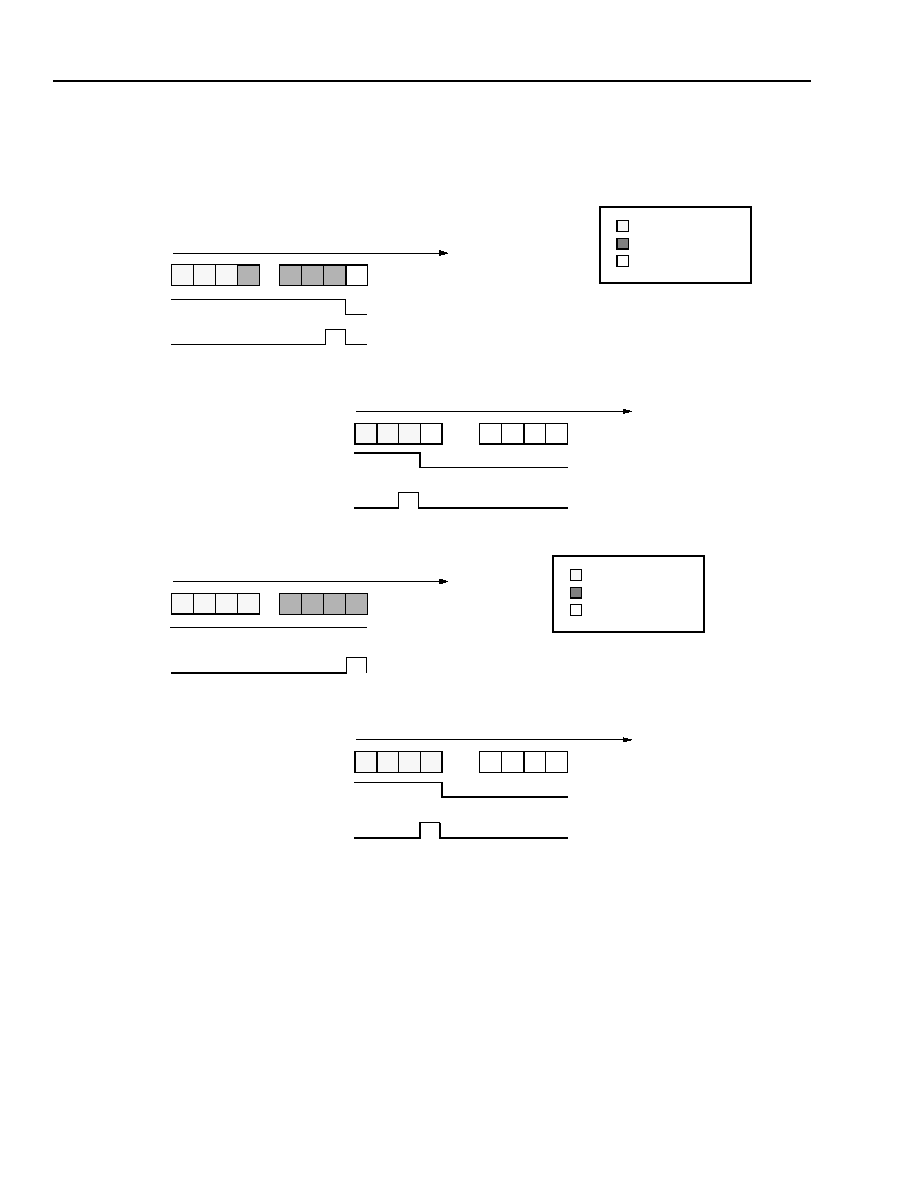

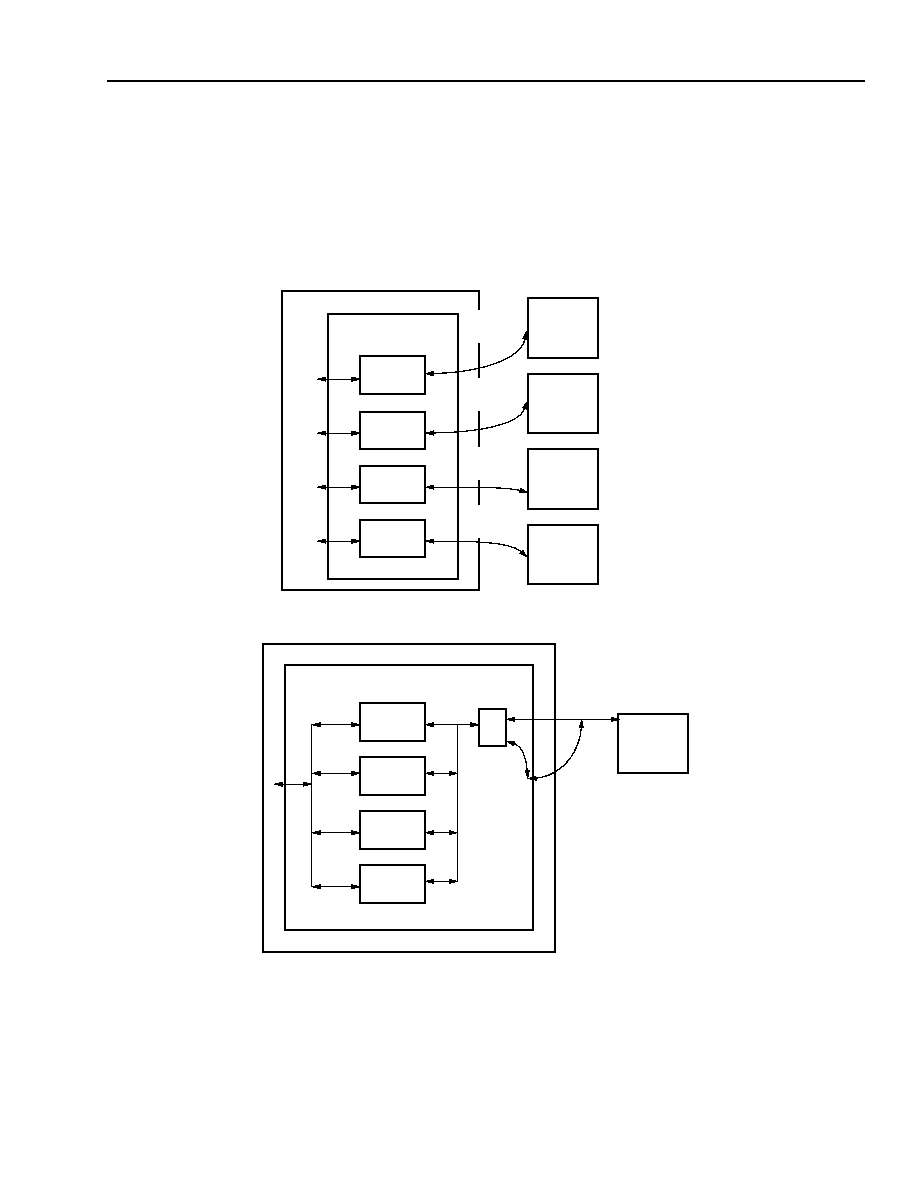

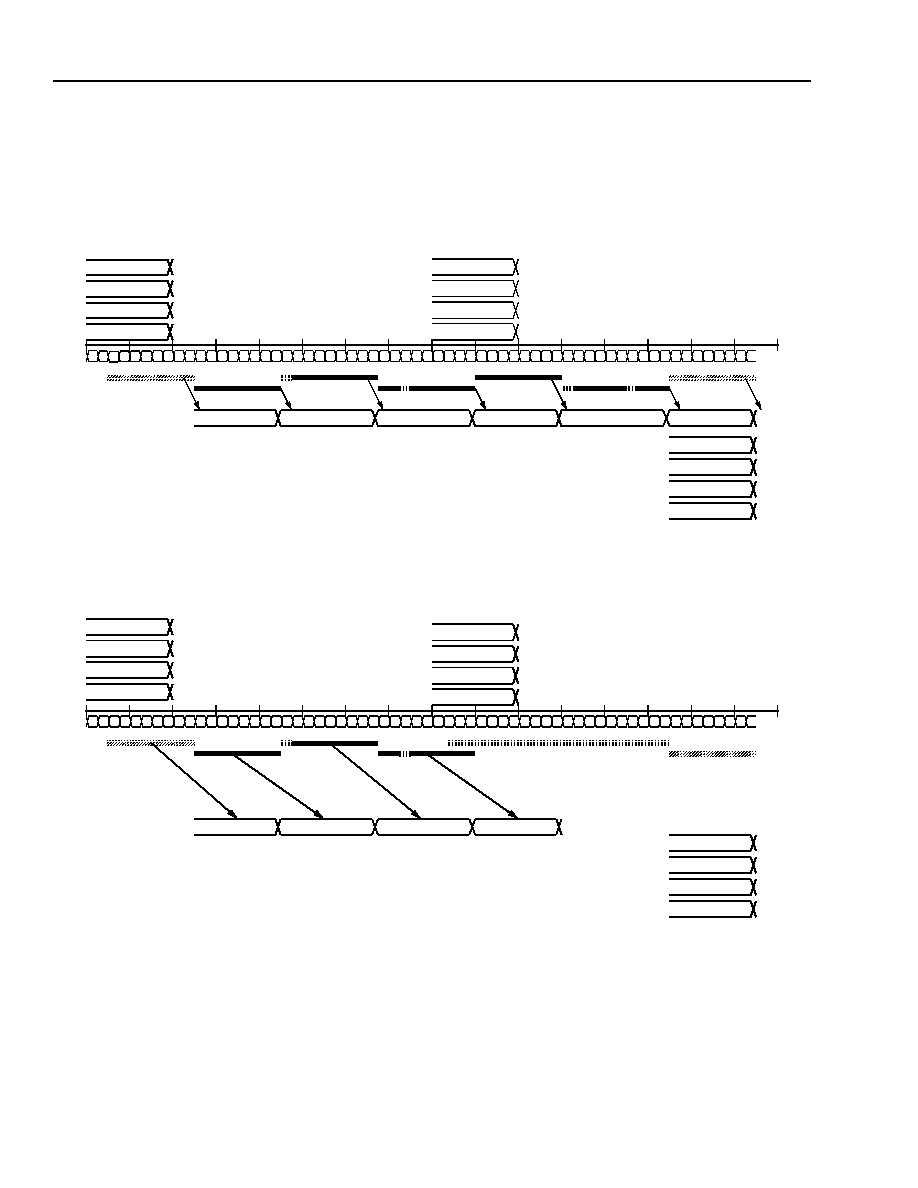

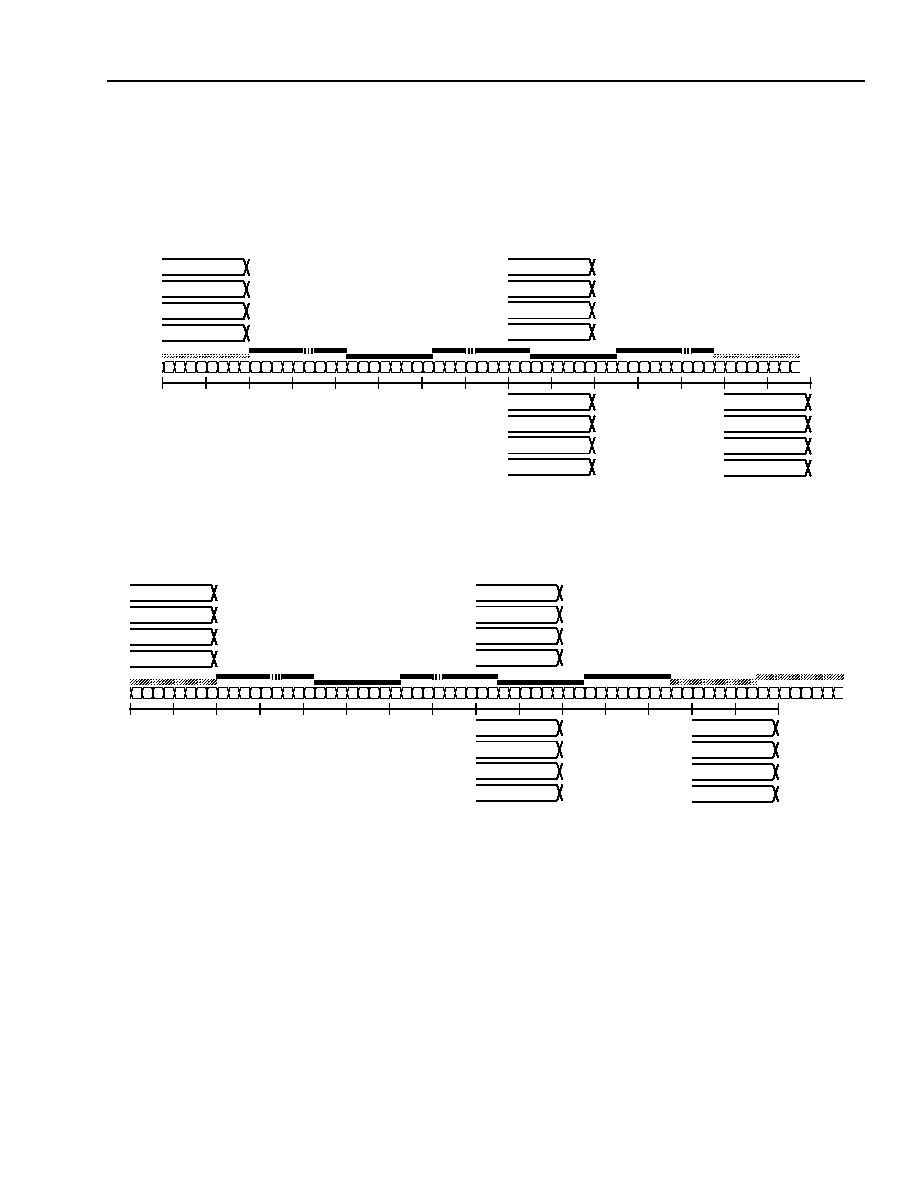

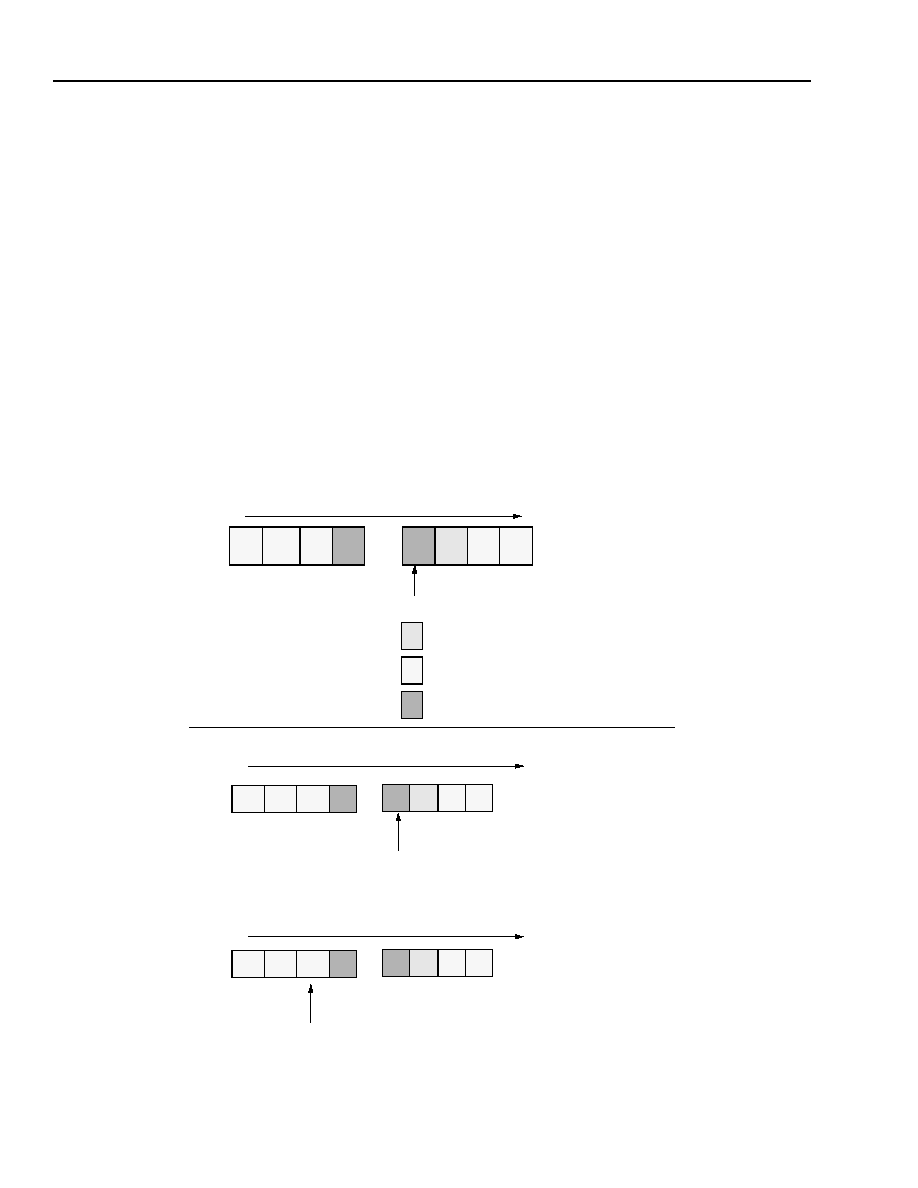

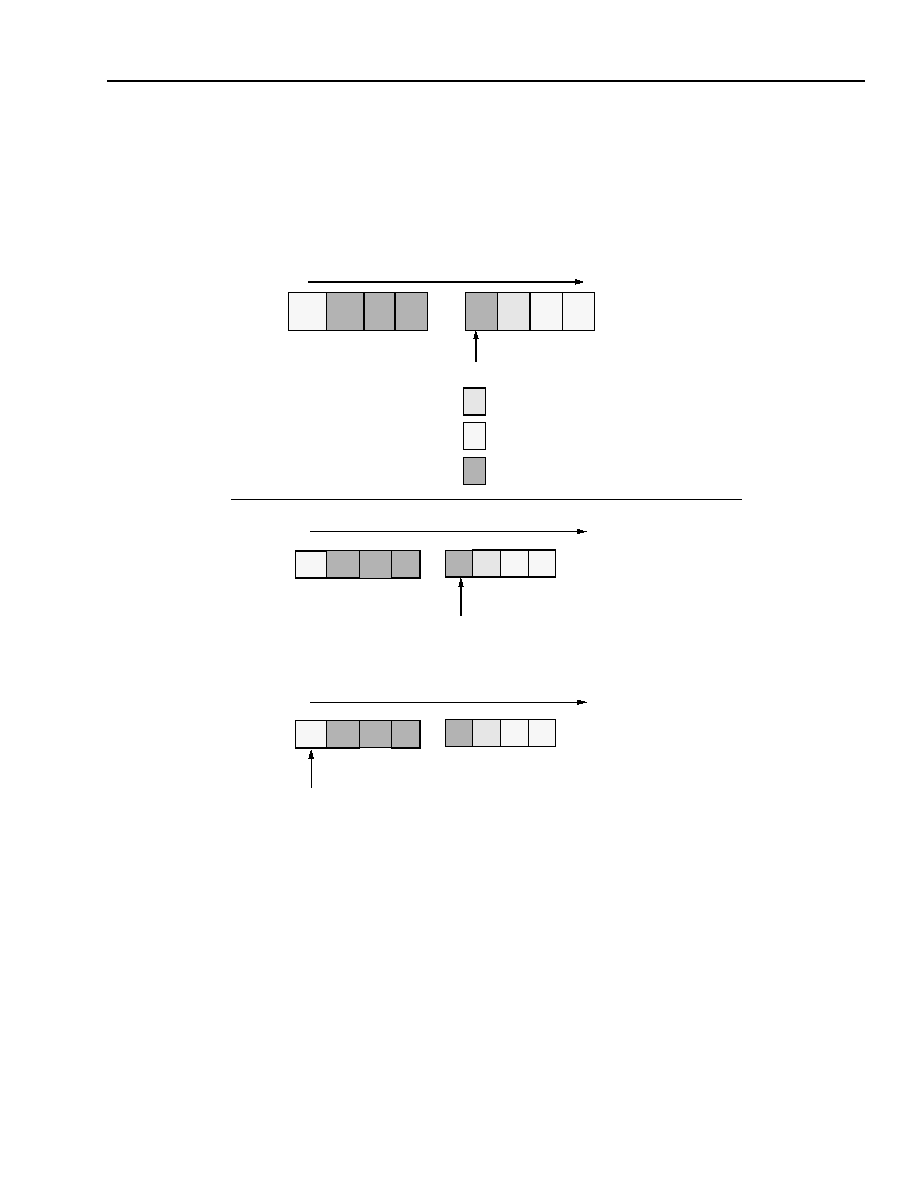

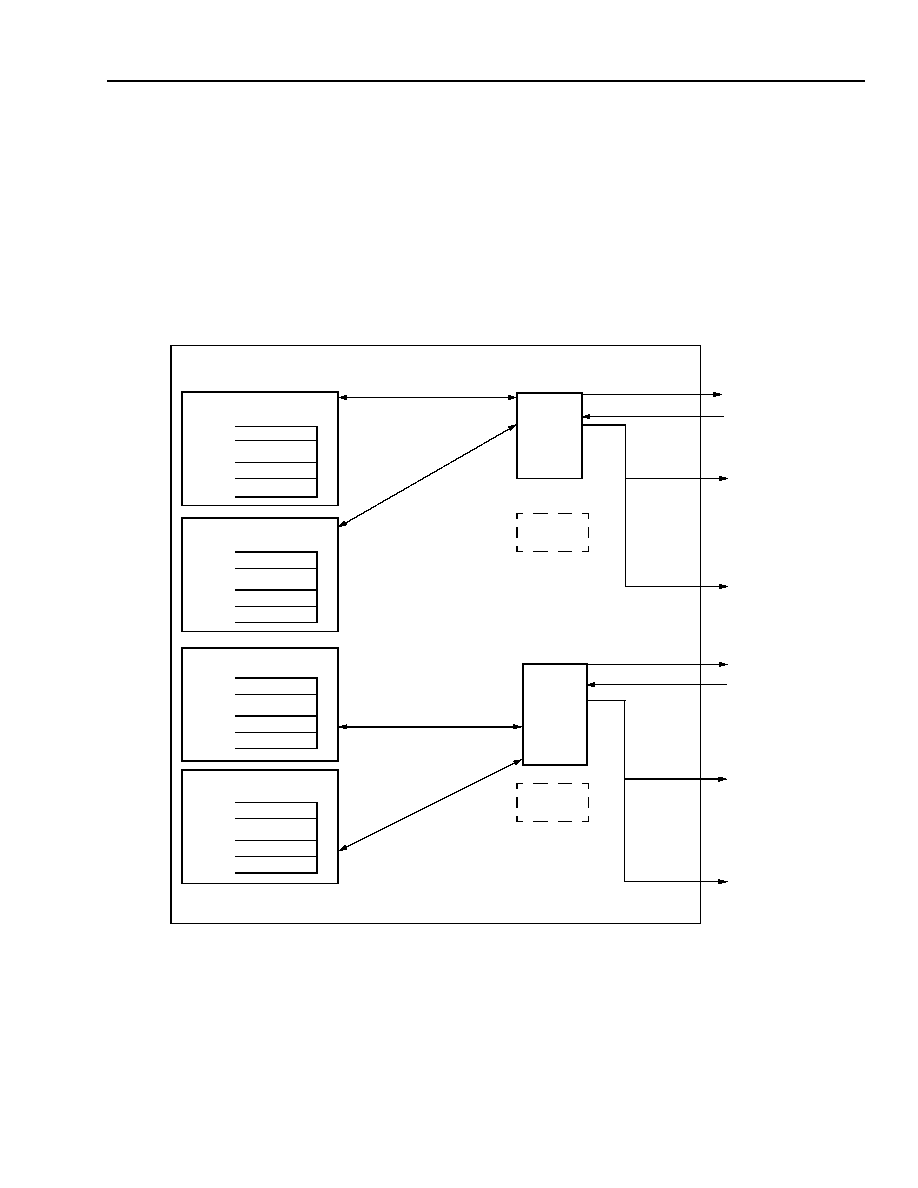

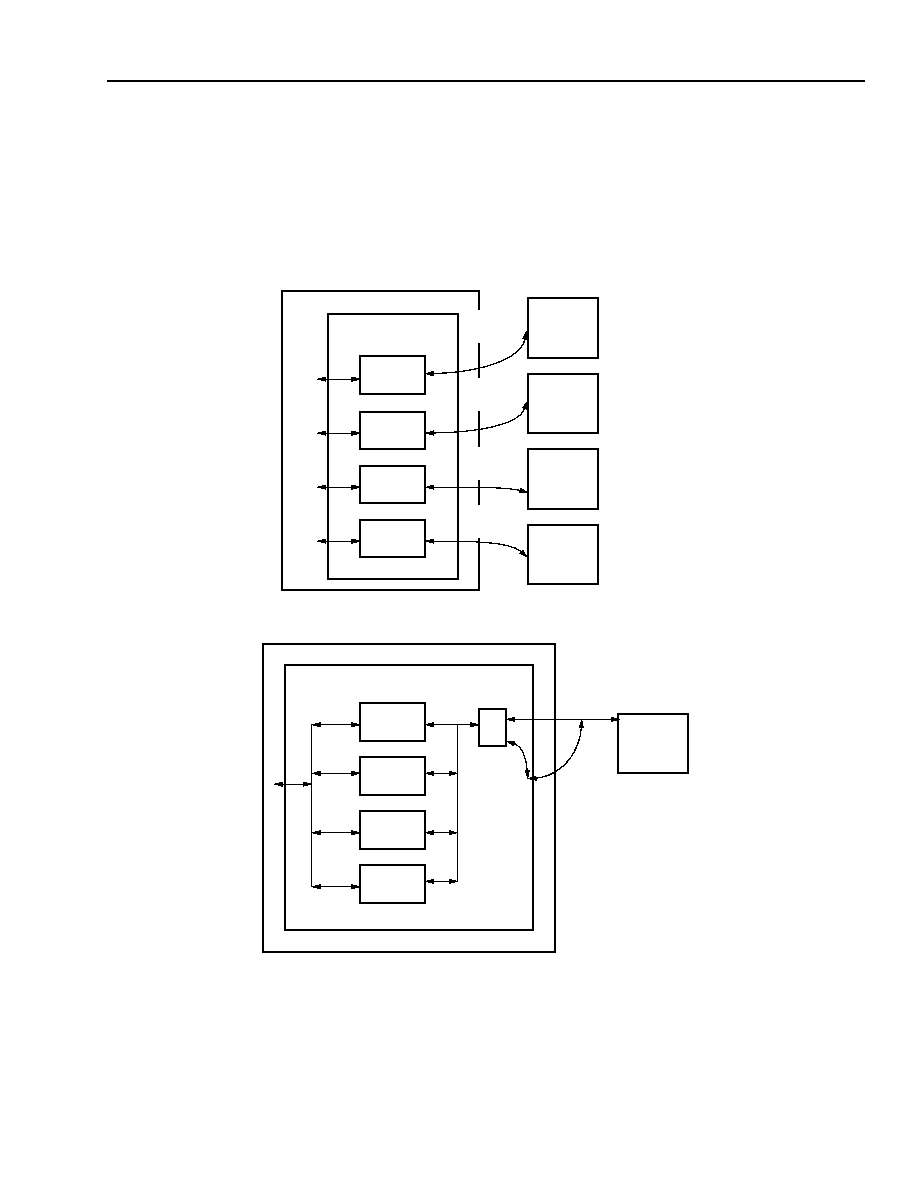

- Pointer Processor (PP)

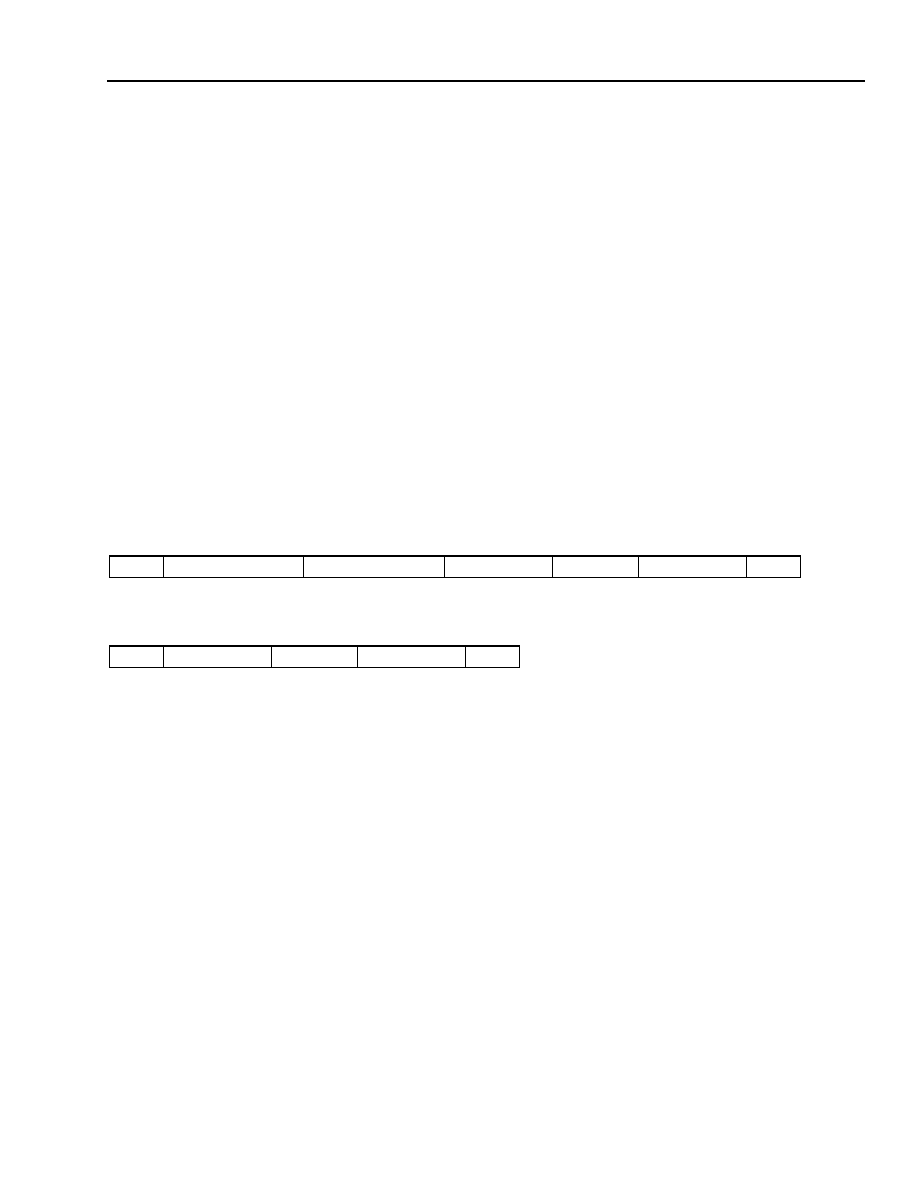

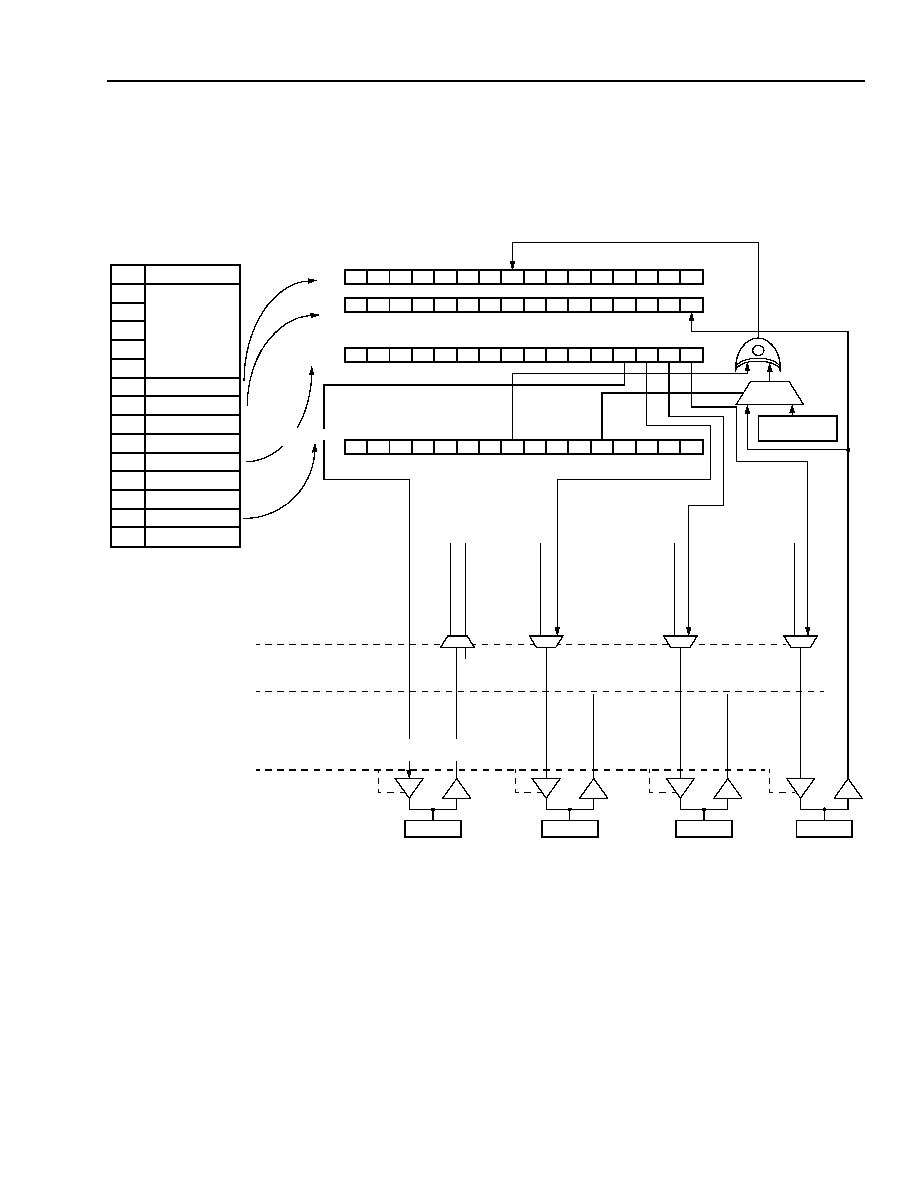

- Path Terminator (PT)

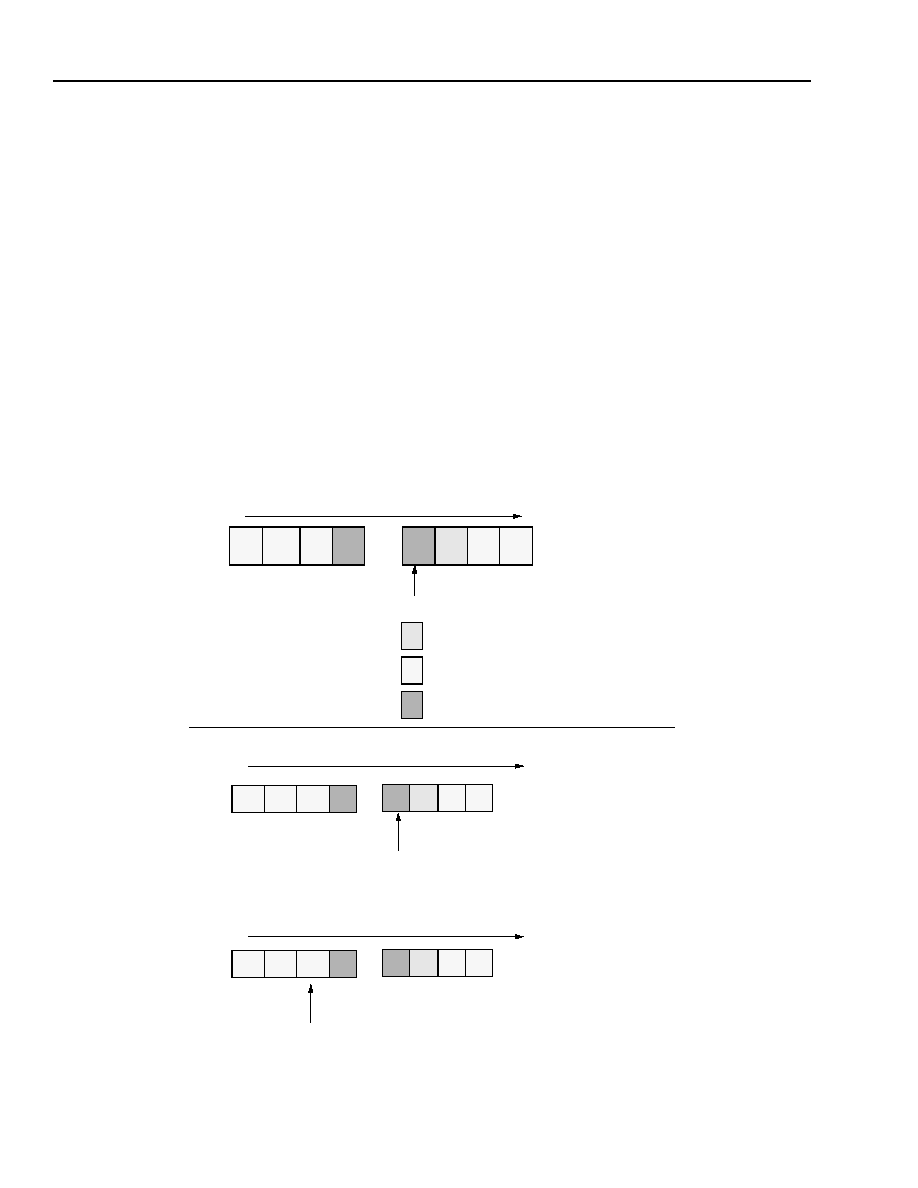

- STS Receive Terminator (RXT) Block

- DS3/E3 Block

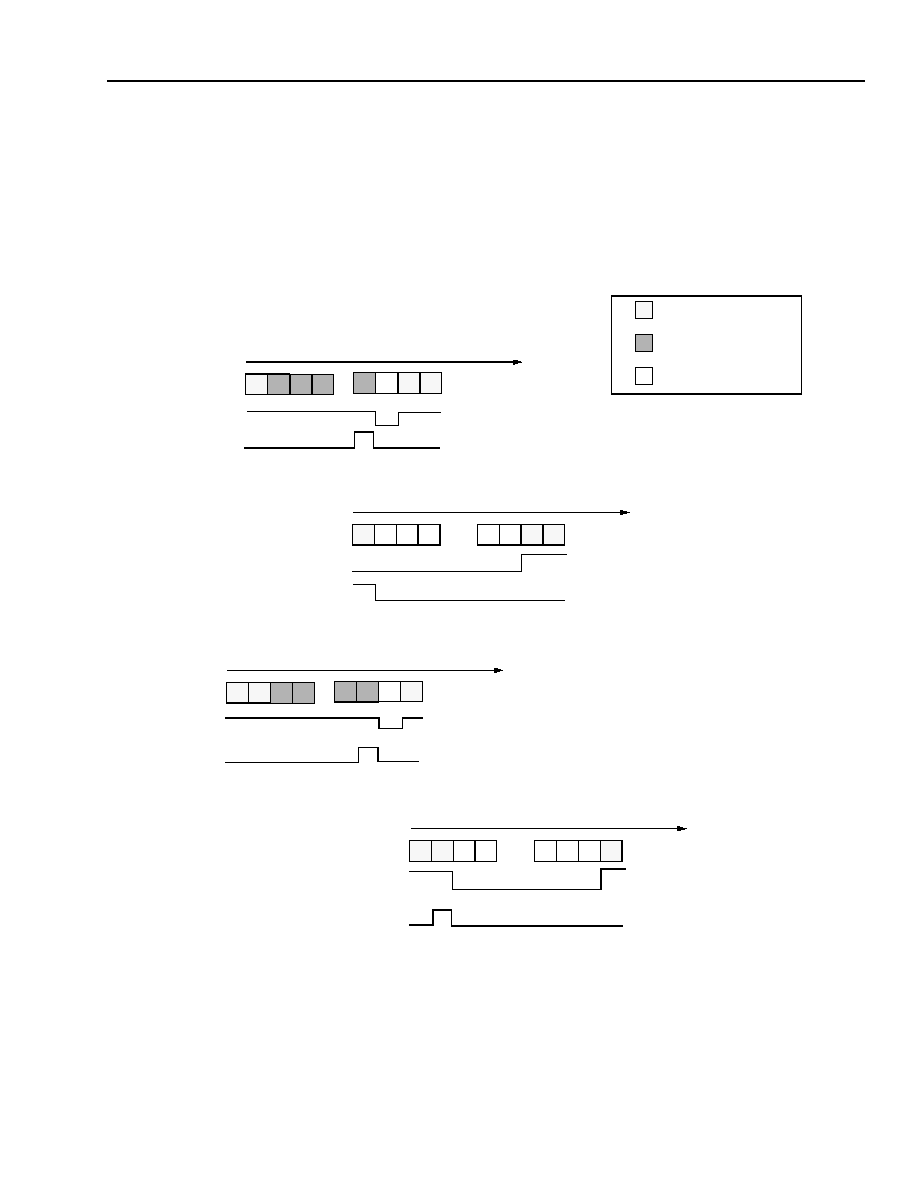

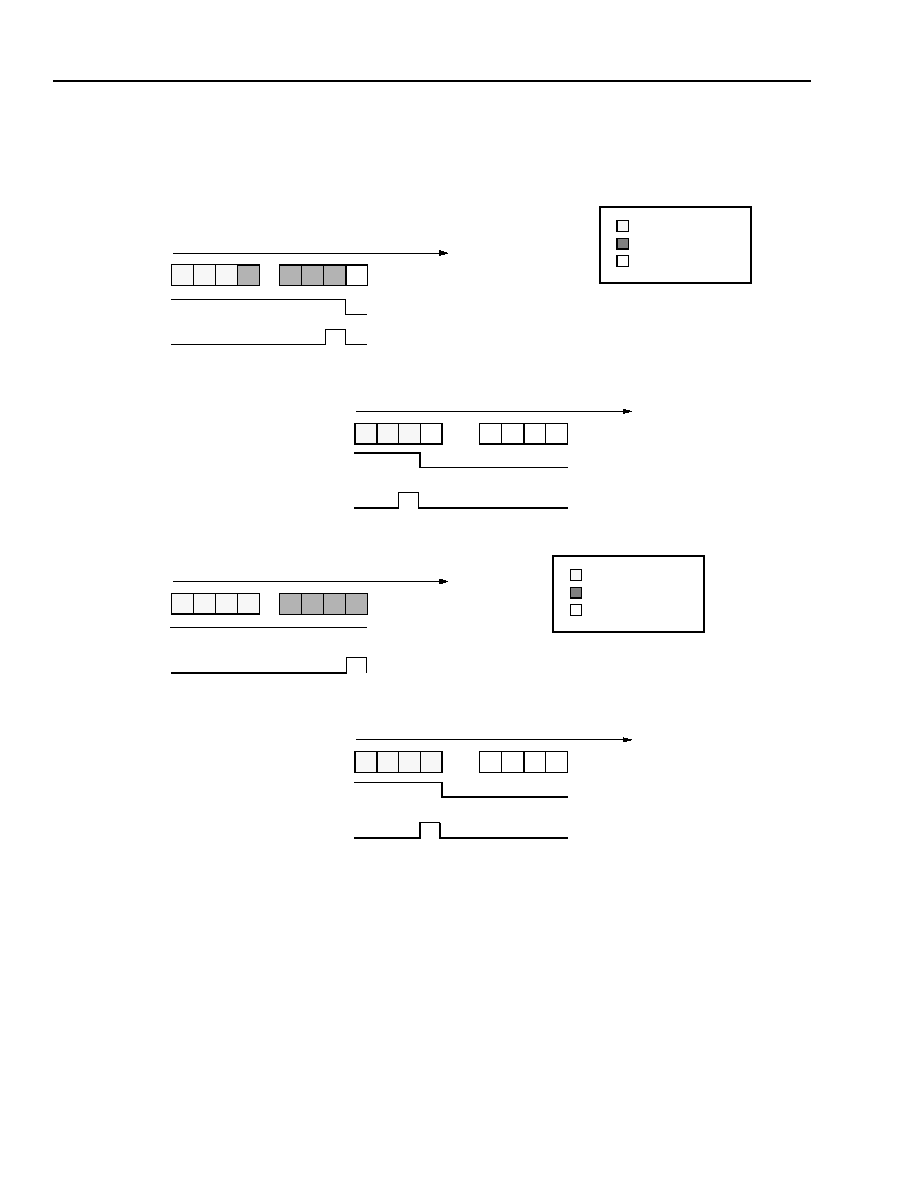

- Receive Sequencer (RXS) Block

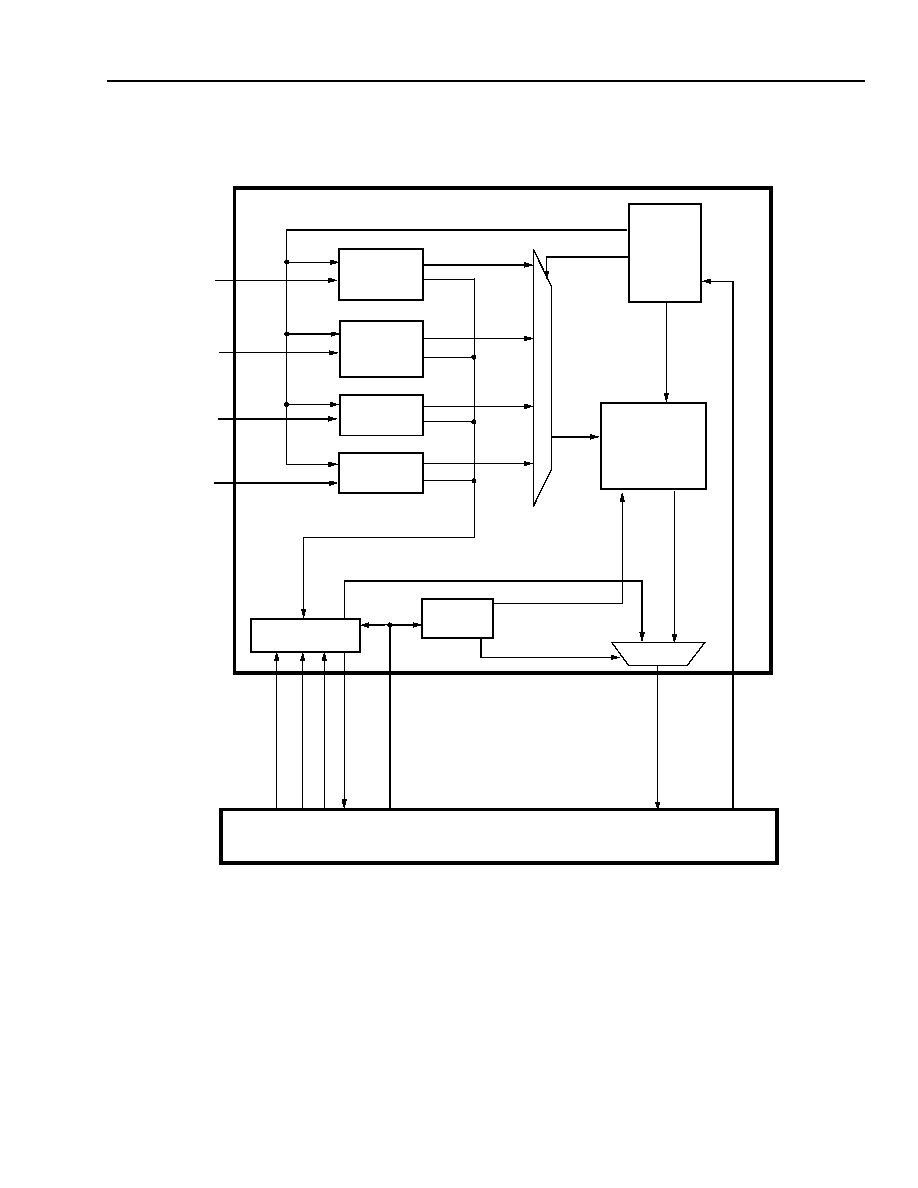

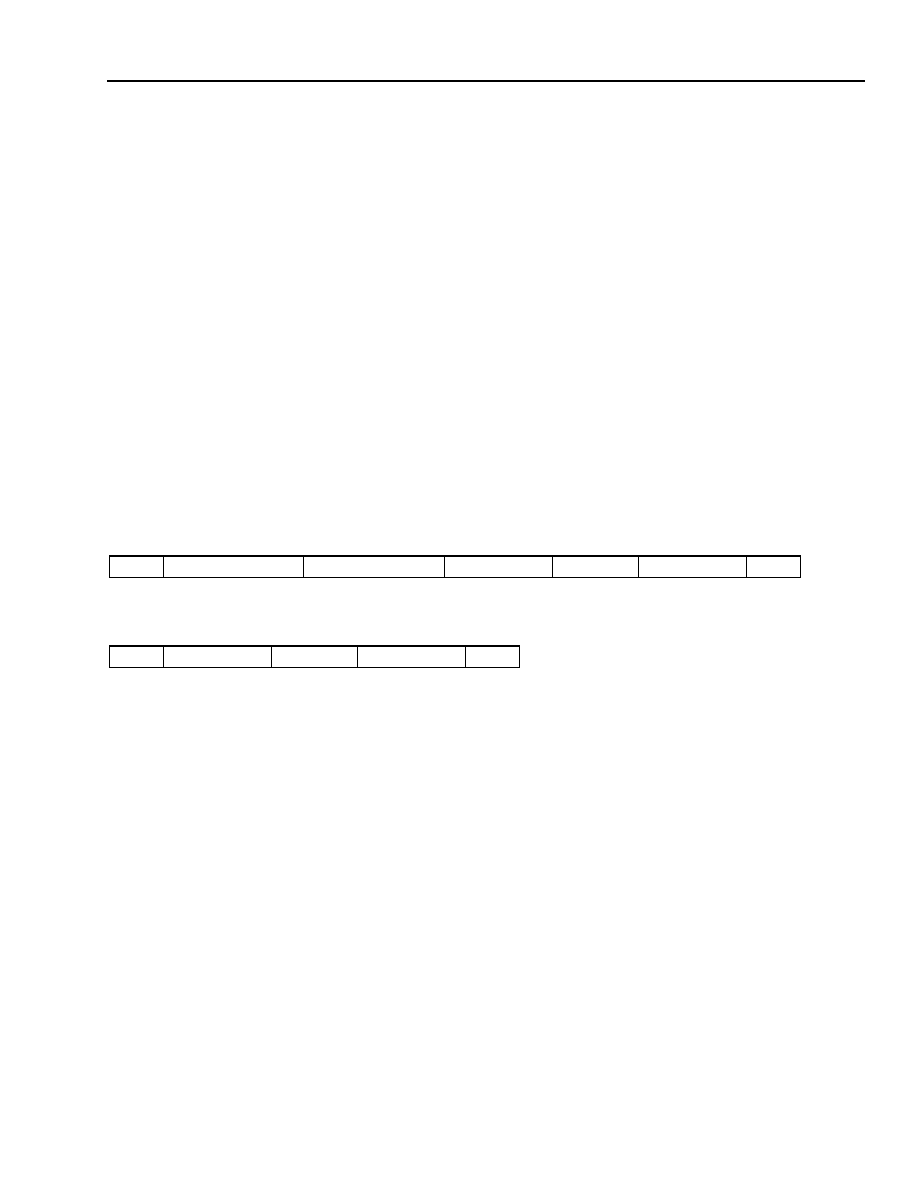

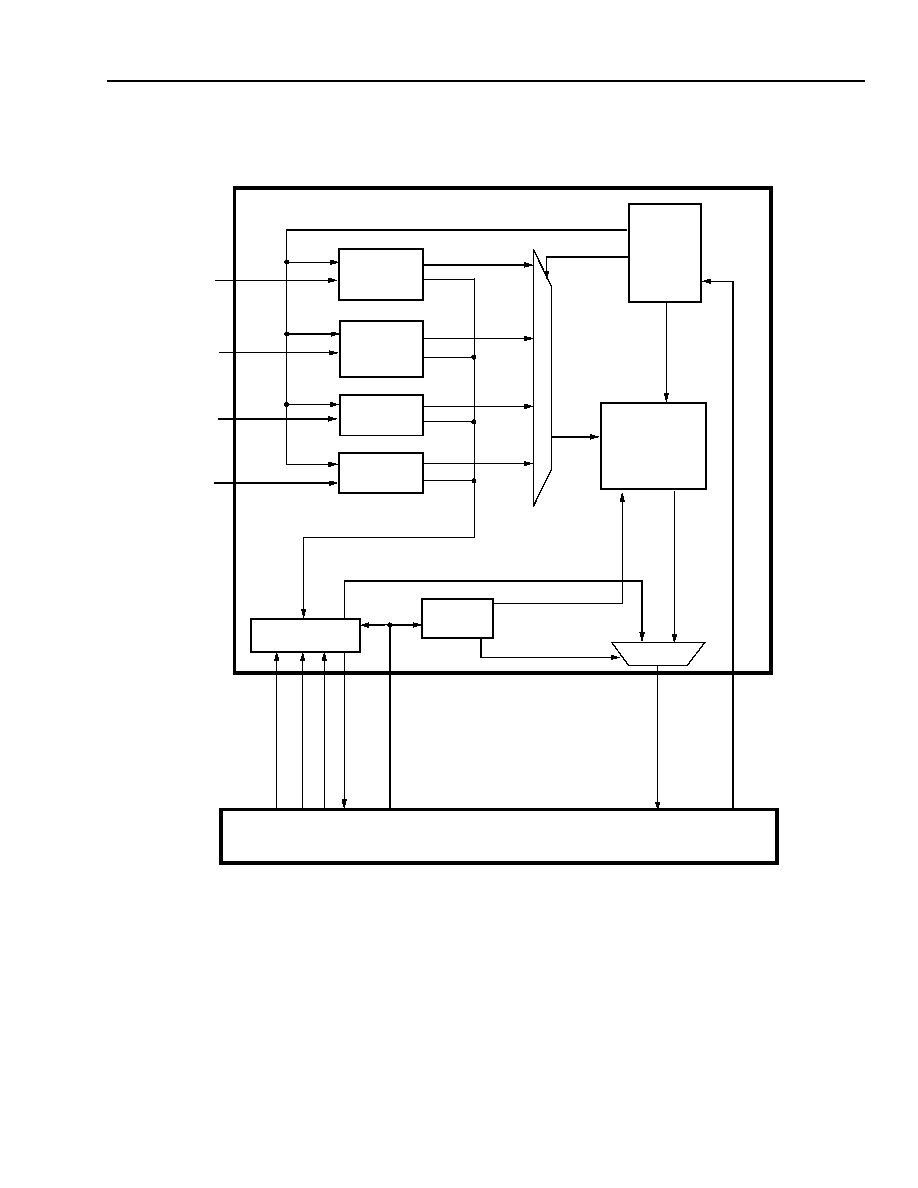

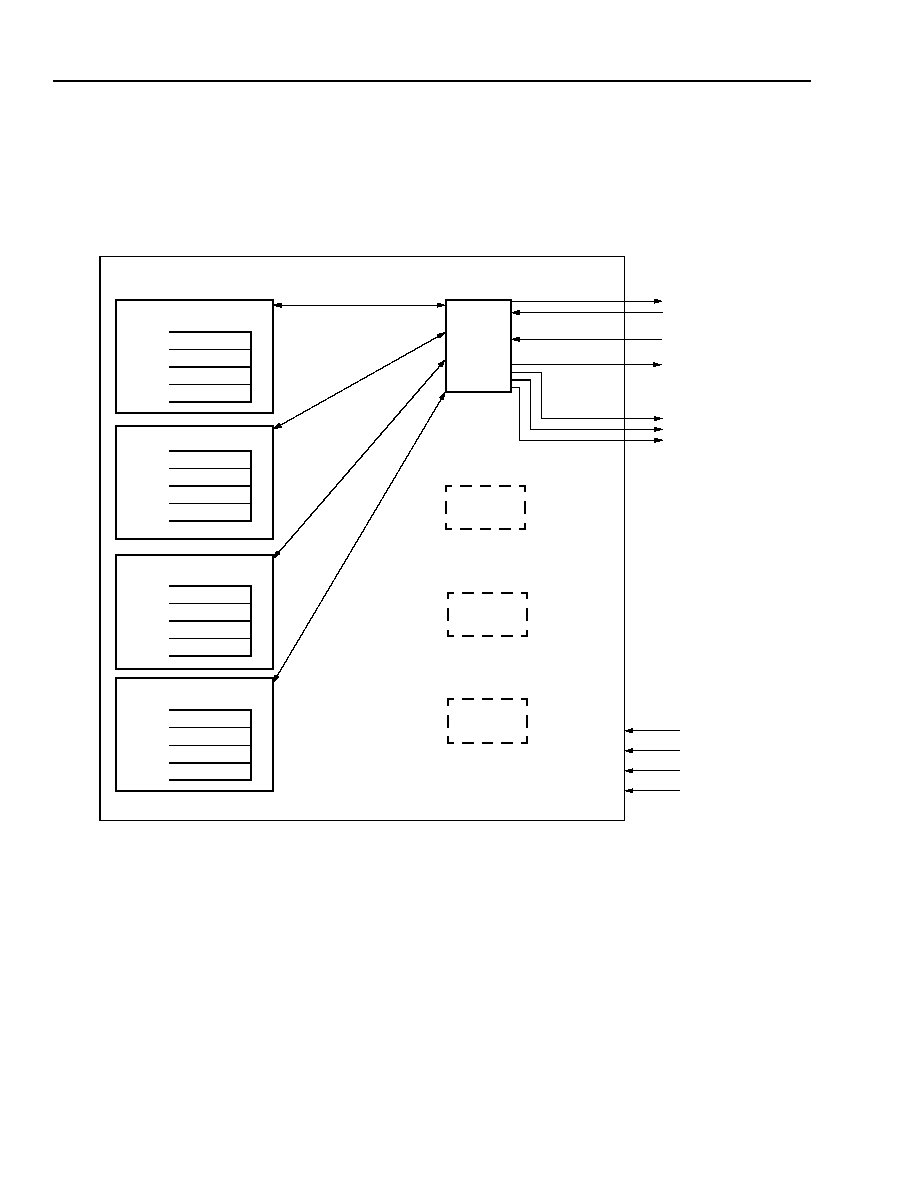

- Data Engine Block

- Data Engine Block-ATM Framer/Frame Inserter Subblock

- Data Engine Block-HDLC Framer and Escaper Subblock

- Data Engine Block-CRC Generator/Checker Subblock

- Data Engine Block-PPP Detach Subblock

- Data Engine Block-Data Engine Counter Subblock

- Data Engine Block-Channel Distribution and Allocation Subblock

- Data Engine Block-GFP General Framing Procedure Subblock

- Data Engine Block Registers

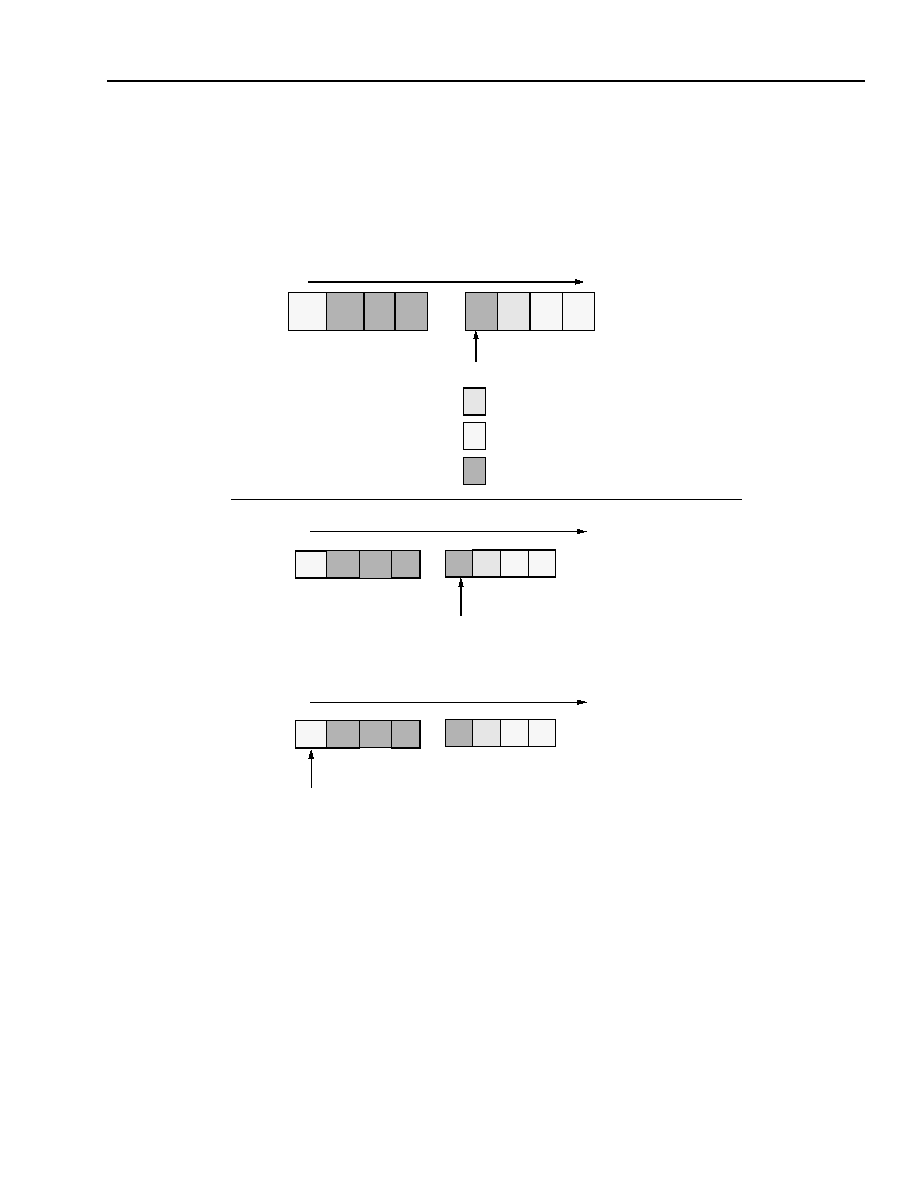

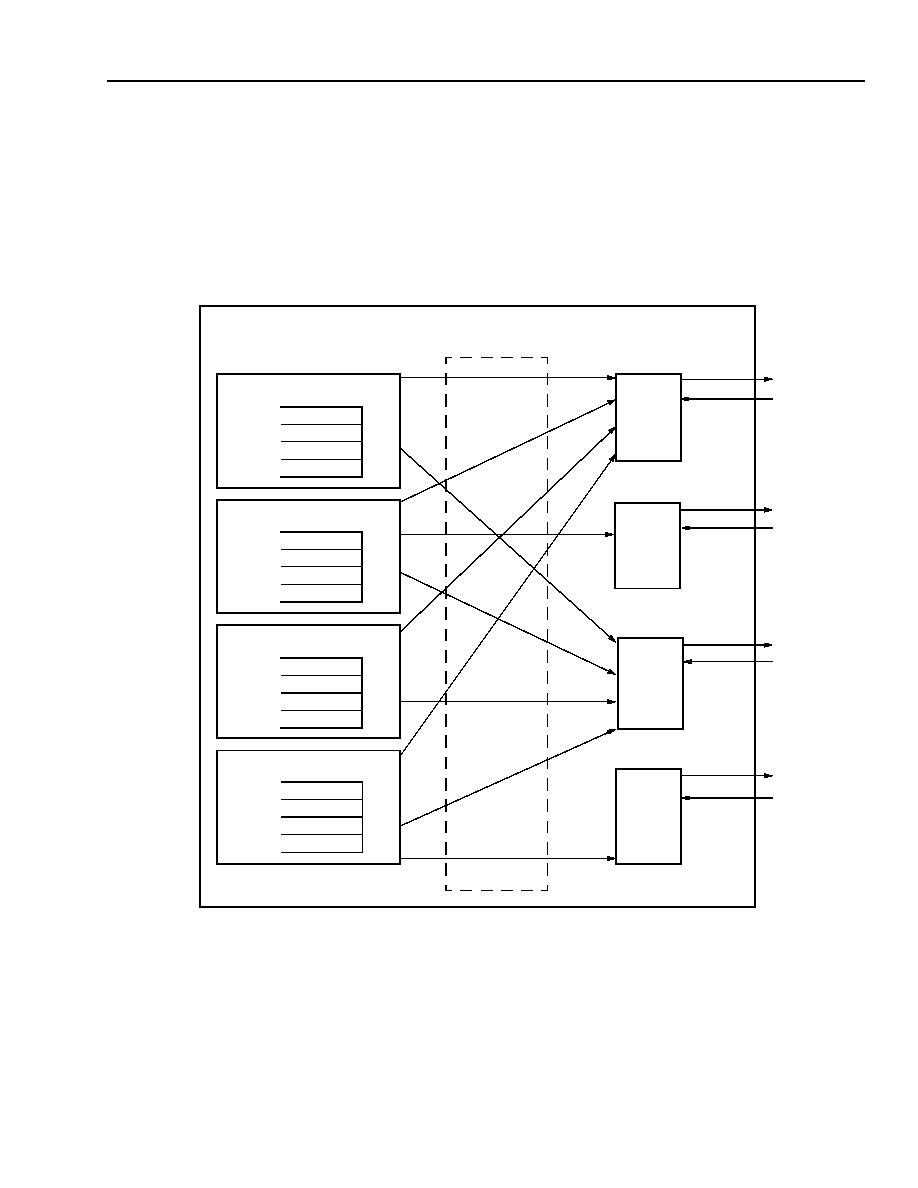

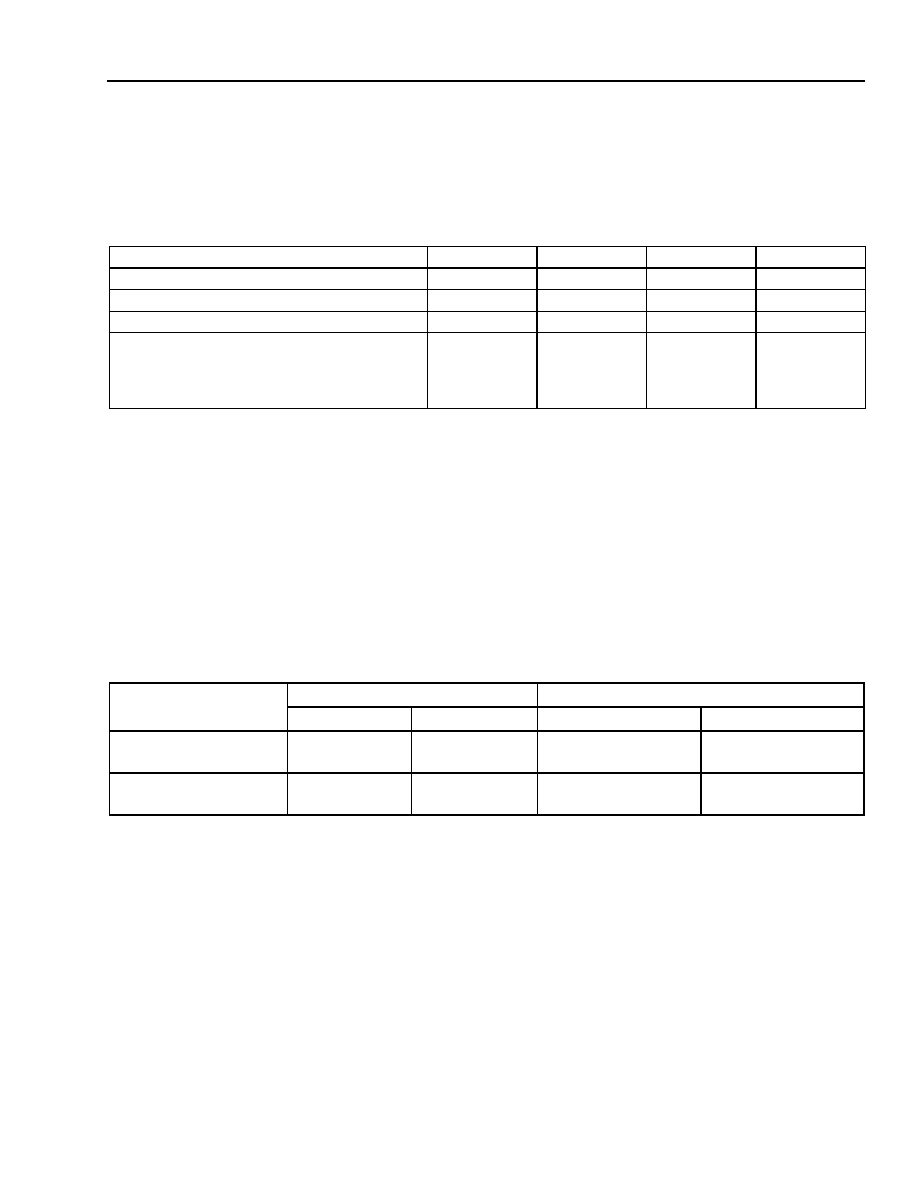

- UTOPIA (UT) Block

- System Interface

- Test

- Absolute Maximum Ratings

- Handling Precautions

- Operating Conditions

- Electrical Characteristics

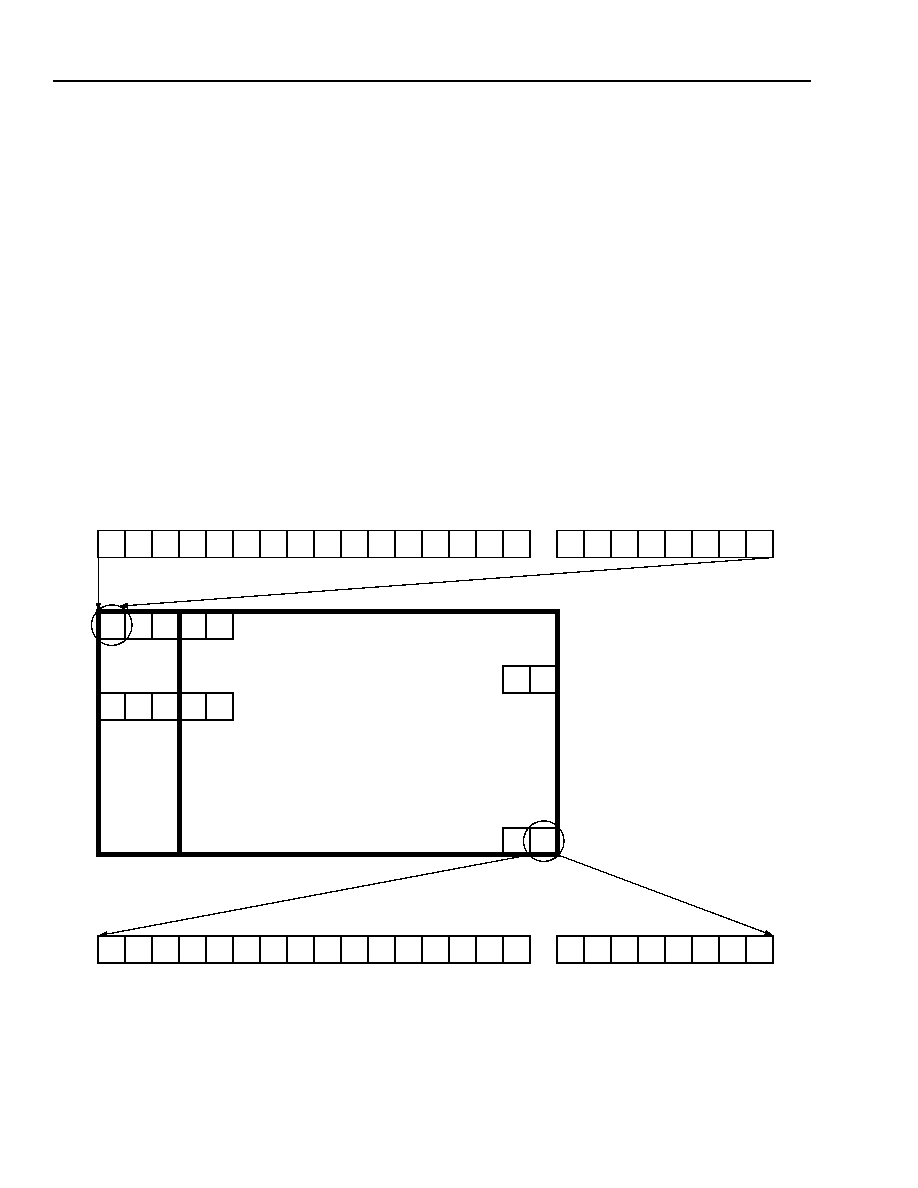

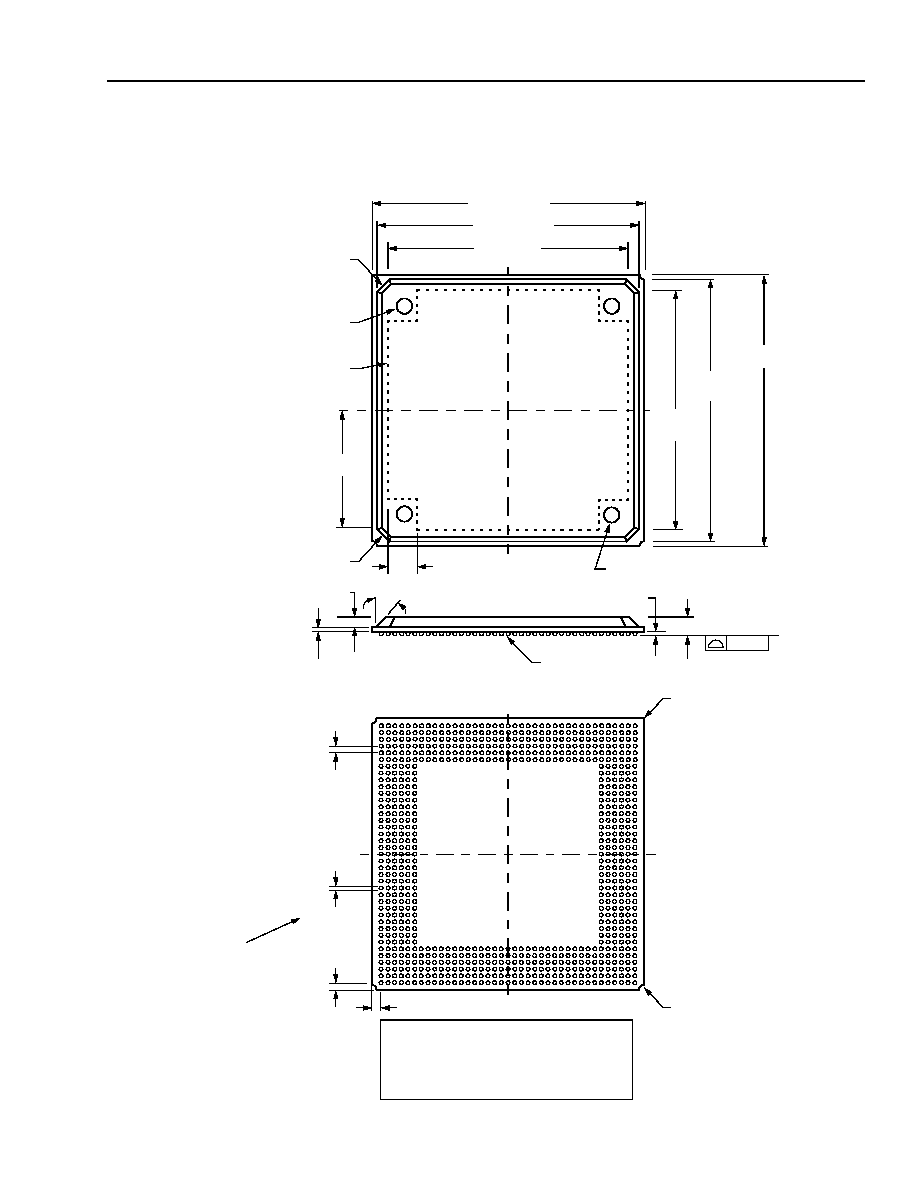

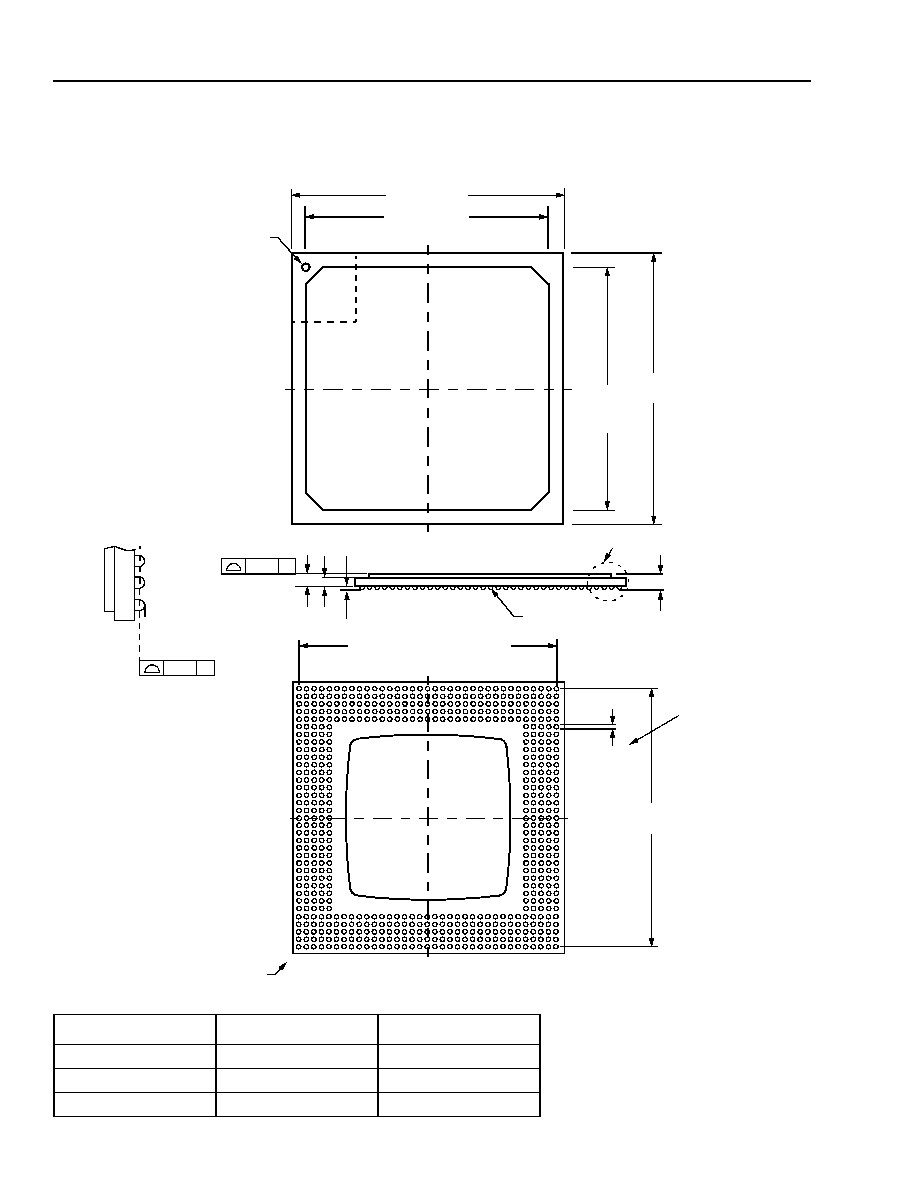

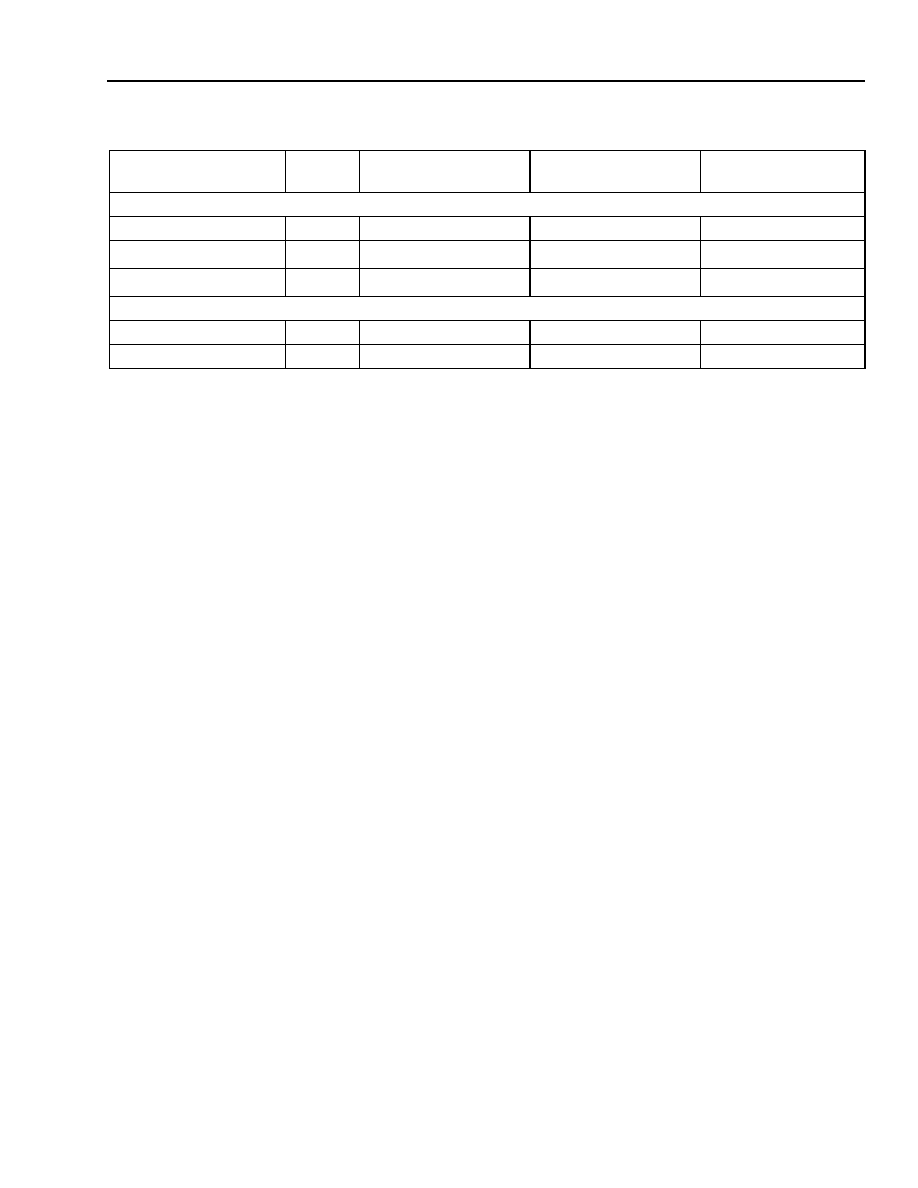

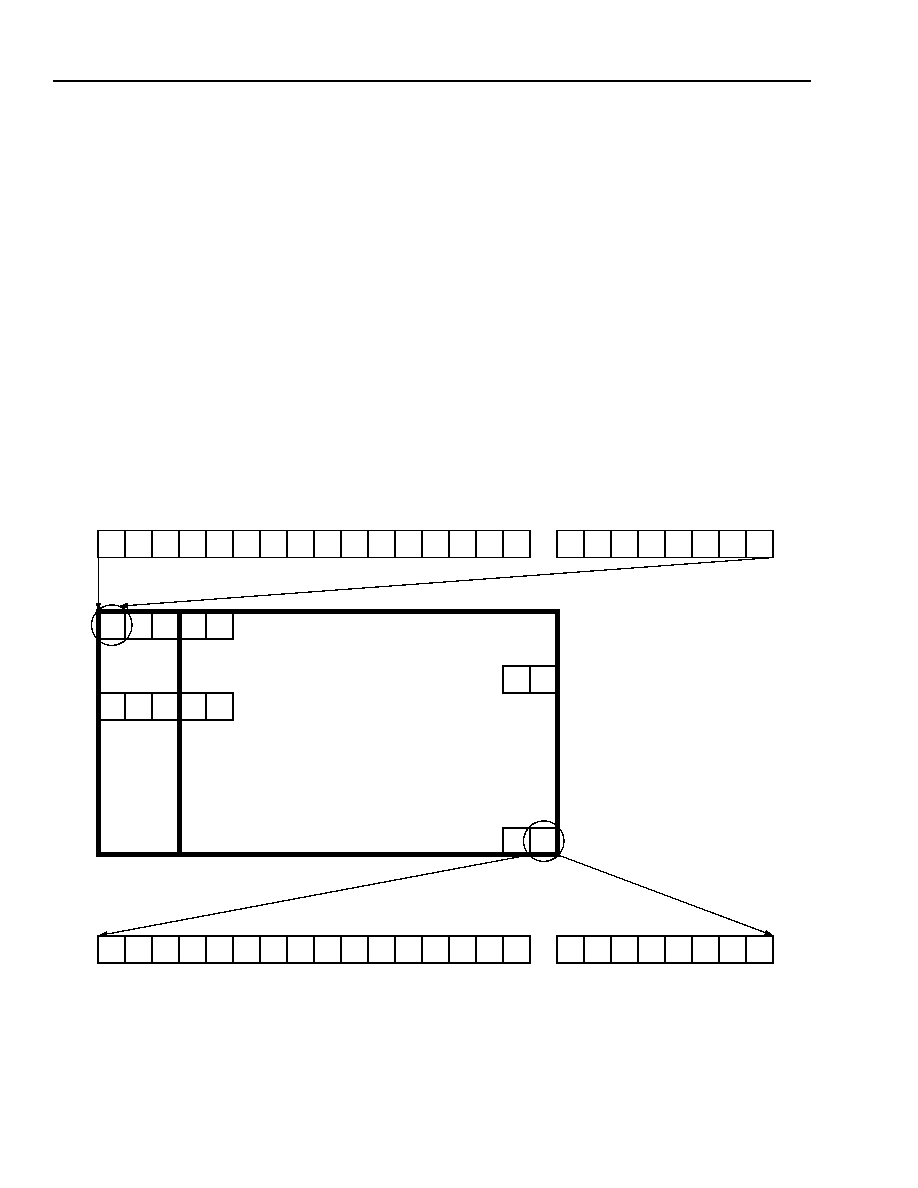

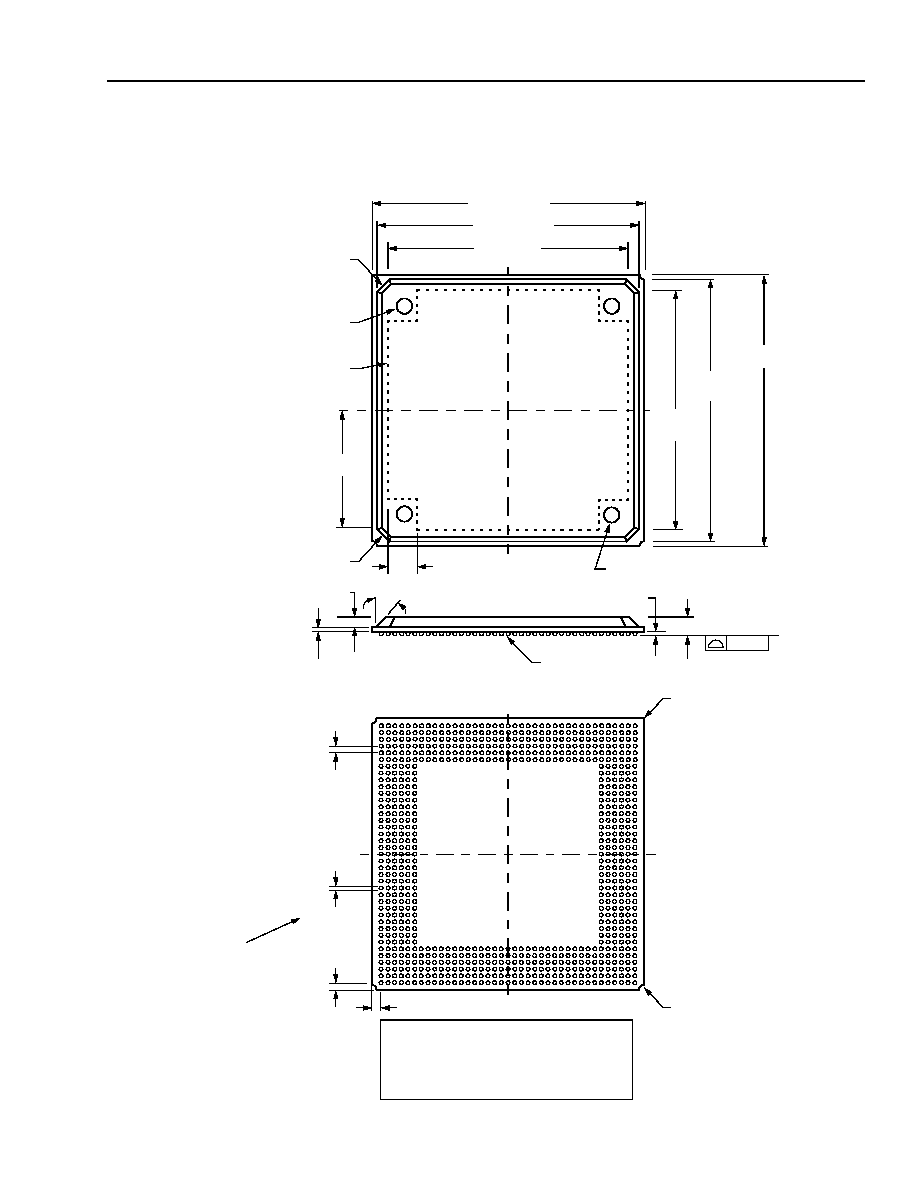

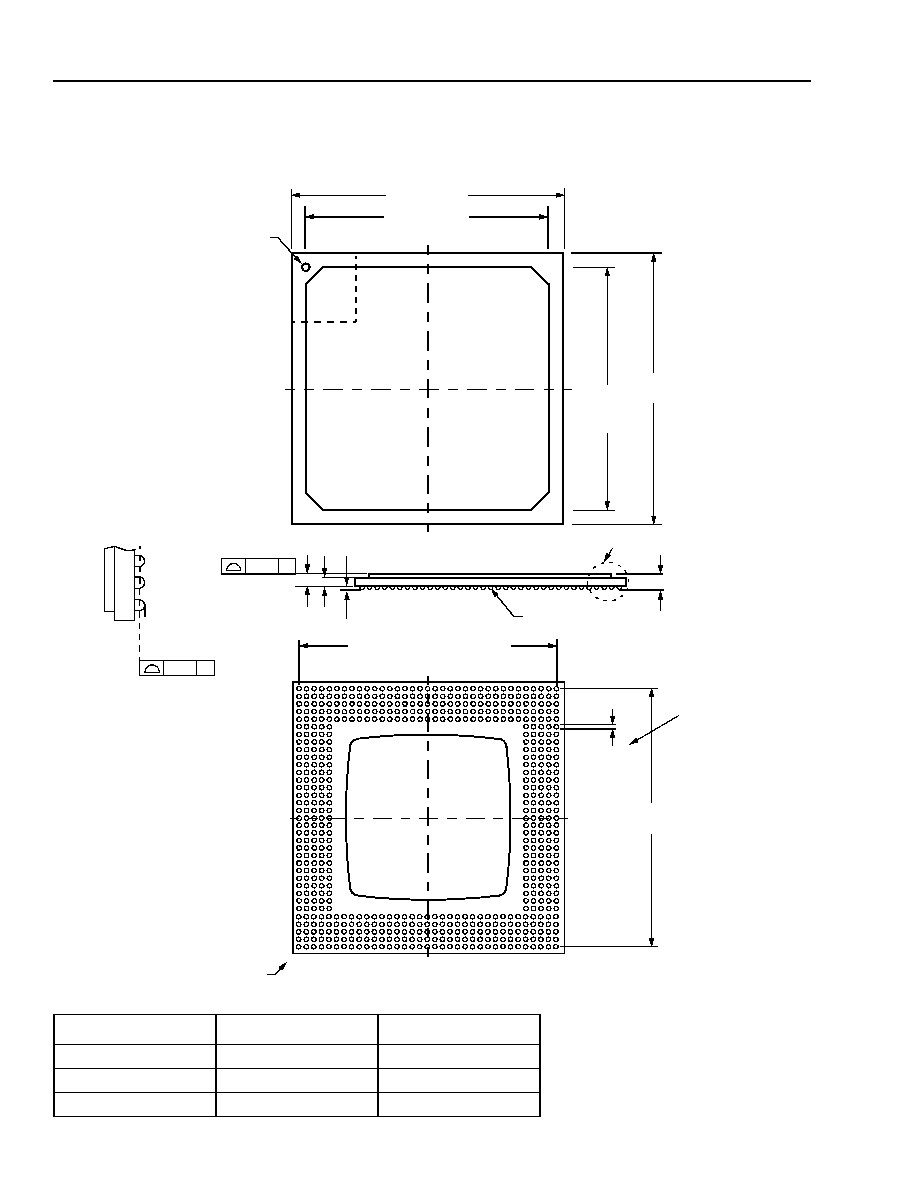

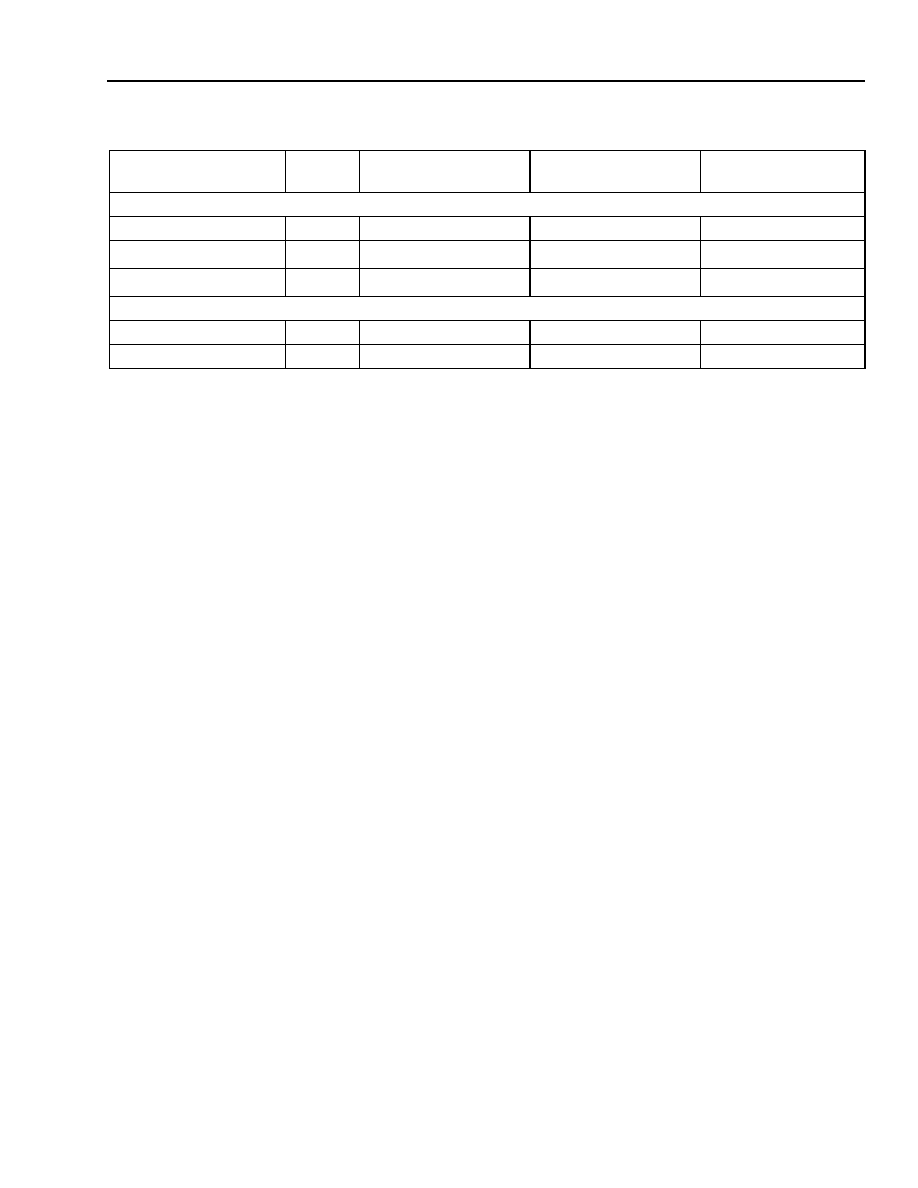

- Outline Diagrams

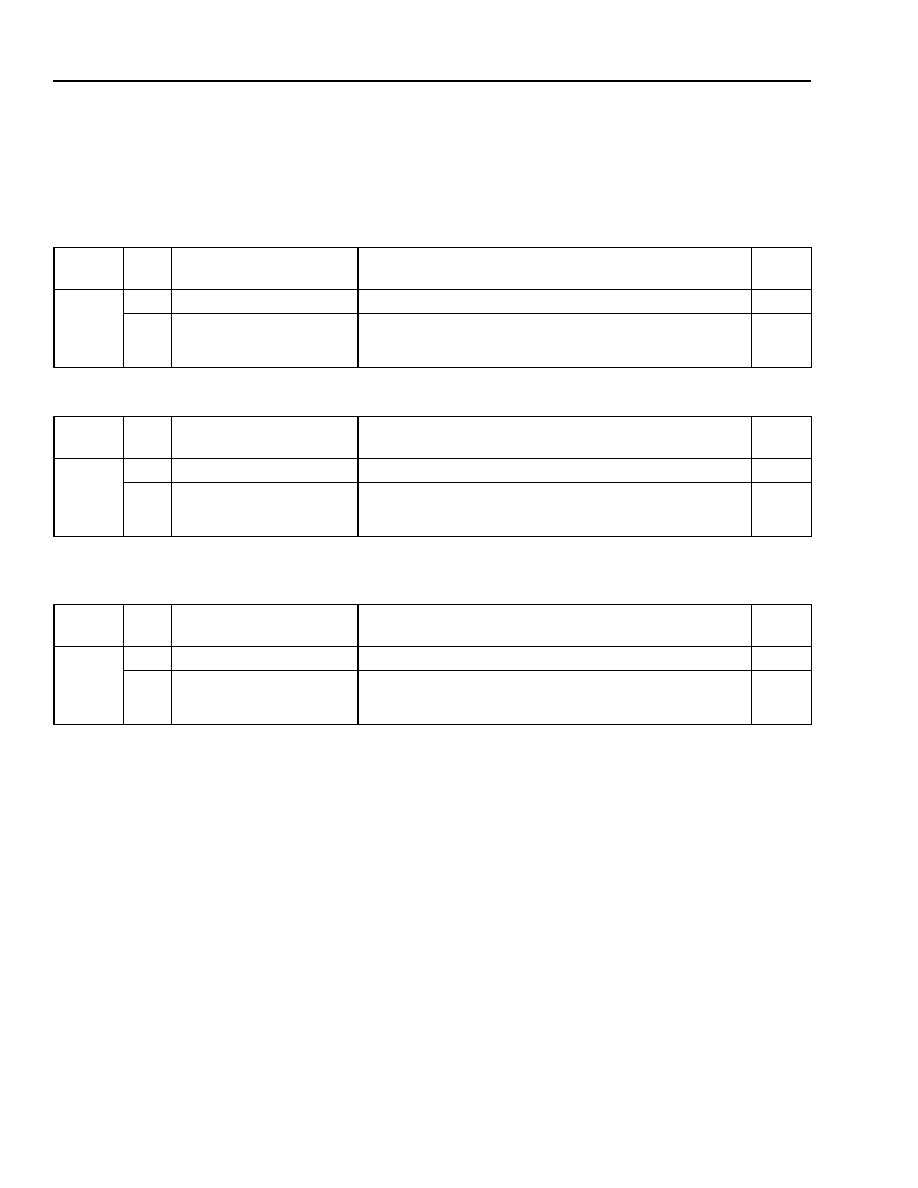

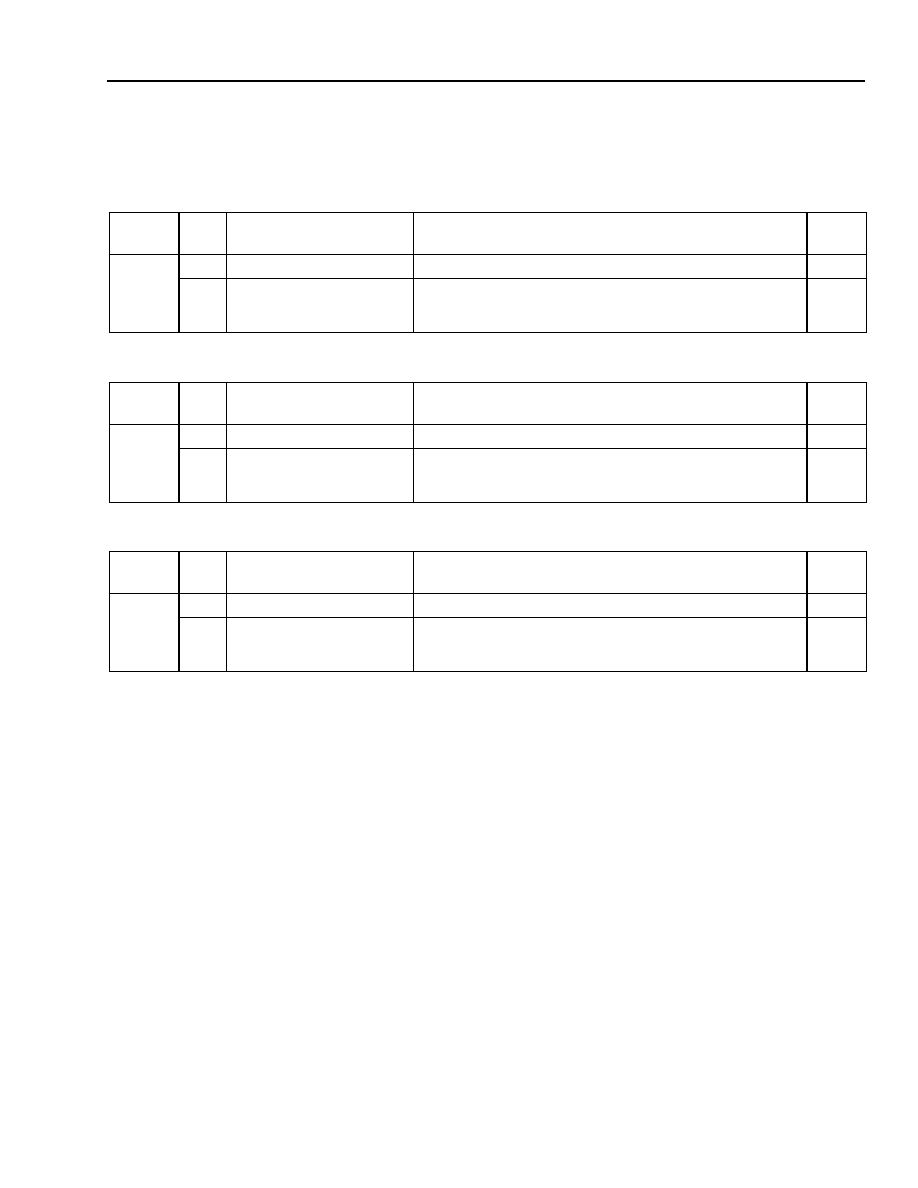

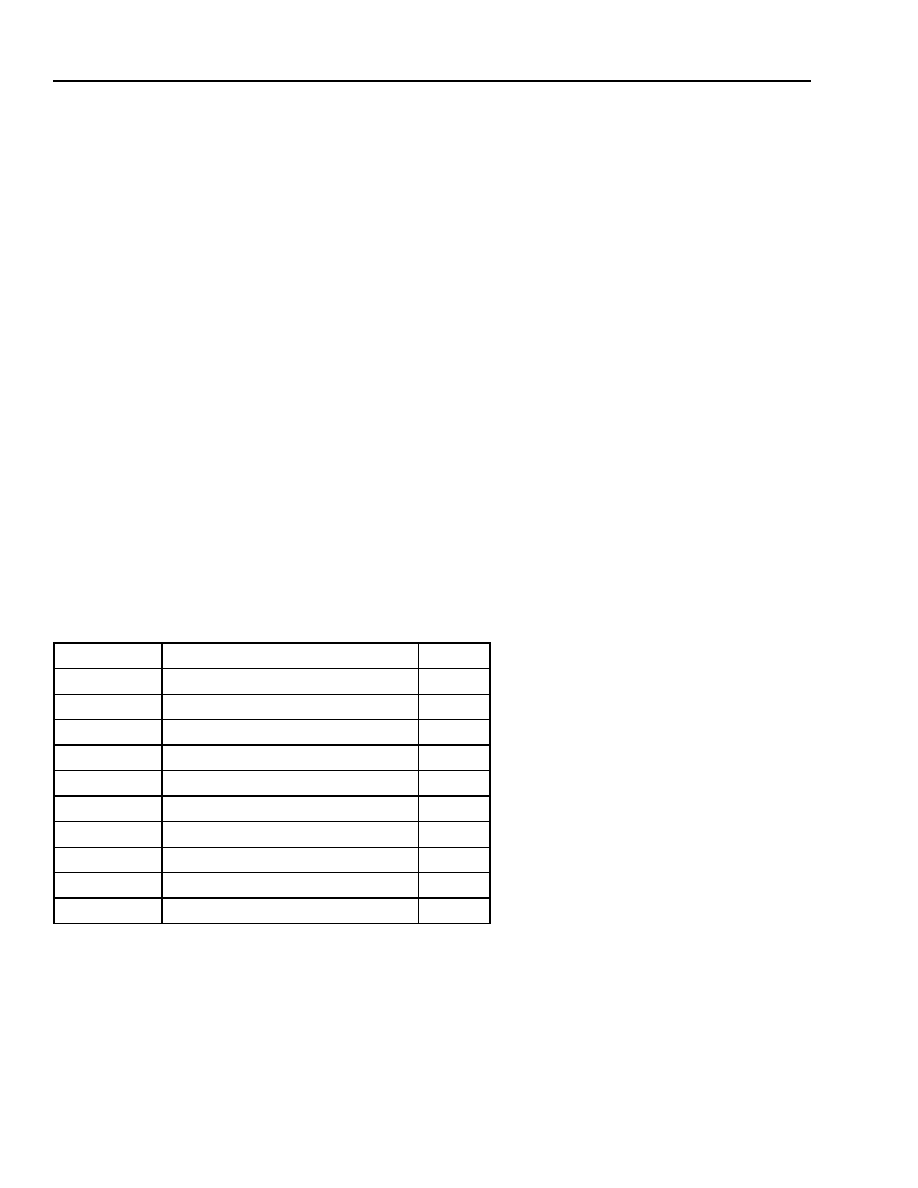

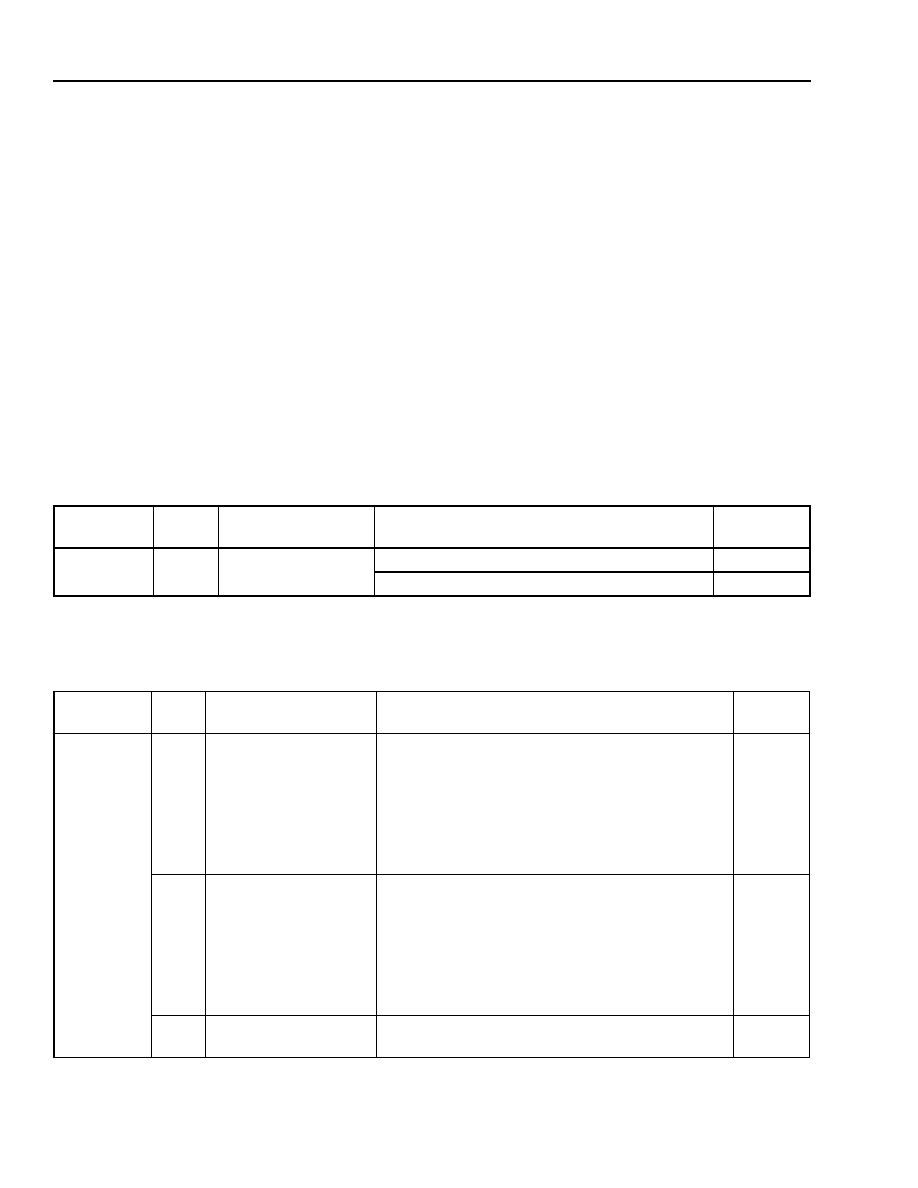

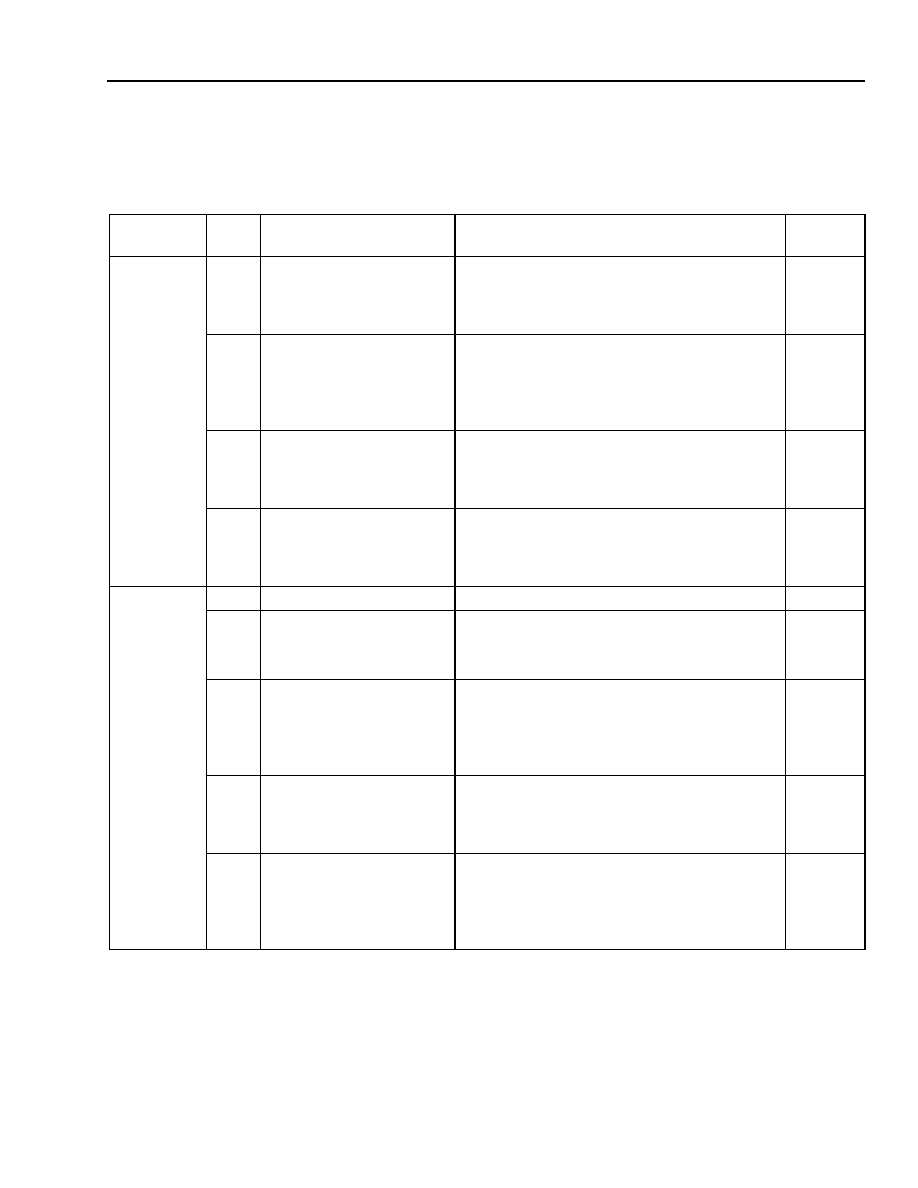

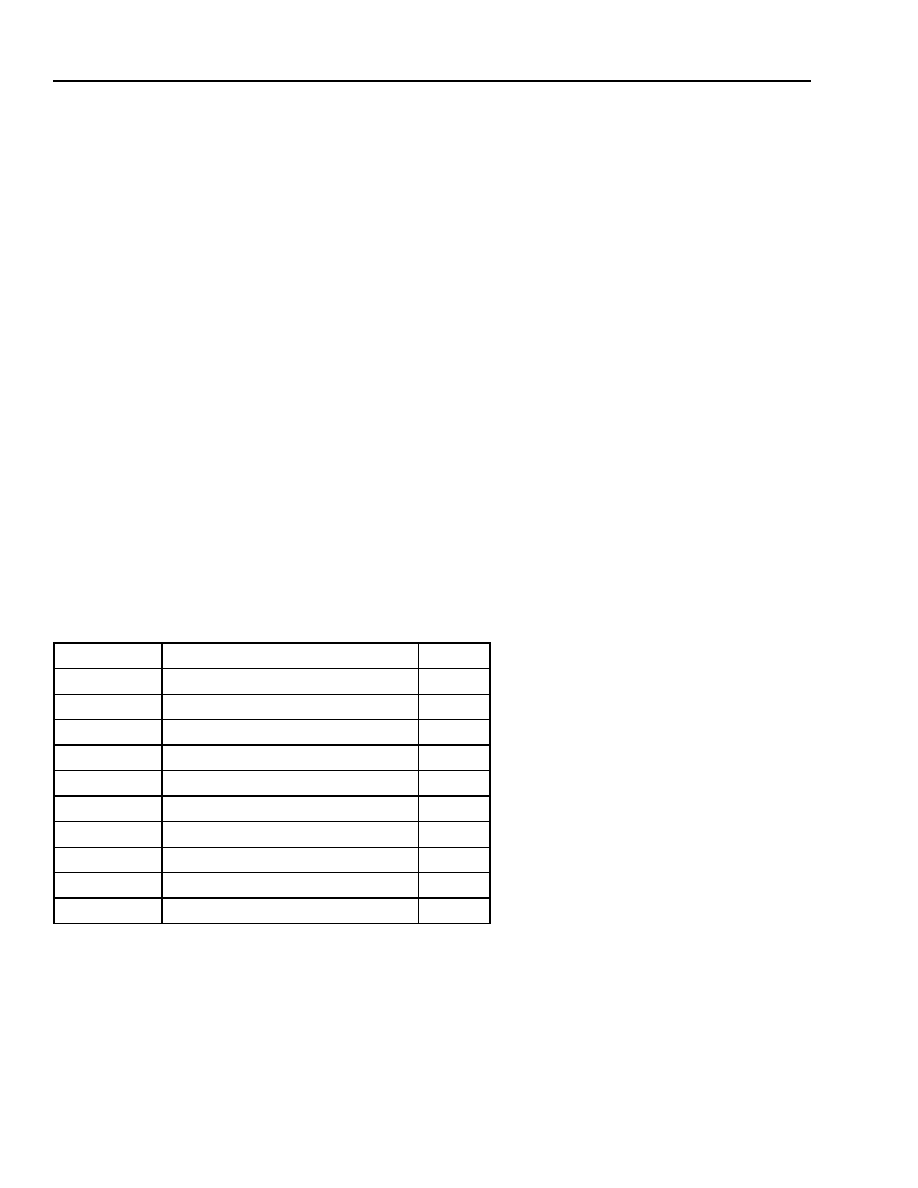

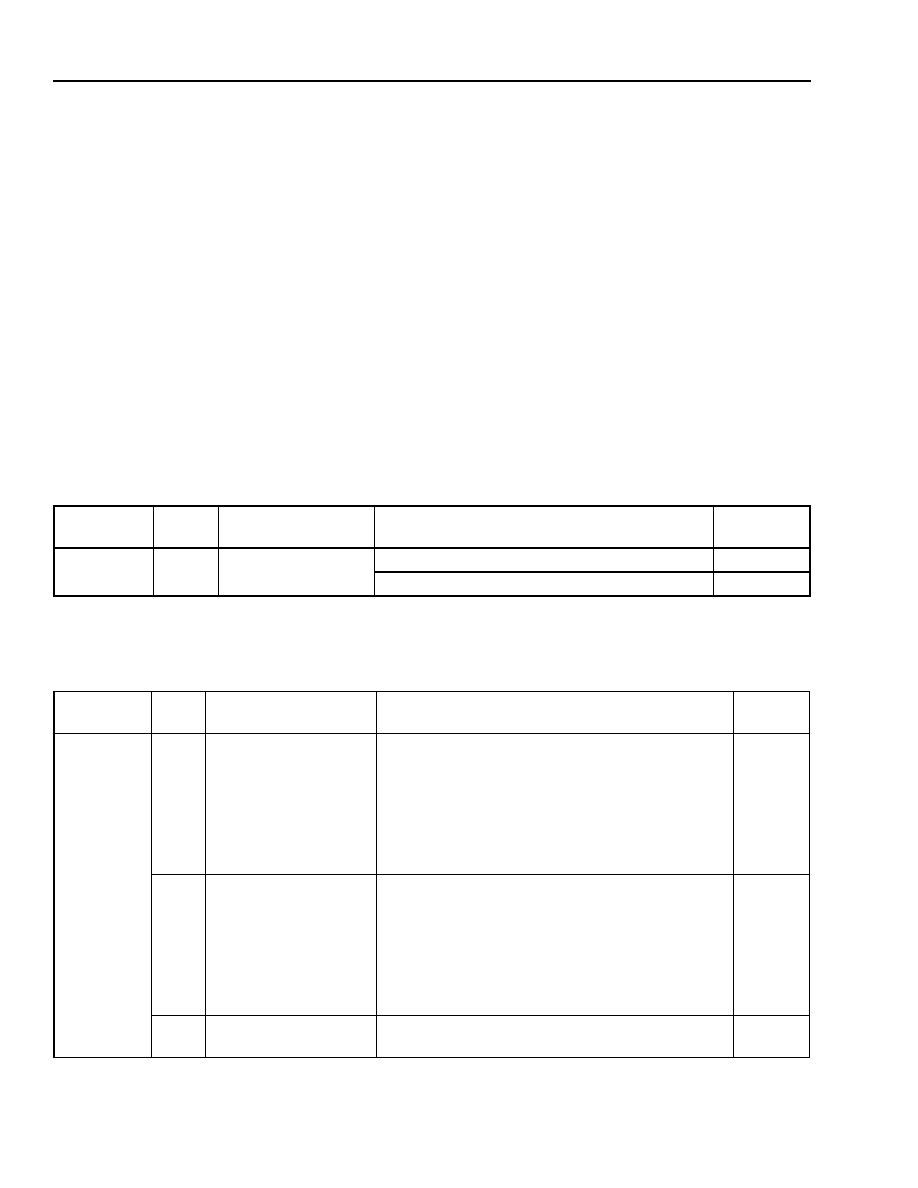

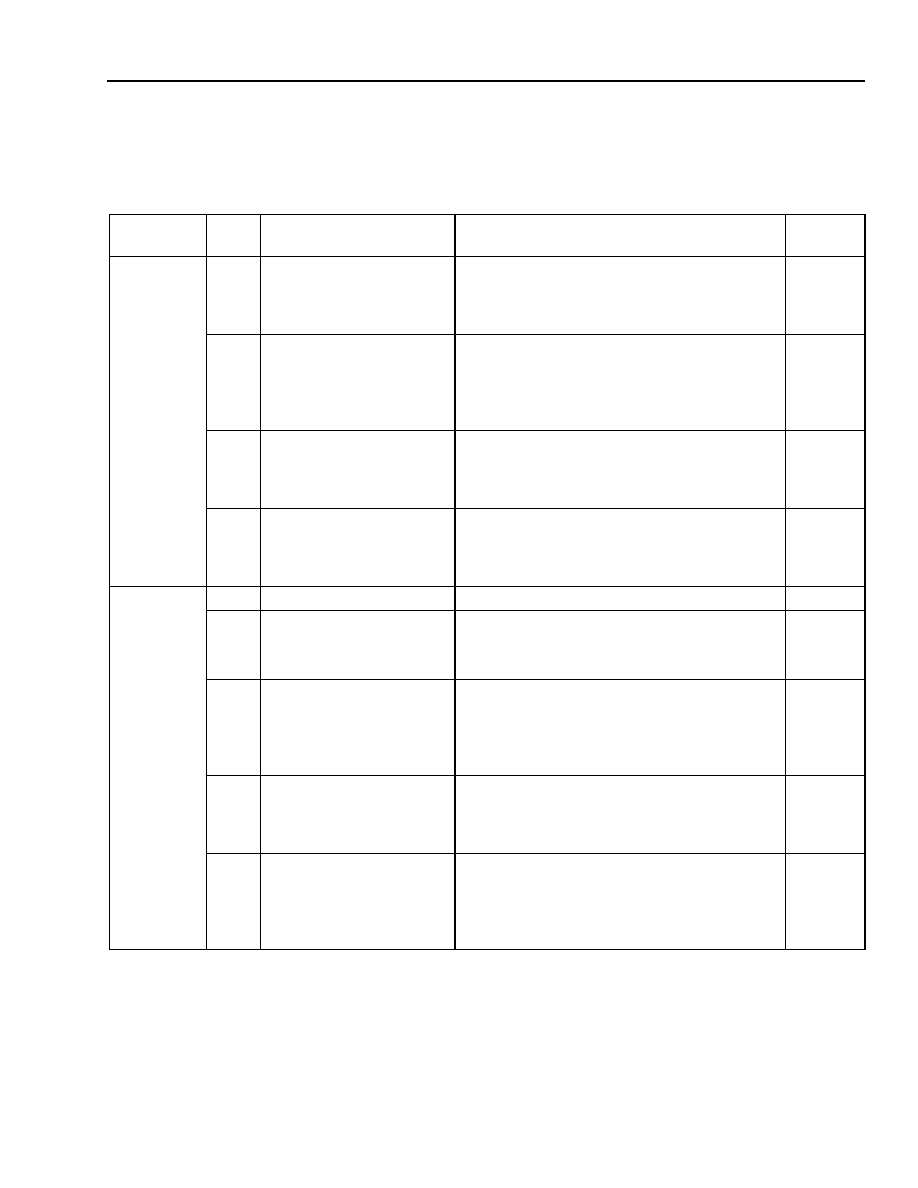

- Ordering Information

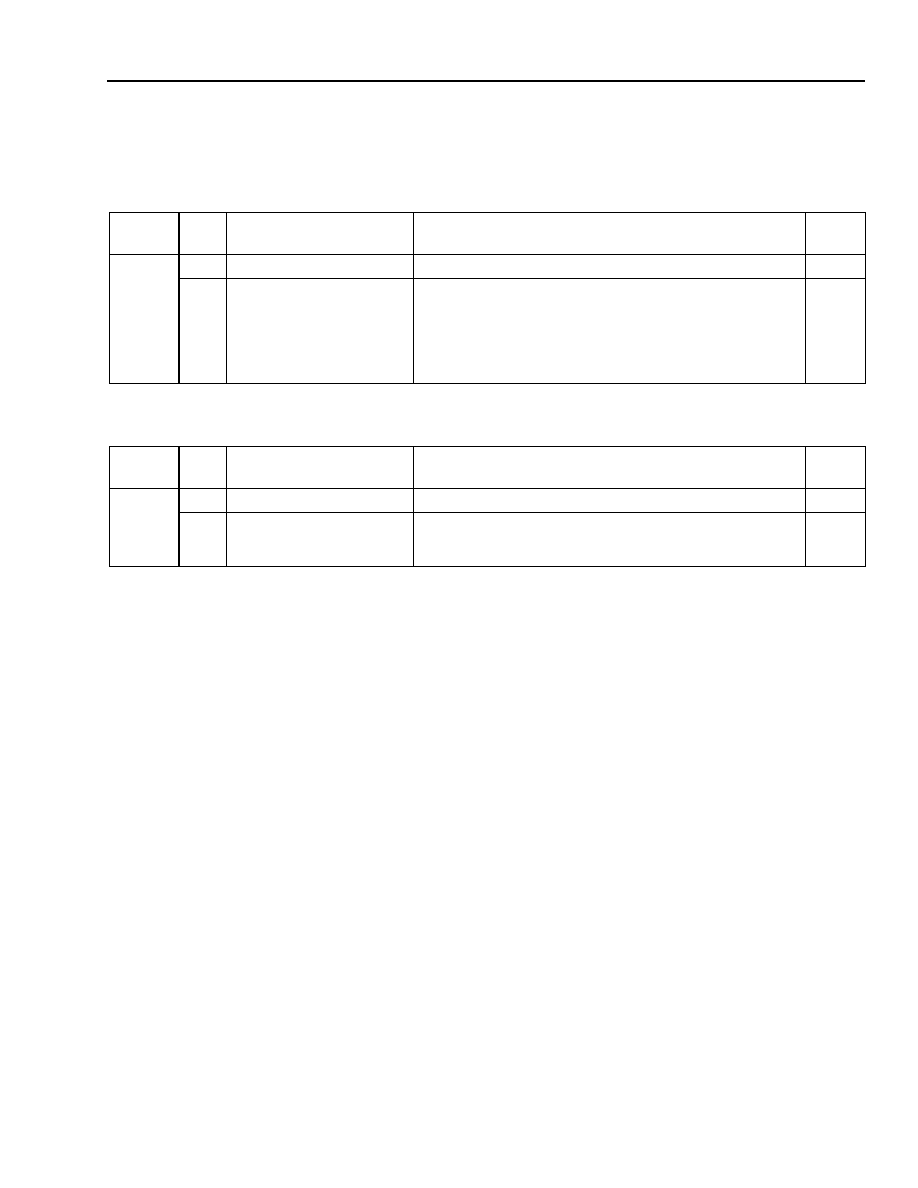

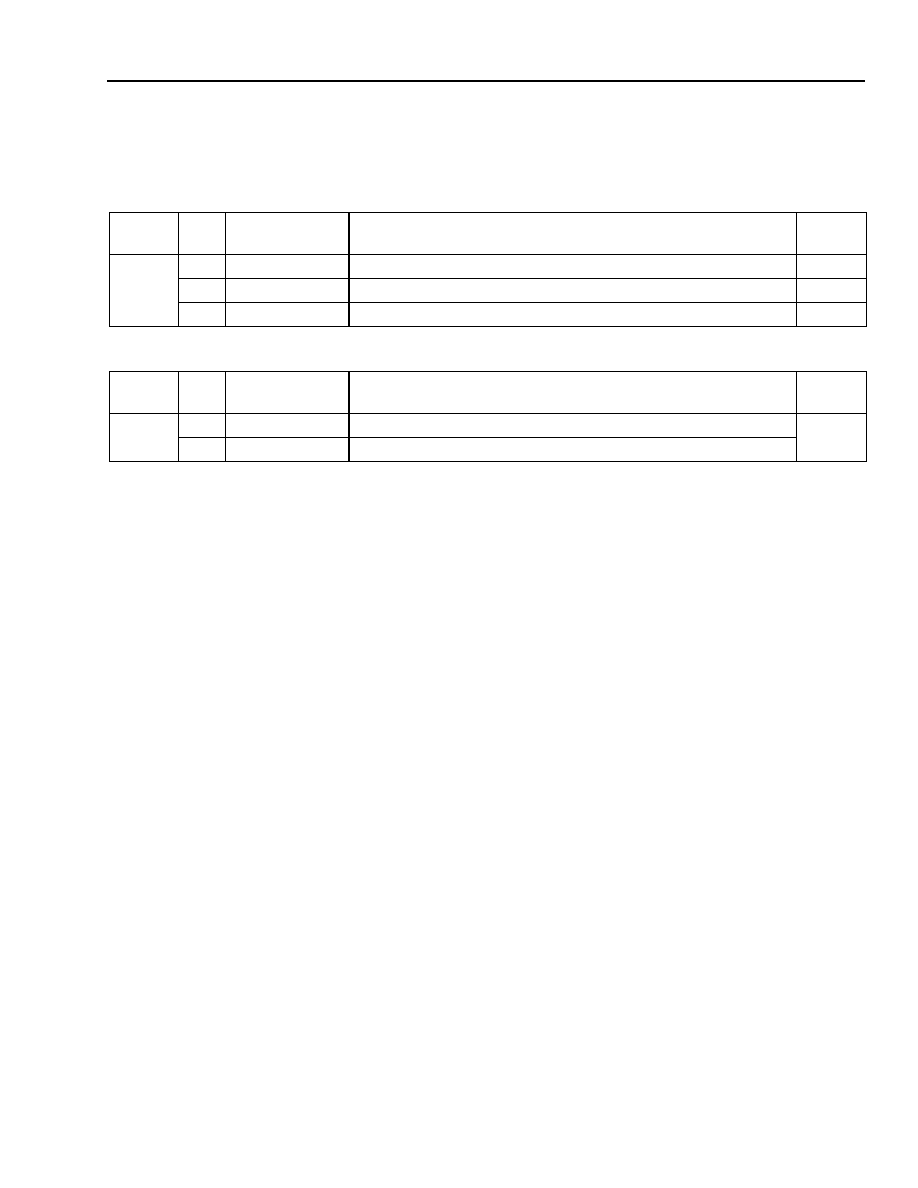

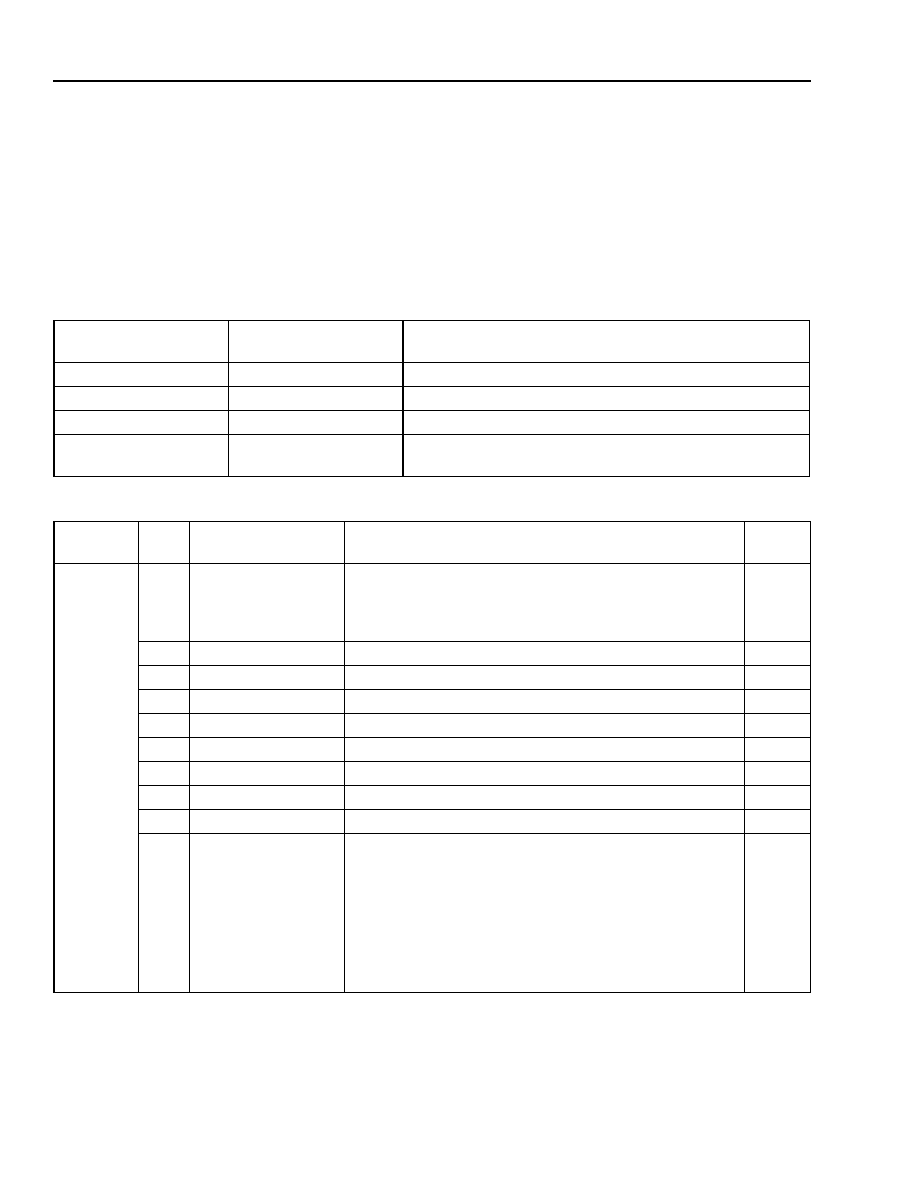

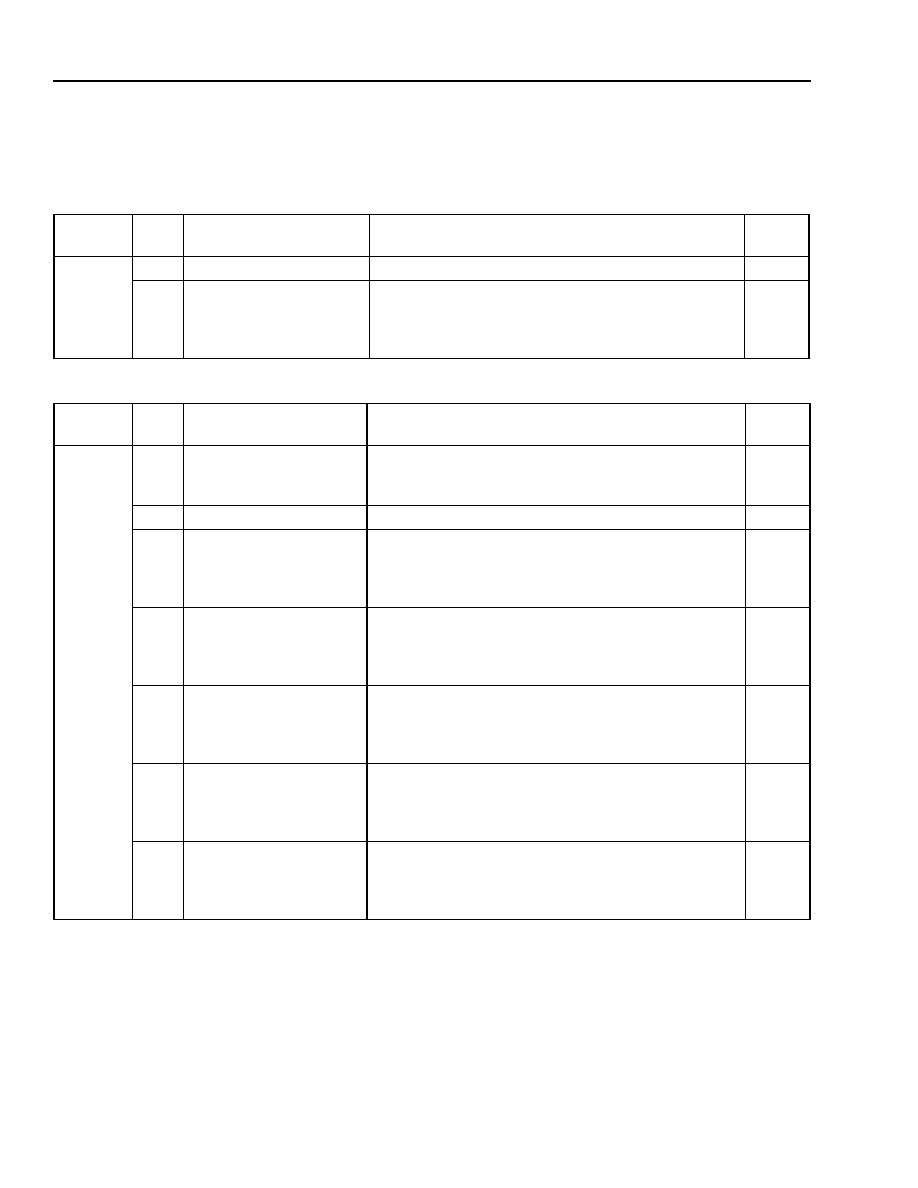

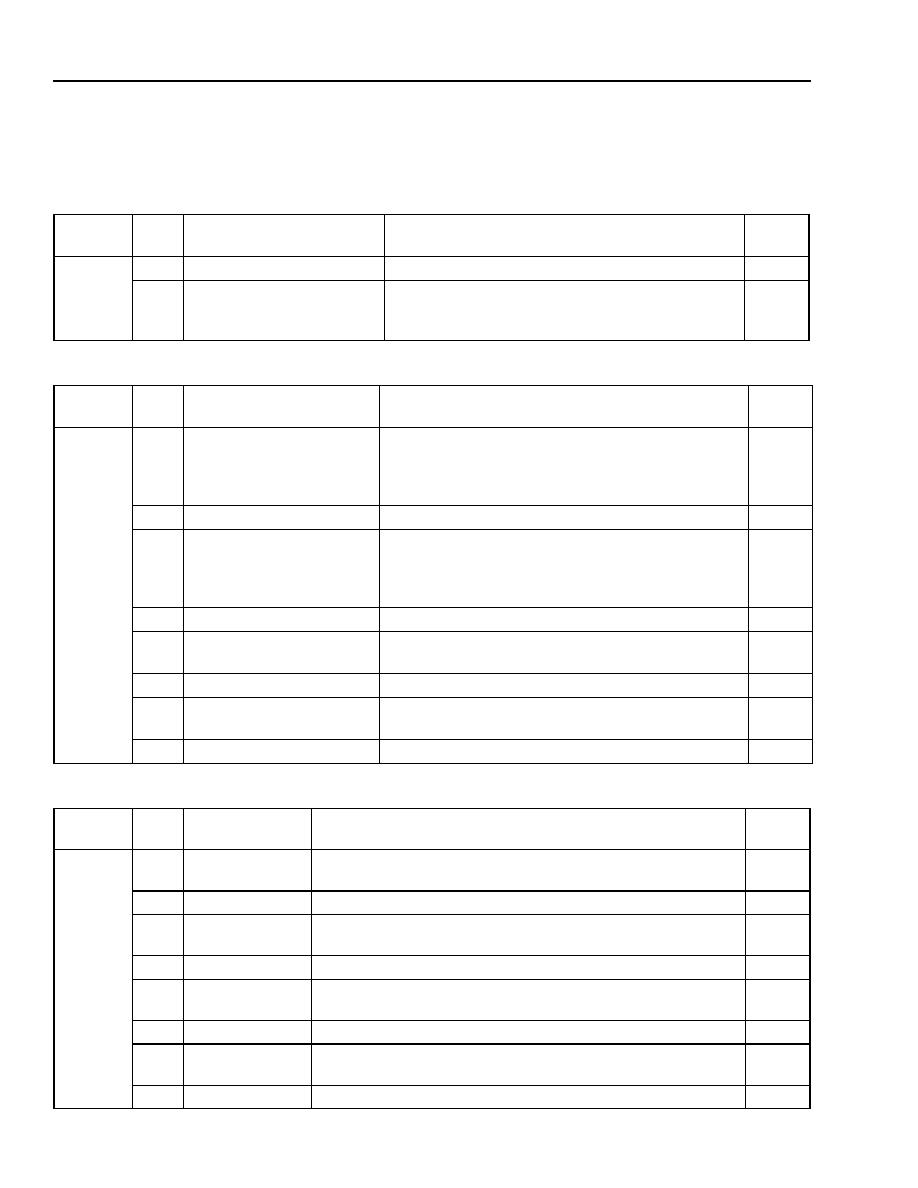

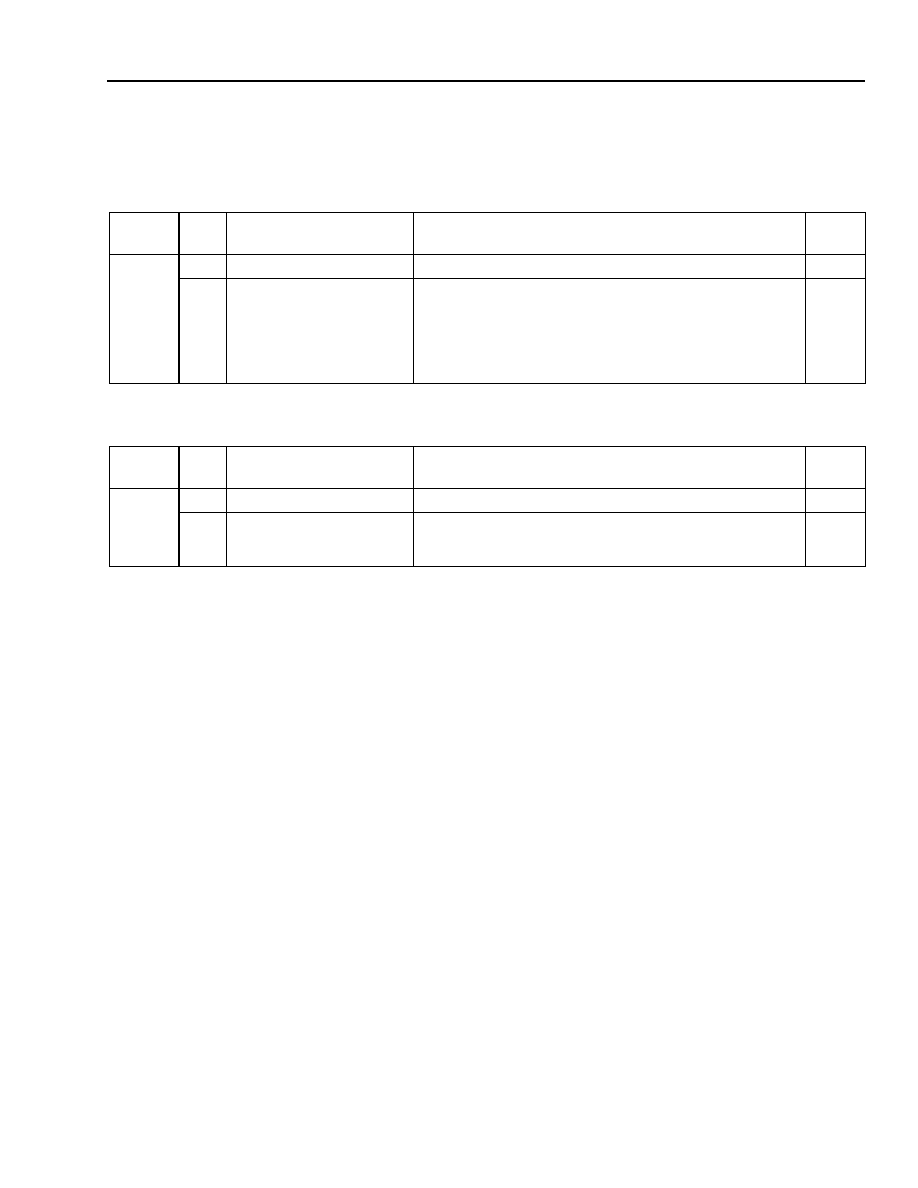

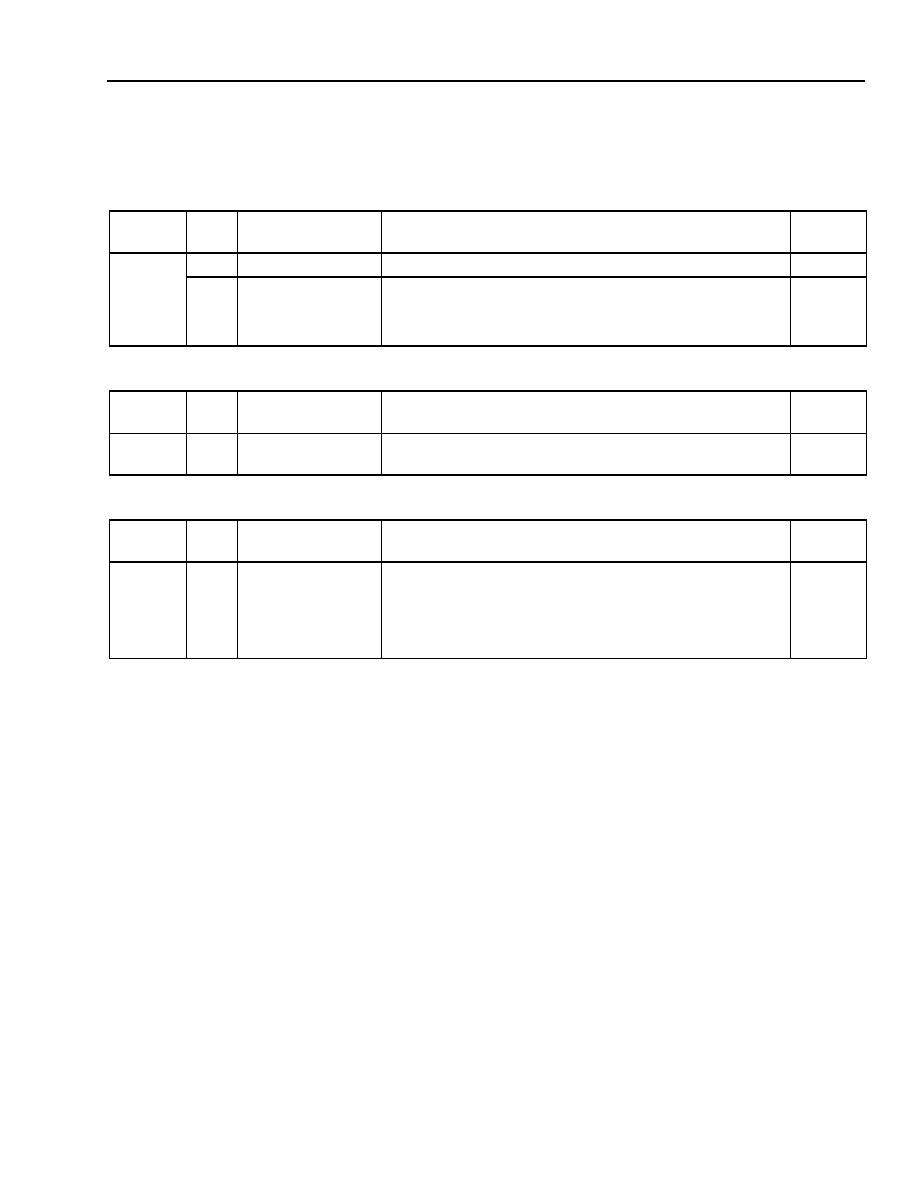

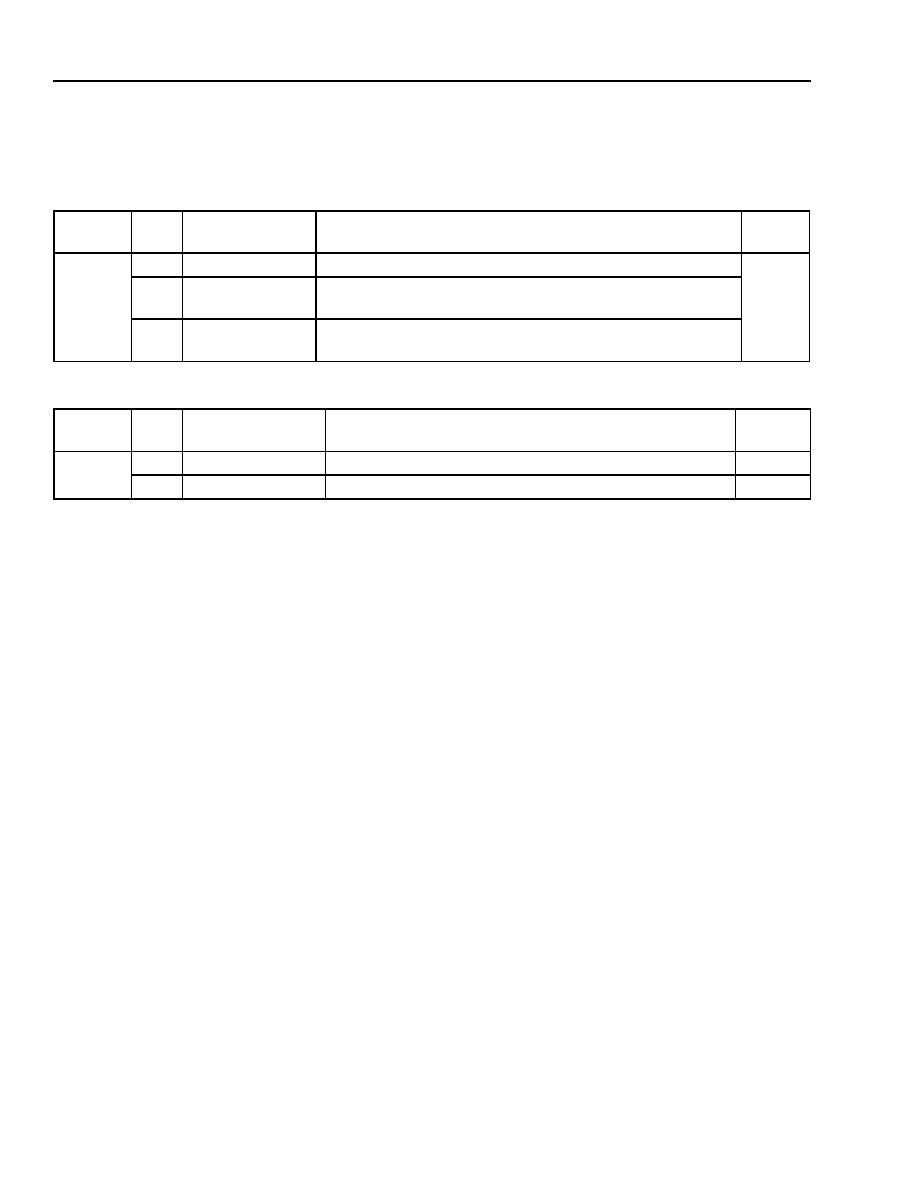

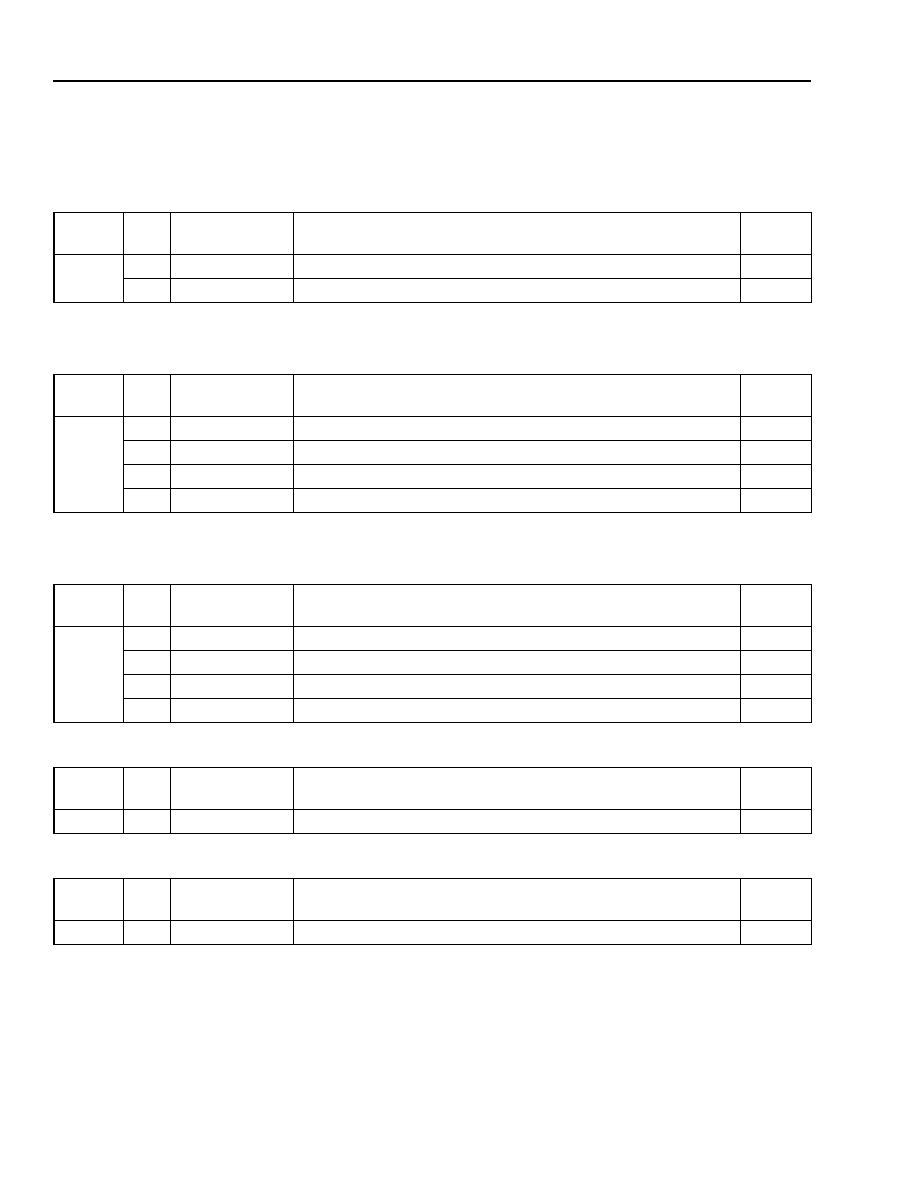

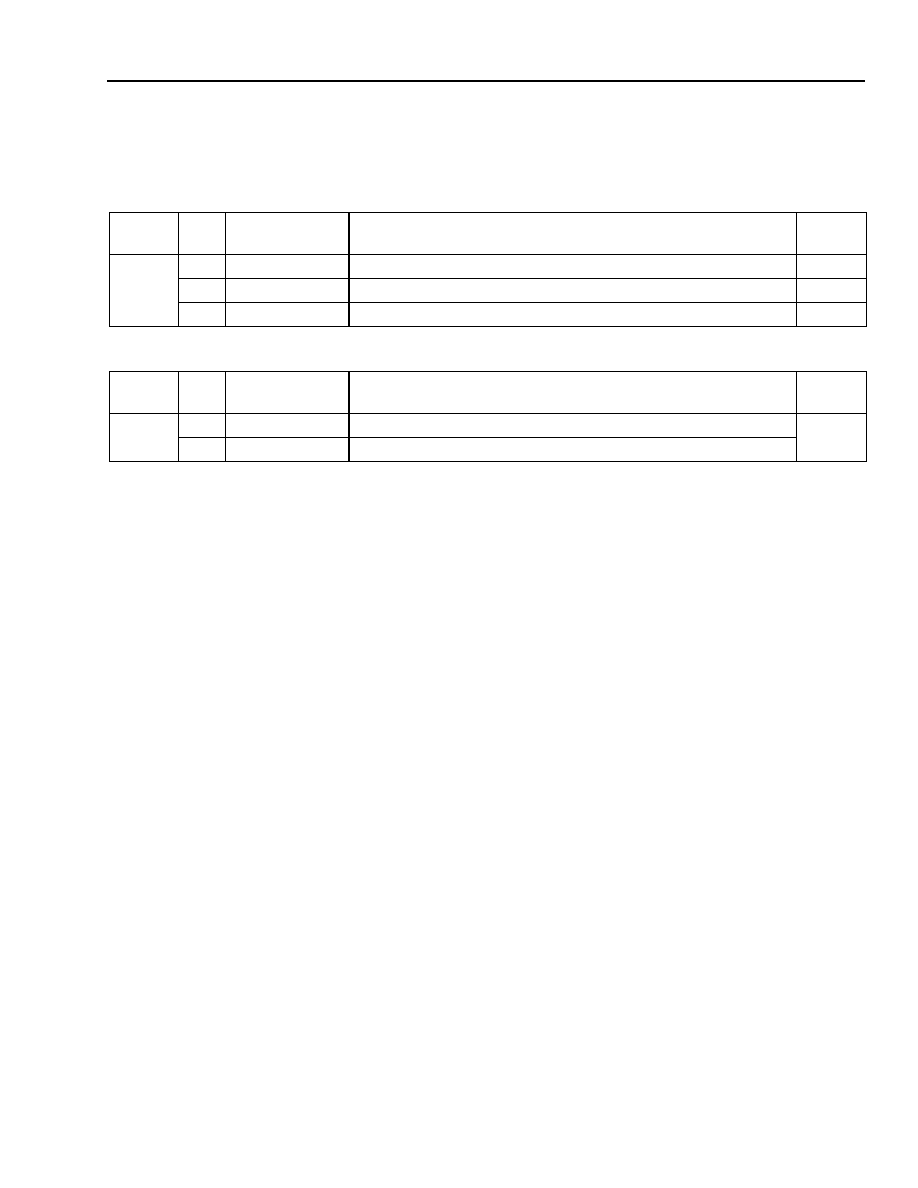

- MARS2G5 P-Pro (TDAT162G52) (Version 2.2 and 2.3 Only)

- MARS2G5 P-Pro (TDAT162G52) (Version 2.3 Only)

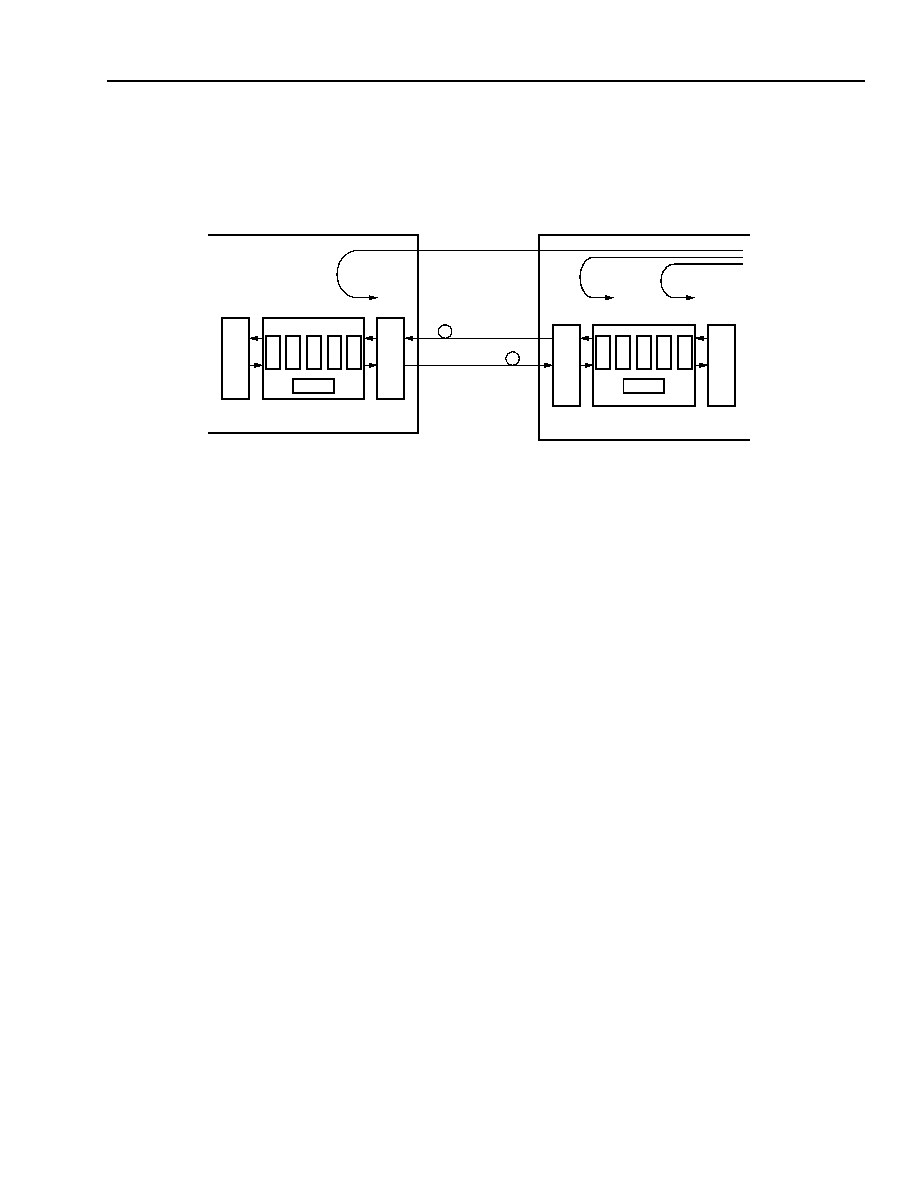

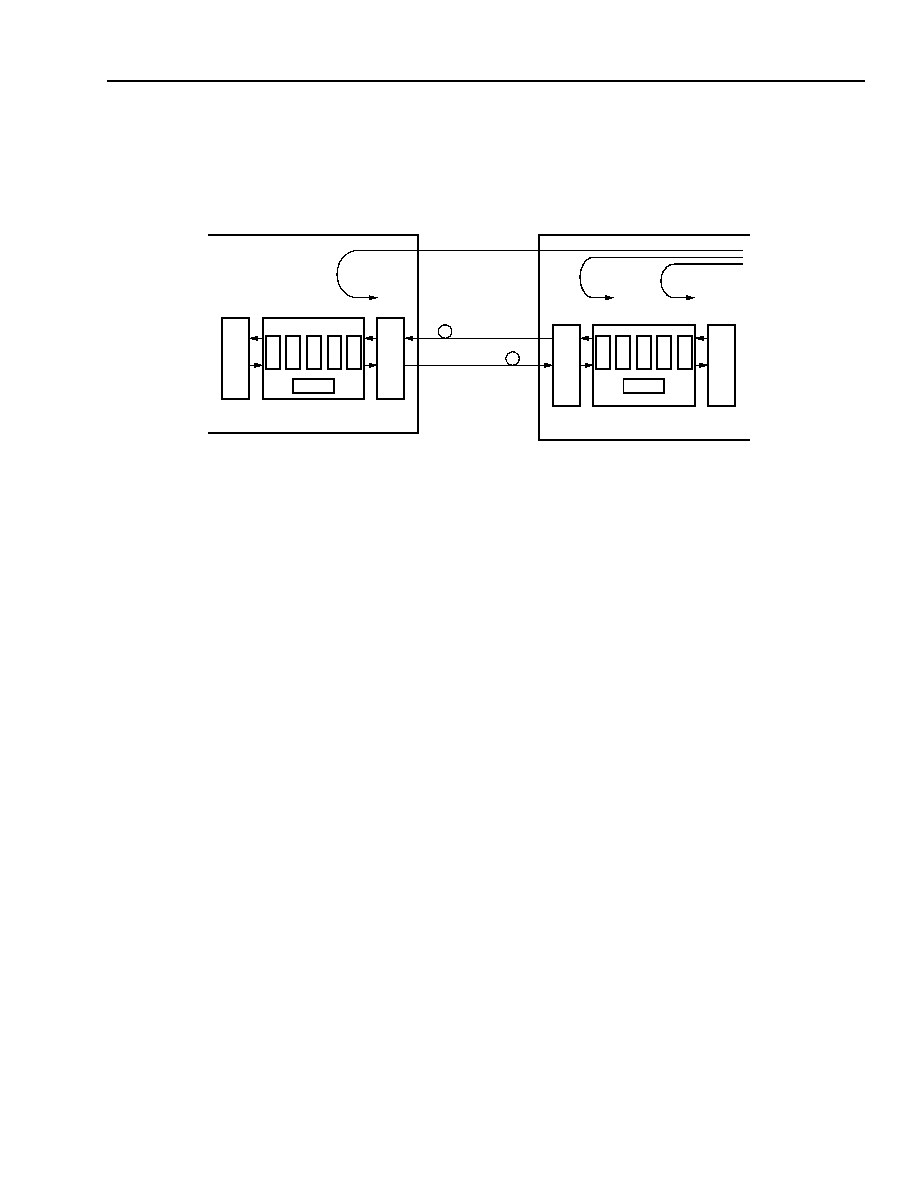

- Appendix: Line Loopback Block

- Appendix: Line Loopback Block Script

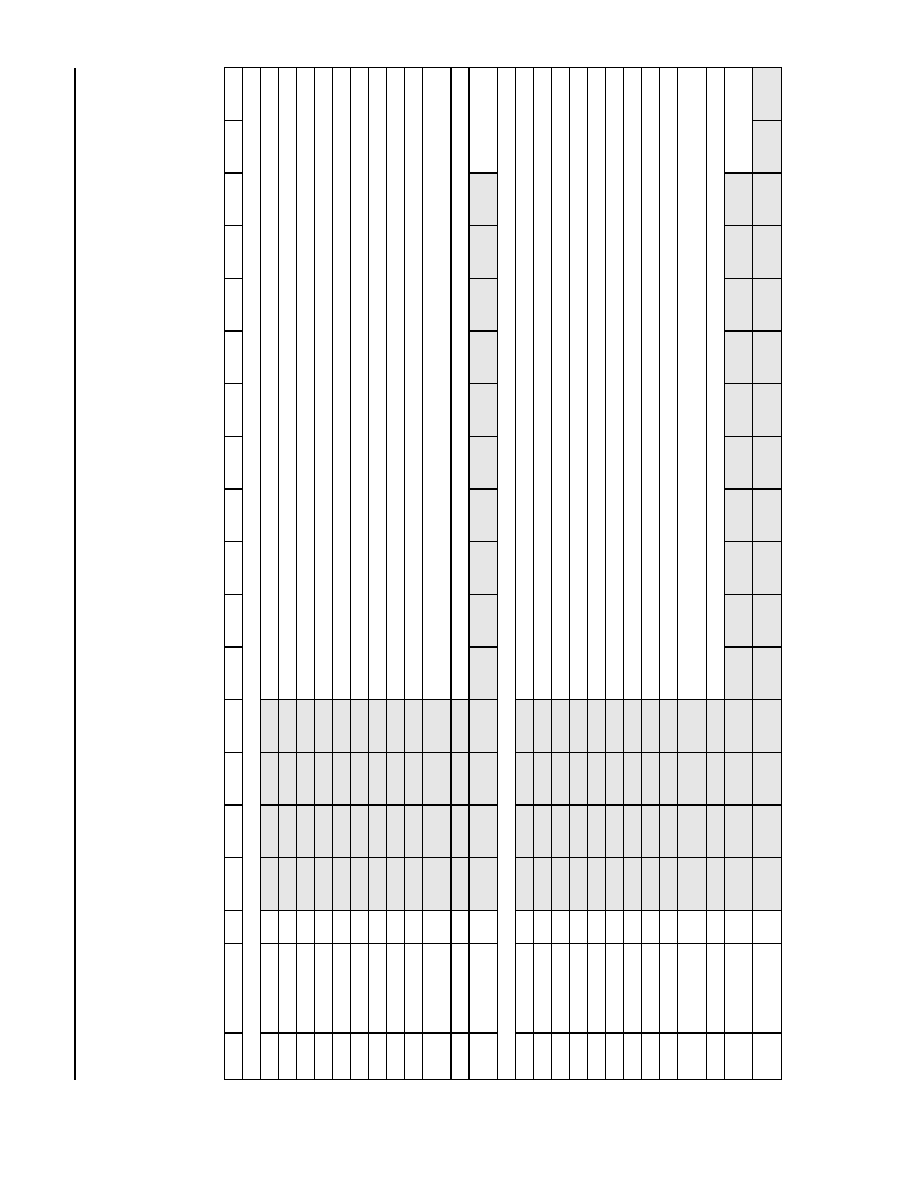

- List of Figures

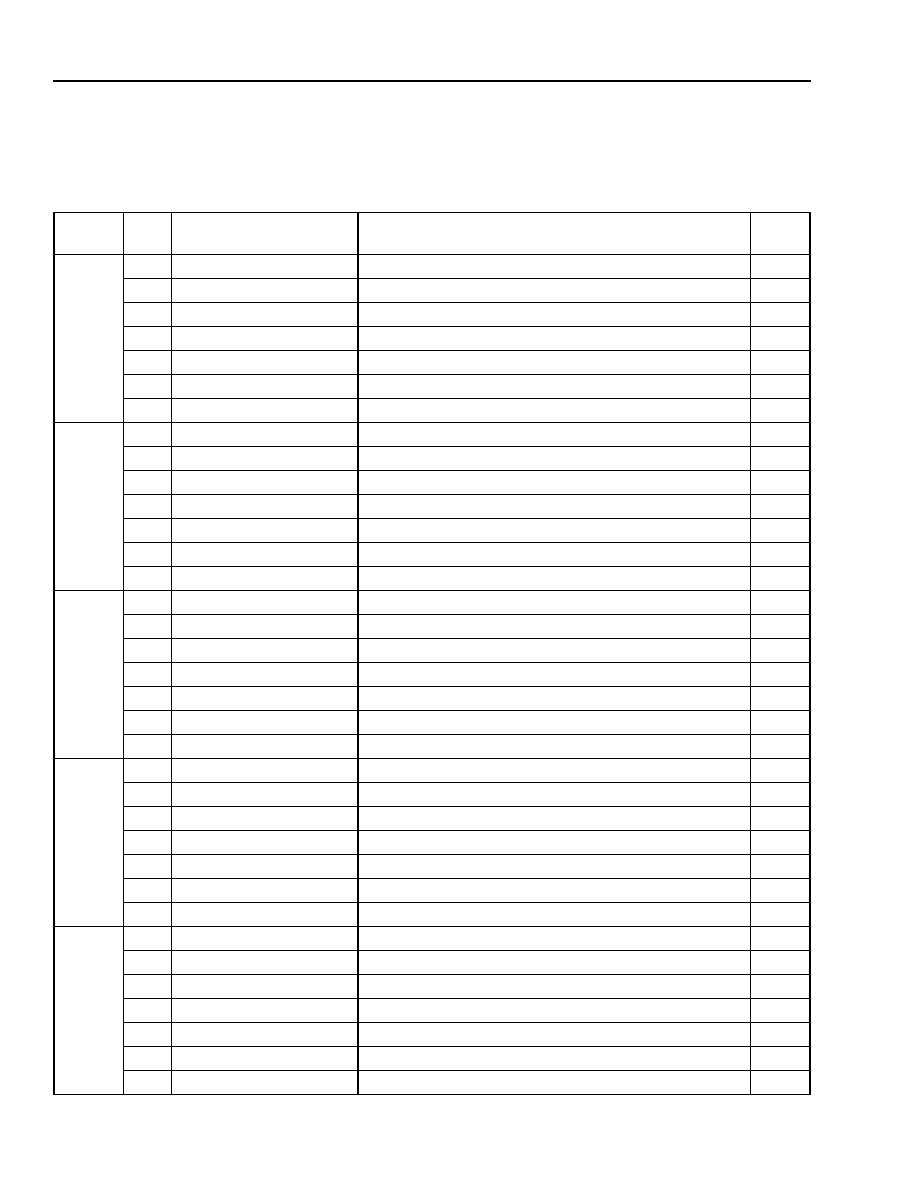

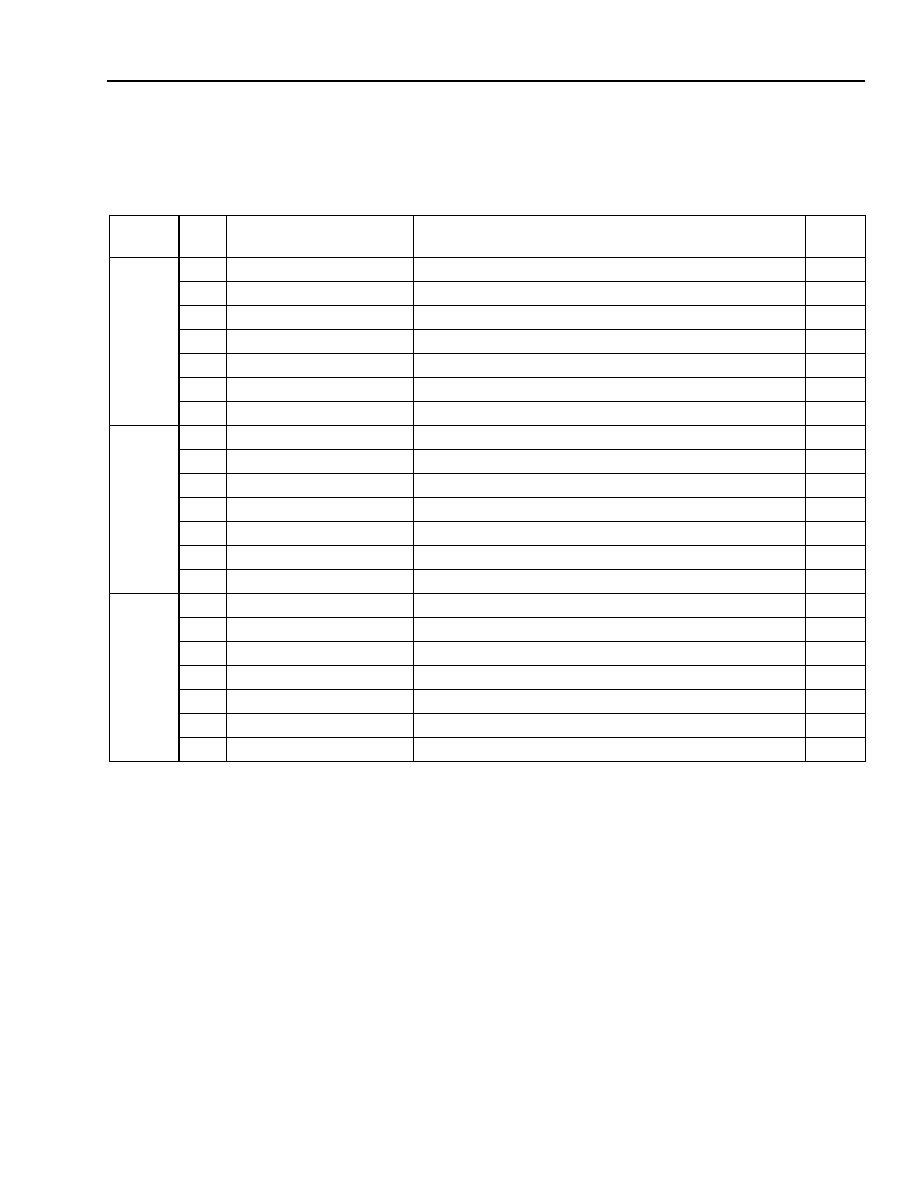

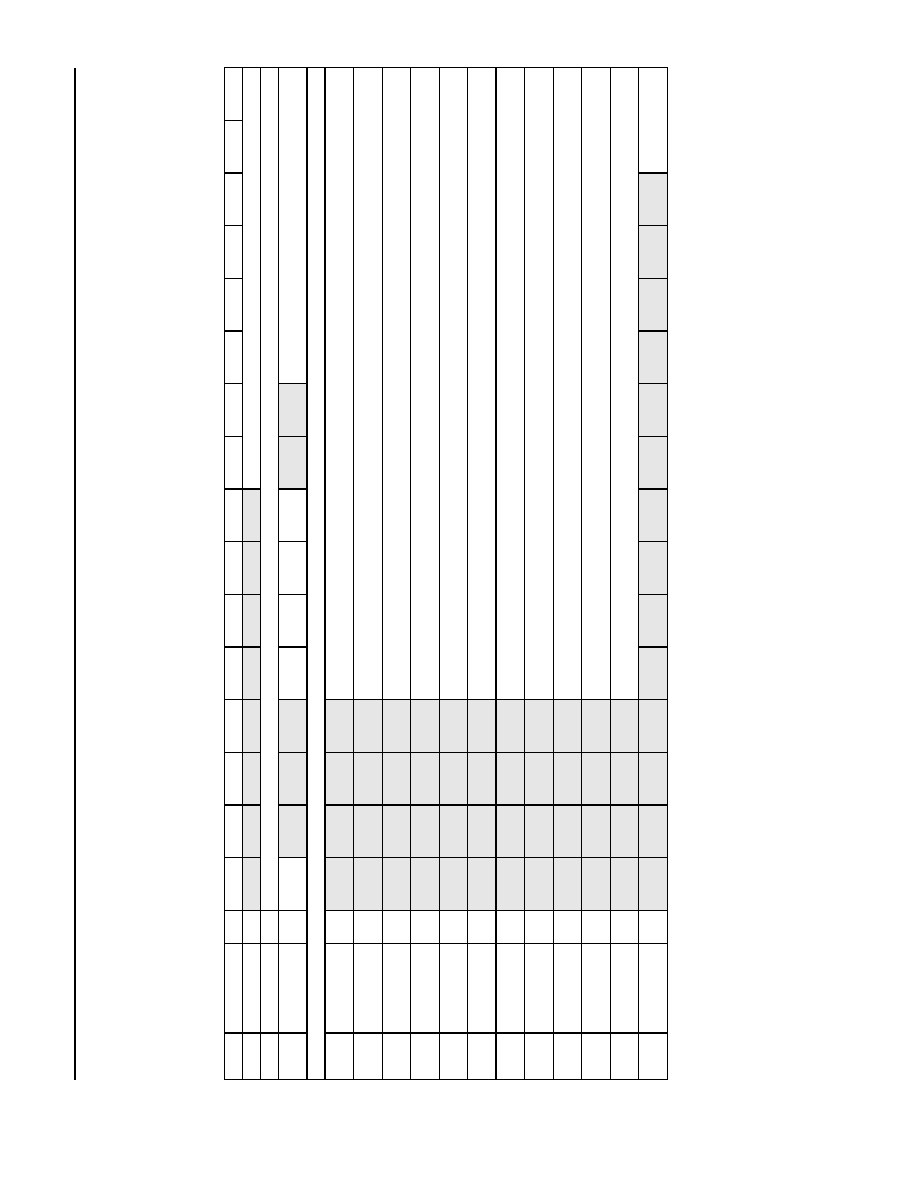

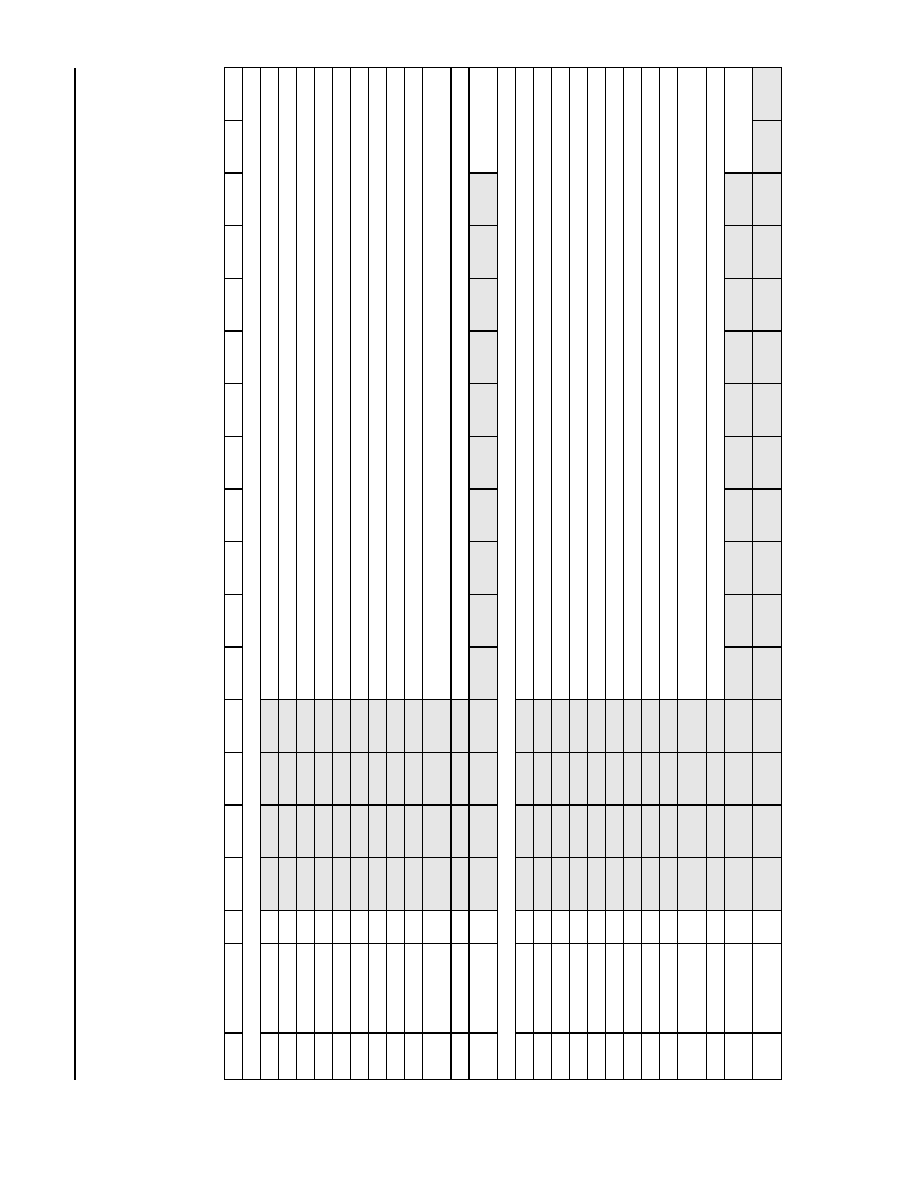

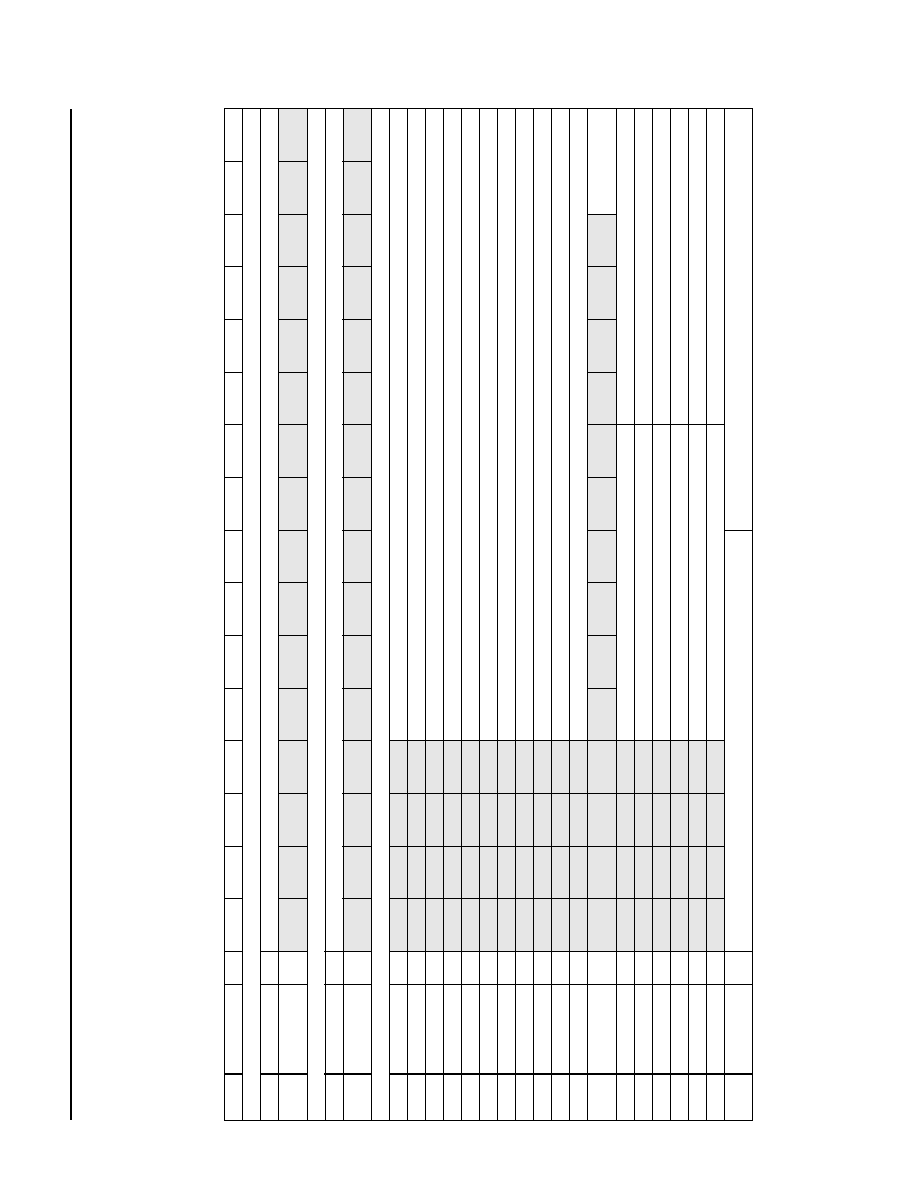

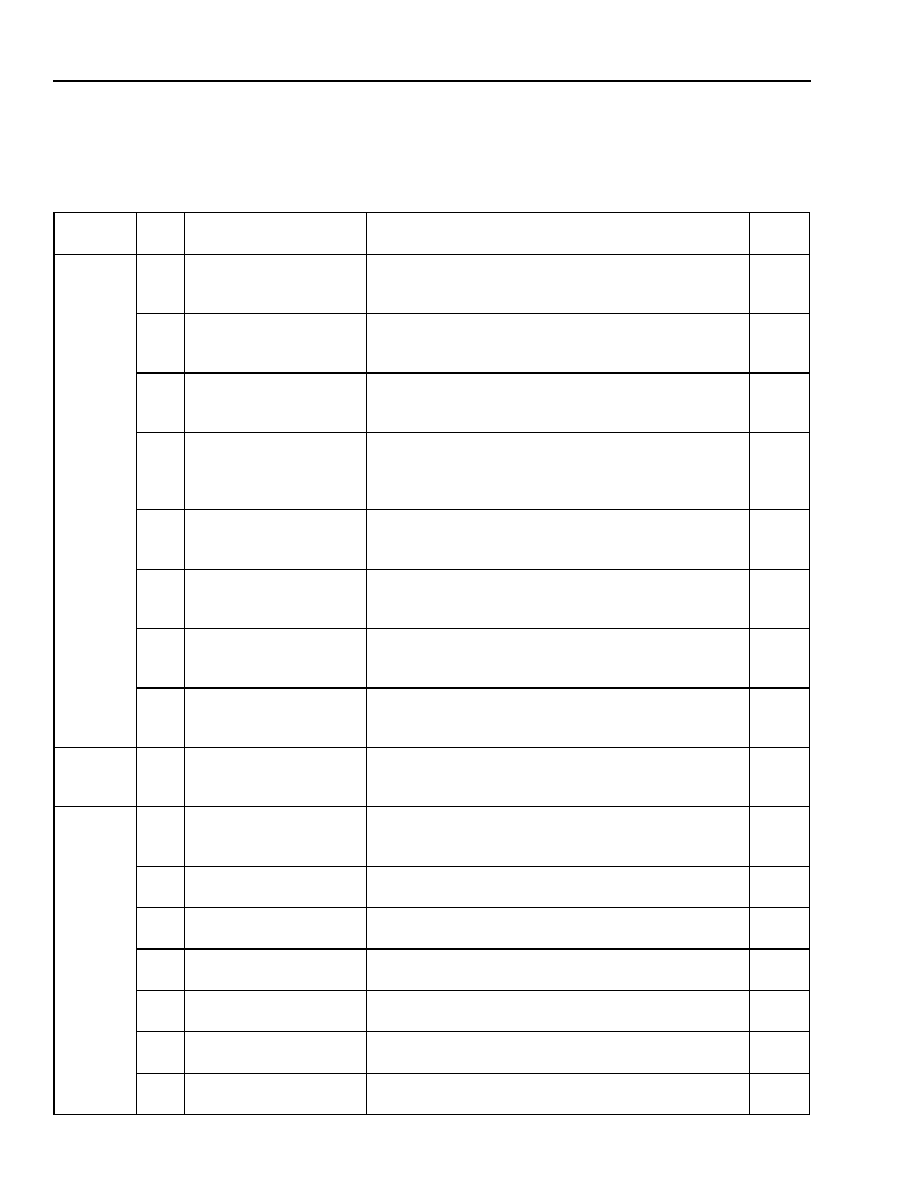

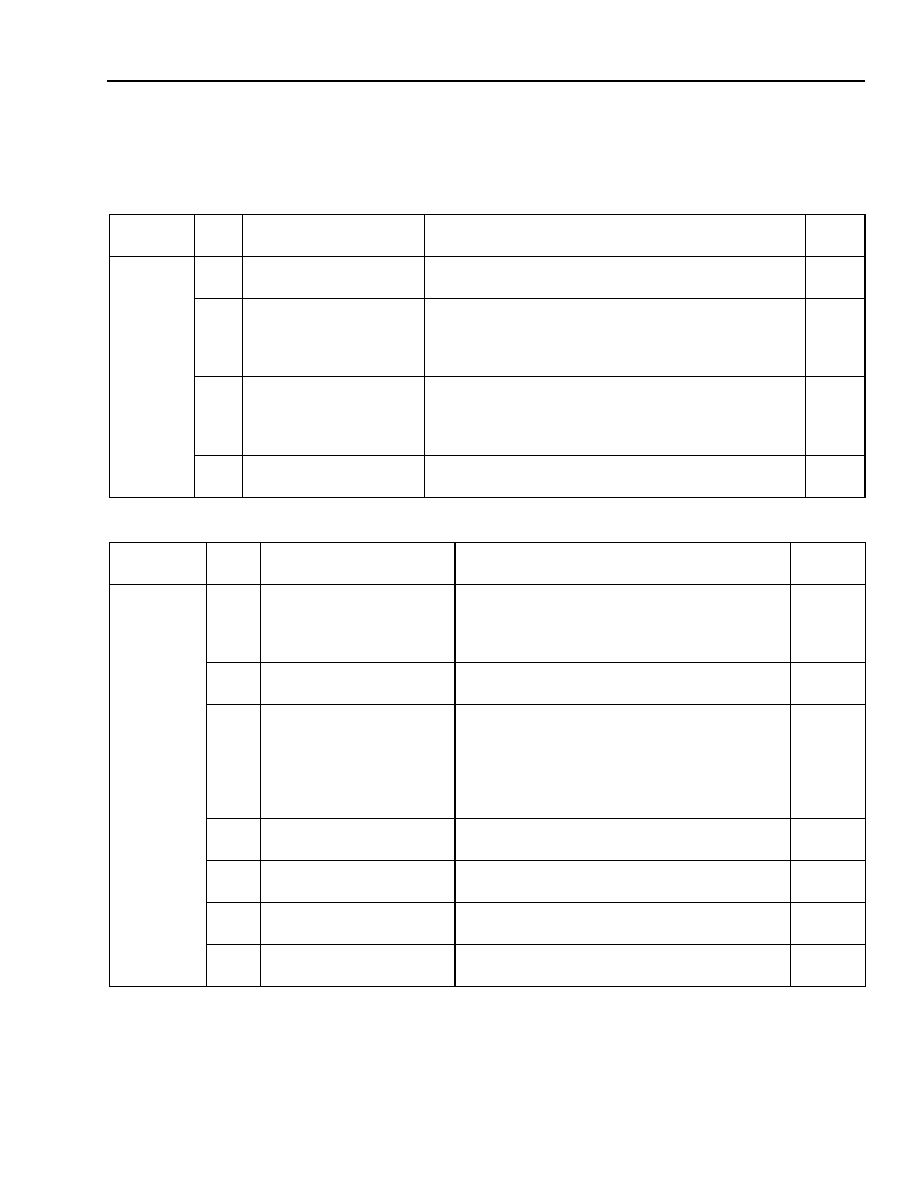

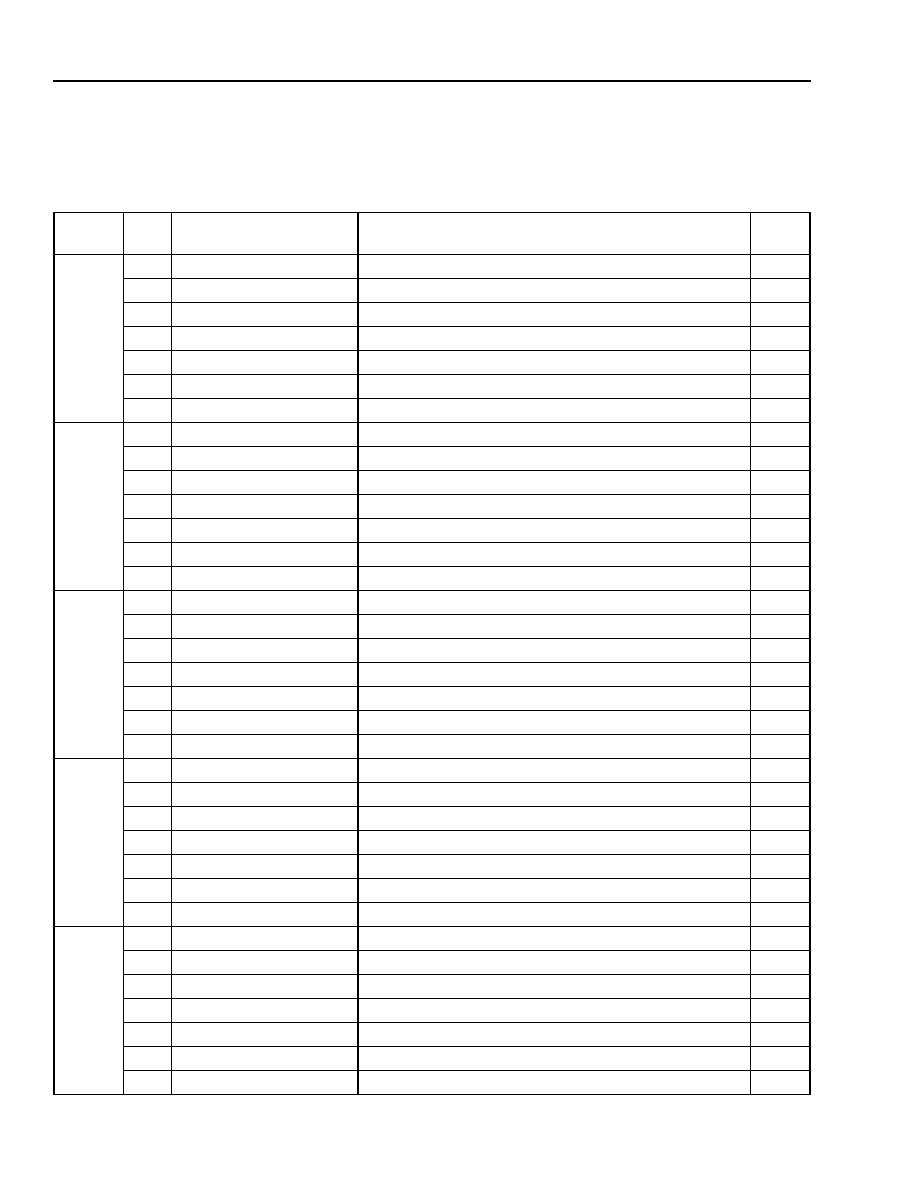

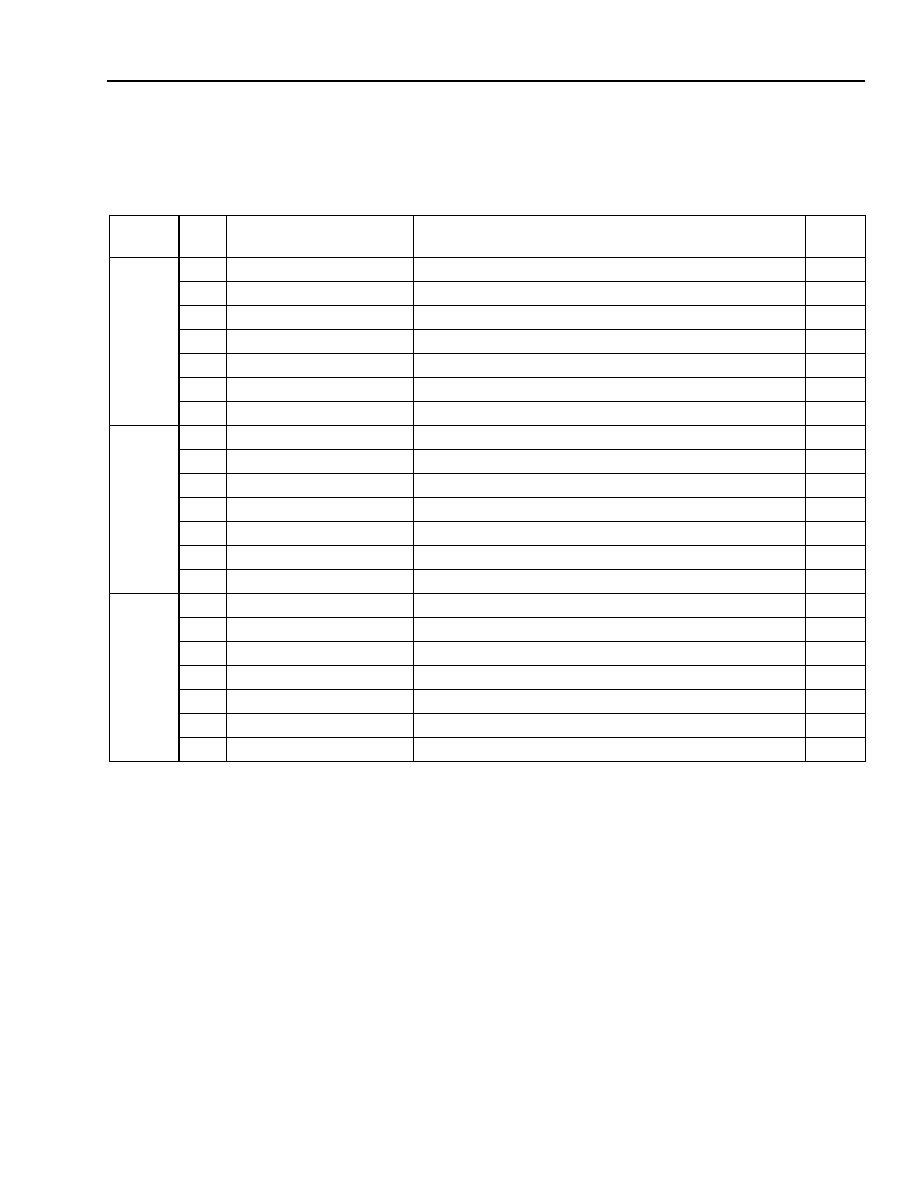

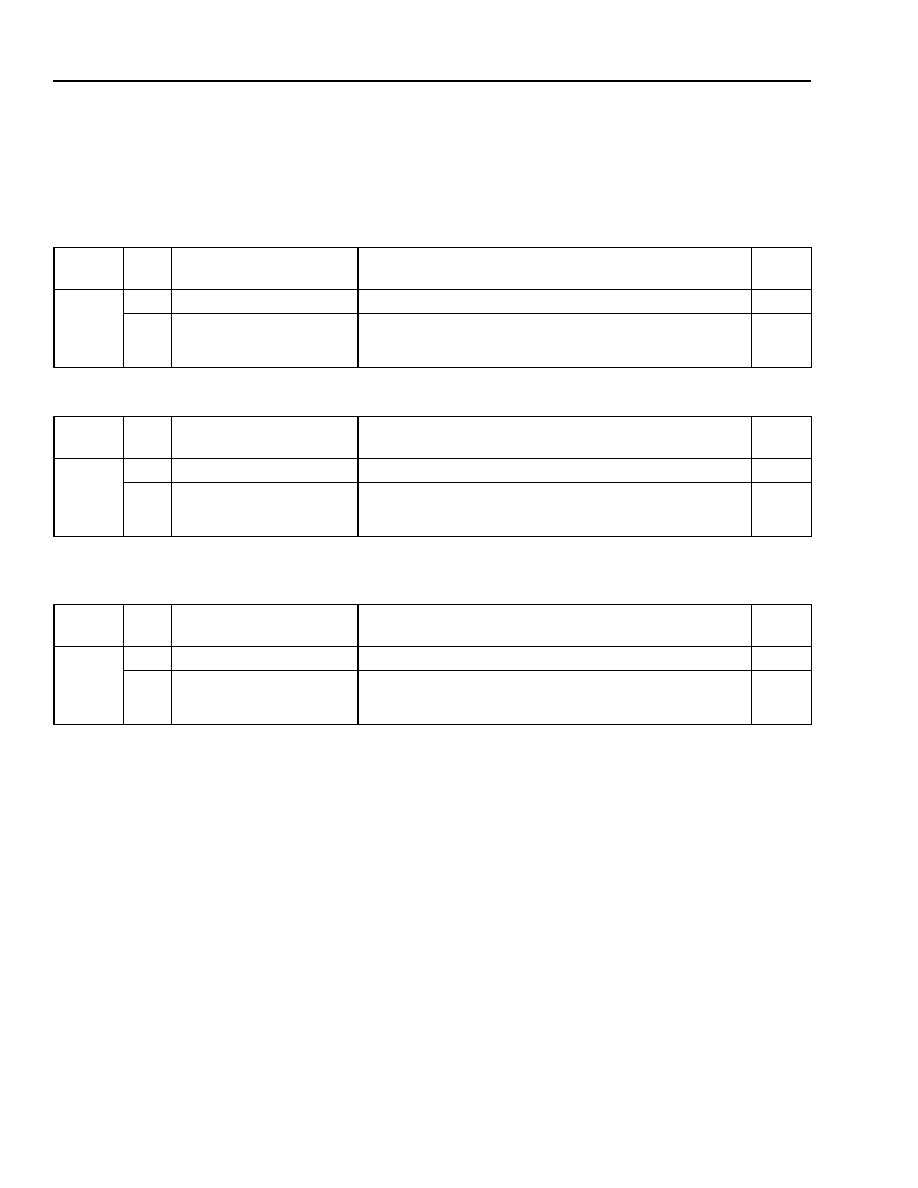

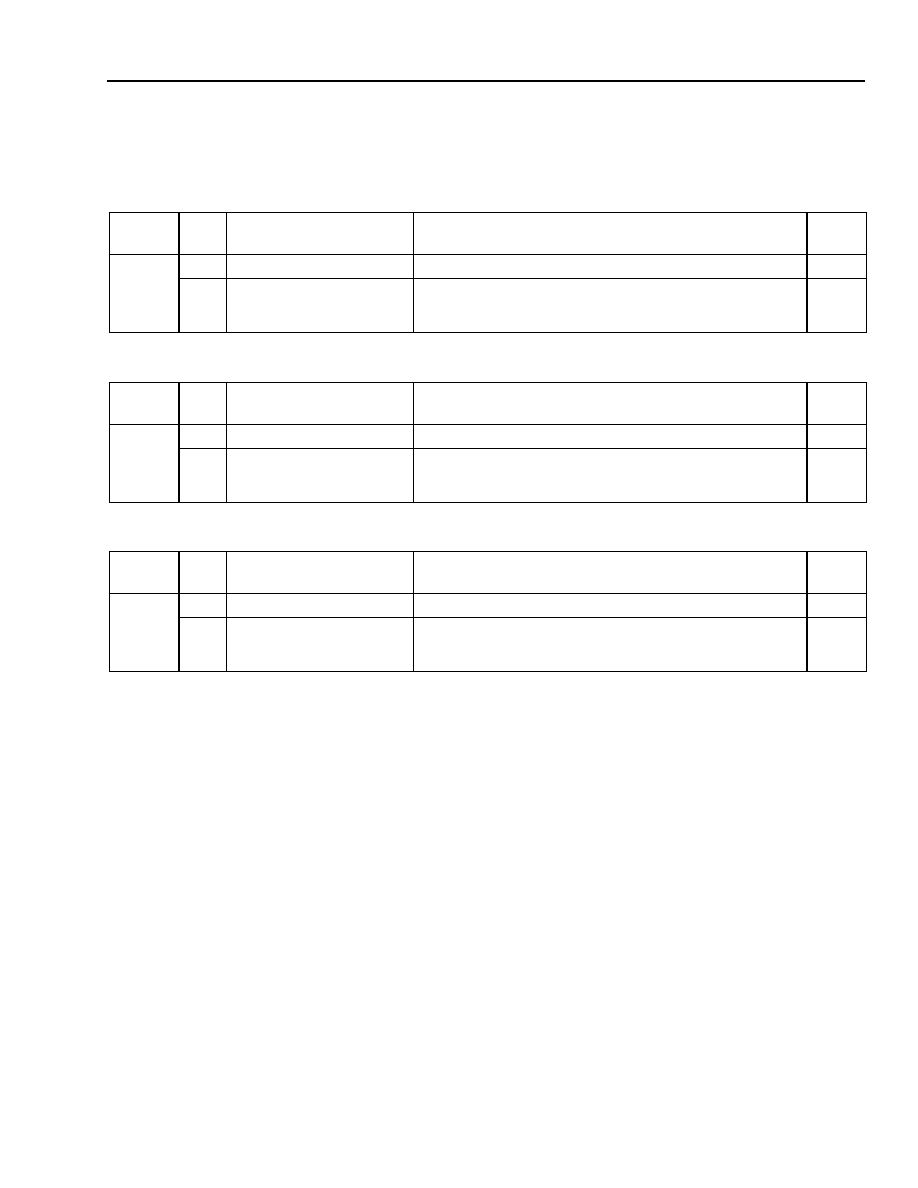

- List of Tables

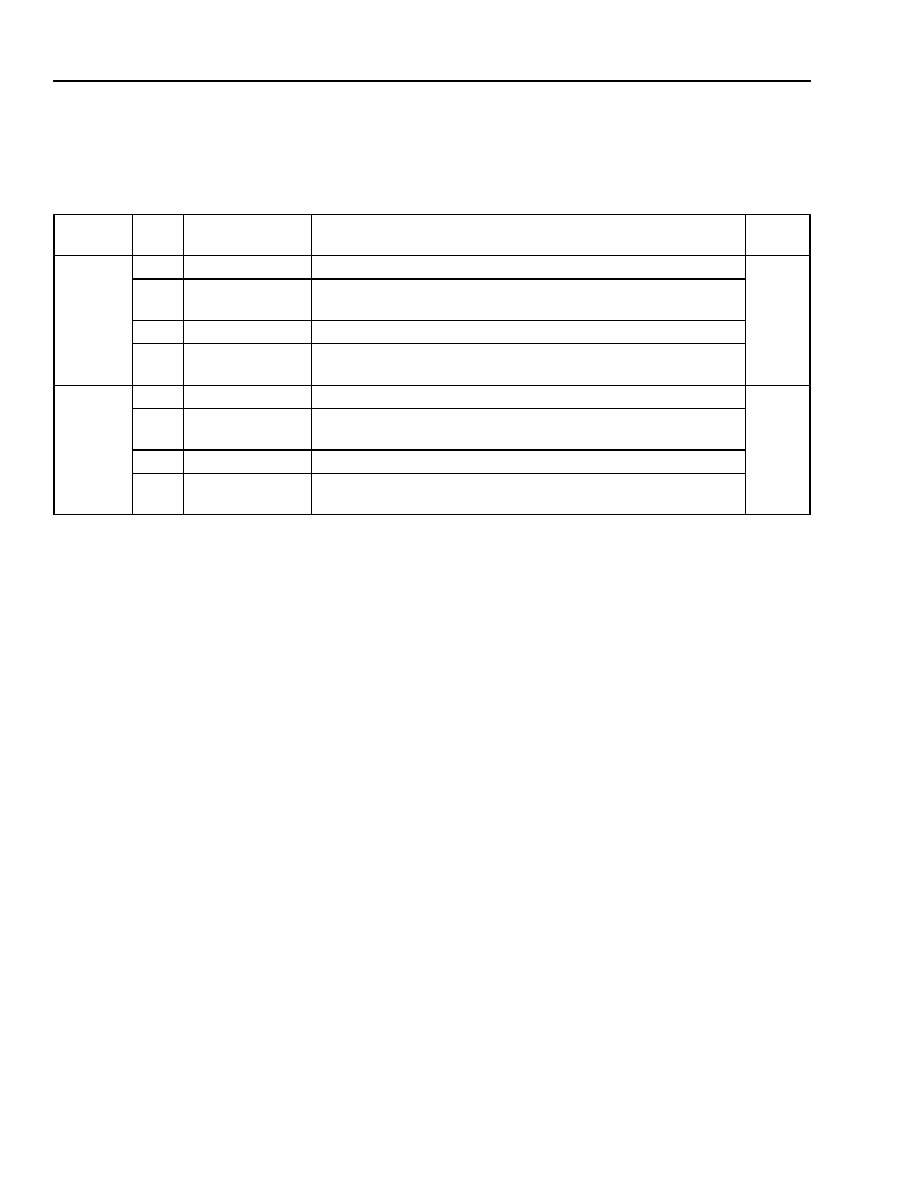

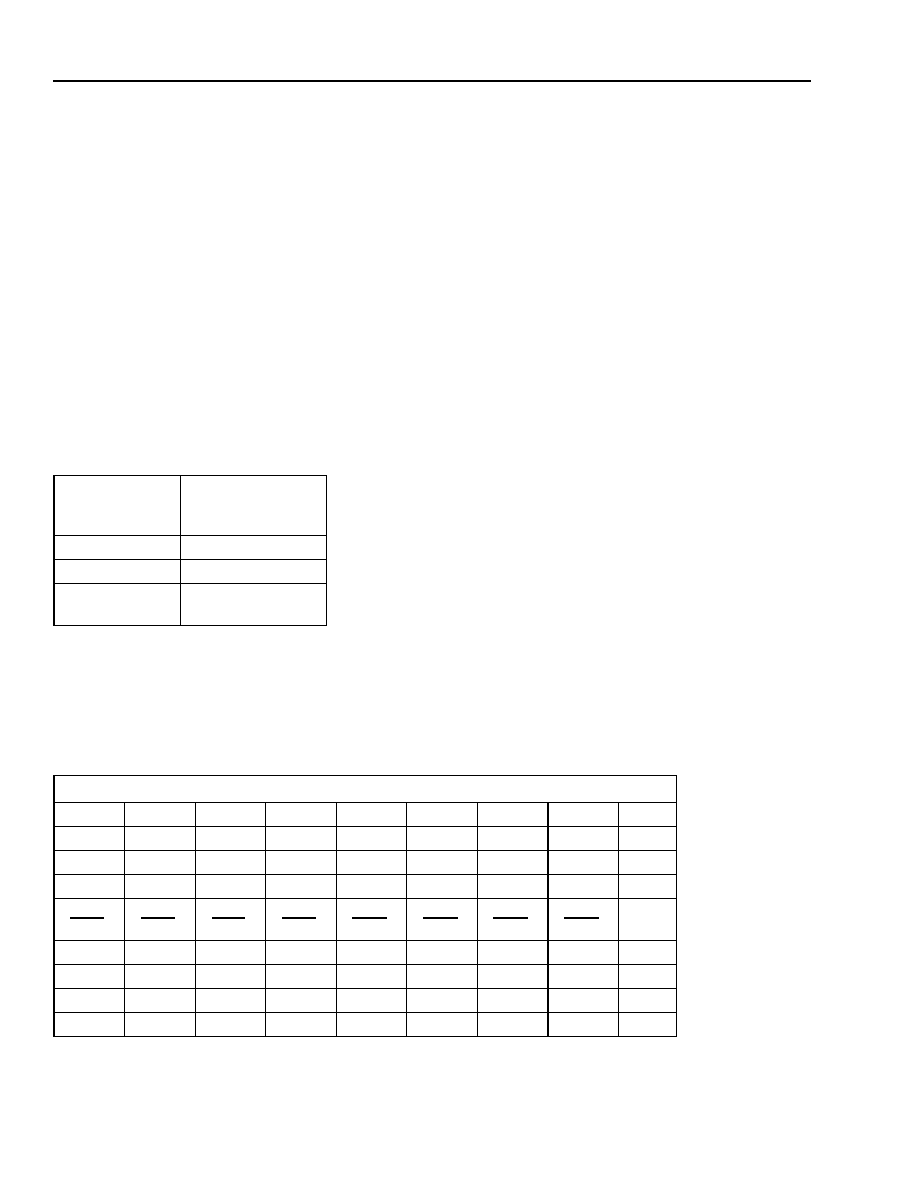

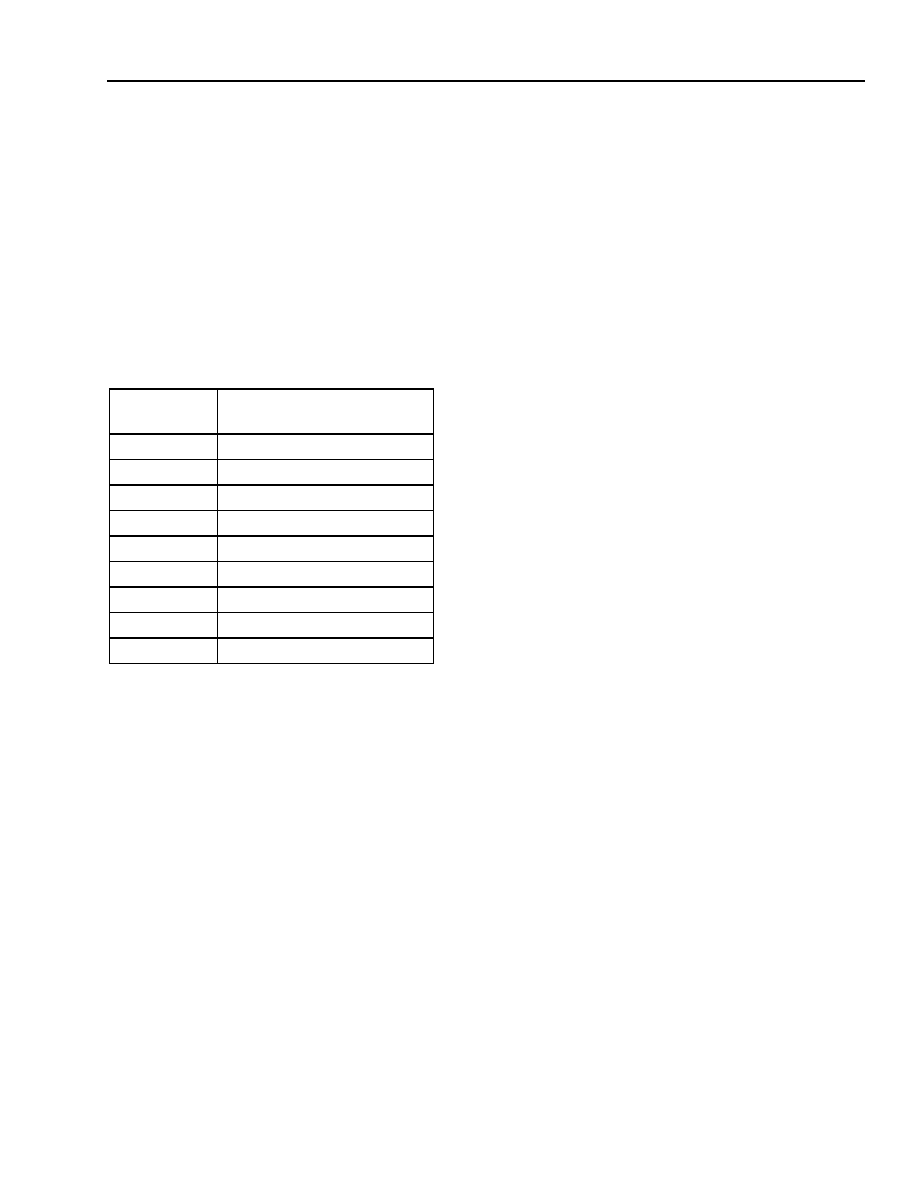

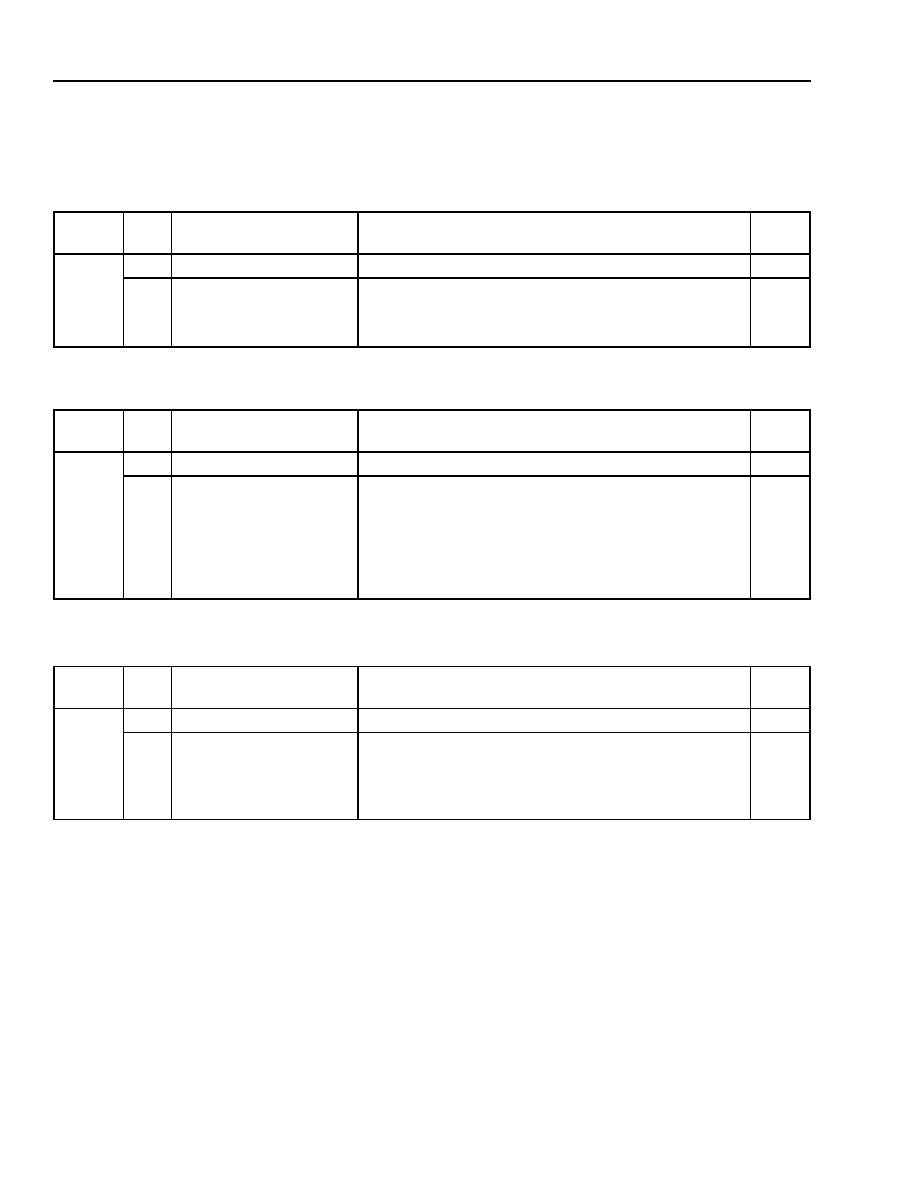

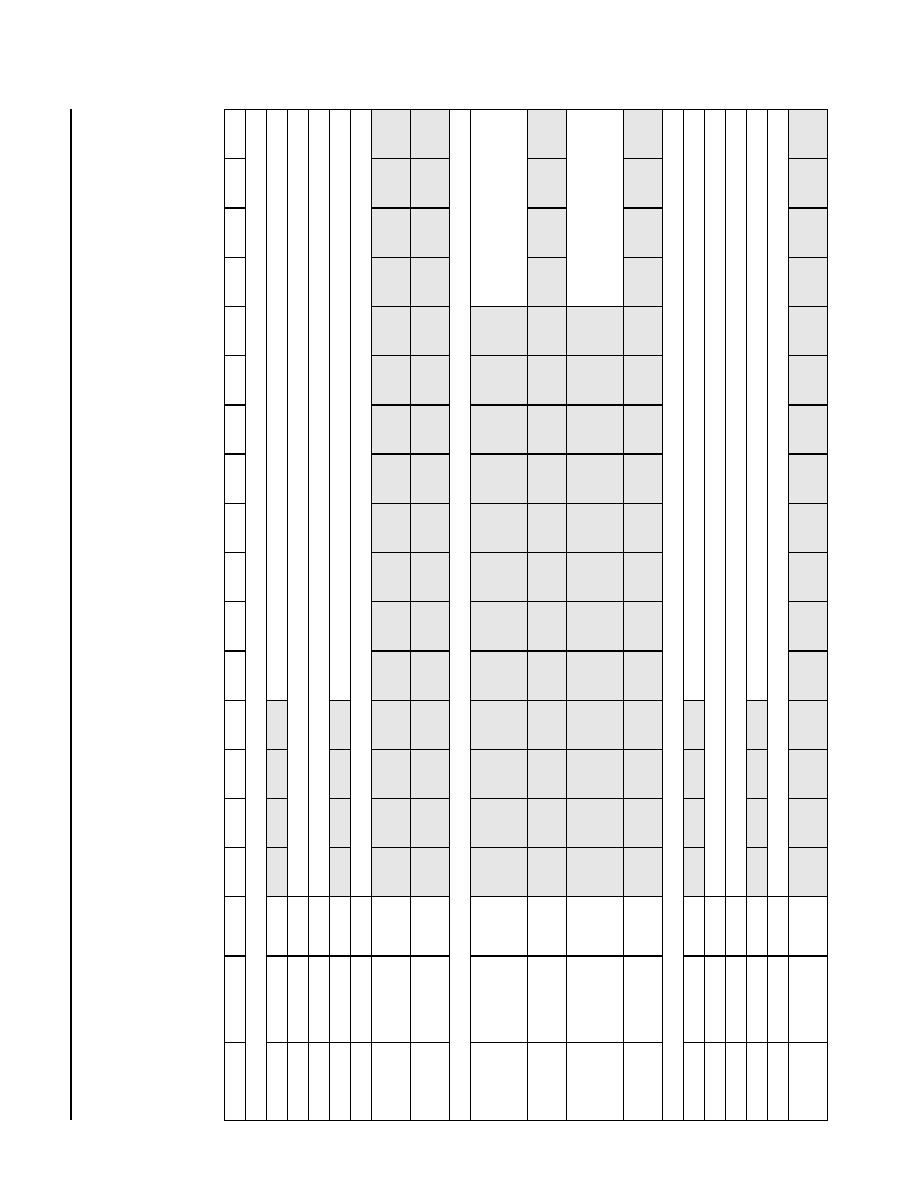

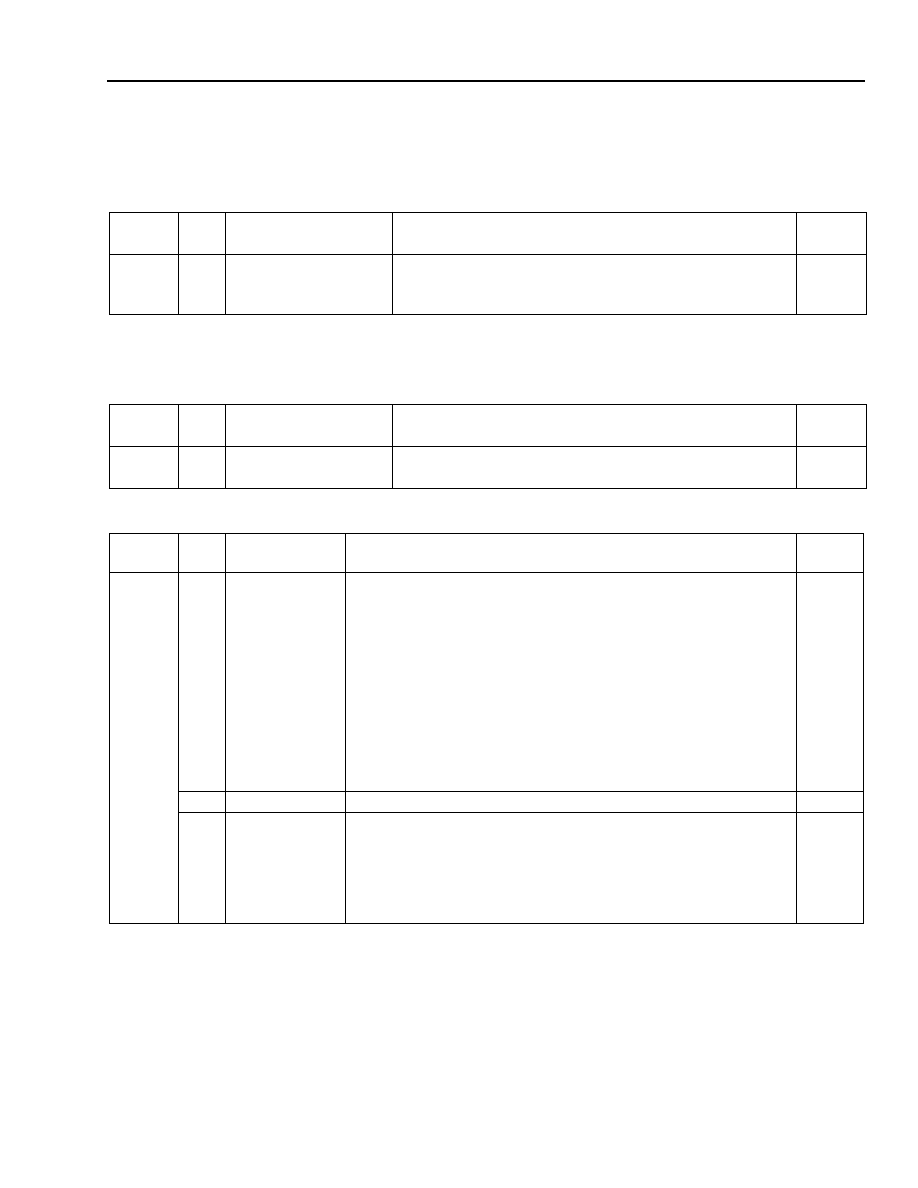

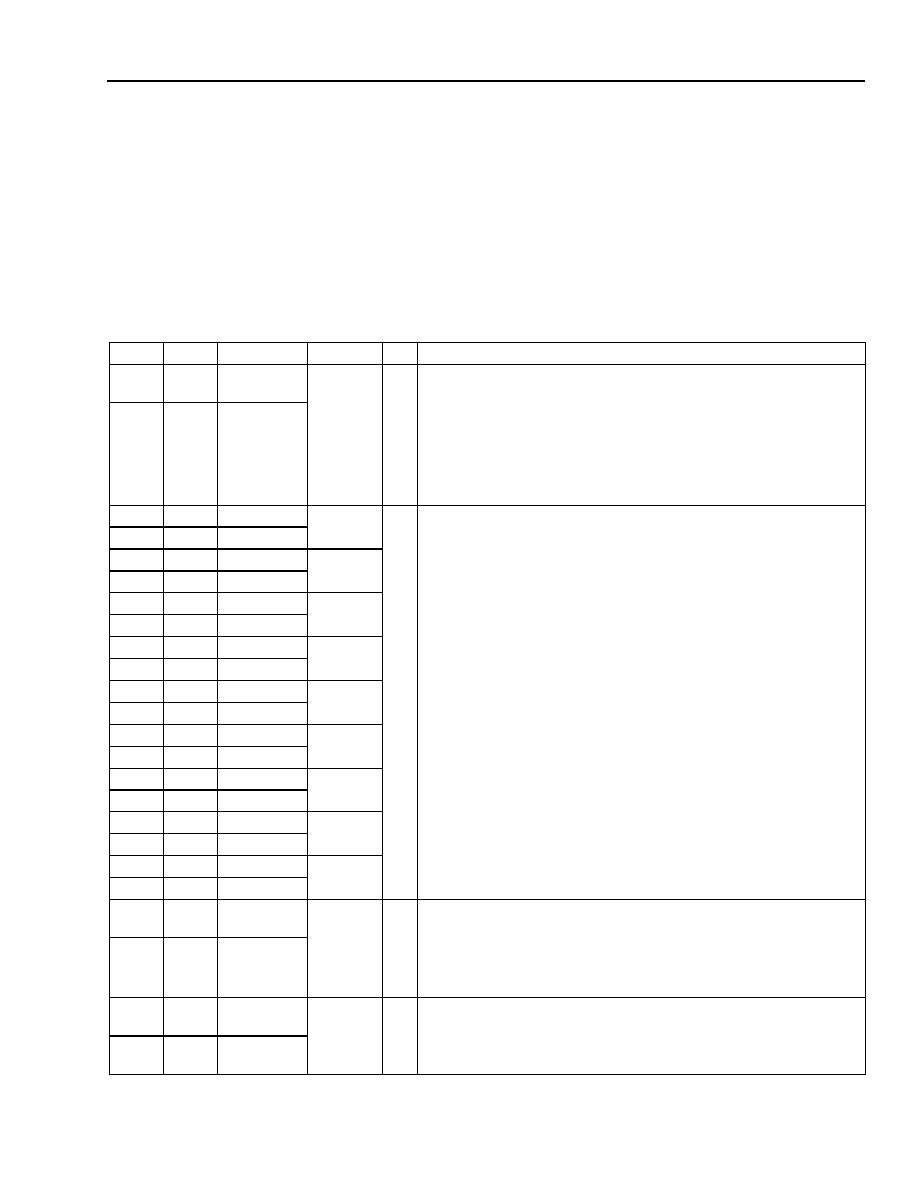

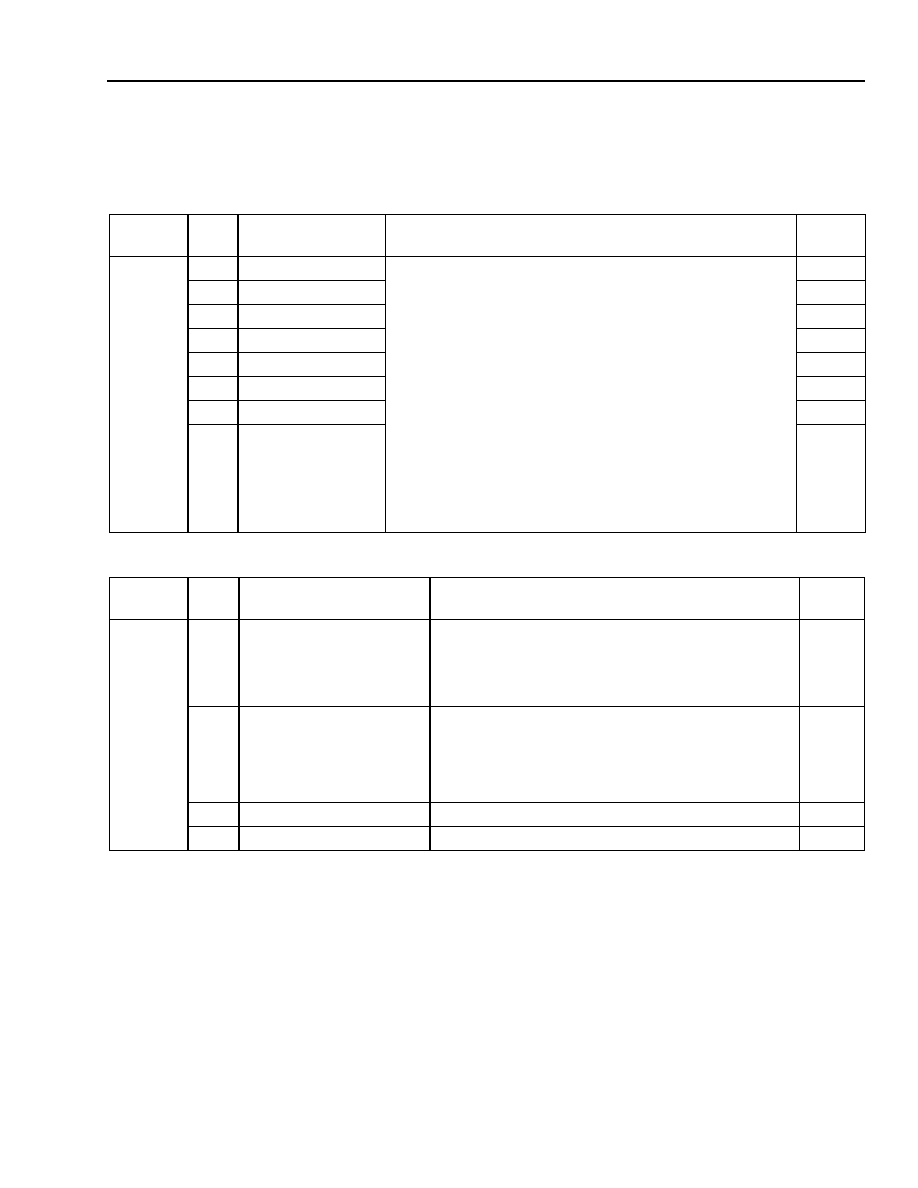

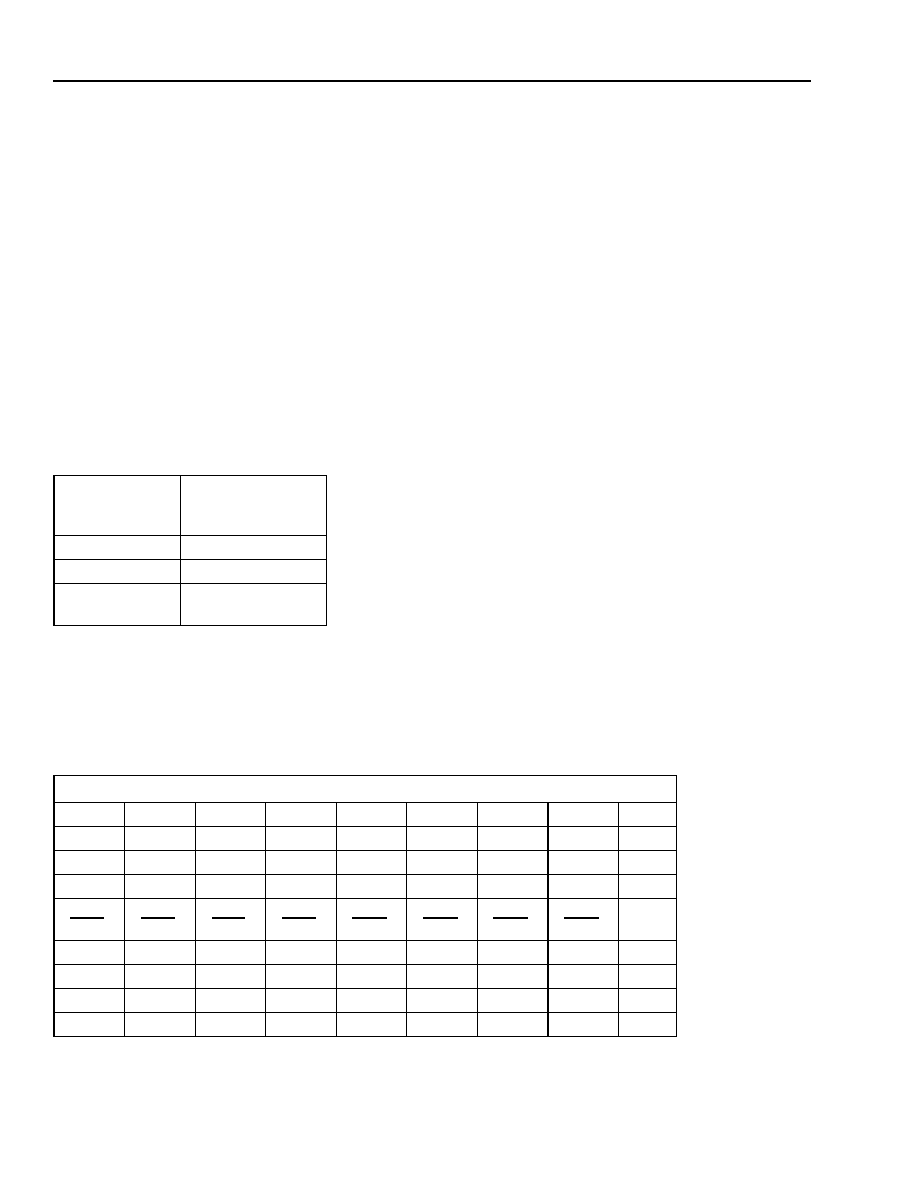

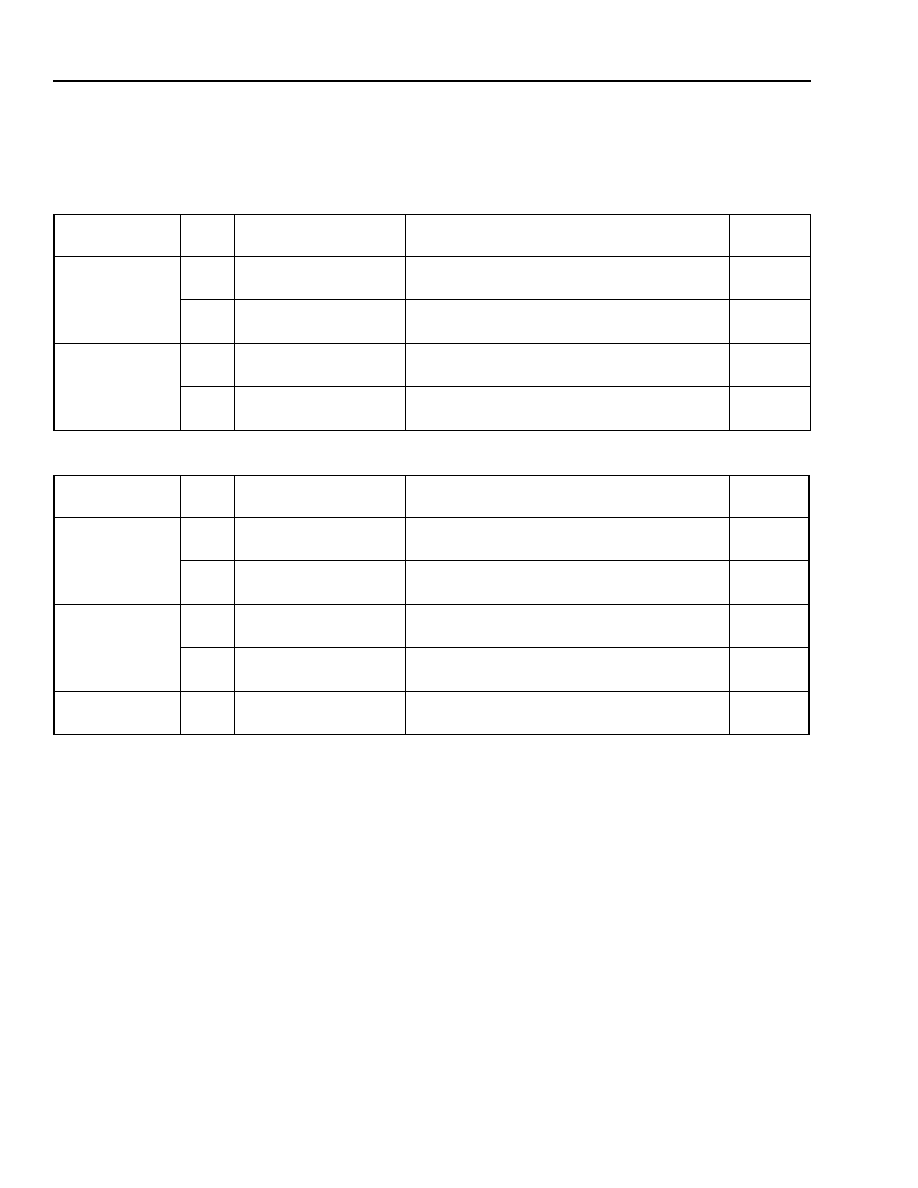

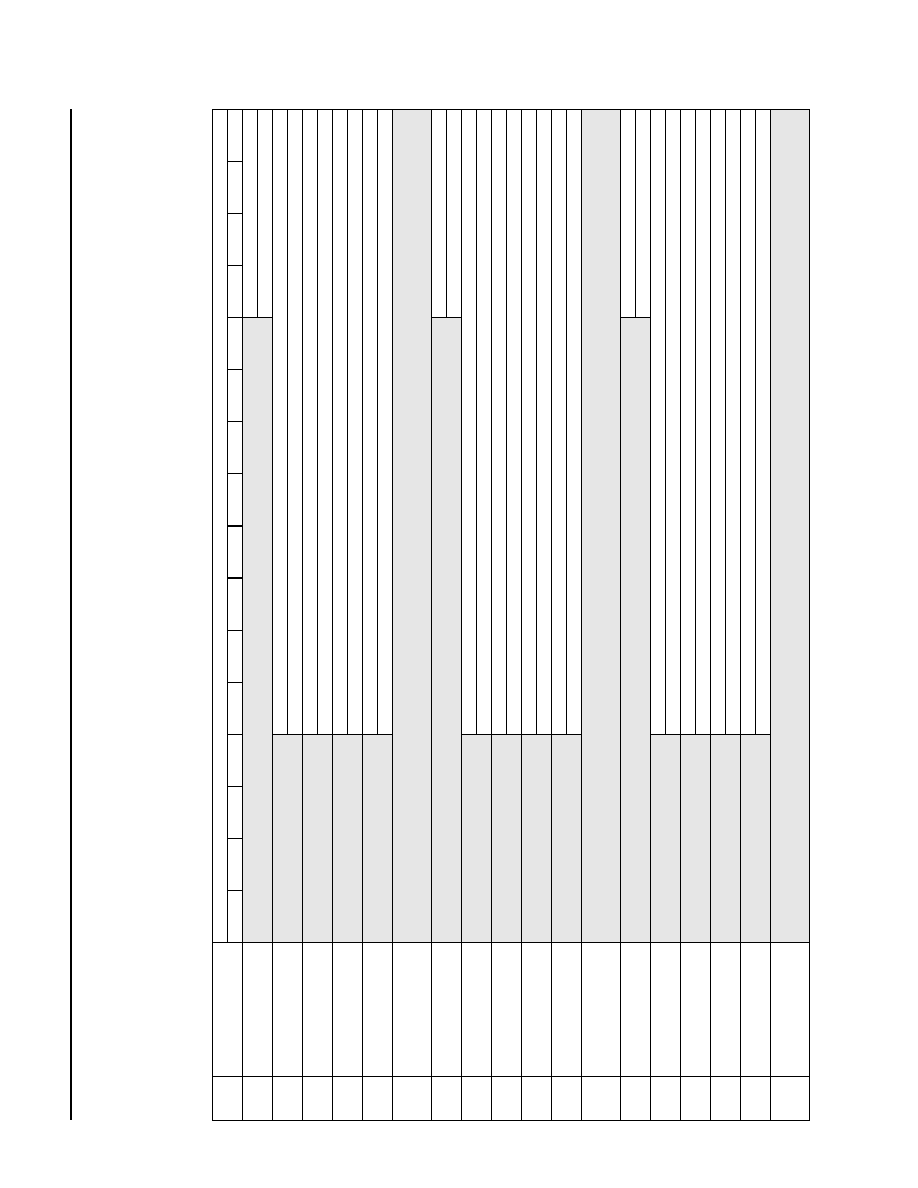

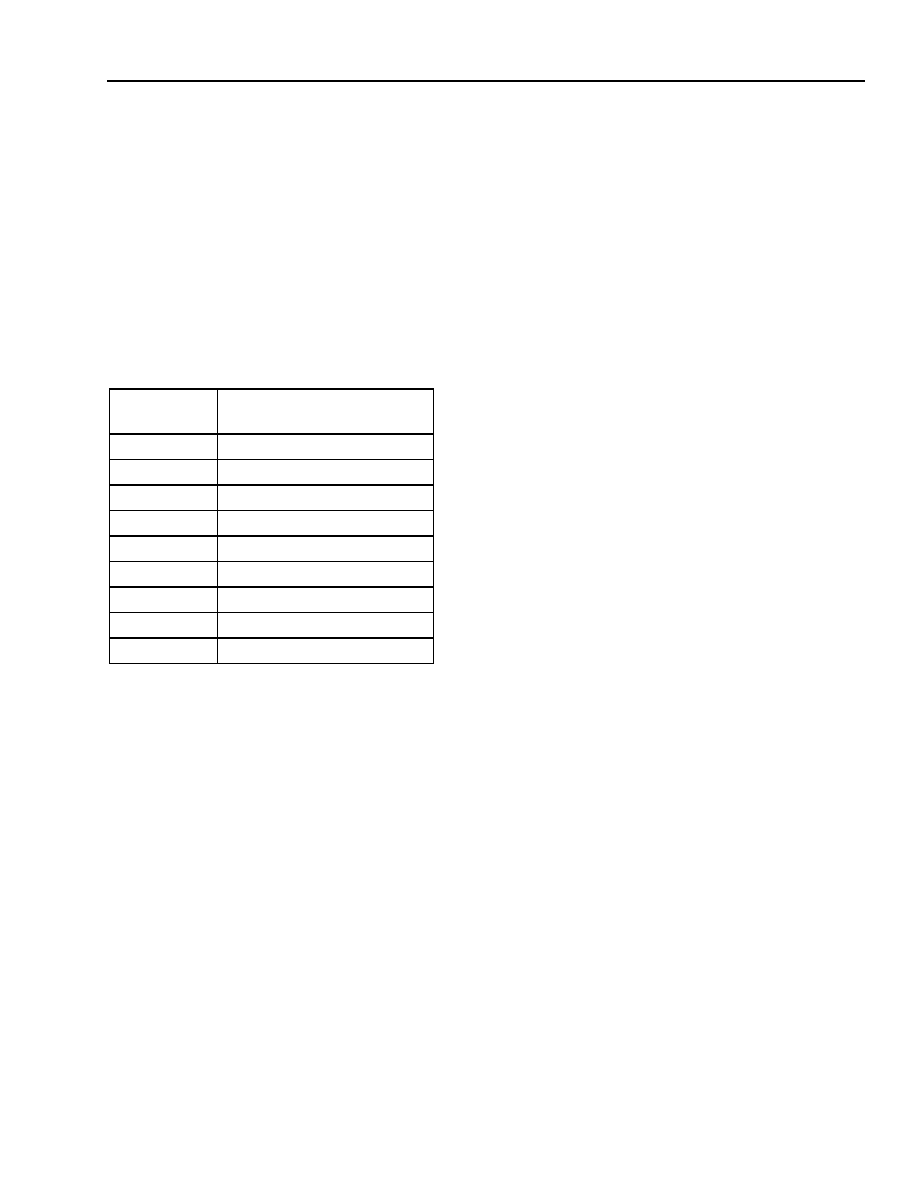

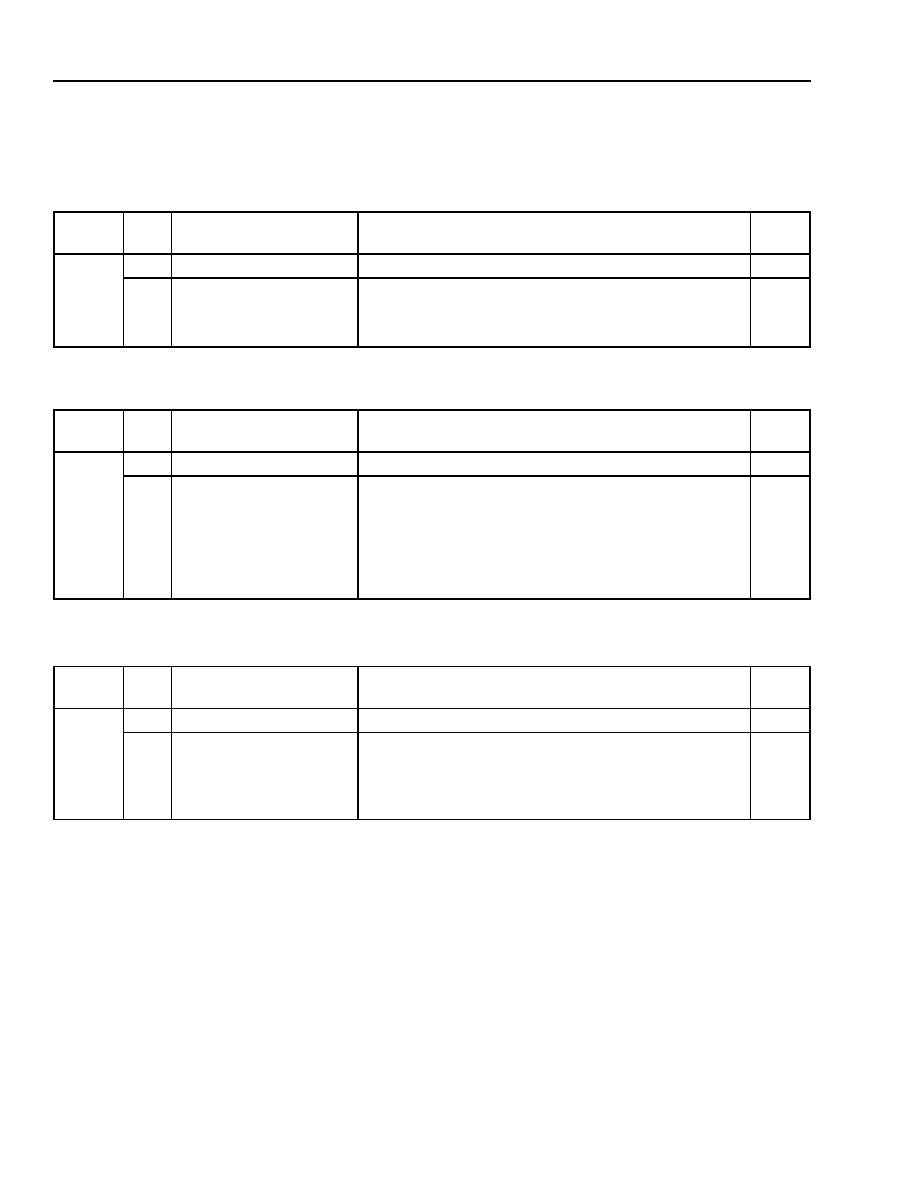

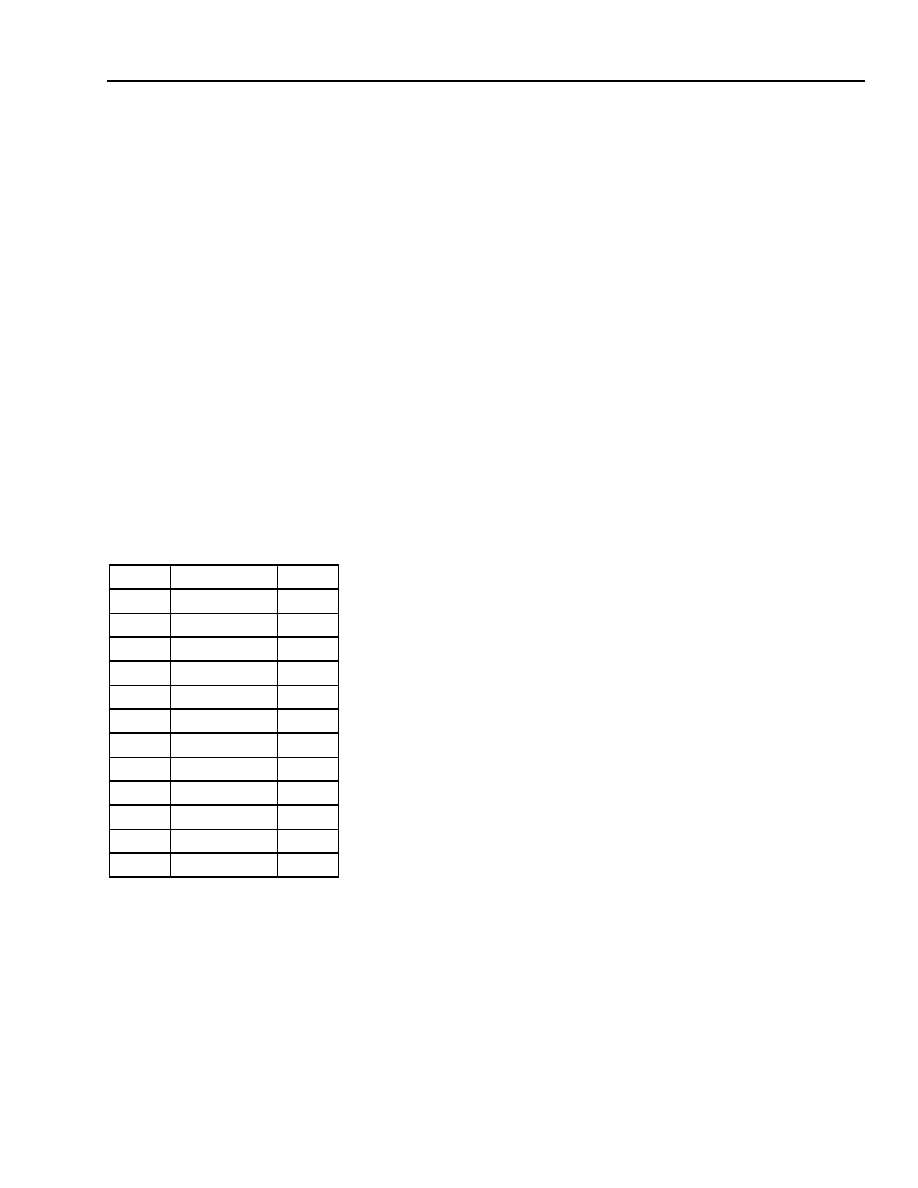

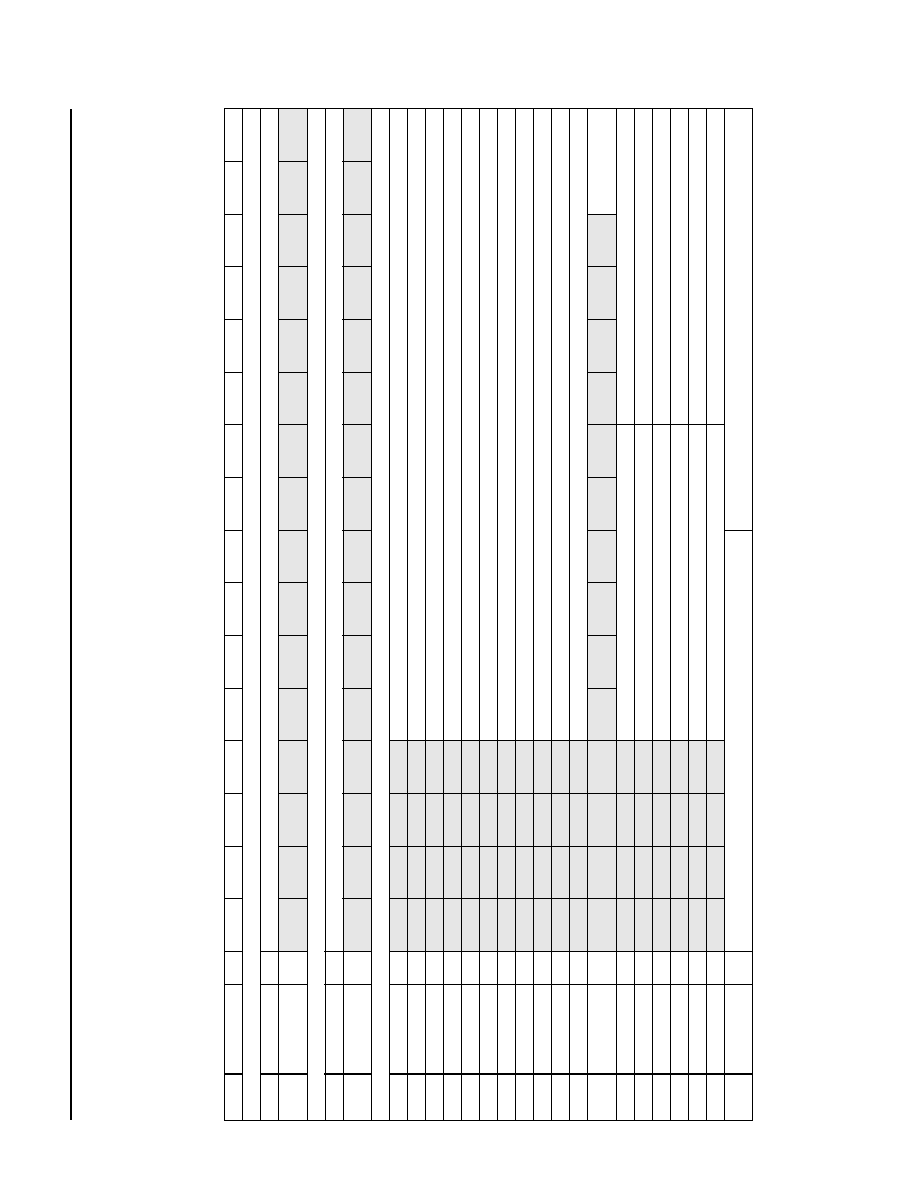

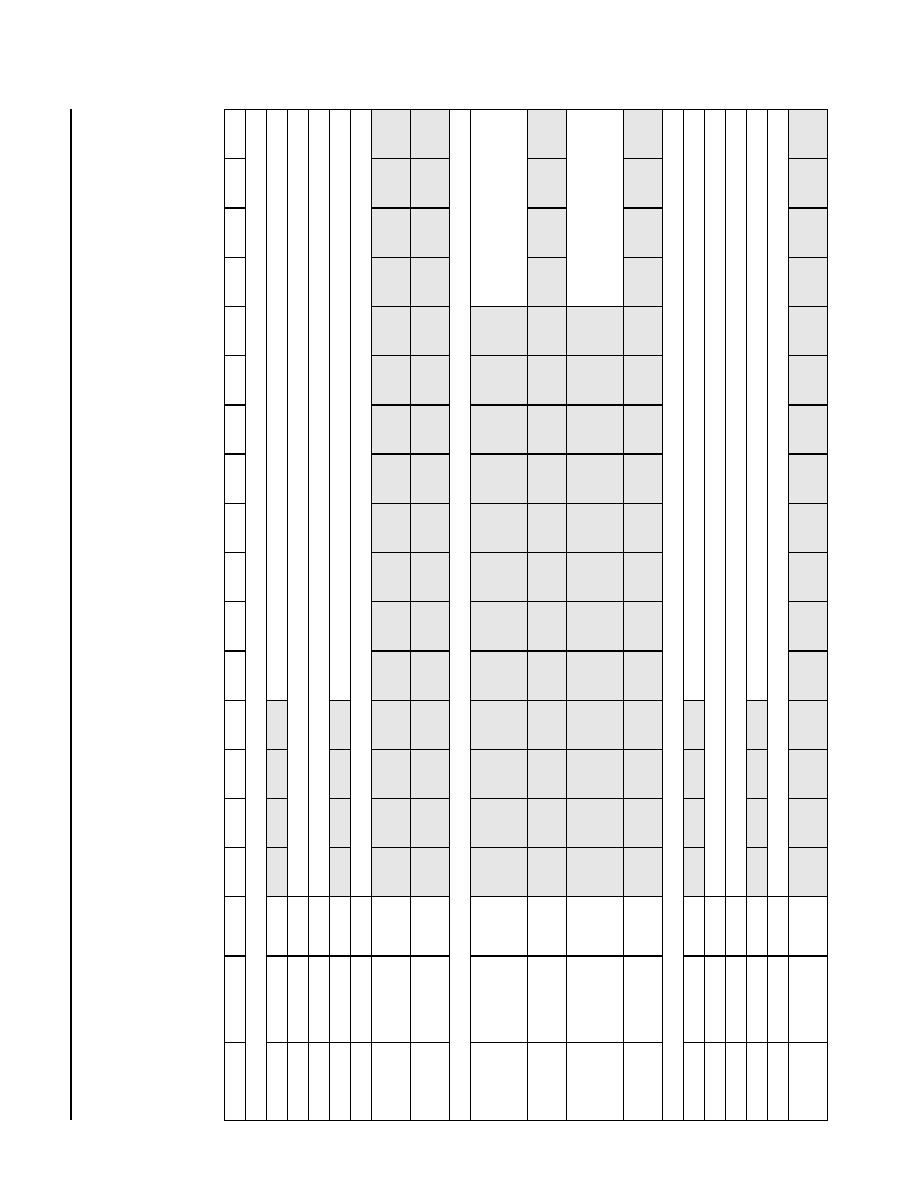

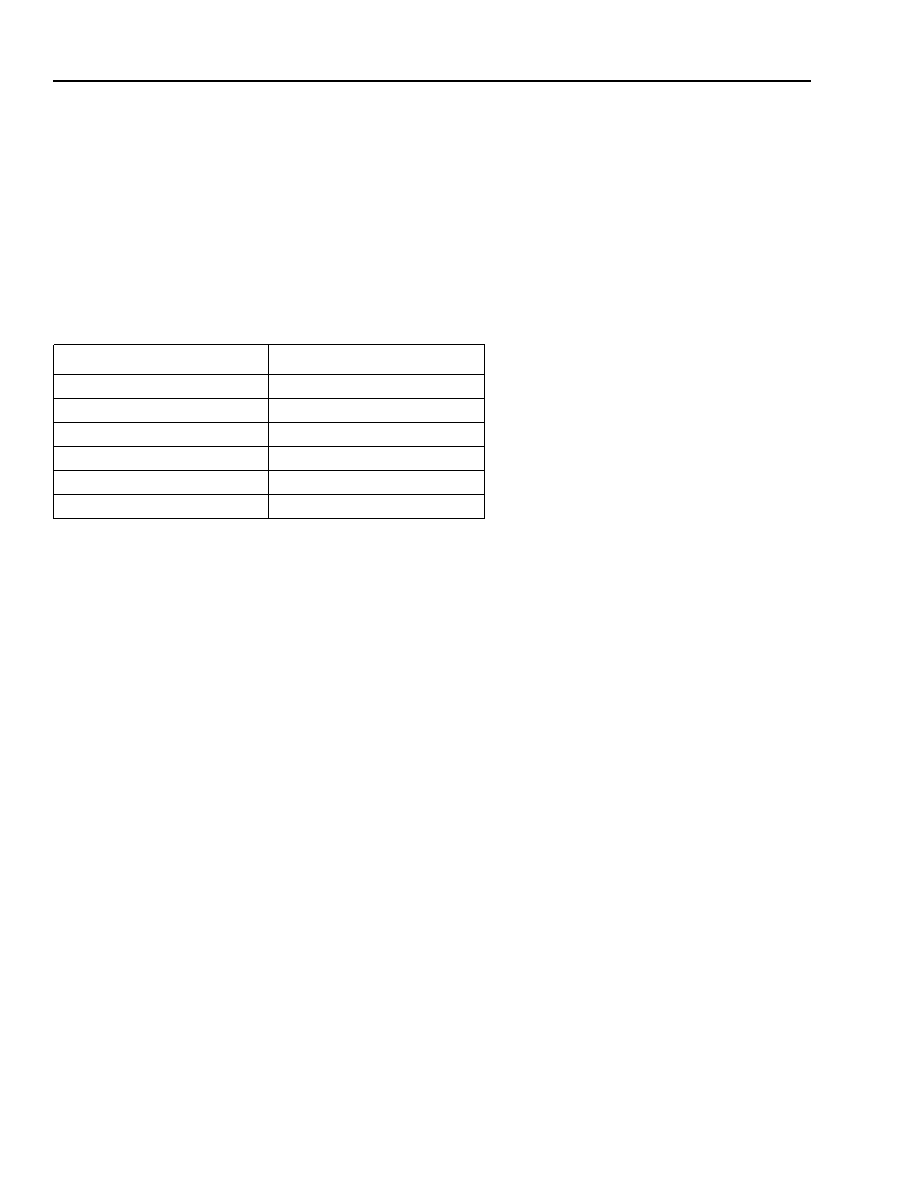

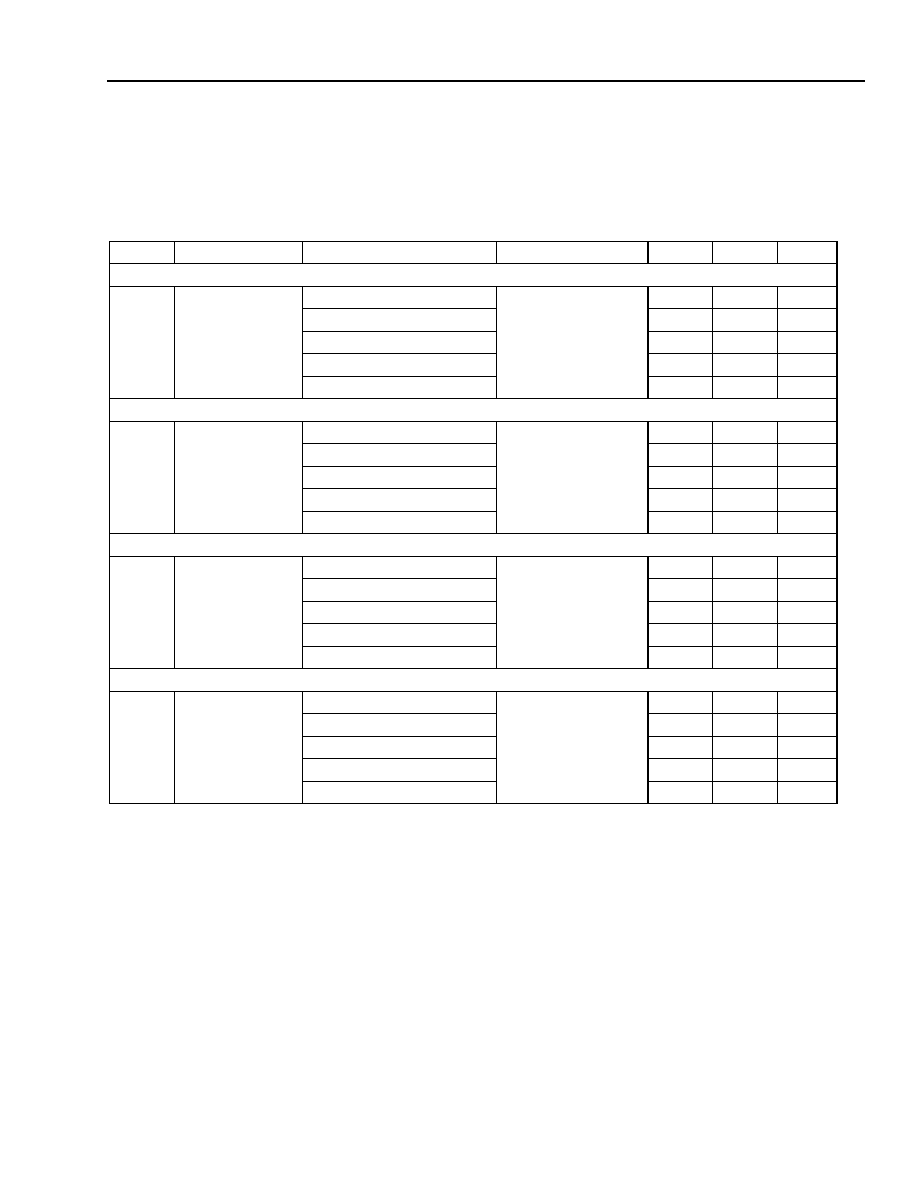

- Table 1. List of the Clock Domains in the MARS2G5 P-Pro, SONET/SDH Mode

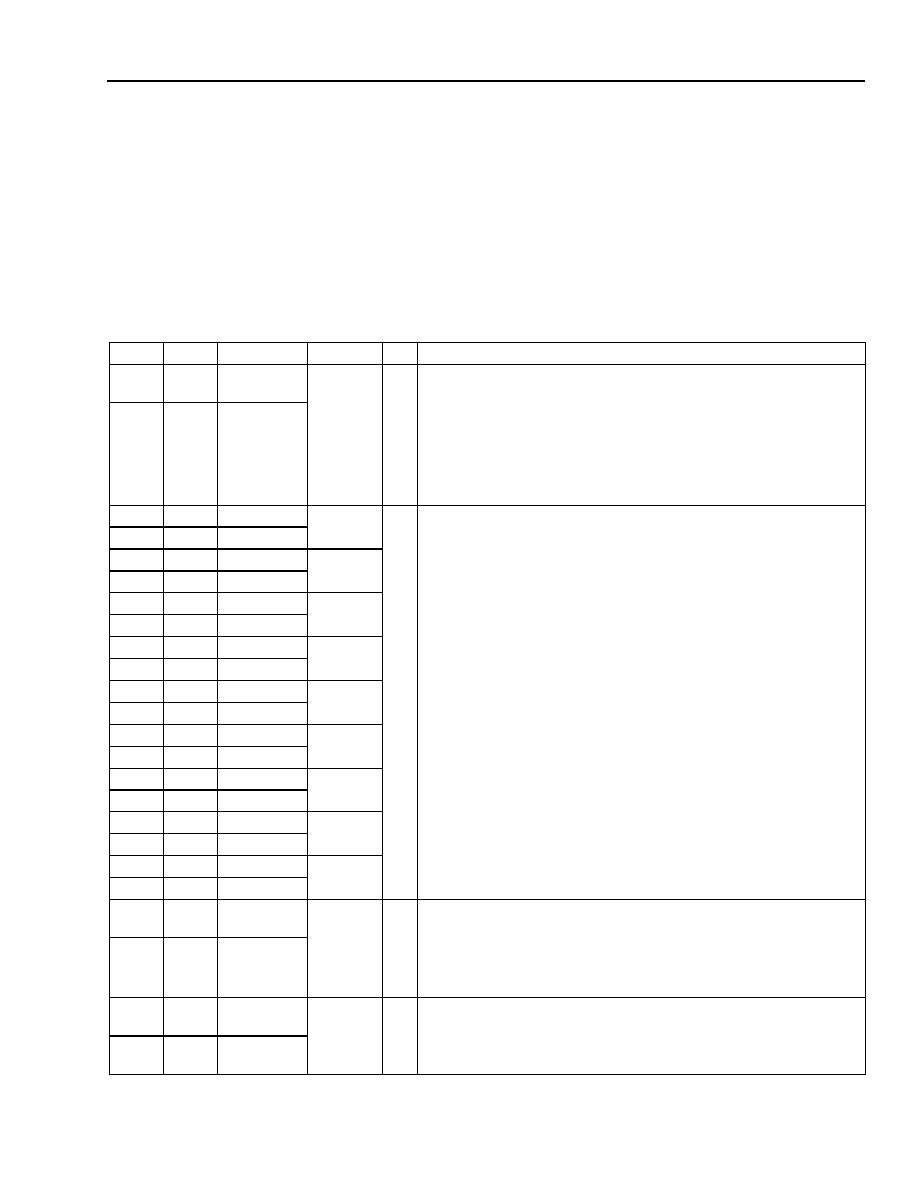

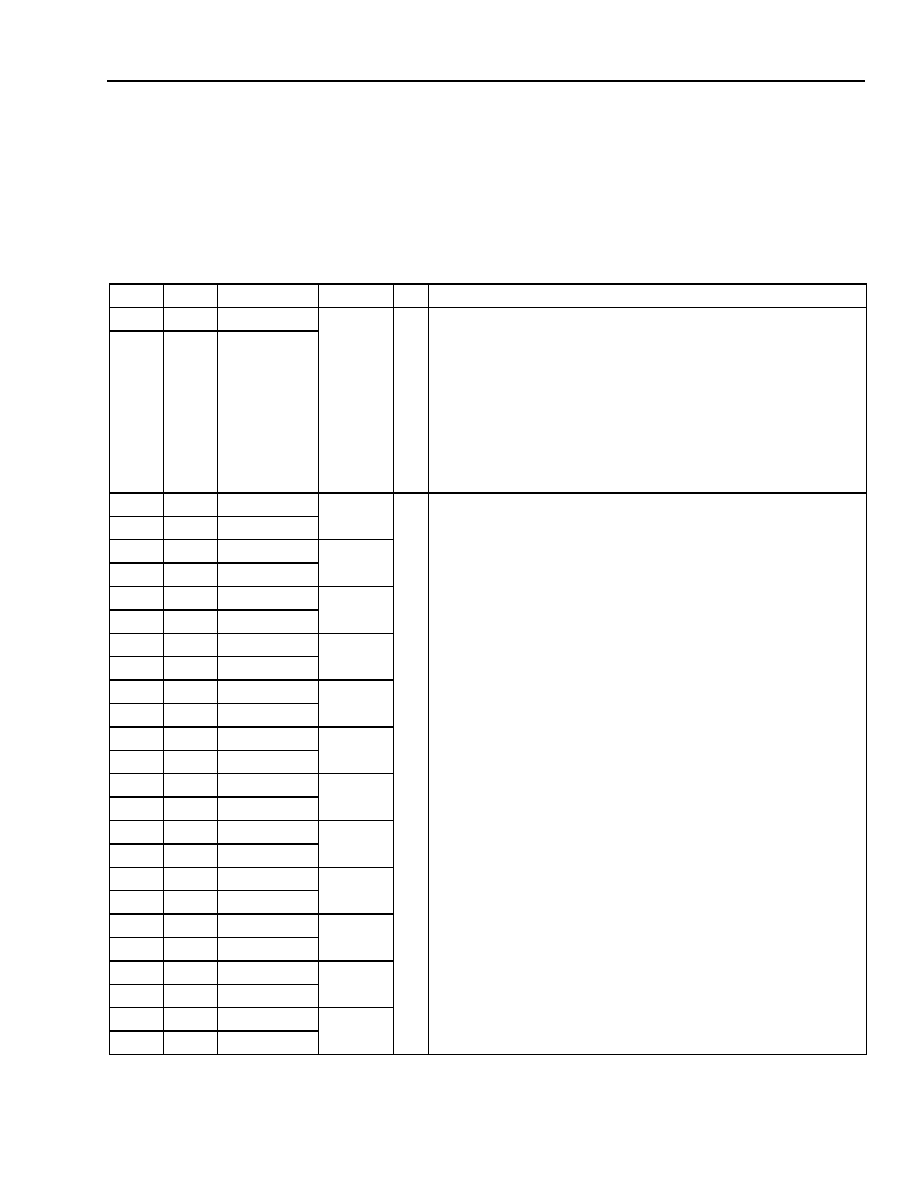

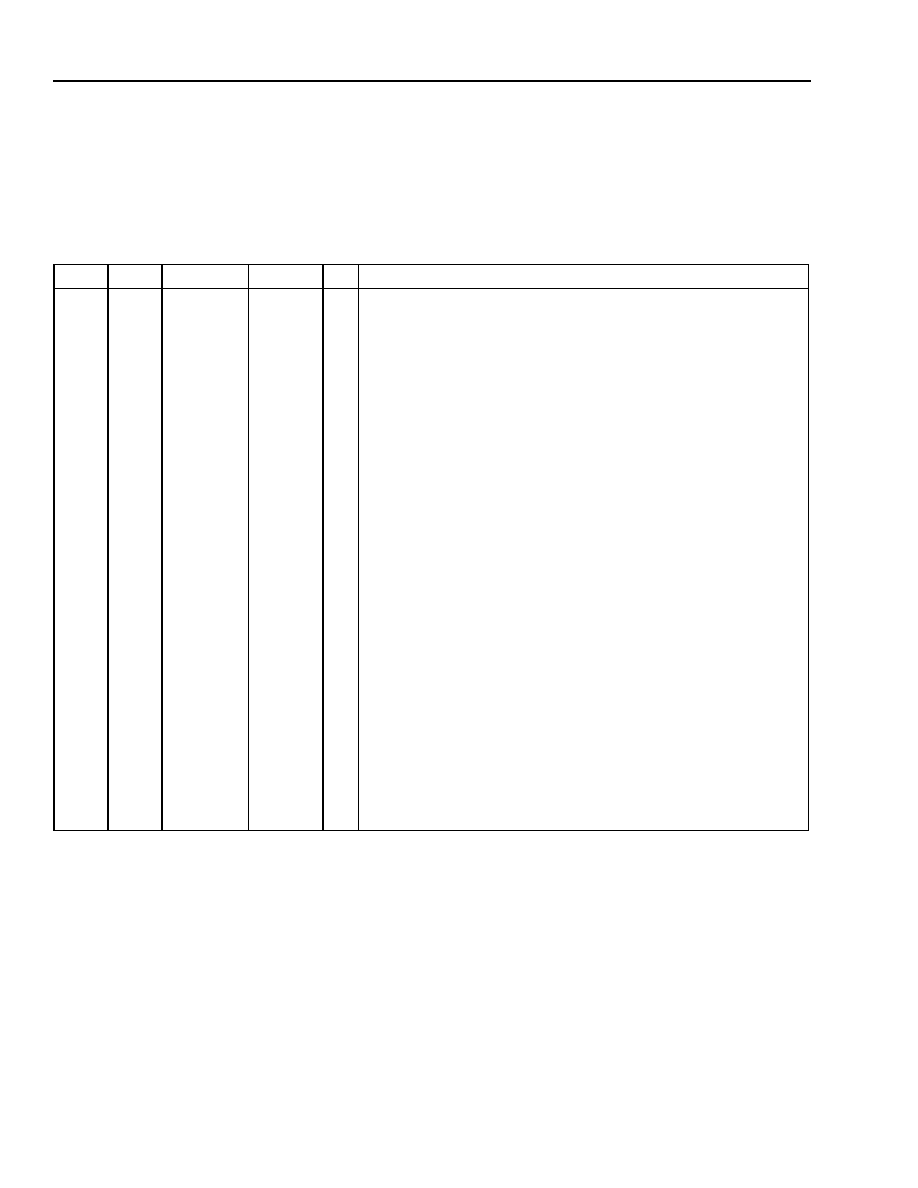

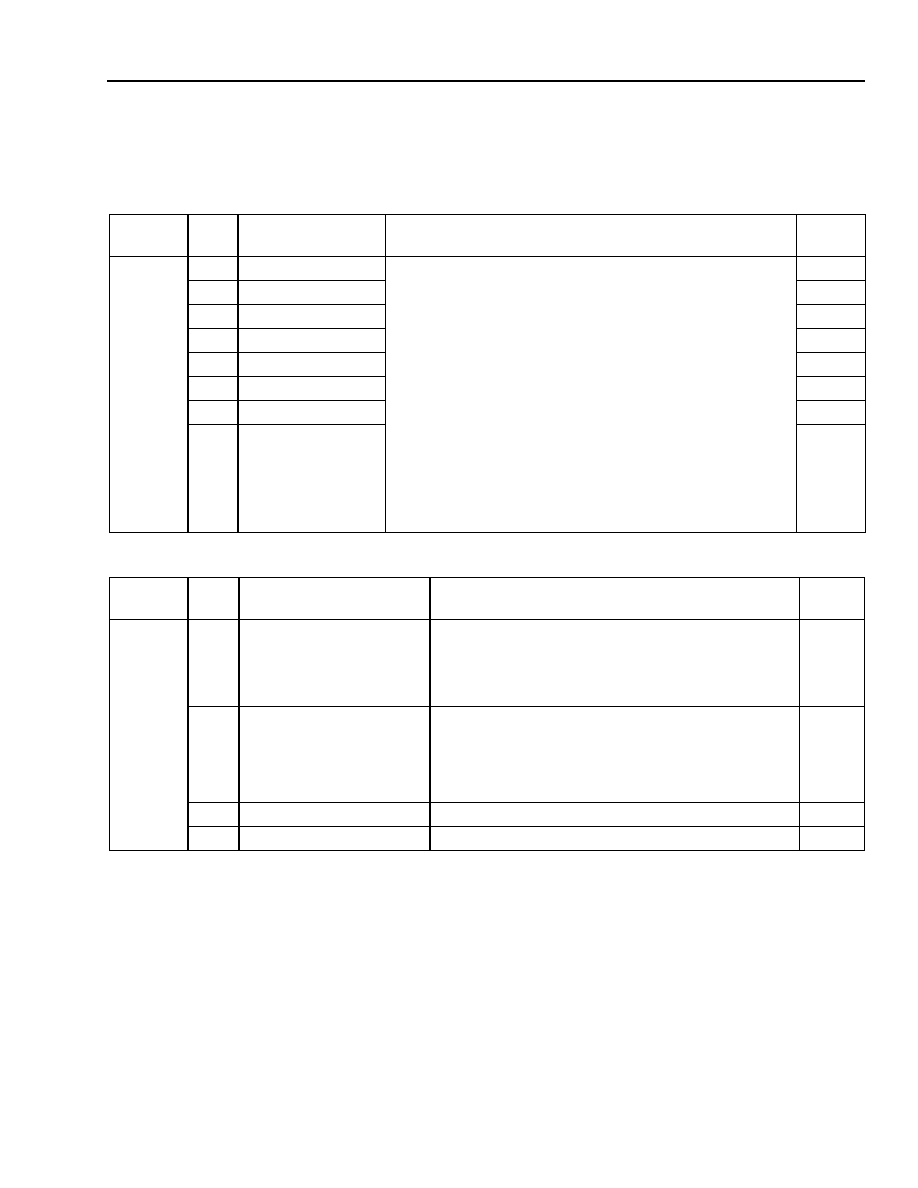

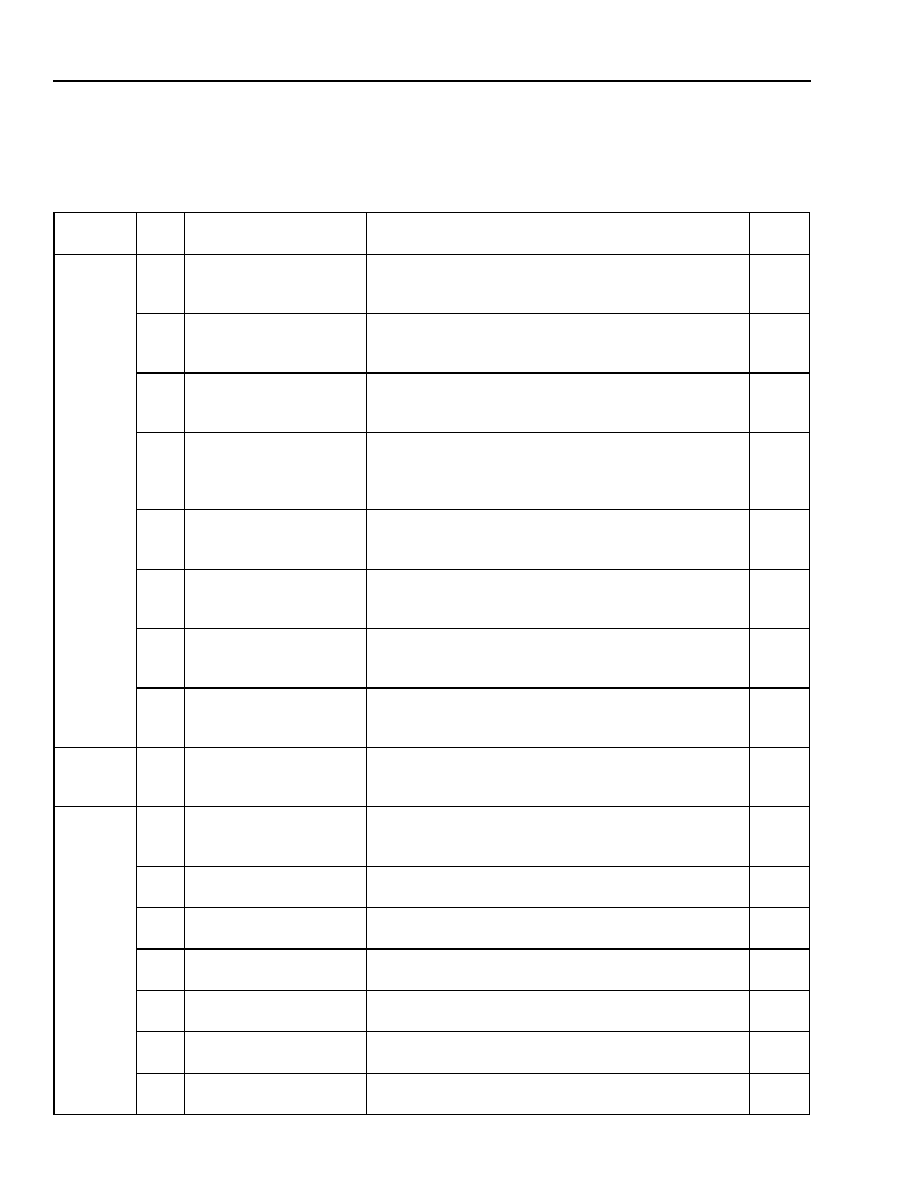

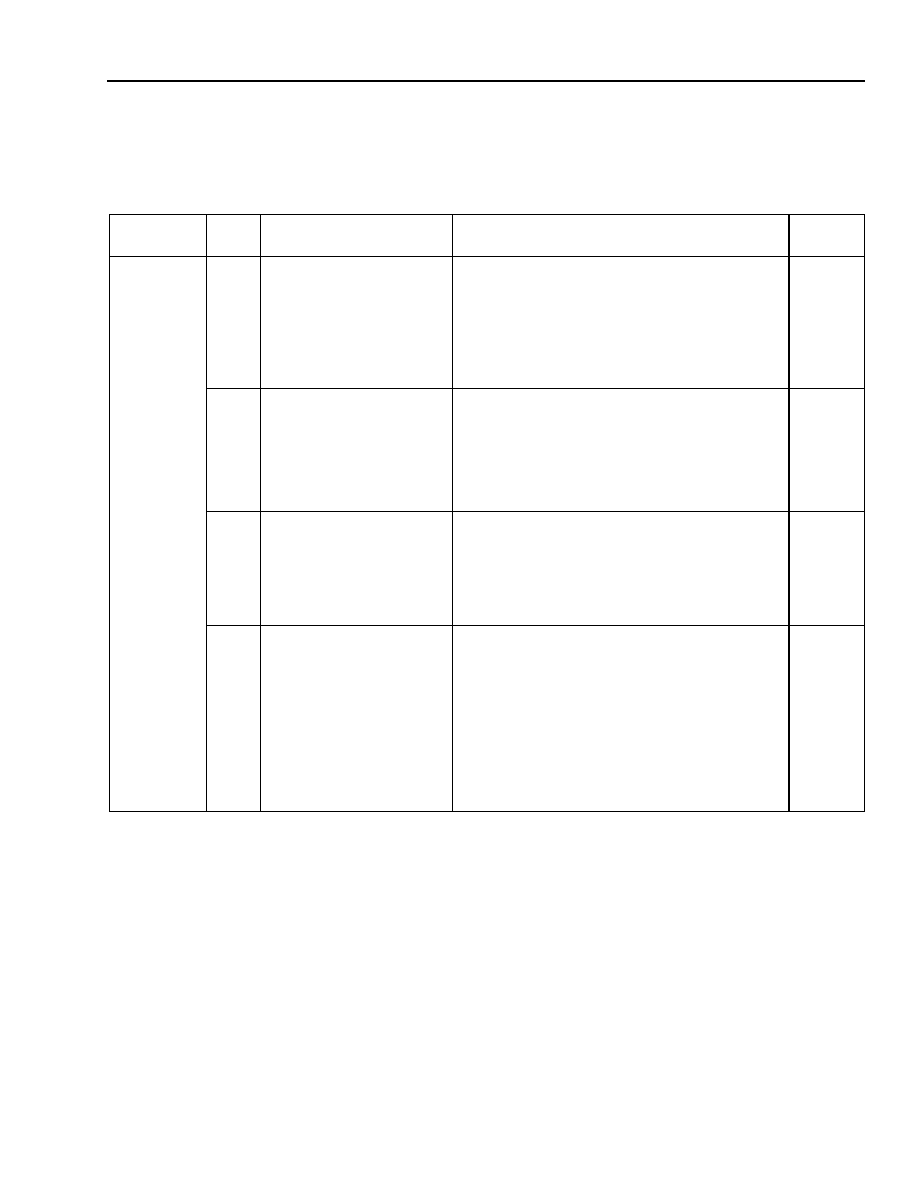

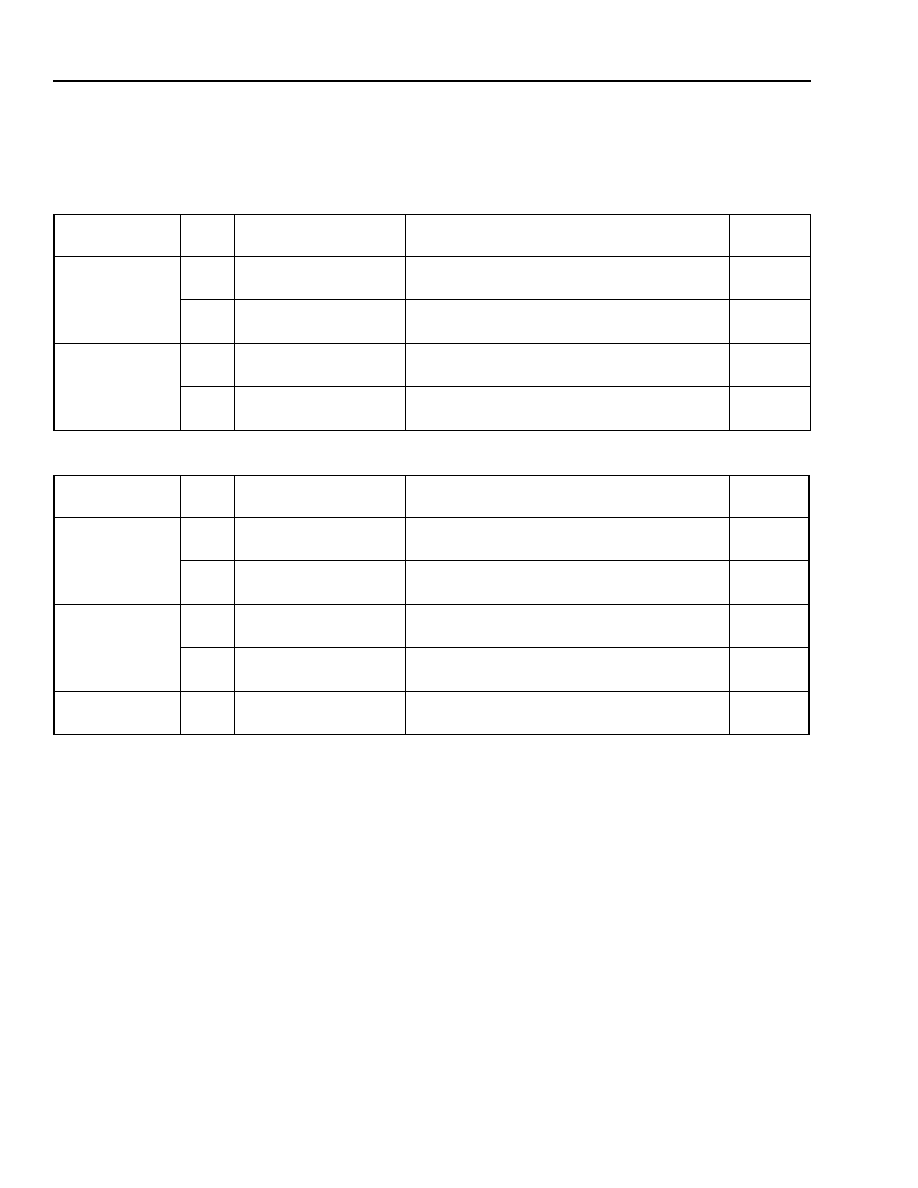

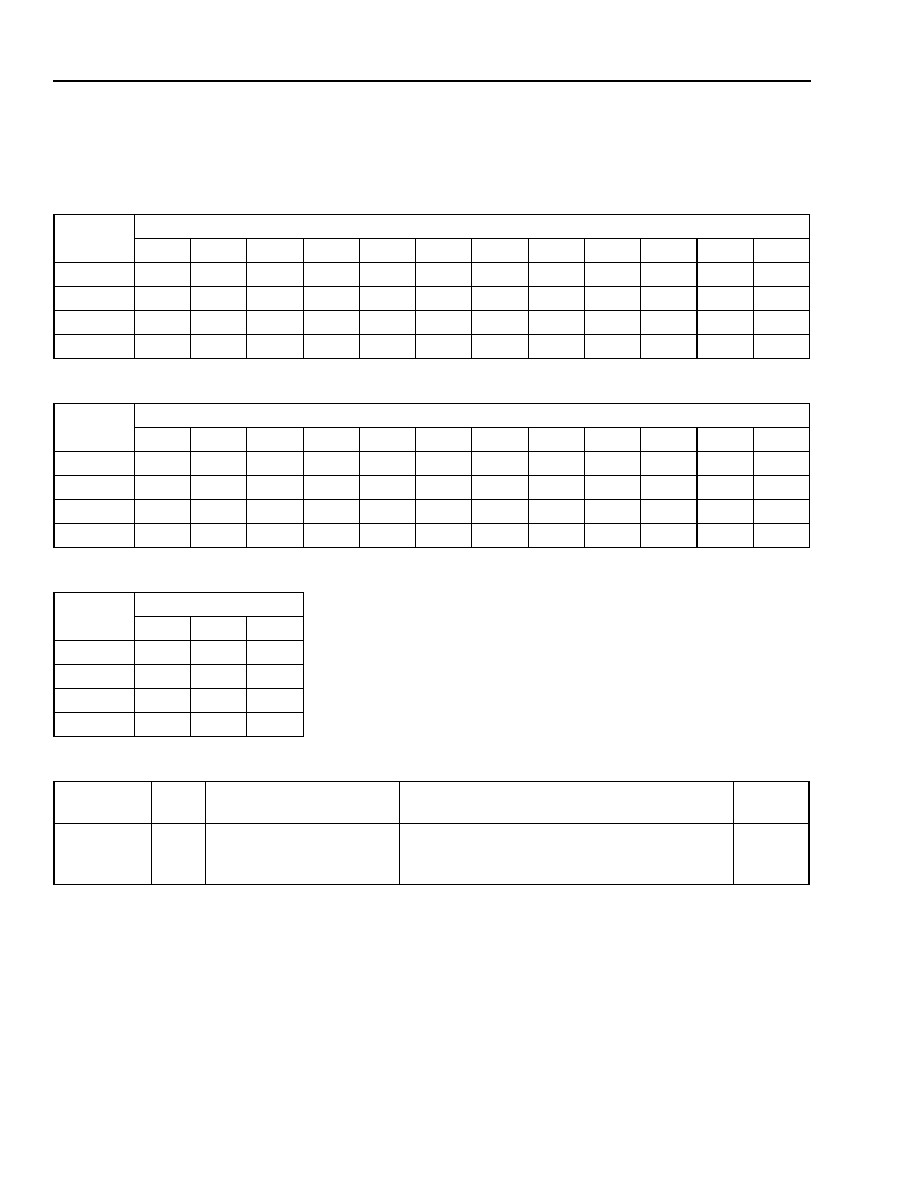

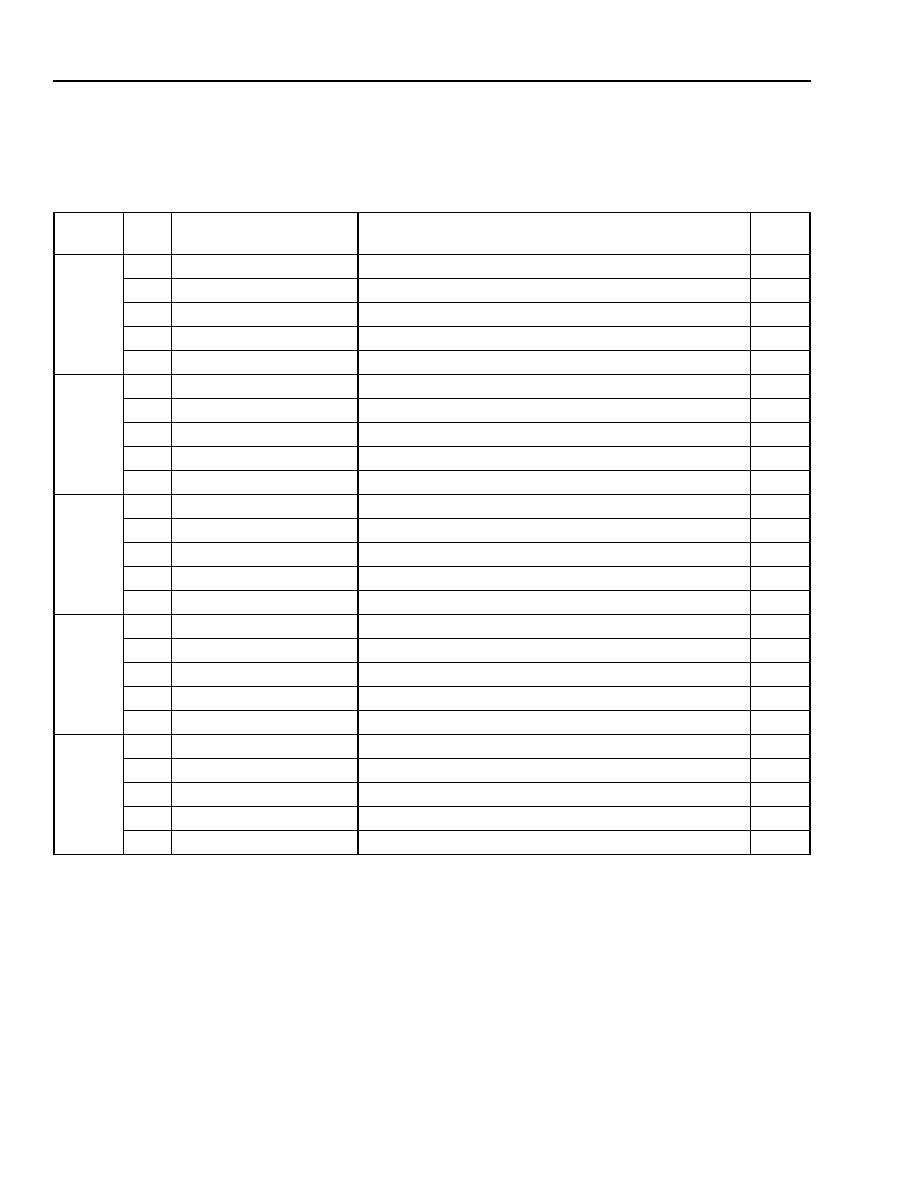

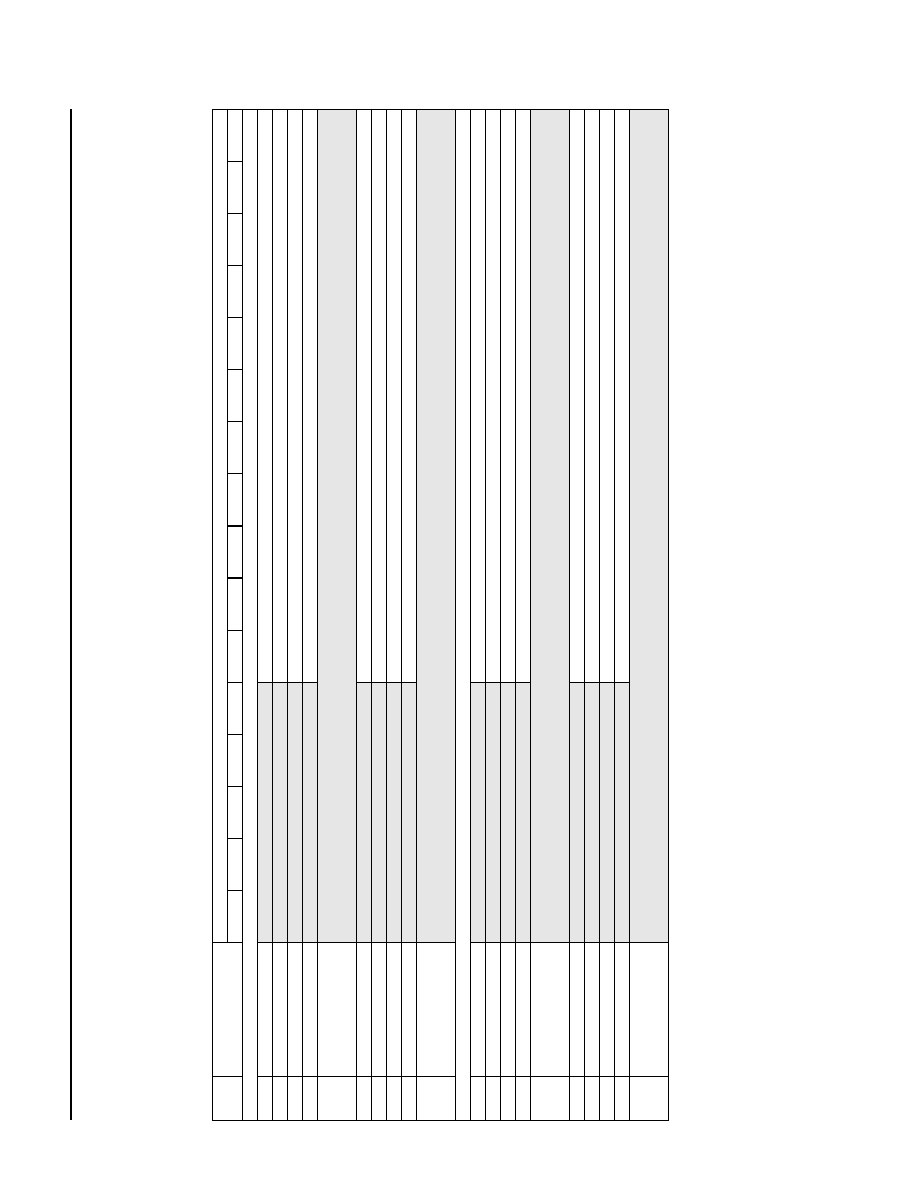

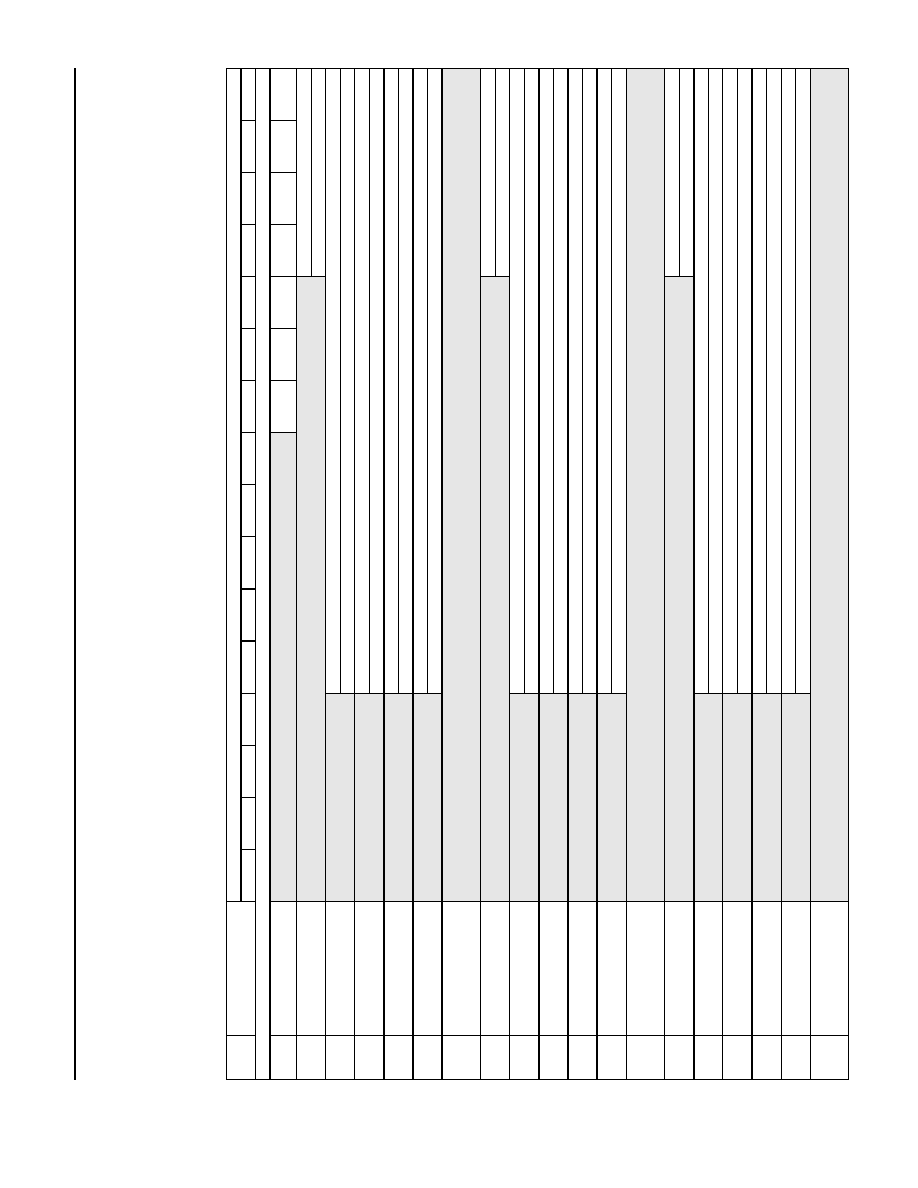

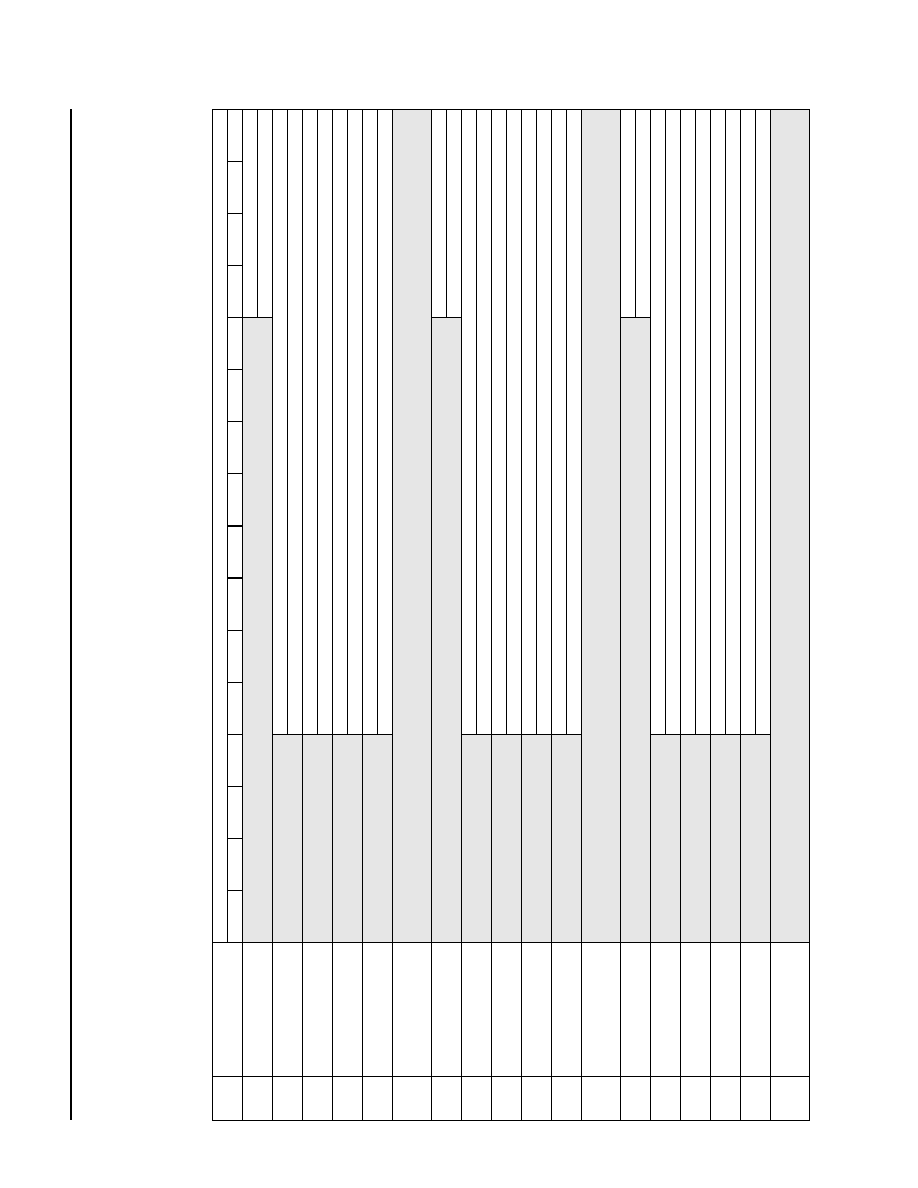

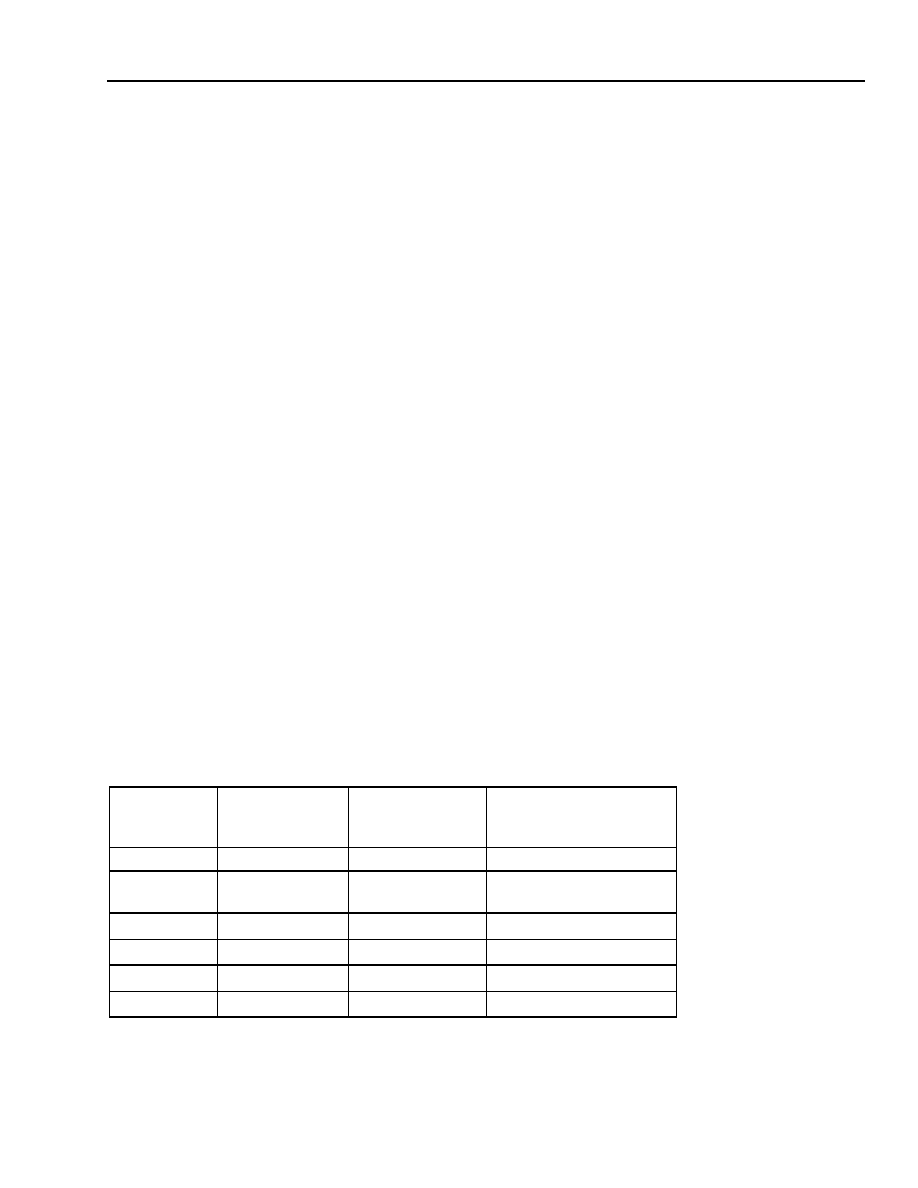

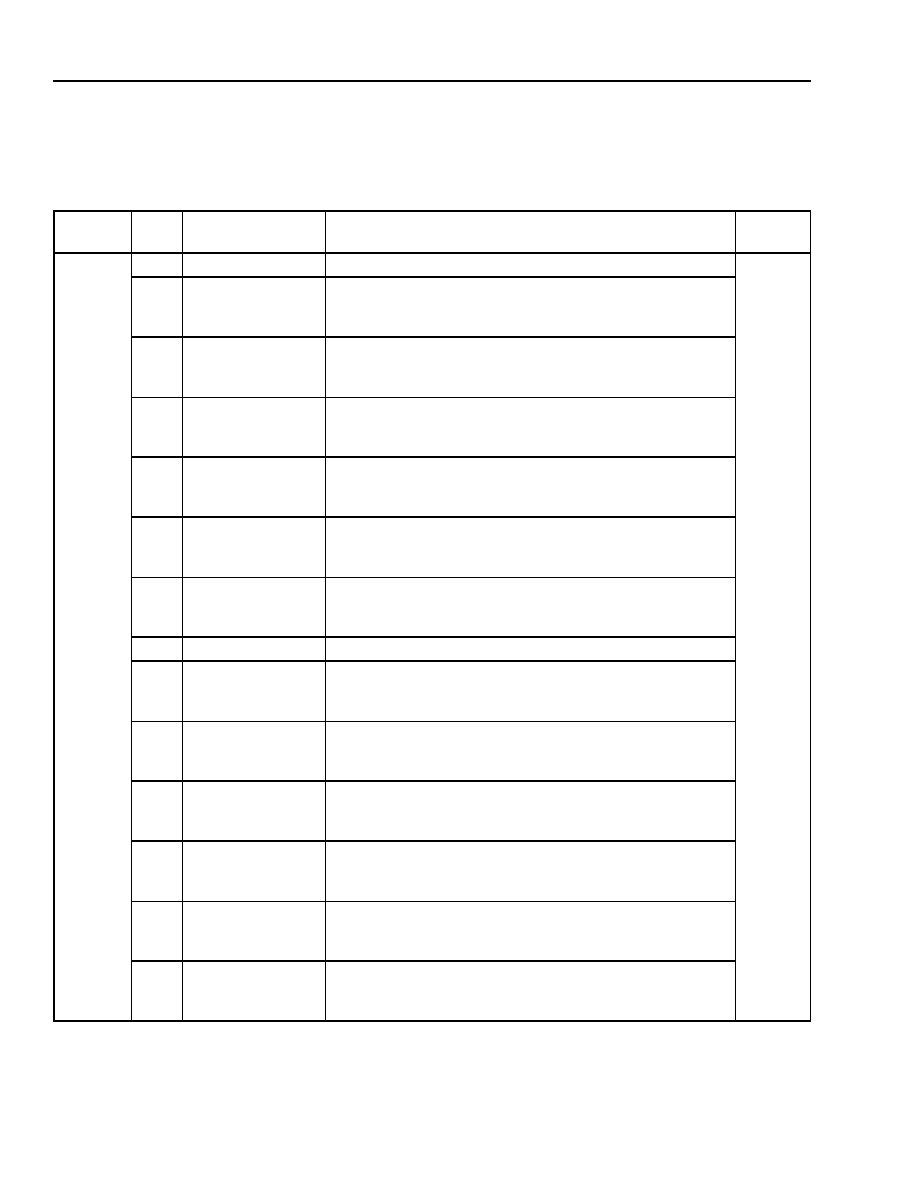

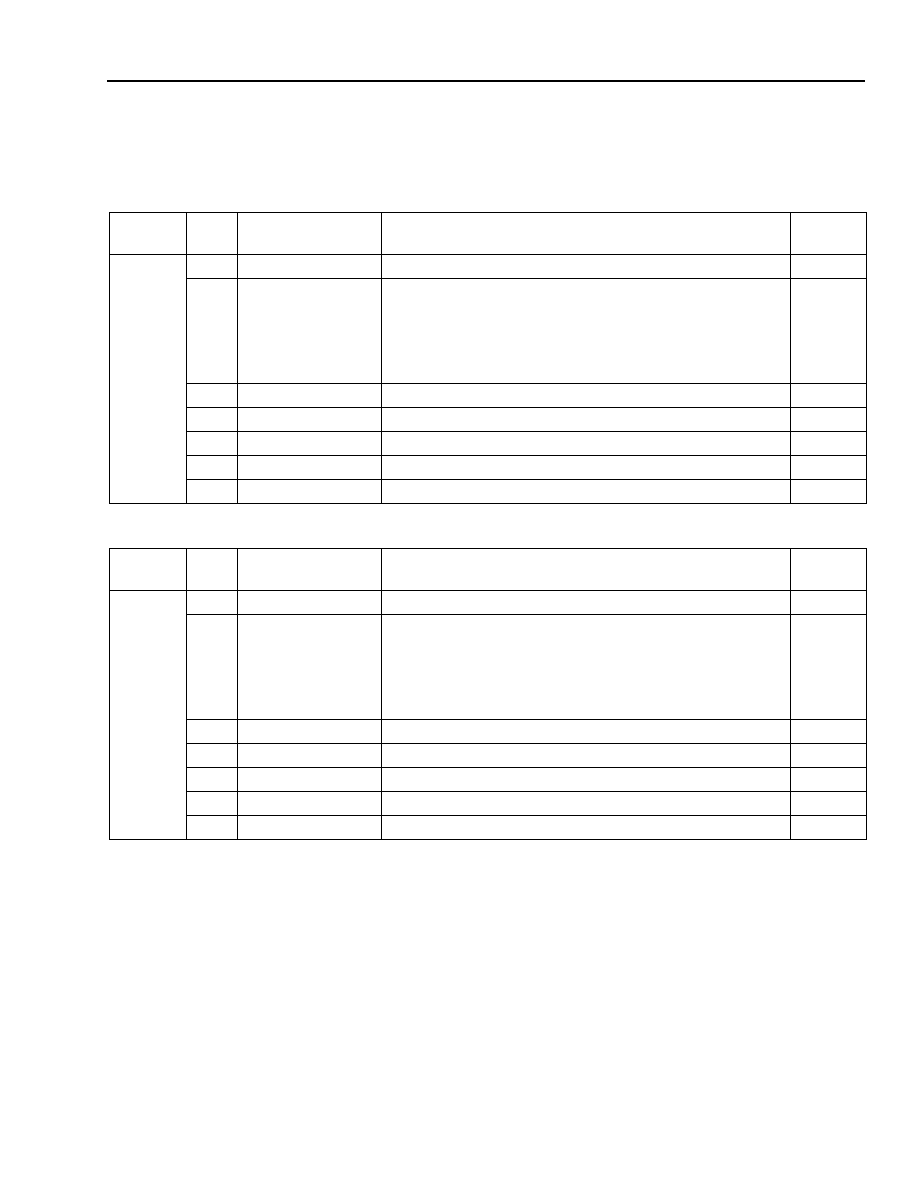

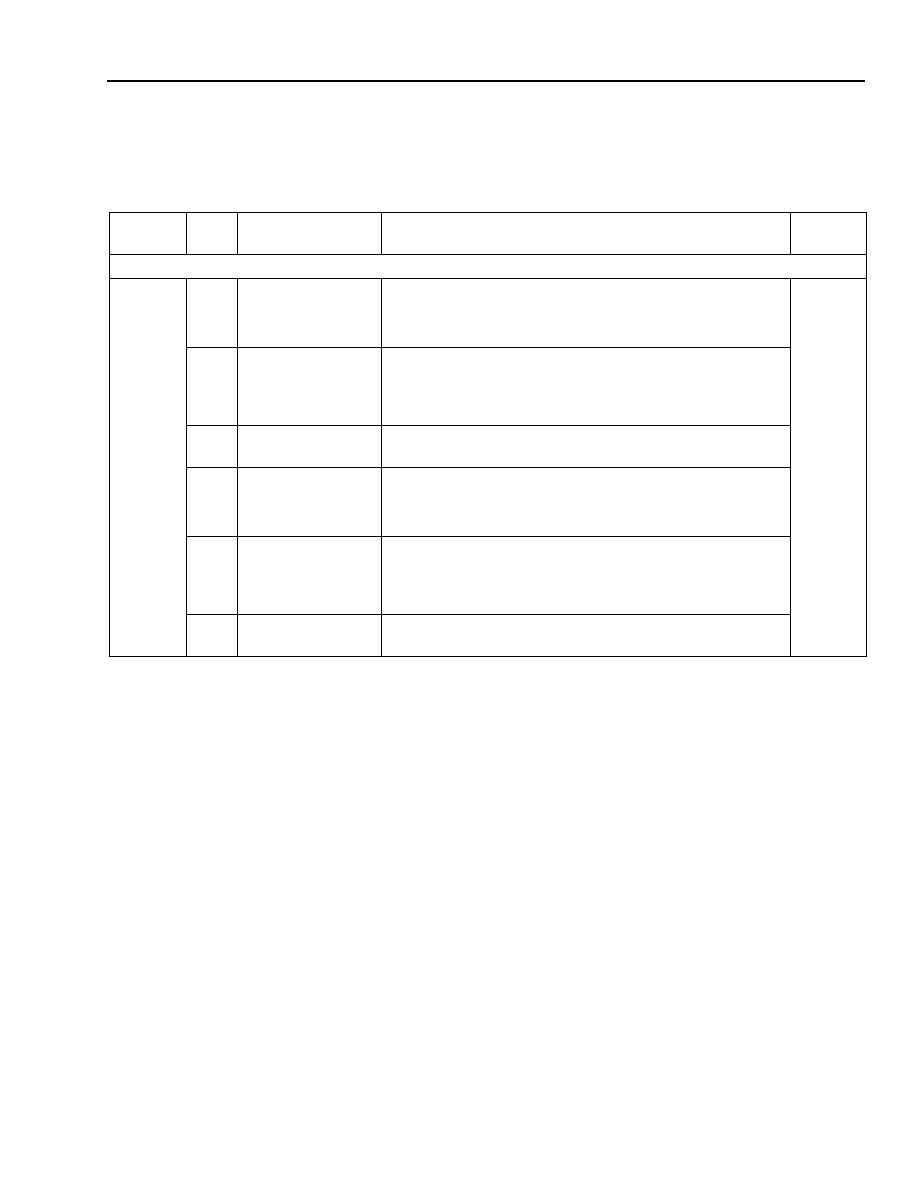

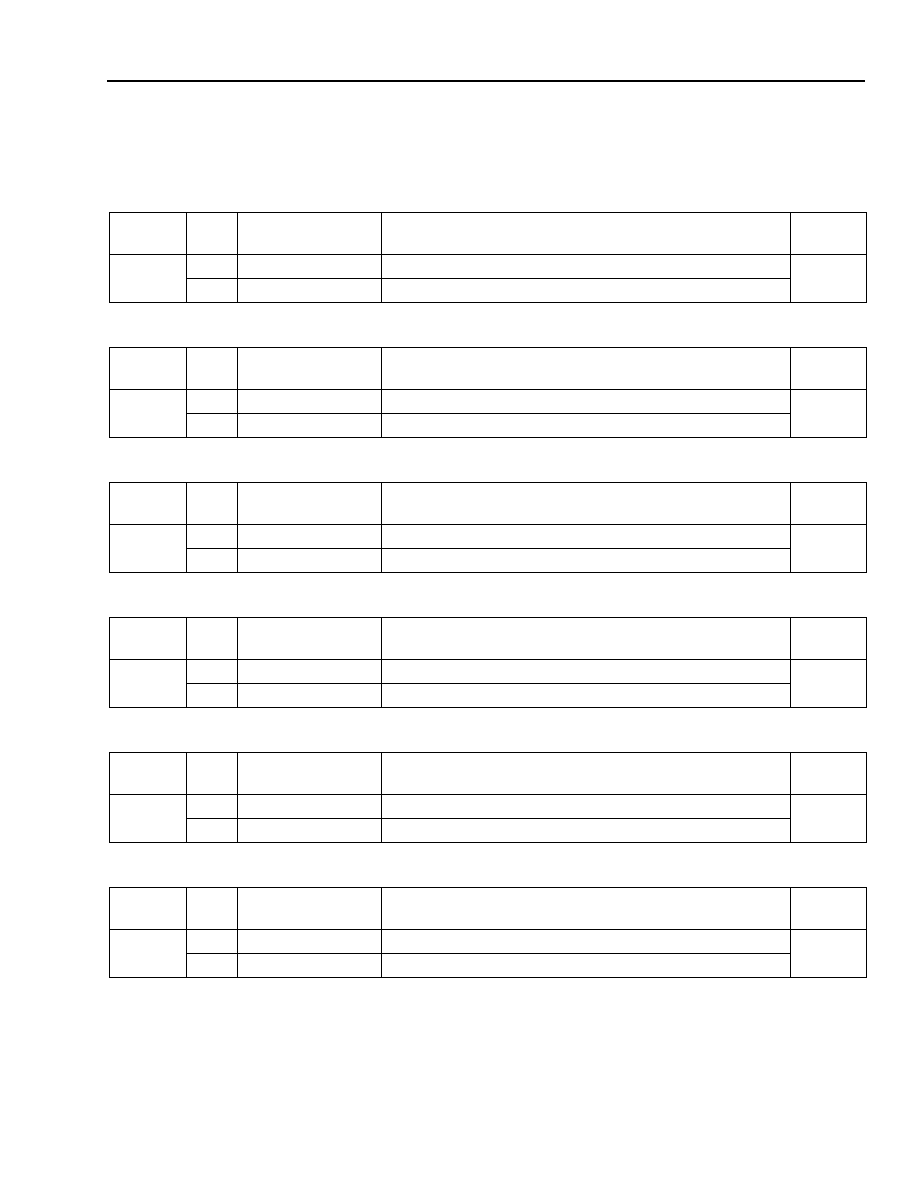

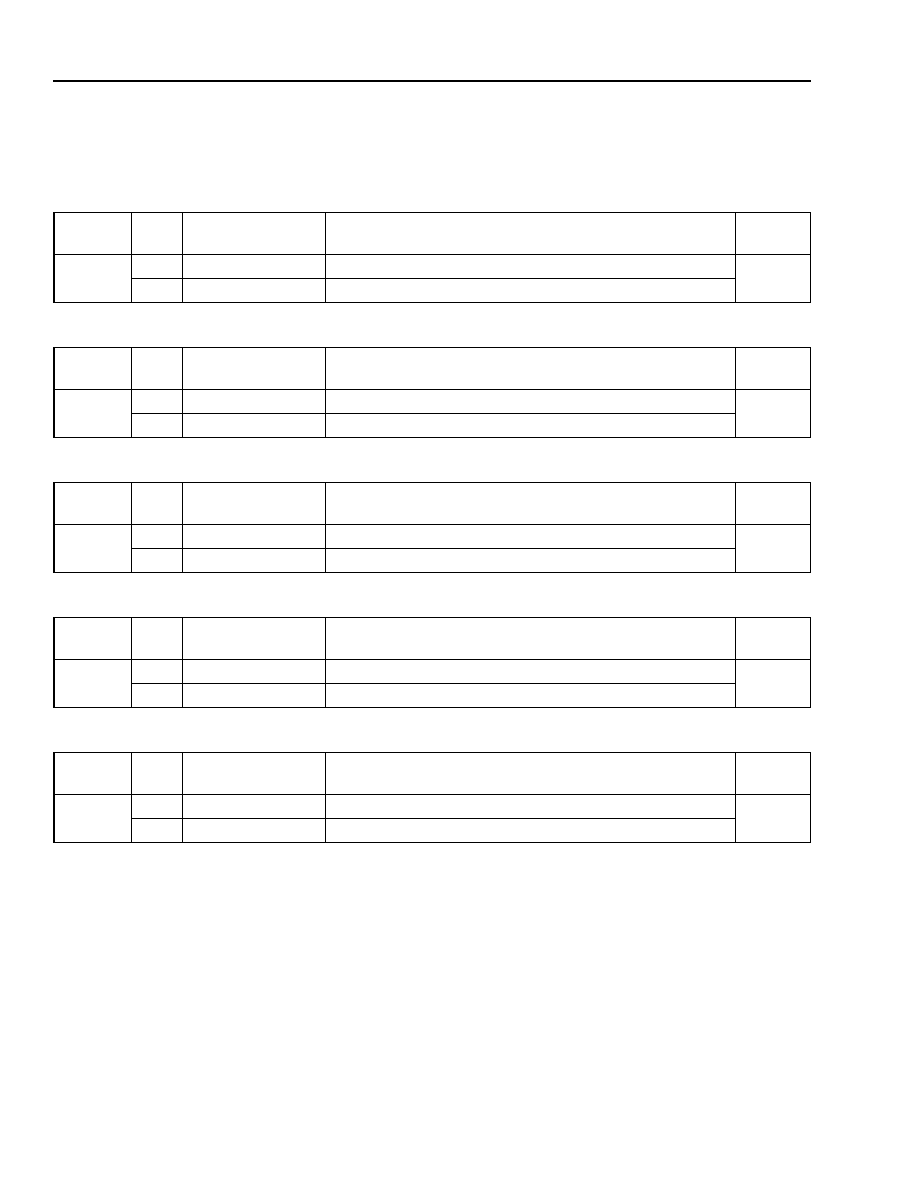

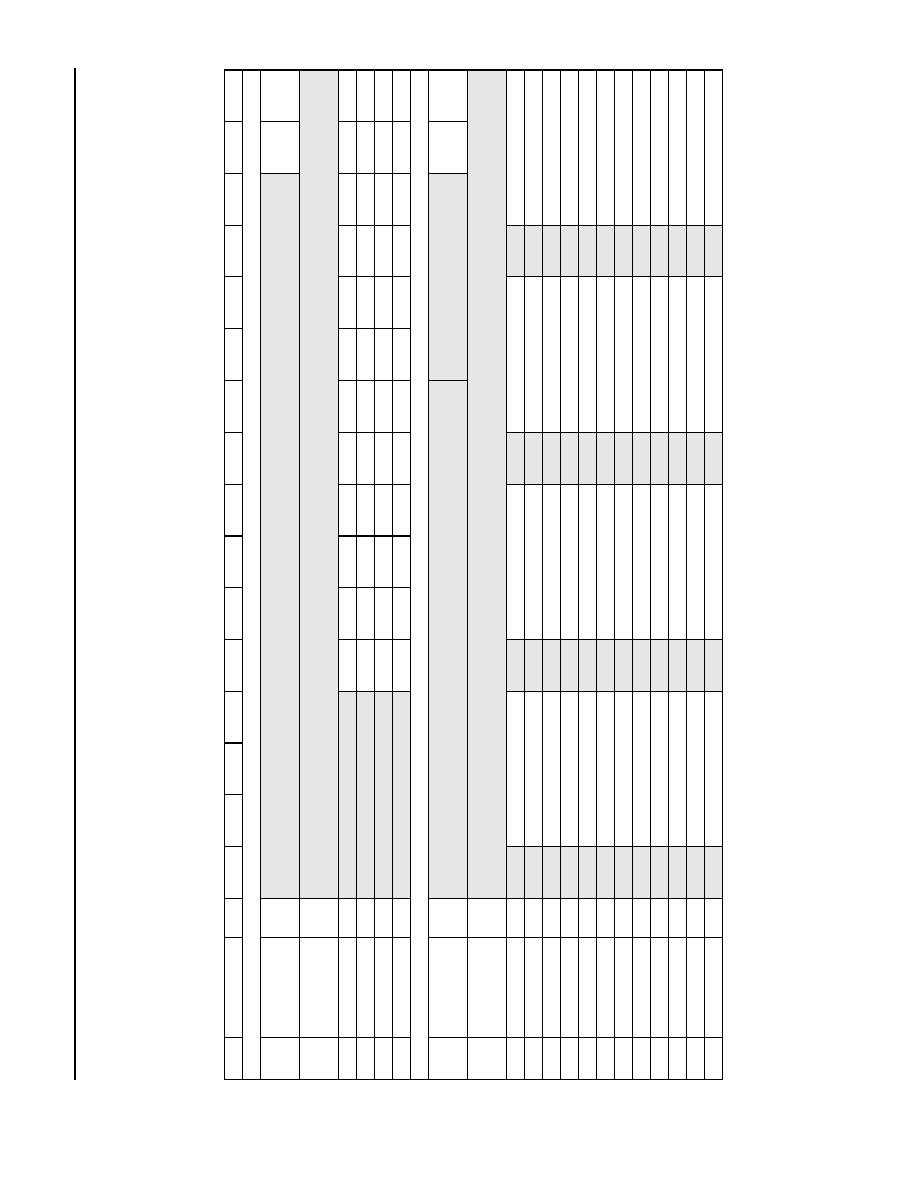

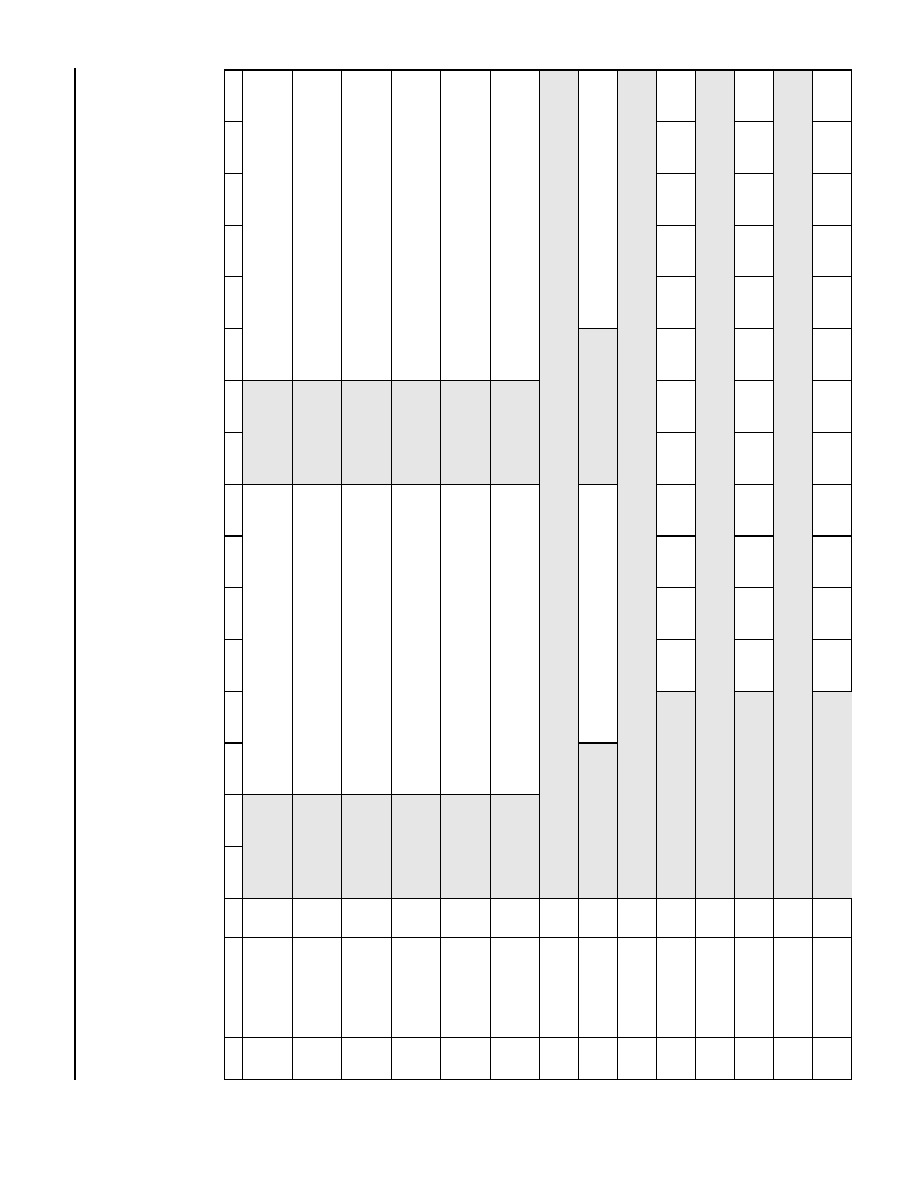

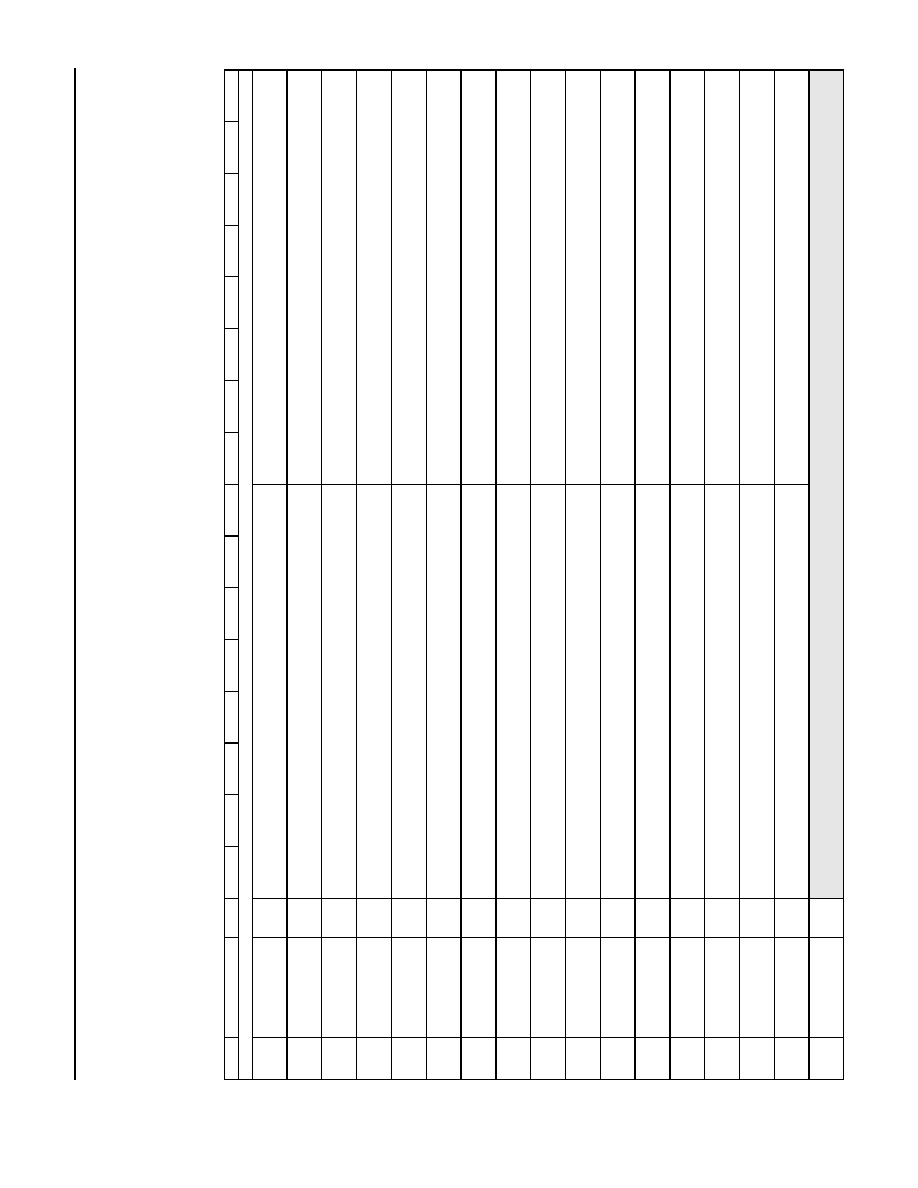

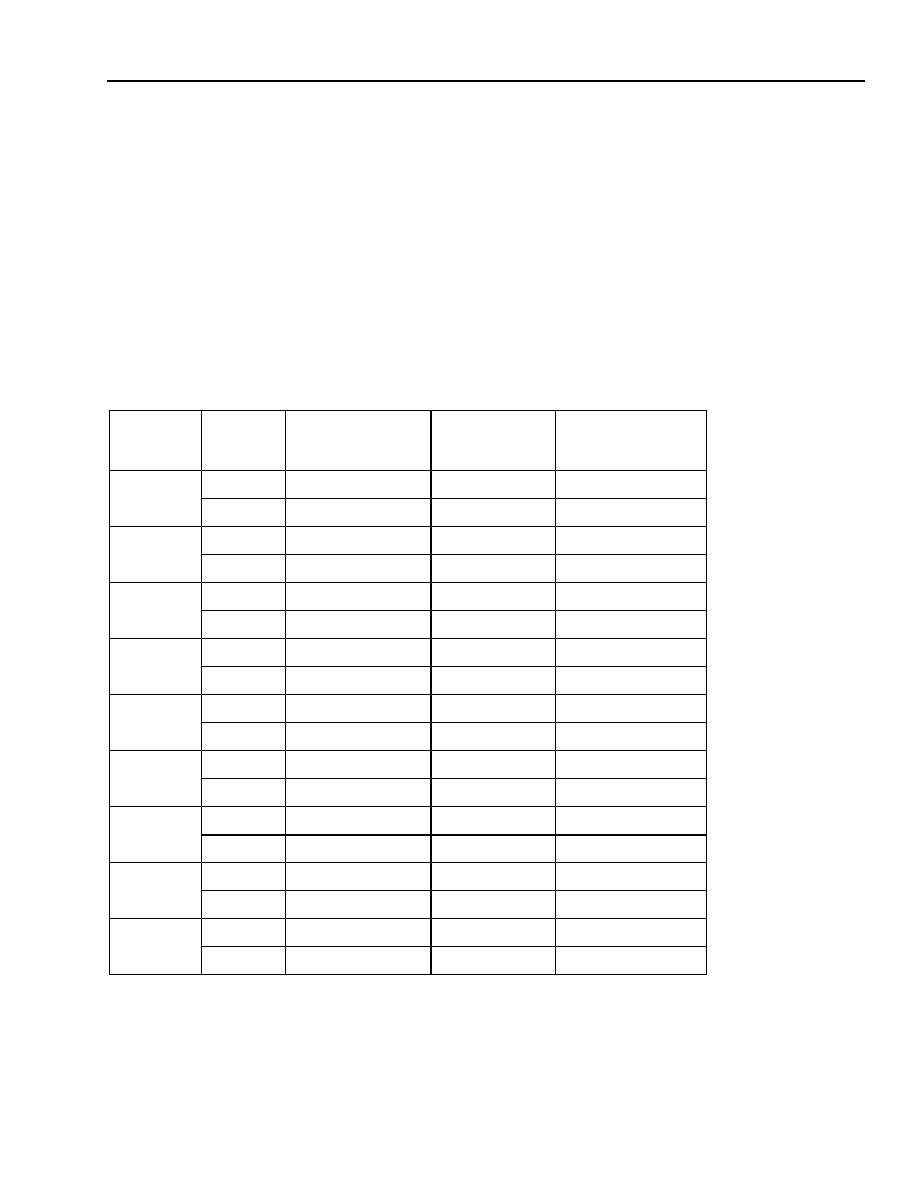

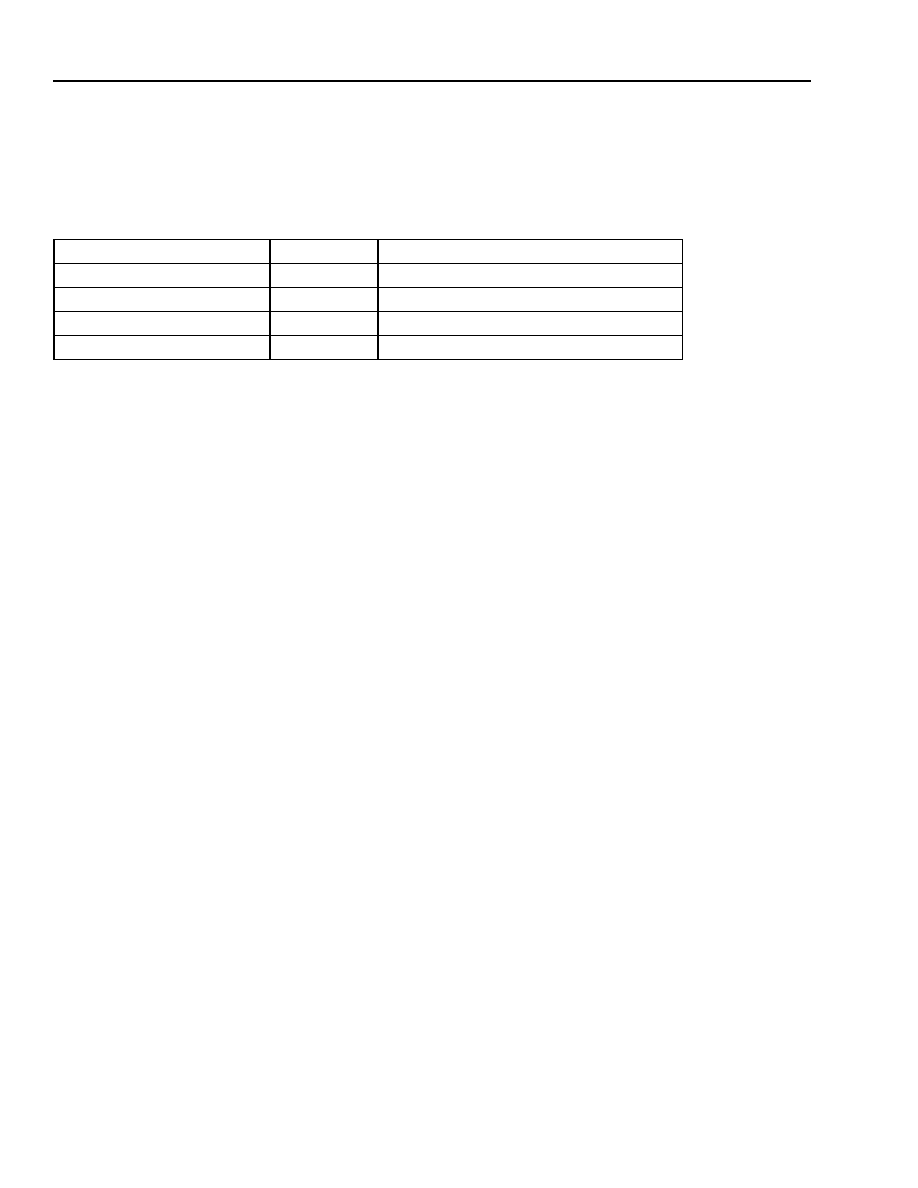

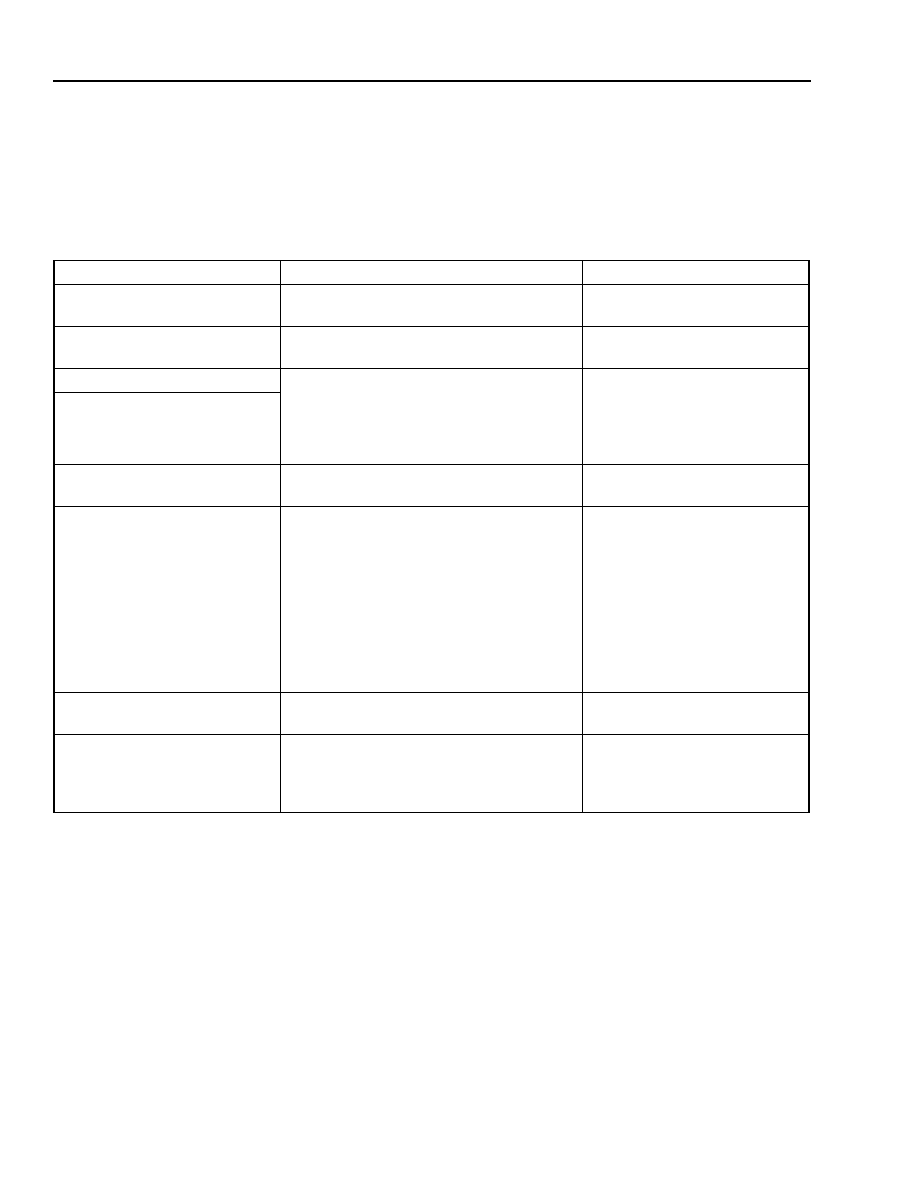

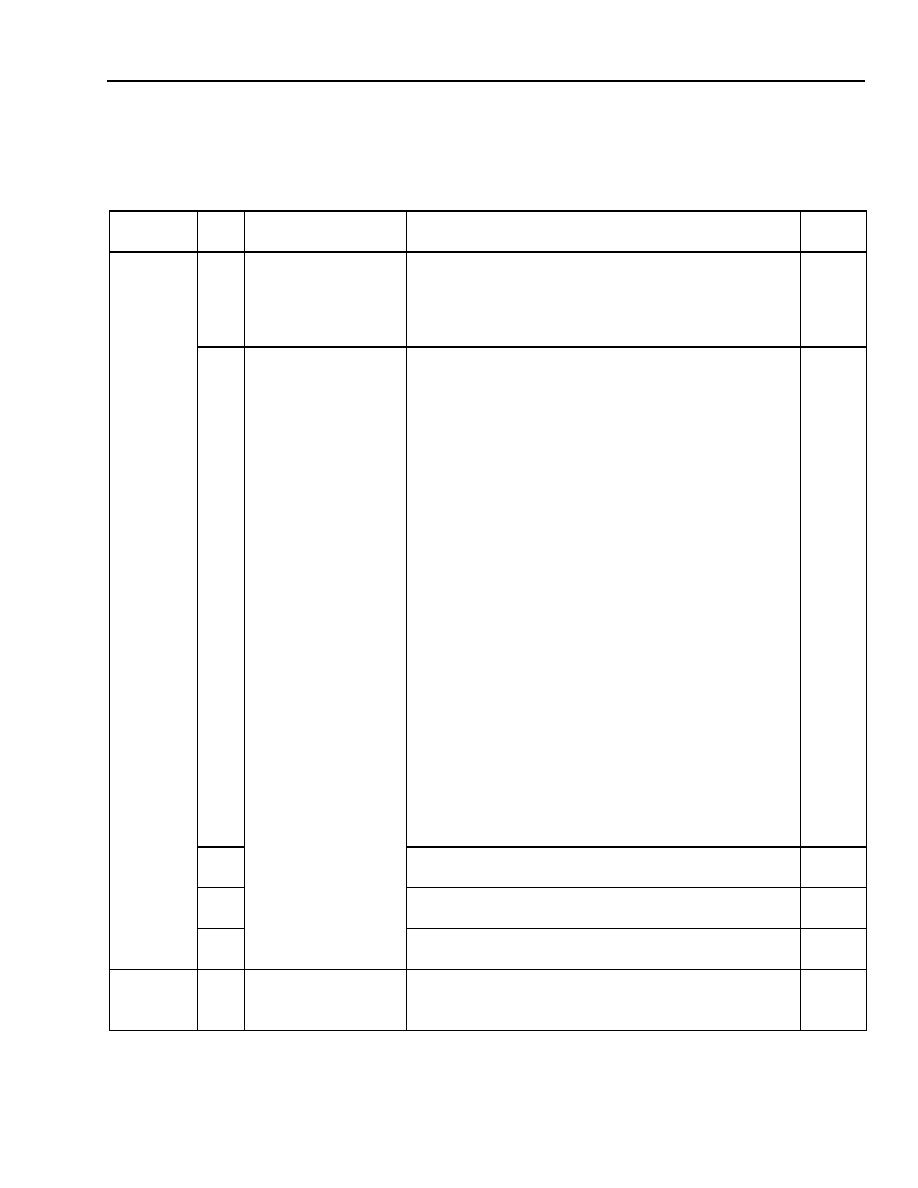

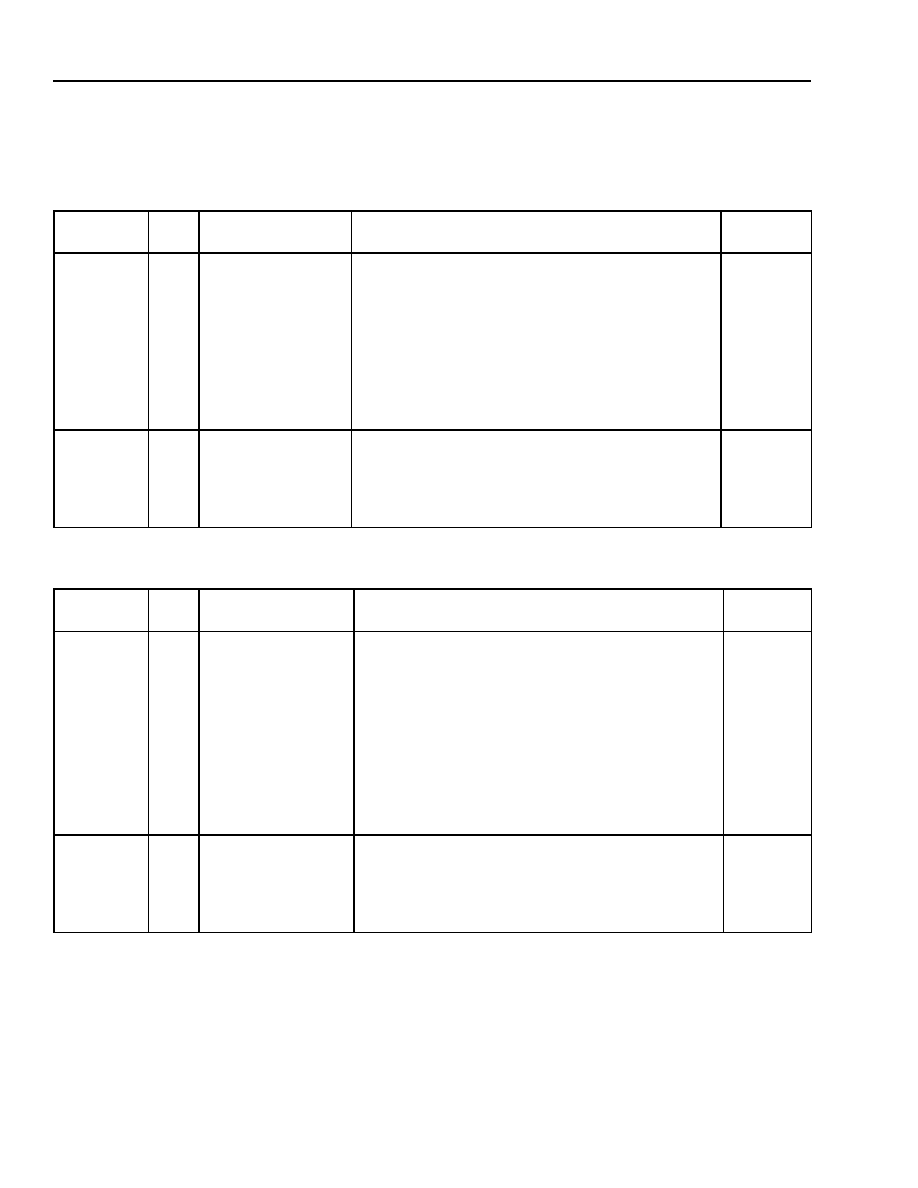

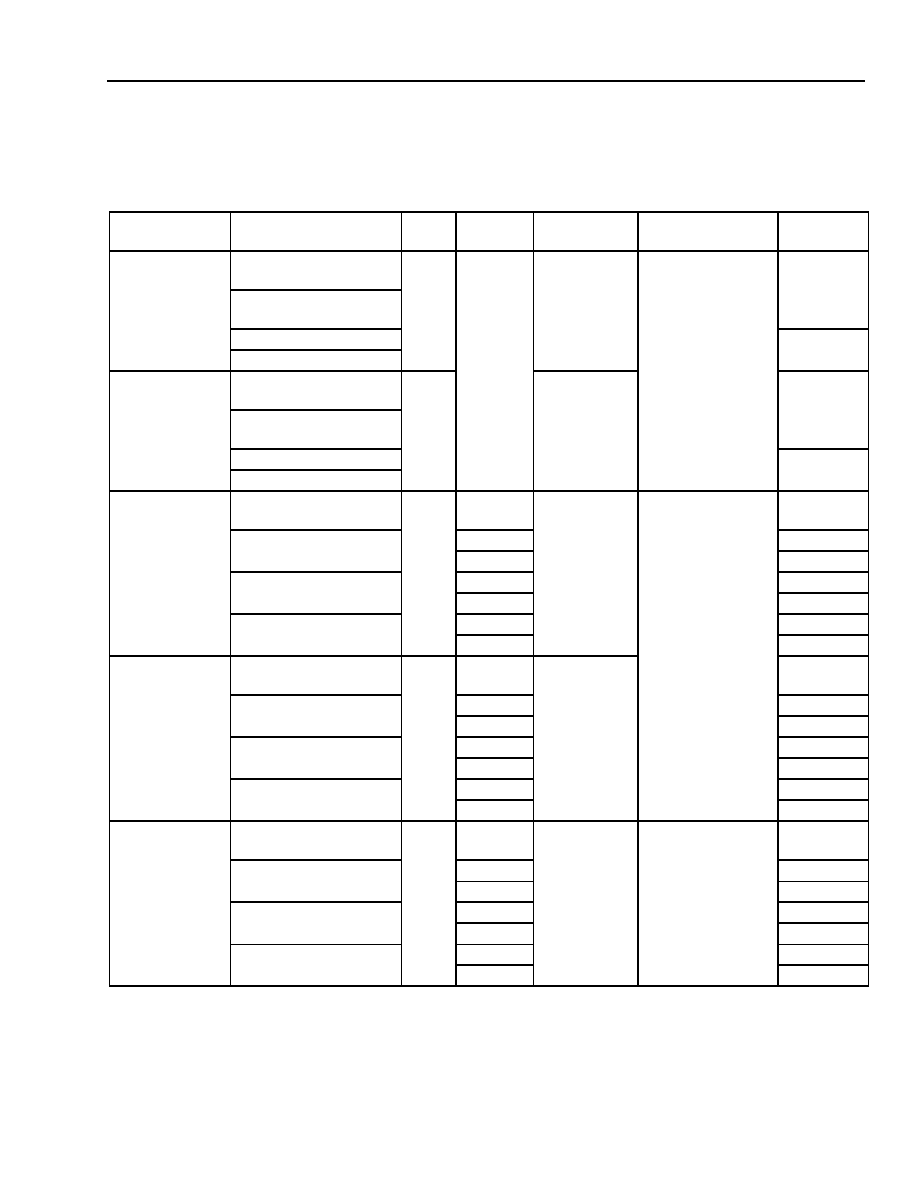

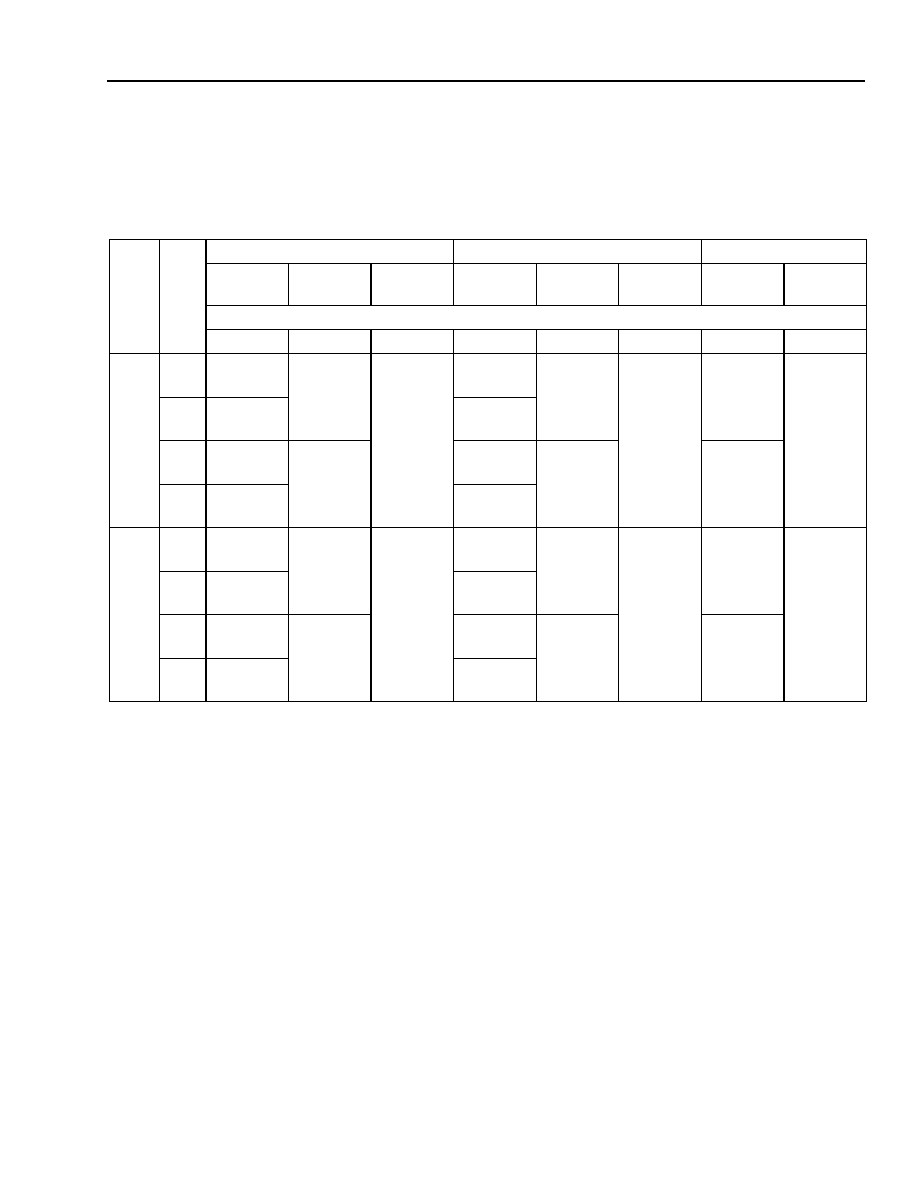

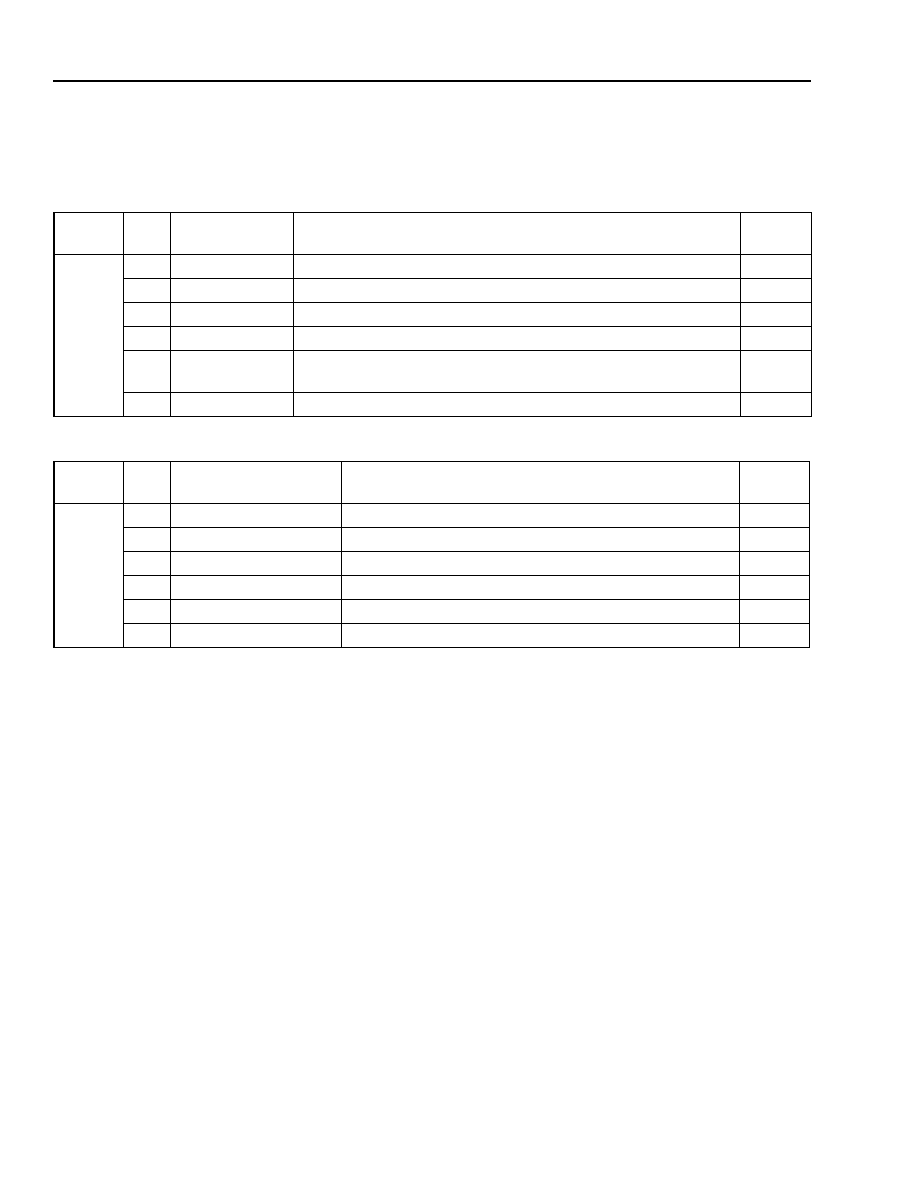

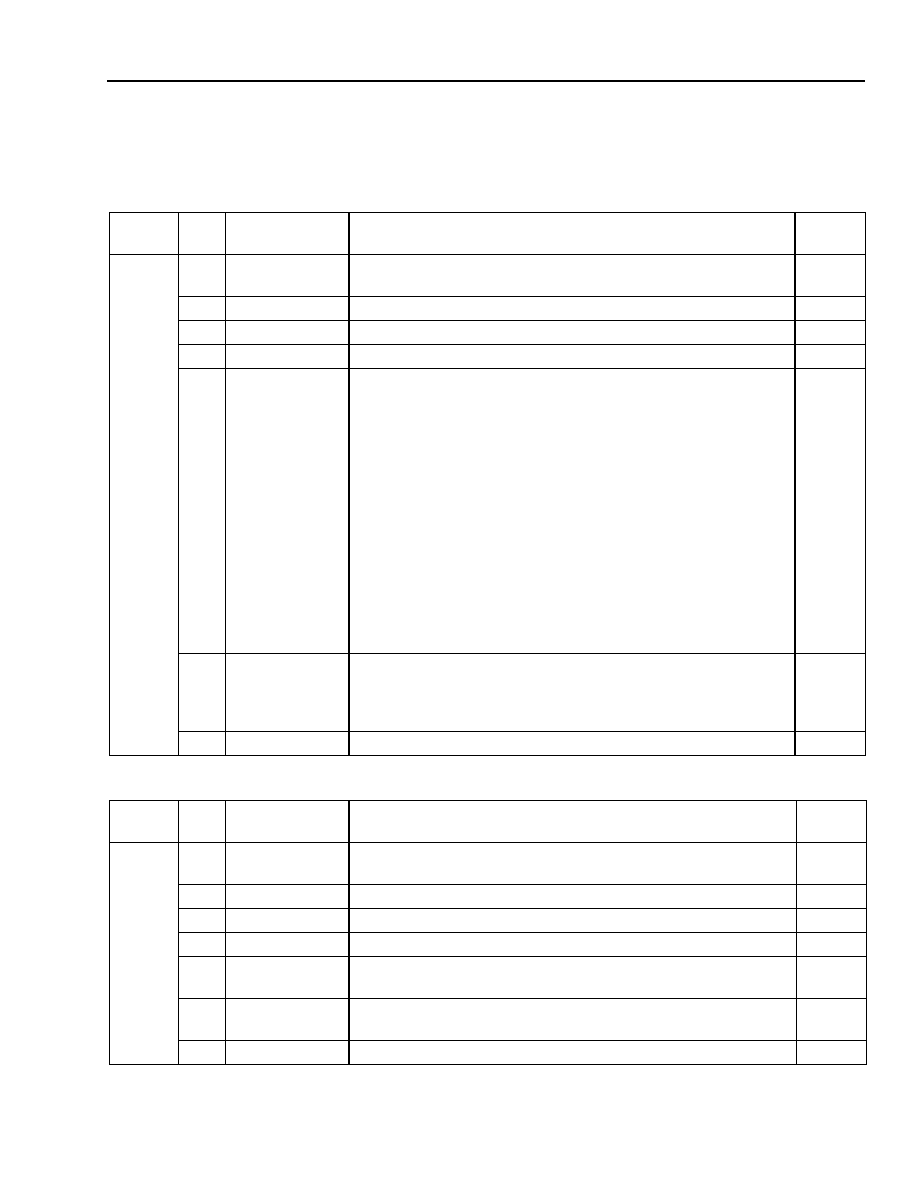

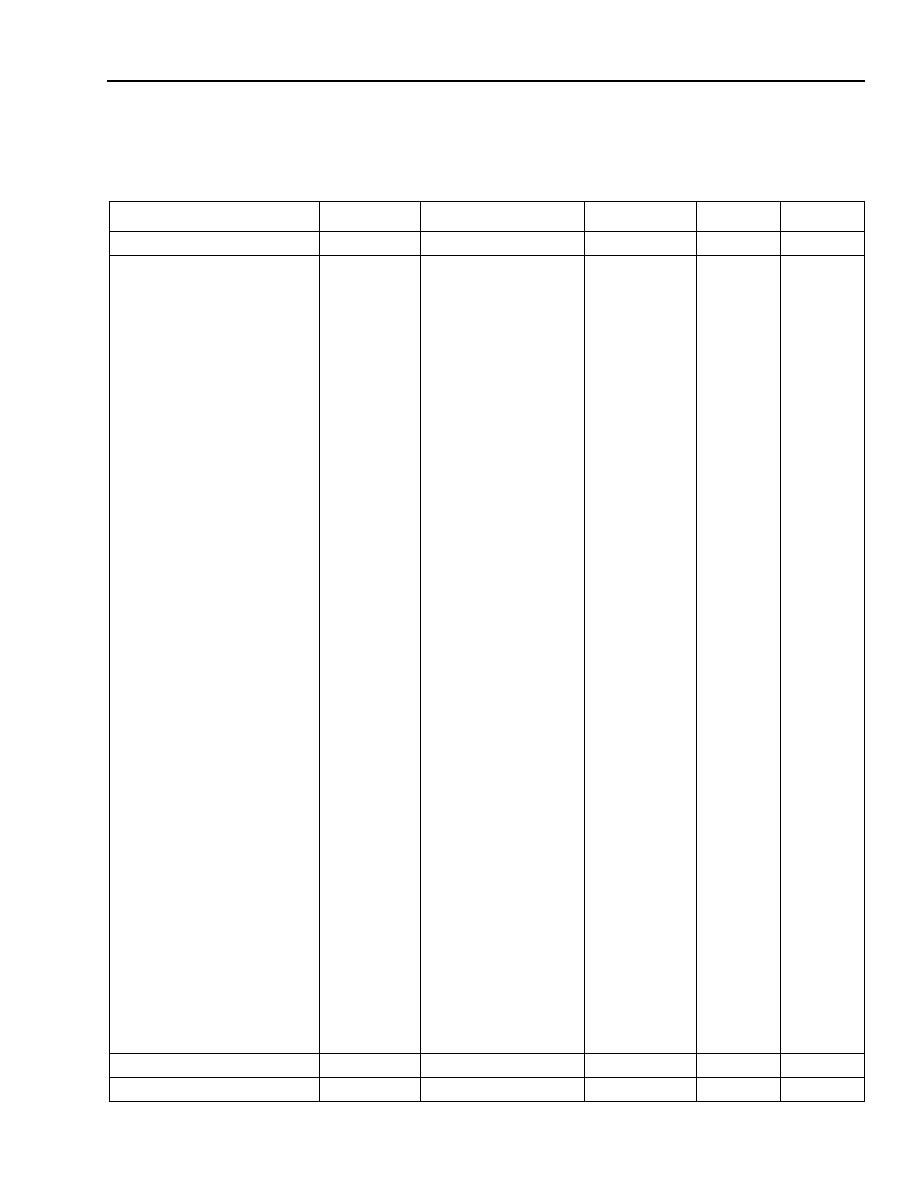

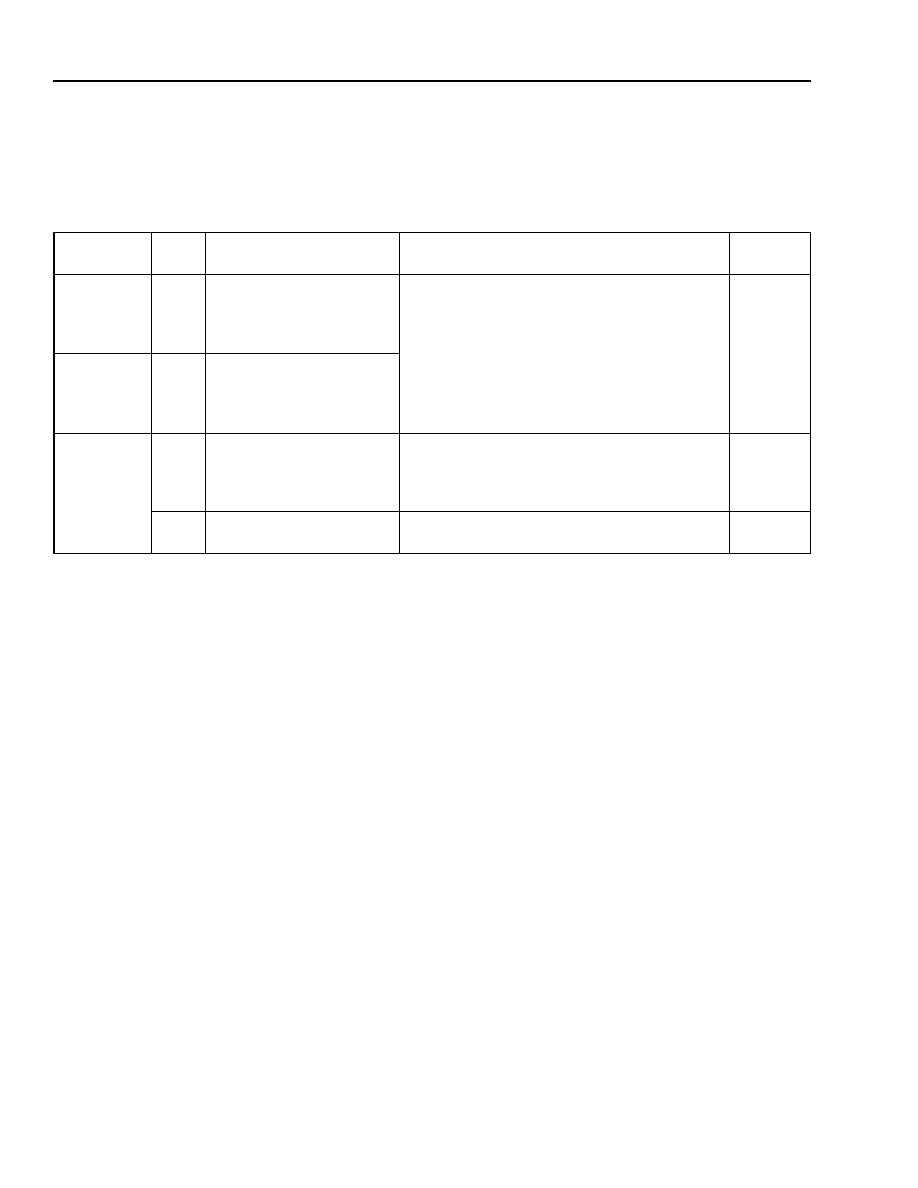

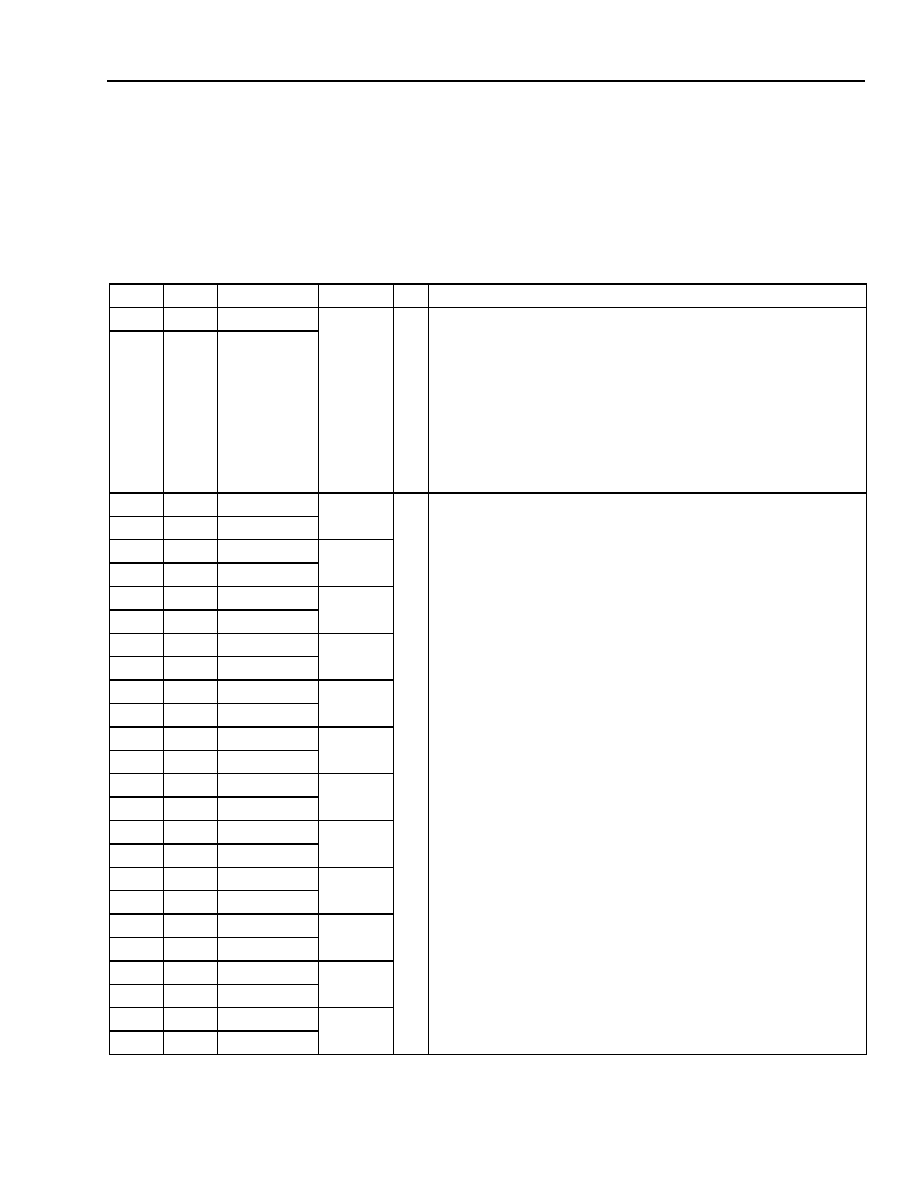

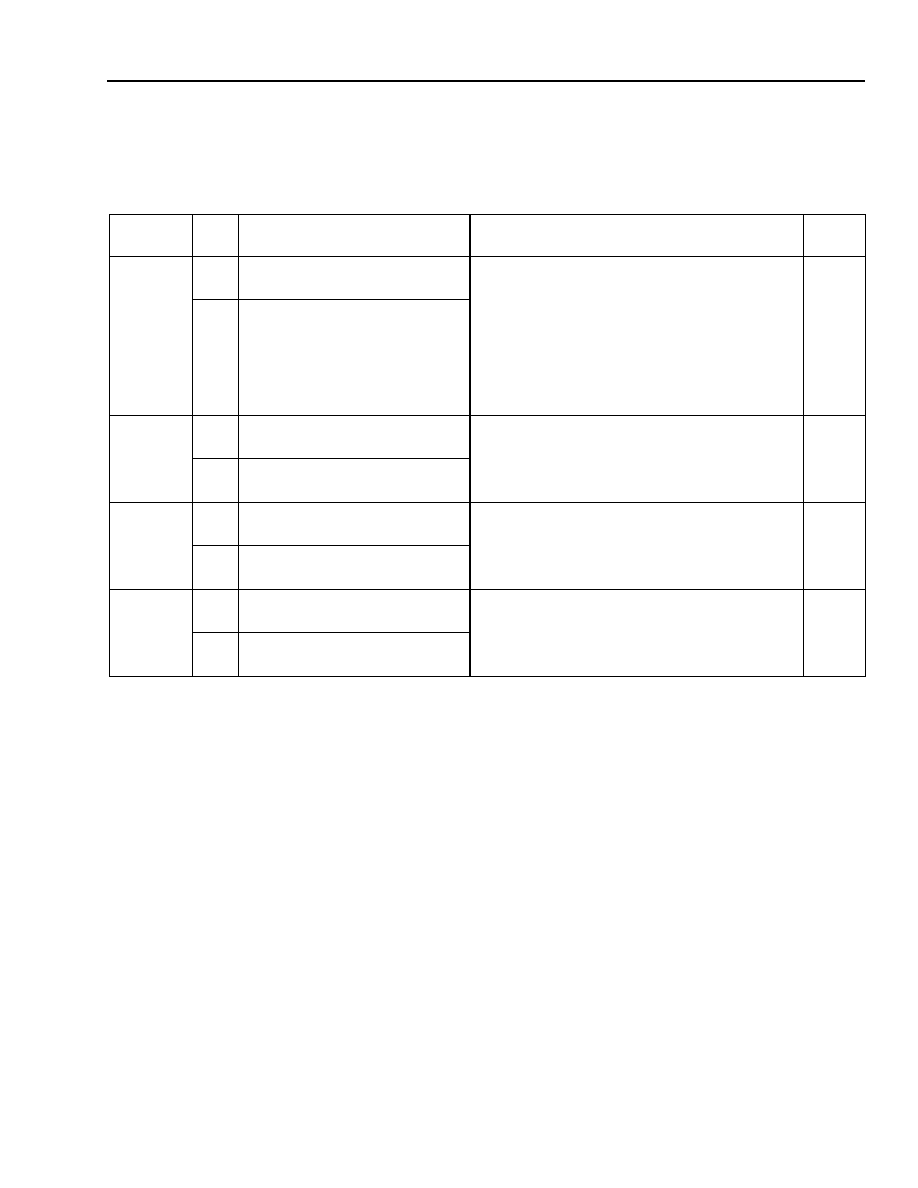

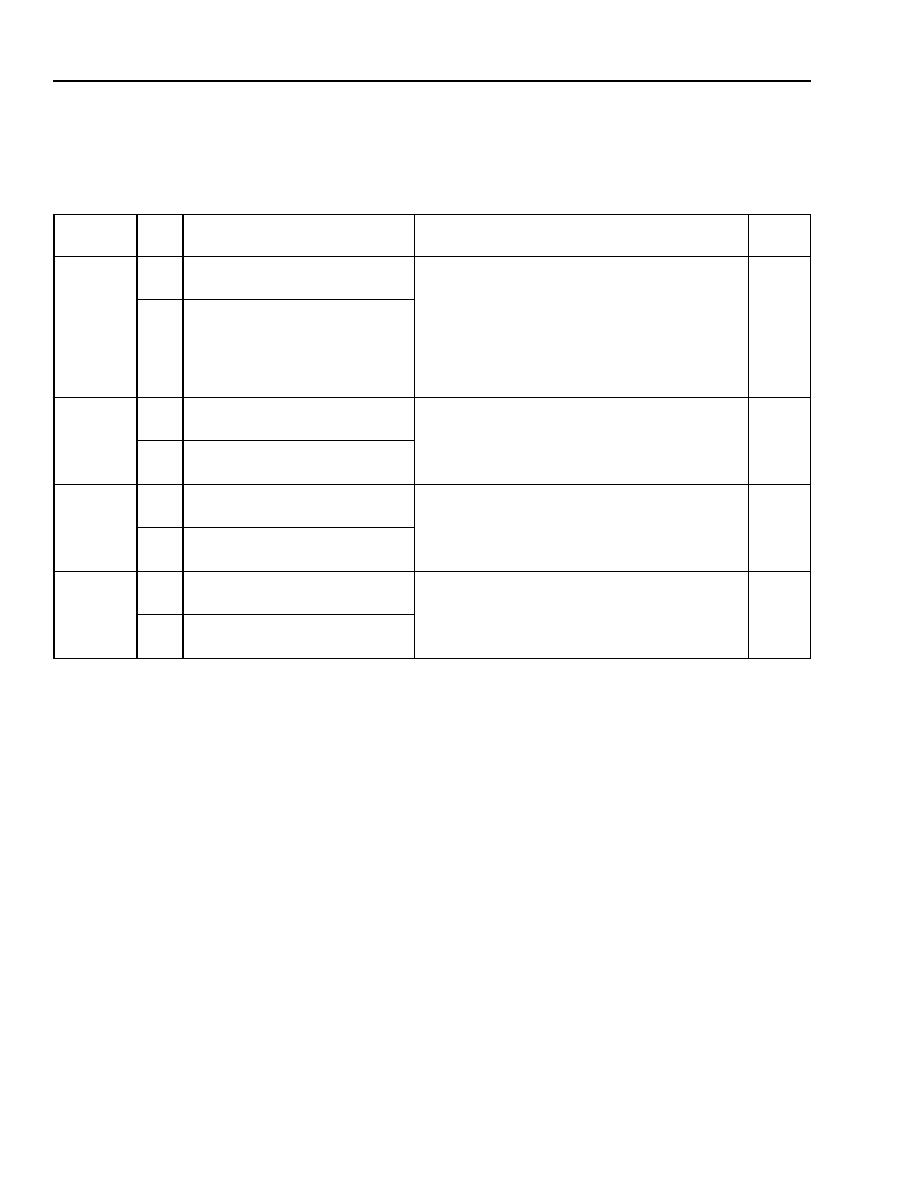

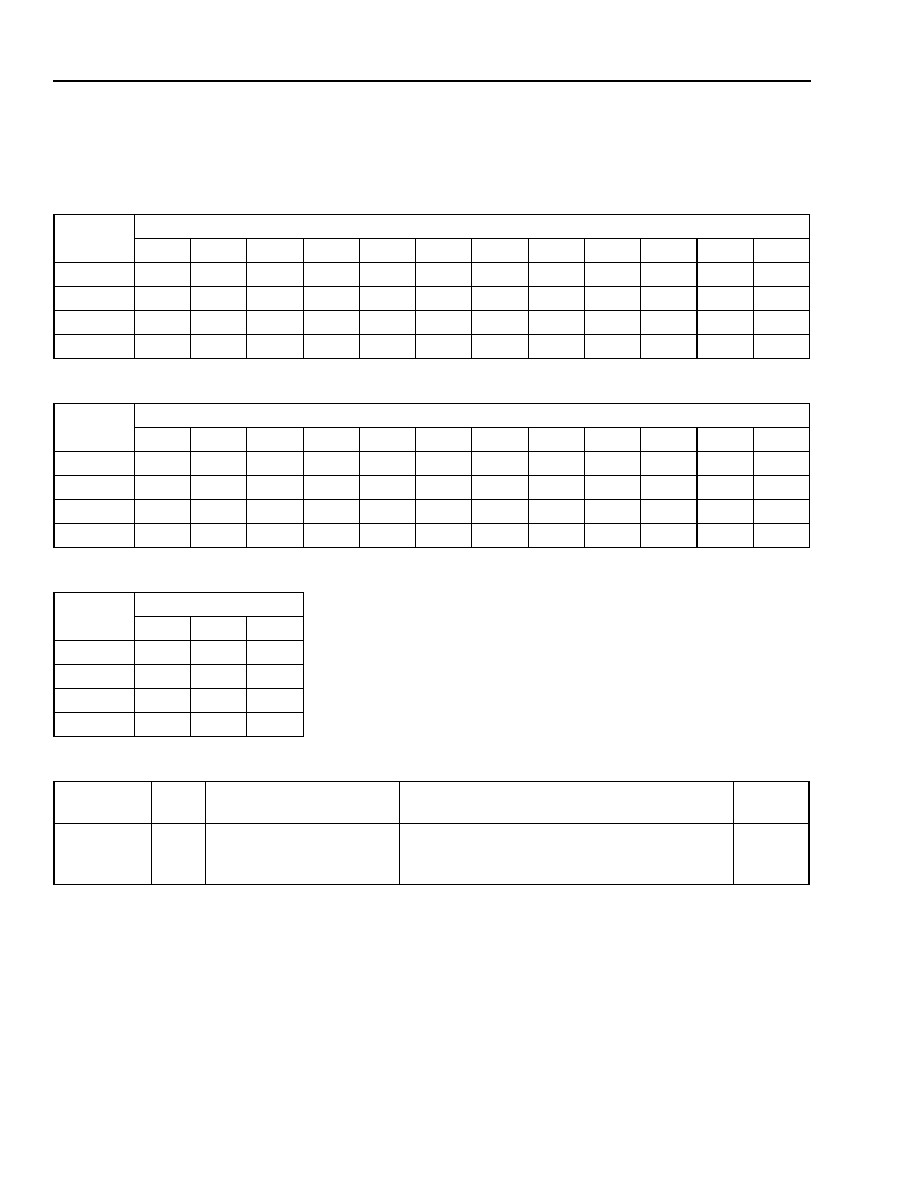

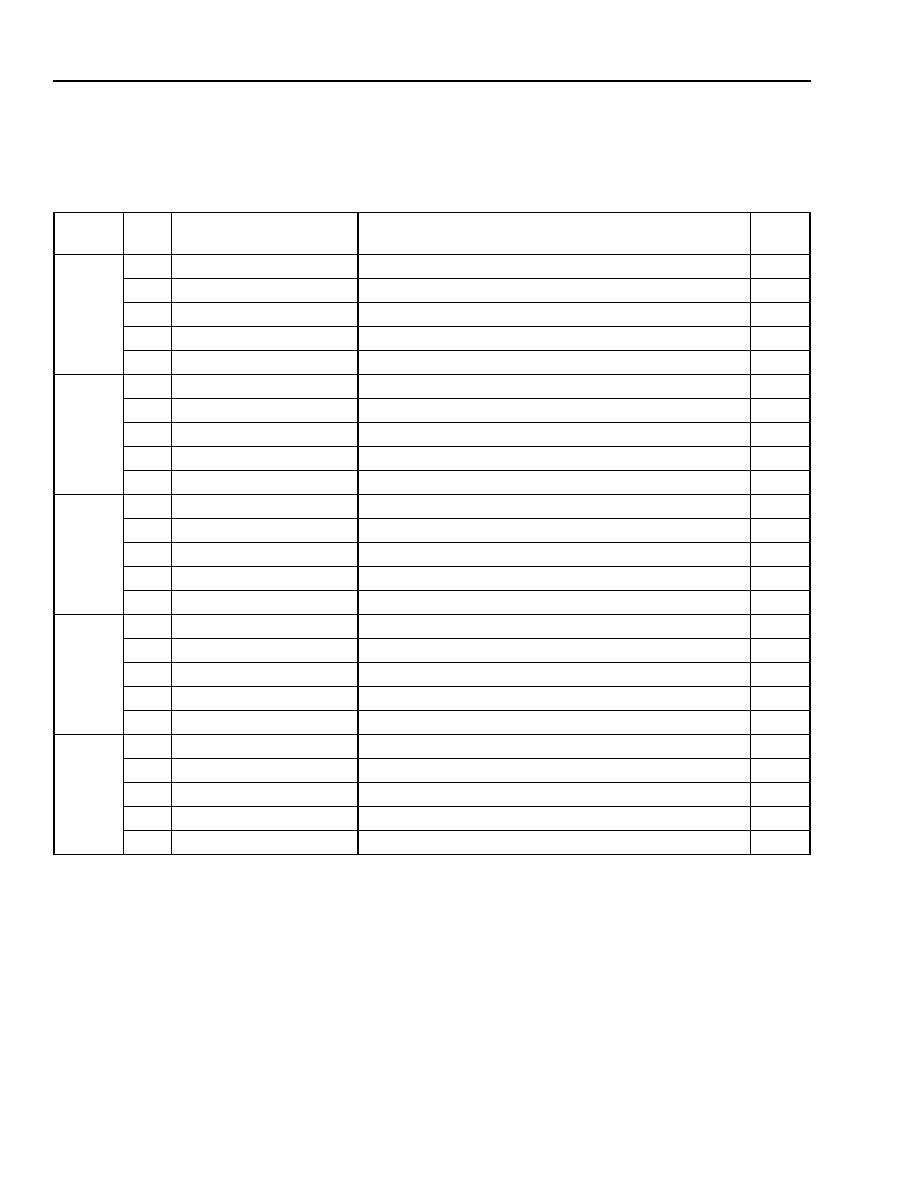

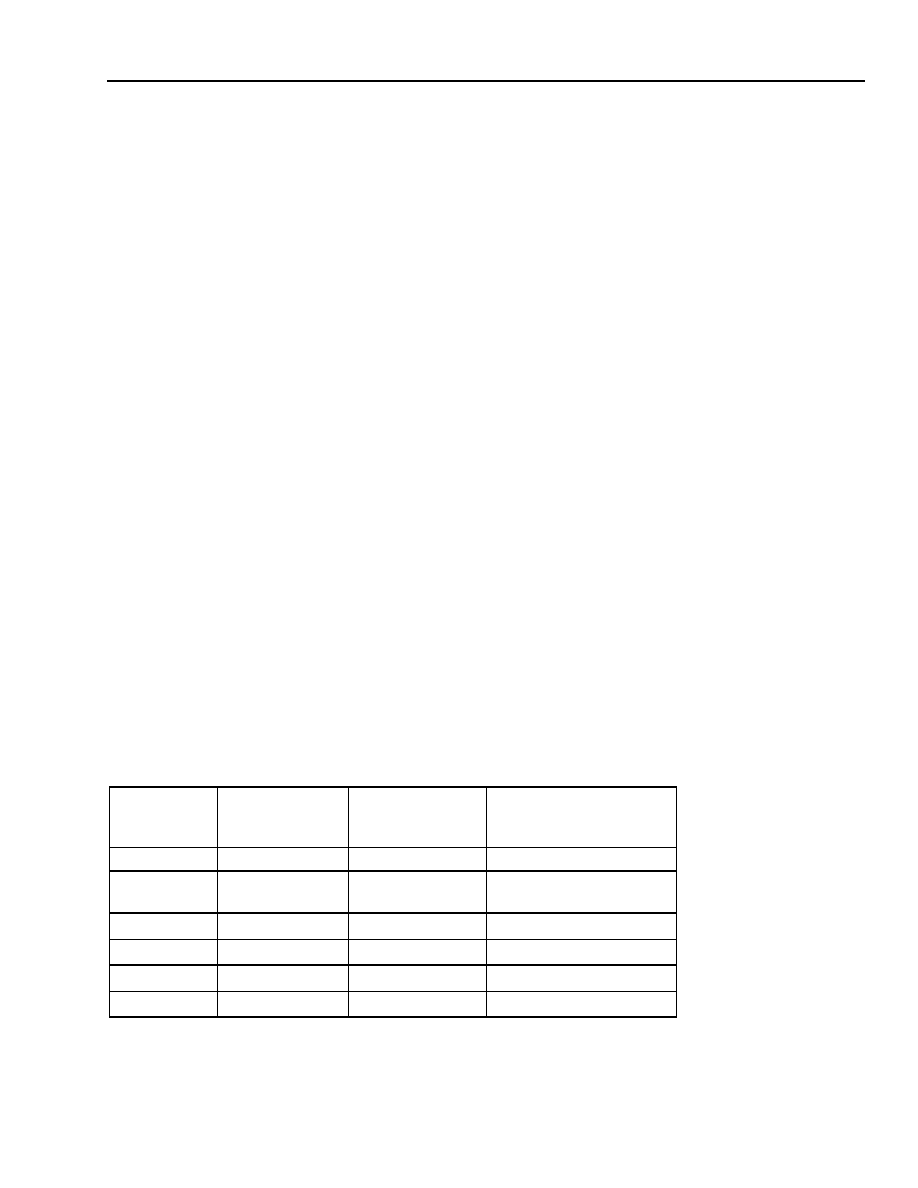

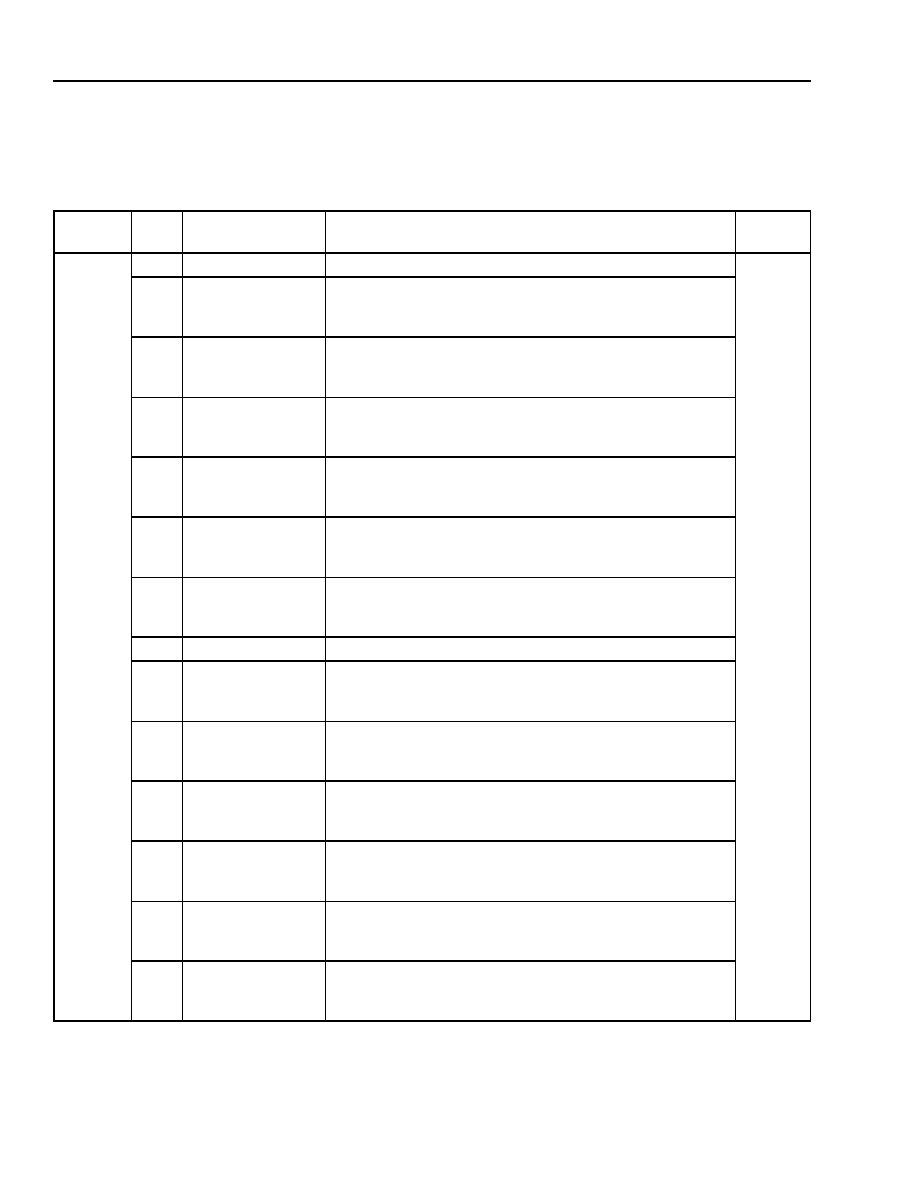

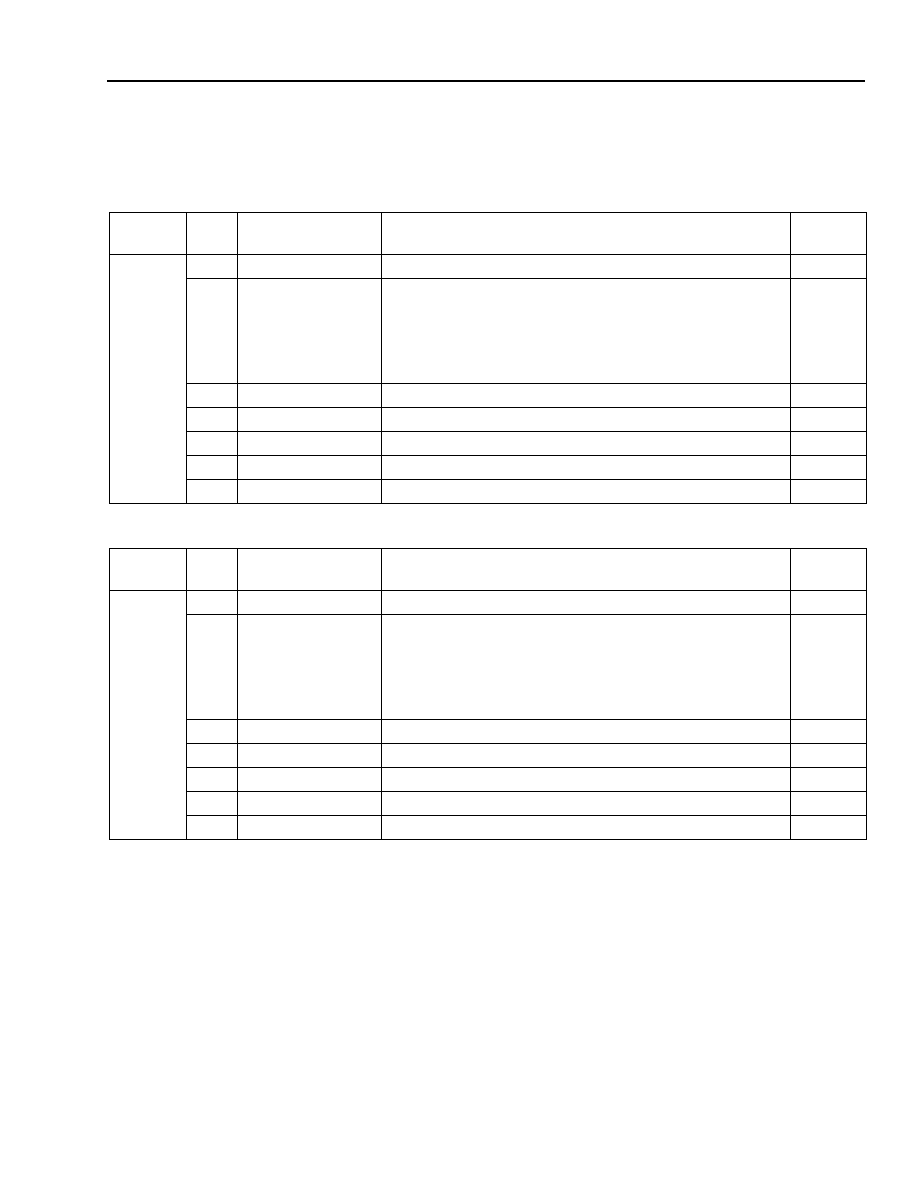

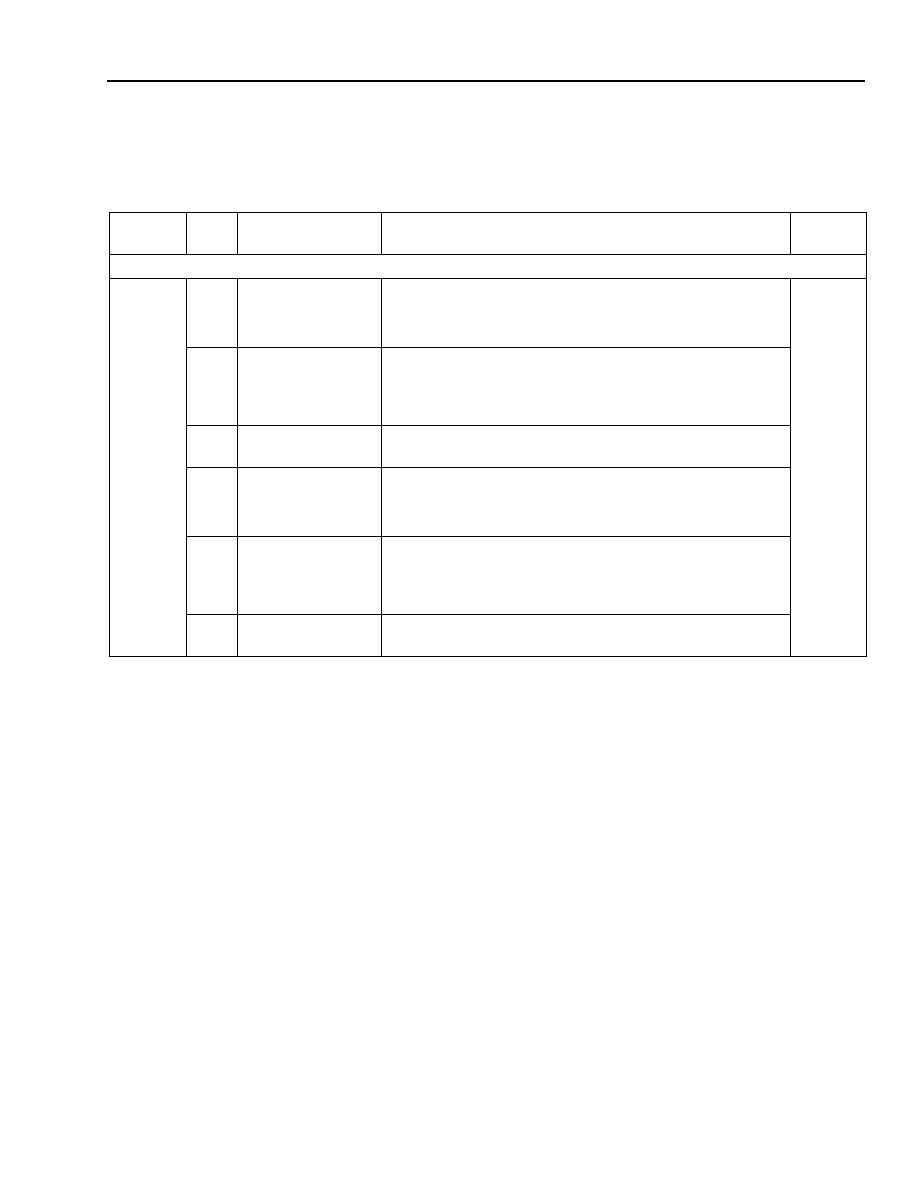

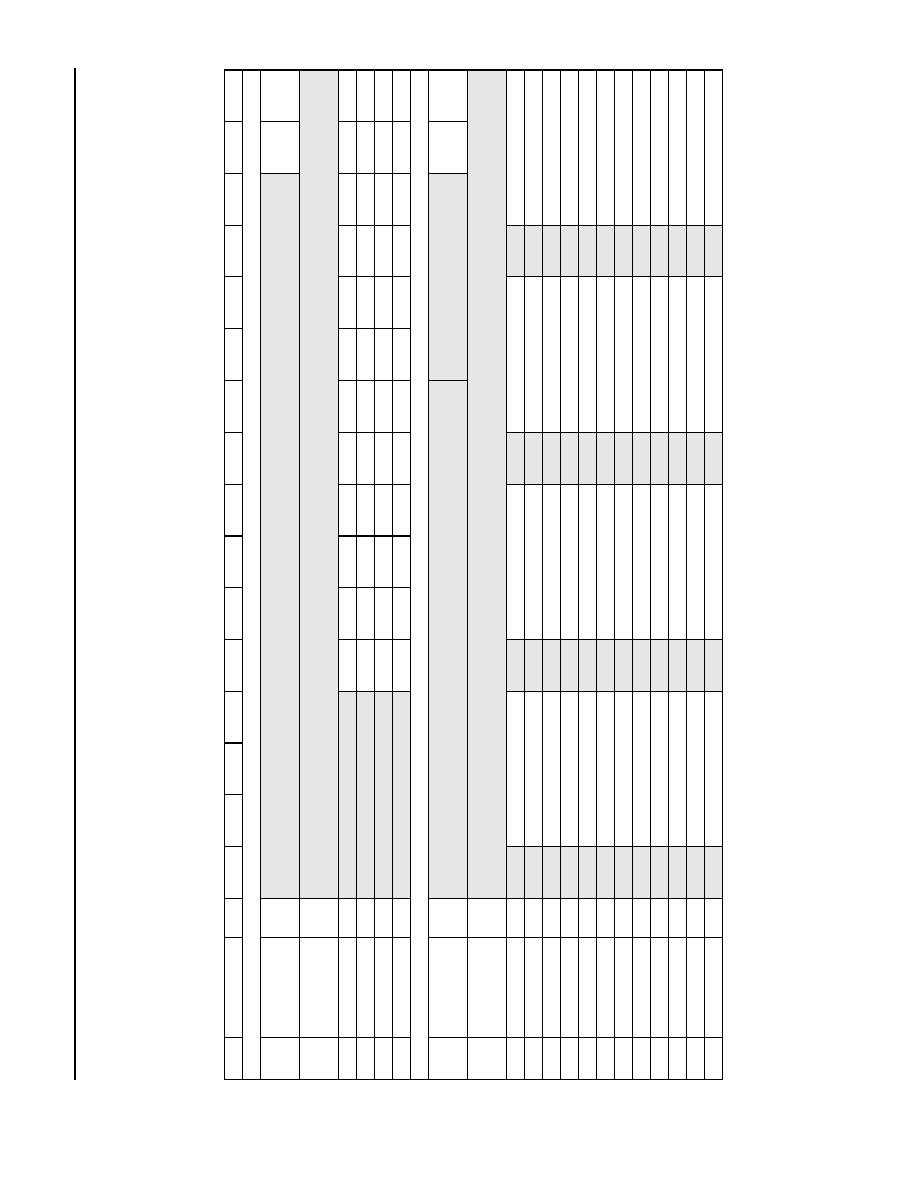

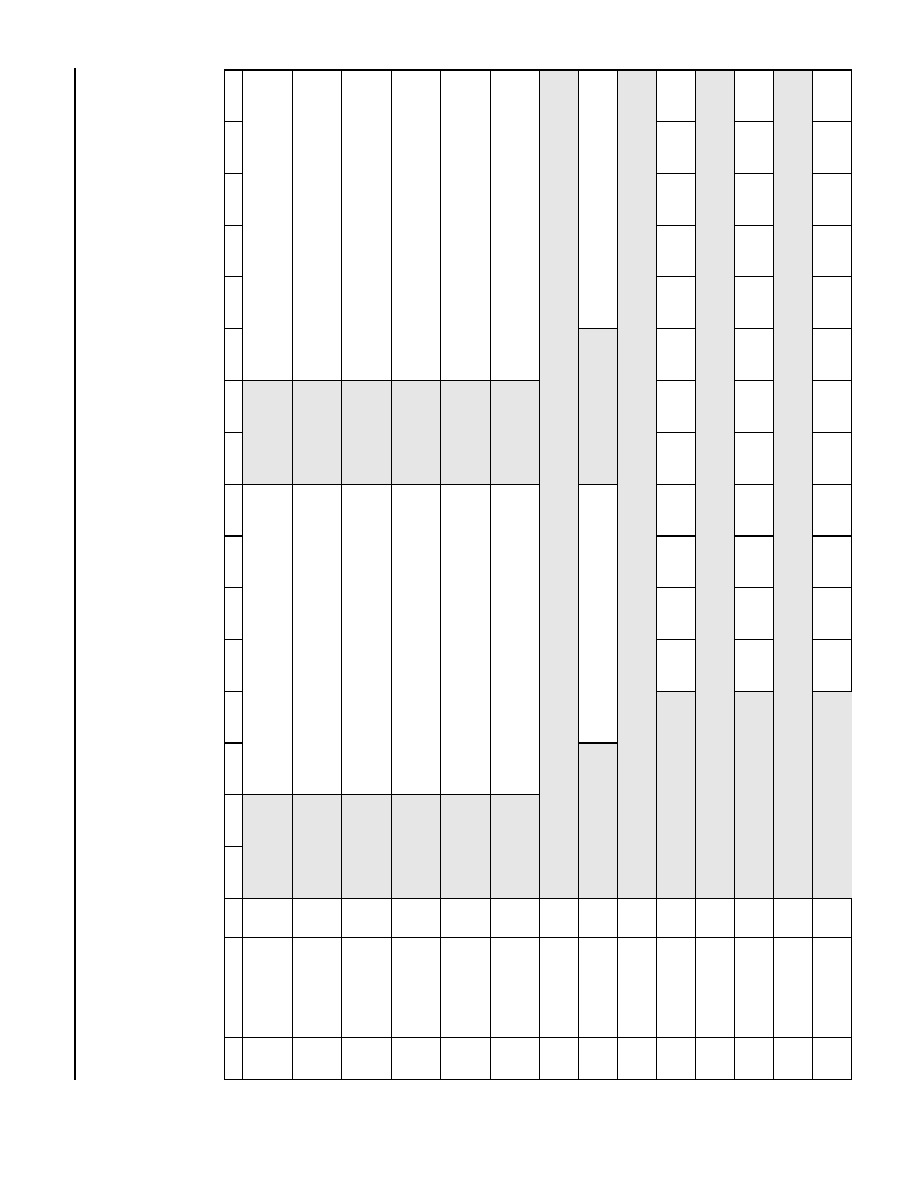

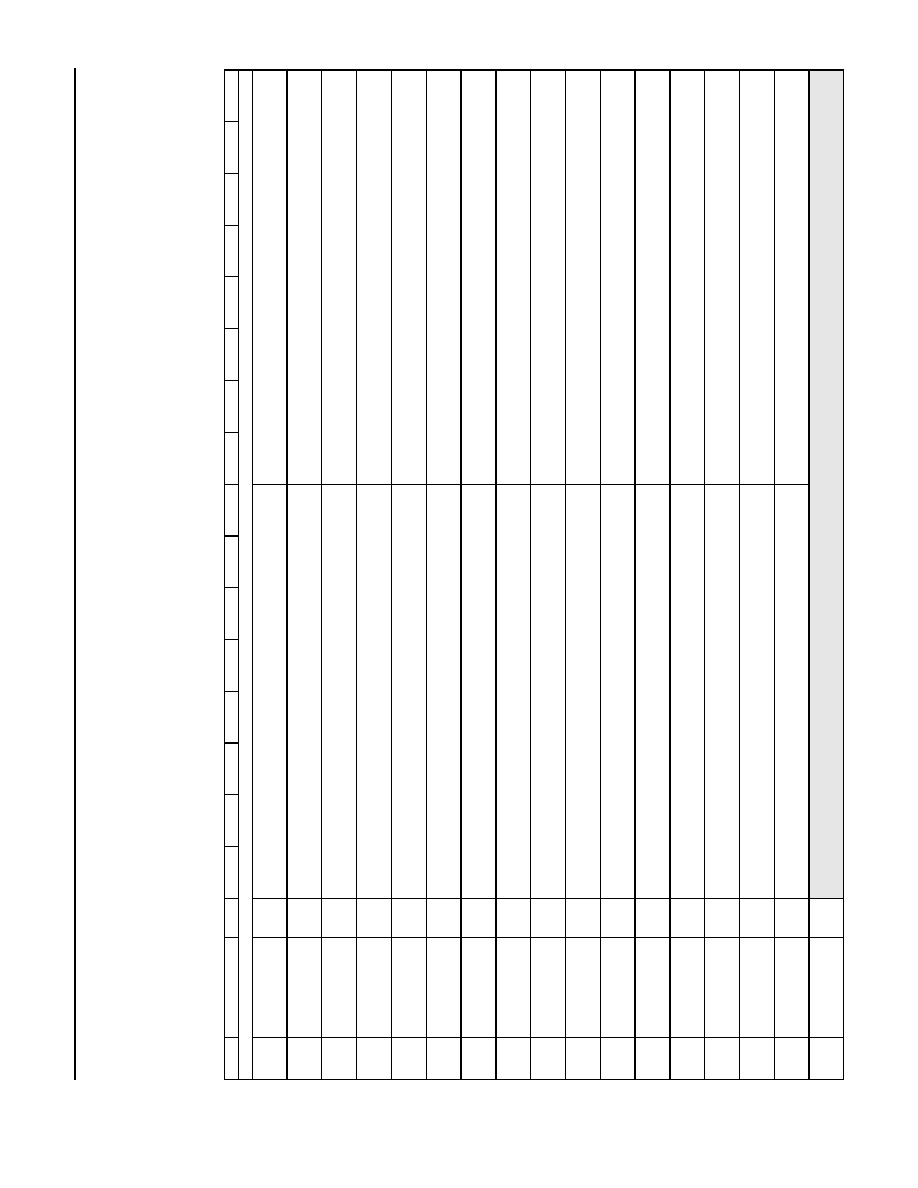

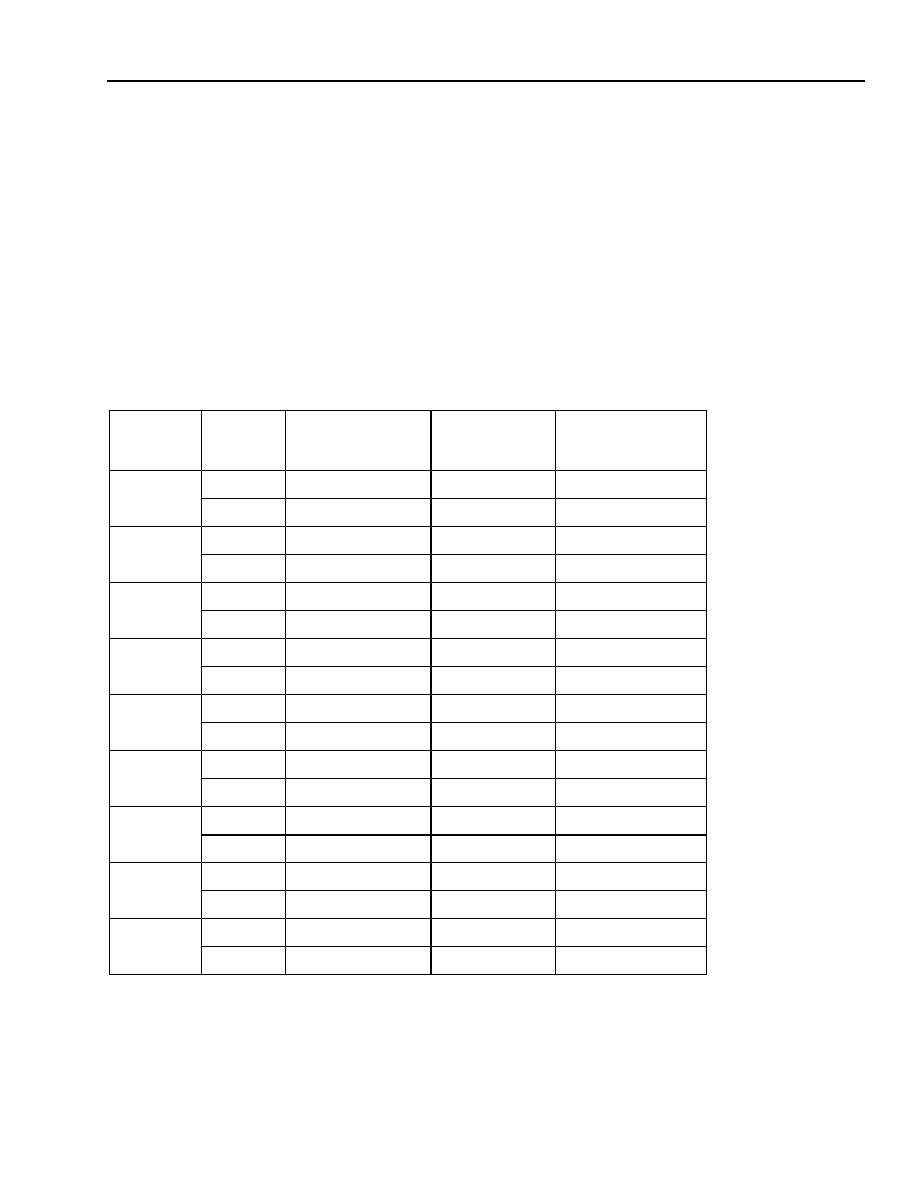

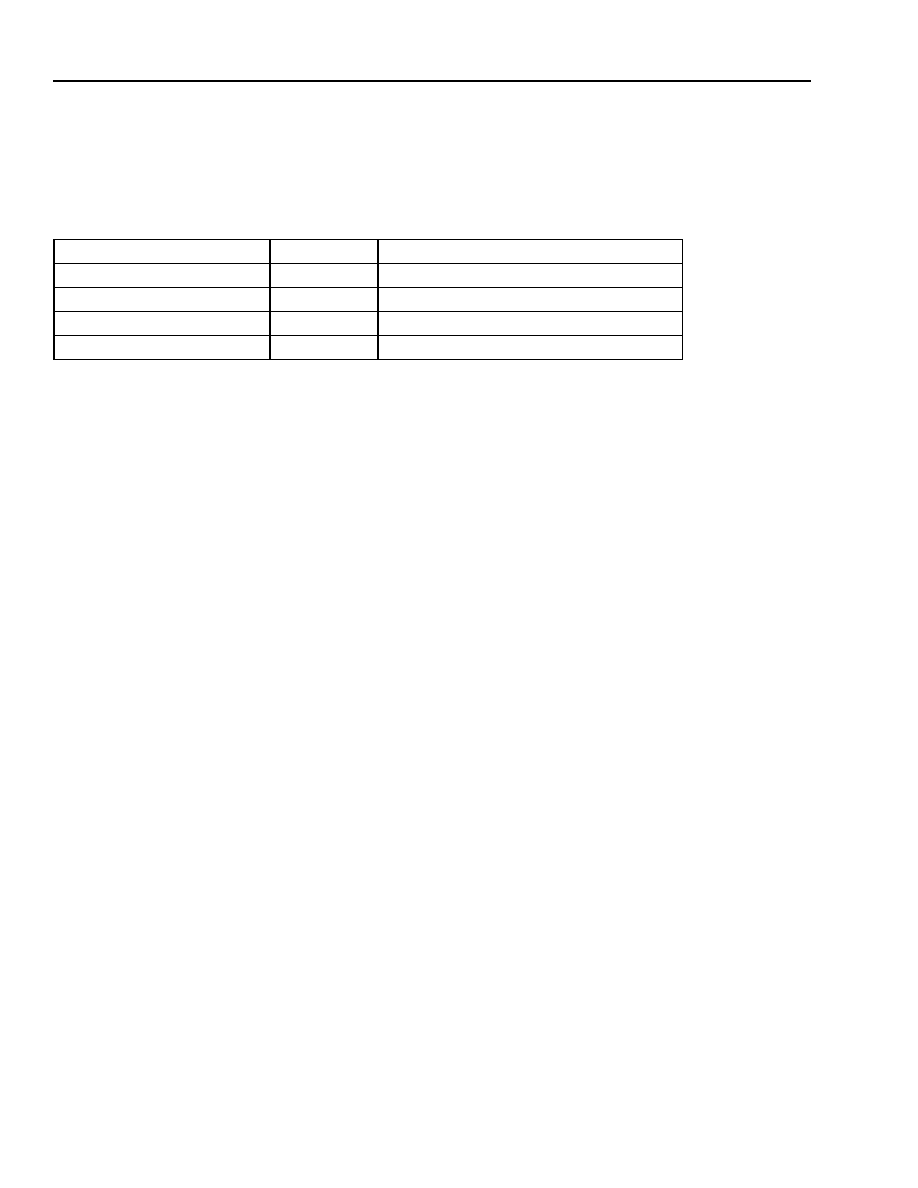

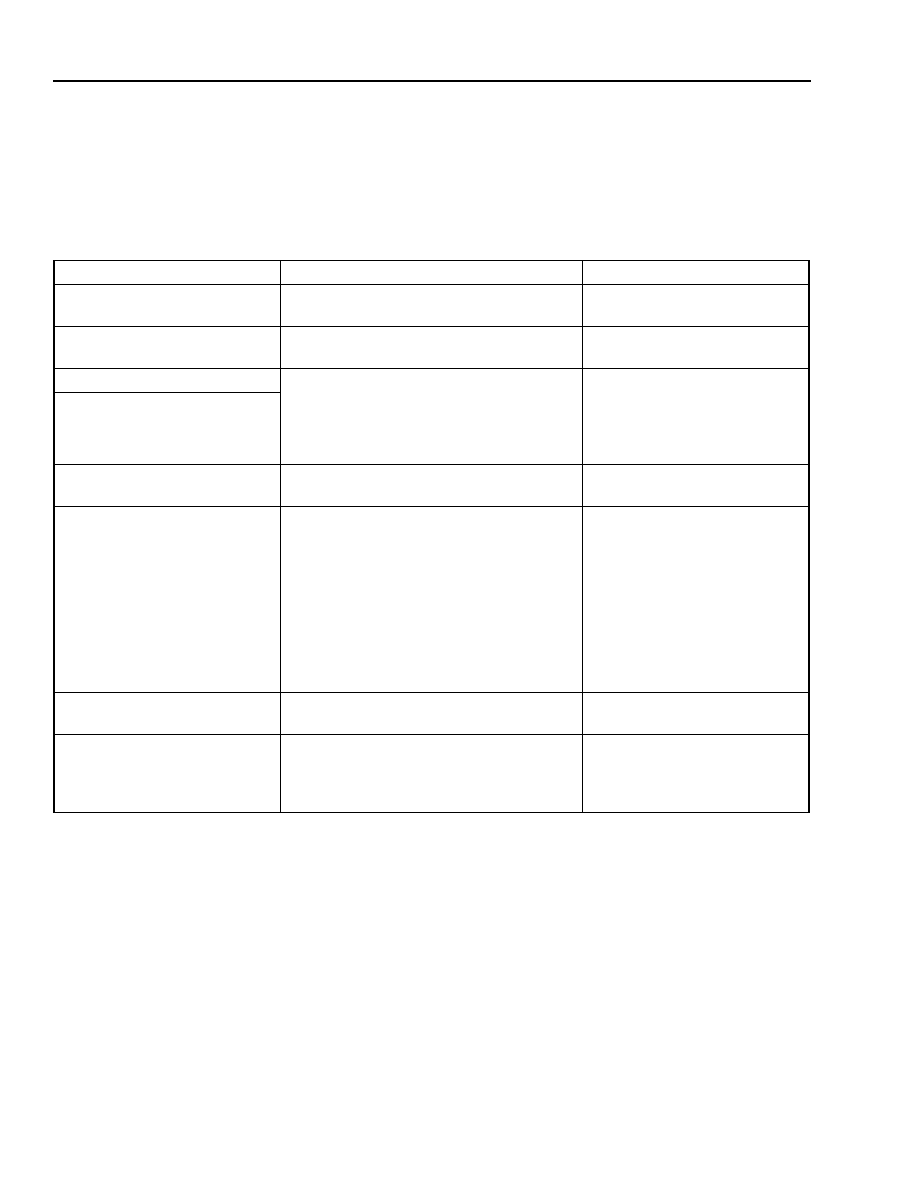

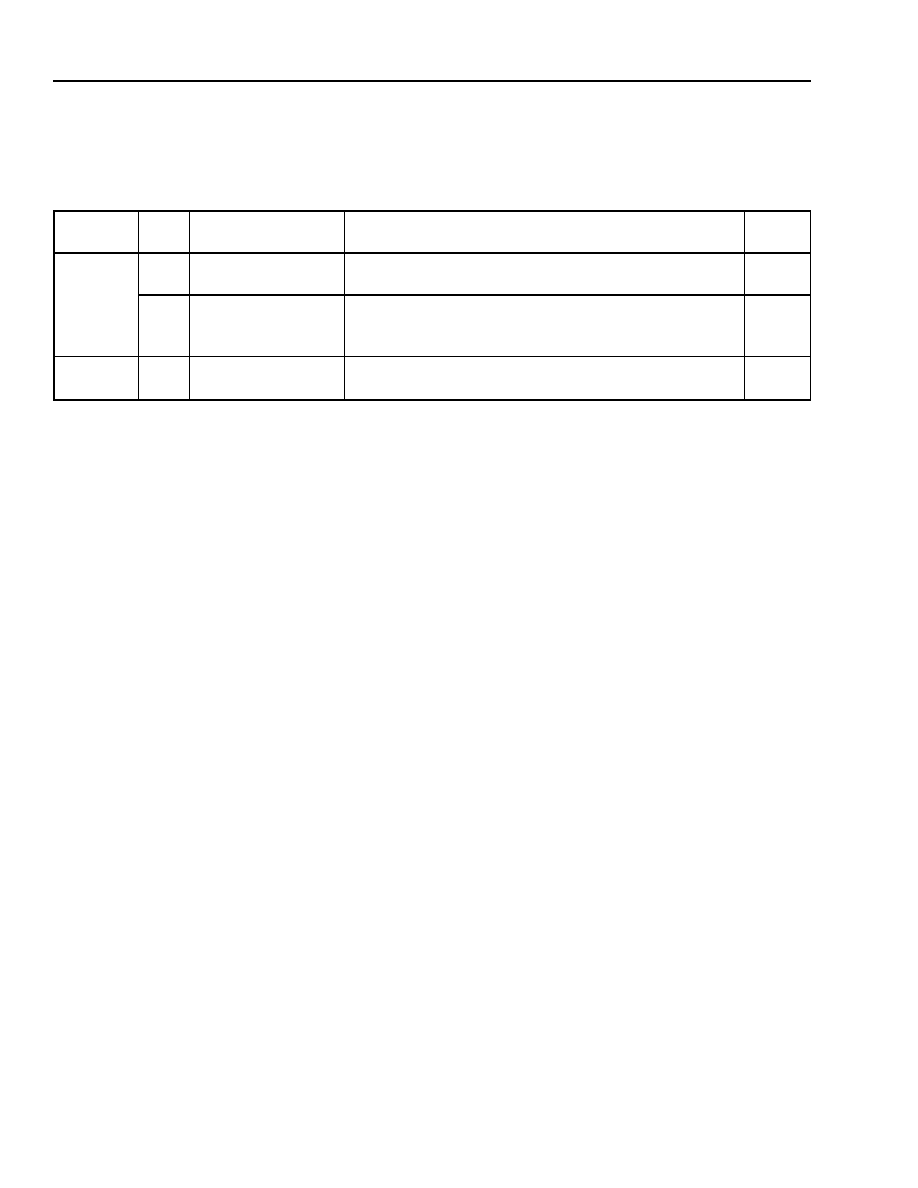

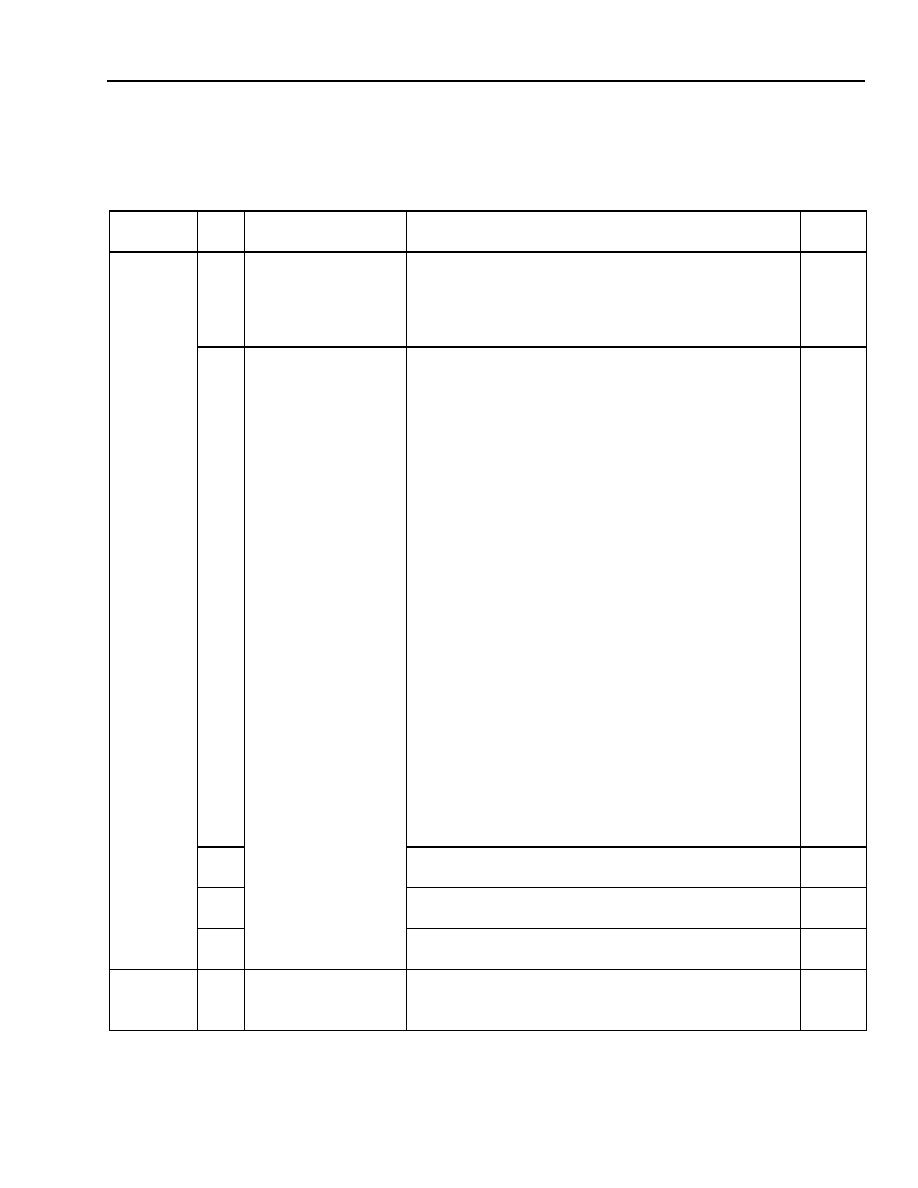

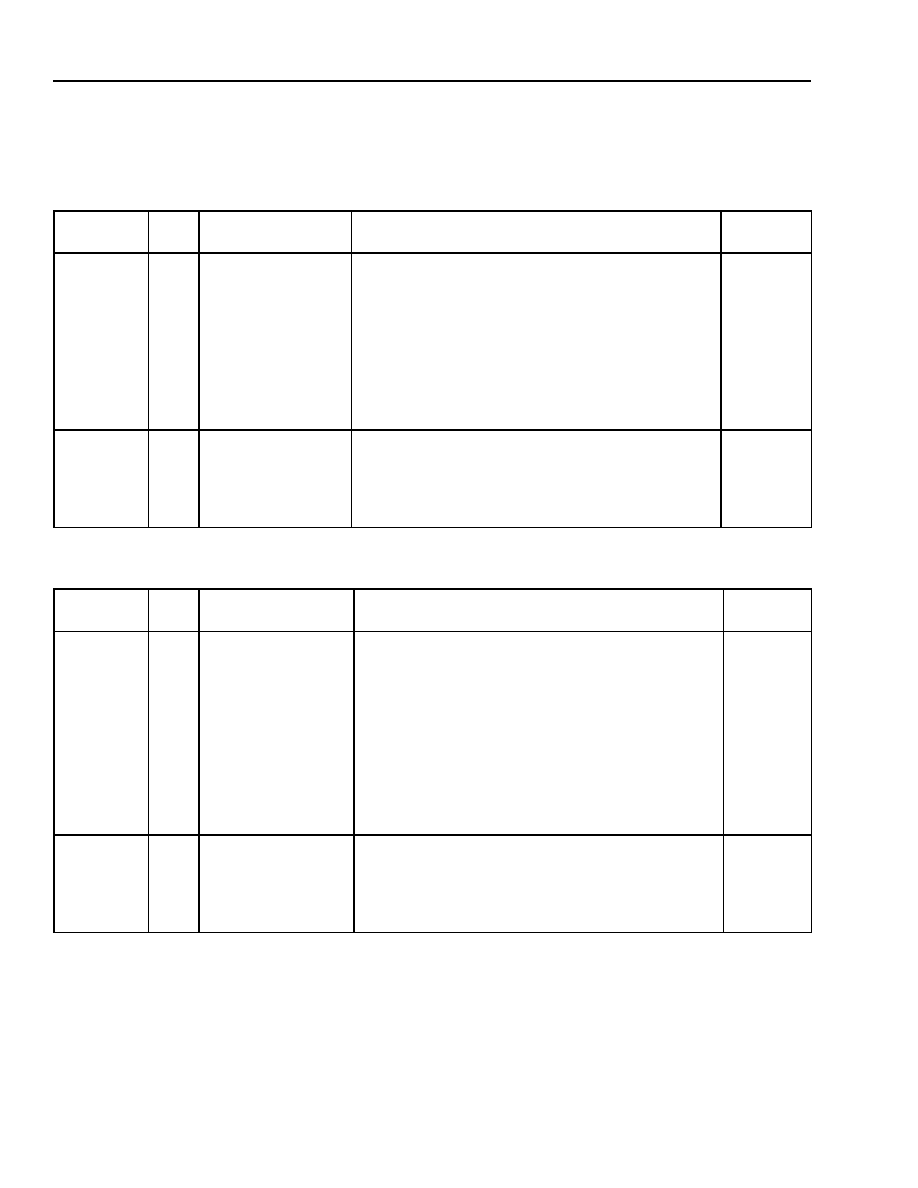

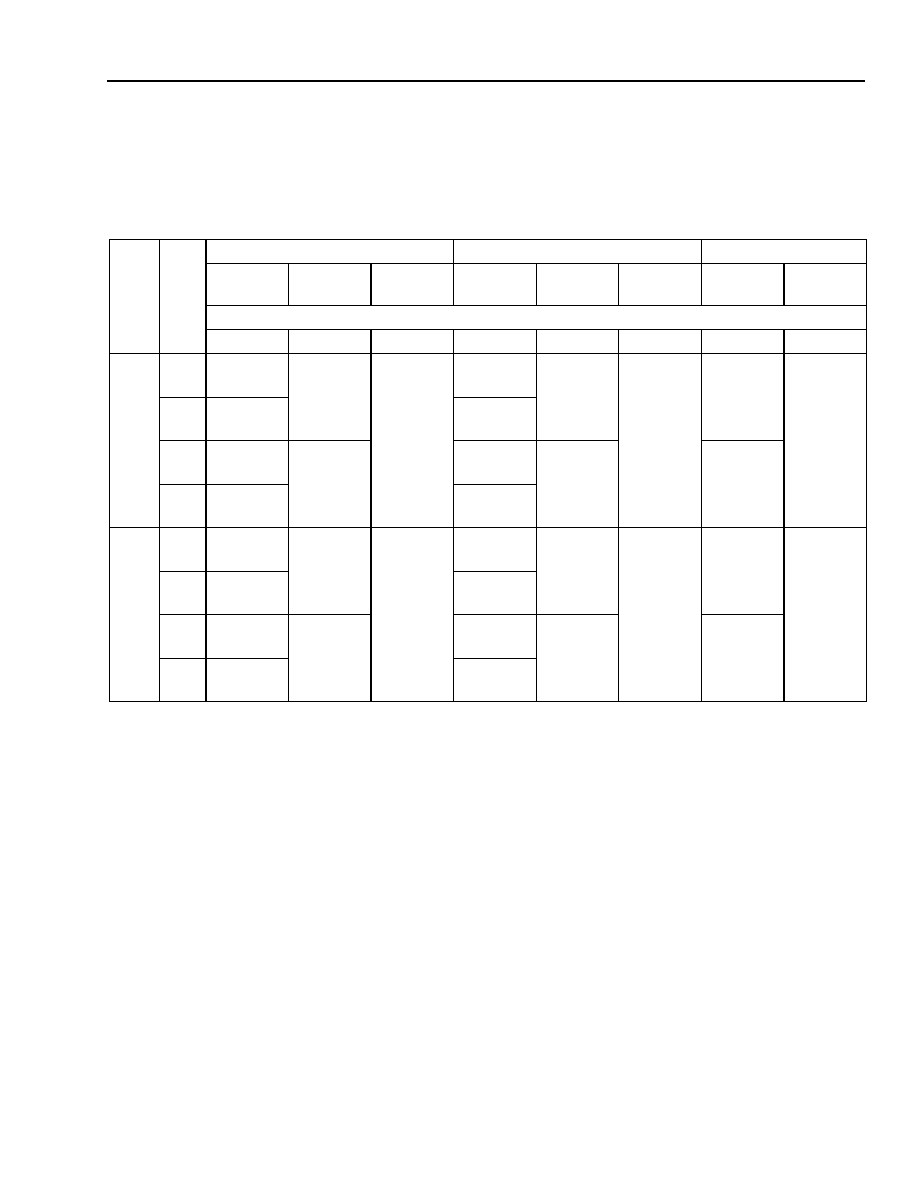

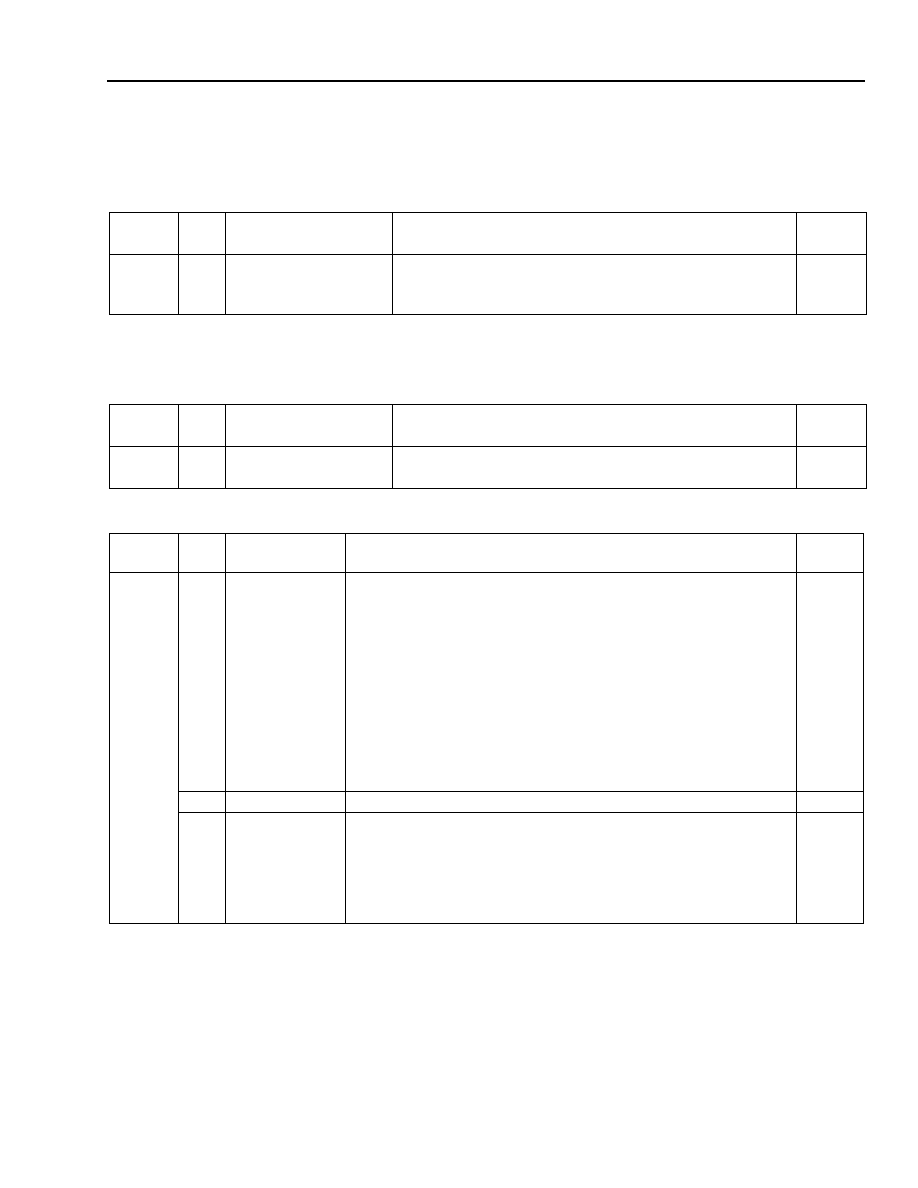

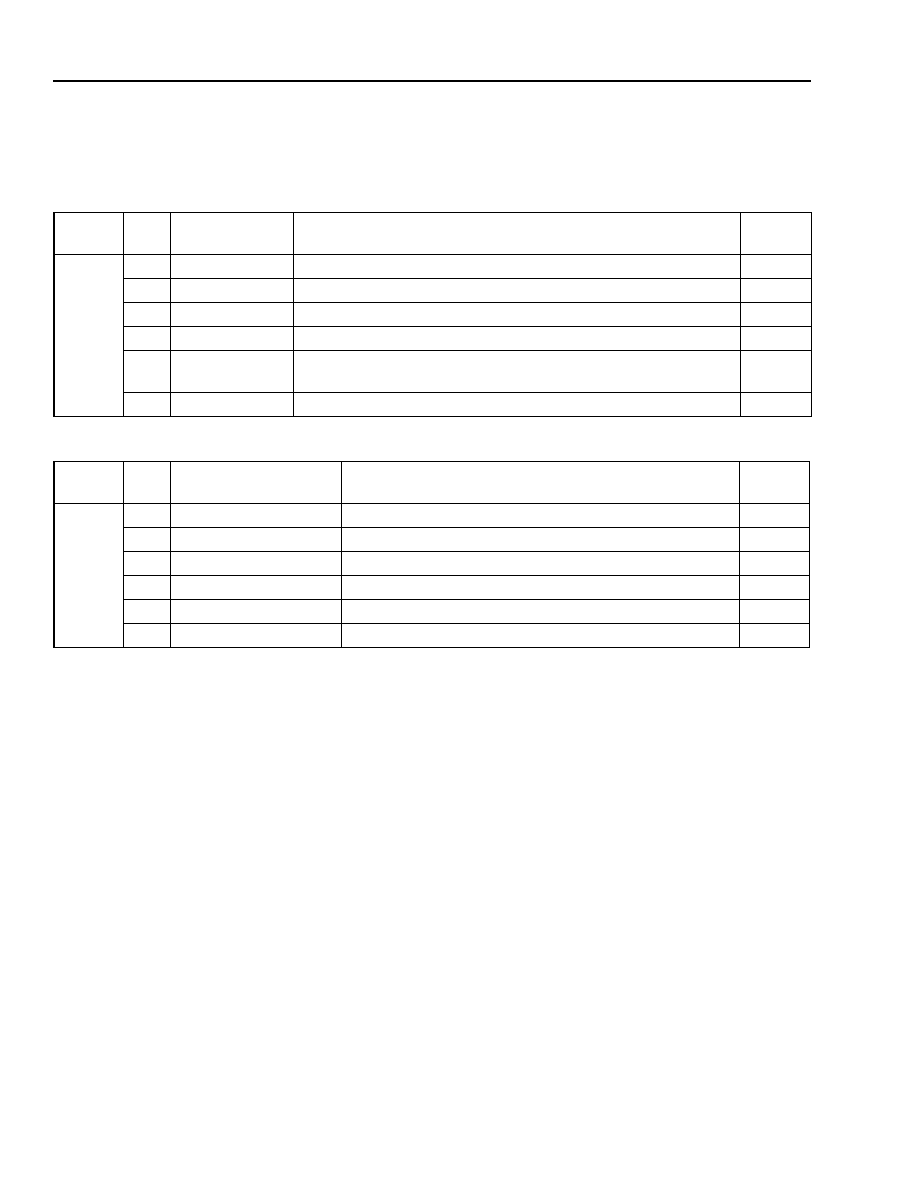

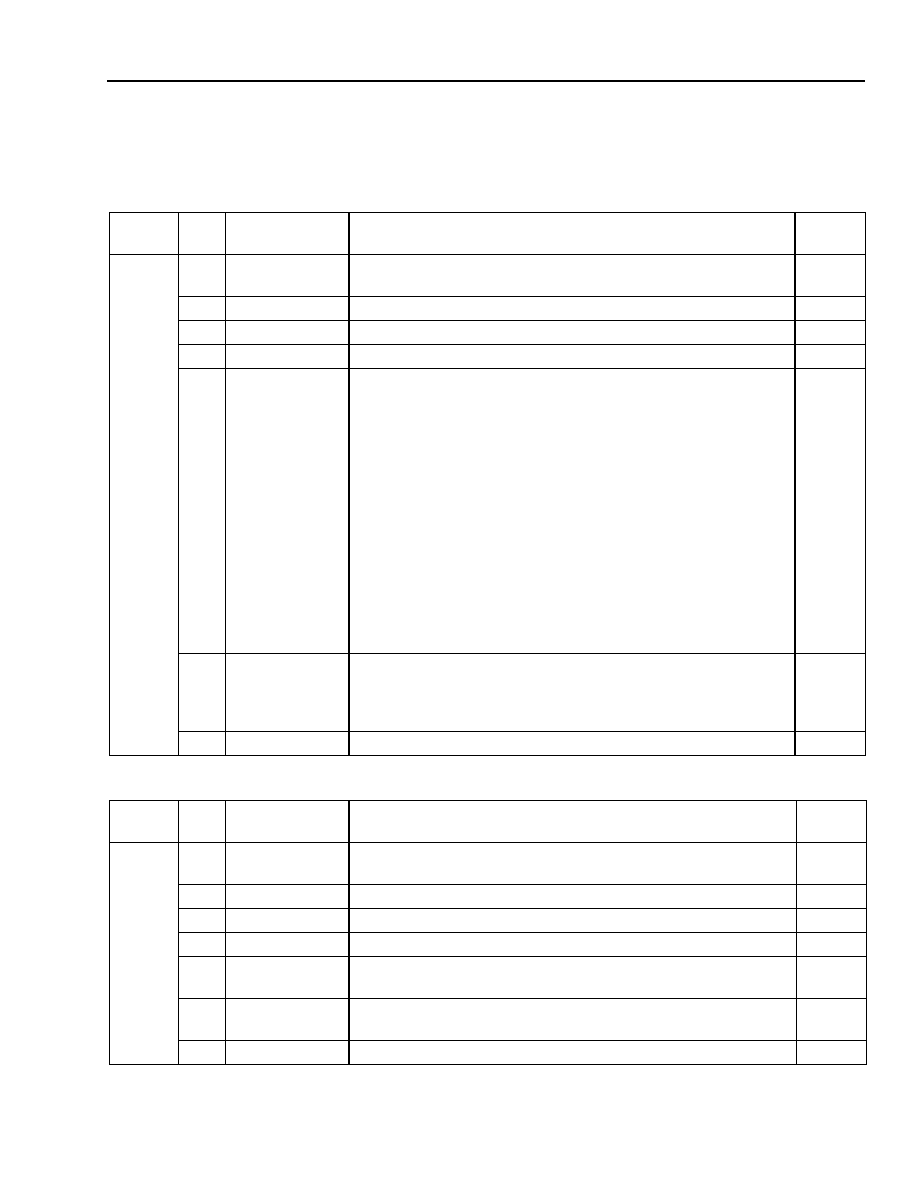

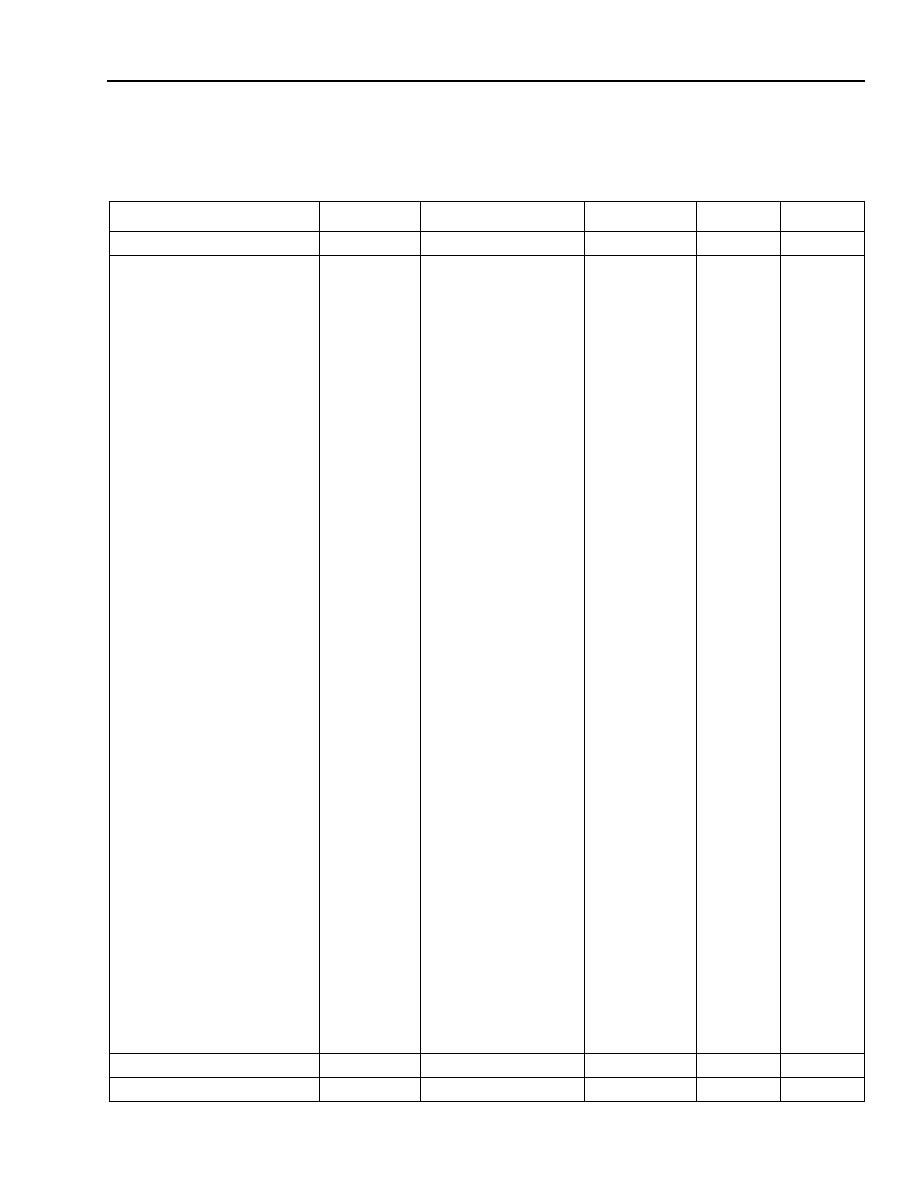

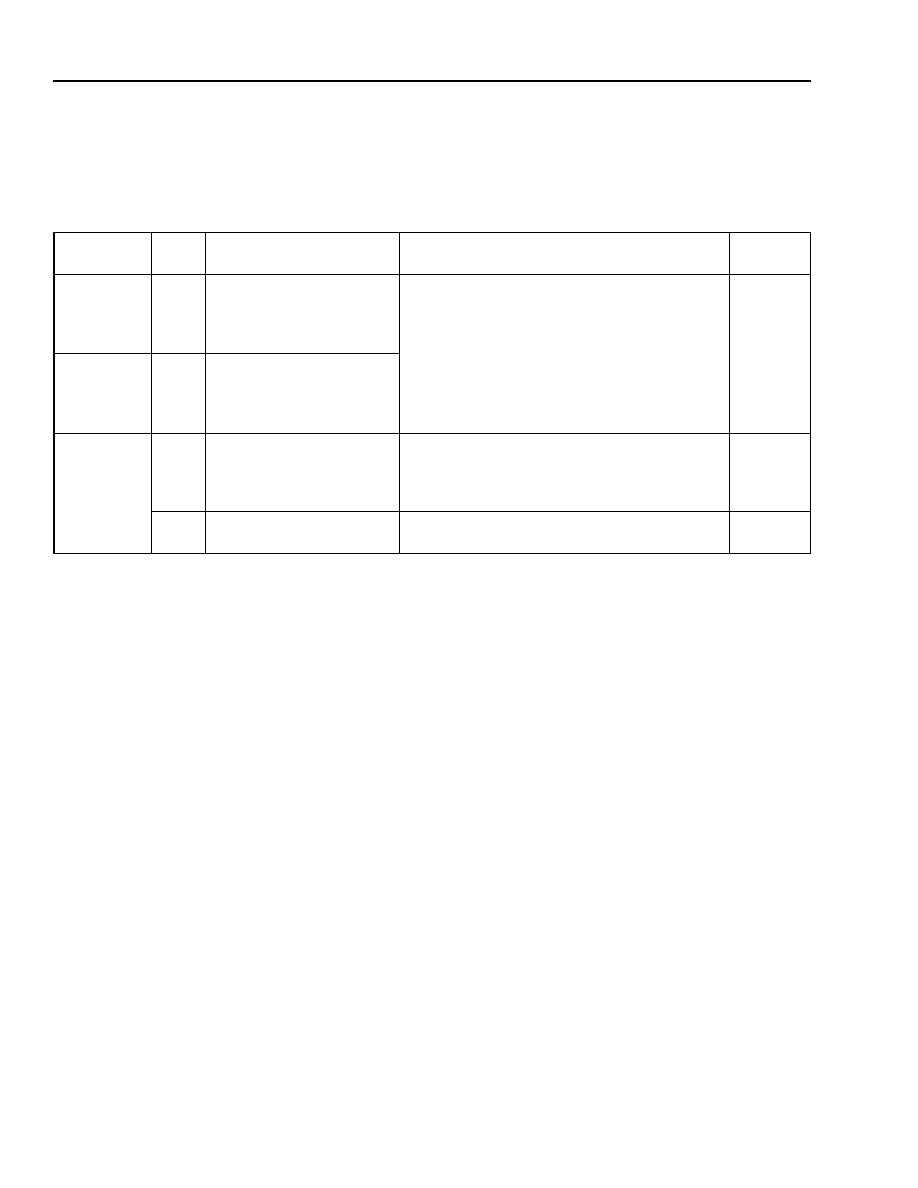

- Table 2. MARS2G5 P-Pro Device Product Line-Data Port Summary

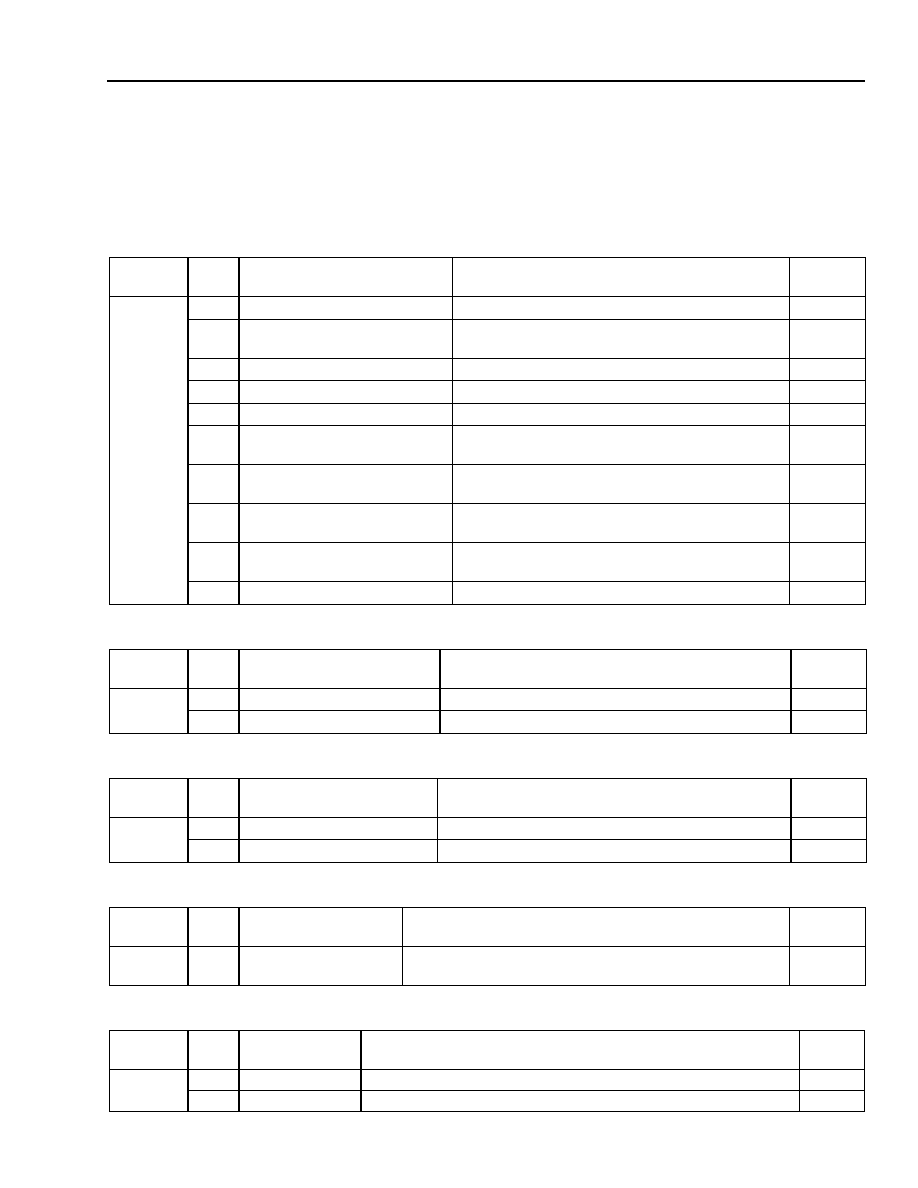

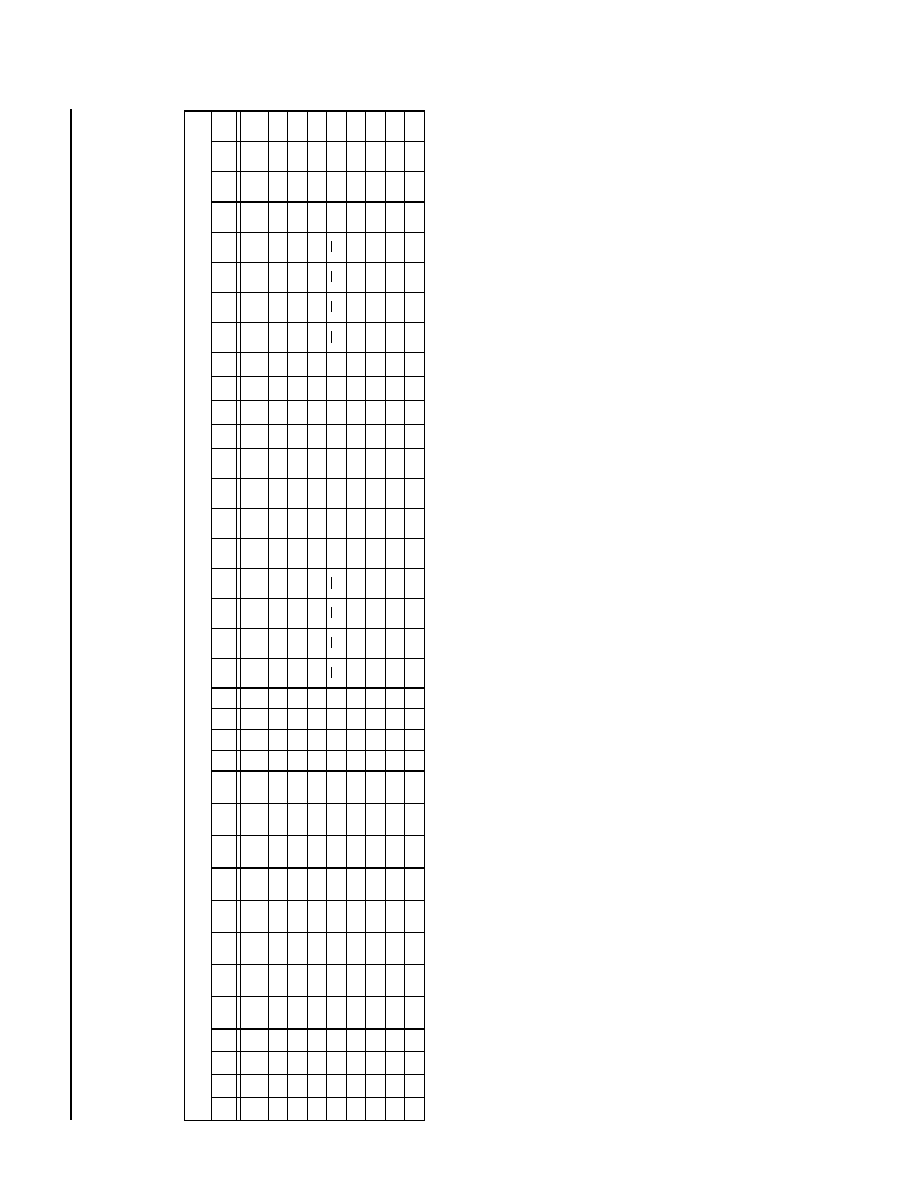

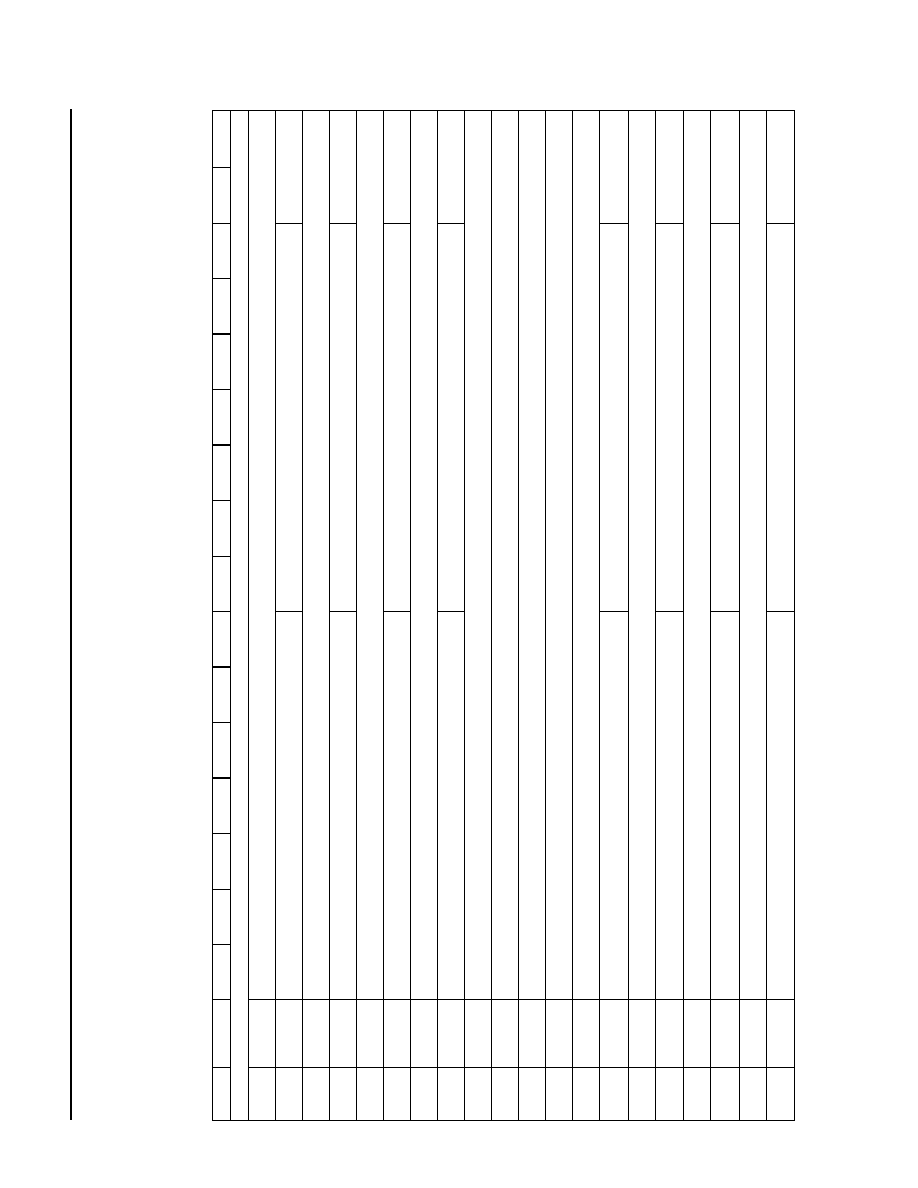

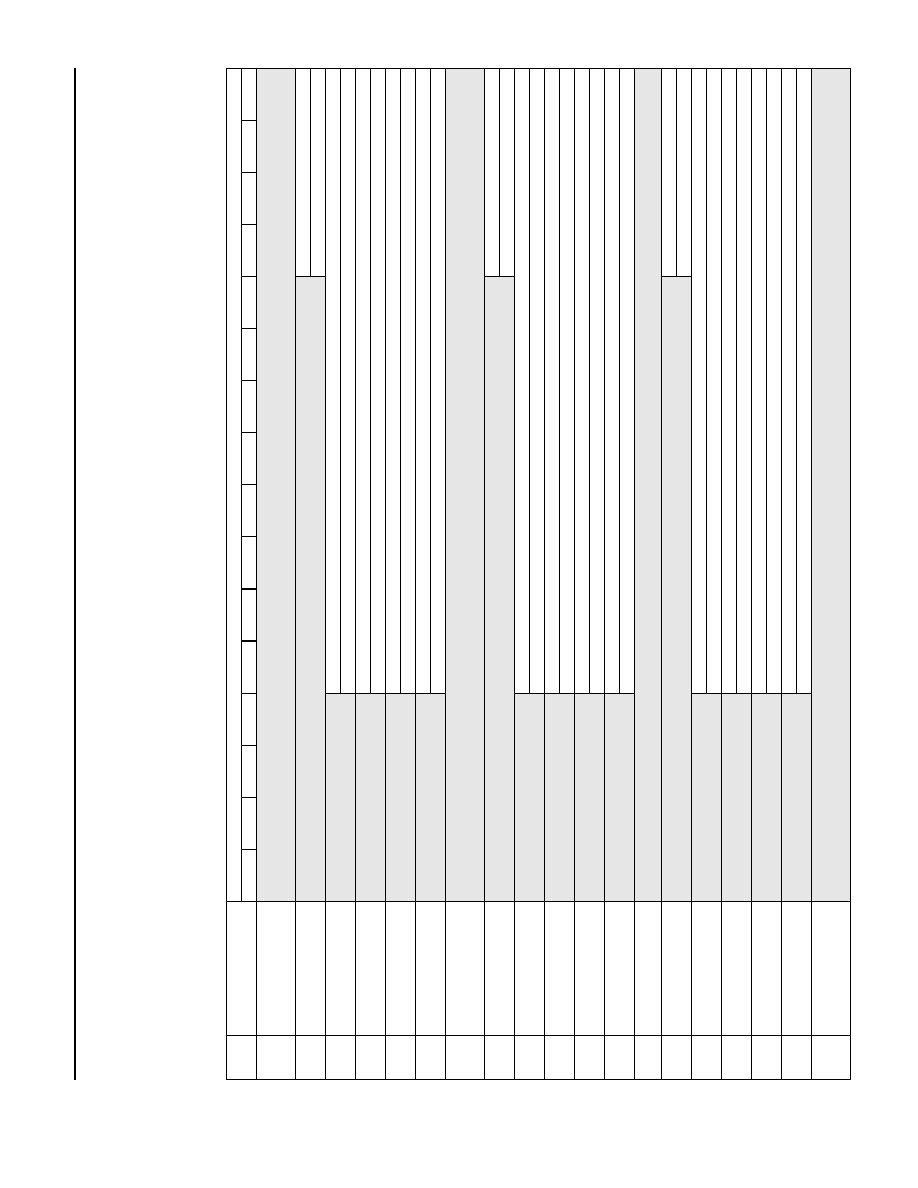

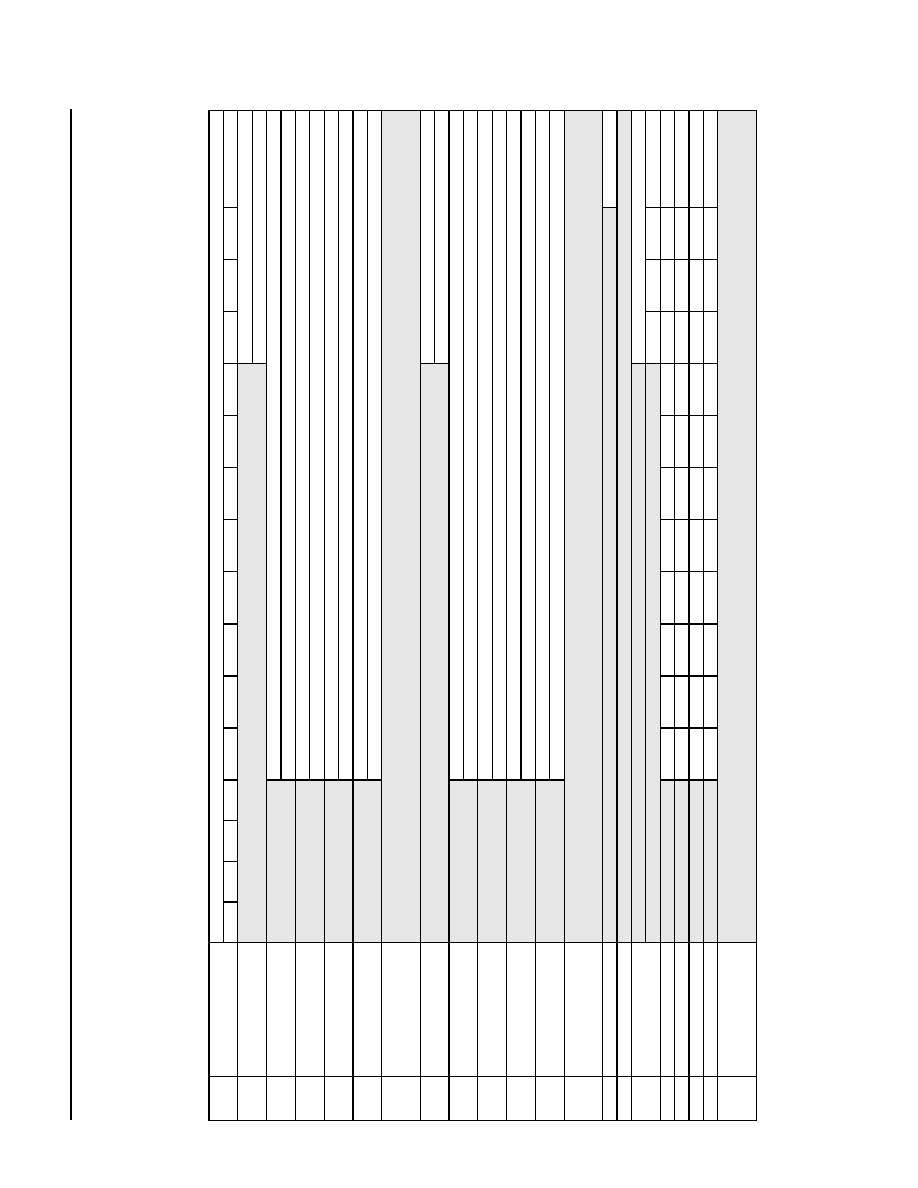

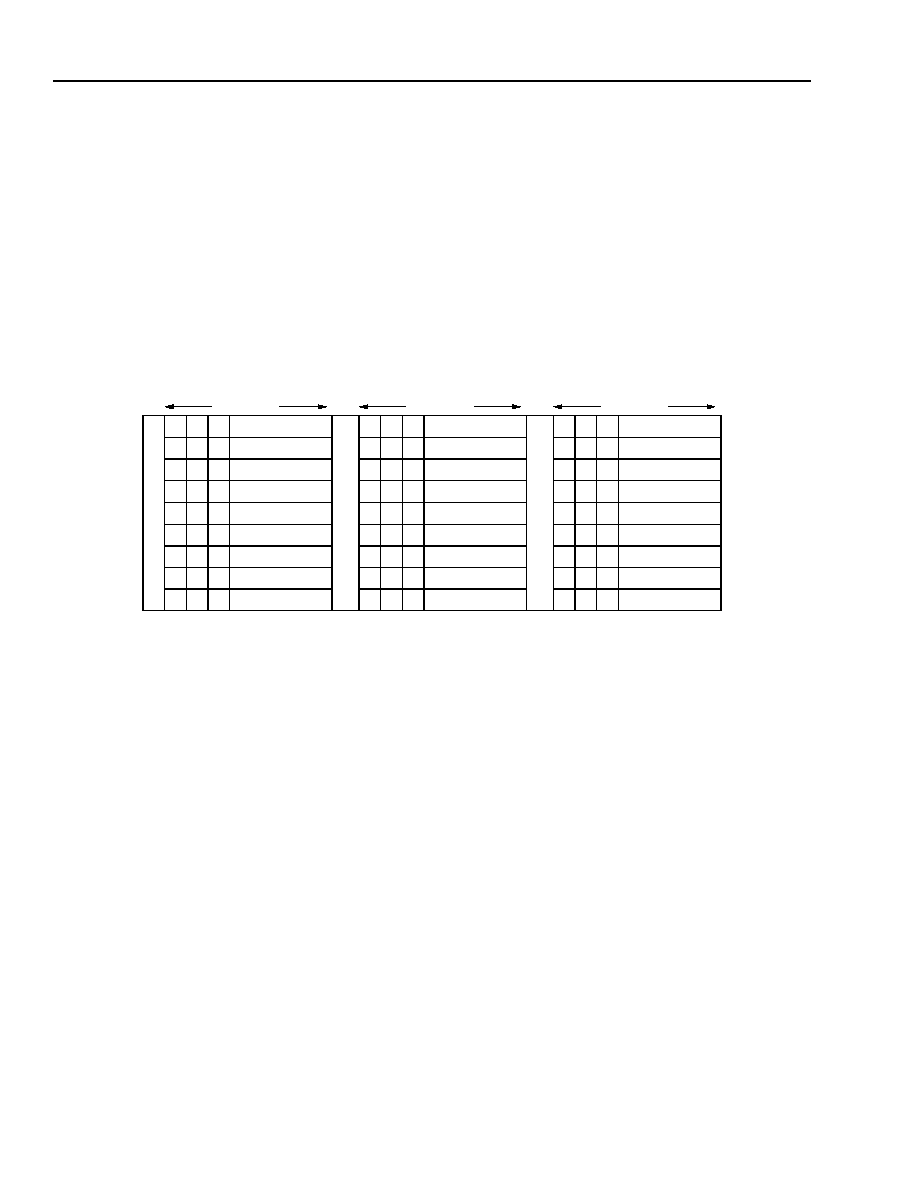

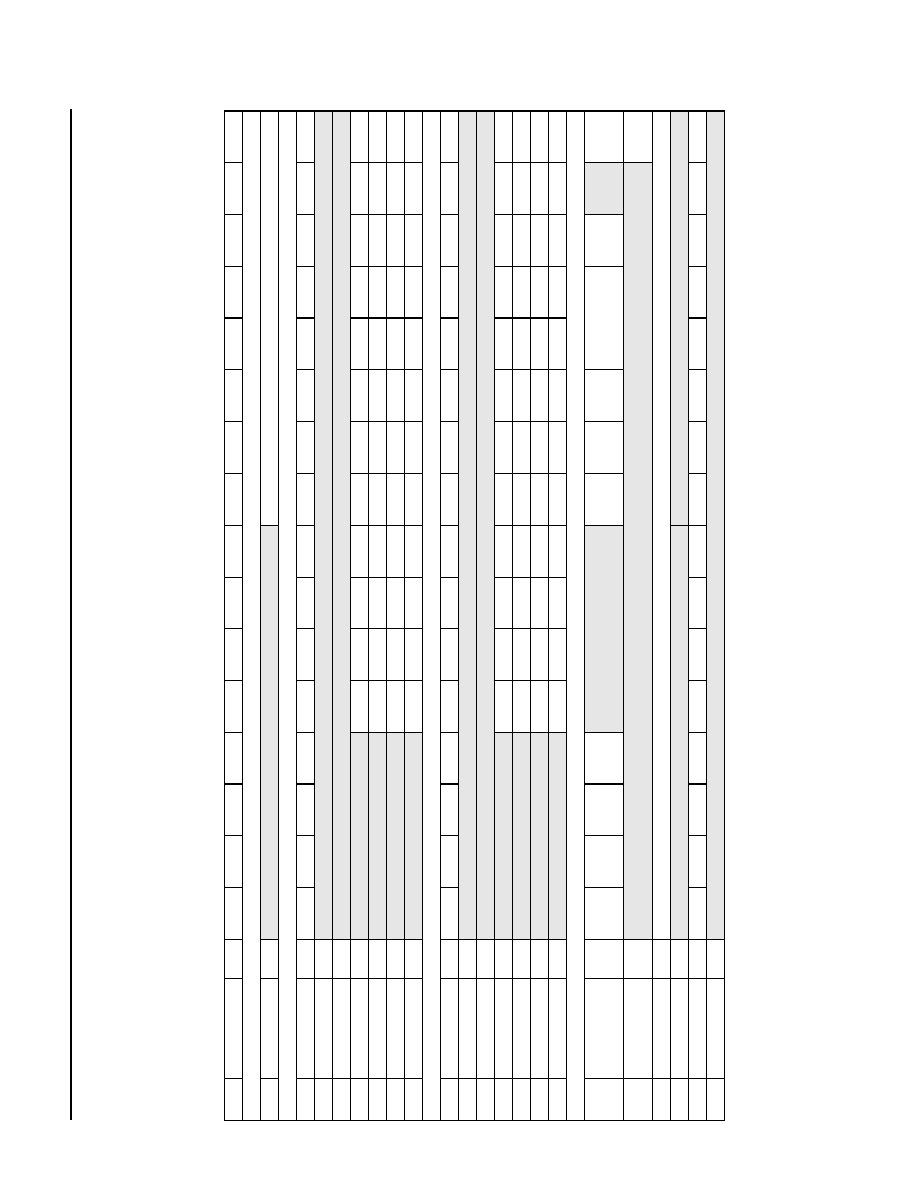

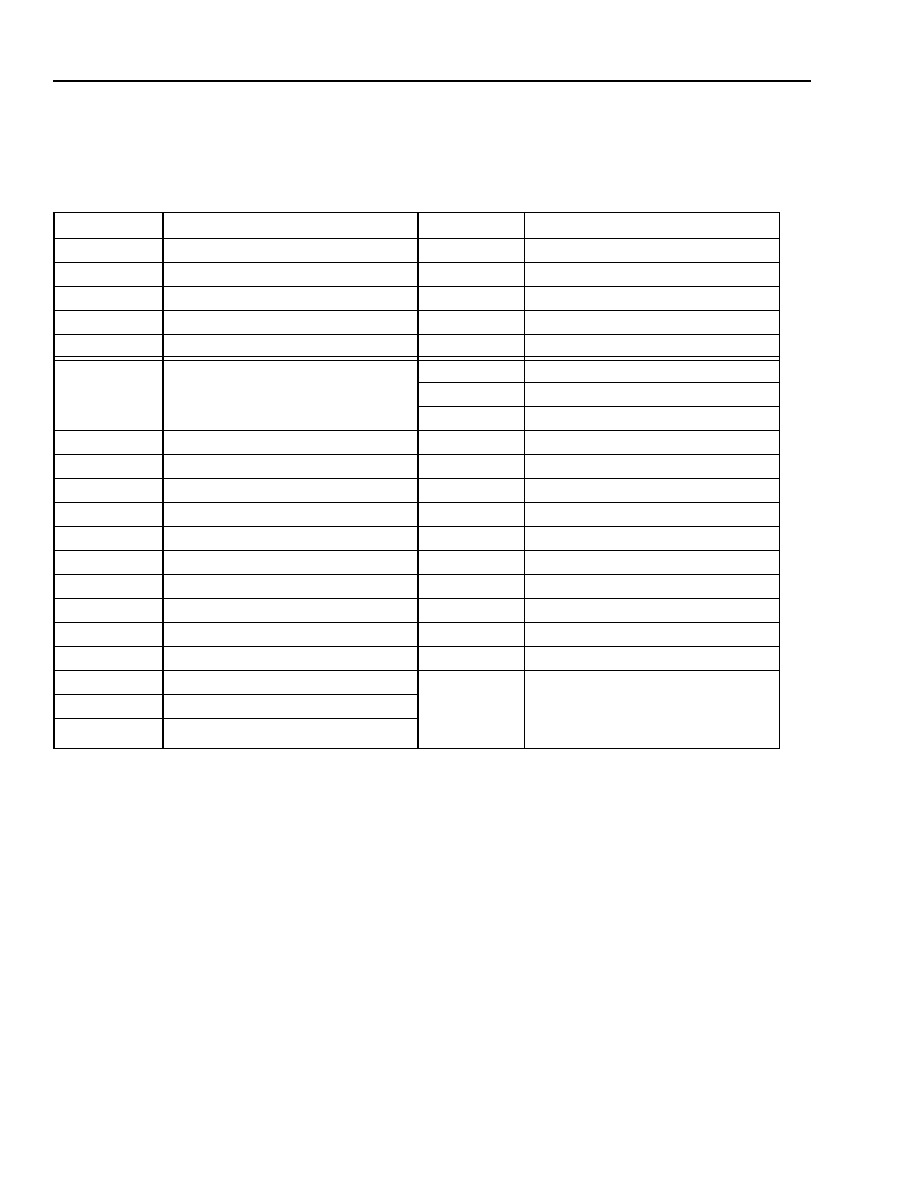

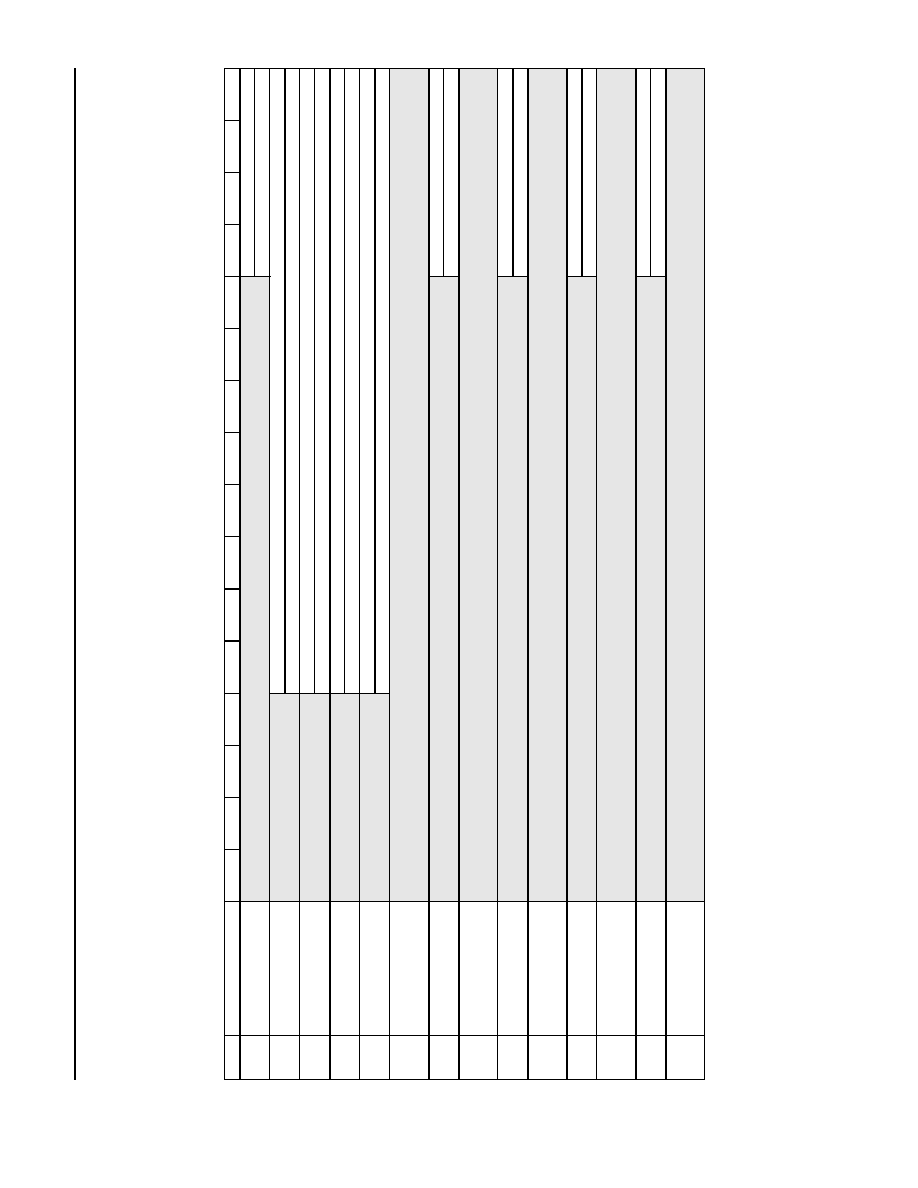

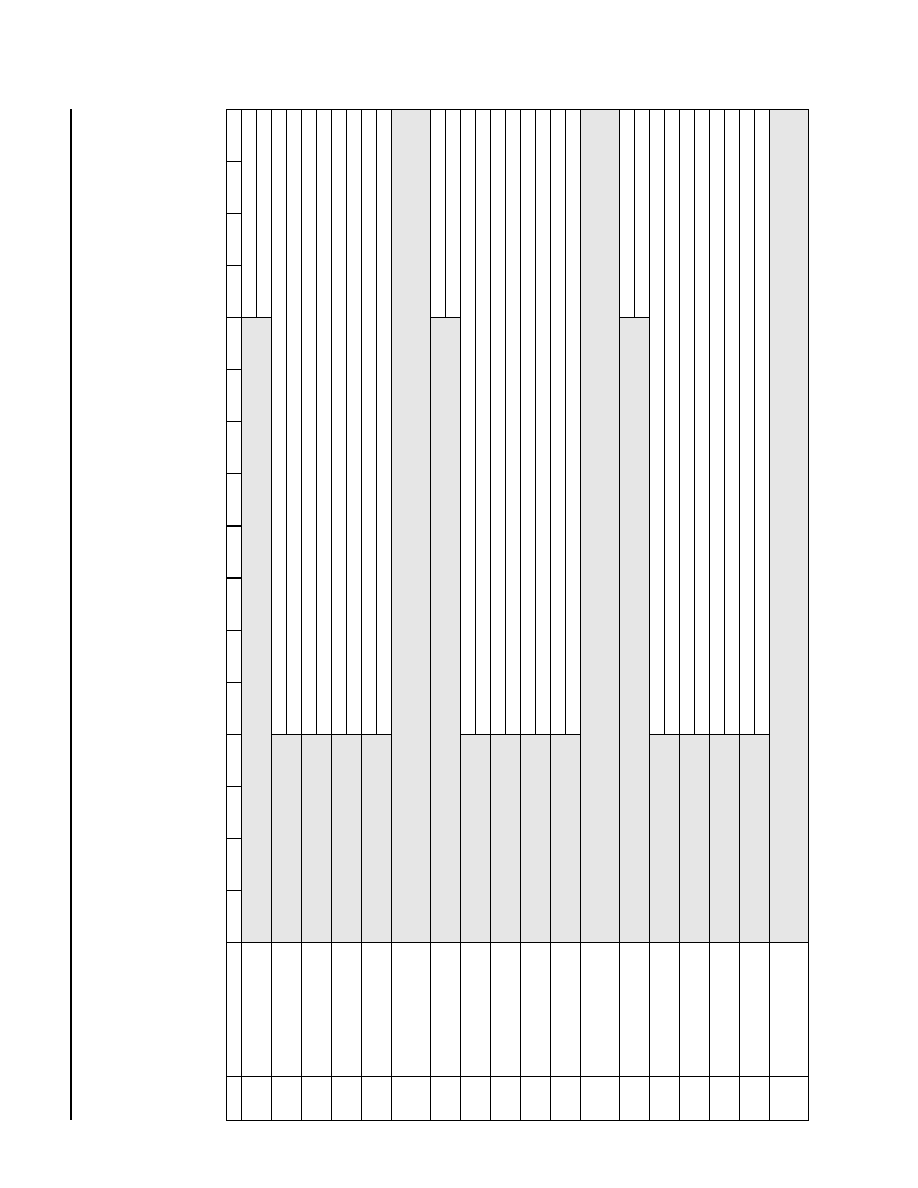

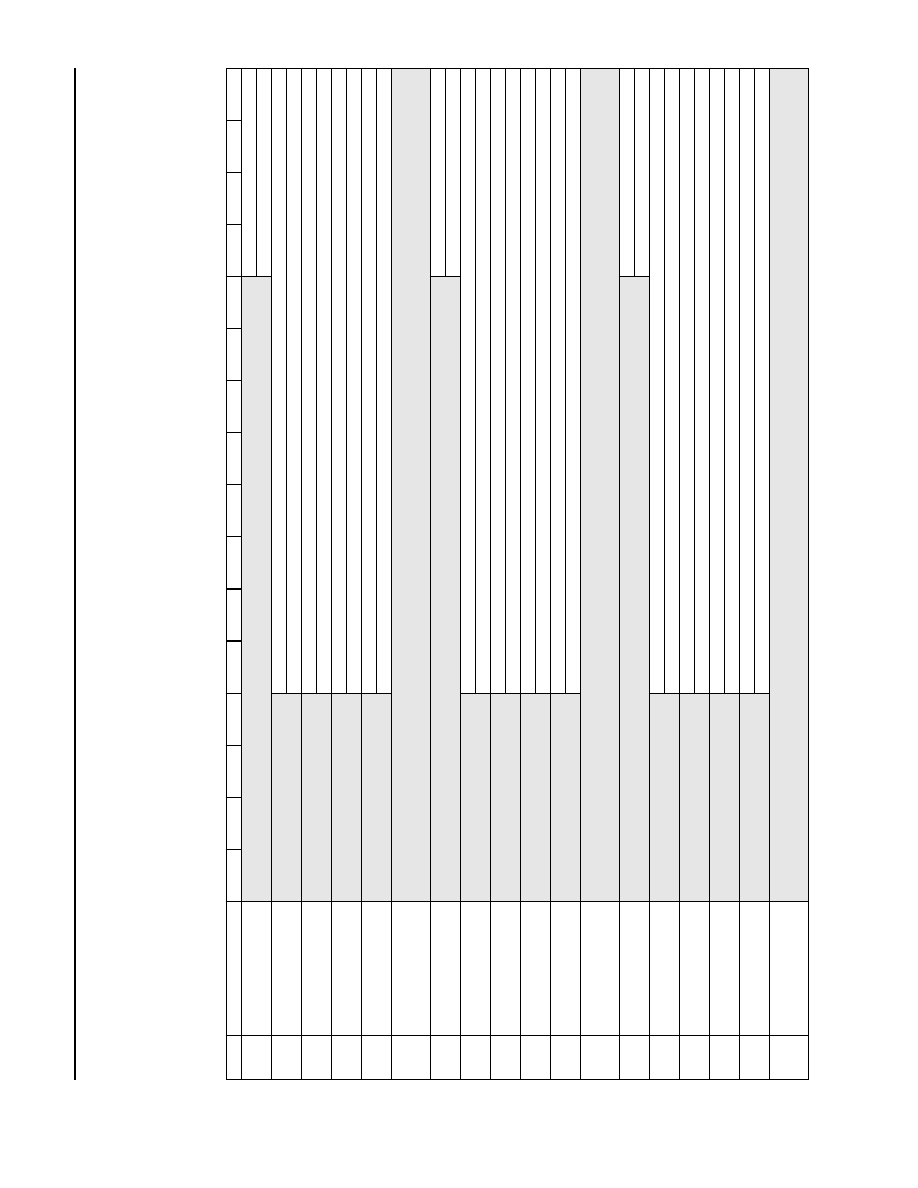

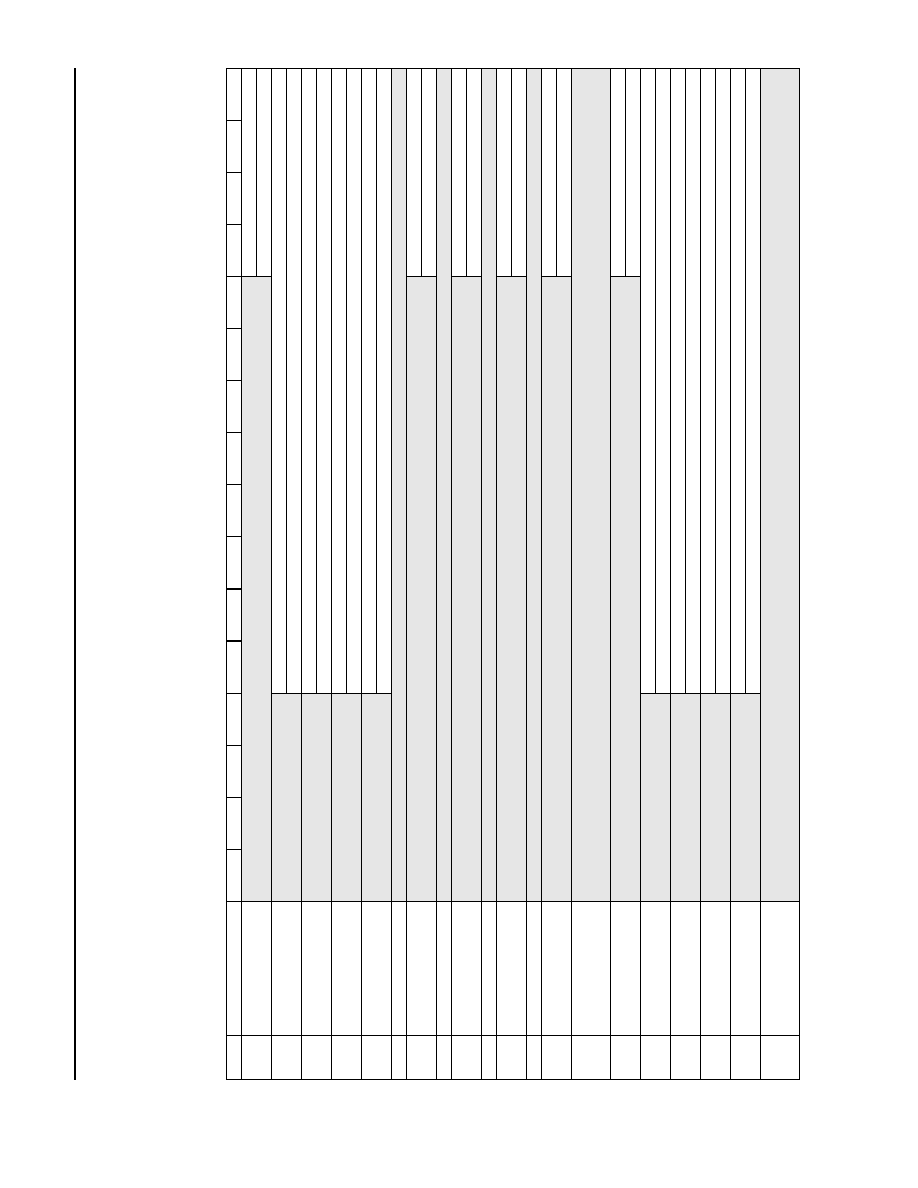

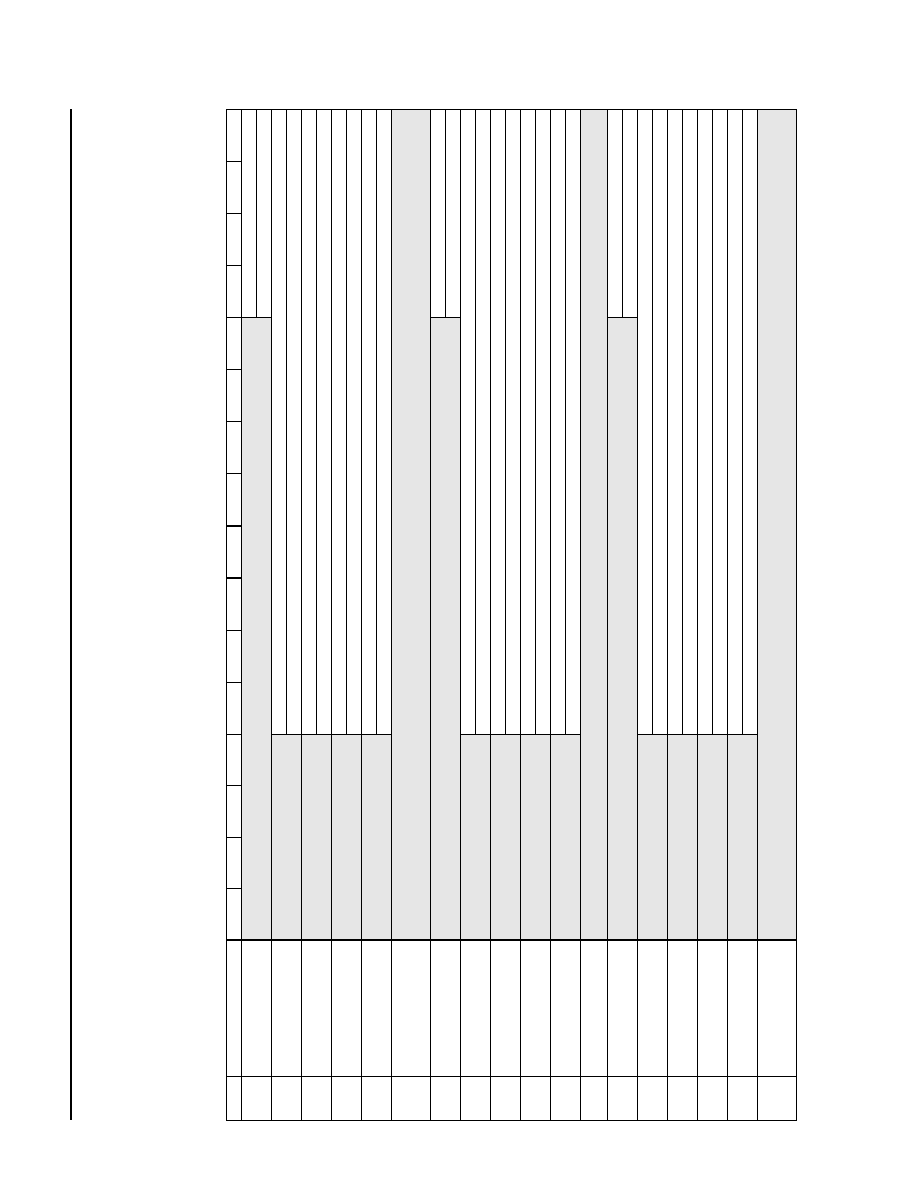

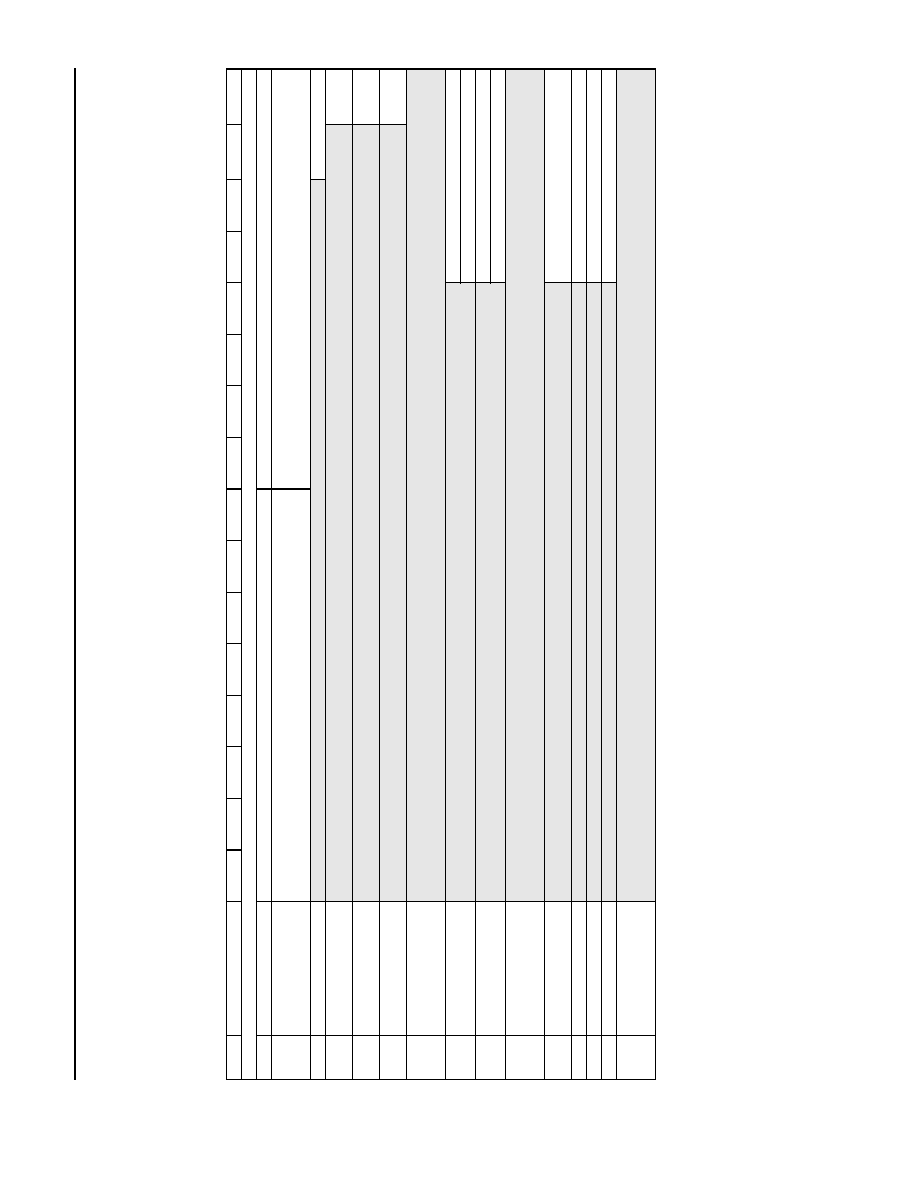

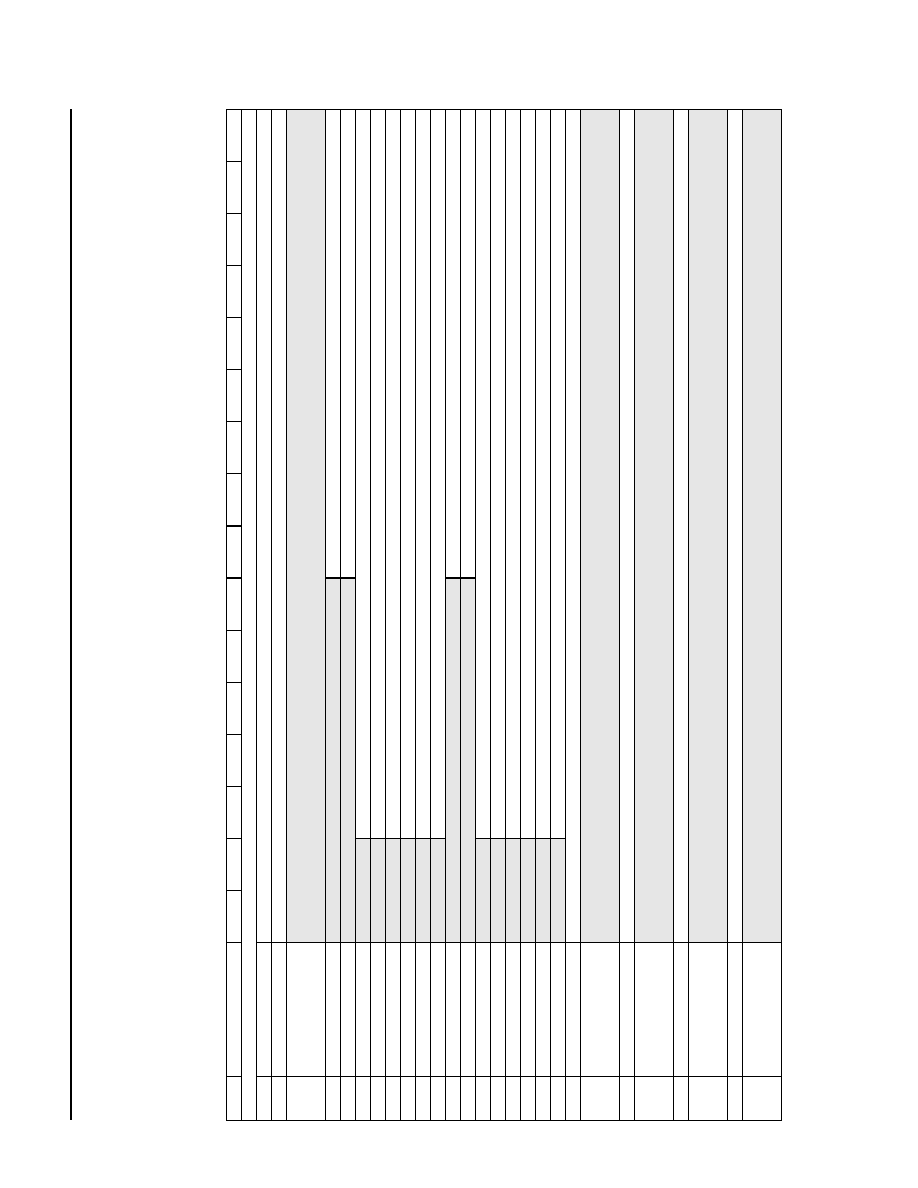

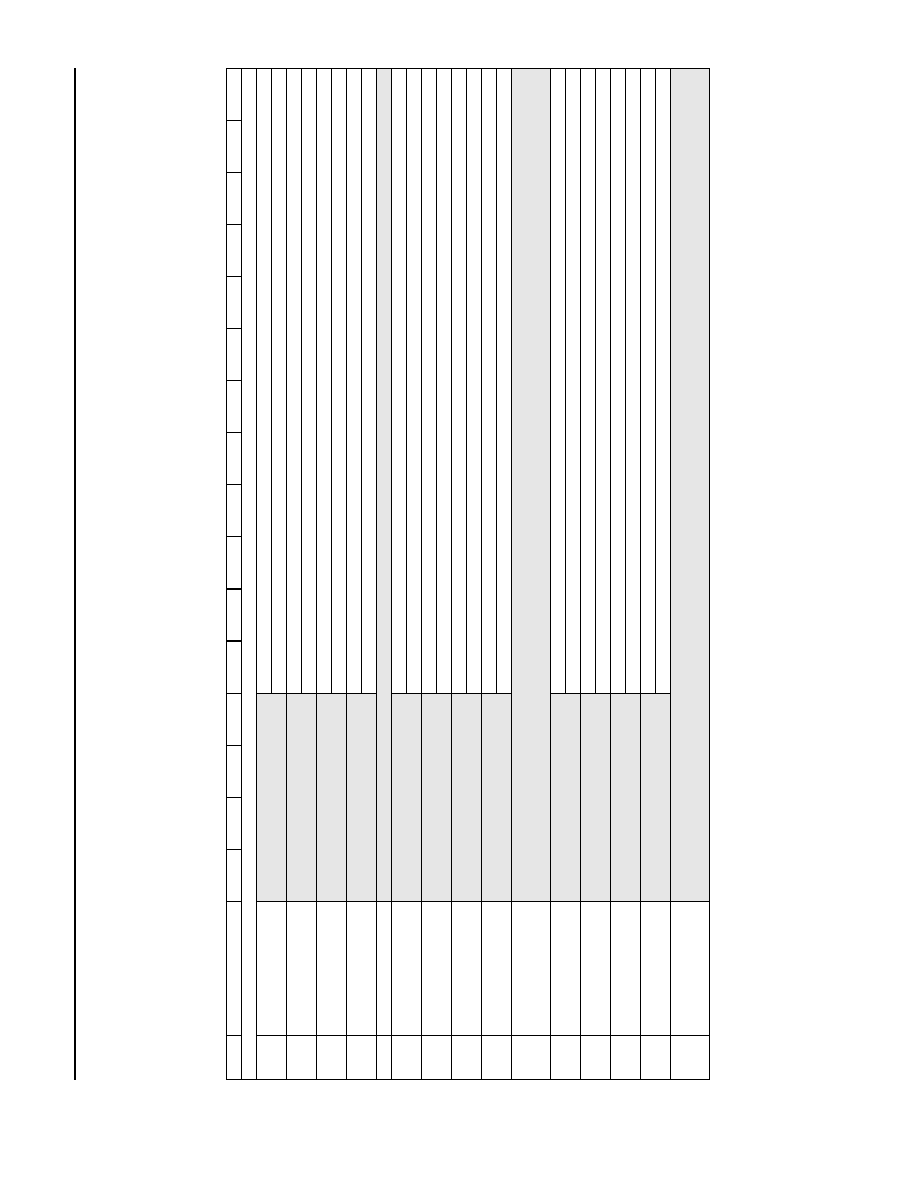

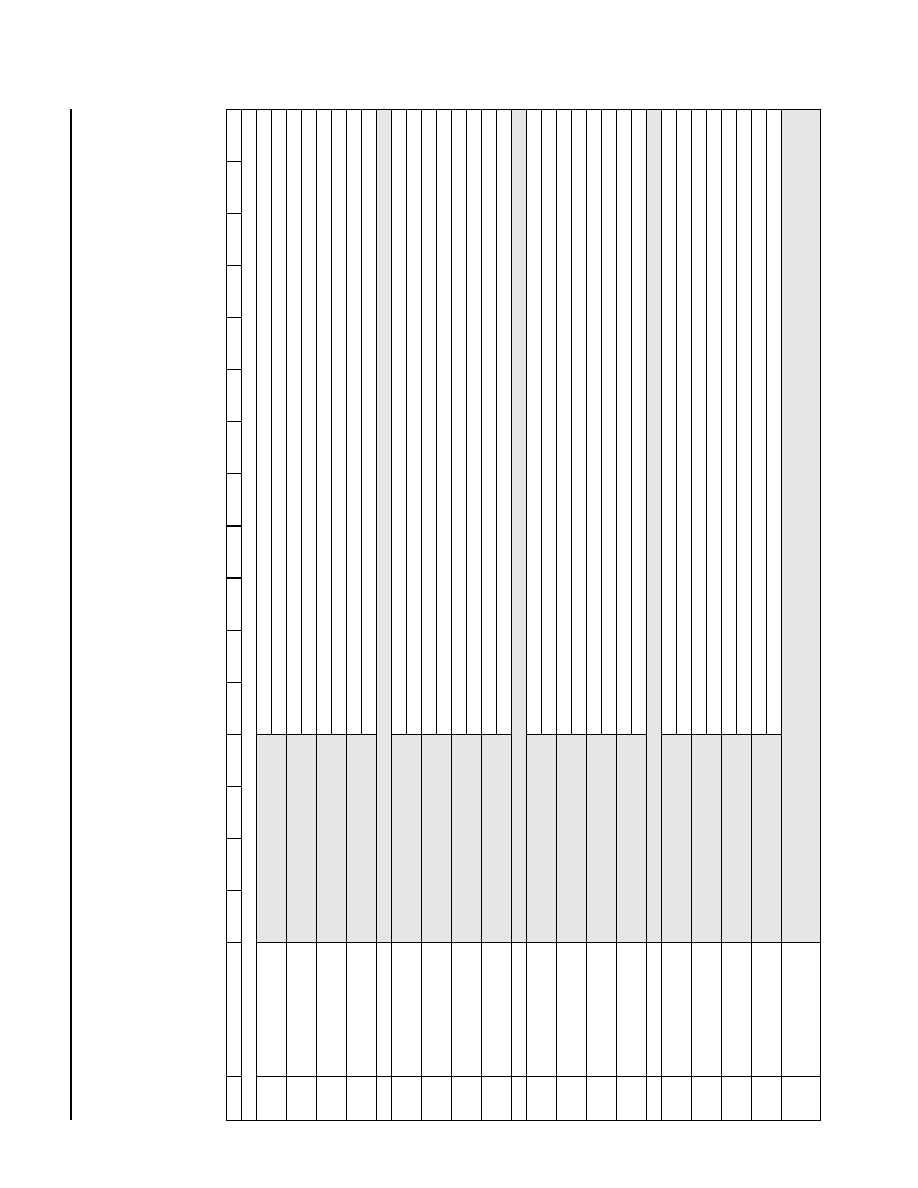

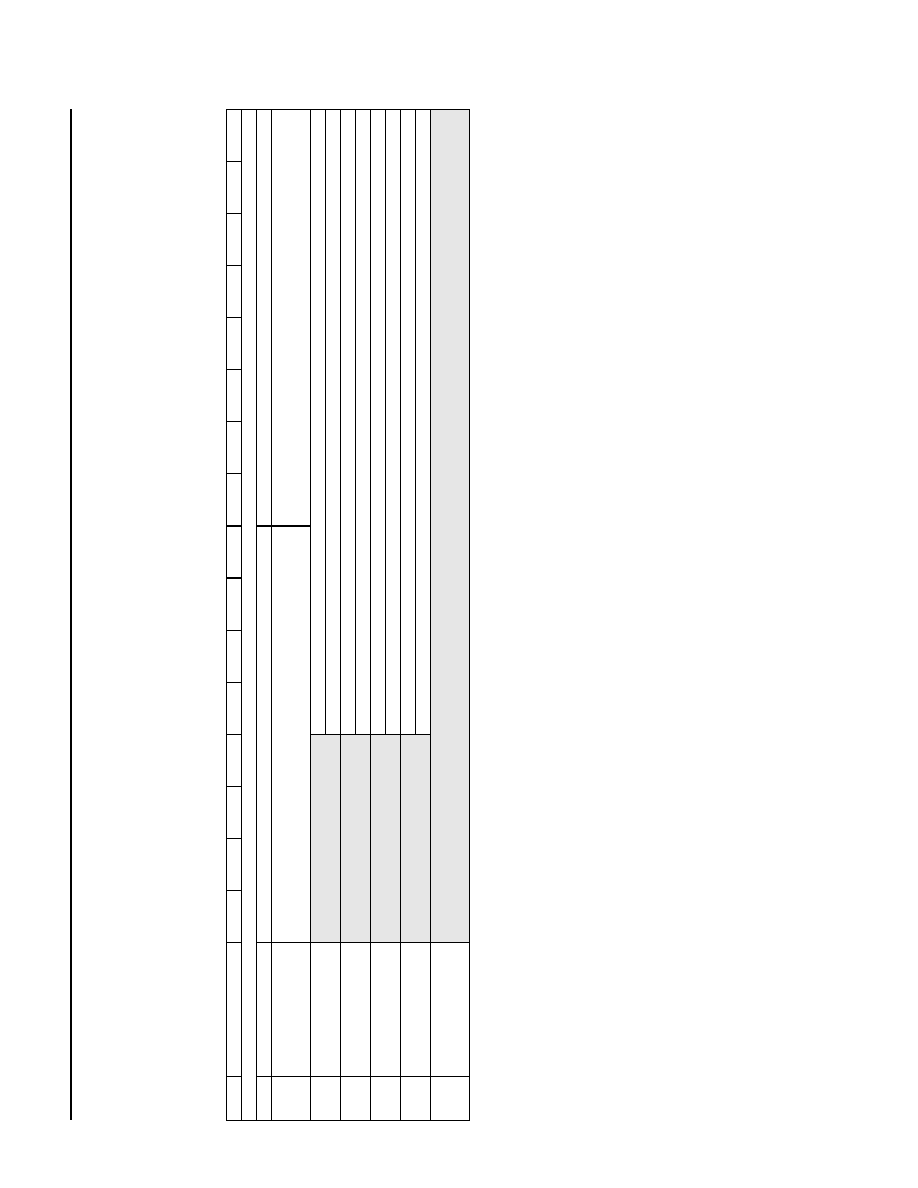

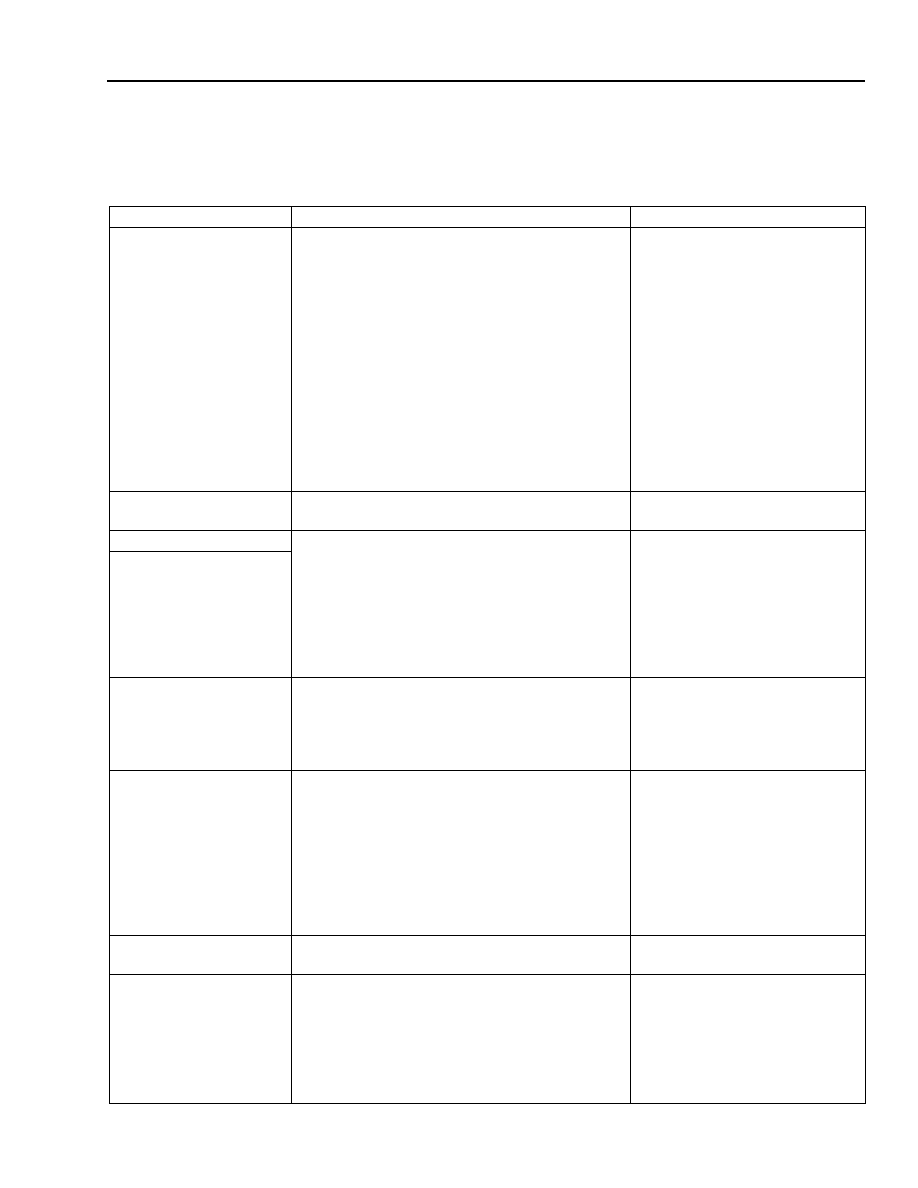

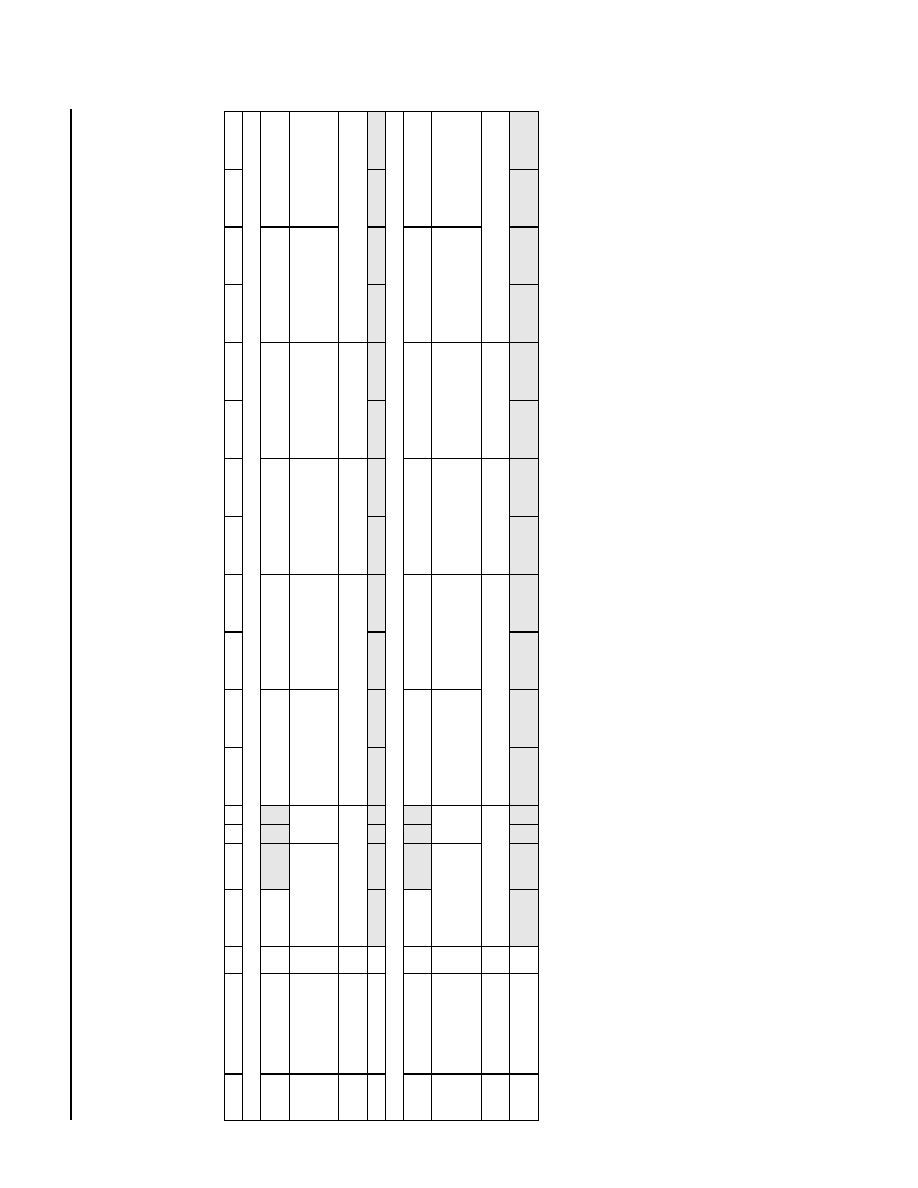

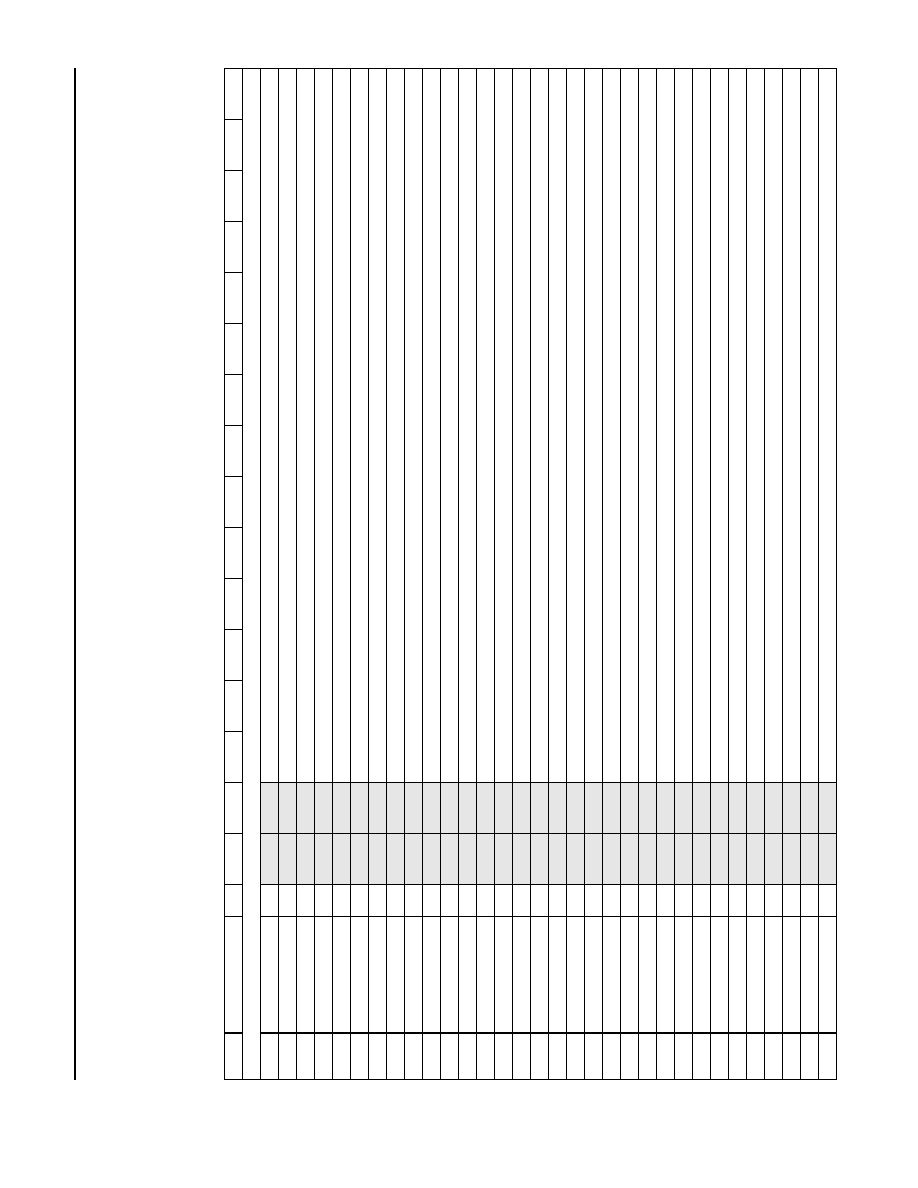

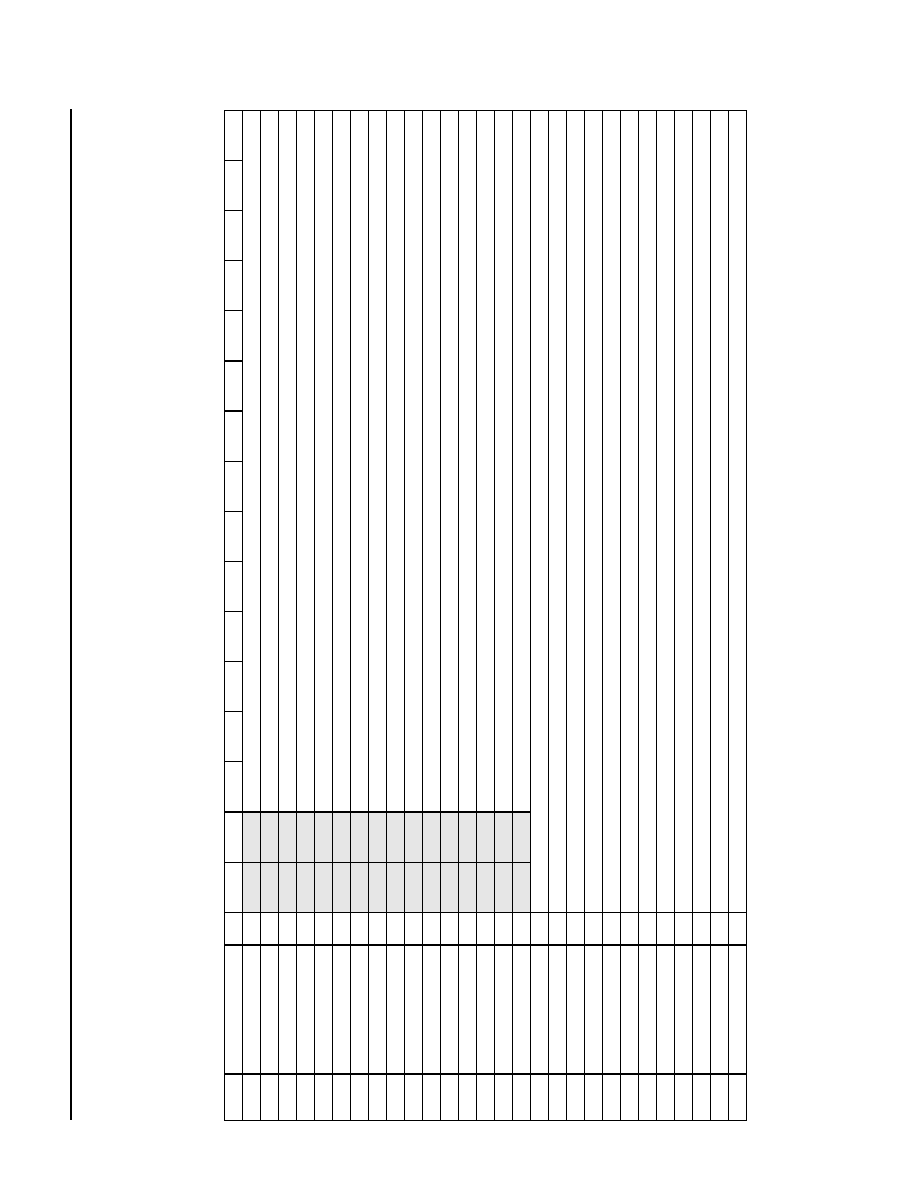

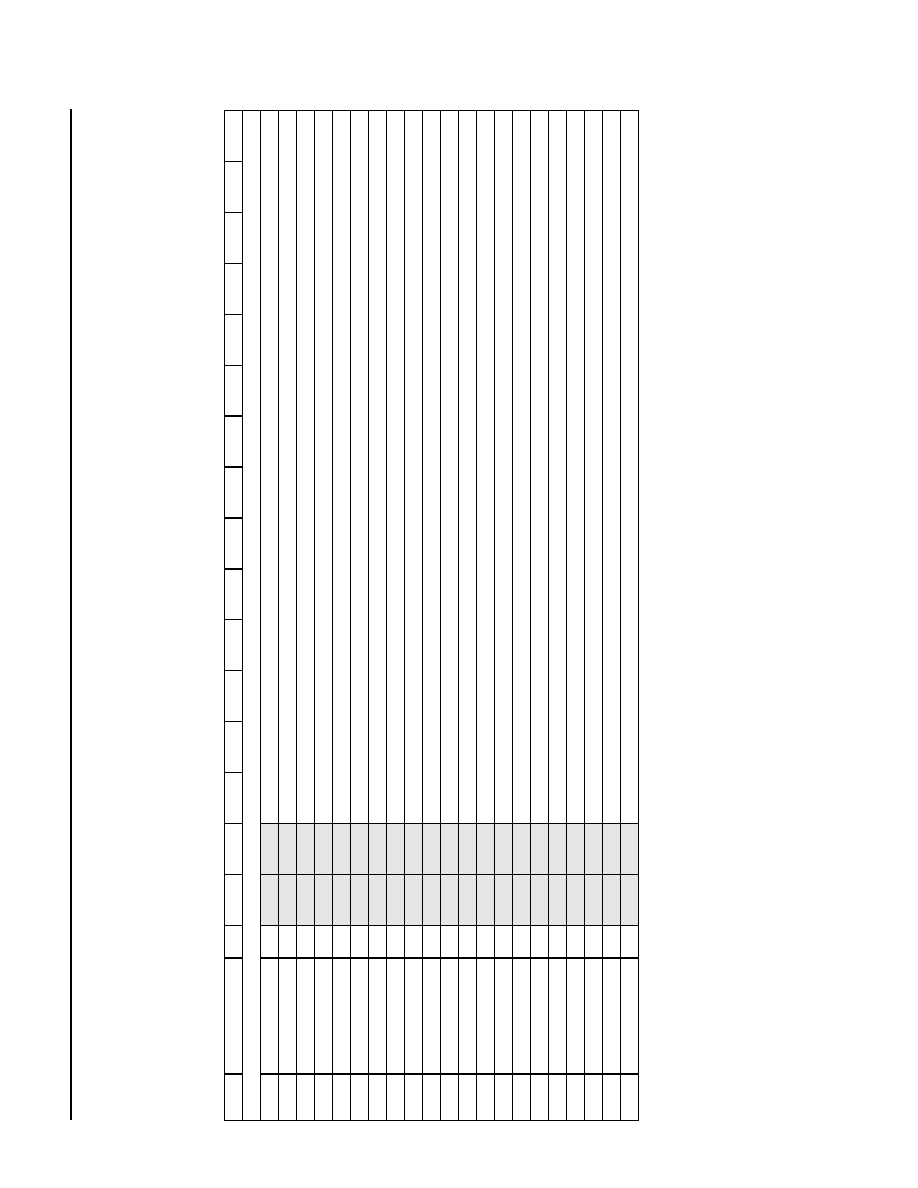

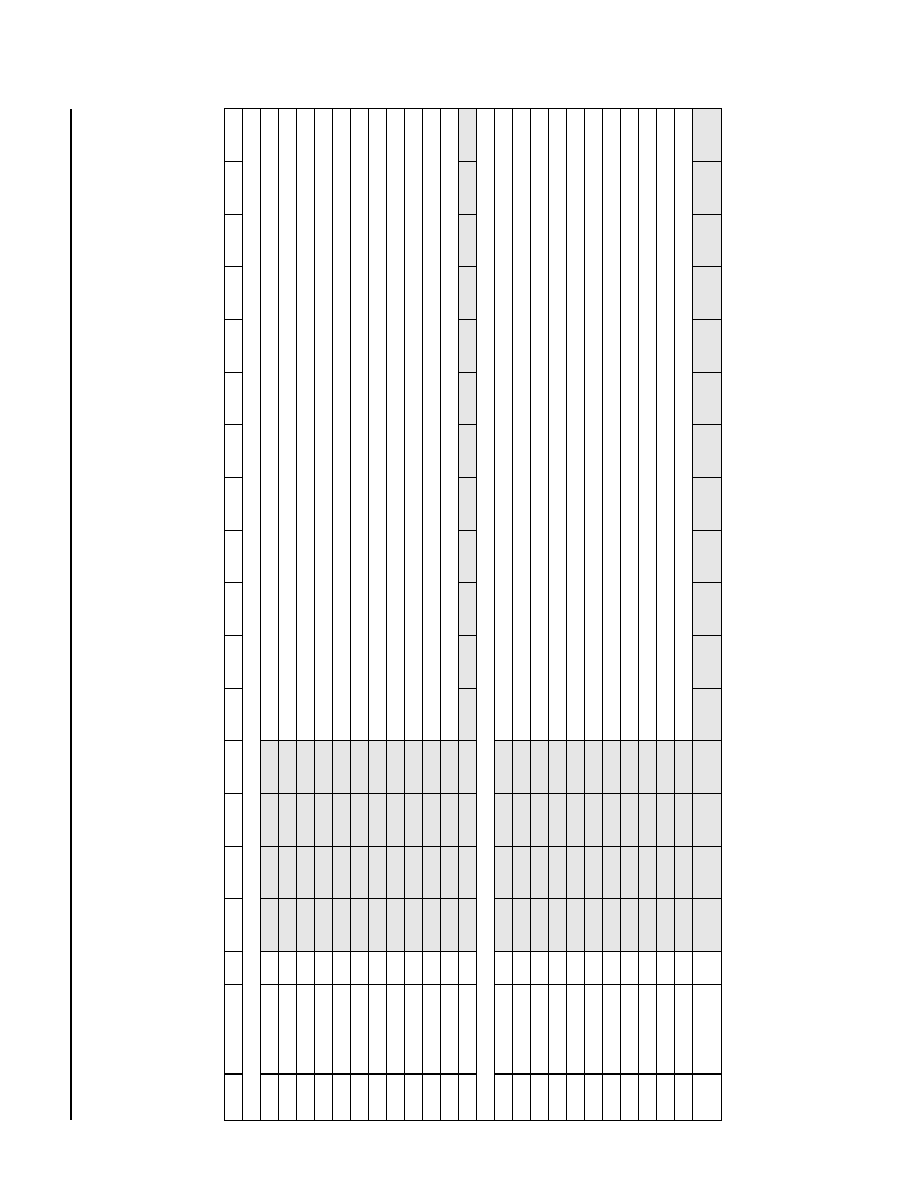

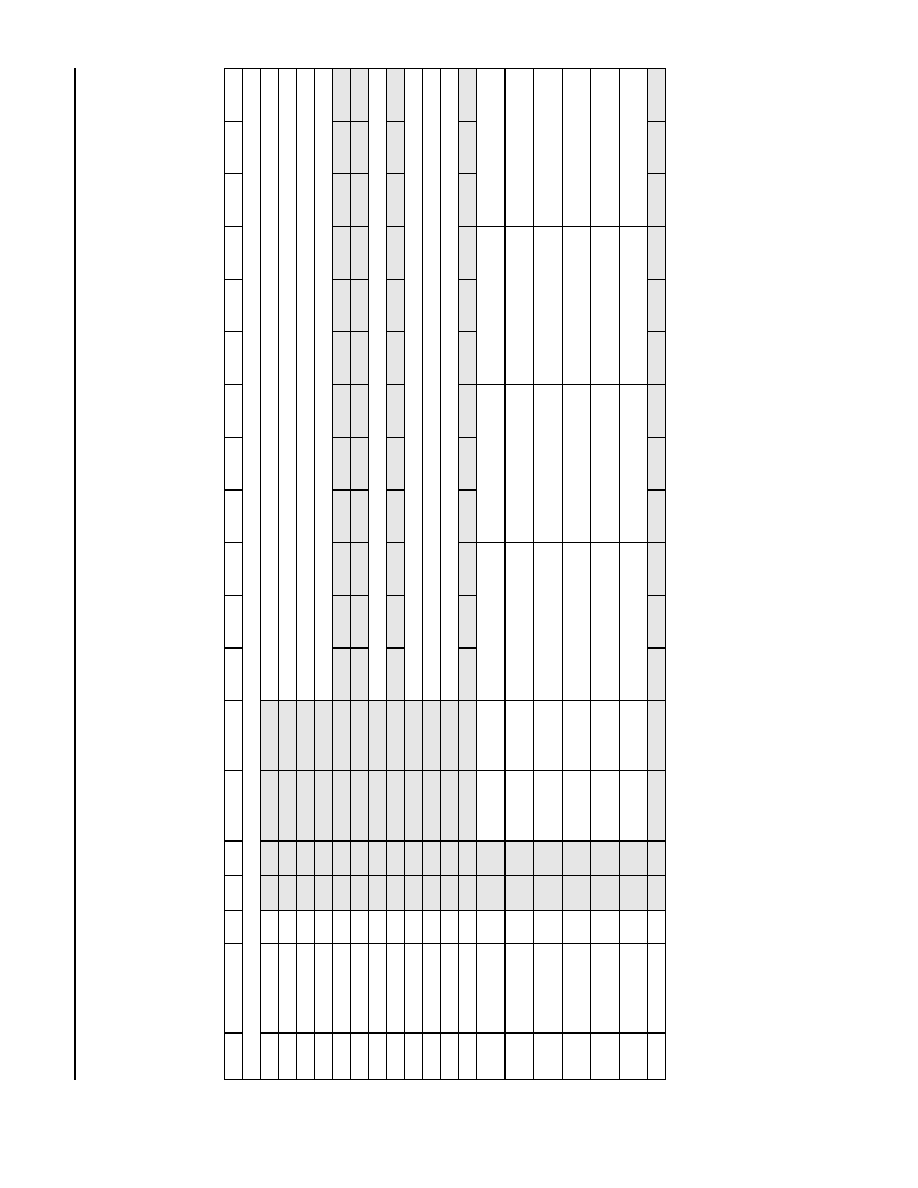

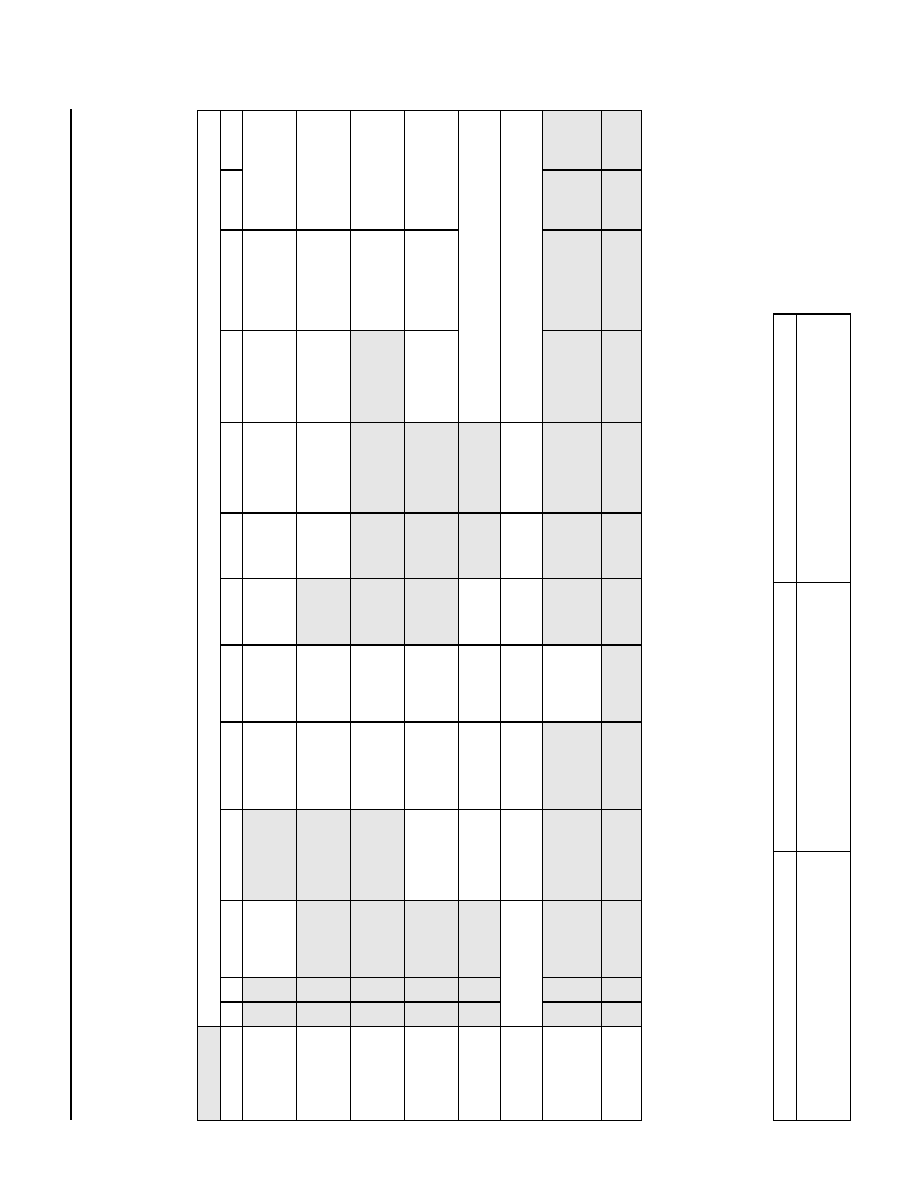

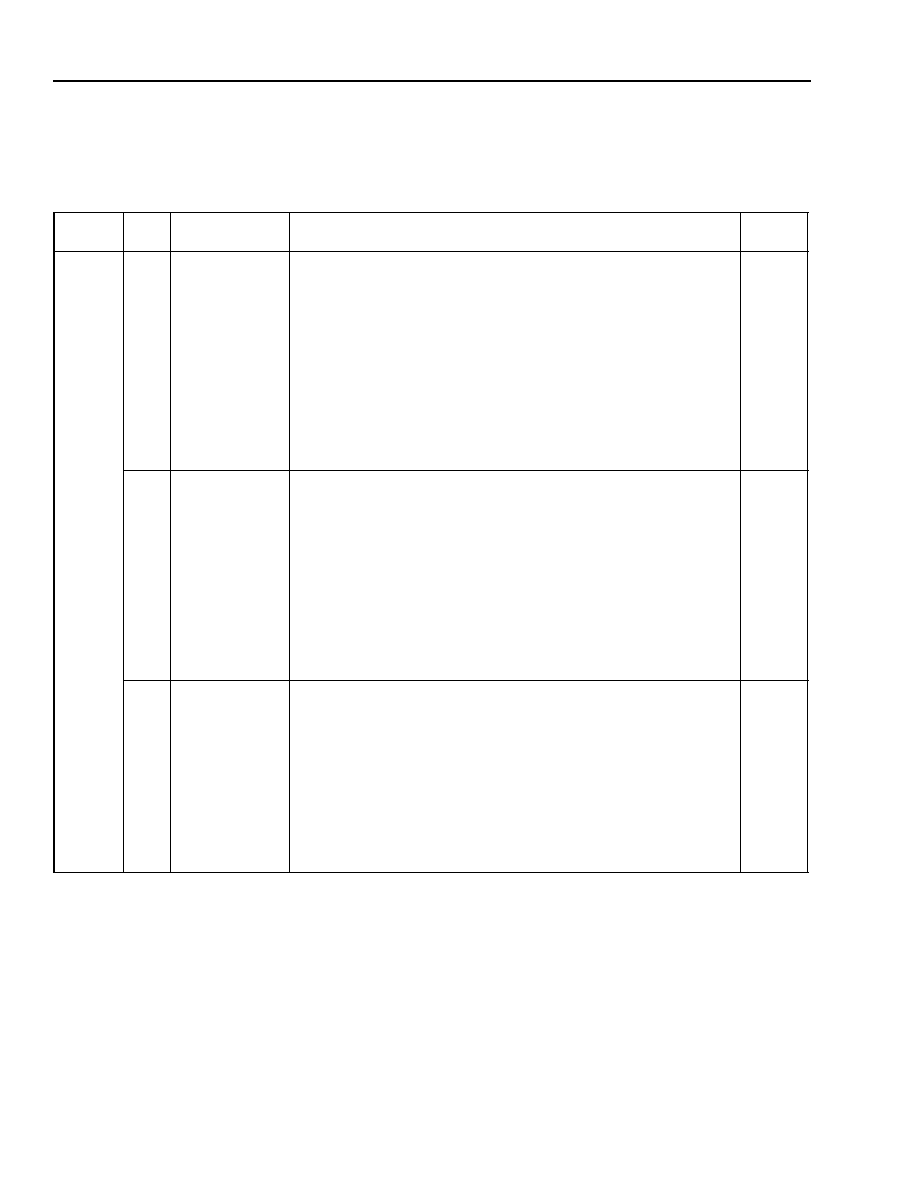

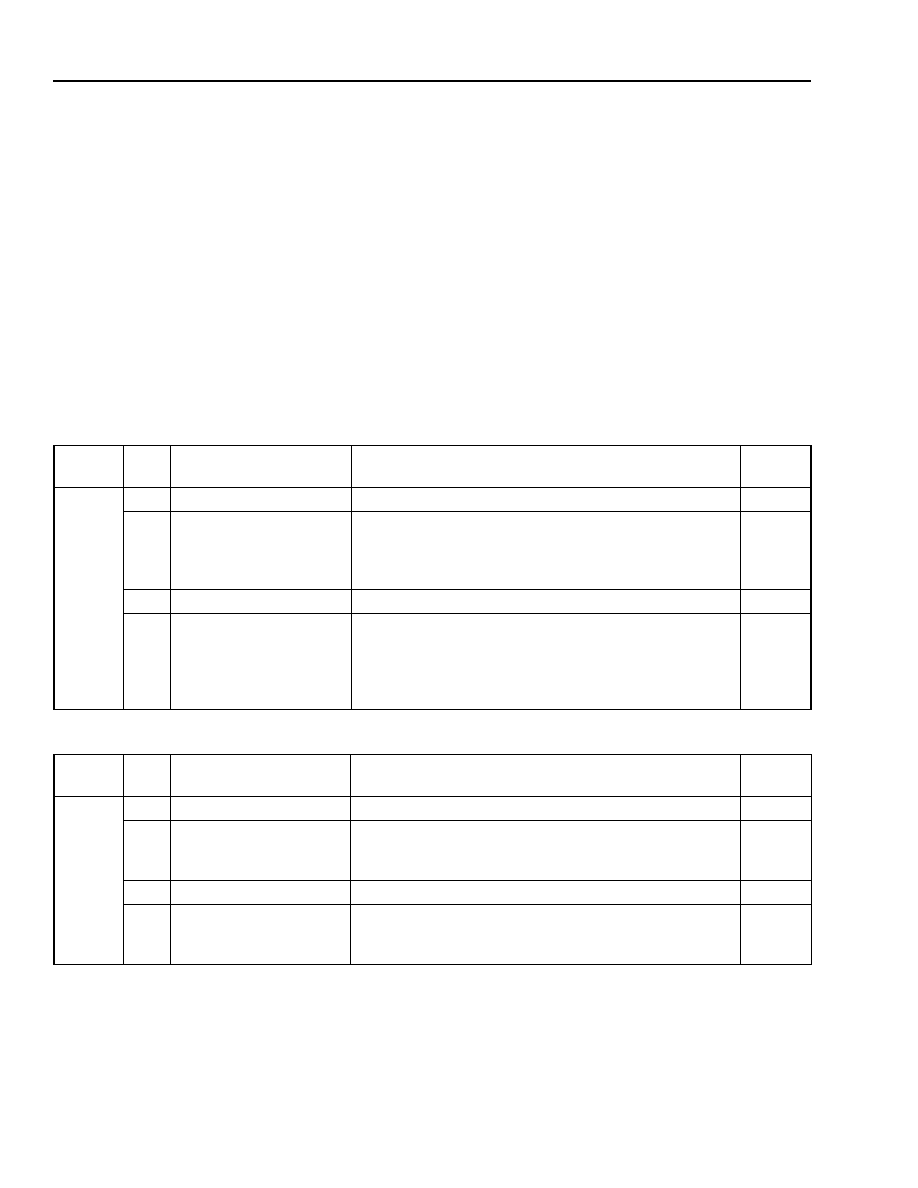

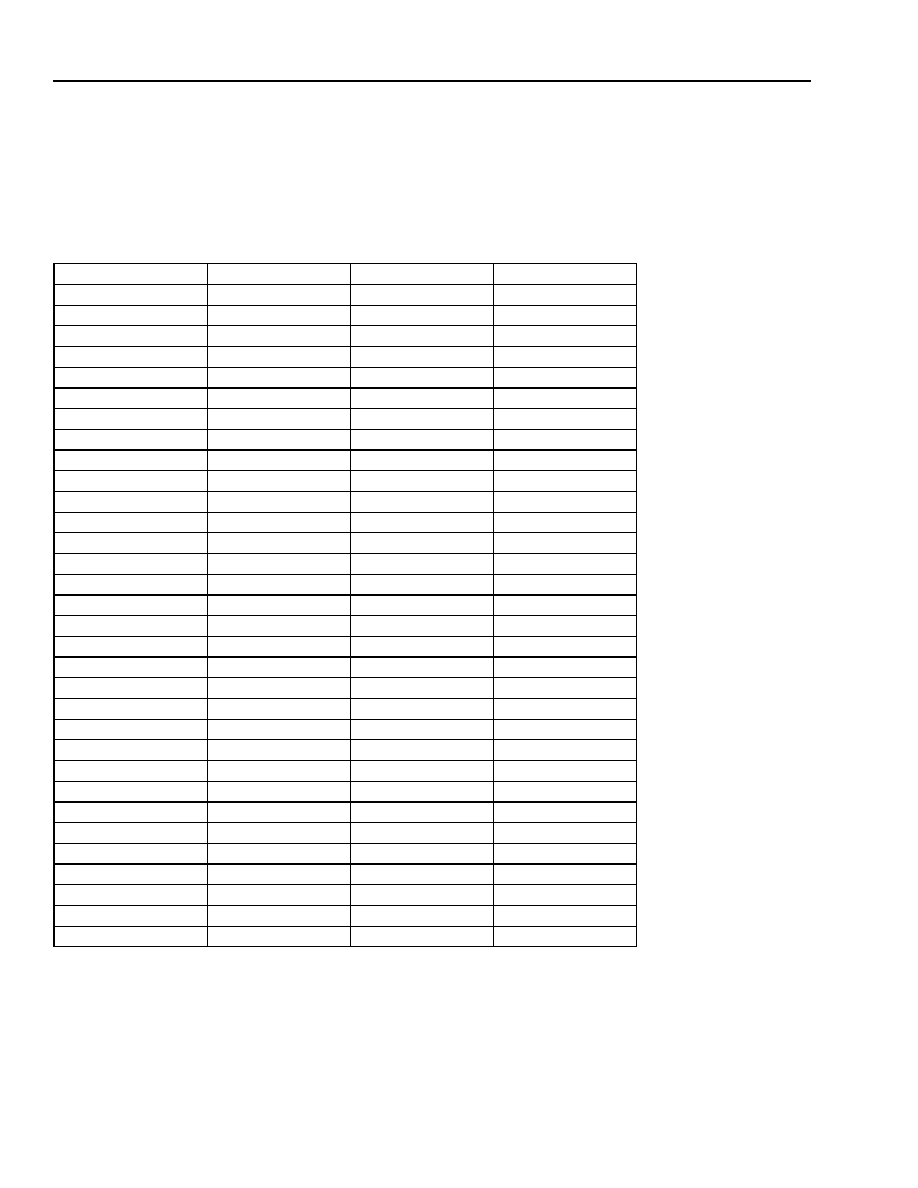

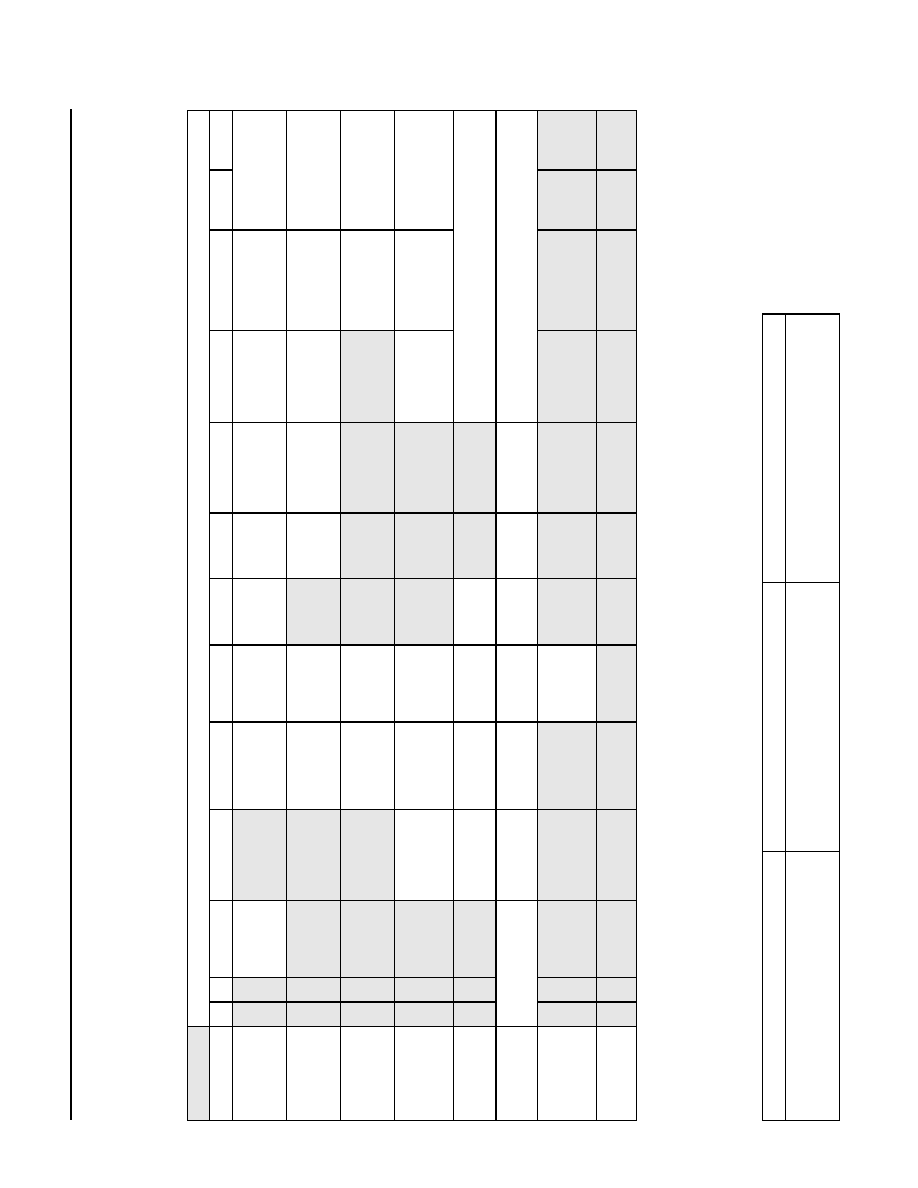

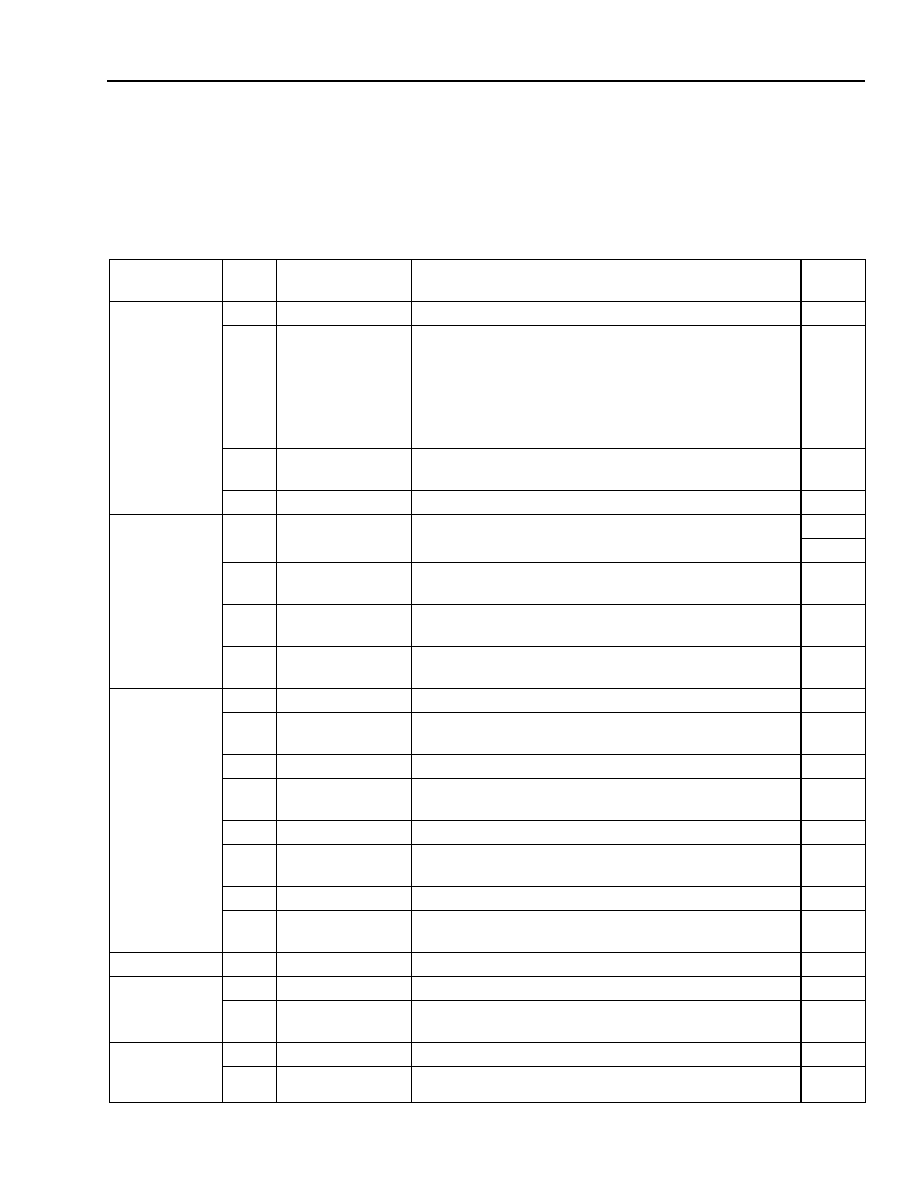

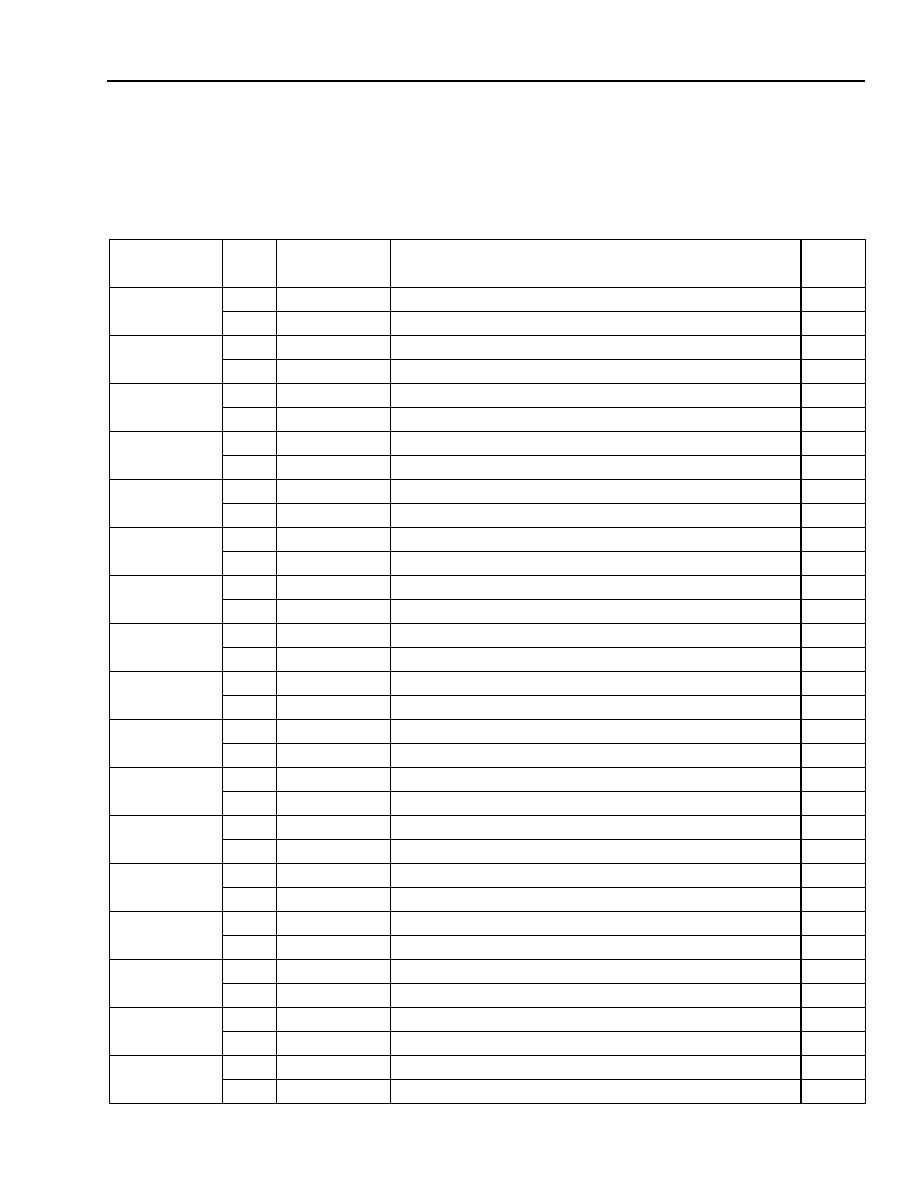

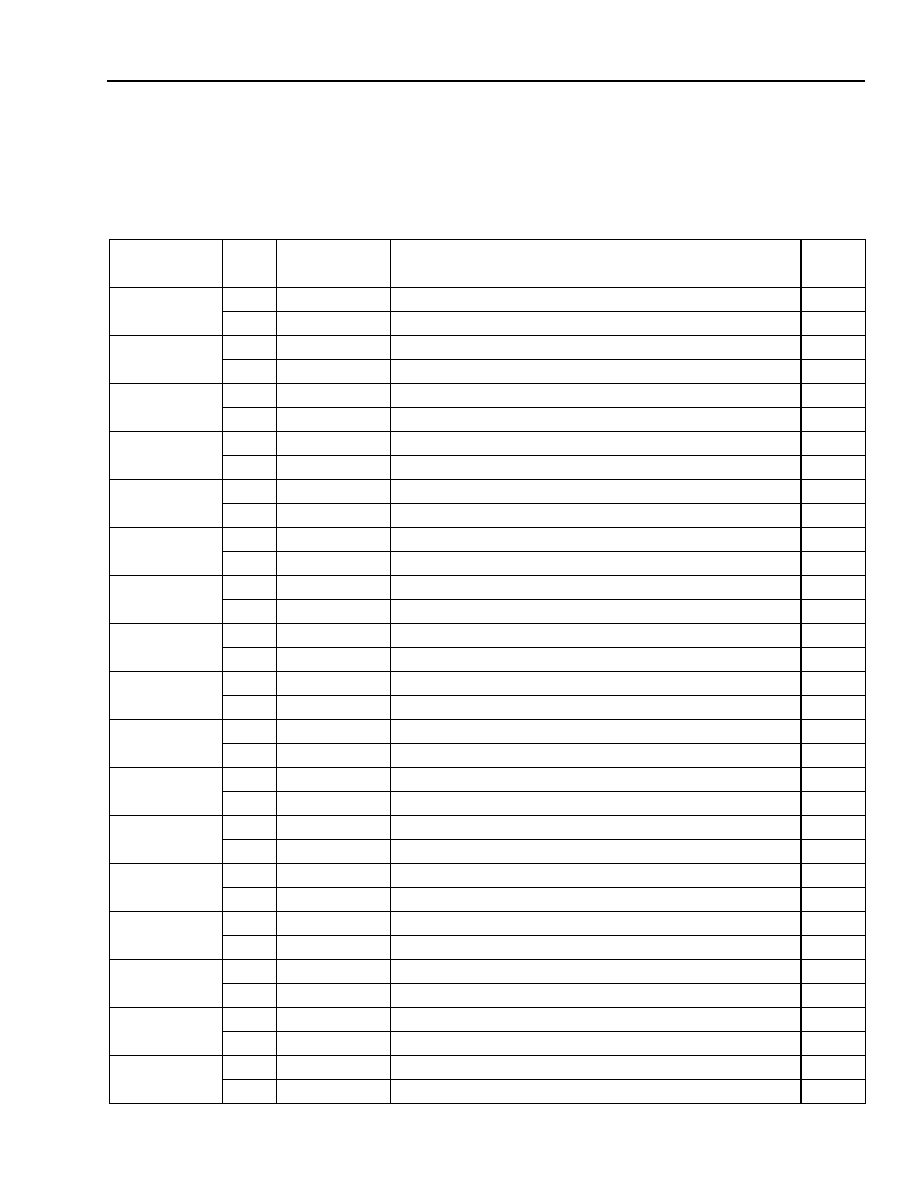

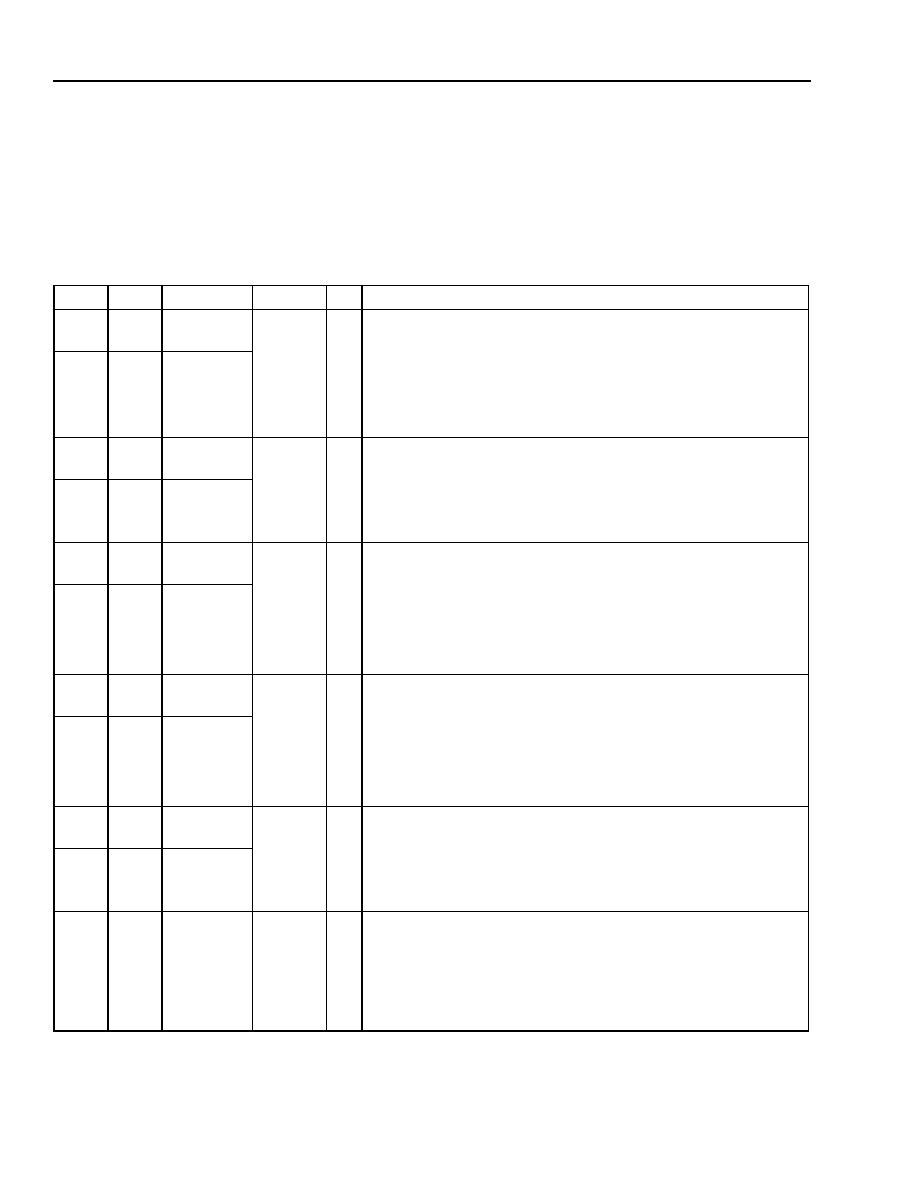

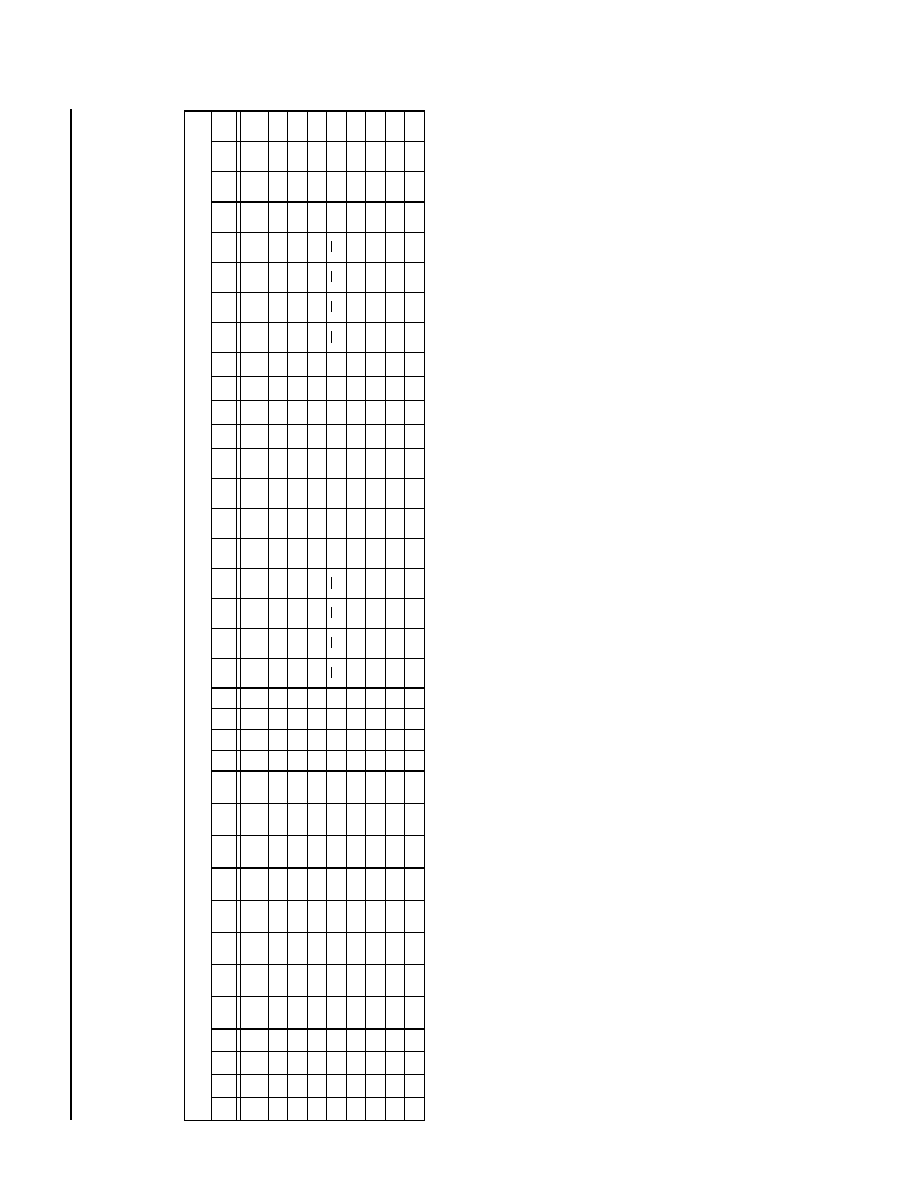

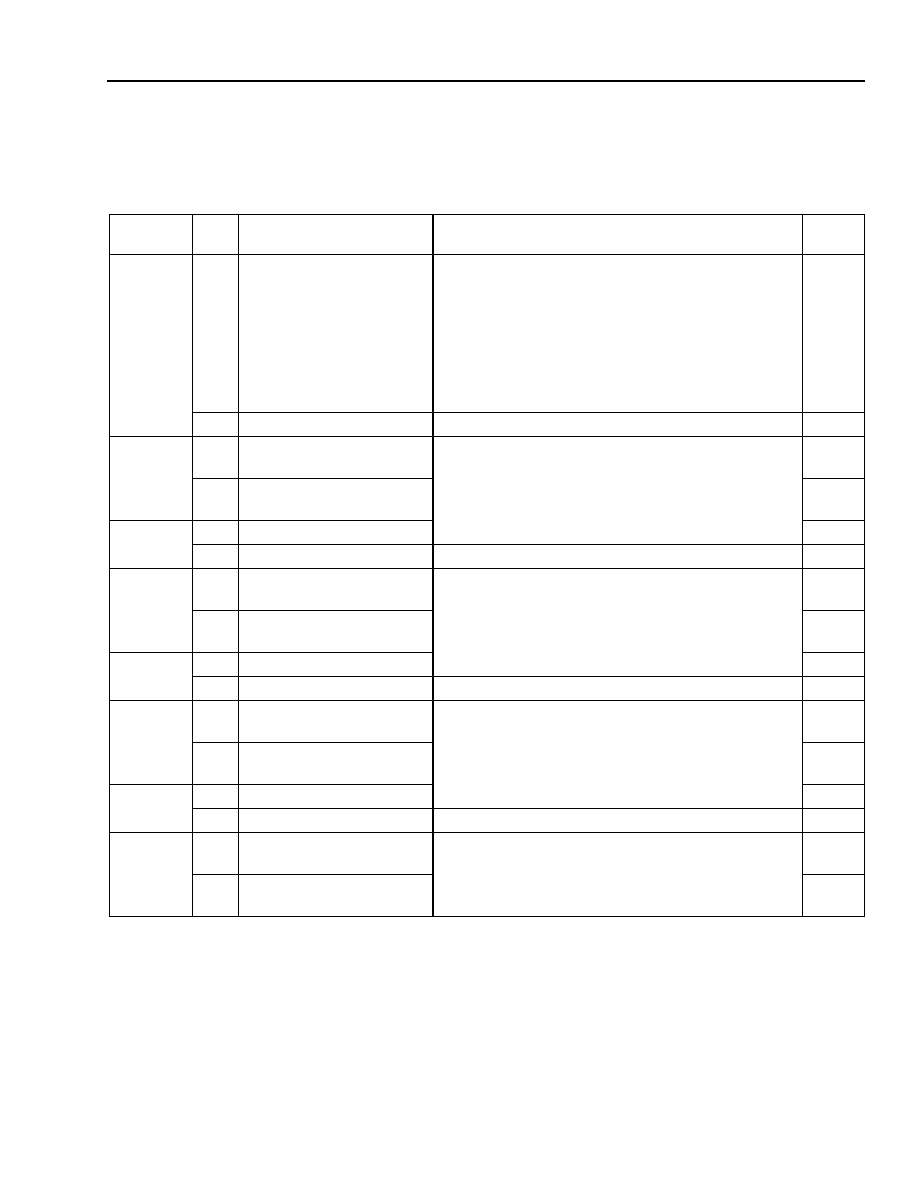

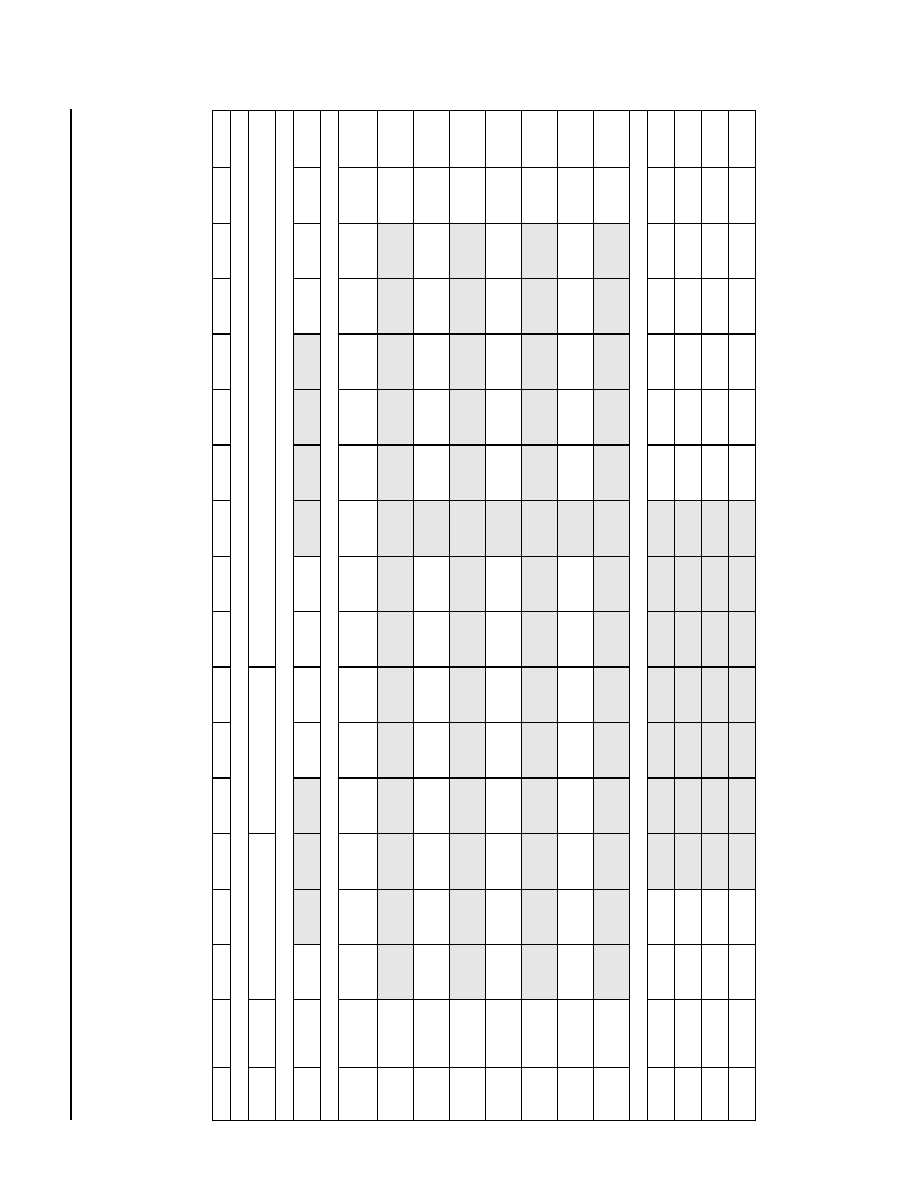

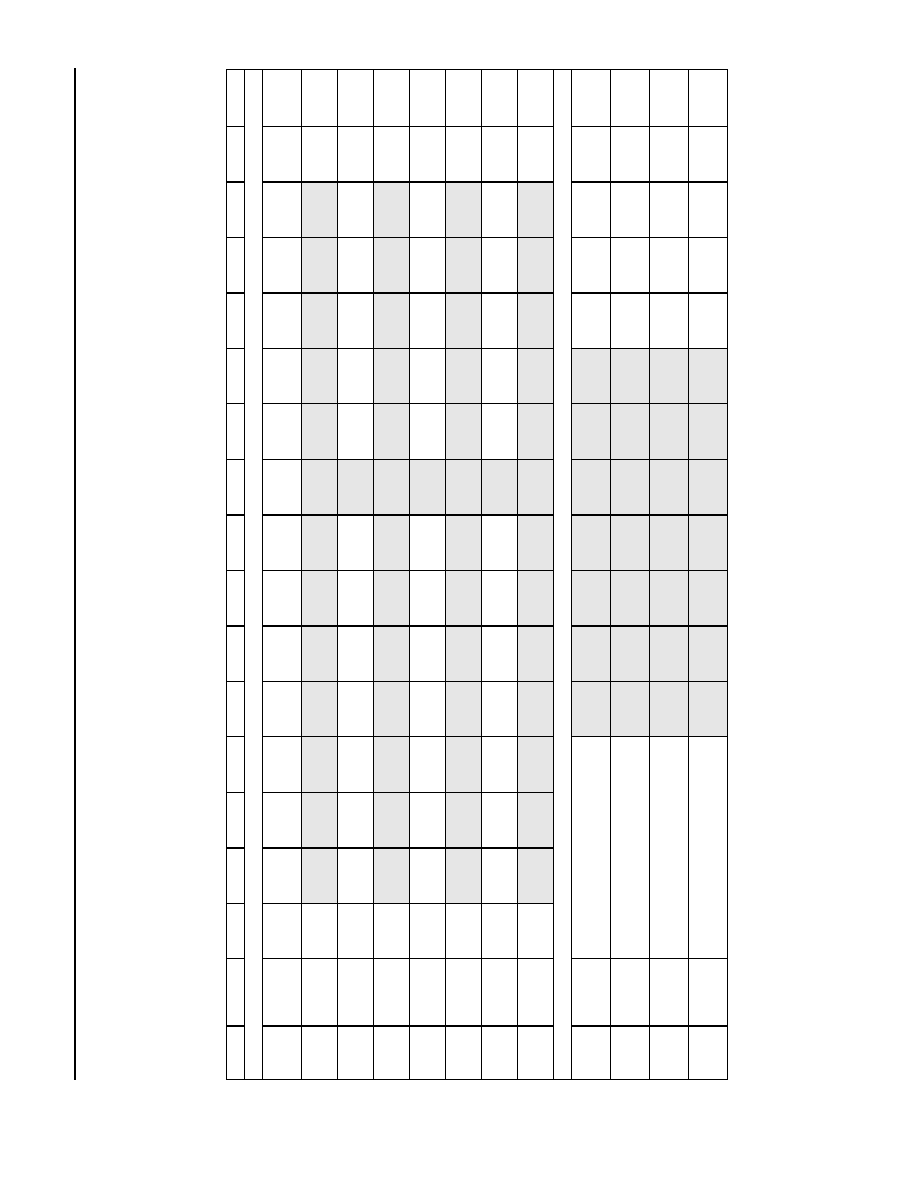

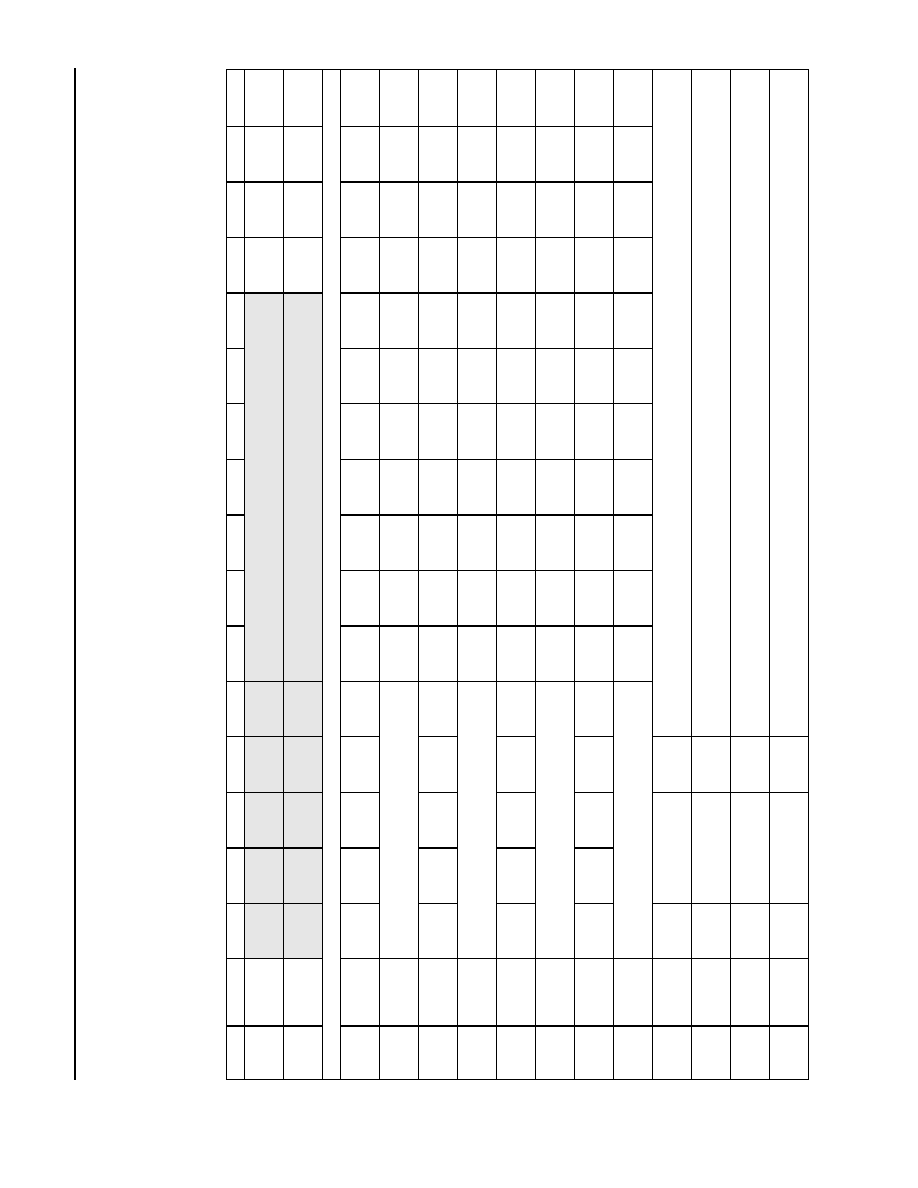

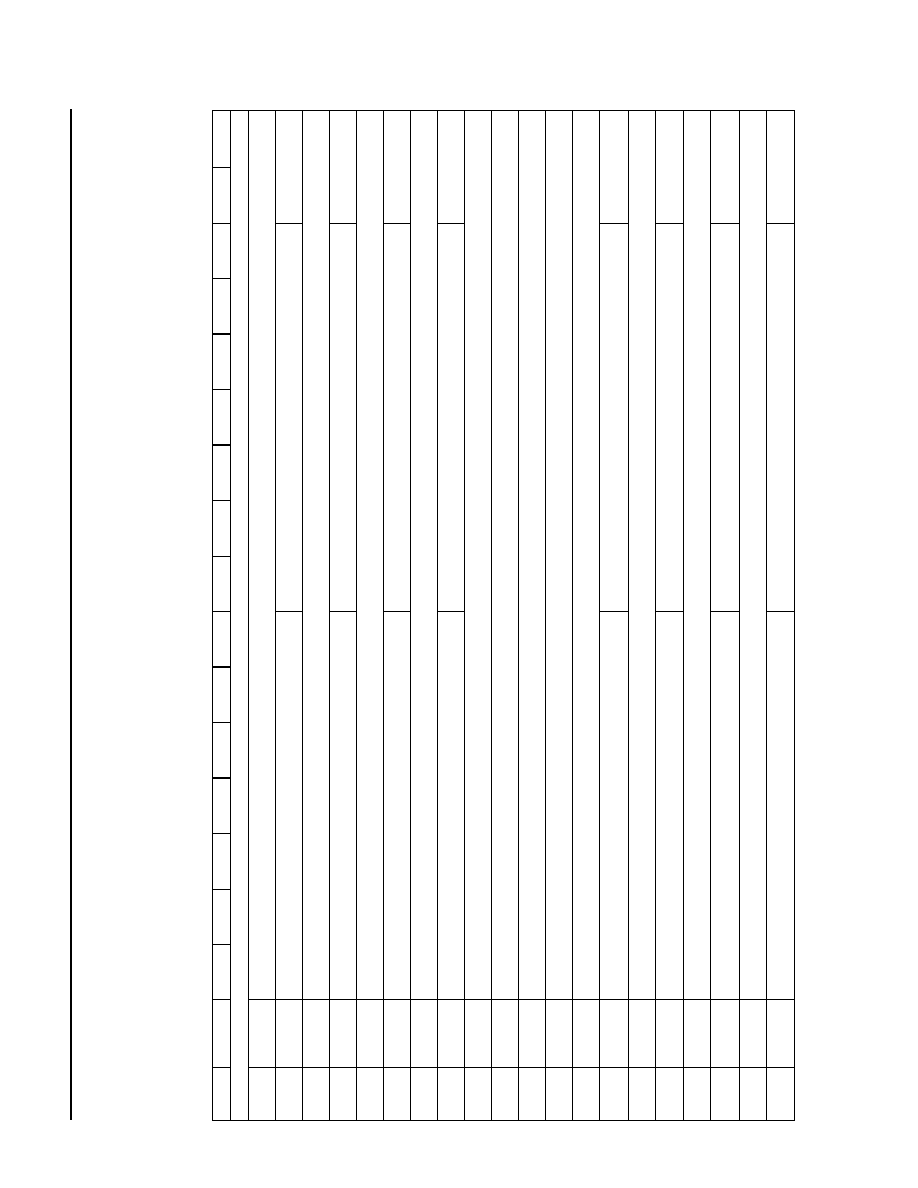

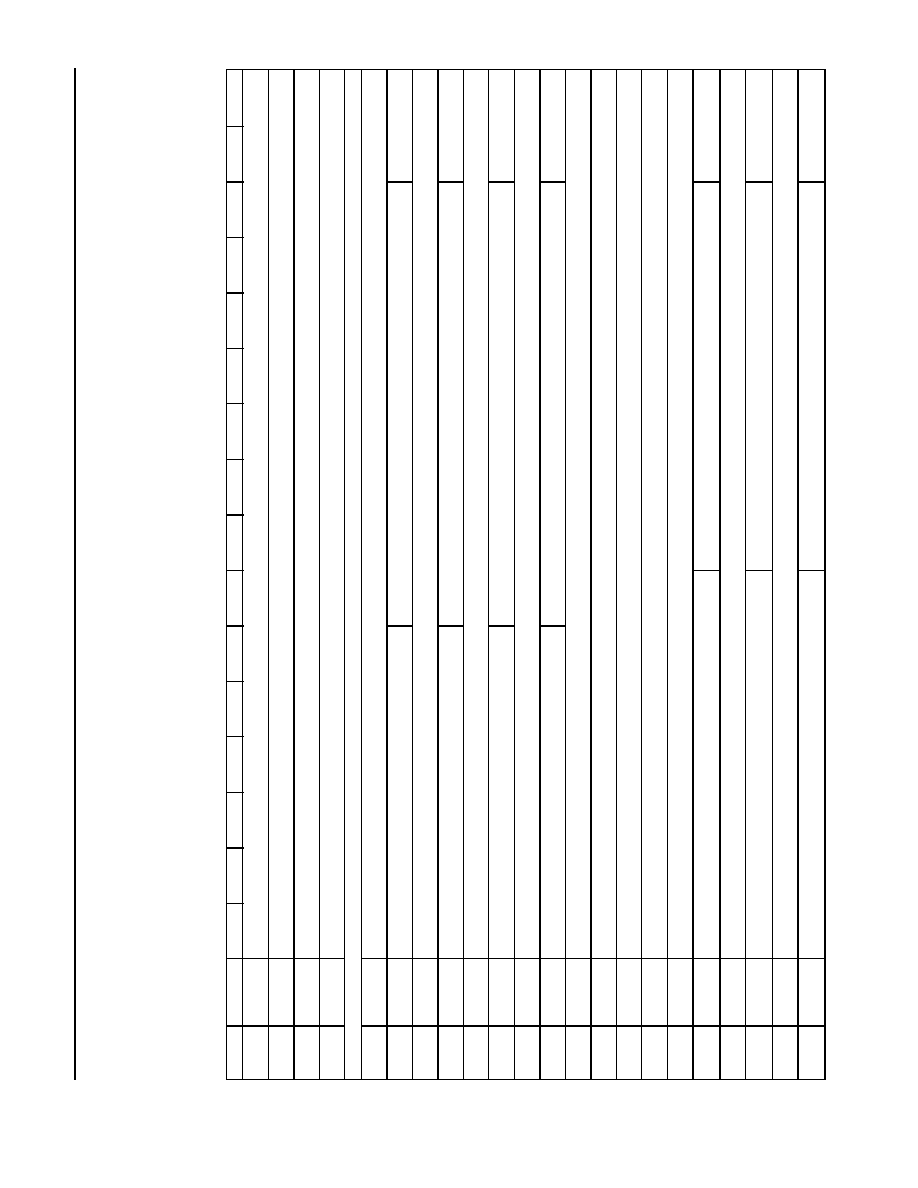

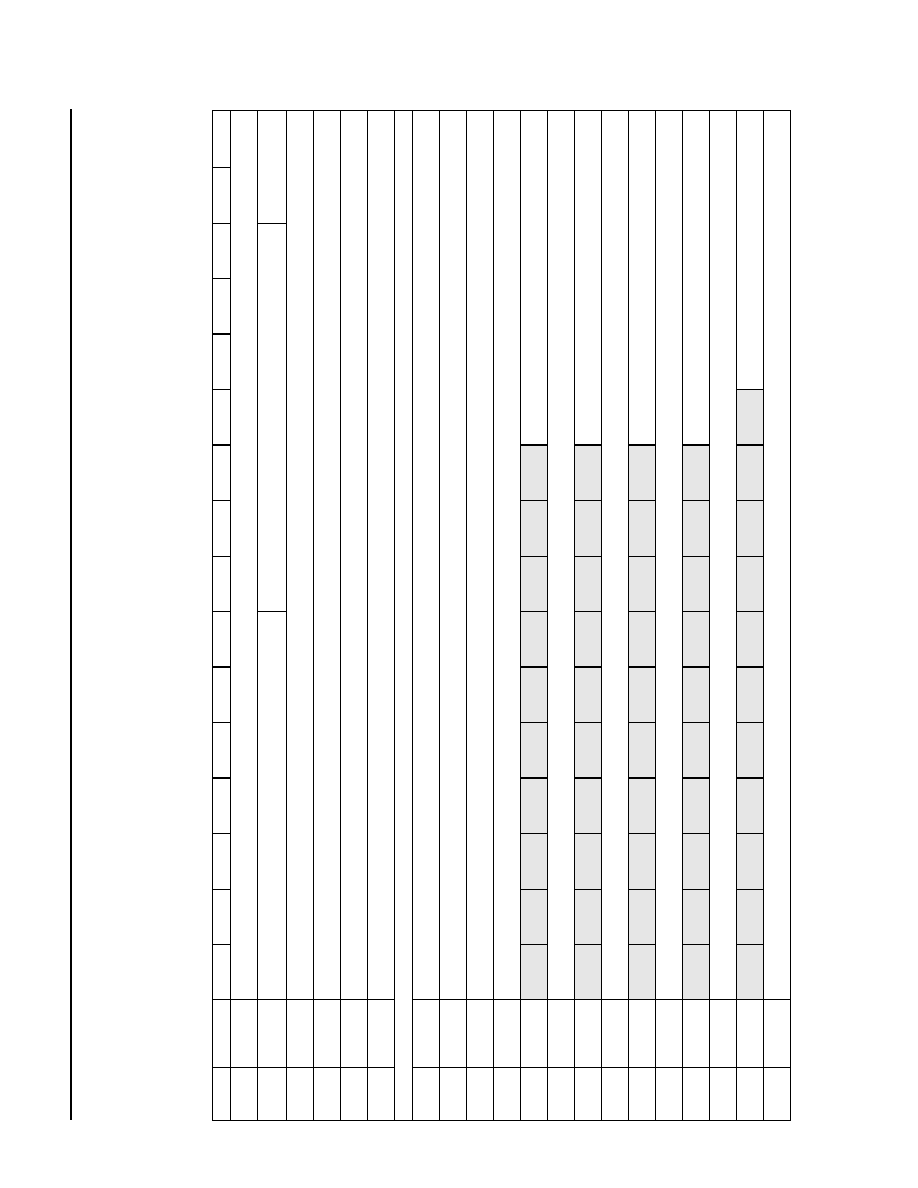

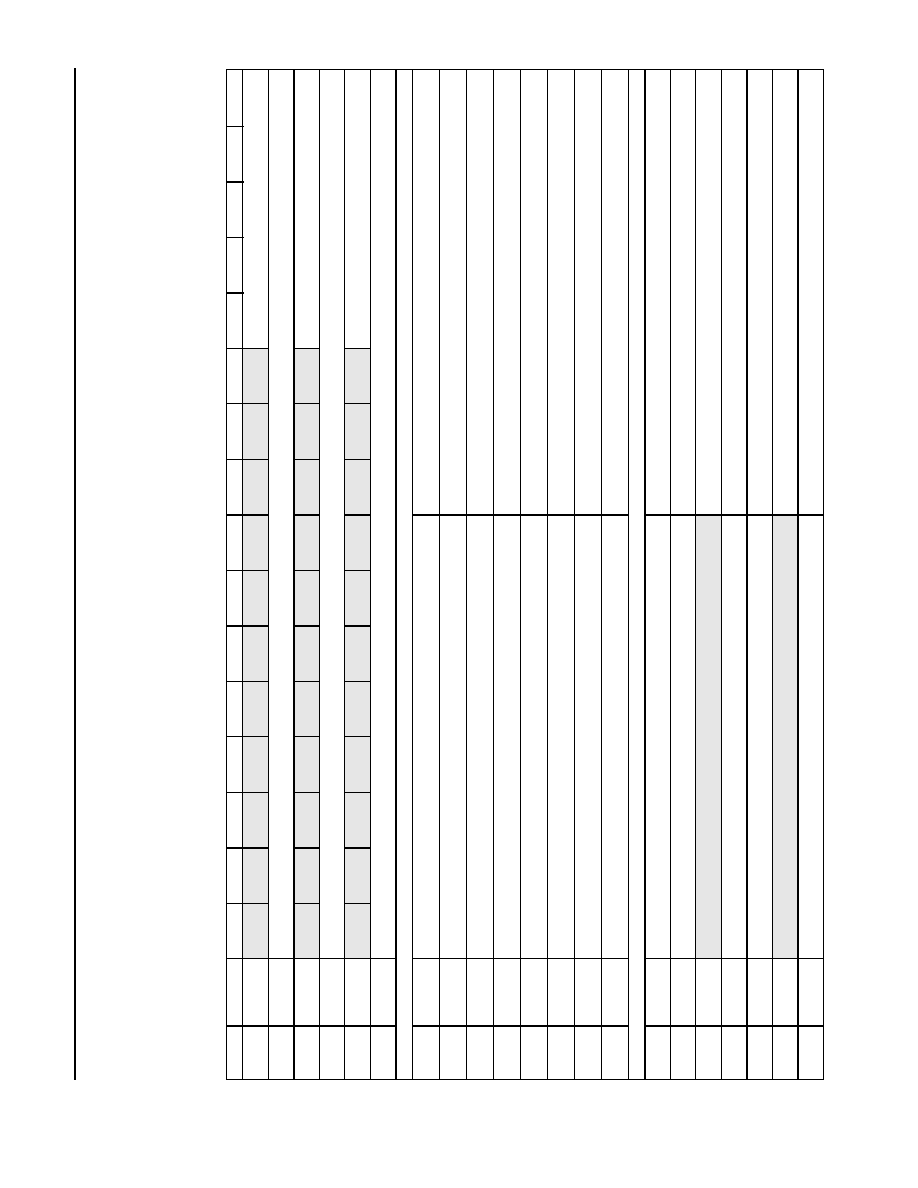

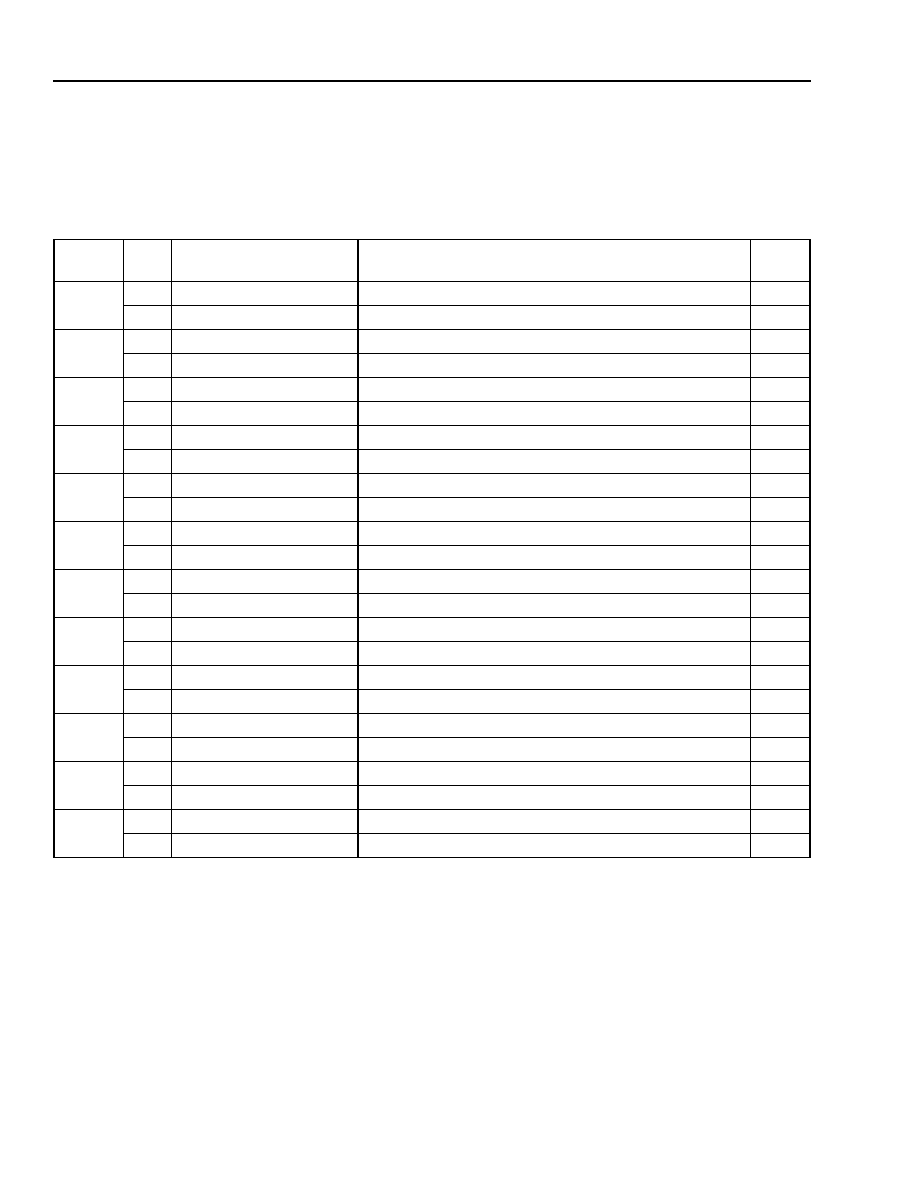

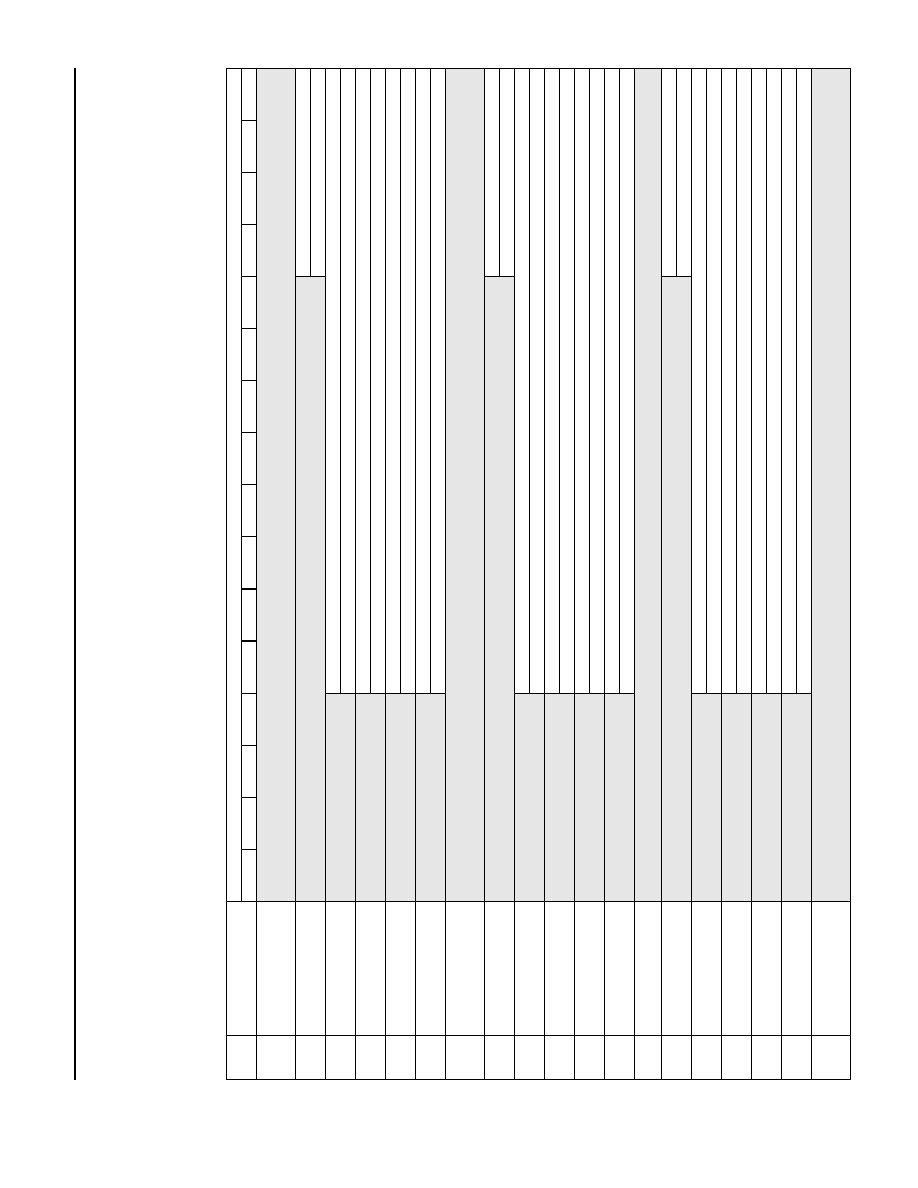

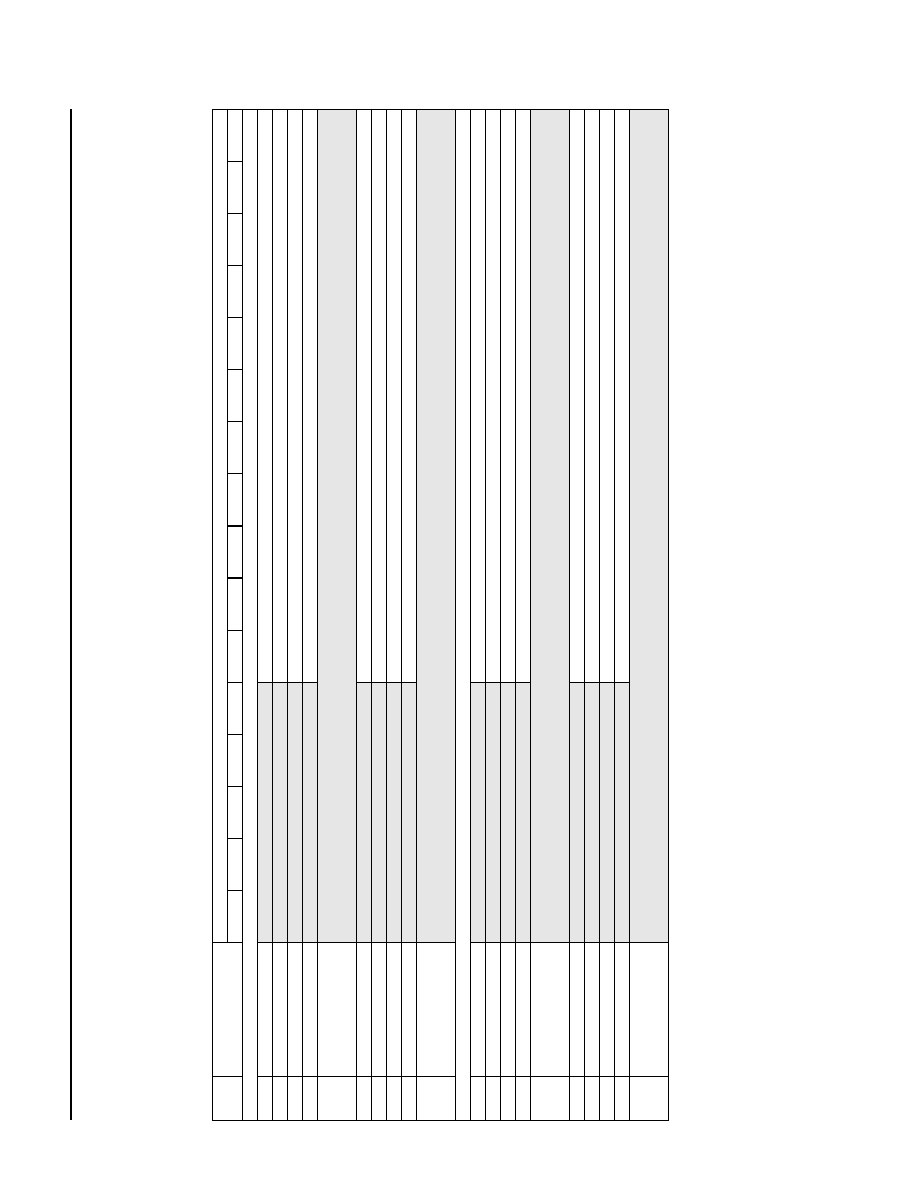

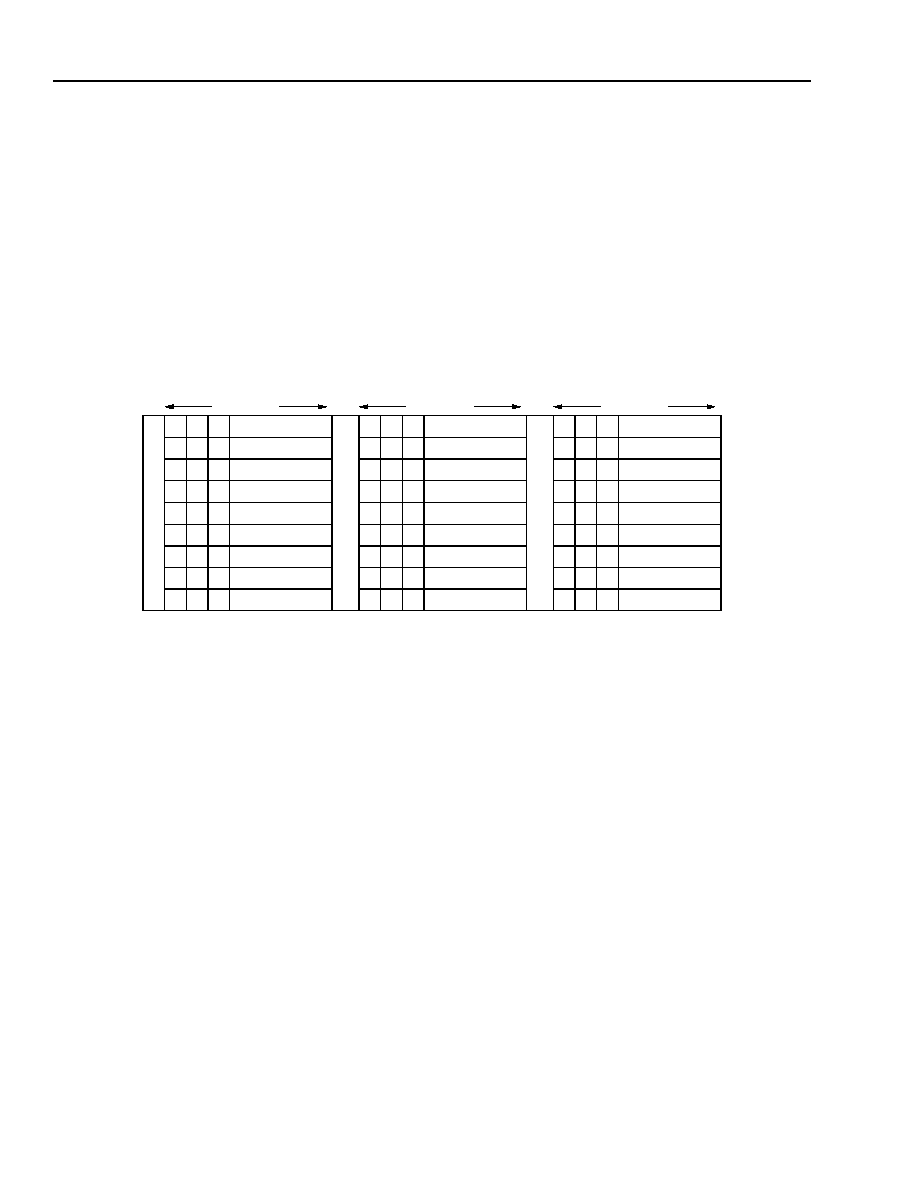

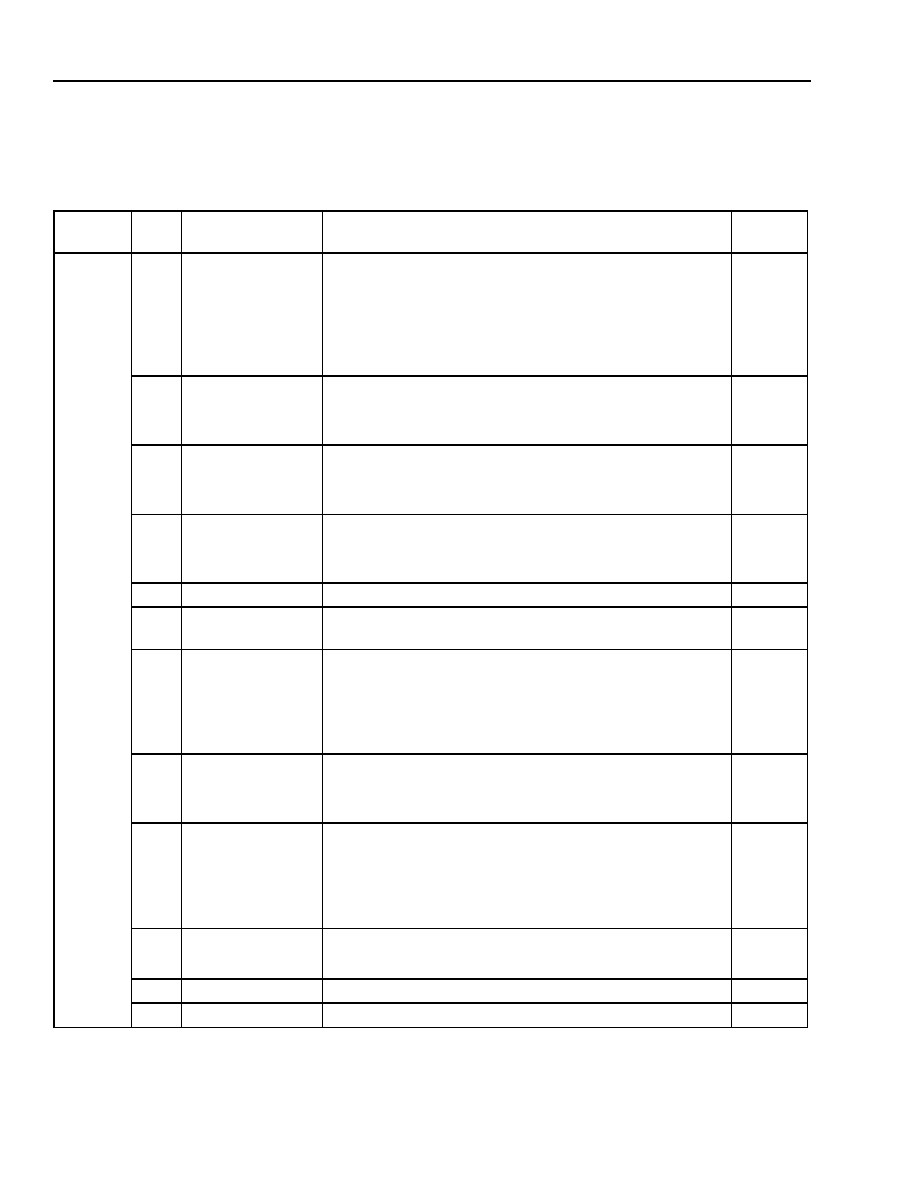

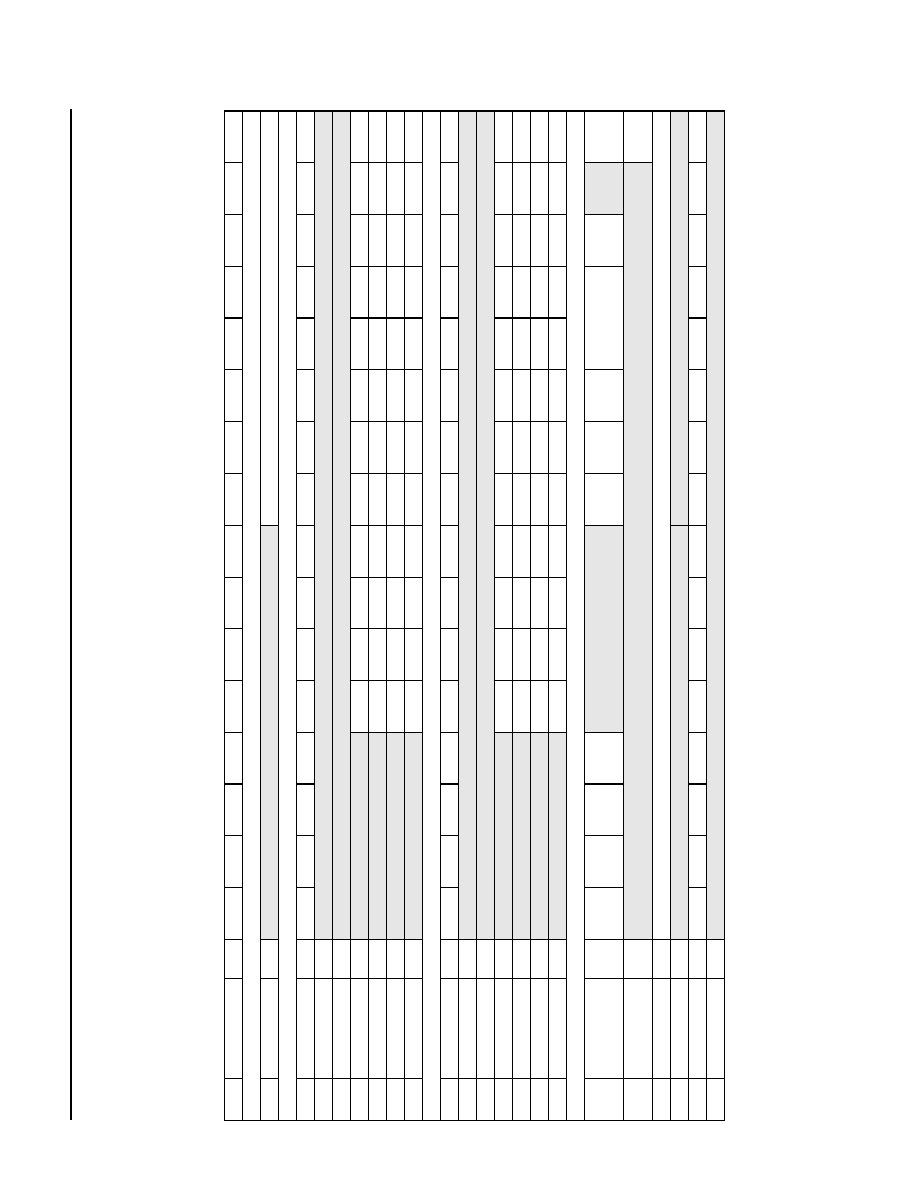

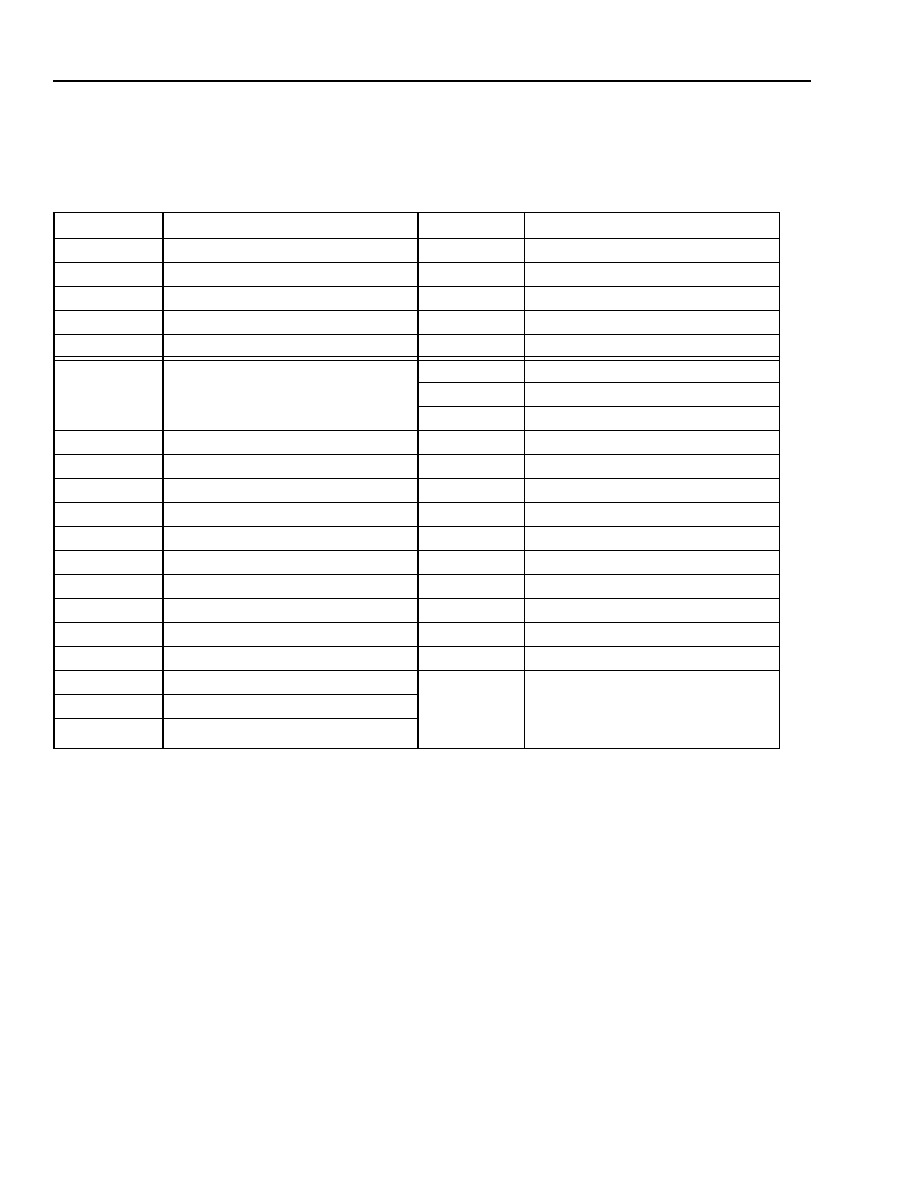

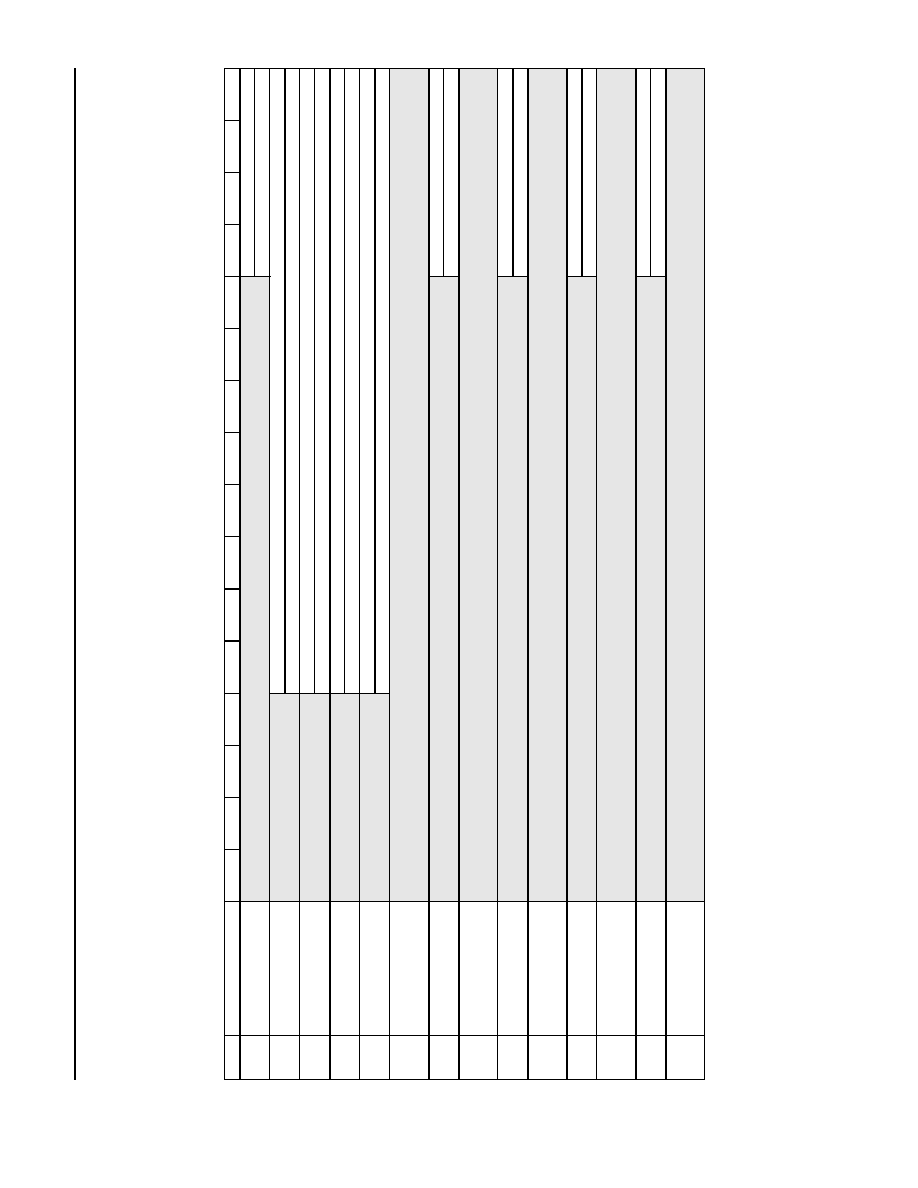

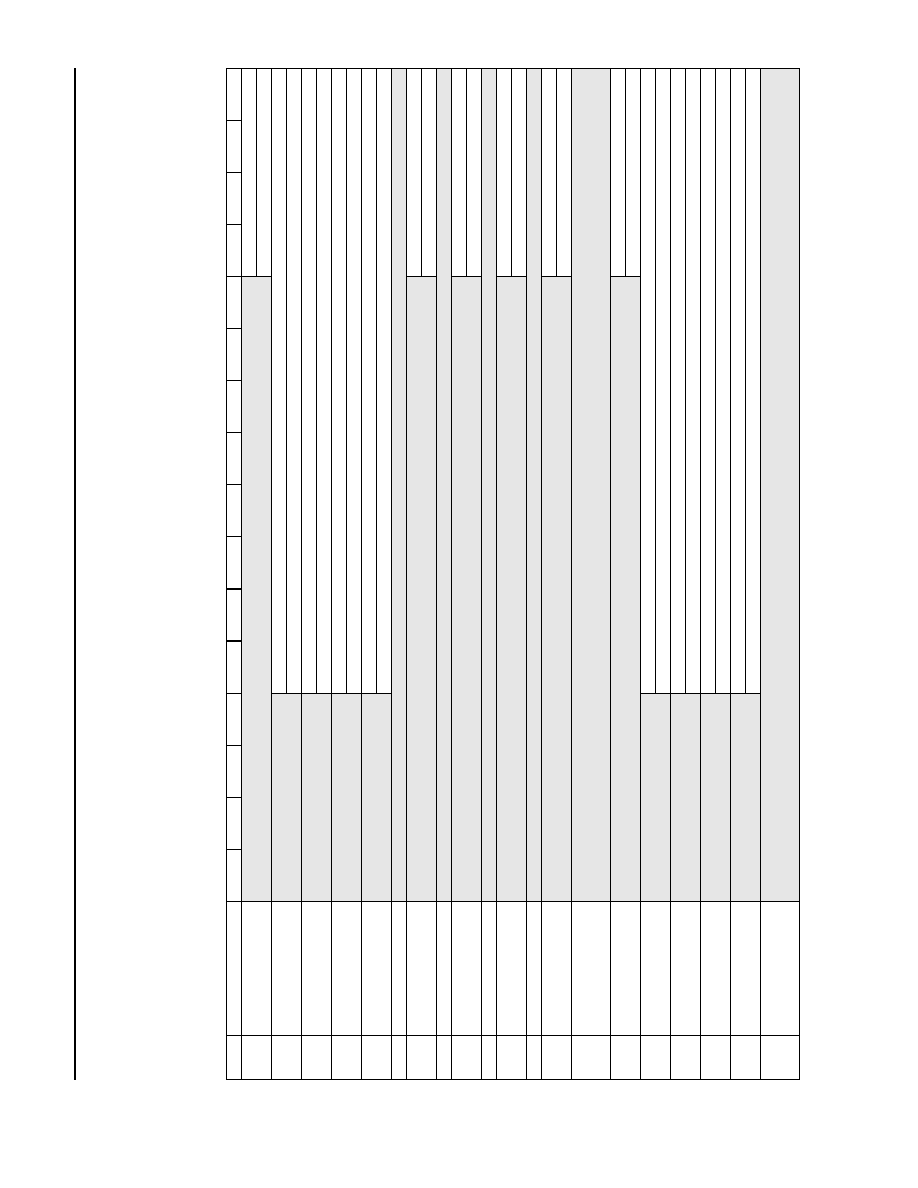

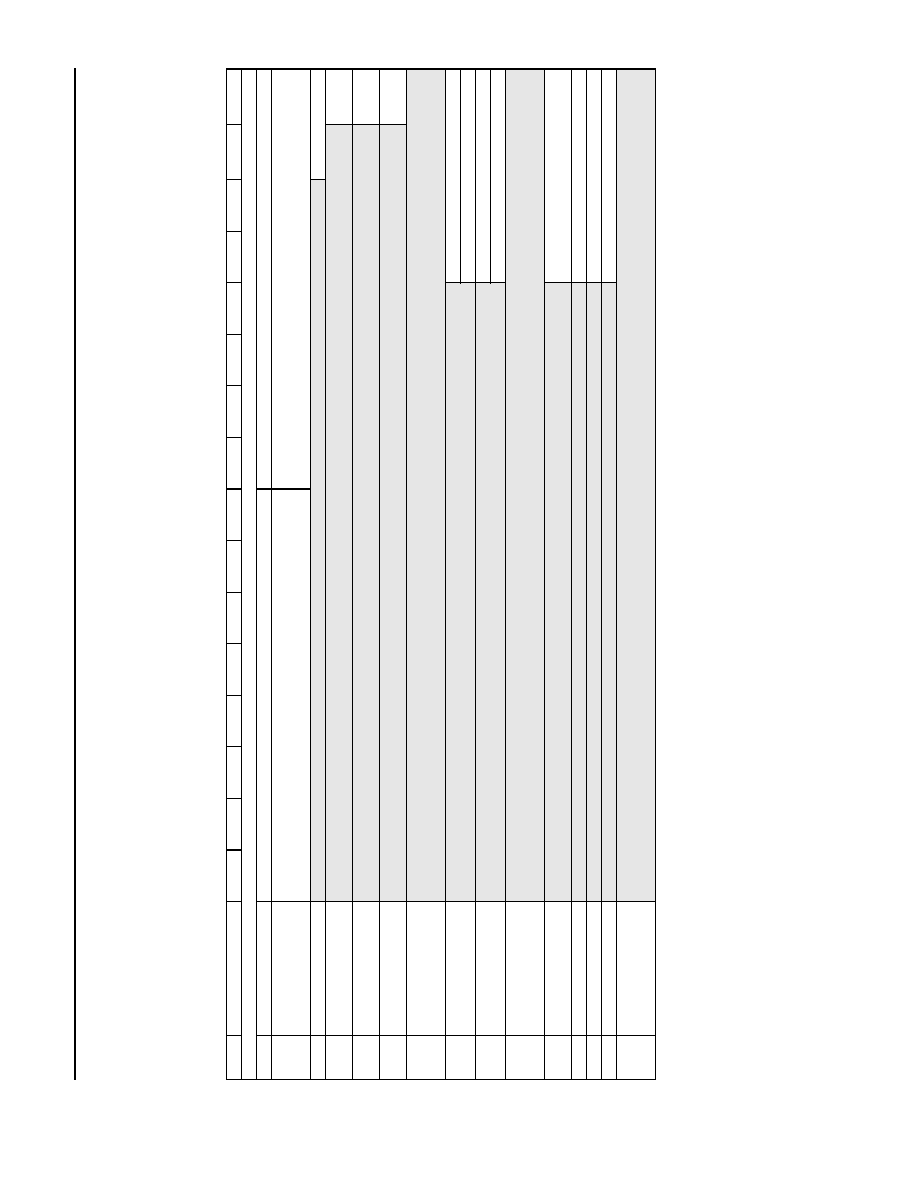

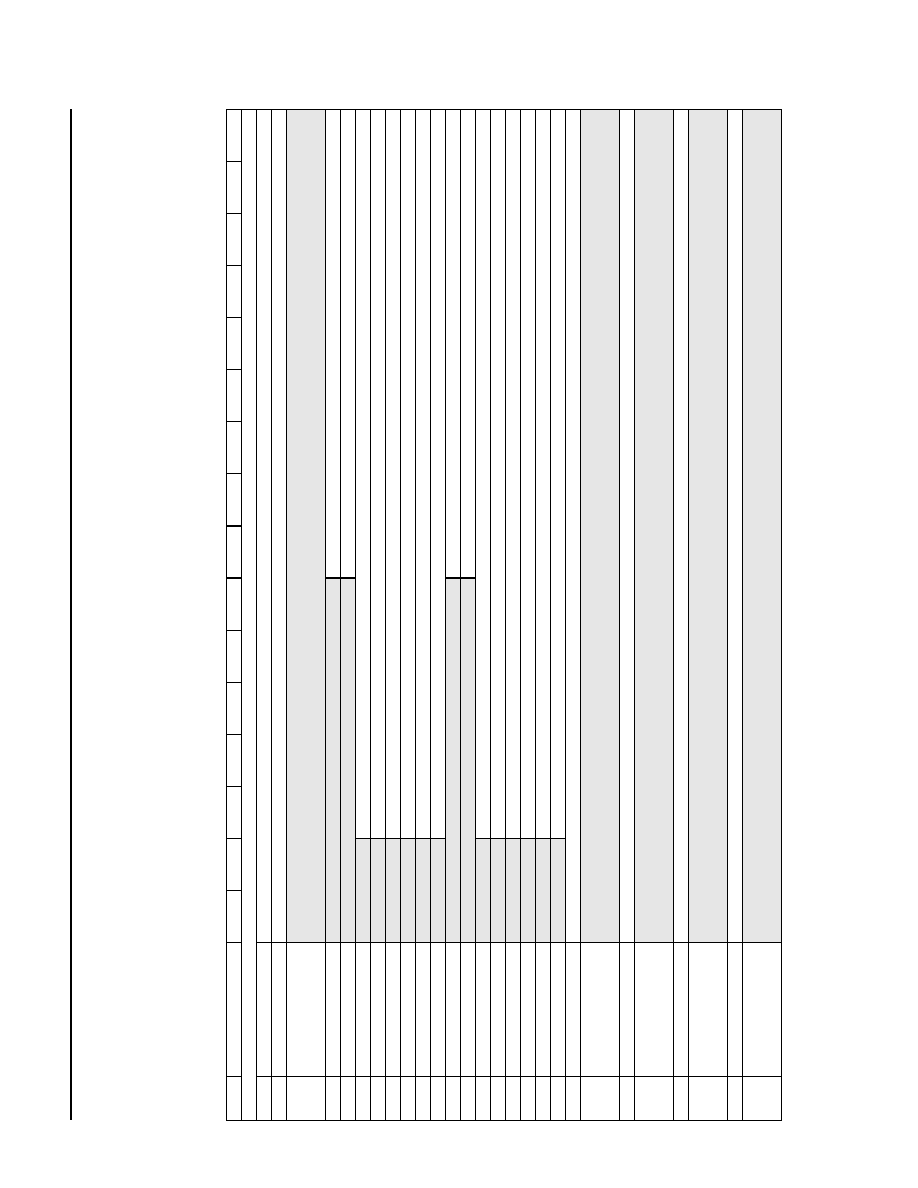

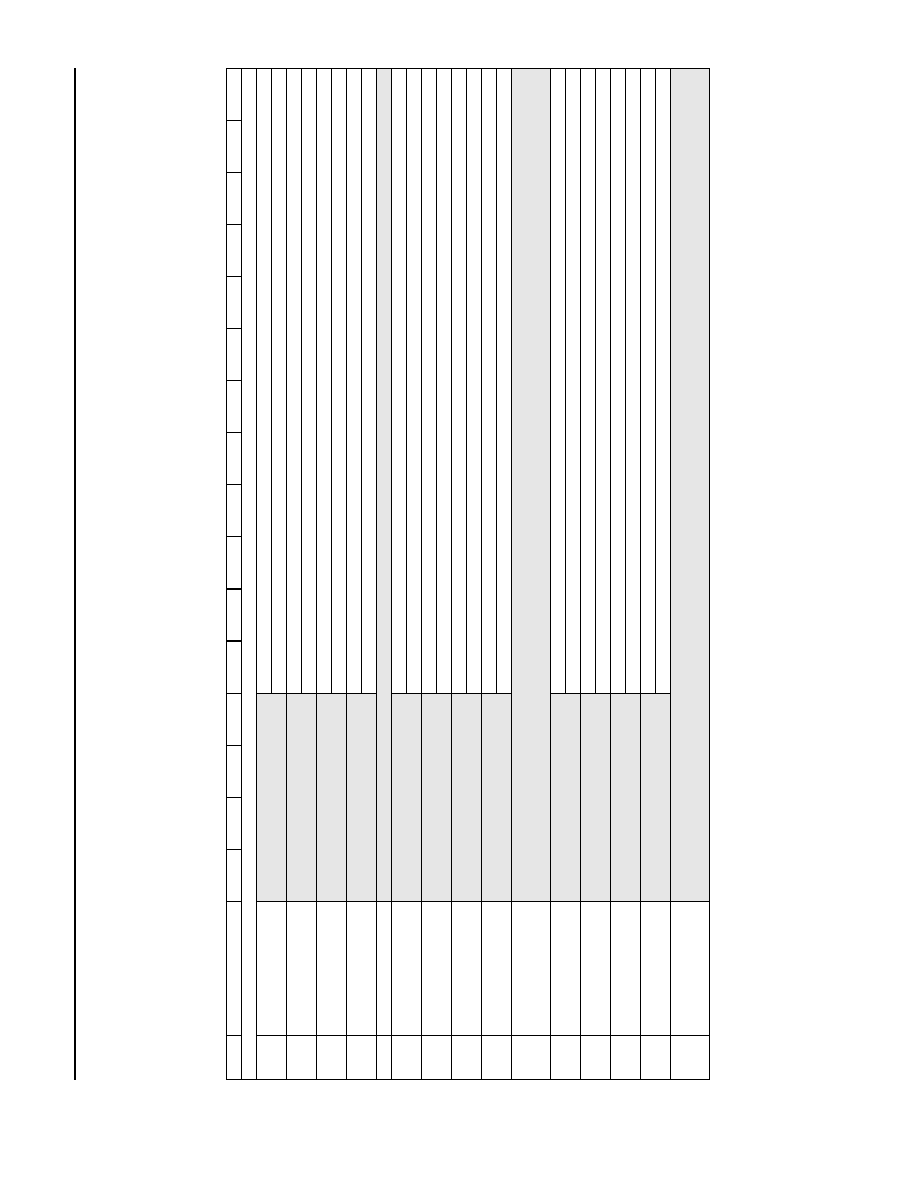

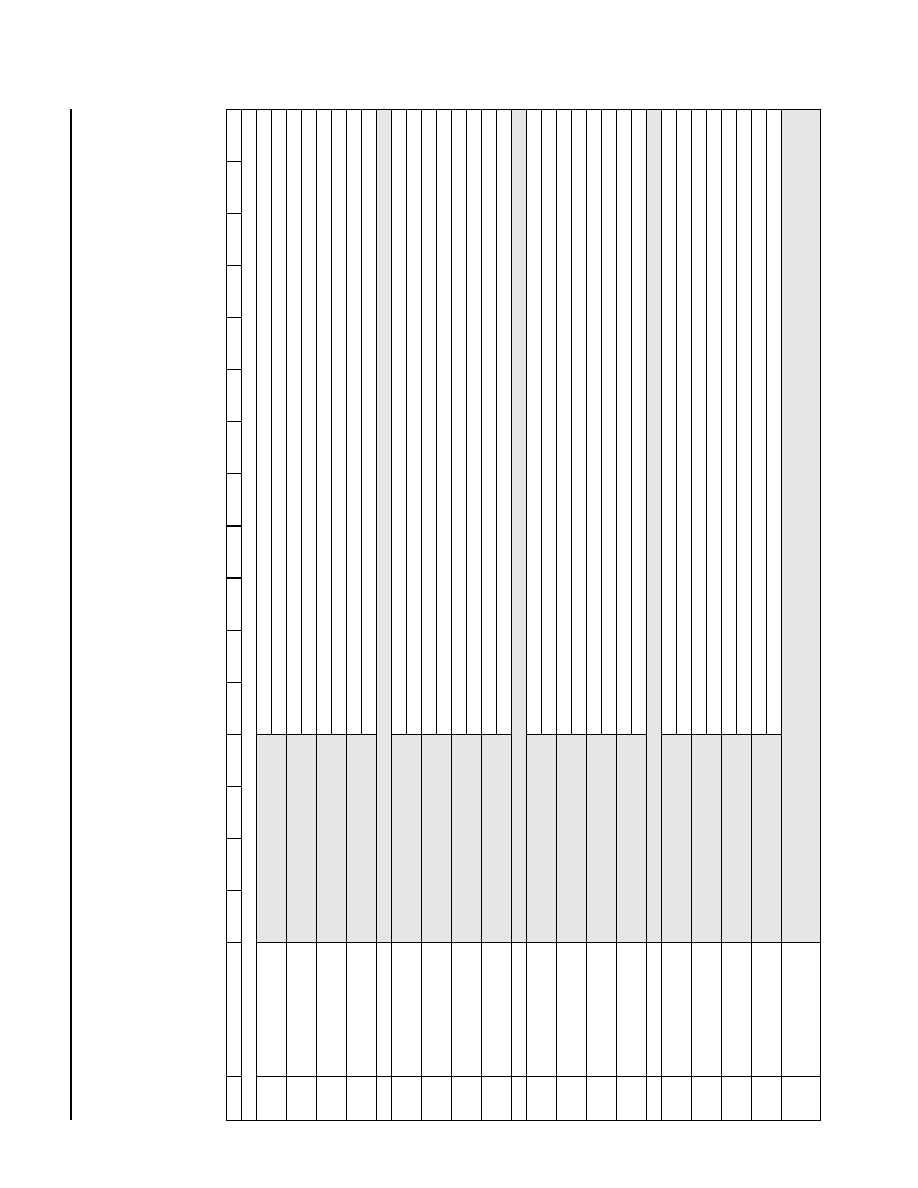

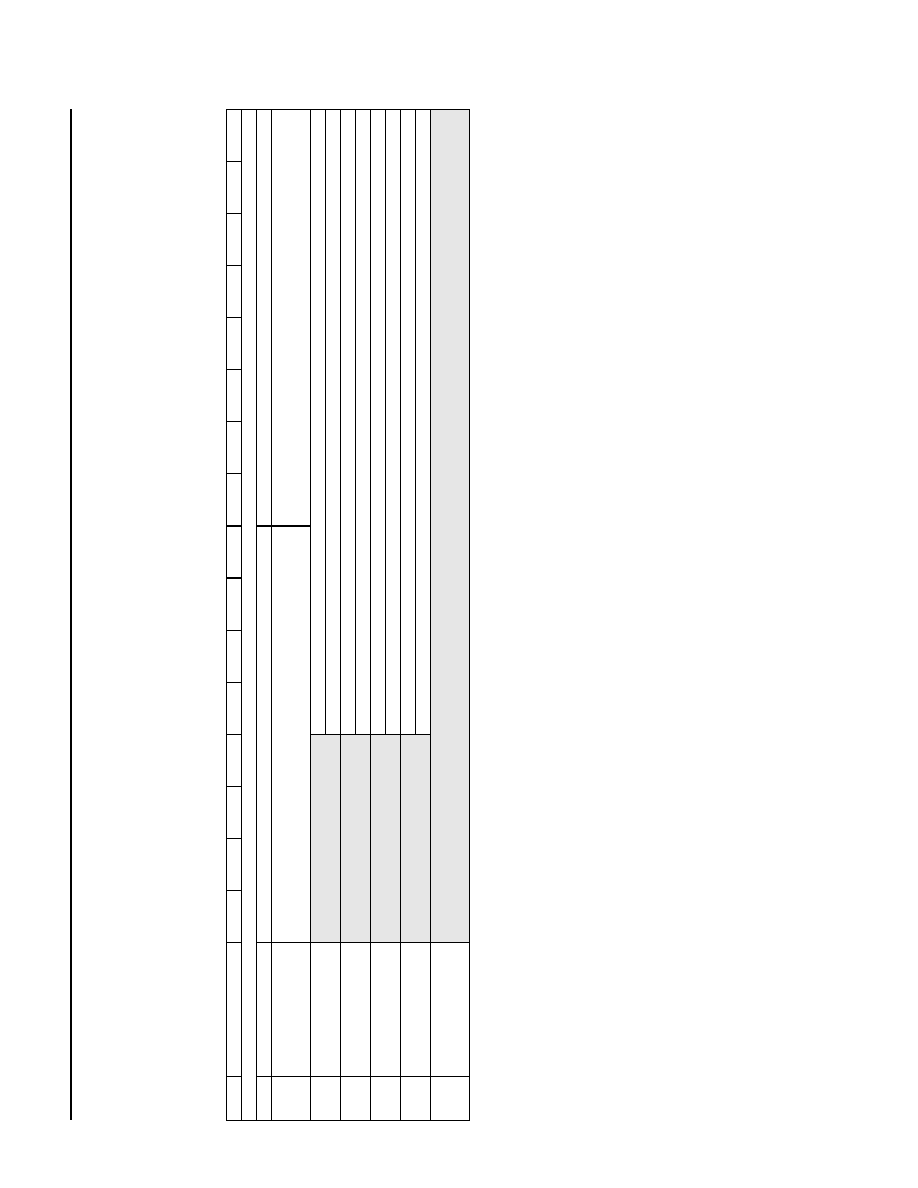

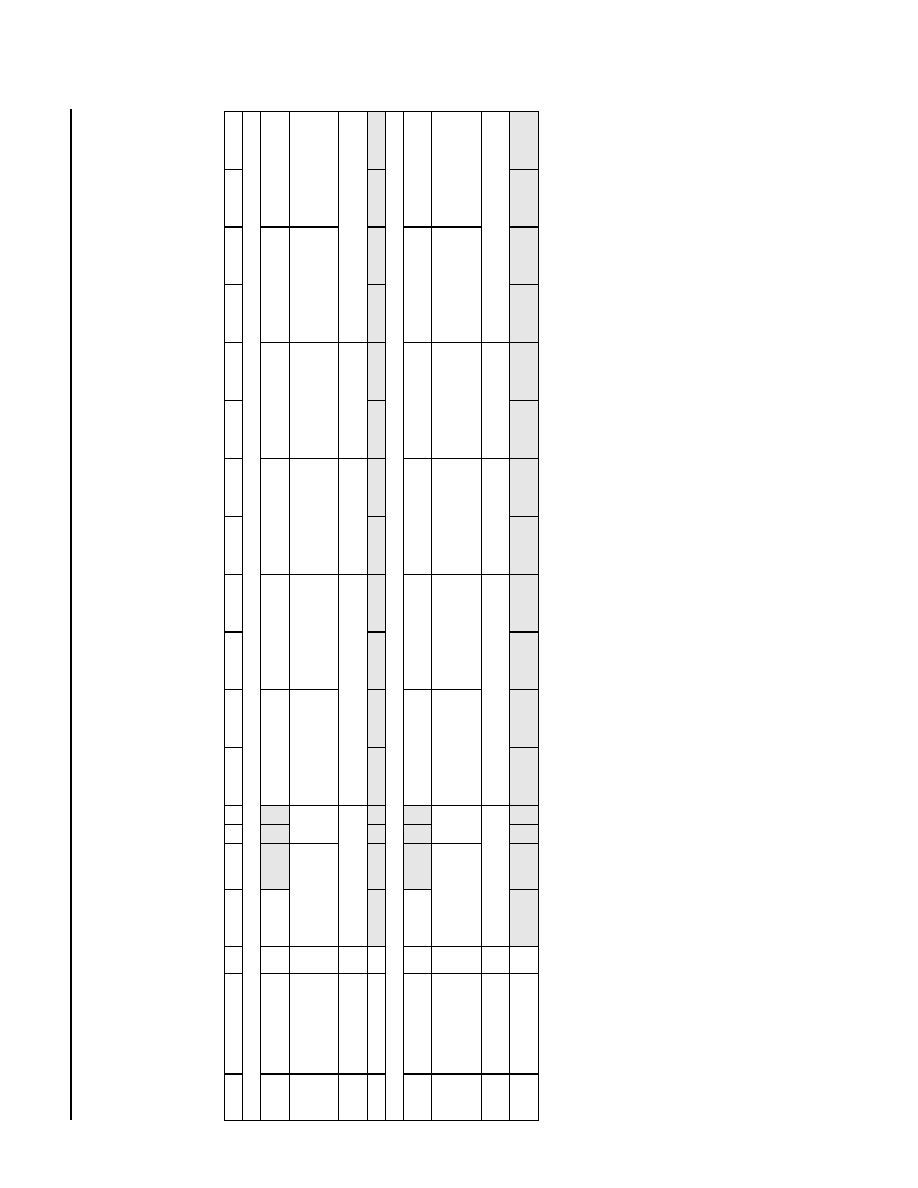

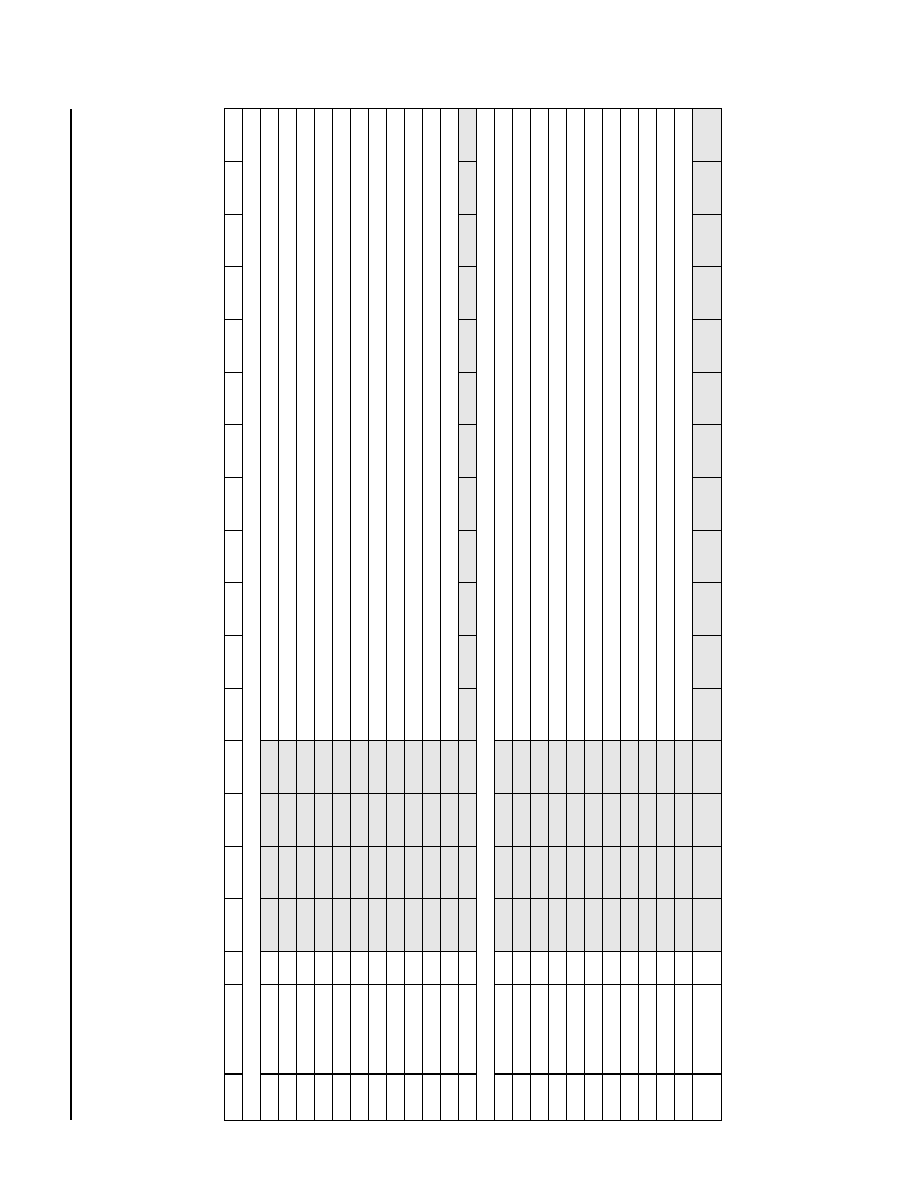

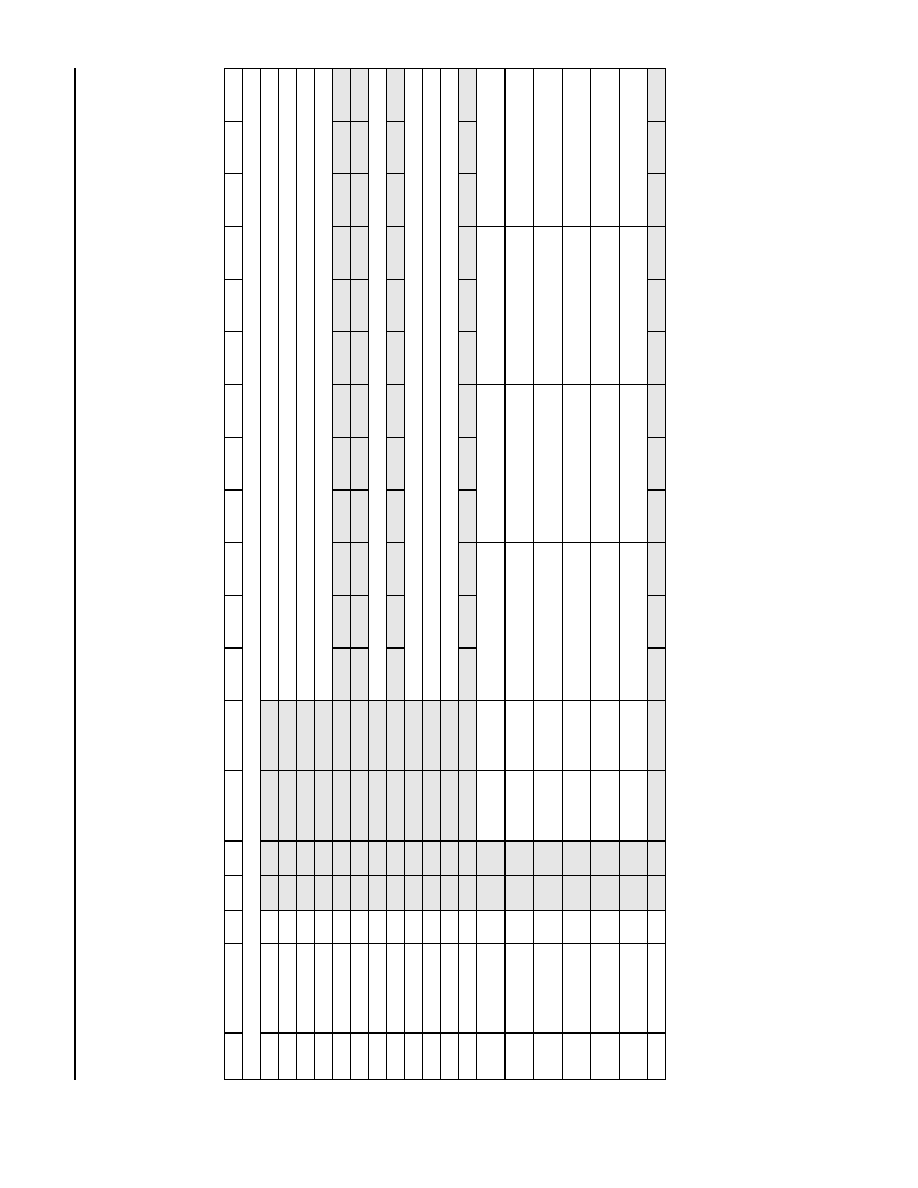

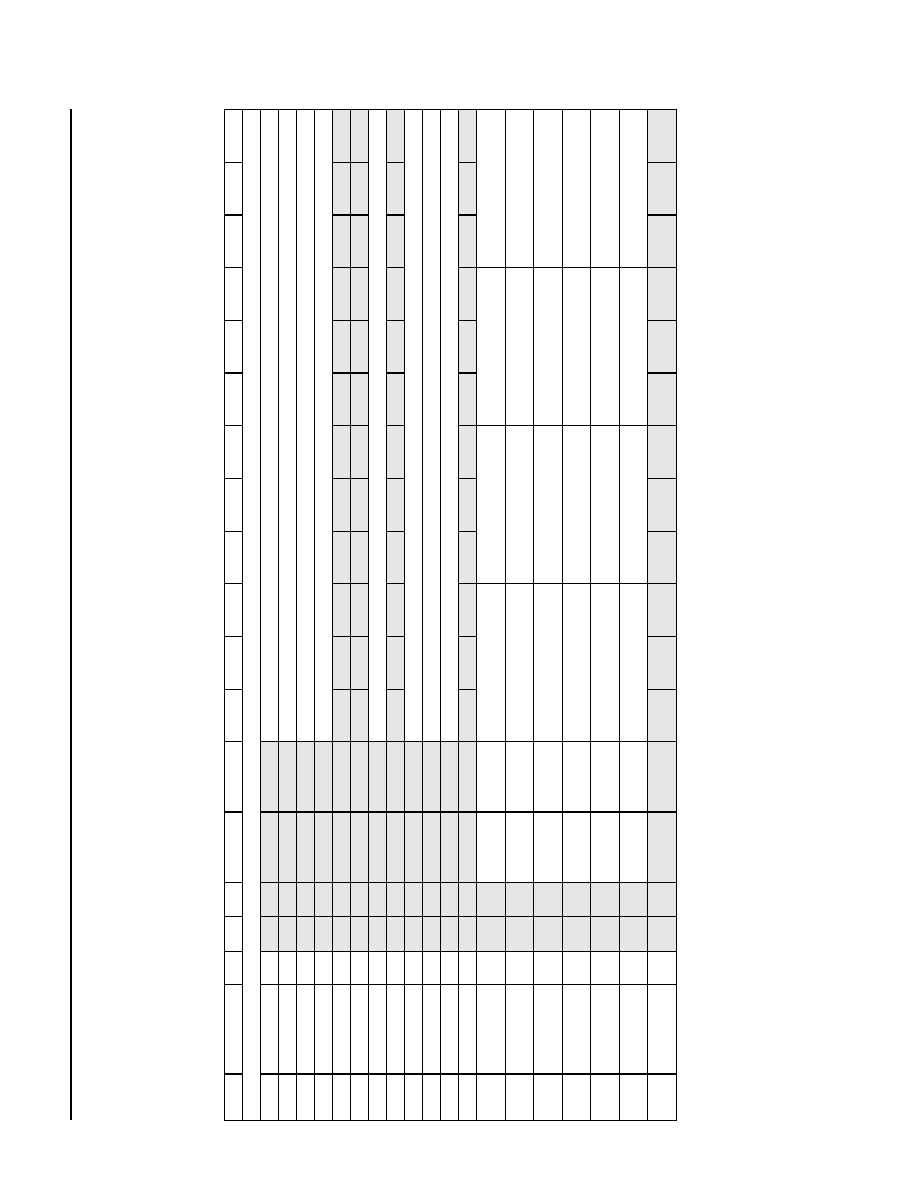

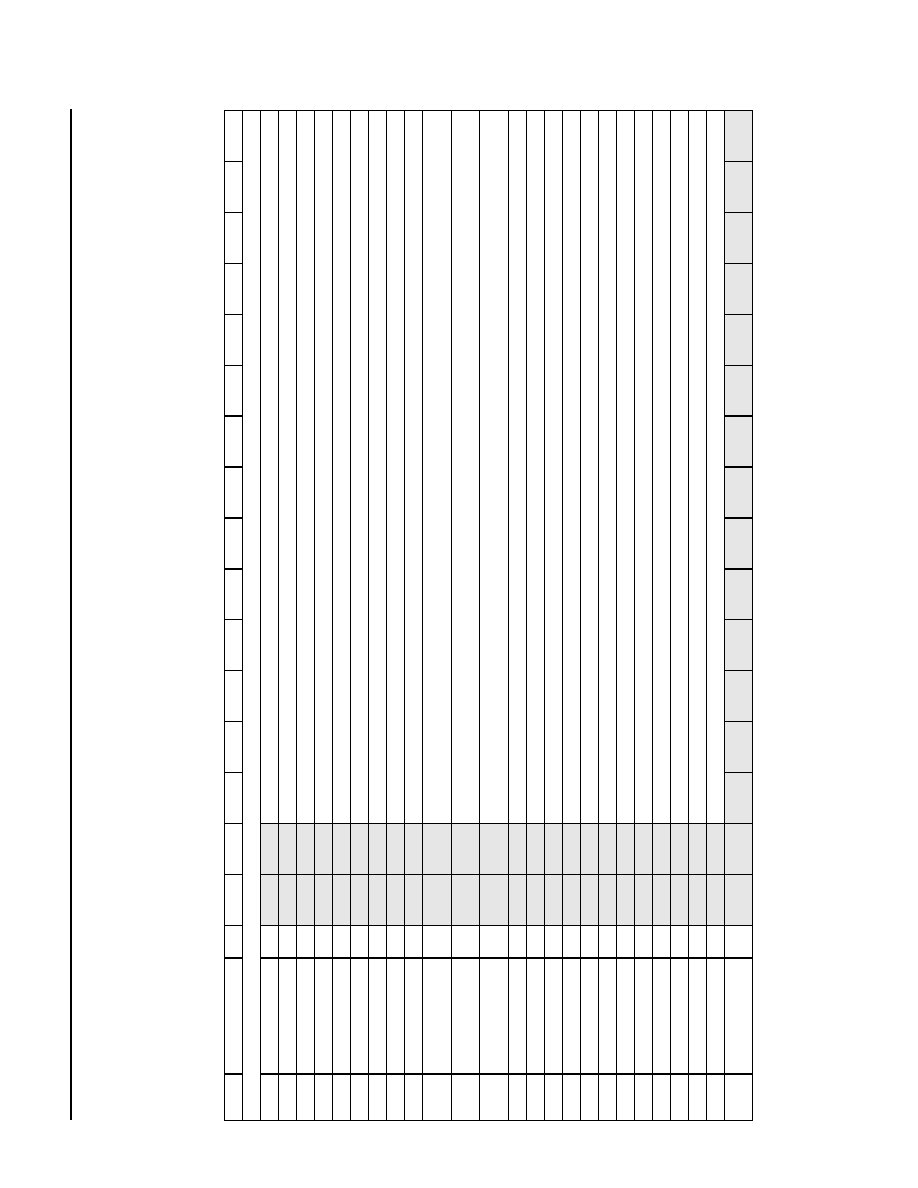

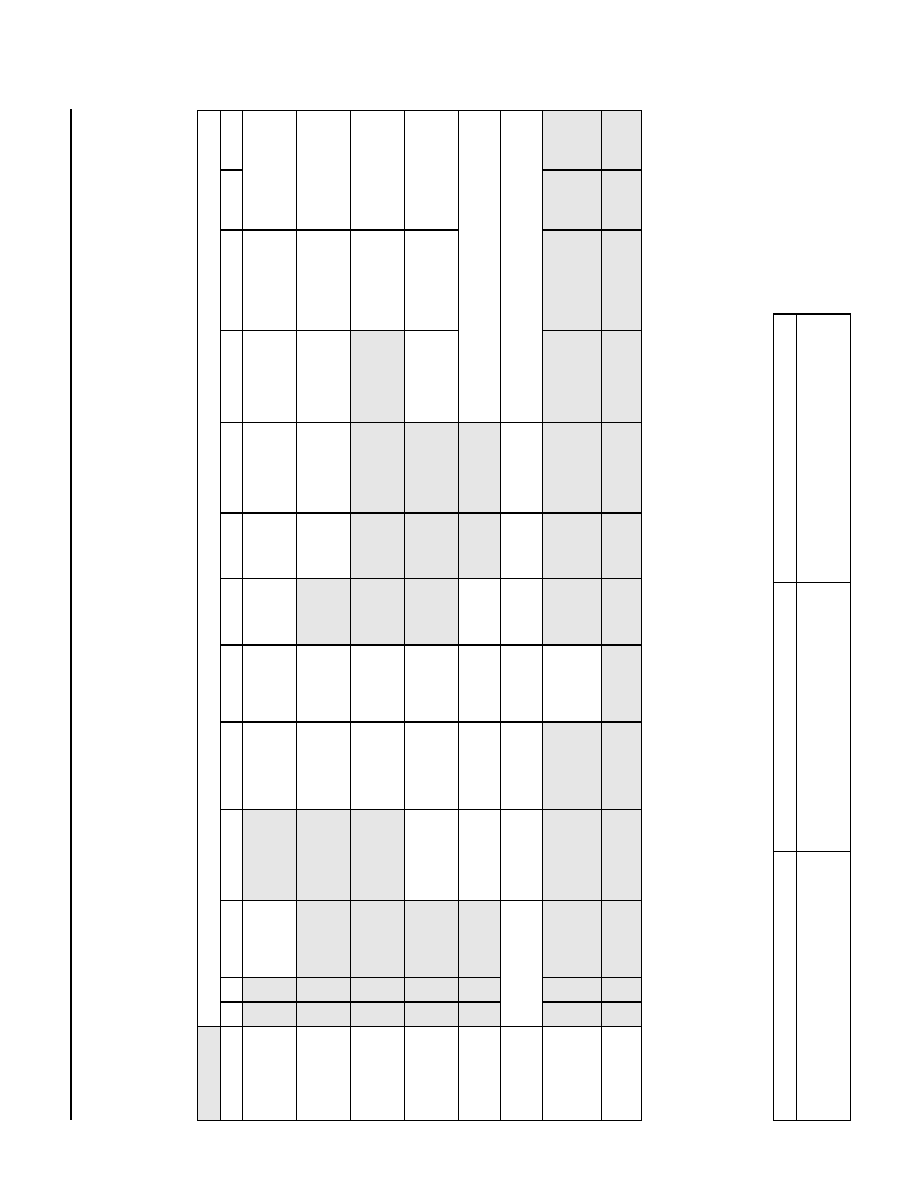

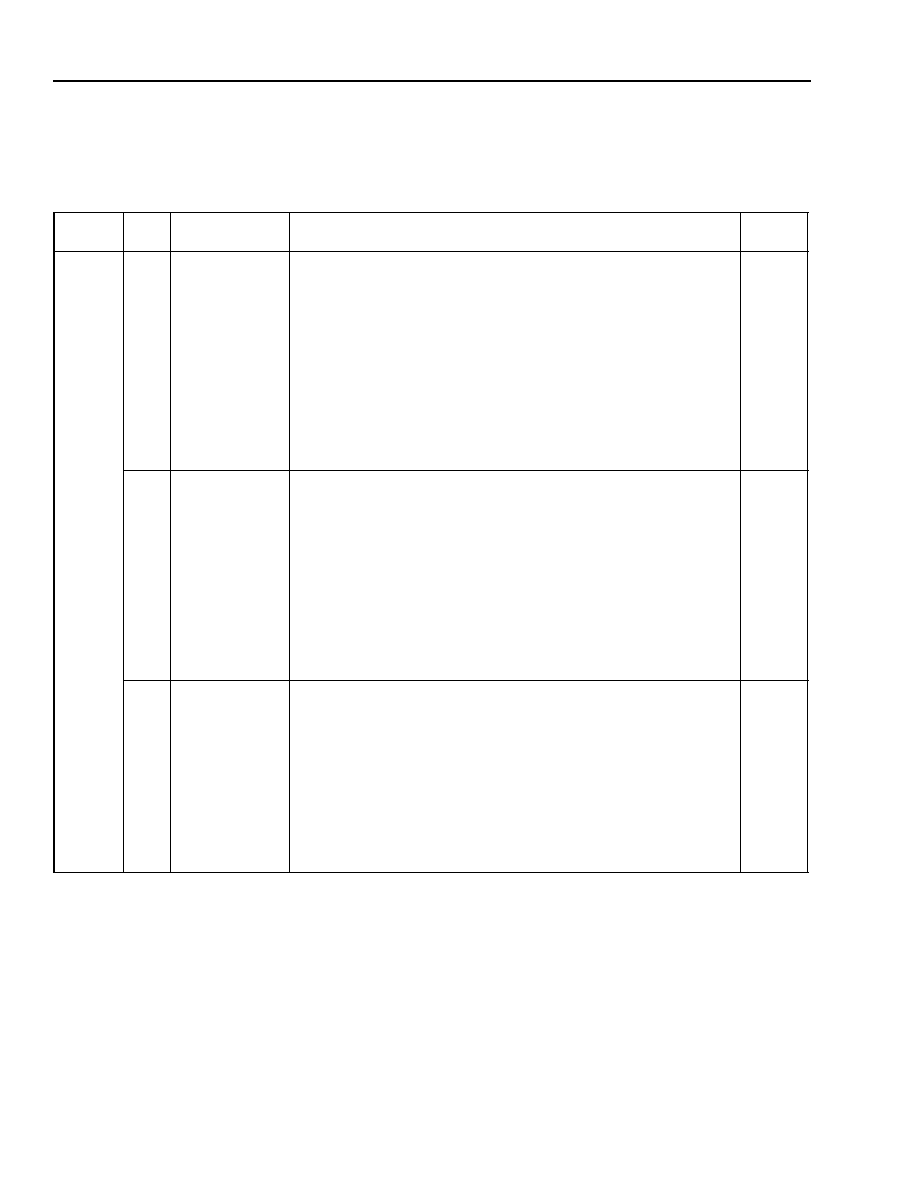

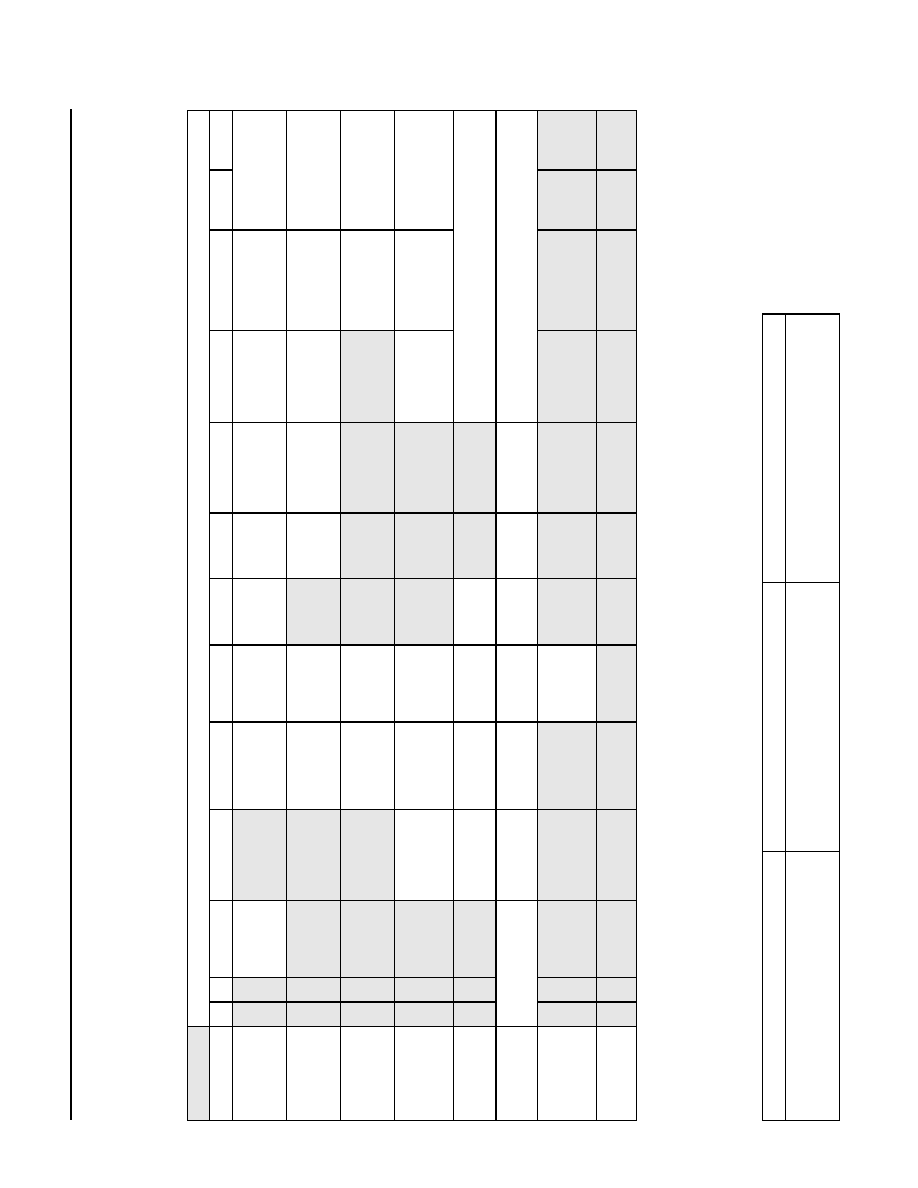

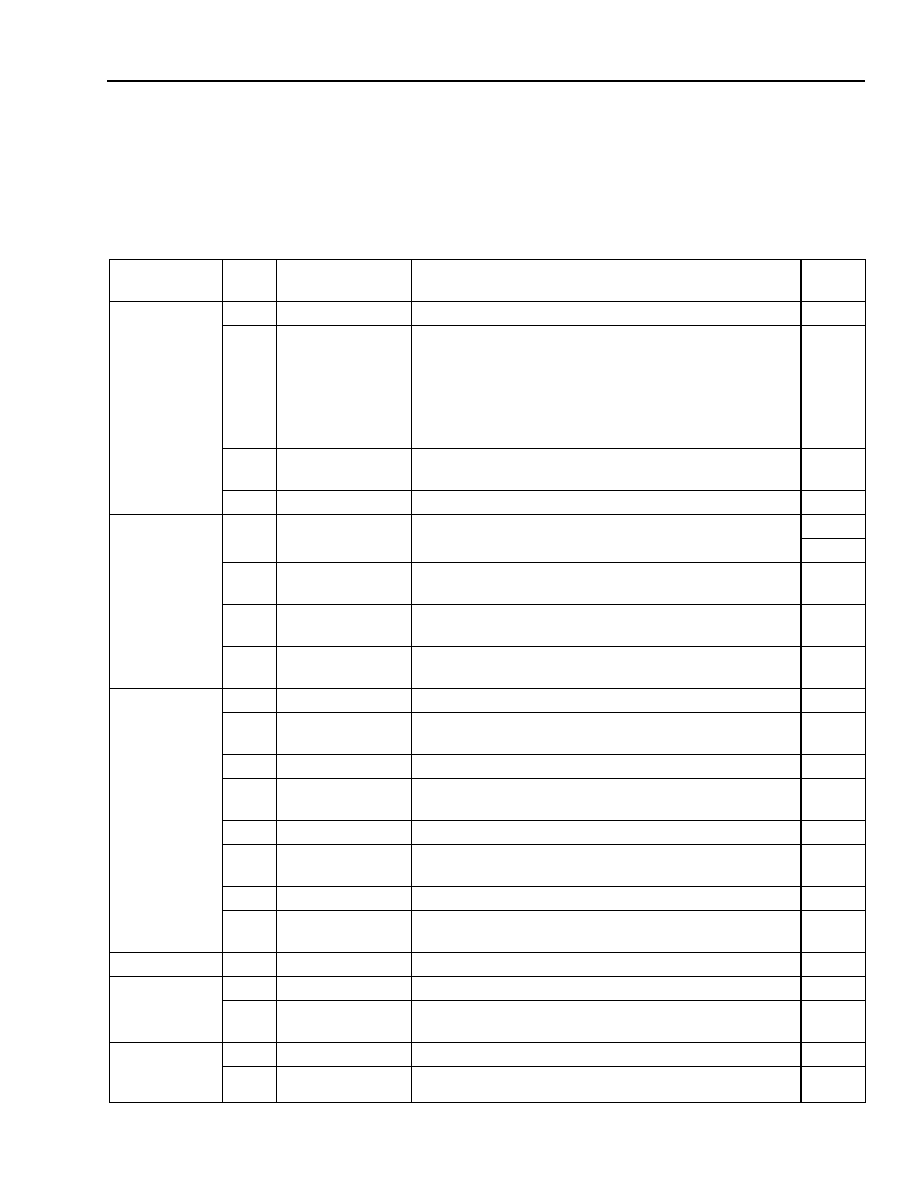

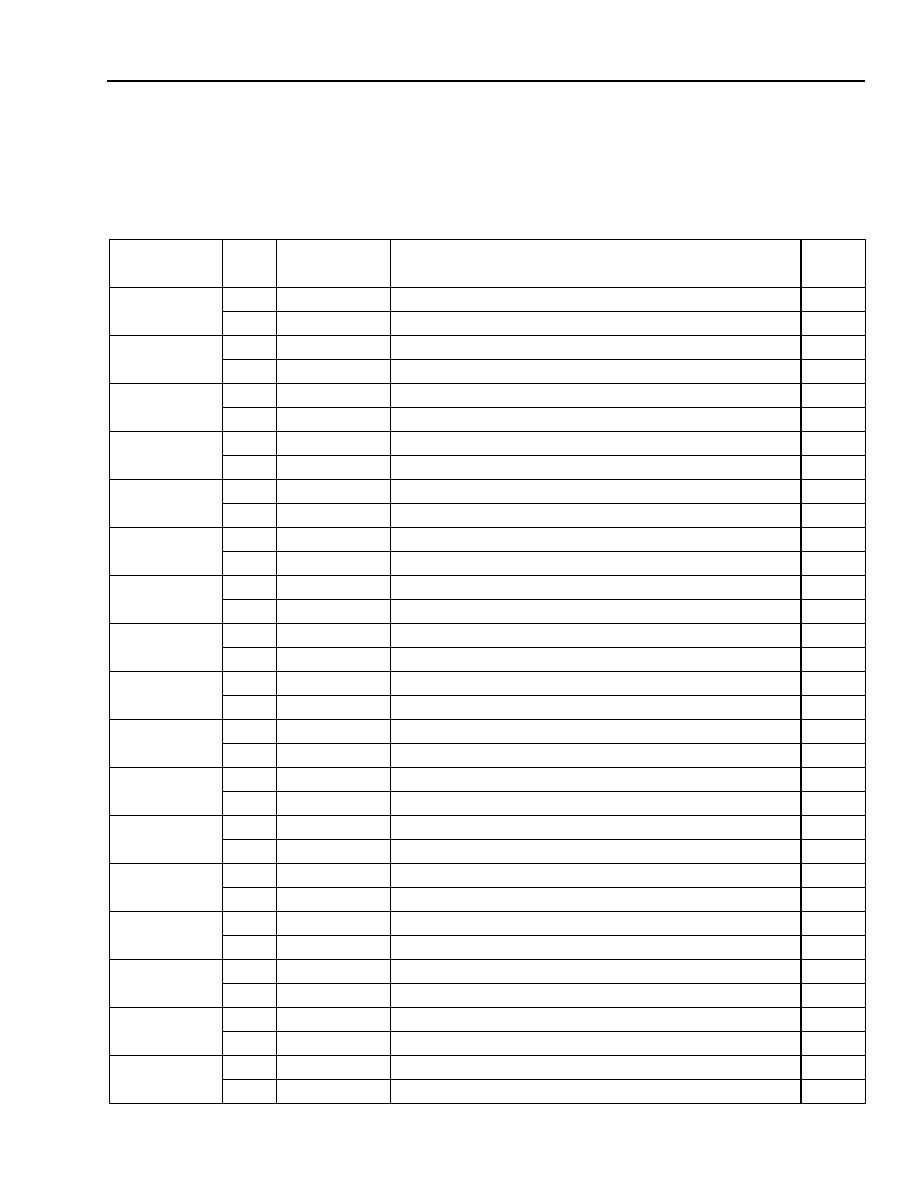

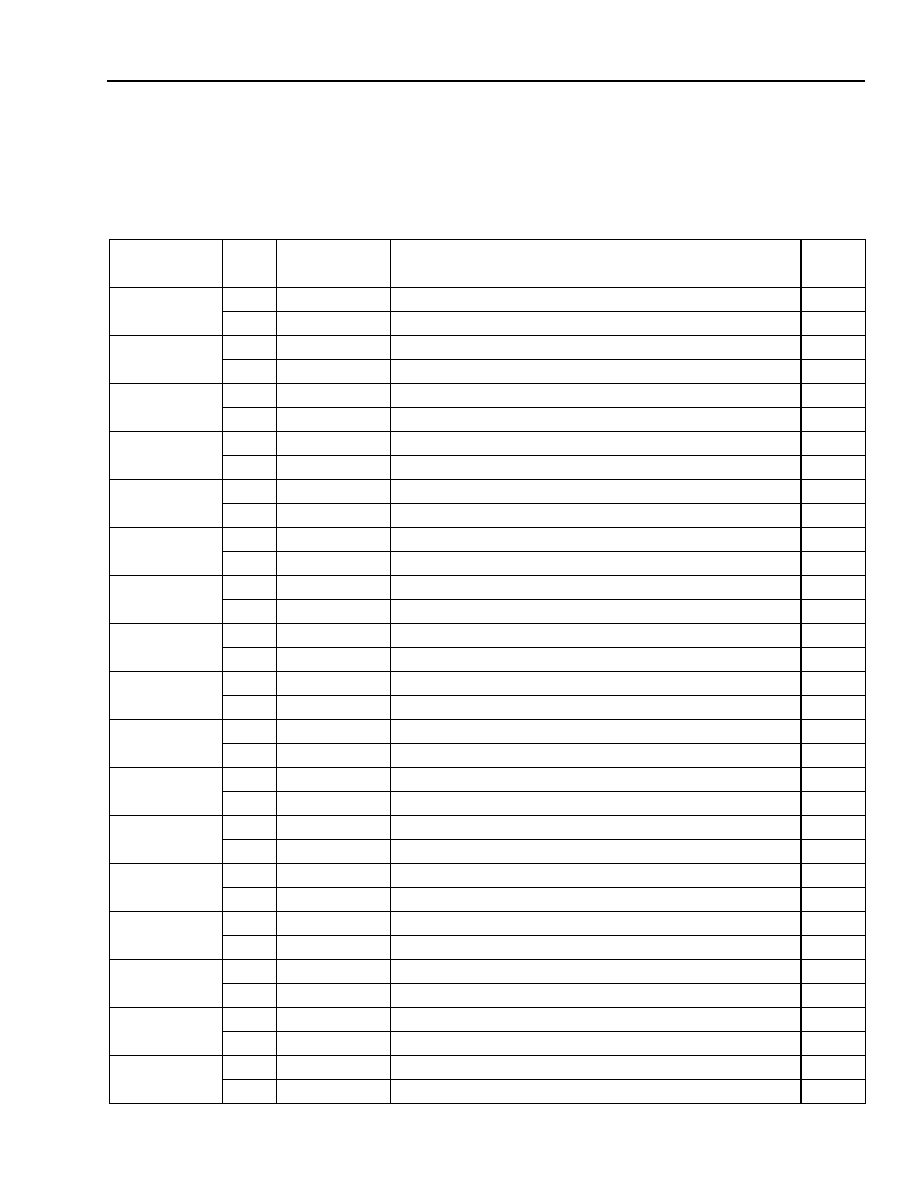

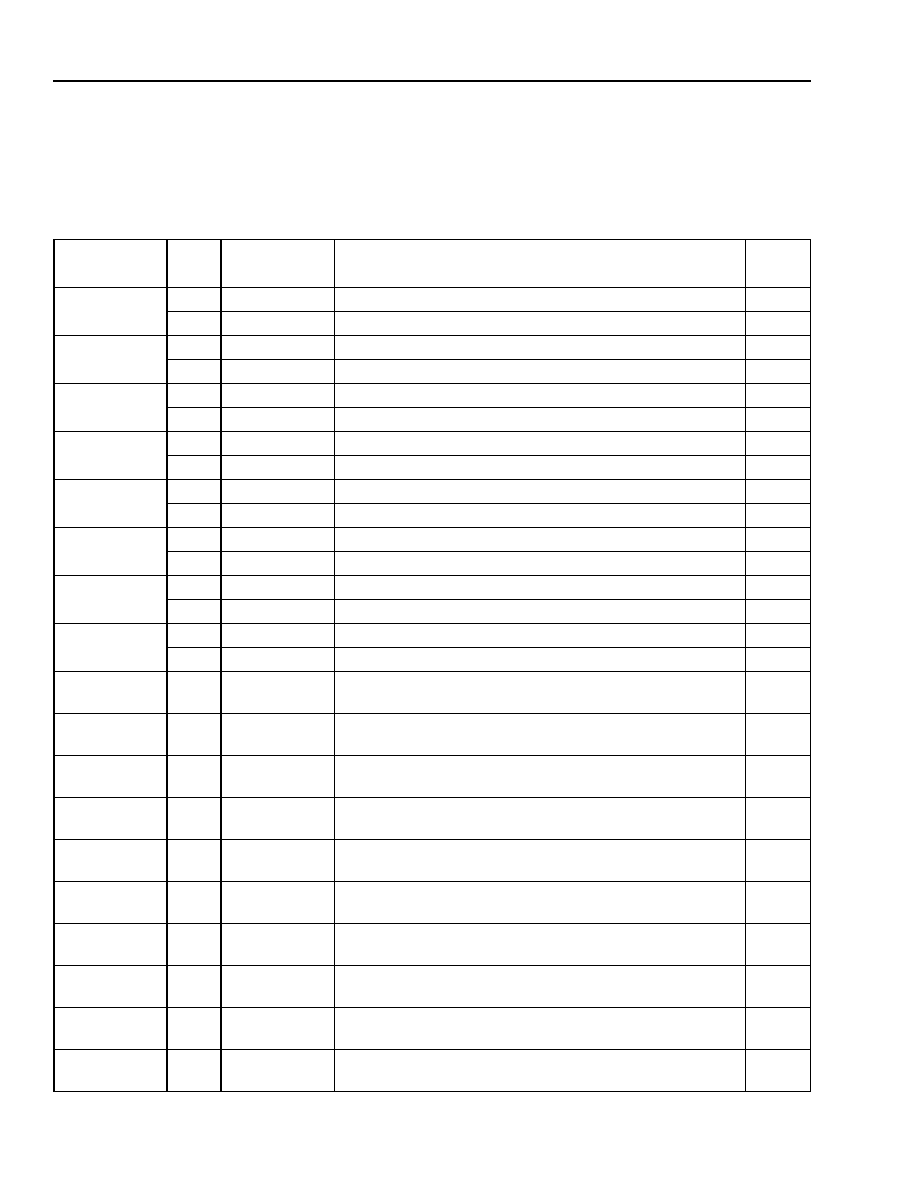

- Table 3. Pin Assignments for 792-Pin PBGA and 600-Pin LBGA by Pin Number Order

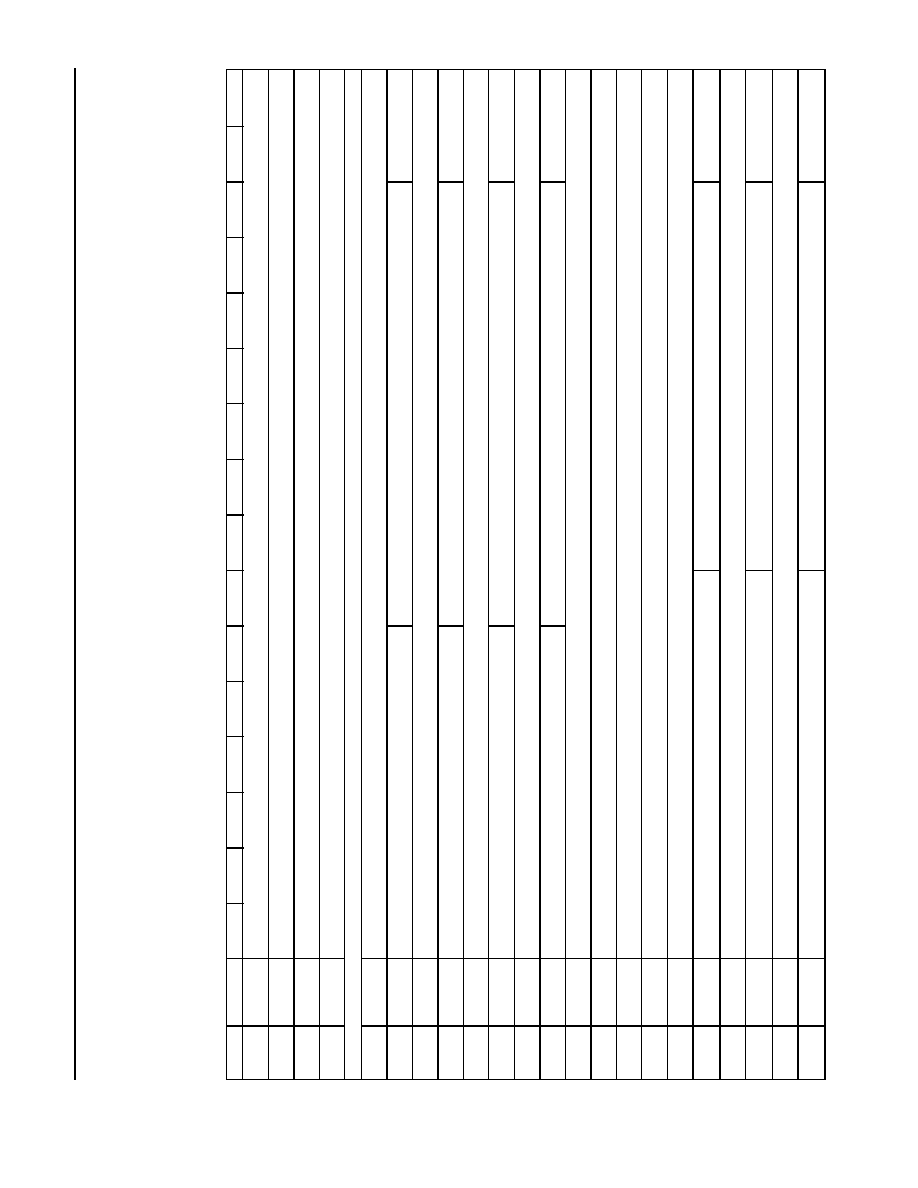

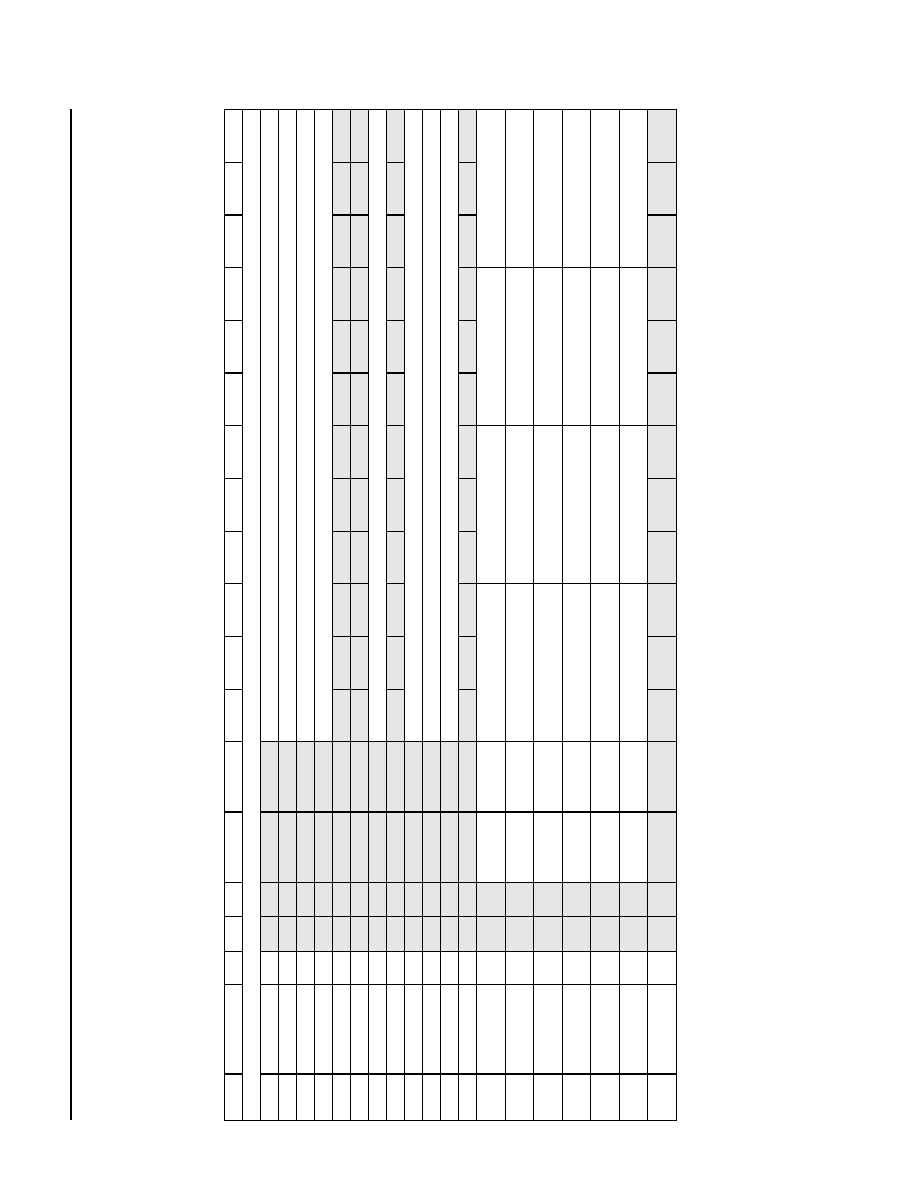

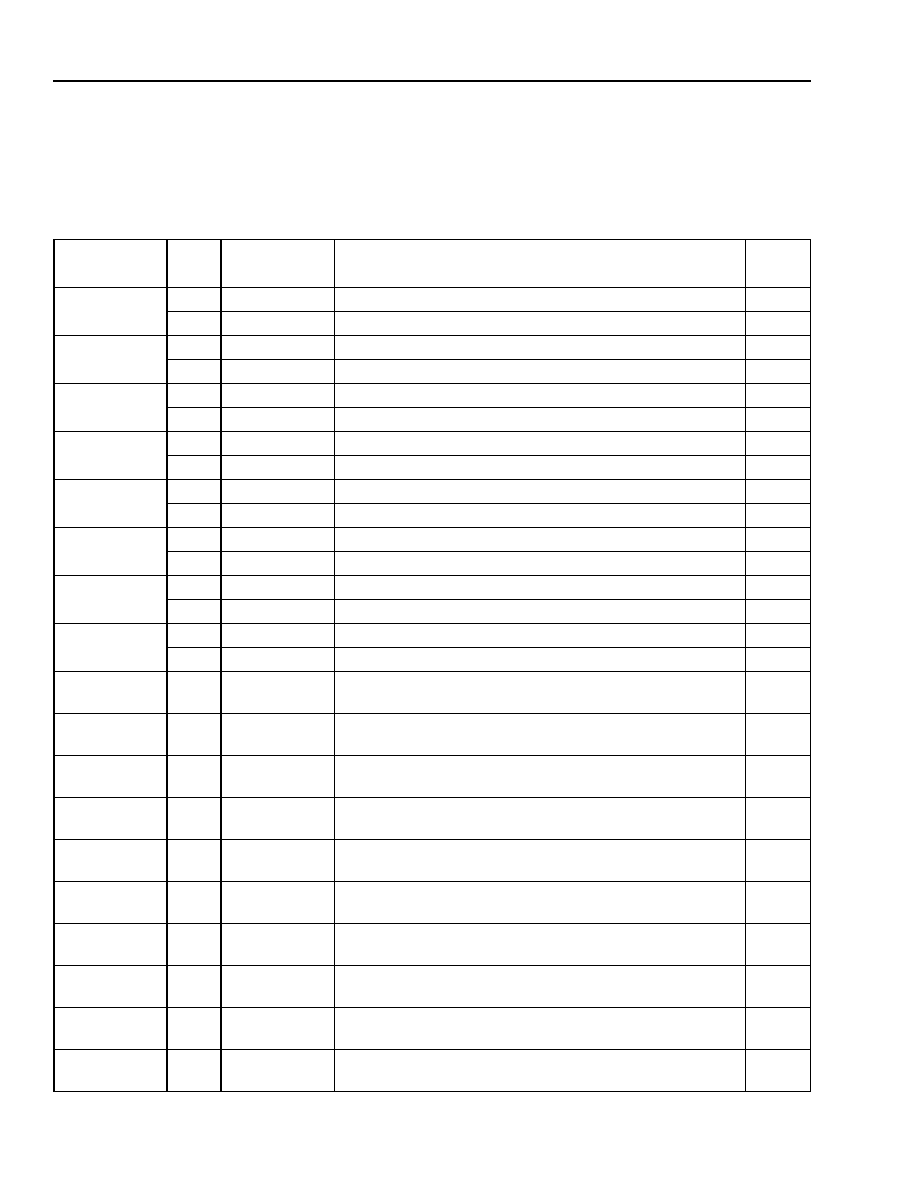

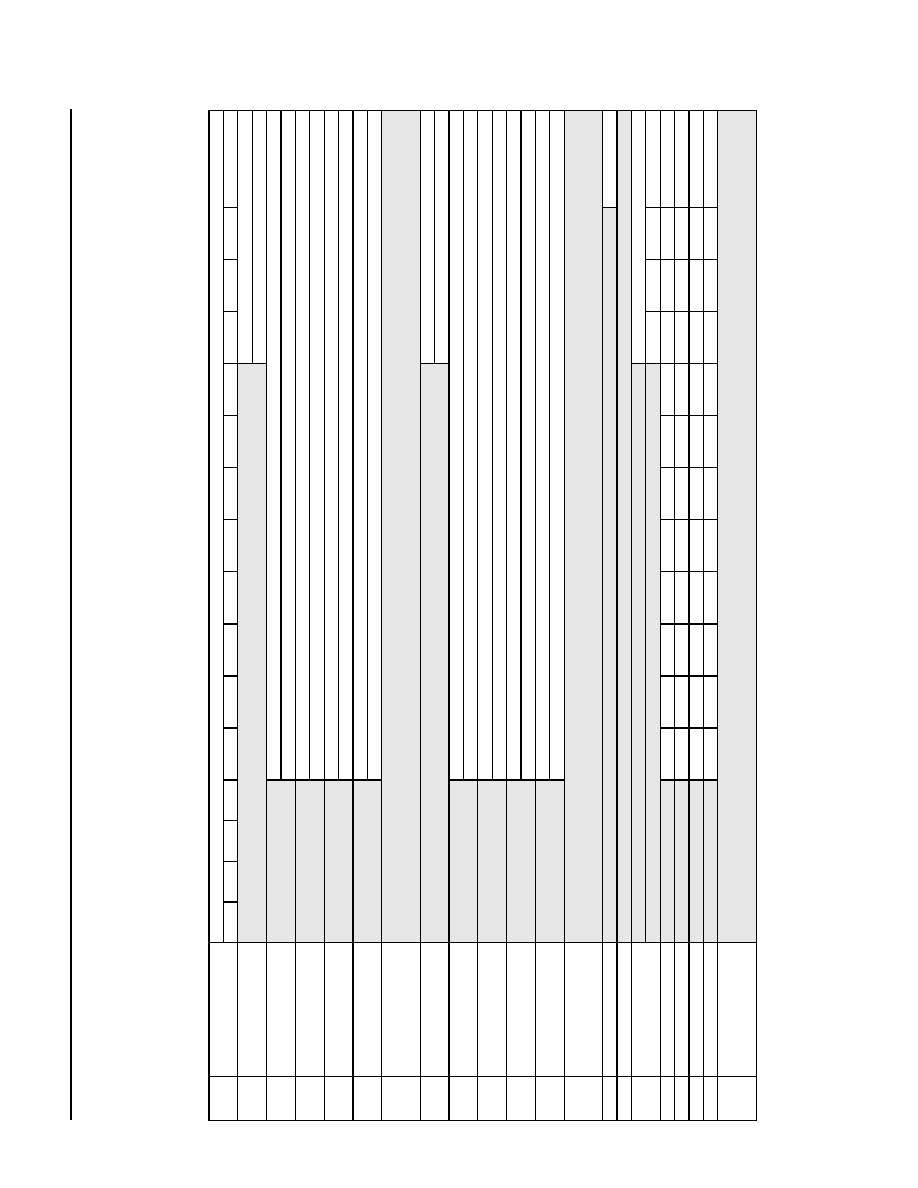

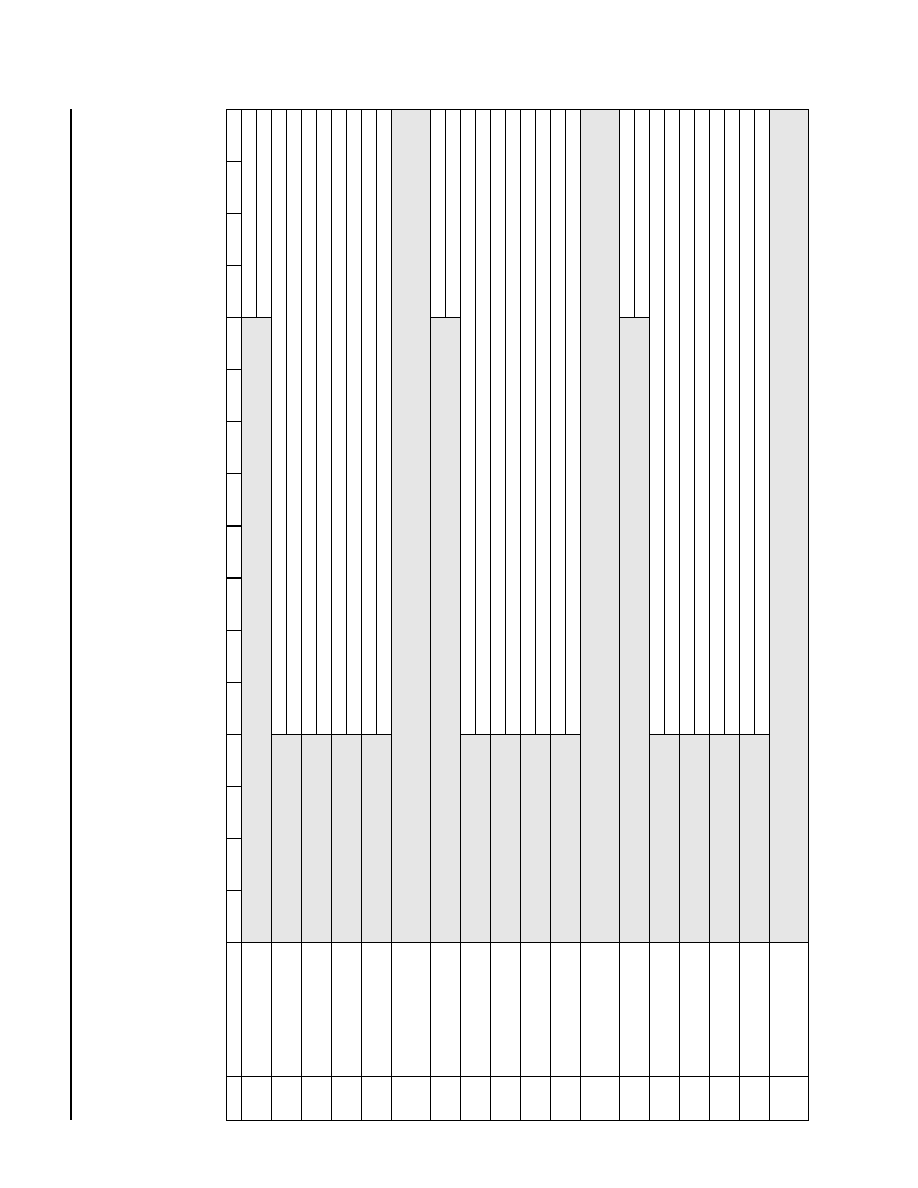

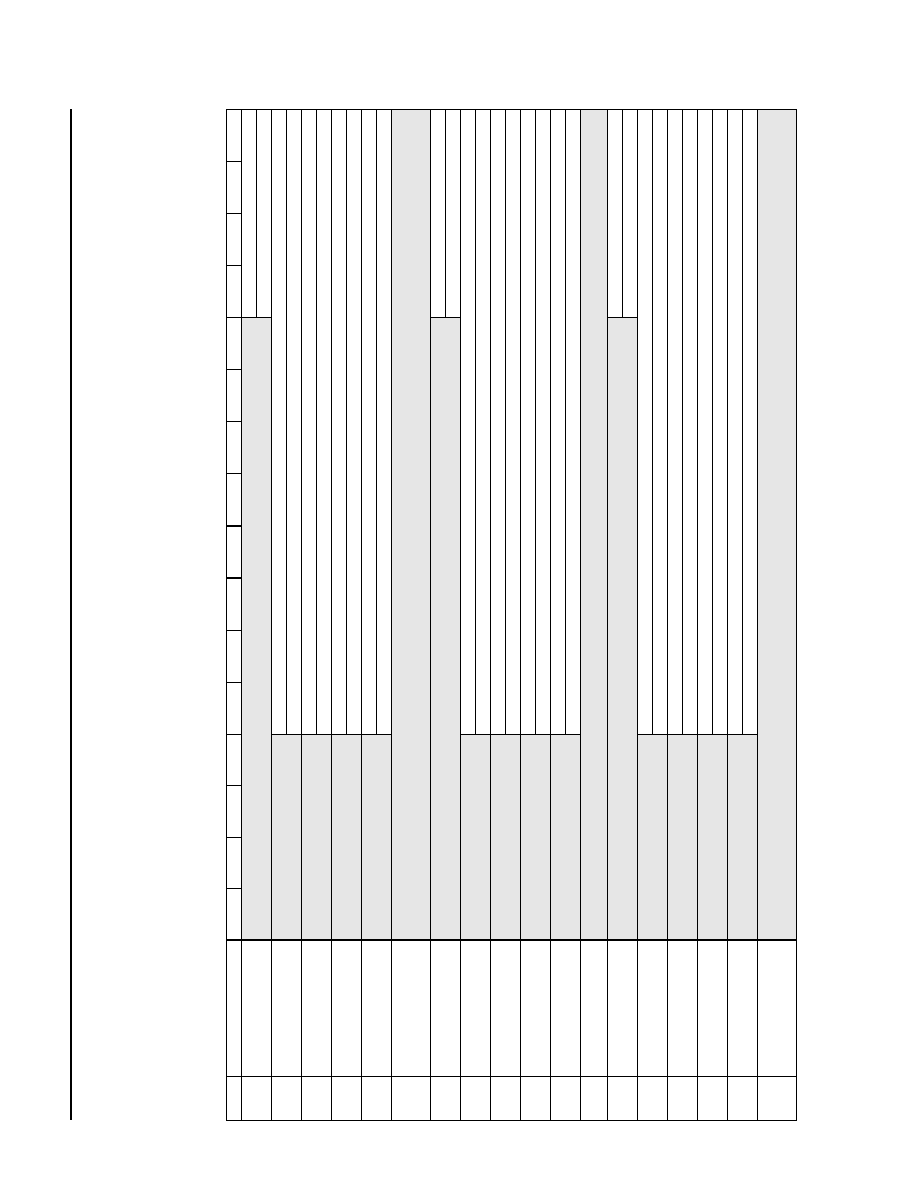

- Table 4. Pin Assignments for 792-Pin PBGA by Signal Name

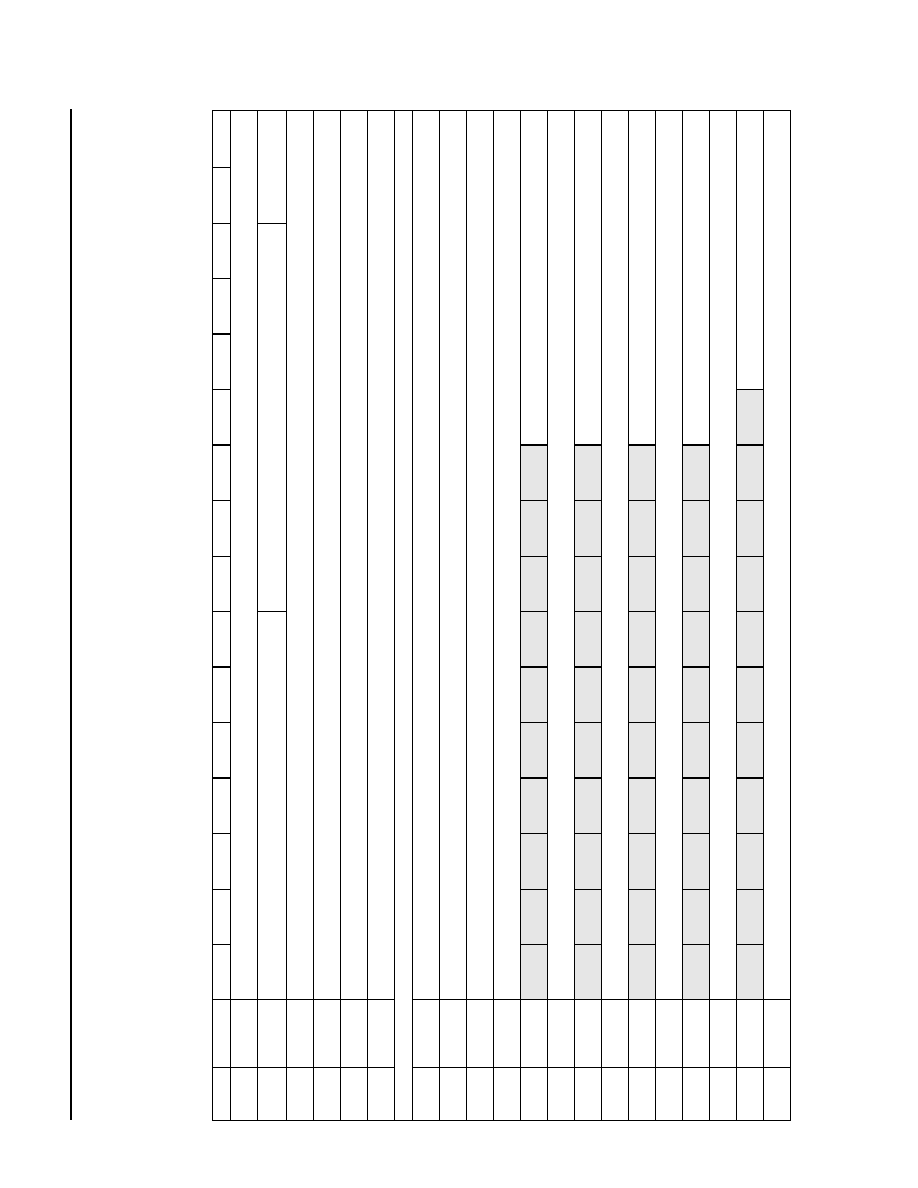

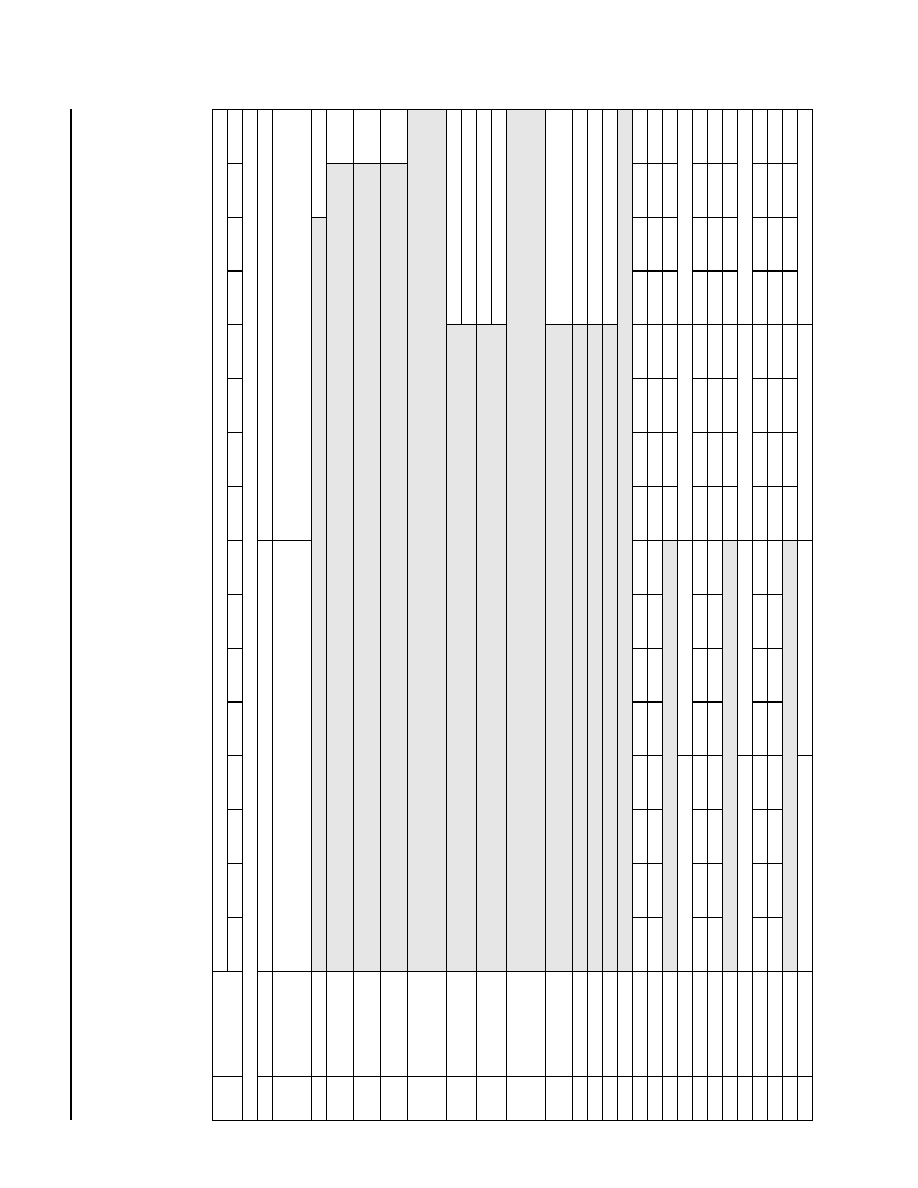

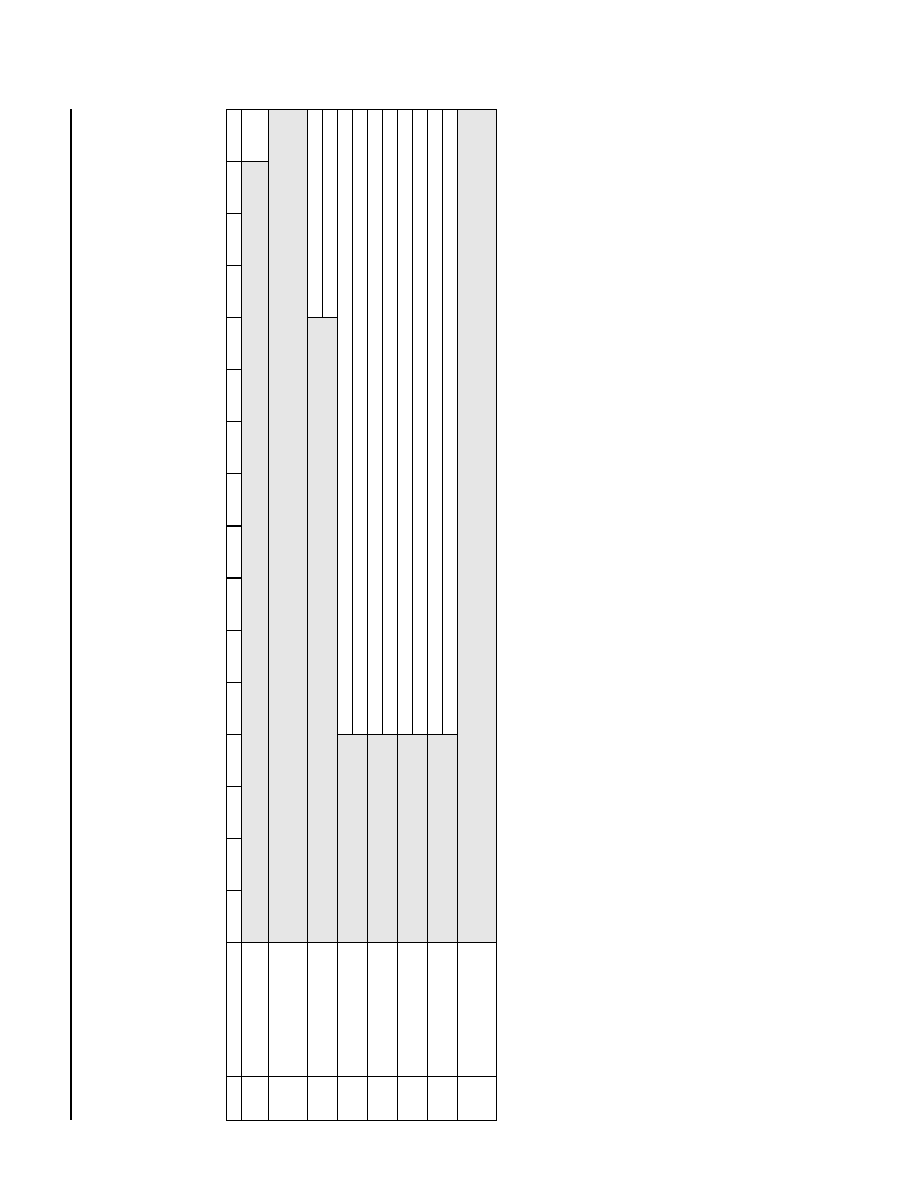

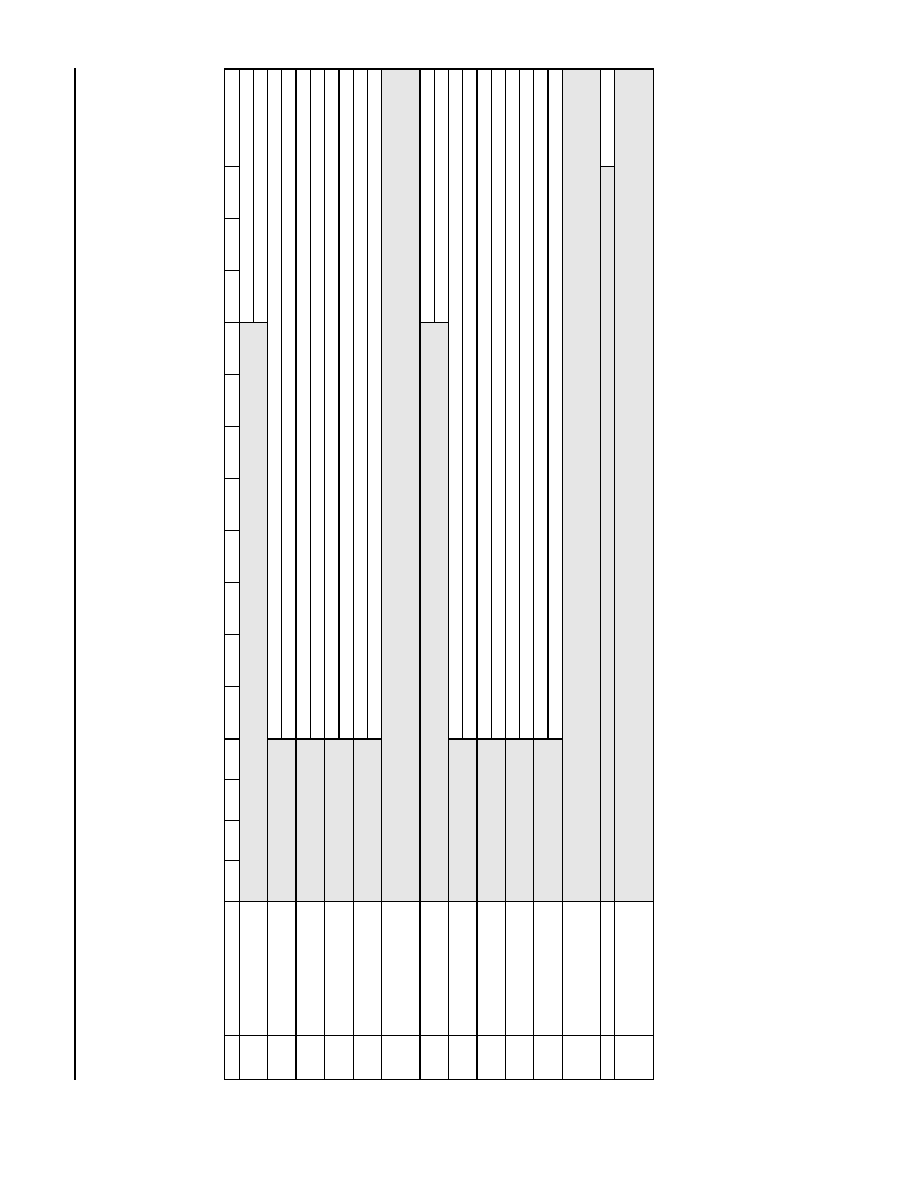

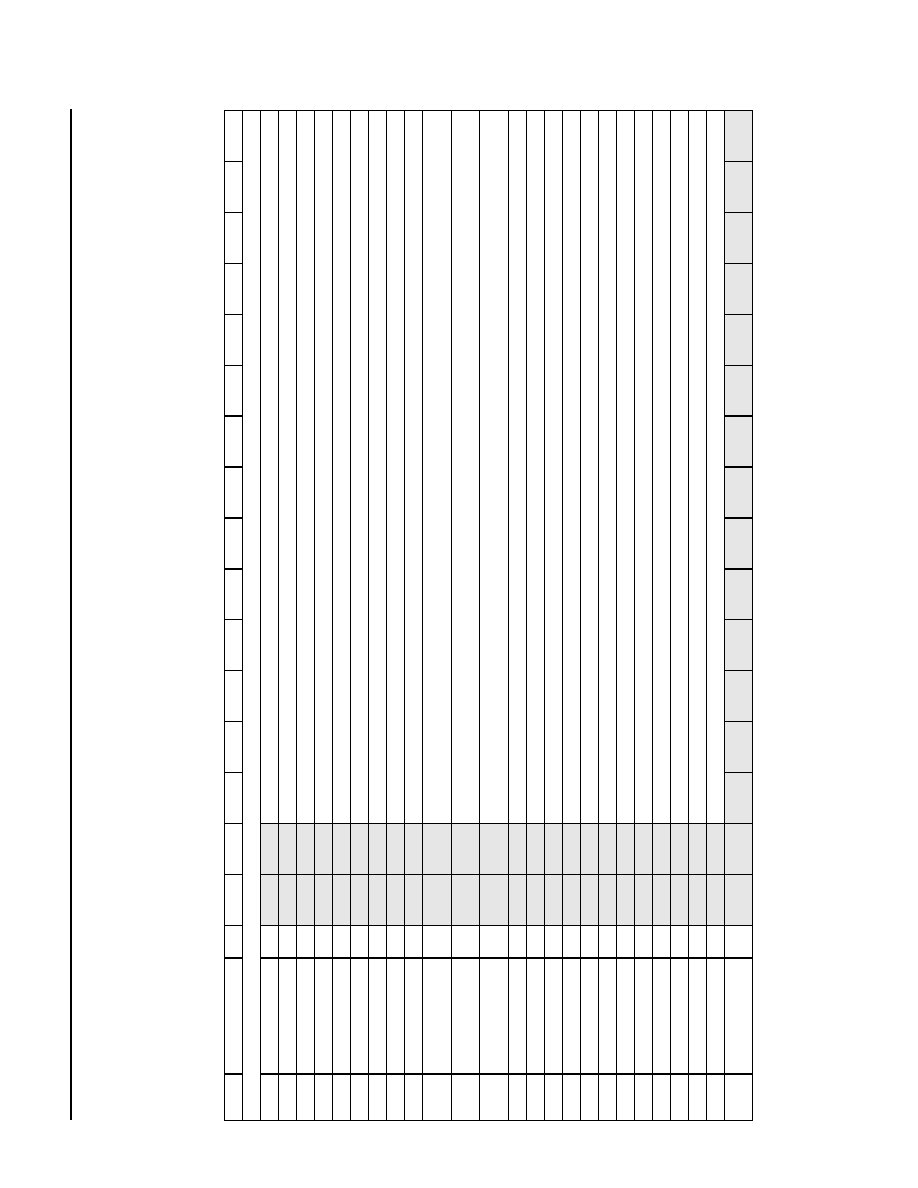

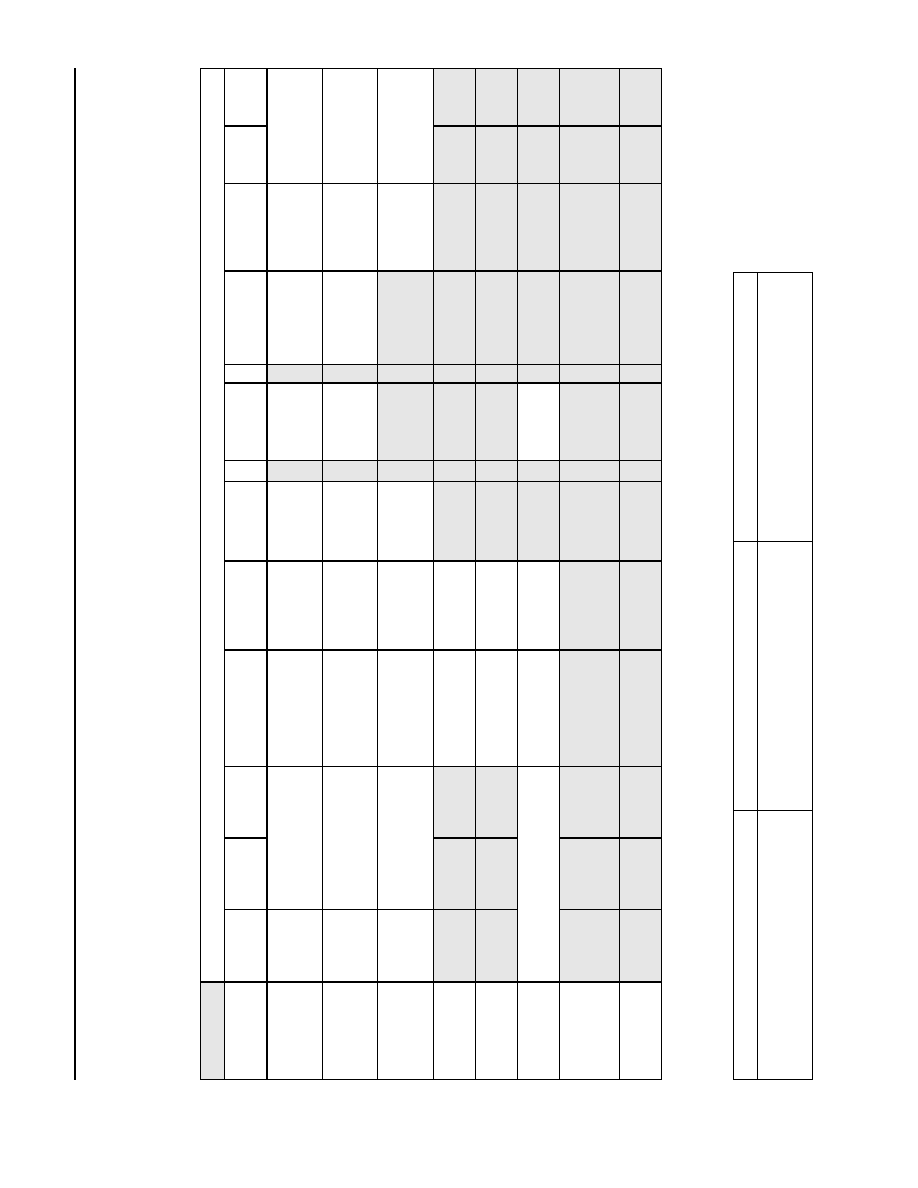

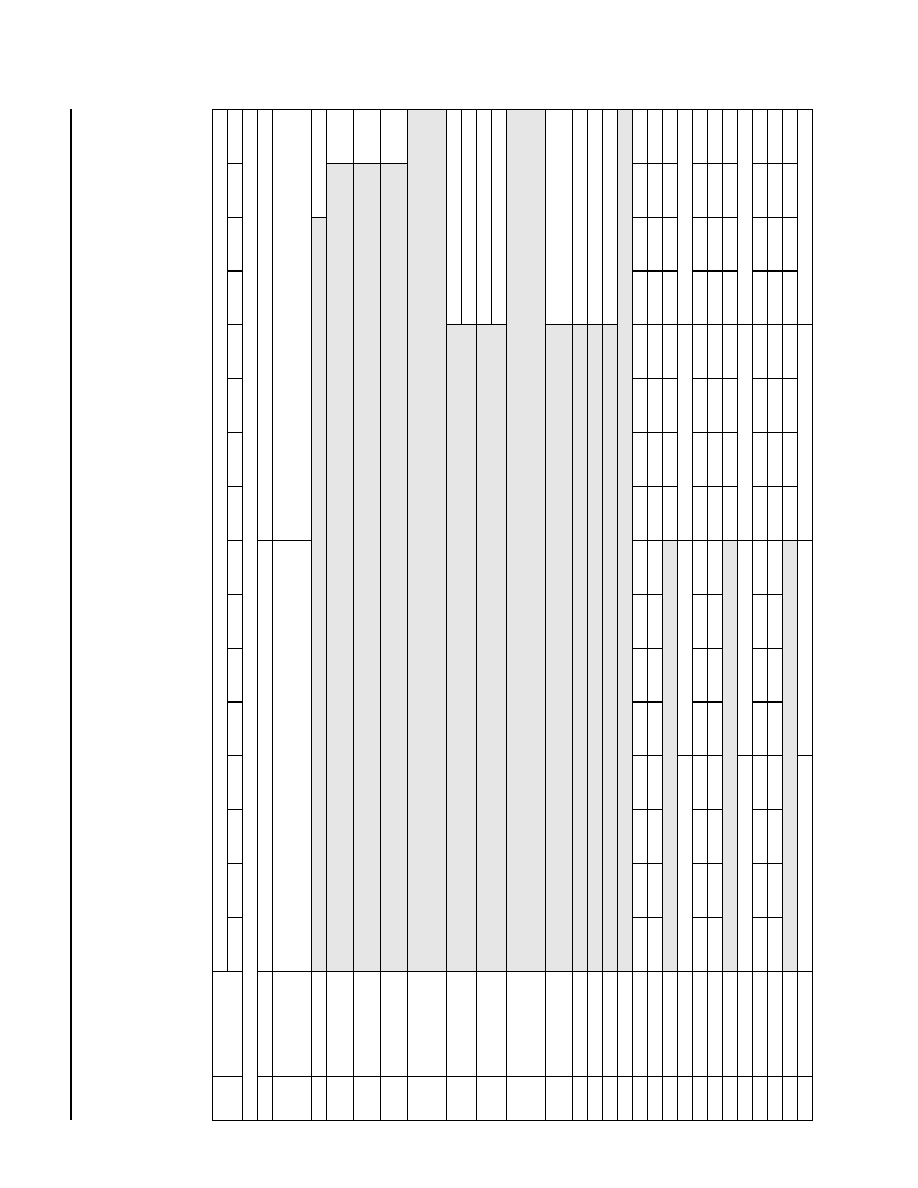

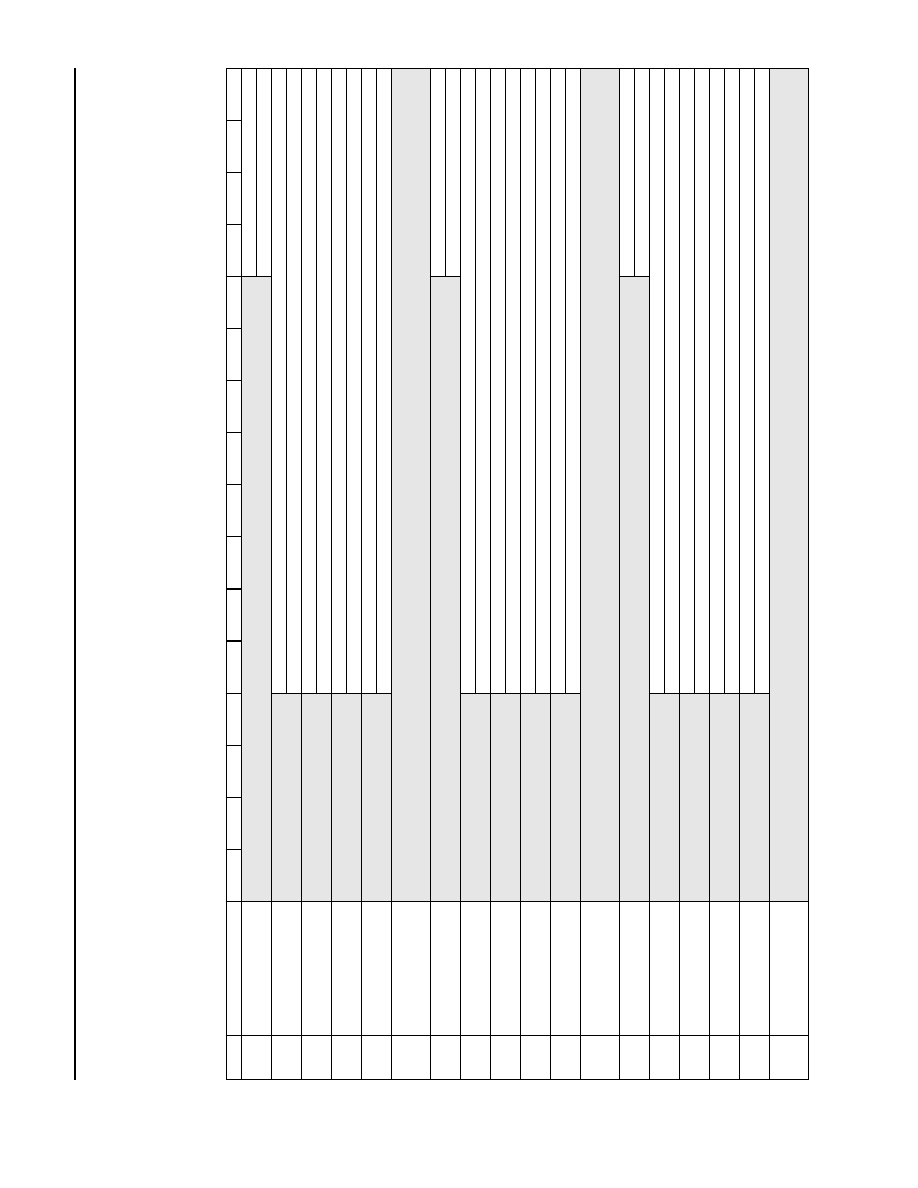

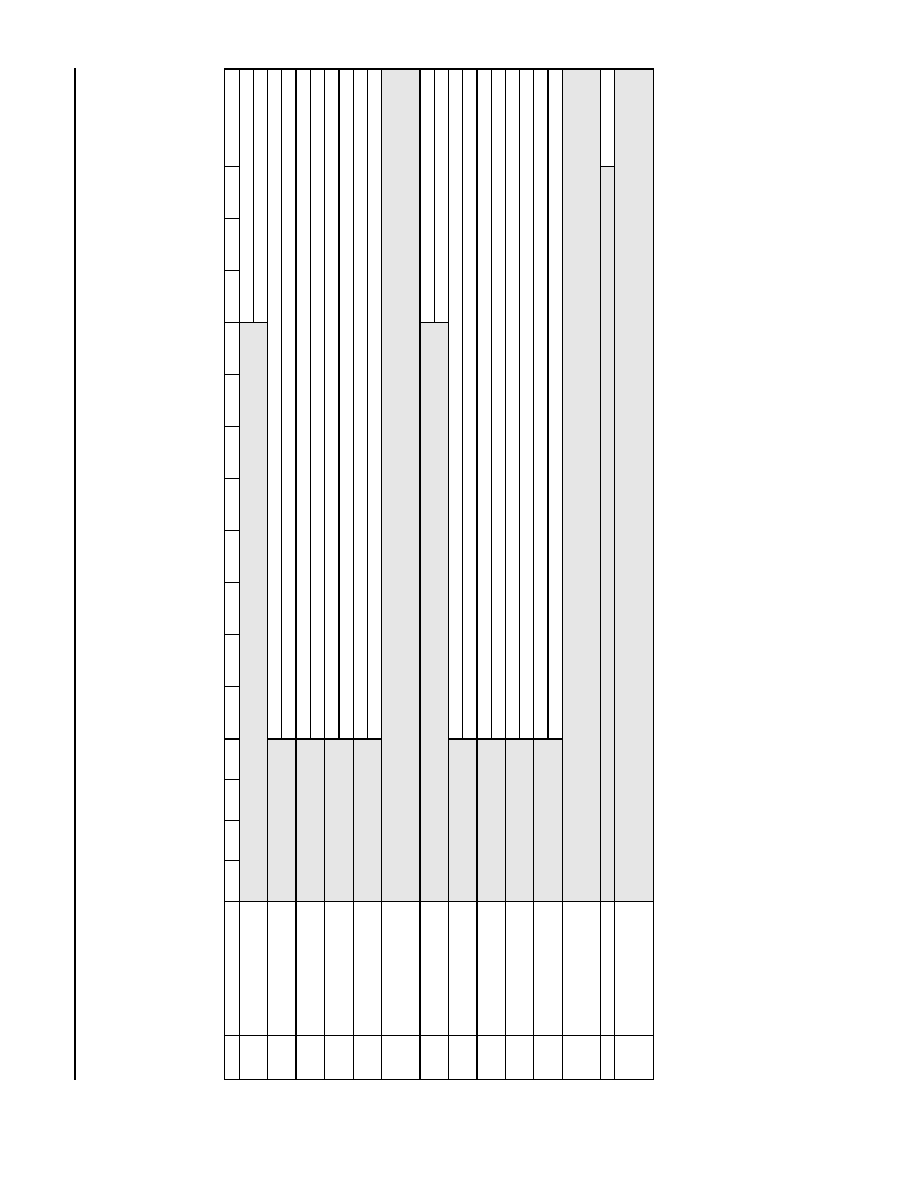

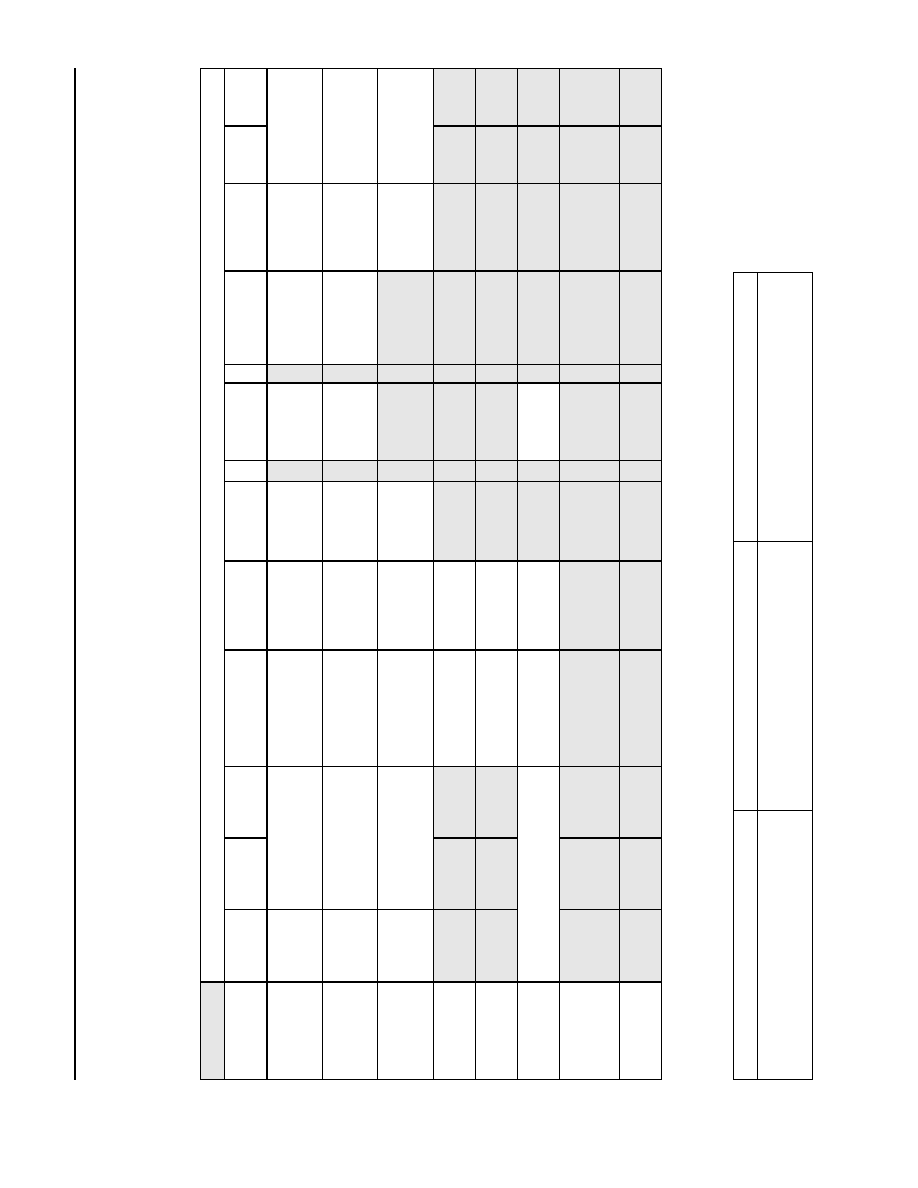

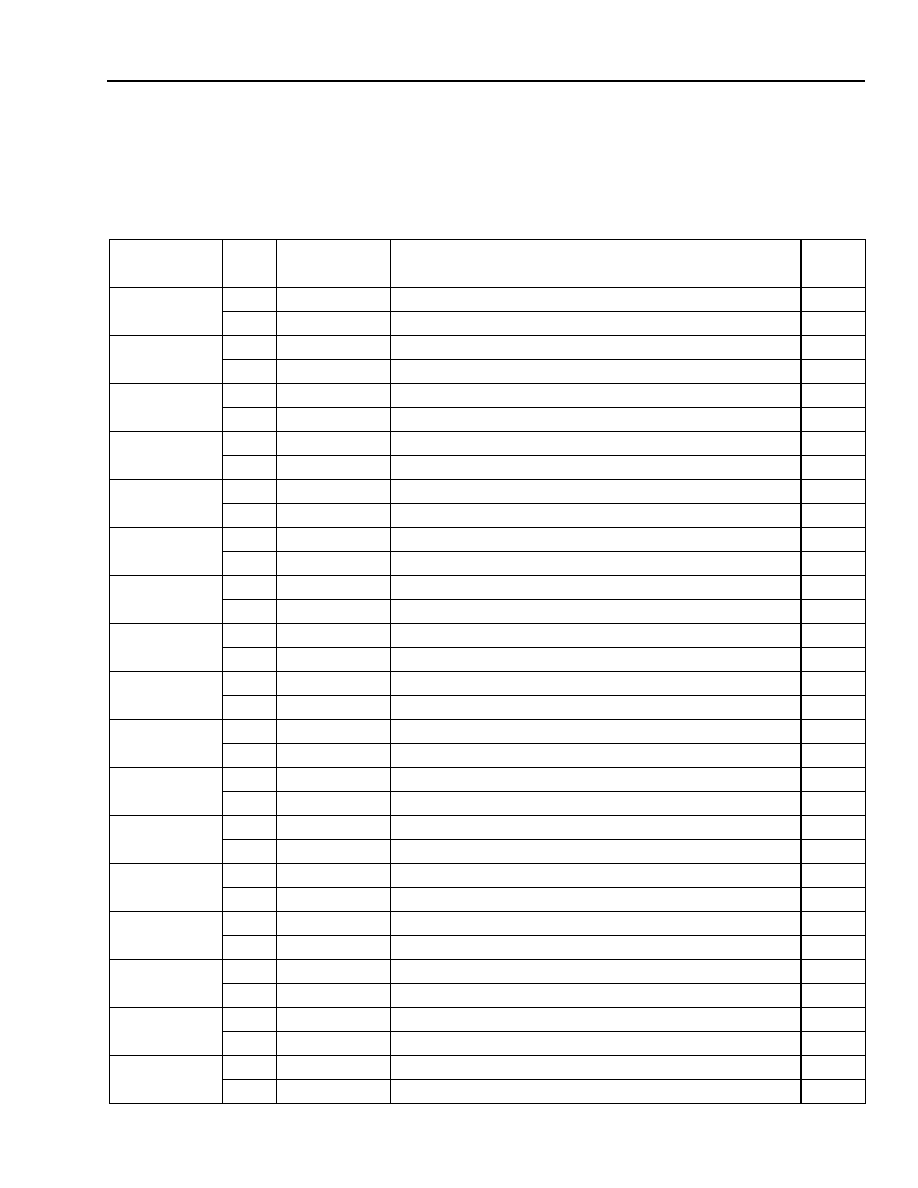

- Table 5. Pin Assignments for 600-Pin LBGA by Pin Number Order

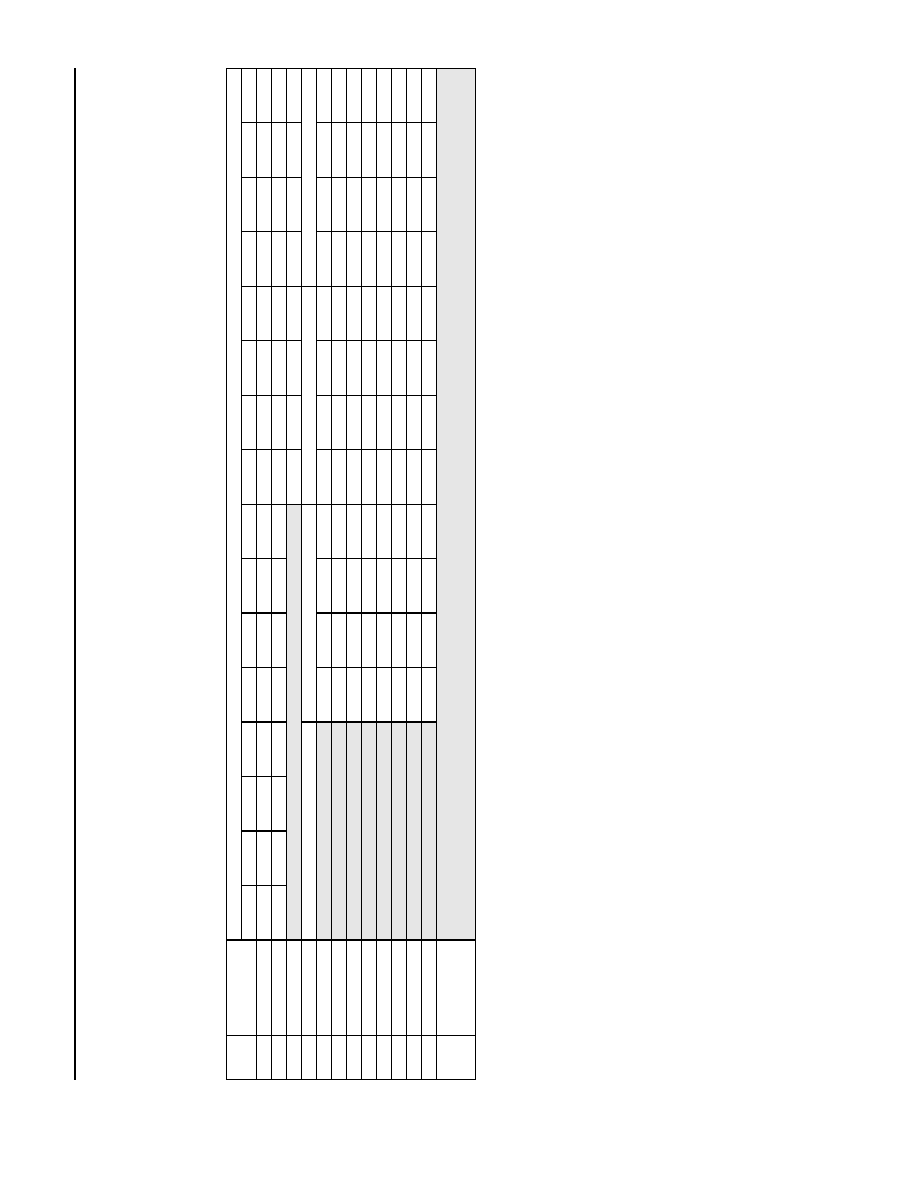

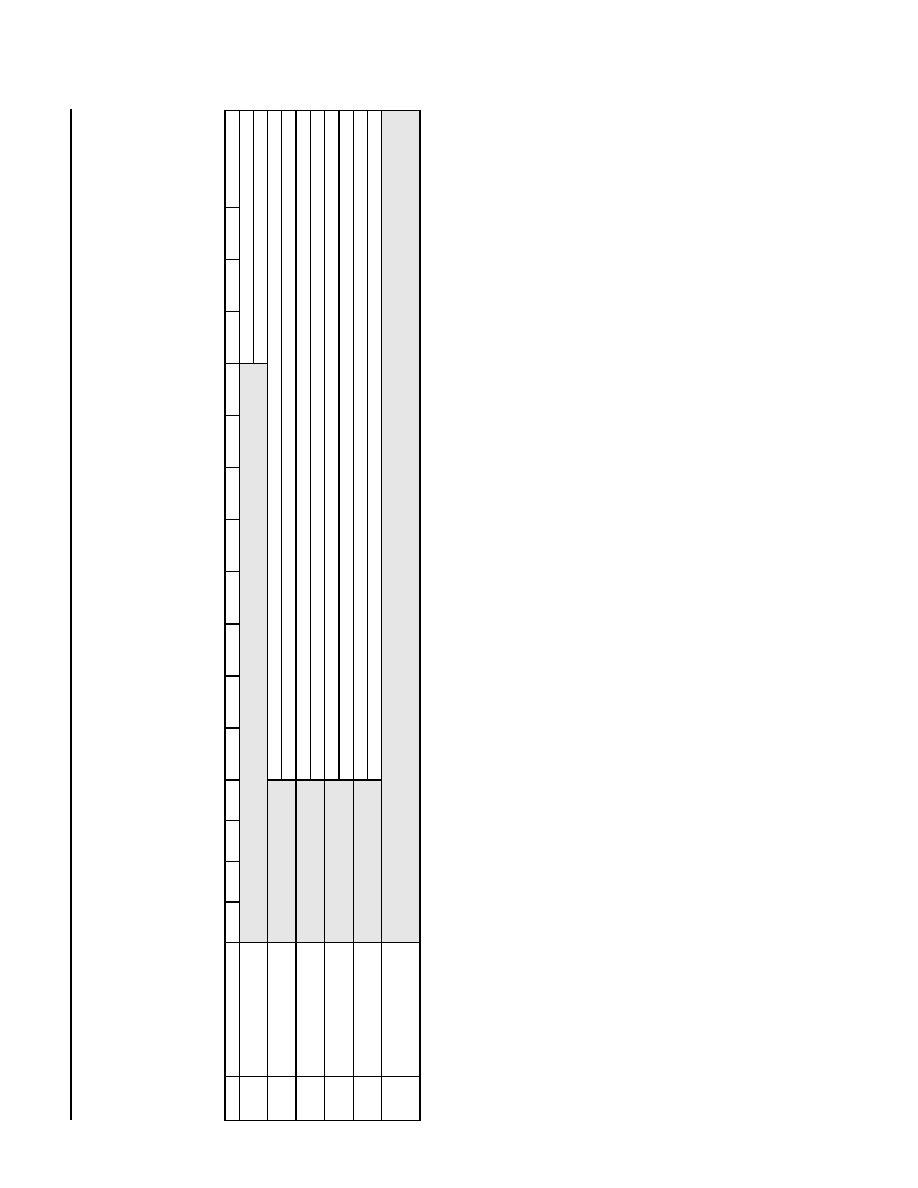

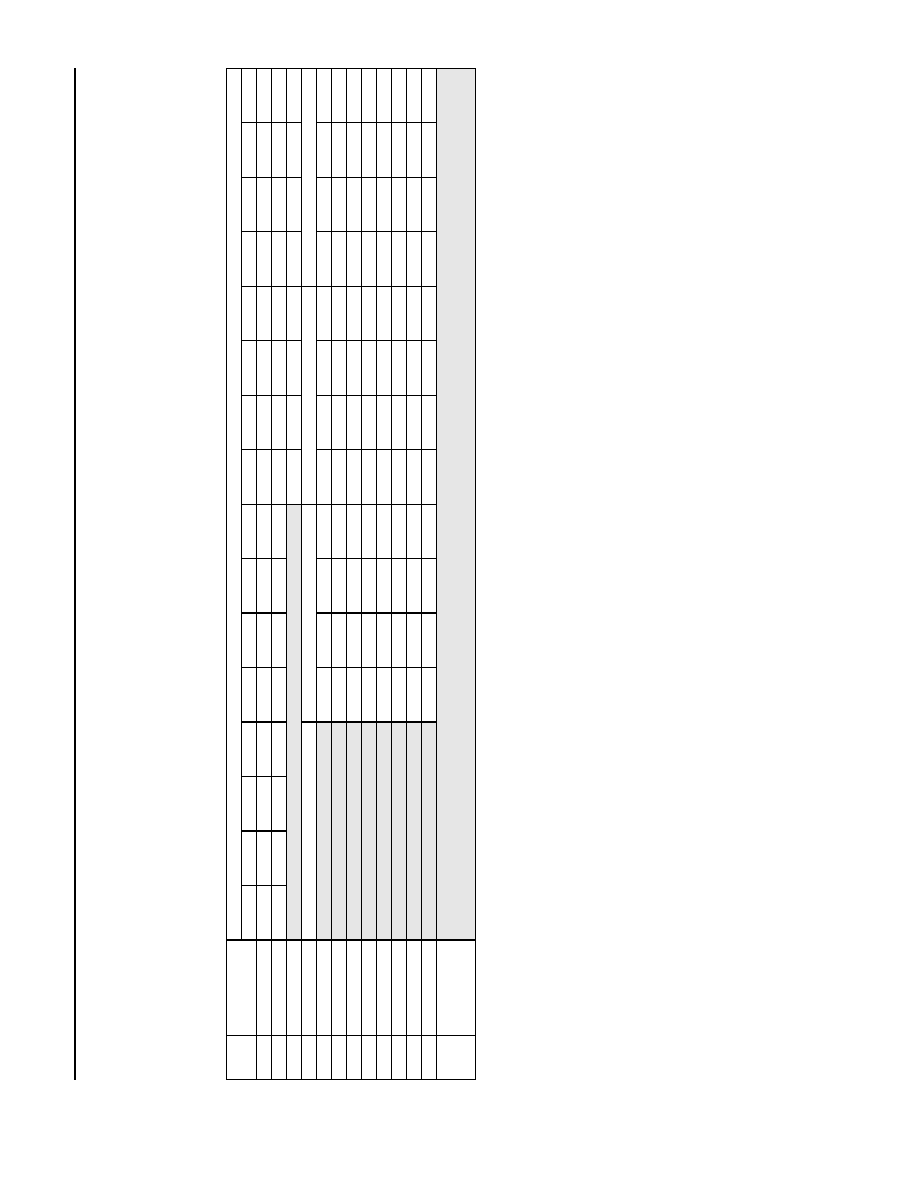

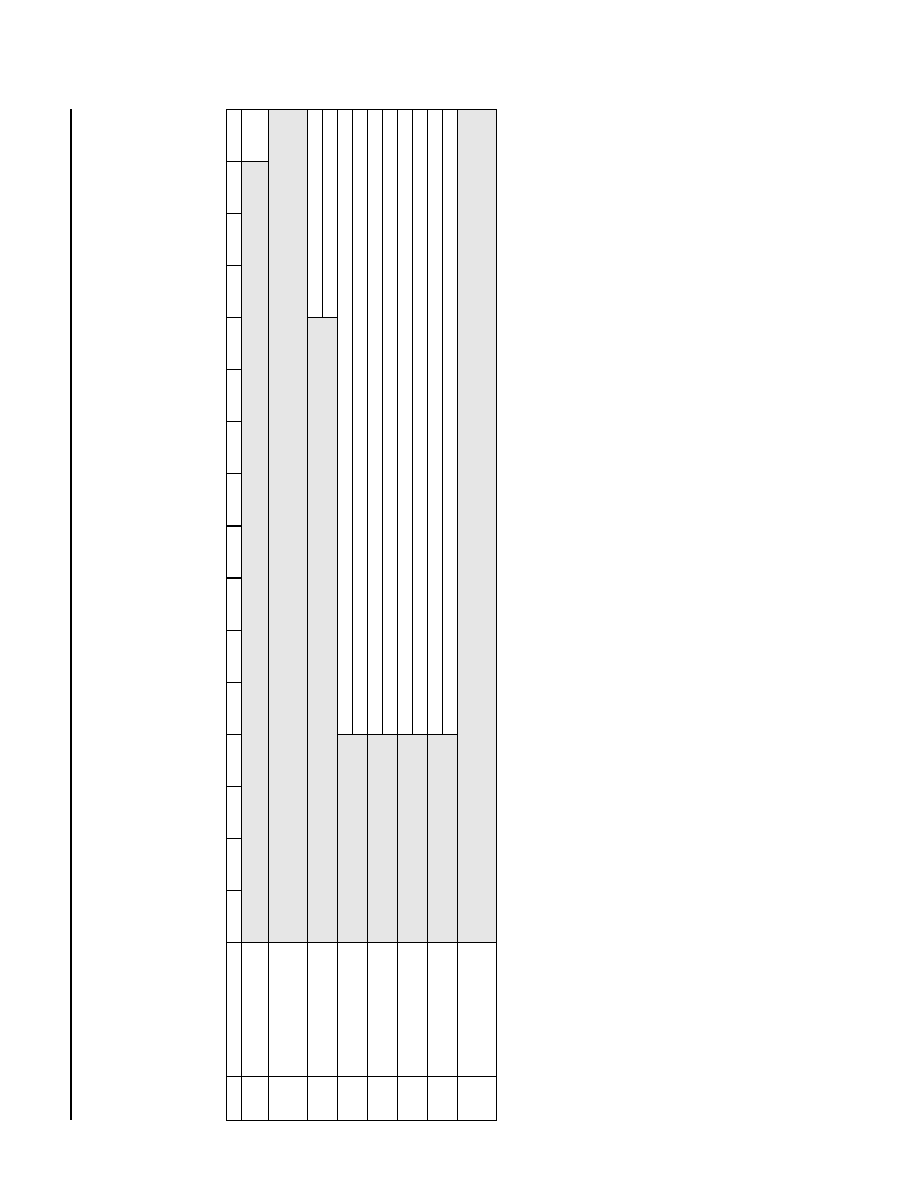

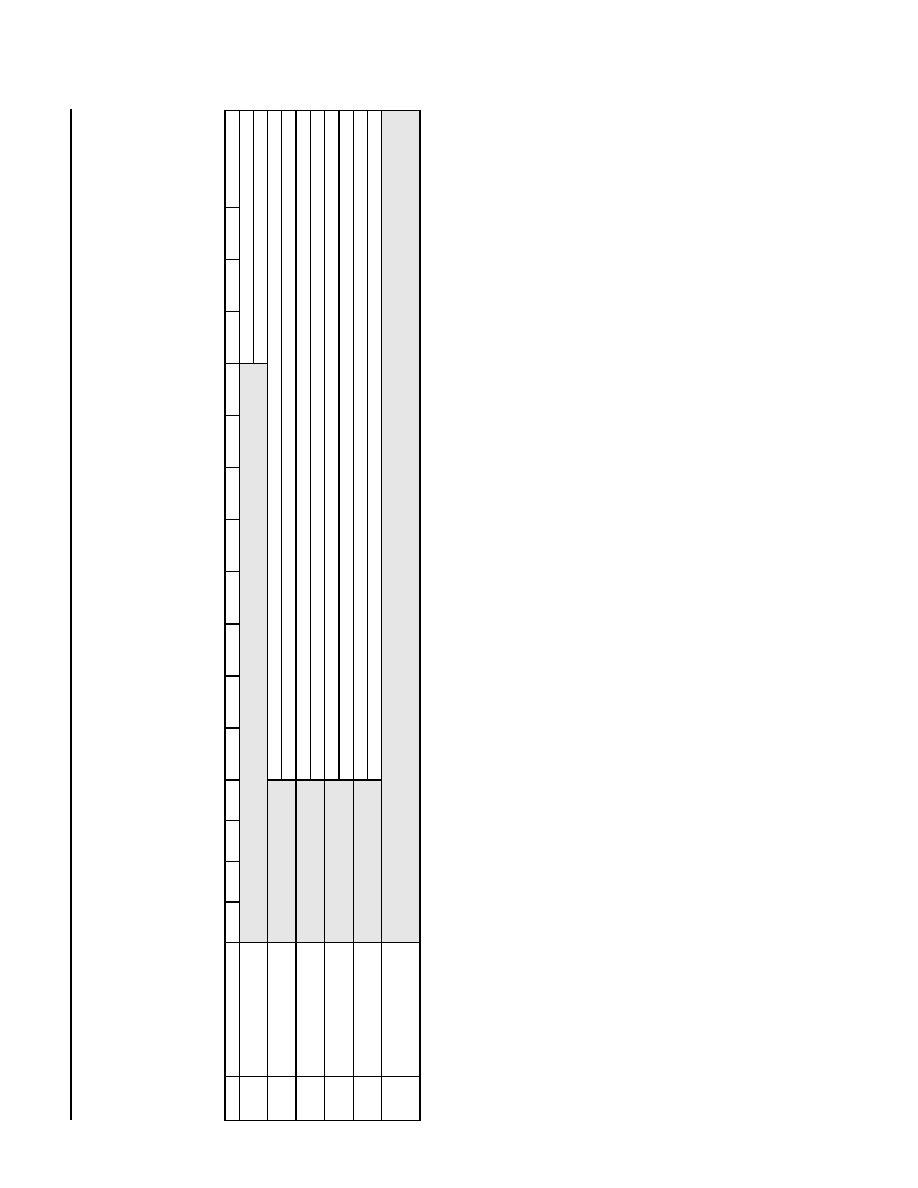

- Table 6. Pin Assignments for 600-Pin LBGA by Signal Name

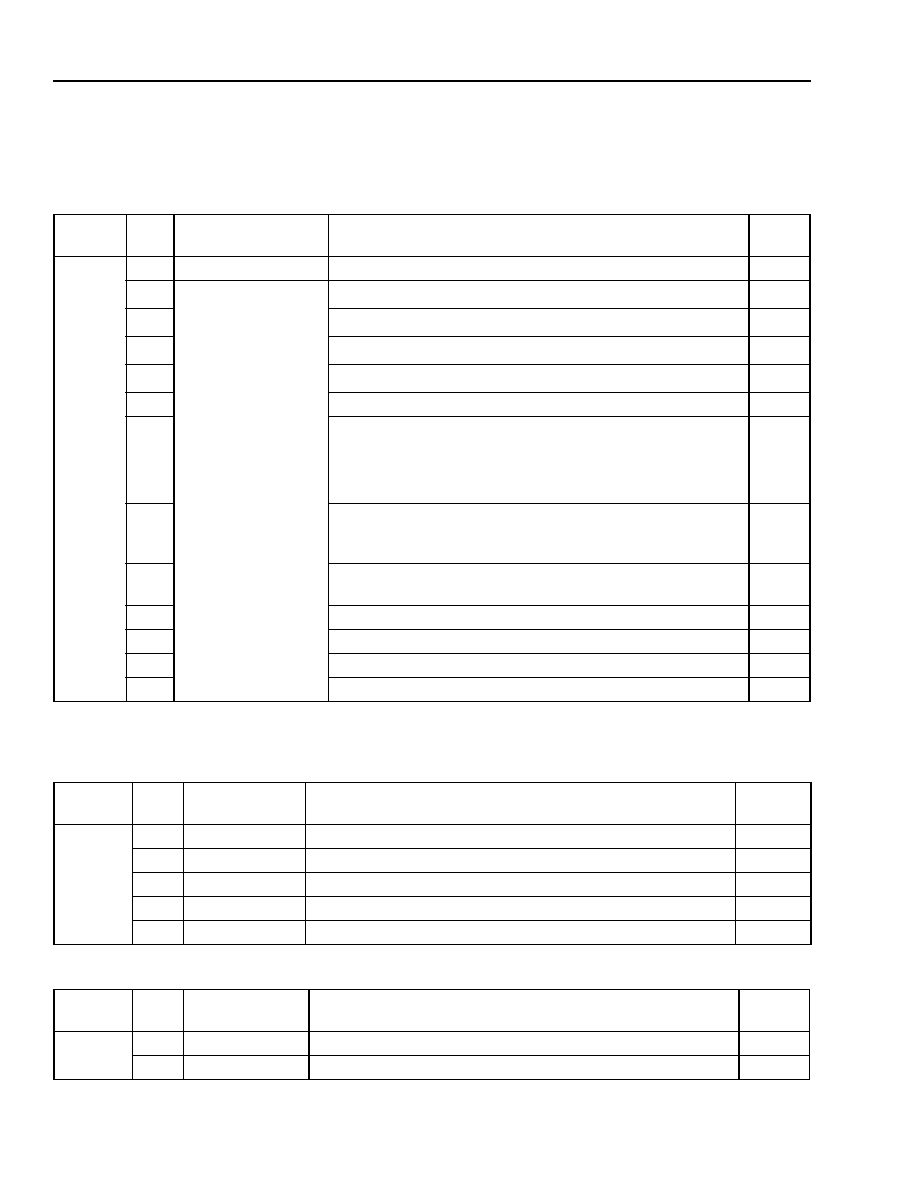

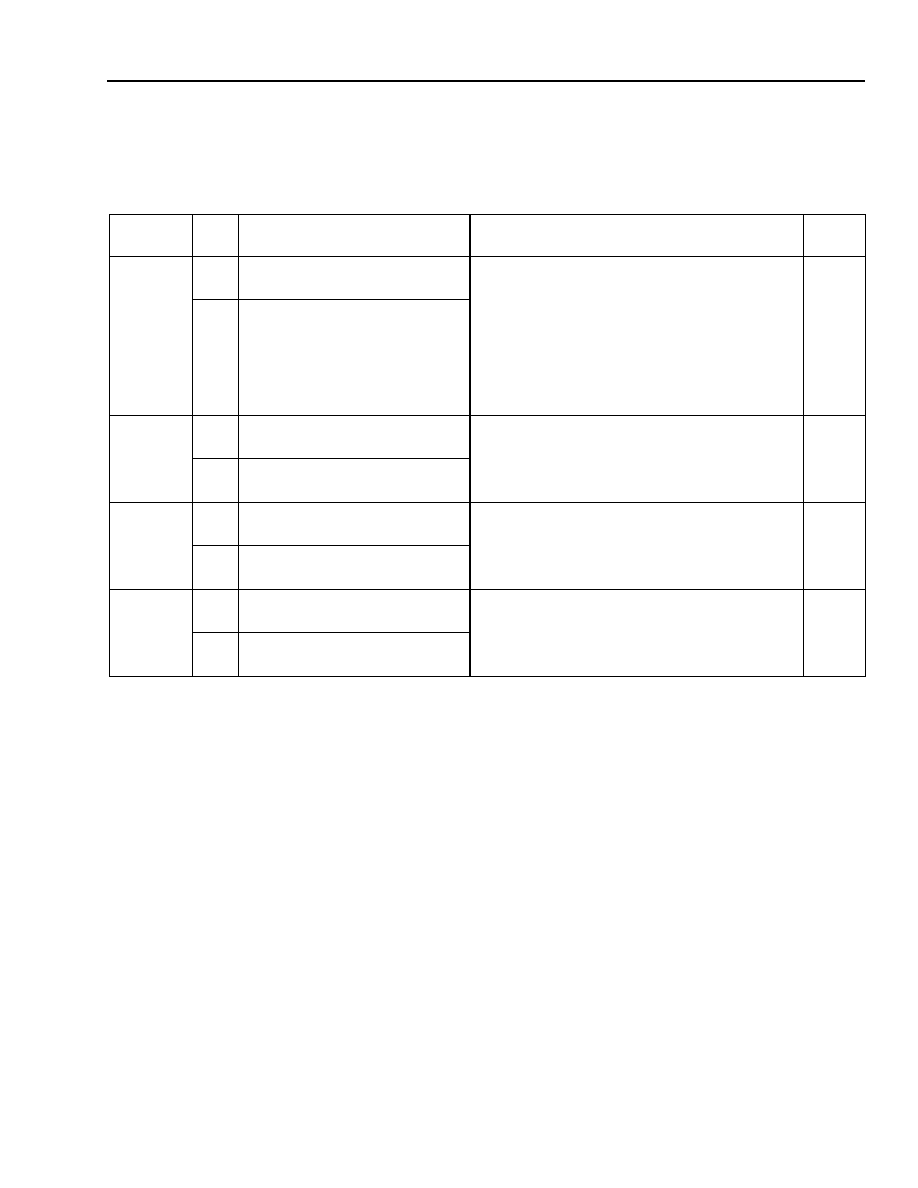

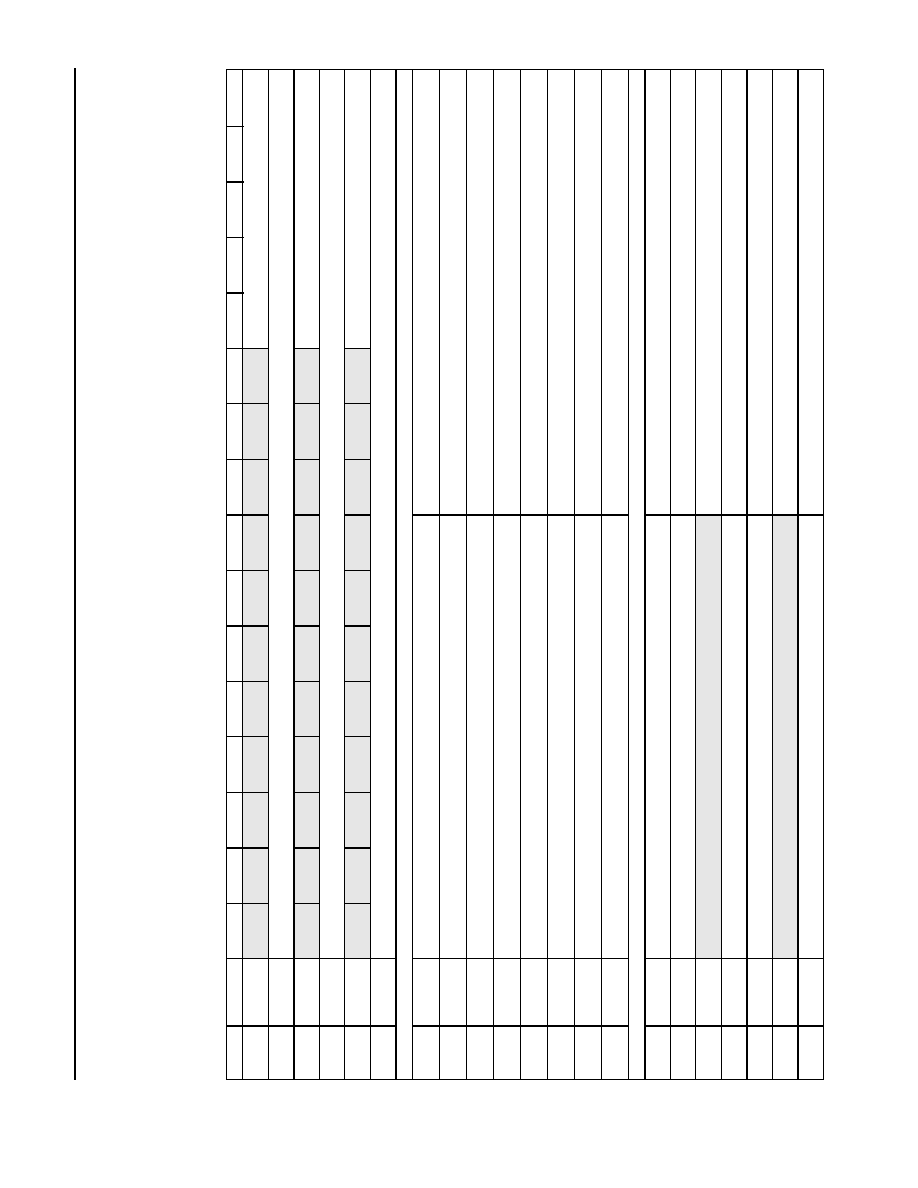

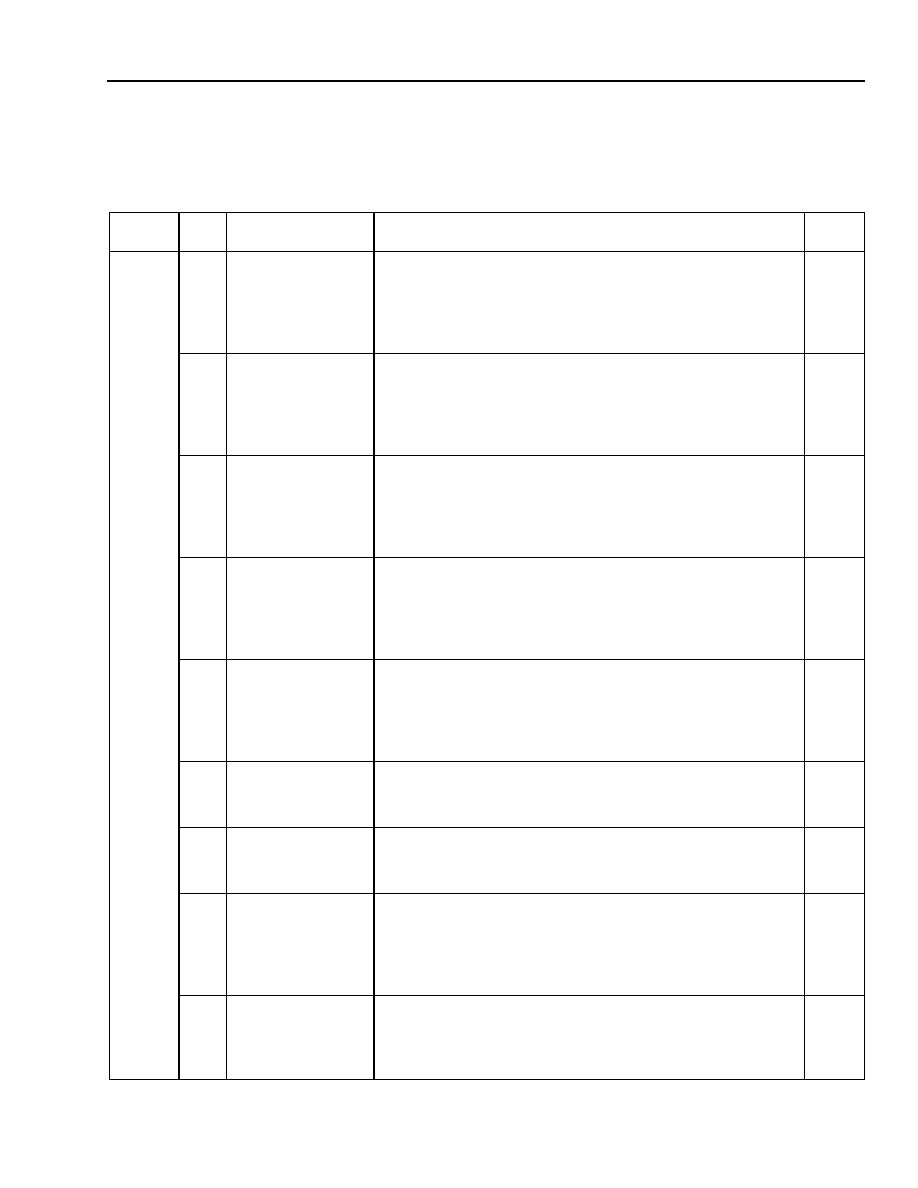

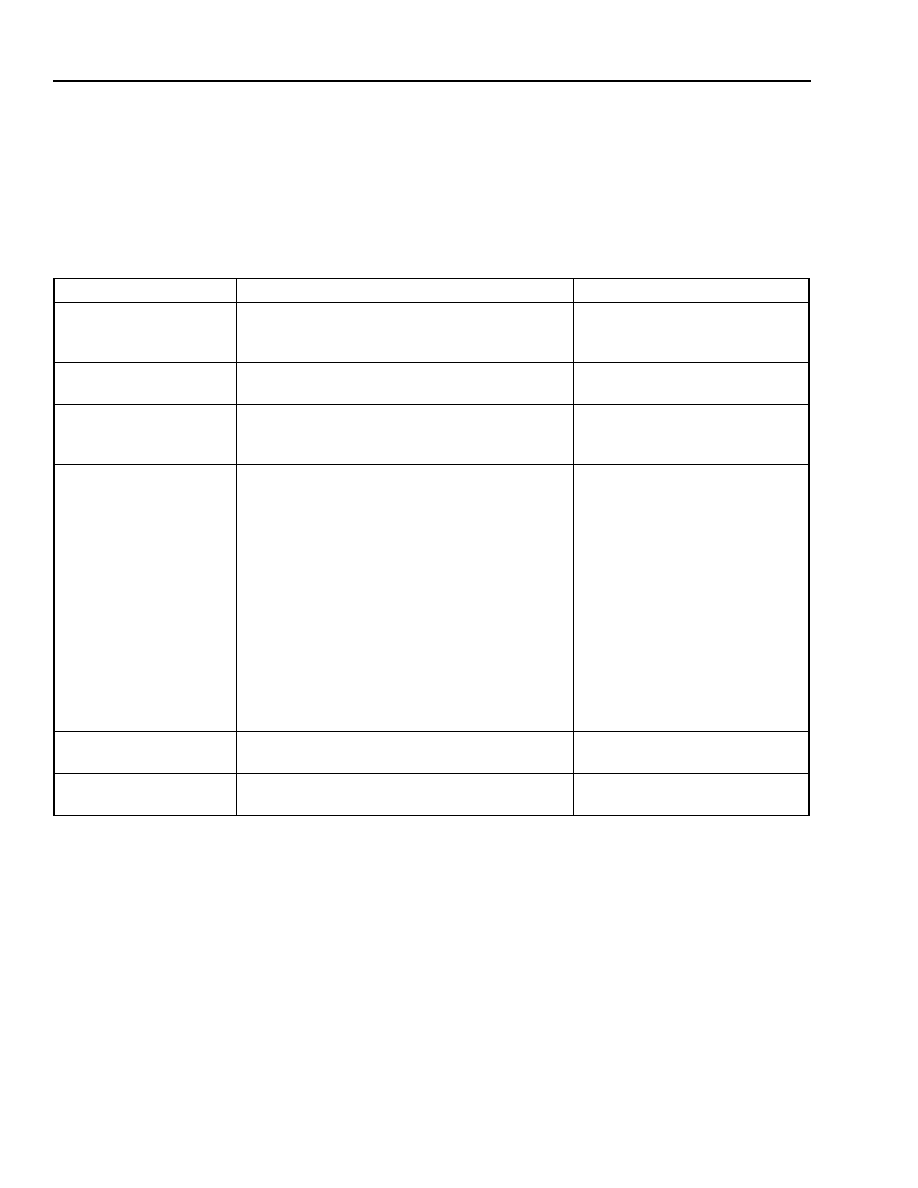

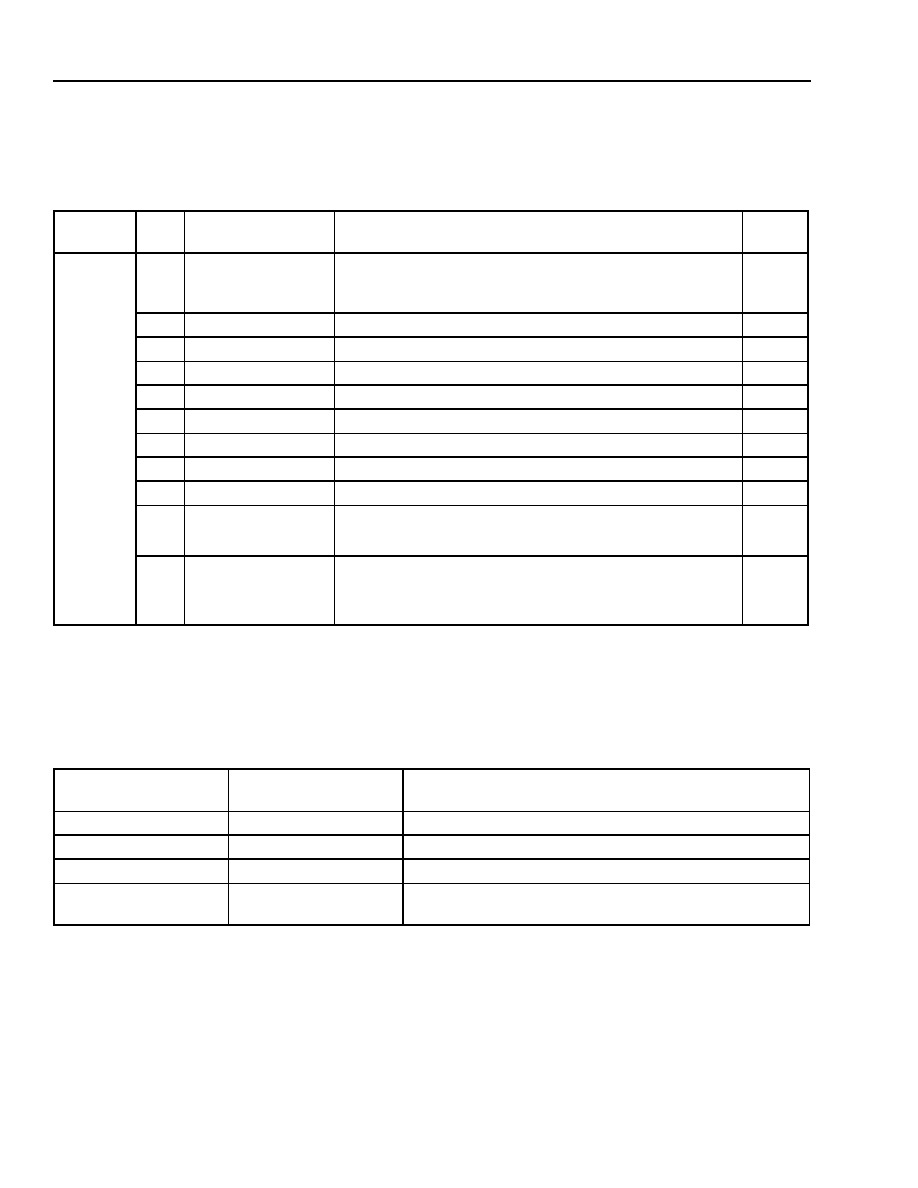

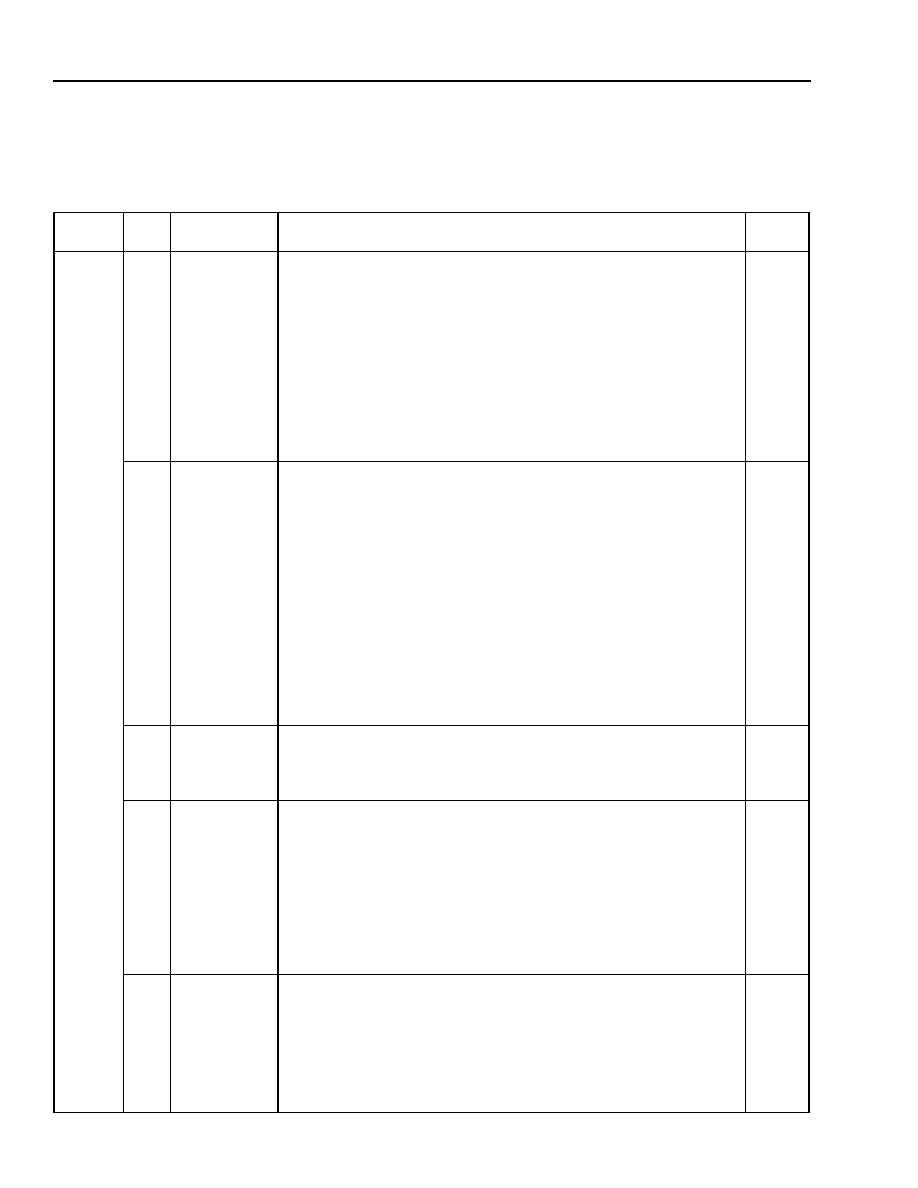

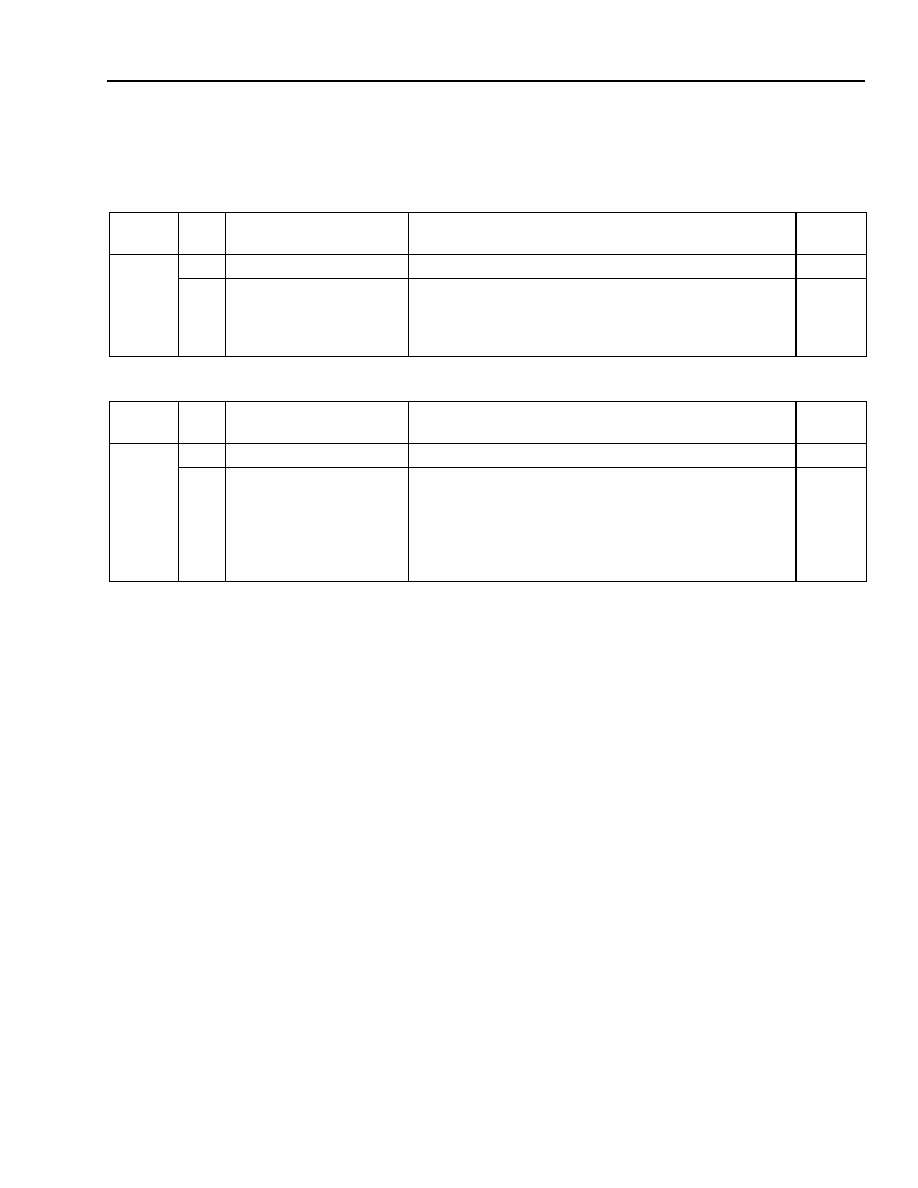

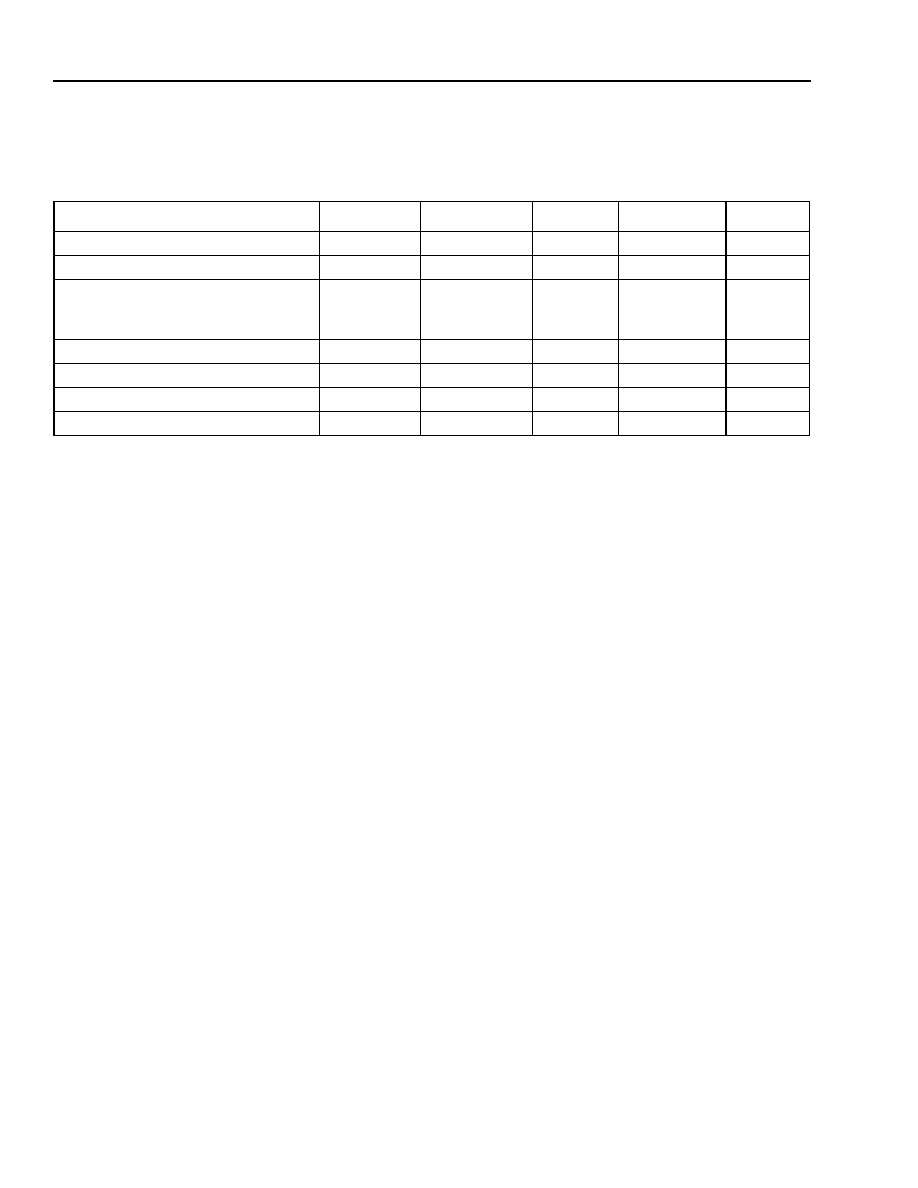

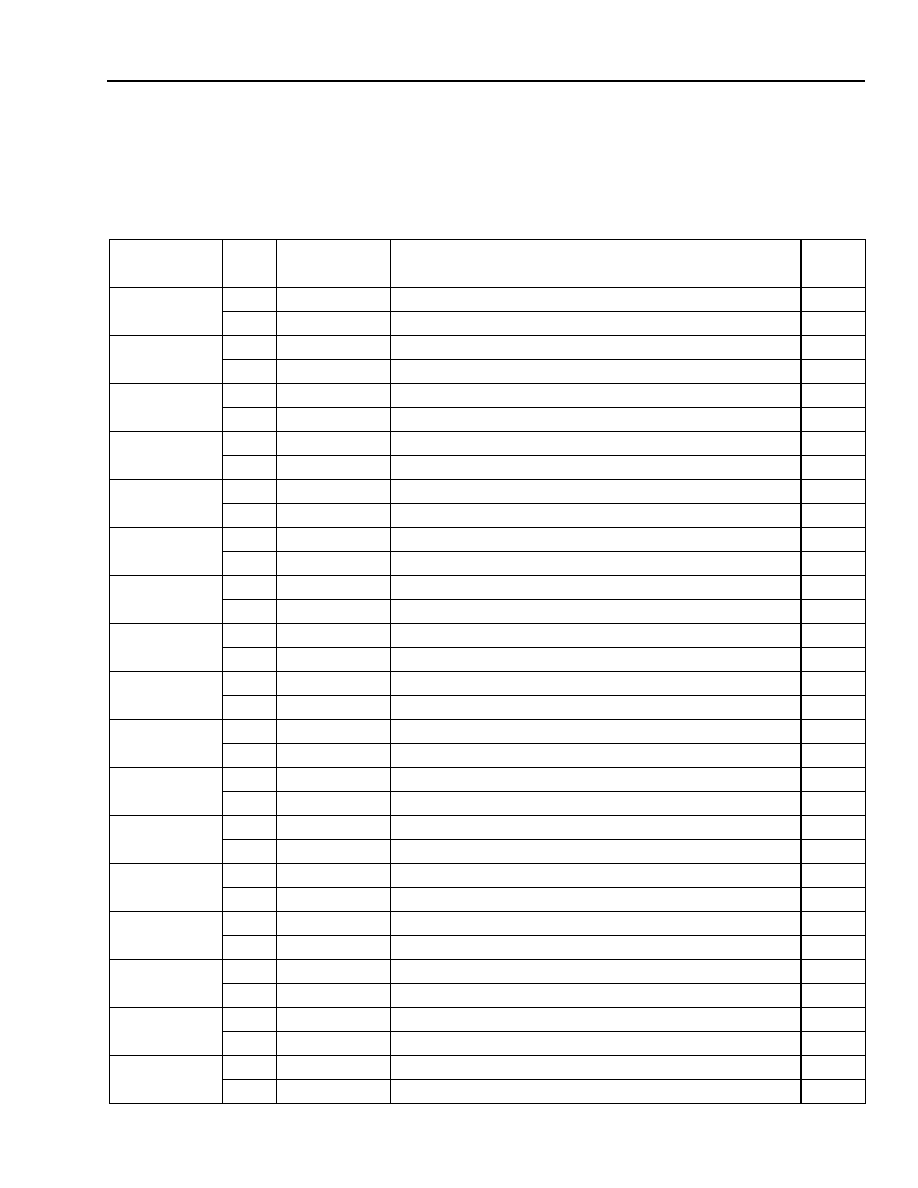

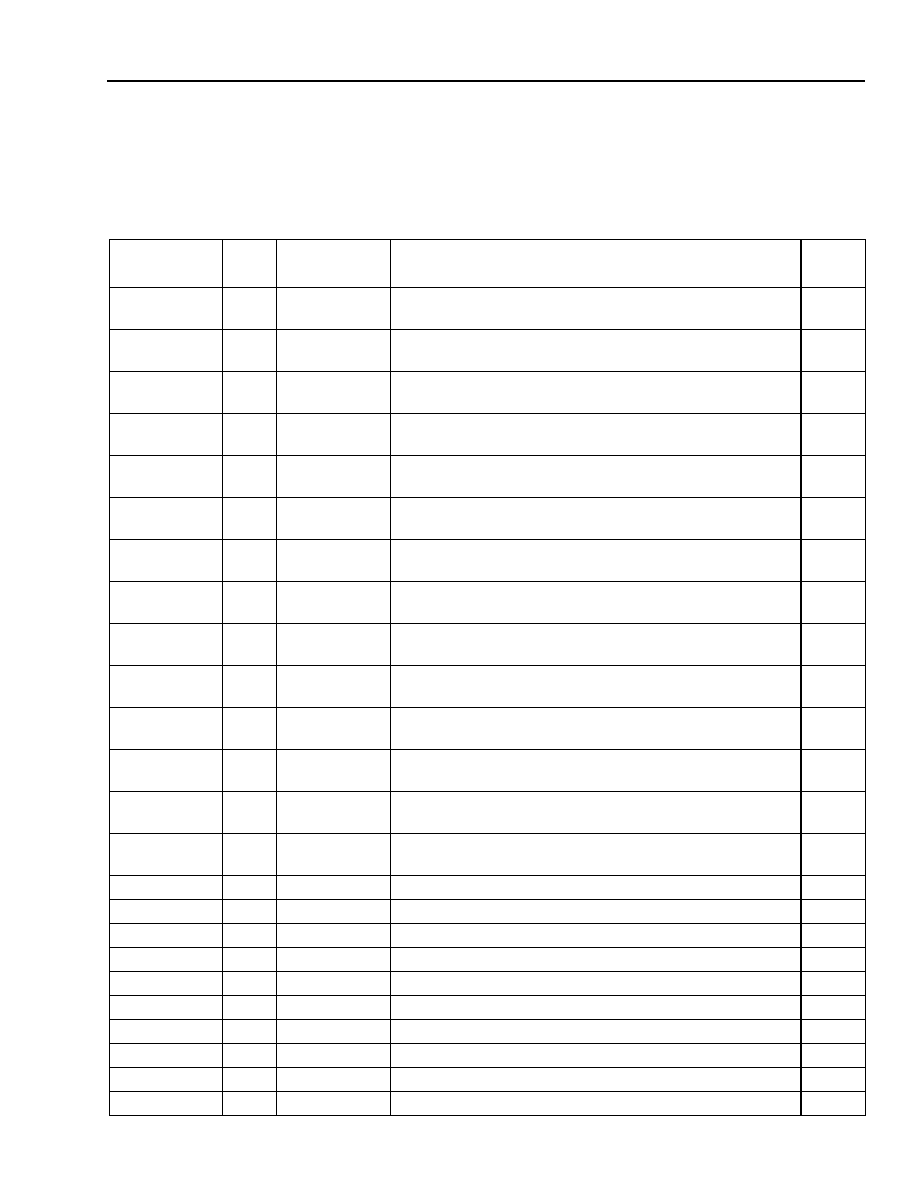

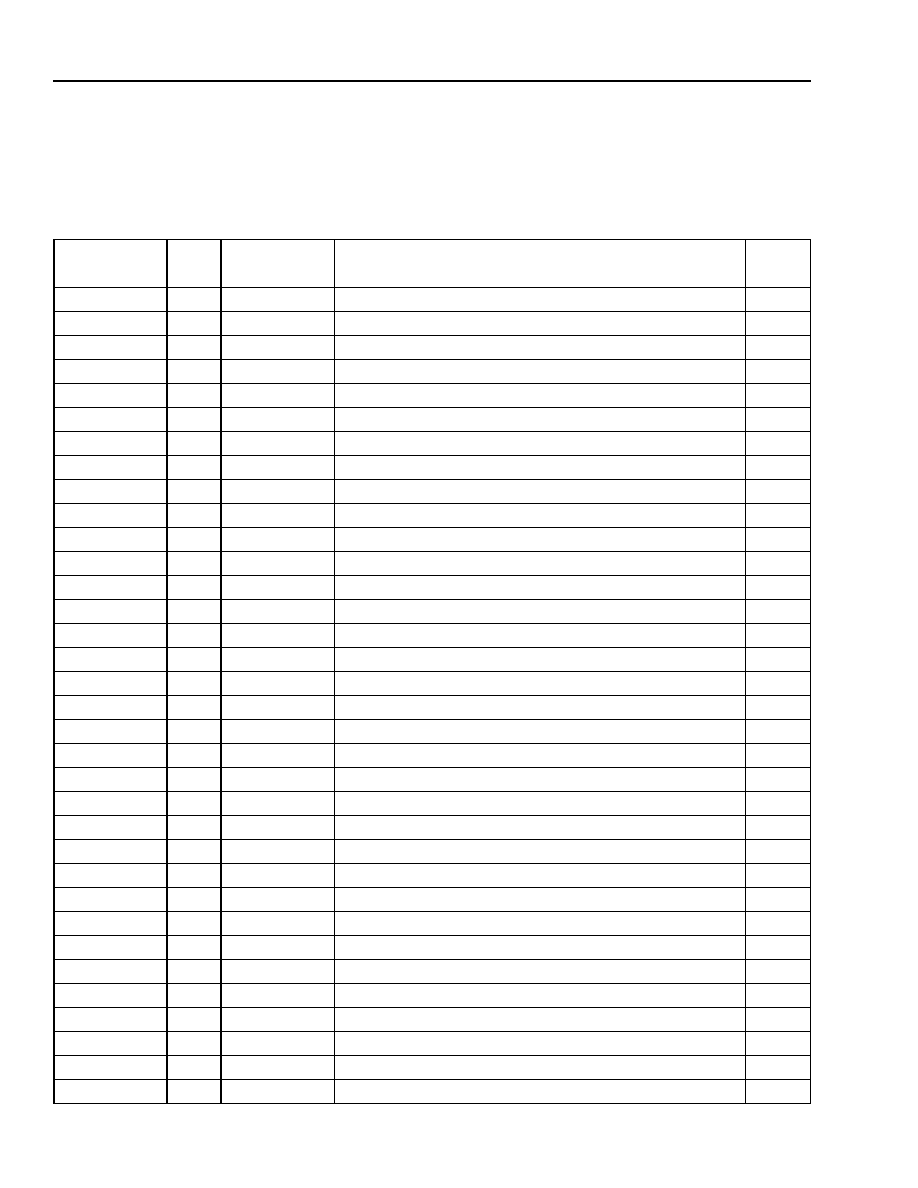

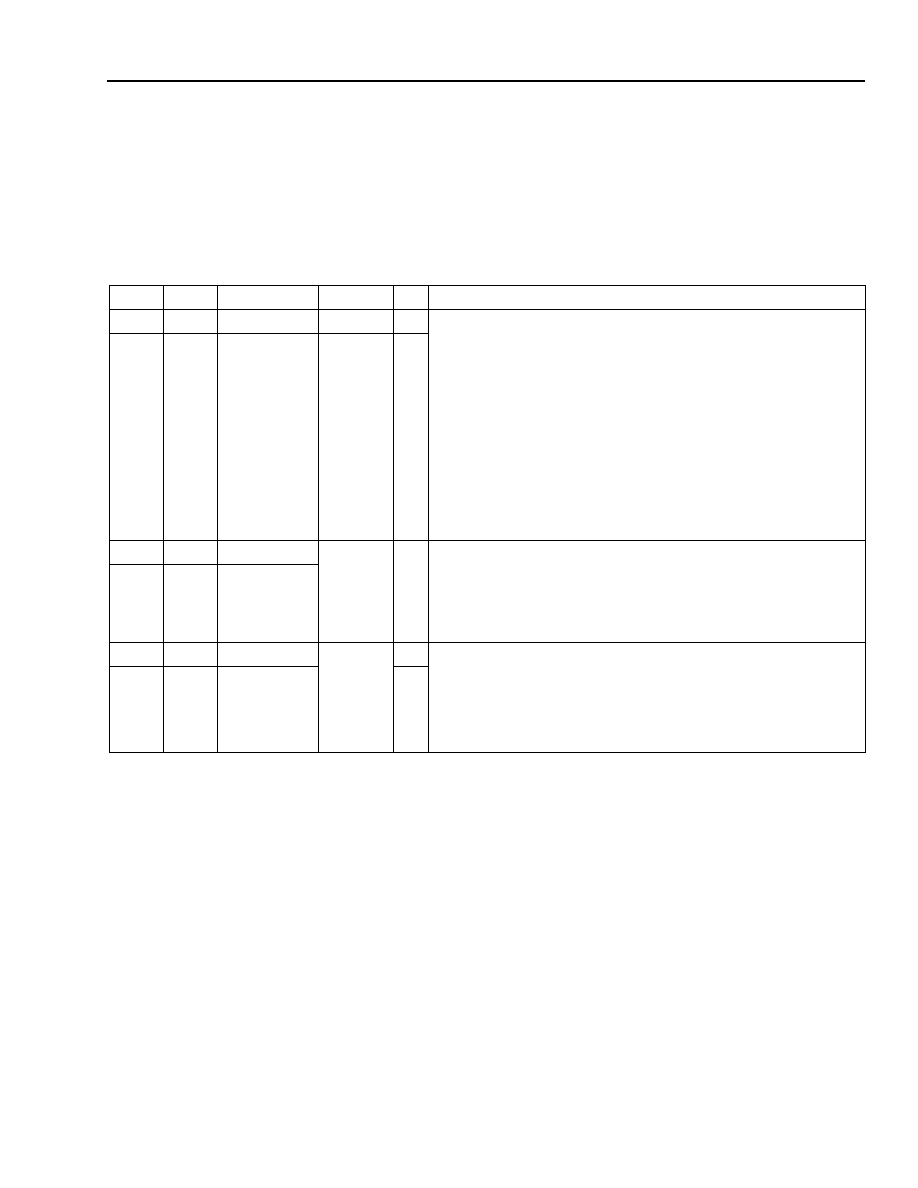

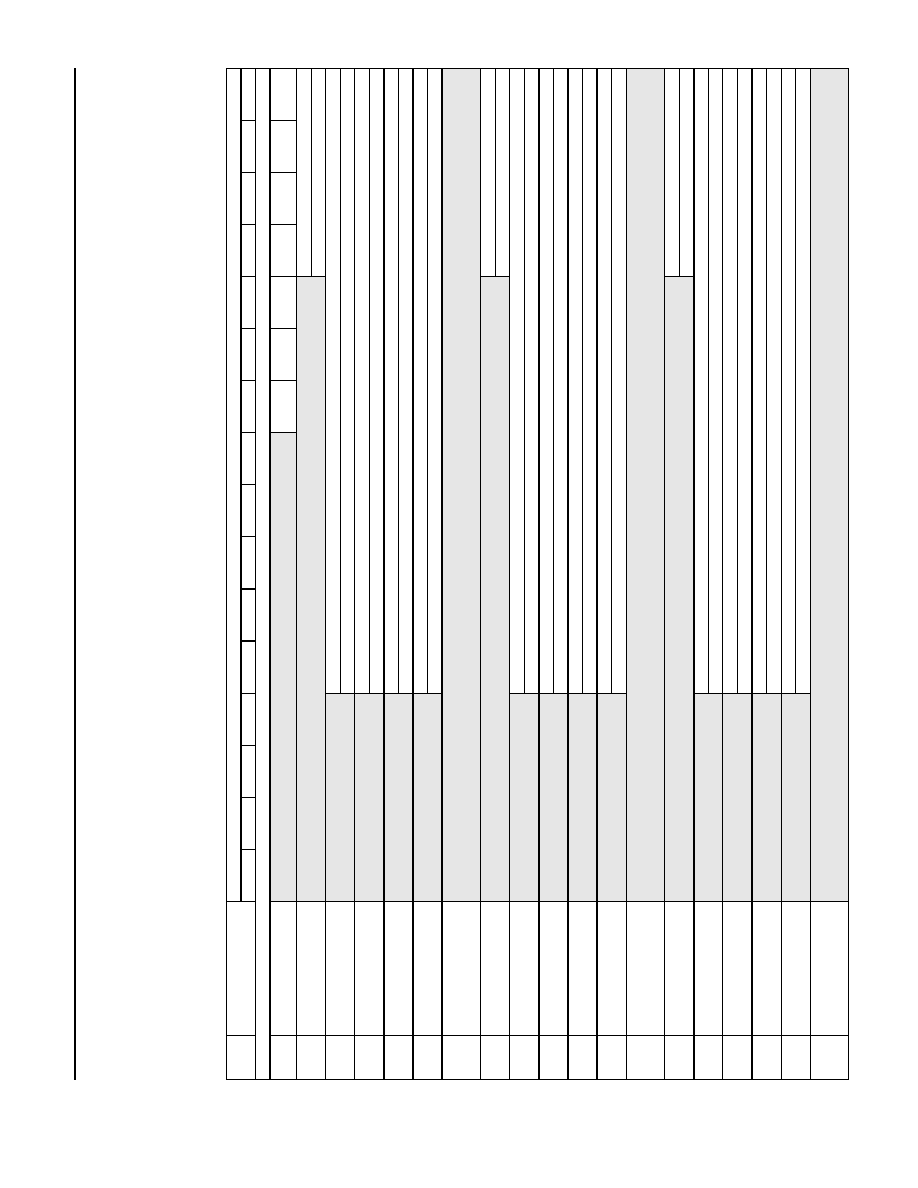

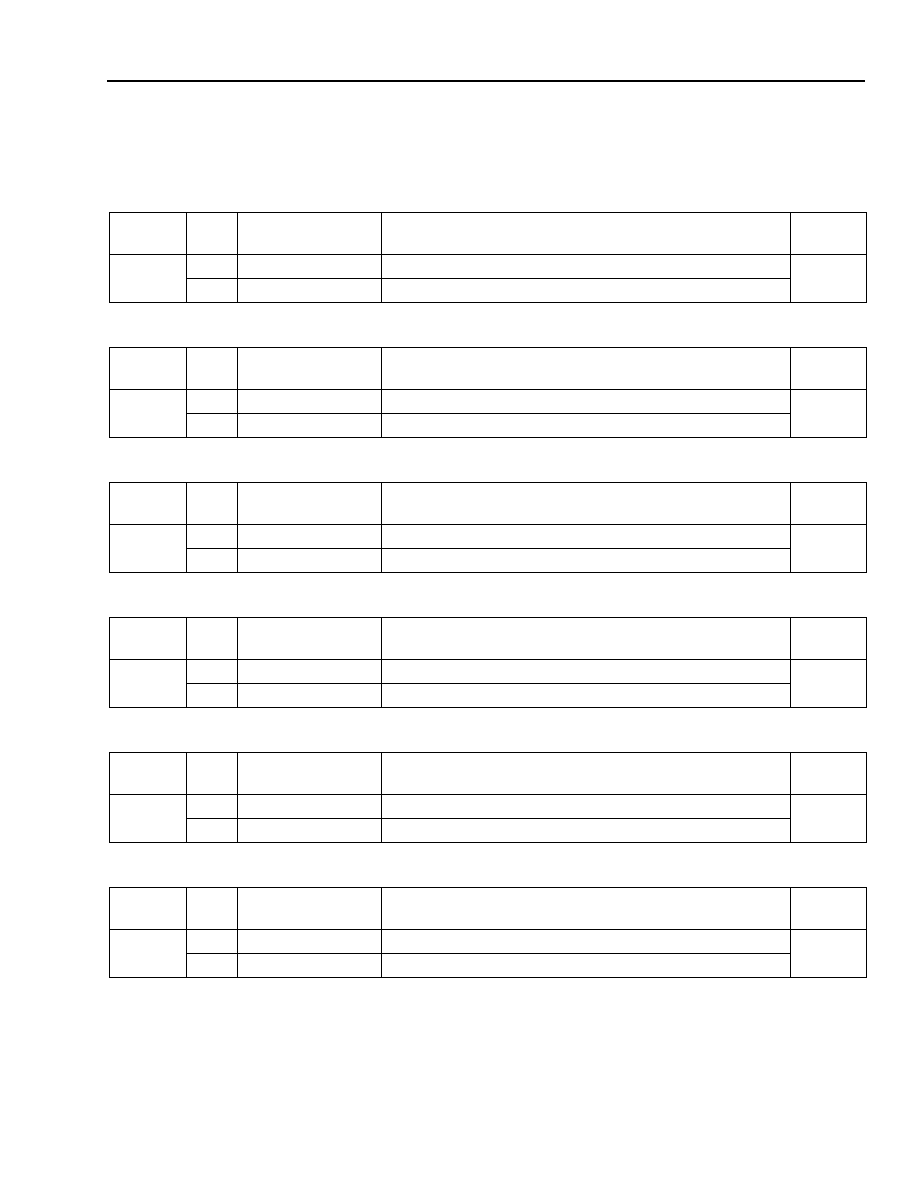

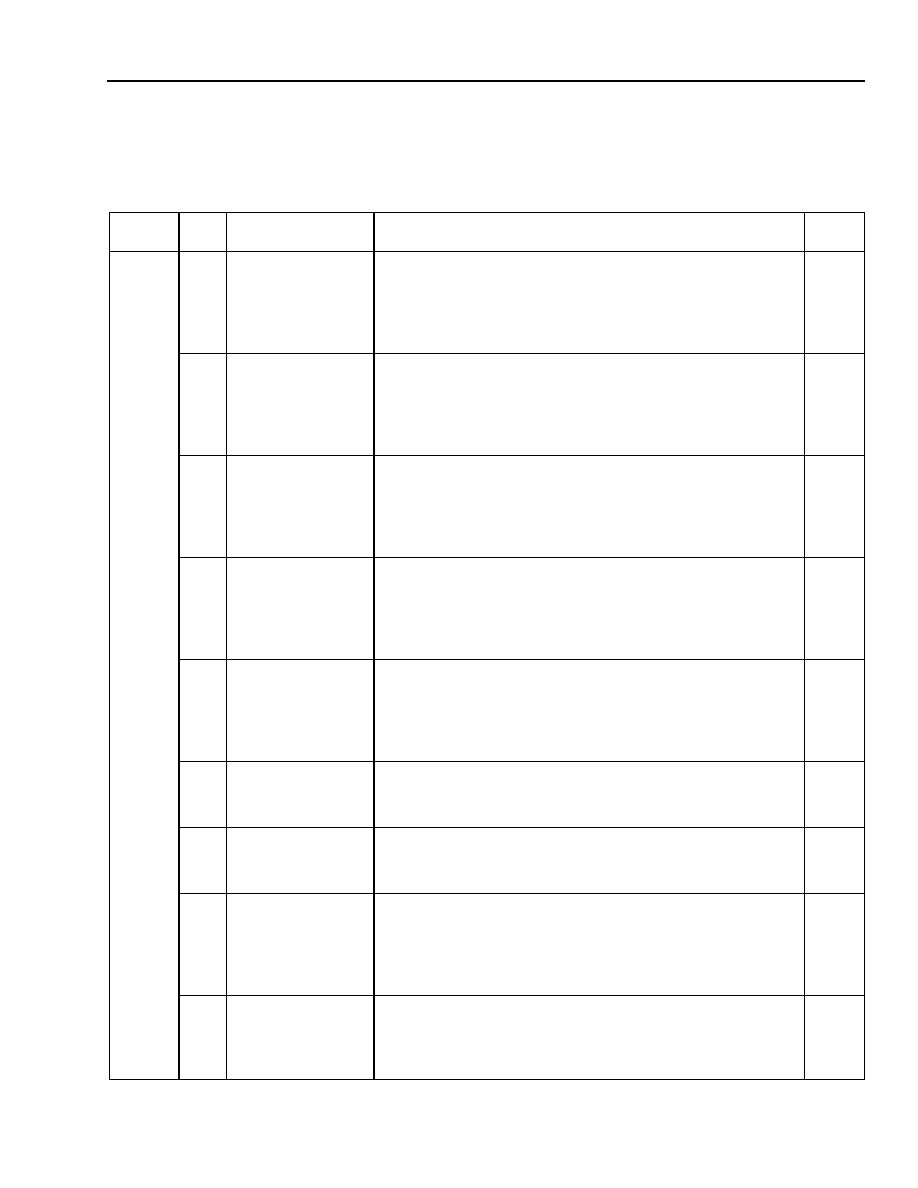

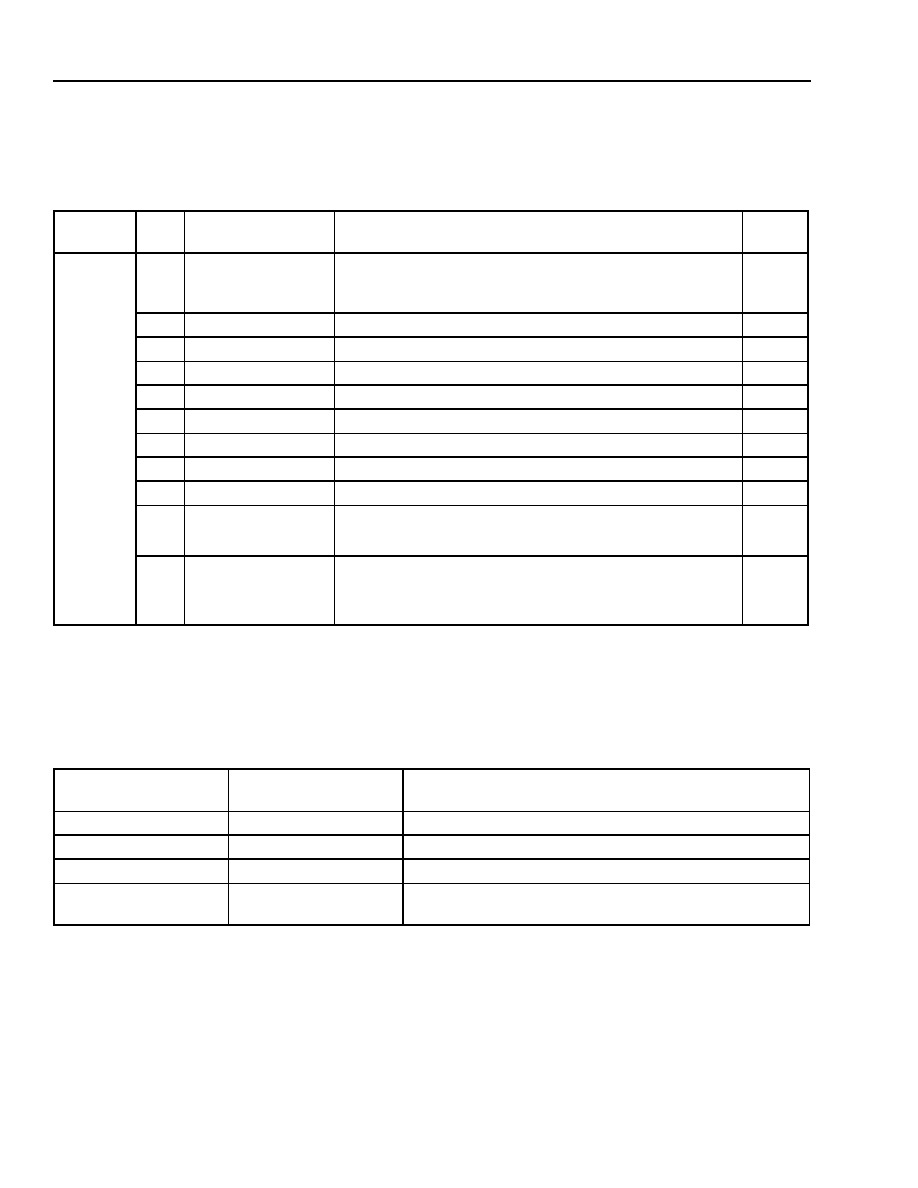

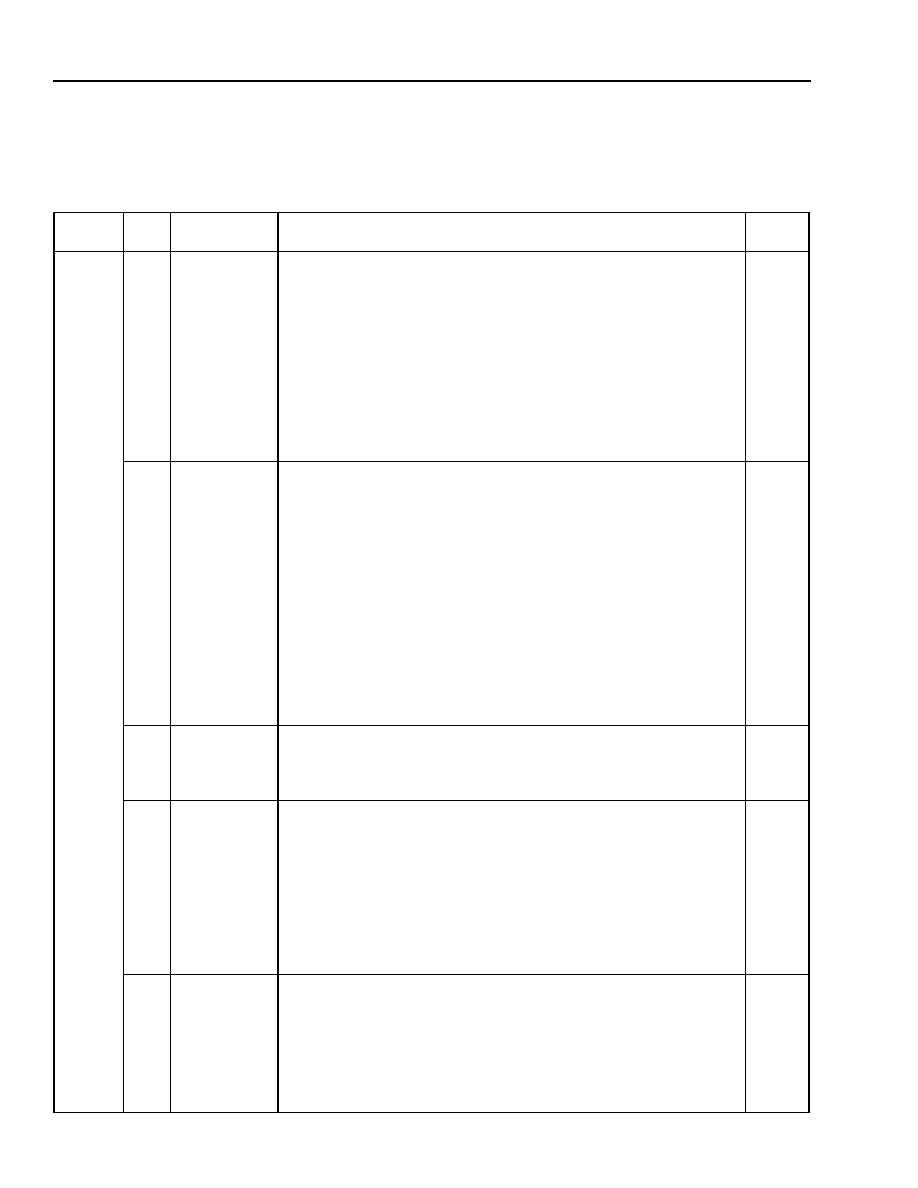

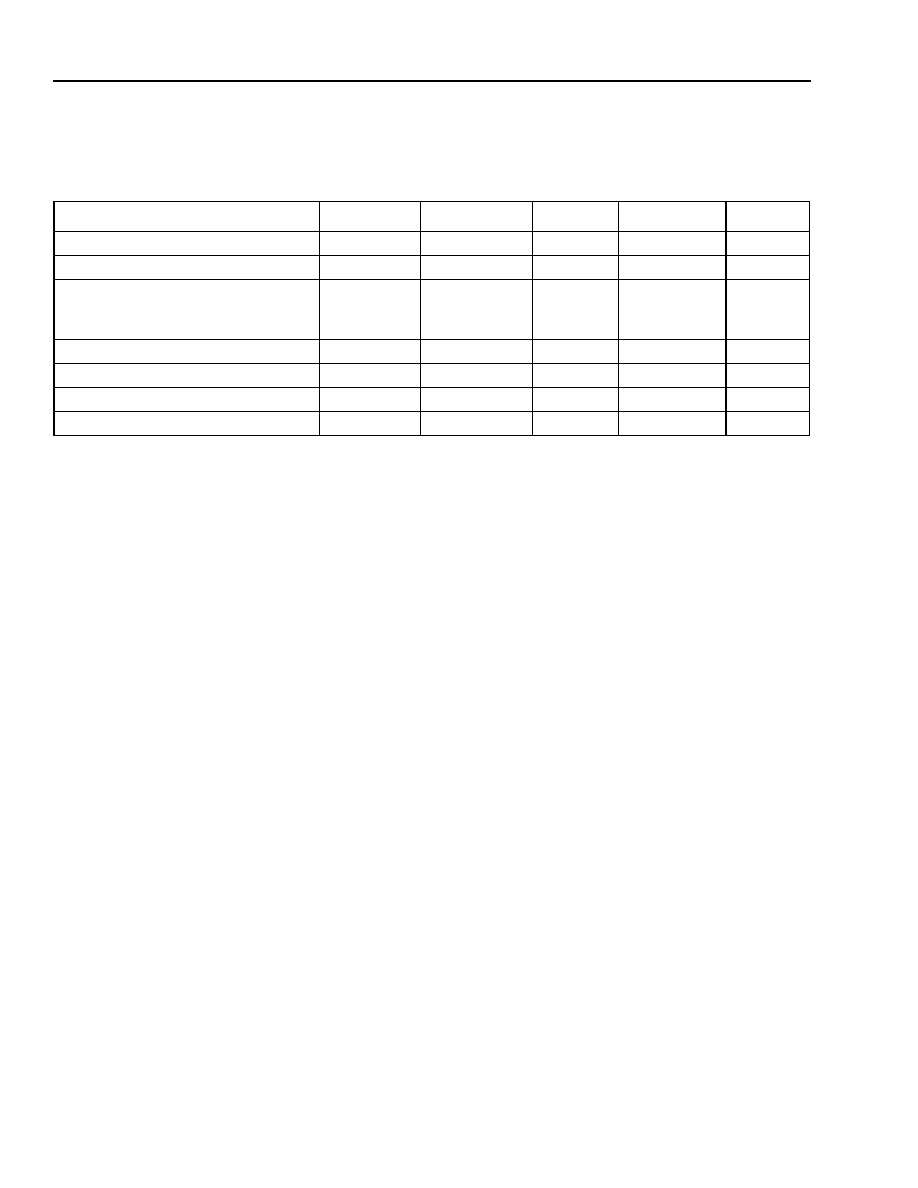

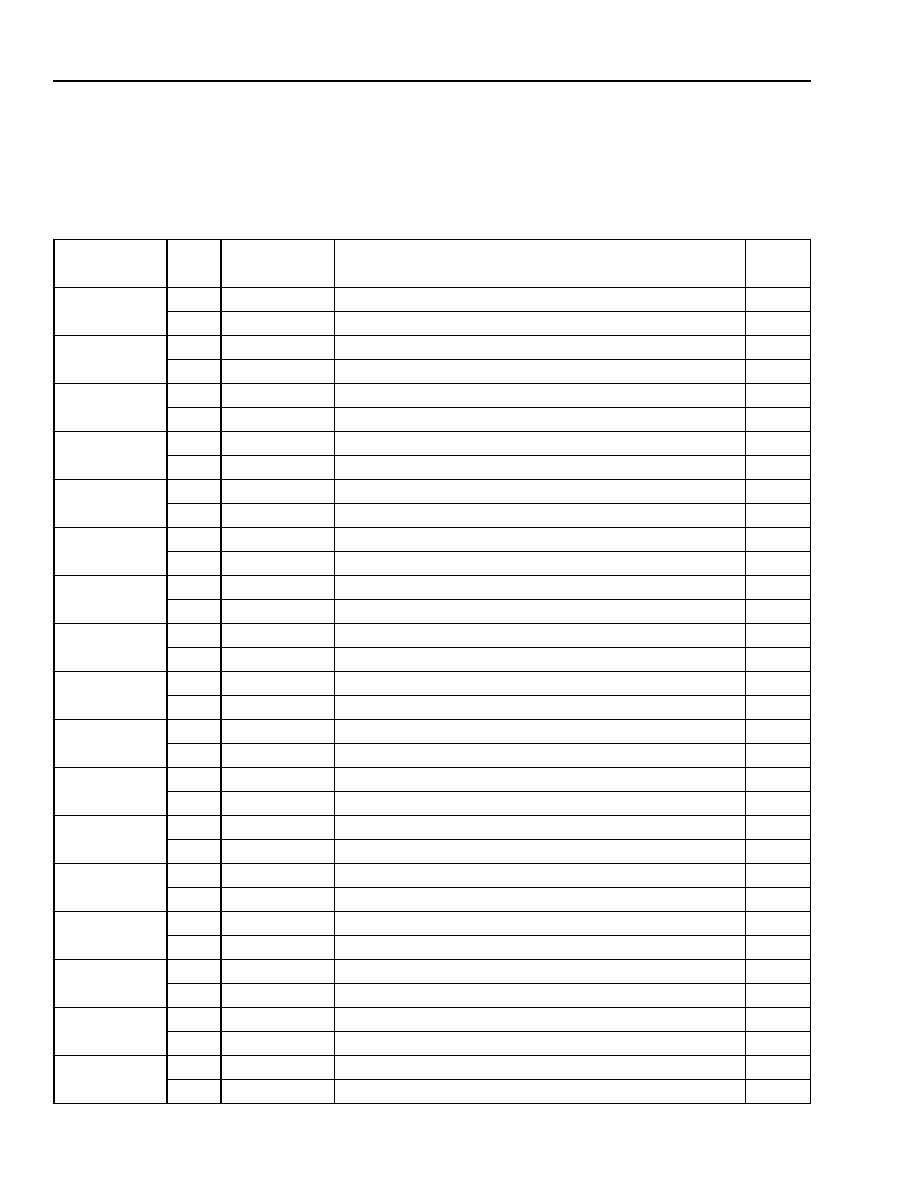

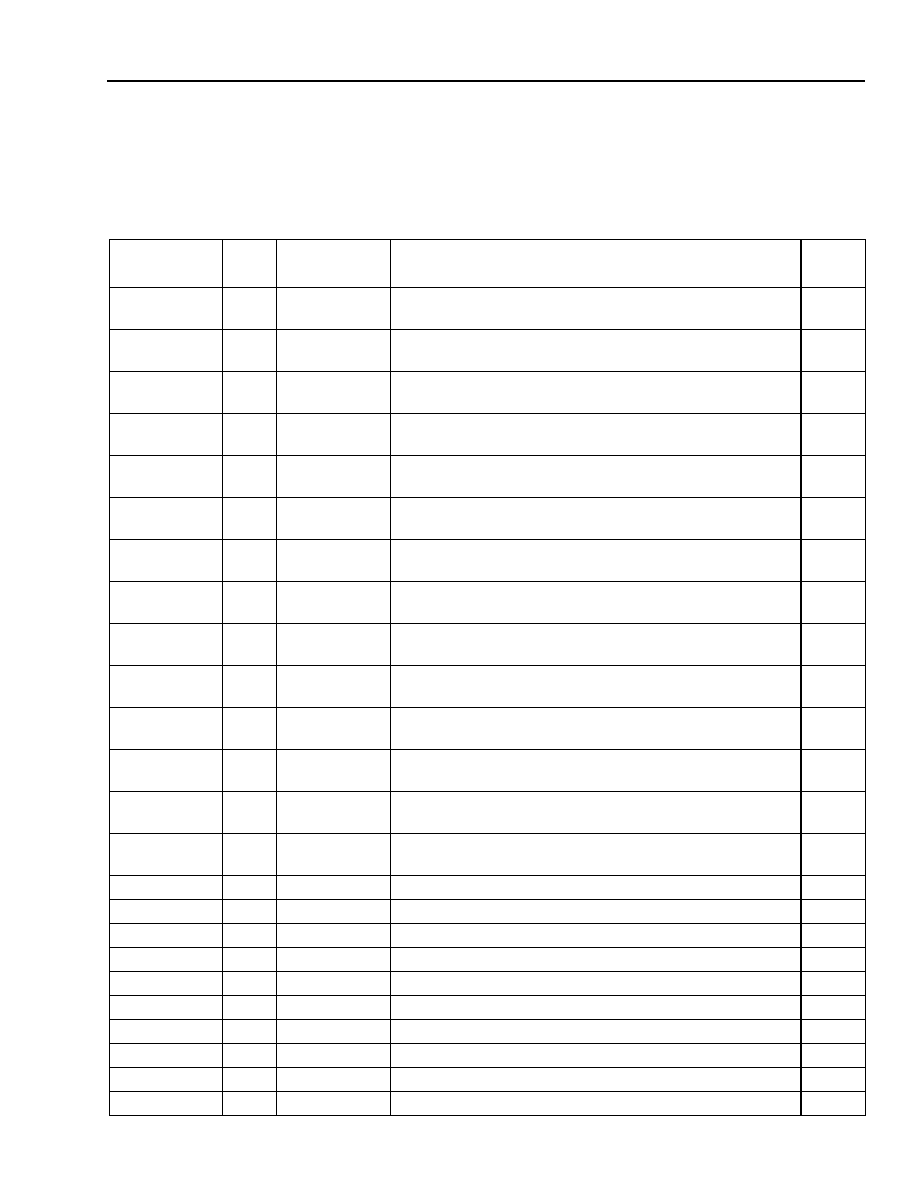

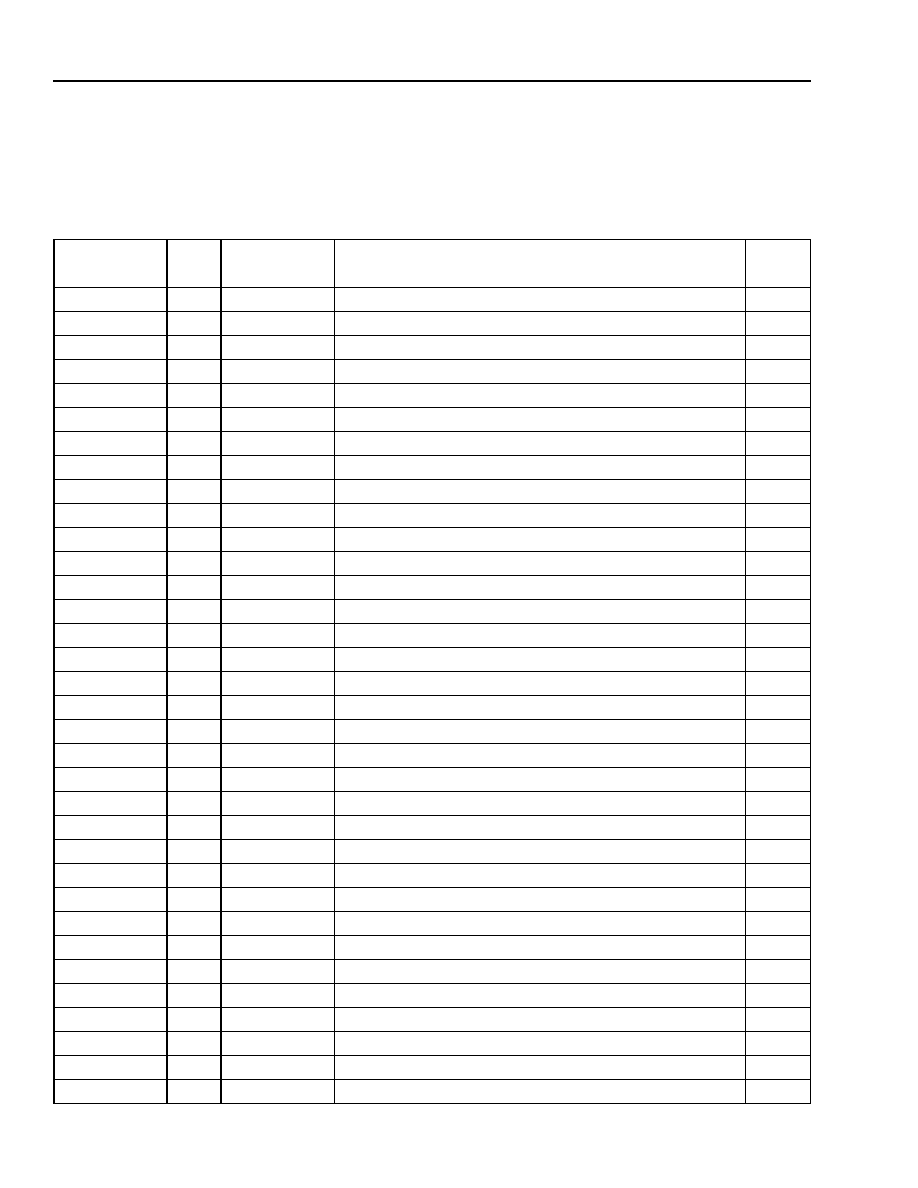

- Table 7. Pin Descriptions-Line Interface Signals

- Table 8. Pin Descriptions-TOH Interface Signals

- Table 9. Pin Descriptions-Enhanced UTOPIA Interface Signals

- Table 10. Pin Descriptions-Microprocessor Interface Signals

- Table 11. Pin Descriptions-General-Purpose I/O Signals: Interface Signals

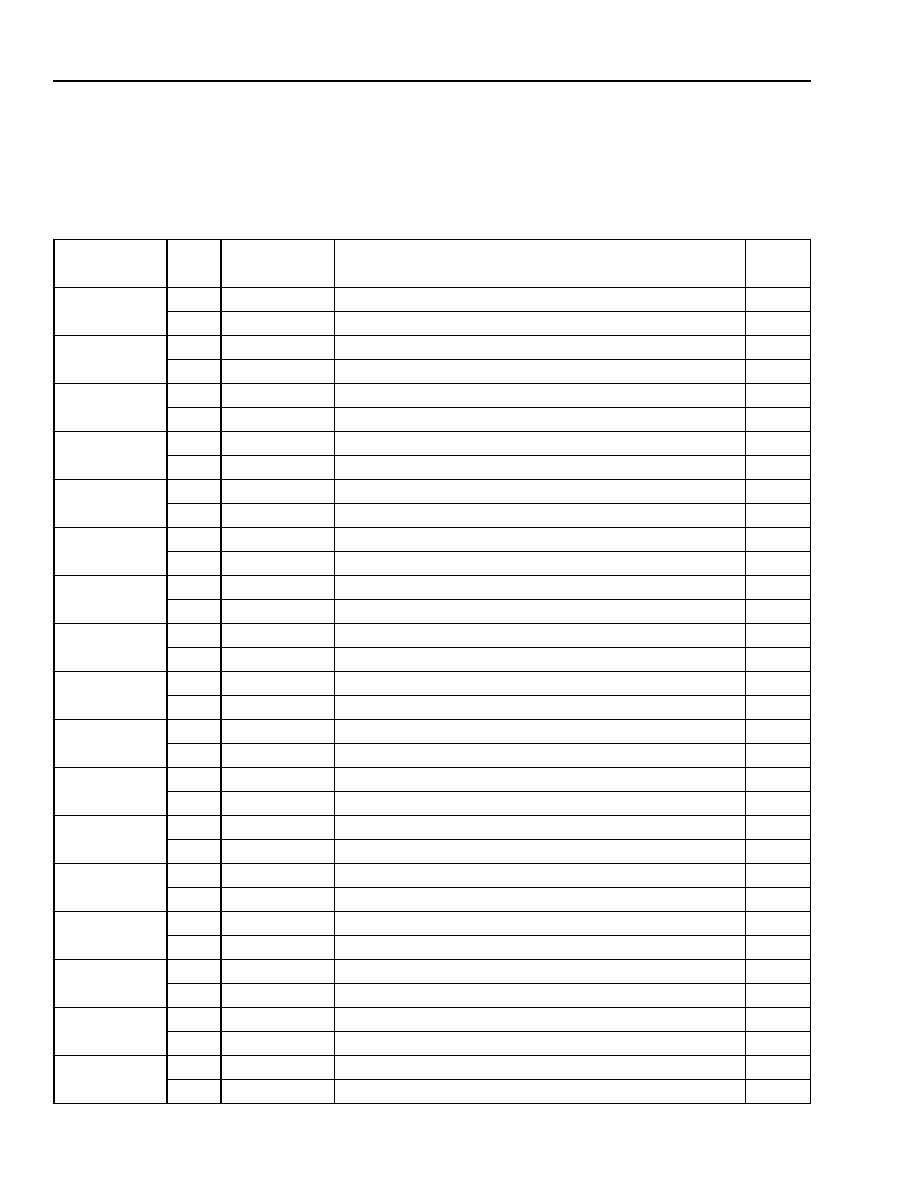

- Table 12. Pin Descriptions-JTAG Interface Signals

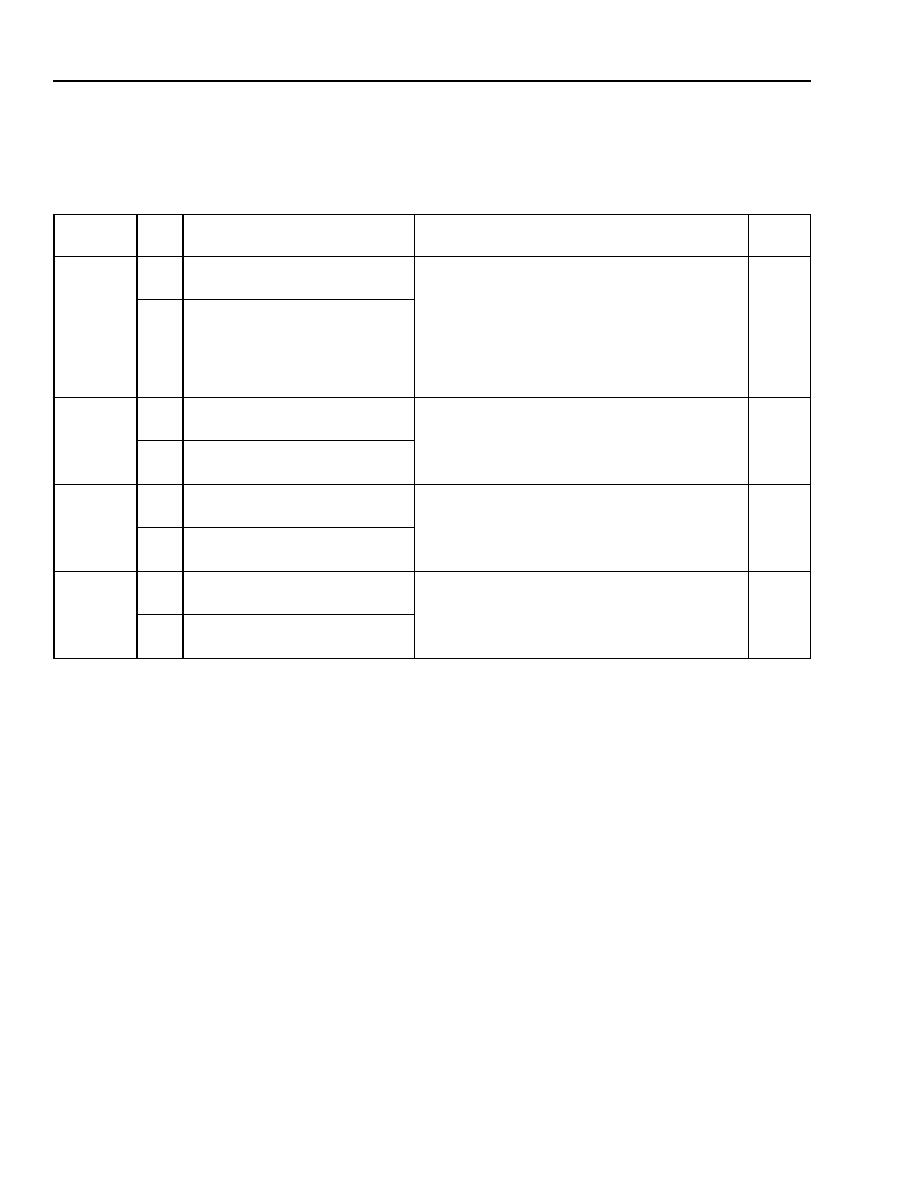

- Table 13. Pin Descriptions-Power Signals

- Table 14. PLL Test Outputs

- Table 15. Pin Descriptions-No-Connect Pins

- Table 16. Leakage Test Pin

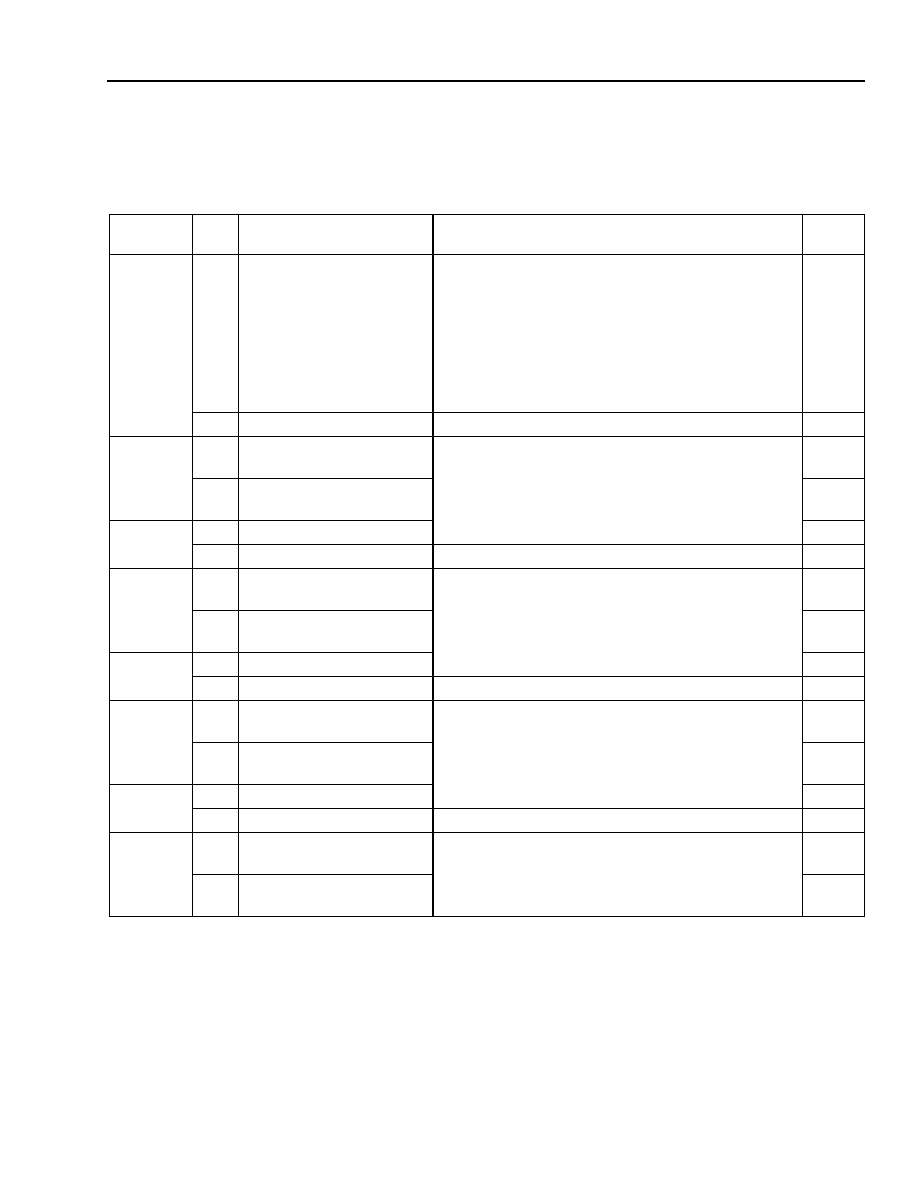

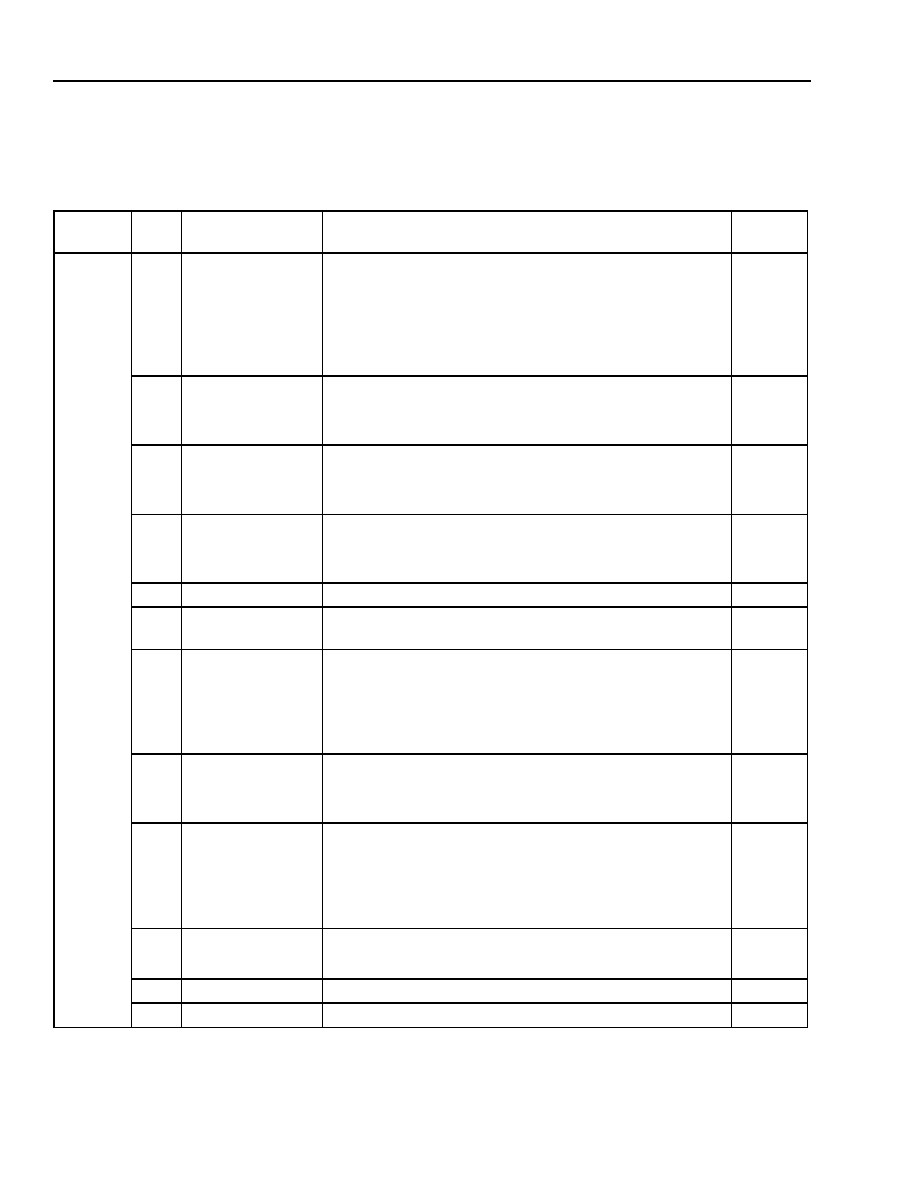

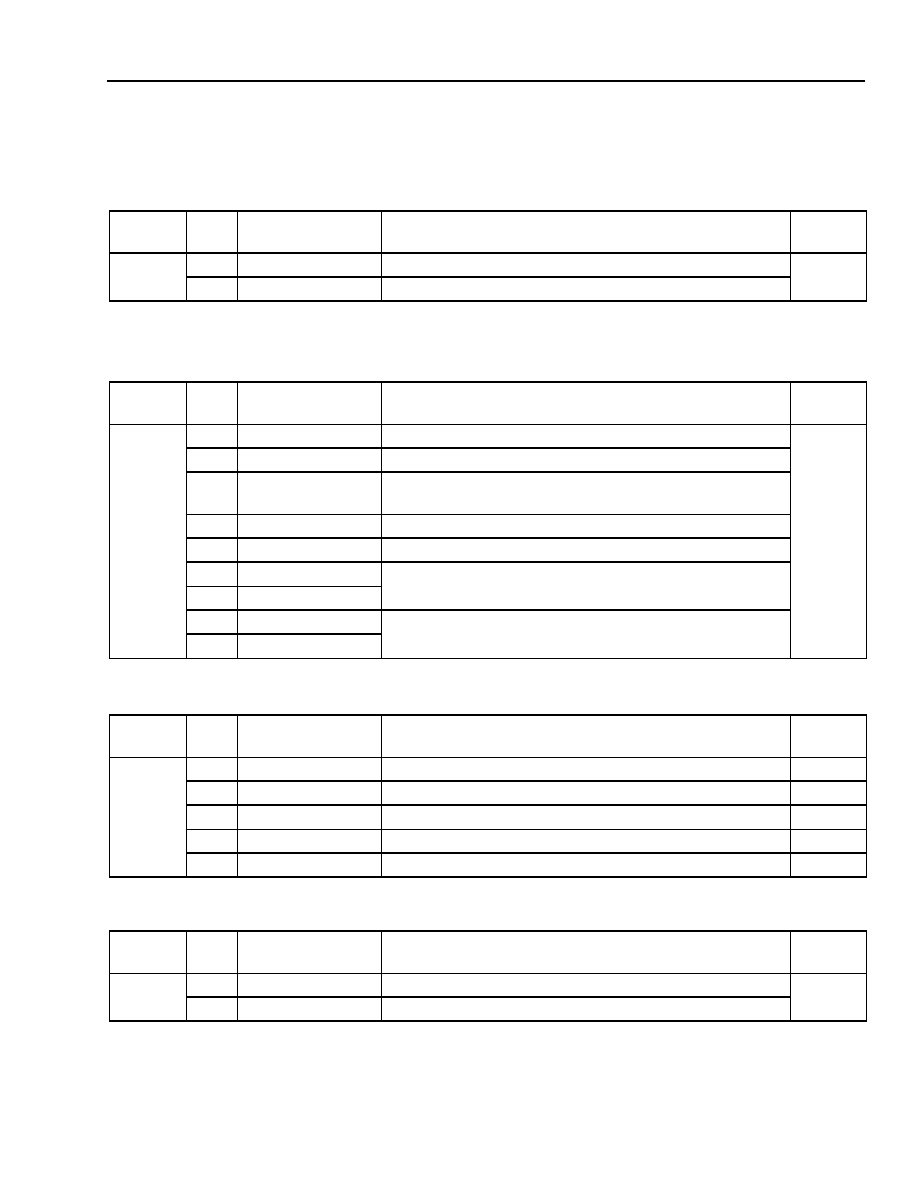

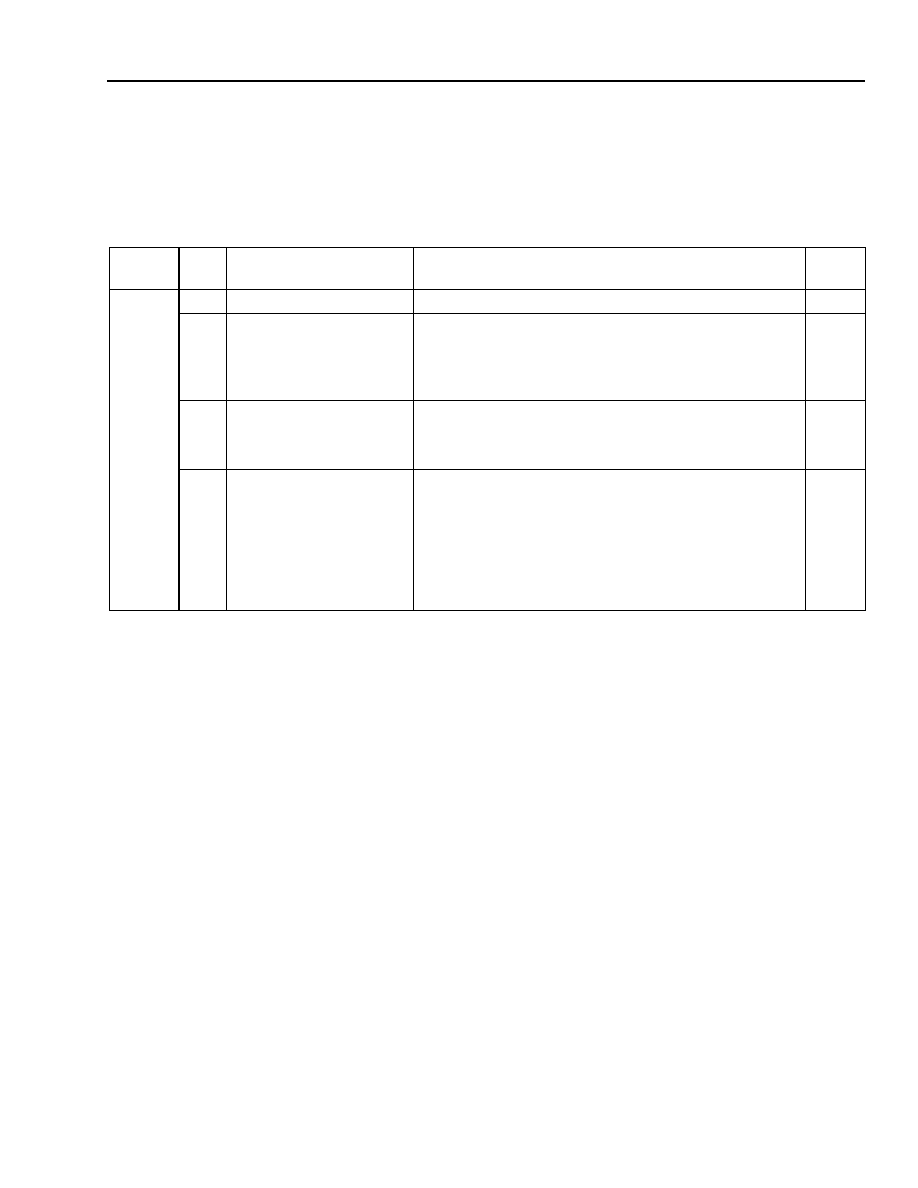

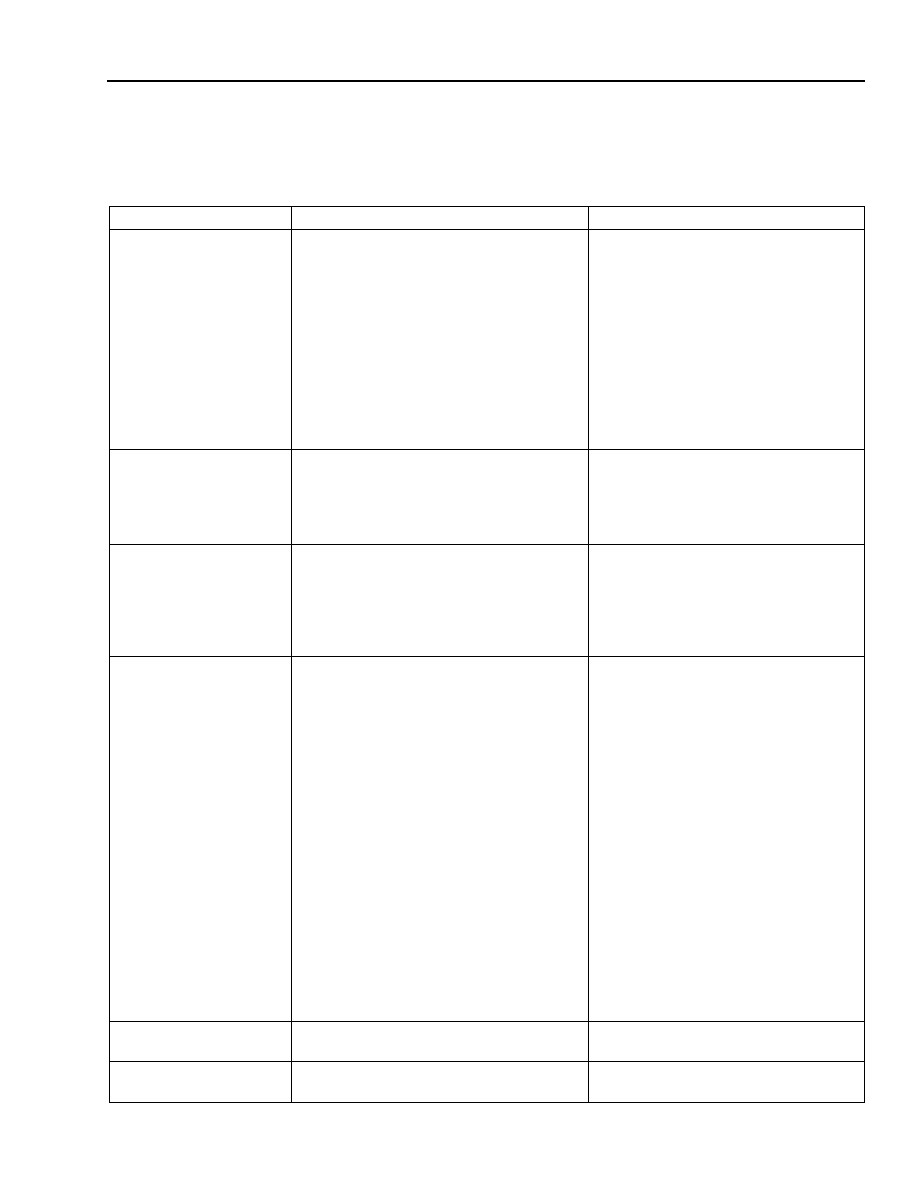

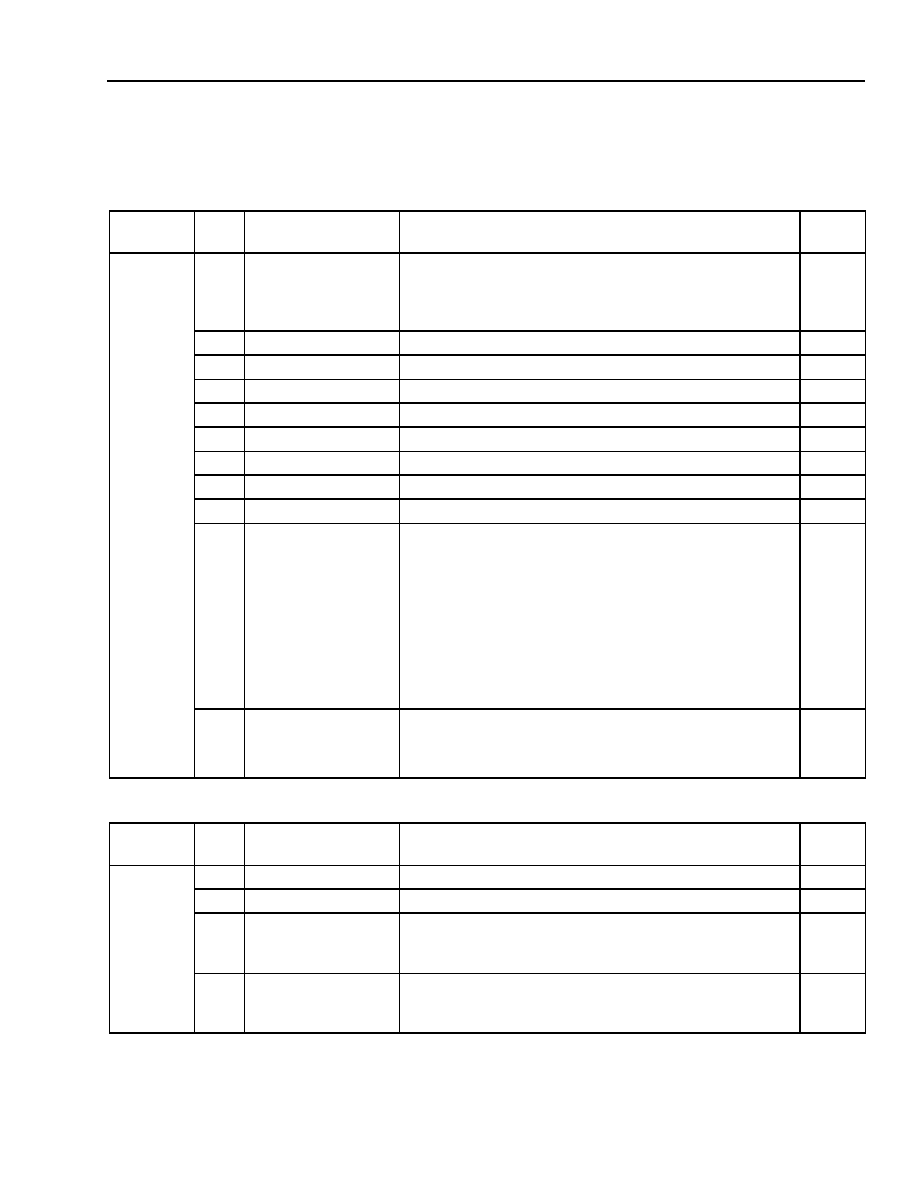

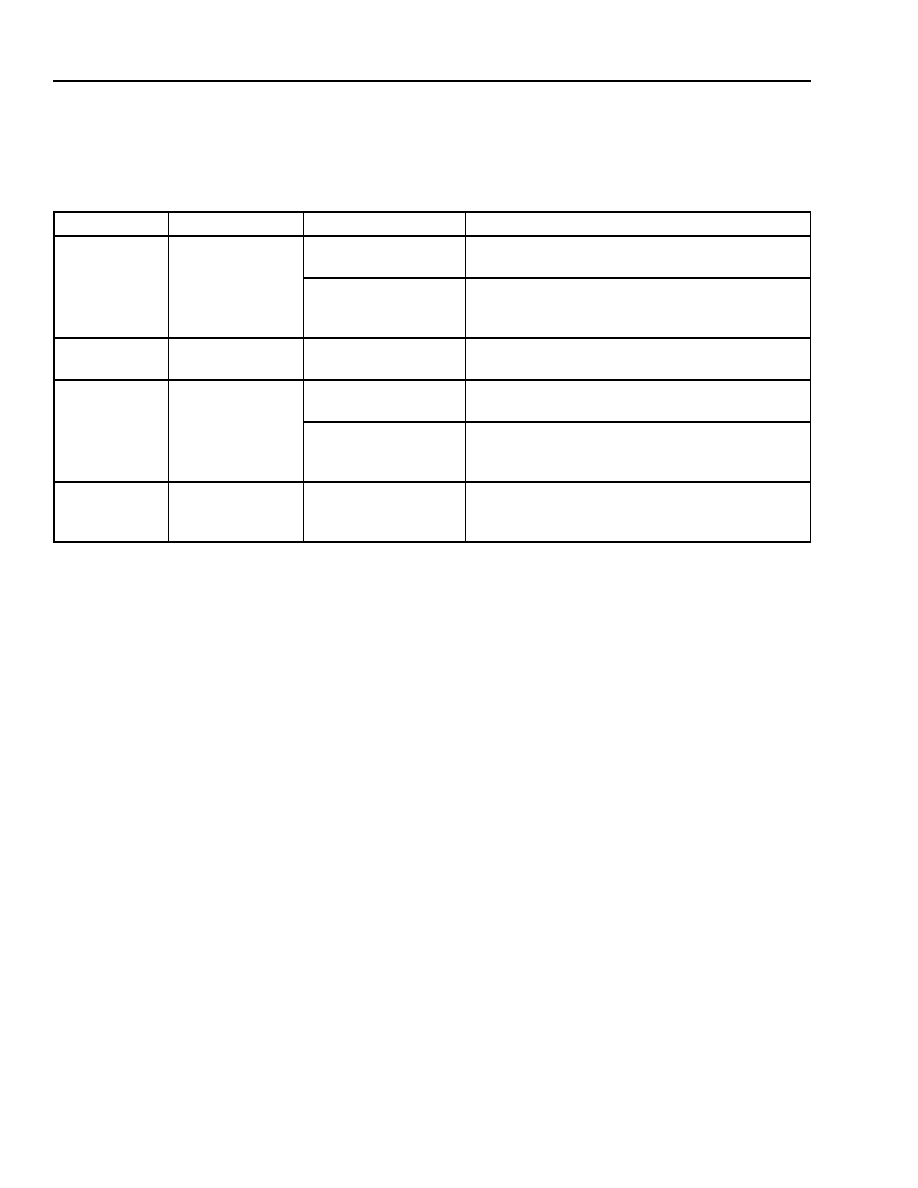

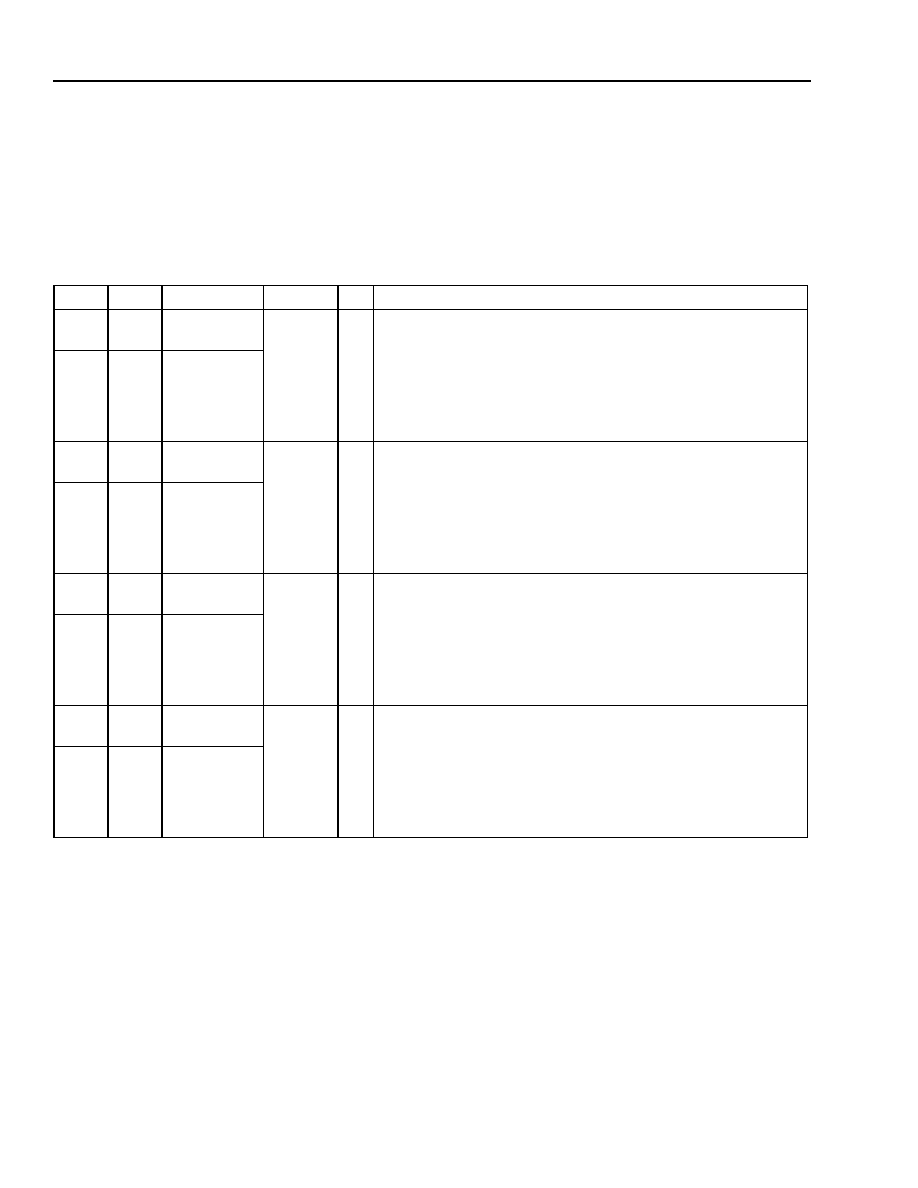

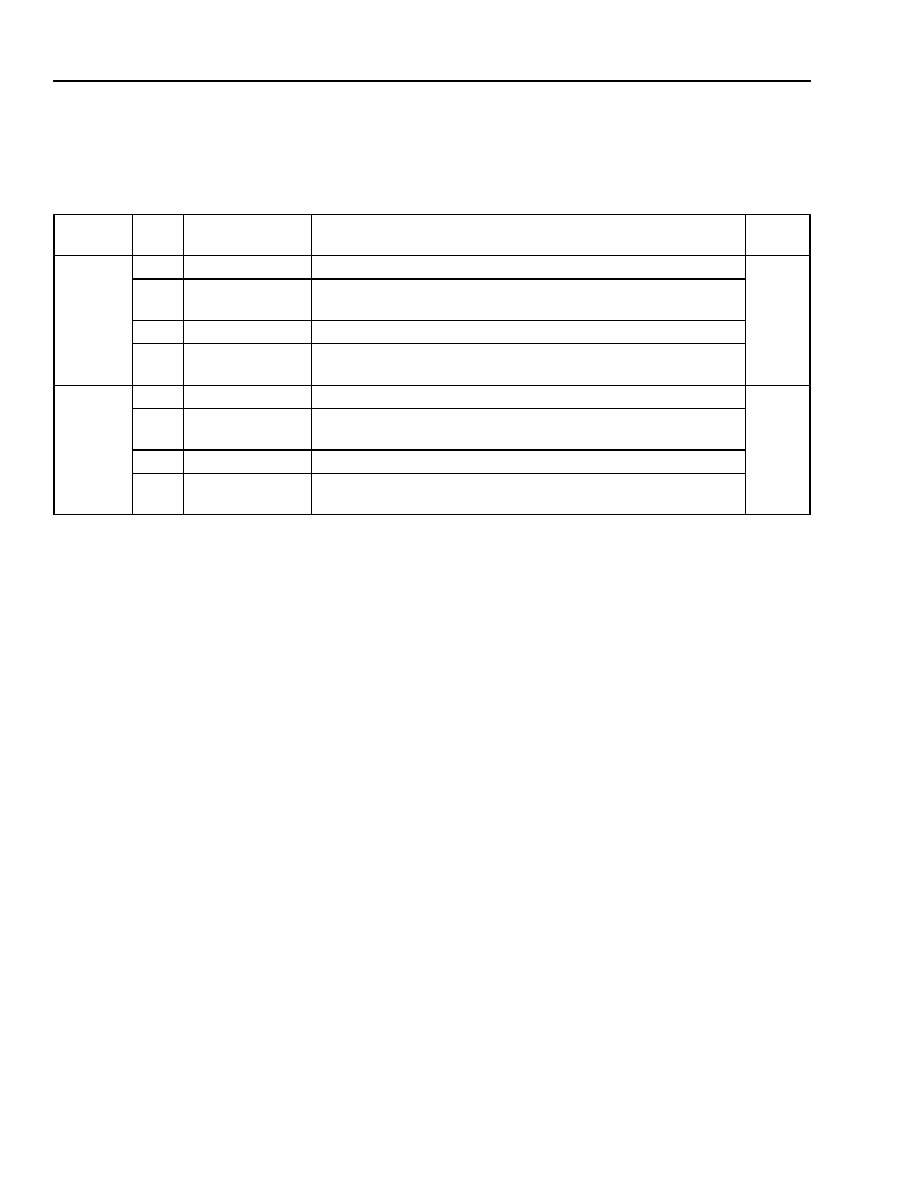

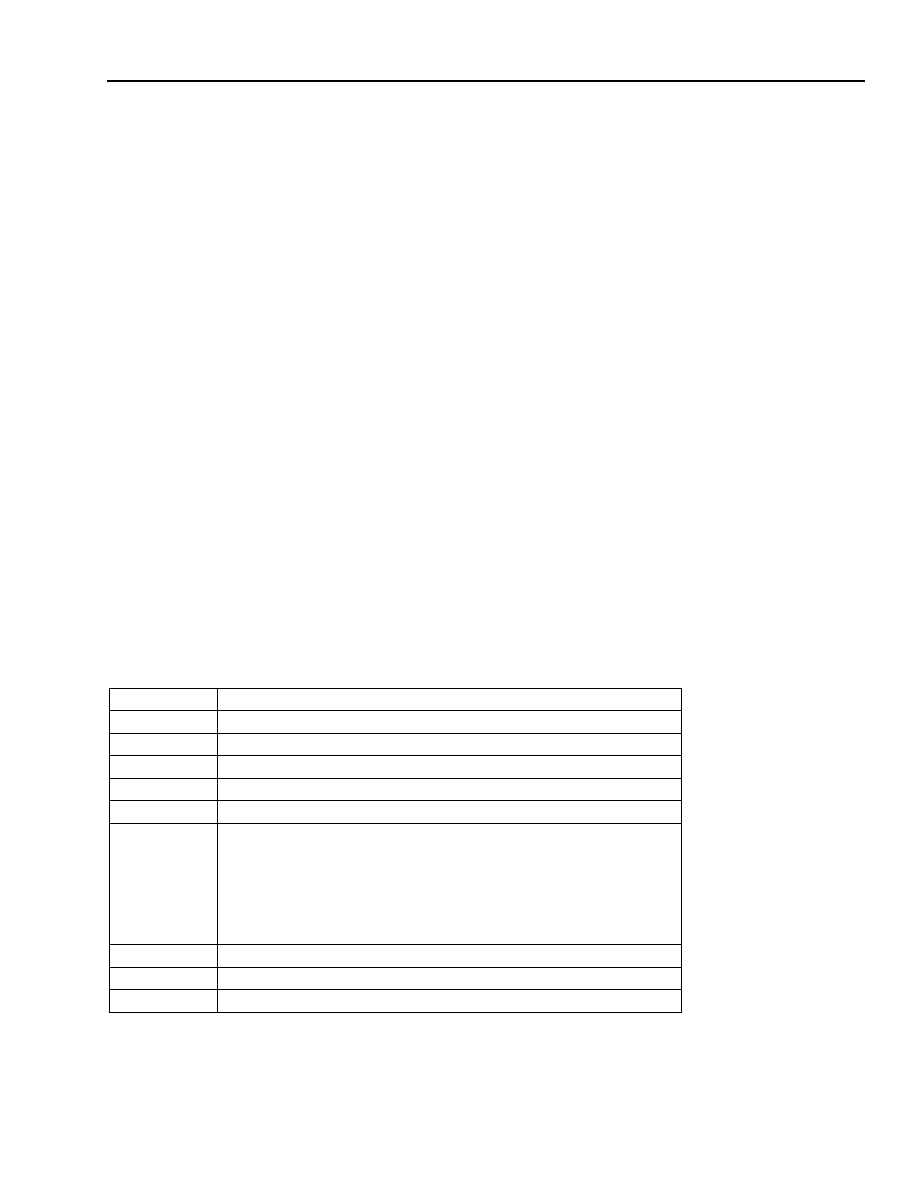

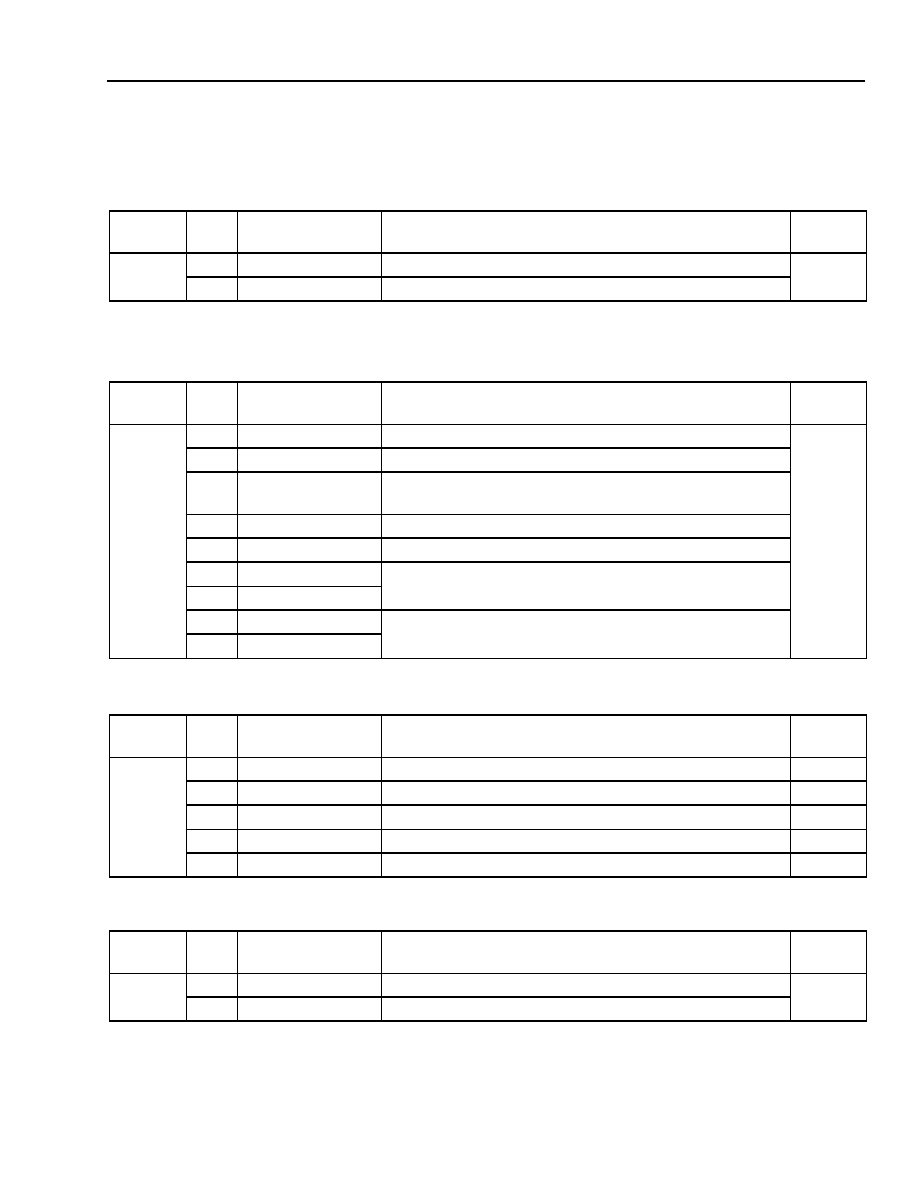

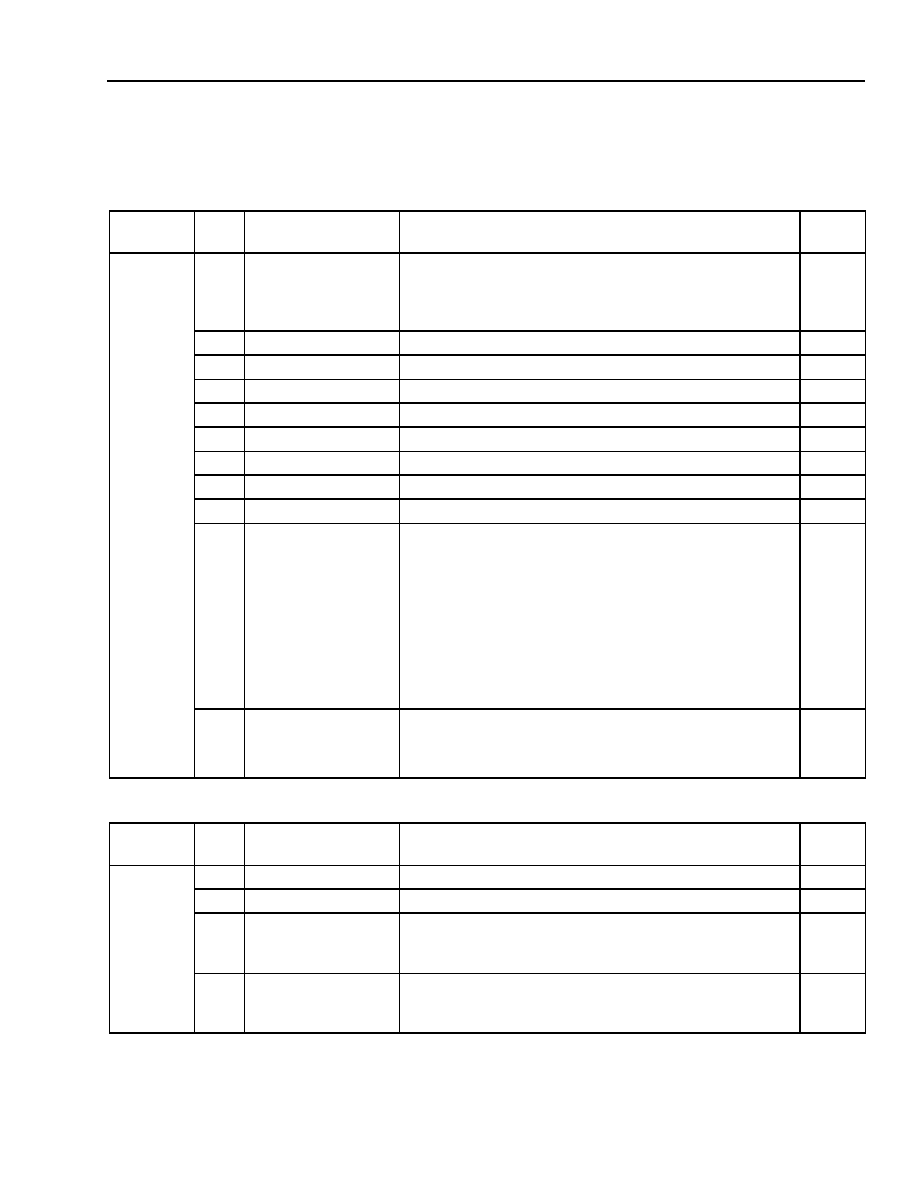

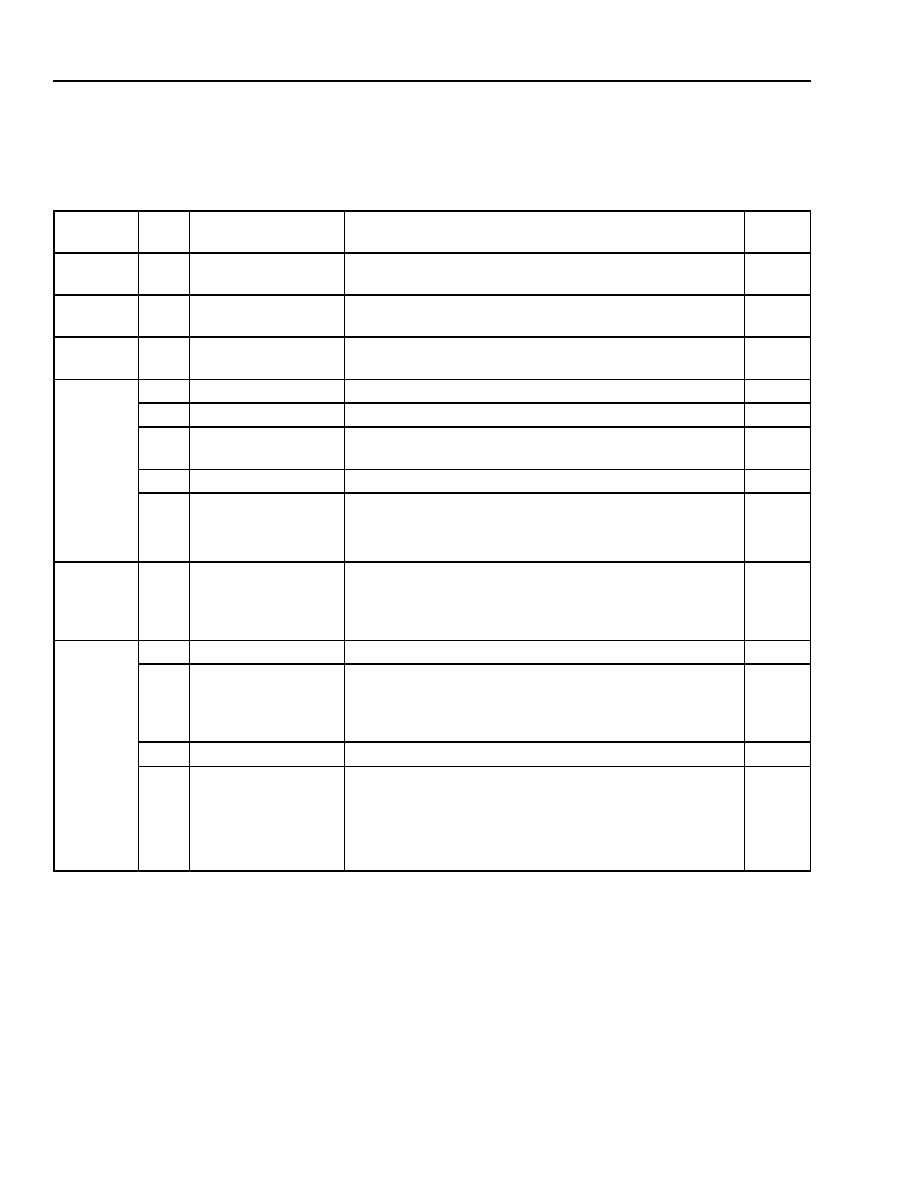

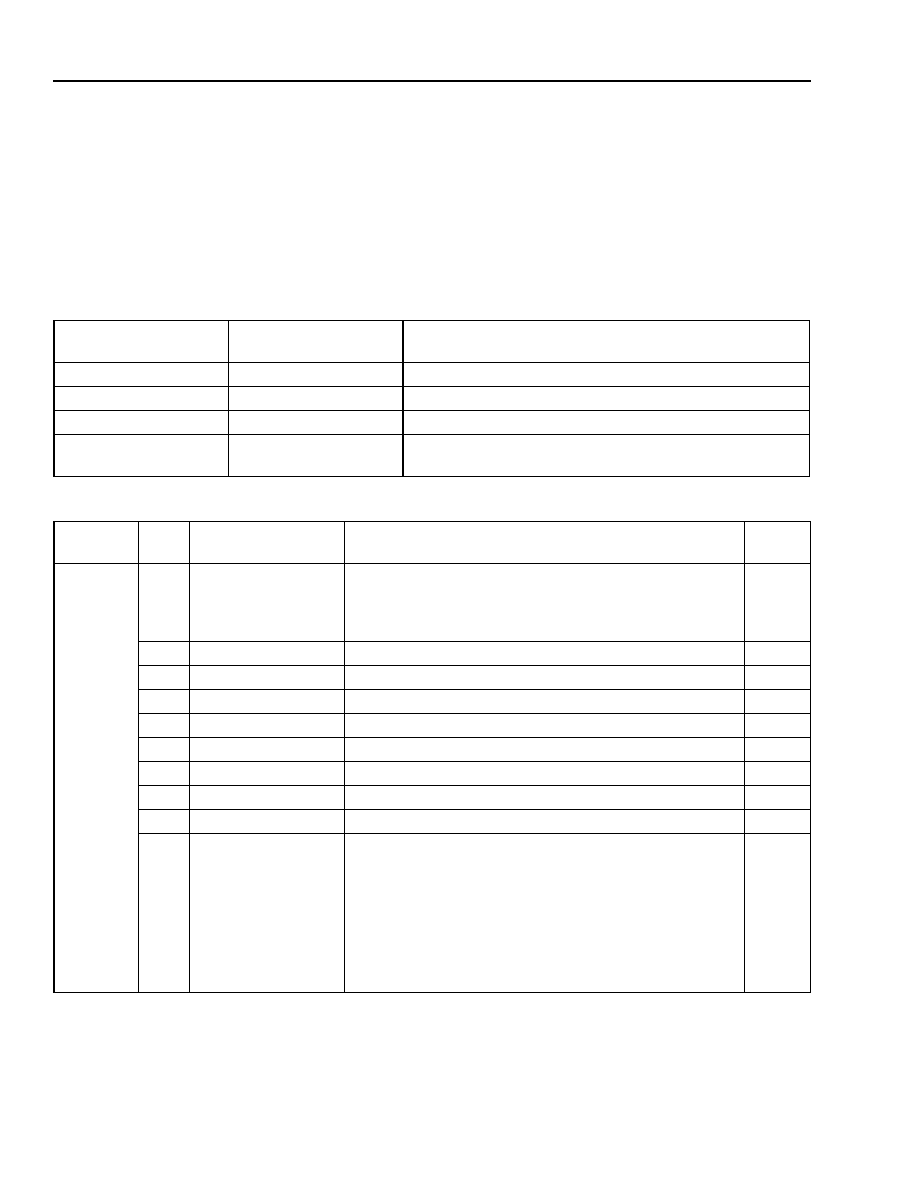

- Table 17. Device Address Space Assignment

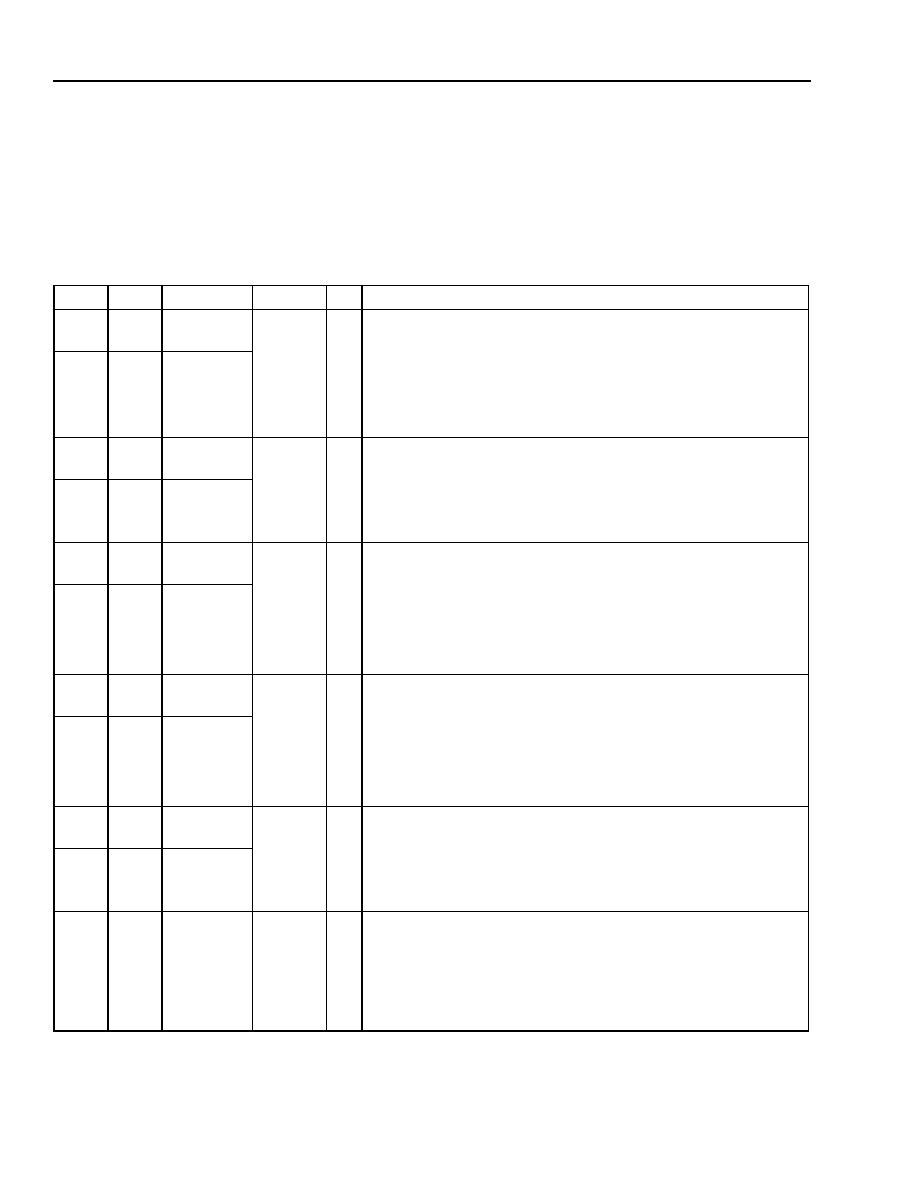

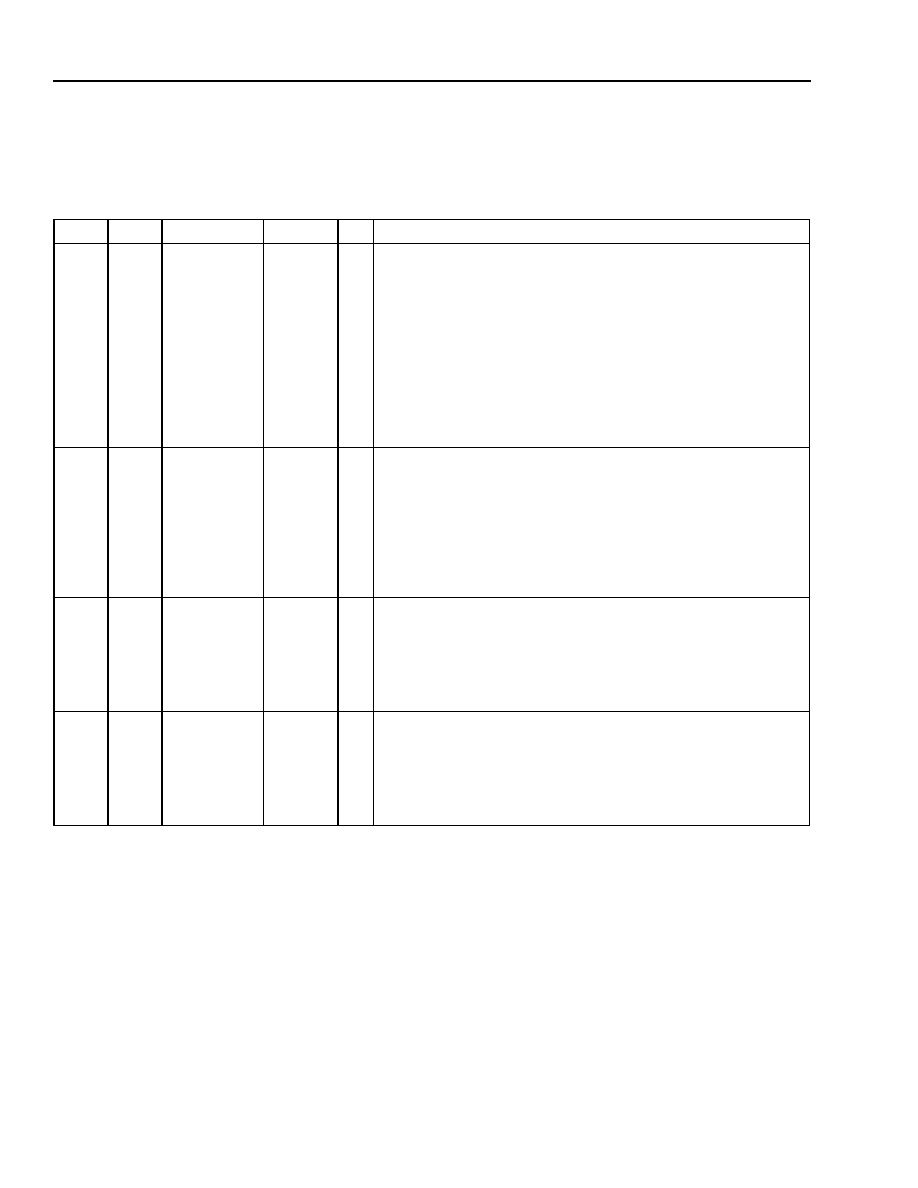

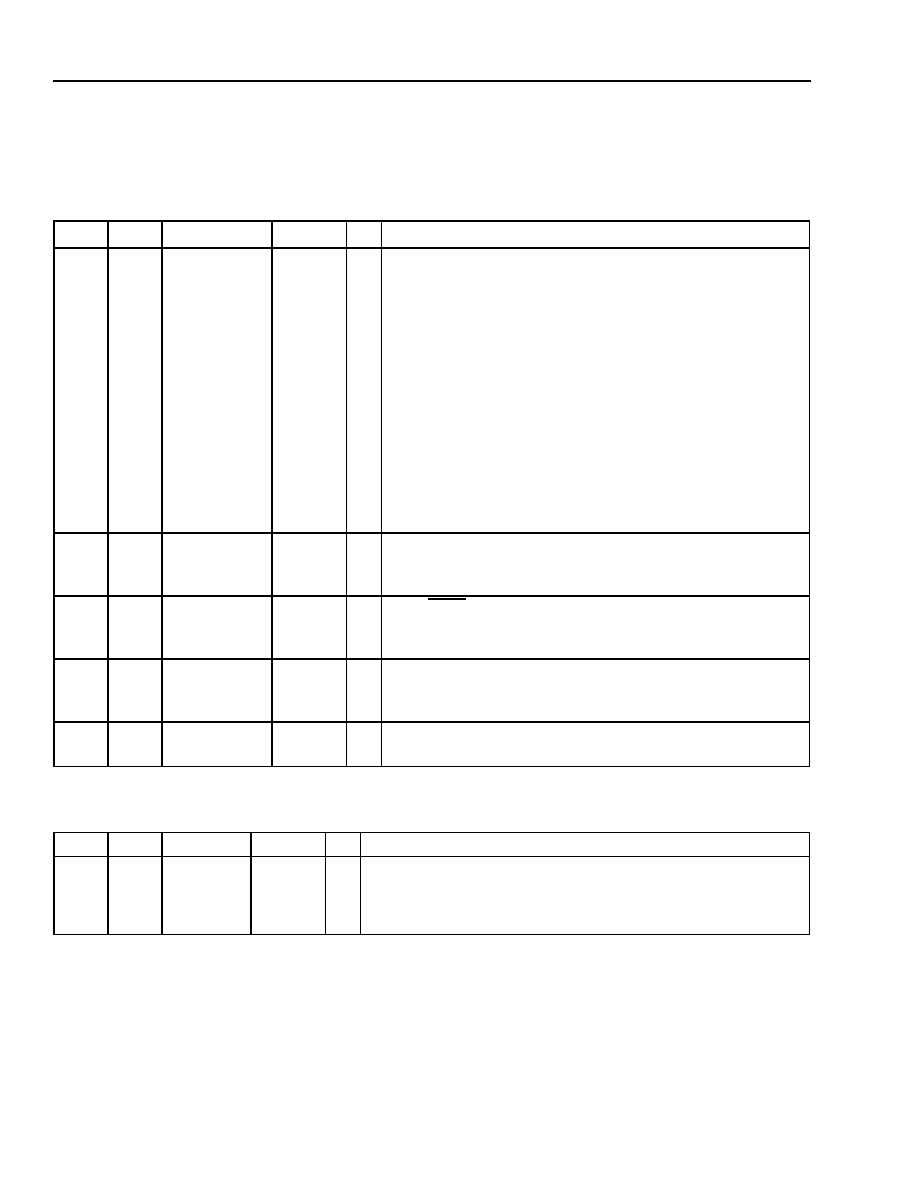

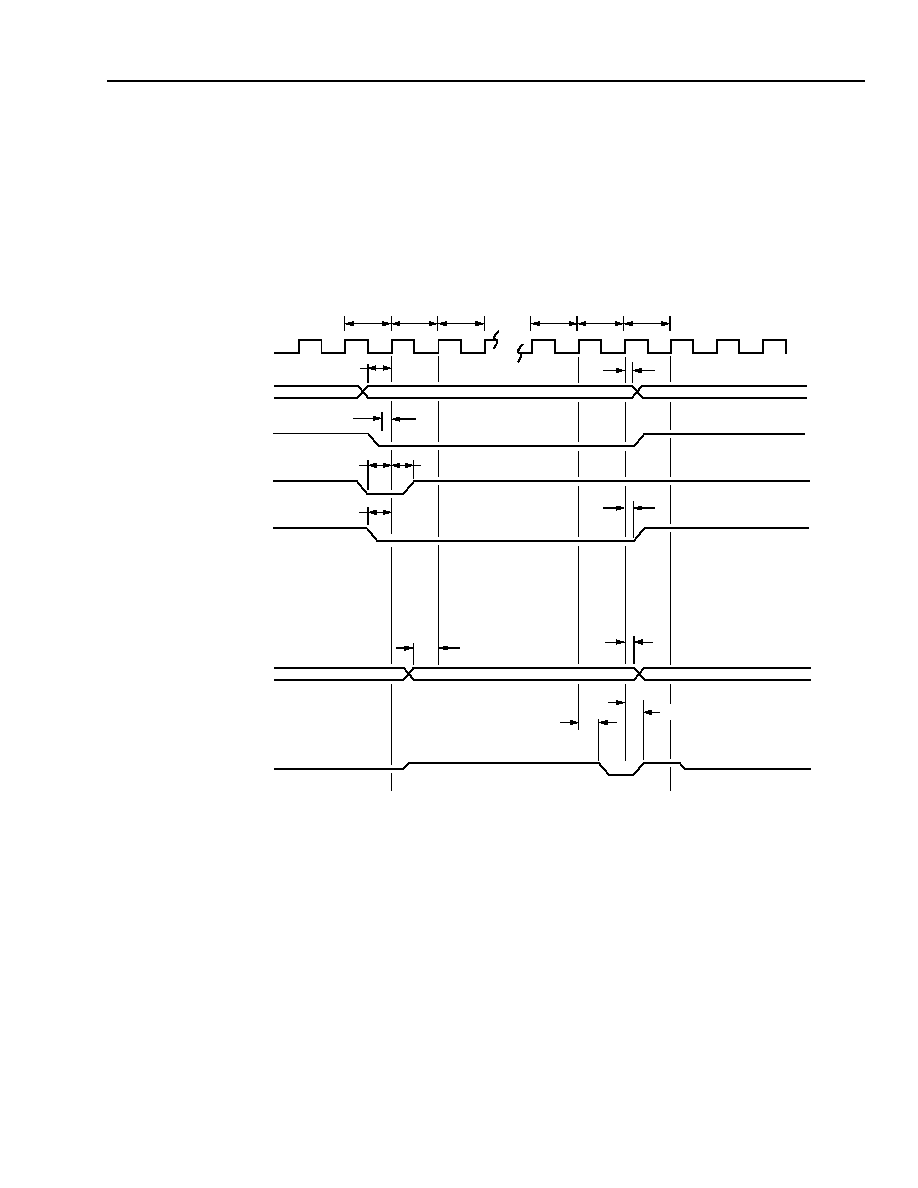

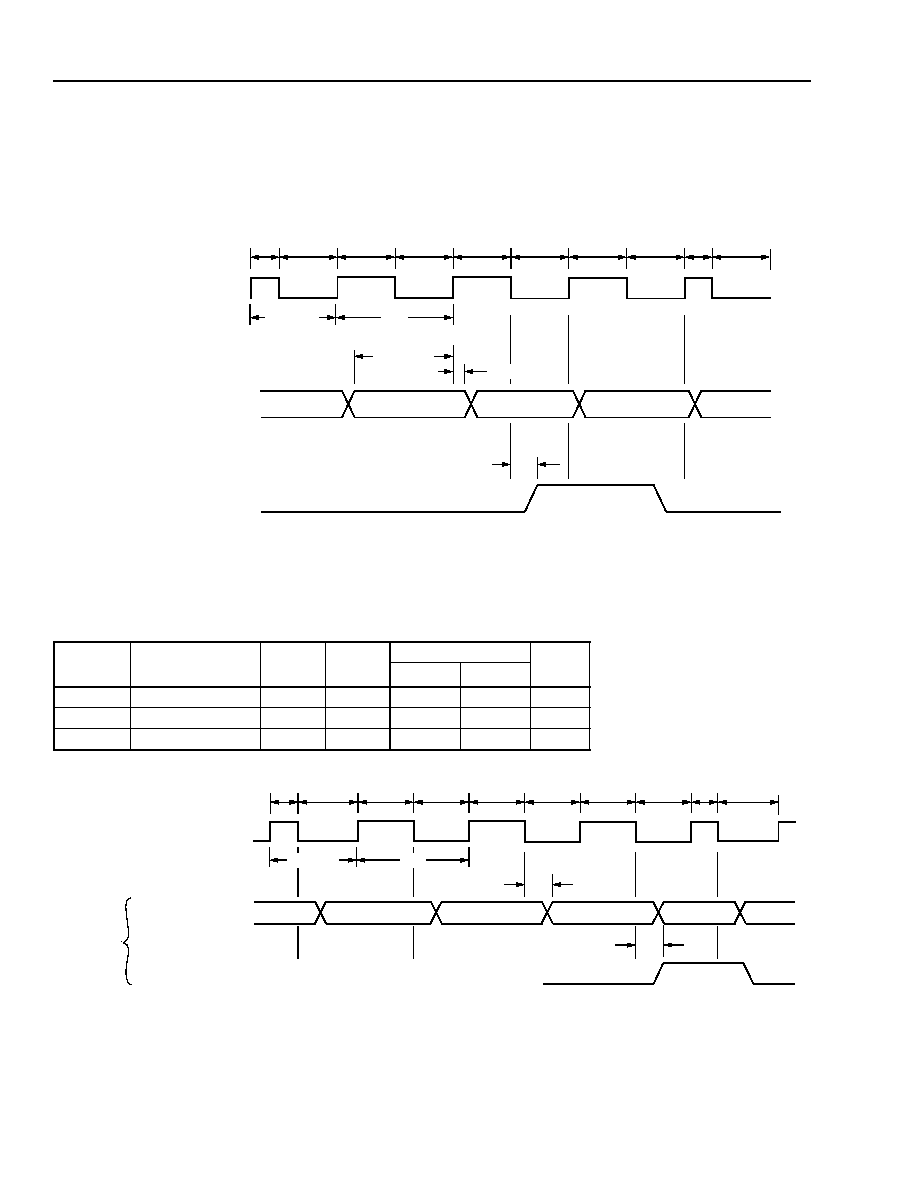

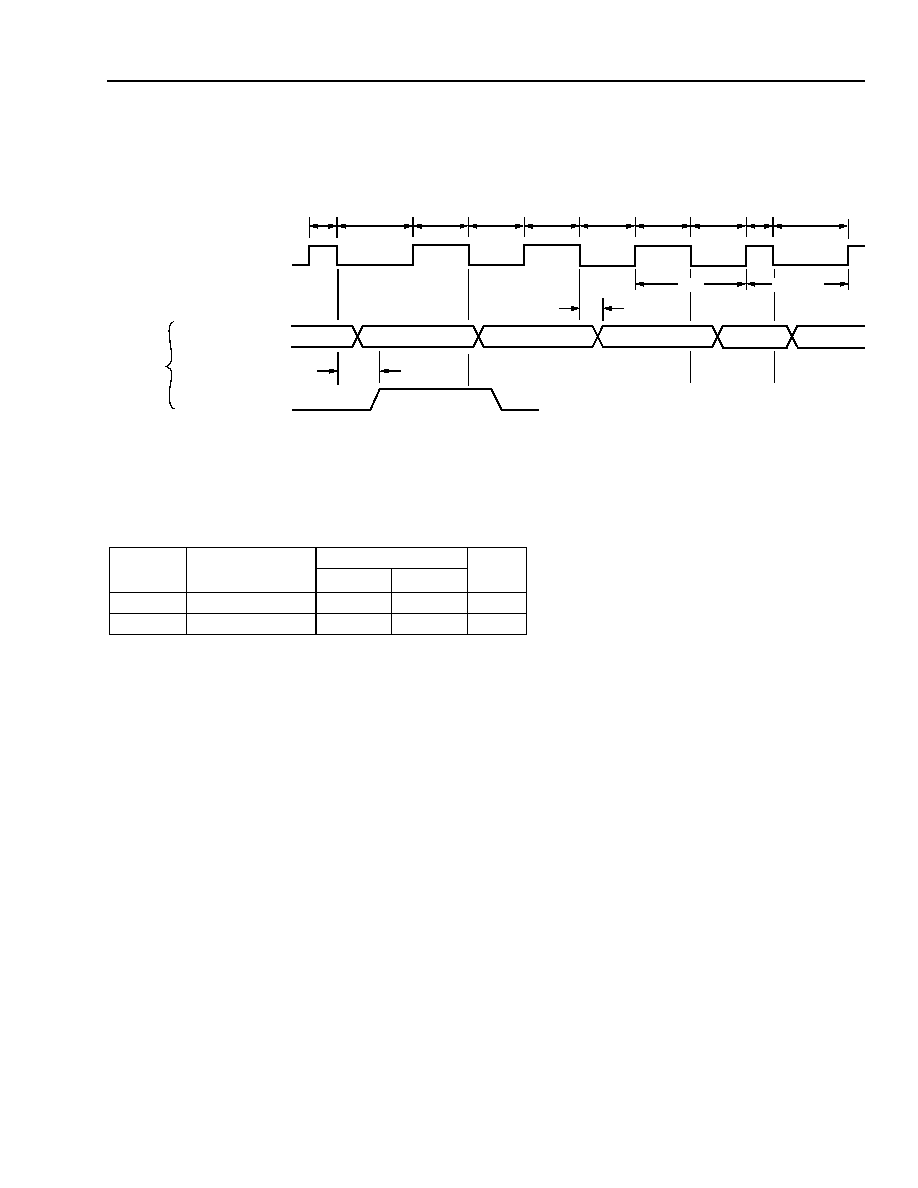

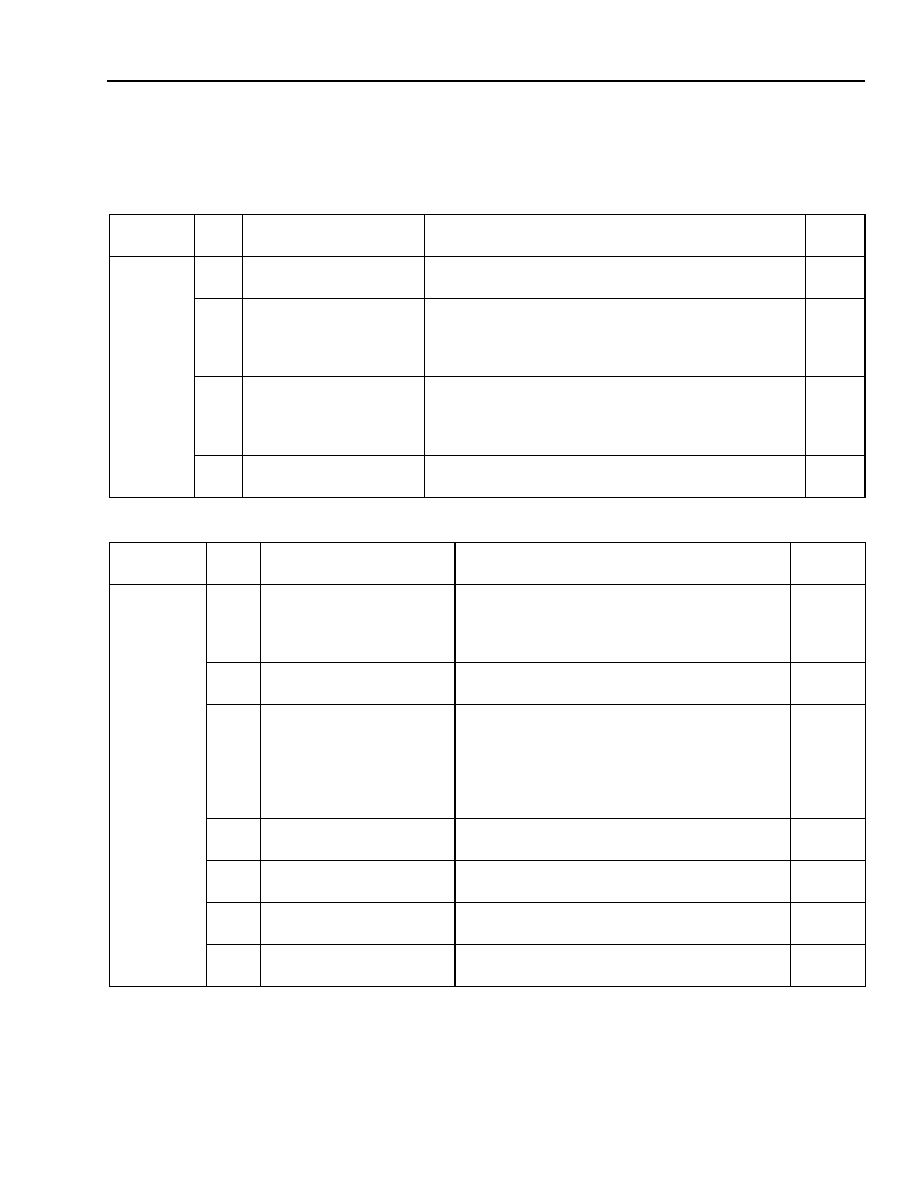

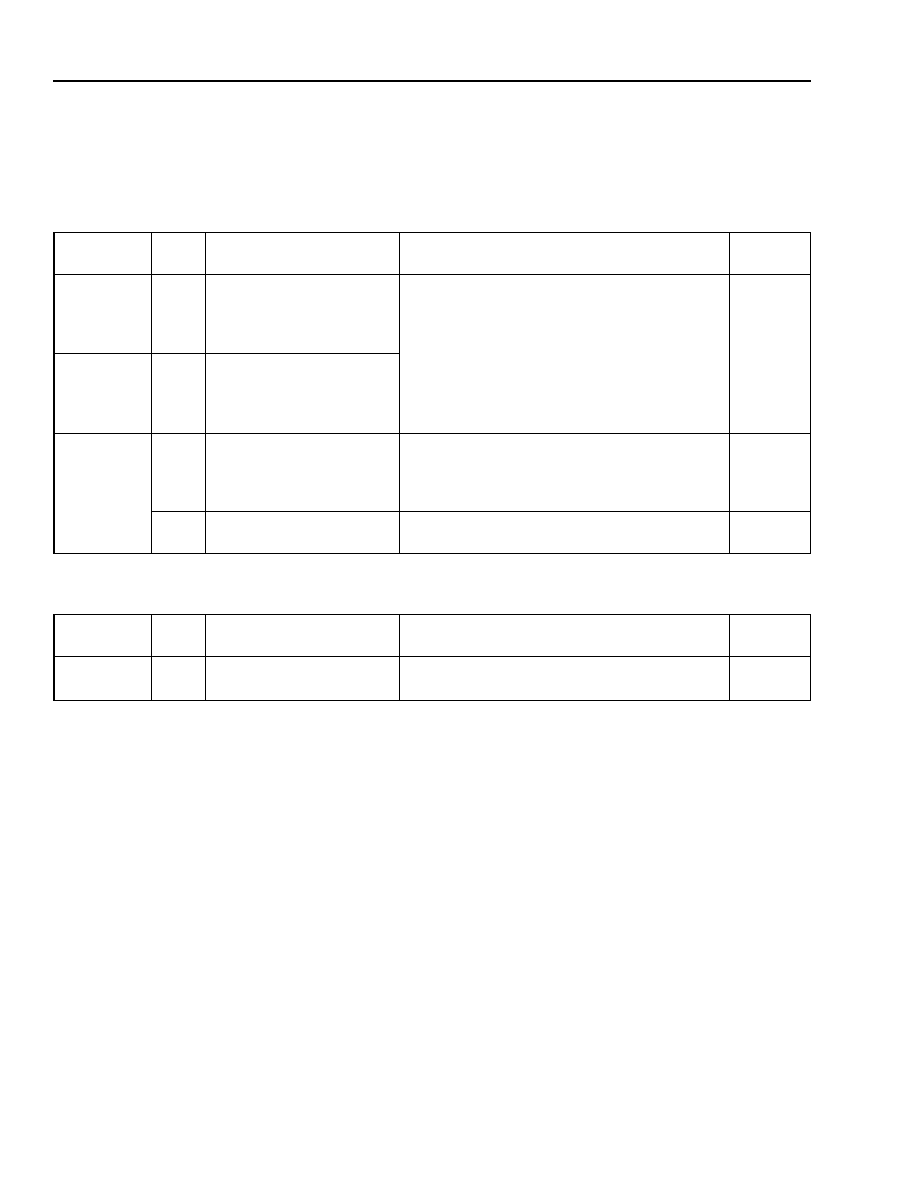

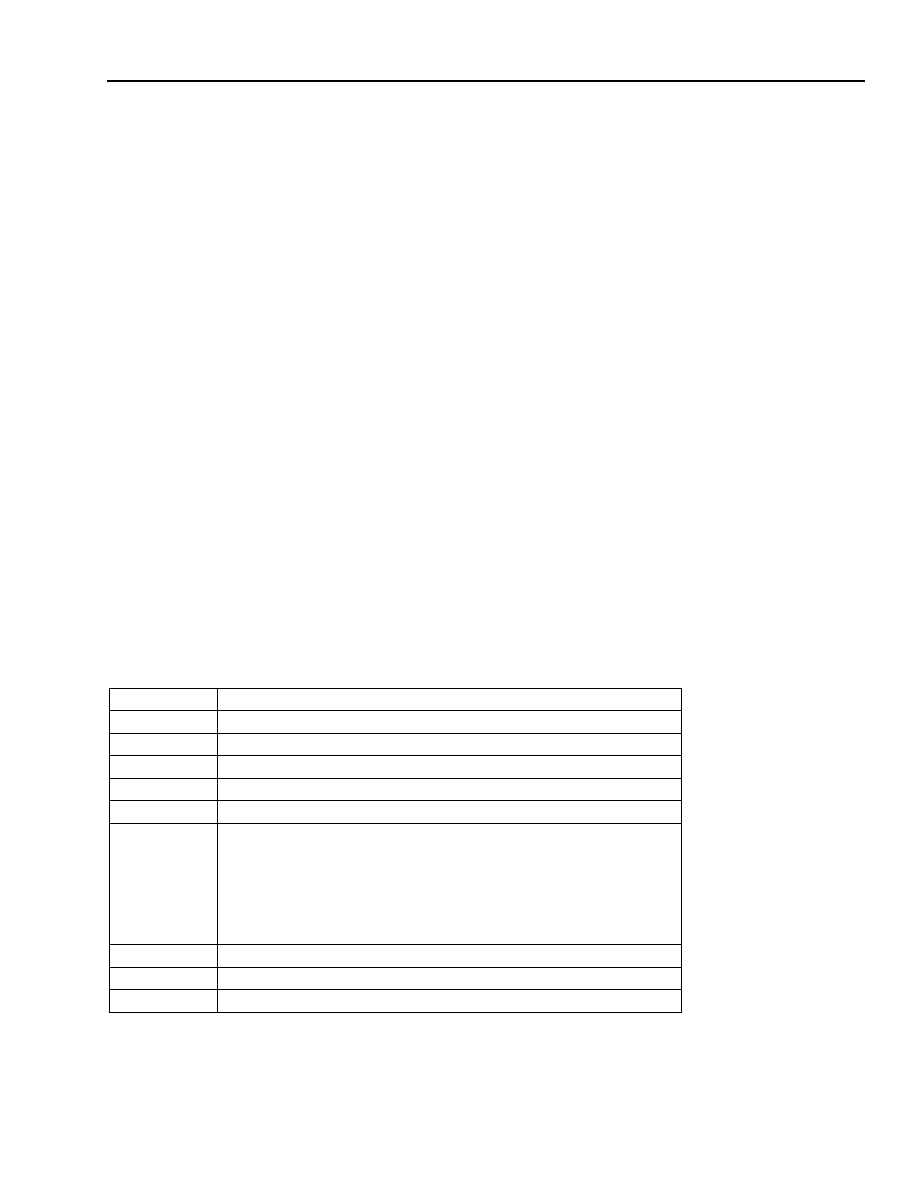

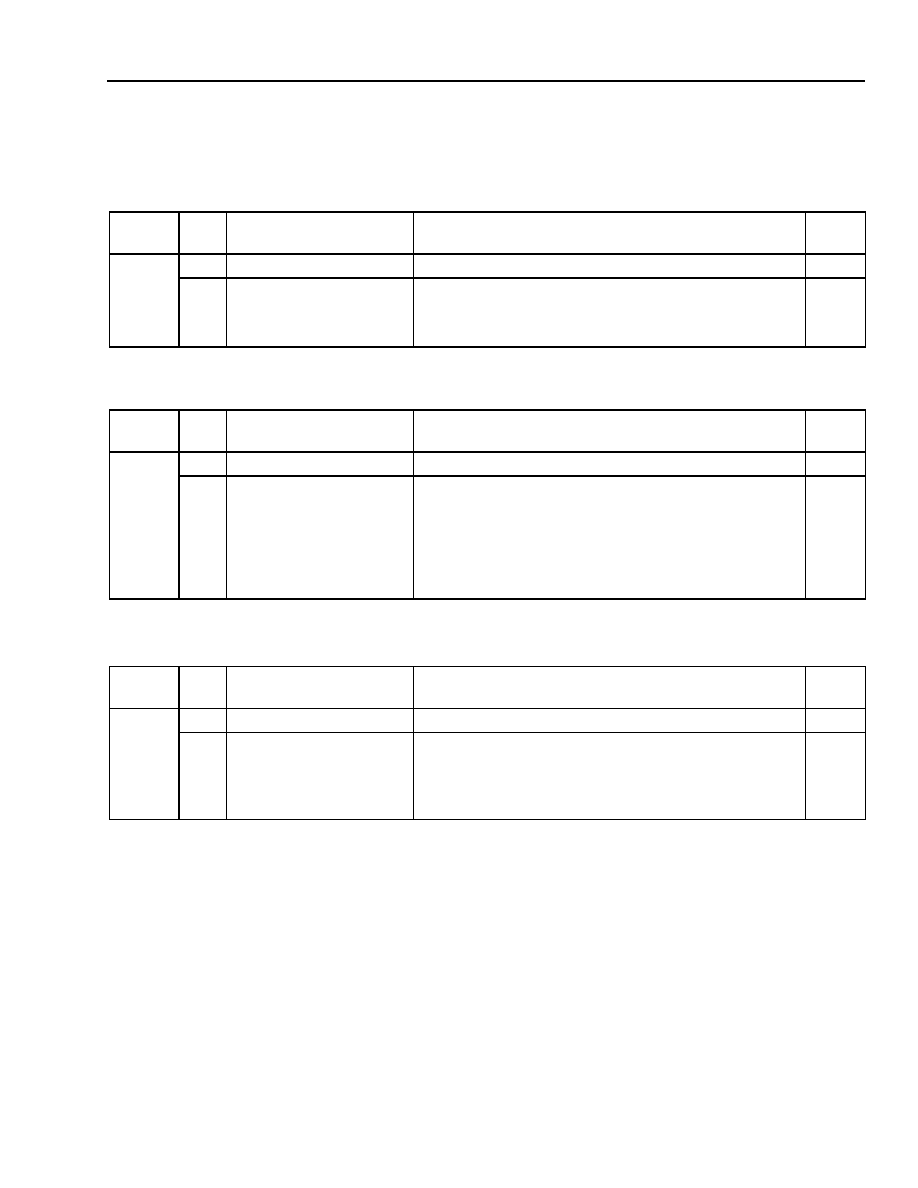

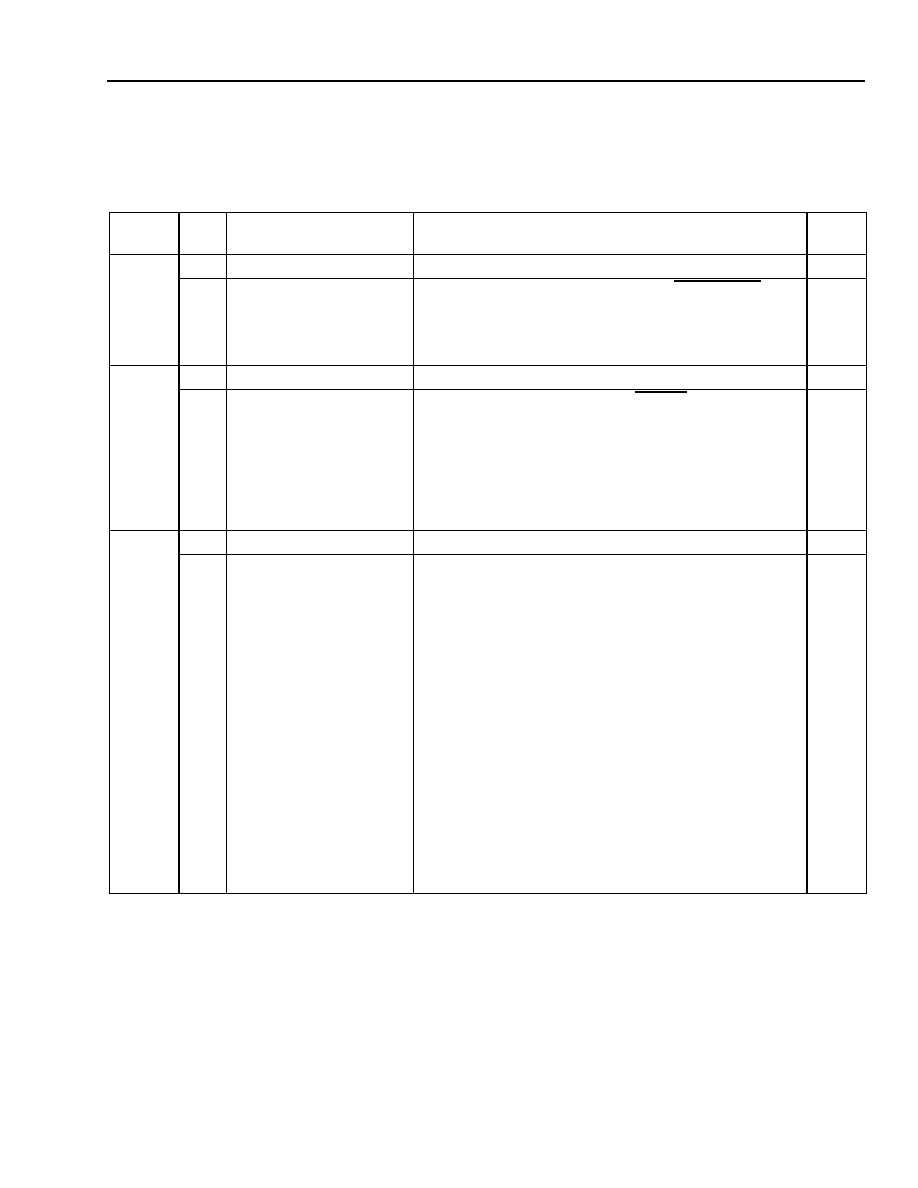

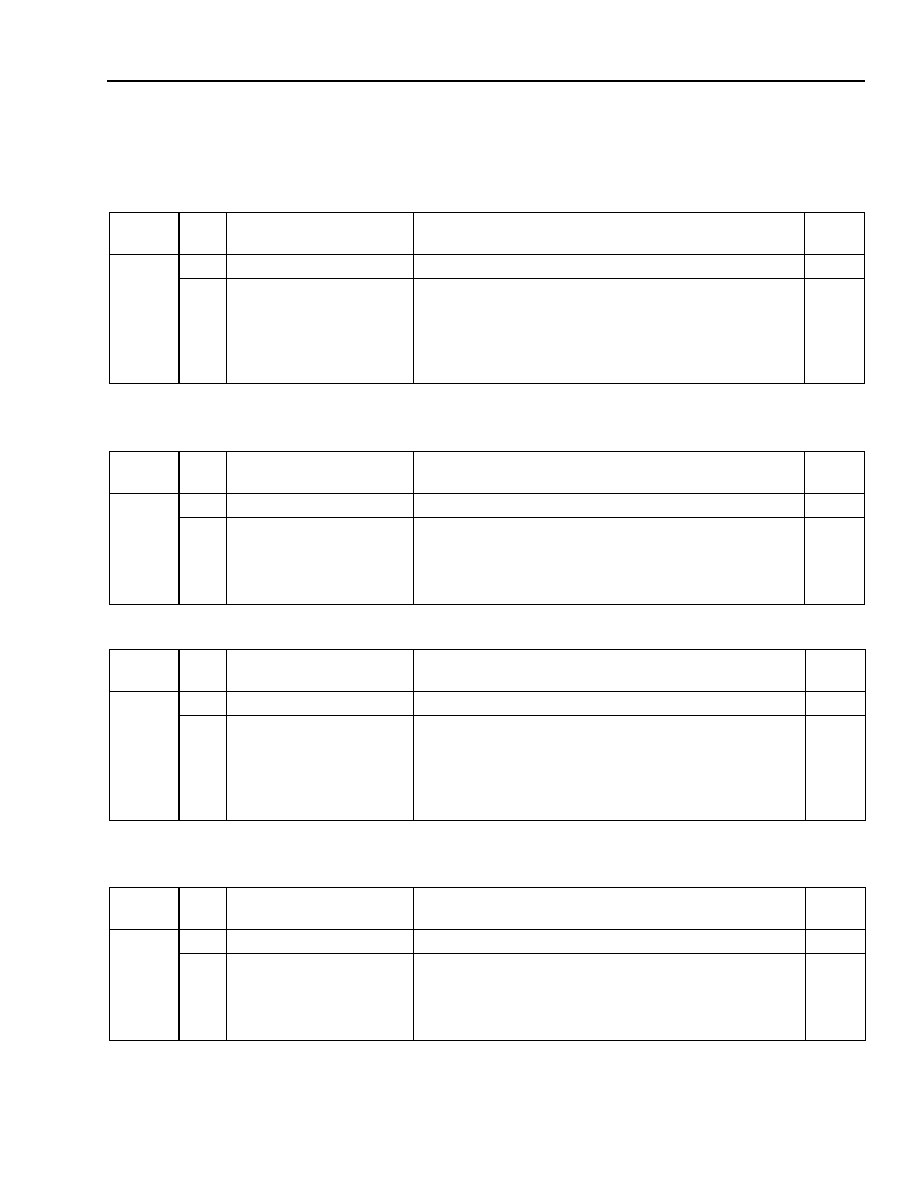

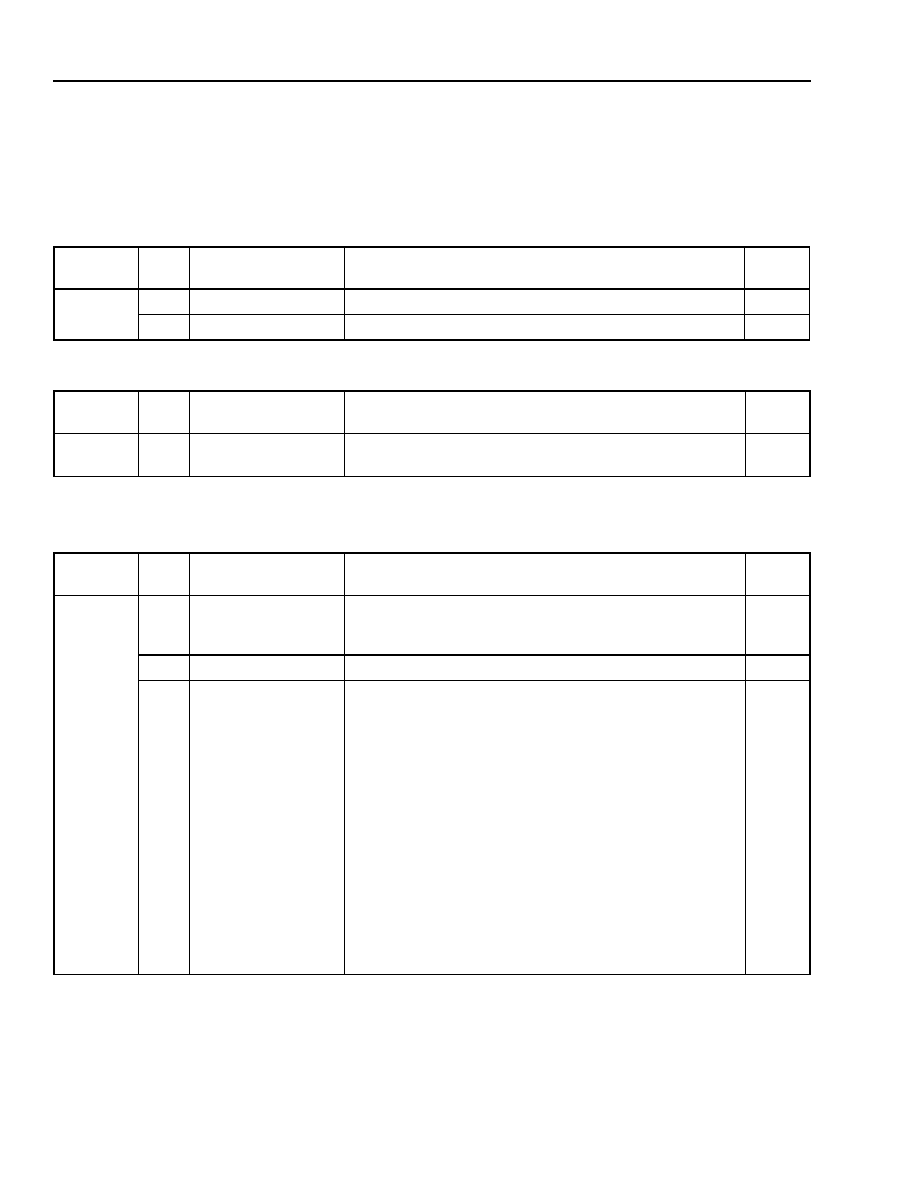

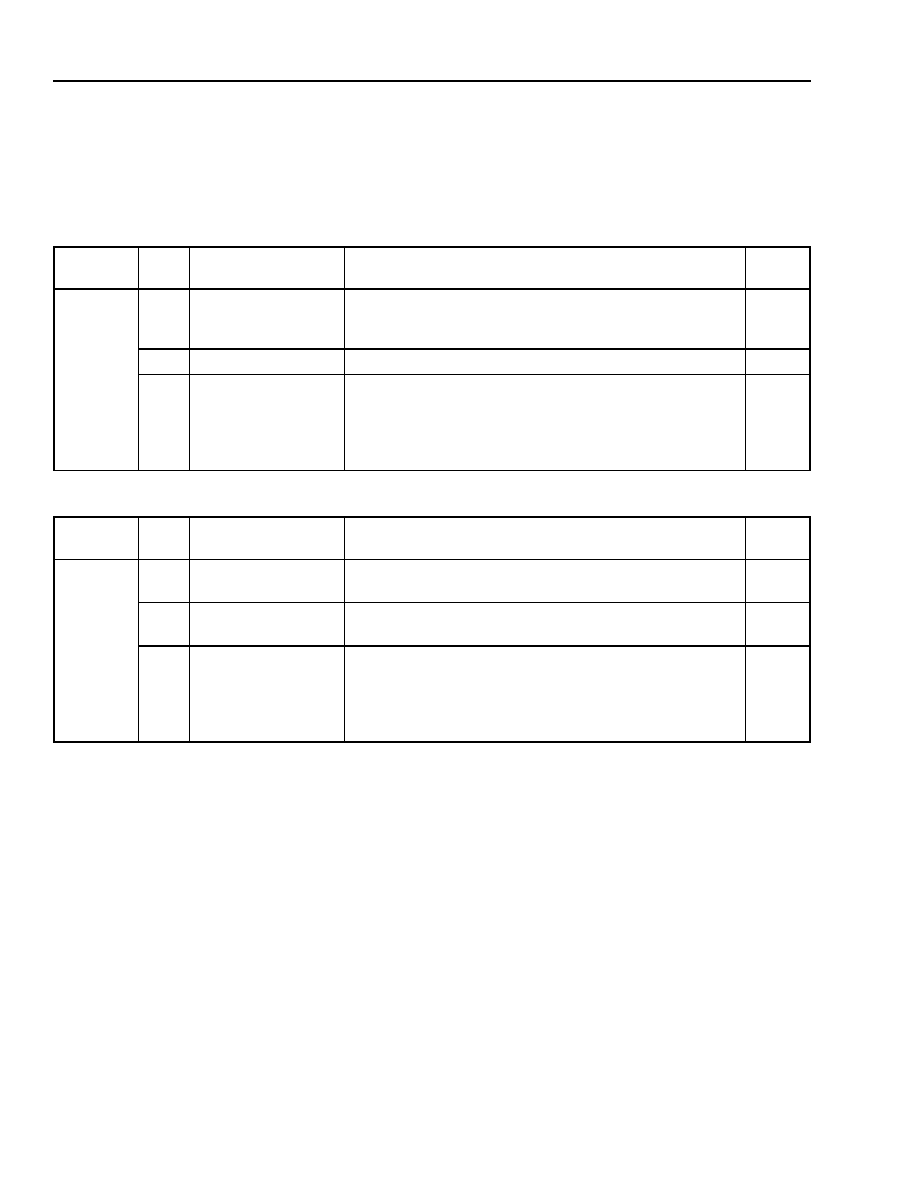

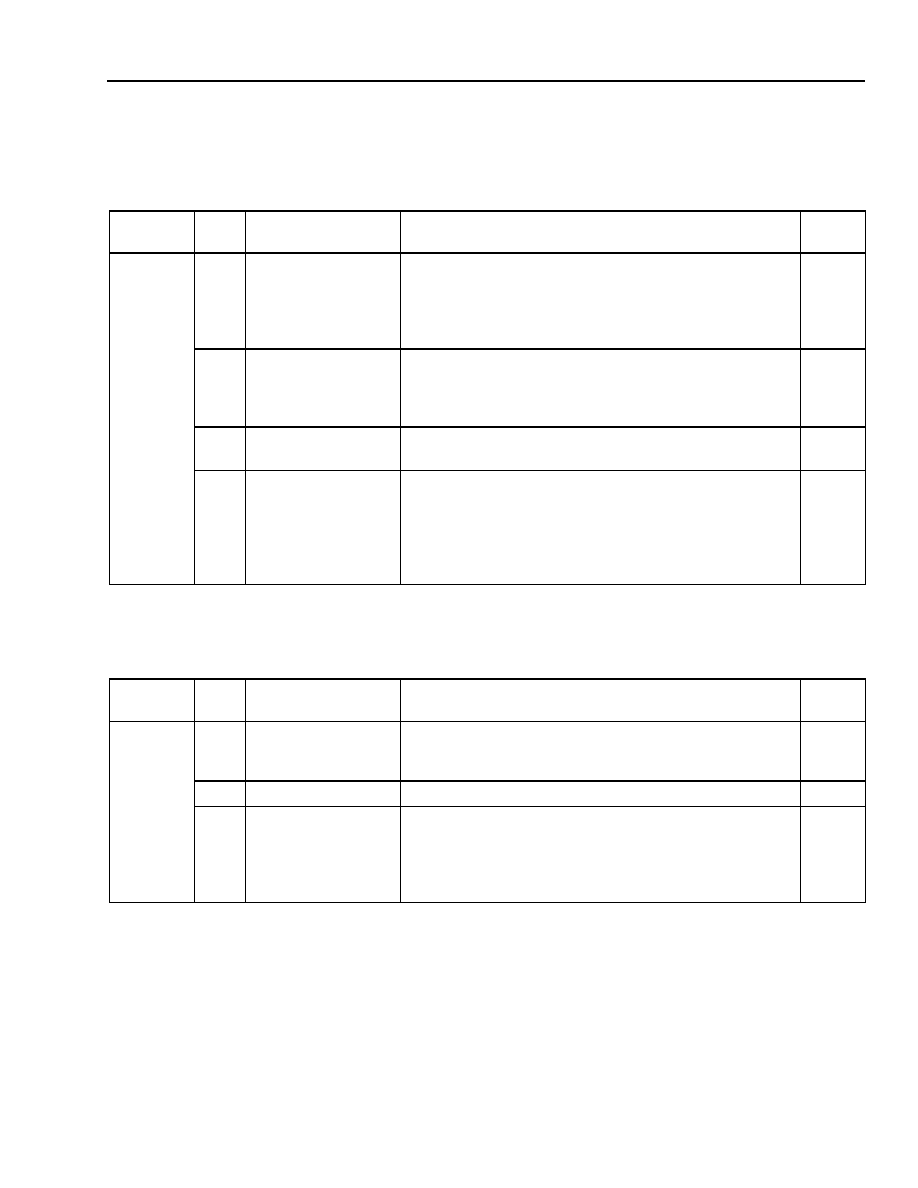

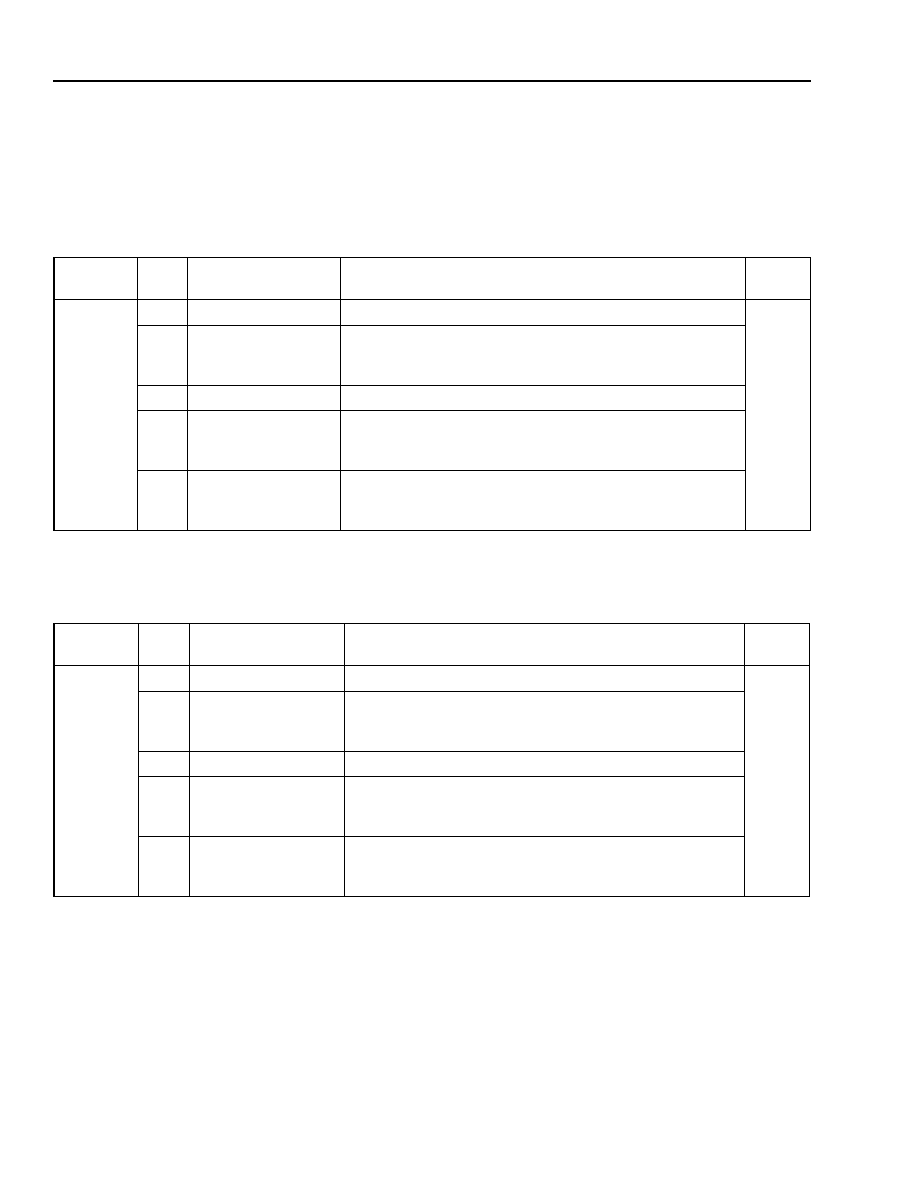

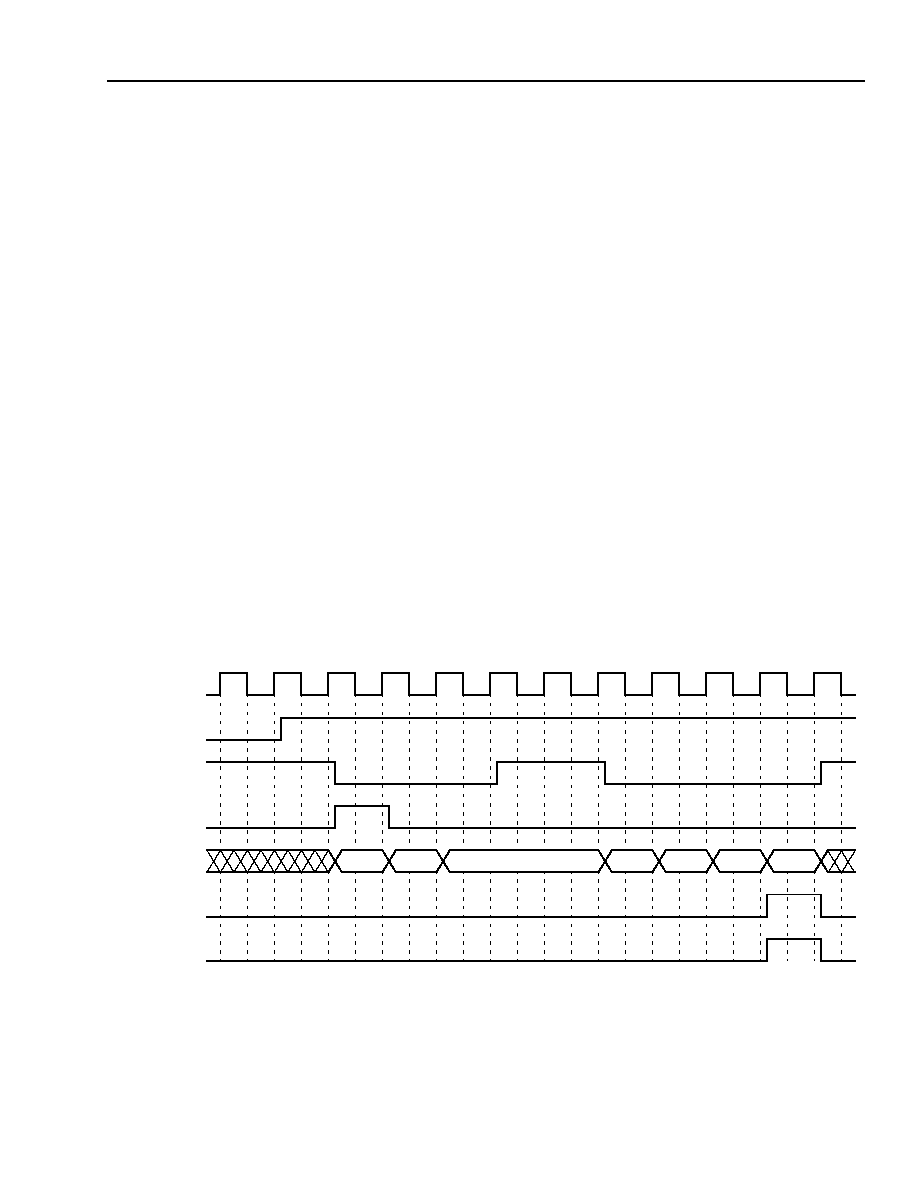

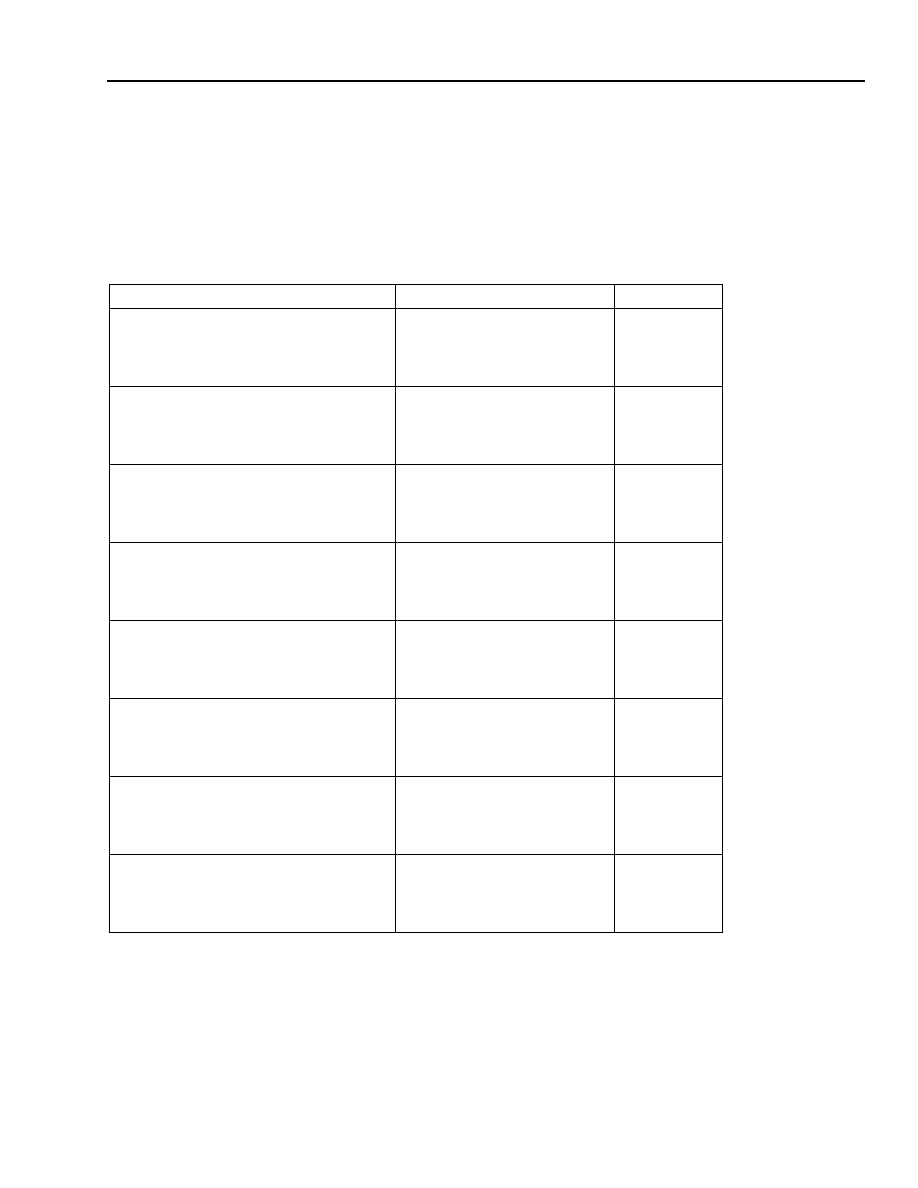

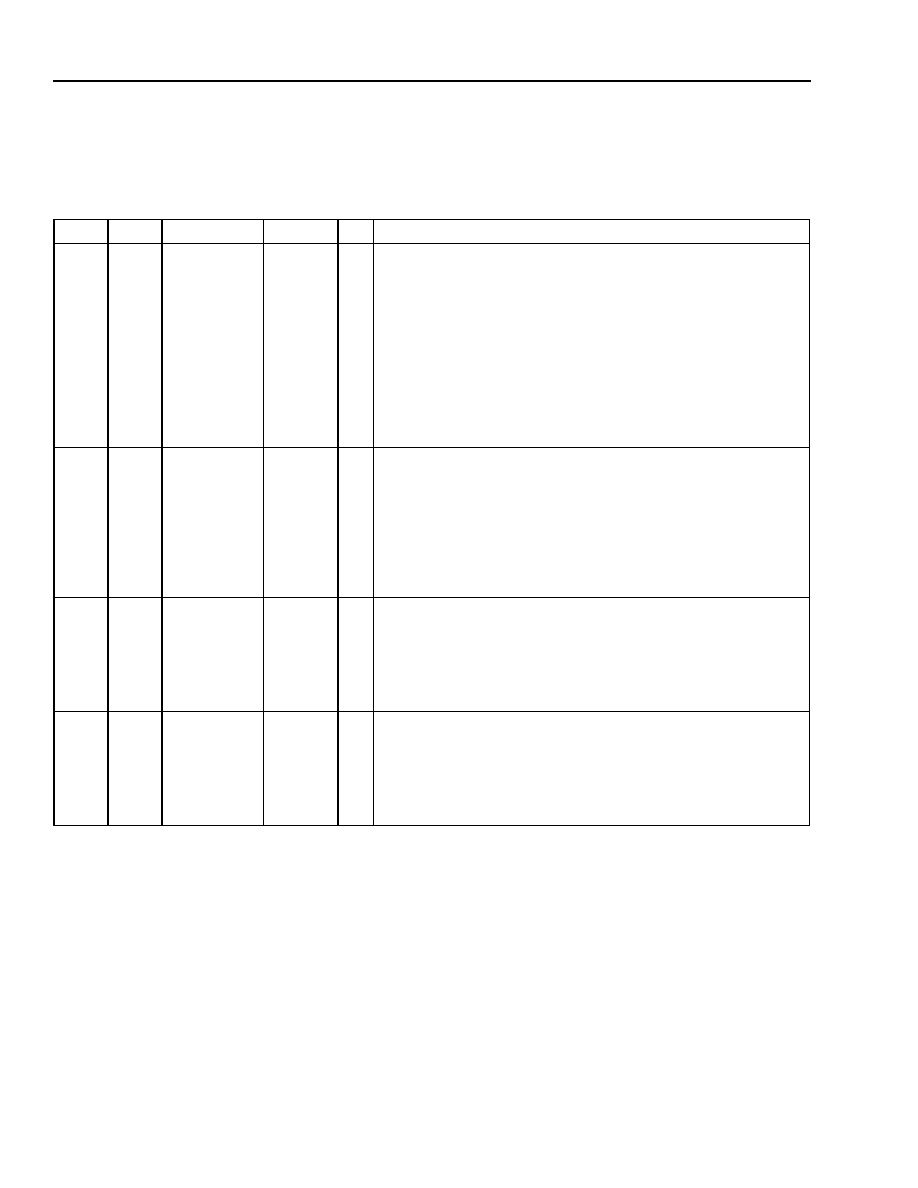

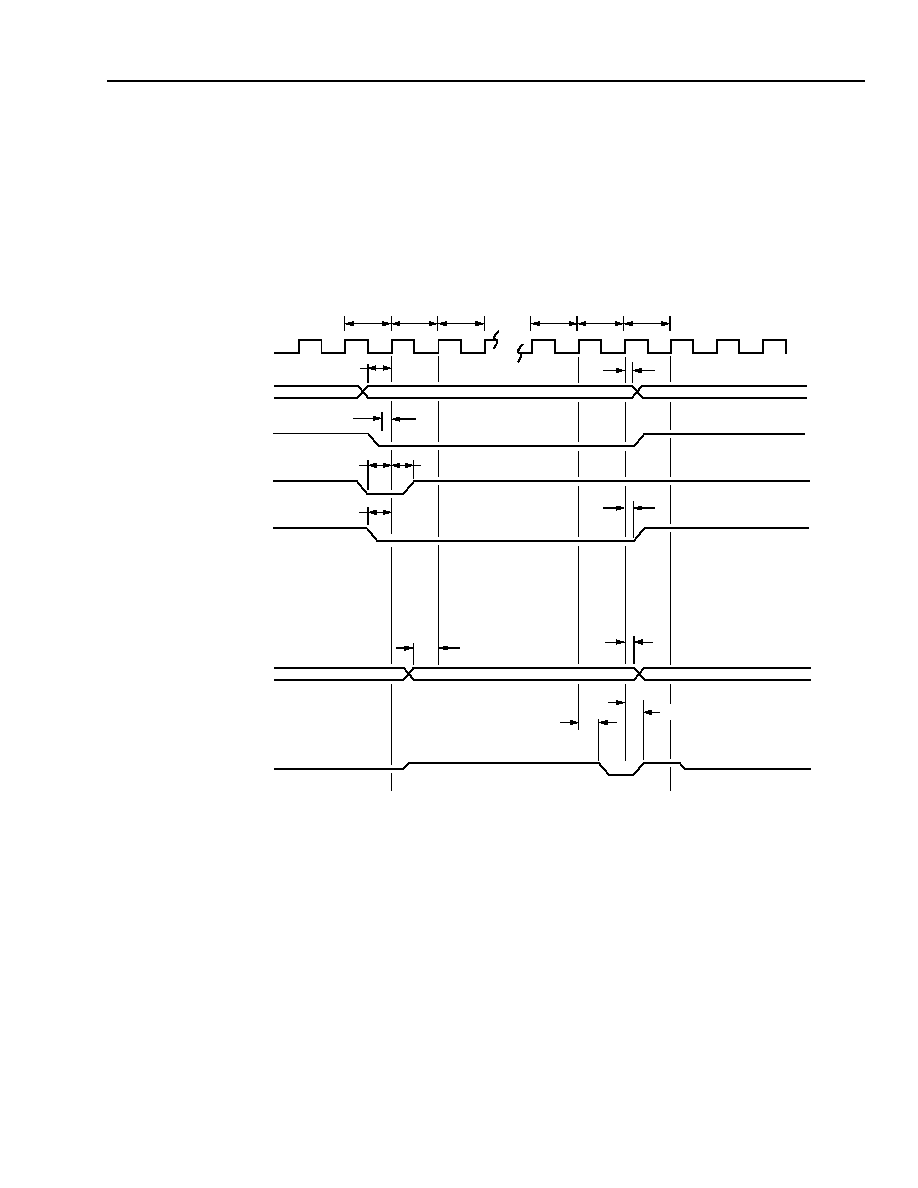

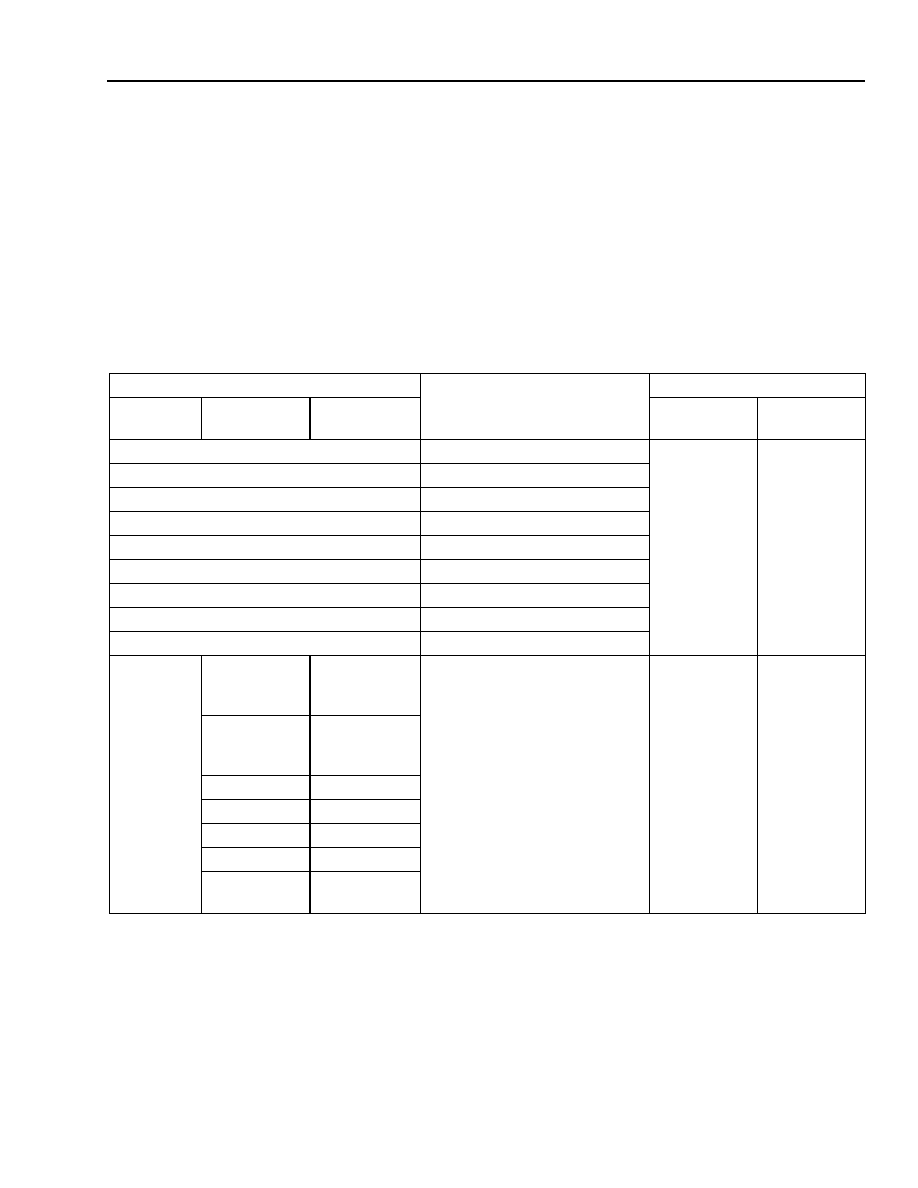

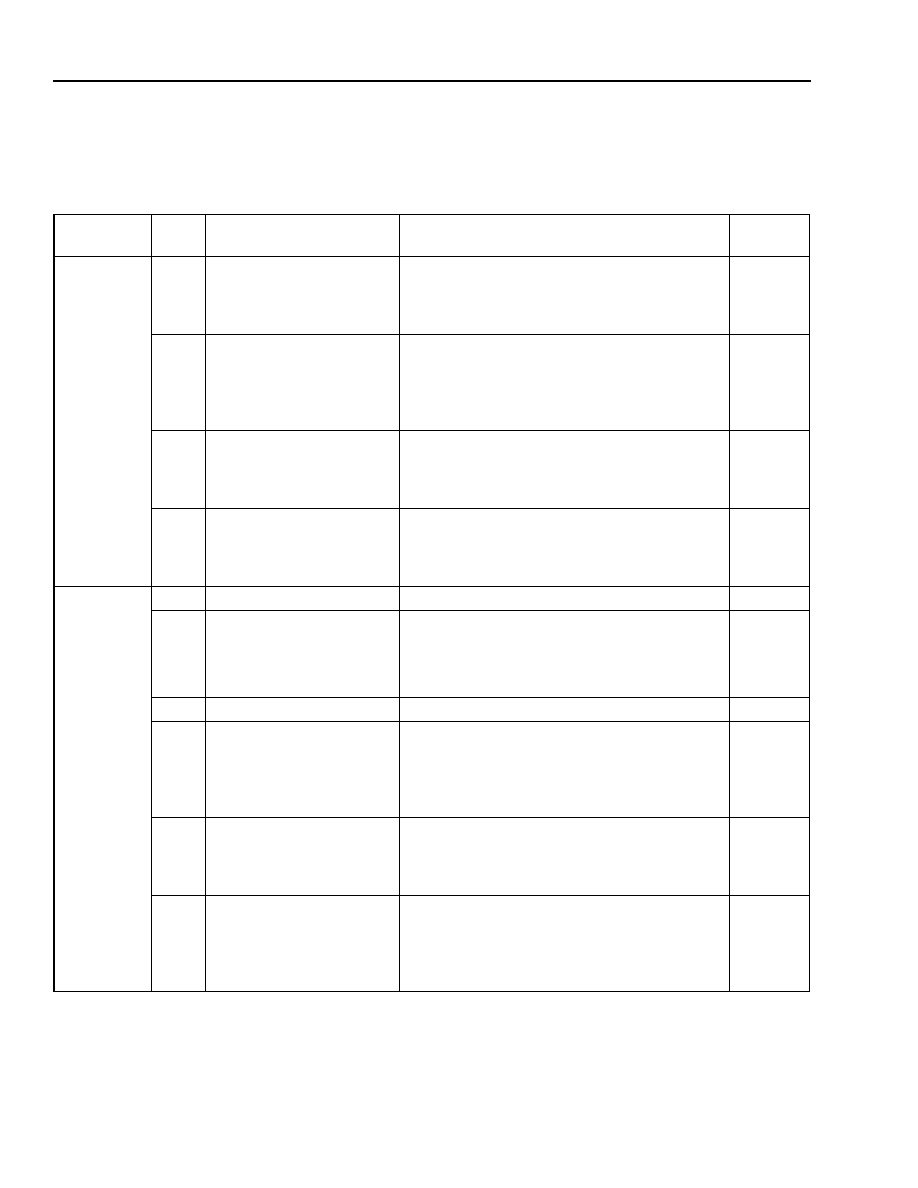

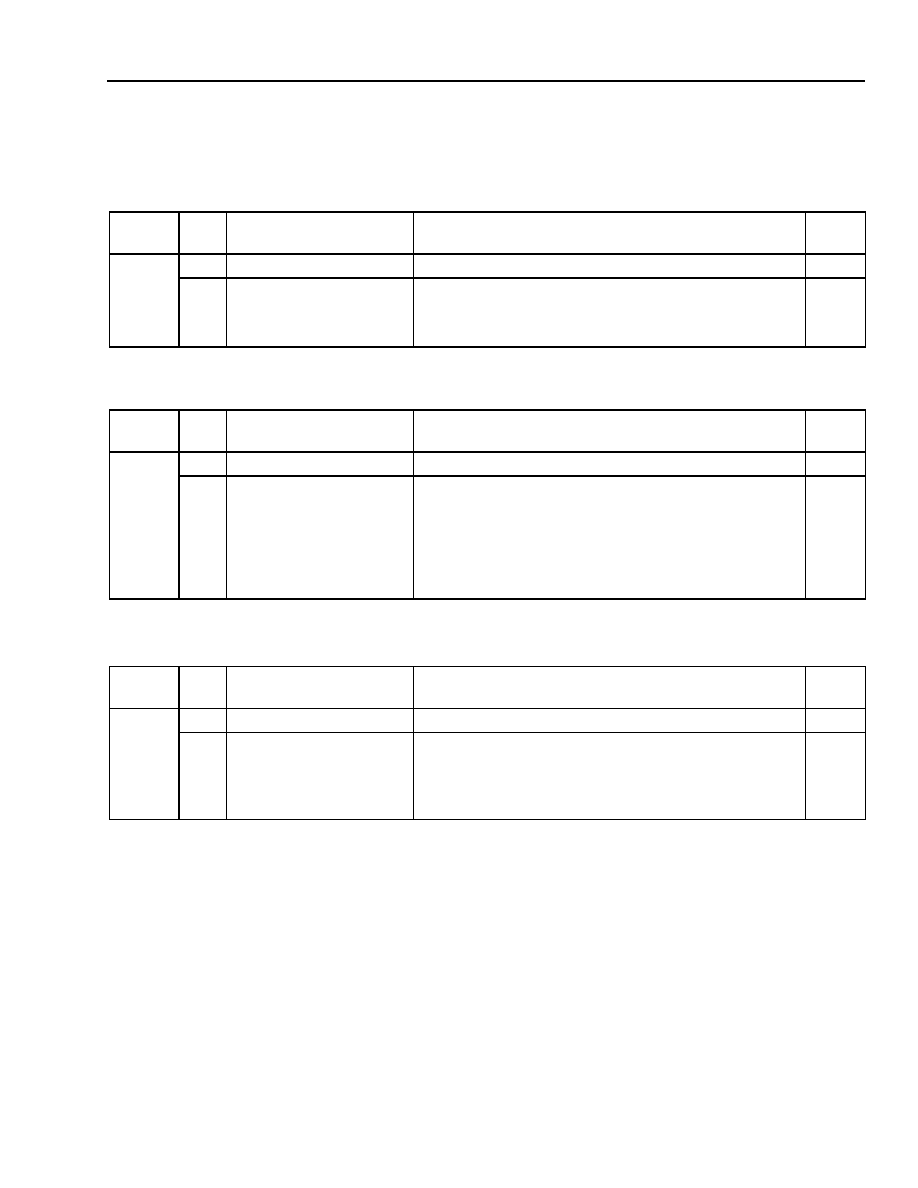

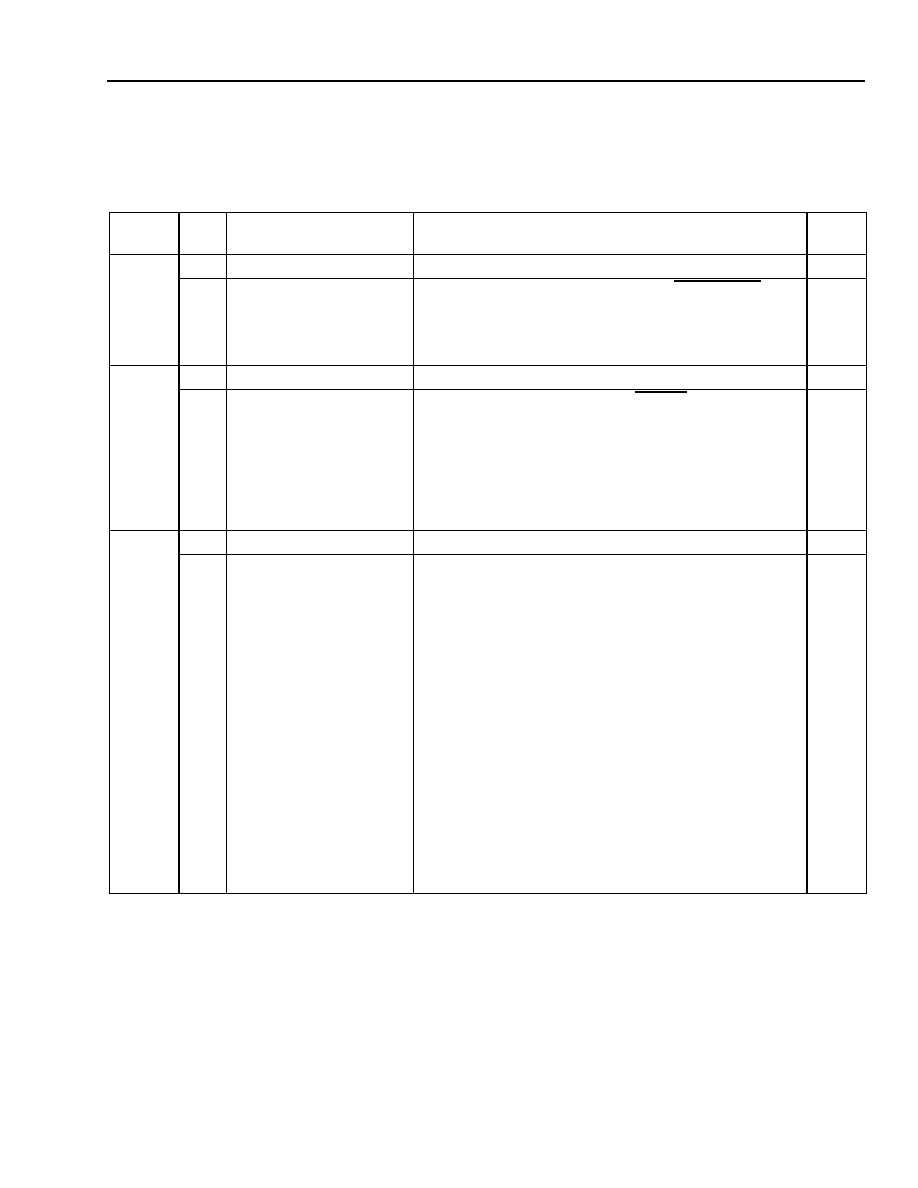

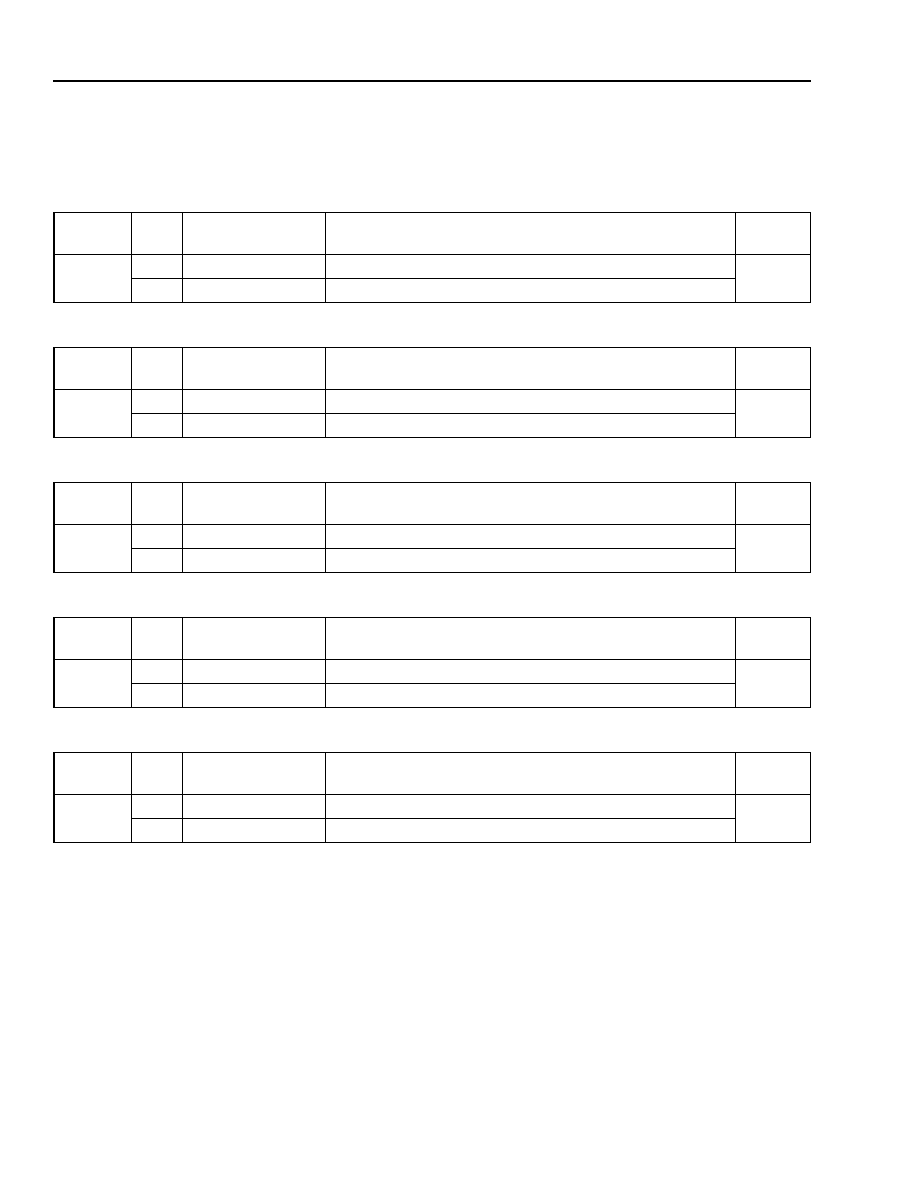

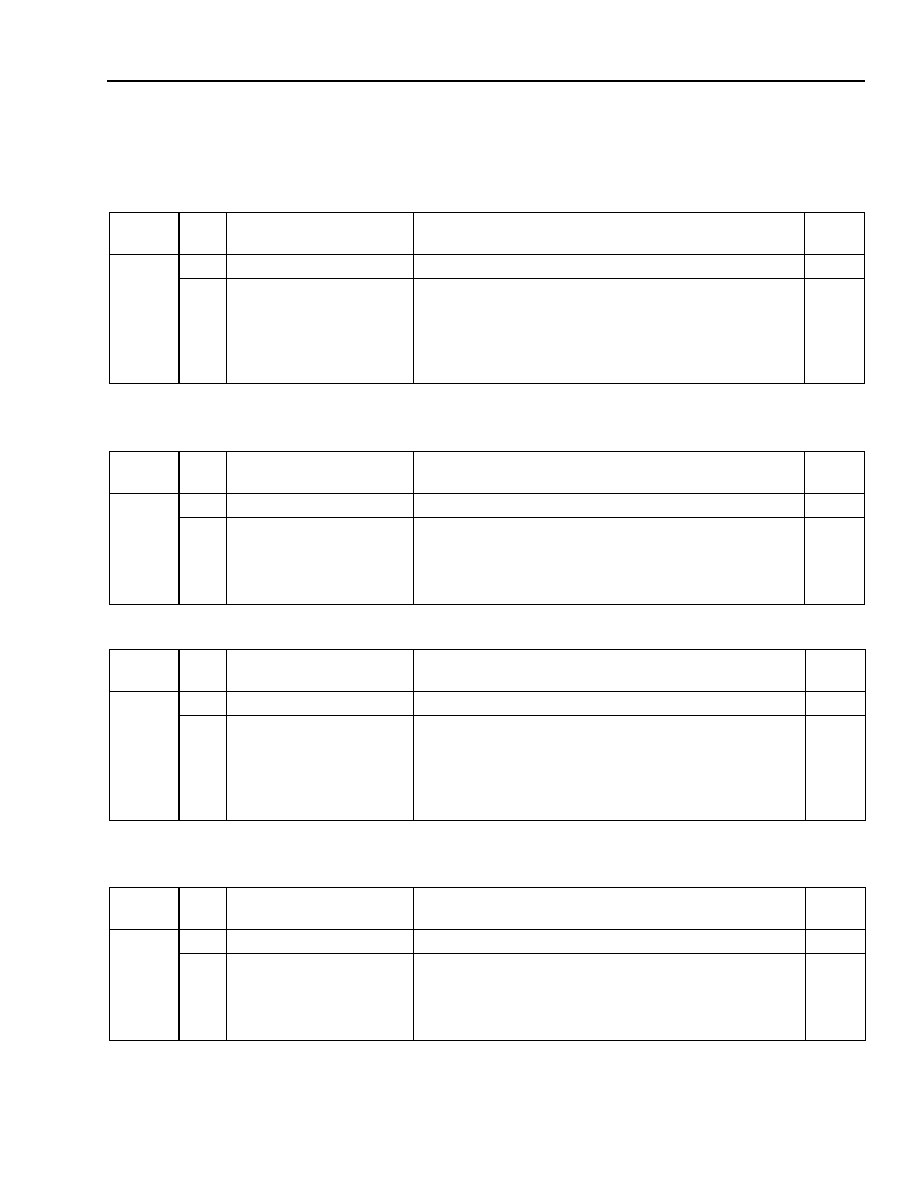

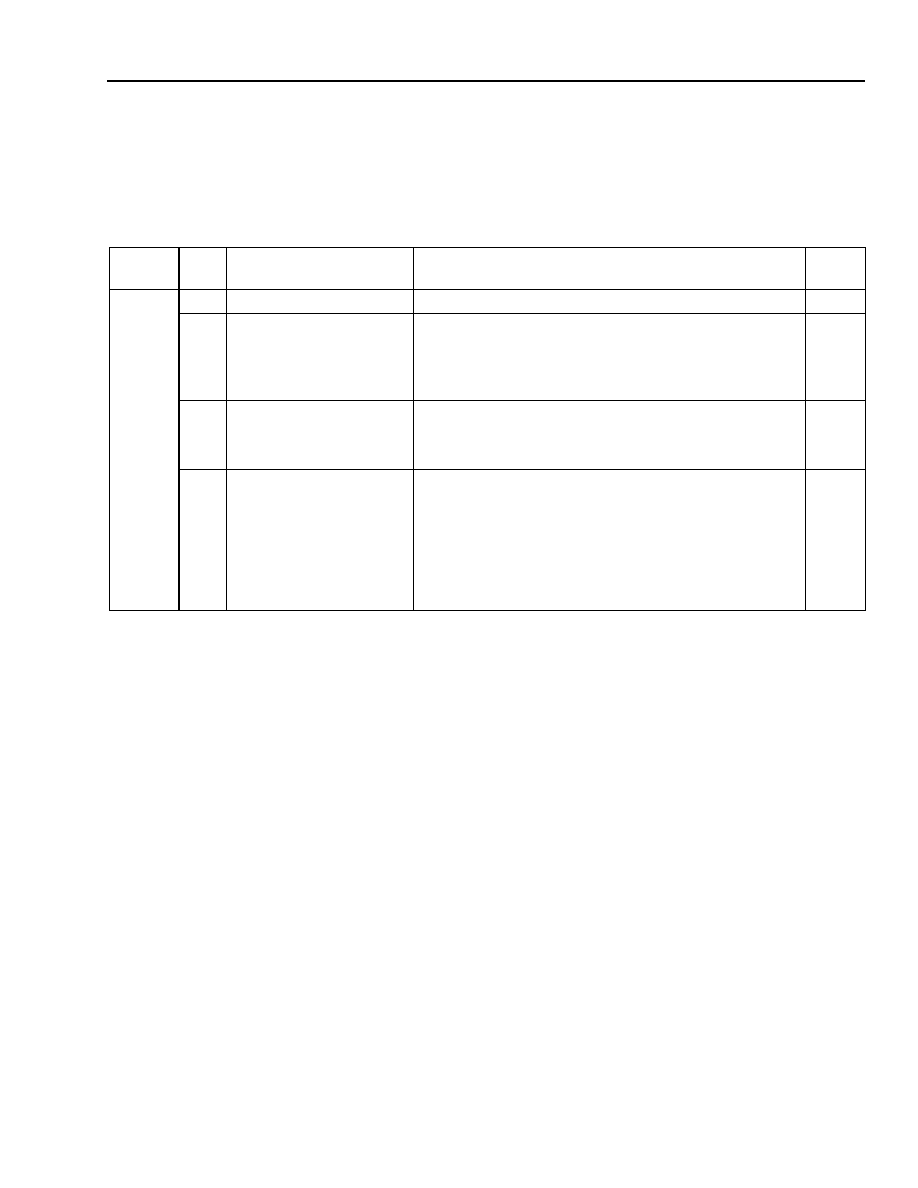

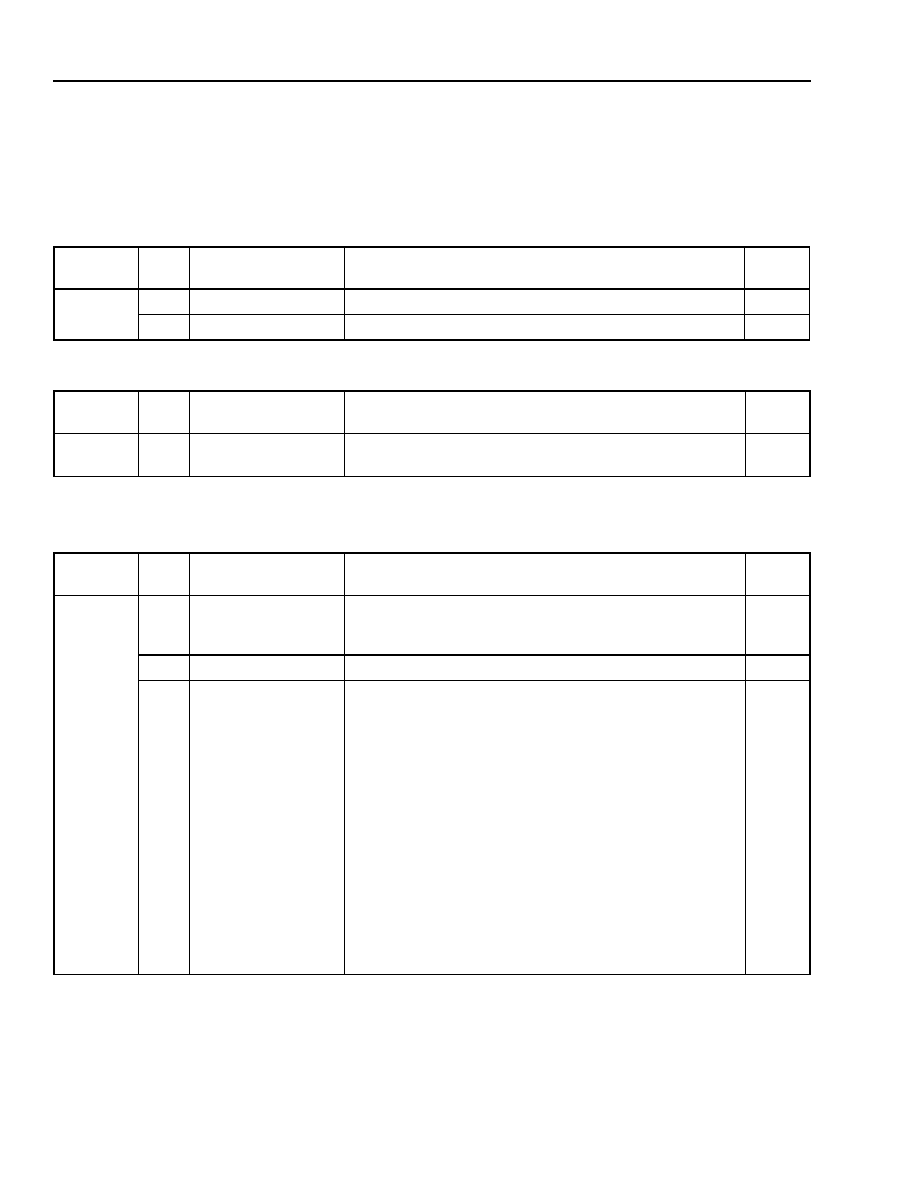

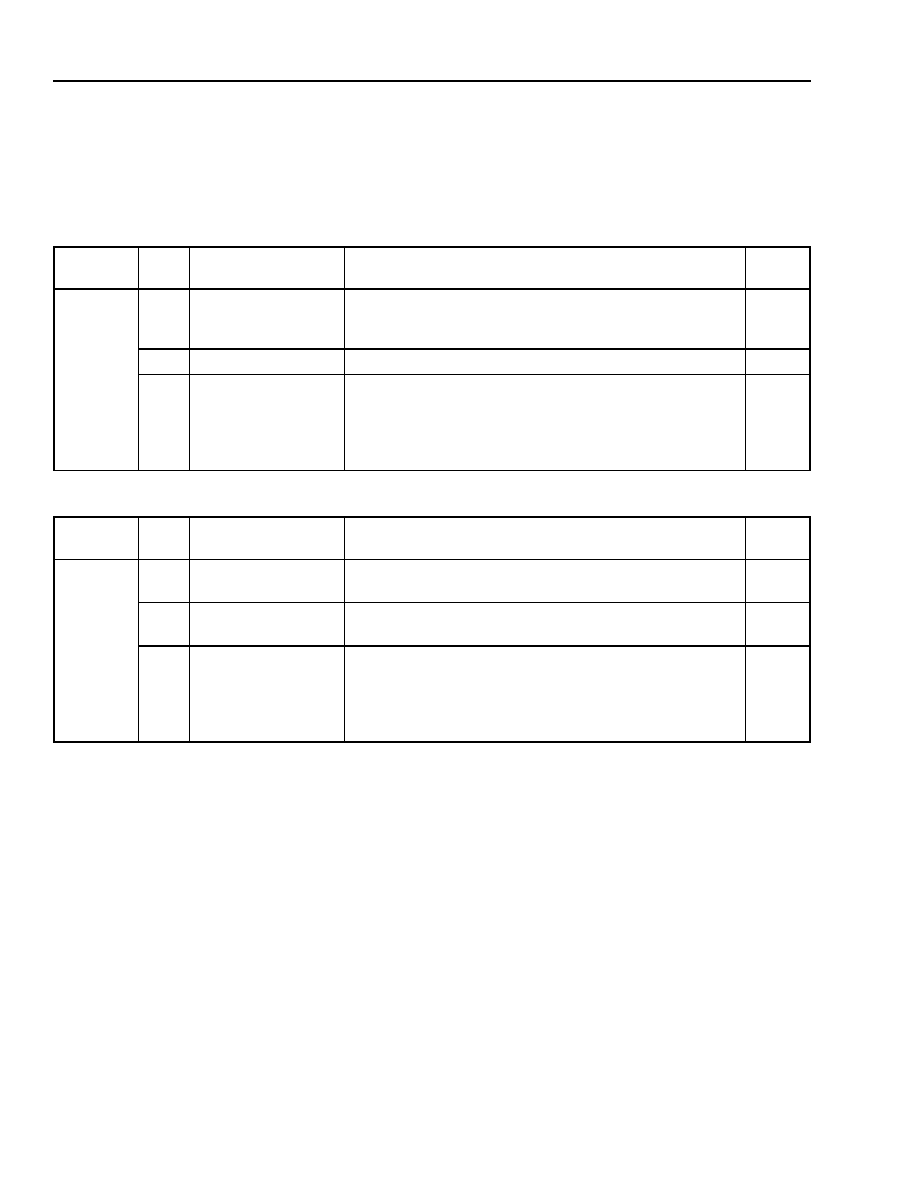

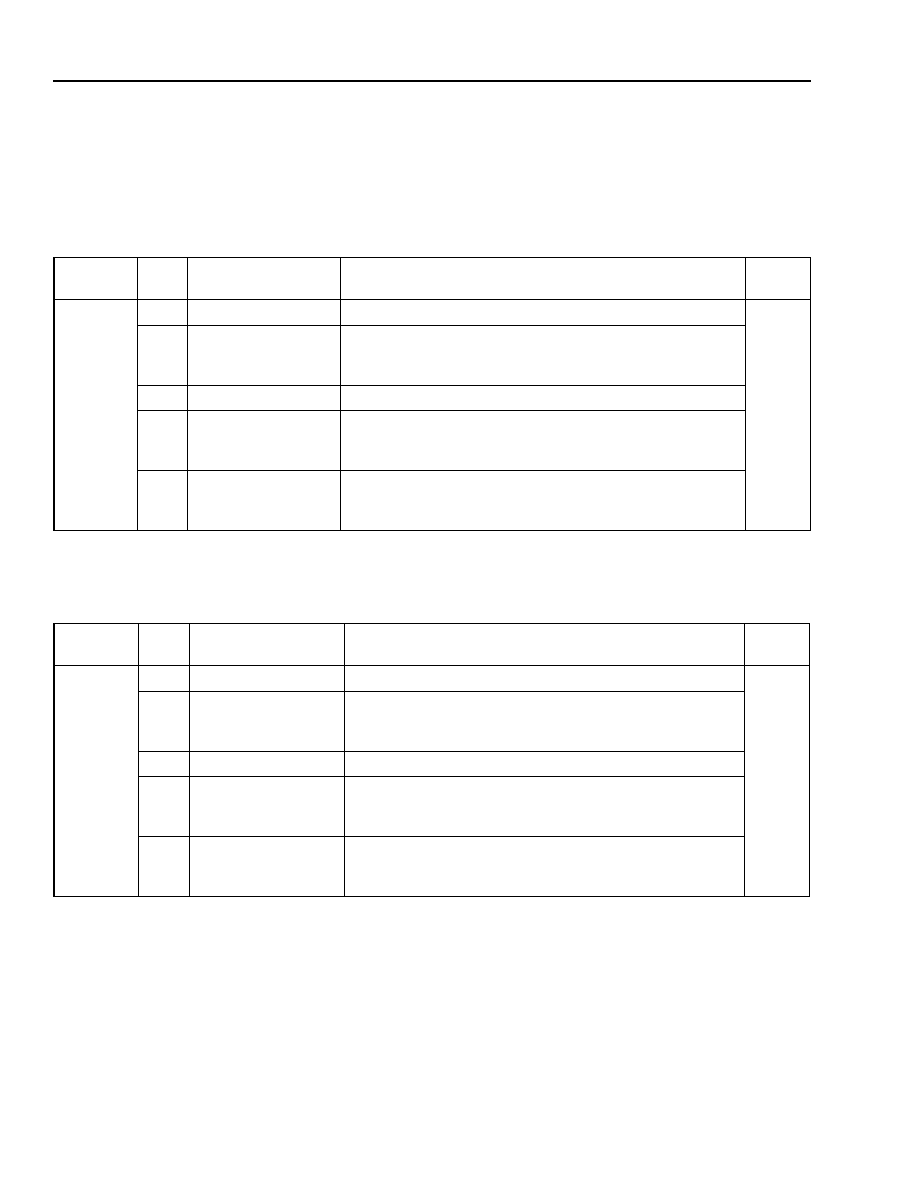

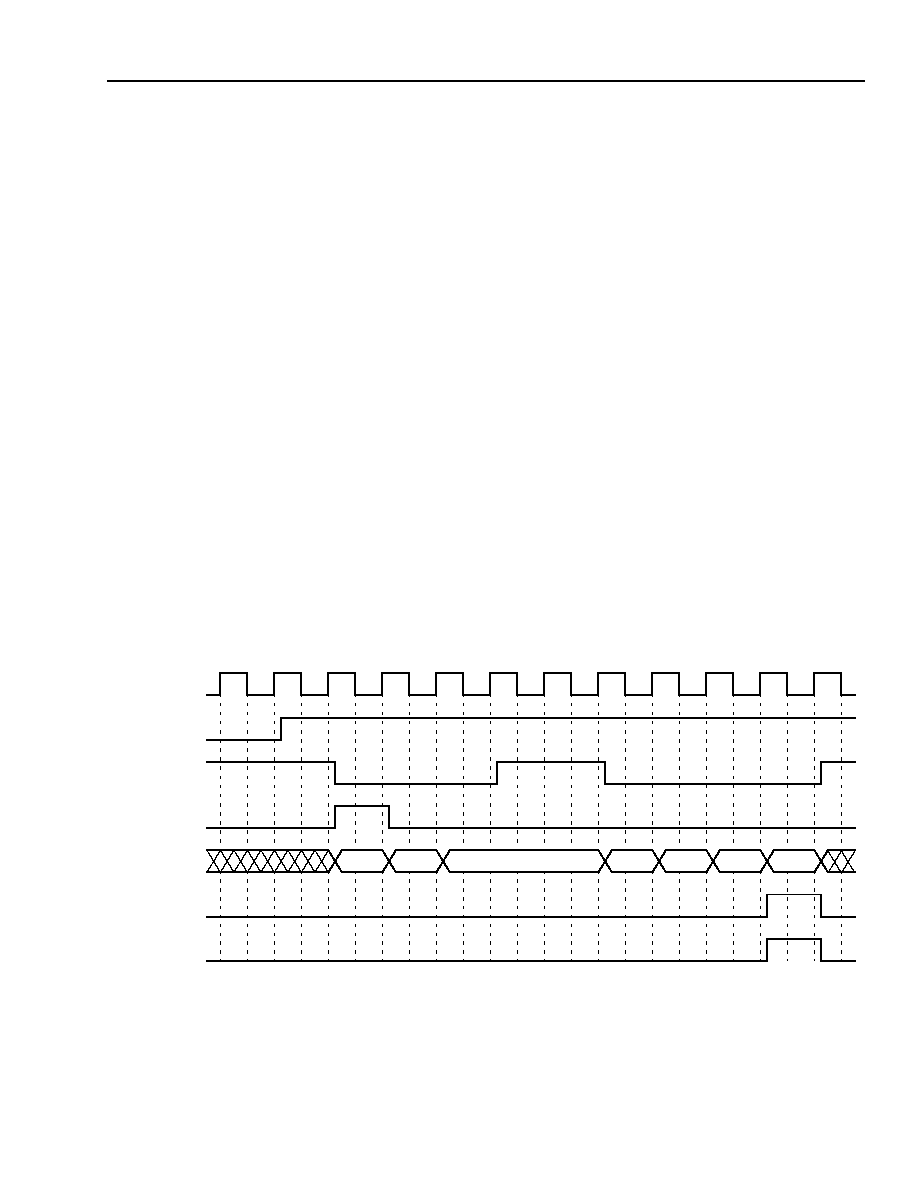

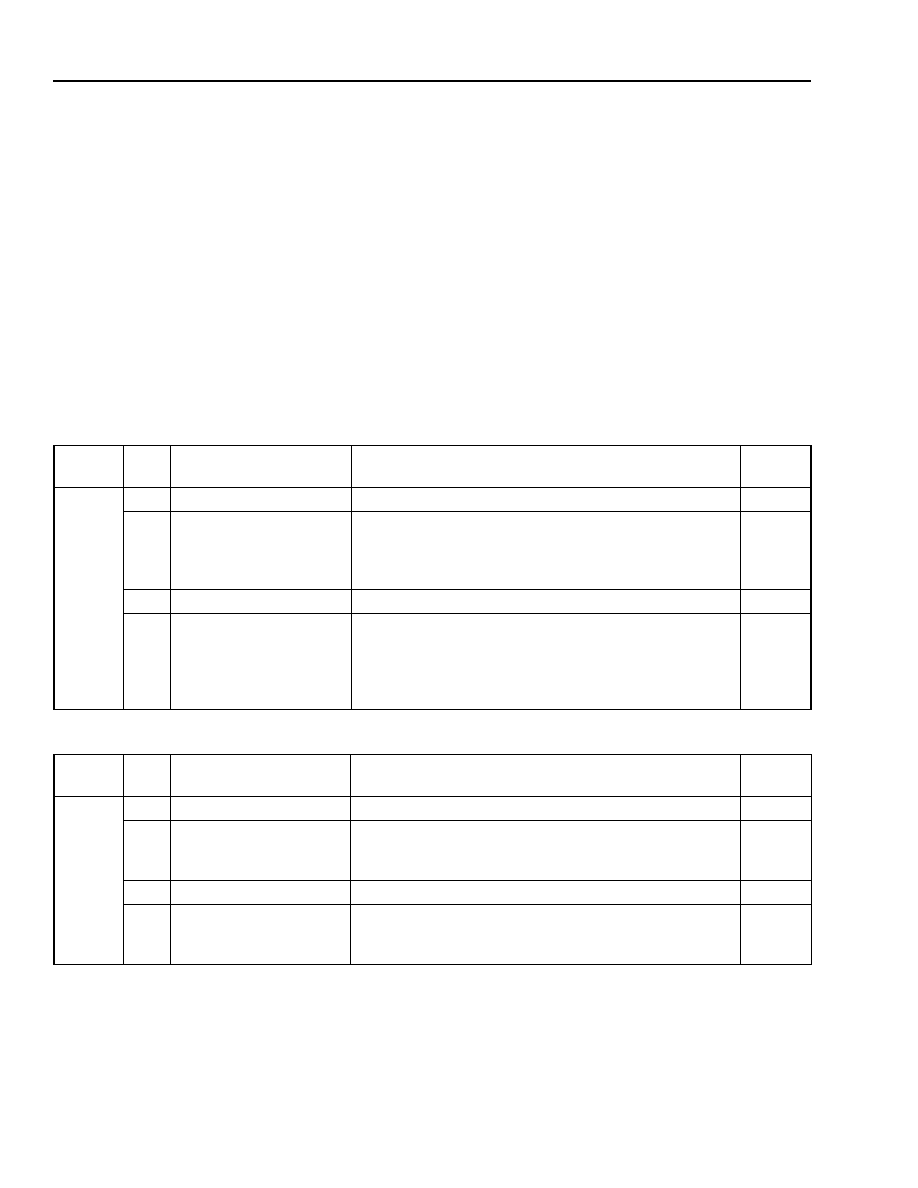

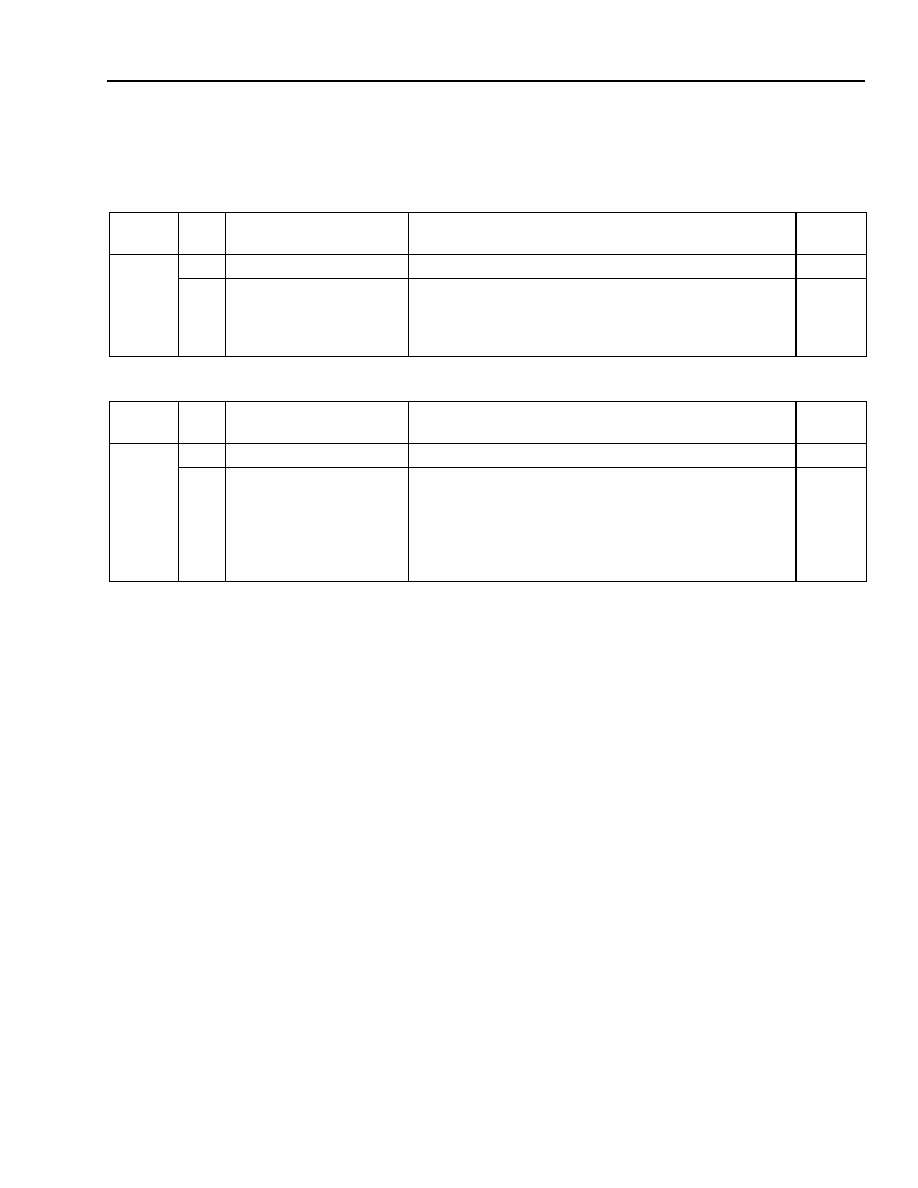

- Table 18. MPU Modes

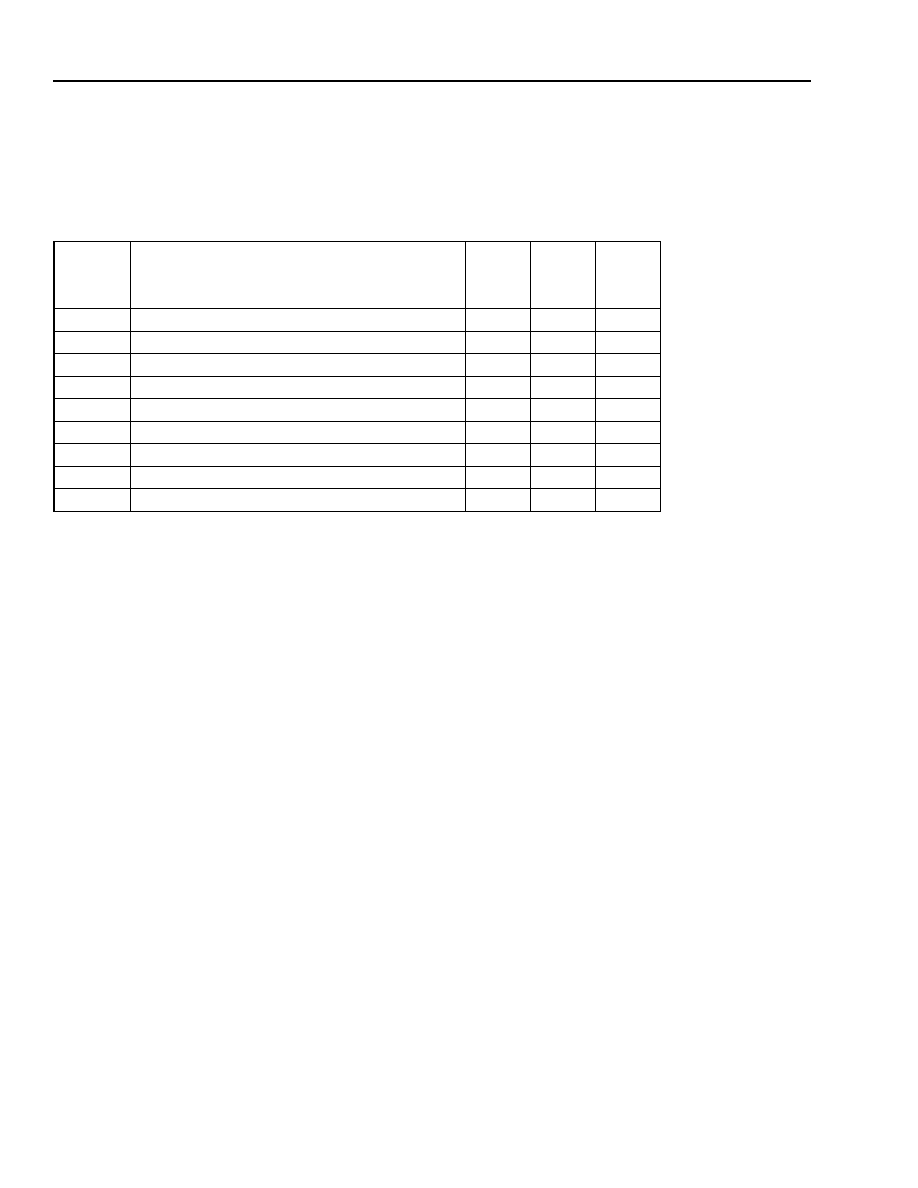

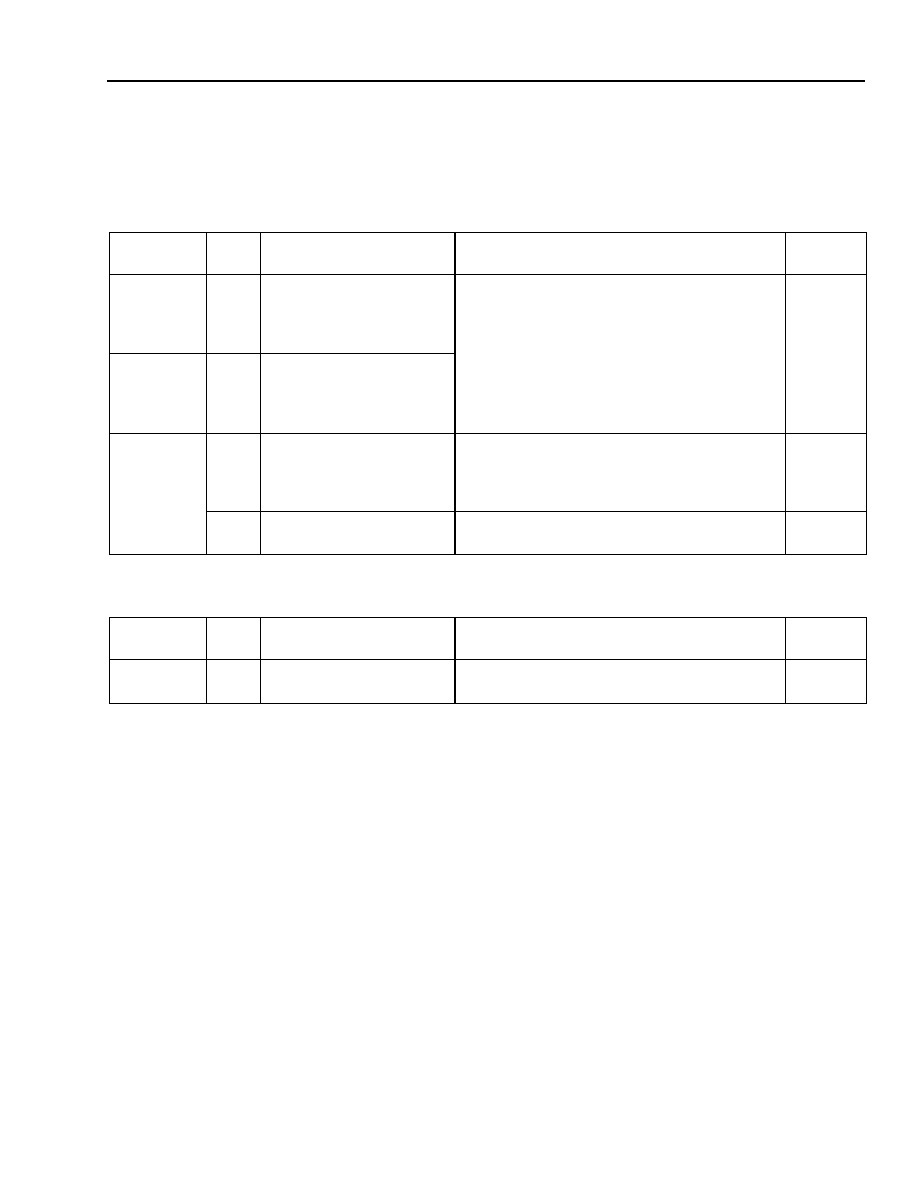

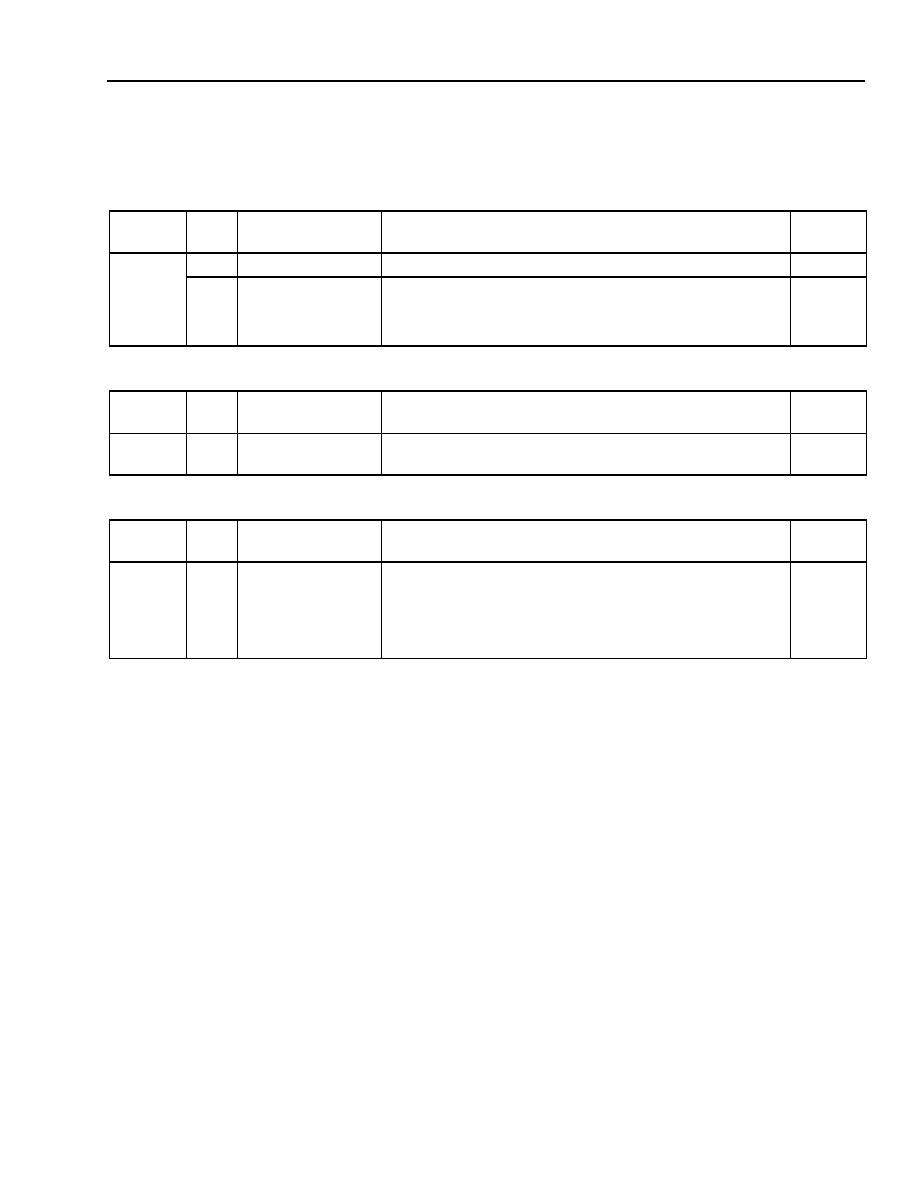

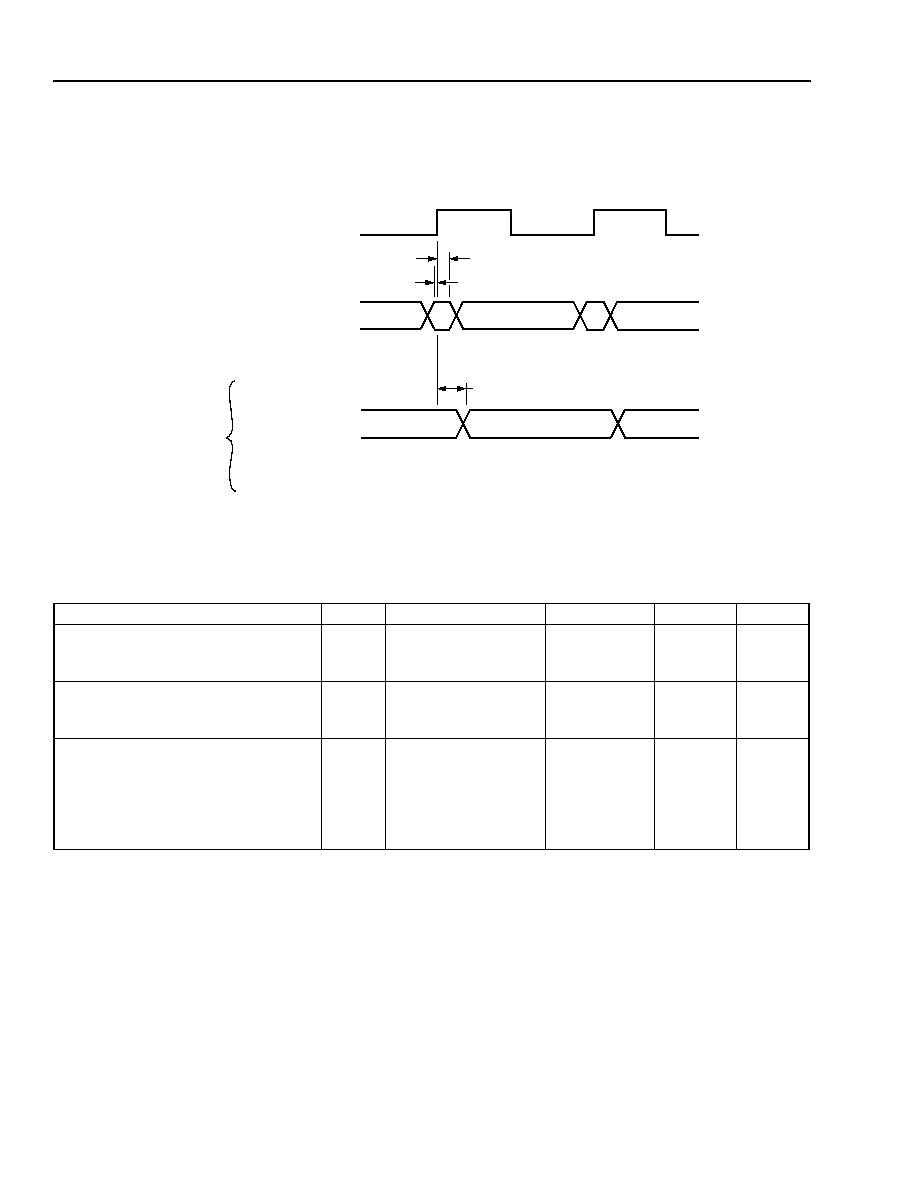

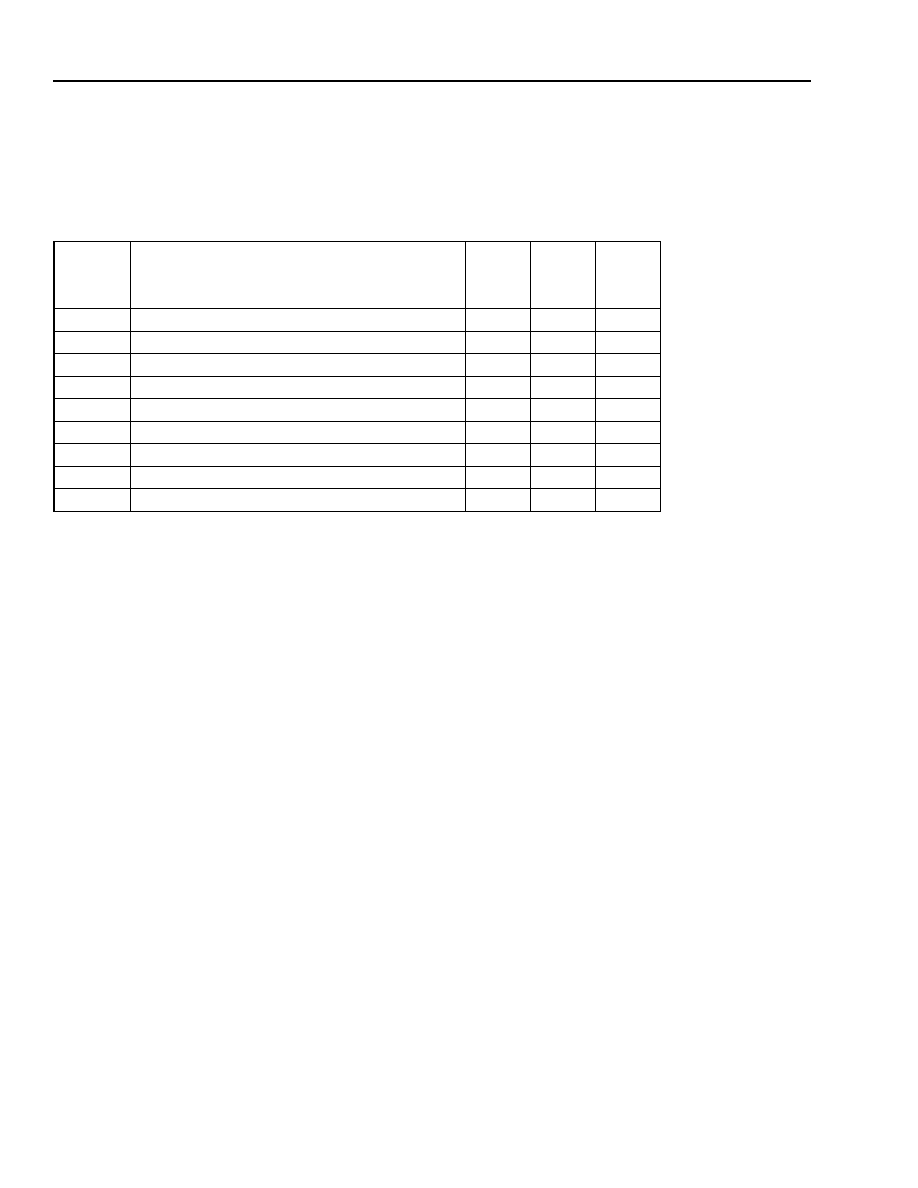

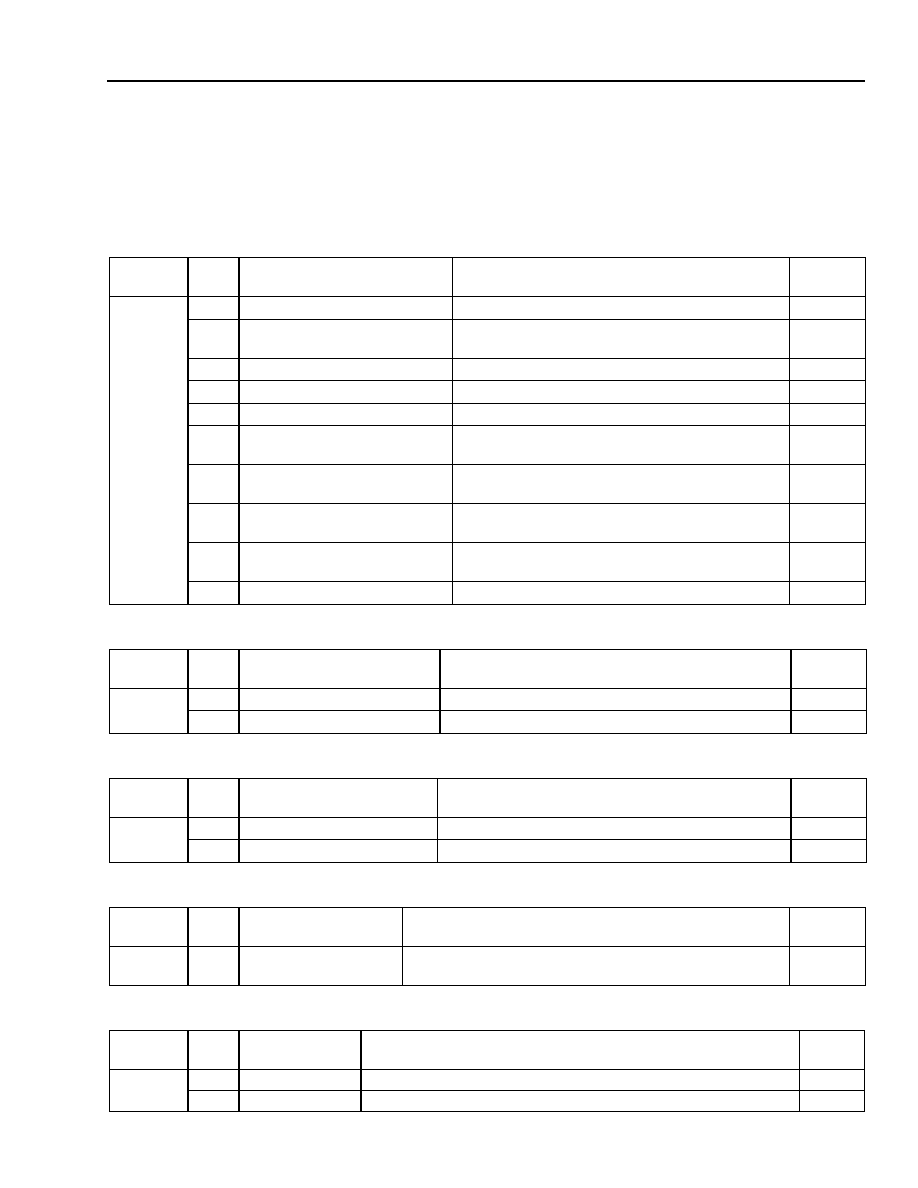

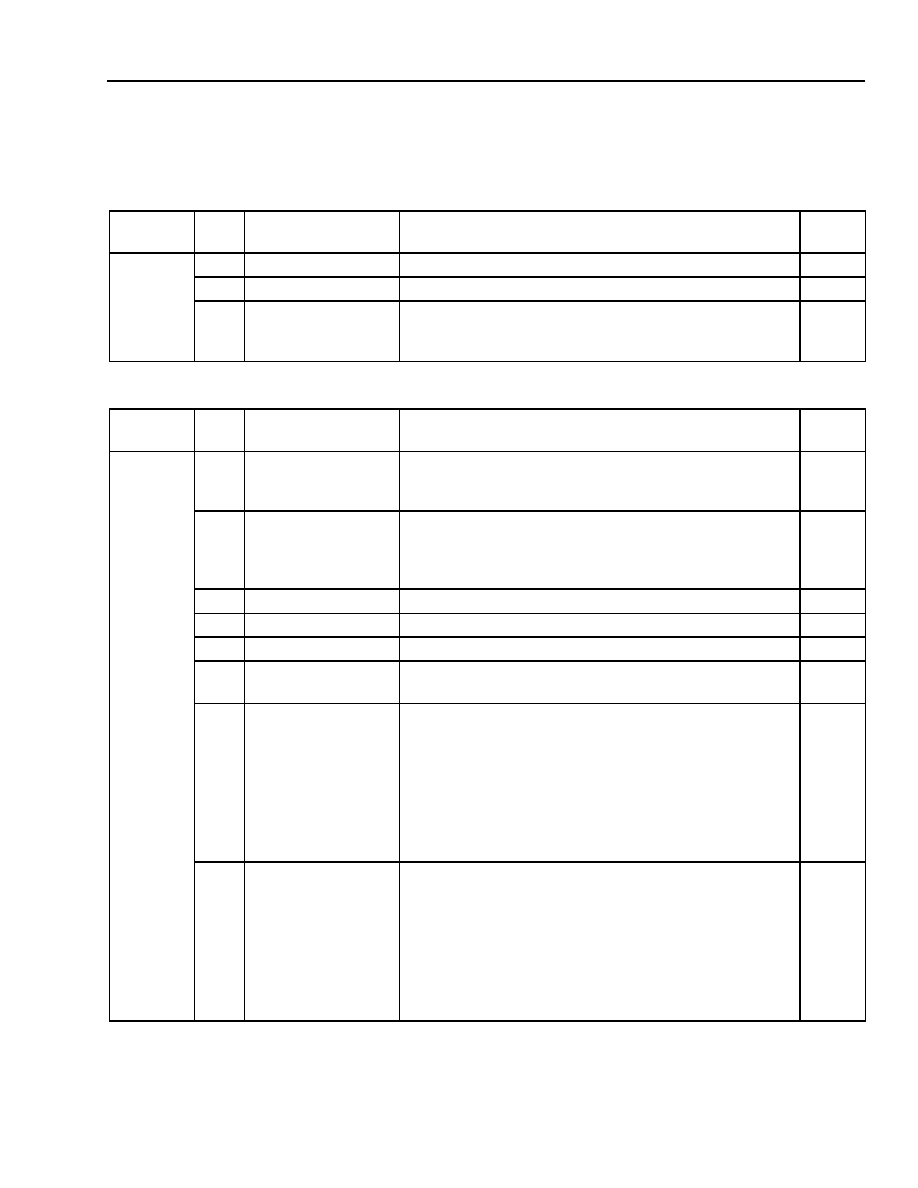

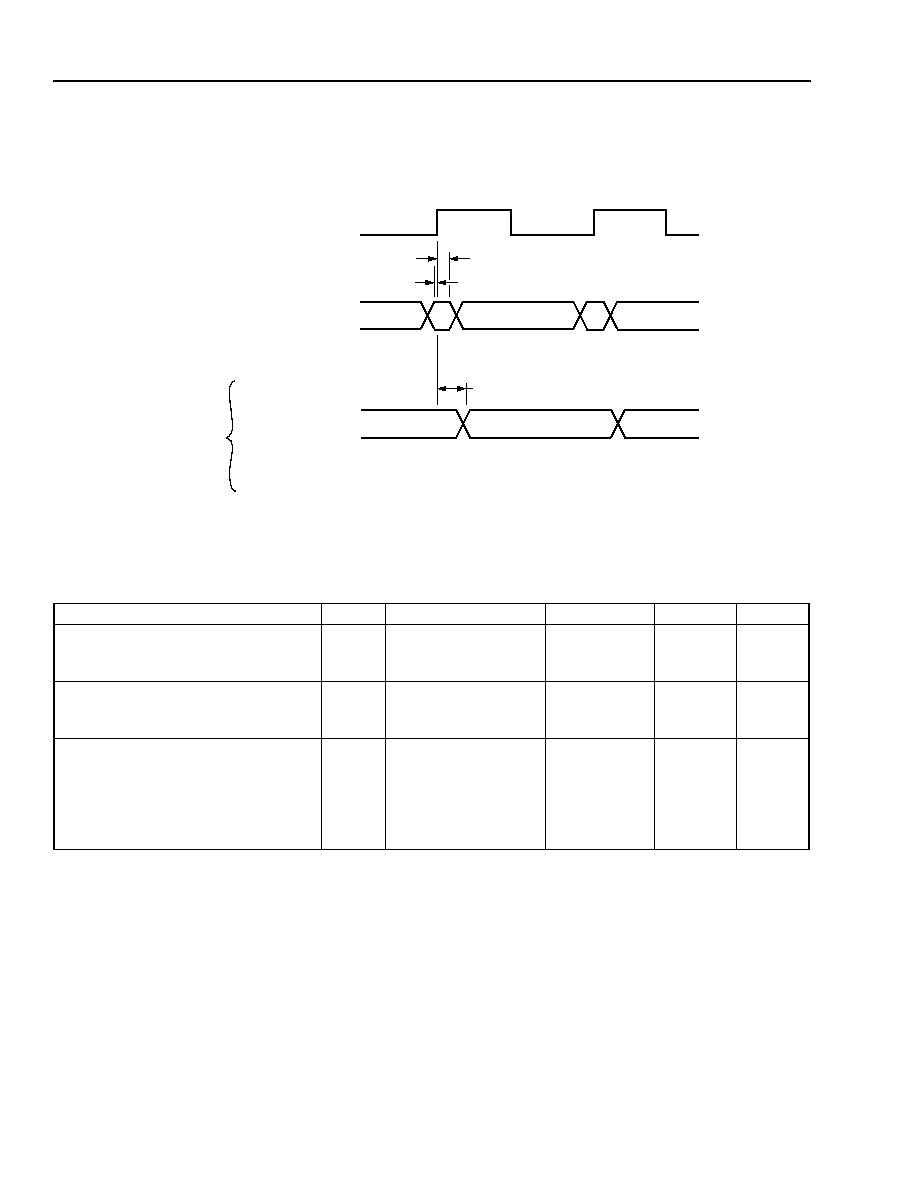

- Table 19. Microprocessor Interface Synchronous Write Cycle Specifications

- Table 20. Microprocessor Interface Synchronous Read Cycle Specifications

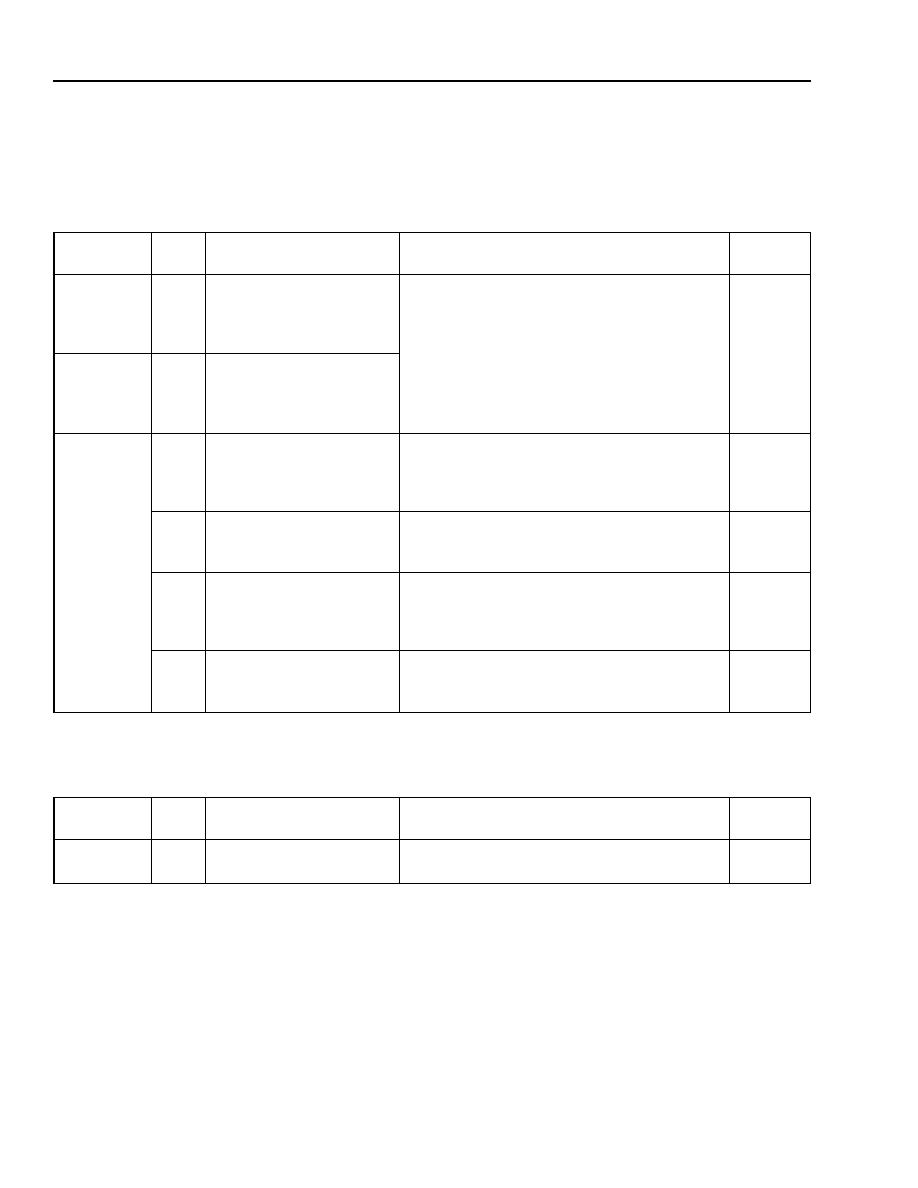

- Table 21. Microprocessor Interface Asynchronous Write Cycle Specifications

- Table 22. Microprocessor Interface Asynchronous Read Cycle Specifications

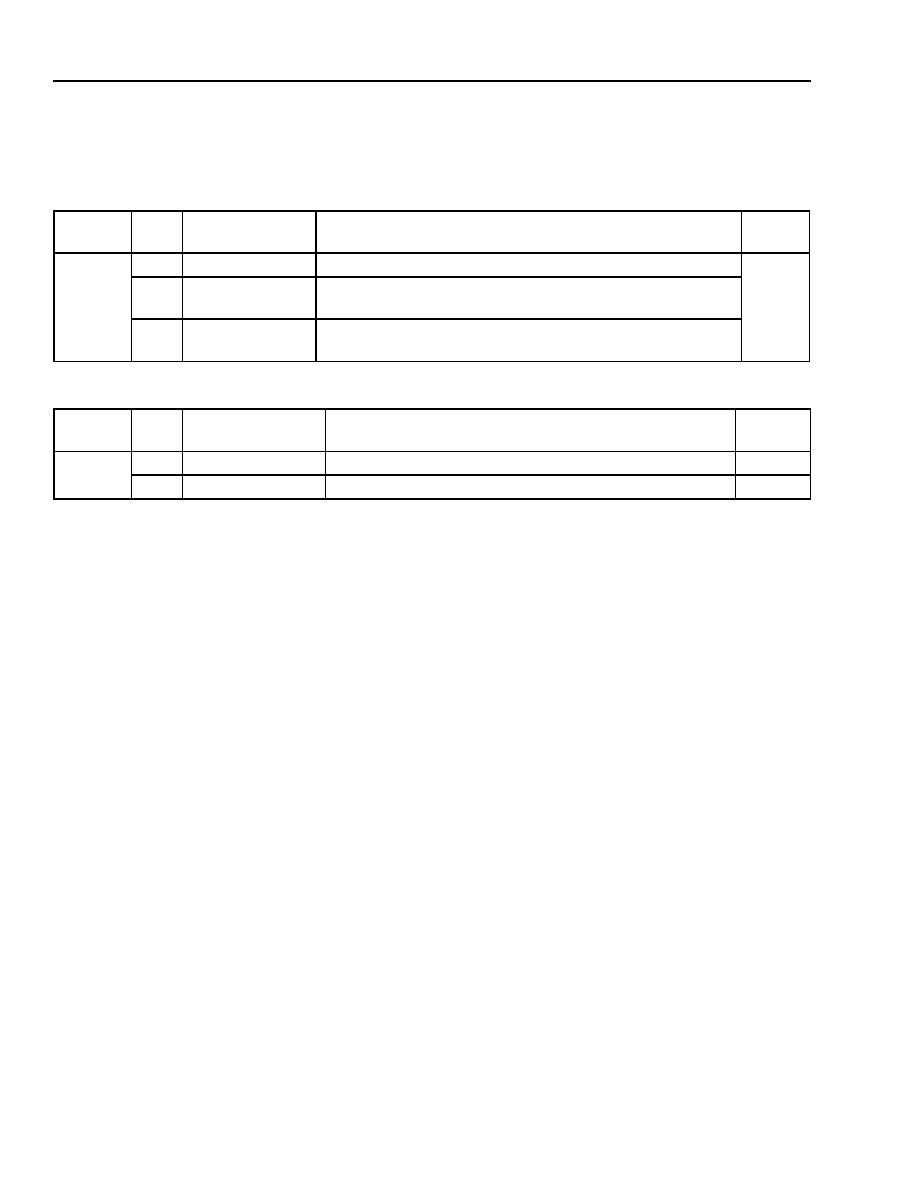

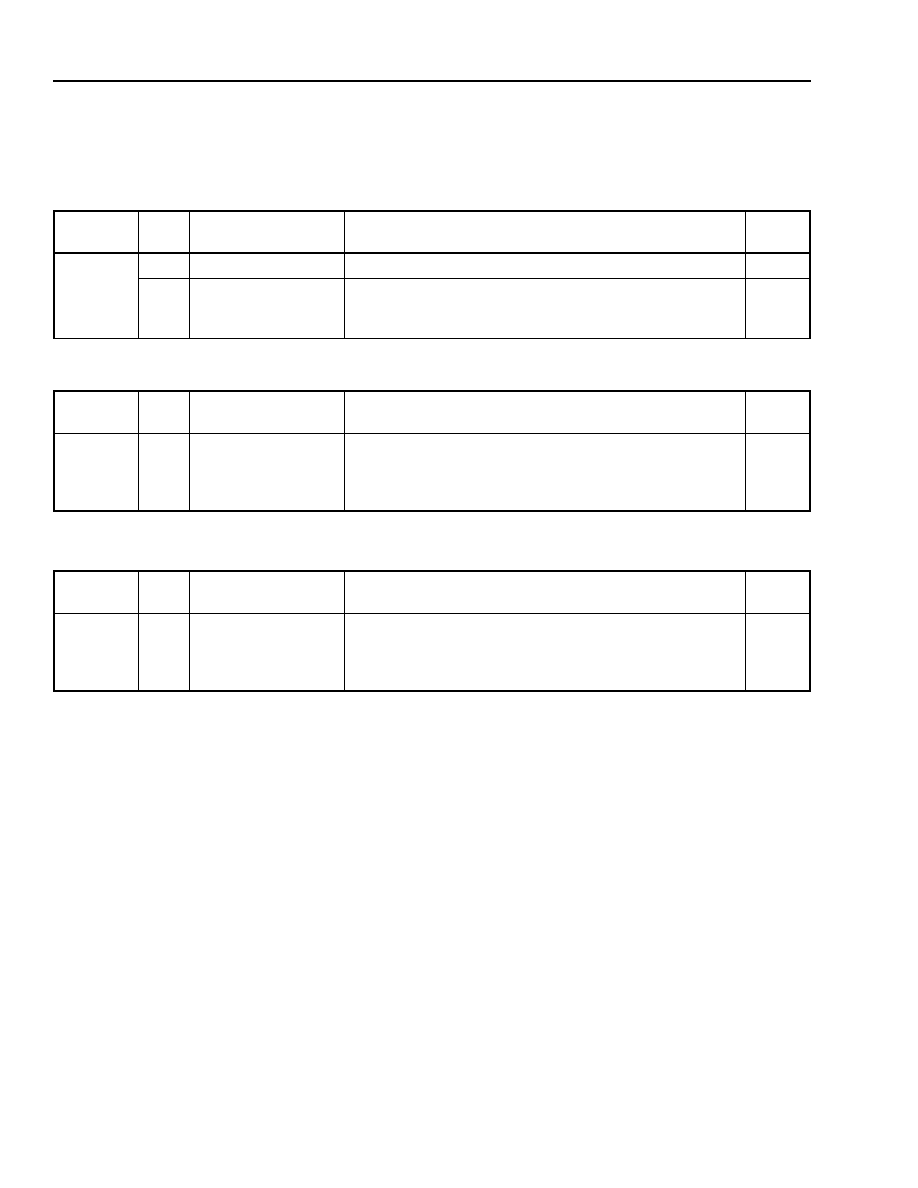

- Table 23. PM Reset Signal Provisioning

- Table 24. MPU_VERR[0-5], Version Control Registers (RO)

- Table 25. MPU_ISR, Interrupt Status Register (RO or COR/W)

- Table 26. MPU_CNDR, Condition Register (RO)

- Table 27. MPU_IMR, Interrupt Mask Register (R/W)

- Table 28. MPU_ICLRR, Interrupt Clear Register (R/W)

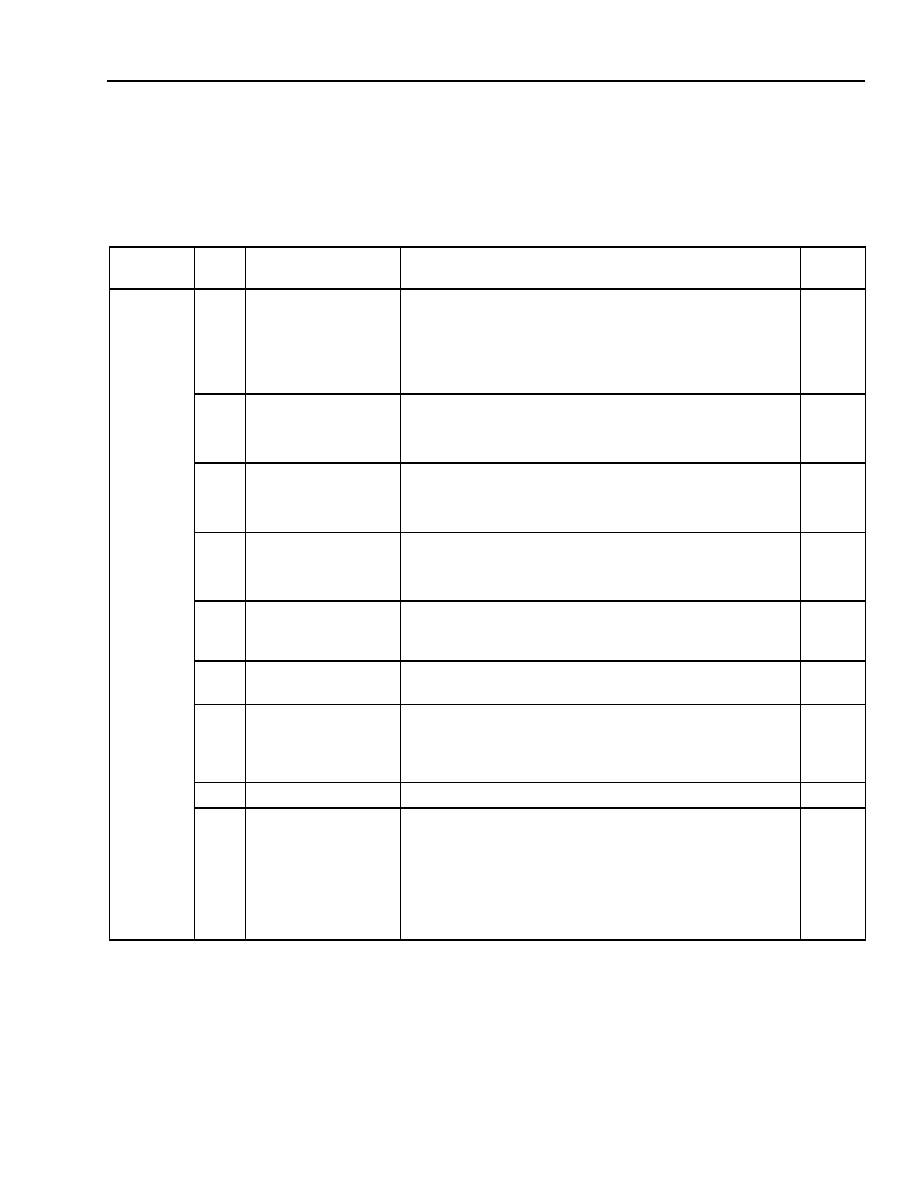

- Table 29. MPU_SWRSR, Software Reset Register (R/W)

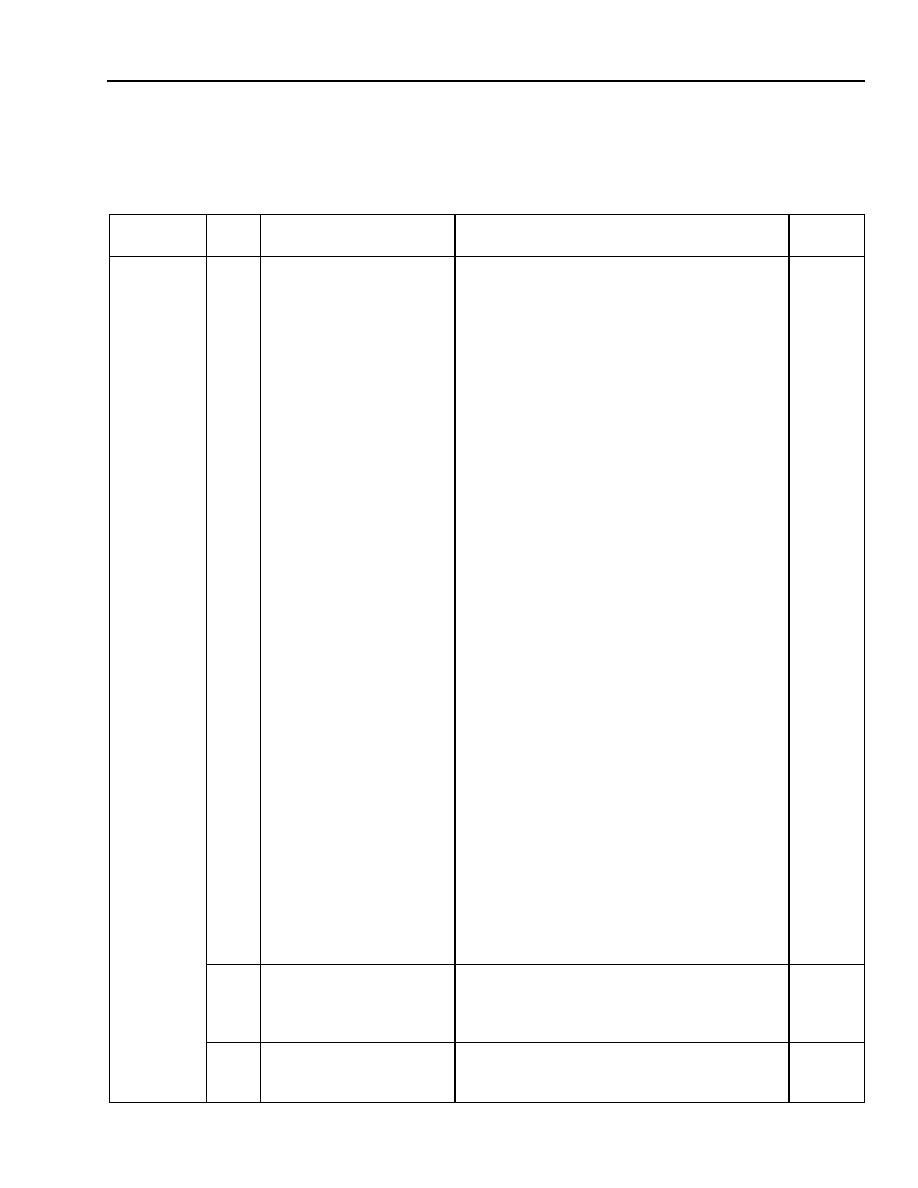

- Table 30. MPU_GPIO_CTLR, GPIO Output Value (R/W)

- Table 31. MPU_PROVISION0, Provisioning Register 0 (R/W)

- Table 32. MPU_PROVISION1, Provisioning Register 1 (R/W)

- Table 33. MPU_LPBKCTLR, Loopback Control Register (R/W)

- Table 34. MPU_GPIOCFG, GPIO Configuration Register (R/W)

- Table 35. MPU_GPIO_OER[1-2], GPIO Output Enable (R/W)

- Table 36. MPU_PDN1, Powerdown Register 1 (R/W)

- Table 37. MPU_PDN2, Powerdown Register 2 (R/W)

- Table 38. MPU_PDN3, Powerdown Register 3 (R/W)

- Table 39. MPU_SCRATCHR, Scratch Register (R/W)

- Table 40. MPU_TDAT16_MODER, MARS2G5 P-Pro Mode Selection Register (R/W)

- Table 41. MPU_LI_MODER, Register (R/W)*

- Table 42. MPU_HSI_TST_CTL, High-Speed Interface Control

- Table 43. MPU_HSI_LPBKR, High-Speed Interface Loopback Register

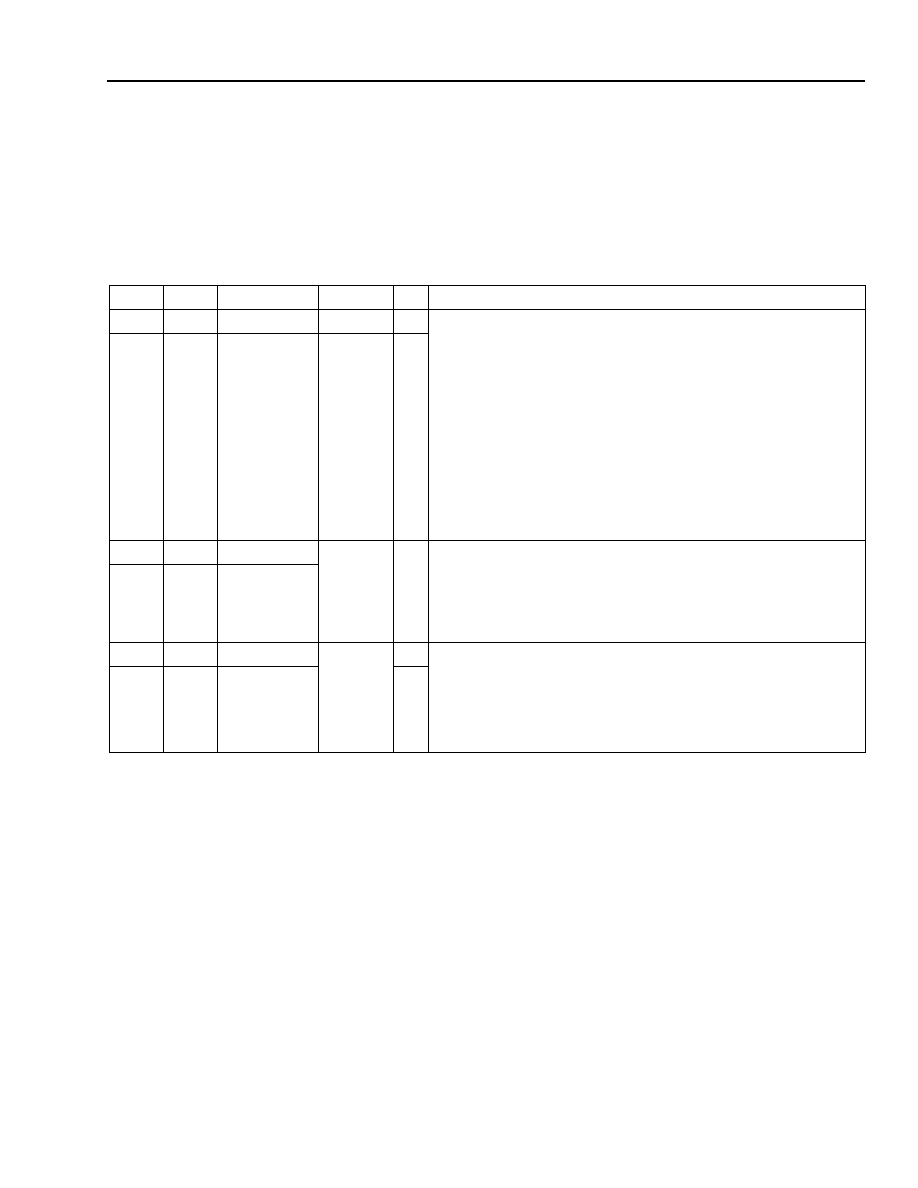

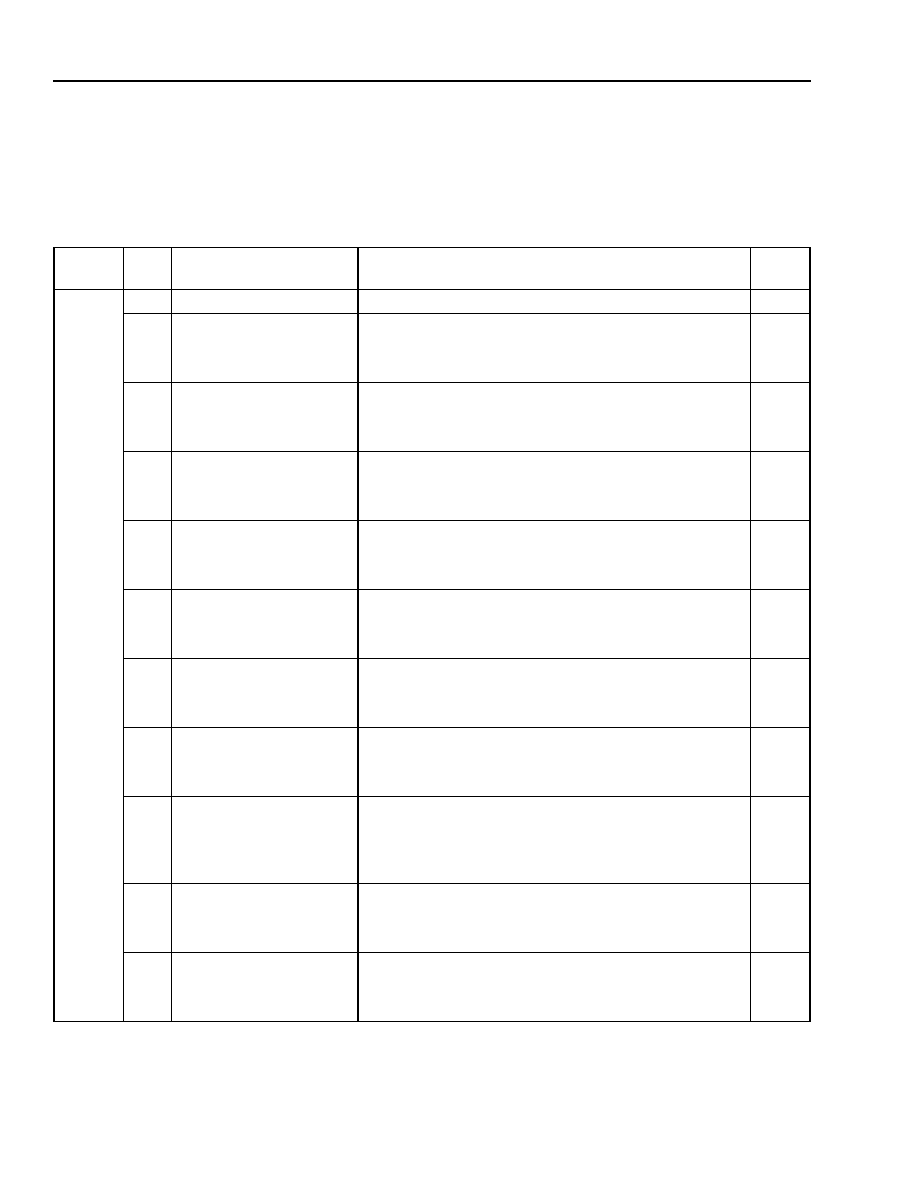

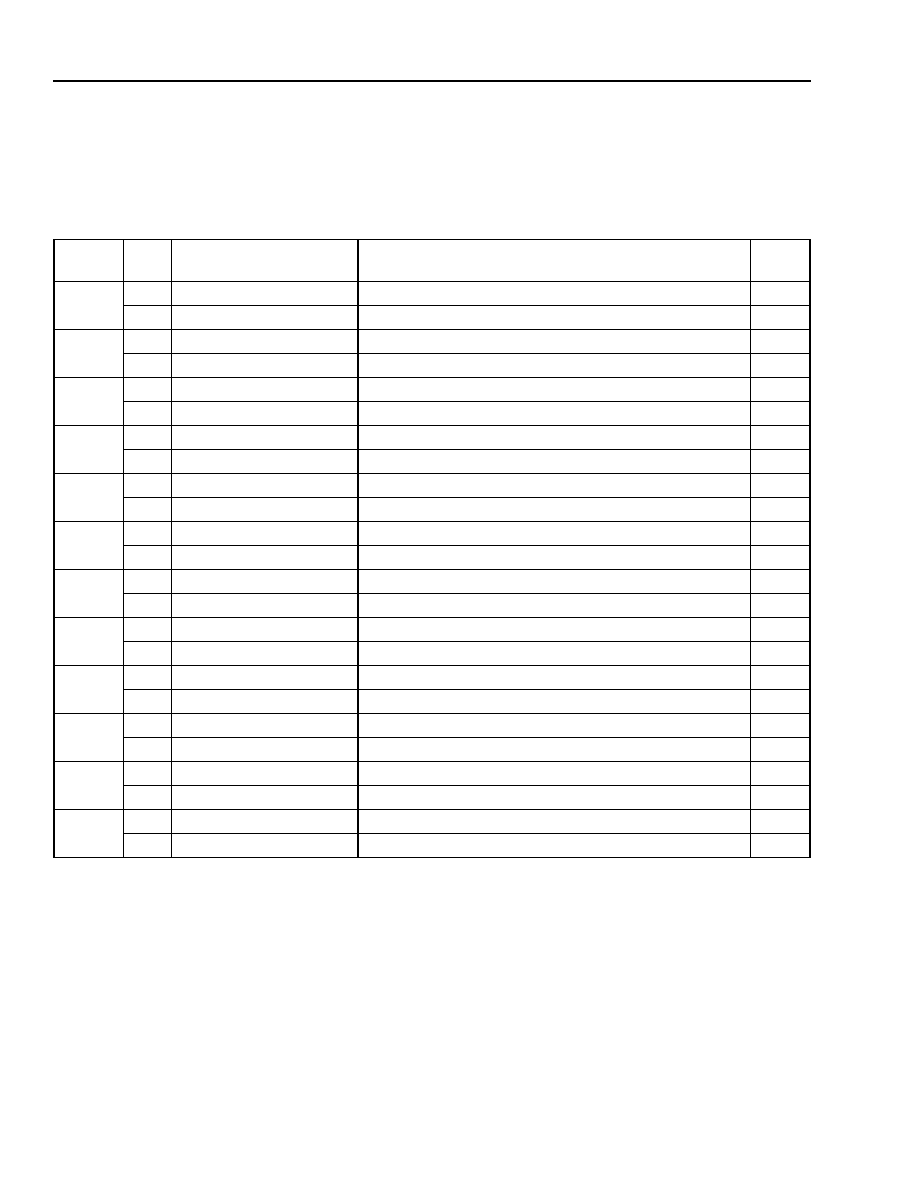

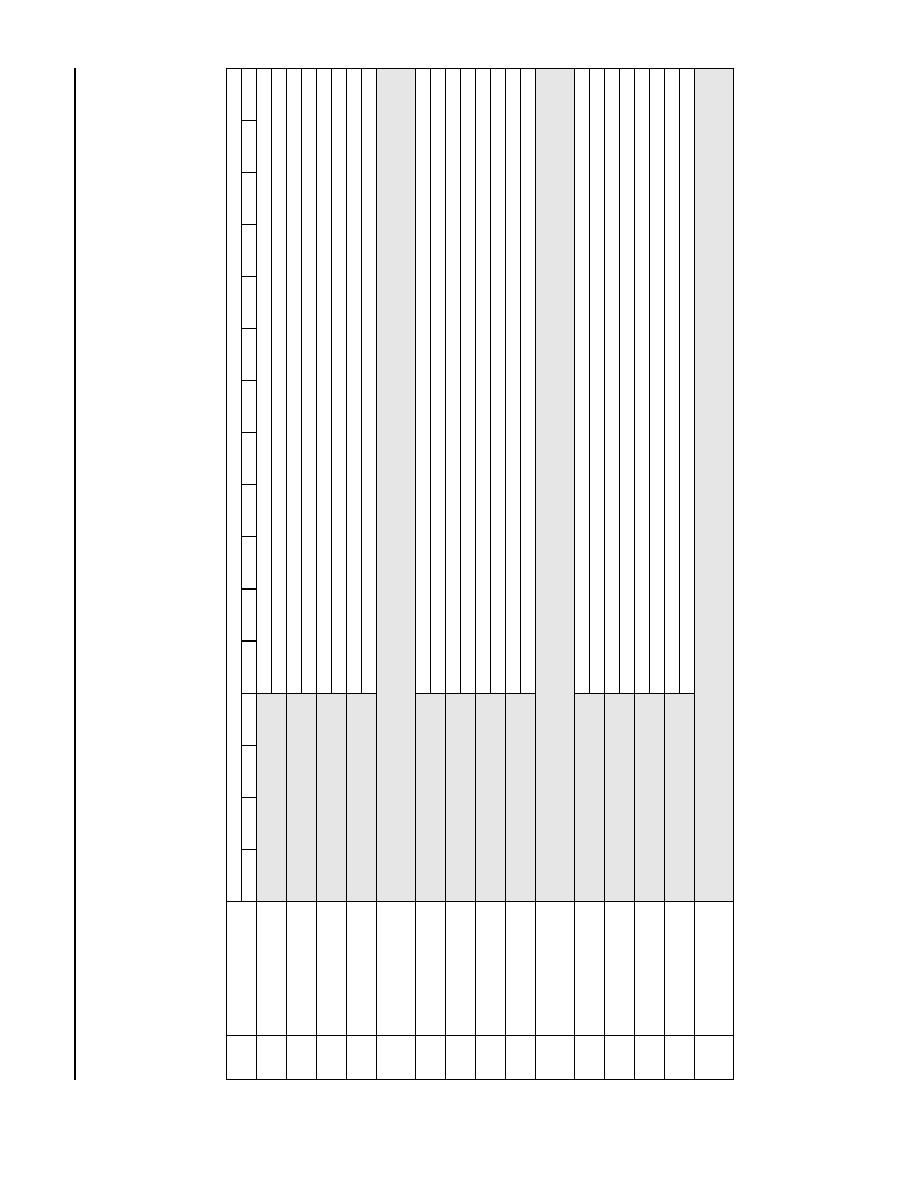

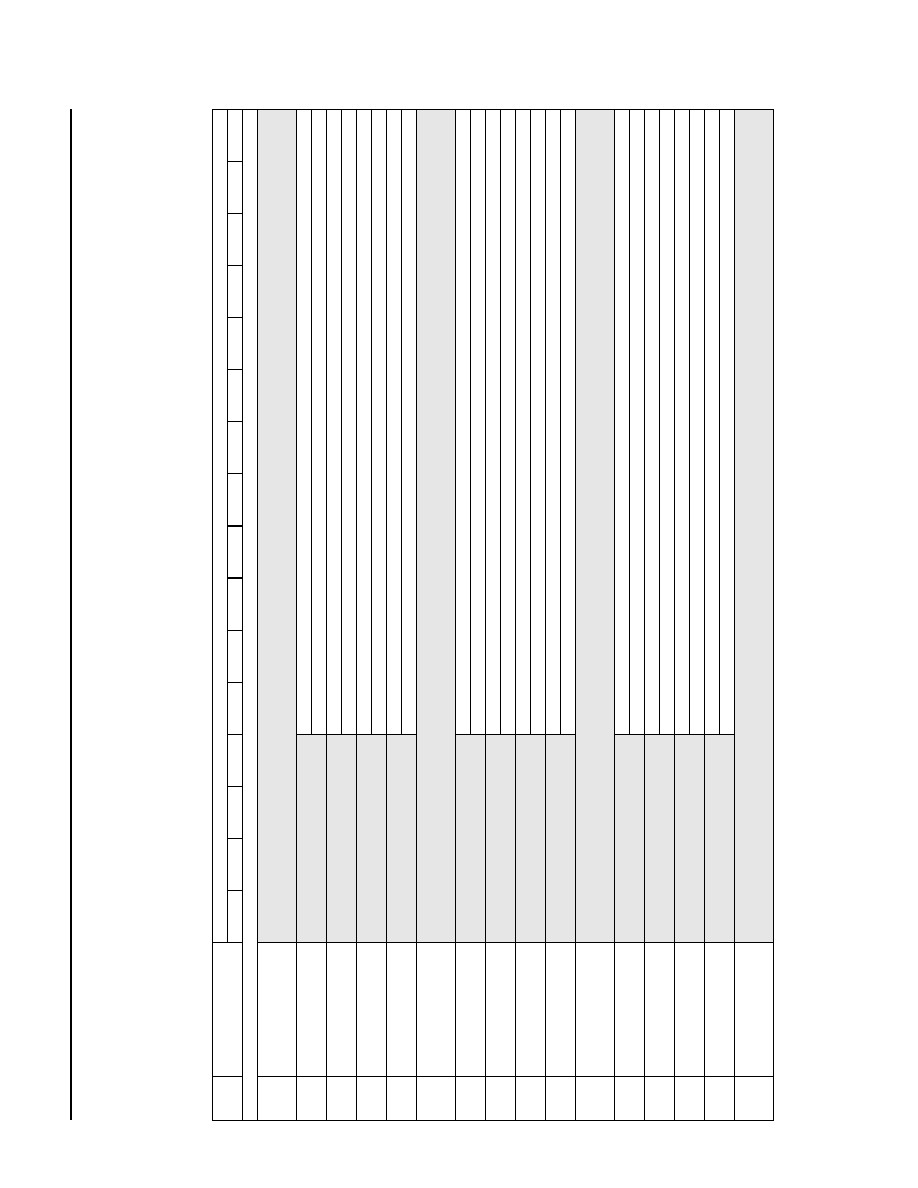

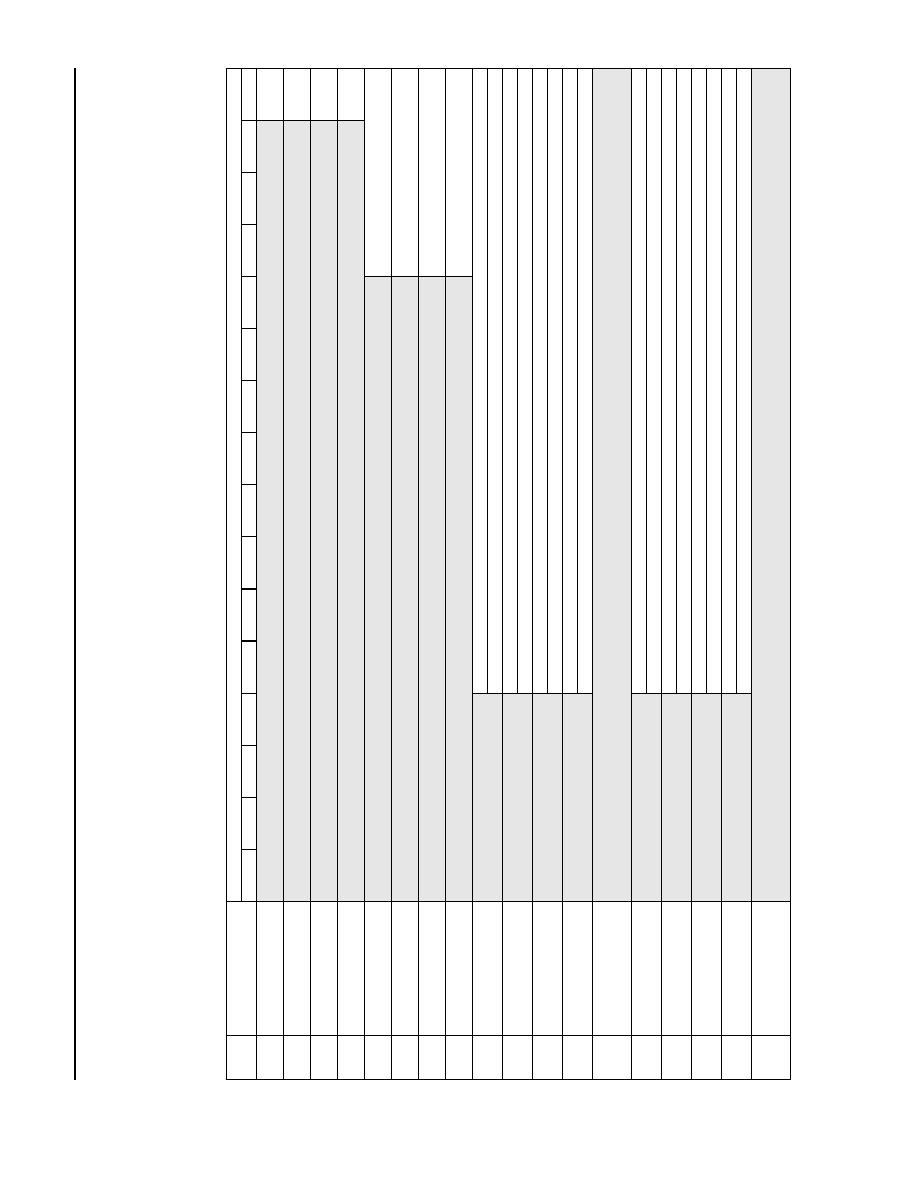

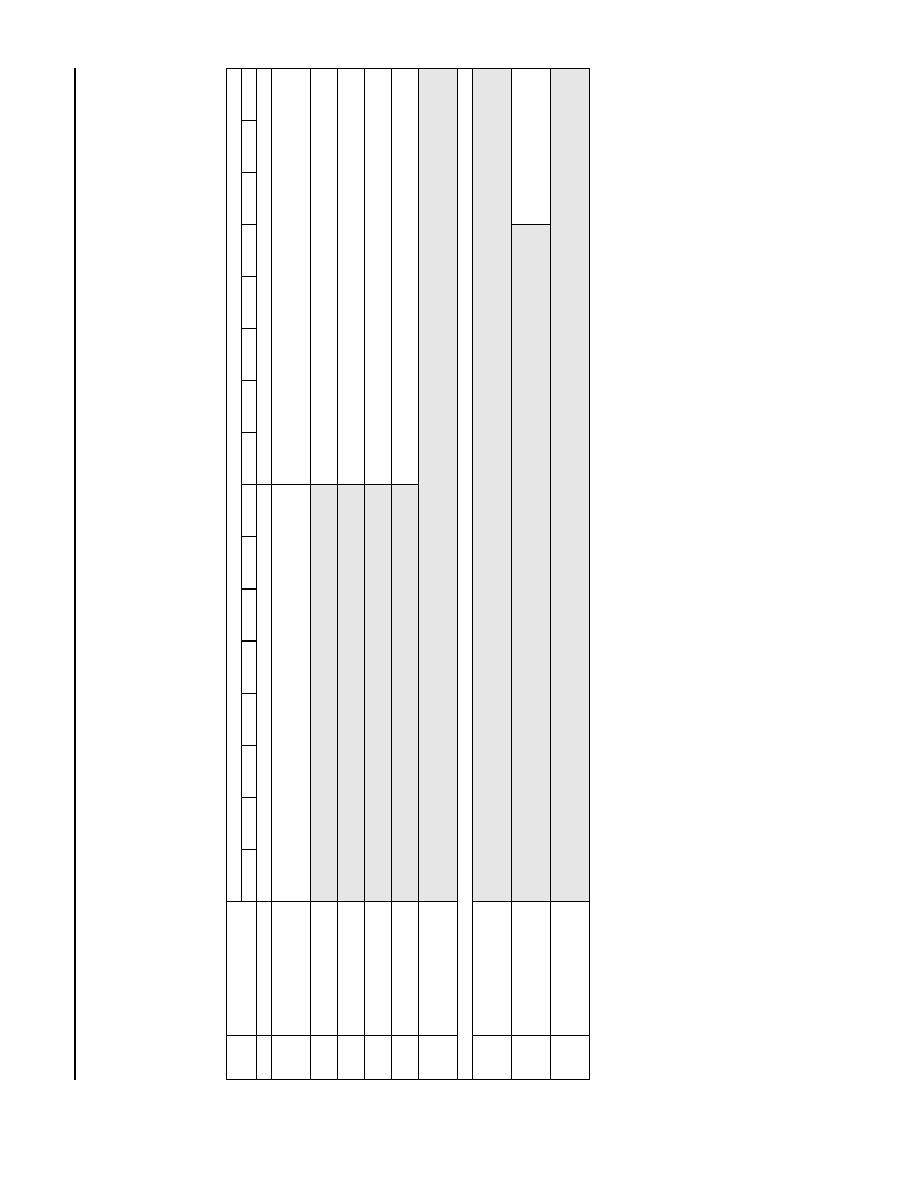

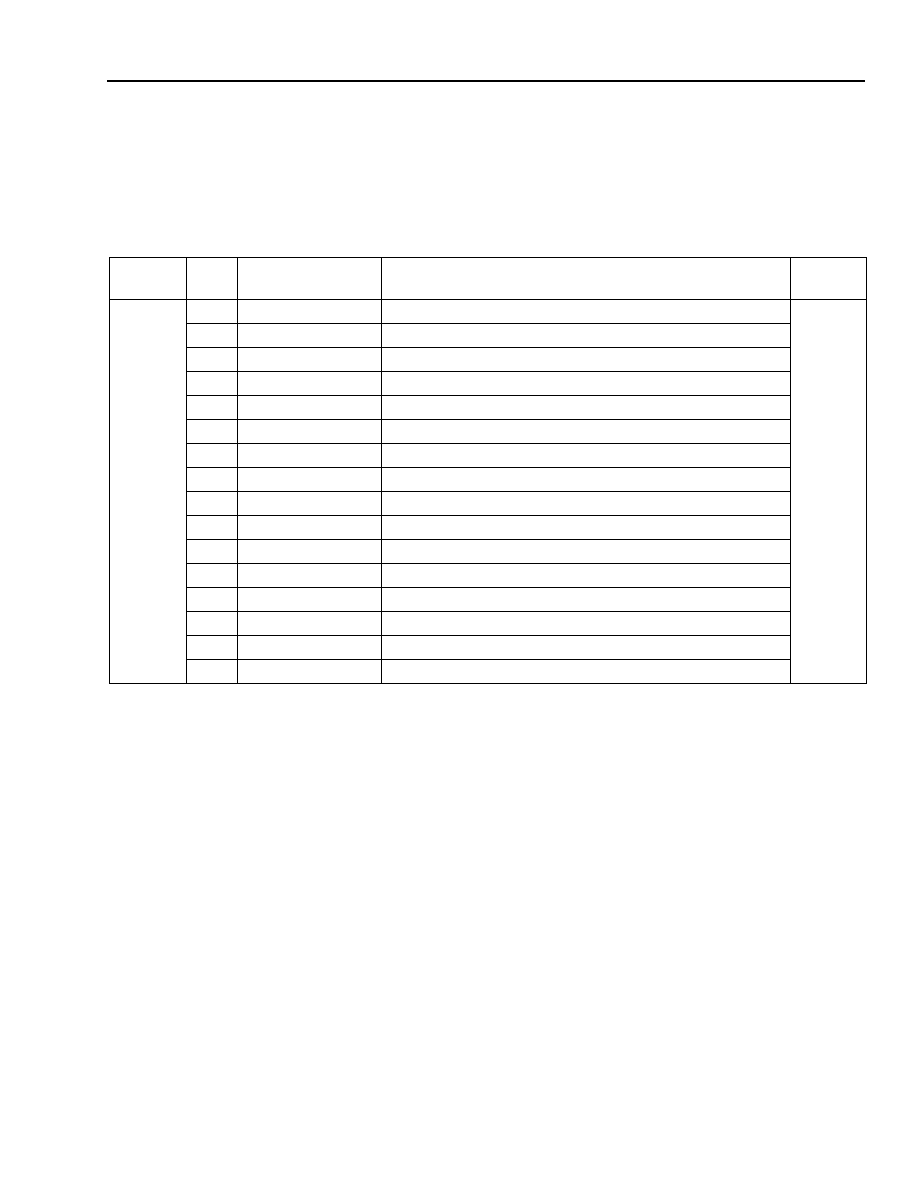

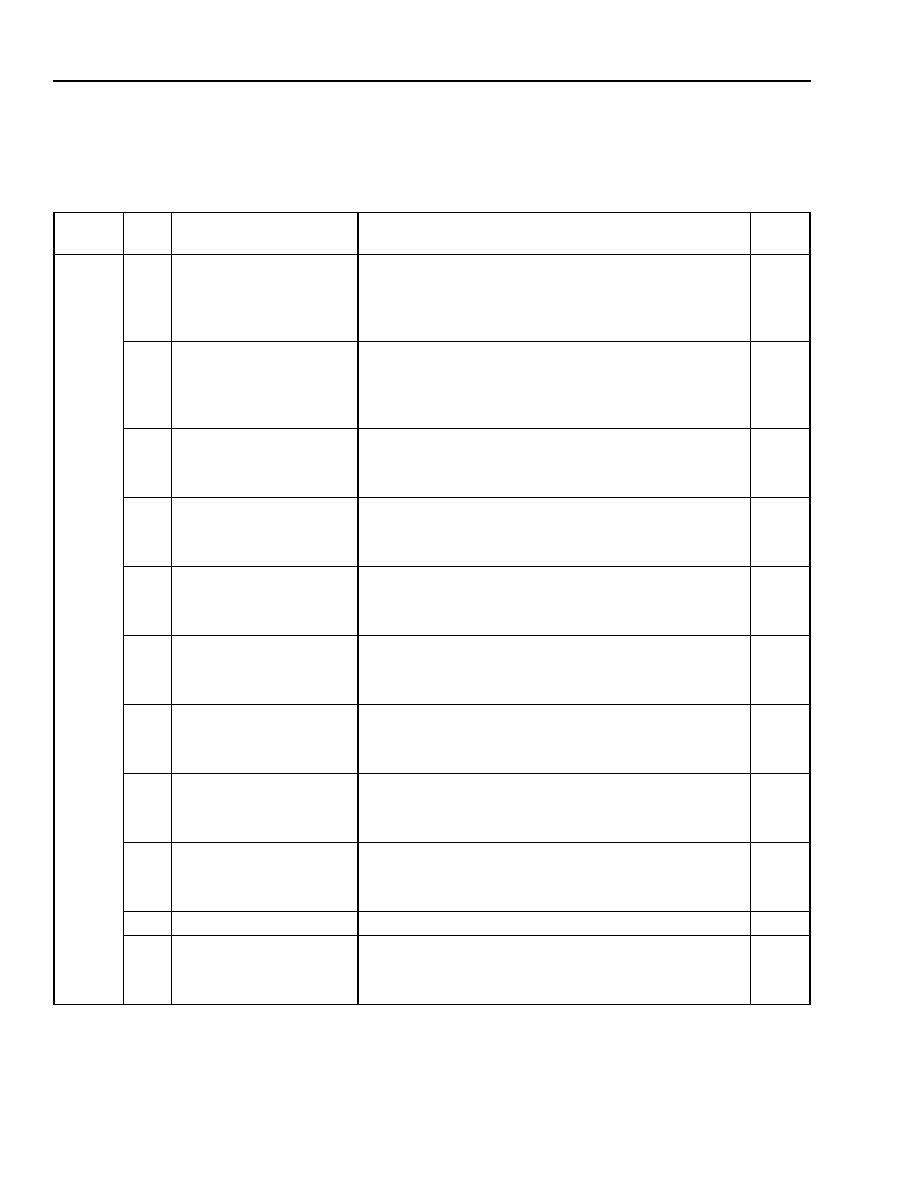

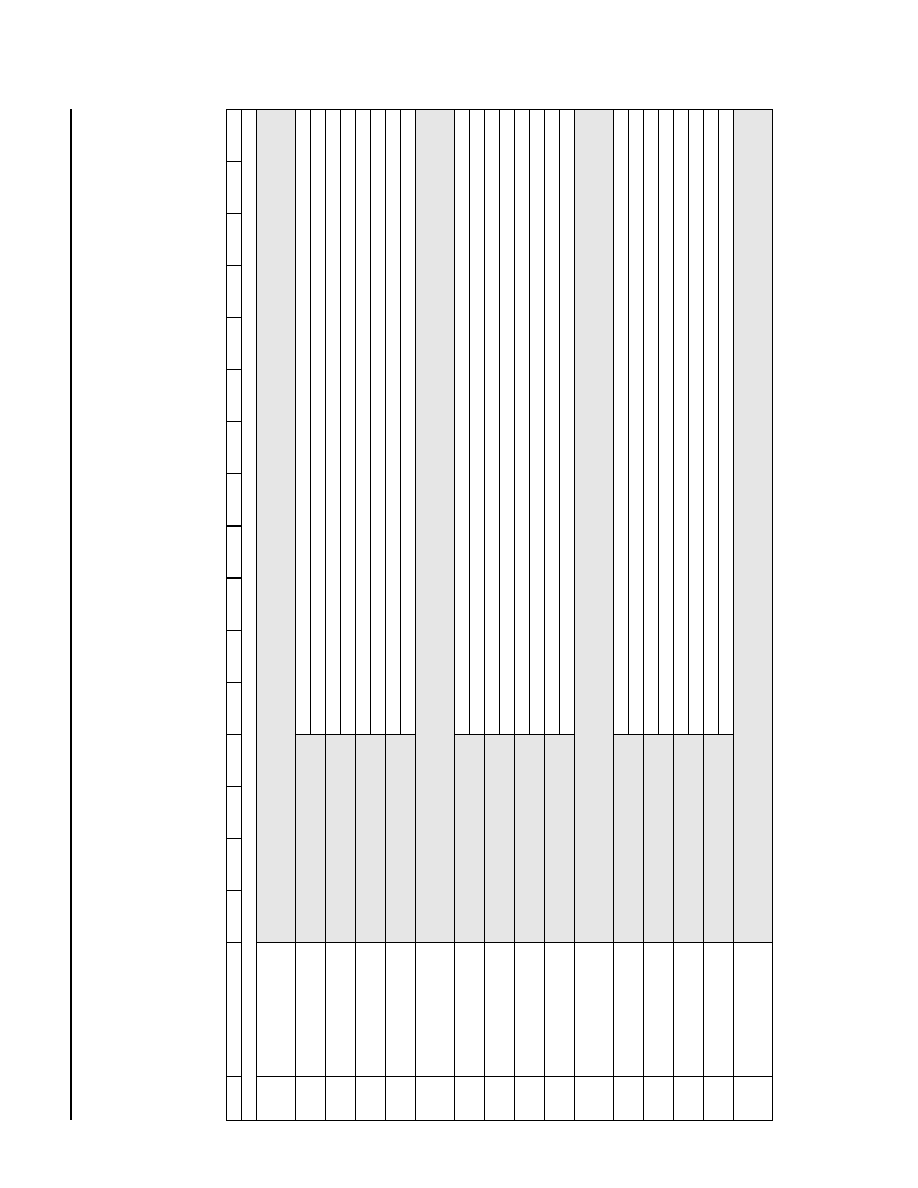

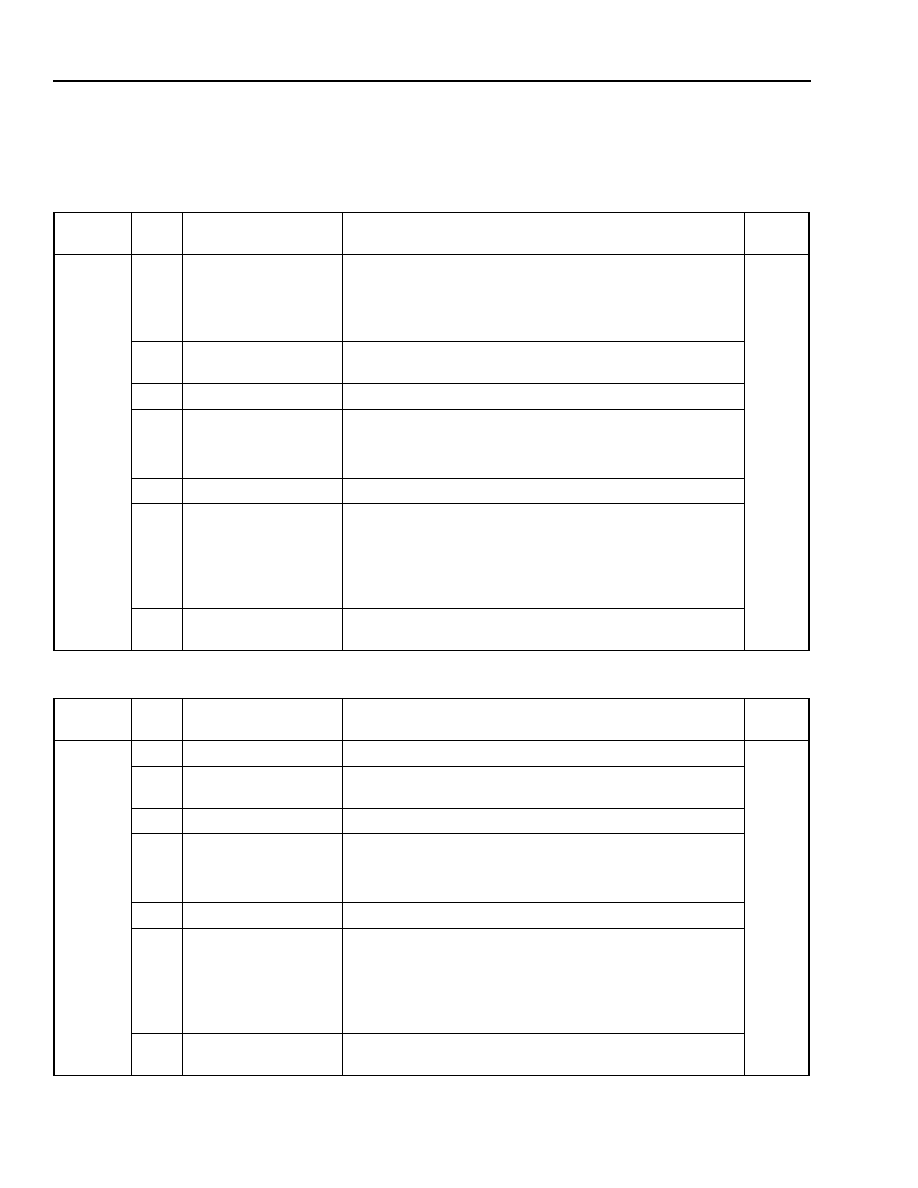

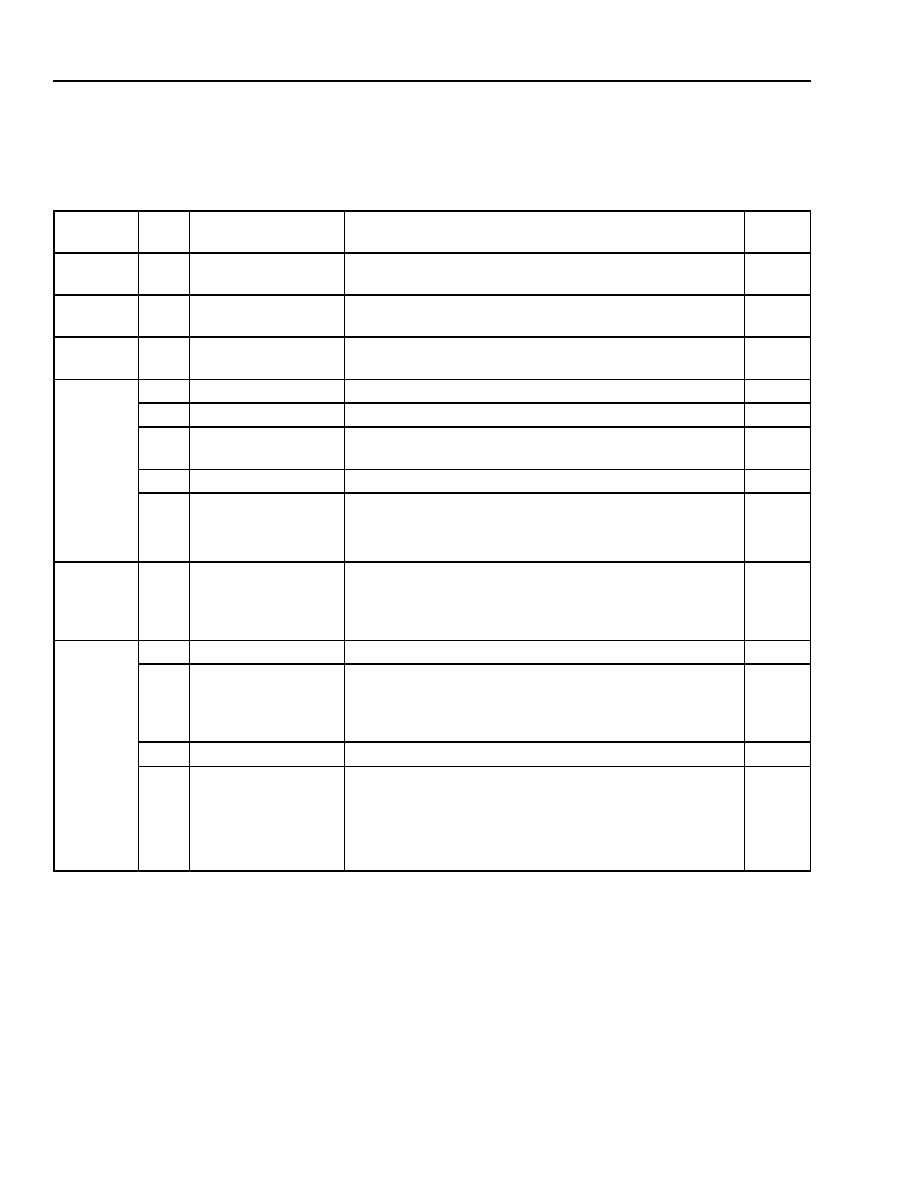

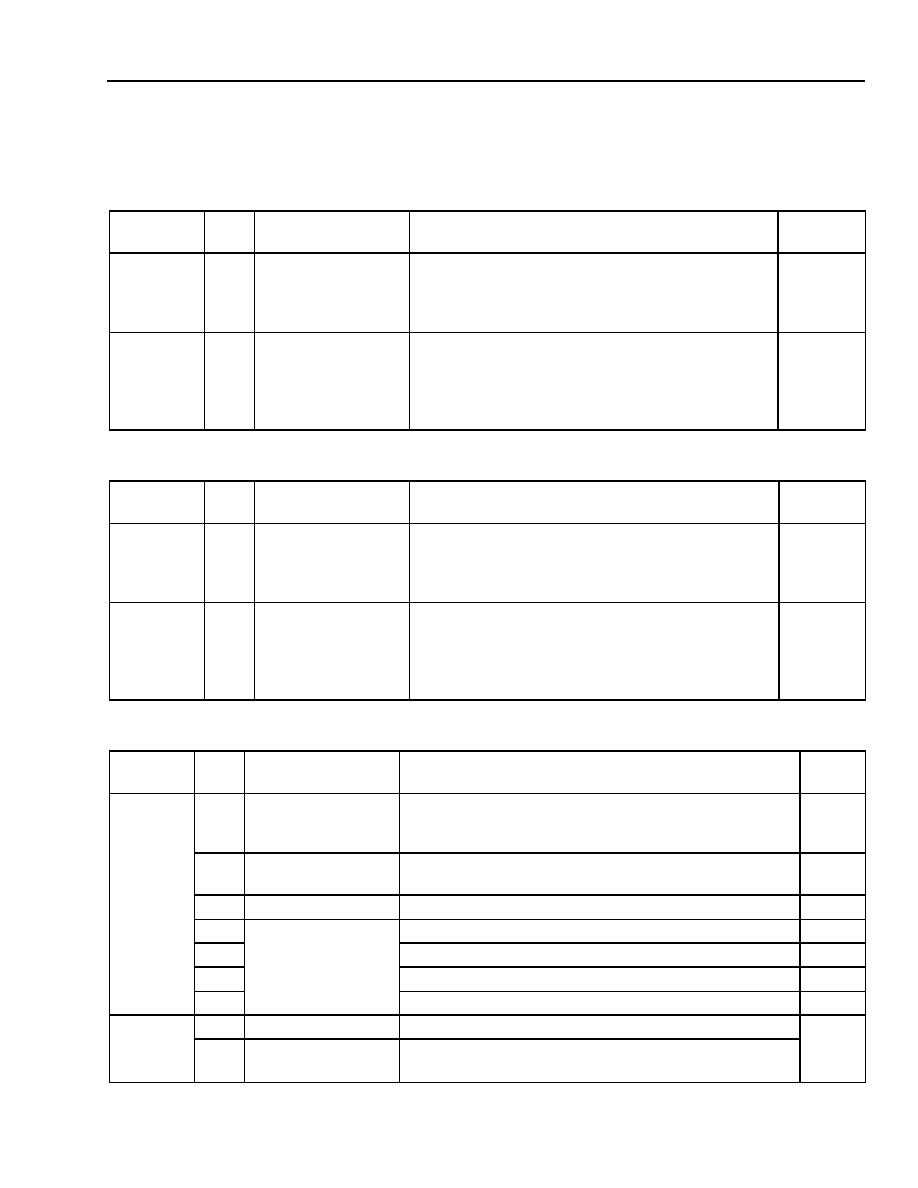

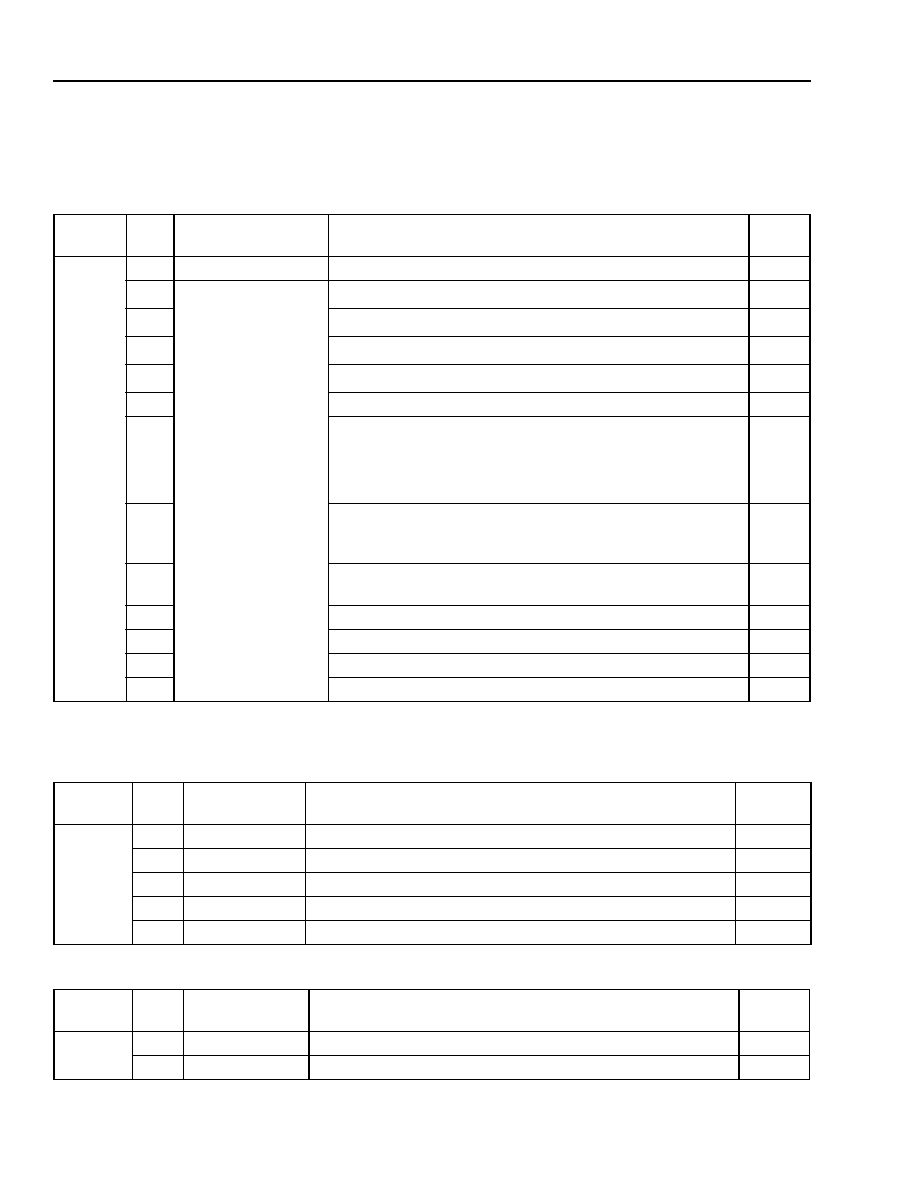

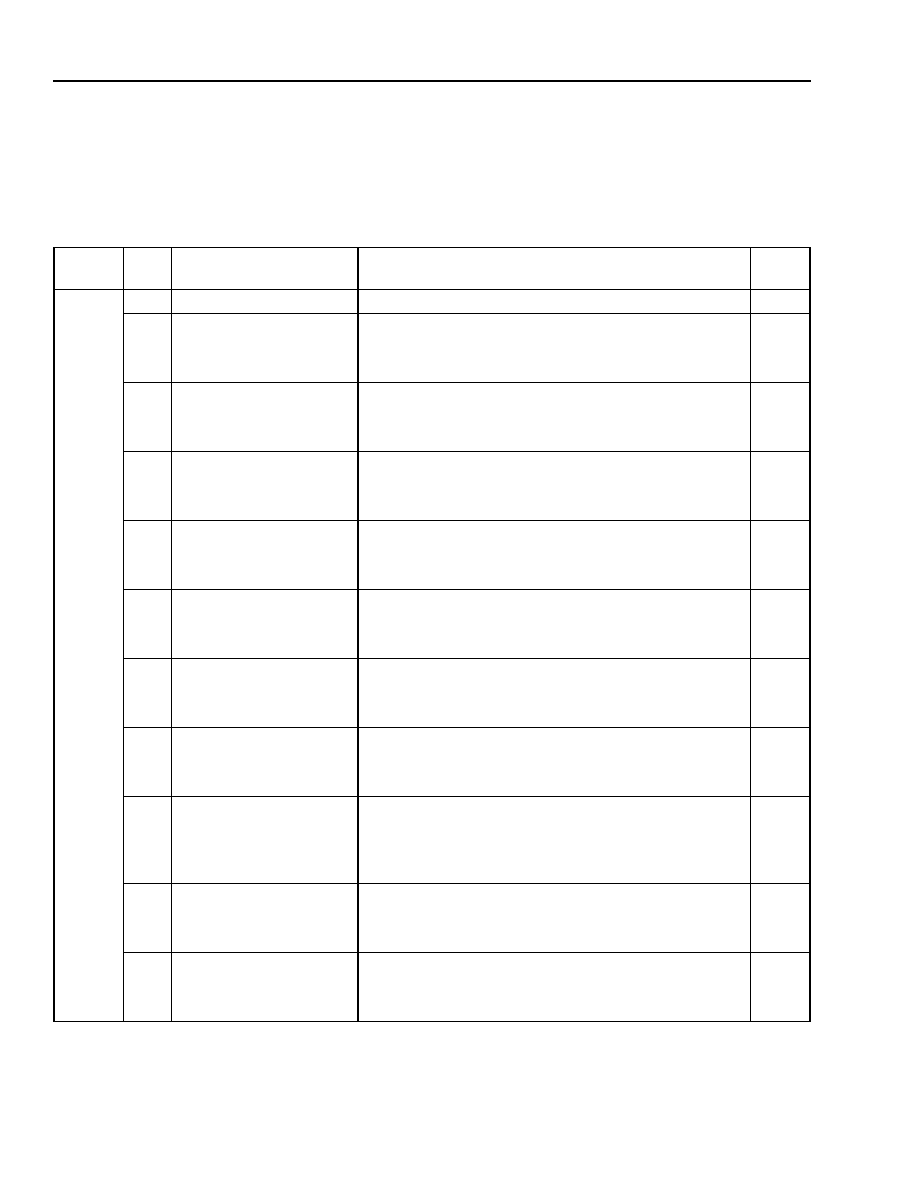

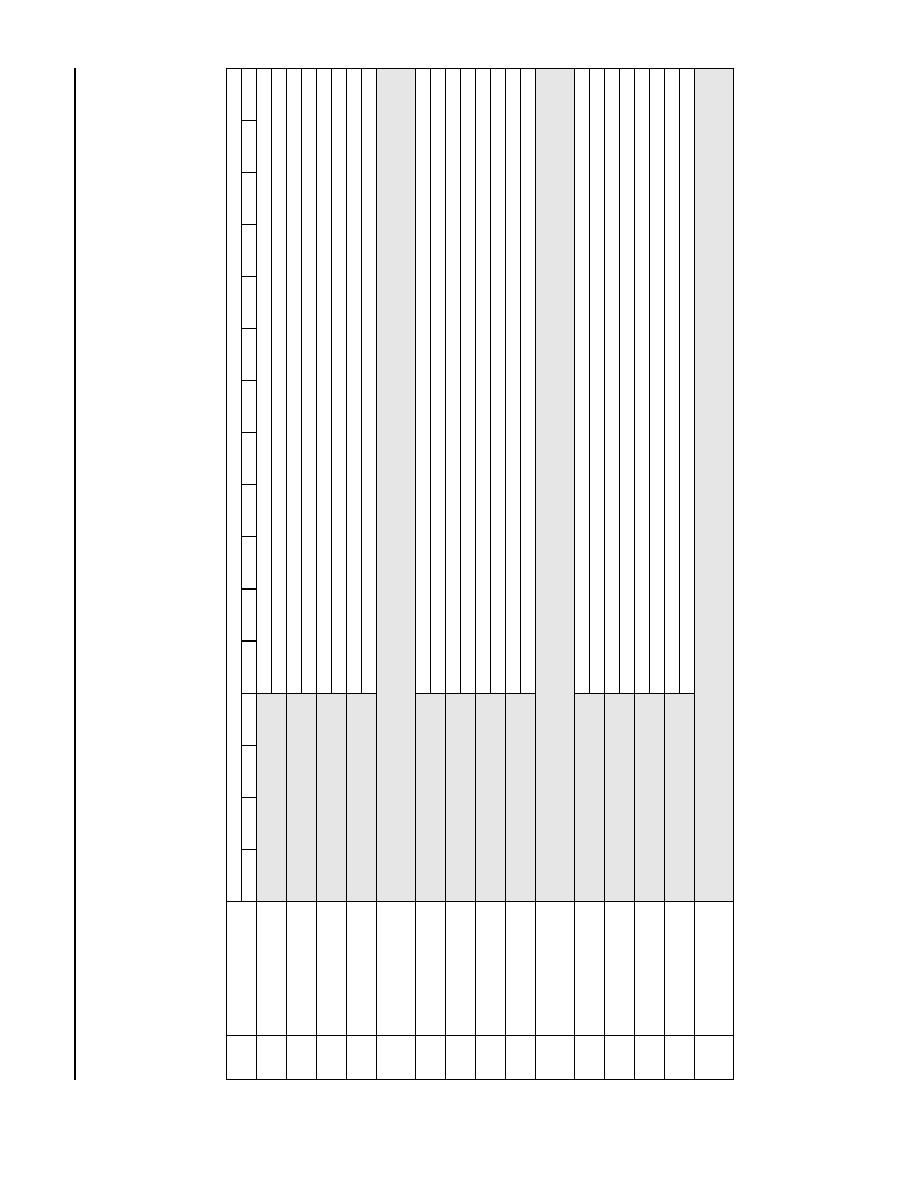

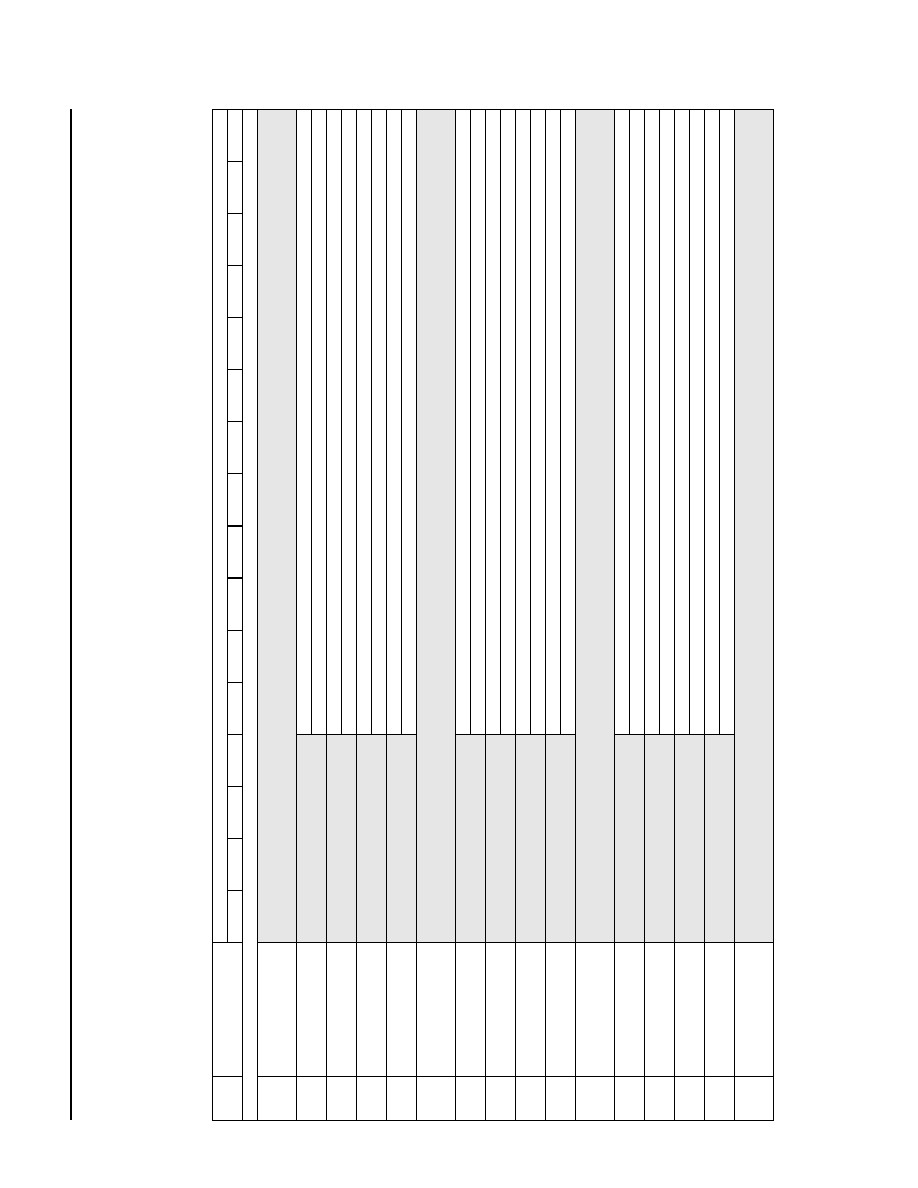

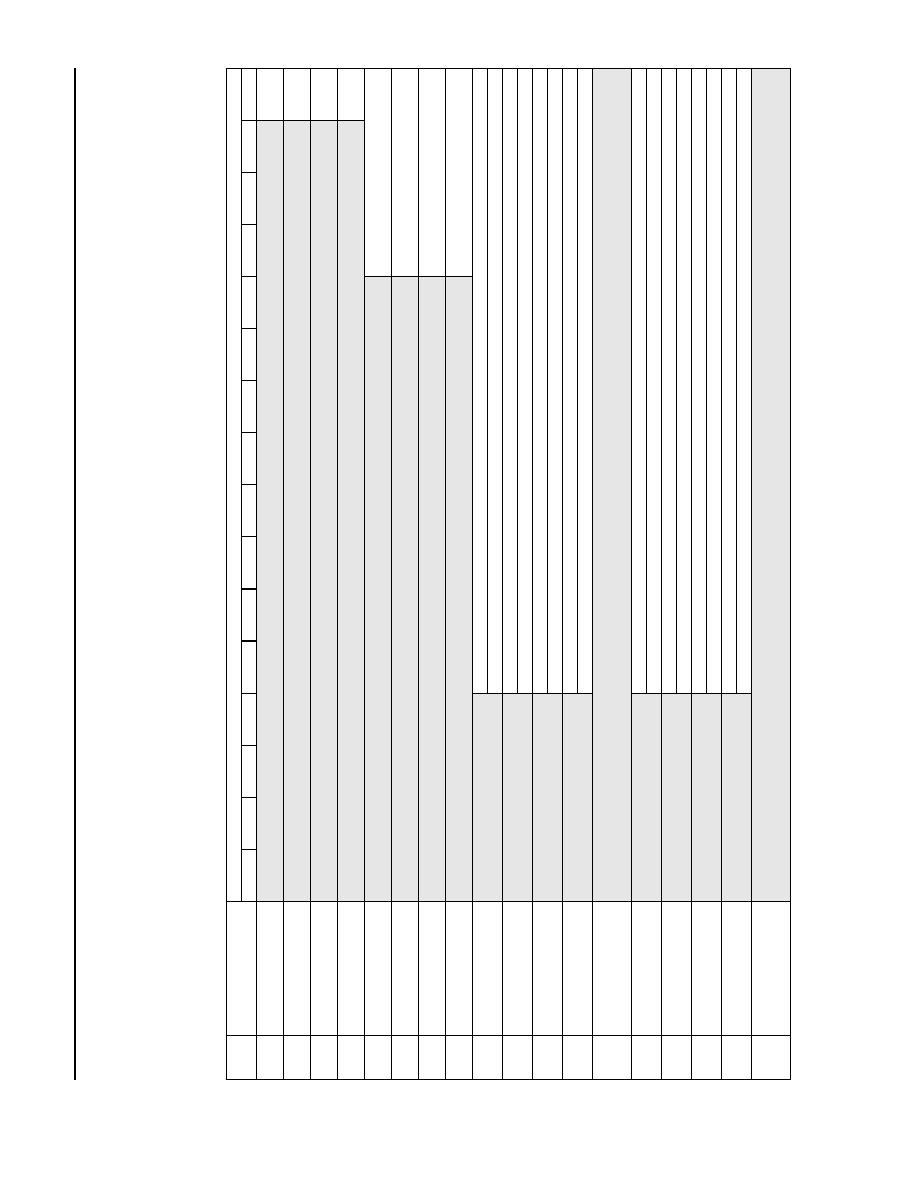

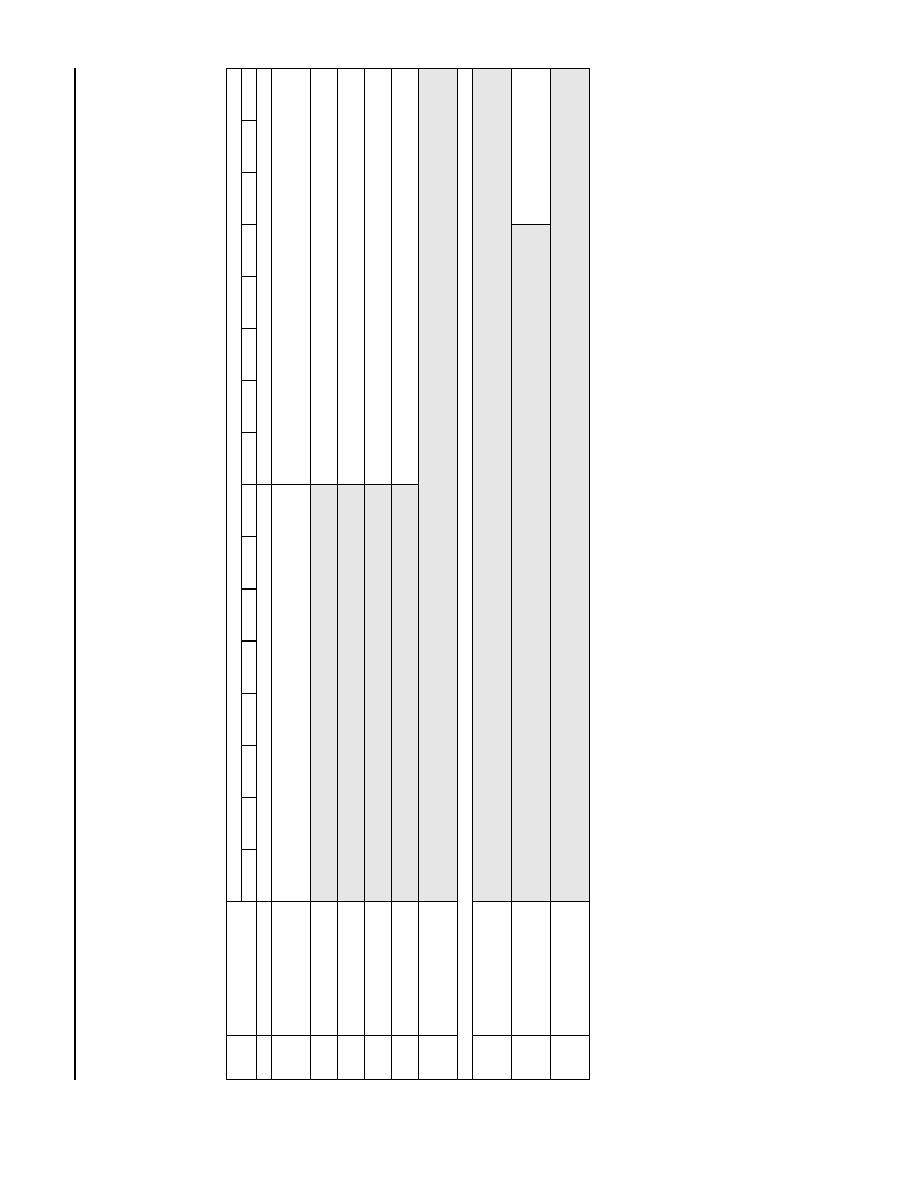

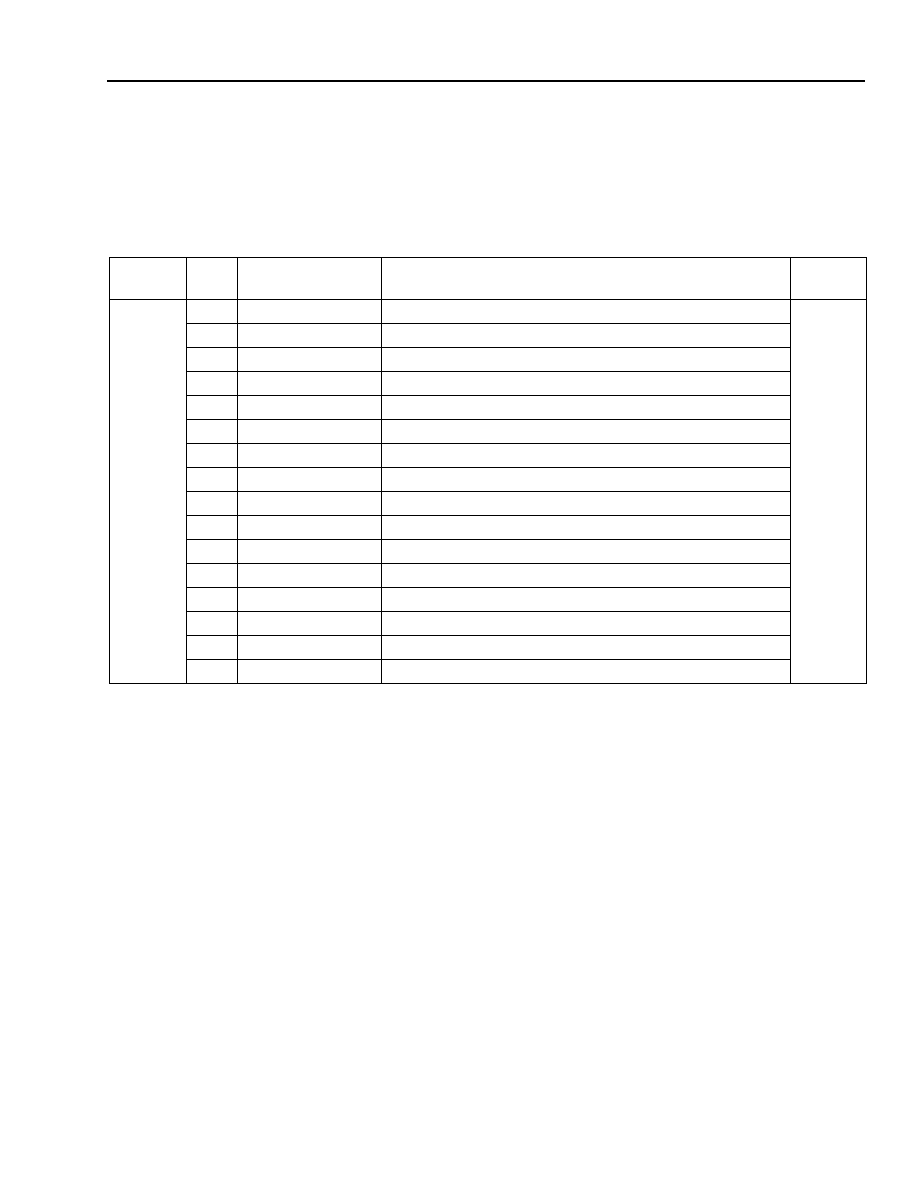

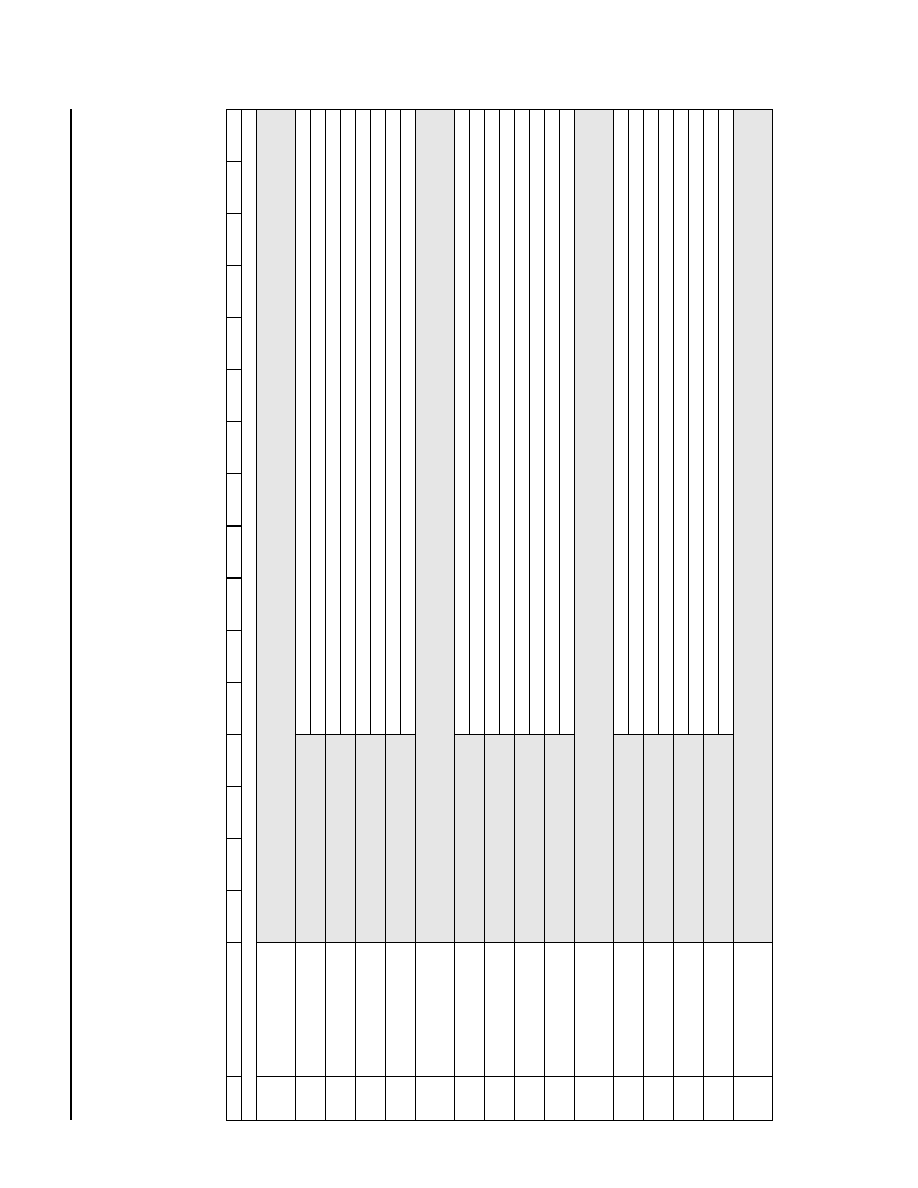

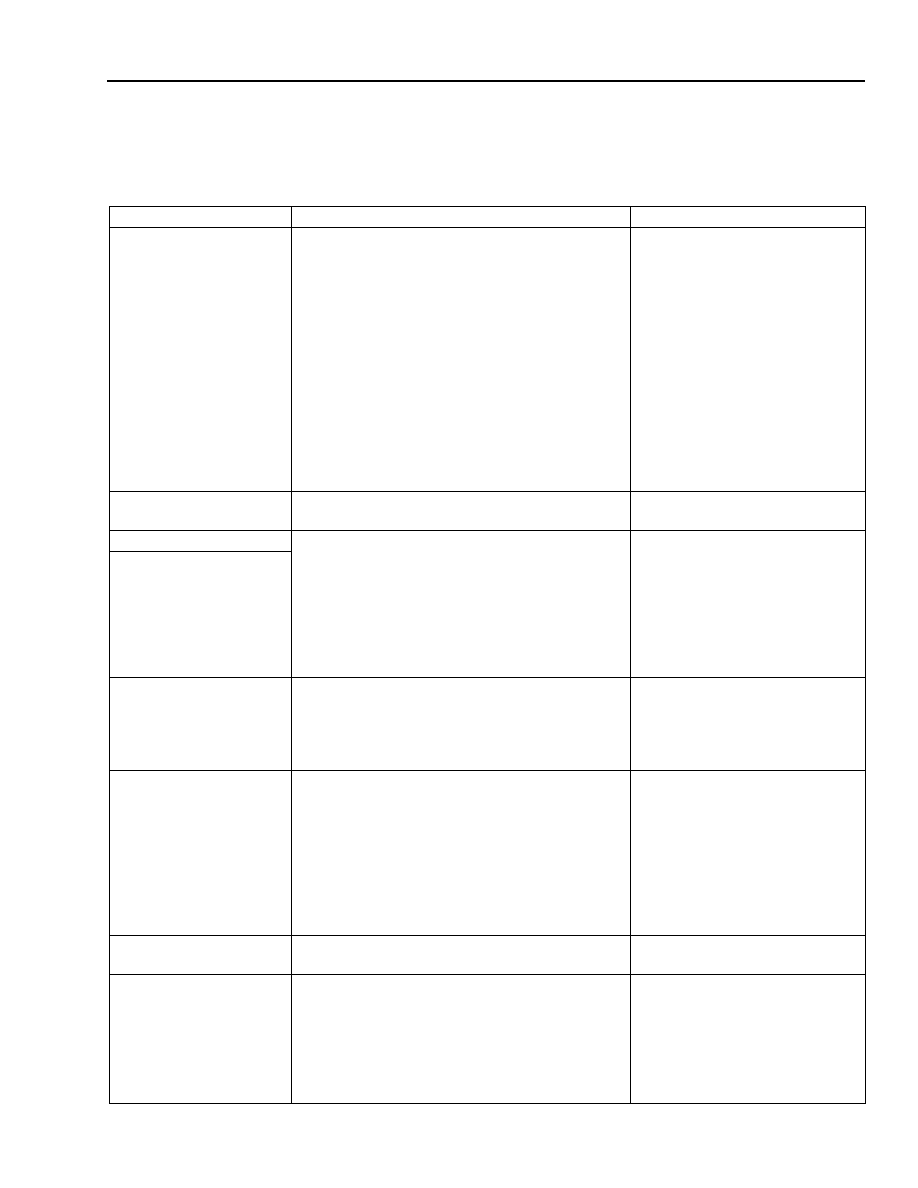

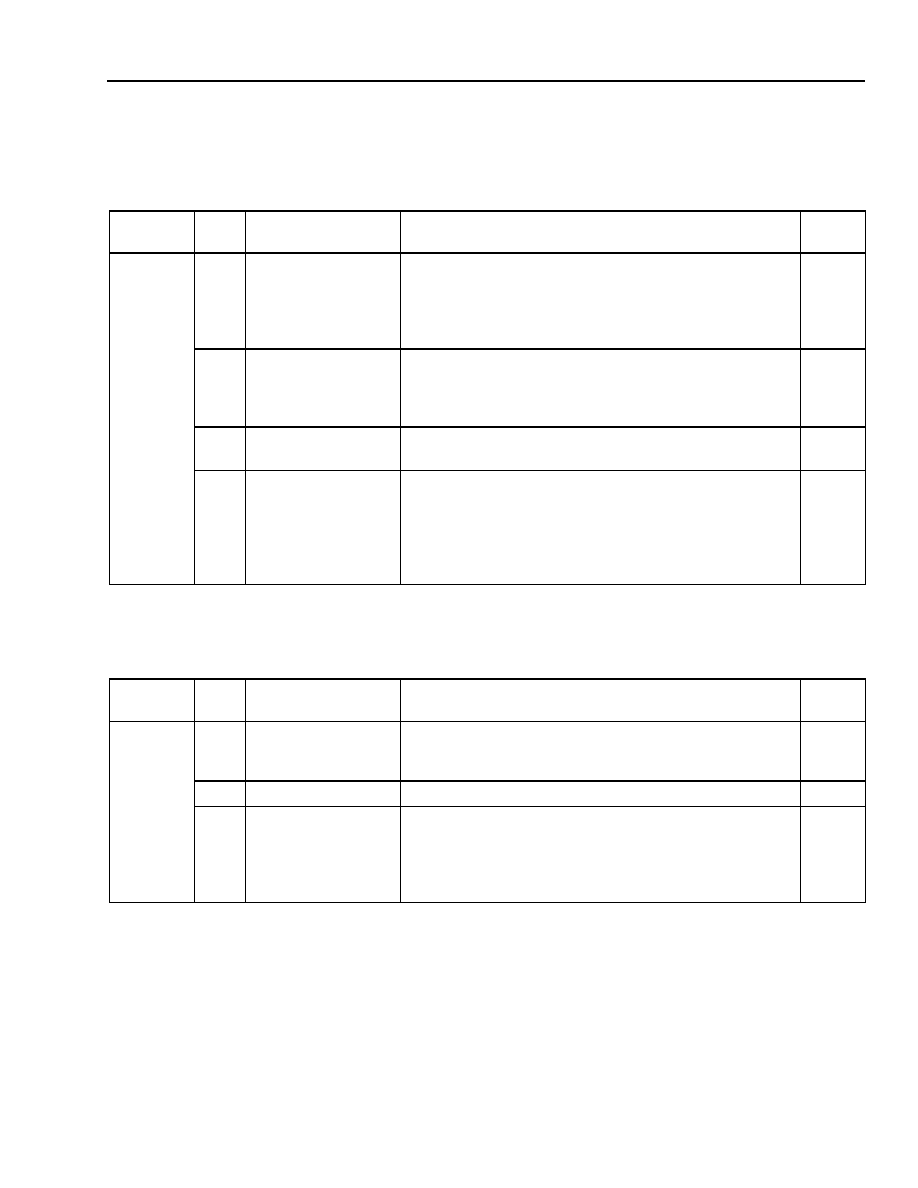

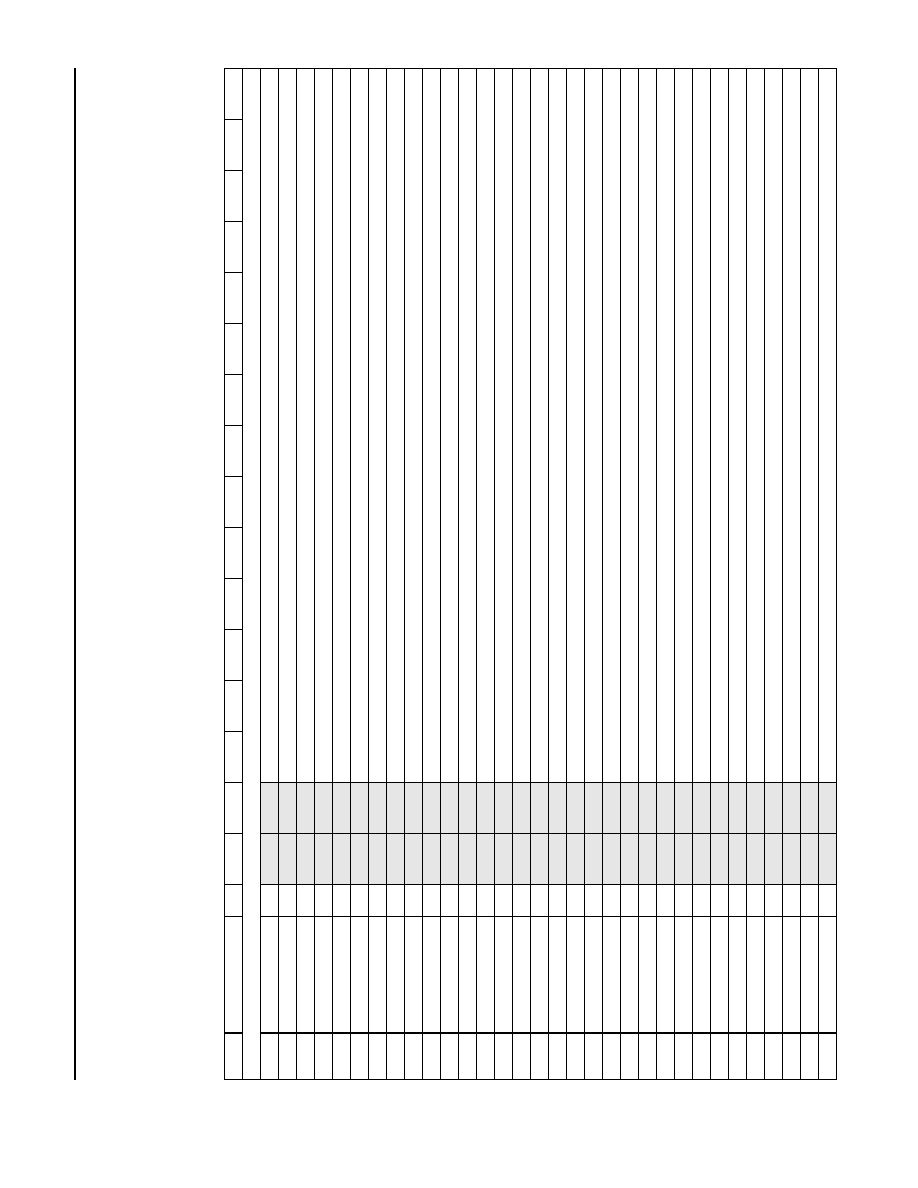

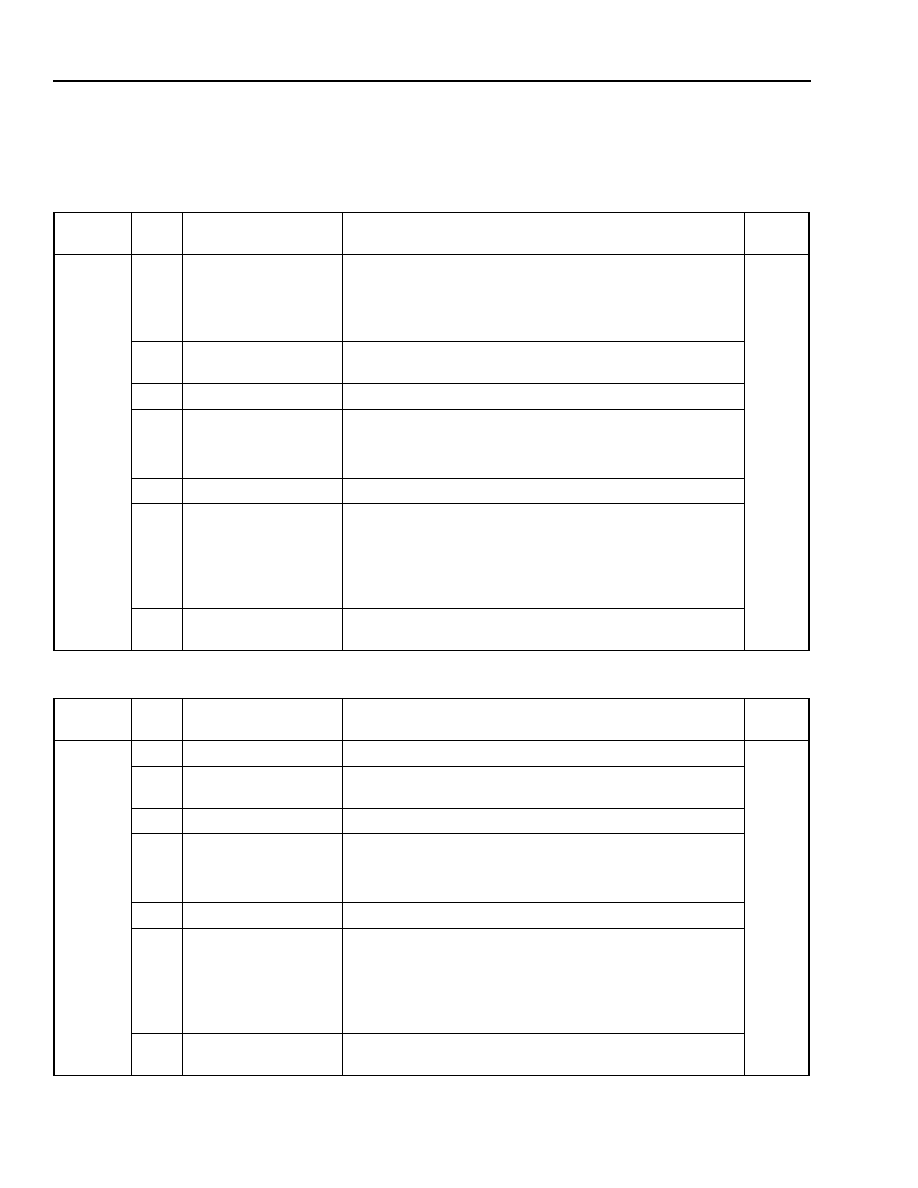

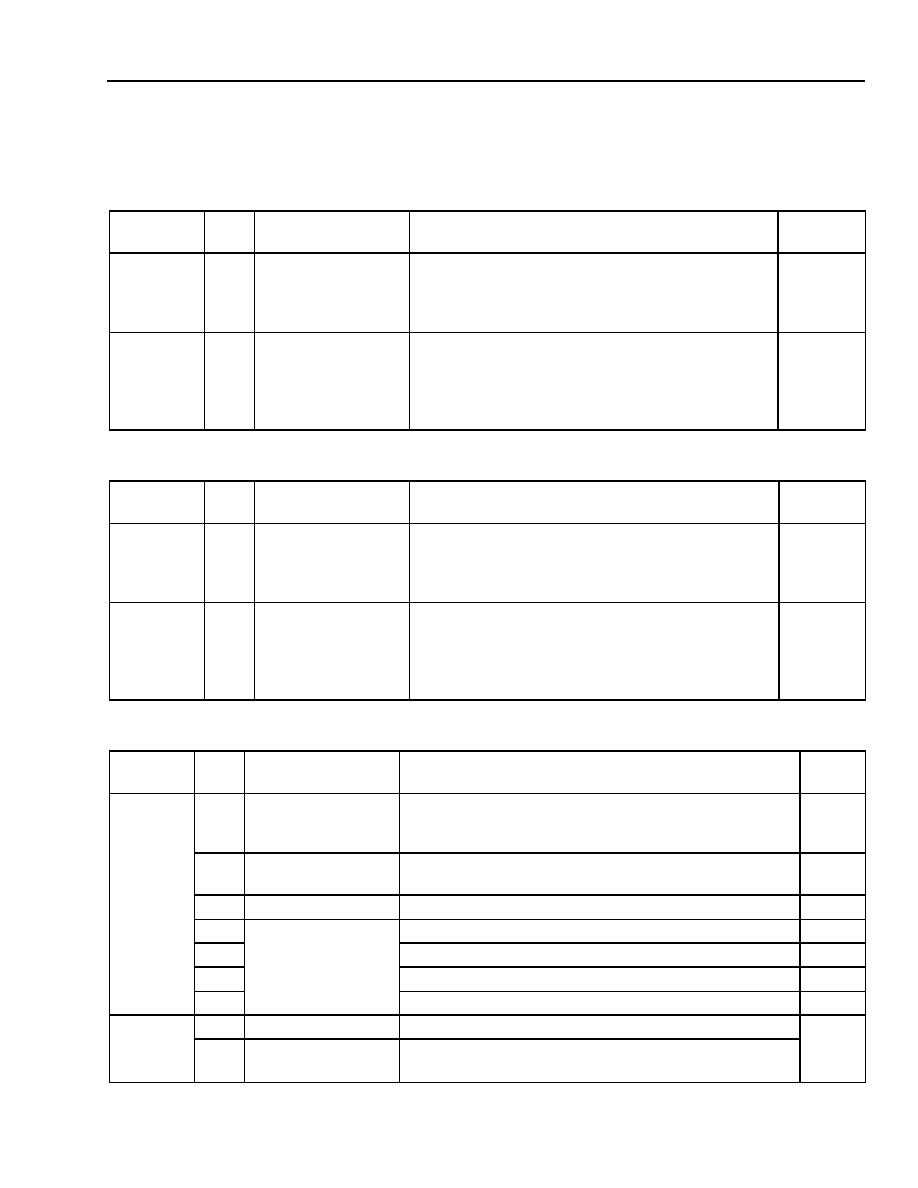

- Table 44. MPU Register Map

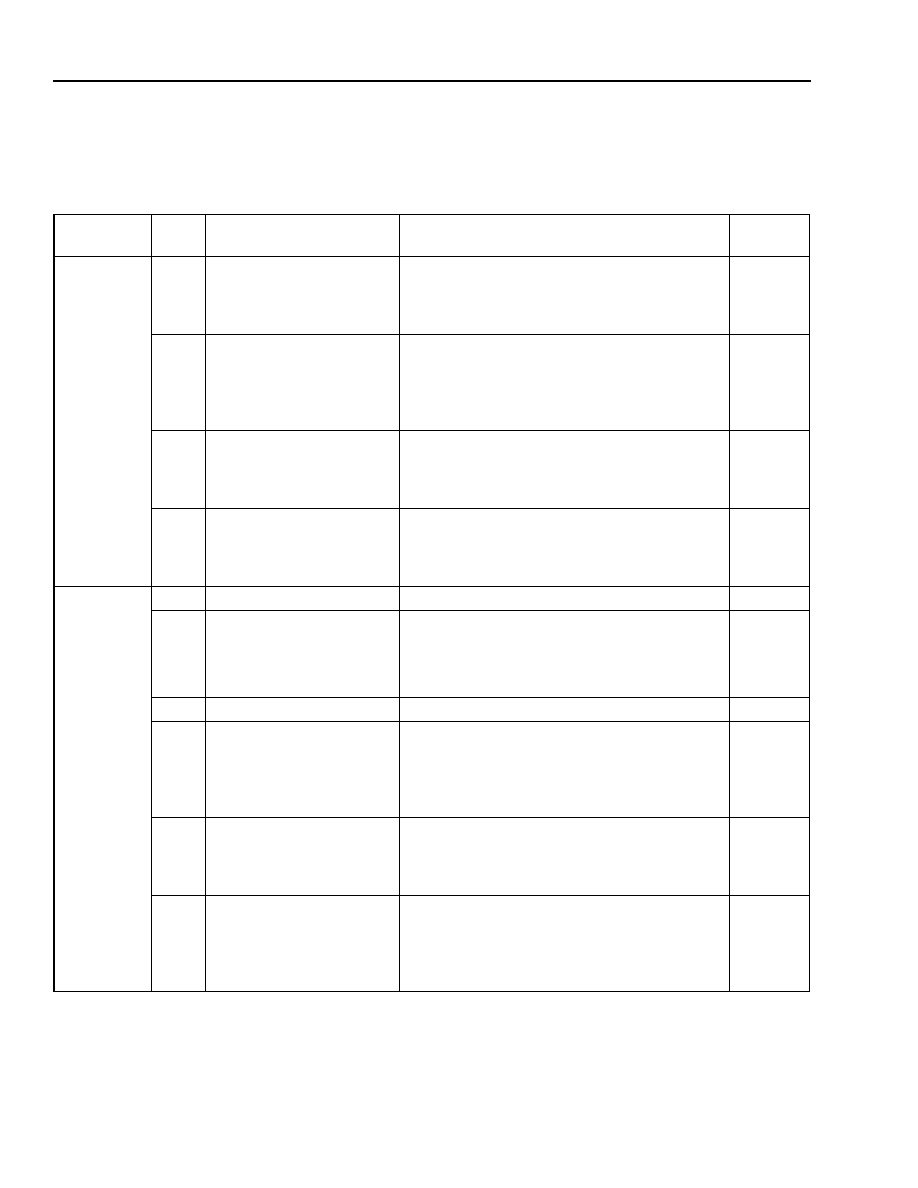

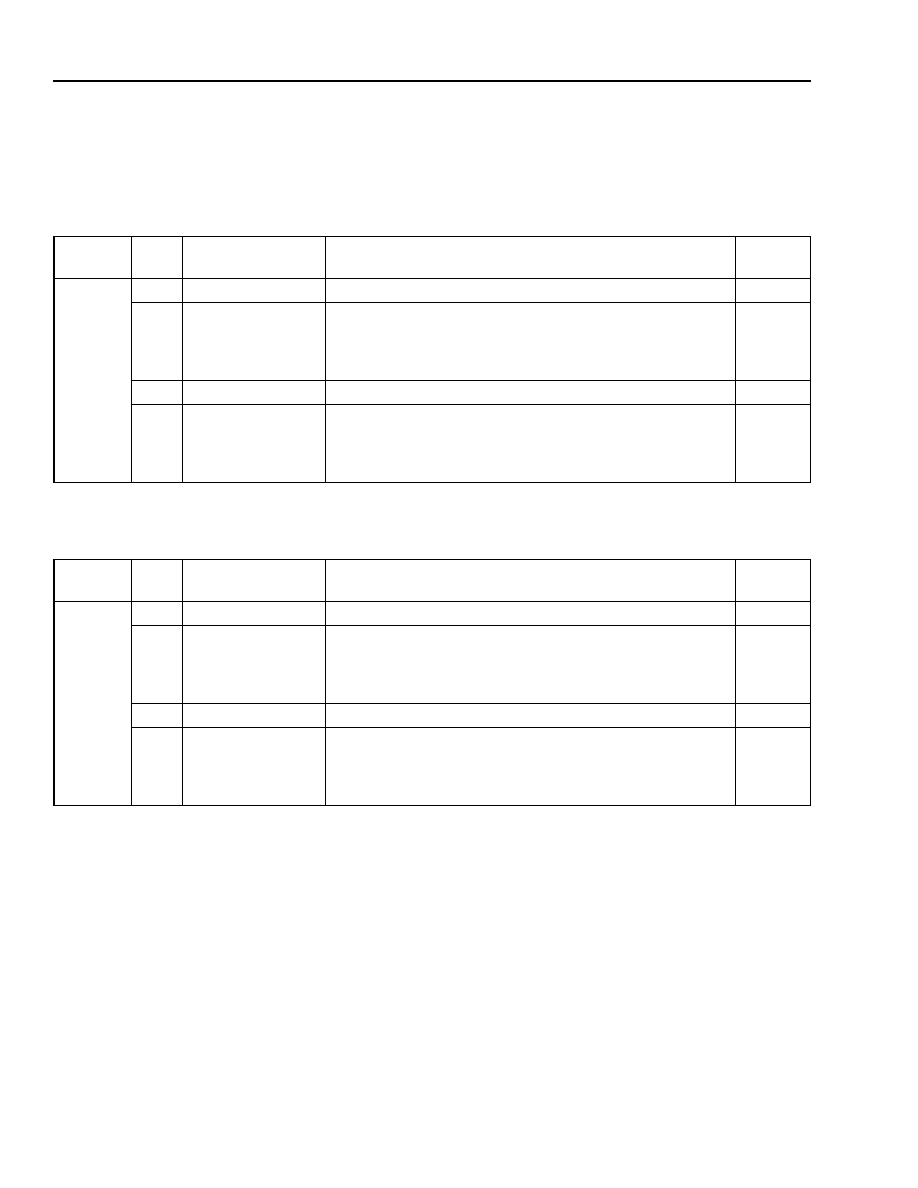

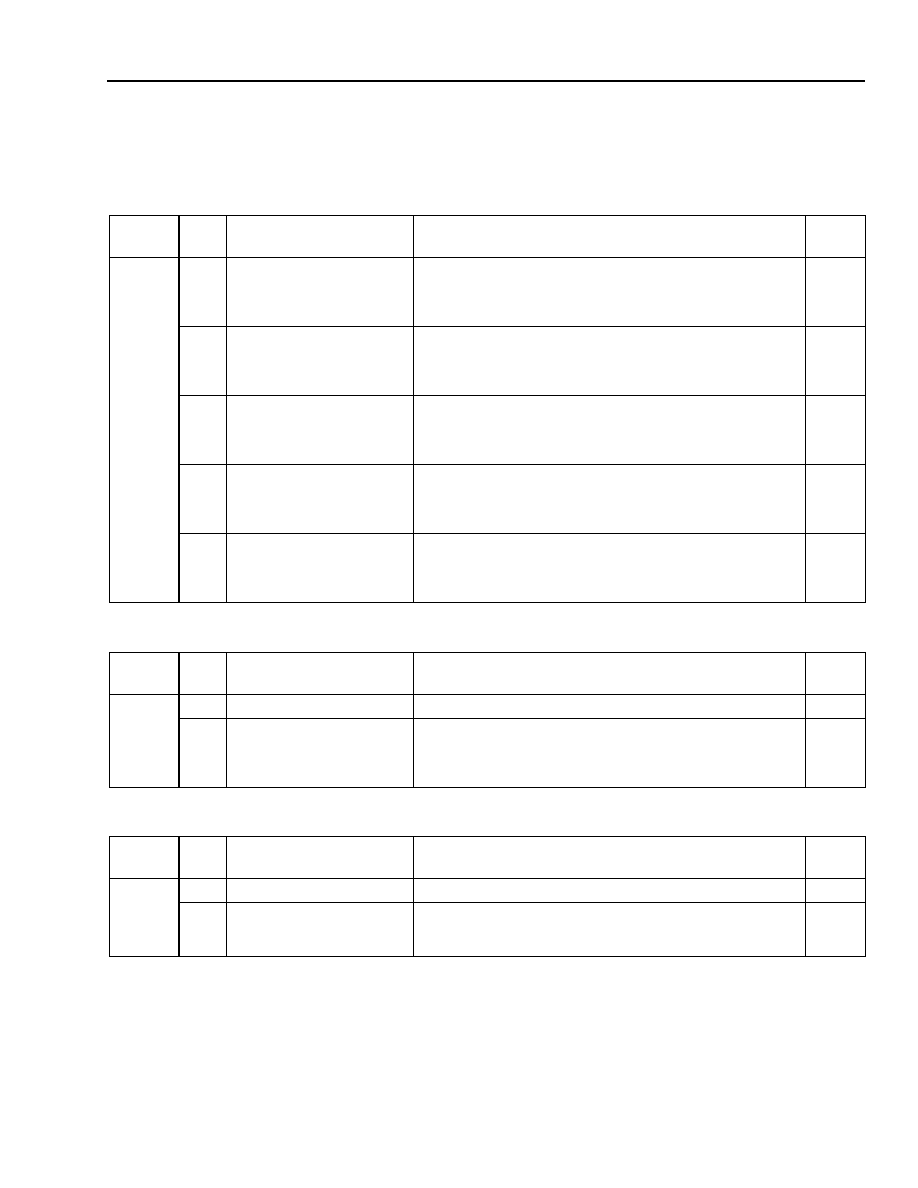

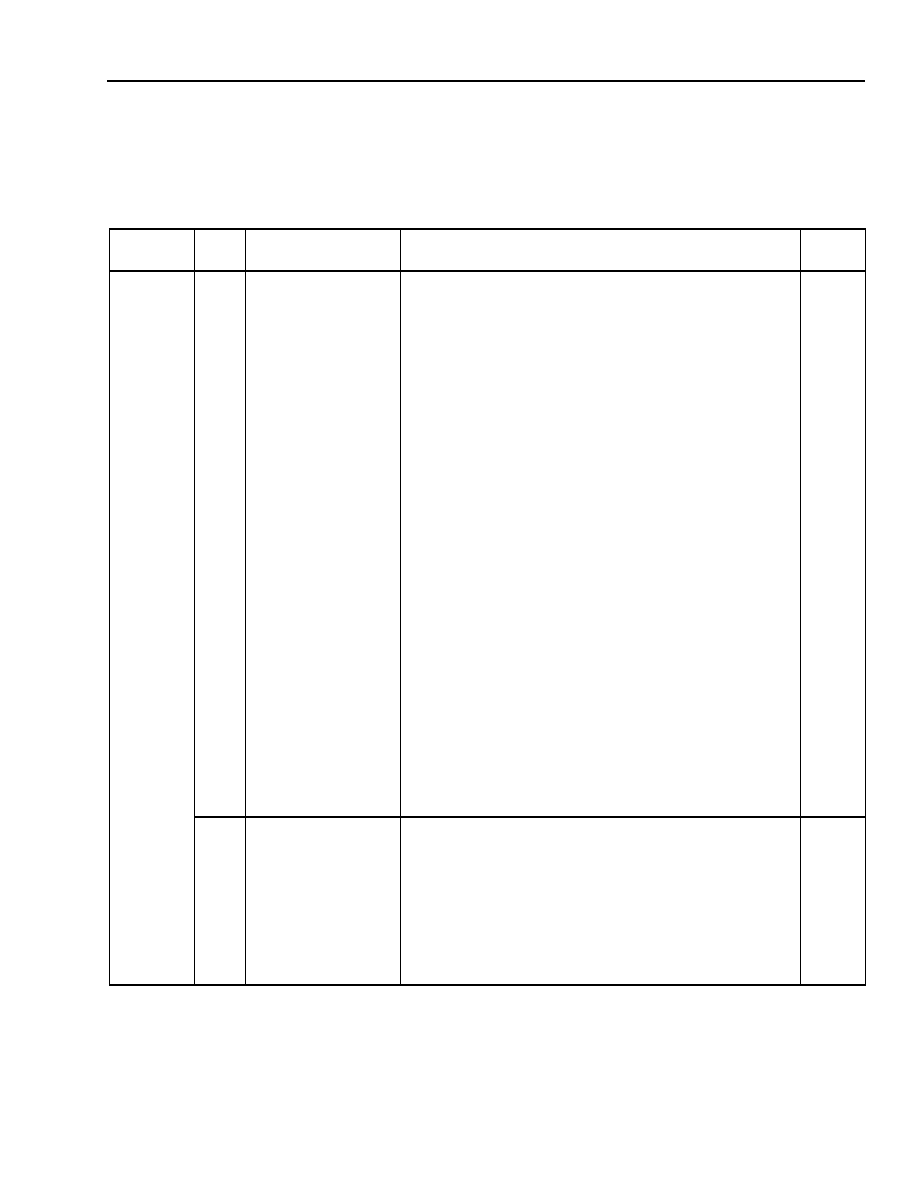

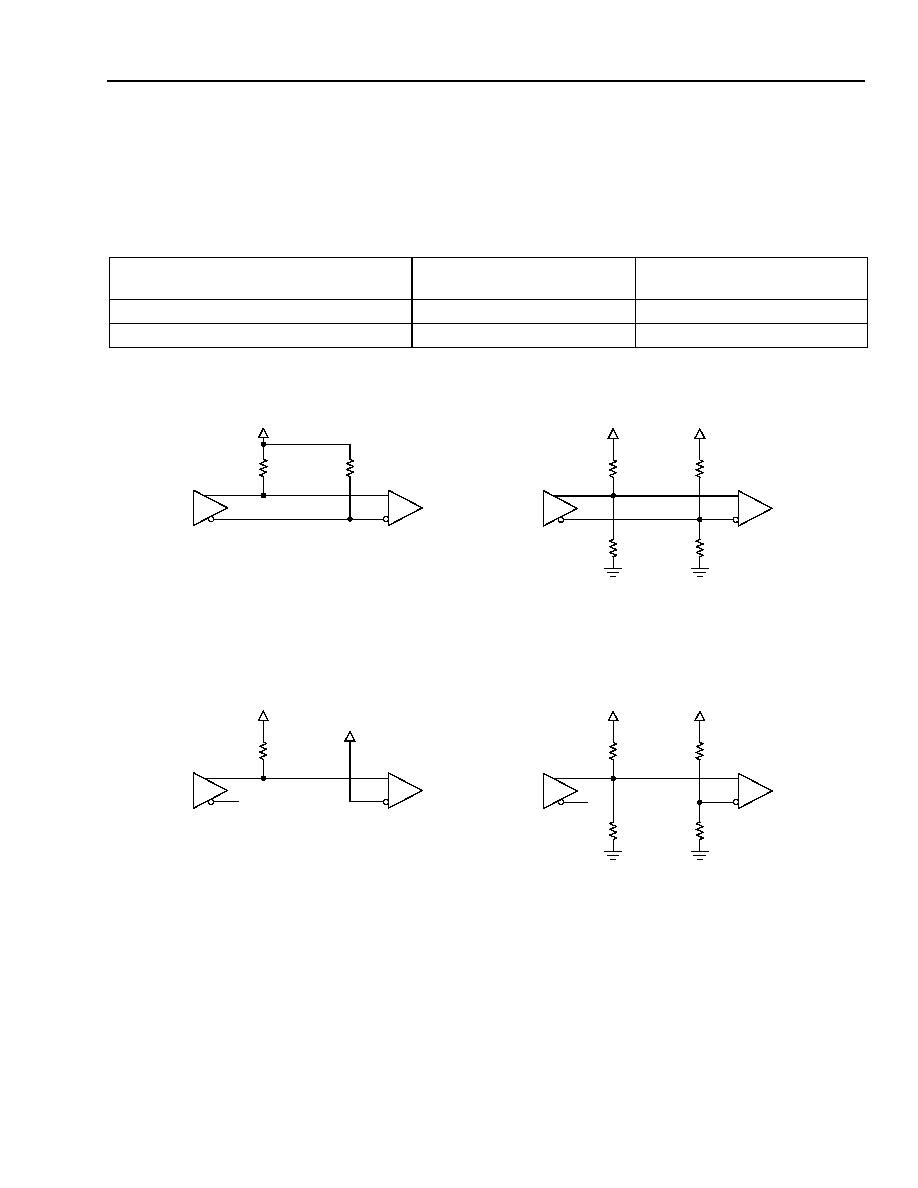

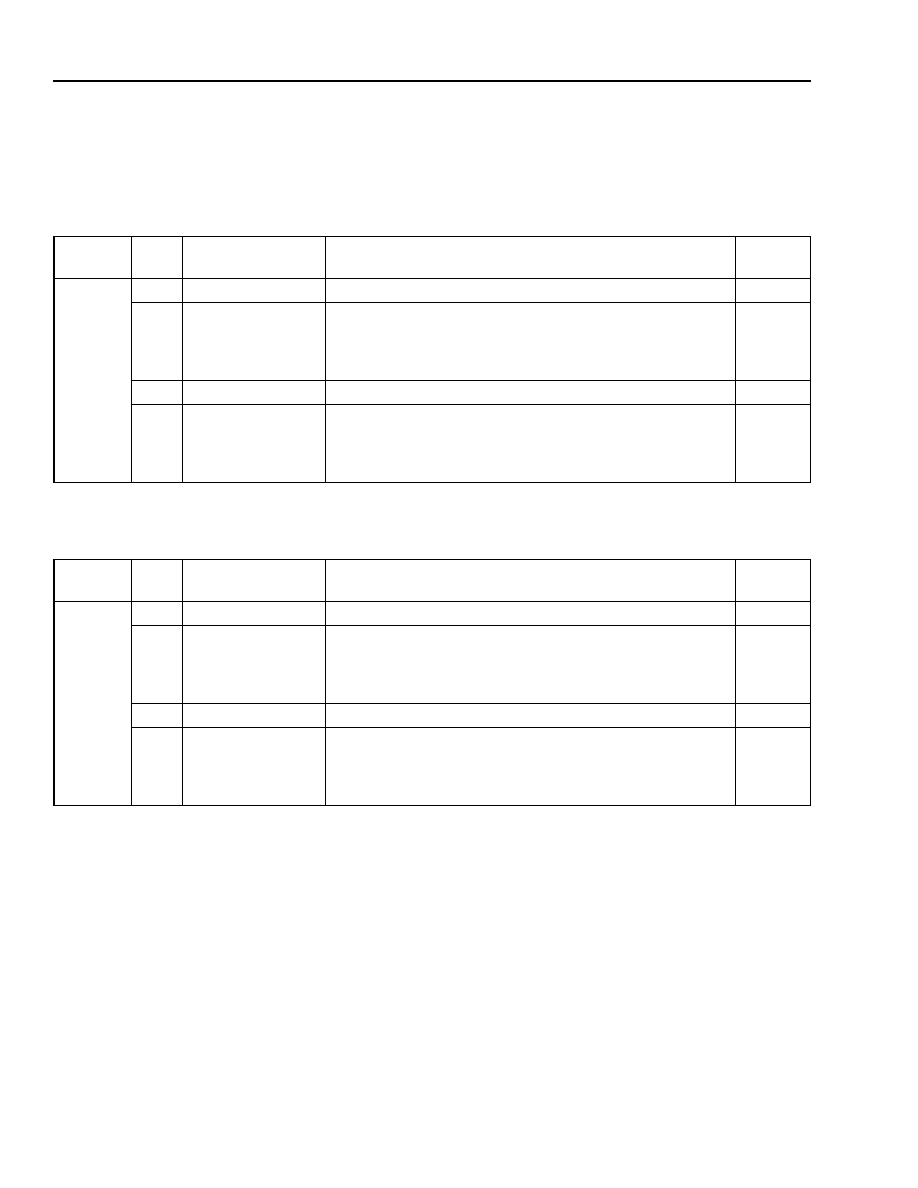

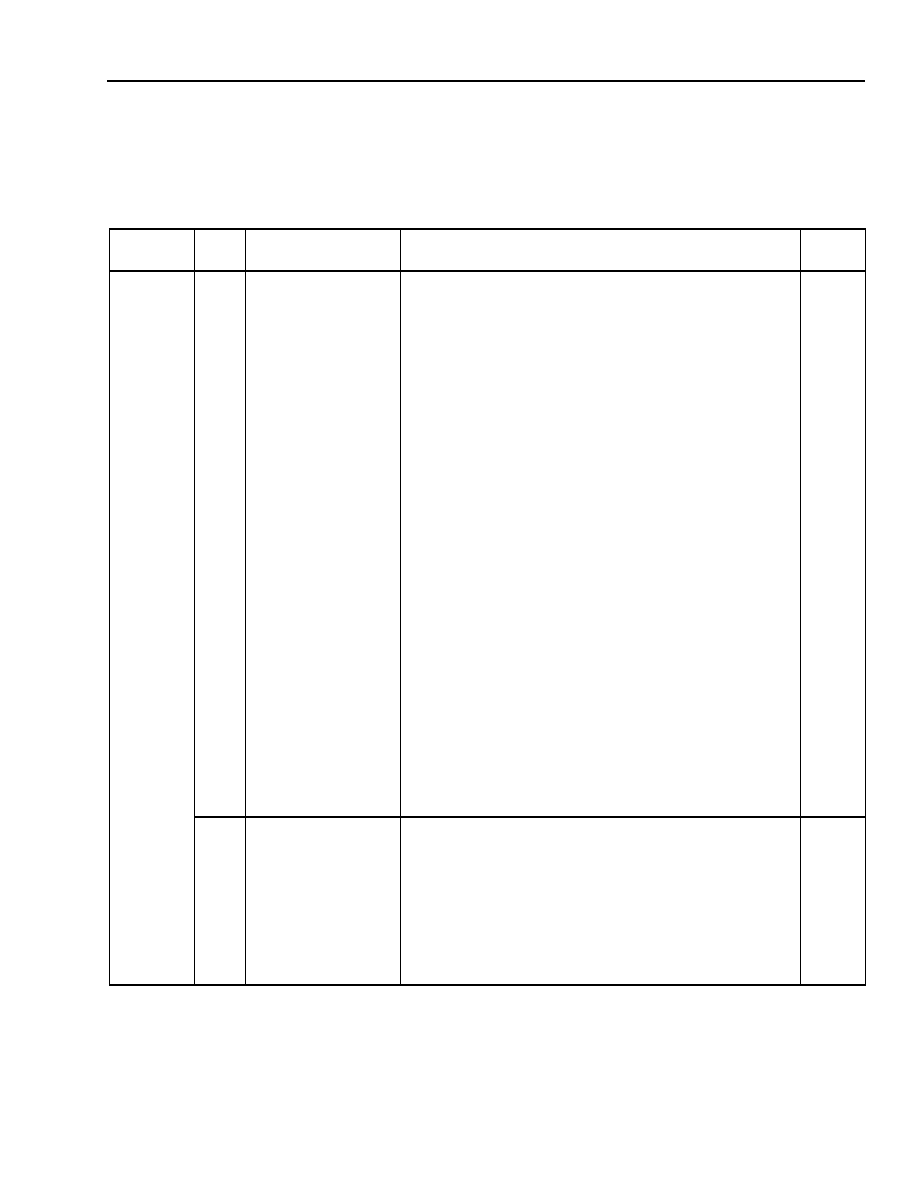

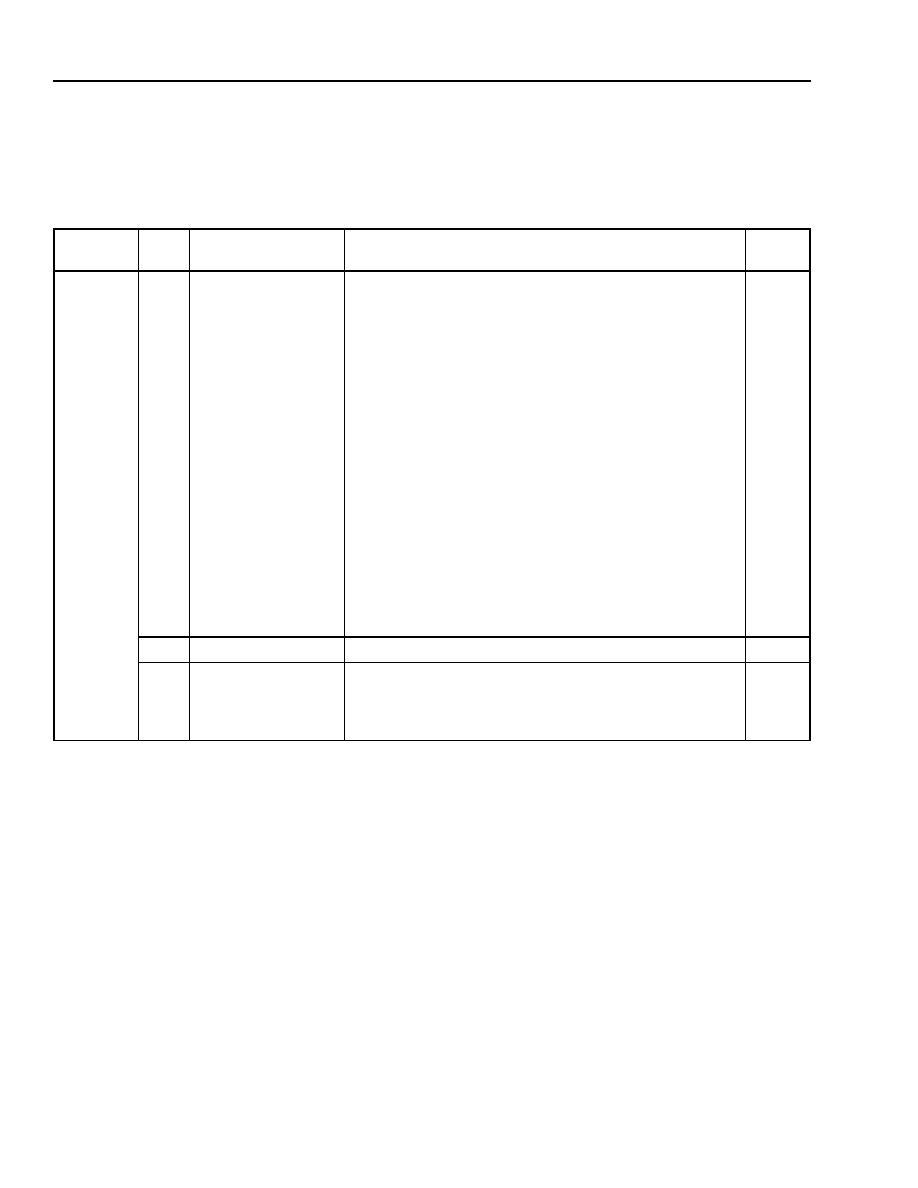

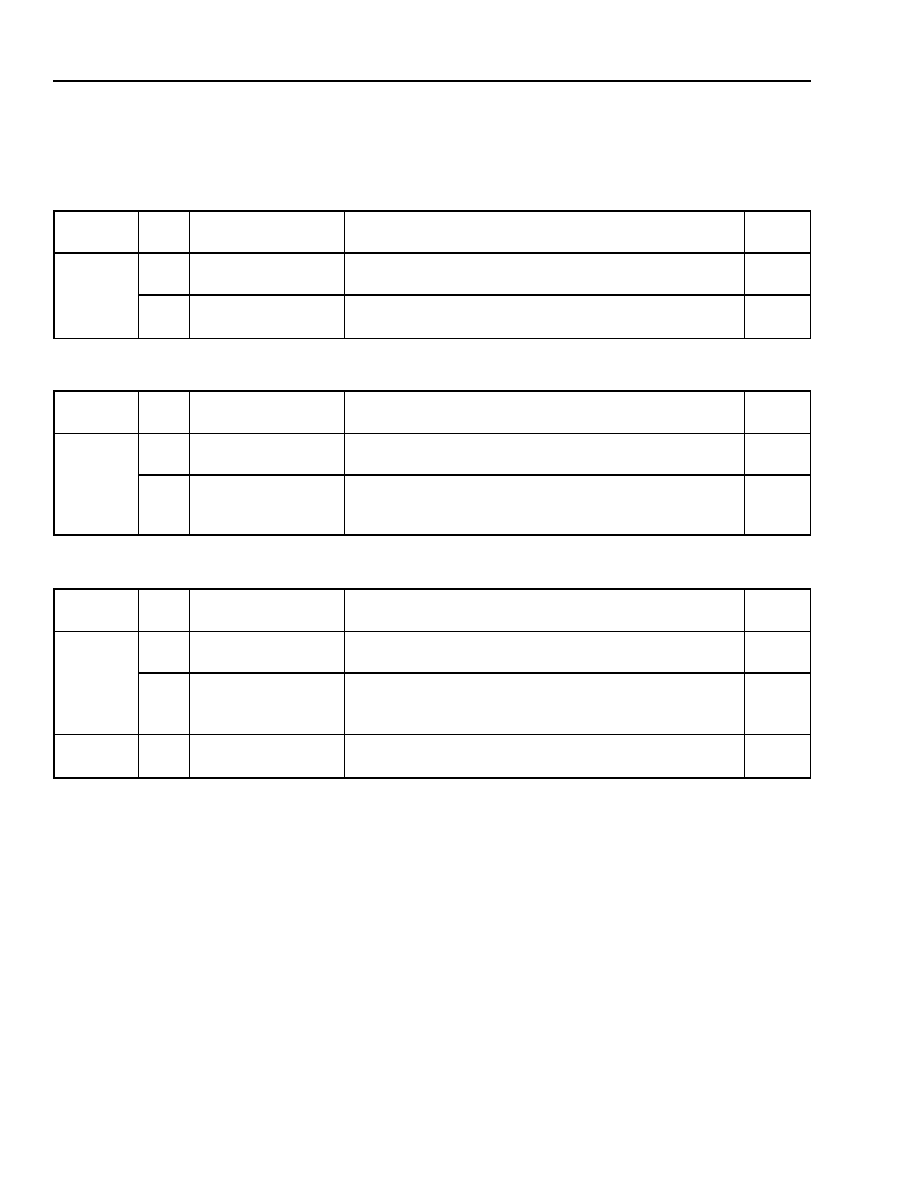

- Table 45. Line Interface Modes

- Table 46. Nominal dc Power for Suggested Terminations

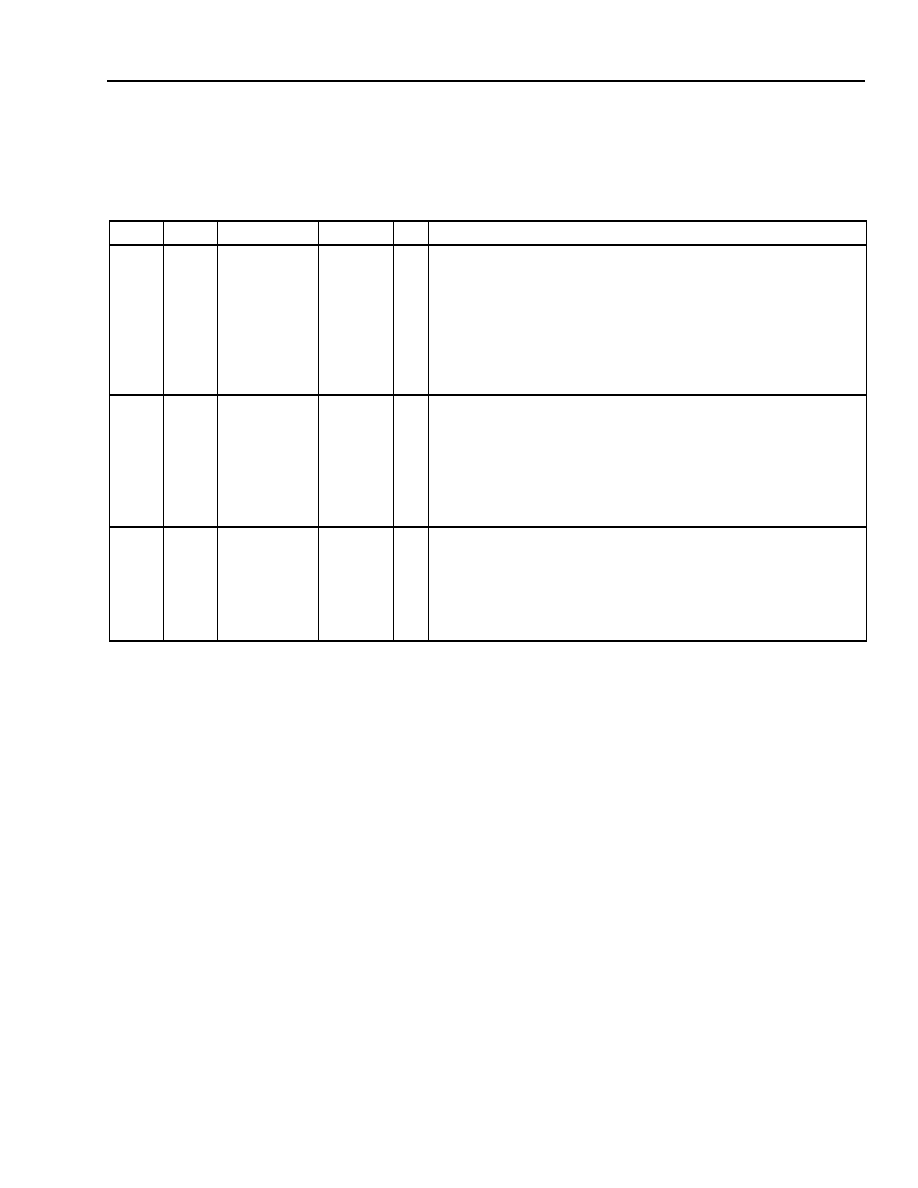

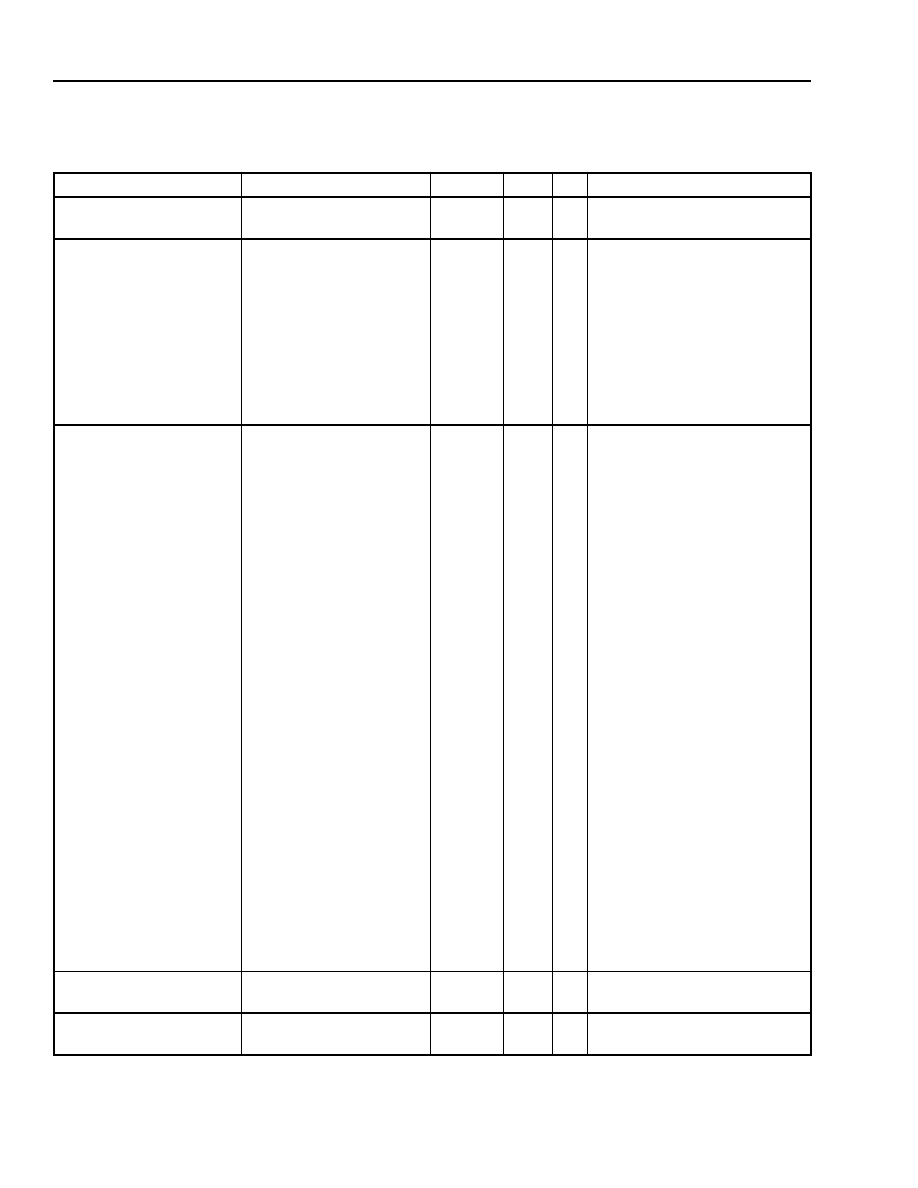

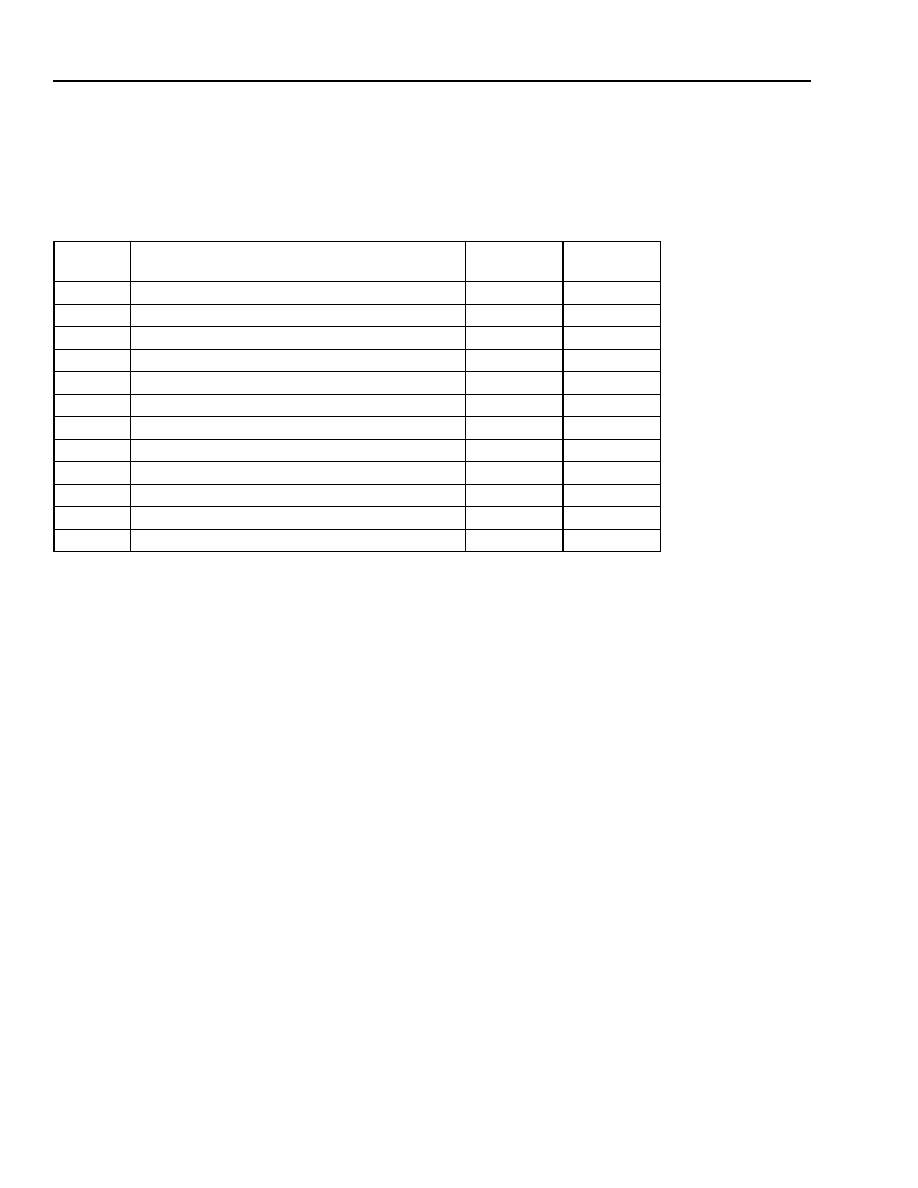

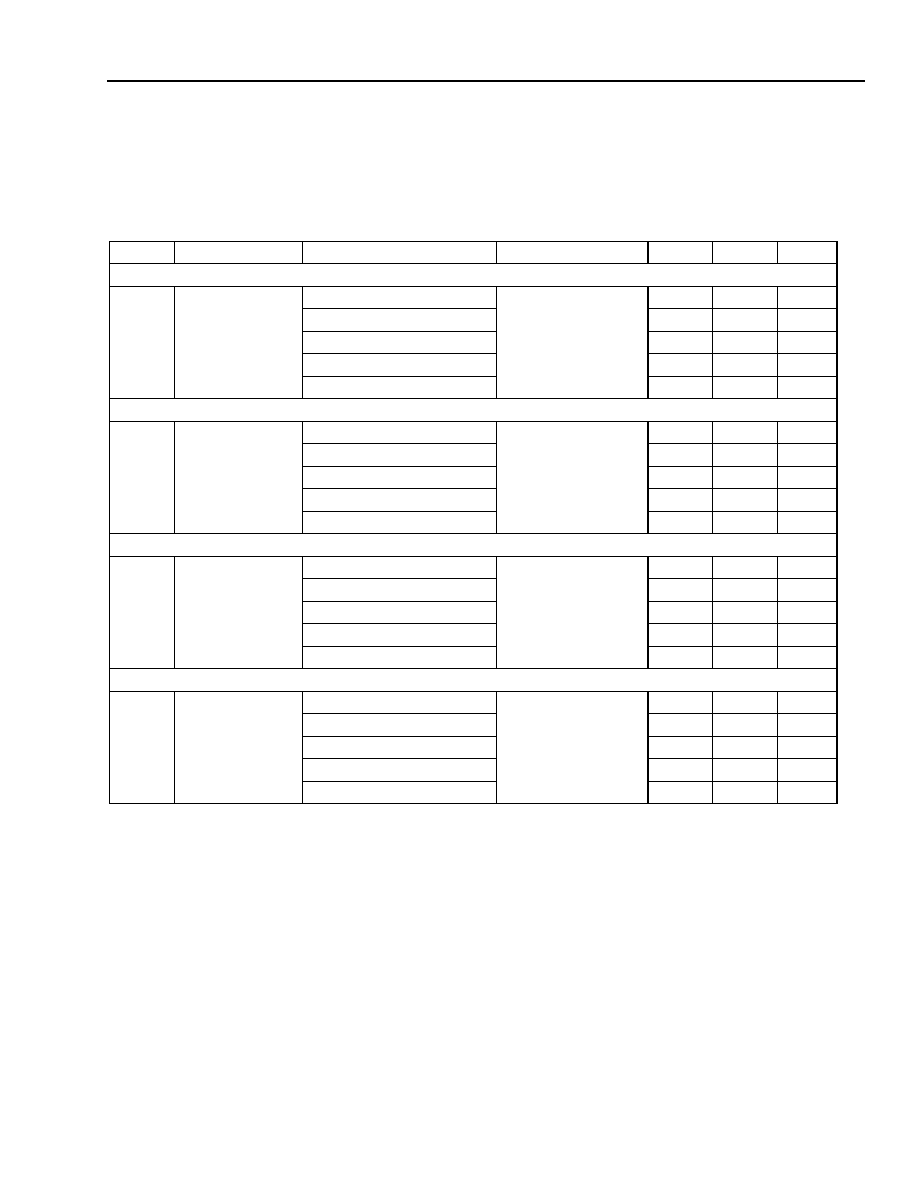

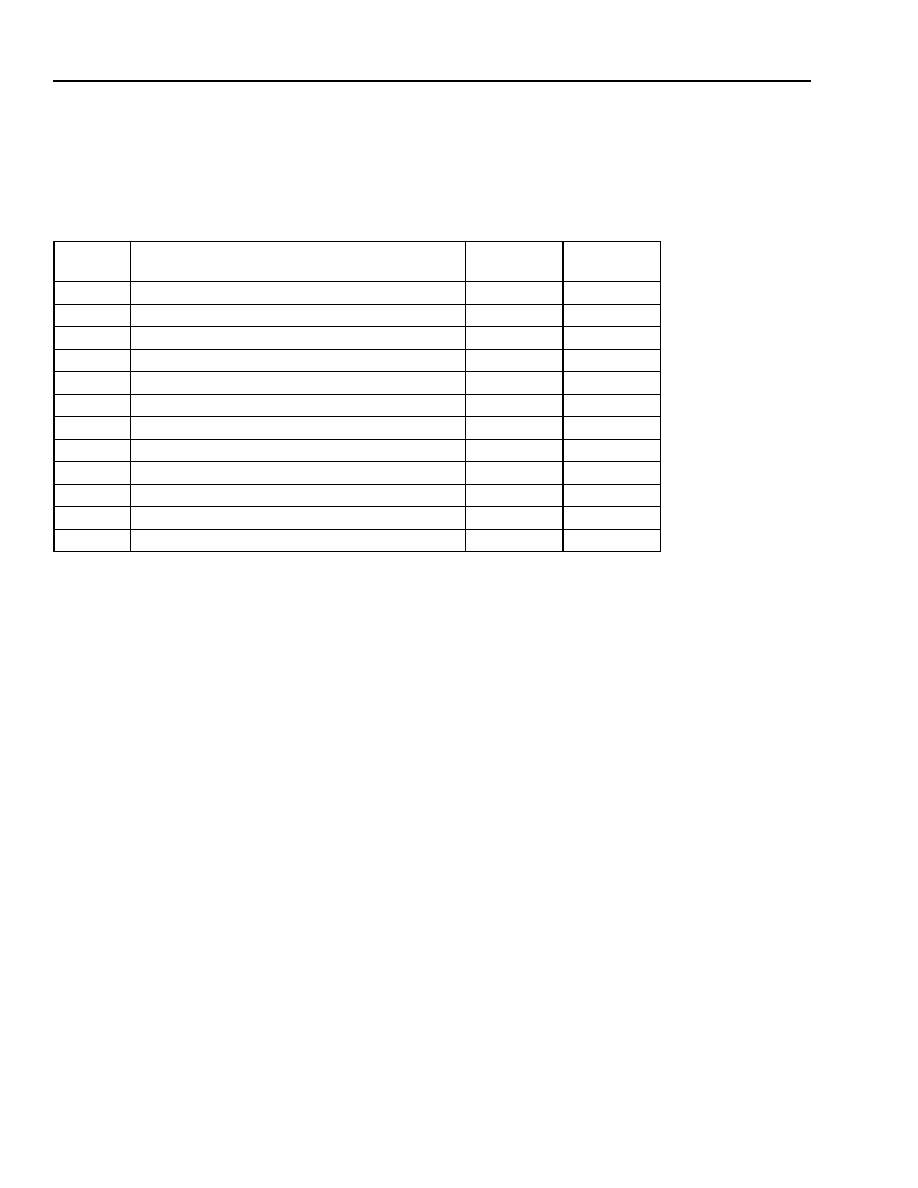

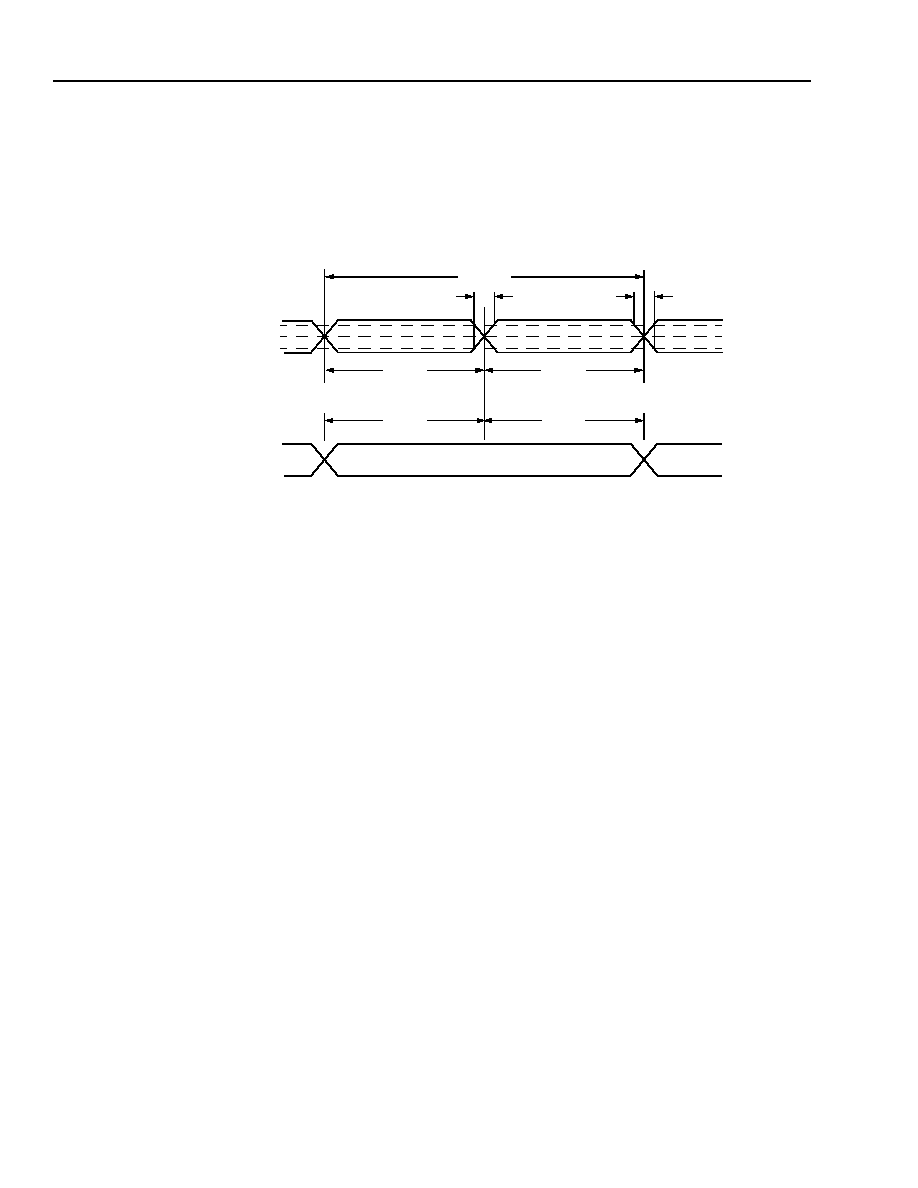

- Table 47. Receive Line-Side Timing Specifications

- Table 48. Transmit Line-Side Timing Specifications

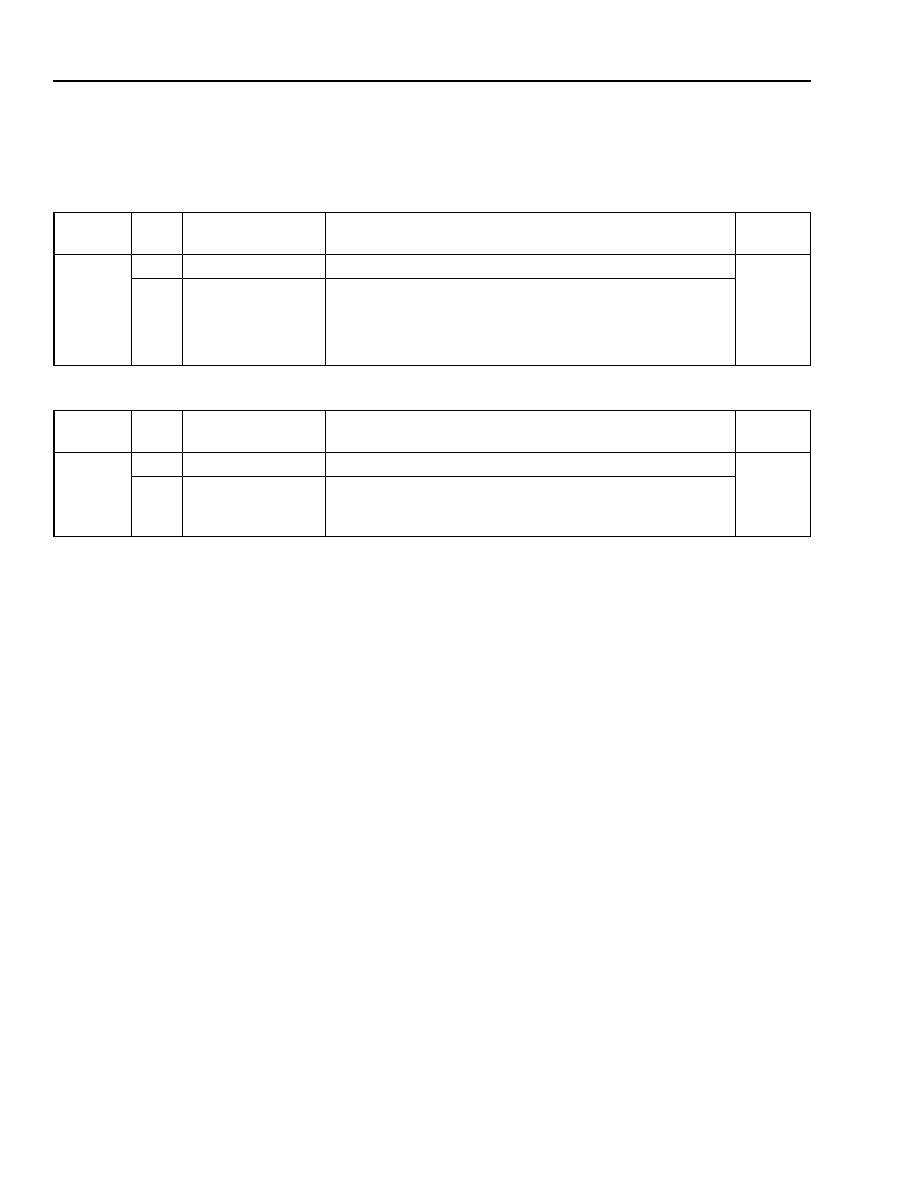

- Table 49. Framing Bytes Observed for Framing Integrity

- Table 50. TOAC Channel Output Versus Time-Slot Assignment

- Table 51. Transport Overhead Bytes Received Via RxTOAC Interface*

- Table 52. TOAC Channel Input Versus Time-Slot Assignments

- Table 53. TTOAC OC-3 Signal Definition*

- Table 54. TTOAC OC-12 Signal Definition

- Table 55. TTOAC OC-48 Signal Definition

- Table 56. TTOAC Control Bits

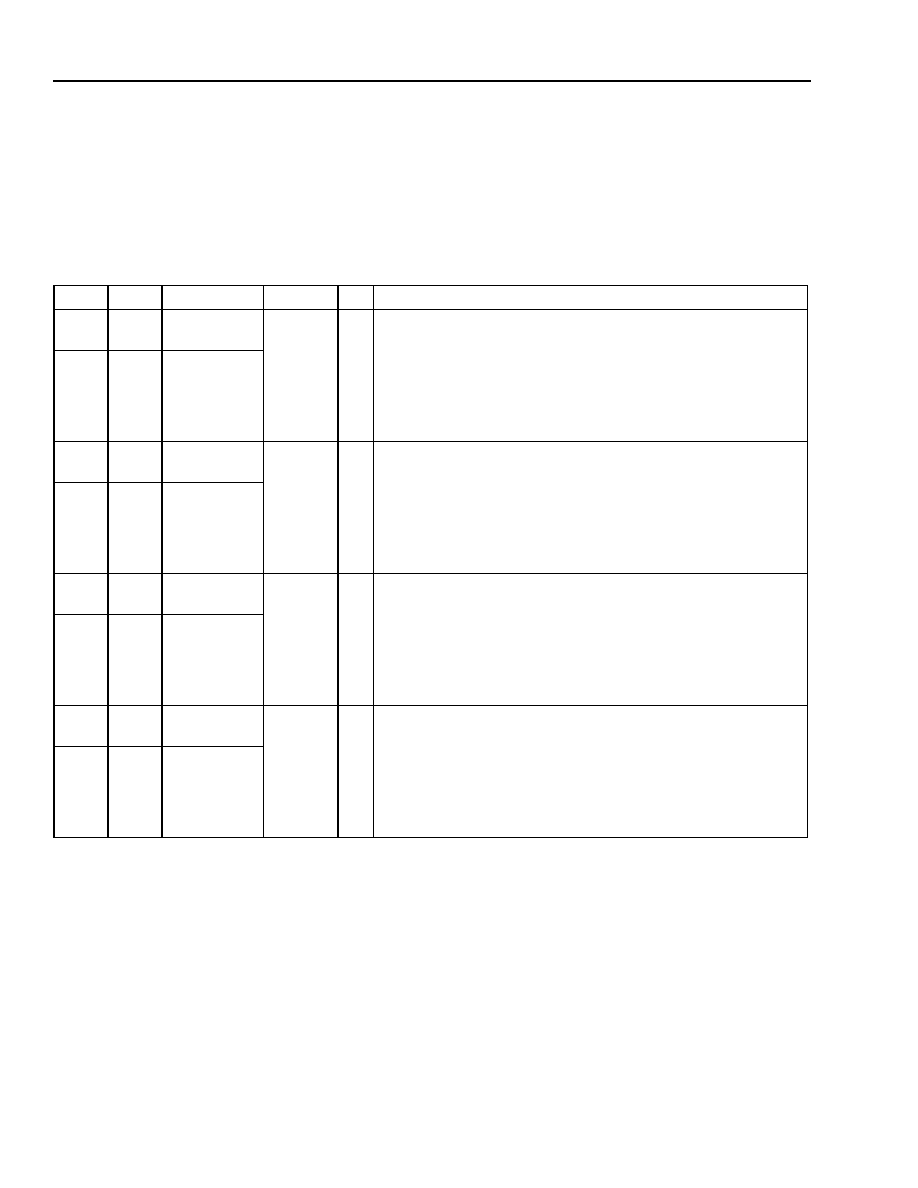

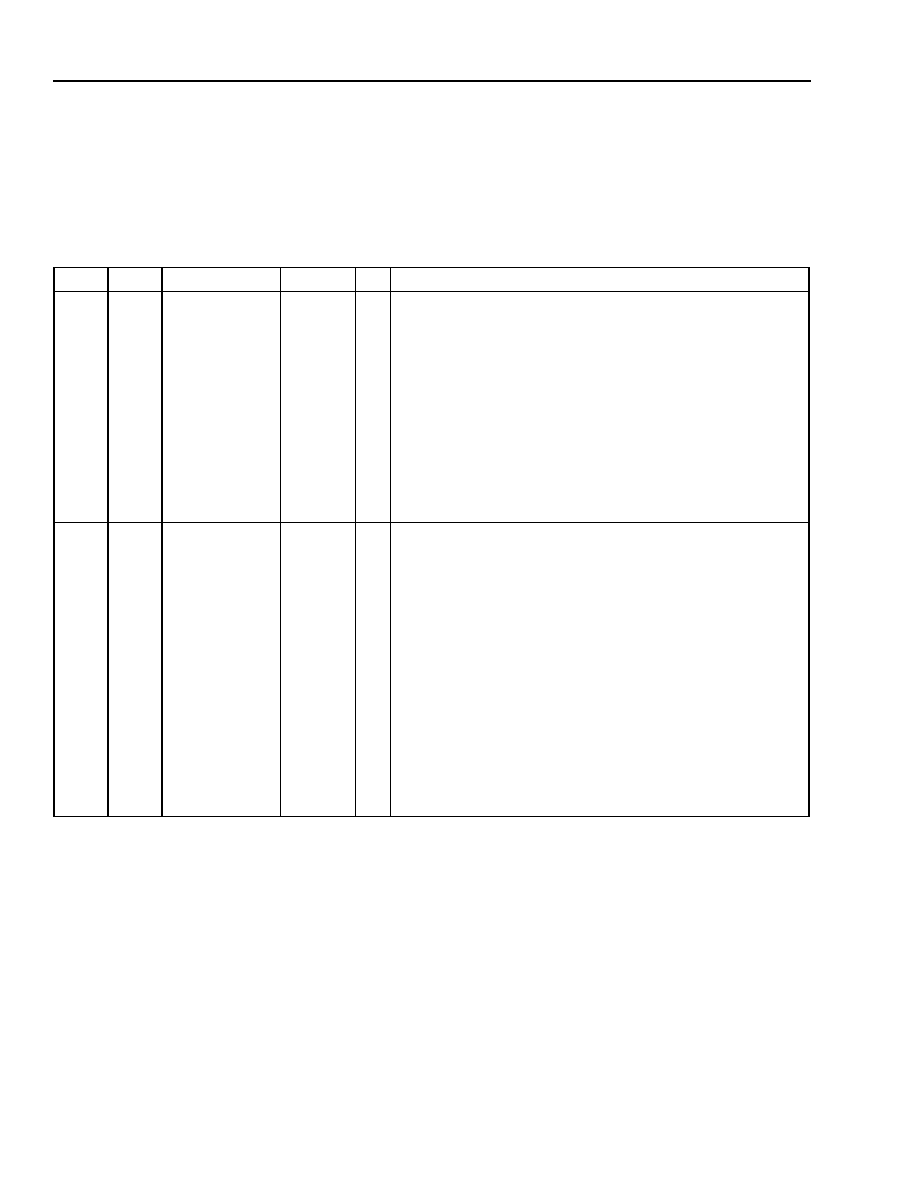

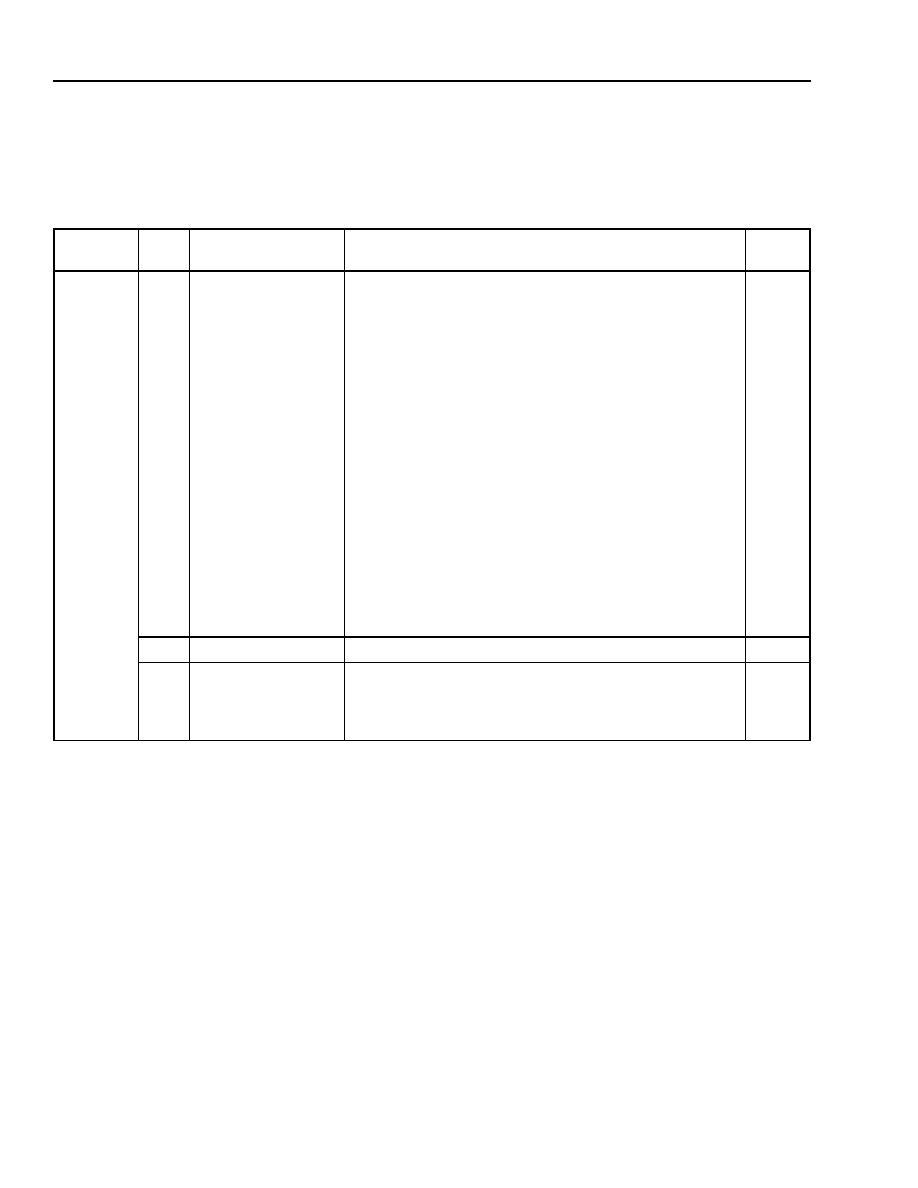

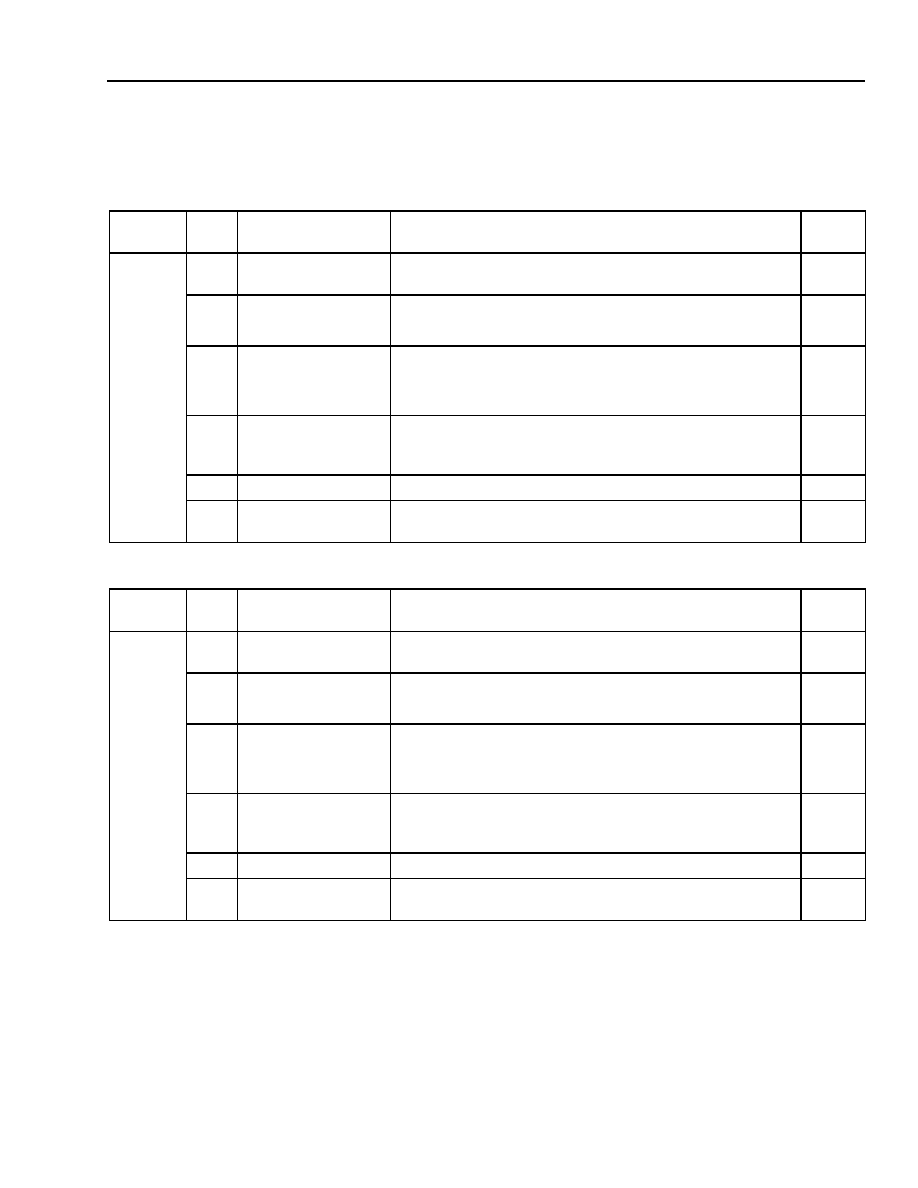

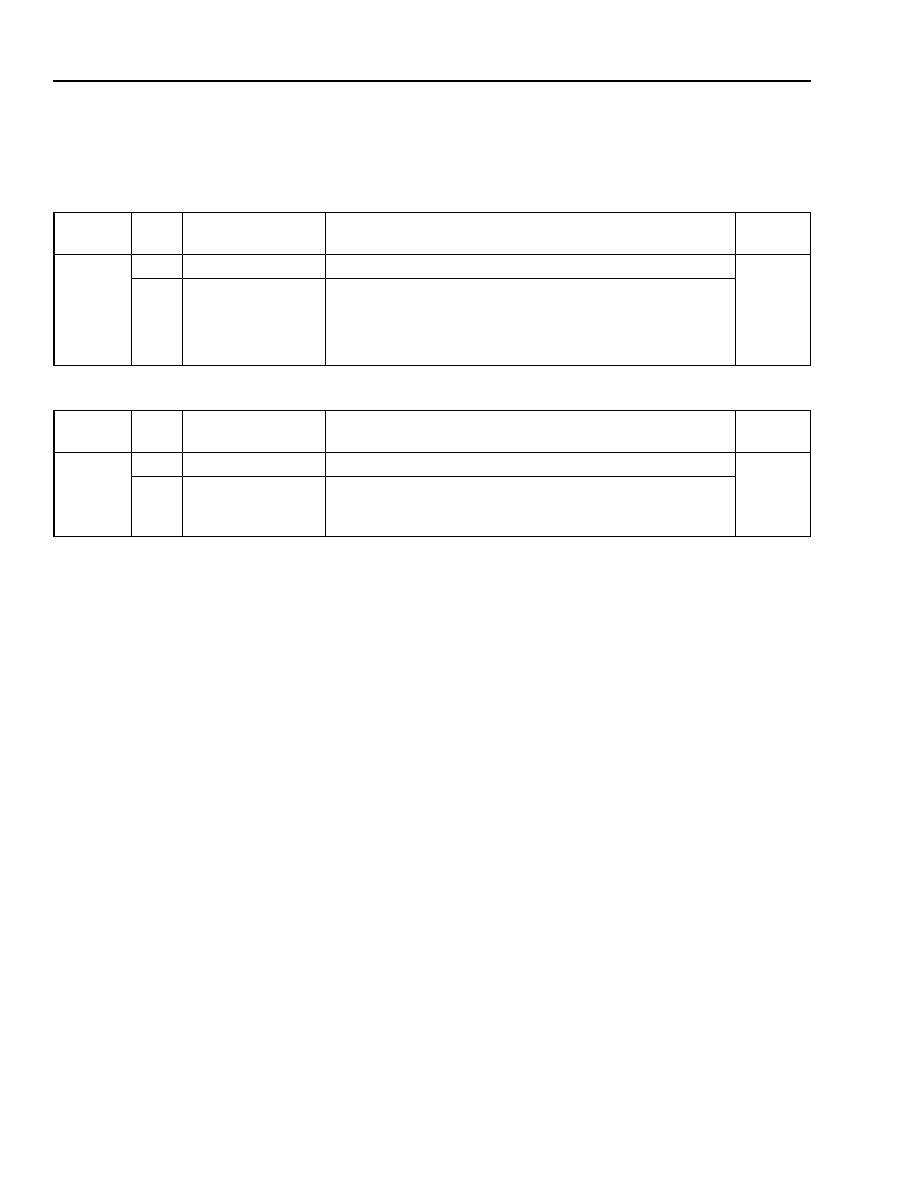

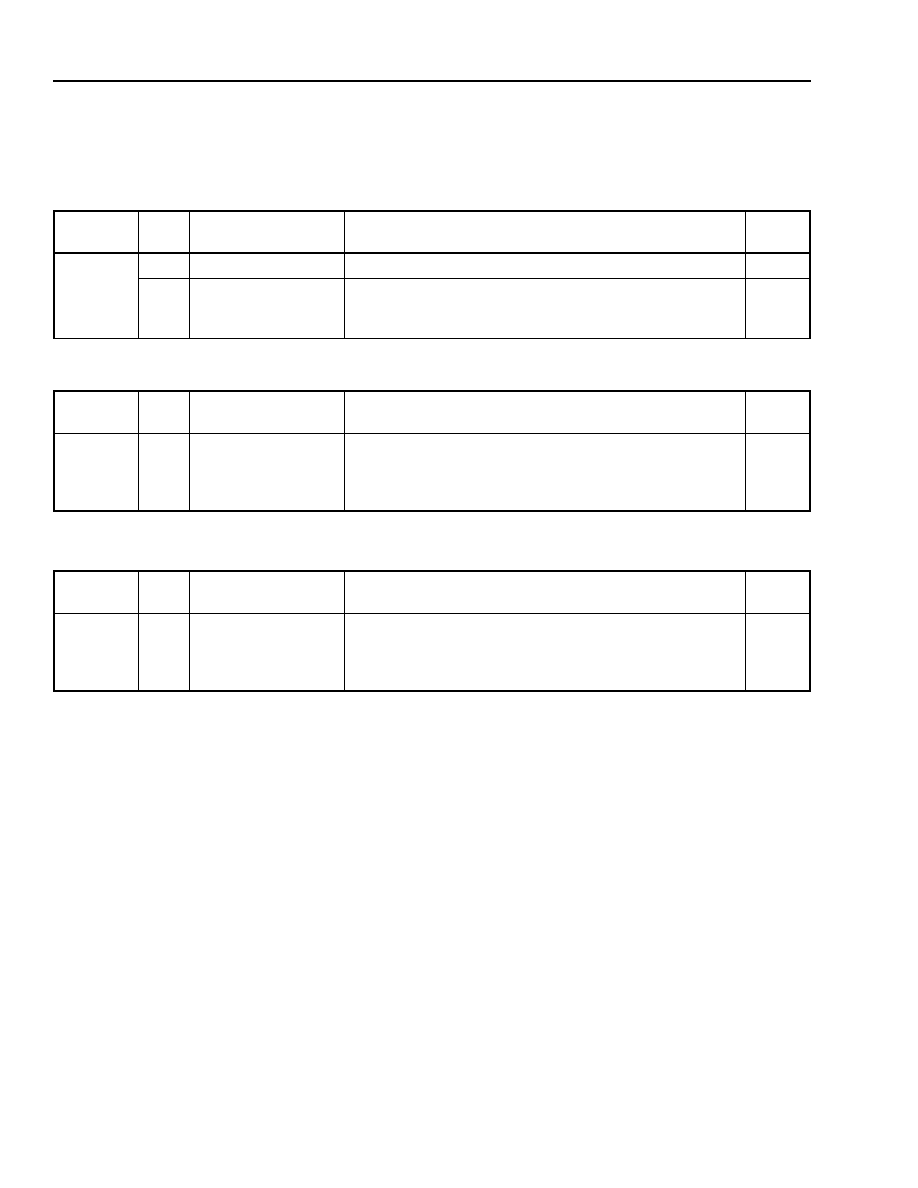

- Table 57. Rx/Tx TOHP-48 Interface Rates

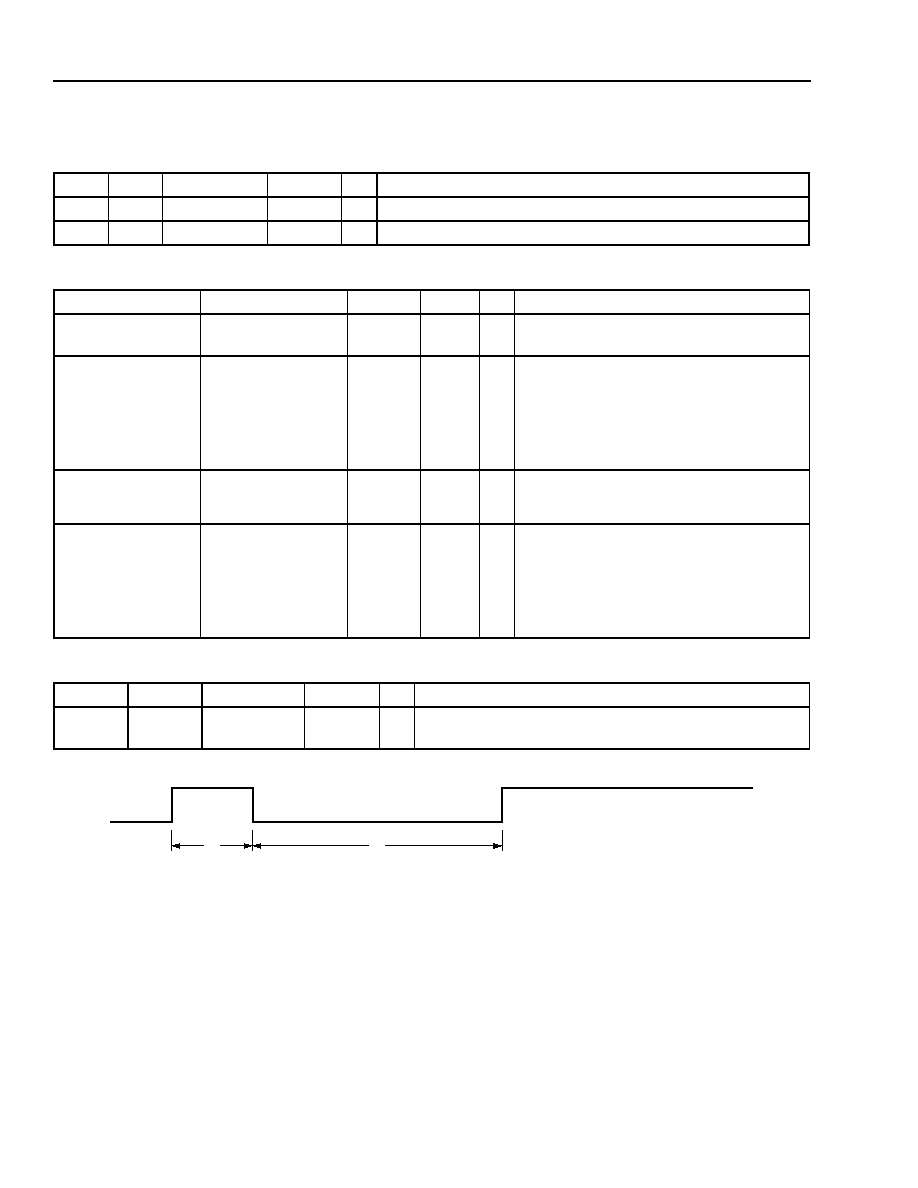

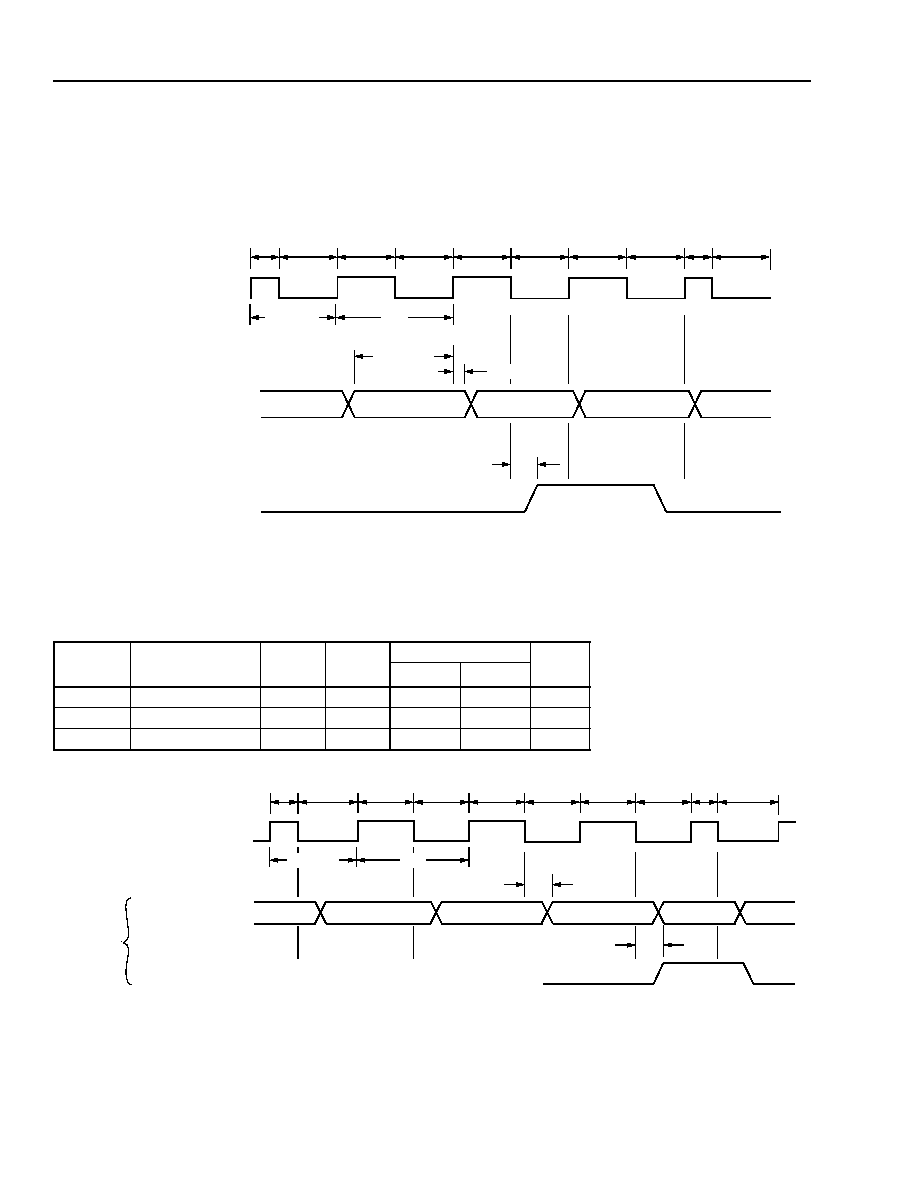

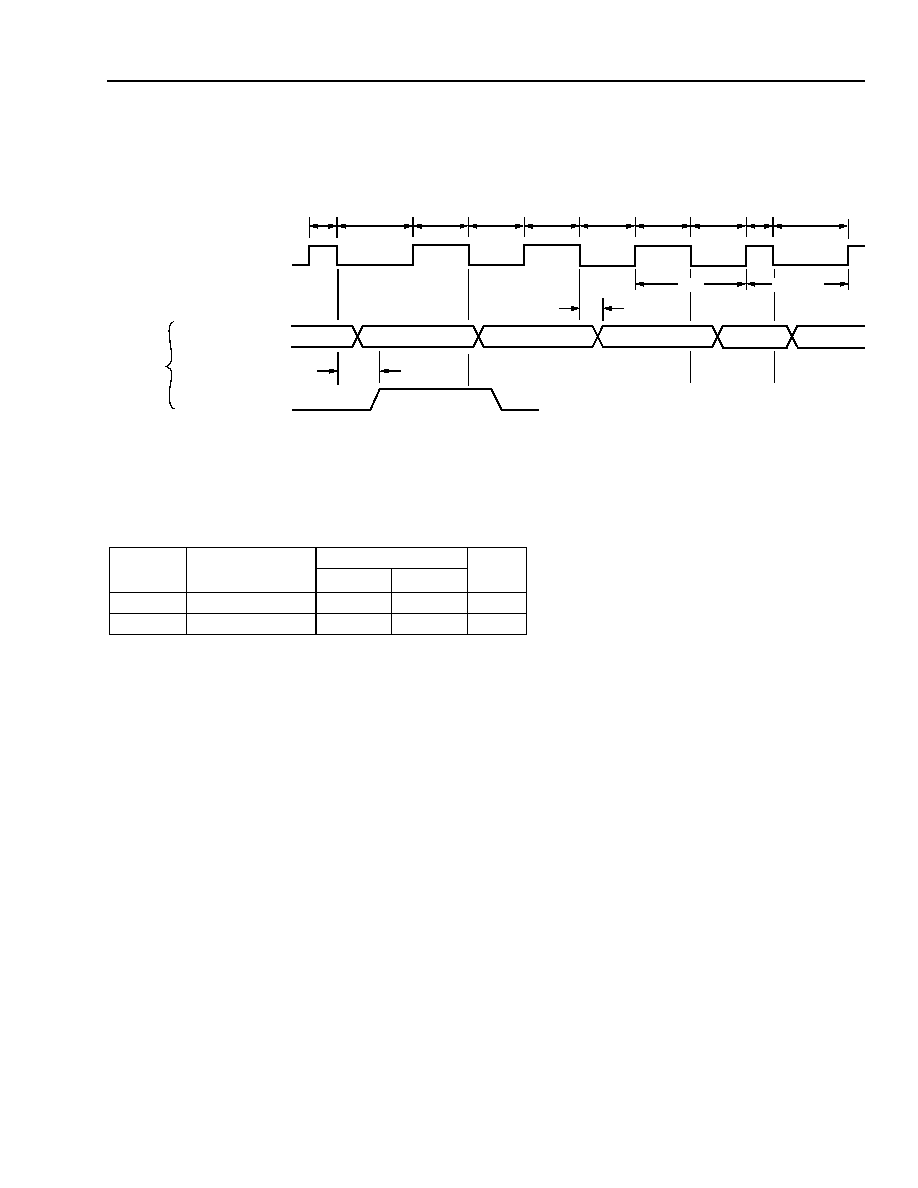

- Table 58. Transmit TOAC Interface Timing Specifications

- Table 59. Receive TOAC Interface Timing Specifications

- Table 60. TOHP_MODE_VERR, Mode (R/W) and Block Version (RO)

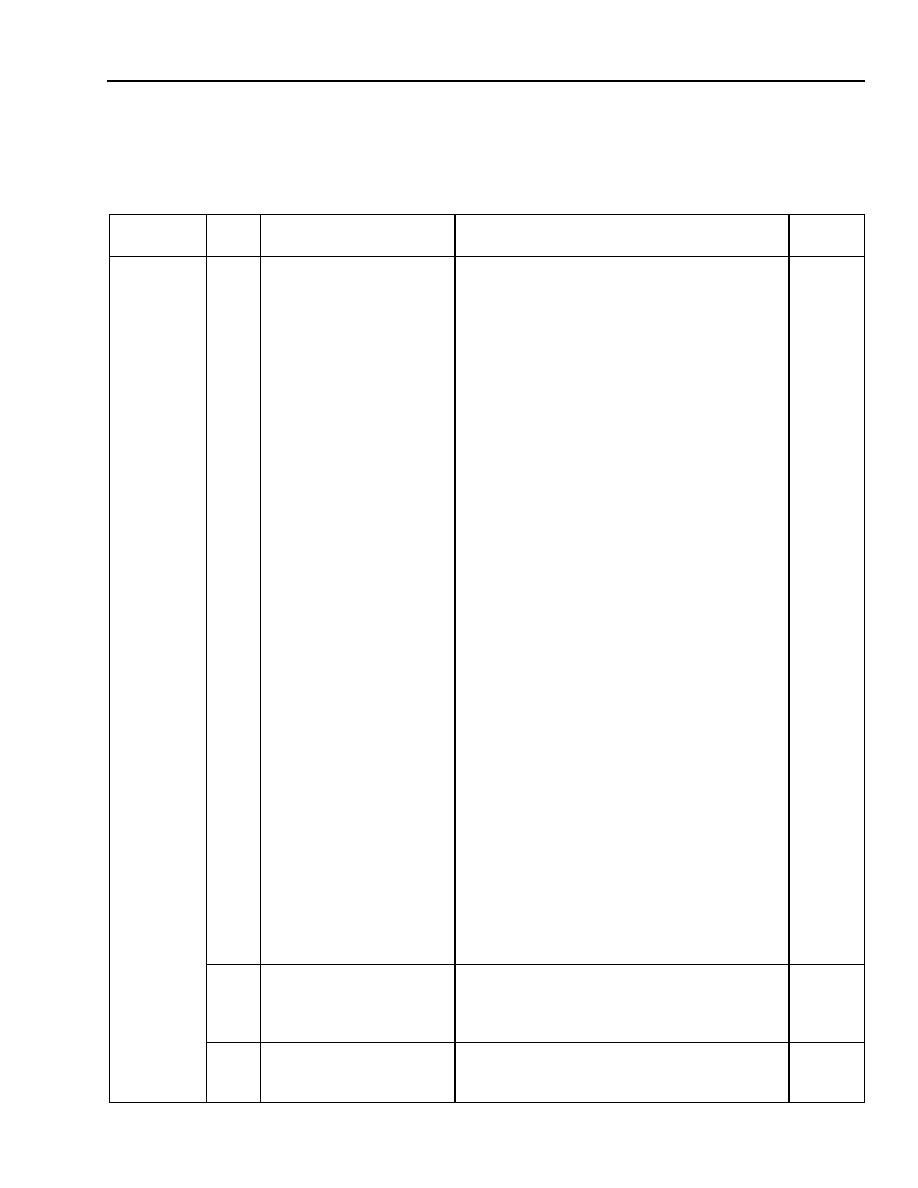

- Table 61. TOHP_CH_INT, Channel Interrupt (R/W, RO)

- Table 62. TOHP_DLT_EVT[A-D][1-2], 0x0802-0x0809, Delta/Event Registers (COR/COW-RO)

- Table 63. TOHP_RX_TX_STATE[A-D], 0x080A-0x080D, Receive/Transmit State Registers (RO)

- Table 64. TOHP_MSK[A-D][1-2], 0x080E-0x0815, Mask Bit Registers (R/W)

- Table 65. TOHP_TRG[A-D], 0x0816-0x0819, Trigger Register 0 ∆ 1 (R/W)

- Table 66. TOHP_CNTD[A-D][1-2], 0x081A-0x0821, Continuous N-Times Detect (CNTD) Values (R/W)

- Table 67. TOHP_RCTL[A-D][1-2], 0x0822-0x0829, Receive Control [1-2] (R/W)

- Table 68. TOHP_RCTL[A-D][3], 0x082A-0x082D, Receive Control 3 (R/W)

- Table 69. TOHP_TCTL[A-D][1-2], 0x082E-0x0835, Transmit Control [1-2] (R/W)

- Table 70. TOHP_TCTL[A-D][3], 0x0836-0x0839, Transmit Control 3 (R/W)

- Table 71. TOHP_SD_SETR[A-D][1-2], 0x083A-0x0841, Signal Degrade BER Algorithm Set Control Registers [1-2] (R/W)

- Table 72. TOHP_SD_SETR[A-D][3], 0x0842-0x0845, Signal Degrade BER Algorithm Set Control Register [3] (R/W)

- Table 73. TOHP_SD_CLEARR[A-D][1-2], 0x0846-0x084D, Signal Degrade BER Algorithm Clear Control Registers [1-2] (R/W)

- Table 74. TOHP_SD_CLEARR[A-D][3], 0x084E-0x0851, Signal Degrade BER Algorithm Clear Control Register [3] (R/W)

- Table 75. TOHP_SF_SETR[A-D][1-2], 0x0852-0x0859, Signal Fail Set BER Algorithm Control Registers [1-2] (R/W)*

- Table 76. TOHP_SF_SETR[A-D][3], 0x085A-0x085D, Signal Fail BER Algorithm Set Control Register [3] (R/W)

- Table 77. TOHP_SF_CLEARR[A-D][1-2], 0x085E-0x0865, Signal Fail BER Algorithm Clear Control Registers [1-2] (R/W)*

- Table 78. TOHP_SF_CLEARR[A-D][3], 0x0866-0x0869, Signal Fail BER Algorithm Clear Control Register [3] (R/W)

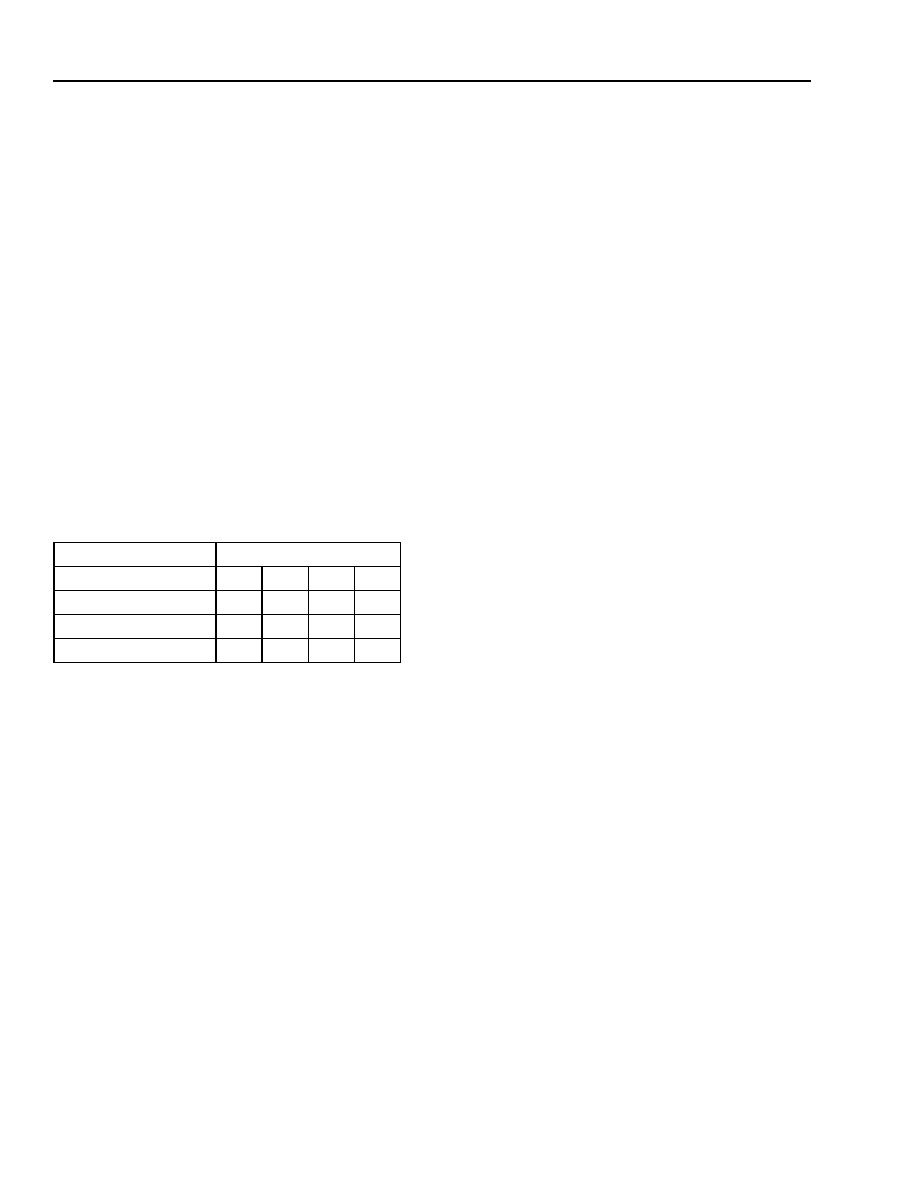

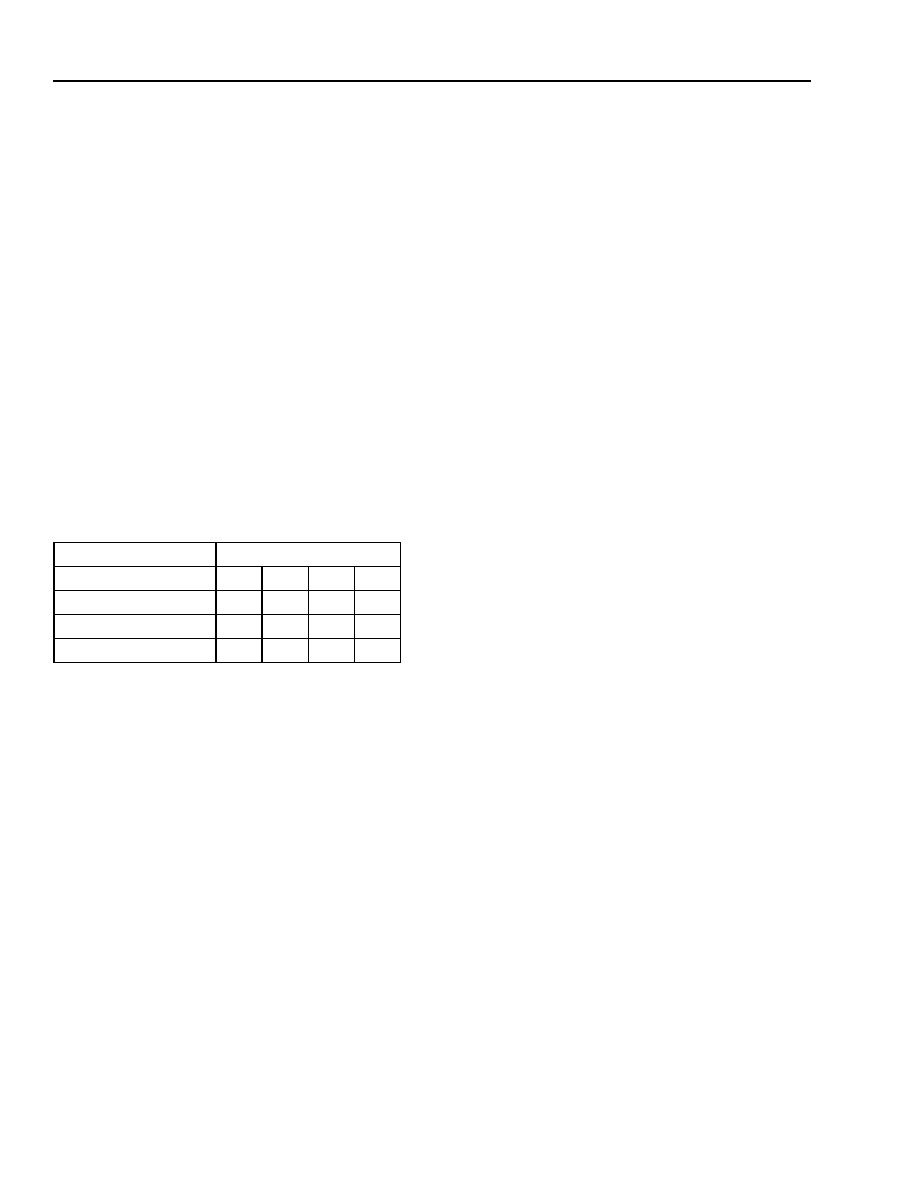

- Table 79. Ns, L, M, and B Values to Set the BER Indicator

- Table 80. Ns, L, M, and B Values to Clear the BER Indicator

- Table 81. TOHP_B1ECNTR[A-D], 0x086A-0x086D, B1 Error Count (RO)

- Table 82. TOHP_B2ECNTR[A-D][1-2], 0x086E-0x0875, B2 Error Count (RO)

- Table 83. TOHP_M1ECNTR[A-D][1-2], 0x0876-0x087D, M1 Error Count (RO)

- Table 84. TOHP_TOH_INSR[A-D][1-2], 0x087E-0x0885, Transmit OH Insert Value (R/W)

- Table 85. TOHP_RMONR[A-D][1-3], 0x0886-0x0891, Receive Monitor Value (RO)

- Table 86. TOHP_RJ0DMONR[A-D][1-32], 0x0892-0x0911, Receive J0/Z0 Monitor Value Registers (RO)

- Table 87. TOHP_TJ0DINSR[A-D][1-32], 0x0912-0x09A9, Transmit J0/Z0 Insert Value Registers (R/W)

- Table 88. TOHP_TZ0DINSR[A-D][1-6], 0x09AA-0x09C1, Transmit Z0 Insert Value Registers (R/W)

- Table 89. Z0 Byte Ordering STS-48 Mode for Z0-1-Z0-47

- Table 90. Z0 Byte Ordering STS-12 Mode for Z0-1-Z0-11

- Table 91. Z0 Byte Ordering STS-3 Mode for Z0-1-Z0-2

- Table 92. TOHP_SCRATCHR, 0x09C2, TOHP-48 Scratch Register (R/W)

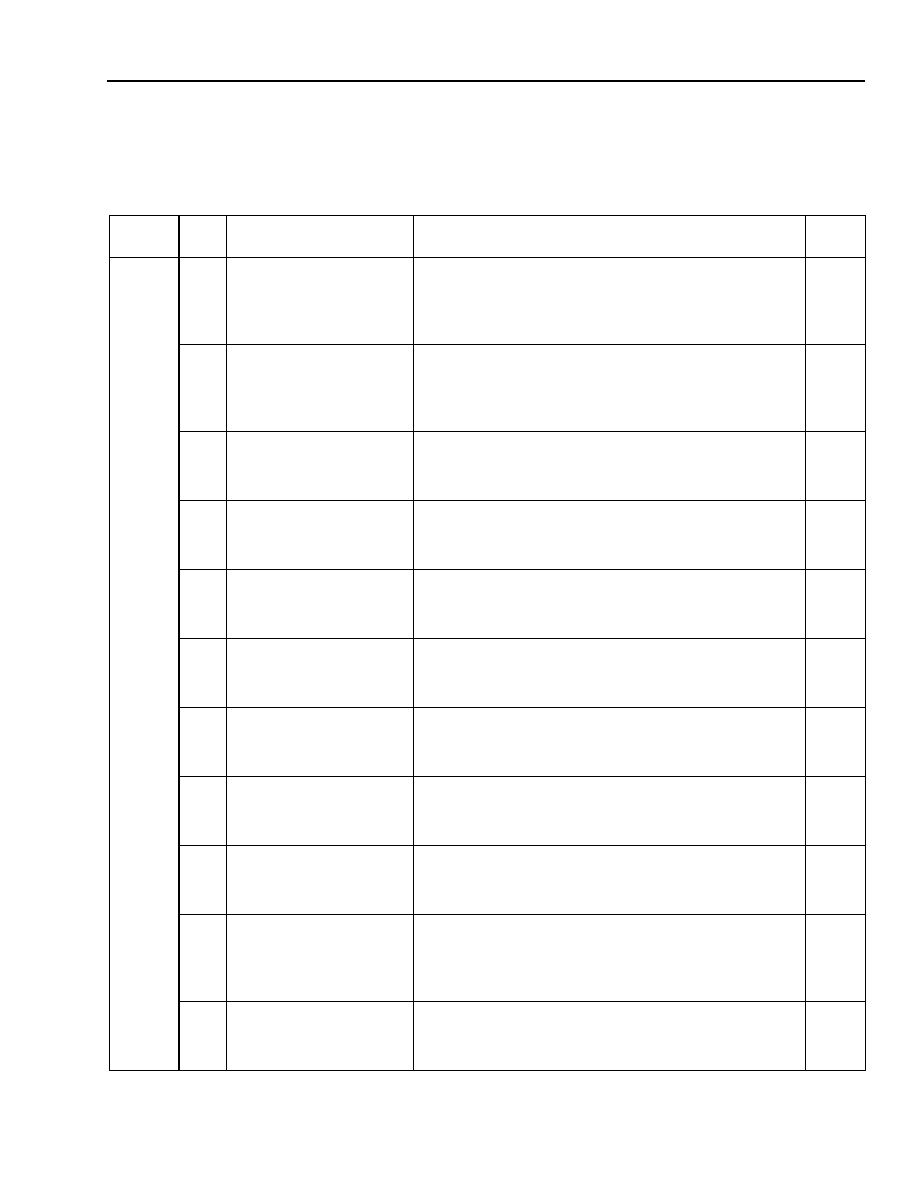

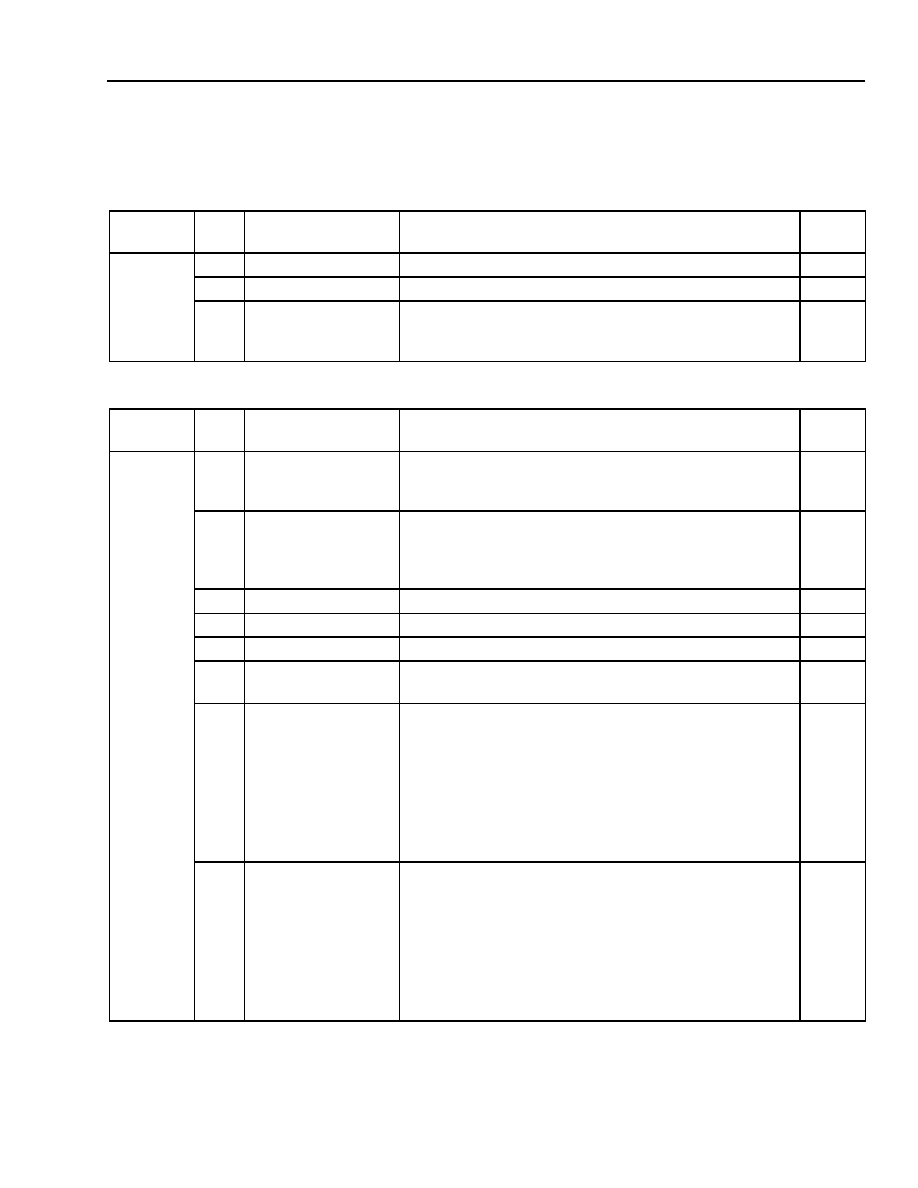

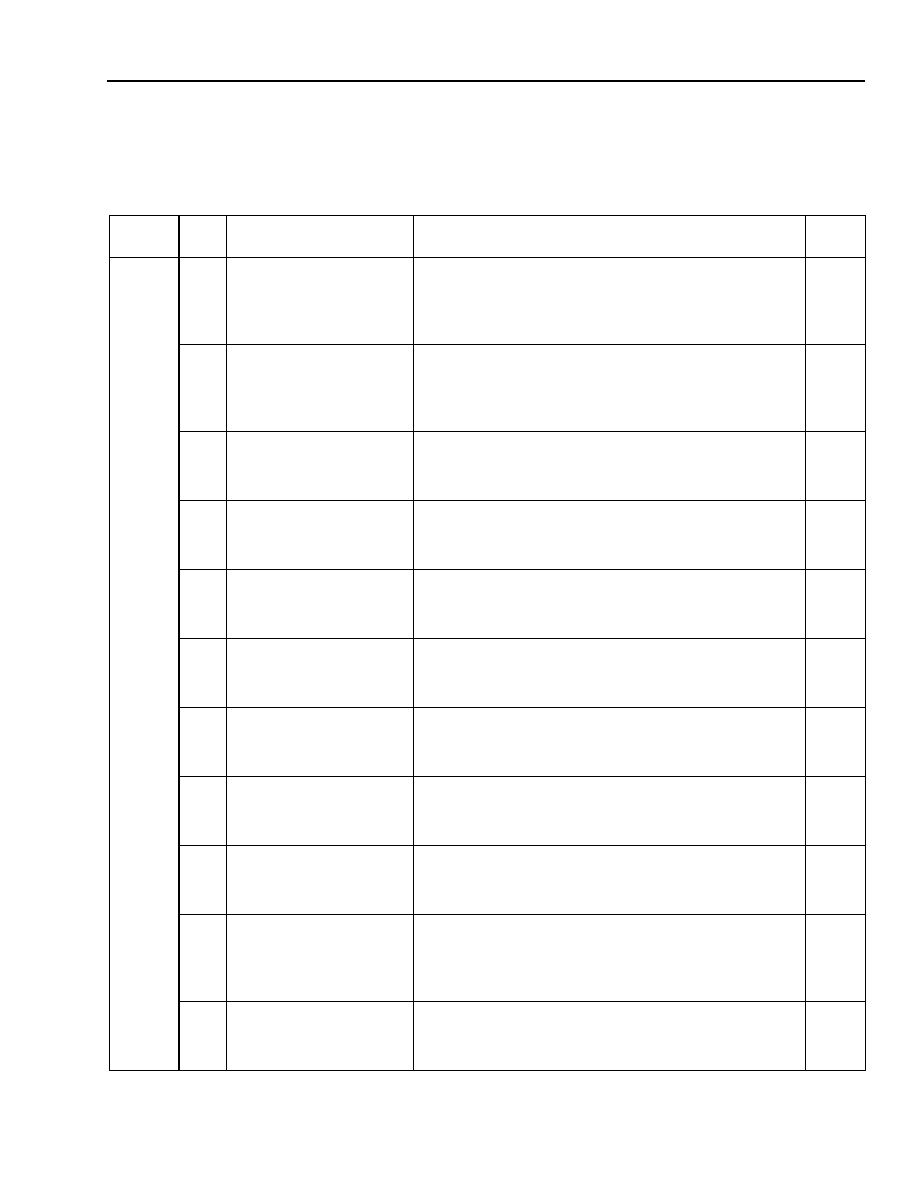

- Table 93. TOHP-48 Register Map

- Table 94. E1/F1 Path Status Definition

- Table 95. RDI-P Codes and Interpretation

- Table 96. PP_IDR, PP Identification Register (RO, Fixed Value)

- Table 97. PP_CORWR, PP Clear on Read/Write Register (R/W, Control)

- Table 98. PP_POH_ALMBNR[1-2], Path Overhead Alarm Status Binning Register (RO)

- Table 99. PP_ES_ALMBNBSR, Elastic Store Overrun/Underrun Alarm Status Binning Bytestream A-D (RO)

- Table 100. PP_TSES_ALMBSR[A-D], Time Slots 1-12 Elastic Store Overrun/Underrun Alarm Bytestream A-D (RO, COR/COW)

- Table 101. PP_SF_ALMBNBSR, Signal Fail Alarm Status Binning Bytestream A-D (RO)

- Table 102. PP_TSSF_ALMBSR[A-D], Time Slots 1-12 Signal Fail Alarm Bytestream A-D (RO, COR/ COW)

- Table 103. PP_RDI_ALMBNBSR, Remote Defect Indicator Alarm Status Binning Bytestream A-D (RO)

- Table 104. PP_TSRDI_ALMBSR[A-D], Time Slots 1-12 Remote Defect Indicator Alarm Bytestream A-D (RO, COR/COW)

- Table 105. PP_PLM_ALMBNBSR, Payload Label Mismatch Alarm Status Binning Bytestream A-D (RO)

- Table 106. PP_TSPLM_ALMBSR[A-D], Time Slots 1-12 Payload Label Mismatch Alarm Bytestream A-D (RO, COR/COW)

- Table 107. PP_UNEQR_ALMBNBSR, Unequipped Received Alarm Status Binning Bytestream A-D (RO)

- Table 108. PP_TSUNEQR_ALMBSR[A-D], Time Slots 1-12 Unequipped Received Alarm Bytestream A-D (RO, COR/COW)

- Table 109. PP_AIS_ALMBNBSR, Alarms Indicator Signal Alarm Status Binning Bytestream A-D (RO)

- Table 110. PP_TSAIS_ALMBSR[A-D], Time Slots 1-12 Alarms Indicator Signal Alarm Bytestream A-D (RO, COR/COW)

- Table 111. PP_LOP_ALMBNBSR, Loss of Pointer Alarm Status Binning Bytestream A-D (RO)

- Table 112. PP_TSLOP_ALMBSR[A-D], Time Slots 1-12 Loss of Pointer Alarm Bytestream A-D (RO, COR/COW)

- Table 113. PP_CNCTMM_ALMBNBSR, Channel Path Concatenation Map Mismatch Alarm Status Binning Bytestream A-D (RO, COR/COW)

- Table 114. PP_USCNCTM_ALMBNBSR, Channel Path Unsupported Concatenation Map Alarm Binning Bytestream A-D (RO, COR/COW)

- Table 115. PP_J1NVLDMSG_ALMBNBSR, Channel Path J1 New Validated Message Alarm Binning Bytestream A-D (RO, COR/COW)

- Table 116. PP_J1MSGMM_ALMBNBSR, Channel Path J1 Message Mismatch Alarm Status Binning Bytestream A-D (RO, COR/COW)

- Table 117. PP_PDI_ALMBNBSR, Payload Defect Indicator Alarm Status Binning Bytestream A-D (RO)

- Table 118. PP_TSPDI_ALMBSR[A-D], Time Slots 1-12 Payload Defect Indicator Alarm Bytestream A-D (RO, COR/COW)

- Table 119. PP_RDI_ALMDBNBSR, Path Overhead STS-1 Remote Defect Indicator Alarm Delta Status Binning Bytestream A-D (RO)

- Table 120. PP_TSRDI_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Remote Defect Indicator Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 121. PP_PLM_ALMDBNBSR, Path Overhead STS-1 Payload Label Mismatch Alarm Delta Status Binning Bytestream A-D (RO)

- Table 122. PP_TSPLM_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Payload Label Mismatch Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 123. PP_UNEQR_ALMDBNBSR, Path Overhead STS-1 Unequipped Received Alarm Delta Status Binning Bytestream A-D (RO)

- Table 124. PP_TSUNEQR_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Unequipped Received Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 125. PP_AIS_ALMDBNBSR, Path Overhead STS-1 Alarm Indicator Signal Alarm Delta Status Binning Bytestream A-D (RO)

- Table 126. PP_TSAIS_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Alarm Indicator Signal Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 127. PP_LOP_ALMDBNBSR, Path Overhead STS-1 Loss of Pointer Alarm Delta Status Binning Bytestream A-D (RO)

- Table 128. PP_TSLOP_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Loss of Pointer Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 129. PP_PTRACCMPIR, Path Trace Access Complete Interrupt (RO, COR/COW)

- Table 130. PP_PDI_ALMDBNBSR, Path Overhead STS-1 Payload Defect Indicator Alarm Delta Status Binning Bytestream A-D (RO)

- Table 131. PP_TSPDI_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Payload Defect Indicator Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 132. STS-1 #12 Channel Path Alarm Binning Status Registers (RO)

- Table 133. STS-1 Channel Path SS New Validated Bits Alarm Status Binning Bytestream A-D (RO)

- Table 134. STS-1 Channel Path Time Slots 1-12 SS New Validated Bits Alarm Status Bytestream A-D (RO, COR/COW)

- Table 135. STS-1 Channel Path SS Bits Mismatch Alarm Status Binning Bytestream A-D (RO)

- Table 136. STS-1 Channel Path Time Slots 1-12 SS Bits Mismatch Alarm Status Bytestream A-D (RO, COR/COW)

- Table 137. PP_POH_ALMBNMR[1-2], Path Overhead Alarm Status Binning Masks (R/W)

- Table 138. PP_ES_ALMBNMBSR, Elastic Store Overrun/Underrun Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 139. PP_TSES_ALMMBSR[A-D], Time Slots 1-12 Elastic Store Overrun/Underrun Alarm Masks Bytestream A-D (R/W)

- Table 140. PP_SF_ALMBNMBSR, Signal Fail Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 141. PP_TSSF_ALMMBSR[A-D], Time Slots 1-12 Signal Fail Alarm Masks Bytestream A-D (R/W)

- Table 142. PP_RDI_ALMBNMBSR, Remote Defect Indicator Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 143. PP_TSRDI_ALMMBSR[A-D], Time Slots 1-12 Remote Defect Indicator Alarm Masks Bytestream A-D (R/W)

- Table 144. PP_PLM_ALMBNMBSR, Payload Label Mismatch Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 145. PP_TSPLM_ALMMBSR[A-D], Time Slots 1-12 Payload Label Mismatch Alarm Masks Bytestream A-D (R/W)

- Table 146. PP_UNEQR_ALMBNMBSR, Unequipped Received Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 147. PP_TSUNEQR_ALMMBSR[A-D], Time Slots 1-12 Unequipped Received Alarm Masks Bytestream A-D (R/W)

- Table 148. PP_AIS_ALMBNMBSR, Alarms Indicator Signal Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 149. PP_TSAIS_ALMMBSR[A-D], Time Slots 1-12 Alarms Indicator Signal Alarm Masks Bytestream A-D (R/W)

- Table 150. PP_LOP_ALMBNMBSR, Loss of Pointer Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 151. PP_TSLOP_ALMMBSR[A-D], Time Slots 1-12 Loss of Pointer Alarm Masks Bytestream A-D (R/W)

- Table 152. PP_CNCTMM_ALMMBSR, Channel Path Concatenation Map Mismatch Alarm Status Masks Bytestream A-D (R/W)

- Table 153. PP_USCNCTM_ALMMBSR, Channel Path Unsupported Concatenation Map Alarm Masks Bytestream A-D (R/W)

- Table 154. PP_J1NVLDMSG_ALMMBSR, Channel Path J1 New Validated Message Alarm Masks Bytestream A-D(R/W)

- Table 155. PP_J1MSGMM_ALMMBSR, Channel Path J1 Message Mismatch Alarm Status Masks Bytestream A-D (R/W)

- Table 156. PP_PDI_ALMBNMBSR, Payload Defect Indicator Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 157. PP_TSPDI_ALMMBSR[A-D], Time Slots 1-12 Payload Defect Indicator Alarm Masks Bytestream A-D (R/W)

- Table 158. PP_RDI_ALMDBNMBSR, Path Overhead STS-1 Remote Defect Indicator Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 159. PP_TSRDI_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Remote Defect Indicator Alarm Delta Masks Bytestream A-D (R/W)

- Table 160. PP_PLM_ALMDBNMBSR, Path Overhead STS-1 Payload Label Mismatch Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 161. PP_TSPLM_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Payload Label Mismatch Alarm Delta Masks Bytestream A-D (R/W)

- Table 162. PP_UNEQR_ALMDBNMBSR, Path Overhead STS-1 Unequipped Received Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 163. PP_TSUNEQR_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Unequipped Received Alarm Delta Masks Bytestream A-D (R/W)

- Table 164. PP_AIS_ALMDBNMBSR, Path Overhead STS-1 Alarm Indicator Signal Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 165. PP_TSAIS_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Alarm Indicator Signal Alarm Delta Masks Bytestream A-D (R/W)

- Table 166. PP_LOP_ALMDBNMBSR, Path Overhead STS-1 Loss of Pointer Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 167. PP_TSLOP_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Loss of Pointer Alarm Delta Masks Bytestream A-D (R/W)

- Table 168. PP_PTRACCMPIR, Path Trace Access Complete Interrupt Mask (R/W)

- Table 169. STS-1 Channel Path SS Bits Mismatch Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 170. STS-1 Channel Path Time Slots 1-12 SS Bits Mismatch Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 171. PP_PDI_ALMDBNMBSR, Path Overhead STS-1 Payload Defect Indicator Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 172. PP_TSPDI_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Payload Defect Indicator Alarm Delta Masks Bytestream A-D (R/W)

- Table 173. STS-1 #12 Channel Path Alarm Binning Mask Status Registers (R/W)

- Table 174. STS-1 Channel Path SS New Validated Bits Alarm Binning Masks Bytestream A-D (R/W)

- Table 175. STS-1 Channel Path Time Slots 1-12 SS New Validated Bits Alarm Masks Bytestream A-D (R/W)

- Table 176. PP_PTRBFR[1-32], Path Trace Buffer Registers 1-32 (R/W)

- Table 177. PP_PTRACCTLR1, Path Trace Access Control Register 1 (R/W)

- Table 178. PP_PTRACCTLR2, Path Trace Access Control Register 2 (R/W)

- Table 179. PP_PTRACCTLR3, Path Trace Access Control Register 3 (R/W)

- Table 180. PP_PTRACBGR, Path Trace Access Begin (WO)

- Table 181. PP_STS12PTRCTLR[1-6], STS-12 Channel Path Trace Control Registers 1-6 (R/W)

- Table 182. STS-12 F2, H4, Z3, Z4, and Z5 Status (RO)

- Table 183. Path F2, H4, Z3, Z4, and Z5 Provisioning Bytestream A-D (R/W, Control)

- Table 184. STS-12 SS Bits Status (RO)

- Table 185. PP_TSRDI_ALMPSBSR[A-D], Time Slots 1-12 RDI Alarm Persistency Bytestream A-D (RO)

- Table 186. PP_TSPLM_ALMPSBSR[A-D], Time Slots 1-12 PLM Alarm Persistency Bytestream A-D (RO)

- Table 187. PP_TSPUNEQ_ALMPSBSR[A-D], Time Slots 1-12 Path Unequipped Alarm Persistency Bytestream A-D (RO)

- Table 188. PP_TSAIS_ALMPSBSR[A-D], Time Slots 1-12 AIS Alarm Persistency Bytestream A-D (RO)

- Table 189. PP_TSLOP_ALMPSBSR[A-D], Time Slots 1-12 LOP Alarm Persistency Bytestream A-D (RO)

- Table 190. PP_TSPDI_ALMPSBSR[A-D], Time Slots 1-12 PDI Alarm Persistency Bytestream A-D (RO)

- Table 191. PP_TSRDI_STBSR[A-D], Time Slots 1-12 RDI State Bytestream A-D (RO)

- Table 192. PP_TSPLM_STBSR[A-D], Time Slots 1-12 PLM State Bytestream A-D (RO)

- Table 193. PP_TSPUNEQ_STBSR[A-D], Time Slots 1-12 Path Unequipped State Bytestream A-D (RO)

- Table 194. PP_TSAIS_STBSR[A-D], Time Slots 1-12 AIS State Bytestream A-D (RO)

- Table 195. PP_TSLOP_STBSR[A-D], Time Slots 1-12 LOP State Bytestream A-D (RO)

- Table 196. PP_TSPDI_STBSR[A-D], Time Slots 1-12 PDI State Bytestream A-D (RO)

- Table 197. PP_SFWSZ_SELR[1-2], Signal Fail Window Size Select Registers 1-2 (R/W, Control)

- Table 198. PP_SFDR[0-7], Signal Fail Detect Threshold Registers 0-7 (R/W, Control)

- Table 199. PP_SFCLRR[0-7], Signal Fail Clear Threshold Registers 0-7 (R/W, Control)

- Table 200. PP_SFWSZR[0-3], Signal Fail Window Size 0/1/2/3 Registers (R/W, Control)

- Table 201. PP_ECNCTM_TSBSR[A-D], Expected Concatenation Map Time Slots 1-12 in Bytestream A-D (R/W)

- Table 202. PP_CNCTCPREN_TSBSR[A-D], Concatenation Compare Enable Time Slots 1-12 in Bytestream A-D (R/W)

- Table 203. PP_RCNCTM_TSBSR[A-D], Received Concatenation Map Time Slots 1-12 in Bytestream A-D (RO)

- Table 204. PP_SWAIS_ISRTR, Software AIS Insert (R/W)

- Table 205. PP_STS12_PINCDECR, STS-12 Pointer Increment/Decrement (R/W)

- Table 206. PP_TSSS_ISRTBSR[A-D], Time Slot 1-Time Slot 12 SS Bits Insert Bytestream A-D (R/W)

- Table 207. PP_TSE1F1_ISRTBSR[A-D], Time Slot 1-Time Slot 12 E1/F1 Insert Bytestream A-D (R/W)

- Table 208. PP_E2_ISRTCTLR[A-D], E2 Insert Control Bytestream A-D (R/W)

- Table 209. PP_TS_INCDECBNR[A-D], Time Slots 1-12 Increment/Decrement Binning Select Bytestream A-D (R/W)

- Table 210. PP_AISONTIM_ISRTR[A-D], STS-12 Pointer Processor Control (R/W)

- Table 211. PP_TSPDIVLD_CTLBSR[A-D], Time Slot 1-Time Slot 12 PDI Validate Control Bytestream A-D (R/W)

- Table 212. PP_EXPC2_PVSNR[1-24], Expected C2 Byte Provisioning (R/W)

- Table 213. PP_TSCBB_ERRBSR[A-D], Time Slot 1-Time Slot 12 Count Block/Bit Errors Bytestream A-D

- Table 214. PP_TS1_6_SSBSRA, PP_TS7_12_SSBSRA, Time Slots 1-12 SS Bits Insertion Value Bytestream A (R/W)

- Table 215. PP_TS1_6_SSBSRB, PP_TS7_12_SSBSRB, Time Slots 1-12 SS Bits Insertion Value Bytestream B (R/W)

- Table 216. PP_TS1_6_SSBSRC, PP_TS7_12_SSBSRC, Time Slots 1-12 SS Bits Insertion Value Bytestream C (R/W)

- Table 217. PP_TS1_6_SSBSRD, PP_TS7_12_SSBSRD, Time Slots 1-12 SS Bits Insertion Value Bytestream D (R/W)

- Table 218. SS Bits Provisioning (R/W)

- Table 219. SS Bits Validation/Compare Period (R/W)

- Table 220. Elastic Store Decrement and Increment (R/W)

- Table 221. Elastic Store Overflow Region (R/W)

- Table 222. PP_TS_E1F1ISRTR[1-24], Time Slots 1-48 E1/F1 Insert

- Table 223. PP_E2_ISRTBSR[A-D], E2 Byte Insert Bytestream A-D

- Table 224. PP_TSMNTR[1-48], Time Slots 1-48 Maintenance (R/W)

- Table 225. PP_PI_LSECINCR[A-D], Pointer Interpreter Last Second Increments Bytestream A-D (RO)

- Table 226. PP_PI_LSECDECR[A-D], Pointer Interpreter Last Second Decrements Bytestream A-D (RO)

- Table 227. PP_PG_LSECINCR[A-D], Pointer Generator Last Second Increments Bytestream A-D (RO)

- Table 228. PP_PG_LSECDECR[A-D], Pointer Generator Last Second Decrements Bytestream A-D (RO)

- Table 229. PP_POH_ALMPMR, Path Overhead Alarm Performance Monitoring (RO)

- Table 230. PP_1BRDI_DPMBSR, Path Overhead One-Bit RDI Defect PM Bytestream A-D (RO)

- Table 231. PP_TS1BRDI_DPMBSR[A-D], Path Overhead Time Slots 1-12 One-Bit RDI Defect PM Bytestream A-D (RO)

- Table 232. PP_ERDI_PDPMBSR, Path Overhead ERDI Payload Defect PM Bytestream A-D (RO)

- Table 233. PP_TSERDI_PDPMBSR[A-D], Path Overhead Time Slots 1-12 ERDI Payload Defect PM Bytestream A-D (RO)

- Table 234. PP_ERDI_CDPMBSR, Path Overhead ERDI Connectivity Defect PM Bytestream A-D (RO)

- Table 235. PP_TSERDI_CDPMBSR[A-D], Path Overhead Time Slots 1-12 ERDI Connectivity Defect PM Bytestream A-D (RO)

- Table 236. PP_ERDI_SDPMBSR, Path Overhead ERDI Server Defect PM Bytestream A-D (RO)

- Table 237. PP_TSERDI_SDPMBSR[A-D], Path Overhead Time Slots 1-12 ERDI Server Defect PM Bytestream A-D (RO)

- Table 238. PP_UNEQR_PMBSR, Path Overhead Unequipped Received PM Bytestream A-D (RO)

- Table 239. PP_TSUNEQR_PMBSR[A-D], Path Overhead Time Slots 1-12 Unequipped Received PM Bytestream A-D (RO)

- Table 240. PP_AIS_PMBSR, Path Overhead Alarm Indicator Signal PM Bytestream A-D (RO)

- Table 241. PP_TSAIS_PMBSR[A-D], Path Overhead Time Slots 1-12 Alarm Indicator Signal PM Bytestream A-D (RO)

- Table 242. PP_LOP_PMBSR, Path Overhead Loss of Pointer PM Bytestream A-D (RO)

- Table 243. PP_TSLOP_PMBSR[A-D], Path Overhead Time Slots 1-12 Loss of Pointer PM Bytestream A-D (RO)

- Table 244. PP_LSECCVP_CPMR[1-48], Last Second CV-P Count Time Slot 1-Time Slot 48 PM (RO)

- Table 245. PP_LSECREIP_CPMR[1-48], Last Second REI-P Count Time Slot 1-Time Slot 48 PM (RO)

- Table 246. PP_TSRDIPR[1-48], Time Slots 1-48 Path RDI Status (RO)

- Table 247. PP_TSC2R[1-24], Time Slots 1-48 Path C2 Status (RO)

- Table 248. PP_TSPDIR[1-24], Time Slots 1-48 Path PDI Status (RO)

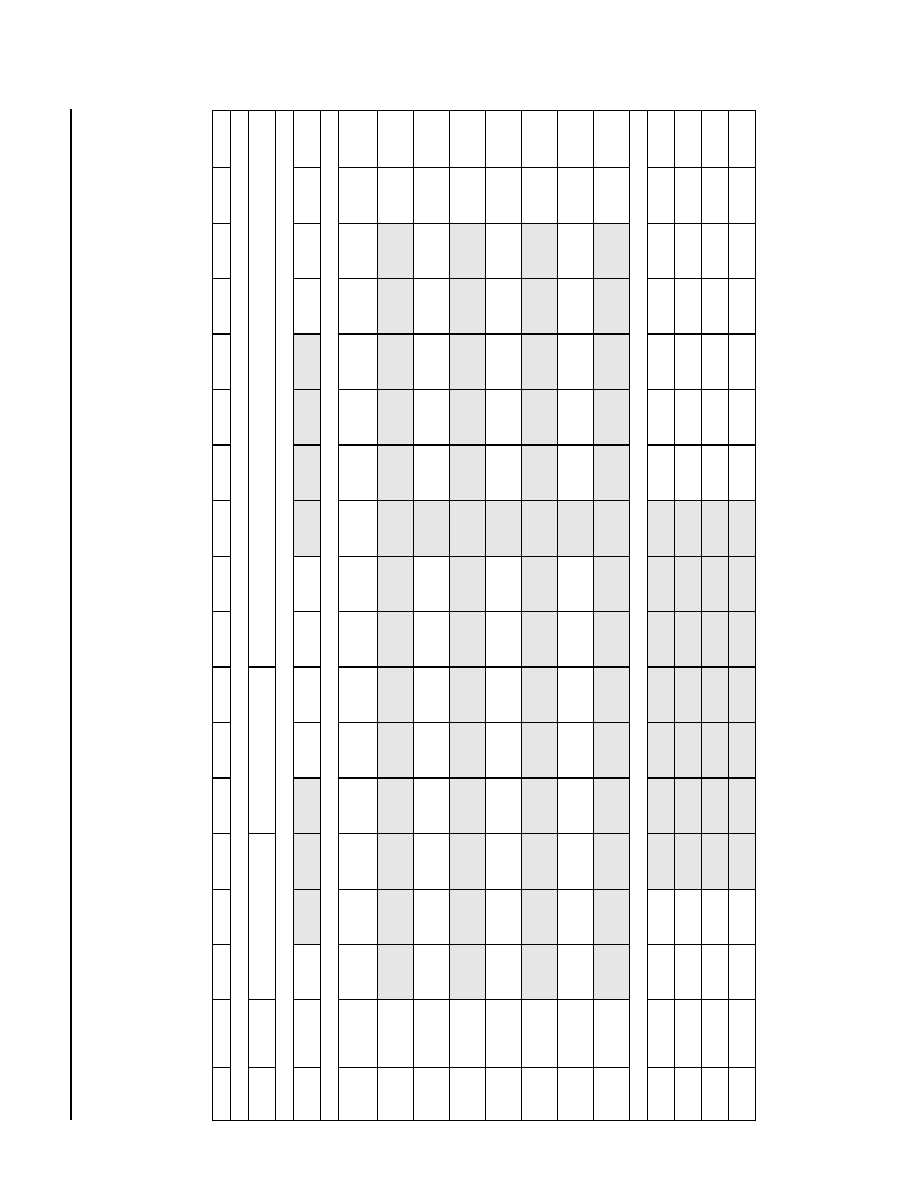

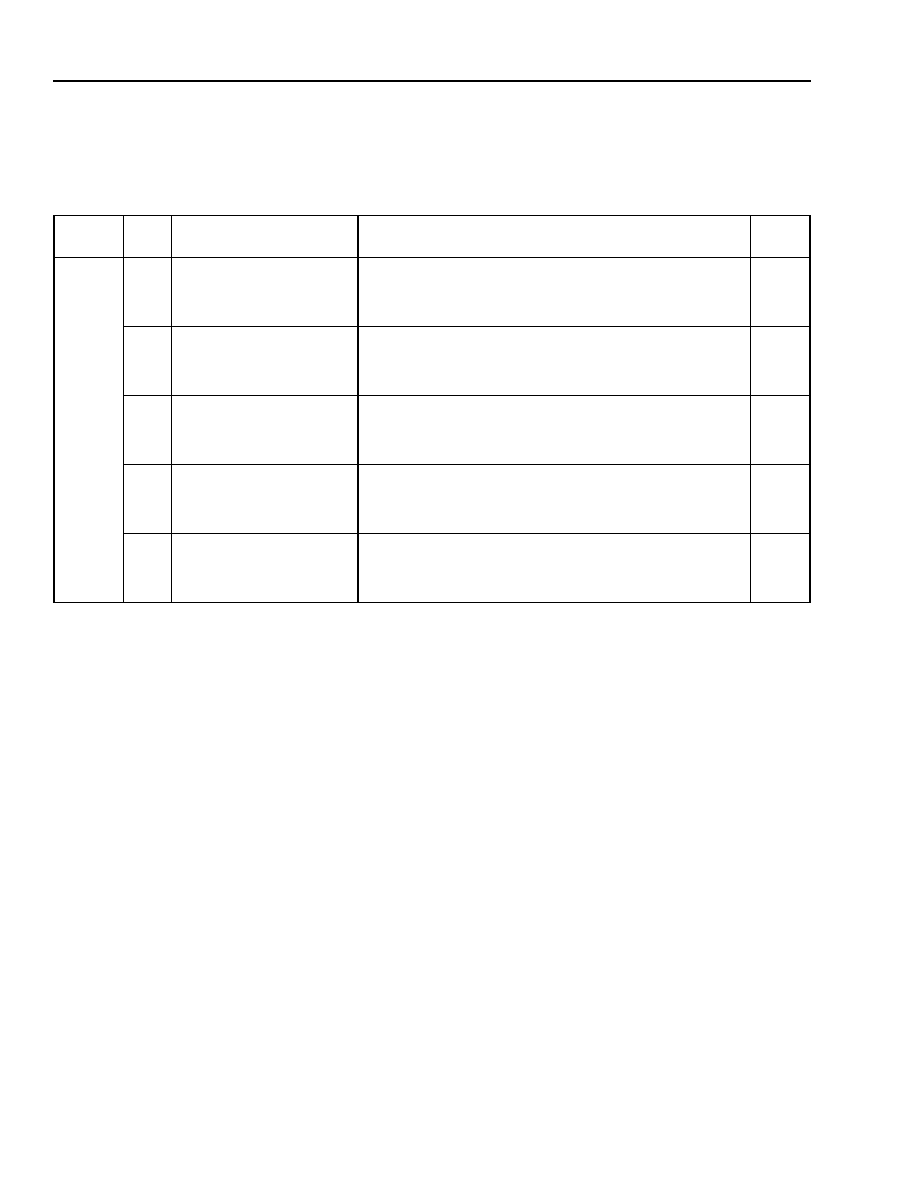

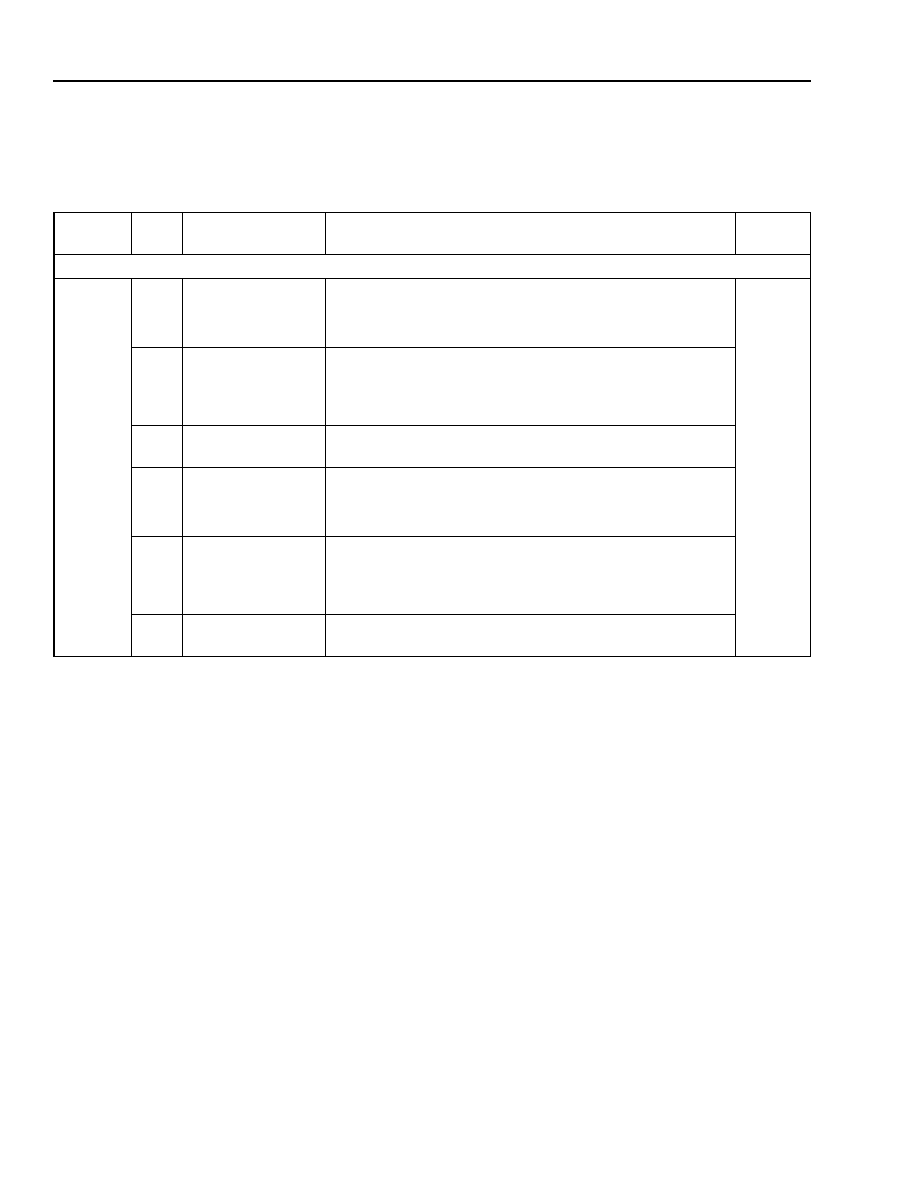

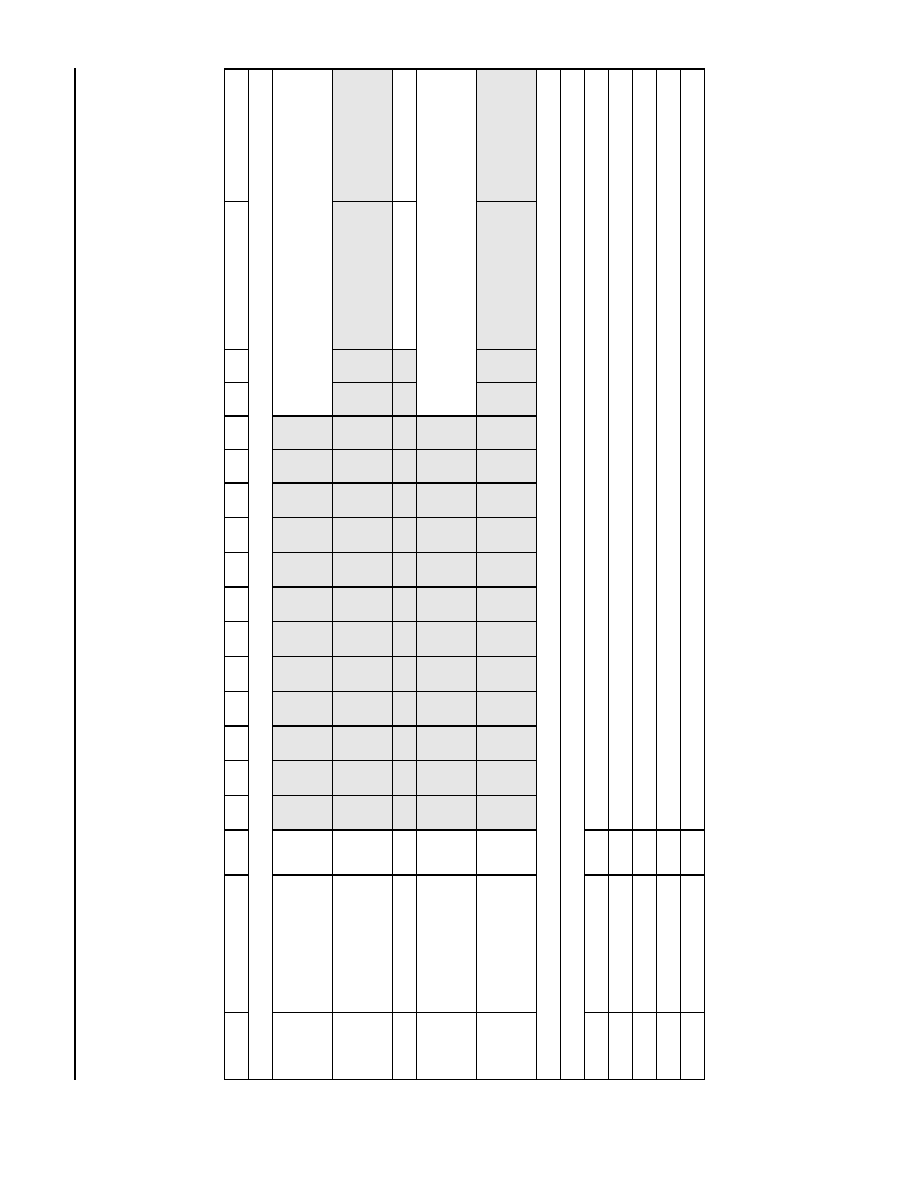

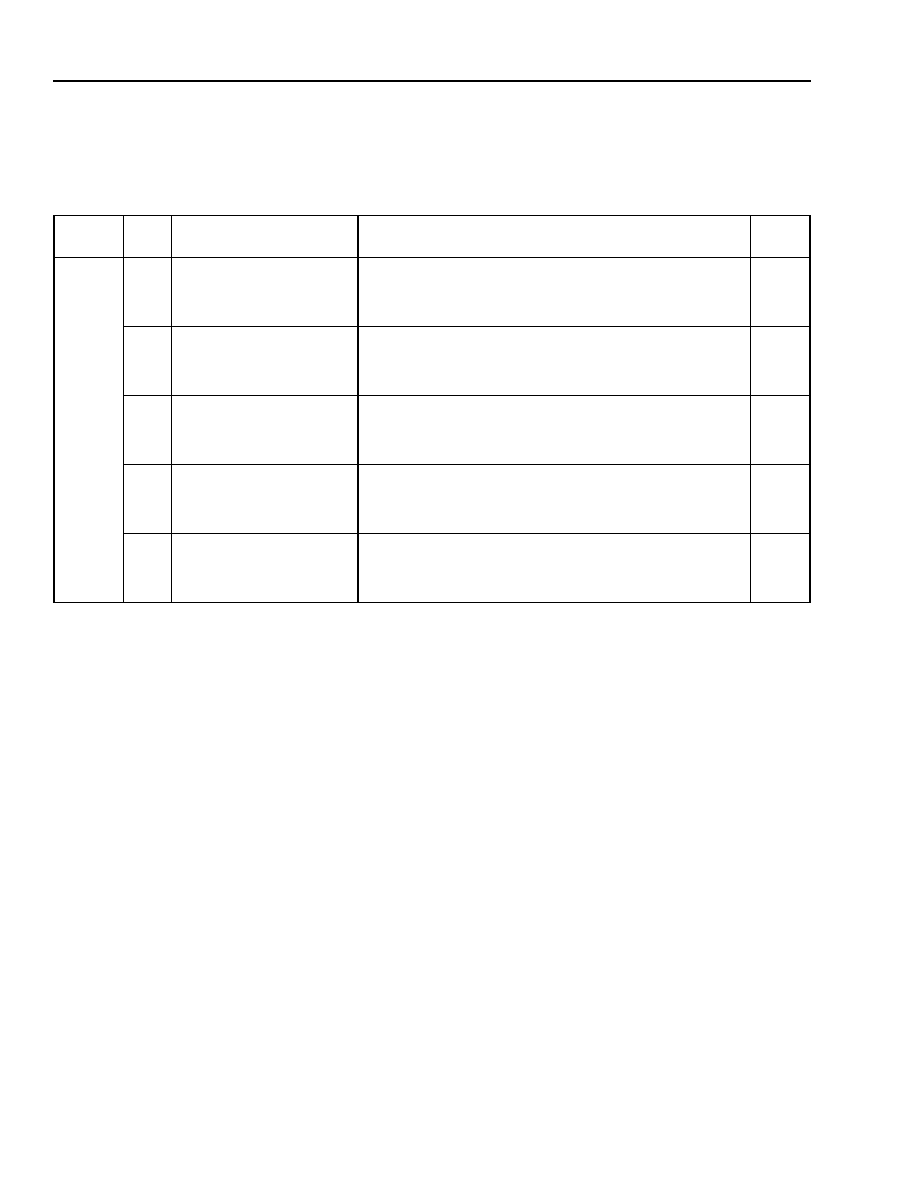

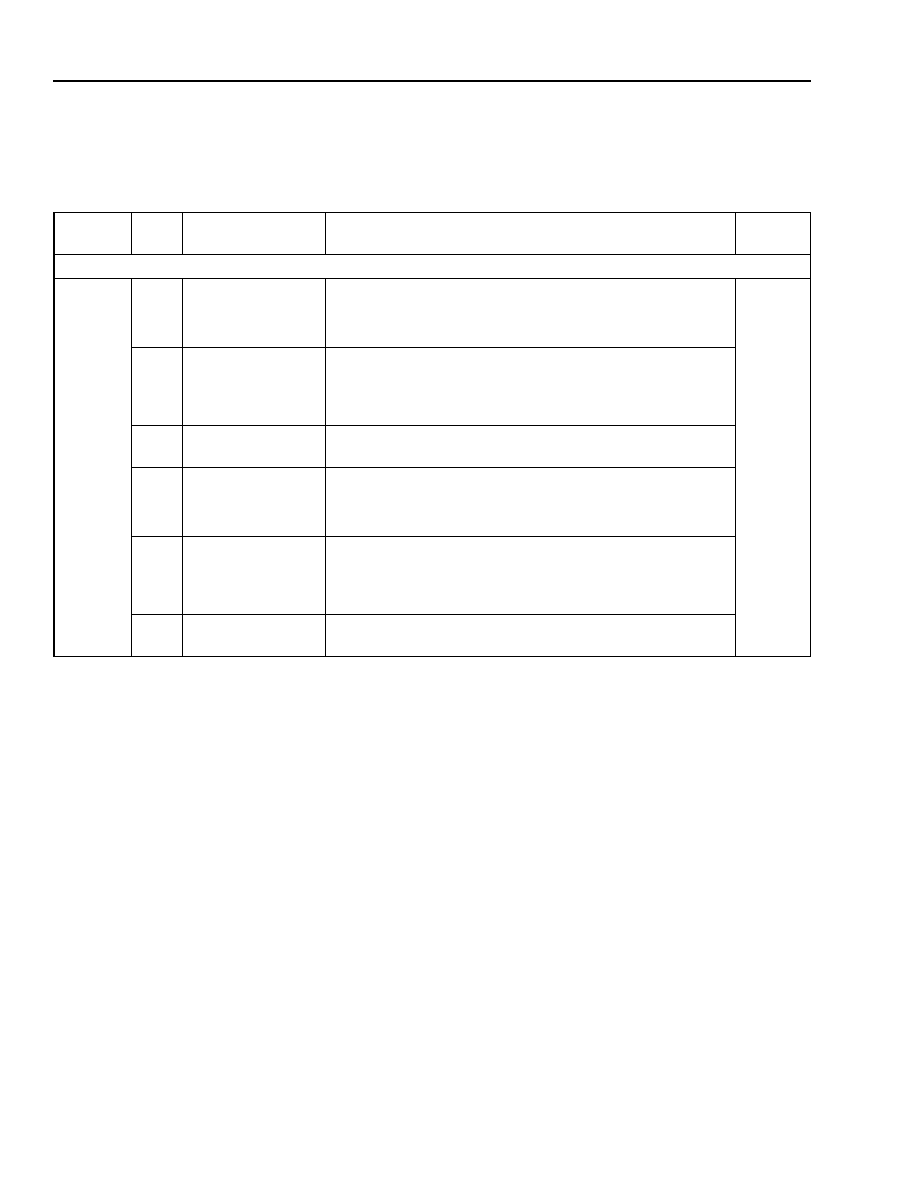

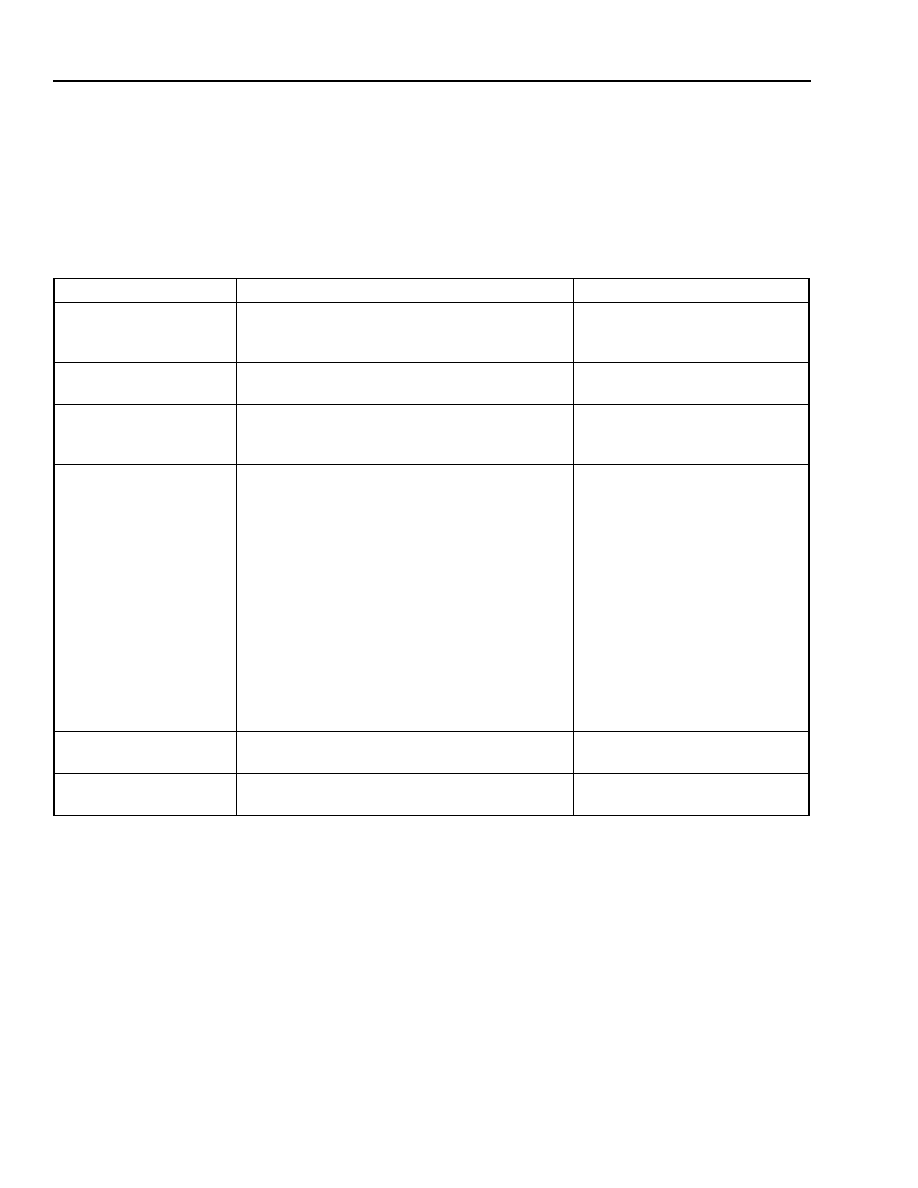

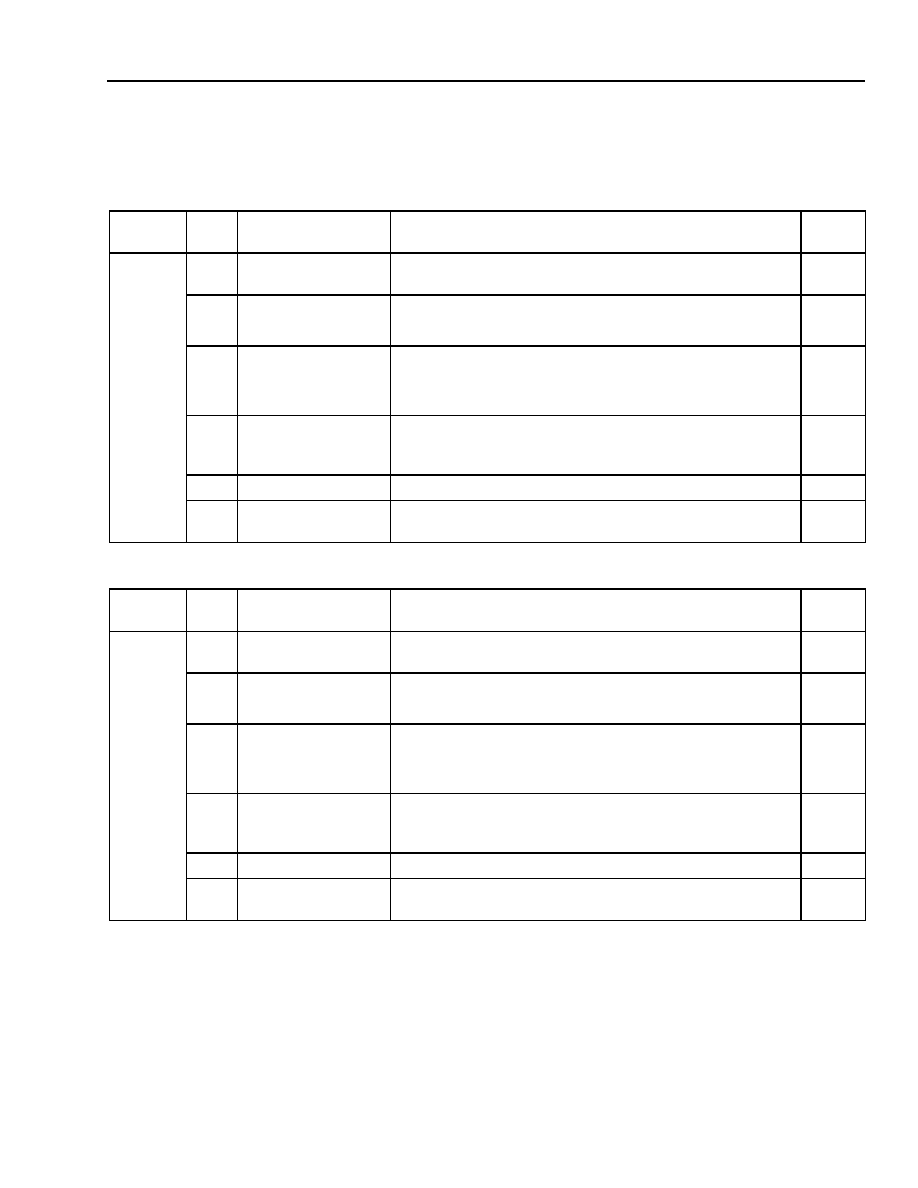

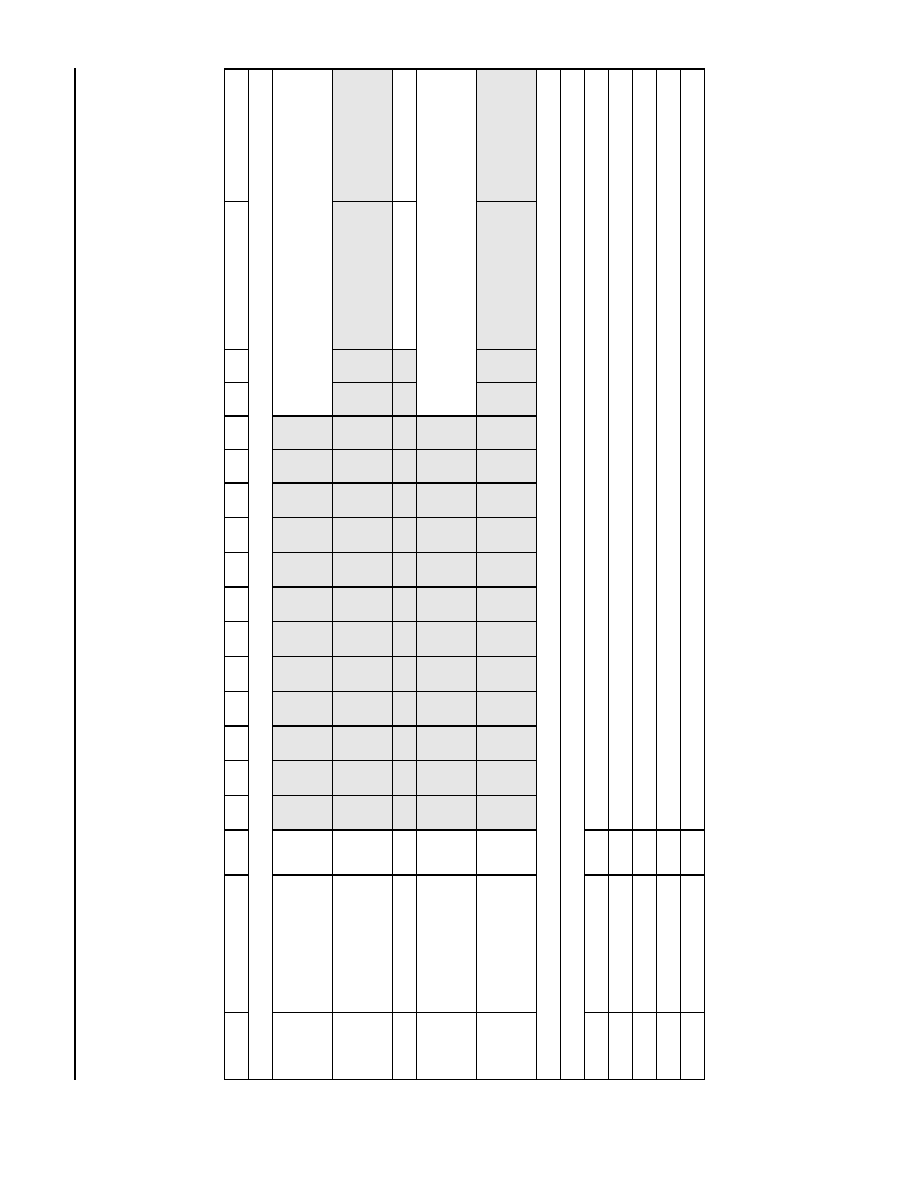

- Table 249. Pointer Processor Register Map

- Table 250. STS-48 Time-Slot Assignments

- Table 251. STS-12 Time-Slot Assignments

- Table 252. STS-3 Time-Slot Assignments

- Table 253. Sequence Register Map TS[0-23]_PM_[A-D]

- Table 254. Logical 16-Channel Configuration Concatenation Register Map CH[0-15]_NC

- Table 255. C2 Path Signal Label

- Table 256. G1 RDI-P Codes

- Table 257. STS-48 Time-Slot Internal Ordering

- Table 258. (PT_TX_VERSION), Version Control (RO)

- Table 259. (PT_TX_CH_INT), Tx Channel Composite Interrupt (RO)

- Table 260. (PT_TX_TS_[A-D]_INT), Tx Time-Slot Composite Interrupt (RO)

- Table 261. (PT_TX_CH_INTMASK), Tx Channel Composite Interrupt Mask (R/W)

- Table 262. (PT_TX_TS[A-D]_INTMASK), Tx Time-Slot Composite Interrupt Mask (R/W)

- Table 263. (PT_TX_MODE), Mode (R/W)

- Table 264. (PT_TX_BANKAorB), Tx_BANKAorB (R/W)

- Table 265. (PT_TX_SCRATCH), SCRATCH (R/W)

- Table 266. (PT_TX_SOFTRST), Tx Channel FIFO Reset (R/W)

- Table 267. (PT_TX_CH_DELTA [0-15]), Tx Channel Delta/Event (COR/W)

- Table 268. (PT_Tx_TS_[A-D]_Delta), Tx Delta/Event Register (COR/W)

- Table 269. (PT_Tx_CH_Status_[0-15]), Transmit Status Register (RO)

- Table 270. (PT_TX_TS_[A-D]0_Status), Transmit Status Register (RO)

- Table 271. (PT_TX_TS_[A-D]1_Status), Transmit Status Register (RO)

- Table 272. (PT_TX_TS_[A-D]2_Status), Transmit Status Register (RO)

- Table 273. (PT_Tx_CH_Mask_[0-15]), Tx Channel Mask Register (R/W)

- Table 274. (PT_Tx_TS_[A-D]_Mask), Tx Mask Register (COR/W)

- Table 275. (PT_Tx_Mask_A_[1-6]), Transmit Provisioning Register (R/W)

- Table 276. (PT_Tx_Mask_B_[1-6]), Transmit Provisioning Register (R/W)

- Table 277. (PT_Tx_Mask_C_[1-6]), Transmit Provisioning Register (R/W)

- Table 278. (PT_Tx_Mask_D_[1-6]), Transmit Provisioning Register (R/W)

- Table 279. (PT_Tx_RW4_[0-15]), Transmit Provisioning Register 4 (R/W)

- Table 280. (PT_Tx_RW1_[0-47]), Transmit Provisioning Register, Per Time Slot (R/W)

- Table 281. (PT_Tx_RW2_[0-15]), Transmit Provisioning Register, Per Channel (R/W)

- Table 282. (PT_Tx_RW3_[0-15]), Transmit Provisioning Register 3 (R/W)

- Table 283. (PT_Tx_alarm_[A-D]_[1]]), TX Alarm Mapper Register 1 (R/W)

- Table 284. (PT_Tx_alarm_[A-D]_[2]]), TX Alarm Mapper Register 2 (R/W)

- Table 285. (PT_Tx_alarm_[A-D]_[3]]), TX Alarm Mapper Register 3 (R/W)

- Table 286. (PT_Tx_alarm_[A-D]_[4]]), TX Alarm Mapper Register 4 (R/W)

- Table 287. (PT_Tx_alarm_[A-D]_[5]]), TX Alarm Mapper Register 5 (R/W)

- Table 288. (PT_Tx_alarm_[A-D]_[6]]), TX Alarm Mapper Register 6 (R/W)

- Table 289. (PT_Tx_RW5_[0-15]), Transmit Provisioning Register 5 (R/W)

- Table 290. (PT_Tx_TIMP_[A-D]), TX TIMP Alarm Register, Per Time Slot (R/W)

- Table 291. (PT_Tx_DS3E3_[A-B]), Transmit Provisioning Register (R/W)

- Table 292. (PT_Tx_STS1_[A-D]), Transmit Provisioning Register (R/W)

- Table 293. (PT_Tx_Cnfg_Alow), Transmit STS Configuration, Time Slots 0-5 (R/W)

- Table 294. (PT_Tx_Cnfg_Ahigh), Transmit STS Configuration, Time Slots 6-11 (R/W)

- Table 295. (PT_Tx_Cnfg_Blow), Transmit STS Configuration, Time Slots 0-5 (R/W)

- Table 296. (PT_Tx_Cnfg_Bhigh), Transmit STS Configuration, Time Slots 6-11 (R/W)

- Table 297. (PT_Tx_Cnfg_Clow), Transmit STS Configuration, Time Slots 0-5 (R/W)

- Table 298. (PT_Tx_Cnfg_Chigh), Transmit STS Configuration, Time Slots 6-11 (R/W)

- Table 299. (PT_Tx_Cnfg_Dlow), Transmit STS Configuration, Time Slots 0-5 (R/W)

- Table 300. (PT_Tx_Cnfg_Dhigh), Transmit STS Configuration, Time Slots 6-11 (R/W)

- Table 301. (PT_Tx_Stuffbyte_cnfg]), Tx Stuff Byte Configuration Register (R/W)

- Table 302. (PT_TX_SEQMAP_A_AB[0-11]), Sequence Map, Bank A, Slices A and B, Per Time Slot (R/W)

- Table 303. (PT_TX_SEQMAP_B_AB[0-11]), Sequence Map, Bank B, Slices A and B, Per Time Slot (R/W)

- Table 304. (PT_TX_SEQMAP_A_CD[0-11]), Sequence Map, Bank A, Slices C and D, Per Time Slot (R/W)

- Table 305. (PT_TX_SEQMAP_B_CD[0-11]), Sequence Map, Bank B, Slices C and D, Per Time Slot (R/W)

- Table 306. (PT_Tx_J1Byte_start_0_[0-31]), Transmit J1 Byte Message Channel 0 (R/W)

- Table 307. (PT_Tx_J1Byte_start_1_[0-31]), Transmit J1 Byte Message Channel 1 (R/W)

- Table 308. (PT_Tx_J1Byte_start_2_[0-31]), Transmit J1 Byte Message Channel 2 (R/W)

- Table 309. (PT_Tx_J1Byte_start_3_[0-31]), Transmit J1 Byte Message Channel 3 (R/W)

- Table 310. (PT_Tx_J1Byte_start_4_[0-31]), Transmit J1 Byte Message Channel 4 (R/W)

- Table 311. (PT_Tx_J1Byte_start_5_[0-31]), Transmit J1 Byte Message Channel 5 (R/W)

- Table 312. (PT_Tx_J1Byte_start_6_[0-31]), Transmit J1 Byte Message Channel 6 (R/W)

- Table 313. (PT_Tx_J1Byte_start_7_[0-31]), Transmit J1 Byte Message Channel 7 (R/W)

- Table 314. (PT_Tx_J1Byte_start_8_[0-31]), Transmit J1 Byte Message Channel 8 (R/W)

- Table 315. (PT_Tx_J1Byte_start_9_[0-31]), Transmit J1 Byte Message Channel 9 (R/W)

- Table 316. (PT_Tx_J1Byte_start_10_[0-31]), Transmit J1 Byte Message Channel 10 (R/W)

- Table 317. (PT_Tx_J1Byte_start_11_[0-31]), Transmit J1 Byte Message Channel 11 (R/W)

- Table 318. (PT_Tx_J1Byte_start_12_[0-31]), Transmit J1 Byte Message Channel 12 (R/W)

- Table 319. (PT_Tx_J1Byte_start_13_[0-31]), Transmit J1 Byte Message Channel 13 (R/W)

- Table 320. (PT_Tx_J1Byte_start_14_[0-31]), Transmit J1 Byte Message Channel 14 (R/W)

- Table 321. (PT_Tx_J1Byte_start_15_[0-31]), Transmit J1 Byte Message Channel 15 (R/W)

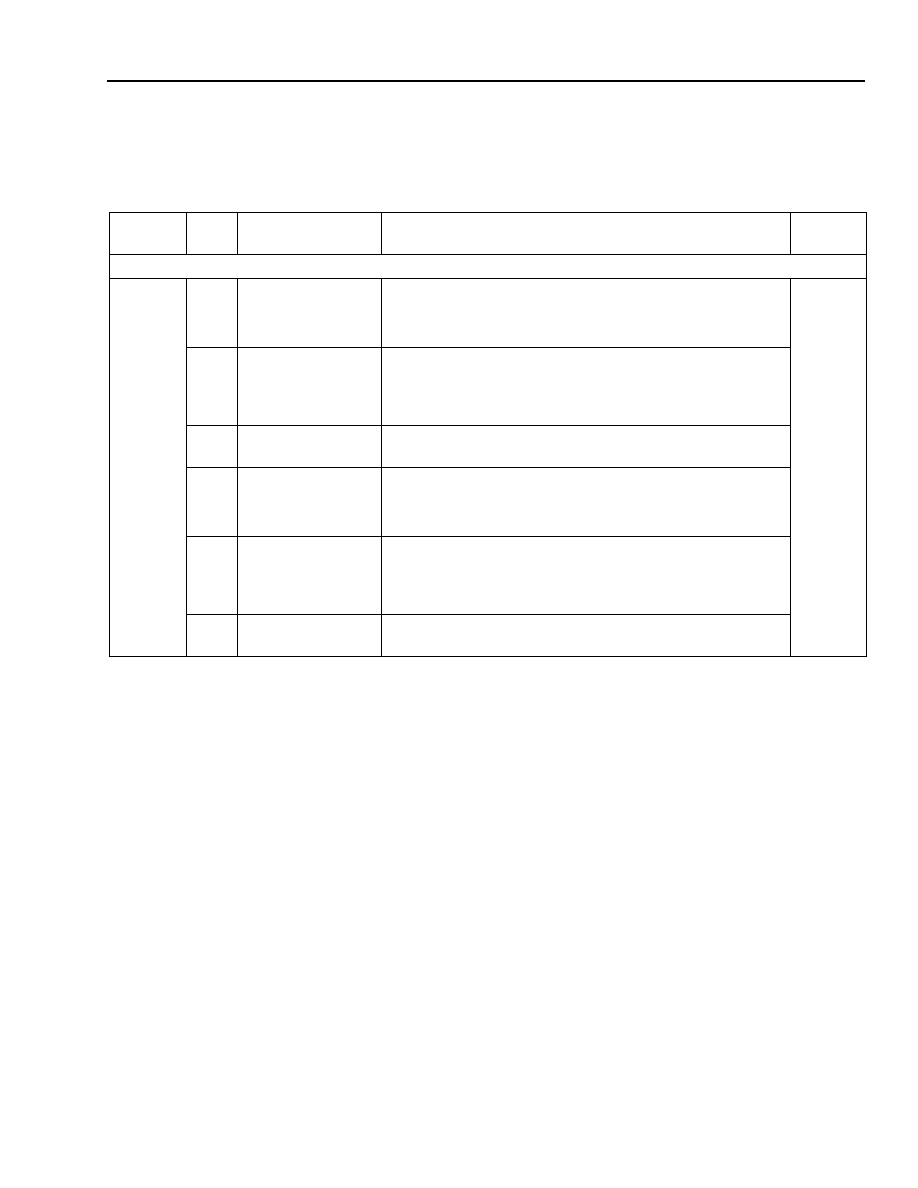

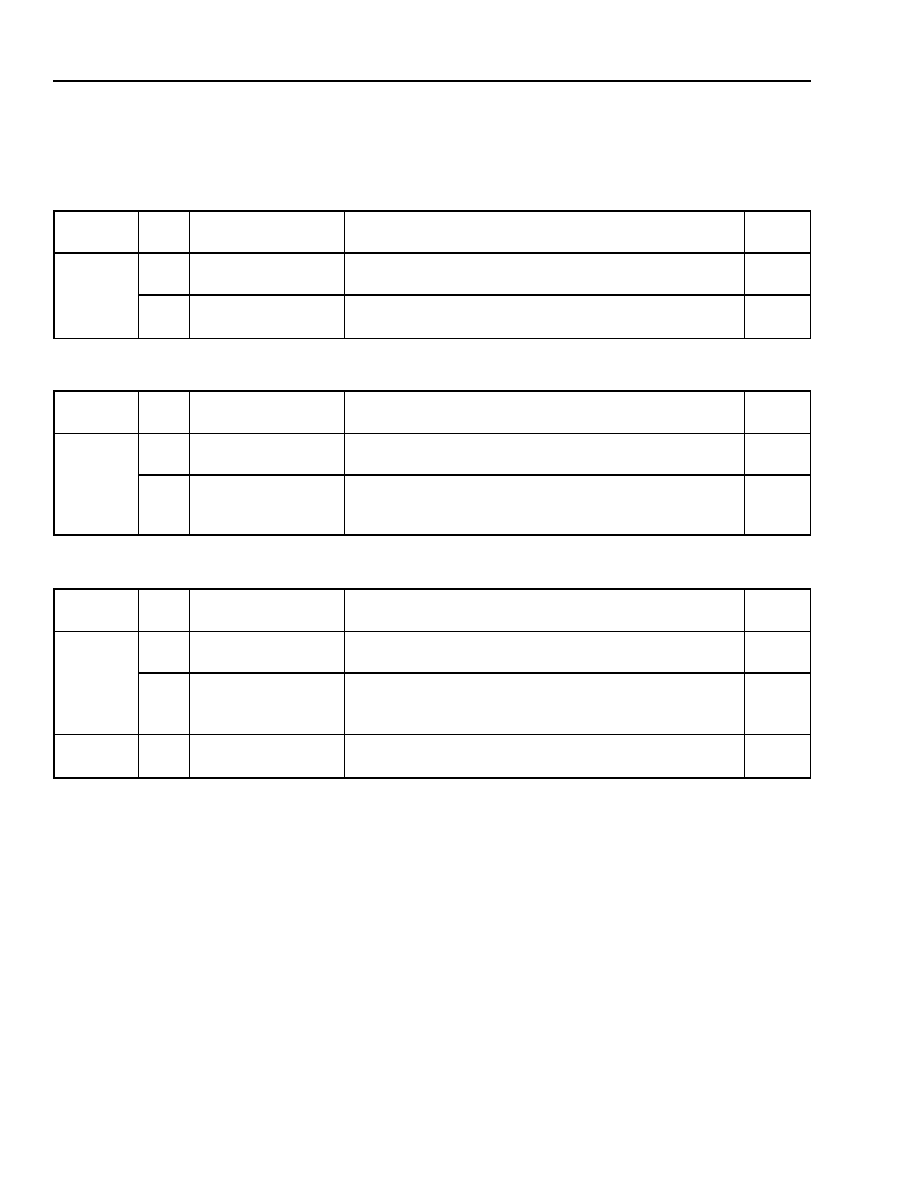

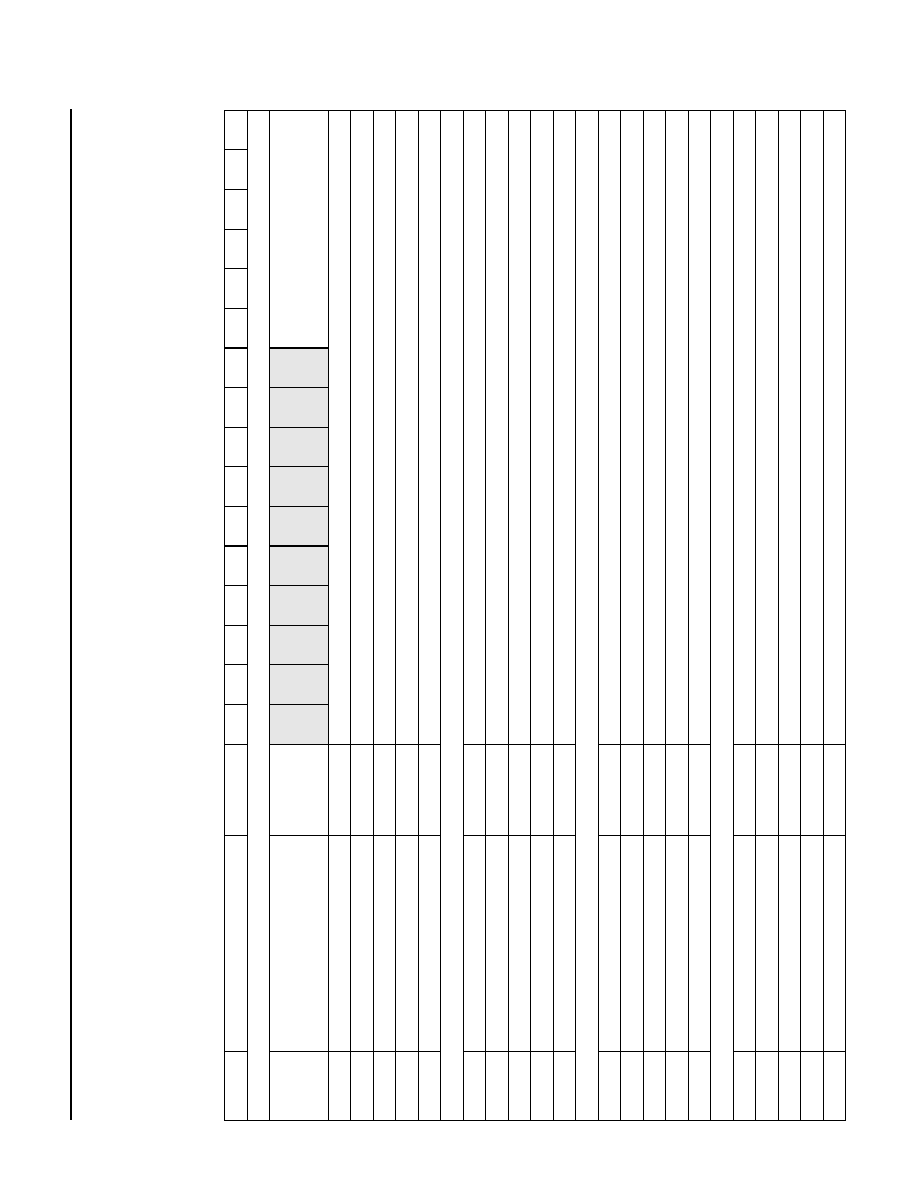

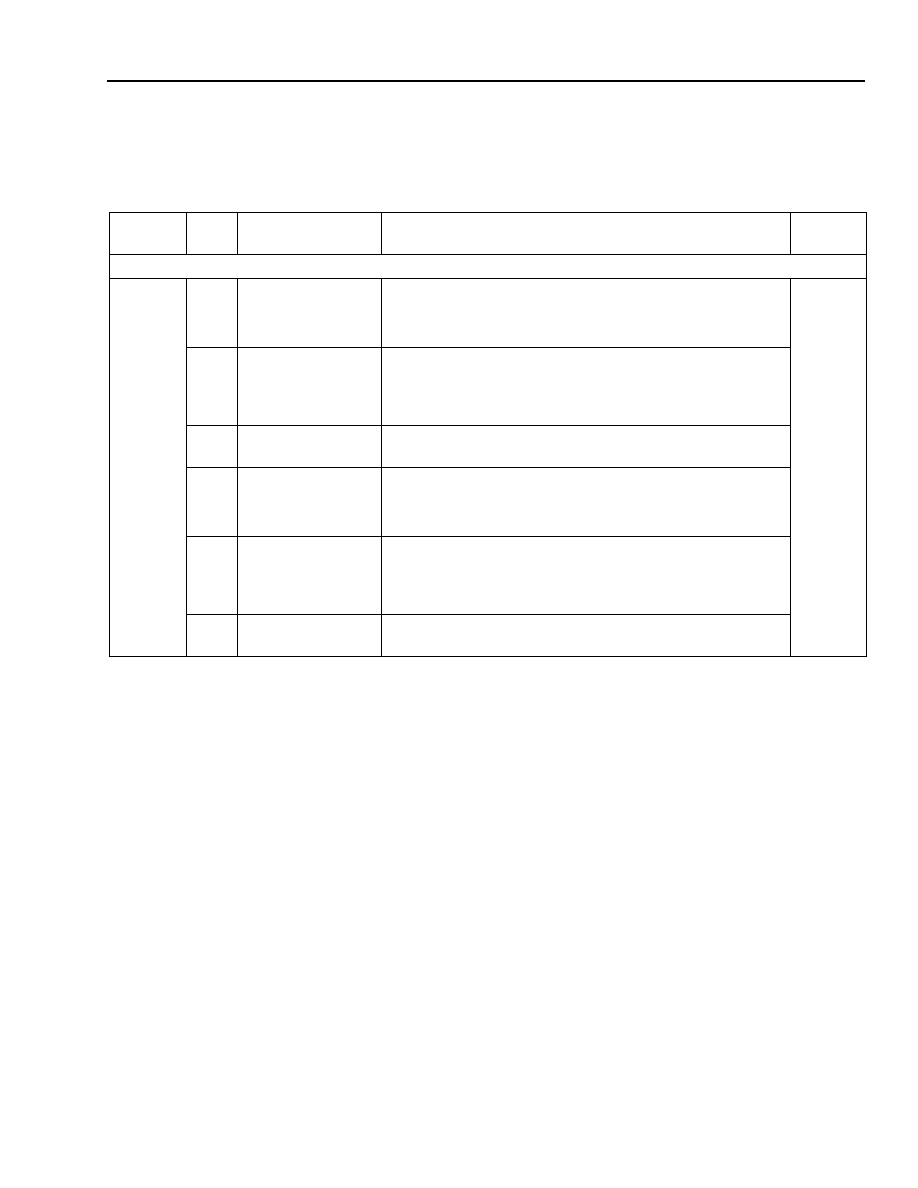

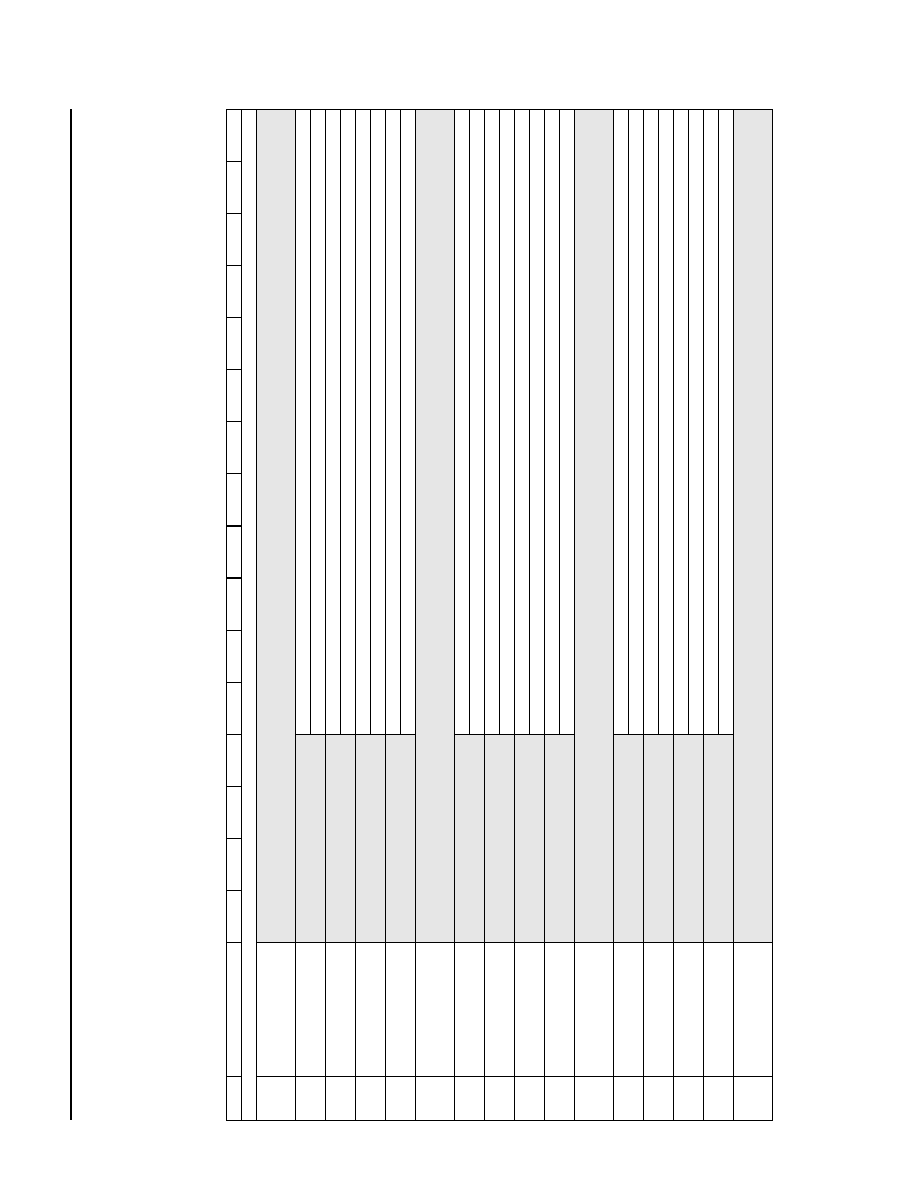

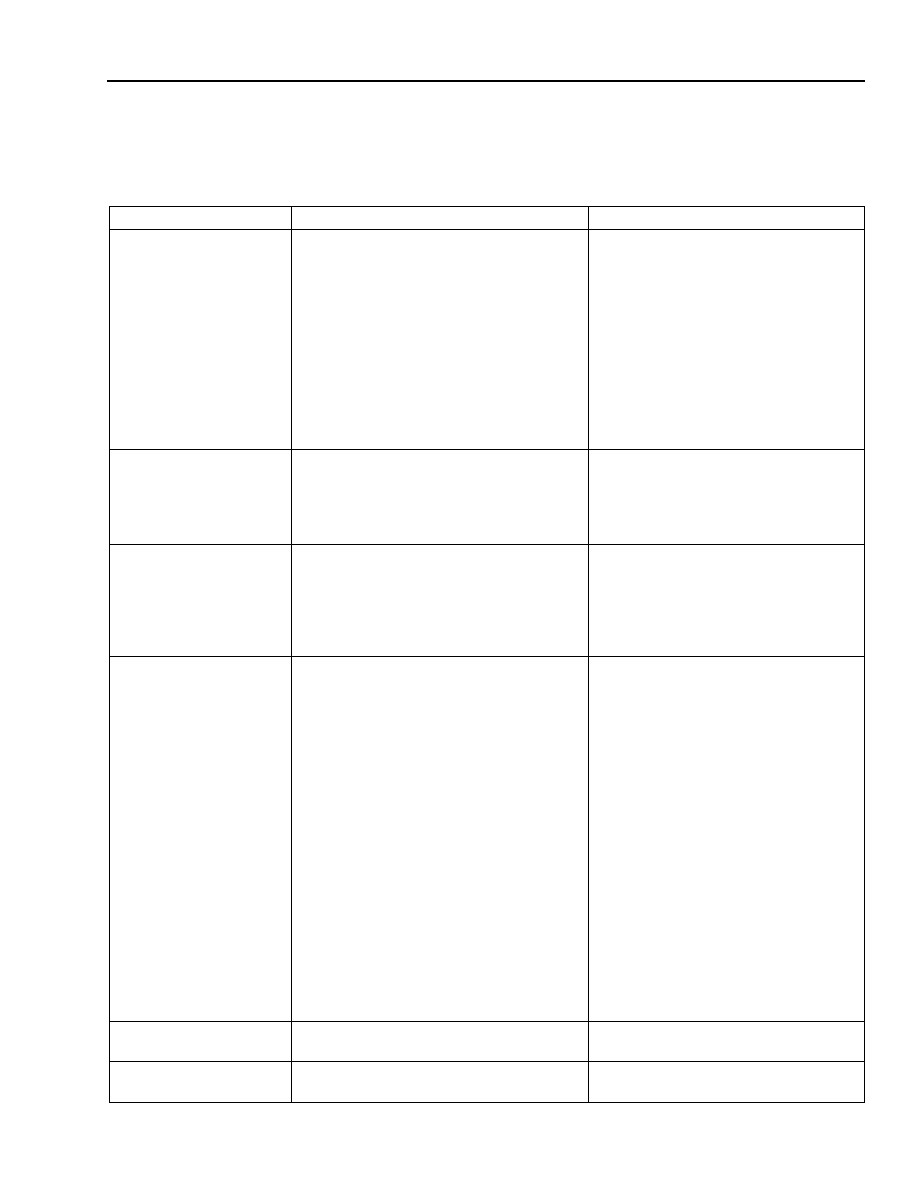

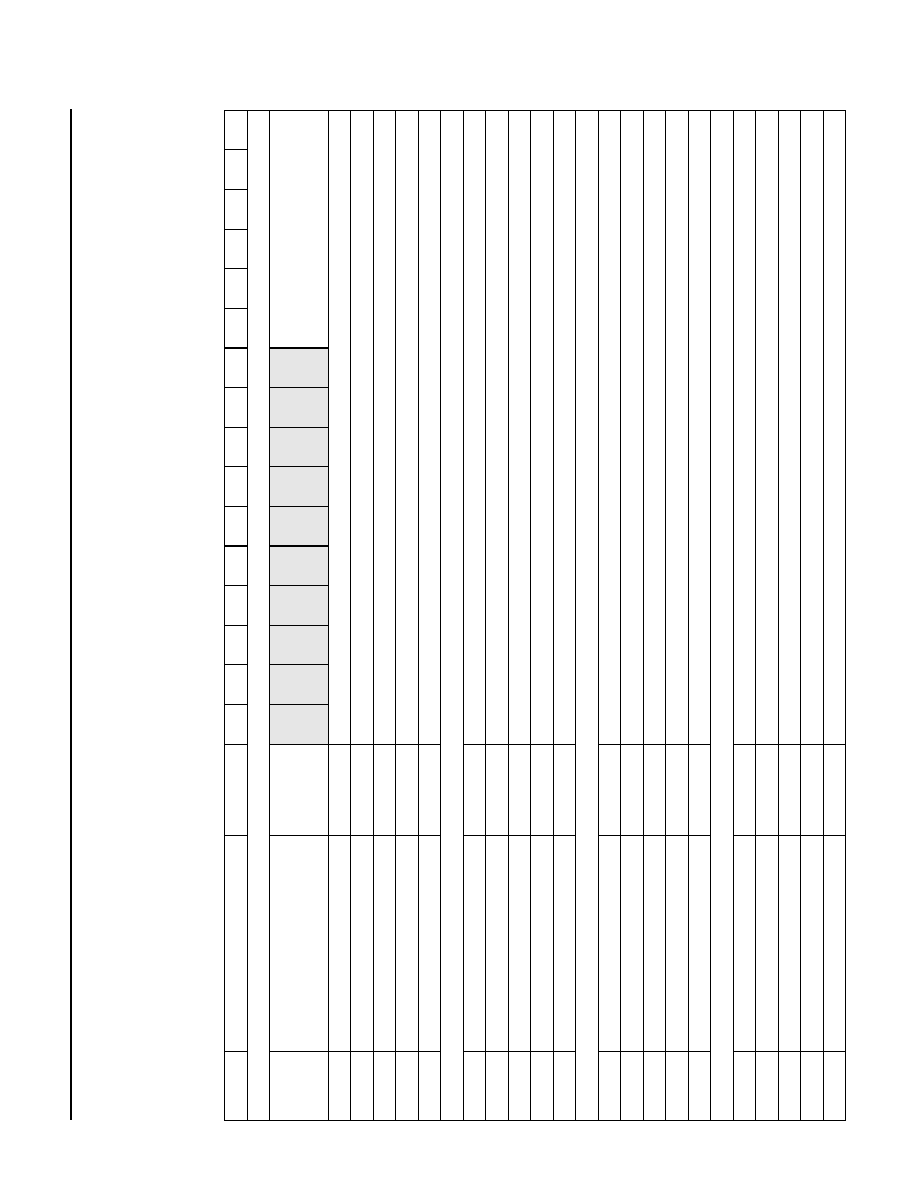

- Table 322. PT Register Map

- Table 323. Path Overhead Extraction Compare Values

- Table 324. Set/Clear Threshold and Window Settings

- Table 325. Default Signal Fail Window Size Settings

- Table 326. STS Path Signal Label Assignments

- Table 327. Payload Label Conditions

- Table 328. RDI-P Codes and Interpretation

- Table 329. RXT_IDR, RXT Identification Register (RO, Fixed Value)

- Table 330. PP_CORWR, PP Clear on Read/Write Register (R/W, Control)

- Table 331. RXT_POH_ALMBNR[1-2], Path Overhead Alarm Status Binning Register (RO)

- Table 332. RXT_SF_ALMBNBSR, Signal Fail Alarm Status Binning Bytestream A-D (RO)

- Table 333. RXT_TSSF_ALMBSR[A-D], Time Slots 1-12 Signal Fail Alarm Bytestream A-D (RO, COR/COW)

- Table 334. RXT_RDI_ALMBNBSR, Remote Defect Indicator Alarm Status Binning Bytestream A-D (RO)

- Table 335. RXT_TSRDI_ALMBSR[A-D], Time Slots 1-12 Remote Defect Indicator Alarm Bytestream A-D (RO, COR/COW)

- Table 336. RXT_PLM_ALMBNBSR, Payload Label Mismatch Alarm Status Binning Bytestream A-D (RO)

- Table 337. RXT_TSPLM_ALMBSR[A-D], Time Slots 1-12 Payload Label Mismatch Alarm Bytestream A-D (RO, COR/COW)

- Table 338. RXT_UNEQR_ALMBNBSR, Unequipped Received Alarm Status Binning Bytestream A-D (RO)

- Table 339. RXT_TSUNEQR_ALMBSR[A-D], Time Slots 1-12 Unequipped Received Alarm Bytestream A- D (RO, COR/COW)

- Table 340. RXT_AIS_ALMBNBSR, Alarms Indicator Signal Alarm Status Binning Bytestream A-D (RO)

- Table 341. PP_TSAIS_ALMBSR[A-D], Time Slots 1-12 Alarms Indicator Signal Alarm Bytestream A-D (RO, COR/COW)

- Table 342. RXT_LOP_ALMBNBSR, Loss of Pointer Alarm Status Binning Bytestream A-D (RO)

- Table 343. RXT_TSLOP_ALMBSR[A-D], Time Slots 1-12 Loss of Pointer Alarm Bytestream A-D (RO, COR/COW)

- Table 344. RXT_CNCTMM_ALMBNBSR, Channel Path Concatenation Map Mismatch Alarm Status Binning Bytestream A-D (RO, COR/COW)

- Table 345. RXT_USCNCTM_ALMBNBSR, Channel Path Unsupported Concatenation Map Alarm Binning Bytestream A-D (RO, COR/COW)

- Table 346. RXT_J1NVLDMSG_ALMBNBSR, Channel Path J1 New Validated Message Alarm Binning Bytestream A-D (RO, COR/COW)

- Table 347. RXT_J1MSGMM_ALMBNBSR, Channel Path J1 Message Mismatch Alarm Status Binning Bytestream A-D (RO, COR/COW)

- Table 348. RXT_PDI_ALMBNBSR, Payload Defect Indicator Alarm Status Binning Bytestream A-D (RO)

- Table 349. RXT_TSPDI_ALMBSR[A-D], Time Slots 1-12 Payload Defect Indicator Alarm Bytestream A-D (RO, COR/COW)

- Table 350. RXT_RDI_ALMDBNBSR, Path Overhead STS-1 Remote Defect Indicator Alarm Delta Status Binning Bytestream A-D (RO)

- Table 351. RXT_TSRDI_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Remote Defect Indicator Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 352. RXT_PLM_ALMDBNBSR, Path Overhead STS-1 Payload Label Mismatch Alarm Delta Status Binning Bytestream A-D (RO)

- Table 353. RXT_TSPLM_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Payload Label Mismatch Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 354. RXT_UNEQR_ALMDBNBSR, Path Overhead STS-1 Unequipped Received Alarm Delta Status Binning Bytestream A-D (RO)

- Table 355. RXT_TSUNEQR_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Unequipped Received Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 356. RXT_AIS_ALMDBNBSR, Path Overhead STS-1 Alarm Indicator Signal Alarm Delta Status Binning Bytestream A-D (RO)

- Table 357. RXT_TSAIS_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Alarm Indicator Signal Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 358. RXT_LOP_ALMDBNBSR, Path Overhead STS-1 Loss of Pointer Alarm Delta Status Binning Bytestream A-D (RO)

- Table 359. RXT_TSLOP_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Loss of Pointer Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 360. RXT_PTRACCMPIR, Path Trace Access Complete Interrupt (RO, COR/COW)

- Table 361. RXT_PDI_ALMDBNBSR, Path Overhead STS-1 Payload Defect Indicator Alarm Delta Status Binning Bytestream A-D (RO)

- Table 362. RXT_TSPDI_ALMDBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Payload Defect Indicator Alarm Delta Bytestream A-D (RO, COR/COW)

- Table 363. RXT_POH_ALMBNMR[1-2], Path Overhead Alarm Status Binning Masks (R/W)

- Table 364. RXT_SF_ALMBNMBSR, Signal Fail Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 365. RXT_TSSF_ALMMBSR[A-D], Time Slots 1-12 Signal Fail Alarm Masks Bytestream A-D (R/W)

- Table 366. RXT_RDI_ALMBNMBSR, Remote Defect Indicator Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 367. RXT_TSRDI_ALMMBSR[A-D], Time Slots 1-12 Remote Defect Indicator Alarm Masks Bytestream A-D (R/W)

- Table 368. RXT_PLM_ALMBNMBSR, Payload Label Mismatch Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 369. RXT_TSPLM_ALMMBSR[A-D], Time Slots 1-12 Payload Label Mismatch Alarm Masks Bytestream A-D (R/W)

- Table 370. RXT_UNEQR_ALMBNMBSR, Unequipped Received Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 371. RXT_TSUNEQR_ALMMBSR[A-D], Time Slots 1-12 Unequipped Received Alarm Masks Bytestream A-D (R/W)

- Table 372. RXT_AIS_ALMBNMBSR, Alarms Indicator Signal Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 373. RXT_TSAIS_ALMMBSR[A-D], Time Slots 1-12 Alarms Indicator Signal Alarm Masks Bytestream A-D (R/W)

- Table 374. RXT_LOP_ALMBNMBSR, Loss of Pointer Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 375. RXT_TSLOP_ALMMBSR[A-D], Time Slots 1-12 Loss of Pointer Alarm Masks Bytestream A-D (R/W)

- Table 376. RXT_CNCTMM_ALMMBSR, Channel Path Concatenation Map Mismatch Alarm Status Masks Bytestream A-D (R/W)

- Table 377. RXT_USCNCTM_ALMMBSR, Channel Path Unsupported Concatenation Map Alarm Masks Bytestream A-D (R/W)

- Table 378. RXT_J1NVLDMSG_ALMMBSR, Channel Path J1 New Validated Message Alarm Masks Bytestream A-D (R/W)

- Table 379. RXT_J1MSGMM_ALMMBSR, Channel Path J1 Message Mismatch Alarm Status Masks Bytestream A-D (R/W)

- Table 380. RXT_PDI_ALMBNMBSR, Payload Defect Indicator Alarm Status Binning Masks Bytestream A-D (R/W)

- Table 381. RXT_TSPDI_ALMMBSR[A-D], Time Slots 1-12 Payload Defect Indicator Alarm Masks Bytestream A-D (R/W)

- Table 382. RXT_RDI_ALMDBNMBSR, Path Overhead STS-1 Remote Defect Indicator Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 383. RXT_TSRDI_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Remote Defect Indicator Alarm Delta Masks Bytestream A-D (R/W)

- Table 384. RXT_PLM_ALMDBNMBSR, Path Overhead STS-1 Payload Label Mismatch Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 385. RXT_TSPLM_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Payload Label Mismatch Alarm Delta Masks Bytestream A-D (R/W)

- Table 386. RXT_UNEQR_ALMDBNMBSR, Path Overhead STS-1 Unequipped Received Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 387. RXT_TSUNEQR_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Unequipped Received Alarm Delta Masks Bytestream A-D (R/W)

- Table 388. RXT_AIS_ALMDBNMBSR, Path Overhead STS-1 Alarm Indicator Signal Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 389. RXT_TSAIS_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Alarm Indicator Signal Alarm Delta Masks Bytestream A-D (R/W)

- Table 390. RXT_LOP_ALMDBNMBSR, Path Overhead STS-1 Loss of Pointer Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 391. RXT_TSLOP_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Loss of Pointer Alarm Delta Masks Bytestream A-D (R/W)

- Table 392. RXT_PTRACCMPIR, Path Trace Access Complete Interrupt Mask (R/W)

- Table 393. RXT_PDI_ALMDBNMBSR, Path Overhead STS-1 Payload Defect Indicator Alarm Delta Status Binning Masks Bytestream A-D (R/W)

- Table 394. RXT_TSPDI_ALMDMBSR[A-D], Path Overhead STS-1 Time Slots 1-12 Payload Defect Indicator Alarm Delta Masks Bytestream A-D (R/W)

- Table 395. RXT_PTRBFR[1-32], Path Trace Buffer Registers 1-32 (R/W)

- Table 396. RXT_PTRACCTLR1, Path Trace Access Control Register 1 (R/W)

- Table 397. RXT_PTRACCTLR2, Path Trace Access Control Register 2 (R/W)

- Table 398. RXT_PTRACCTLR3, Path Trace Access Control Register 3 (R/W)

- Table 399. RXT_PTRACBGR, Path Trace Access Begin (WO)

- Table 400. RXT_STS12PTRCTLR[1-6], STS-12 Channel Path Trace Control Registers 1-6 (R/W)

- Table 401. RXT_TSRDI_ALMPSBSR[A-D], Time Slots 1-12 RDI Alarm Persistency Bytestream A-D (RO)

- Table 402. RXT_TSPLM_ALMPSBSR[A-D], Time Slots 1-12 PLM Alarm Persistency Bytestream A-D (RO)

- Table 403. RXT_TSPUNEQ_ALMPSBSR[A-D], Time Slots 1-12 Path Unequipped Alarm Persistency Bytestream A-D (RO)

- Table 404. RXT_TSAIS_ALMPSBSR[A-D], Time Slots 1-12 AIS Alarm Persistency Bytestream A-D (RO)

- Table 405. RXT_TSLOP_ALMPSBSR[A-D], Time Slots 1-12 LOP Alarm Persistency Bytestream A-D (RO)

- Table 406. RXT_TSPDI_ALMPSBSR[A-D], Time Slots 1-12 PDI Alarm Persistency Bytestream A-D (RO)

- Table 407. RXT_TSRDI_STBSR[A-D], Time Slots 1-12 RDI State Bytestream A-D (RO)

- Table 408. RXT_TSPLM_STBSR[A-D], Time Slots 1-12 PLM State Bytestream A-D (RO)

- Table 409. RXT_TSPUNEQ_STBSR[A-D], Time Slots 1-12 Path Unequipped State Bytestream A-D (RO)

- Table 410. RXT_TSAIS_STBSR[A-D], Time Slots 1-12 AIS State Bytestream A-D (RO)

- Table 411. RXT_TSLOP_STBSR[A-D], Time Slots 1-12 LOP State Bytestream A-D (RO)

- Table 412. RXT_TSPDI_STBSR[A-D], Time Slots 1-12 PDI State Bytestream A-D (RO)

- Table 413. RXT_SFWSZ_SELR[1-2], Signal Fail Window Size Select Registers 1-2 (R/W, Control)

- Table 414. RXT_SFDR[0-7], Signal Fail Detect Threshold Registers 0-7 (R/W, Control)

- Table 415. RXT_SFCLRR[0-7], Signal Fail Clear Threshold Registers 0-7 (R/W, Control)

- Table 416. RXT_SFWSZR[0-3], Signal Fail Window Size 0-3 Registers (R/W, Control)

- Table 417. RXT_ECNCTM_TSBSR[A-D], Expected Concatenation Map Time Slots 1-12 in Bytestream A-D (R/W, Control)

- Table 418. RXT_CNCTCPREN_TSBSR[A-D], Concatenation Compare Enable Time Slots 1-12 in Bytestream A-D (R/W, Control)

- Table 419. RXT_RCNCTM_TSBSR[A-D], Received Concatenation Map Time Slots 1-12 in Bytestream A-D (RO)

- Table 420. RXT_SWAIS_ISRTR, Software AIS Insert (R/W, Control)

- Table 421. RXT_AISONUNEQ_PR[A-D], Time Slot 1-Time Slot 12 AIS Insert on UNEQ-P Bytestream A-D (R/W, Control)

- Table 422. RXT_AISONPLM_PR[A-D], Time Slot 1-Time Slot 12 AIS Insert on PLM-P Bytestream A-D (R/W, Control)

- Table 423. RXT_AISONTIM_PR[A-D], Time Slot 1-Time Slot 12 Software AIS Insert on TIM-P Bytestream A-D (R/W, Control)

- Table 424. RXT_STS12_PINCDECR, STS-12 Pointer Increment/Decrement (R/W, Control)

- Table 425. RXT_TS_INCDECBNR[A-D], Time Slots 1-12 Increment/Decrement Binning Select Bytestream A-D (R/W, Control)

- Table 426. RXT_TSPDIVLD_CTLBSR[A-D], Time Slot 1-Time Slot 12 PDI Validate Control Bytestream A-D (R/W, Control)

- Table 427. RXT_EXPC2_PVSNR[1-24], Expected C2 Byte Provisioning (R/W, Control)

- Table 428. RXT_TSCBB_ERRBSR[A-D], Time Slot 1-Time Slot 12 Count Block/Bit Errors Bytestream A-D

- Table 429. RXT_TSMNTR[1-48], Time Slots 1-48 Maintenance (R/W, Control)

- Table 430. RXT_PI_LSECINCR[A-D], Pointer Interpreter Last Second Increments Bytestream A-D (RO)

- Table 431. RXT_PI_LSECDECR[A-D], Pointer Interpreter Last Second Decrements Bytestream A-D (RO)

- Table 432. RXT_POH_ALMPMR, Path Overhead Alarm Performance Monitoring (RO)

- Table 433. RXT_1BRDI_DPMBSR, Path Overhead One-Bit RDI Defect PM Bytestream A-D (RO)

- Table 434. RXT_TS1BRDI_DPMBSR[A-D], Path Overhead Time Slots 1-12 One-Bit RDI Defect PM Bytestream A-D (RO)

- Table 435. RXT_ERDI_PDPMBSR, Path Overhead ERDI Payload Defect PM Bytestream A-D (RO)

- Table 436. RXT_TSERDI_PDPMBSR[A-D], Path Overhead Time Slots 1-12 ERDI Payload Defect PM Bytestream A-D (RO)

- Table 437. RXT_ERDI_CDPMBSR, Path Overhead ERDI Connectivity Defect PM Bytestream A-D (RO)

- Table 438. RXT_TSERDI_CDPMBSR[A-D], Path Overhead Time Slots 1-12 ERDI Connectivity Defect PM Bytestream A-D (RO)

- Table 439. RXT_ERDI_SDPMBSR, Path Overhead ERDI Server Defect PM Bytestream A-D (RO)

- Table 440. RXT_TSERDI_SDPMBSR[A-D], Path Overhead Time Slots 1-12 ERDI Server Defect PM Bytestream A-D (RO)

- Table 441. RXT_UNEQR_PMBSR, Path Overhead Unequipped Received PM Bytestream A-D (RO)

- Table 442. RXT_TSUNEQR_PMBSR[A-D], Path Overhead Time Slots 1-12 Unequipped Received PM Bytestream A-D (RO)

- Table 443. RXT_AIS_PMBSR, Path Overhead Alarm Indicator Signal PM Bytestream A-D (RO)

- Table 444. RXT_TSAIS_PMBSR[A-D], Path Overhead Time Slots 1-12 Alarm Indicator Signal PM Bytestream A-D (RO)

- Table 445. RXT_LOP_PMBSR, Path Overhead Loss of Pointer PM Bytestream A-D (RO)

- Table 446. RXT_TSLOP_PMBSR[A-D], Path Overhead Time Slots 1-12 Loss of Pointer PM Bytestream A-D (RO)

- Table 447. RXT_LSECCVP_CPMR[1-48], Last Second CV-P Count Time Slot 1-Time Slot 48 PM (RO)

- Table 448. RXT_LSECREIP_CPMR[1-48], Last Second REI-P Count Time Slot 1-Time Slot 48 PM (RO)

- Table 449. RXT_TSRDIPR[1-48], Time Slots 1-48 Path RDI Status (RO)

- Table 450. RXT_TSC2R[1-24], Time Slots 1-48 Path C2 Status (RO)

- Table 451. RXT_TSPDIR[1-24], Time Slots 1-48 Path PDI Status (RO)

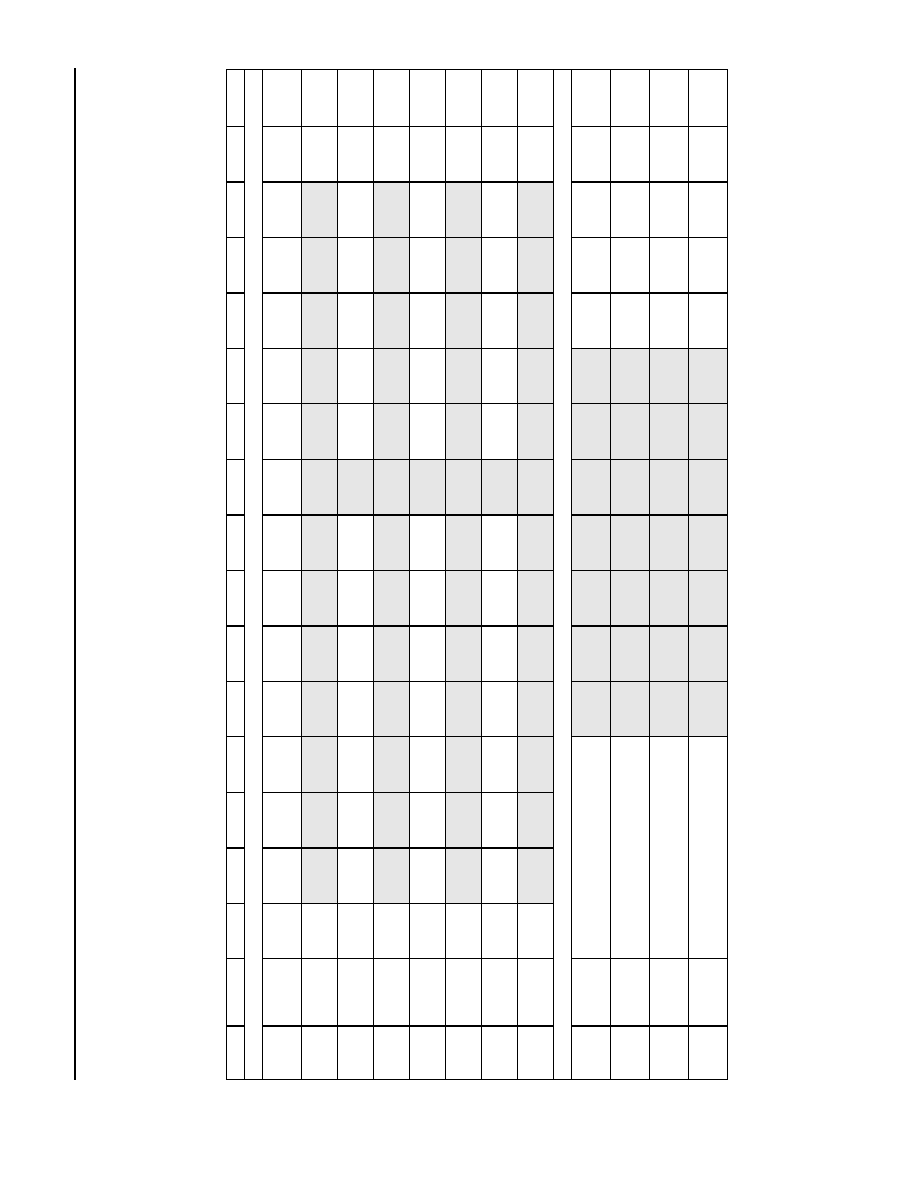

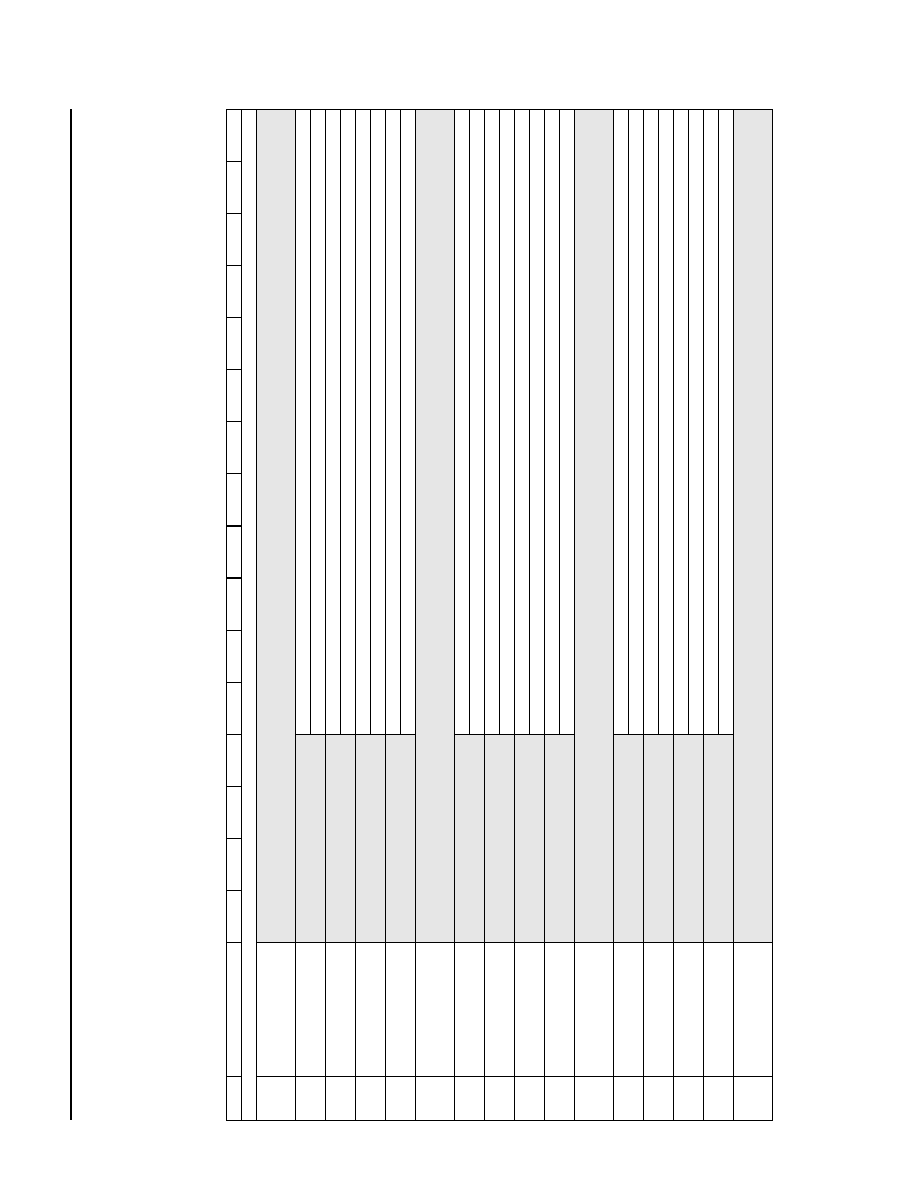

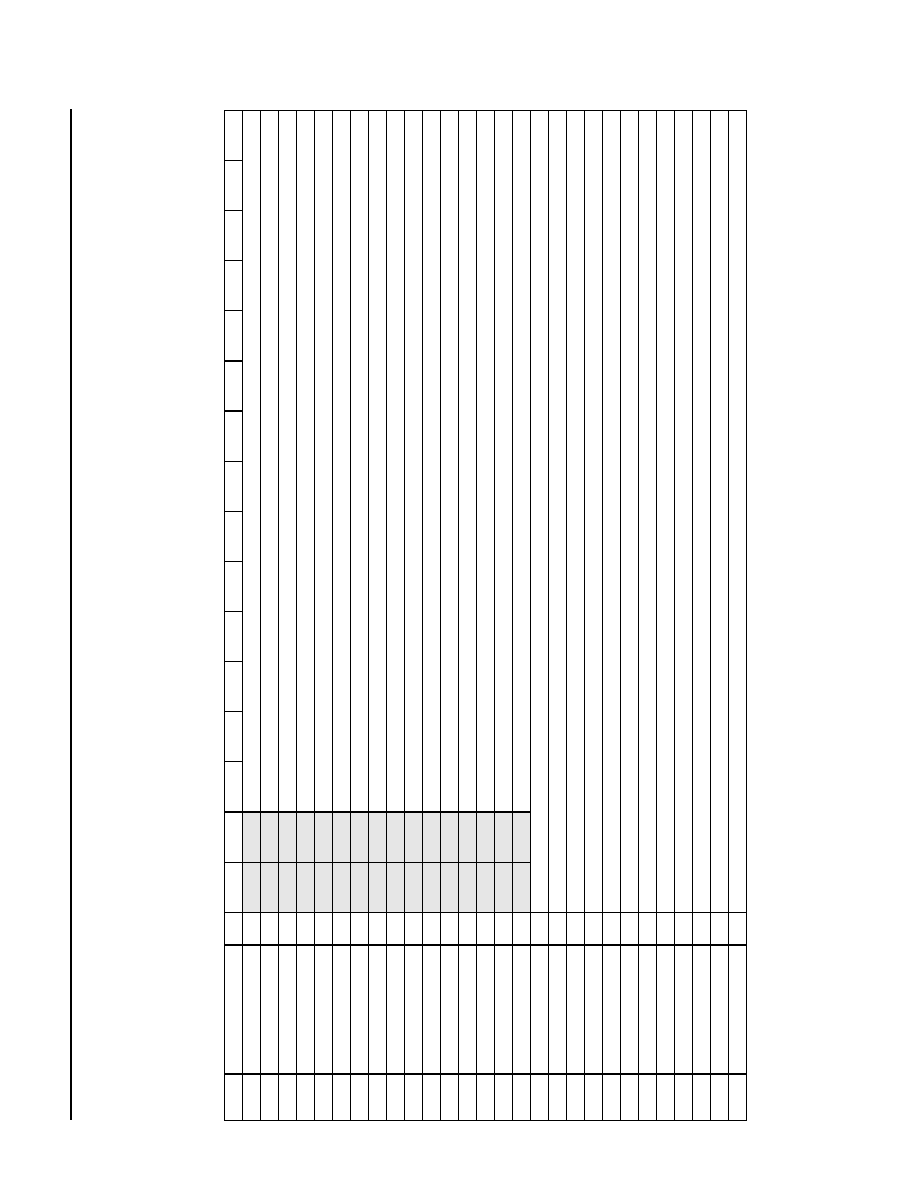

- Table 452. RXT Register Map

- Table 453. Overhead Bits Defined in a 44.736 Mbits/s Multiframe Structure

- Table 454. RAI Code Words

- Table 455. POI Values

- Table 456. G1 Byte Definition

- Table 457. Trailer Length

- Table 458. PLCP Nibble Stuff Sequence

- Table 459. C-Bit Insert

- Table 460. Overhead Allocation at 34,368 kbits/s

- Table 461. MA Byte Description

- Table 462. G.751 E3 Frame Format

- Table 463. E3-PLCP Mapping of ATM Cells

- Table 464. Path Overhead Identifier Codes (POI)

- Table 465. PLCP G1 byte

- Table 466. C1 Values and Transmit Insert Sequence

- Table 467. Receive Mode Control Signals

- Table 468. Transmit Mode Control Signals

- Table 469. G.751 E3 Frame Transmit Overhead Operation

- Table 470. G.751 E3 Frame Receive Overhead Operation

- Table 471. G.751 E3-PLCP Transmit Overhead Operation

- Table 472. G.751 E3-PLCP Receive Overhead Operation

- Table 473. G.832 E3 Transmit Frame Overhead Operation

- Table 474. G.832 E3 Receive Frame Overhead Operation

- Table 475. PRBS Receive (Monitor) Pattern Control Signals

- Table 476. PRBS Transmit Pattern Control Signals

- Table 477. DS3E3_VERR, Version Control (RO)

- Table 478. DS3_SCRATCHR, Scratch Register (R/W)

- Table 479. DS3_CORW_GPOSEL, Clear-on-Read/Clear-on-Write Global Select for Delta/Event Registers (R/W)

- Table 480. DS3FRMD_A, DS3 Out-of-Frame Delta (COR/COW)

- Table 481. DS3LOFD_A, DS3 Loss-of-Frame Delta (COR/COW)

- Table 482. DS3SEFD_A, DS3 Severely Errored Frame (SEF) Delta (COR/COW)

- Table 483. DS3AISD_A, DS3 AIS Detection Delta (COR/COW)

- Table 484. DS3IDLED_A, DS3 Idle Detection Delta (COR/COW)

- Table 485. DS3CBD_A, DS3 C-Bit Detect Delta (COR/COW)

- Table 486. DS3RAID_A, DS3 X-Bit Detect Delta (COR/COW)

- Table 487. DS3FEACALMD_A, DS3 Far-End Alarm and Control (FEAC) RAI Delta (COR/COW)

- Table 488. DS3FEACCTLD_A, DS3 Far-End Alarm and Control (FEAC) Control Delta (COR/COW)

- Table 489. DS3_PLCPOOFD_A, PLCP Out-of-Frame Monitor Delta (COR/COW)

- Table 490. DS3_PLCPRAID_A, PLCP RAI (G1[3]) Monitoring Delta (COR/COW)

- Table 491. DS3_RXPRBS_SYNCD_A, PRBS Detector Sync Delta (COR/COW)

- Table 492. DS3FRMD_B, DS3 Out-of-Frame Delta (COR/COW)

- Table 493. DS3LOFD_B, DS3 Loss-of-Frame Delta (COR/COW)

- Table 494. DS3SEFD_B, DS3 Severely Errored Frame (SEF) Delta (COR/COW)

- Table 495. DS3AISD_B, DS3 AIS Detection Delta (COR/COW)

- Table 496. DS3IDLED_B, DS3 Idle Detection Delta (COR/COW)

- Table 497. DS3CBD_B, DS3 C-Bit Detect Delta (COR/COW)

- Table 498. DS3RAID_B, DS3 X-Bit Detect Delta (COR/COW)

- Table 499. DS3FEACALMD_B, DS3 Far-End Alarm and Control (FEAC) RAI Delta (COR/COW)

- Table 500. DS3FEACCTLD_B, DS3 Far-End Alarm and Control (FEAC) Control Delta (COR/COW)

- Table 501. DS3_PLCPOOFD_B, PLCP Out-of-Frame Monitor Delta (COR/COW)

- Table 502. DS3_PLCPRAID_B, PLCP RAI (G1[3]) Monitoring Delta (COR/COW)

- Table 503. DS3_RXPRBS_SYNCD_B, PRBS Detector Sync Delta (COR/COW)

- Table 504. DS3_TXFIFOERRE, FIFO Overflow Indicator Event (COR/COW)

- Table 505. DS3_TXEOPERRER, EOP Marker Error Event (COR/COW)

- Table 506. DS3FRMM_A, DS3 Out-of-Frame Mask (R/W)

- Table 507. DS3LOFM_A, DS3 Loss-of-Frame Mask (R/W)

- Table 508. DS3SEFM_A, DS3 Severely Errored Frame (SEF) Mask (R/W)

- Table 509. DS3AISM_A, DS3 AIS Detection Mask (R/W)

- Table 510. DS3IDLEM_A, DS3 Idle Detection Mask (R/W)

- Table 511. DS3CBM_A, DS3 C-Bit Detect Mask (R/W)

- Table 512. DS3RAIM_A, DS3 X-Bit Detect Mask (R/W)

- Table 513. DS3FEACALMM_A, DS3 Far-End Alarm and Control (FEAC) Alarm Mask (R/W)

- Table 514. DS3FEACCTLM_A, DS3 Far-End Alarm and Control (FEAC) Control Mask (R/W)

- Table 515. DS3_PLCPOOFM_A, PLCP Out-of-Frame Monitor Mask (R/W)

- Table 516. DS3_PLCPRAIM_A, PLCP RAI (G1[3]) Monitoring Mask (R/W)

- Table 517. DS3_RXPRBS_SYNCM_A, PRBS Detector Sync Mask (R/W)

- Table 518. DS3_DS3FRMM_B, DS3 Out-of-Frame Mask (R/W)

- Table 519. DS3LOFM_B, DS3 Loss-of-Frame Mask (R/W)

- Table 520. DS3SEFM_B, DS3 Severely Errored Frame (SEF) Mask (R/W)

- Table 521. DS3AISM_B, DS3 AIS Detection Mask (R/W)

- Table 522. DS3IDLEM_B, DS3 Idle Detection Mask (R/W)

- Table 523. DS3CBM_B, DS3 C-Bit Detect Mask (R/W)

- Table 524. DS3RAIM_B, DS3 X-Bit Detect Mask (R/W)

- Table 525. DS3FEACALMM_B, DS3 Far-End Alarm and Control (FEAC) Alarm Mask (R/W)

- Table 526. DS3FEACCTLM_B, DS3 Far-End Alarm and Control (FEAC) Control Mask (R/W)

- Table 527. DS3_PLCPOOFM_B, PLCP Out-of-Frame Monitor Mask (R/W)

- Table 528. DS3_PLCPRAIM_B, PLCP RAI (G1[3]) Monitoring Mask (R/W)

- Table 529. DS3_RXPRBS_SYNCM_B, PRBS Detector Sync Mask (R/W)

- Table 530. DS3_TXFIFOERRM, FIFO Overflow Indicator Mask (R/W)

- Table 531. DS3_TXEOPERRM, EOP Marker Error Mask (R/W)

- Table 532. DS3FRM_A, DS3 Out-of-Frame State (RO)

- Table 533. DS3LOF_A, DS3 Loss-of-Frame State (RO)

- Table 534. DS3SEF_A, DS3 Severely Errored Frame (SEF) (RO)

- Table 535. DS3AIS_A, DS3 AIS Detection (RO)

- Table 536. DS3IDLE_A, DS3 Idle Detection (RO)

- Table 537. DS3CB_A, DS3 C-Bit Detect (RO)

- Table 538. DS3RAI_A, DS3 X-Bit Detect (RO)

- Table 539. DS3FEACALM_A, DS3 Far-End Alarm and Control (FEAC) (RO)

- Table 540. DS3FEACCTL_A, DS3 Far-End Alarm and Control (FEAC) (RO)

- Table 541. DS3_PLCPOOF_A, PLCP Out-of-Frame Monitor (RO)

- Table 542. DS3_PLCPRAI_A, PLCP RAI (G1[3]) Monitoring (RO)

- Table 543. DS3_RXPRBS_SYNC_A, PRBS Detector Sync State (RO)

- Table 544. DS3FEACCODE_A[1-6], DS3 Far-End Alarm and Control (FEAC) (RO)

- Table 545. DS3_RXPRBSERRCNT_A, PRBS Error Counter (RO)

- Table 546. DS3FRM_B, DS3 Out-of-Frame State (RO)

- Table 547. DS3LOF_B, DS3 Loss-of-Frame State (RO)

- Table 548. DS3SEF_B, DS3 Severely Errored Frame (SEF) (RO)

- Table 549. DS3AIS_B, DS3 AIS Detection (RO)

- Table 550. DS3IDLE_B, DS3 Idle Detection (RO)

- Table 551. DS3CB_B, DS3 C-Bit Detect (RO)

- Table 552. DS3RAI_B, DS3 X-Bit Detect (RO)

- Table 553. DS3FEACALM_B, DS3 Far-End Alarm and Control (FEAC) (RO)

- Table 554. DS3FEACCTL_B, DS3 Far-End Alarm and Control (FEAC) (RO)

- Table 555. DS3_PLCPOOF_B, PLCP Out-of-Frame Monitor (RO)

- Table 556. DS3_PLCPRAI_B, PLCP RAI (G1[3]) Monitoring (RO)

- Table 557. DS3_RXPRBS_SYNC_B, PRBS Detector Sync State (RO)

- Table 558. DS3FEACCODE_B[1-6], DS3 Far-End Alarm and Control (FEAC) (RO)

- Table 559. DS3_RXPRBSERRCNT_B, PRBS Error Counter (RO)

- Table 560. DS3_RXMODE_A_1, Receive Interface A Control Register 1 (R/W)

- Table 561. DS3_RXMODE_A_2, Receive Interface A Control Register 2 (R/W)

- Table 562. DS3_RXPRBS_A, Receive PRBS (R/W)

- Table 563. DS3_RXMODE_B_1, Receive Interface B Control Register 1 (R/W)

- Table 564. DS3_RXMODE_B_2, Receive Interface B Control Register 2 (R/W)

- Table 565. DS3_RXPRBS_B, Receive PRBS (R/W)

- Table 566. DS3_RXDS3FBIT_A[1-12], DS3 F-Bit and M-Bit Error Count (RO)

- Table 567. DS3_RXDS3_CVP_P_A[1-12], DS3 P-Bit CVP-P Error Counter (CVP-P) (RO)

- Table 568. DS3_RXDS3_CVCP_P_A[1-12], DS3 CP-Bit Error Counter (CVCP-P) (RO)

- Table 569. DS3_RXDS3FEBE_A[1-12], DS3 FEBE Error Counter (CVCP-PFE) (RO)

- Table 570. DS3_RXPLCPB1ECNT_A[1-12], PLCP B1 Error Count (RO)

- Table 571. DS3_PLCPFEBECNT_A[1-12], PLCP FEBE (G1[7:4]) Error Count (RO)

- Table 572. DS3_RXDS3FBIT_B[1-12], DS3 F-Bit and M-Bit Error Count (RO)

- Table 573. DS3_RDS3_CVP_P_B[1-12], DS3 P-Bit CVP-P Error Counter (CVP-P)

- Table 574. DS3_RXDS3_CVCP_P_B[1-12], DS3 CP-Bit Error Counter (CVCP-P) (RO)

- Table 575. DS3_RXDS3FEBE_B[1-12], DS3 FEBE Error Counter (CVCP-PFE) (RO)

- Table 576. DS3_RXPLCPB1ECNT_B[1-12], PLCP B1 Error Count (RO)

- Table 577. DS3_PLCPFEBECNT_B[1-12], PLCP FEBE (G1[7:4]) Error Count (RO)

- Table 578. DS3_TDS3PLCPCTL1_CHD[1-16], Transmit PLCP (R/W)

- Table 579. DS3_TDS3CTL_CHD[1-16], Transmit DS3 (R/W)

- Table 580. DS3_TXPRBSCTL_[1-2], Transmit PRBS Control (R/W)

- Table 581. DS3_TXFEBEDINS, Transmit Blank Request Counter Reset (R/W)

- Table 582. DS3_TXFIFO, Transmit FIFO Min/Max Thresholds (R/W)

- Table 583. DS3E3_VERR, Version Control (RO)

- Table 584. E3_SCRATCHR, Scratch Register (R/W)

- Table 585. E3_CORW_GPOSEL, Clear-on-Read/Clear-on-Write Global Select for Delta/Event Registers (R/W)

- Table 586. E3FRMD_A, E3 Out-of-Frame Delta (COR/COW)

- Table 587. E3LOFD_A, E3 Loss-of-Frame Delta (COR/COW)

- Table 588. E3_TR_MISMATCHD_A, E3 Delta (COR/COW)

- Table 589. E3AISD_A, E3 AIS Detection Delta (COR/COW)

- Table 590. E3_D_A, E3 Delta (COR/COW)

- Table 591. E3_MA_SSMD_A, E3 Delta (COR/COW)

- Table 592. E3_D_A, E3 Delta (COR/COW)

- Table 593. E3_MA_PTD_A, E3 Delta (COR/COW)

- Table 594. E3_PLCP_LOFD_A, E3 Delta (COR/COW)

- Table 595. E3_PLCPOOFD_A, PLCP Out-of-Frame Monitor Delta (COR/COW)

- Table 596. E3_PLCPASD_A, PLCP (G1[3]) Monitoring Delta (COR/COW)

- Table 597. E3FRMD_B, E3 Out-of-Frame Delta (COR/COW)

- Table 598. E3LOFD_B, E3 Loss-of-Frame Delta (COR/COW)

- Table 599. E3_TR_MISMATCHD_B, E3 Delta (COR/COW)

- Table 600. E3AISD_B, E3 AIS Detection Delta (COR/COW)

- Table 601. E3_D_B, E3 Delta (COR/COW)

- Table 602. E3_MA_SSMD_B, E3 Delta (COR/COW)

- Table 603. E3_D_B, E3 Delta (COR/COW)

- Table 604. E3_MA_PTD_B, E3 Delta (COR/COW)

- Table 605. E3_PLCP_LOFD_B, E3 Delta (COR/COW)

- Table 606. E3_PLCPOOFD_B, PLCP Out-of-Frame Monitor Delta (COR/COW)

- Table 607. E3_PLCP_G1_ASD_B, PLCP (G1[3]) Monitoring Delta (COR/COW)

- Table 608. E3FRMM_A, E3 Out-of-Frame Mask (R/W)

- Table 609. E3LOFM_A, E3 Loss-of-Frame Mask (R/W)

- Table 610. E3SEFM_A, E3 Severely Errored Frame (SEF) Mask (R/W)

- Table 611. E3AISM_A, E3 AIS Detection Mask (R/W)

- Table 612. E3_M_A, E3 Mask (R/W)

- Table 613. E3MAM_A, E3 MA-Bit Detect Mask (R/W)

- Table 614. E3_M_A, E3 Detect Mask (R/W)

- Table 615. E3_MA_PTM_A, E3 Mask (R/W)

- Table 616. E3_PLCP_LOFM_A, E3 Mask (R/W)

- Table 617. E3_PLCPOOFM_A, PLCP Out-of-Frame Monitor Mask (R/W)

- Table 618. DS3_PLCPASM_A, PLCP (G1[3]) Monitoring Mask (R/W)

- Table 619. E3FRMM_B, E3 Out-of-Frame Mask (R/W)

- Table 620. E3LOFM_B, E3 Loss-of-Frame Mask (R/W)

- Table 621. E3SEFM_B, E3 Severely Errored Frame (SEF) Mask (R/W)

- Table 622. E3AISM_B, E3 AIS Detection Mask (R/W)

- Table 623. E3_M_B, E3 Mask (R/W)

- Table 624. E3MAM_B, E3 MA-Bit Detect Mask (R/W)

- Table 625. E3_M_B, E3 Detect Mask (R/W)

- Table 626. E3_MA_PTM_B, E3 Mask (R/W)

- Table 627. E3_PLCP_LOFM_B, E3 Mask (R/W)

- Table 628. E3_PLCPOOFM_B, PLCP Out-of-Frame Monitor Mask (R/W)

- Table 629. E3_PLCPASM_B, PLCP (G1[3]) Monitoring Mask (R/W)

- Table 630. E3FRM_A, E3 Out-of-Frame State (RO)

- Table 631. E3LOF_A, E3 Loss-of-Frame State (RO)

- Table 632. E3SEF_A, E3 Severely Errored Frame (SEF) (RO)

- Table 633. E3AIS_A, E3 AIS Detection (RO)

- Table 634. E3E3_A, E3 Detect (RO)

- Table 635. E3_PLCP_LOF_A, E3 PLCP Loss-of-Frame Monitor (RO)

- Table 636. E3_PLCPOOF_A, PLCP Out-of-Frame Monitor (RO)

- Table 637. E3_PLCPAS_A, PLCP (G1[3]) Monitoring (RO)

- Table 638. E3SSMCODE_A[1-6], E3 (RO)

- Table 639. E3FRM_B, E3 Out-of-Frame State (RO)

- Table 640. E3LOF_B, E3 Loss-of-Frame State (RO)

- Table 641. E3SEF_B, E3 Severely Errored Frame (SEF) (RO)

- Table 642. E3AIS_B, E3 AIS Detection (RO)

- Table 643. E3_B, E3 Detect (RO)

- Table 644. E3_PLCP_LOF_B, E3 PLCP Loss-of-Frame Monitor (RO)

- Table 645. E3_PLCPOOF_B, PLCP Out-of-Frame Monitor (RO)

- Table 646. E3_PLCPAS_B, PLCP (G1[3]) Monitoring (RO)

- Table 647. E3SSMCODE_B[1-6], E3 (RO)

- Table 648. E3_RXMODE_A_1, Receive Interface A Control Register 1 (R/W)

- Table 649. E3_RXMODE_A_2, Receive Interface A Control Register 2 (R/W)

- Table 650. RDS3E3_A, Receive Mode Control (R/W)

- Table 651. E3_RXMODE_B_1, Receive Interface B Control Register 1 (R/W)

- Table 652. E3_RXMODE_B_2, Receive Interface B Control Register 2 (R/W)

- Table 653. RDS3E3_B, Receive Mode Control

- Table 654. E3PROV_1, E3 Provisioning Parameters (Per Block) (R/W)

- Table 655. E3PROV_2, E3 PLCP Provisioning Parameters (Per Block) (R/W)

- Table 656. E3PROV_3, E3 AIS Provisioning Parameters (Per Block) (R/W)

- Table 657. E3PROV_4, E3 Provisioning Parameters (Per Block) (R/W)

- Table 658. E3PROV_5, E3 Provisioning Parameters (Per Block) (R/W)

- Table 659. E3_MA_MF_[A-B], E3 Provisioning Parameters

- Table 660. E3_TR_NMODE_[A-B][1-2], (R/W)

- Table 661. E3PLCP_MON[A-B][1-2], (RO)

- Table 662. E3_MA_REI_ERRCNT_A[1-12], E3 MA REI Error Count (RO)

- Table 663. E3_B1_ERRCNT_A[1-12], E3 B1 Error Counter (RO)

- Table 664. E3_RXPLCPB1ECNT_A[1-12], PLCP B1 Error Count (RO)

- Table 665. E3_PLCPFEBECNT_A[1-12], PLCP FEBE (G1[7:4]) Error Count (RO)

- Table 666. E3_MA_REI_ERRCNT_B[1-12], E3 MA REI Error Count (RO)

- Table 667. E3_B1_ERRCNT_B[1-12], E3 B1 Error Counter (RO)

- Table 668. E3_RXPLCPB1ECNT_B[1-12], PLCP B1 Error Count (RO)

- Table 669. E3_PLCPFEBECNT_B[1-12], PLCP FEBE (G1[7:4]) Error Count (RO)

- Table 670. E3_TE3PLCPCTL1_CHD[1-16], Transmit PLCP (R/W)

- Table 671. E3_TE3CTL_CHD[1-16], Transmit E3 (R/W)

- Table 672. E3_TXFEBEDINS, Transmit PLCP FEBE Insert Data Value for All Channel (R/W)

- Table 673. TXE3PLCP_P[1-3], Transmit G.751 E3 PLCP Z1-Z3, F1 Insert Control (R/W)

- Table 674. TXTRACE[1-16]_B[1-8], Transmit E3 G.832 Trail Trace (TR) Insert Registers (128 Locations) (R/W)

- Table 675. Receive E3 (G.832) Trail Trace Expected/Captured Value-Expected/Capture Format Same as Transmit Insert Format

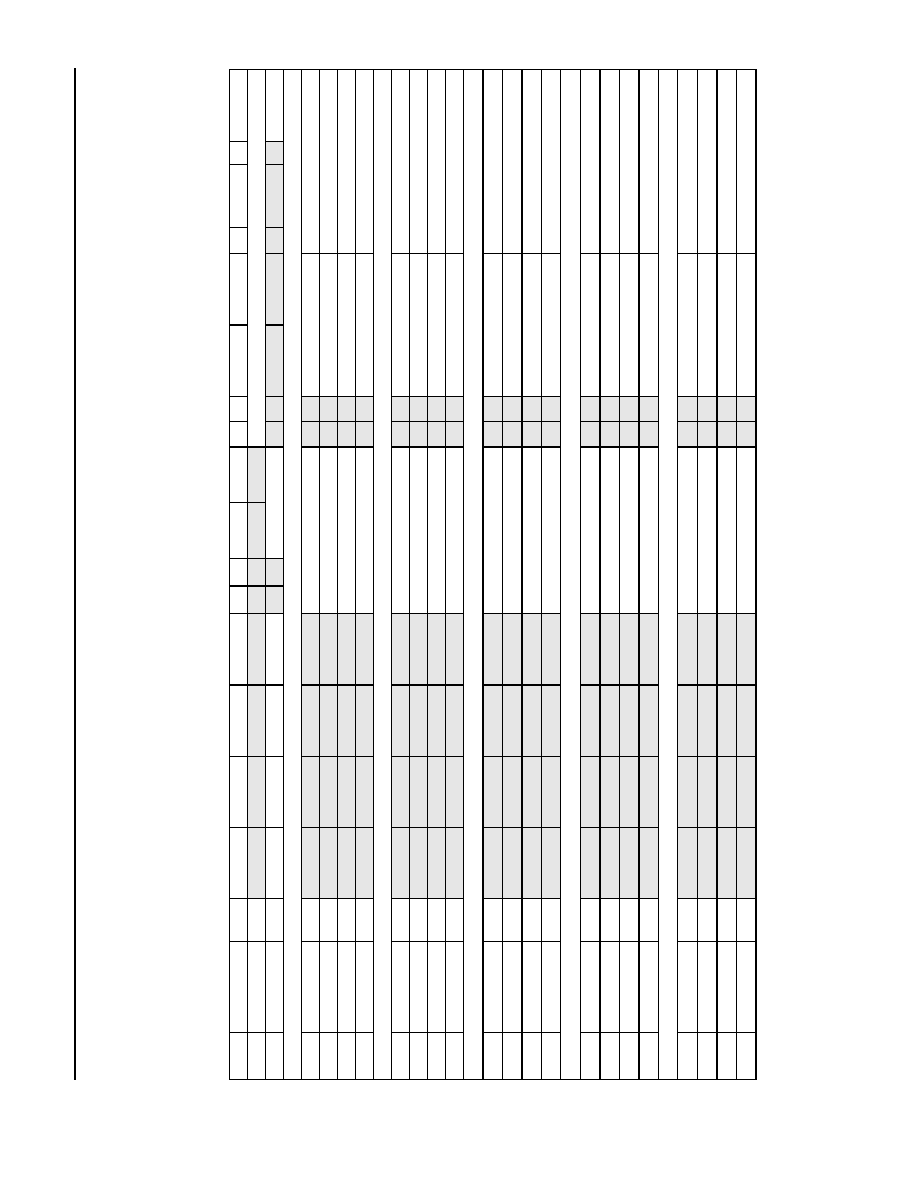

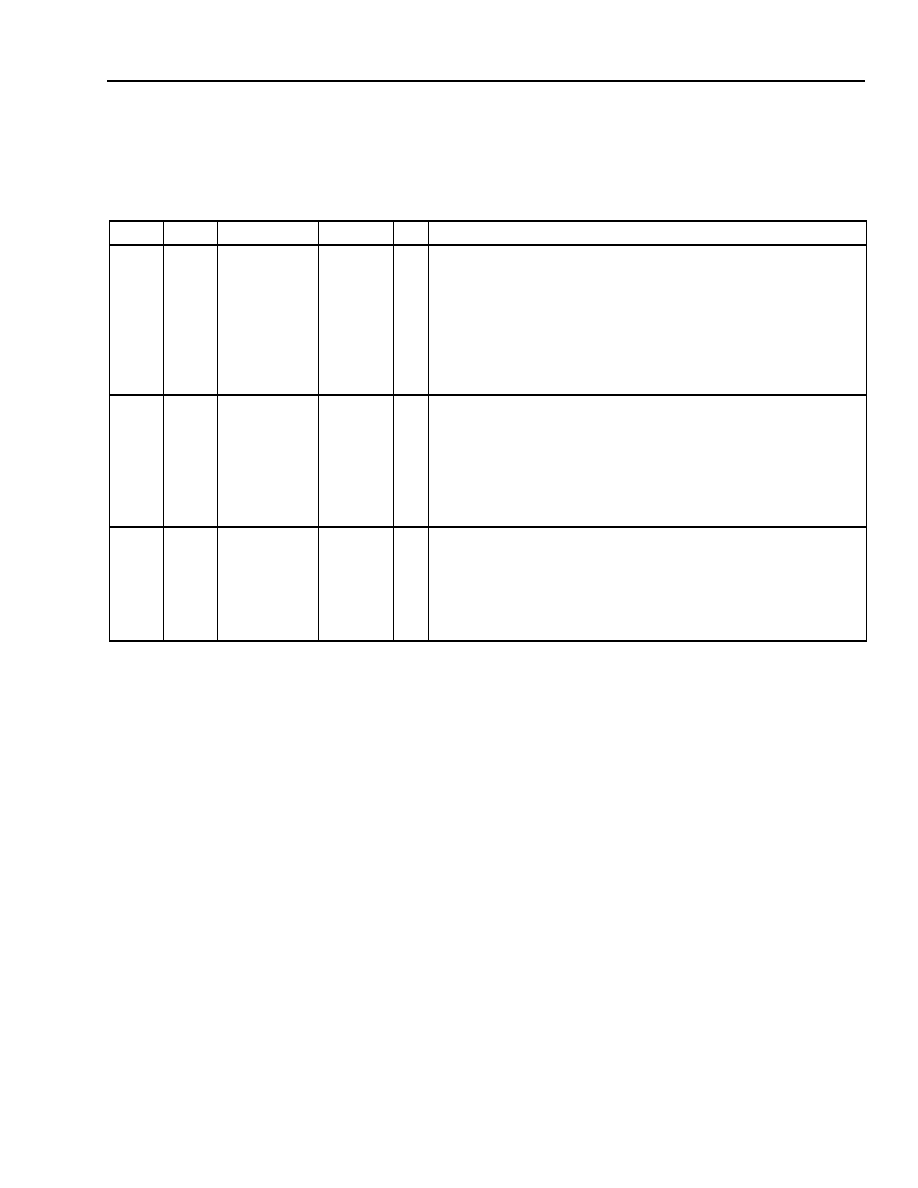

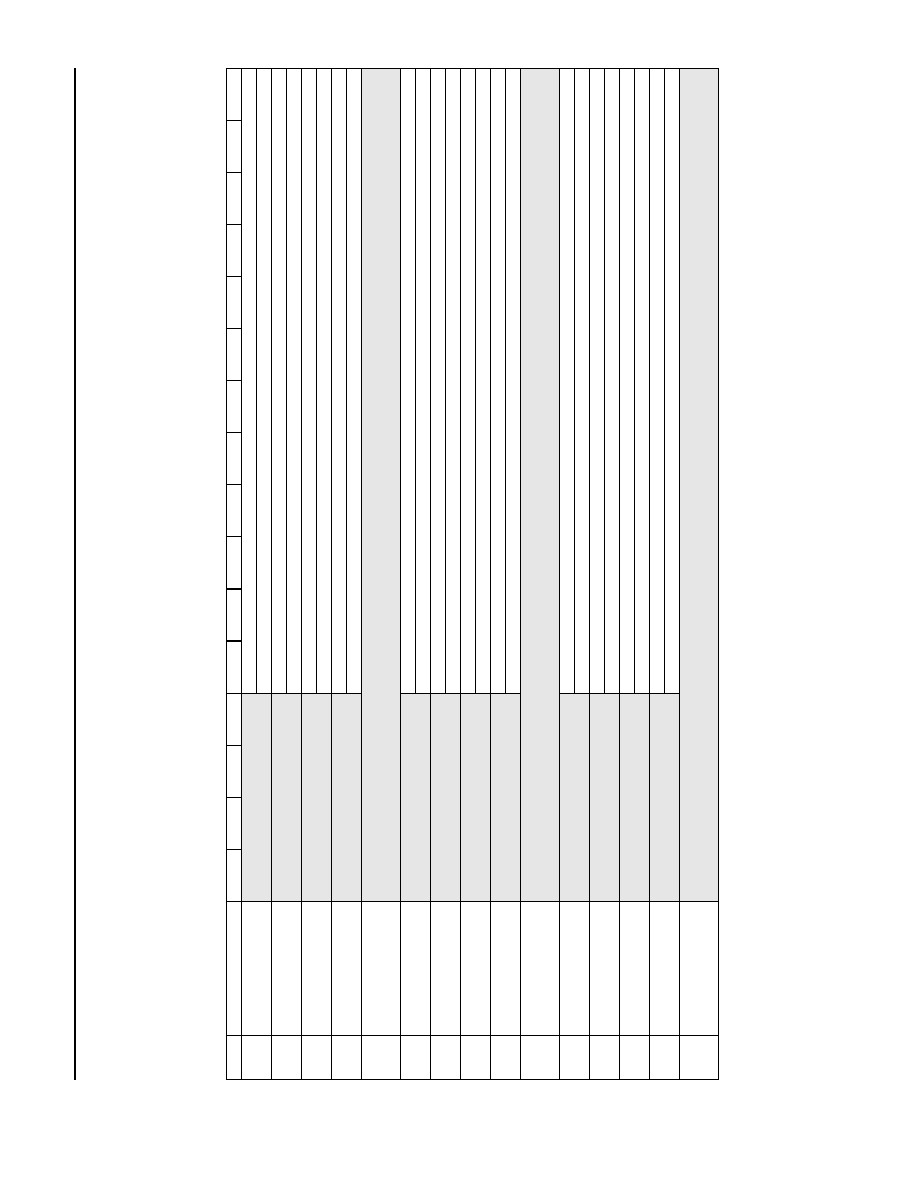

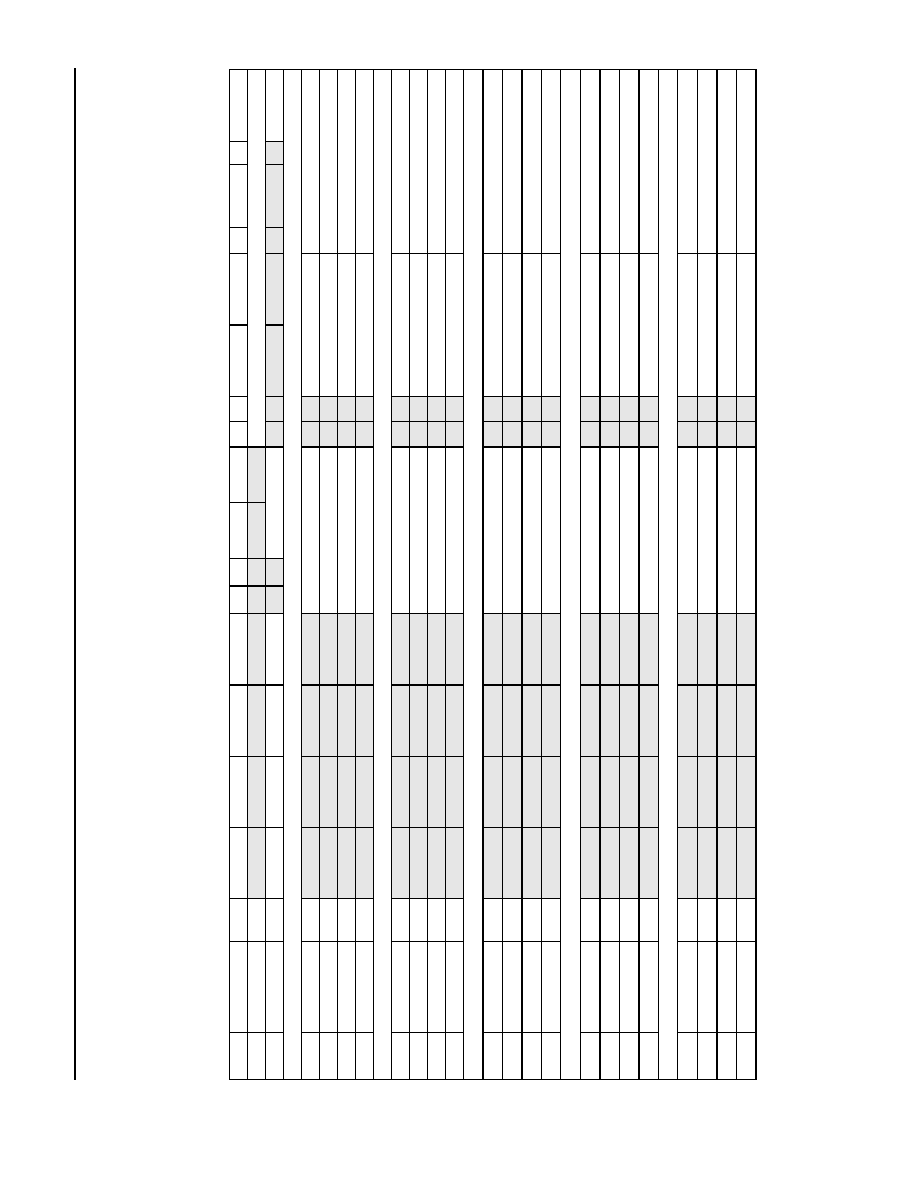

- Table 676. DS3 Register Map

- Table 677. E3 Register Map

- Table 678. STS-1 Mapping of DS3 Information

- Table 679. (RXSVERSION) Version Control (RO)

- Table 680. RXS_CONTROL, Receive Sequencer Control Register (R/W)

- Table 681. RXS_TS[0-11][A-D], X Sequence Map Register (R/W)

- Table 682. RYS_TS[0-11][A-D], Y Sequence Map Register (R/W)

- Table 683. DS3 Support Registers

- Table 684. RXS PRBS Control Register for Monitor 1 (R/W)

- Table 685. RXS PRBS Control Register for Monitor 2 (R/W)

- Table 686. RXS PRBS Status Register for Monitor 1 (Mixed)

- Table 687. RXS PRBS Status Register for Monitor 2 (Mixed)

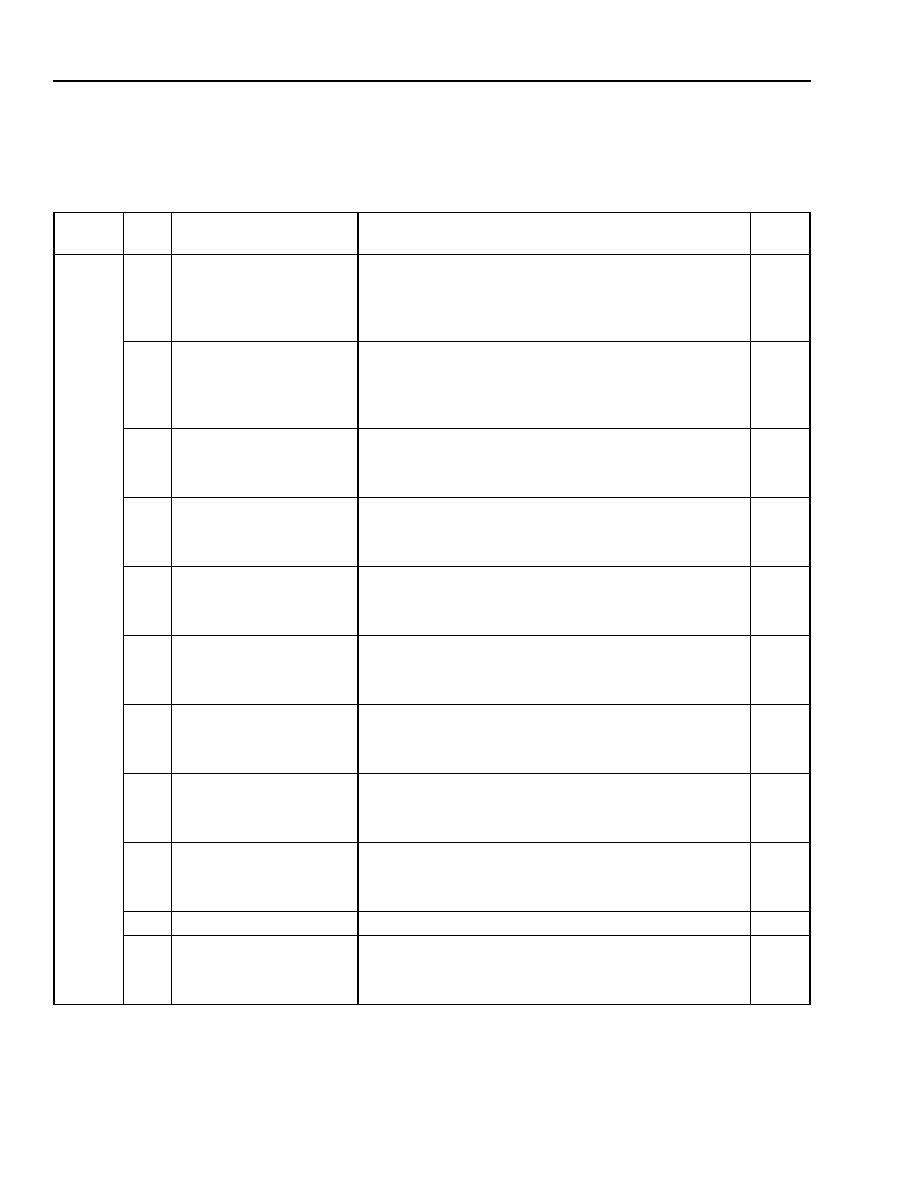

- Table 688. Sequencer Register Map 1 Field Definition

- Table 689. Sequencer Register Map 2 Field Definition

- Table 690. General Registers (RO)

- Table 691. CORWN Register (R/W)

- Table 692. TXMUX Mask Register (R/W)

- Table 693. RXMUX Mask Register (R/W)

- Table 694. FIFO Control (FC) Bandwidth Register (R/W)

- Table 695. DE Scratch Register (R/W)

- Table 696. Counter Interrupts (COR/COW)

- Table 697. GFP Message Interrupts (COR/COW)

- Table 698. Composite Interrupt Register for GFP Interrupts at the Channel Level (COR/COW)

- Table 699. ATM Frame State Interrupts (COR/COW)

- Table 700. ATM Cool Interrupts (COR/COW)

- Table 701. CDA MAP0 Register (R/W)

- Table 702. CDA MAP Control Register (R/W)

- Table 703. CDA MAP1 Register (R/W)

- Table 704. ATM Framer Idle Cell Match Mask (R/W)

- Table 705. ATM_LCD[0-15] (R/W)

- Table 706. ATM_LCDCLK (R/W)

- Table 707. ATM_IN_LCD_MASK (R/W)

- Table 708. ATM_OUT_LCD_MASK (R/W)

- Table 709. ATM_IN_LCD (COR/COW)

- Table 710. ATM_OUT_LCD (COR/COW)

- Table 711. ATM Framer Idle Cell (R/W)

- Table 712. ATM Unassigned Cell Match/Register (R/W)

- Table 713. ATM Unassigned Cell (R/W)

- Table 714. ATM Frame State Channel [0-15] Registers (RO)

- Table 715. ATM Configuration Registers (R/W)

- Table 716. Rx Channel [0-15] Payload Type and Control (R/W)

- Table 717. Rx Payload Type and Payload Control Summary Table

- Table 718. GFP State Register (R/W, RO)

- Table 719. Registers 0x6470-0x6473 A Message Mailbox Registers (RO)

- Table 720. A Message Mailbox Registers (RO)

- Table 721. Registers 1168-1171 A Message Mailbox Registers (RO)

- Table 722. Registers 1184-1187 B Message Mailbox Registers (RO)

- Table 723. B Message Mailbox Registers (RO)

- Table 724. B Message Mailbox Registers (RO)

- Table 725. GFP Interrupt Masks R/W

- Table 726. Per-Channel Framer State

- Table 727. GFP Interrupts (COW)

- Table 728. GFP Receive Configuration Registers (R/W)

- Table 729. PPP Detach Channel 0-15 PPP Protocol Check (R/W)

- Table 730. PPP Detach Programmable PPP Protocol Register 0-11 (R/W)

- Table 731. PPP Detach Channel 0-15 PPP Header Search (R/W)

- Table 732. ATM Null Cell Register in TX (R/W)

- Table 733. ATM Header Error Register in Tx (R/W)

- Table 734. CRC Transmit Registers (R/W)

- Table 735. GFP Transmit Registers (R/W)

- Table 736. GFP Transmit Registers (RO)

- Table 737. GFP Transmit Registers (R/W)

- Table 738. HDLC-Tx Dry Character

- Table 739. HDLC-Tx FIFO Threshold

- Table 740. Tx Payload Type and Control (R/W)

- Table 741. Tx Payload Type and Payload Control Summary Table

- Table 742. ATM/HDLC/GFP Framer-Condition Counter 1 (PMRST Update) (RO)

- Table 743. ATM/HDLC/GFP Framer-Condition Counter 2 (PMRST Update) (RO

- Table 744. CRC Checker-Bad Packet Counter (PMRST Update) (RO)

- Table 745. PPP Detach-Bad Header Counter (PMRST Update) (RO)

- Table 746. Interrupts and Interrupt Masks for Packet Counters (R/W)

- Table 747. Interrupts for Packet Counters (COR/COW)

- Table 748. Transmit (Tx) Good Packet Counter (PMRST Update) (RO)

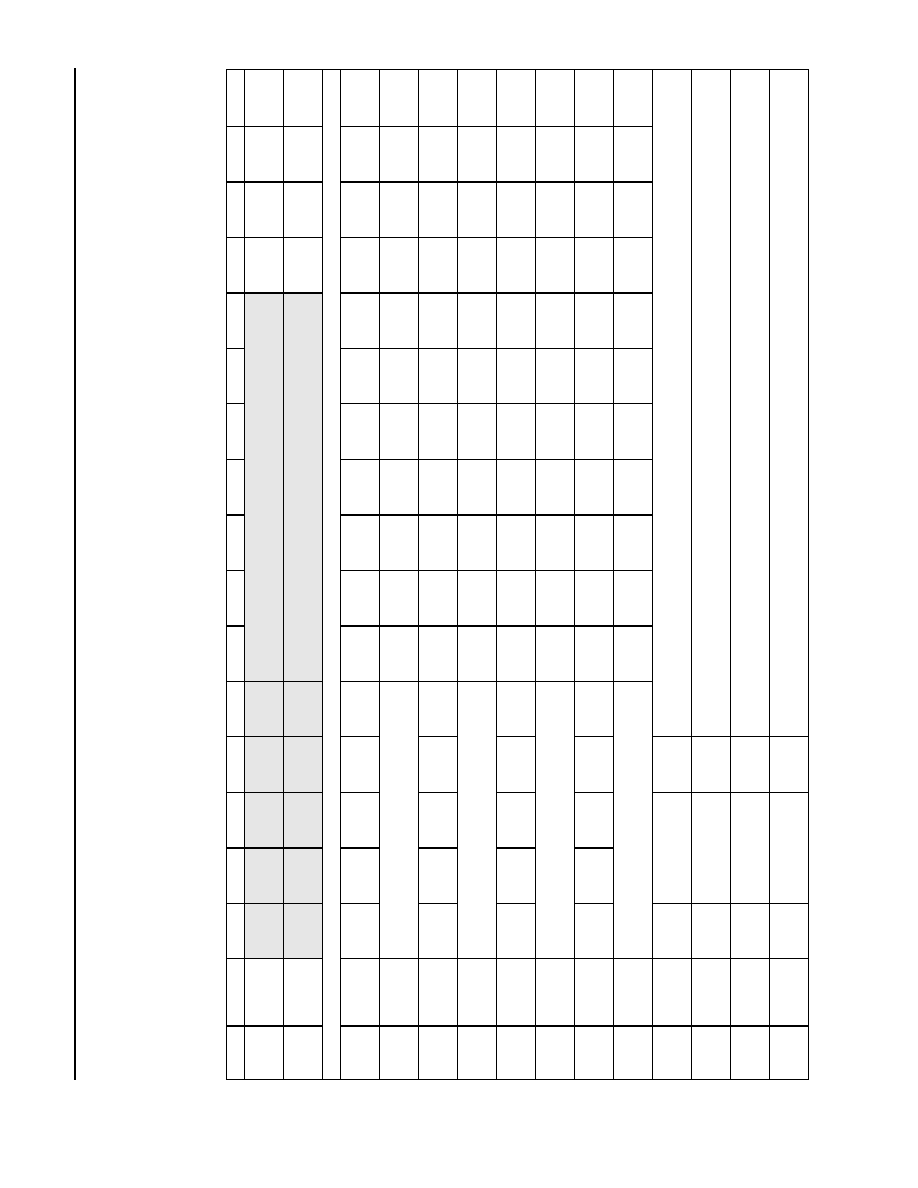

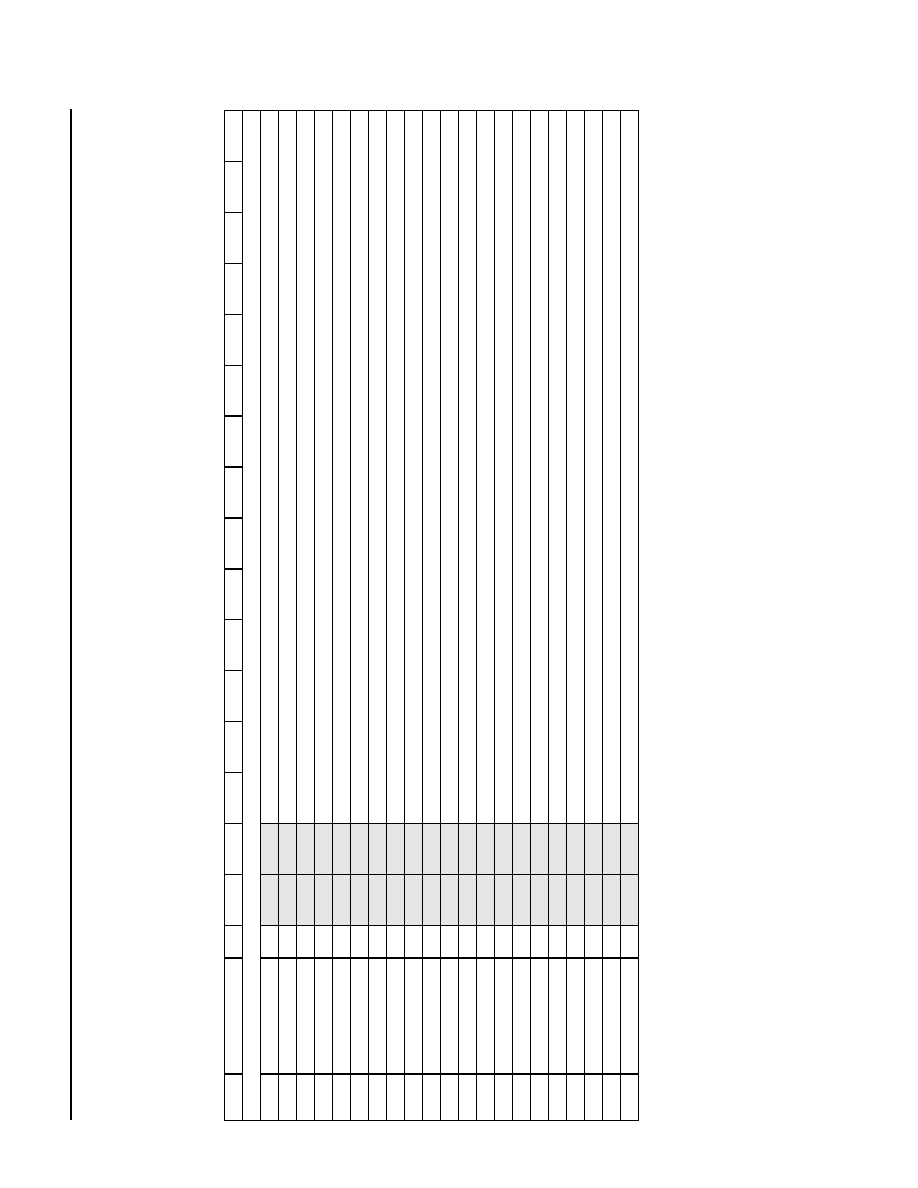

- Table 749. DE Register Map

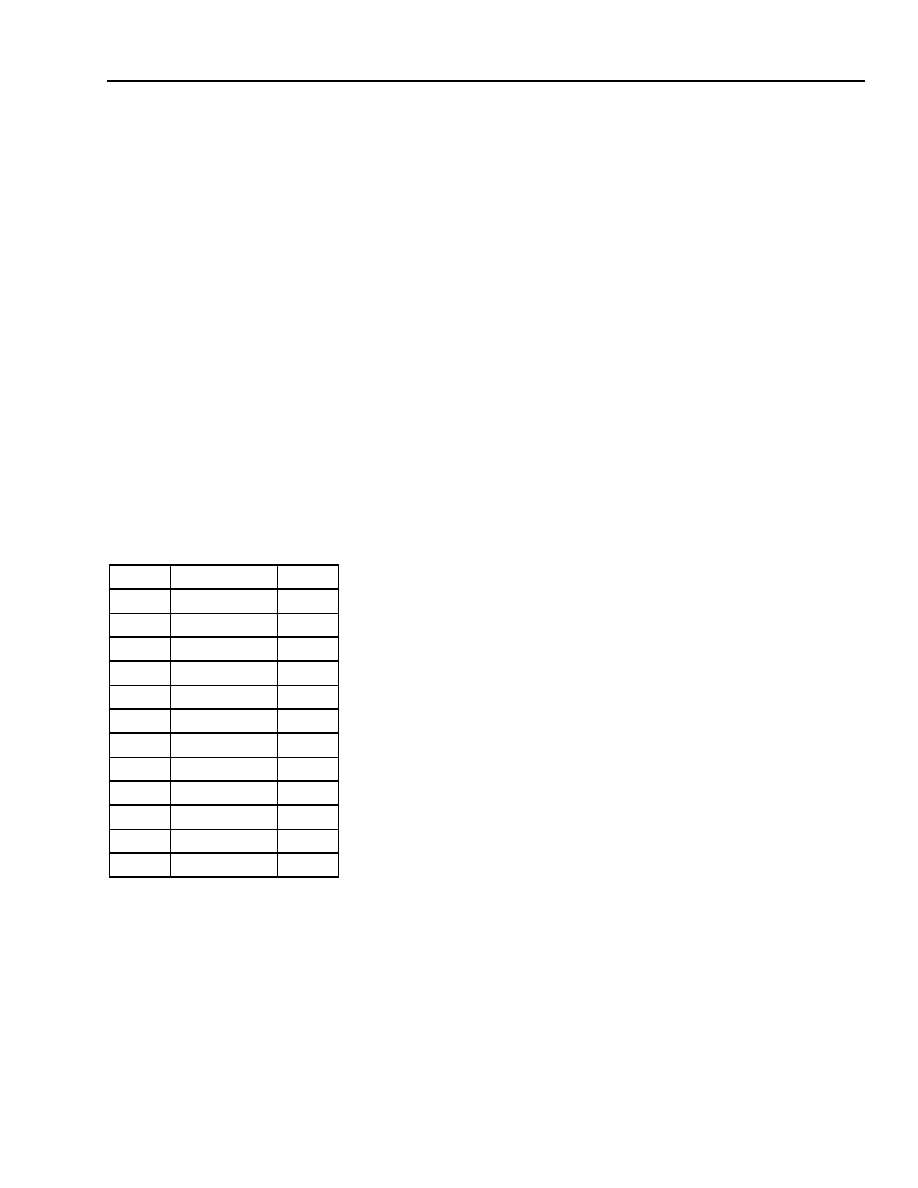

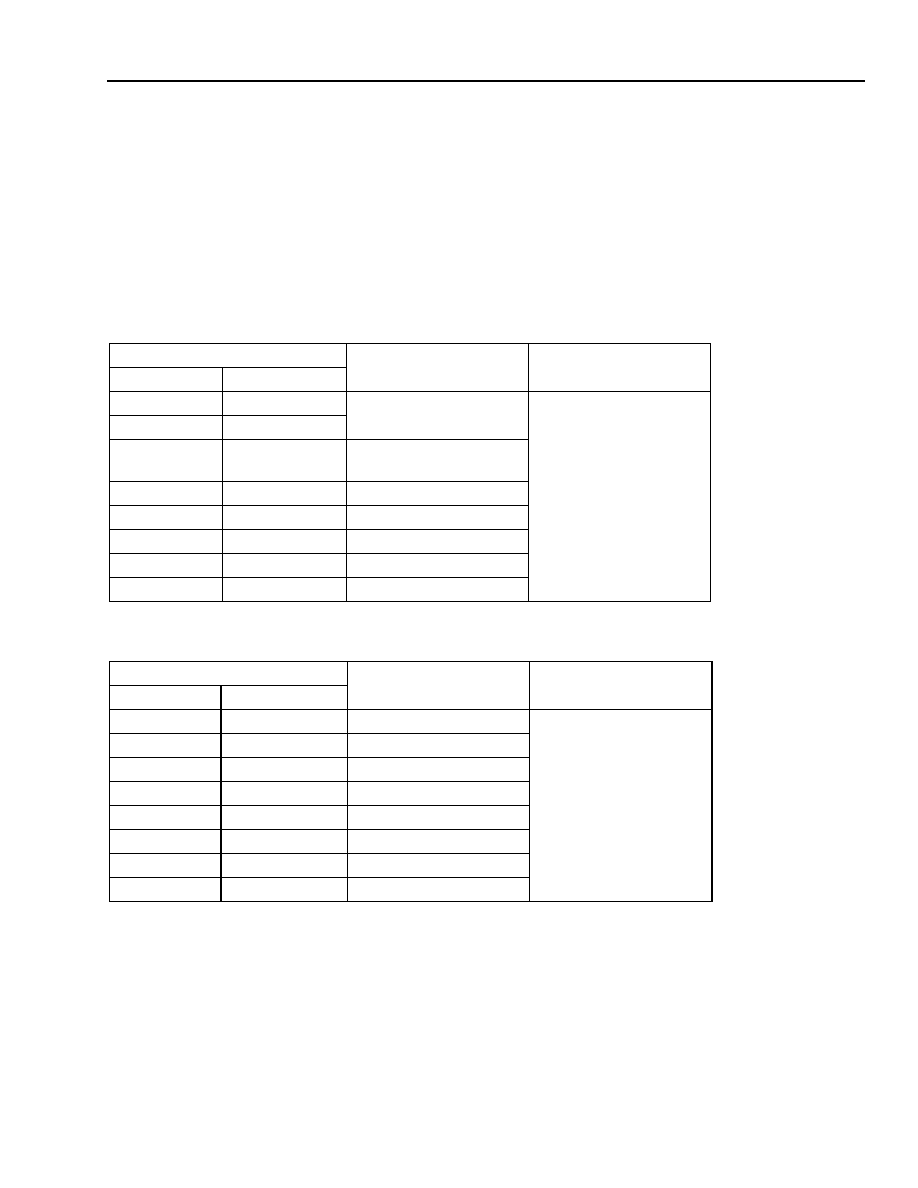

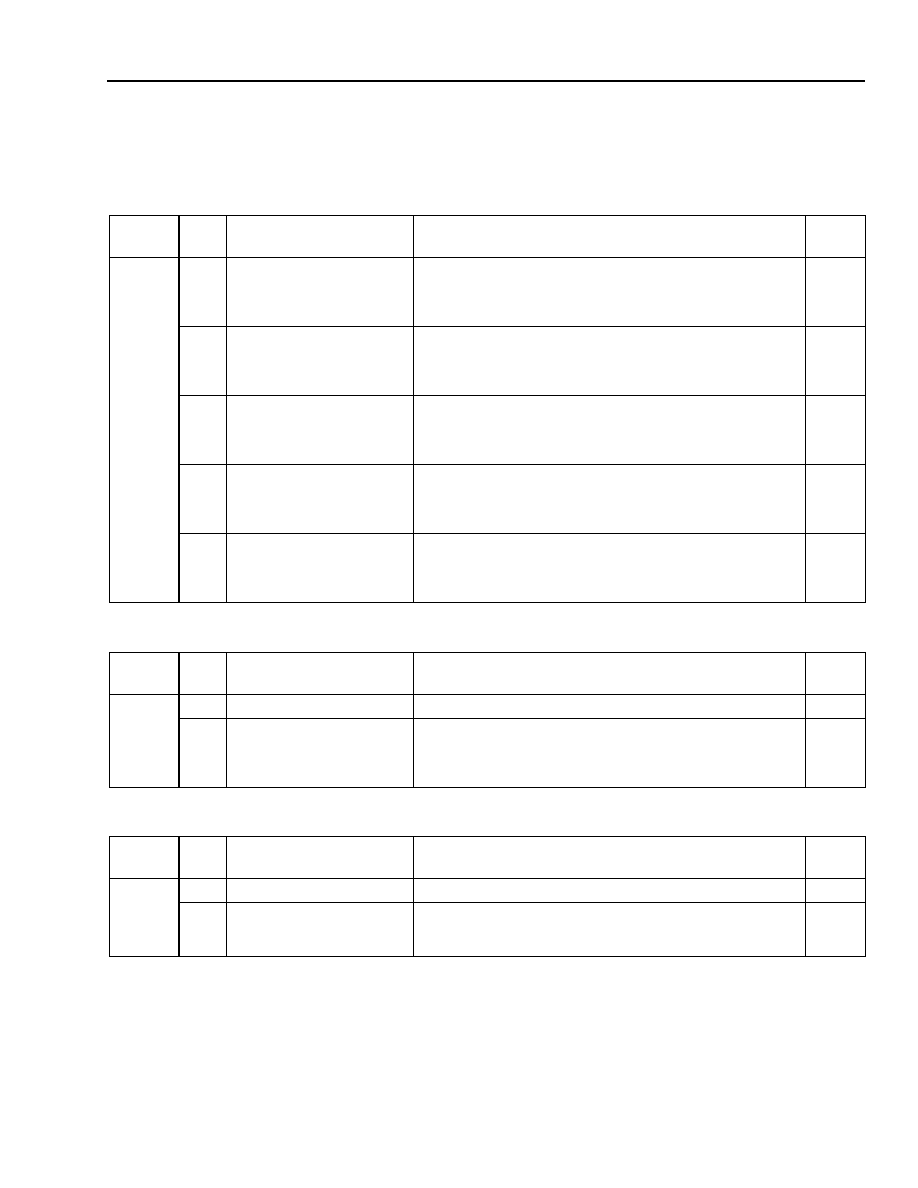

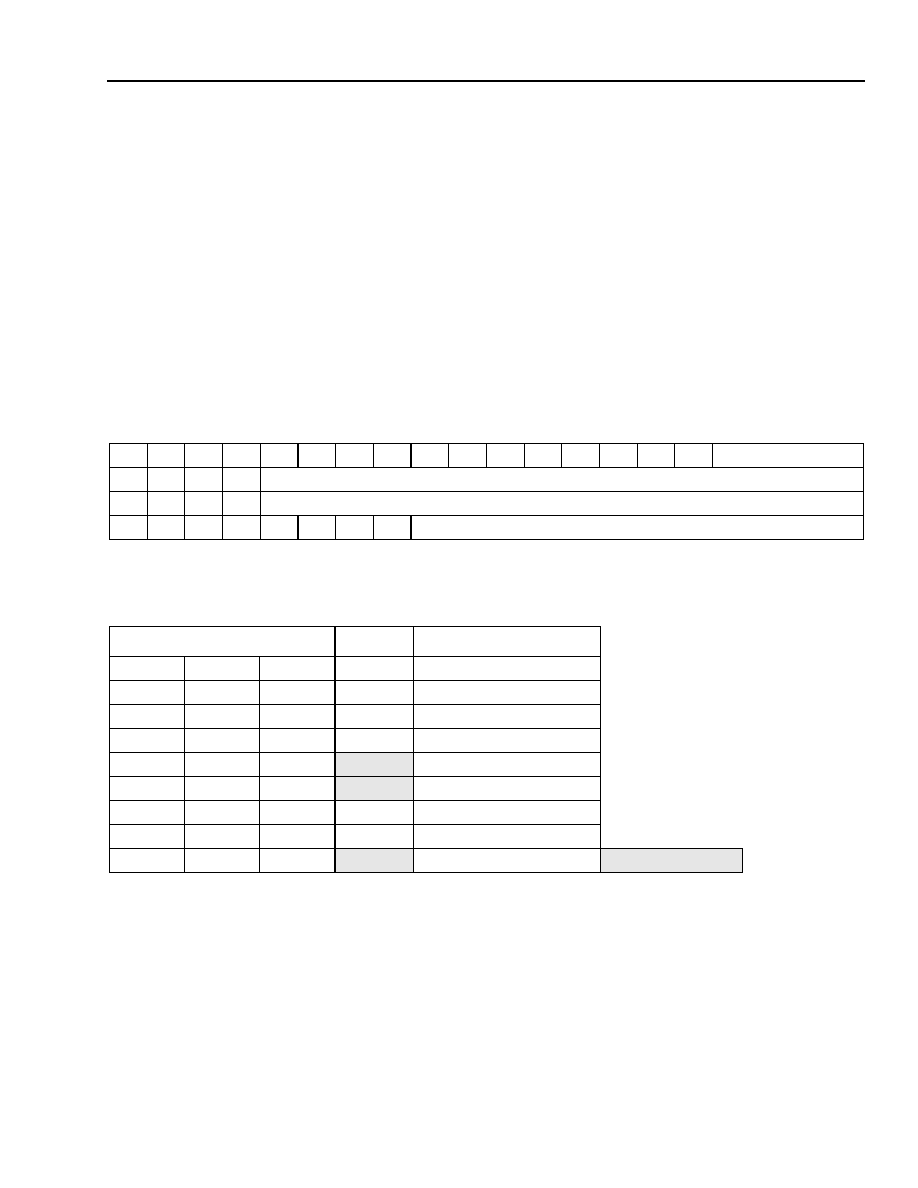

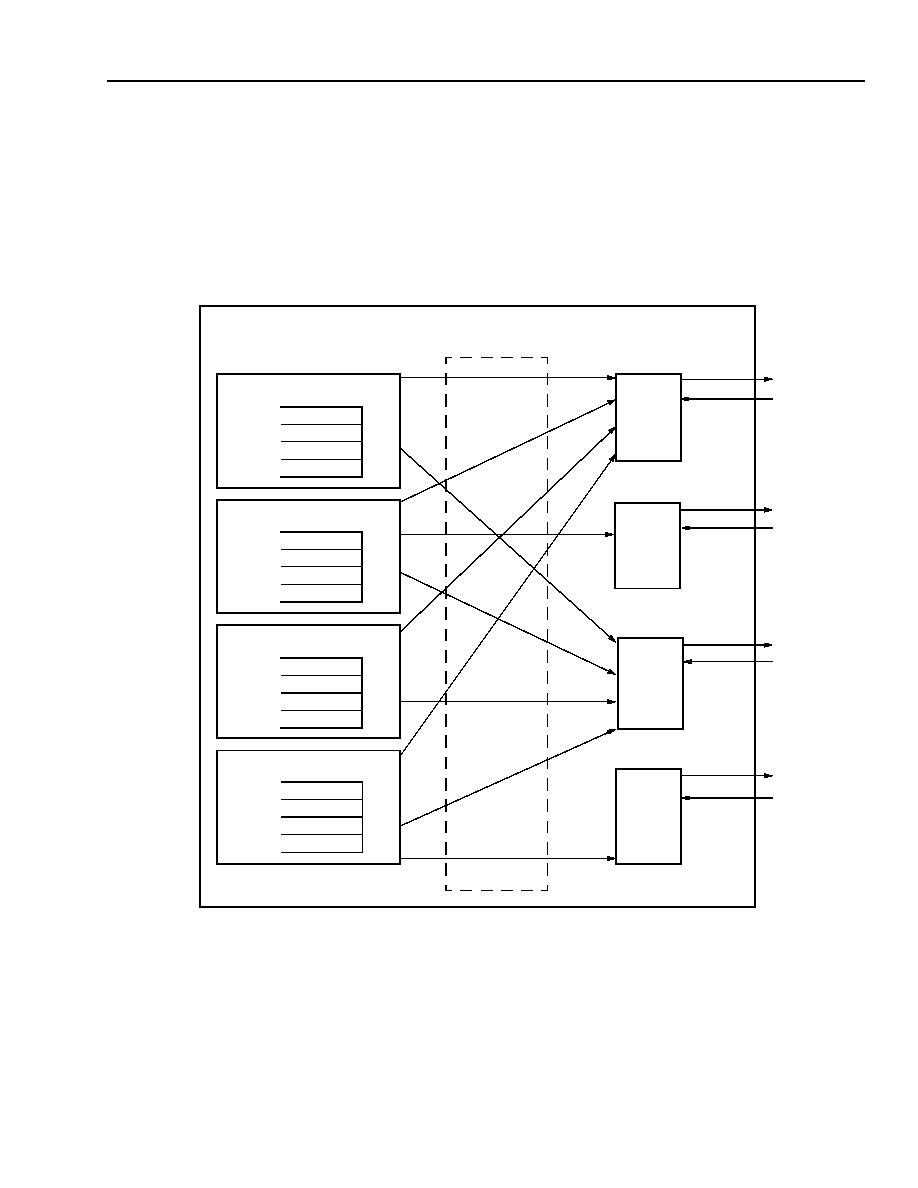

- Table 750. Slices, Channels, and Channel IDs

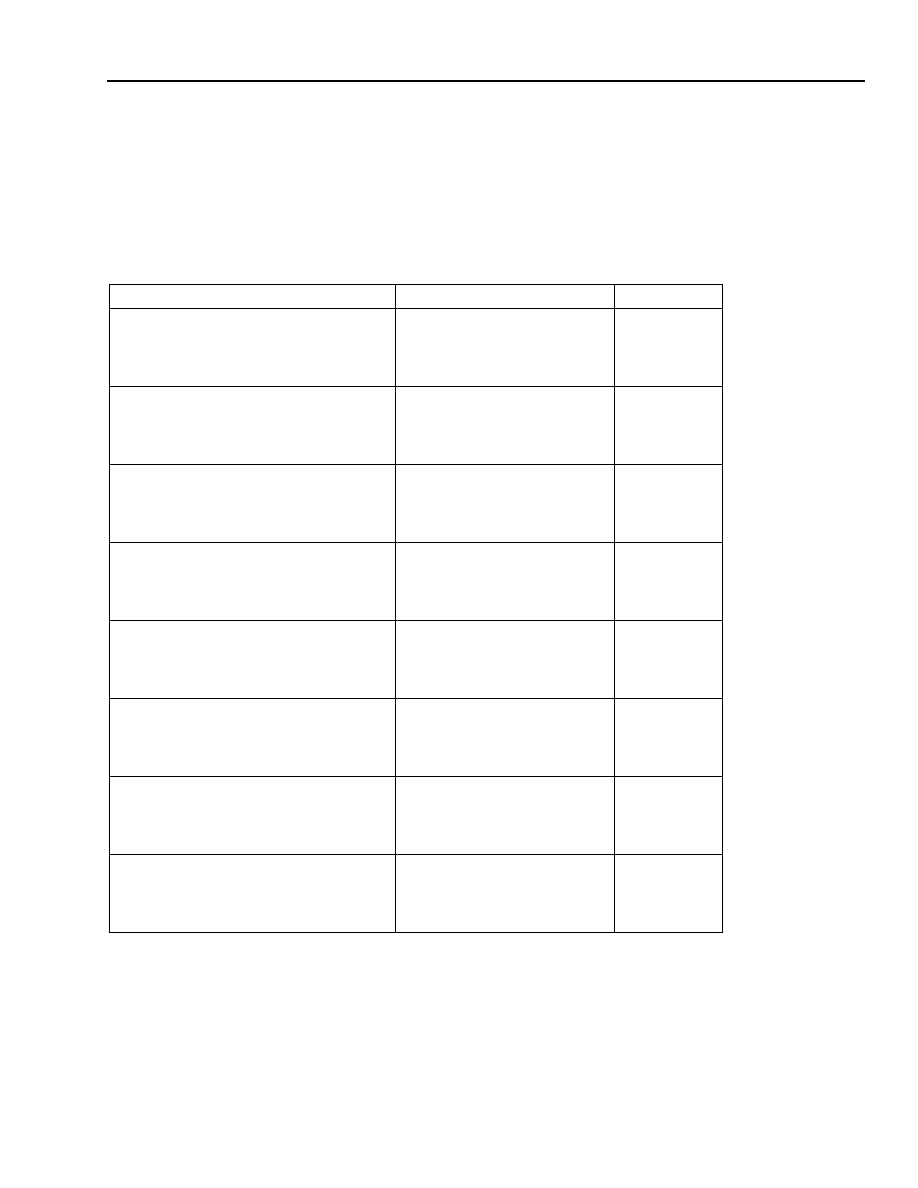

- Table 751. UTOPIA Traffic Types

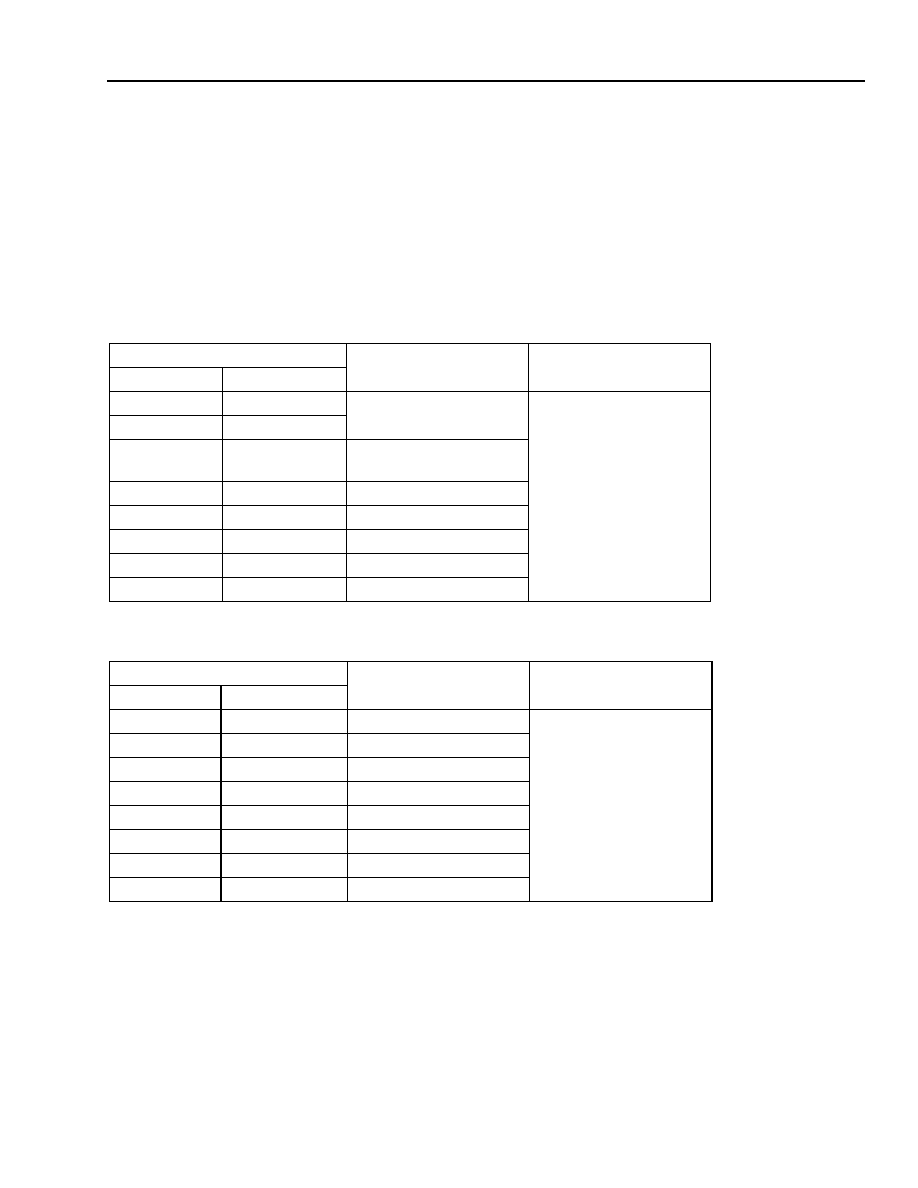

- Table 752. Interface Configurations Supported

- Table 753. UTOPIA Address Modes

- Table 754. MARS2G5 P-ProLT/MARS2G5 P-Pro UTOPIA (Virtual) Address Pin Mappings

- Table 755. PHY Channel Address Allocation Related to Status Signal

- Table 756. UTOPIA Tx Interface Pins that Have Different Meanings in Different Modes

- Table 757. UTOPIA Rx Interface Pins that Have Different Meanings in Different Modes

- Table 758. Channel B0/B1 Ganging Settings for ATM Cells

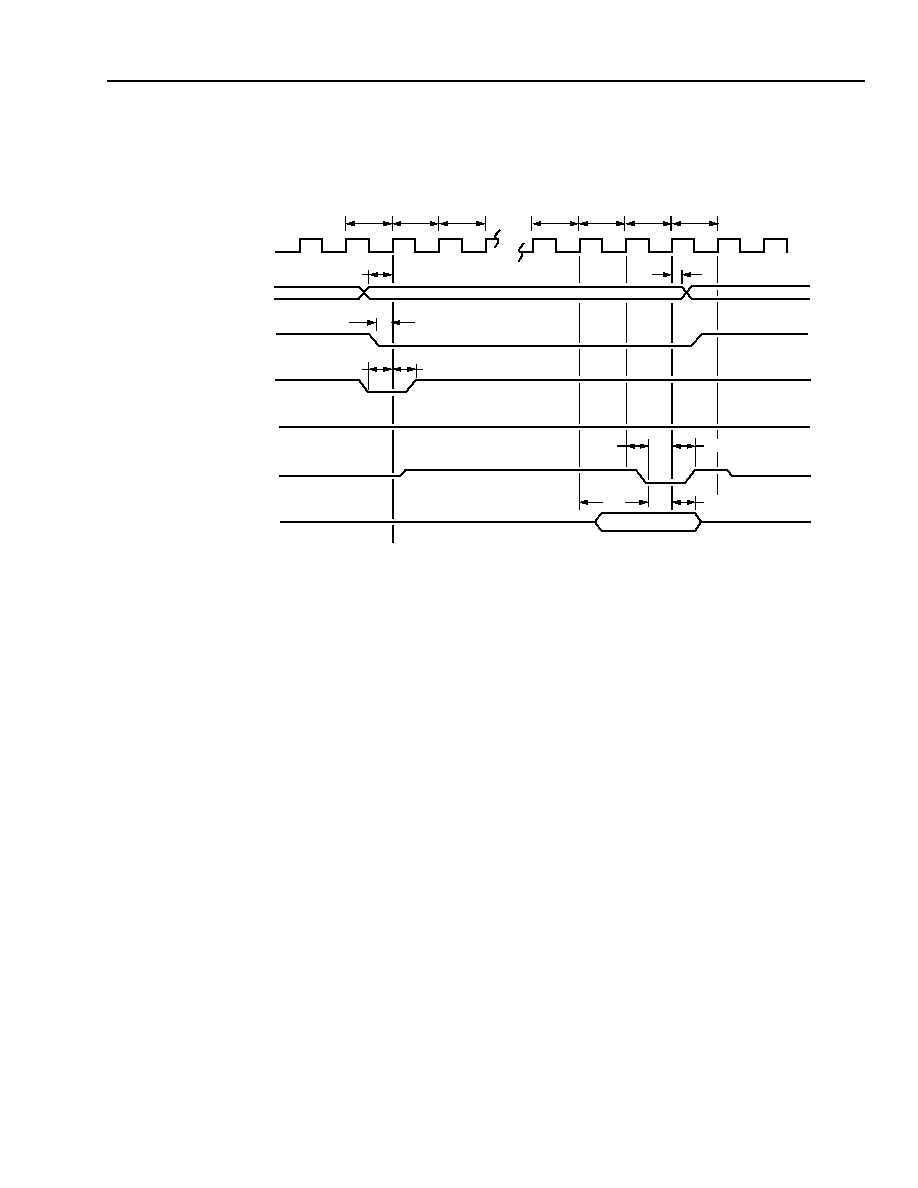

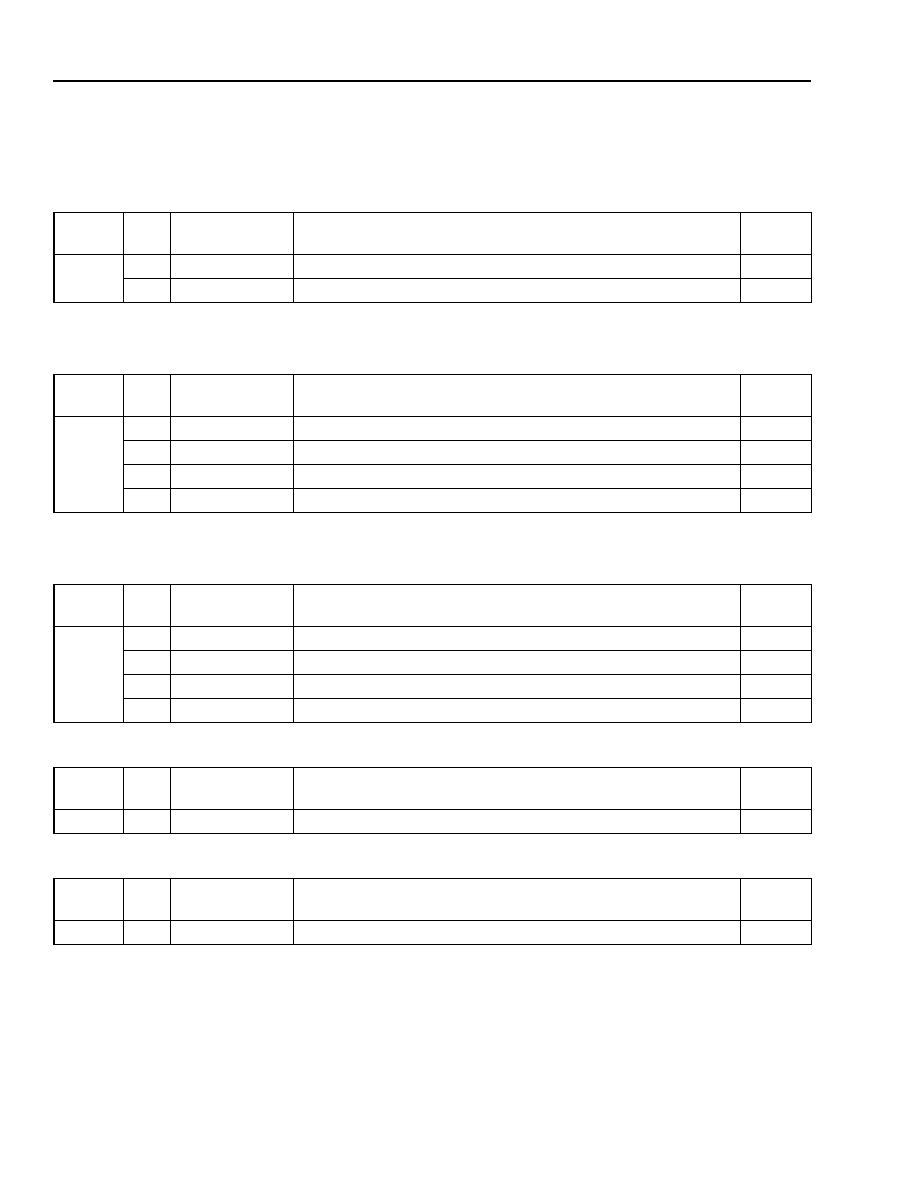

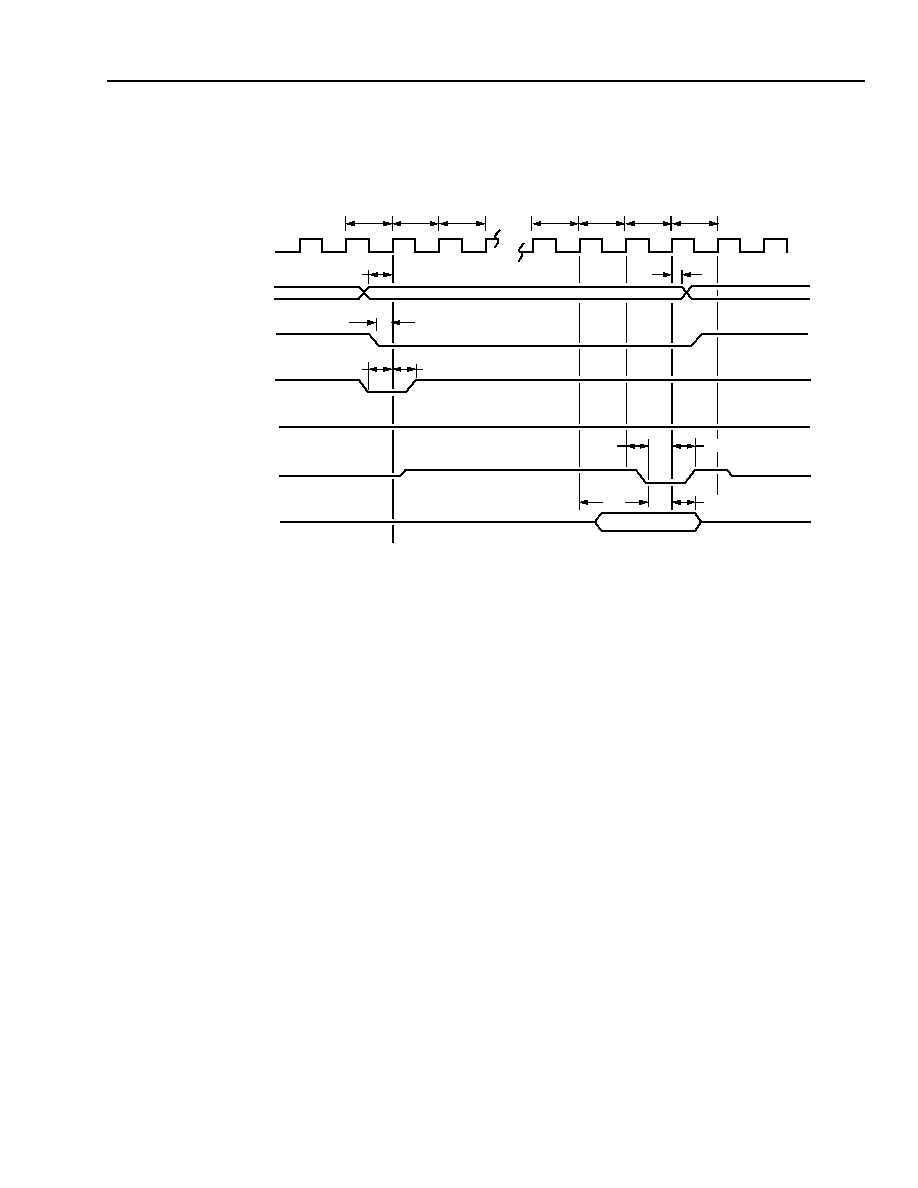

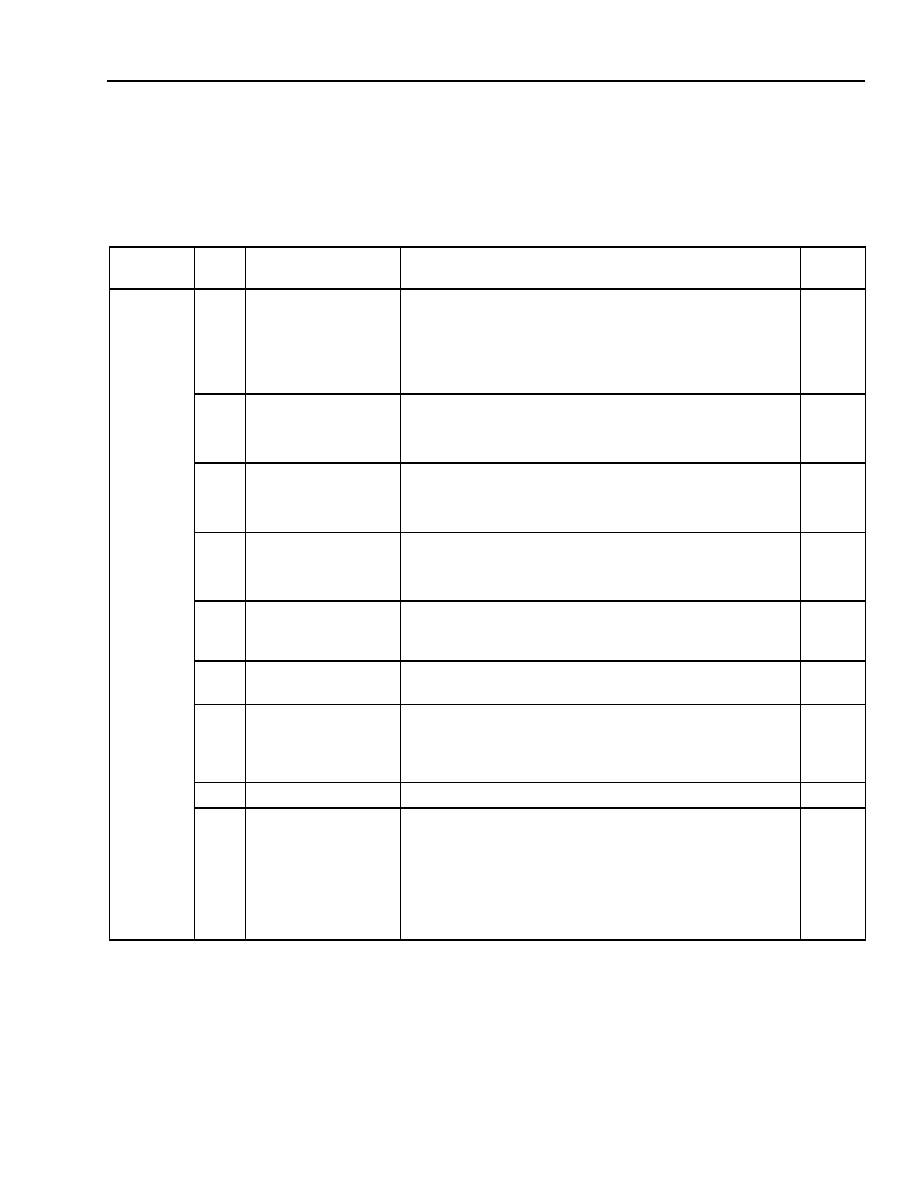

- Table 759. Transmit UTOPIA Interface Timing Specifications

- Table 760. Receive UTOPIA Interface Timing Specifications

- Table 761. UTOPIA Interface Clock Specifications

- Table 762. (UTVER) Version Control (RO)

- Table 763. (XBARCFGRX) Cross-Bar Configuration Register for Rx (R/W)

- Table 764. (XBARCFGTX) Cross-Bar Configuration Register for Tx (R/W)

- Table 765. (INTSTATUS) Interrupts (RO)

- Table 766. (INTMASK) Interrupt Masks (R/W)

- Table 767. (ARST) ARST Register (R/W)

- Table 768. (CORWN) Clear-On-Read or Clear-On-Write Select Register (R/W)

- Table 769. UTOPIA Provisioning Field Description

- Table 770. Rx/Tx UTOPIA Interface A-D Provisioning Registers

- Table 771. (PARERRA_PM) Interface A Error Count in PMRST Mode (RO)

- Table 772. (PARERRA) Interface A Error Count (RO/COR)

- Table 773. (RXMODEA) Rx Interface A Provisioning Registers (R/W)

- Table 774. (TXMODEA) Tx Interface A Provisioning Registers (R/W)

- Table 775. (TxWC[A-D]) Channel A-D Transmit Wait Register (R/W)

- Table 776. UTOPIA Channel [A-D](0-3) Provisioning Registers

- Table 777. (INTA0) Channel A0-Overflow/Underflow (COR/COW)

- Table 778. (INTA0m) Channel A0-Overflow/Underflow Mask (R/W)

- Table 779. (RxProvA0) Channel A0-Provisioning Registers (R/W)

- Table 780. (TxProvA0) Channel A0-Provisioning Registers (R/W)

- Table 781. (RxThA0) Channel A0-Provisioning Registers (R/W)

- Table 782. (TxThA0) Channel A0-Provisioning Registers (R/W)

- Table 783. (RxThMinA0) Channel A0-Provisioning Registers (R/W)

- Table 784. (TxThMaxA0) Channel A0-Provisioning Registers (R/W)

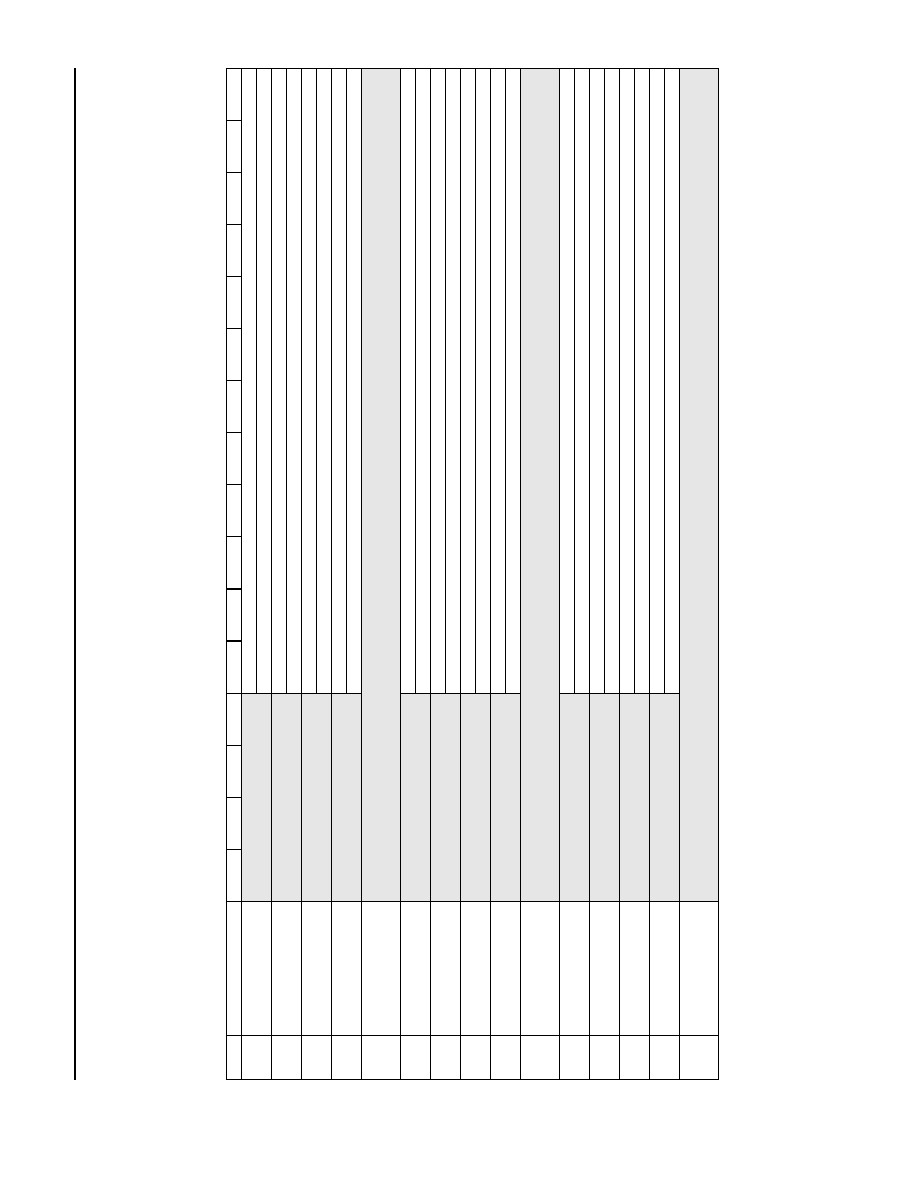

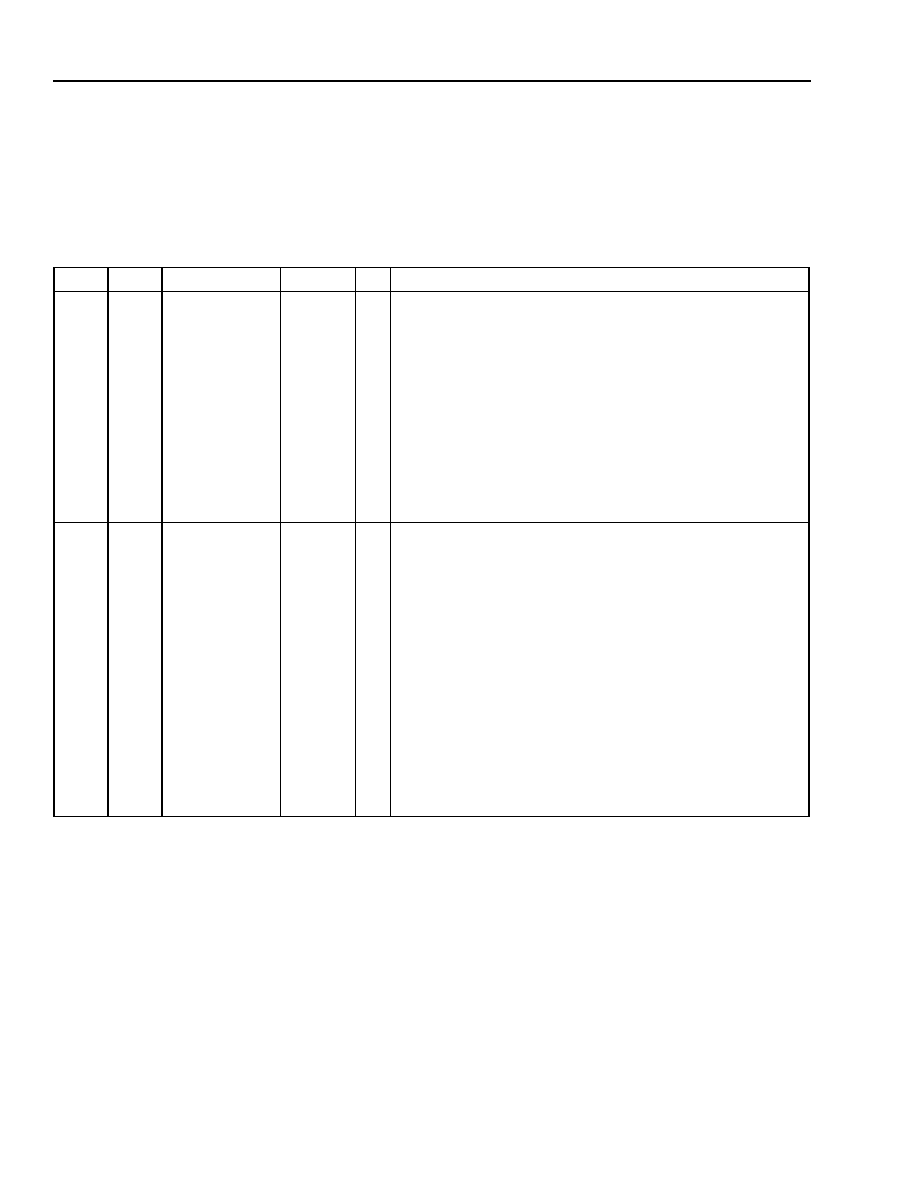

- Table 785. UT Register Map

- Table 786. JTAG ID Register Codings

- Table 787. ESD Threshold Voltage

- Table 788. LVTTL 3.3 V Logic Interface Characteristics

- Table 789. LVPECL 3.3 V Logic Interface Characteristics

- Table 790. Substrate Thickness

- Table 791. Loopback Mode

- Table 792. Connection Memory Map (WO)

- Contact Us

Data Sheet

August 18, 2004

MARS

Æ

2G5 P-Pro (TDAT162G52) SONET/SDH

155/622/2488 Mbits/s Data Interface

Features

One of the next-generation, system-on-a-chip

devices of Agere Systems' multiservice access &

rate solutions MARS

TM

family of framers.

Transmission convergence and SONET/SDH ter-

minal functionality for linear networks.

Versatile IC supports 155/622/2488 Mbits/s

SONET/SDH interface solutions for packet over

SONET (POS), packet over fiber (POF), or asyn-

chronous transfer mode (ATM) applications.

Low-power 1.6 V/3.3 V operation.

SONET/SDH Interface

Termination of quad STS-3/STM-1,

quad STS-12/STM-4, or single STS-48/STM-16.

Supports overhead processing for transport and

path overhead bytes.

Optional insertion and extraction of overhead bytes

via serial overhead interface.

STS pointer processing to align the receive frame

to the system frame.

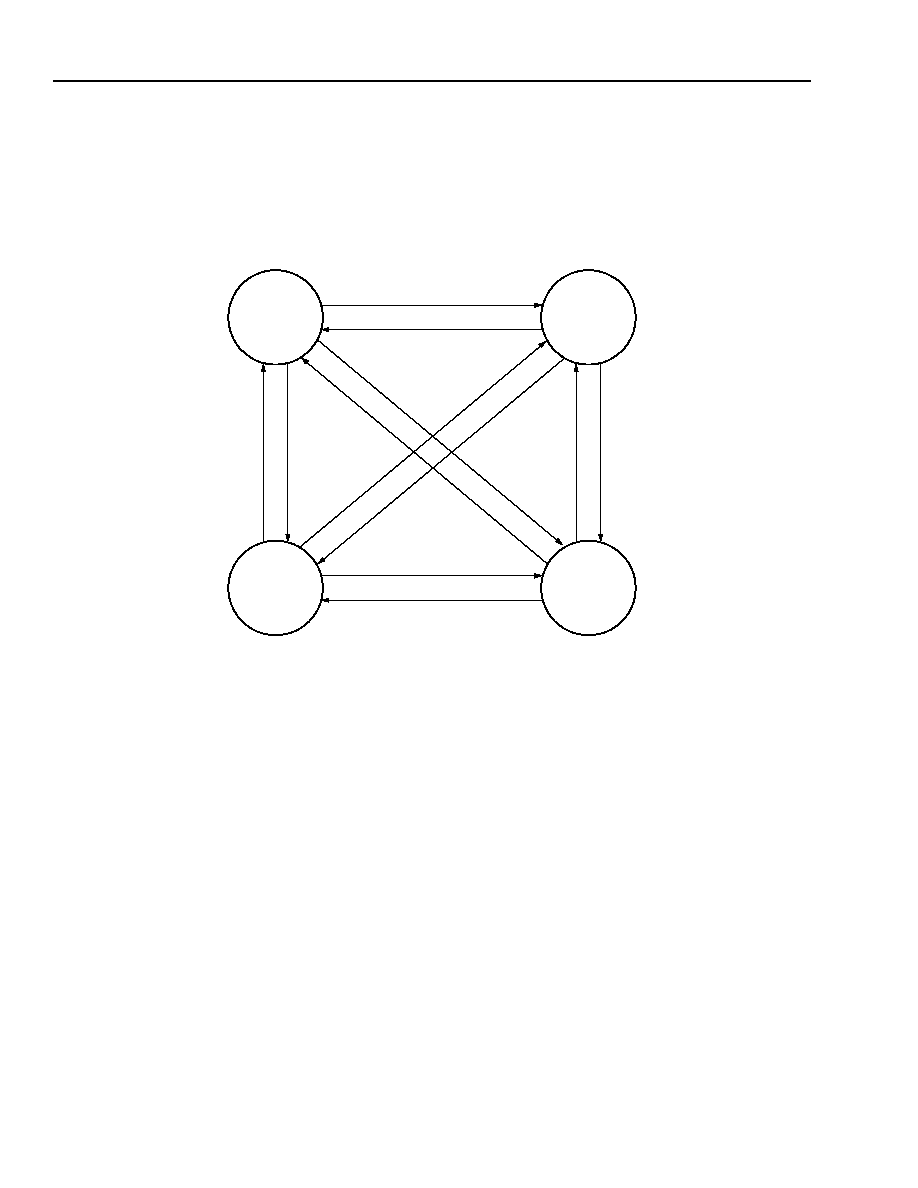

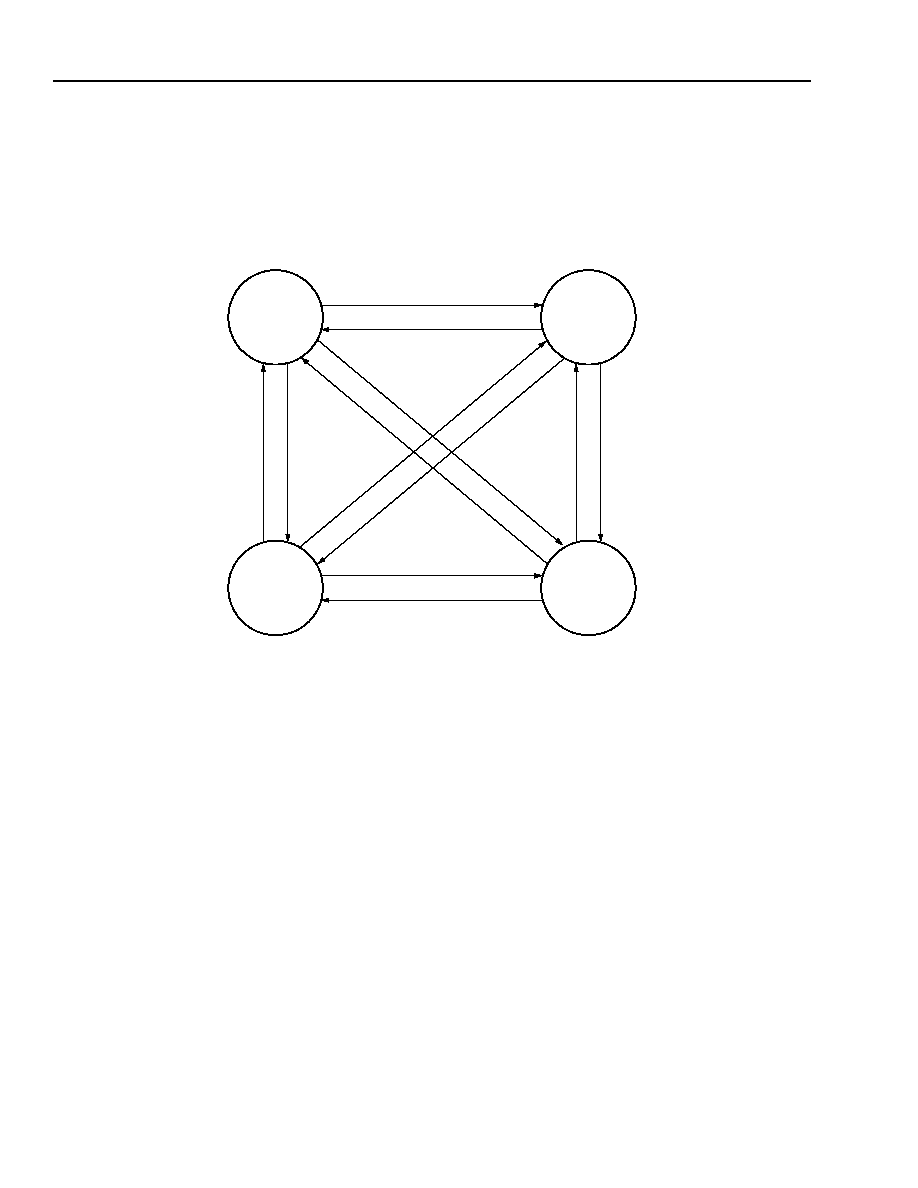

Support for 1 + 1 and 1:1 linear networks.

Full path termination and SPE extraction/insertion.

SONET/SDH compliant condition and alarm

reporting.

Handles all concatenation levels of STS-3c to

STS-48c (in multiples of 3: e.g., 3c, 6c, 9c, etc.).

Built-in diagnostic loopback modes.

Compliant with the following Telcordia Technolo-

gies

Æ

, ANSI

Æ

, and ITU standards:

-- GR-253 CORE: SONET Transport Systems:

Common Generic Criteria.

-- ITU-T G.707: Network Node Interface for the

Synchronous Digital Hierarchy.

-- ITU-T G.803: Architecture of Transport Net-

works Based on the Synchronous Digital Hierar-

chy.

-- T1.105: SONET-Basic Description including

Multiplex Structure, Rates, and Formats.

-- T1.105.02 SONET-Payload Mappings.

-- T1.105.03 SONET-Jitter at Network Interfaces.

-- T1.105.06 SONET Physical Layer Specifica-

tions.

-- T1.105.07 SONET-Sub-STS-1 Interface Rates

and Formats Specification.

-- ITU-T I.432: B-ISDN User-Network Interface-

Physical Layer Specification.

-- IETF RFC 2615: PPP over SONET/SDH.

-- IETF RFC 1661: The Point-to-Point Protocol

(PPP).

-- IETF RFC 1662: PPP in HDLC-like Framing.

Data Processing

Provisionable data engine supports payload inser-

tion/extraction for PPP, ATM, or HDLC streams.

Extraction and insertion of DS3 frames containing

HDLC or ATM data streams for up to 16 channels.

Integrated UTOPIA Level 2 and Level 3 compatible

physical layer interface for packets or ATM cells.

Provides/supports internal E3 mapping.

Supports DS3/PLCP and clear channel DS3 map-

ping.

Insertion and extraction of up to 16 separate data

channels.

Direct cell/packet over fiber interface device.

Compliant with ATM forum, ITU standards, and

IETF standards.

Supports generic framing procedure (GFP) proto-

col.

Interfaces

Enhanced UTOPIA interface for cell and packet

transfer.

IEEE

Æ

1149.1 port with BIST, scan, and boundry

scan.

Microprocessor Interface

Up to 66 MHz synchronous.

16-bit address and 16-bit data interface.

Synchronous or asynchronous modes available.

Configurable to operate with most commercial

microprocessors.

MARS2G5 P-Pro (TDAT162G52) SONET/SDH

Data Sheet

155/622/2488 Mbits/s Data Interface

August 18, 2004

2

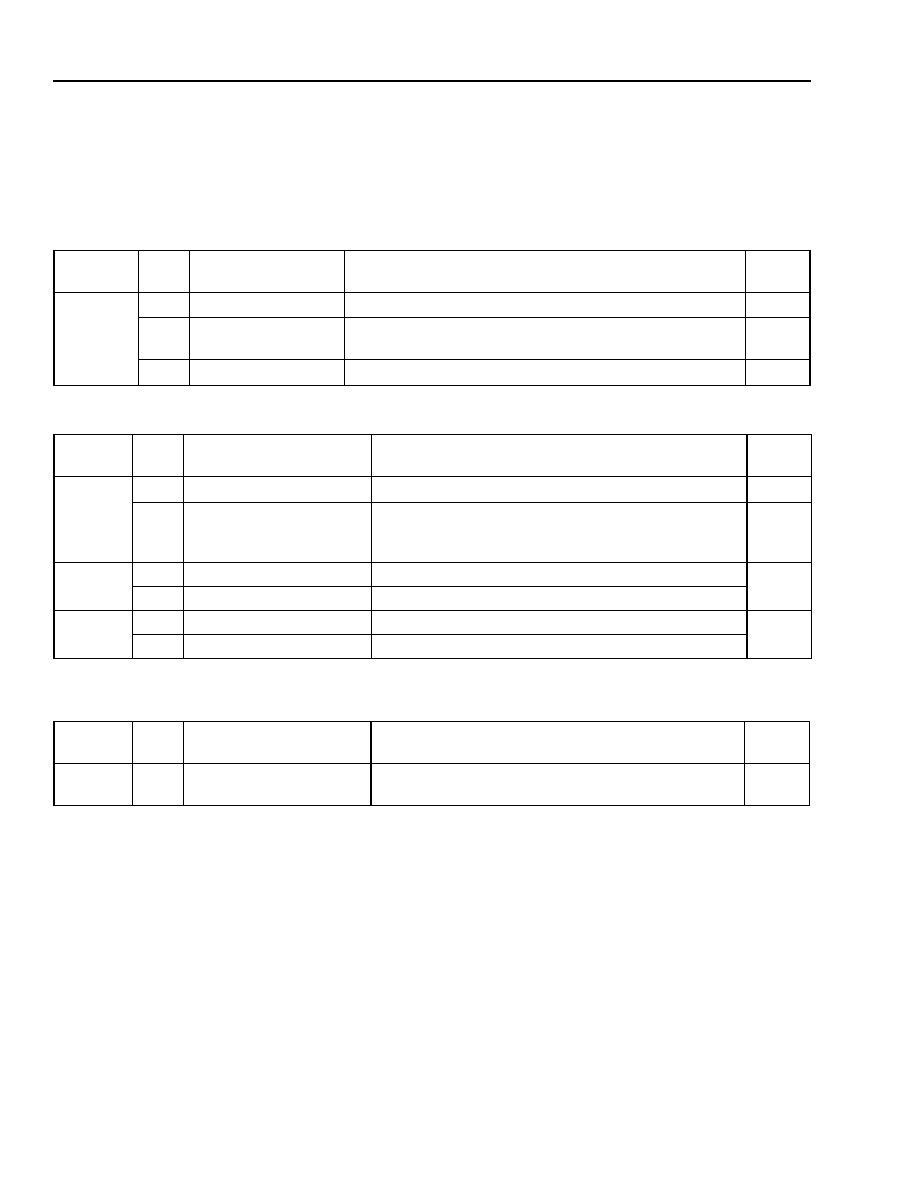

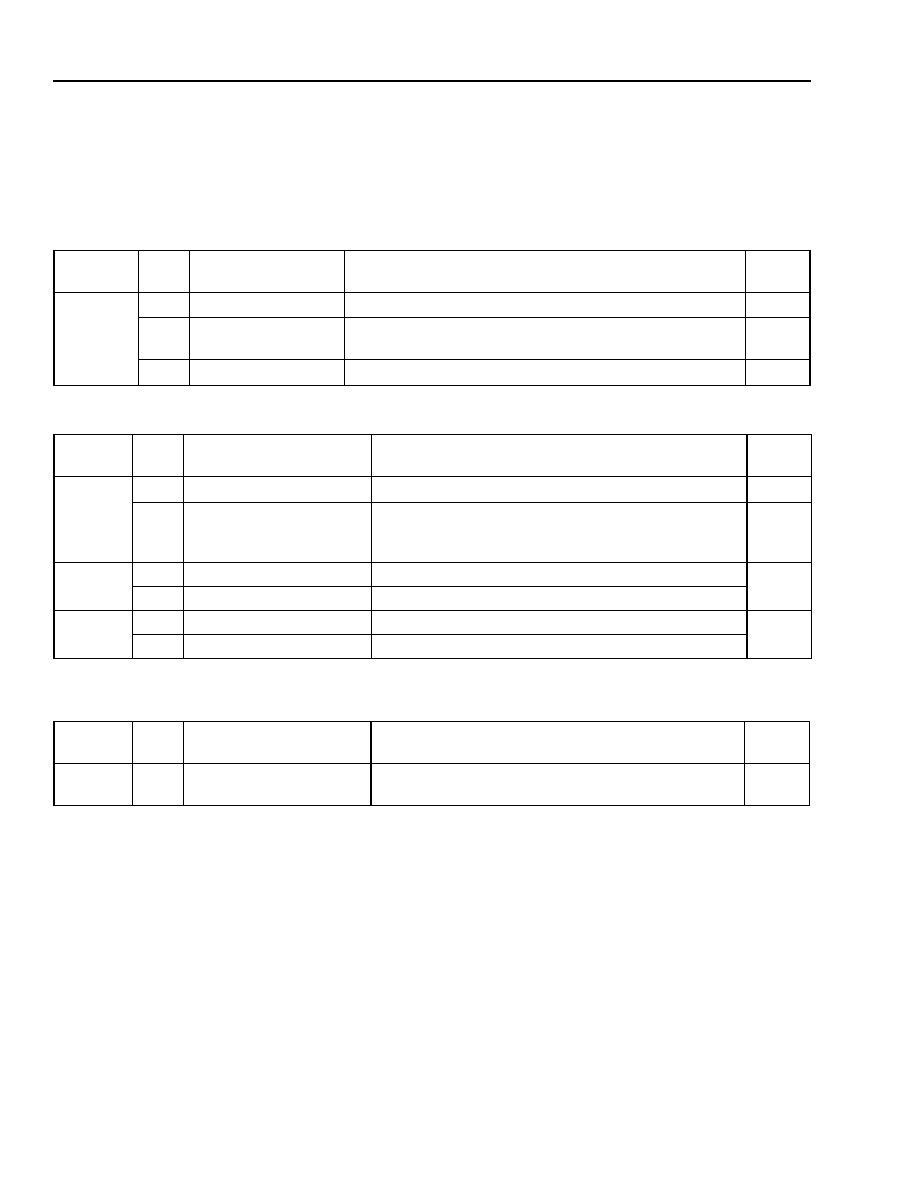

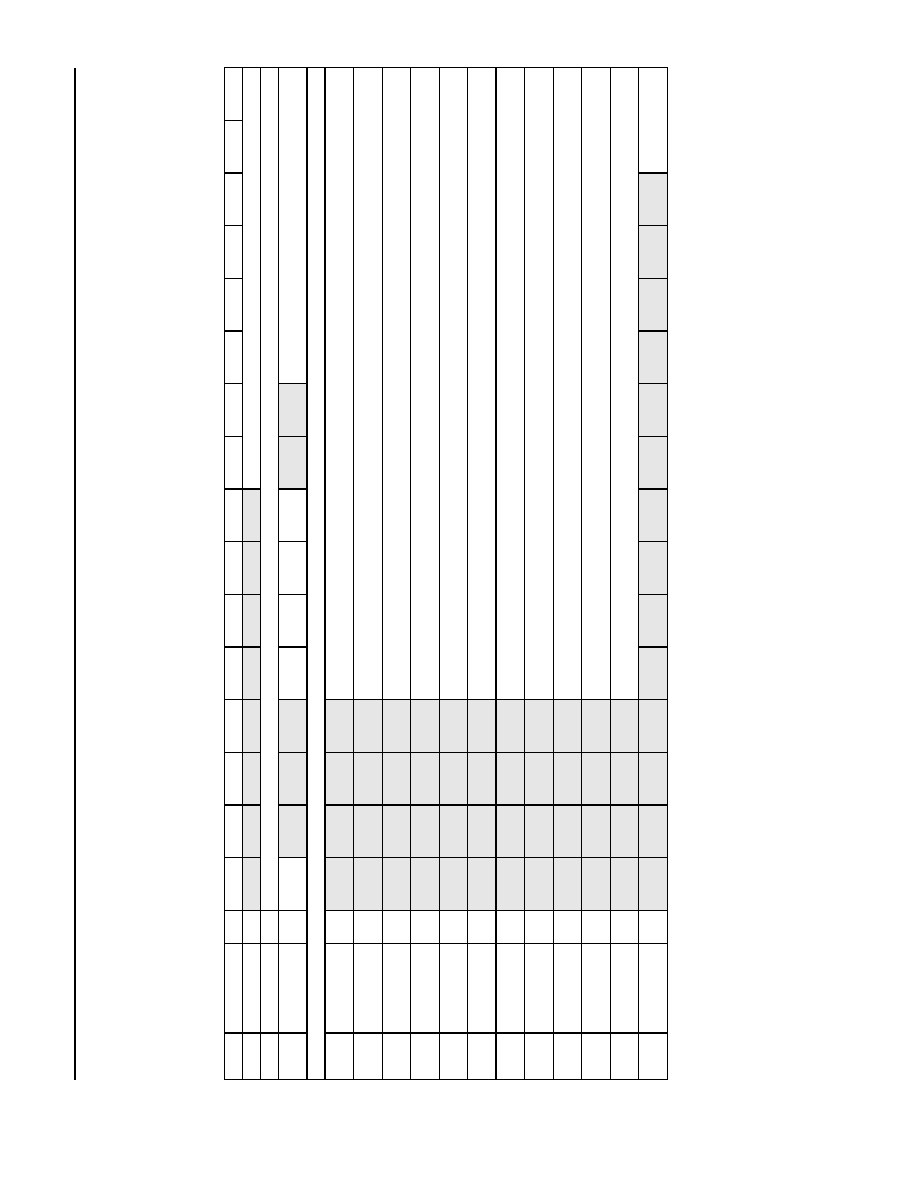

Table of Contents

Contents

Page

Agere Systems Inc.

Features ................................................................................................................................................................... 1

SONET/SDH Interface ....................................................................................................................................... 1

Data Processing................................................................................................................................................. 1

Interfaces ........................................................................................................................................................... 1

Microprocessor Interface ................................................................................................................................... 1

Description.............................................................................................................................................................. 27

Generic Framing Procedure (GFP) .................................................................................................................. 28

Target Applications Supported ............................................................................................................................... 29

MARS2G5 P-Pro (600-Pin LBGA and 792-Pin PBGA) .................................................................................... 29

MARS1G2 P-Pro (TDAT161G2) (792-Pin PBGA) ........................................................................................... 30

MARS622 P-Pro (TDAT12622) (792-Pin PBGA) ............................................................................................. 31

Overview................................................................................................................................................................. 32

Clocking ........................................................................................................................................................... 34

MARS2G5 P-Pro (792-Pin PBGA) Low-Speed Devices Available......................................................................... 36

MARS1G2 P-Pro (TDAT161G2) (792-Pin PBGA) ........................................................................................... 36

MARS622 P-Pro (TDAT12622) (792-Pin PBGA) ............................................................................................. 36

MARS2G5 P-Pro Device Product Line Table Summaries...................................................................................... 37

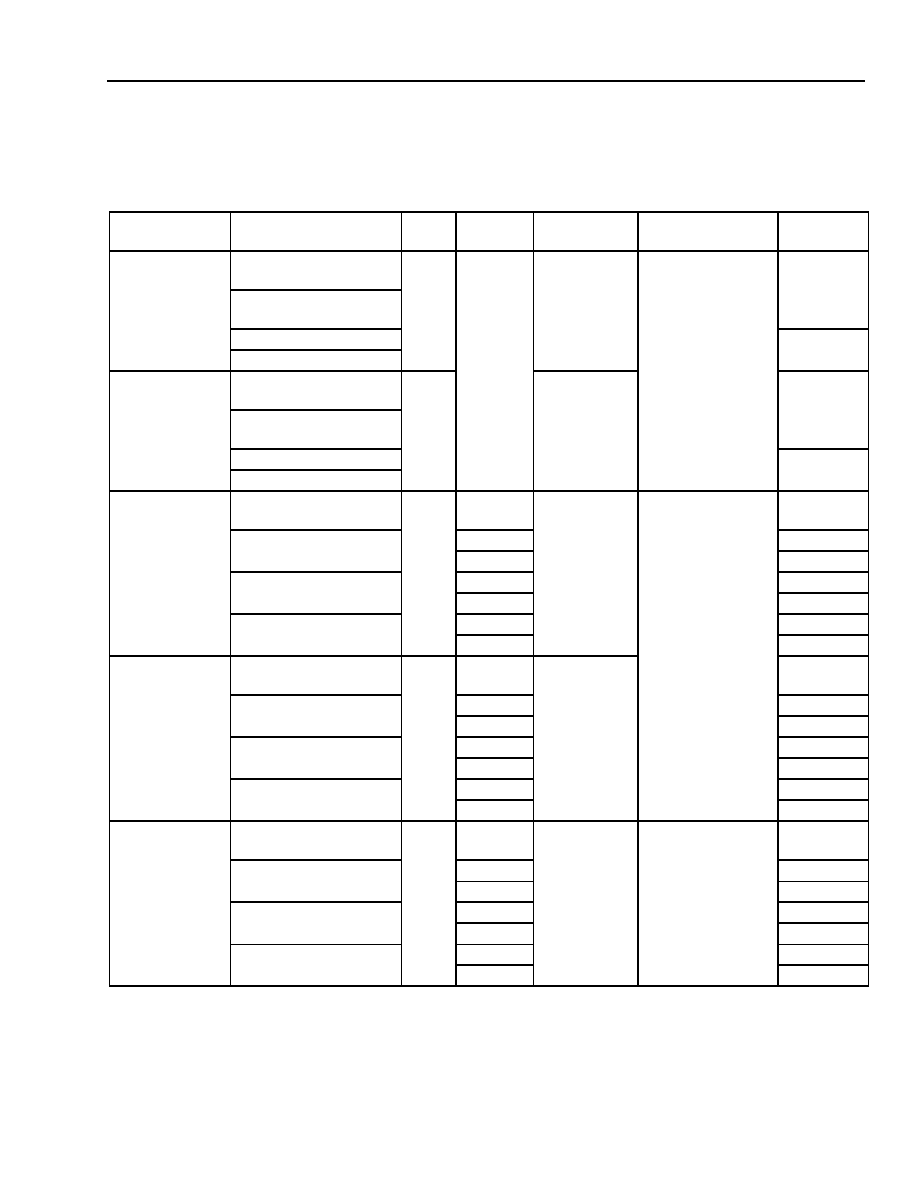

Pin Information ....................................................................................................................................................... 38

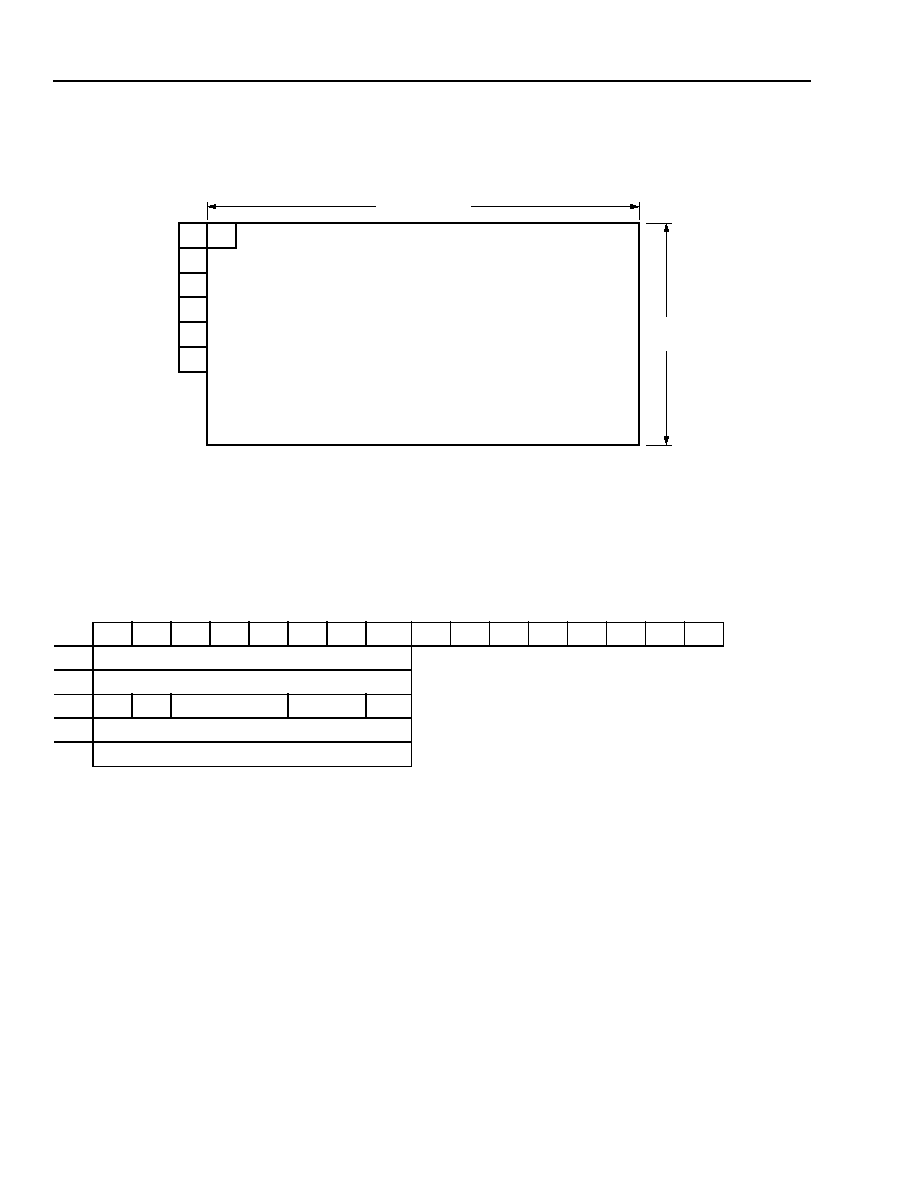

792-Pin PBGA Pin Assignments ...................................................................................................................... 38

600-Pin LBGA Pin Assignments ...................................................................................................................... 87

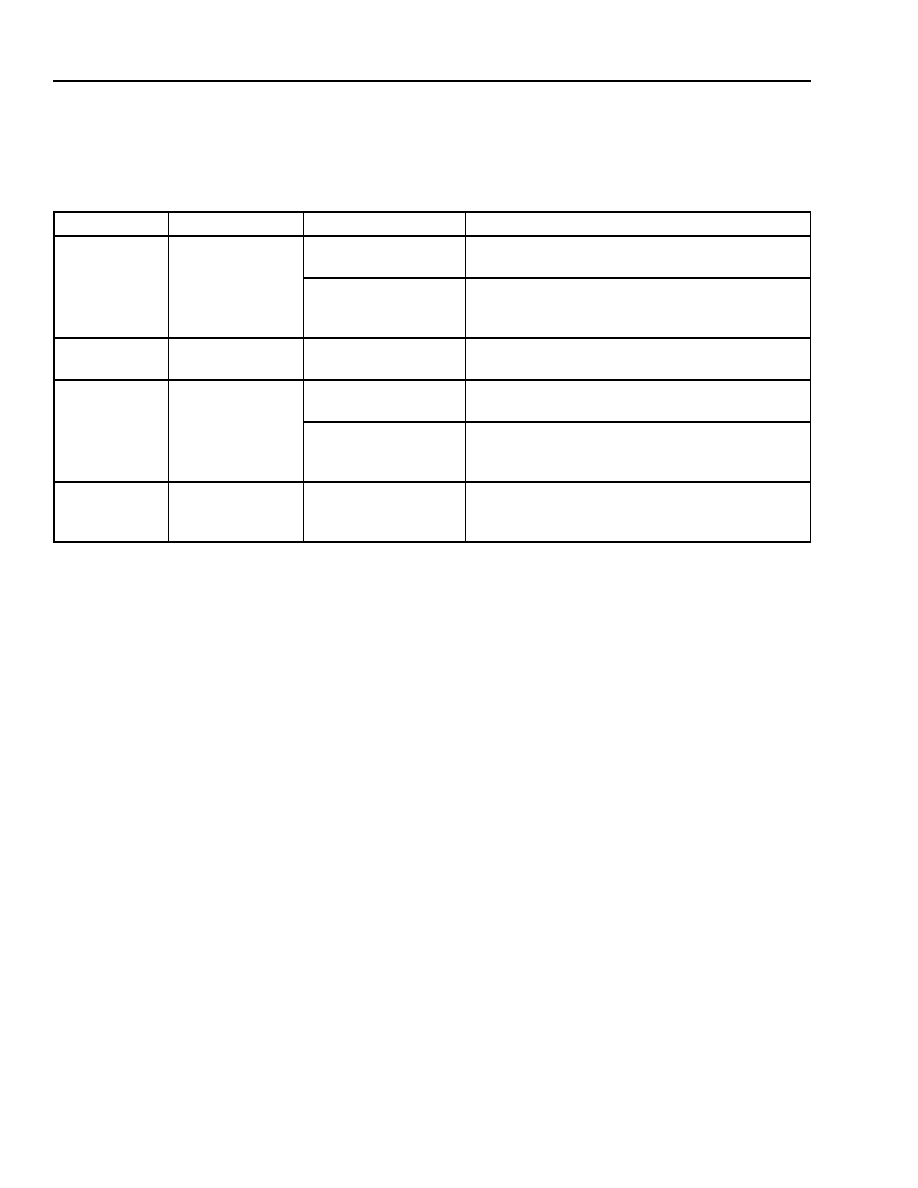

Pin Descriptions...................................................................................................................................................... 97

Microprocessor (MPU) Interface........................................................................................................................... 123

Device Address Space Assignments ............................................................................................................. 123

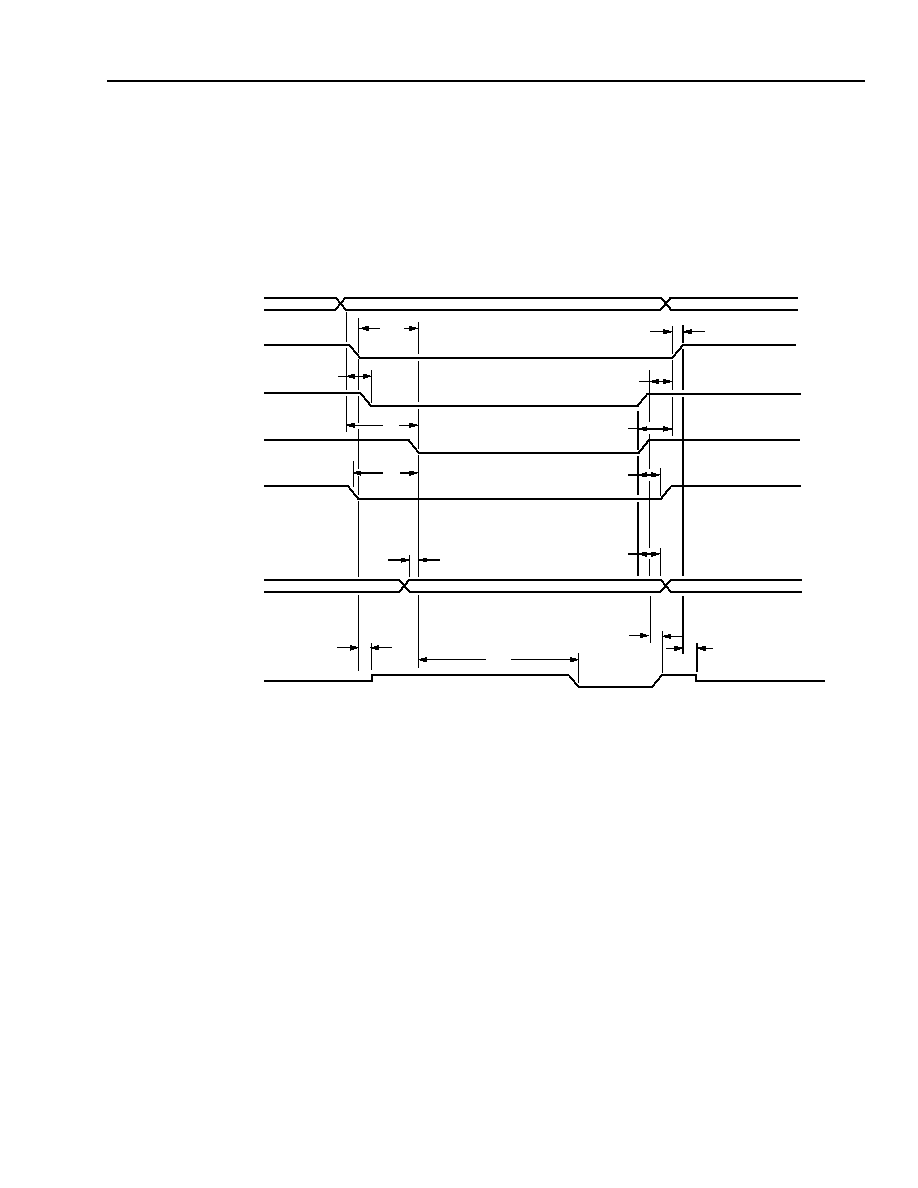

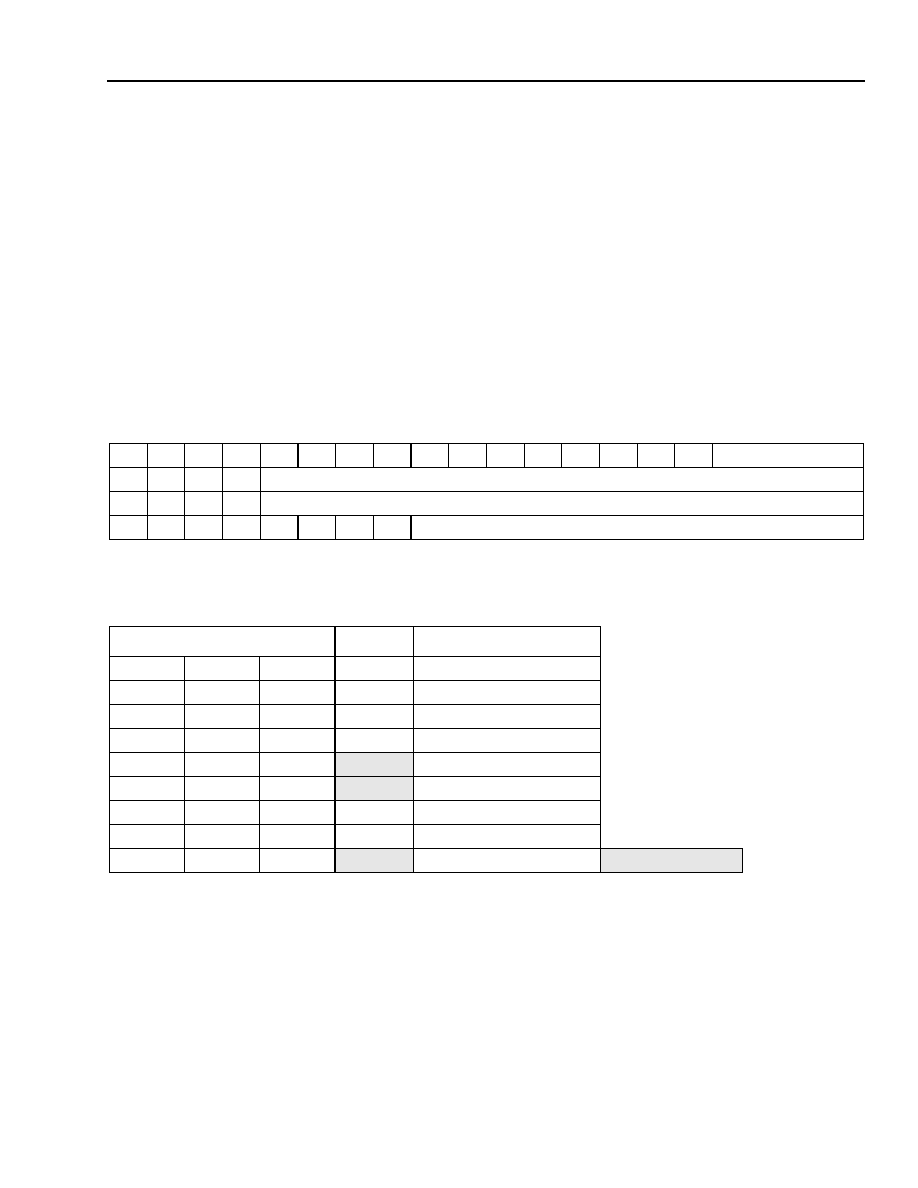

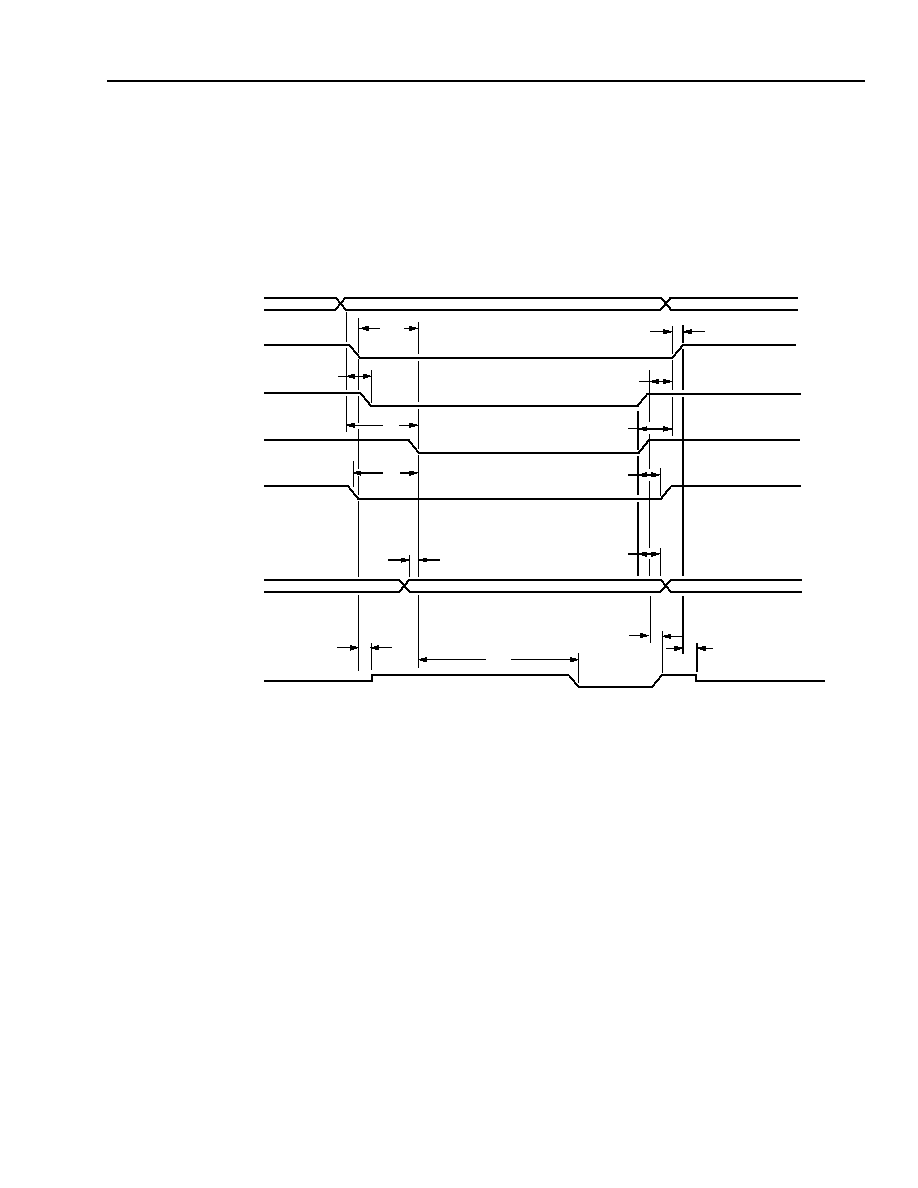

Microprocessor Interface Modes.................................................................................................................... 124

Microprocessor Interface Timing.................................................................................................................... 125

Necessary Register Provisioning Sequence and Clocks ............................................................................... 133

Clocks Required for MPU Read or Write of MARS2G5 P-Pro Registers....................................................... 134

Performance Monitor (PM) Reset .................................................................................................................. 158

General-Purpose Input/Output Interface ........................................................................................................ 160

Interrupts ........................................................................................................................................................ 162

Loopback Operation....................................................................................................................................... 163

MPU Register Descriptions ............................................................................................................................ 164

MPU Register Map......................................................................................................................................... 173

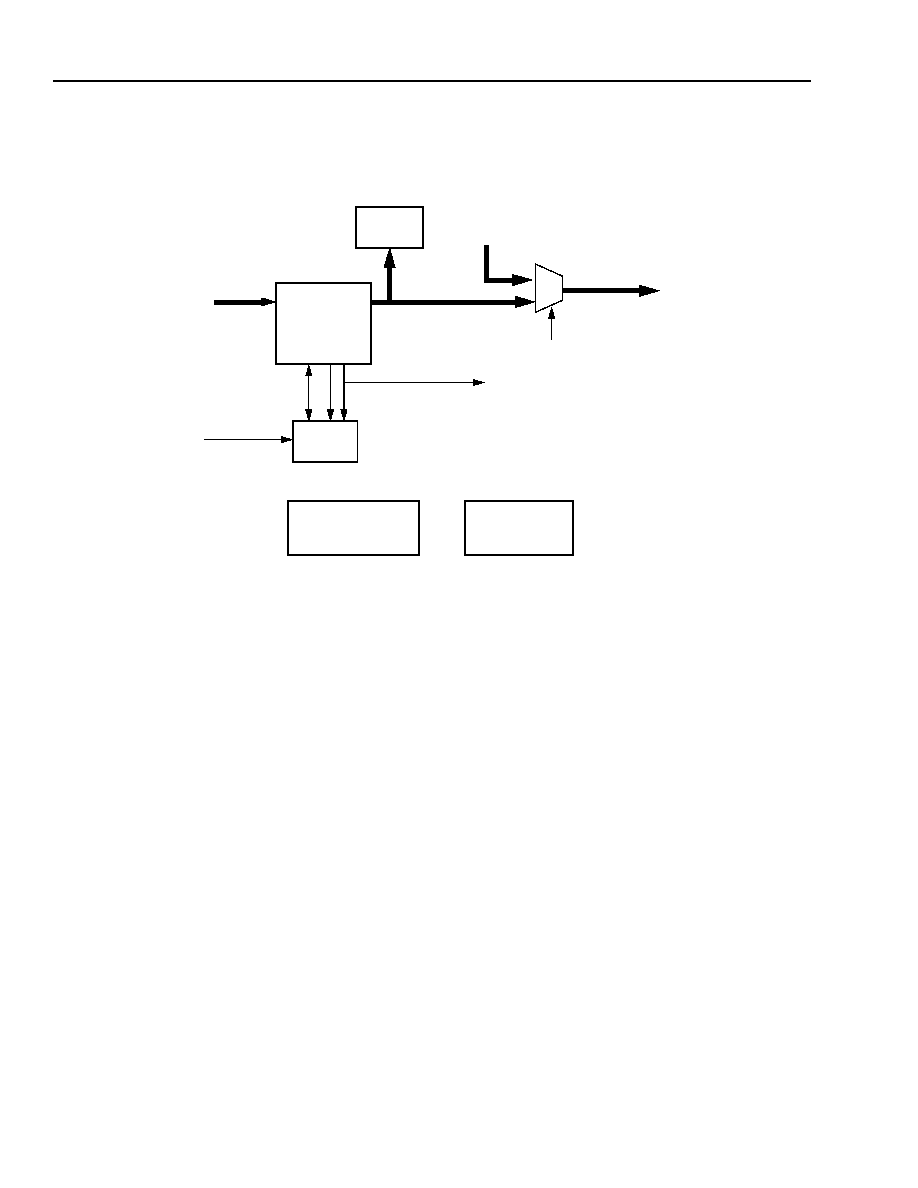

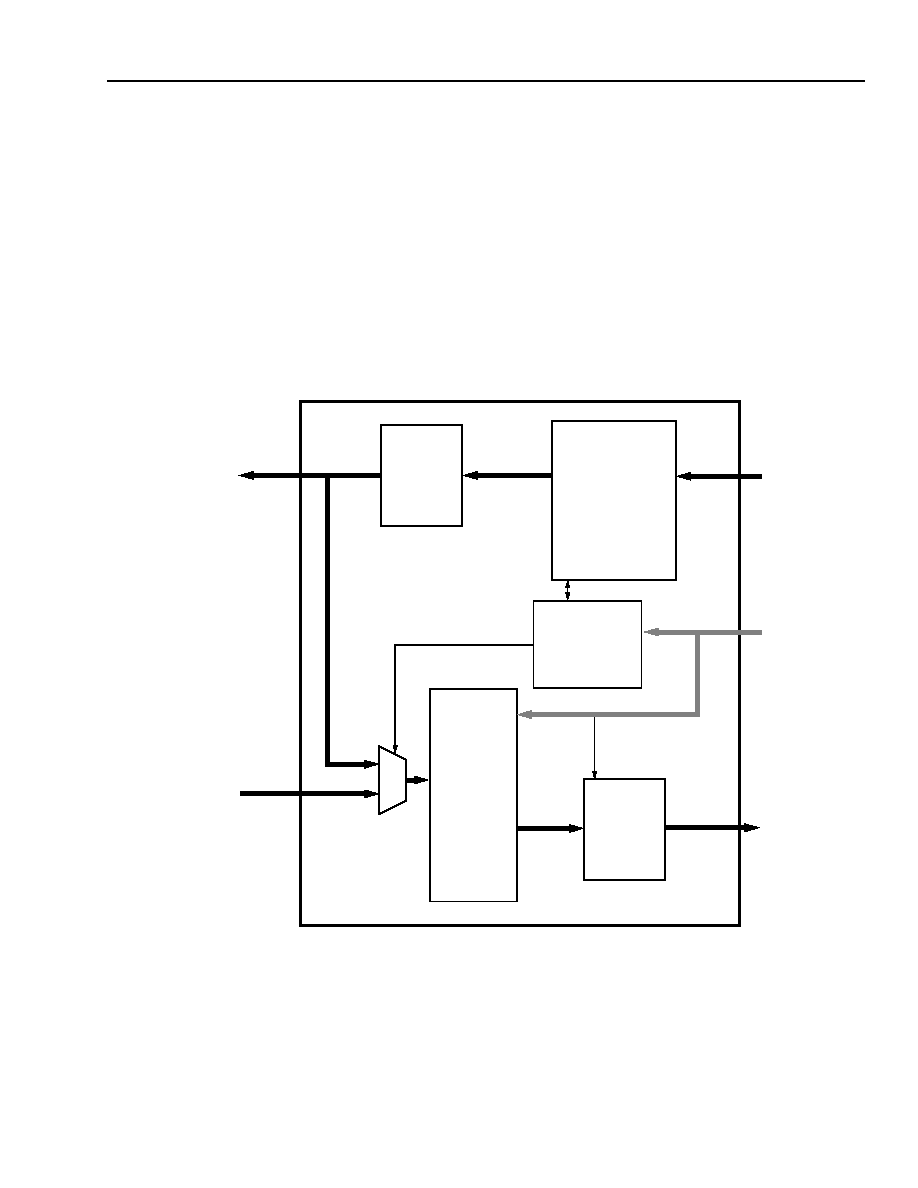

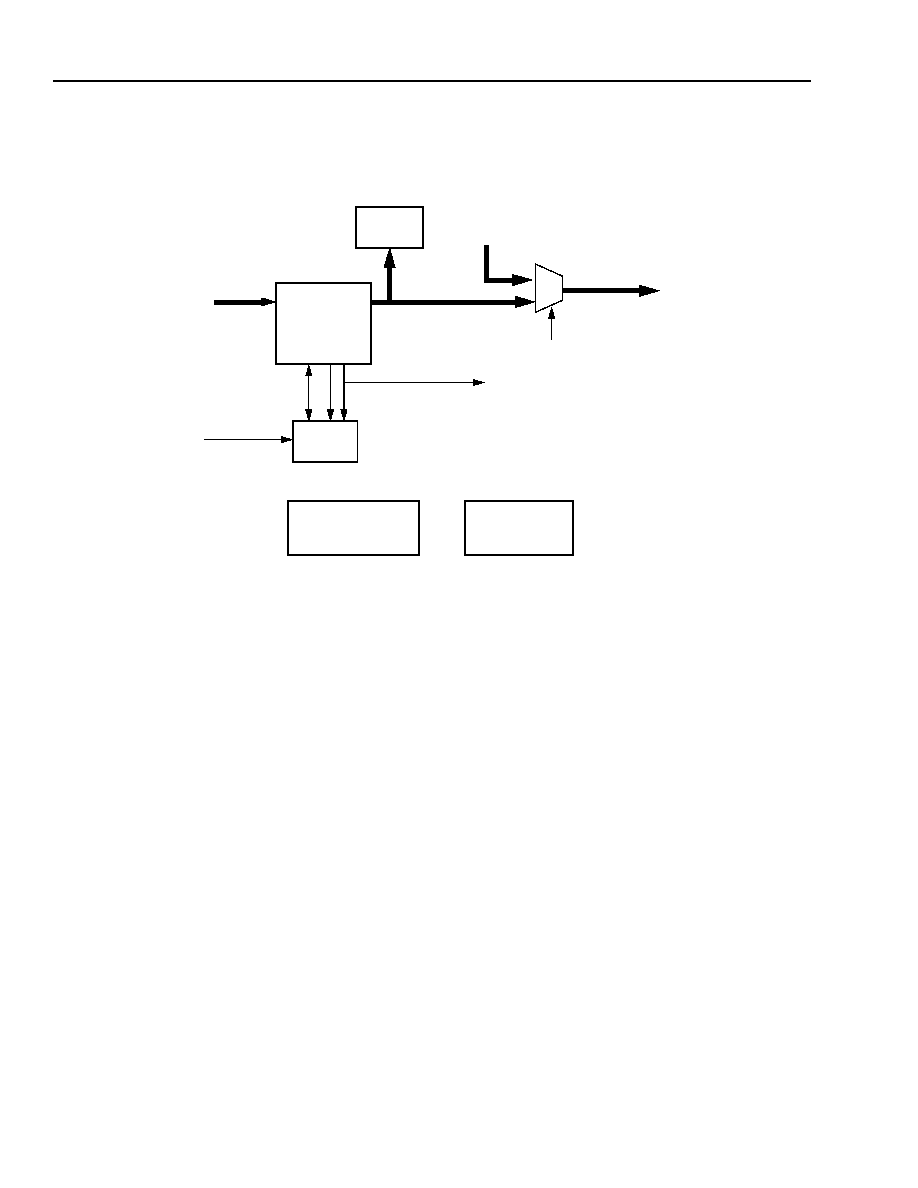

Functional Description .......................................................................................................................................... 175

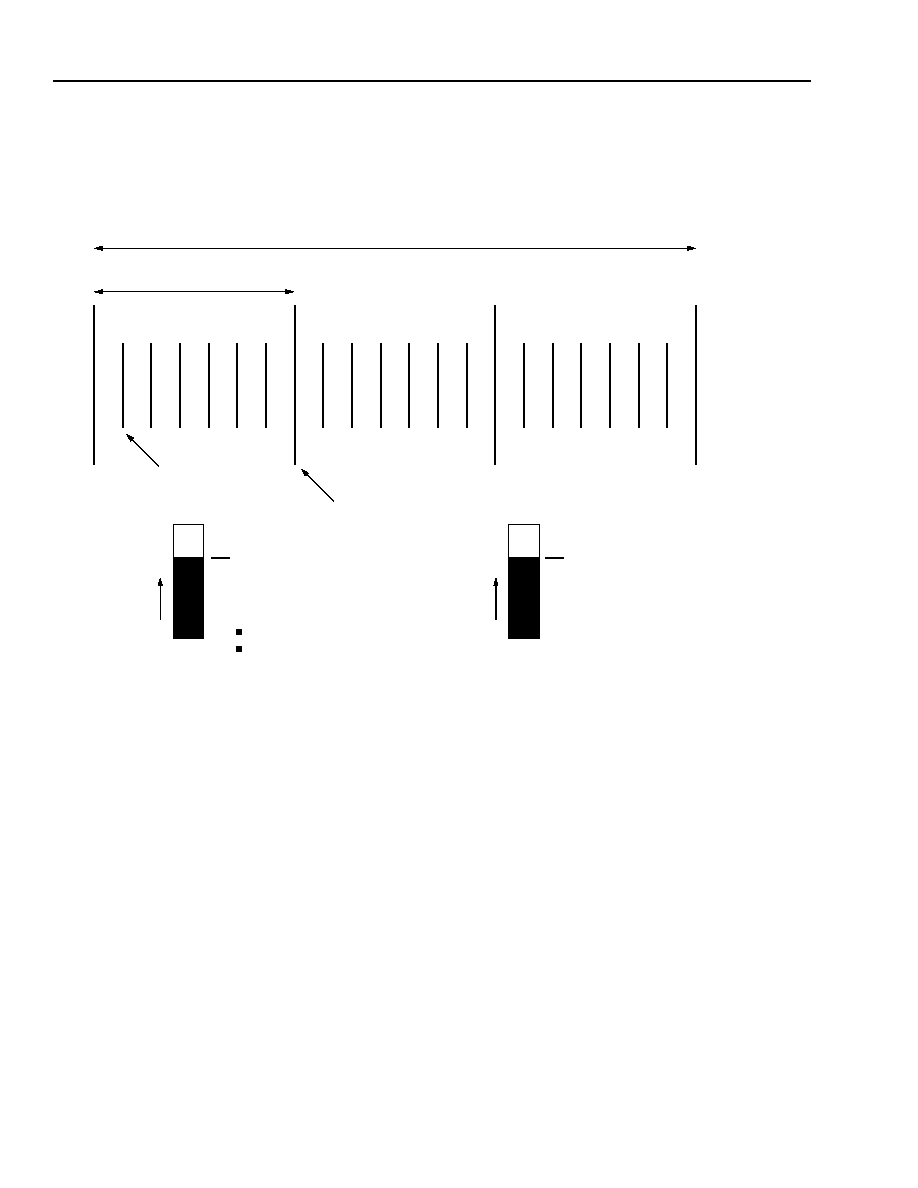

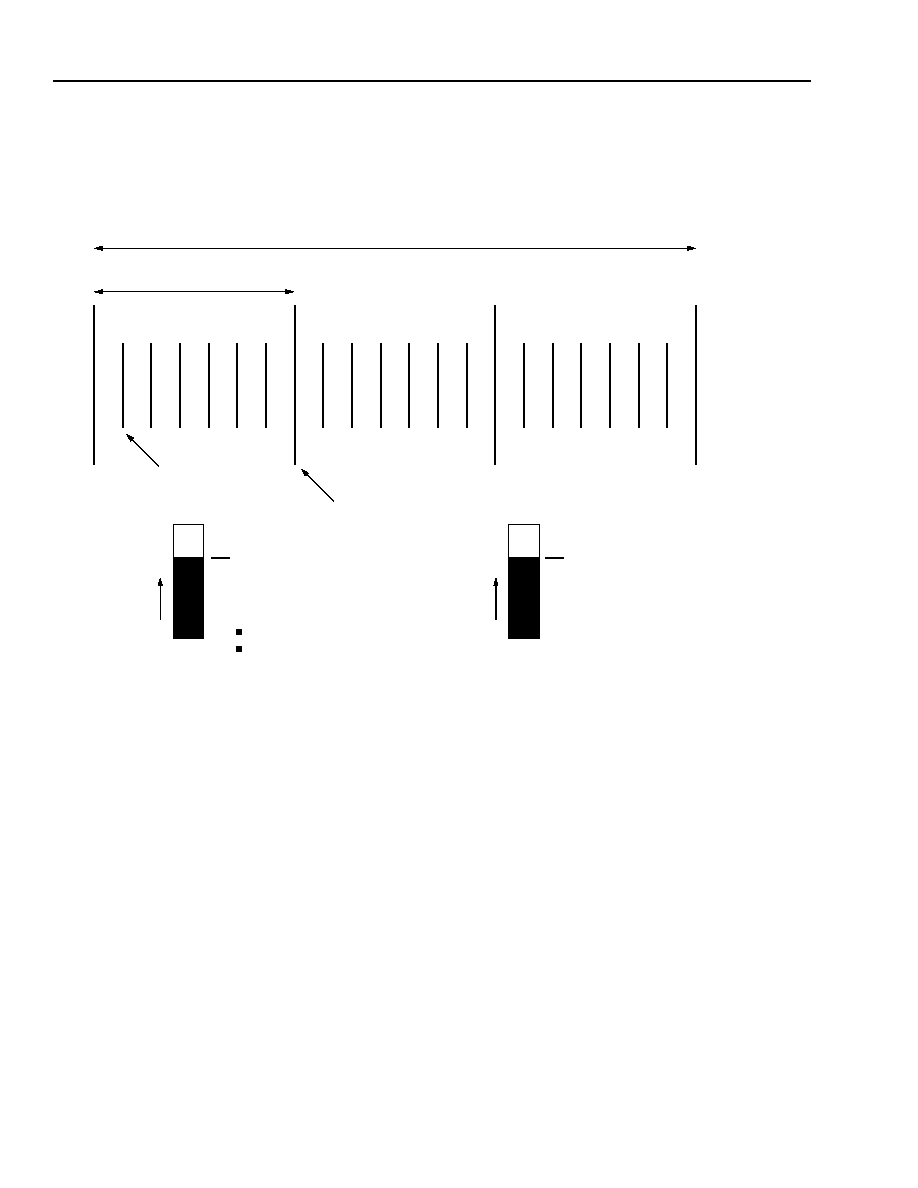

Line Interface........................................................................................................................................................ 176

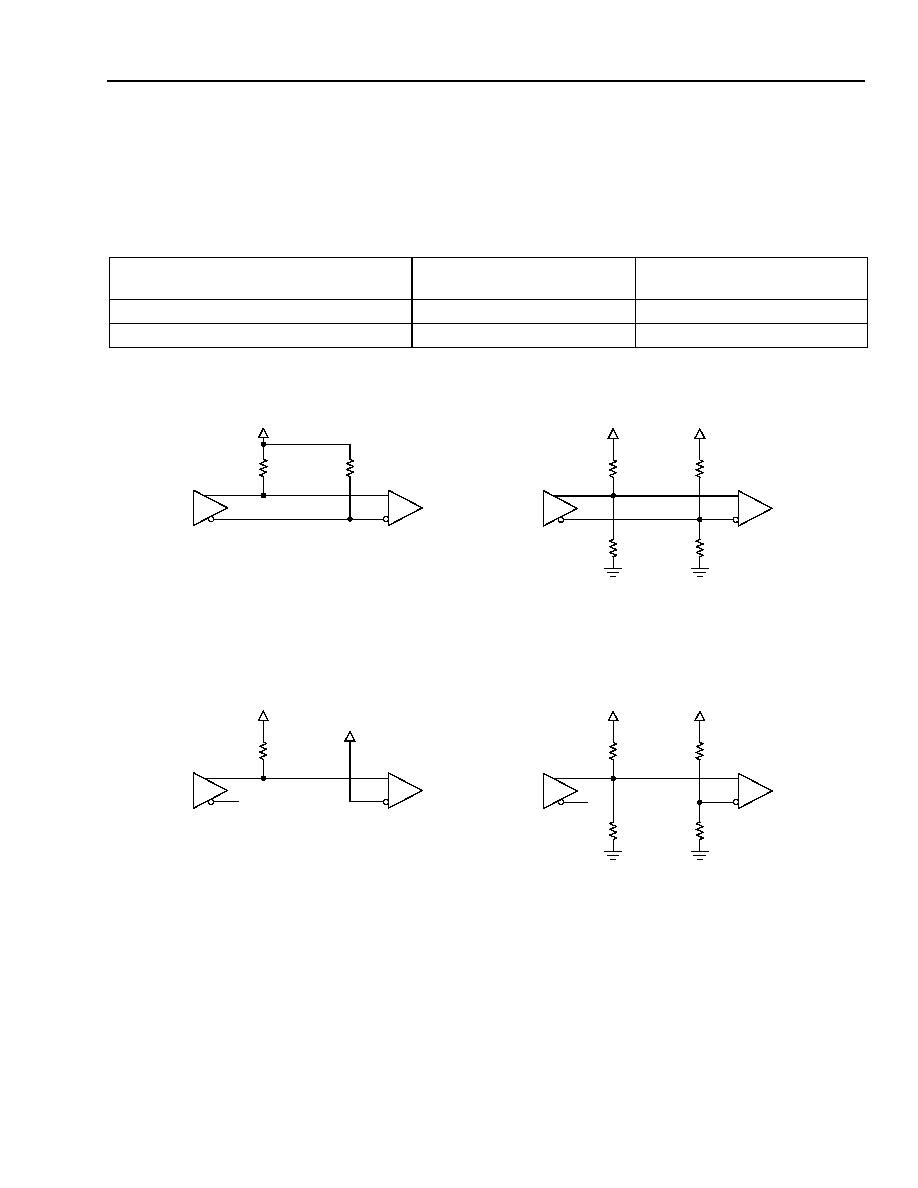

LVPECL I/O Termination and Load Specifications ........................................................................................ 178

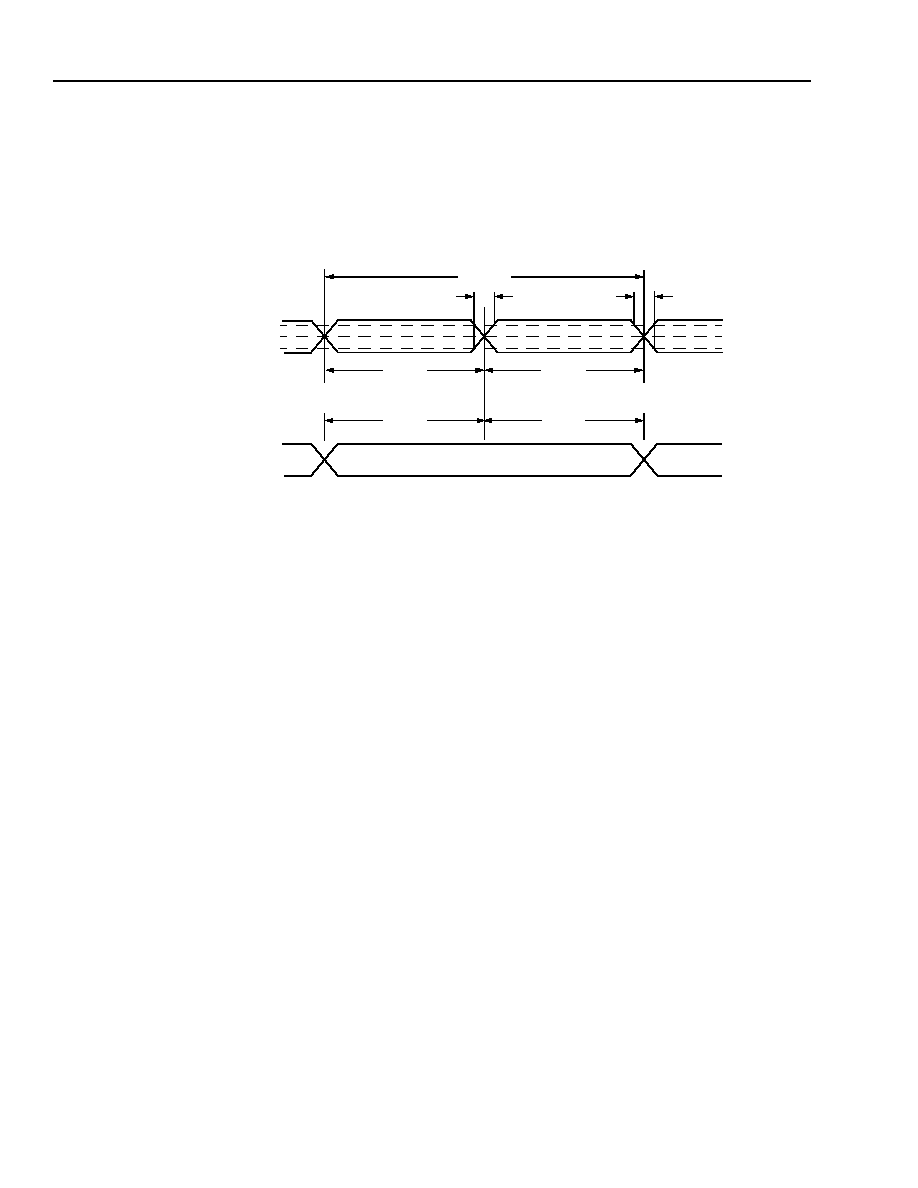

Line Interface I/O Timing................................................................................................................................ 180

Transport Overhead Processor (TOHP-48) Block................................................................................................ 184

Introduction .................................................................................................................................................... 184

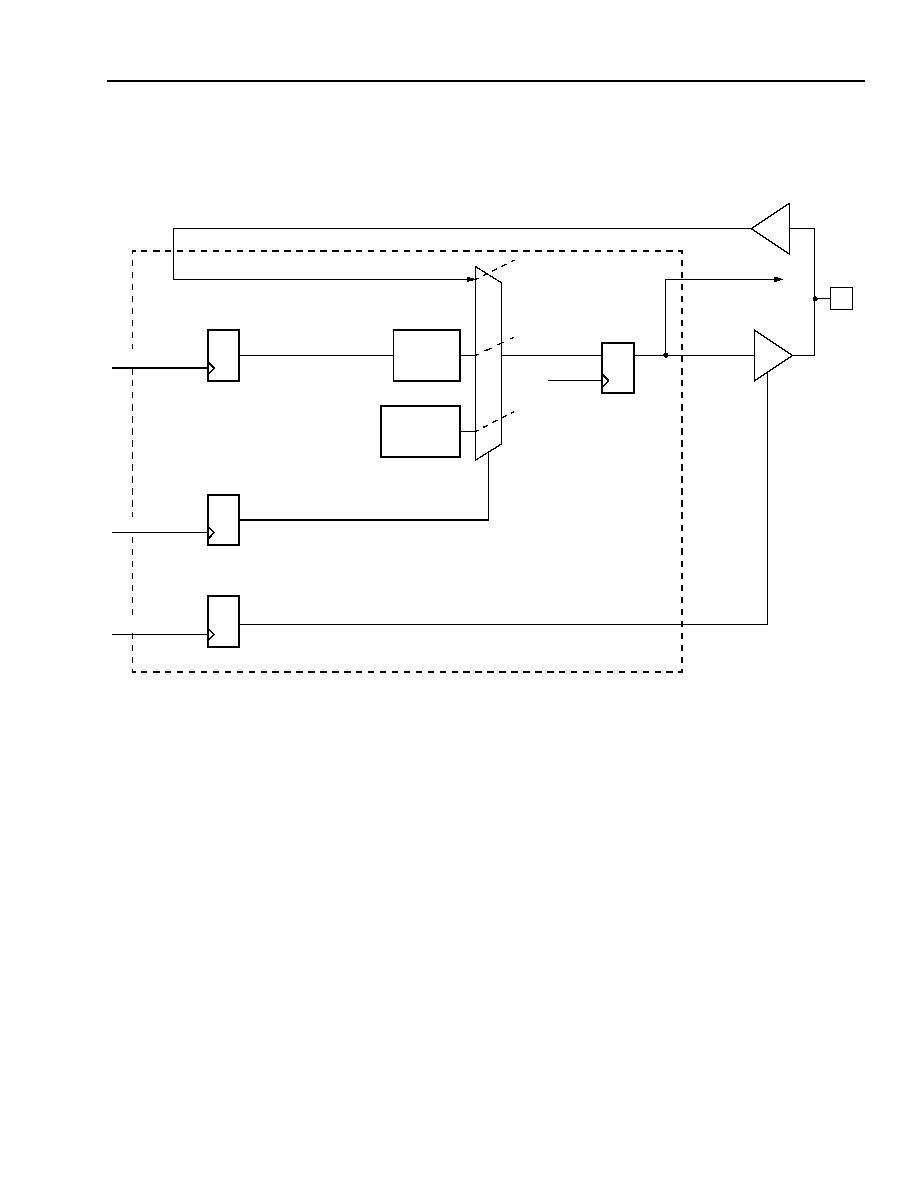

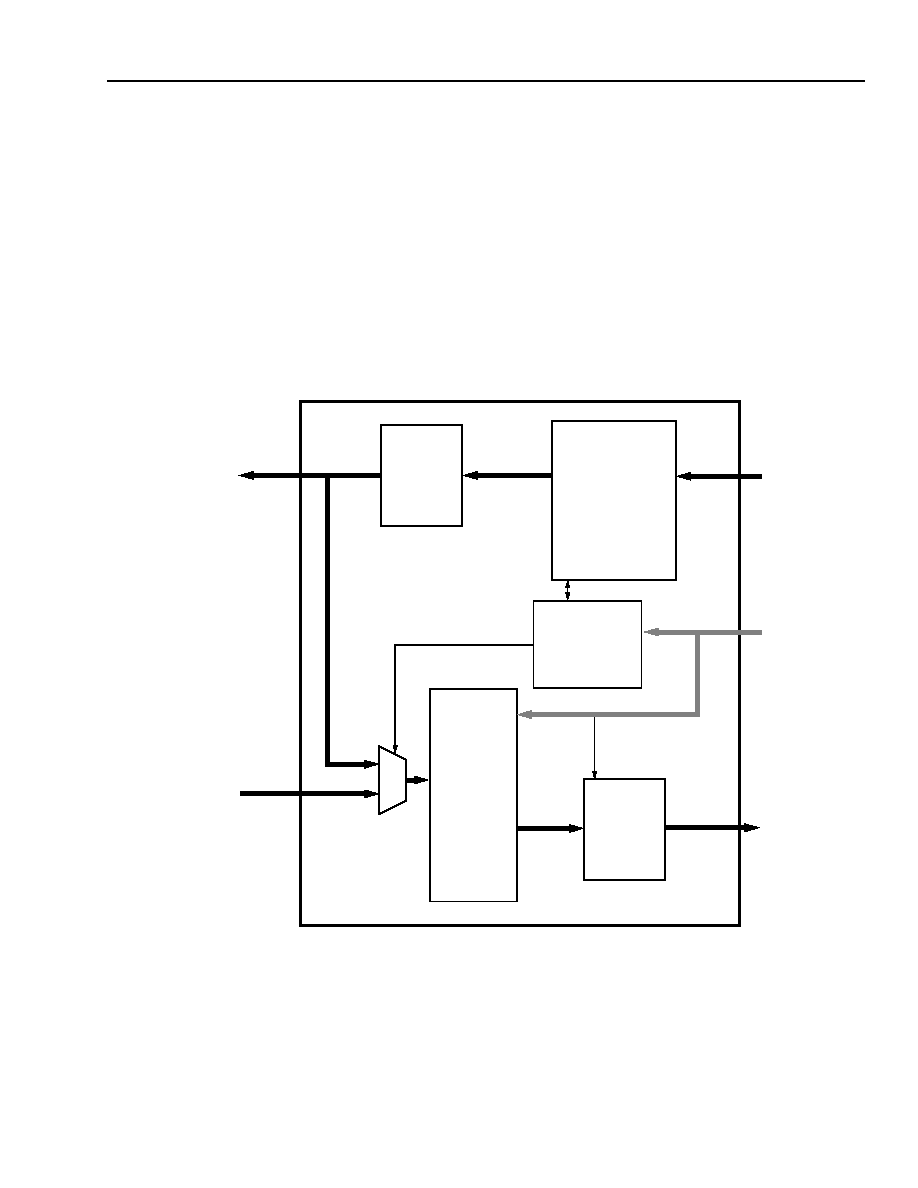

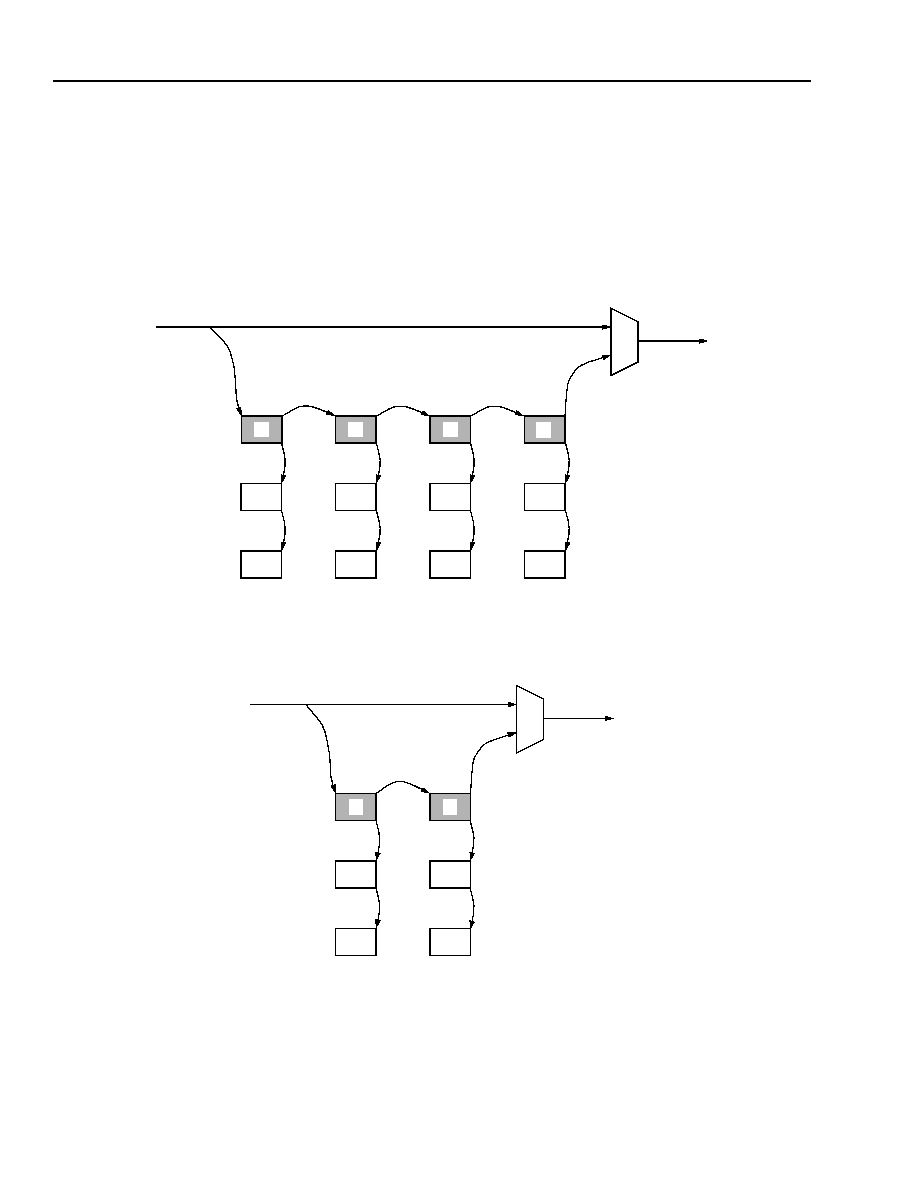

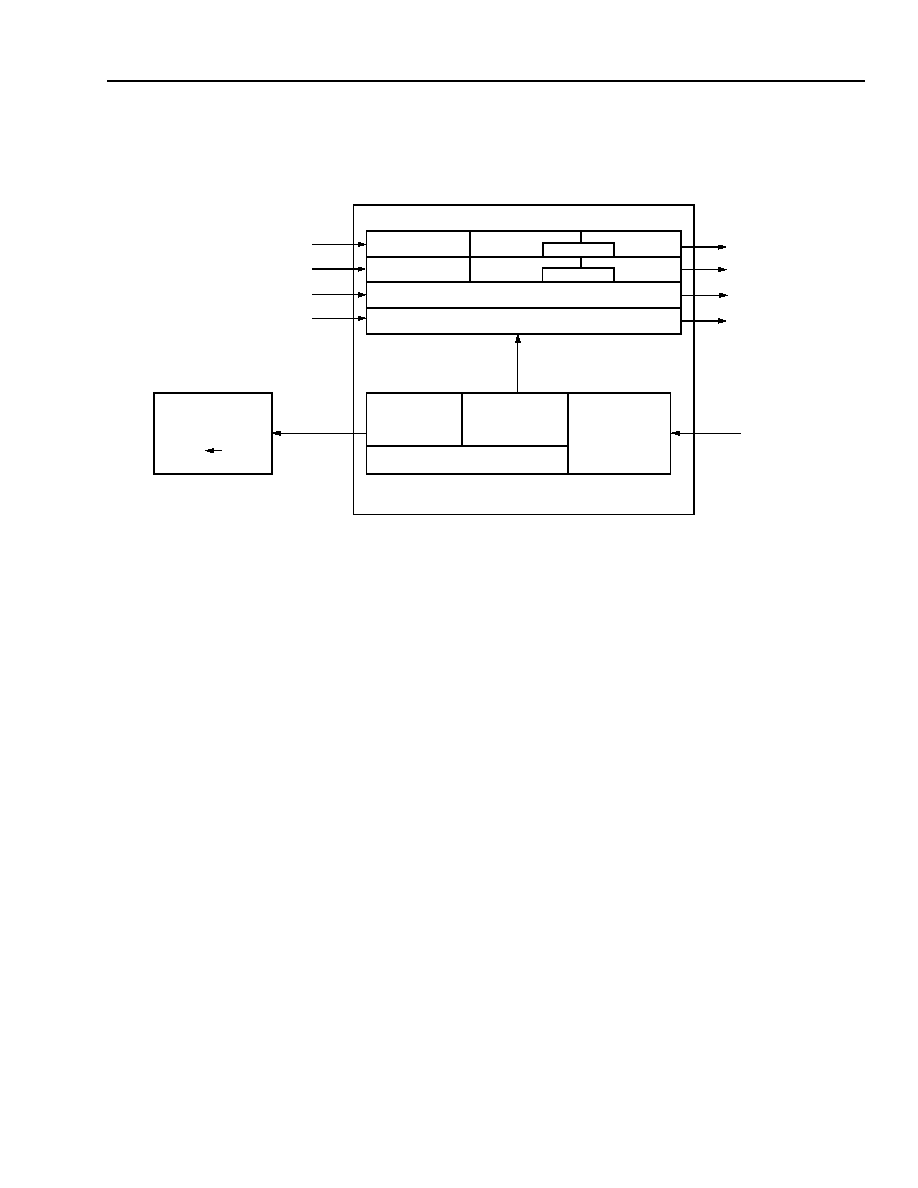

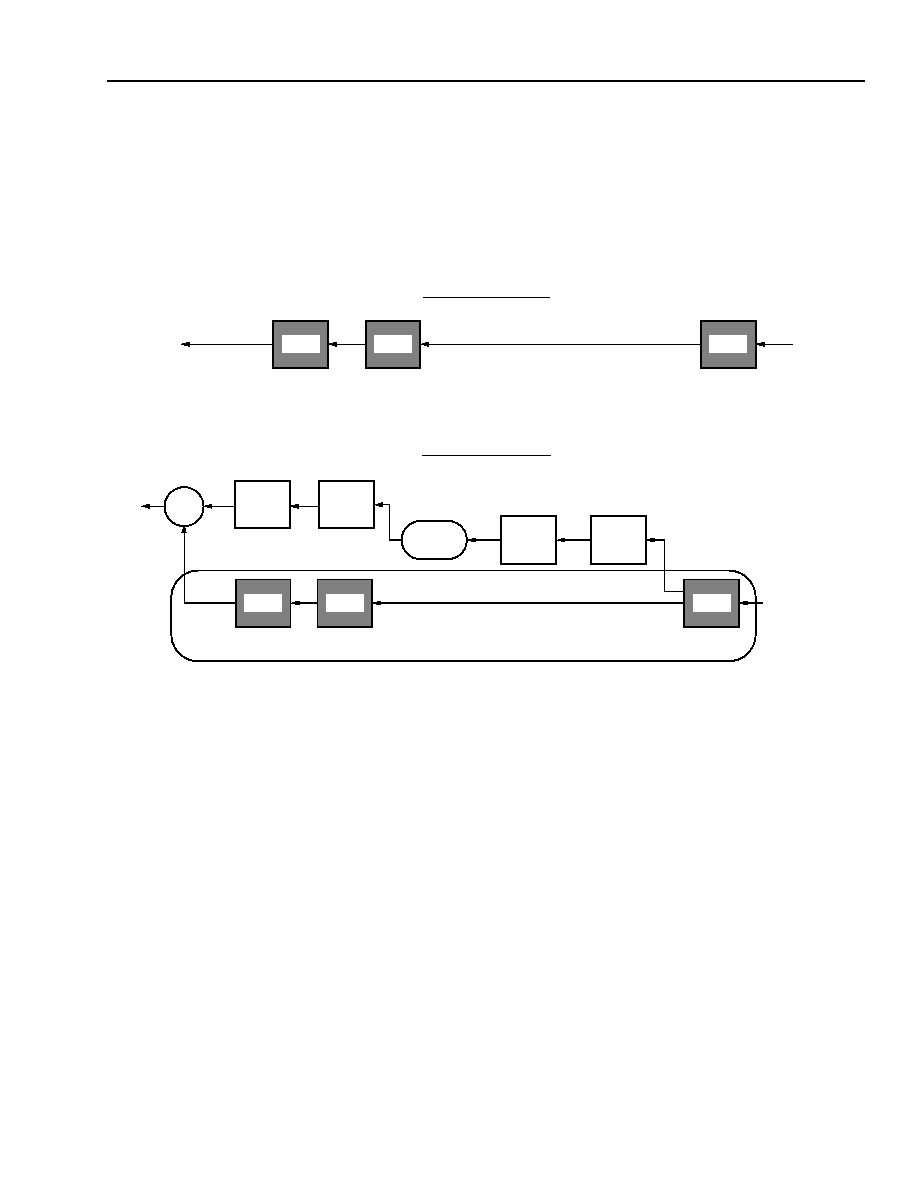

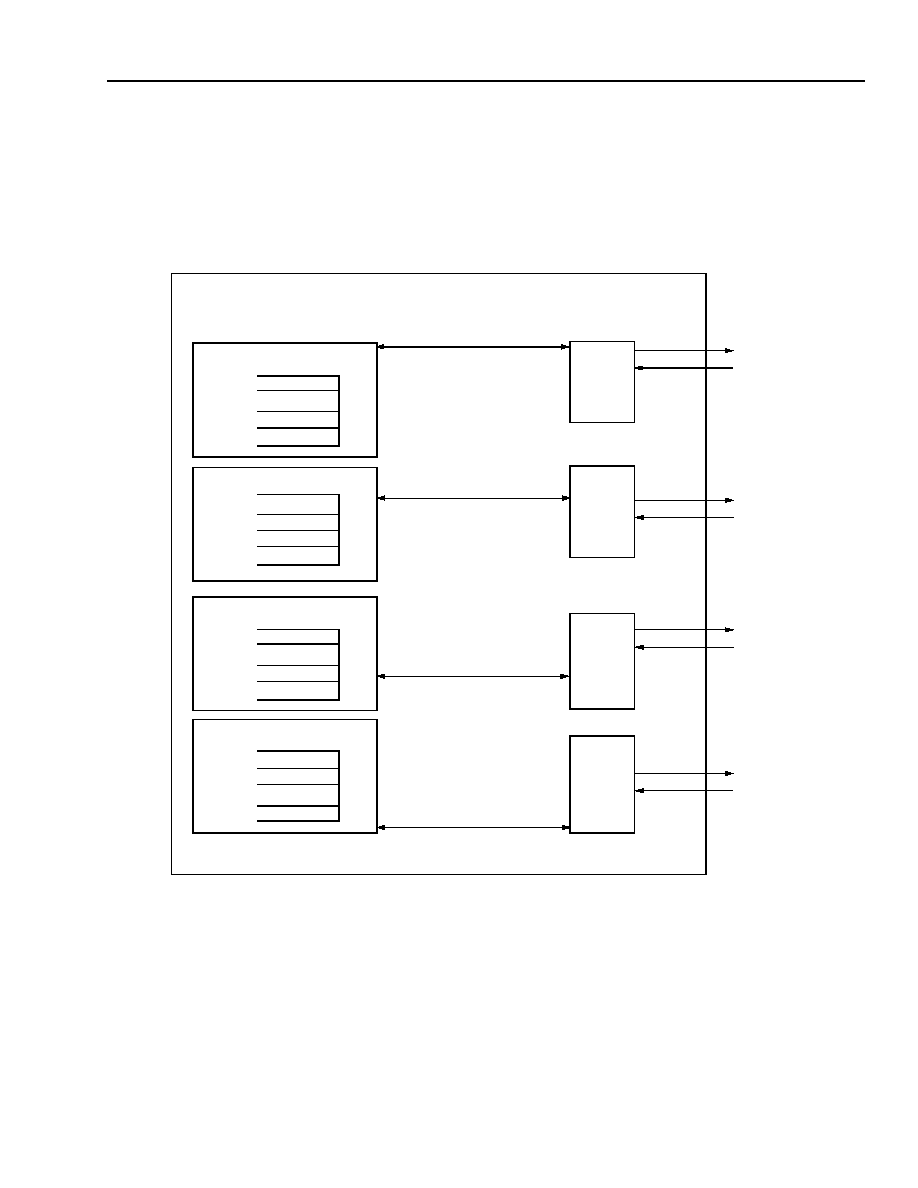

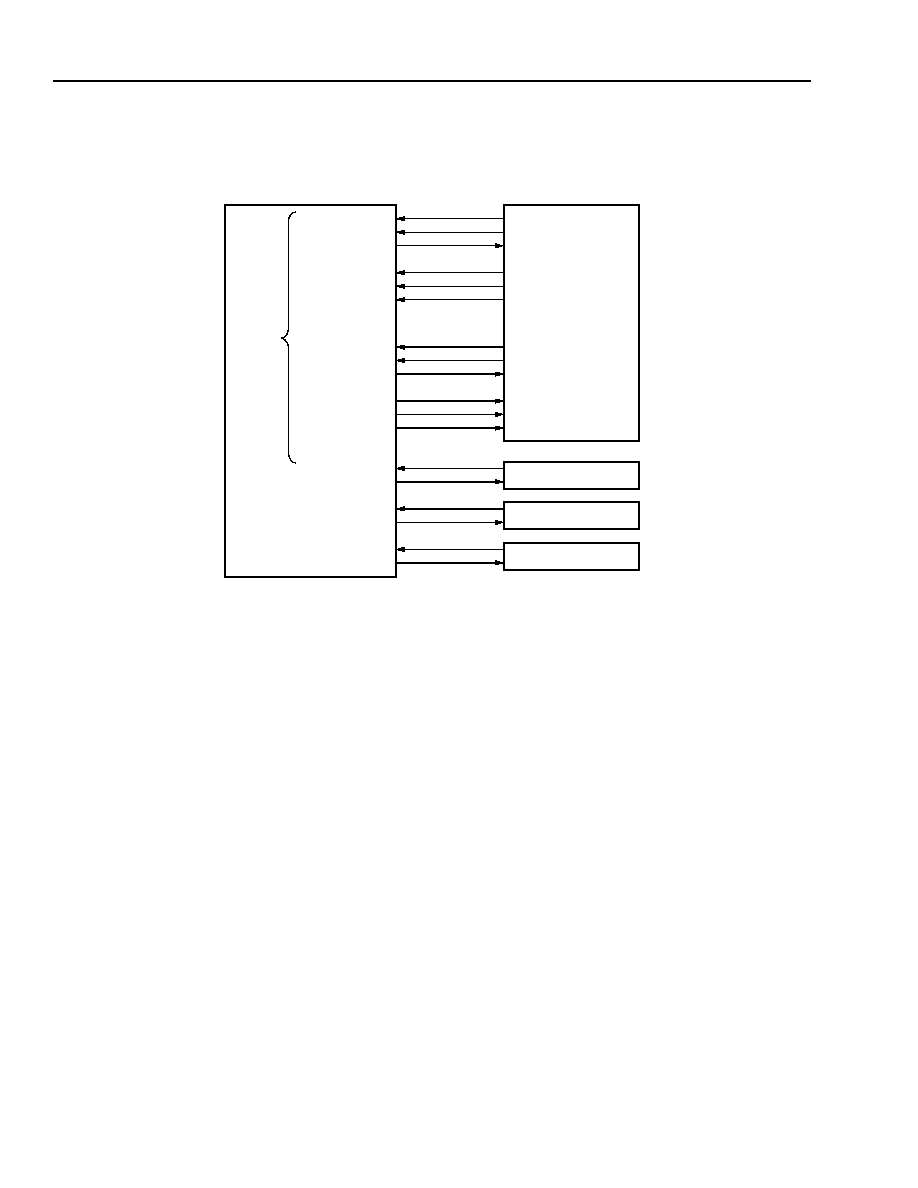

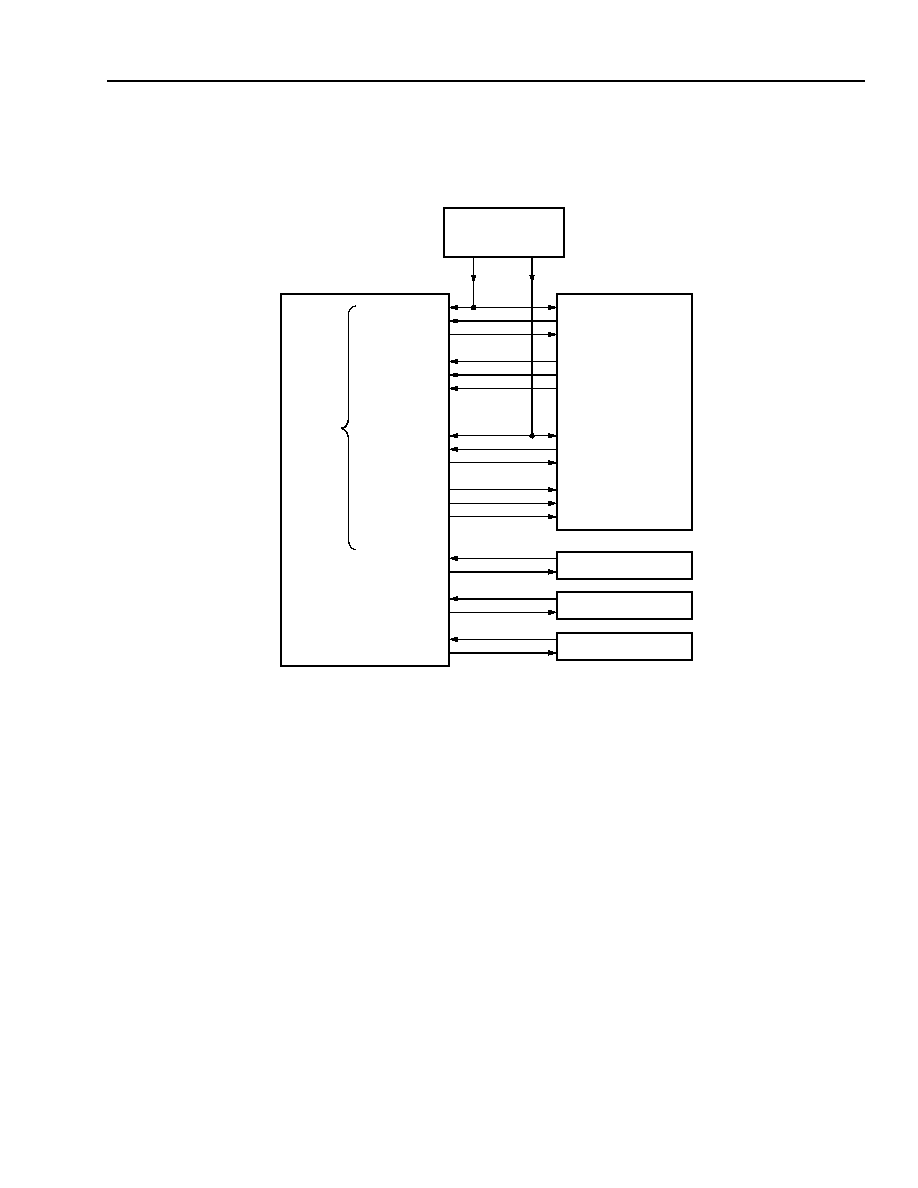

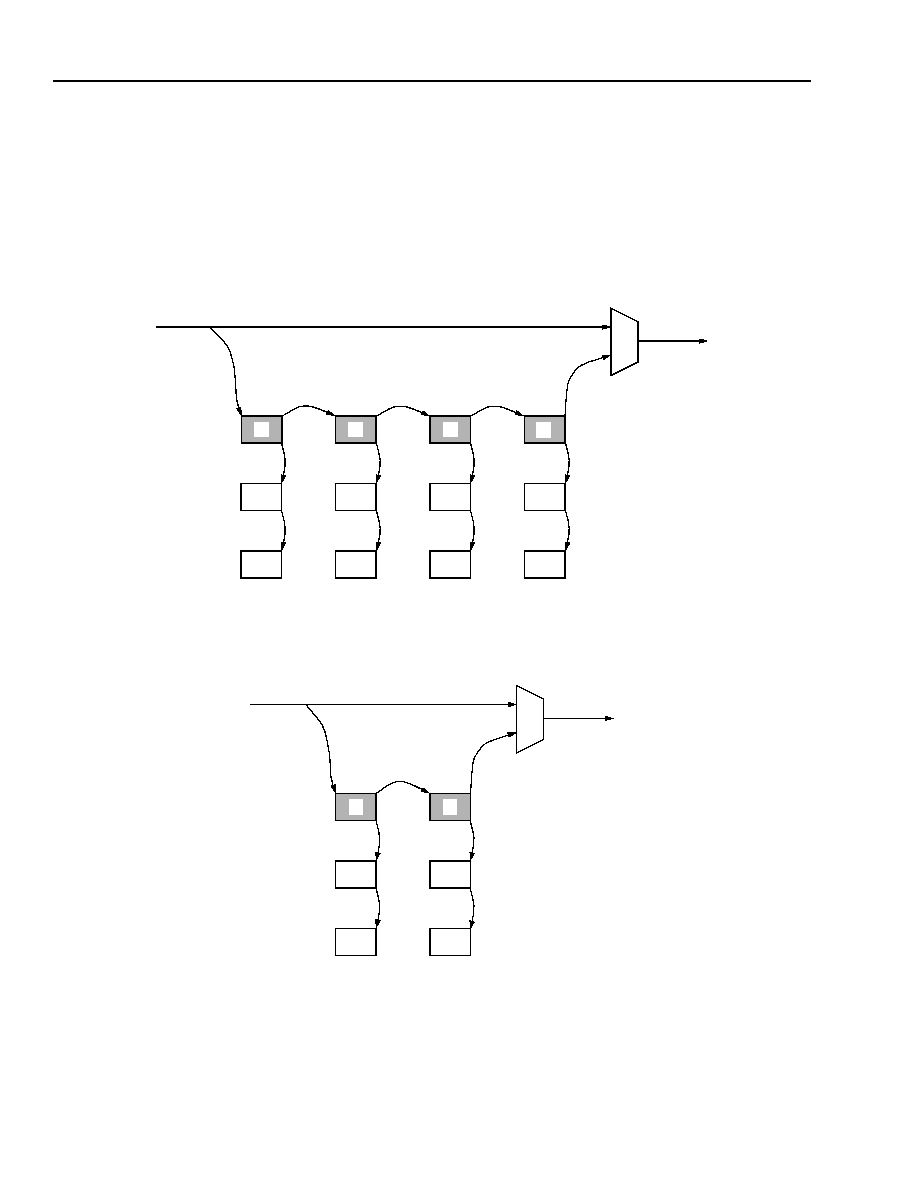

TOHP-48 Functional Block Diagram .............................................................................................................. 184

Enhancements ............................................................................................................................................... 186

APSMON and K2MON Processing (Including K1K2 Validation and Pass Through) ..................................... 186

TOHP-48 Receive Direction........................................................................................................................... 187

Transmit Direction (to SONET/SDH line) ....................................................................................................... 197

Receive/Transmit TOHP-48 Interface ............................................................................................................ 204

TOHP-48 Register Descriptions..................................................................................................................... 208

TOHP-48 Register Map ................................................................................................................................. 237

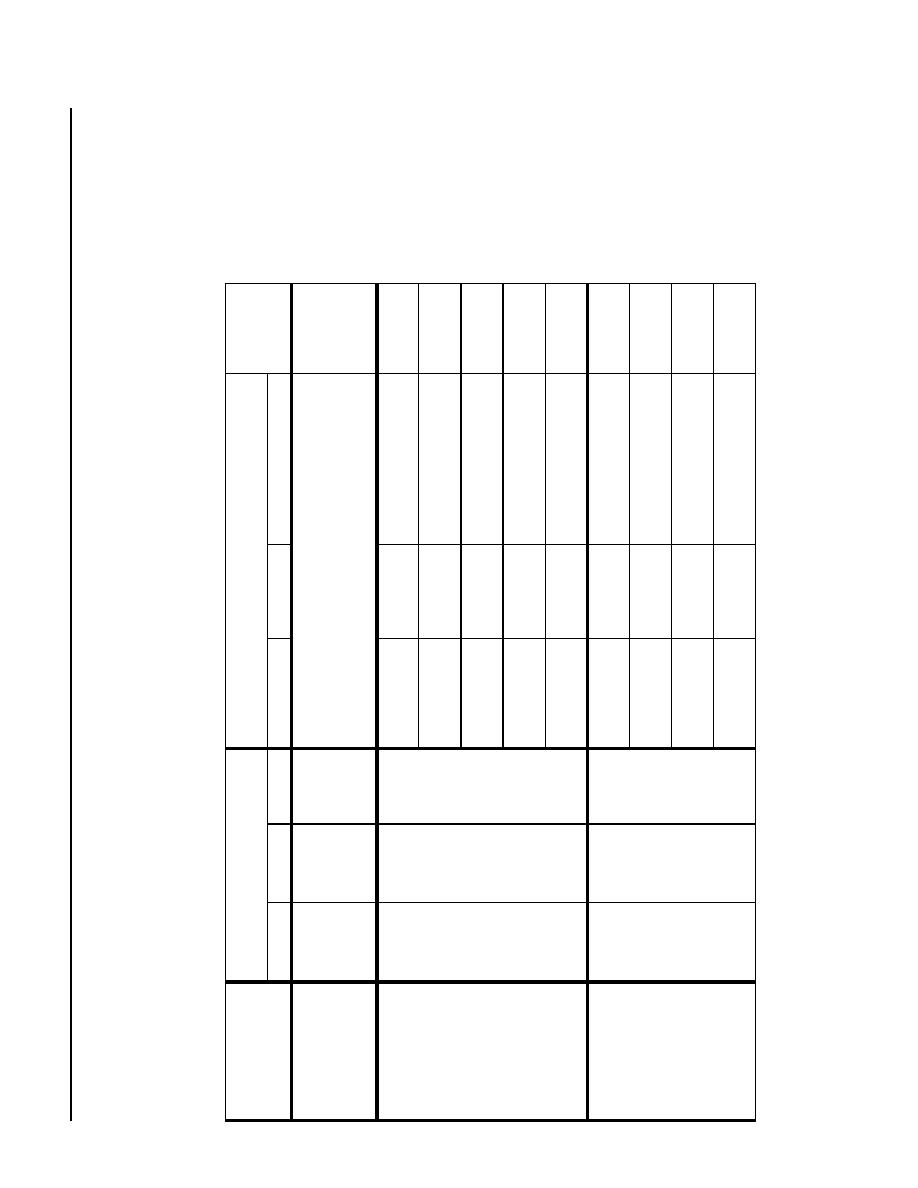

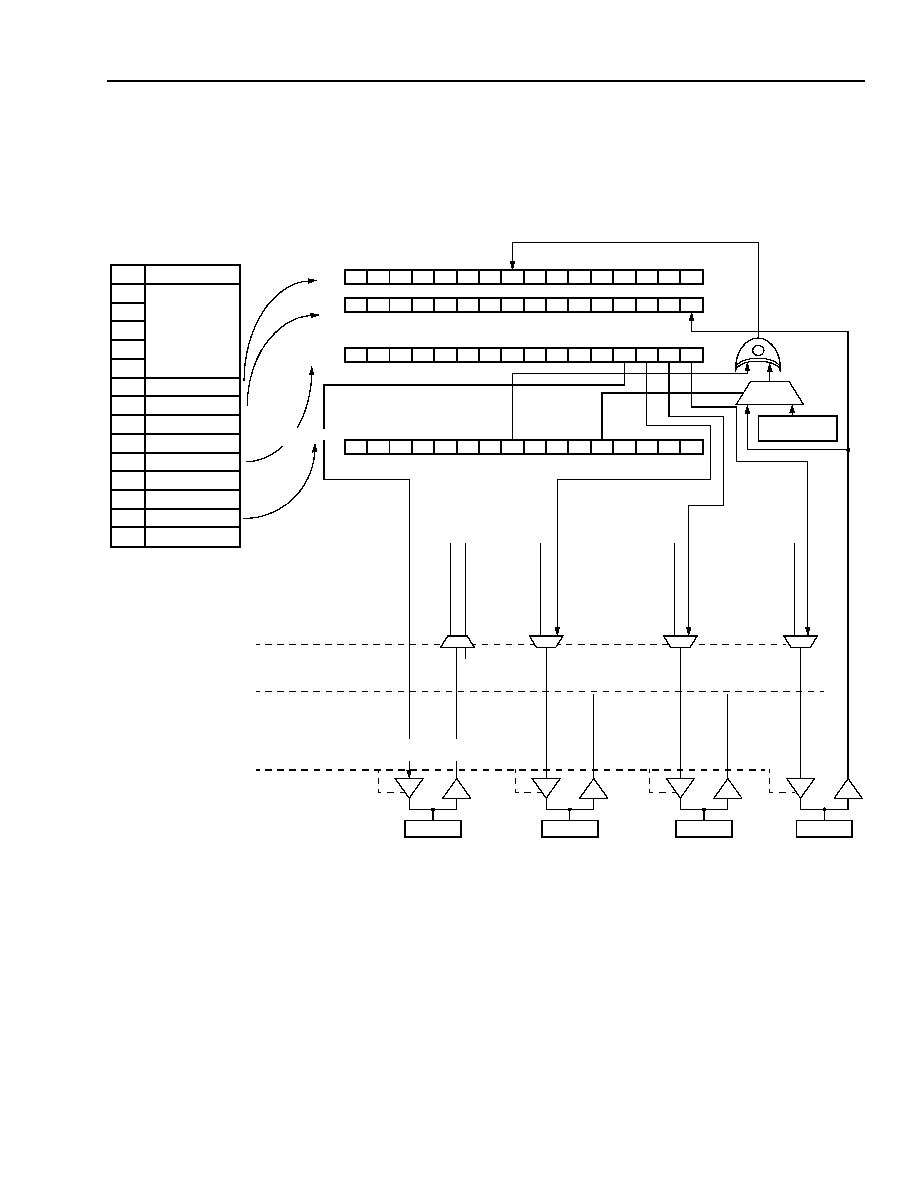

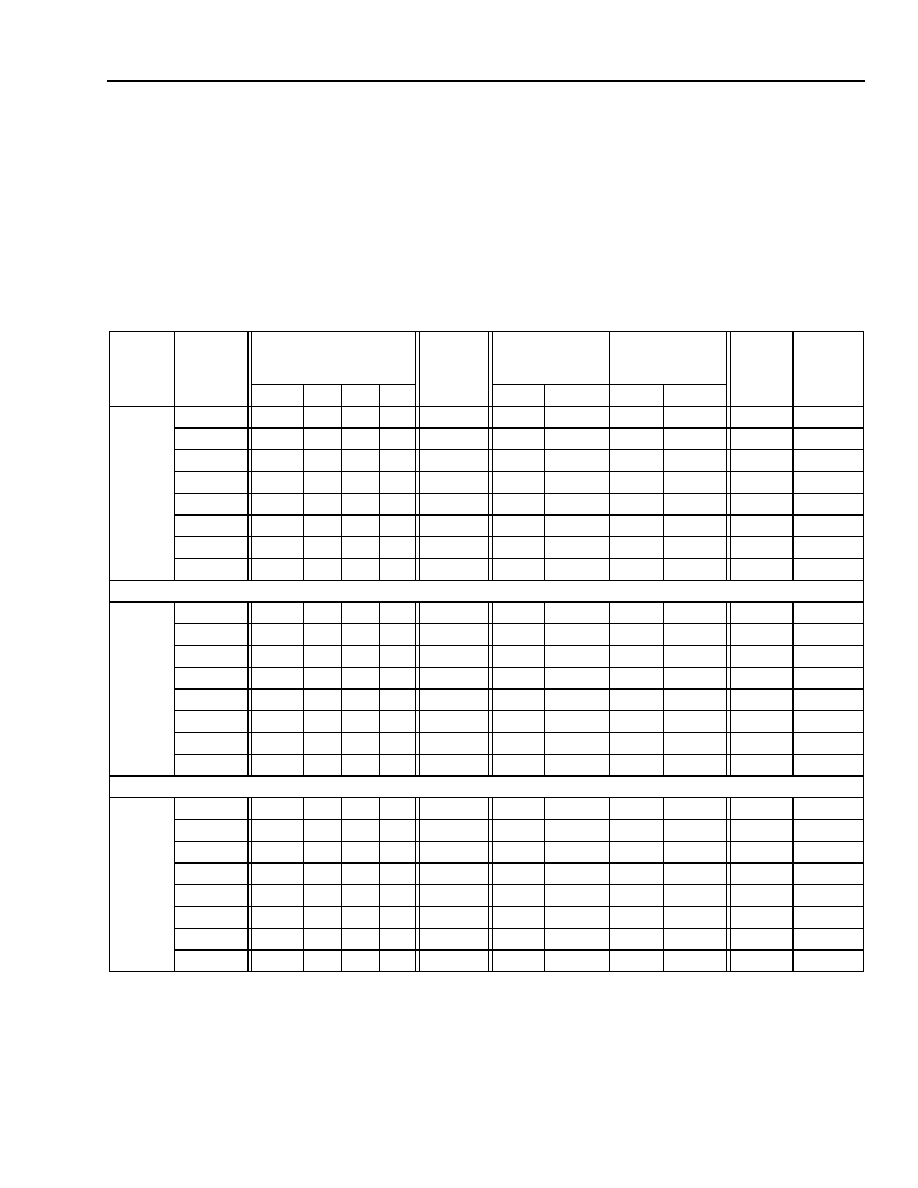

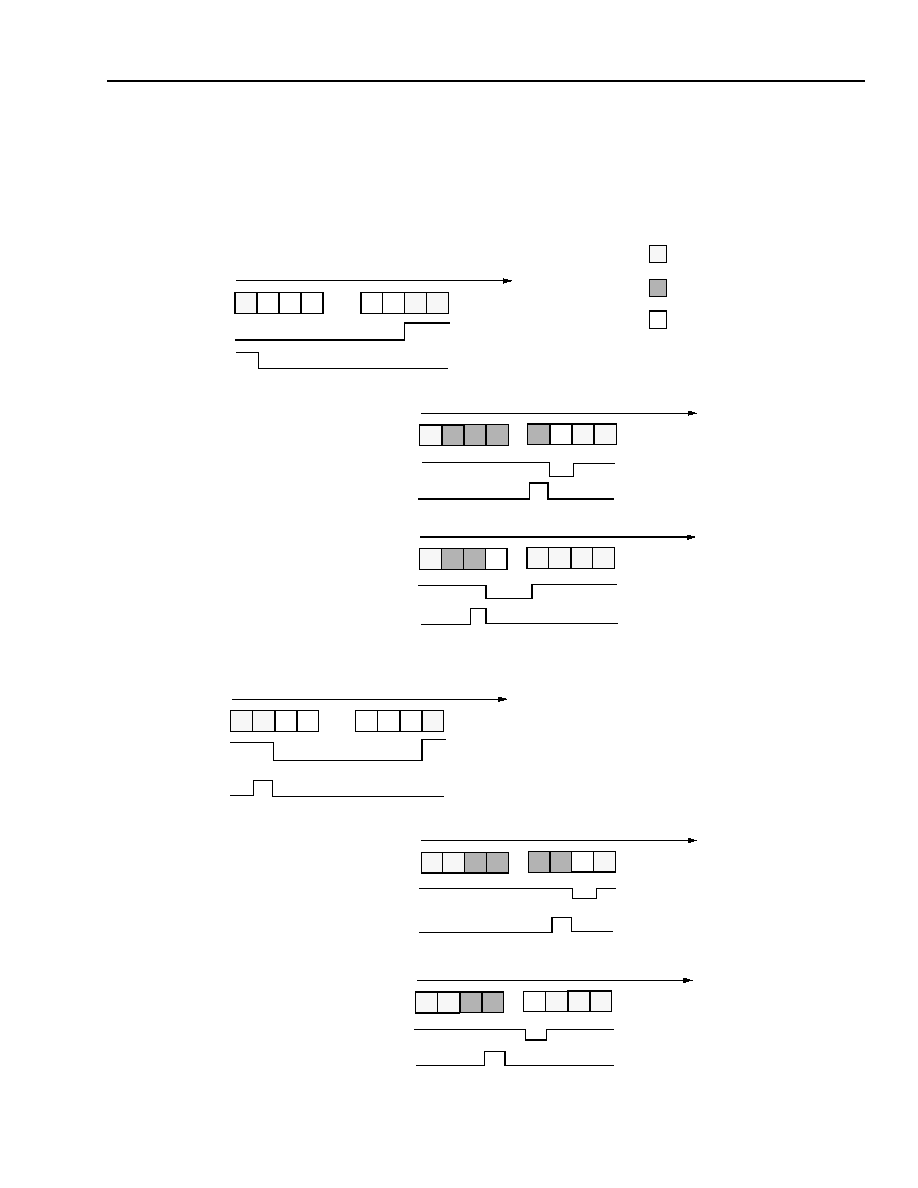

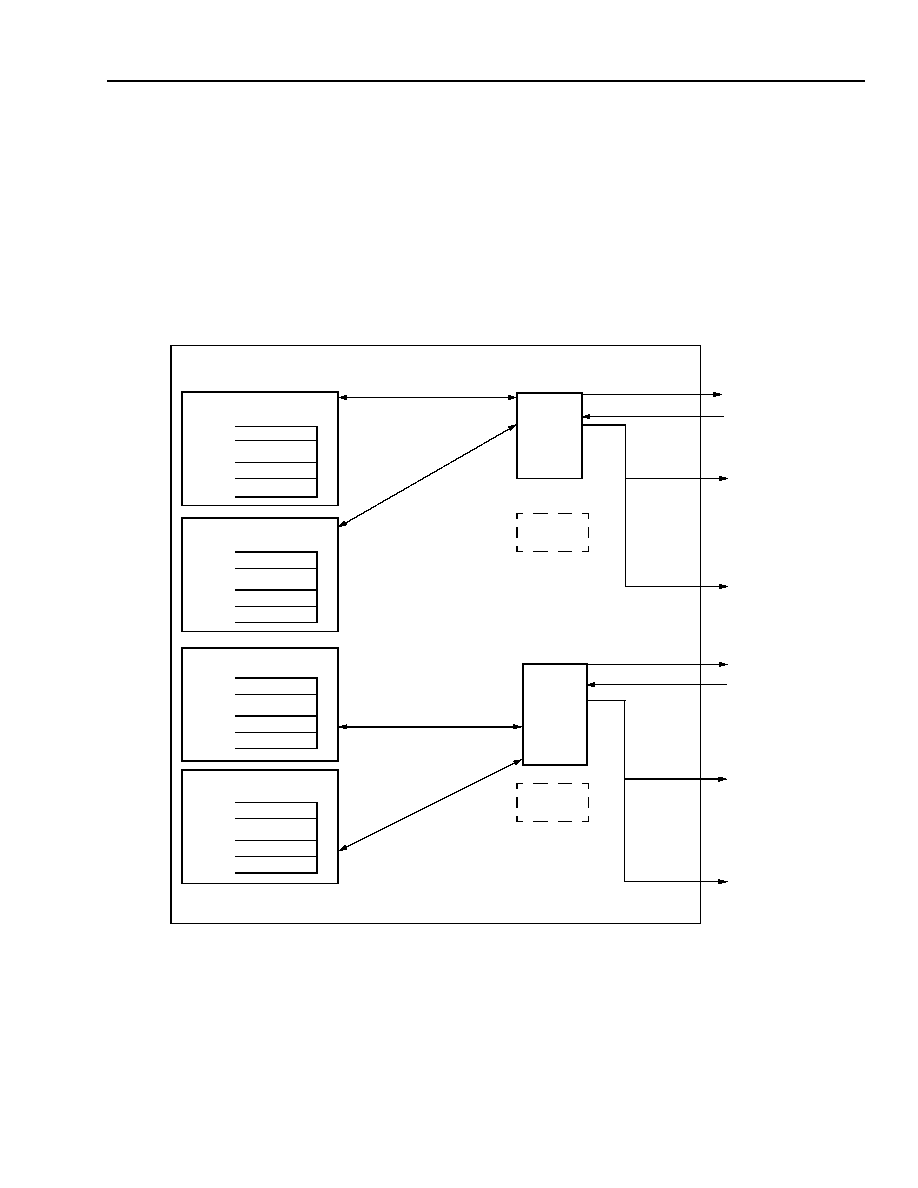

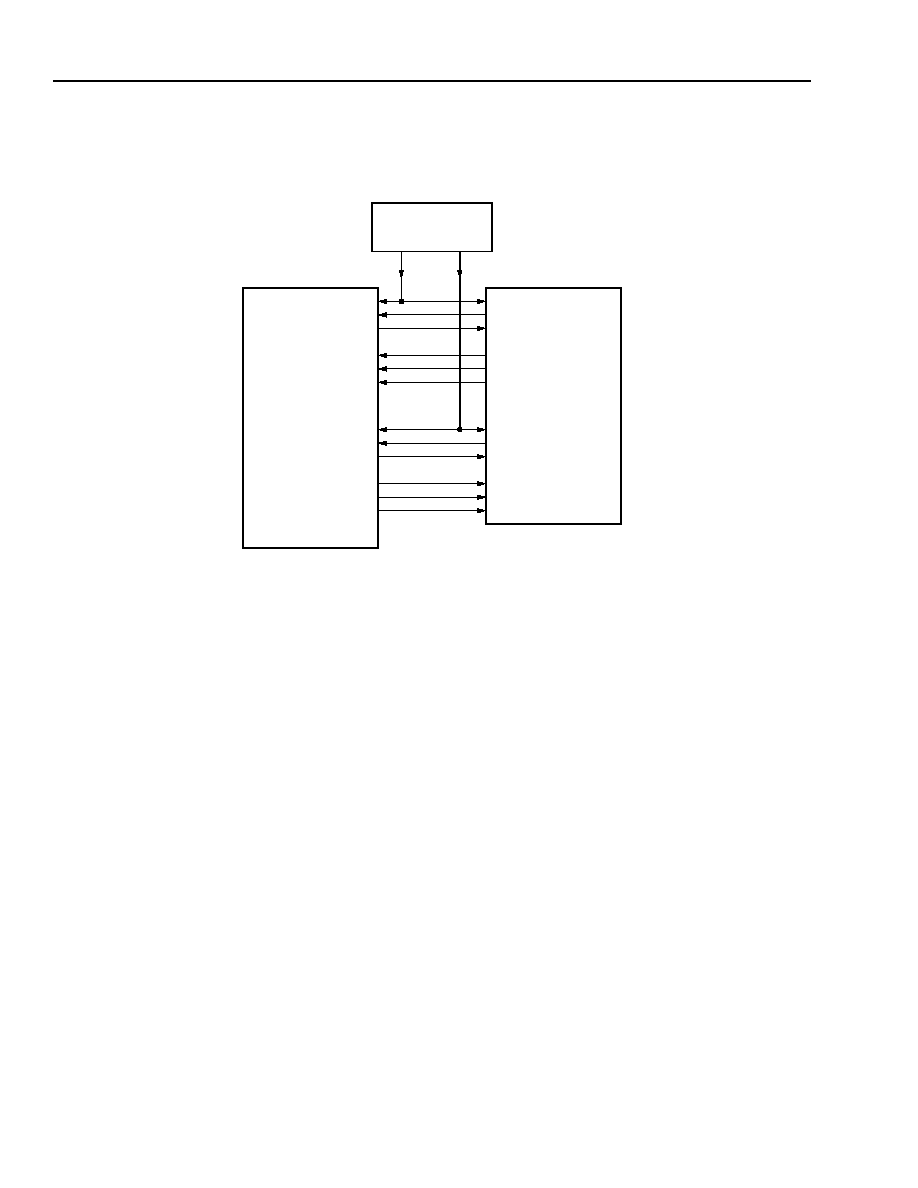

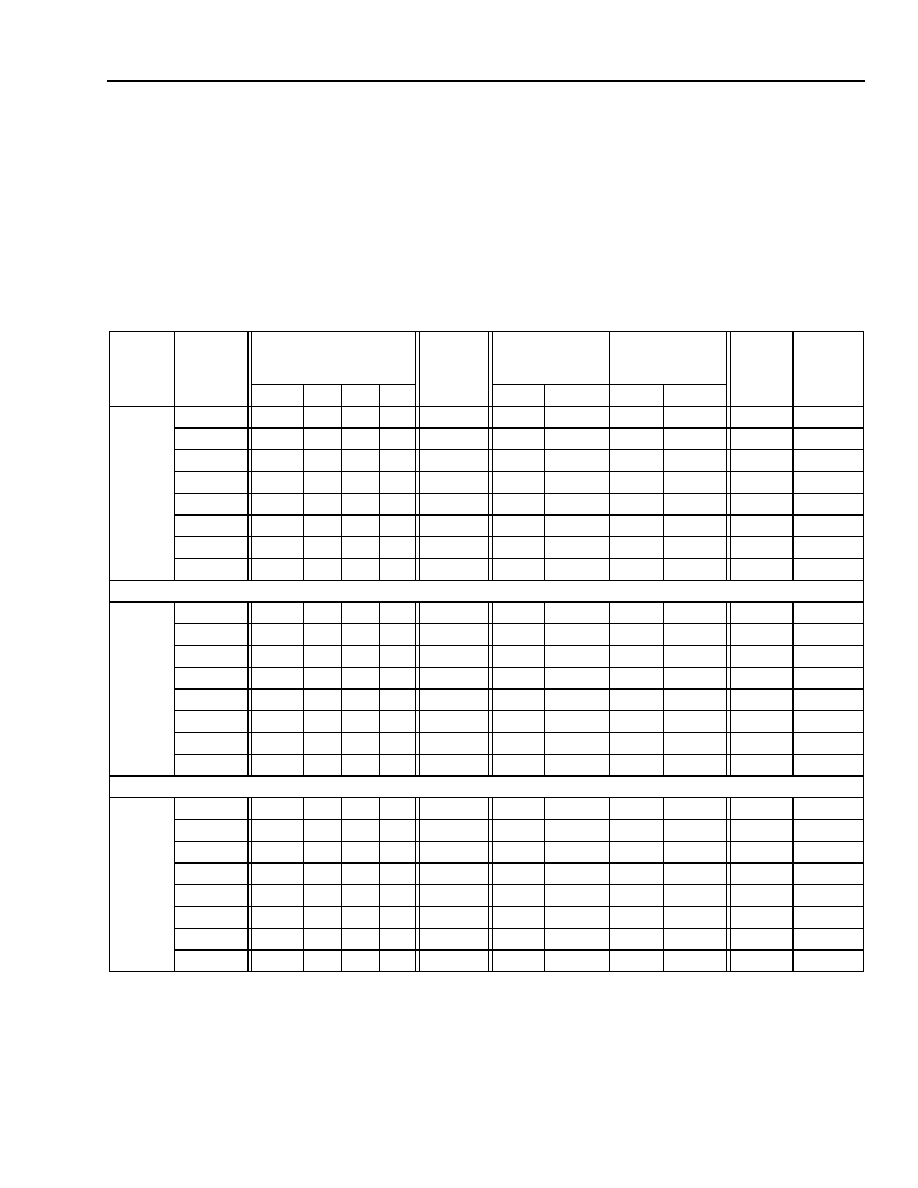

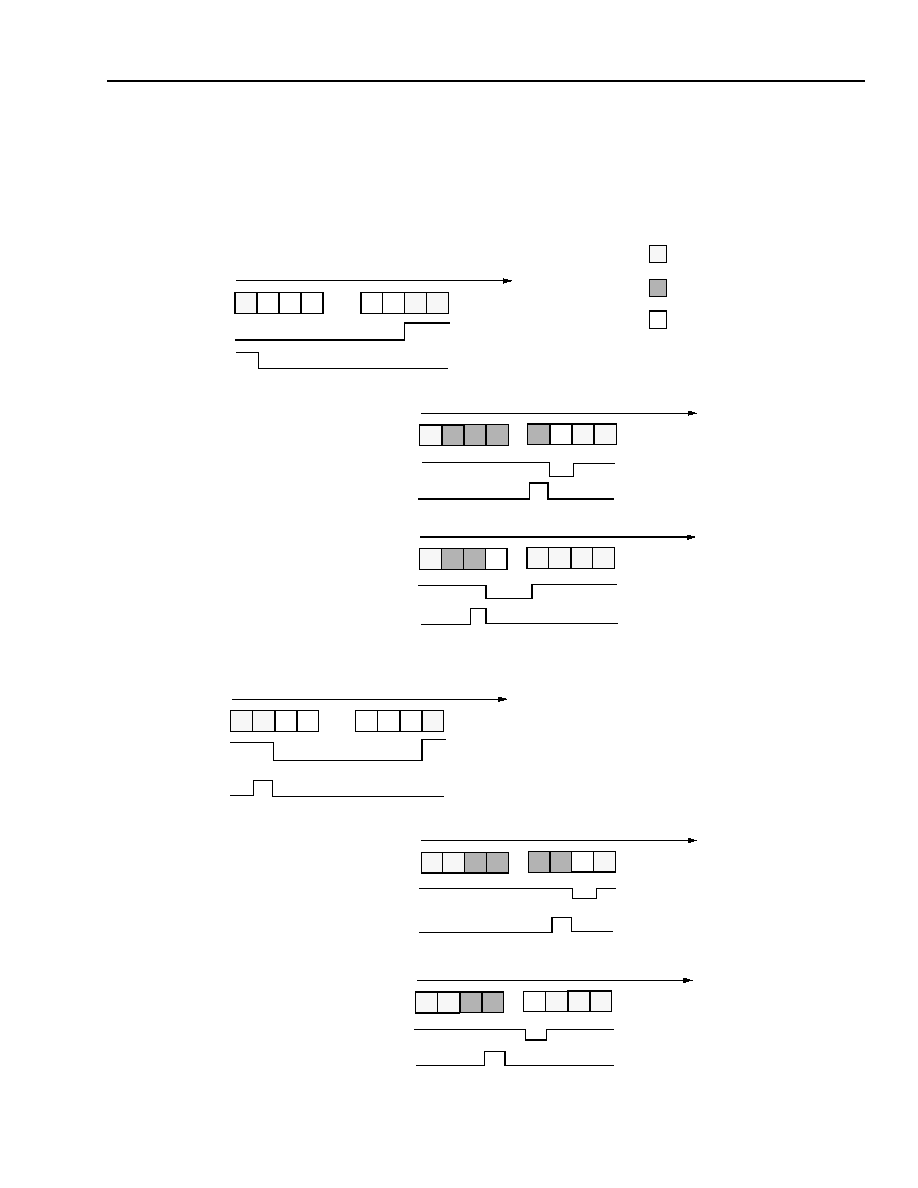

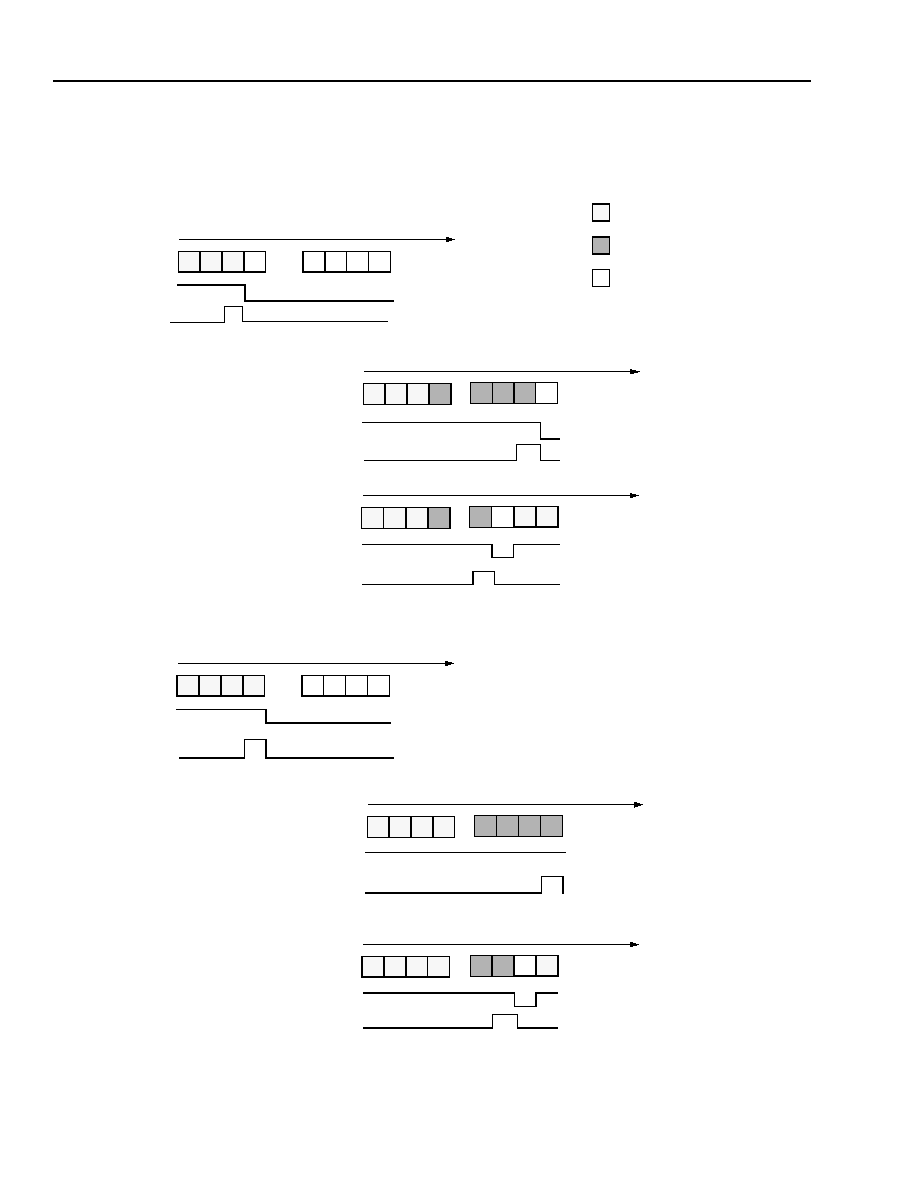

Pointer Processor (PP)......................................................................................................................................... 247

Introduction .................................................................................................................................................... 247

Detailed Description ....................................................................................................................................... 250

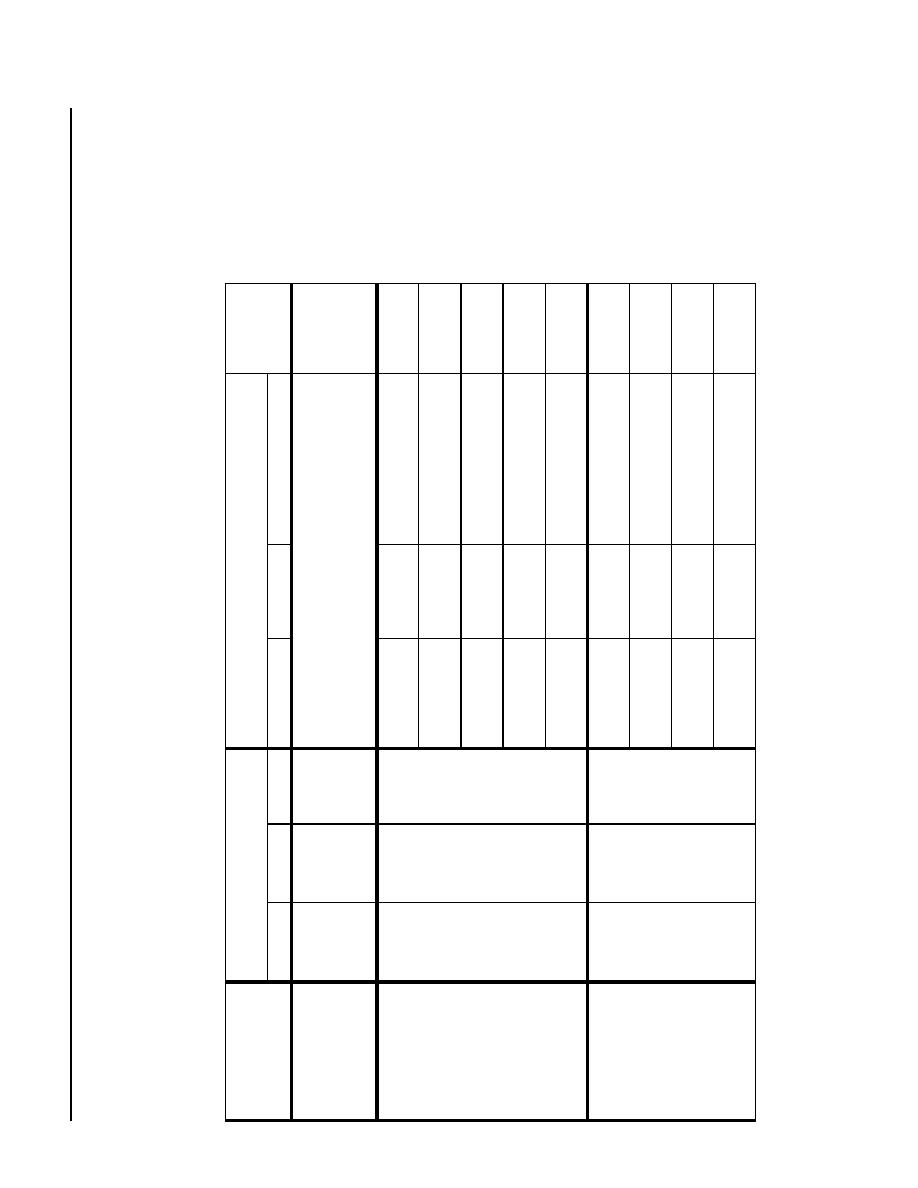

PP Register Map Overview ............................................................................................................................ 257

PP Register Descriptions ............................................................................................................................... 258

Data Sheet

MARS2G5 P-Pro (TDAT162G52) SONET/SDH

August 18, 2004

155/622/2488 Mbits/s Data Interface

3

Agere Systems Inc.

Contents

Page

Table of Contents

(continued)

PP Register Map ............................................................................................................................................ 317

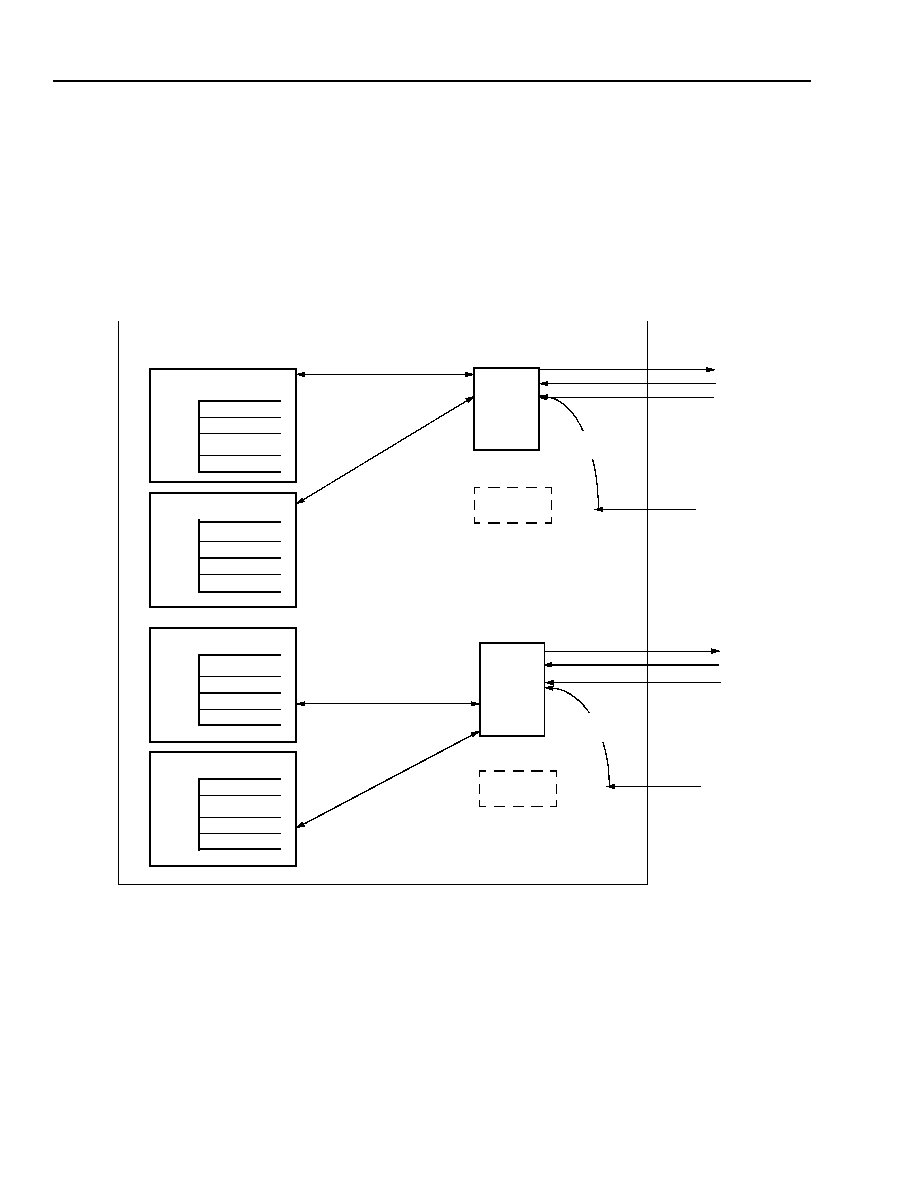

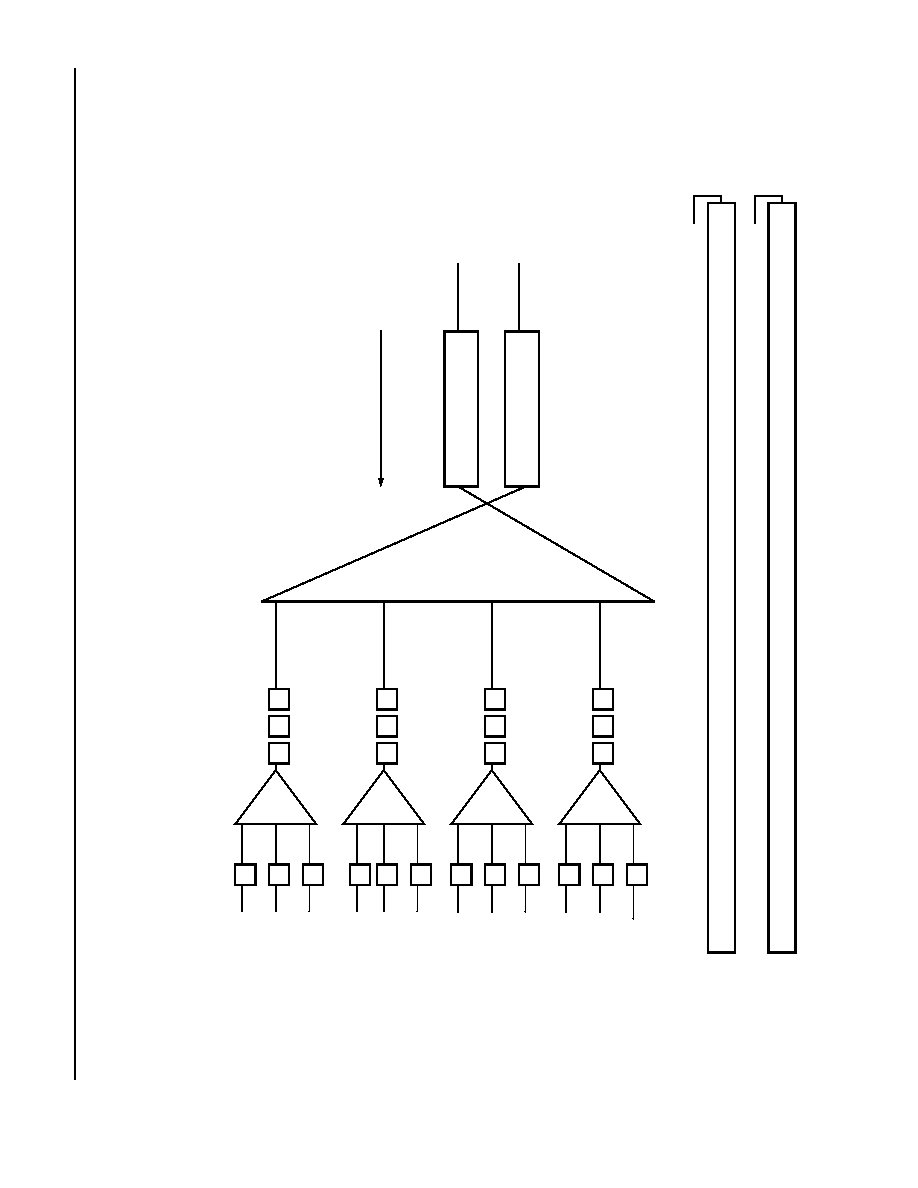

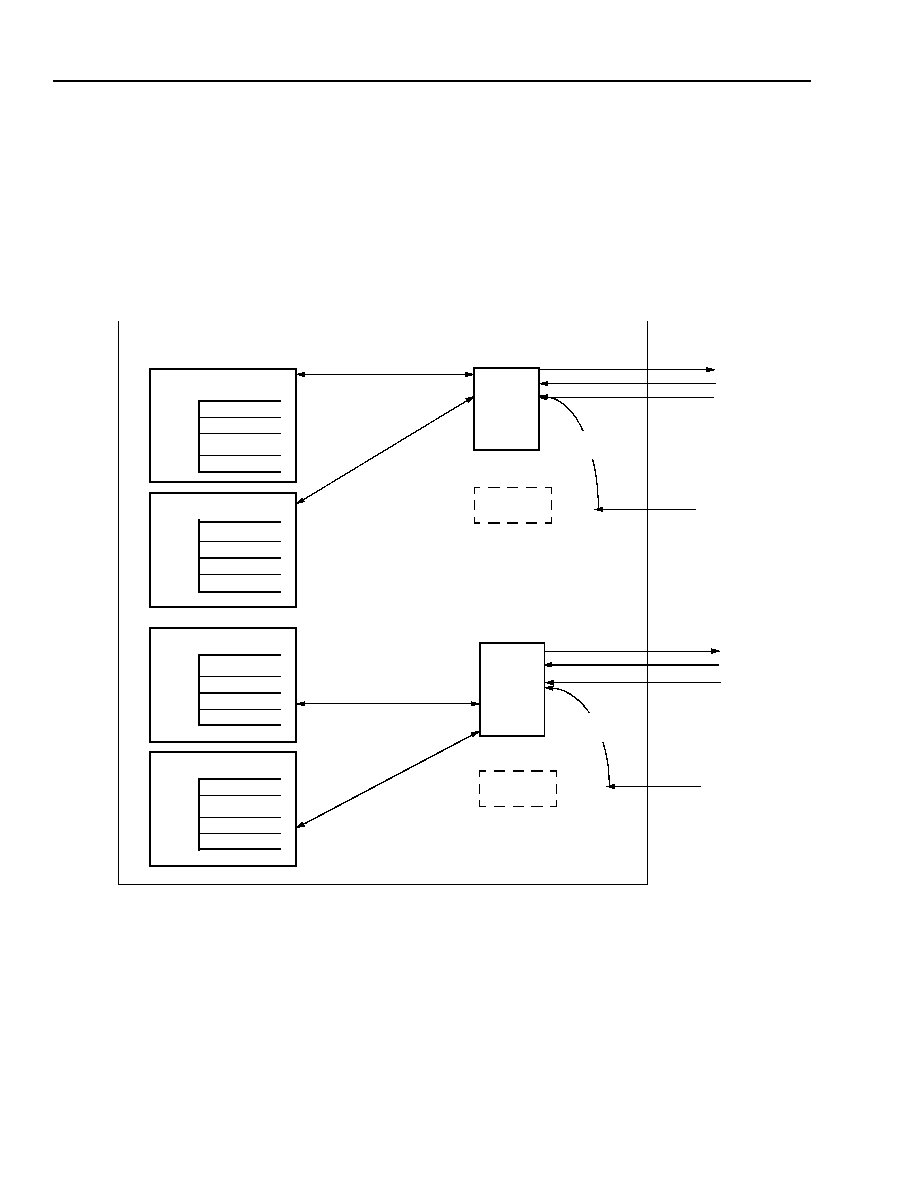

Path Terminator (PT)............................................................................................................................................ 345

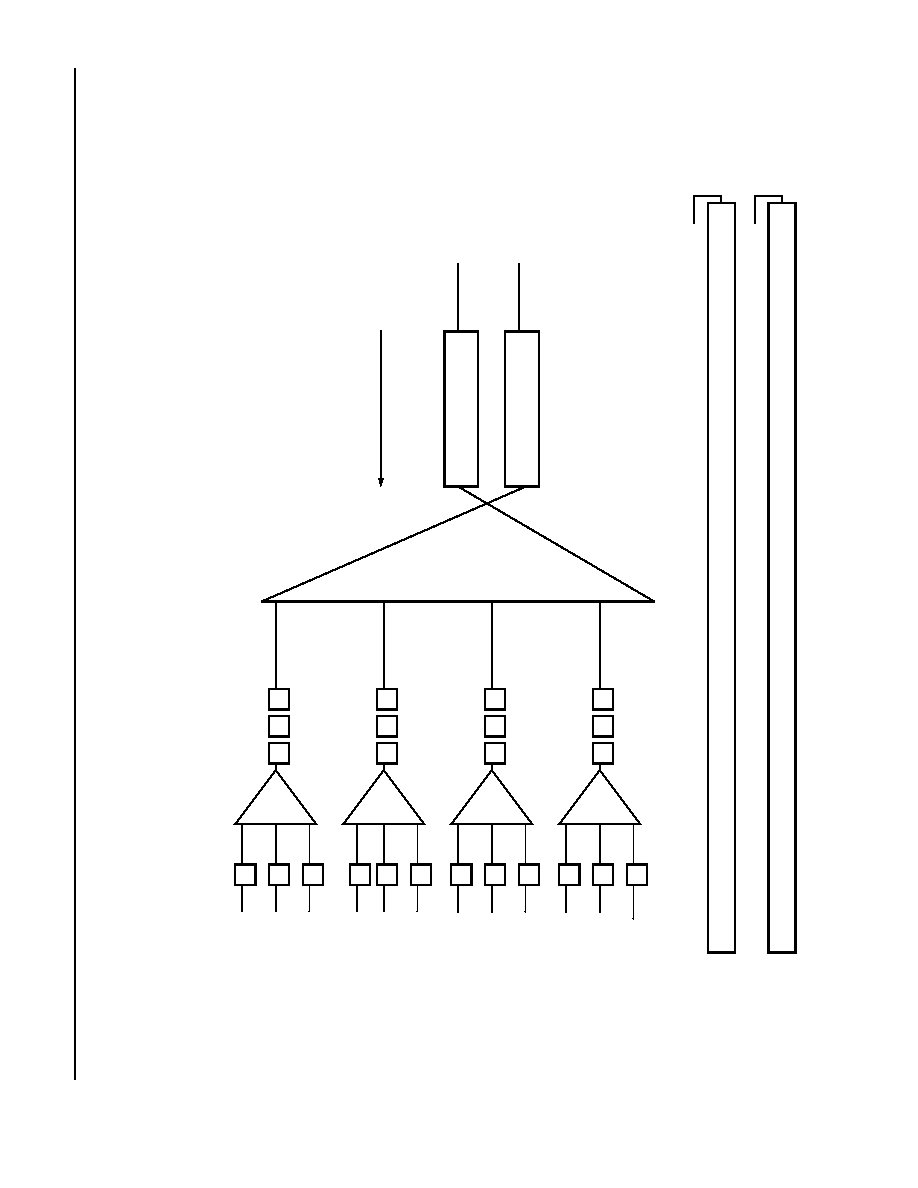

Introduction .................................................................................................................................................... 345

SPE Mapper................................................................................................................................................... 346

Supported SPE Formats ................................................................................................................................ 349

SPE Mapper Architecture............................................................................................................................... 352

Transpose Block ............................................................................................................................................ 356

PT Register Descriptions ............................................................................................................................... 357

PT Register Map (Entire PT Except RXT Block)............................................................................................ 385

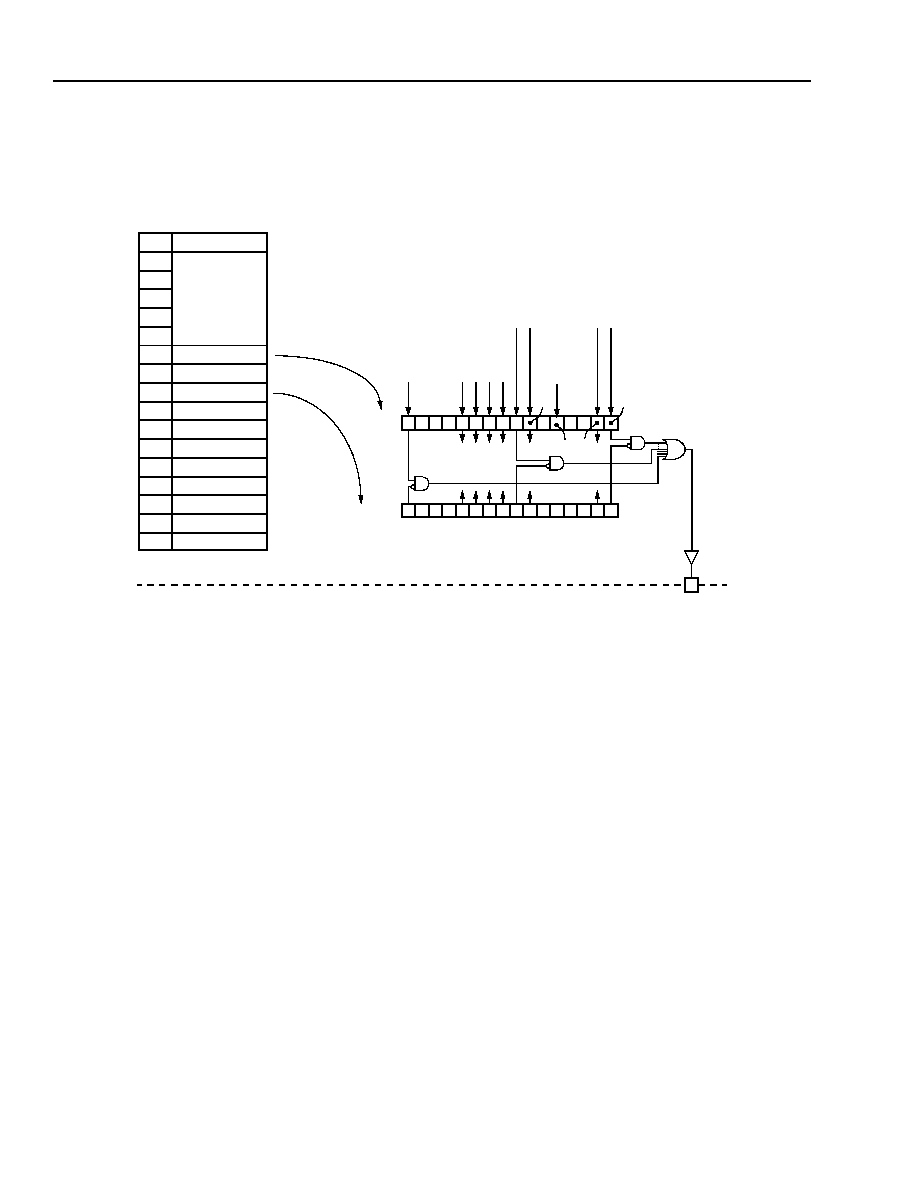

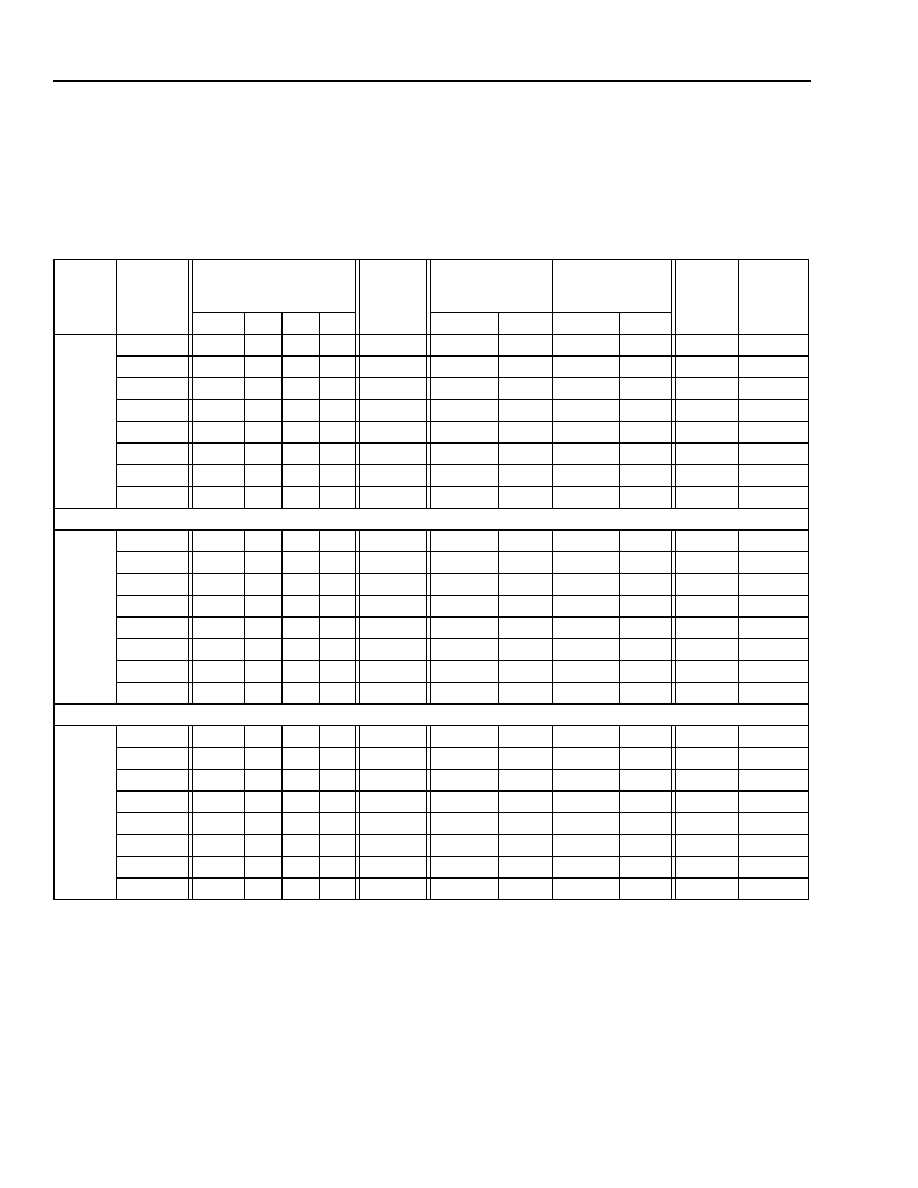

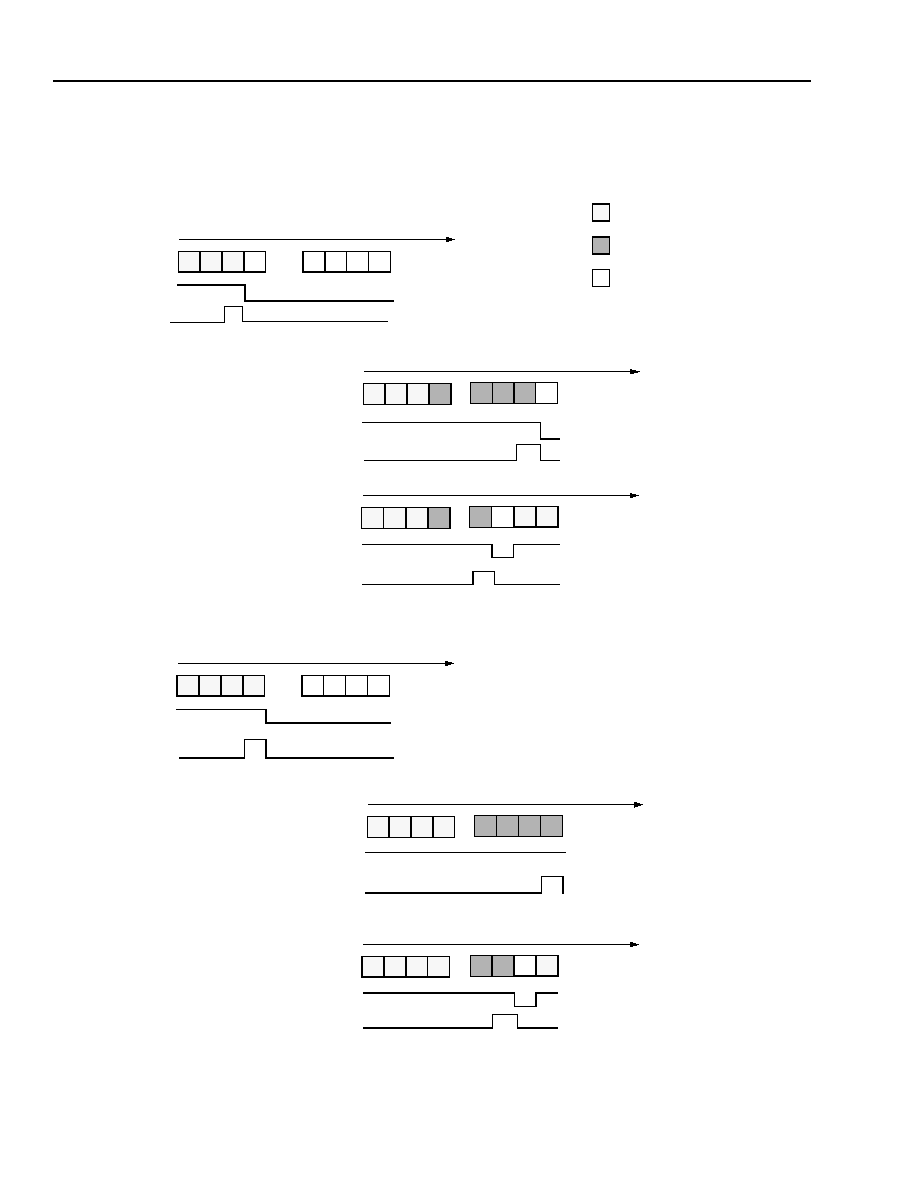

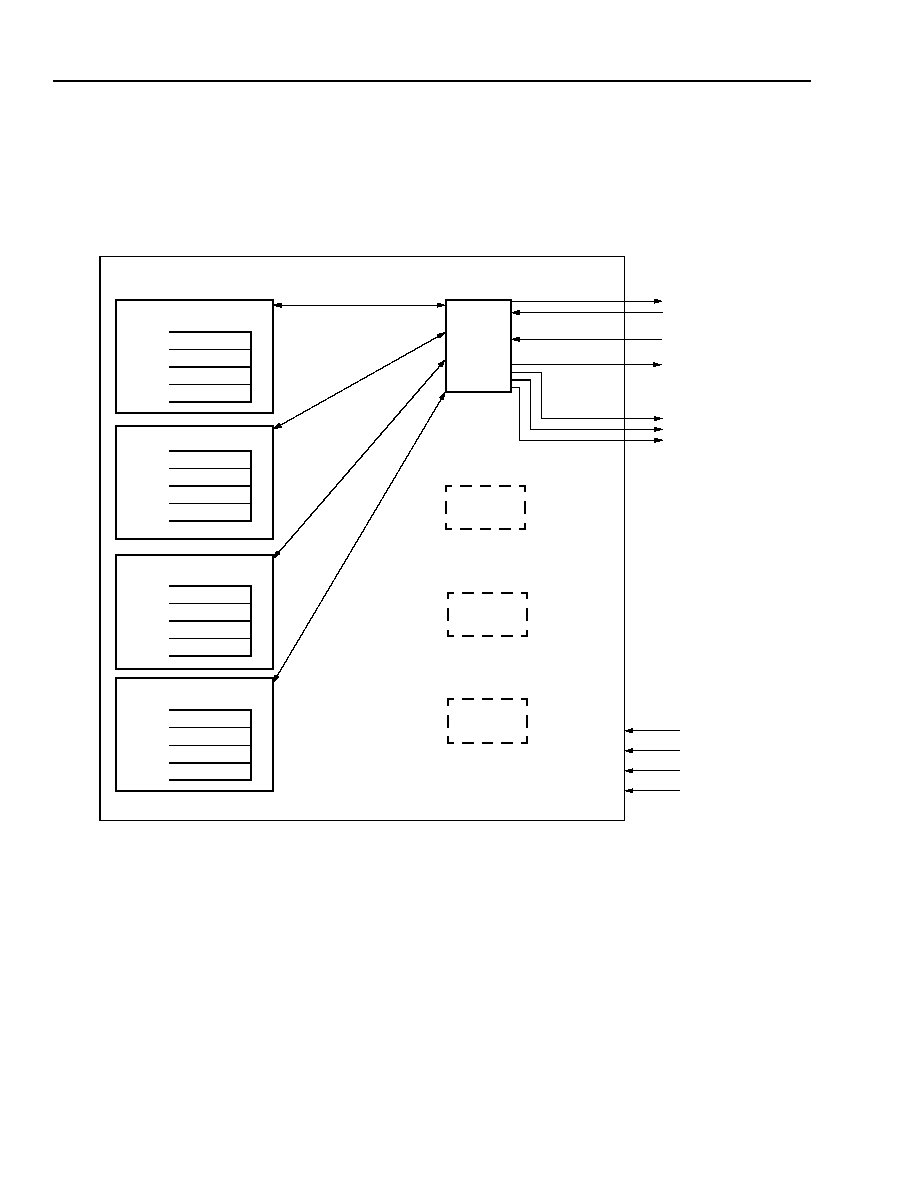

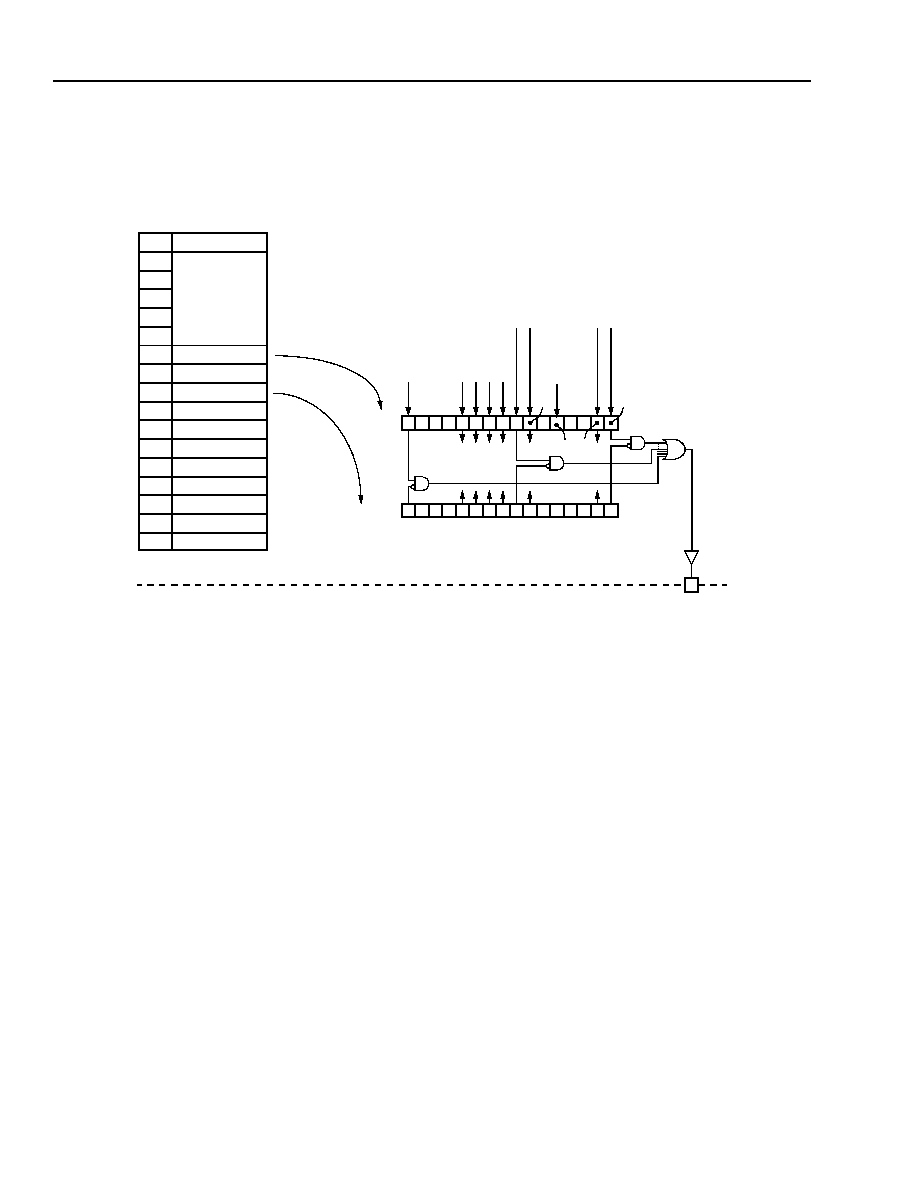

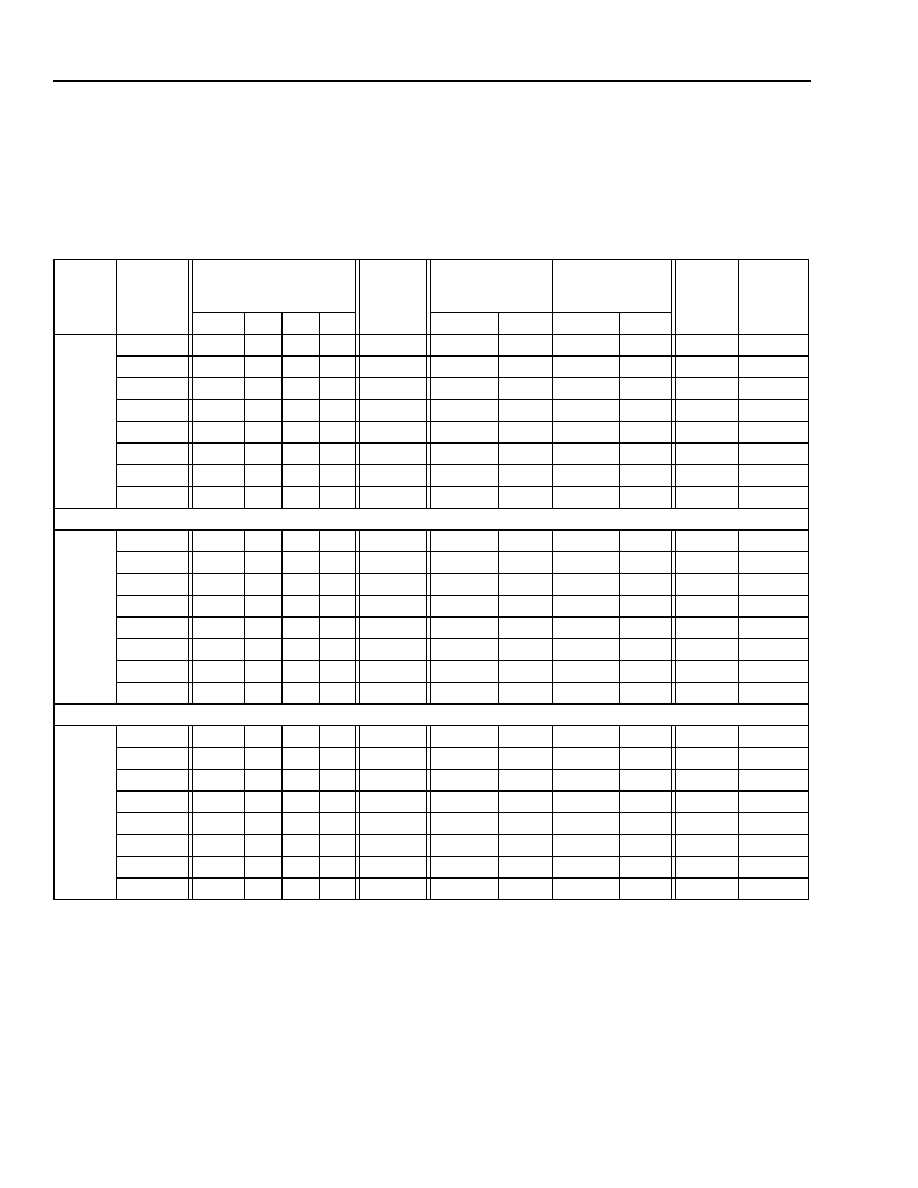

STS Receive Terminator (RXT) Block.................................................................................................................. 391

Introduction .................................................................................................................................................... 391

Receive Timing Functions.............................................................................................................................. 393

Pointer Interpreter Functions.......................................................................................................................... 394

Concatenation ................................................................................................................................................ 398

RXT Register Descriptions............................................................................................................................. 414

RXT Register Map.......................................................................................................................................... 460

DS3/E3 Block ....................................................................................................................................................... 486

DS3 Functional Description............................................................................................................................ 486

DS3 Transmit Direction .................................................................................................................................. 494