| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TECO3264 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- Features

- Applications

- Description

- Block Diagram

- Pin Information

- Functional Description

- External Control Connection

- Parameters

- Parameter Map

- Register Architecture

- Absolute Maximum Ratings

- Recommended Operating Conditions

- Electrical Characteristics

- Physical Characteristics

- Outline Diagram

- Ordering Information

- DS99-241PDH Replaces DS98-409TIC to Incorporate the Following Updates

- List of Figures

- List of Tables

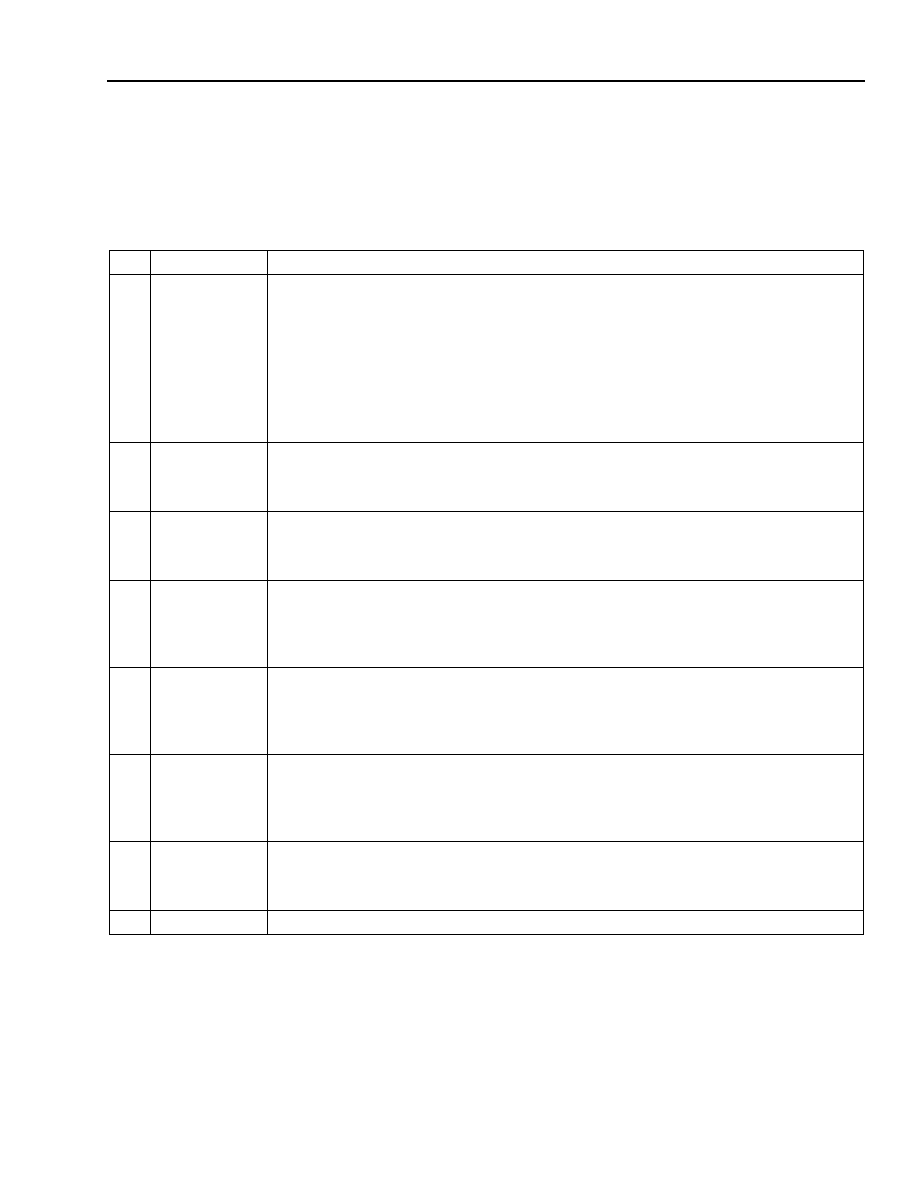

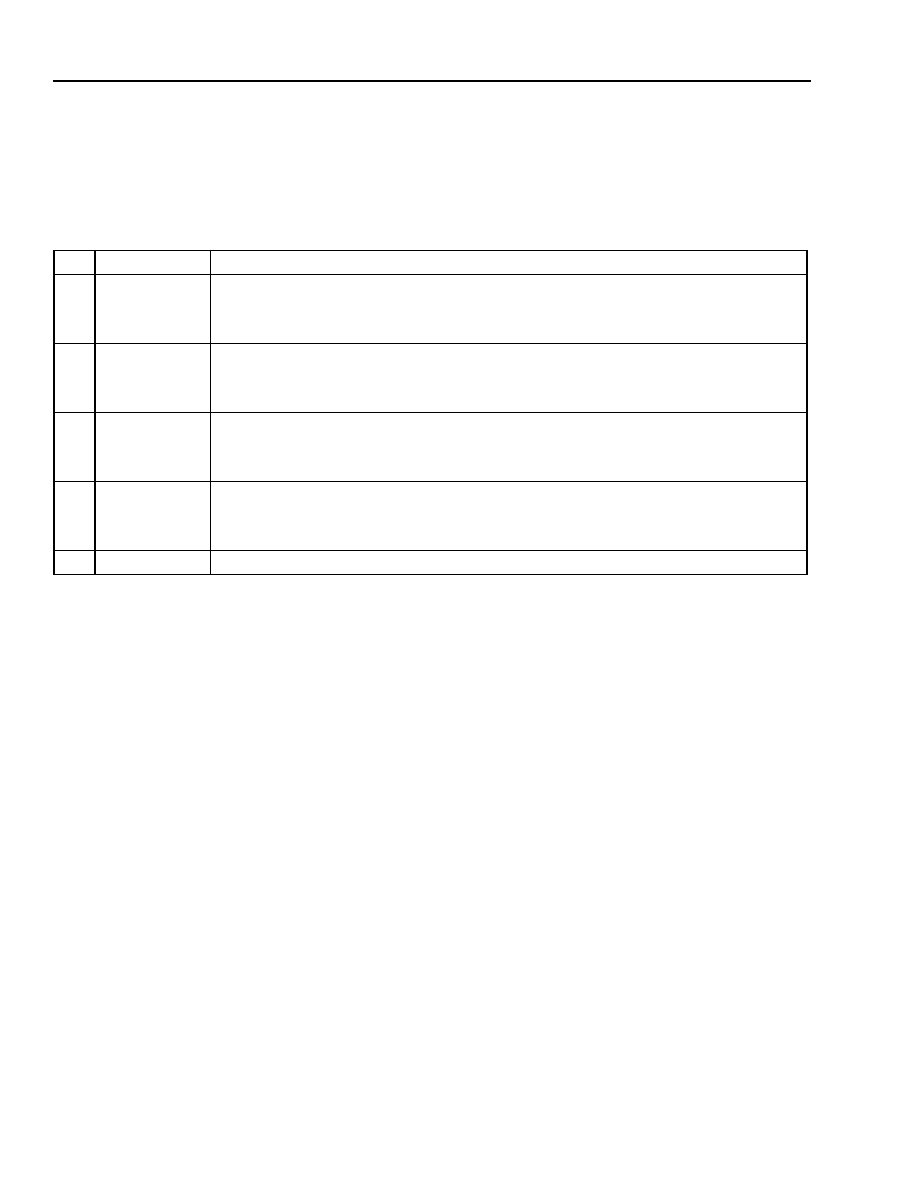

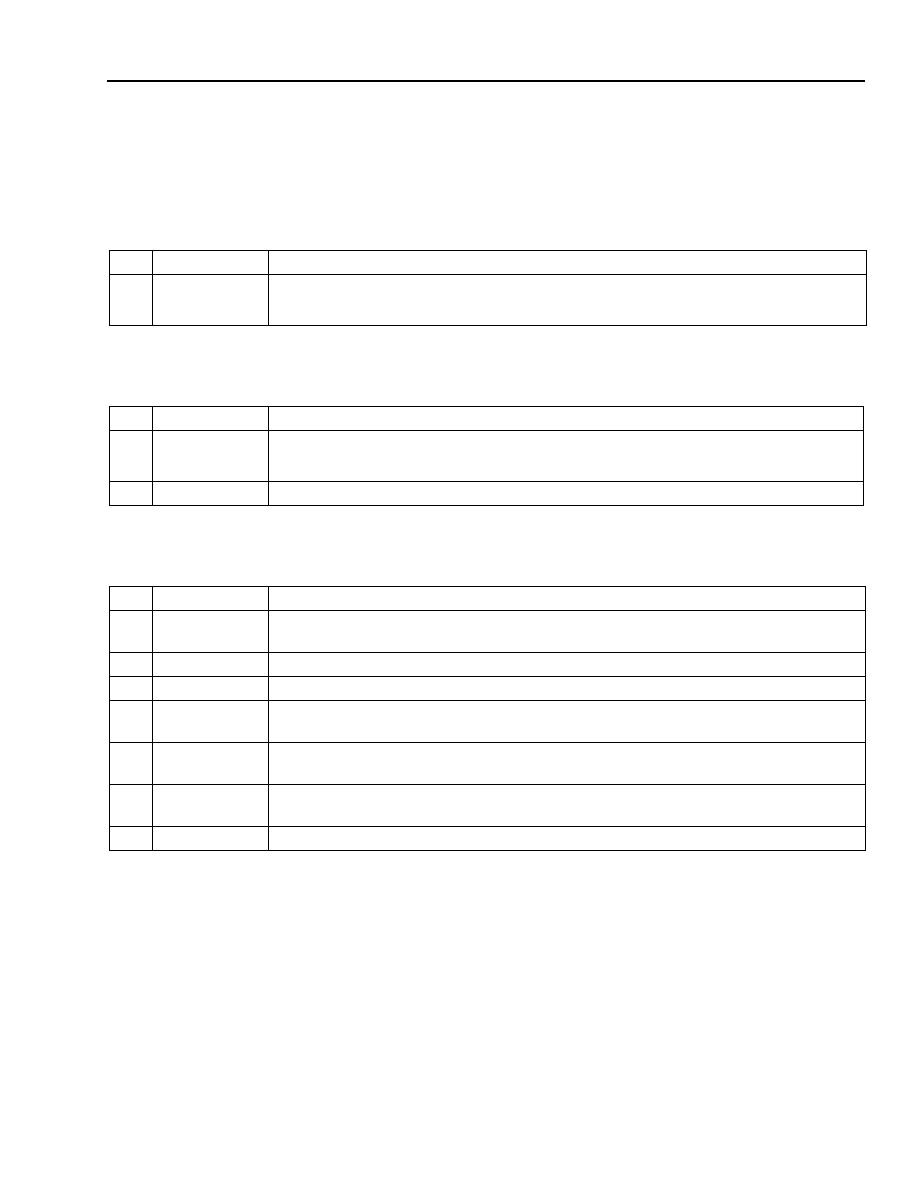

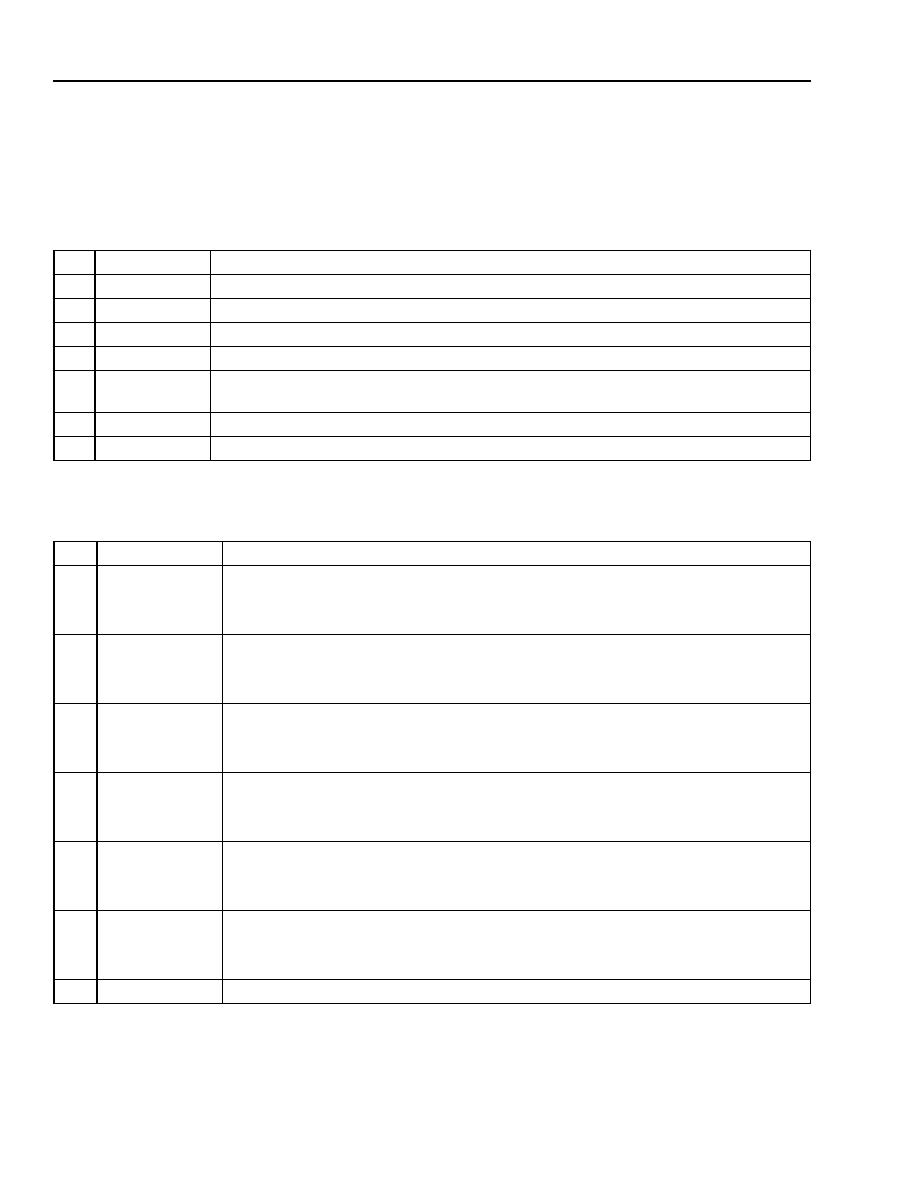

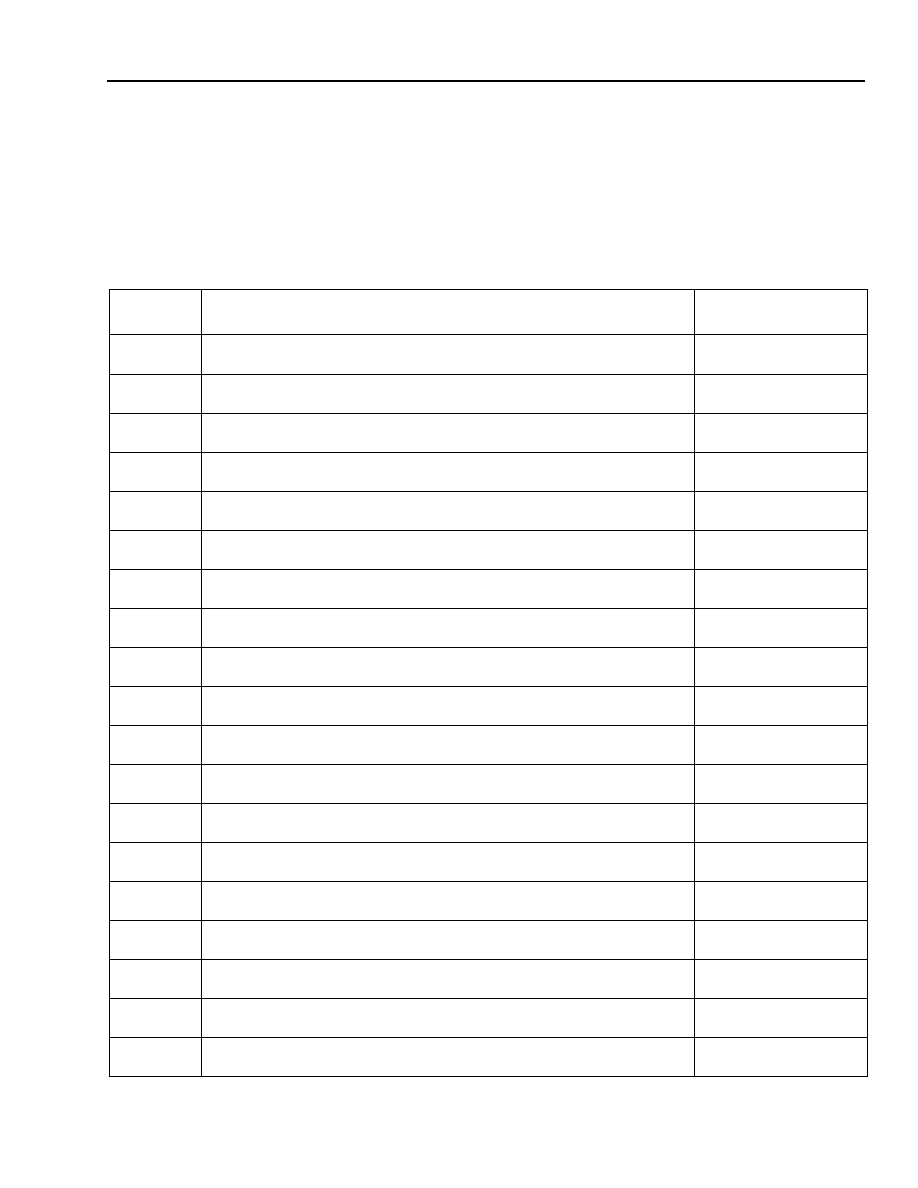

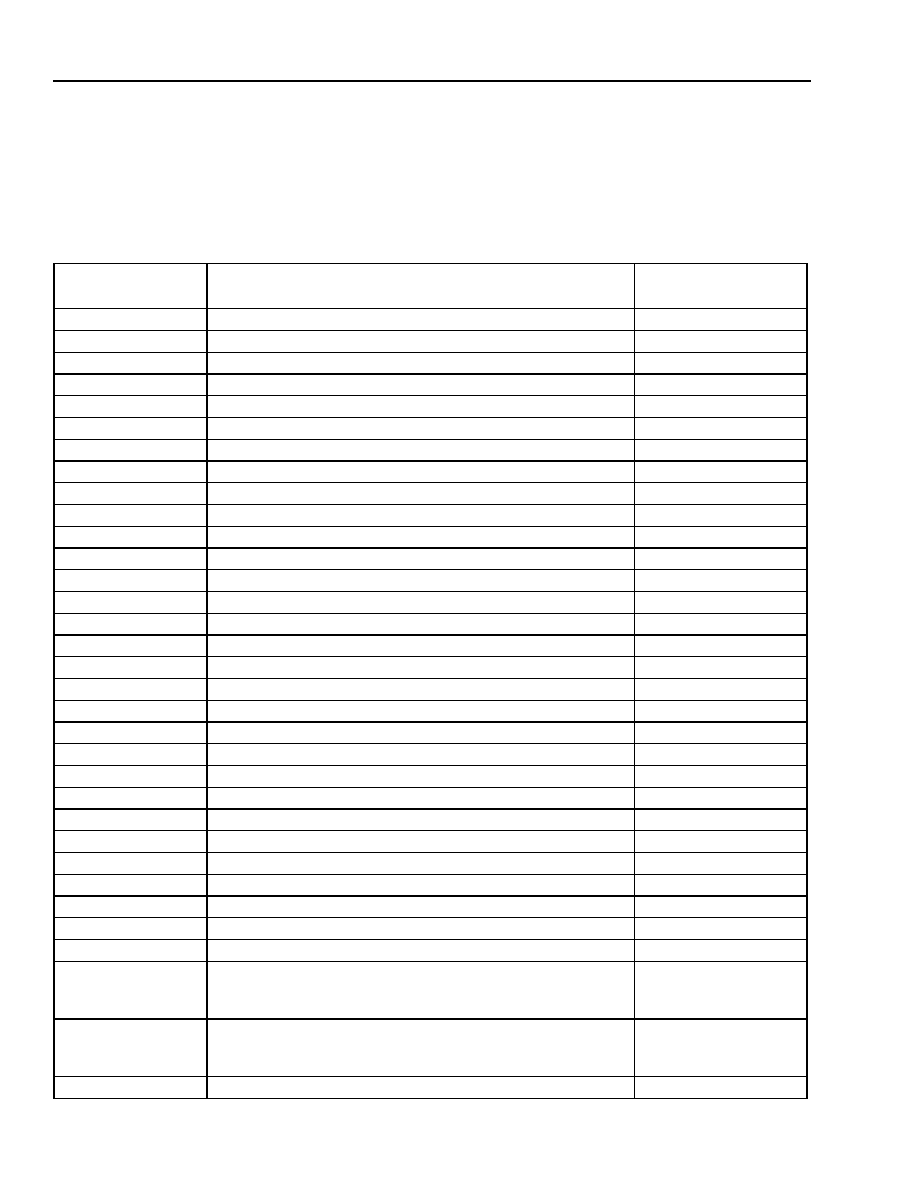

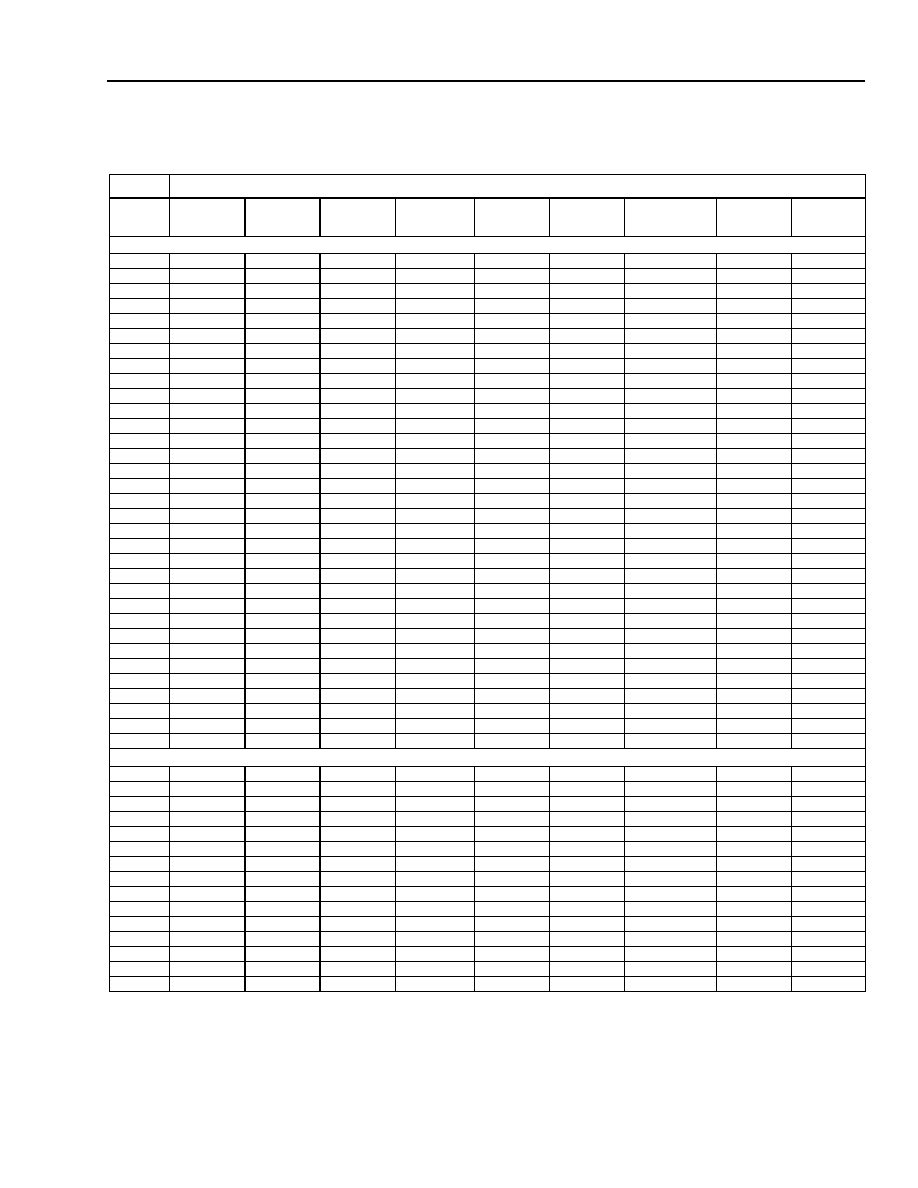

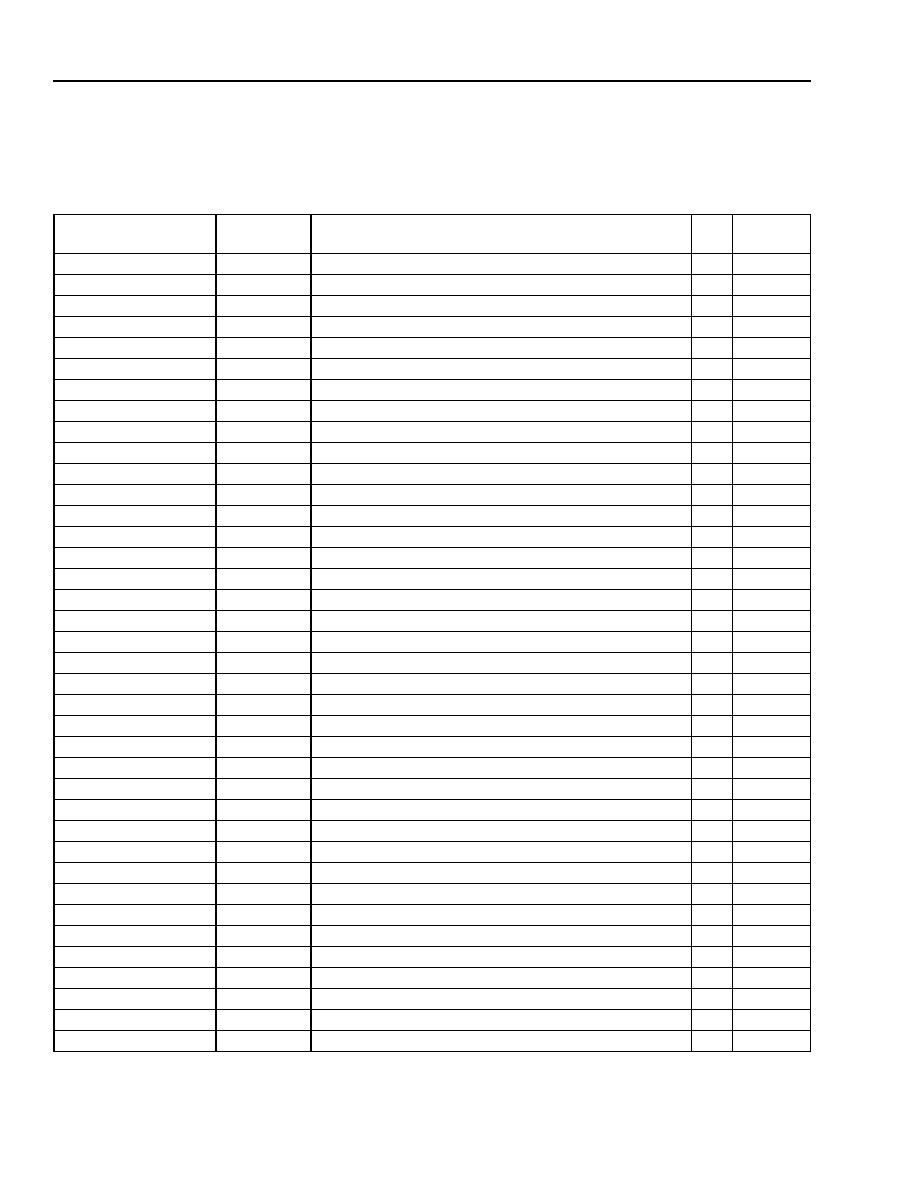

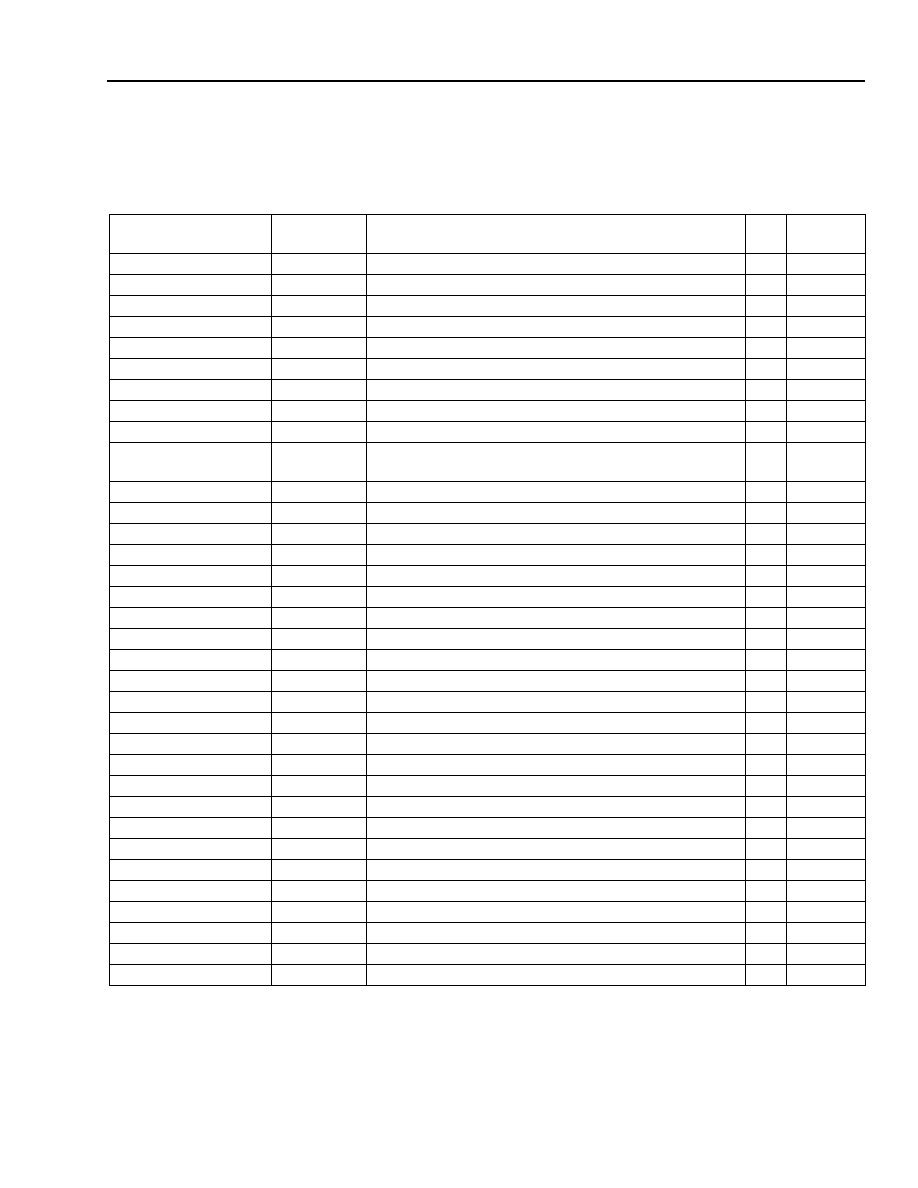

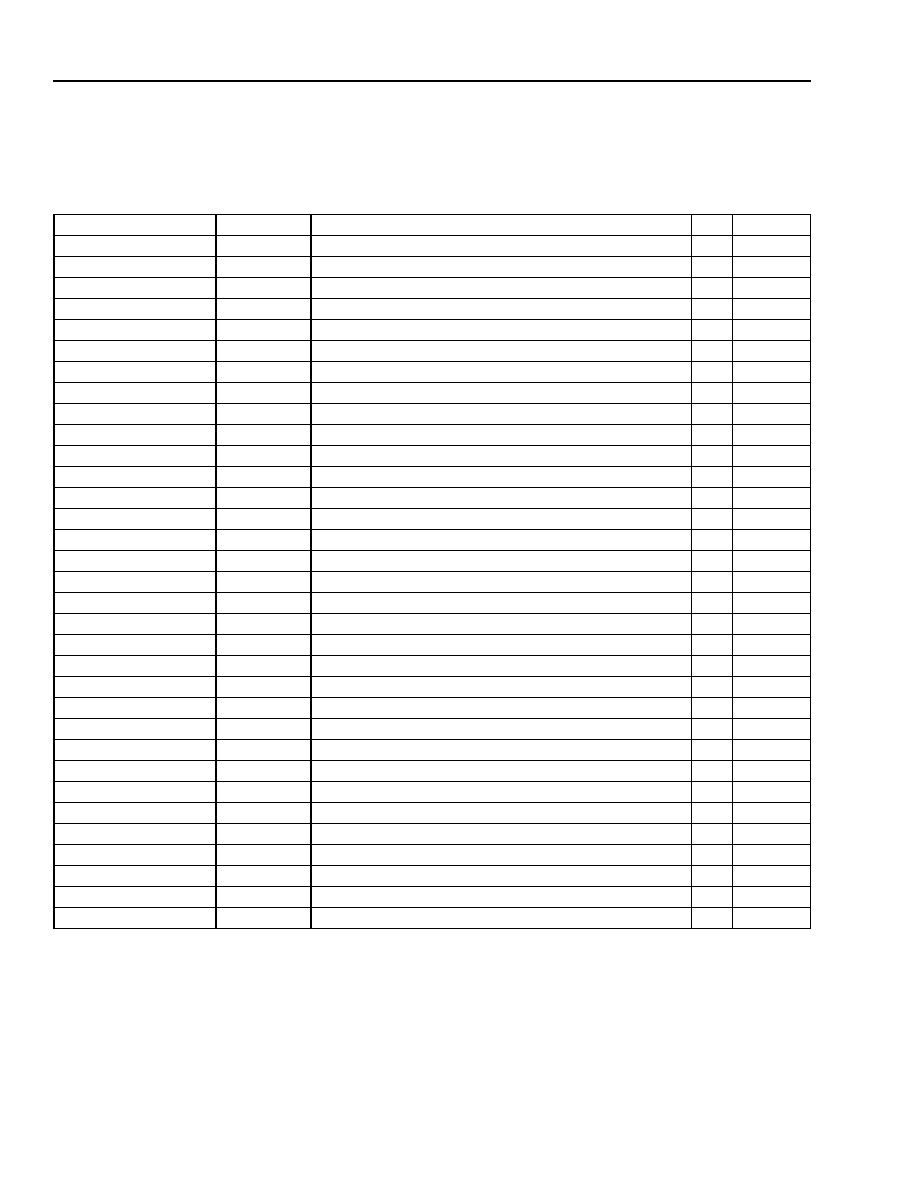

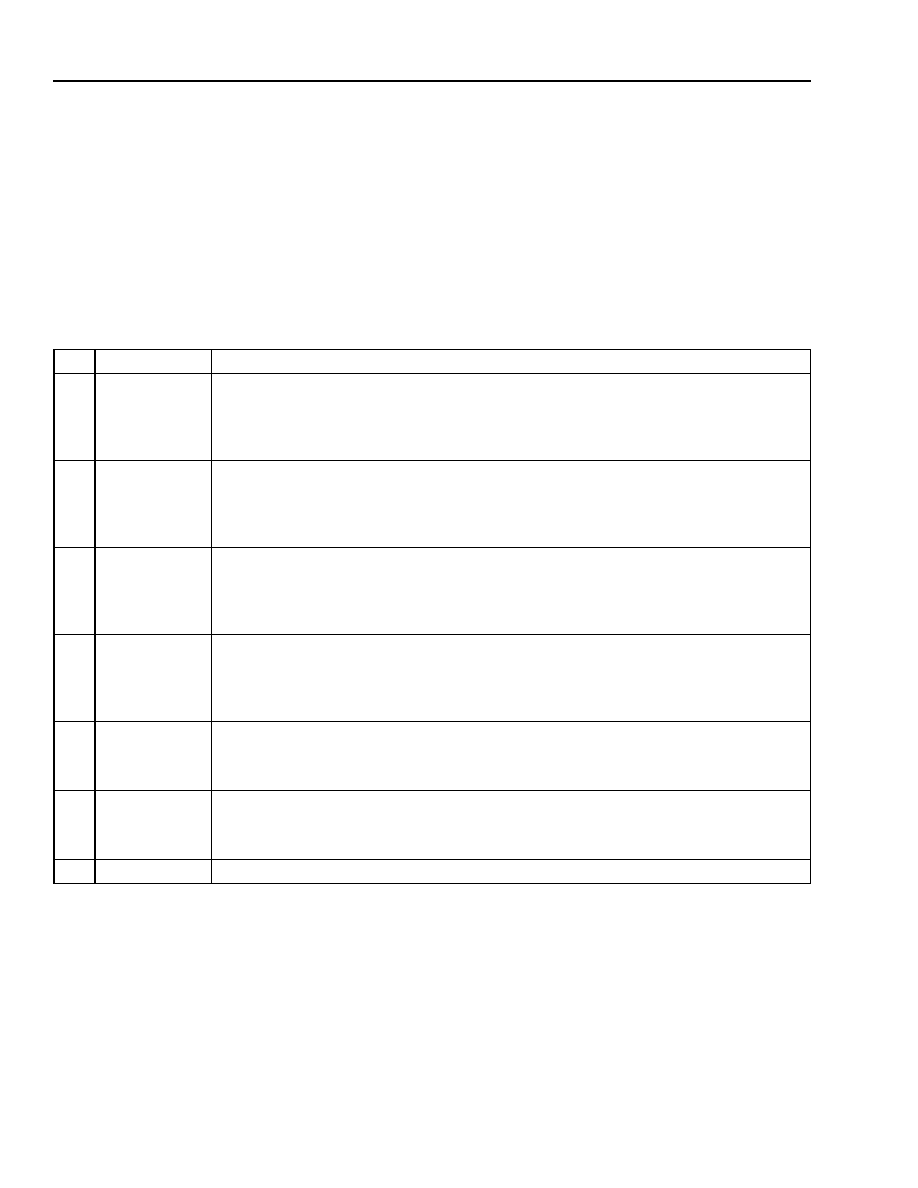

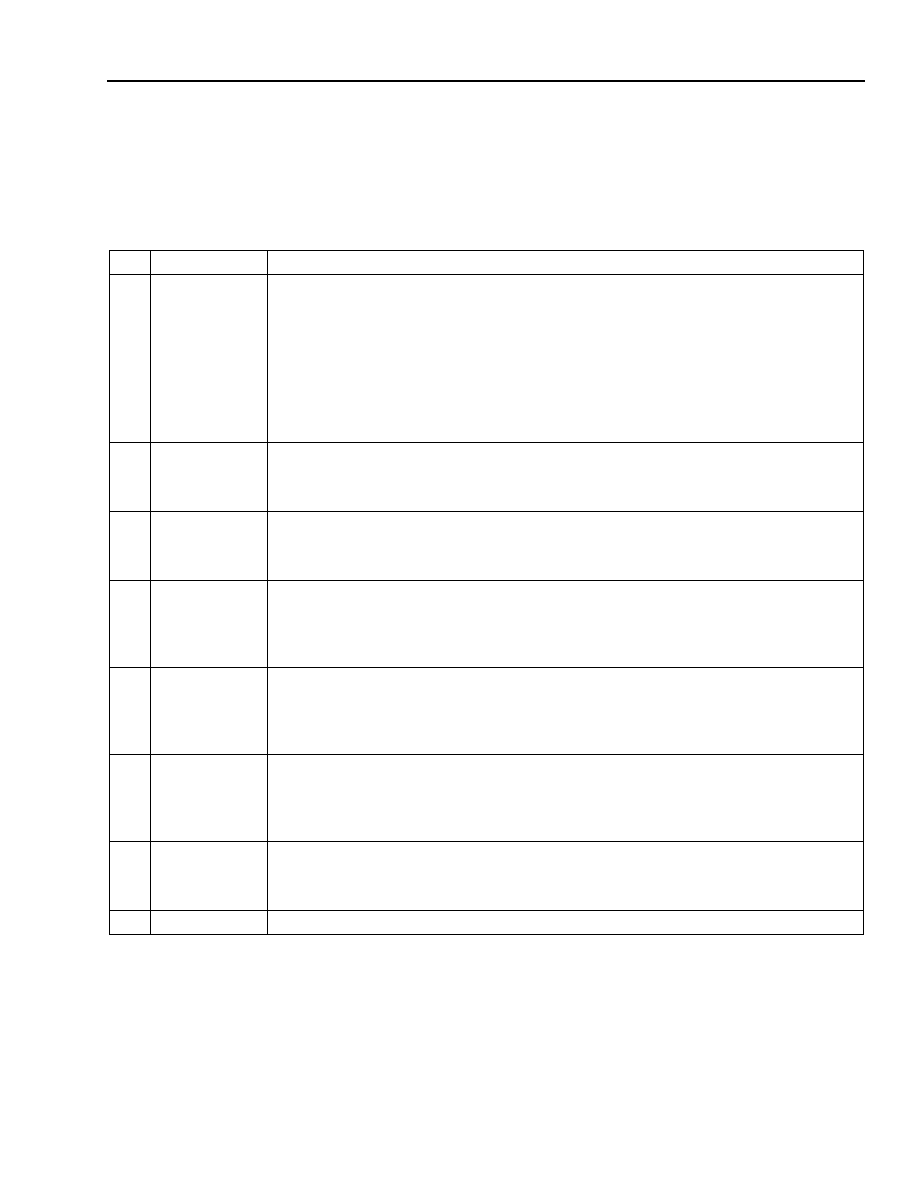

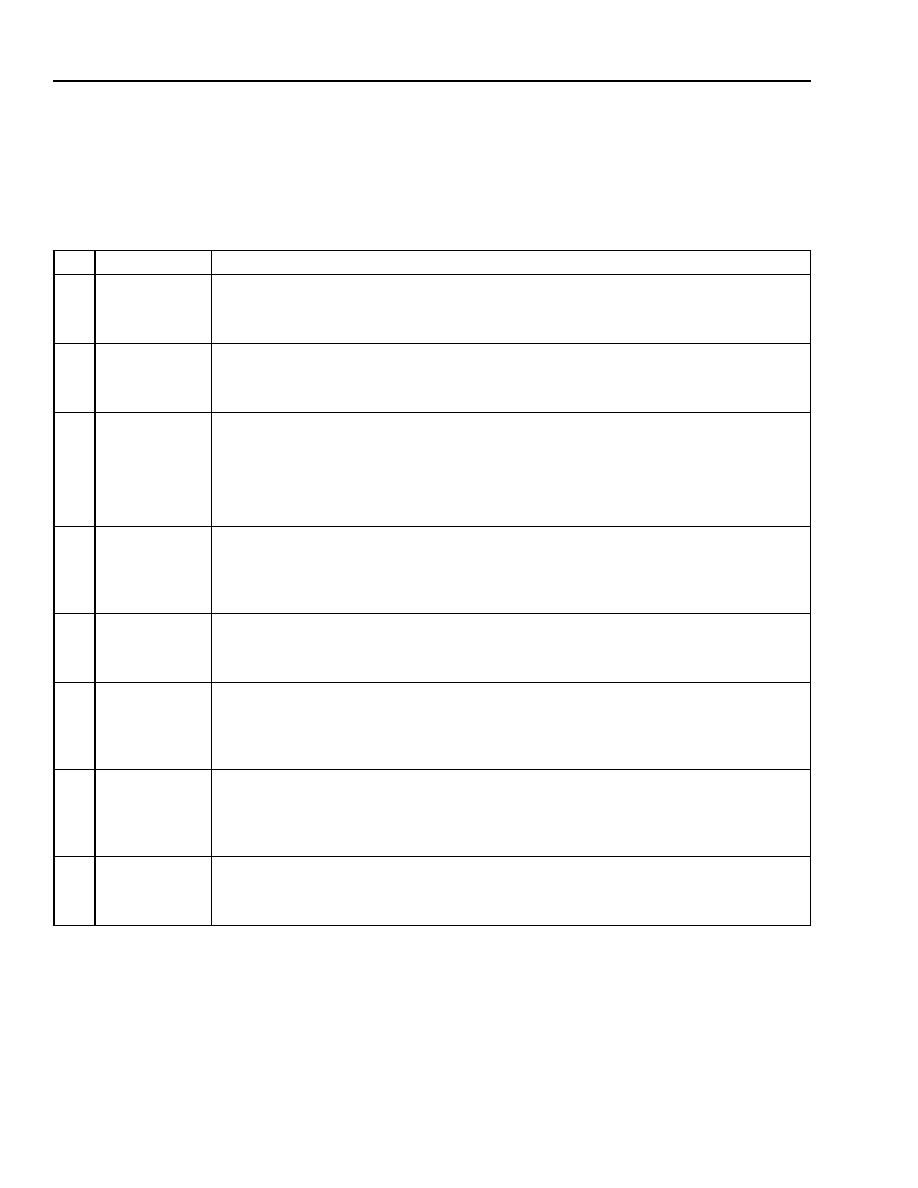

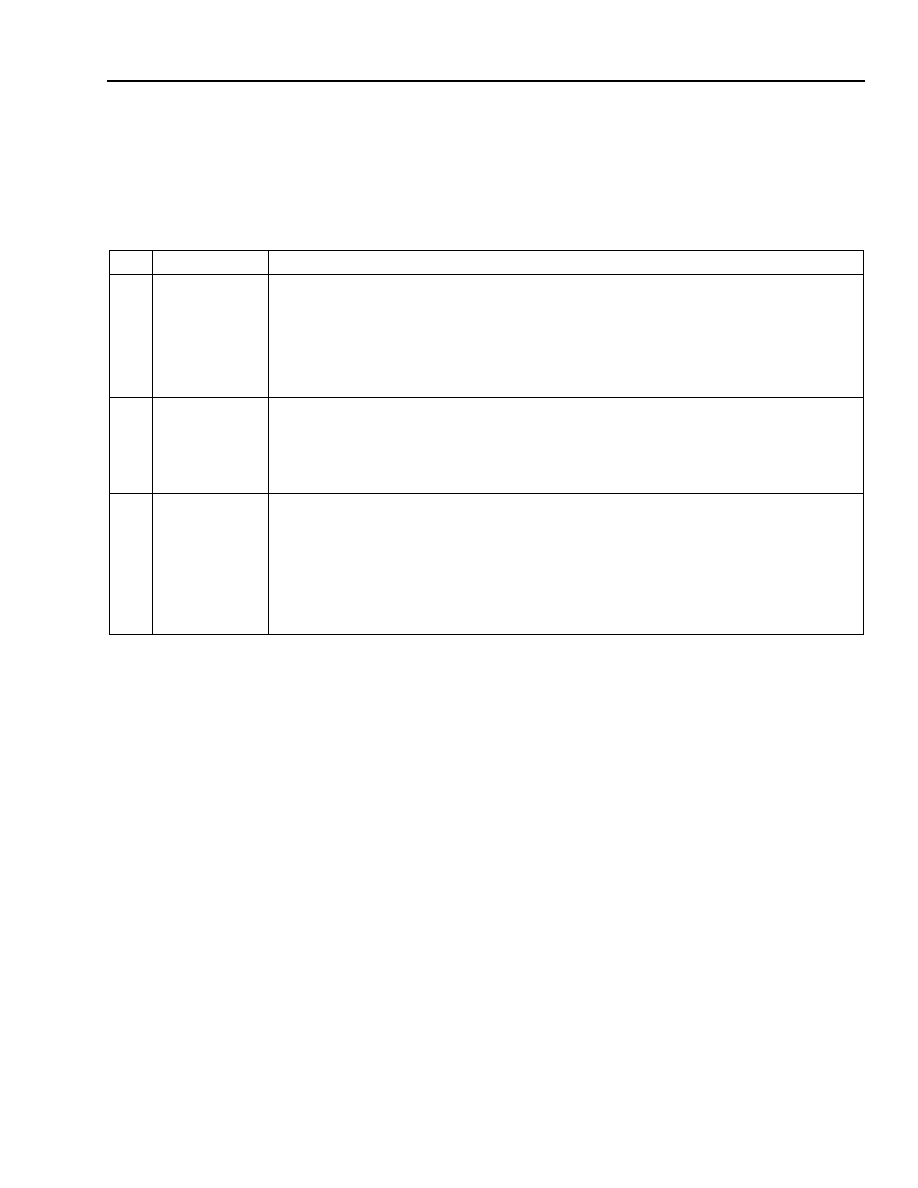

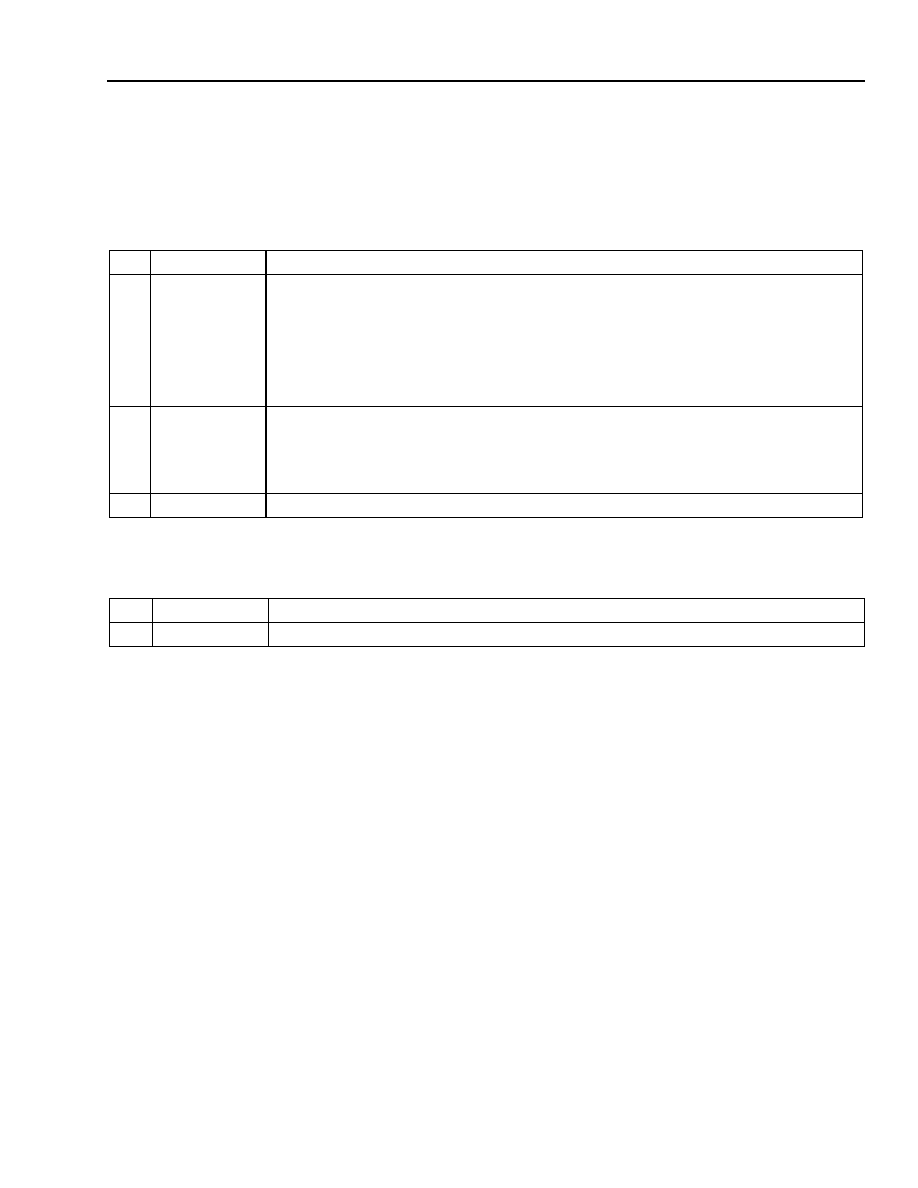

- Table 1. Pin Descriptions

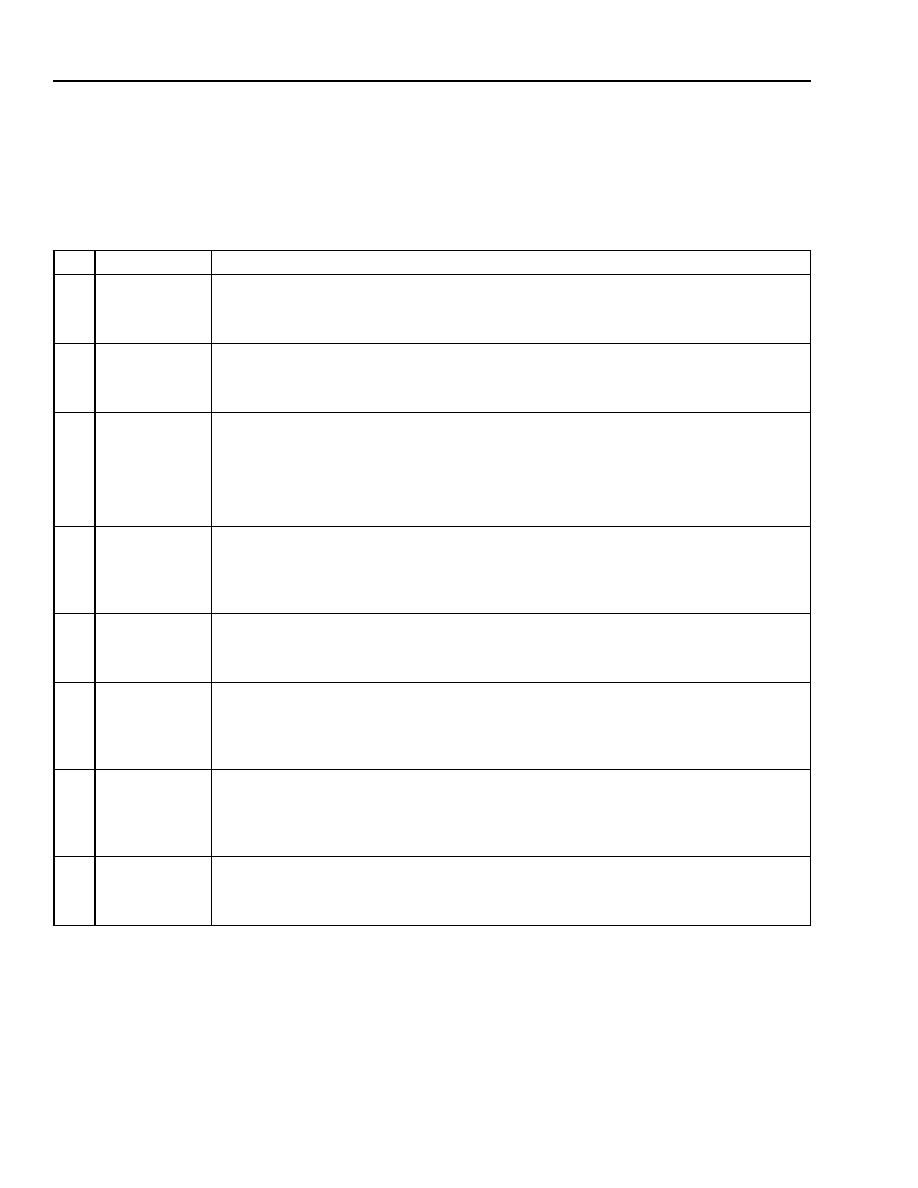

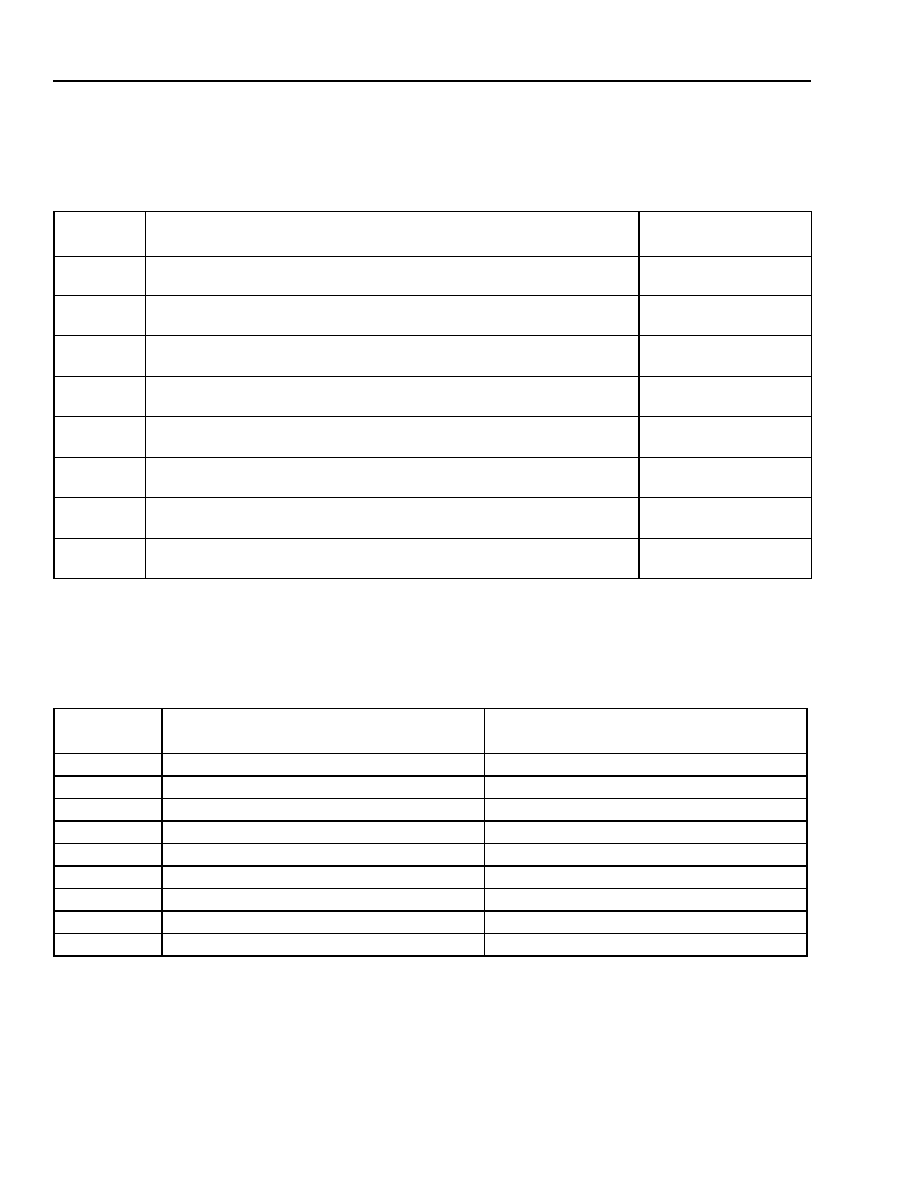

- Table 2. Microprocessor Interface Control I/O

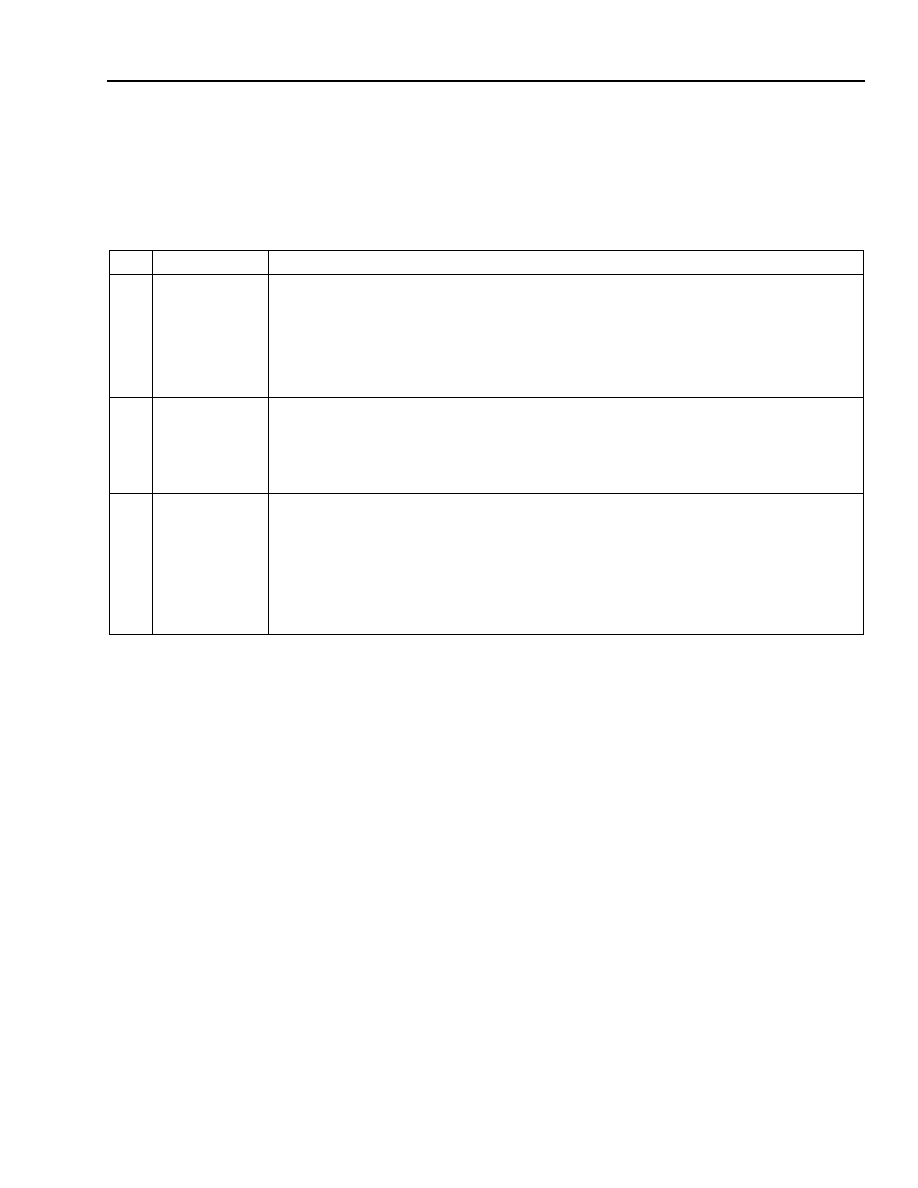

- Table 3. Relationship Between CET and CER, When CMS = 1

- Table 4. Relationship Between CET and CER, When CMS = 0

- Table 5. Programming Values (CER = Decimal) for [X, Y]RBOFF, When CMS = 1

- Table 6. Programming Values (CET = Decimal) for [C, E]XBOFF, When CMS = 1

- Table 7. Programming Values (CER = Decimal) for [X, Y]RBOFF, When CMS = 0

- Table 8. Programming Values (CET = Decimal) for [C, E]XBOFF, When CMS = 0

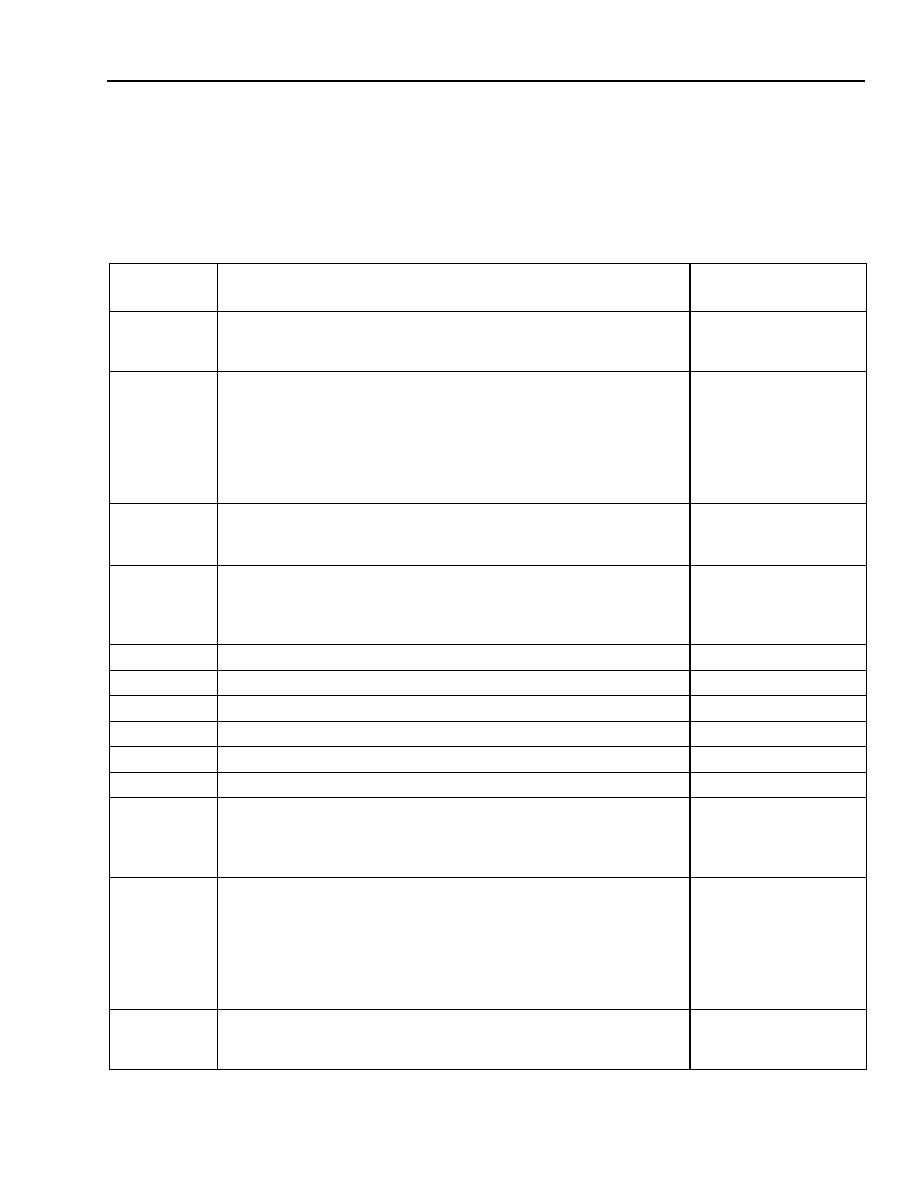

- Table 9. Transmission Parameter Settings and Description for Waveforms in Figure 15, PCM Input/Ou...

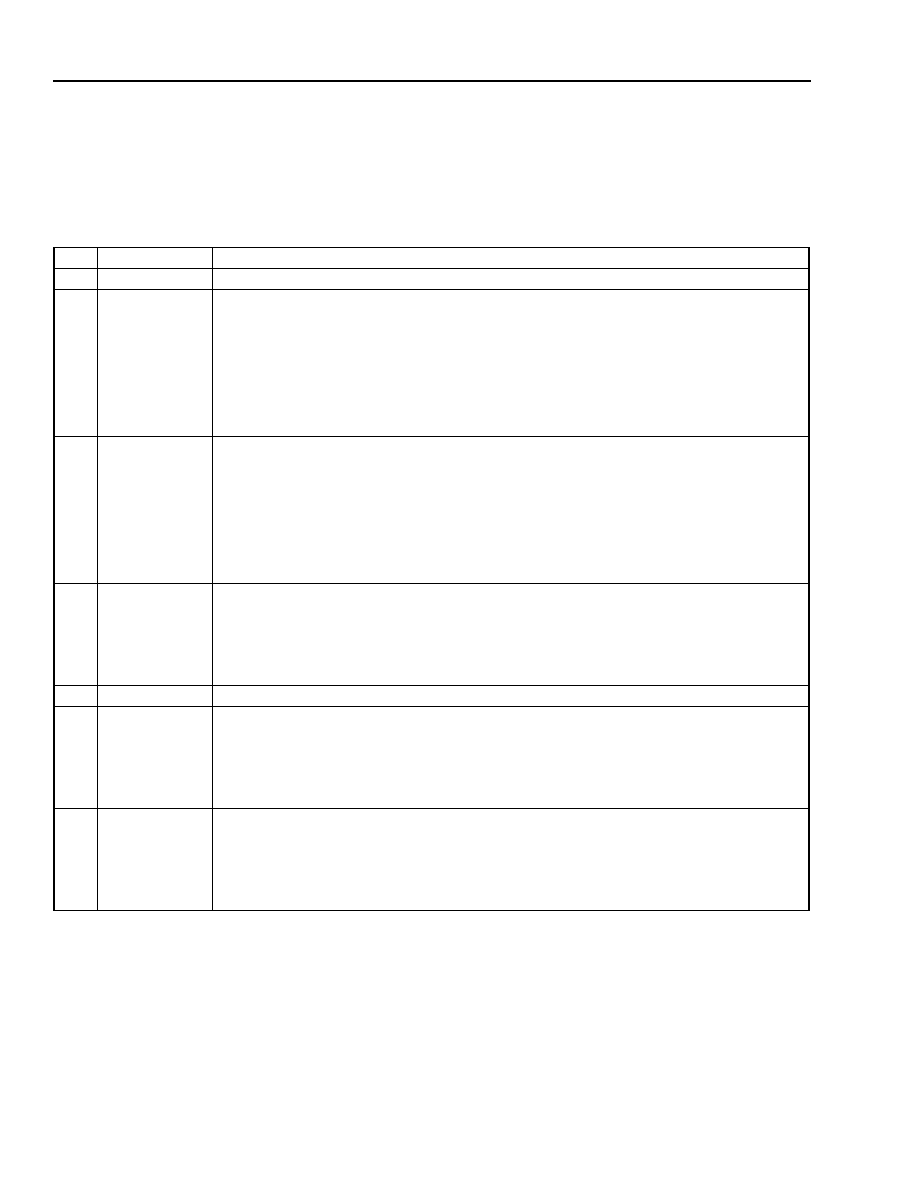

- Table 10. H-Register Display Output Format

- Table 11. Per-Channel Control Parameters

- Table 12. Mask Parameters

- Table 13. EC Parameters

- Table 14. Transmission Parameters

- Table 15. Tone Disabler Parameters

- Table 16. Nonlinear Processor Parameters

- Table 17. Control Parameters

- Table 18. Test and Diagnostic Parameters

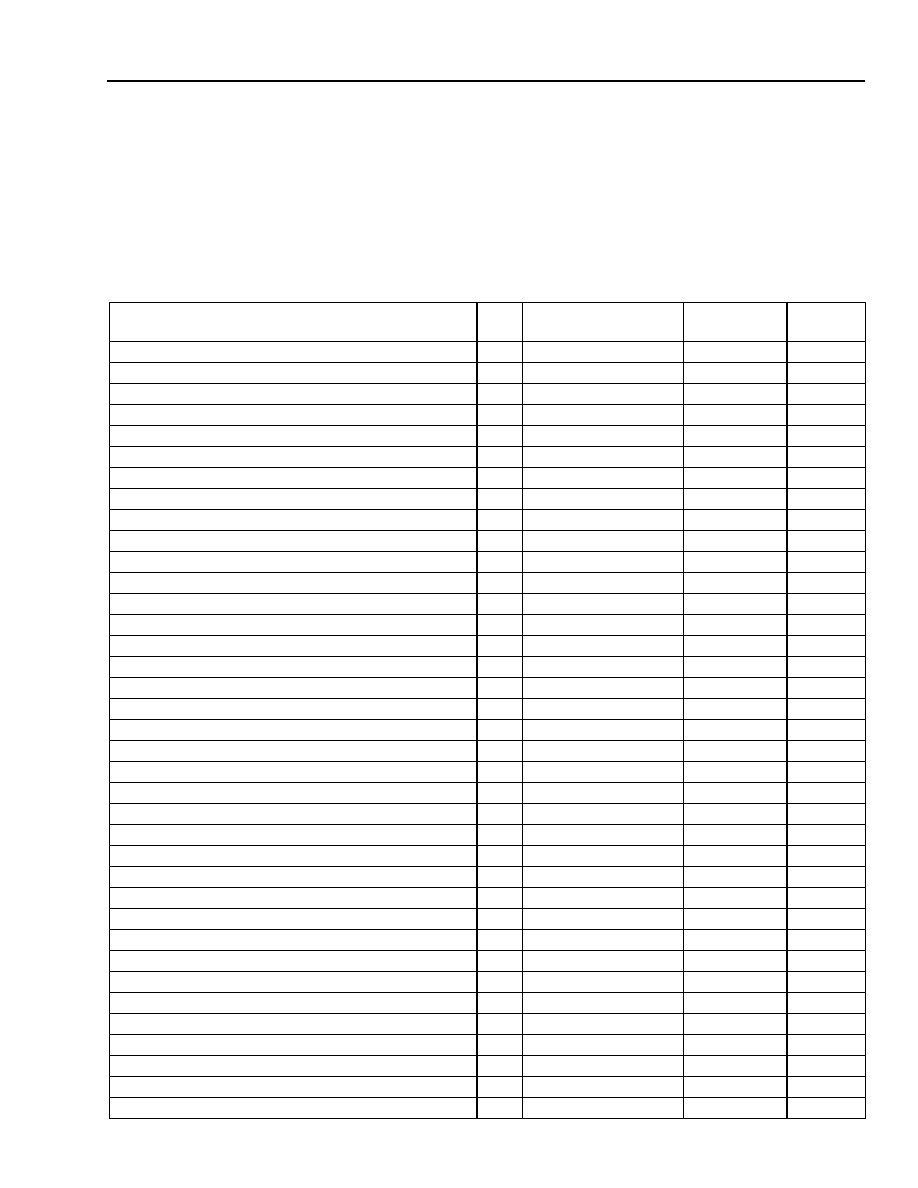

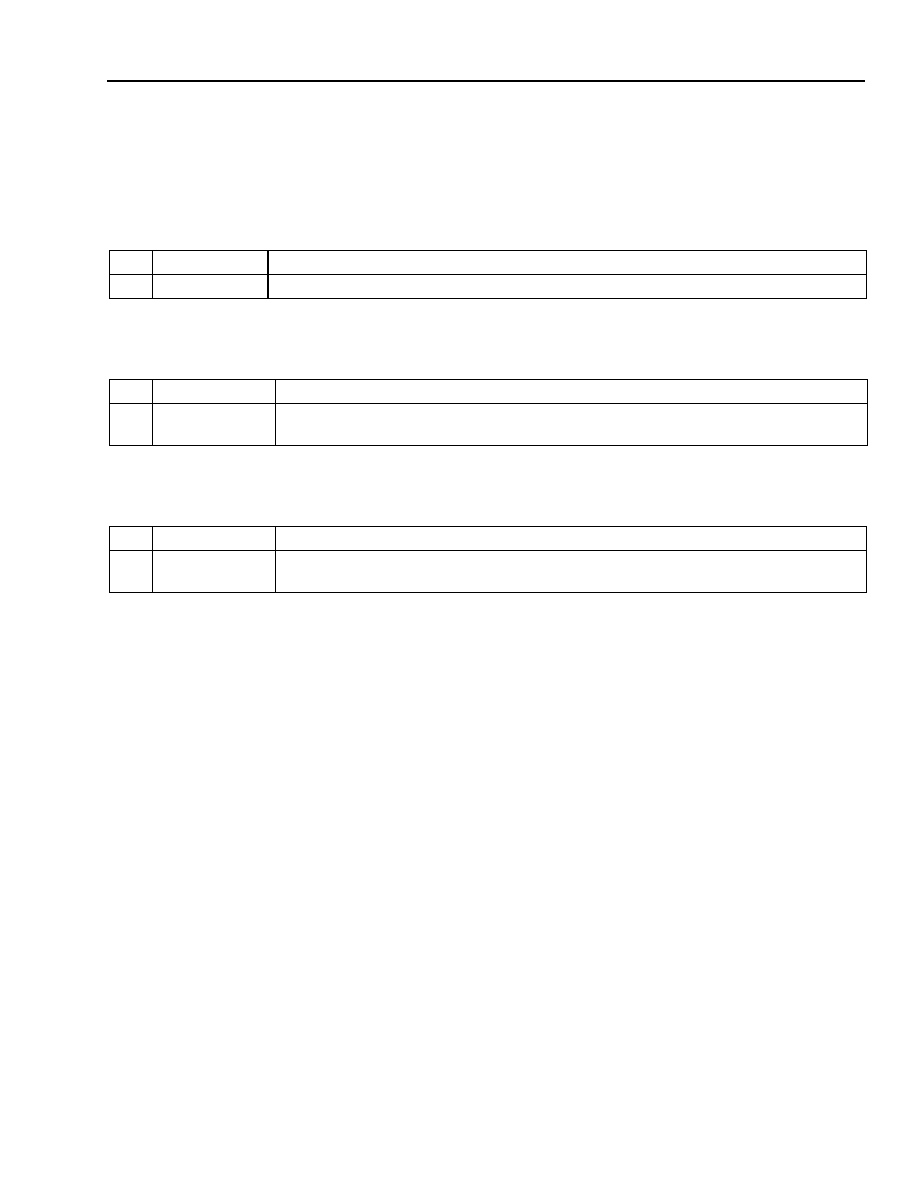

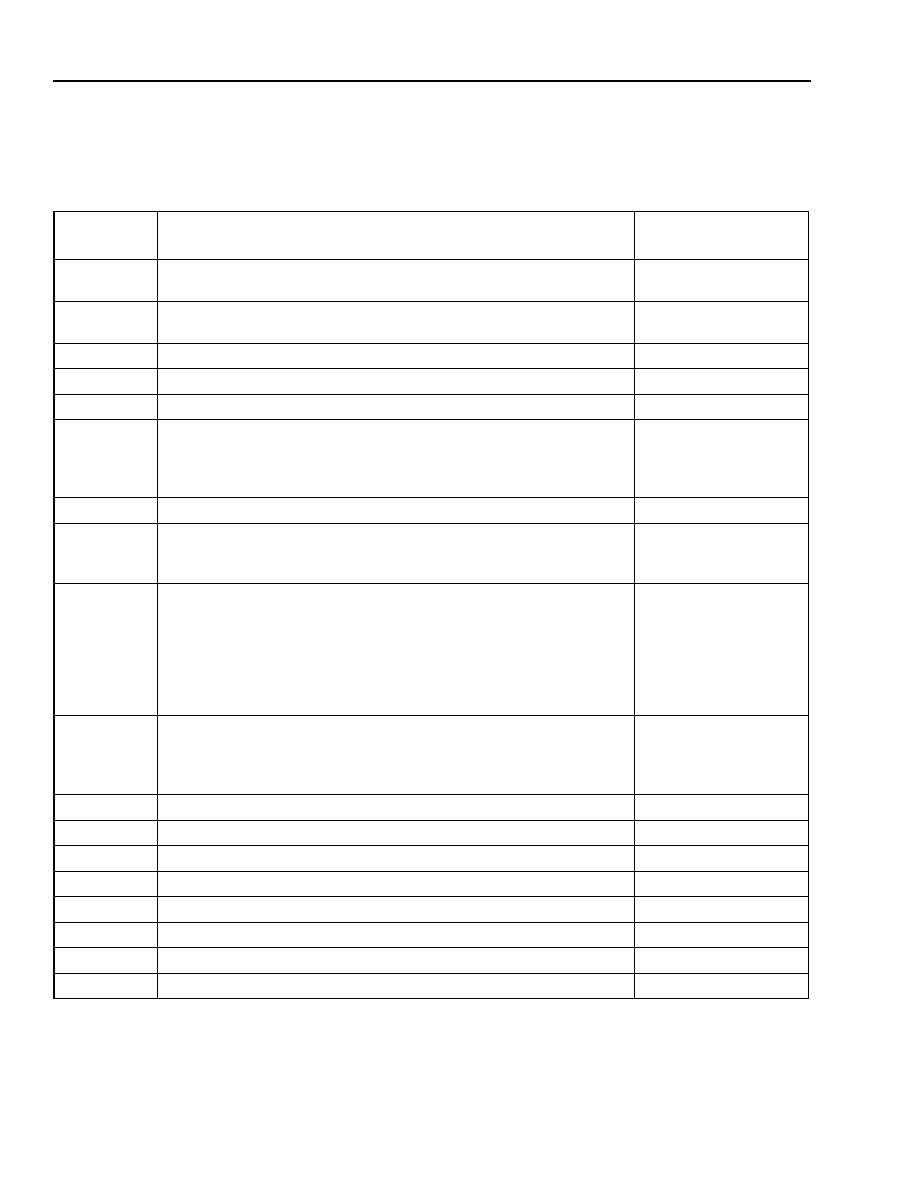

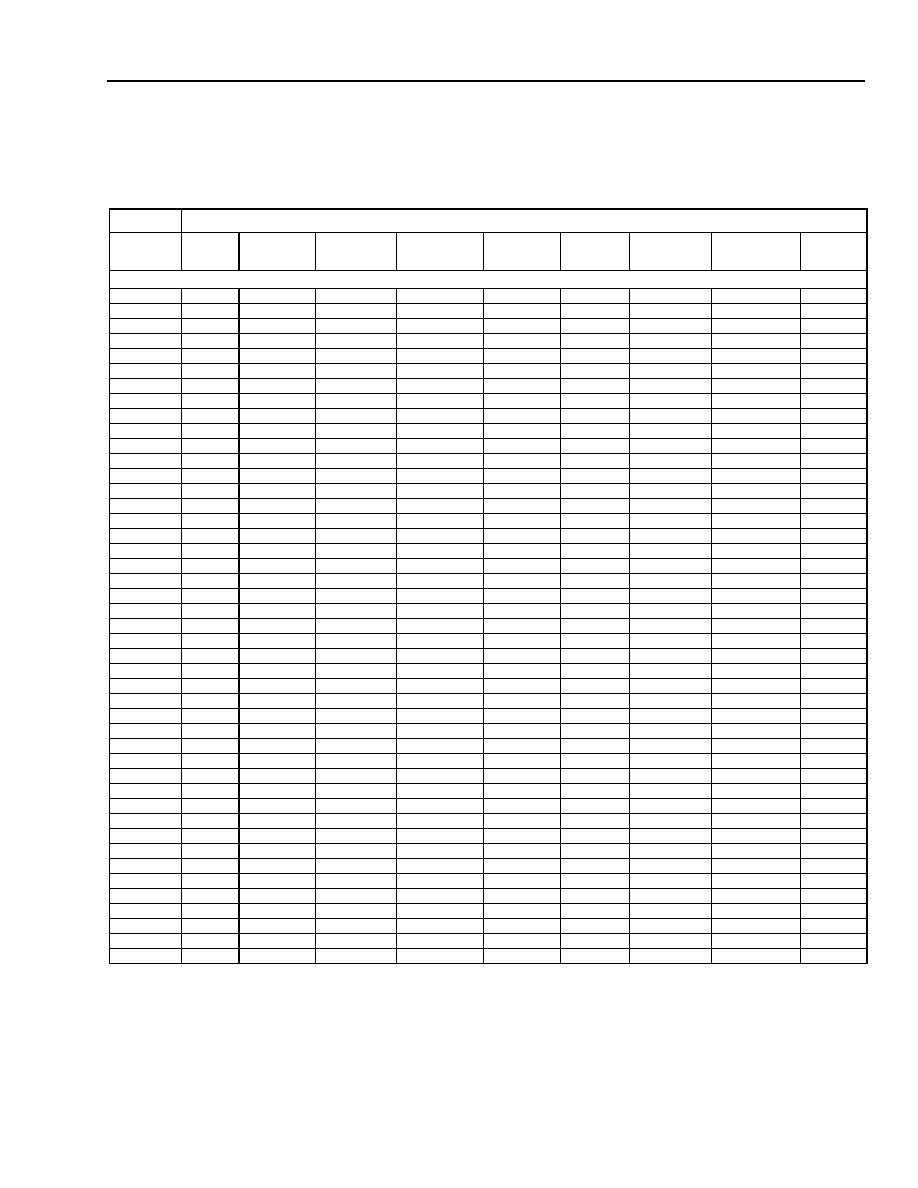

- Table 19. Parameter Address Map

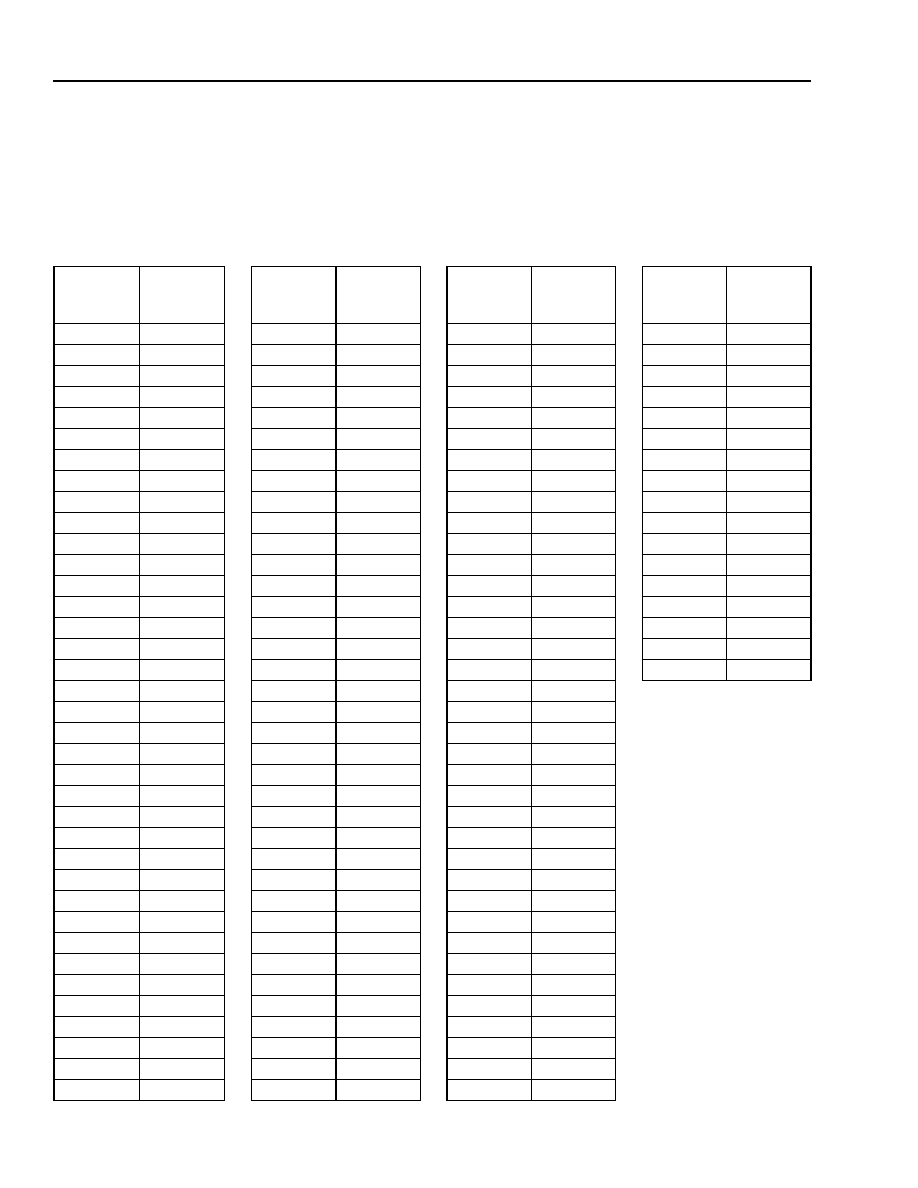

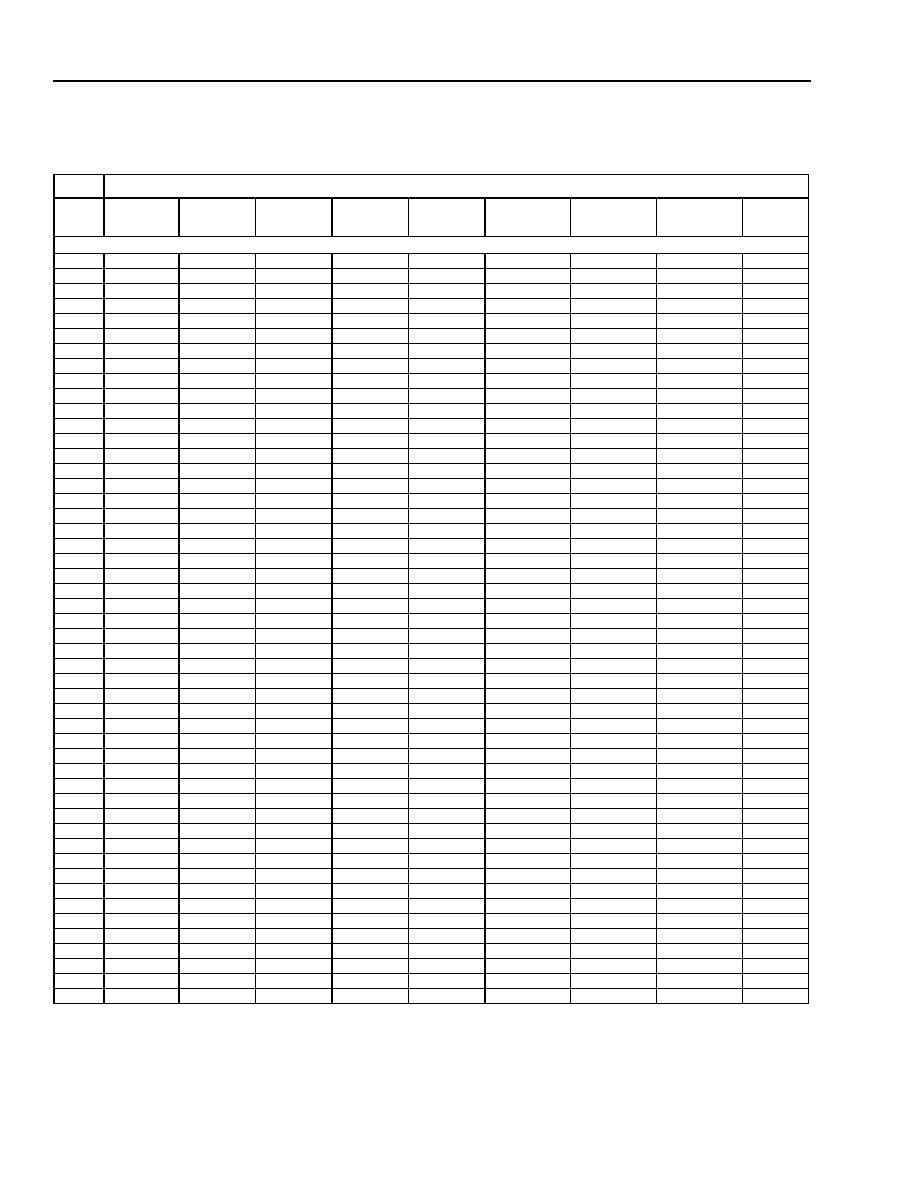

- Table 20. Recommended Register Values for DS1 (µ-Law) and 2.048 Mbits/s Rate

- Table 21. Recommended Register Values for E1 (A-Law)

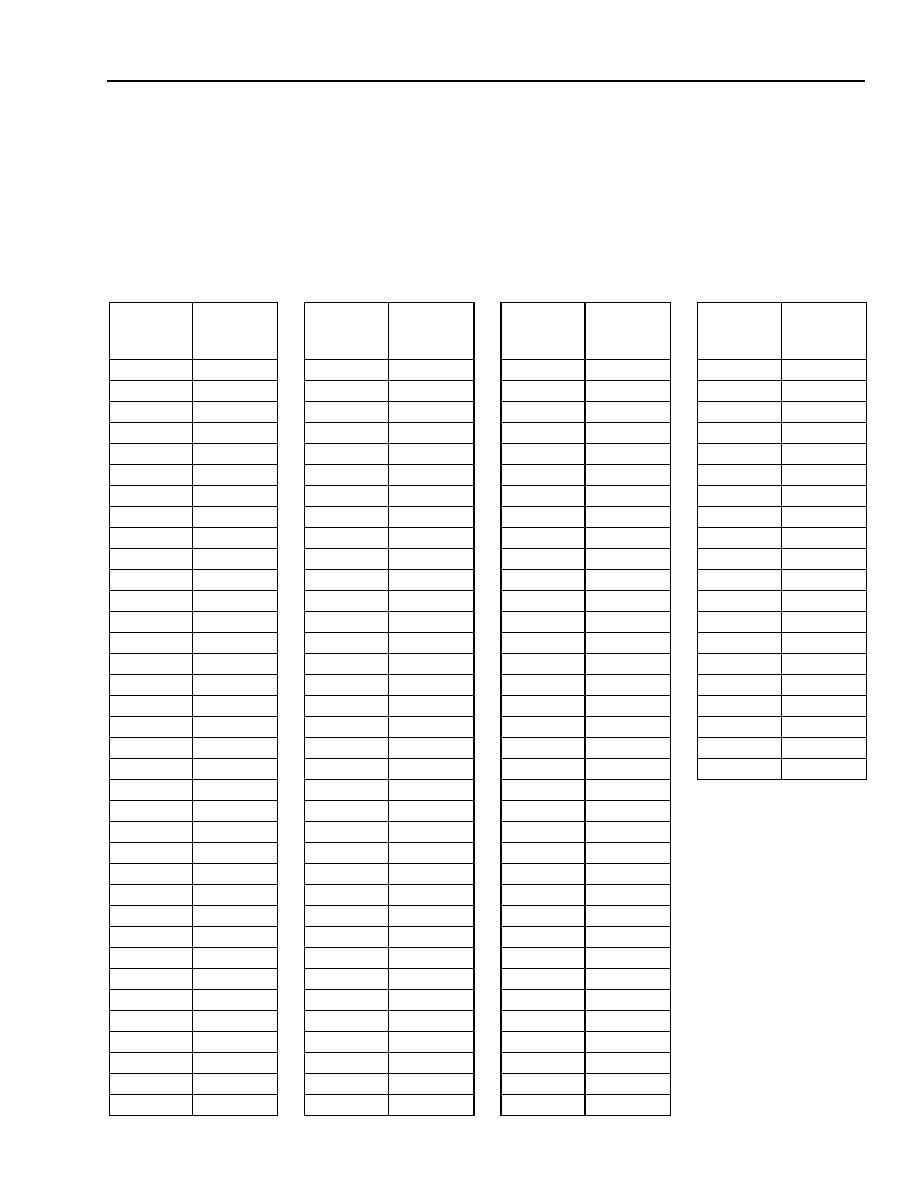

- Table 22. Function Name to Symbol and Register Address Index

- Table 23. Symbol to Register Address and Function Name Index

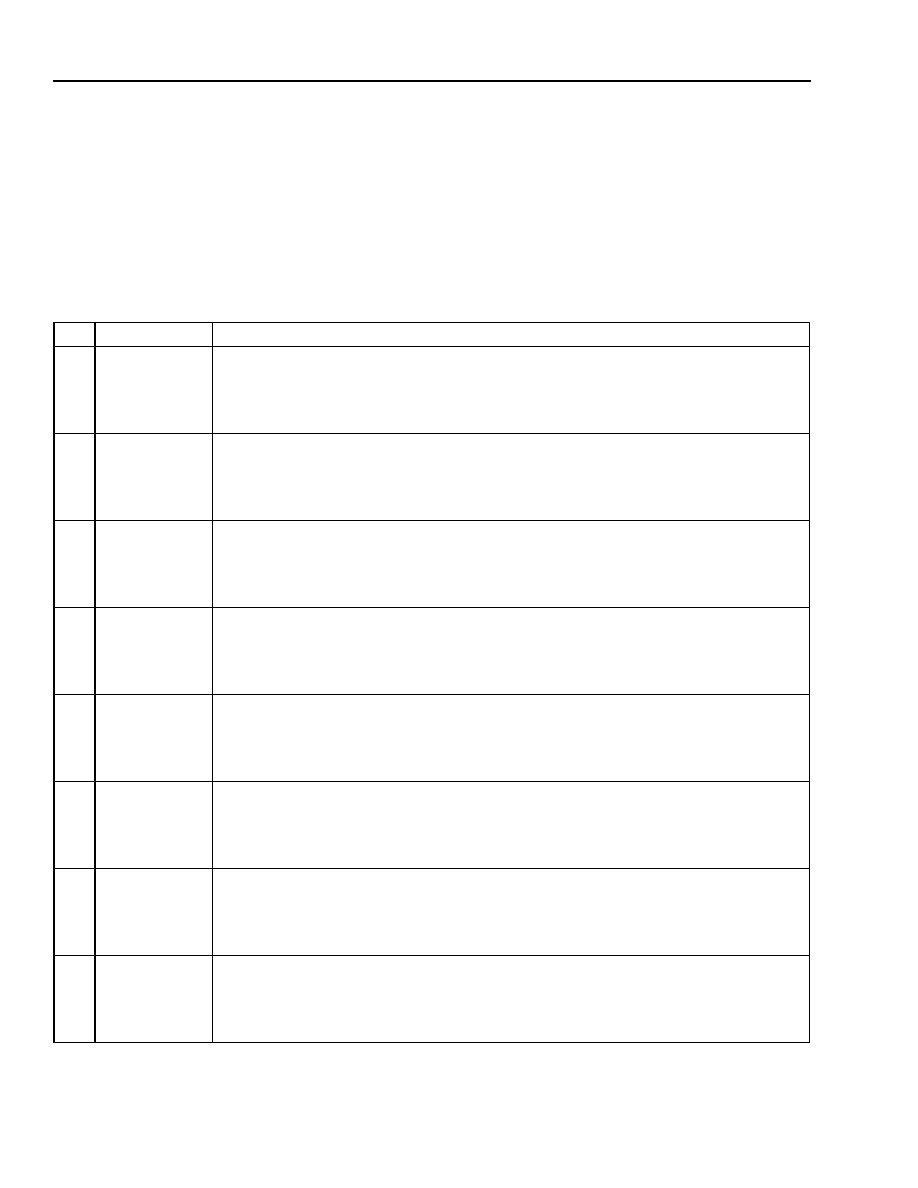

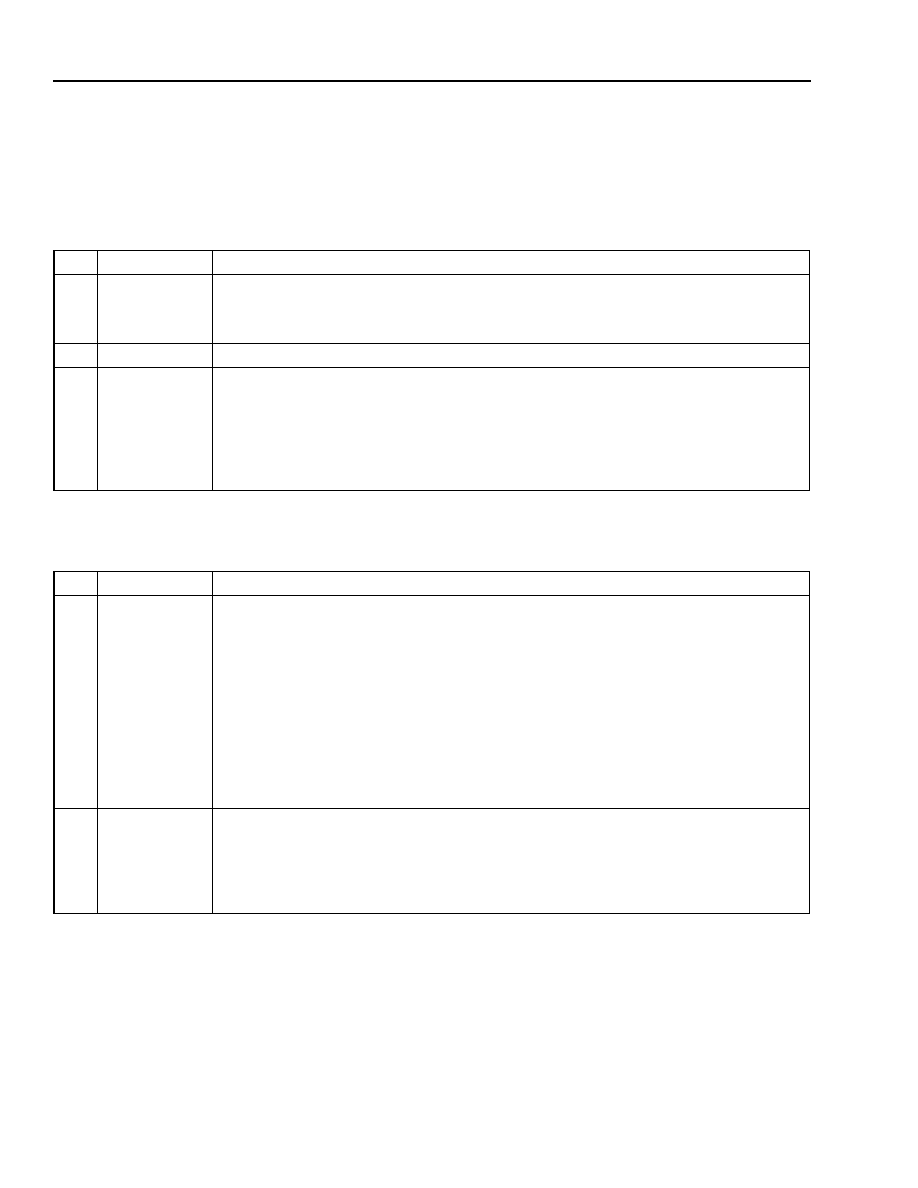

- Table 24. Per-Channel Control Parameters

- Table 25. Tone Disabler Masks 1 Register (020) [00]

- Table 26. Tone Disabler Masks 2 Register (021) [02]

- Table 27. Nonlinear Processor (NLP) Control Masks Register (022) [41]

- Table 28. H-Register Control Options (023) [80]

- Table 29. Leak Control Register (024) [A1]

- Table 30. Filter and Tone Detector 2 Controls Register (025) [0C]

- Table 31. Far-End Speech Threshold 1 Register (026) [9B]

- Table 32. Far-End Speech Threshold 2 Register (027) [02]

- Table 33. Narrowband Energy Peak Factor Register (028) [18]

- Table 34. Wideband Energy Peak Factor Register (029) [18]

- Table 35. Highway Bit Rate Register (02A) [05]

- Table 36. X Parity Register (02B) [00]

- Table 37. Test 1 Register (02C) [00]

- Table 38. Test 2 Register (02D) [00]

- Table 39. A-Law/µ-Law Linear Conversion Register (02E) [1B for DS1, 09 for E1]

- Table 40. C Port Control Register (02F) [F8]

- Table 41. X-C Bulk Time-Slot Delay Register (030) [19]

- Table 42. Y-E Bulk Time-Slot Delay Register (031) [15]

- Table 43. X Input Format Register (032) [02]

- Table 44. Edge Sampling Register (033) [02]

- Table 45. SRAM Control Register (034) [01]

- Table 46. Y Port Control 1 Register (035) [02]

- Table 47. Y Port Control 2 Register (036) [07 for DS1, 05 for E1]

- Table 48. Y Test Data 1 Register (037) [00]

- Table 49. Y Test Data 2 Register (038) [00]

- Table 50. E and Y EMP Gain Filter Constant Register (039) [80]

- Table 51. E Port Control 1 Register (03A) [F7 for DS1, F6 for E1]

- Table 52. E Port Control 2 Register (03B) [08]

- Table 53. Reserved (03C) [00]

- Table 54. Low-Peak Count Register (03D) [84]

- Table 55. High-Peak Count Register (03E) [E3]

- Table 56. Interval Count Register (03F) [E4]

- Table 57. Good Intervals VPA Register (040) [00]

- Table 58. Good Intervals Declare Register (041) [70]

- Table 59. Phase Reversal Interval Minimum Register (042) [CA]

- Table 60. Phase Reversal Interval Maximum Register (043) [8A]

- Table 61. Tone Detector Declarations Register (044) [AC]

- Table 62. Low Voice Path Assurance (VPA) Count Register (045) [5F]

- Table 63. High VPA Count Register (046) [22]

- Table 64. VPA Power Minimum Register (047) [0C]

- Table 65. Tone Detector Power Minimum Register (048) [0E]

- Table 66. Phase Reversal Interval Maximum Register (049) [4D]

- Table 67. Tone Detector Threshold Register (04A) [90]

- Table 68. Y Energy Threshold Register (04B) [7F]

- Table 69. Noise Matching Enable Register (04C) [20]

- Table 70. Near-End Speech Hangover Register (04D) [F0]

- Table 71. Í Noise Floor Estimate Maximum 1 Register (04E) [1F]

- Table 72. Í Noise Floor Estimate Maximum 2 Register (04F) [00]

- Table 73. Gamma Í Noise Floor Register (050) [02]

- Table 74. Clamp Í Noise Floor 1 Register (051) [FF]

- Table 75. Clamp Í Noise Floor 2 Register (052) [3F]

- Table 76. Noise Floor Estimate High Hysteresis Threshold 1 Register (053) [00]

- Table 77. Variable Loss Noise Matching Select Register (054) [00]

- Table 78. Noise Floor Estimate Low Hysteresis Threshold Register (055) [08]

- Table 79. NLP Freeze, Soft NLP Select Register (056) [80]

- Table 80. Noise Floor Estimate Register (057) [21]

- Table 81. Spectrally Matched Noise Matching Select Register (058) [B0]

- Table 82. Soft NLP Number Interval Time Steps 1 Register (059) [08]

- Table 83. Soft NLP Number Interval Time Steps 2 Register (05A) [00]

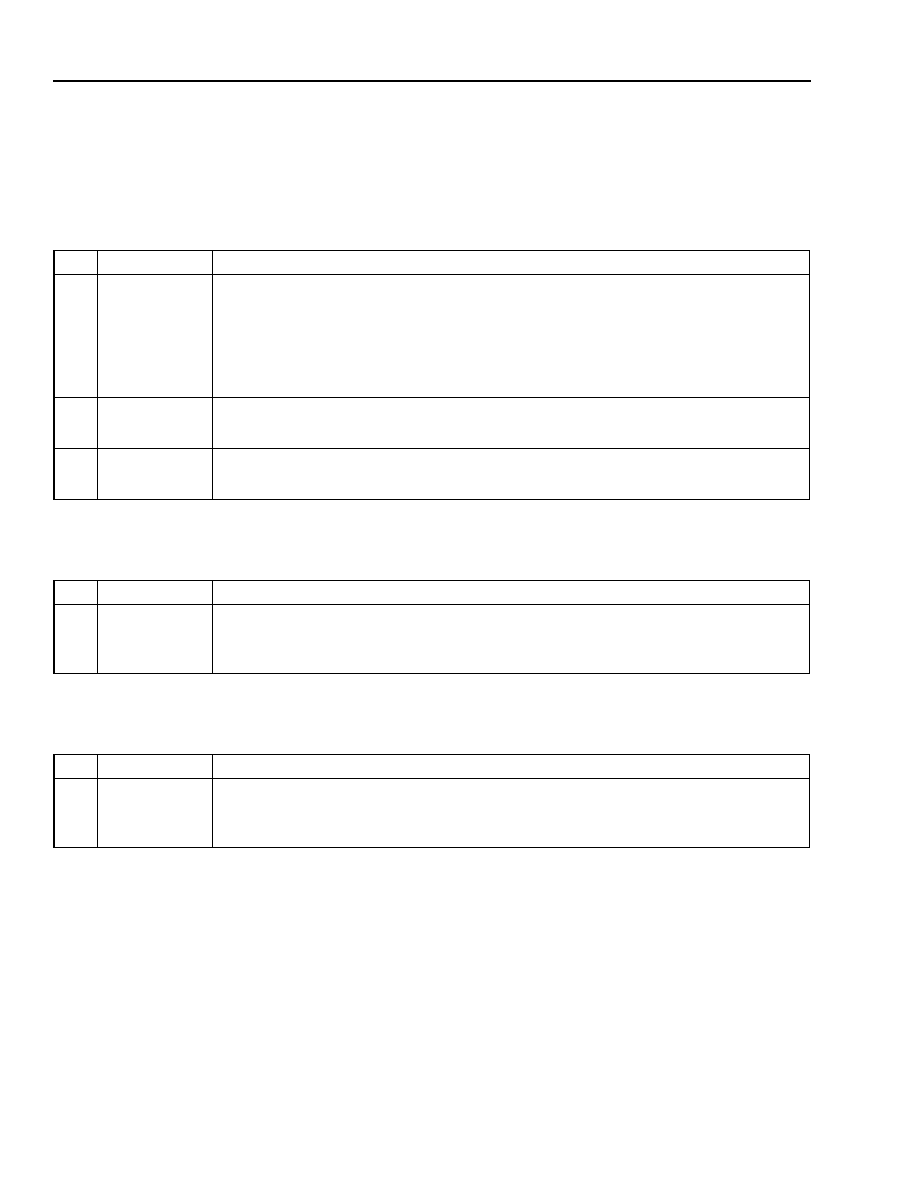

- Table 84. Soft NLP Interval Steps Register (05B) [20]

- Table 85. Loss Increment Attenuated Í 1 Register (05C) [4C]

- Table 86. Loss Increment Attenuated Í 2 Register (05D) [8A]

- Table 87. Í Zero Crossing Threshold Register (05E) [00]

- Table 88. Soft NLP Incremental Loss Factor 1 Register (05F) [00]

- Table 89. Soft NLP Incremental Loss Factor 2 Register (060) [1E]

- Table 90. Reserved Register (061) [00]

- Table 91. State Variable Test 1 Register (062) [00]

- Table 92. State Variable Test 2 Register (063) [00]

- Table 93. State Variable Test 3 Register (064) [00]

- Table 94. Convolution Update Processor Disable Register (065) [00]

- Table 95. Test Control Register (066) [00]

- Table 96. X and Y Loss Pads Register (067) [00]

- Table 97. E and Y Exponentially Mapped (EMP) Filter Time Constant Register (068) [01]

- Table 98. Fast Convergence Register (069) [60]

- Table 99. Slow Convergence Gain Register (06A) [40]

- Table 100. Fast Convergence Beta 1 Register (06B) [12]

- Table 101. Fast Convergence Beta 2 Register (06C) [05]

- Table 102. Slow Convergence Beta 1 Register (06D) [12]

- Table 103. Slow Convergence Beta 2 Register (06E) [05]

- Table 104. Fast Convergence Gain Time Register (06F) [20]

- Table 105. Fast Convergence NLP Beta Time Register (070) [20]

- Table 106. Alpha Voice Hybrid Return Loss Threshold (071) [40]

- Table 107. Echo Cancellation Convergence Register (072) [05]

- Table 108. Alpha Data Hybrid Return Loss Threshold Register (073) [40]

- Table 109. Near-End Speech 1 Hangover Register (074) [FF]

- Table 110. NLP Hangover Register (075) [10]

- Table 111. Near-End Speech 3 Hangover Register (076) [00]

- Table 112. Fast Convergence Threshold Register (077) [AA]

- Table 113. Transient NLP Threshold Register (078) [00]

- Table 114. H-Reset Threshold Register (079) [00]

- Table 115. Near-End Speech Compare Threshold Register (07A) [00]

- Table 116. Test Channel Offset Register (07B) [03]

- Table 117. NLP Operate Time Double Register (07C) [A3]

- Table 118. High-Side 2100 Hz Peak Count Register (07D) [A4]

- Table 119. Enable Í Threshold Register (07E) [18]

- Table 120. Enable Í Threshold Register (07F) [C0]

- Table 121. Error Indicators 1 Register (100)

- Table 122. Interupt Masks 1 Register (101)

- Table 123. Error Indicators 2 Register (102)

- Table 124. Interrupt Masks 2 Register (103)

- Table 125. C Test Data Register (104)

- Table 126. E Test Data Bits [7:0] Register (105)

- Table 127. E Test Data Bits [15:8] Register (106)

- Table 128. Tone Detector Indicator Registers (107Ñ10E)

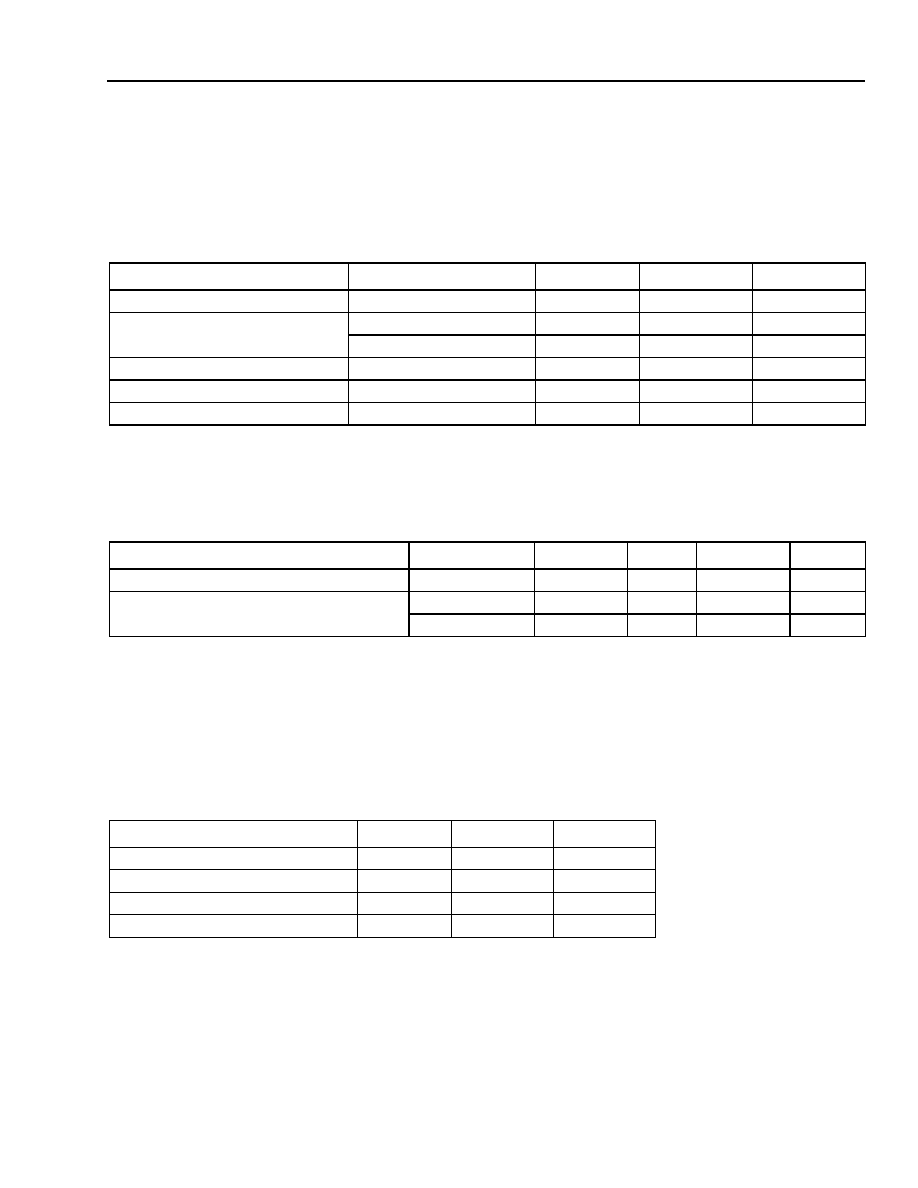

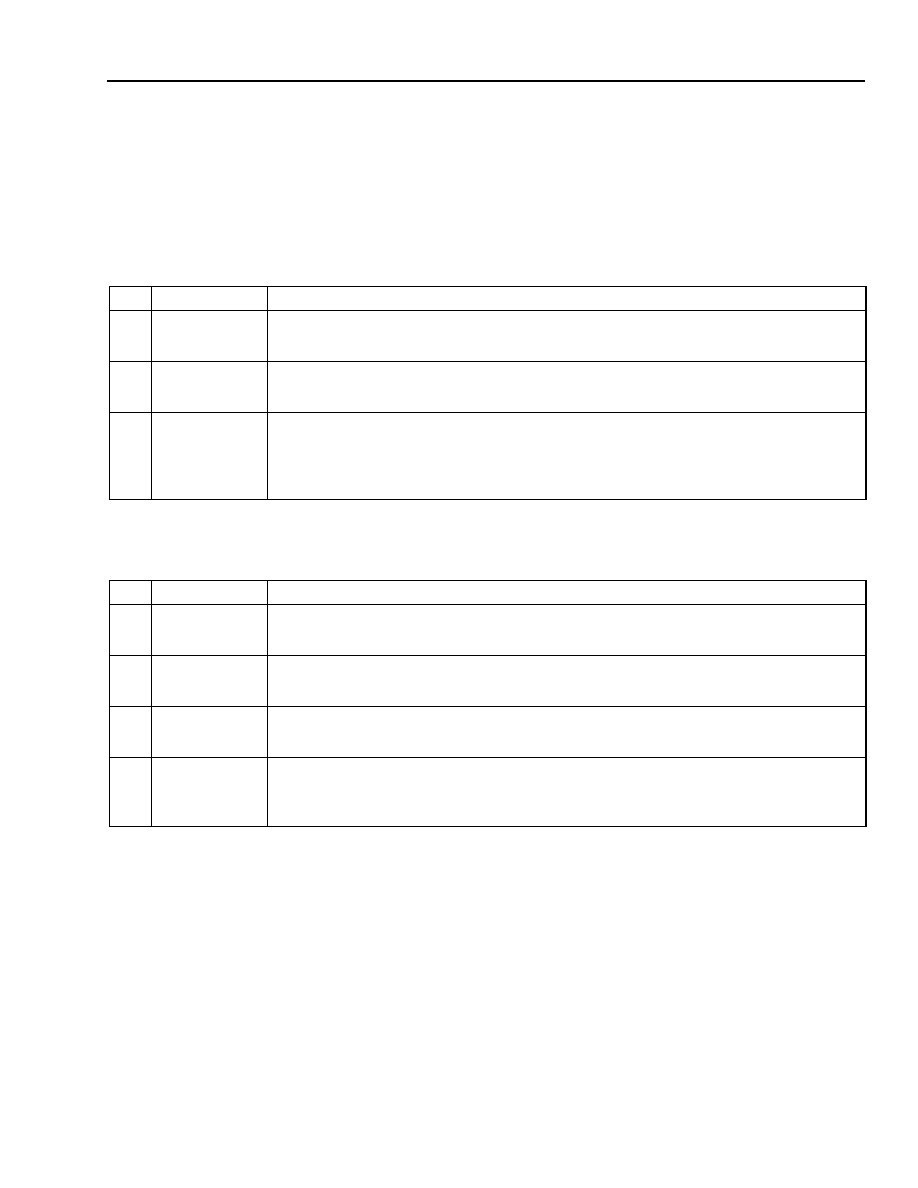

- Table 129. Absolute Maximum Ratings

- Table 130. Recommended Operating Conditions

- Table 131. Input and High-Impedance Leakage Current

- Table 132. Clock Input Specification

- Table 133. Other Input Specifications

- Table 134. Output Signal Specification

- Contact Us

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

Features

Overall Device

s

Dual-convergence voiceband echo canceller (EC).

s

32 independent and individually controlled echo

canceller channels.

s

Stable performance across virtually all network

hybrid conditions.

s

Multiple-channel processing modes:

-- Echo cancelling ON/OFF.

-- µ-law to A-law and A-law to µ-law conversion.

-- 64-clear.

s

Tail-end delay up to 64 ms.

s

Flexible integrated nonlinear processor.

s

Automatic echo path change detection.

s

PCM interface supporting µ-law, A-law, and linear

formats.

s

Two independent tone disablers.

s

Two-band tone detection.

s

Multiple-configuration options for tone disabling:

-- 2100 Hz.

-- 2100 Hz with phase reversal only.

-- 2010 VPA.

-- Dual band.

-- None.

s

Integrated data storage in on-chip SRAM.

s

Integrated PLL for high-speed operations.

s

High-speed microprocessor interface configurable

to operate with most commercial microprocessors.

s

Built-in self-test and boundary scan.

s

IEEE

*1149.1 boundary scan (JTAG).

s

ITU-T G.165, G.168 compliance.

s

Highly provisionable and highly observable.

s

Selectable 3.3 V or 5.0 V tolerant inputs.

s

0 ∞C to 85 ∞C temperature range.

s

Typical power dissipation: 700 mW--900 mW.

s

160-pin, plastic, metric quad flat pack with heat

spreader (MQFPH) package.

*

IEEE

is a registered trademark of The Institute of Electrical and

Electronics Engineers, Inc.

Applications

s

Digital terrestrial communication networks

s

Digital wireless communications networks

s

Digital personal communication networks

s

Voiceband telephony

-- Voice calls

-- Low-speed modem calls

-- Voice over Internet

-- Packetized voice (e.g., frame relay, ATM)

s

Centralized applications

-- Local exchange (LEC) office

-- Interexchange (IEC) office

-- Mobile telephone switching office (MTSO)

-- Base-station controllers

-- Packetized voice equipment

Description

The TECO3264 32-channel echo canceller (EC)

device is a 3.3 V, CMOS, very large-scale integration

(VLSI) component offering 32 independent channels

of echo cancellation. Packaged in a 160-pin, plastic,

metric quad flat pack with heat speader (MQFPH)

and handling up to 64 ms of tail-end delay, this

device combines high performance, high channel

density, low power dissipation, high flexibility, excel-

lent maintenance capability, and low cost into a sin-

gle package.

The TECO3264 32-channel echo canceller provides

echo cancellation for both T1 and E1 systems. The

device operates from a single 3.3 V supply and

requires only an external 8.192 MHz clock and 8 kHz

frame sync.

Built-in self-test logic affords easy device verification

while integrated boundary-scan capability reduces

board verification time and cost.

A high-speed microprocessor interface and full user

provisionability on device pins provide maximum flex-

ibility.

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

2

Lucent Technologies Inc.

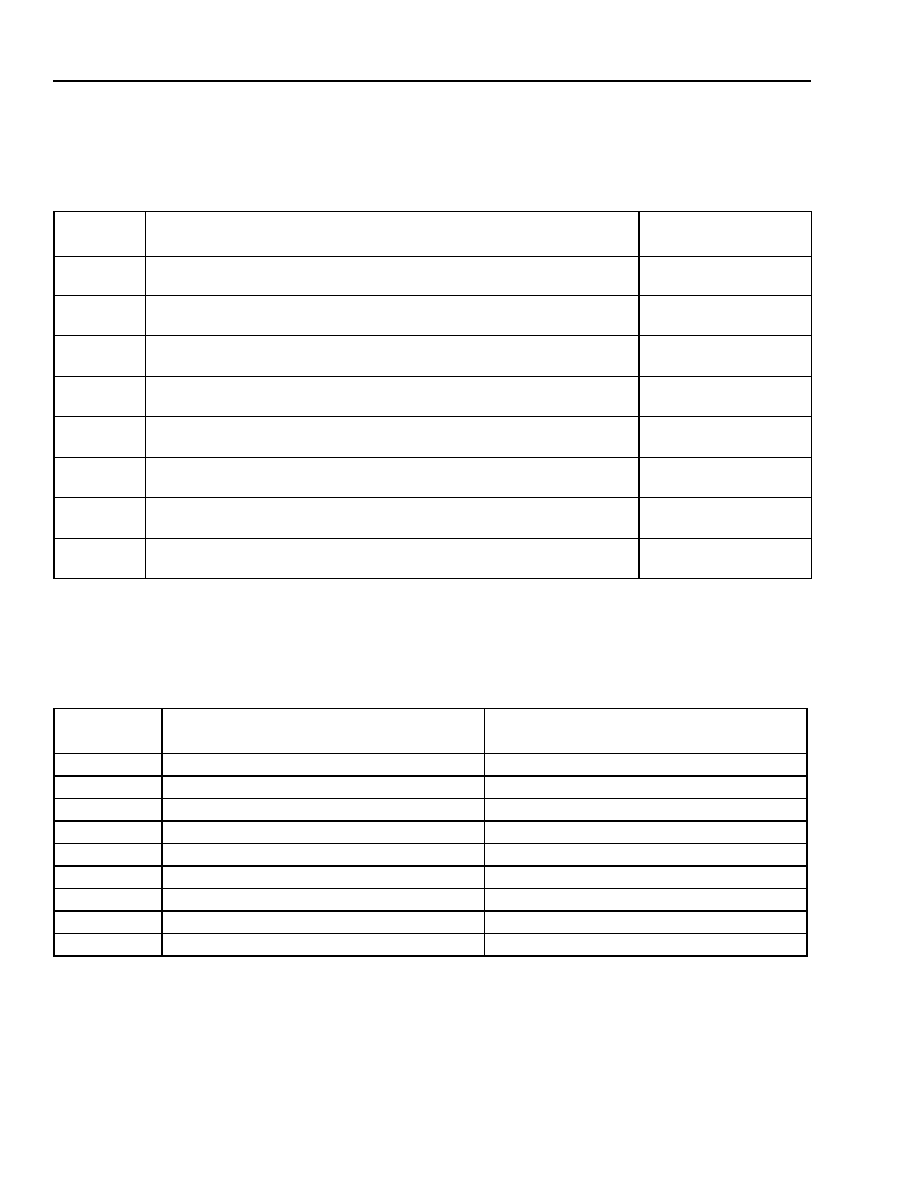

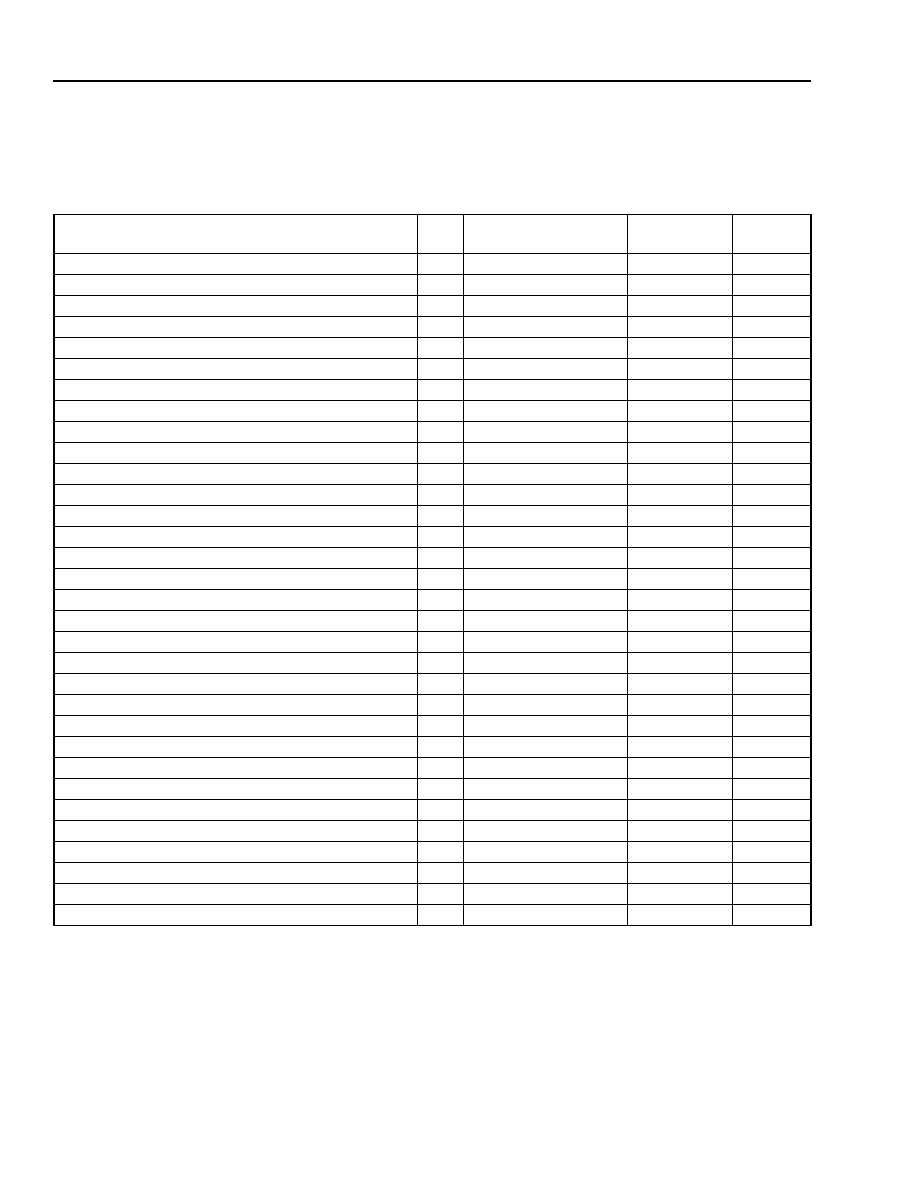

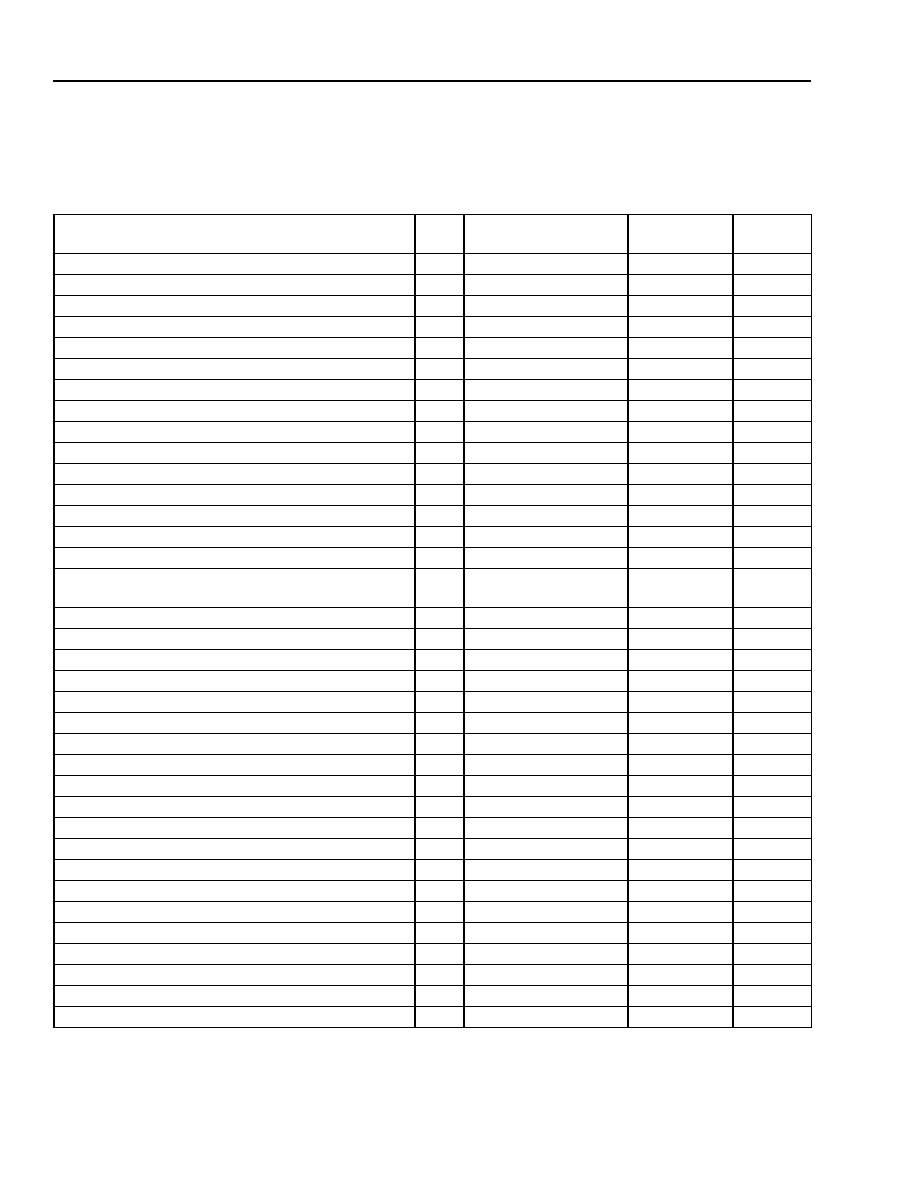

Table of Contents

Contents

Page

Features ................................................................................................................................................................... 1

Overall Device .............................................................................................................................................. 1

Applications .............................................................................................................................................................. 1

Description................................................................................................................................................................ 1

Block Diagram .......................................................................................................................................................... 8

Pin Information ......................................................................................................................................................... 9

Pin Assignment ............................................................................................................................................ 9

Pin Descriptions ......................................................................................................................................... 10

Functional Description ............................................................................................................................................ 13

X(PCM/Linear) Highway Control (XPCM) .................................................................................................. 13

Y(PCM/Linear) Highway Control (YPCM) .................................................................................................. 13

E(PCM/Linear) Highway Control (EPCM) .................................................................................................. 13

Convolution/Update Processor (CUP)........................................................................................................ 13

Nonlinear Processor (NLP) ........................................................................................................................ 13

Tone Disablers (TD1, TD2) ........................................................................................................................ 13

Microprocessor Interface and Control (MPIC)............................................................................................ 13

External Control Connection................................................................................................................................... 14

Microprocessor Interface and Control (MPIC)............................................................................................ 14

Channel Status and Control ....................................................................................................................... 19

PCM Input/Output (I/O) Timing and Register Control................................................................................. 20

H-Register Channel Status......................................................................................................................... 30

Parameters ............................................................................................................................................................. 34

Parameter Overview................................................................................................................................... 34

Per-Channel Control Parameters ............................................................................................................... 34

Mask Bits.................................................................................................................................................... 35

Echo Canceller (EC) Parameters ............................................................................................................... 36

PCM Transmission Parameters ................................................................................................................. 37

Tone Disabler Parameters ......................................................................................................................... 40

Nonlinear Processor Parameters ............................................................................................................... 41

Control Parameters .................................................................................................................................... 42

Test and Diagnostic Parameters ................................................................................................................ 43

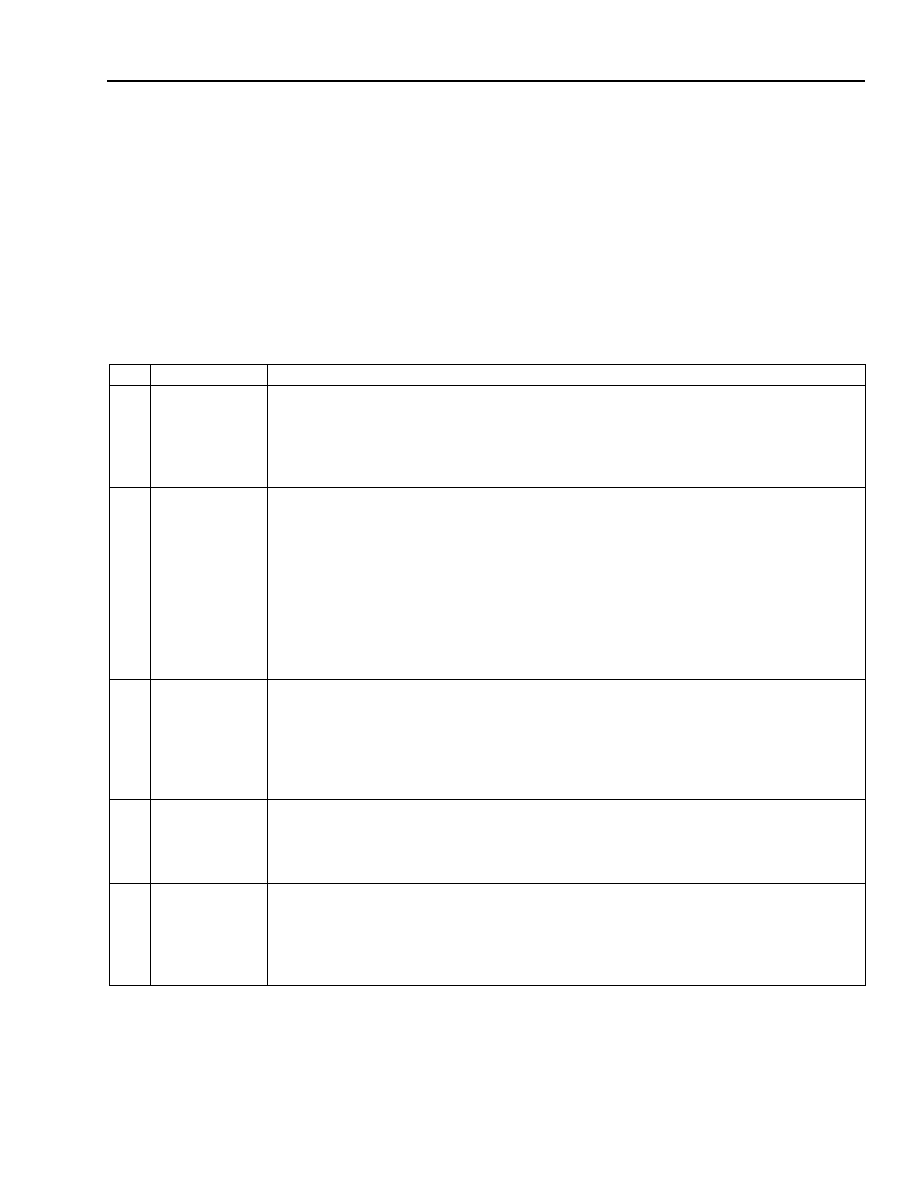

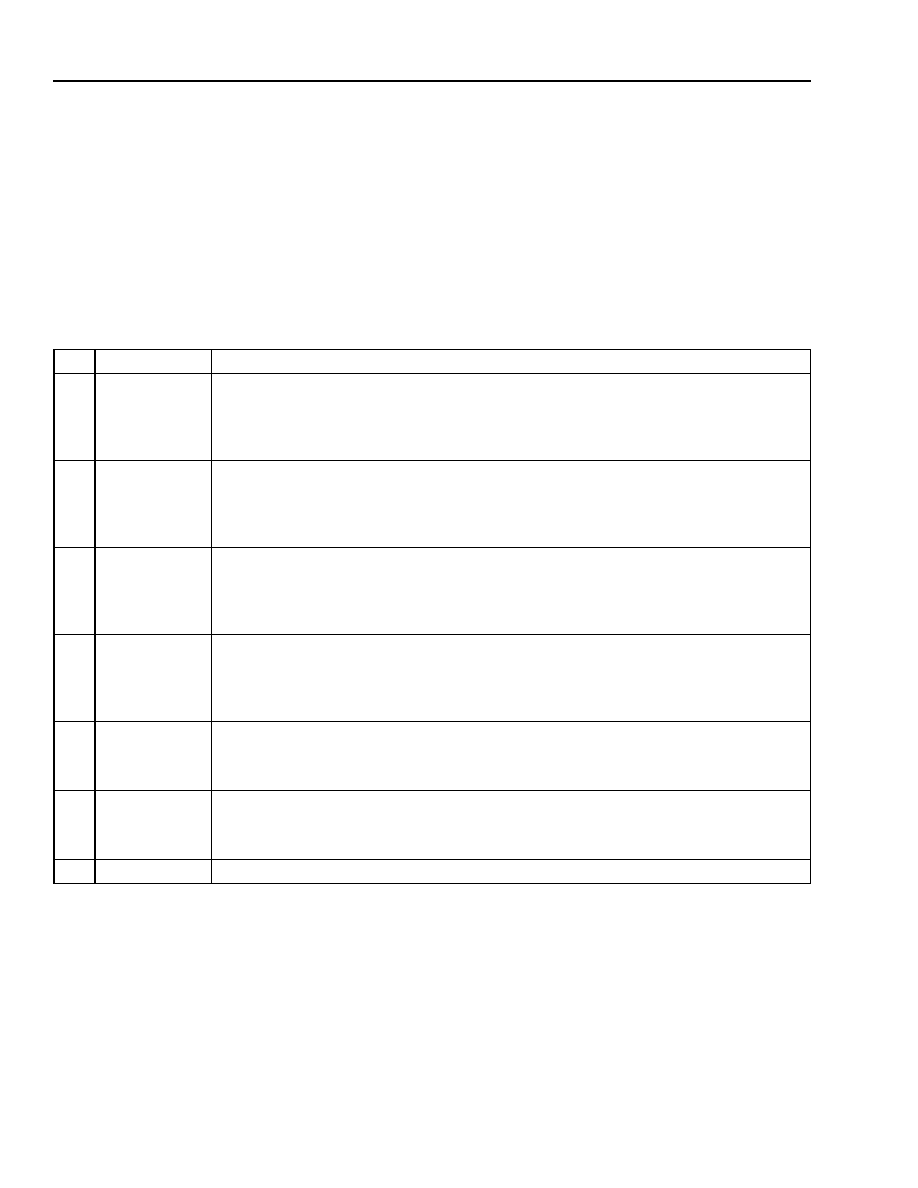

Parameter Map....................................................................................................................................................... 45

Register Architecture .............................................................................................................................................. 48

Register Scopes ......................................................................................................................................... 48

Registers, Functions, Symbols--Information Presentations ...................................................................... 49

Recommended Register Values................................................................................................................. 50

Notation and Format: Bits per Parameter and Bits in Registers................................................................. 50

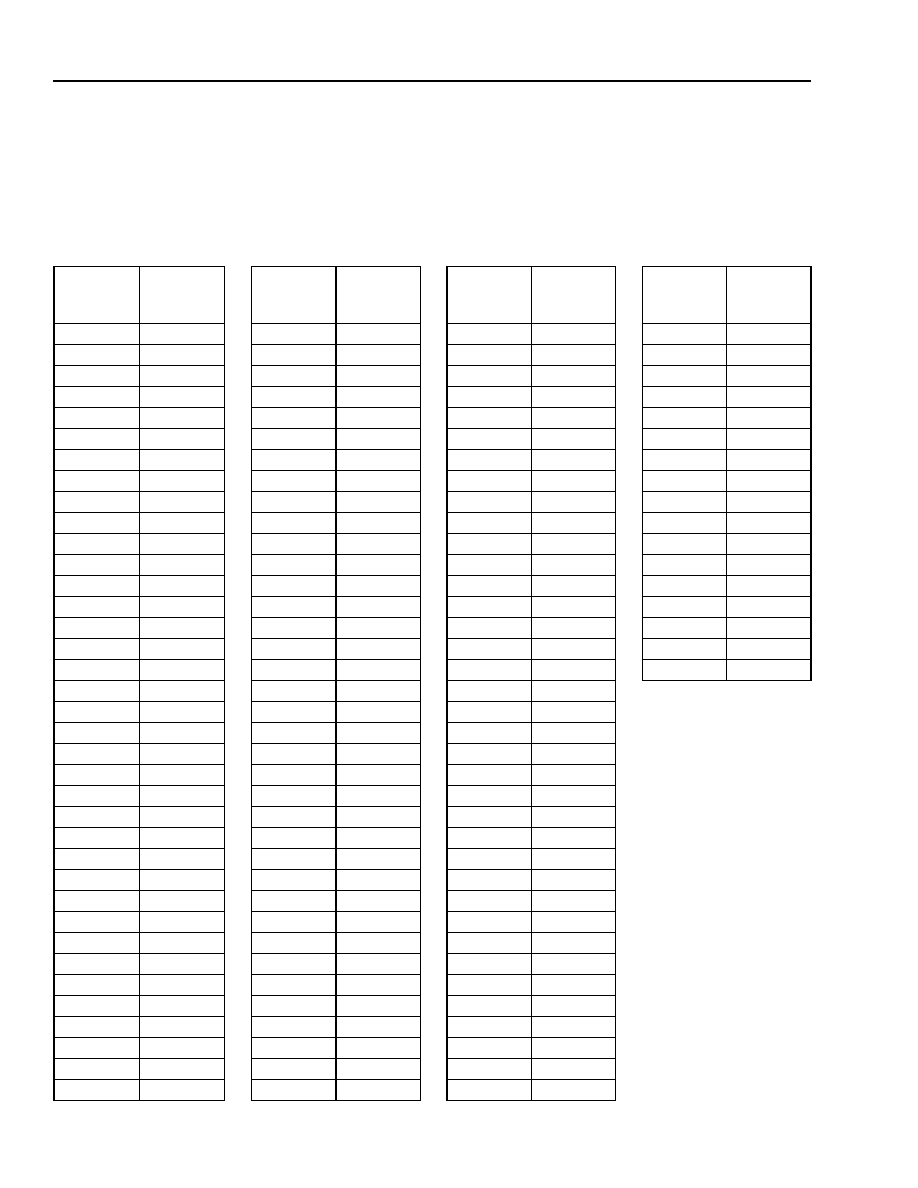

Recommended Register Values for DS1 (µ-Law) ...................................................................................... 51

Recommended Register Values for E1 (A-Law) ........................................................................................ 52

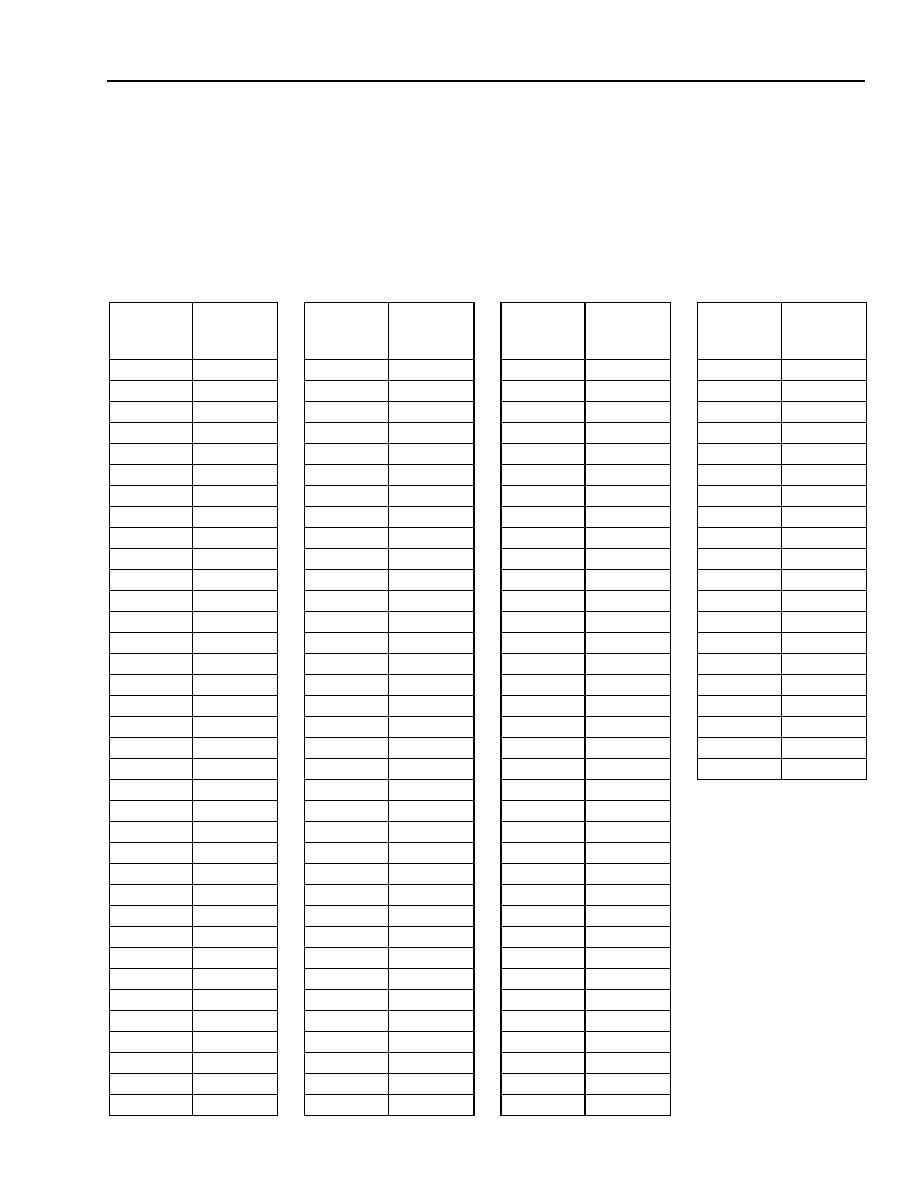

Function Name to Symbol and Register Address Index............................................................................. 53

Symbol to Register Address and Function Name Index............................................................................. 59

Page 0 Read/Write Registers 000--07FE.................................................................................................. 65

Page 1 Read-Only Registers 100--10E................................................................................................... 114

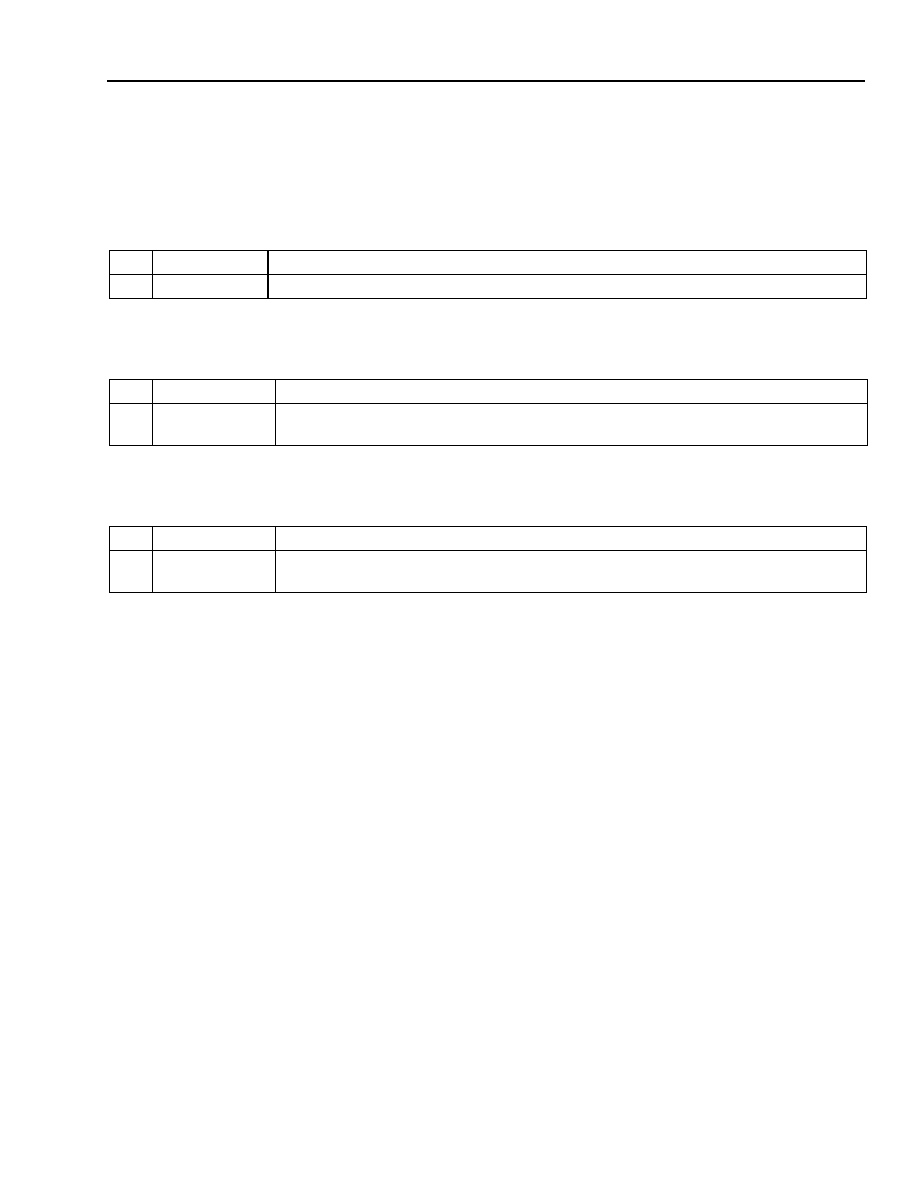

Absolute Maximum Ratings.................................................................................................................................. 119

Recommended Operating Conditions .................................................................................................................. 119

Electrical Characteristics ...................................................................................................................................... 119

Input and High-Impedance Leakage Current ........................................................................................... 119

Clock Input Specifications ........................................................................................................................ 120

Other Input Specifications ........................................................................................................................ 121

Output Signal Specification ...................................................................................................................... 123

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

3

Lucent Technologies Inc.

Table of Contents

(continued)

Contents

Page

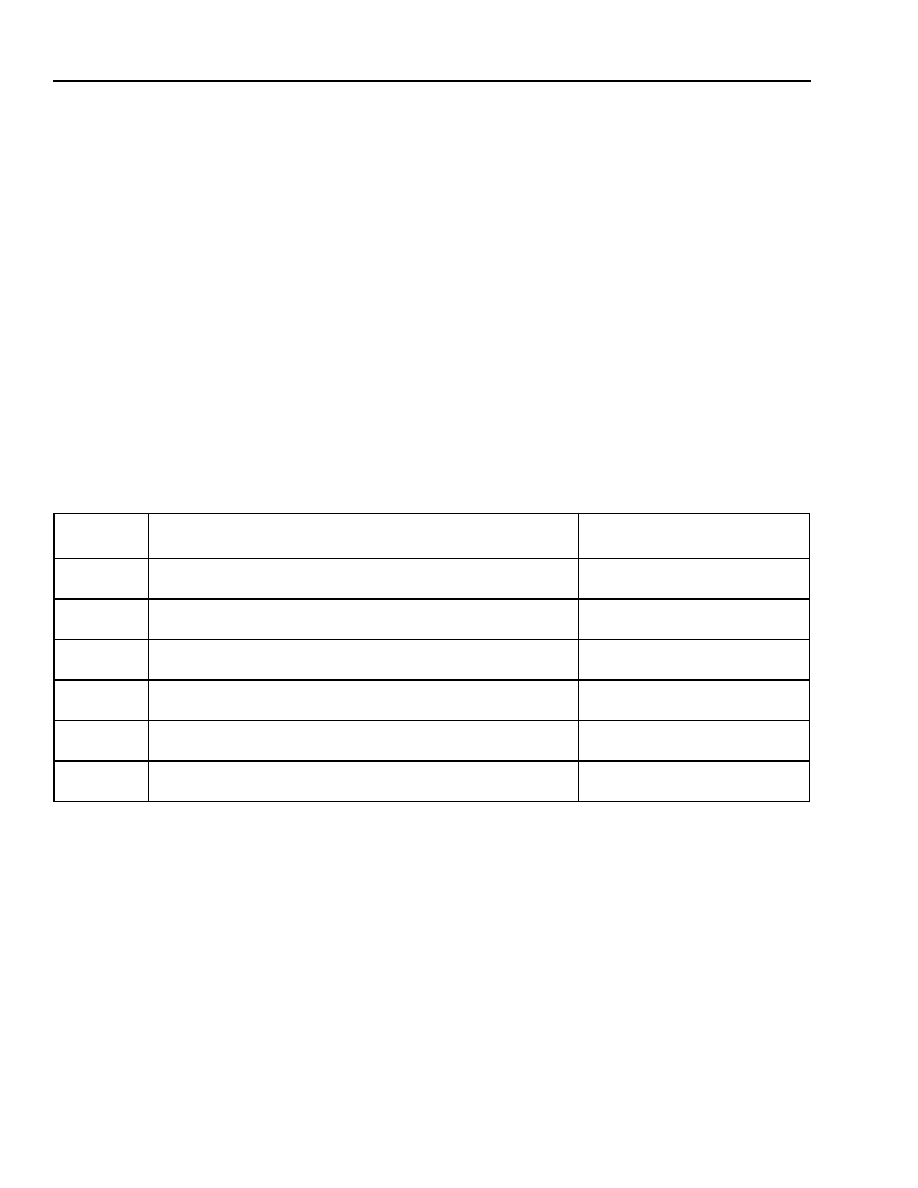

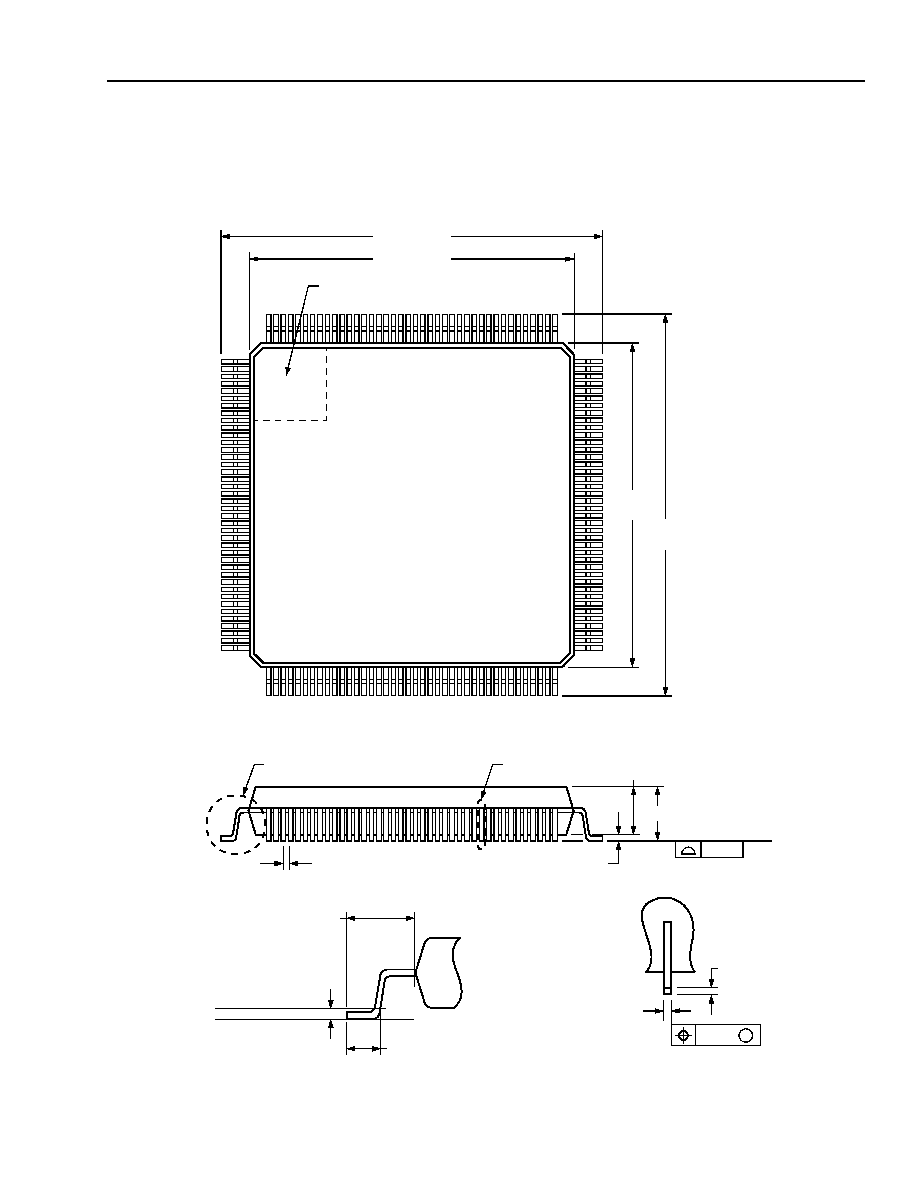

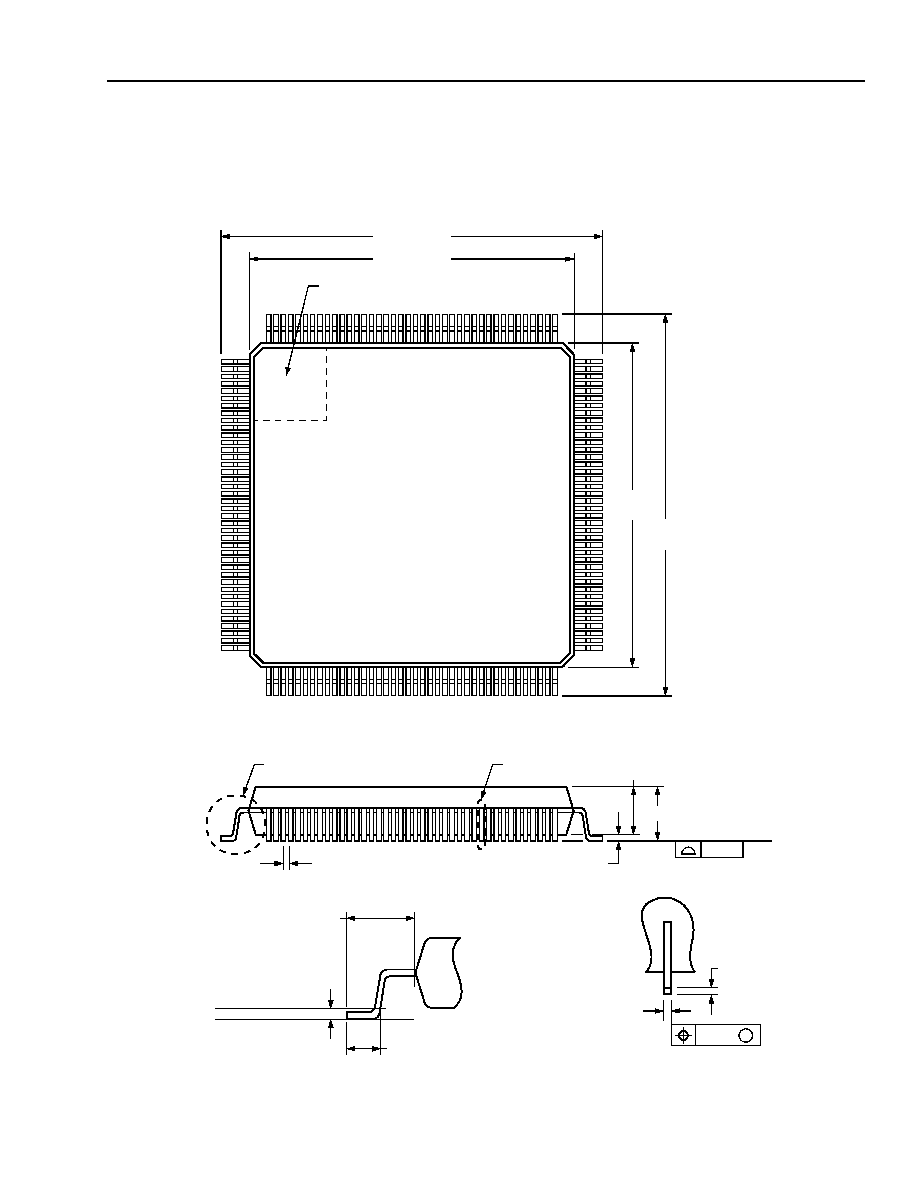

Physical Characteristics ........................................................................................................................................124

Outline Diagram ....................................................................................................................................................125

160-Pin MQFPH........................................................................................................................................125

Ordering Information .............................................................................................................................................126

DS99-241PDH Replaces DS98-409TIC to Incorporate the Following Updates....................................................126

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

4

Lucent Technologies Inc.

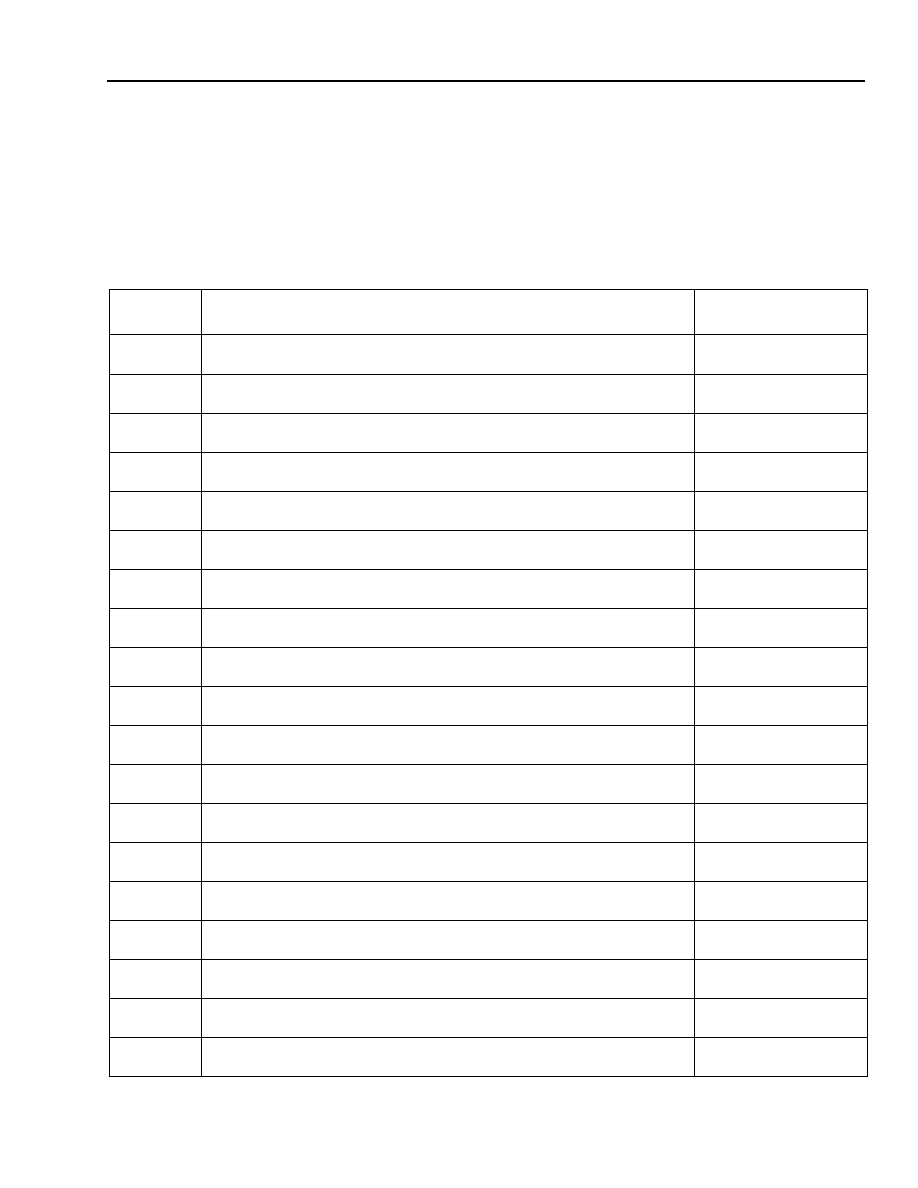

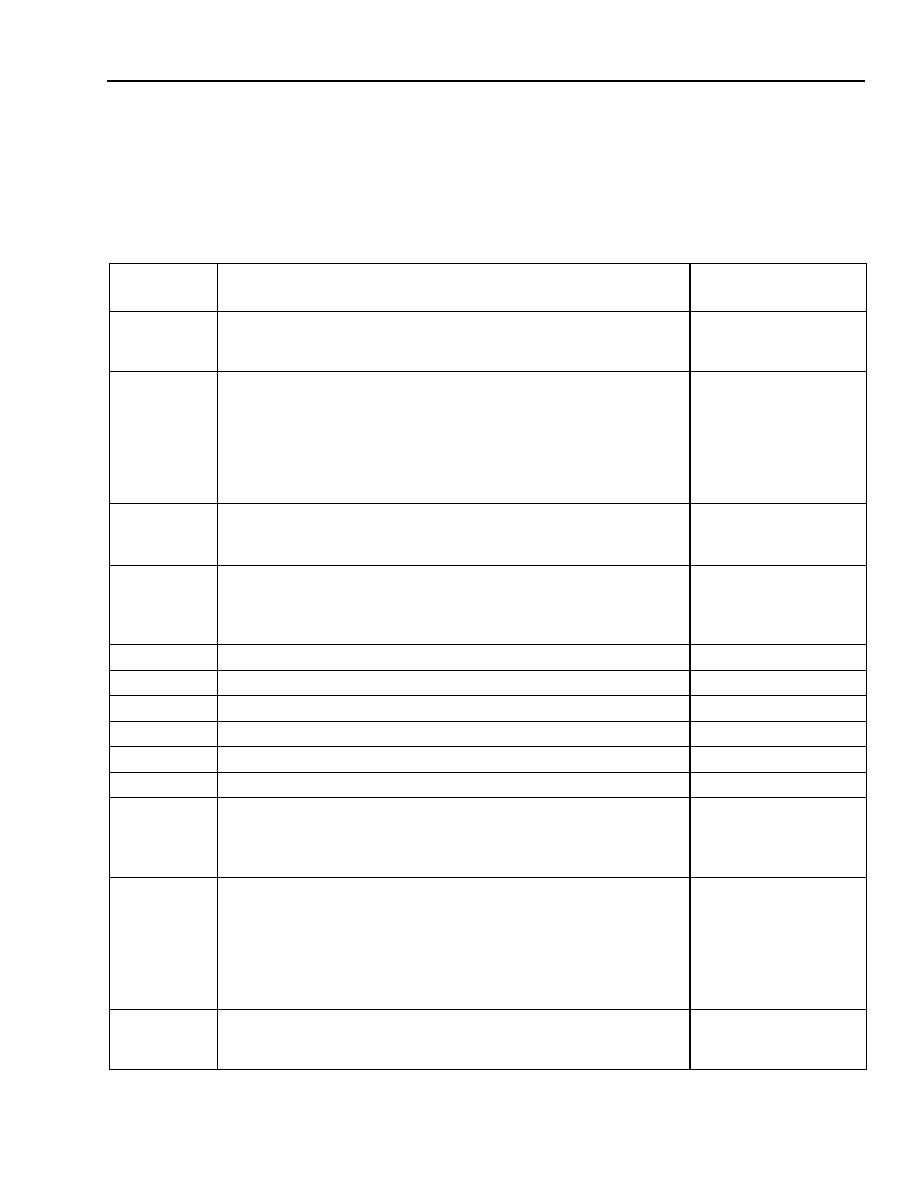

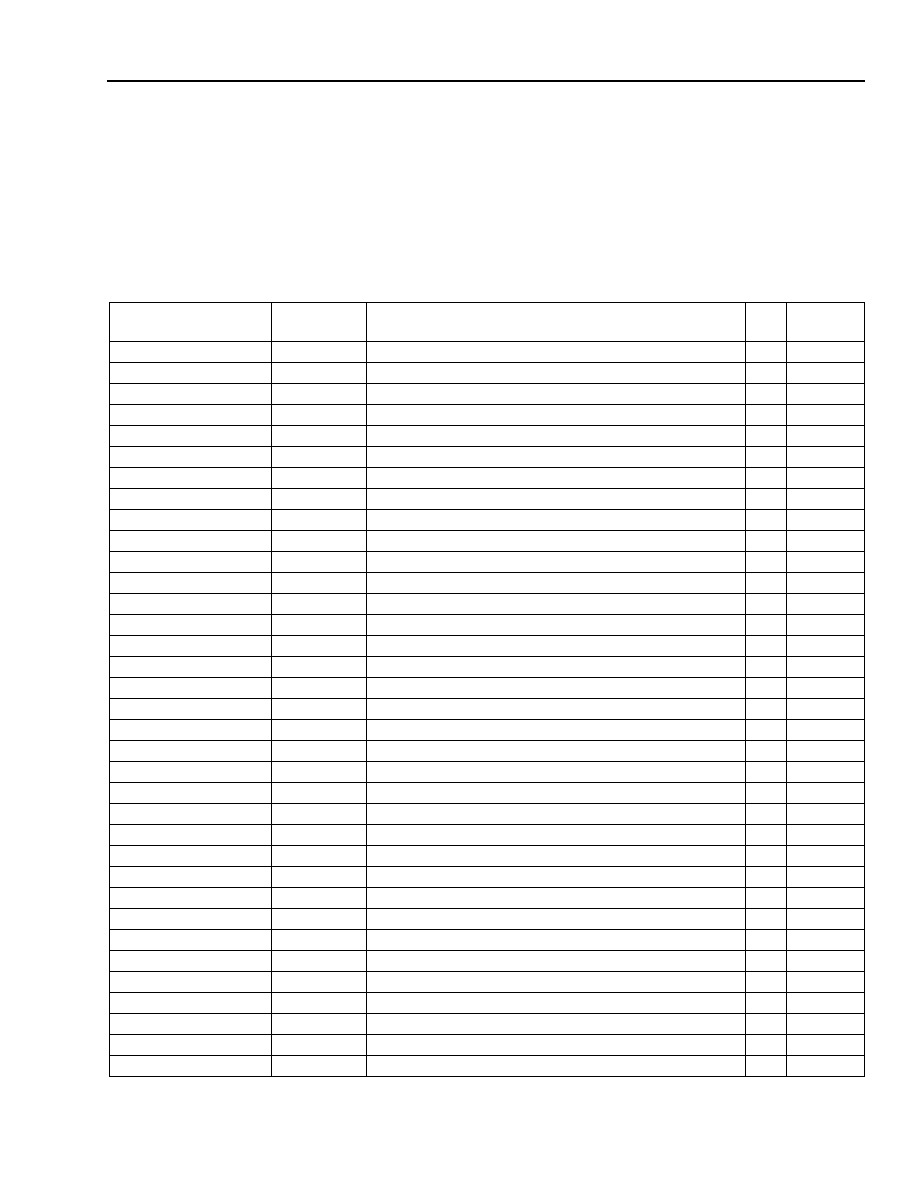

List of Figures

Figures

Page

Figure 1. 32-Channel Echo Canceller Block Diagram .............................................................................................. 8

Figure 2. Pin Assignment ......................................................................................................................................... 9

Figure 3. MPIC Write Cycle (UP_MODE = 1)......................................................................................................... 17

Figure 4. MPIC Read Cycle (UP_MODE = 1) ........................................................................................................ 17

Figure 5. MPIC Write Cycle (UP_MODE = 0)......................................................................................................... 18

Figure 6. MPIC Read Cycle (UP_MODE = 0) ........................................................................................................ 18

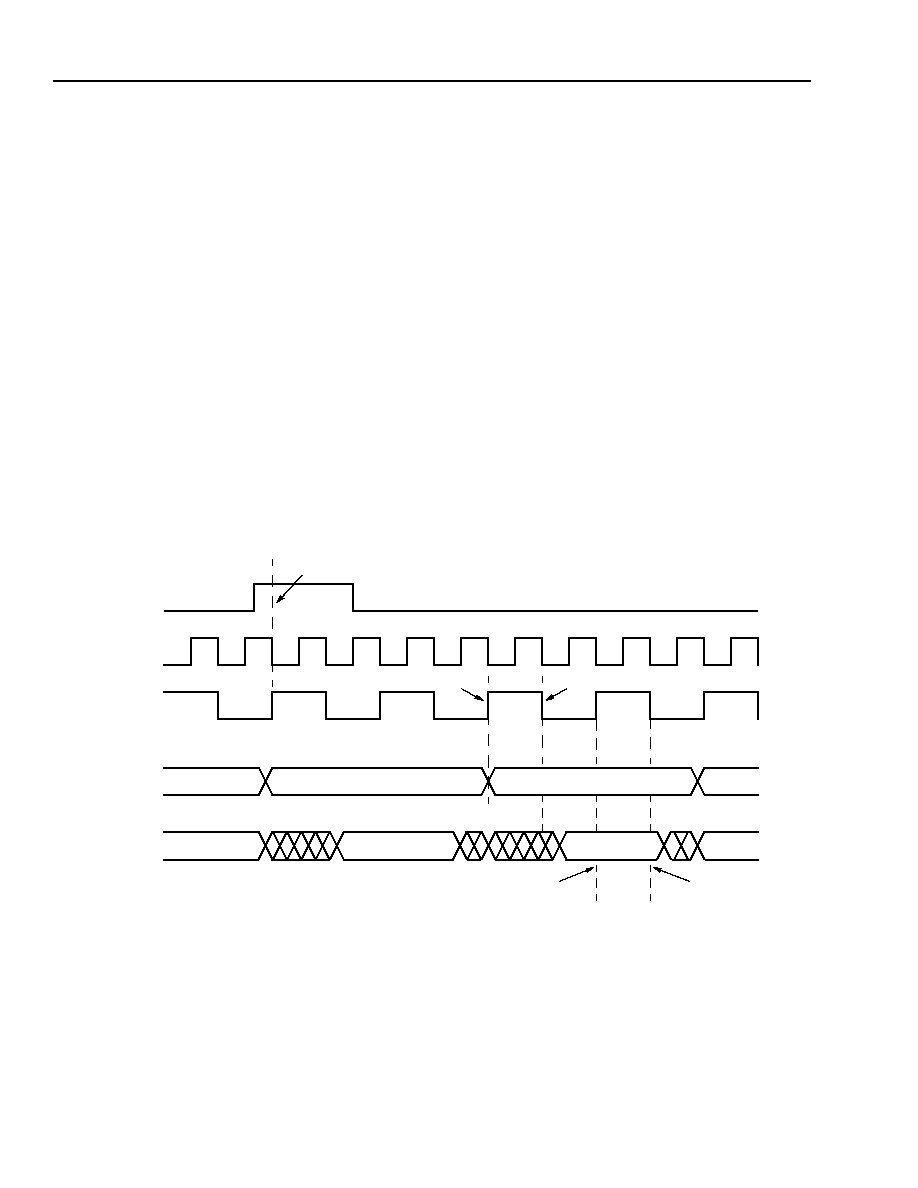

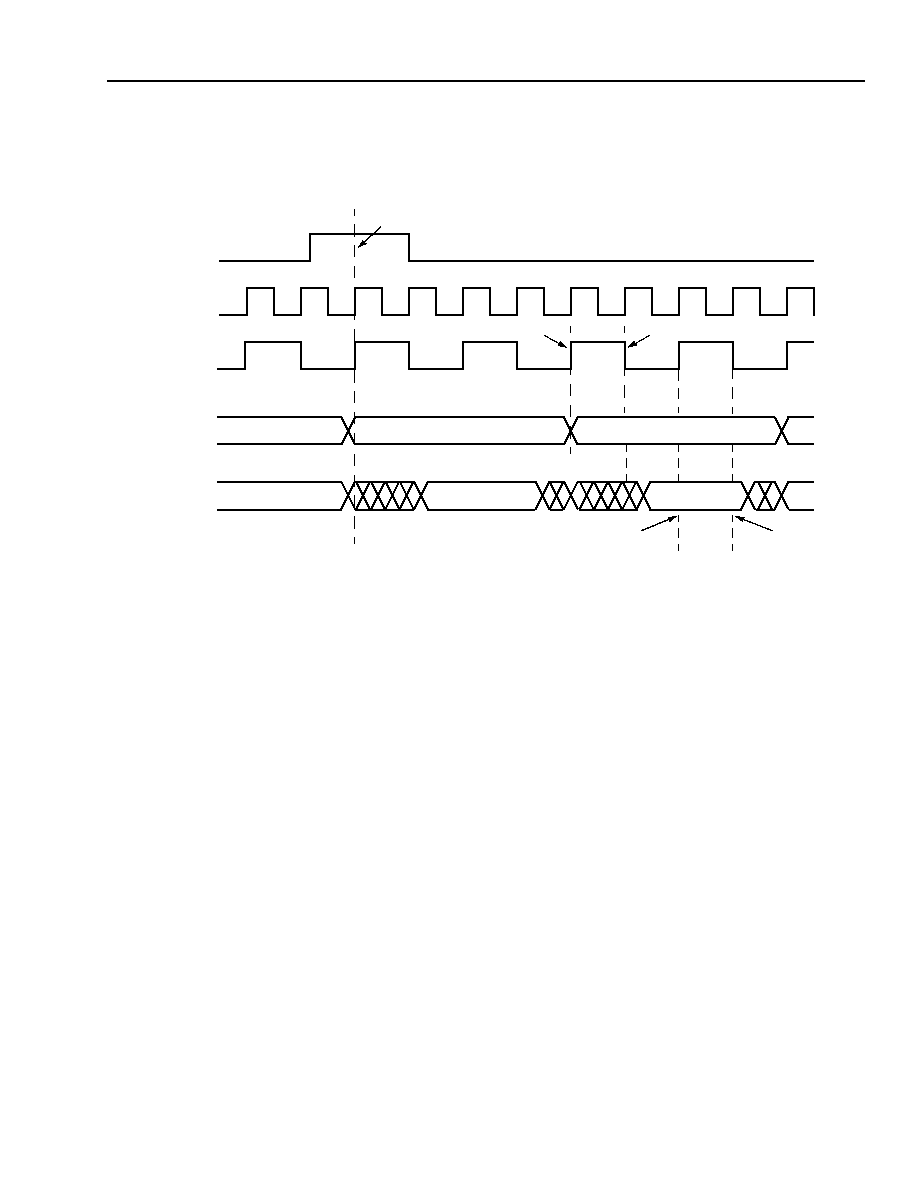

Figure 7. Control and Status Timing....................................................................................................................... 19

Figure 8. SYNC and PCM Timing for DS1 and CEPT Frame ................................................................................ 20

Figure 9. Interface Timing (SYNC, 8 kHz) .............................................................................................................. 21

Figure 10. Interface Timing (CK8M Clock) ............................................................................................................. 21

Figure 11. 4.096 MHz Reference Clock (FE = 0, CK8M Falling Edge) .................................................................. 22

Figure 12. 4.096 MHz Reference Clock (FE = 1, CK8M Rising Edge) ................................................................... 23

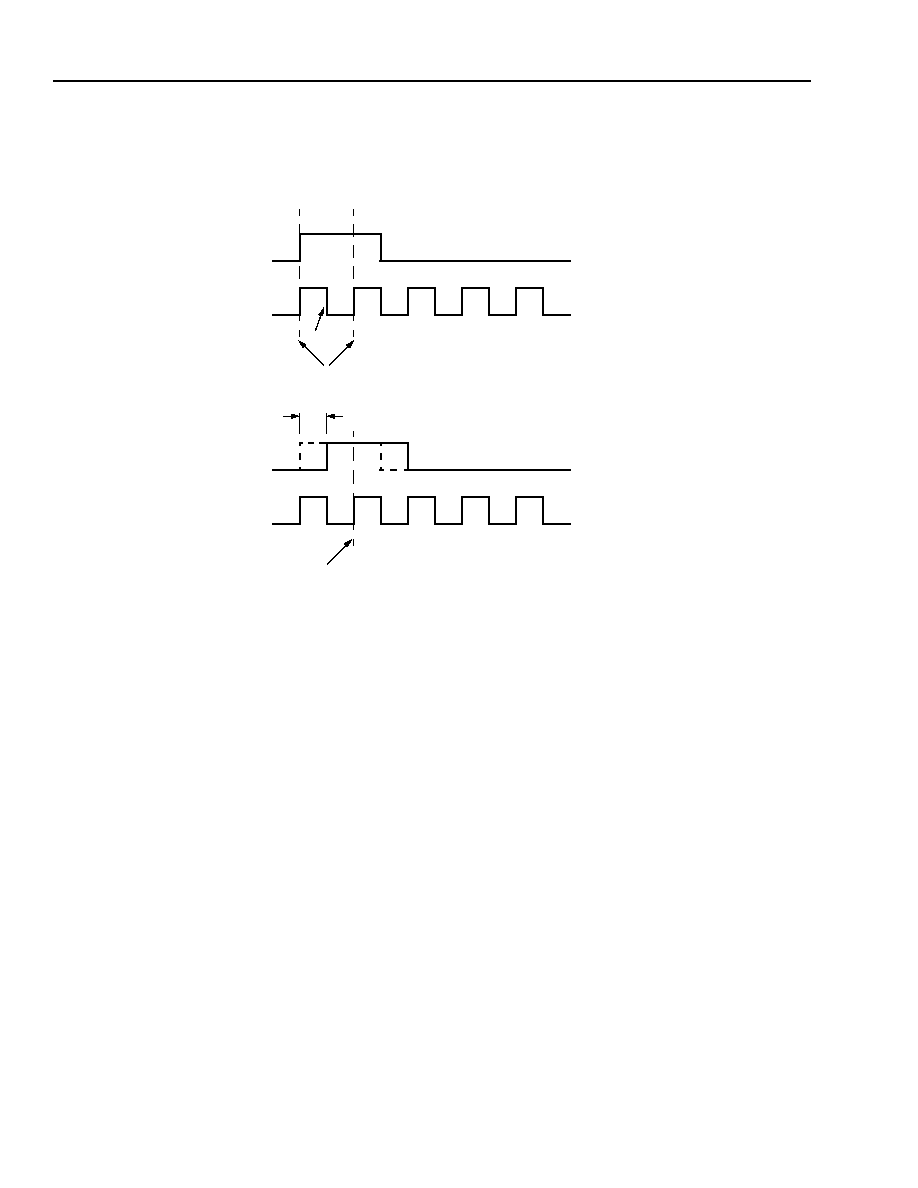

Figure 13. Received and Transmit Offsets Related to Received and Transmit Data ............................................. 25

Figure 14. SYNC Shifted to Edge of CK8M............................................................................................................ 26

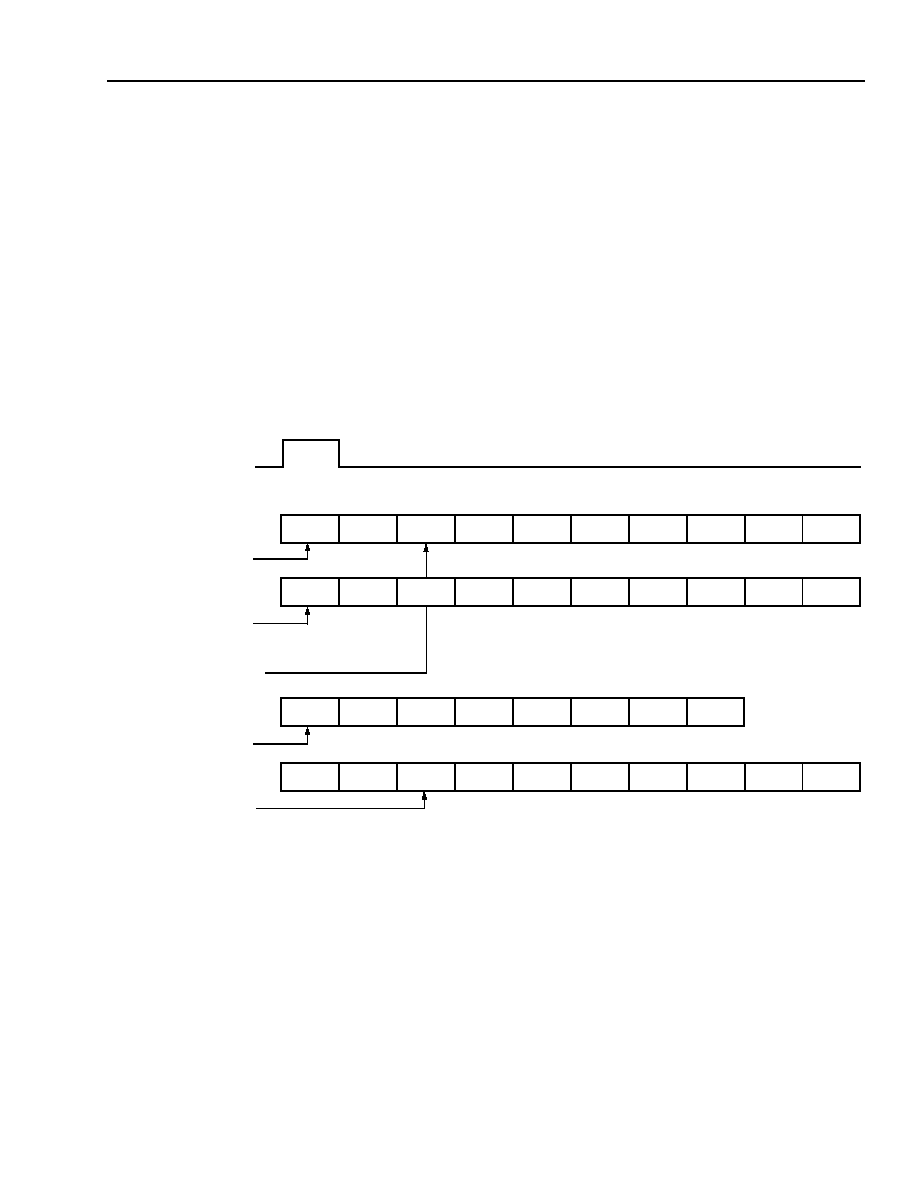

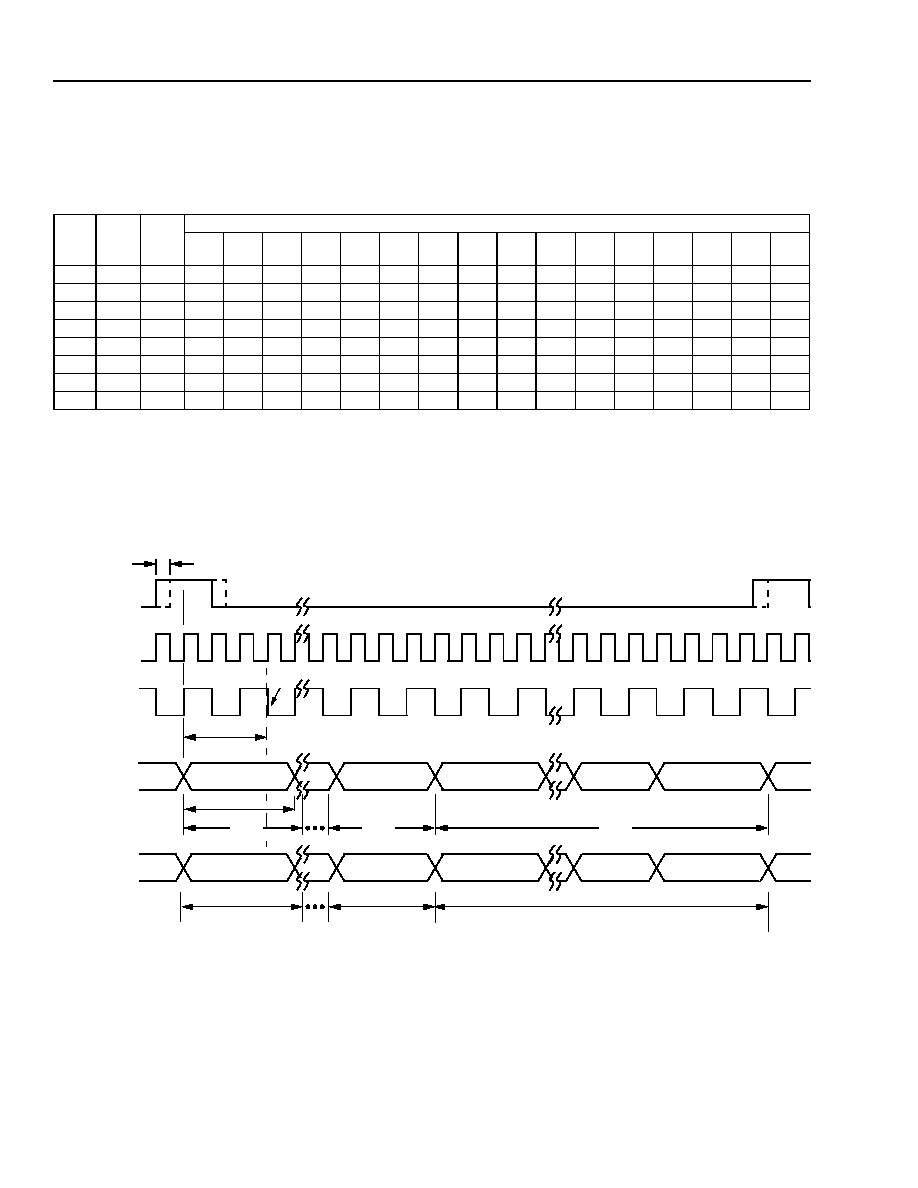

Figure 15. PCM Input/Output Transmission Parameter Settings ........................................................................... 28

Figure 16. HSYNC, Frames, Bits, etc., Relationship .............................................................................................. 30

Figure 17. HSYNC, HDSP Relationship ................................................................................................................. 30

Figure 18. Clock Input Signals.............................................................................................................................. 120

Figure 19. Setup and Hold Times......................................................................................................................... 122

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

5

Lucent Technologies Inc.

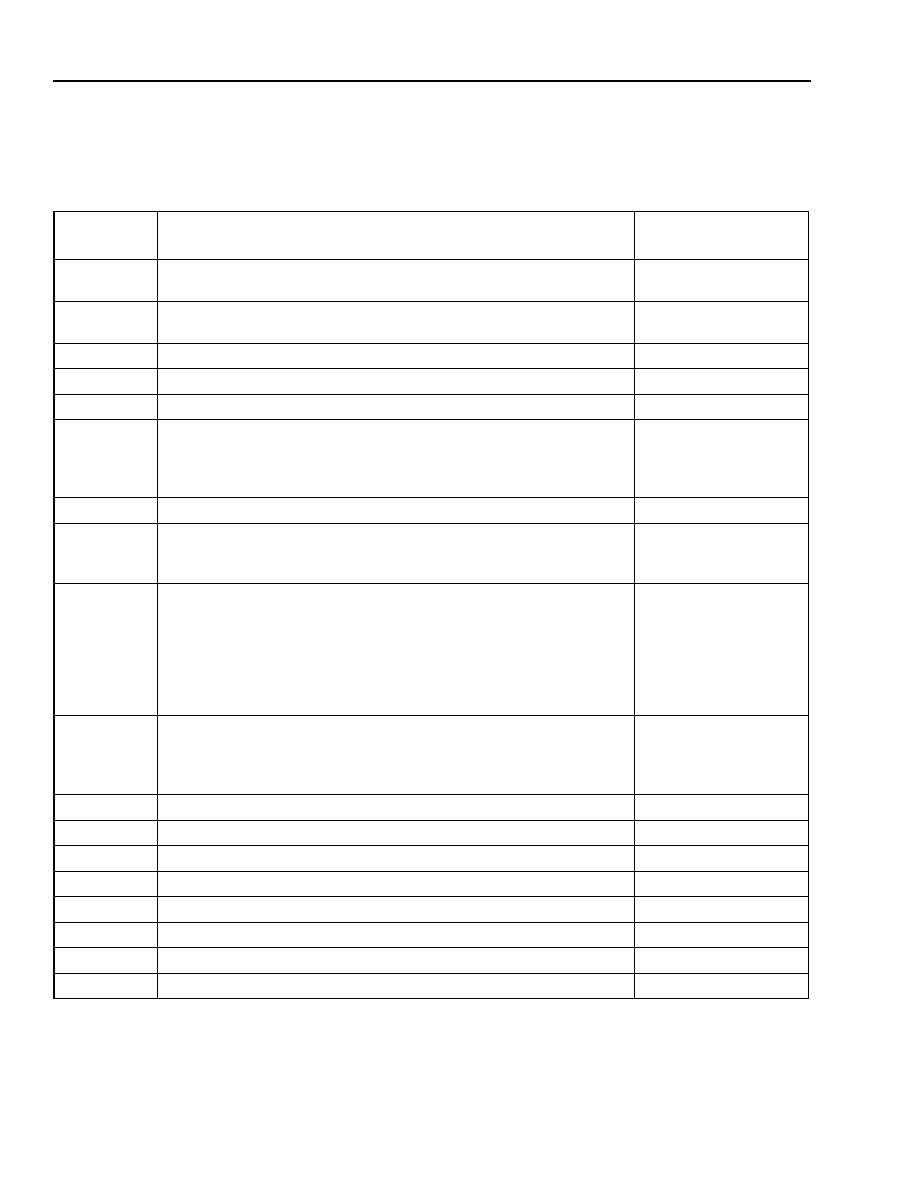

List of Tables

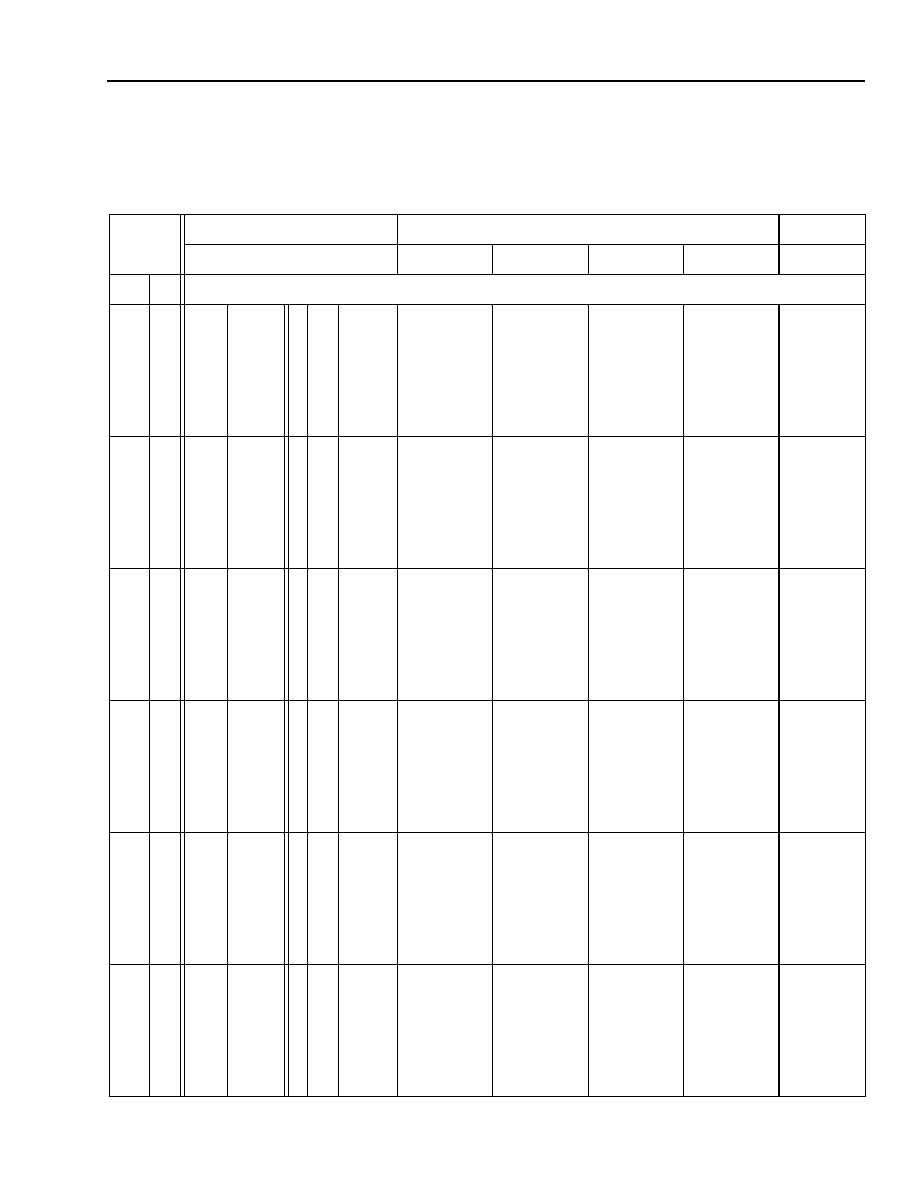

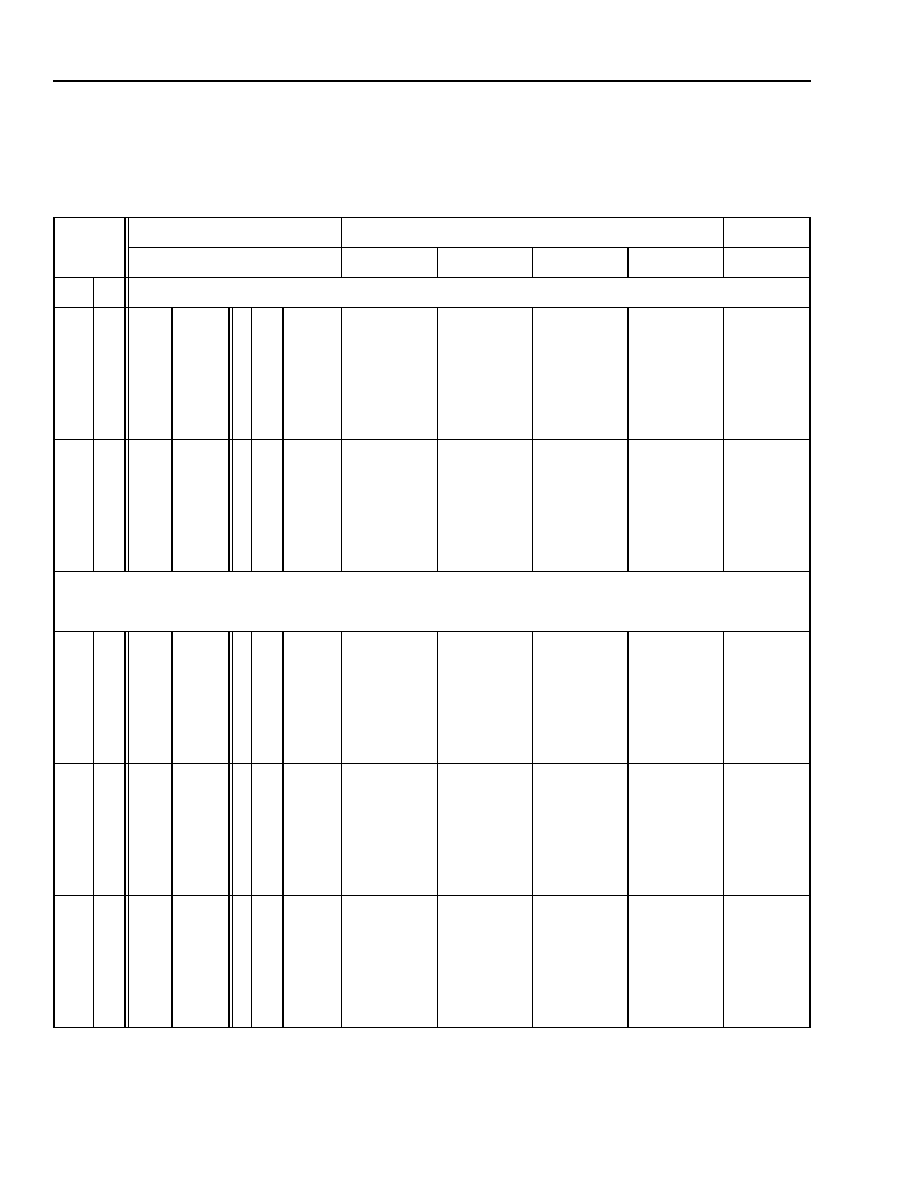

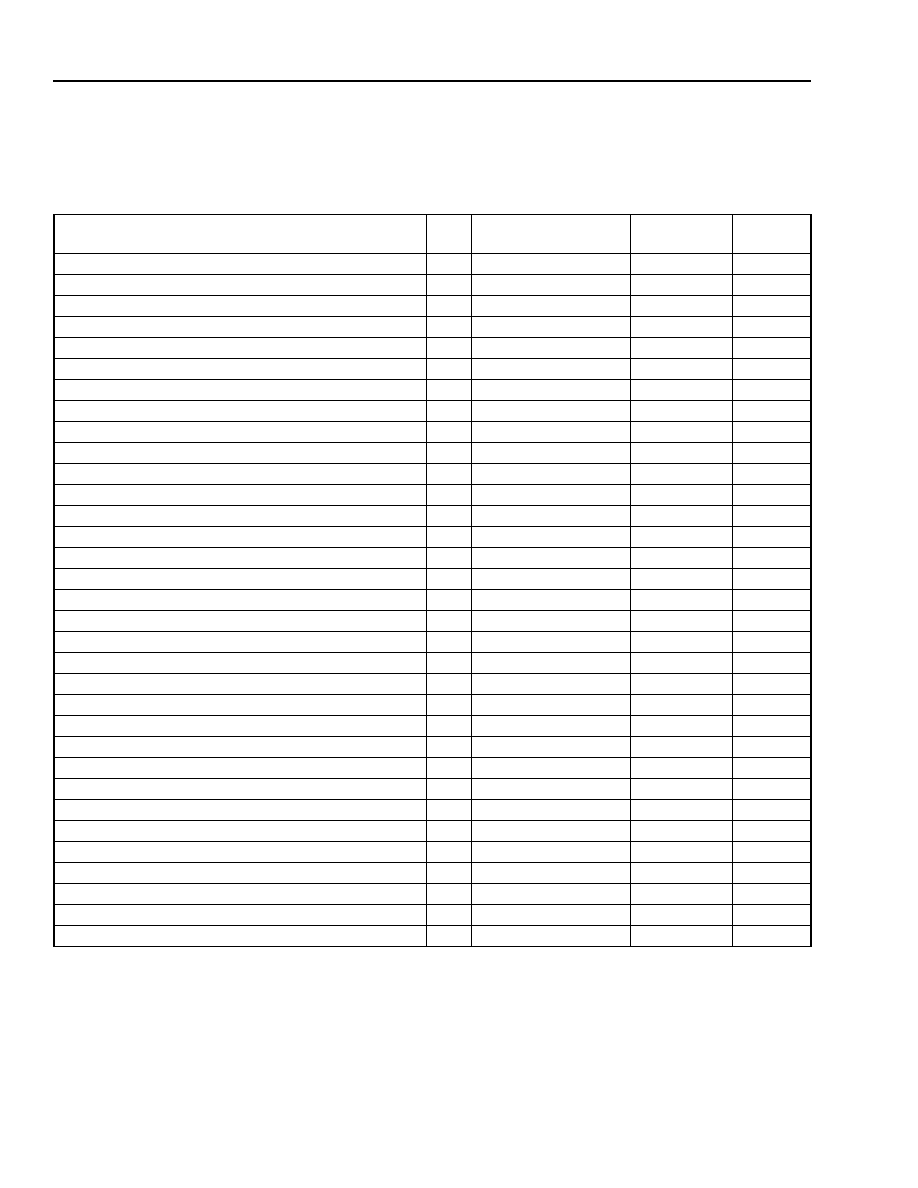

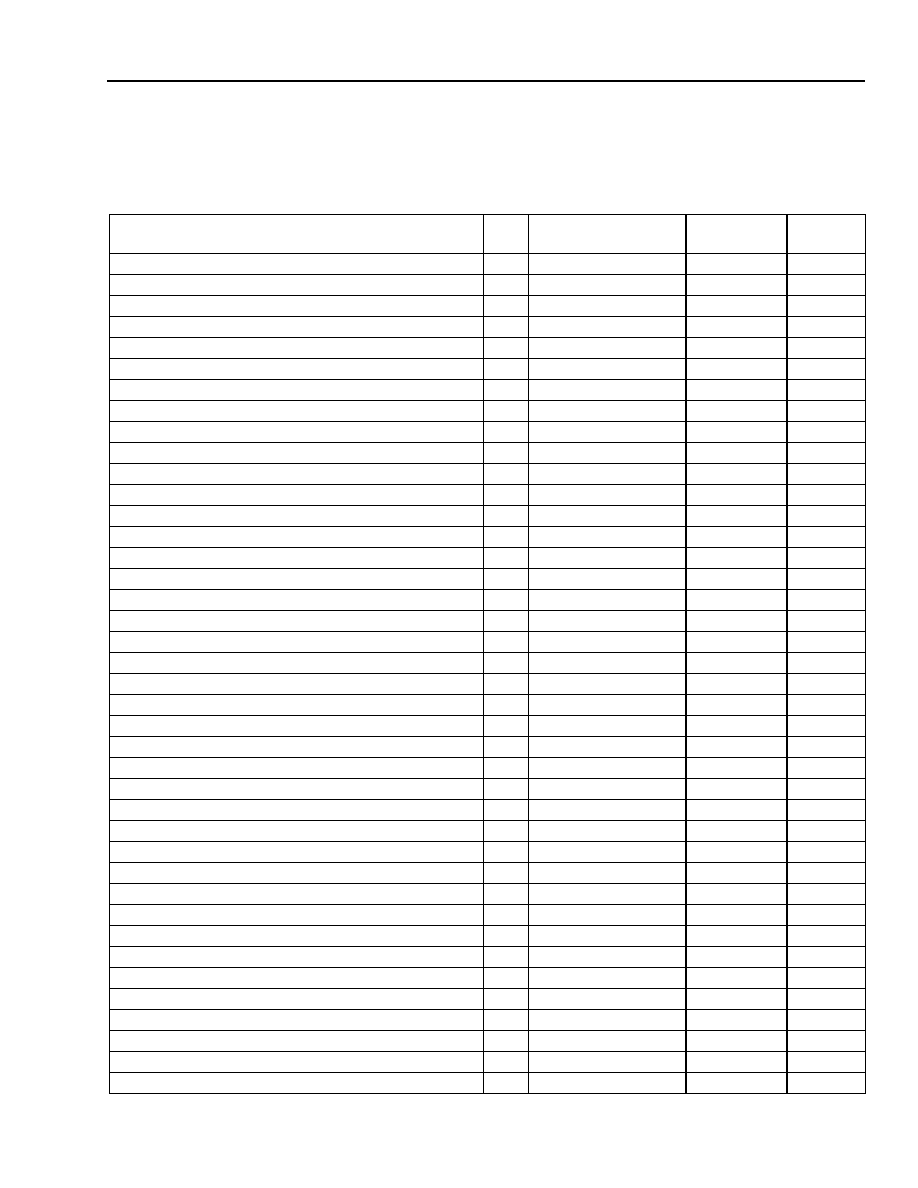

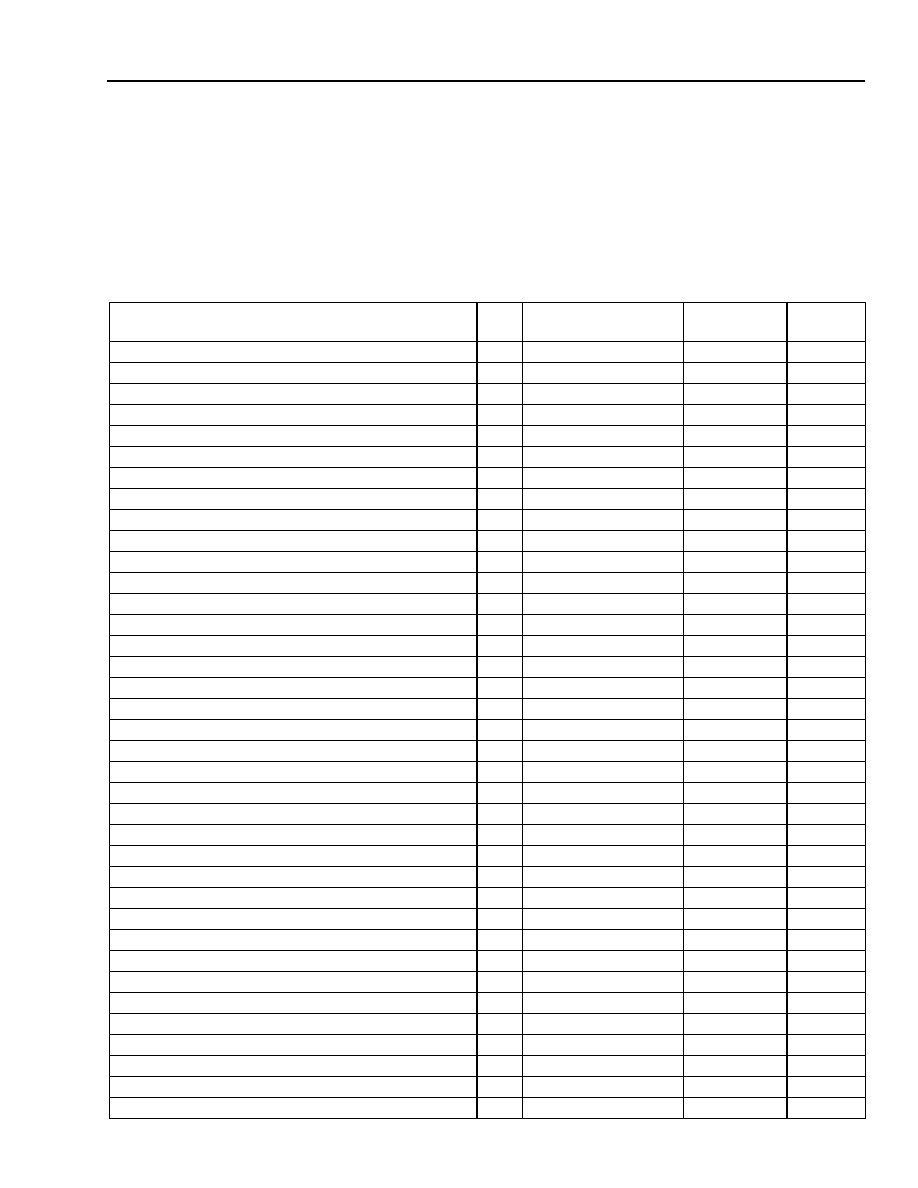

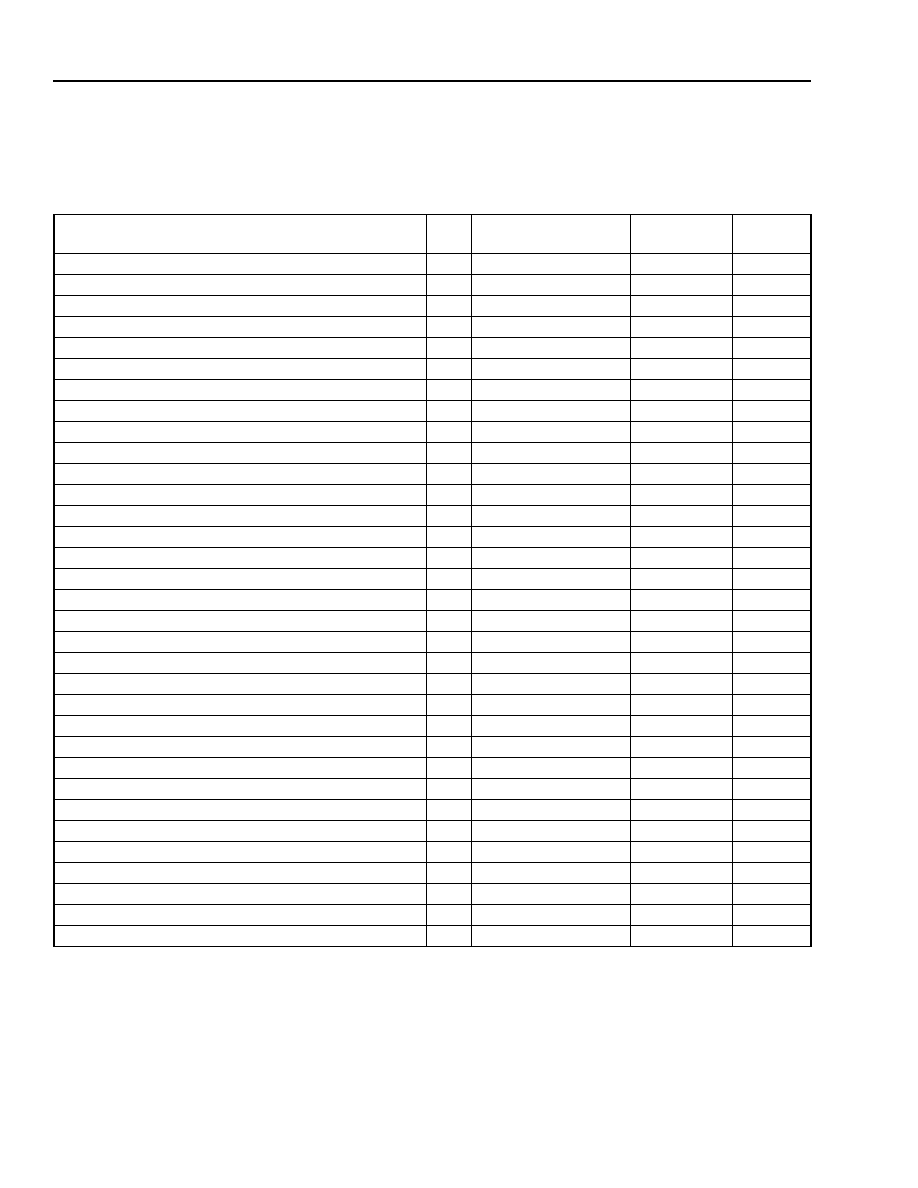

Tables

Page

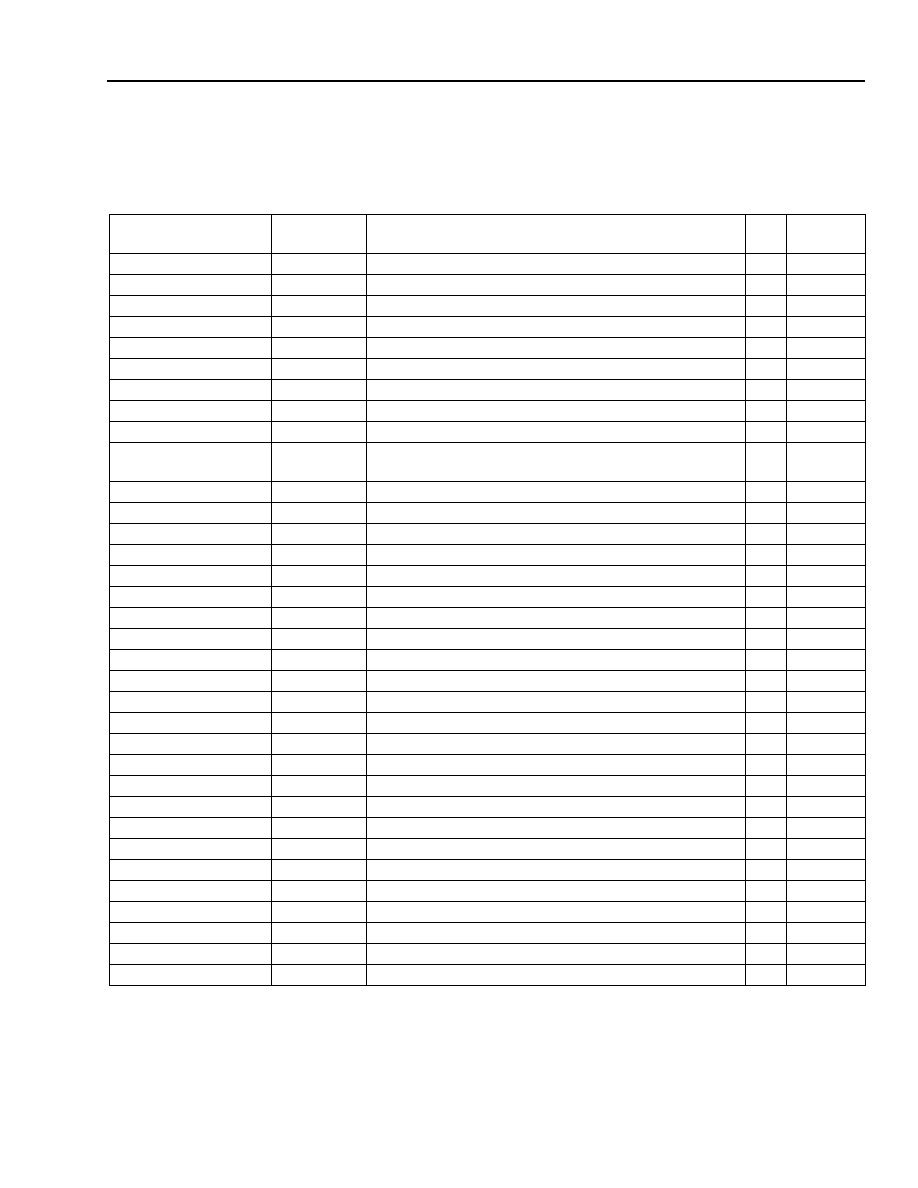

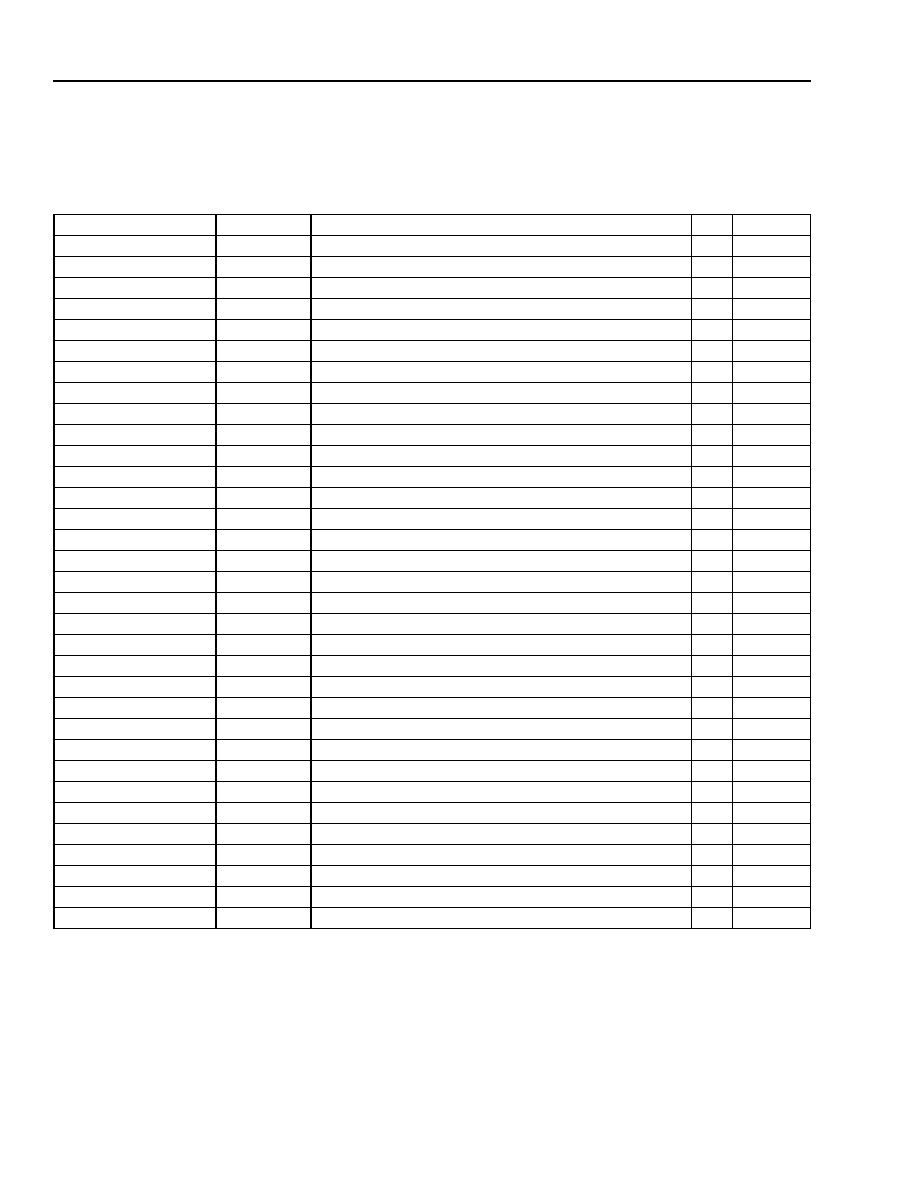

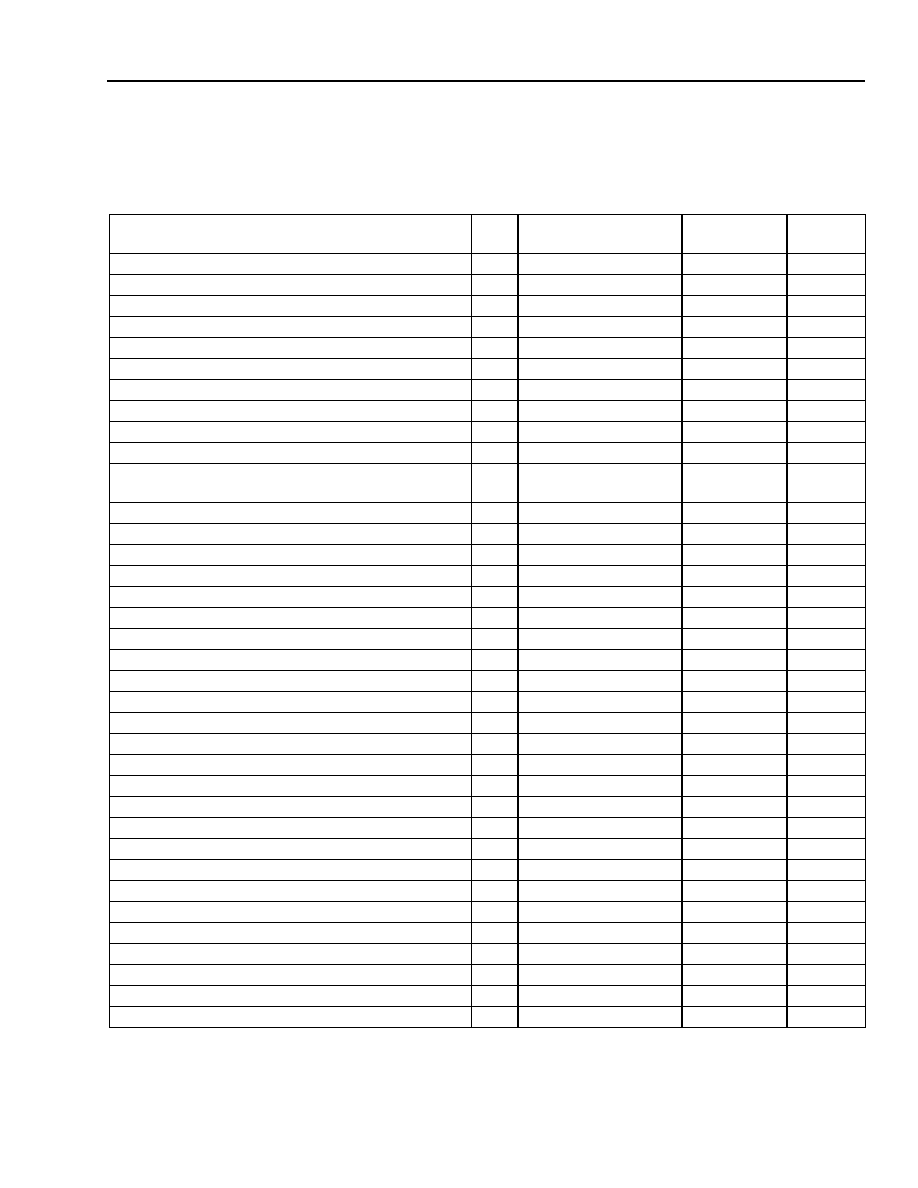

Table 1. Pin Descriptions ........................................................................................................................................10

Table 2. Microprocessor Interface Control I/O ........................................................................................................16

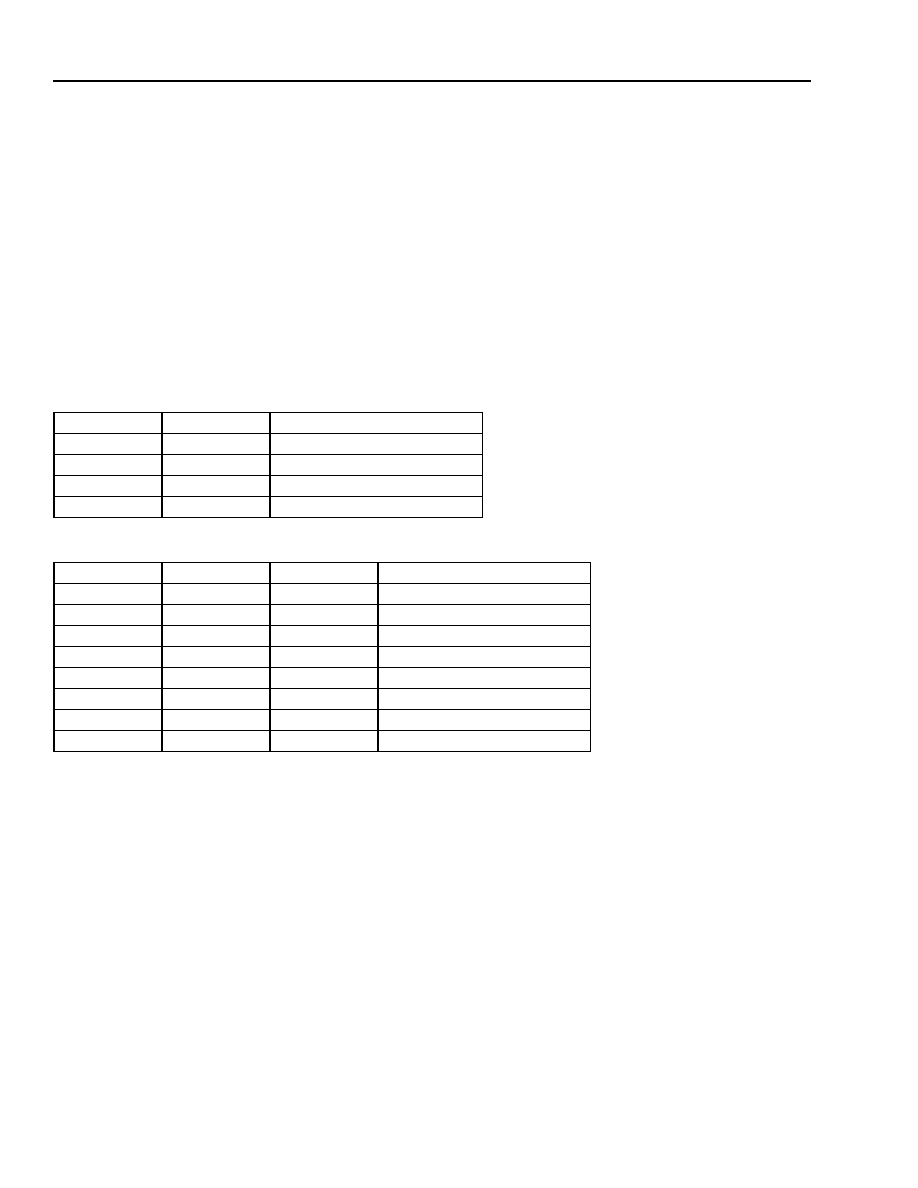

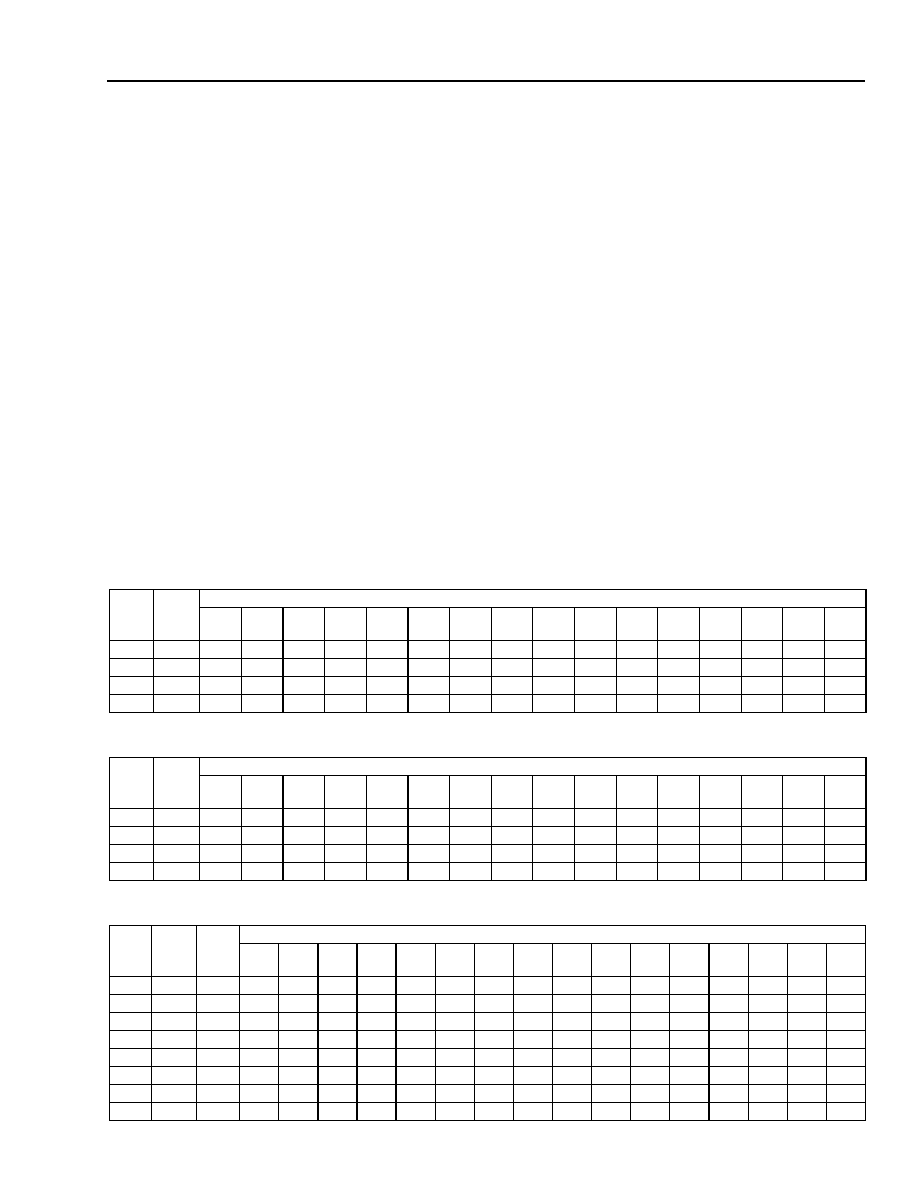

Table 3. Relationship Between CET and CER, When CMS = 1 .............................................................................24

Table 4. Relationship Between CET and CER, When CMS = 0 .............................................................................24

Table 5. Programming Values (CER = Decimal) for [X, Y]RBOFF, When CMS = 1 ...............................................27

Table 6. Programming Values (CET = Decimal) for [C, E]XBOFF, When CMS = 1 ...............................................27

Table 7. Programming Values (CER = Decimal) for [X, Y]RBOFF, When CMS = 0 ...............................................27

Table 8. Programming Values (CET = Decimal) for [C, E]XBOFF, When CMS = 0 ...............................................28

Table 9. Transmission Parameter Settings and Description for Waveforms in Figure 15, PCM Input/Output

Transmission Parameter Settings ............................................................................................................29

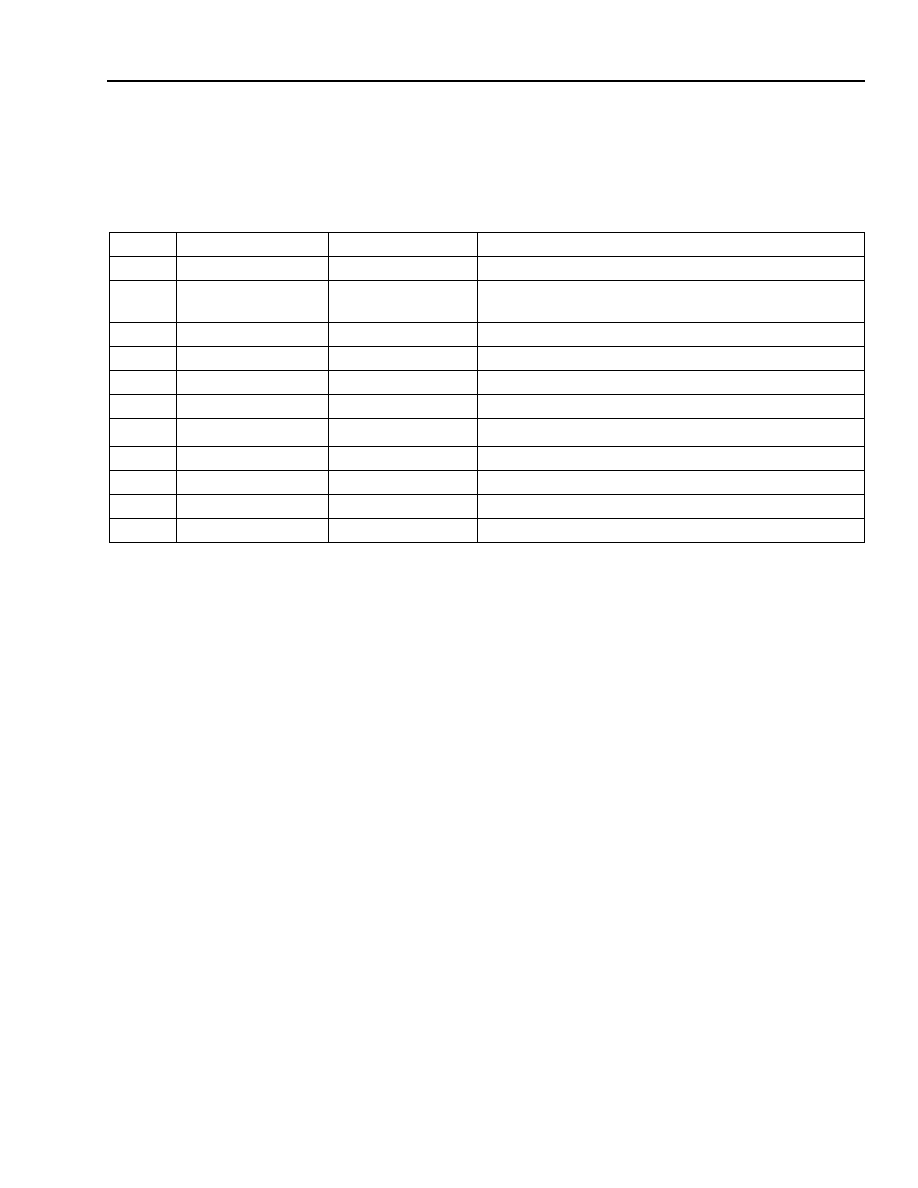

Table 10. H-Register Display Output Format ..........................................................................................................31

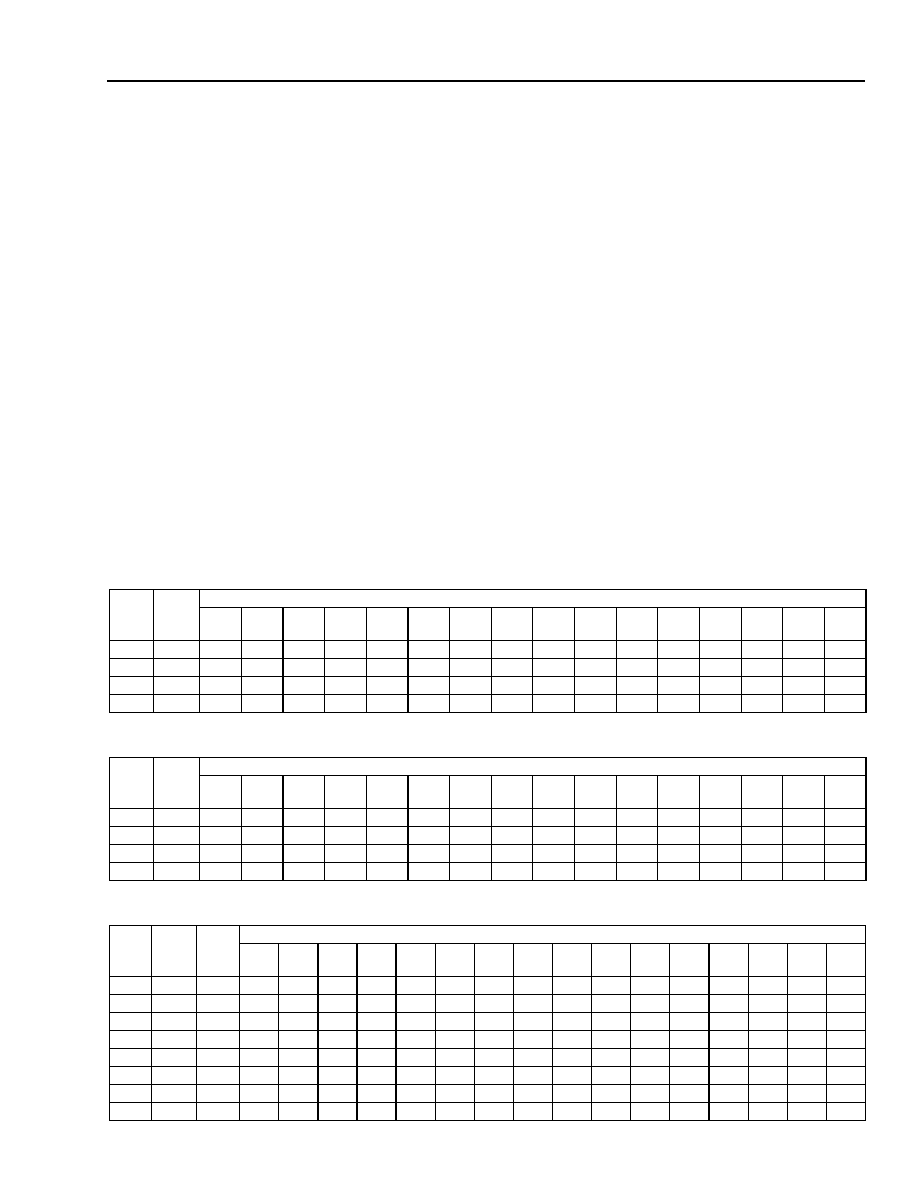

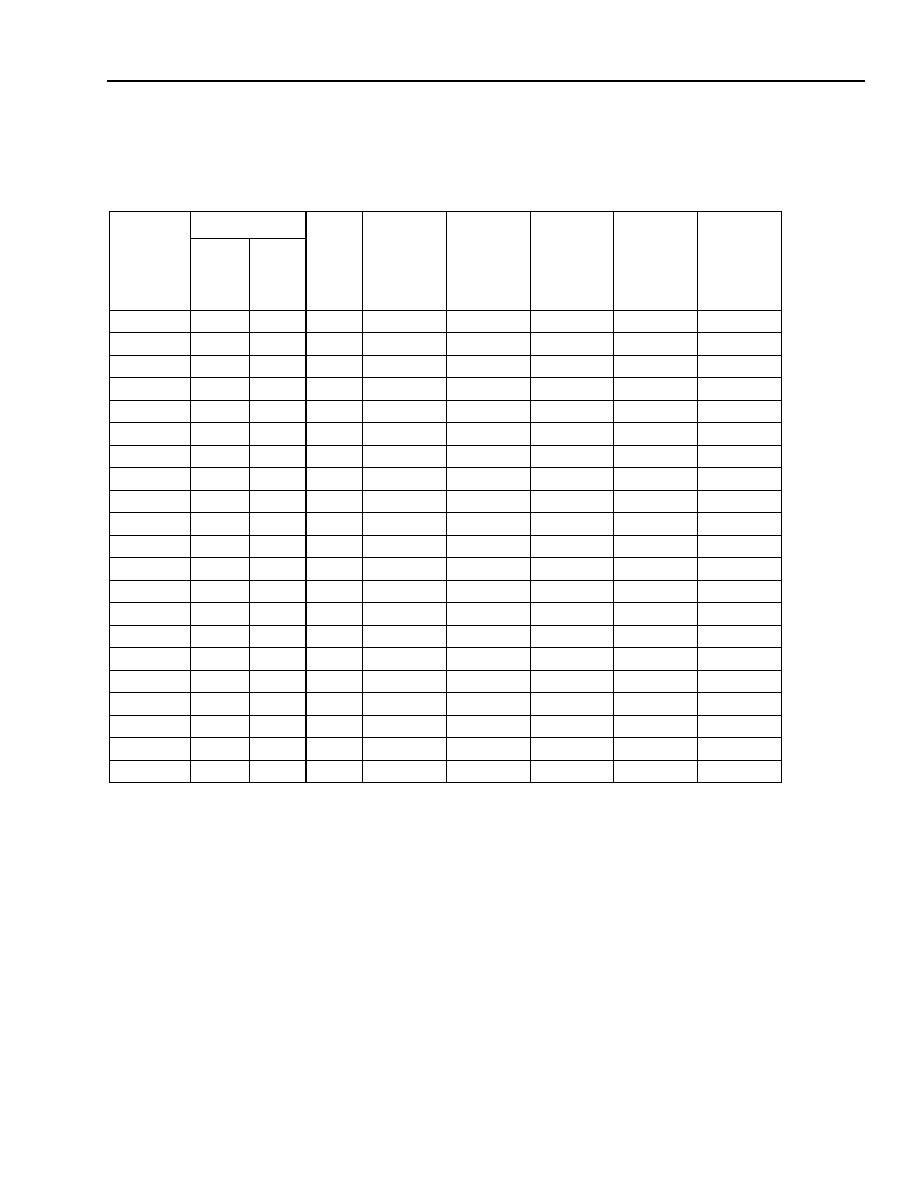

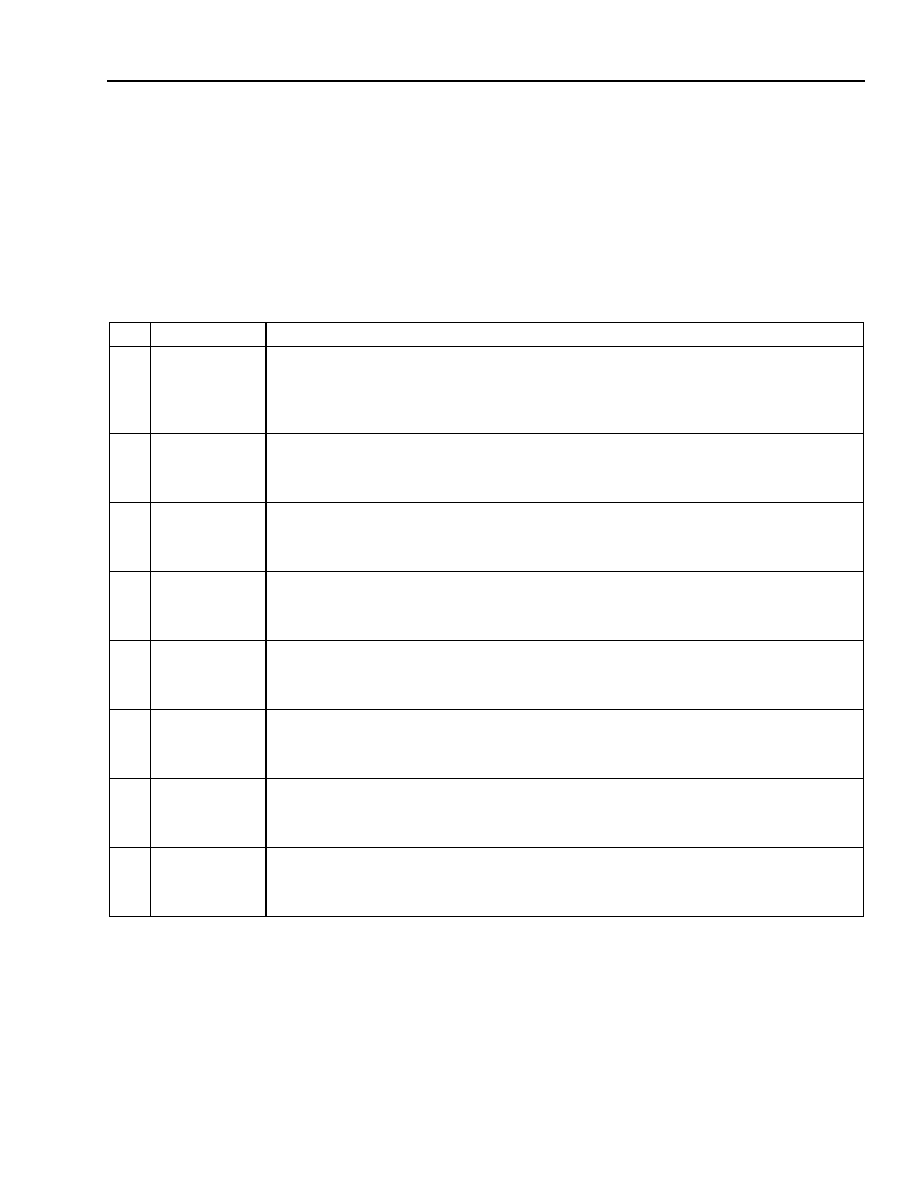

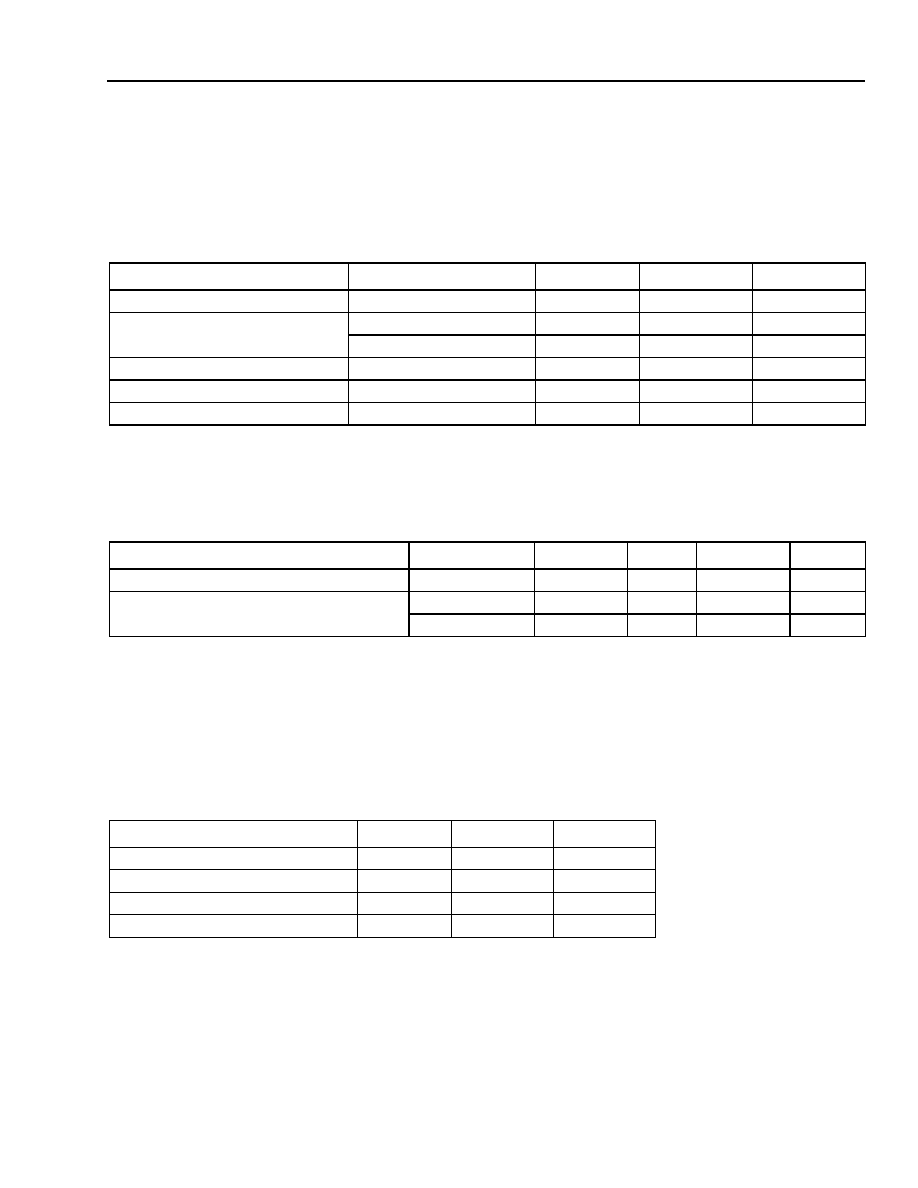

Table 11. Per-Channel Control Parameters ............................................................................................................34

Table 12. Mask Parameters ....................................................................................................................................35

Table 13. EC Parameters........................................................................................................................................36

Table 14. Transmission Parameters .......................................................................................................................37

Table 15. Tone Disabler Parameters ......................................................................................................................40

Table 16. Nonlinear Processor Parameters ............................................................................................................41

Table 17. Control Parameters .................................................................................................................................42

Table 18. Test and Diagnostic Parameters.............................................................................................................43

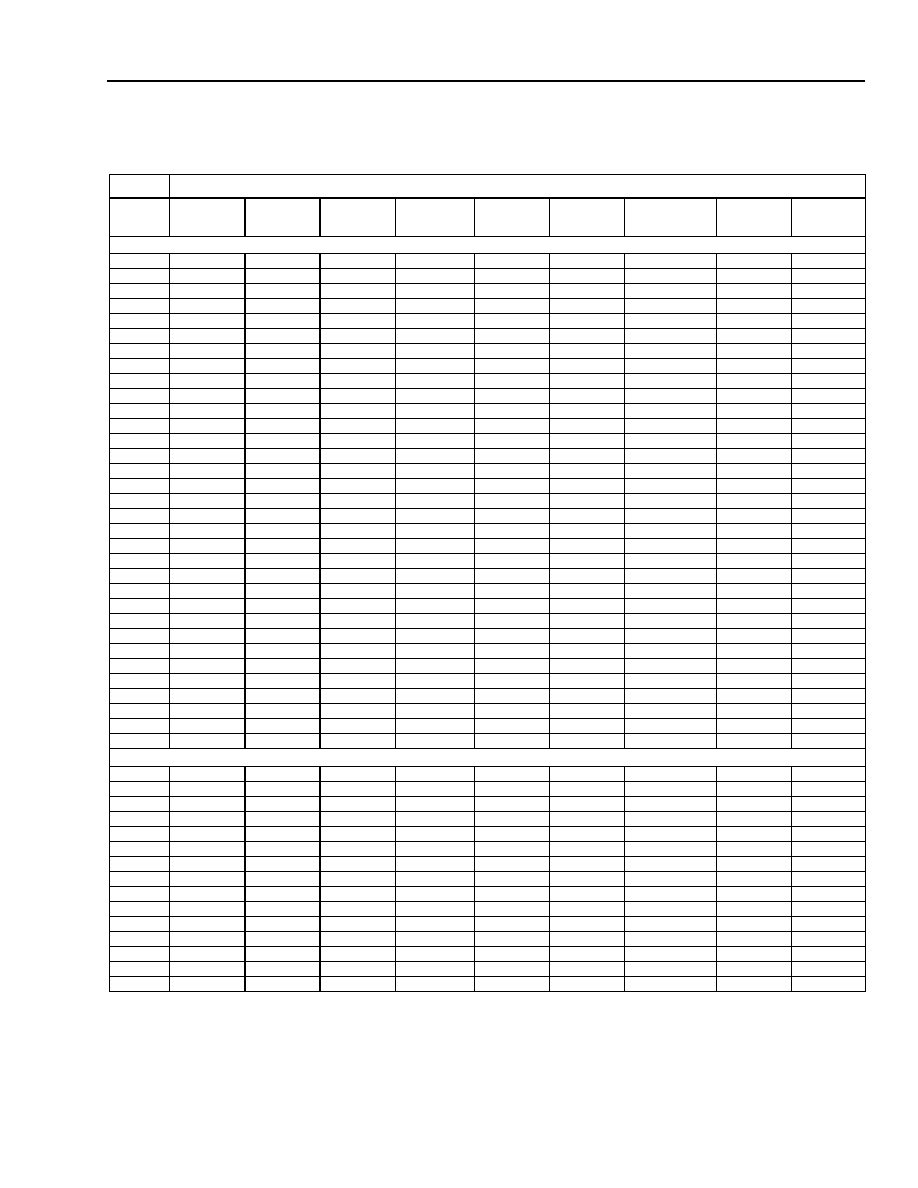

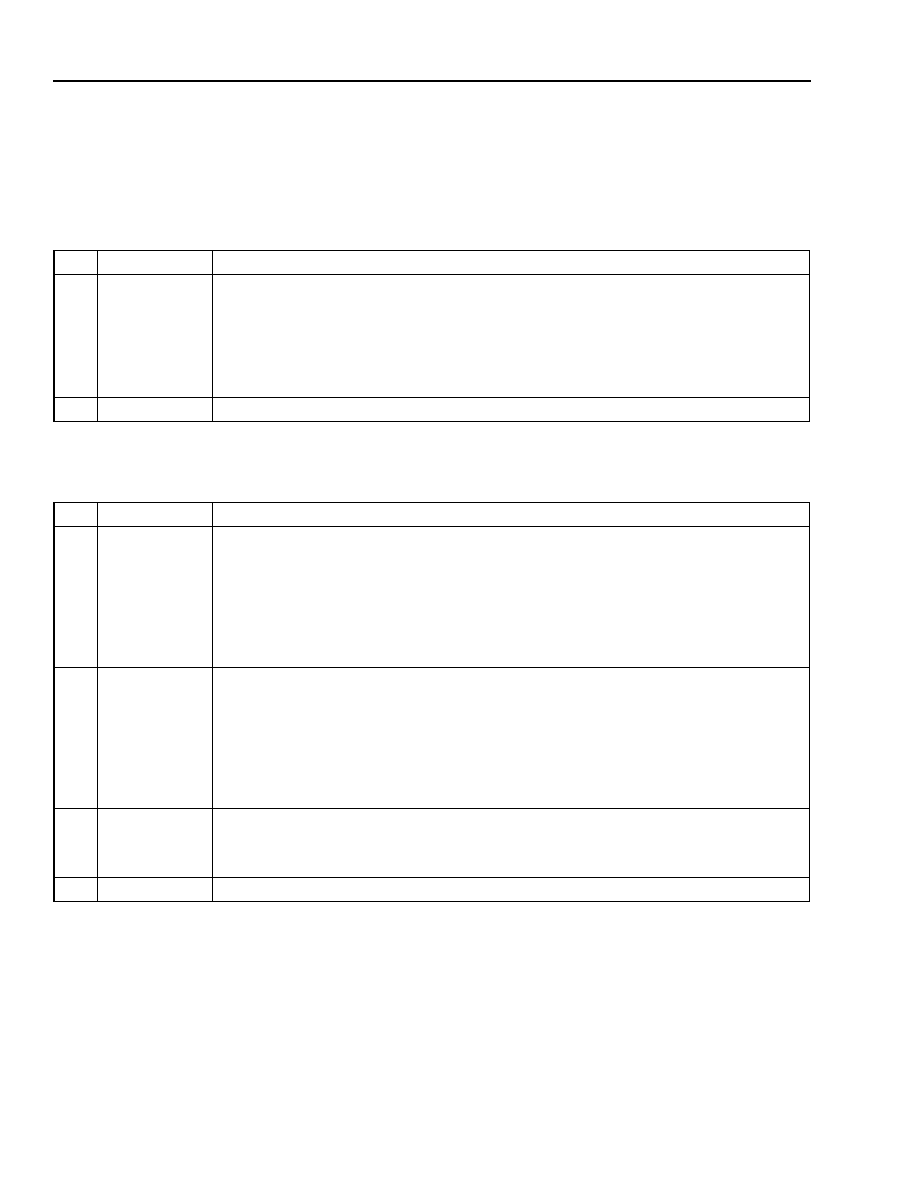

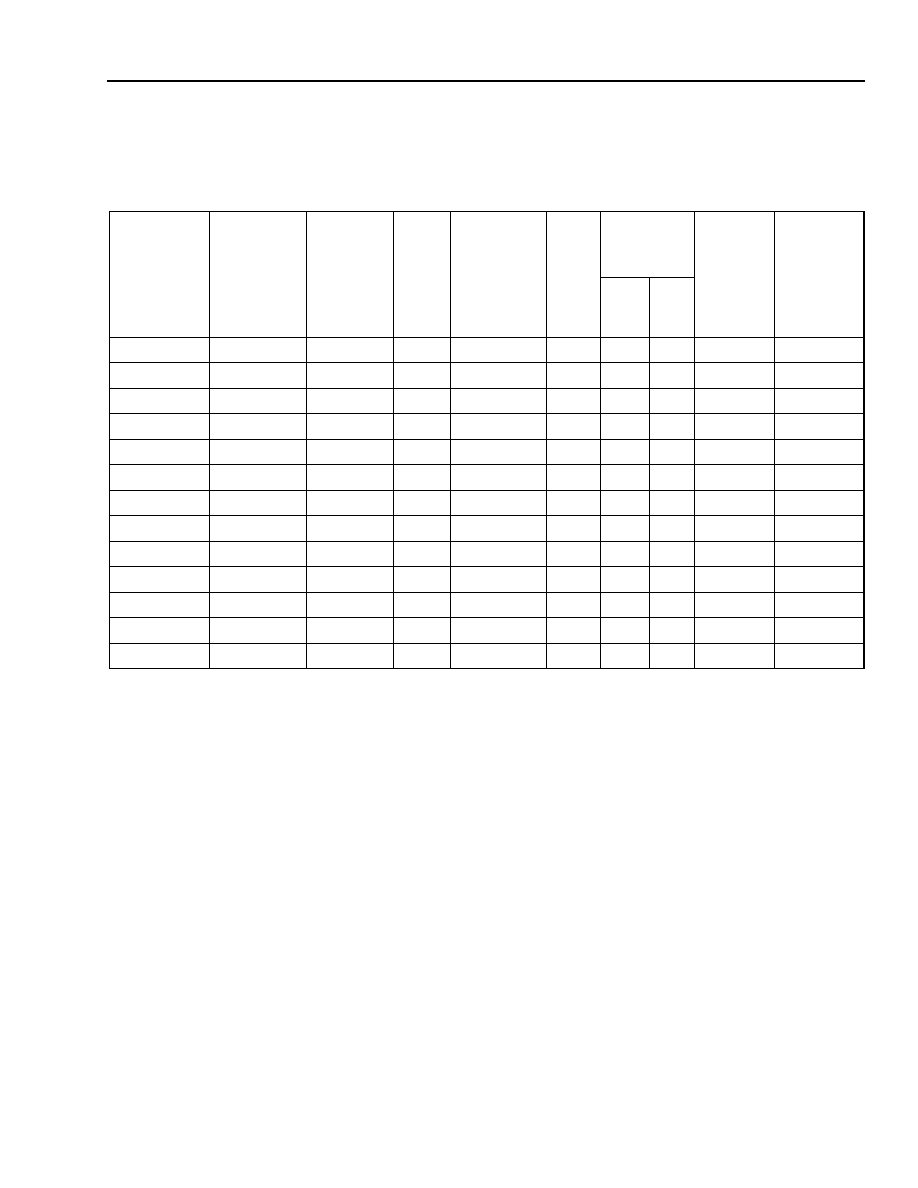

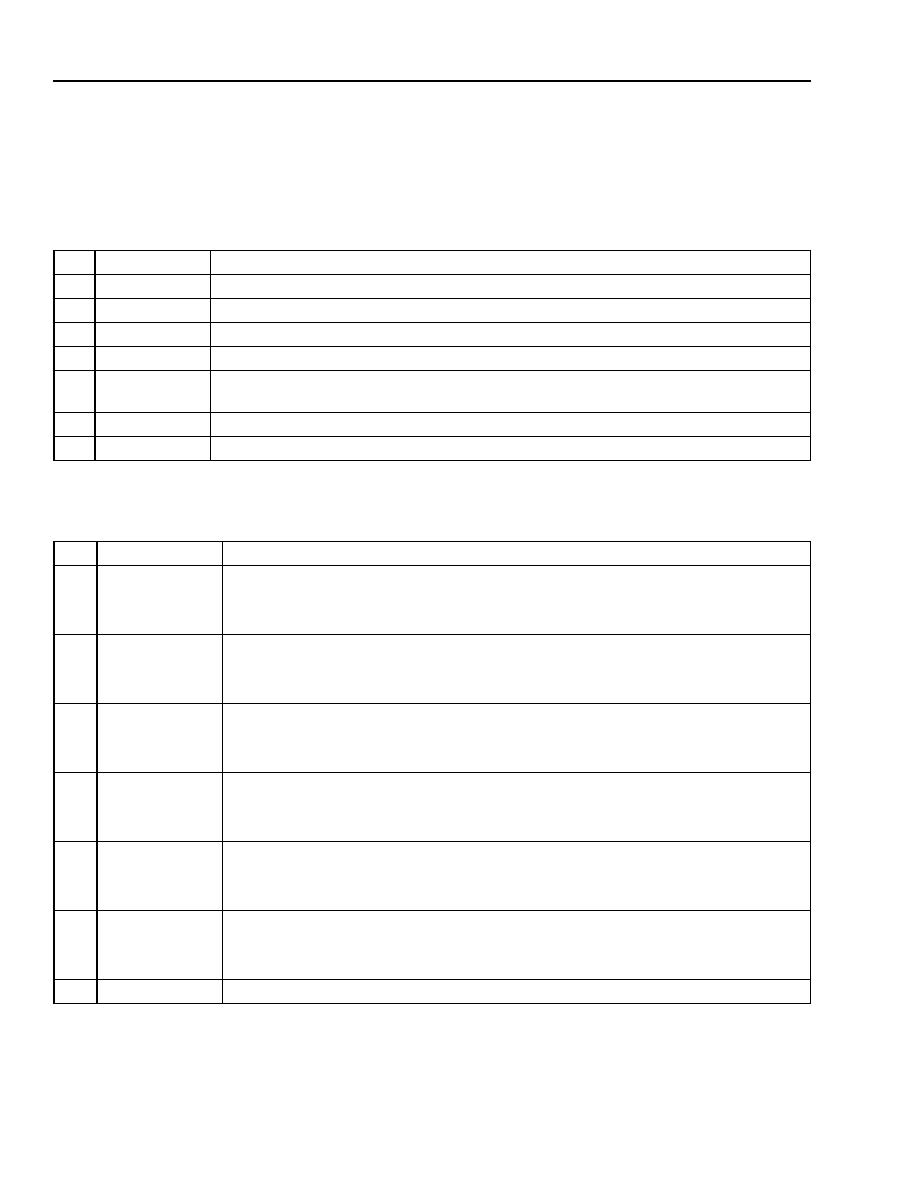

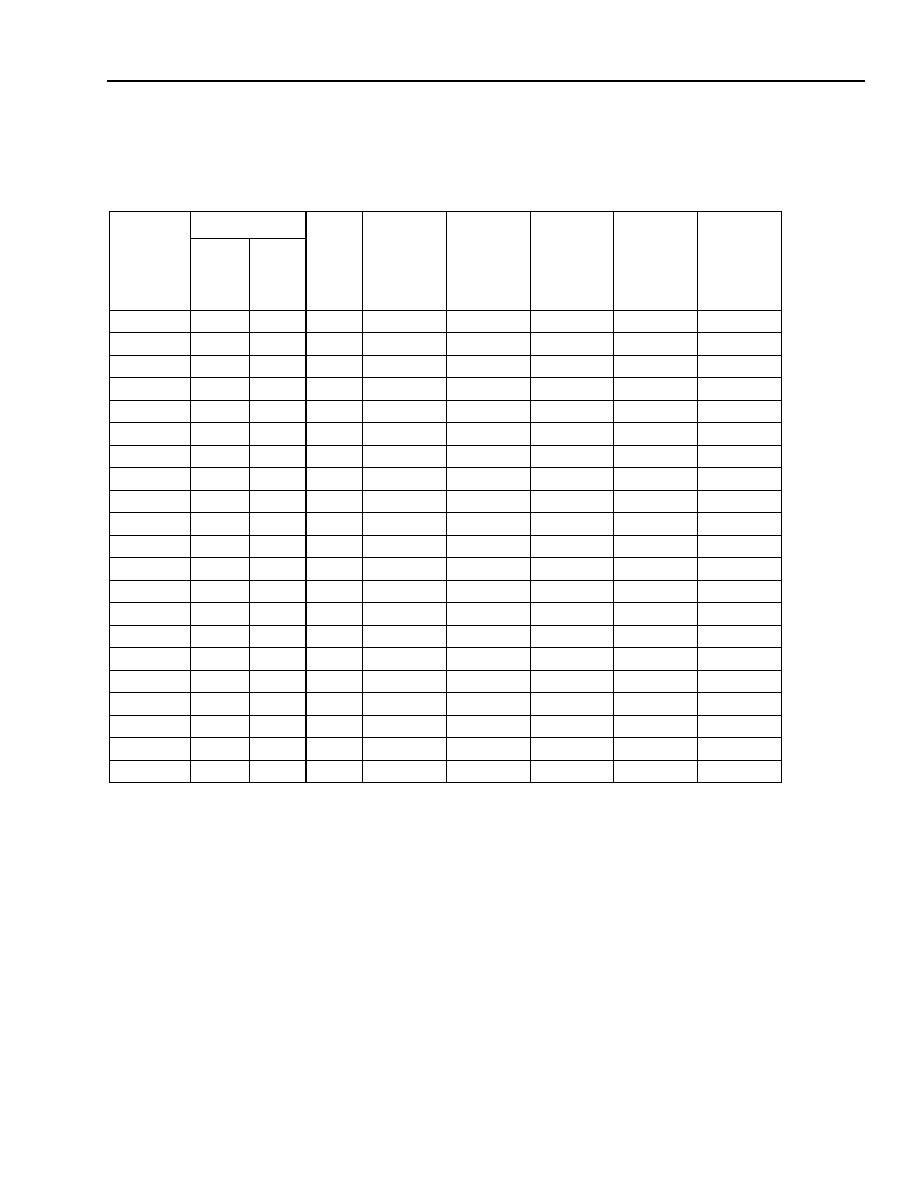

Table 19. Parameter Address Map .........................................................................................................................45

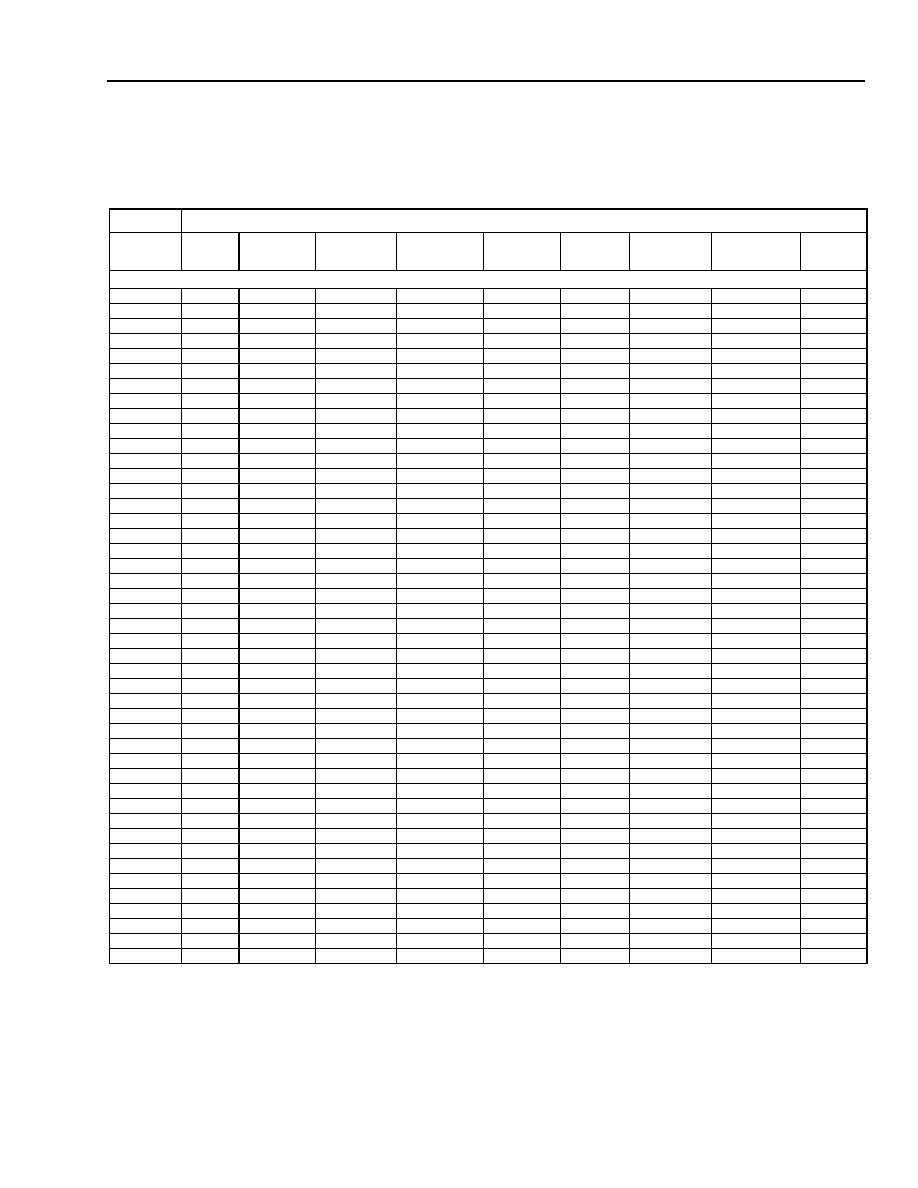

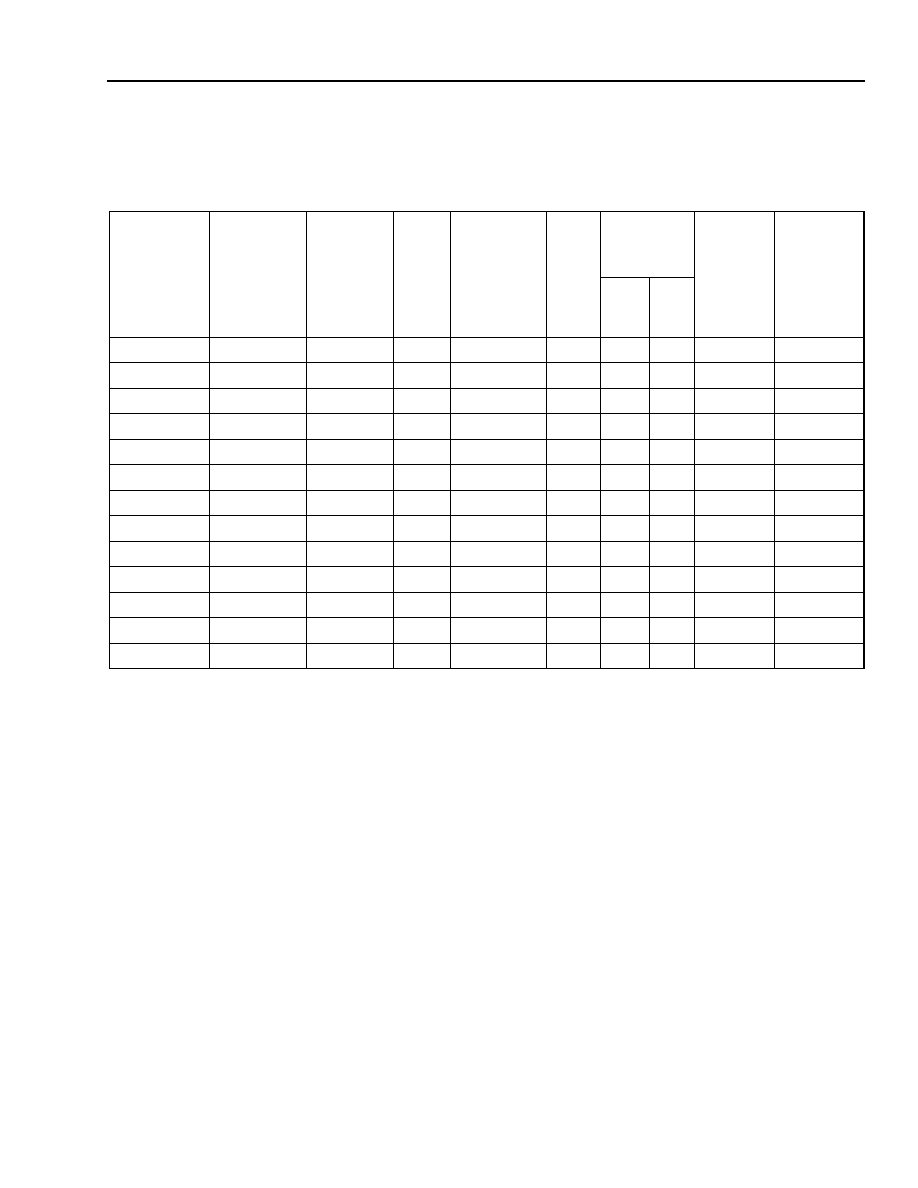

Table 20. Recommended Register Values for DS1 (µ-Law) and 2.048 Mbits/s Rate .............................................51

Table 21. Recommended Register Values for E1 (A-Law) .....................................................................................52

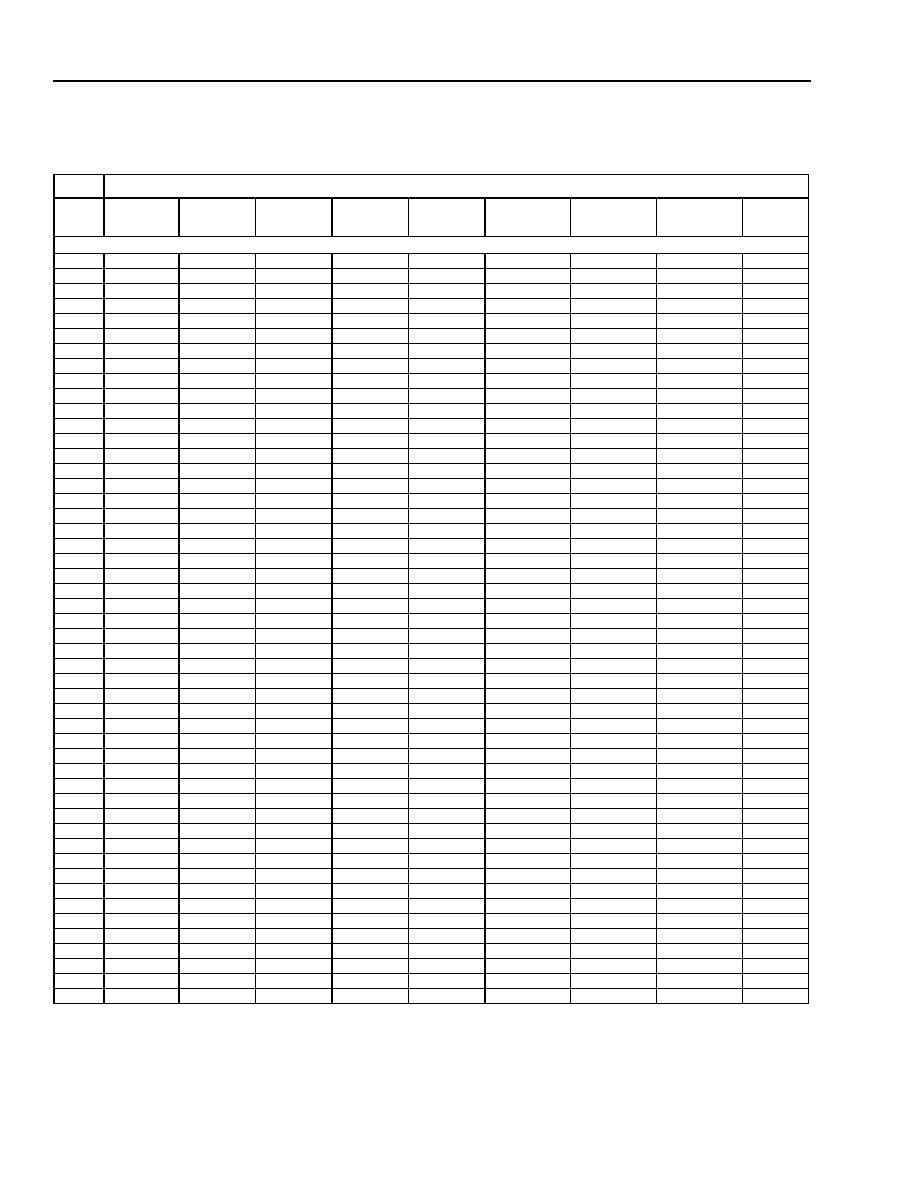

Table 22. Function Name to Symbol and Register Address Index .........................................................................53

Table 23. Symbol to Register Address and Function Name Index .........................................................................59

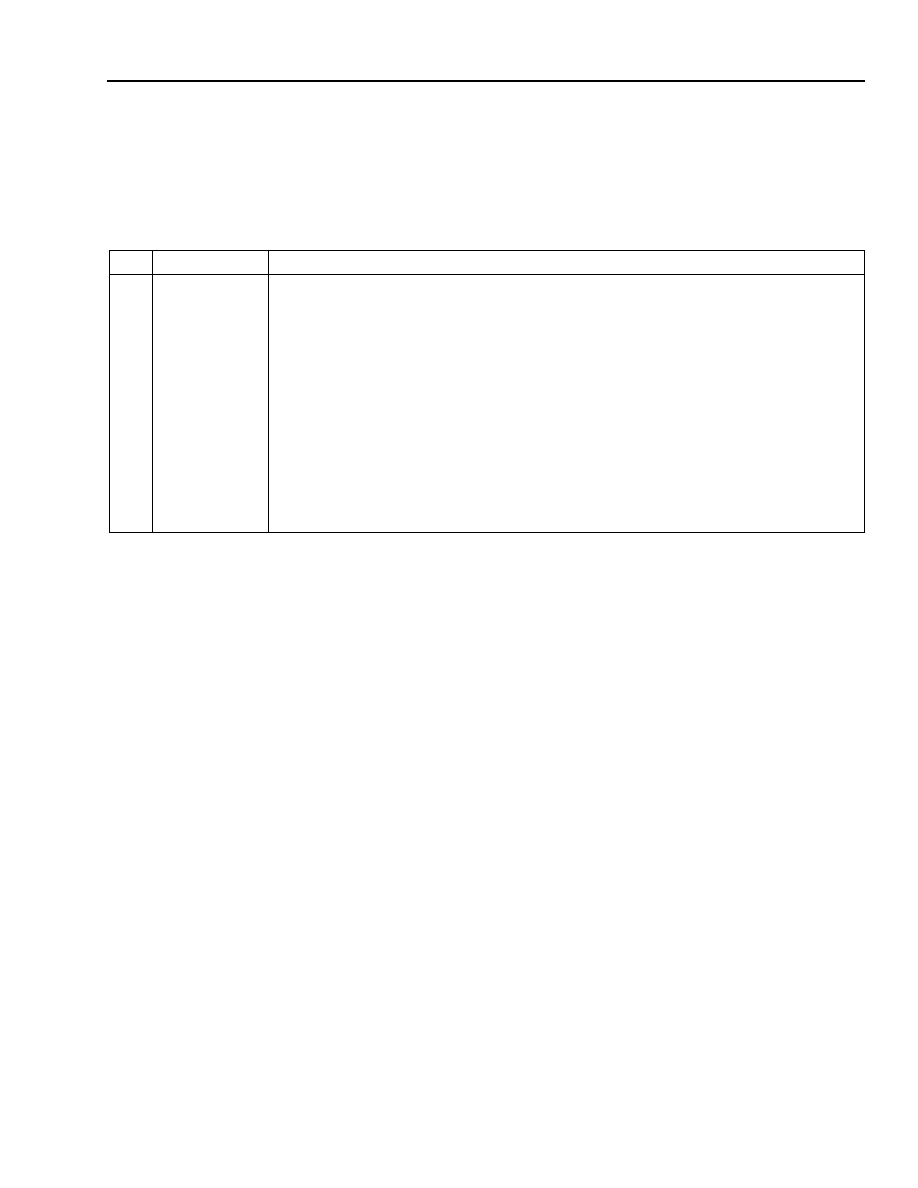

Table 24. Per-Channel Control Parameters ............................................................................................................65

Table 25. Tone Disabler Masks 1 Register (020) [00].............................................................................................67

Table 26. Tone Disabler Masks 2 Register (021) [02].............................................................................................68

Table 27. Nonlinear Processor (NLP) Control Masks Register (022) [41] ..............................................................69

Table 28. H-Register Control Options (023) [80].....................................................................................................70

Table 29. Leak Control Register (024) [A1].............................................................................................................71

Table 30. Filter and Tone Detector 2 Controls Register (025) [0C].........................................................................72

Table 31. Far-End Speech Threshold 1 Register (026) [9B] ...................................................................................73

Table 32. Far-End Speech Threshold 2 Register (027) [02] ...................................................................................73

Table 33. Narrowband Energy Peak Factor Register (028) [18] .............................................................................73

Table 34. Wideband Energy Peak Factor Register (029) [18] ................................................................................74

Table 35. Highway Bit Rate Register (02A) [05] .....................................................................................................74

Table 36. X Parity Register (02B) [00] ....................................................................................................................75

Table 37. Test 1 Register (02C) [00] .......................................................................................................................75

Table 38. Test 2 Register (02D) [00] .......................................................................................................................75

Table 39. A-Law/µ-Law Linear Conversion Register (02E) [1B for DS1, 09 for E1]................................................76

Table 40. C Port Control Register (02F) [F8] ..........................................................................................................77

Table 41. X-C Bulk Time-Slot Delay Register (030) [19].........................................................................................77

Table 42. Y-E Bulk Time-Slot Delay Register (031) [15] .........................................................................................78

Table 43. X Input Format Register (032) [02]..........................................................................................................78

Table 44. Edge Sampling Register (033) [02] .........................................................................................................78

Table 45. SRAM Control Register (034) [01] ..........................................................................................................79

Table 46. Y Port Control 1 Register (035) [02] ........................................................................................................79

Table 47. Y Port Control 2 Register (036) [07 for DS1, 05 for E1] ..........................................................................80

Table 48. Y Test Data 1 Register (037) [00] ...........................................................................................................81

Table 49. Y Test Data 2 Register (038) [00] ...........................................................................................................81

Table 50. E and Y EMP Gain Filter Constant Register (039) [80] ...........................................................................81

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

6

Lucent Technologies Inc.

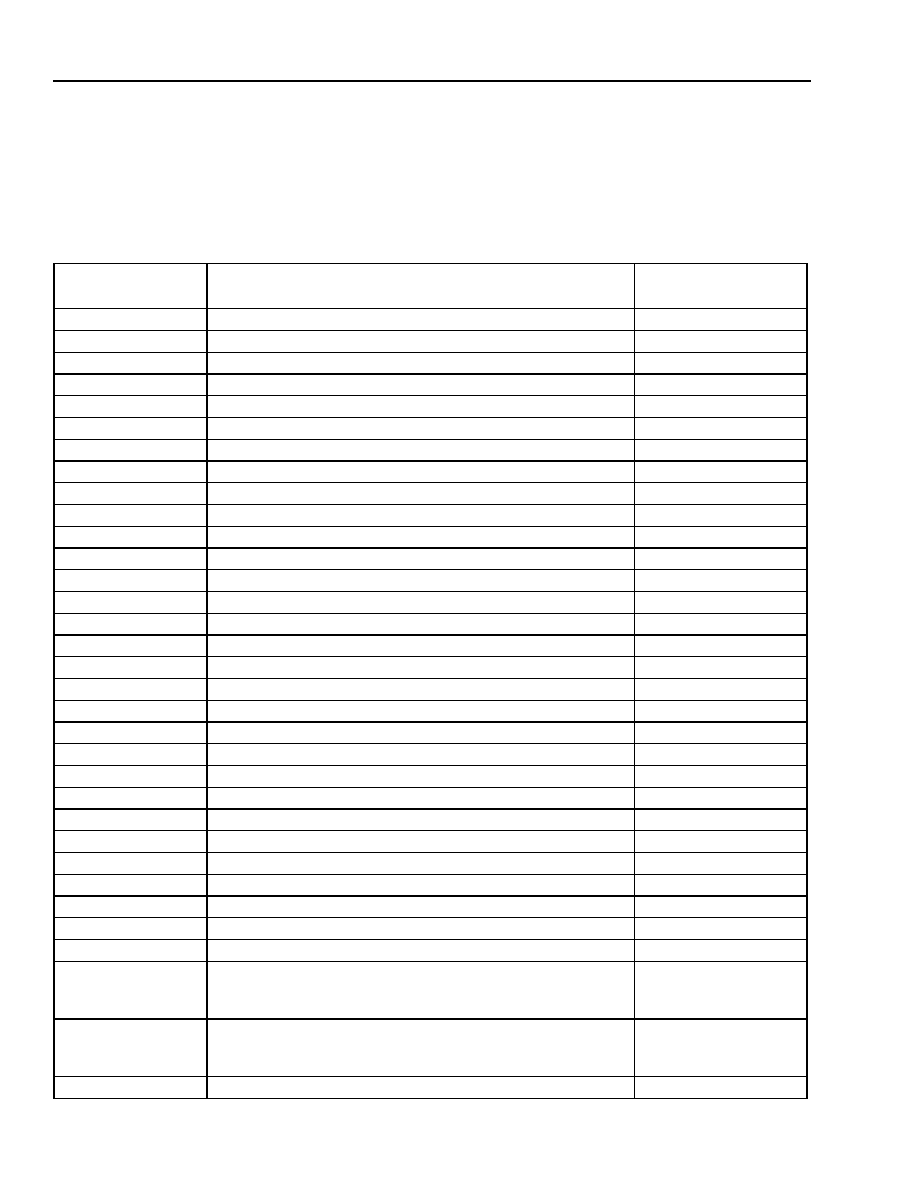

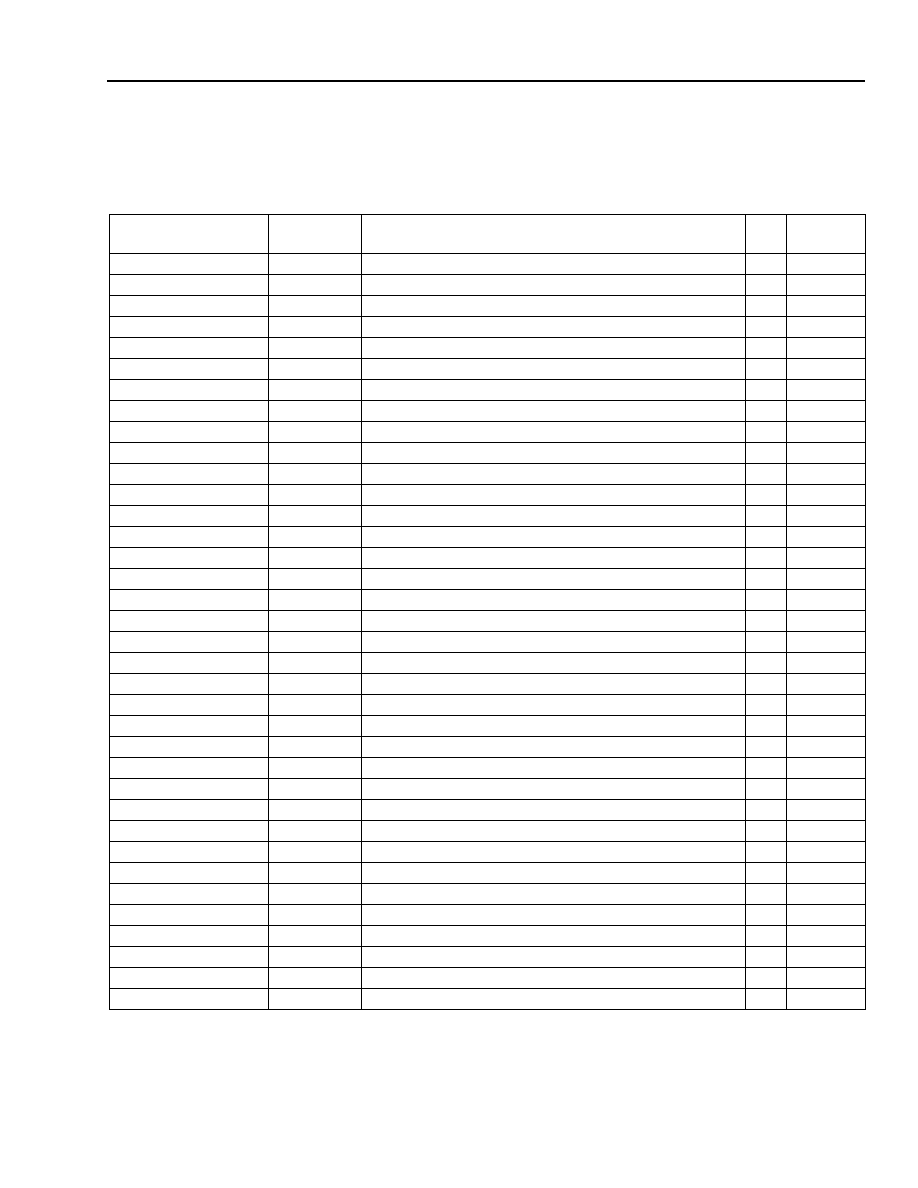

List of Tables

(continued)

Tables

Page

Table 51. E Port Control 1 Register (03A) [F7 for DS1, F6 for E1]......................................................................... 82

Table 52. E Port Control 2 Register (03B) [08]....................................................................................................... 83

Table 53. Reserved (03C) [00] ............................................................................................................................... 83

Table 54. Low-Peak Count Register (03D) [84]...................................................................................................... 84

Table 55. High-Peak Count Register (03E) [E3]..................................................................................................... 84

Table 56. Interval Count Register (03F) [E4].......................................................................................................... 85

Table 57. Good Intervals VPA Register (040) [00] ................................................................................................. 85

Table 58. Good Intervals Declare Register (041) [70] ............................................................................................ 85

Table 59. Phase Reversal Interval Minimum Register (042) [CA] .......................................................................... 86

Table 60. Phase Reversal Interval Maximum Register (043) [8A].......................................................................... 86

Table 61. Tone Detector Declarations Register (044) [AC] .................................................................................... 87

Table 62. Low Voice Path Assurance (VPA) Count Register (045) [5F] ................................................................ 87

Table 63. High VPA Count Register (046) [22]....................................................................................................... 88

Table 64. VPA Power Minimum Register (047) [0C] .............................................................................................. 88

Table 65. Tone Detector Power Minimum Register (048) [0E]............................................................................... 88

Table 66. Phase Reversal Interval Maximum Register (049) [4D] ......................................................................... 89

Table 67. Tone Detector Threshold Register (04A) [90]......................................................................................... 89

Table 68. Y Energy Threshold Register (04B) [7F] ................................................................................................ 90

Table 69. Noise Matching Enable Register (04C) [20] ........................................................................................... 90

Table 70. Near-End Speech Hangover Register (04D) [F0]................................................................................... 91

Table 71. Í Noise Floor Estimate Maximum 1 Register (04E) [1F] ........................................................................ 91

Table 72. Í Noise Floor Estimate Maximum 2 Register (04F) [00]......................................................................... 92

Table 73. Gamma Í Noise Floor Register (050) [02].............................................................................................. 92

Table 74. Clamp Í Noise Floor 1 Register (051) [FF]............................................................................................. 92

Table 75. Clamp Í Noise Floor 2 Register (052) [3F]............................................................................................. 93

Table 76. Noise Floor Estimate High Hysteresis Threshold 1 Register (053) [00] ................................................. 93

Table 77. Variable Loss Noise Matching Select Register (054) [00] ...................................................................... 94

Table 78. Noise Floor Estimate Low Hysteresis Threshold Register (055) [08] ..................................................... 94

Table 79. NLP Freeze, Soft NLP Select Register (056) [80] .................................................................................. 95

Table 80. Noise Floor Estimate Register (057) [21] ............................................................................................... 95

Table 81. Spectrally Matched Noise Matching Select Register (058) [B0] ............................................................. 96

Table 82. Soft NLP Number Interval Time Steps 1 Register (059) [08].................................................................. 96

Table 83. Soft NLP Number Interval Time Steps 2 Register (05A) [00] ................................................................. 97

Table 84. Soft NLP Interval Steps Register (05B) [20] ........................................................................................... 97

Table 85. Loss Increment Attenuated Í 1 Register (05C) [4C]............................................................................... 98

Table 86. Loss Increment Attenuated Í 2 Register (05D) [8A]............................................................................... 98

Table 87. Í Zero Crossing Threshold Register (05E) [00]...................................................................................... 99

Table 88. Soft NLP Incremental Loss Factor 1 Register (05F) [00]........................................................................ 99

Table 89. Soft NLP Incremental Loss Factor 2 Register (060) [1E] ..................................................................... 100

Table 90. Reserved Register (061) [00] ............................................................................................................... 100

Table 91. State Variable Test 1 Register (062) [00] ............................................................................................. 100

Table 92. State Variable Test 2 Register (063) [00] ............................................................................................. 101

Table 93. State Variable Test 3 Register (064) [00] ............................................................................................. 101

Table 94. Convolution Update Processor Disable Register (065) [00] ................................................................. 101

Table 95. Test Control Register (066) [00] ........................................................................................................... 102

Table 96. X and Y Loss Pads Register (067) [00] ................................................................................................ 102

Table 97. E and Y Exponentially Mapped (EMP) Filter Time Constant Register (068) [01] ................................. 103

Table 98. Fast Convergence Register (069) [60] ................................................................................................. 104

Table 99. Slow Convergence Gain Register (06A) [40]........................................................................................ 104

Table 100. Fast Convergence Beta 1 Register (06B) [12].................................................................................... 104

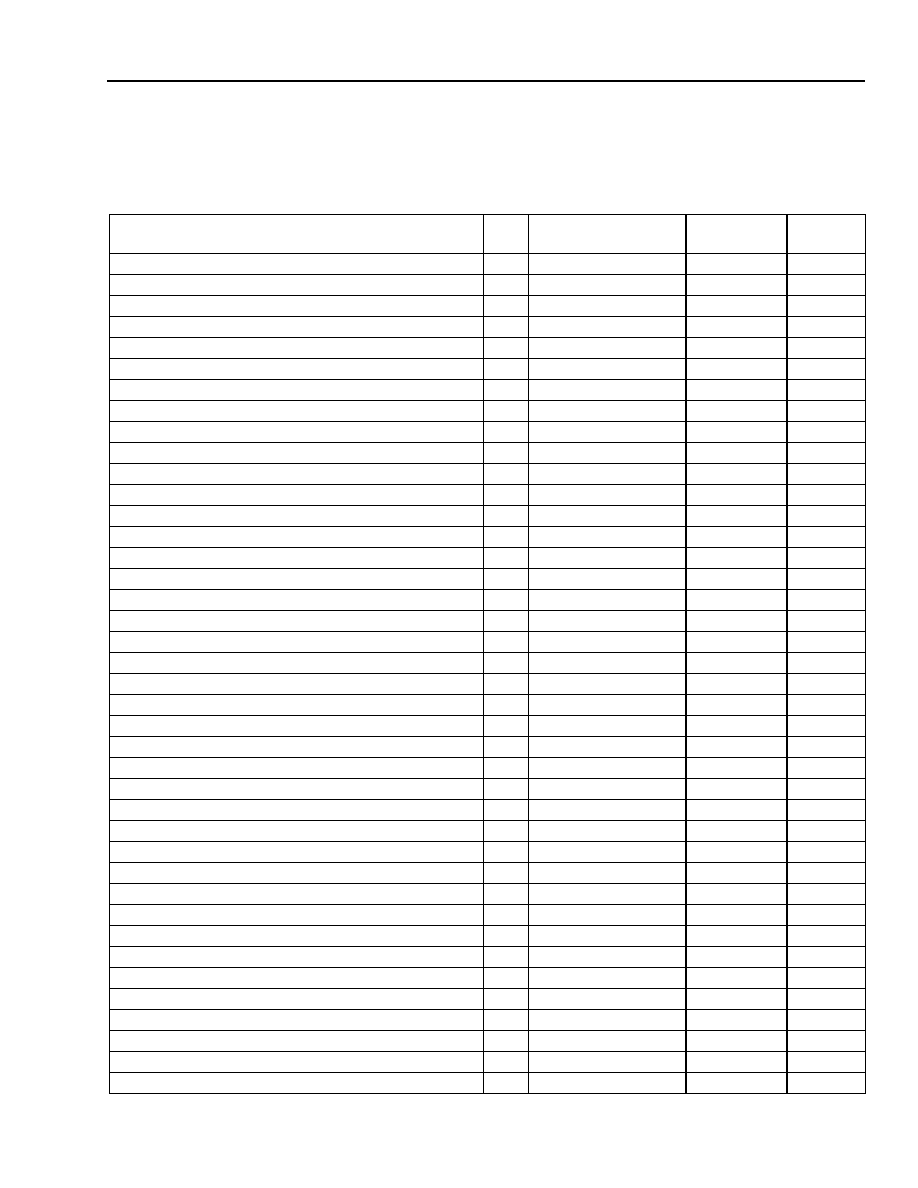

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

7

Lucent Technologies Inc.

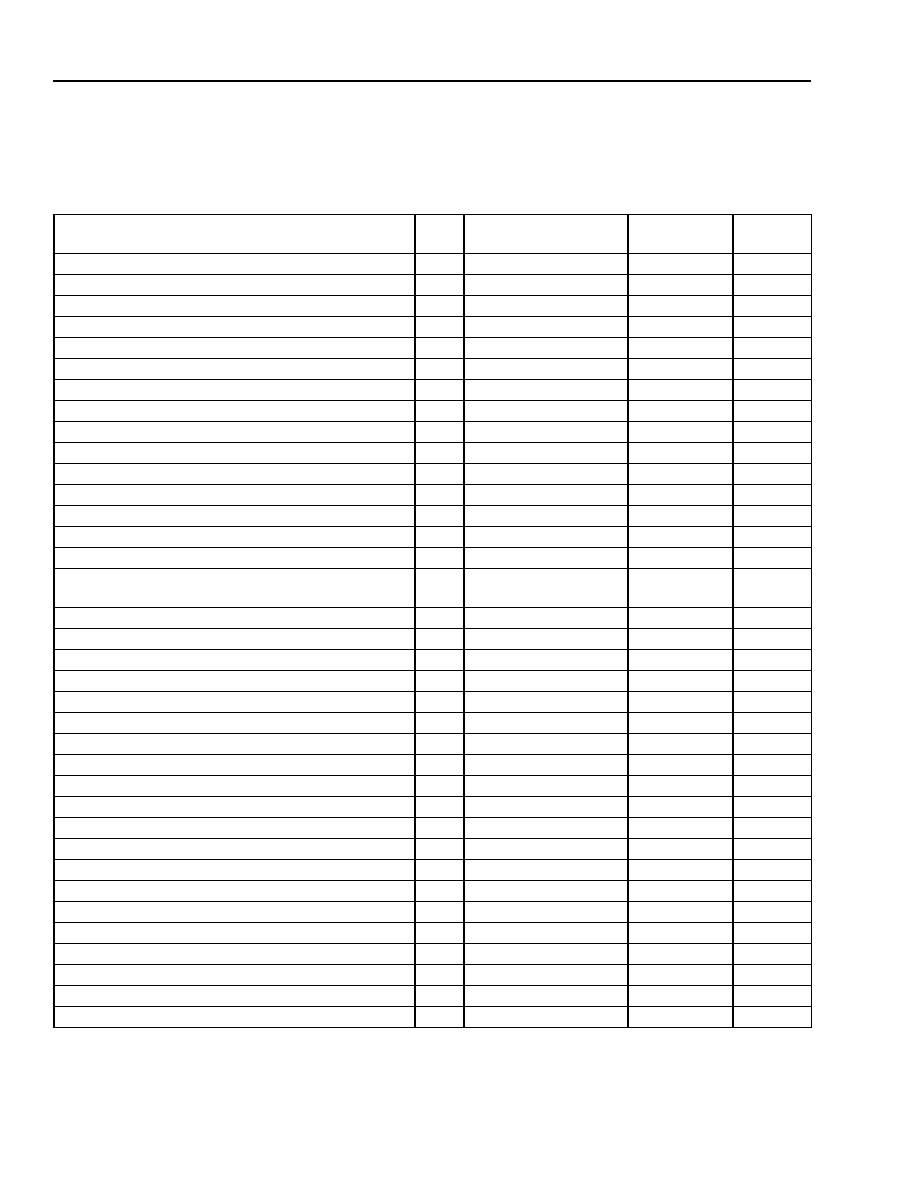

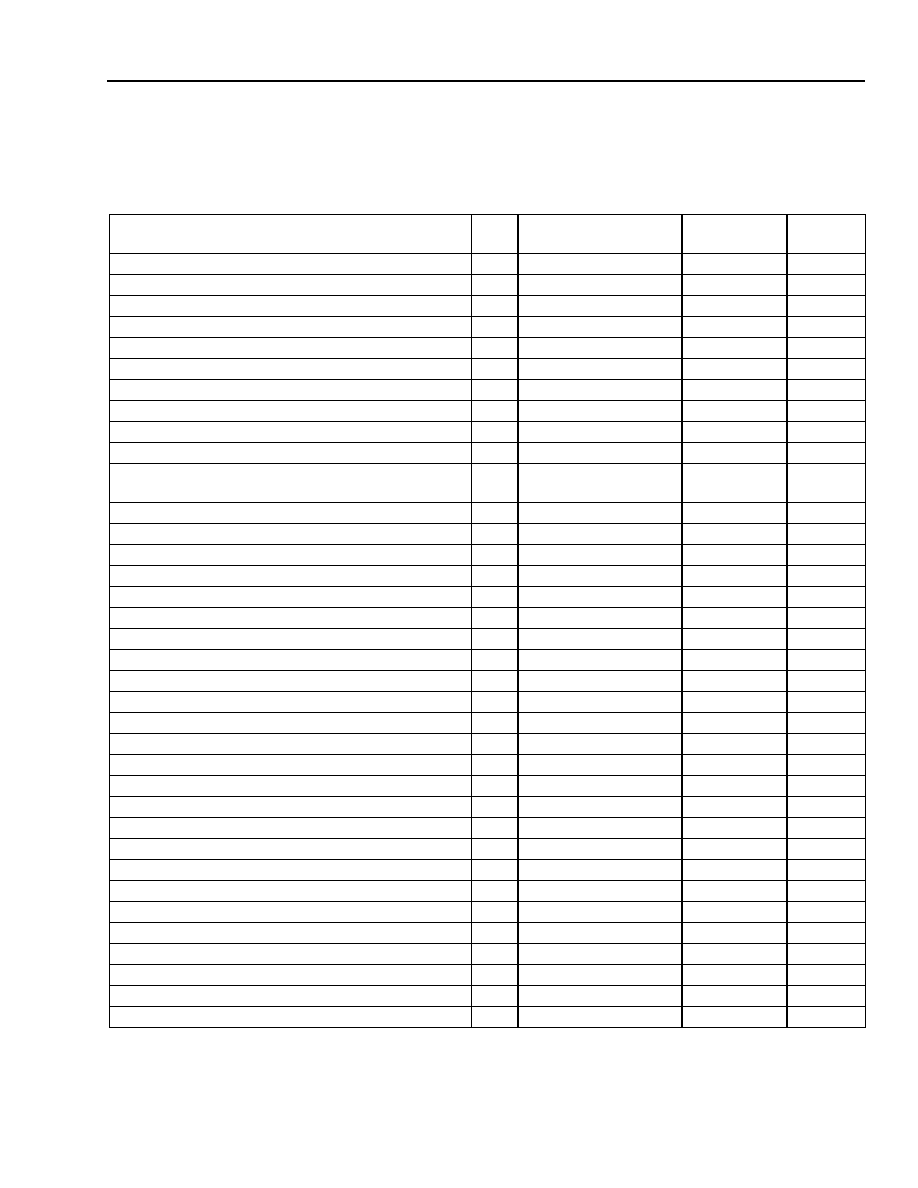

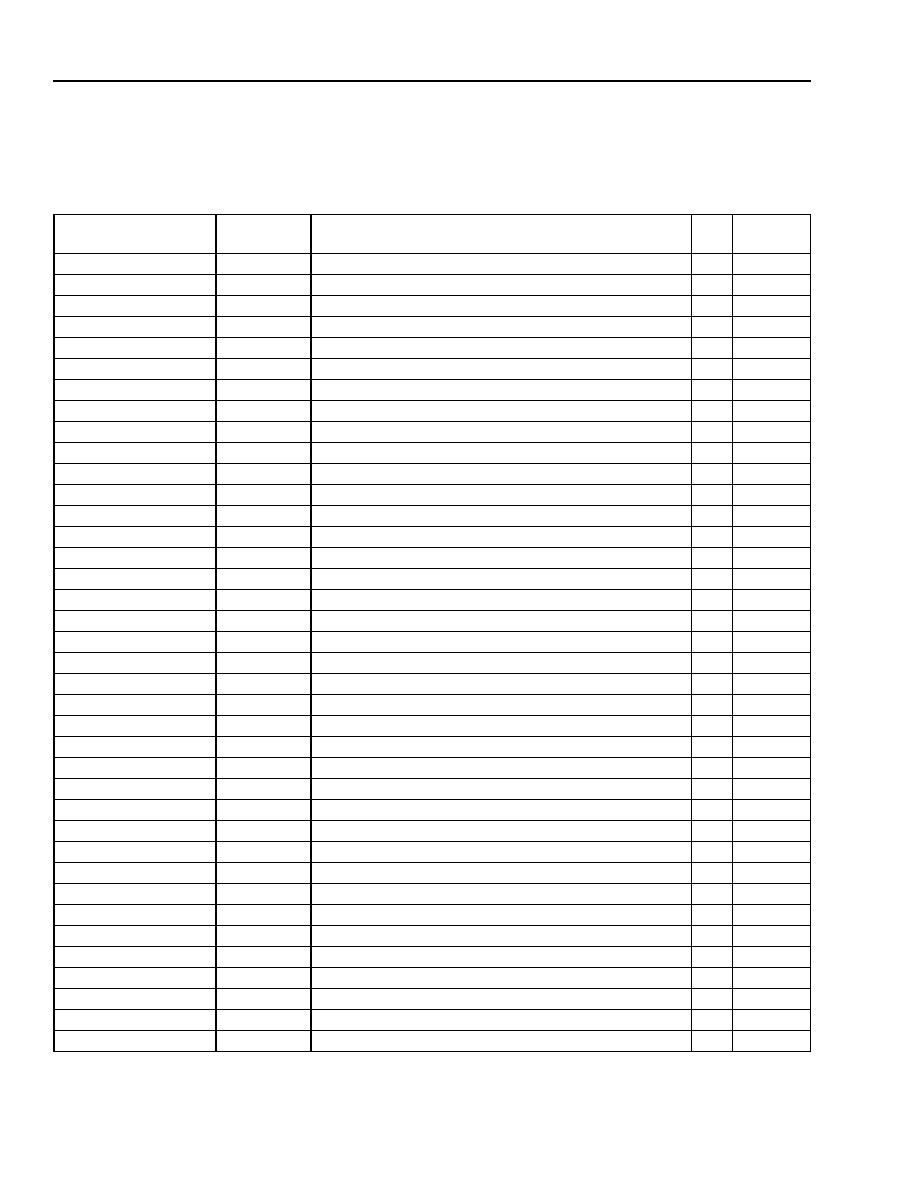

List of Tables

(continued)

Tables

Page

Table 101. Fast Convergence Beta 2 Register (06C) [05] ....................................................................................105

Table 102. Slow Convergence Beta 1 Register (06D) [12] ...................................................................................105

Table 103. Slow Convergence Beta 2 Register (06E) [05] ...................................................................................106

Table 104. Fast Convergence Gain Time Register (06F) [20] ..............................................................................106

Table 105. Fast Convergence NLP Beta Time Register (070) [20].......................................................................107

Table 106. Alpha Voice Hybrid Return Loss Threshold (071) [40] ........................................................................107

Table 107. Echo Cancellation Convergence Register (072) [05] ..........................................................................108

Table 108. Alpha Data Hybrid Return Loss Threshold Register (073) [40] ...........................................................109

Table 109. Near-End Speech 1 Hangover Register (074) [FF] .............................................................................109

Table 110. NLP Hangover Register (075) [10] ......................................................................................................110

Table 111. Near-End Speech 3 Hangover Register (076) [00] .............................................................................110

Table 112. Fast Convergence Threshold Register (077) [AA] ..............................................................................110

Table 113. Transient NLP Threshold Register (078) [00] .....................................................................................111

Table 114. H-Reset Threshold Register (079) [00] ...............................................................................................111

Table 115. Near-End Speech Compare Threshold Register (07A) [00]................................................................111

Table 116. Test Channel Offset Register (07B) [03] .............................................................................................112

Table 117. NLP Operate Time Double Register (07C) [A3] ..................................................................................112

Table 118. High-Side 2100 Hz Peak Count Register (07D) [A4] ..........................................................................113

Table 119. Enable Í Threshold Register (07E) [18] ..............................................................................................113

Table 120. Enable Í Threshold Register (07F) [C0] .............................................................................................113

Table 121. Error Indicators 1 Register (100) .........................................................................................................114

Table 122. Interupt Masks 1 Register (101) ..........................................................................................................115

Table 123. Error Indicators 2 Register (102) .........................................................................................................116

Table 124. Interrupt Masks 2 Register (103).........................................................................................................116

Table 125. C Test Data Register (104) .................................................................................................................117

Table 126. E Test Data Bits [7:0] Register (105) ..................................................................................................117

Table 127. E Test Data Bits [15:8] Register (106) ................................................................................................117

Table 128. Tone Detector Indicator Registers (107--10E) ...................................................................................118

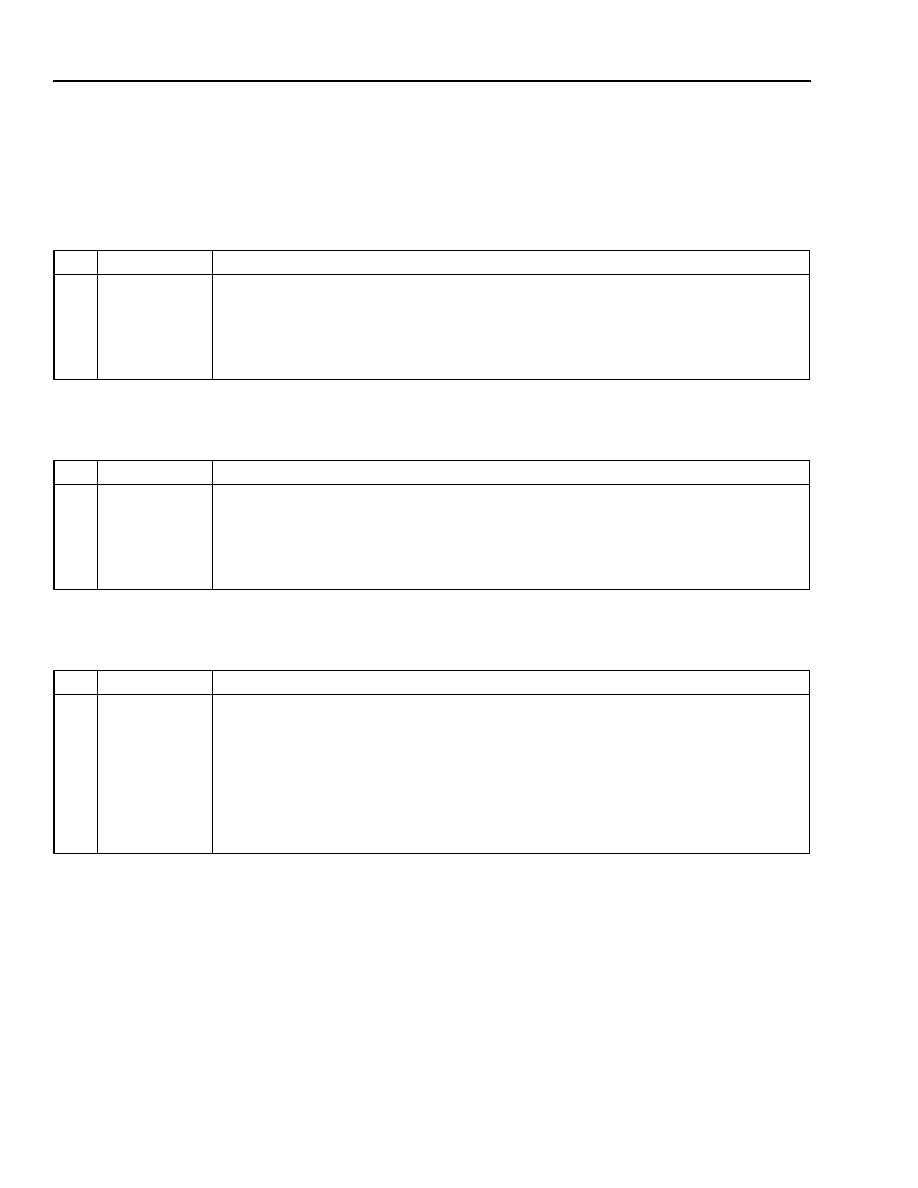

Table 129. Absolute Maximum Ratings ................................................................................................................119

Table 130. Recommended Operating Conditions .................................................................................................119

Table 131. Input and High-Impedance Leakage Current ......................................................................................119

Table 132. Clock Input Specification .....................................................................................................................120

Table 133. Other Input Specifications ...................................................................................................................121

Table 134. Output Signal Specification .................................................................................................................123

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

8

Lucent Technologies Inc.

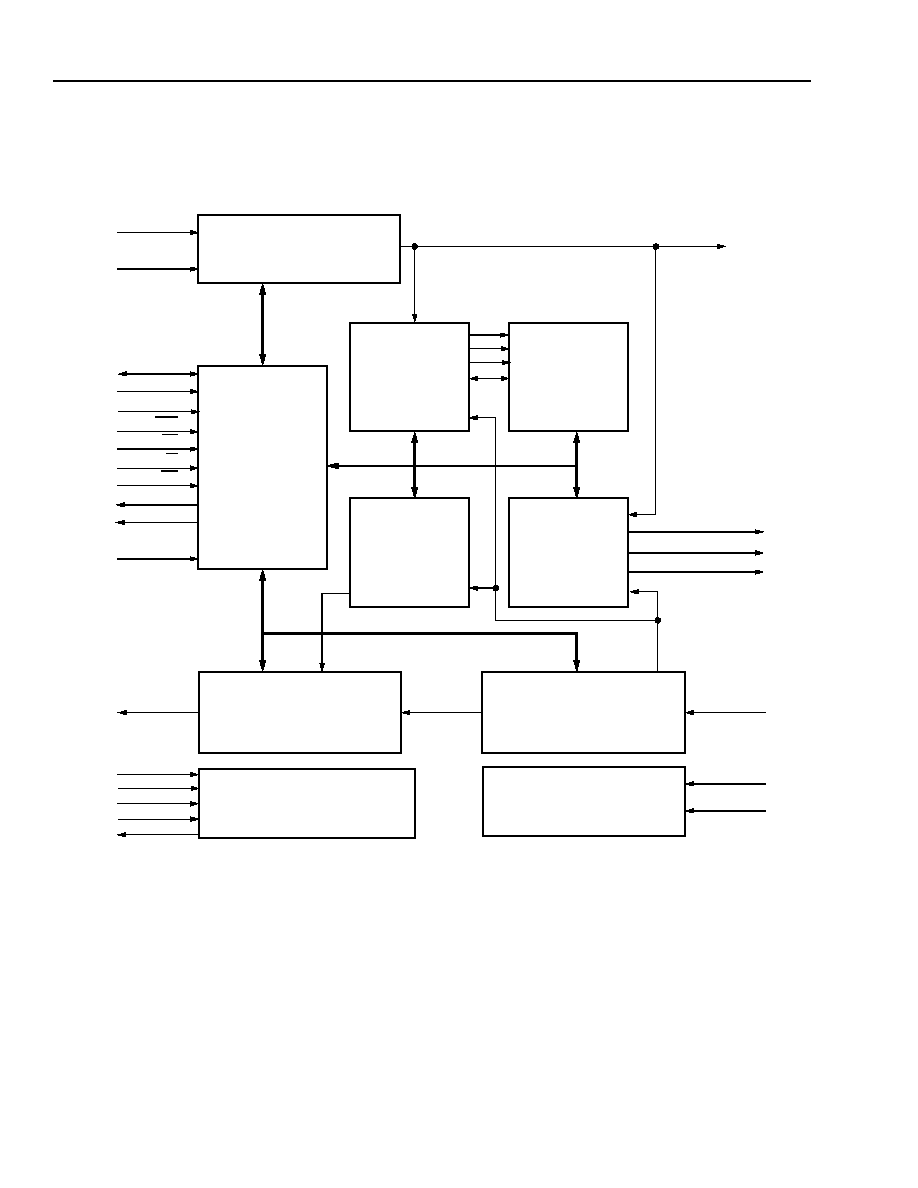

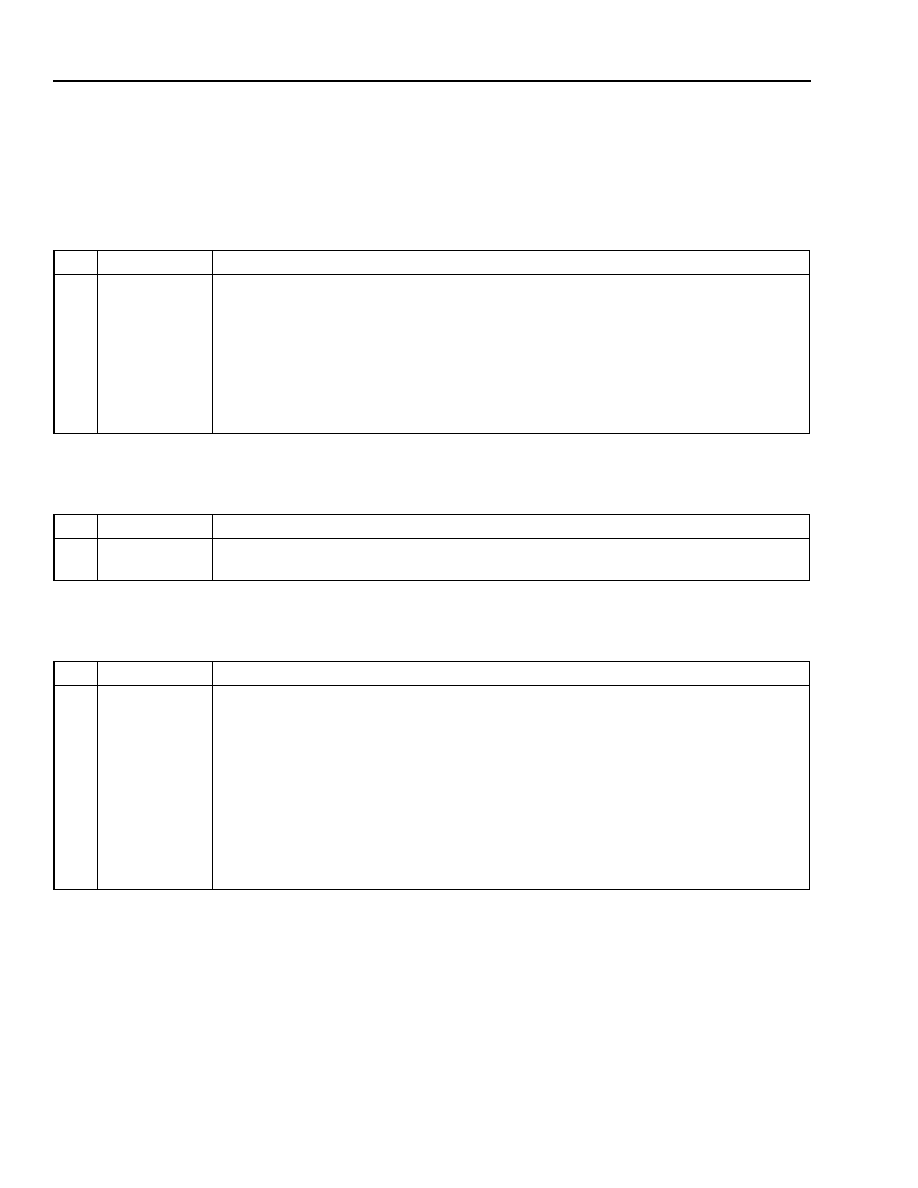

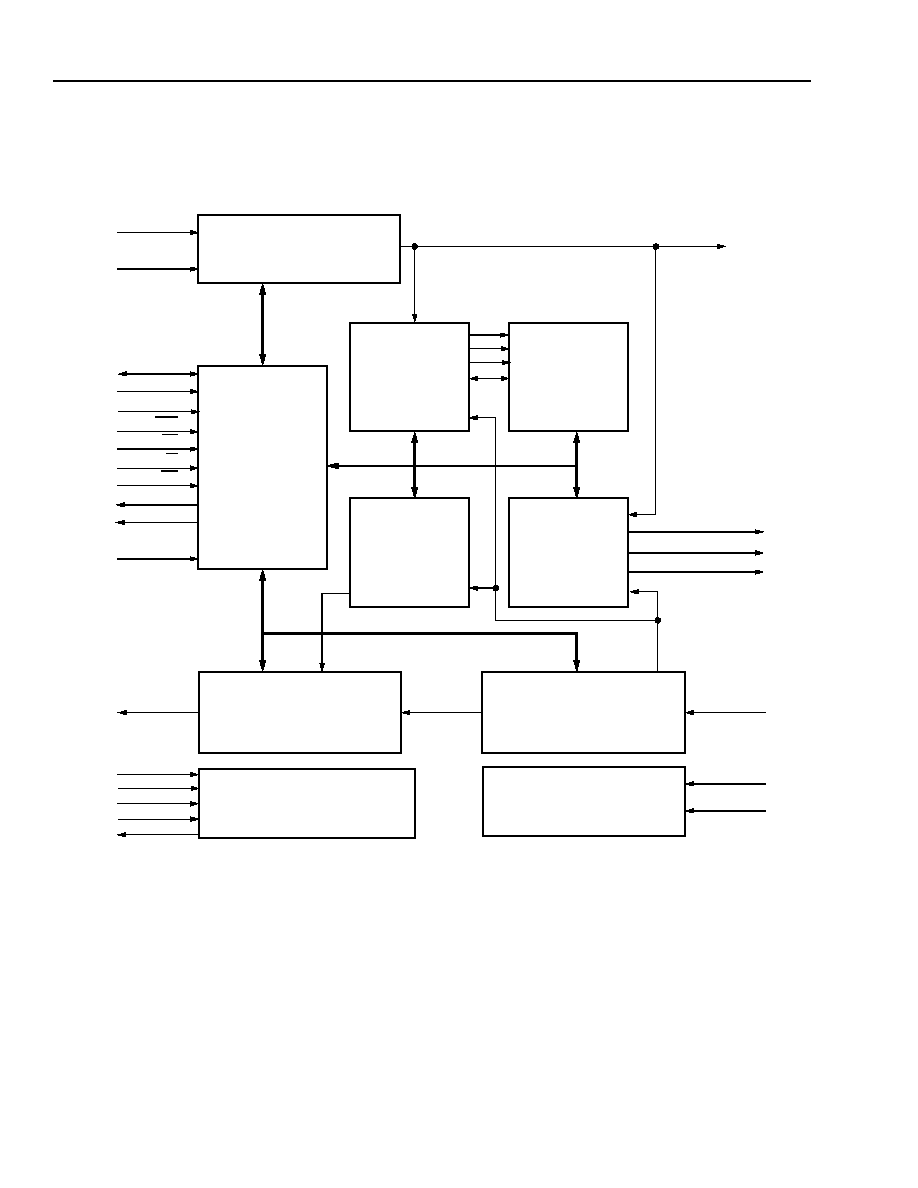

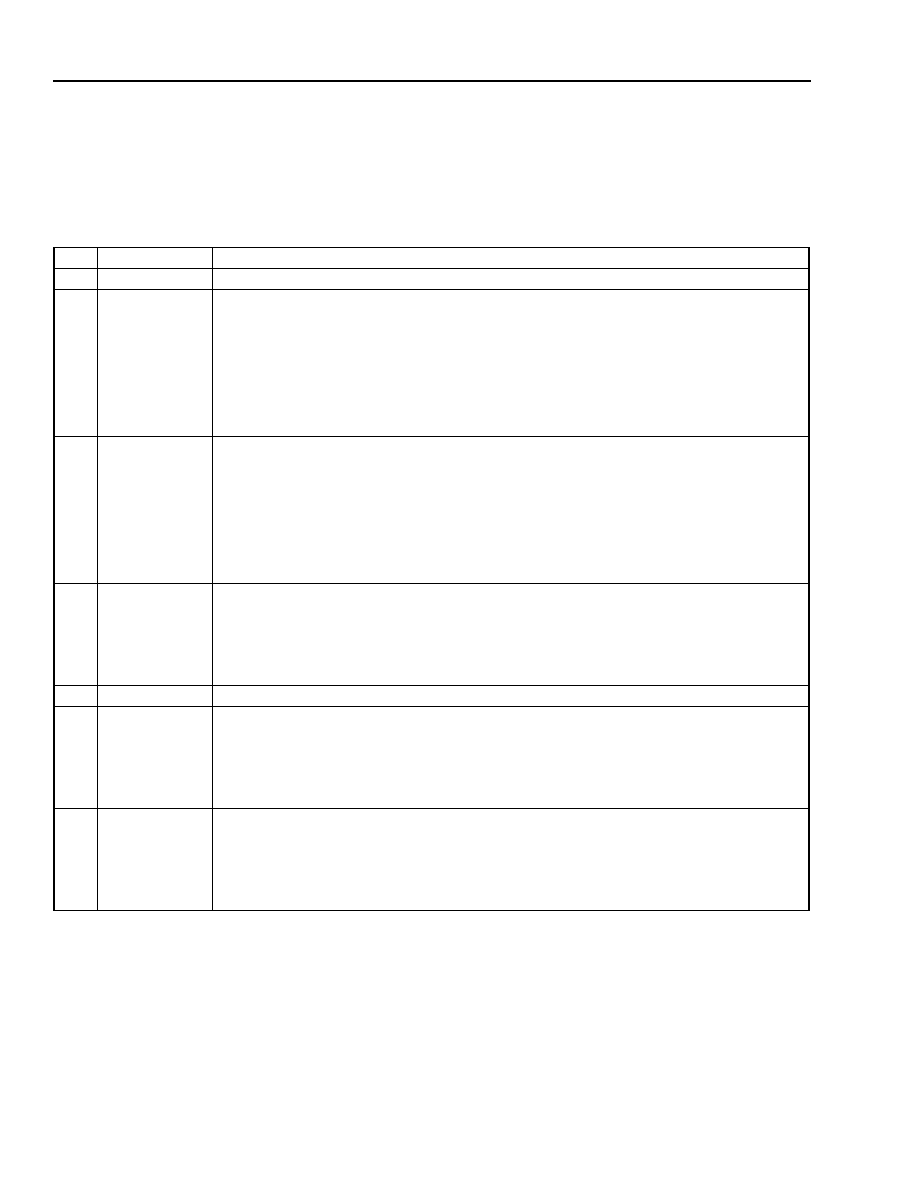

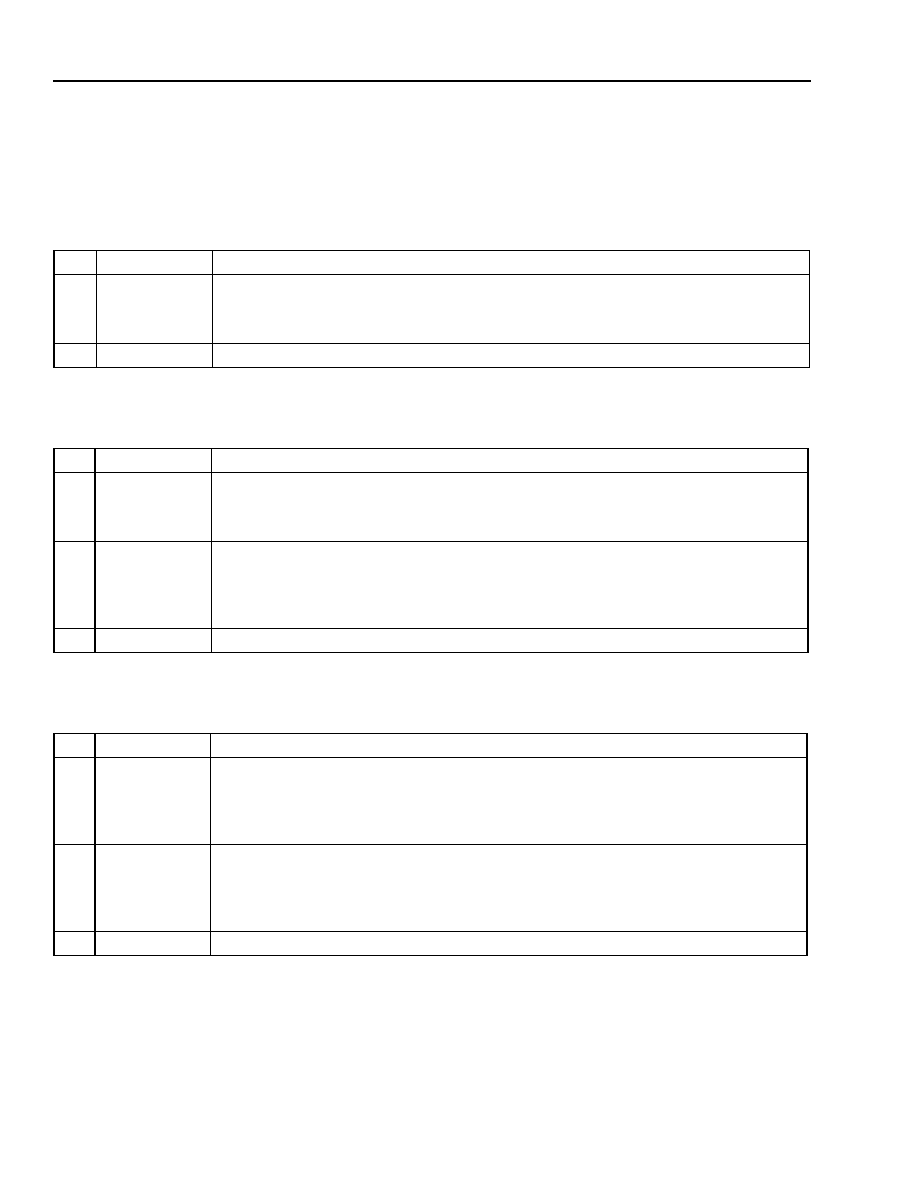

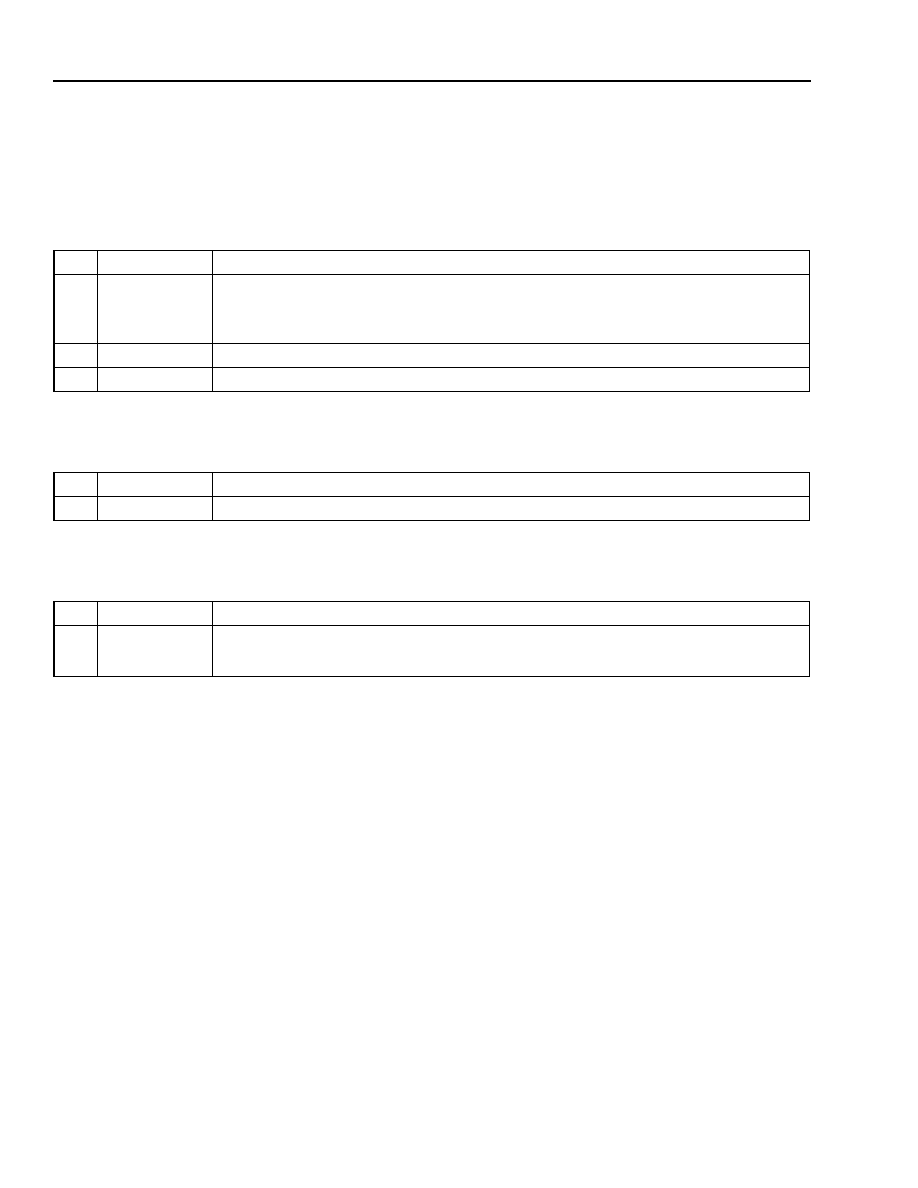

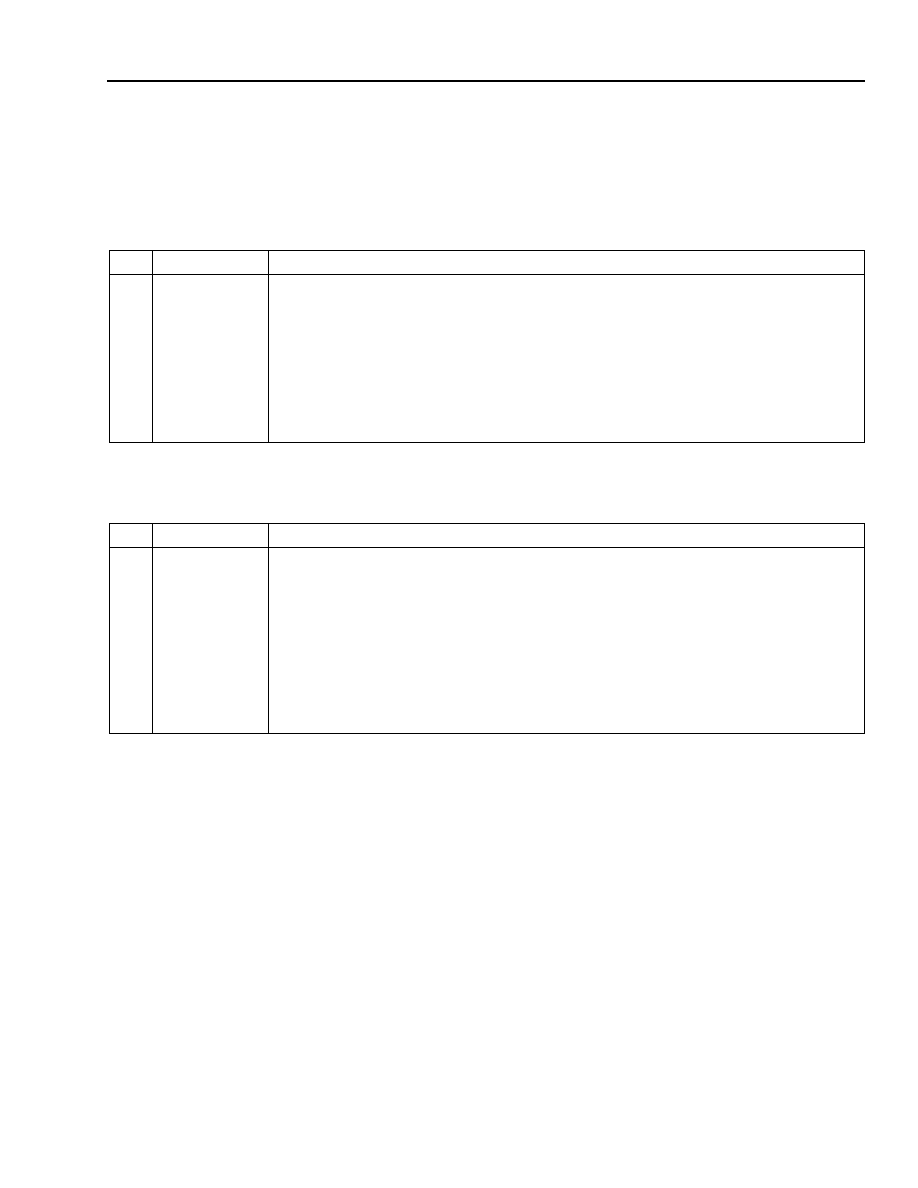

Block Diagram

The TECO3264 32-channel echo canceller block diagram is shown in Figure 1, 32-Channel Echo Canceller Block

Diagram.

5-5252(F).cr.2

* Active-high or active-low depends on microprocessor (

Intel

or

Motorola

).

Intel

is a registered trademark of Intel Corporation.

Motorola

is a registered trademark of Motorola, Inc.

Figure 1. 32-Channel Echo Canceller Block Diagram

TIMING

TEST ACCESS

E(PCM/LINEAR)

MICROPROCESSOR

CONVOLUTION

SRAM

NONLINEAR

TONE

Y(PCM/LINEAR)

CK8M

TONE

TDPR

VPA

YPCM

SYNC

TDO

CPCM

XPCM

XLINEAR

AS

ALE

UPMD

A[9:0]

D[7:0]

R/W

DS

DTACK*

INT*

RST

EPCM

TRST

TCK

TDI

TMS

UPDATE

PROCESSOR

X(PCM/LINEAR) HIGHWAY

CONTROL BLOCK

(XPCM)

INTERFACE

AND

CONTROL

BLOCK

PROCESSOR

HIGHWAY CONTROL BLOCK

(EPCM)

PORT CONTROLLER

HIGHWAY CONTROL BLOCK

(YPCM)

GENERATOR

DISABLER

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

9

Lucent Technologies Inc.

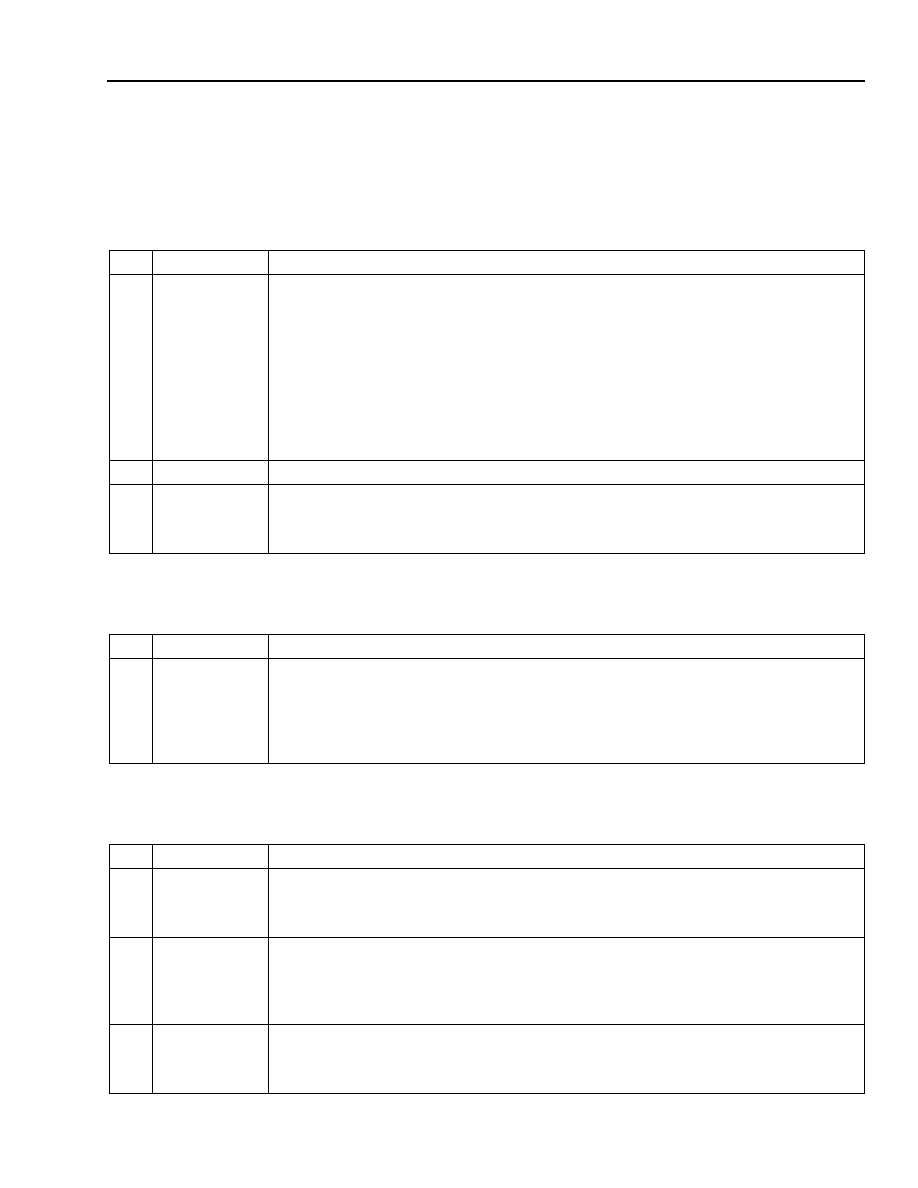

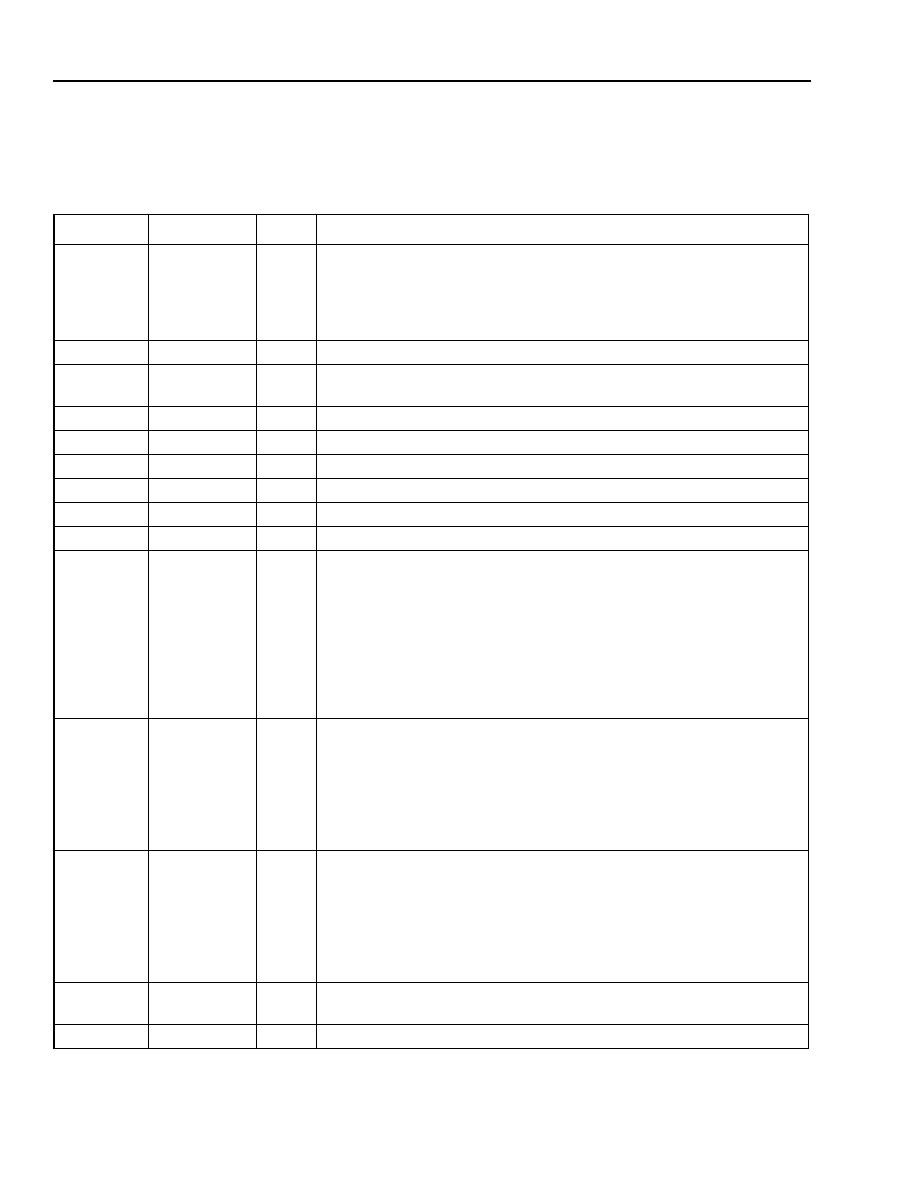

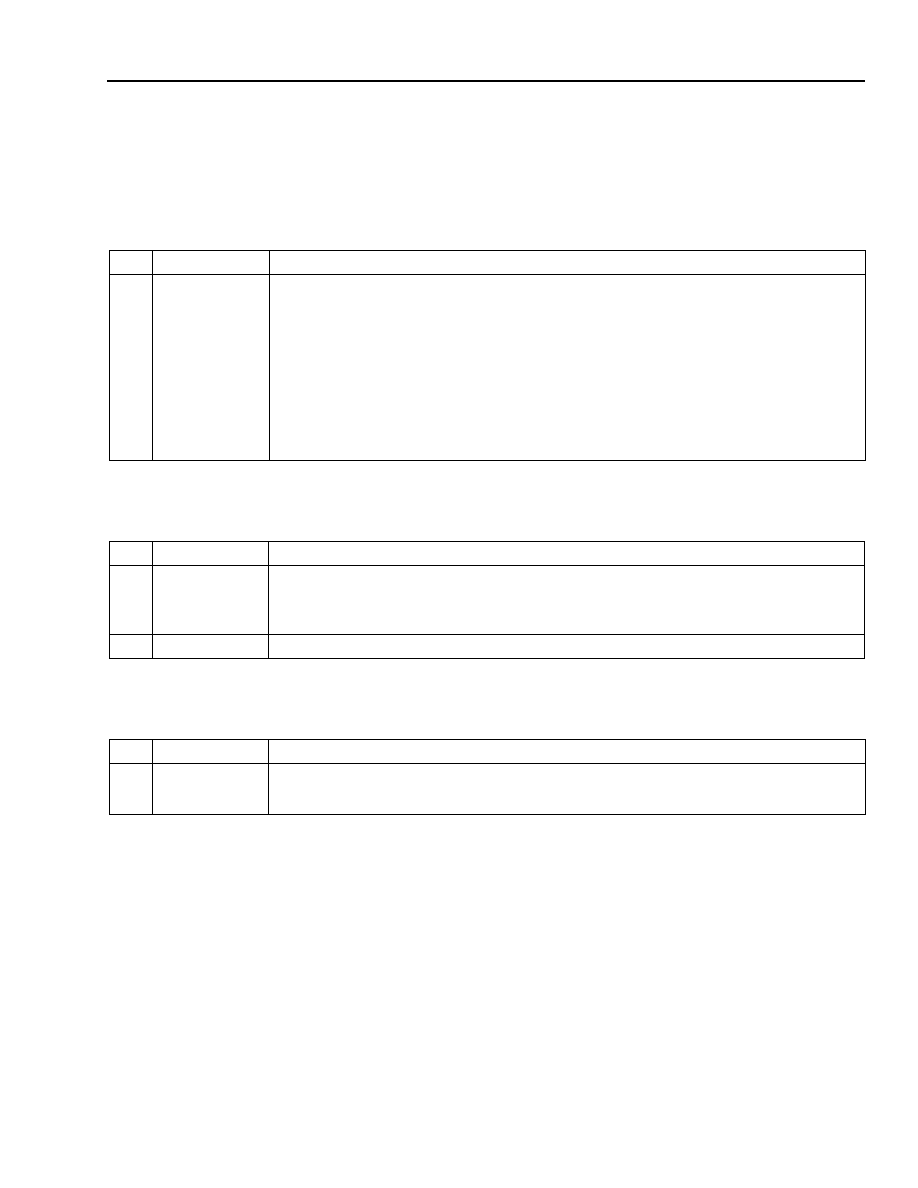

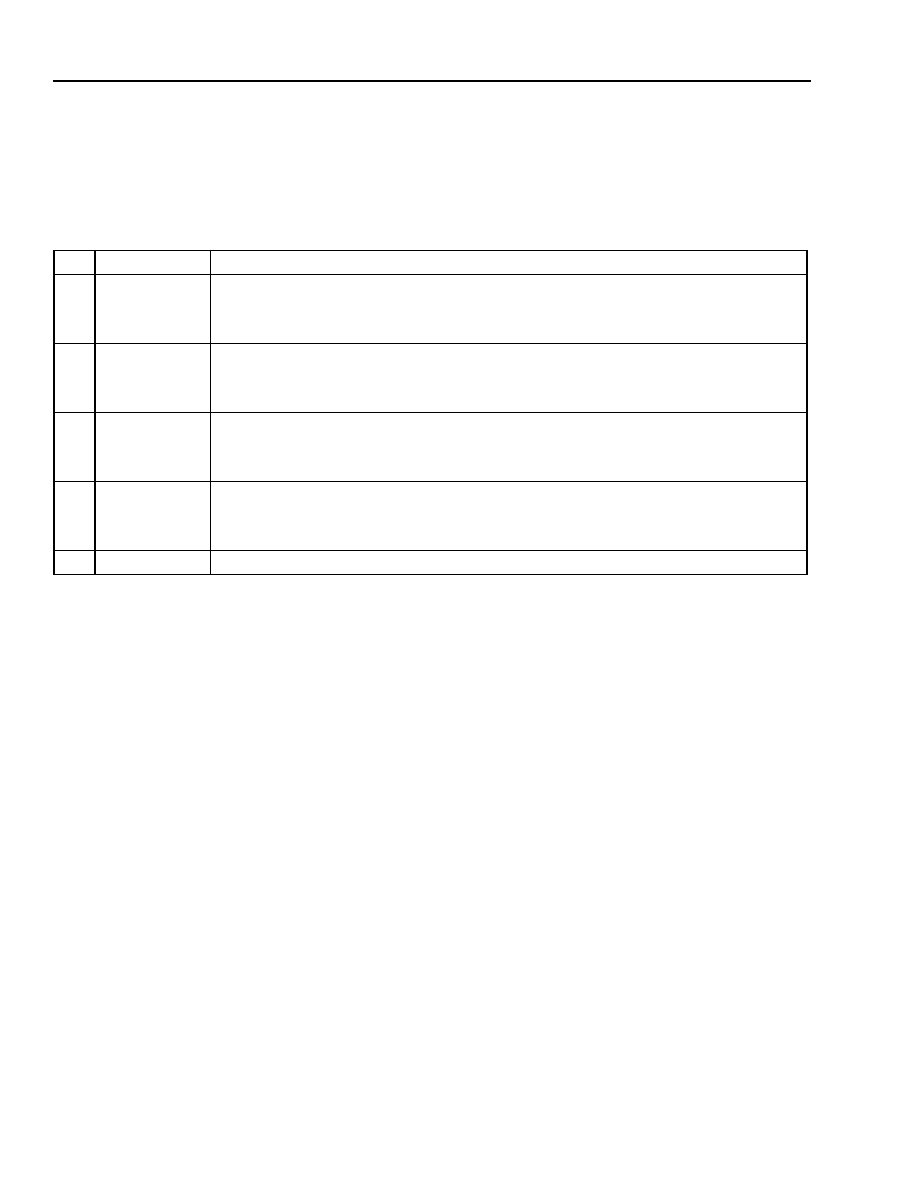

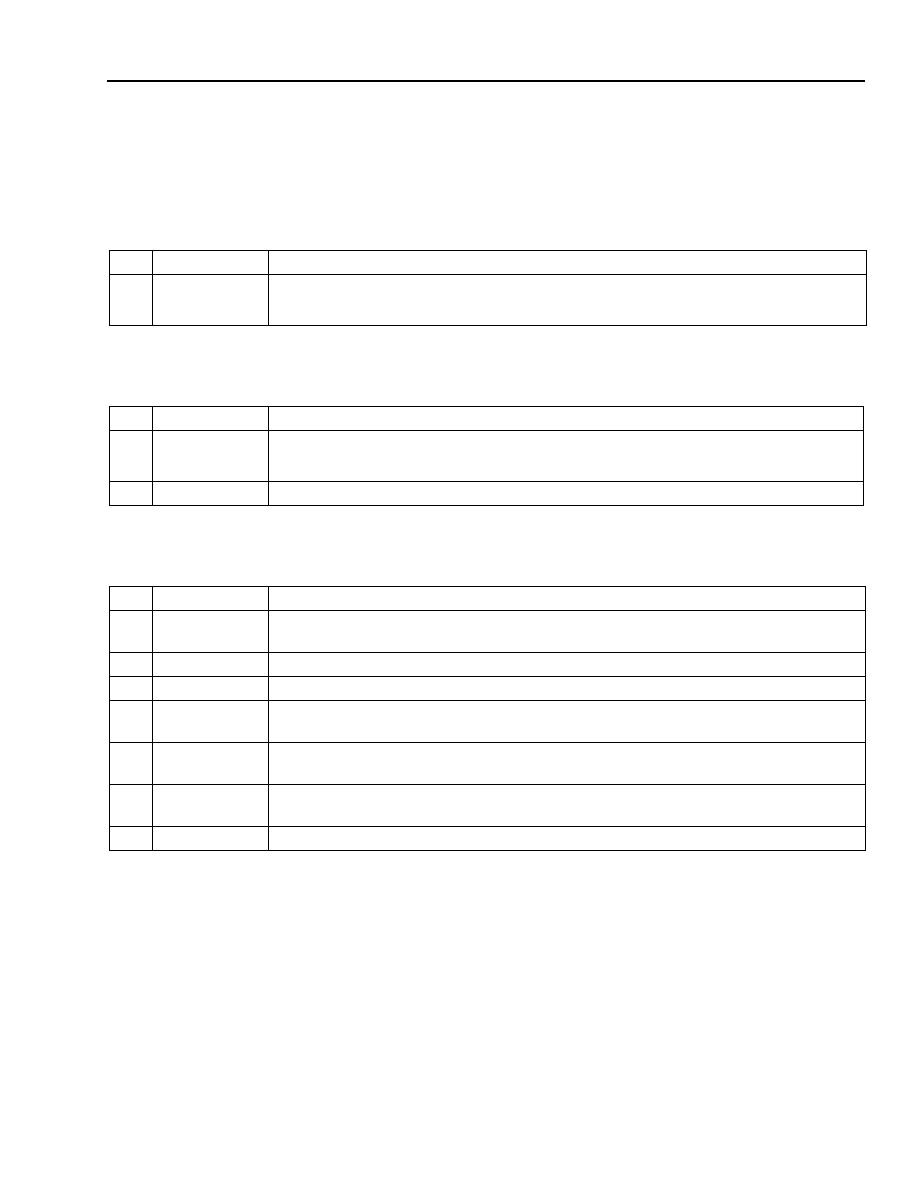

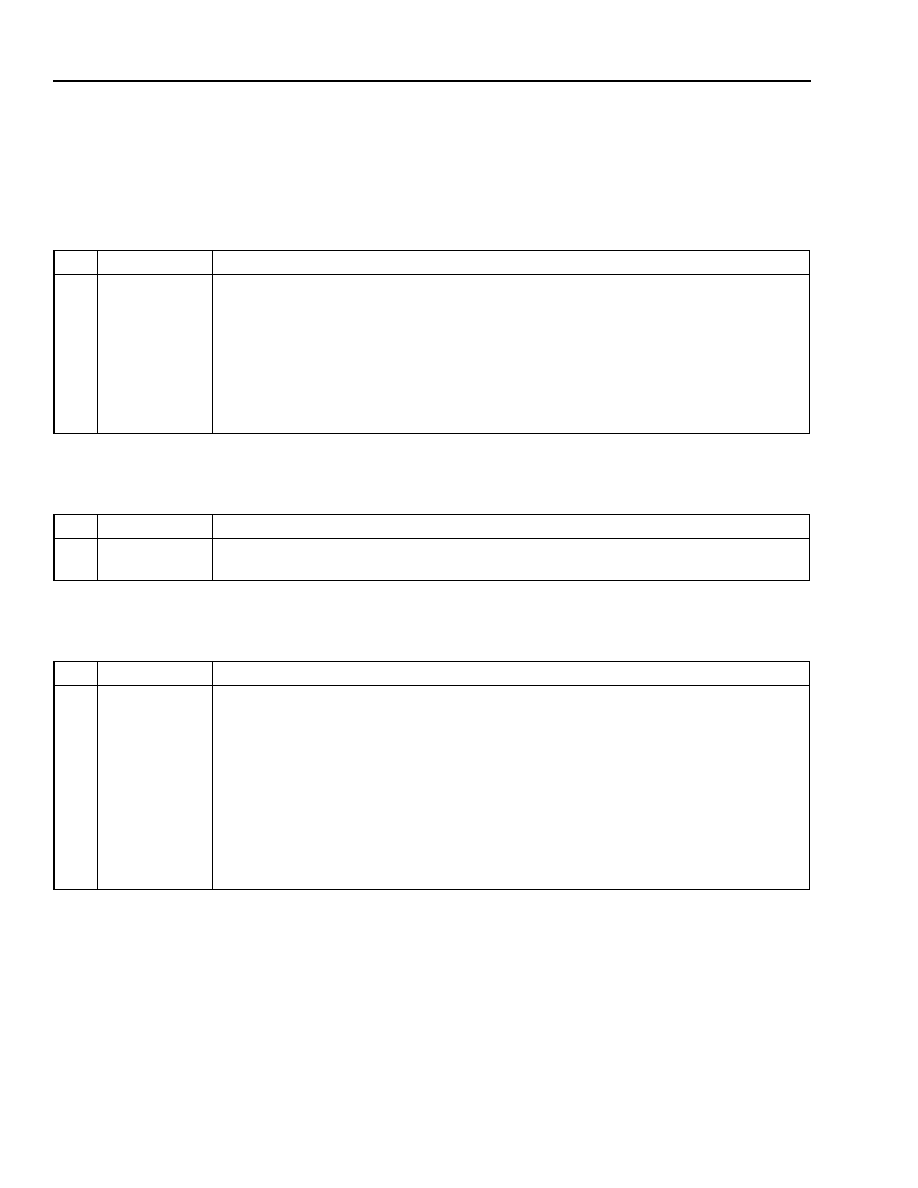

Pin Information

Pin Assignment

5-5316(F)r.6

Note:

INT, DTACK is active-high when interfacing with

Intel

microprocessors.

INT, DTACK is active-low when interfacing with

Motorola

microprocessors.

Figure 2. Pin Assignment

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

42

43

44

45

46

47

49

50

51

52

53

54

55

57

61

62

63

65

67

69

70

71

72

73

74

75

76

77

79

80

56

58

59

66

48

64

41

60

68

78

TD

O

SC

AN

CK

32

TS

TM

D

HIG

H

Z

VS

S

IN

T

TO

N

E

TD

P

R

VP

A

HDS

P

VD

D

H

SYN

C

TE

S

T

1

VS

S

TE

S

T

5

TE

S

T

6

VD

D

CK

8M

CK

65E

X

T

VS

S

CCK

8P

CCK

8N

V

DD_P

L

L

CD0

VSS_

P

L

L

CD1

CD2

CD4

VD

D

TE

S

T

0

TE

S

T

2

TE

S

T

3

SL

O

W

DT

A

C

K

TE

S

T

7

VD

D

TE

S

T

4

C

KEX

T

CD3

159

158

157

156

155

154

152

151

150

149

148

147

146

144

140

139

138

136

134

132

131

130

129

128

127

126

125

124

122

121

145

143

142

135

153

137

160

141

133

123

D3

D2

D1

D0

VSS

XL

IN

EA

R

SYN

C

VD

D

CP

CM

EPC

M

CA

14

CA

13

VSS

CA

11

CA

8

CA

7

CA

6

VSS

CA

3

CA

1

VD

D

CA

0

CW

E

CRO

E

CB

WE

[D]

VSS

CB

WE

[C]

CB

WE

[B

]

VD

D

CA

12

CA

10

CA

9

CA

4

XPC

M

CA

5

VD

D

VD

D

CA

2

CB

WE

[A

]

YPC

M

119

118

117

116

115

114

112

111

110

109

108

107

106

104

100

99

98

96

94

92

91

90

89

88

87

86

85

84

82

81

105

103

102

95

113

97

120

101

93

83

CD35

CD34

CD33

VDD

CD32

CD31

CD29

VSS

CD28

CD27

CD26

CD25

VDD

CD23

CD20

CD19

CD18

VDD

CD15

CD13

VSS

CD12

CD11

CD10

CD9

VDD

CD8

CD7

CD5

VSS

CD24

CD22

CD21

CD16

CD30

CD17

VSS

VSS

CD14

CD6

D4

D5

D6

D7

A0

VDD

A2

A3

A4

A5

VSS

A6

A7

A9

AS

DS

UPMD

RST

VSS

NLPFRZ

NLPEN

HRST

HFRZ

VDD

CALLB

VSC

TDI

TCK

TMS

VSS

A8

VDD5

ALE

ECDIS

A1

R/W

VSS

VDD

ENBP

TRST

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

10

Lucent Technologies Inc.

Pin Information

(continued)

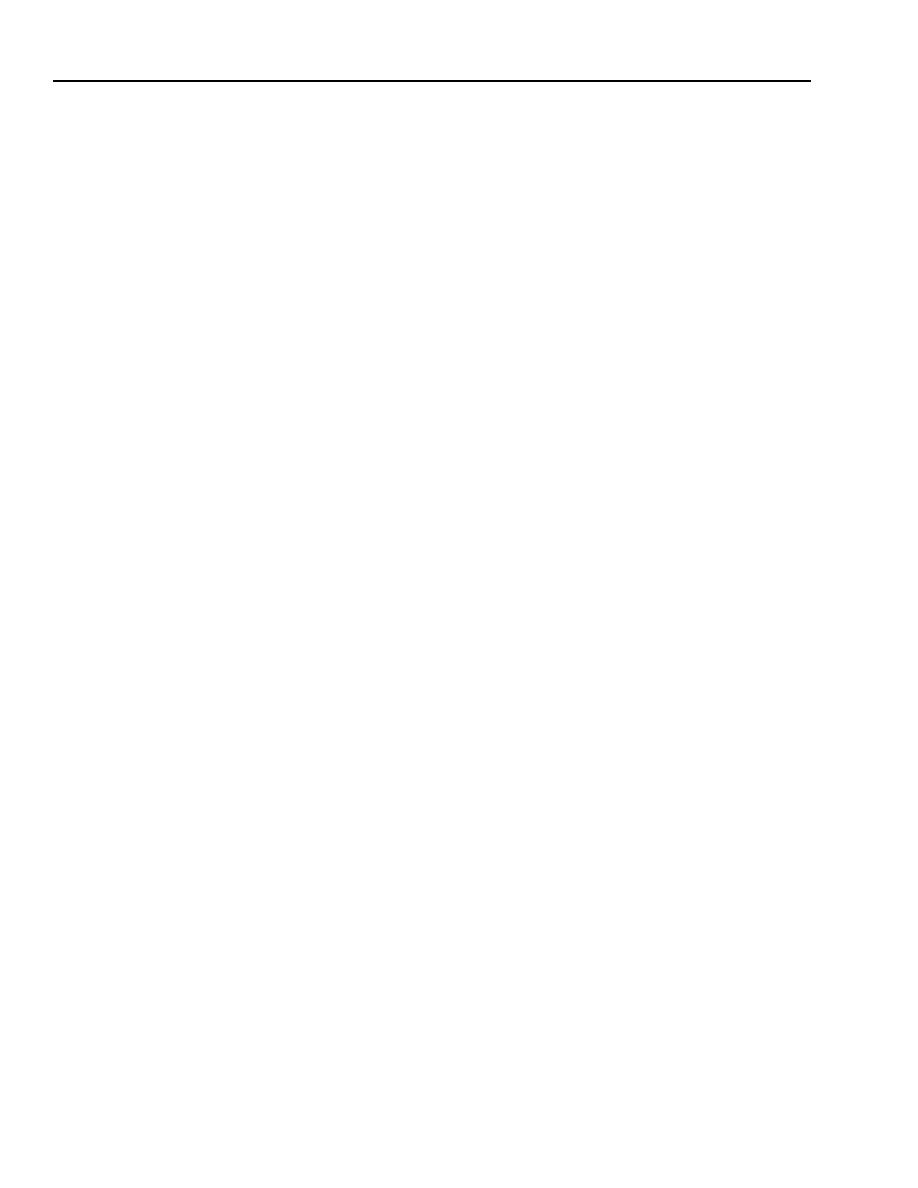

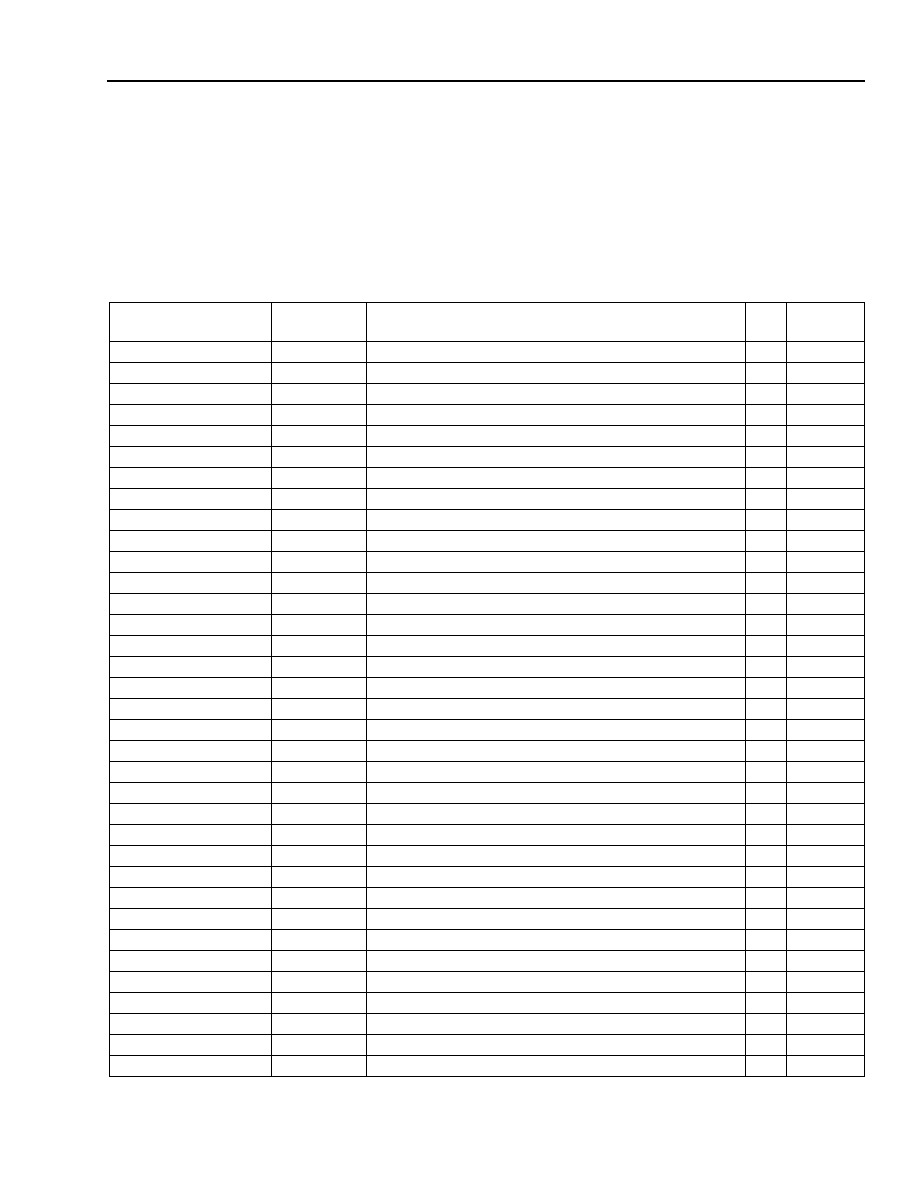

Pin Descriptions

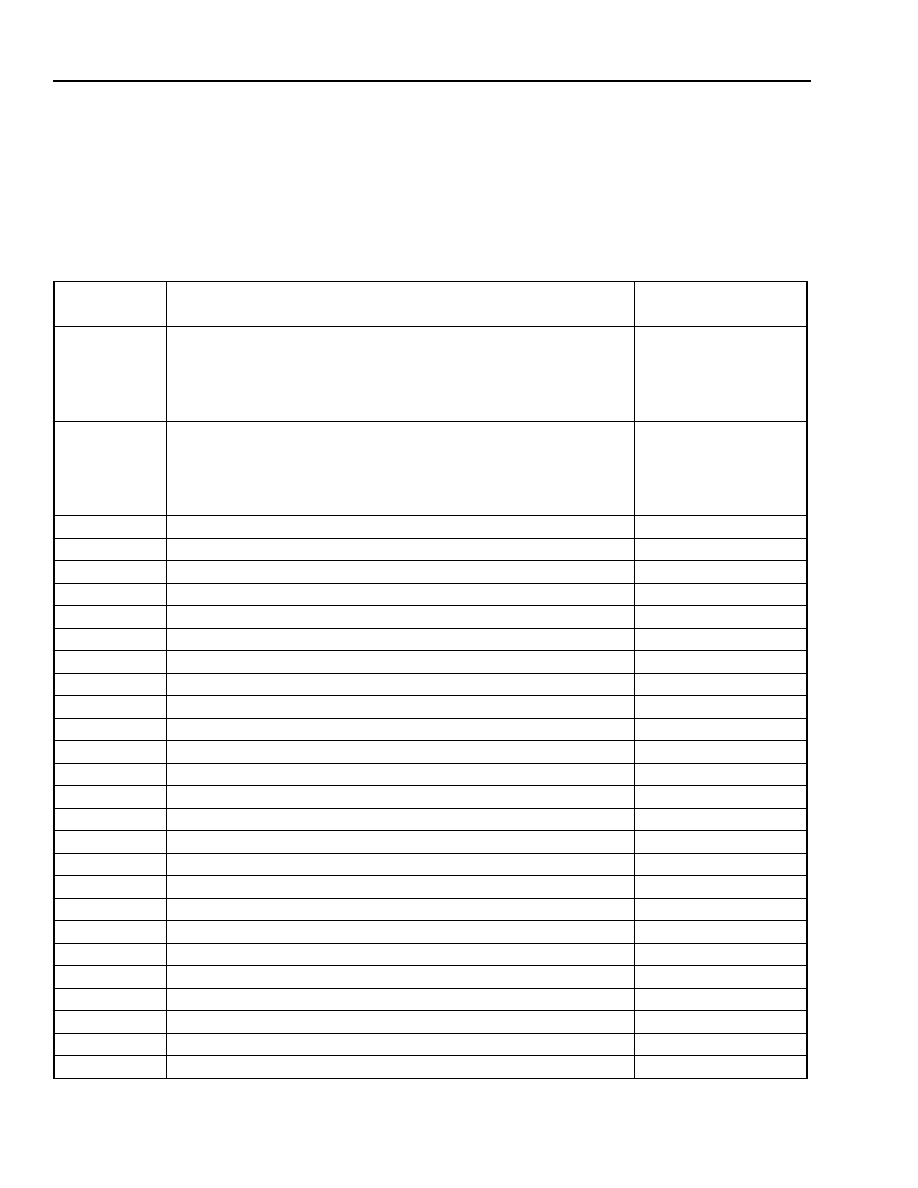

Table 1. Pin Descriptions

* I

u

indicates an internal pull-up.

Pin

Symbol

Type*

Description

152

YPCM

I

2.048/4.096 Mbits/s Near Input Serial PCM Data Stream.

153

XPCM

I

2.048/4.096 Mbits/s Far Input Serial PCM Data Stream.

154

XLINEAR

I

4.096 Mbits/s Far Input Linear PCM from Optional Coprocessor.

69

CK65EXT

I

External Clock @ 65.536 MHz. This clock is primarily intended for

factory test and should be tied low for normal use.

67

CK8M

I

Input Clock. This input clock controls the rate at which information is

sent or received on both the transmit and receive PCM streams. It

operates at 8.192 MHz.

151 SYNC

I

Frame Synchronization. The rising edge of this signal, which has a

frequency of 8 kHz, marks the beginning of a data frame. The SYNC

clock can be detected on either a rising or falling edge of CK8M by

programming the frame edge (FE) register bit. Individual time slots are

determined relative to the detection of the SYNC clock. SYNC clock

should be high for a minimum of 244 ns.

68

CKEXT

I

External/Internal Clock Select. A low on this pin will select the internal

65.536 MHz clock.

26

ECDIS

I

256 kHz Per-Channel Echo Canceller On/Off Control Stream.

(1 = on; 0 = off.)

28

ENBP

I

256 kHz Per-Channel 64-Clear On/Off Control Stream.

(1 = on; 0 = off.)

29

NLPFRZ

I

256 kHz Per-Channel NLP Freeze Control Stream.

(1 = freeze; 0 = no freeze.)

30

NLPEN

I

256 kHz Per-Channel NLP On/Off Control Stream.

(1 = on; 0 = off.)

31

HRST

I

256 kHz Per-Channel H-Reset Control Stream.

(1 = reset; 0 = no reset.)

32

HFRZ

I

256 kHz Per-Channel H-Freeze Control Stream.

(1 = freeze; 0 = no freeze.)

34

CALLB

I

256 kHz Per-Channel Call Boundary Control Stream.

(0

1 transition = call boundary event; otherwise, no call boundary

event.)

35

VSC

I

256 kHz Per-Channel Voice/Data Call Indication.

(1 = data; 0 = voice.)

19

ALE

I

Microprocessor Interface Address Latch Enable (Active-Low).

21

AS

I

Microprocessor Interface Address Strobe (Active-Low).

22

DS

I

Microprocessor Interface Data Strobe (Active-Low).

23

UPMD

I

Microprocessor Interface Mode. (1 =

Motorola

; 0 =

Intel

.)

24

R/W

I

Microprocessor Interface Read/Write Control. (1 = read; 0 = write.)

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

11

Lucent Technologies Inc.

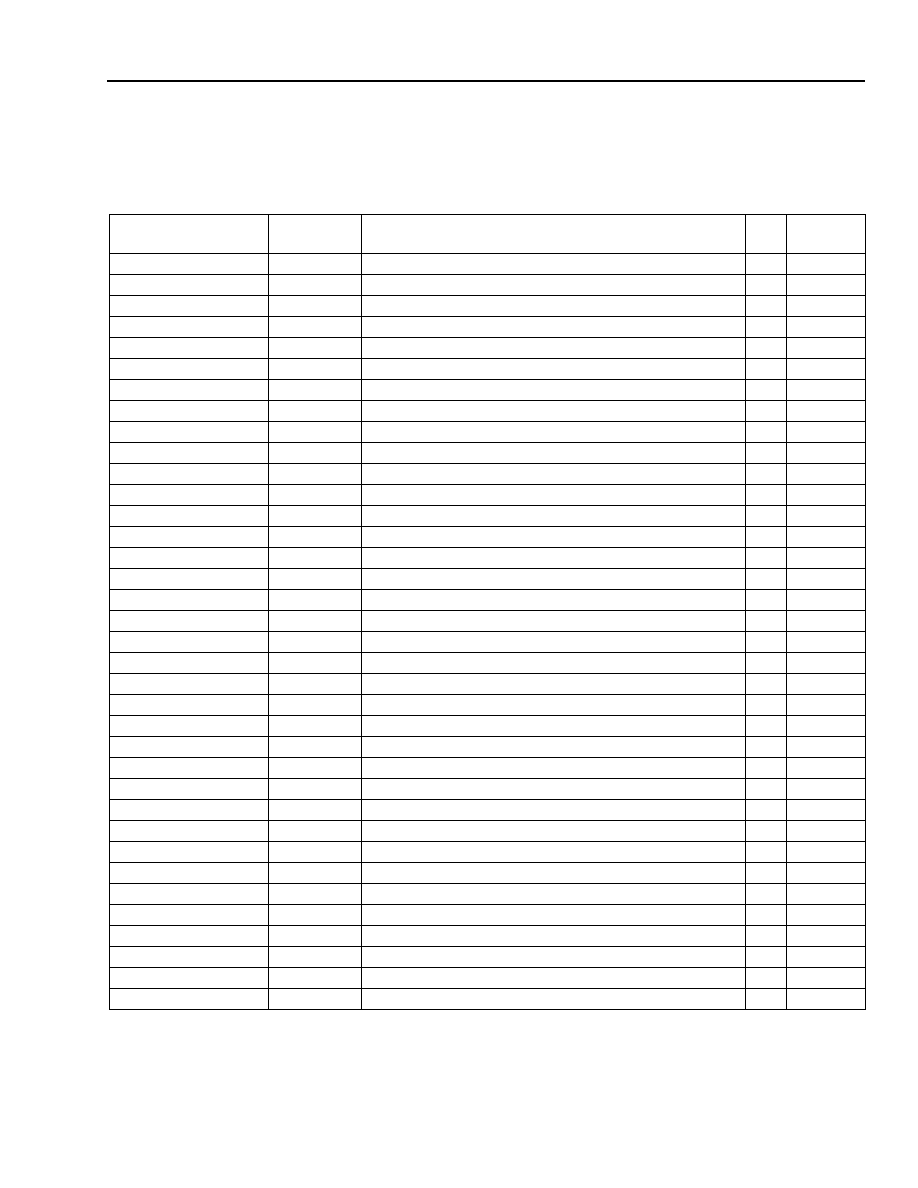

Pin Information

(continued)

Pin Descriptions

(continued)

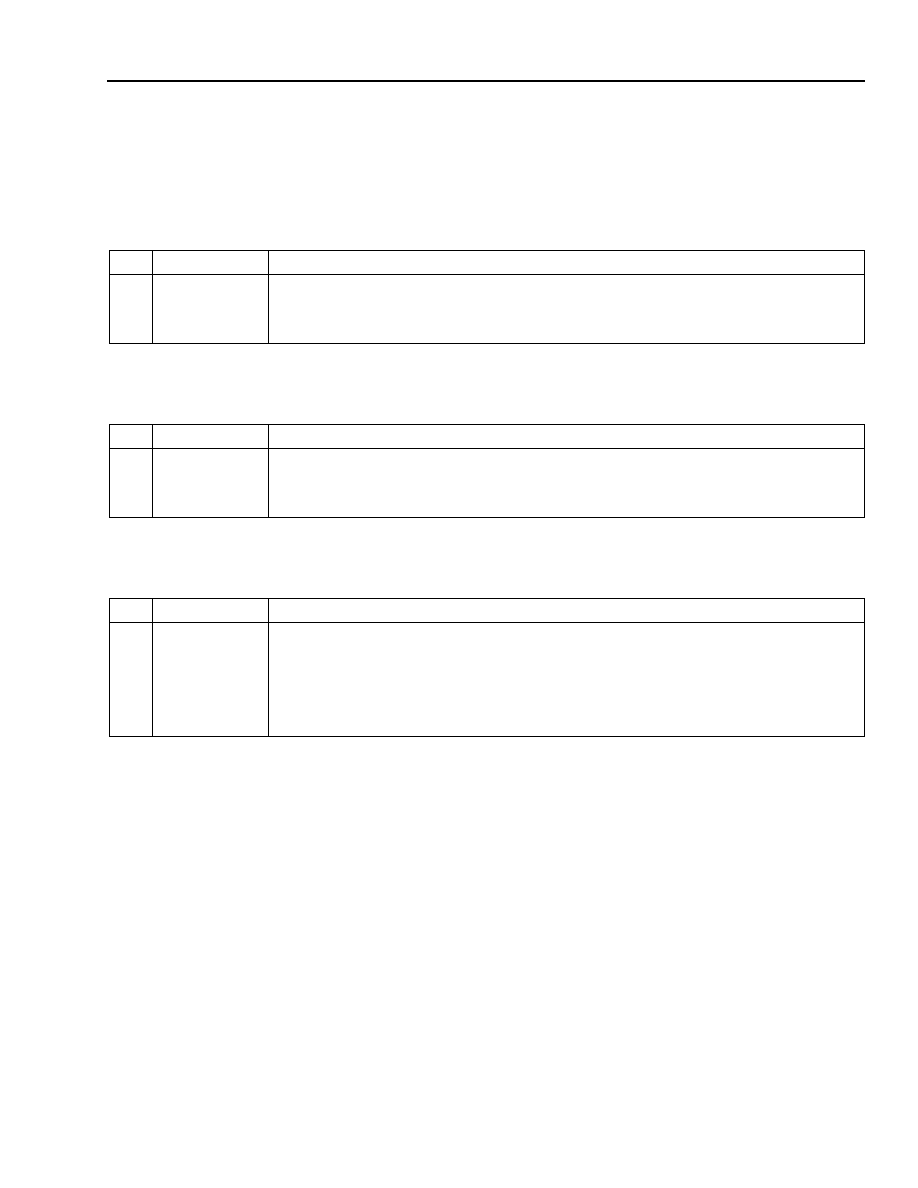

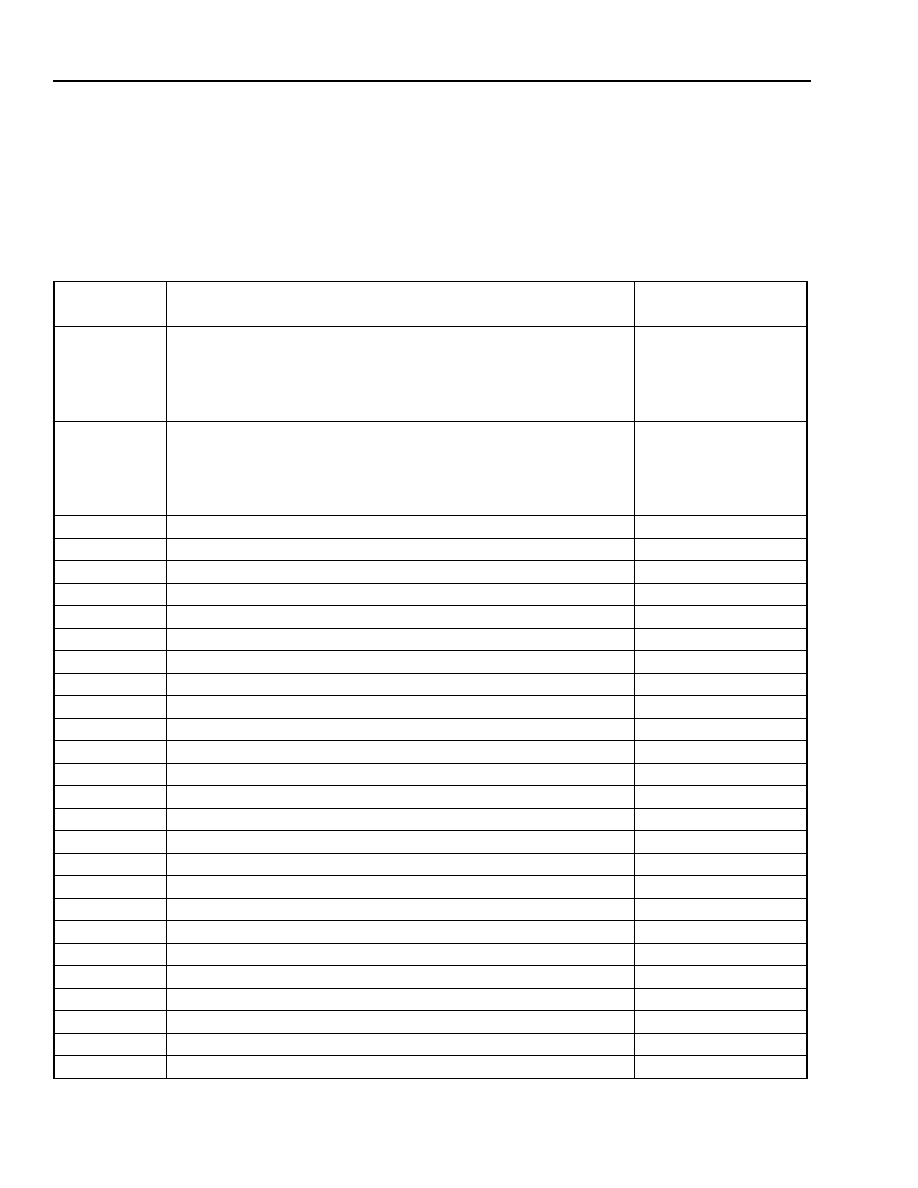

Table 1. Pin Descriptions (continued)

* I

u

indicates an internal pull-up.

Pin

Symbol

Type*

Description

48

DTACK

O

Microprocessor Interface Write Acknowledge. DTACK is active-high in

the

Intel

mode and active-low in the

Motorola

mode. For the family of

Intel

8086 microprocessors, DTACK corresponds to RDY.

49

INT

O

Microprocessor Interrupt. INT is active-low in the

Motorola

mode and

active-high in the

Intel

mode, i.e.,

Intel

8086 family. In other

Intel

devices,

INT may be an active-low signal depending on the device.

6, 8--12,

14--17

A[0:9]

I

Microprocessor Interface Address Bus.

156--159,

2--5

D[0:7]

I/O

8-Bit Microprocessor Data Bus.

36

TDI

I

u

Boundary-Scan Test Data Input.

37

TCK

I

Boundary-Scan Test Clock Input. TCK must have a clock input at all

times to keep the TAP controller in an idle state.

38

TRST

I

u

Boundary-Scan Test Input. If not used, this pin must be held low.

39

TMS

I

u

Boundary-Scan Test Mode Select.

42

TDO

O

Boundary-Scan Data Output.

43

SCAN

I

SCAN Mode Switch. Leave unconnected for normal operation.

45

TSTMD

I

Static Test Enable for SCAN. Leave unconnected for normal operation.

46

HIGHZ

I

u

Force All Outputs to High-Impedance (Active-Low).

66

SLOW

I

u

Test Input. Leave unconnected for normal operation.

25

RST

I

Chip Reset (Active-High). Must be active for 500

µ

s.

18

V

DD

5

I

5.0 V Supply. For 5.0 V tolerant I/O; otherwise, connect to 3.3 V supply

(V

DD

).

148

EPCM

O

2.048/4.096 Mbits/s Far Output Serial PCM Data Stream.

149

CPCM

O

2.048/4.096 Mbits/s Near Output Serial PCM Data Stream.

71, 72

CCK8[P, N]

O

Balanced 8.192 MHz Clock Output (Factory Use Only).

44

CK32

O

32.768 MHz Clock Output for H-Register Data.

55

HSYNC

O

H-Register Data Sync Pulse. Occurs once per 16

µ

s and is one

32.768 MHz clock cycle wide.

53

HDSP

O

H-Register Data Clocked Out at 32.768 Mbits/s.

50

TONE

O

256 kHz Straight Tone Output.

51

TDPR

O

256 kHz Phase Reversed Tone Output.

52

VPA

O

256 kHz Voice Path Assurance Output.

127

CROE

O

(Factory Use.) This pin must be left unconnected.

128

CWE

O

(Factory Use.) This pin must be left unconnected.

122--124,

126

CBWE[A:D]

O

(Factory Use.) These pins must be left unconnected.

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

12

Lucent Technologies Inc.

Pin Information

(continued)

Pin Descriptions

(continued)

Table 1. Pin Descriptions (continued)

Pin

Symbol

Type

Description

129,

131--134,

136--139,

141--144,

146, 147

CA[0:14]

O

(Factory Use.) These pins must be left unconnected.

56

TEST0

O

256 kHz Per-Channel NLP On/Off Status. (1 = on; 0 = off.)

57

TEST1

O

256 kHz Per-Channel Far-End Speech (FES) Status.

(1 = FES declared; 0 = FES not declared.)

58

TEST2

O

256 kHz Per-Channel 64-Clear Status. (1 = on; 0 = off.)

59

TEST3

O

256 kHz Per-Channel EC Status. (1 = off; 0 = on.)

60

TEST4

O

256 kHz Per-Channel H-Reset Status. (1 = reset; 0 = not reset.)

62

TEST5

O

256 kHz Per-Channel H-Freeze Status. (1 = frozen; 0 = not frozen.)

63

TEST6

O

4.096 Mbits/s Í Linear PCM Data.

64

TEST7

O

256 kHz Per-Channel Convergence Mode. (1 = fast; 0 = slow.)

74, 76--79,

82--85,

87--90,

92--95,

97--100,

102--105,

107--110,

112--115,

117--119

CD[0:35]

I/O

(Factory Use.) These pins must be left unconnected.

7, 20, 33,

41, 54, 65,

80, 86, 96,

106, 116,

121, 130,

140, 150,

160

V

DD

Power

3.3 V.

1, 13, 27,

40, 47, 61,

70, 81, 91,

101, 111,

120, 125,

135, 145,

155

V

SS

Ground Ground.

73

V

DD_PLL

Power

3.3 V. Recommended bypass capacitors 10 µF, 0.047 µF, and 2700 pF,

between V

DD_PLL

and V

SS_PLL

.

75

V

SS_PLL

Ground Ground.

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

13

Lucent Technologies Inc.

Functional Description

X(PCM/Linear) Highway Control (XPCM)

XPCM provides all the PCM transport and format con-

version functions for the X to C direction of the trans-

mission. In addition, it provides a separate linear X

input which can be used to interface an external copro-

cessor device. The block also provides parallel linear

and companded PCM outputs to the convolution pro-

cessor, control, and tone disabler blocks. The parity

detection and generation as well as EC vector X test

data insertion and C data readback functions are also

performed in this block. Programmable bulk delay on

the PCM data is provided to allow up to one complete

frame delay through the device. A high-pass filter

(>10 Hz) is provided for x(t) prior to the convolution/

update block.

Y(PCM/Linear) Highway Control (YPCM)

YPCM implements the YPCM input functions and for-

mat conversion to linear for the convolution processing.

Parity detection is performed on the YPCM input, and

errors are reported to the control interface. The EC

vector Y test data insertion function is performed in this

block. Programmable bulk delay is provided to allow

arbitrary time-slot alignment of the Y input signal rela-

tive to the sync pulse. A high-pass filter (>10 Hz) is pro-

vided for y(t) prior to the convolution/update block.

E(PCM/Linear) Highway Control (EPCM)

EPCM performs the EPCM output formatting and EC

enable/disable and bypass functions. Conversion from

linear to companded PCM format is provided. Parity

generation on the EPCM output signal is performed.

Delay equalization for the EC enable/disable and

bypass functions is accomplished by the use of pro-

grammable bulk delay blocks. An additional program-

mable bulk delay block allows up to one full frame

delay for the Y to E direction of the transmission.

Convolution/Update Processor (CUP)

The primary function of the convolution/update proces-

sor (CUP) is to create a replica, (t), of the echo path

impulse response, h(t). The PCM samples at the C port

of the canceller are convolved with (t) to generate an

estimate, (t), of the echo signal y(t). The echo esti-

mate, (t), is subtracted from the echo signal, y(t), to

form the error signal, (t) ( is pronounced as ehat),

which is the main output from the convolution/update

processor.

In order to make the convergence time independent of

signal power, the gain is normalized by a measure of C

signal power before being applied to the update func-

tion. The power measure is the larger of the power esti-

mated from the sum of squares of the samples in the

register, or the power estimated from the peak signal in

the register multiplied by a peak factor.

An H-reset input is provided that sets all H taps to zero.

H-register freeze is achieved in the controller by setting

both the gain and leak values equal to zero. The

H reset must be applied for 500 ms. A serial H-register

display output is provided via HDSP (pin 53).

Nonlinear Processor (NLP)

The nonlinear processor (NLP) provides all the func-

tions necessary for the processing of the residual echo.

When enabled, the NLP can select from a variety of

alternate signal sources to switch into the signal path

for transmission on the EPCM output. These alternate

sources include quiet, noise matching, colored noise

matching, or a variably attenuated (t). The main func-

tion of the NLP is to generate these alternate sources

and switch the appropriate source into the signal path

when enabled by the control function. The NLP accepts

parametric inputs which determine the nature of the

selected alternate signal source. With the soft NLP

mode, the chosen comfort noise is inserted in a grad-

ual programmable fashion.

Tone Disablers (TD1, TD2)

The tone disabler functions (TD1, TD2) provide the

means to disable the echo cancellation function when

data or other specified tone signals are transmitted

through the echo canceller. This is accomplished by

detecting 2100 Hz tones with or without phase rever-

sals. The tone detection is performed on a per-channel

basis for both X and Y directions. The tone disablers

are tunable and capable of detecting tones in fre-

quency range and signal levels that are compliant for

voice path assurance (VPA) detection.

Microprocessor Interface and Control

(MPIC)

The microprocessor interface and control block func-

tion is to provide microprocessor access to the control,

provisioning, status, and alarm registers of the echo

canceller and to generate the signals required to con-

trol the operation of all echo canceller functions. The

functions performed in the MPIC block are described in

greater detail in the External Control Connection sec-

tion on page 14.

h^

h^

y^

y^

e^

e^

e^

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

14

Lucent Technologies Inc.

External Control Connection

Microprocessor Interface and Control

(MPIC)

As given in the Functional Description section on

page 13, the microprocessor interface and control

block functions to (1) provide microprocessor access

to the control, provisioning, option, status, and alarm

registers of the echo canceller and (2) to generate the

signals required to control the operation of all echo

canceller functions. The following paragraphs

describe the functions performed in the MPIC block.

The internal register description sections which follow

detail the parameter register information and format

for each of the user-provisionable device characteris-

tics.

Channel Control (CHAN_CTRL)

The channel control function combines inputs from the

tone disabler with the user-provisionable mask and

enable register information and external inputs to gen-

erate the channel bypass and canceller enable signals.

Narrowband Energy Detector (NBE)

The narrowband energy detector measures the X sig-

nal input characteristics to differentiate between wide-

band and narrowband signals. Based on this

determination, the near-end speech detector threshold

is provisioned. In addition, this information is used in

setting the gain applied in the echo cancellation.

Near-End Speech Detectors (NES)

The function of the near-end speech detectors is to dif-

ferentiate between far-end echo and near-end speech

at the Y input port of the canceller. The H-register

updates should only be allowed if the Y input signal is

due to far-end echo and not due to near-end speech.

Two measures of near-end speech are provided.

The near-end speech detector compares the magni-

tude of the samples in the X register to the magnitude

of the Y samples. By comparing the relative magni-

tudes of the X samples and Y samples, the existence

of near-end speech can be deduced.

Far-End Speech Detector (FES)

The function of the far-end speech detector is to deter-

mine whether there is any far-end speech present. If

there is no far-end speech, there can be no echo signal

and the H-register updates should be frozen.

In the far-end speech detector, the X sample magni-

tude is compared to a threshold parameter value and a

far-end speech condition is asserted whenever the

threshold value is exceeded.

H-Register Freeze

The H-register update is frozen whenever:

s

NBE is declared and NBE detection is unmasked, or

s

NES is declared and NES detection is unmasked, or

s

FES is not declared and FES detection is unmasked,

or

s

External freeze is requested via the microprocessor

interface or external input.

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

15

Lucent Technologies Inc.

External Control Connection

(continued)

Microprocessor Interface and Control

(MPIC)

(continued)

Fast/Slow Convergence Control (F_CONV)

NLP threshold and gain are the primary parameters

that determine convergence rate of the canceller. The

gain calculation function provisions a value for the gain

parameter and a value for the occurrence of any single

unmasked event.

The four events which cause the fast convergence

parameters to be chosen are:

1. H-register reset

2. External event such as call boundary

3. VPA tone detection

4. samples > Y samples times a threshold parameter

There is a serial output that indicates, on a per-

channel basis, the convergence mode of each channel.

See output pin TEST7.

Transient NLP Control (TRNLP)

The transient NLP control circuit can enable the NLP

whenever the power in (t) exceeds the power in Y by

a programmable threshold. These conditions exist on a

transient basis and generally indicate that the echo

canceller is not converged.

NLP Control

The NLP control function enables the NLP whenever

the magnitude of (t) exceeds the maximum magni-

tude of the samples in the X register times the NLP

threshold selected by the F_CONV function when this

feature is enabled.

The NLP may also be enabled by external command

via the microprocessor interface or external input.

e^

e^

e^

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

16

Lucent Technologies Inc.

External Control Connection

(continued)

Microprocessor Interface and Control (MPIC)

(continued)

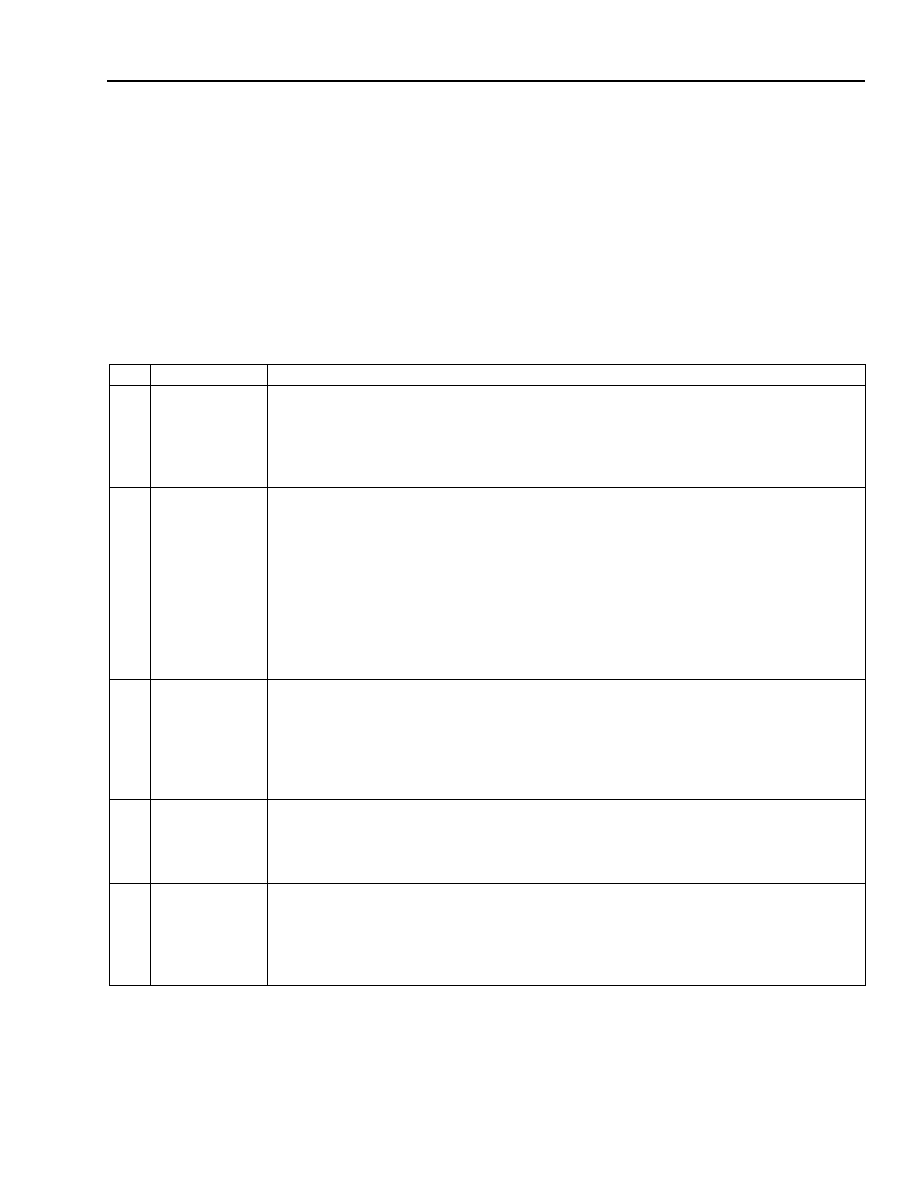

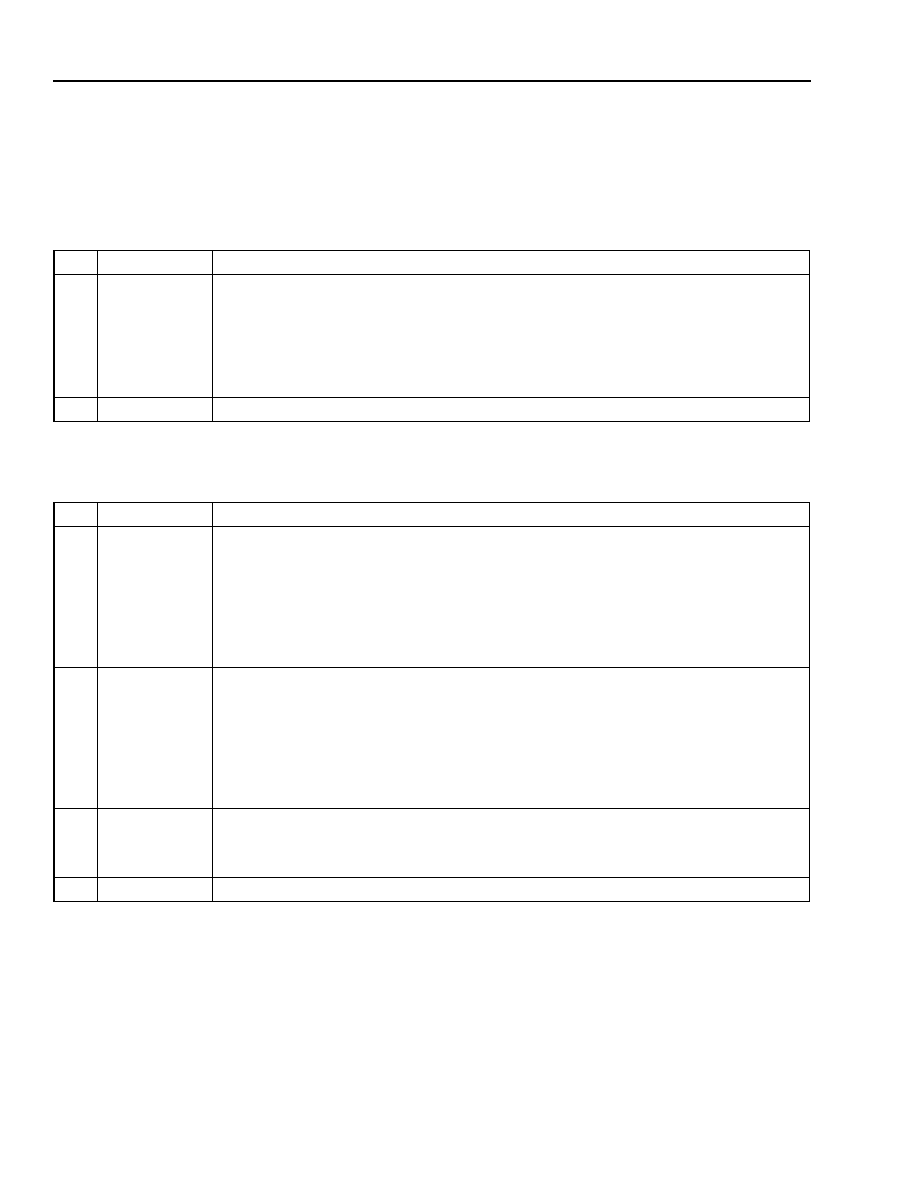

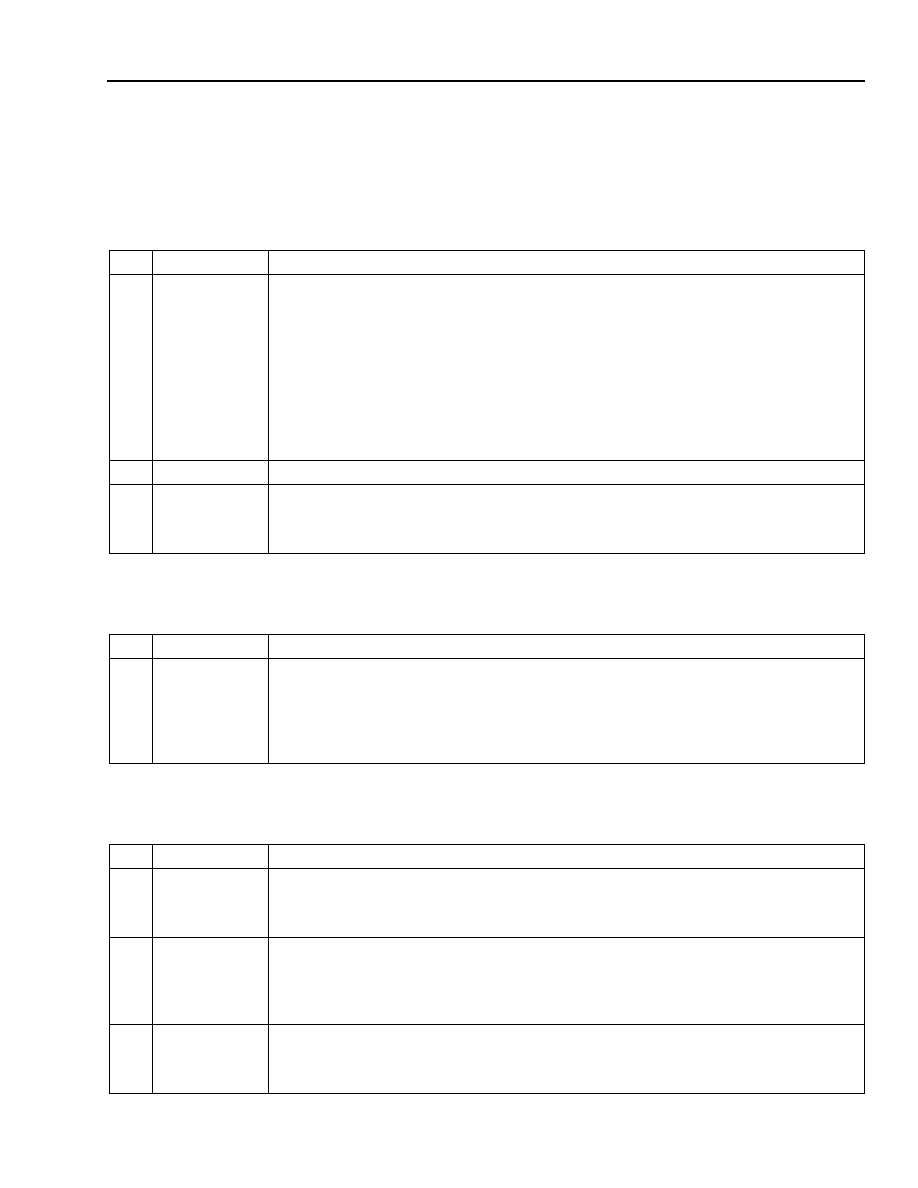

Microprocessor Interface

This interface provides microprocessor access to the control, provisioning, option, parameter, status, and alarm

registers, all of which are directly accessible via the address and data buses. Interrupt capability is also provided at

this interface.

1. All status and alarm registers are maskable and exercisable under microprocessor control.

2. The microprocessor has read and write access to the control, provisioning, option, parameter, and mask regis-

ters and read-only access to the status and alarm registers. Alarm registers are cleared when read by the micro-

processor. Microprocessor writes and reads at this interface are asynchronous to the clock.

3. The chip has access to the control, provisioning, option, and parameter registers and read-only access to the

status and alarm registers.

4. An interrupt signal is generated whenever any unmasked alarm condition is detected.

In order to provide flexibility in the choice of a microprocessor, two interface modes are supported. The primary

mode uses separate address and data buses, and interfaces directly with the

Motorola MC68000

* microprocessor

family. This mode is patterned on the microprocessor interfaces found in the T7270 Time-Slot Interchanger and

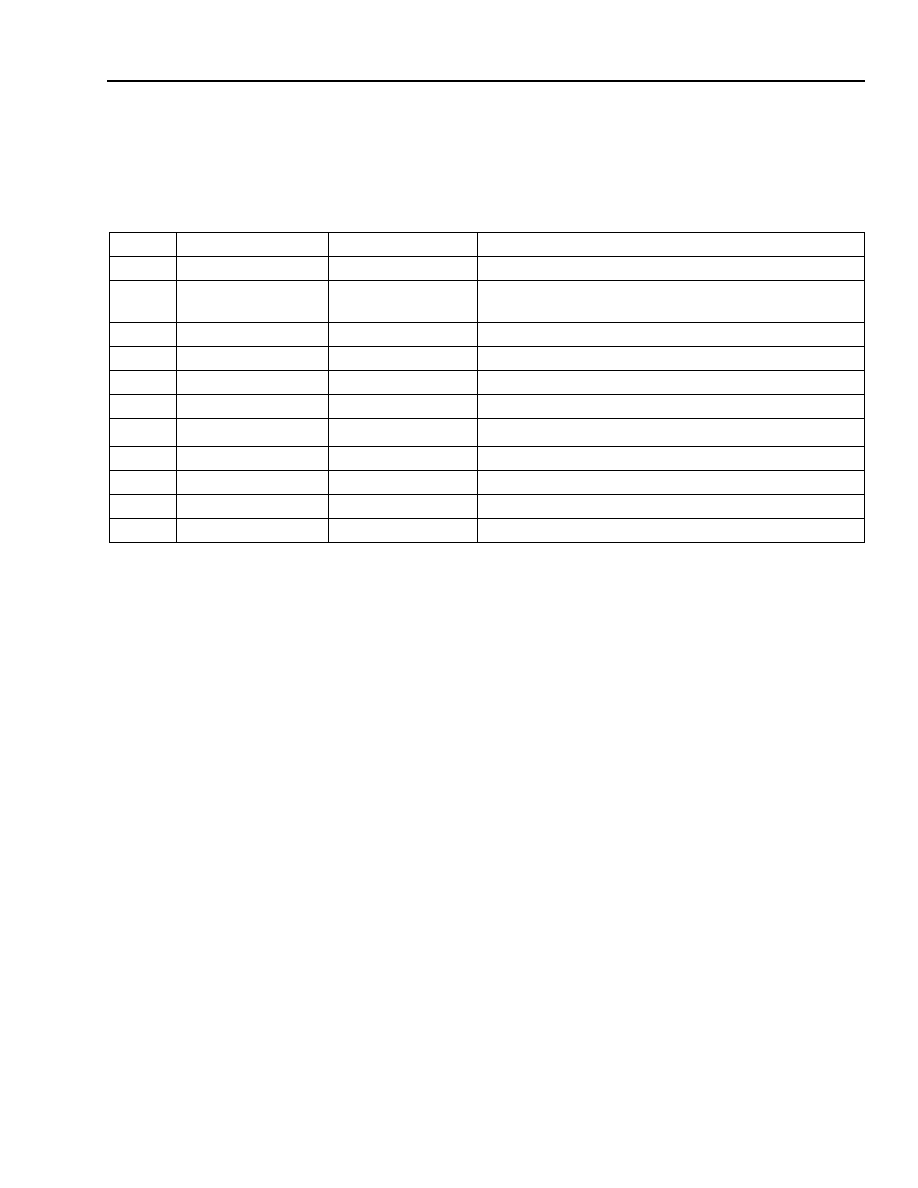

T7230 Primary Access Framer/Controller. Pin definitions for each of the modes are defined in Table 2. The I/O

specifications for these pins are defined in Table 2, Figure 3, MPIC Write Cycle (UP_MODE = 1), and Figure 4,

MPIC Read Cycle (UP_MODE = 1) for UP_MODE = 1 (

Motorola

mode), and Figure 5, MPIC Write Cycle

(UP_MODE = 0) and Figure 6, MPIC Read Cycle (UP_MODE = 0) for UP_MODE = 0 (

Intel

mode).

*

MC68000

is a trademark of Motorola, Inc.

* In other

Intel

devices, INT may be an active-low signal, depending on the device.

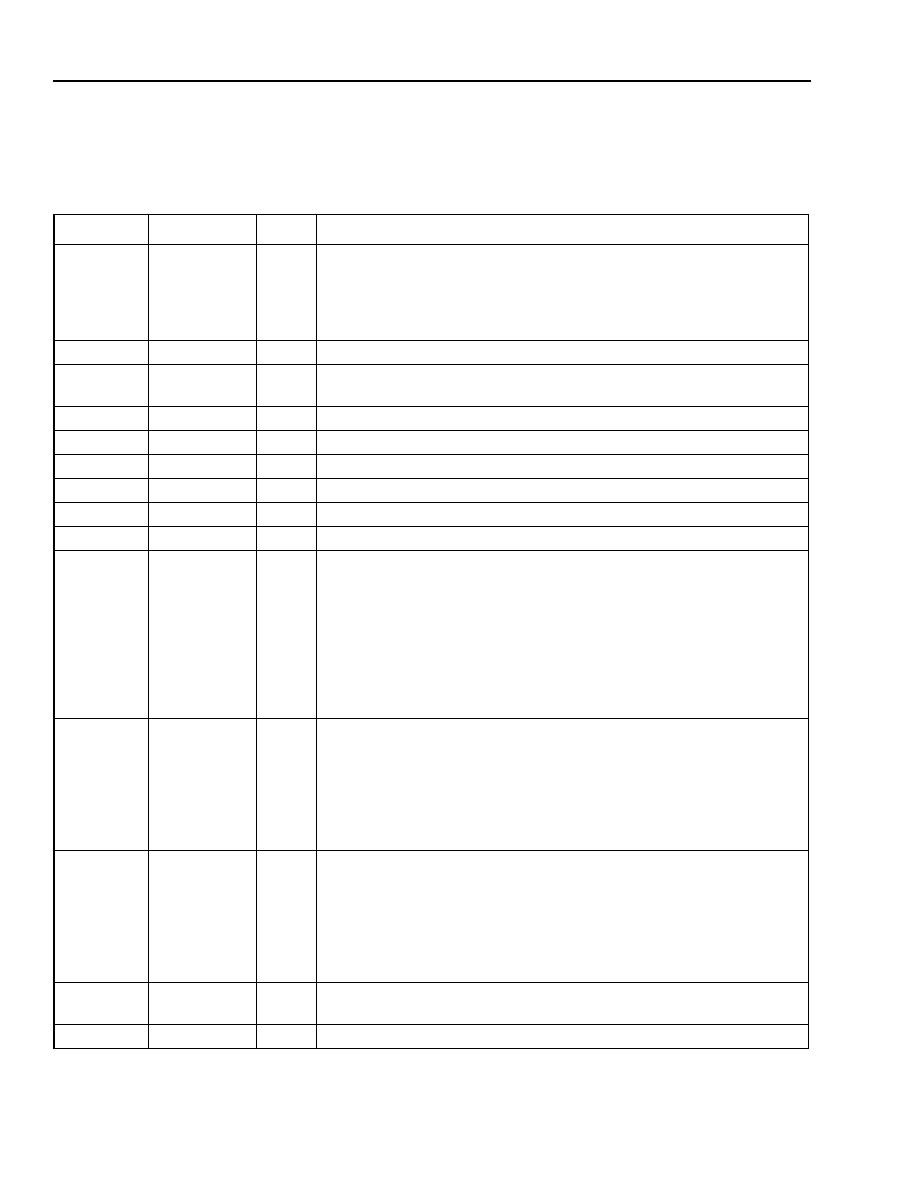

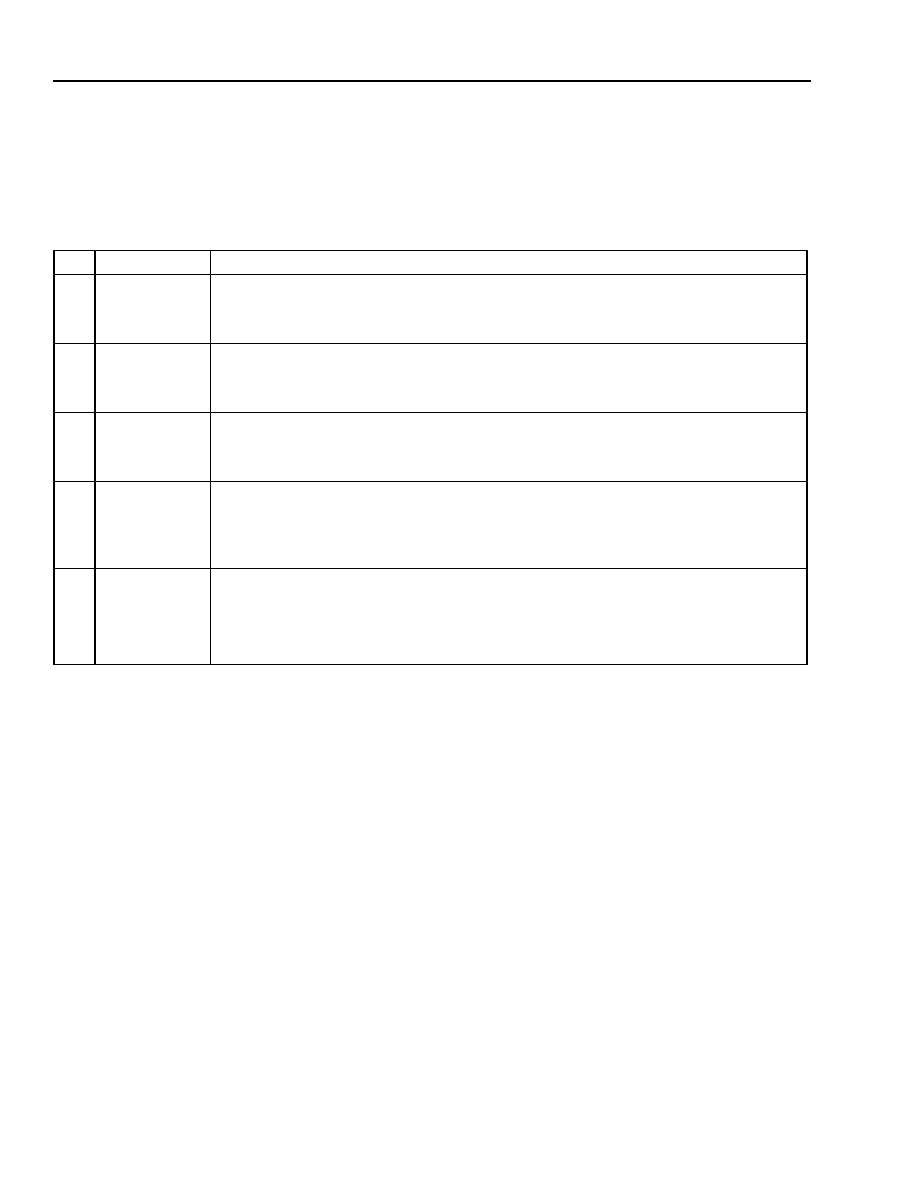

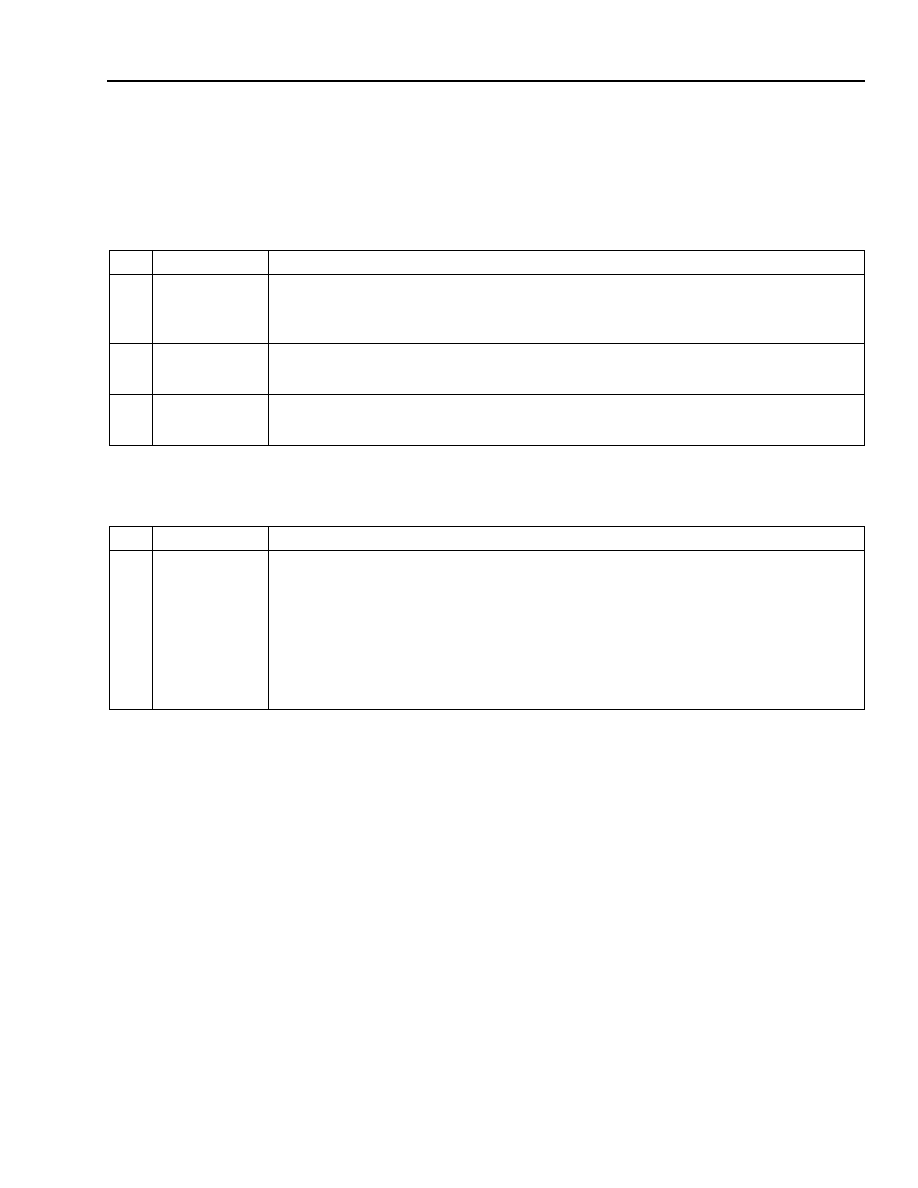

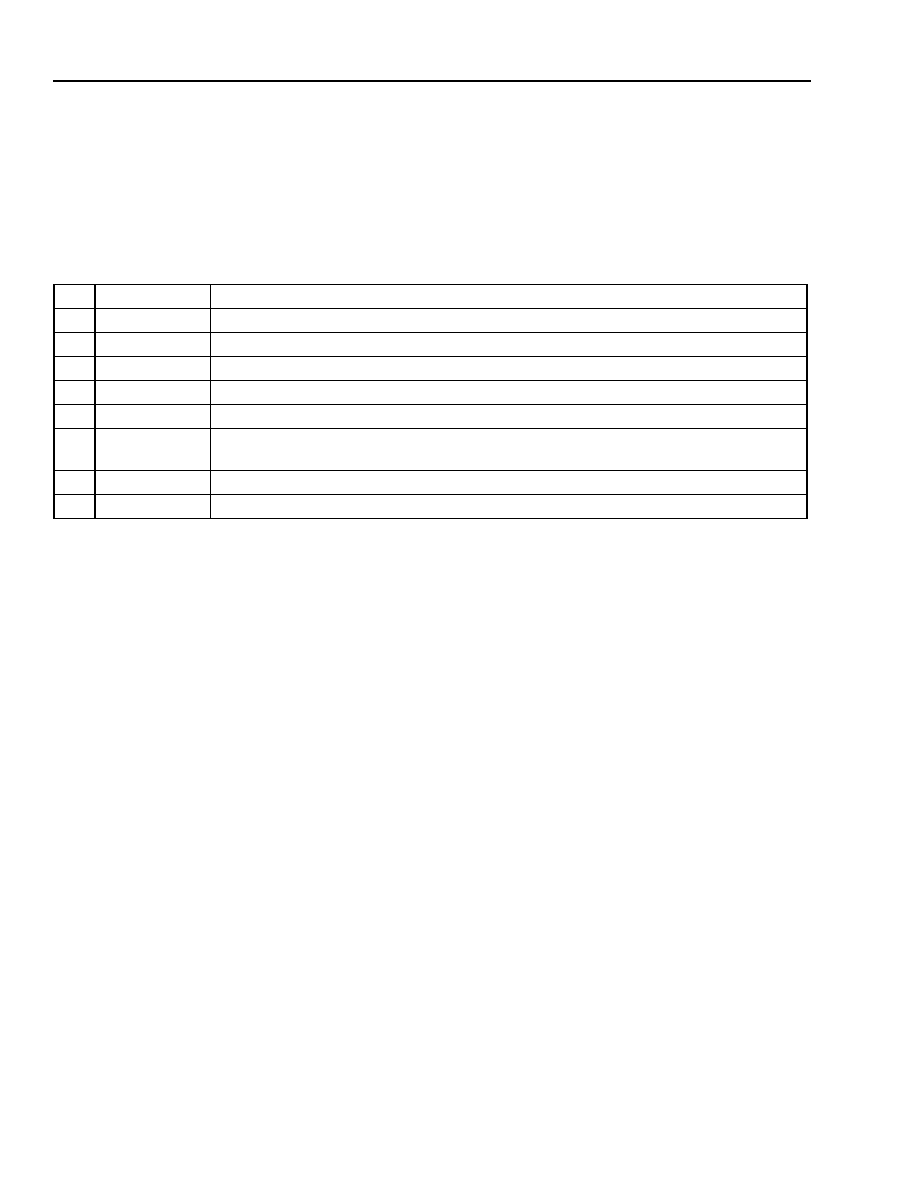

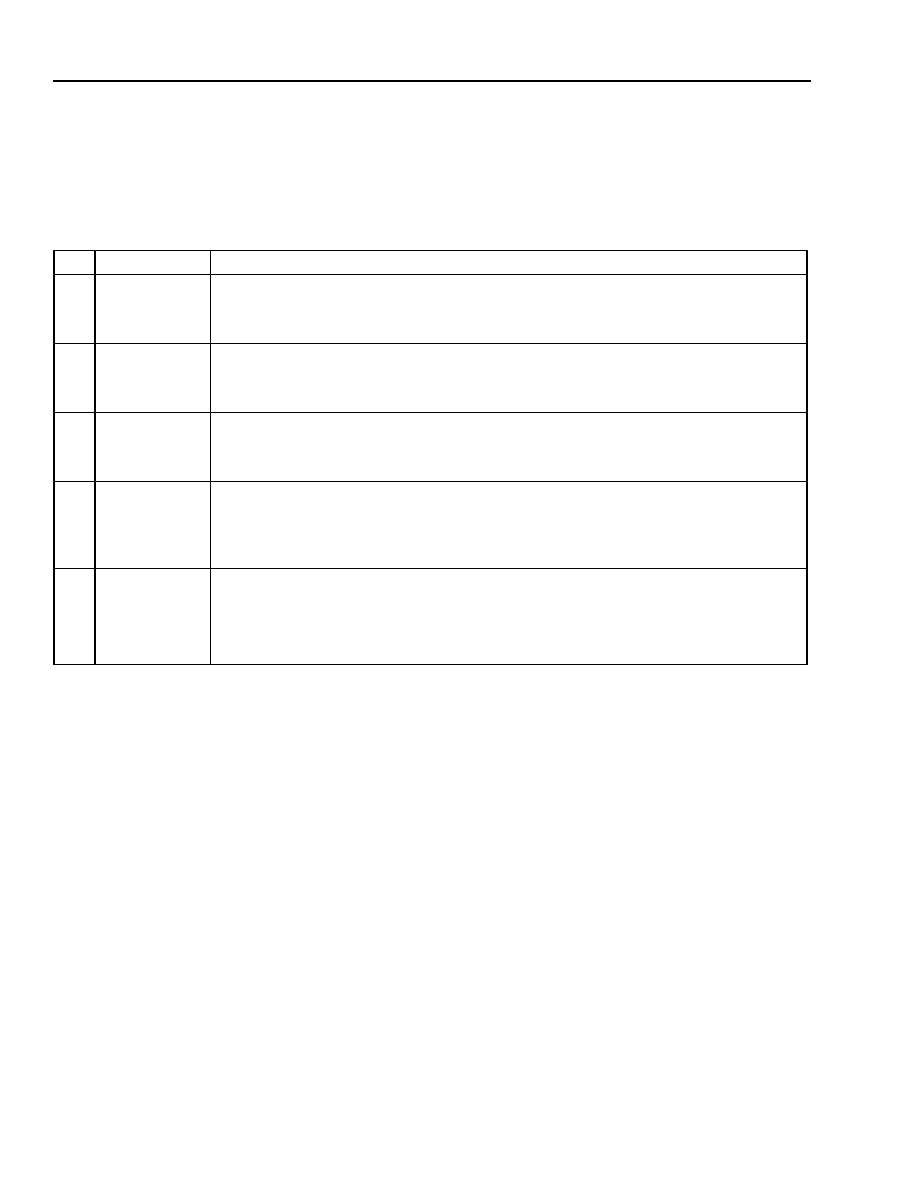

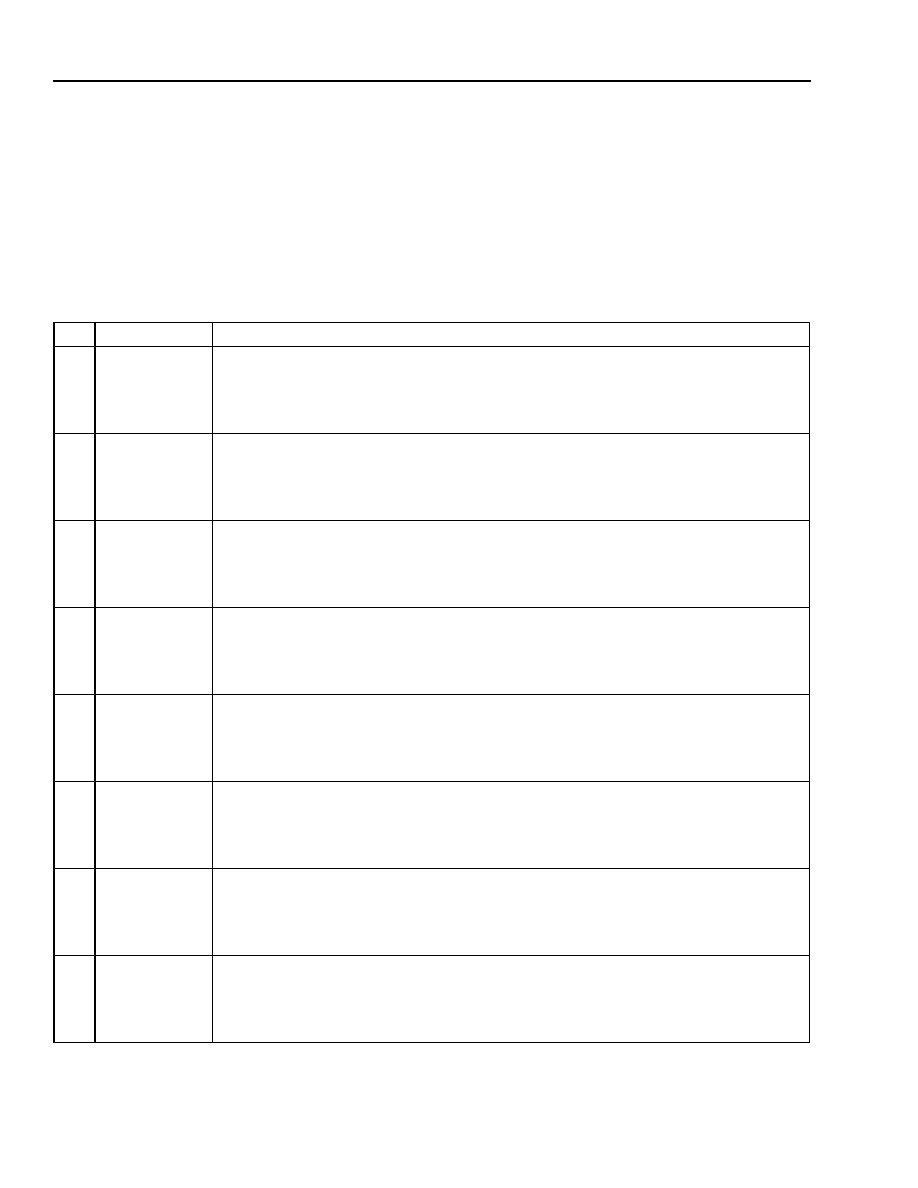

Table 2. Microprocessor Interface Control I/O

Device Pin

Name

Pin

Number

Type

Microprocessor Mode

Intel

Mode

Motorola

Mode

UP_MODE

23

I

UP_MODE = 0

UP_MODE = 1

ALE

19

I

Address Latch Enable (ALE)

(1 to 0 transition)

Not Used (ALE = 1)

D0--D7

(156--159,

2--5)

I/O

Data Bus

Data Bus

A0--A9

(6, 8--12,

14--17)

I

Address Bus

Address Bus

AS

21

I

Chip Select (CS) (active-low)

Address Strobe (active-low)

R/W

24

I

Read Cycle (RD) (active-low)

Read/Write Select

DS

22

I

Write Cycle (WR) (active-low)

Data Strobe (active-low)

DTACK

48

O

Ready (RDY for 8086 family)

(TECO3264 and

Intel

devices are

active-high.)

Data Transfer Acknowledge

(TECO3264 and

Motorola

devices

are active-low.)

INT

49

O

Interrupt (TECO3264 is active-high,

but

Intel

8086 family* is active-low.)

Interrupt (TECO3264 and

Motorola

devices are active-low.)

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

17

Lucent Technologies Inc.

External Control Connection

(continued)

Microprocessor Interface and Control (MPIC)

(continued)

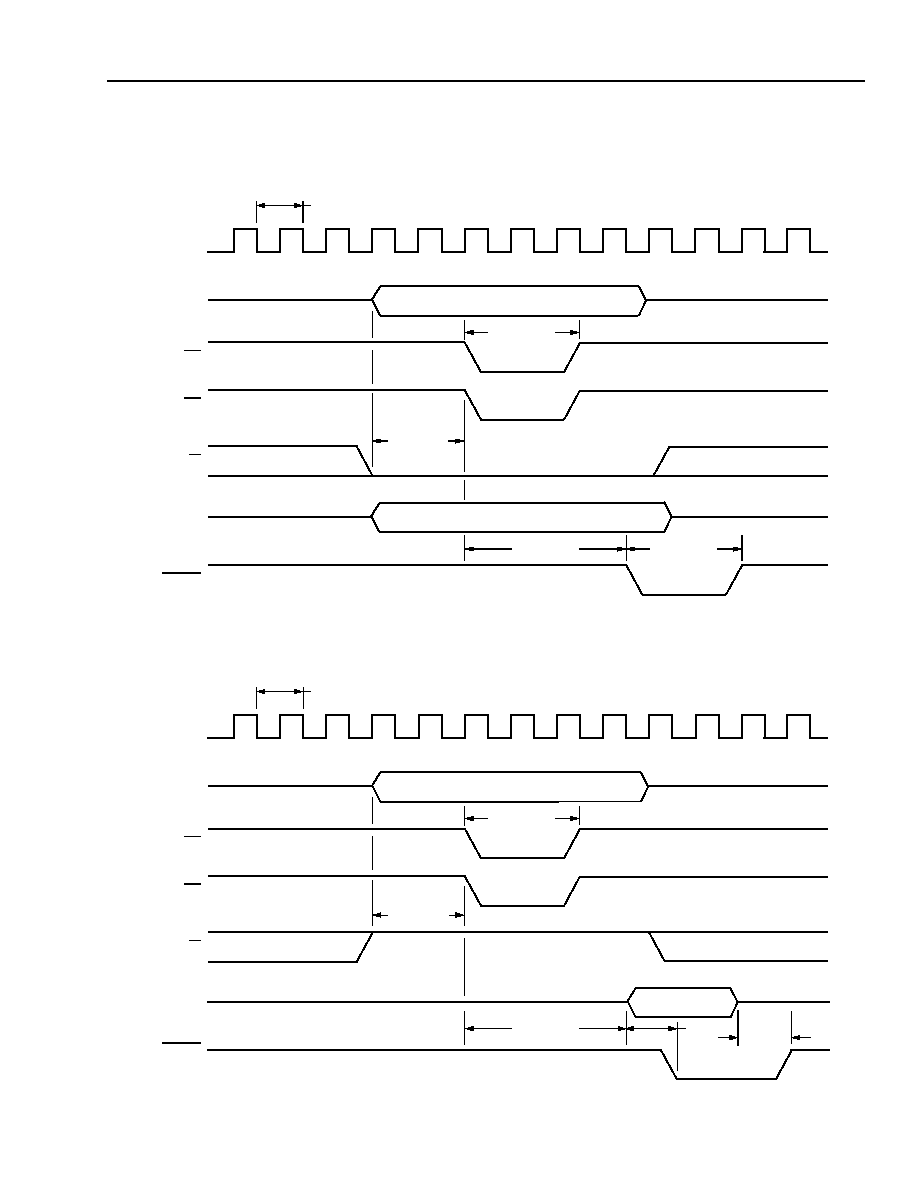

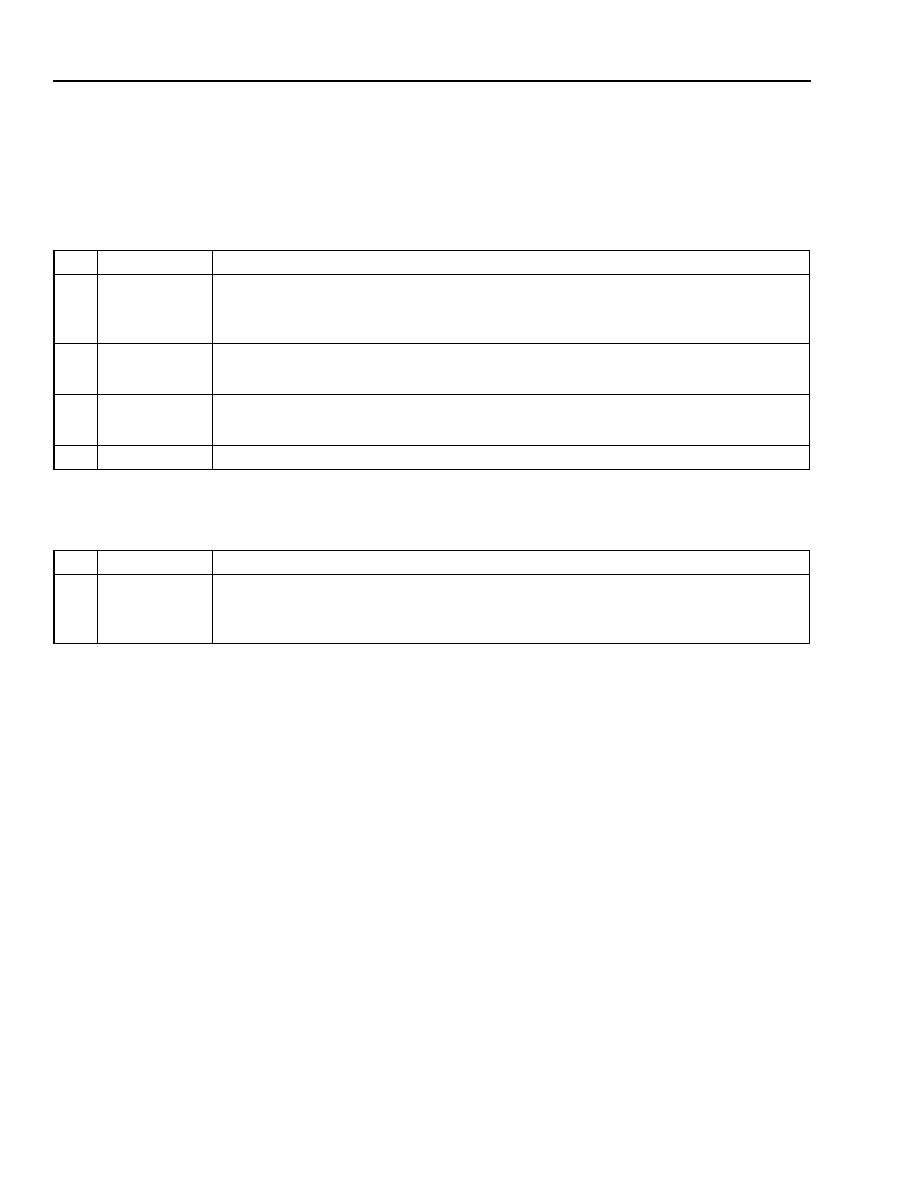

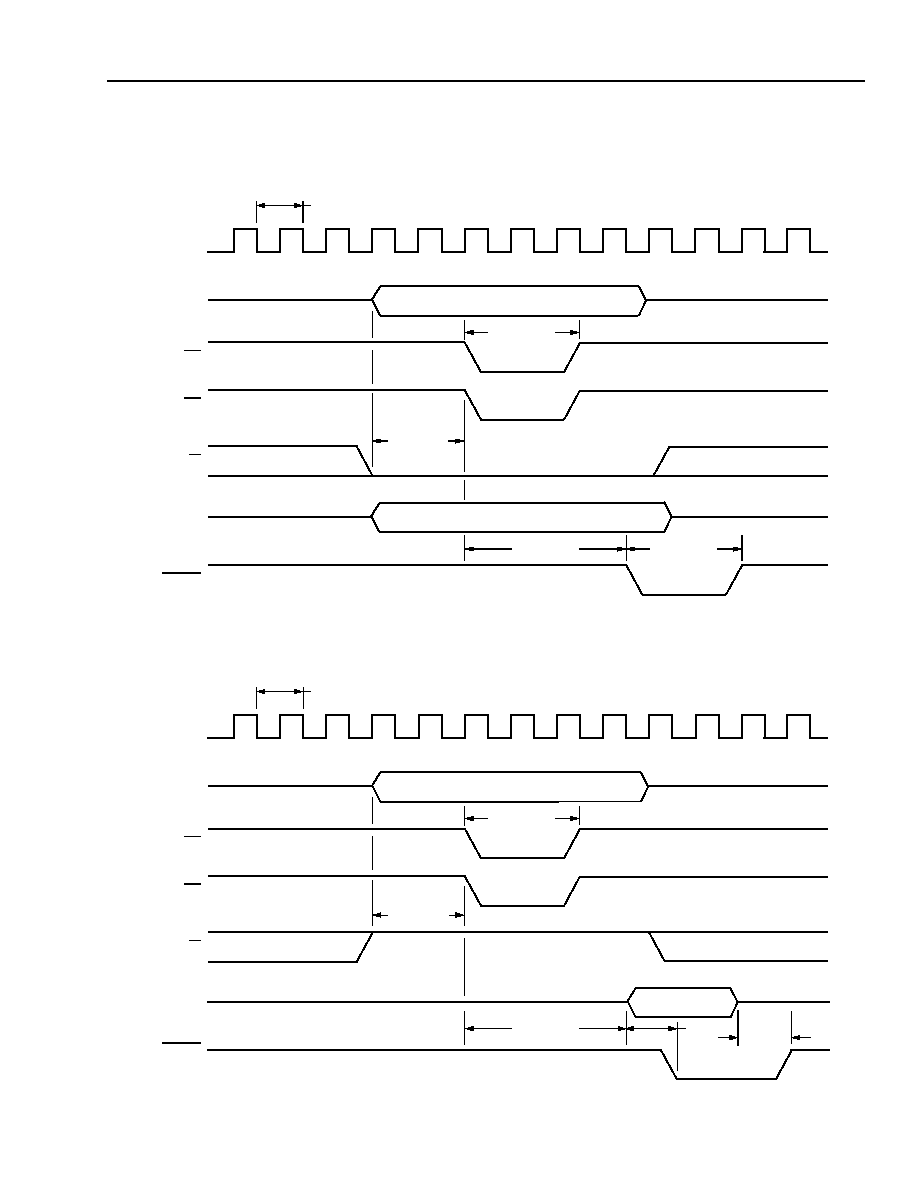

5-5345(F)r.7

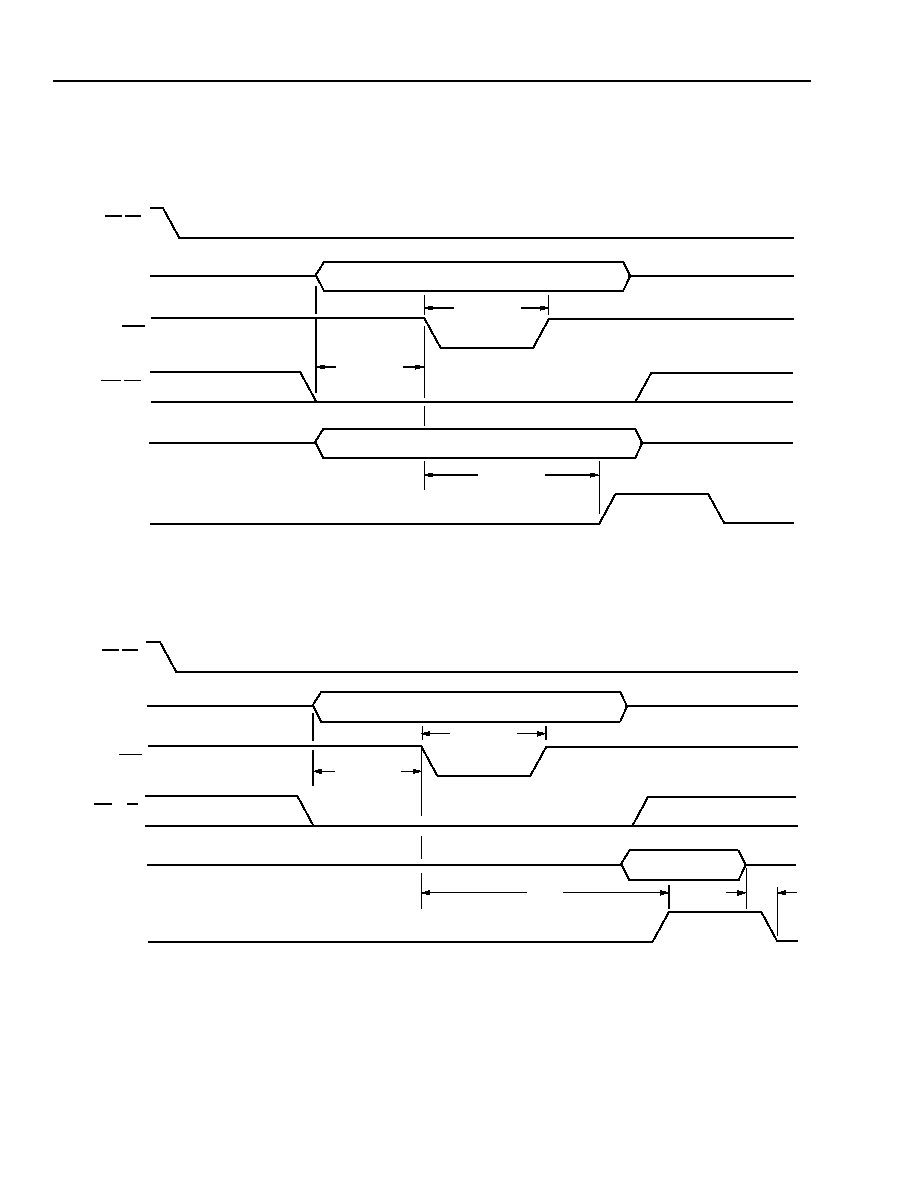

Figure 3. MPIC Write Cycle (UP_MODE = 1)

5-5346(F)r.8

Figure 4. MPIC Read Cycle (UP_MODE = 1)

VALID

VALID

60 ns MIN

0 ns MIN

90 ns MIN

A[0:9]

AS

DS

R/W

D[0:7]

DTACK

60 ns MIN

30.5 ns

32 MHz CLOCK

(INTERNAL)

VALID

60 ns MIN

0 ns MIN

A[0:9]

AS

DS

R/W

30.5 ns

32 MHz CLOCK

(INTERNAL)

VALID OUT

D[0:7]

DTACK

30 ns

30 ns

90 ns MAX

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

18

Lucent Technologies Inc.

External Control Connection

(continued)

Microprocessor Interface and Control (MPIC)

(continued)

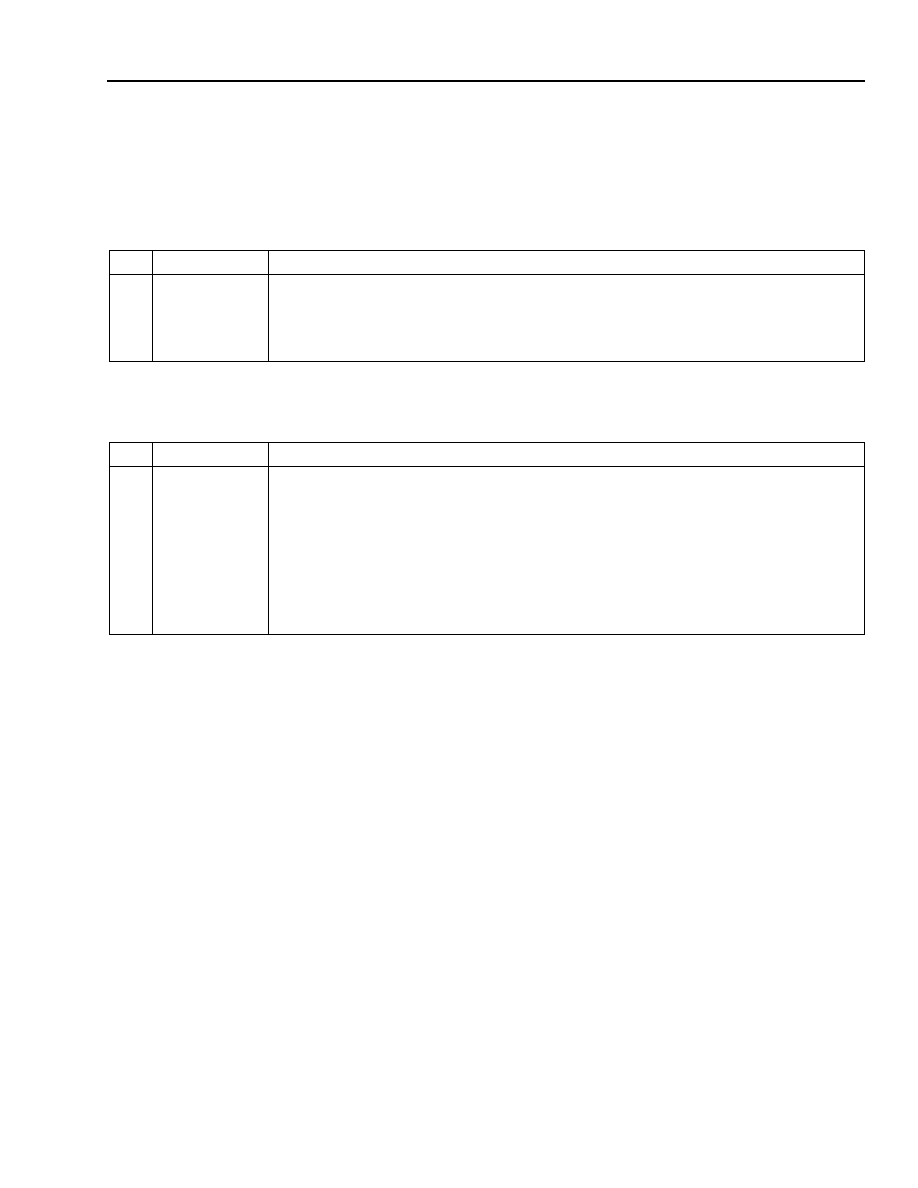

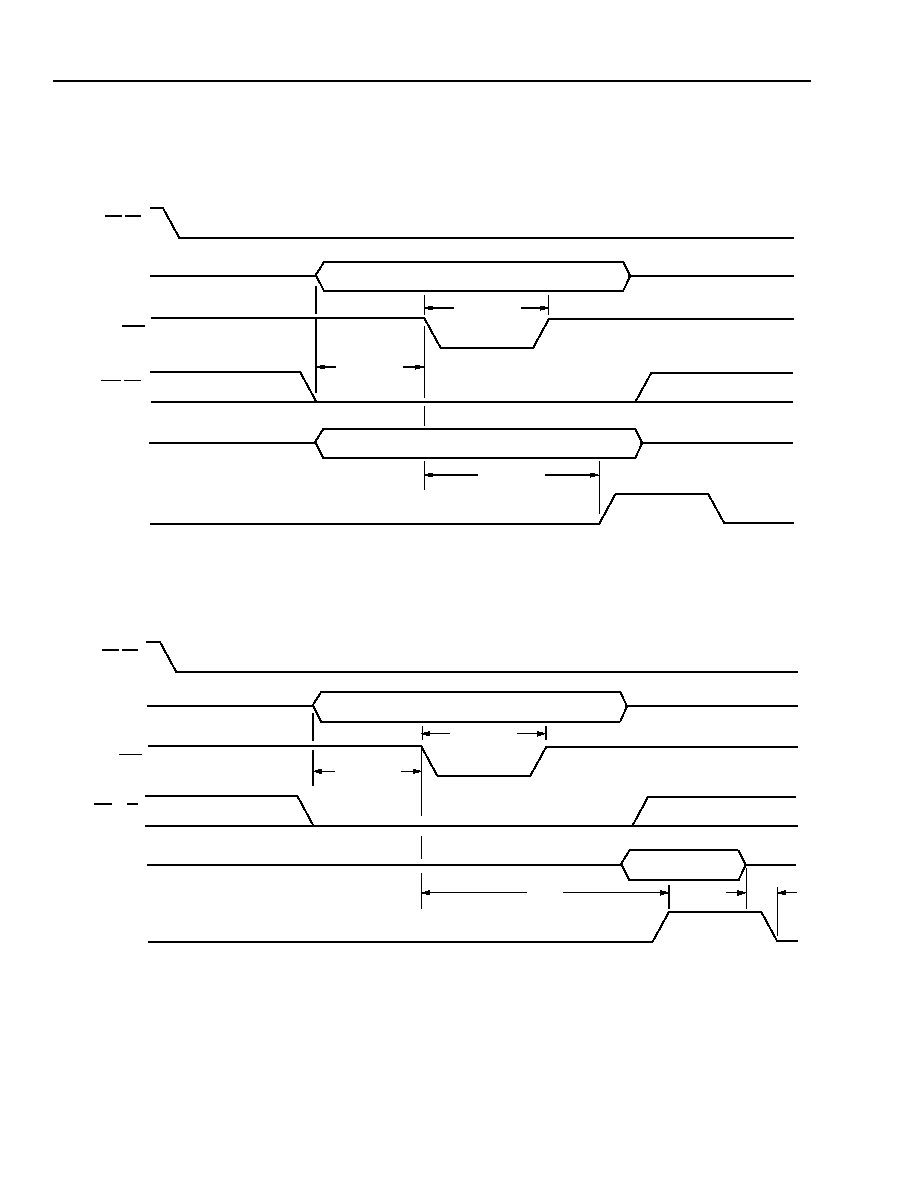

5-5345(F).ar.6

* See Table 2, Microprocessor Interface Control I/O, on page 16.

Figure 5. MPIC Write Cycle (UP_MODE = 0)

5-5346(F).ar.7

* See Table 2, Microprocessor Interface Control I/O, on page 16.

Figure 6. MPIC Read Cycle (UP_MODE = 0)

VALID

VALID

60 ns MIN

15 ns MIN

75 ns MIN

A[0:9]

ALE

CS[AS]

WR[DS]

D[0:7]

RDY[DTACK*]

VALID OUT

60 ns MIN

A[0:9]

ALE

RD[R/W]

D[0:7]

RDY[DTACK*]

75 ns

20 ns

VALID

CS[AS]

15 ns MIN

Data Sheet

August 1999

TECO3264 32-Channel Echo Canceller

19

Lucent Technologies Inc.

External Control Connection

(continued)

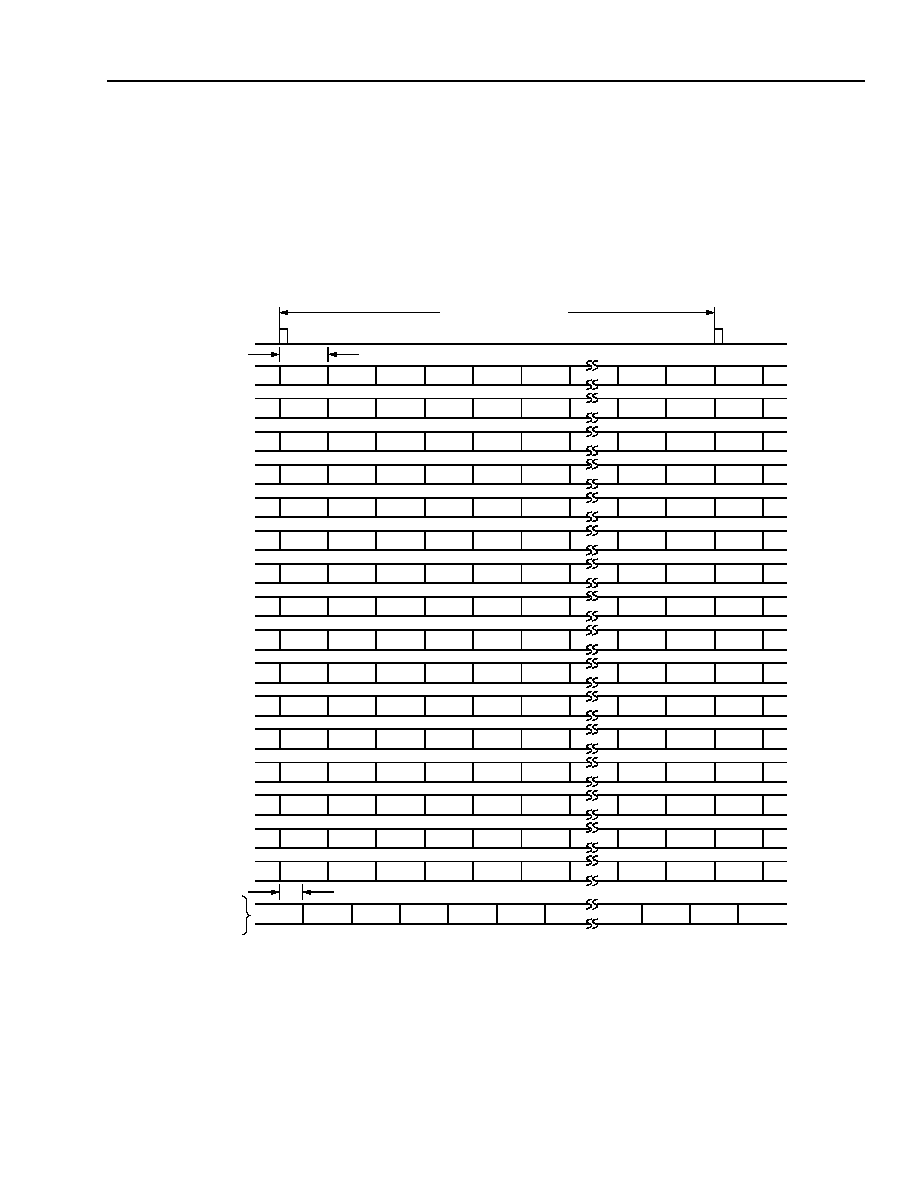

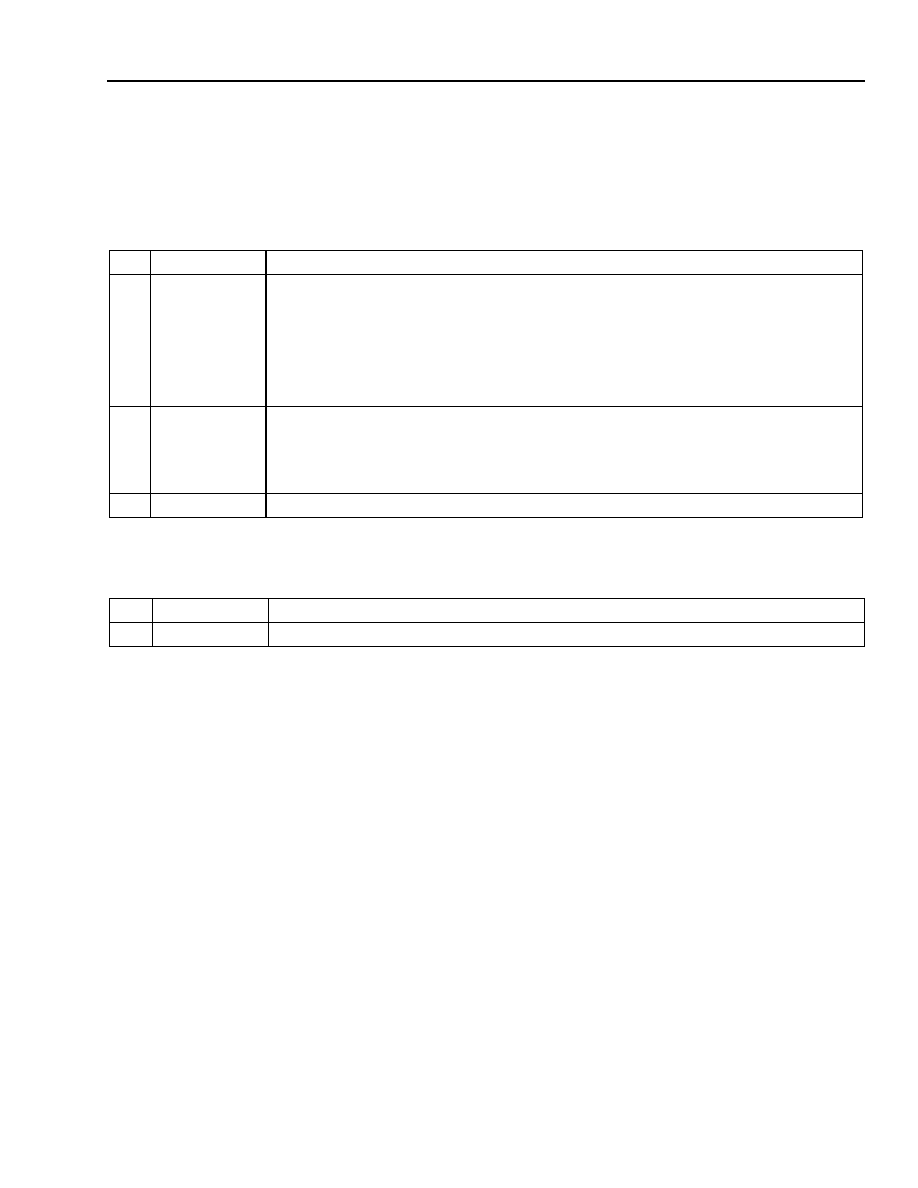

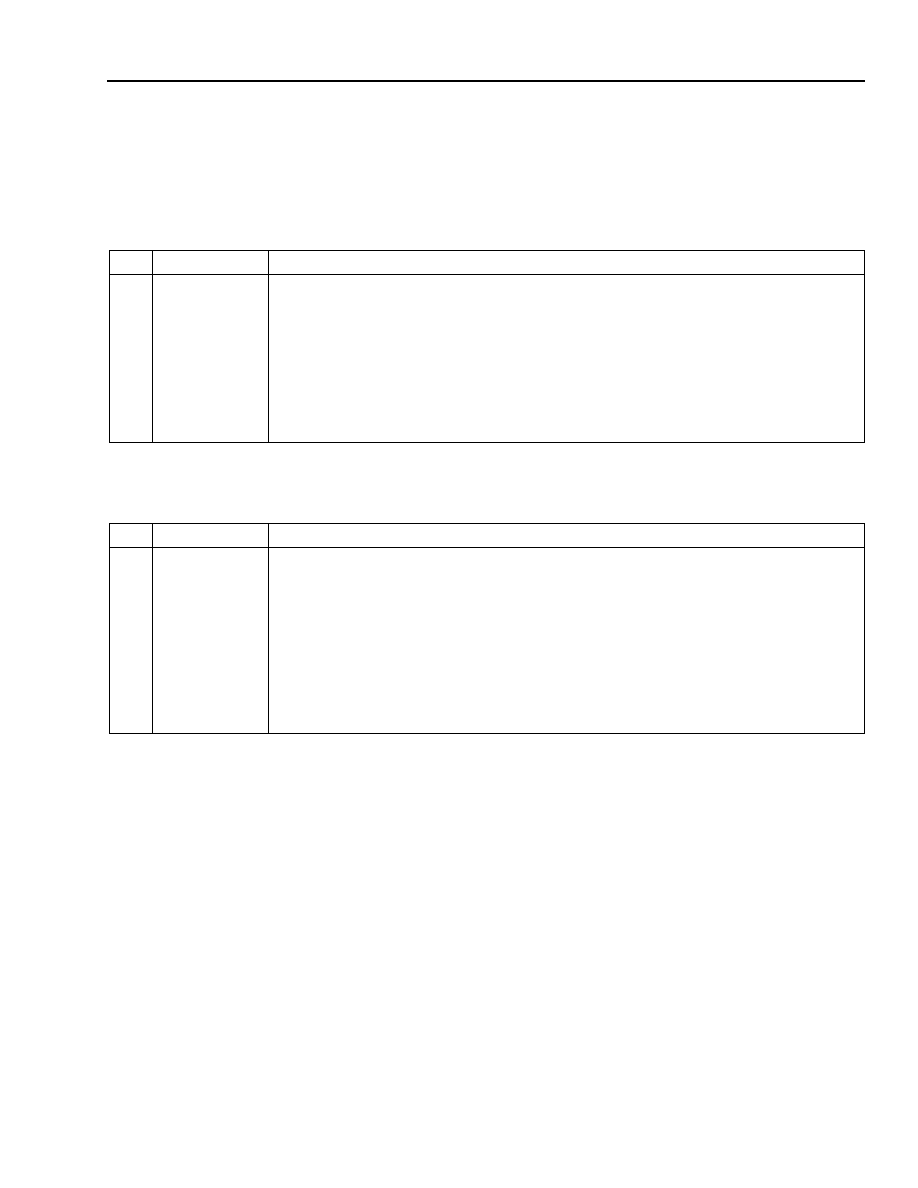

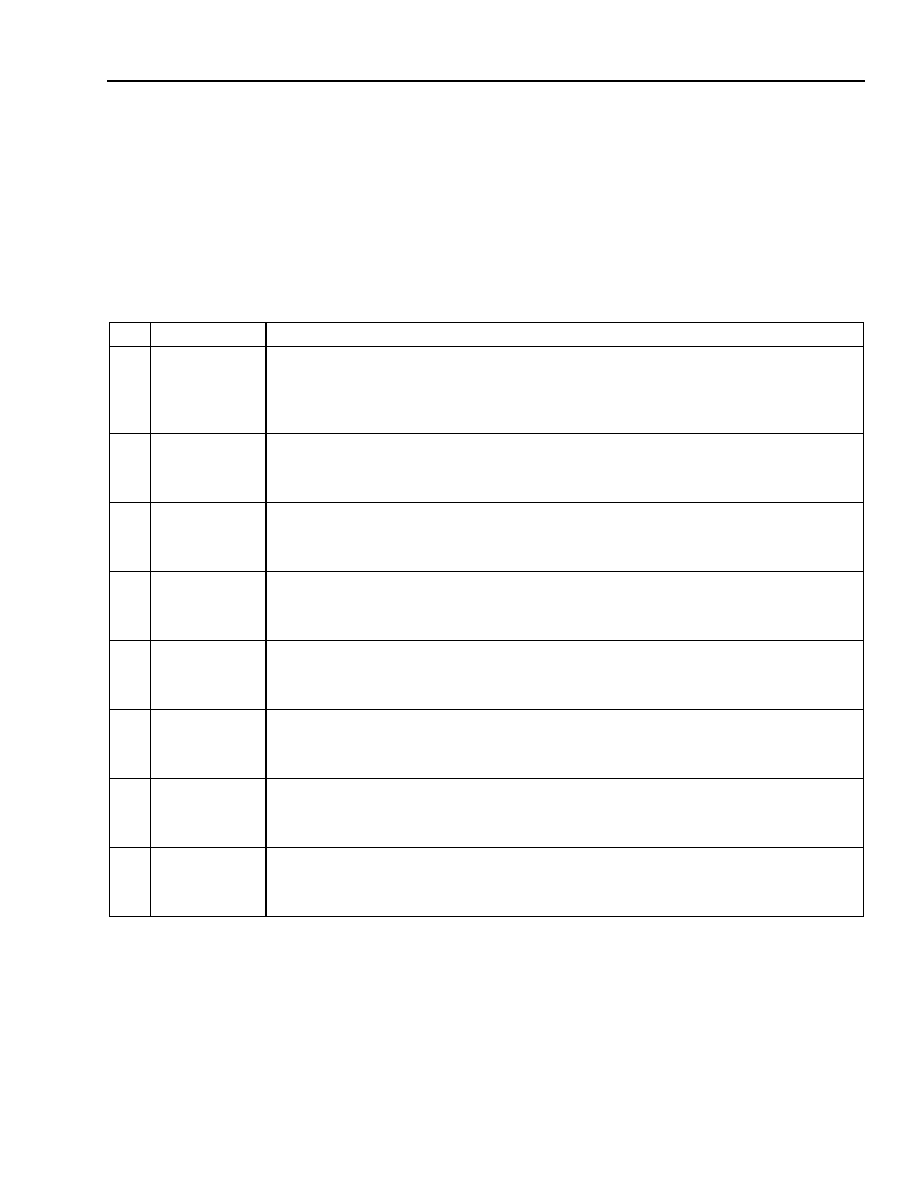

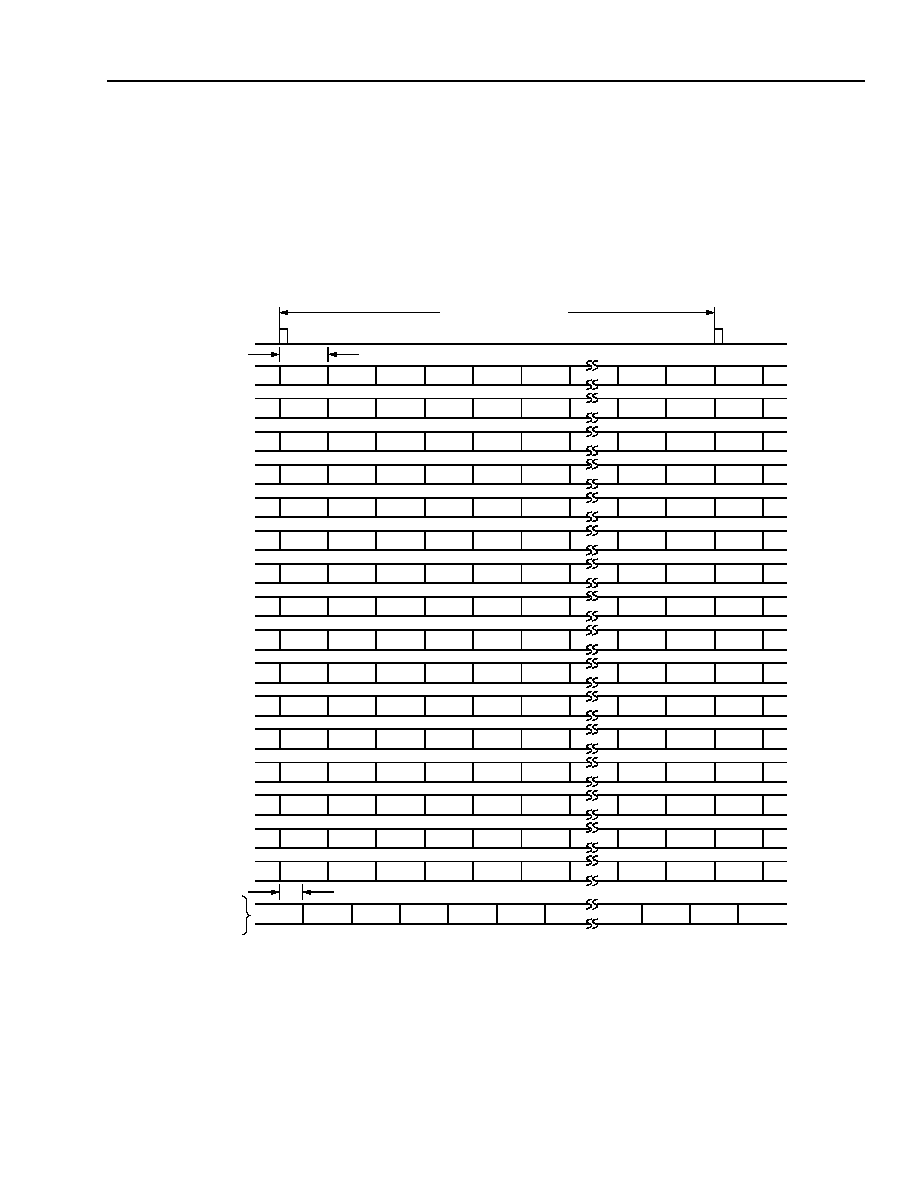

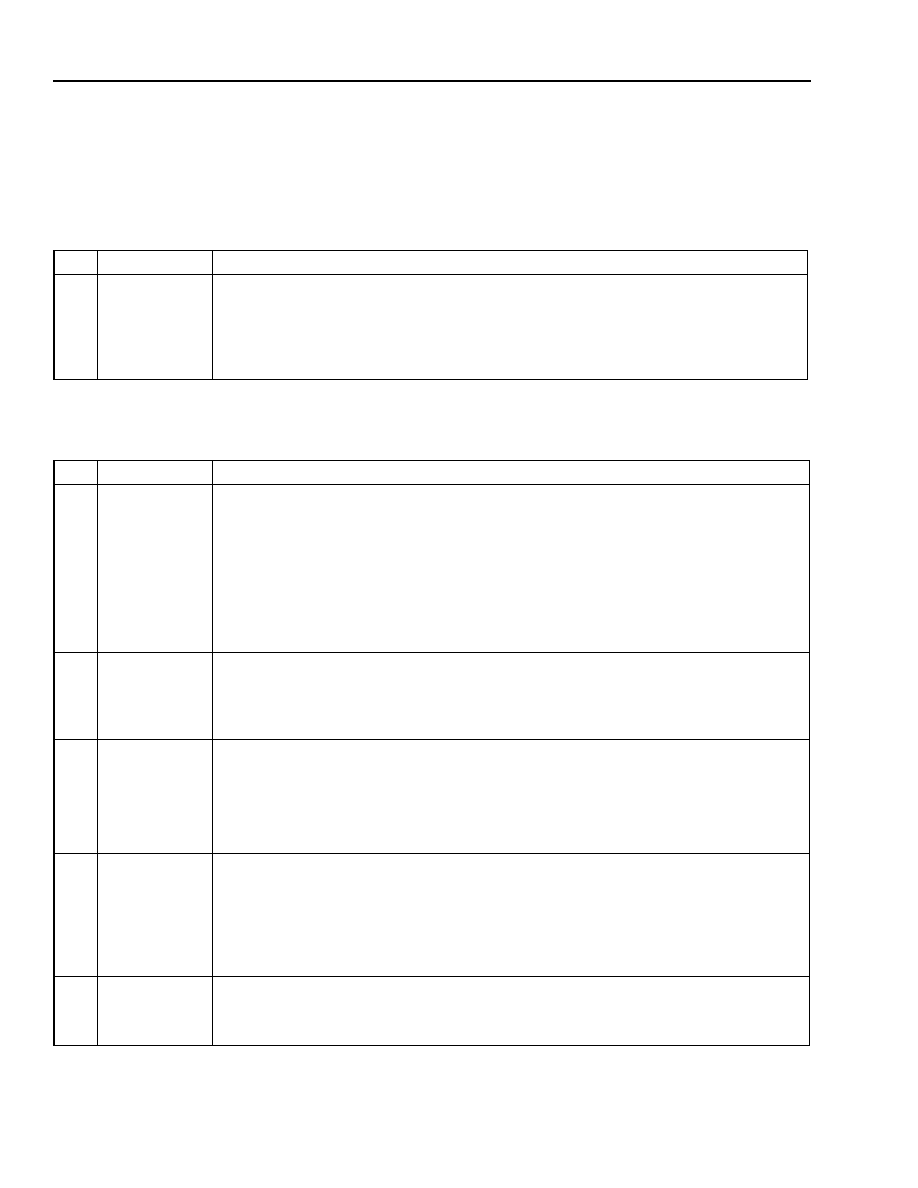

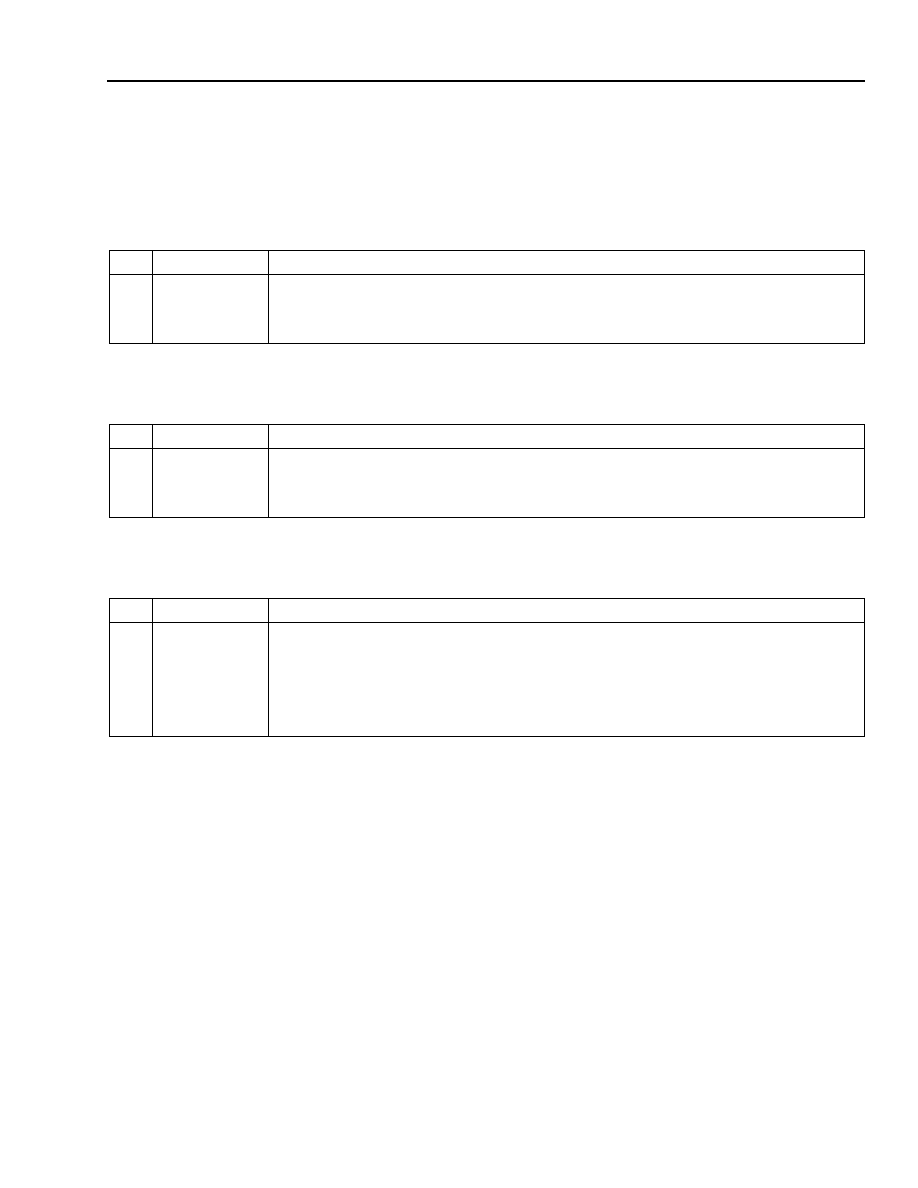

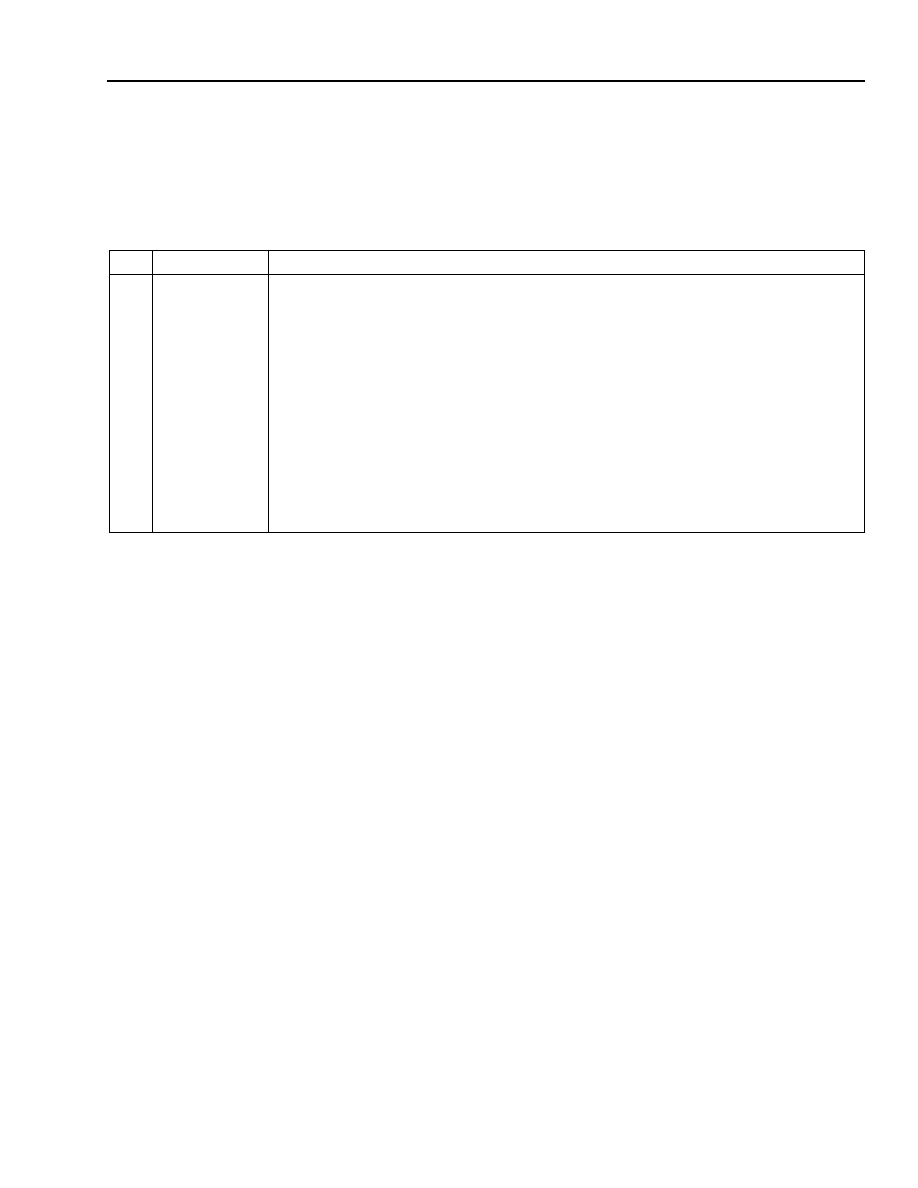

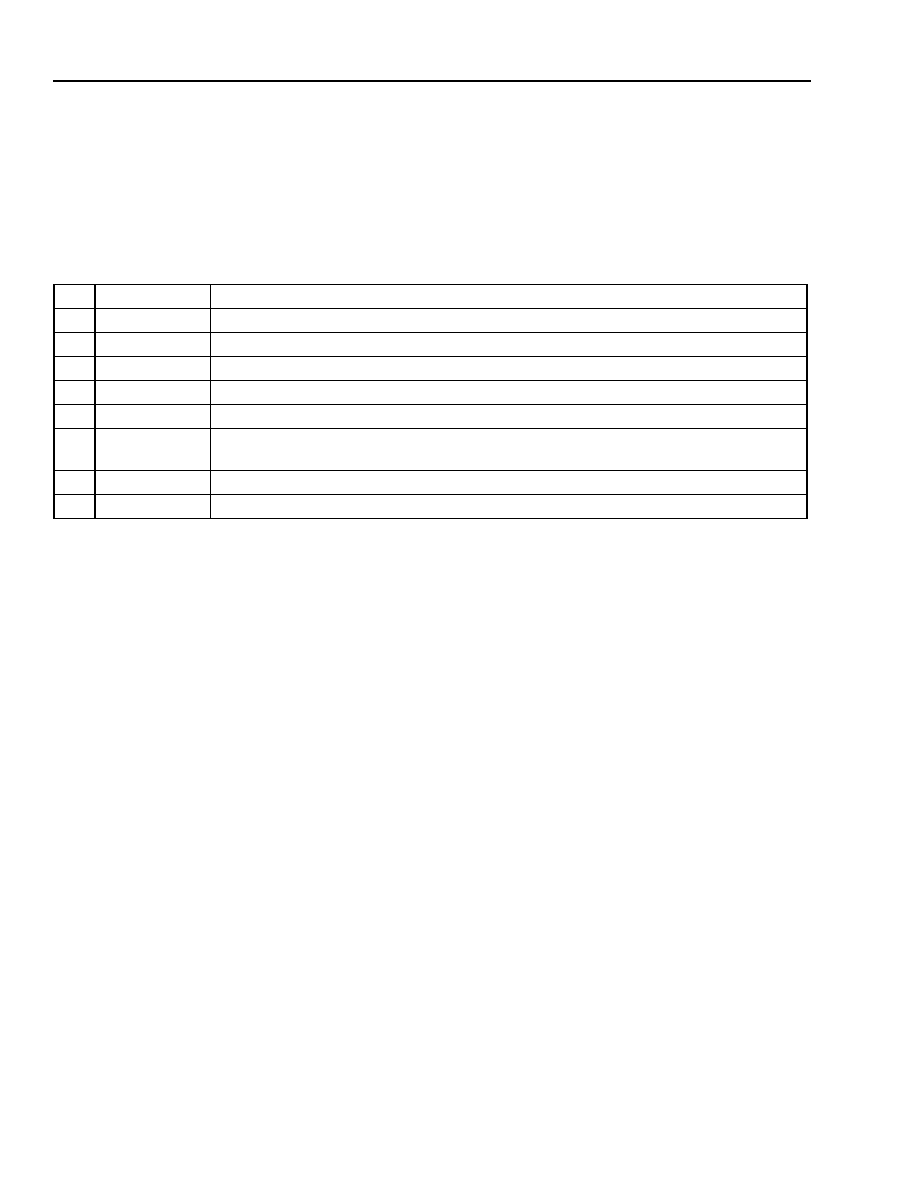

Channel Status and Control

The TECO3264 implements a highly provisionable architecture that offers per-channel control and status for

numerous functions via the respective data I/O pins. These I/O per-channel control and status pins include ENBP,

NLPFRZ, NLPEN, HRST, HFRZ, CALLB, VSC, TEST[0:7], TONE, TDPR, and VPA. For information on their pin

numbers and functions, please refer to Pin Descriptions, Table 1, on page 10. Figure 7, Control and Status Timing

shows the channel alignment for each control and status signal.

5-4902(F).ar.3

Note: There are 32 bits/frame for each serial stream. TS# represents the time-slot number.

Figure 7. Control and Status Timing

ECDIS

ENBP

TS31

TS0

TS1

TS2

TS3

TS4

TS29

TS30

TS31

TS31

TS0

TS1

TS2

TS3

TS4

TS29

TS30

TS31

TS26

TS27

TS28

TS29

TS30

TS31

TS24

TS25

TS26

TS27

TS28

TS29

TS30

TS31

TS0

TS25

TS26

TS27

TS29

TS30

TS31

TS0

TS1

TS2

TS27

TS28

TS29

TS28

TS29

TS30

TS31

TS0

TS1

TS26

TS27

TS28

TS26

TS27

TS28

TS29

TS30

TS31

TS24

TS25

TS26

TS26

TS27

TS28

TS29

TS30

TS31

TS24

TS25

TS26

NLPFRZ

NLPEN

HRST

HFRZ

CALLB

VSC

TS26

TS27

TS28

TS29

TS30

TS31

TS24

TS25

TS26

TS26

TS27

TS28

TS29

TS30

TS31

TS24

TS25

TS26

TS30

TS31

TS0

TS1

TS2

TS3

TS28

TS29

TS30

TS25

TS26

TS27

TS28

TS29

TS30

TS23

TS24

TS25

TS28

TS29

TS30

TS31

TS0

TS1

TS26

TS27

TS28

TS29

TS30

TS31

TS0

TS1

TS2

TS27

TS28

TS29

TS25

TS26

TS27

TS28

TS29

TS30

TS23

TS24

TS25

SYNC

125

µ

s FRAME

TS30

TS31

TS0

TS1

TS2

TS3

TS29

TS30

TS31

TONE

1.95

µ

s

TDPR

VPA

TEST0

TEST1

TS26

TS27

TS28

TS29

TS30

TS31

TS24

TS25

TS26

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

3.9

µ

s

Data Sheet

TECO3264 32-Channel Echo Canceller

August 1999

20

Lucent Technologies Inc.

External Control Connection

(continued)

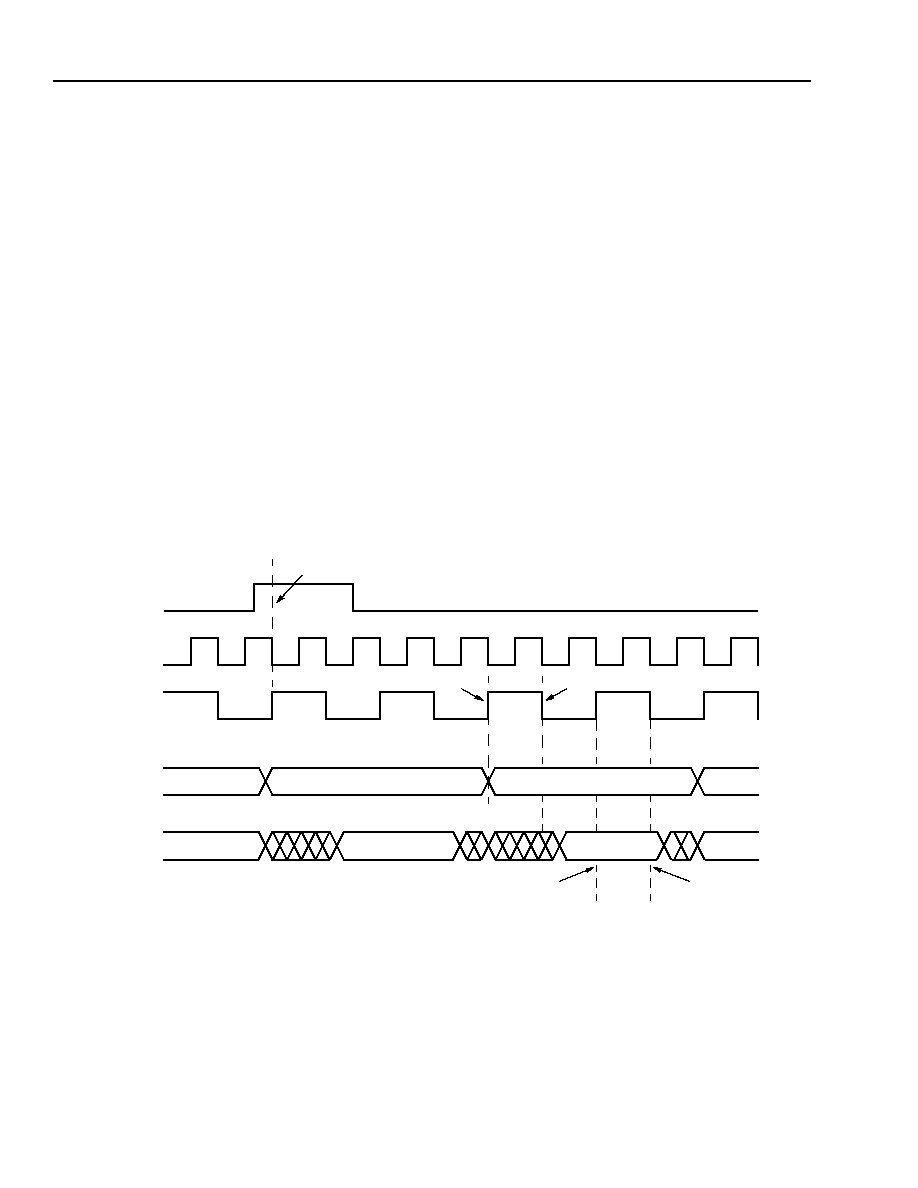

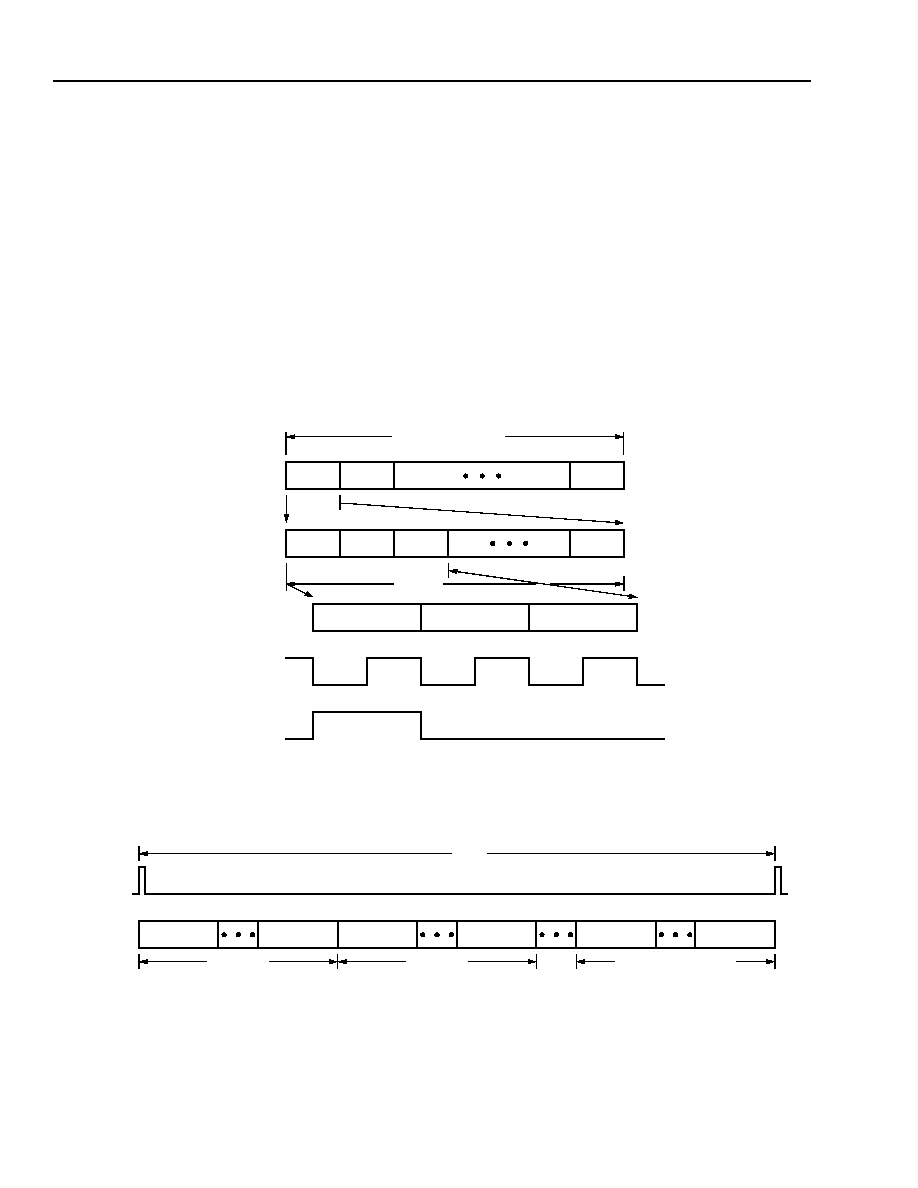

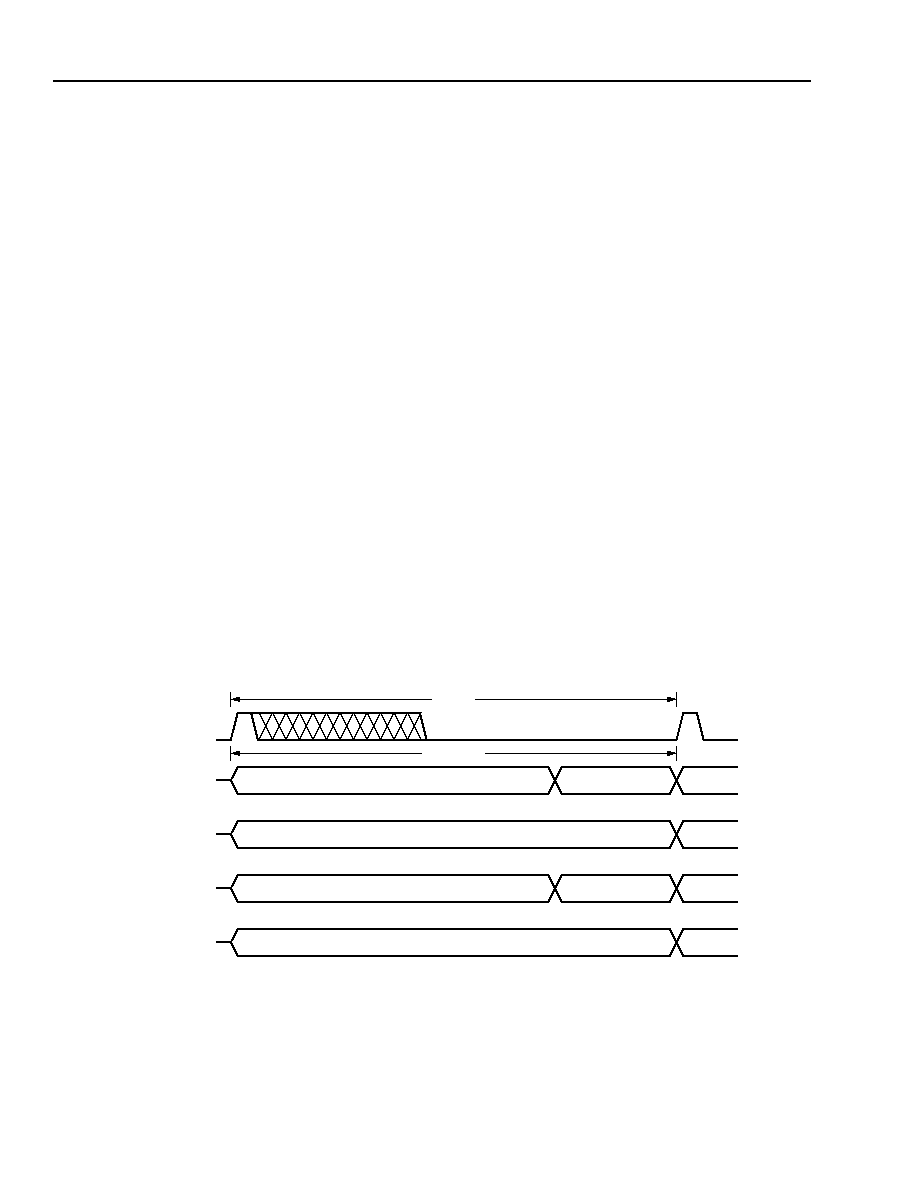

PCM Input/Output (I/O) Timing and Register Control

The TECO3264 has a number of configurable parameters pertaining to the PCM data, the synchronization (SYNC,

8 kHz) clock, and the input clock (8.192 MHz). The only input clock that is required is the 8.192 MHz clock--there

are no other frequency options. The PCM ports support either 4.096 Mbits/s or 2.048 Mbits/s serial data. Proper

PCM timing is controlled through the use of programmable registers. Table 14, Transmission Parameters, on page

37 gives a description of the control features necessary to establish proper data and clock synchronization.

Transmission parameters can be set to sample the data wherever it needs to work. Essentiall y, the user will choose

to sample the data synchronously at either 4.096 Mbits/s or 2.048 Mbits/s and the transmission parameters can

vary the phase of the sampling relative to the sync pulse. For example, in cases when the [C, E] PCM data is not

properly aligned to time slot 0 (TS0) relative to the synchronization clock, then a combination of the bit offset

parameters (CXBOFF, XRBOFF, YRBOFF, EXBOFF), the bulk time-slot delay parameters [X, Y]DLY[4:0], and the

transmit clock edge parameters [C, E]XCE can be adjusted to fix the problem. Any properly formed 2.048 Mbits/s

(or 4.096 Mbits/s) serial stream can be made to work by adjusting these parameters.

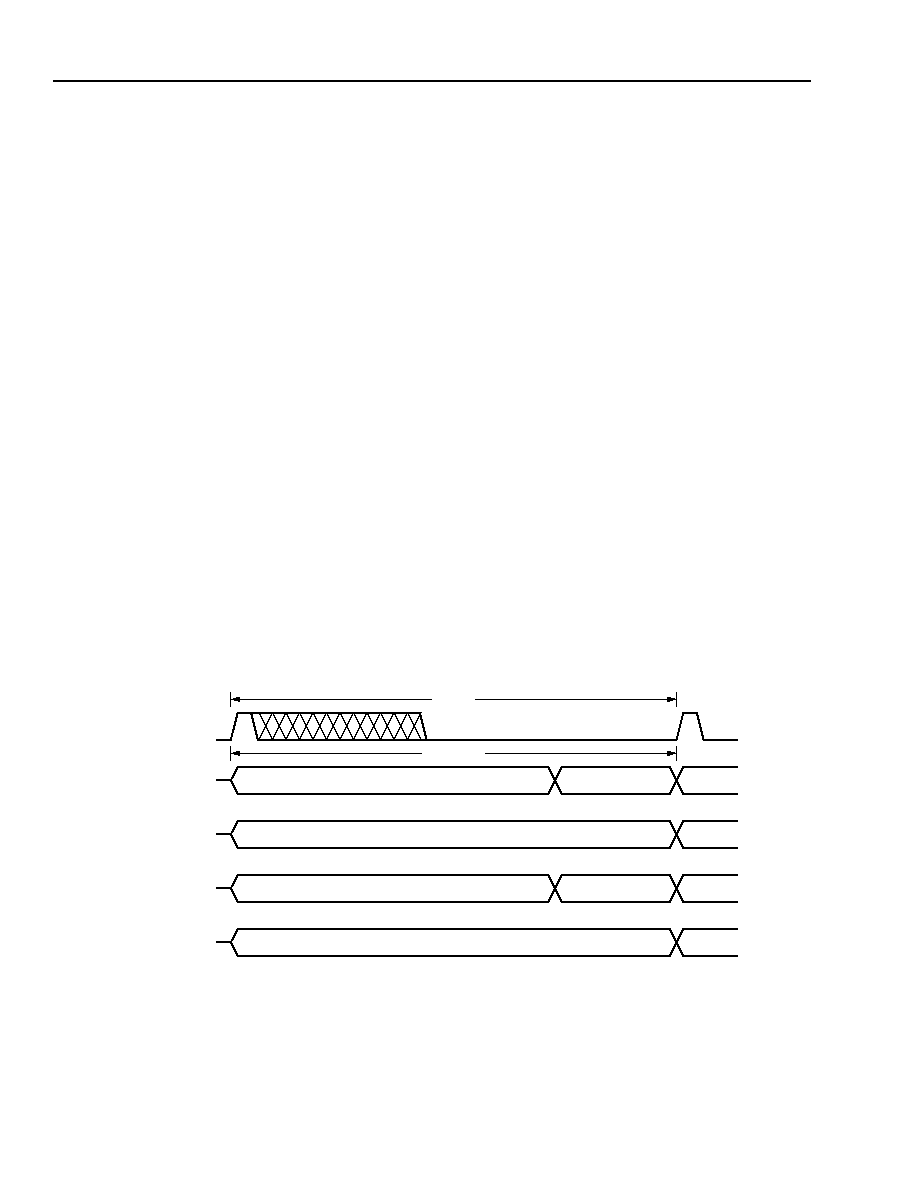

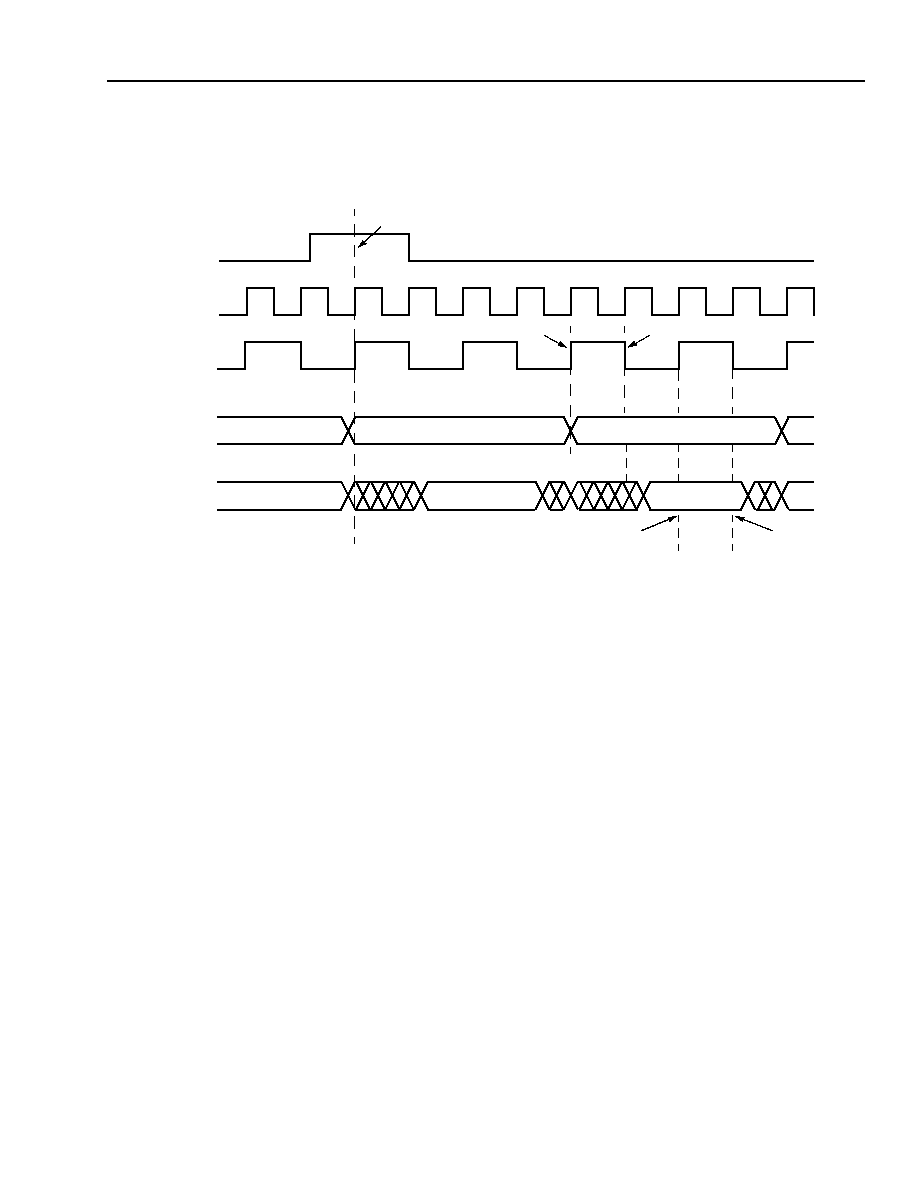

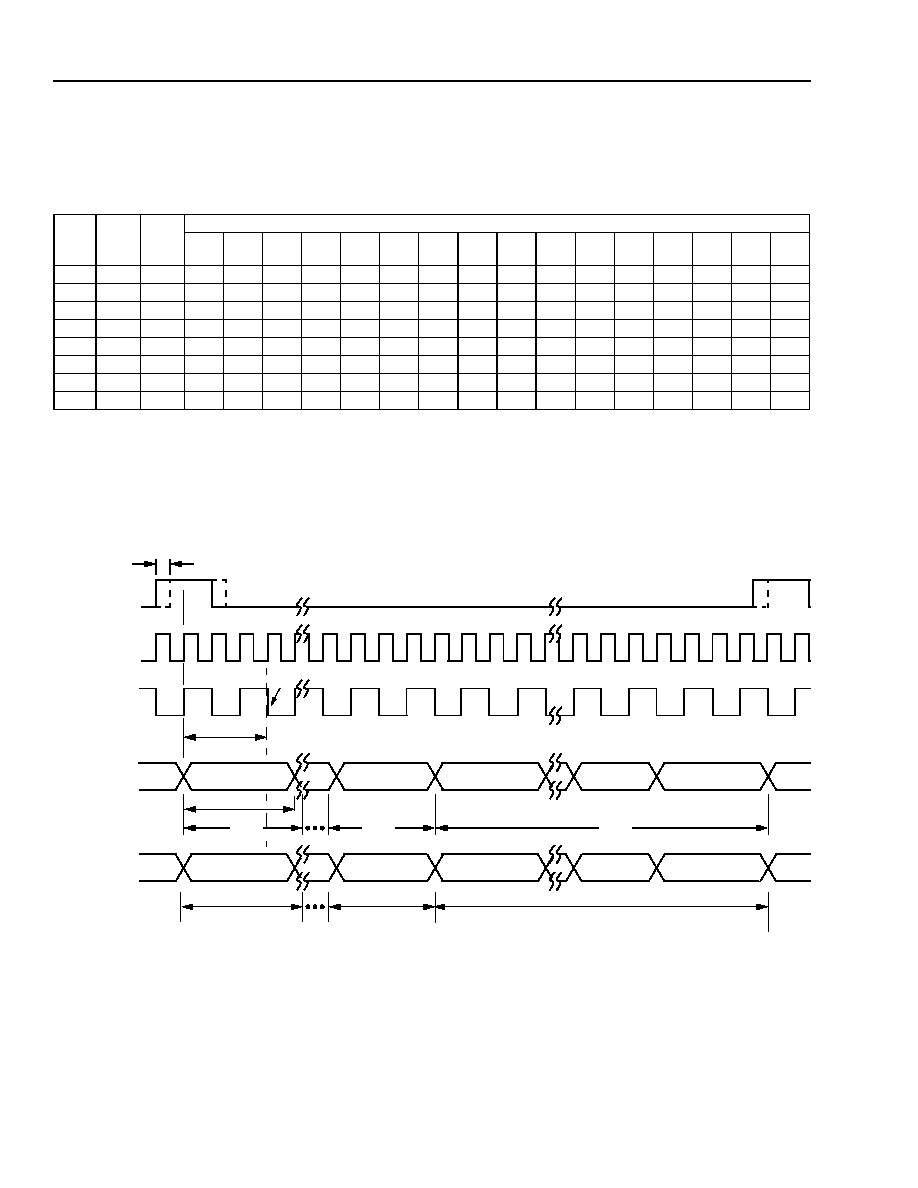

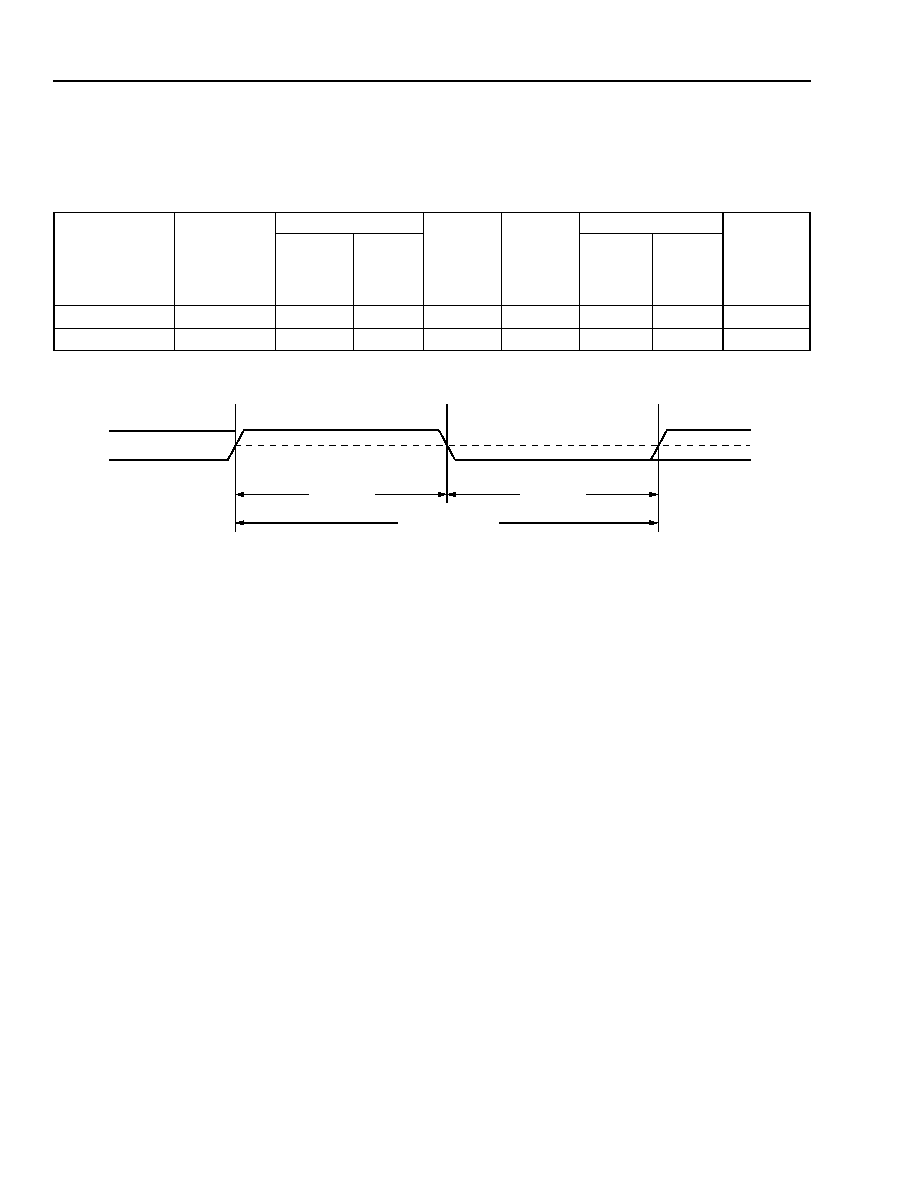

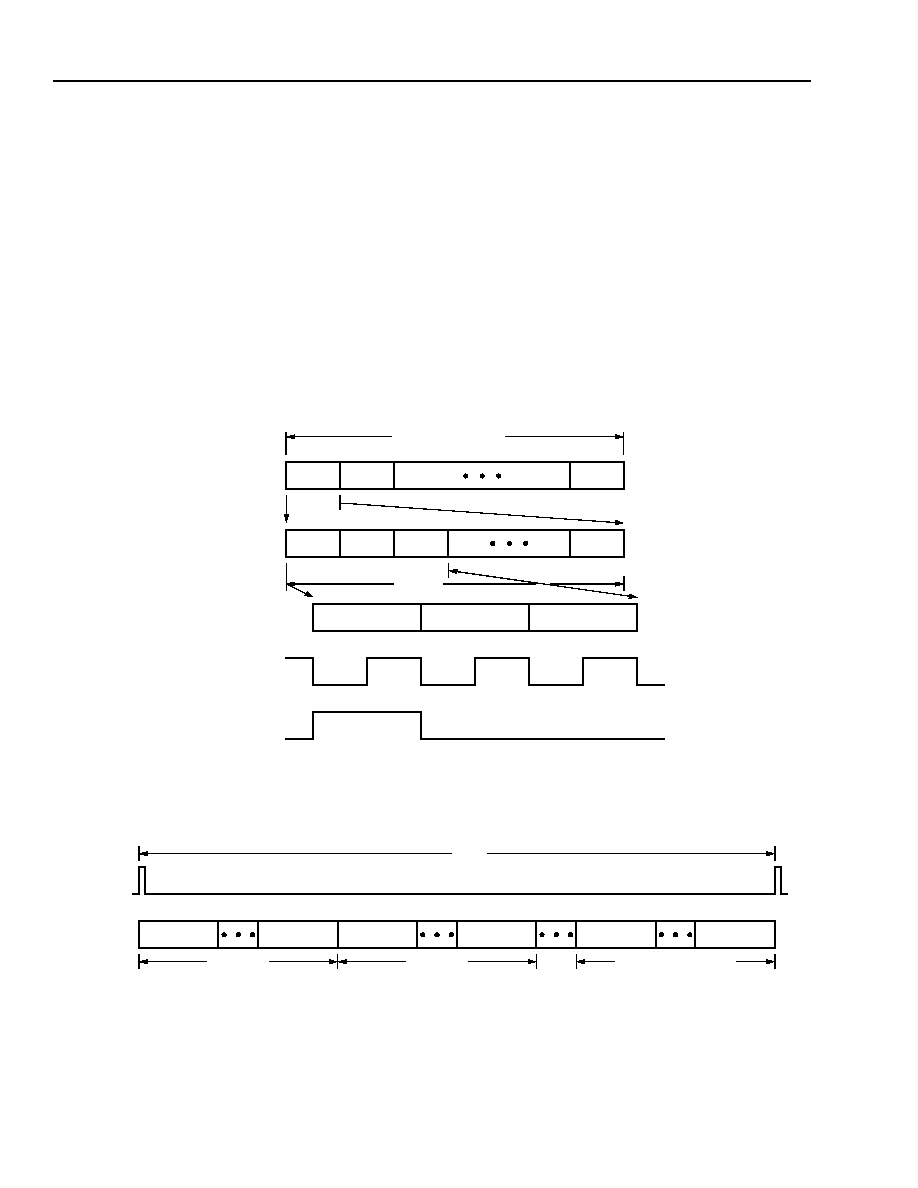

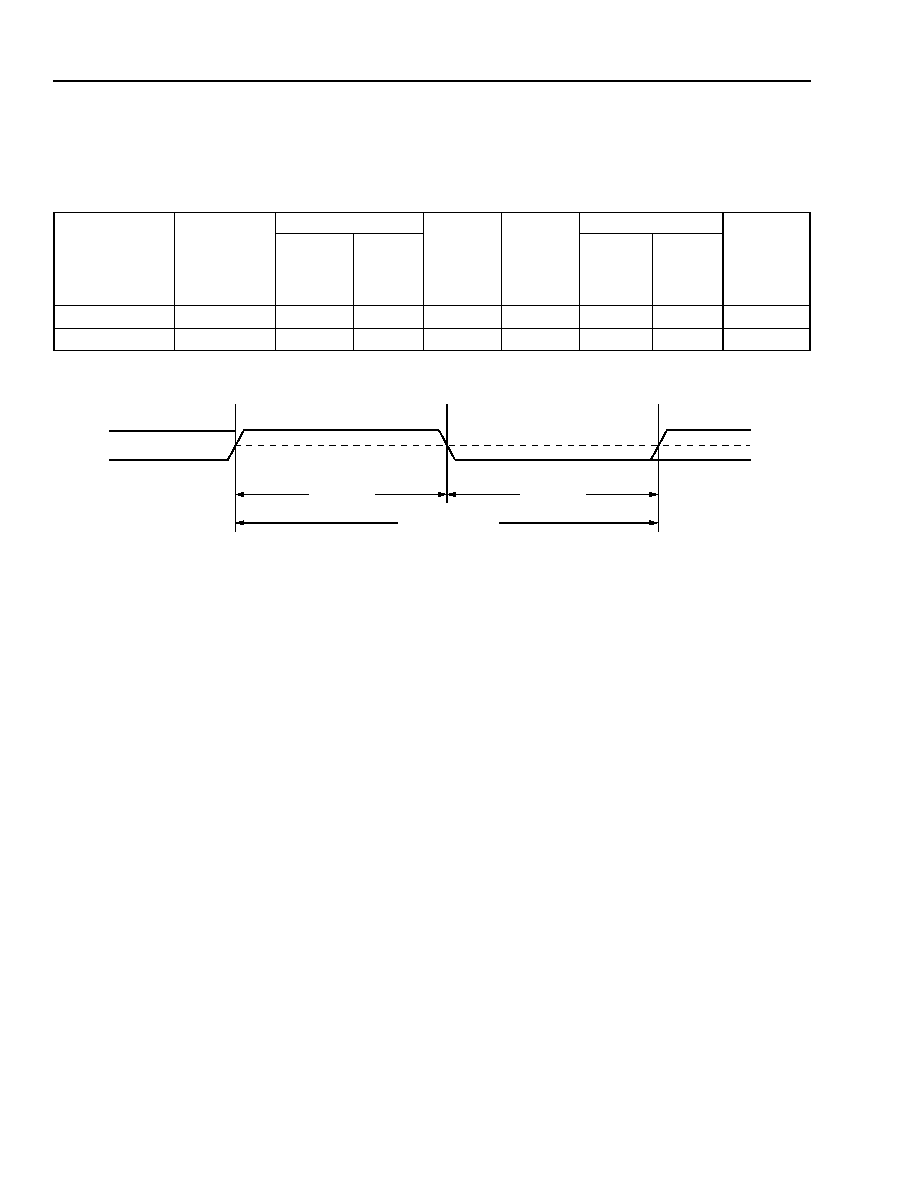

PCM I/O Frame Timing

Figure 8, SYNC and PCM Timing for DS1 and CEPT Frame illustrates the SYNC and PCM timing for both DS1 and