| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TMUX03155 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- Features

- Applications

- Description

- Nomenclature Assumptions

- Block Diagram

- Pin Information

- Mode Control Signals (See Register Description on page 54.)

- STS-1 Mode

- Transmit Direction Overview

- Receive Direction Overview

- Maintenance Functions

- Typical Uses

- Microprocessor Interface

- Absolute Maximum Ratings

- Handling Precautions

- Operating Conditions

- Electrical Characteristics

- Timing Characteristics

- Outline Diagram

- Ordering Information

- DS01-194PDH Replaces DS00-213TIC to Incorporate the Following Updates

- List of Figures

- List of Tables

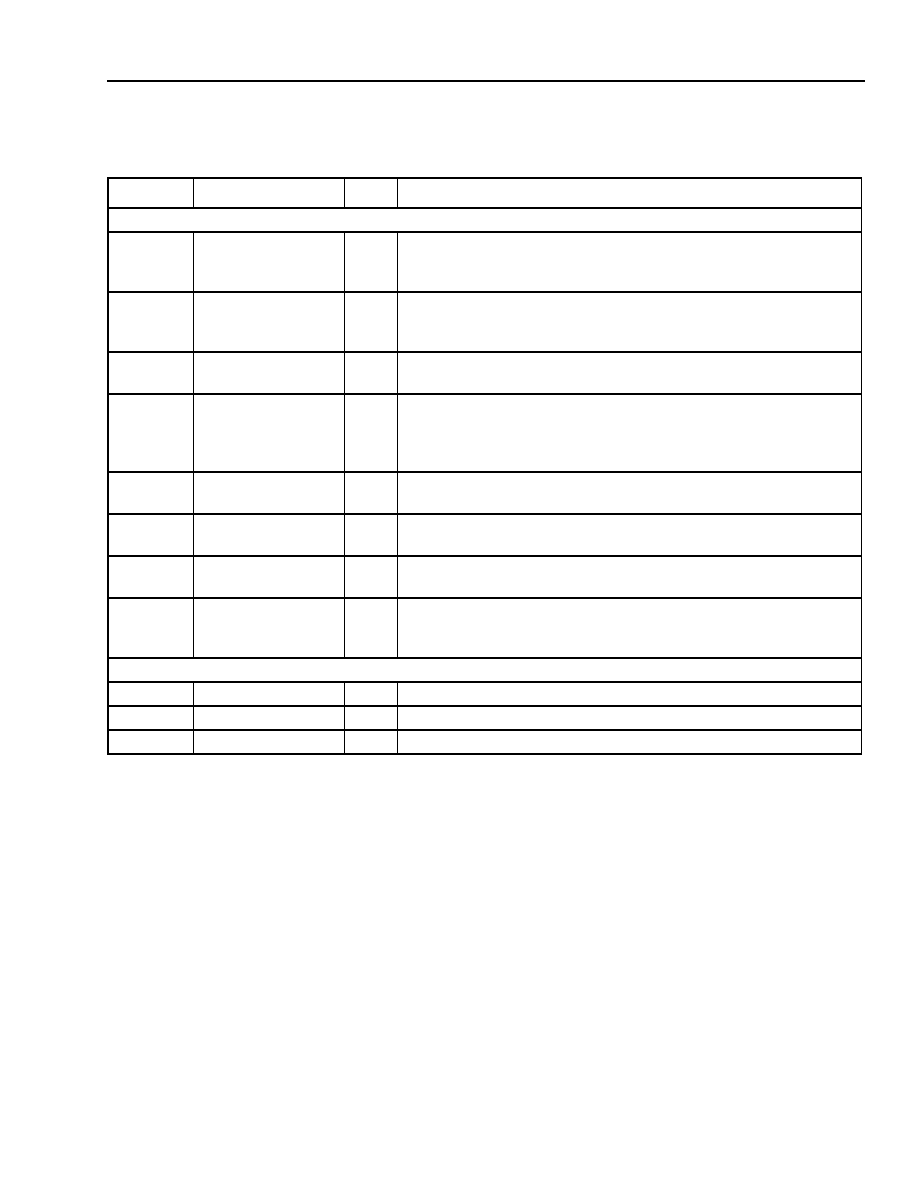

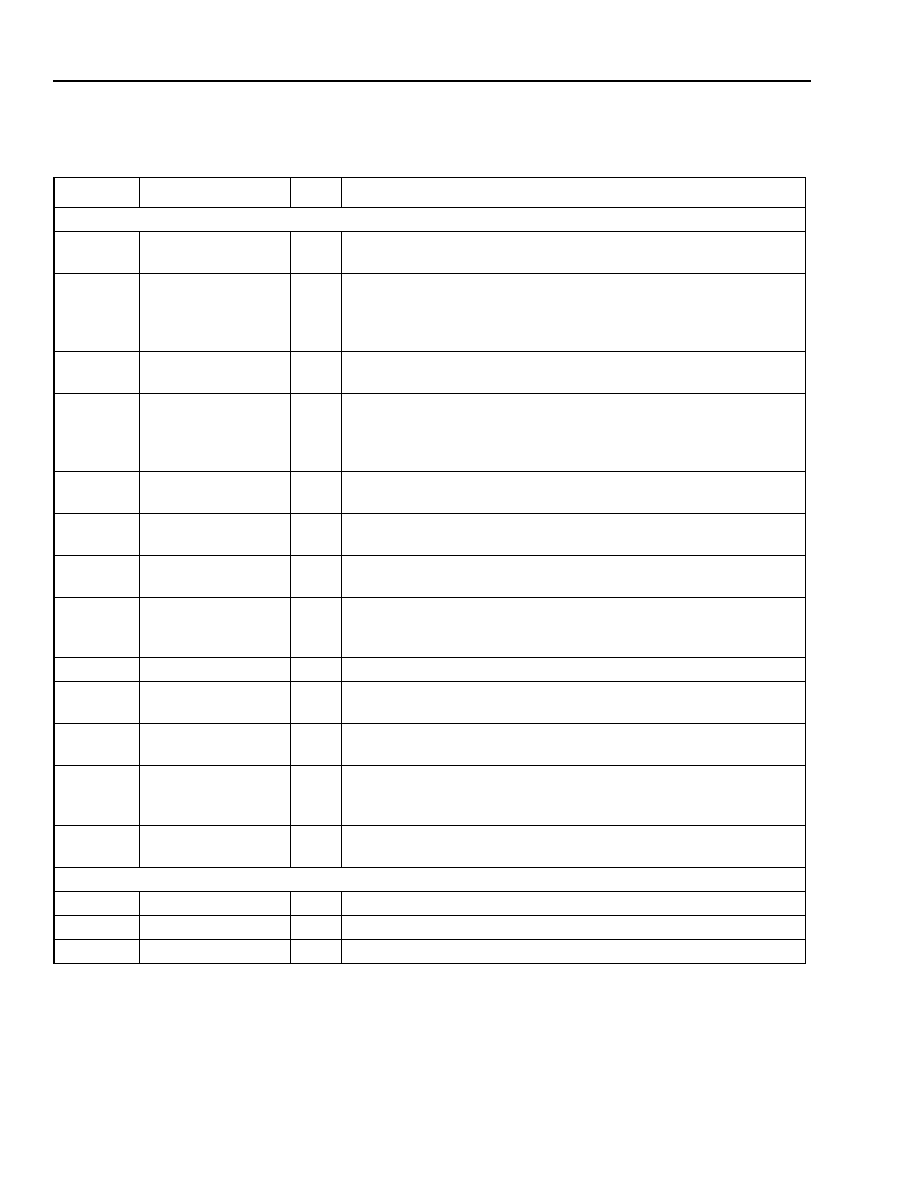

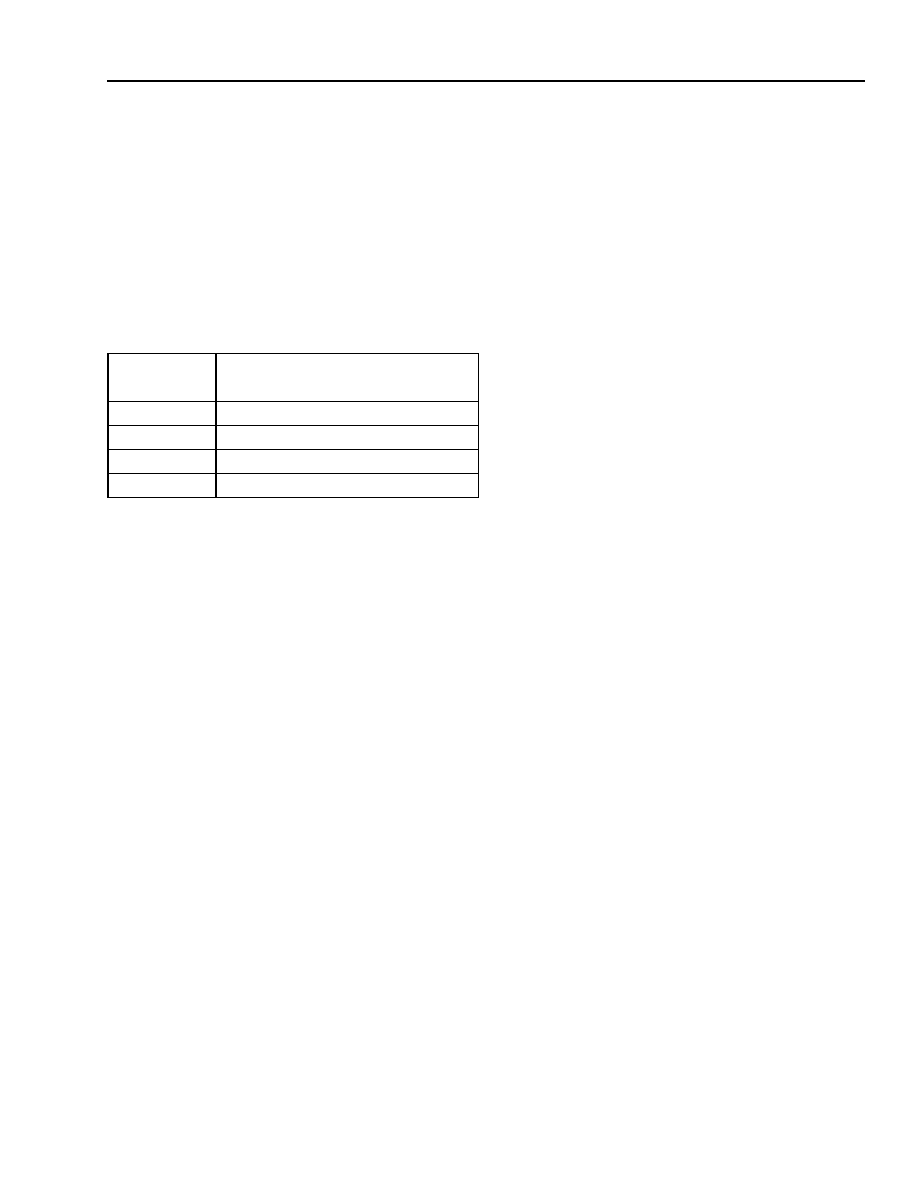

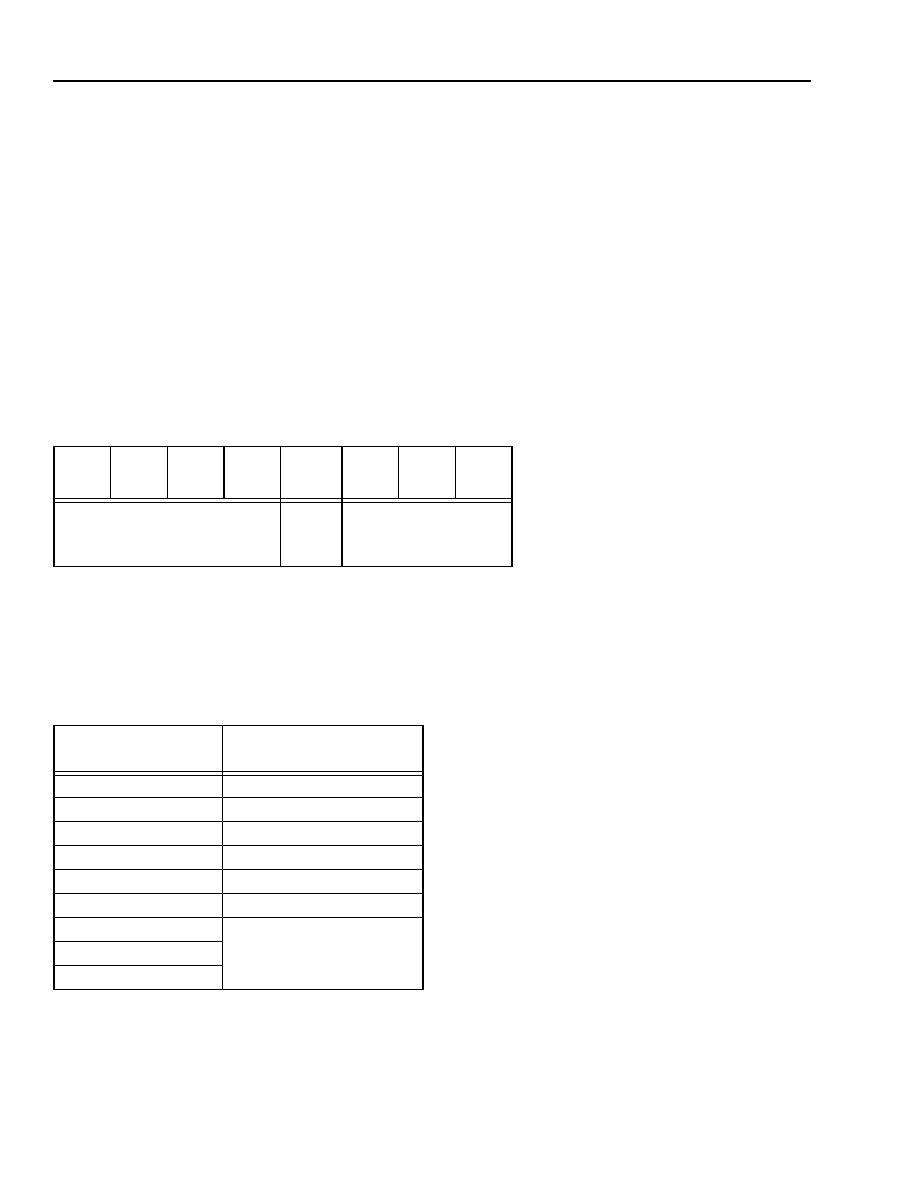

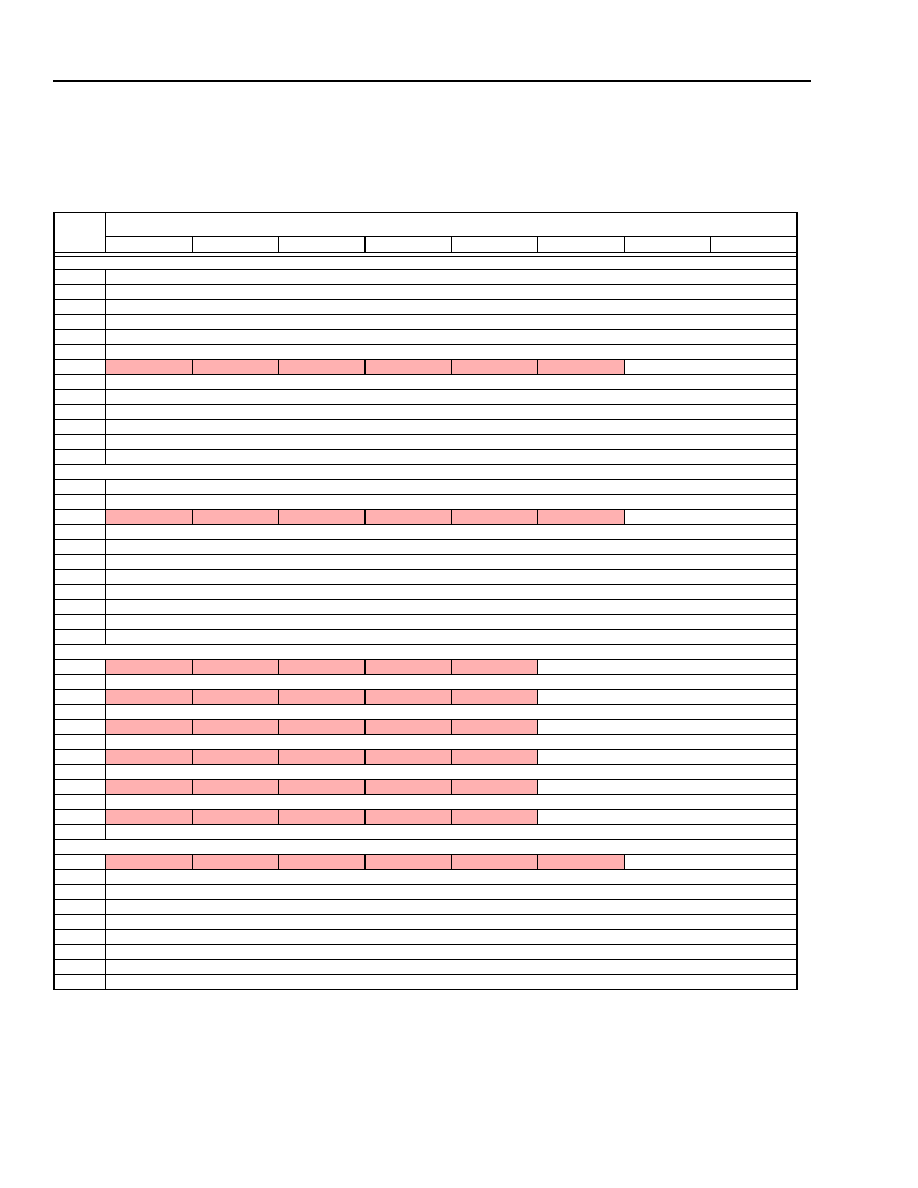

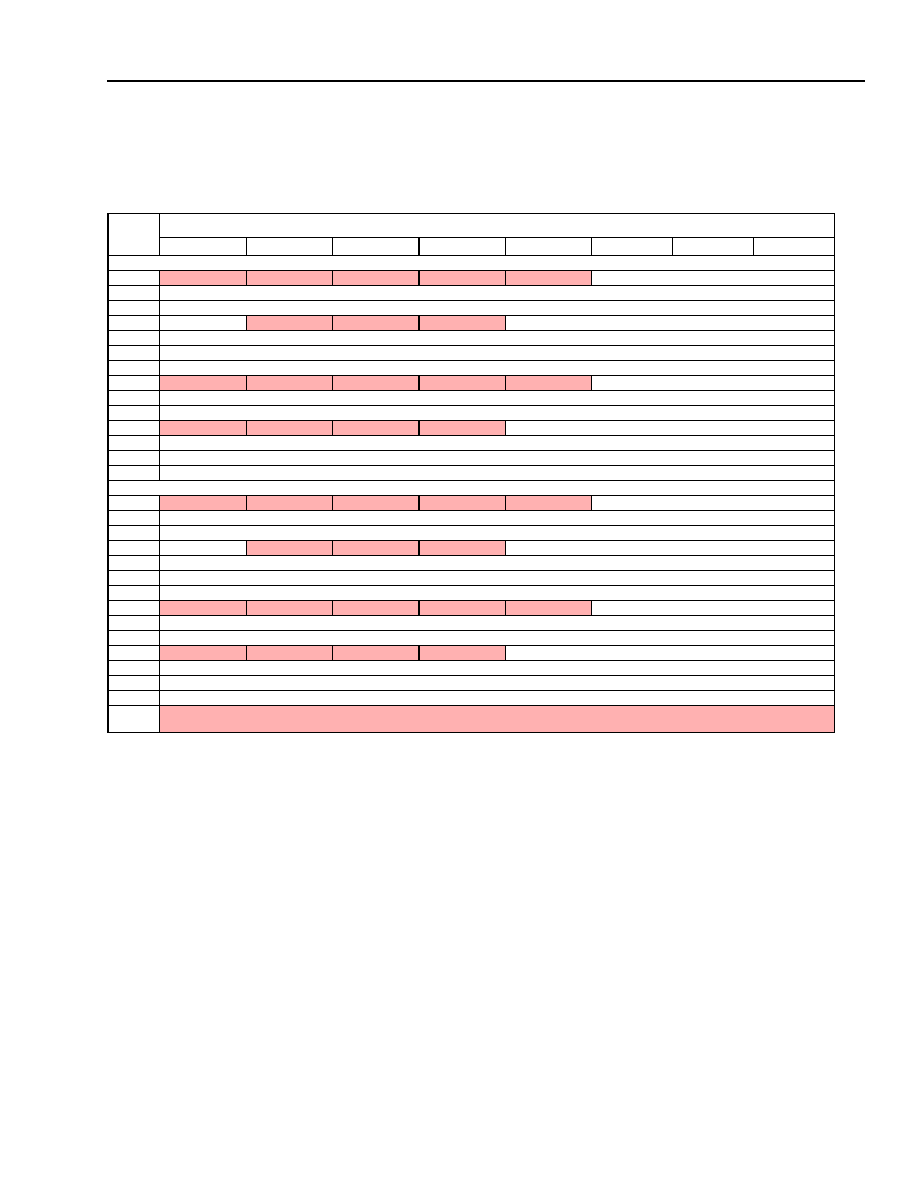

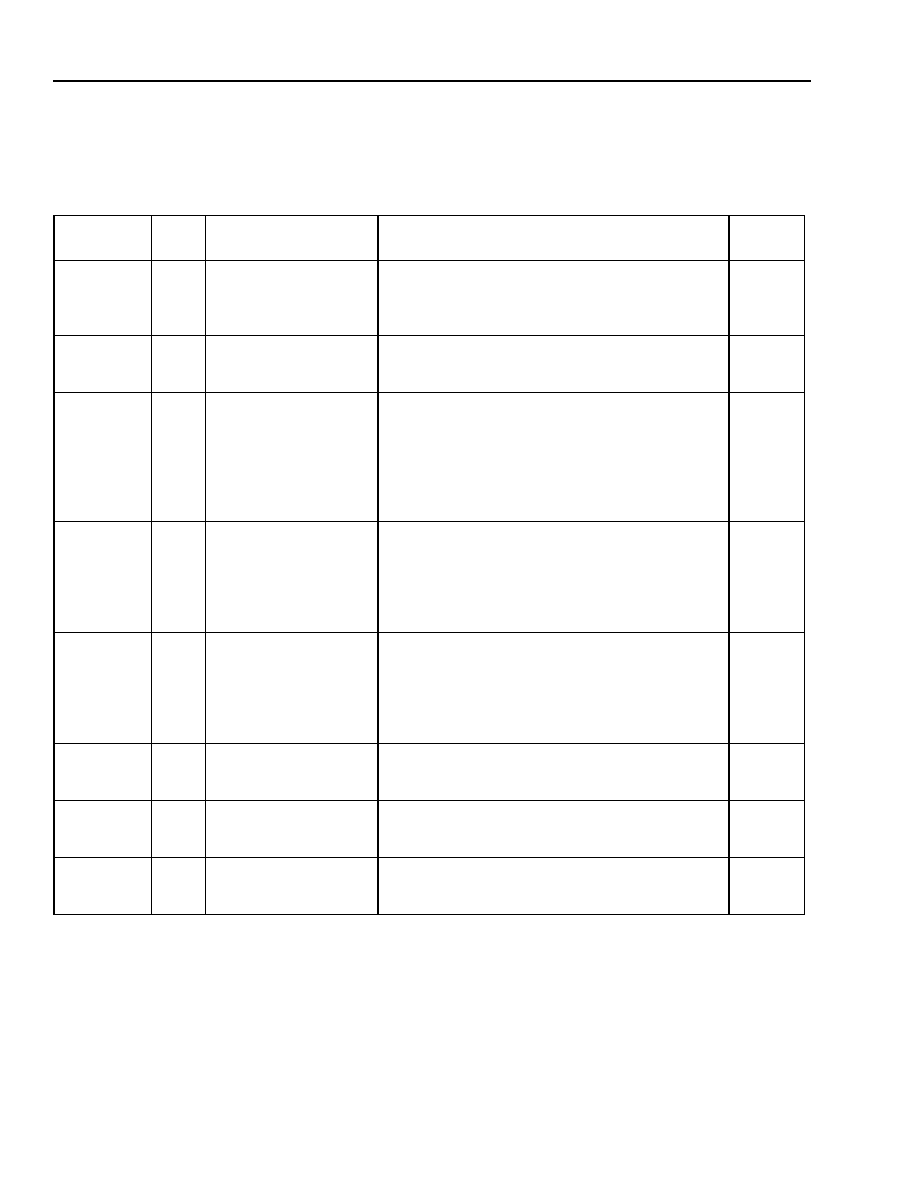

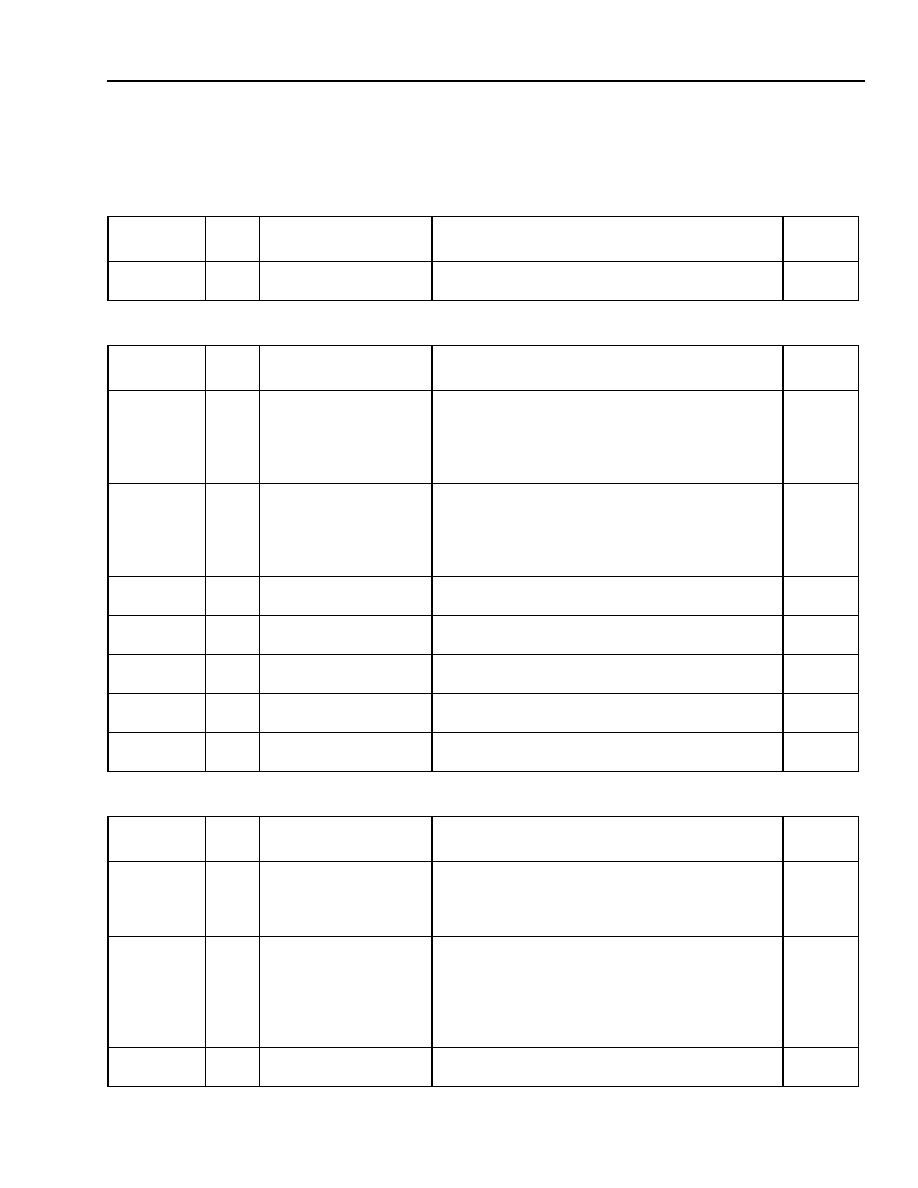

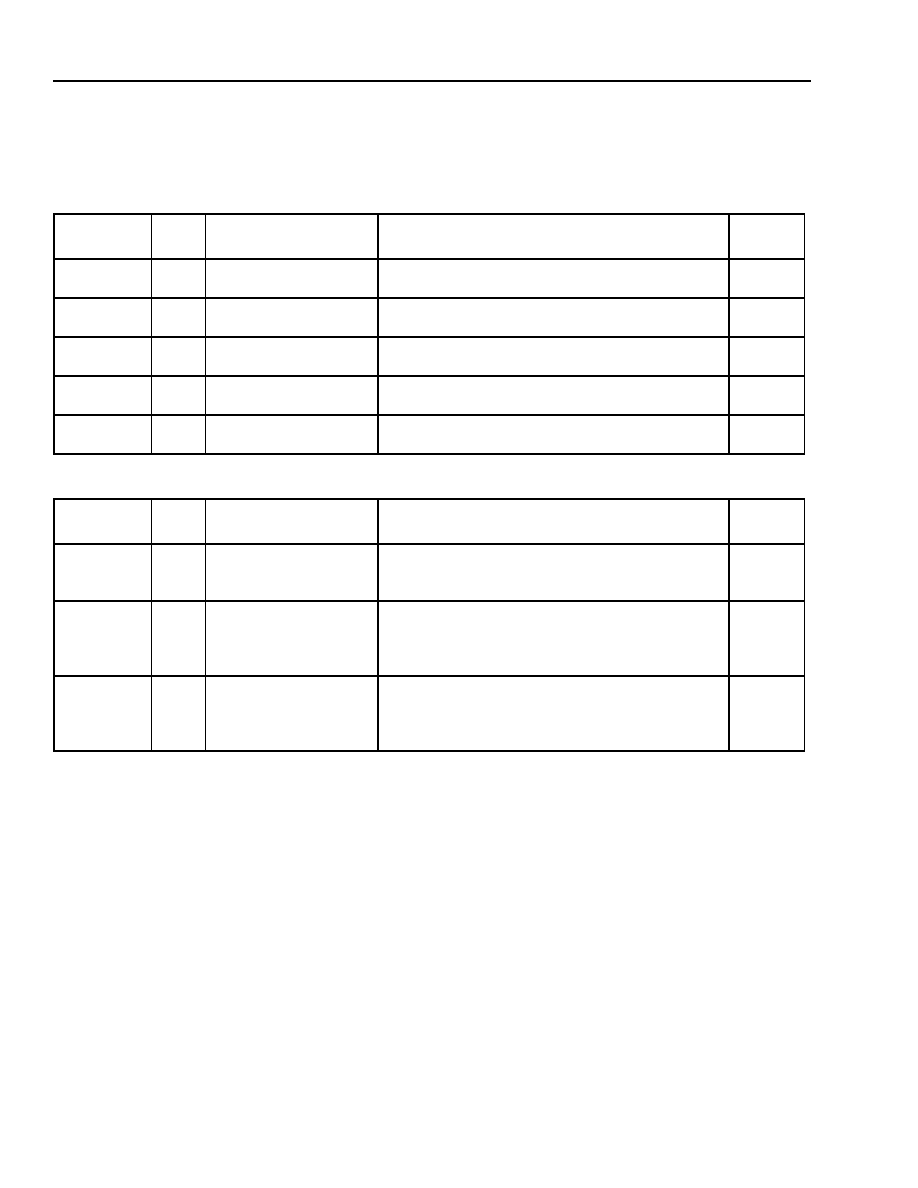

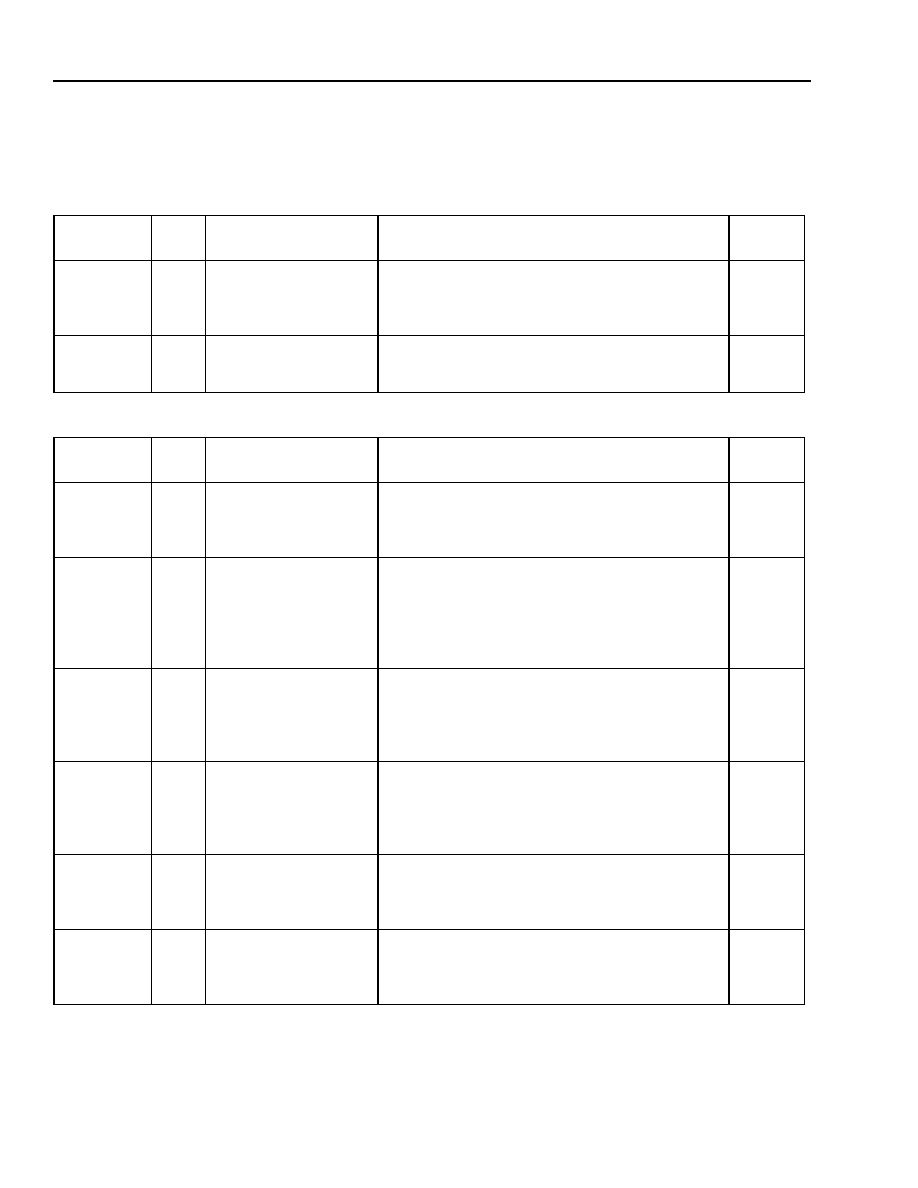

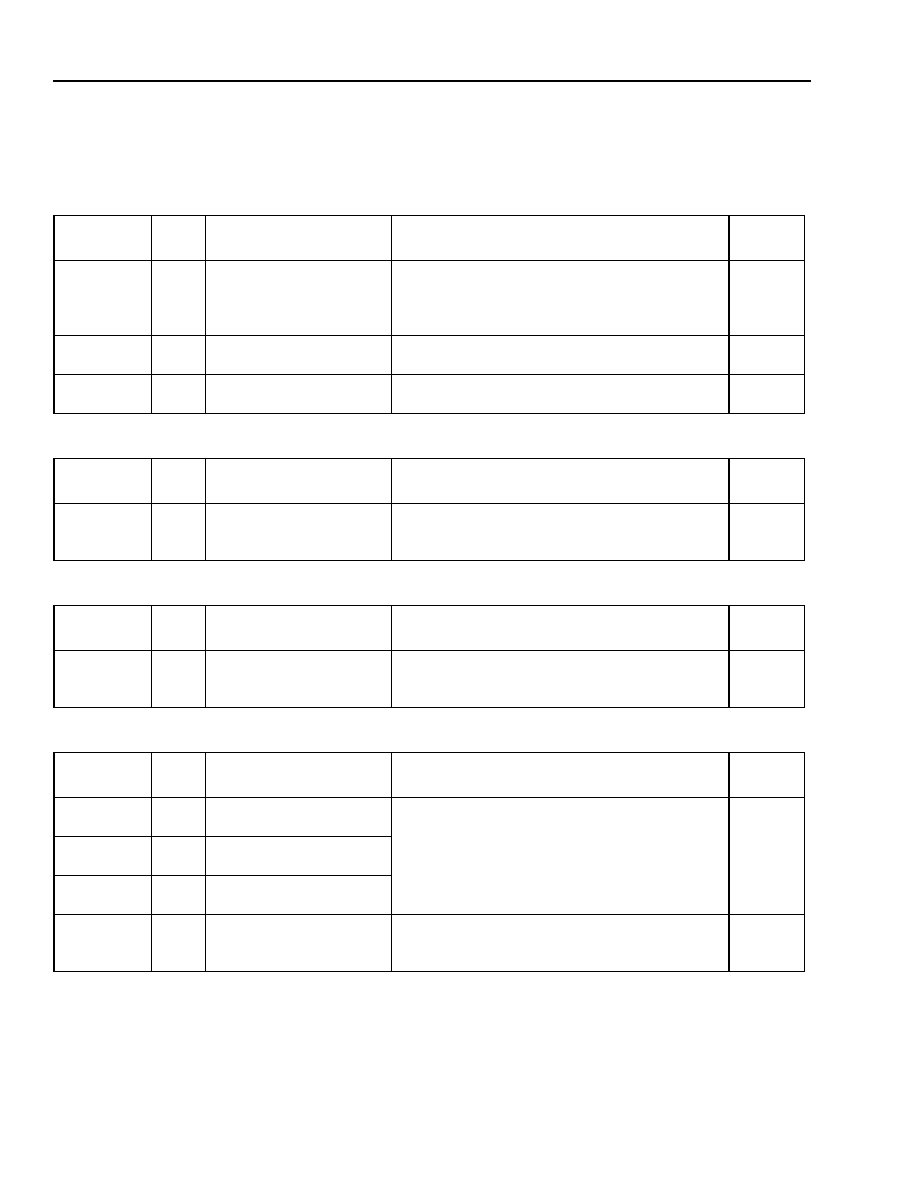

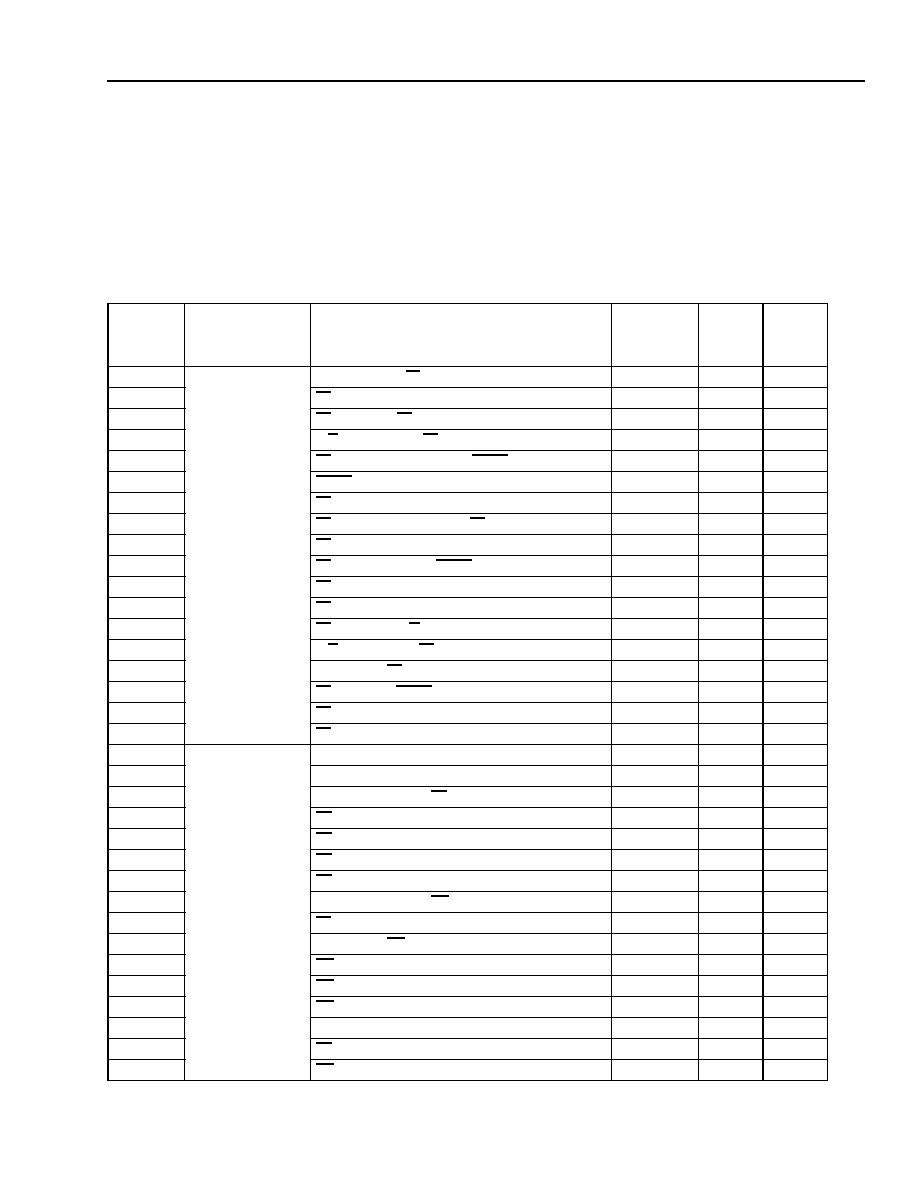

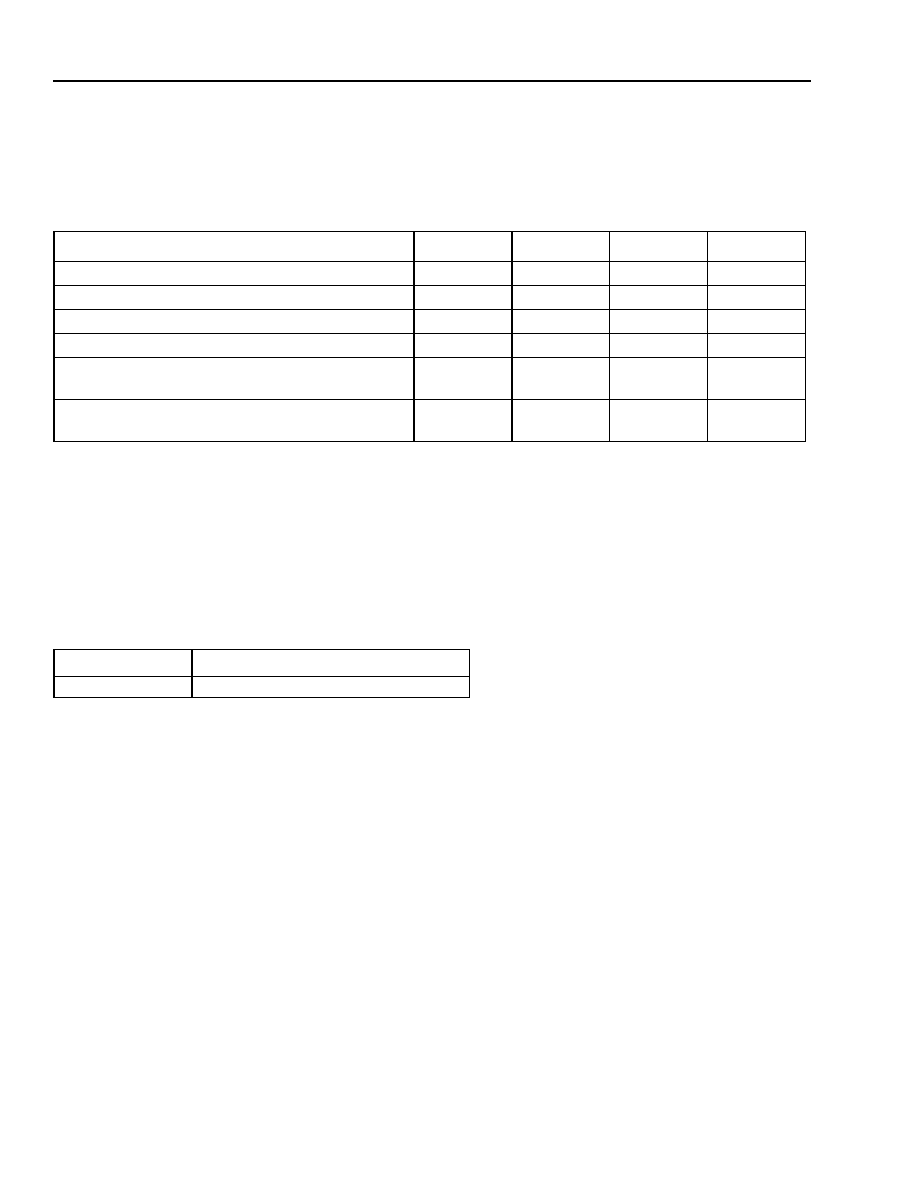

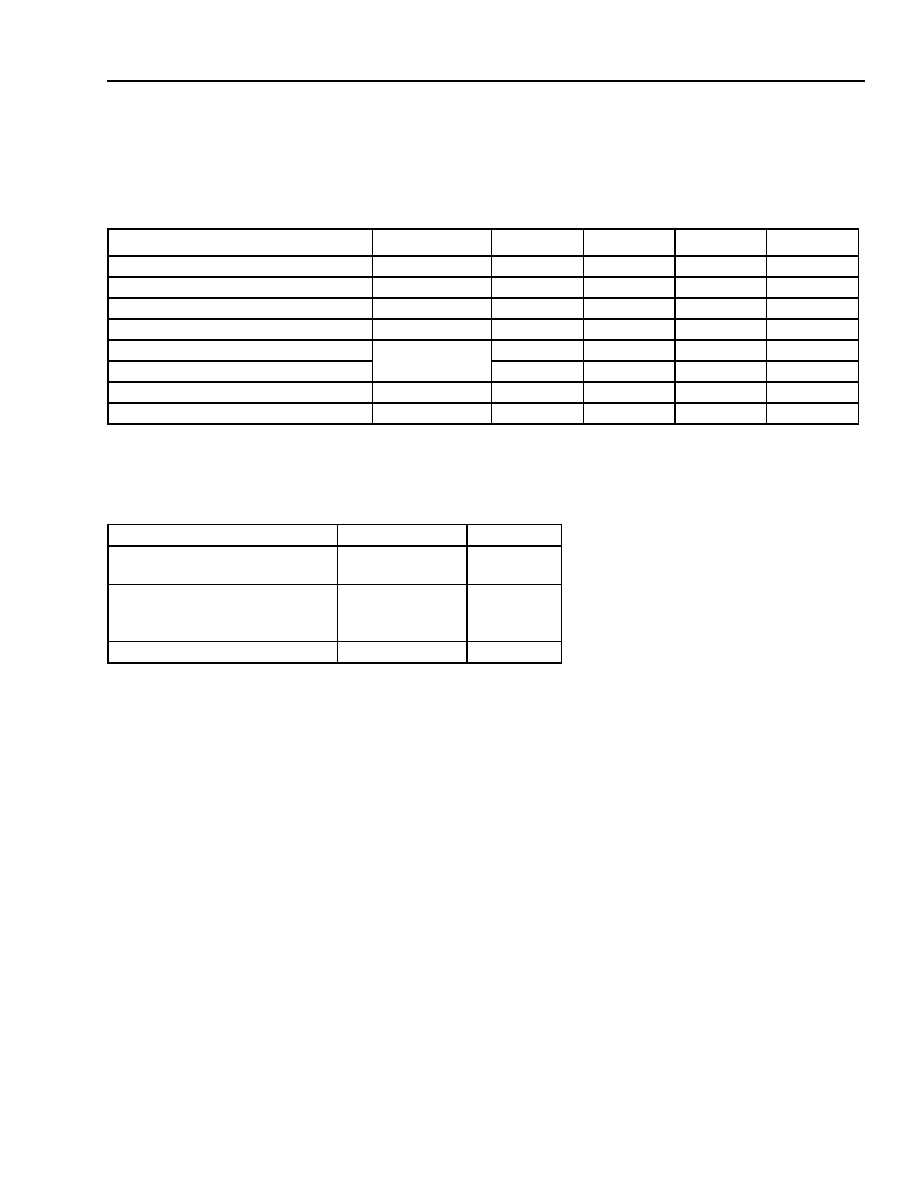

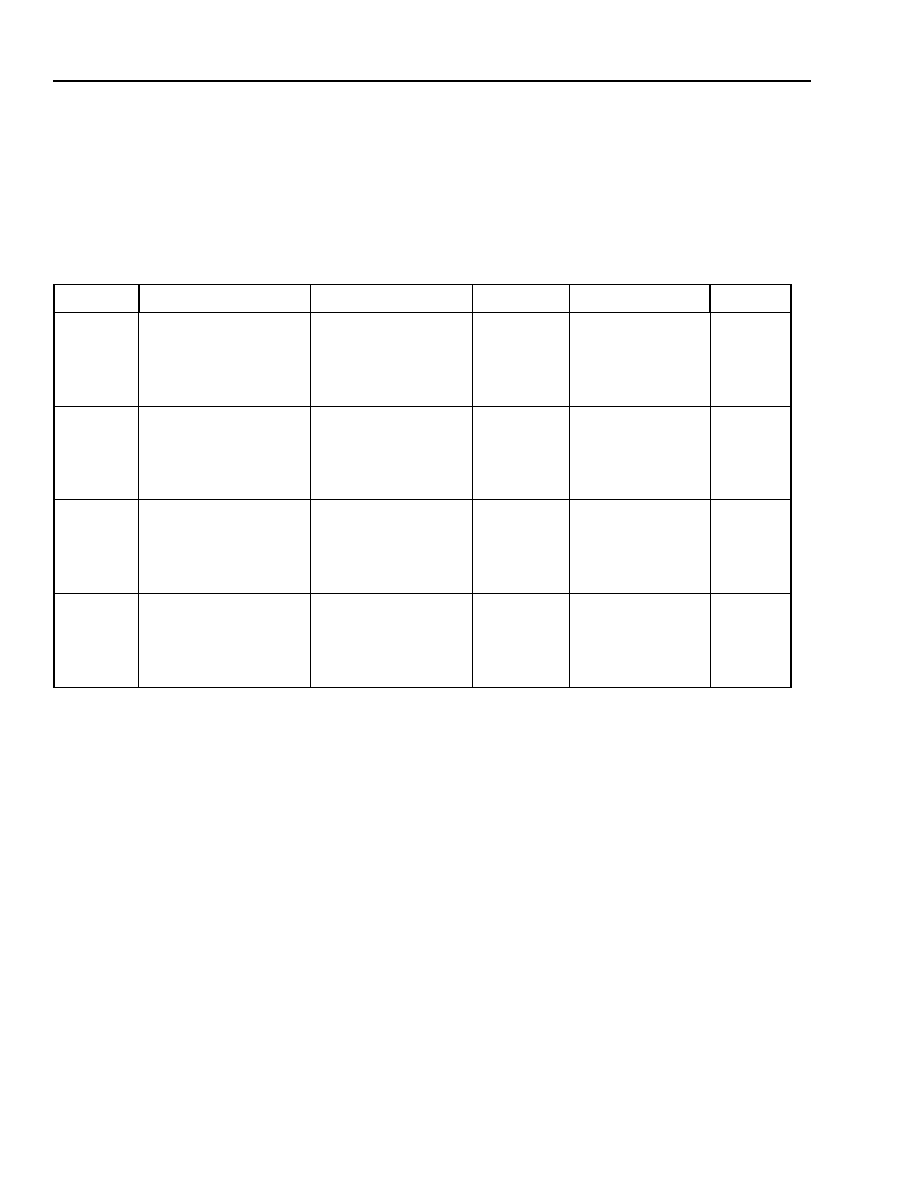

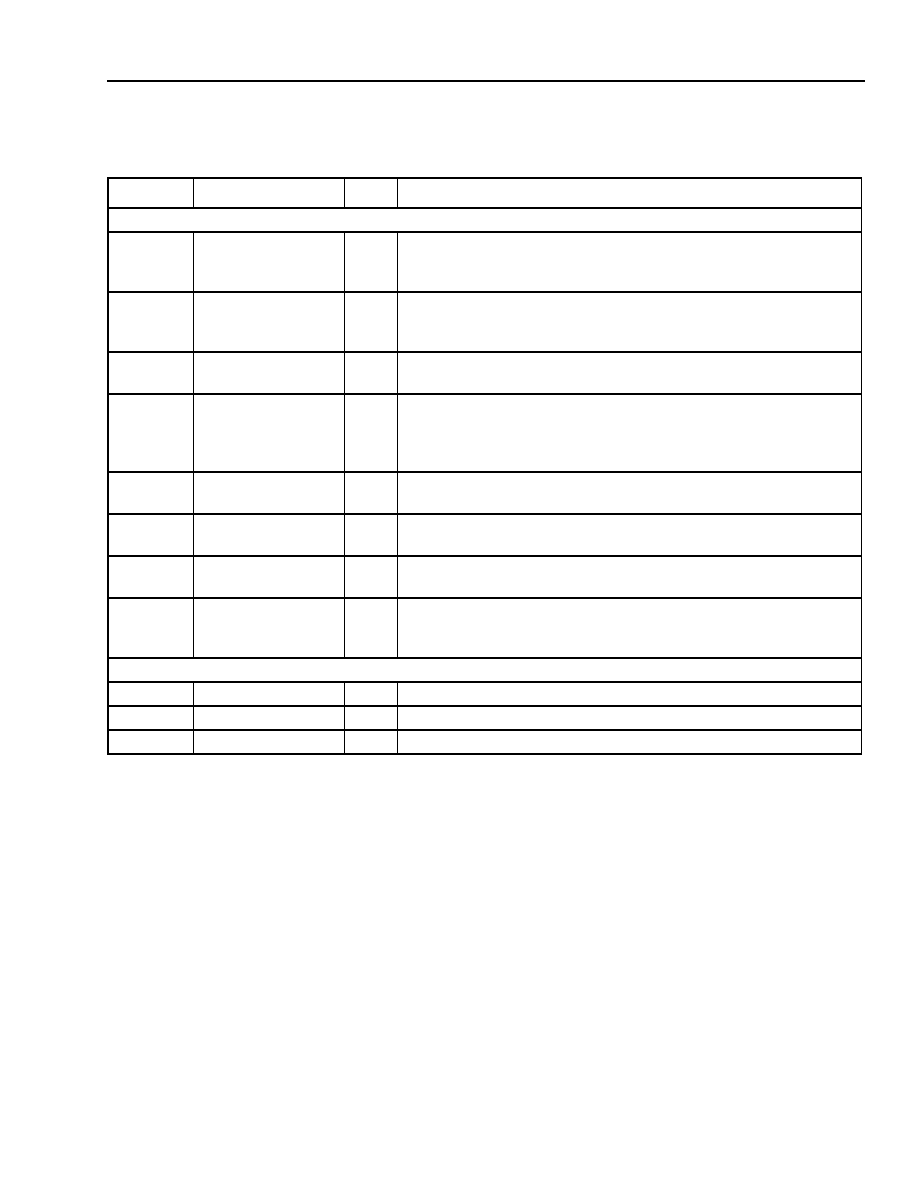

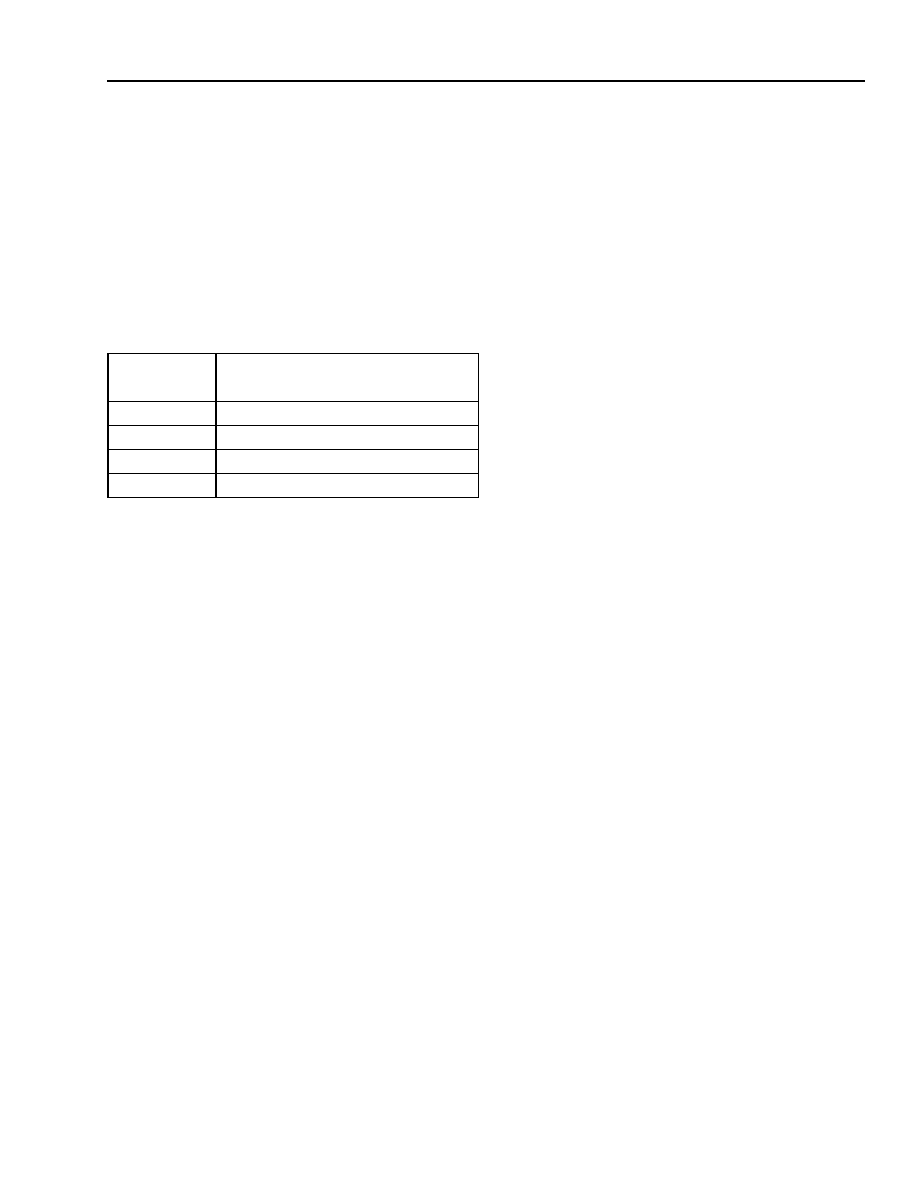

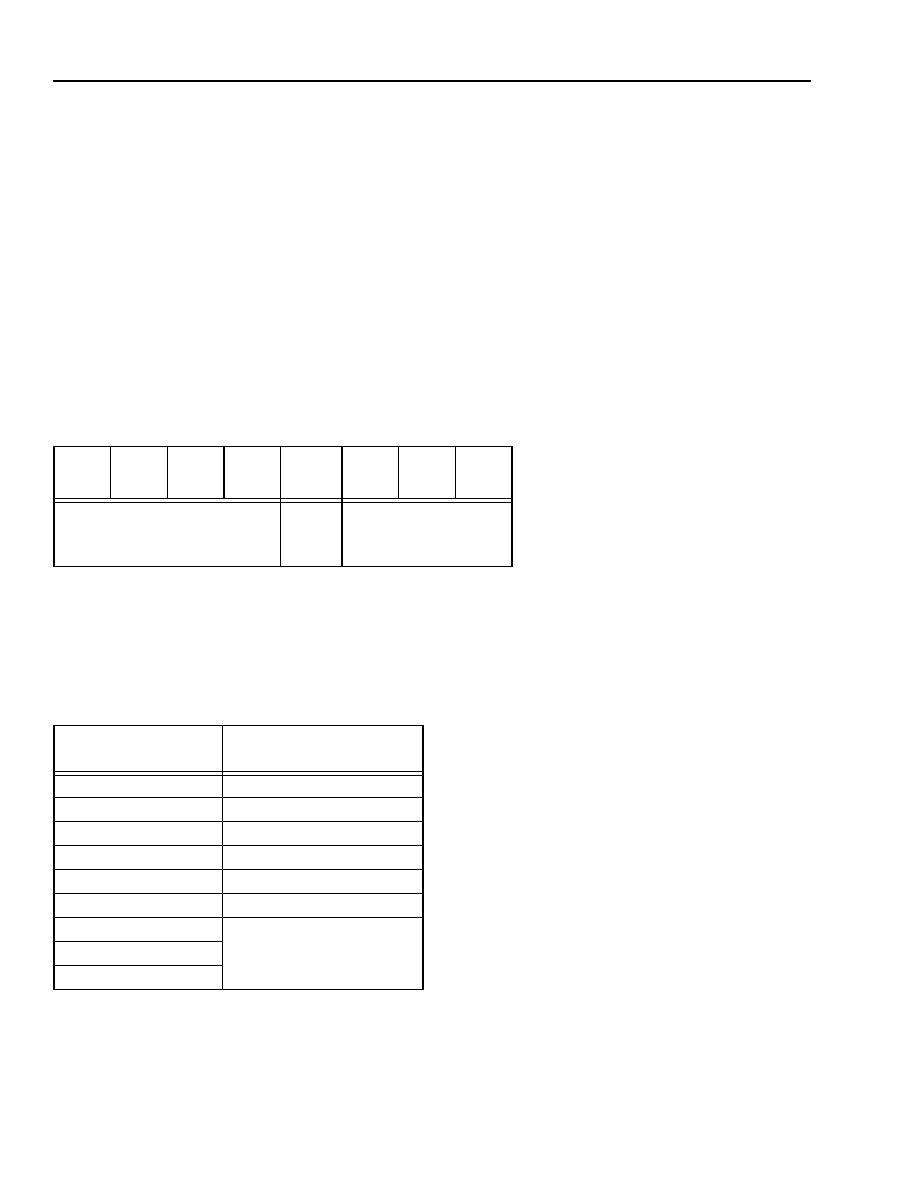

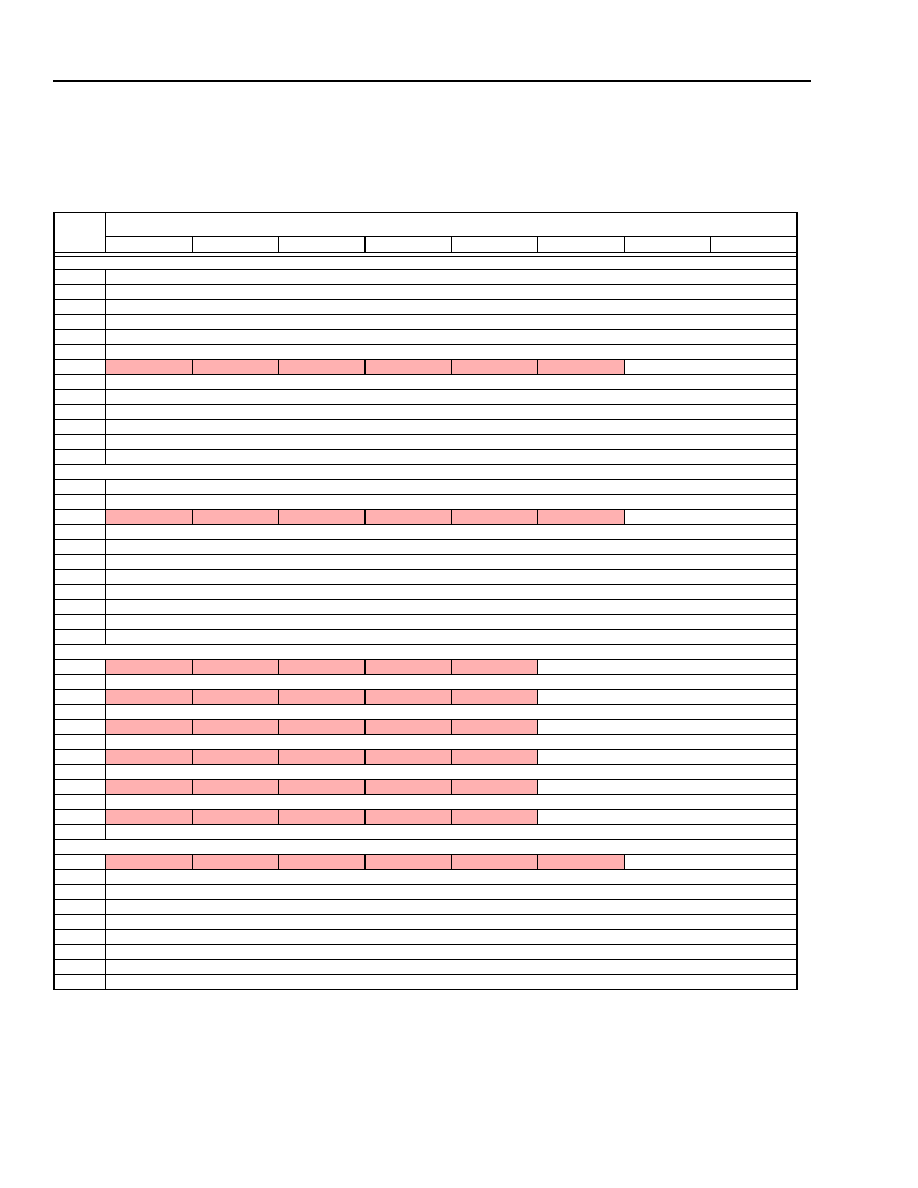

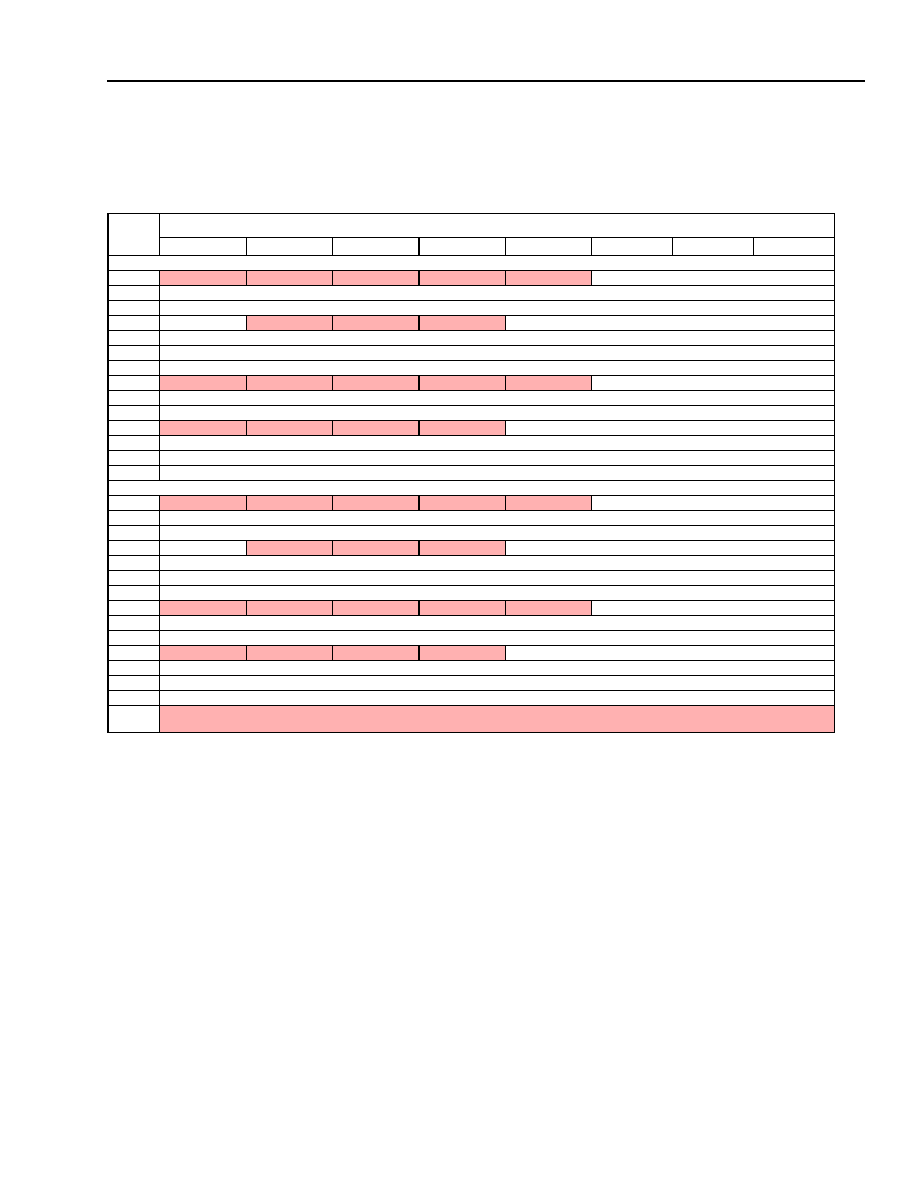

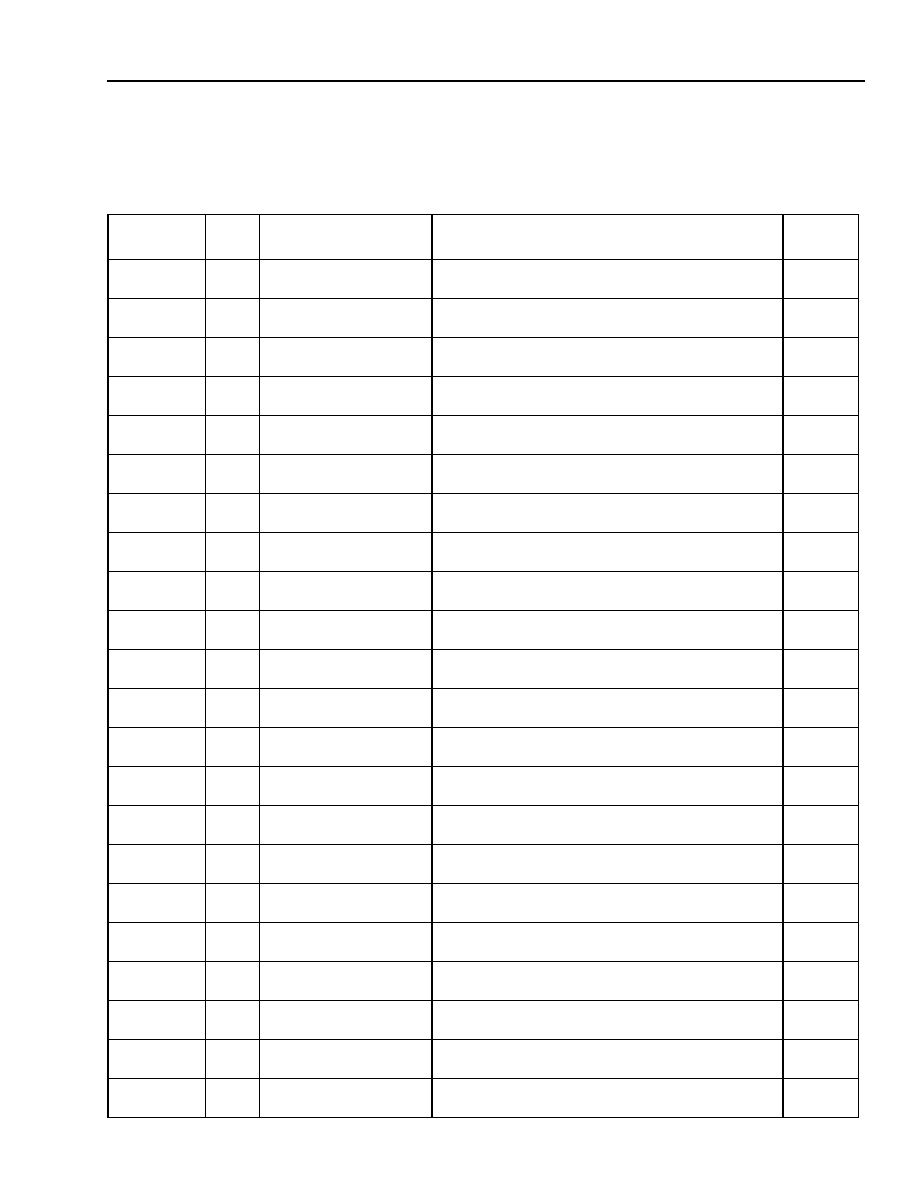

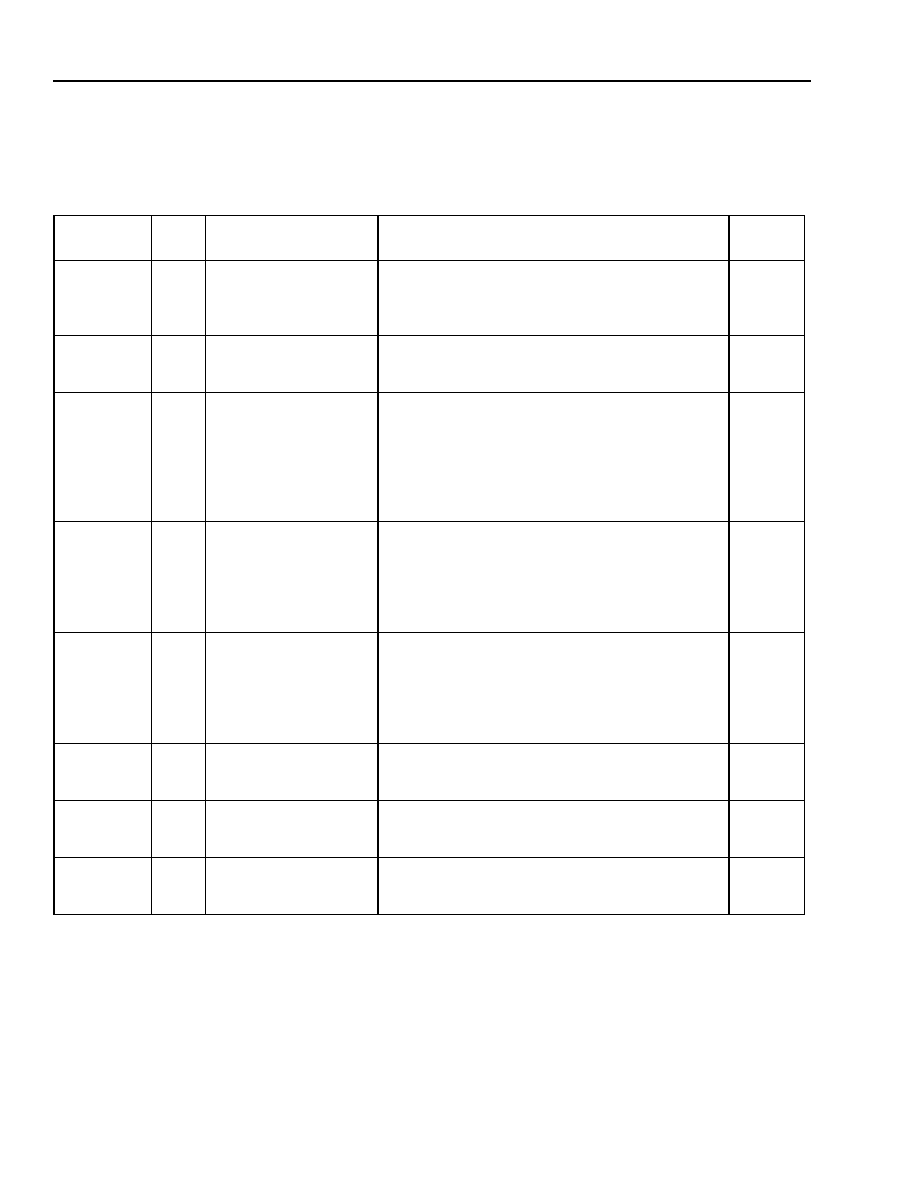

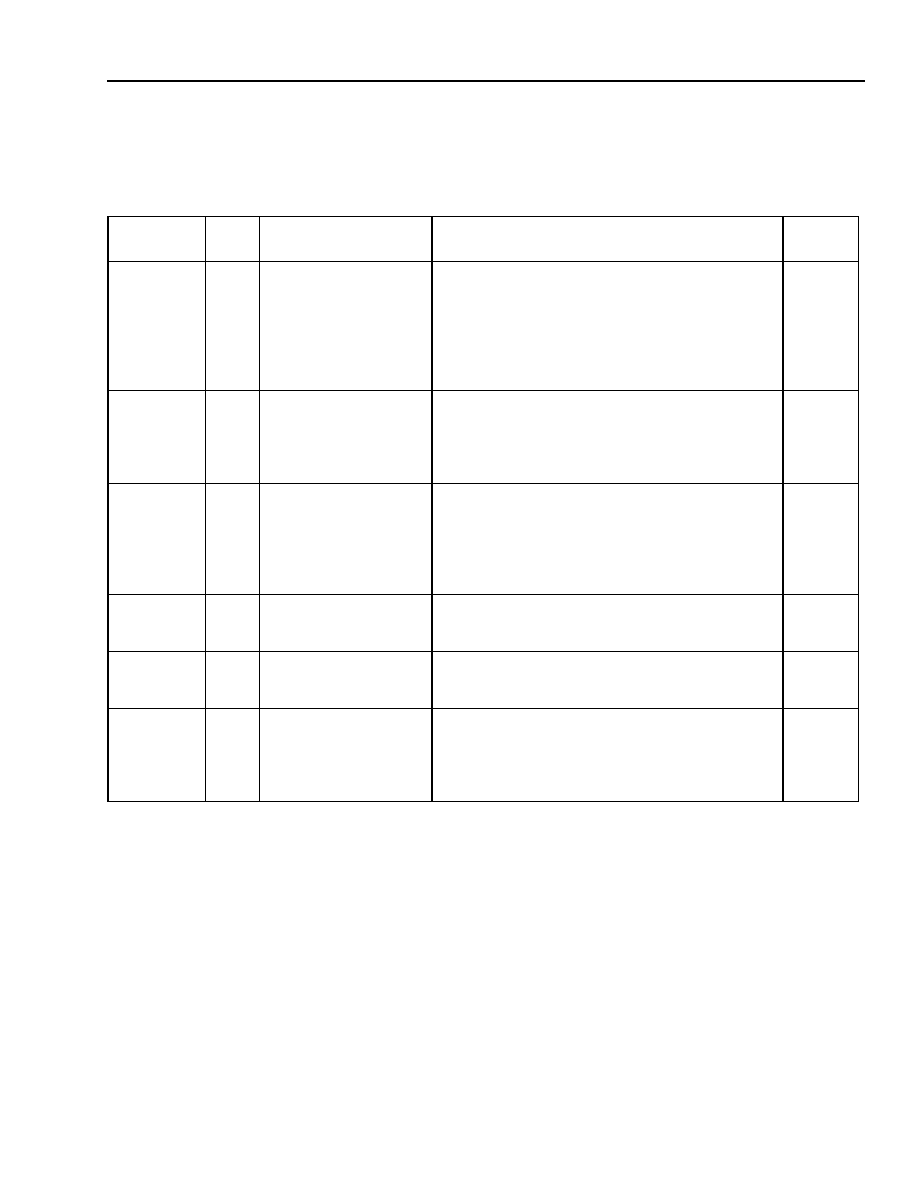

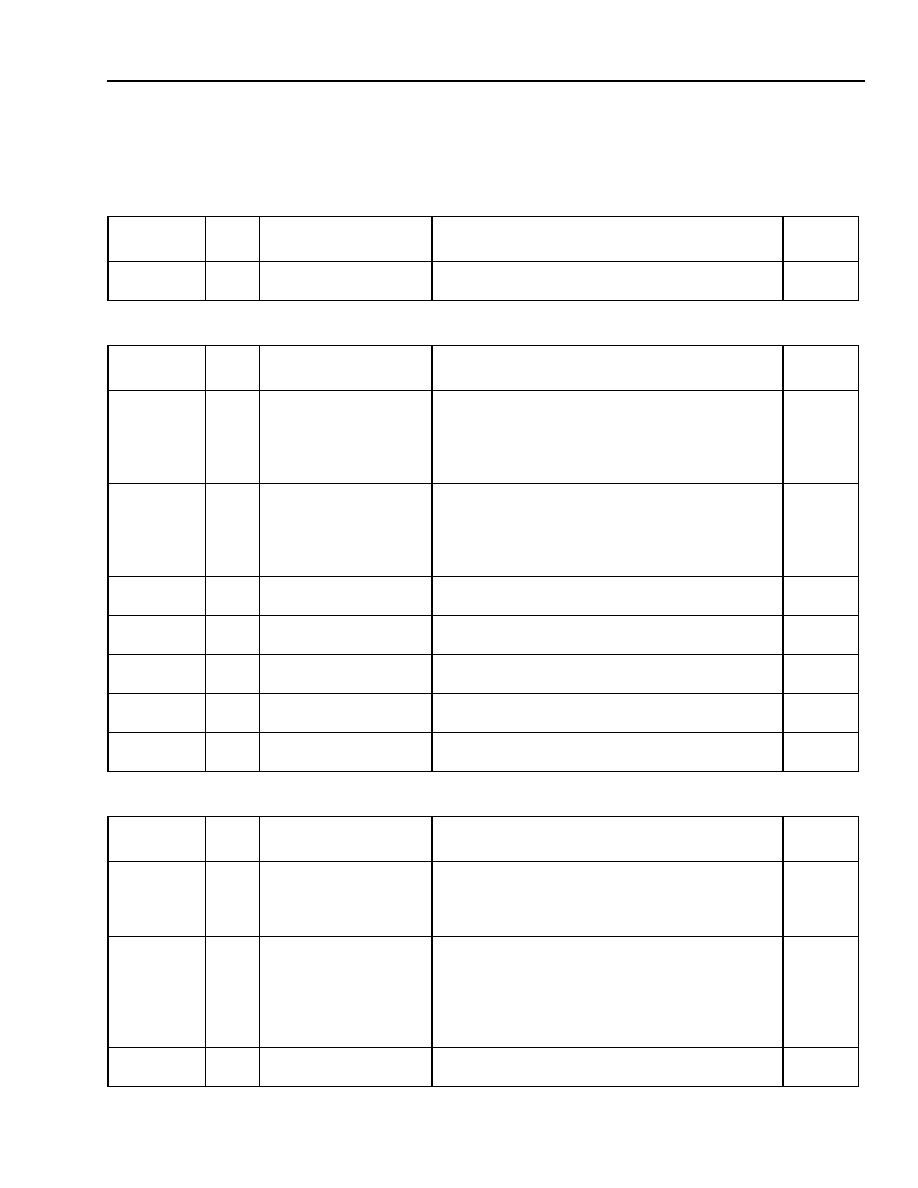

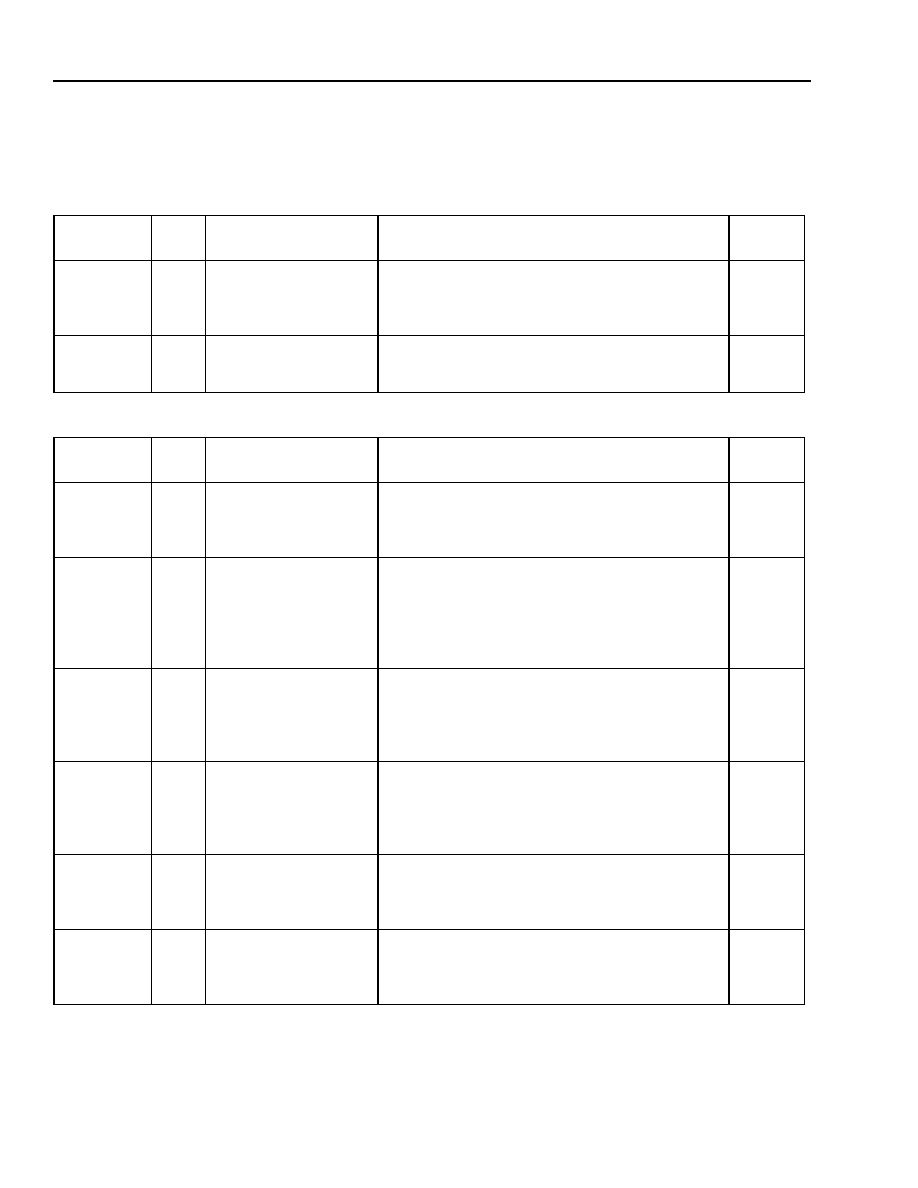

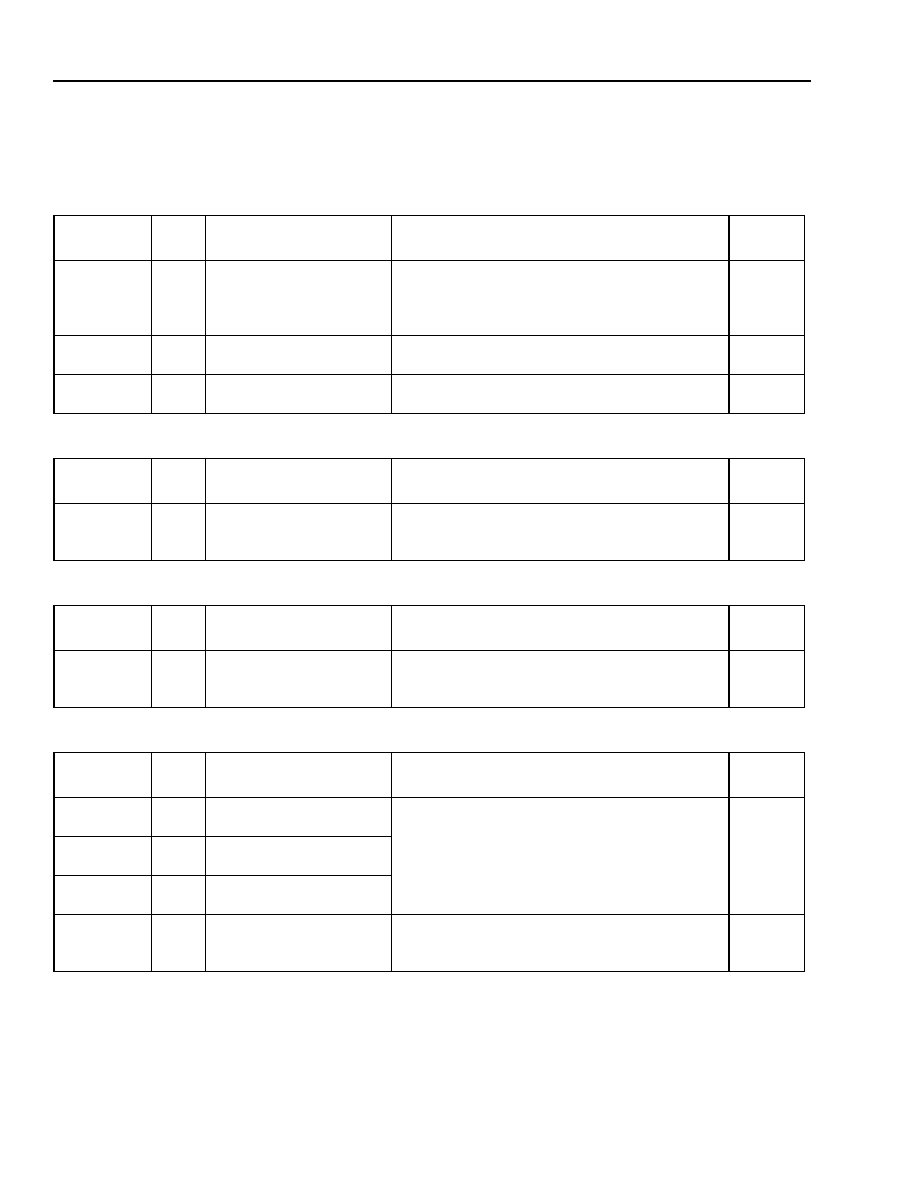

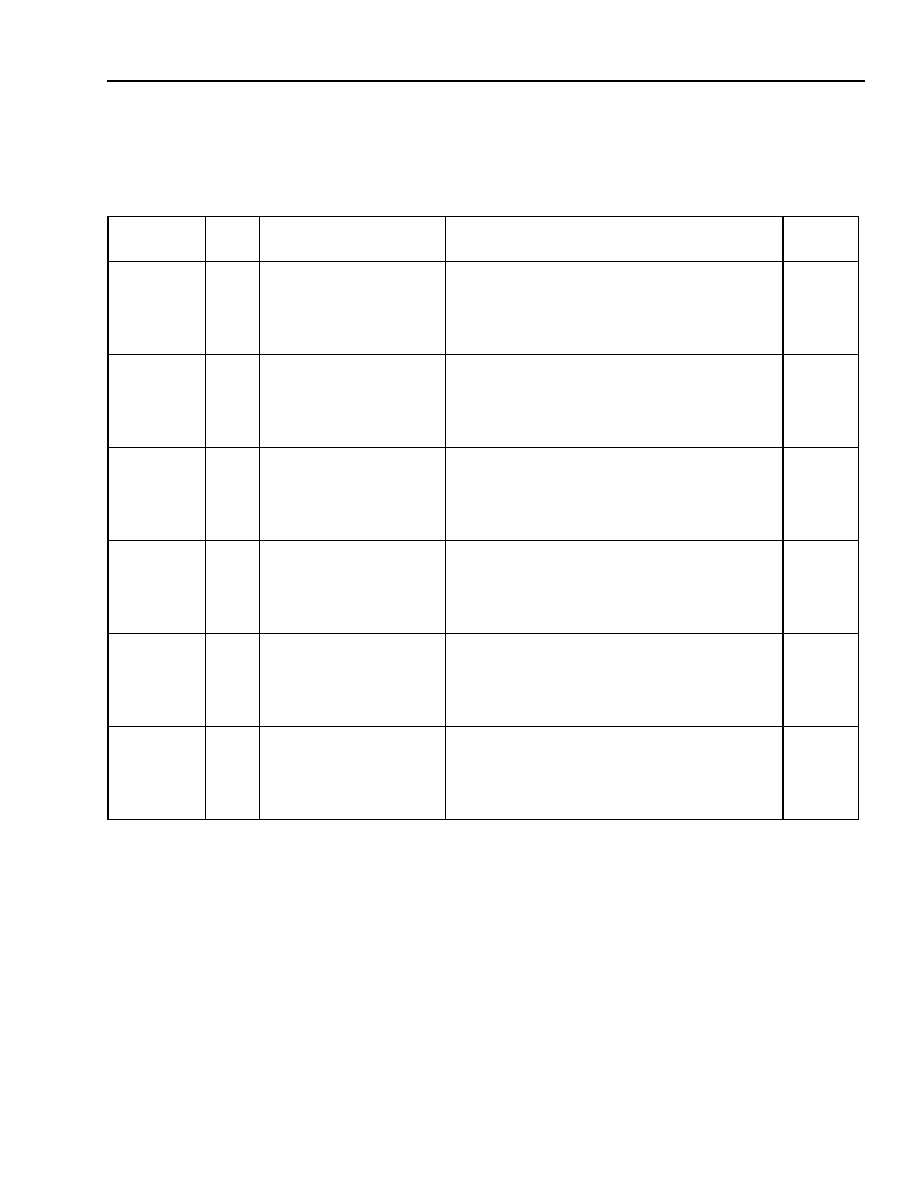

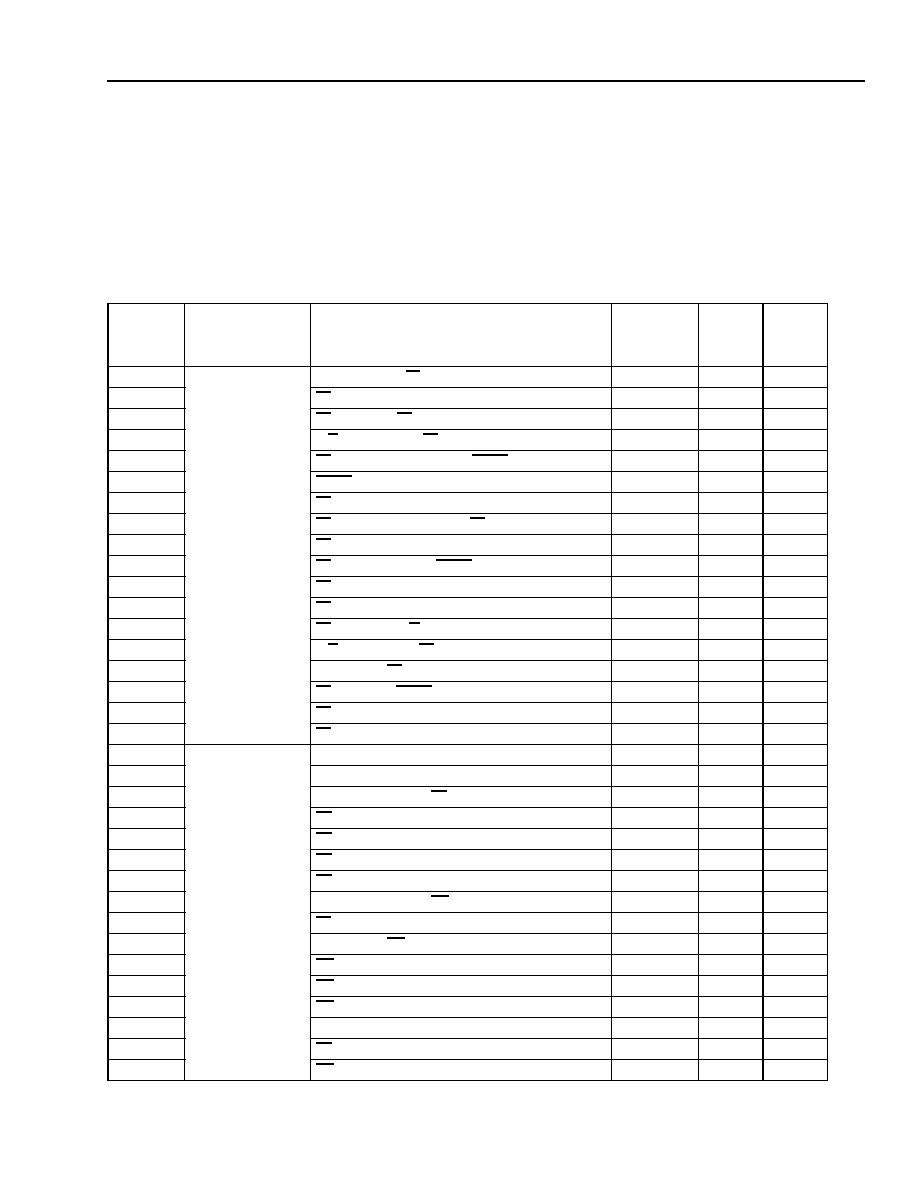

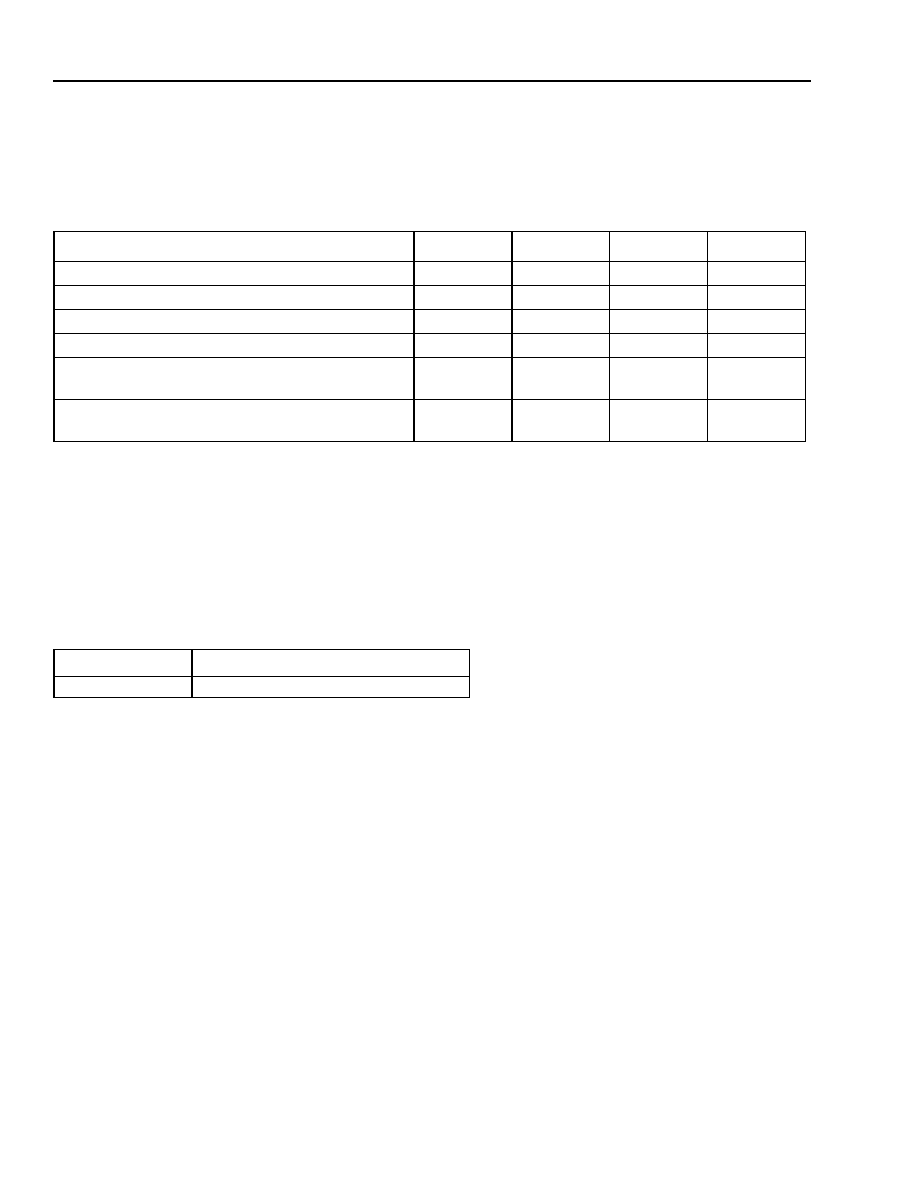

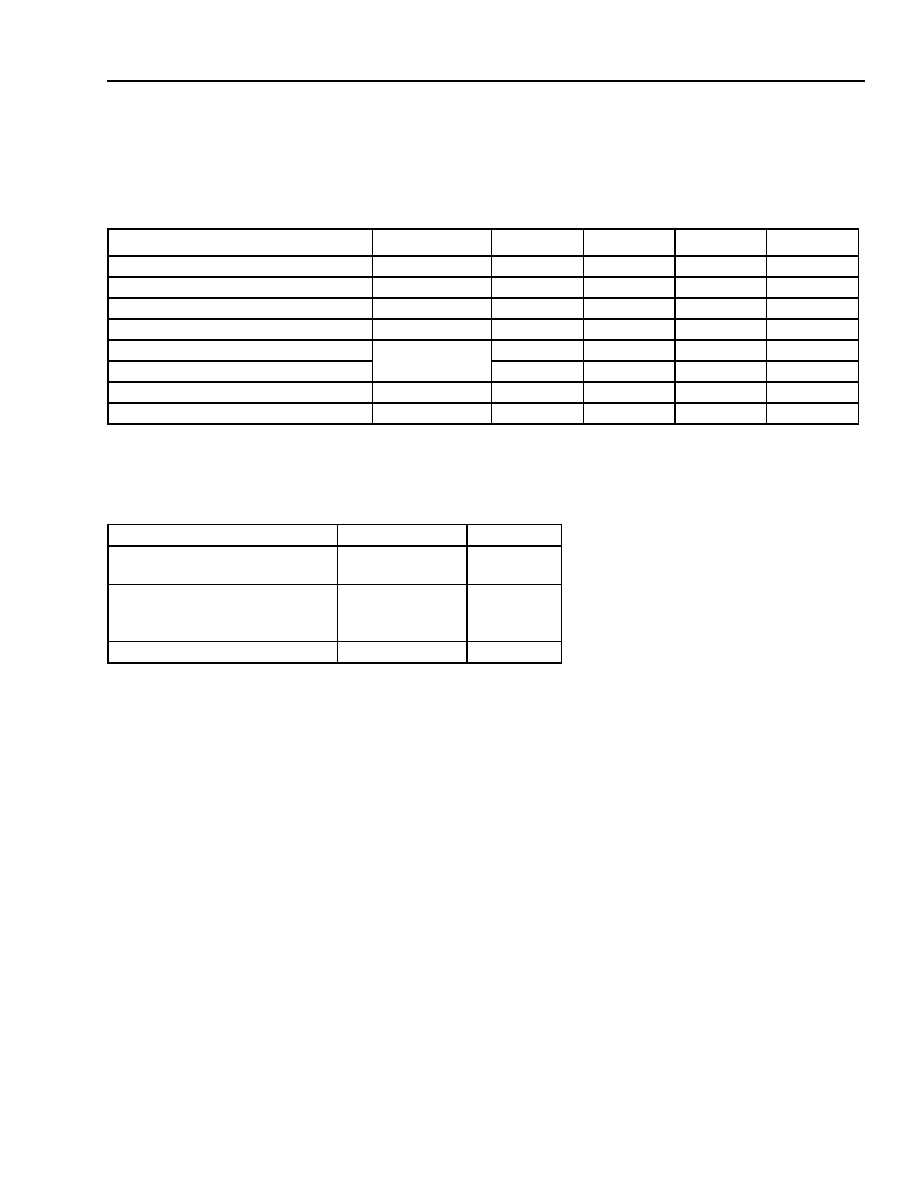

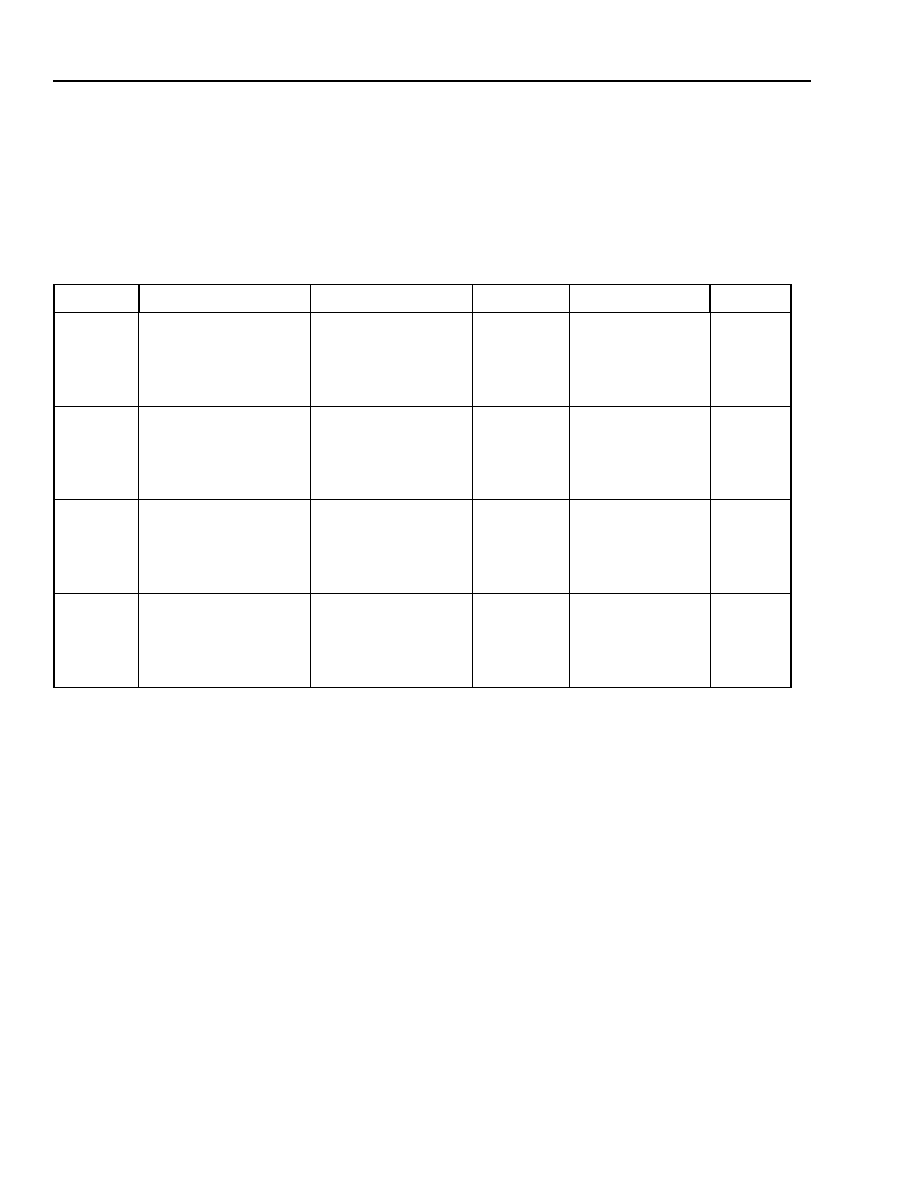

- Table 1. Pin Descriptions for the 208-Pin SQFP Package

- Table 2. Input/Output Summary

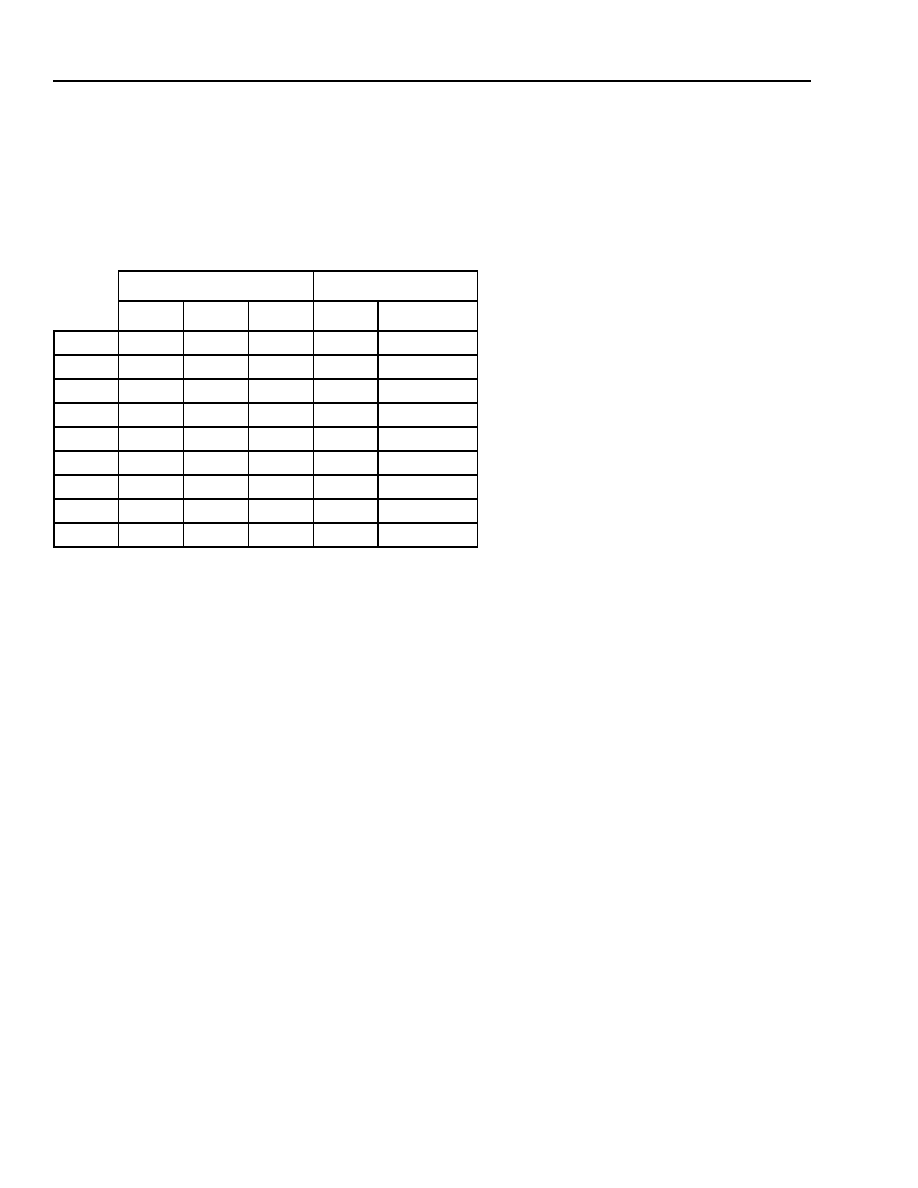

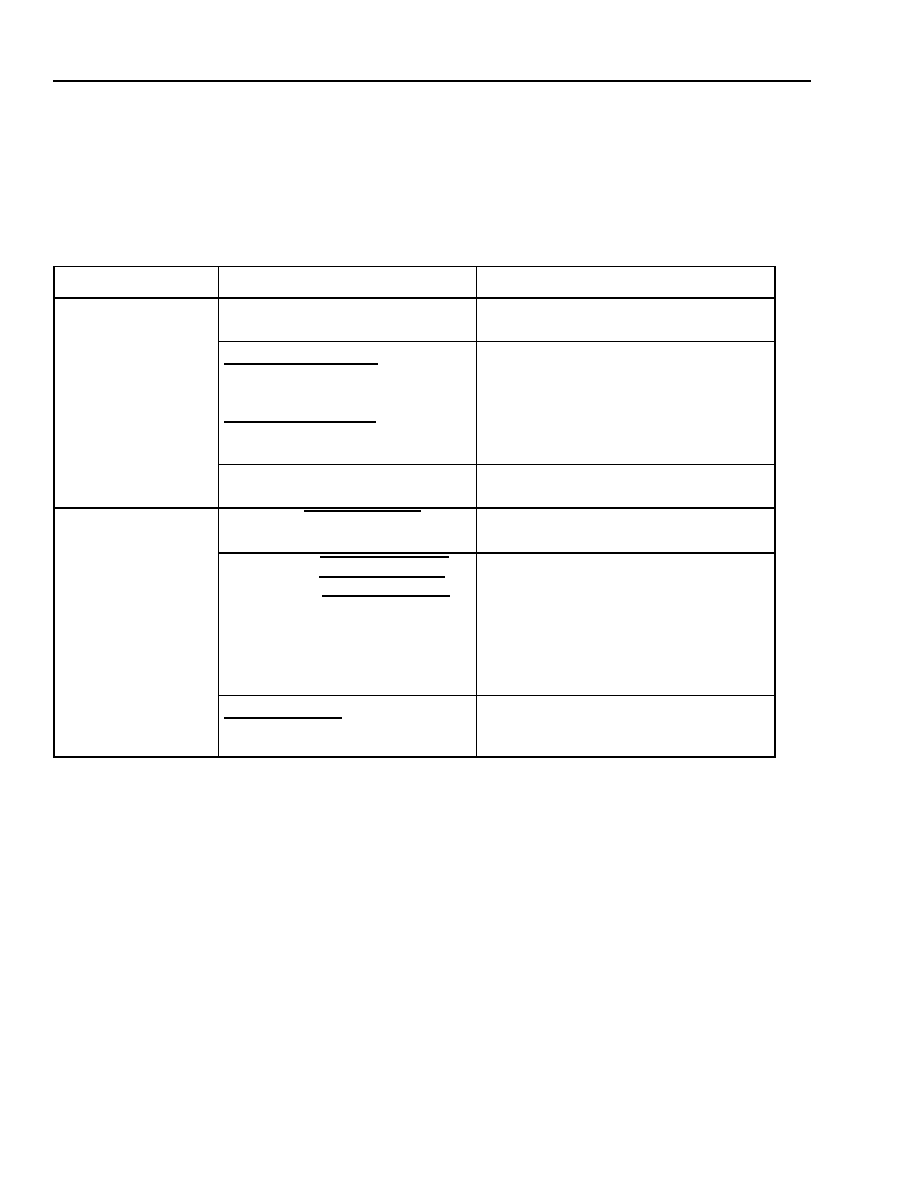

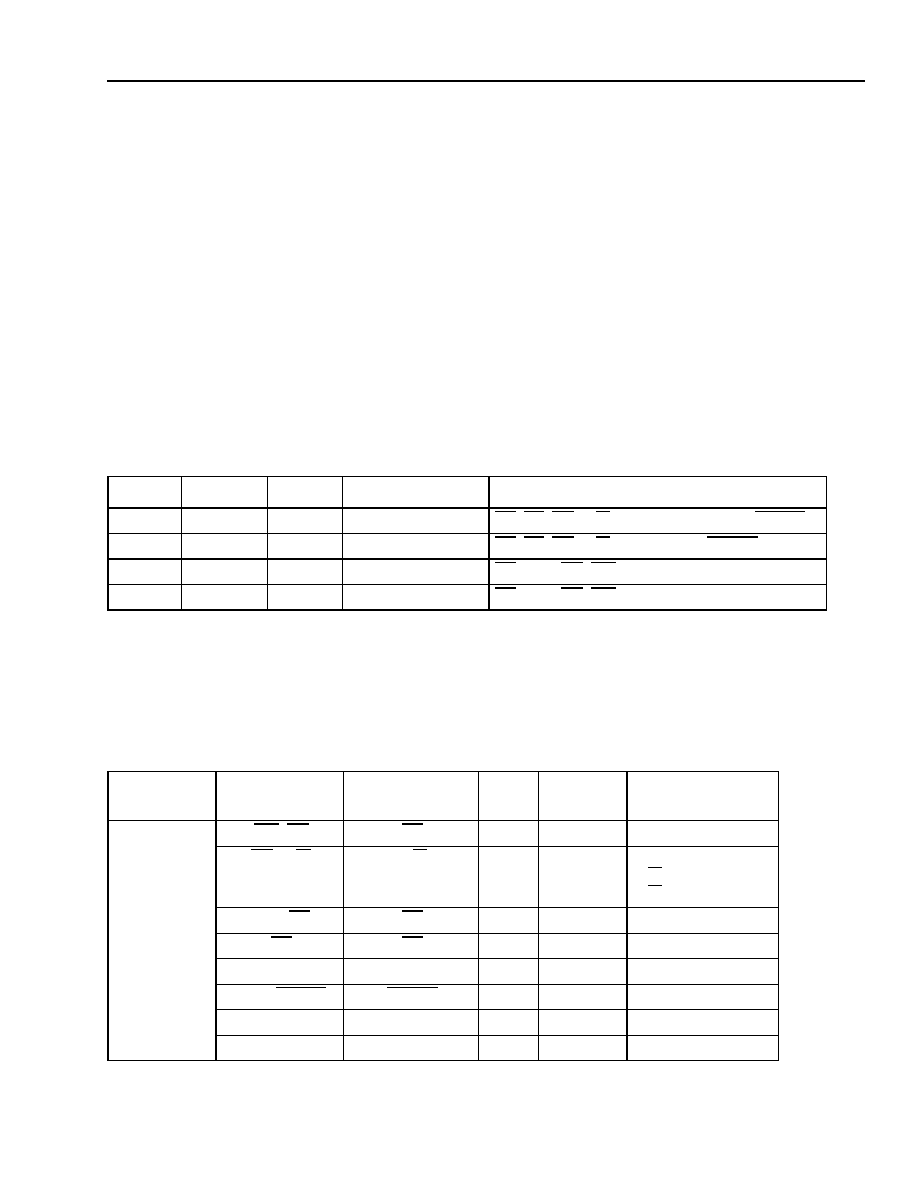

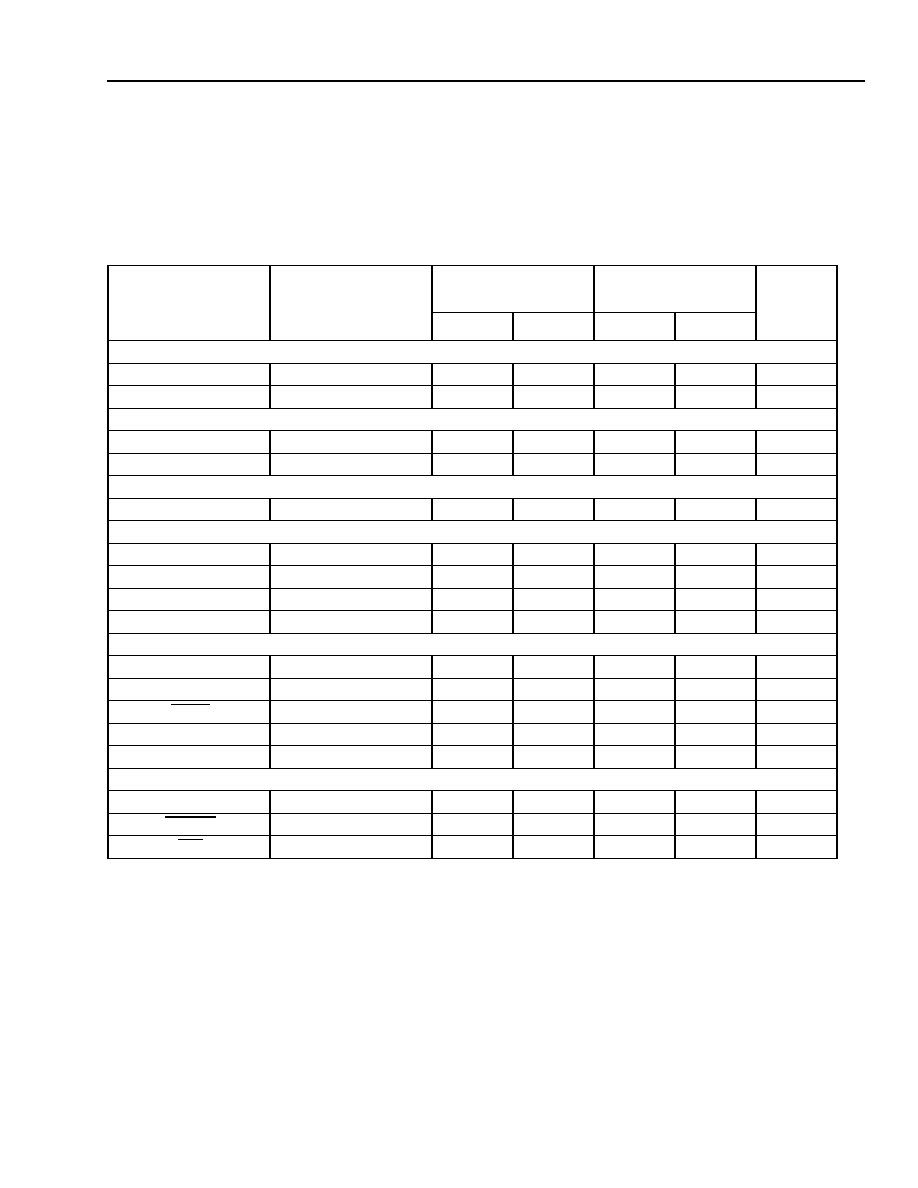

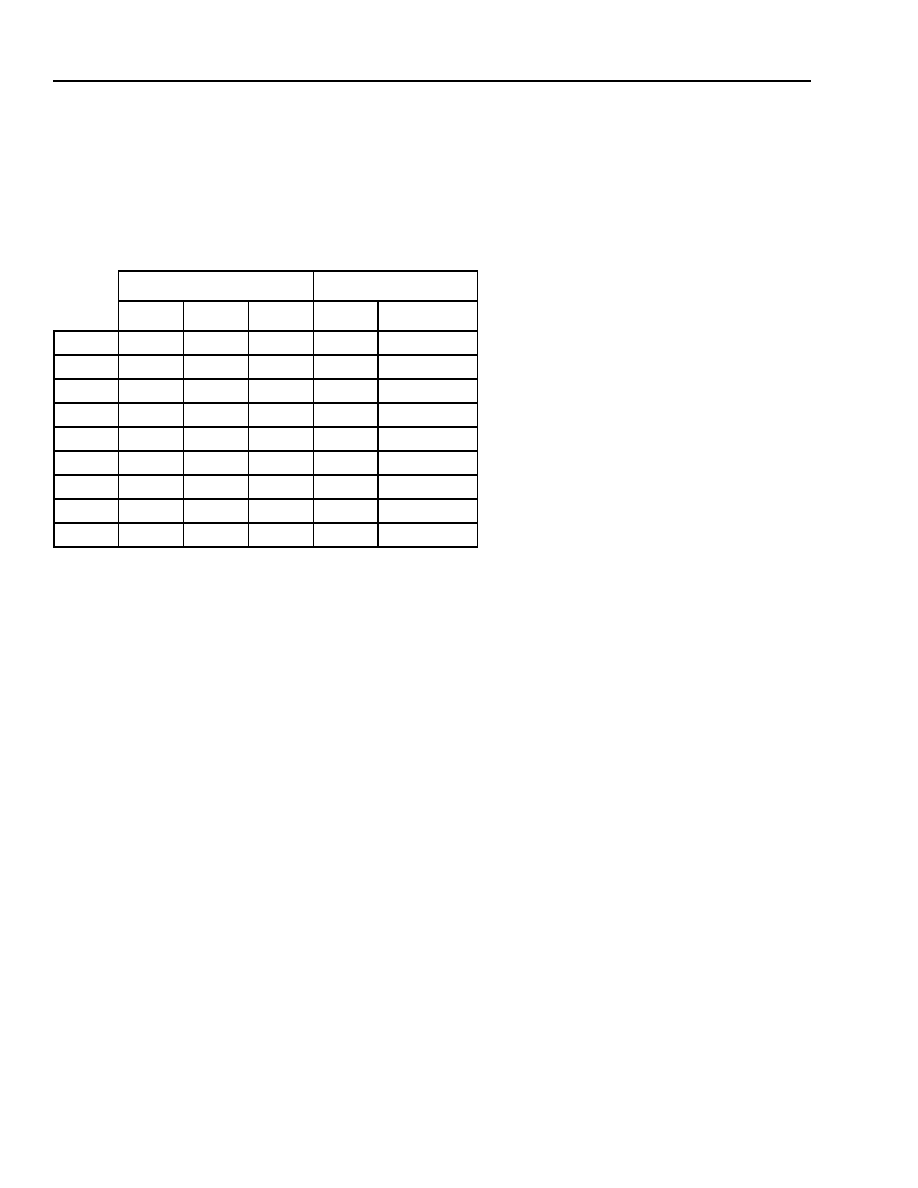

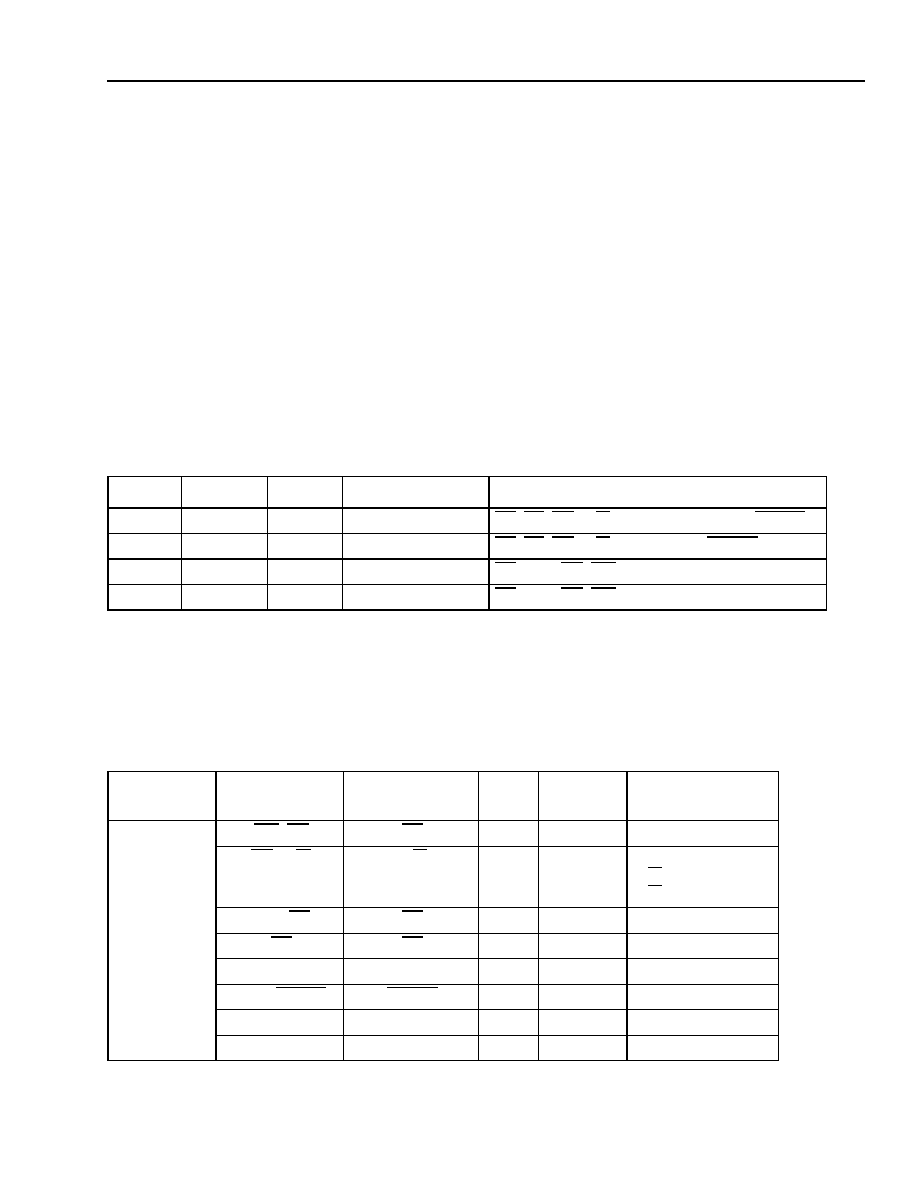

- Table 3. Transmit Mode Control Signals

- Table 4. Receive Mode Control

- Table 5. Input Select Control

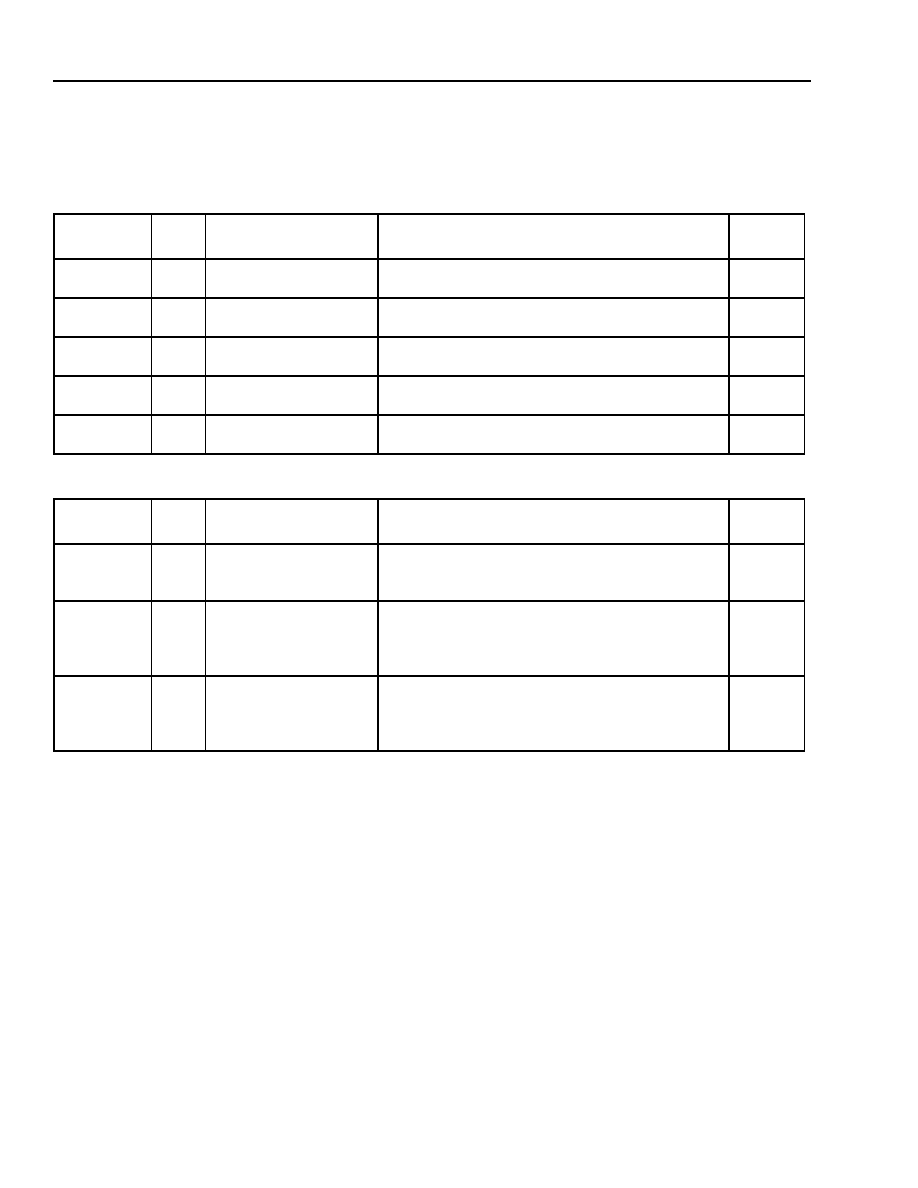

- Table 6. Expected STS-1/AU-3 Input Frame Format

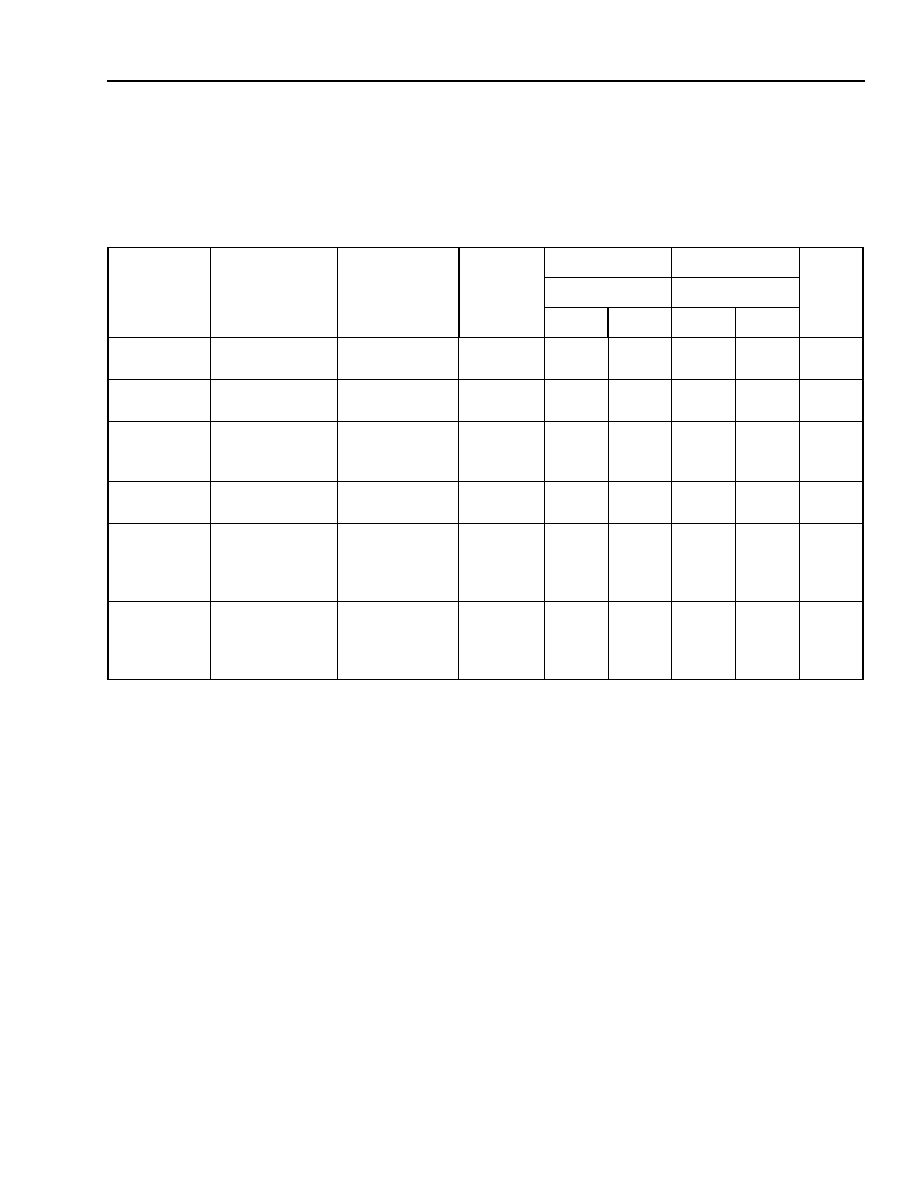

- Table 7. STS-3 Output Overhead Format

- Table 8. STM-1 (AU-4) Output Overhead Format

- Table 9. STS-1/AU-3 Format and Overhead Control Summary

- Table 10. STS-1/AU-3 Output Select Control

- Table 11. Monitors Disabled During Failure Conditions

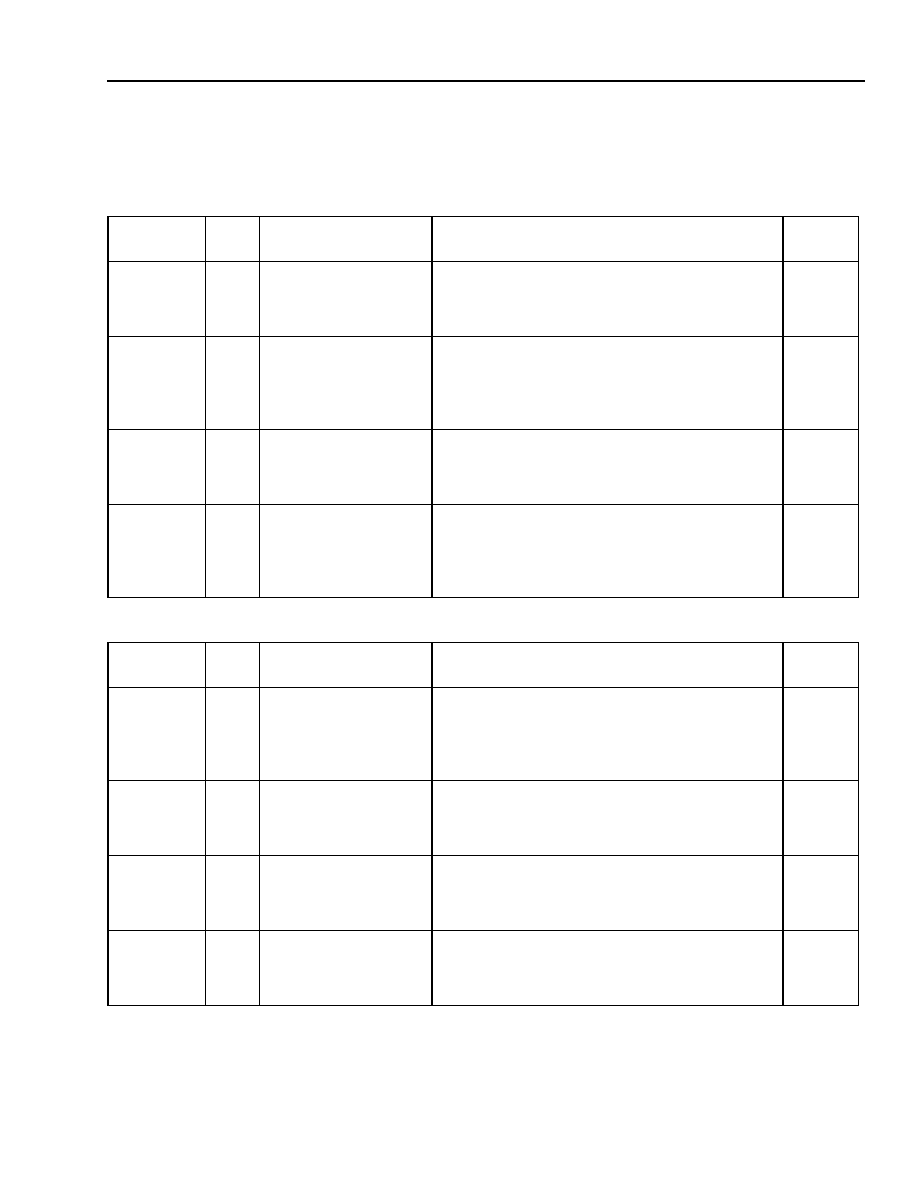

- Table 12. SFEBE Values

- Table 13. G1 ByteÑAU-4 Mode Only

- Table 14. PFEBE Values

- Table 15. Value Offset Load Values

- Table 16. Transport Overhead Byte AccessÑTransmit Direction

- Table 17. TTOAC Control Bits

- Table 18. STS-1/AU-3 Overhead Control

- Table 19. Transport Overhead Byte AccessÑReceive Direction

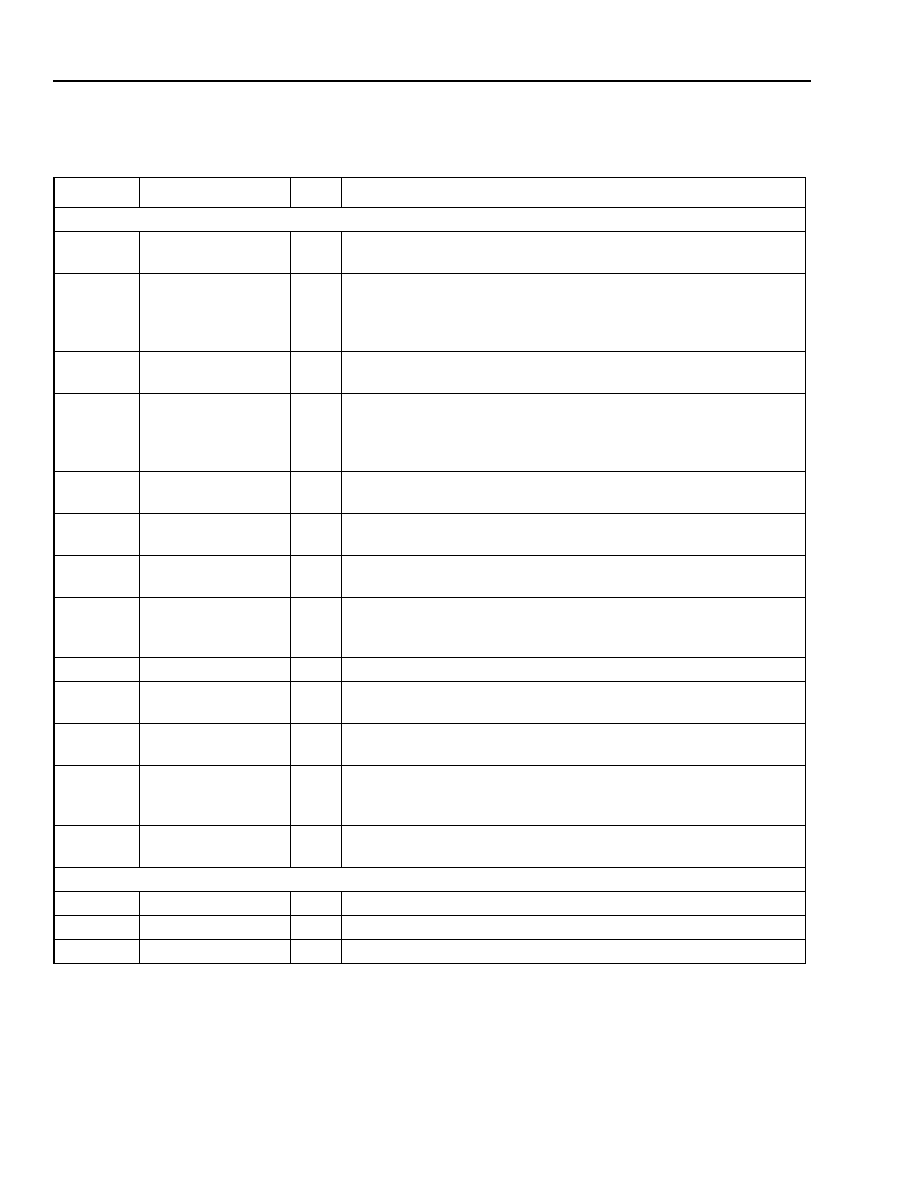

- Table 20. Microprocessor Configuration Modes

- Table 21. MODE [1Ñ4] Microprocessor Pin Definitions

- Table 22. Device-Level Register Map

- Table 23. Page 0ÑJ1 Byte Insert and Monitor

- Table 24. Page 1ÑError Counters

- Table 25. Page 2ÑBER Algorithm Parameters

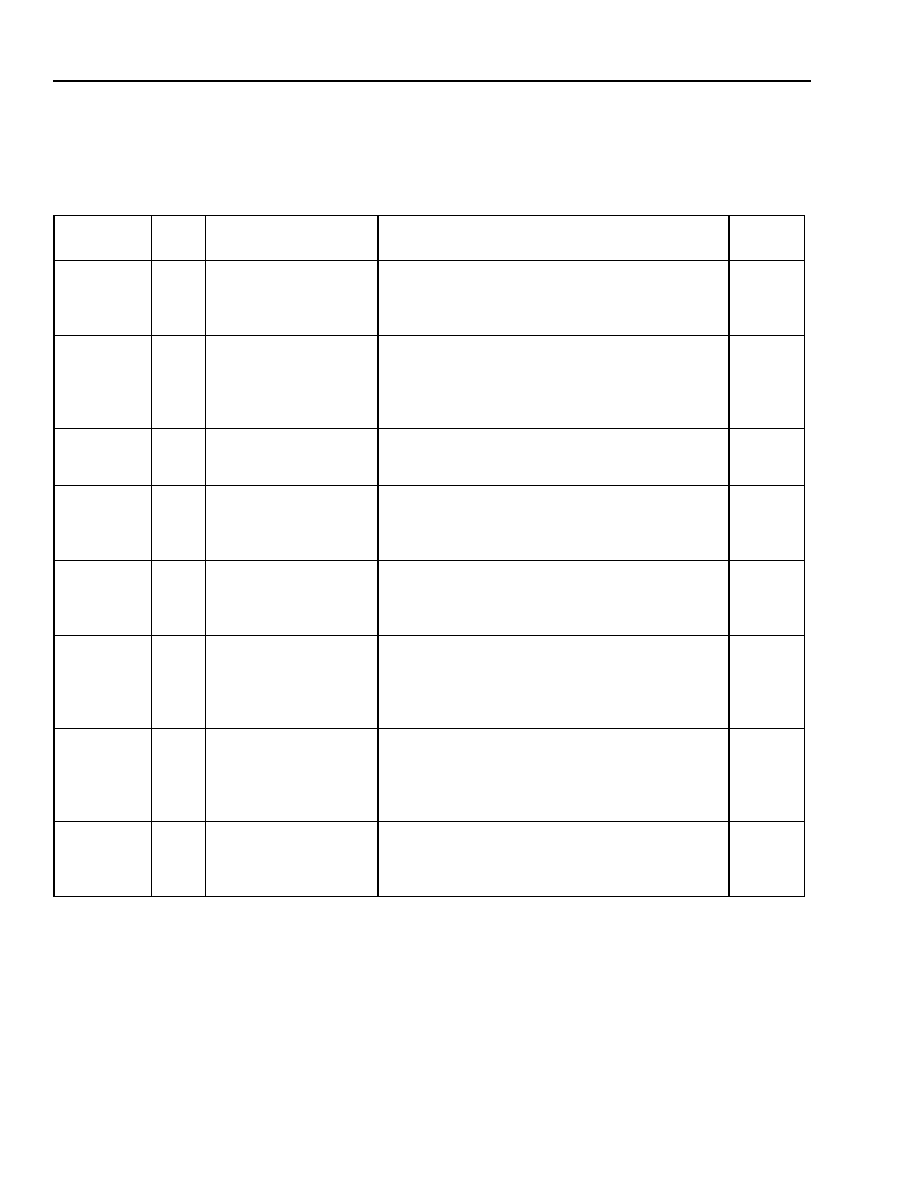

- Table 26. Register 0 (RO)

- Table 27. Registers 1Ñ3 (RO)

- Table 28. Registers 4, 5: One-Shot Register 0 ∆ 1 (R/W)

- Table 29. Register 6: Scratch Register (R/W)

- Table 30. Registers 7Ñ15: Delta/Event (COR-RO)

- Table 31. Registers 16Ñ24: Mask Bits (R/W)

- Table 32. Registers 25Ñ51: State Bits (RO)

- Table 33. Register 52: Mode Control (R/W)

- Table 34. Register 53: Low-Speed Transmit Common Signals (R/W)

- Table 35. Register 54Ñ59: Transmit Low-Speed Port Input Control (R/W)

- Table 36. Registers 60, 61: Transmit High-Speed Clock/Port Control (R/W)

- Table 37. Register 62: Transmit High-Speed Control Signals (R/W)

- Table 38. Register 62, and Page 0, Registers 128Ñ191: Transmit High-Speed J1 Insert (R/W)

- Table 39. Register 62, 69: Transmit High-Speed Control Signals (R/W)

- Table 40. Register 62, 66: Transmit High-Speed Control Signals (R/W)

- Table 41. Registers 63Ñ65: Trace/Growth Bytes (R/W)

- Table 42. Register 66: Transmit F1 Data Byte (R/W)

- Table 43. Registers 67 and 68: K1 and K2 Insert Bytes (R/W)

- Table 44. Register 69: Transmit Sync Status Byte (R/W)

- Table 45. Register 70: Path Signal Trace Byte (R/W)

- Table 46. Register 71: Path User Channel Byte (R/W)

- Table 47. Register 72: Path Growth Byte (R/W)

- Table 48. Register 73: Tandem Connection Byte (R/W)

- Table 49. Register 74: Transmit High-Speed Line RDI Insertion Inhibit Bits (R/W)

- Table 50. Register 75: Transmit High-Speed Path RDI Insertion Inhibit Bits (R/W)

- Table 51. Register 76: Transmit High-Speed Error Insert Control Parameters (R/W)

- Table 52. Register 77: Transmit High-Speed Error Insert Control Parameters (R/W)

- Table 53. Register 78: Transmit High-Speed Error Insert (R/W)

- Table 54. Register 79: Receive/Transmit TOAC Control (R/W)

- Table 55. Registers 80, 81: Transmit TOAC Control (R/W)

- Table 56. Register 83, 84: Transmit High-Speed STS-3/STM-1 Output Frame Offset (R/W)

- Table 57. A1-1 Alignment Parameters

- Table 58. BITCNT Alignment Table

- Table 59. Register 85: Receive High/Low-Speed Port Control (R/W)

- Table 60. Register 86: Receive J1 and Receive Low-Speed Port Select Control (R/W)

- Table 61. Register 87: STS-1/AU-3 Receive Control Bits (R/W)

- Table 62. Register 88: STS-1/AU-3 Receive Low-Speed AIS Inhibit Control Bits (R/W)

- Table 63. Registers 88, 89: STS-1/AU-3 Loss of Signal Detector (R/W)

- Table 64. Register 90Ñ95: Continuous N Times Detect (CNTD) Values (R/W)

- Table 65. Register 95: Continuous N Times Detect (CNTD) B1 Control Bit (R/W)

- Table 66. Register 96: Test Pattern Drop Control and Status

- Table 67. Register 97: Test Pattern Drop Error Counter (RO)

- Table 68. Register 98: Receive Low-Speed Overhead Control Bits (R/W)

- Table 69. Register 99: Receive Low-Speed BIP Error Insert (R/W)

- Table 70. Registers 100Ñ102: Receive Low-Speed Overhead Control Bits (R/W)

- Table 71. Register 103: Receive Low-Speed L-RDI Inhibit Control (R/W)

- Table 72. Registers 104Ñ106: Receive Low-Speed C1 Byte (R/W)

- Table 73. Registers 107Ñ109: Receive Low-Speed F1 Byte (R/W)

- Table 74. Registers 110Ñ115: Receive Low-Speed K1, K2 Byte Insert (R/W)

- Table 75. Registers 116Ñ118: Receive Low-Speed Pass Control (R/W)

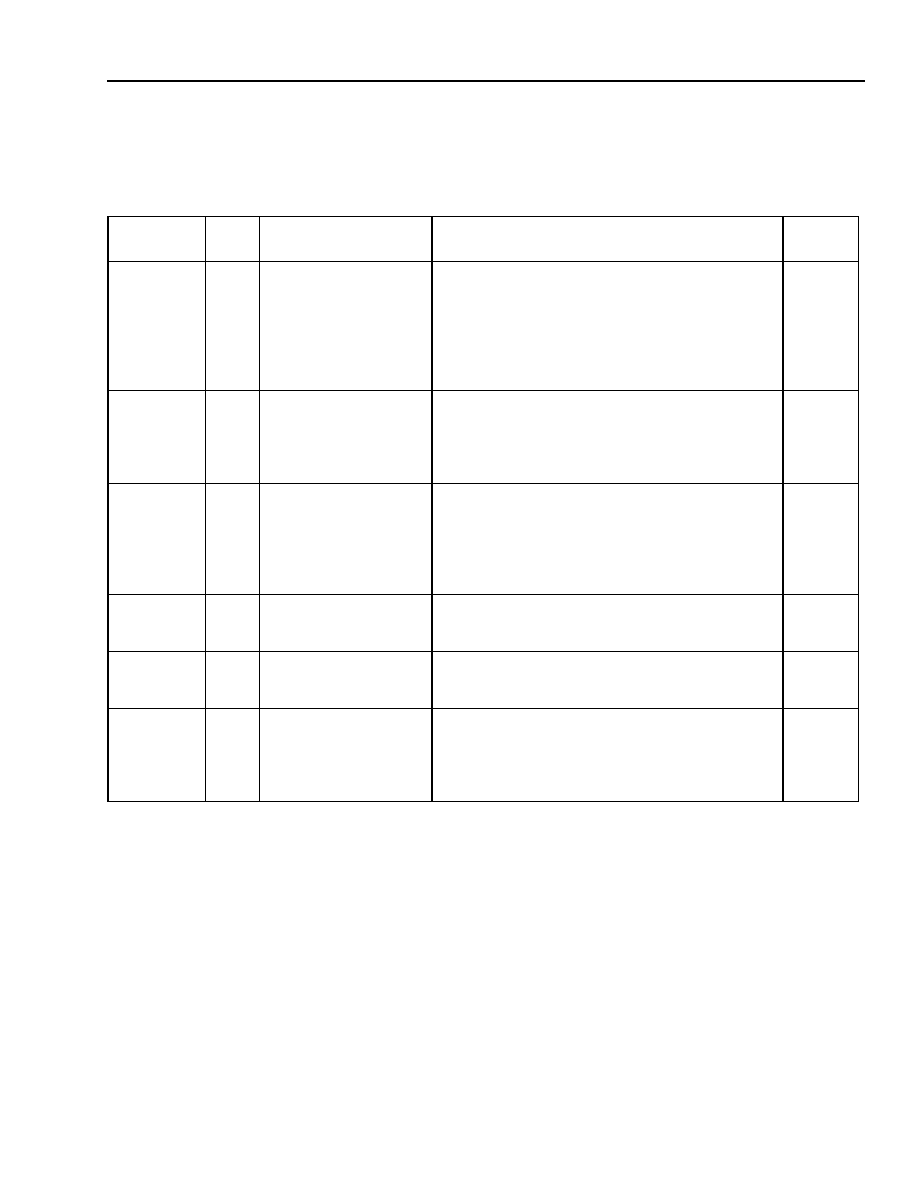

- Table 76. Register 127: Page Control Register (R/W)

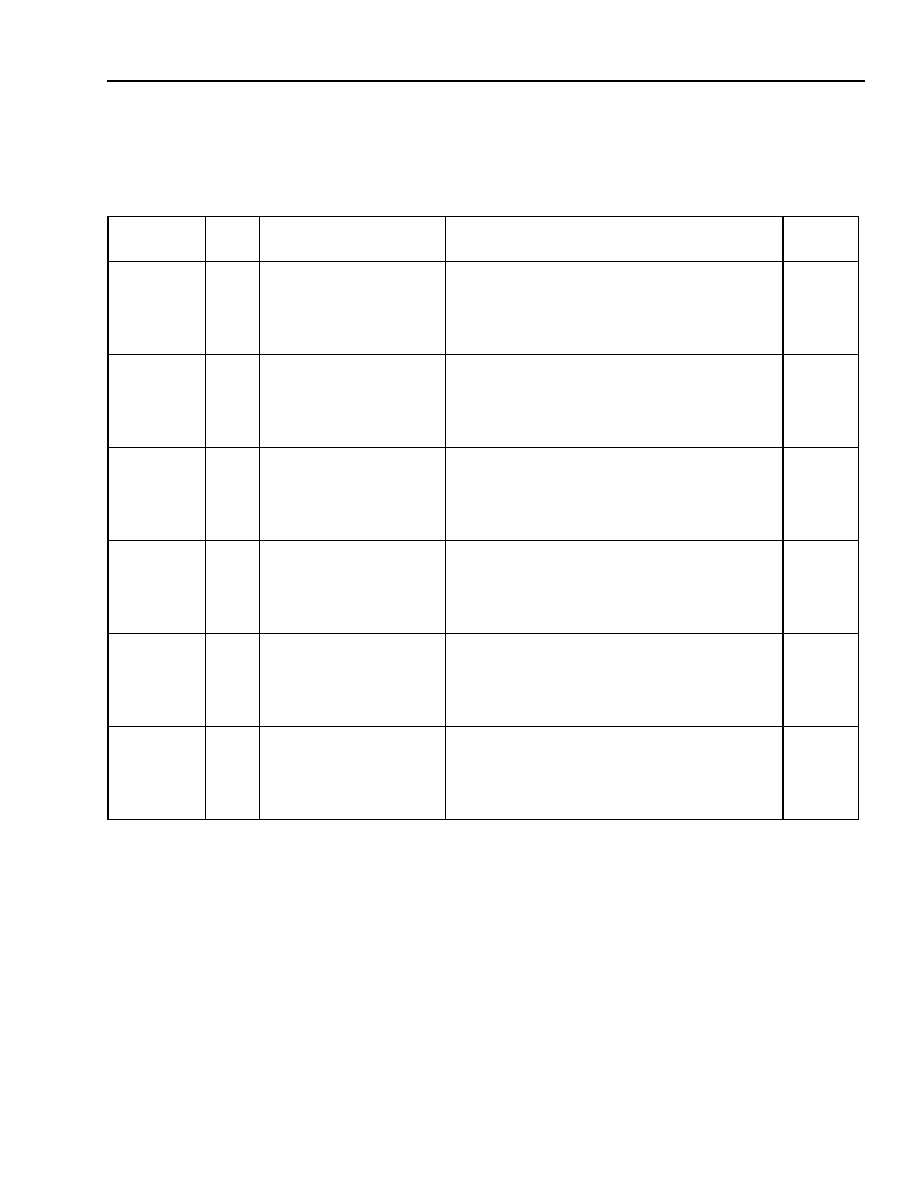

- Table 77. Page 0 - Registers 128Ñ191: J1 Insert Parameters (R/W)

- Table 78. Page 0 - Registers 192Ñ255: J1 Monitor Bytes (RO)

- Table 79. Page 1 - Registers 128Ñ133: STS-1/AU-3 B1 BIP Error Counters (RO)

- Table 80. Page 1 - Registers 134Ñ140: STS-1/AU-3 B2 BIP Error Counters (RO)

- Table 81. Page 1 - Registers 141Ñ142: STS-3/STM-1 (AU-4) B1 Error Count (RO)

- Table 82. Page 1 - Registers 143Ñ145: STS-3/STM-1 (AU-4) B2 Error Count (RO)

- Table 83. Page 1 - Registers 146Ñ151: STS-3/STM-1 (AU-4) B3 Error Count (RO)

- Table 84. Page 1 - Registers 152Ñ163: STS-3/STM-1 (AU-4) Pointer Increment/Decrement Counter (RO)

- Table 85. Page 1 - Registers 164Ñ166: Receive High-Speed SFEBE Count (RO)

- Table 86. Page 1 - Registers 167Ñ172: Receive High-Speed Path FEBE Count (RO)

- Table 87. Page 2 - Register 131 (R/W)

- Table 88. Page 2 - Registers 128Ñ141 (R/W)

- Table 89. Page 2 - Register 145 (R/W)

- Table 90. Page 2 - Registers 142Ñ155 (R/W)

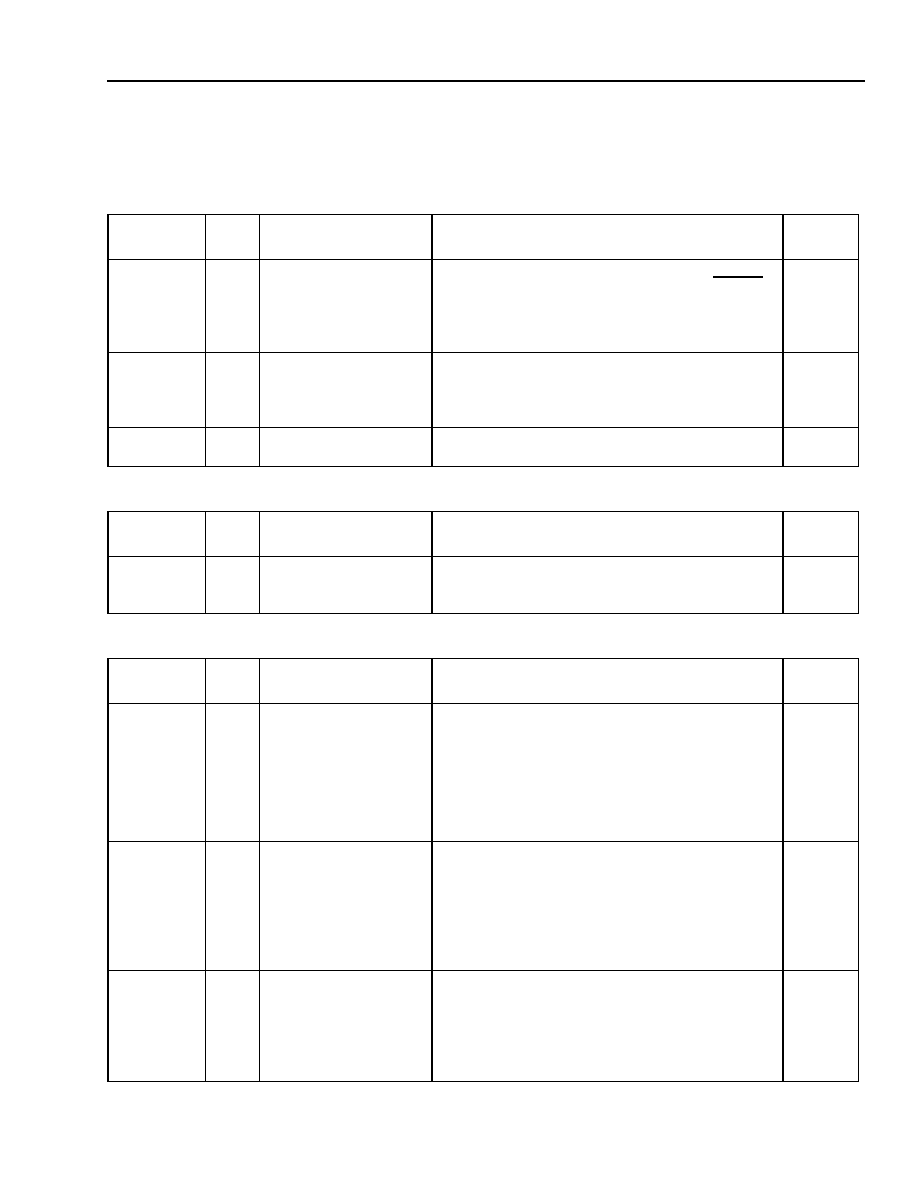

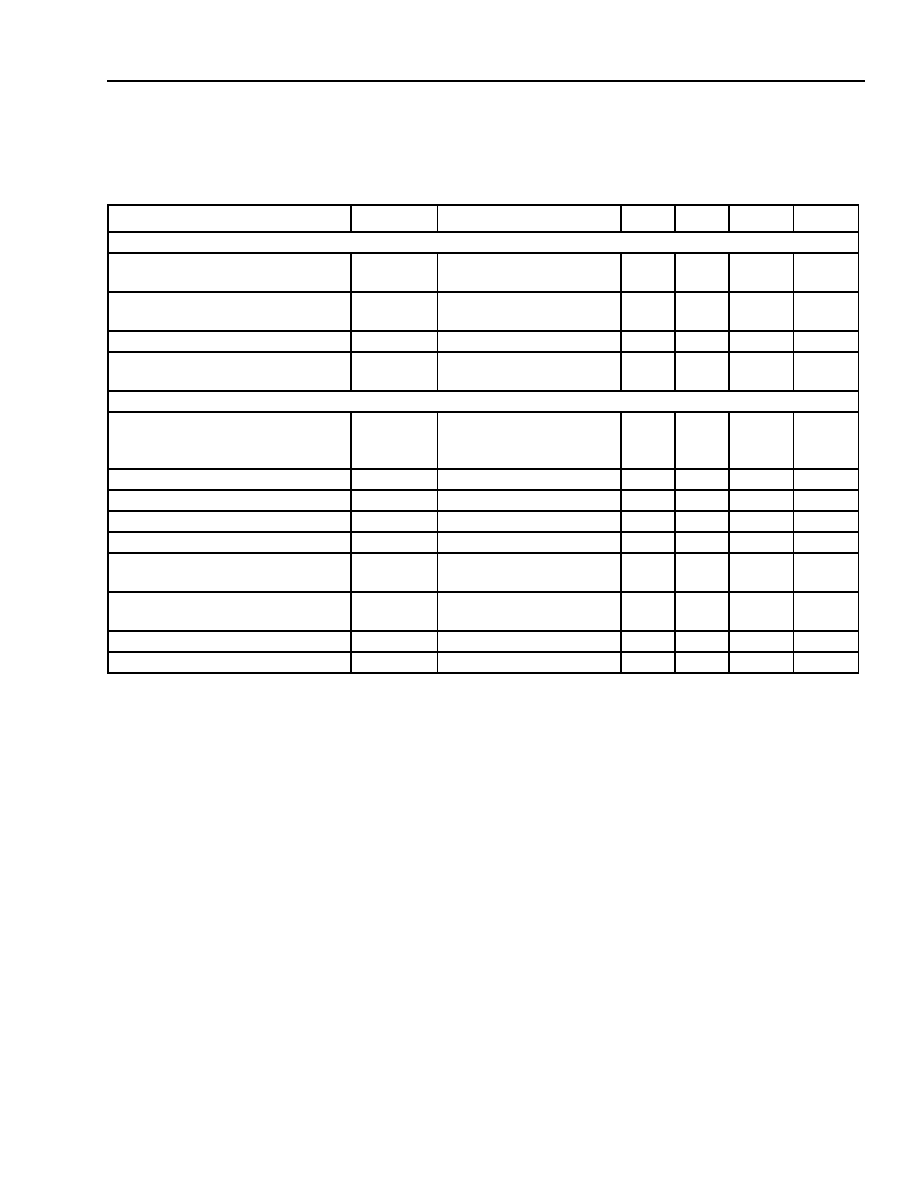

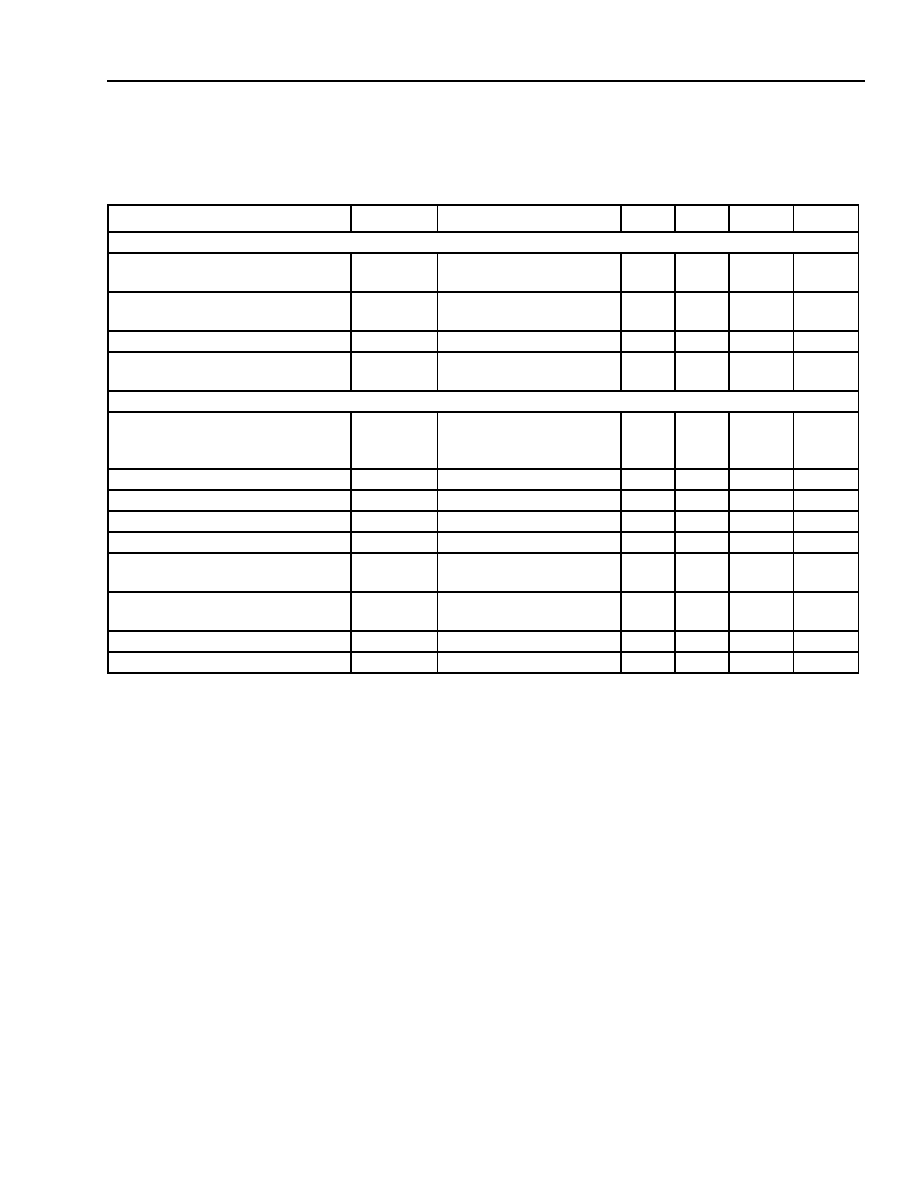

- Table 91. Microprocessor Interface I/O Timing Specifications

- Table 92. Recommended Operating Conditions

- Table 93. Power Measurements (VDD = 3.3 V, 23 ∞C)

- Table 94. Logic Interface Characteristics

- Table 95. LVDS Interface Characteristics

- Table 96. Input Clock Specifications

- Table 97. Input Timing Specifications

- Table 98. Output Clock Specifications

- Table 99. Output Timing Specifications

- Contact Us

Preliminary Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Features

I

Multiplexes three STS-1 signals into a SONET

STS-3 signal.

I

Multiplexes three AU-3 signals into an SDH STM-1

(AU-4) signal via a TUG-3 construction.

I

Demultiplexes three STS-1 signals from a SONET

STS-3 signal.

I

Demultiplexes three AU-3 signals from an SDH

STM-1 (AU-4) signal via a TUG-3 deconstruction.

I

High-speed microprocessor interface configurable

to operate with most commercial microprocessors.

I

Detects STS-3/STM-1 (AU-4) loss-of-signal (LOS)

conditions.

I

Detects STS-3/STM-1 (AU-4) out-of-frame and

loss-of-frame (OOF/LOF) conditions.

I

Provides an 8-bit bus interface at the STS-1/AU-3

rate.

I

Provides a bit serial, nibble-wide, or byte-wide

interface at STS-3/STM-1 (AU-4) rate.

I

Provides STS-3/STM-1 (AU-4) selectable scram-

bler/descrambler functions and B1/B2/B3 genera-

tion/detection.

I

Accepts bit rate, nibble rate, or byte rate high-

speed clocks (155.52 MHz, 38.88 MHz, or

19.44 MHz, respectively).

I

STS-3/STM-1 (AU-4) internal clock and data

recovery. Meets type B jitter tolerance of ITU-T

G.958. Accommodates 0.5 UI jitter up to 20 MHz.

155.52 MHz input reference clock for on-chip PLL.

Has on-chip PLL for clock synthesis, requiring only

one external resistor. No output clock drift in

absence of data transitions once lock is acquired.

I

STS-1 termination mode.

I

≠40 ∞C to +85 ∞C temperature range.

I

208-pin, shrink quad flat pack (SQFP) package.

I

Complies with GR-253-CORE (12/95), G.707

(3/96), G.783(1/94).

Applications

I

SONET/SDH line termination equipment.

I

SDH path origination and termination equipment.

I

SONET/SDH add/drop multiplexers.

I

SONET/SDH cross connects.

I

SONET/SDH test equipment.

Description

The TMUX03155 STS-3/STM-1 (AU-4) multiplexer

device provides three modes of operation: STS-3,

STM-1 (AU-4), and STS-1

modes. In STS-3 mode,

the TMUX03155 device provides all of the functions

necessary to multiplex and demultiplex up to three

STS-1 signals to/from a SONET STS-3 signal. In

AU-4 mode, the TMUX03155 provides the functional-

ity to multiplex and demultiplex up to three AU-3 sig-

nals to/from an STM-1 (AU-4) signal. In STS-1 mode,

the high-speed side of the TMUX03155 operates at

51.84 MHz and can be used for STS-1 termination

and for accessing transport overhead in the SONET

frame.

On the STS-3/STM-1 (AU-4) side, the device

can be configured for either a 1-bit serial data inter-

face, a 4-bit parallel (nibble-wide) data interface, or

an 8-bit parallel (byte-wide) data interface. This

allows the device to drive an OC3 optical signal

directly or to allow for modular growth in terminal or

add/drop applications. On the STS-1/AU-3 side, the

TMUX03155 device provides a bus mode that can

communicate with up to three STS-1/AU-3 devices at

19.44 Mbits/s. The TMUX03155 is designed to inter-

face with the Agere Systems Inc. TMPR28051

device, or equivalent, providing complete mapping/

unmapping from/to an STS-3/STM-1 (AU-4) signal

for up to 84 DS1 or 63 E1 signals.

Table of Contents

Contents

Page

2

Agere Systems Inc.

Preliminary Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Features ...................................................................................................................................................................1

Applications ..............................................................................................................................................................1

Description ................................................................................................................................................................1

Nomenclature Assumptions ......................................................................................................................................7

Block Diagram ..........................................................................................................................................................7

Pin Information .........................................................................................................................................................9

Summary of I/O Pins .........................................................................................................................................15

Mode Control Signals (See Register Description on page 54.) ..............................................................................16

STS-1 Mode ...........................................................................................................................................................16

Transmit Direction Overview ..................................................................................................................................17

STS-1/AU-3 Bus Mode Input Retiming ..............................................................................................................17

Input Select Control ...........................................................................................................................................17

STS-1/AU-3 Inputs ............................................................................................................................................17

Out-of-Frame (OOF) and Loss-of-Frame (LOF) Monitoring ..............................................................................18

Descramble Enable/Disable ..............................................................................................................................18

Monitor B1 and B2 Errors ..................................................................................................................................19

H4 Multiframe and Pointer Monitor (AU-4 Mode Only) ......................................................................................19

STS-3 Generate ................................................................................................................................................20

Transport Overhead Access Channel (TOAC) Insert ........................................................................................23

STS-3/STM-1 (AU-4) Scramble Enable ............................................................................................................23

STS-3/STM-1 (AU-4) B1, B2, and B3 BIP Generation ......................................................................................23

STS-3/STM-1 (AU-4) Loopback Control ............................................................................................................23

STS-3/STM-1 (AU-4) Output Interface ..............................................................................................................23

Receive Direction Overview ...................................................................................................................................23

Input Retime ......................................................................................................................................................24

Clock and Data Recovery ..................................................................................................................................24

STS-3/STM-1 (AU-4) Framing ...........................................................................................................................24

Loss of Signal ....................................................................................................................................................24

Loopback Select Logic ......................................................................................................................................25

RSTS-3/STM-1 (AU-4) Frame Synchronous Descrambling (SONET/SDH) .....................................................25

TOAC Drop ........................................................................................................................................................25

B1, B2, and B3 Checking ..................................................................................................................................25

Monitoring Functions .........................................................................................................................................25

Pointer Interpretation .........................................................................................................................................25

Data Demultiplex and Conversion (AU-4 Mode Only) .......................................................................................26

STS-1/AU-3 Output Byte Control ......................................................................................................................26

B1 and B2 Generate ..........................................................................................................................................26

STS-1/AU-3 Output Scramble ...........................................................................................................................27

Output Selection Logic ......................................................................................................................................27

Output Data Formatter ......................................................................................................................................27

Maintenance Functions ..........................................................................................................................................27

Maintenance Functions Disabled During Failure Conditions .............................................................................28

Common Maintenance and Control Functions ..................................................................................................28

Transmit Functions ............................................................................................................................................30

Receive Functions .............................................................................................................................................38

Typical Uses ...........................................................................................................................................................45

Section and Line Termination Multiplex ............................................................................................................45

Add/Drop Multiplex ............................................................................................................................................46

Digital Cross Connect ........................................................................................................................................46

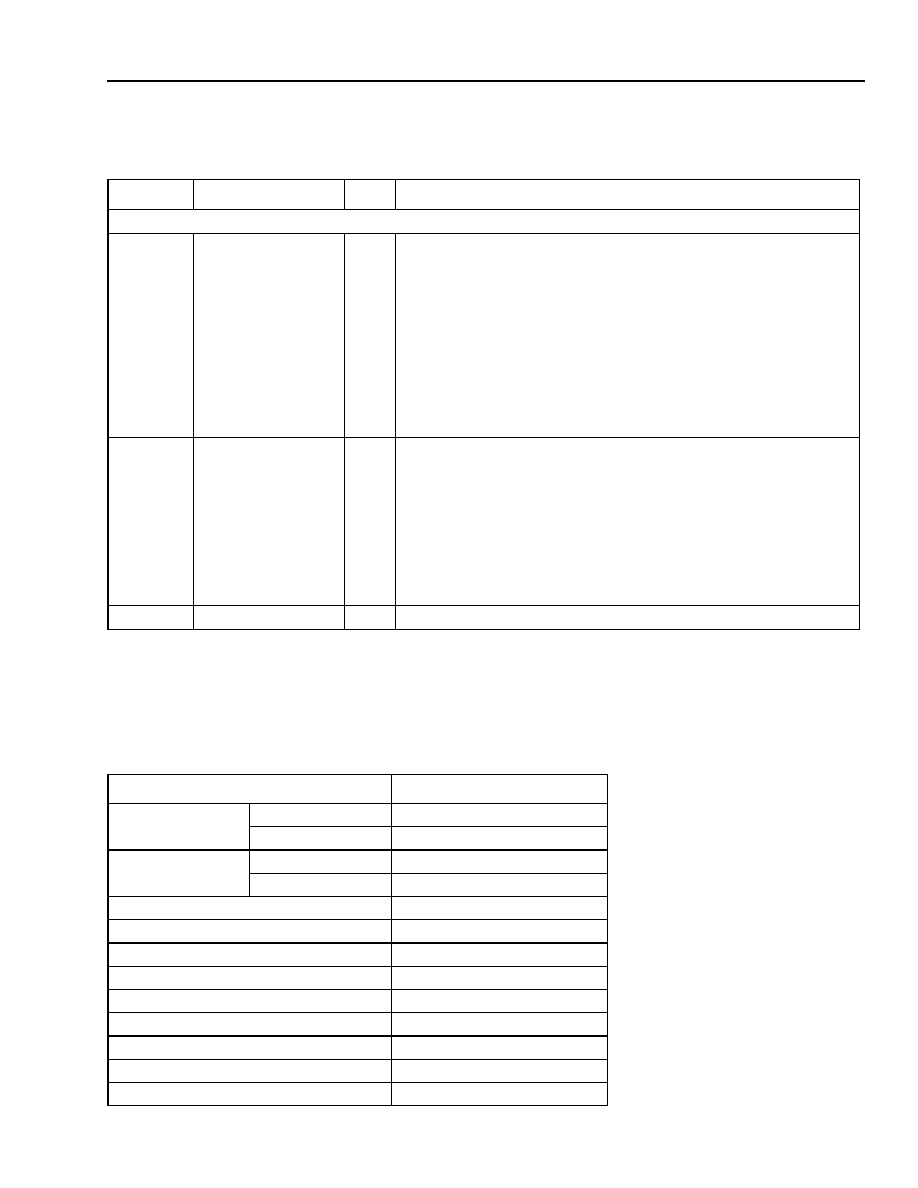

Microprocessor Interface ........................................................................................................................................47

Overview ...........................................................................................................................................................47

Table of Contents

(continued)

Contents

Page

Agere Systems Inc.

3

Preliminary Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Microprocessor Configuration Modes ................................................................................................................47

Microprocessor Interface Pinout Descriptions ...................................................................................................47

Microprocessor Interface Register Architecture ................................................................................................49

Register Description ..........................................................................................................................................54

I/O Timing ........................................................................................................................................................101

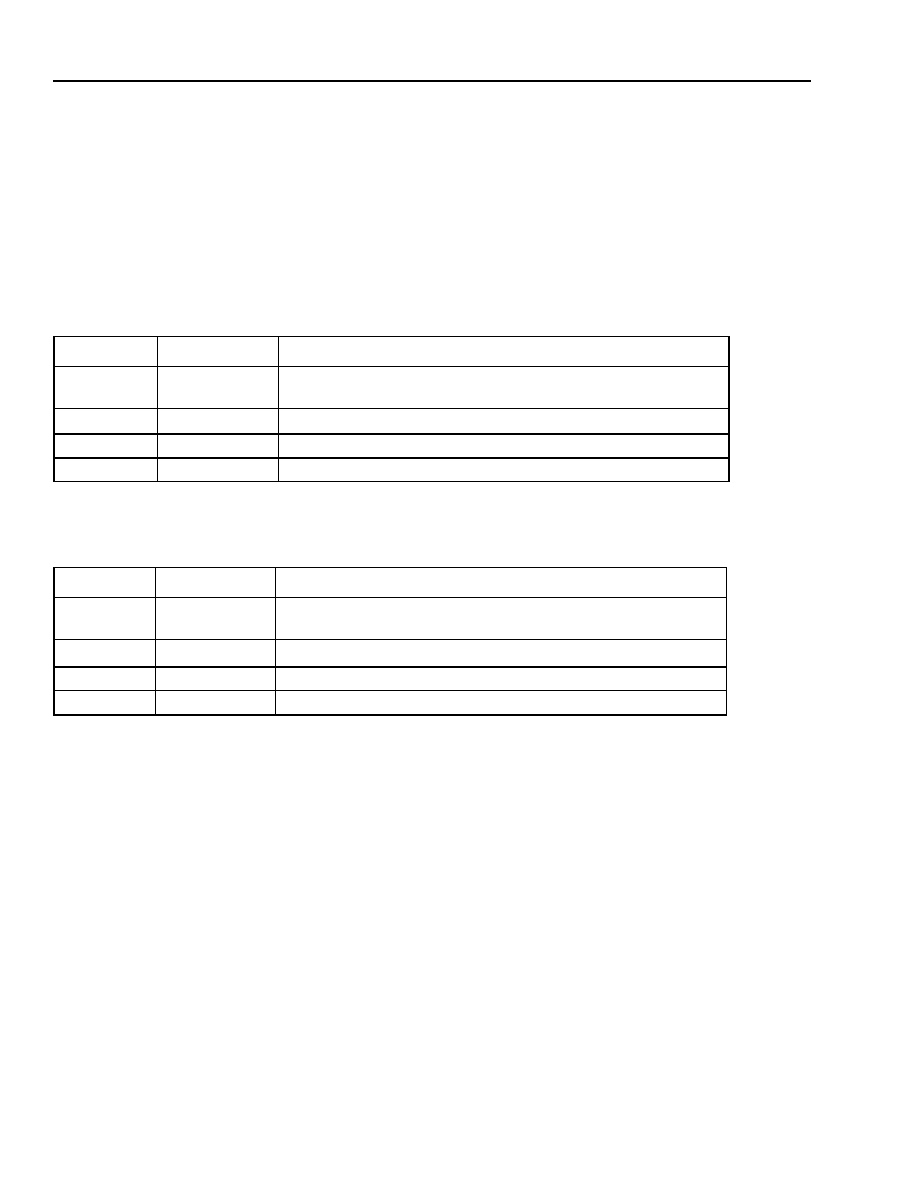

Absolute Maximum Ratings ..................................................................................................................................106

Handling Precautions ...........................................................................................................................................106

Operating Conditions ............................................................................................................................................107

Electrical Characteristics ......................................................................................................................................108

Timing Characteristics ..........................................................................................................................................110

Operational Timing ..........................................................................................................................................110

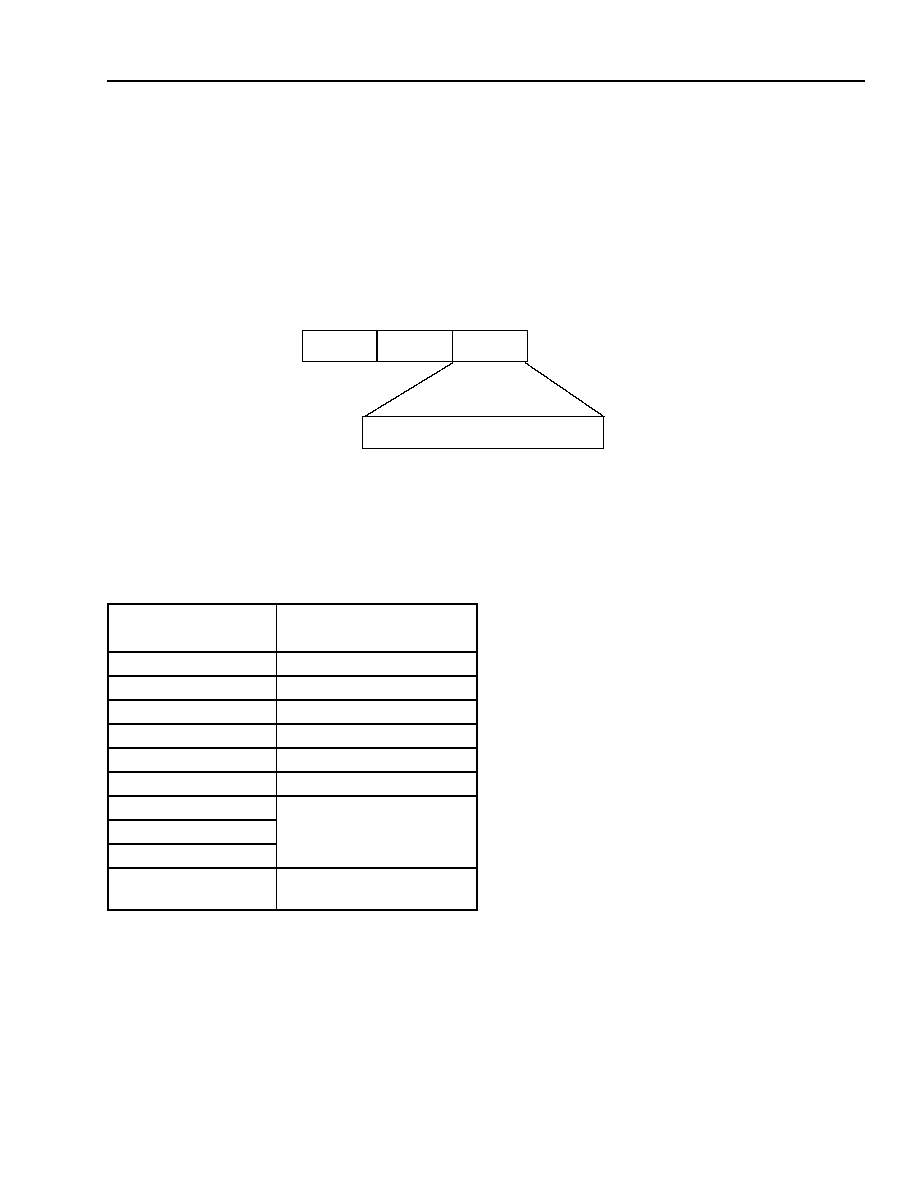

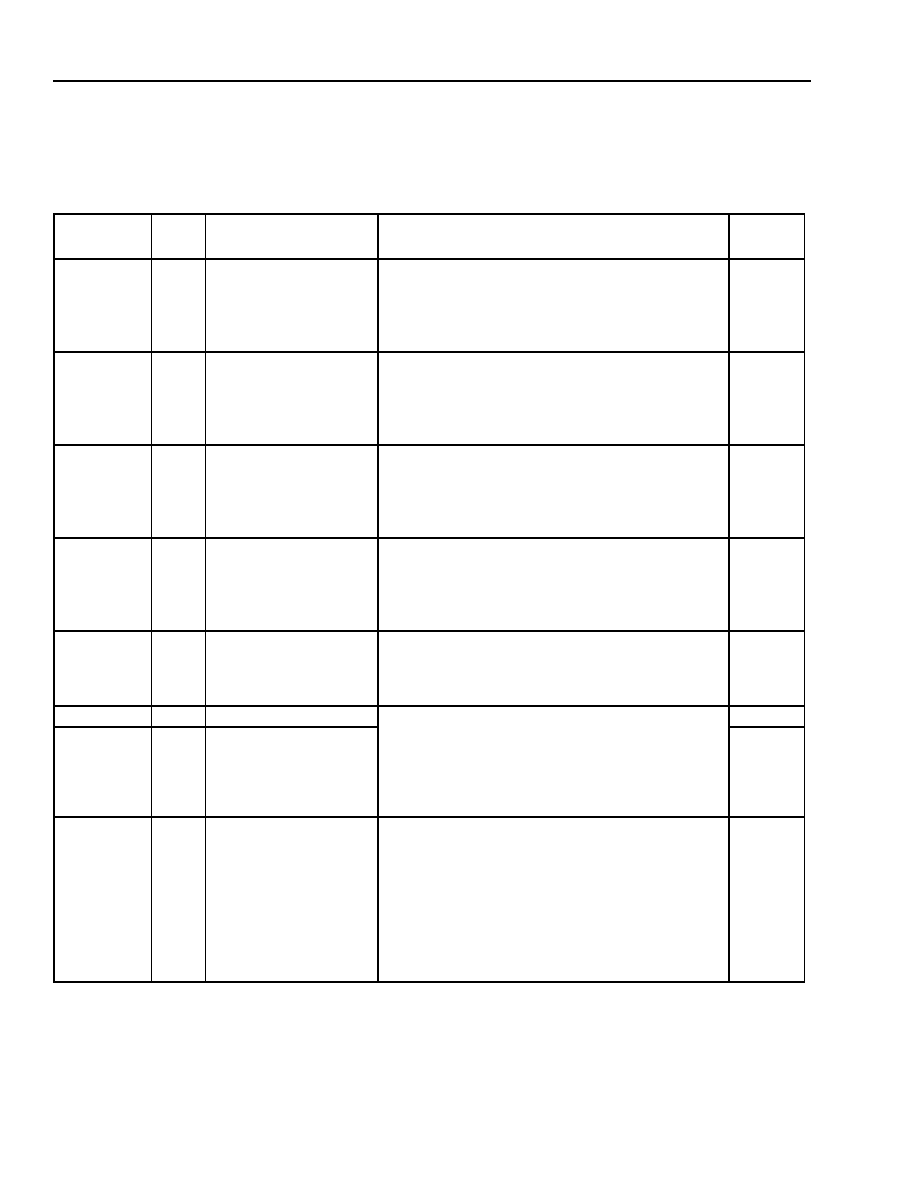

Outline Diagram ....................................................................................................................................................117

208-Pin SQFP .................................................................................................................................................117

Ordering Information .............................................................................................................................................118

DS01-194PDH Replaces DS00-213TIC to Incorporate the Following Updates ...................................................118

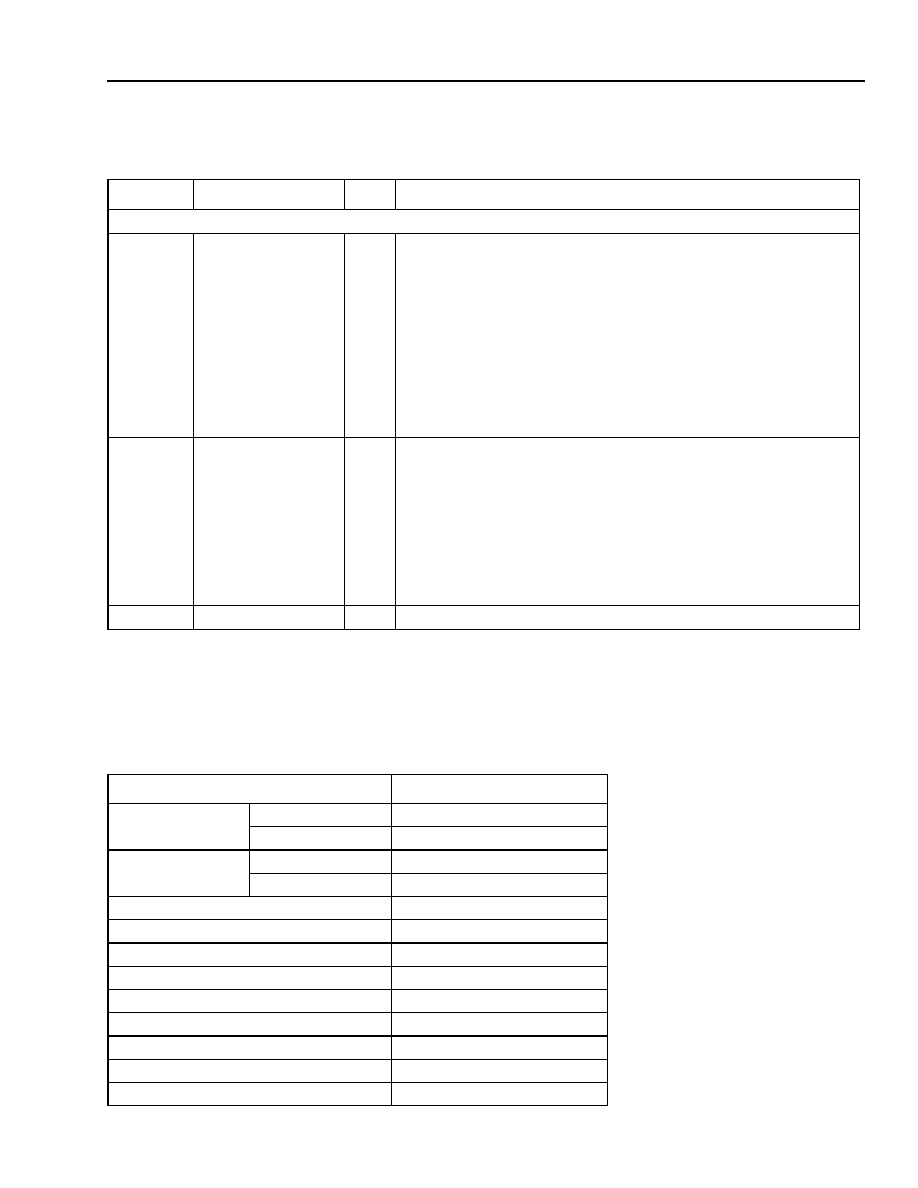

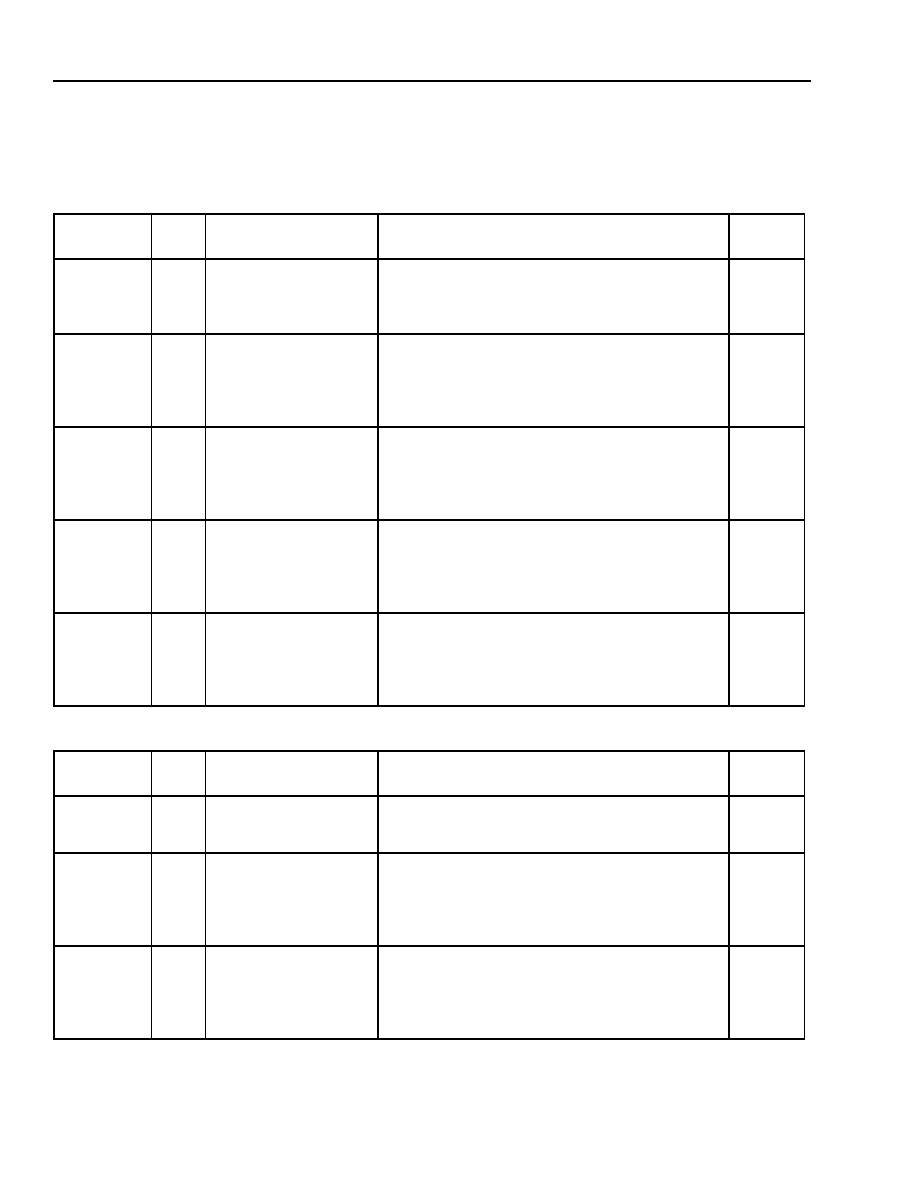

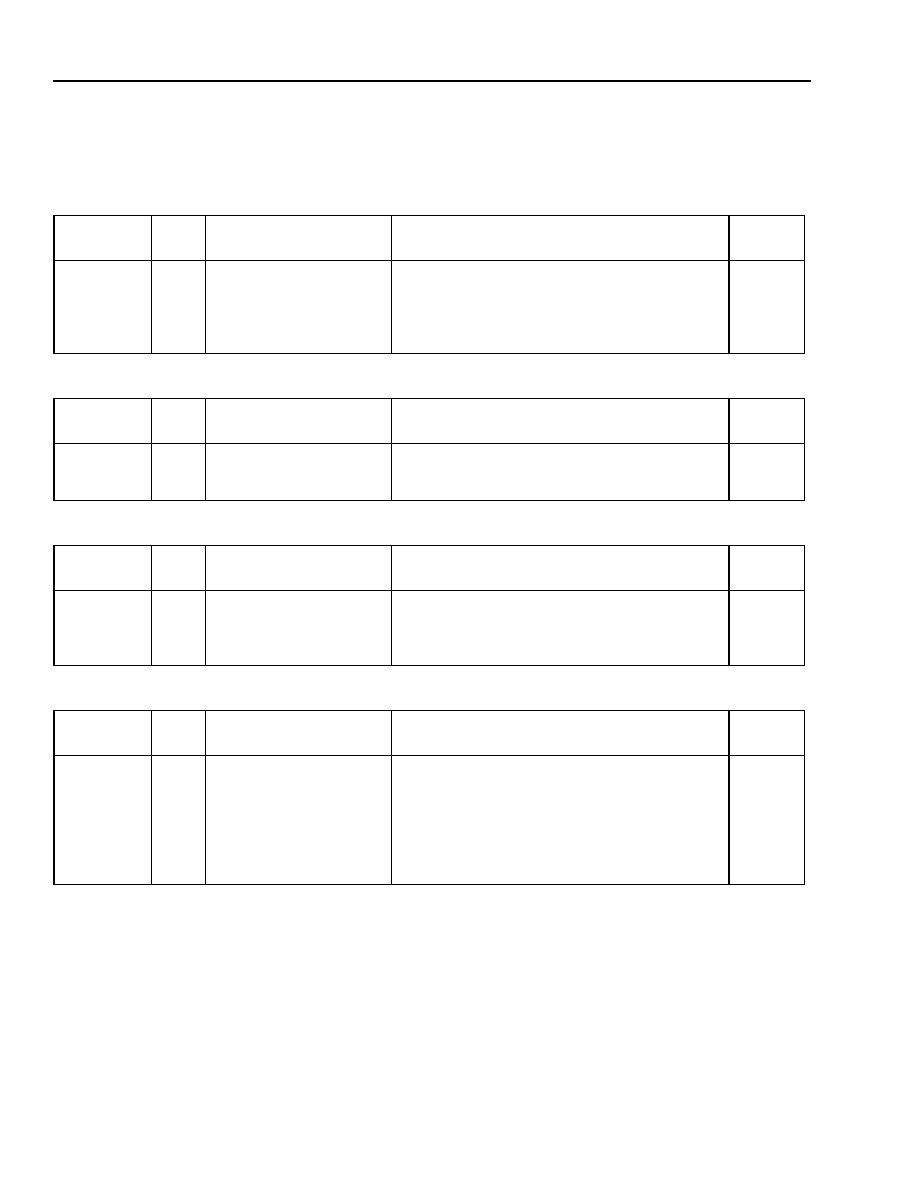

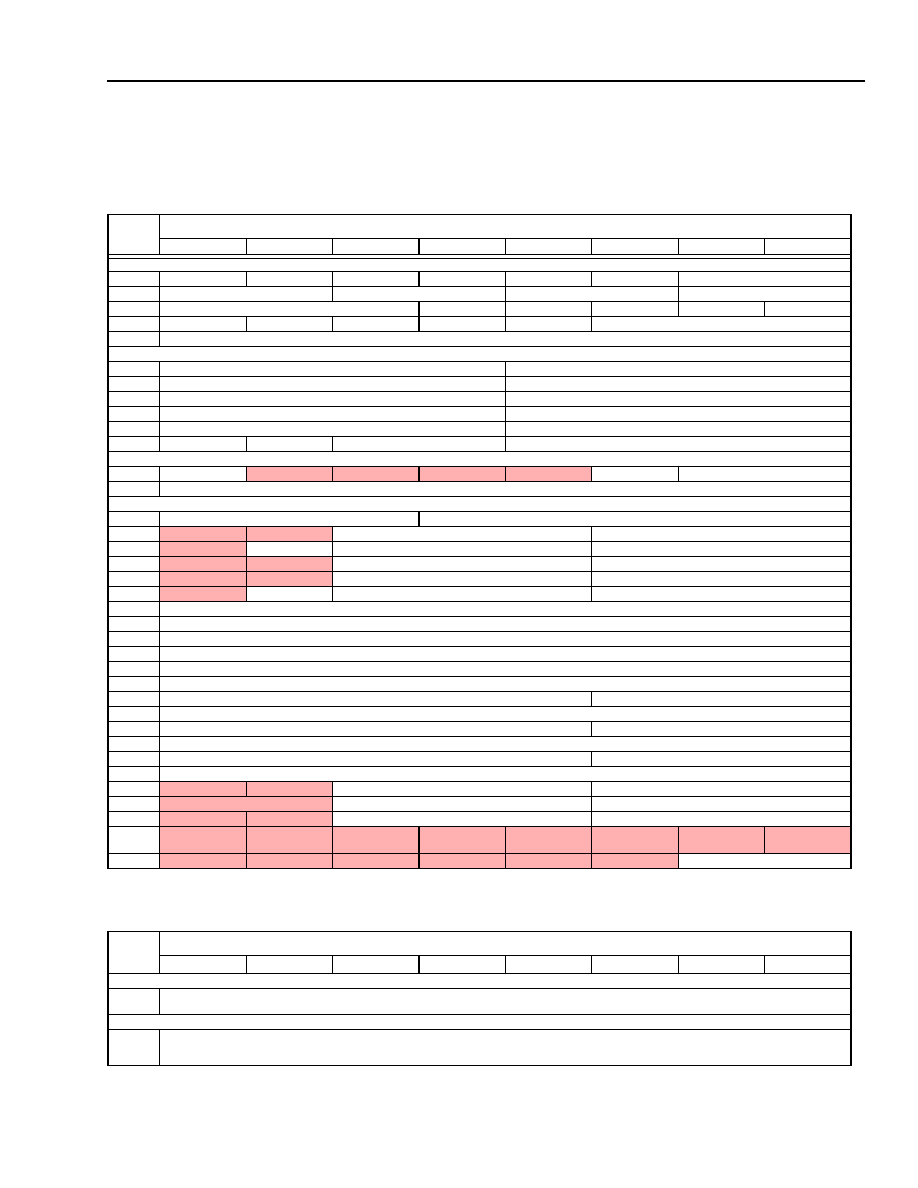

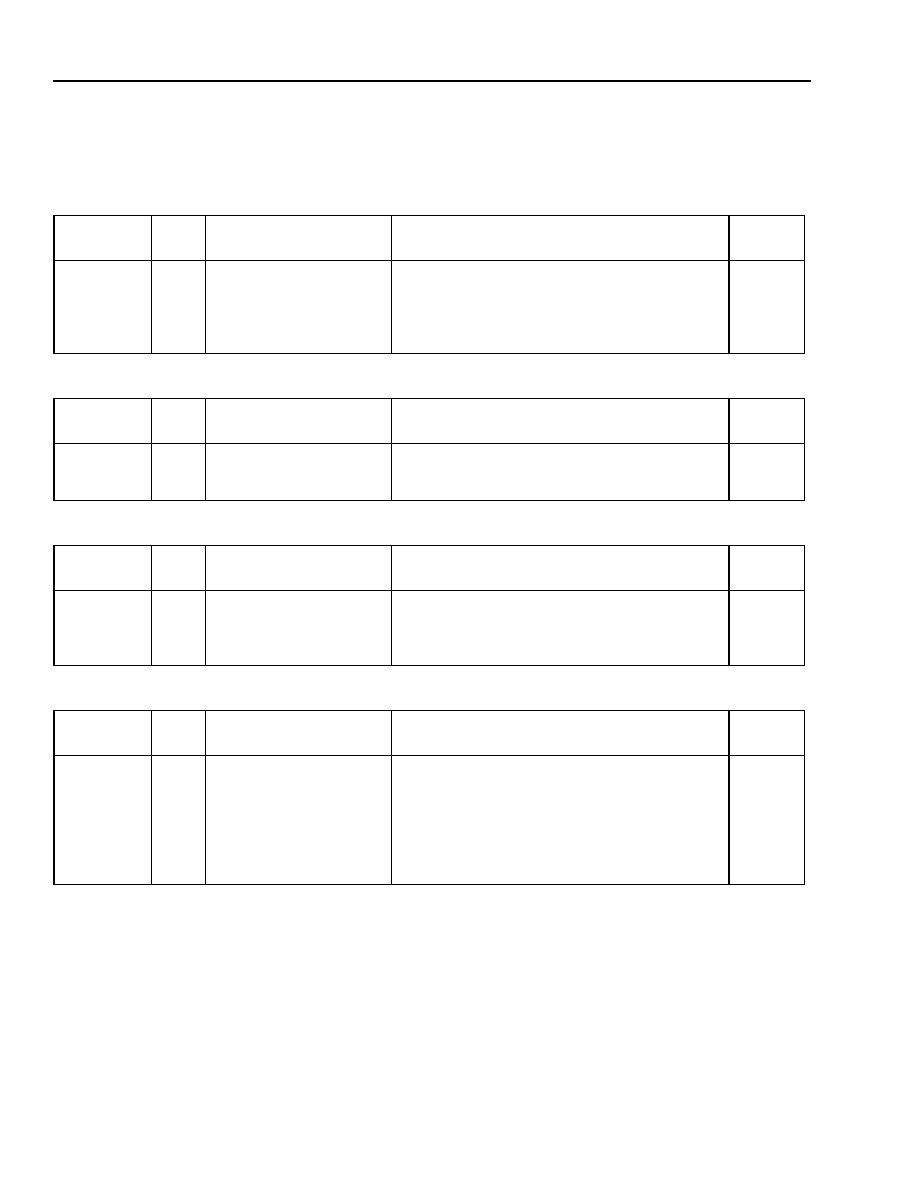

List of Figures

Contents

Page

4

Agere Systems Inc.

Preliminary Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

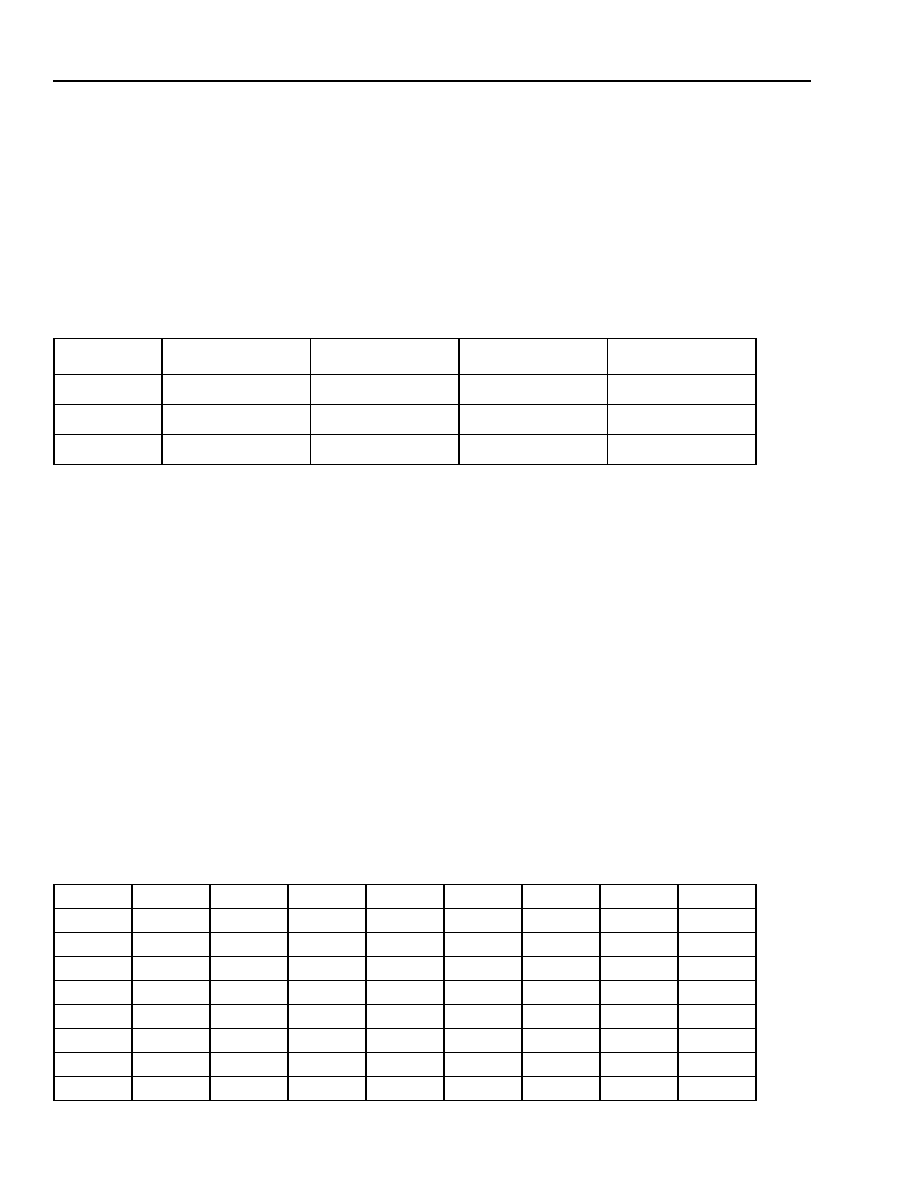

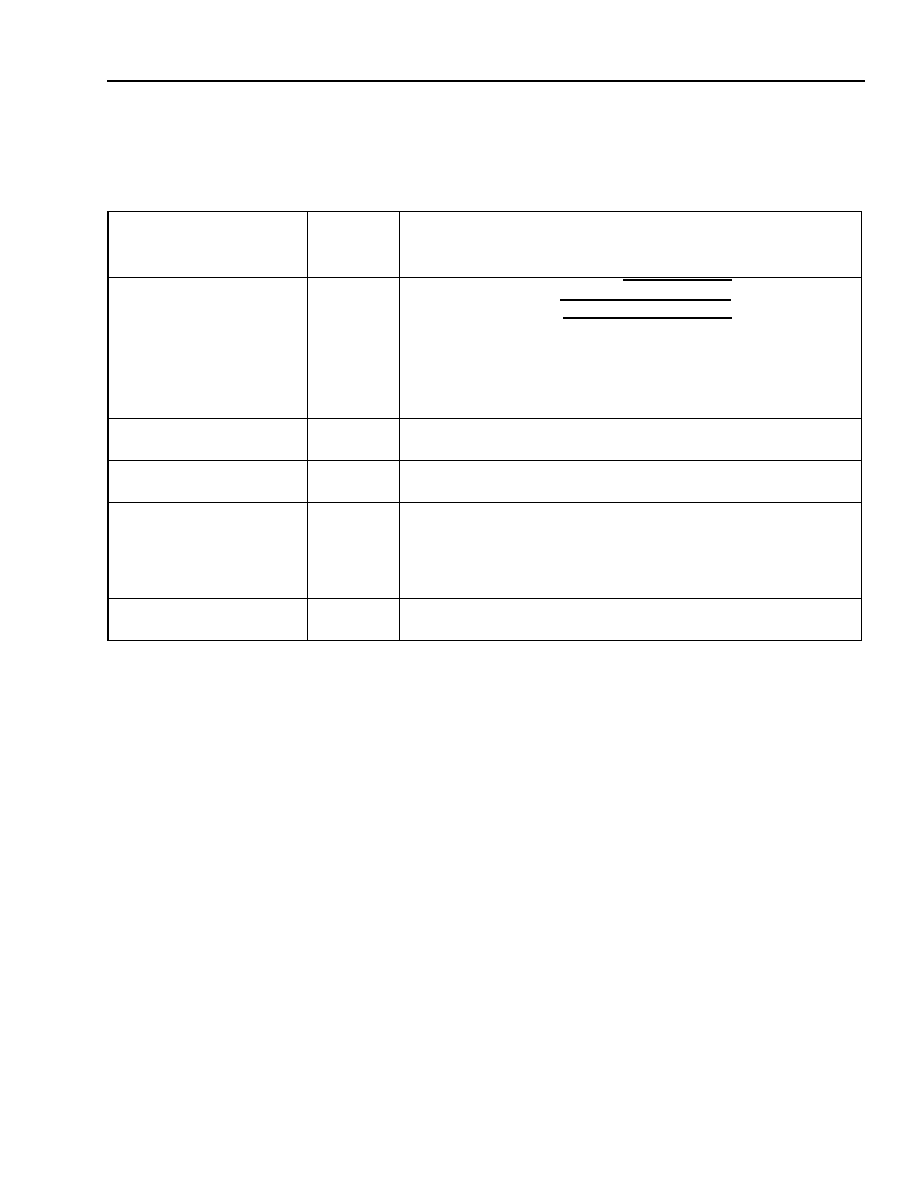

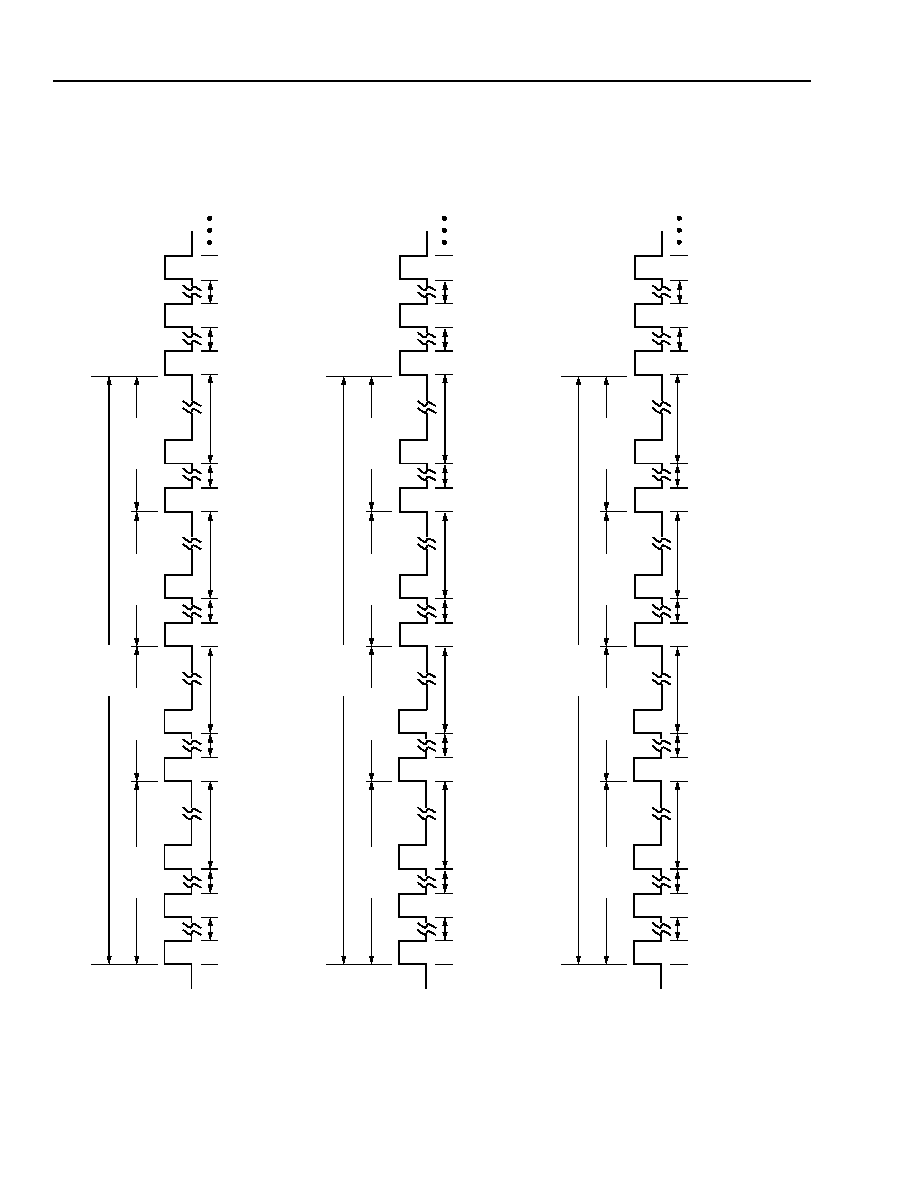

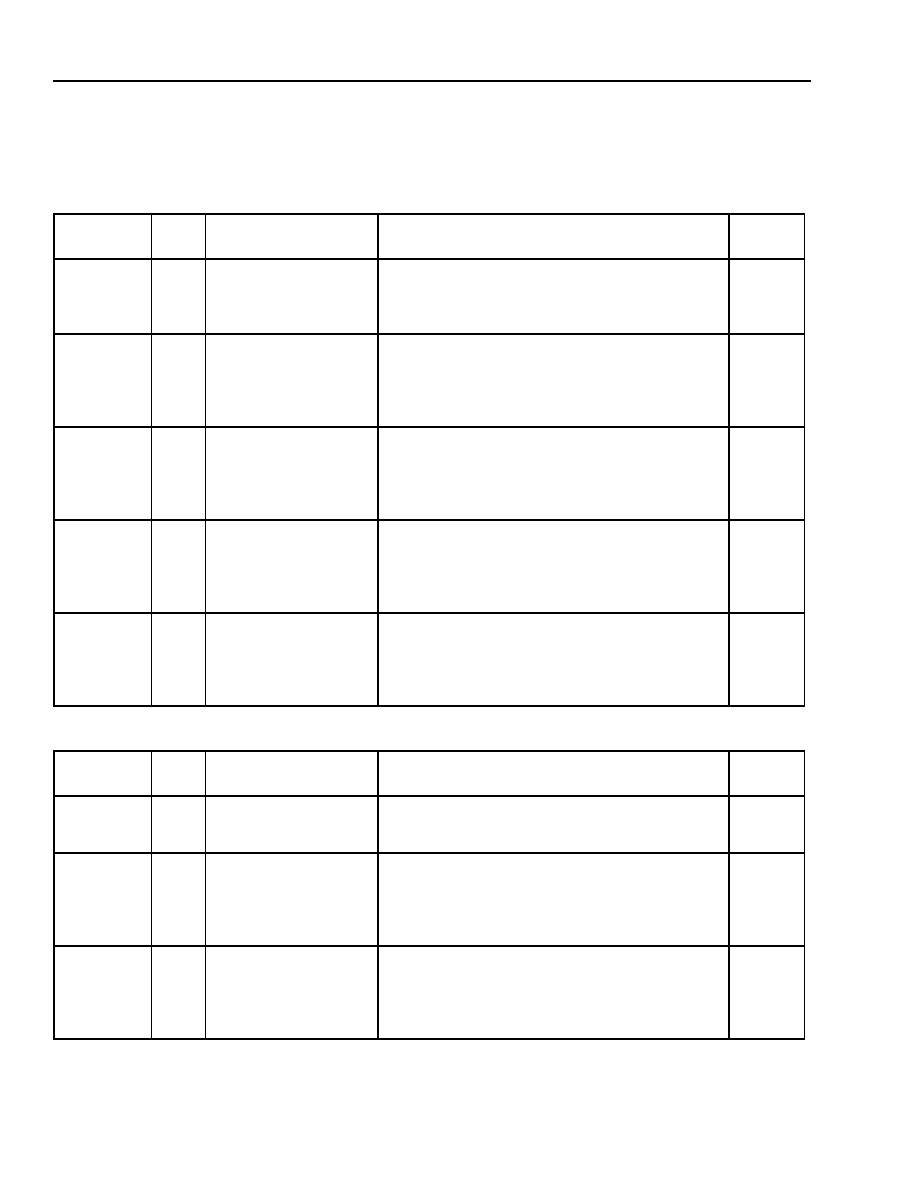

Figure 1. TMUX03155 Block Diagram ................................................................................................................... 8

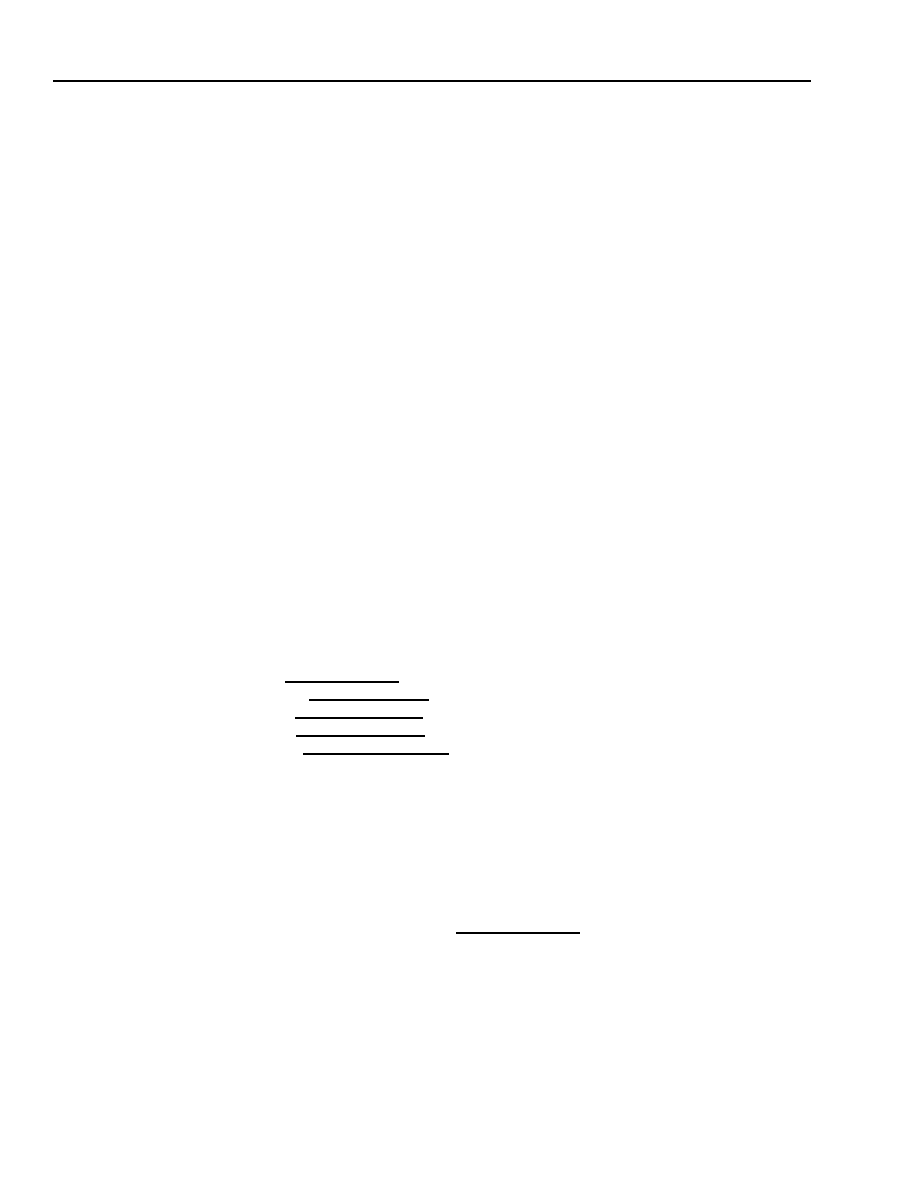

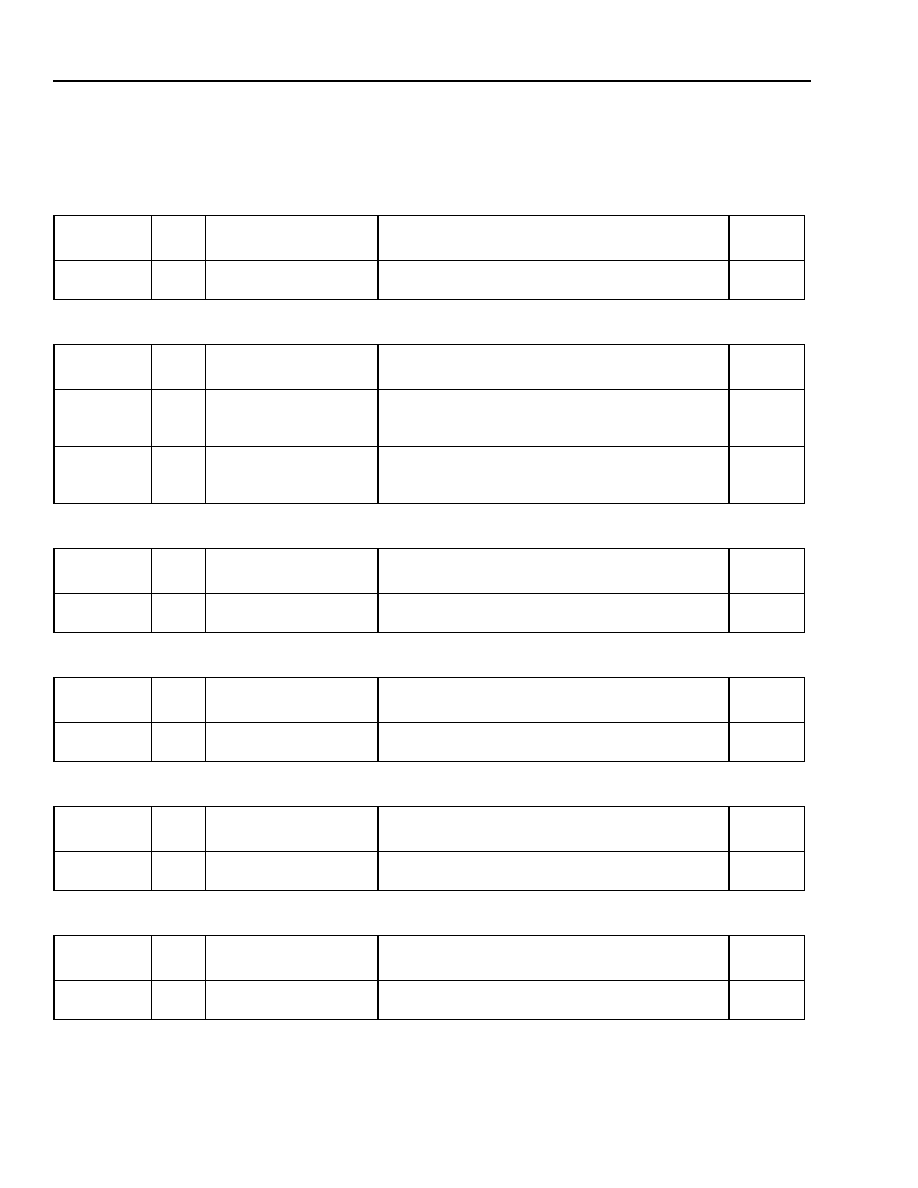

Figure 2. Pinout of 208 SQFP Device ................................................................................................................... 9

Figure 3. SFEBE Location ................................................................................................................................... 33

Figure 4. Line Termination Multiplex ................................................................................................................... 45

Figure 5. Add/Drop Multiplex ............................................................................................................................... 46

Figure 6. Digital Cross Connect ........................................................................................................................... 46

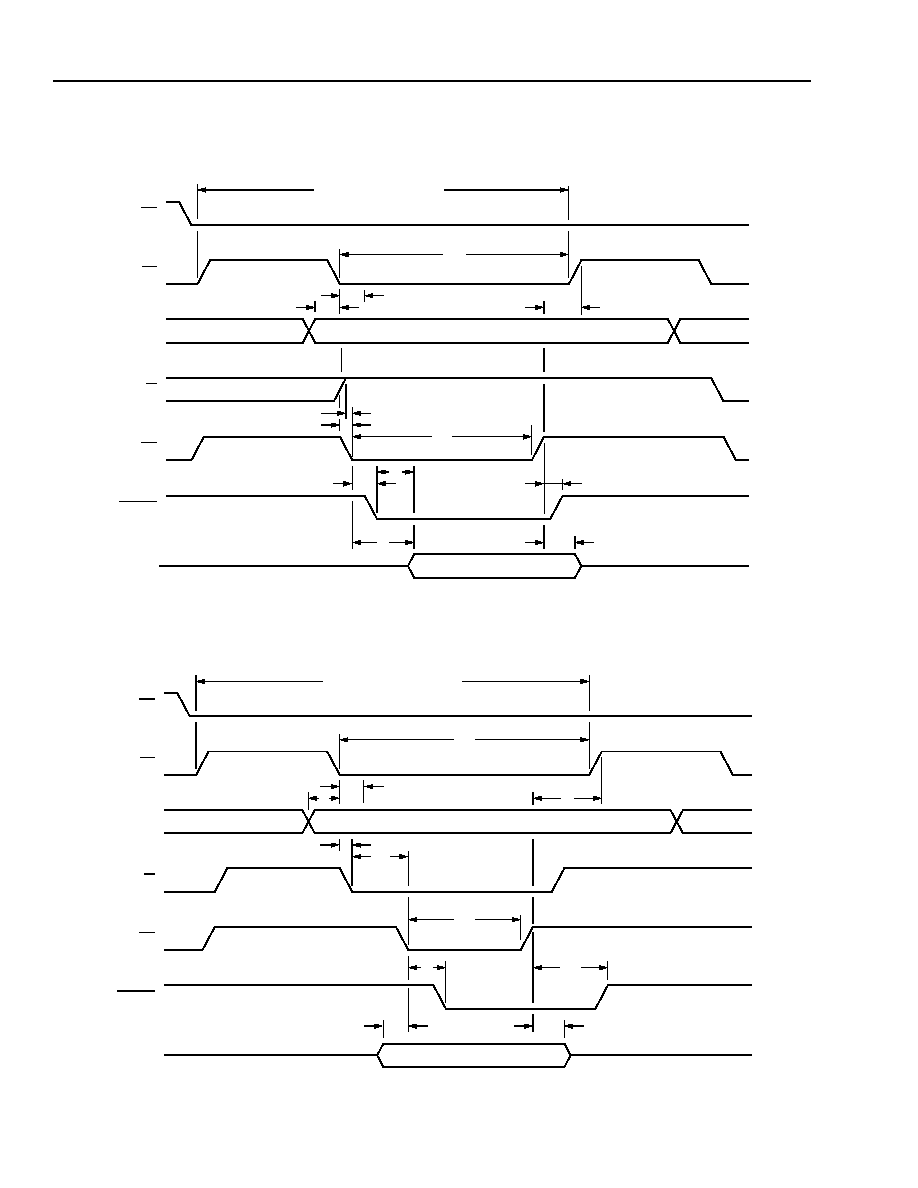

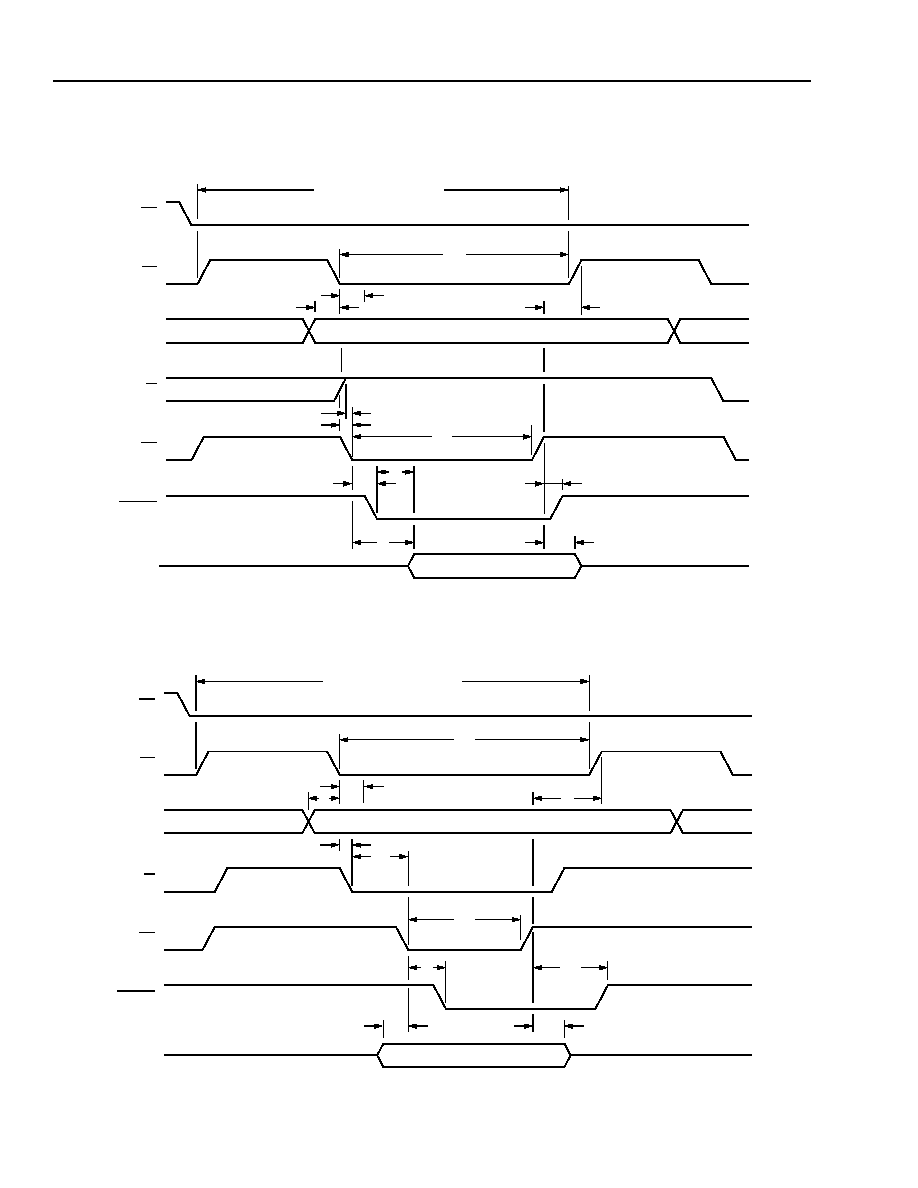

Figure 7. MODE 1--Read Cycle Timing (MPMODE = 0, MPMUX = 0) ............................................................ 102

Figure 8. MODE 1--Write Cycle Timing (MPMODE = 0, MPMUX = 0) ............................................................. 102

Figure 9. MODE 2--Read Cycle Timing (MPMODE = 0, MPMUX = 1) ............................................................ 103

Figure 10. MODE 2--Write Cycle Timing (MPMODE = 0, MPMUX = 1) ........................................................... 103

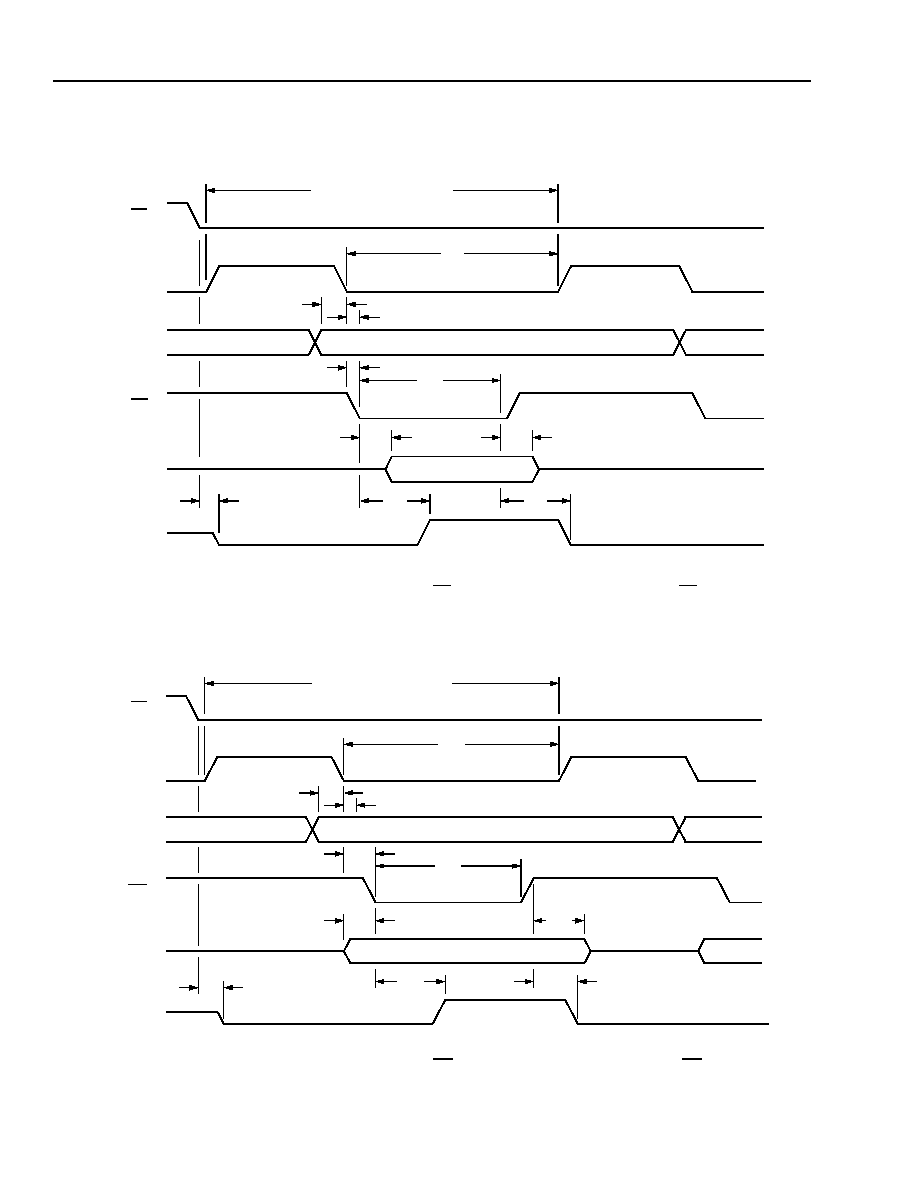

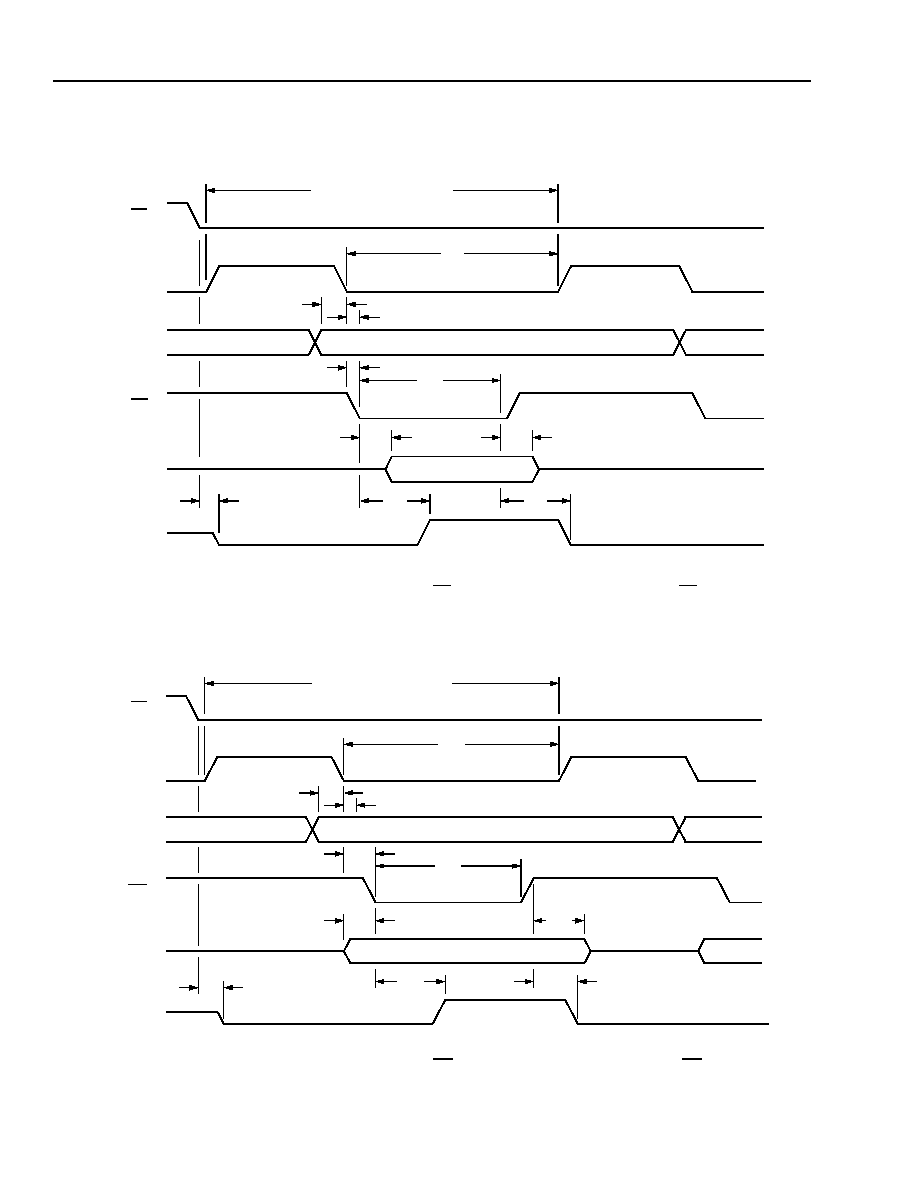

Figure 11. MODE 3--Read Cycle Timing (MPMODE = 1, MPMUX = 0) .......................................................... 104

Figure 12. MODE 3--Write Cycle Timing (MPMODE = 1, MPMUX = 0) ........................................................... 104

Figure 13. MODE 4--Read Cycle Timing (MPMODE = 1, MPMUX = 1) .......................................................... 105

Figure 14. MODE 4--Write Cycle Timing (MPMODE = 1, MPMUX = 1) ........................................................... 105

Figure 15. Single-Ended Input Specification ..................................................................................................... 108

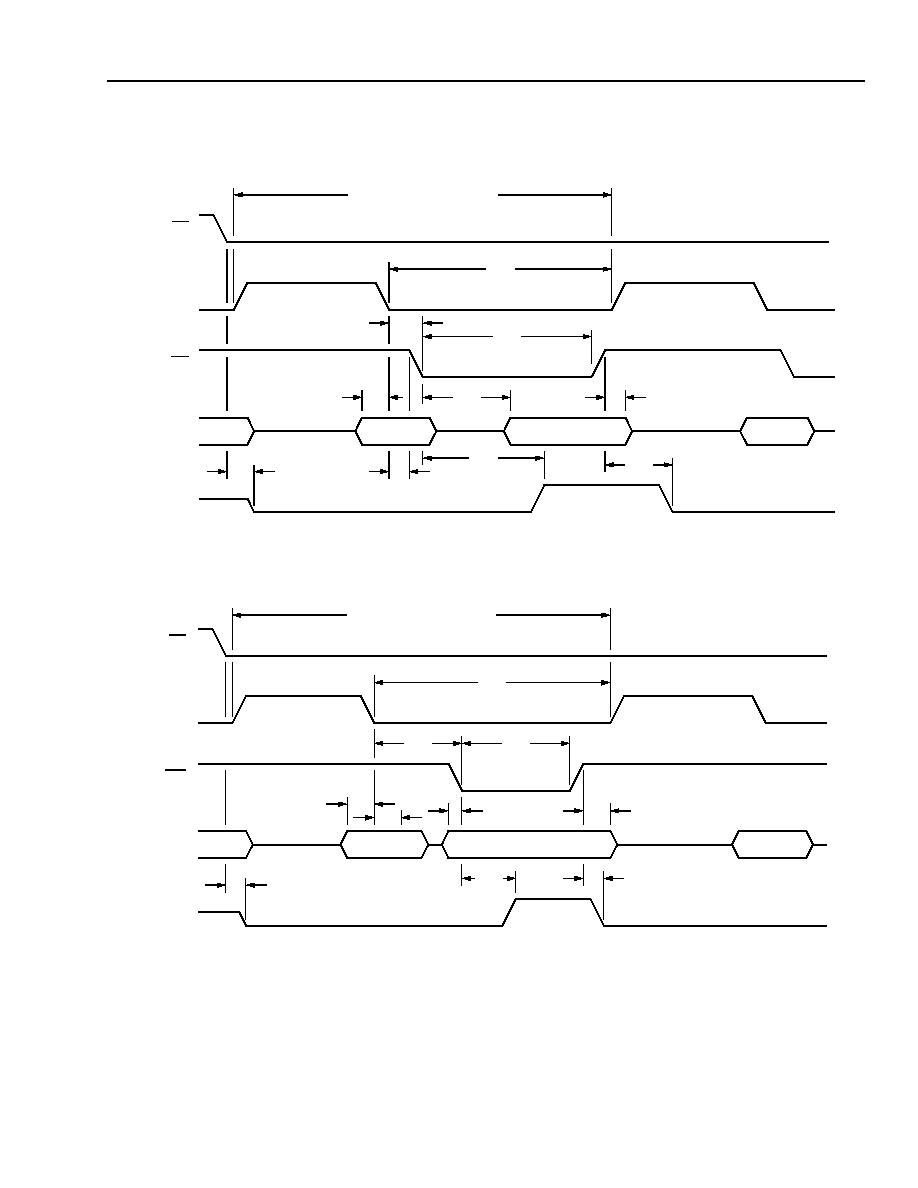

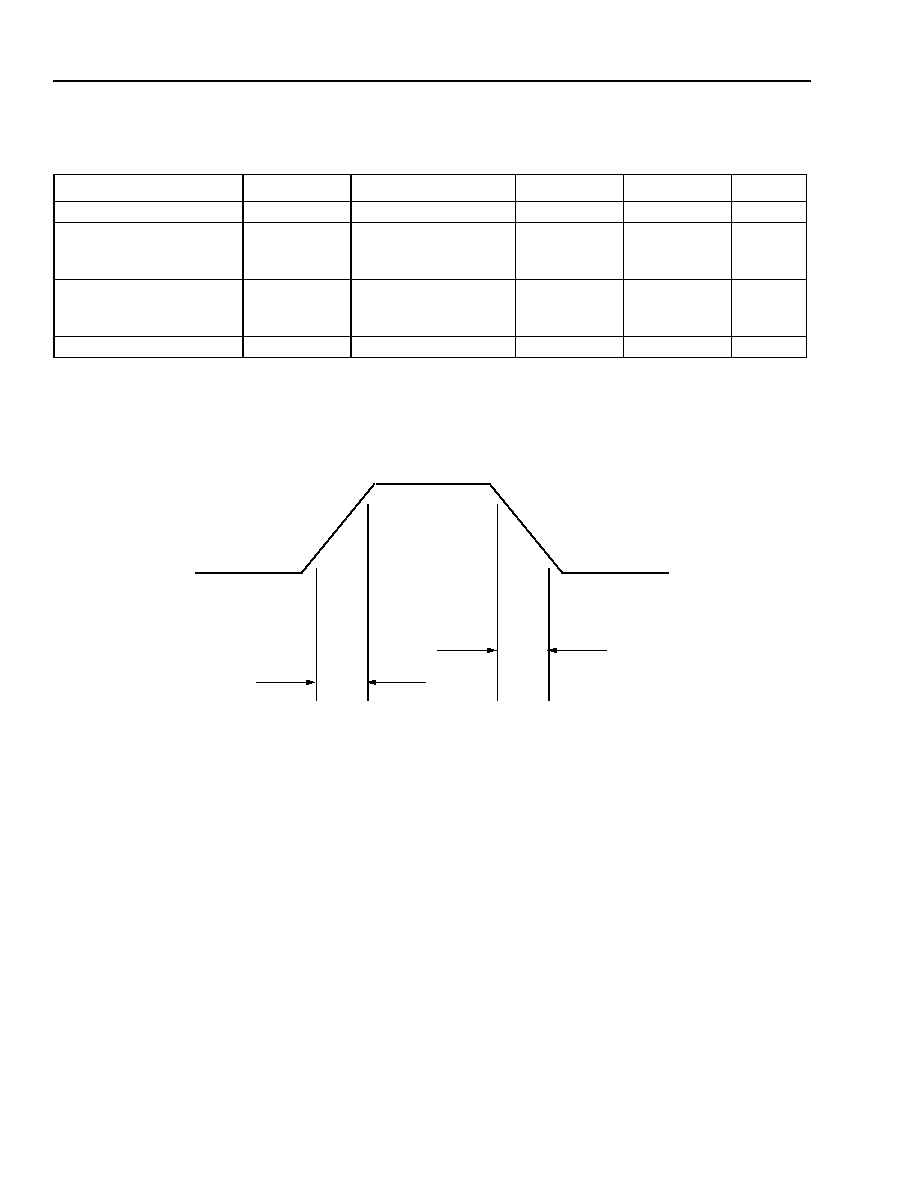

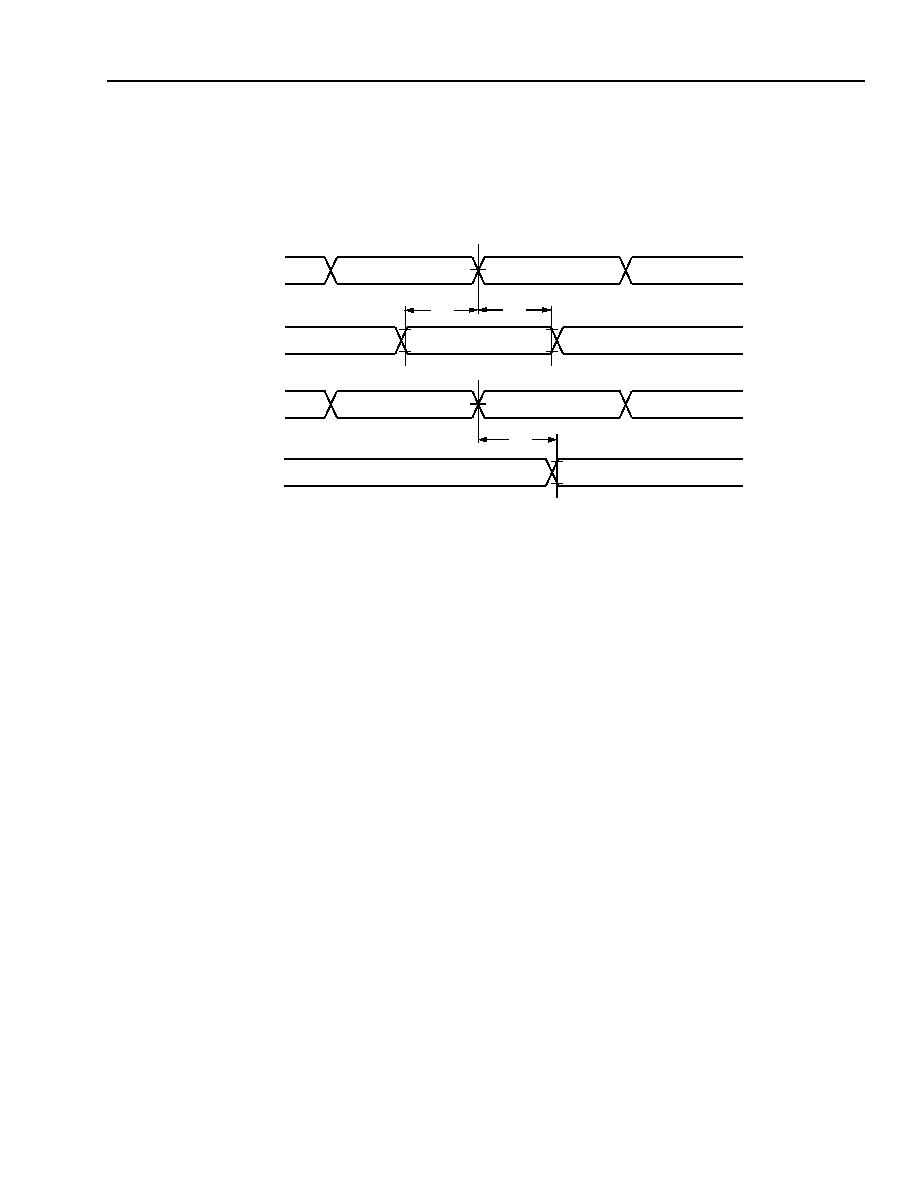

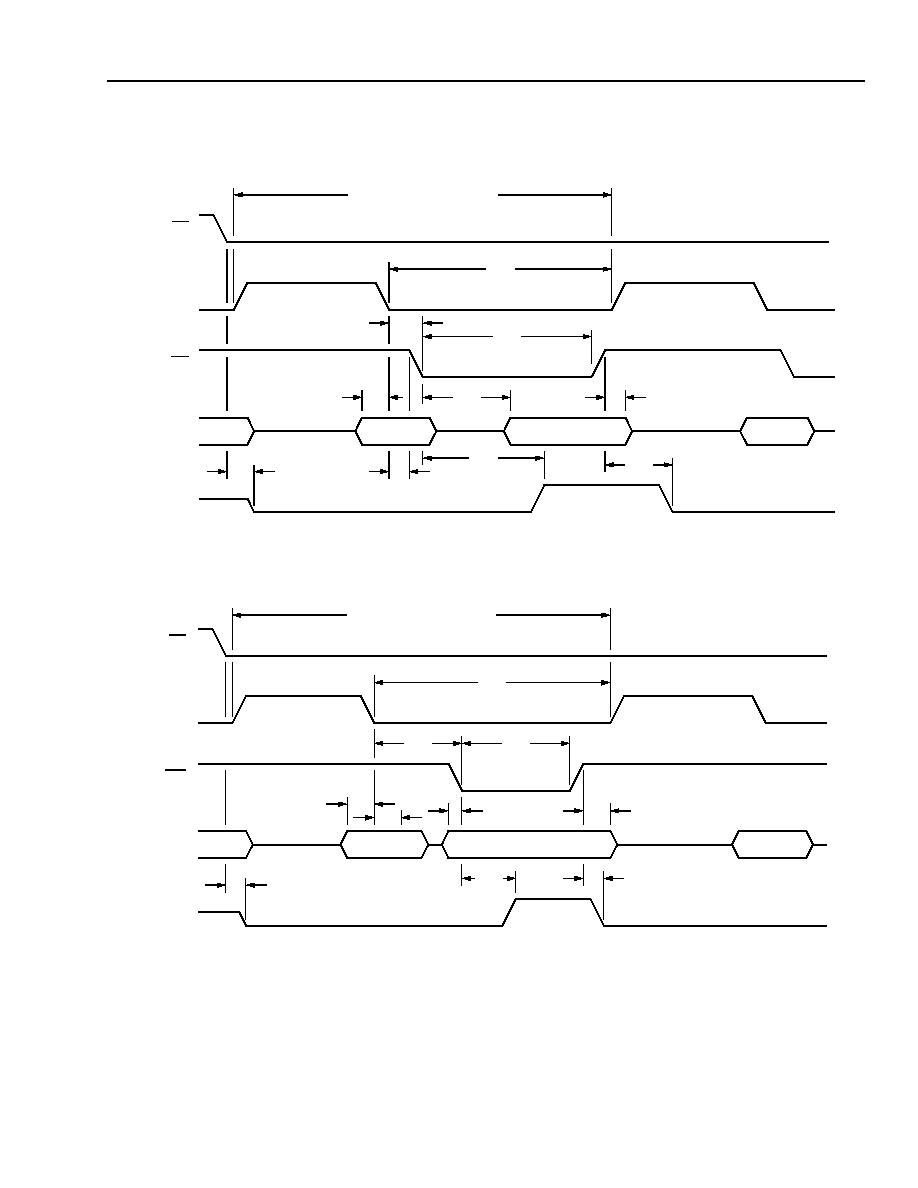

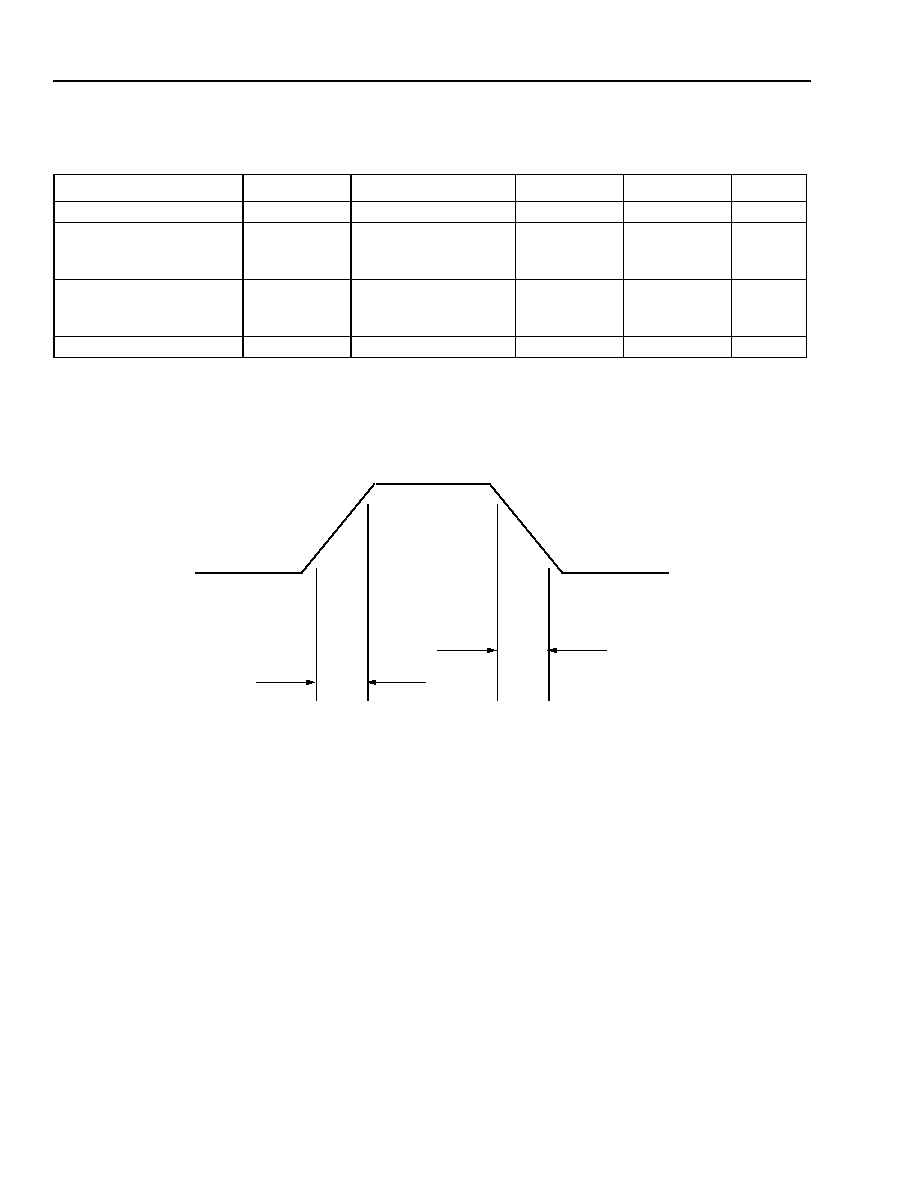

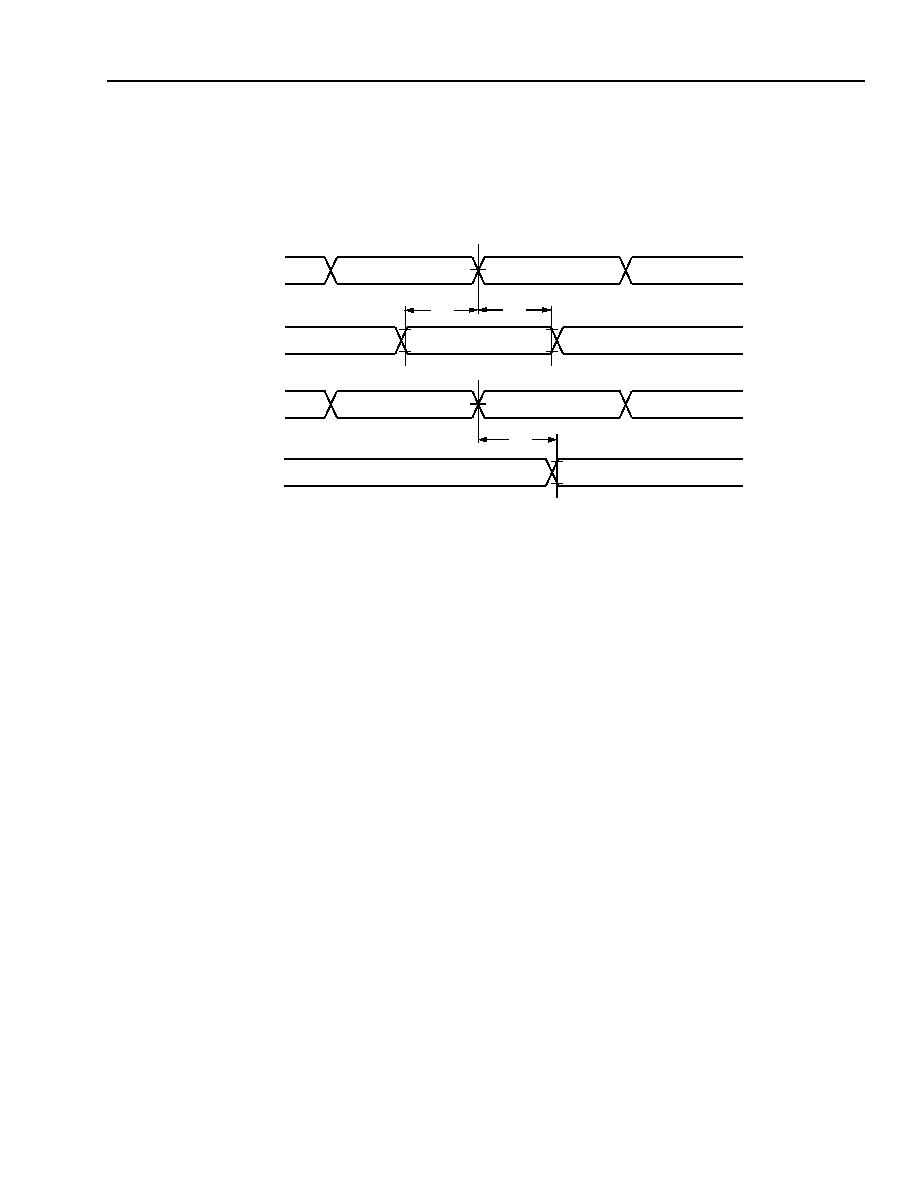

Figure 16. THSJ0J1V1I Signal Structure Definition ........................................................................................... 112

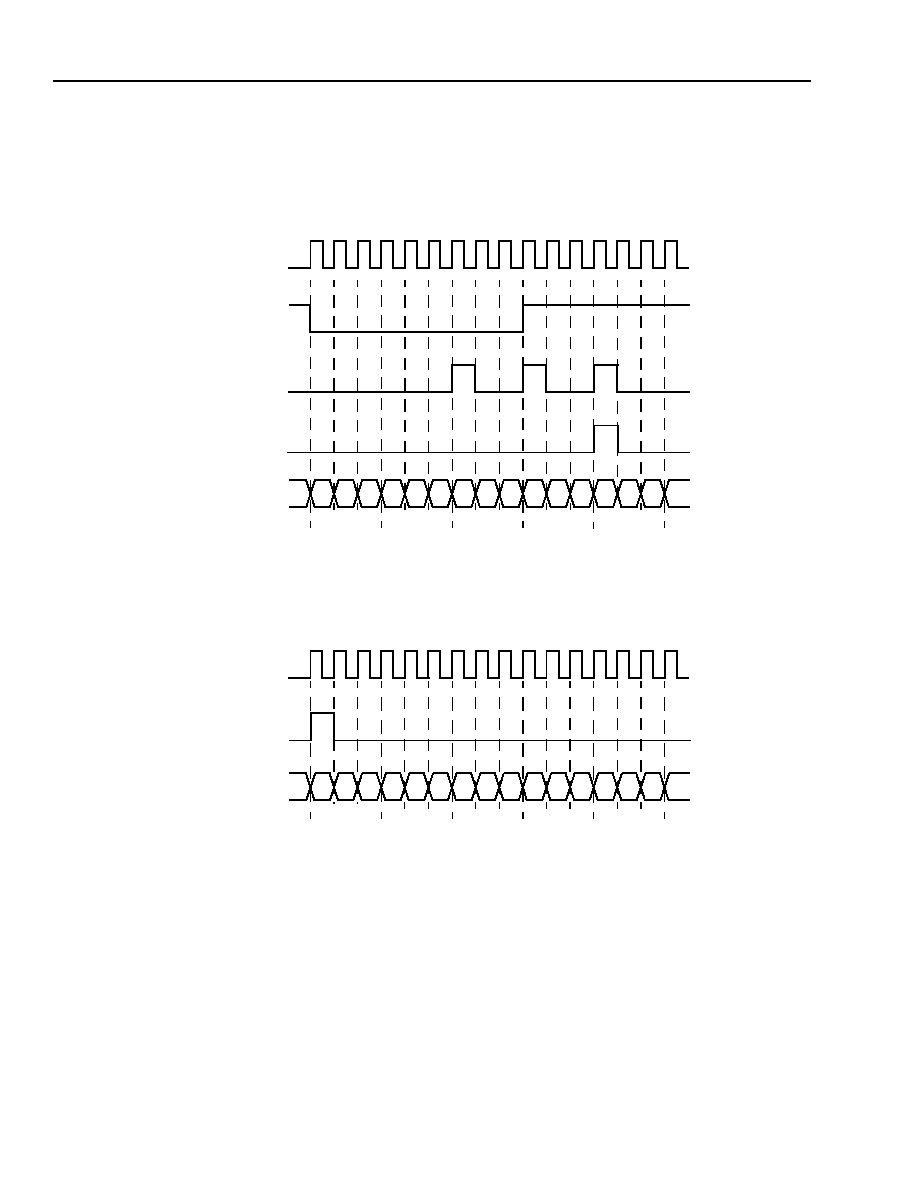

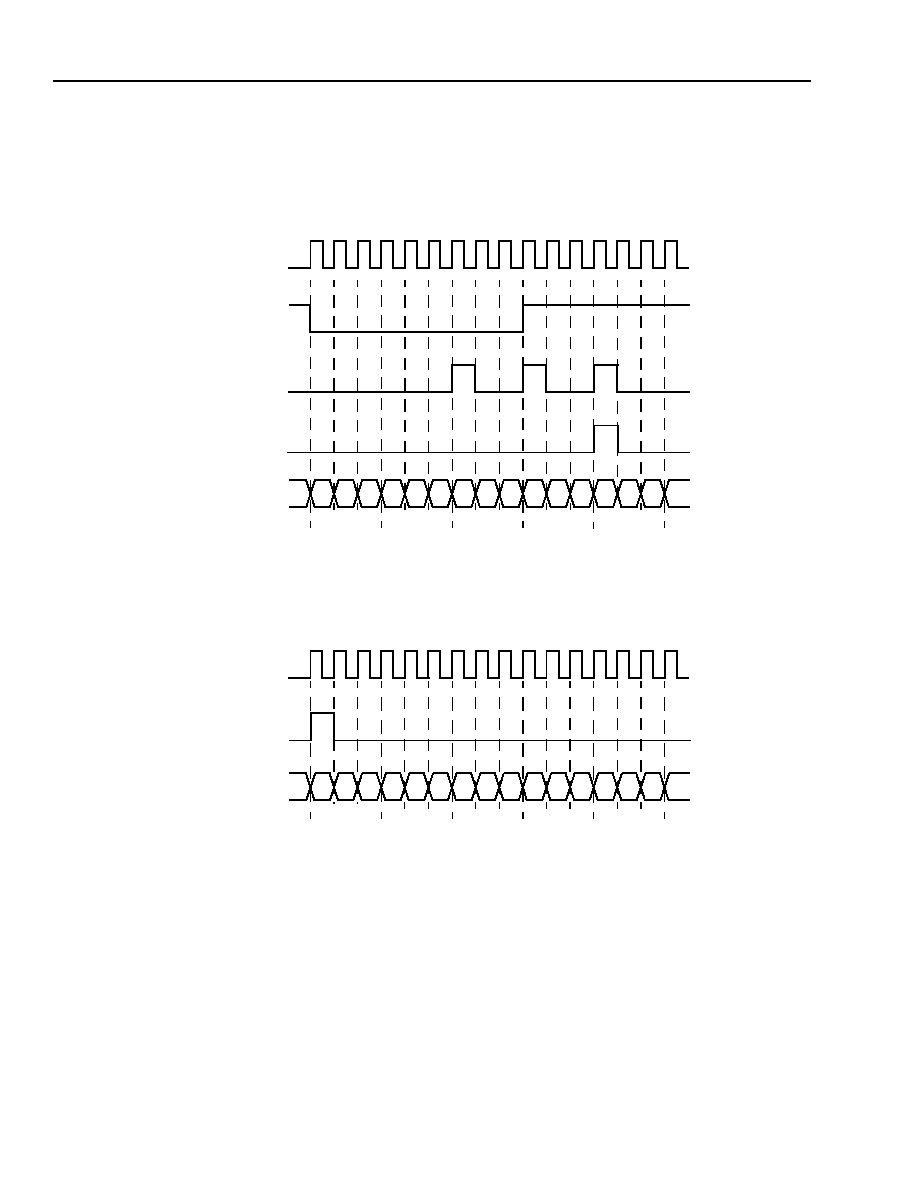

Figure 17. Interface Data Timing ....................................................................................................................... 115

Figure 18. Bus Interface Signals ....................................................................................................................... 116

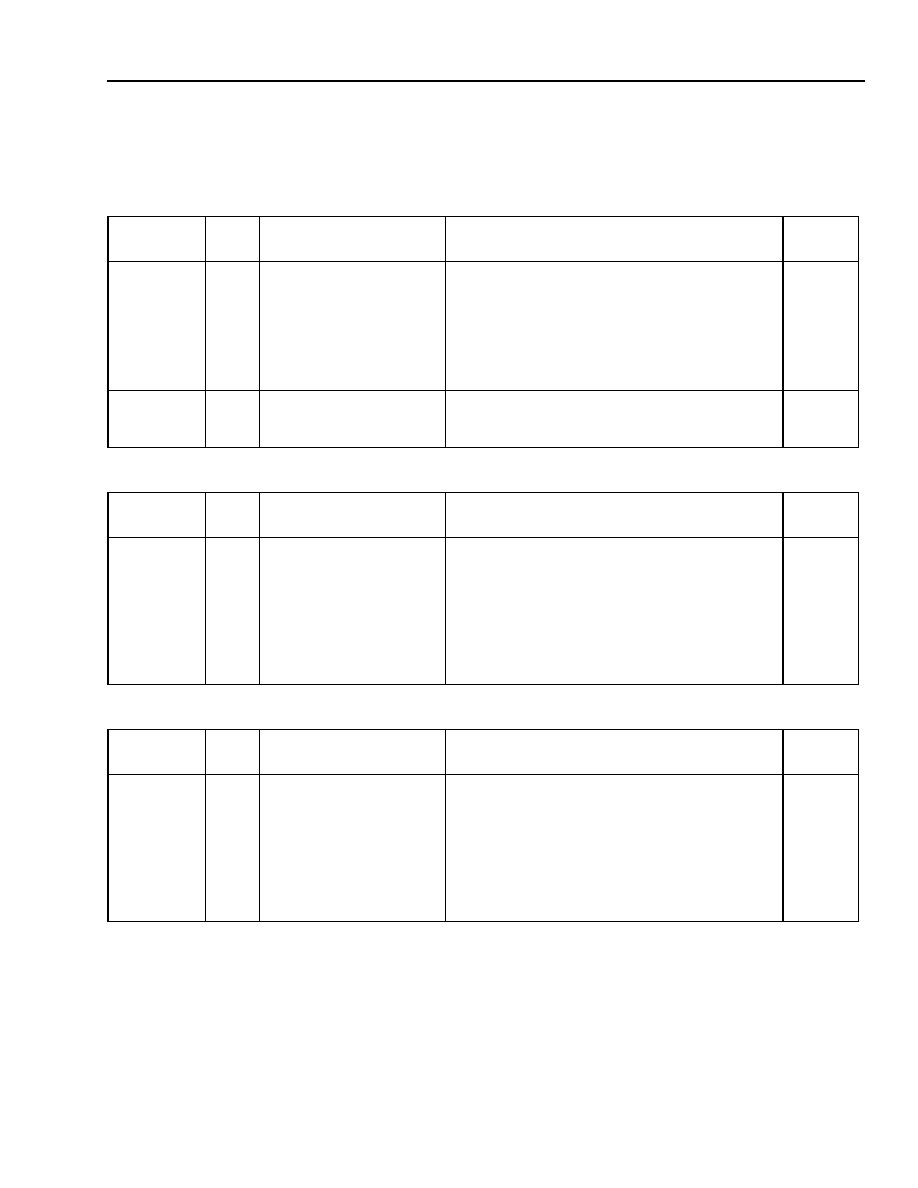

List of Tables

Contents

Page

Agere Systems Inc.

5

Preliminary Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

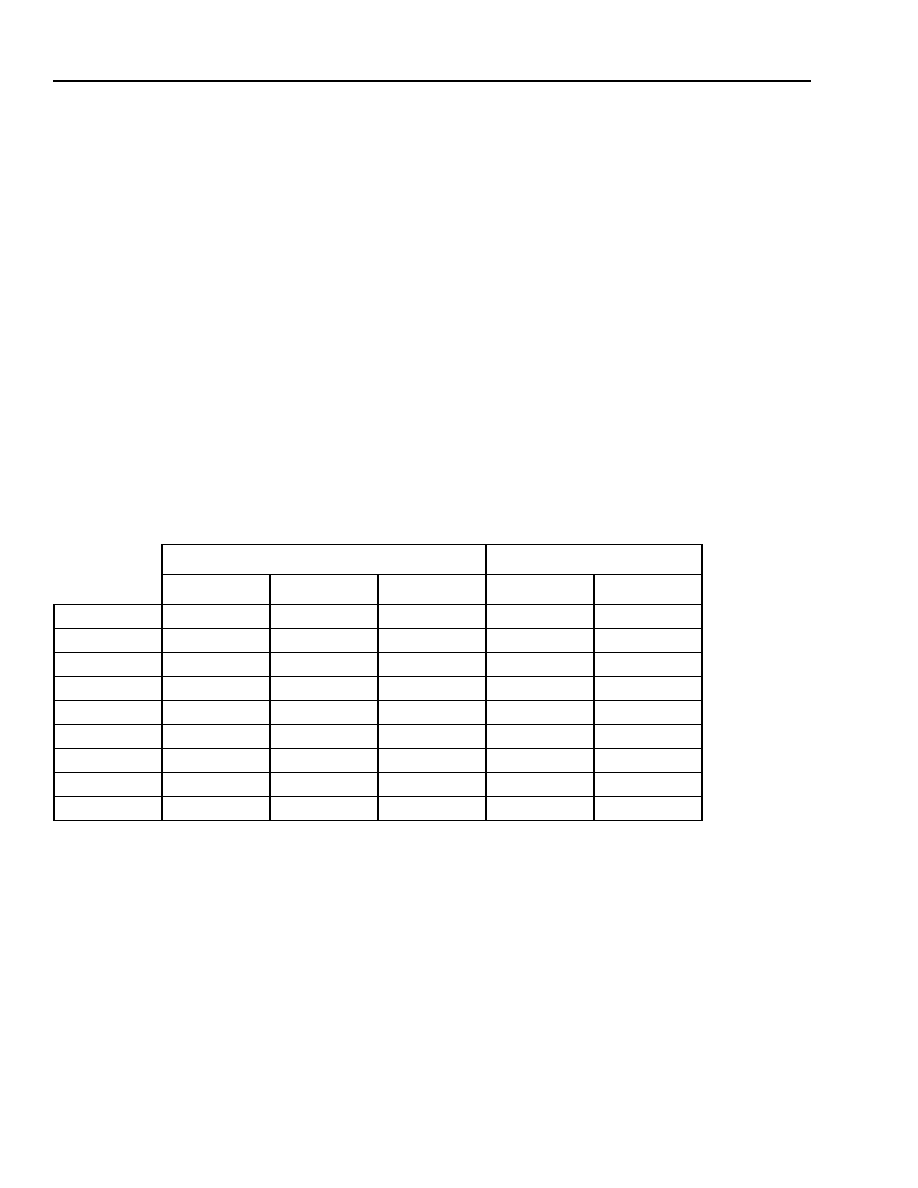

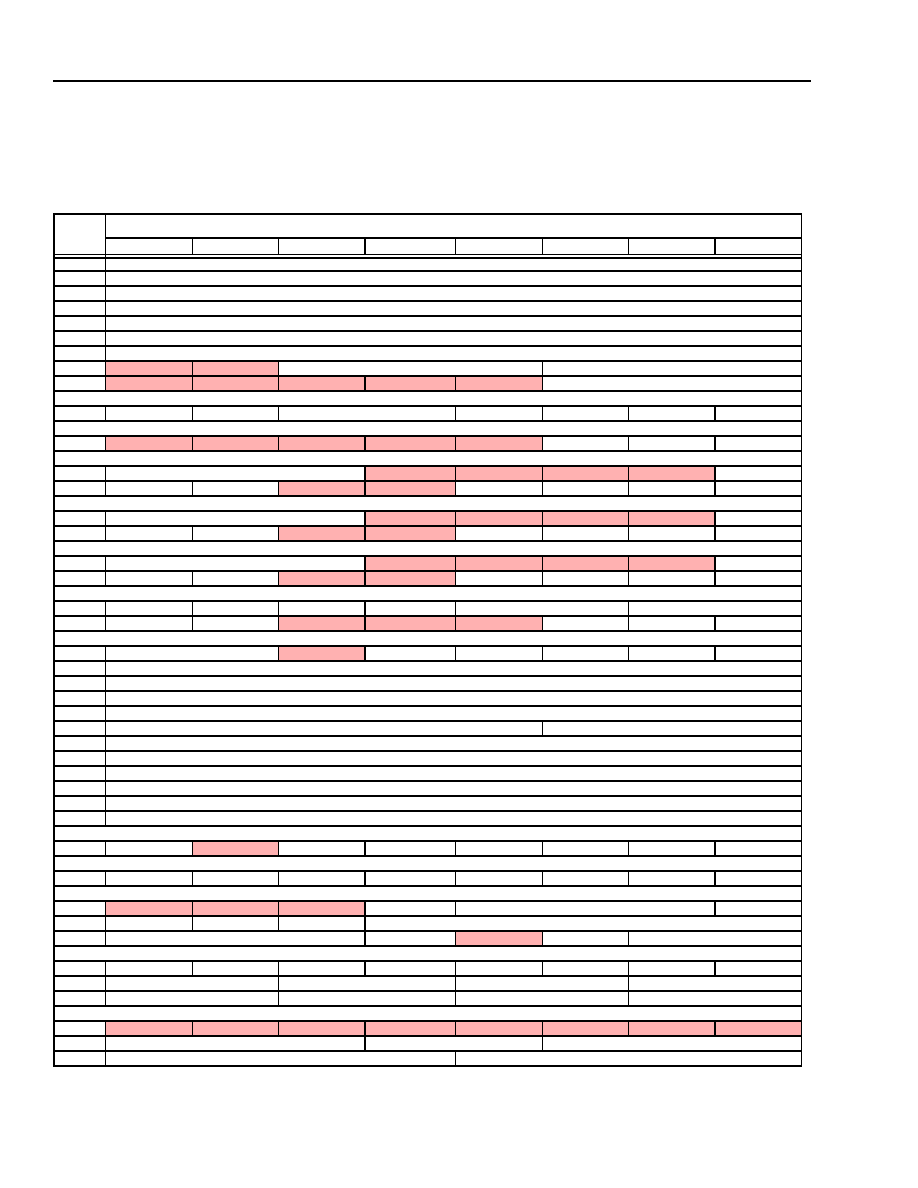

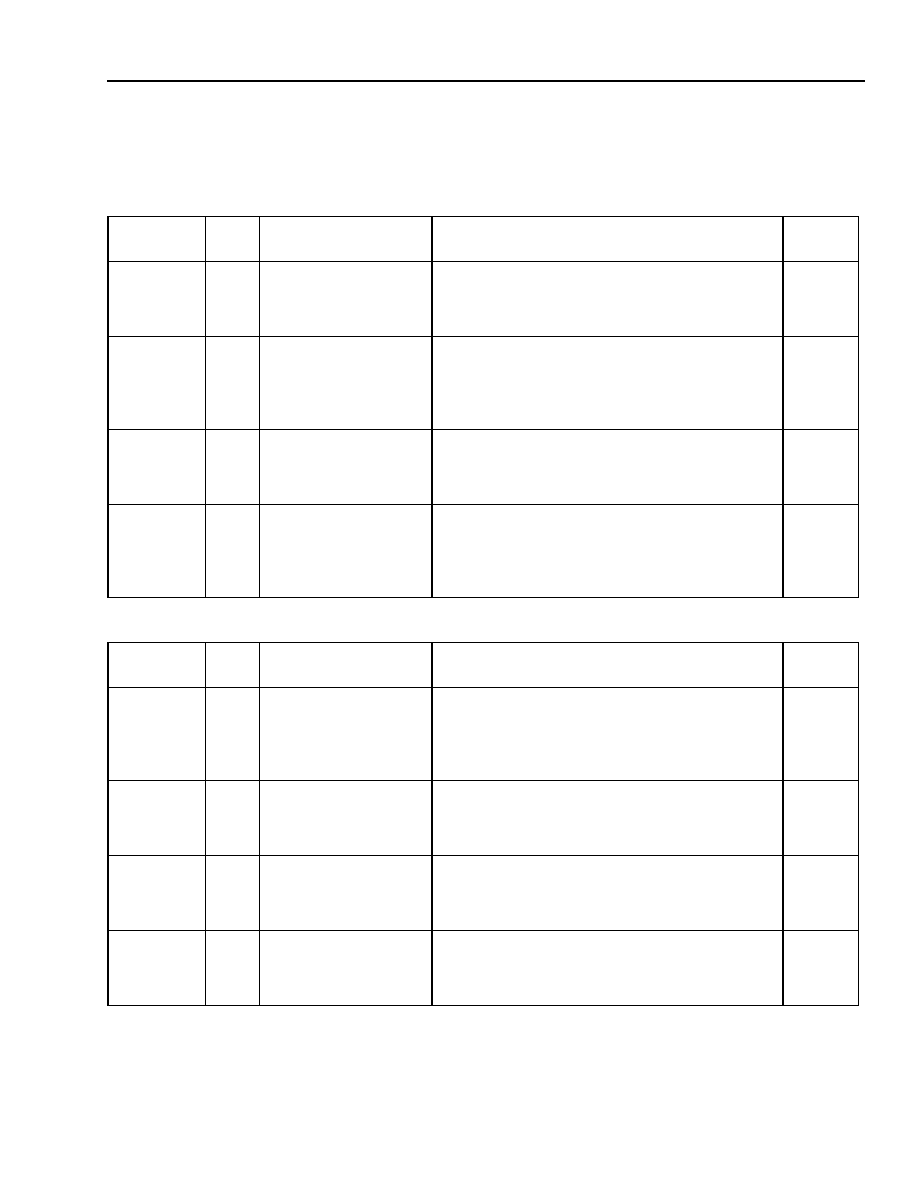

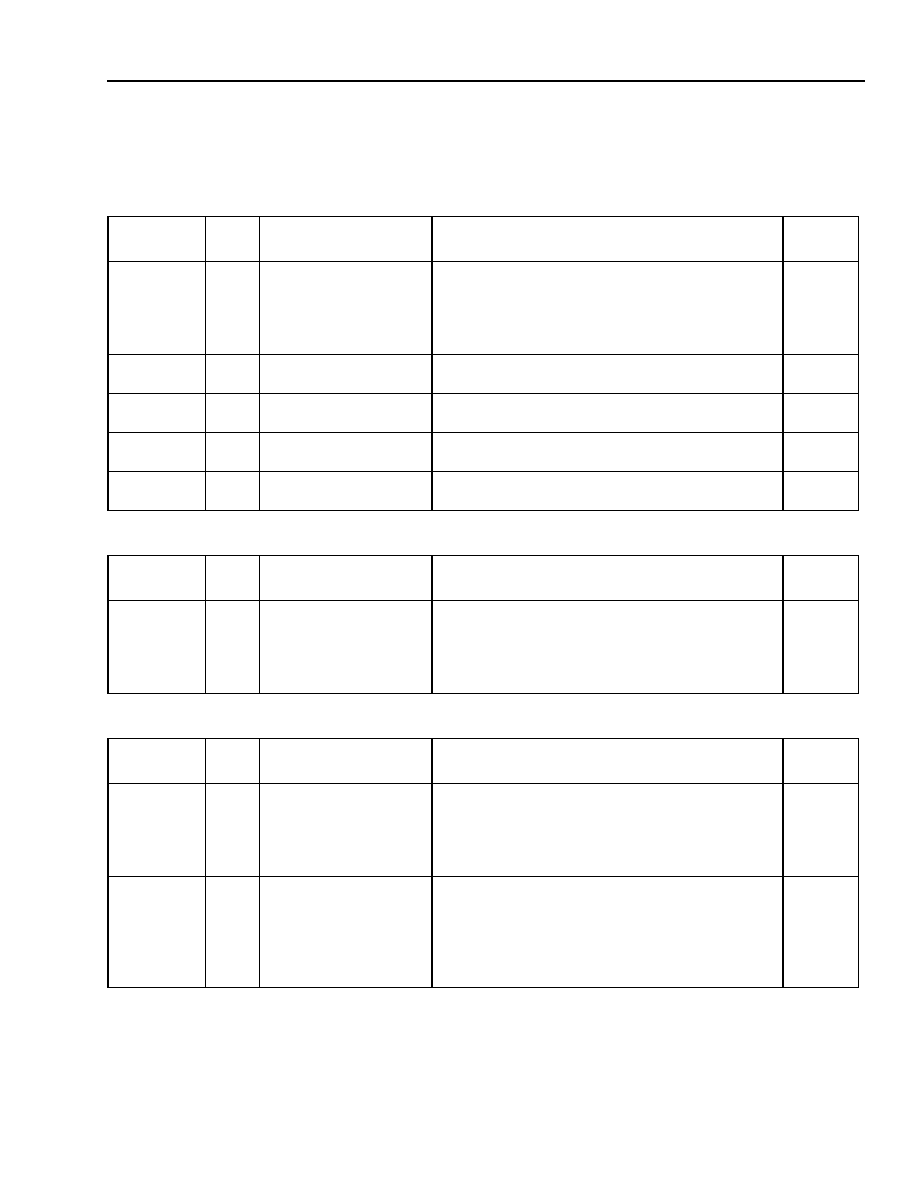

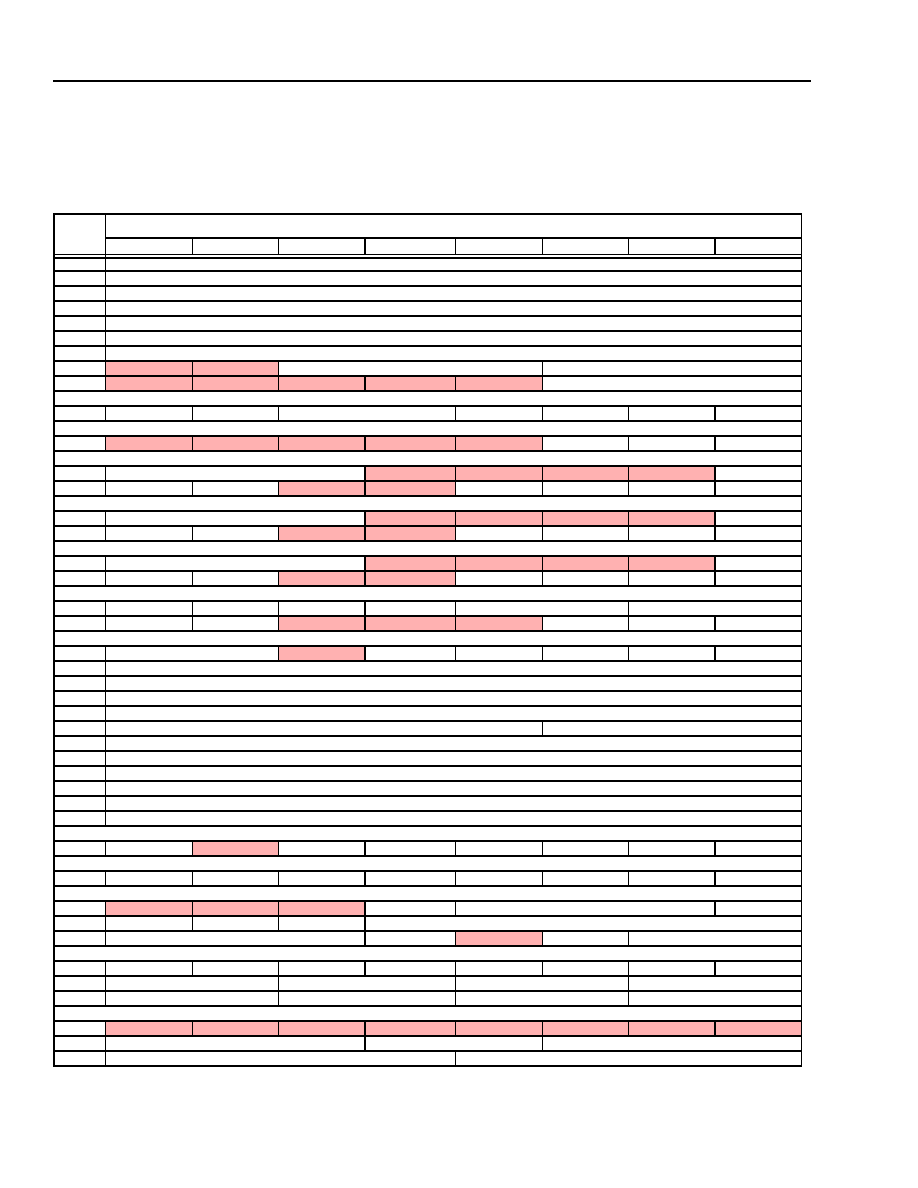

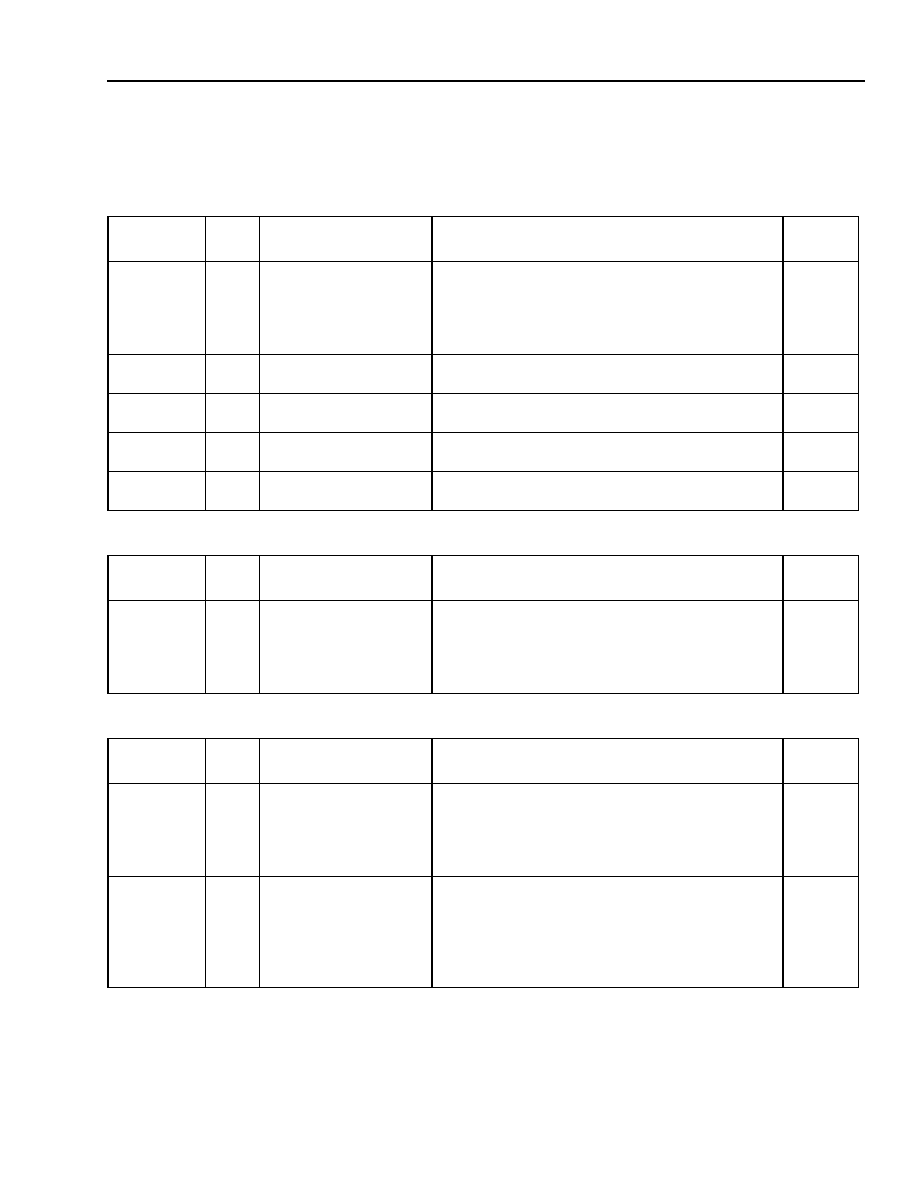

Table 1. Pin Descriptions for the 208-Pin SQFP Package .................................................................................. 10

Table 2. Input/Output Summary .......................................................................................................................... 15

Table 3. Transmit Mode Control Signals ............................................................................................................. 16

Table 4. Receive Mode Control ........................................................................................................................... 16

Table 5. Input Select Control ............................................................................................................................... 17

Table 6. Expected STS-1/AU-3 Input Frame Format .......................................................................................... 18

Table 7. STS-3 Output Overhead Format ........................................................................................................... 20

Table 8. STM-1 (AU-4) Output Overhead Format ............................................................................................... 21

Table 9. STS-1/AU-3 Format and Overhead Control Summary .......................................................................... 26

Table 10. STS-1/AU-3 Output Select Control ...................................................................................................... 27

Table 11. Monitors Disabled During Failure Conditions ...................................................................................... 28

Table 12. SFEBE Values ..................................................................................................................................... 33

Table 13. G1 Byte--AU-4 Mode Only ................................................................................................................. 34

Table 14. PFEBE Values ..................................................................................................................................... 34

Table 15. Value Offset Load Values .................................................................................................................... 36

Table 16. Transport Overhead Byte Access--Transmit Direction ....................................................................... 36

Table 17. TTOAC Control Bits ............................................................................................................................. 37

Table 18. STS-1/AU-3 Overhead Control ............................................................................................................ 42

Table 19. Transport Overhead Byte Access--Receive Direction ........................................................................ 44

Table 20. Microprocessor Configuration Modes .................................................................................................. 47

Table 21. MODE [1--4] Microprocessor Pin Definitions ...................................................................................... 47

Table 22. Device-Level Register Map ................................................................................................................. 49

Table 23. Page 0--J1 Byte Insert and Monitor .................................................................................................... 51

Table 24. Page 1--Error Counters ...................................................................................................................... 52

Table 25. Page 2--BER Algorithm Parameters .................................................................................................. 53

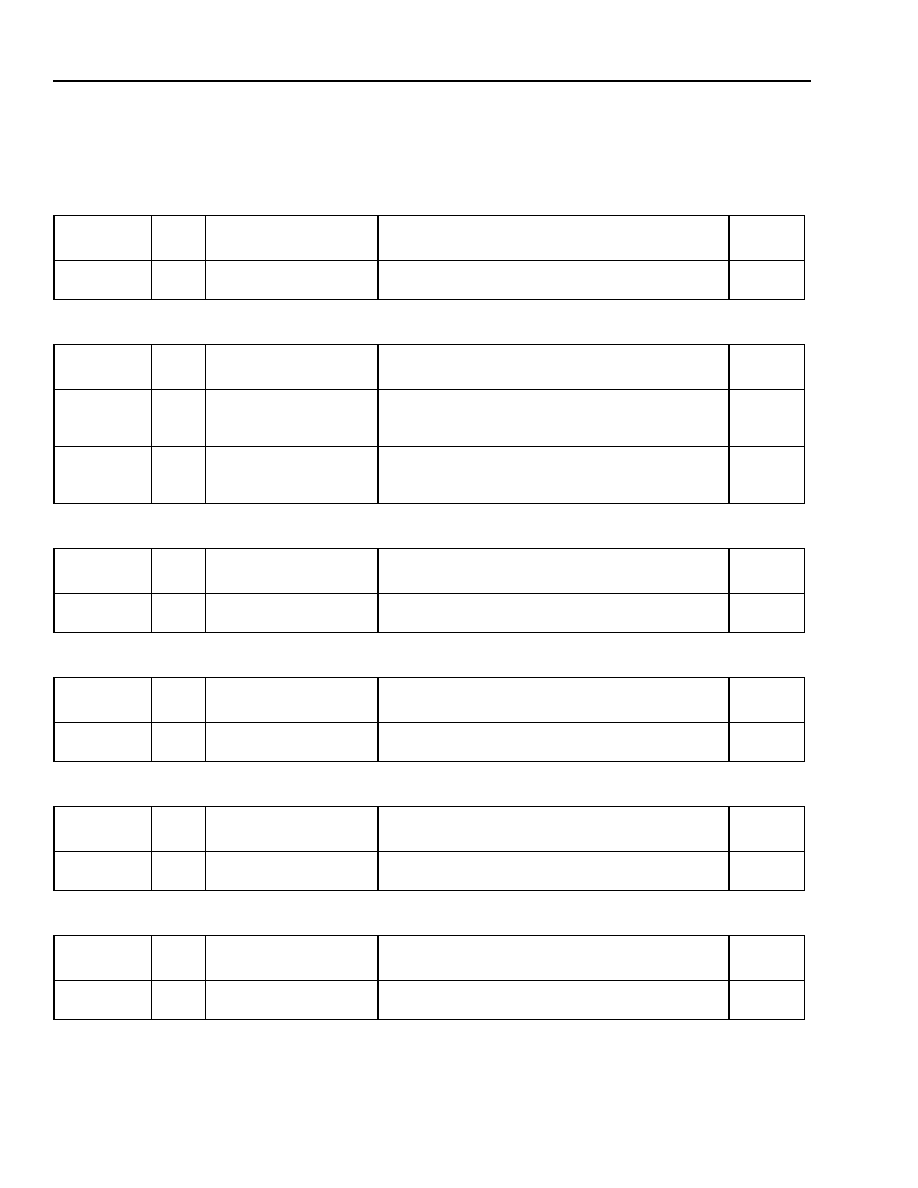

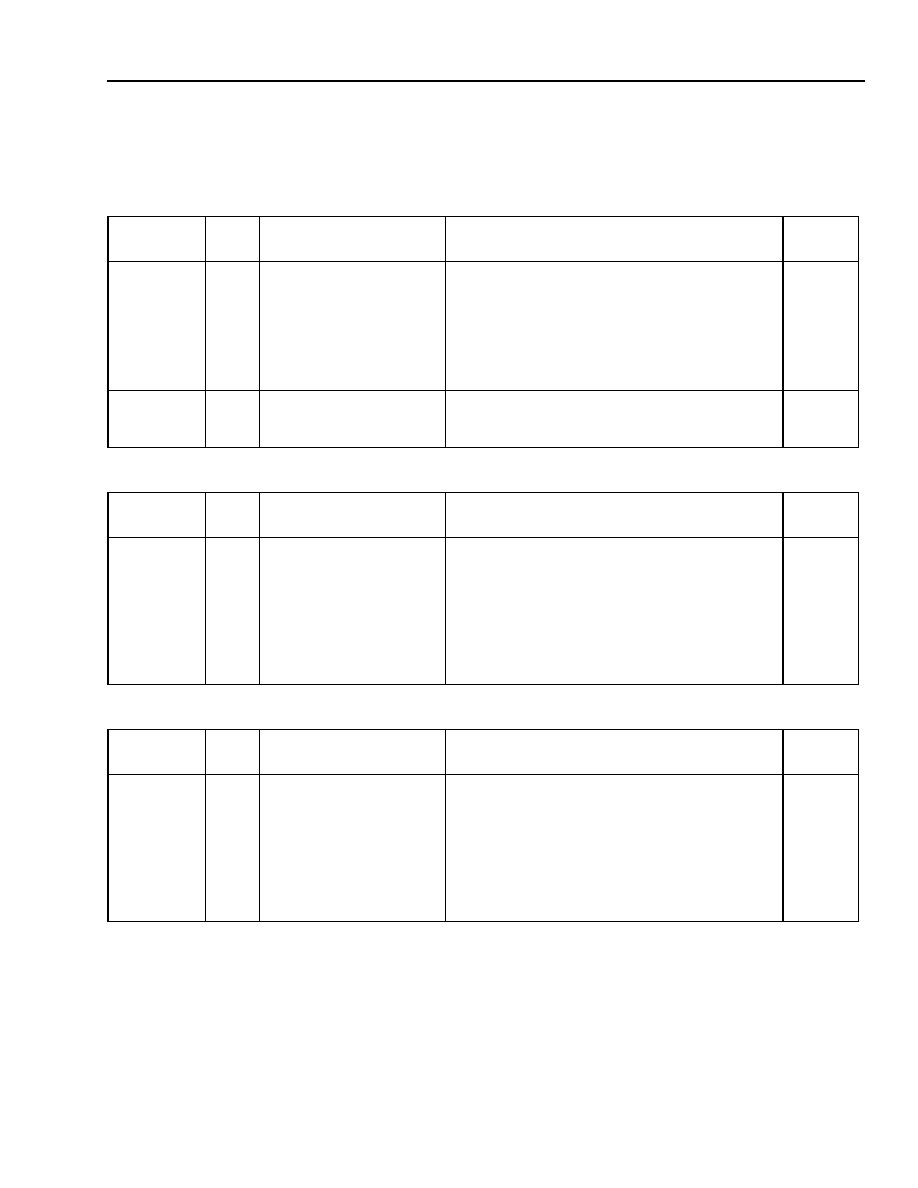

Table 26. Register 0 (RO) ................................................................................................................................... 54

Table 27. Registers 1--3 (RO) ............................................................................................................................ 54

Table 28. Registers 4, 5: One-Shot Register 0

1 (R/W) .................................................................................. 54

Table 29. Register 6: Scratch Register (R/W) ..................................................................................................... 55

Table 30. Registers 7--15: Delta/Event (COR-RO) ............................................................................................ 55

Table 31. Registers 16--24: Mask Bits (R/W) ..................................................................................................... 60

Table 32. Registers 25--51: State Bits (RO) ....................................................................................................... 62

Table 33. Register 52: Mode Control (R/W) ........................................................................................................ 64

Table 34. Register 53: Low-Speed Transmit Common Signals (R/W) ................................................................ 65

Table 35. Register 54--59: Transmit Low-Speed Port Input Control (R/W) ........................................................ 66

Table 36. Registers 60, 61: Transmit High-Speed Clock/Port Control (R/W) ...................................................... 67

Table 37. Register 62: Transmit High-Speed Control Signals (R/W) .................................................................. 68

Table 38. Register 62, and Page 0, Registers 128--191: Transmit High-Speed J1 Insert (R/W) ....................... 69

Table 39. Register 62, 69: Transmit High-Speed Control Signals (R/W) ............................................................ 69

Table 40. Register 62, 66: Transmit High-Speed Control Signals (R/W) ............................................................ 69

Table 41. Registers 63--65: Trace/Growth Bytes (R/W) ..................................................................................... 69

Table 42. Register 66: Transmit F1 Data Byte (R/W) .......................................................................................... 70

Table 43. Registers 67 and 68: K1 and K2 Insert Bytes (R/W) ........................................................................... 70

Table 44. Register 69: Transmit Sync Status Byte (R/W) ................................................................................... 70

Table 45. Register 70: Path Signal Trace Byte (R/W) ......................................................................................... 70

Table 46. Register 71: Path User Channel Byte (R/W) ....................................................................................... 70

Table 47. Register 72: Path Growth Byte (R/W) .................................................................................................. 70

Table 48. Register 73: Tandem Connection Byte (R/W) ..................................................................................... 71

Table 49. Register 74: Transmit High-Speed Line RDI Insertion Inhibit Bits (R/W) ............................................ 71

Table 50. Register 75: Transmit High-Speed Path RDI Insertion Inhibit Bits (R/W) ............................................ 71

Table 51. Register 76: Transmit High-Speed Error Insert Control Parameters (R/W) ......................................... 72

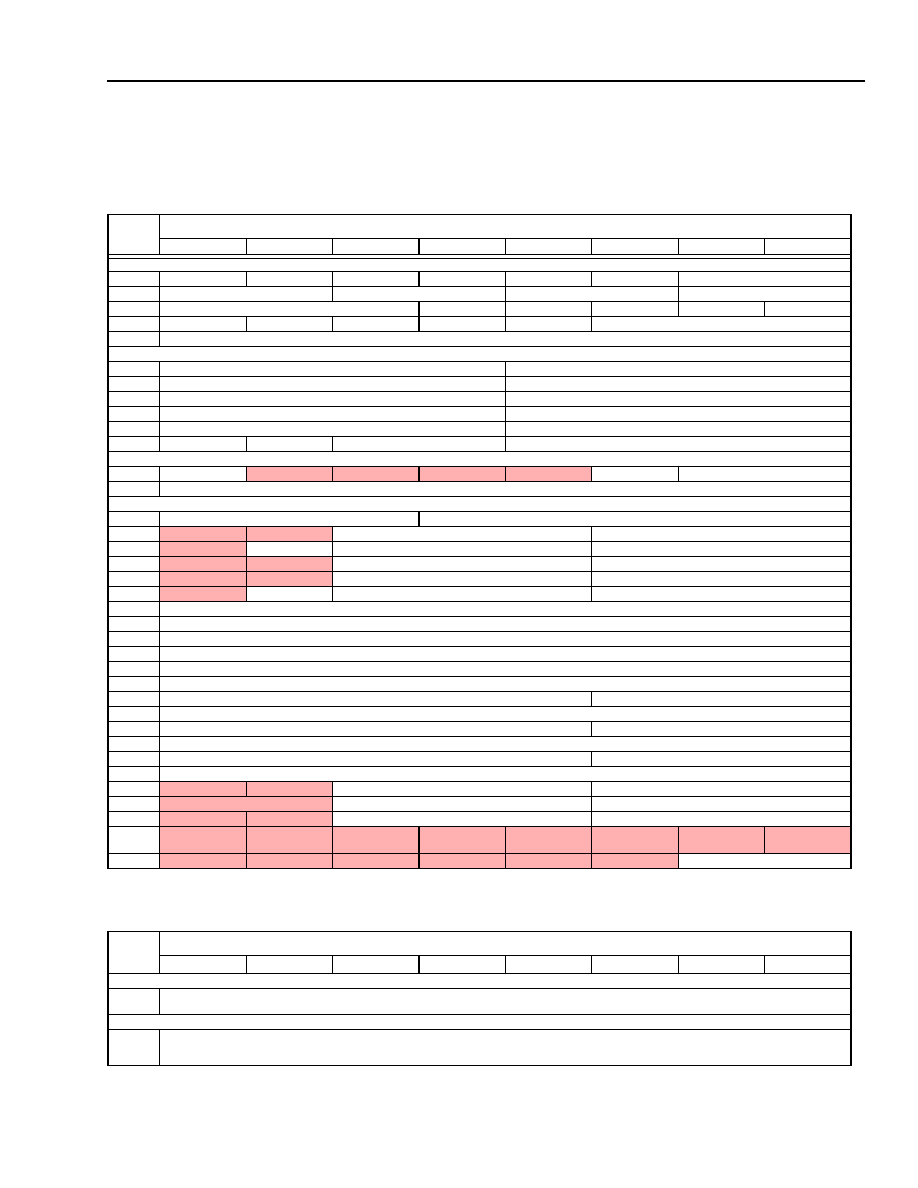

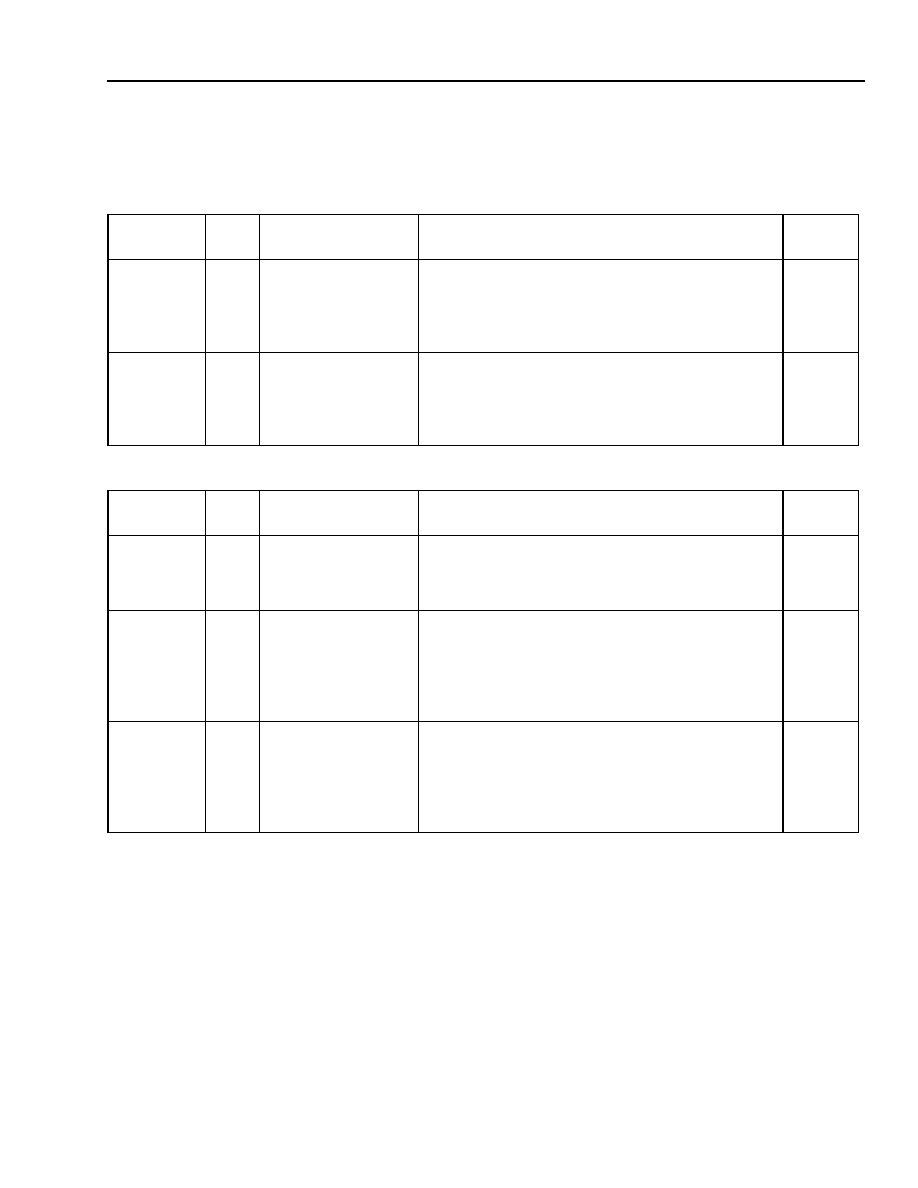

List of Tables

(continued)

Contents

Page

6

Agere Systems Inc.

Preliminary Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Table 52. Register 77: Transmit High-Speed Error Insert Control Parameters (R/W) ......................................... 73

Table 53. Register 78: Transmit High-Speed Error Insert (R/W) ......................................................................... 73

Table 54. Register 79: Receive/Transmit TOAC Control (R/W) .......................................................................... 74

Table 55. Registers 80, 81: Transmit TOAC Control (R/W) ................................................................................ 75

Table 56. Register 83, 84: Transmit High-Speed STS-3/STM-1 Output Frame Offset (R/W) ............................. 77

Table 57. A1-1 Alignment Parameters ................................................................................................................ 80

Table 58. BITCNT Alignment Table ..................................................................................................................... 80

Table 59. Register 85: Receive High/Low-Speed Port Control (R/W) ................................................................. 81

Table 60. Register 86: Receive J1 and Receive Low-Speed Port Select Control (R/W) ..................................... 82

Table 61. Register 87: STS-1/AU-3 Receive Control Bits (R/W) ......................................................................... 82

Table 62. Register 88: STS-1/AU-3 Receive Low-Speed AIS Inhibit Control Bits (R/W) .................................... 83

Table 63. Registers 88, 89: STS-1/AU-3 Loss of Signal Detector (R/W) ............................................................ 83

Table 64. Register 90--95: Continuous N Times Detect (CNTD) Values (R/W) ................................................. 83

Table 65. Register 95: Continuous N Times Detect (CNTD) B1 Control Bit (R/W) ............................................. 85

Table 66. Register 96: Test Pattern Drop Control and Status ............................................................................. 86

Table 67. Register 97: Test Pattern Drop Error Counter (RO) ............................................................................ 86

Table 68. Register 98: Receive Low-Speed Overhead Control Bits (R/W) ......................................................... 86

Table 69. Register 99: Receive Low-Speed BIP Error Insert (R/W) .................................................................... 87

Table 70. Registers 100--102: Receive Low-Speed Overhead Control Bits (R/W) ............................................ 87

Table 71. Register 103: Receive Low-Speed L-RDI Inhibit Control (R/W) .......................................................... 88

Table 72. Registers 104--106: Receive Low-Speed C1 Byte (R/W) .................................................................. 88

Table 73. Registers 107--109: Receive Low-Speed F1 Byte (R/W) ................................................................... 88

Table 74. Registers 110--115: Receive Low-Speed K1, K2 Byte Insert (R/W) .................................................. 88

Table 75. Registers 116--118: Receive Low-Speed Pass Control (R/W) ........................................................... 89

Table 76. Register 127: Page Control Register (R/W) ........................................................................................ 90

Table 77. Page 0 - Registers 128--191: J1 Insert Parameters (R/W) ................................................................ 90

Table 78. Page 0 - Registers 192--255: J1 Monitor Bytes (RO) ......................................................................... 90

Table 79. Page 1 - Registers 128--133: STS-1/AU-3 B1 BIP Error Counters (RO) ........................................... 90

Table 80. Page 1 - Registers 134--140: STS-1/AU-3 B2 BIP Error Counters (RO) ........................................... 91

Table 81. Page 1 - Registers 141--142: STS-3/STM-1 (AU-4) B1 Error Count (RO) ......................................... 91

Table 82. Page 1 - Registers 143--145: STS-3/STM-1 (AU-4) B2 Error Count (RO) ......................................... 91

Table 83. Page 1 - Registers 146--151: STS-3/STM-1 (AU-4) B3 Error Count (RO) ......................................... 92

Table 84. Page 1 - Registers 152--163: STS-3/STM-1 (AU-4) Pointer Increment/Decrement Counter (RO) .... 92

Table 85. Page 1 - Registers 164--166: Receive High-Speed SFEBE Count (RO) ........................................... 92

Table 86. Page 1 - Registers 167--172: Receive High-Speed Path FEBE Count (RO) ..................................... 93

Table 87. Page 2 - Register 131 (R/W) ............................................................................................................... 93

Table 88. Page 2 - Registers 128--141 (R/W) .................................................................................................... 94

Table 89. Page 2 - Register 145 (R/W) ............................................................................................................... 97

Table 90. Page 2 - Registers 142--155 (R/W) .................................................................................................... 97

Table 91. Microprocessor Interface I/O Timing Specifications .......................................................................... 101

Table 92. Recommended Operating Conditions ............................................................................................... 107

Table 93. Power Measurements (VDD = 3.3 V, 23 ◊C) .................................................................................... 107

Table 94. Logic Interface Characteristics .......................................................................................................... 108

Table 95. LVDS Interface Characteristics ......................................................................................................... 109

Table 96. Input Clock Specifications ................................................................................................................. 110

Table 97. Input Timing Specifications ................................................................................................................ 111

Table 98. Output Clock Specifications ............................................................................................................... 113

Table 99. Output Timing Specifications ............................................................................................................. 114

Agere Systems Inc.

7

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Description

(continued)

Automatic receive monitoring functions can be config-

ured to provide an interrupt to the control system, or

the device can be operated in a polled mode.

Built-in loopback at both the STS-1/AU-3 and STS-3/

STM-1 (AU-4) interfaces provides maximum flexibility

for use in a number of SONET/SDH products including

path termination multiplexers, add/drop multiplexers,

and digital cross connects.

A high-speed microprocessor interface and full user

programmability on STS-1/AU-3 to STS-3/STM-1 (AU-

4) slot insertion and drop provide maximum flexibility

for I/O configuration.

Nomenclature Assumptions

Throughout this document, certain assumptions are

made about nomenclature. The transmission path that

outputs the STS-3/STM-1 (AU-4) signal is called the

transmit direction, while the transmission path that

receives the STS-3/STM-1 (AU-4) signal is referred to

as the receive path. The low-speed (LS) side of the

device transmits or receives the STS-1/AU-3 signals,

while the high-speed (HS) side of the device transmits

or receives the STS-3/STM-1 (AU-4) signal.

The LSB (least significant bit) of a byte is labeled 0 and

the MSB (most significant bit) is labeled N ≠ 1, where N

is the total number of bits in the word. A signal that

ends in [3--1][7:0] implies there are three separate sig-

nals, each containing 8 bits.

A control bit that has only one function causes that

function to be active when the control bit is set to a

logic 1. For example, setting RLSCLKINV, 0x57 to a

logic 1 causes the low-speed output clock to be

inverted. A control bit with two names performs the first

choice when set to a logic 0 and the second choice

when set to a logic 1. For example, TSONET_SDH,

0x34 when set to a logic 0 puts the transmit direction in

the SONET mode and when set to a logic 1 puts the

transmit direction in SDH mode.

Where necessary to avoid confusion, numbers may be

expressed using a format to specify their base. The fol-

lowing are examples:

I

9\D = 9 decimal.

I

0x04 = 04 hexadecimal.

I

11\B = 11 binary.

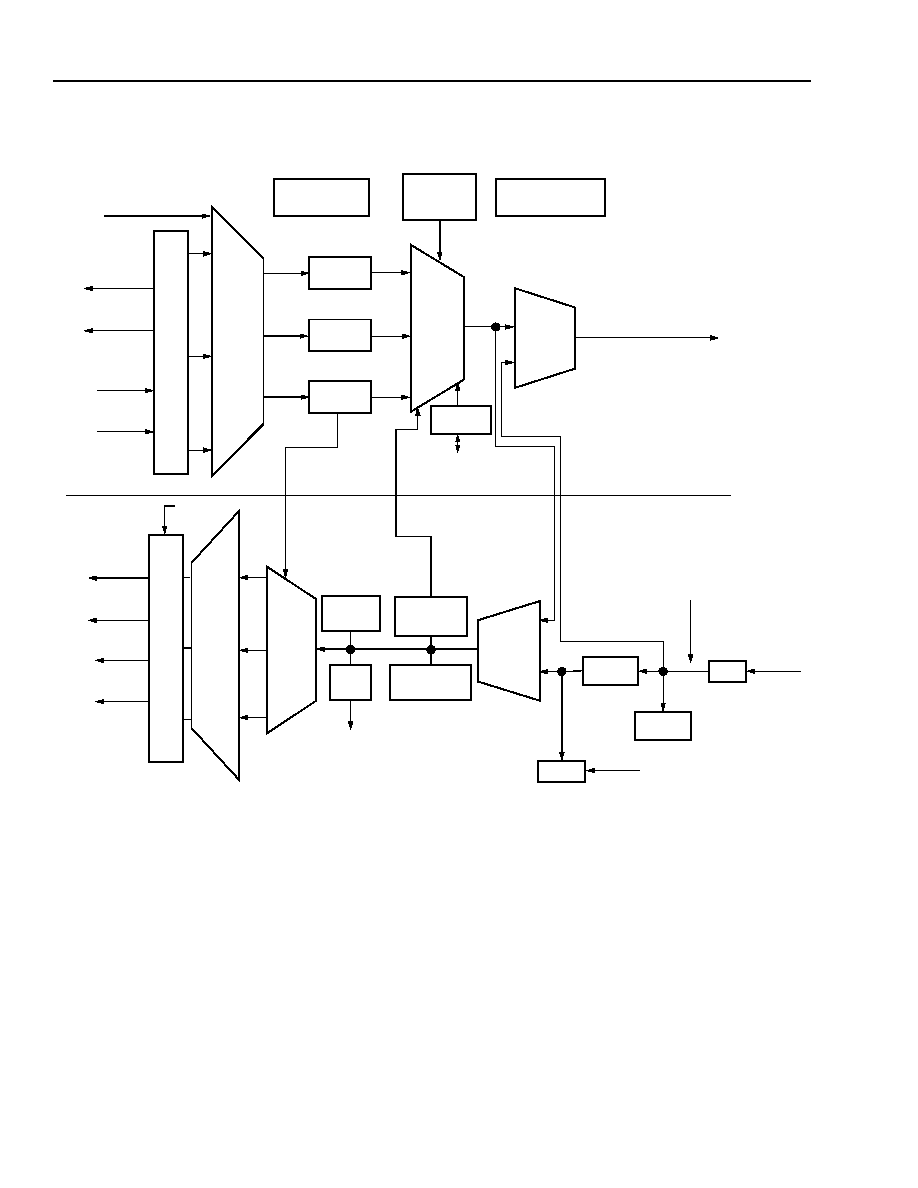

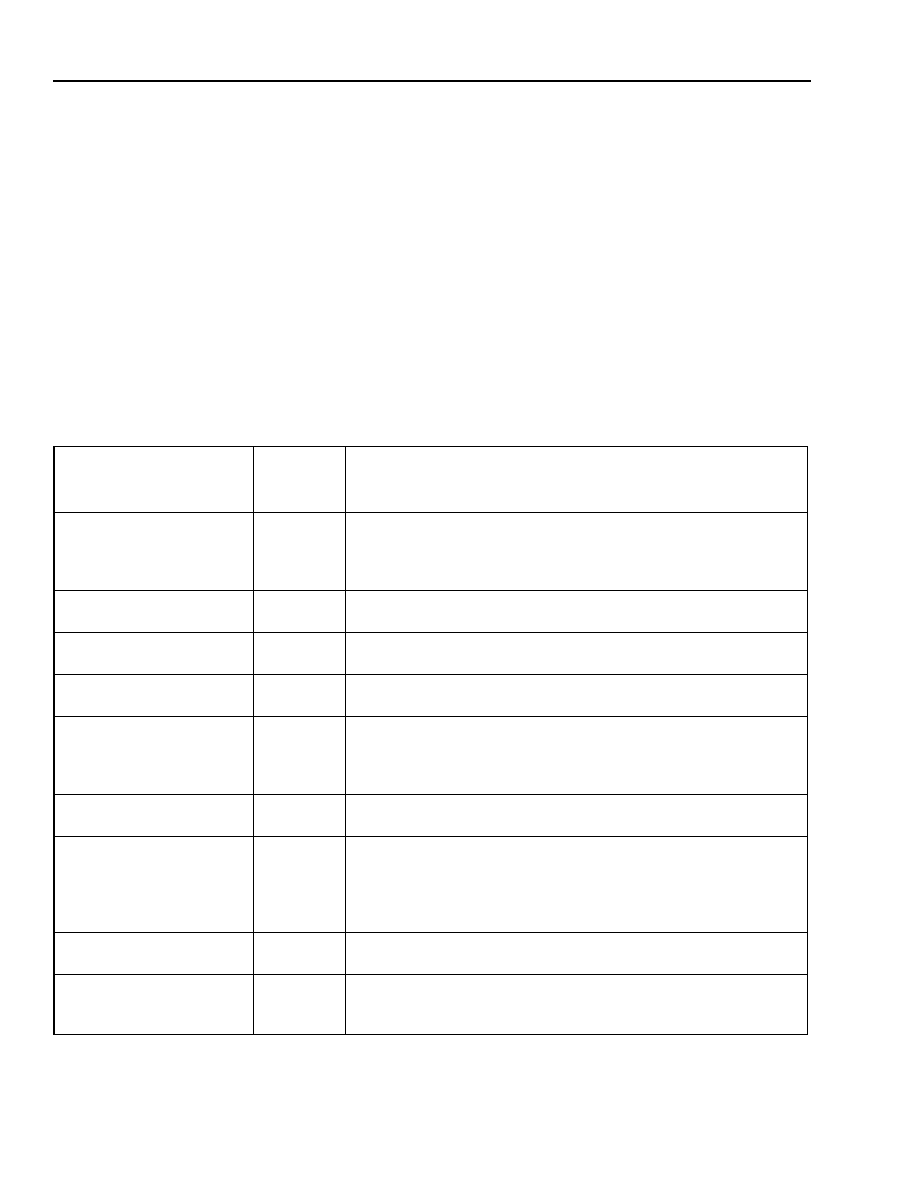

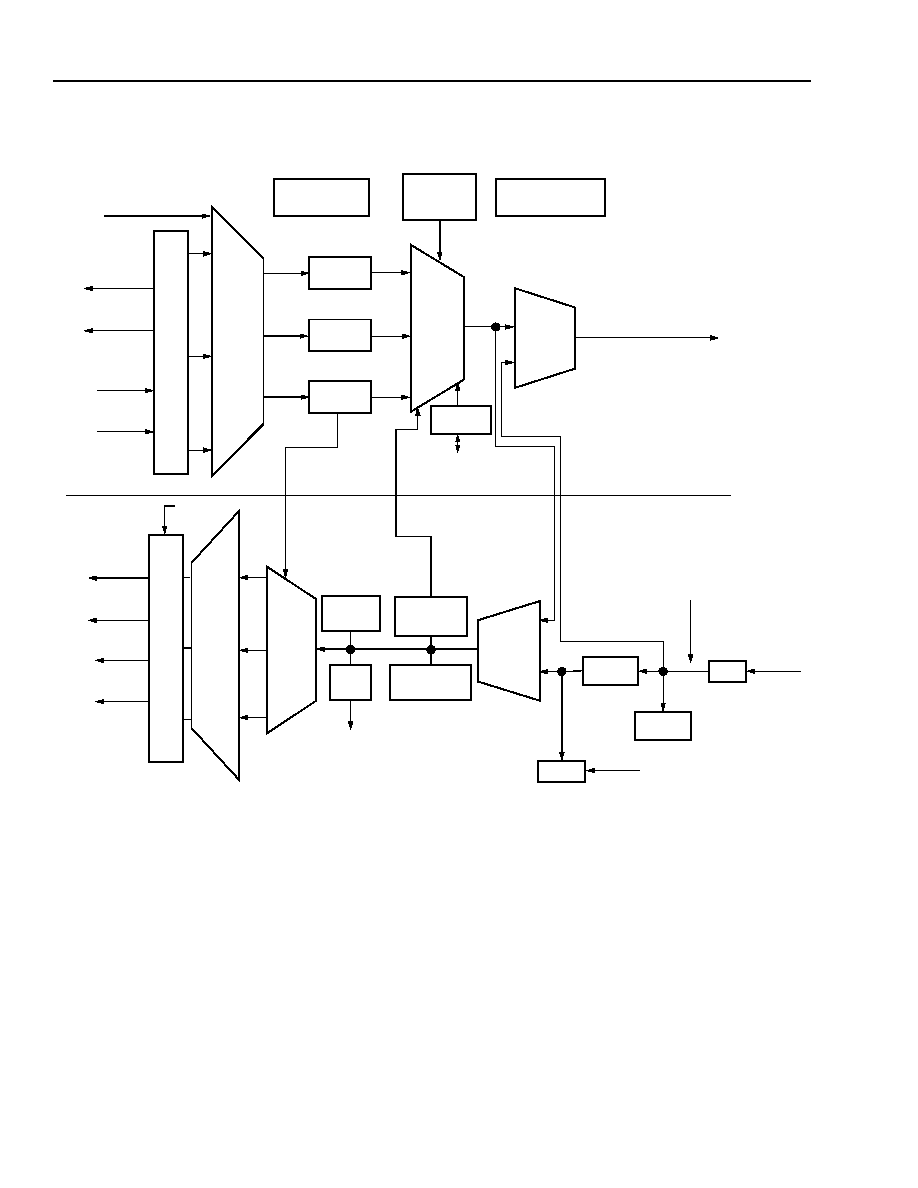

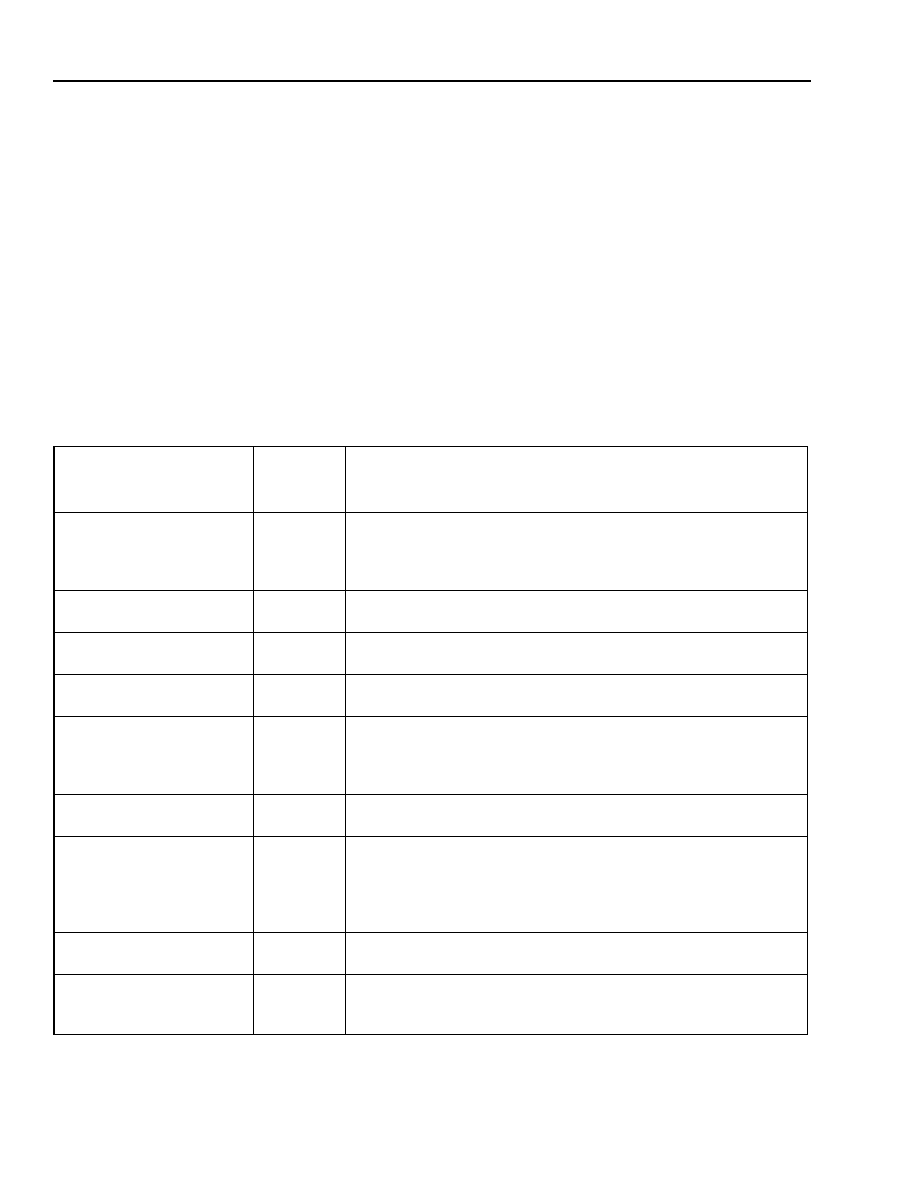

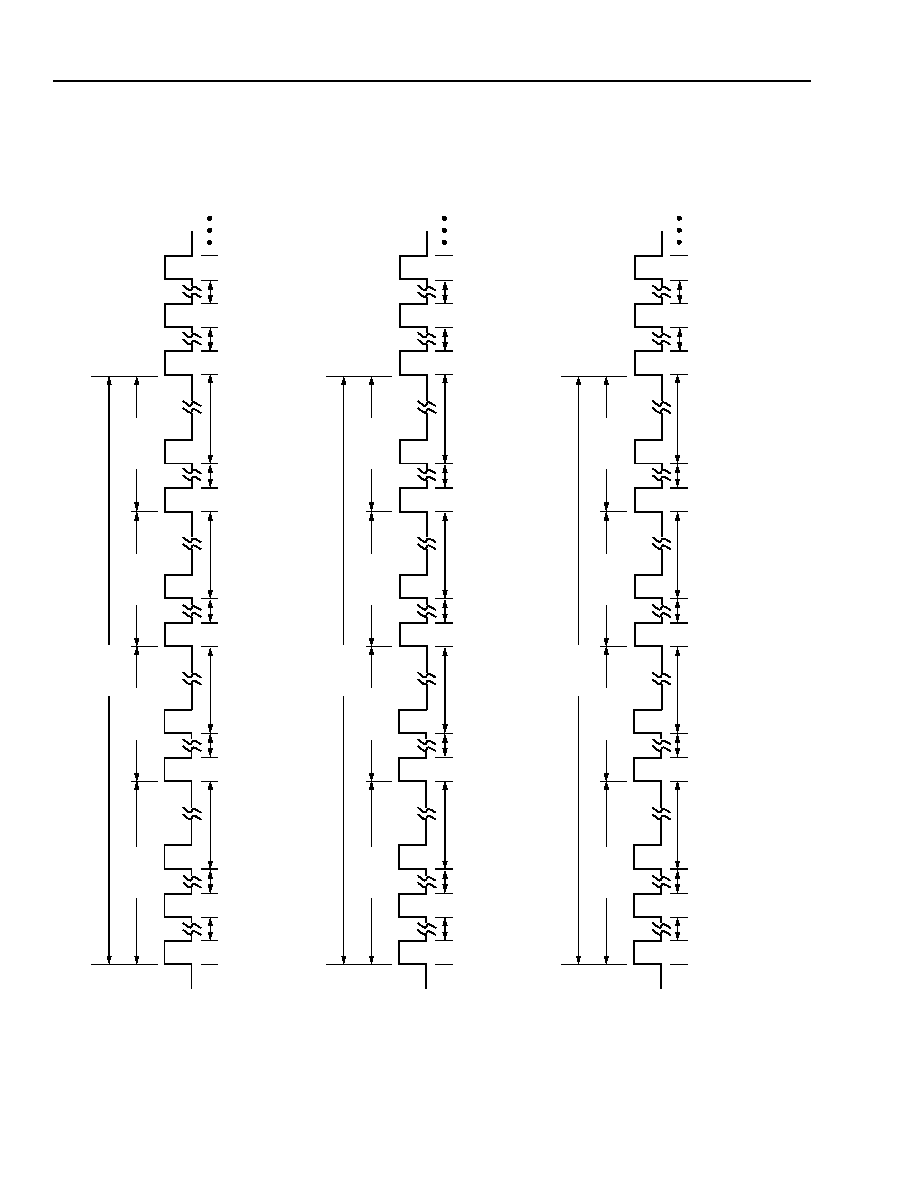

Block Diagram

In the transmit direction, the device outputs a clock and

sync and accepts bused data [7:0] and a parity signal

from up to three devices. The device outputs one data

bundle at the STS-3/STM-1 (AU-4) rate (clock, sync,

data [7:0], and parity bit). A local clock and optional

frame sync signal are needed for operation of the

device. A transport overhead access channel (TOAC)

is provided to allow overwriting of the transport over-

head bytes in the output STS-3/STM-1 (AU-4) frame.

In the receive direction, the device accepts one STS-3/

STM-1 (AU-4) bundle (clock, data, parity). Optional

clock and data recovery is available on the STS-3/

STM-1 (AU-4) receive input. The device also accepts a

loss-of-signal indication from an external source. The

device outputs three STS-1/AU-3 signals over a bus

interface (clock, data, J0 time, parity). The STS-3/STM-

1 (AU-4) input clock is used to clock this direction. A

transport overhead access channel is provided for

additional external monitoring of the incoming transport

overhead of the STS-3/STM-1 (AU-4) frame. A pointer

interpreter is provided to monitor path functions.

The device also has loopback capabilities at the STS-

1/AU-3 and STS-3/STM-1 (AU-4) interfaces. In addi-

tion, the device supports STS-1 termination. An 8-bit

microprocessor interface, JTAG control logic, and in-

circuit test capabilities are also provided.

8

Agere Systems Inc.

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Block Diagram

(continued)

5-5294(F).ar.8

Figure 1. TMUX03155 Block Diagram

TOAC

DROP

3:1

MUX

LOGIC

SPE

GENERATE

1:3

DEMUX

LOGIC

LOOPBACK

SELECT

LOGIC

TRANSPORT

OVERHEAD

LOSS OF

CLOCK

BER

MONITOR

#1R

#2R

#3R

#1T, #2T, #3T

#1R, #2R, #3R

SELECT/

LOGIC

MULTI-

CAST

OVERHEAD

MONITOR

TOAC

INSERT

MICROPROCESSOR

LOCAL CLOCK

GENERATION

TRANSMIT DIRECTION

RECEIVE DIRECTION

S#1T

S#2T

S#3T

TLSCLKO

#1T

#2T

#3T

OVERHEAD

MONITOR

INTERFACE

OVERHEAD

MONITOR

BU

S

CO

N

T

RO

L

DROP

SELECT/

LOGIC

LOOPBACK

SELECT

LOGIC

ADD

TLSSPEO,

TLSPARI

TLSDATA[7:0]I

RLSCLKO

BU

S

CO

N

T

RO

L

RLSJ0TIMEO

RLSPARO

RLSDATA[7:0]O

TTOACCLKO (5.184 MH

Z

),

POINTER

INTERPRETER

AND PATH

MONITORS

LOS

FRAMER

RHSLOSEXTI

TTOACSYNCO (8 kH

Z

),

TTOACDATAI (5.184 Mbits/s)

TLSV1TIMEO

(19.44 MHz)

(19.44 MHz)

RTOACCLKO (5.184 MH

Z

),

RTOACSYNCO (8 kH

Z

),

RTOACDATAO (5.184 Mbits/s)

THSSCLKOT/C (155.52 MH

Z

),

THSSSYNCOT/C (8 kH

Z

),

THSSDATAOT/C (155.52 Mbits/s)

OR

RHSSCLKIT/C (155.52 MH

Z

)

RHSSDATAIT/C (155.52 Mbits/s)

OR

MULTI-

CAST

TLSC1J1V1TIMEO,

THSCLKO (38.88 MHz OR 19.44 MHz),

THSSYNCO (8 kH

Z

),

THSDATA[7:0]O (38.88 Mbits/s OR 19.44 Mbits/s),

RHSCLKI (38.88 MHz OR 19.44 MHz),

RHSDATA[7:0]I (38.88 Mbits/s OR 19.44 Mbits/s),

THSPARO (38.88 Mbits/s OR 19.44 Mbits/s)

RHSPARI (38.88 Mbits/s OR 19.44 Mbits/s)

CDR

Agere Systems Inc.

9

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

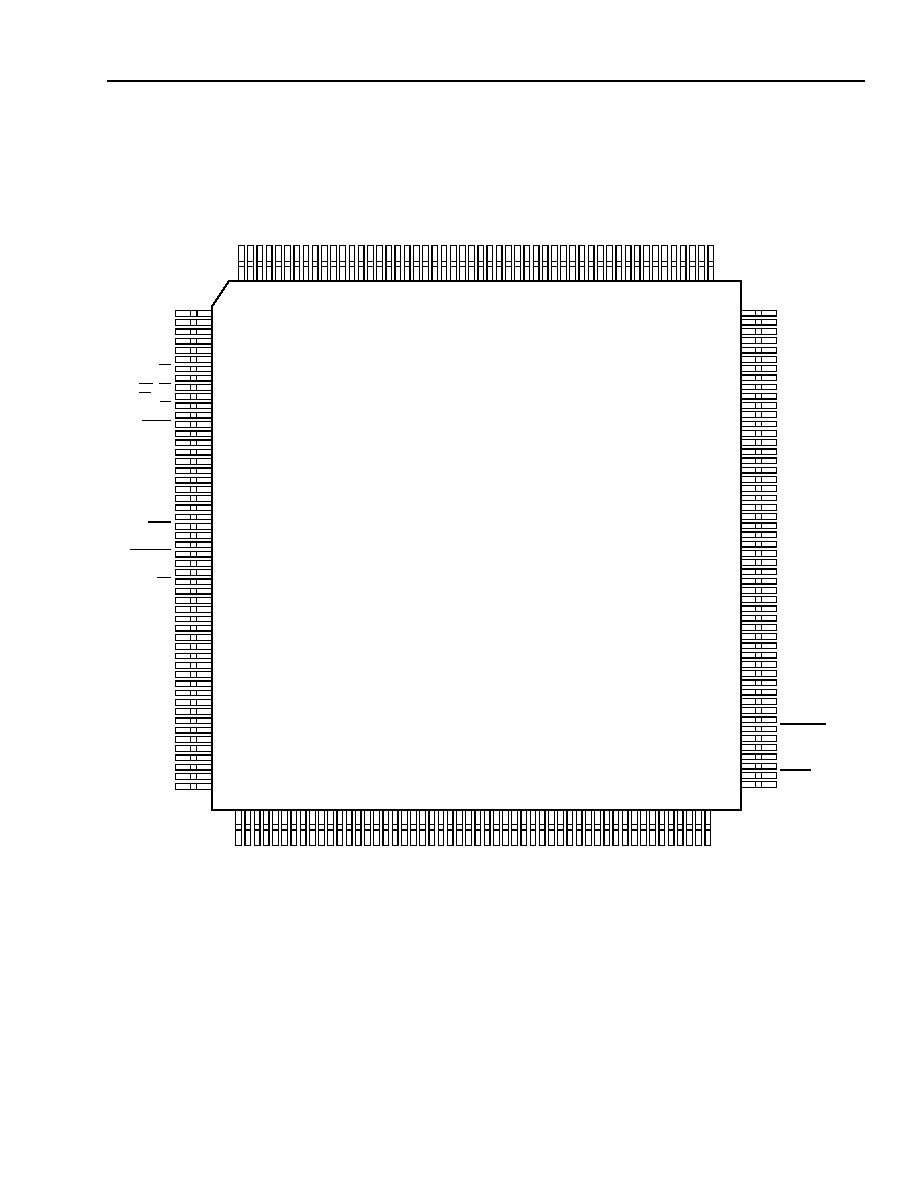

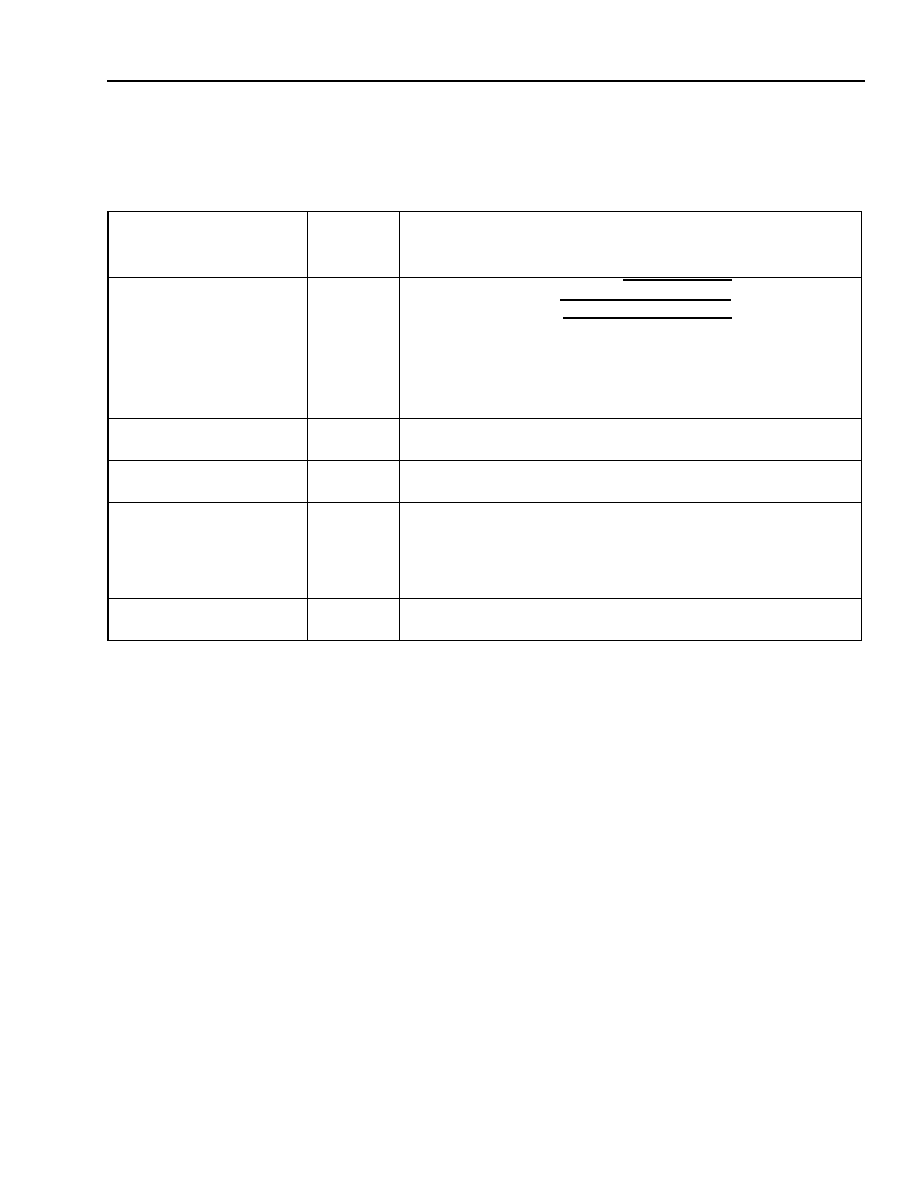

Pin Information

5-4873(F)

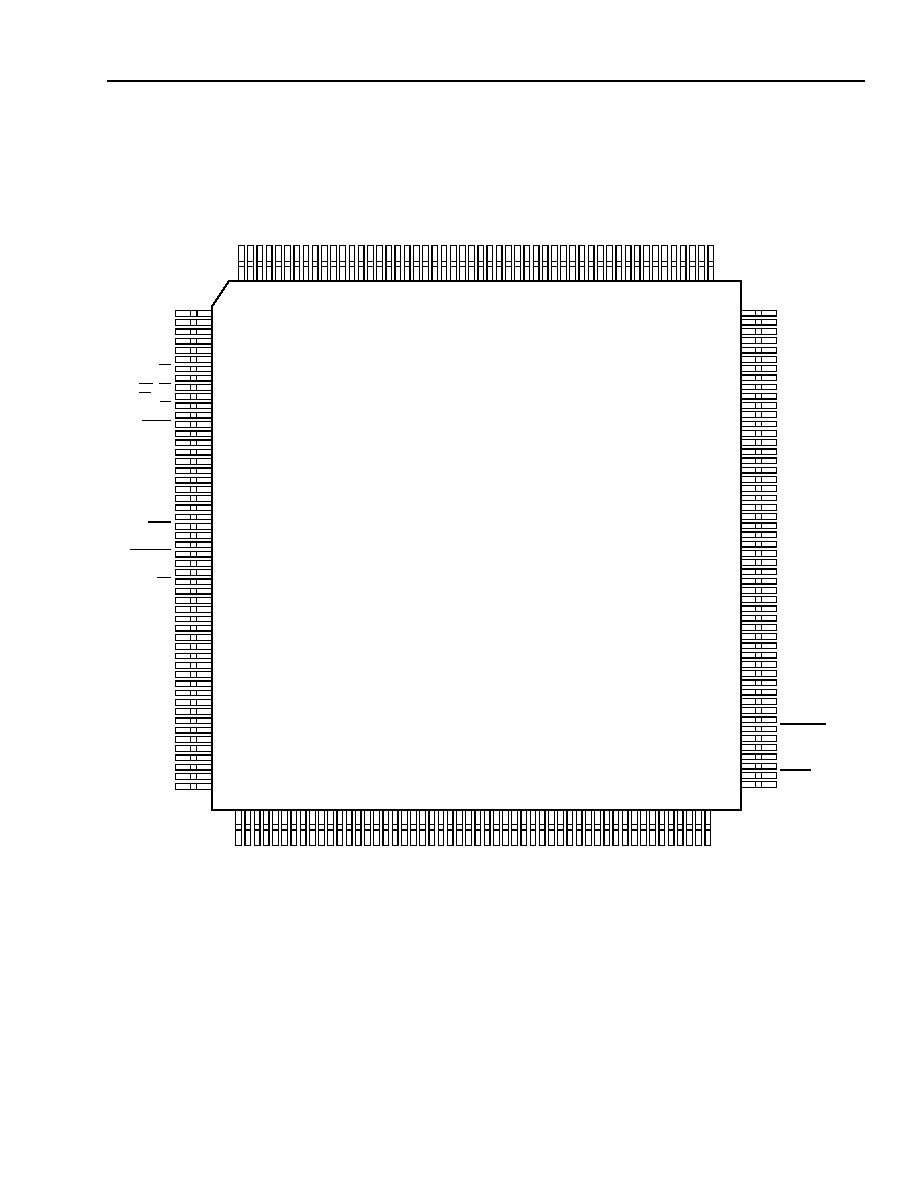

Figure 2. Pinout of 208 SQFP Device

The pin descriptions for the 208 SQFP package follow in Table 1 on page 10.

NC

VSS

MODE0

MODE1

VDD

REF5VTOL

THSJ0J1V1I

VSS

THSCLKI

VDD

LVDS_REFSEL

CTAP_THSSCLKI

VDD

THSSCLKIT

THSSCLKIC

CTAP_THSSJ0J1V1I

THSSJ0J1V1IT

THSSJ0J1V1IC

VDD

THSSCLKOT

THSSCLKOC

VSS

THSSSYNCOT

THSSSYNCOC

THSSDATAOT

THSSDATAOC

VDD

LVDS_REF10

LVDS_REF14

LVDS_RESHI

LVDS_RESLO

VSS

RHSSCLKIT

RHSSCLKIC

CTAP_RHSSCLKI

VDD

VSS

RHSSDATAIT

RHSSDATAIC

CTAP_RHSSDATAI

VDD

VSS

CDR_TSTMUXO

RCDR10K2GND

NC

RSTN_TST

THSCLKO

THSSYNCO

NC

NC

RESET

VSS

VSS

VSS

AD5

AD6

AD7

NC

CS

INT

WR_DS

RD_RW

ALE_AS

VDD

RDY_DTACK

MPMUX

MPMODE

MPMODE3ALE

VDD

NC

NC

TCLK

VSS

TDI

TMS

TRST

TDO

VDD

SCAN_EN

TEST_MODE

NC

ICT

VSS

REF5VTOL

NC

NC

NC

VDD

TTOACCLKO

TTOACSYNCO

TTOACDATAI

VDD

RTOACCLKO

RTOACSYNCO

RTOACDATAO

VDD

NC

NC

NC

NC

RHSLOSEXTI

RHSCLKI

VSS

NC

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

VS

S

VS

S

RHSP

A

RI

RHSDA

T

A

7

I

RHSDA

T

A

6

I

RHSDA

T

A

5

I

RHSDA

T

A

4

I

RHSDA

T

A

3

I

RHSDA

T

A

2

I

RHSDA

T

A

1

I

RHSDA

T

A

0

I

NC

VD

D

NC NC NC NC NC NC NC

VD

D

VS

S

NC NC NC NC

VS

S

VD

D

NC NC NC

VS

S

VD

D

NC NC NC NC NC NC NC

VD

D

T

H

SDA

T

A0

O

T

H

SDA

T

A1

O

T

H

SDA

T

A2

O

T

H

SDA

T

A3

O

T

H

SDA

T

A4

O

T

H

SDA

T

A5

O

T

H

SDA

T

A6

O

T

H

SDA

T

A7

O

T

H

SP

ARO VS

S

NC

53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104

NC VS

S

AD

4

AD

3

AD

2

AD

1

AD

0

A7 A6 A5 A4 A3 VD

D

A2 A1 A0 RL

SP

ARO

RE

SER

V

E

D

RL

SDA

T

A0

O

RL

SDA

T

A1

O

RL

SDA

T

A2

O

VS

S

RL

SDA

T

A3

O

RL

SDA

T

A4

O

RL

SDA

T

A5

O

RL

SDA

T

A6

O

VS

S

RL

SDA

T

A7

O

VD

D

RL

SCL

K

O

NC VS

S

RL

SJ0

T

IM

E

O

NC T

L

S

SPE

O

TL

SV

1

T

I

M

E

0

TL

SC

L

K

O

T

L

S

J

0

J

1V

1T

I

M

E

O

TL

SD

A

T

A7

I

TL

SD

A

T

A6

I

VD

D

TL

SD

A

T

A5

I

TL

SD

A

T

A4

I

TL

SD

A

T

A3

I

TL

SD

A

T

A2

I

TL

SD

A

T

A1

I

TL

SD

A

T

A0

I

TL

SP

AR

I

NC NC VS

S

VS

S

208 207 206 205 204 203 202 201 200 199 198 197 196 195 194 193 192 191 190 189 188 187 186 185 184 183 182 181 180 179 178 177 176 175 174 173 172 171 170 169 168 167 166 165 164 163 162 161 160 159 158 157

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

10

10

Agere Systems Inc.

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Pin Information

(continued)

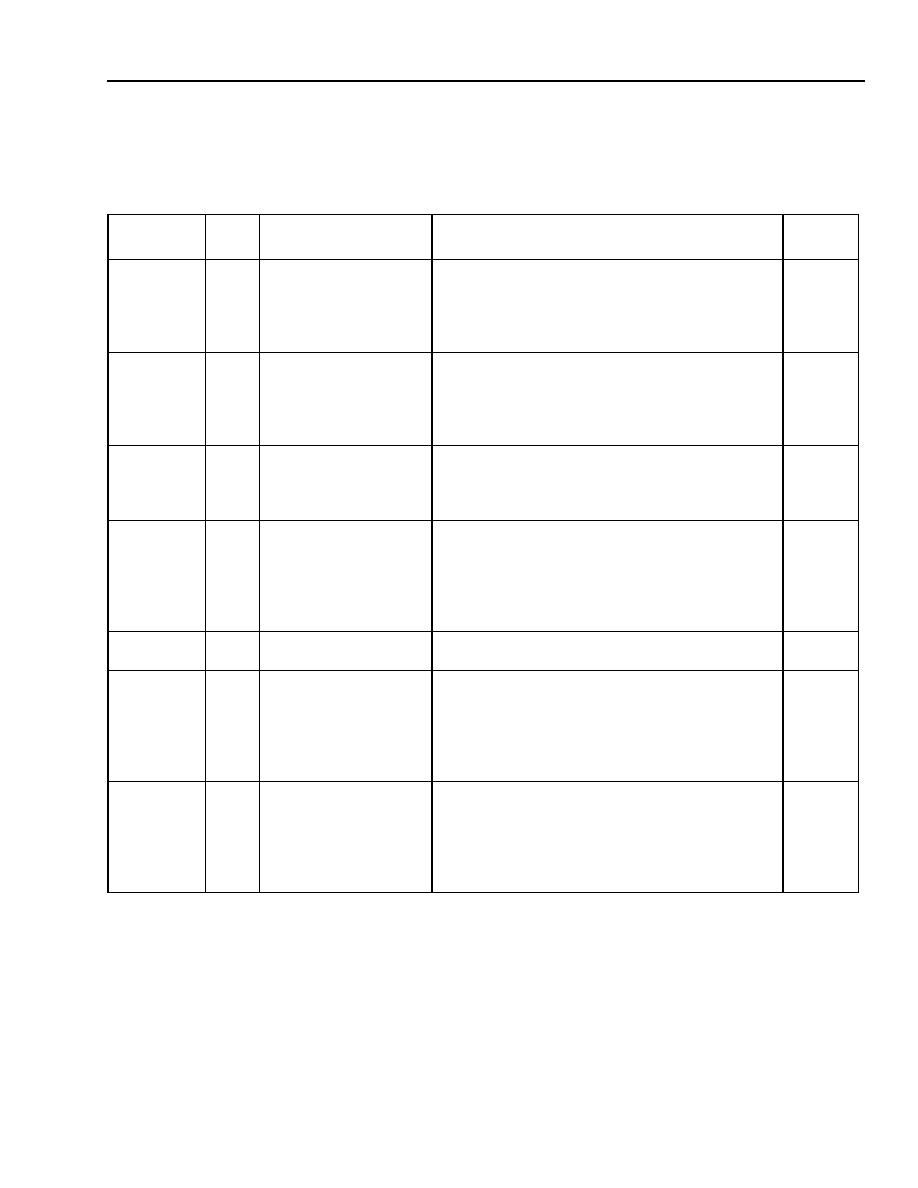

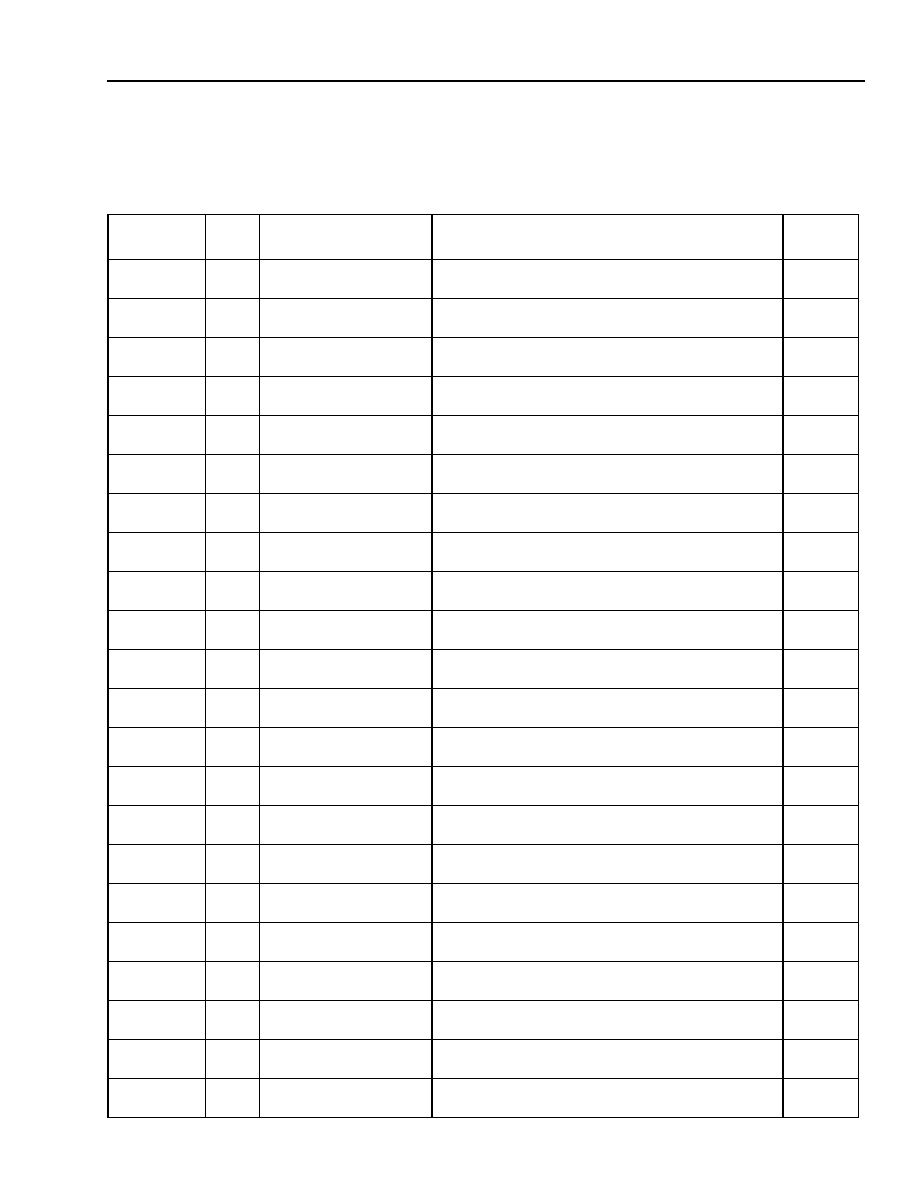

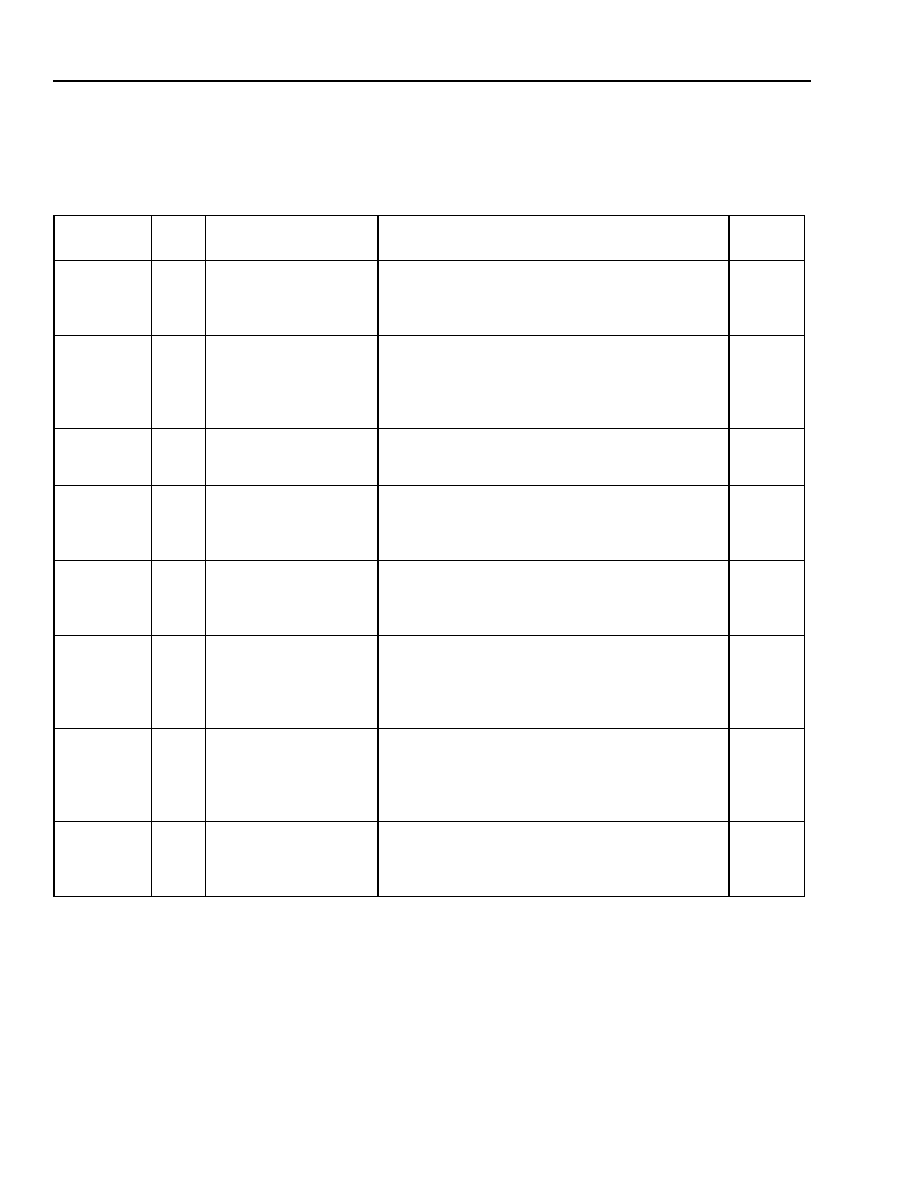

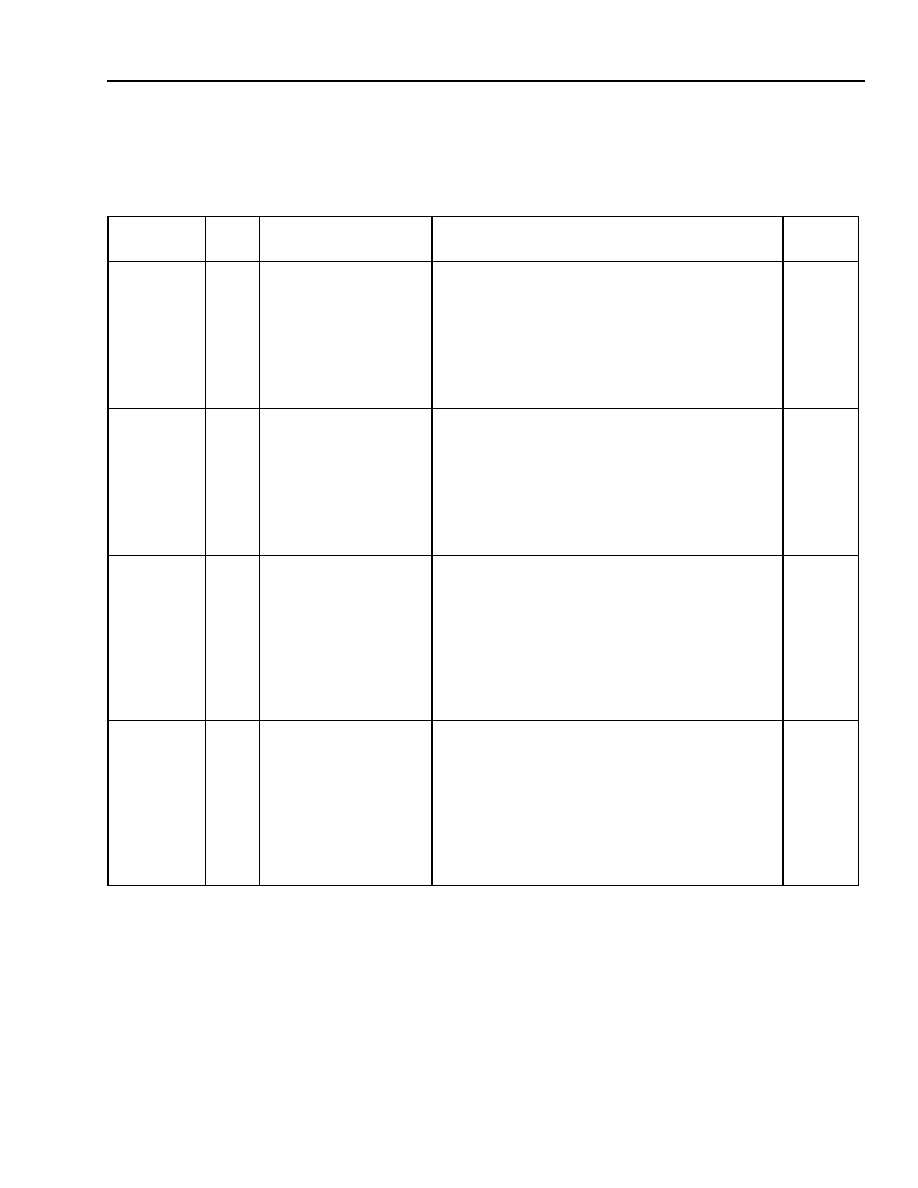

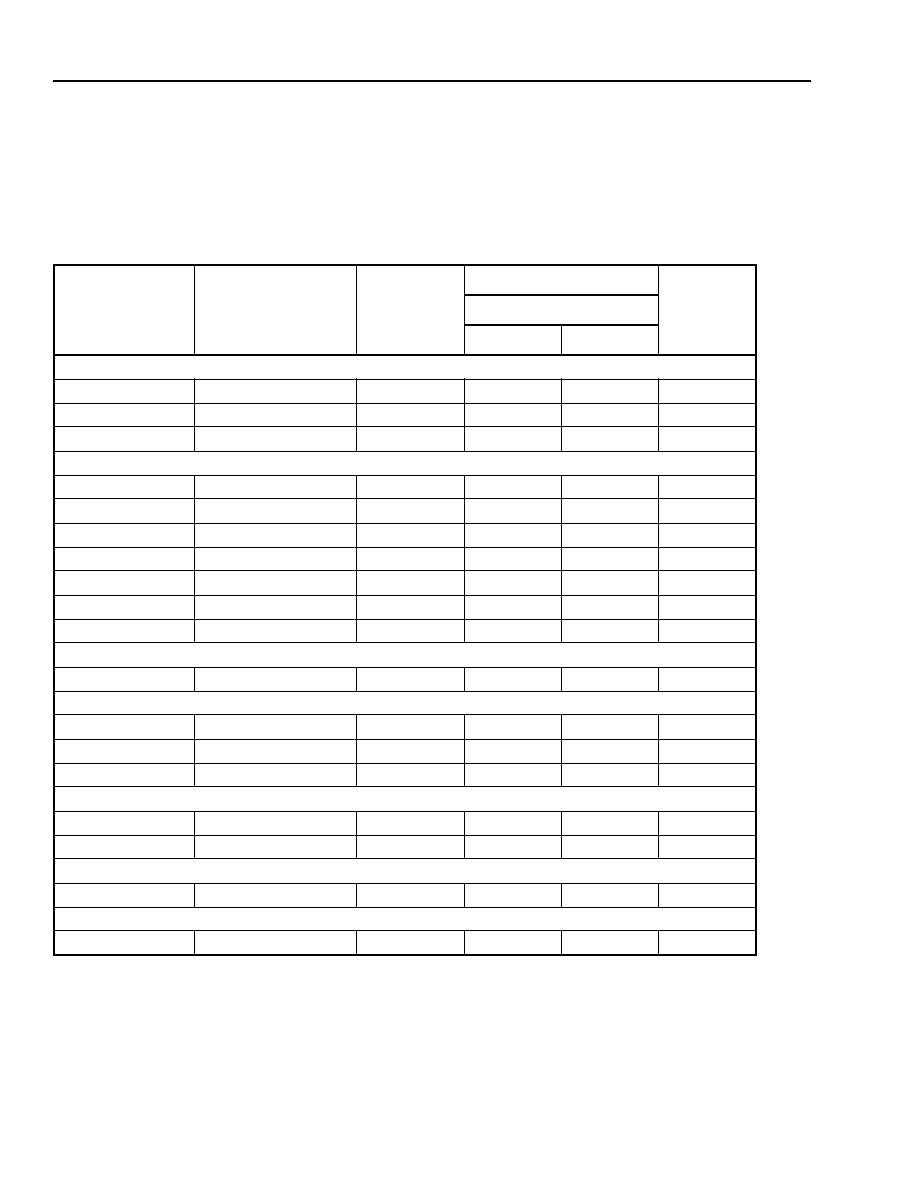

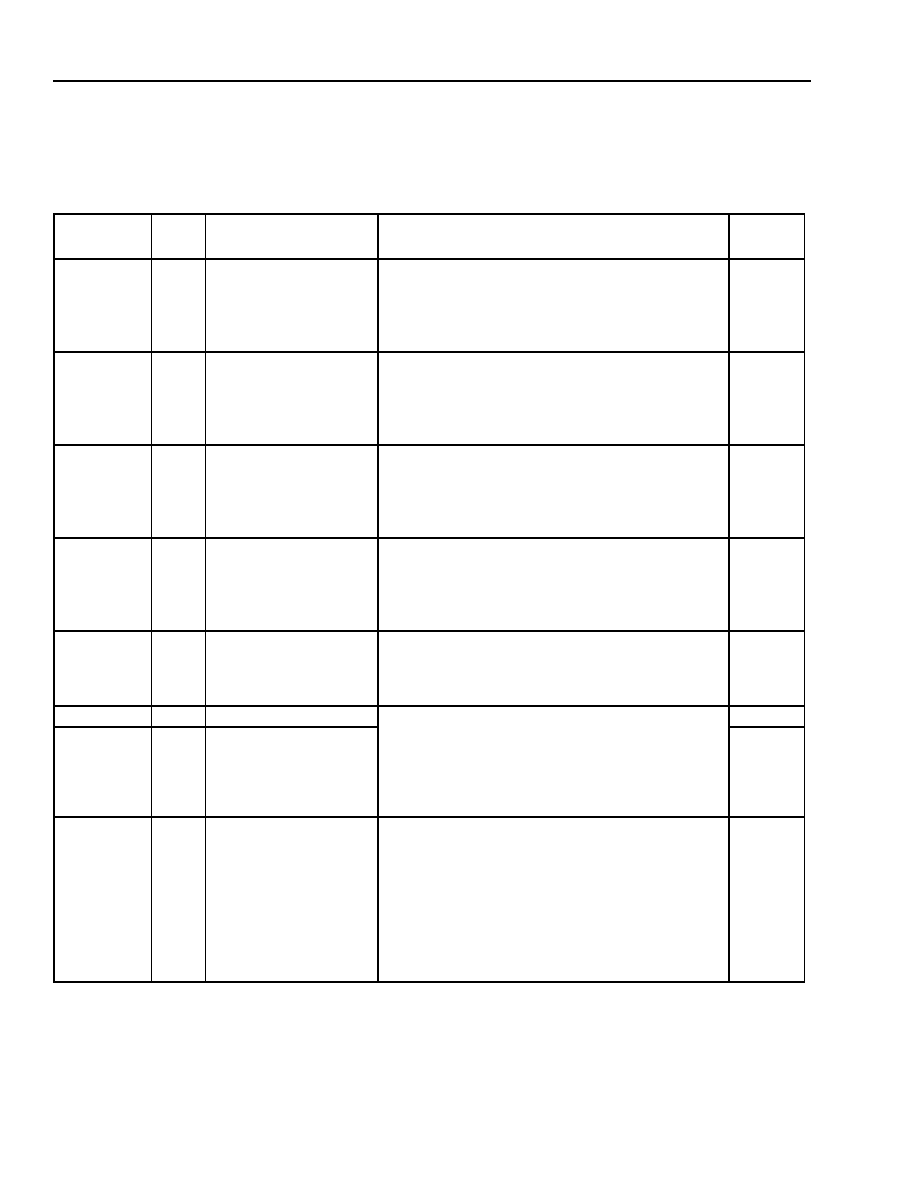

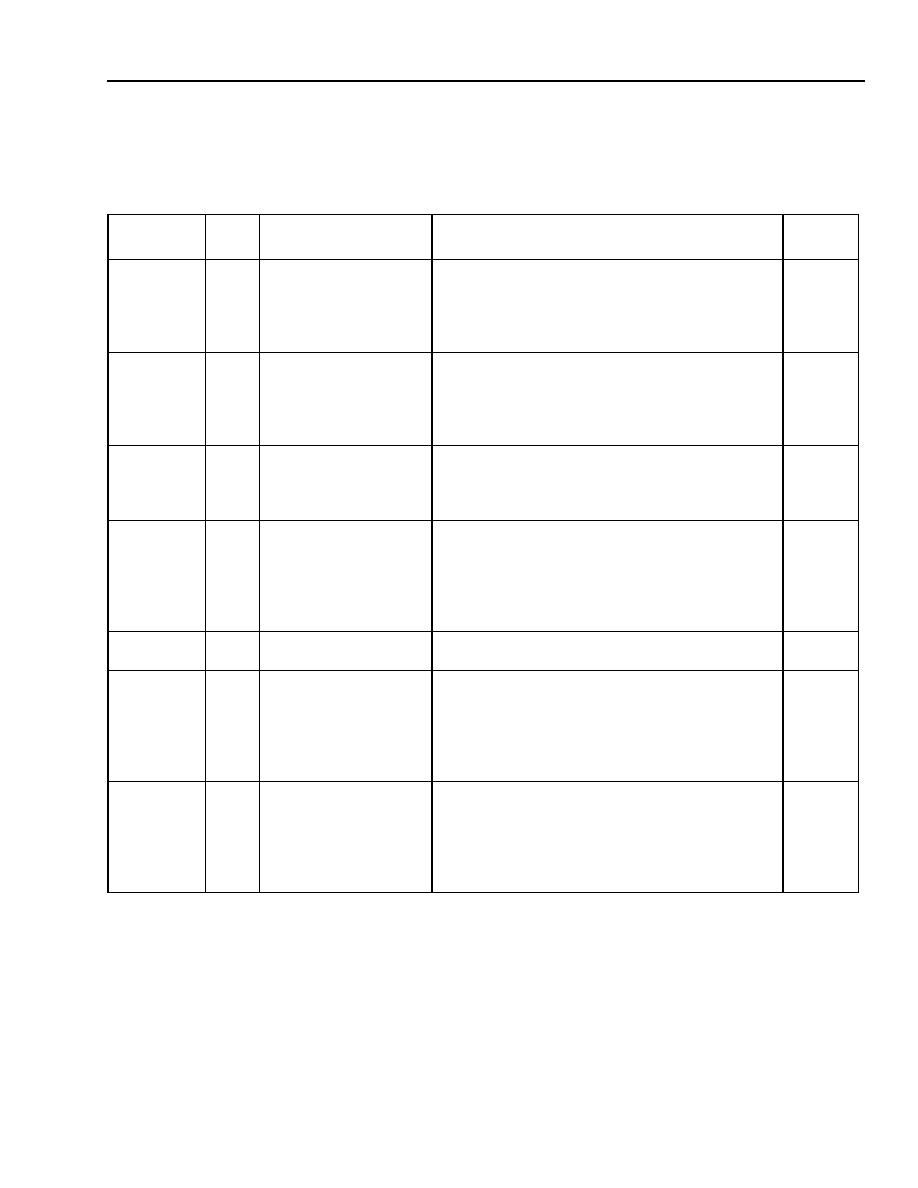

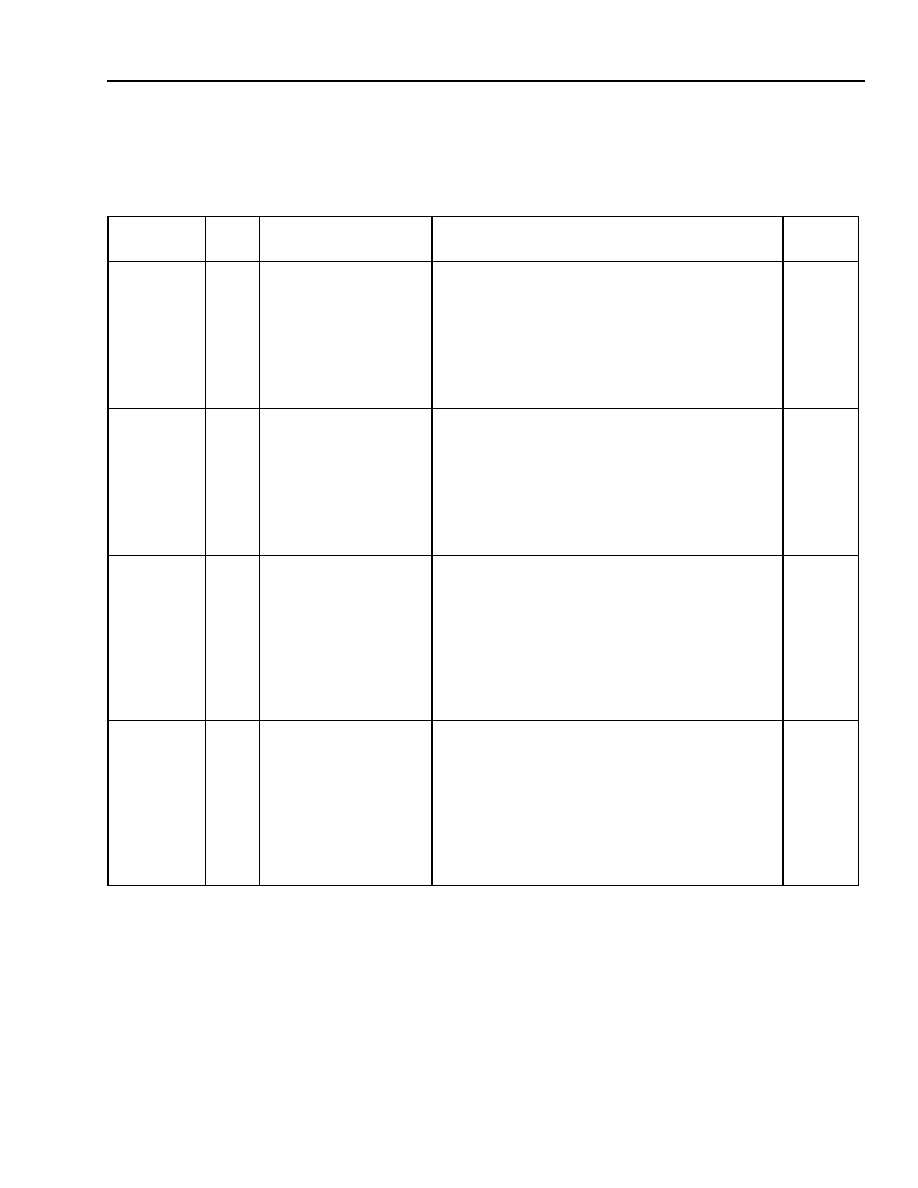

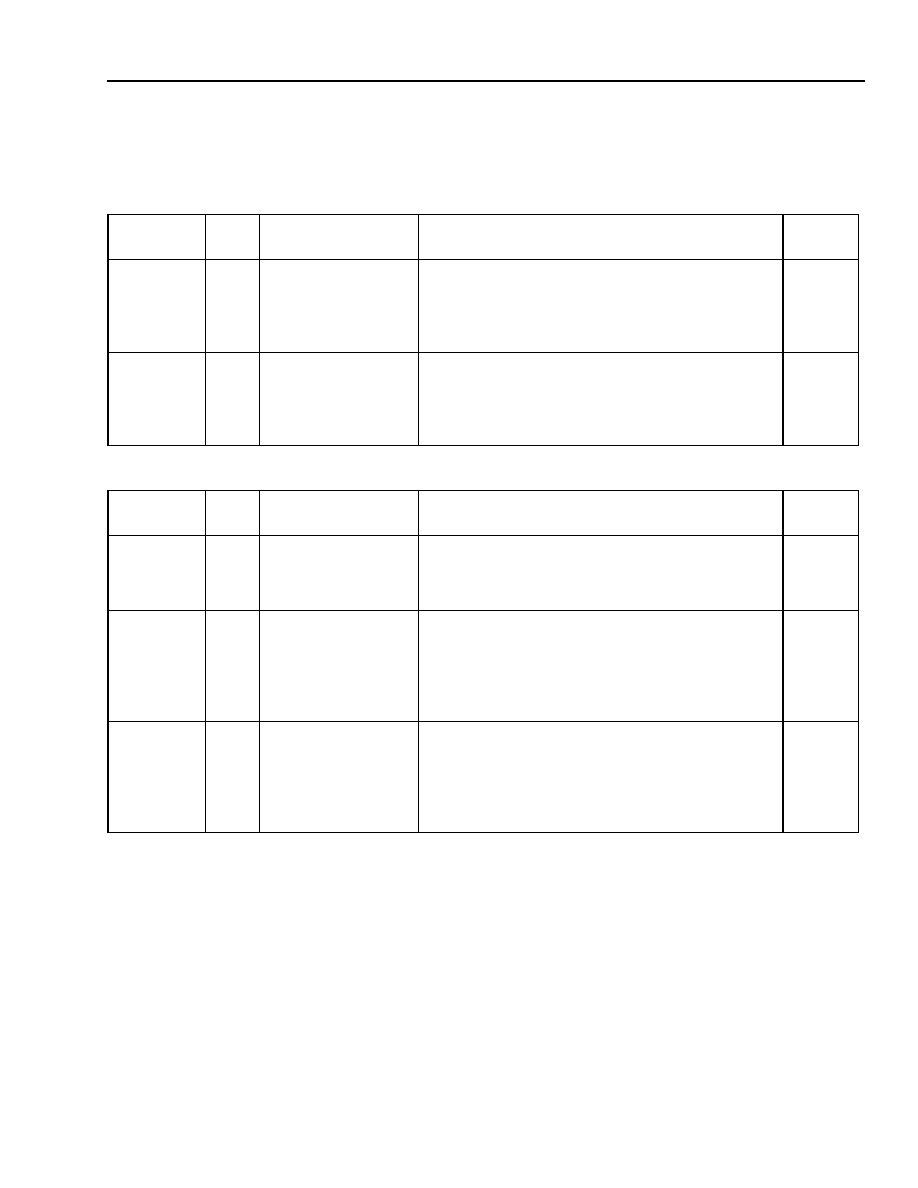

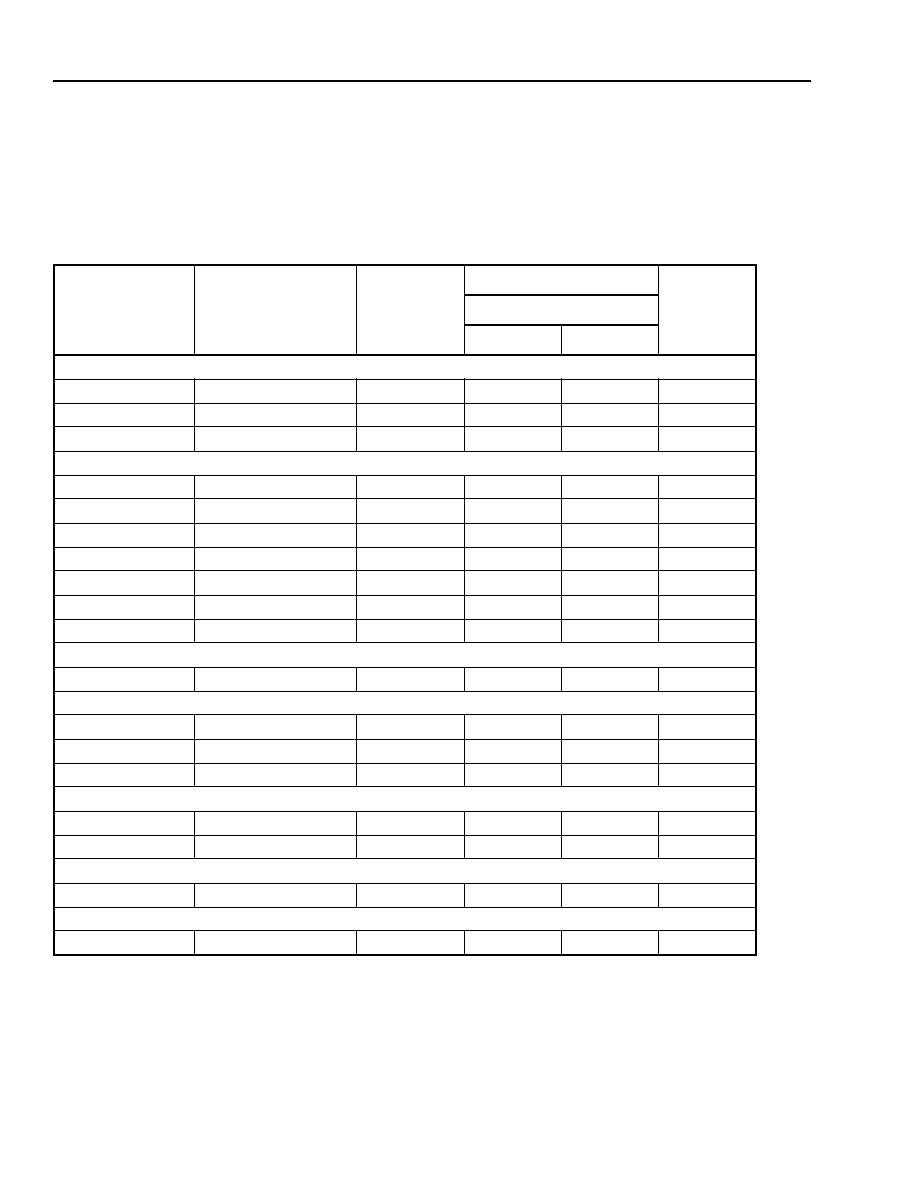

Table 1. Pin Descriptions for the 208-Pin SQFP Package

* Pin order follows symbol order, e.g., pin 170 refers to TLSDATA7I.

I = input, O = output, I/O = bidirectional signal, I

d

= input with internal pull-down (~20 kW), I

u

= input with internal pull-up (~100 kW), I

diff

or

O

diff

= differential input or output. All I/O not explicitly stated with a buffer type are 5 V compatible. They will tolerate 5 V at their inputs or out-

puts. LVDS = low-voltage differential signal.

Pin*

Symbol

Type

Name/Description

Transmit Direction Signals

143, 142

THSSCLKIT/C

I

diff

LVDS

Transmit High-Speed Serial Clock Input. The transmit clock can

either be 155.52 MHz (serial), 38.88 MHz (nibble), or 19.44 MHz

(byte).

145

CTAP_THSSCLKI

I

Center Tap for Transmit High-Speed Serial Clock Input. The cen-

ter tap input provides for center-tapped common-mode termination.

This input should be terminated through an external capacitor to

ground (approximately 0.1 µF).

140, 139

THSSJ0J1V1IT/C

I

diff

LVDS

Transmit High-Speed Serial Sync Input. The transmit sync signal

is active during J0 time (8 kHz), J11 time, and V11 time (2 kHz). This

signal is active-high and is optional. (See Figure 16 on page 112 for

details.)

141

CTAP_THSSJ0J1V1I

I

Center Tap for Transmit High-Speed Serial Sync Input. The cen-

ter tap input provides for center-tapped common-mode termination.

This input should be terminated through an external capacitor to

ground (approximately 0.1 µF).

148

THSCLKI

I

d

Transmit High-Speed Clock Input. The transmit clock can either be

38.88 MHz (nibble) or 19.44 MHz (byte).

150

THSJ0J1V1I

I

d

Transmit High-Speed Sync Input. The transmit sync signal is active

during J0 time (8 kHz), J11 time, and V11 time (2 kHz). This signal is

active-high and is optional.

172

TLSCLKO

O

Transmit Low-Speed Output Clock. The STS-1/AU-3 clock will be

19.44 MHz.

174

TLSSPEO

O

Transmit Low-Speed Synchronous Payload Envelope (SPE). The

STS-1/AU-3 SPE signal is low when the transport overhead is on the

input bus (TLSDATA[7:0]I). (See Figure 18 on page 116 for details.)

171

TLSJ0J1V1TIMEO

O

Transmit Low-Speed J0, J1, and V1 Time Signal. J0 time is

defined when TLSSPEO is a logic 0, TLSJ0J1V1TIMEO is a logic 1,

TLSV1TIMEO is a logic 0, and the J0 byte is on the input bus. J1 time

is defined when TLSSPEO is a logic 1, TLSJ0J1V1TIMEO is a logic

1, TLSV1TIMEO is a logic 0, and J11 is on the input bus. (See Figure

18 on page 116 for details.)

173

TLSV1TIMEO

O

Transmit Low-Speed V1 Time. This signal is active-high when the

current frame contains the V1 byte. V1 time is defined when

TLSSPEO is a logic 1, TLSJ0J1V1TIMEO is a logic 1, and

TLSV1TIMEO is a logic 1. (See Figure 18 on page 116 for details.)

170, 169,

167--162

TLSDATA[7:0]I

I

d

Transmit Low-Speed Data. TLSDATA7I is the most significant bit of

the input byte. (See Figure 18 on page 116 for details.)

Agere Systems Inc.

11

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Pin Information

(continued)

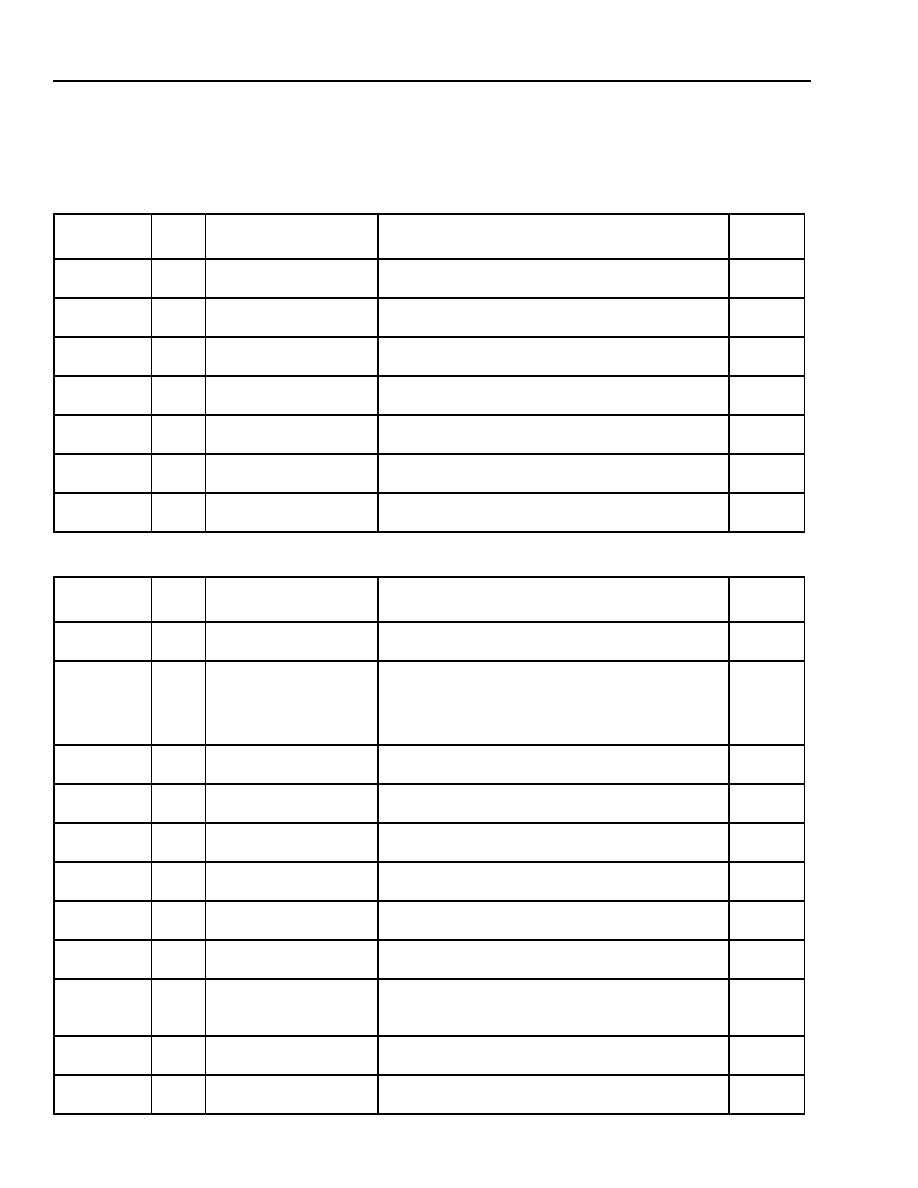

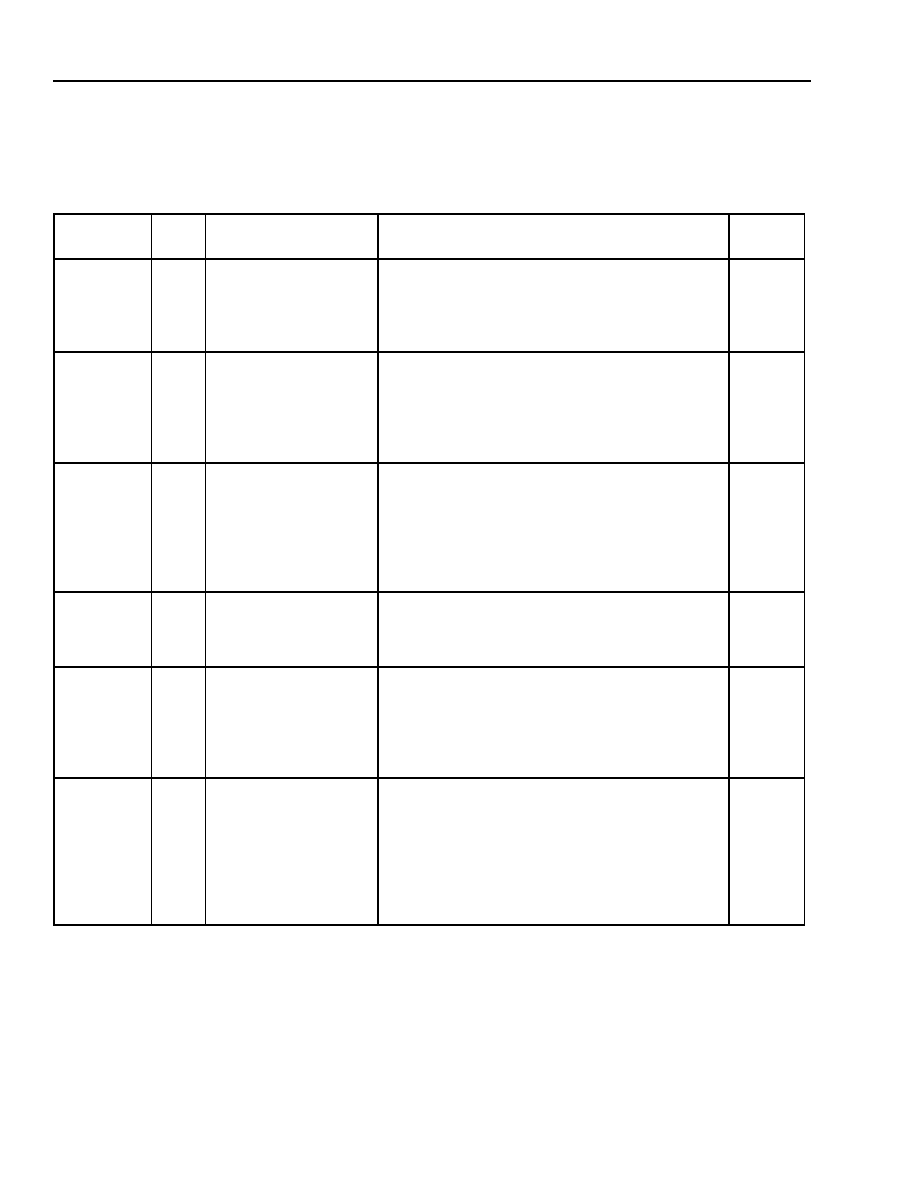

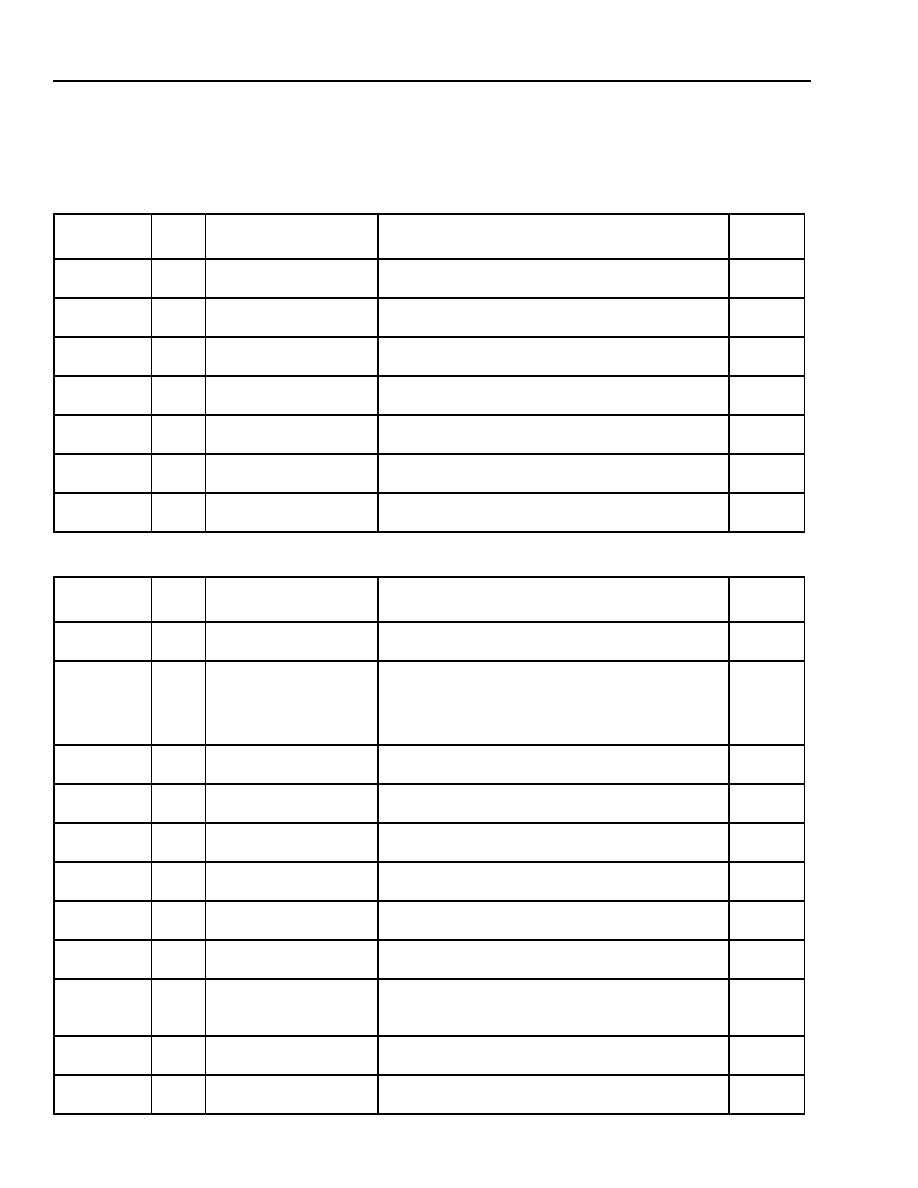

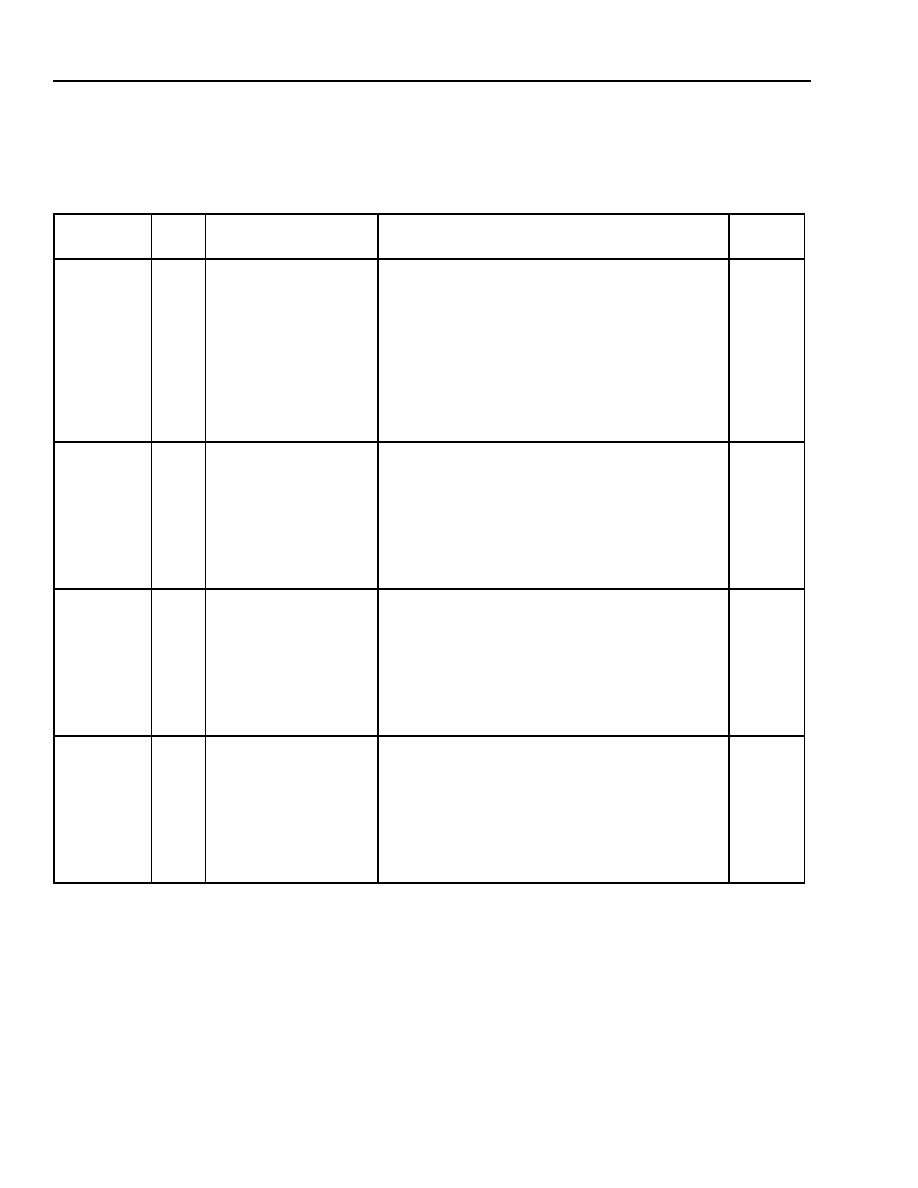

Table 1. Pin Descriptions for the 208-Pin SQFP Package (continued)

* Pin order follows symbol order, e.g., pin 170 refers to TLSDATA7I.

I = input, O = output, I/O = bidirectional signal, I

d

= input with internal pull-down (~20 kW), I

u

= input with internal pull-up (~100 kW), I

diff

or

O

diff

= differential input or output. All I/O not explicitly stated with a buffer type are 5 V compatible. They will tolerate 5 V at their inputs or out-

puts. LVDS = low-voltage differential signal.

Pin*

Symbol

Type

Name/Description

Transmit Direction Signals (continued)

161

TLSPARI

I

u

Transmit Low-Speed Parity Bit. The STS-1/AU-3 parity input is

only defined for byte-wide data. The device can be provisioned to

receive either odd or even parity.

137, 136

THSSCLKOT/C

O

diff

LVDS

Transmit High-Speed Serial Clock. The STS-3/STM-1 (AU-4) clock

will be 155.52 MHz for serial output data; otherwise, this output is

placed in a high-impedance state.

134, 133

THSSSYNCOT/C

O

diff

LVDS

Transmit High-Speed Serial Sync. The STS-3/STM-1 (AU-4) 8 kHz

frame sync is coincident with the first or last bit of the frame.

132,131

THSSDATAOT/C

O

diff

LVDS

Transmit High-Speed Serial Data. If the device is operating in the

serial mode, then this output is used as the differential data pin. In

nibble or parallel output mode, this output is placed in a high-

impedance state.

110

THSCLKO

O

Transmit High-Speed Clock. The STS-3/STM-1 (AU-4) clock is

38.88 MHz for nibble data, or 19.44 MHz for byte-wide data.

109

THSSYNCO

O

Transmit High-Speed Sync. The STS-3/STM-1 (AU-4) 8 kHz frame

sync is coincident with the first or last nibble/byte of the frame.

101--94

THSDATA[7:0]O

O

Transmit High-Speed Data. Bit 7 is the most significant bit in nibble

or byte mode.

102

THSPARO

O

Transmit High-Speed Parity. The parity output is only defined for

nibble or byte-wide data. The device can be provisioned to source

either an odd or even parity bit.

STS-3/STM-1 (AU-4) Transport Overhead Access Channel (TOAC) Insert

37

TTOACCLKO

O

Transmit TOAC Clock. (5.184 MHz.)

38

TTOACSYNCO

O

Transmit TOAC Sync. (8 kHz.)

39

TTOACDATAI

I

d

Transmit TOAC Data. (5.184 Mbits/s.)

12

12

Agere Systems Inc.

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

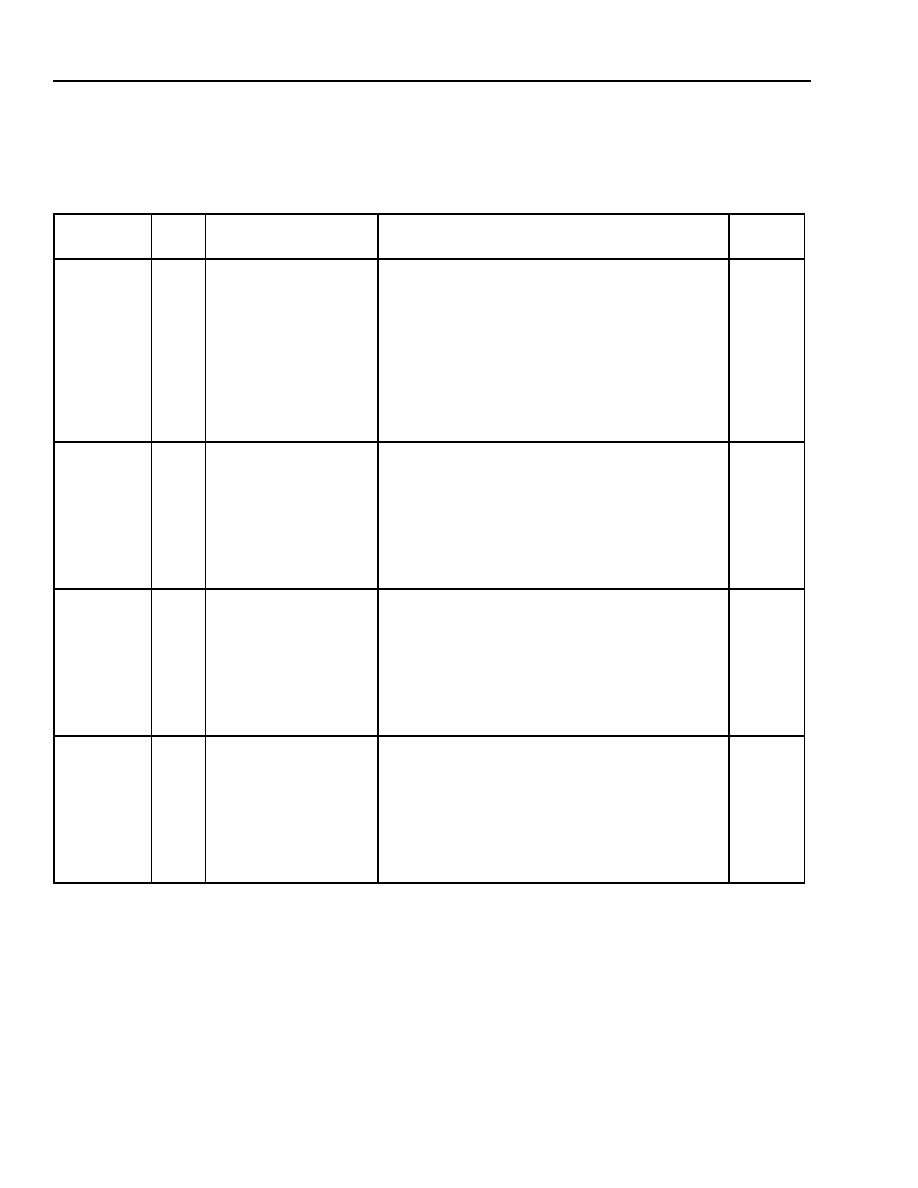

Pin Information

(continued)

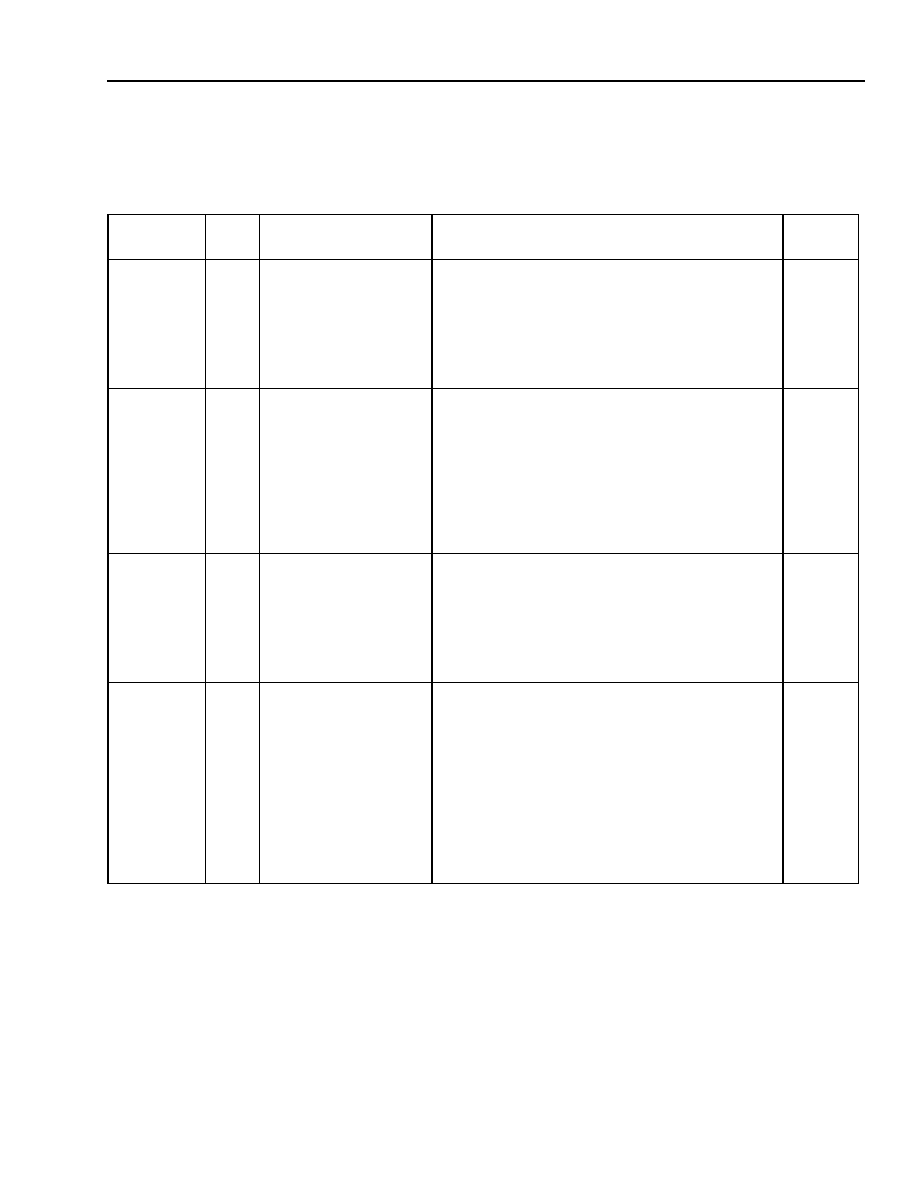

Table 1. Pin Descriptions for the 208-Pin SQFP Package (continued)

* Pin order follows symbol order, e.g., pin 170 refers to TLSDATA7I.

I = input, O = output, I/O = bidirectional signal, I

d

= input with internal pull-down (~20 kW), I

u

= input with internal pull-up (~100 kW), I

diff

or

O

diff

= differential input or output. All I/O not explicitly stated with a buffer type are 5 V compatible. They will tolerate 5 V at their inputs or out-

puts. LVDS = low-voltage differential signal.

Pin*

Symbol

Type

Name/Description

Receive Direction Signals

124, 123

RHSSCLKIT/C

I

diff

LVDS

Receive High-Speed Serial Clock Input. The STS-3/STM-1

(AU-4) serial clock is 155.52 MHz.

122

CTAP_RHSSCLKI

I

Center Tap for Receive High-Speed Serial Clock Input. The cen-

ter tap input provides for center-tapped common-mode termination.

This input should be terminated through an external capacitor to

ground (approximately 0.1 µF).

119, 118

RHSSDATAIT/C

I

diff

LVDS

Receive High-Speed Serial Data Input. The STS-3/STM-1 (AU-4)

serial data is 155.52 Mbits/s.

117

CTAP_RHSSDATAI

I

Center Tap for Receive High-Speed Serial Data Input. The center

tap input provides for center-tapped common-mode termination. This

input should be terminated through an external capacitor to ground

(approximately 0.1 µF).

113

RCDR10K2GND

I

Receive CDR Bias Resistor Input. Must be tied to ground, through

an external 10 k

±1% resistor.

50

RHSCLKI

I

d

Receive High-Speed Clock Input. The STS-3/STM-1 (AU-4) clock

is 38.88 MHz (nibble), or 19.44 MHz for byte-wide data.

56--63

RHSDATA[7:0]I

I

d

Receive High-Speed Data Inputs. Data bit 7 is the most significant

bit in nibble or byte mode.

55

RHSPARI

I

u

Receive High-Speed Input Parity. The parity input is only defined

for nibble- or byte-wide data. The device can be provisioned to

accept either odd or even parity.

49

RHSLOSEXTI

I

d

Receive High-Speed Loss of Signal. This is an active-high signal.

179

RLSCLKO

O

Receive STS-1/AU-3 Output Clock. The STS-1/AU-3 clock will be

19.44 MHz for byte-wide data (bus mode).

176

RLSJ0TIMEO

O

Receive STS1/AU-3 Output J0 Time. This signal will be active

(logic 1) each time the J0 byte is output.

181,

183--186,

188--190

RLSDATA[7:0]O

O

Receive STS-1/AU-3 Output Data. RLSDATA7O is the most signifi-

cant bit of the output byte.

192

RLSPARO

O

Receive STS-1/AU-3 Output Parity. The device can be provisioned

to source either an odd or even parity bit per byte transfer.

STS-3/STM-1 (AU-4) Transport Overhead Access Channel (TOAC) Drop

41

RTOACCLKO

O

Receive TOAC Clock. (5.184 MHz.)

42

RTOACSYNCO

O

Receive TOAC Sync. (8 kHz.)

43

RTOACDATAO

O

Receive TOAC Data. (5.184 Mbits/s.)

Agere Systems Inc.

13

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Pin Information

(continued)

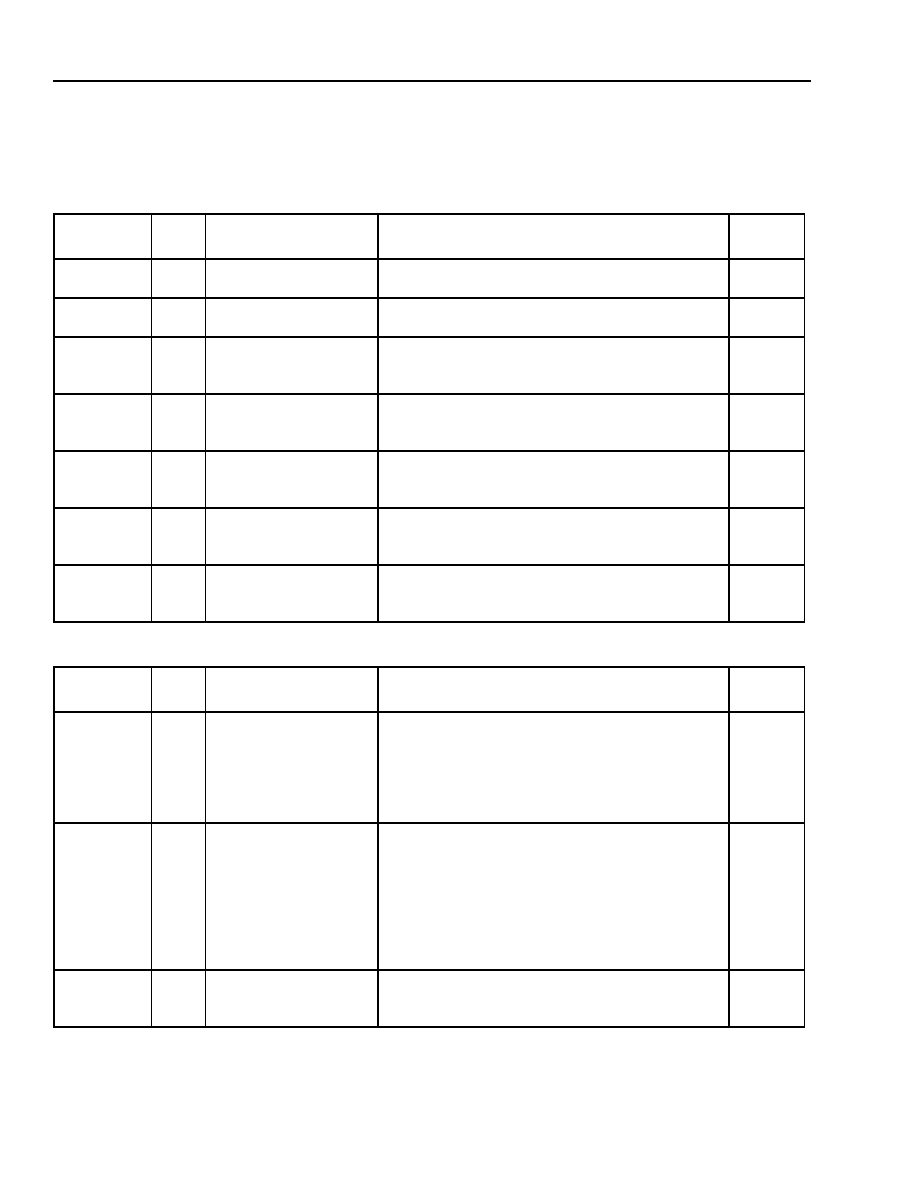

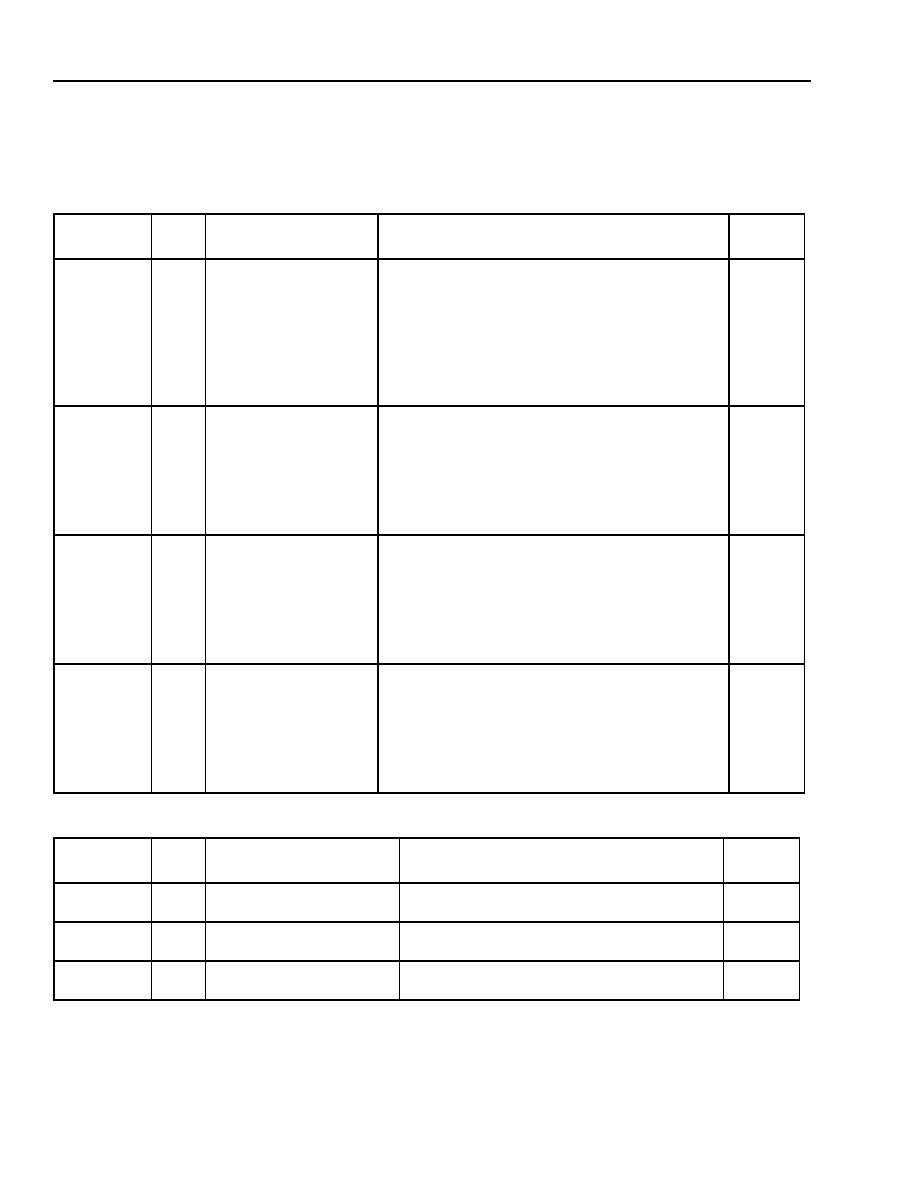

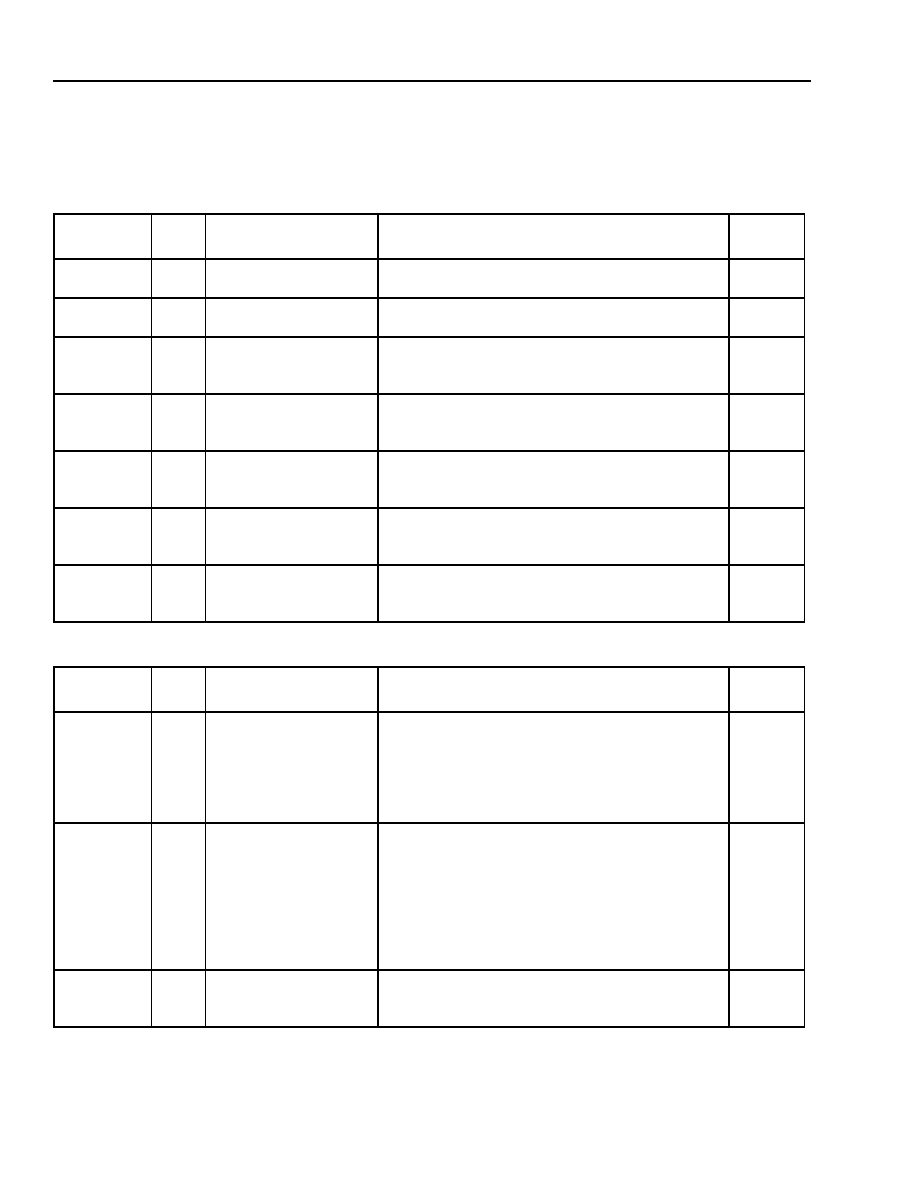

Table 1. Pin Descriptions for the 208-Pin SQFP Package (continued)

* Pin order follows symbol order, e.g., pin 170 refers to TLSDATA7I.

I = input, O = output, I/O = bidirectional signal, I

d

= input with internal pull-down (~20 kW), I

u

= input with internal pull-up (~100 kW), I

diff

or

O

diff

= differential input or output. All I/O not explicitly stated with a buffer type are 5 V compatible. They will tolerate 5 V at their inputs or out-

puts. LVDS = low-voltage differential signal.

Pin*

Symbol

Type

Name/Description

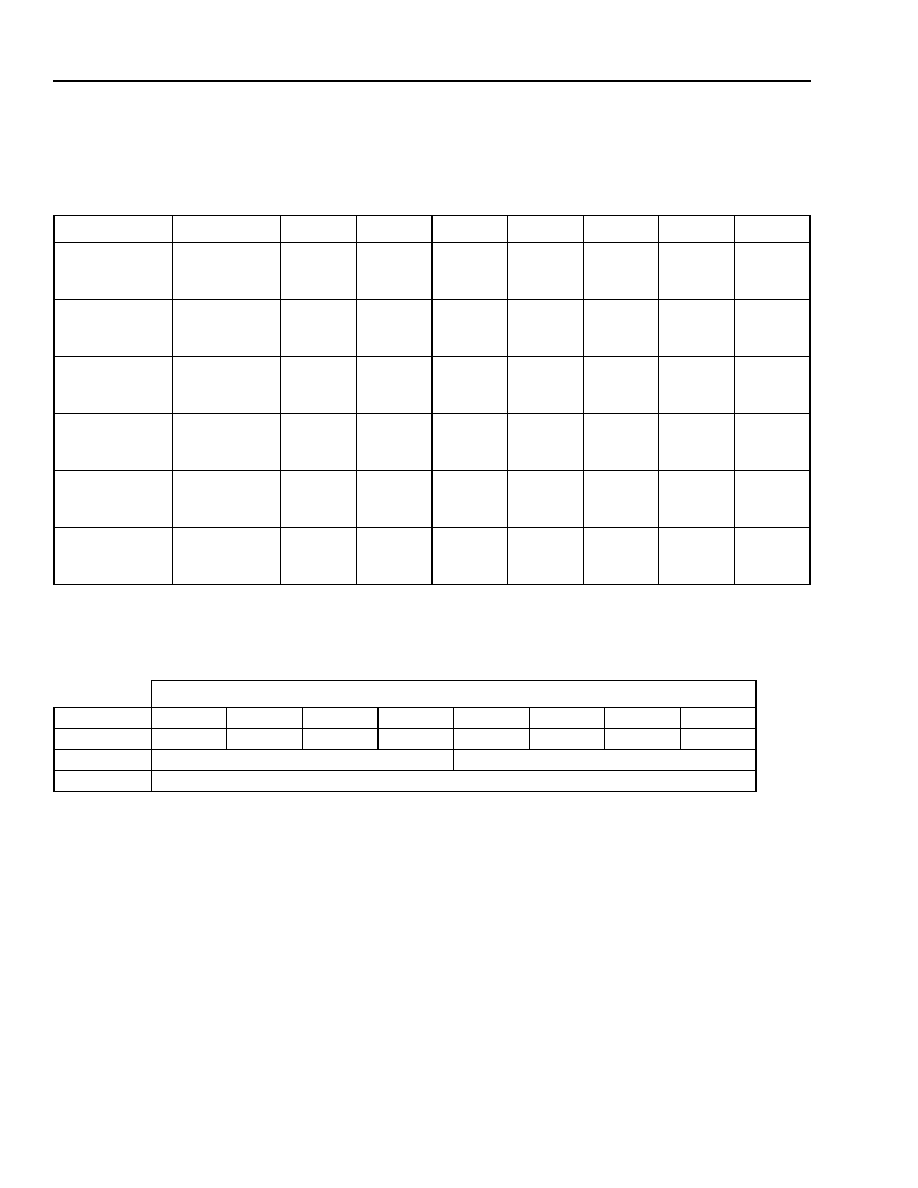

Mode/In-Circuit Test and Reset Control Inputs

30

ICT

I

u

In-Circuit Test Control (Active-Low). If

ICT

is forced low, certain

output pins are placed in the high-impedance state.

106

RESET

I

u

Hardware Reset (Active-Low). If

RESET

is forced low, all internal

states in the transceiver paths are reset and data flow through each

channel will be interrupted.

111

RSTN_TST

I

u

Test Reset (Active-Low). This pin is for test purposes only; it should

be left unconnected.

153, 154

MODE [1:0]

I

u

, I

d

Mode Control. Normal STS-3/STM-1 mode set MODE [1:0] = 10.

STS-1 mode set MODE [1:0] = 00

Microprocessor Interface

14

MPMUX

I

Microprocessor Multiplex Mode. Setting MPMUX = 1 allows the

microprocessor interface to accept the multiplexed address and data

signals. Setting MPMUX = 0 allows the microprocessor interface to

accept demultiplexed (separate) address and data signals.

15

MPMODE

I

Microprocessor Mode. When MPMODE = 1, the device uses the

address latch enable type microprocessor read/write protocol with

separate read and write controls. Setting MPMODE = 0 allows the

device to use the address strobe type microprocessor read/write pro-

tocol with a separate data strobe and a combined read/write control.

16

MPMODE3ALE

I

u

Microprocessor MODE3 ALE Enable. When the device is in

MODE3 (MPMODE = 1 and MPMUX = 0), the ALE signal can be

used to retime the address or the address bus can be used directly

without being retimed. This is an active-high signal.

9

WR_DS

I

Write (Active-Low). If MPMODE = 1, this pin is asserted low by the

microprocessor to initiate a write cycle.

Data Strobe (Active-Low). If MPMODE = 0, this pin becomes the

data strobe for the microprocessor. When R/W = 0 (write), a low

applied to this pin latches the signal on the data bus into internal reg-

isters.

11

ALE_AS

I

Address Latch Enable. If MPMODE = 1, this pin becomes the

address latch enable for the microprocessor. When this pin transi-

tions from high to low, the address bus inputs are latched into the

internal registers.

Address Strobe (Active-Low). If MPMODE = 0, this pin becomes

the address strobe for the microprocessor. When this pin transitions

from high to low, the address bus inputs are latched into the internal

registers.

10

RD_R/W

I

Read (Active-Low). If MPMODE = 1, this pin is asserted low by the

microprocessor to initiate a read cycle.

Read/Write. If MPMODE = 0, this pin is asserted high by the micro-

processor to indicate a read cycle or asserted low to indicate a write

cycle.

14

14

Agere Systems Inc.

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Pin Information

(continued)

Table 1. Pin Descriptions for the 208-Pin SQFP Package (continued)

* Pin order follows symbol order, e.g., pin 170 refers to TLSDATA7I.

I = input, O = output, I/O = bidirectional signal, I

d

= input with internal pull-down (~20 kW), I

u

= input with internal pull-up (~100 kW), I

diff

or

O

diff

= differential input or output. All I/O not explicitly stated with a buffer type are 5 V compatible. They will tolerate 5 V at their inputs or out-

puts. LVDS = low-voltage differential signal.

Pin*

Symbol

Type

Name/Description

Microprocessor Interface (continued)

7

CS

I

u

Chip Select (Active-Low). This pin is asserted low by the micropro-

cessor to enable the microprocessor interface. If MPMUX = 1, an

internal 100 k

pull-up is on this pin.

8

INT

O

Interrupt. This pin is asserted high to indicate an interrupt produced

by an alarm condition. The activation of this pin can be masked by

the microprocessor by setting the appropriate mask bits.

13

RDY_DTACK

O

Ready. If MPMODE = 1, this pin is asserted high to indicate the

device has completed a read or write operation. This pin is in a high-

impedance state when CS is high.

Data Transfer Acknowledge (Active-Low). If MPMODE = 0, this

pin is asserted low to indicate the device has completed a read or

write operation.

5--3,

206--202

AD[7:0]

I/O

Microprocessor Interface Address/Data Bus. If MPMUX = 0,

these pins become the bidirectional, 3-state data bus. If MPMUX = 1,

these pins become the multiplexed address/data bus.

201--197,

195--193

A[7:0]

I

d

Microprocessor Interface Address. If MPMUX = 0, these pins

become the address bus for the microprocessor interface registers.

JTAG Signals

20

TCLK

I

u

JTAG Clock.

22

TDI

I

u

JTAG Input Data.

23

TMS

I

u

JTAG Mode Select.

24

TRST

I

u

JTAG Reset (Active-Low).

25

TDO

O

JTAG Output Data.

SCAN Specific Inputs

27

SCAN_EN

I

u

Scan Enable. Place device in scan mode (active-low).

28

TEST_MODE

I

d

Test Mode. Disable all clocks and async resets (active-high).

114

CDR_TSTMUX0

O

CDR Test Output. Test purpose only.

LVDS Control Signals

146

LVDS_REFSEL

I

u

LVDS Reference Select. If LVDS_REFSEL = 0, then use external

1.0 and 1.4 reference voltages. If LVDS_REFSEL = 1, then use inter-

nal references.

129

LVDS_REF10

I

1.0 V Reference for LVDS Buffers. This signal is optional.

128

LVDS_REF14

I

1.4 V Reference for LVDS Buffers. This signal is optional.

127

LVDS_RESHI

I

LVDS Resistor Pins. A 100

±1% resistor must be placed between

these two pins when using the LVDS buffers.

126

LVDS_RESLO

I

Agere Systems Inc.

15

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Pin Information

(continued)

Table 1. Pin Descriptions for the 208-Pin SQFP Package (continued)

* Pin order follows symbol order, e.g., pin 170 refers to TLSDATA7I.

I = input, O = output, I/O = bidirectional signal, I

d

= input with internal pull-down (~20 kW), I

u

= input with internal pull-up (~100 kW), I

diff

or

O

diff

= differential input or output. All I/O not explicitly stated with a buffer type are 5 V compatible. They will tolerate 5 V at their inputs or out-

puts. LVDS = low-voltage differential signal.

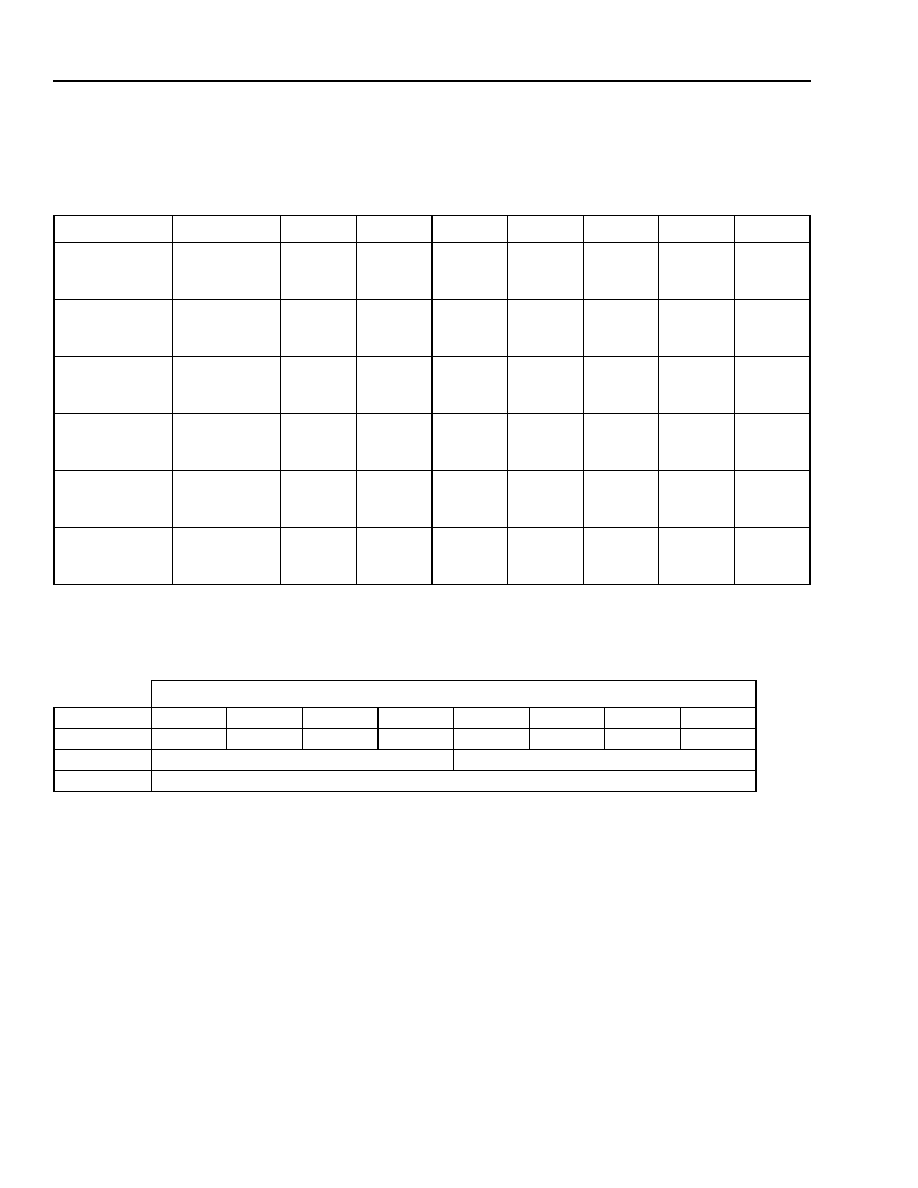

Summary of I/O Pins

Pin*

Symbol

Type

Name/Description

Power and Ground Pins

1--2, 21

31, 51,

53--54,

74, 79, 84,

103, 105,

115, 120,

125, 135,

149, 155,

157--158,

177, 182,

187, 207

V

SS

I

Ground Reference.

12, 17, 26,

36, 40, 44,

65, 73, 80,

85, 93,

116, 121,

130, 138,

144, 147,

152, 168,

180, 196

V

DD

I

Power Supply for Digital Circuitry.

151, 32

REF5VTOL

I

5 V Tolerant Reference Voltage.

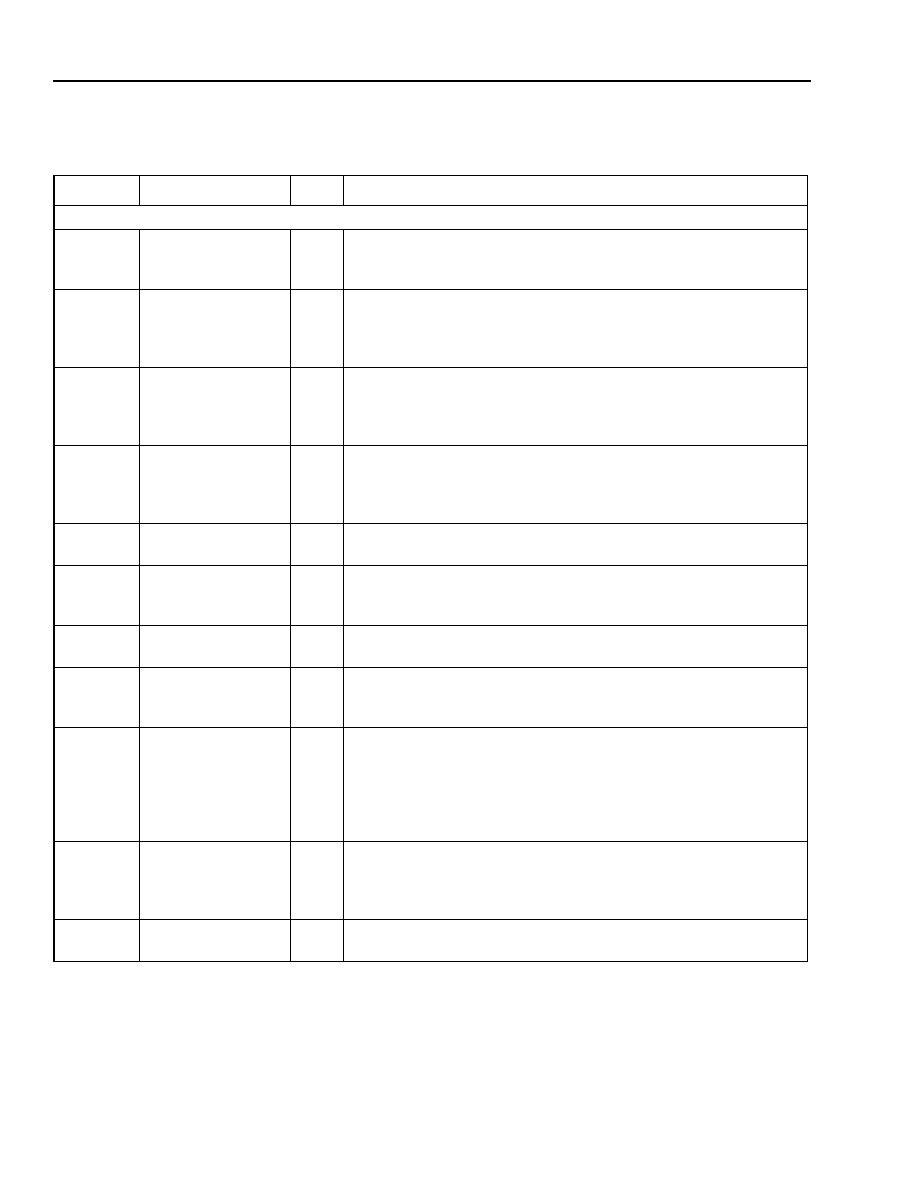

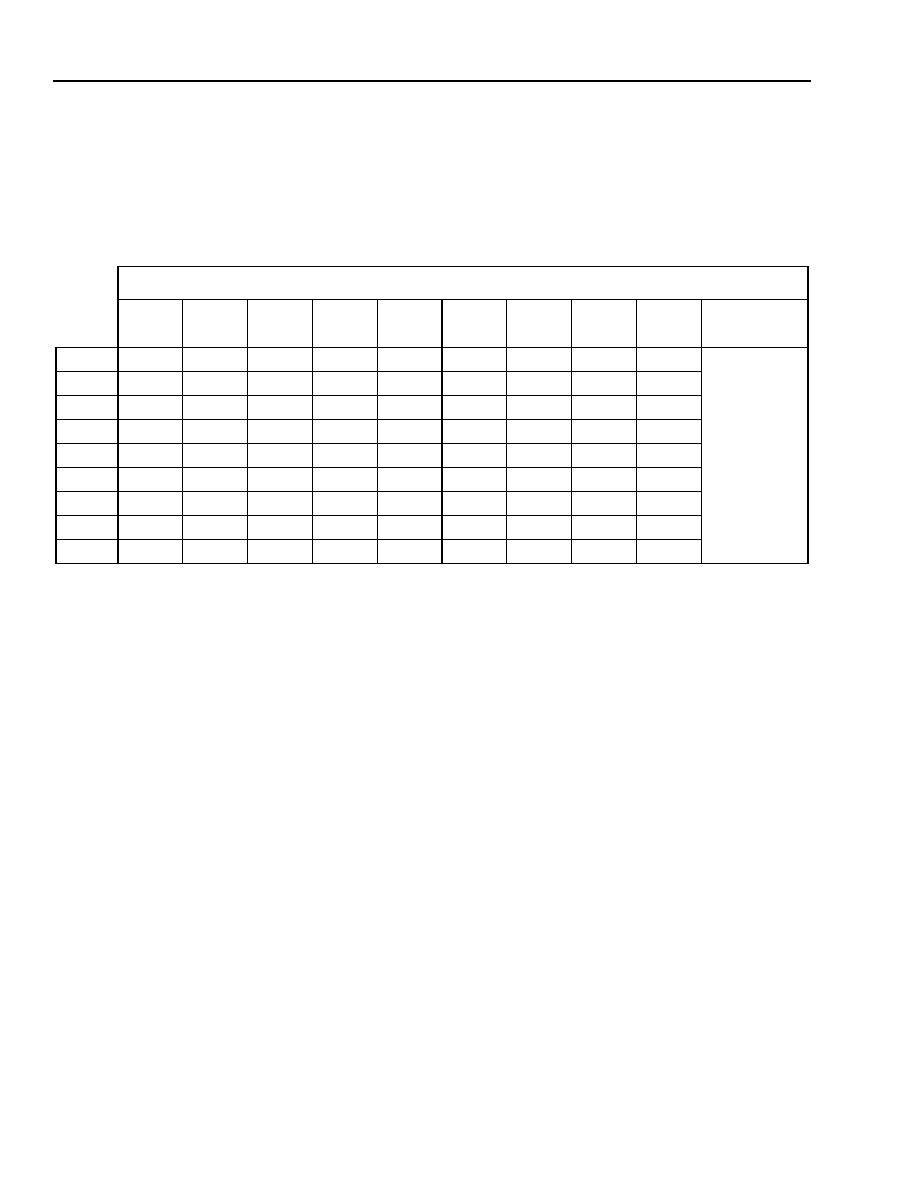

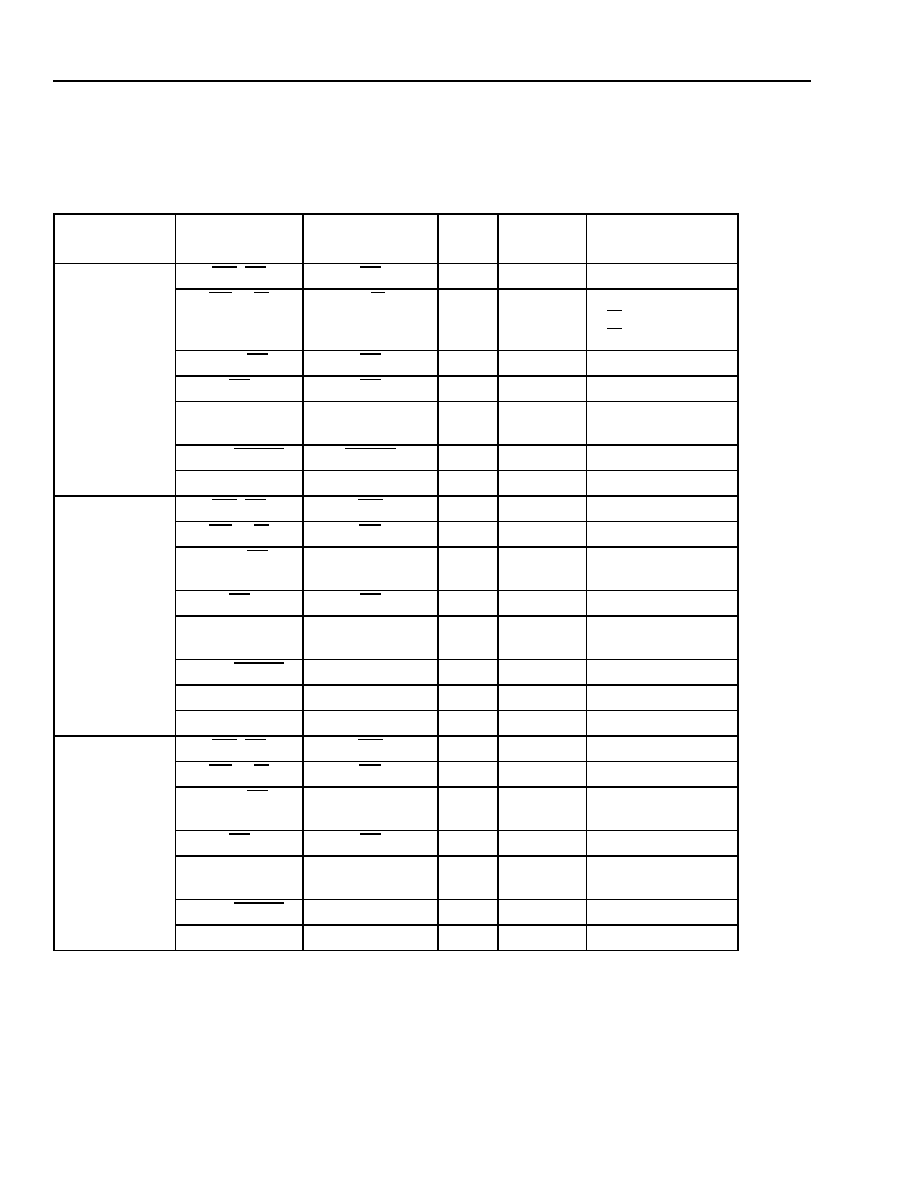

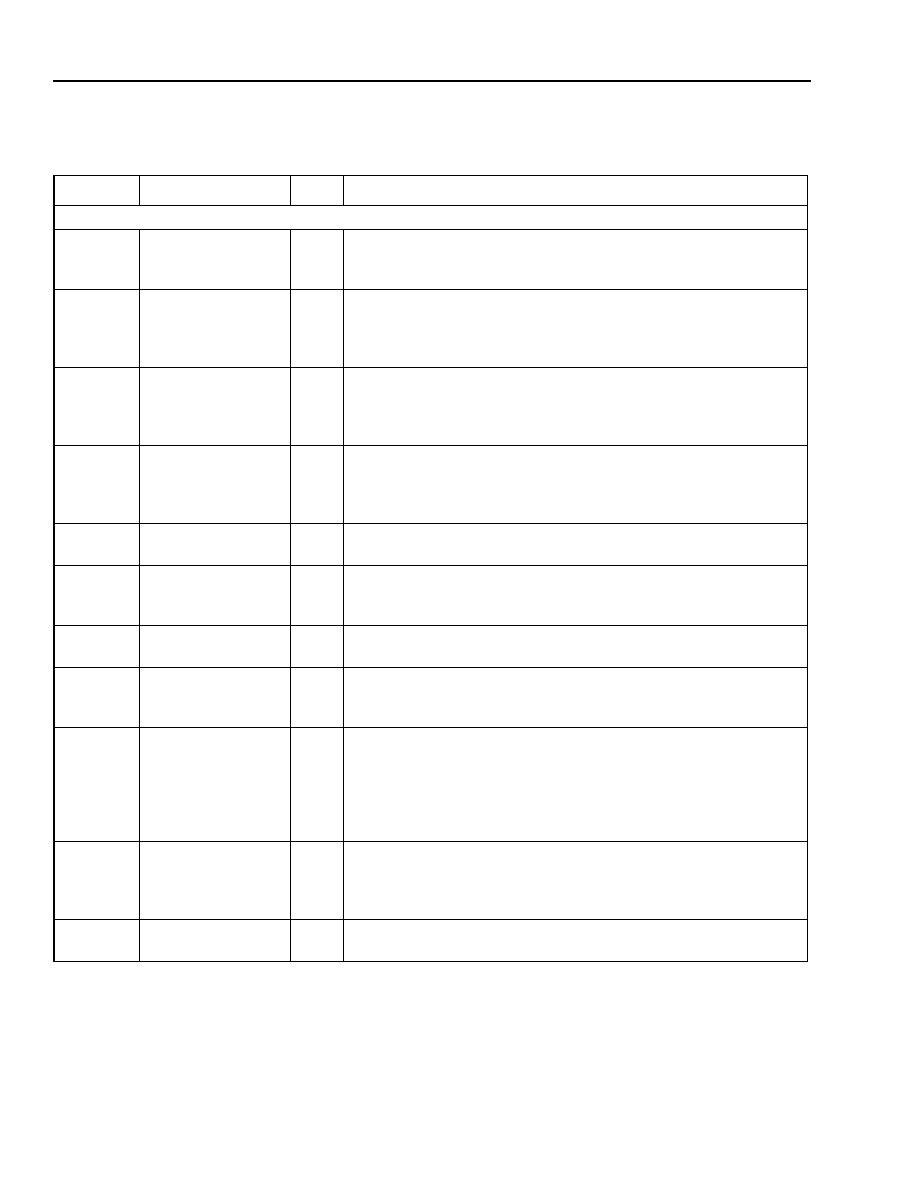

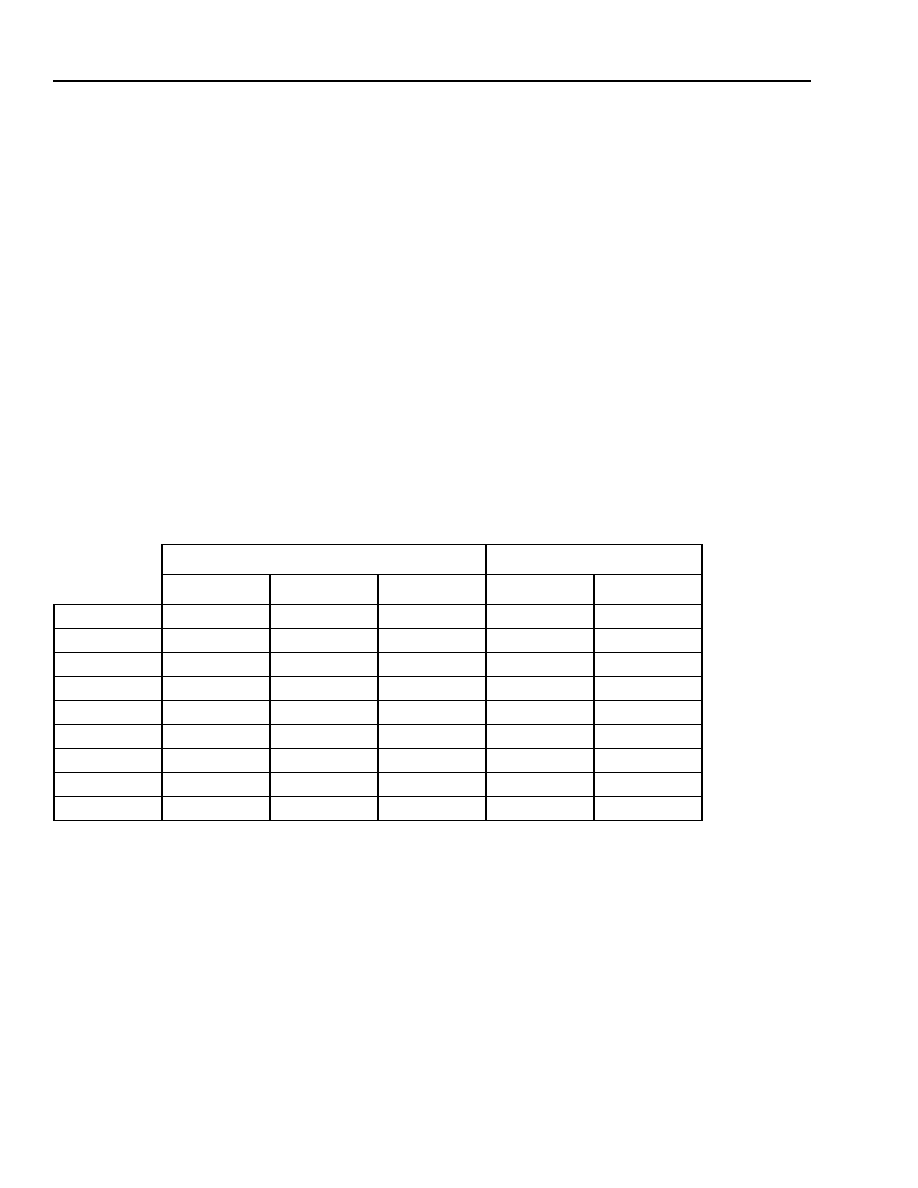

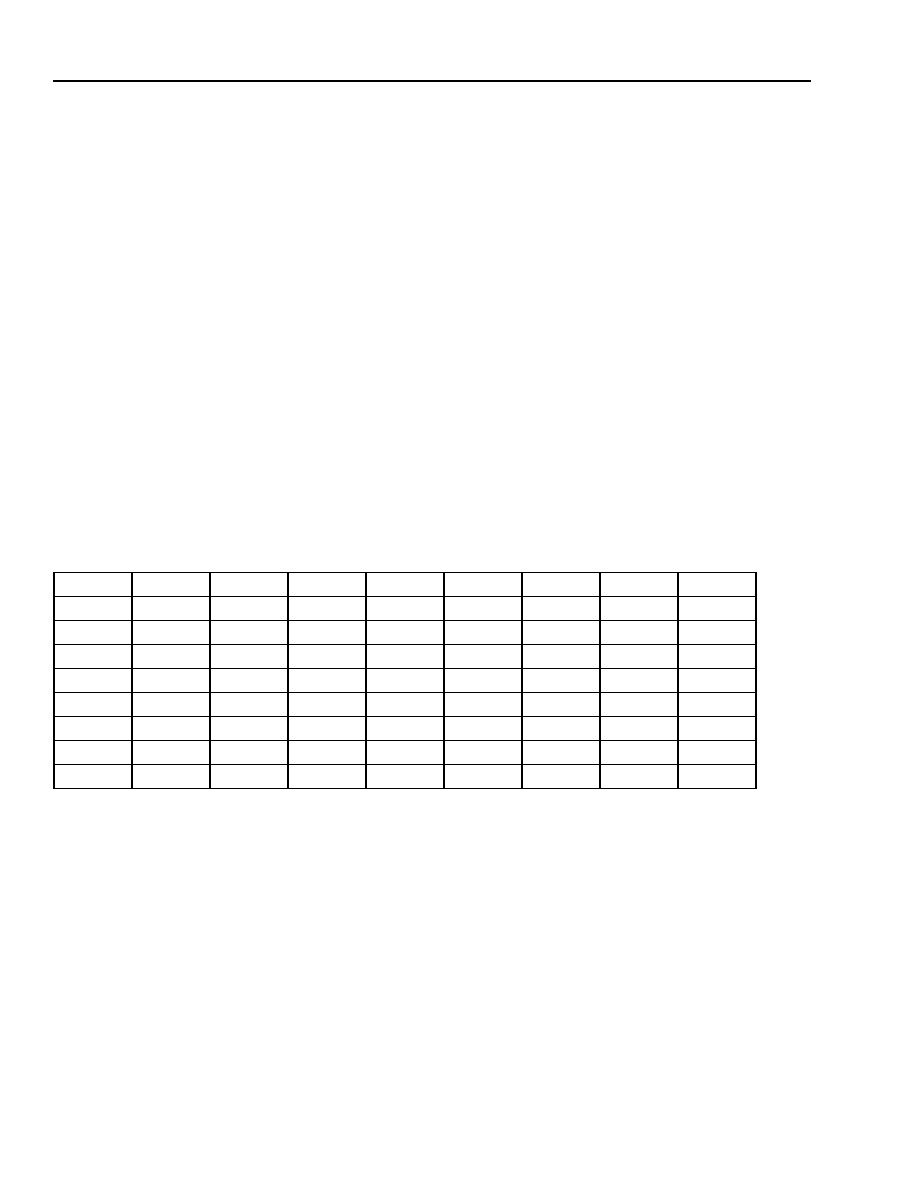

Table 2. Input/Output Summary

Type

Number of Pins

Input

Differential

8

Single Ended

57

Output

Differential

6

Single Ended

35

Bidirectional

8

Total Signal

114

No Connect (Reserved)

45

REF5VTOL

2

LVDS_REF10

1

LVDS_REF14

1

V

DD

21

V

SS

(GND)

24

Total Package

208 SQFP

16

16

Agere Systems Inc.

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

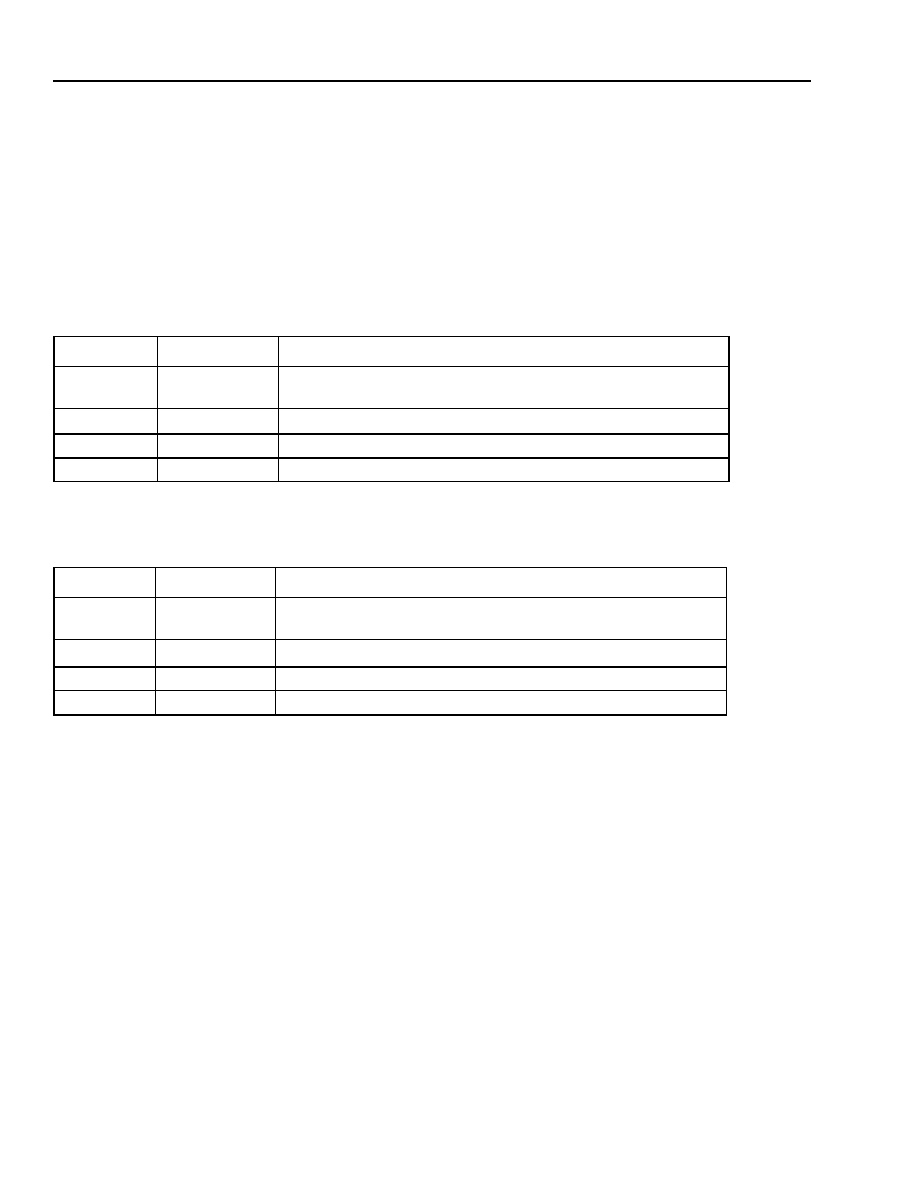

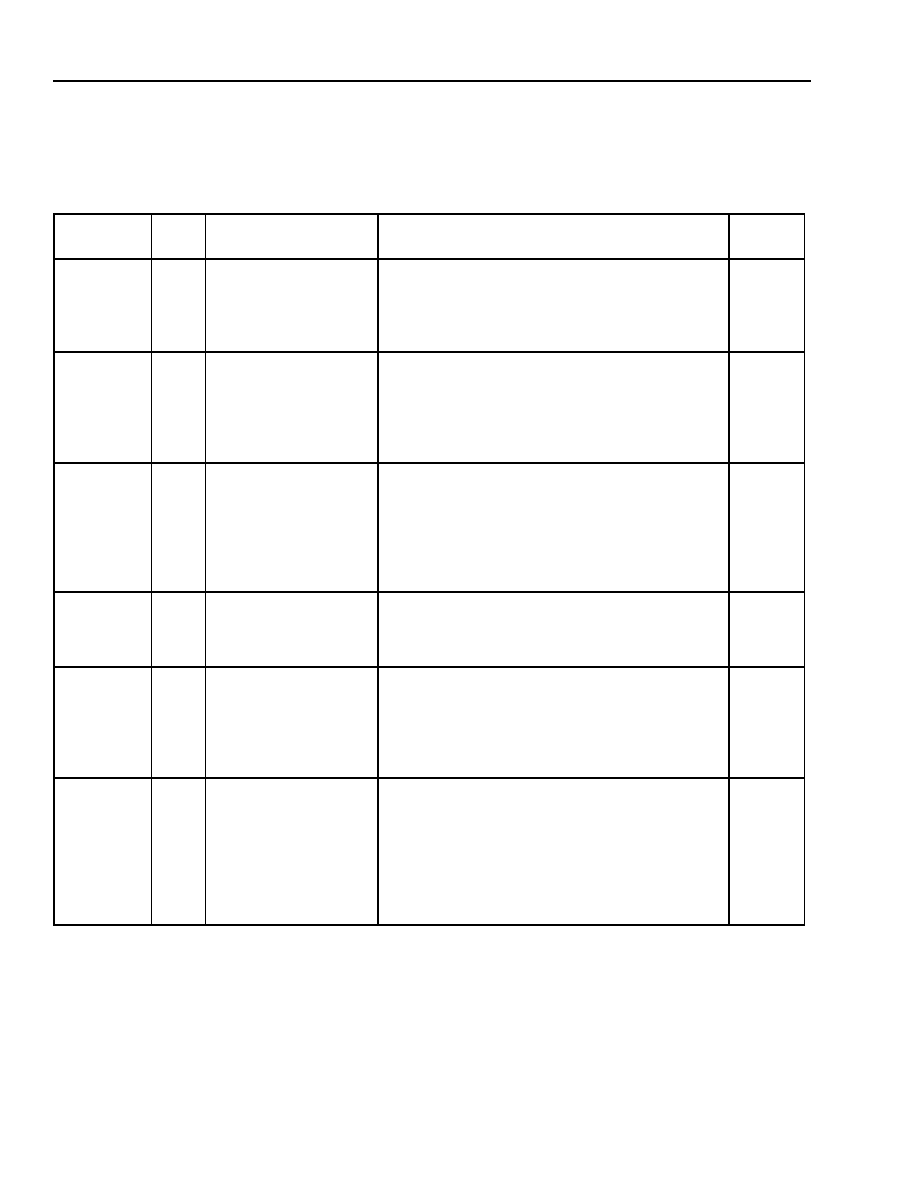

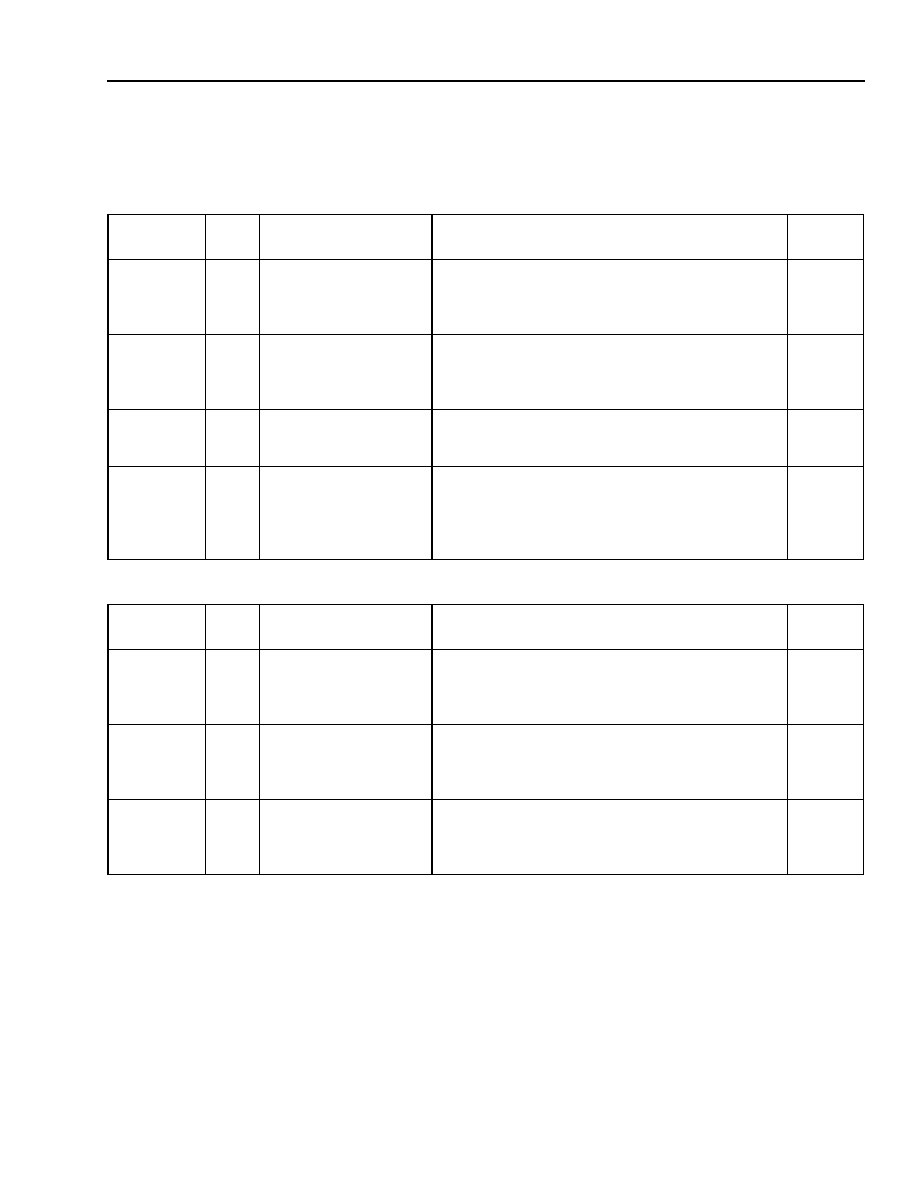

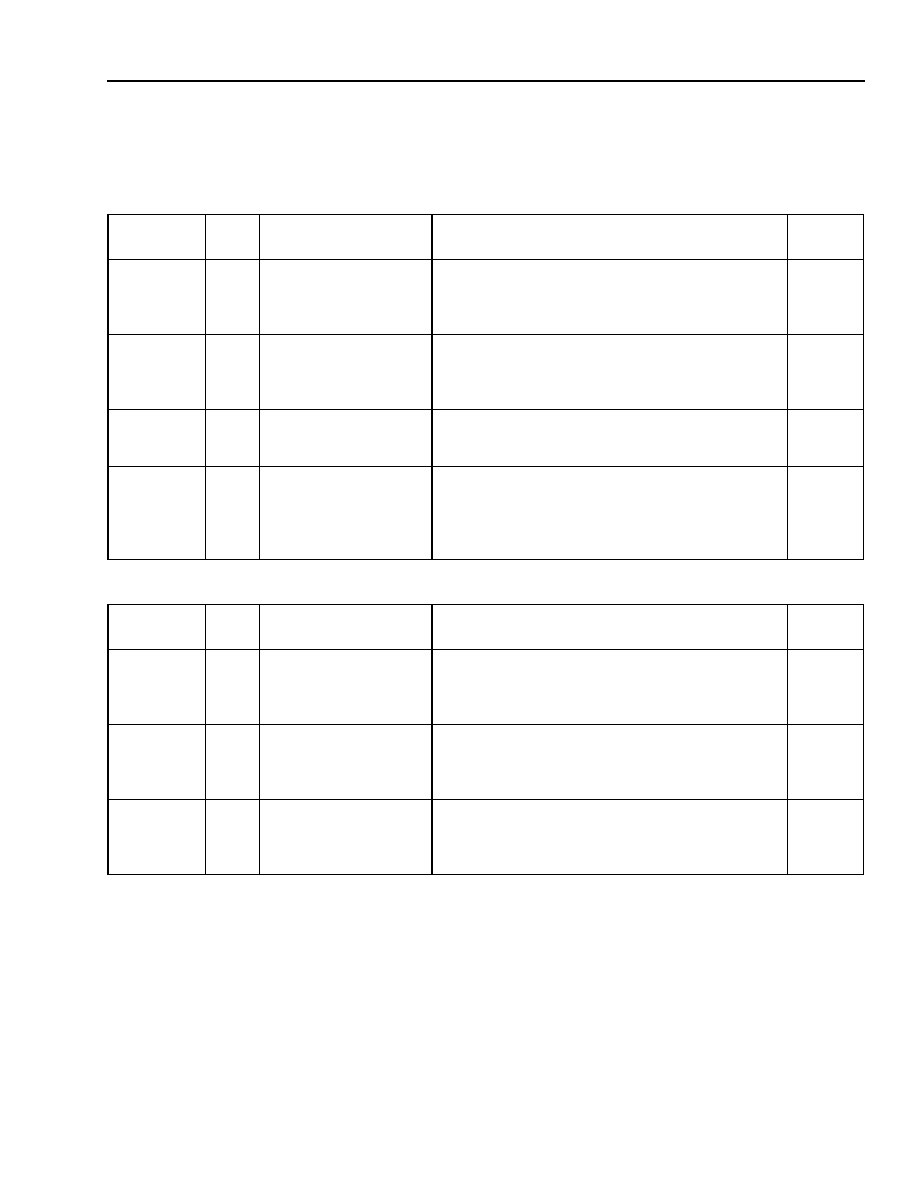

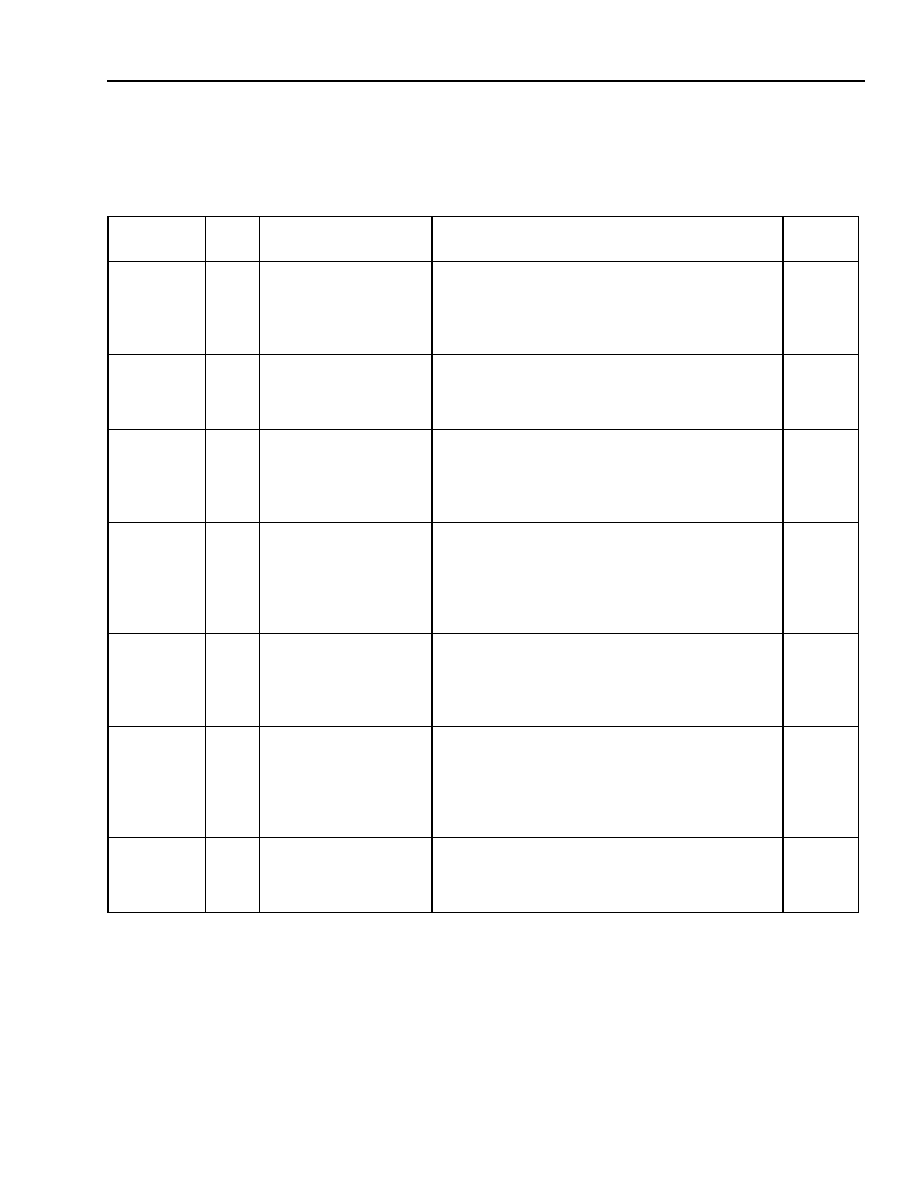

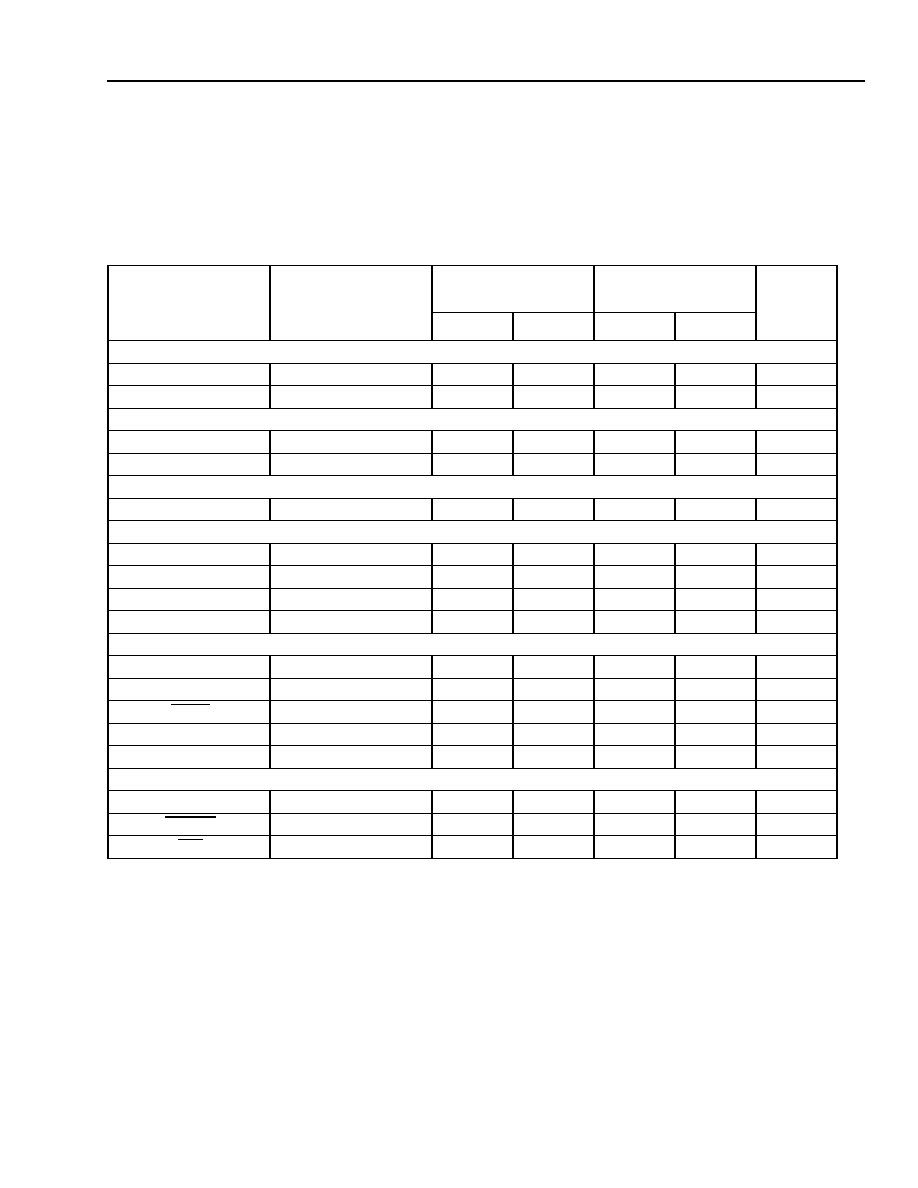

Mode Control Signals

(See Register Description on page 54.)

The device is controlled by four control signals: T/RSONET_SDH and T/RSTS3_AU4, 0x34. These signals control

the following:

I

The type of input signal to expect (low-speed (LS) side--STS-1/AU-3).

I

The expected high-speed (HS) input/output signal format--STS-3/STM-1 (AU-4), or STS-1.

I

The default byte value in the outgoing HS frame.

These provisioning signals are summarized in Table 3 and Table 4.

STS-1 Mode

In STS-1 mode, all other device functions remain the same as in STS-3/STM-1 mode; except, the device runs at

one-third the STS-3/STM-1 rate and operates on a single STS-1 frame. The high-speed side operates in the follow-

ing three modes: 1) as a 51.84 Mbits/s serial interface, 2) as a parallel 12.96 MHz nibble wide, 3) or as a 6.48 MHz

byte-wide interface. The low-speed STS-1/AU-3 side operates at 6.48 Mbytes/s and communicates with a single

STS-1/AU-3 device (TMPR28051). Since the TOAC interface provides access to the transport overhead in a single

STS-1 frame, its clock and data operate at 1.782 MHz, while the sync runs at 8 kHz. For STS-1 mode, set both

mode pins 153 and 154 to a logic 0, and set all mode control bits TSTS3_AU4, TSONET_SDH, RSTS3_AU4,

RSONET_SDH, 0x34, to a logic 0.

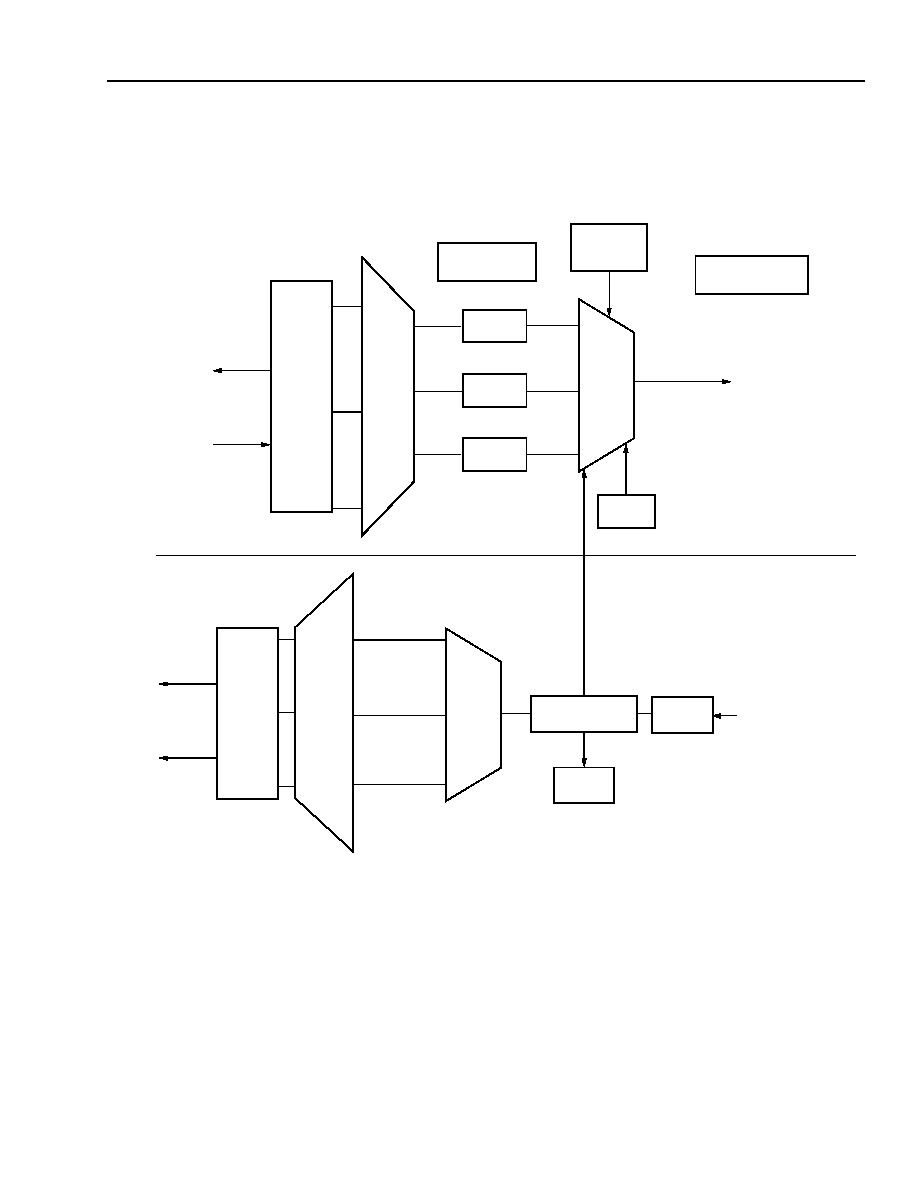

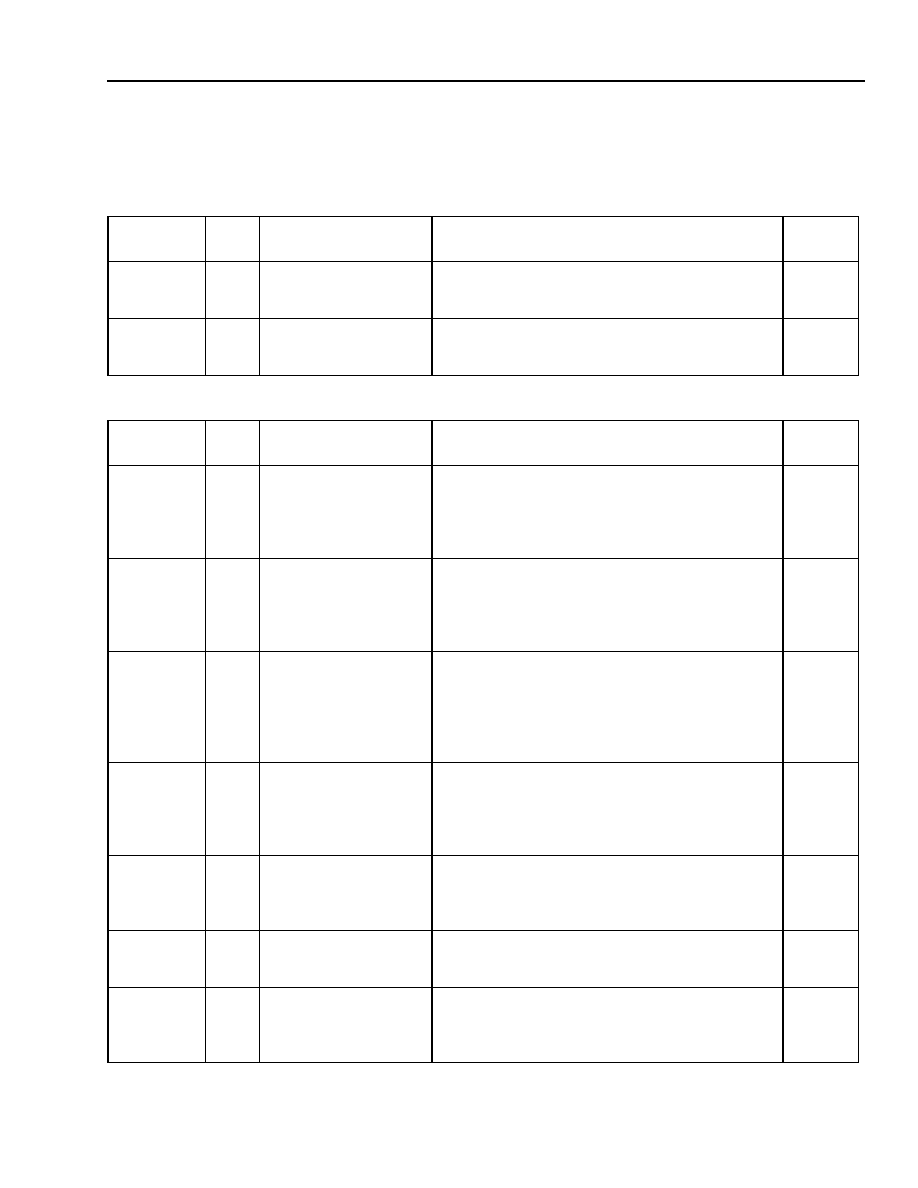

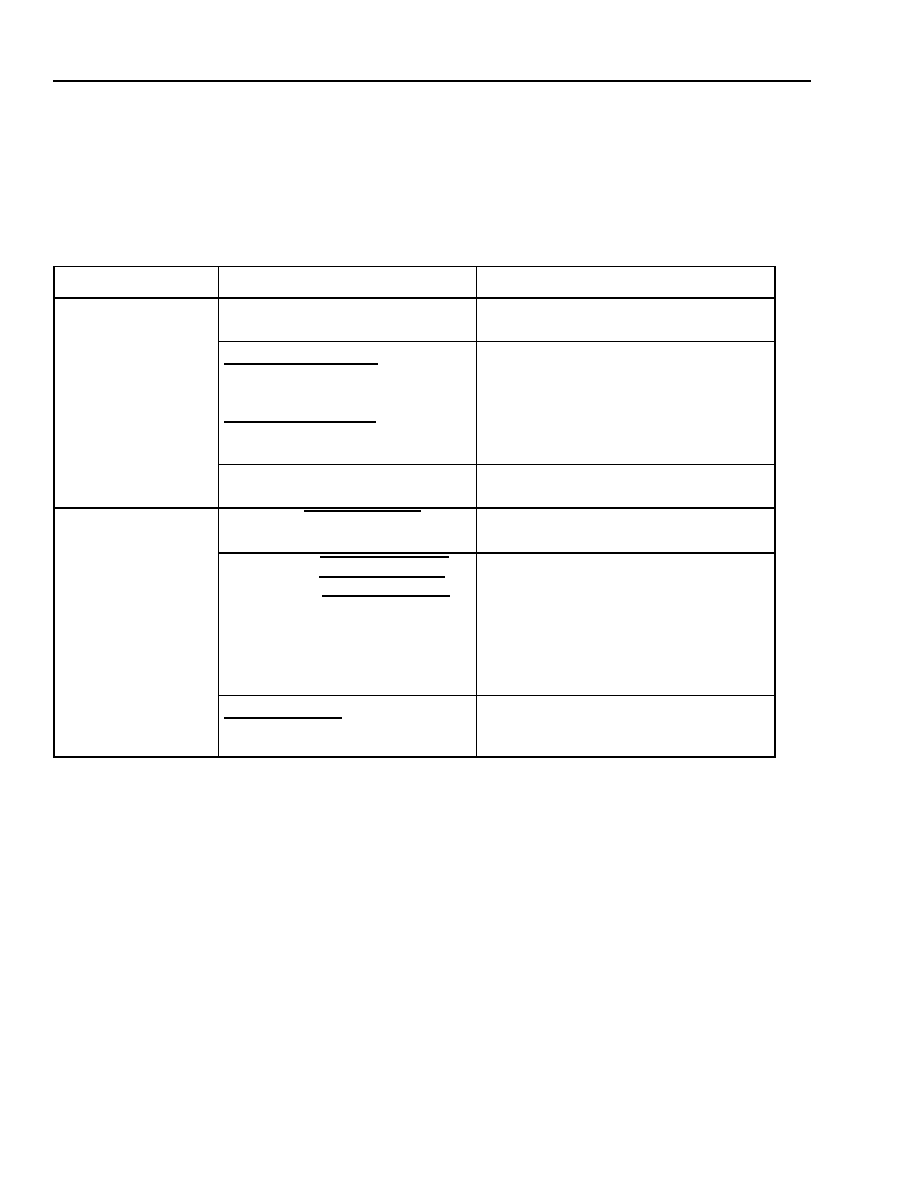

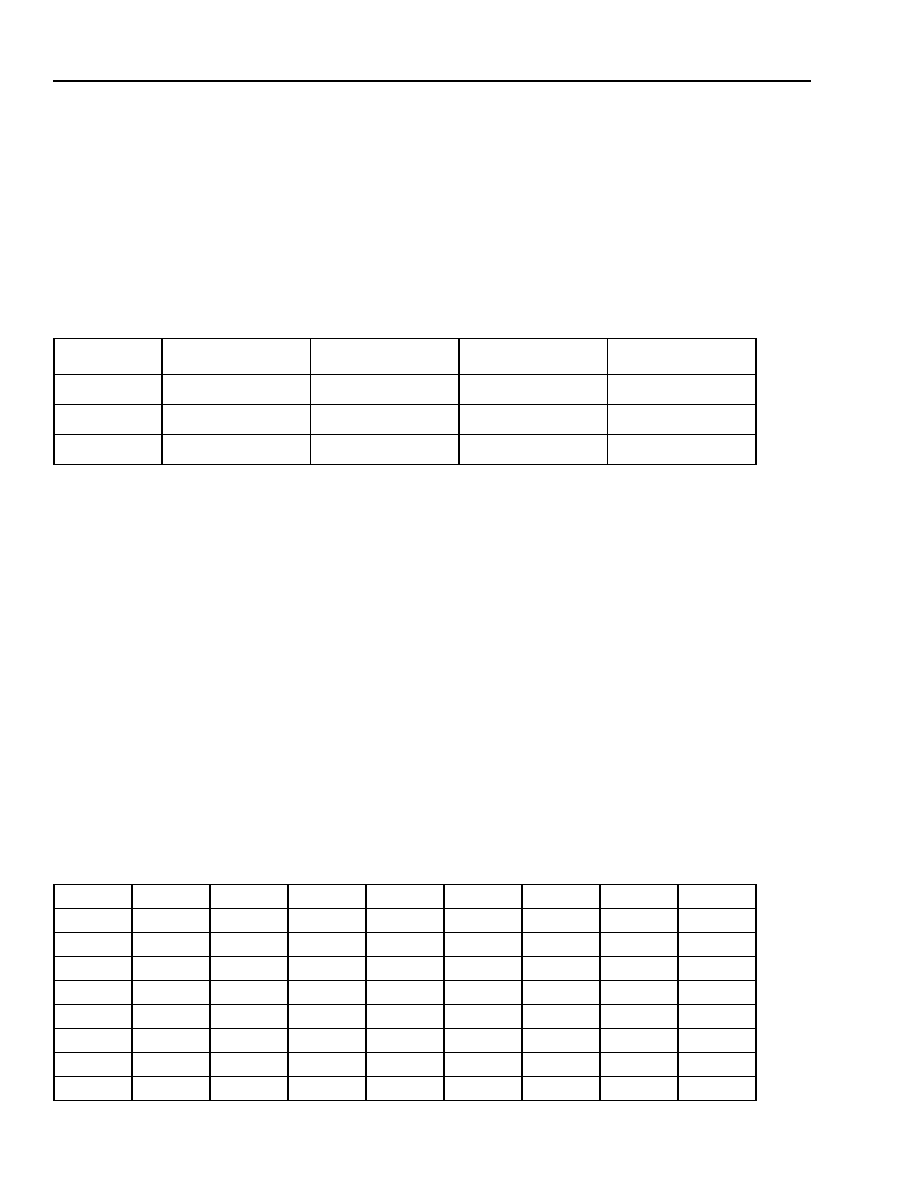

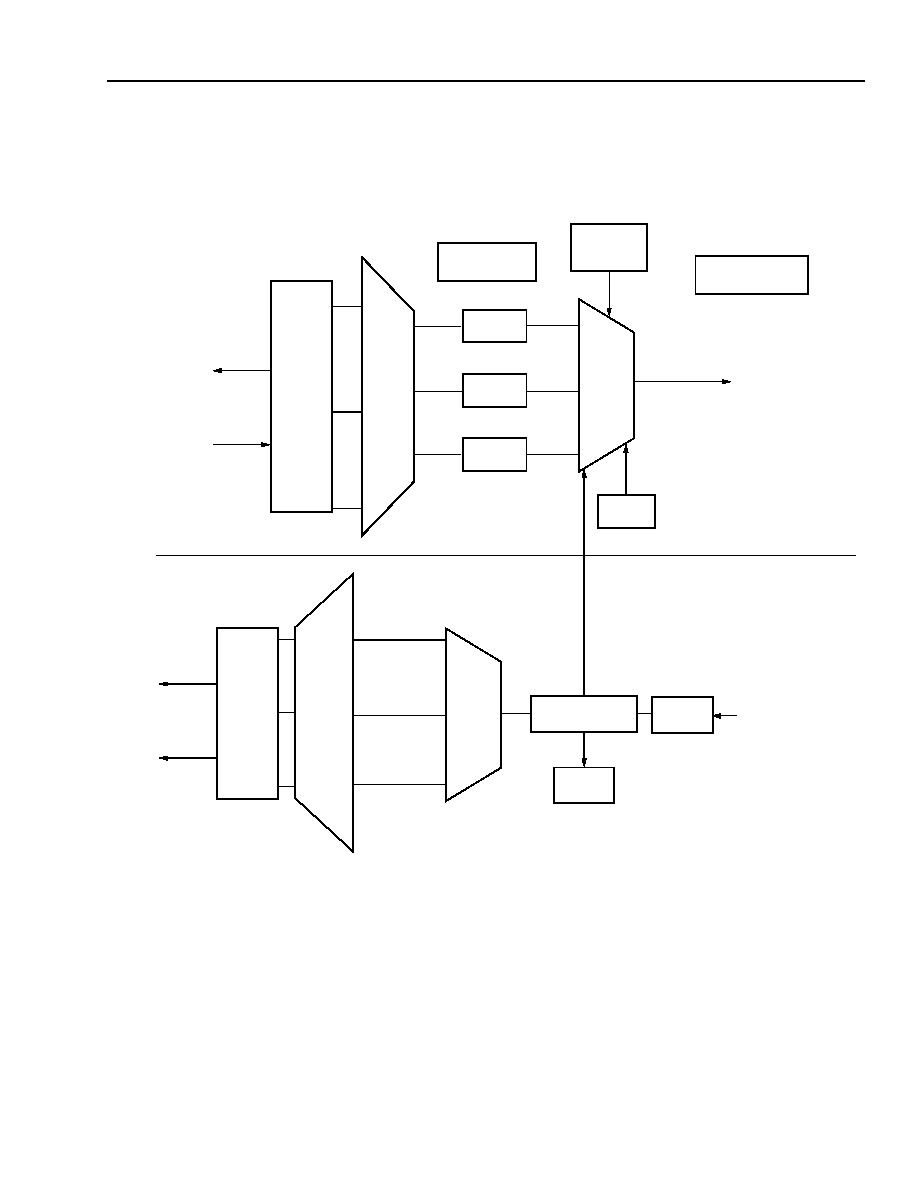

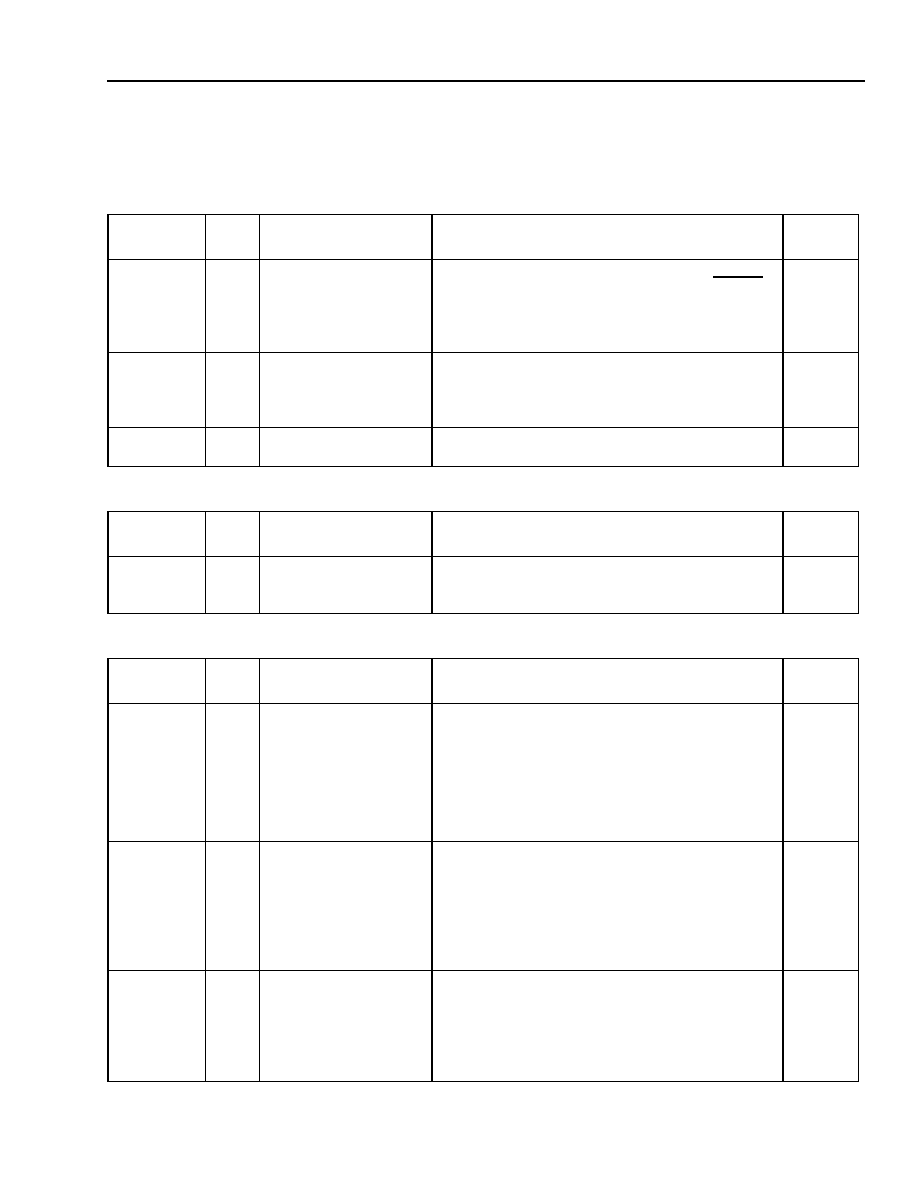

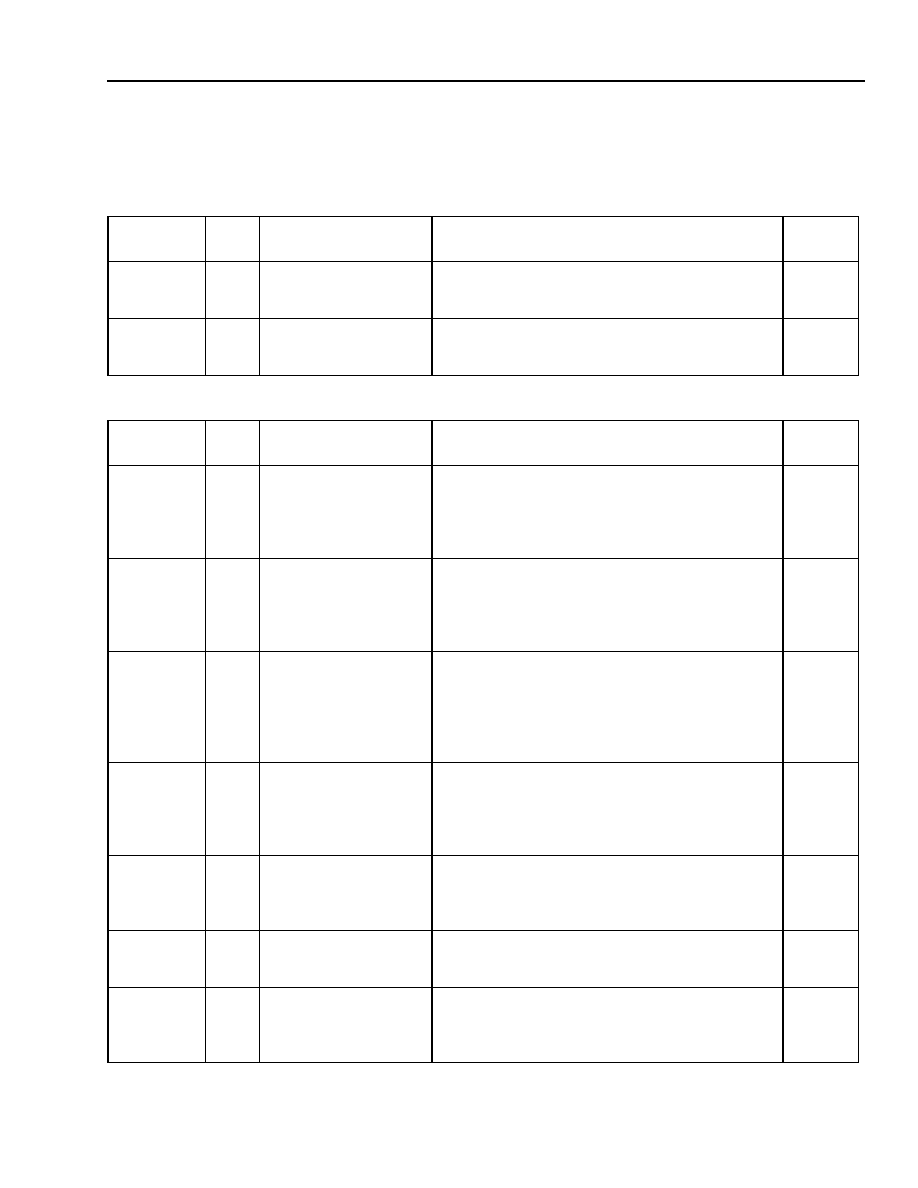

Table 3. Transmit Mode Control Signals

TSTS3_AU4

TSONET_SDH

Description

0 = STS-3

0 = SONET

1

1. SONET = OOF 0

1, 4 times detect; default output byte = 0x00.

Three STS-1 inputs multiplexed to an STS-3 output. Also used for

STS-1 mode. See STS-1 Mode section for details.

1 = AU-4

0 = SONET

*

Three AU-3 signals multiplexed to an STM-1 (AU-4) signal.

0 = STS-3

1 = SDH

2

2. SDH = OOF 0

1, 5 times detect; default output byte = 0xFF.

Three STS-1 inputs multiplexed to an STS-3 output.

1 = AU-4

1 = SDH

Three AU-3 signals multiplexed to an STM-1 (AU-4) signal.

Table 4. Receive Mode Control

RSTS3_AU4 RSONET_SDH

Description

0 = STS-3

0 = SONET

1

1. SONET = OOF 0

1, 4 times detect; default output byte = 0x00; ignore SS bits.

One STS-3 input demultiplexed to three STS-1 outputs. Also used

for STS-1 mode. See STS-1 Mode section for details.

1 = AU-4

0 = SONET

*

One STM-1 (AU-4) input demultiplexed to three AU-3 outputs.

0 = STS-3

1 = SDH

2

2. SDH = OOF 0

1, 5 times detect; default output byte = 0xFF; verify SS bits = 10.

One STS-3 input demultiplexed to three STS-1 outputs.

1 = AU-4

1 = SDH

One STM-1 (AU-4) input demultiplexed to three AU-3 outputs.

Agere Systems Inc.

17

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

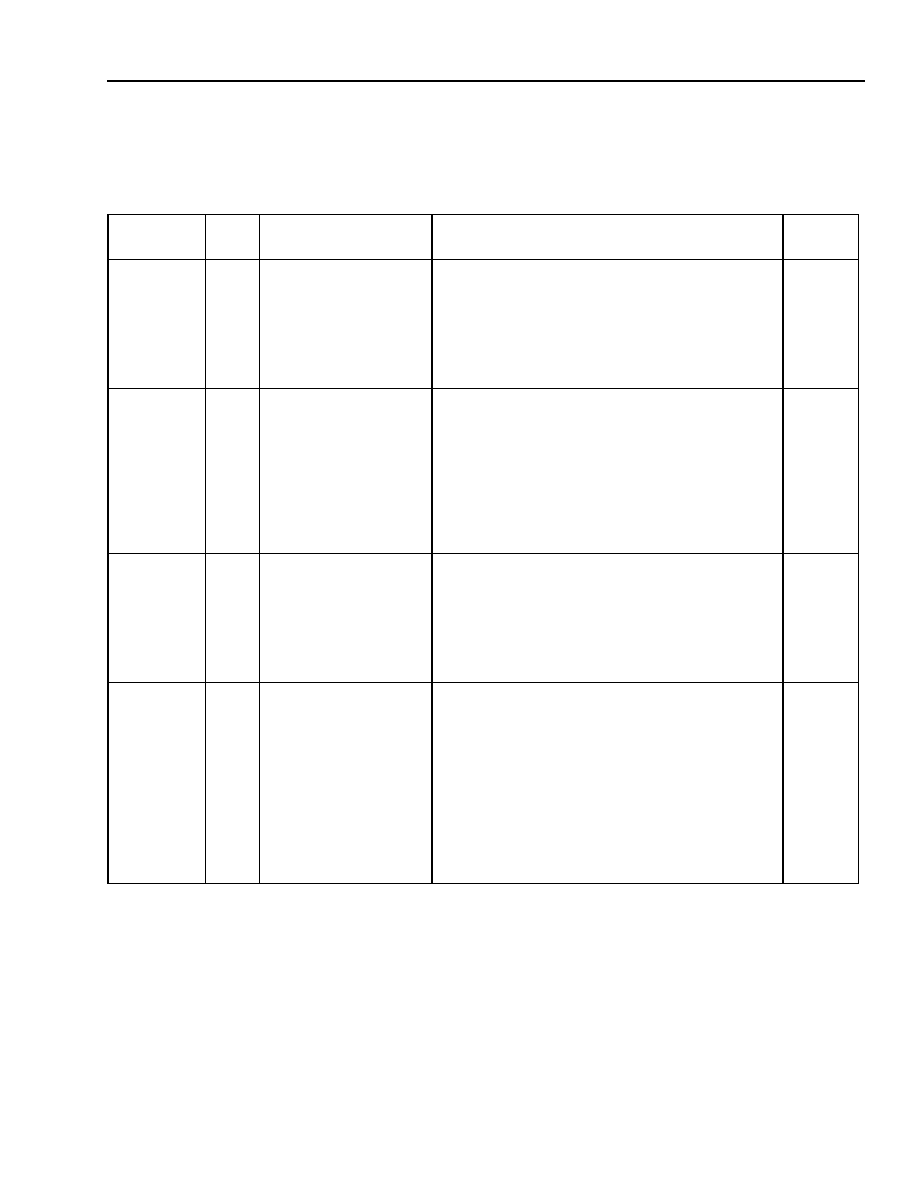

Transmit Direction Overview

The following major functions are performed in the transmit direction: STS-1/AU-3 bus mode retiming, input select

control, STS-1/AU-3 inputs, out-of-frame (OOF) and loss-of frame (LOF) monitoring, descramble enable/disable,

monitor B1 and B2 errors, H4 multiframe and pointer monitor (AU-4 mode only), STS-3 generate, STM-1 (AU-4)

frame generation (AU-4 mode), transport overhead access channel (TOAC) insert, STS-3/STM-1 (AU-4) scramble

enable, STS-3/STM-1 (AU-4) loopback control, and STS-3/STM-1 (AU-4) output interface.

STS-1/AU-3 Bus Mode Input Retiming

The bus mode provides a single byte-wide bus and parity bit that is shared with up to three devices at

19.44 Mbits/s. The device will source a clock (19.44 MHz), synchronous payload envelope (SPE) indicator, J0J1V1

indicator, and V1 time indicator signals toward the downstream devices. These signals guarantee frame alignment

between all three STS-1/AU-3 inputs and H4 byte multiframe values (AU-4 mode). The V1 time signal can be dis-

abled under software control (TLSV1DISABLE, 0x35).

The clock can be inverted leaving the device (TLSCLKINV, 0x35). An odd/even parity bit (TLSVOEPAR, 0x35) is

verified per byte transfer (TLSPARE[3--1], TLSPARM[3--1], 0x07, 0x10).

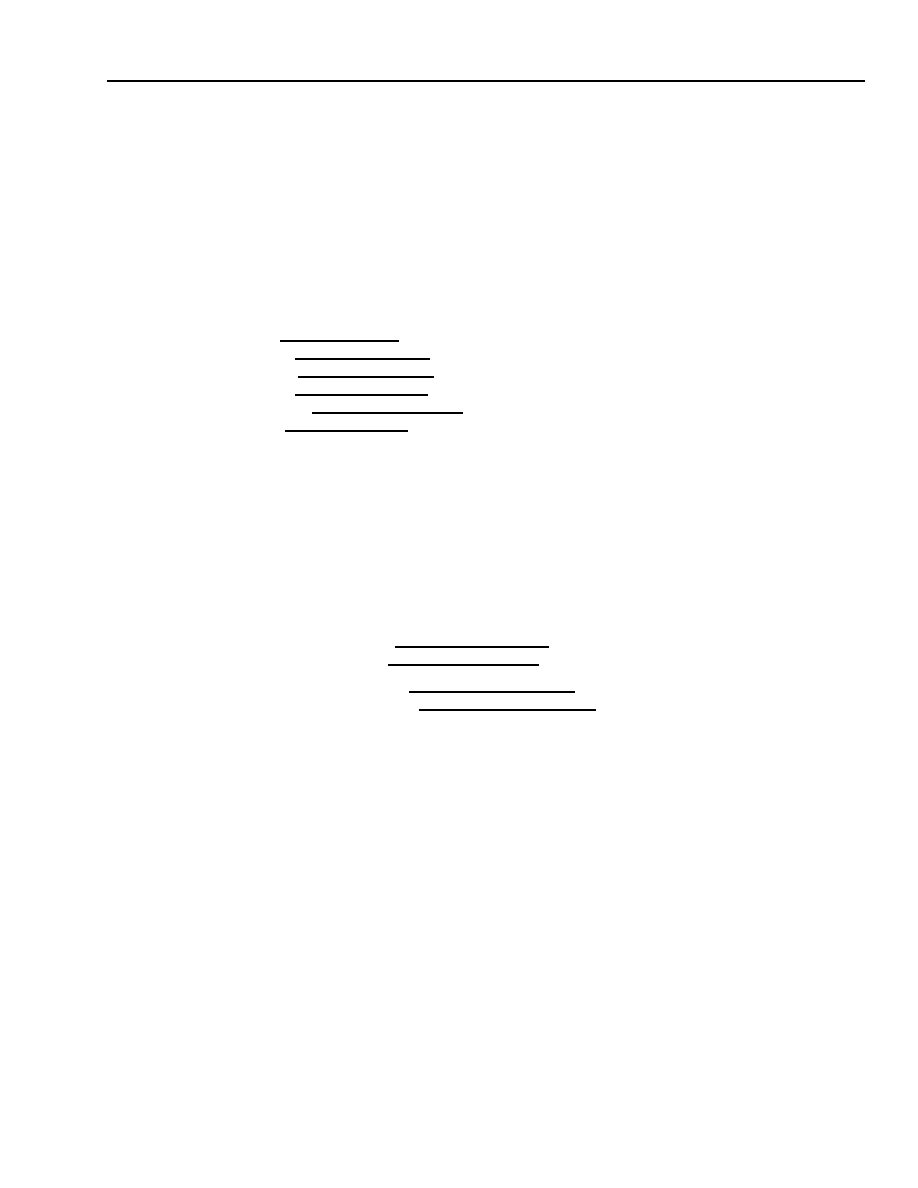

Input Select Control

This function determines which signals are multiplexed to form the STS-3 signal. These control bits (TSEL[3--

1][2:0], 0x3A, 0x38, 0x36) allow loopback (STS-1/AU-3-R to STS-1/AU-3-T), input shuffle, and multicast opera-

tions to be possible. The selected STS-1/AU-3 inputs are labeled S#1T, S#2T, and S#3T in Figure 1.

STS-1/AU-3 Inputs

The SONET/SDH STS-1/AU-3 frame is comprised of 9 rows x 90 columns that repeat at an 8 kHz rate. Each col-

umn is 1-byte wide. The frame contains three columns of transport overhead, one column of path overhead, and

86 columns of payload. For column byte definitions, see Table 6 on page 18.

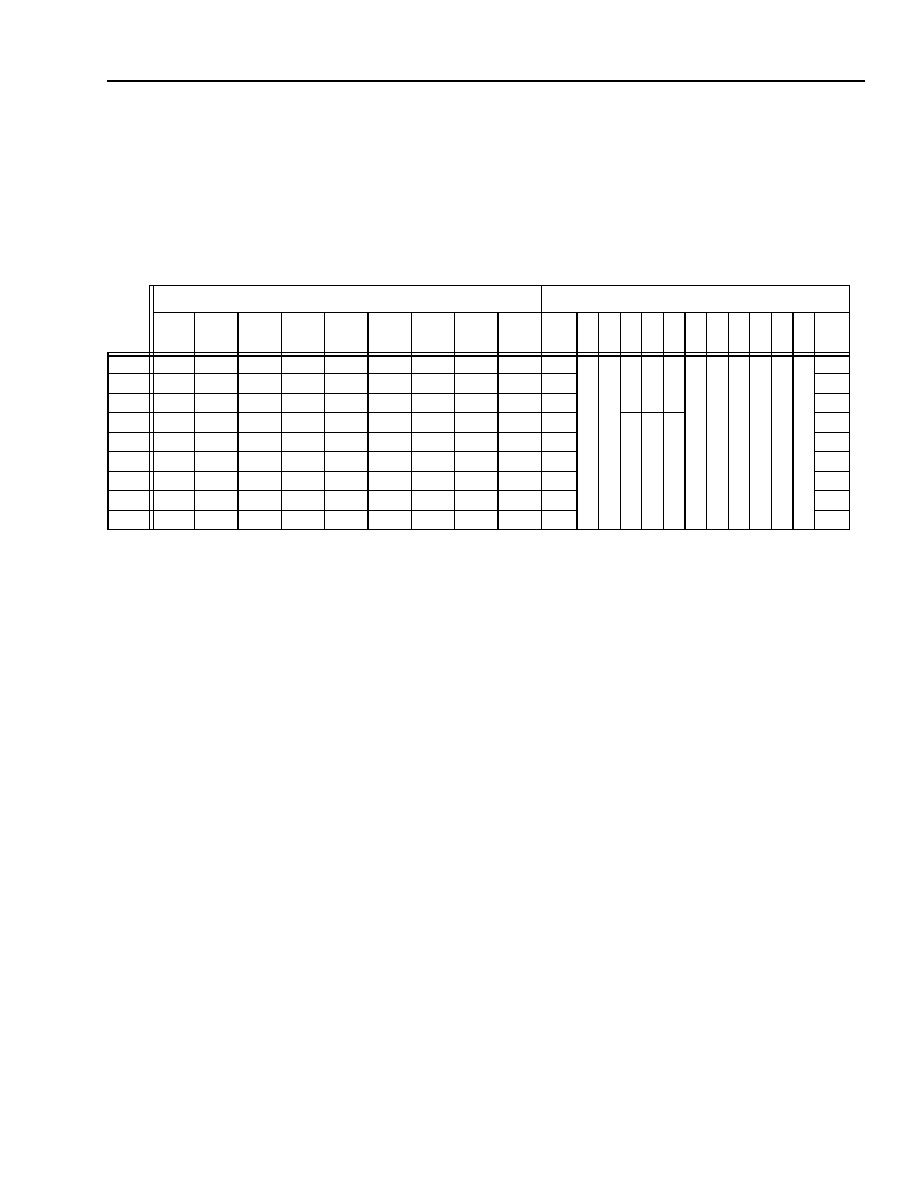

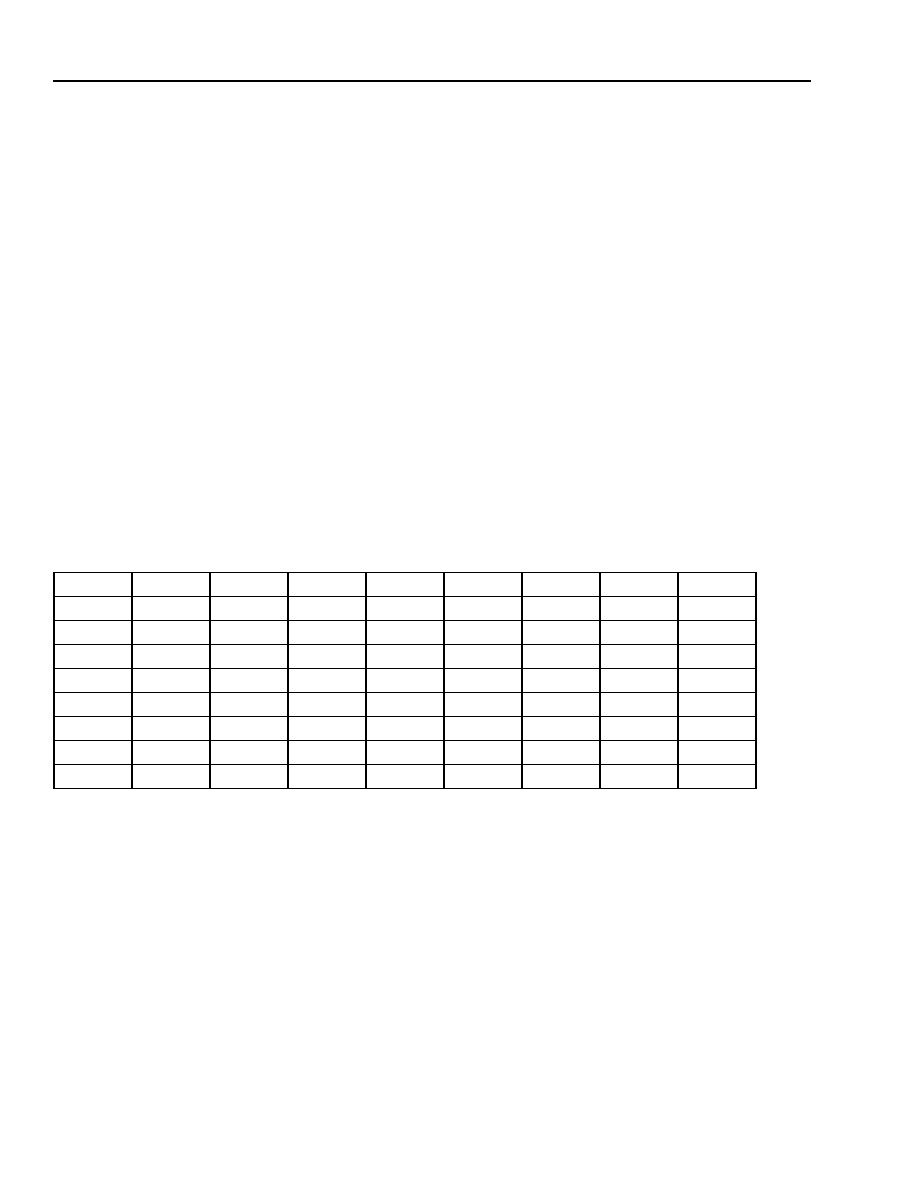

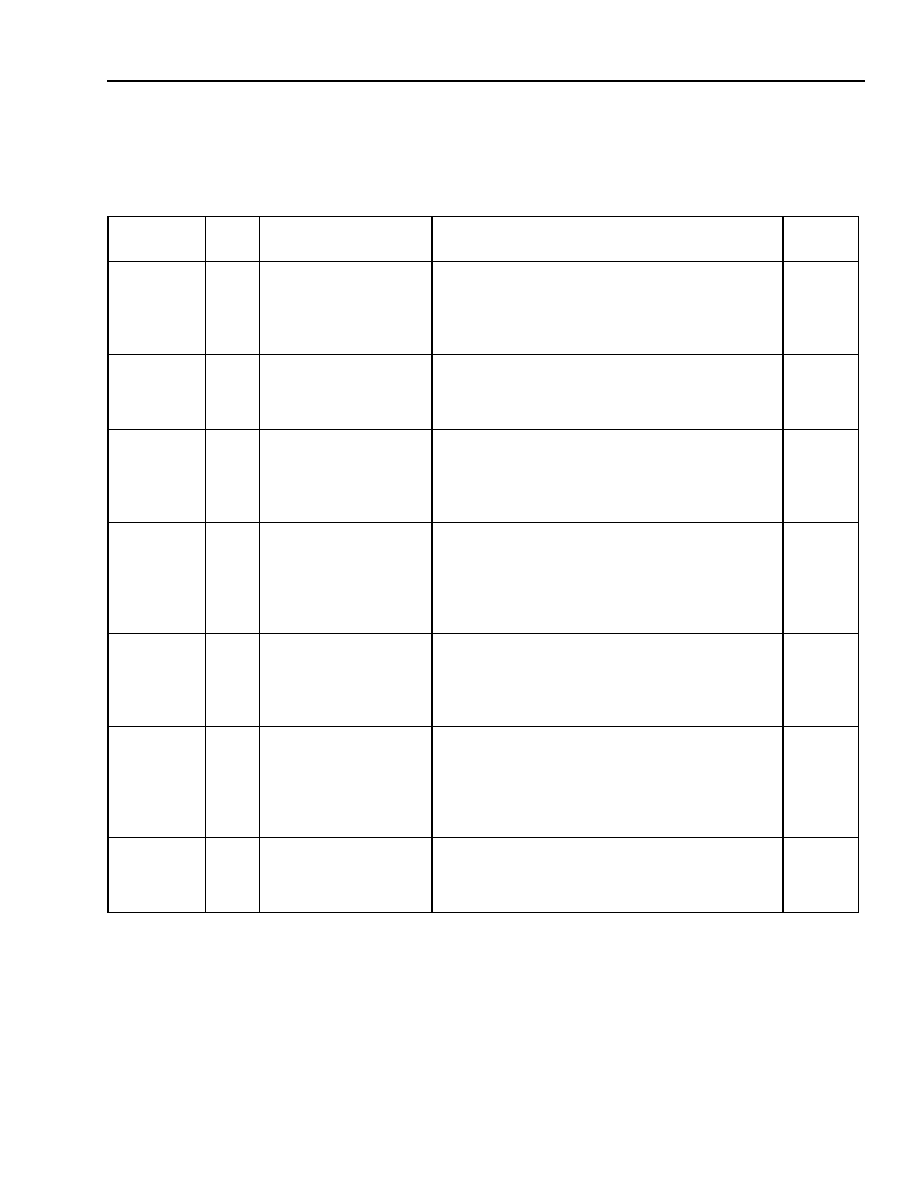

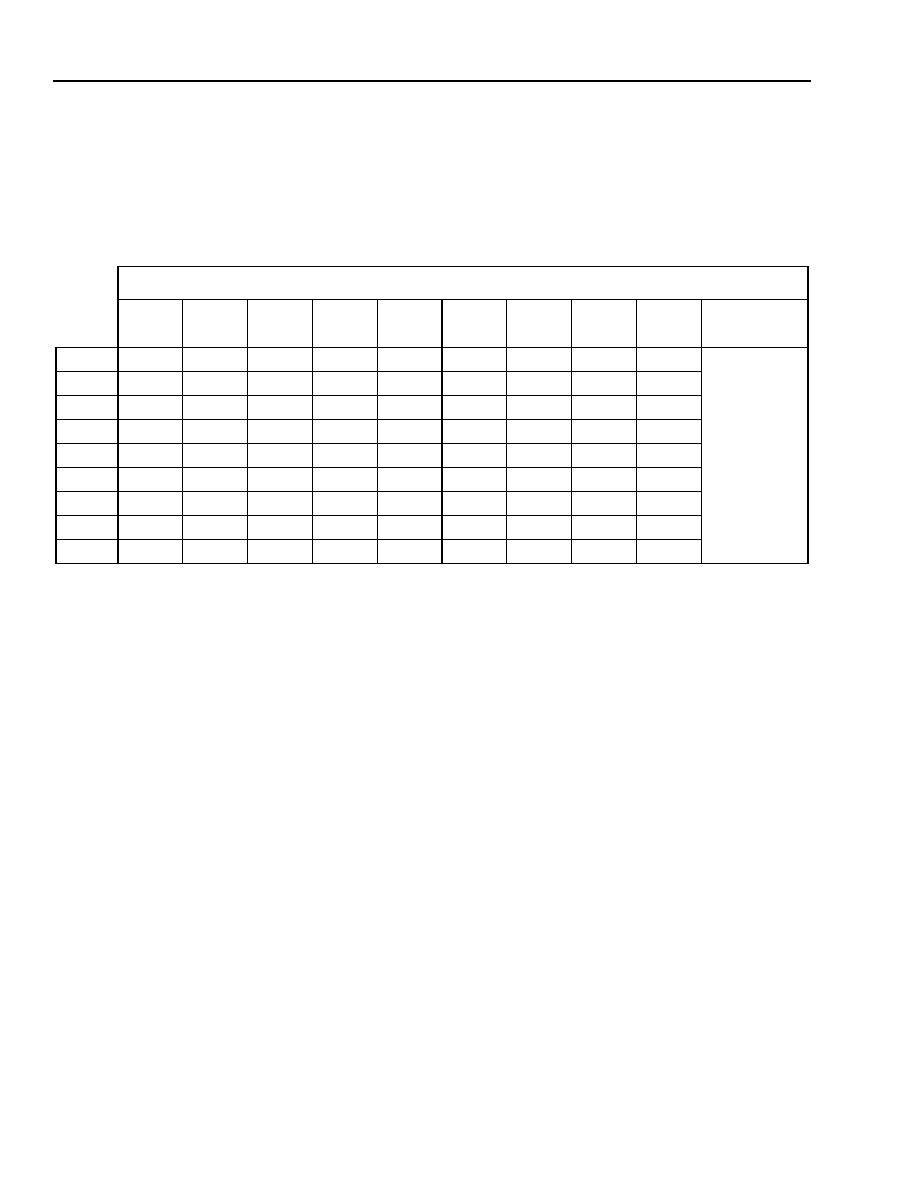

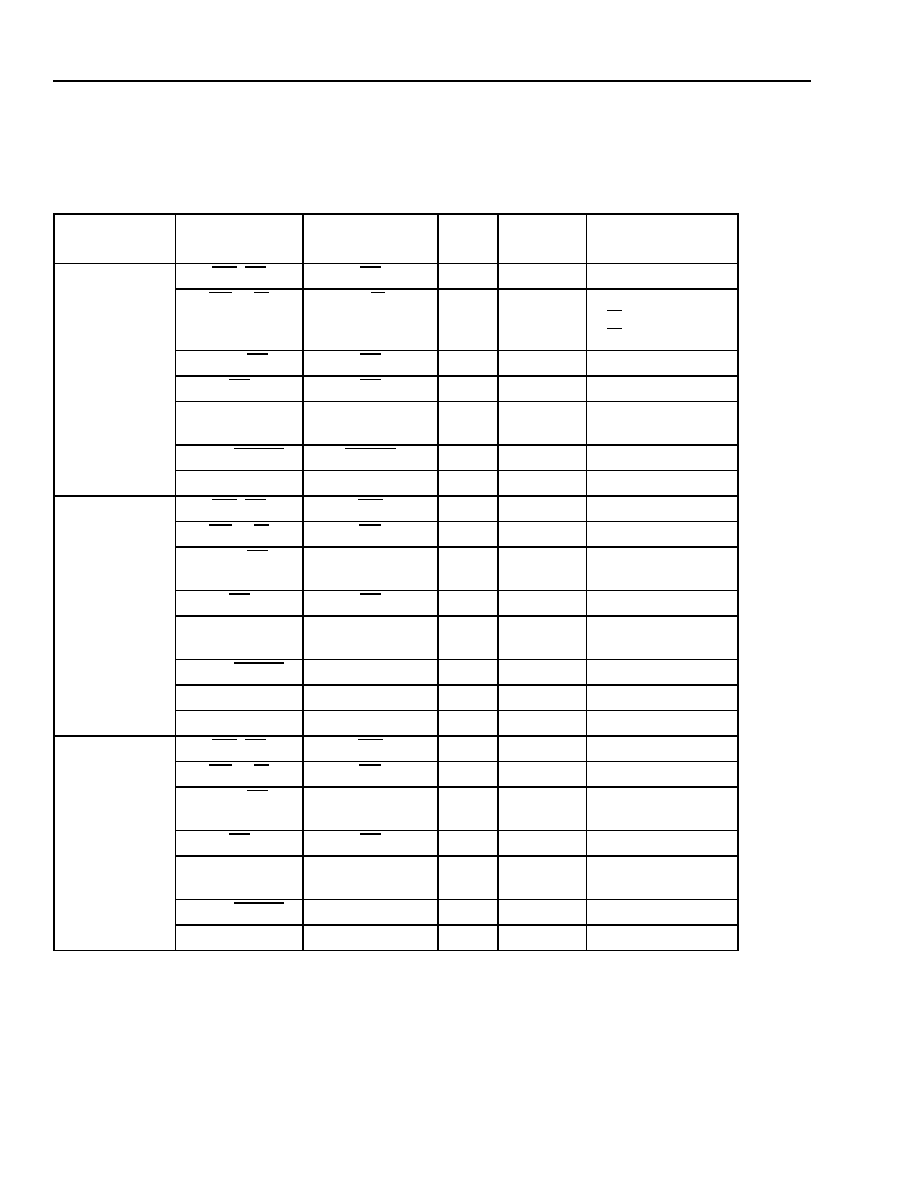

Table 5. Input Select Control

TSEL

[3--1][2:0]

Output

000 (0)

STS-1/AU-3 #1 Transmit

001 (1)

STS-1/AU-3 #2 Transmit

010 (2)

STS-1/AU-3 #3 Transmit

011 (3)

STS-1/AU-3 #1 Receive (Loopback)

STS3 Mode Only

100 (4)

STS-1/AU-3 #2 Receive (Loopback)

STS3 Mode Only

101 (5)

STS-1/AU-3 #3 Receive (Loopback)

STS3 Mode Only

110 (6)

STS-1/AU-3 #1 Transmit

111 (7)

STS-1/AU-3 #1 Transmit

18

18

Agere Systems Inc.

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Transmit Direction Overview

(continued)

STS-1/AU-3 Inputs

(continued)

The 27 bytes of transport overhead from each STS-1/AU-3 input must be aligned* (A1-1, A1-2, A1-3 must all be

coincident from all three STS-1/AU-3 inputs) and are allocated as shown in Table 6

.

Monitored in STS-1 mode.

Monitored in AU-4 mode.

Note: X = don't care (payload).

The path overhead (POH) can start anywhere within the SPE and cannot be accessed in the STS-3 mode.

In the AU-4 mode, the pointer is fixed at 522\D; therefore, the J1 byte will always be in row 1, column 4. The H4

byte is the only valid byte in the POH and all other bytes are ignored.

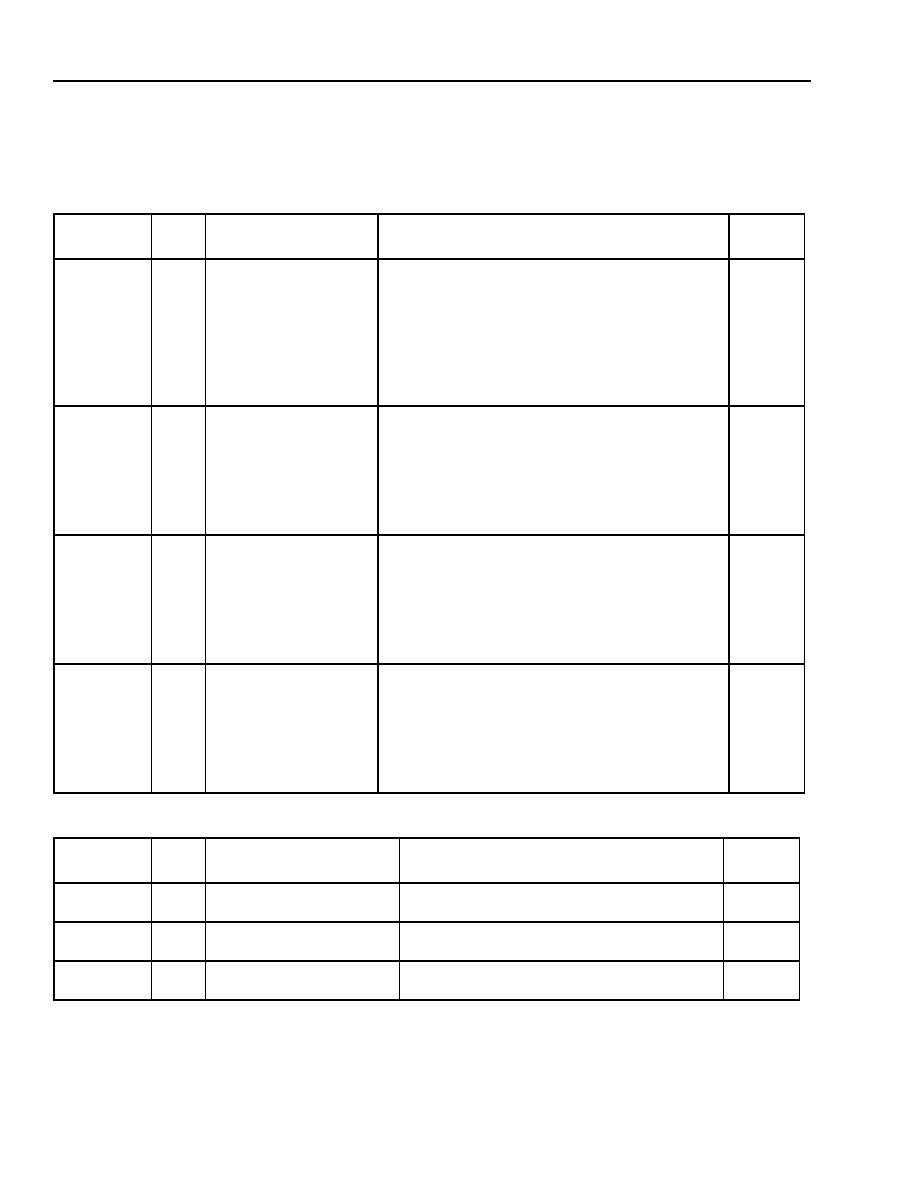

Out-of-Frame (OOF) and Loss-of-Frame (LOF) Monitoring

The device monitors for out-of-frame (OOF) and loss-of-frame (LOF) states on each selected STS-1/AU-3 input

(TLSOOF[3--1], TLSOOFD[3--1], TLSOOFM[3--1], TLSLOF[3--1], TLSLOFD[3--1, TLSLOFM[3--1], 0x08,

0x11, 0x19). Each input will be considered out-of-frame until two successive framing patterns (0xF628) separated

in time by 125 µs occur without framing byte errors. Each selected STS-1/AU-3 input will be considered in frame

until five (SDH)/four (SONET) successive frames separated in time by 125 µs occur with errored framing patterns.

The device will be considered in the LOF state when an OOF condition persists for 24 consecutive frames (3 ms)

or clear when the OOF condition is inactive for 24 consecutive frames (3 ms) with the correct framing patterns

spaced 125 µs apart.

Descramble Enable/Disable

Each selected STS-1/AU-3 input can be descrambled (TLSDSCR[3--1], 0x3A, 0x38, 0x36) according to the

frame synchronous descrambling sequence 1 + x

6

+ x

7

. The sequence is reset to 1111111 at the beginning of the

byte following the C1 byte and descrambles all of the STS-1/AU-3 data except the A1, A2, and J0 bytes. Writing a

logic 1 to the appropriate bit causes the selected STS-1/AU-3 signal to be descrambled.

* Can be provided by the Agere TMPR28051 mapper device.

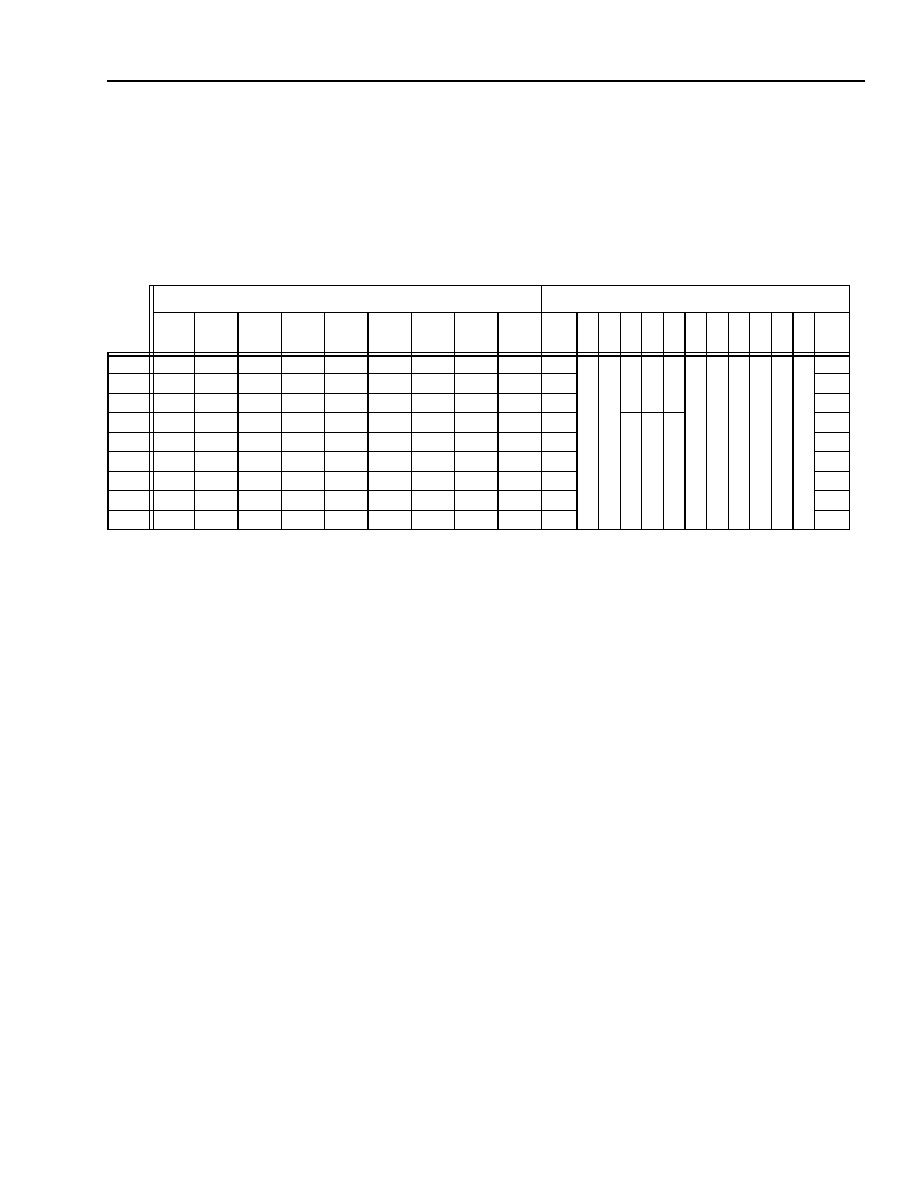

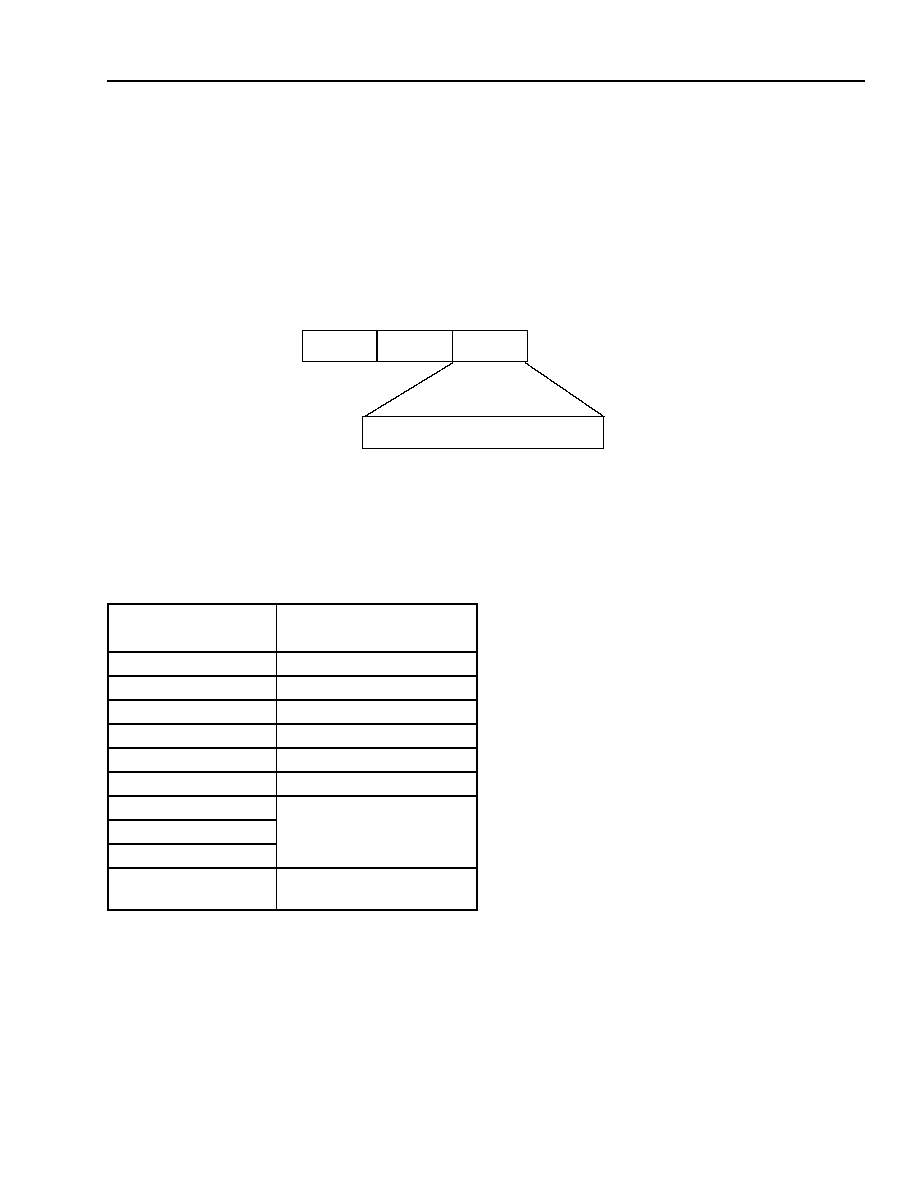

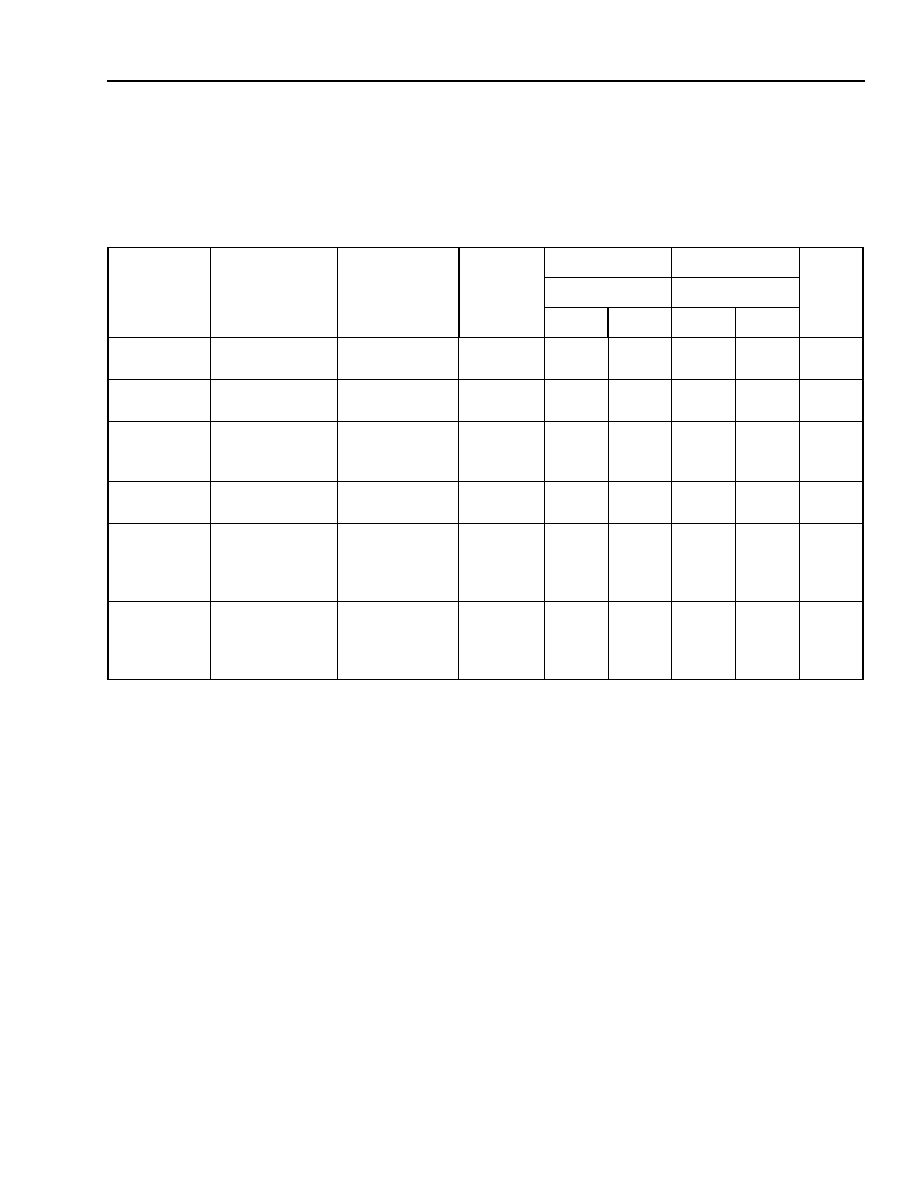

Table 6. Expected STS-1/AU-3 Input Frame Format

Transport Overhead

Payload

Col. 1

Col. 2

Col. 3

Col. 4

Col. 5--90

Row 1

A1

A2

J0

J1

X

Row 2

B1

E1

F1

B3

X

Row 3

D1

D2

D3

C2

X

Row 4

H1

H2

H3

G1

X

Row 5

B2

K1

K2

F2

X

Row 6

D4

D5

D6

H4

X

Row 7

D7

D8

D9

Z3

X

Row 8

D10

D11

D12

Z4

X

Row 9

S1

M0

E2

Z5

X

Agere Systems Inc.

19

Data Sheet

April 2001

TMUX03155 STS-3/STM-1 (AU-4) Multiplexer/Demultiplexer

Transmit Direction Overview