Data Sheet, Revision 3

September 21, 2005

TSI-1

1k x 1k Time-Slot Interchanger

1 Introduction

The last issue of this data sheet was August 31, 2005. A change history is included in Section

11 Change History on page

61

. Red change bars have been installed on all text, figures, and tables that were added or changed. All changes to the text

are highlighted in red. Changes within figures, and the figure title itself, are highlighted in red, if feasible. Formatting or

grammatical changes have not been highlighted. Deleted sections, paragraphs, figures, or tables will be specifically

mentioned.

This document consists of two major sections:

The

TSI-1

device hardware description. This section contains ball information, operating conditions, dc electrical charac-

teristics, timing diagrams, ac characteristics, and packaging information.

The

TSI-1

device register description. This section contains register information.

1.1 Related Documents

The documentation package for this device consists of the following documents:

The TSI-1 1k x 1k Time-Slot Interchanger Product Brief, the TSI Family Selection Guide, the TSI-1 1k x 1k Time-Slot

Interchanger Data Sheet (this document), and the TSI-1 Time-Slot Interchanger System Design Guide.

These documents are available on the public website shown below.

If the reader displays this document using Acrobat Reader

�

, clicking on any blue text will bring the reader to that reference

point.

To access related documents, including the documents mentioned above, please go to the following public website, or con-

tact your Agere representative (see the last page of this document).

http://www.agere.com/telecom/time_slot_interchangers.html

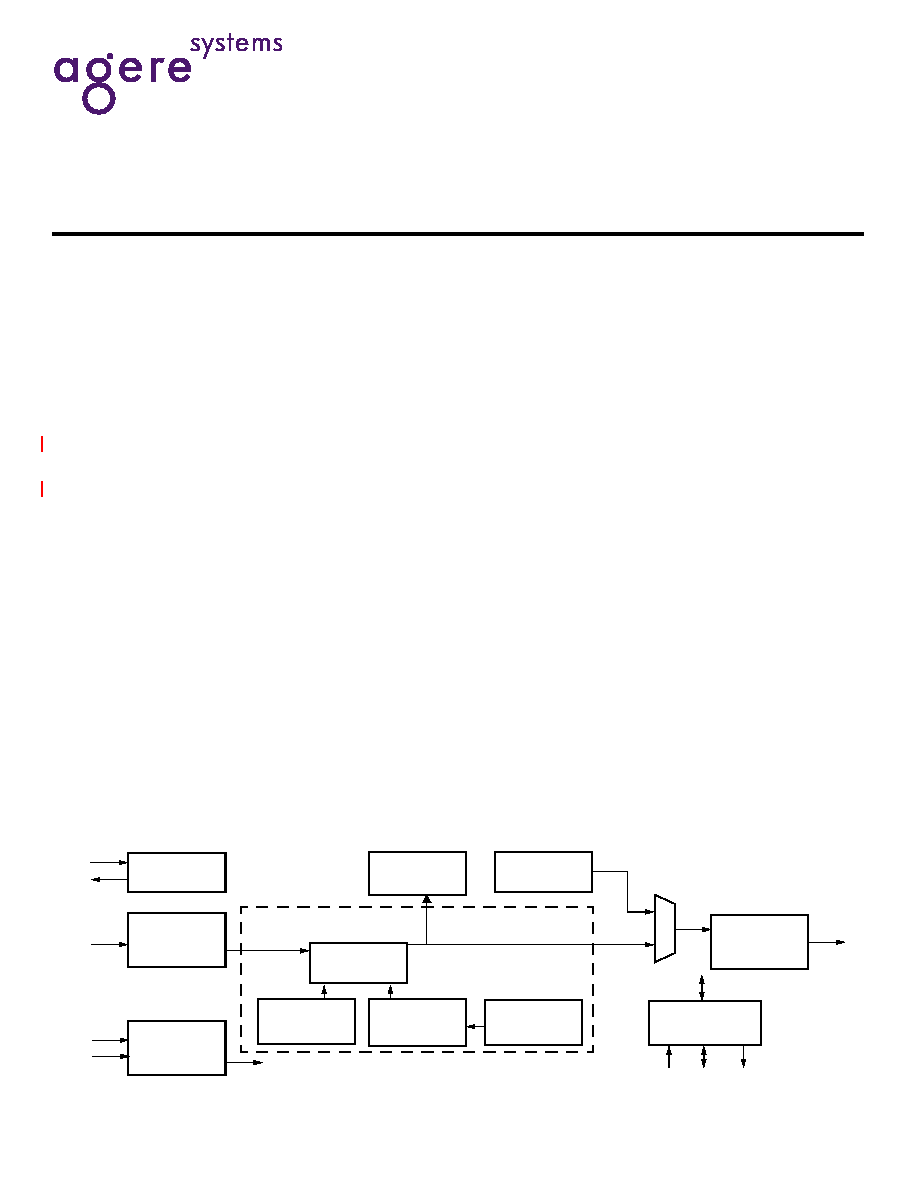

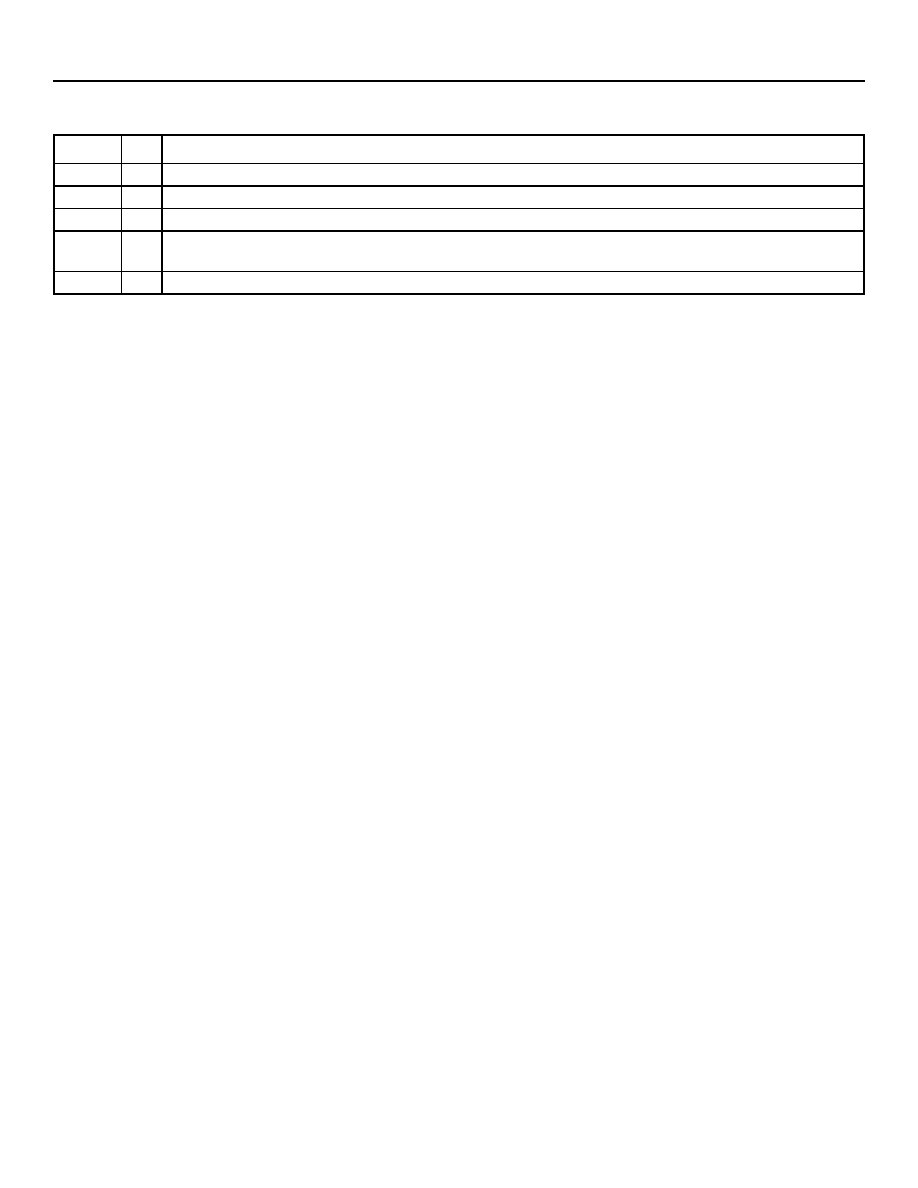

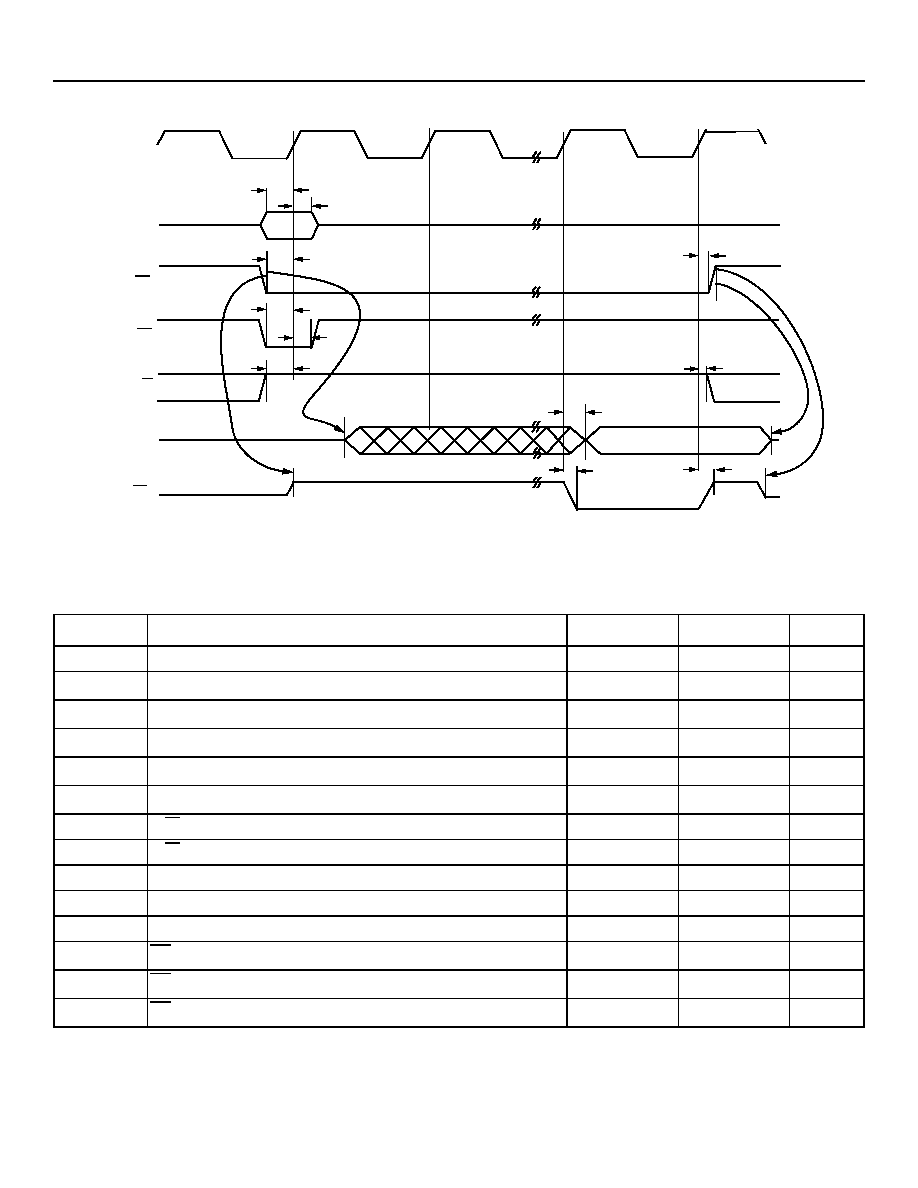

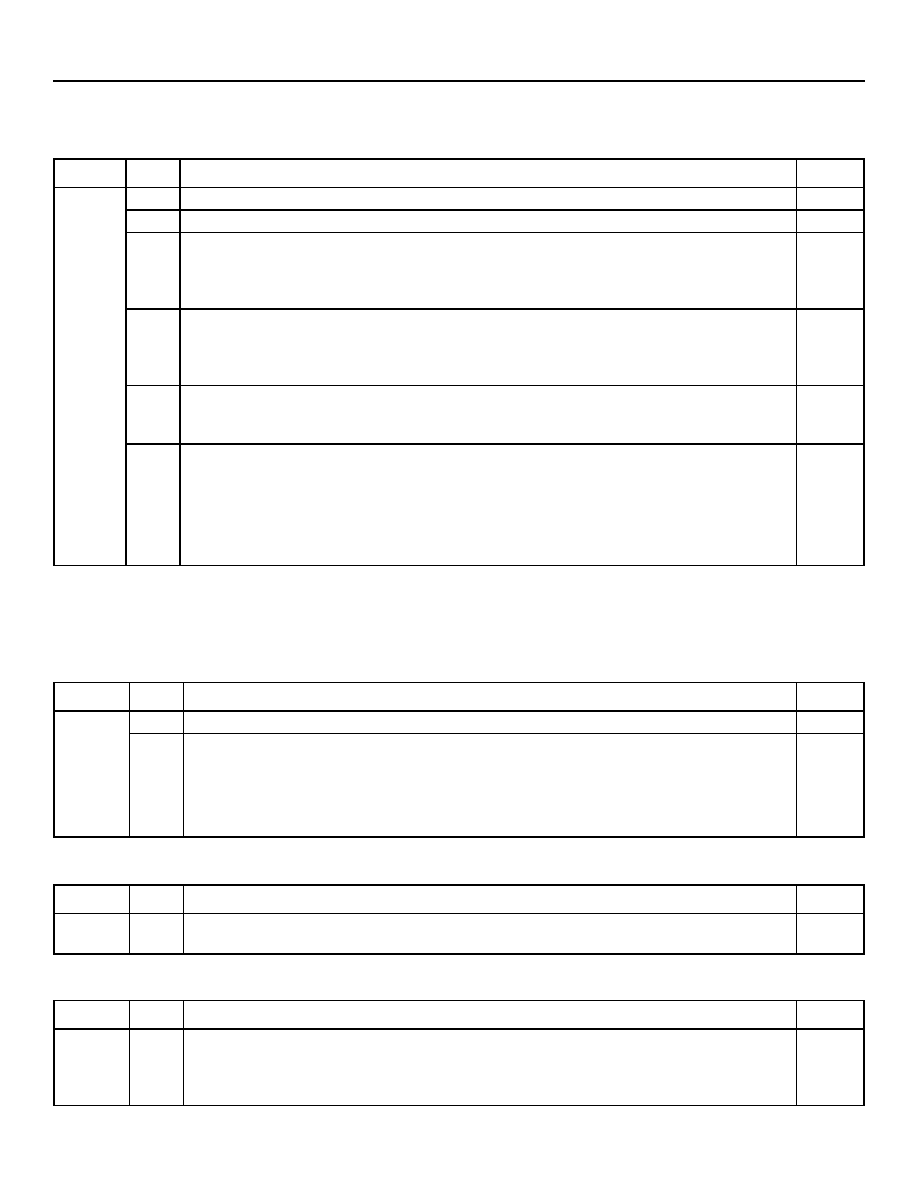

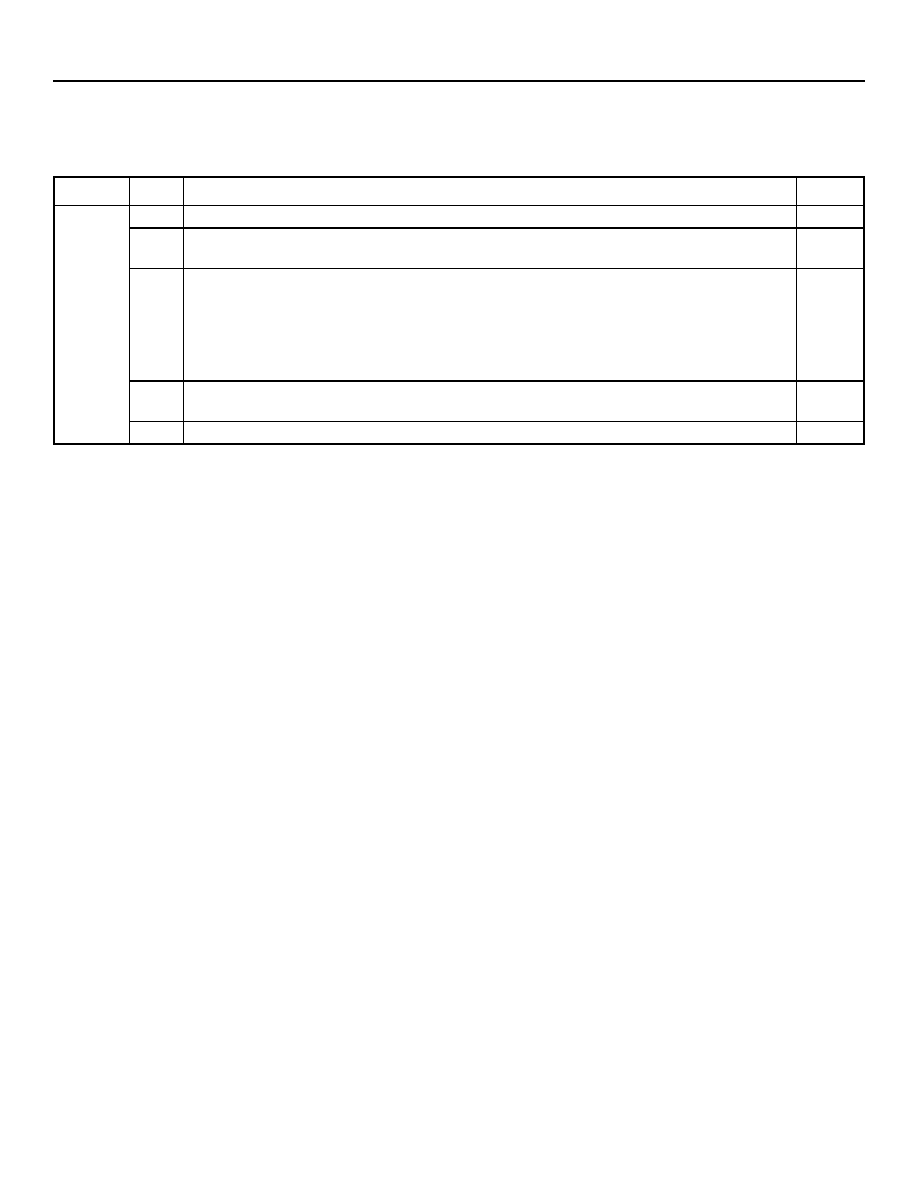

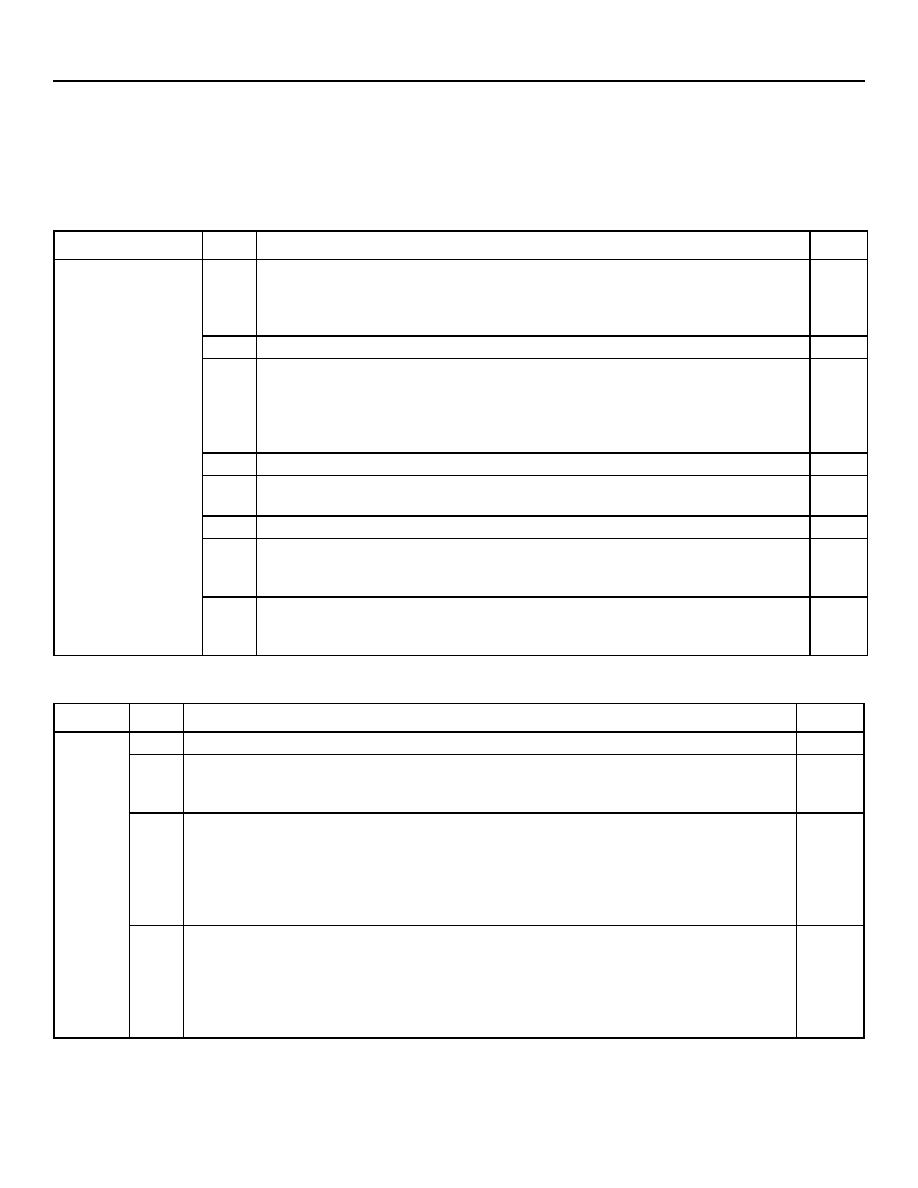

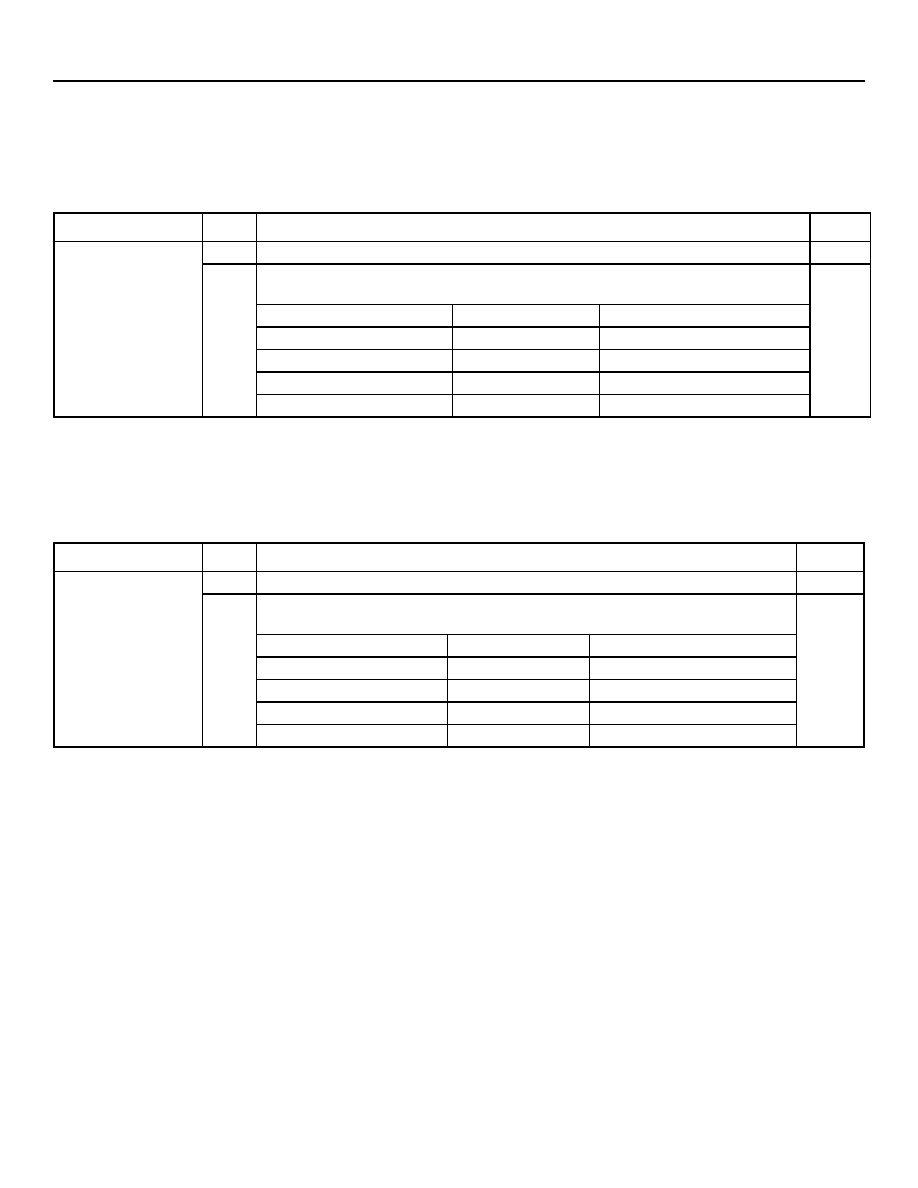

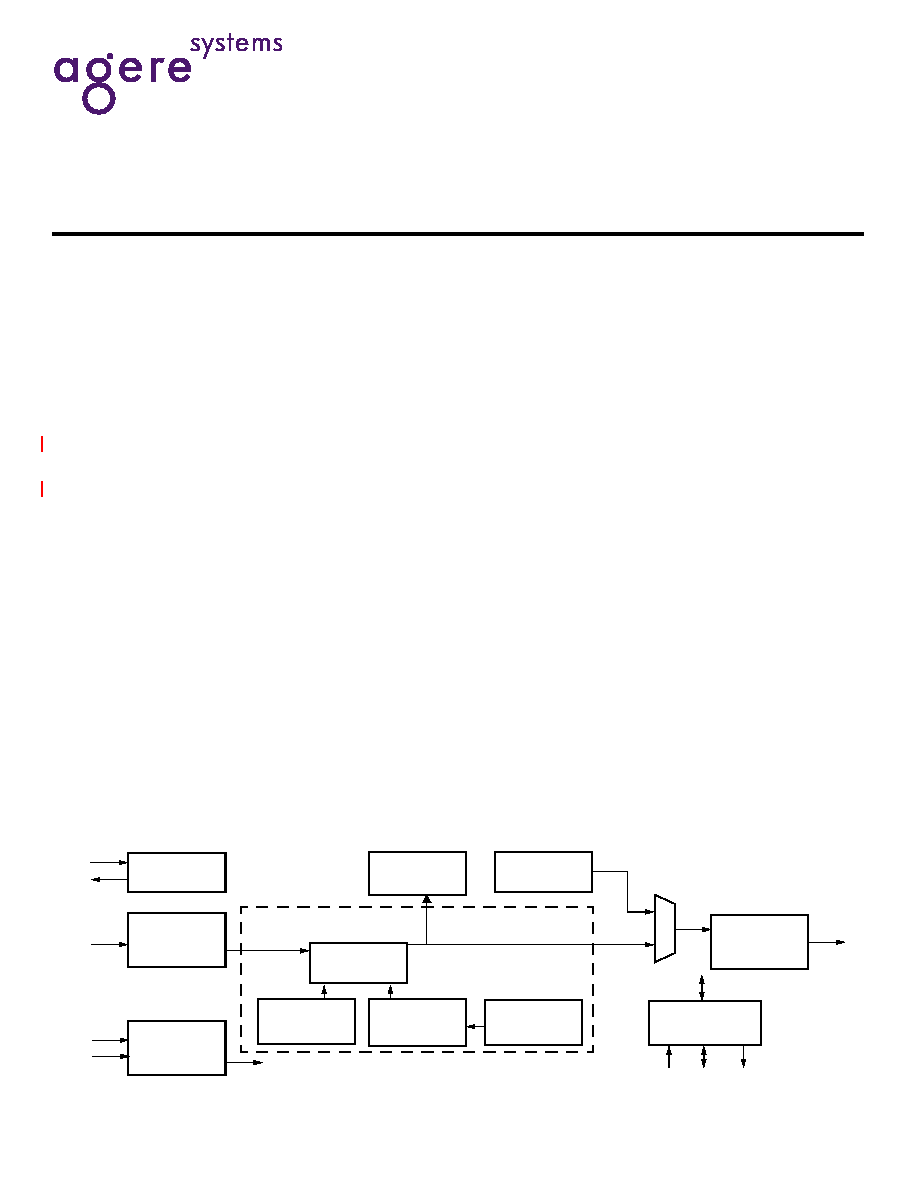

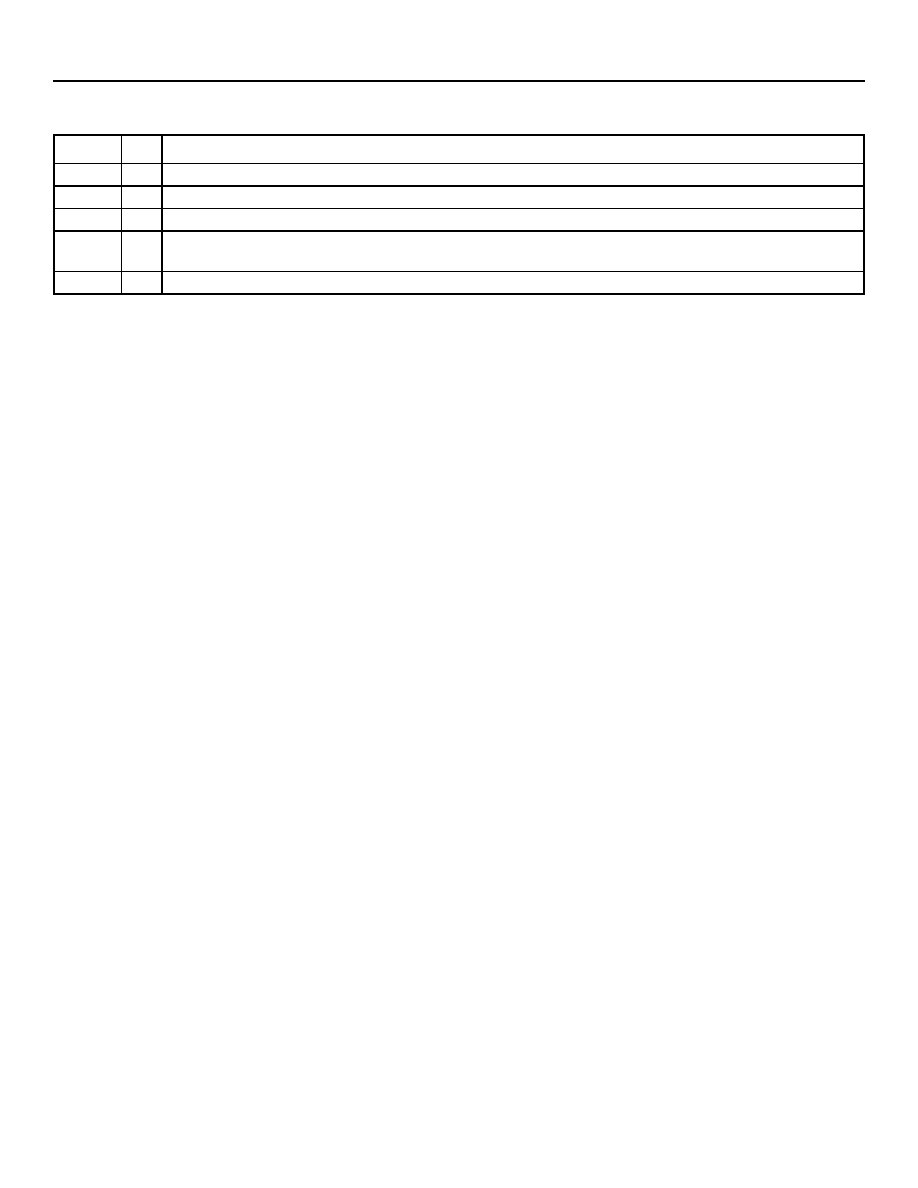

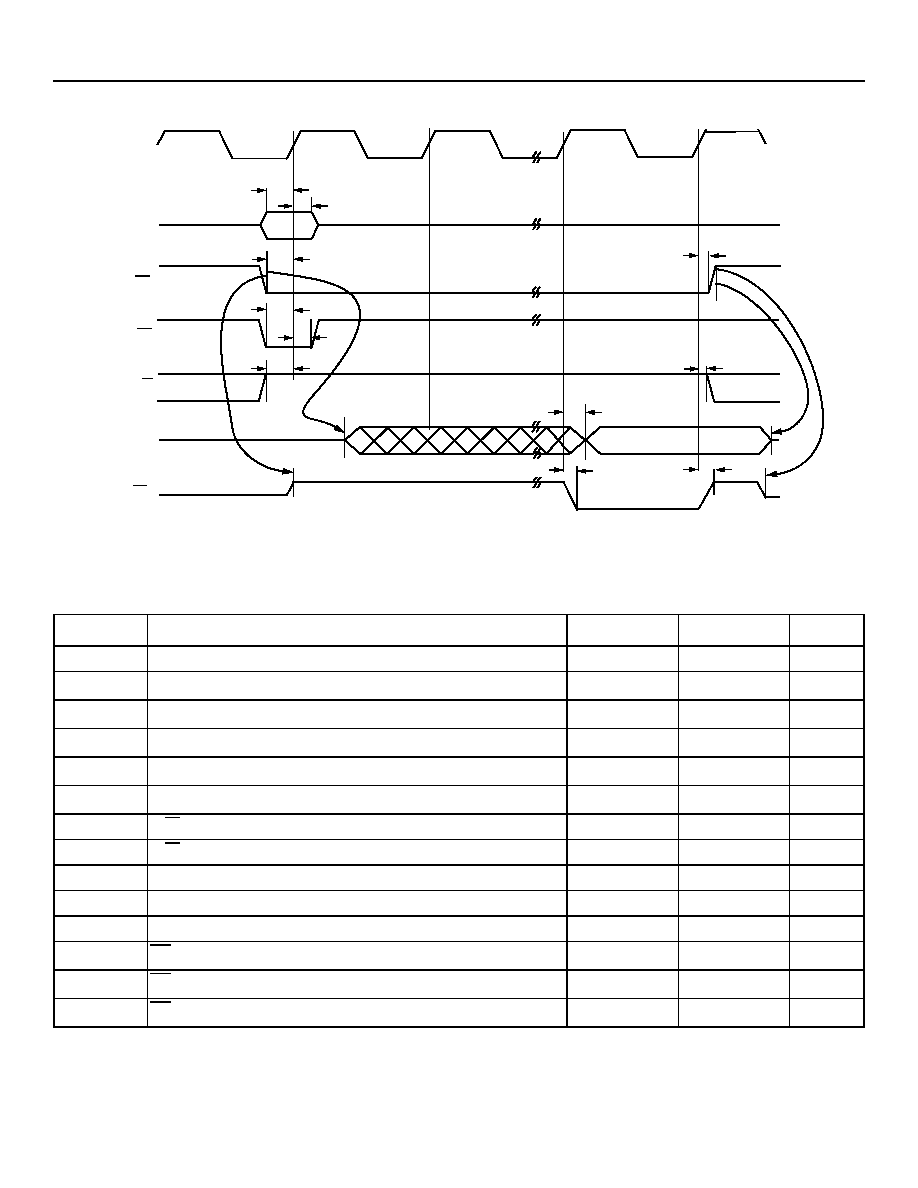

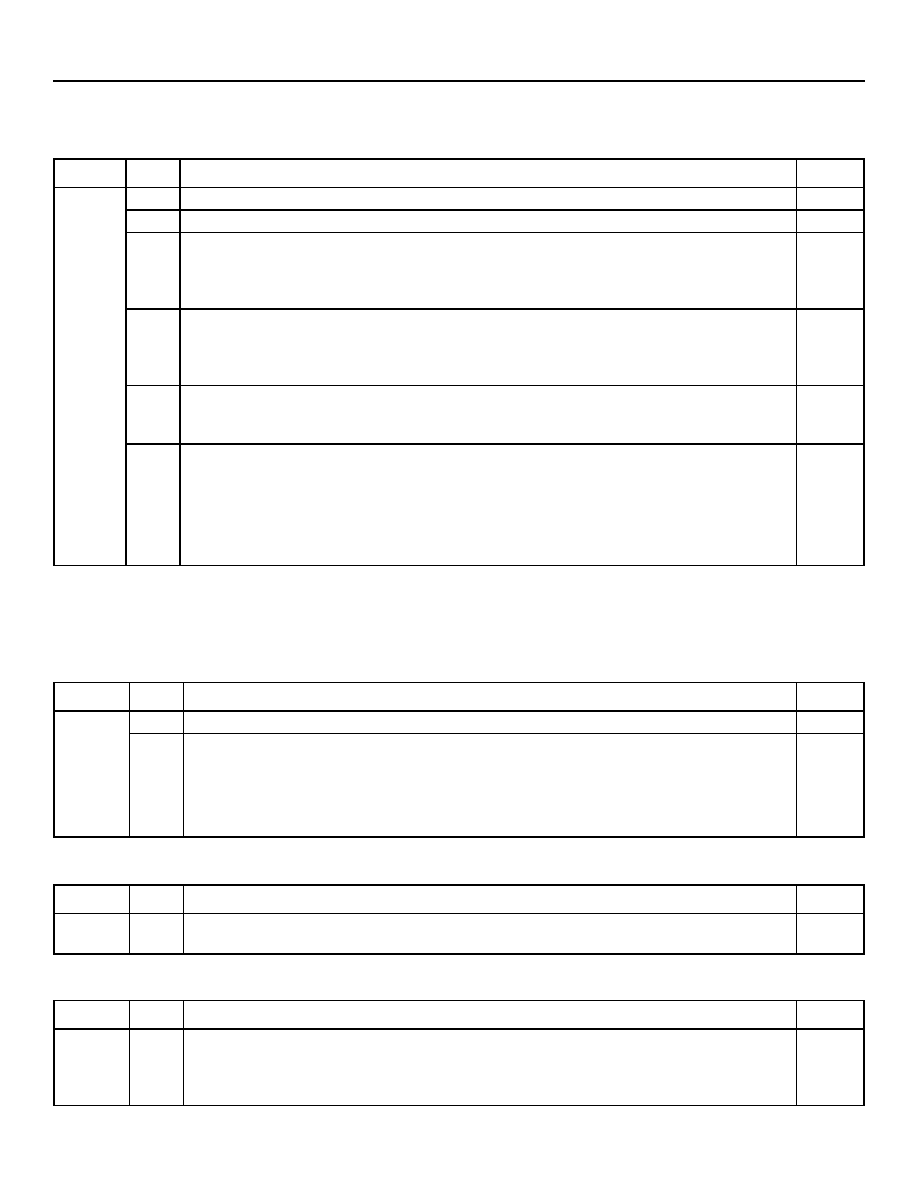

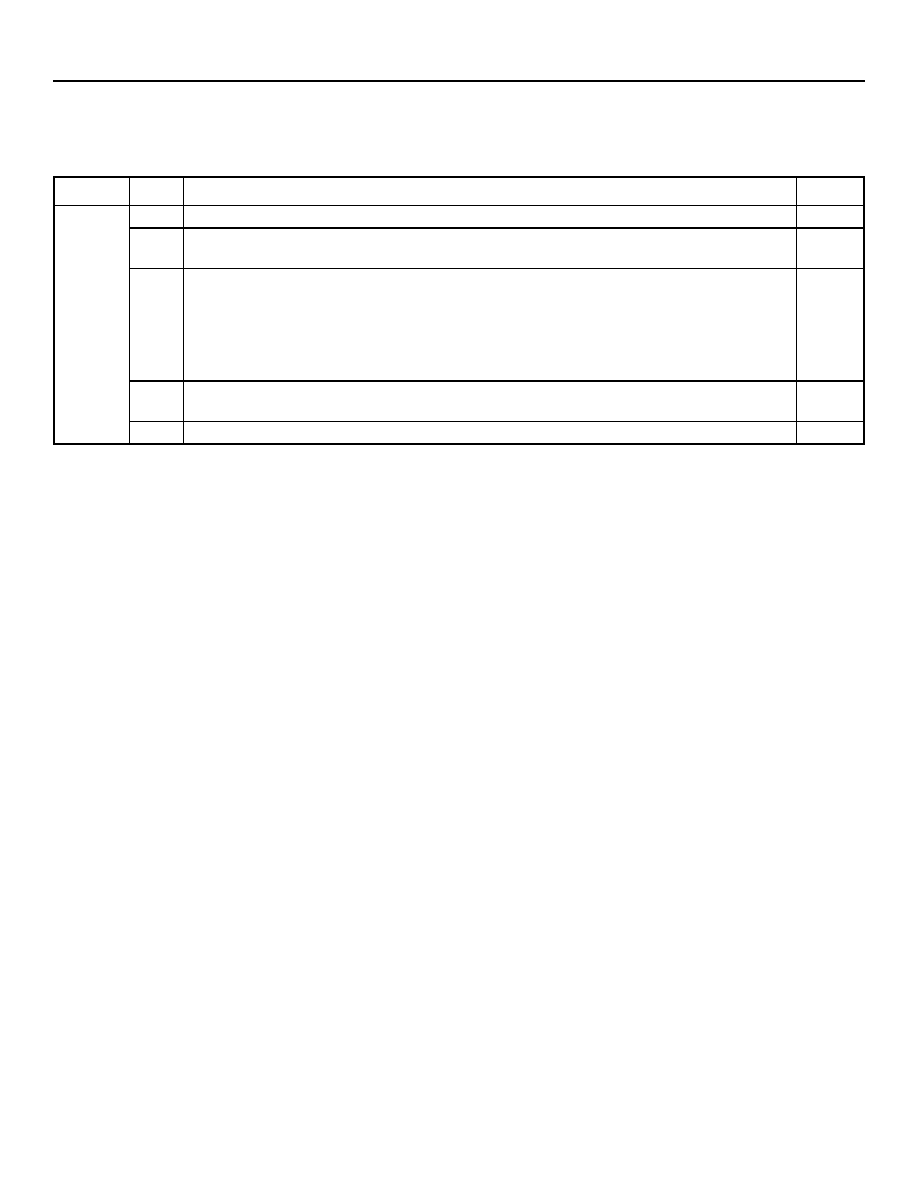

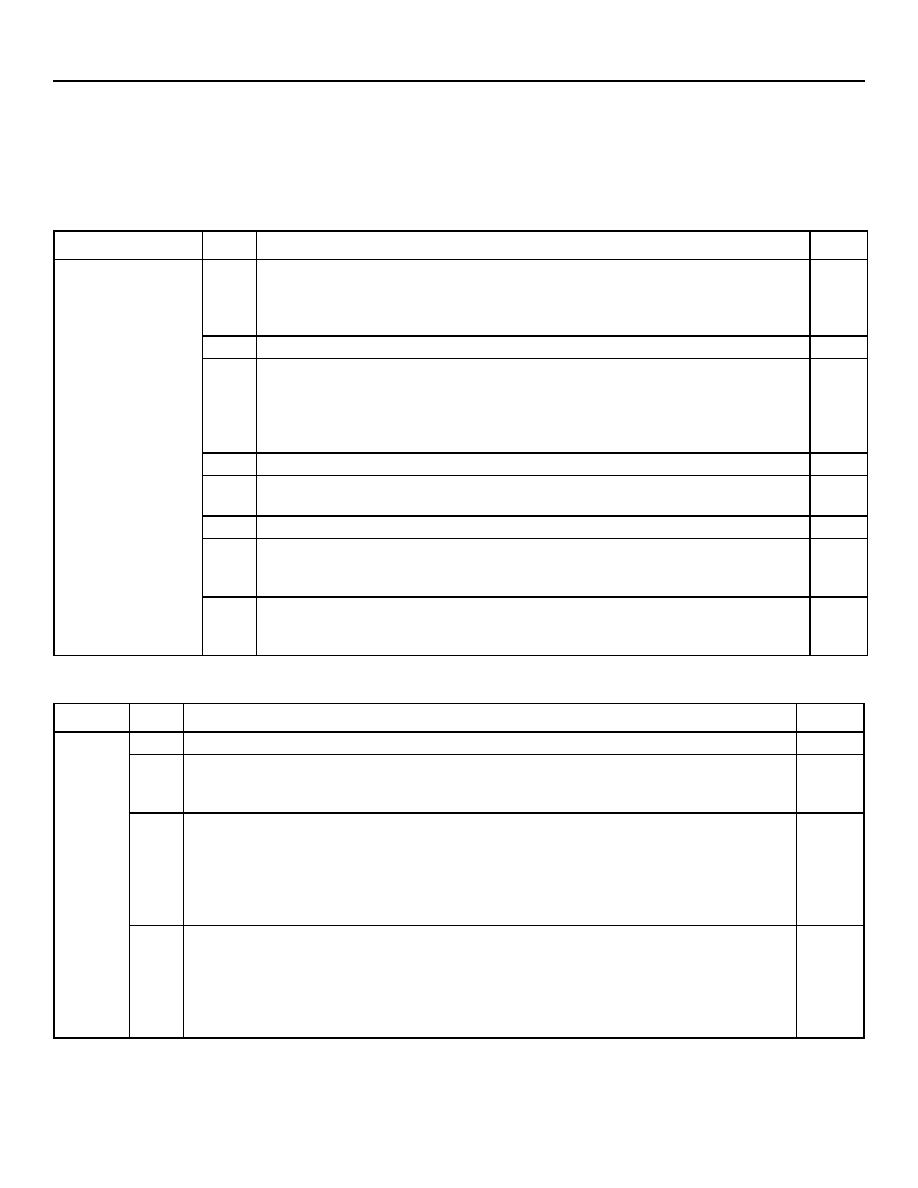

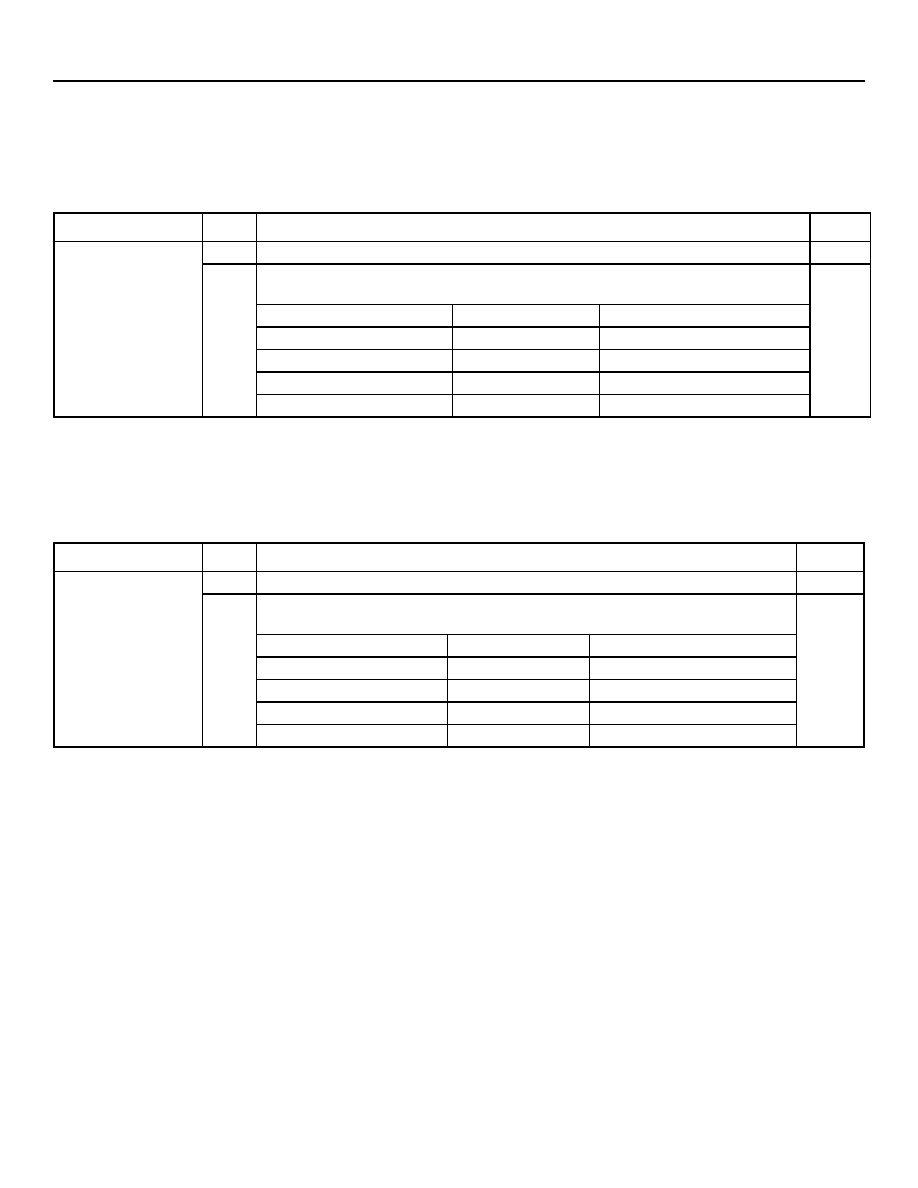

1.2 Block Diagram and High-Level Interface Definition

Figure 1-1. Block Diagram and High-Level Interface Definition

TEST ACCESS

PORT

READ ADDRESS

COUNTER

CONNECTION

STORE

WRITE ADDRESS

COUNTER

DATA

STORE

MICROPROCESSOR

INTERFACE

TRANSMIT

CHI

TEST PATTERN

GENERATOR

TEST PATTERN

MONITOR

CLOCK

GENERATOR

RECEIVE

CHI

16

16

1k x 1k

Switch Fabric

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

Table of Contents

Contents

Page

2

2

Agere Systems Inc.

1 Introduction .........................................................................................................................................................................1

1.1 Related Documents .....................................................................................................................................................1

1.2 Block Diagram and High-Level Interface Definition .....................................................................................................1

2 Ball Information ...................................................................................................................................................................7

2.1 Top View Ball Diagram ................................................................................................................................................7

2.2 Package Ball Assignments ..........................................................................................................................................8

2.3 Package Ball Matrix ...................................................................................................................................................10

2.3.1 Top View ..........................................................................................................................................................10

2.3.2 Bottom View .....................................................................................................................................................11

2.4 Ball Types ..................................................................................................................................................................12

2.5 Ball Definitions ...........................................................................................................................................................12

3 Operating Conditions and Reliability ................................................................................................................................15

3.1 Absolute Maximum Ratings .......................................................................................................................................15

3.2 Recommended Operating Conditions .......................................................................................................................15

3.3 Handling Precautions ................................................................................................................................................15

3.4 Thermal Parameters (Definitions and Values) ...........................................................................................................16

3.5 Power Consumption ..................................................................................................................................................17

4 dc Electrical Characteristics .............................................................................................................................................18

5 Timing Diagrams and ac Characteristics ..........................................................................................................................19

6 Register Description .........................................................................................................................................................31

6.1 Device Addressing Notes ..........................................................................................................................................31

6.2 Acronyms Used .........................................................................................................................................................31

6.3 Address Map .............................................................................................................................................................31

6.4 Register Summary .....................................................................................................................................................32

6.5 Global Control Registers ...........................................................................................................................................34

6.6 Connection Store Generator Registers .....................................................................................................................39

6.7 Test Pattern Generator and Monitor Registers ..........................................................................................................44

6.8 Concentration Highway Configuration Registers .......................................................................................................48

7 Switch Fabric Control .......................................................................................................................................................54

8 Connection Store ..............................................................................................................................................................58

9 Outline Diagrams ..............................................................................................................................................................60

10 Ordering Information .......................................................................................................................................................61

11 Change History ...............................................................................................................................................................61

11.1 Navigating Through an Adobe Acrobat Document ..................................................................................................61

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Table of Contents

(continued)

Contents

Page

Agere Systems Inc.

3

Table 2-1. Package Ball Assignments in Signal Name Order.................................................................................................8

Table 2-2. Package Ball Assignments (Top View) ................................................................................................................10

Table 2-3. Package Ball Assignments (Bottom View)........................................................................................................... 11

Table 2-4. Ball Types ............................................................................................................................................................12

Table 2-5. Timing Port ..........................................................................................................................................................12

Table 2-6. Transmit and Receive Concentration Highways ..................................................................................................12

Table 2-7. Control Port..........................................................................................................................................................13

Table 2-8. Initialization and Test Access...............................................................................................................................13

Table 2-9. Power Balls..........................................................................................................................................................14

Table 3-1. Absolute Maximum Ratings .................................................................................................................................15

Table 3-2. Operating Conditions ...........................................................................................................................................15

Table 3-3. ESD Tolerance.....................................................................................................................................................15

Table 3-4. Thermal Parameter Values ..................................................................................................................................16

Table 3-5. Power Consumption ............................................................................................................................................17

Table 4-1. CMOS Inputs .......................................................................................................................................................18

Table 4-2. CMOS Outputs ....................................................................................................................................................18

Table 4-3. CMOS Bidirectionals (DATA[15:0]) ......................................................................................................................18

Table 5-1. CHICLK Timing Specifications.............................................................................................................................19

Table 5-2. MPUCLK Timing Specifications ...........................................................................................................................19

Table 5-3. CMOS Output ac Timing Specification * ..............................................................................................................20

Table 5-4. CHI Interface Timing ............................................................................................................................................21

Table 5-5. CHI 3-State Output Control..................................................................................................................................27

Table 5-6. Microprocessor Port Timing--Read Cycle...........................................................................................................28

Table 5-7. Microprocessor Port Timing--Write Cycle ...........................................................................................................29

Table 6-1. Address Map........................................................................................................................................................31

Table 6-2. Global Registers ..................................................................................................................................................32

Table 6-3. Connection Store Generator Registers................................................................................................................32

Table 6-4. Test Pattern Generator and Monitor Registers ....................................................................................................33

Table 6-5. Concentration Highway Configuration Registers .................................................................................................33

Table 6-6. Switch Fabric Control...........................................................................................................................................33

Table 6-7. Connection Store .................................................................................................................................................34

Table 6-8. Reserved Registers .............................................................................................................................................34

Table 6-9. Version_Control (Read Only)...............................................................................................................................34

Table 6-10. Chip_Identity (Read Only) .................................................................................................................................34

Table 6-11. Summary_Interrupt_Status (Read Only)............................................................................................................35

Table 6-12. Summary_Interrupt_Mask (Read/Write) ............................................................................................................35

Table 6-13. CPU_Access_Error (CORWN) ..........................................................................................................................36

Table 6-14. CPU_Access_Error_Mask (Read/Write)............................................................................................................36

Table 6-15. Global_Control (Read/Write) .............................................................................................................................37

Table 6-16. PLL_Control (Read/Write) .................................................................................................................................38

Table 6-17. Power_Control (Read/Write)..............................................................................................................................38

Table 6-18. Invalid_Address_Trap (Read Only)....................................................................................................................38

Table 6-19. Scratch_Register (Read/Write)..........................................................................................................................38

Table 6-20. Reserved_0 (Read/Write) ..................................................................................................................................39

Table 6-21. CSG_Control (Read/Write) ................................................................................................................................39

Table 6-22. CSG_Status (Read Only)...................................................................................................................................40

Table 6-23. CSG_Starting_Address (Read/Write) ................................................................................................................40

Table 6-24. CSG_Ending_Address (Read/Write) .................................................................................................................40

Table 6-25. CSG_Write_Enable_Low (Read/Write)..............................................................................................................40

Table 6-26. CSG_Write_Enable_High (Read/Write).............................................................................................................40

Table 6-27. CSG_Seed_Low (Read/Write)...........................................................................................................................41

Table 6-28. CSG_Seed_High (Read/Write)..........................................................................................................................41

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

Table of Contents

(continued)

Tables

Page

4

4

Agere Systems Inc.

Table 6-29. CSG_OR_Mask_Low (Read/Write) ...................................................................................................................41

Table 6-30. CSG_OR_Mask_High (Read/Write) ..................................................................................................................41

Table 6-31. CSG_AND_Mask_Low (Read/Write).................................................................................................................42

Table 6-32. CSG_AND_Mask_High (Read/Write) ................................................................................................................42

Table 6-33. CS_Stream_Control (Read/Write) .....................................................................................................................42

Table 6-34. CSG_Configuration (Read/Write) ......................................................................................................................43

Table 6-35. TPG_Configuration (Read/Write).......................................................................................................................44

Table 6-36. TPG_User_Pattern (Read/Write).......................................................................................................................44

Table 6-37. TPM_Configuration (Read/Write) ......................................................................................................................45

Table 6-38. TPM_User_Pattern (Read/Write).......................................................................................................................45

Table 6-39. TPM_Error_Count (Sat/Roll*) ............................................................................................................................46

Table 6-40. TPG_Inject_Error_Count (Write Only) ...............................................................................................................46

Table 6-41. TPG_Data_Invert_Mask (Read/Write) ...............................................................................................................46

Table 6-42. TPM_Status (Read Only)...................................................................................................................................47

Table 6-43. TPM_Status_Mask (Read/Write) .......................................................................................................................47

Table 6-44. Receive_CHI_Configuration (Read/Write).........................................................................................................48

Table 6-45. Receive_CHI_Status (CORWN) Receive_CHI_Status (CORWN).....................................................................48

Table 6-46. Receive_CHI_Status_Mask (Read/Write)..........................................................................................................49

Table 6-47. Receive_CHI_Global_Configuration (Read/Write) ............................................................................................49

Table 6-48. Transmit_CHI_Configuration (Read/Write) ........................................................................................................50

Table 6-49. Transmit_CHI_Status (CORWN) .......................................................................................................................51

Table 6-50. Transmit_CHI_Status_Mask (Read/Write).........................................................................................................51

Table 6-51. Transmit_CHI_Global_Configuration (Read/Write)............................................................................................52

Table 6-52. Receive_CHI_Time_Slot_Offset (Read/Write)...................................................................................................53

Table 6-53. Transmit_CHI_Time_Slot_Offset (Read/Write)..................................................................................................53

Table 7-1. SF_Status (CORWN)...........................................................................................................................................54

Table 7-2. SF_Status_Mask (Read/Write) ............................................................................................................................54

Table 7-3. Data_Store_Time_Slot_Capture_Select (Read/Write).........................................................................................55

Table 7-4. Data_Store_Captured_Data (Read Only) ............................................................................................................55

Table 7-5. Connection_Store_Parity_Error_Address_Trap (CORWN) .................................................................................56

Table 7-6. Receive_Link_Offset (Read Only) .......................................................................................................................56

Table 7-7. Transmit_Link_Offset (Read/Write) .....................................................................................................................56

Table 7-8. Wide_Mode_Control (Read/Write).......................................................................................................................57

Table 8-1. Low_Control_Word (Read/Write).........................................................................................................................58

Table 8-2. High_Control_Word (Read/Write) ........................................................................................................................59

Table 10-1. Ordering Information..........................................................................................................................................61

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Table of Contents

(continued)

Figures

Page

Agere Systems Inc.

5

Figure 1-1. Block Diagram and High-Level Interface Definition..............................................................................................1

Figure 2-1. Package Diagram (Top View) ..............................................................................................................................7

Figure 5-1. CHICLK Timing Specifications ...........................................................................................................................19

Figure 5-2. MPUCLK Timing Specifications .........................................................................................................................19

Figure 5-3. ac Timing Specification ......................................................................................................................................20

Figure 5-4. CHI Interface Timing ..........................................................................................................................................21

Figure 5-5. Typical Receive CHI Timing with 16.384 Mbits/s Data and 16.384 MHz CHICLK.............................................22

Figure 5-6. Transmit CHI Timing with 16.384 Mbits/s Data and 16.384 MHz CHICLK ........................................................22

Figure 5-7. Typical Receive CHI Timing with 8.192 Mbits/s Data and 16.384 MHz CHICLK...............................................23

Figure 5-8. Transmit CHI Timing with 8.192 Mbits/s Data and 16.384 MHz CHICLK ..........................................................23

Figure 5-9. Typical Receive CHI Timing with 4.096 Mbits/s Data and 16.384 MHz CHICLK...............................................24

Figure 5-10. Transmit CHI Timing with 4.096 Mbits/s Data and 16.384 MHz CHICLK ........................................................24

Figure 5-11. Typical Receive CHI Timing with 2.048 Mbits/s Data and 16.384 MHz CHICLK.............................................25

Figure 5-12. Transmit CHI Timing with 2.048 Mbits/s Data and 16.384 MHz CHICLK ........................................................25

Figure 5-13. Typical Receive CHI Timing with 8.192 Mbits/s Data and 8.192 MHz CHICLK...............................................26

Figure 5-14. Transmit CHI Timing with 8.192 Mbits/s Data and 8.192 MHz CHICLK ..........................................................26

Figure 5-15. CHI 3-State Output Control ..............................................................................................................................27

Figure 5-16. Microprocessor Port Timing--Read Cycle .......................................................................................................28

Figure 5-17. Microprocessor Port Timing--Write Cycle .......................................................................................................29

Figure 6-1. Transmit CHI Configuration (R/W) .....................................................................................................................50

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

6

6

Agere Systems Inc.

Hardware Description

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

7

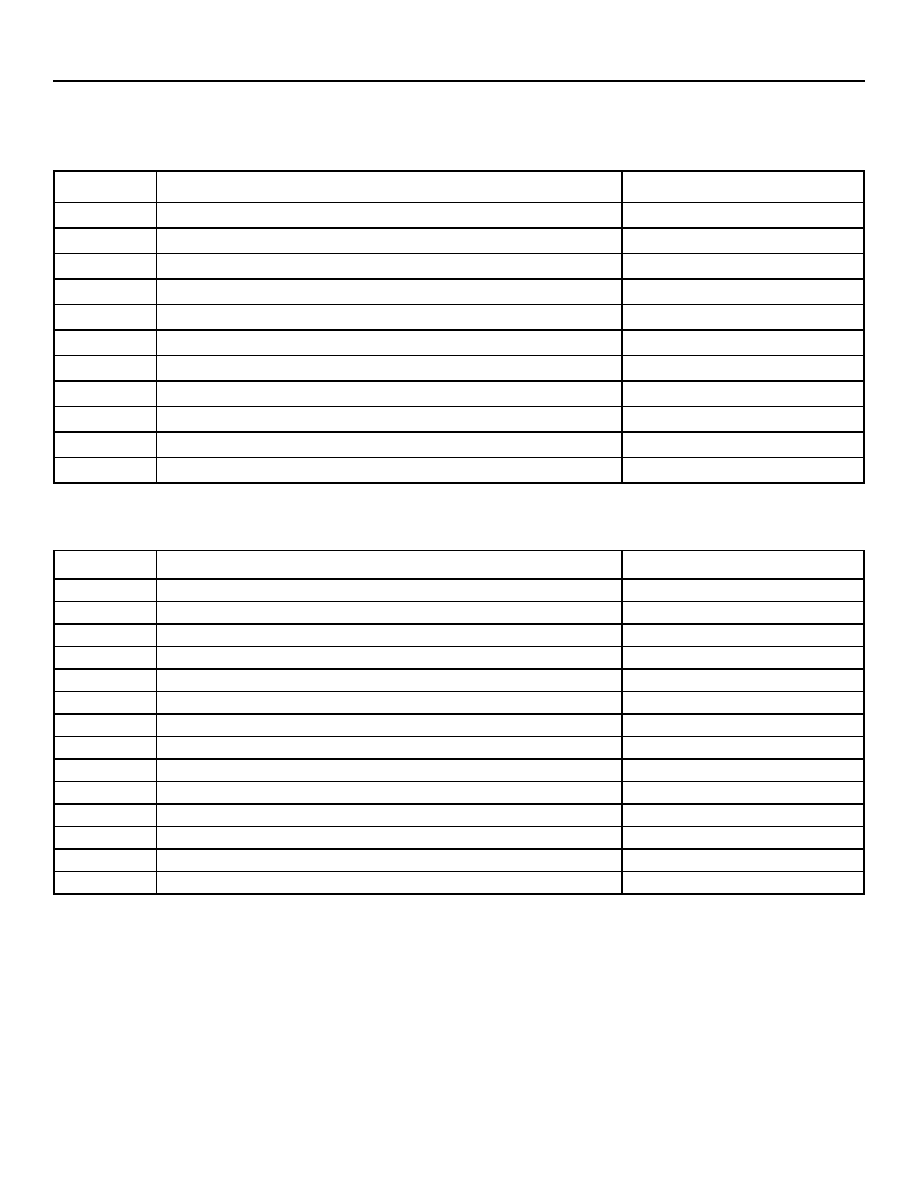

2 Ball Information

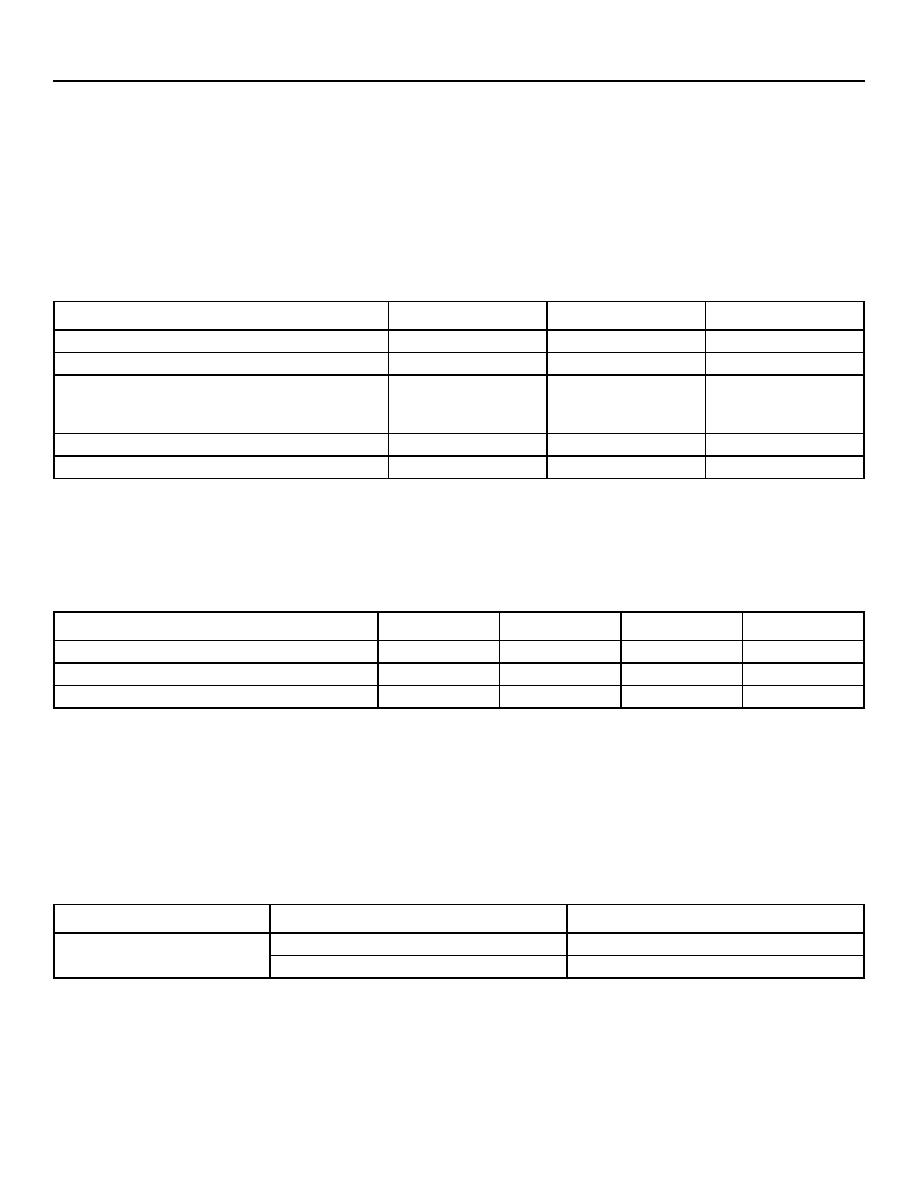

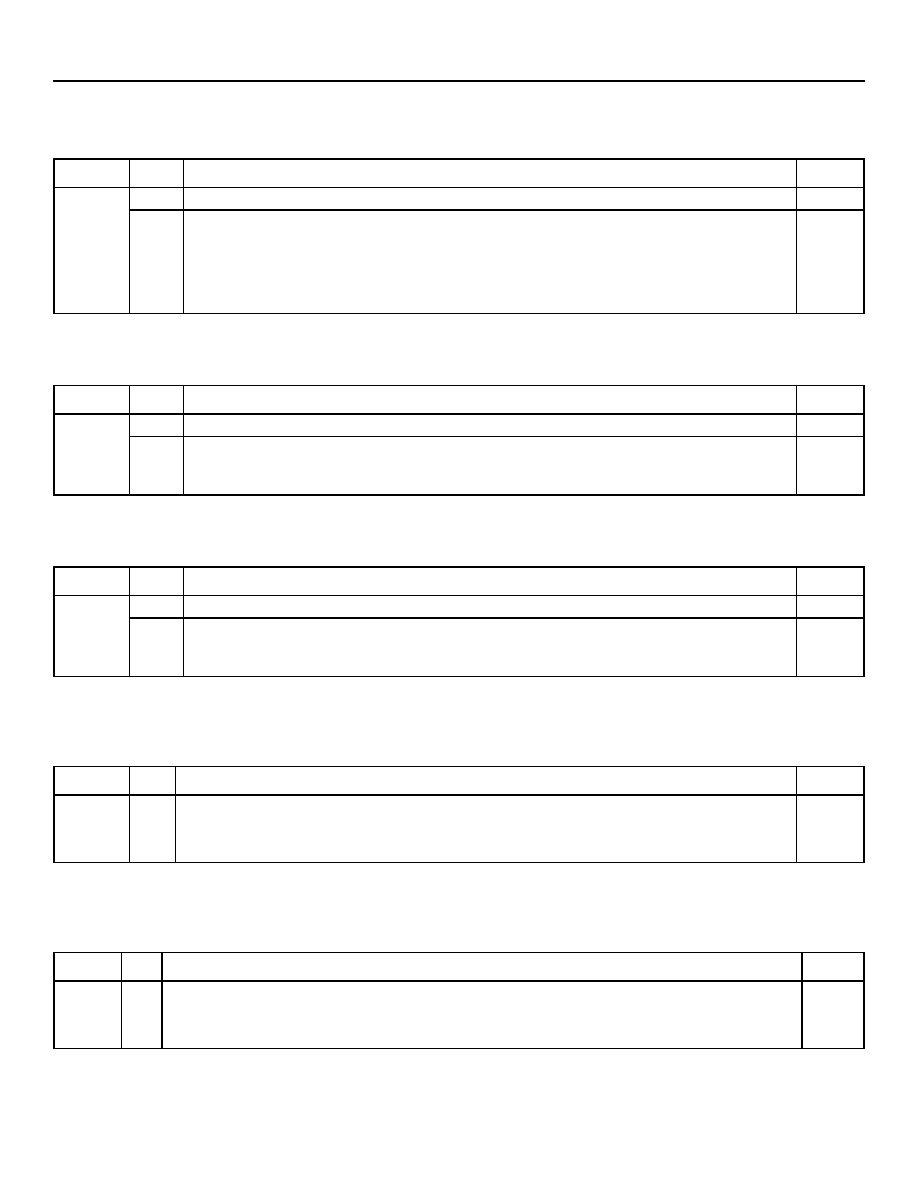

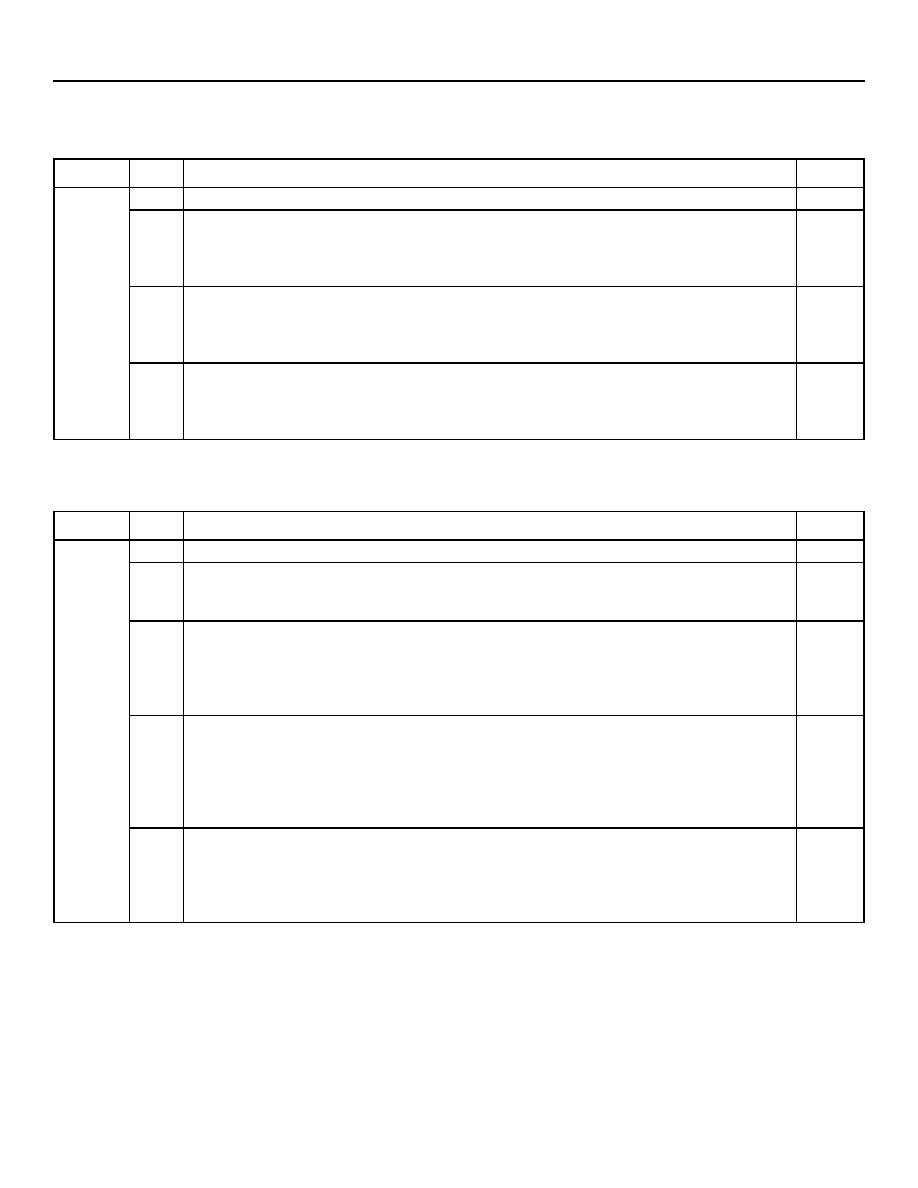

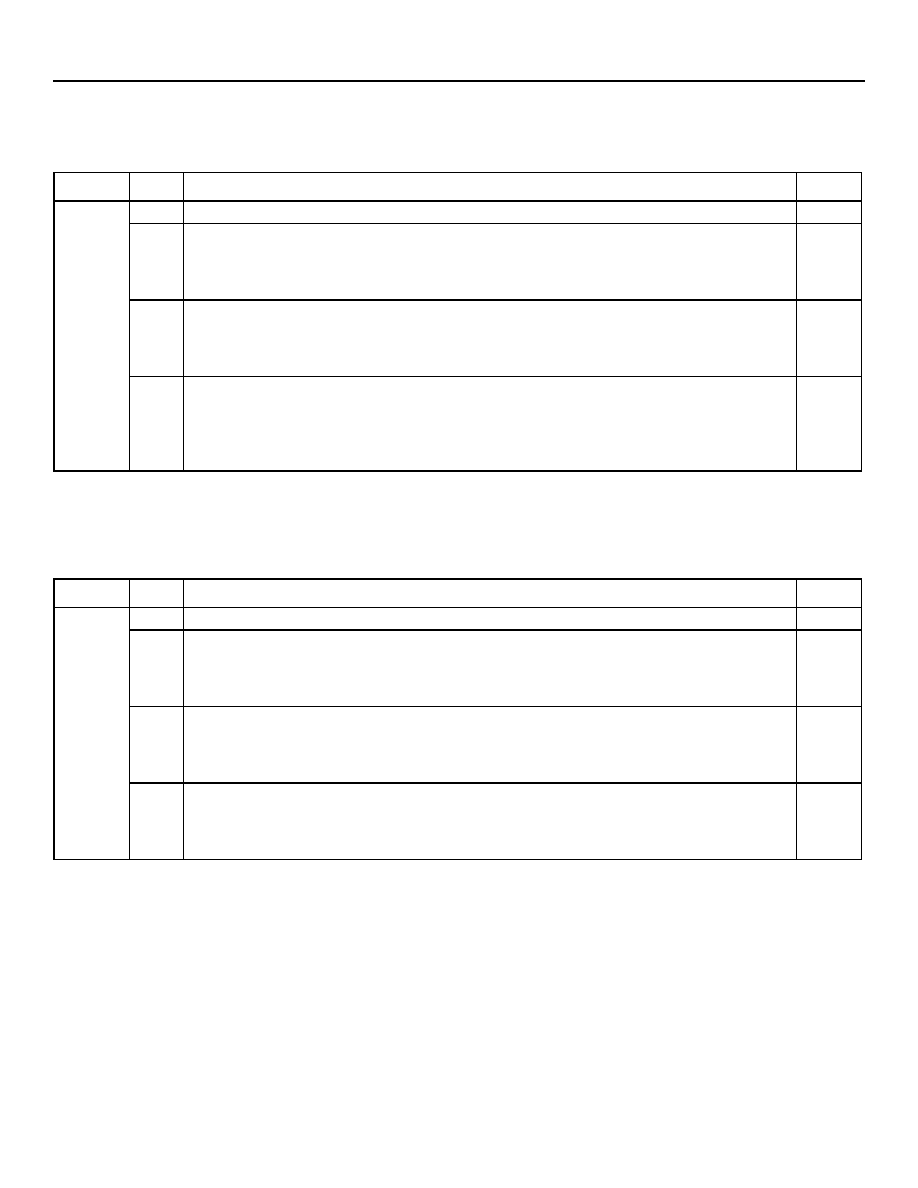

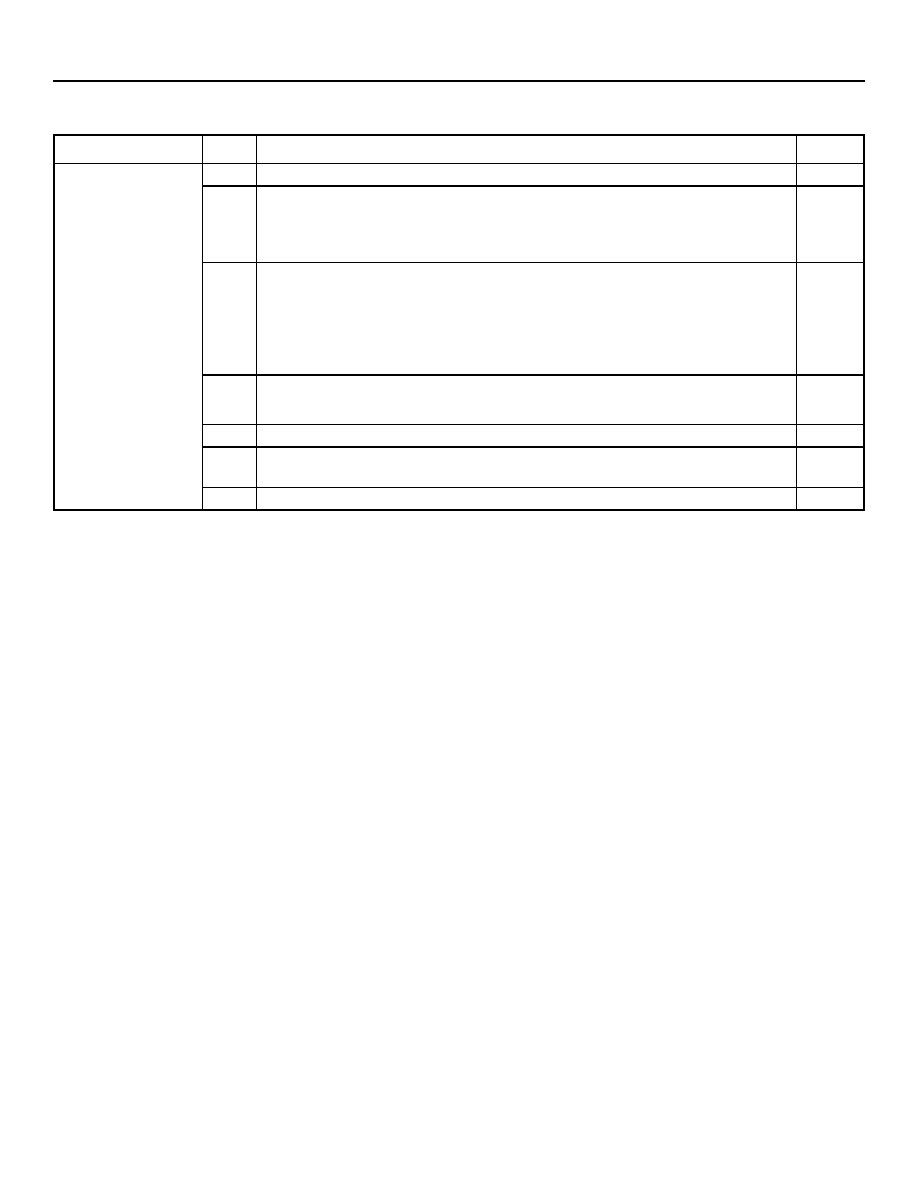

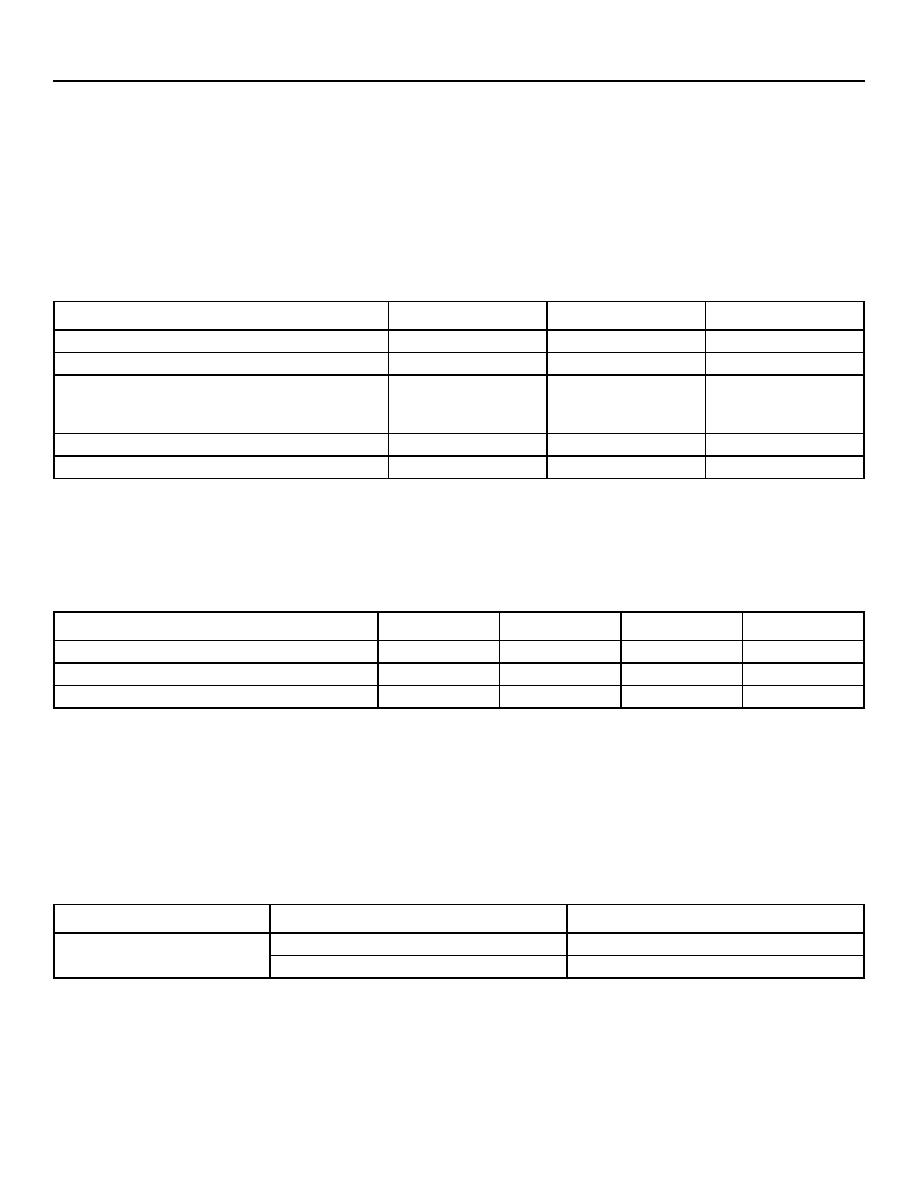

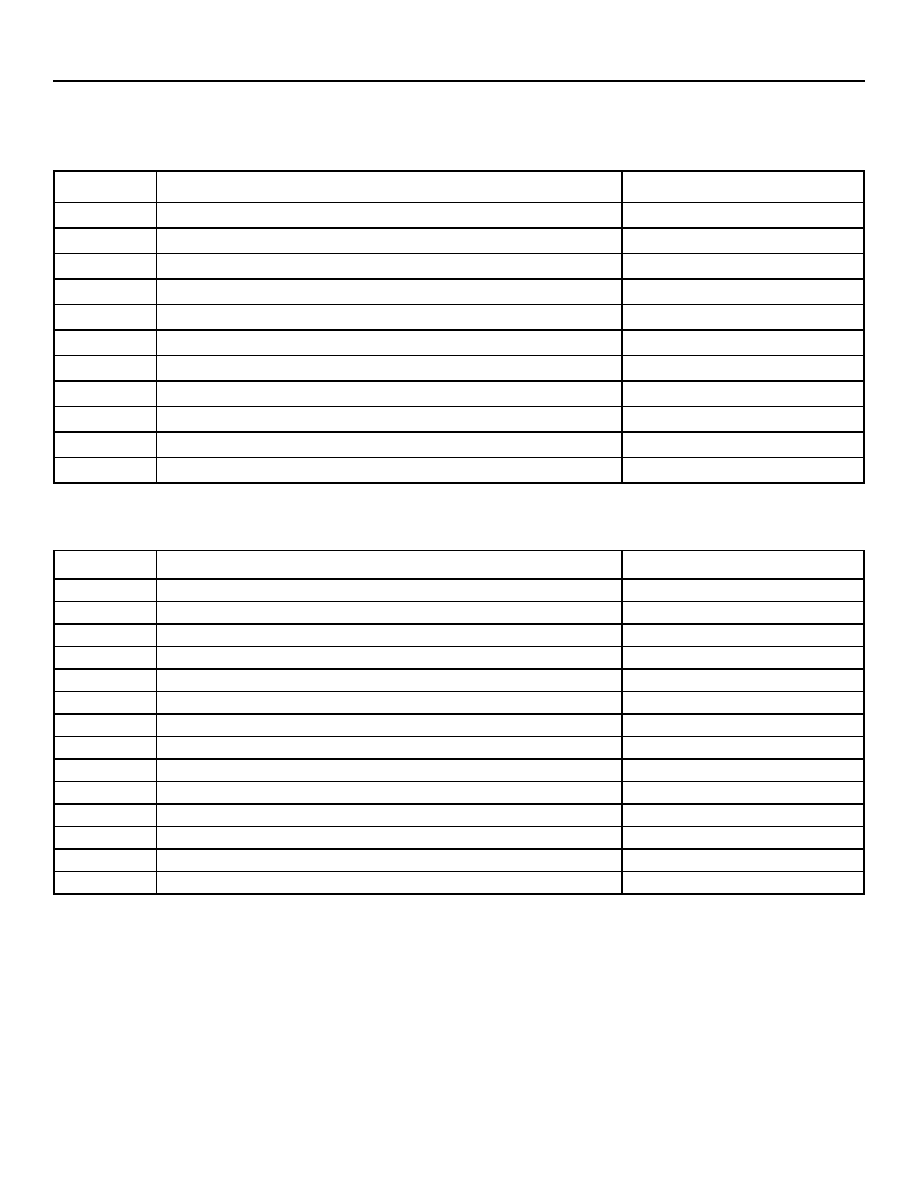

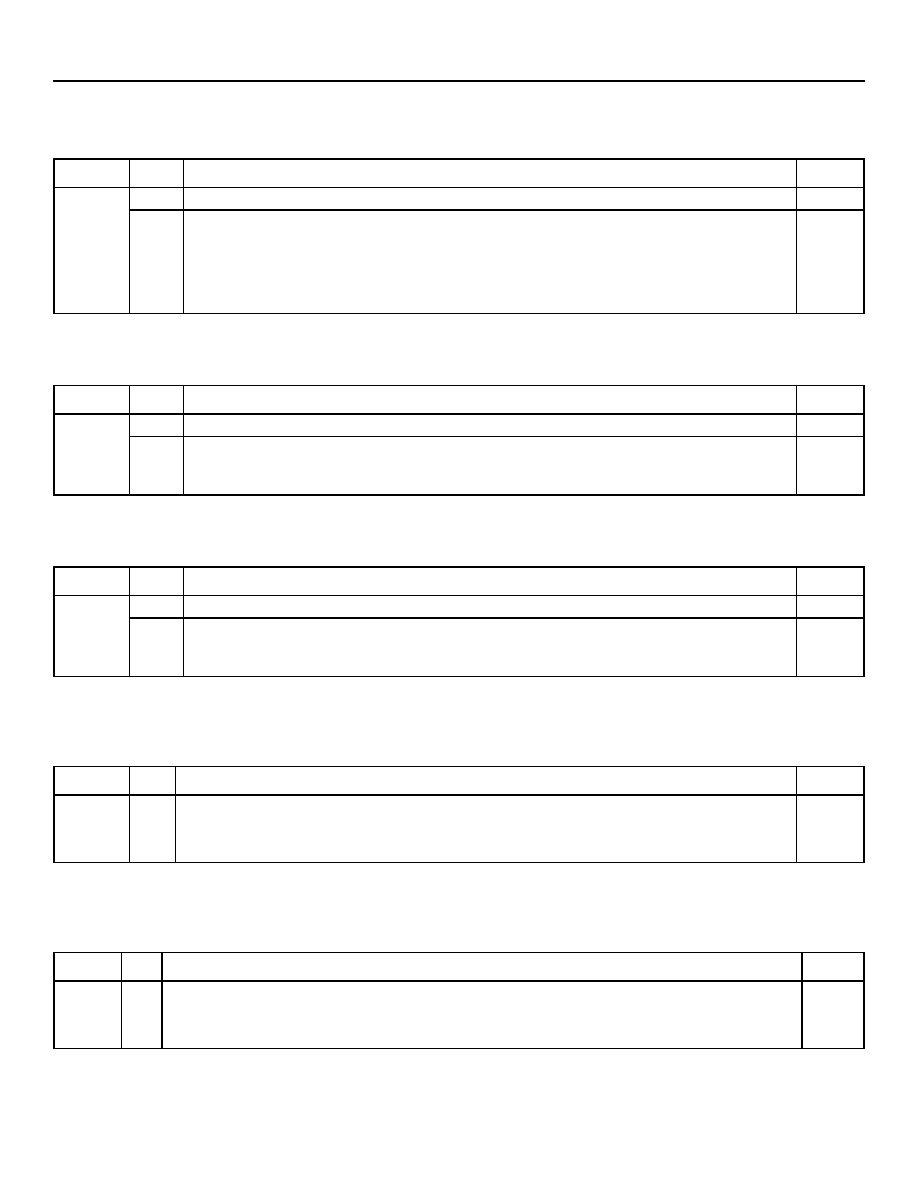

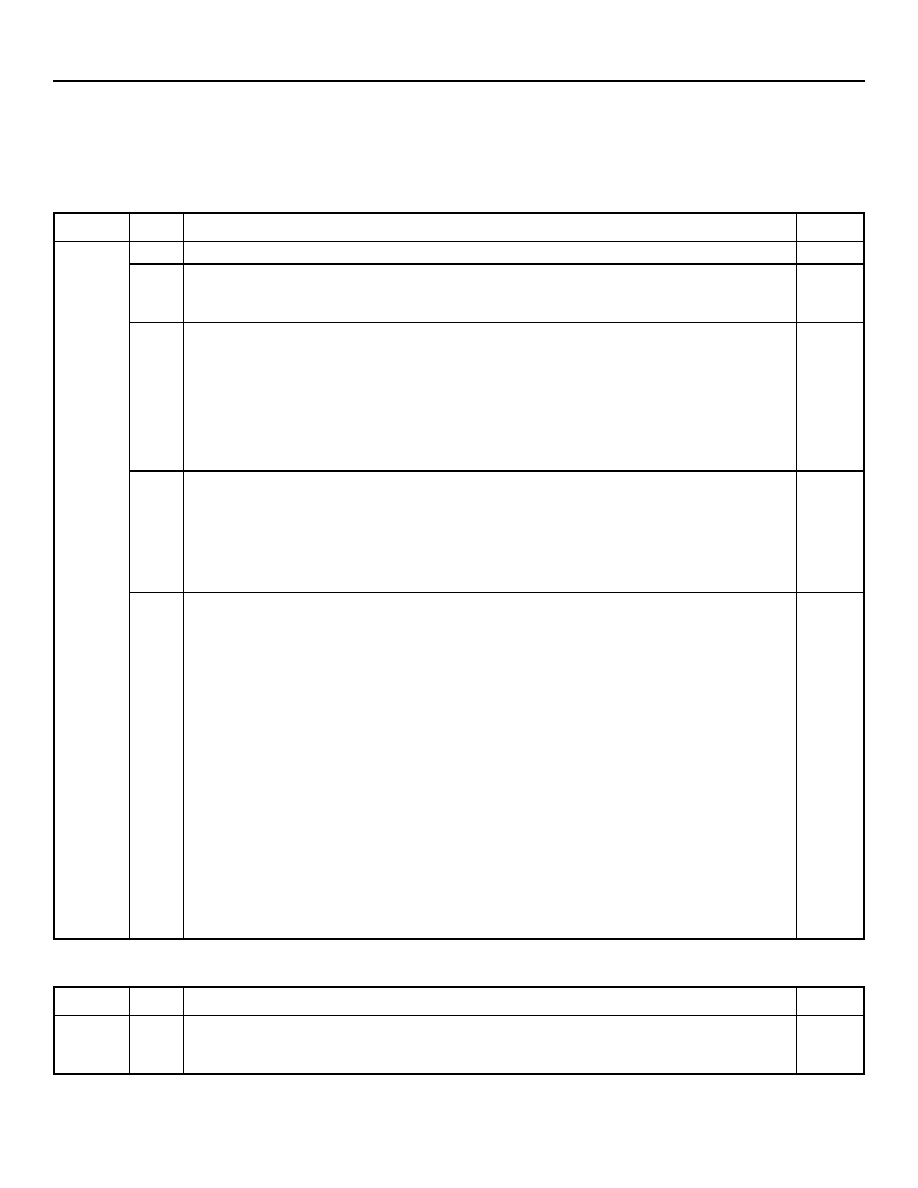

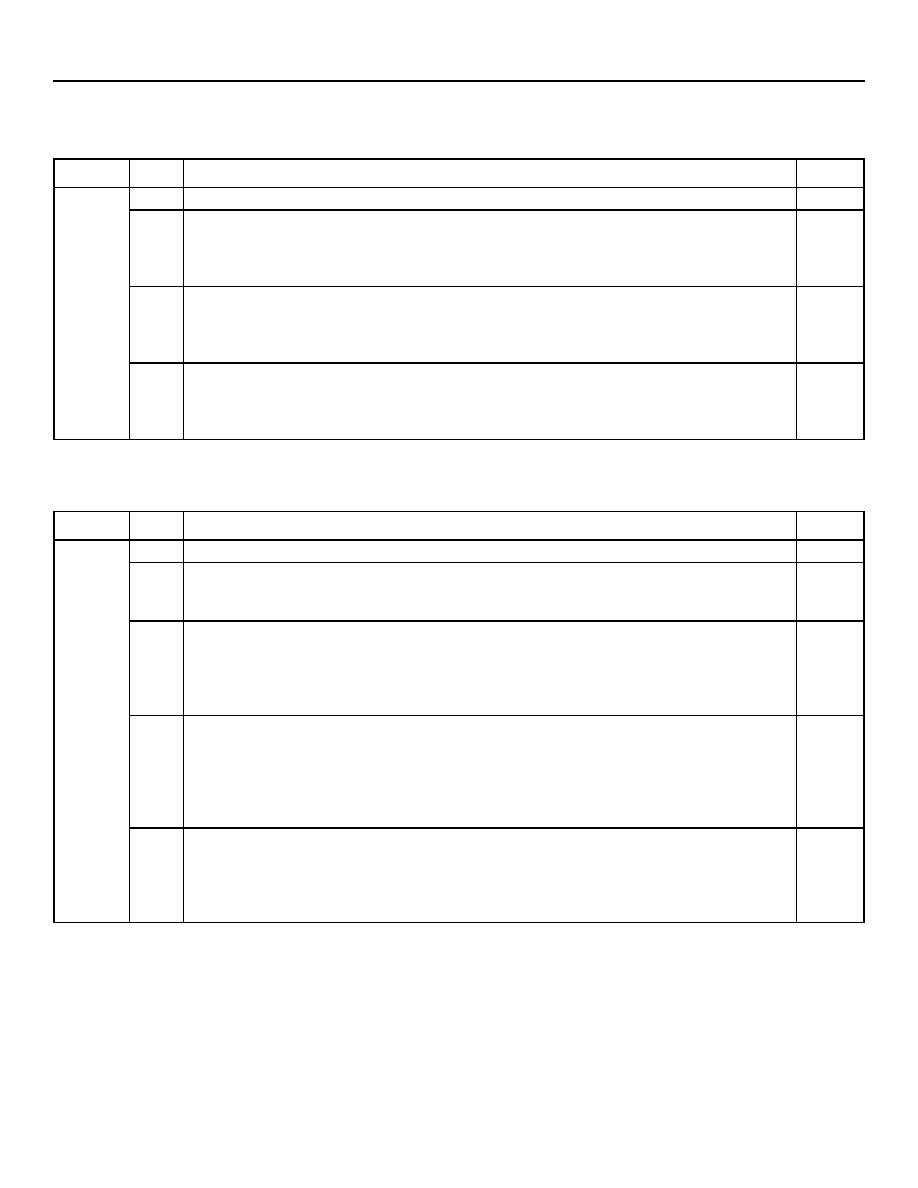

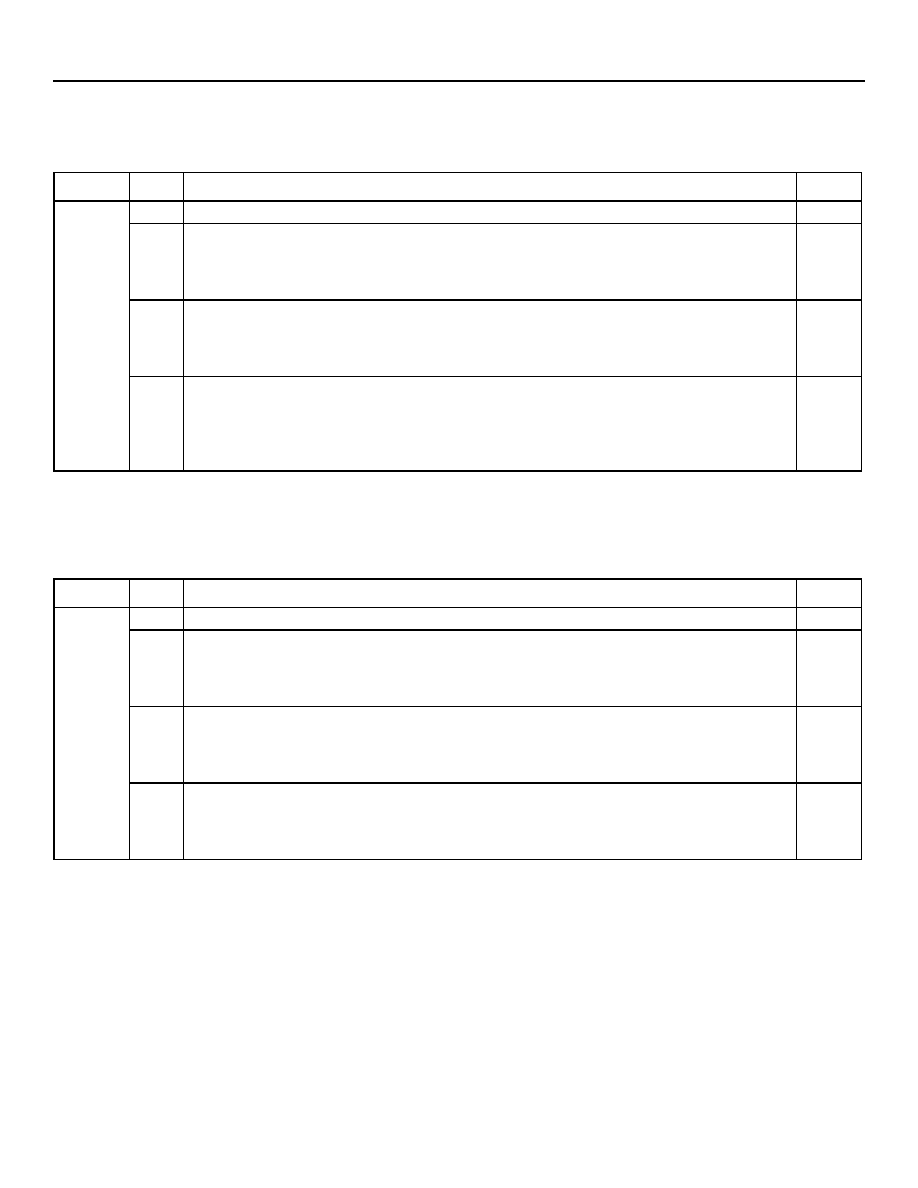

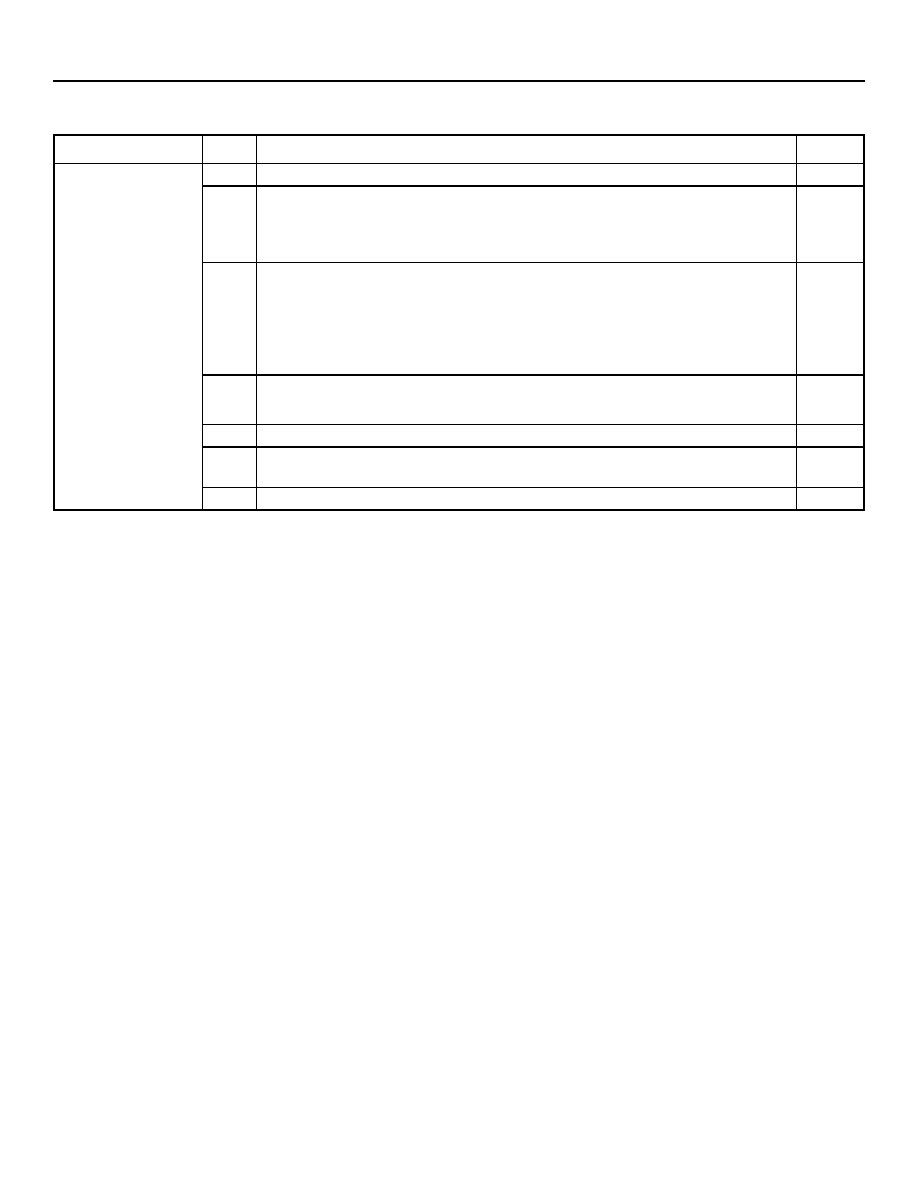

2.1 Top View Ball Diagram

The device is housed in a 240-ball plastic ball grid array. Figure 2-1 shows the ball arrangement viewed from the top of the

package. The balls are spaced on a 1.0 mm pitch.

Figure 2-1. Package Diagram (Top View)

B

C

A

E

F

D

H

J

G

L

M

K

P

R

N

U

V

T

2

3

1

5

6

4

8

7

10

11

9

13

14

12

16

15

17

18

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

8

8

Agere Systems Inc.

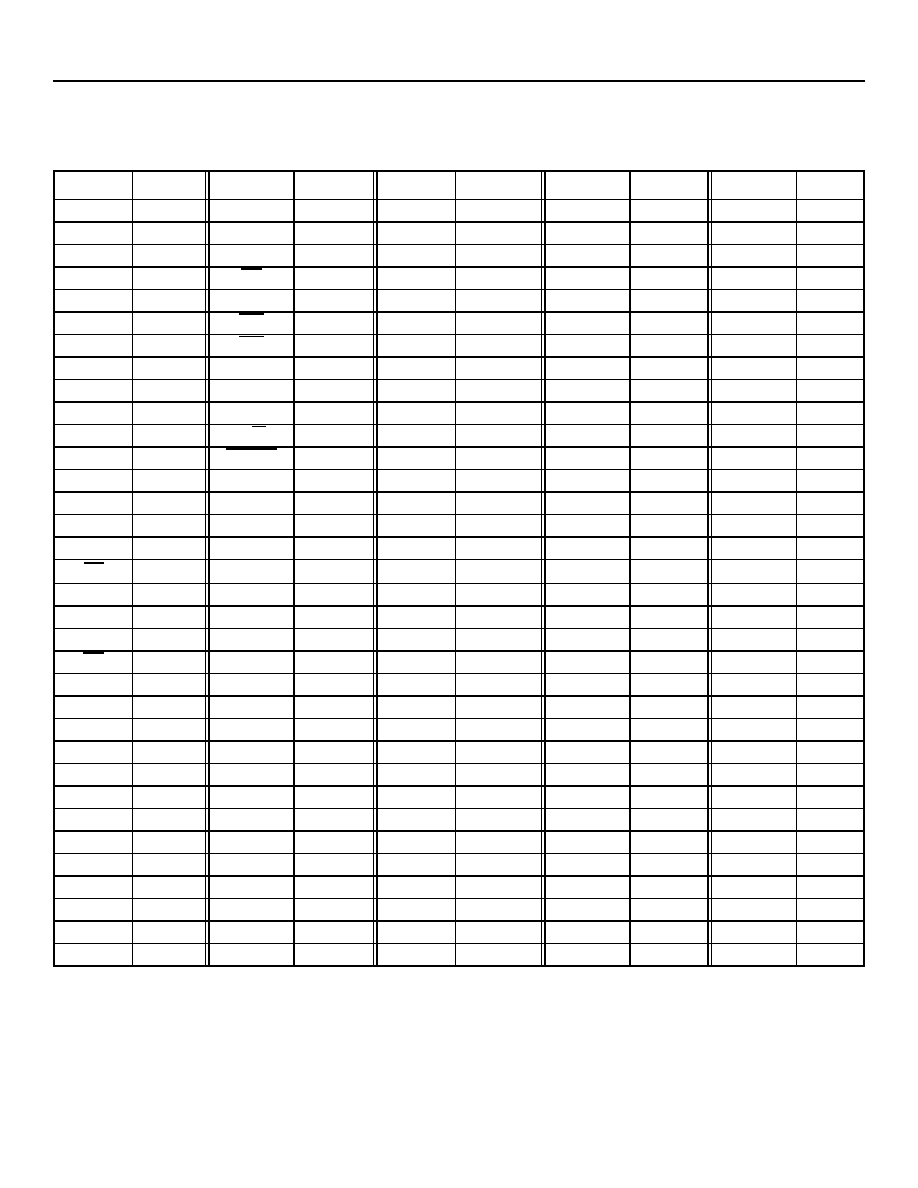

2.2 Package Ball Assignments

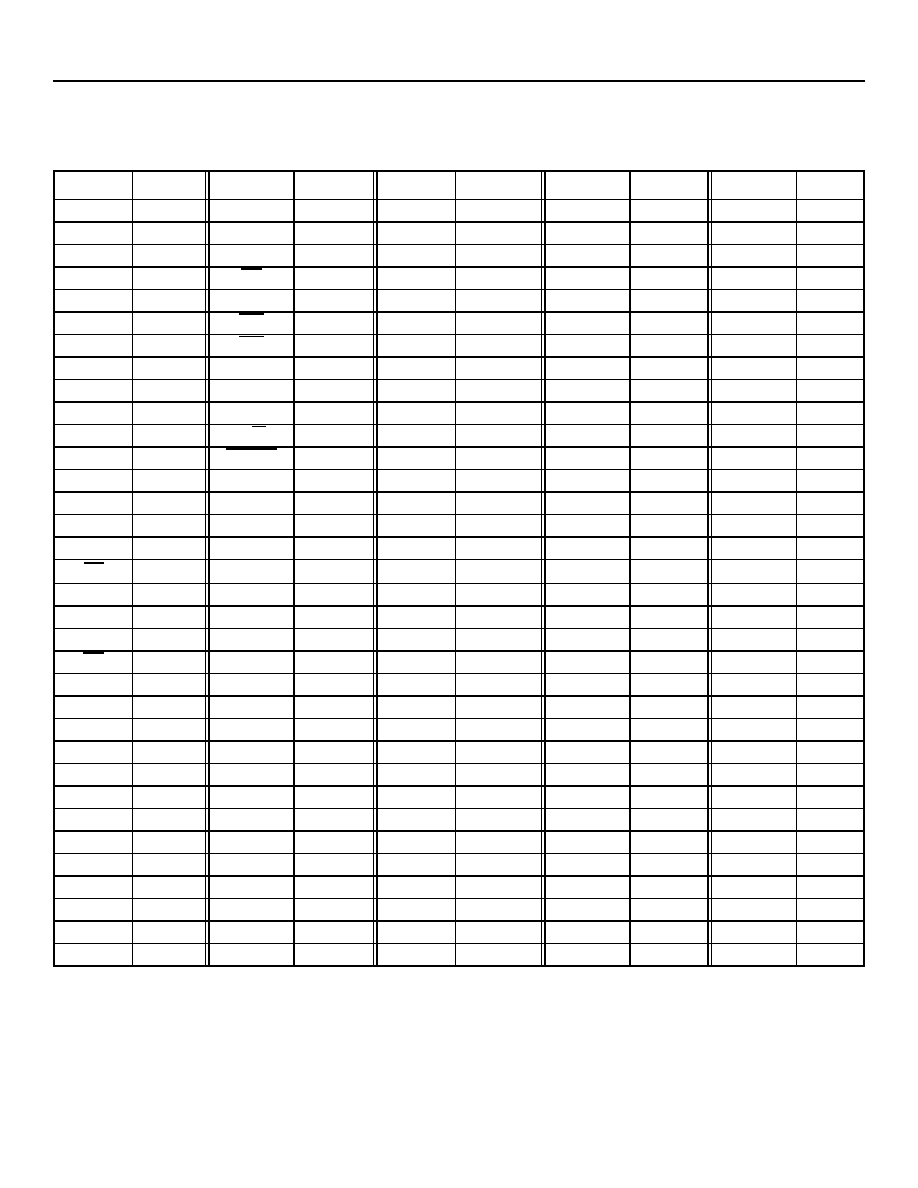

Table 2-1. Package Ball Assignments in Signal Name Order

Symbol

Ball Symbol

Ball

Symbol

Ball

Symbol

Ball

Symbol

Ball

ADDR00

A17

DATA13

P18

RXD11

V7

TXD08

F1

V

DD15

D13

ADDR01

A16

DATA14

P17

RXD12

T8

TXD09

G3

V

DD15

D14

ADDR02

A15

DATA15

P16

RXD13

U8

TXD10

G2

V

DD15

G4

ADDR03

A14

DT

H17

RXD14

V8

TXD11

G1

V

DD15

H4

ADDR04

A13

FSYNC

T11

RXD15

U9

TXD12

H2

V

DD15

L4

ADDR05

A12

HIZ

R17

NC

V9

TXD13

H1

V

DD15

M4

ADDR06

A11

INT

H16

NC

V10

TXD14

J2

V

DD15

R7

ADDR07

A10

MPUCLK

K15

NC

U10

TXD15

J1

V

DD15

R8

ADDR08

A9

PAR0

R18

NC

V11

NC

K1

V

DD15

R11

ADDR09

A8

PAR1

P15

NC

U11

NC

K2

V

DD15

R12

ADDR10

A7

R/W

J17

NC

V12

NC

L1

V

DD33

C9

ADDR11

A6

RESET

H15

NC

U12

NC

L2

V

DD33

C10

ADDR12

A5

RSV1

F17

NC

V13

NC

M1

V

DD33

C17

ADDR13

A4

RSV2

F18

NC

U13

NC

M2

V

DD33

D9

ADDR14

A3

RSV3

E15

NC

V14

NC

N1

V

DD33

D10

ADDR15

A2

RSV4

E16

NC

U14

NC

N2

V

DD33

E3

AS

J16

RSV5

E17

NC

V15

NC

N3

V

DD33

F3

CHICLK

R16

RSV6

D17

NC

U15

NC

P1

V

DD33

F15

CKSPD0

E18

RSV7

B18

NC

T15

NC

P2

V

DD33

H3

CKSPD1

D16

RSV8

C18

NC

V16

NC

R1

V

DD33

J3

CS

J18

RSV9

D18

NC

U16

NC

R2

V

DD33

K16

DATA00

K18

RSV10

T18

TCK

G17

NC

T1

V

DD33

P3

DATA01

K17

RSV11

V17

TDI

G16

NC

T2

V

DD33

R3

DATA02

L18

RXD00

V2

TDO

G18

NC

U1

V

DD33

T5

DATA03

L17

RXD01

U3

TMS

G15

V

DD15

C5

V

DD33

T6

DATA04

L16

RXD02

V3

TRSTN

H18

V

DD15

C6

V

DD33

T9

DATA05

M18

RXD03

U4

TXD00

B1

V

DD15

C7

V

DD33

T10

DATA06

M17

RXD04

V4

TXD01

C2

V

DD15

C12

V

DD33

T14

DATA07

M16

RXD05

U5

TXD02

C1

V

DD15

C13

V

DD33

T17

DATA08

M15

RXD06

V5

TXD03

D2

V

DD15

C14

V

DDPLL

R14

DATA09

N18

RXD07

U6

TXD04

D1

V

DD15

D5

NC

K3

DATA10

N17

RXD08

V6

TXD05

E2

V

DD15

D6

NC

T4

DATA11

N16

RXD09

T7

TXD06

E1

V

DD15

D7

V

SS

A1

DATA12

N15

RXD10

U7

TXD07

F2

V

DD15

D12

V

SS

A18

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

9

Symbol

Ball Symbol

Ball

Symbol

Ball

Symbol

Ball

Symbol

Ball

V

SS

B2

V

SS

C8

V

SS

J9

V

SS

R4

V

SS

B3

V

SS

C11

V

SS

J10

V

SS

R5

V

SS

B4

V

SS

C15

V

SS

J11

V

SS

R6

V

SS

B5

V

SS

C16

V

SS

J15

V

SS

R9

V

SS

B6

V

SS

D3

V

SS

K4

V

SS

R10

V

SS

B7

V

SS

D4

V

SS

K8

V

SS

R15

V

SS

B8

V

SS

D8

V

SS

K9

V

SS

T3

V

SS

B9

V

SS

D11

V

SS

K10

V

SS

T12

V

SS

B10

V

SS

D15

V

SS

K11

V

SS

T13

V

SS

B11

V

SS

E4

V

SS

L3

V

SS

T16

V

SS

B12

V

SS

F4

V

SS

L8

V

SS

U2

V

SS

B13

V

SS

F16

V

SS

L9

V

SS

U17

V

SS

B14

V

SS

H8

V

SS

L10

V

SS

U18

V

SS

B15

V

SS

H9

V

SS

L11

V

SS

V1

V

SS

B16

V

SS

H10

V

SS

L15

V

SS

V18

V

SS

B17

V

SS

H11

V

SS

M3

V

SSPLL

R13

V

SS

C3

V

SS

J4

V

SS

N4

V

SS

C4

V

SS

J8

V

SS

P4

Table 2-1. Package Ball Assignments in Signal Name Order (continued)

TSI-1

1k x 1k Time-Slot Interchanger

Data Sheet, Revision 3

September 21, 2005

10

Agere Systems Inc.

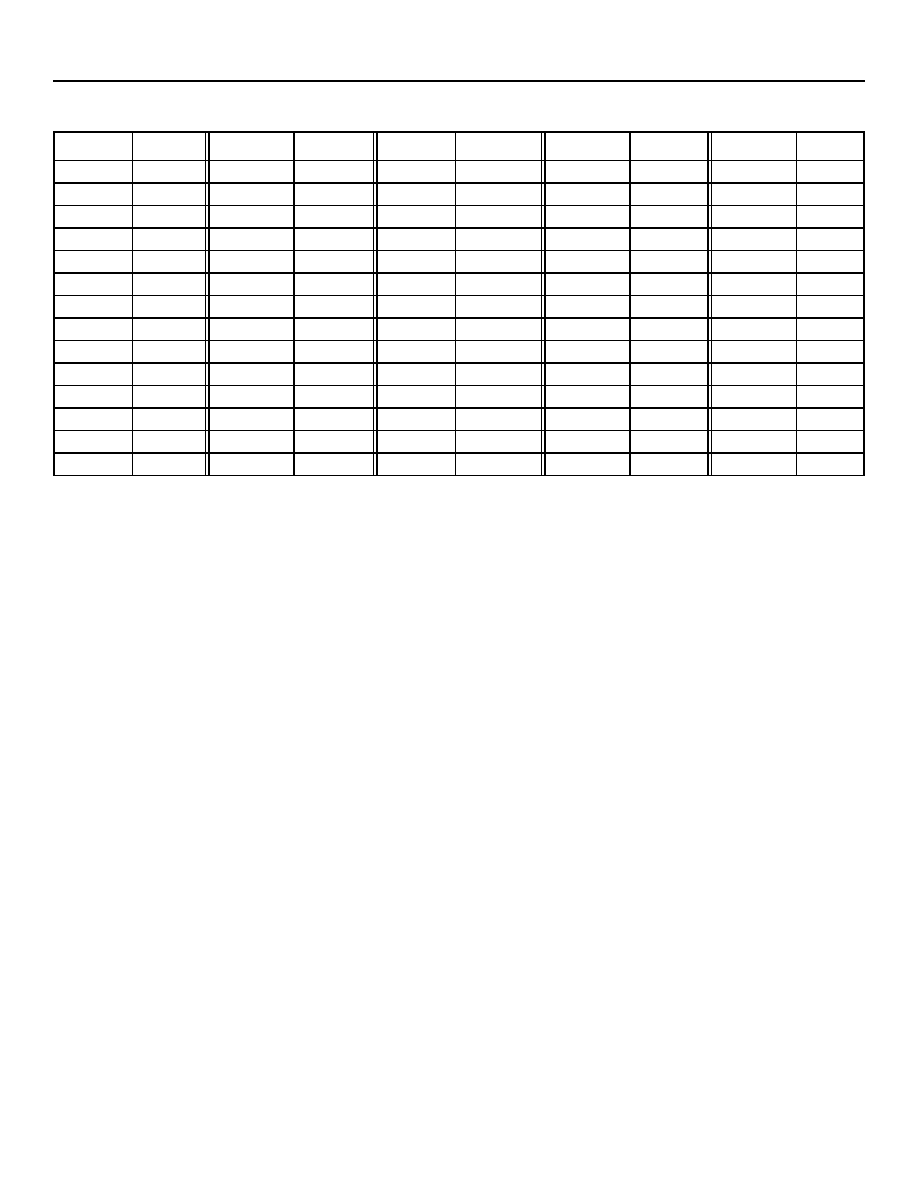

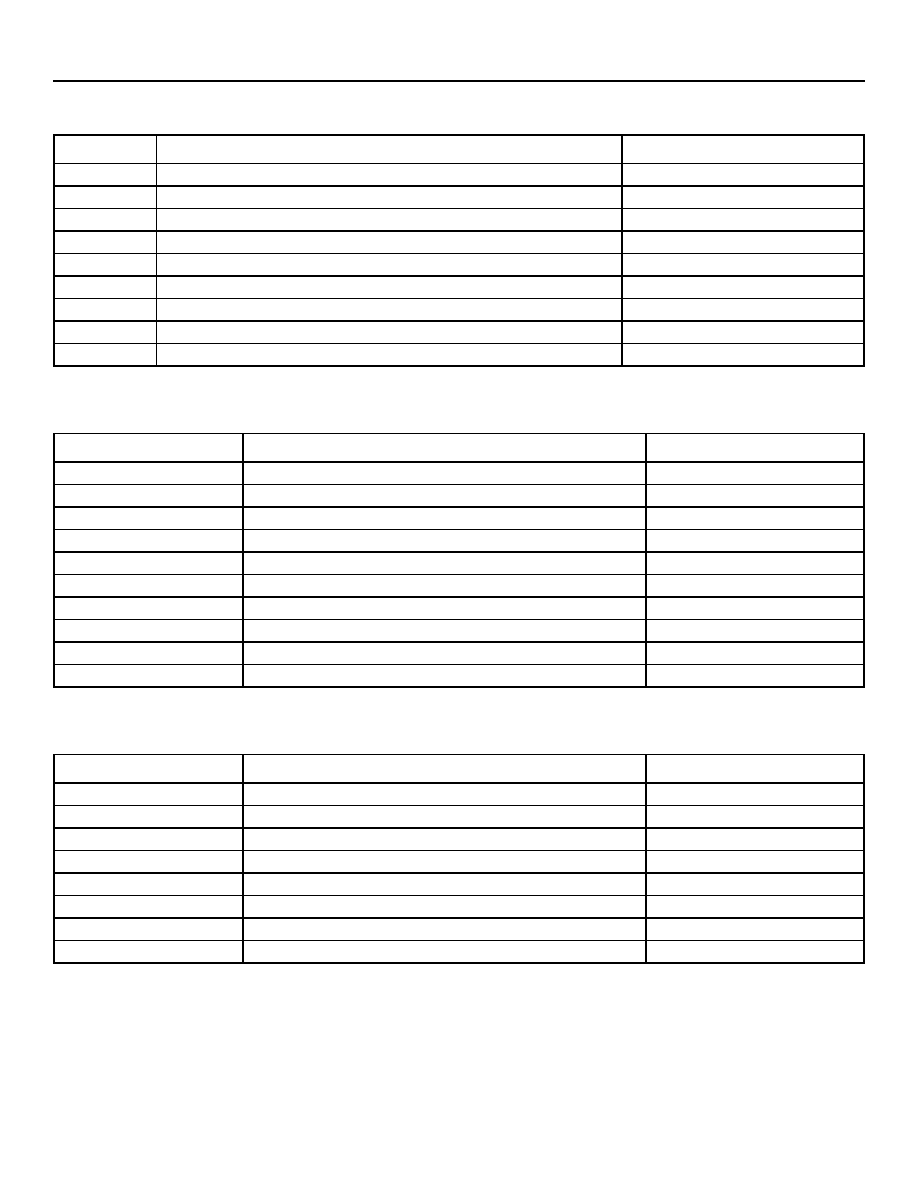

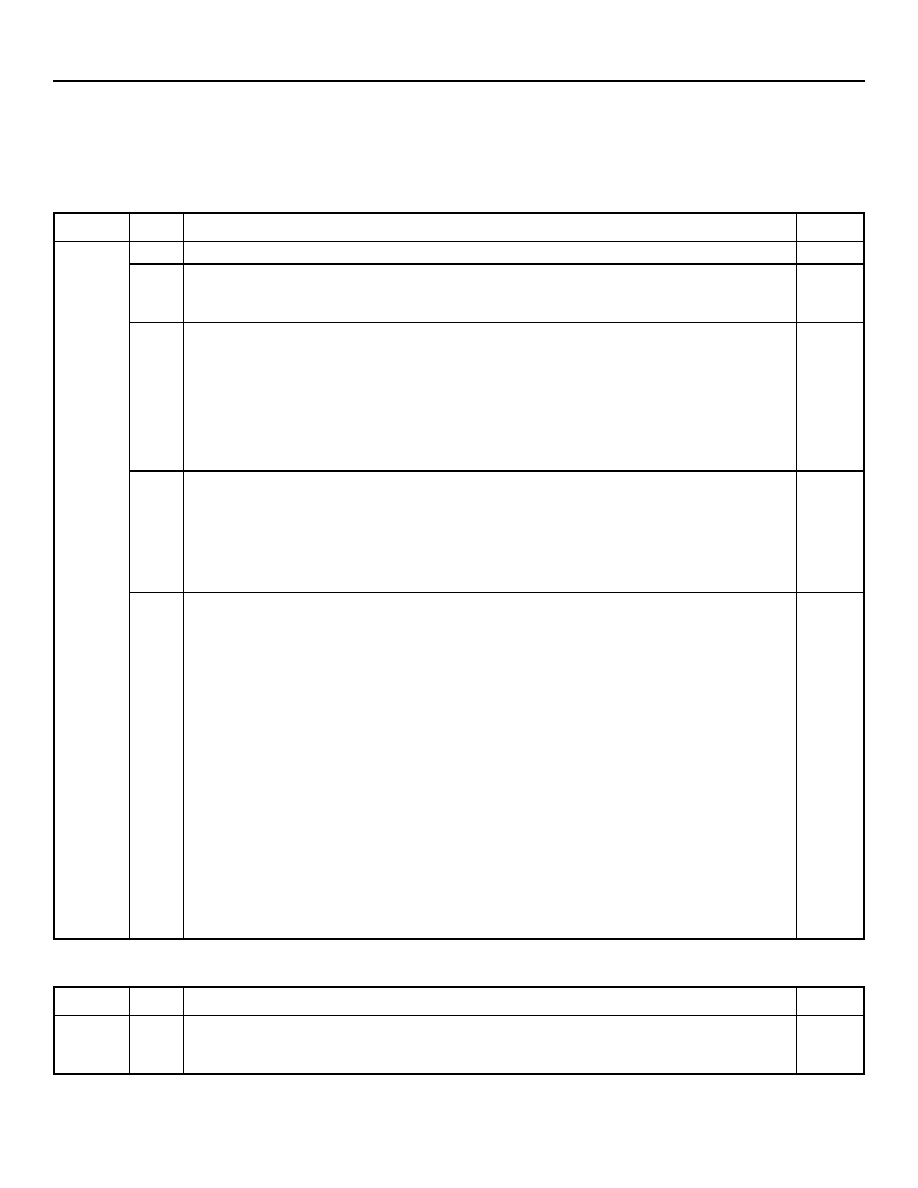

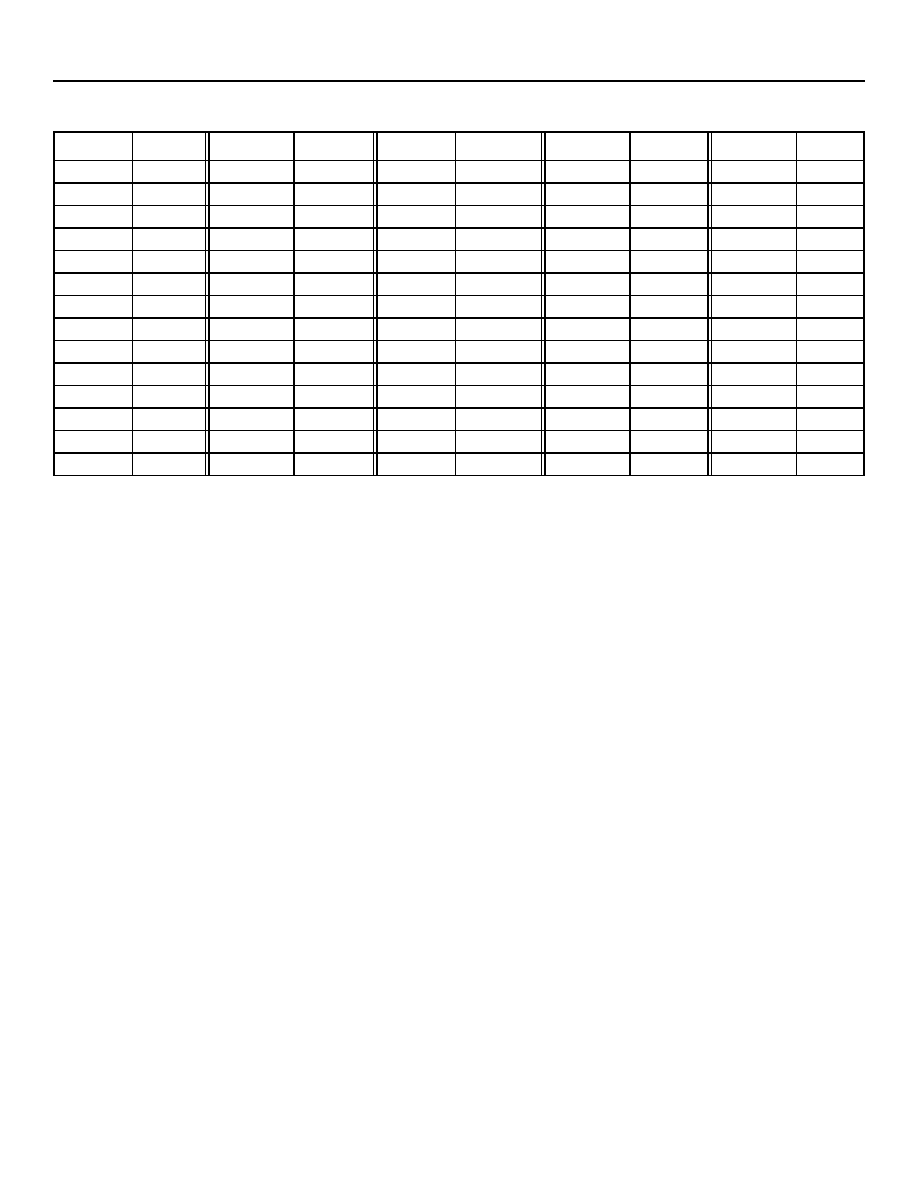

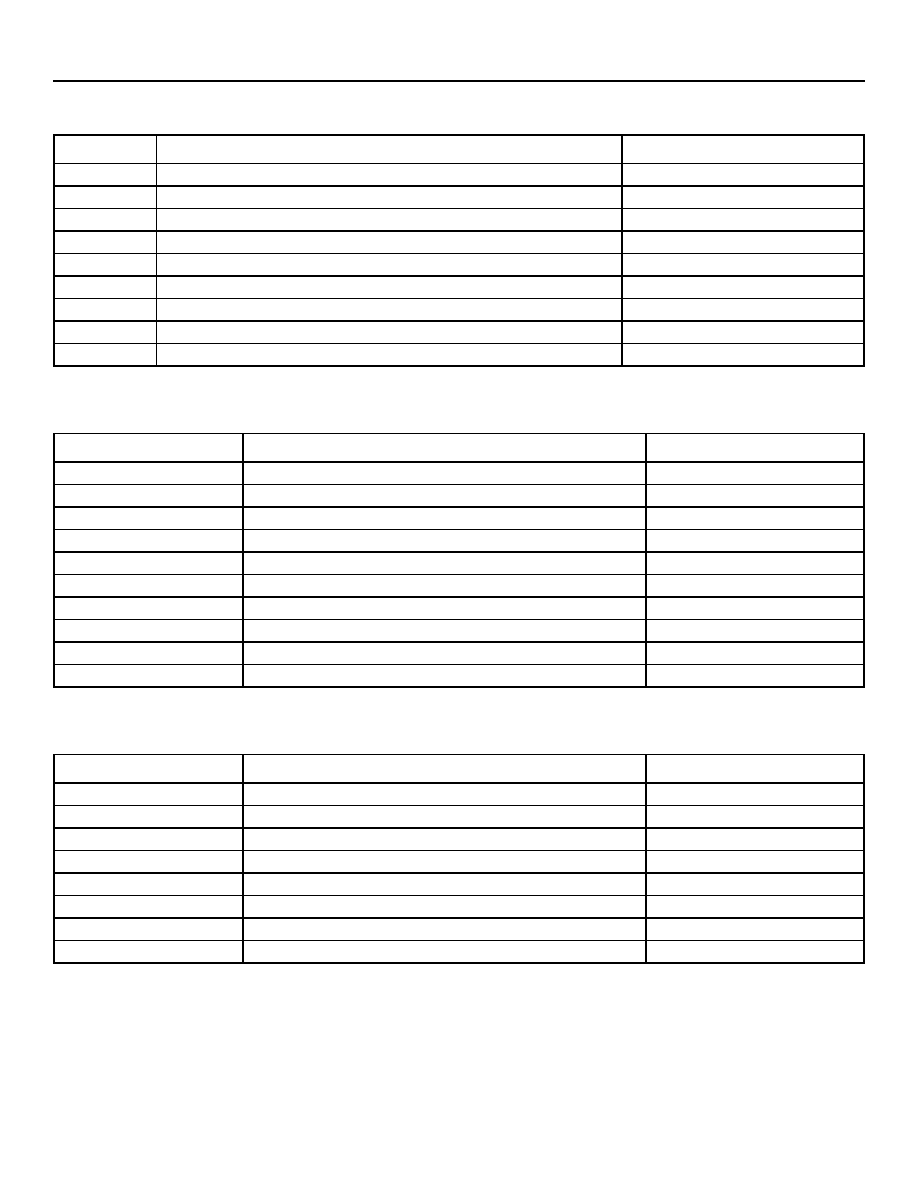

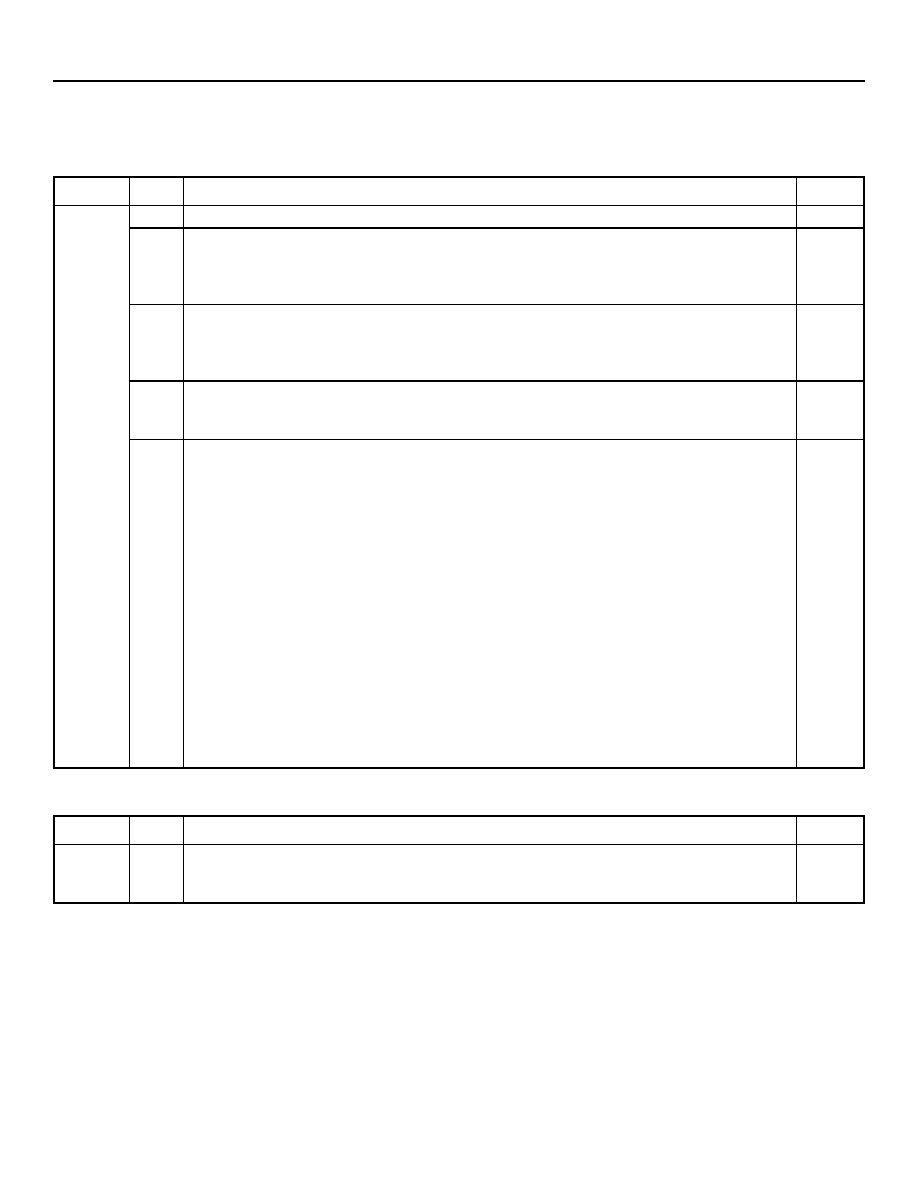

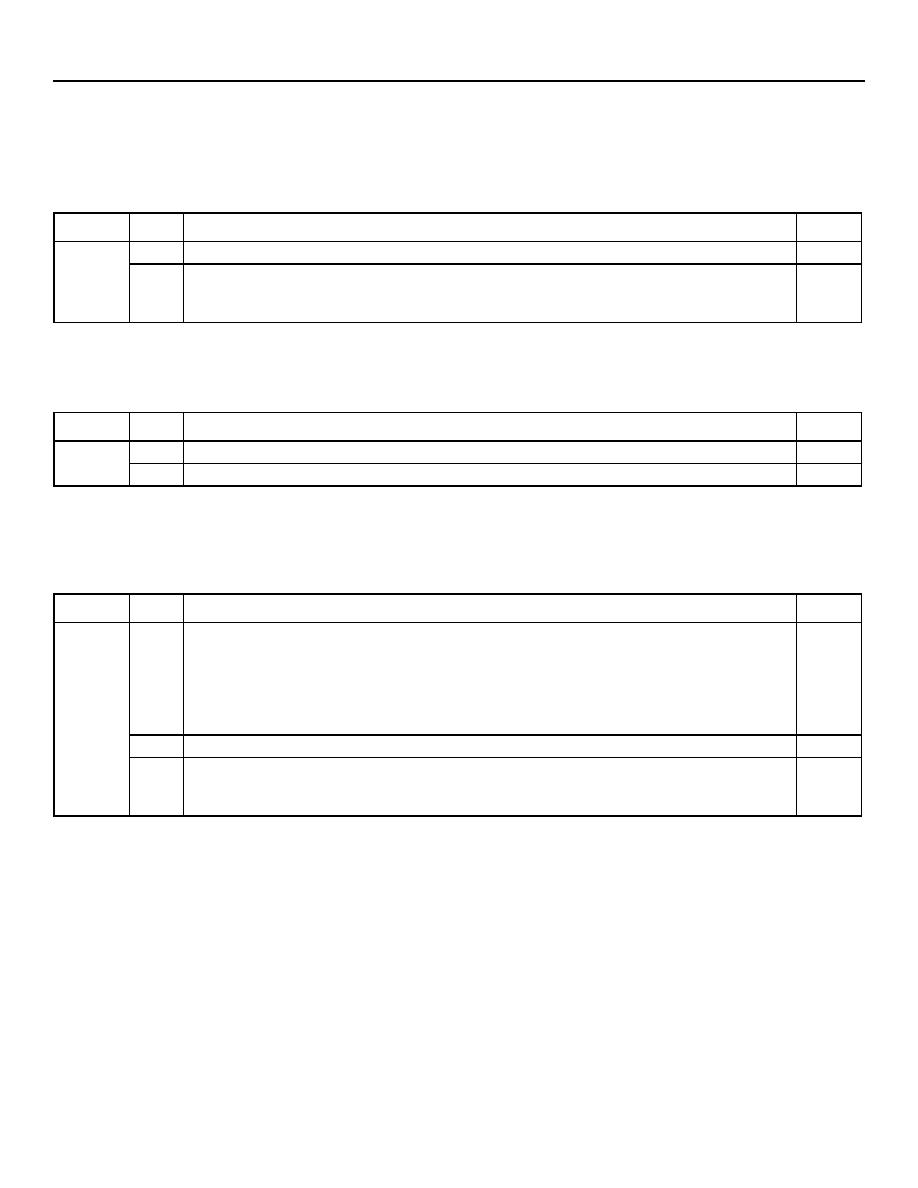

2.3 Package Ball Matrix

2.3.1 Top View

Table 2-2. Package Ball Assignments (Top View)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

A

V

SS

ADDR15 ADDR14 ADDR13 ADDR12 ADDR11 ADDR10 ADDR09 ADDR08 ADDR07 ADDR06 ADDR05 ADDR04 ADDR03

ADDR02

ADDR01

ADDR00

V

SS

B

TXD00

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

RSV7

C

TXD02

TXD01

V

SS

V

SS

V

DD15

V

DD15

V

DD15

V

SS

V

DD33

V

DD33

V

SS

V

DD15

V

DD15

V

DD15

V

SS

V

SS

V

DD33

RSV8

D

TXD04

TXD03

VSS

VSS

VDD15

VDD15

VDD15

VSS

VDD33

VDD33

V

SS

V

DD15

V

DD15

V

DD15

V

SS

CKSPD1

RSV6

RSV9

E

TXD06

TXD05

VDD33

VSS

--

--

--

--

--

--

--

--

--

--

RSV3

RSV4

RSV5

CKSPD0

F

TXD08

TXD07

VDD33

VSS

--

--

--

--

--

--

--

--

--

--

V

DD33

V

SS

RSV1

RSV2

G

TXD11

TXD10

TXD09

VDD15

--

--

--

--

--

--

--

--

--

--

TMS

TDI

TCK

TDO

H

TXD13

TXD12

VDD33

VDD15

--

--

--

VSS

VSS

VSS

V

SS

--

--

--

RESET

INT

DT

TRSTN

J

TXD15

TXD14

VDD33

VSS

--

--

--

VSS

VSS

VSS

V

SS

--

--

--

V

SS

AS

R/W

CS

K

NC

NC

NC

VSS

--

--

--

VSS

VSS

VSS

V

SS

--

--

--

MPUCLK

V

DD33

DATA01

DATA00

L

NC

NC

VSS

VDD15

--

--

--

VSS

VSS

VSS

V

SS

--

--

--

V

SS

DATA04

DATA03

DATA02

M

NC

NC

VSS

VDD15

--

--

--

--

--

--

--

--

--

--

DATA08

DATA07

DATA06

DATA05

N

NC

NC

NC

VSS

--

--

--

--

--

--

--

--

--

--

DATA12

DATA11

DATA10

DATA09

P

NC

NC

VDD33

VSS

--

--

--

--

--

--

--

--

--

--

PAR1

DATA15

DATA14

DATA13

R

NC

NC

VDD33

VSS

VSS

VSS

VDD15

VDD15

VSS

VSS

V

DD15

V

DD15

V

SSPLL

V

DDPLL

V

SS

CHICLK

HIZ

PAR0

T

NC

NC

VSS

NC

VDD33

VDD33

RXD09

RXD12

VDD33

VDD33

FSYNC

V

SS

V

SS

V

DD33

NC

V

SS

V

DD33

RSV10

U

NC

VSS

RXD01

RXD03

RXD05

RXD07

RXD10

RXD13

RXD15

NC

NC

NC

NC

NC

NC

NC

V

SS

V

SS

V

VSS

RXD00

RXD02

RXD04

RXD06

RXD08

RXD11

RXD14

NC

NC

NC

NC

NC

NC

NC

NC

RSV11

V

SS

Data Sheet, Revision 3

September 21, 2005

TSI-1

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

11

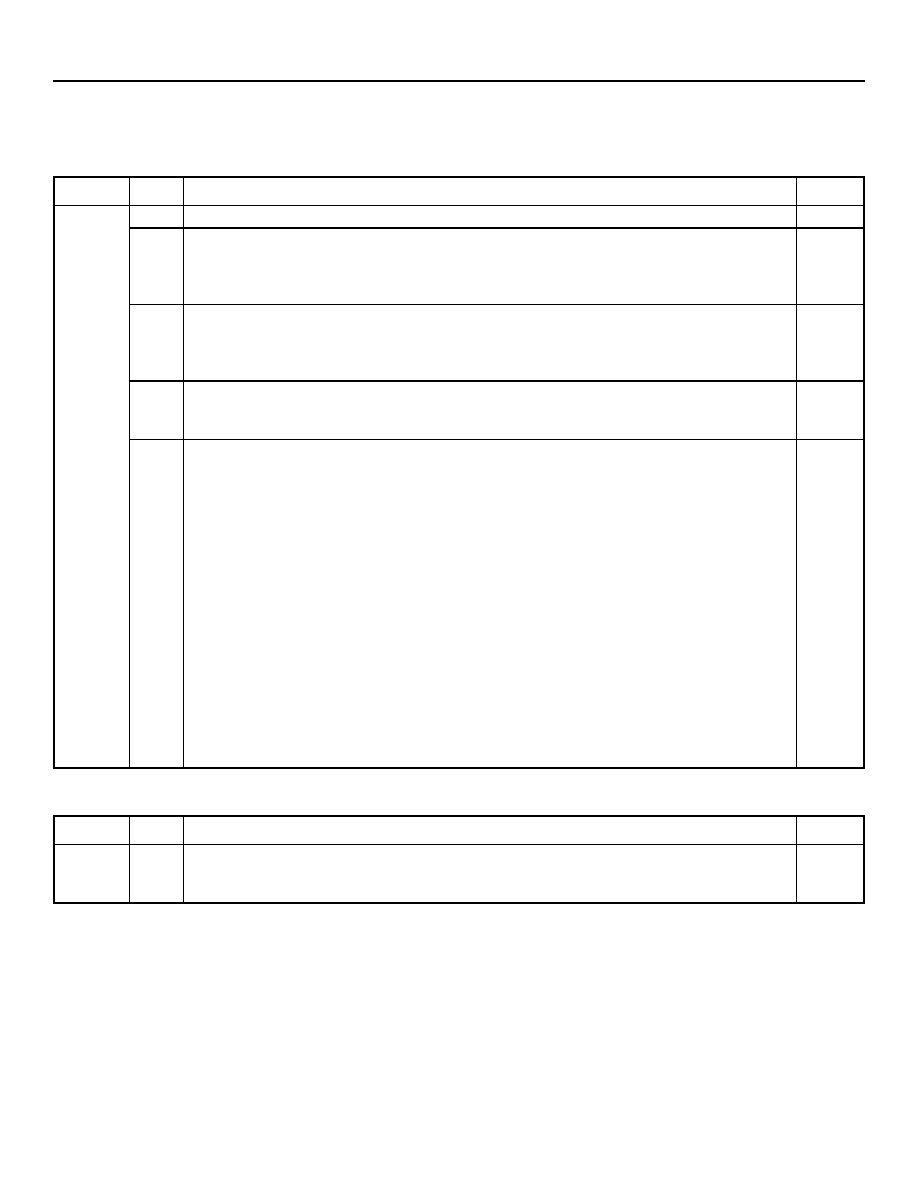

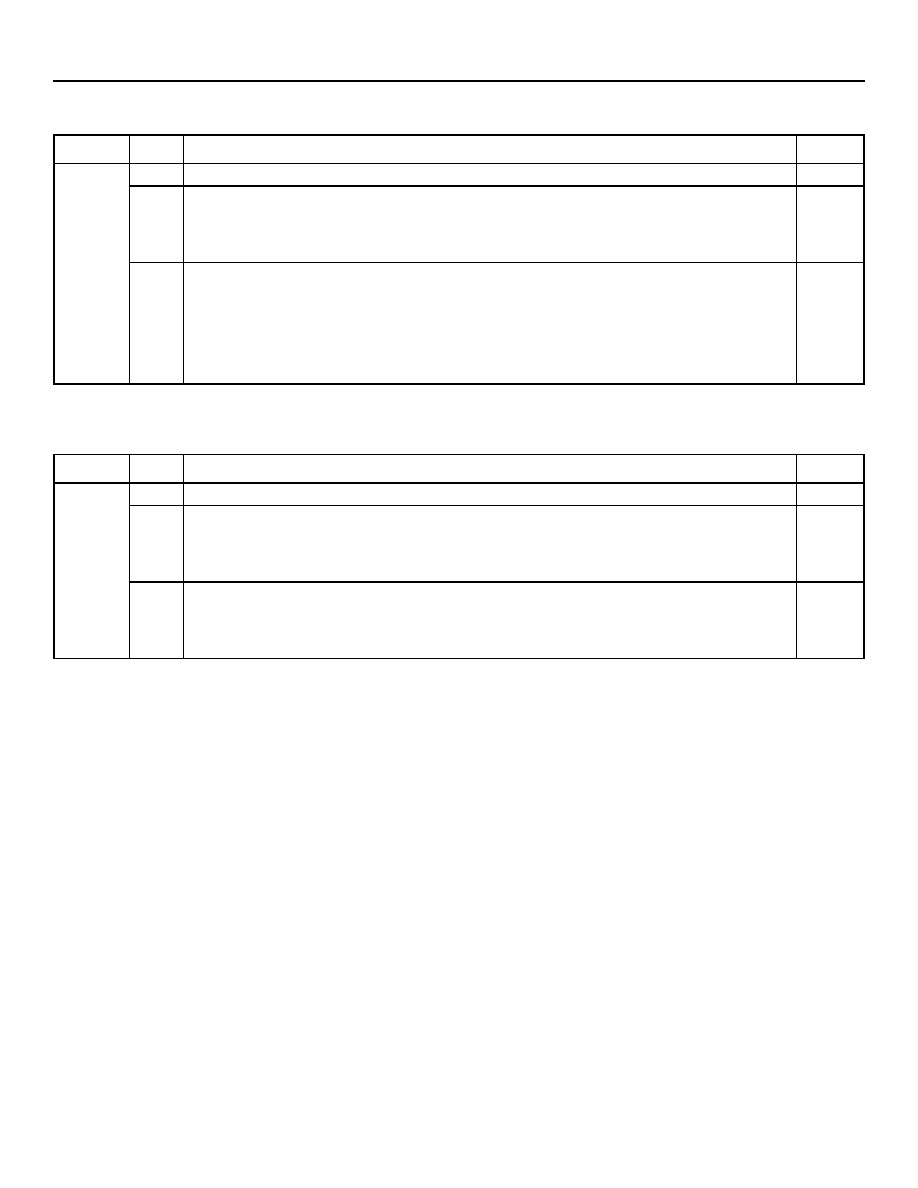

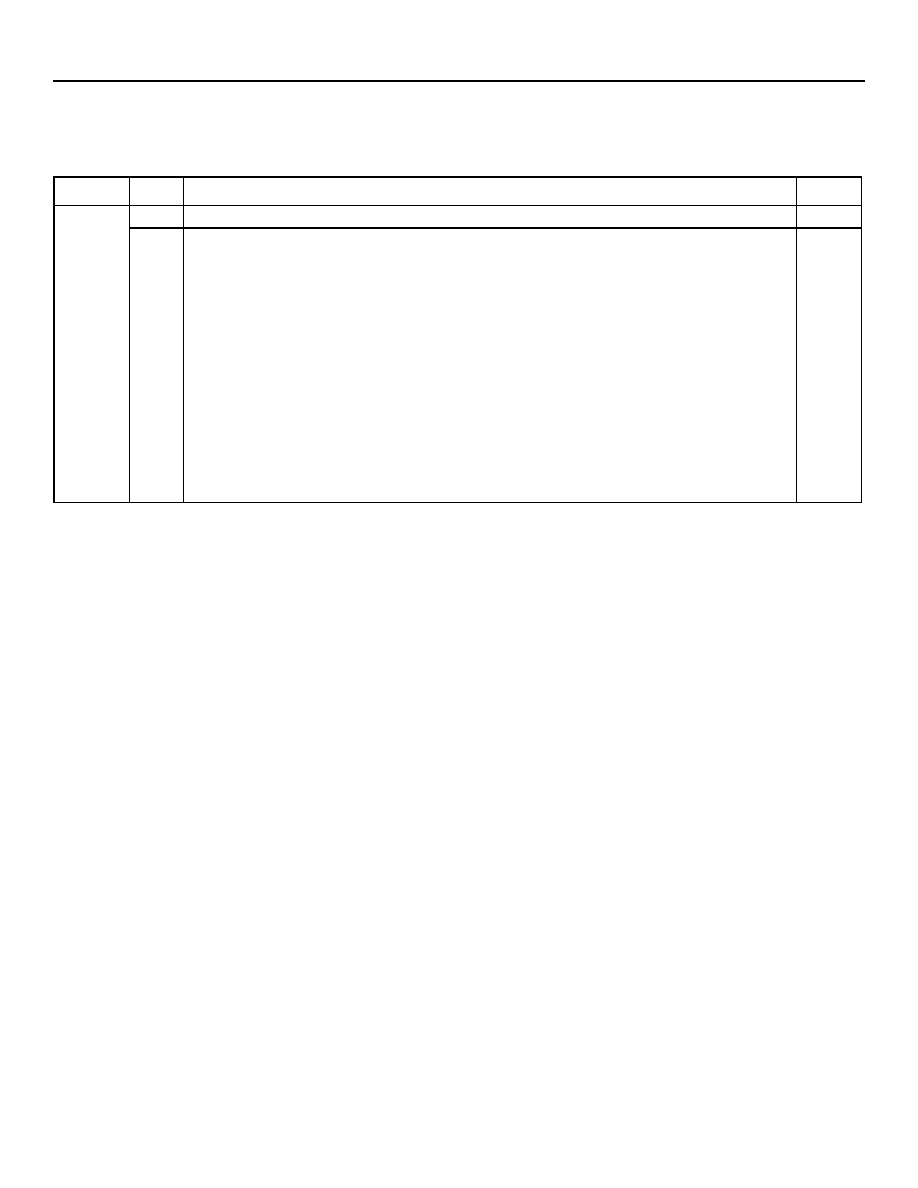

2.3.2 Bottom View

Table 2-3. Package Ball Assignments (Bottom View)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

V

VSS

RXD00

RXD02

RXD04

RXD06

RXD08

RXD11

RXD14

NC

NC

NC

NC

NC

NC

NC

NC

RSV11

V

SS

U

NC

VSS

RXD01

RXD03

RXD05

RXD07

RXD10

RXD13

RXD15

NC

NC

NC

NC

NC

NC

NC

V

SS

V

SS

T

NC

NC

VSS

NC

VDD33

VDD33

RXD09

RXD12

VDD33

VDD33

FSYNC

V

SS

V

SS

V

DD33

NC

V

SS

V

DD33

RSV10

R

NC

NC

VDD33

VSS

VSS

VSS

VDD15

VDD15

VSS

VSS

V

DD15

V

DD15

V

SSPLL

V

DDPLL

V

SS

CHICLK

HIZ

PAR0

P

NC

NC

VDD33

VSS

--

--

--

--

--

--

--

--

--

--

PAR1

DATA15

DATA14

DATA13

N

NC

NC

NC

VSS

--

--

--

--

--

--

--

--

--

--

DATA12

DATA11

DATA10

DATA09

M

NC

NC

VSS

VDD15

--

--

--

--

--

--

--

--

--

--

DATA08

DATA07

DATA06

DATA05

L

NC

NC

VSS

VDD15

--

--

--

VSS

VSS

VSS

V

SS

--

--

--

V

SS

DATA04

DATA03

DATA02

K

NC

NC

NC

VSS

--

--

--

VSS

VSS

VSS

V

SS

--

--

--

MPUCLK

V

DD33

DATA01

DATA00

J

TXD15

TXD14

VDD33

VSS

--

--

--

VSS

VSS

VSS

V

SS

--

--

--

V

SS

AS

R/W

CS

H

TXD13

TXD12

VDD33

VDD15

--

--

--

VSS

VSS

VSS

V

SS

--

--

--

RESET

INT

DT

TRSTN

G

TXD11

TXD10

TXD09

VDD15

--

--

--

--

--

--

--

--

--

--

TMS

TDI

TCK

TDO

F

TXD08

TXD07

VDD33

VSS

--

--

--

--

--

--

--

--

--

--

V

DD33

V

SS

RSV1

RSV2

E

TXD06

TXD05

VDD33

VSS

--

--

--

--

--

--

--

--

--

--

RSV3

RSV4

RSV5

CKSPD0

D

TXD04

TXD03

VSS

VSS

VDD15

VDD15

VDD15

VSS

VDD33

VDD33

V

SS

V

DD15

V

DD15

V

DD15

V

SS

CKSPD1

RSV6

RSV9

C

TXD02

TXD01

V

SS

V

SS

V

DD15

V

DD15

V

DD15

V

SS

V

DD33

V

DD33

V

SS

V

DD15

V

DD15

V

DD15

V

SS

V

SS

V

DD33

RSV8

B

TXD00

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

RSV7

A

V

SS

ADDR15 ADDR14 ADDR13 ADDR12 ADDR11 ADDR10 ADDR09 ADDR08 ADDR07 ADDR06 ADDR05 ADDR04 ADDR03

ADDR02

ADDR01

ADDR00

V

SS

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

12

12

Agere Systems Inc.

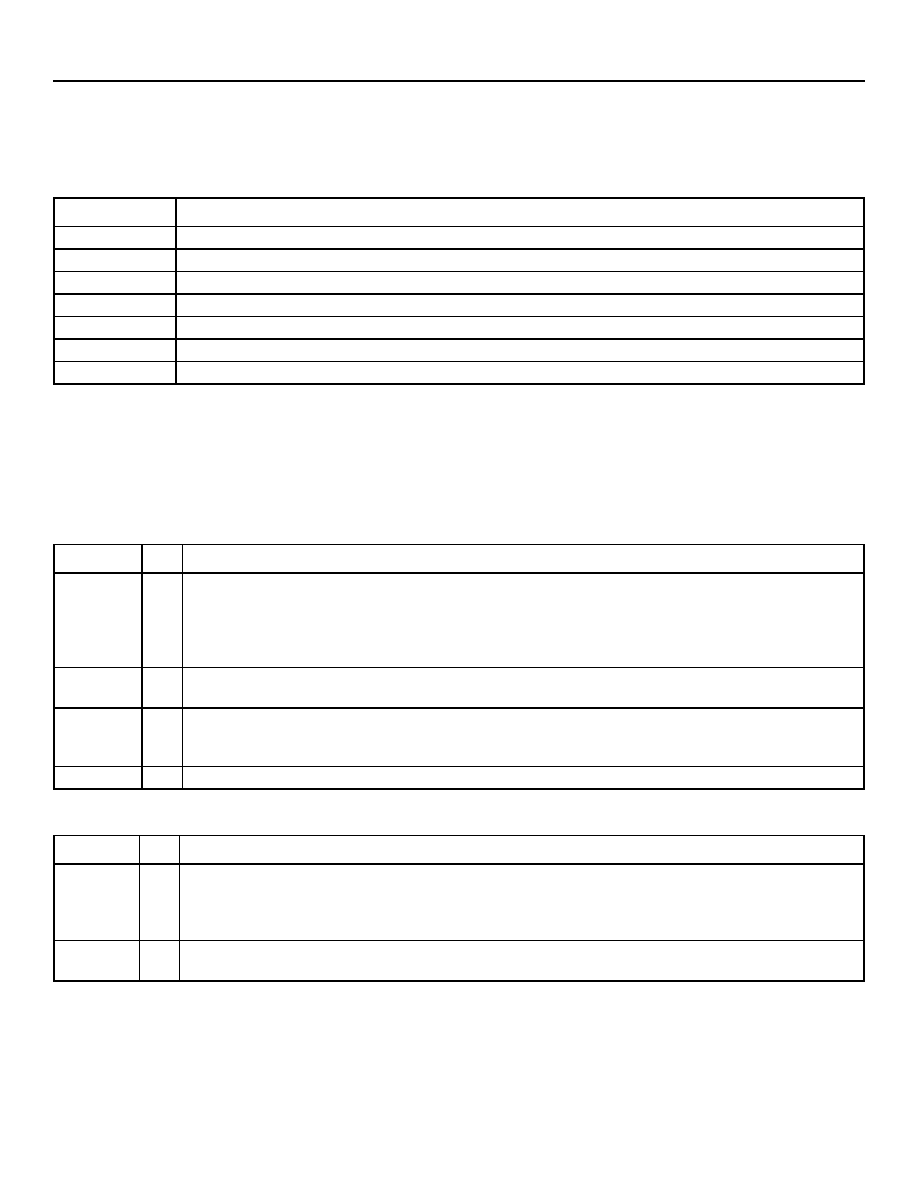

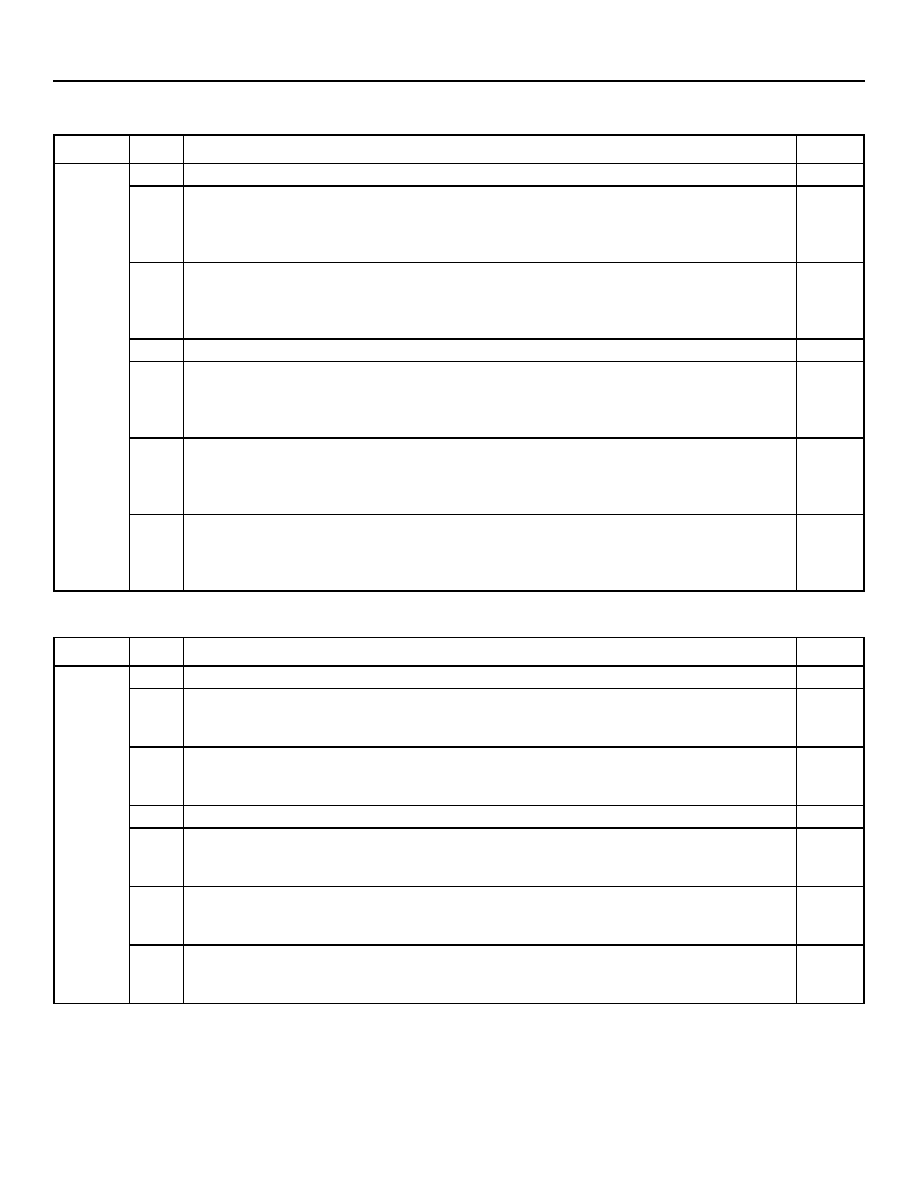

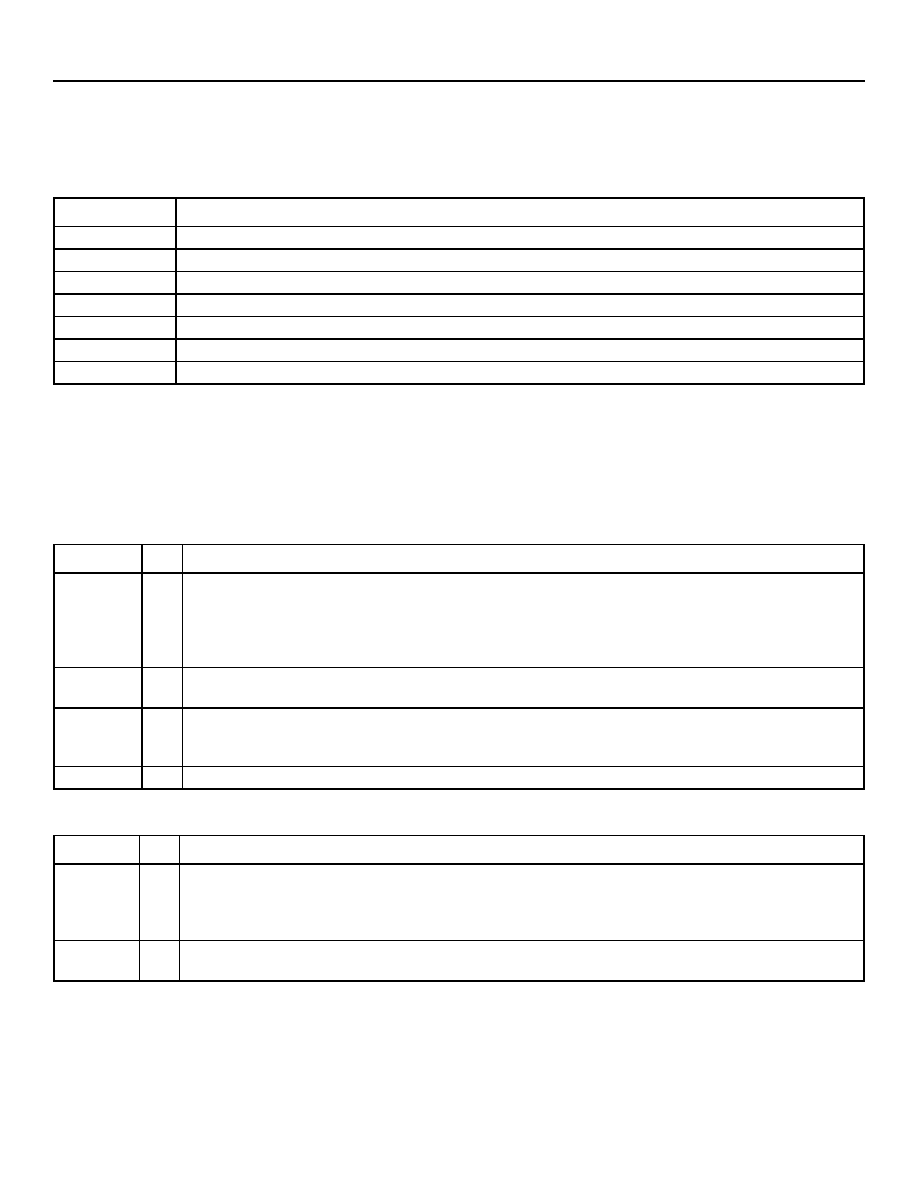

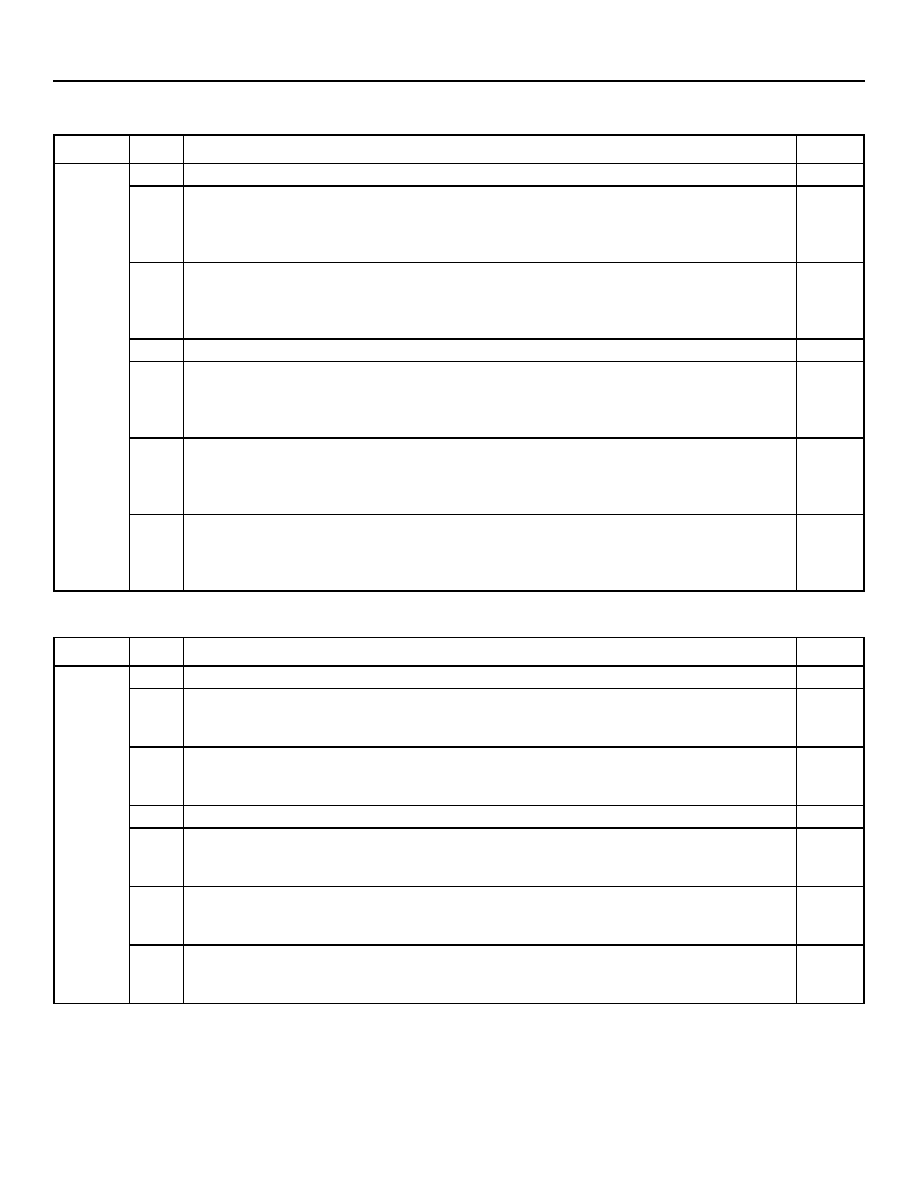

2.4 Ball Types

This table describes each type of input, output, and I/O ball used in the device.

2.5 Ball Definitions

This section describes the function of each of the device balls. The balls are listed by ball name. The static parameters (drive

currents, switching thresholds, etc.) for each ball type (input, output, etc.) are described in

Table 4-1 on page 18

through

Table 4-3

.

Table 2-4. Ball Types

Type Label

Description

I

CMOS input, TTL switching thresholds.

I pd

CMOS input, TTL switching thresholds with internal pull-down resistor.

I pu

CMOS input, TTL switching thresholds with internal pull-up resistor.

O

CMOS output.

O od

Open-drain output.

I/O

Bidirectional ball. CMOS input with TTL switching thresholds and CMOS output.

P

Power and ground.

Table 2-5. Timing Port

Ball Name Type

Name/Description

FSYNC

I

Frame Synchronization. This signal indicates the beginning of a 125 �s frame event (8 kHz). The

FSYNC ball can be programmed as active-low or active-high, but its polarity is the same for all

concentration highway interfaces (CHI). FSYNC can be sampled on either the positive or negative

edge of CHICLK. Time-slot numbers and bit offsets for each CHI are assigned relative to the detection

of FSYNC.

CHICLK

I

Clock. This is the master synchronous clock for the transmit and receive concentration highways. The

frequency can be 8.192 MHz or 16.384 MHz. It must be at least as fast as the highest CHI data rate.

CKSPD0

I

Clock Speed. Static control input that should be tied according to the frequency of CHICLK. If CHICLK

is connected to an 8.192 MHz source, CKSPD0 should be tied to V

SS

. If CHICLK is connected to a

16.384 MHz source, CKSPD0 should be tied to V

DD33

.

CKSPD1

I pd Clock Speed. Reserved, leave disconnected. 20 k

pull-down resistor.

Table 2-6. Transmit and Receive Concentration Highways

Ball Name Type

Name/Description

RXD[15:0] I pd Receive Data [15:0]. Receive concentration highways. These are serial, synchronous data streams,

which may be individually programmed to operate at 2.048 Mbits/s, 4.096 Mbits/s, 8.192 Mbits/s, or

16.384 Mbits/s. They carry 32, 64, 128, or 256 time slots (respectively) each occupying eight

contiguous bits. 20 k

pull-down resistor.

TXD[15:0]

O

Transmit Data [15:0]. These are output concentration highway data streams with data rate options

identical to the RXD inputs.

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

13

Table 2-7. Control Port

Ball Name Type

Name/Description

MPUCLK

I

Processor Clock. This clock is used to sample address, data, and control signals from the

microprocessor. This clock must be within the range of 0 MHz--66 MHz. Required for operation.

CS

I

Chip Select. Active-low chip select. This input is held low for the duration of any read or write access

to the device. Required for operation.

AS

I

Address Strobe. Active-low address strobe that is one MPUCLK cycle wide at the start of a

microprocessor access cycle to the device. This is used to initiate a microprocessor access. Required

for operation.

R/W

I

Read/Write. Cycle selection. R/W is set high during a read cycle, or set low for a write cycle.

Required for operation.

ADDR[15:0] I pu Address [15:0]. ADDR[15] is the most significant bit and ADDR[0] is the least significant bit for

addressing all the internal registers during microprocessor access cycles. All addresses are 16-bit

word addresses; therefore, in a typical application ADDR[0] of the device would be connected to

address bit 1 of a byte addressable system address bus. Required for operation. 200 k

pull-up

resistor.

Note: The device is little-endian; the least significant byte is stored in the lowest address and the

most significant byte is stored in the highest address. Care must be exercised when

connecting to microprocessors that use big-endian byte ordering.

DATA[15:0]

I/O Data [15:0]. Data bus for all transfers between the microprocessor and the internal registers. The

balls are inputs during write cycles and outputs during read cycles. DATA[15] is the most significant

bit, and DATA[0] is the least significant bit. Required for operation.

PAR[1:0]

I/O Control Port Parity [1:0]. Byte-wide parity bits for data. PAR[1] is the parity for DATA[15:8], and

PAR[0] is the parity for DATA[7:0]. The parity sense (even or odd) is application programmable via a

register bit in the device. Not required for operation.

DT

O

Data Transfer Acknowledge. Active-low for one MPUCLK cycle. Indicates that data has been written

during write cycles or that data is valid during read cycles. High impedance when CS is a 1 and driven

when CS is 0. Required for operation.

INT

O od Interrupt. This output is asserted low to indicate that an interrupt condition has occurred. This signal

remains active-low until the interrupt status register has been cleared or masked.

Table 2-8. Initialization and Test Access

Ball Name Type

Name/Description

RESET

I pu Reset. Global reset, active-low. Initializes all internal registers to their default state. The reset occurs

asynchronously, but RESET should be held low for at least two CHICLK periods. 20 k

pull-up resistor.

TCK

I pu Test Clock. This signal provides timing for the boundary-scan and test access port (TAP) controller.

Should be static, except during boundary-scan testing. 20 k

pull-up resistor.

TDI

I pu Test Data In. Data input for the boundary-scan. Sampled on the rising edge of TCK. 20 k

pull-up

resistor.

TMS

I pu Test Mode Select (Active-Low). Controls boundary-scan test operations. TMS is sampled on the rising

edge of TCK. 20 k

pull-up resistor.

TRSTN

I pd Test Reset (Active-Low). This signal is an asynchronous reset for the TAP controller. 20 k

pull-down

resistor.

TDO

O

Test Data Out. Updated on the falling edge of TCK. The TDO output is high impedance except when

scanning out test data.

HIZ

I pu Output Enable. All output and bidrectional buffers will be high-impedance when this input is low unless

boundary scan is enabled (TRSTN = 1). 20 k

pull-up resistor.

RSV[11:1]

-- Reserved [11:1]. These balls are used by Agere Systems during the manufacturing process; they must

be left unconnected.

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

14

14

Agere Systems Inc.

Table 2-9. Power Balls

Symbol Type

Name/Description

V

DD33

P

I/O Power. Power supply balls for the I/O pads (3.3 V � 5%).

V

DD15

P

Core Power. Power supply balls for the core (1.5 V � 5%).

V

SS

P

Ground. Common ground balls for 3.3 V and 1.5 V supplies.

V

DDPLL

P

PLL Power. 1.5 V power supply for the internal phase-locked loop. Must include local 0.01 �F capacitor to

V

SSPLL

.

V

SSPLL

P

PLL Ground. Isolated ground for the internal phase-locked loop.

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

15

3 Operating Conditions and Reliability

3.1 Absolute Maximum Ratings

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute

stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those

given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can

adversely affect device reliability.

3.2 Recommended Operating Conditions

Table 3-2 lists the voltages, along with the tolerances, that are required for proper operation of the device.

3.3 Handling Precautions

Although electrostatic discharge (ESD) protection circuitry has been designed into this device, proper precautions must be

taken to avoid exposure to ESD and electrical overstress (EOS) during all handling, assembly, and test operations. Agere

employs both a human-body model (HBM) and a charged-device model (CDM) qualification requirement in order to deter-

mine ESD-susceptibility limits and protection design evaluation. ESD voltage thresholds are dependent on the circuit param-

eters used in each of the models, as defined by JEDEC's JESD22-A114 (HBM) and JESD22-C101 (CDM) standards.

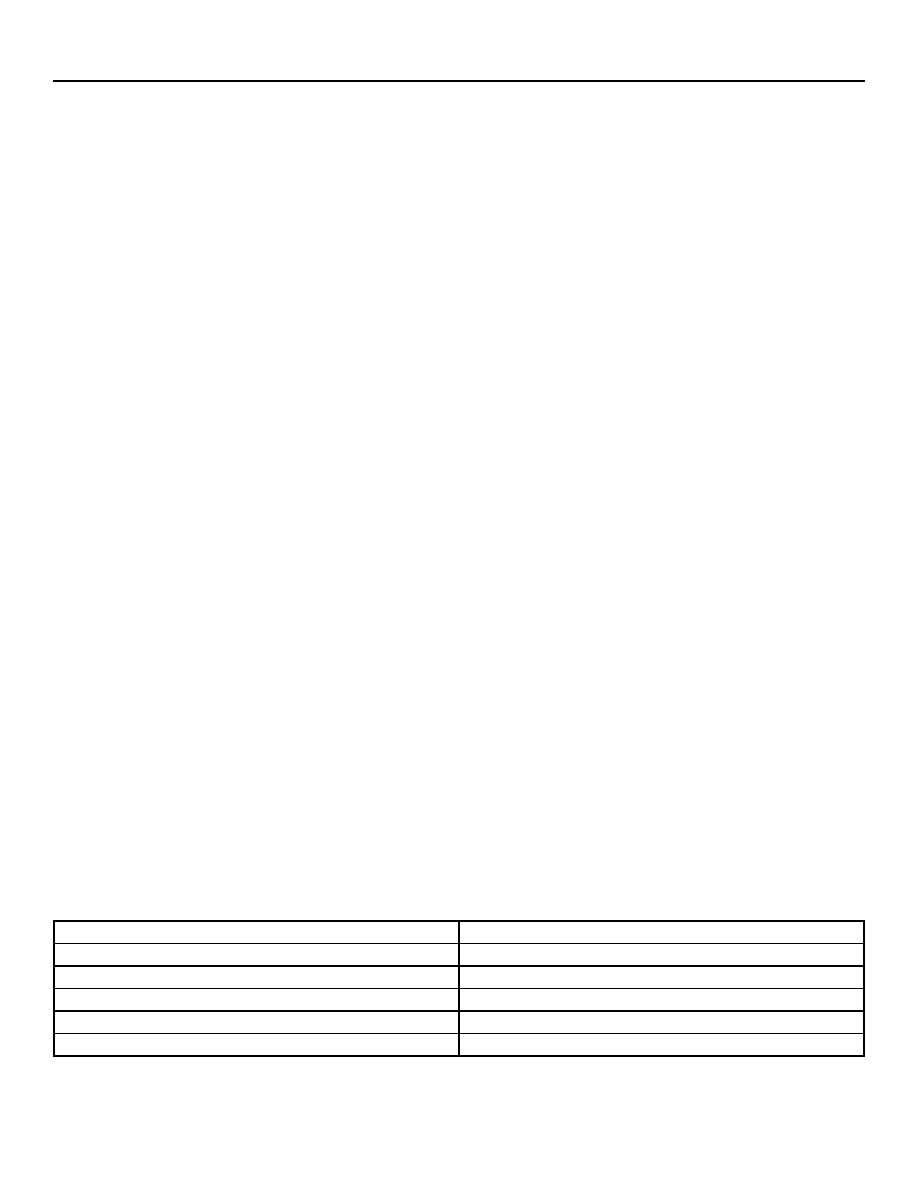

Table 3-1. Absolute Maximum Ratings

Parameter

Min

Max

Unit

Supply Voltage (V

DD33

)

�0.5

4.2

V

Supply Voltage (V

DD15

)

�0.5

1.8

V

Input Voltage:

TXD[15:0]

All Other Inputs

�0.5

�0.3

5.5

V

DD33

+ 0.3

V

V

Storage Temperature

�40

125

�C

Junction Temperature

--

125

�C

Table 3-2. Operating Conditions

Parameter

Min

Typ

Max

Unit

Supply Voltage (V

DD33

)

3.14

3.3

3.47

V

Supply Voltage (V

DD15

)

1.4

1.5

1.6

V

Ambient Temperature

�40

--

85

�C

Table 3-3. ESD Tolerance

Device

Voltage

Type

TSI-1

2,000 V

HBM (human-body model)

500 V

CDM (charged-device model)

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

16

16

Agere Systems Inc.

3.4 Thermal Parameters (Definitions and Values)

System and circuit board level performance depends not only on device electrical characteristics, but also on device thermal

characteristics. The thermal characteristics frequently determine the limits of circuit board or system performance, and they

can be a major cost adder or cost avoidance factor. When the die temperature is kept below 125 �C, temperature-activated

failure mechanisms are minimized. The thermal parameters that Agere provides for its packages help the chip and system

designer choose the best package for their applications, including allowing the system designer to thermally design and in-

tegrate their systems.

It should be noted that all the parameters listed below are affected, to varying degrees, by package design (including paddle

size) and choice of materials, the amount of copper in the test board or system board, and system airflow.

JA

- Junction to Air Thermal Resistance

JA

is a number used to express the thermal performance of a part under JEDEC standard natural convection conditions.

JA

is calculated using the following formula:

JA

= (T

J

� T

amb

) / P; where P = power

JMA

- Junction to Moving Air Thermal Resistance

JMA

is effectively identical to

JA

but represents performance of a part mounted on a JEDEC four layer board inside a wind

tunnel with forced air convection.

JMA

is reported at airflows of 200 LFPM and 500 LFPM (linear feet per minute), which

roughly correspond to 1 m/s and 2.5 m/s (respectively).

JMA

is calculated using the following formula:

JMA

= (T

J

� T

amb

) / P

JC

- Junction to Case Thermal Resistance

JC

is the thermal resistance from junction to the top of the case. This number is determined by forcing nearly 100% of the

heat generated in the die out the top of the package by lowering the top case temperature. This is done by placing the top

of the package in contact with a copper slug kept at room temperature using a liquid refrigeration unit.

JC

is calculated using

the following formula:

JC

= (T

J

� T

C

) / P

JB

- Junction to Board Thermal Resistance

JB

is the thermal resistance from junction to board. This number is determined by forcing the heat generated in the die out

of the package through the leads or balls by lowering the board temperature and insulating the package top. This is done

using a special fixture, which keeps the board in contact with a water chilled copper slug around the perimeter of the package

while insulating the package top.

JB

is calculated using the following formula:

JB

= (T

J

� T

B

) / P

JT

- Junction Temperature to Case Temperature

JT

correlates the junction temperature to the case temperature. It is generally used by the customer to infer the junction

temperature while the part is operating in their system. It is not considered a true thermal resistance.

JT

is calculated using

the following formula:

JT

= (T

J

� T

C

) / P

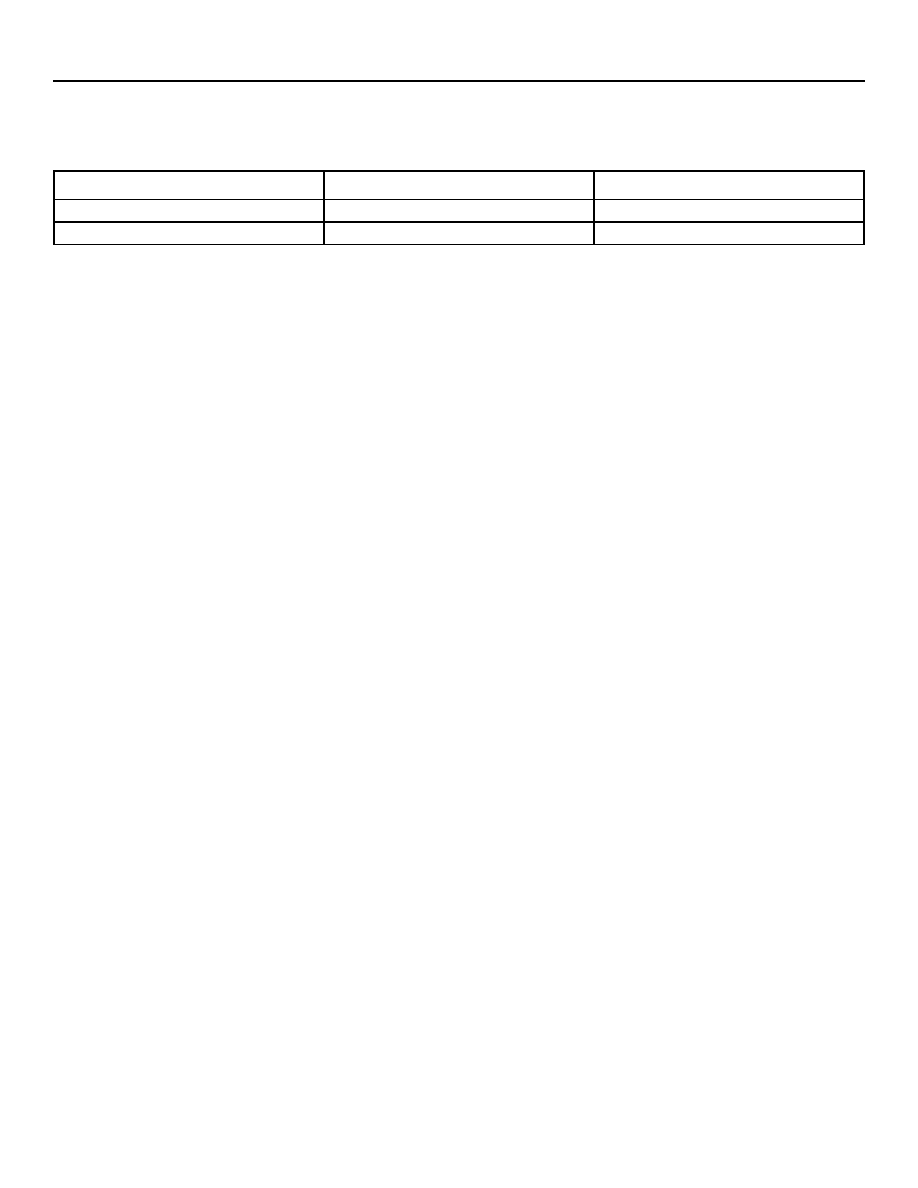

Table 3-4. Thermal Parameter Values

Parameter

Temperature �C/Watt

JA

25.1

JMA

(1 m/s)

21.4

JMA

(2.5 m/s)

18.8

JC

5.8

JB

13.0

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

17

3.5 Power Consumption

Table 3-5. Power Consumption

Supply Voltage

Typ

*

* MPUCLK = 66 MHz, CHICLK = 16.384 MHz, TA = 25 �C, all CHIs active, all outputs loaded with 50 pF.

Max

V

DD33

100 mW at 3.3 V

150 mW at 3.47 V

V

DD15

275 mW at 1.5 V

325 mW at 1.6 V

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

18

18

Agere Systems Inc.

4 dc Electrical Characteristics

This section describes all the static parameters associated with all the ball types used in the device.

* Excludes current due to pull-up or pull-down resistors.

Table 4-1. CMOS Inputs

Parameter

Symbol

Conditions

Min

Typ

Max

Unit

Input Leakage Current

I

IL

V

SS

< V

IN

< V

DD33

--

--

1*

�A

High-input Voltage

V

IH

--

2.0

--

V

DD33

+ 0.3

V

Low-input Voltage

V

IL

--

�0.3

--

0.8

V

Input Capacitance

C

I

--

--

2.5

--

pF

Table 4-2. CMOS Outputs

Parameter

Symbol

Conditions

Min

Typ

Max

Unit

Output Voltage Low

V

OL

I

OL

= �10 mA

--

--

0.4

V

Output Voltage High

V

OH

I

OL

= 10 mA

2.4

--

--

V

Output Current Low

I

OL

--

--

--

10

mA

Output Current High

I

OH

--

--

--

10

mA

Output Capacitance

C

O

--

--

3

--

pF

HIZ Output Leakage Current

I

OZ

--

--

--

10

�A

Table 4-3. CMOS Bidirectionals (DATA[15:0])

Parameter

Symbol

Conditions

Min

Typ

Max

Unit

Leakage Current

I

L

V

SS

< V

IN

< V

DD33

--

--

11

�A

High-input Voltage

V

IH

--

2.0

--

V

DD33

+ 0.3

V

Low-input Voltage

V

IL

--

�0.3

--

0.8

V

Biput Capacitance

C

IB

--

--

5.0

--

pF

Output Voltage Low

V

OL

I

OL

= �10 mA

--

--

0.4

V

Output Voltage High

V

OH

I

OL

= 10 mA

2.4

--

--

V

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

19

5 Timing Diagrams and ac Characteristics

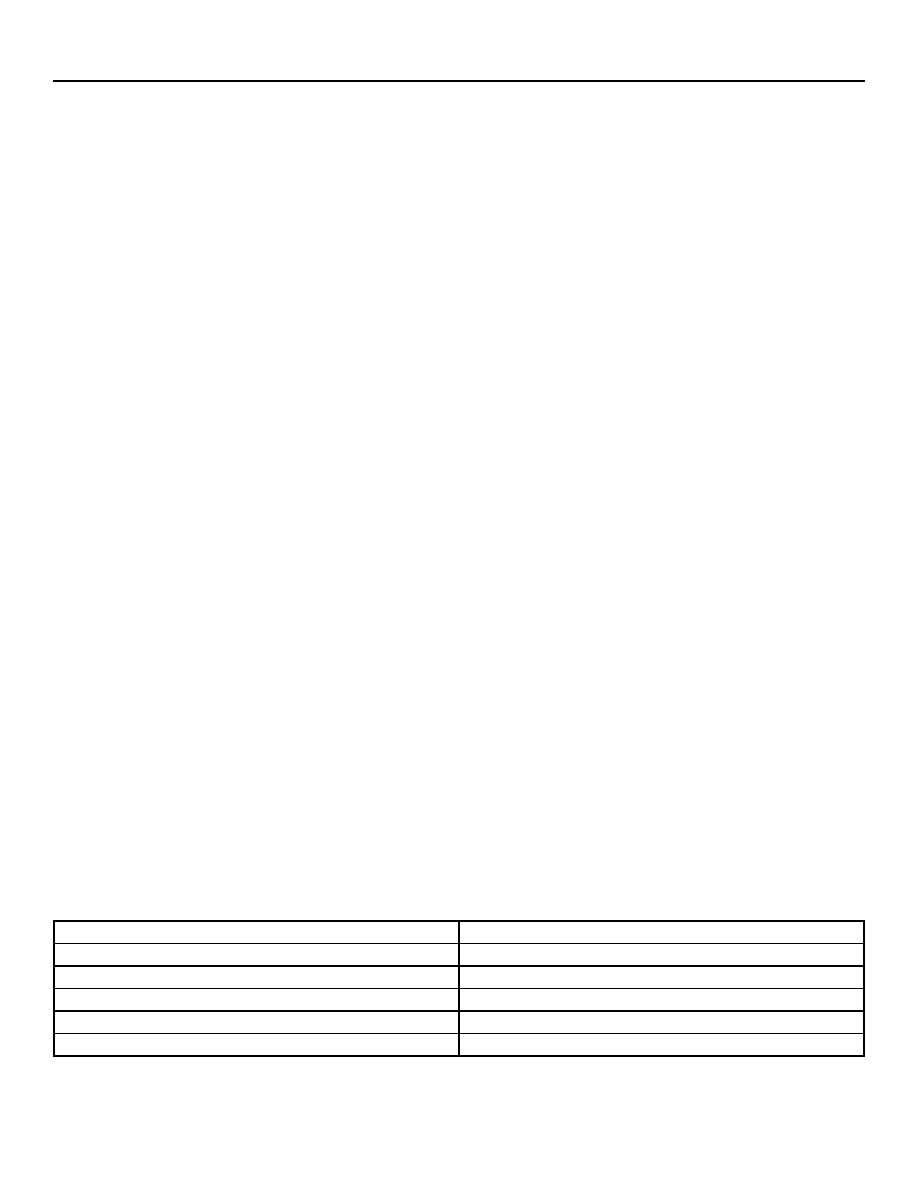

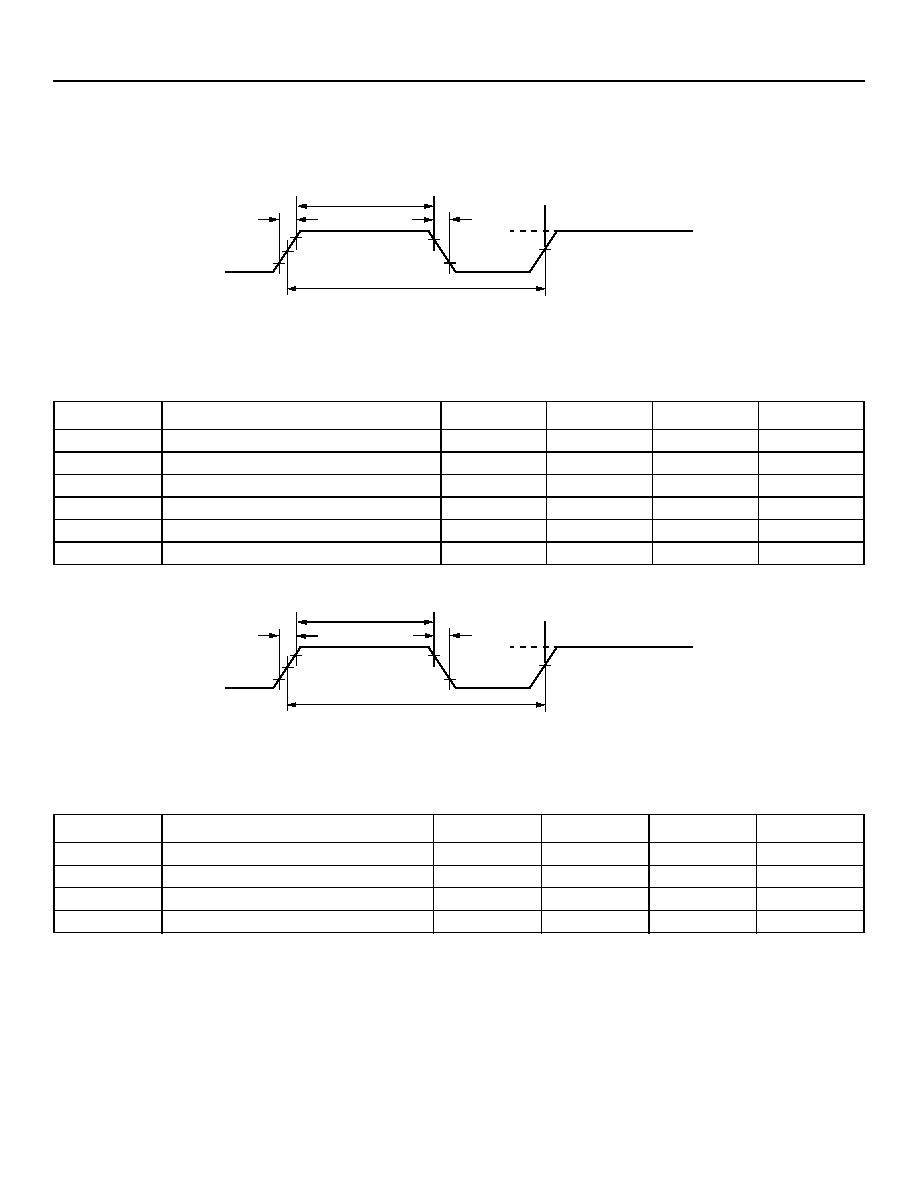

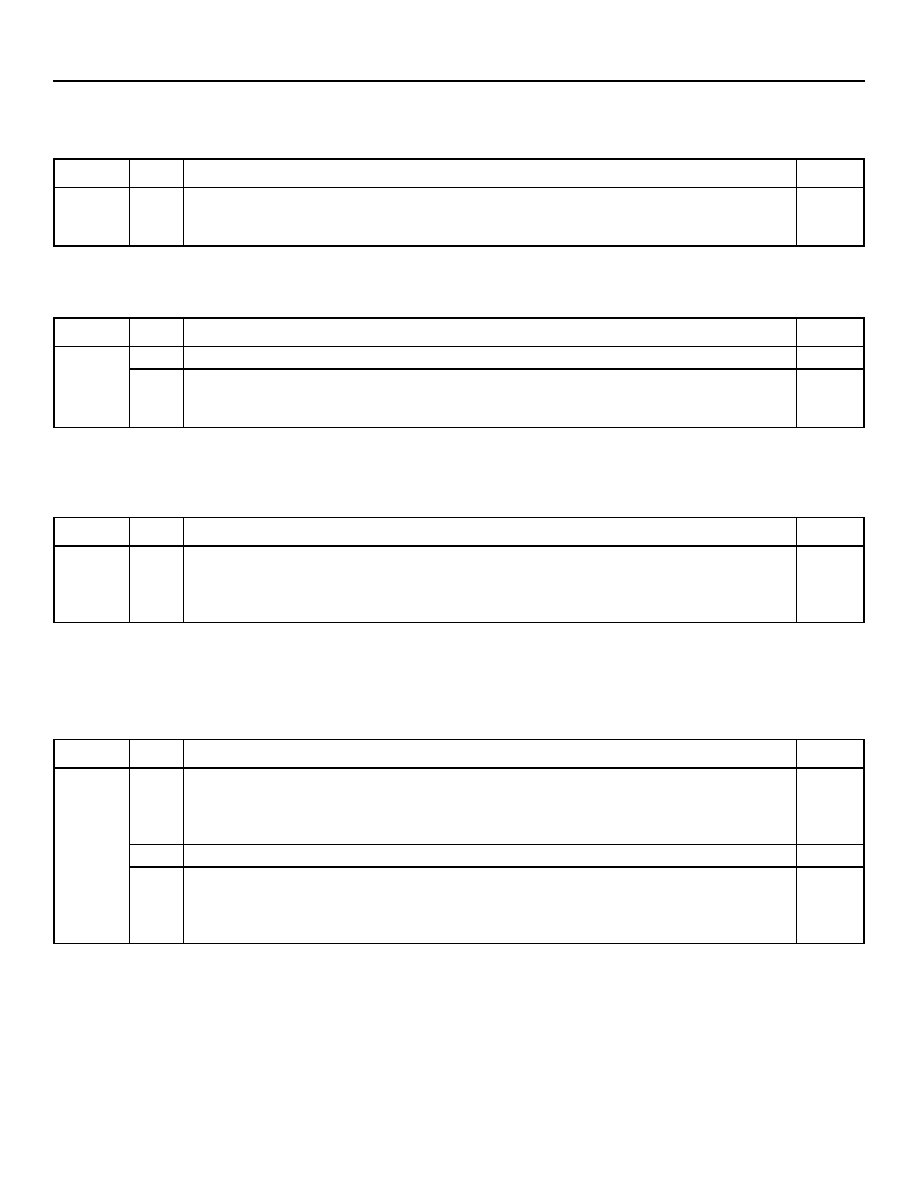

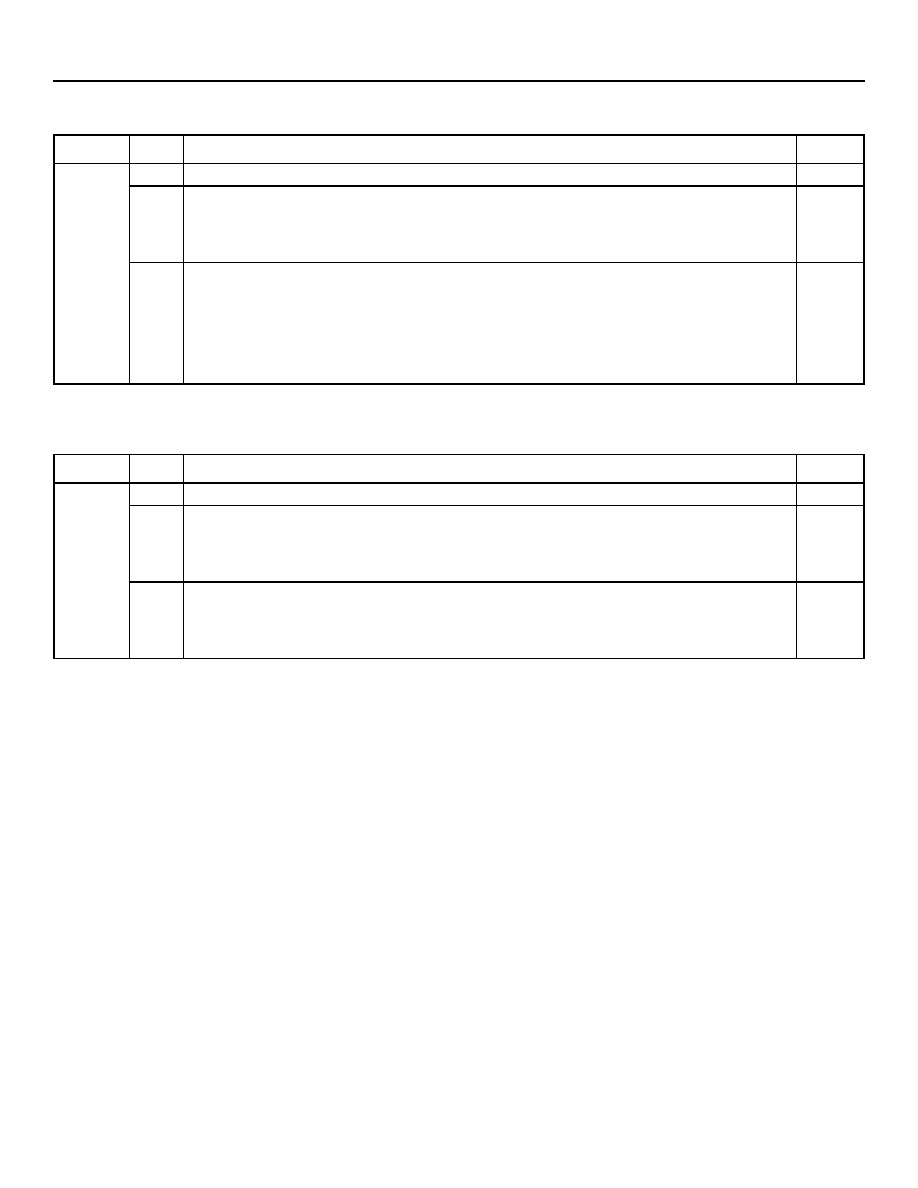

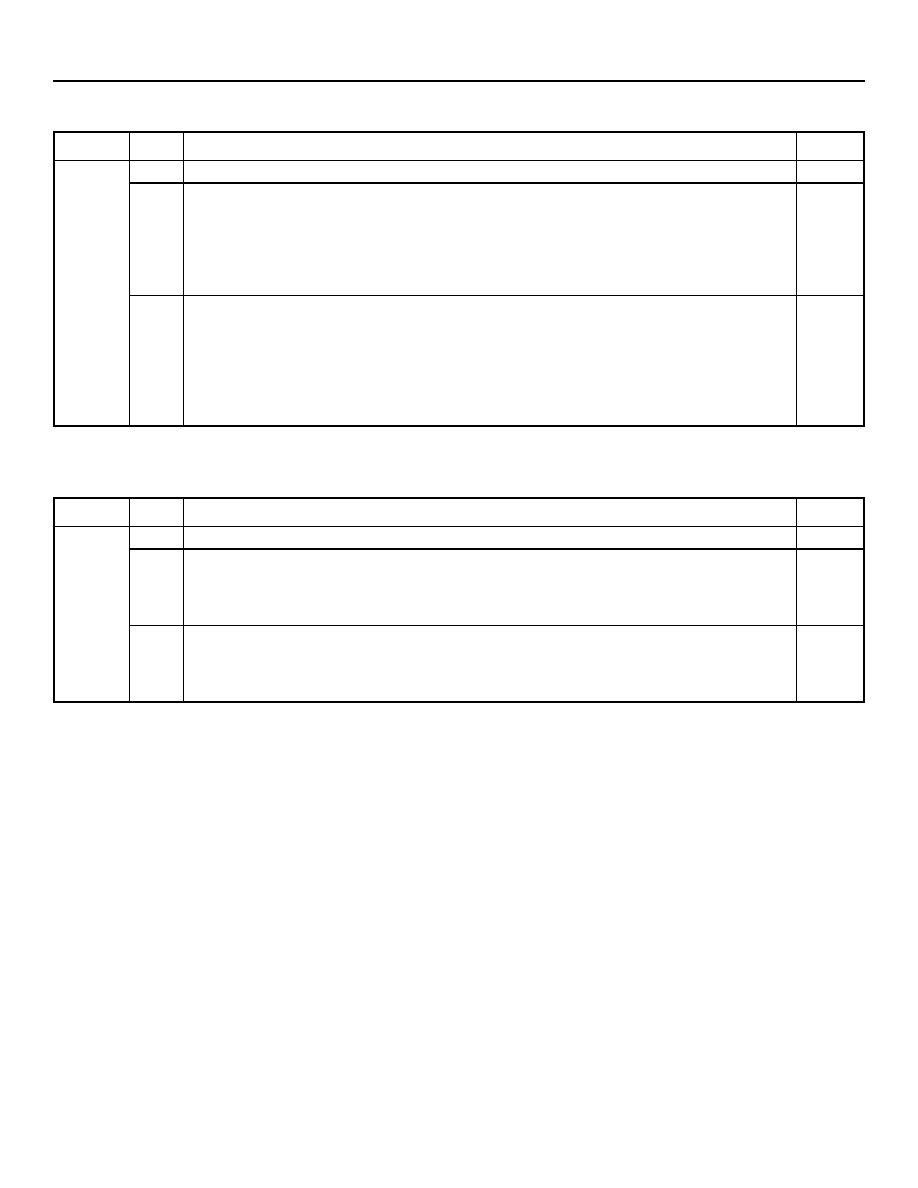

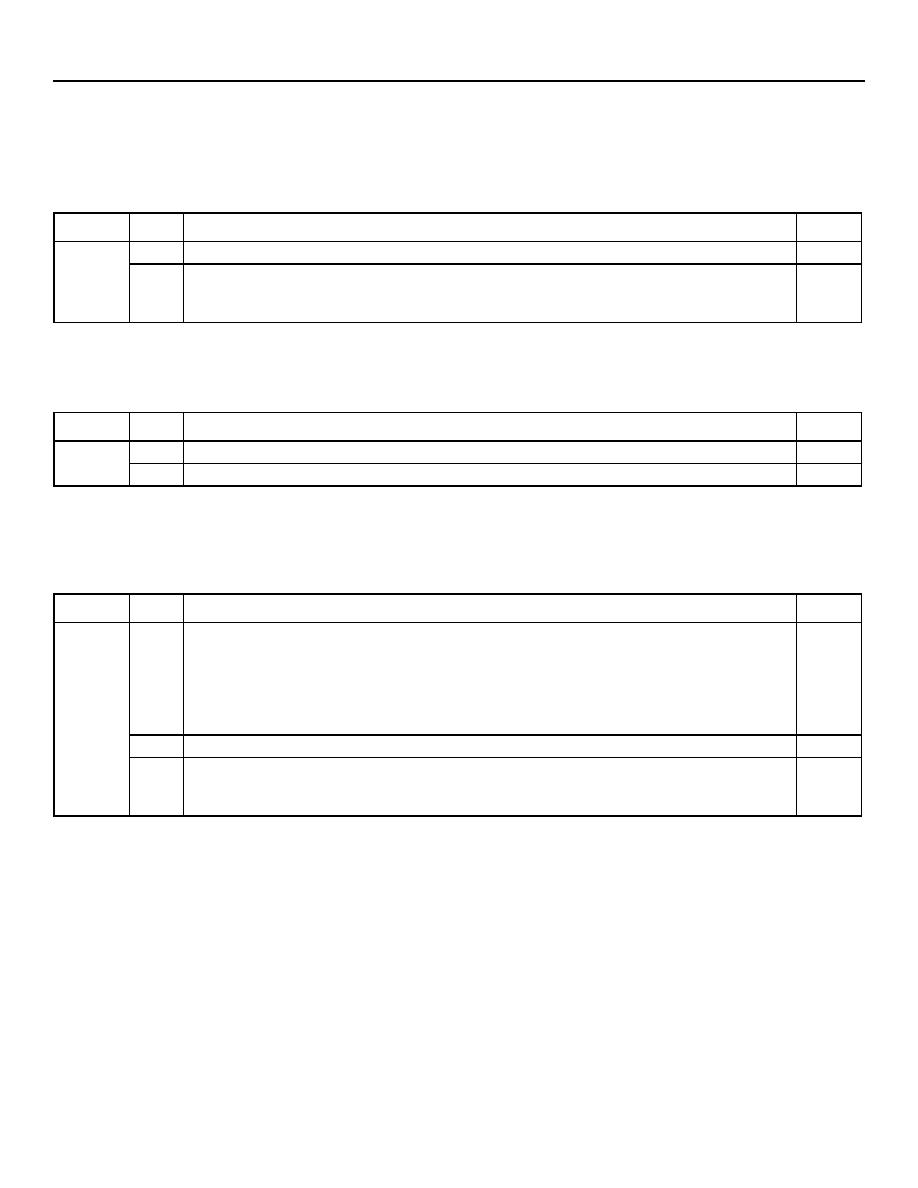

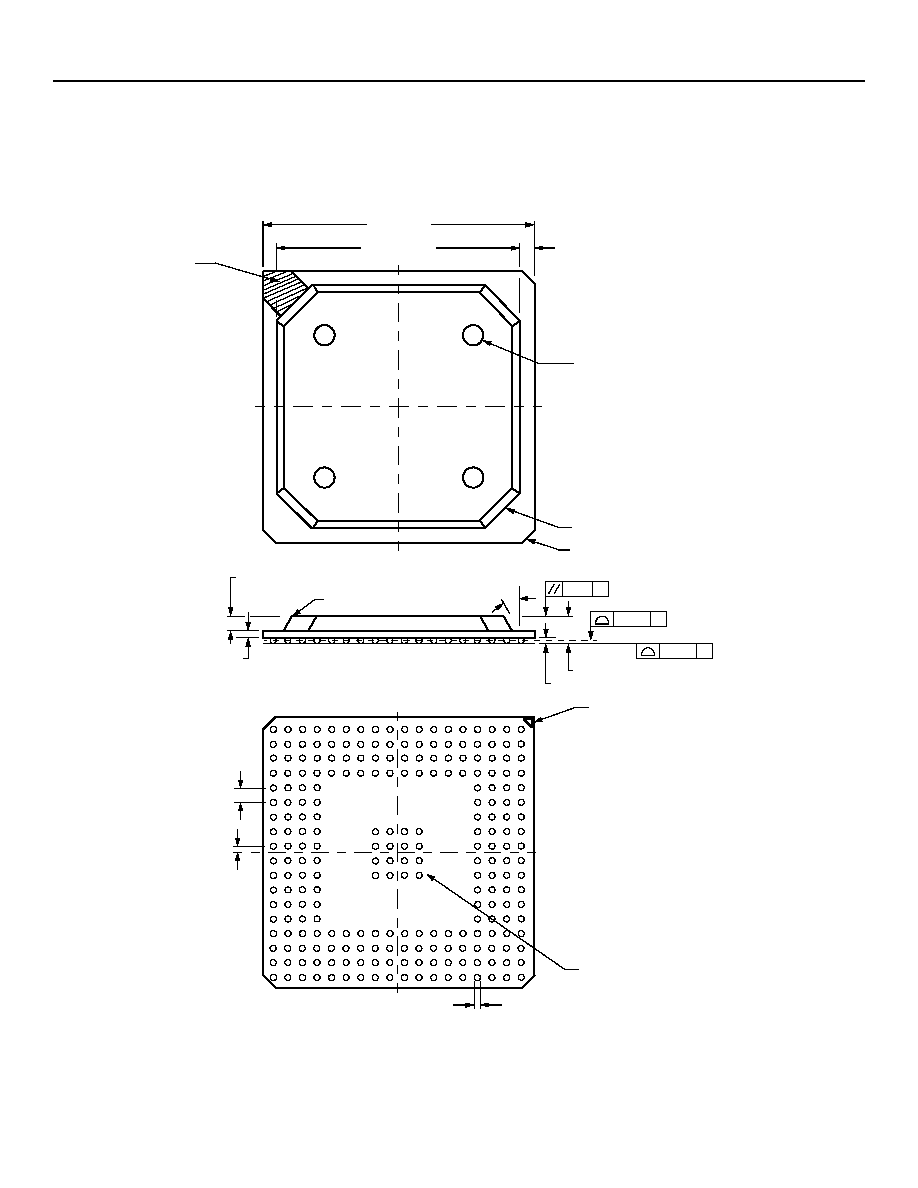

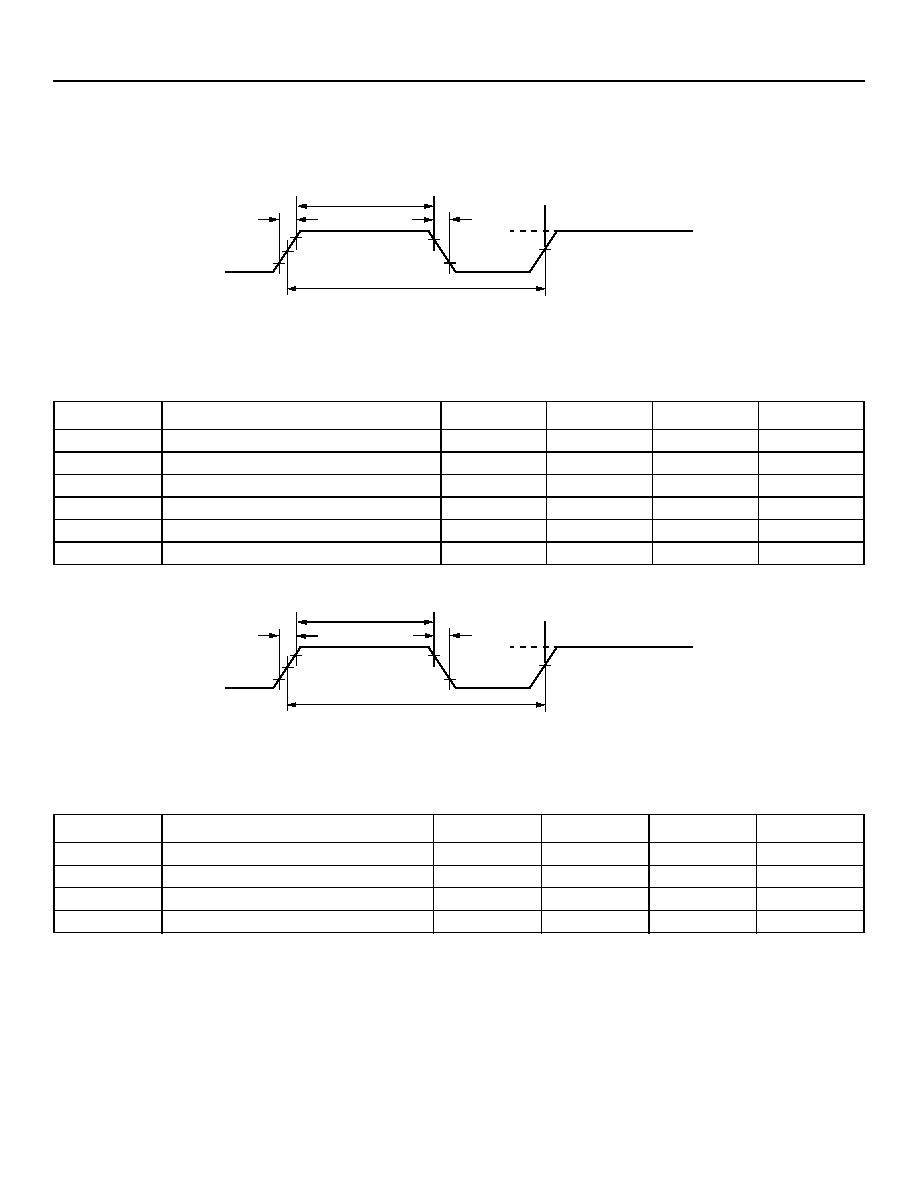

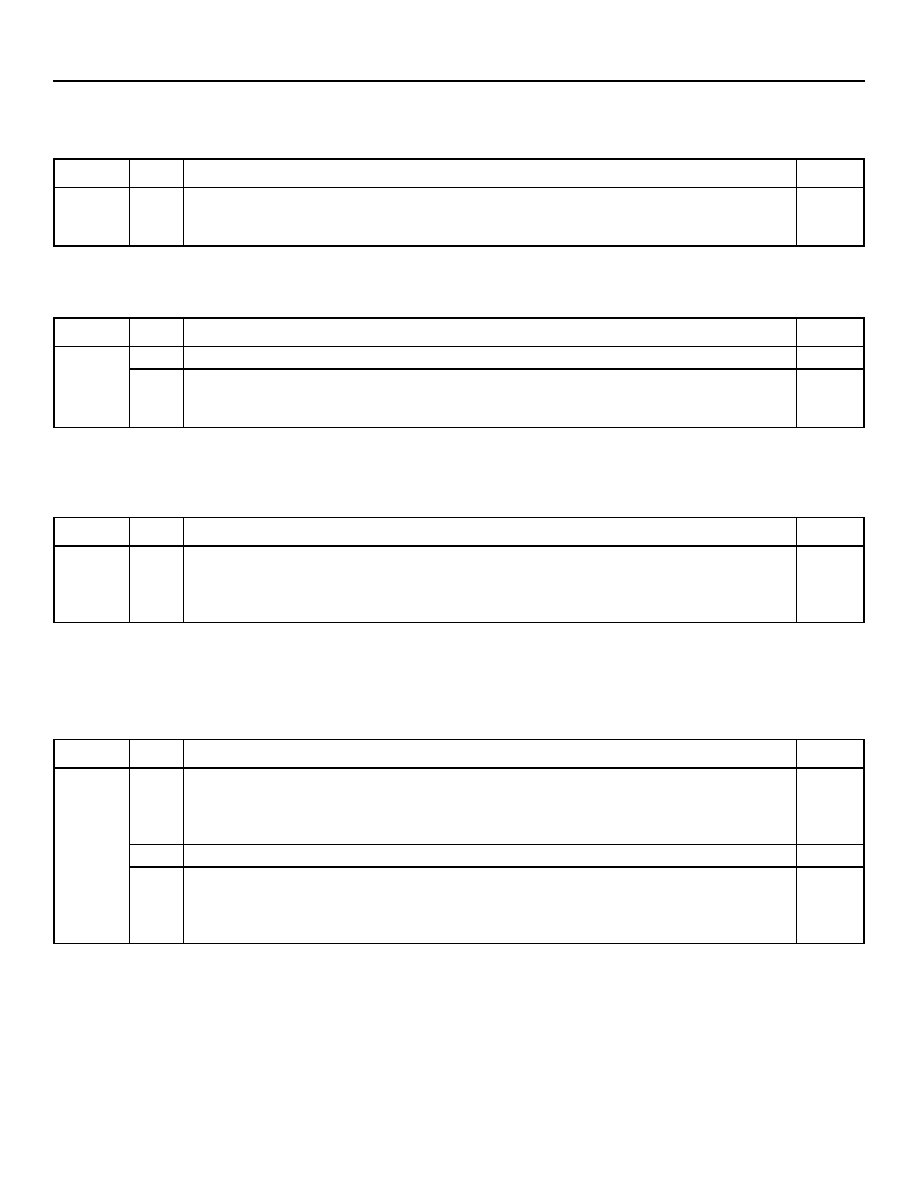

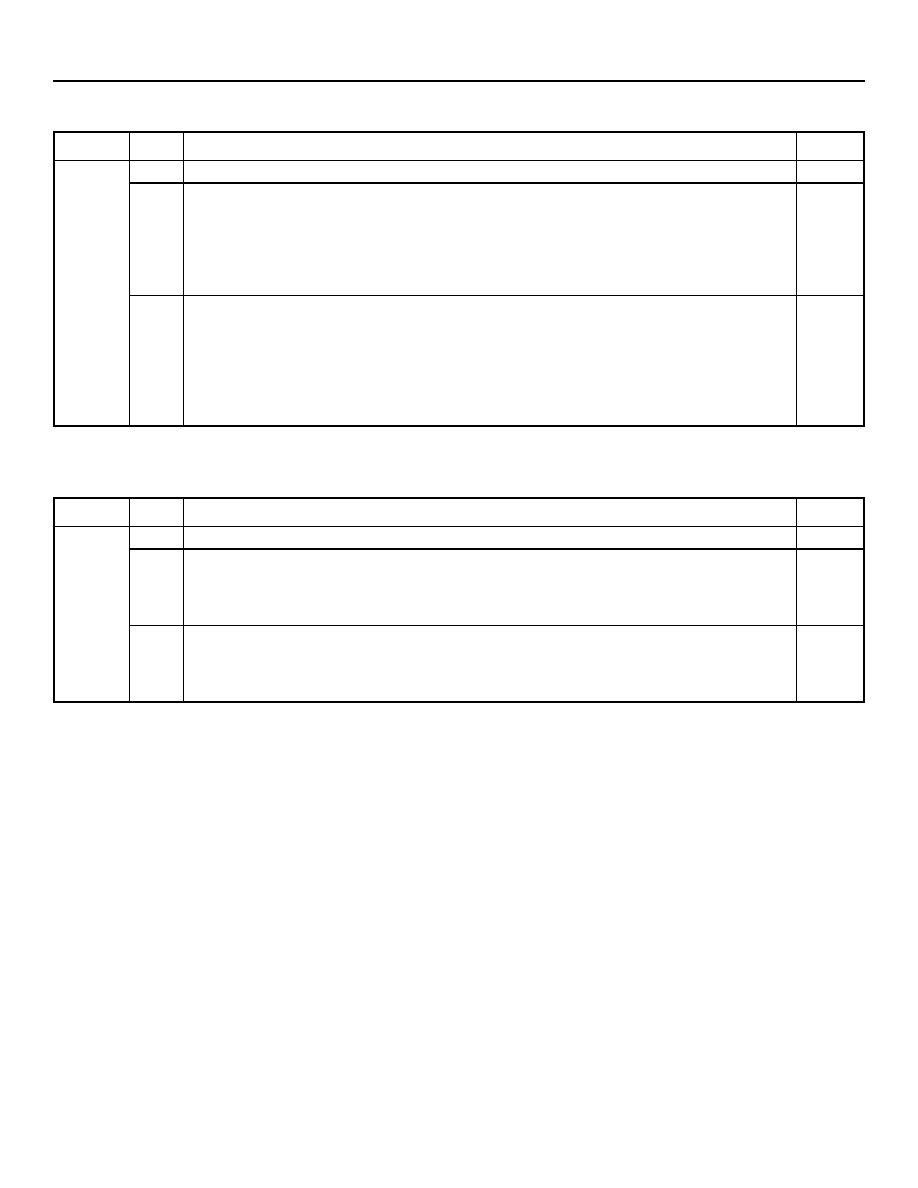

Figure 5-1 and Figure 5-2 describe the timing specifications for the input clocks

Figure 5-1. CHICLK Timing Specifications

* V

IH

to V

IH

or V

IL

to V

IL

.

Figure 5-2. MPUCLK Timing Specifications

* V

IH

to V

IH

or V

IL

to V

IL

.

Table 5-1. CHICLK Timing Specifications

Parameter

Description

Min

Typ

Max

Unit

t

1

CHICLK Rise Time

--

2

7

ns

t

2

CHICLK Width (8.192 MHz)*

48.84

--

73.24

ns

t

2

CHICLK Width (16.384 MHz)*

24.42

--

36.62

ns

t

3

CHICLK Fall Time

--

2

7

ns

t

4

CHICLK Period (8.192 MHz)

--

122.07

--

ns

t

4

CHICLK Period (16.384 MHz)

--

61.03

--

ns

Table 5-2. MPUCLK Timing Specifications

Parameter

Description

Min

Typ

Max

Unit

t

5

MPUCLK Rise Time

--

2

7

ns

t

6

MPUCLK Width*

6.06

--

--

ns

t

7

MPUCLK Fall Time

--

2

7

ns

t

8

MPUCLK Period

15.2

--

--

ns

t

1

V

DD33

V

IL

V

IH

V

IH

V

IL

t

3

t

4

50%

t

2

t

5

V

DD33

V

IL

V

IH

V

IH

V

IL

t

7

t

8

50%

t

6

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

20

20

Agere Systems Inc.

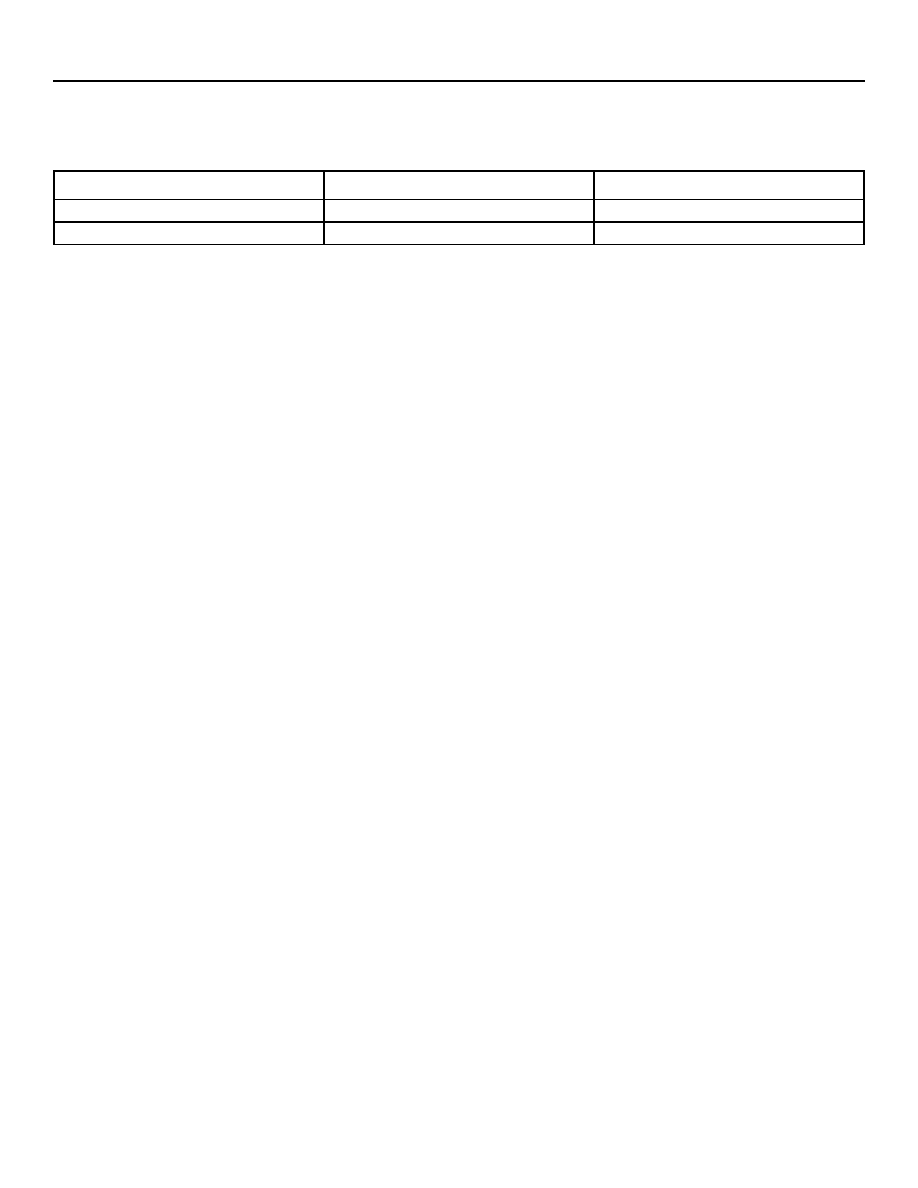

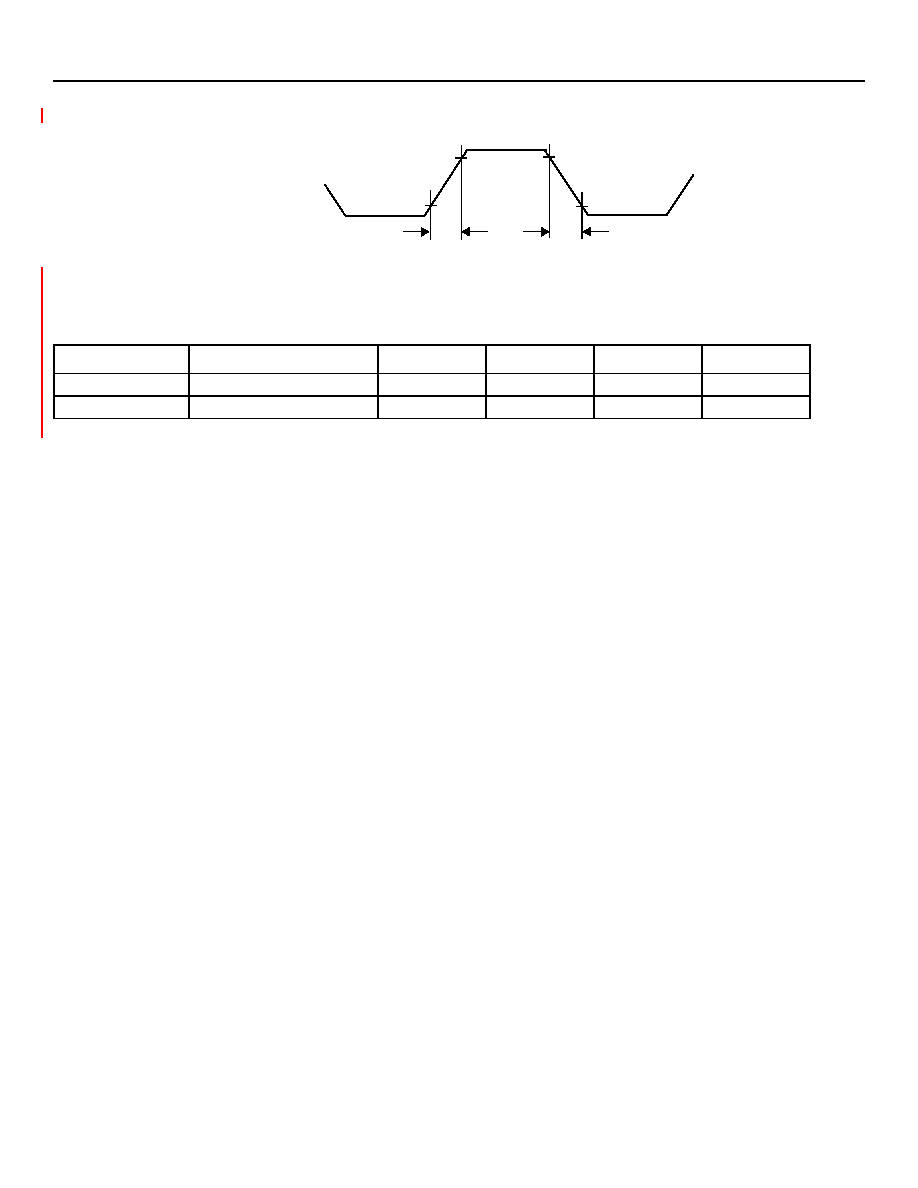

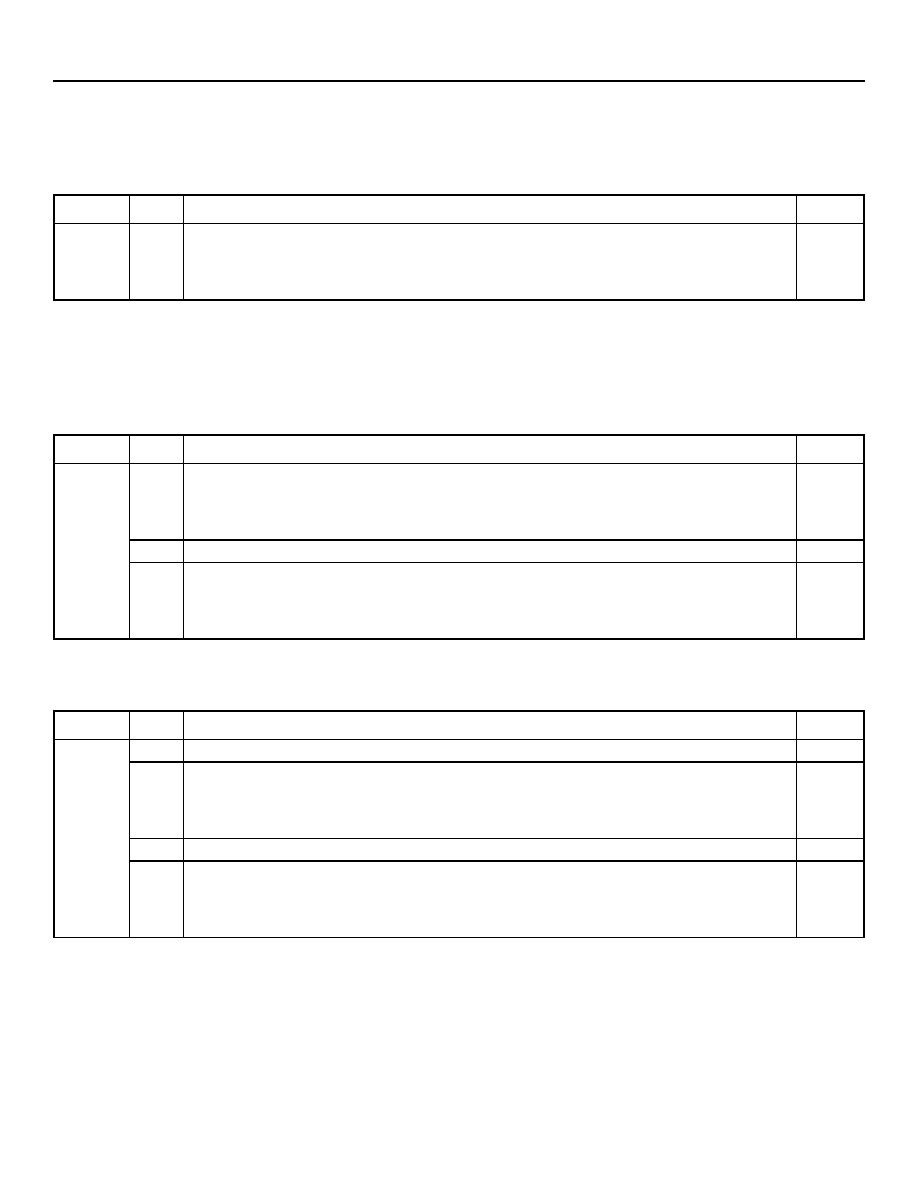

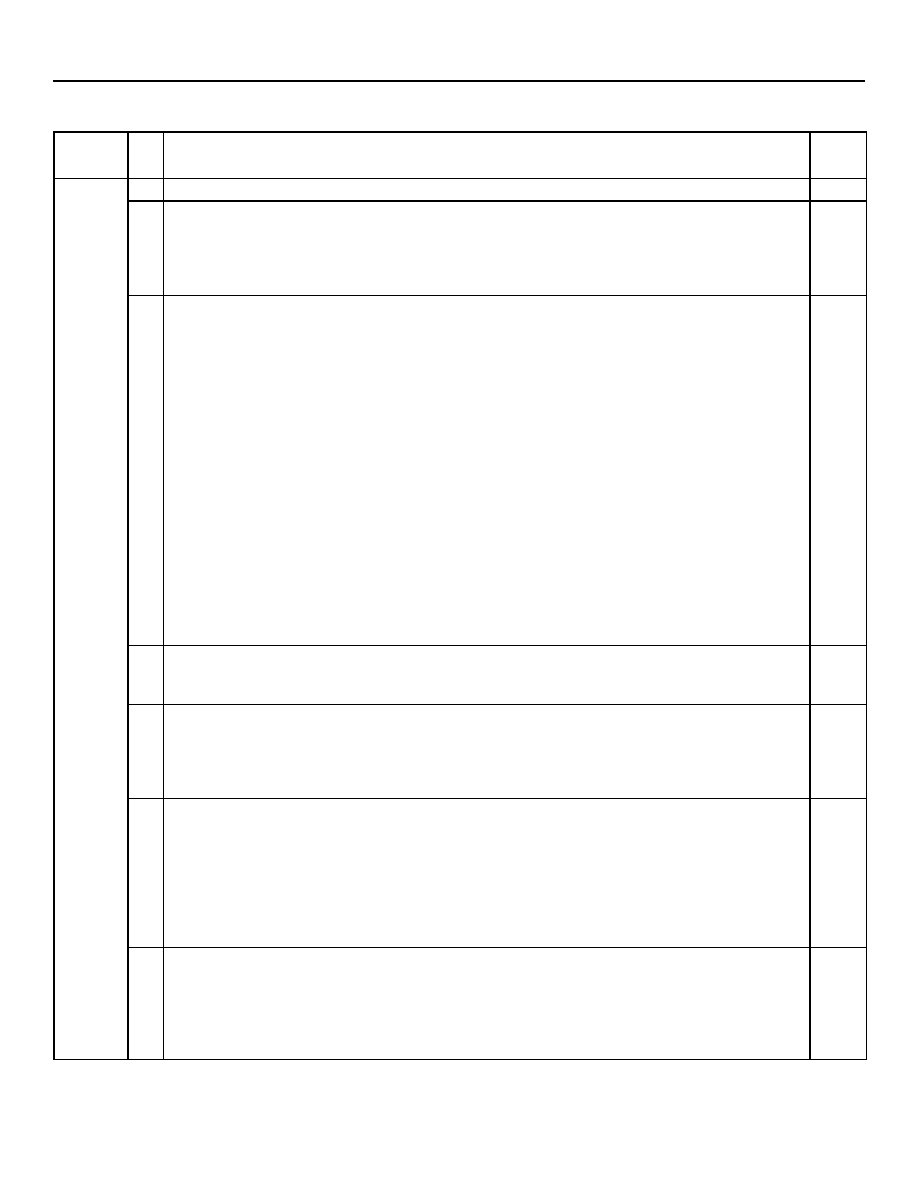

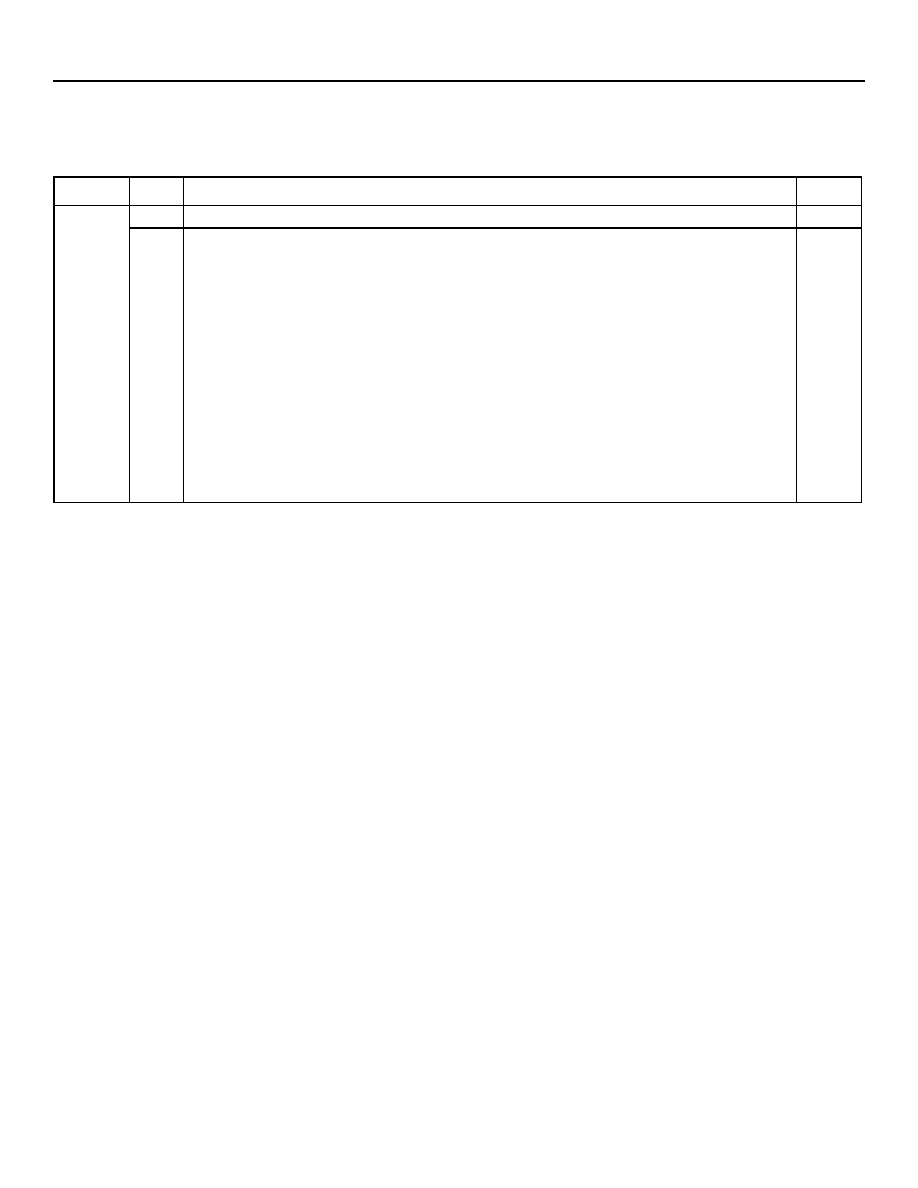

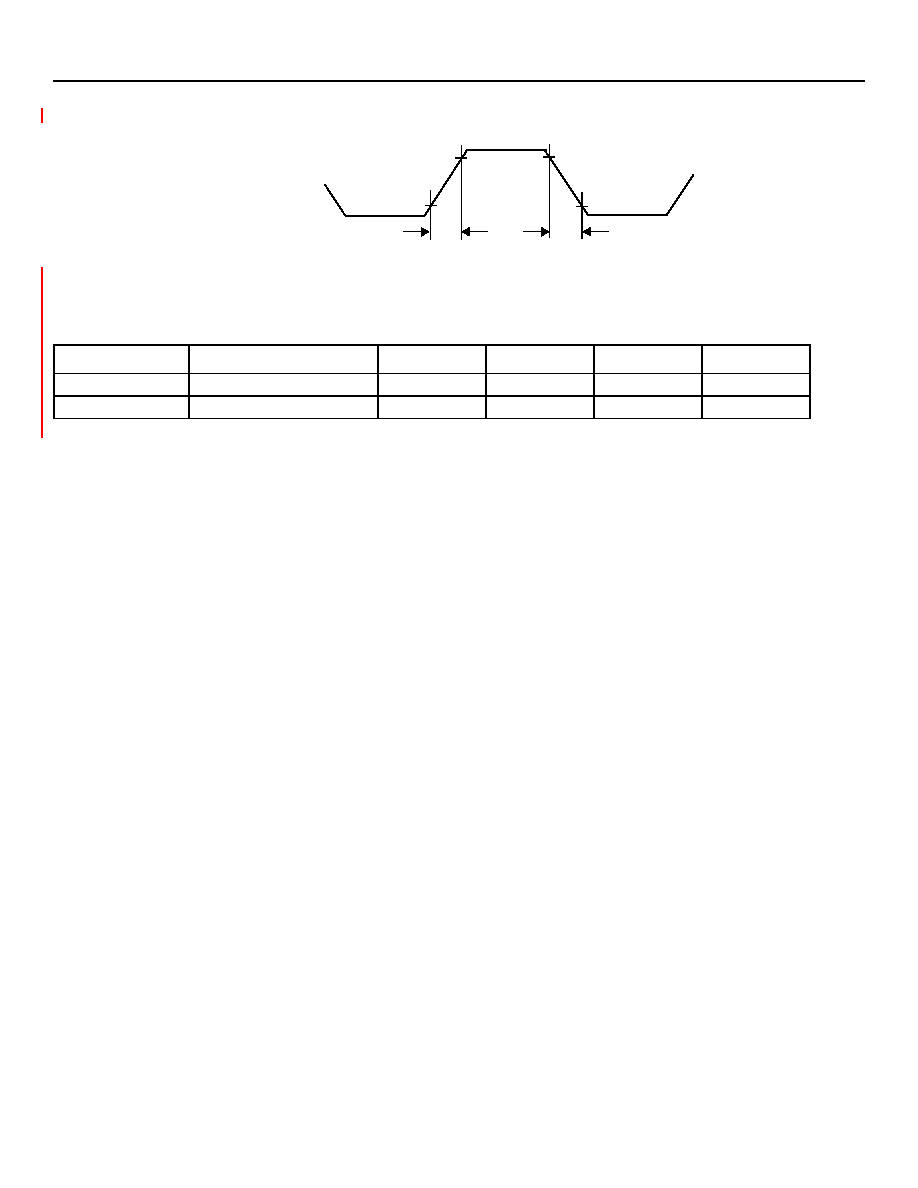

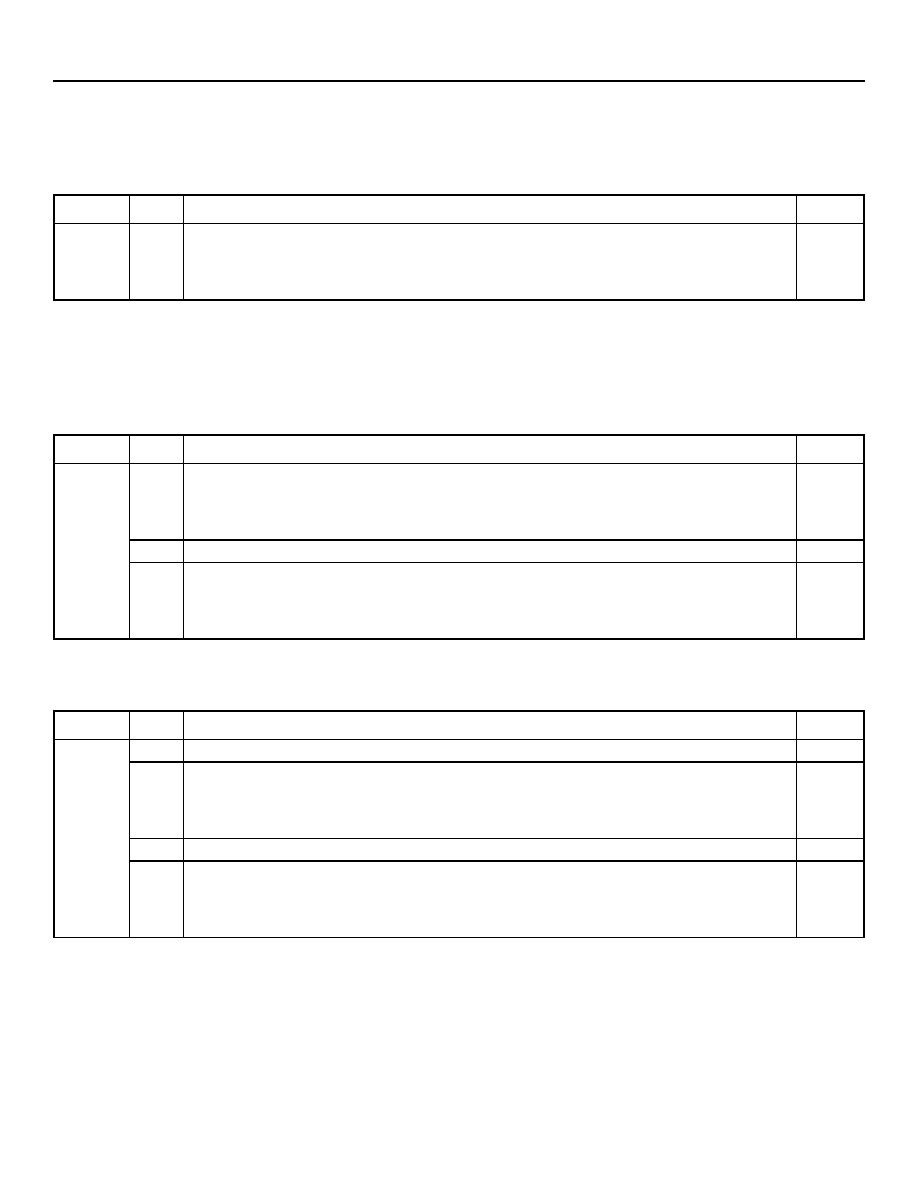

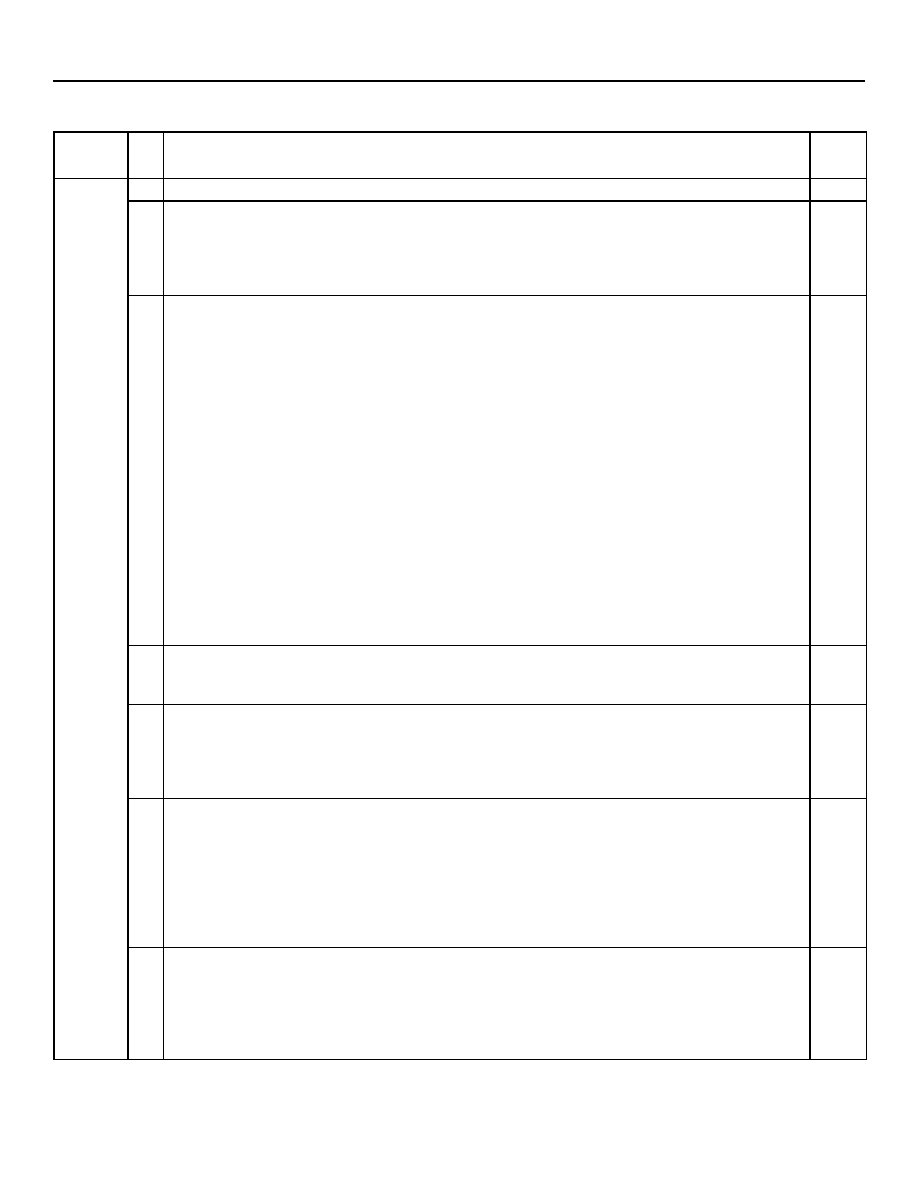

Figure 5-3 shows the ac timing specifications for the

CMOS outputs on the

device.

Figure 5-3. ac Timing Specification

* Test load = 50 pF (total).

Table 5-3. CMOS Output ac Timing Specification *

Parameter

Description

Min

Typ

Max

Unit

t

9

Rise Time (20%--80%)

--

1.5

7

ns

t

10

Fall Time (80%--20%)

--

1.5

7

ns

20%

80 %

20 %

80 %

t9

t10

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

21

Note: This figure assumes the device is programmed to sample FSYNC on the rising edge of CHICLK.

Figure 5-4. CHI Interface Timing

* Applies if Driver_Enable_Control = 01. For Driver_Enable_Control = 11 refer to

Figure 5-15, CHI 3-State Output Control on page 27

.

All timing specifications apply under the following conditions:

If FS is active-low.

If the falling edge of CHICLK is specified as the active edge.

At all RXD and TXD rates (16.384 Mbits/s, 8.192 Mbits/s, 4.096 Mbits/s, or 2.048 Mbits/s) with a CHICLK frequency of

16.384 MHz or 8.192 MHz.

Table 5-4. CHI Interface Timing

Parameter

Description

Min

Max

Unit

t

13

FSYNC Setup Time to Active CHICLK Edge

10

--

ns

t

14

FSYNC Hold Time from Active CHICLK Edge

5

--

ns

t

15

RXD Setup to Active CHICLK Edge

10

--

ns

t

16

RXD Hold Time from Active CHICLK Edge

5

--

ns

t

17

TXD High Z to Data Valid

--

15

ns

t

18

TXD Propagation Delay from Active CHICLK Edge

2

12

ns

t

19

Transmit Data High Impedance*

--

15

ns

t

18

t

19

TXD

CHICLK

t

13

t

14

t

17

RXD

FSYNC

t

15

t

16

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

22

22

Agere Systems Inc.

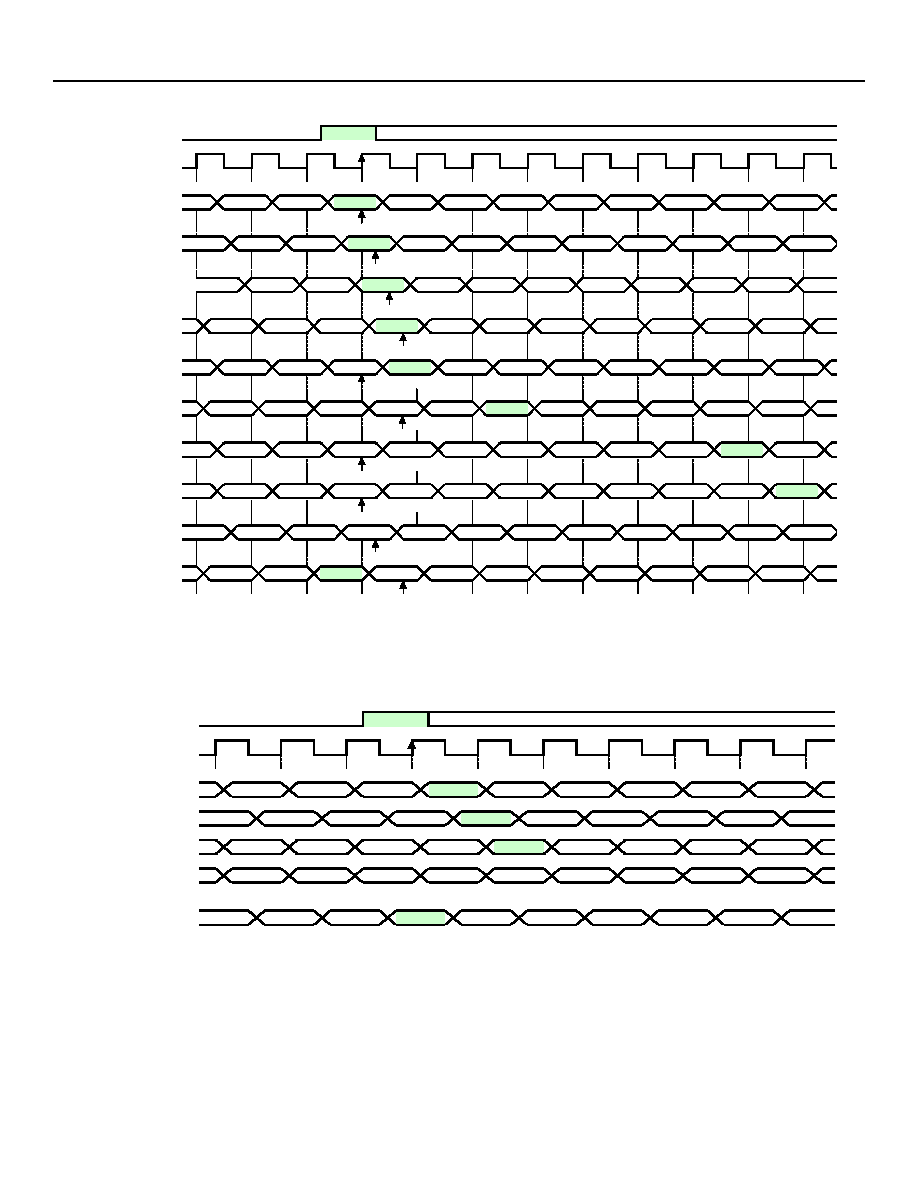

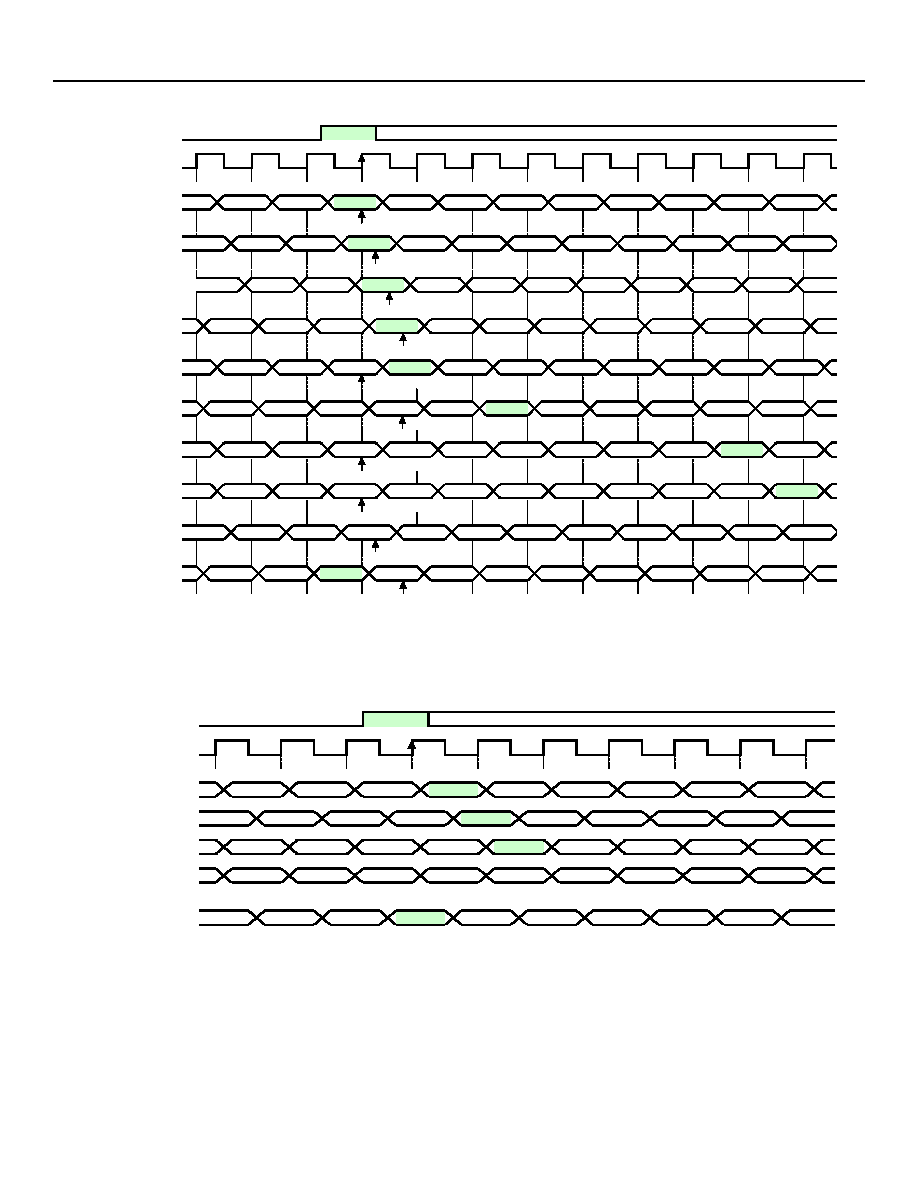

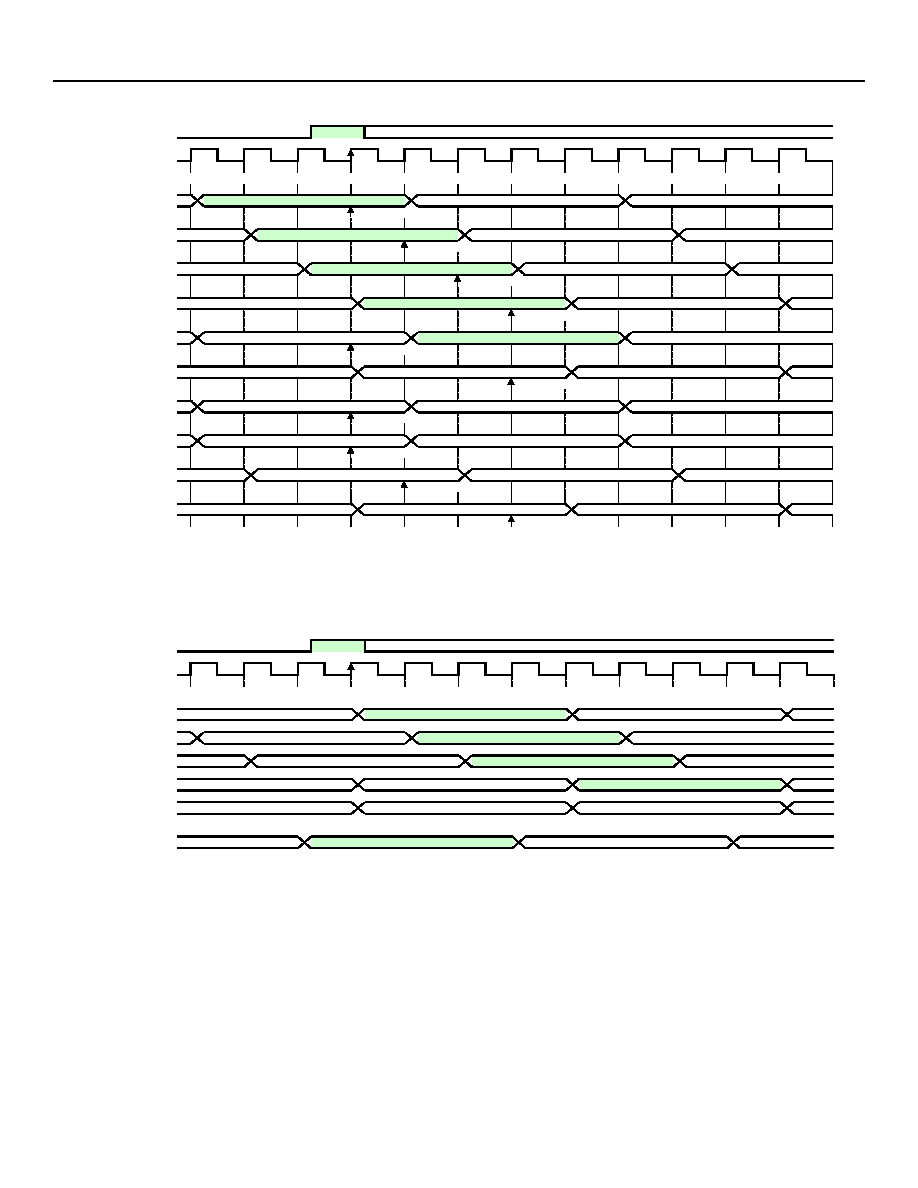

Note: For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the CHICLK.

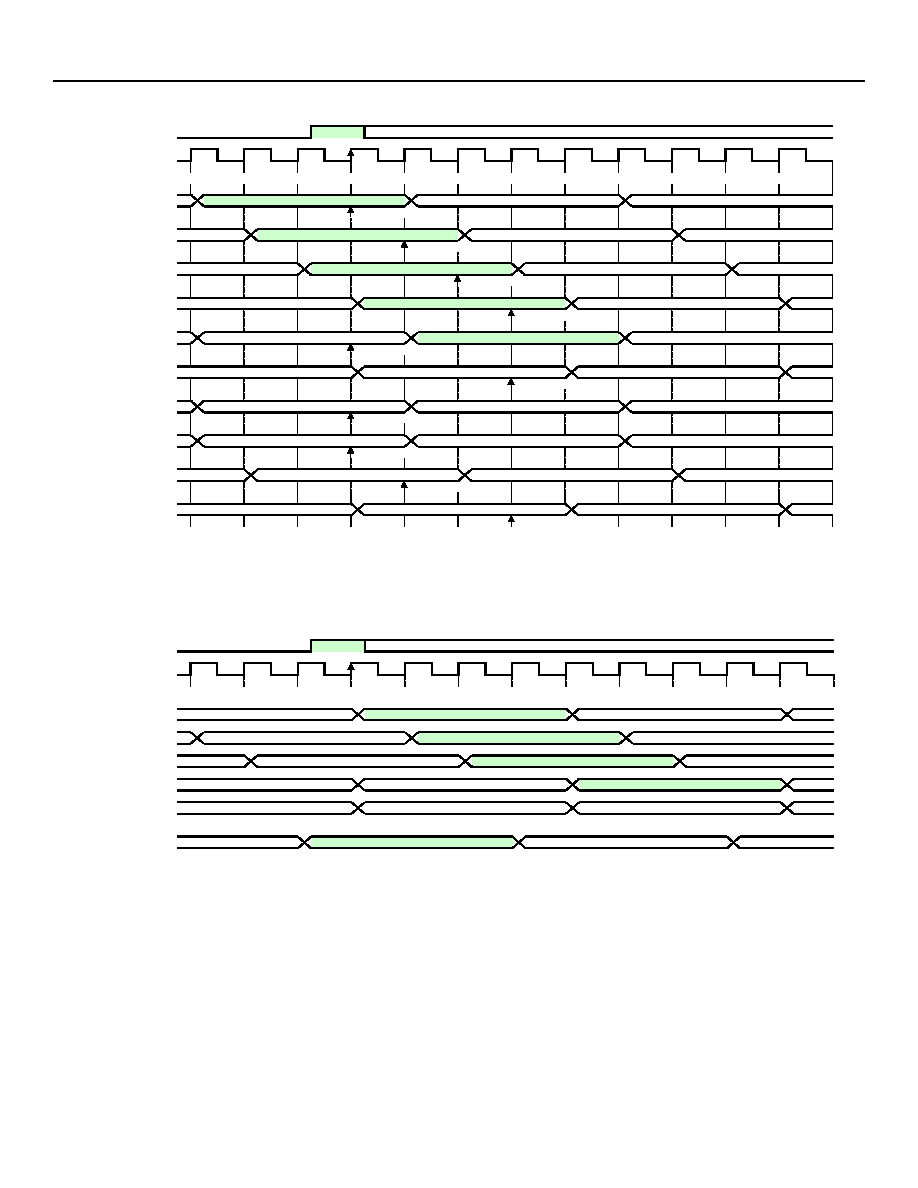

Figure 5-5. Typical Receive CHI Timing with 16.384 Mbits/s Data and 16.384 MHz CHICLK

Notes:

1/4 bit offset not valid with 16 Mbits/s data.

For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the

CHICLK.

Figure 5-6. Transmit CHI Timing with 16.384 Mbits/s Data and 16.384 MHz CHICLK

FSYNC

CHICLK

w/ 0 offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ bit offset = 1

data sampled

w/ 2� bit offset

data sampled

w/ bit offset = 7

data sampled

data sampled

data sampled

data sampled

w/ TS offset = 1,

bit offset = 0

TS254 B6

TS254 B7

TS255 B0

TS0 B1

TS0 B0

TS255 B1

TS255 B2

TS255 B3

TS255 B4

TS0 B4

TS0 B5

TS254 B7

TS255 B0

TS255 B1

TS255 B2

TS255 B3

TS255 B4

TS255 B5

TS255 B6

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS255 B6

TS255 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS0 B5

TS255 B6

TS255 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS0 B5

TS255 B5

TS255 B3

TS255 B4

TS255 B5

TS255 B5

TS255 B6

TS255 B7

TS255 B6

TS255 B7

TS255 B6

TS255 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS255 B6

TS255 B7

TS255 B5

TS255 B7

TS0 B 0

w/ TS offset = 13,

bit offset = 3�

TS242 B3

TS242 B4

TS242 B5

TS243 B4

TS243 B5

TS242 B6

TS242 B7

TS243 B0

TS243 B1

TS255 B7

TS0 B0

TS243 B2

TS243 B3

TS0 B5

TS0 B6

TS0 B3

TS0 B4

TS0 B1

TS0 B2

TS0 B3

TS0 B7

TS1 B0

TS0 B1

TS0 B2

w/ TS offset = 255,

bit offset = 7�

TS255 B6

TS0 B4

TS0 B0

TS255 B6

TS255 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS0 B5

FSYNC

CHICLK

w/ 0 offset

w/ � bit offset

w/ bit offset = 1

w/ TS offset = 255,

bit offset = 7�

TS255 B6

TS255 B7

TS0 B0

w/ TS offset = 1,

bit offset = 0

TS0 B2

TS0 B3

TS0 B4

TS254 B5

TS254 B6

TS254 B7

TS255 B0

TS255 B4

TS255 B5

TS0 B3

TS0 B4

TS255 B1

TS255 B2

TS255 B3

TS0 B0

TS0 B1

TS255 B4

TS255 B5

TS255 B5

TS255 B6

TS255 B7

TS0 B0

TS0 B3

TS0 B4

TS0 B5

TS0 B5

TS0 B1

TS0 B2

TS0 B1

TS0 B2

TS255 B6

TS255 B7

TS255 B5

TS255 B6

TS255 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

23

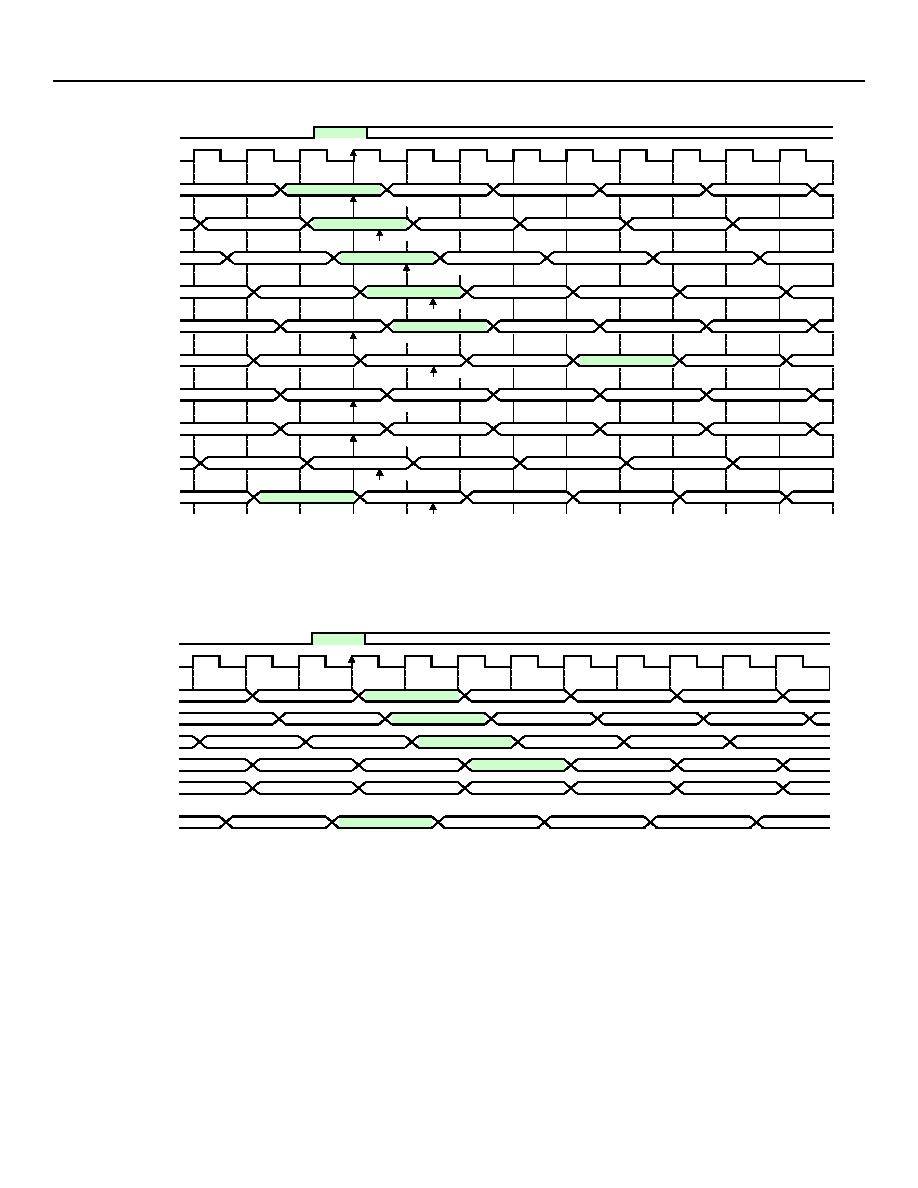

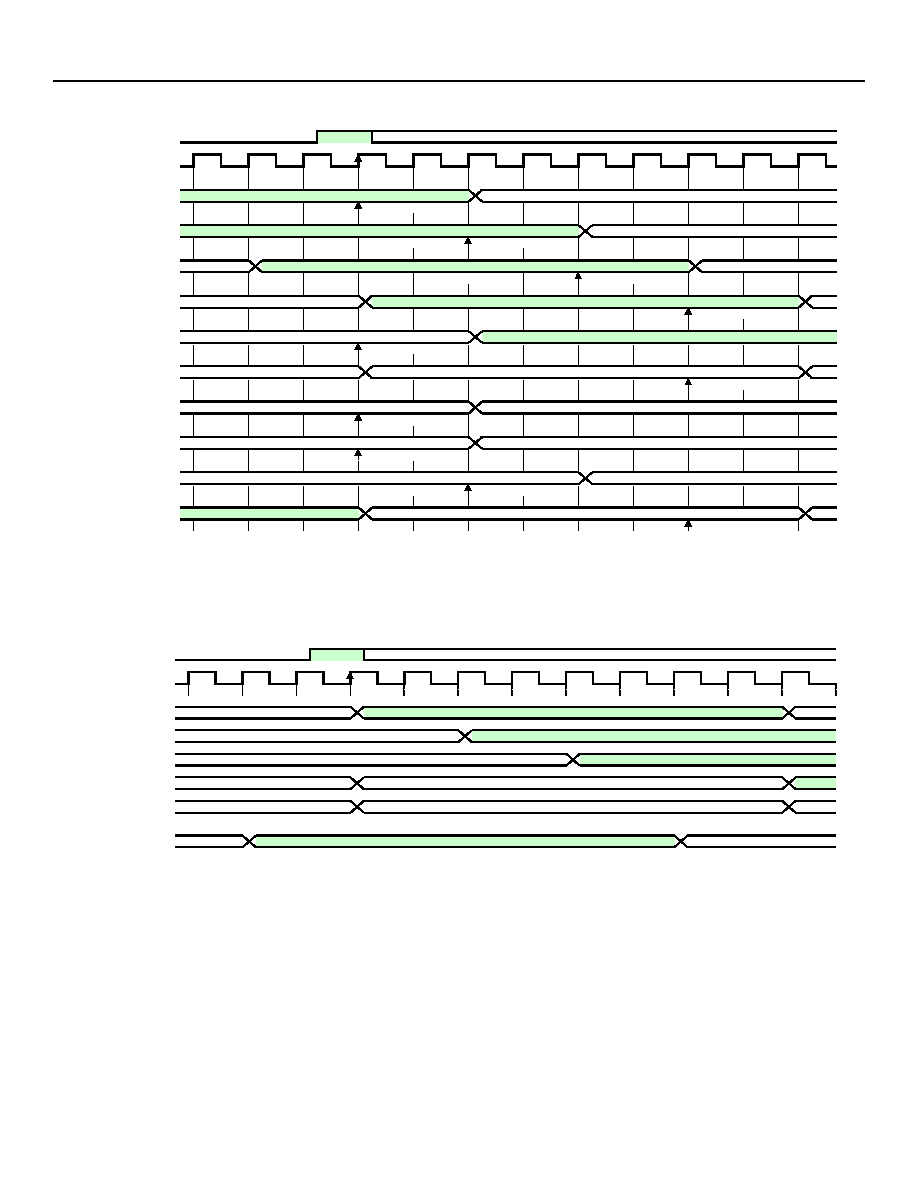

Note: For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the CHICLK.

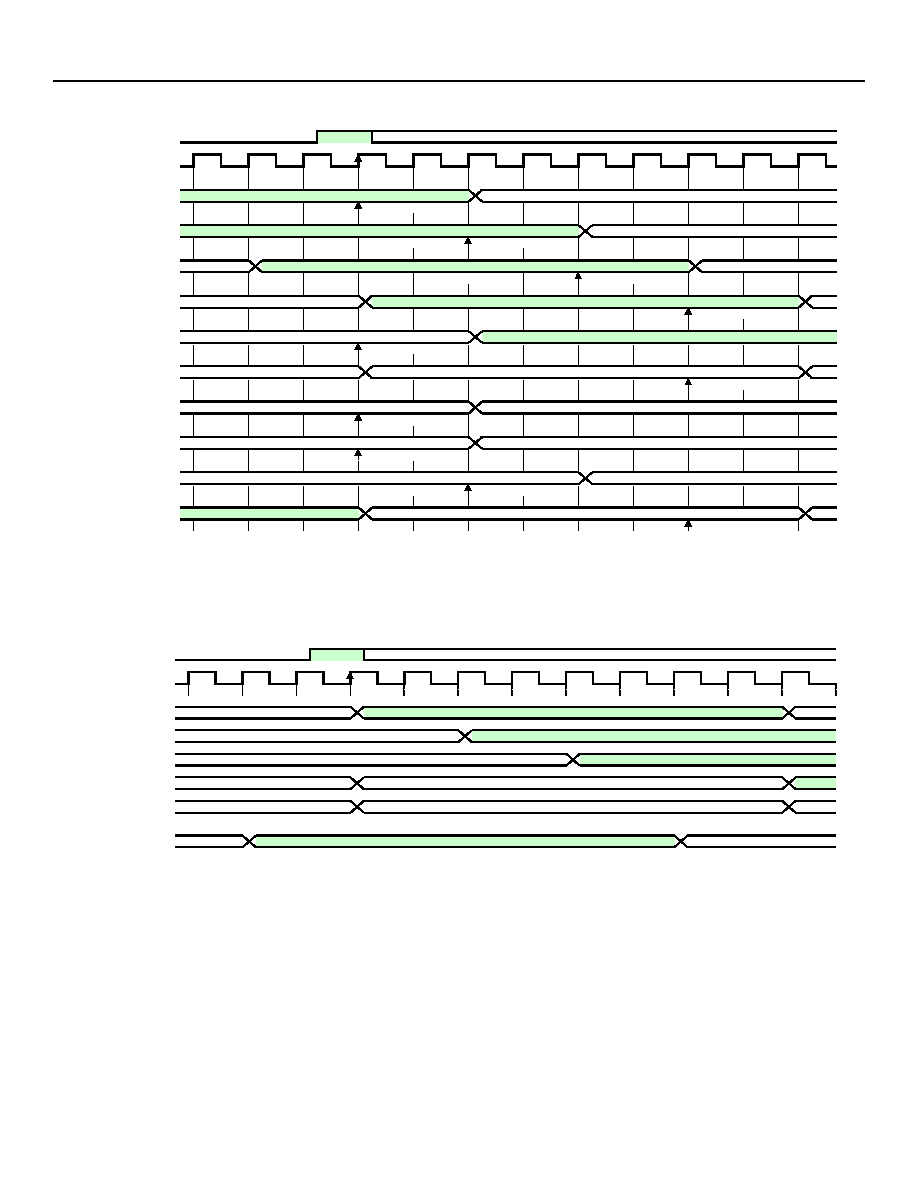

Figure 5-7. Typical Receive CHI Timing with 8.192 Mbits/s Data and 16.384 MHz CHICLK

Note: For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the CHICLK.

Figure 5-8. Transmit CHI Timing with 8.192 Mbits/s Data and 16.384 MHz CHICLK

FSYNC

CHICLK

w/ 0 offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ bit offset = 1

data sampled

w/ 2� bit offset

data sampled

w/ bit offset = 7

data sampled

data sampled

data sampled

data sampled

TS0 B2

TS0 B3

TS0 B4

w/ TS offset = 127,

bit offset = 7�

TS 127 B7

TS0 B0

TS0 B1

TS127 B2

TS127 B3

TS127 B4

w/ TS offset = 13,

bit offset = 3�

TS114 B4

TS114 B5

TS114 B6

TS114 B7

TS115 B0

TS115 B1

w/ TS offset = 1,

bit offset = 0

TS126 B7

TS127 B0

TS127 B1

TS127 B4

TS127 B5

TS 127 B4

TS127 B5

TS127 B0

TS127 B1

TS127 B2

TS127 B3

TS127 B6

TS127 B7

TS0 B2

TS0 B3

TS0 B2

TS0 B3

TS0 B0

TS0 B1

TS127 B6

TS127 B7

TS0 B0

TS0 B1

TS 127 B6

TS127 B7

TS0 B0

TS0 B1

TS0 B3

TS0 B4

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

FSYNC

CHICLK

w/ 0 offset

w/ � bit offset

w/ � bit offset

w/ bit offset = 1

TS 127 B6

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B2

TS0 B3

TS127 B6

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS127 B6

TS127 B7

TS0 B0

TS0 B1

TS 127 B5

TS127 B6

TS127 B7

TS0 B0

w/ TS offset = 1,

bit offset = 0

TS127 B7

TS0 B0

TS0 B1

w/ TS offset = 127,

bit offset = 7�

TS 126 B6

TS126 B7

TS127 B0

TS127 B1

TS0 B2

TS0 B3

TS0 B1

TS0 B2

TS127 B2

TS127 B3

TS0 B3

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

24

24

Agere Systems Inc.

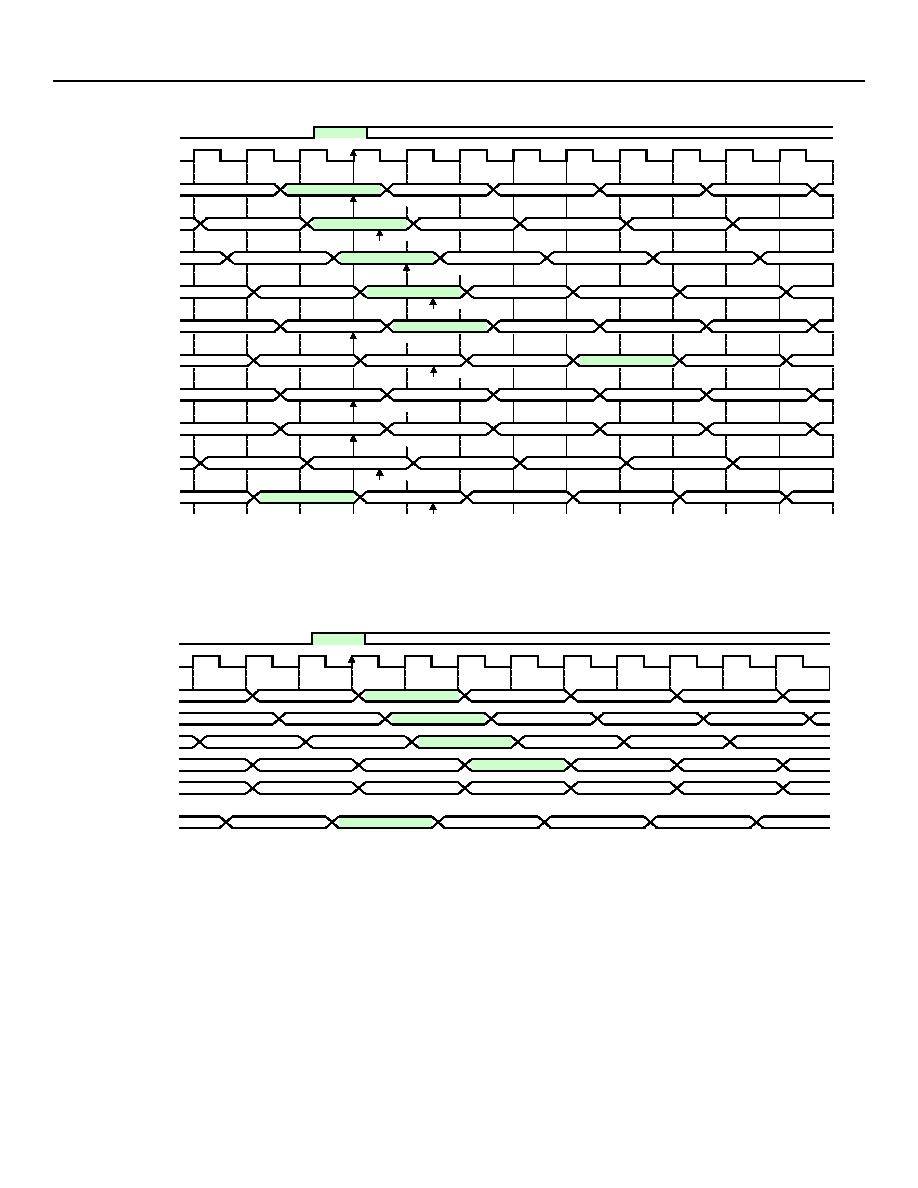

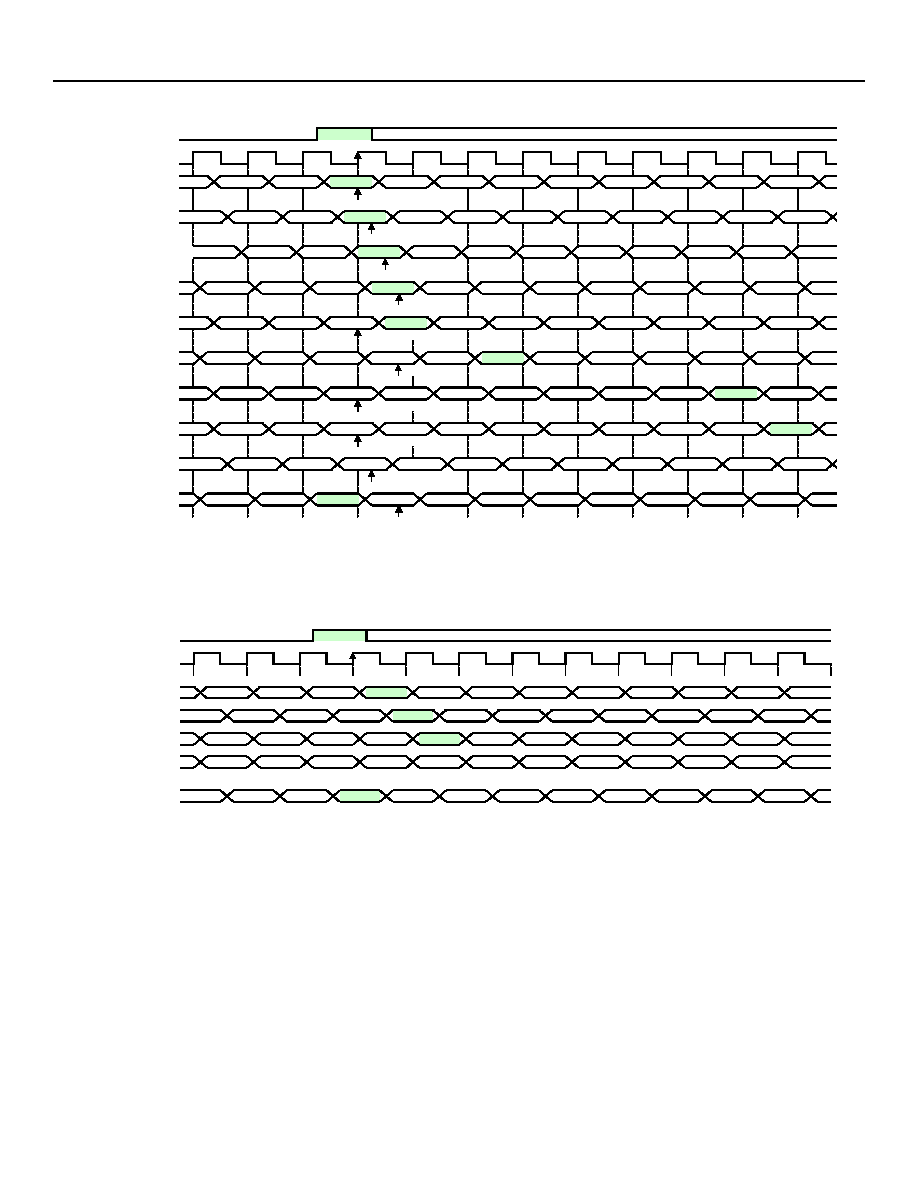

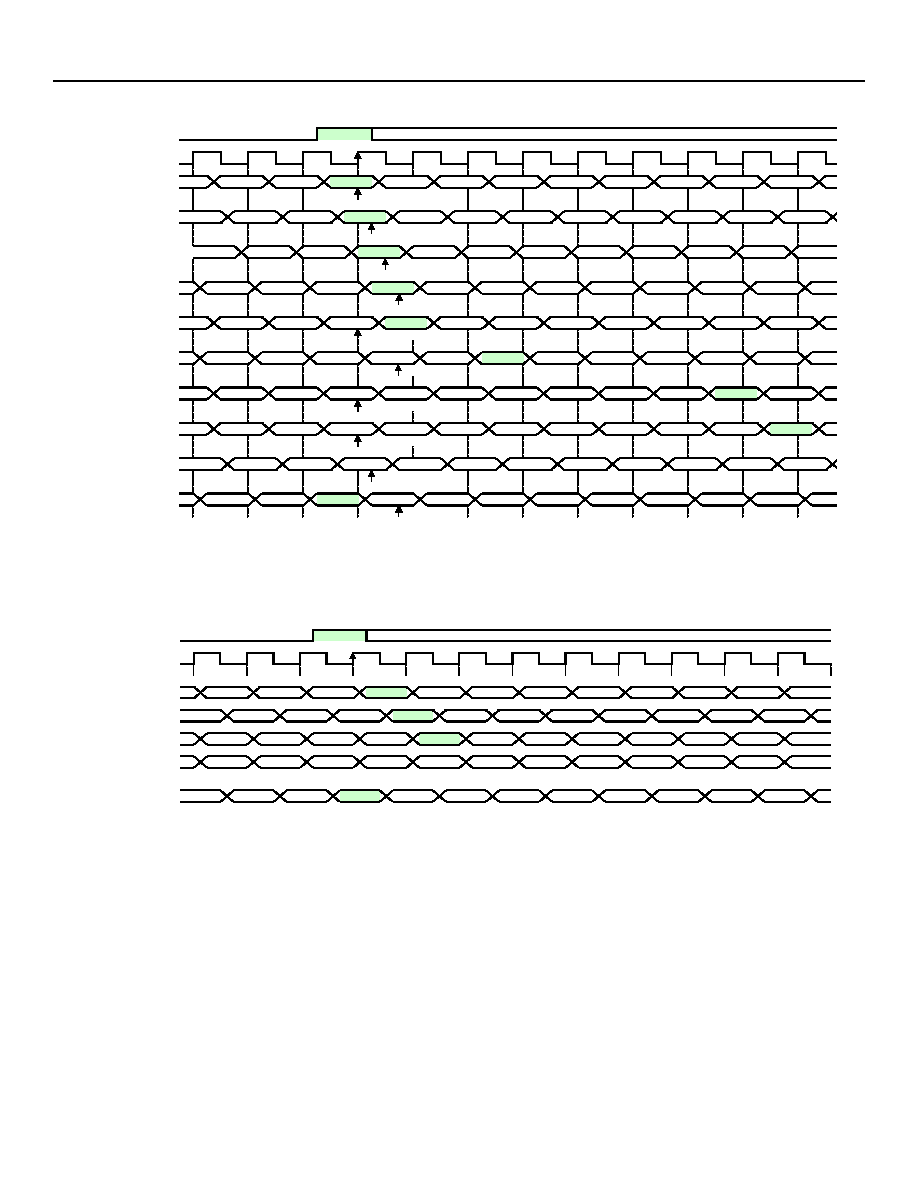

Note: For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the CHICLK.

Figure 5-9. Typical Receive CHI Timing with 4.096 Mbits/s Data and 16.384 MHz CHICLK

Note: For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the CHICLK.

Figure 5-10. Transmit CHI Timing with 4.096 Mbits/s Data and 16.384 MHz CHICLK

FSYNC

CHICLK

w/ 0 offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ bit offset = 1

data sampled

w/ 2� bit offset

data sampled

w/ bit offset = 7

data sampled

data sampled

data sampled

data sampled

TS50 B7

w/ TS offset = 63,

bit offset = 7�

TS0 B0

TS0 B1

TS0 B2

w/ TS offset = 13,

bit offset = 3�

TS50 B4

TS50 B5

TS50 B6

w/ TS offset = 1,

bit offset = 0

TS63 B0

TS63 B1

TS63 B2

TS63 B5

TS63 B6

TS63 B7

TS63 B1

TS63 B2

TS63 B3

TS63 B7

TS0 B0

TS0 B1

TS63 B7

TS0 B0

TS0 B1

TS63 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B0

TS0 B1

TS0 B2

TS63 B7

TS0 B0

TS0 B1

TS0 B2

FSYNC

CHICLK

w/ 0 offset

w/ � bit offset

w/ � bit offset

w/ bit offset = 1

w/ TS offset = 63,

bit offset = 7�

TS62 B7

TS63 B0

TS63 B1

w/ TS offset = 1,

bit offset = 0

TS63 B6

TS63 B7

TS0 B0

TS63 B7

TS0 B0

TS0 B1

TS0 B2

TS63 B6

TS63 B7

TS0 B0

TS0 B1

TS63 B7

TS0 B0

TS0 B1

TS63 B7

TS0 B0

TS0 B1

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

25

Note: For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the CHICLK.

Figure 5-11. Typical Receive CHI Timing with 2.048 Mbits/s Data and 16.384 MHz CHICLK

Note: For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the CHICLK.

Figure 5-12. Transmit CHI Timing with 2.048 Mbits/s Data and 16.384 MHz CHICLK

FSYNC

CHICLK

w/ 0 offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ bit offset = 1

data sampled

w/ 2� bit offset

data sampled

w/ bit offset = 7

data sampled

data sampled

data sampled

data sampled

w/ TS offset = 31,

bit offset = 7�

TS0 B0

TS0 B1

TS0

w/ TS offset = 1,

bit offset = 0

TS31 B0

TS31 B1

w/ TS offset = 13,

bit offset = 3�

TS18 B5

TS18 B6

TS31 B5

TS31 B6

TS31

TS31 B1

TS31 B2

TS31 B7

TS0 B0

TS0

TS31 B7

TS0 B0

TS0 B0

TS0 B1

TS0 B0

TS0 B1

TS31 B7

TS0 B0

TS0 B1

FSYNC

CHICLK

w/ 0 offset

w/ � bit offset

w/ � bit offset

w/ bit offset = 1

TS30 B7

TS31 B0

TS31 B01

w/ TS offset = 1,

bit offset = 0

TS31 B7

TS0 B0

TS0 B1

w/ TS offset = 31,

bit offset = 7�

TS31 B7

TS0 B0

TS31 B6

TS31 B7

TS0 B0

TS31 B7

TS0 B0

TS0 B1

TS31 B7

TS0 B0

TSI-1

Data Sheet, Revision 3

1k x 1k Time-Slot Interchanger

September 21, 2005

26

26

Agere Systems Inc.

Note: For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the CHICLK.

Figure 5-13. Typical Receive CHI Timing with 8.192 Mbits/s Data and 8.192 MHz CHICLK

Notes:

1/4 bit offset not valid with 8 MHz data and 8 MHz clock.

For this timing diagram, it is assumed that FSYNC has been programmed to be active-high, and to be sampled by the rising edge of the

CHICLK.

Figure 5-14. Transmit CHI Timing with 8.192 Mbits/s Data and 8.192 MHz CHICLK

FSYNC

CHICLK

w/ 0 offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ � bit offset

data sampled

w/ bit offset = 1

data sampled

w/ 2� bit offset

data sampled

w/ bit offset = 7

data sampled

data sampled

data sampled

data sampled

TS0 B5

TS0 B6

TS0 B7

TS1 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

w/ TS offset = 127,

bit offset = 7�

TS127 B6

TS127 B7

TS0 B0

TS115 B2

TS115 B3

TS115 B4

TS115 B5

TS114 B6

TS114 B7

TS115 B0

TS115 B1

w/ TS offset = 13,

bit offset = 3�

TS114 B3

TS114 B4

TS114 B5

TS127 B5

TS127 B6

TS127 B7

TS0 B0

TS0 B 0

TS0 B1

w/ TS offset = 1,

bit offset = 0

TS126 B6

TS126 B7

TS127 B0

TS127 B1

TS127 B2

TS127 B3

TS127 B4

TS0 B3

TS126 B7

TS127 B0

TS127 B1

TS127 B2

TS127 B3

TS127 B4

TS127 B5

TS127 B6

TS127 B7

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS127 B3

TS127 B4

TS127 B5

TS127 B6

TS0 B5

TS127 B5

TS127 B6

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS127 B5

TS127 B6

TS127 B7

TS0 B0

TS0 B2

TS0 B3

TS0 B4

TS0 B5

TS127 B6

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS0 B5

TS127 B6

TS127 B7

TS0 B0

TS0 B1

TS127 B6

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS0 B5

FSYNC

CHICLK

w/ 0 offset

w/ � bit offset

w/ bit offset = 1

TS127 B5

w/ TS offset = 127,

bit offset = 7�

TS127 B6

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS0 B5

TS0 B4

w/ TS offset = 1,

bit offset = 0

TS126 B5

TS126 B6

TS126 B7

TS127 B0

TS127 B1

TS127 B2

TS127 B3

TS127 B4

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS127 B4

TS127 B5

TS127 B6

TS127 B7

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS127 B5

TS127 B6

TS127 B7

TS0 B0

TS127 B5

TS127 B6

TS127 B7

TS0 B0

TS0 B1

TS0 B2

TS0 B3

TS0 B4

TS0 B5

Data Sheet, Revision 3

TSI-1

September 21, 2005

1k x 1k Time-Slot Interchanger

Agere Systems Inc.

27

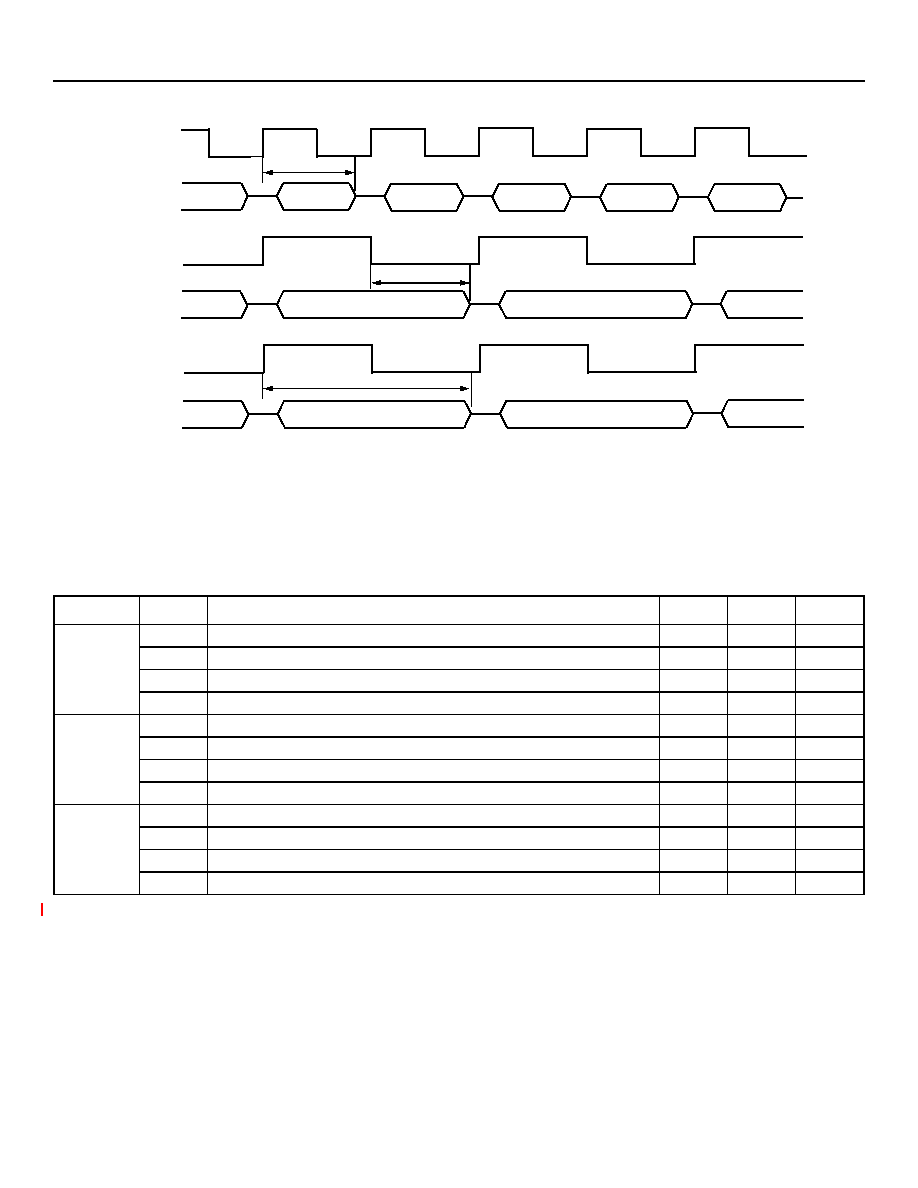

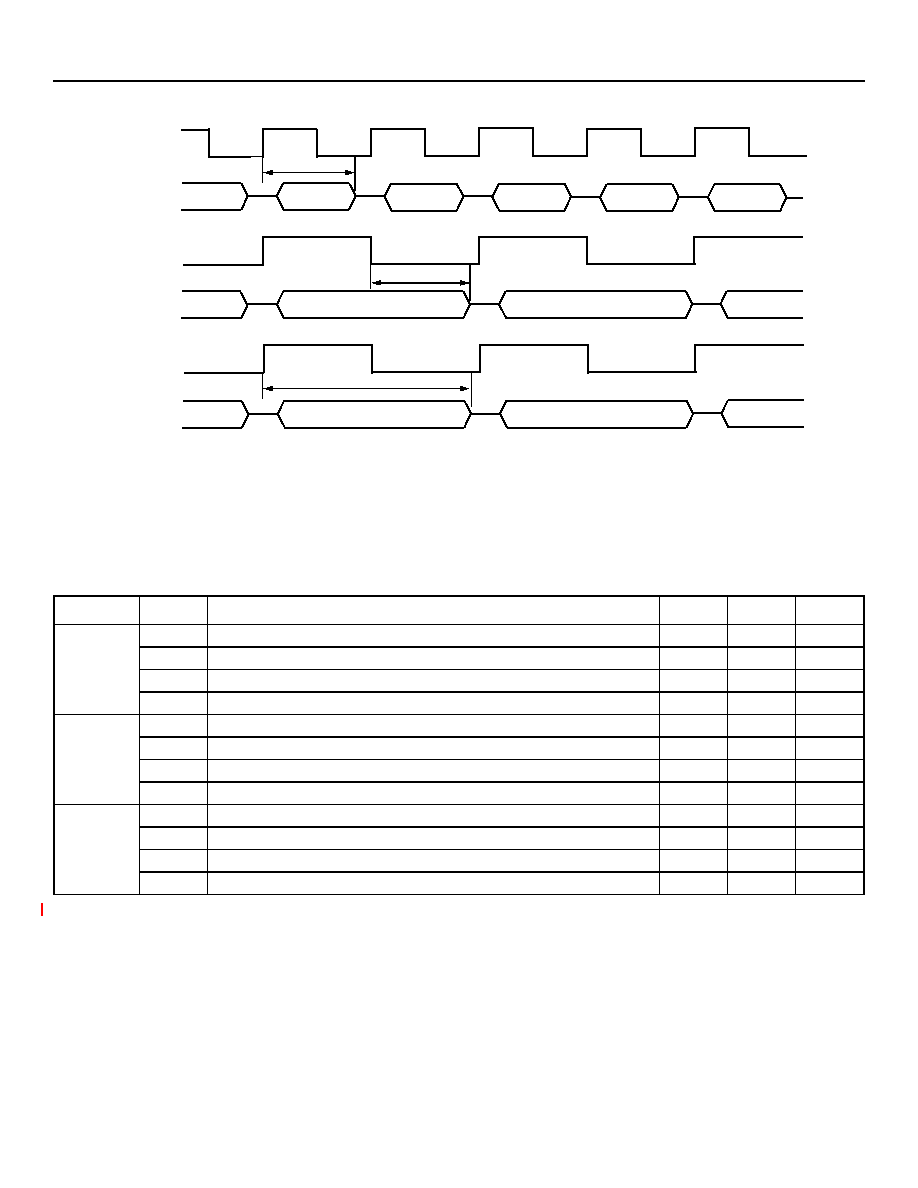

Figure 5-15. CHI 3-State Output Control

Table 5-5. CHI 3-State Output Control

Control in the table below refers to bits [6:4] in