Document Outline

- Features

- Applications

- Description

- Pin Information

- Functional Description

- Microprocessor Interface

- Absolute Maximum Ratings

- Handling Precautions

- Recommended Operating Conditions

- Electrical Characteristics

- Timing Characteristics

- Outline Diagram

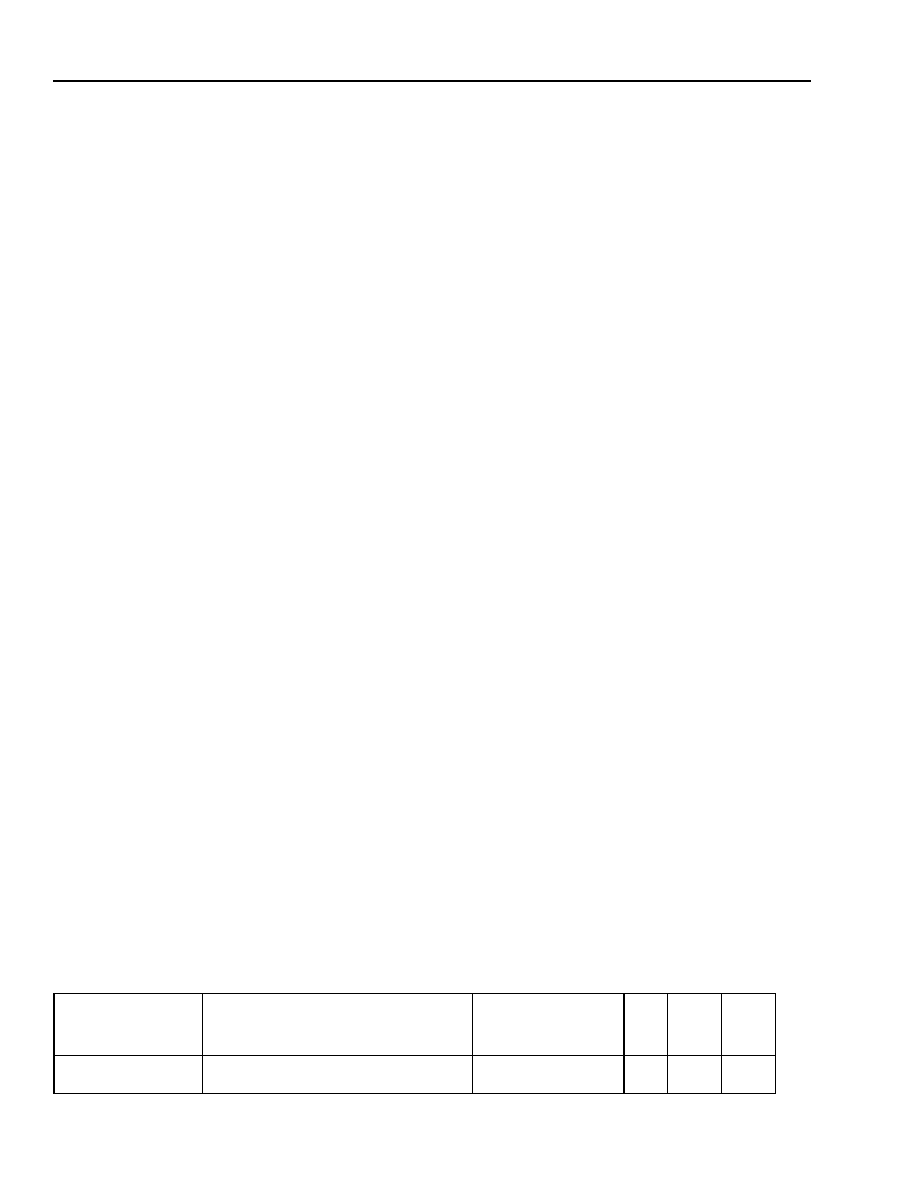

- Ordering Information

- List of Figures

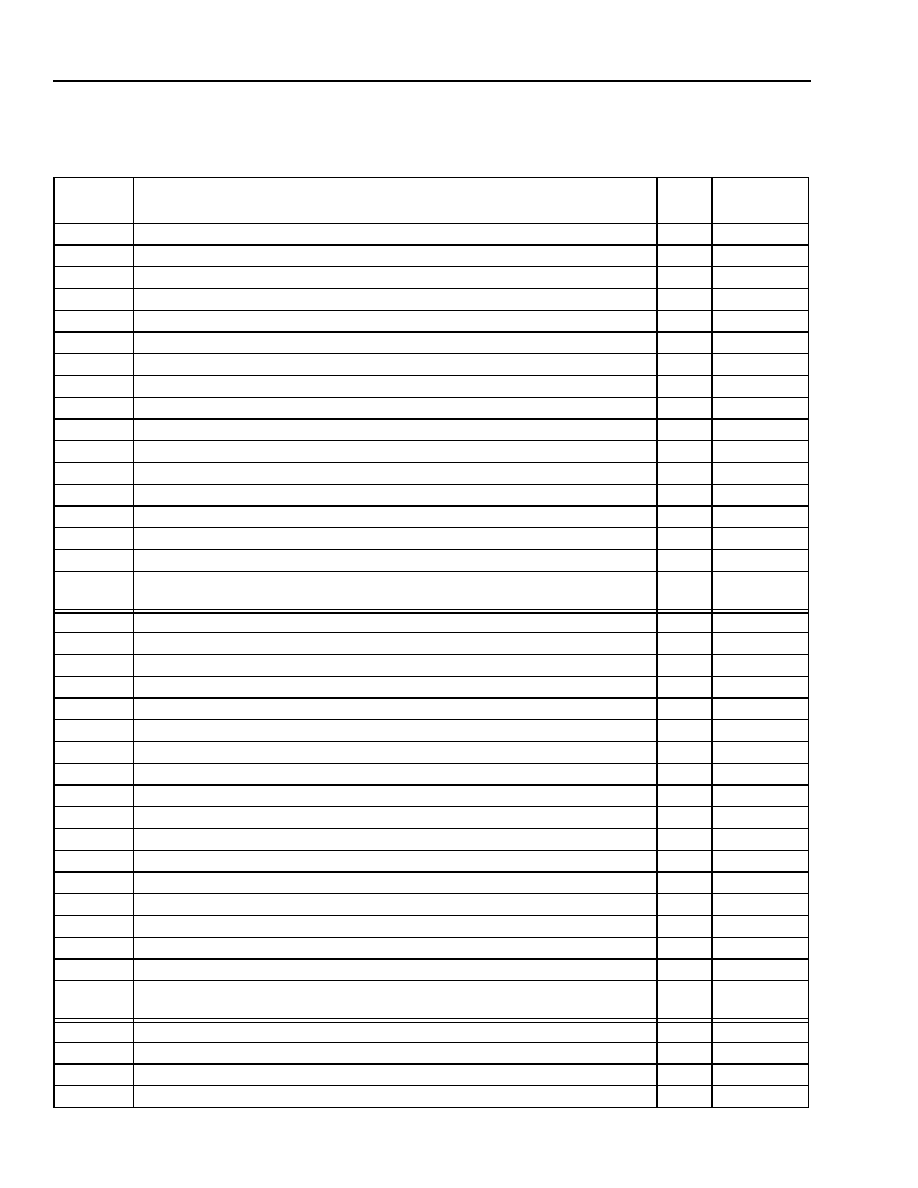

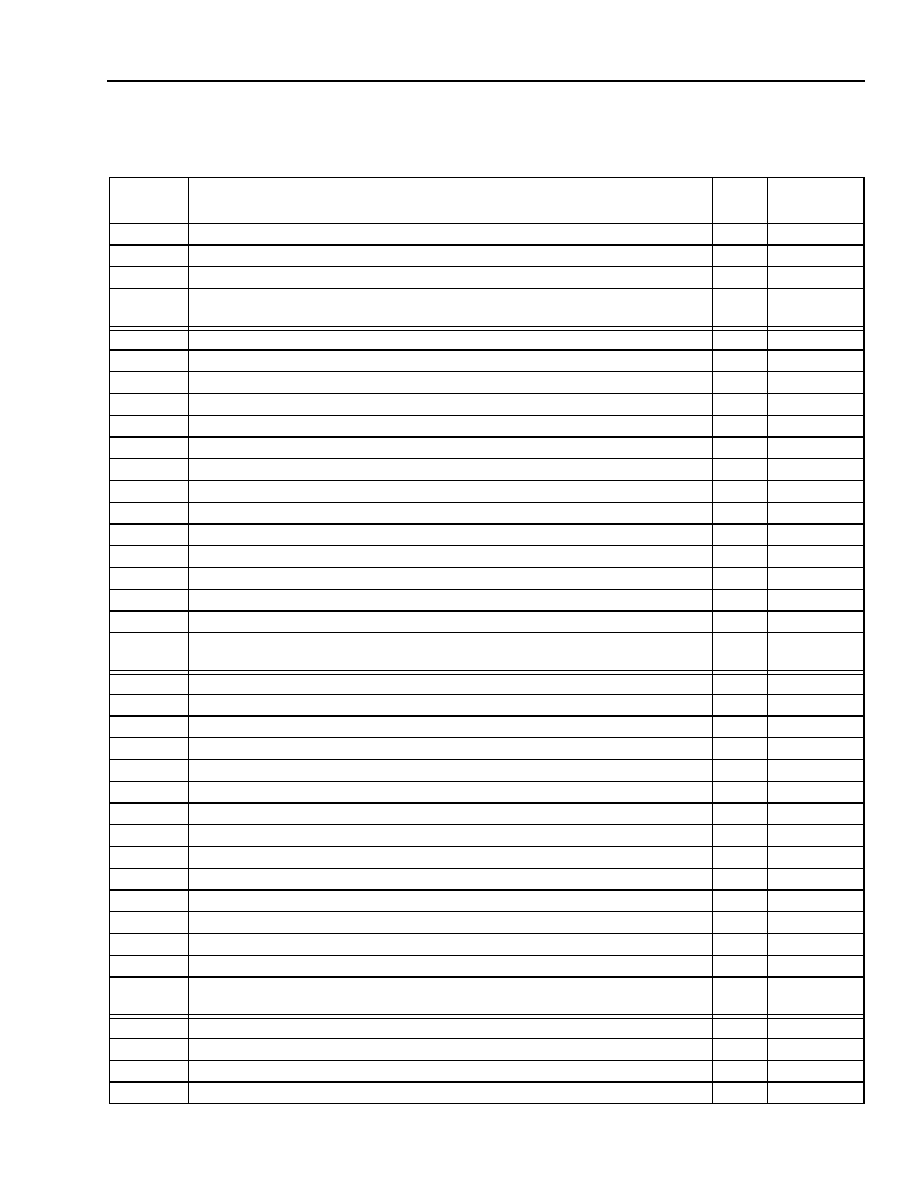

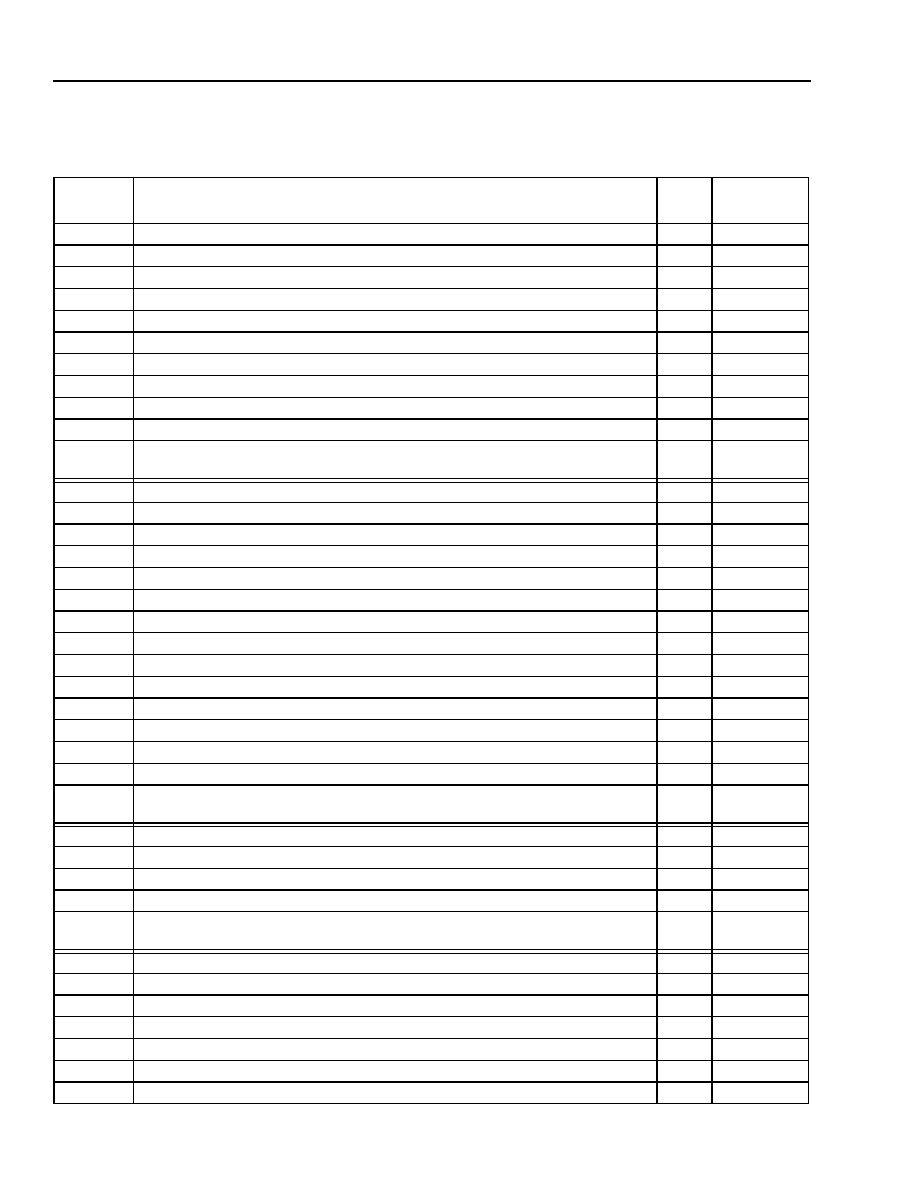

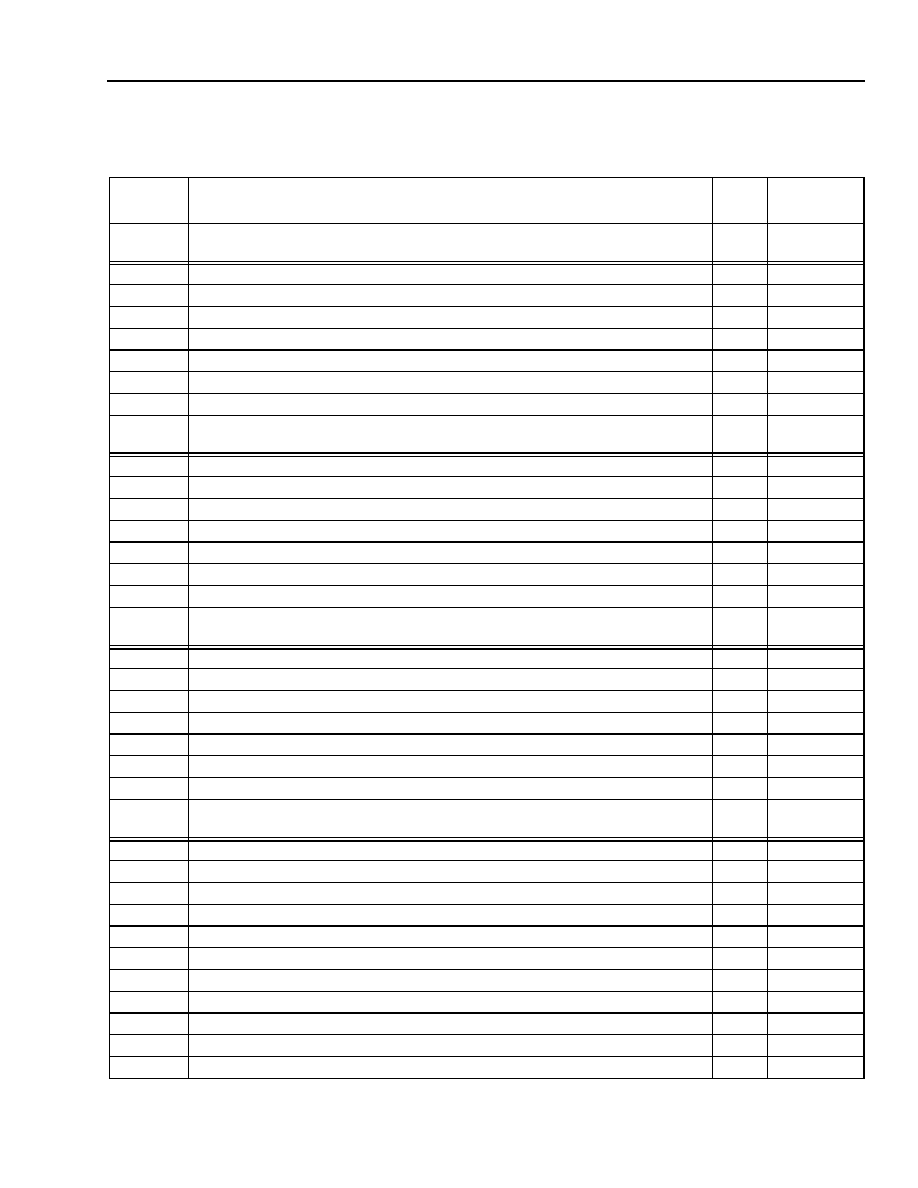

- List of Tables

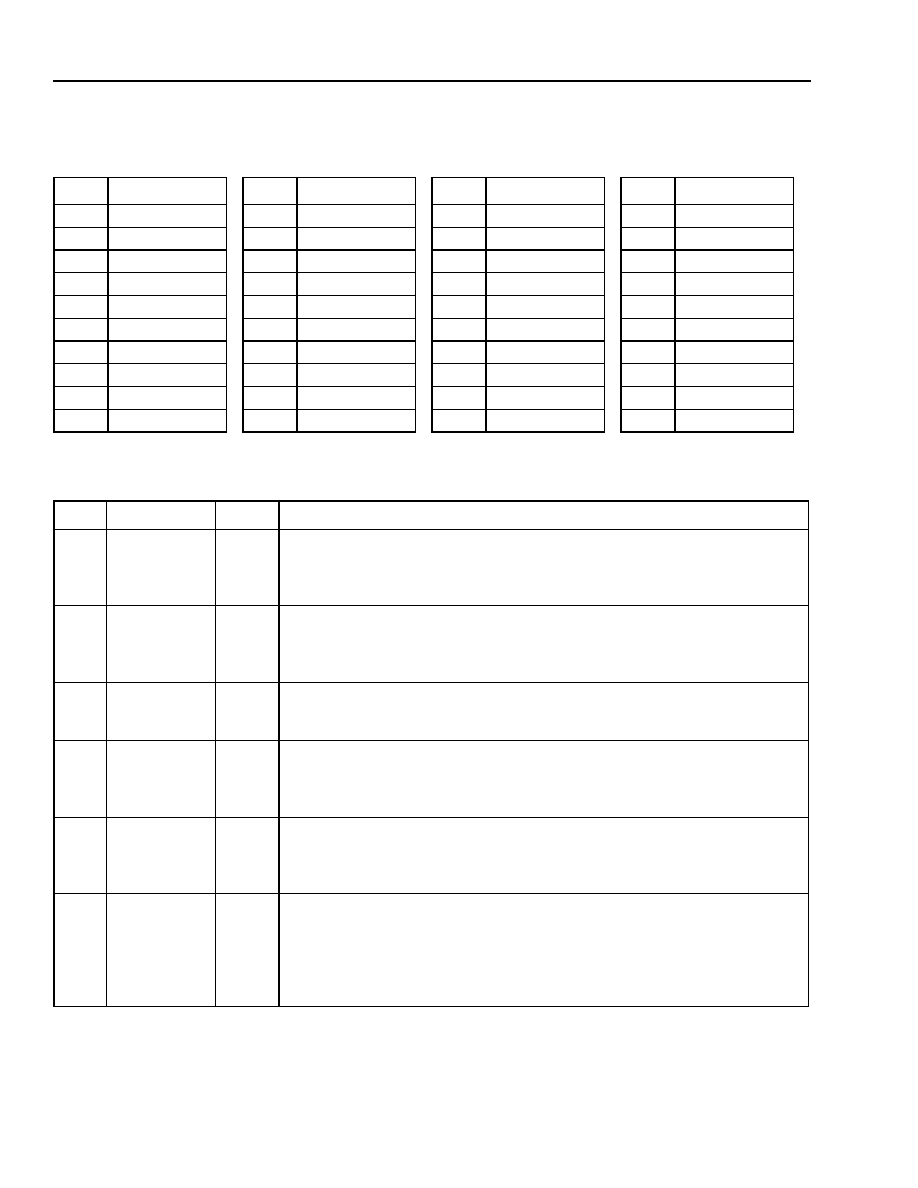

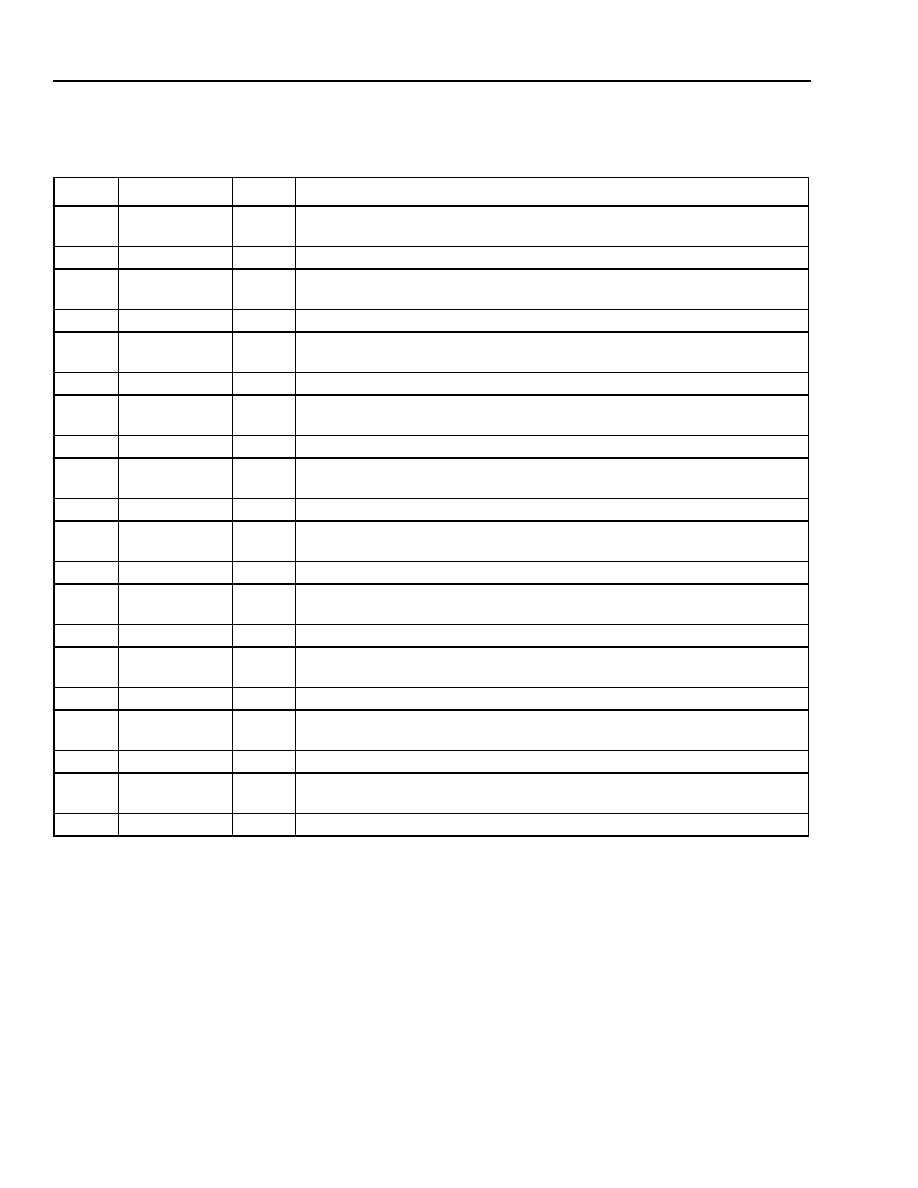

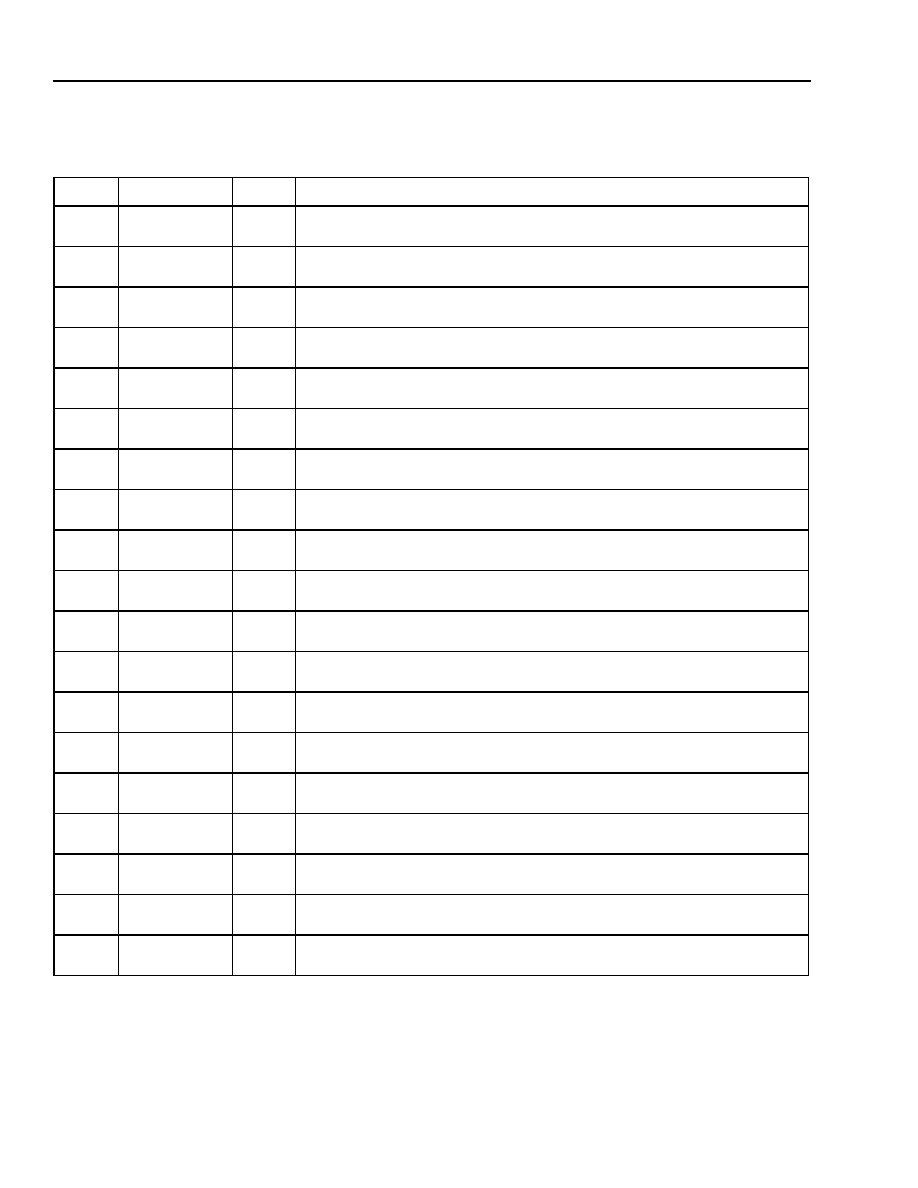

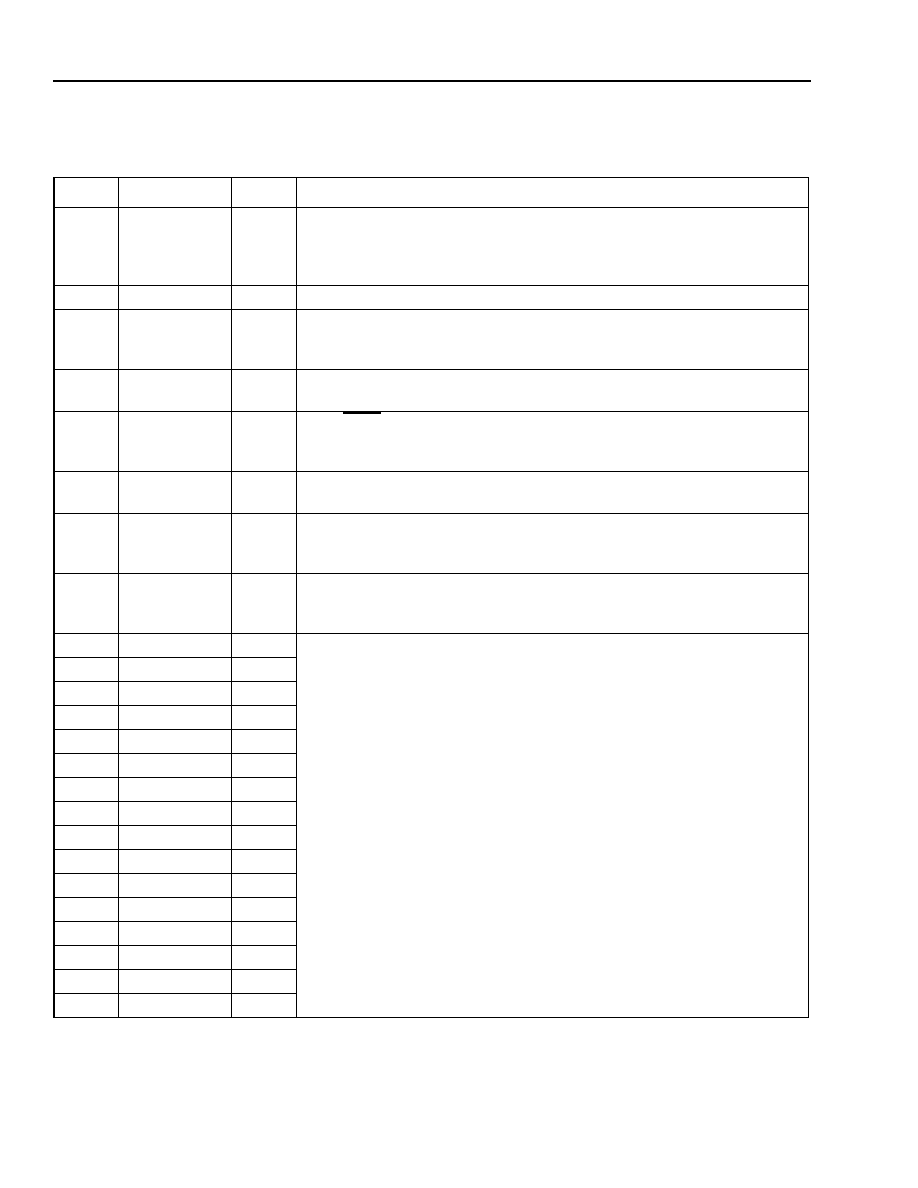

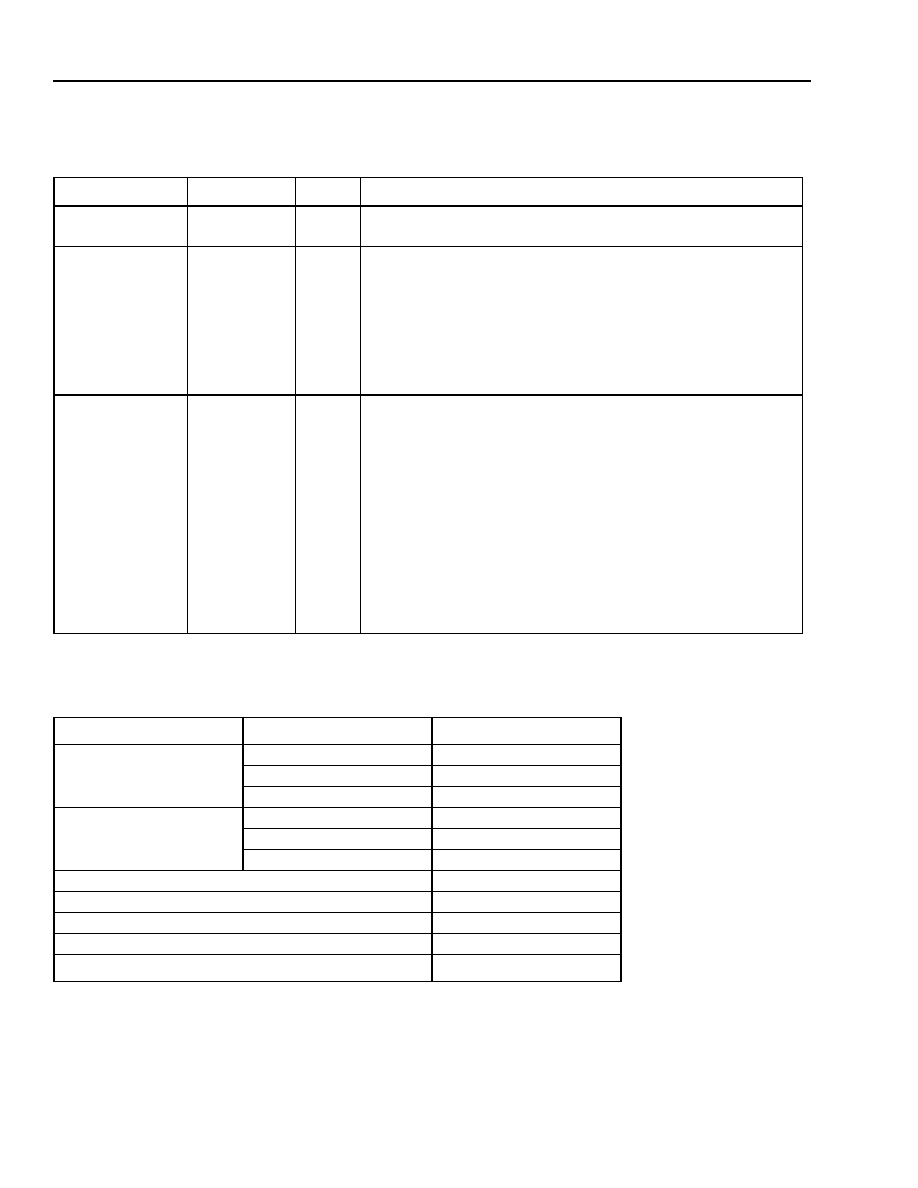

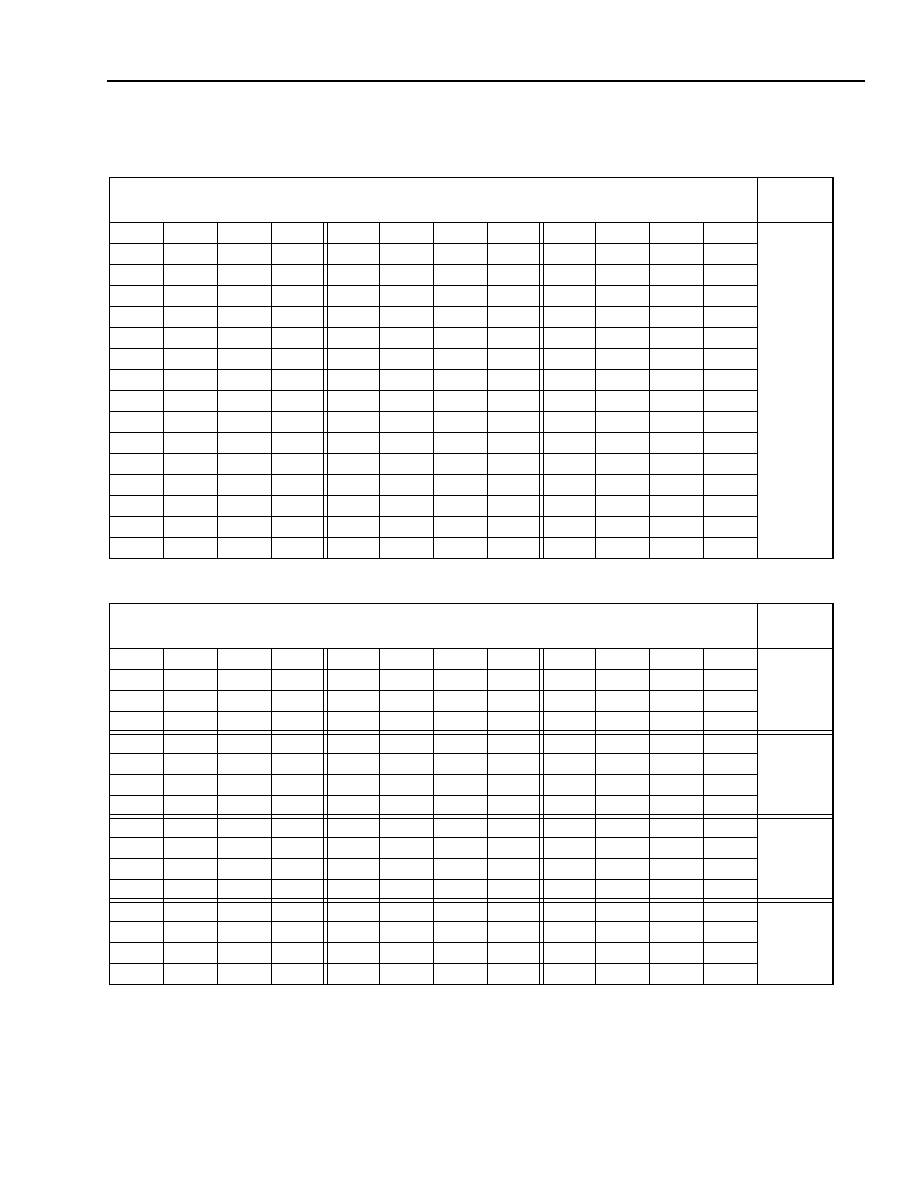

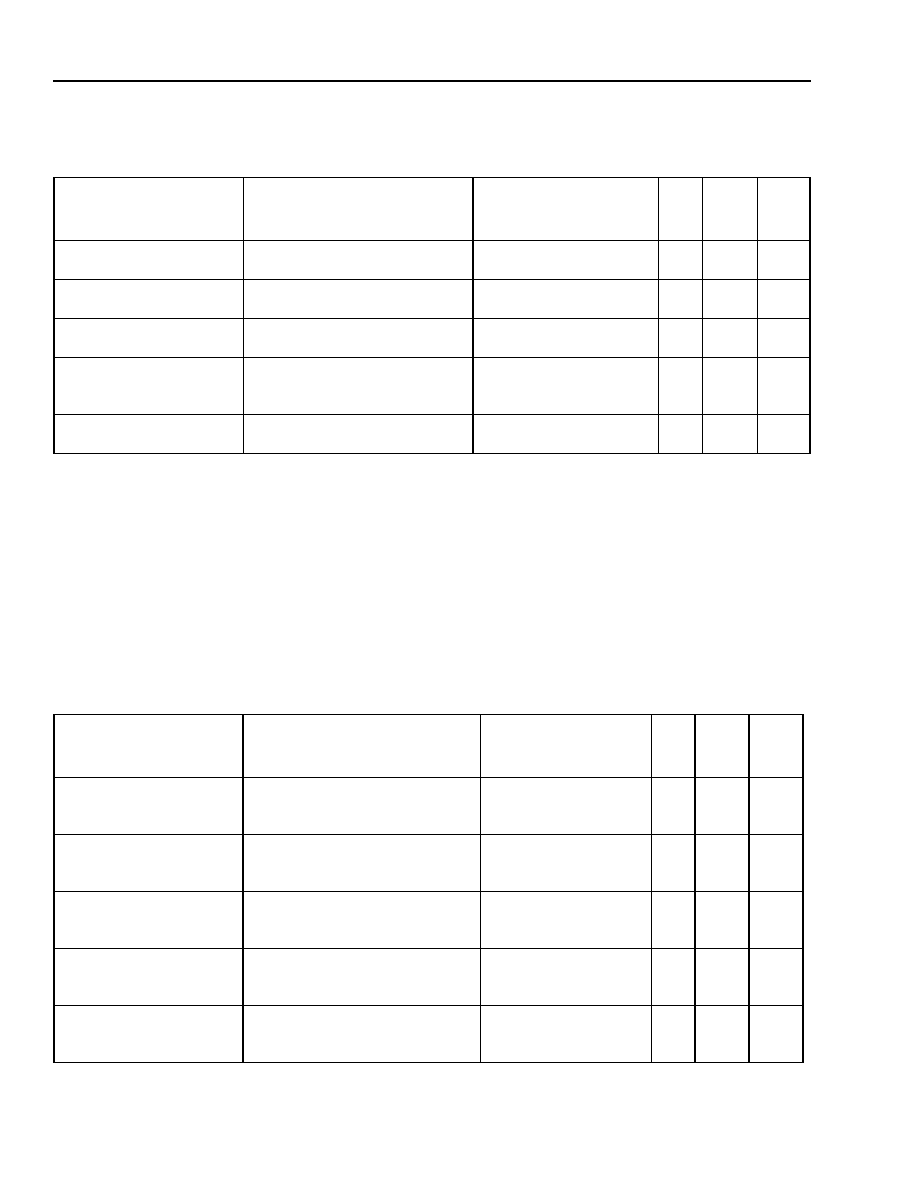

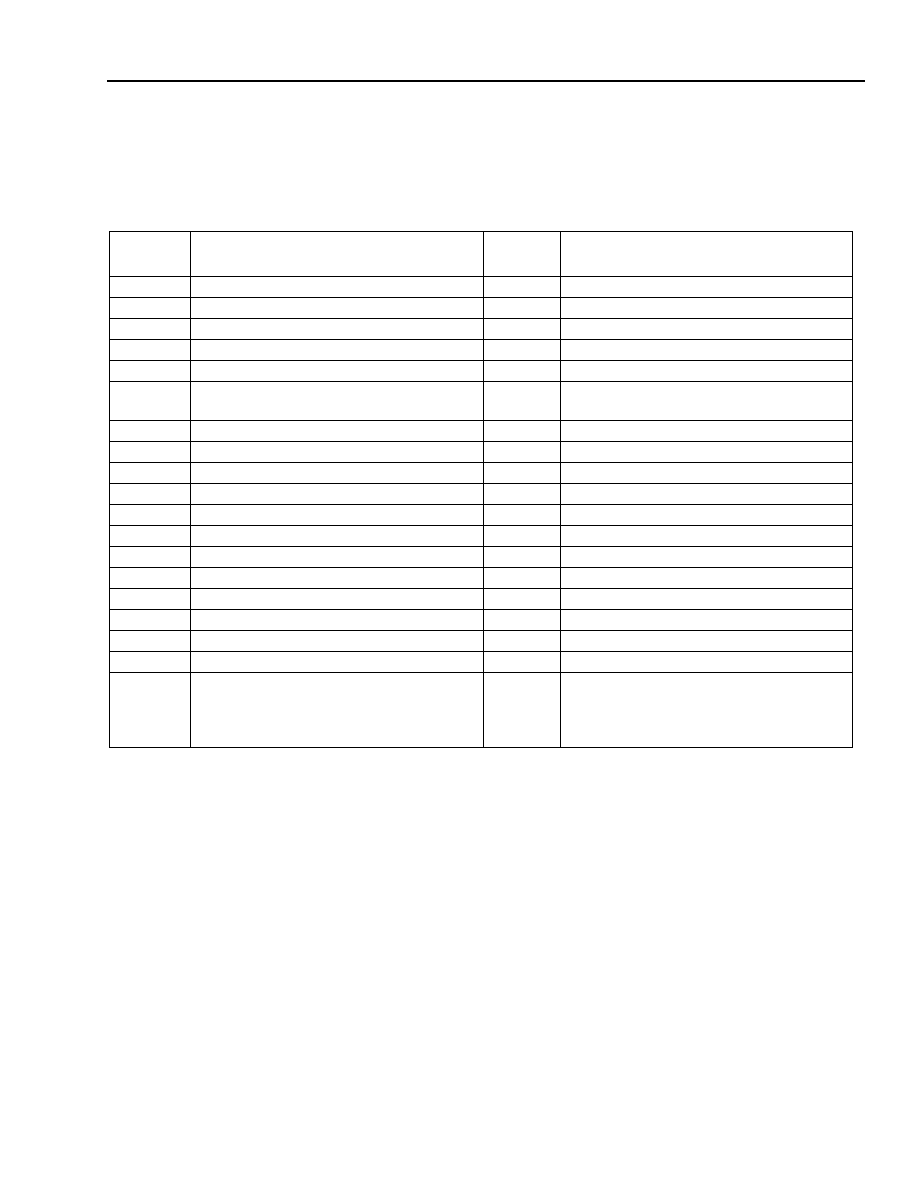

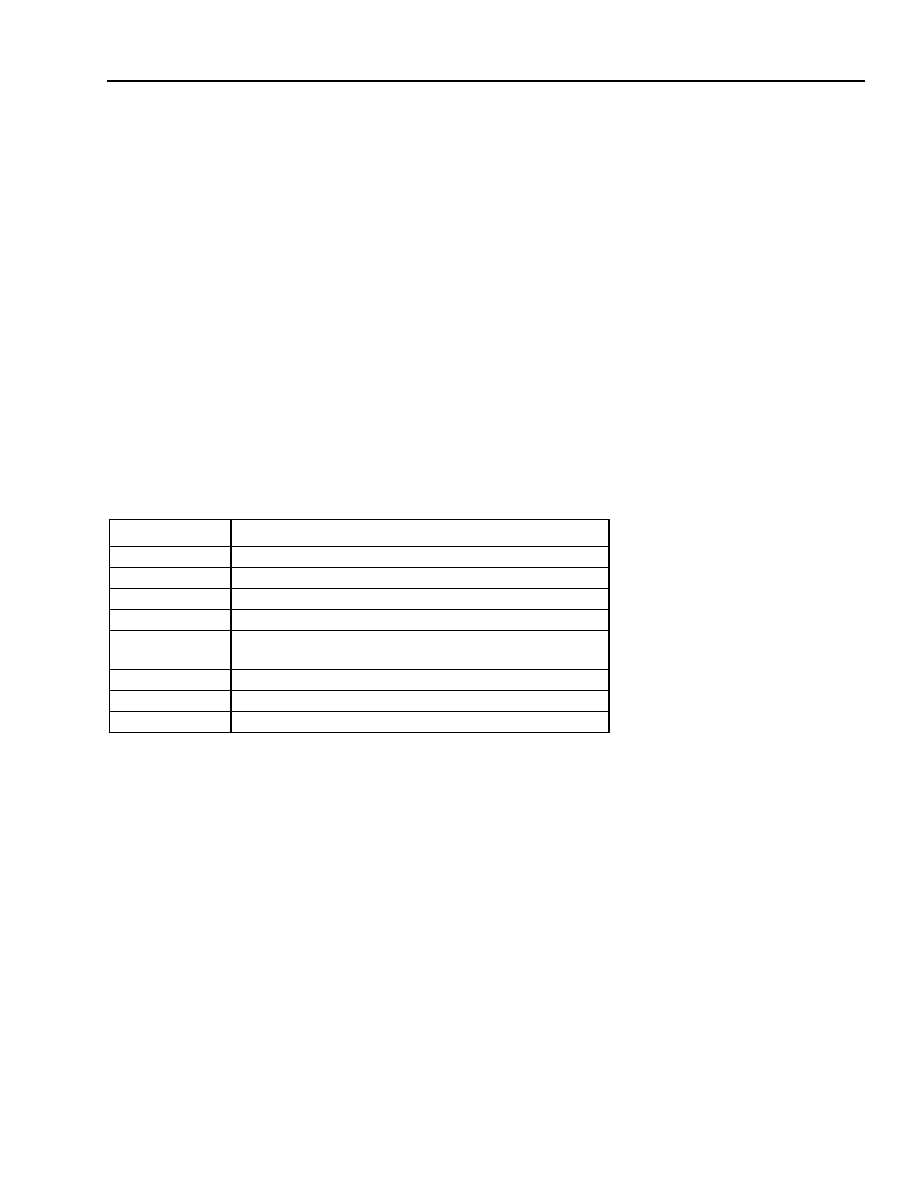

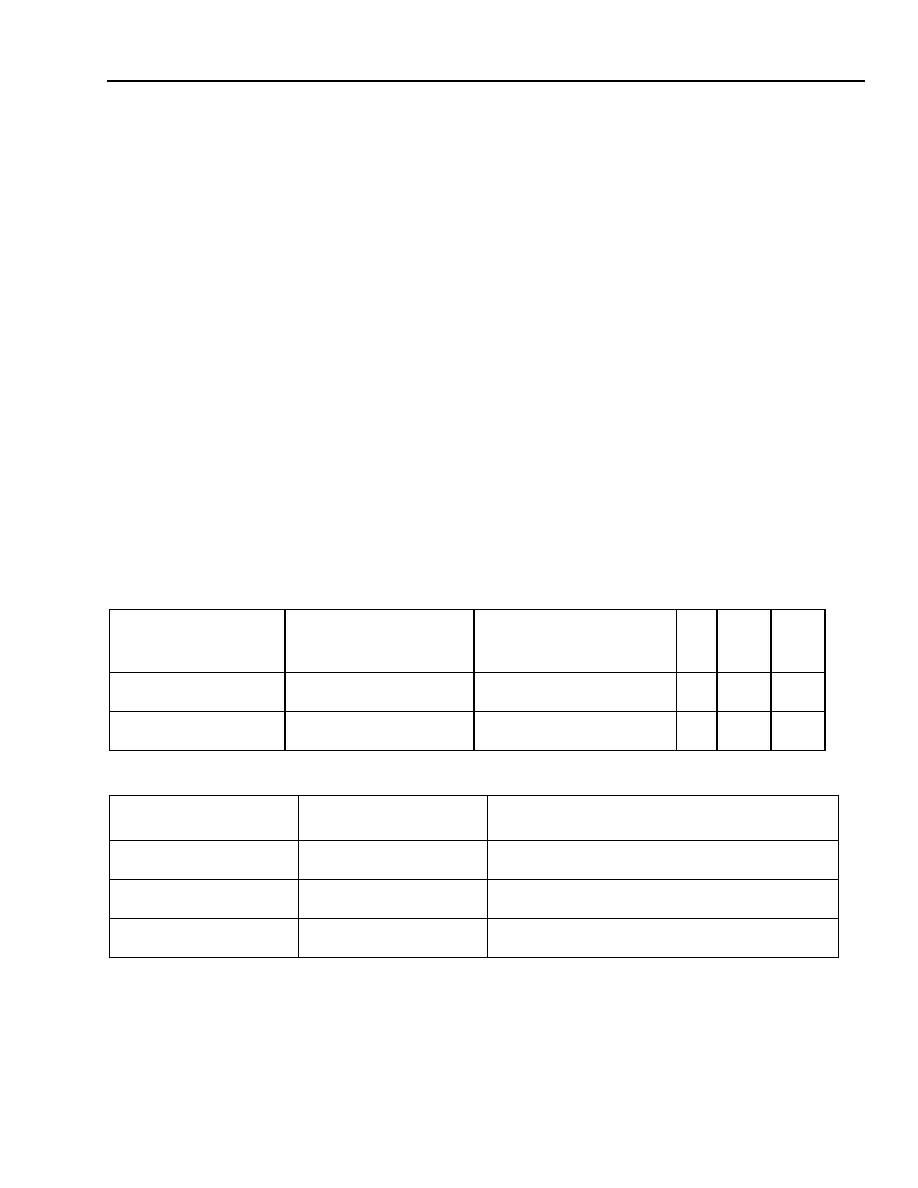

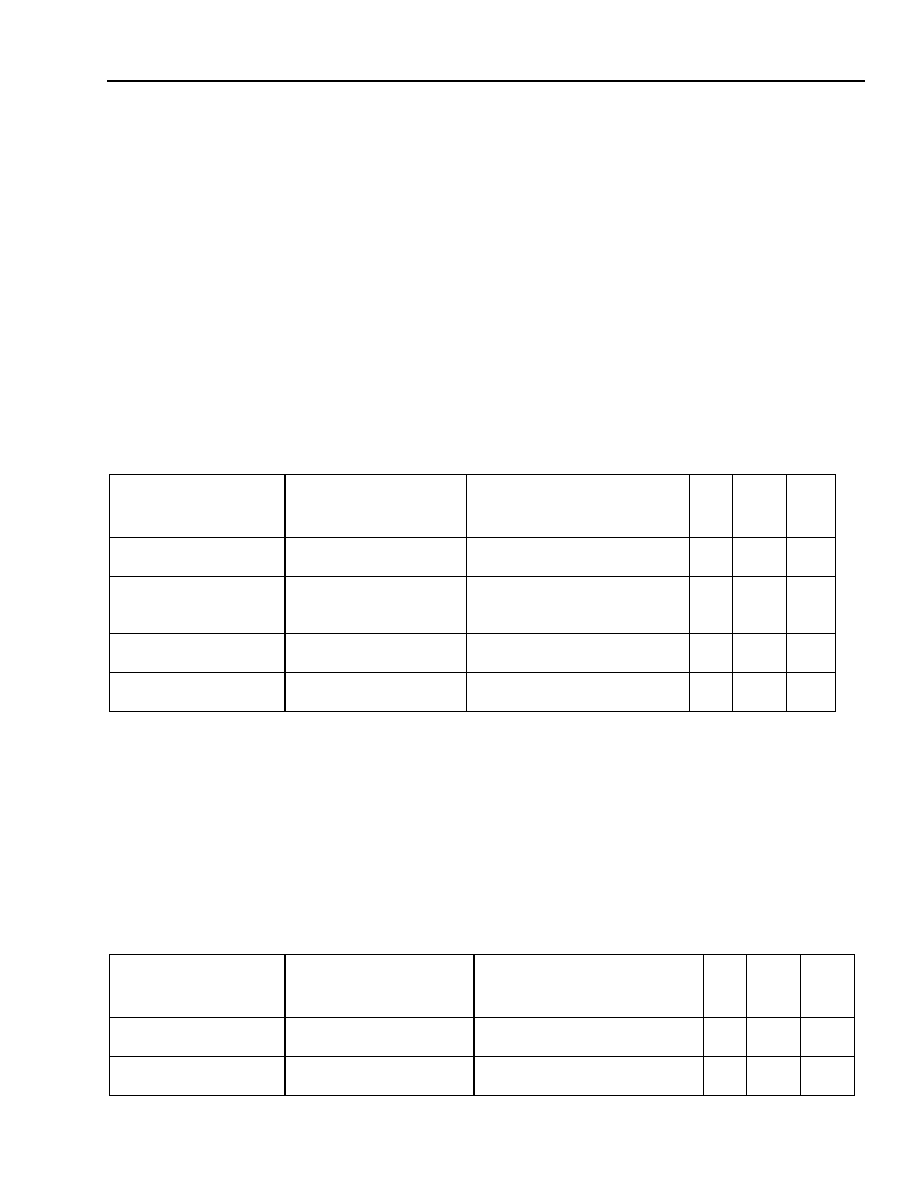

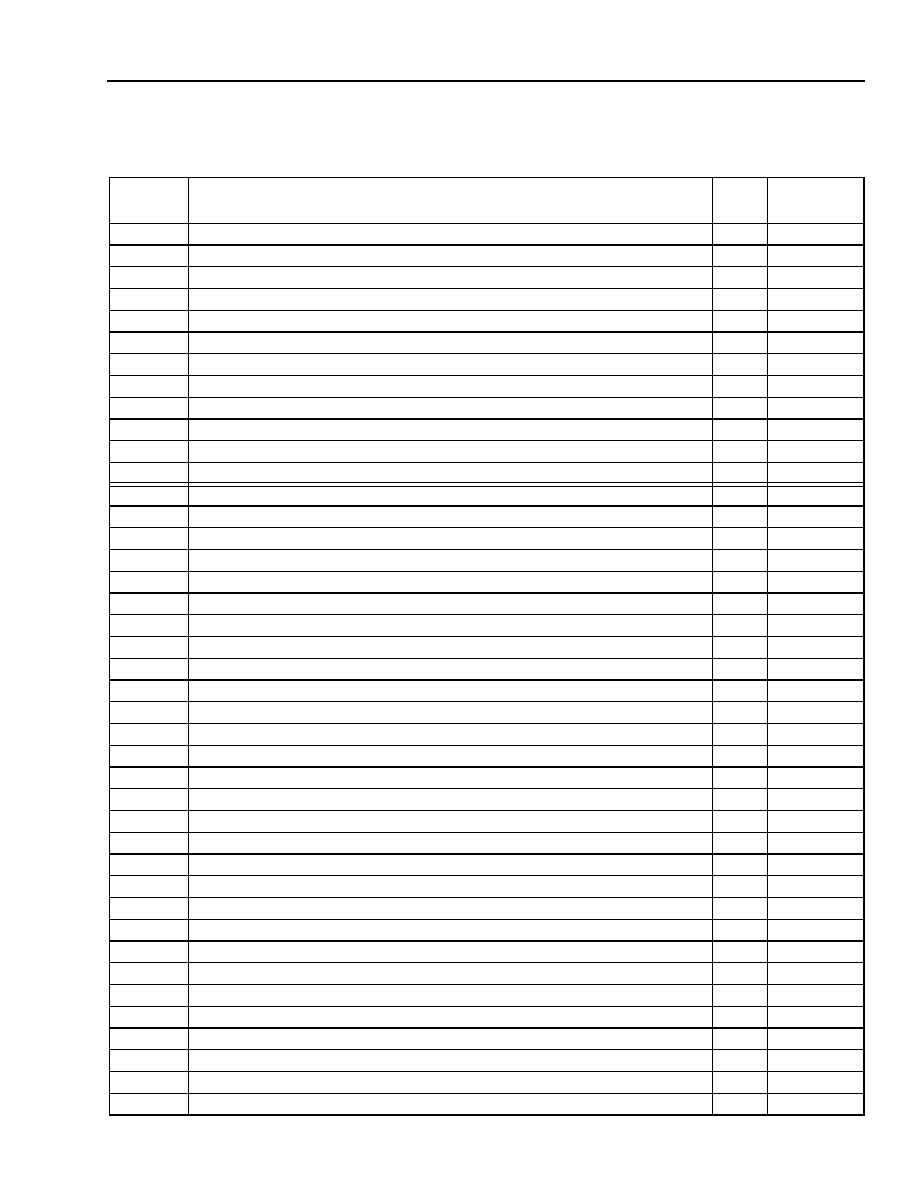

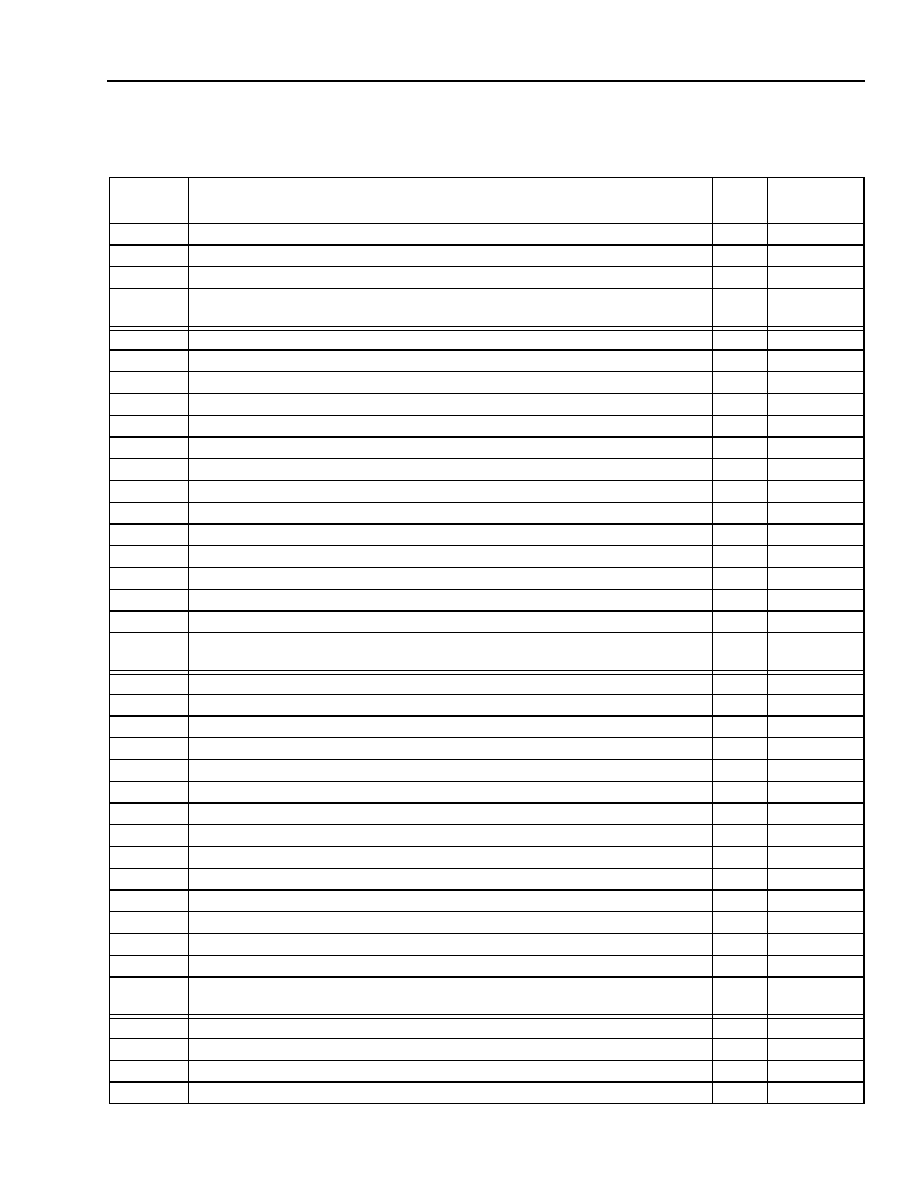

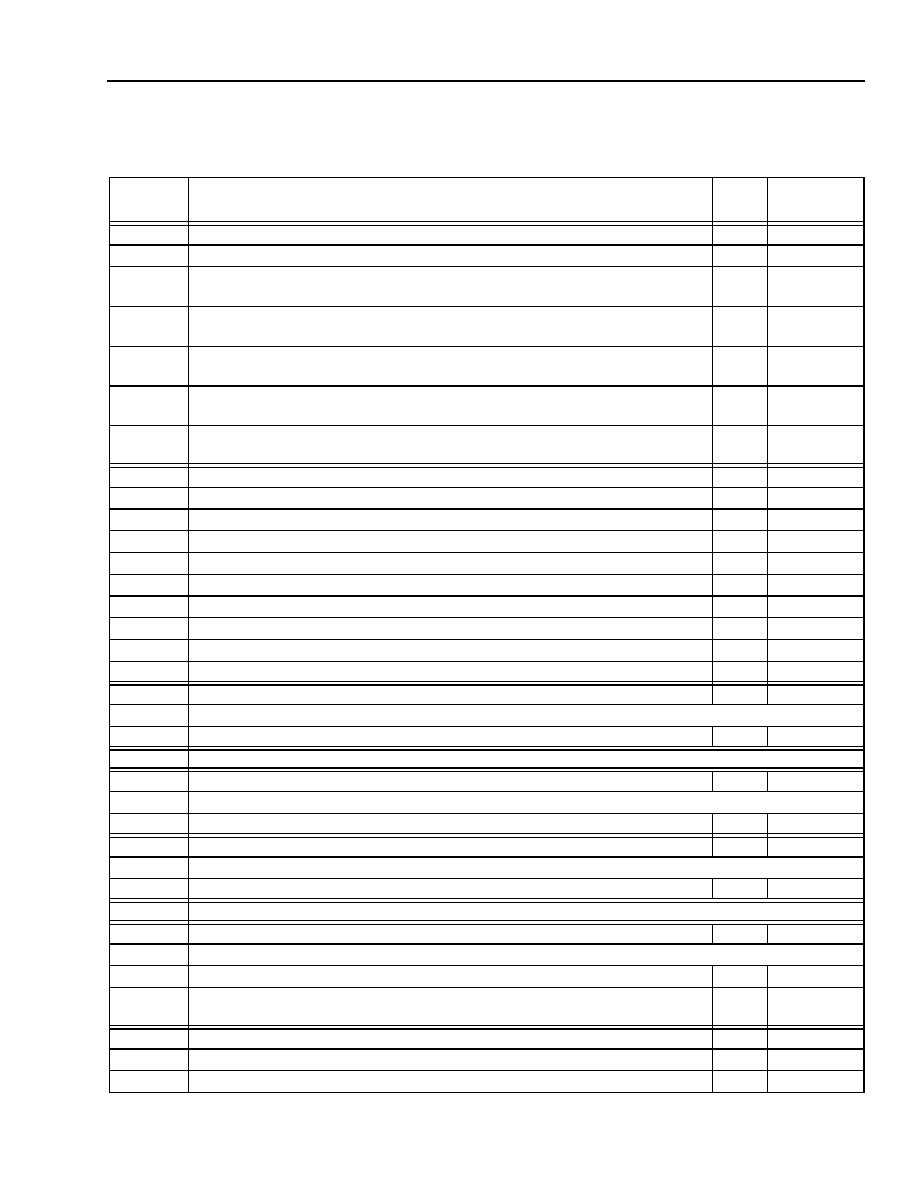

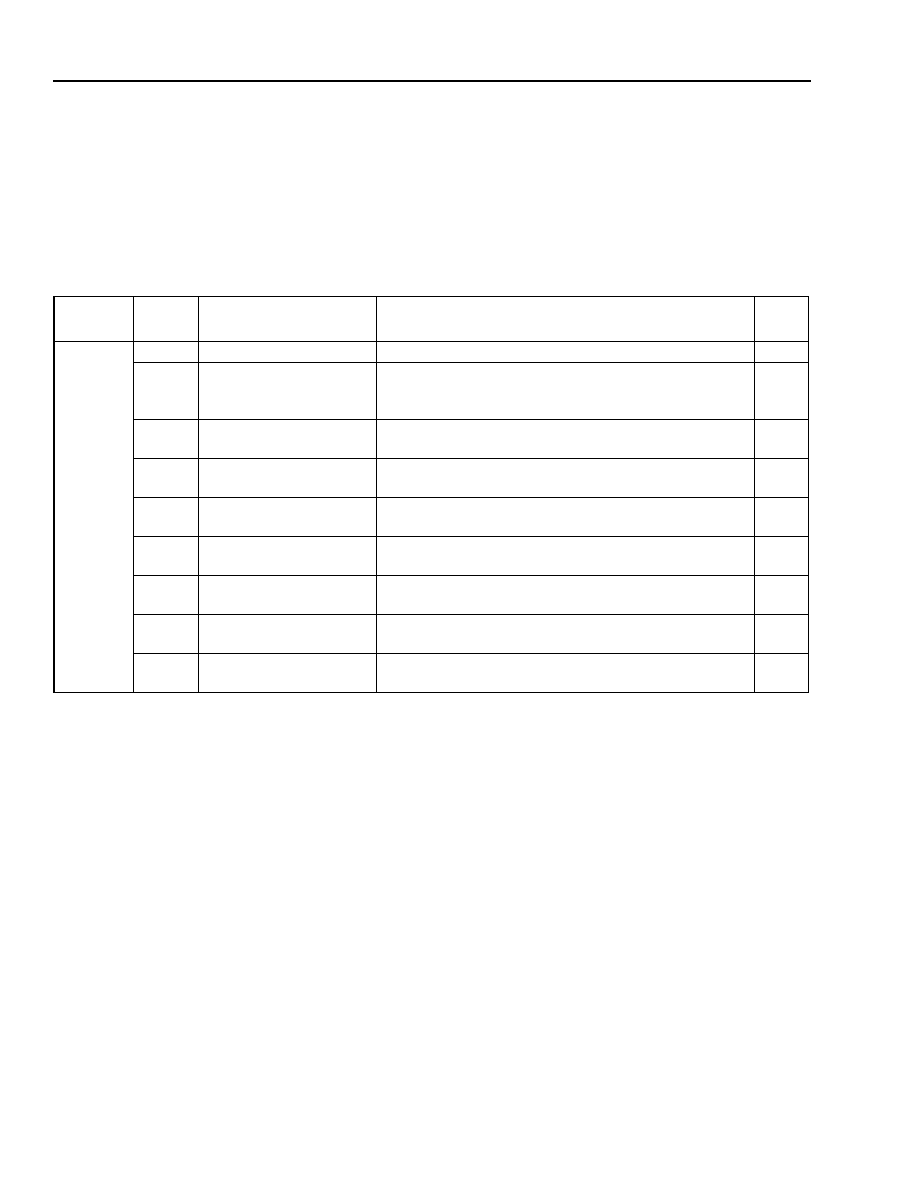

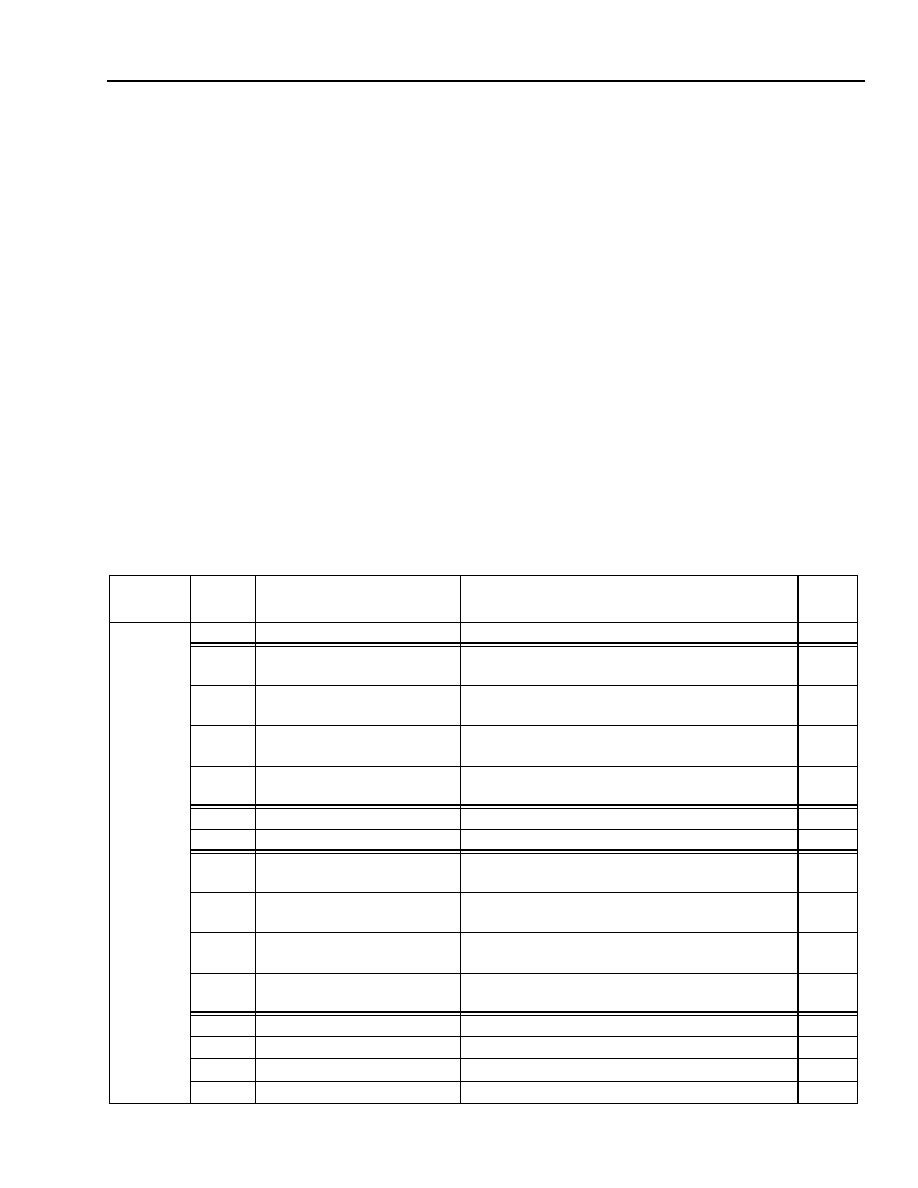

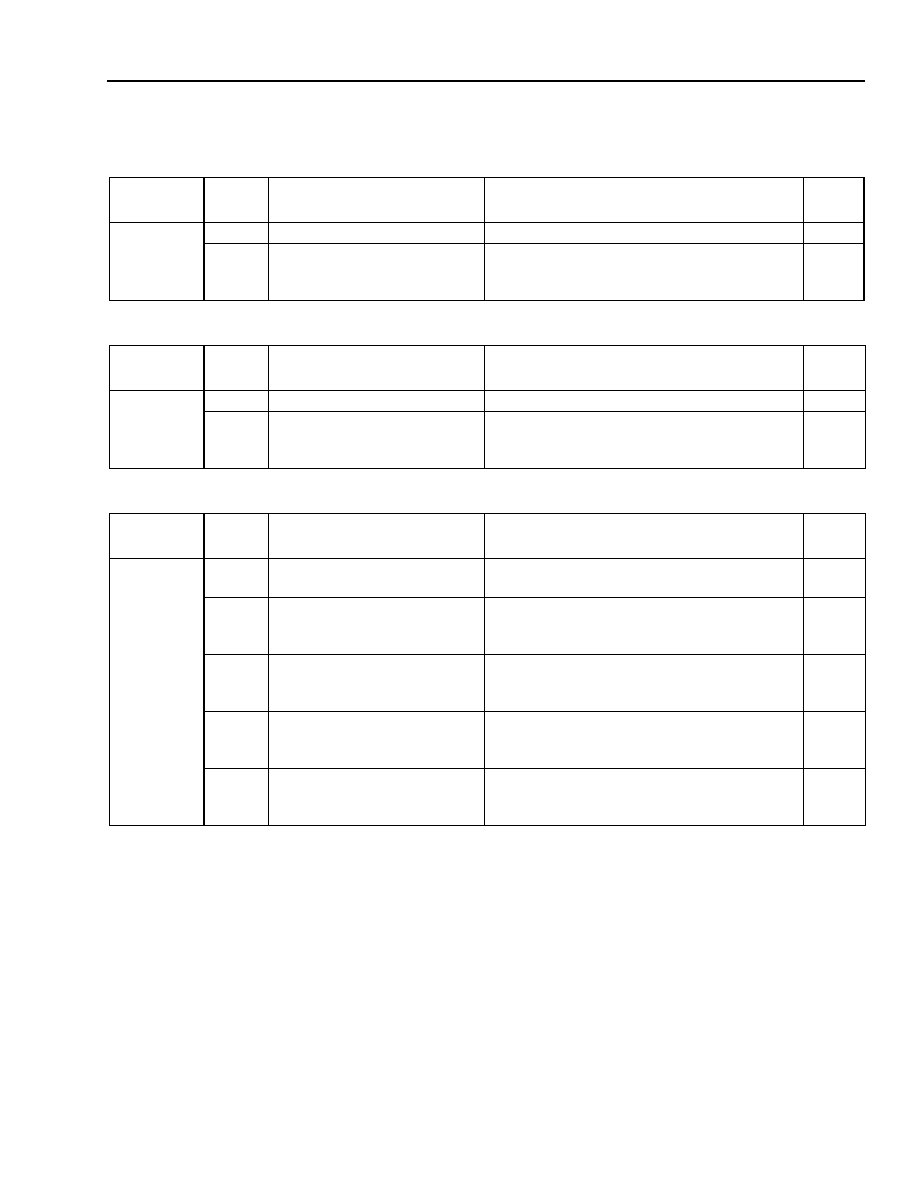

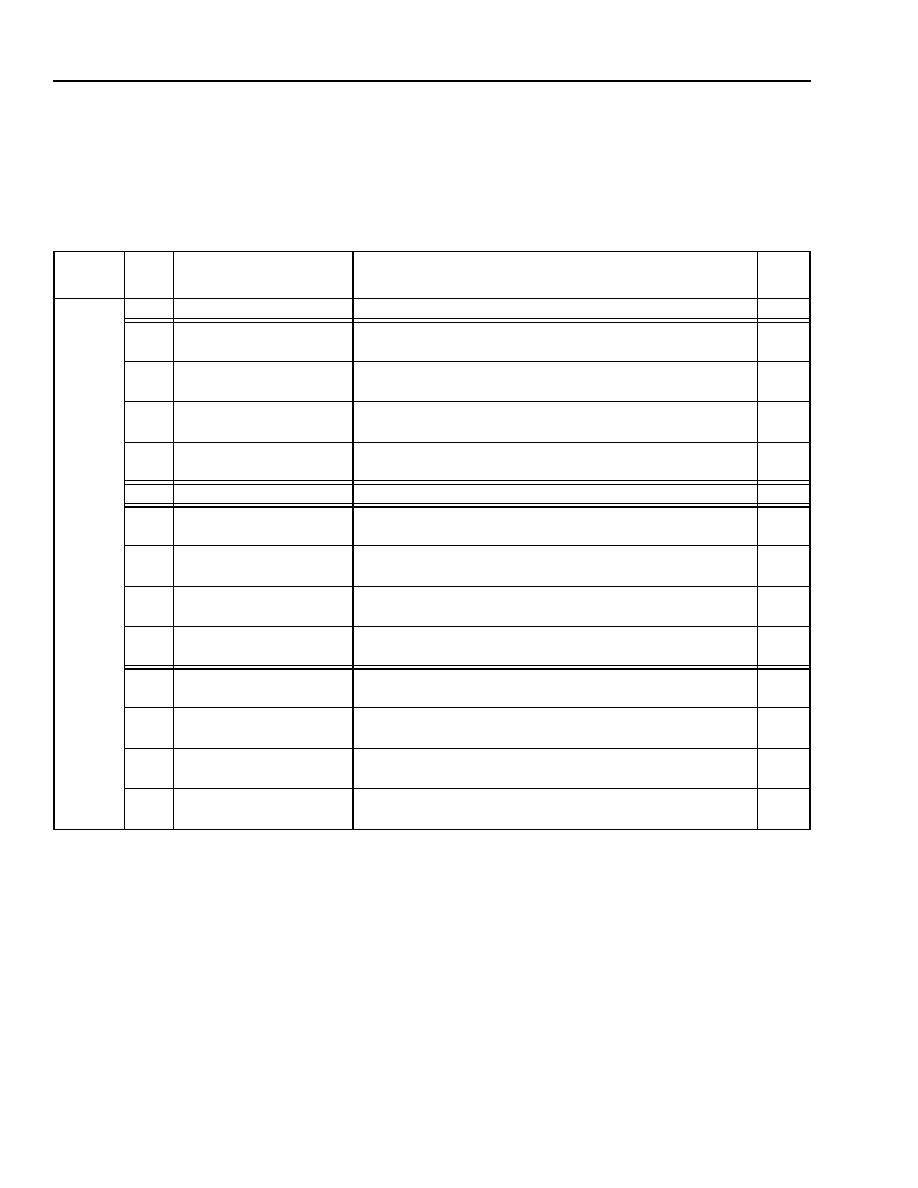

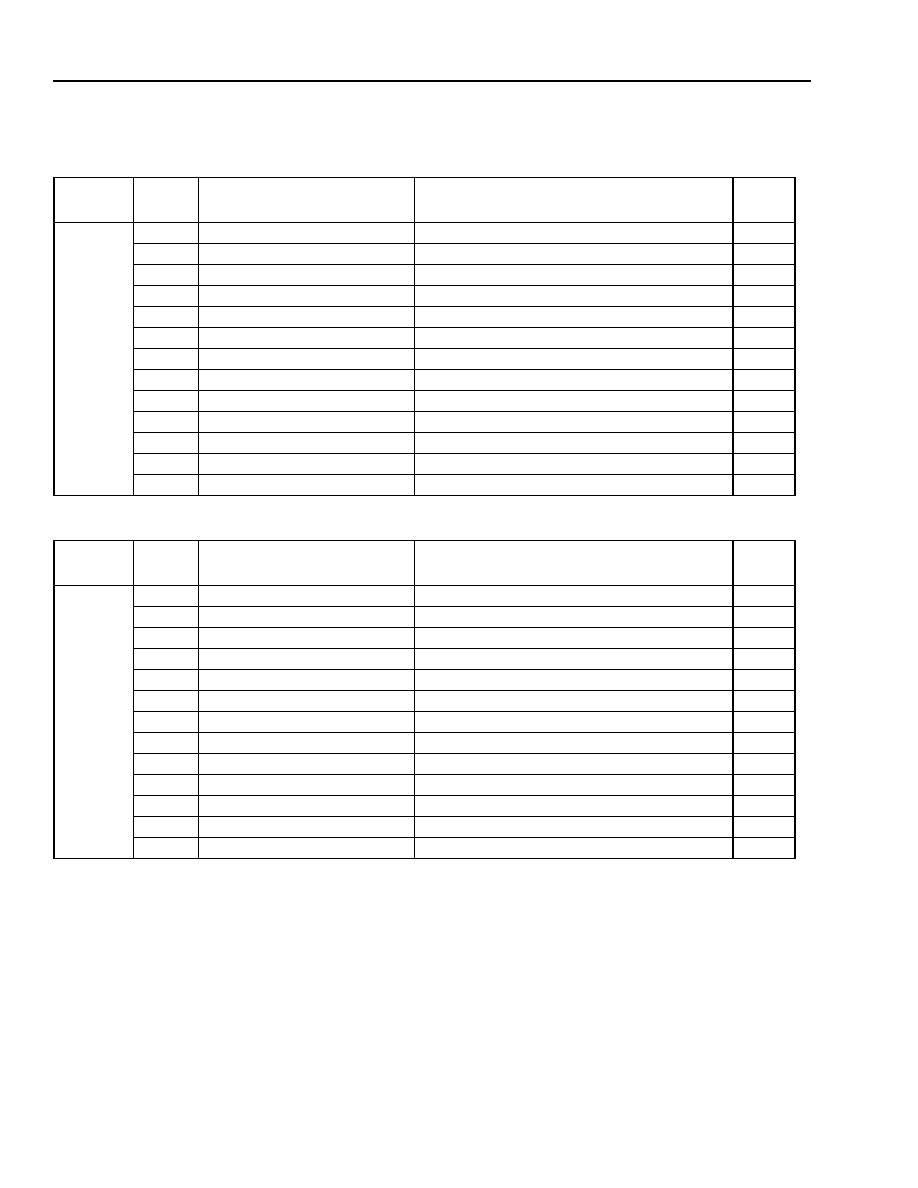

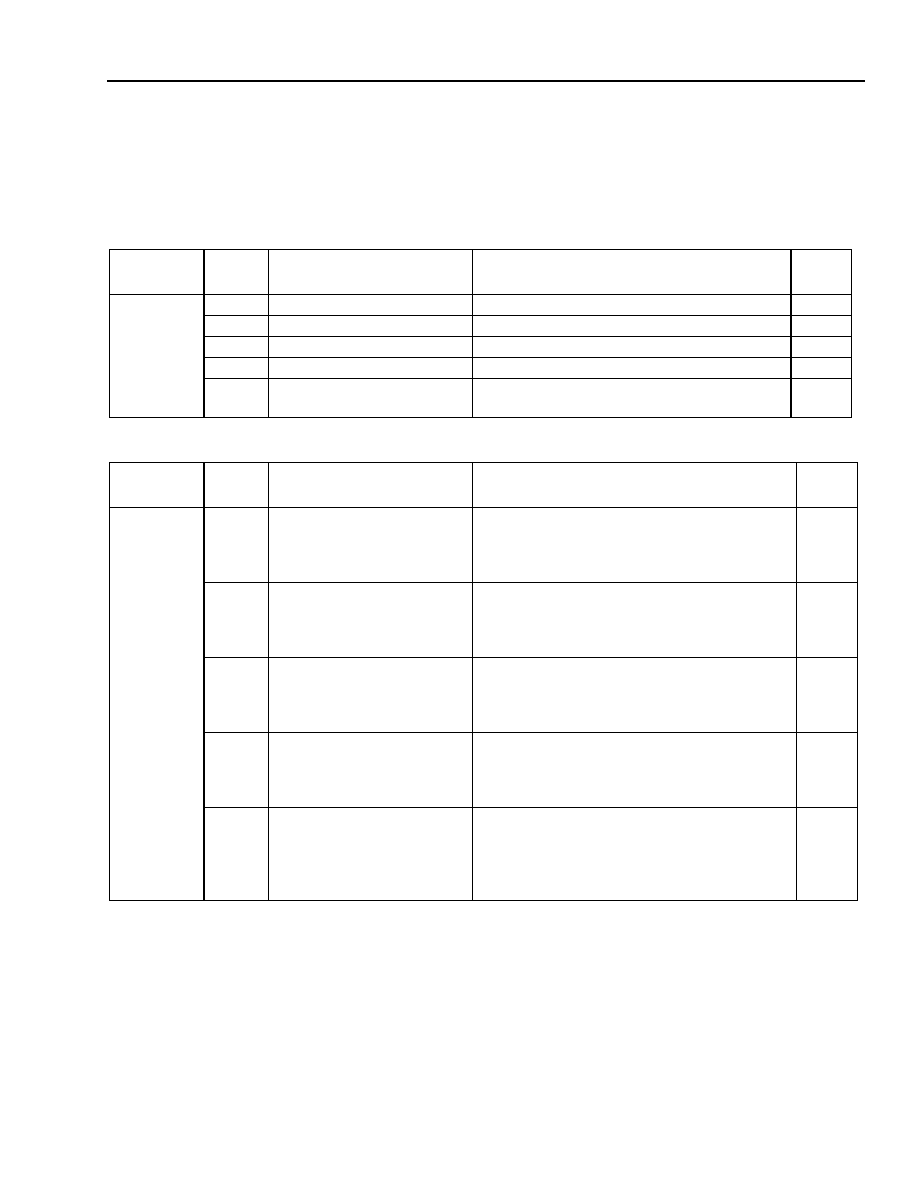

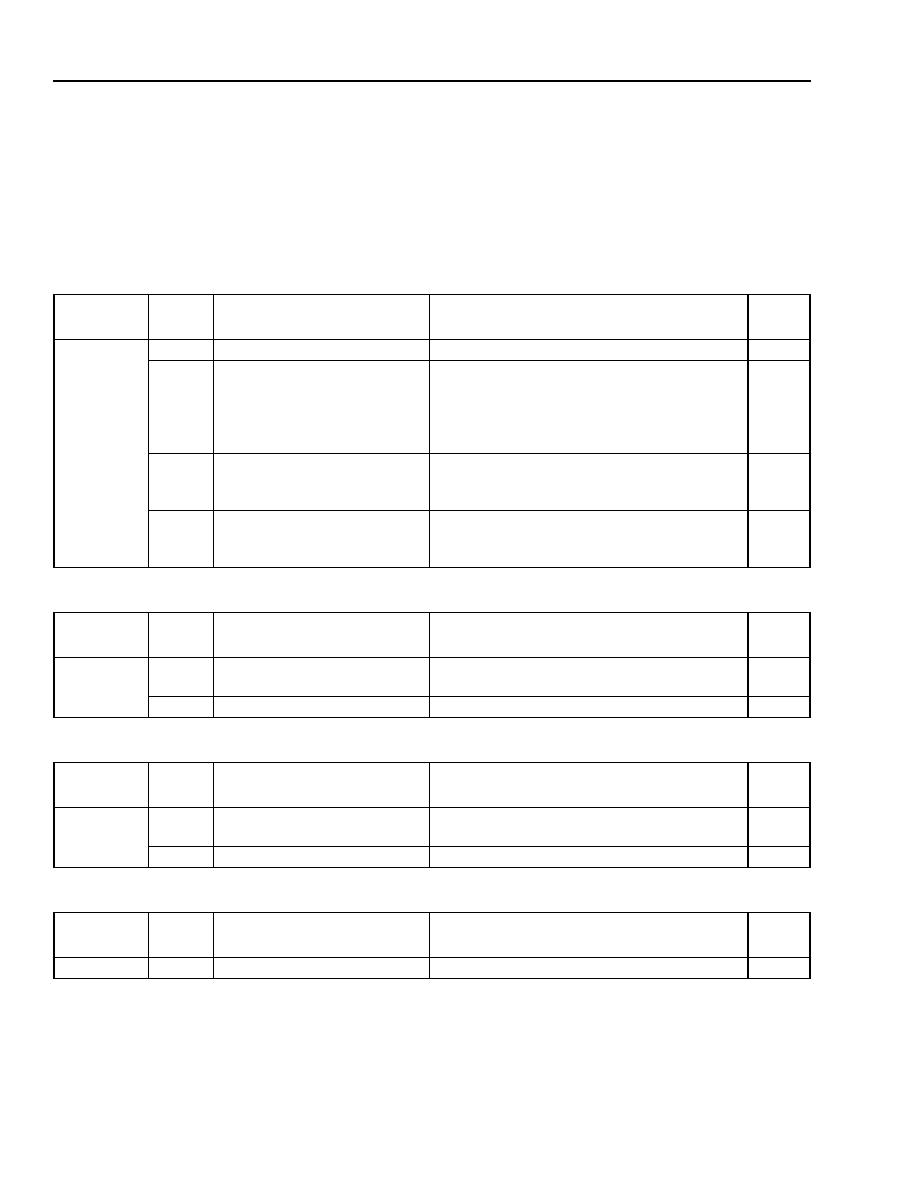

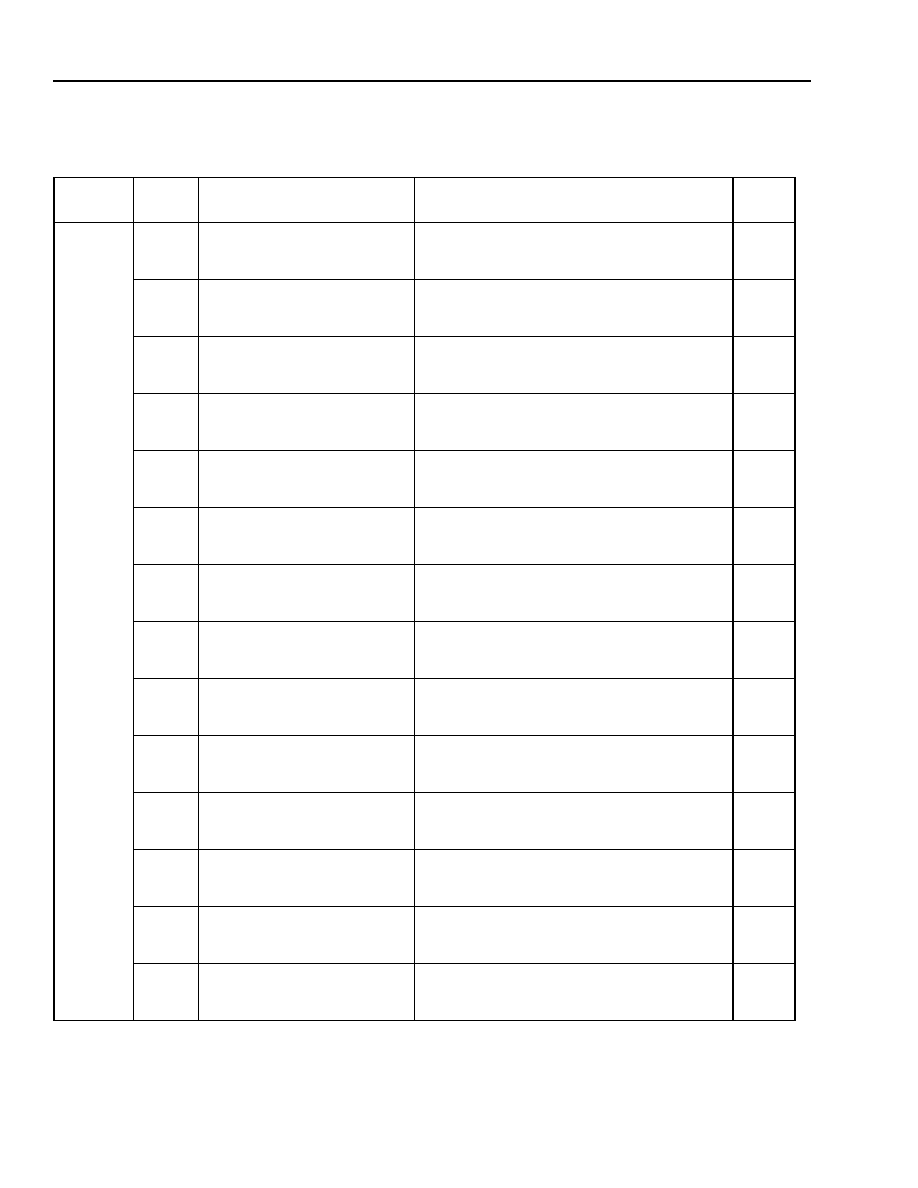

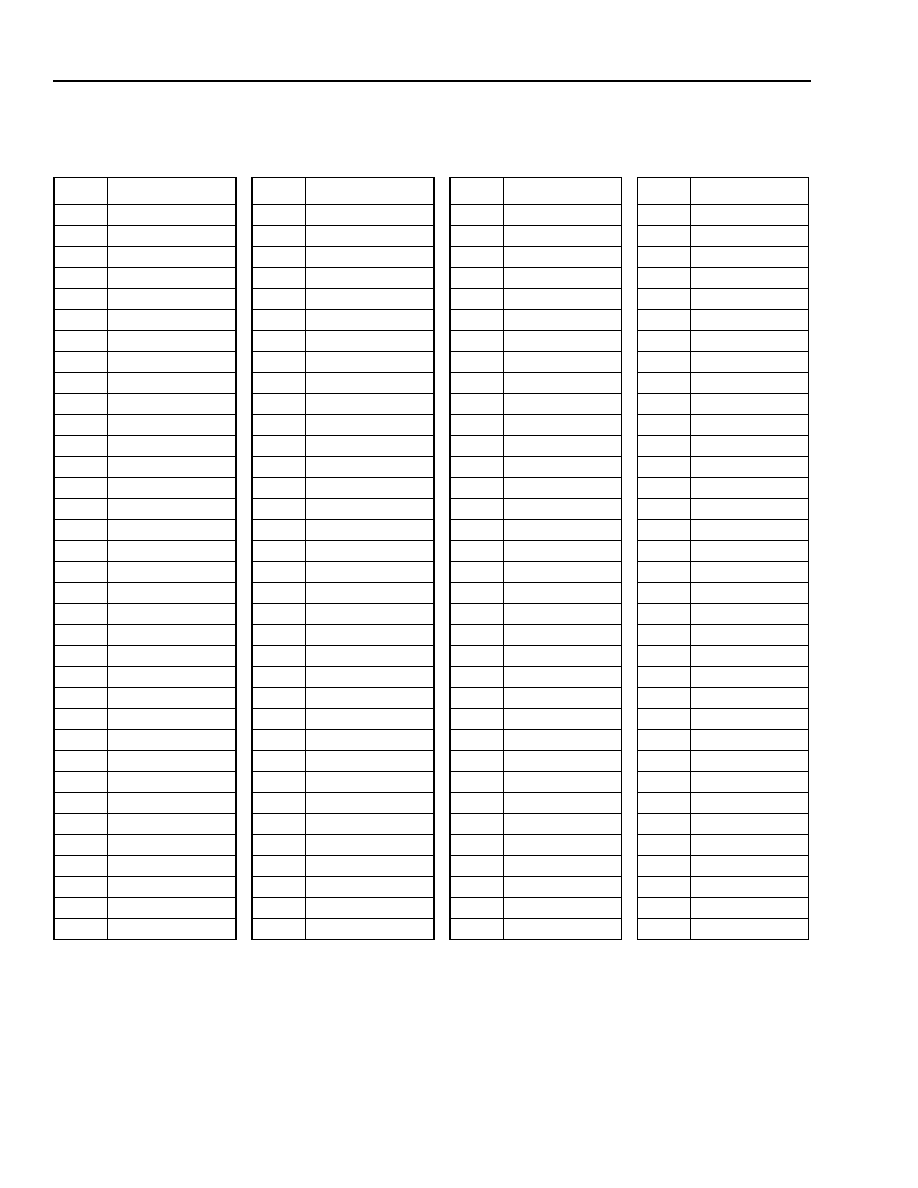

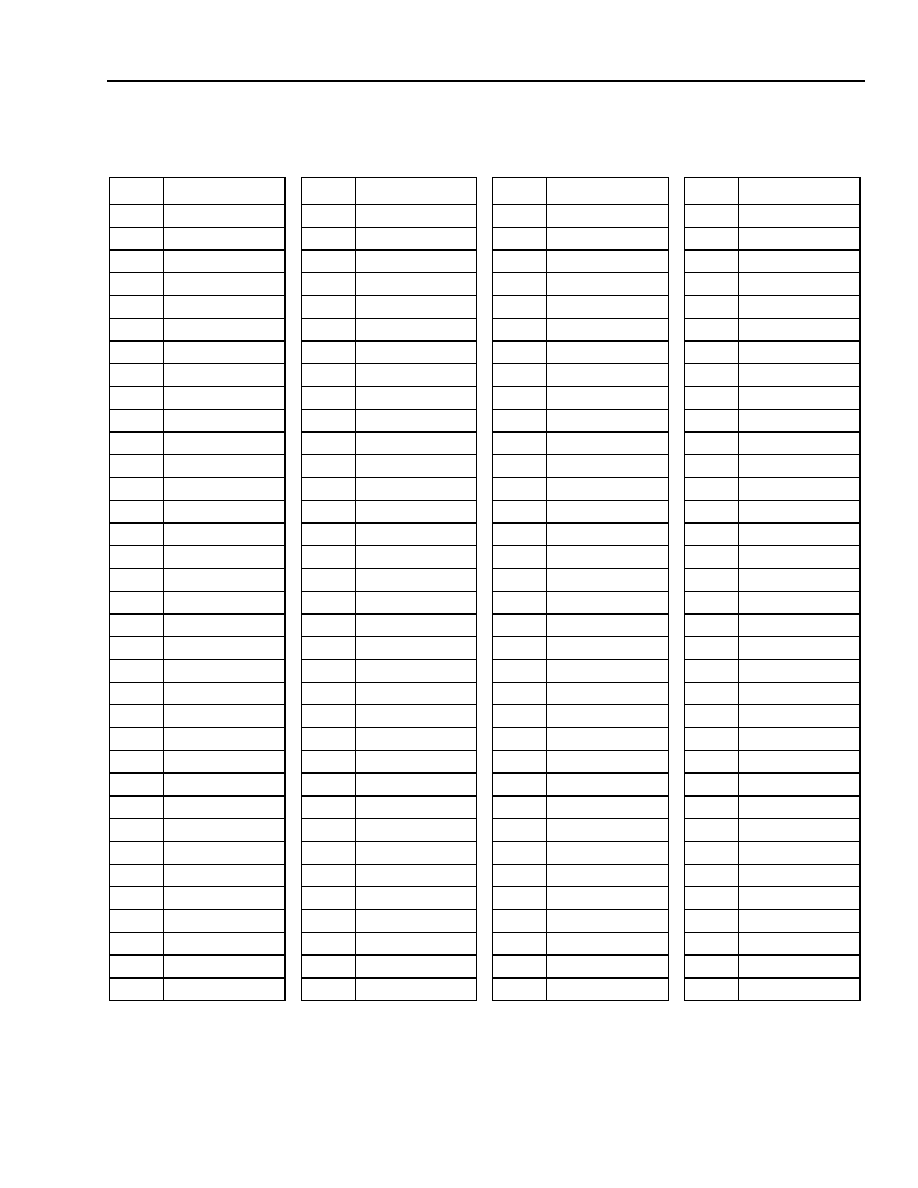

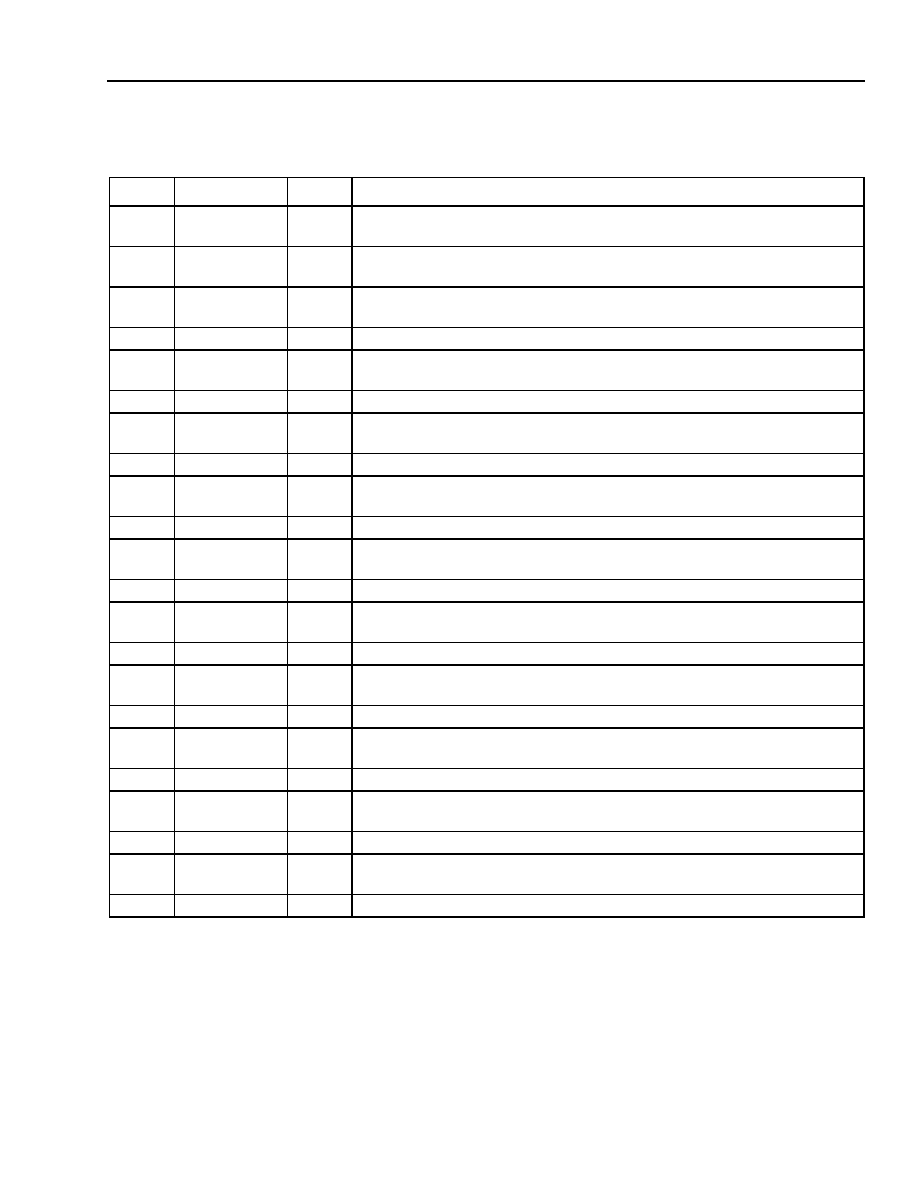

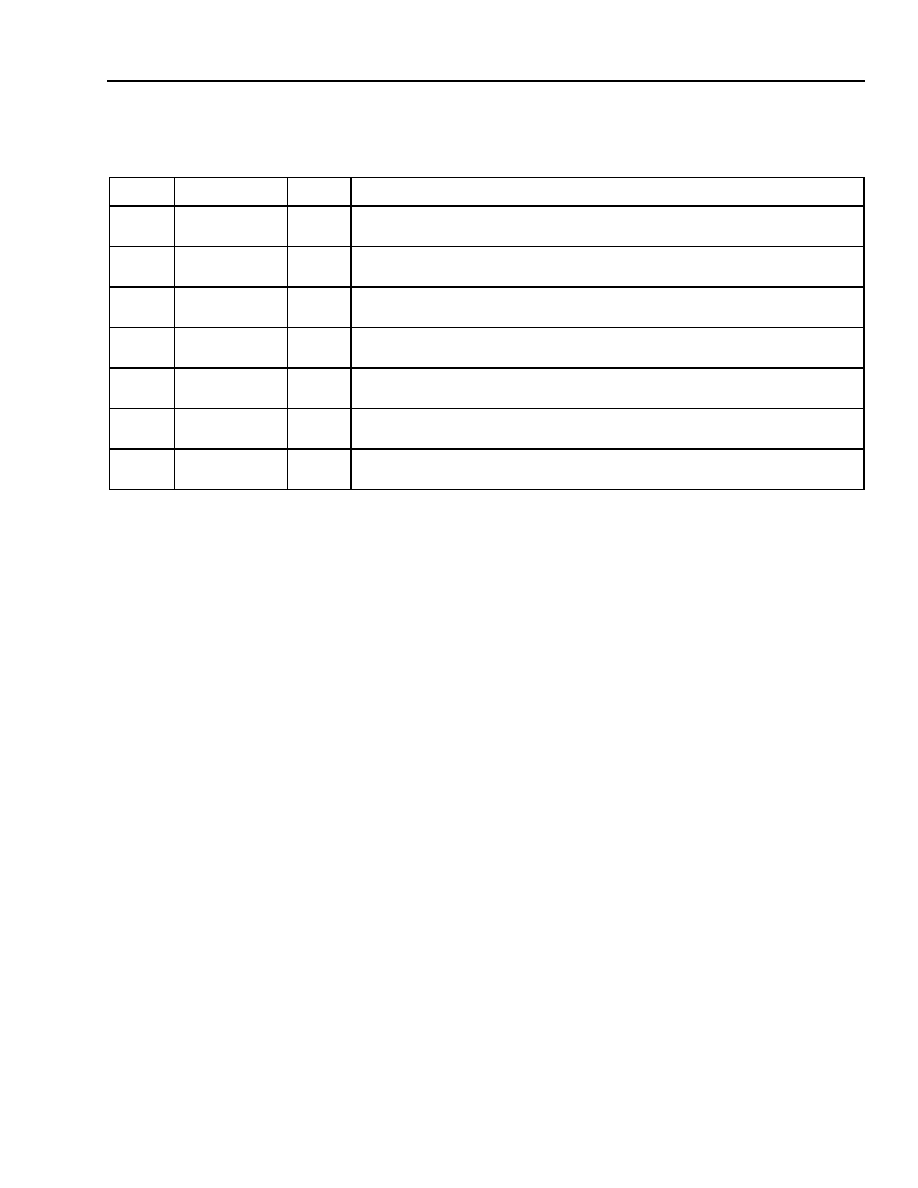

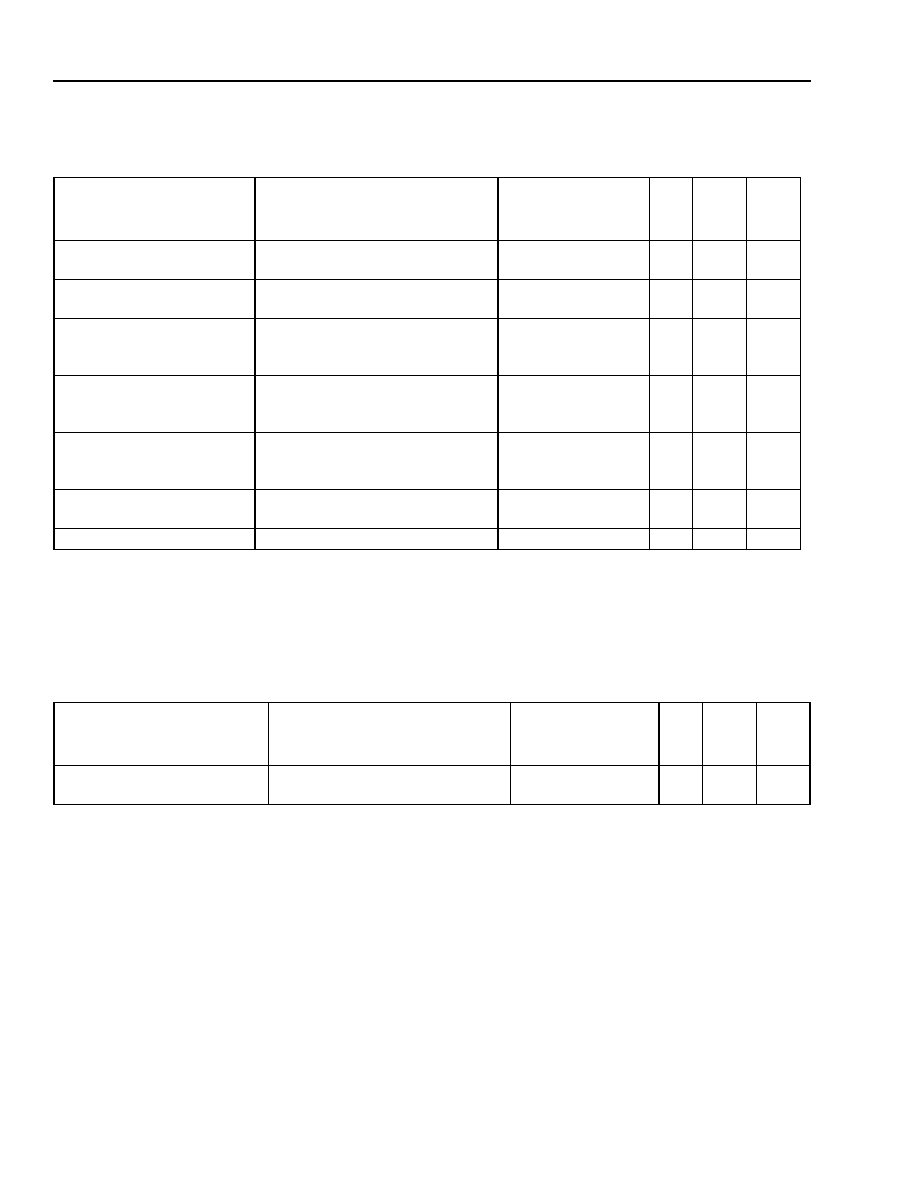

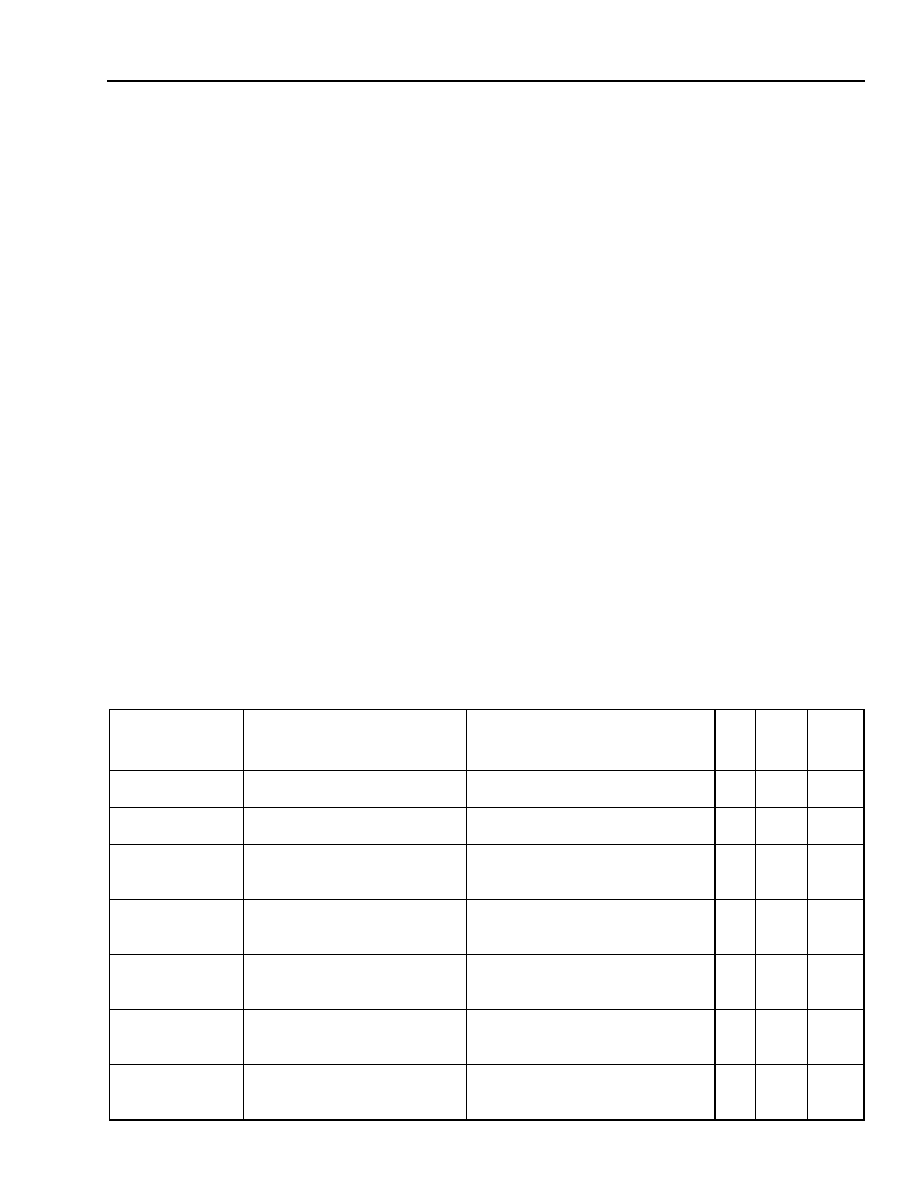

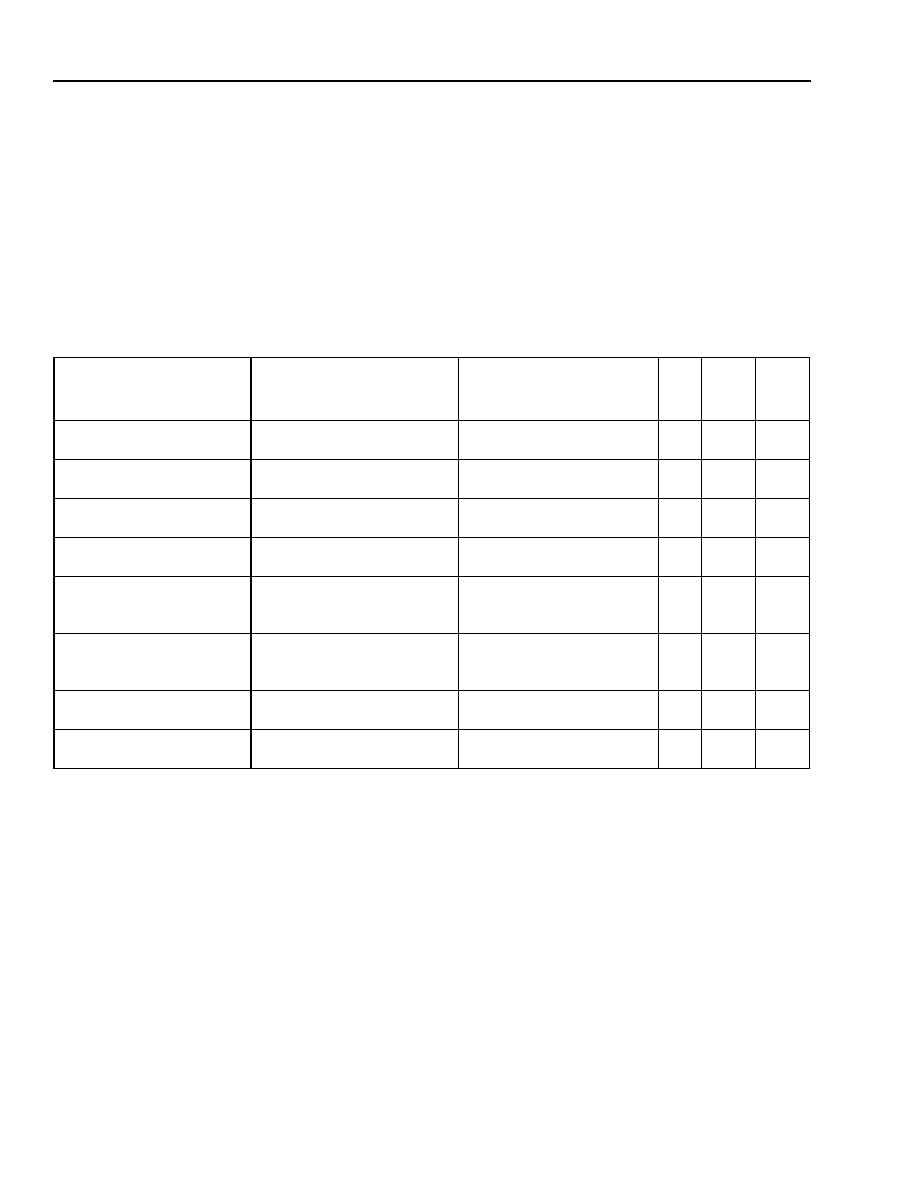

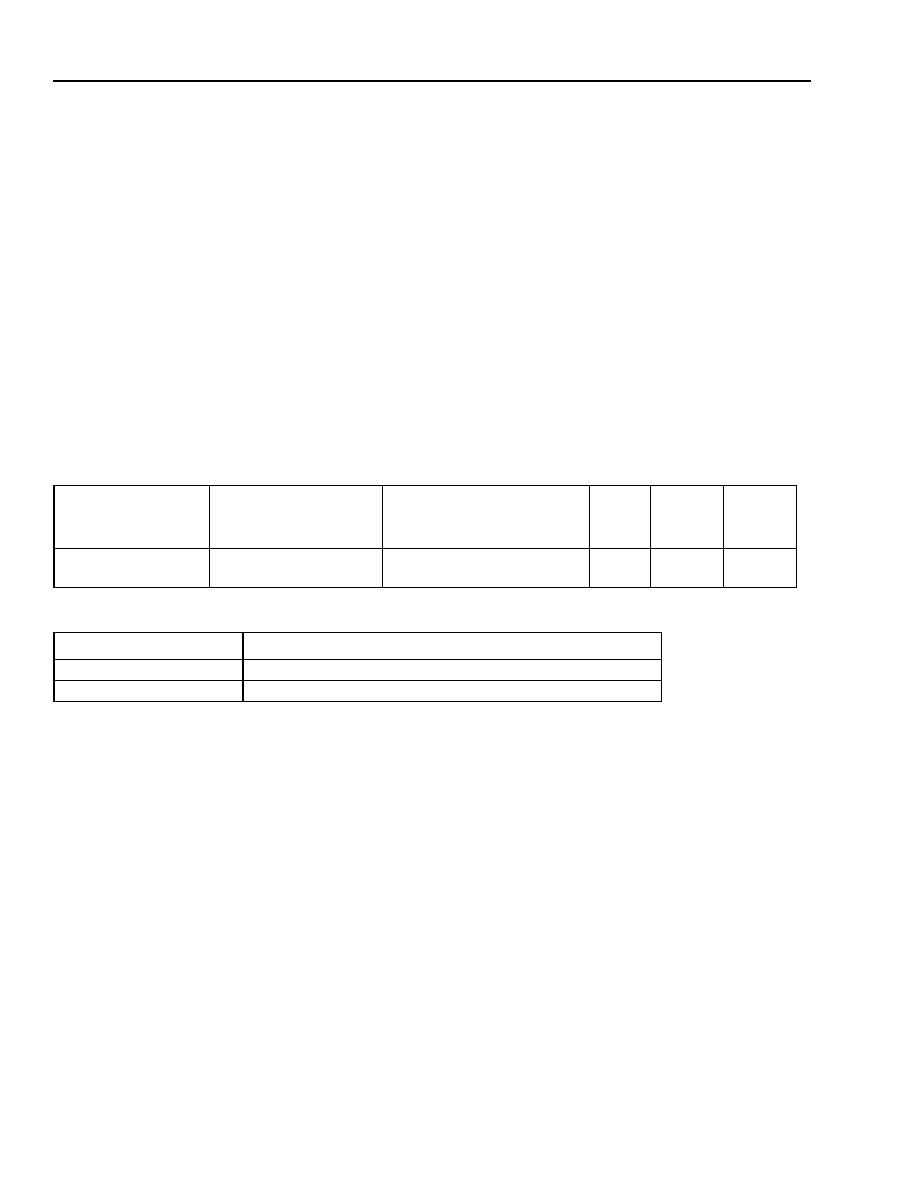

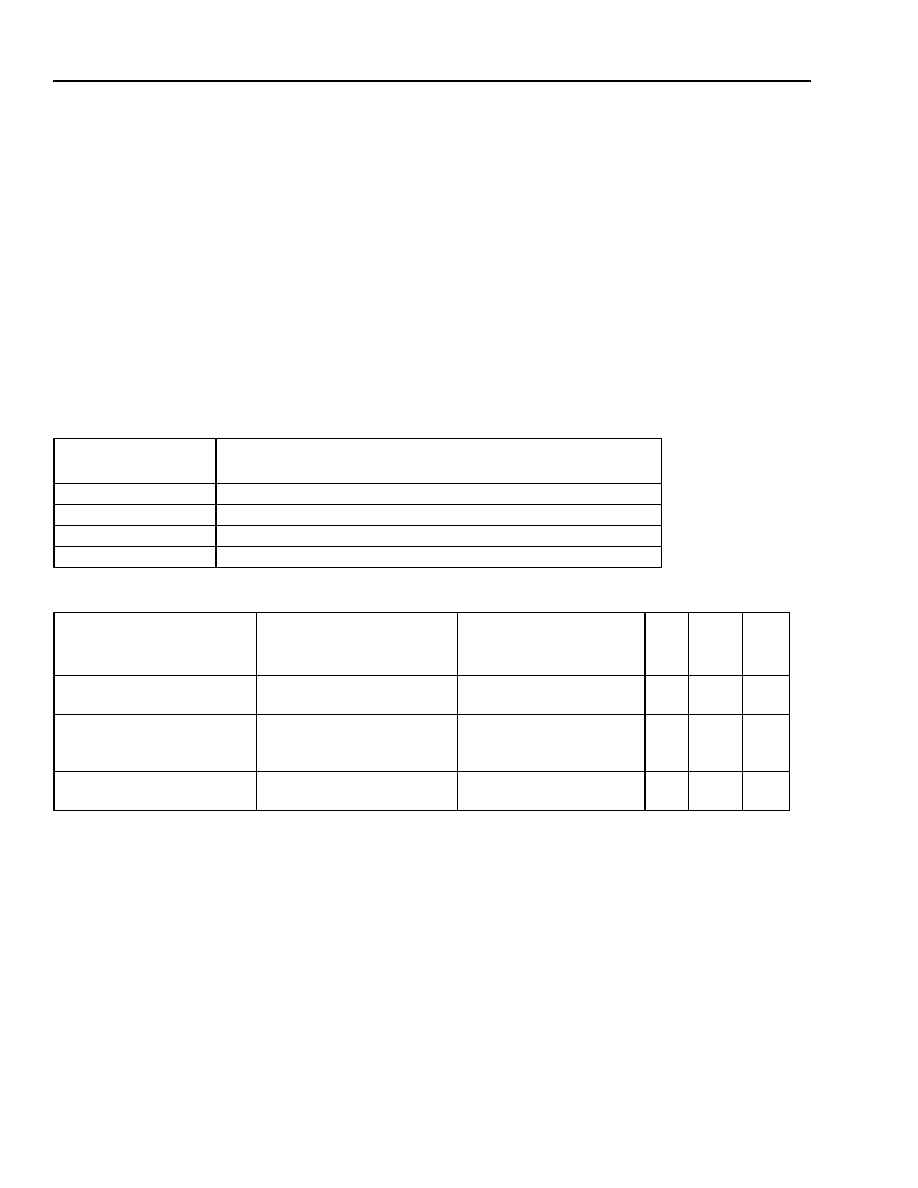

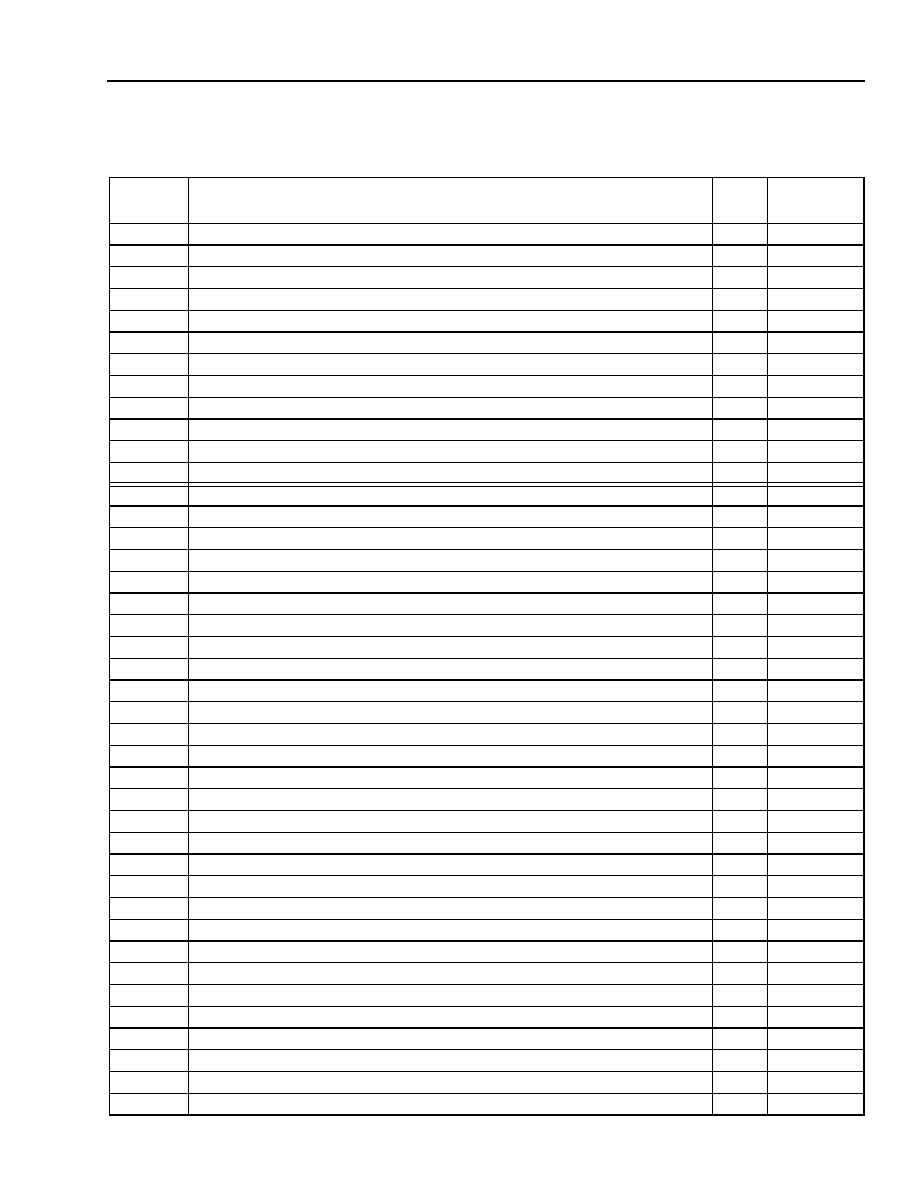

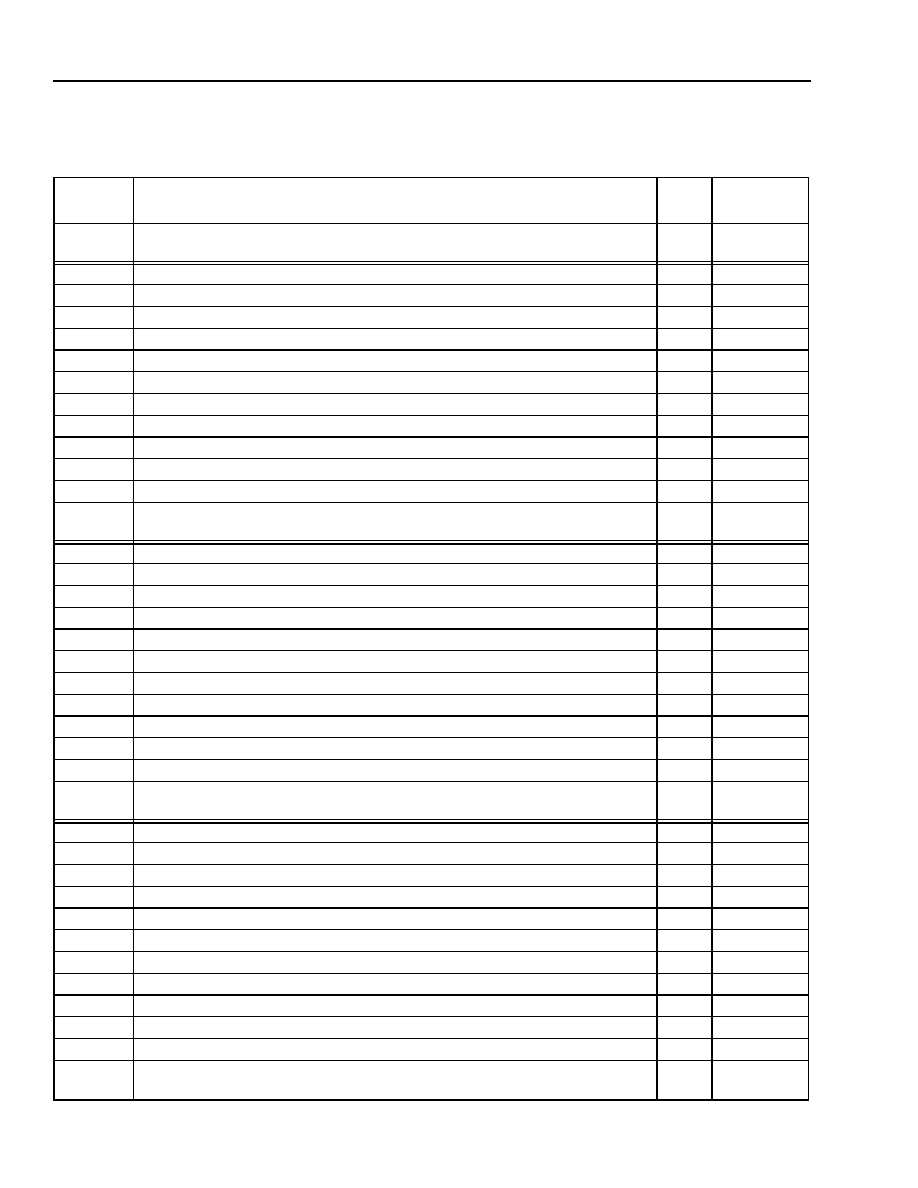

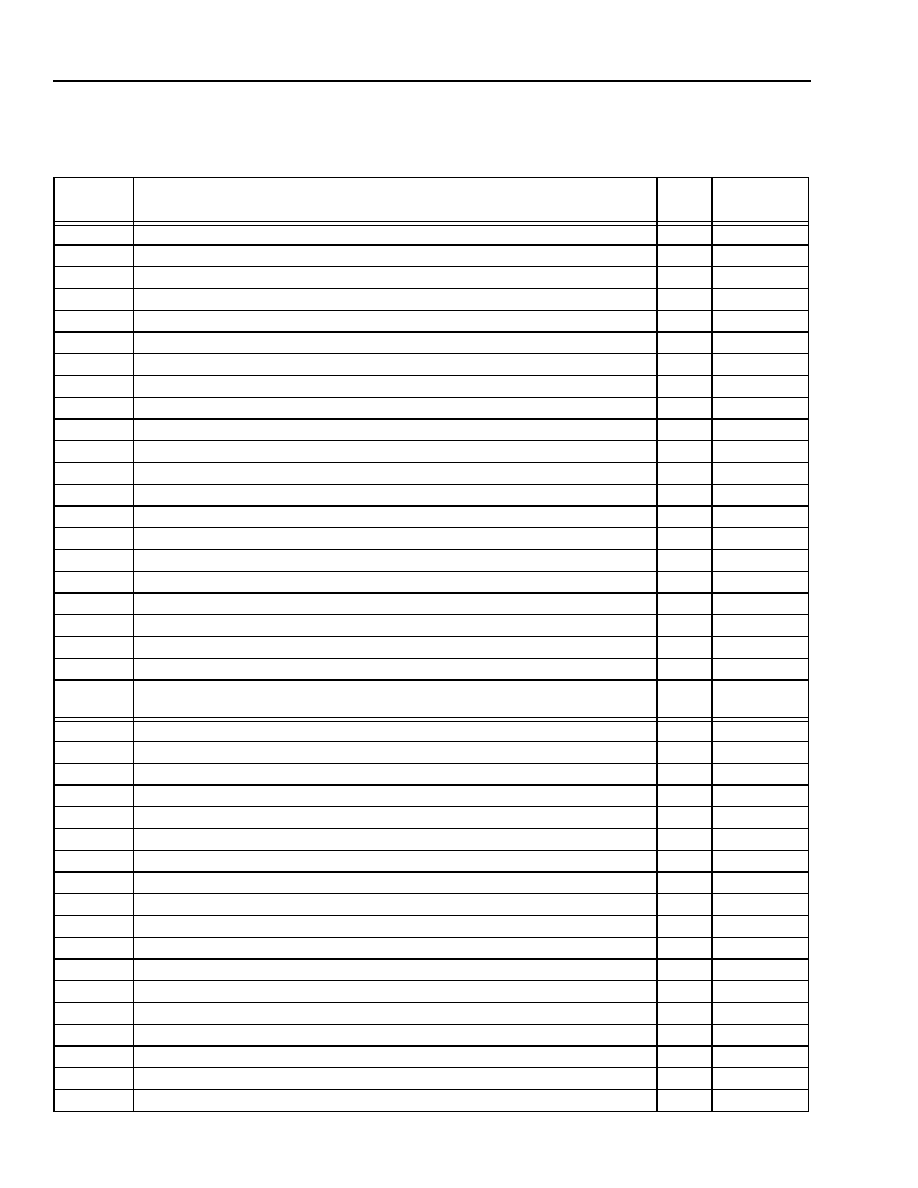

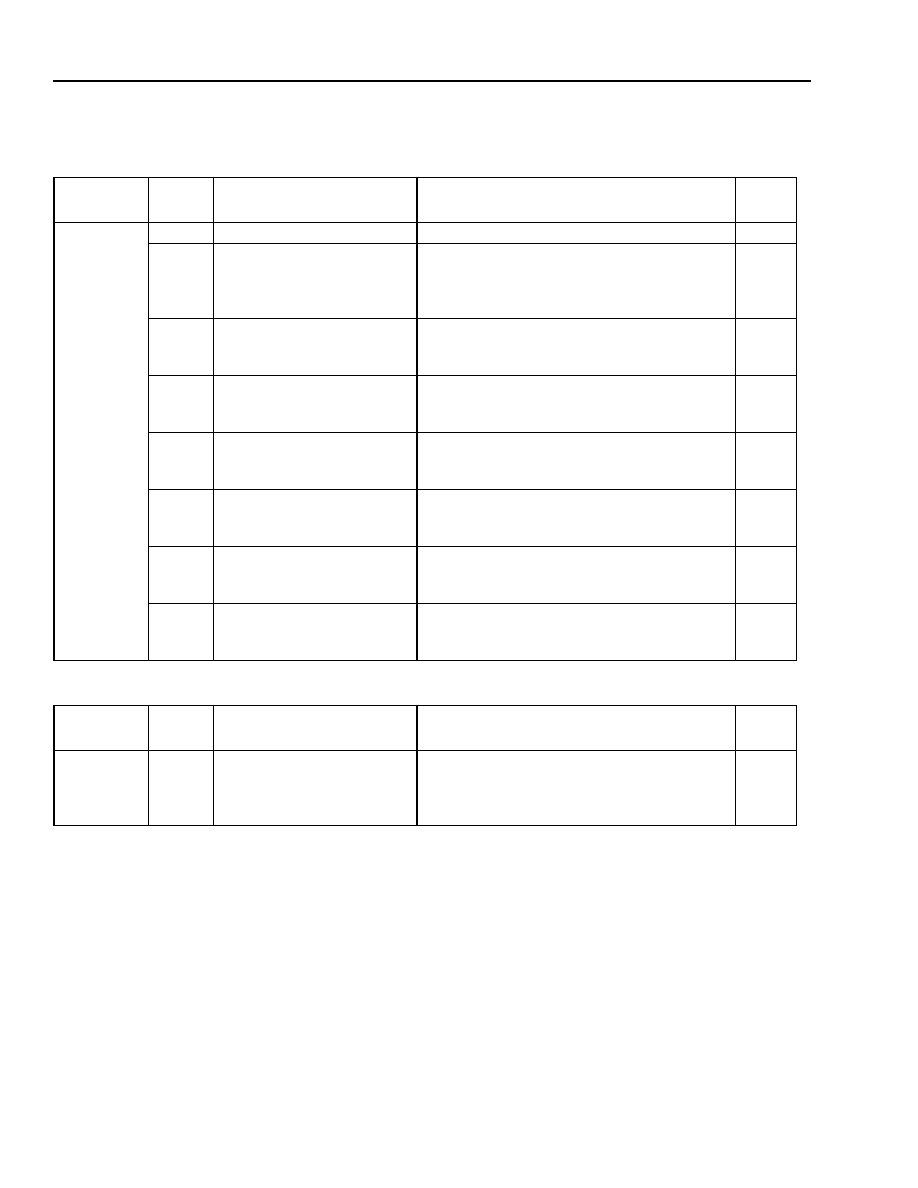

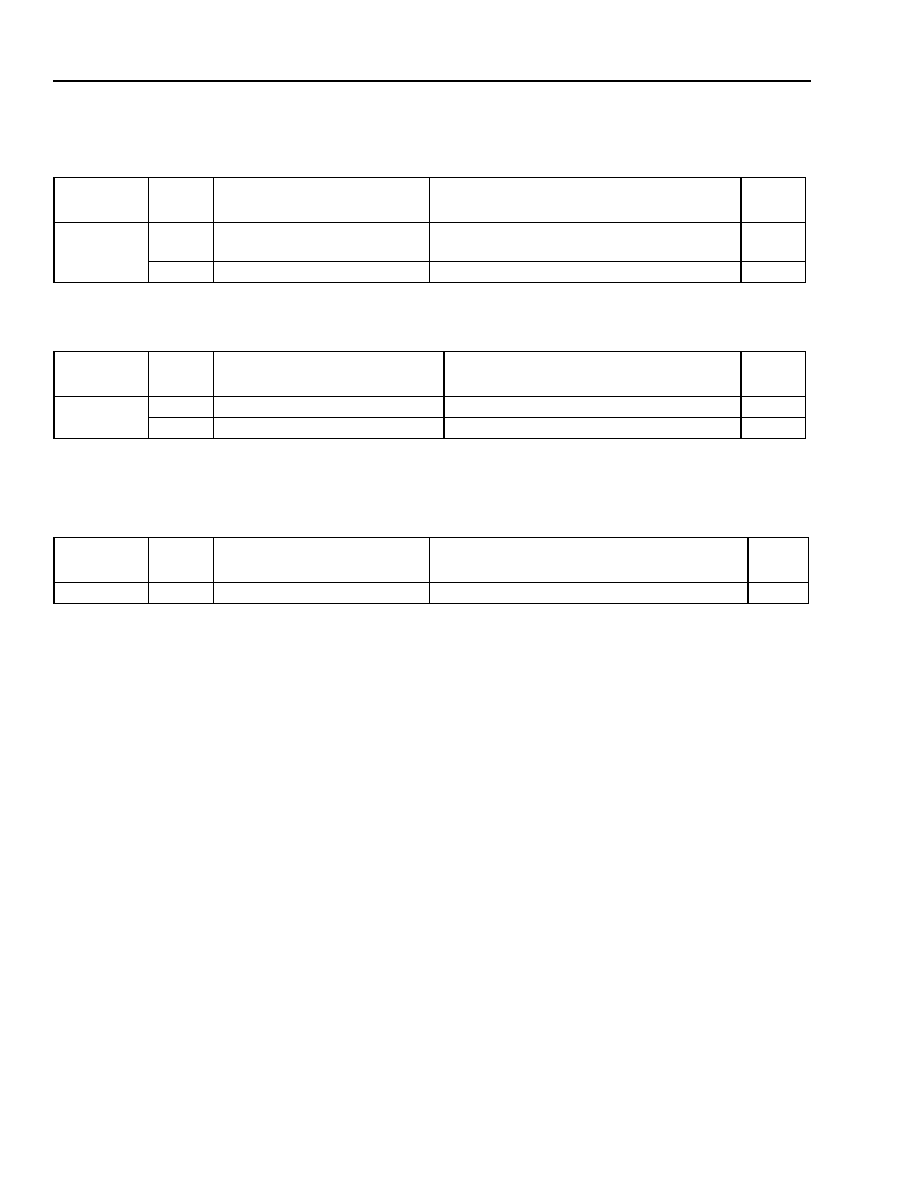

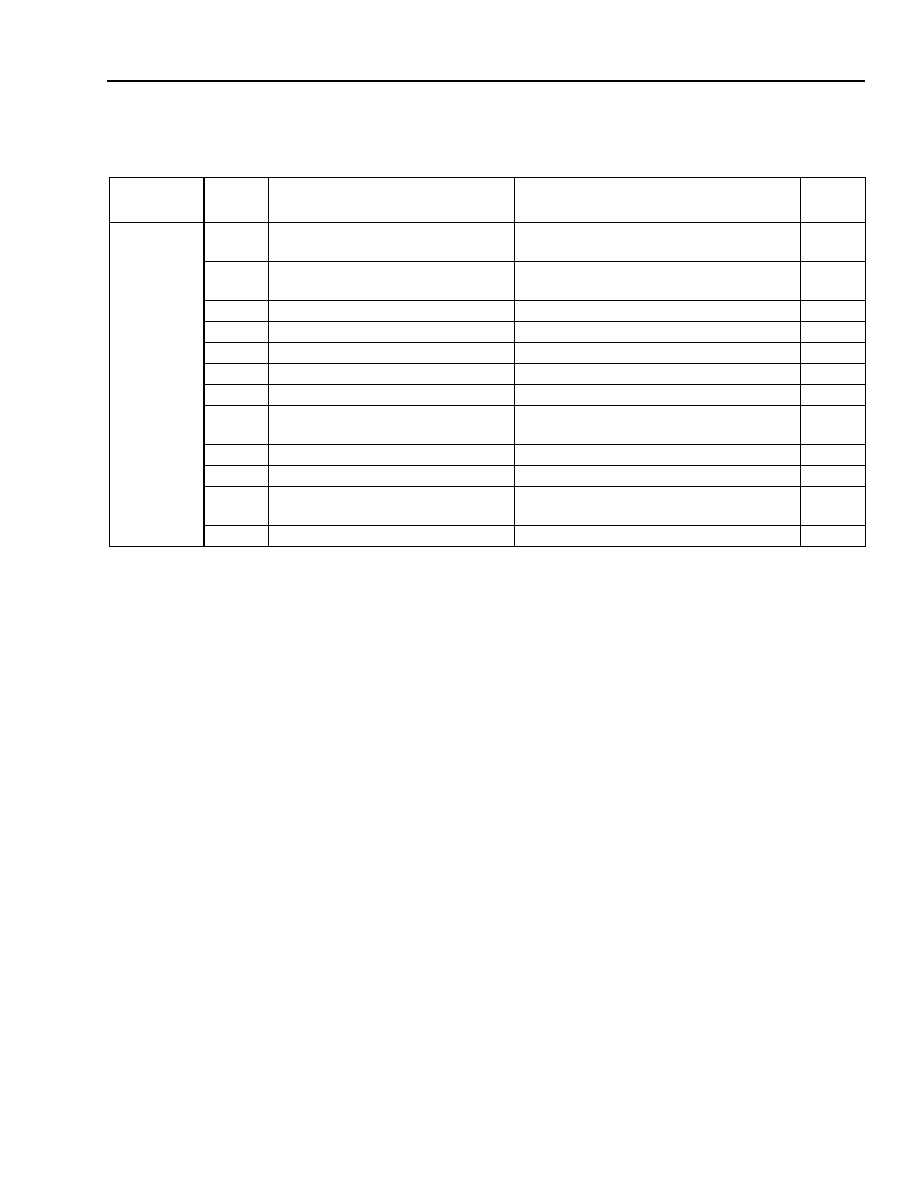

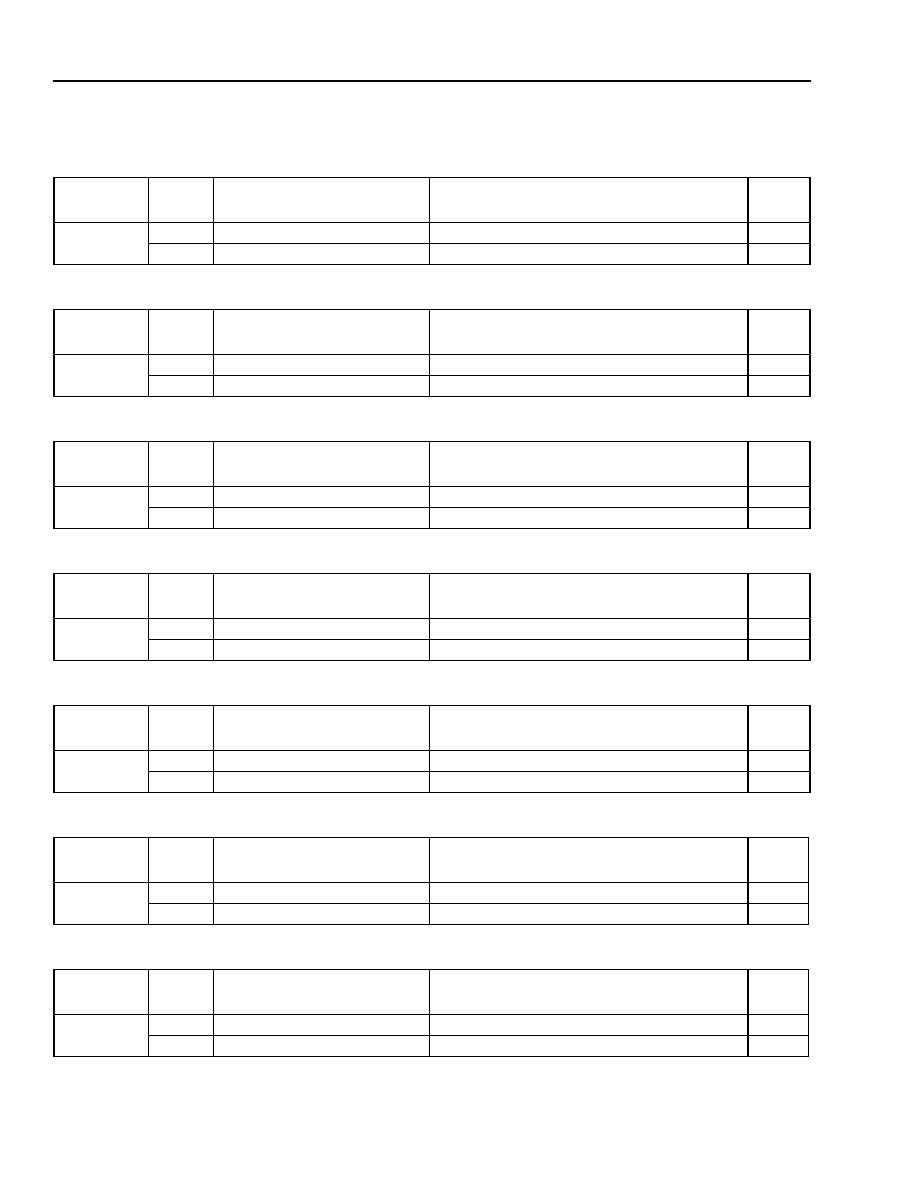

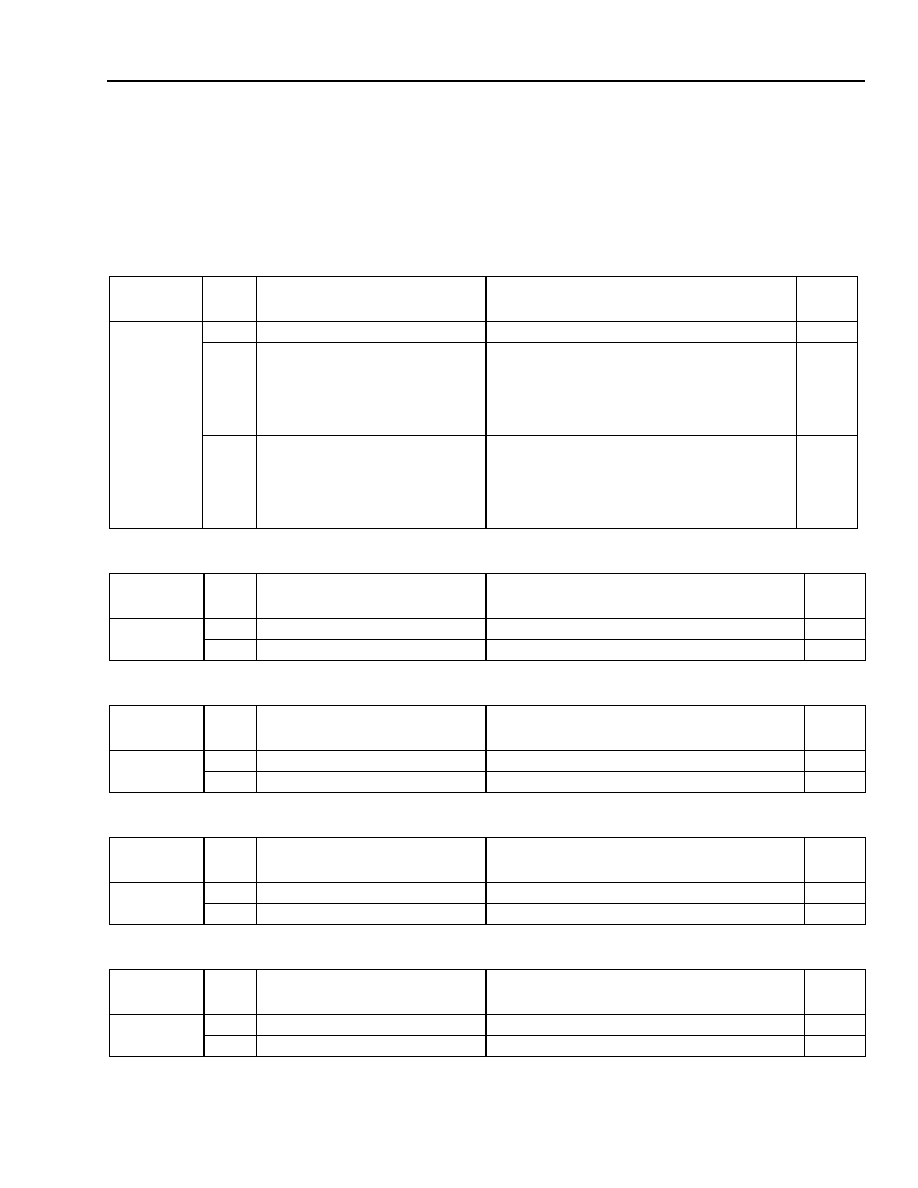

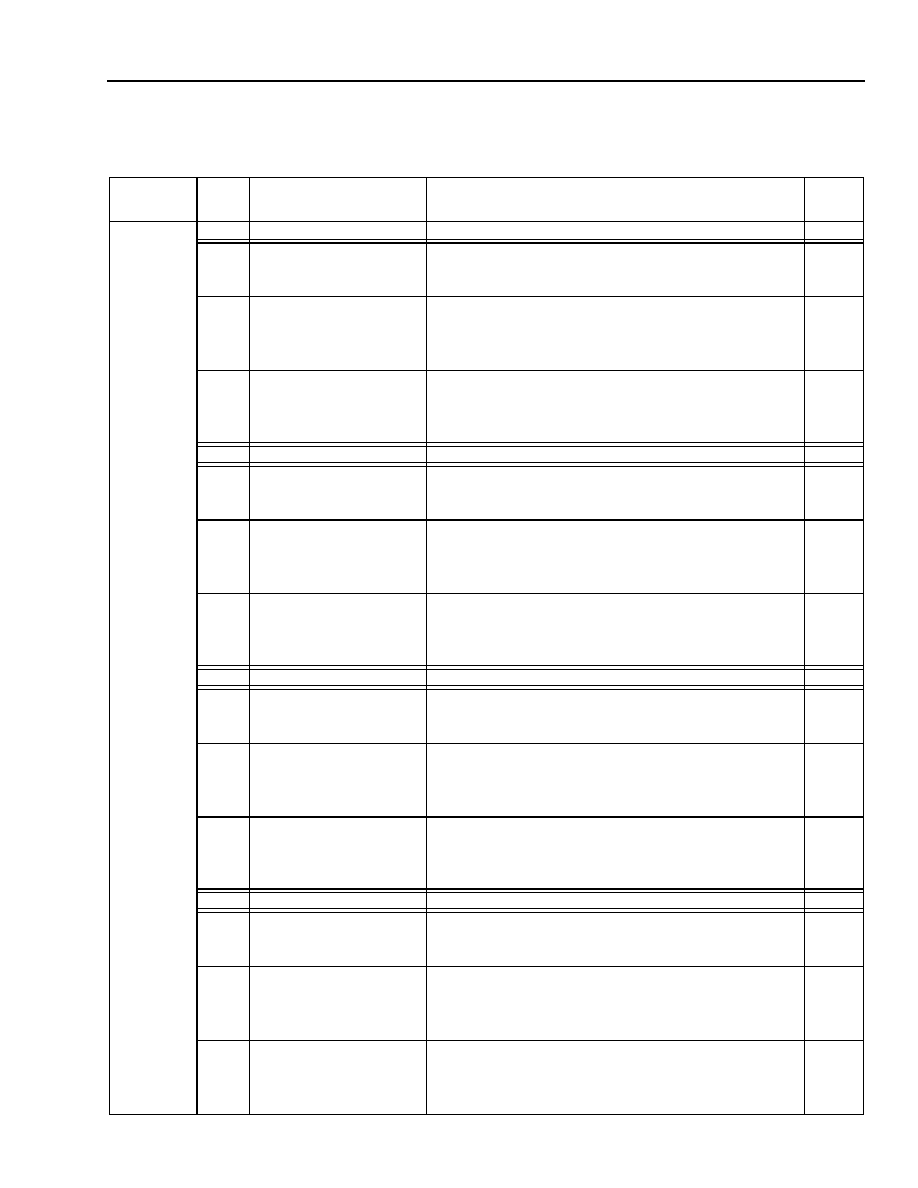

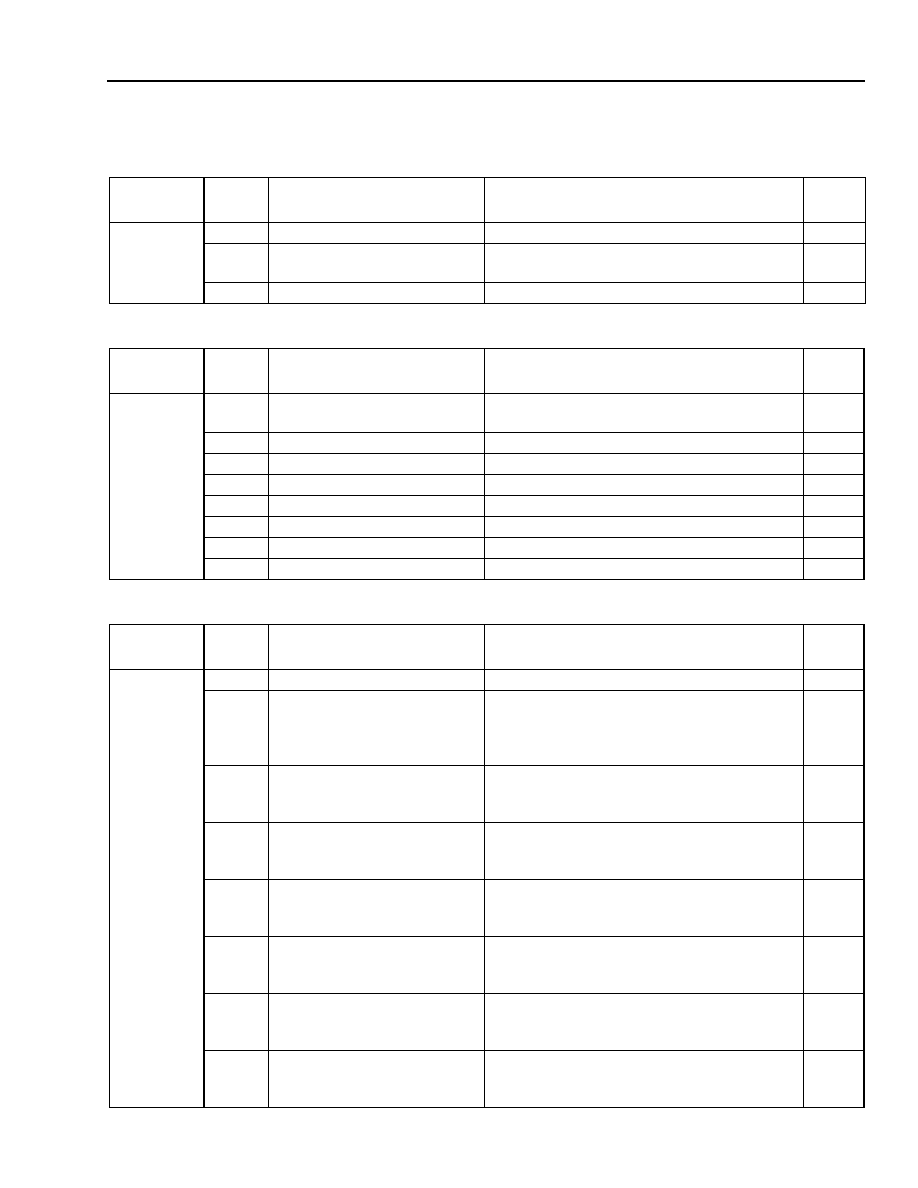

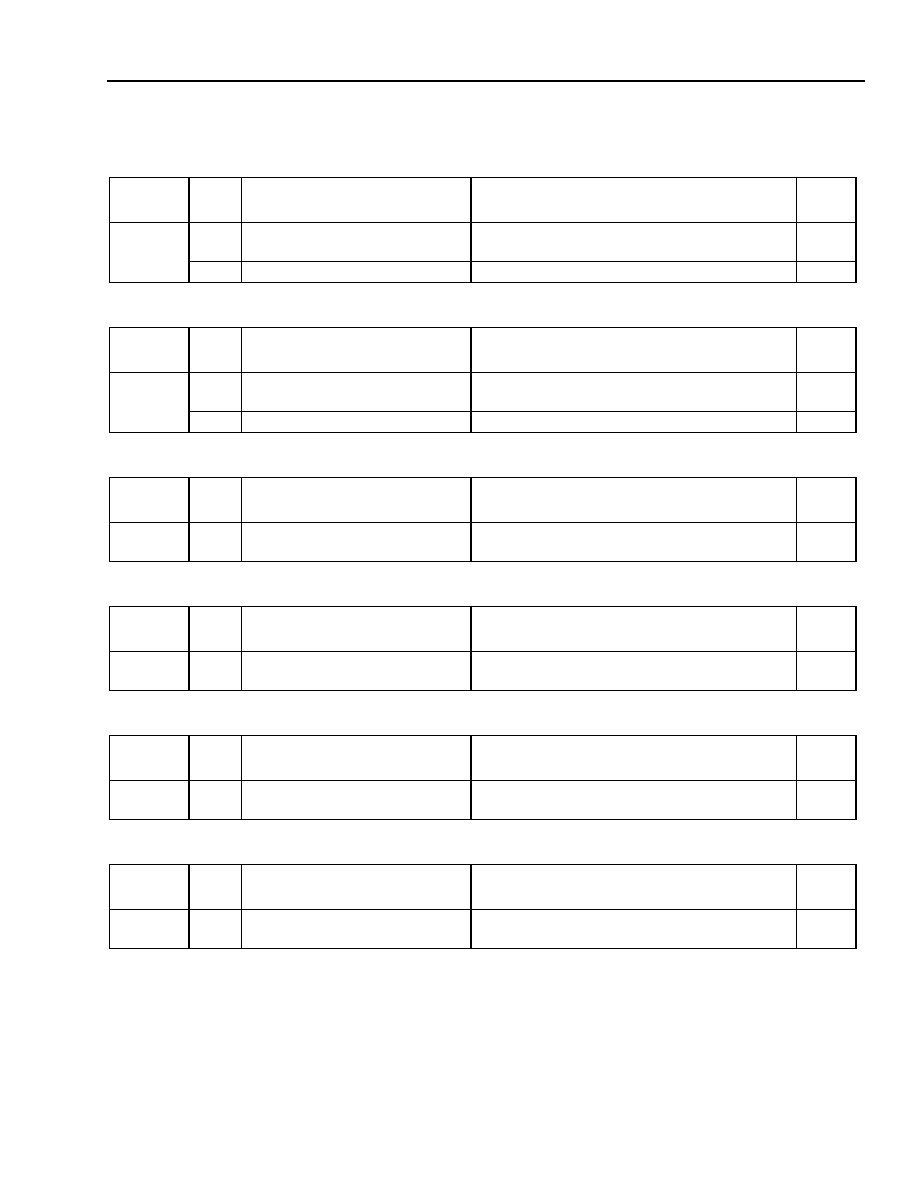

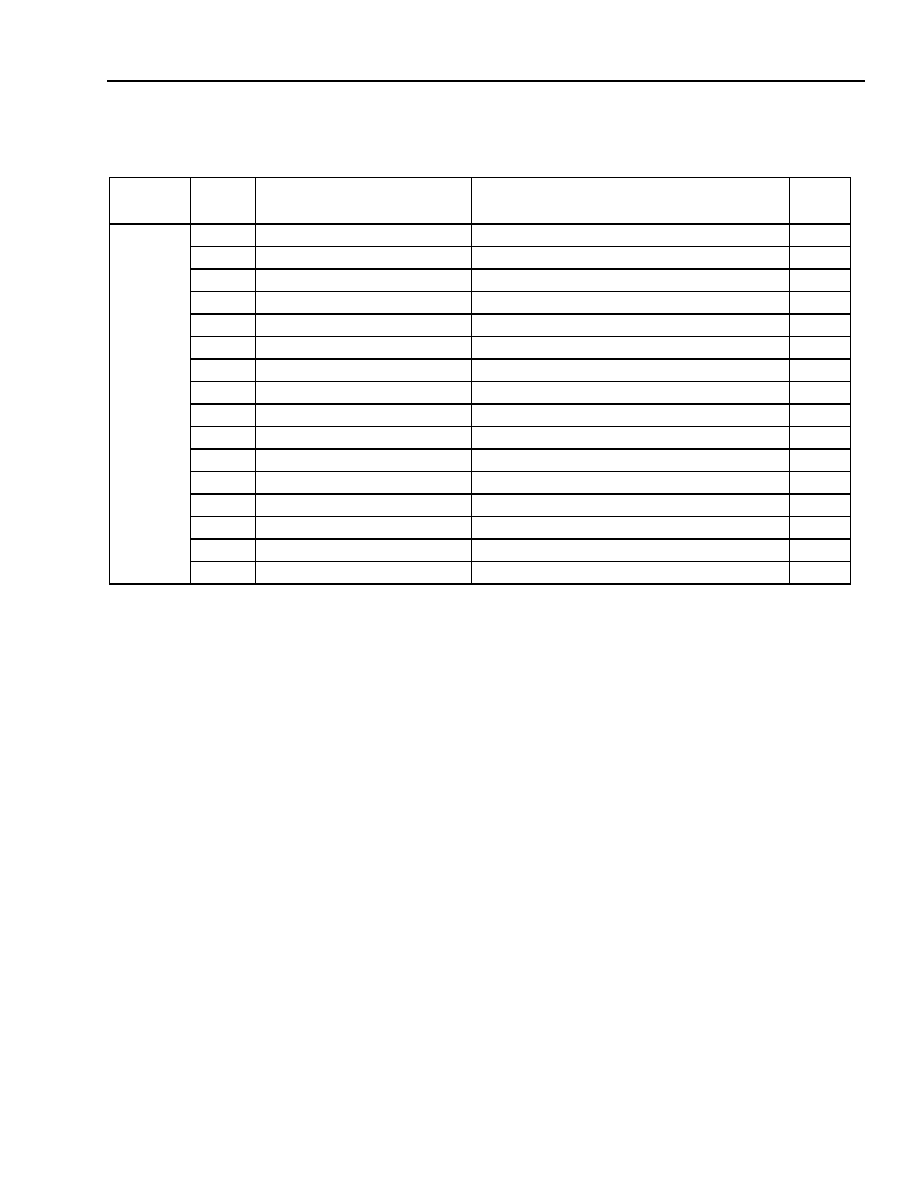

- Table 1. Pin Assignments for 600-Pin LBGA by Pin Number Order

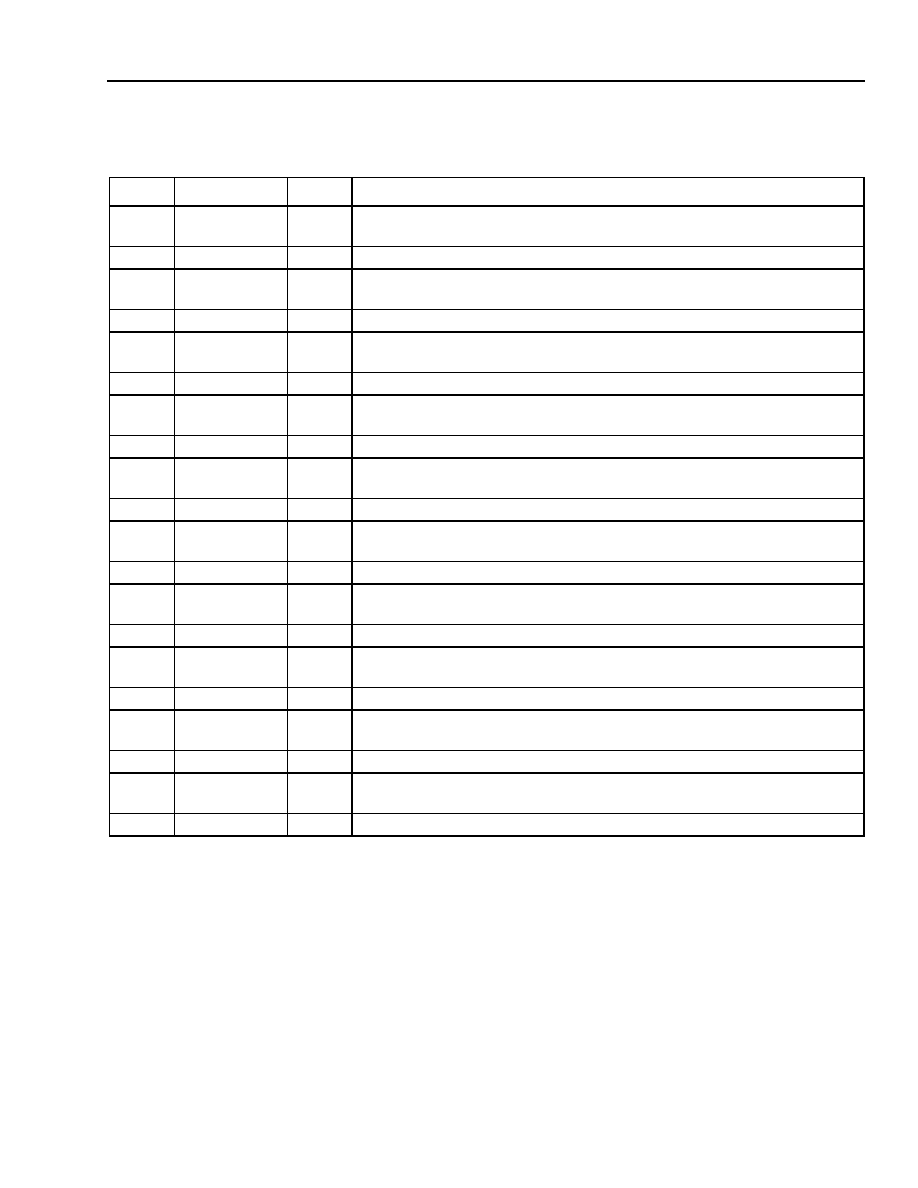

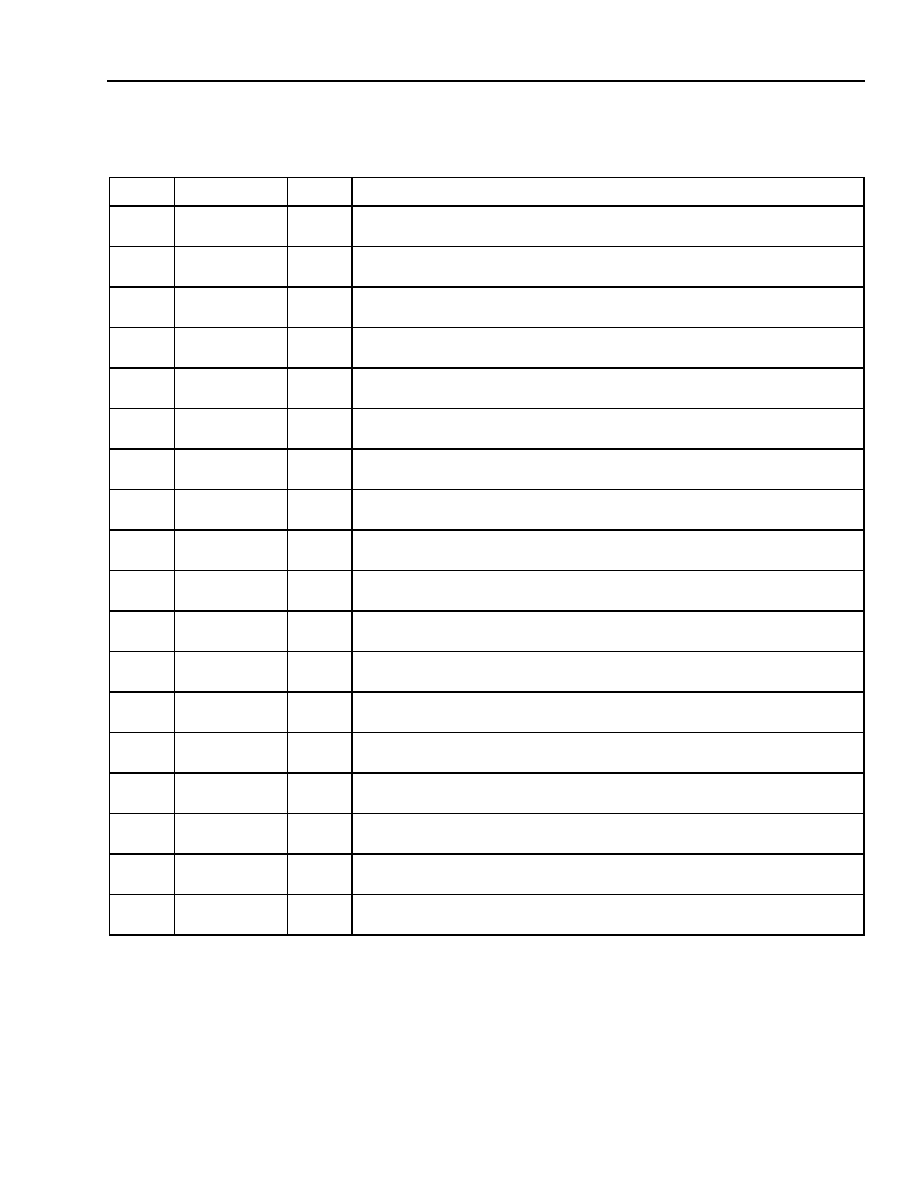

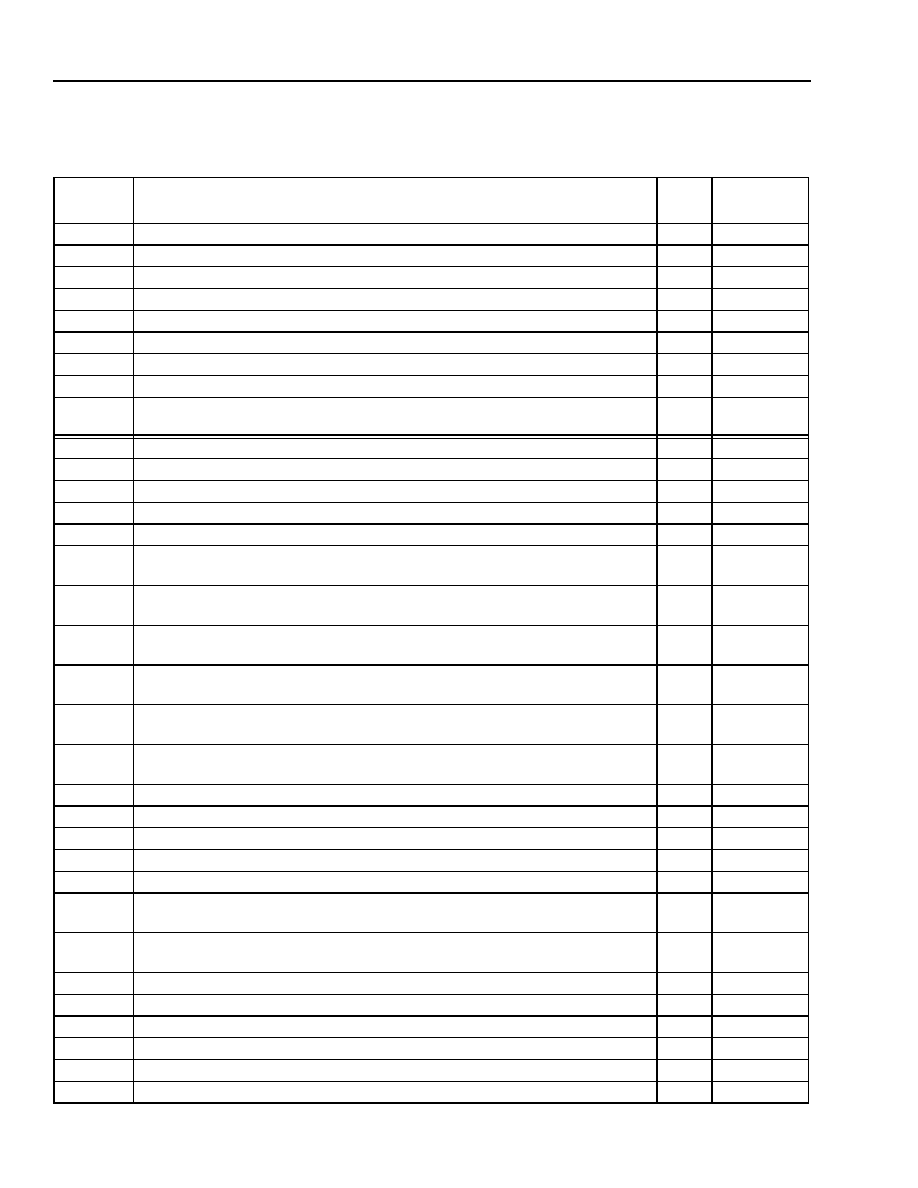

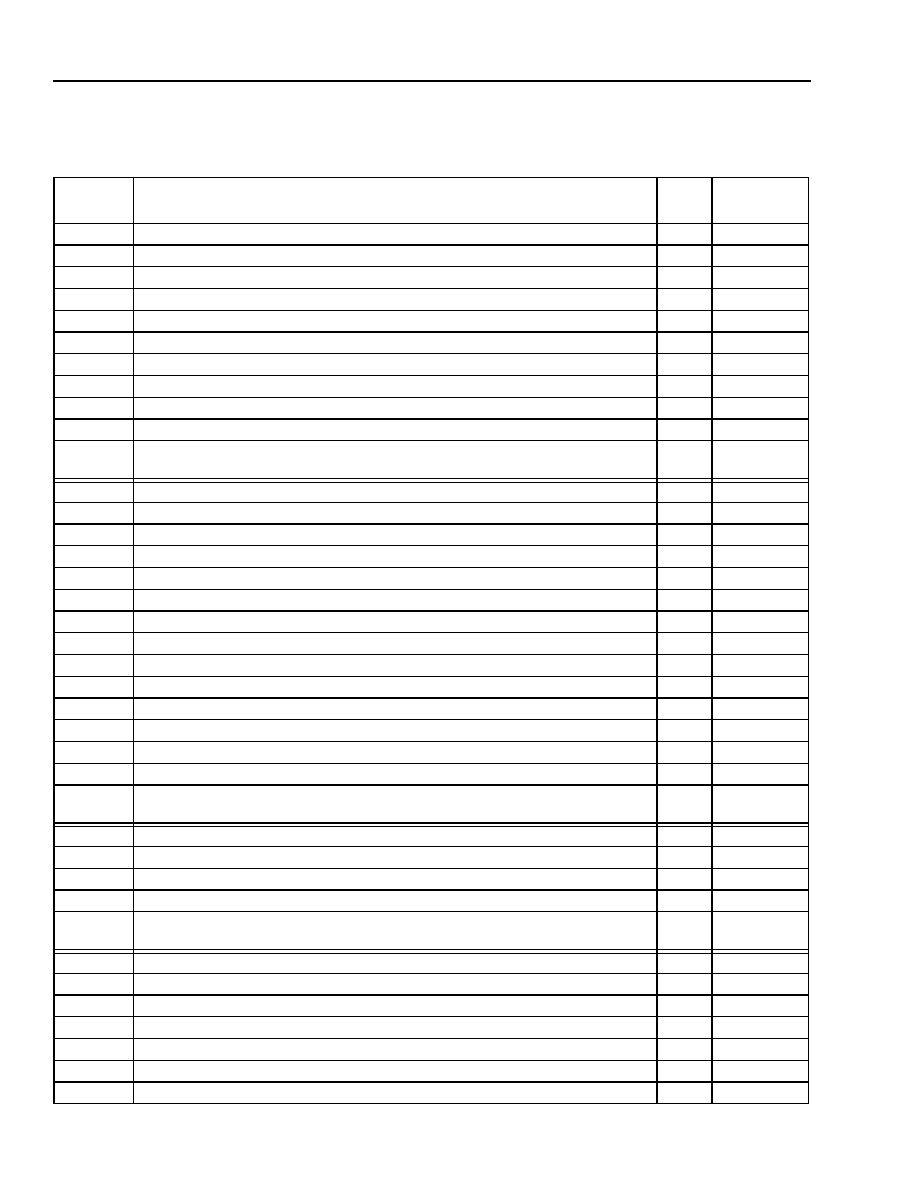

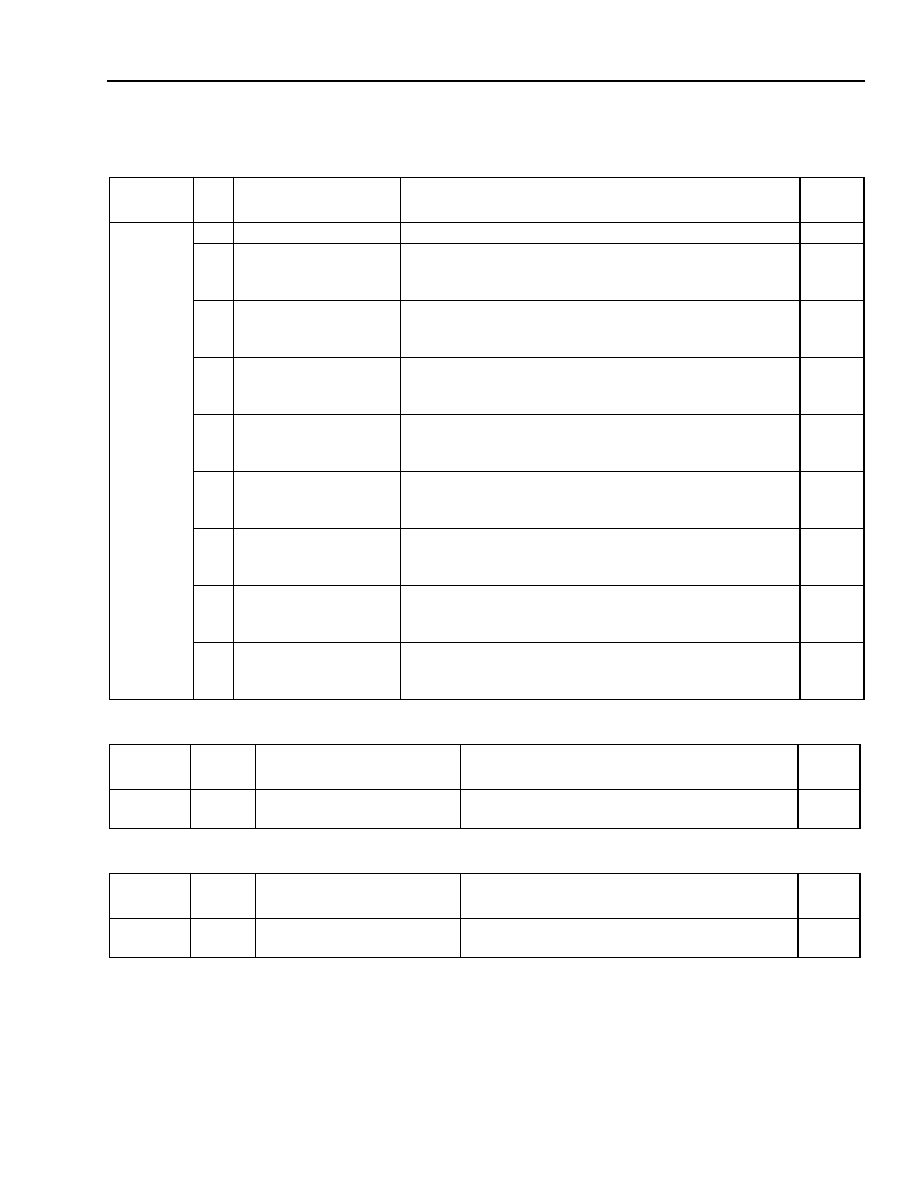

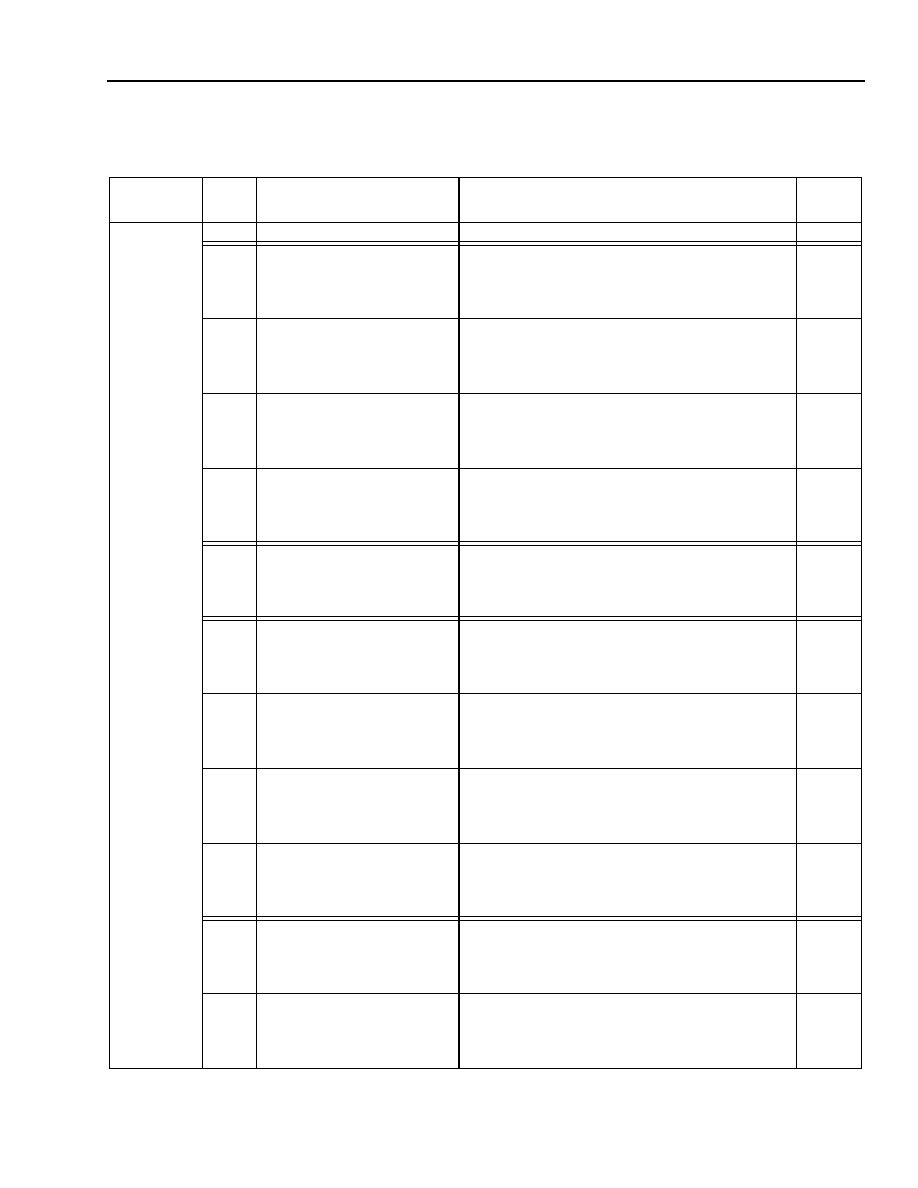

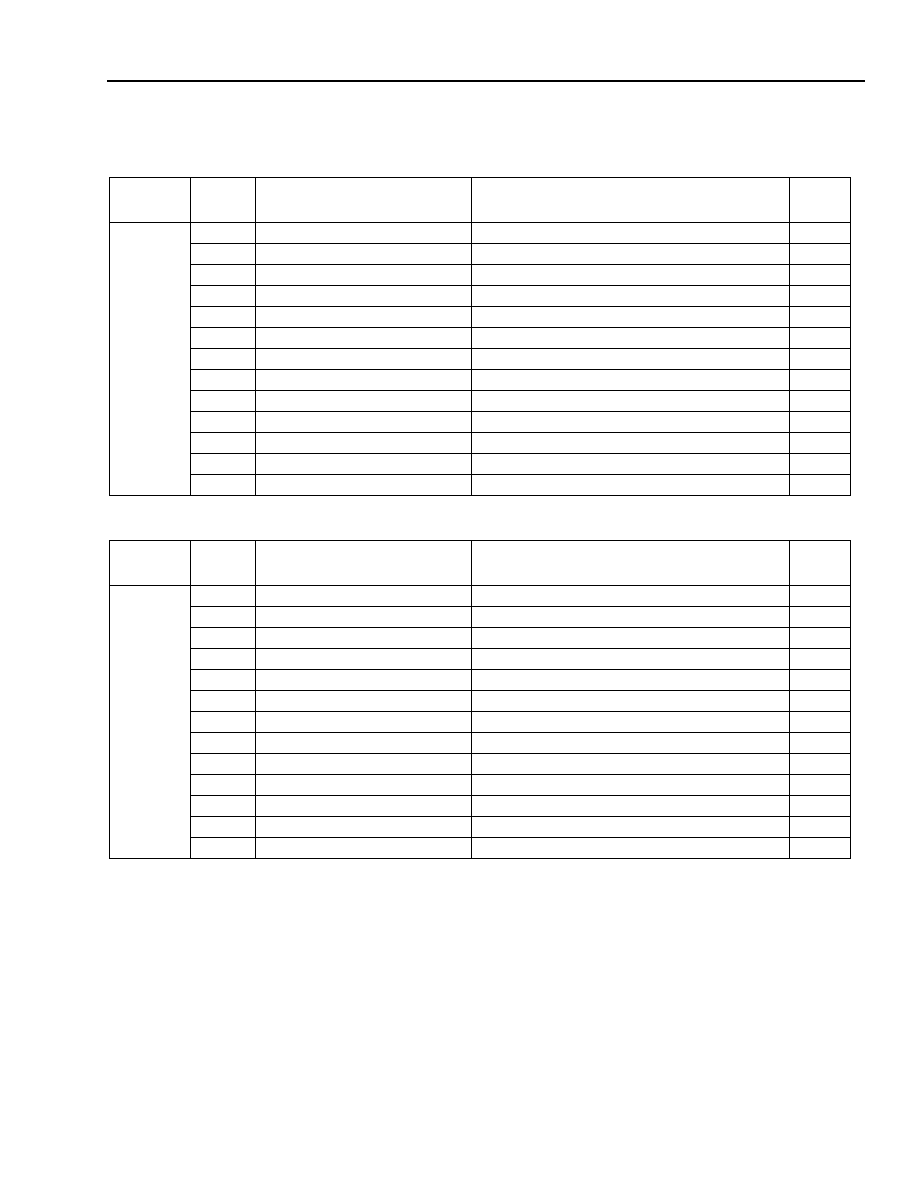

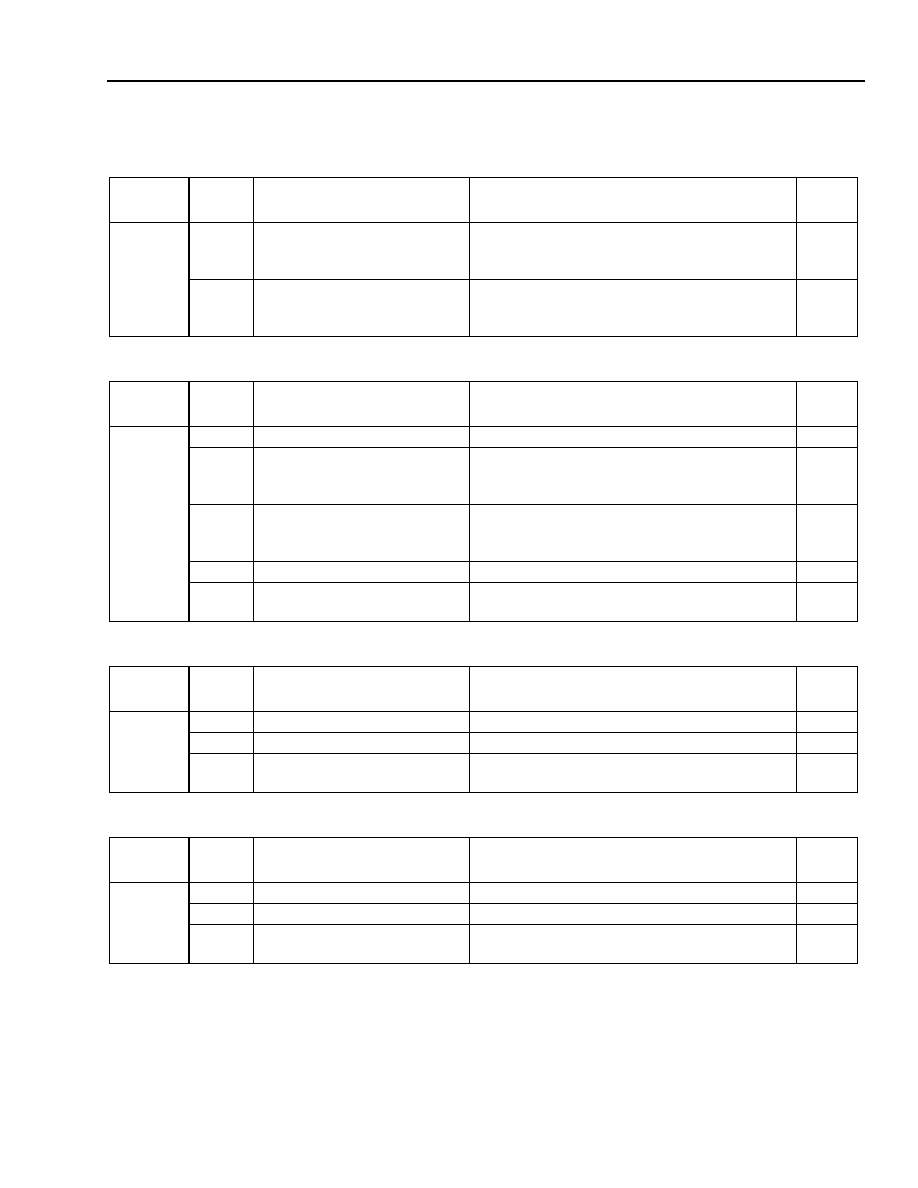

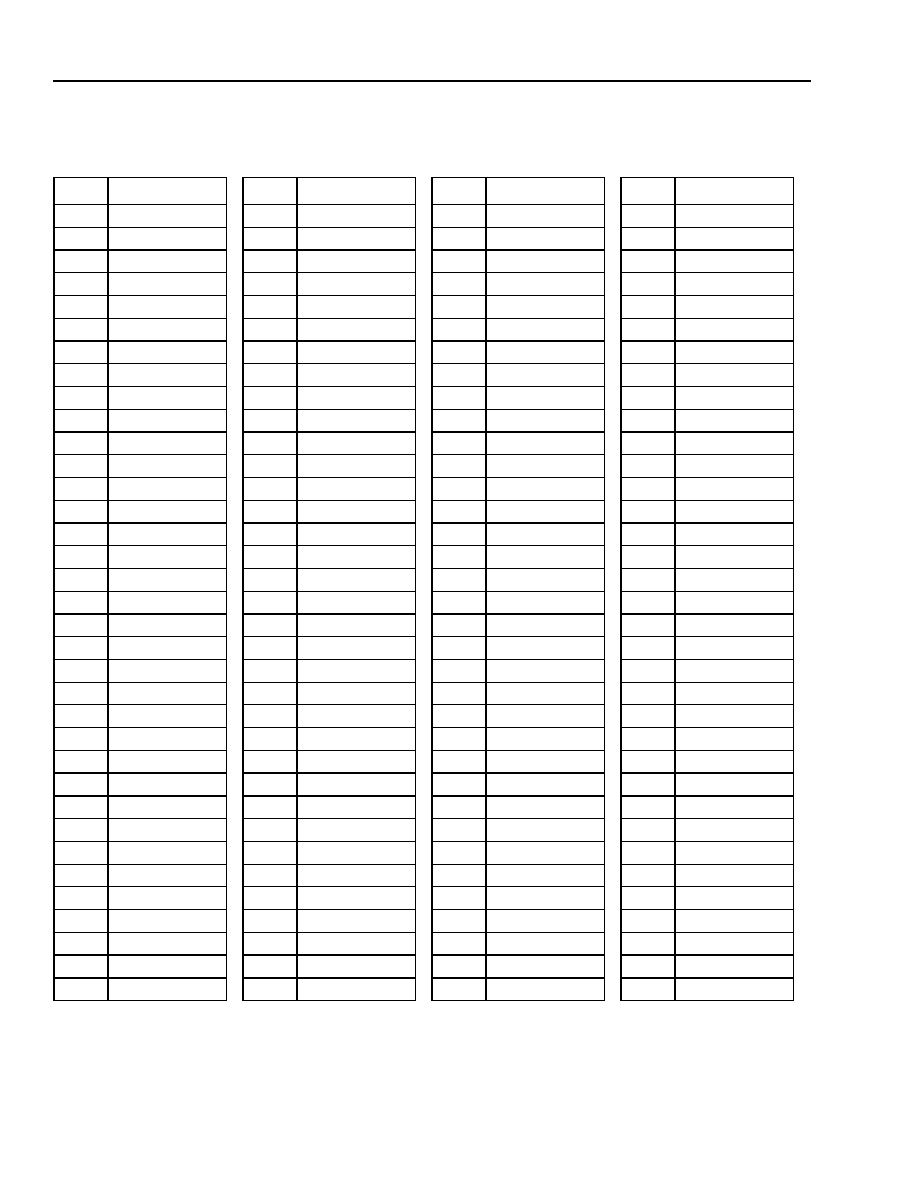

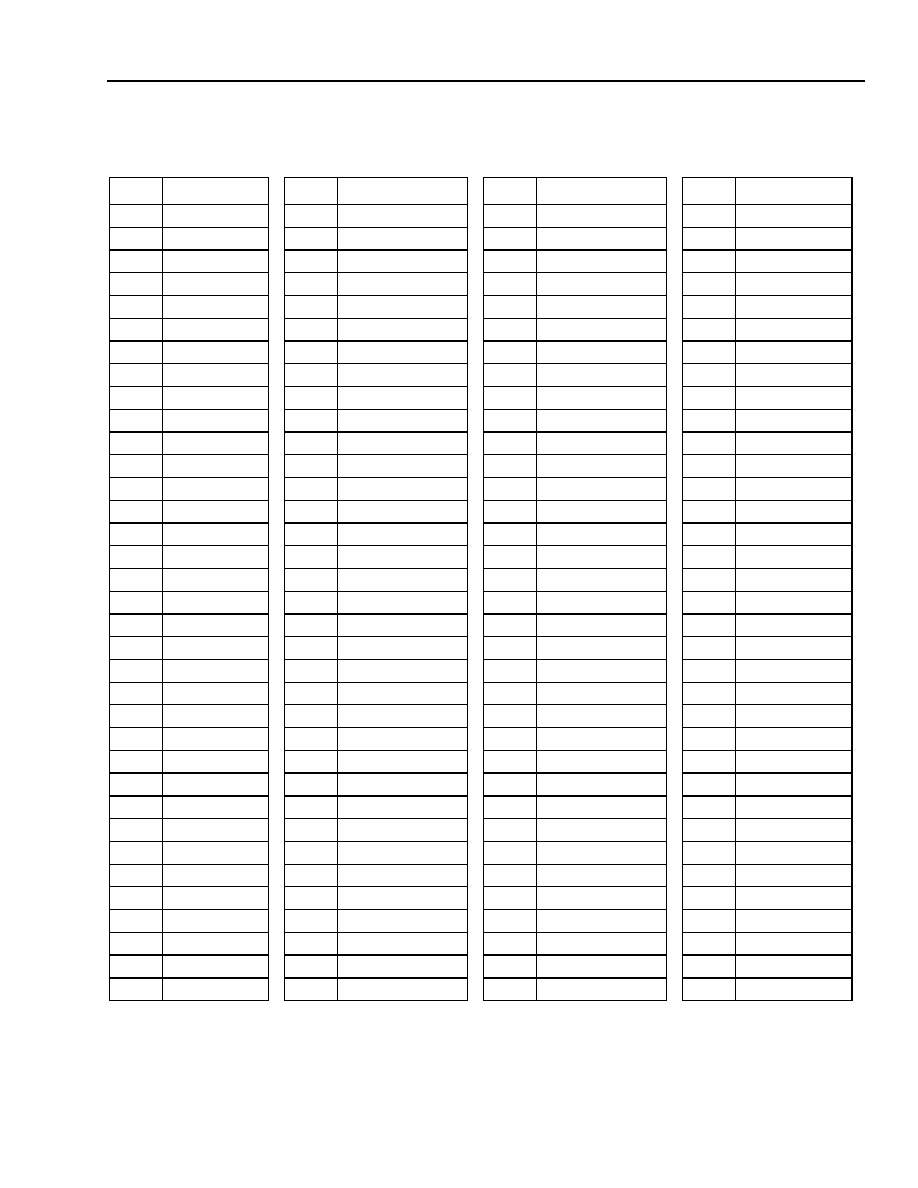

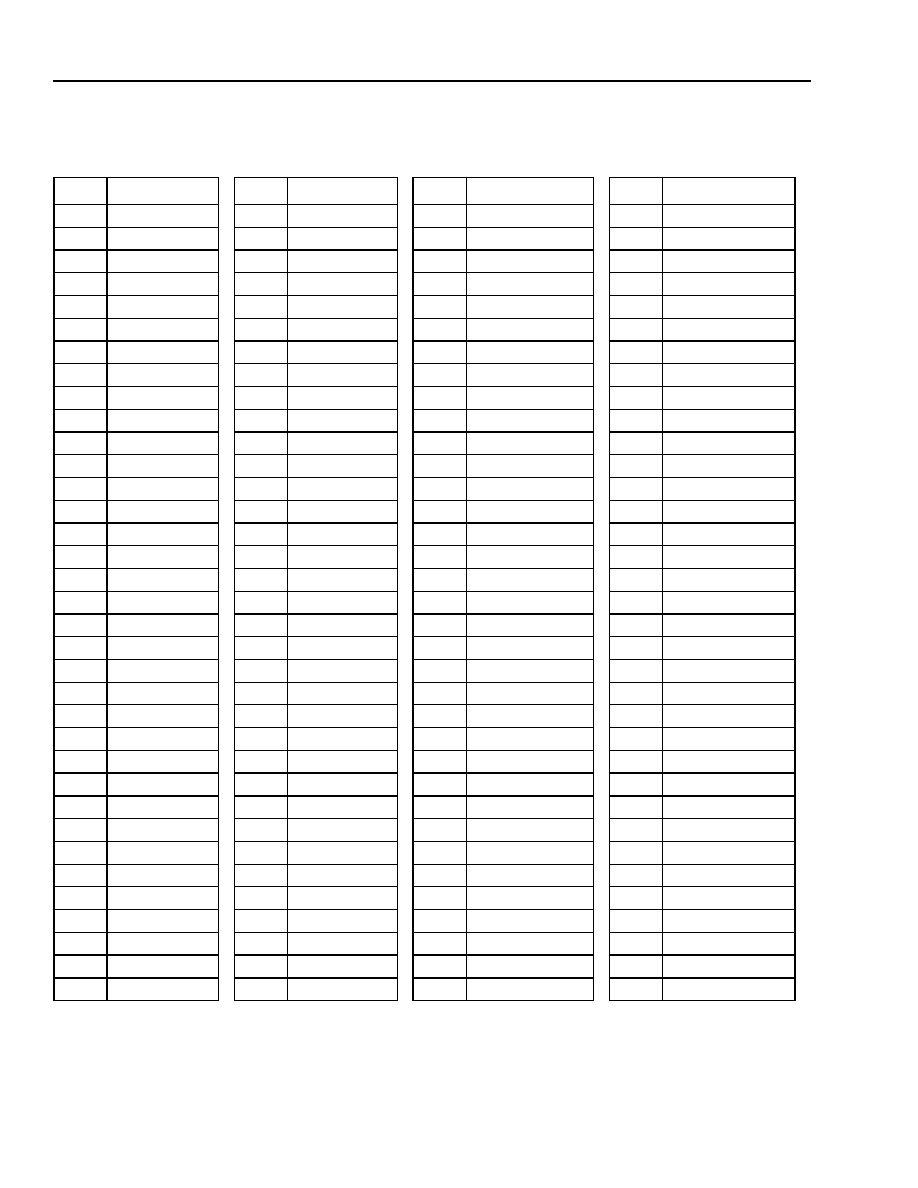

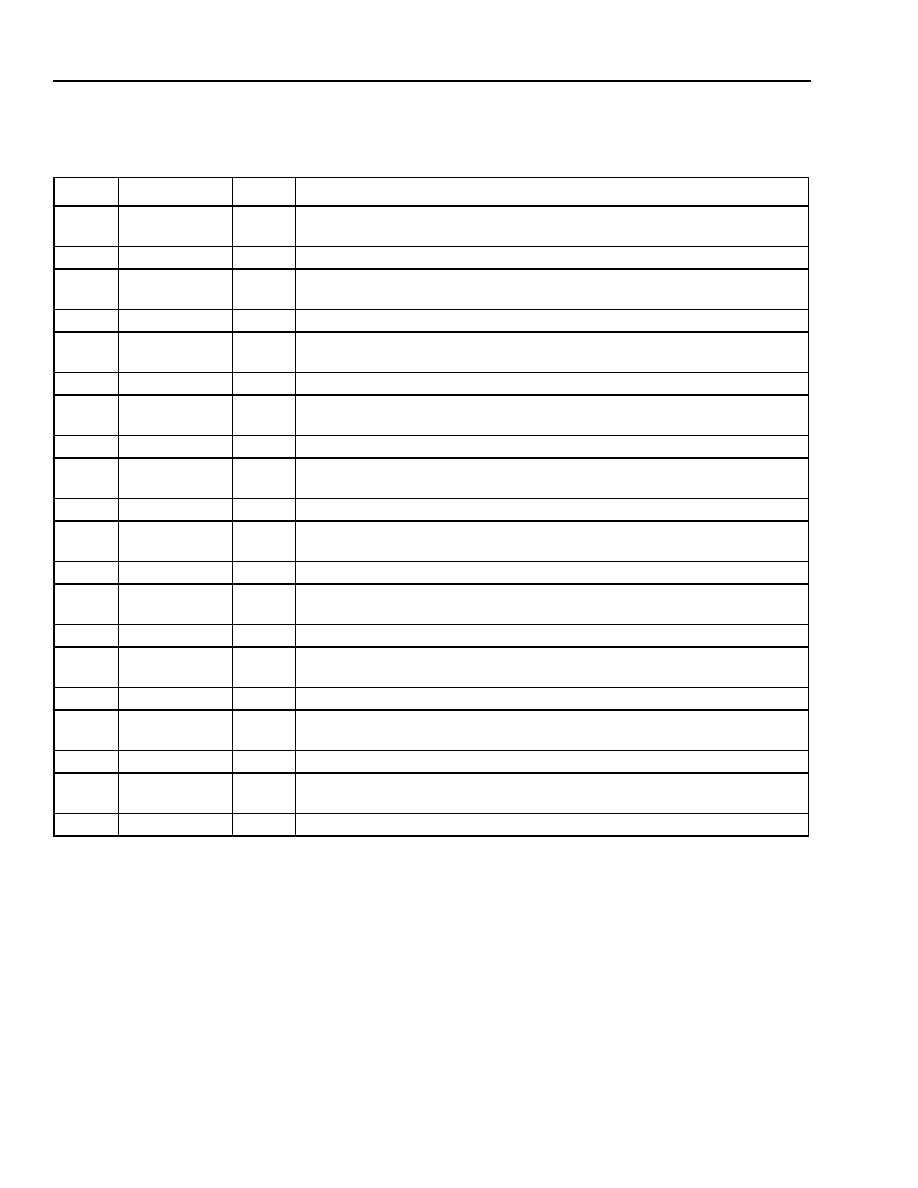

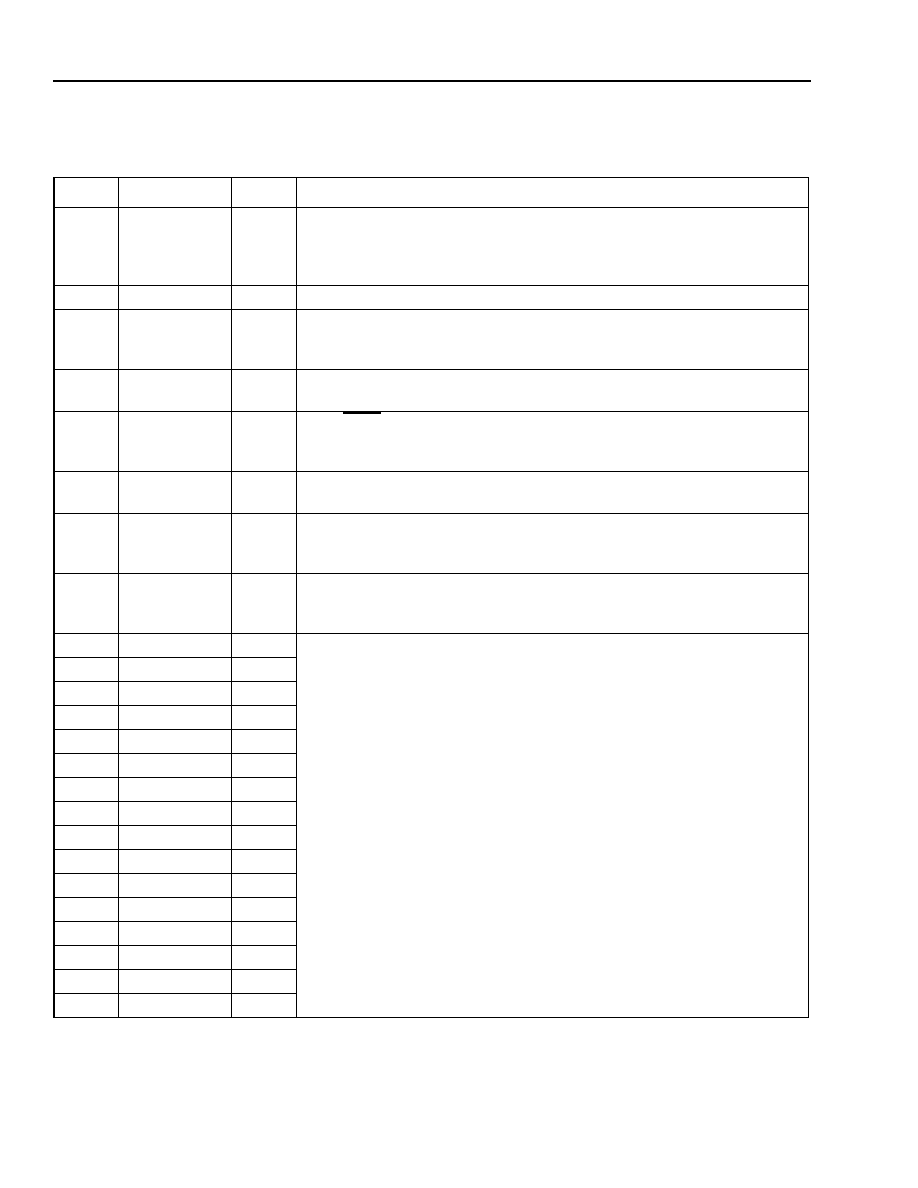

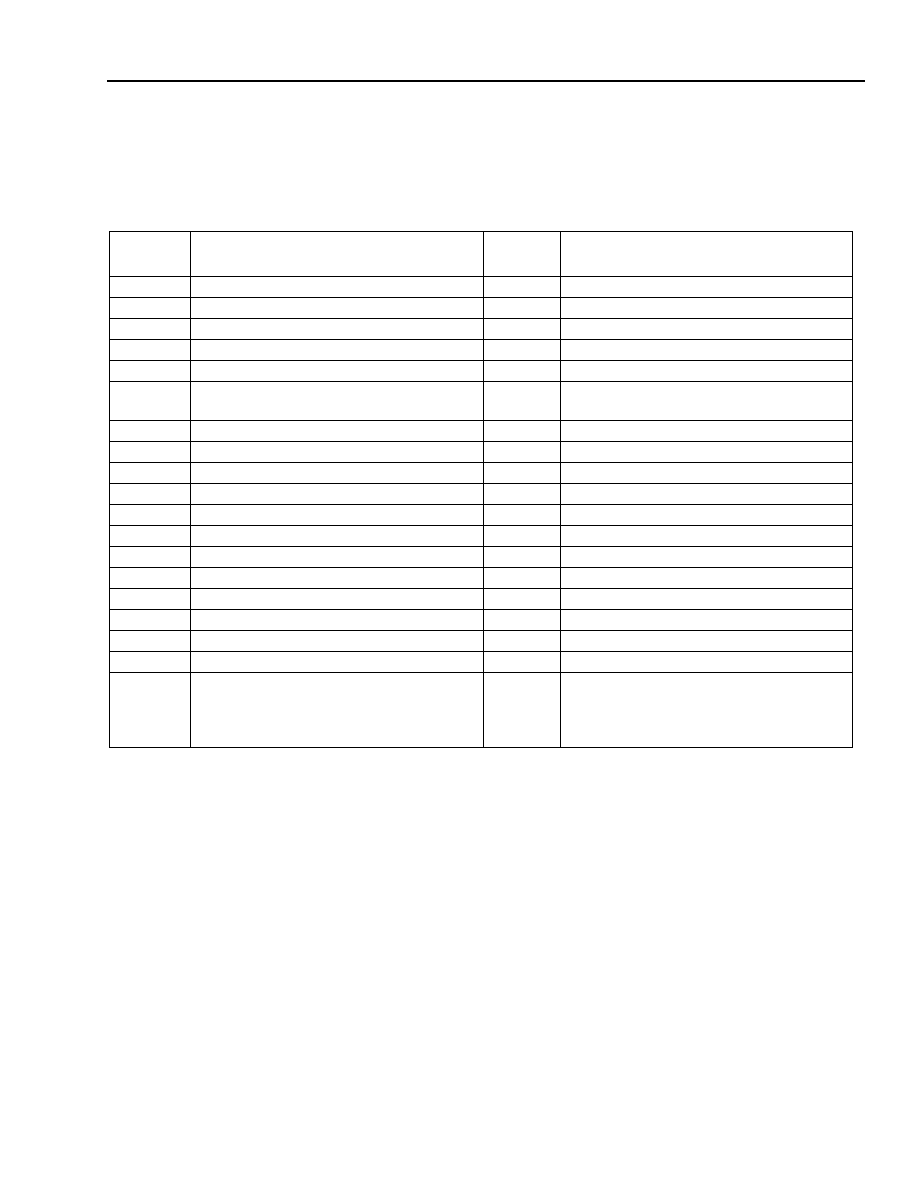

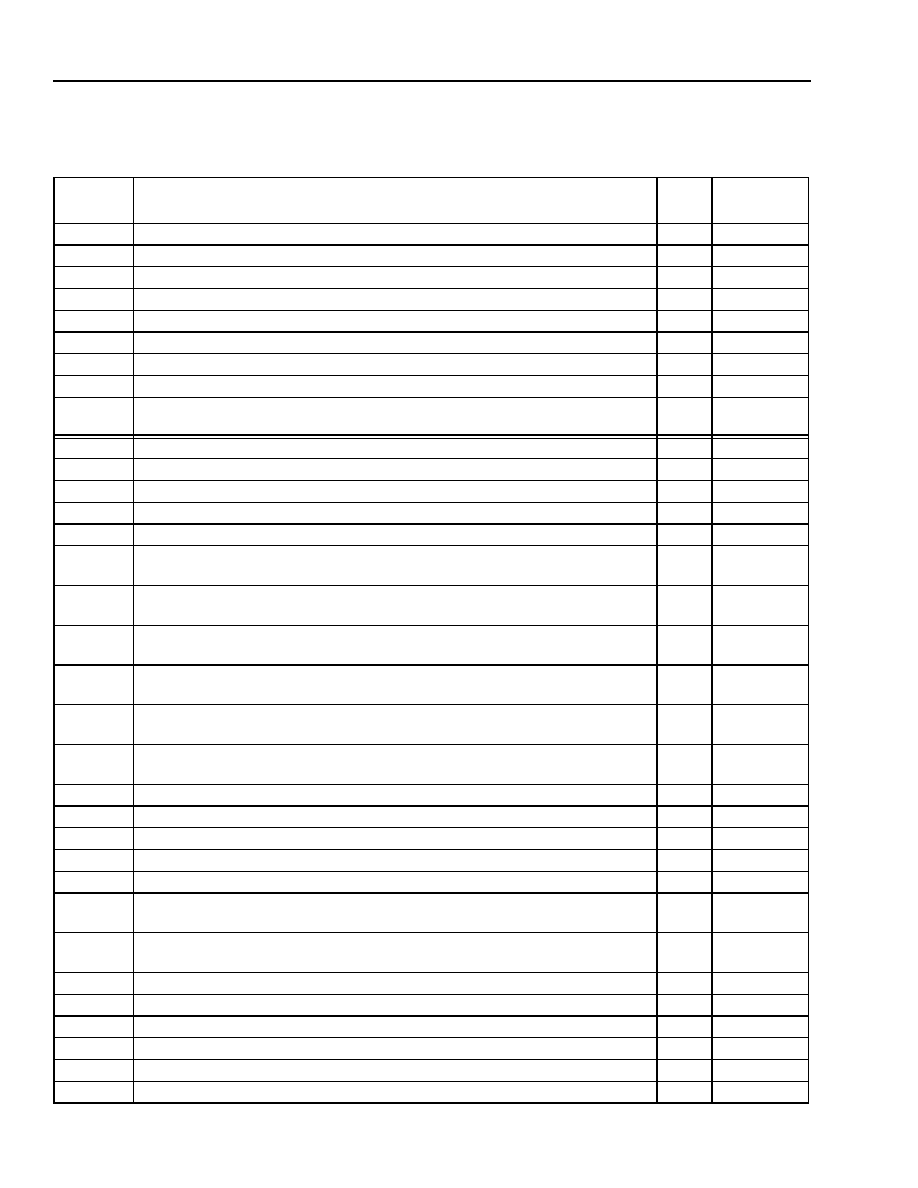

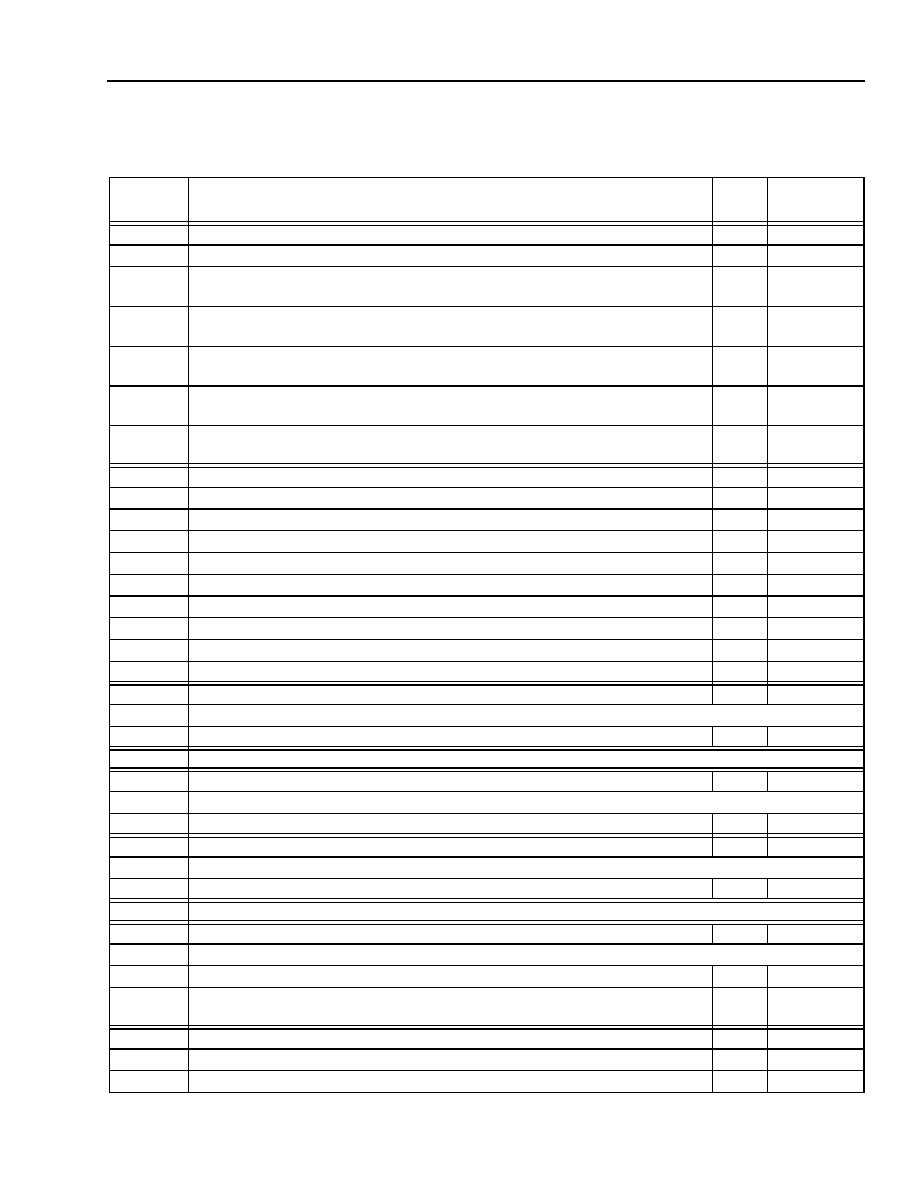

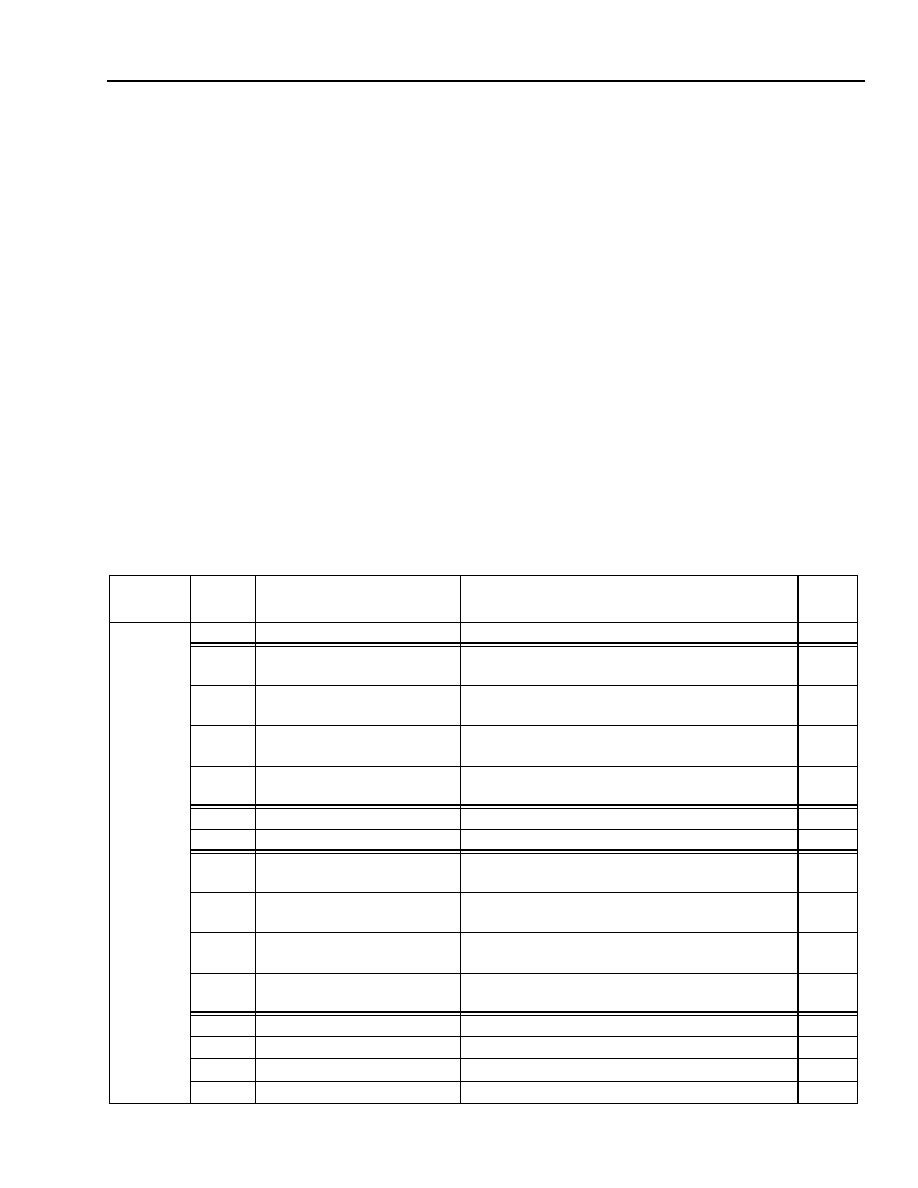

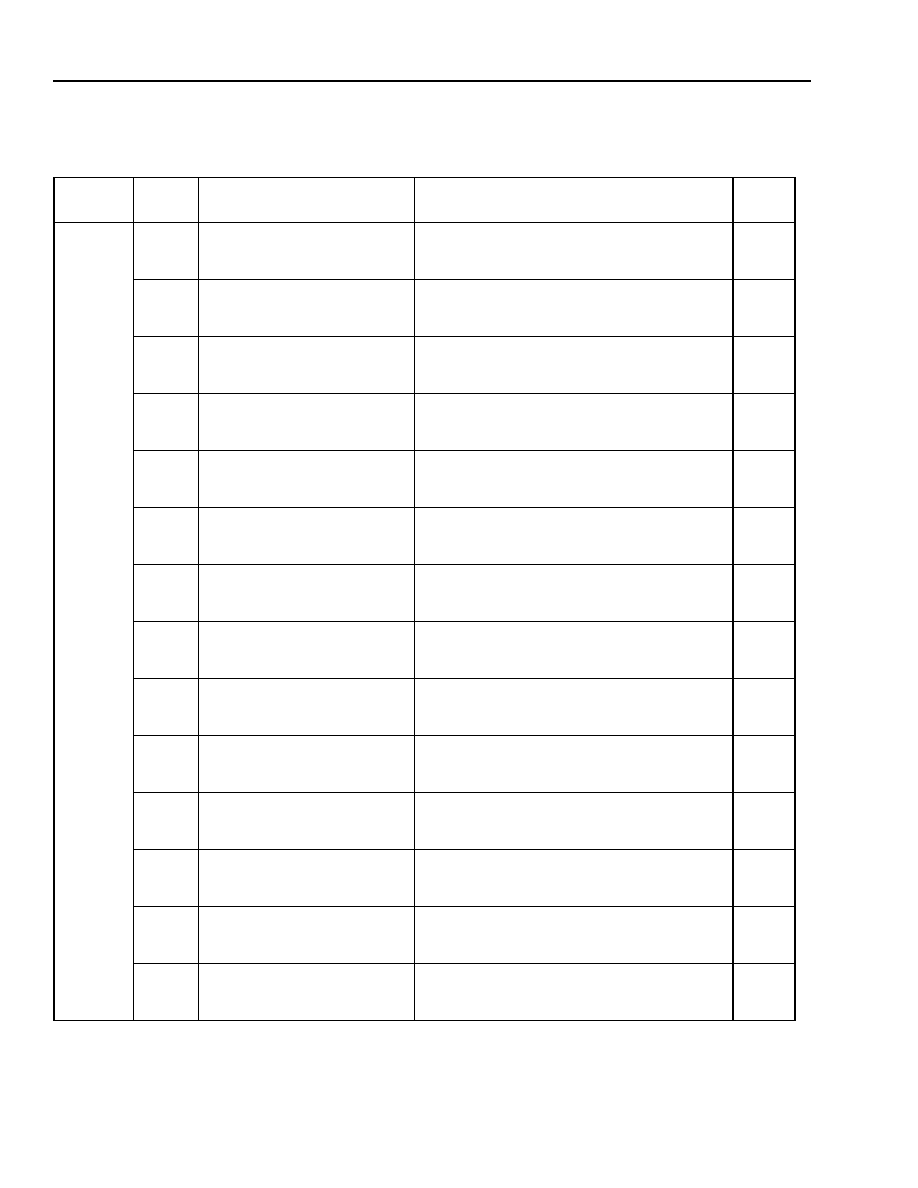

- Table 2. Pin Assignments for 600-Pin LBGA by Signal Name Order

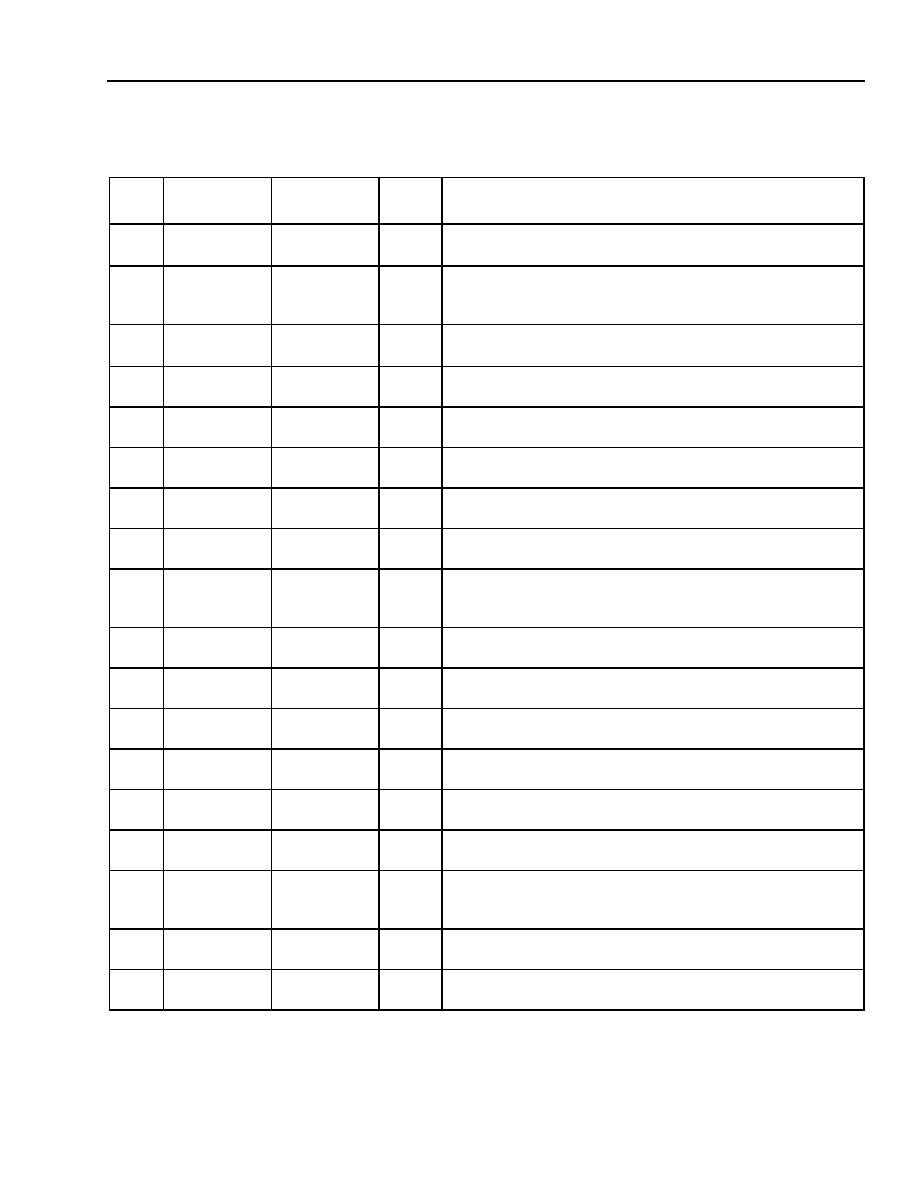

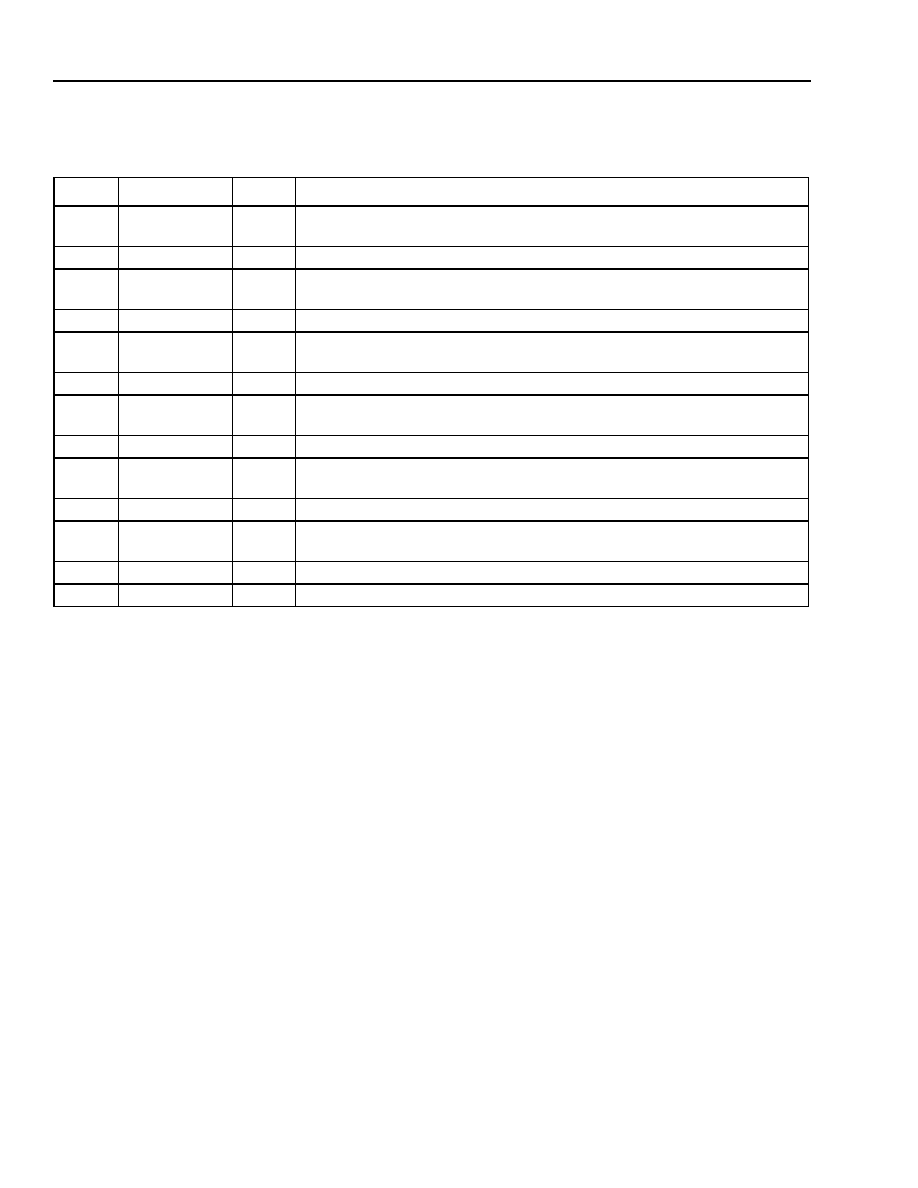

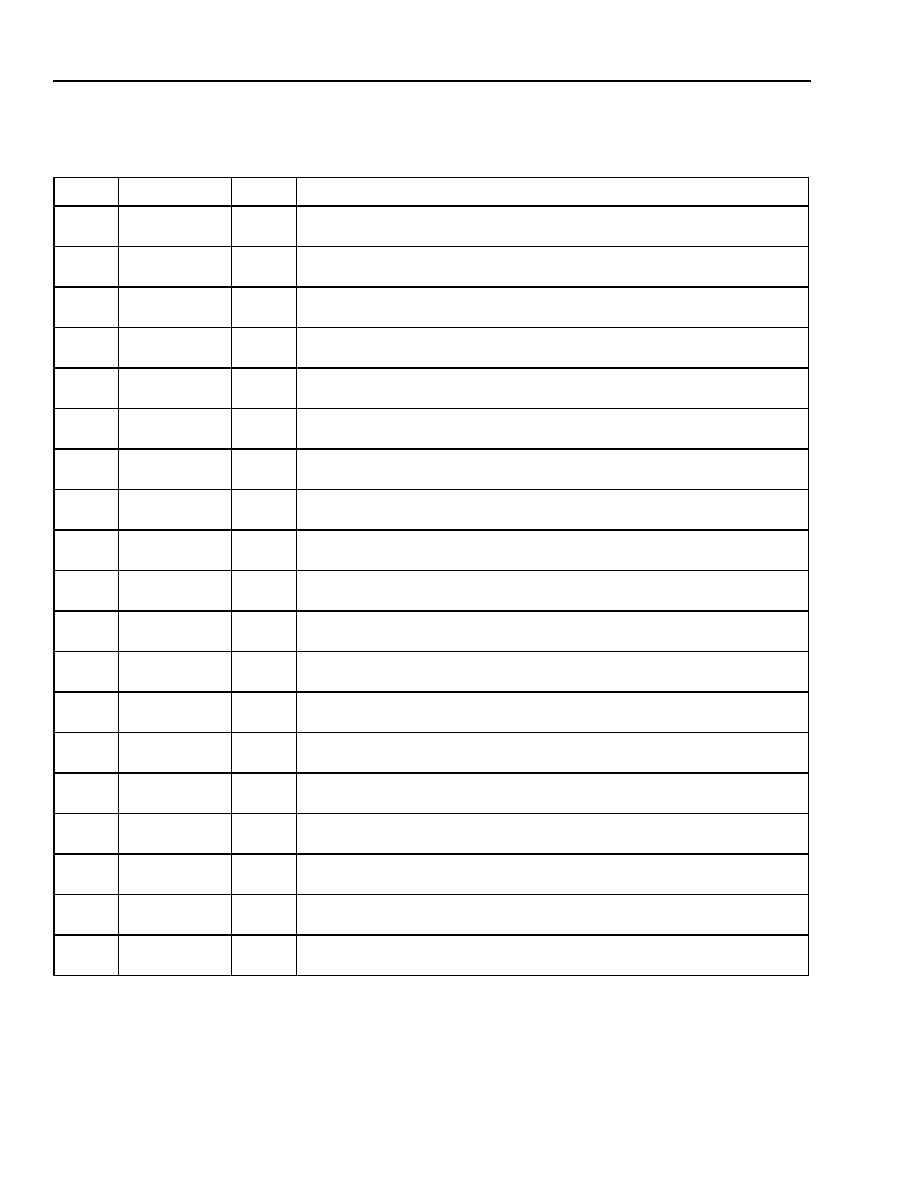

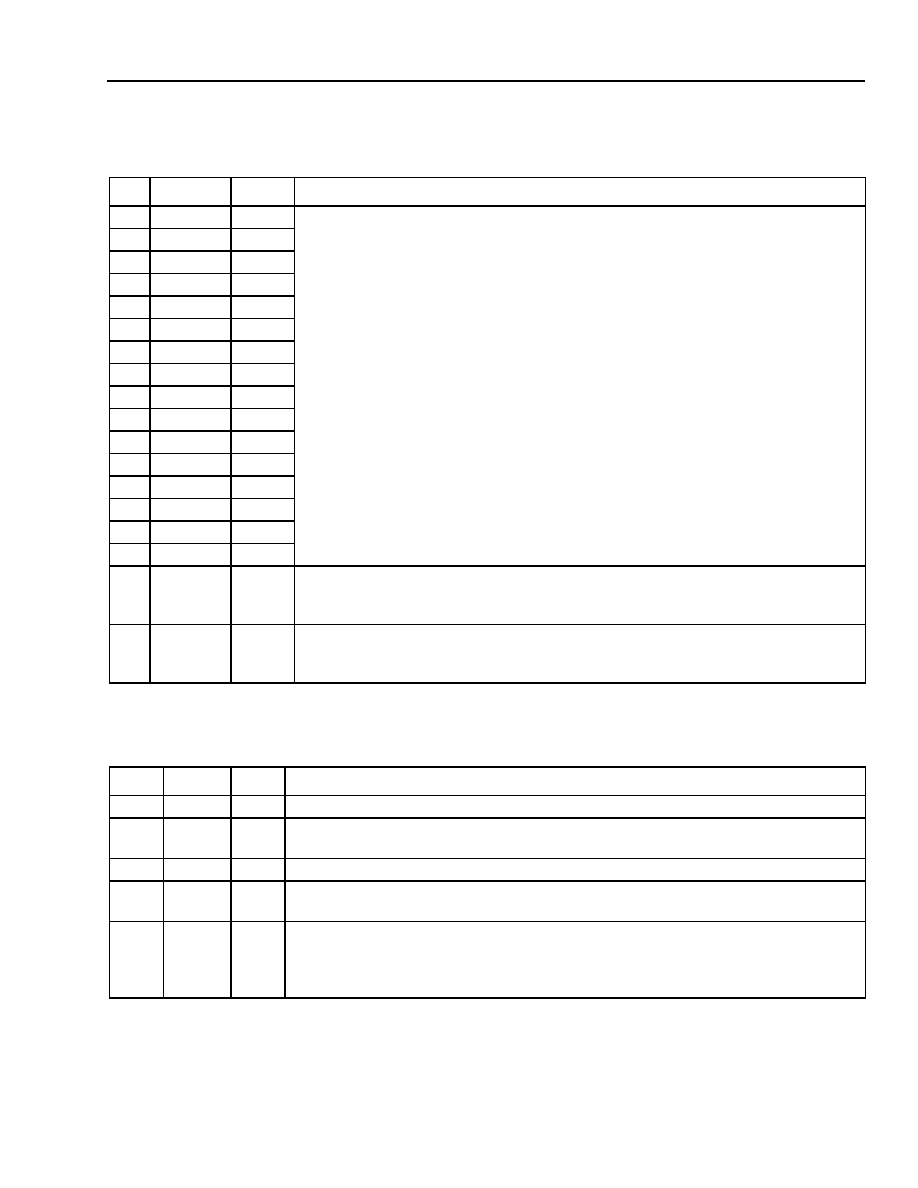

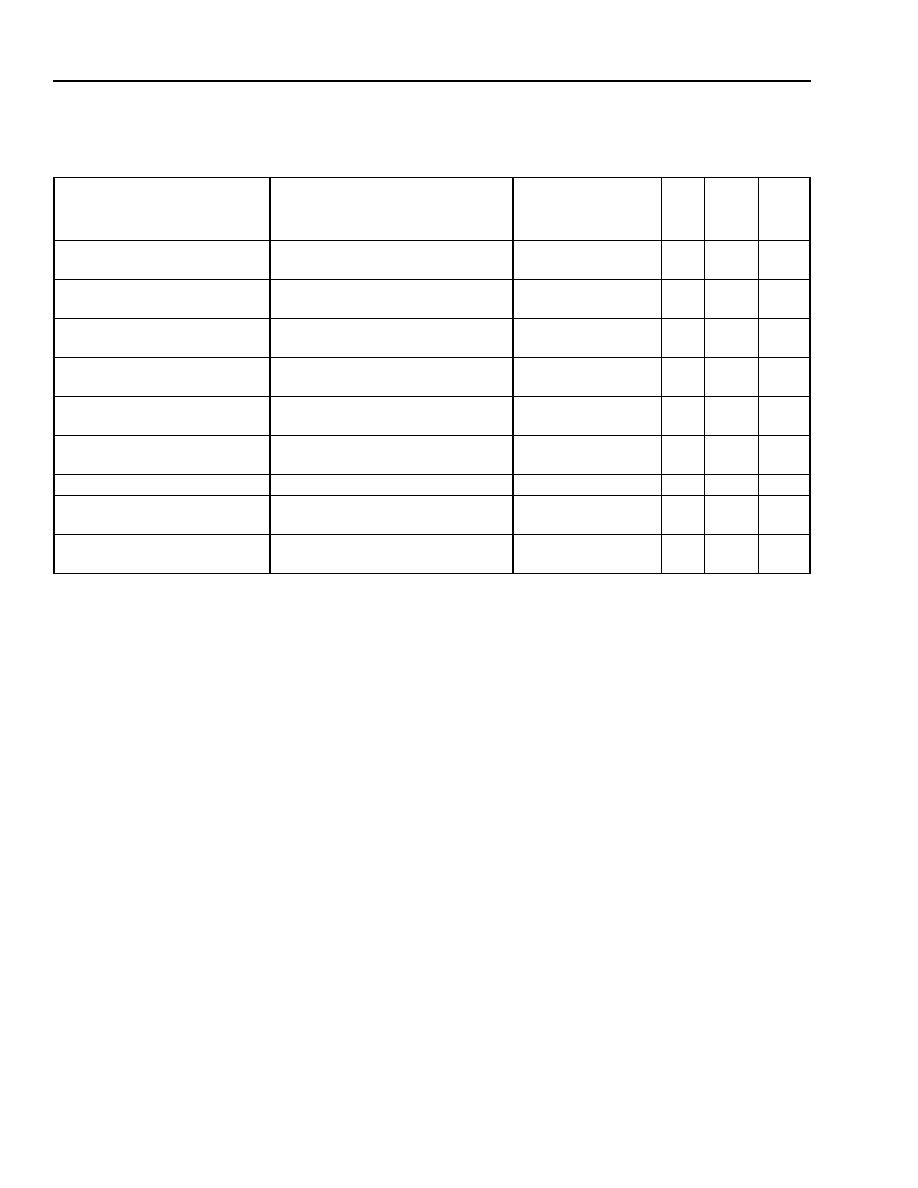

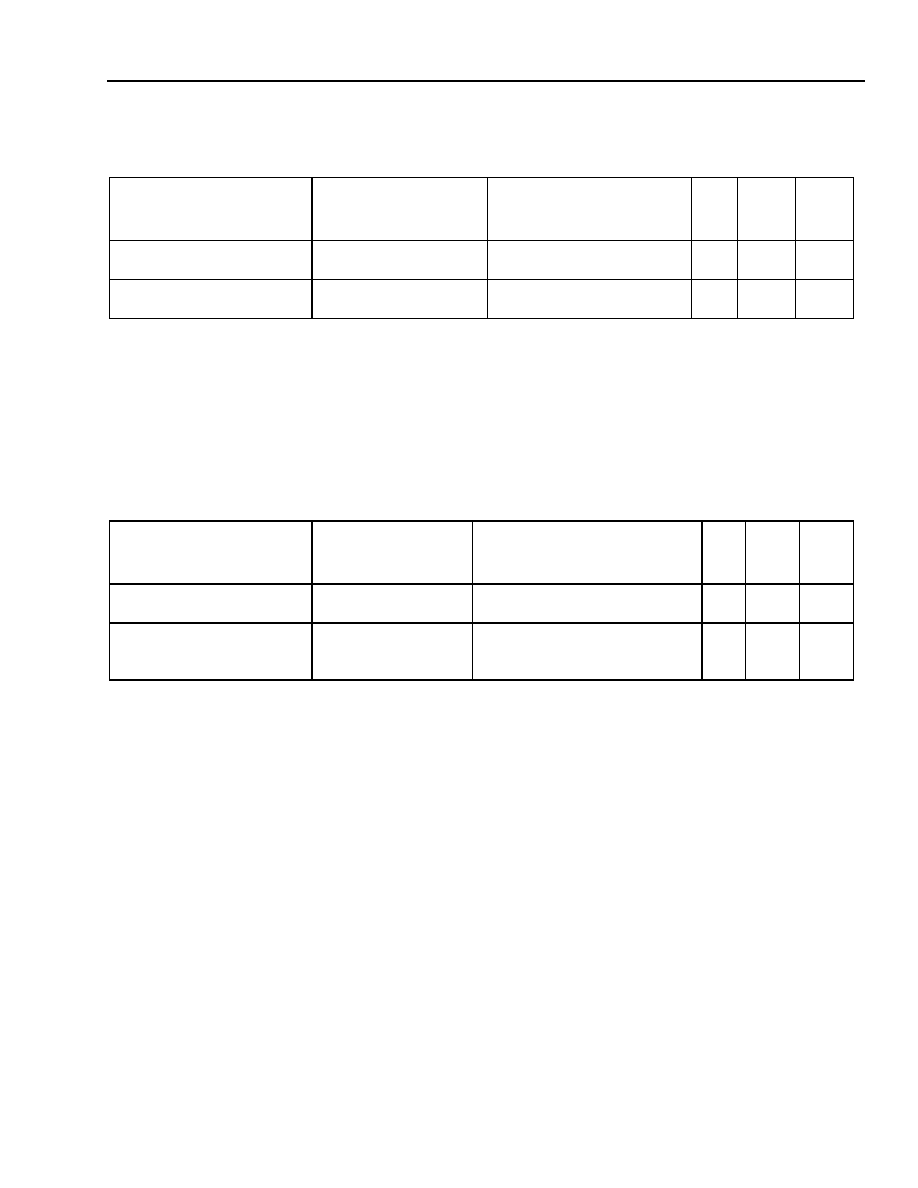

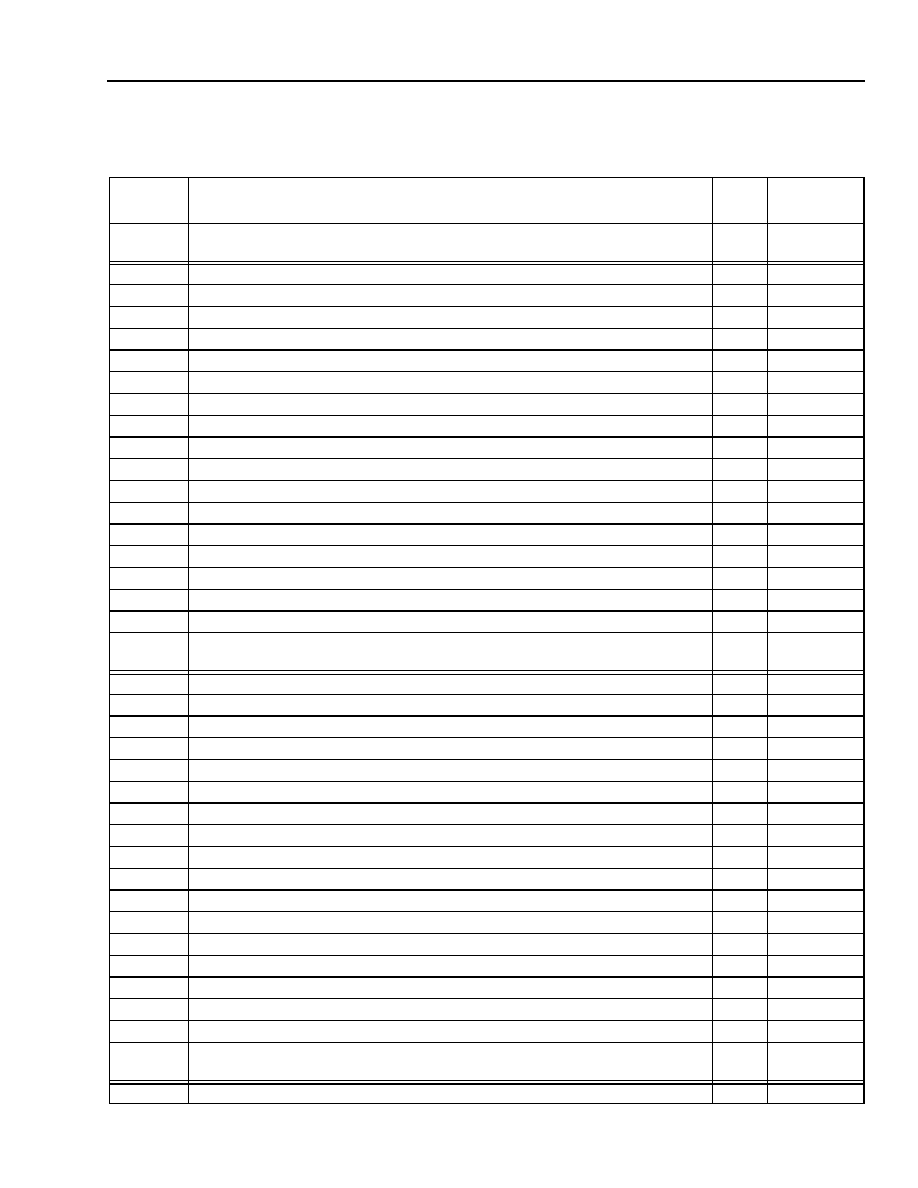

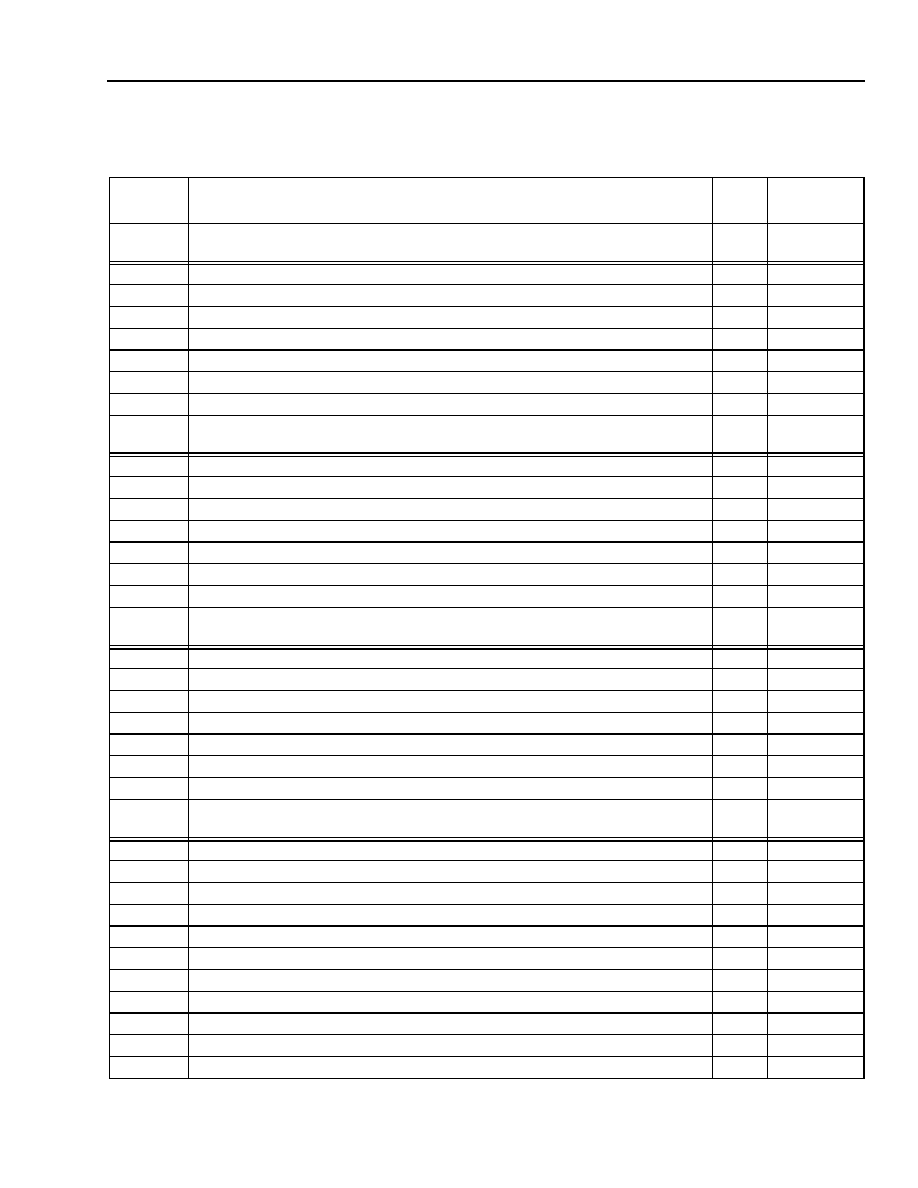

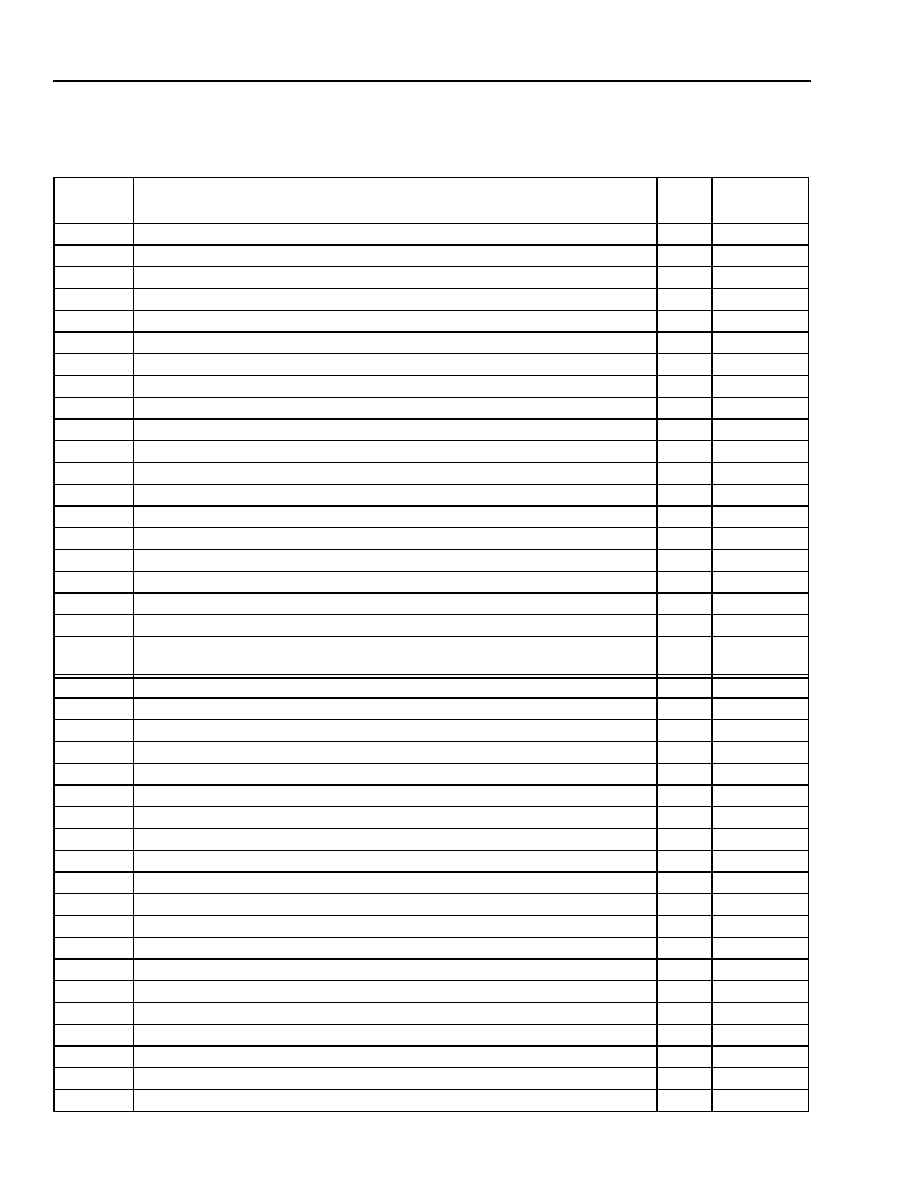

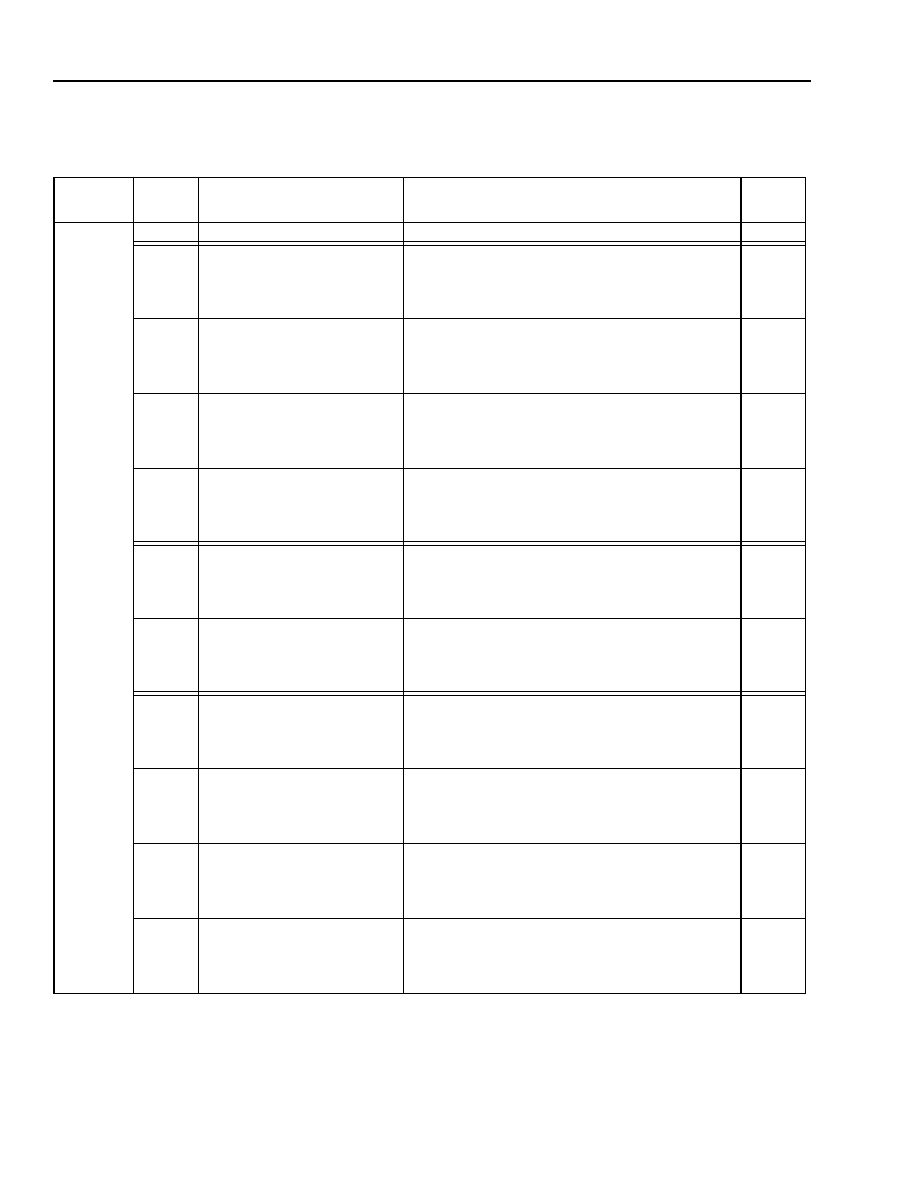

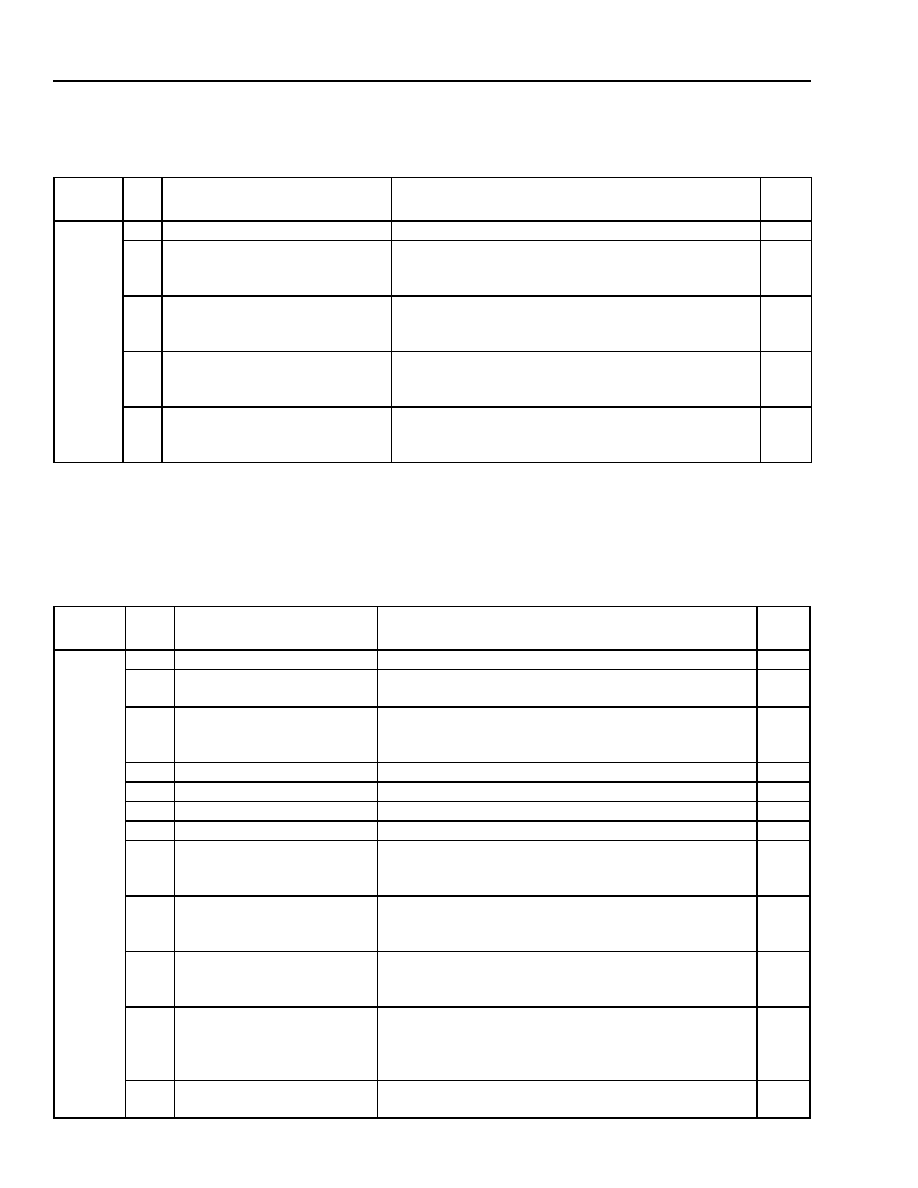

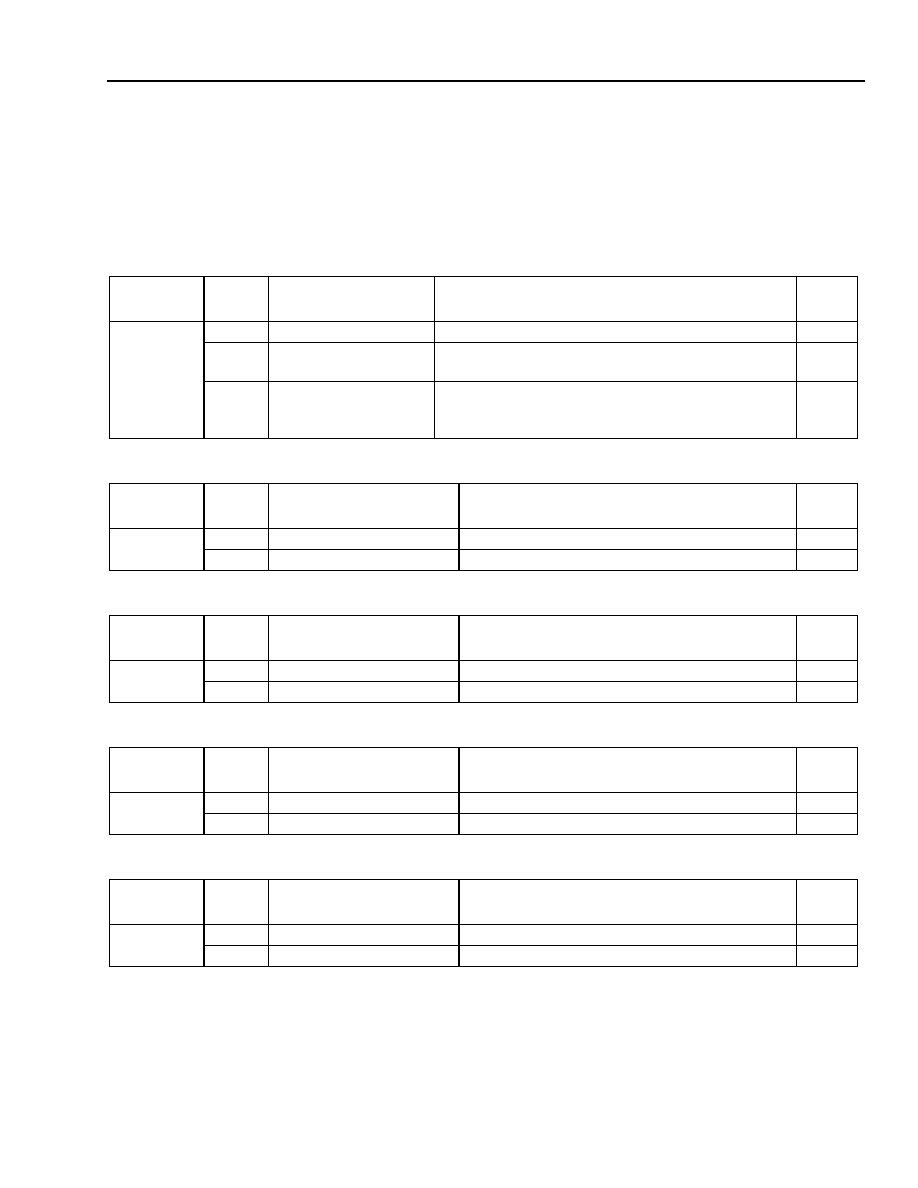

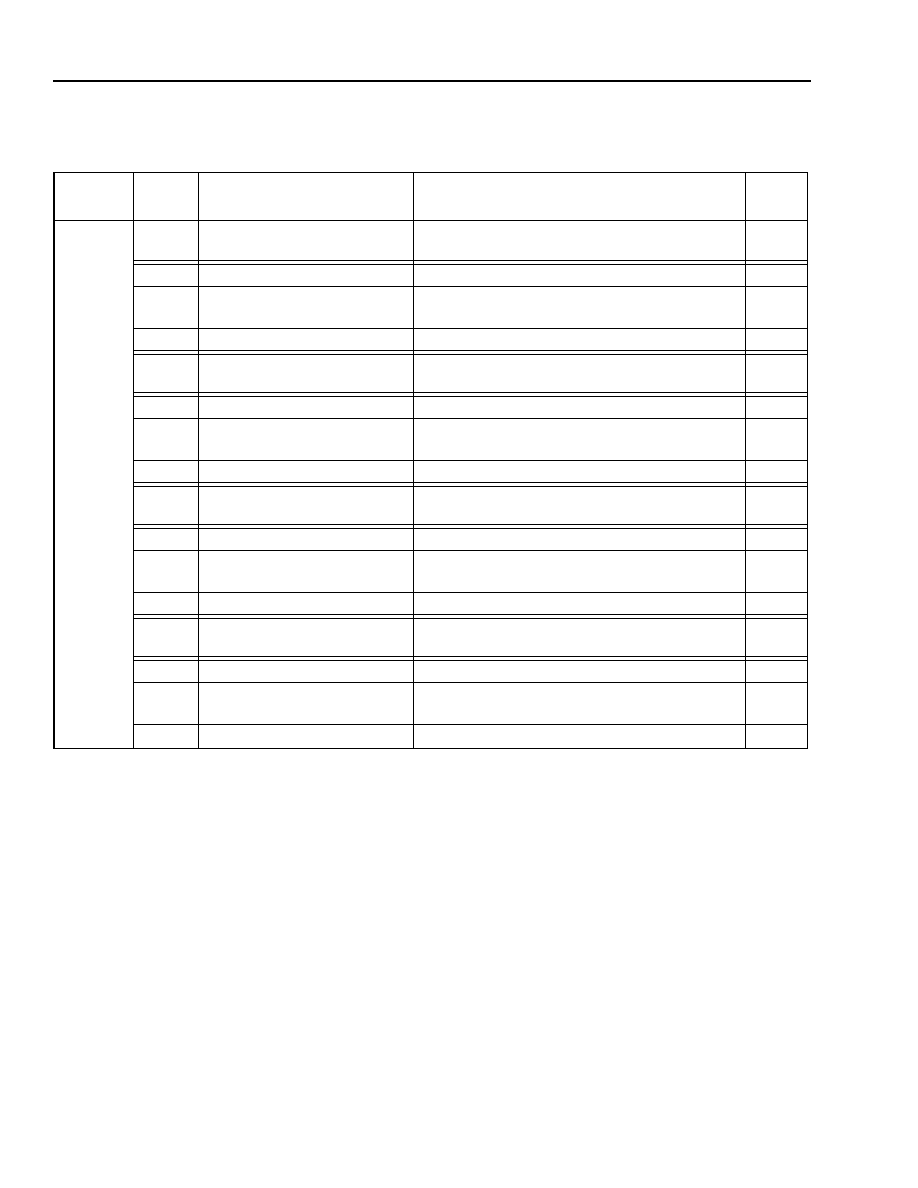

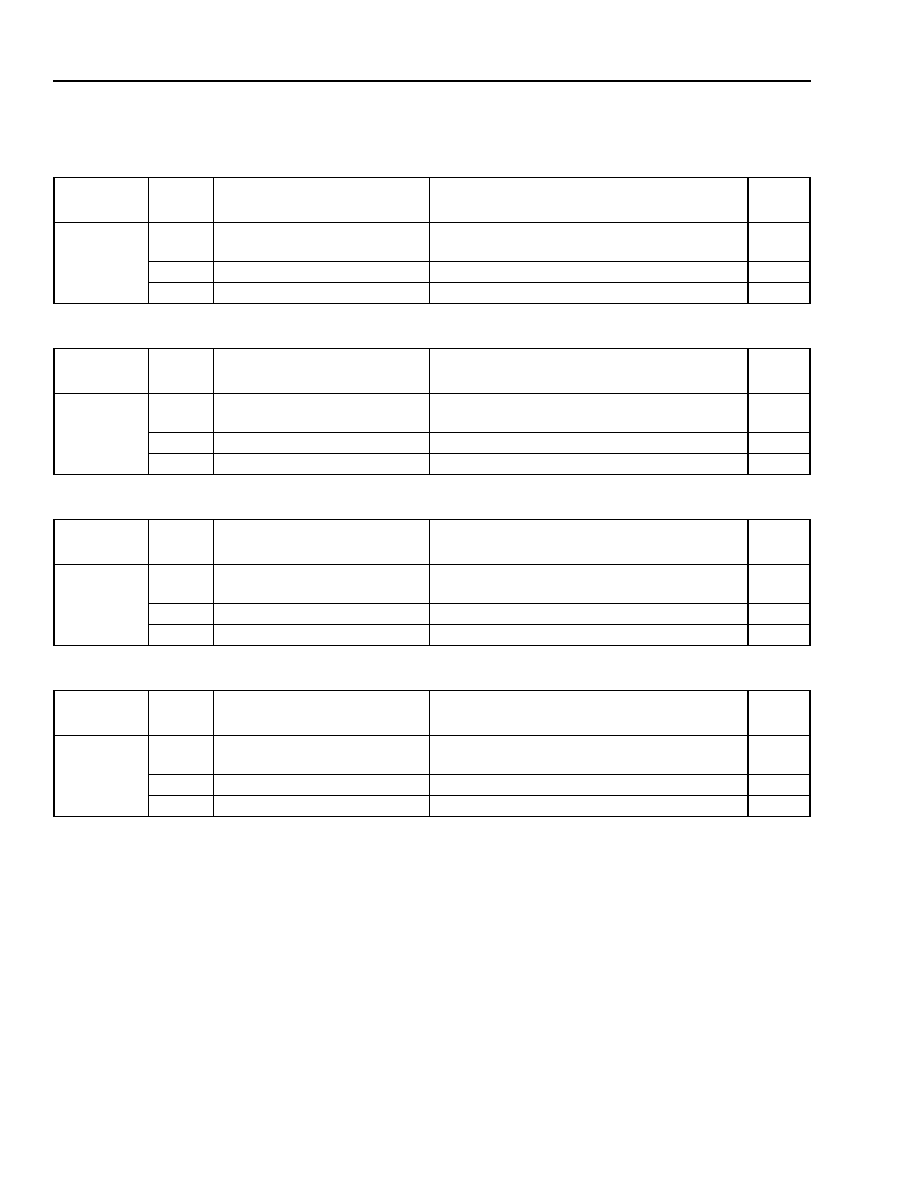

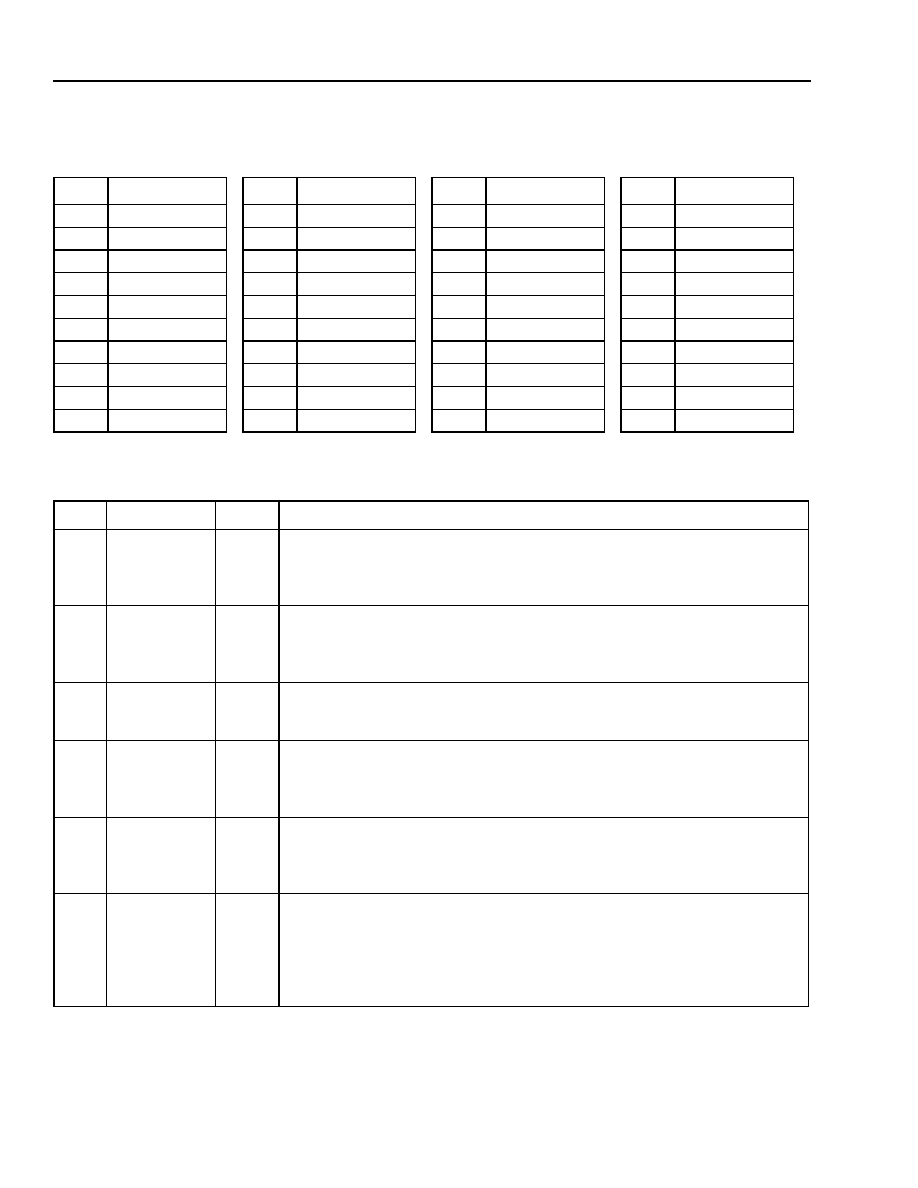

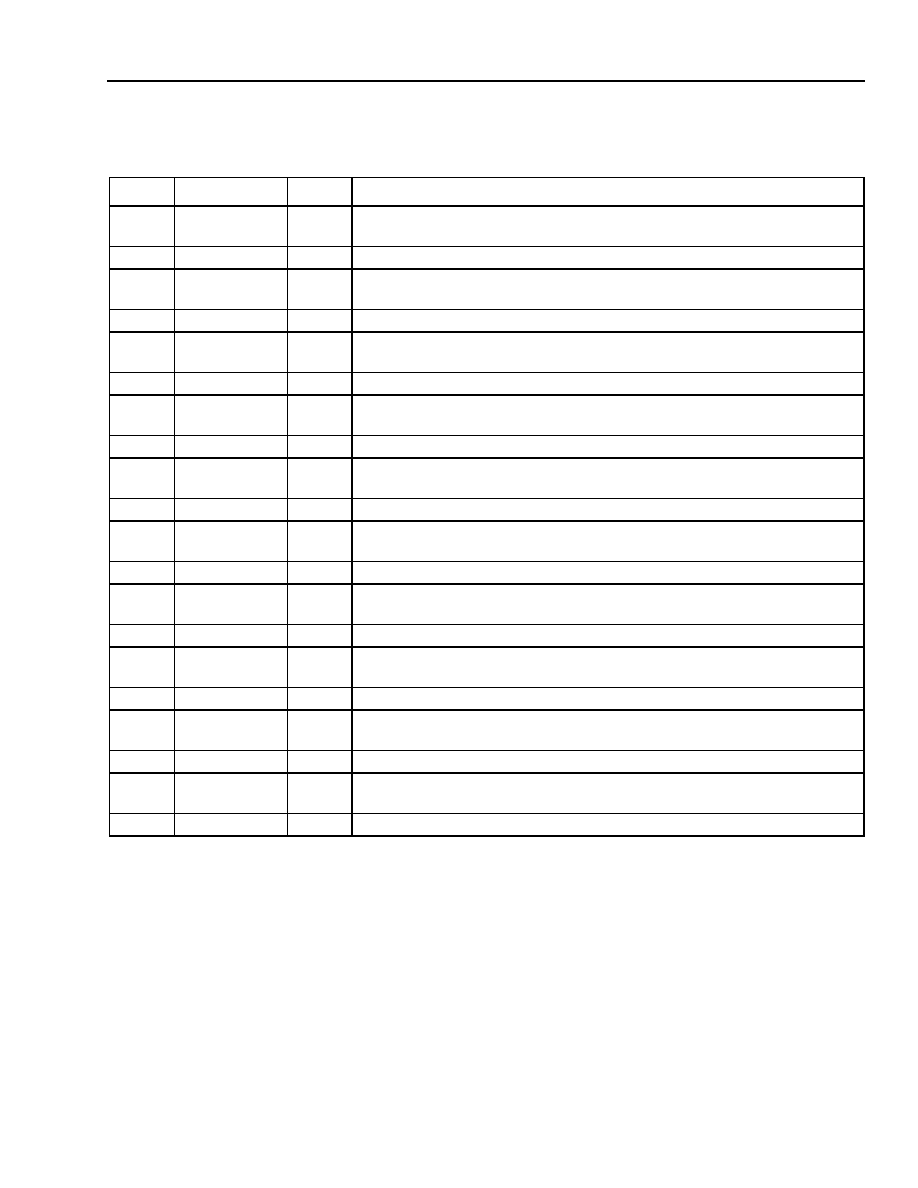

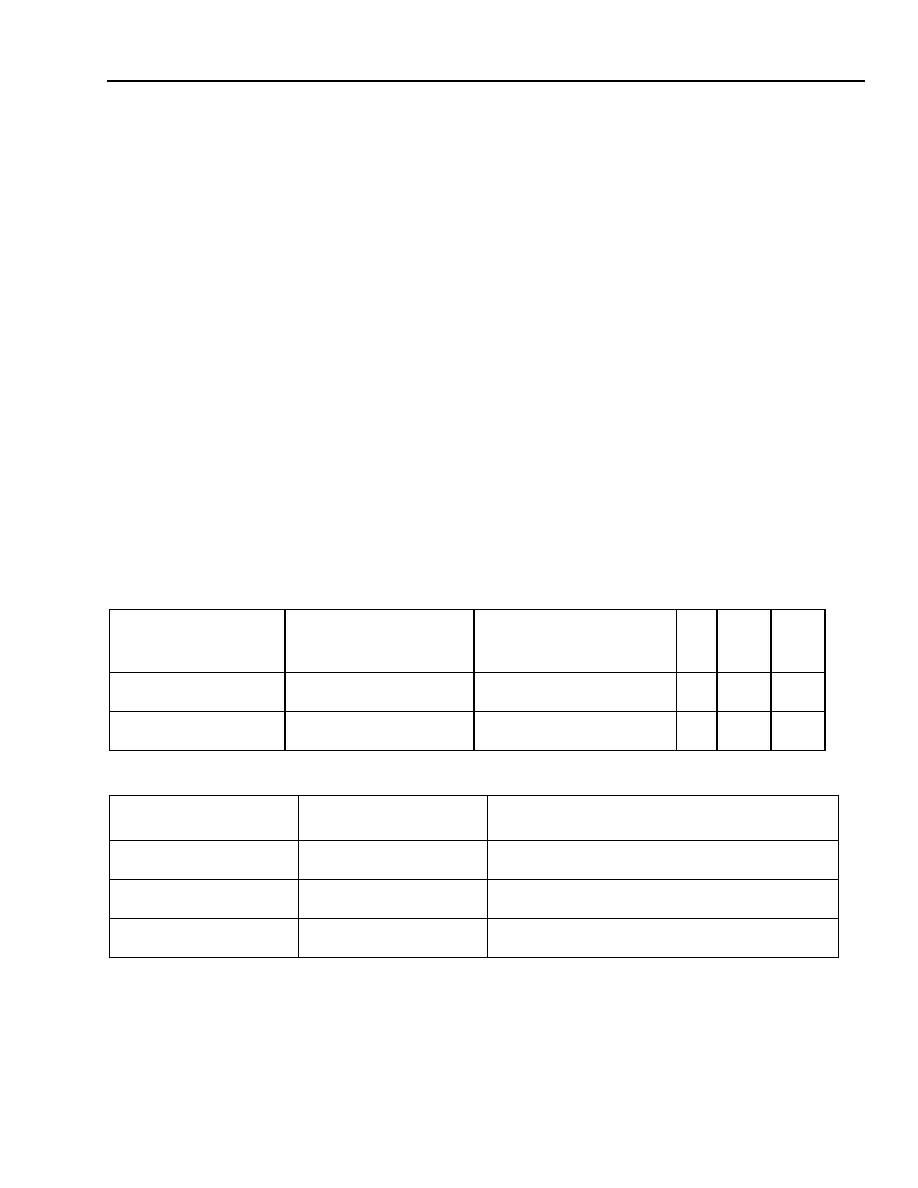

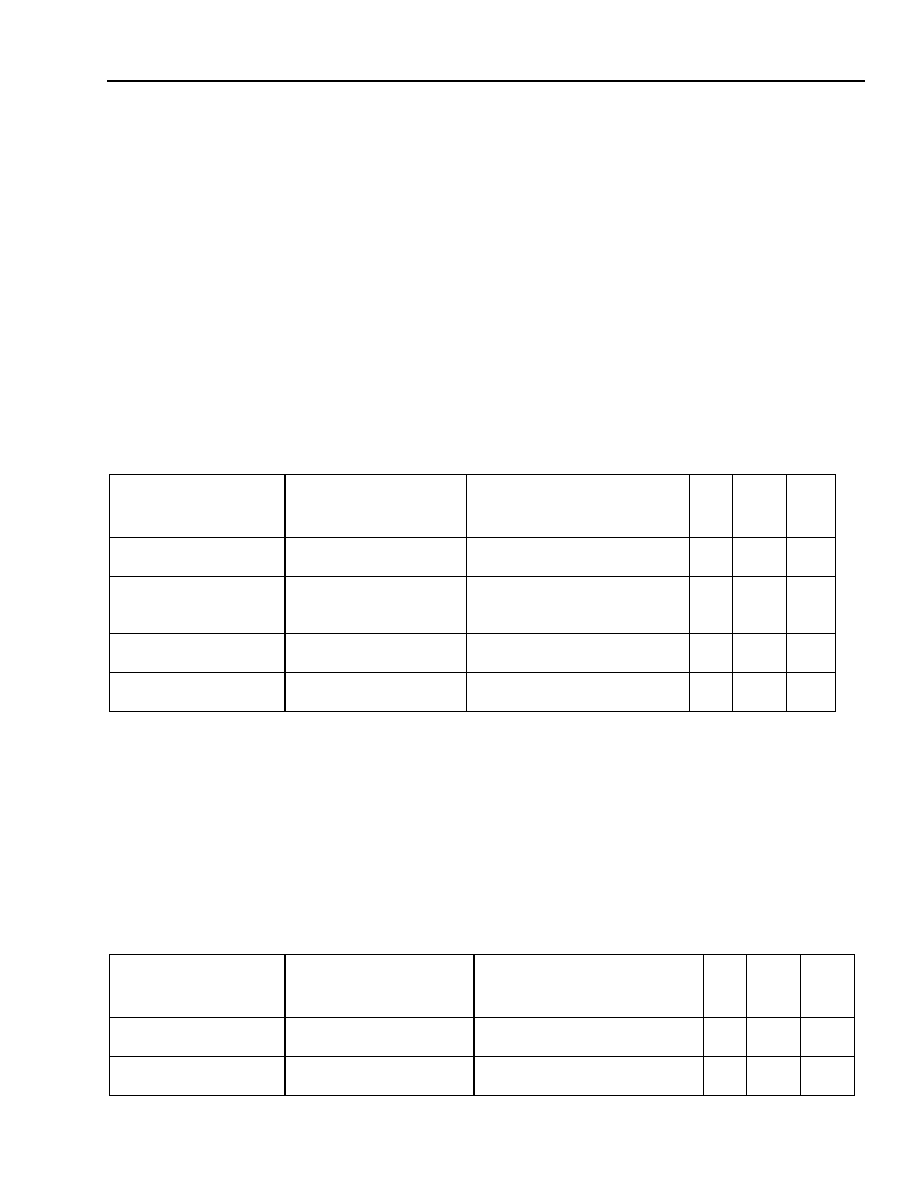

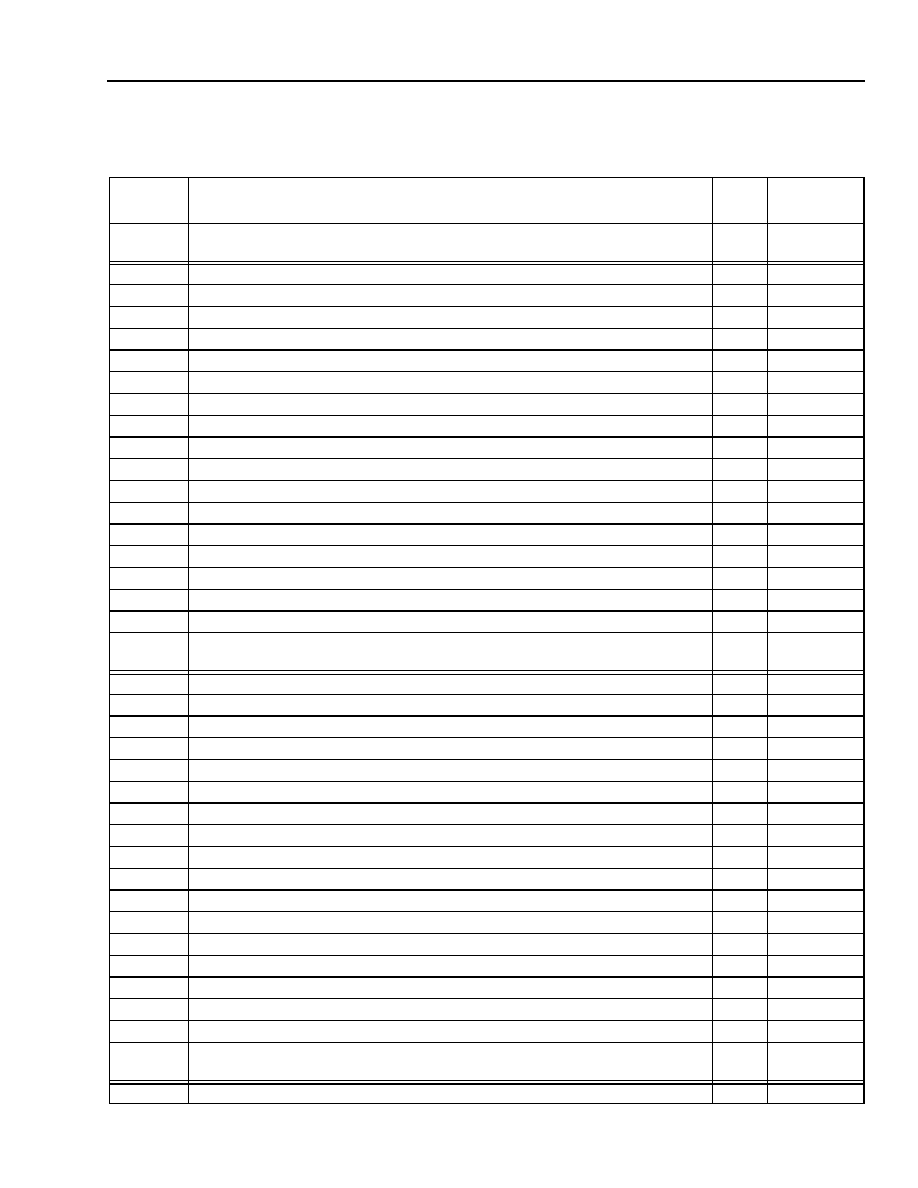

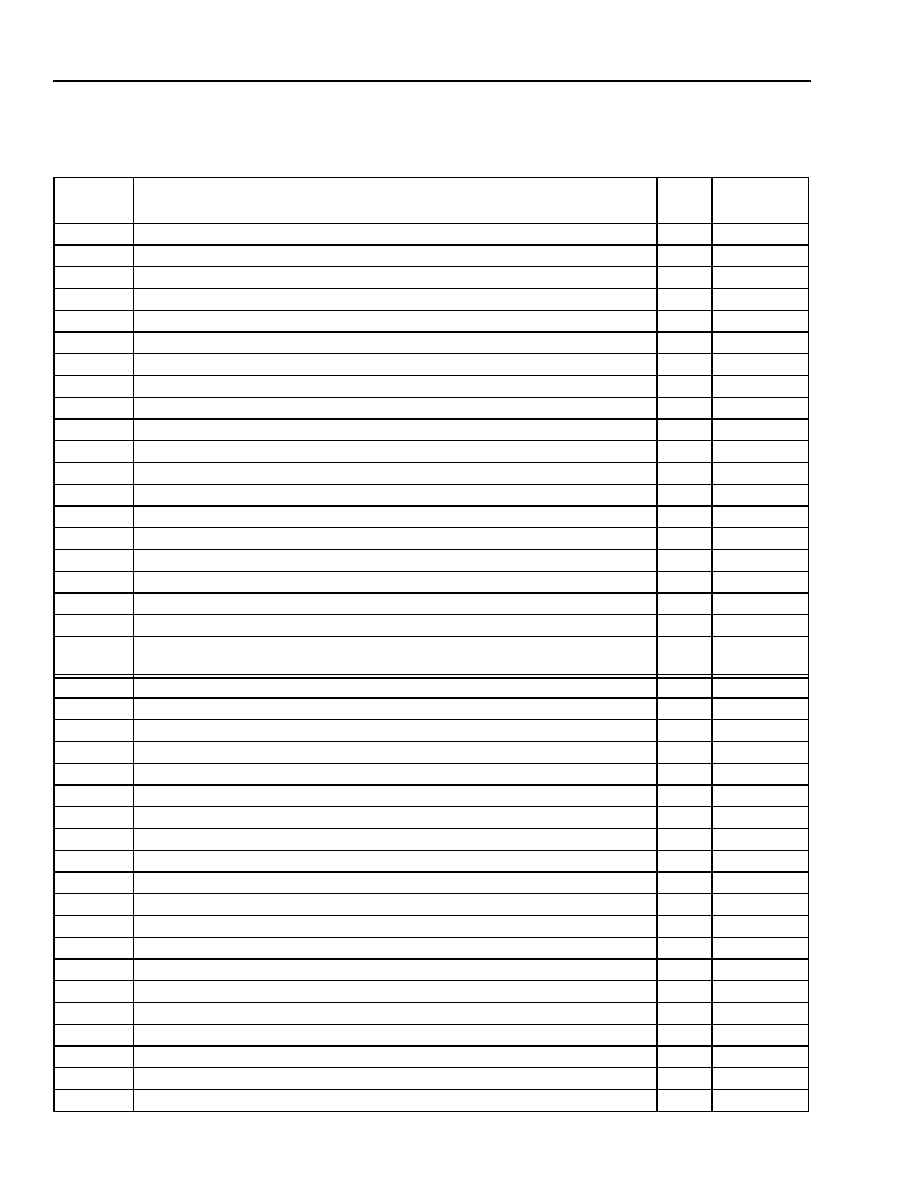

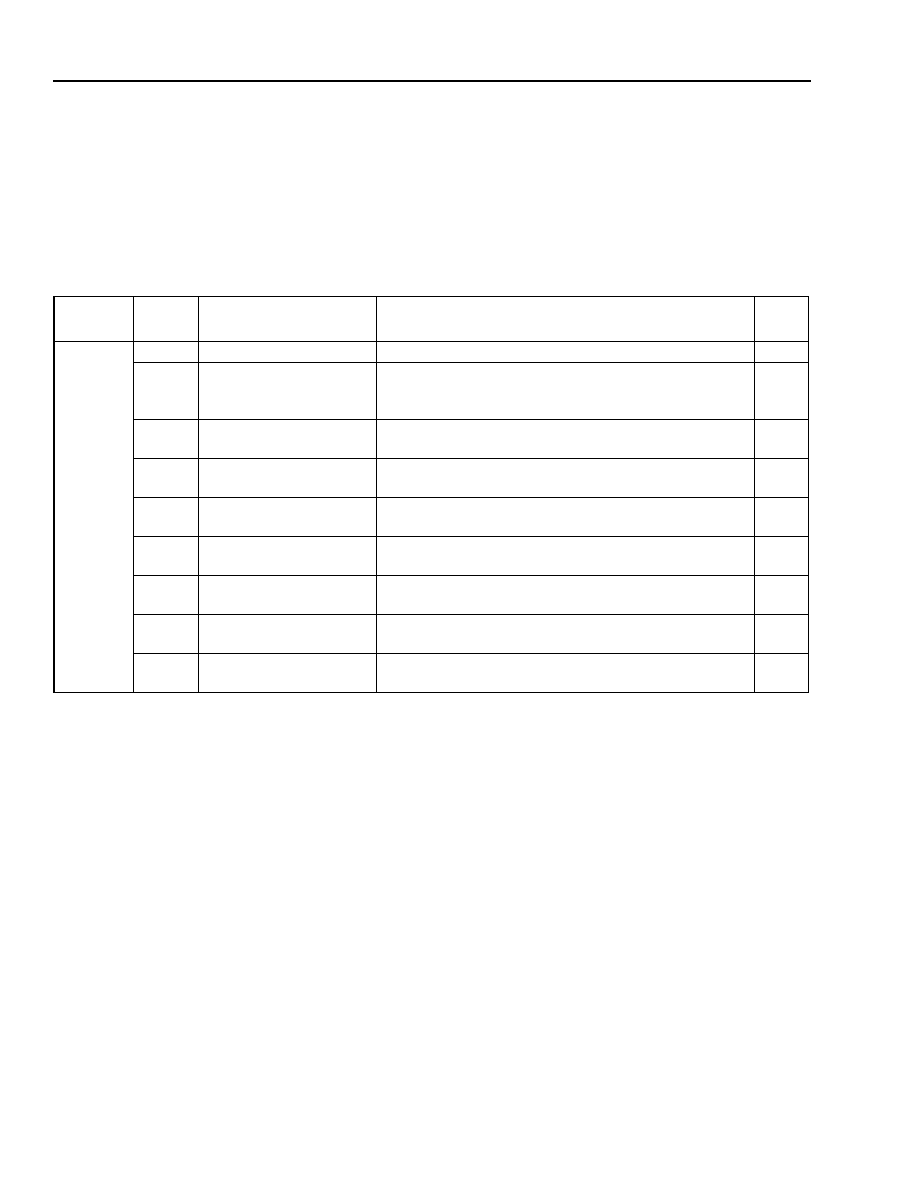

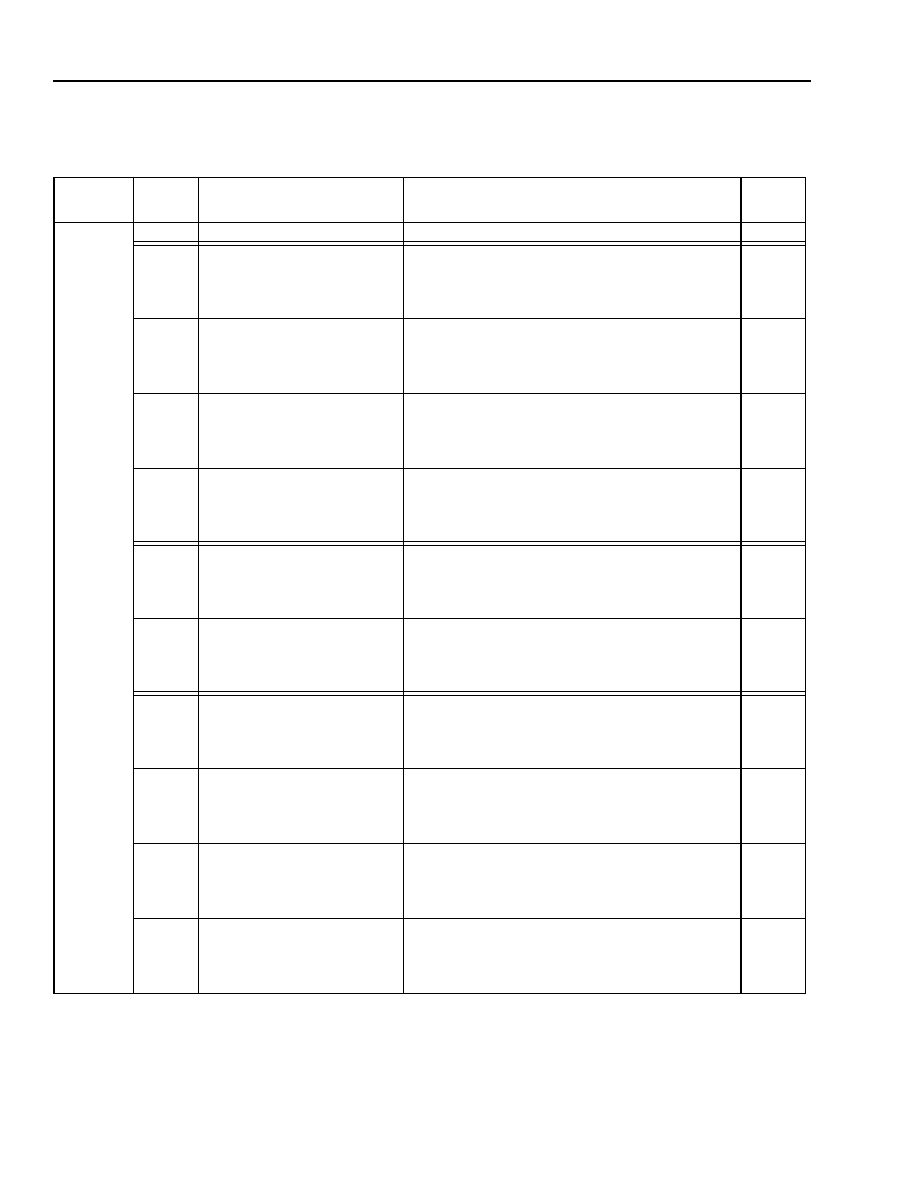

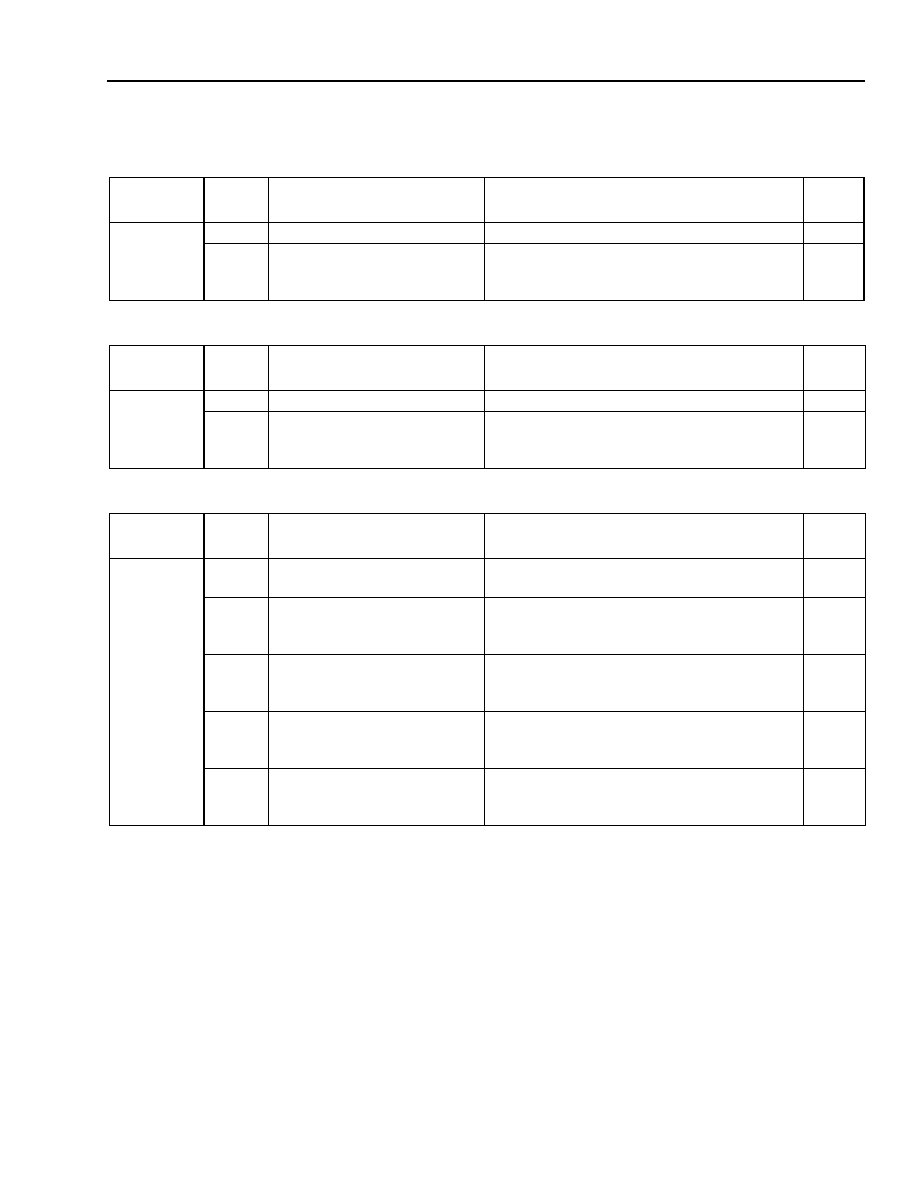

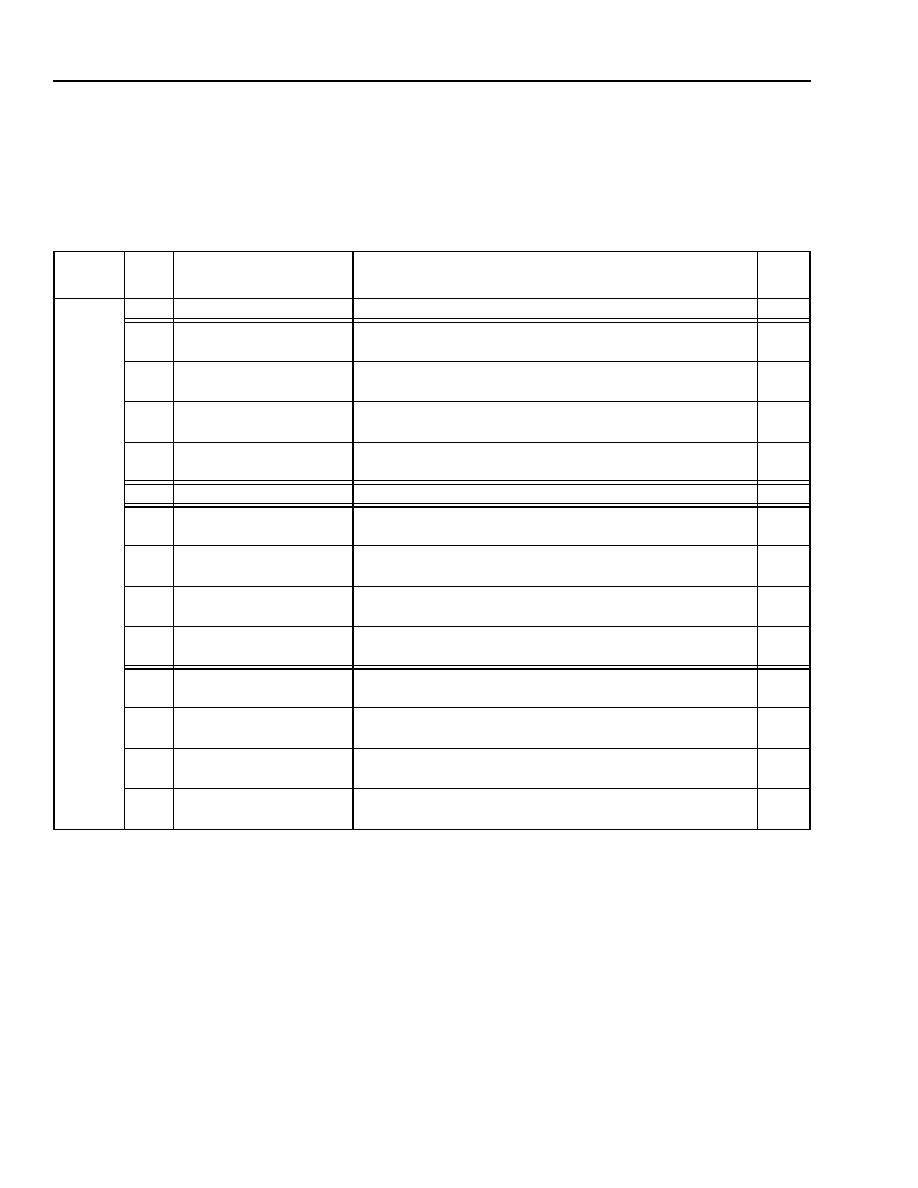

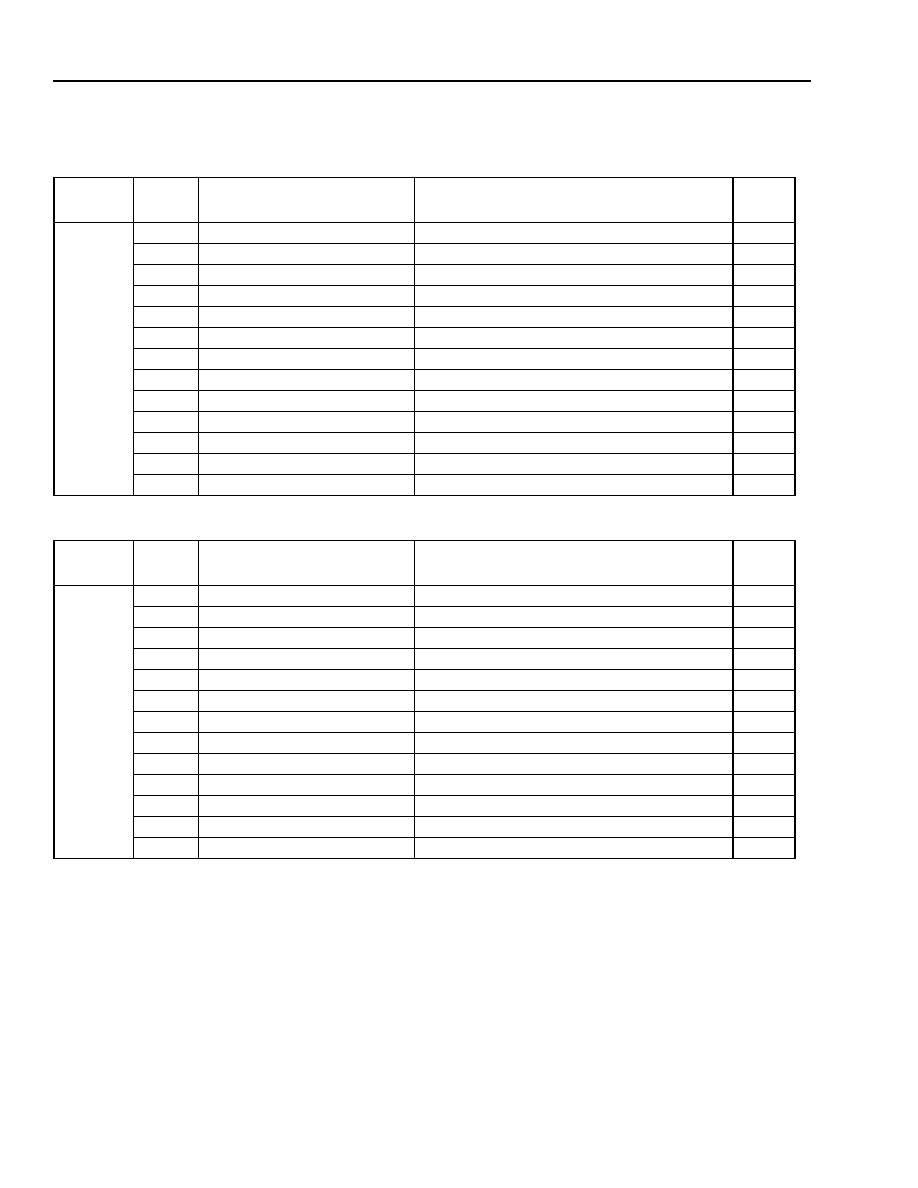

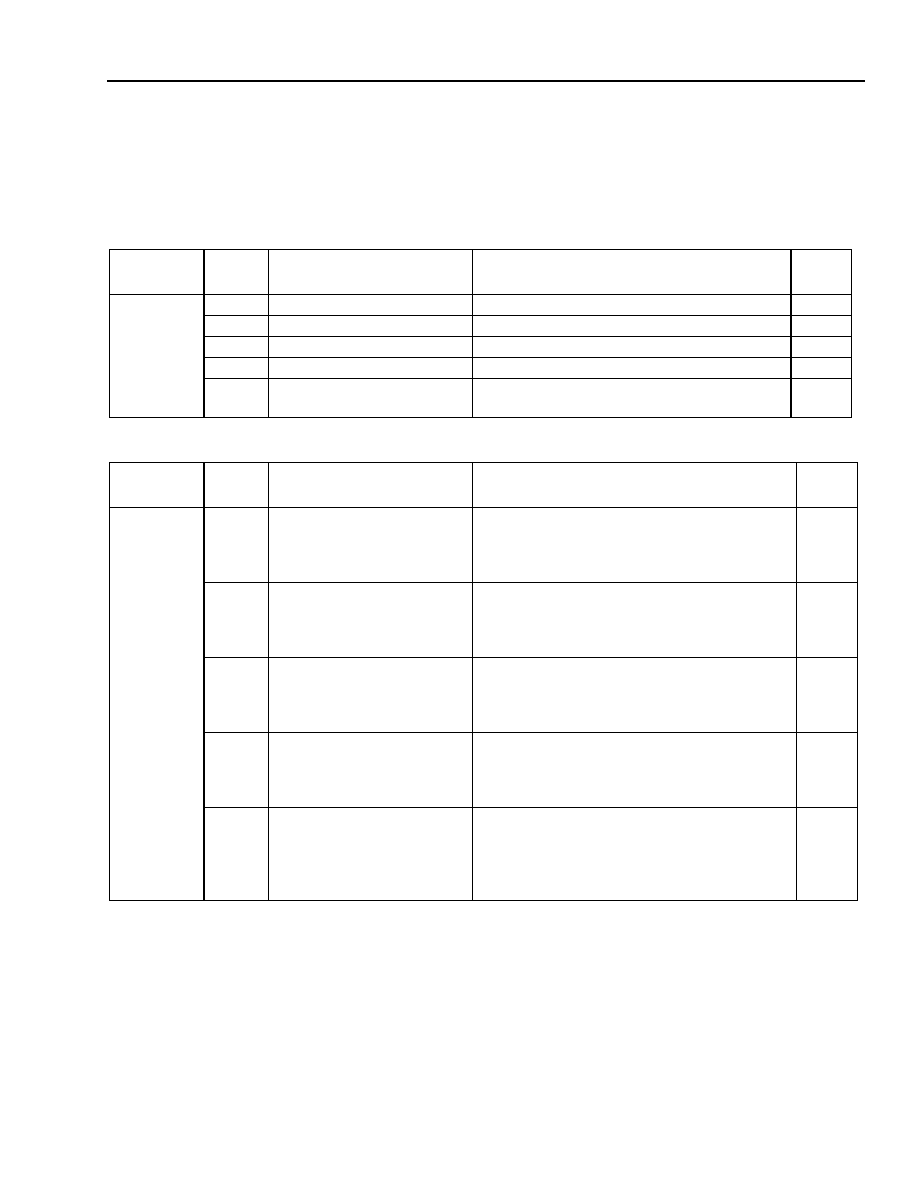

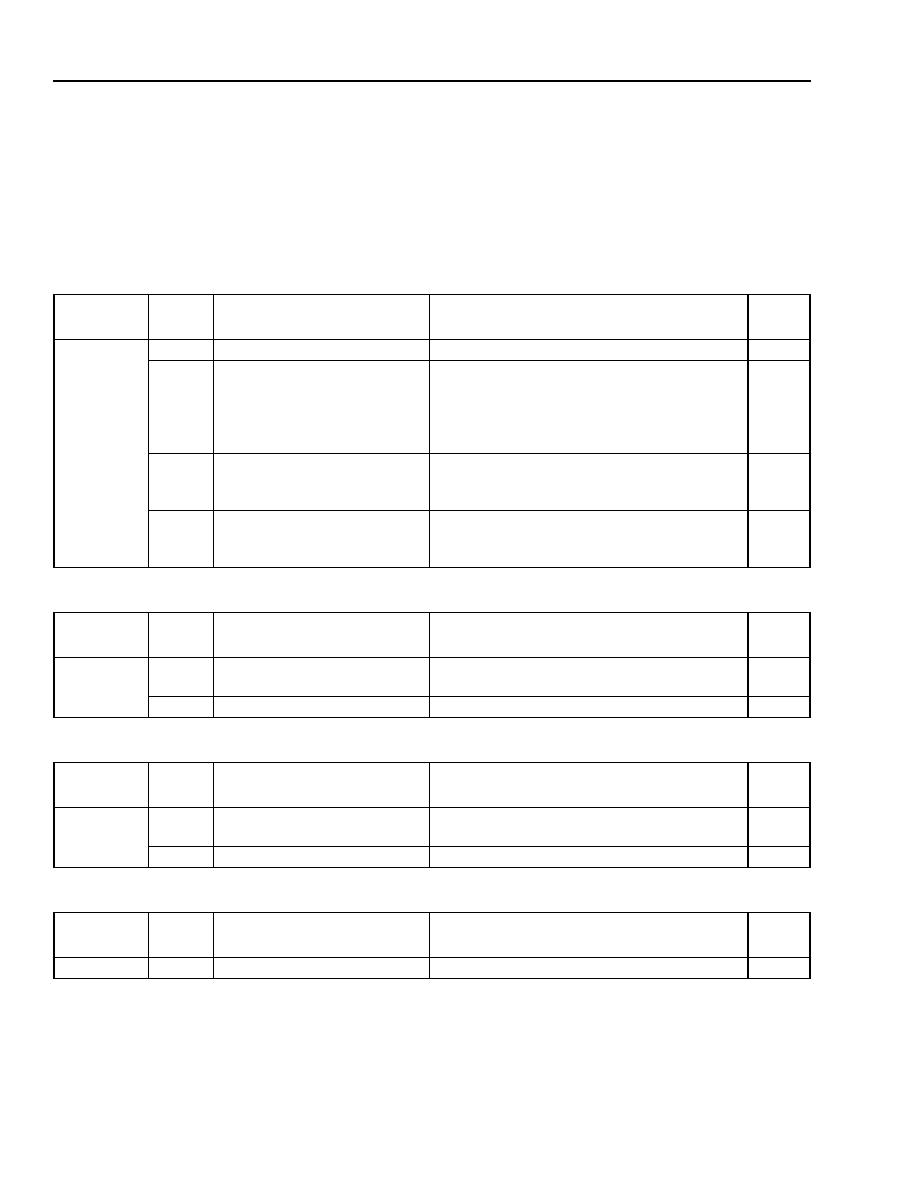

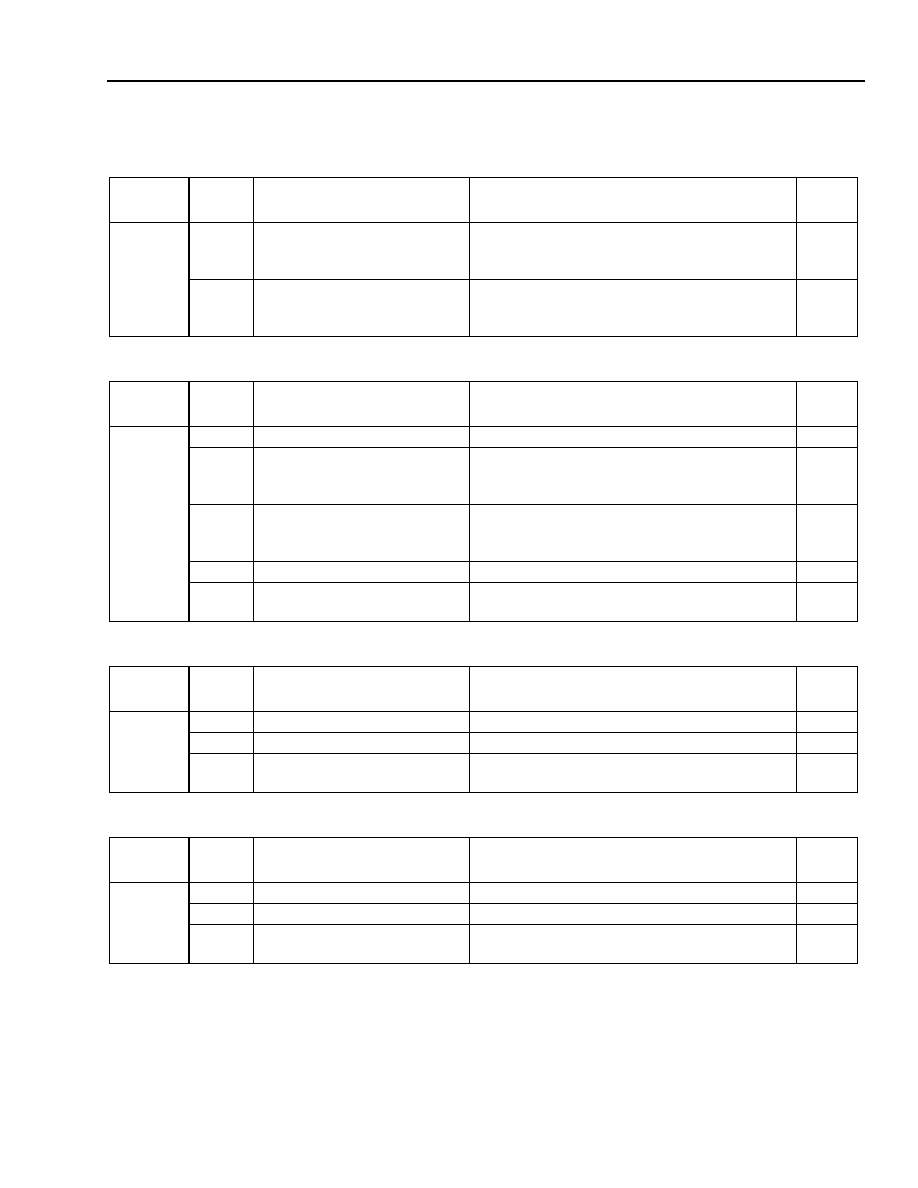

- Table 3. Pin DescriptionsĄSystem Control

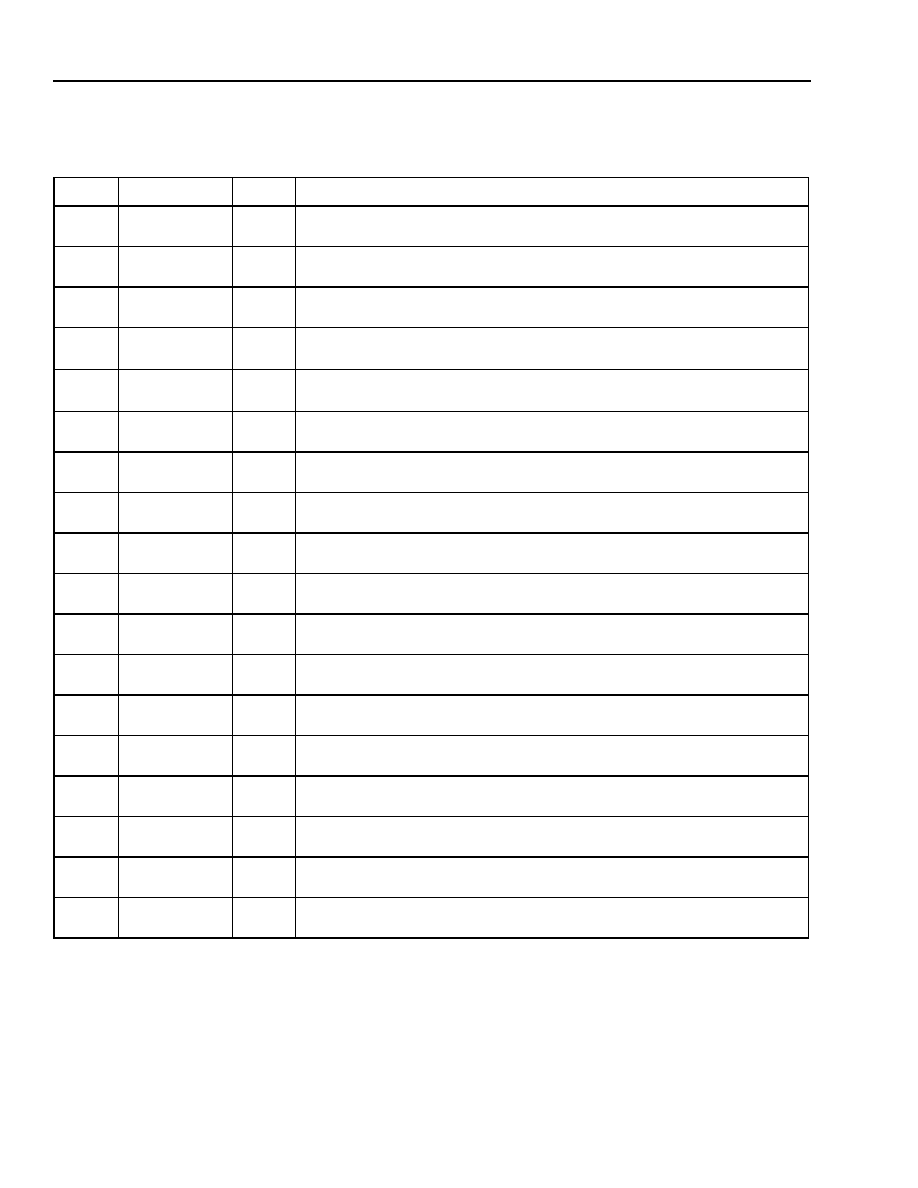

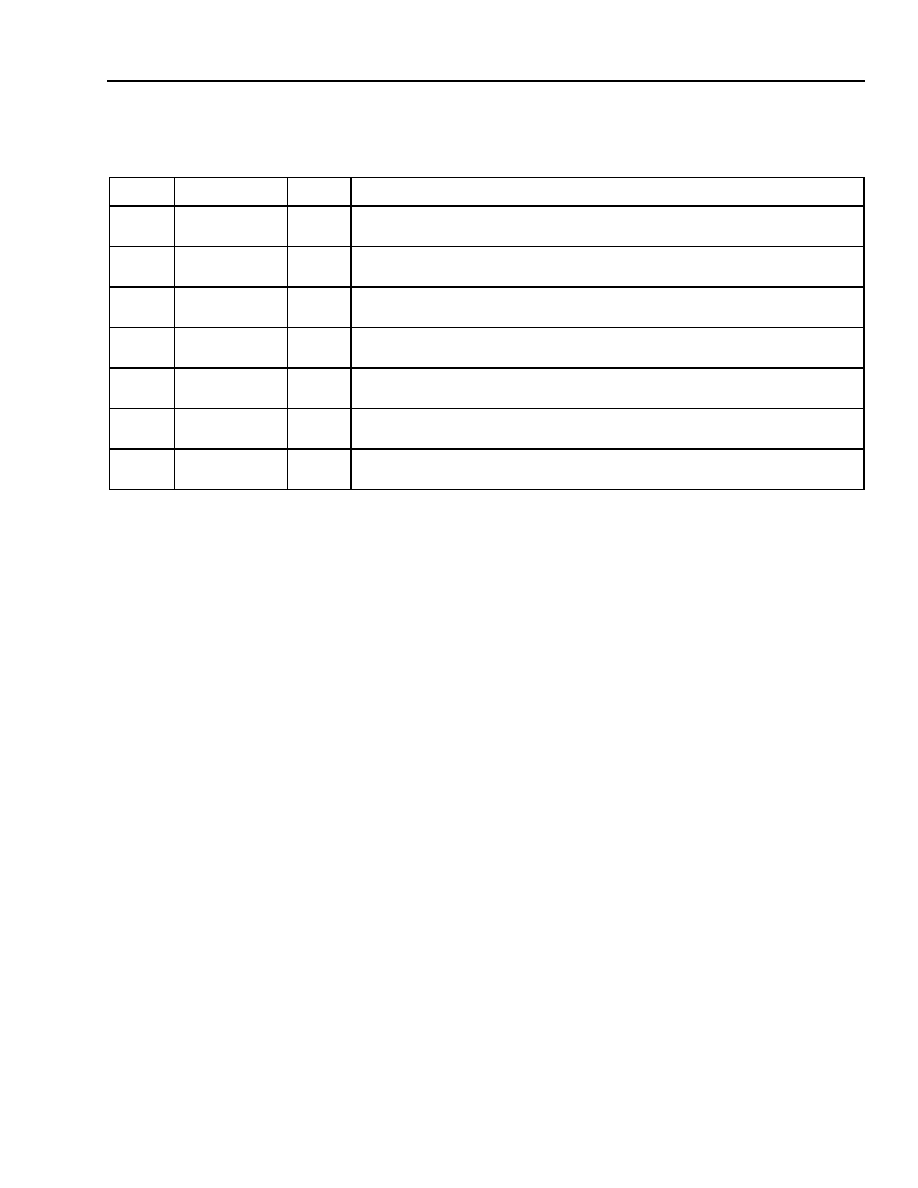

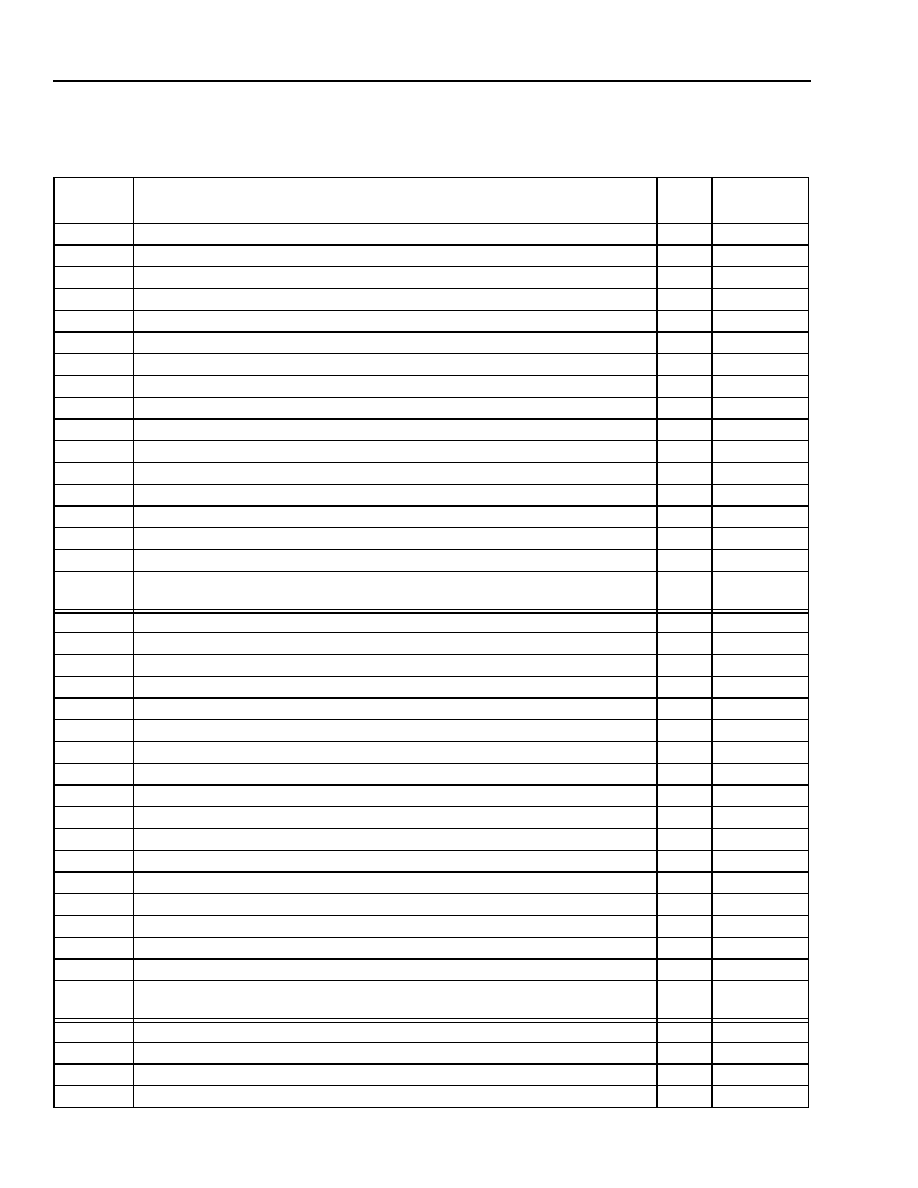

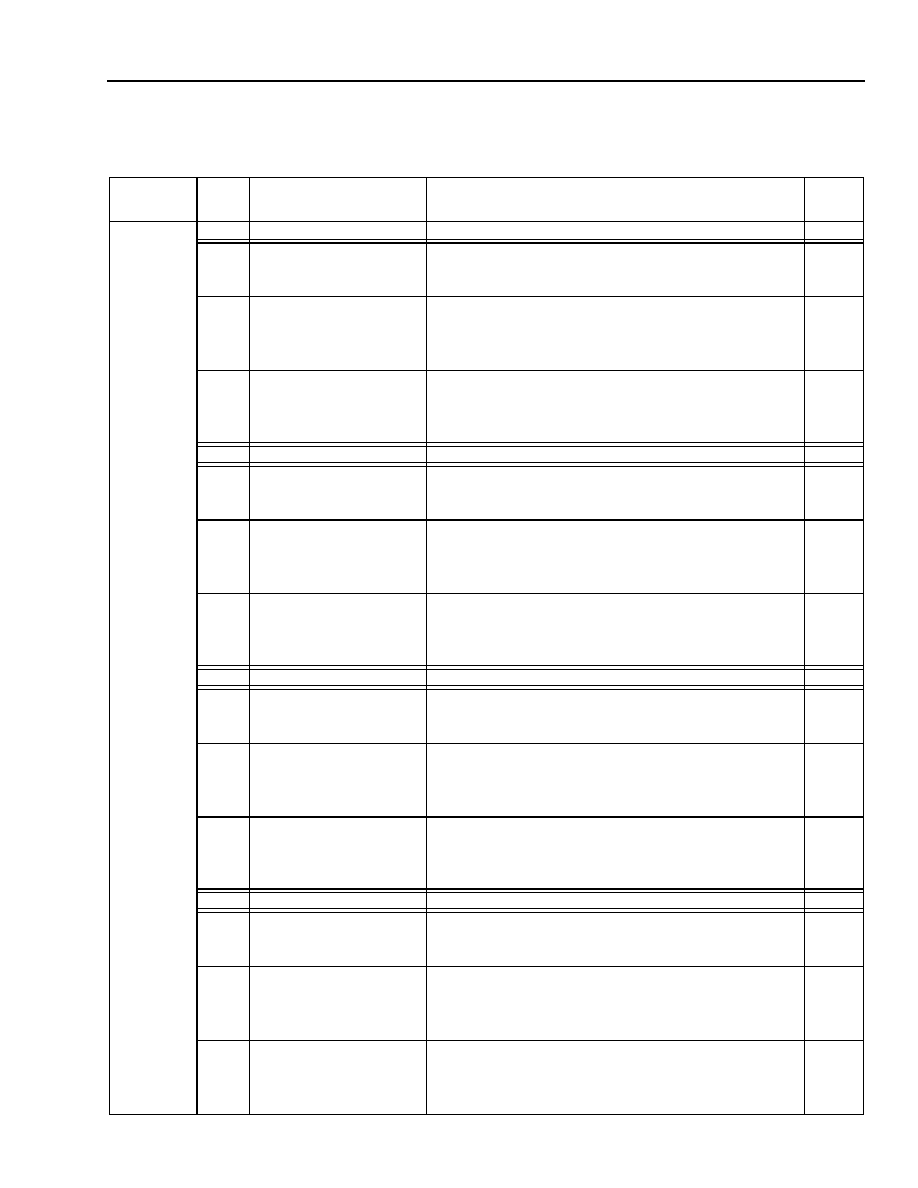

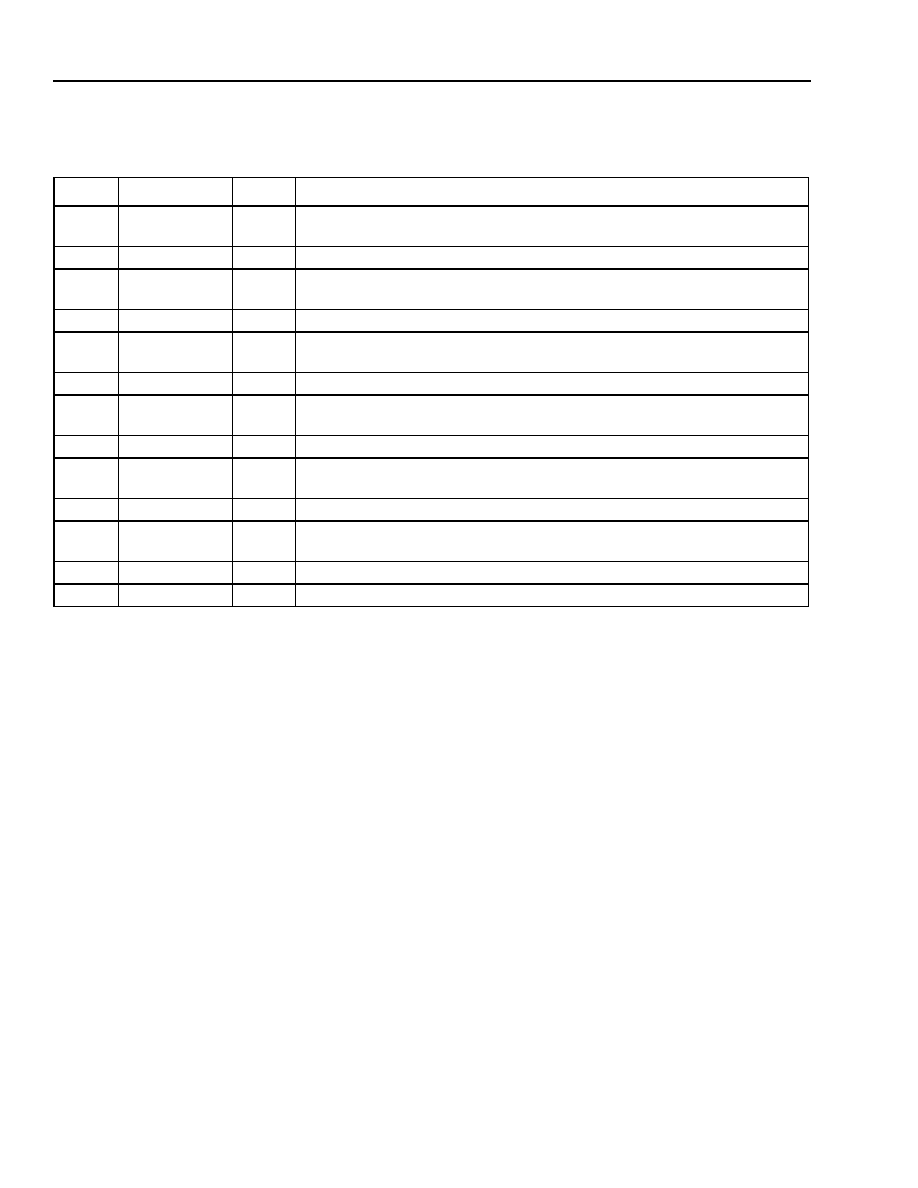

- Table 4. Pin DescriptionsĄReceive Line Interface

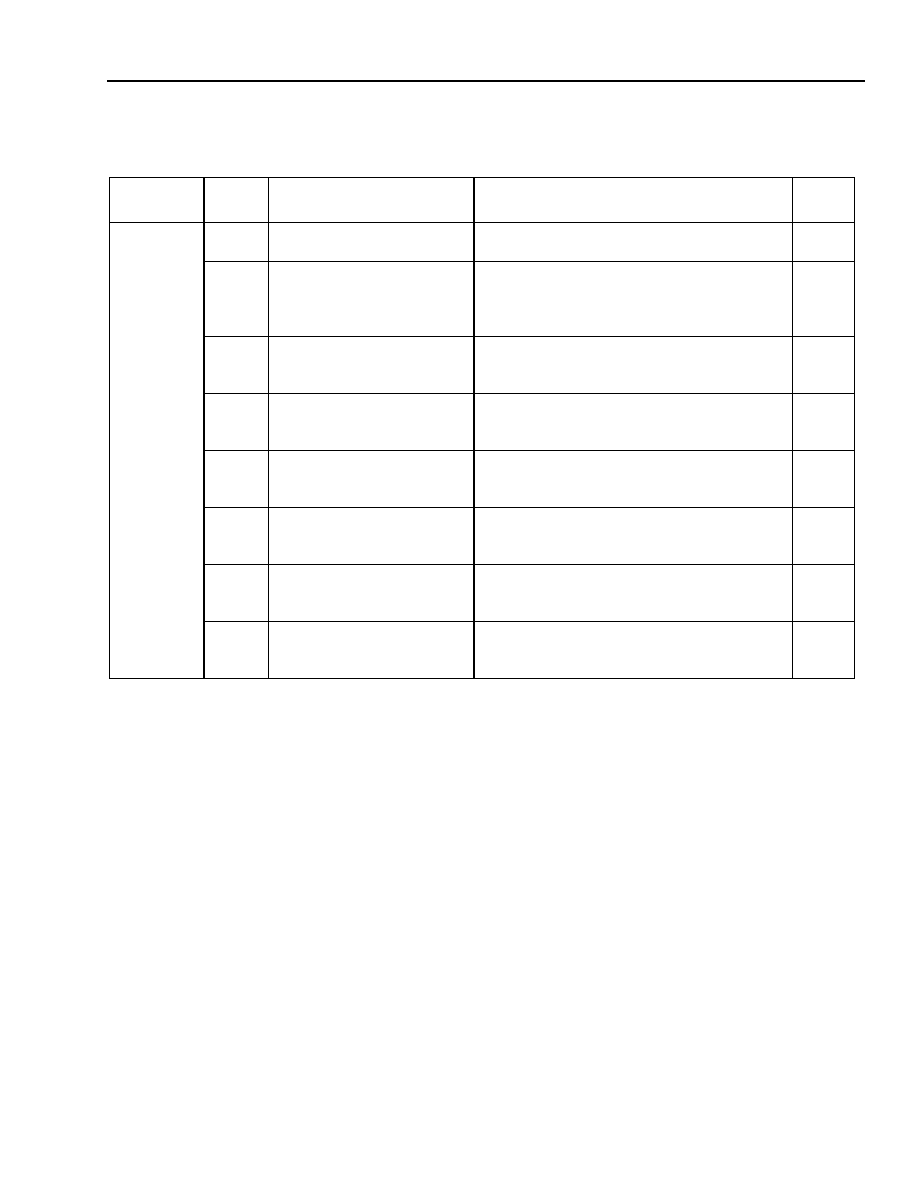

- Table 5. Pin DescriptionsĄTransmit Line Interface

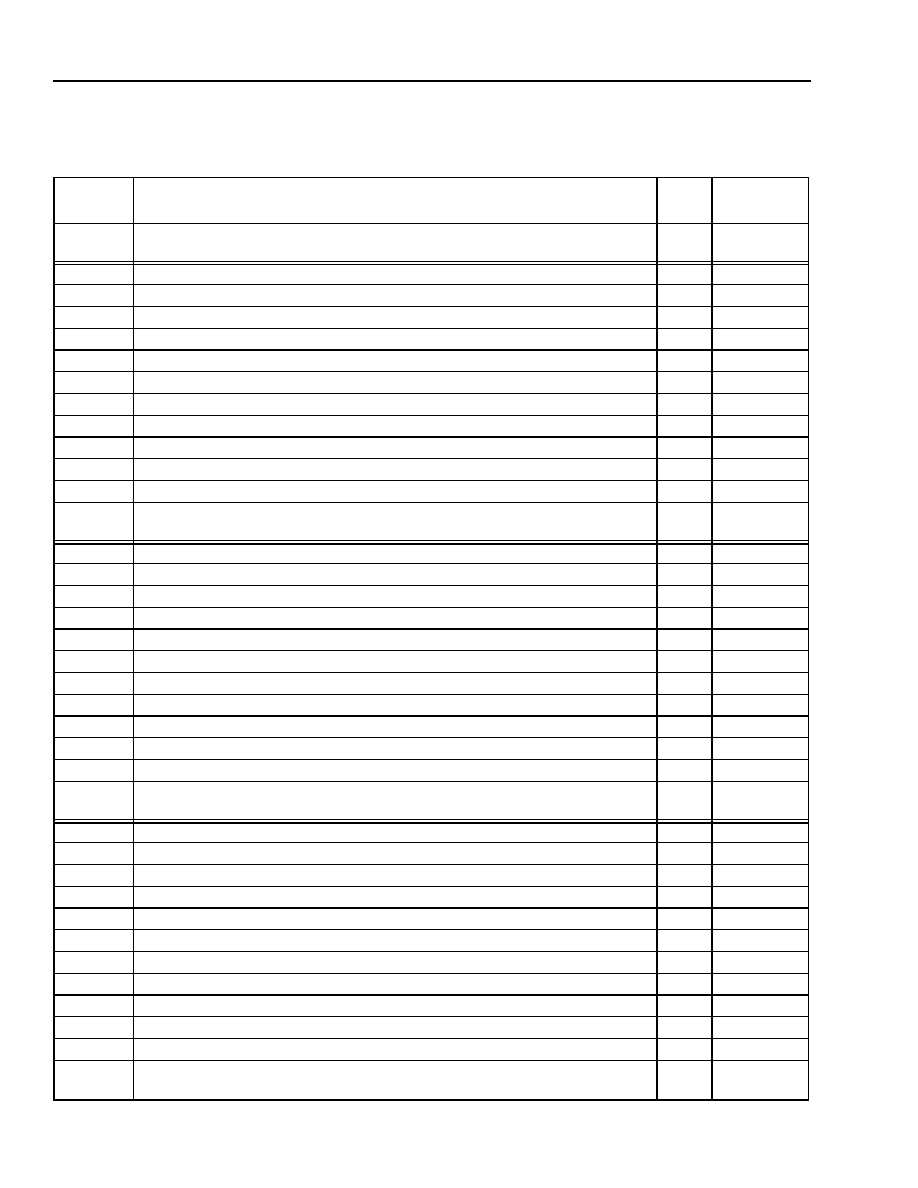

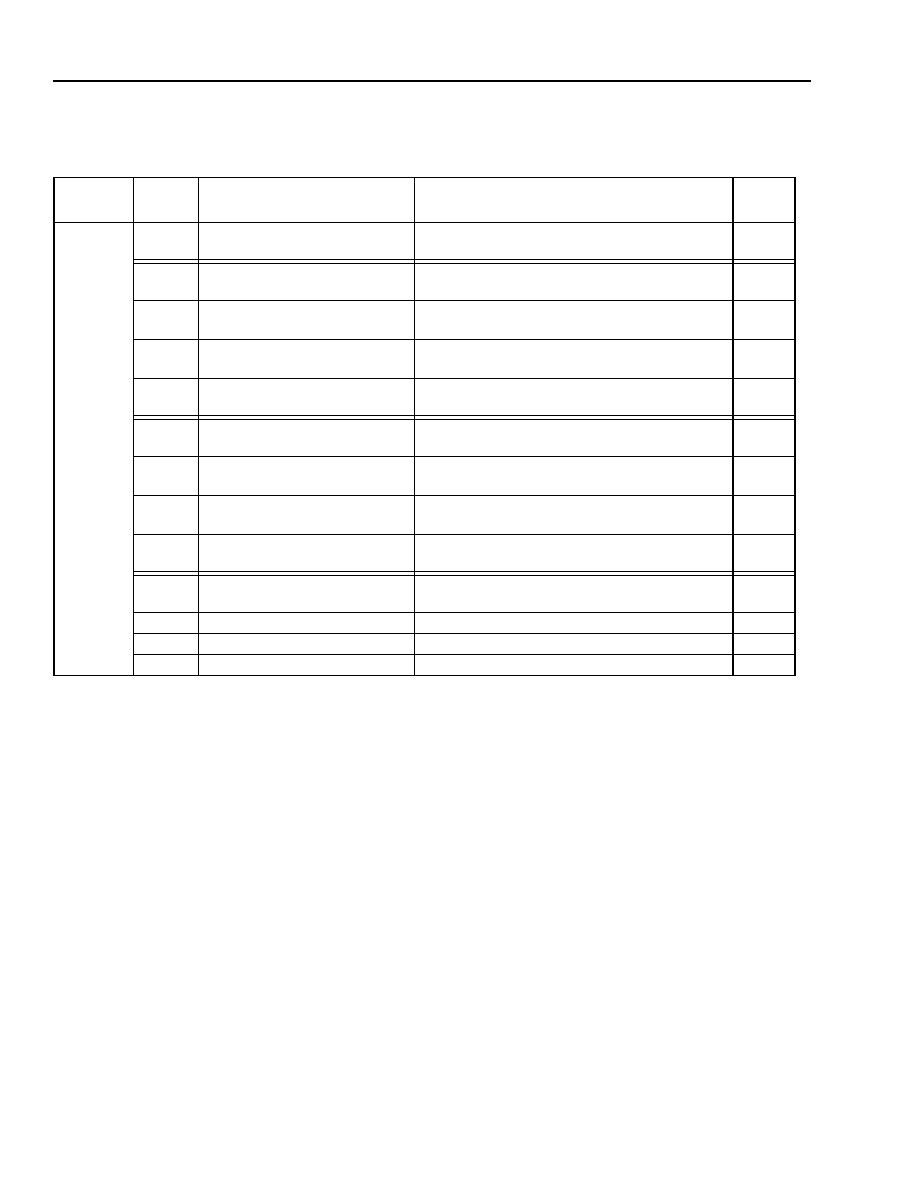

- Table 6. Pin DescriptionsĄLVDS Reference, Line Interface

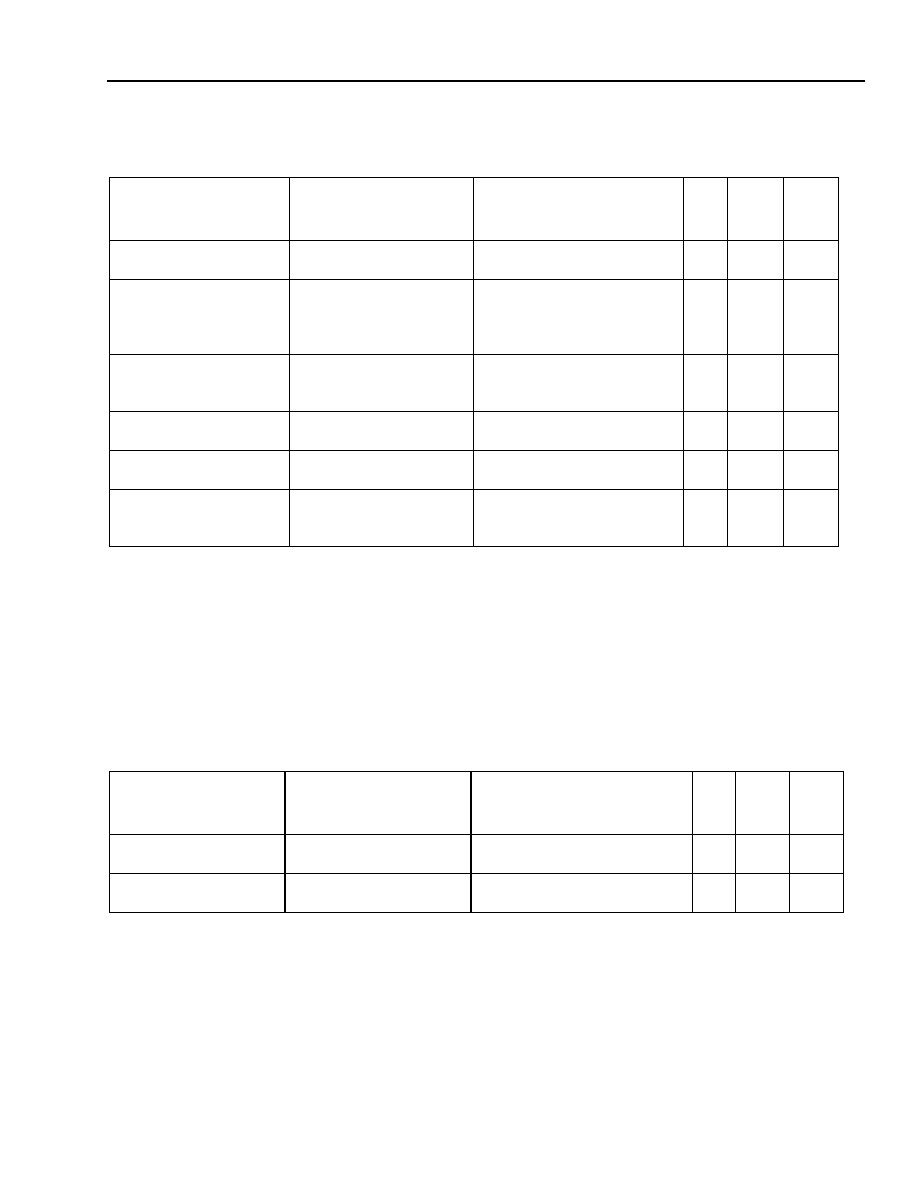

- Table 7. Pin DescriptionsĄReceive Drop Equipment Interface

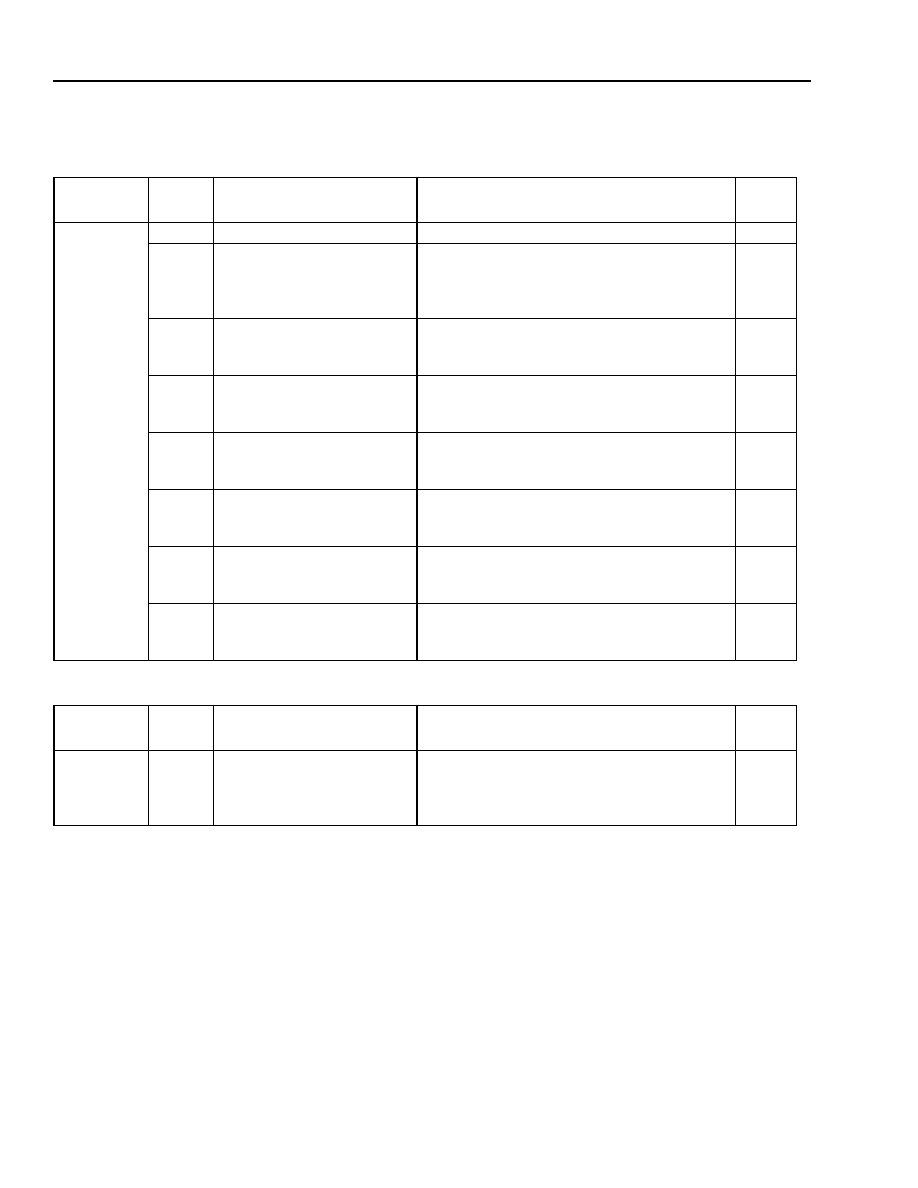

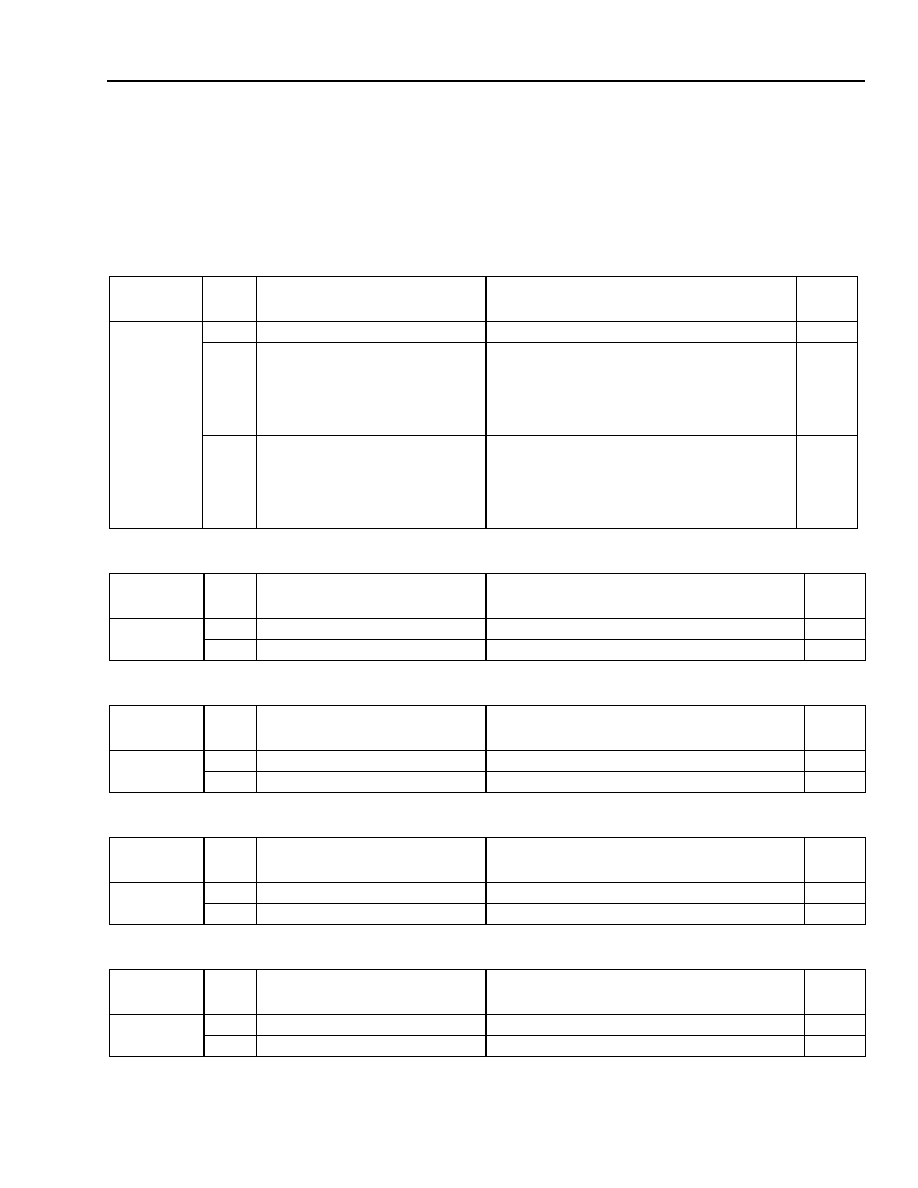

- Table 8. Pin DescriptionsĄTransmit Add Equipment Interface

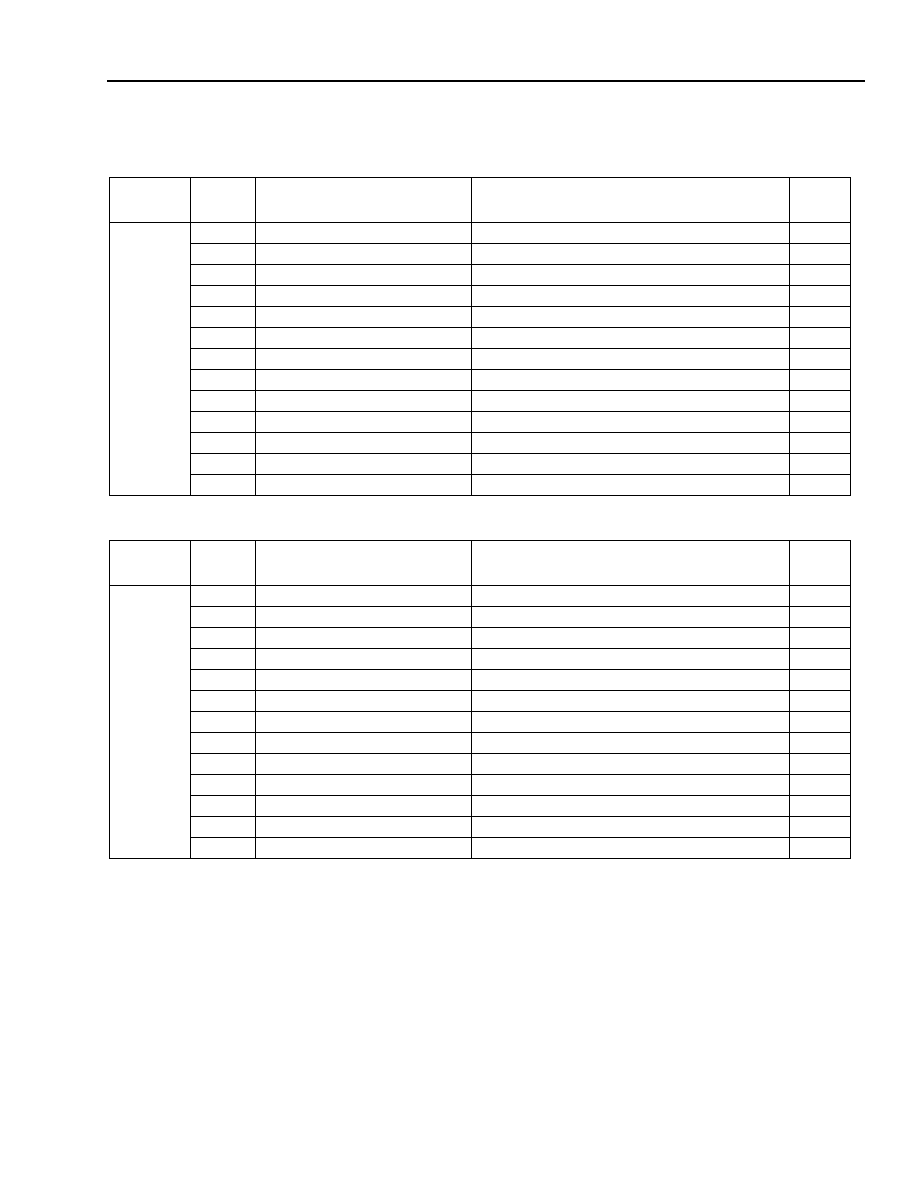

- Table 9. Pin DescriptionsĄLVDS Reference, Equipment Interface

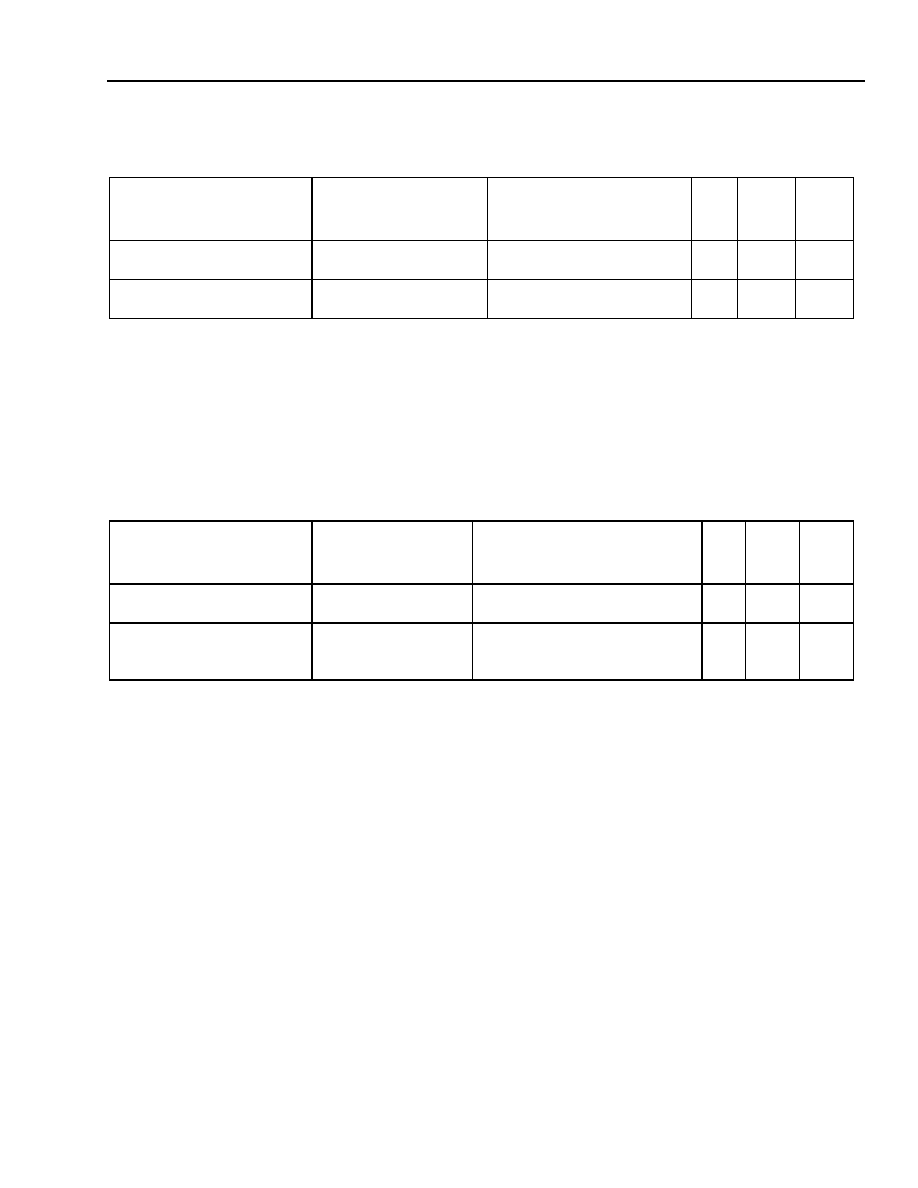

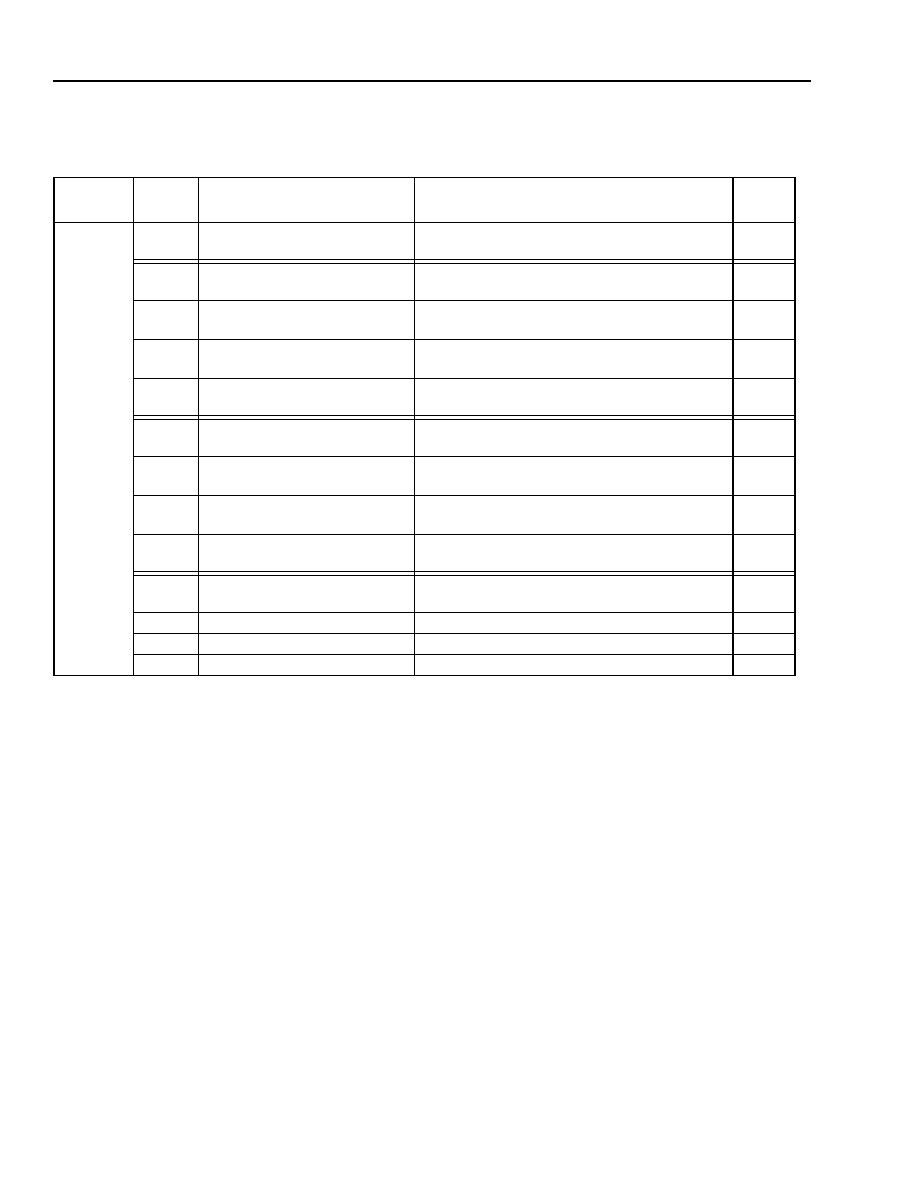

- Table 10. Pin DescriptionsĄTransport Overhead Interface

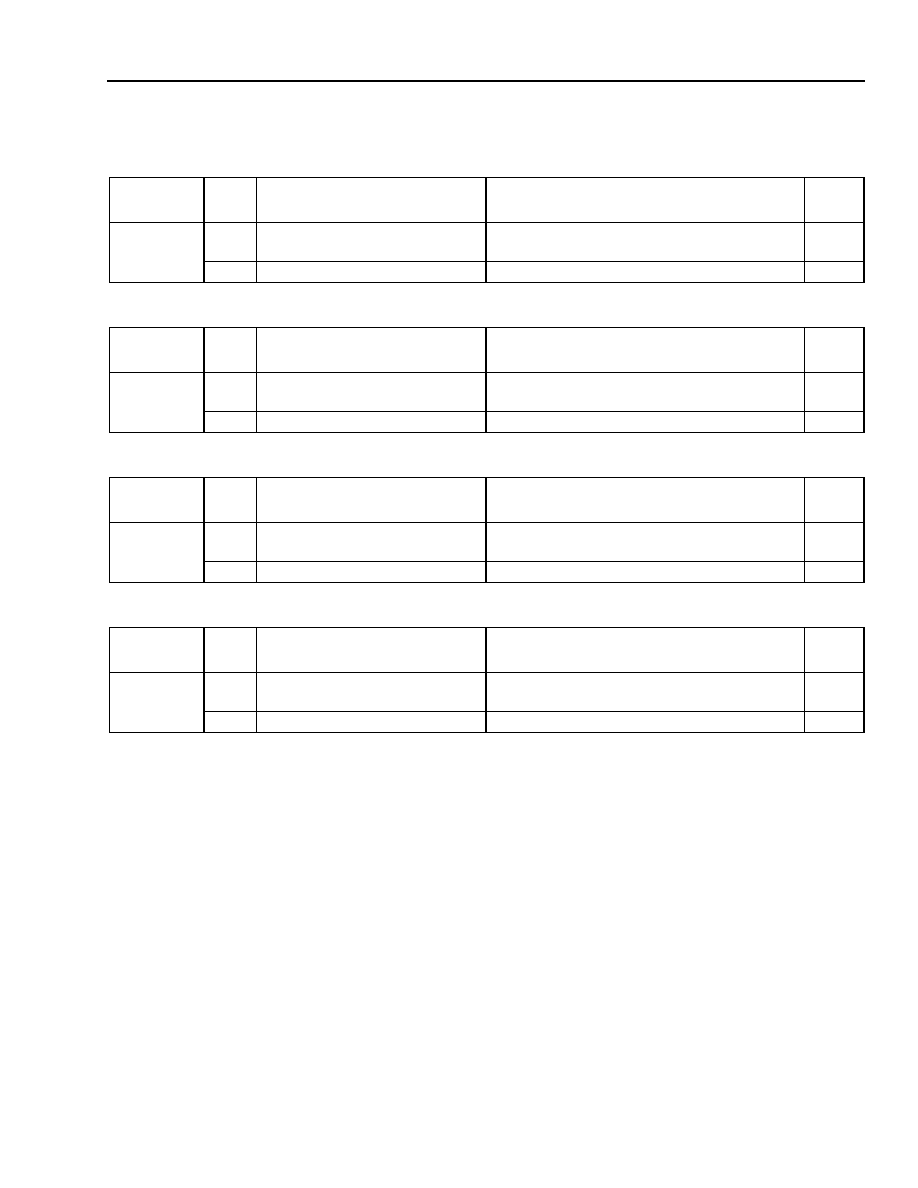

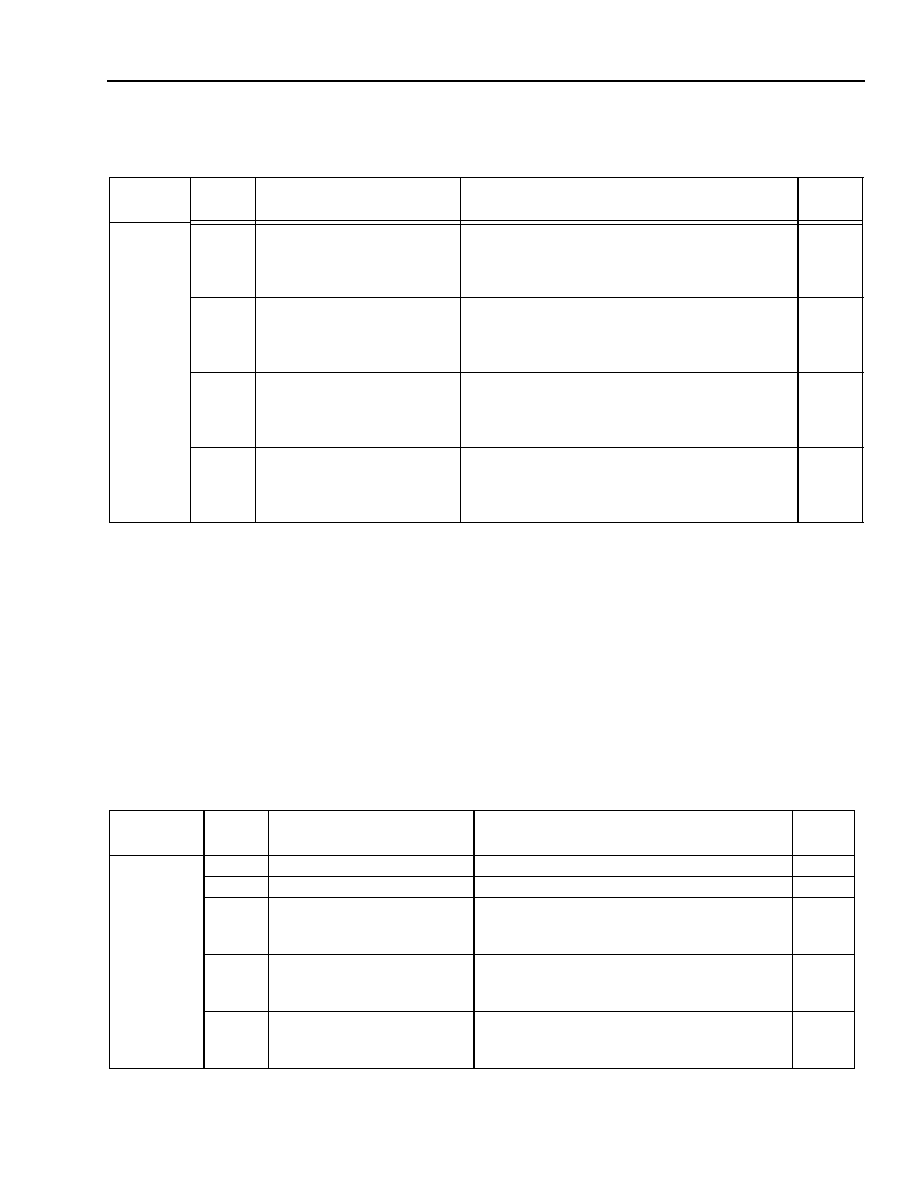

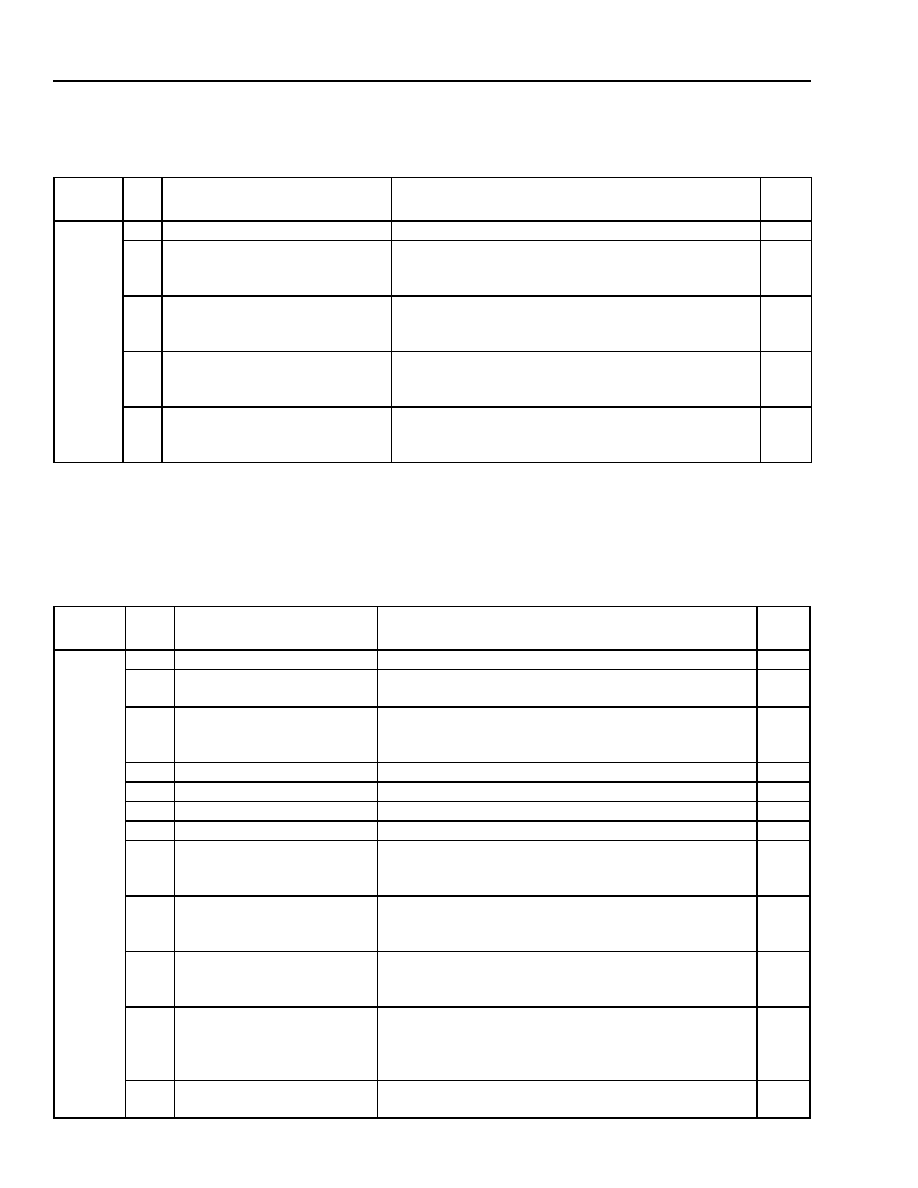

- Table 11. Pin DescriptionsĄMicroprocessor Interface

- Table 12. Pin DescriptionsĄJTAG Interface

- Table 13. Pin DescriptionsĄPLL References

- Table 14. Pin DescriptionsĄPower and Ground

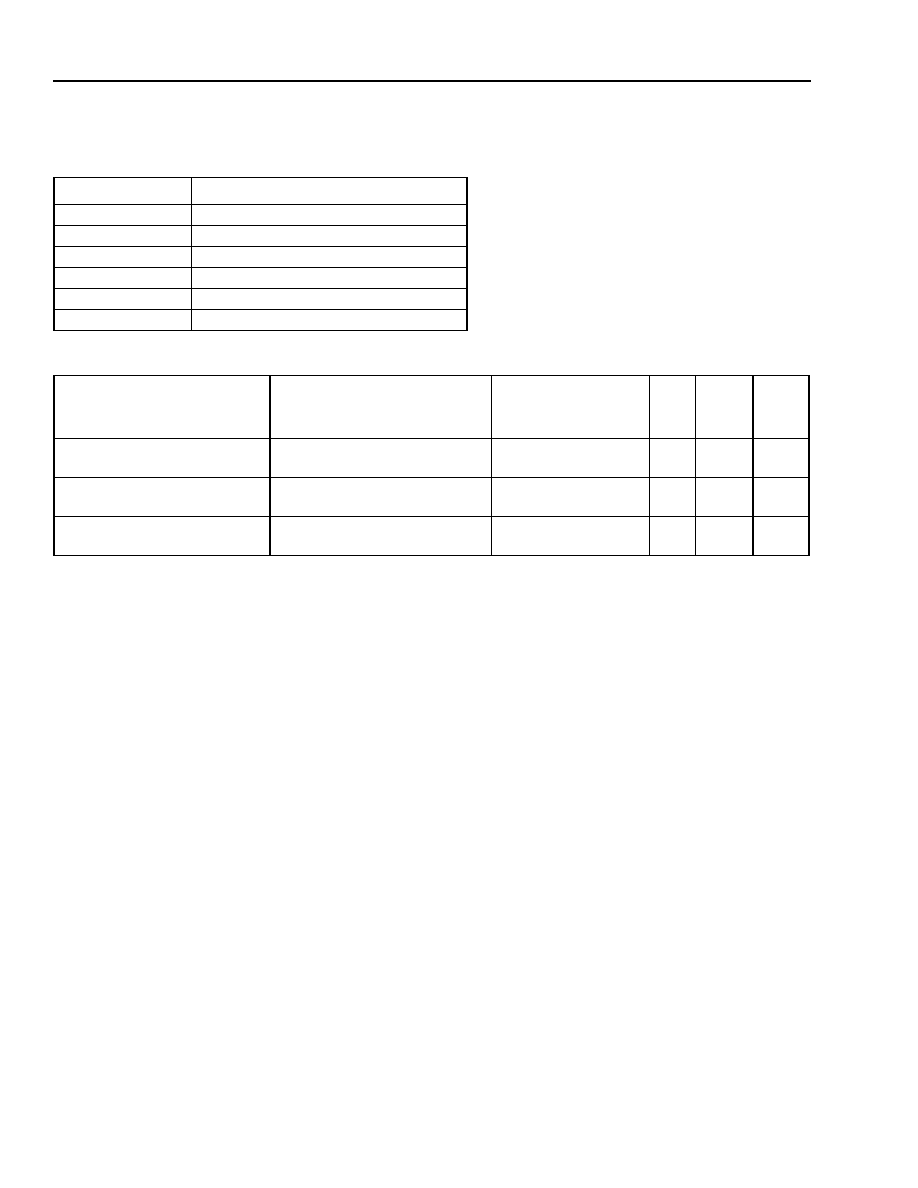

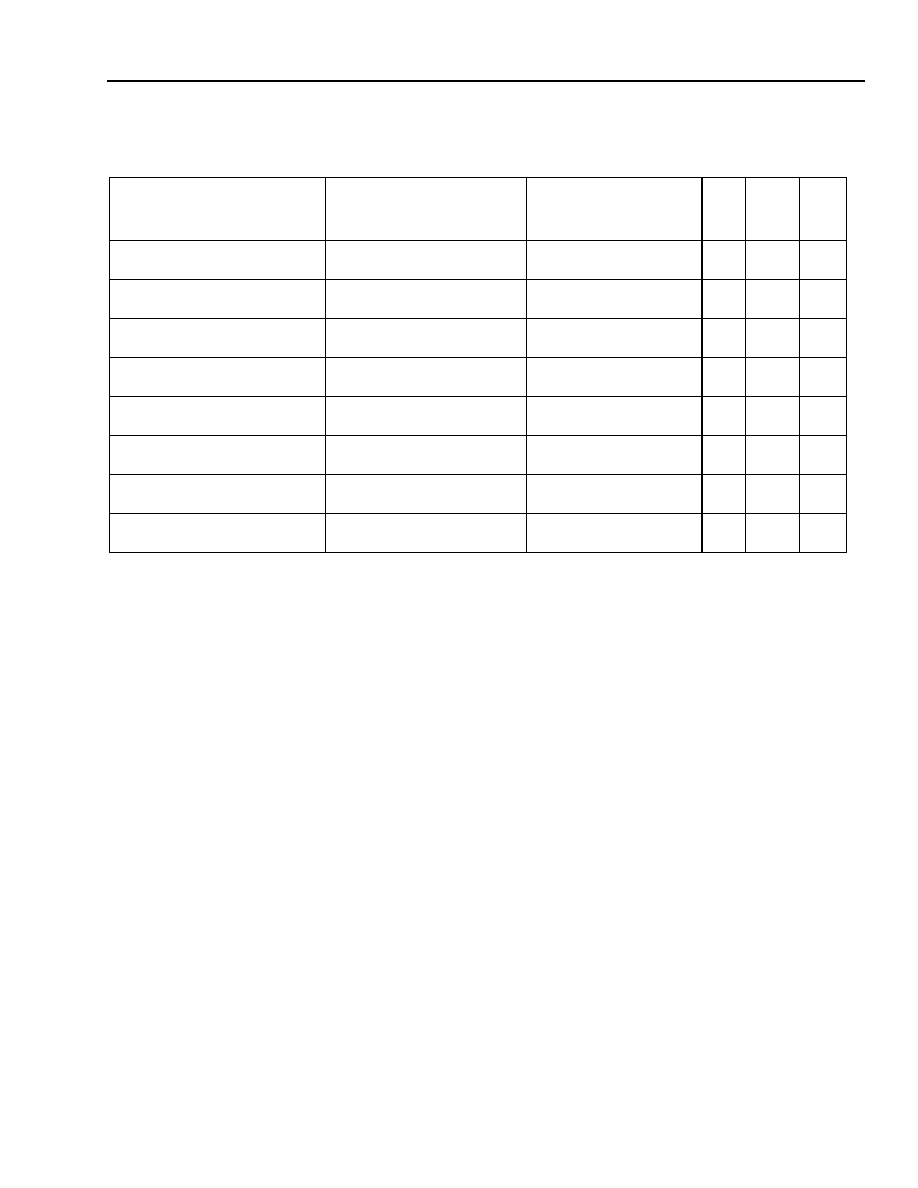

- Table 15. Pin Summary

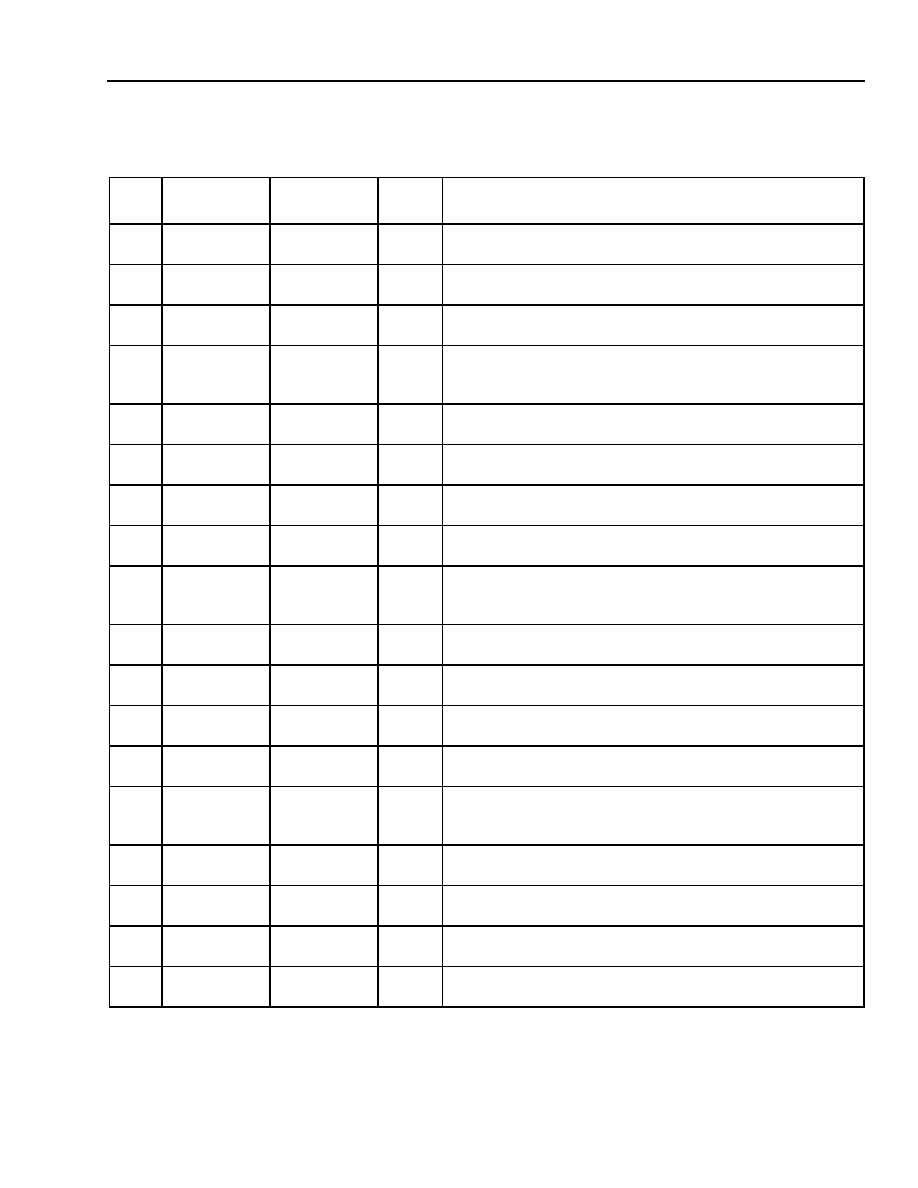

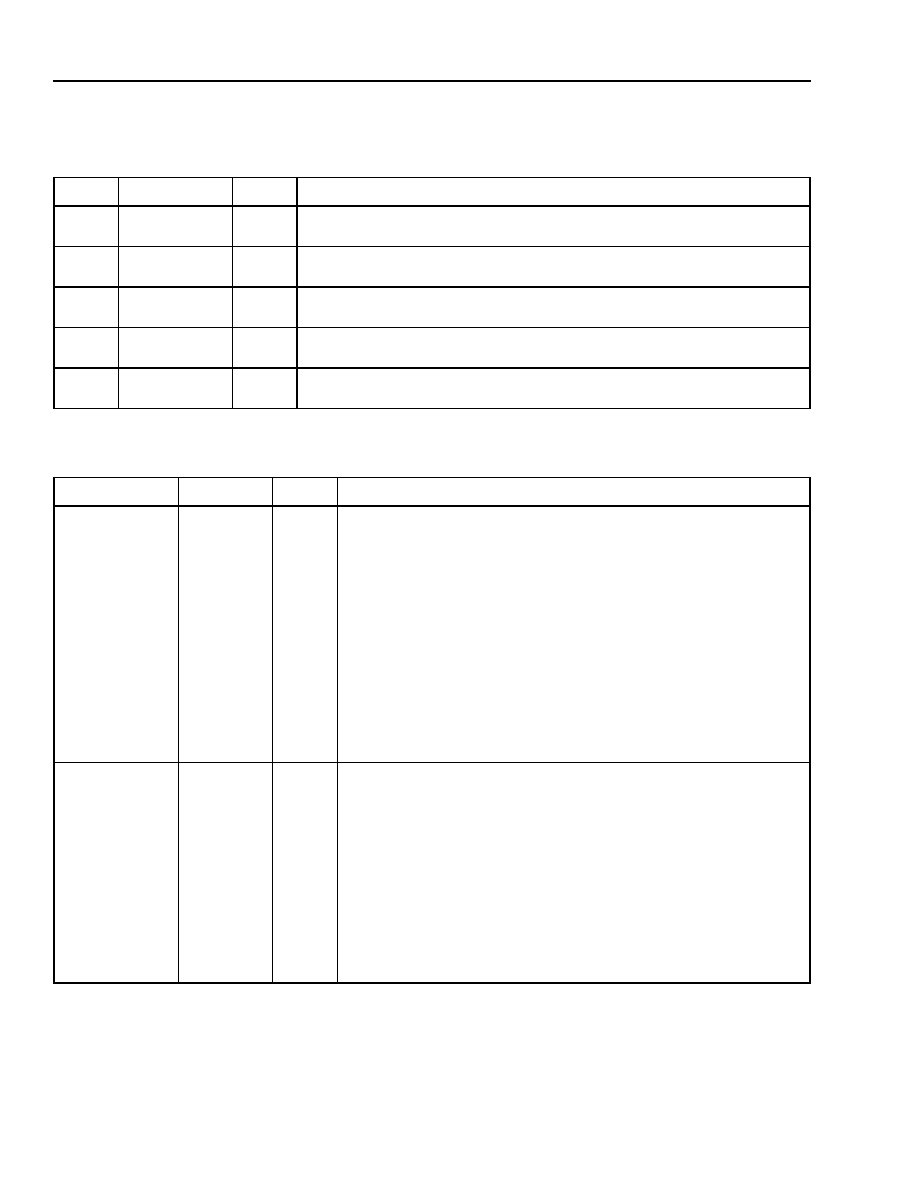

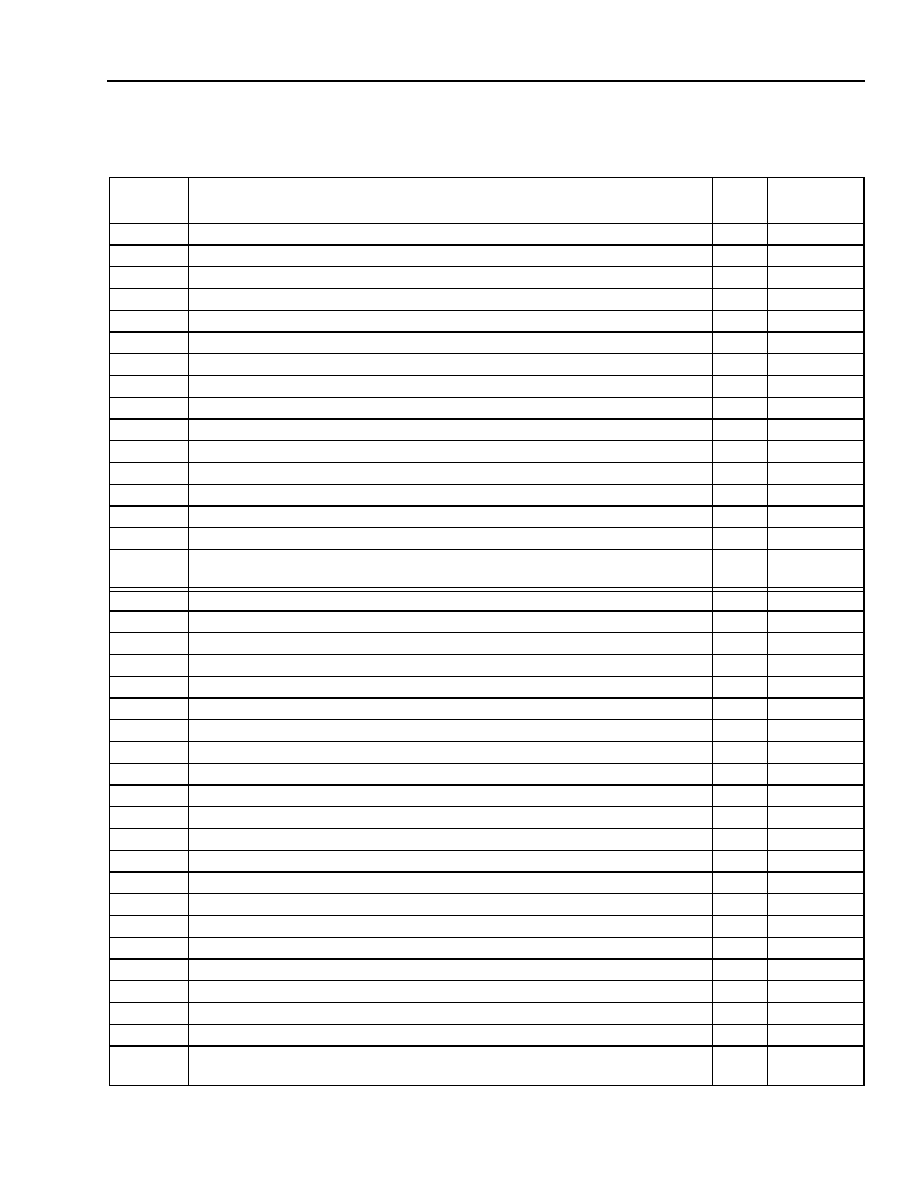

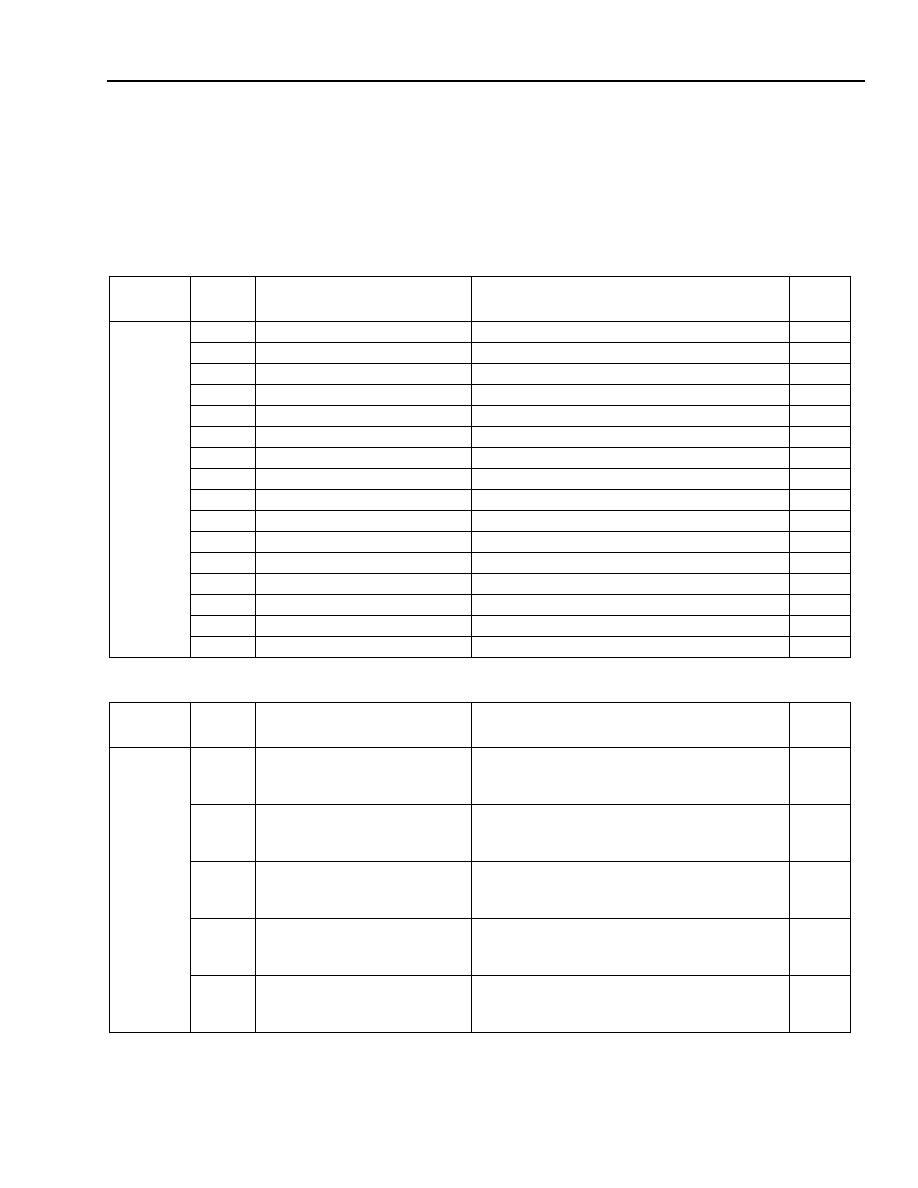

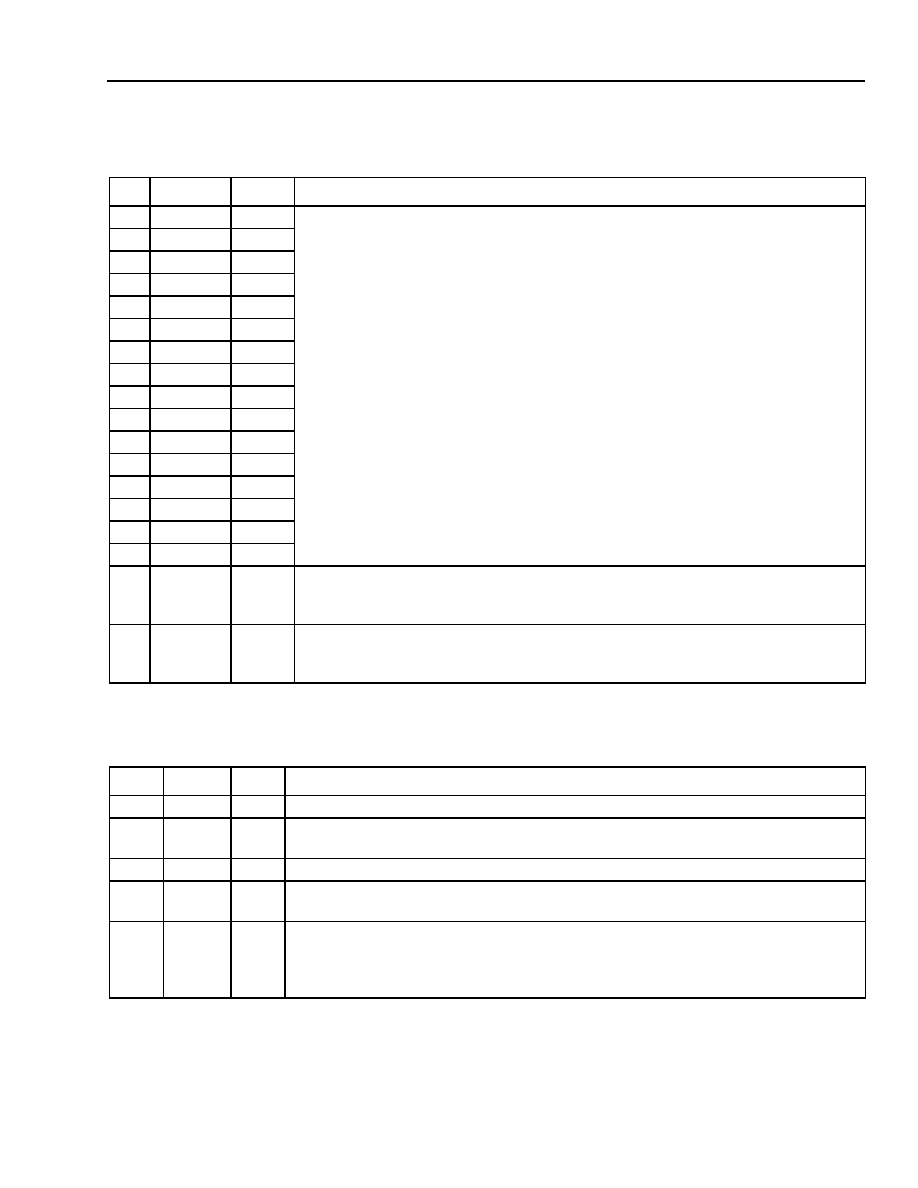

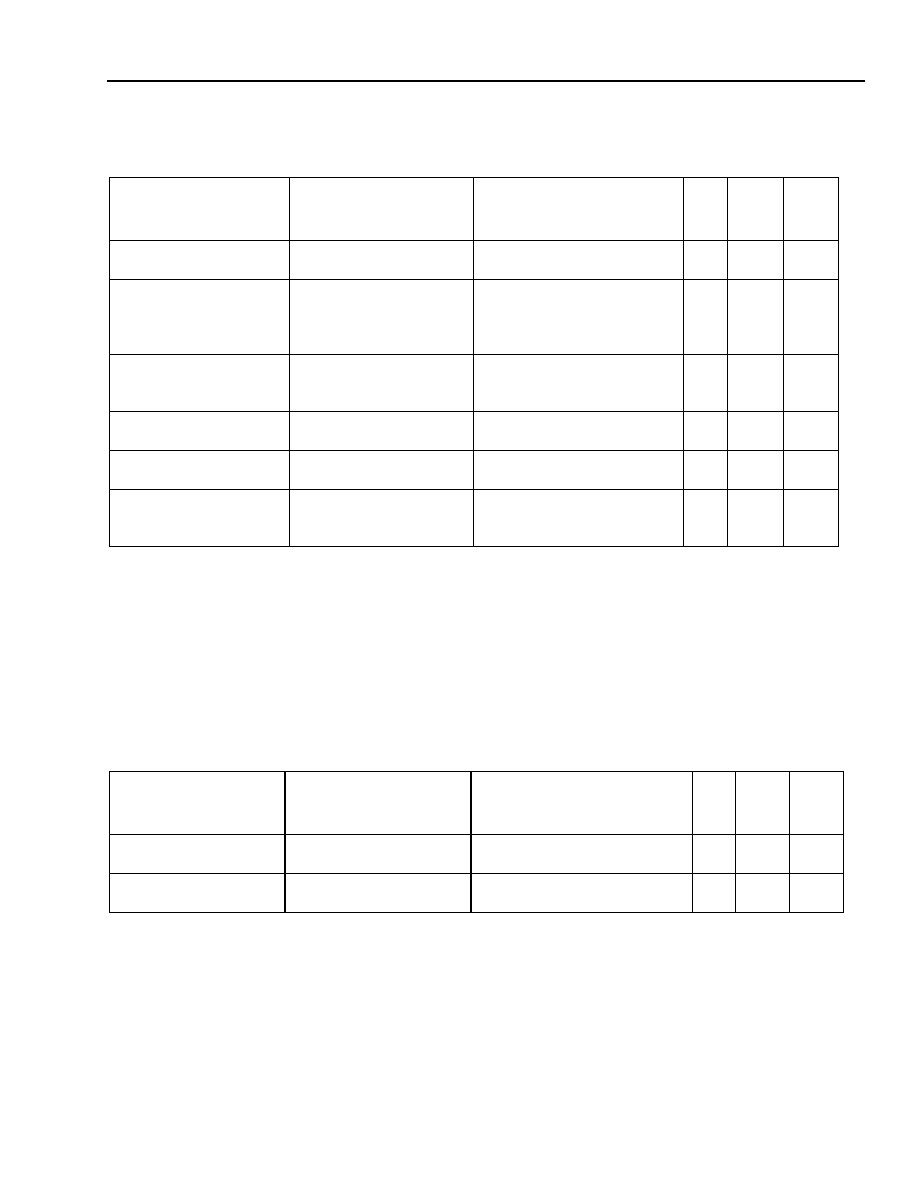

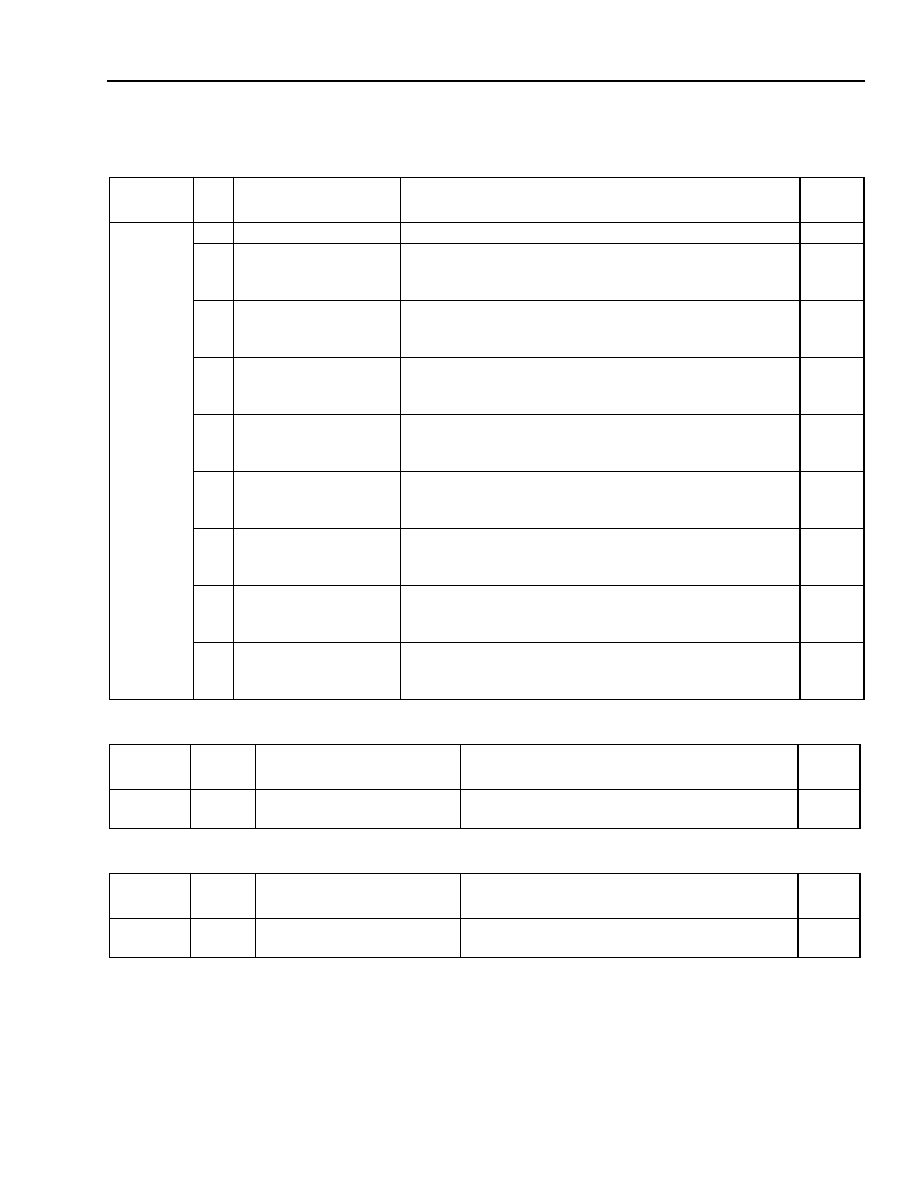

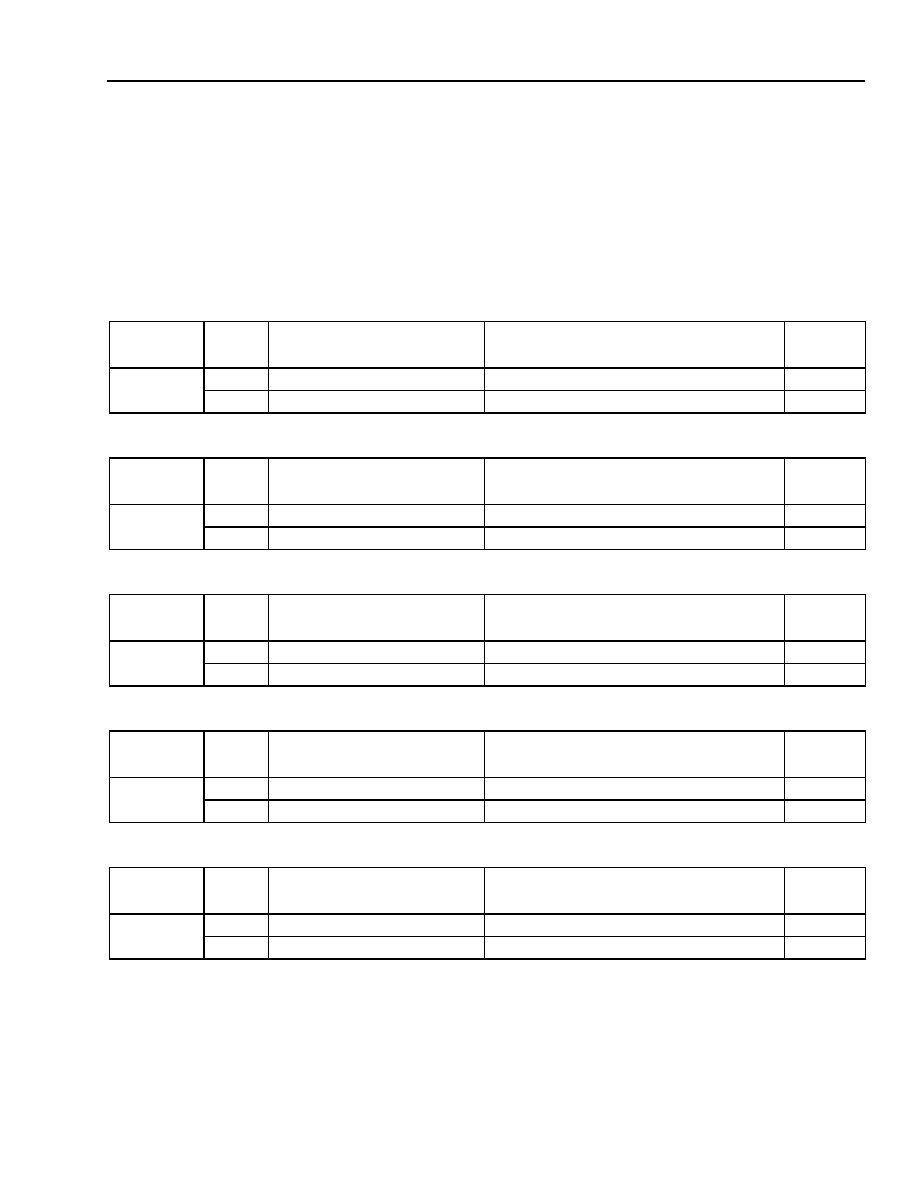

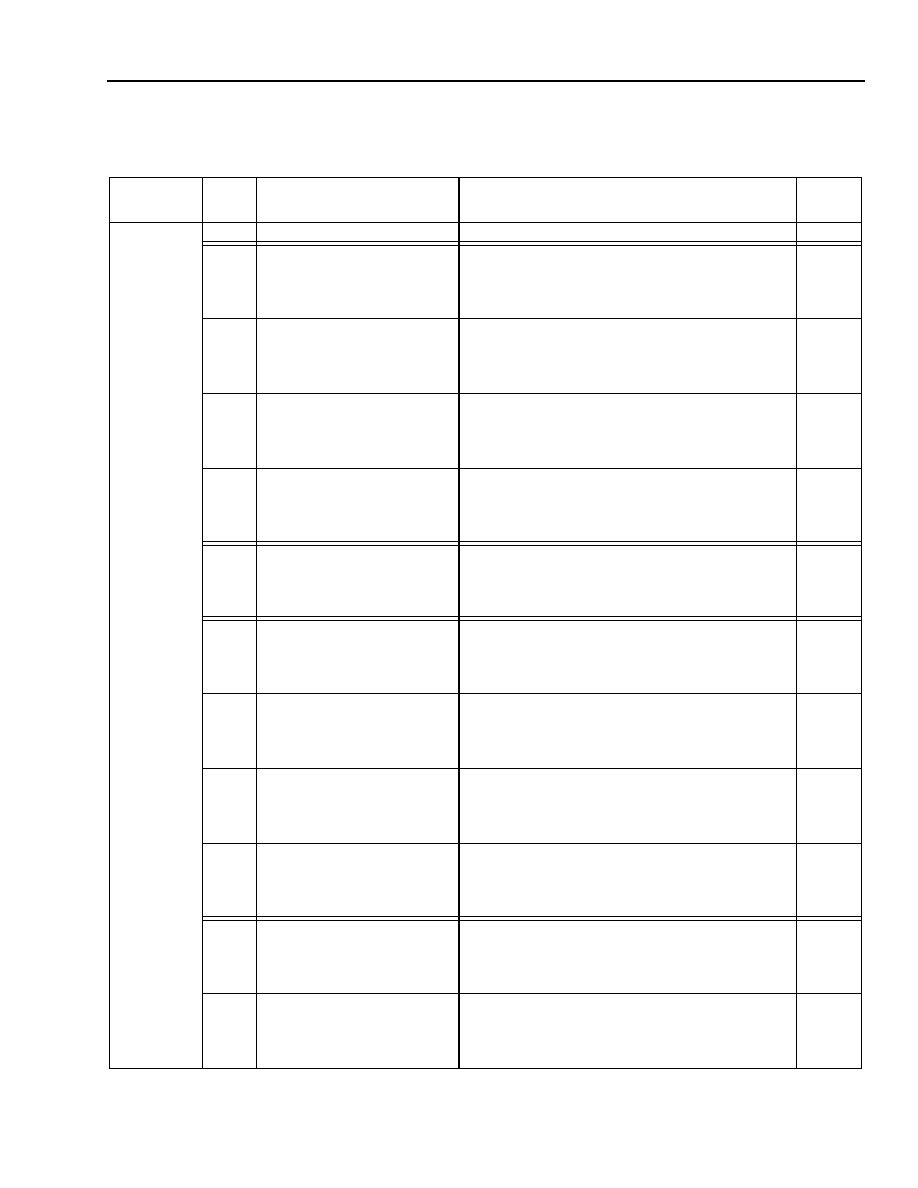

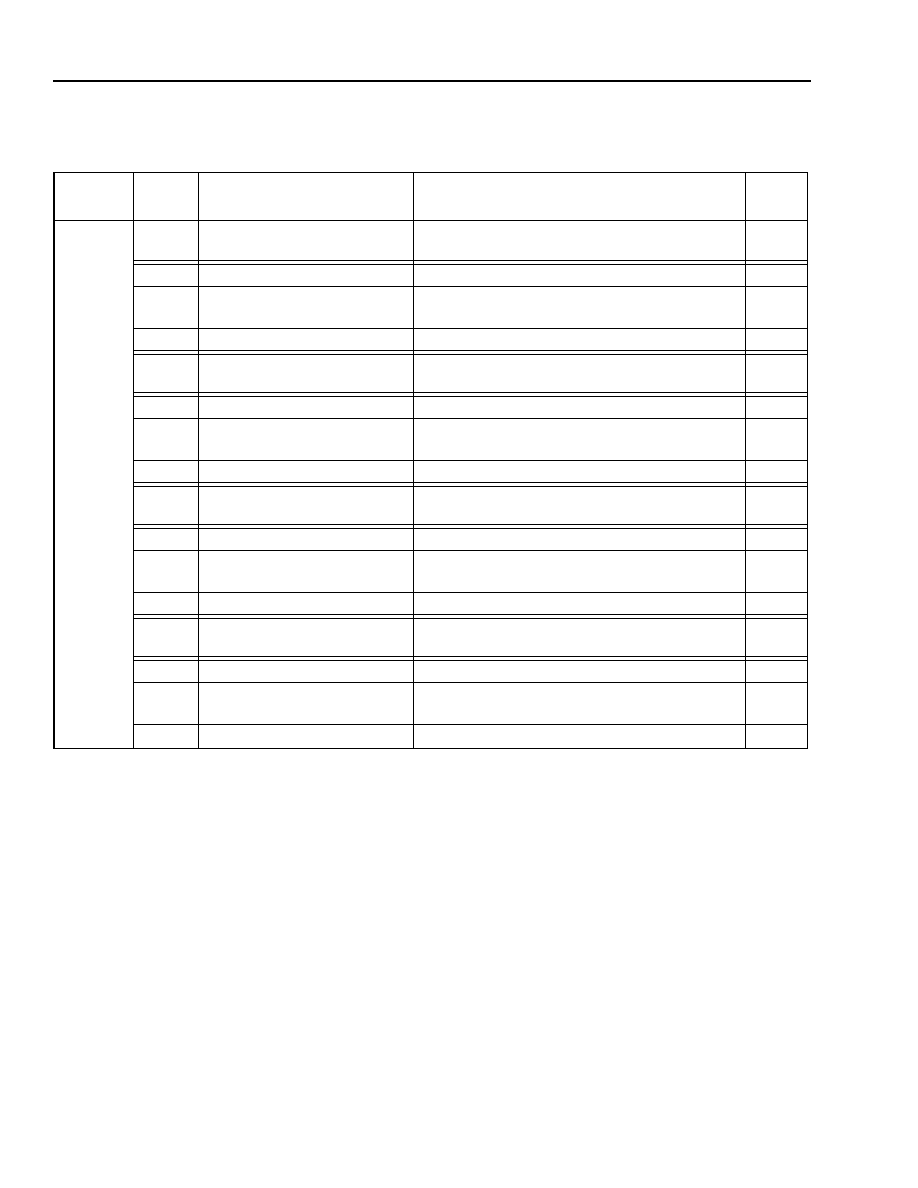

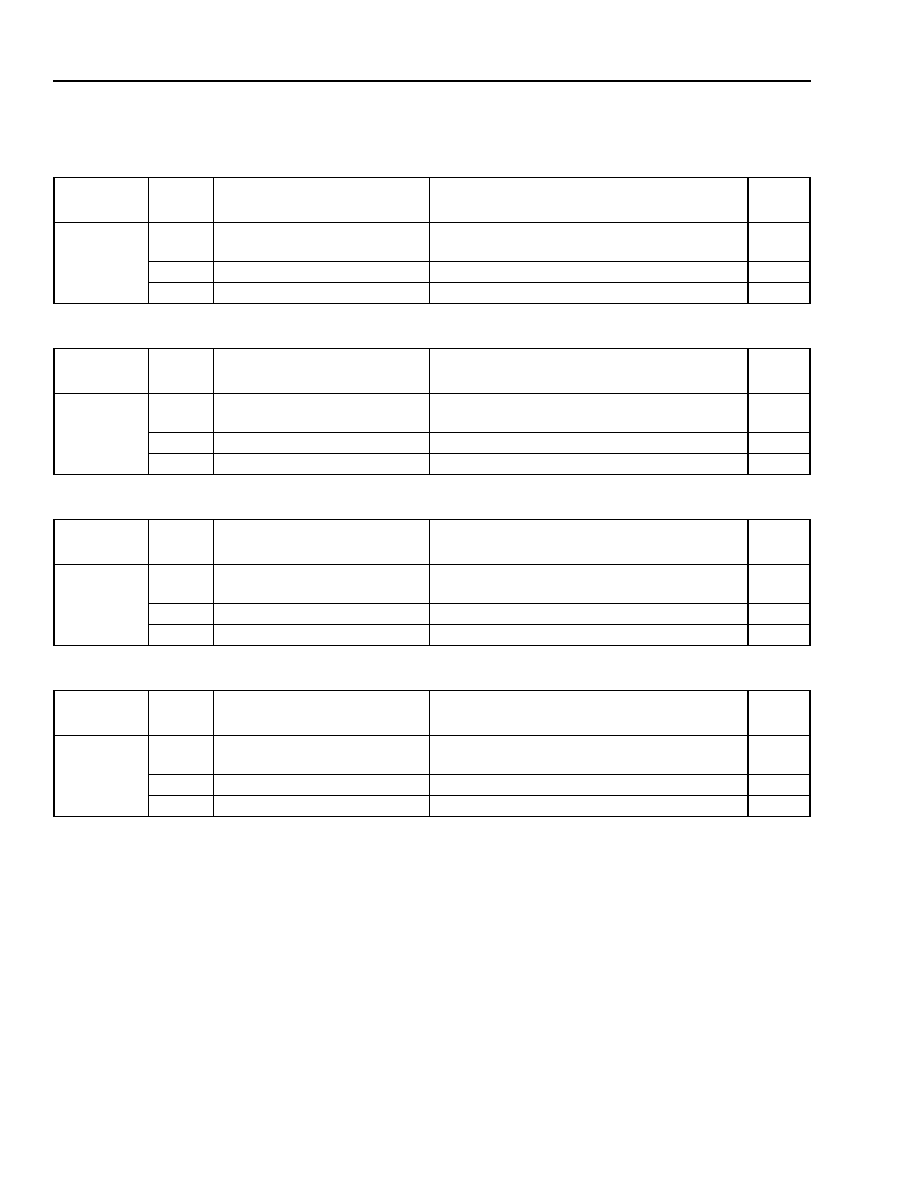

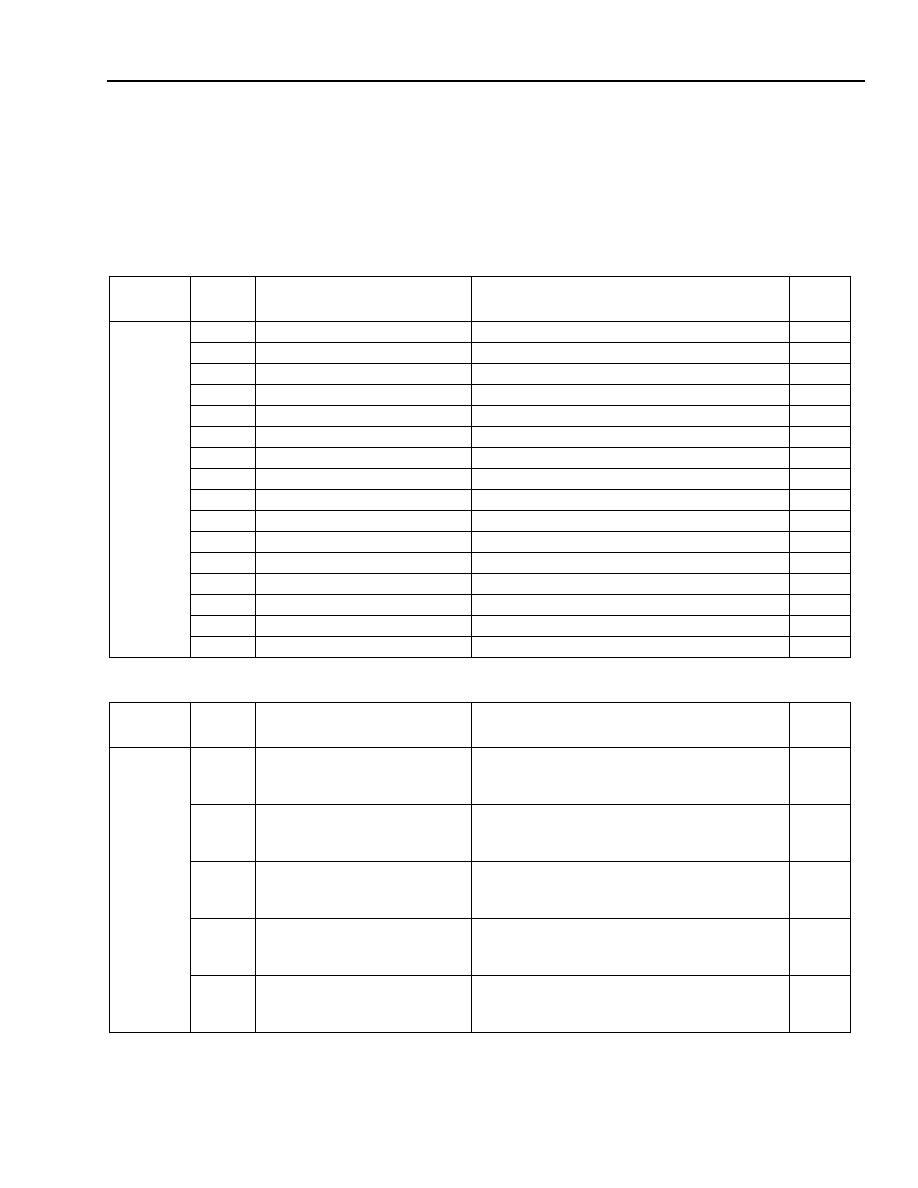

- Table 16. LOS Detector Register Summary

- Table 17. Framer Register Summary

- Table 18. Descrambler Register Summary

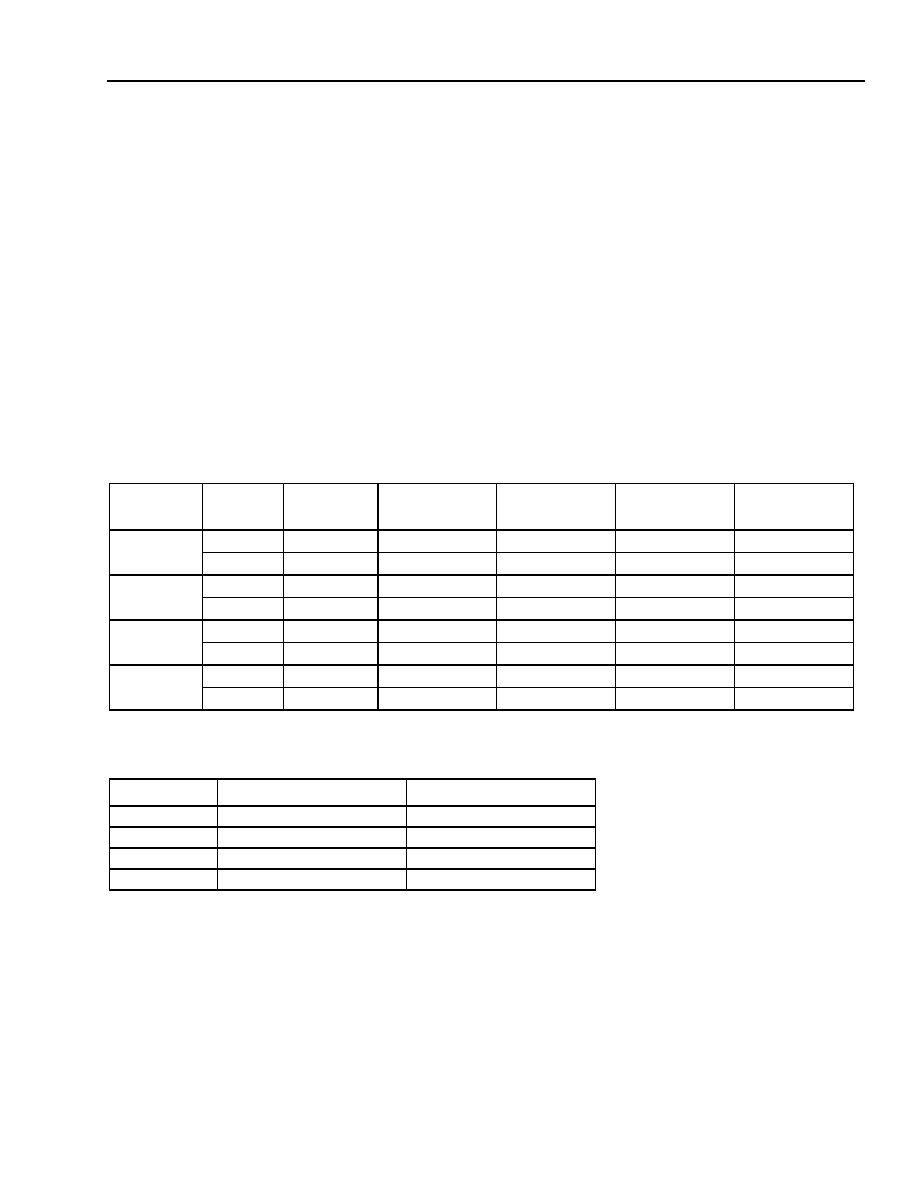

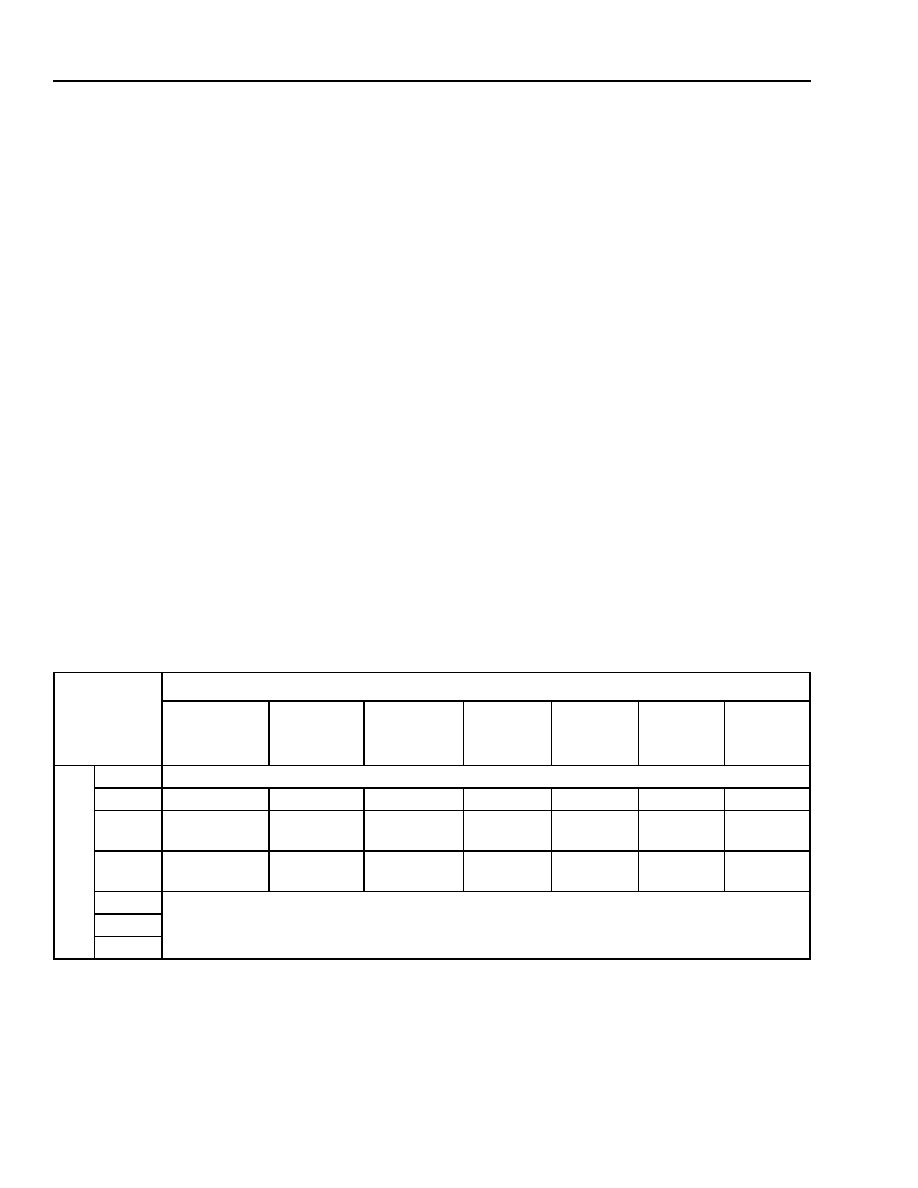

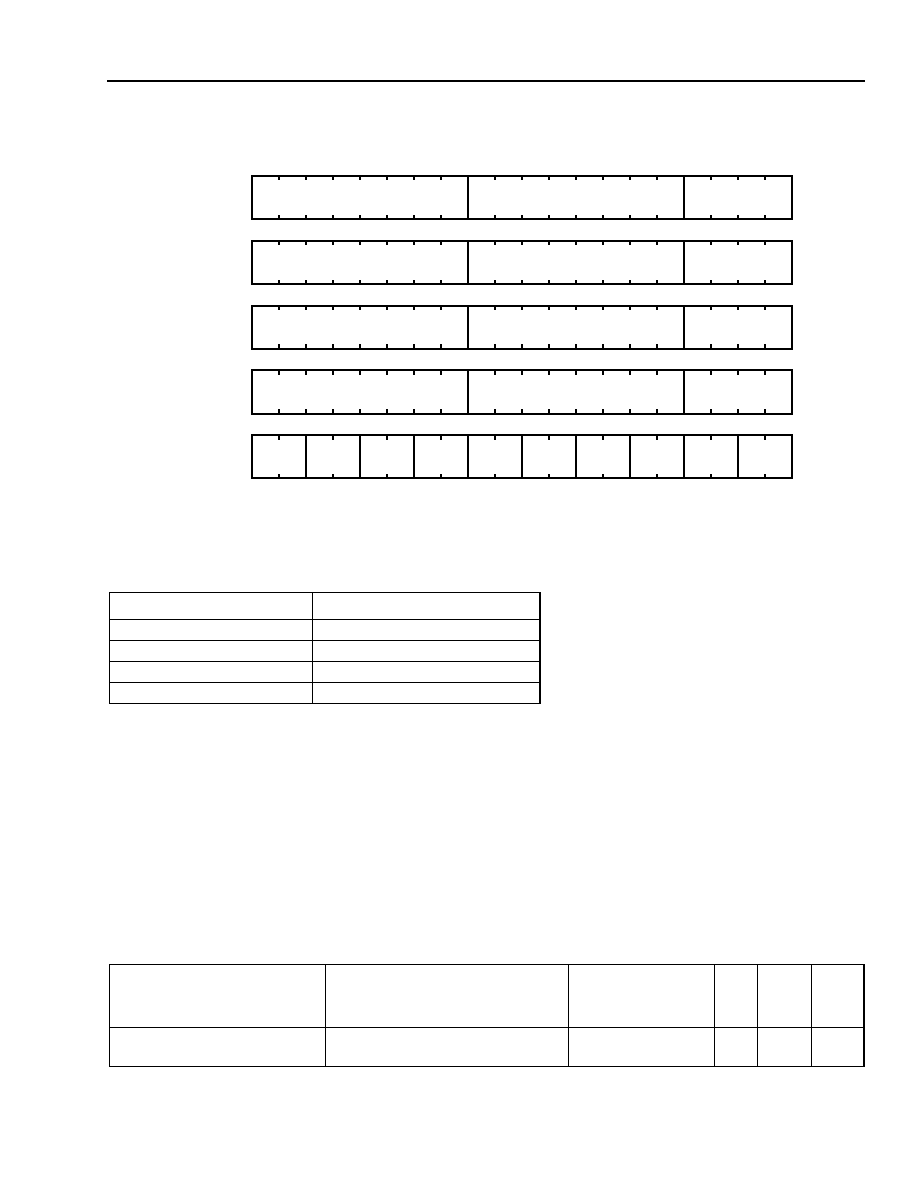

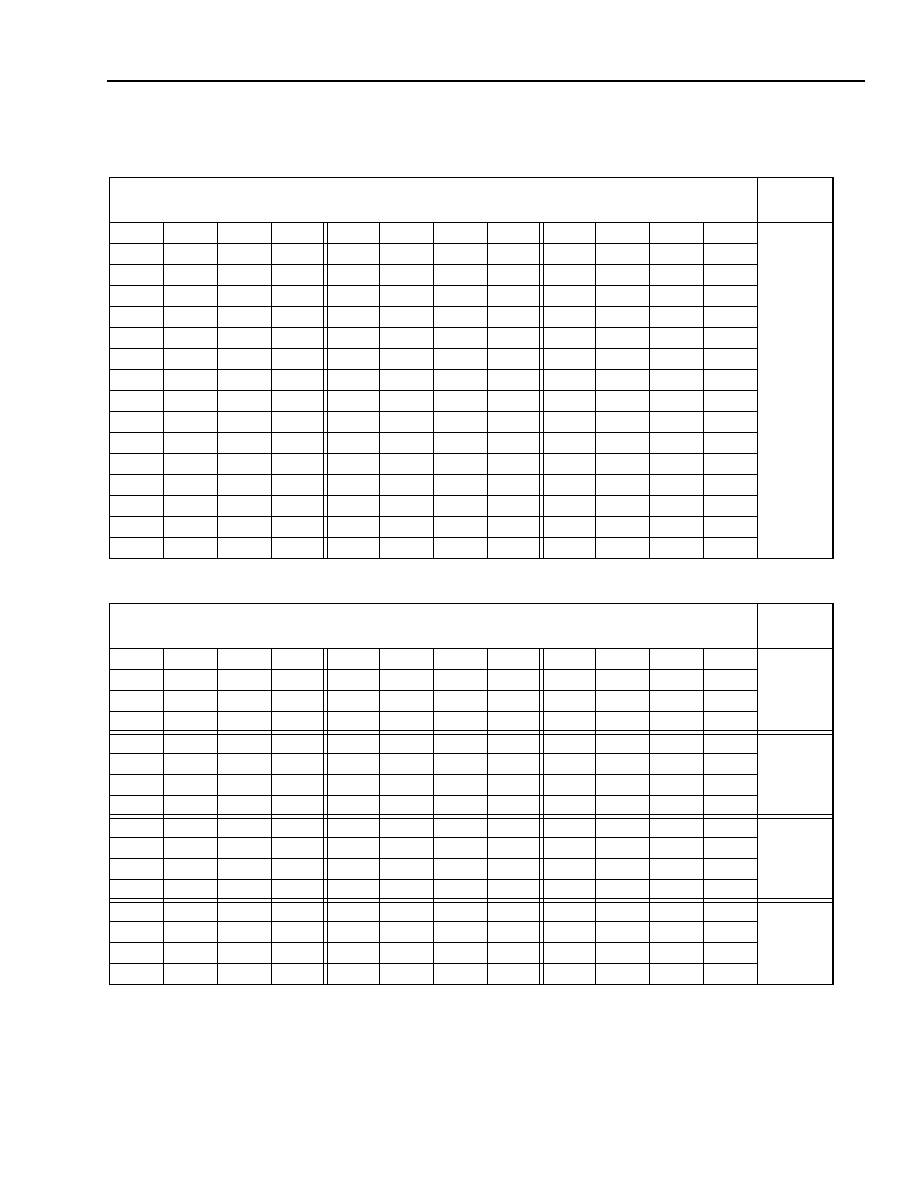

- Table 19. STS-192 Byte Ordering

- Table 20. STS-48 Byte Ordering

- Table 21. Receive Overhead Serial Links Register Summary

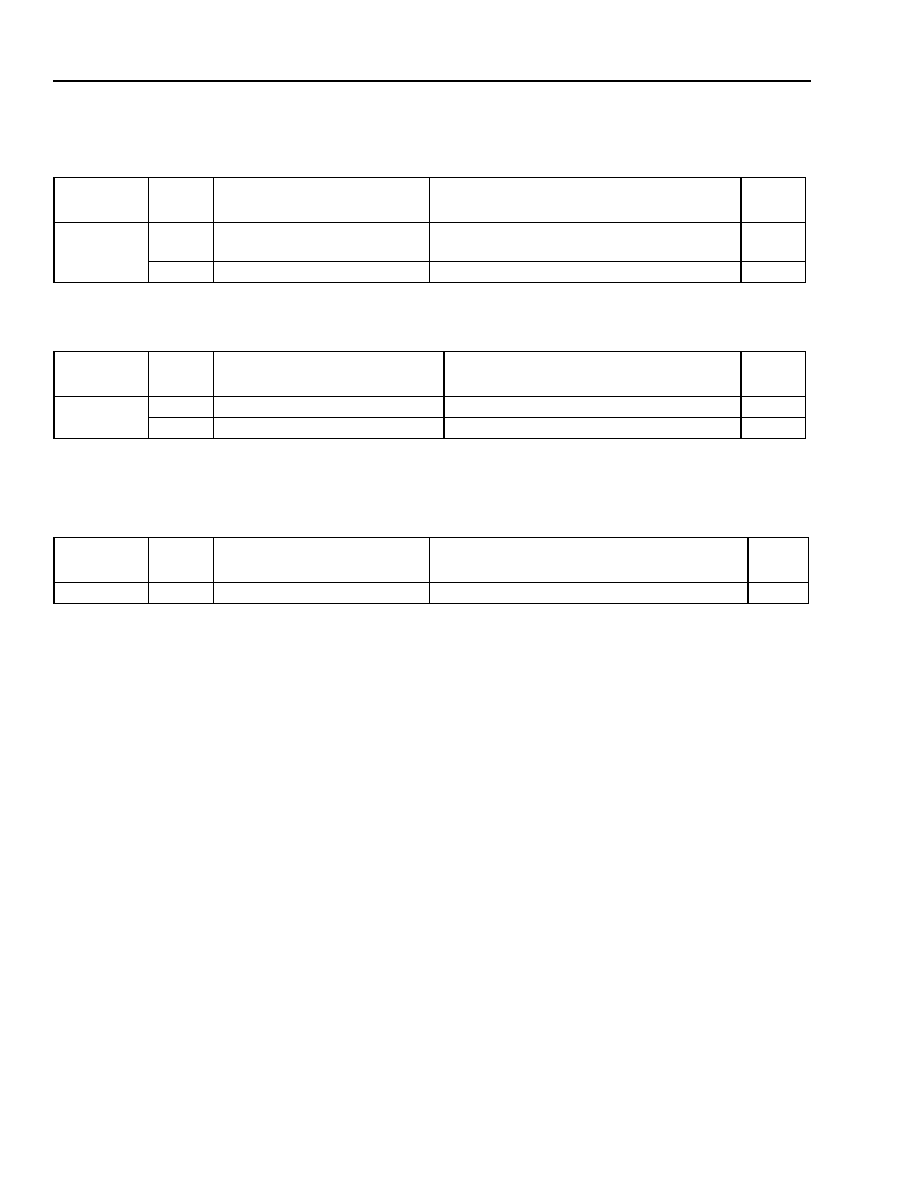

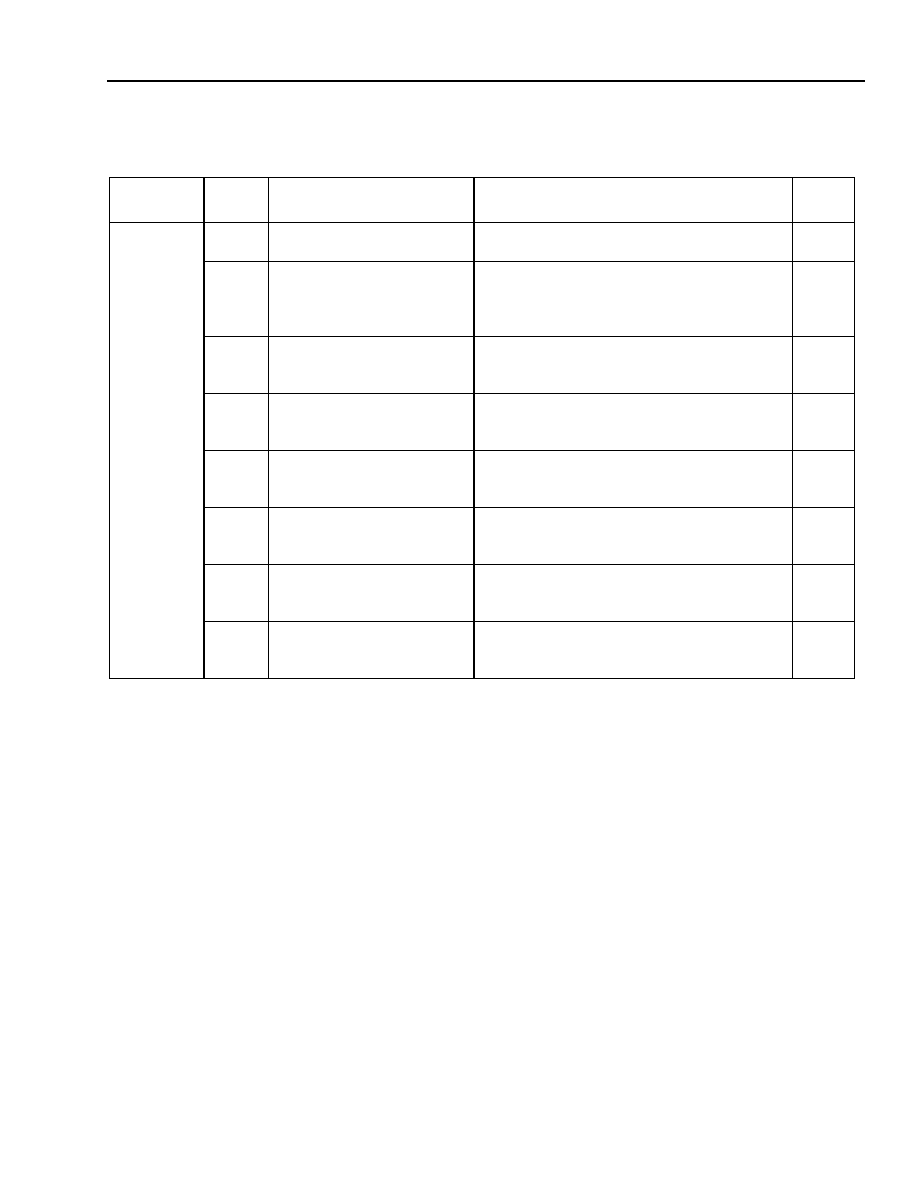

- Table 22. J0 Register Summary

- Table 23. B1 Register Summary

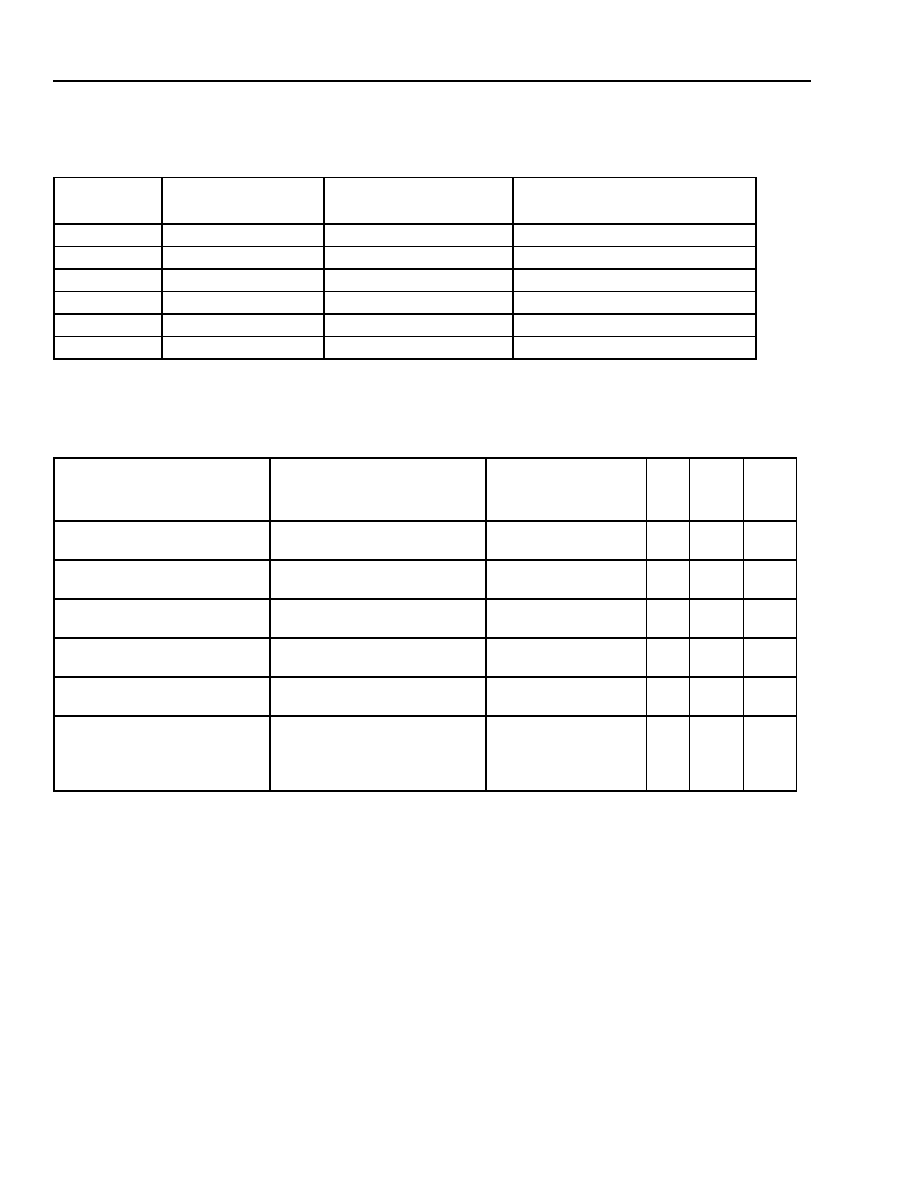

- Table 24. BER Threshold Time and Error Limits for Line SD and SF Detection

- Table 25. B2 Register Summary

- Table 26. APS Channel (K1 and K2) Register Summary

- Table 27. Synchronization Status (S1) Register Summary

- Table 28. Line REI (M1) Register Summary

- Table 29. STS-12 Byte Ordering

- Table 30. Pointer Interpreter Register Summary

- Table 31. Elastic Store Register Summary

- Table 32. Pointer Generator Bypass Register Summary

- Table 33. AIS-P Insertion Conditions

- Table 34. Path AIS Insertion Register Summary

- Table 35. Concatenation Register Summary

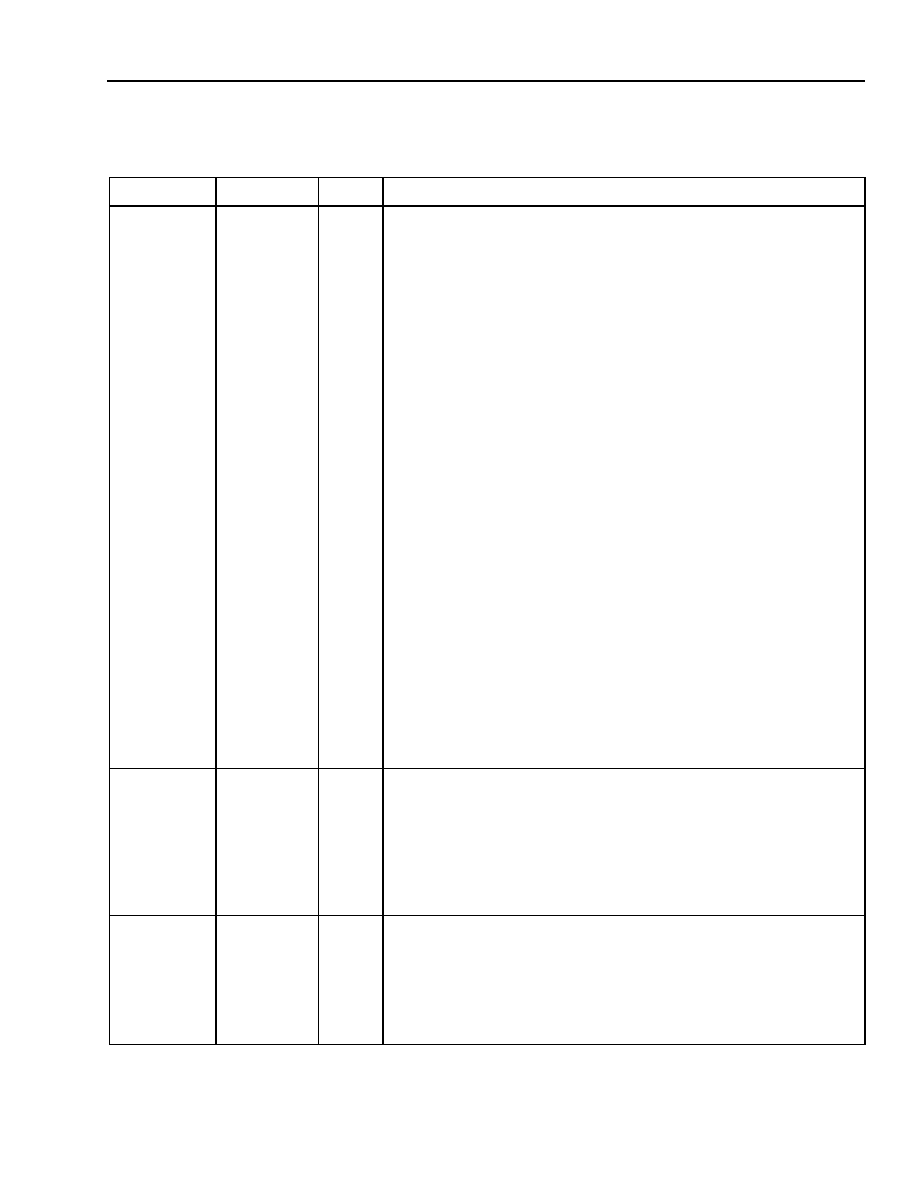

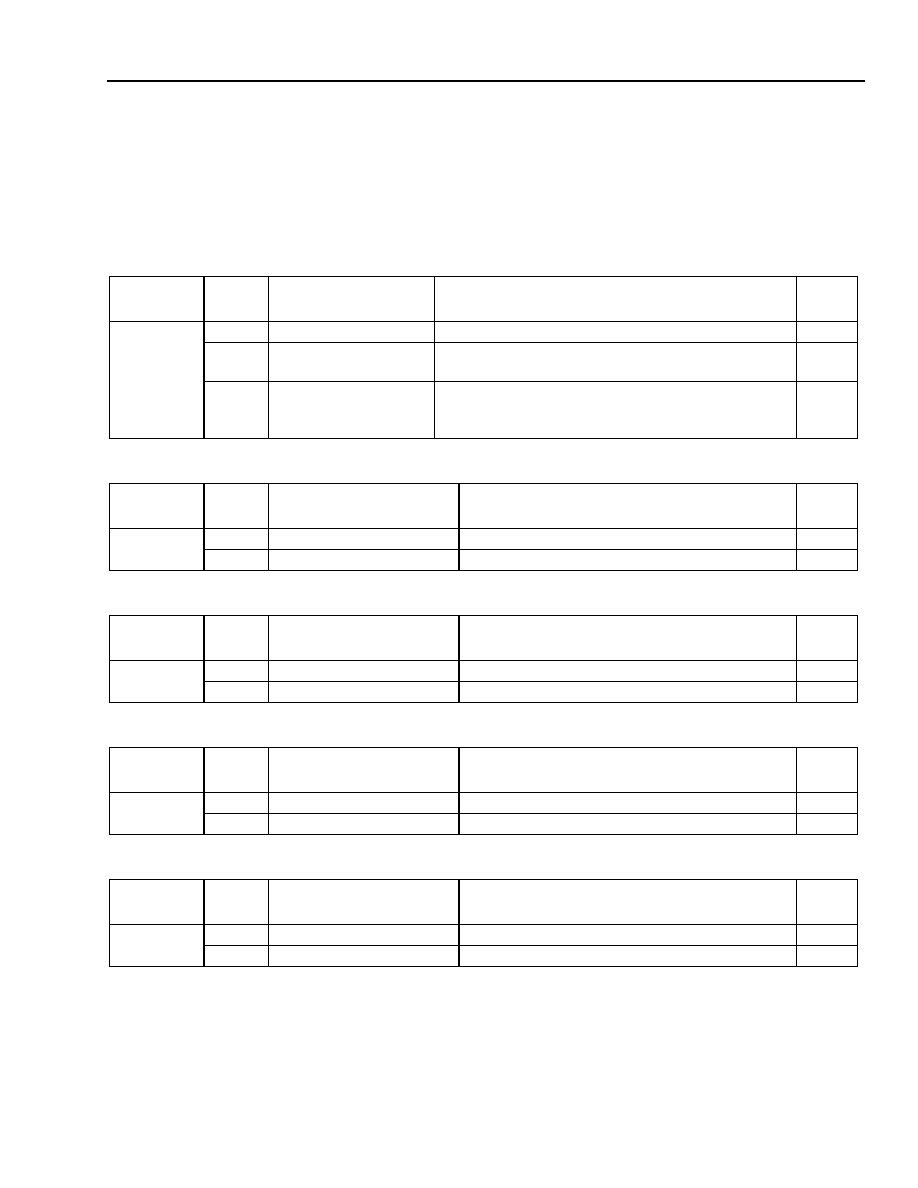

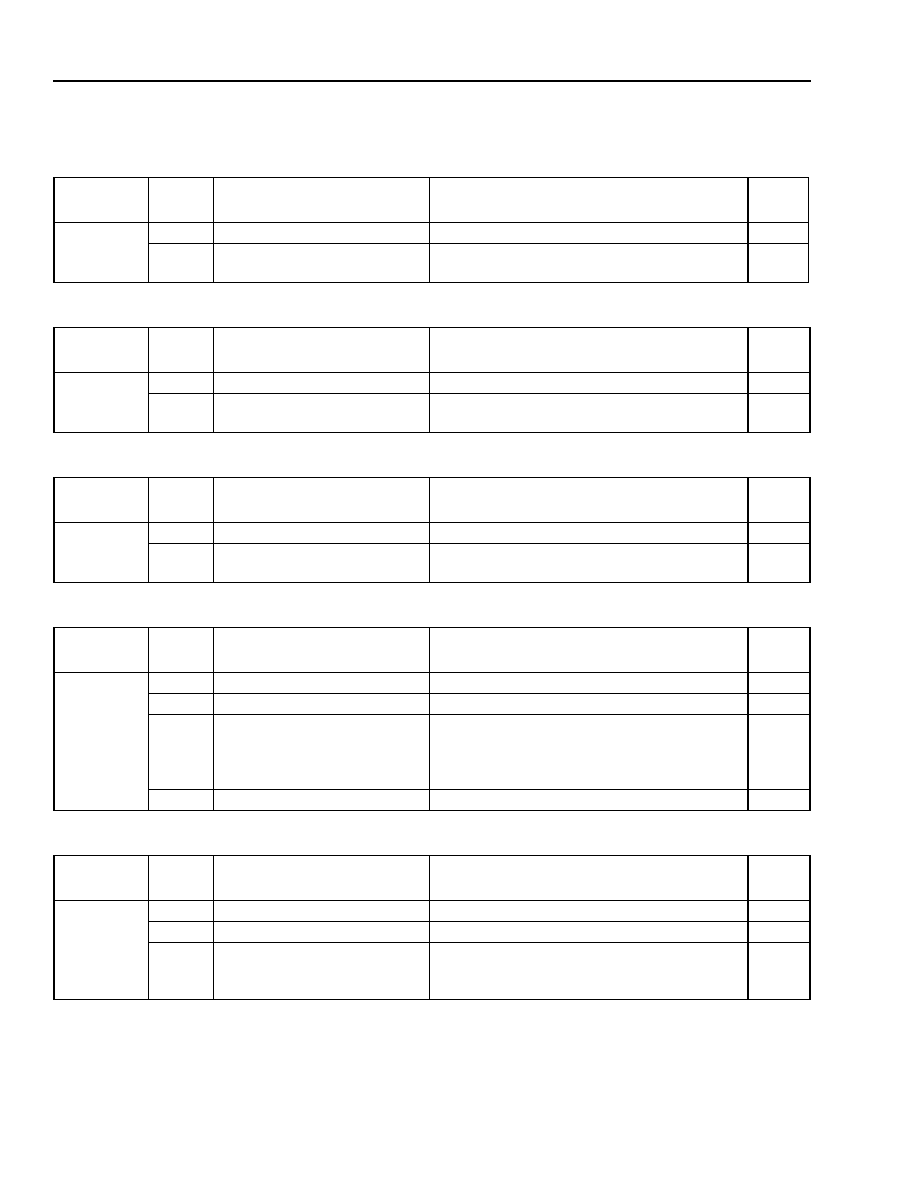

- Table 36. Pointer Justification Binning Register Summary

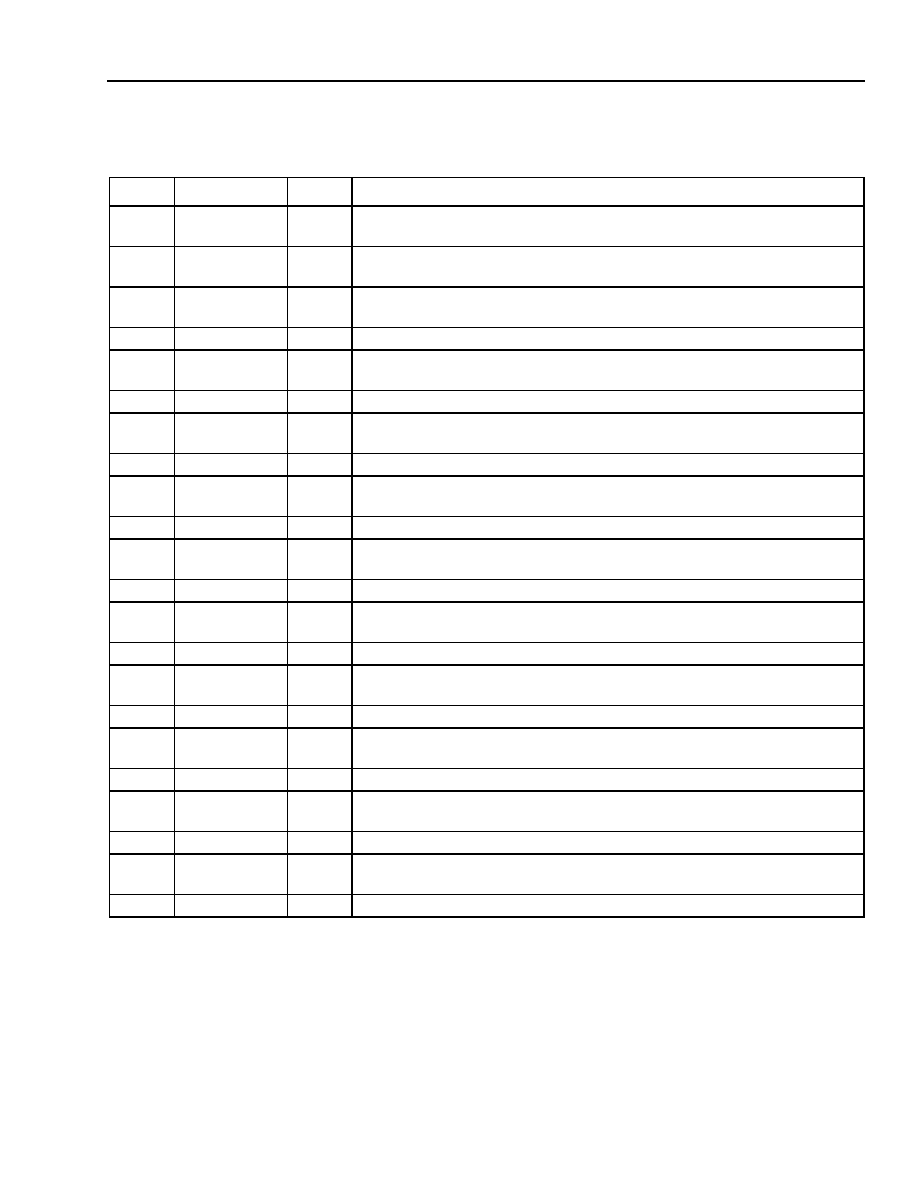

- Table 37. J1 Register Summary

- Table 38. BER Threshold Time Window and Error Limits for Path SF Detection

- Table 39. Time Window Sizes for Path SF Detection

- Table 40. B3 Register Summary

- Table 41. STS Path Signal Label Assignments

- Table 42. Path Signal Label (C2) Alarm Scenarios

- Table 43. C2 Register Summary

- Table 44. RDI-P Codes and Interpretation

- Table 45. G1 Register Summary

- Table 46. Path Alarm Information Encoding

- Table 47. Line Alarm Information Encoding

- Table 48. Drop Interface Overhead and Scrambling Register Summary

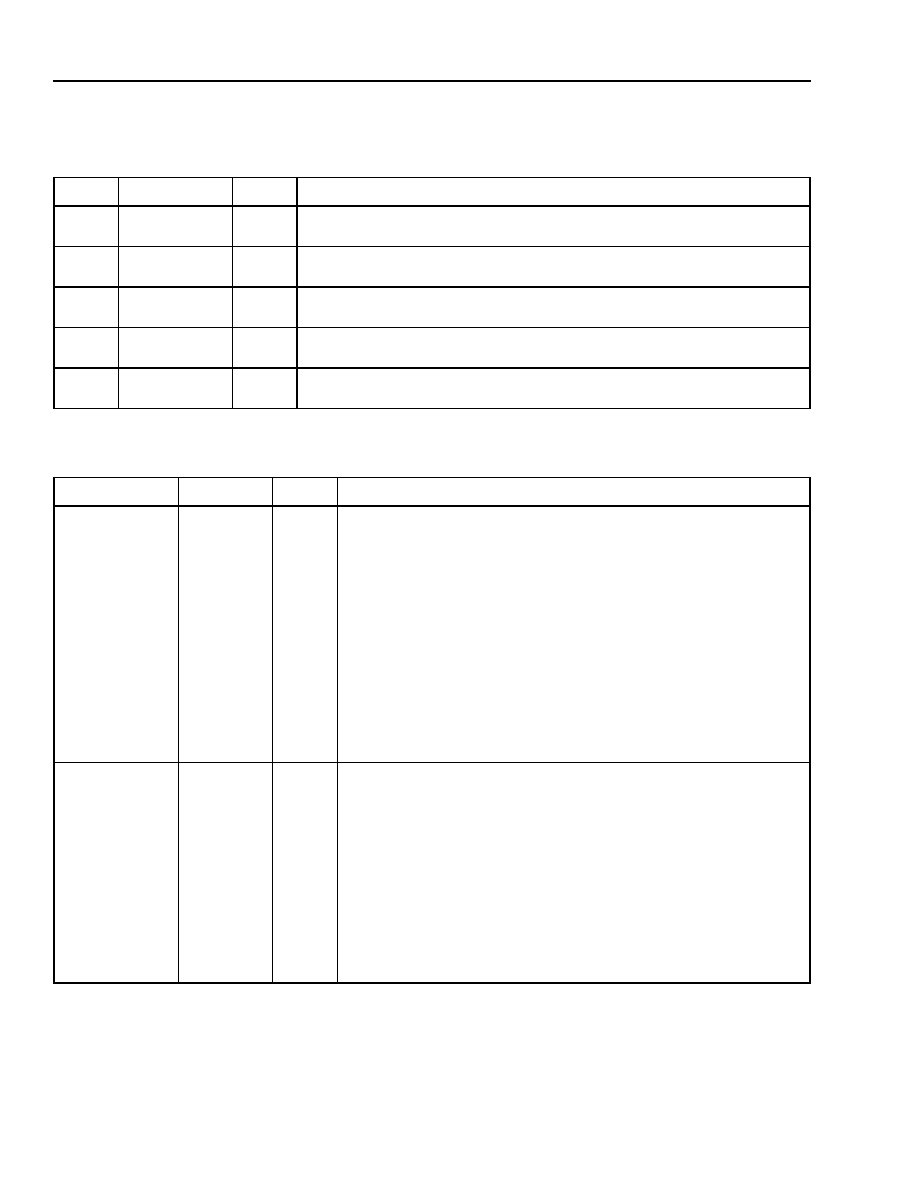

- Table 49. Timing Enable Bit Definitions

- Table 50. Receive Data Path Parity Register Summary

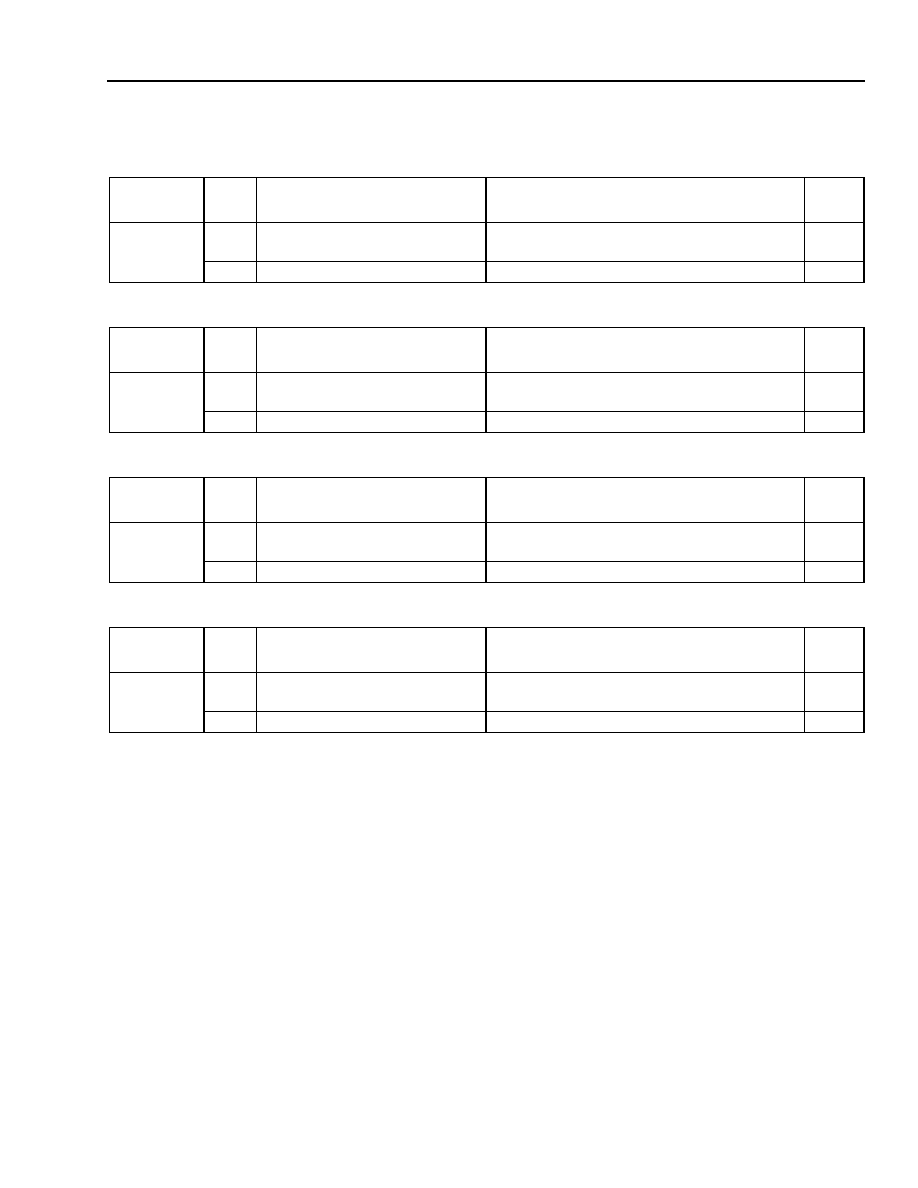

- Table 51. LTE Transmit Channel RegistersĄRegenerator Loopback Summary

- Table 52. Regenerator Loopback Bit Definitions

- Table 53. Path AIS Insertion Encoding

- Table 54. Add Interface Overhead and Scrambling Register Summary

- Table 55. Transmit Synchronization Buffer Register Summary

- Table 56. Frame Pulse Provisioning Bit Definitions

- Table 57. Transmit Framing Register Summary

- Table 58. LTE Transmit Channel RegistersĄTOH Transparency Summary

- Table 59. TOH Transparency Bit Definitions

- Table 60. Transmit Overhead Serial Links Register Summary

- Table 61. Transmit Section Trace (J0) Register Summary

- Table 62. Transmit B1 Register Summary

- Table 63. Transmit STS Payload Pointer Register Summary

- Table 64. Transmit B2 Register Summary

- Table 65. K Byte Select Control Bits

- Table 66. Transmit APS Channel (K1K2) Register Summary

- Table 67. Transmit Synchronization Status (S1) Register Summary

- Table 68. Transmit M1 Register Summary

- Table 69. Transmit Line Scrambler Register Summary

- Table 70. Transmit Data Path Parity Register Summary

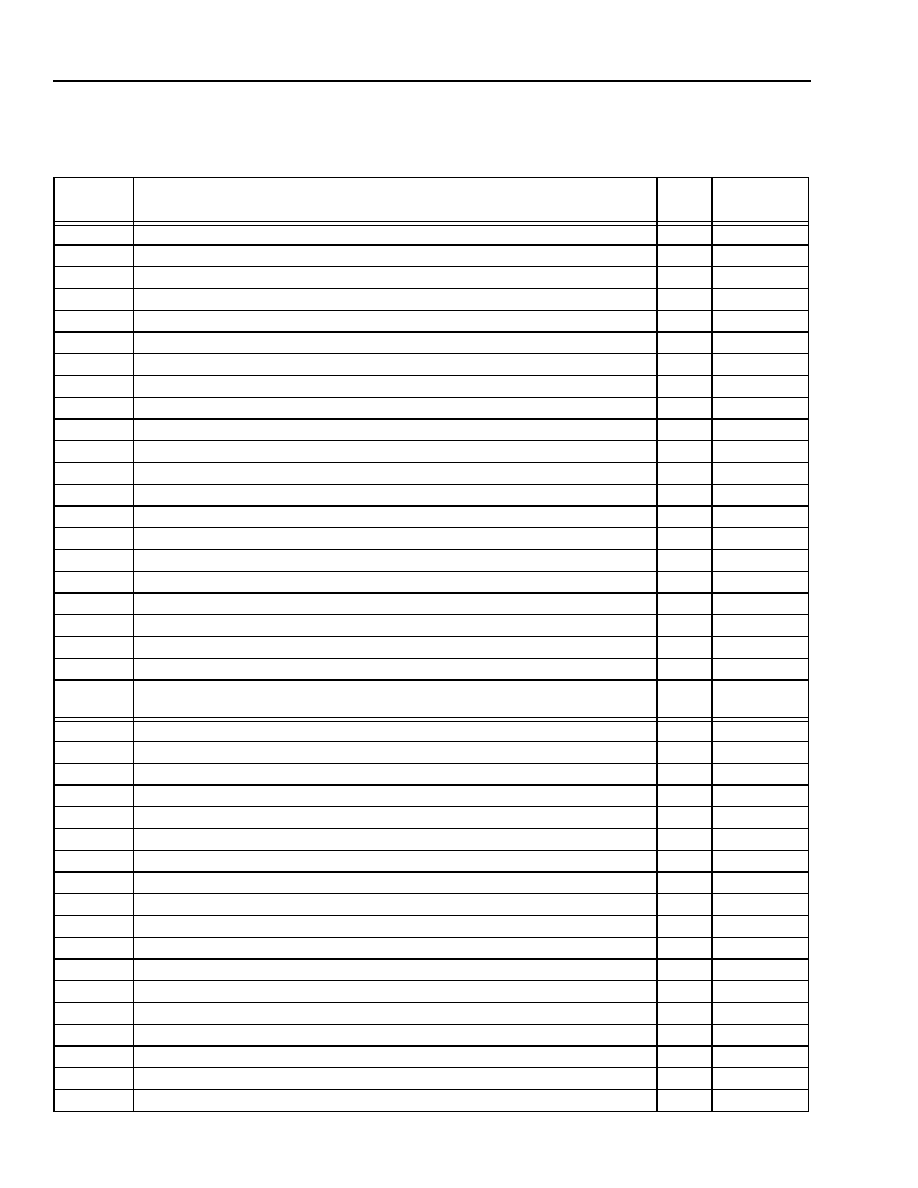

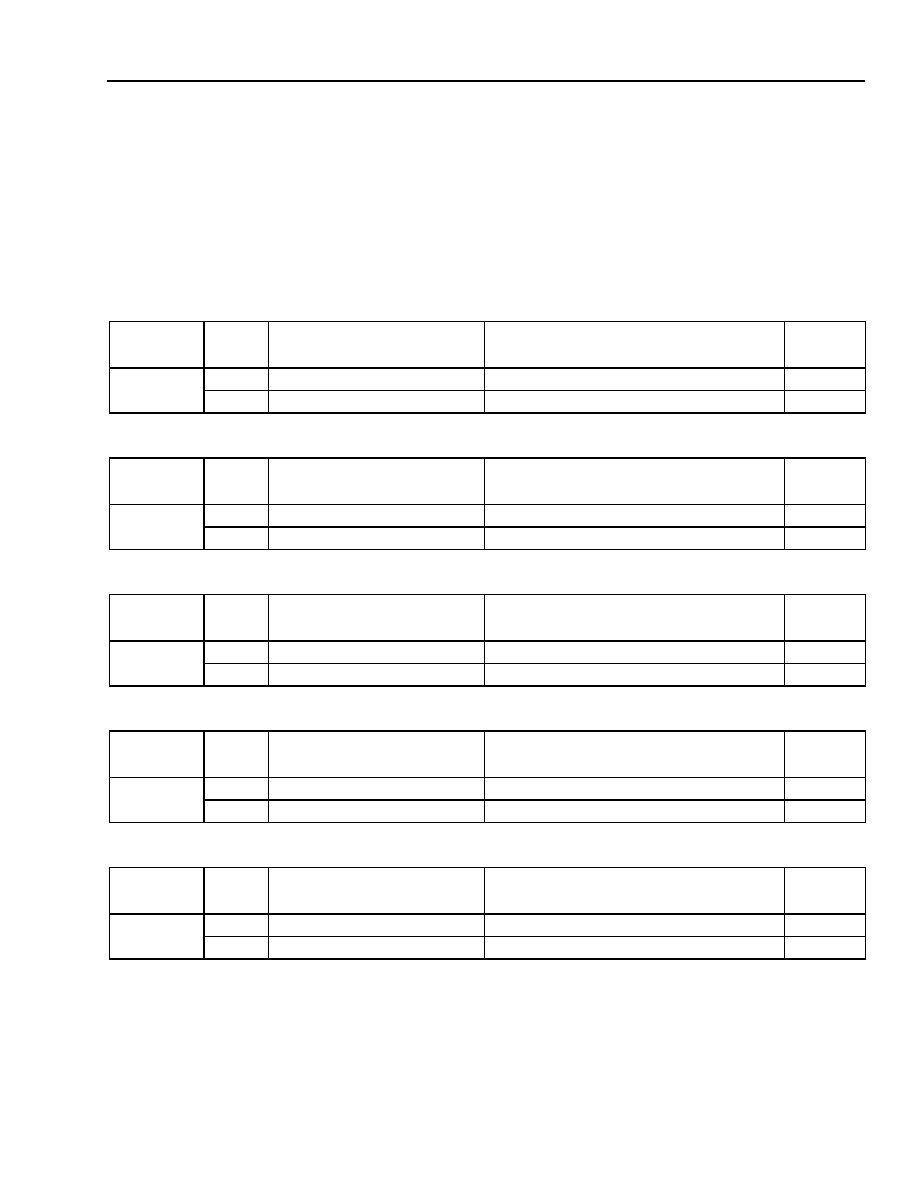

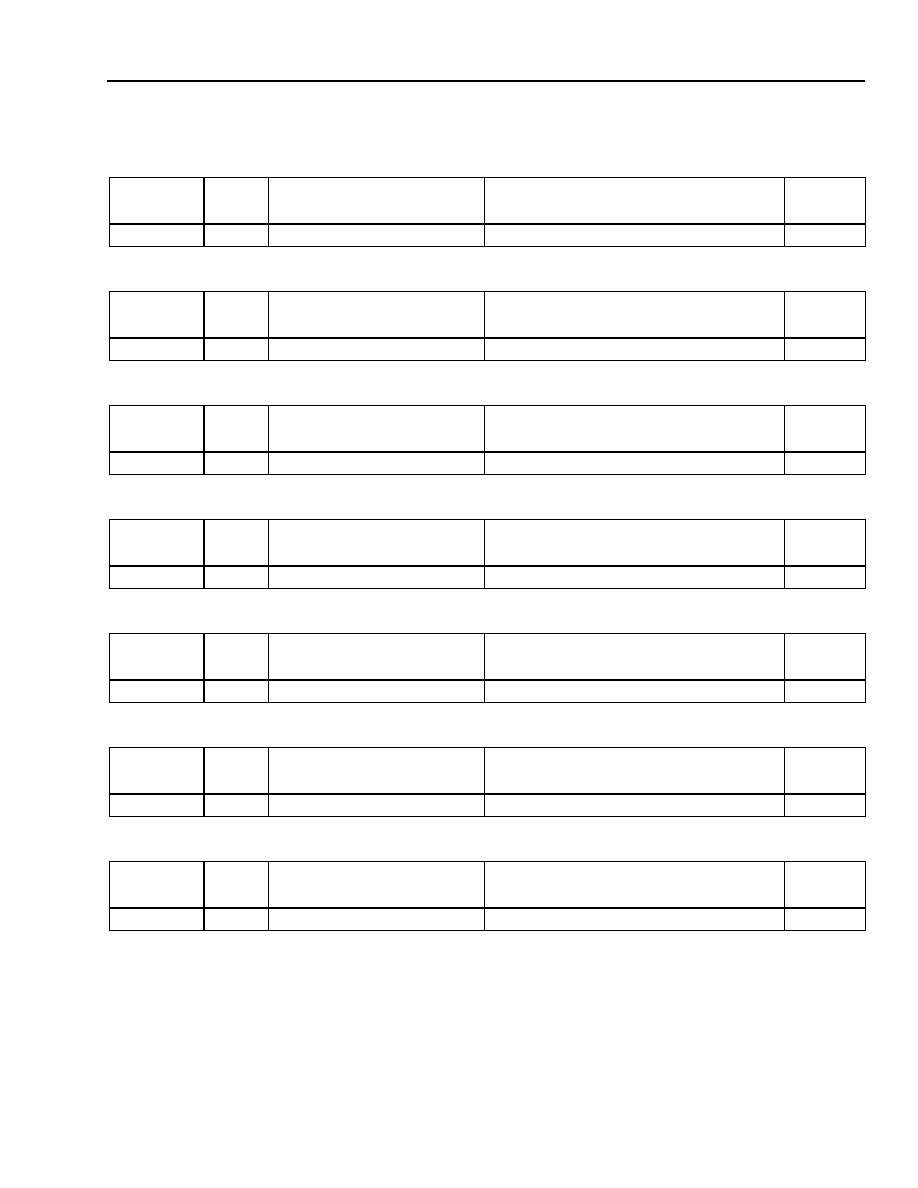

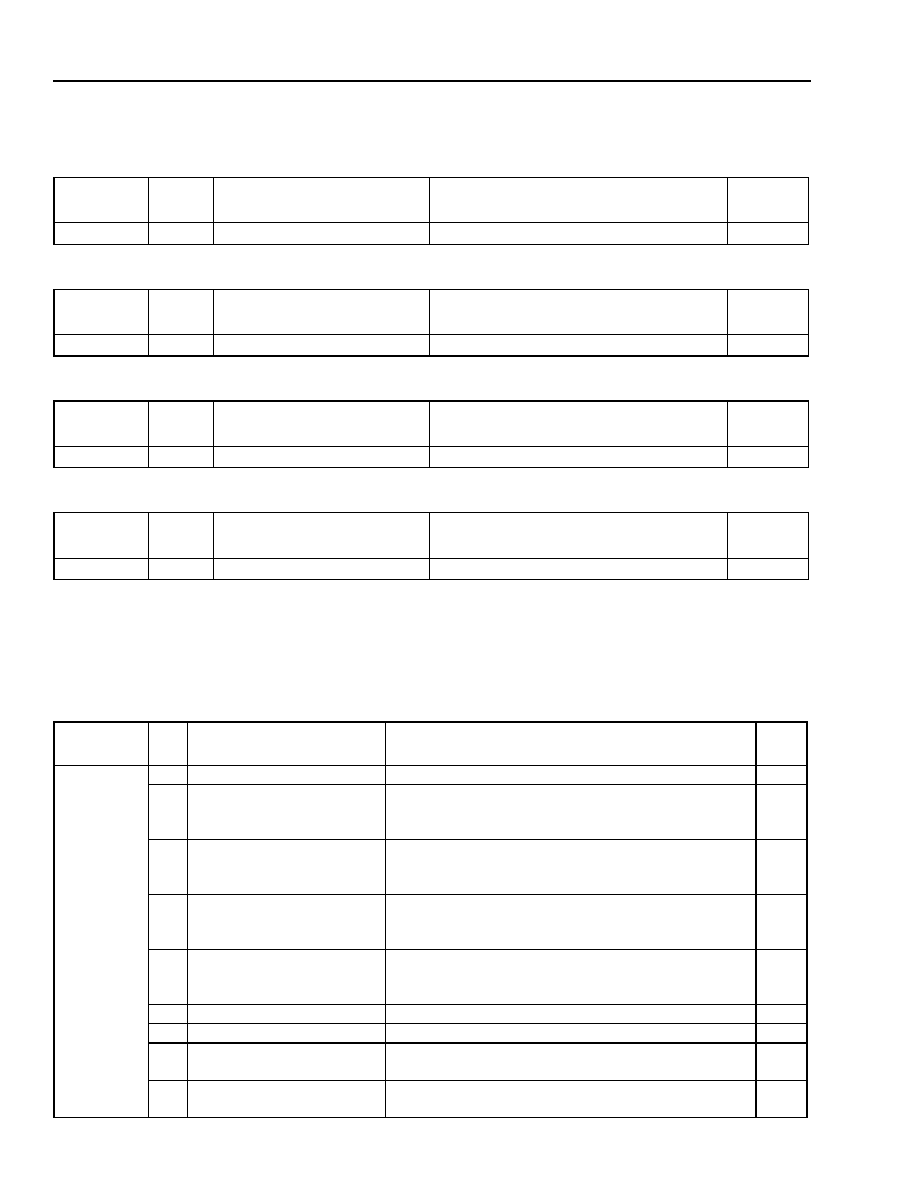

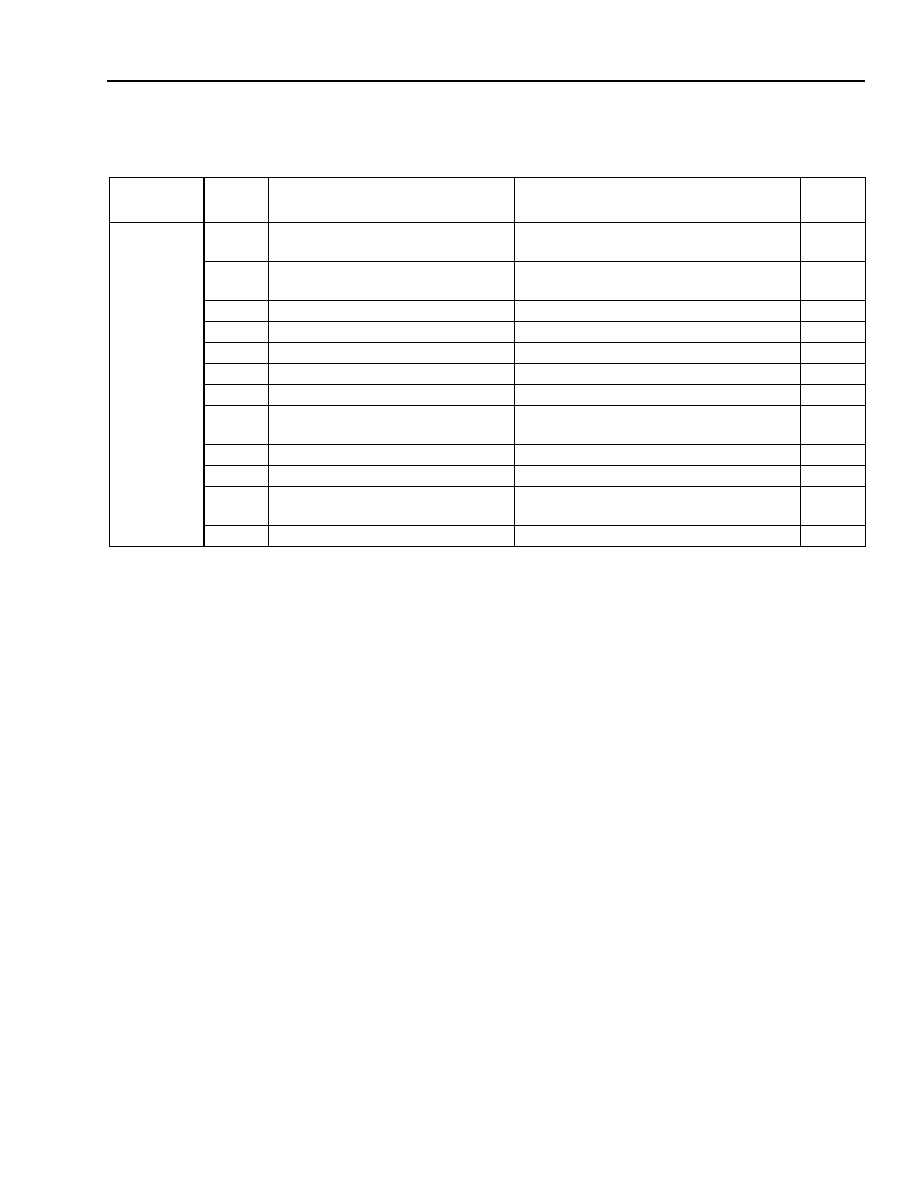

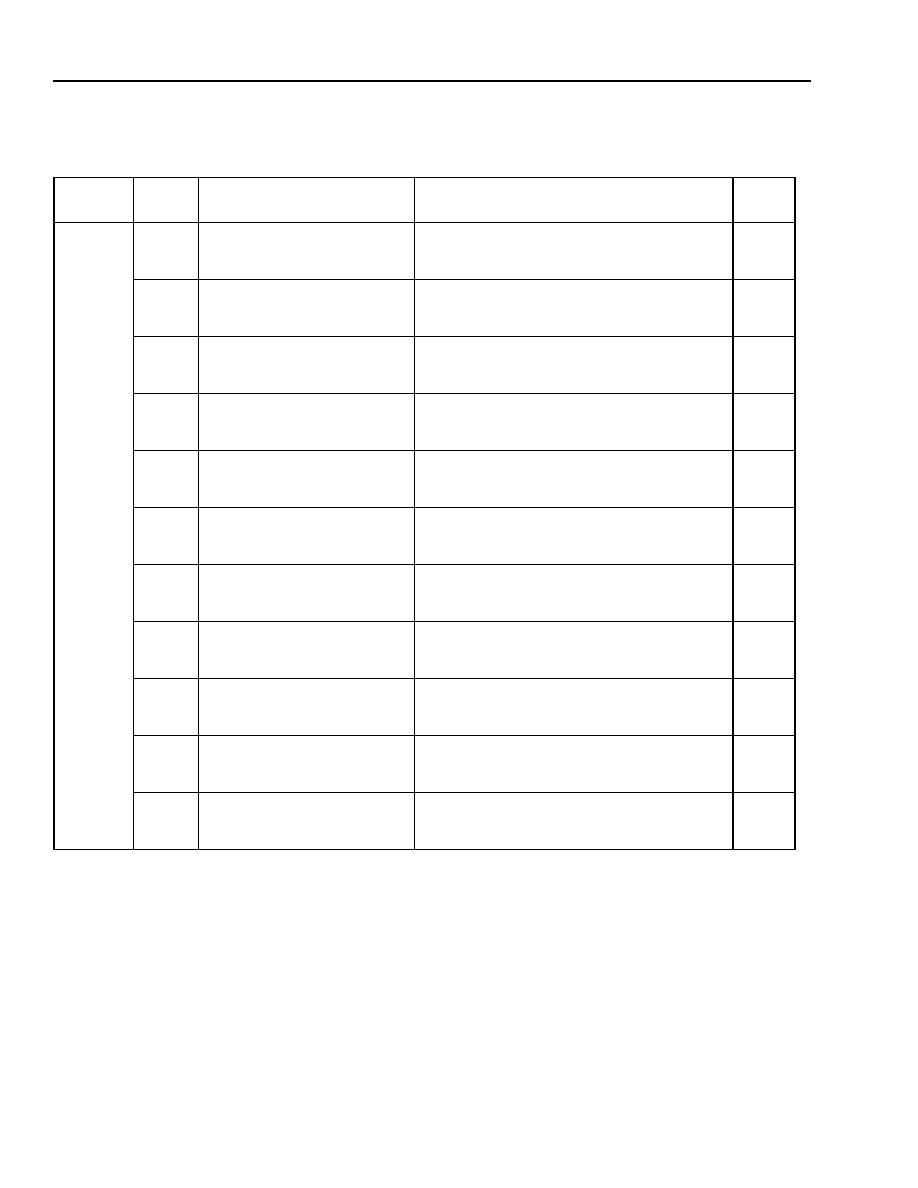

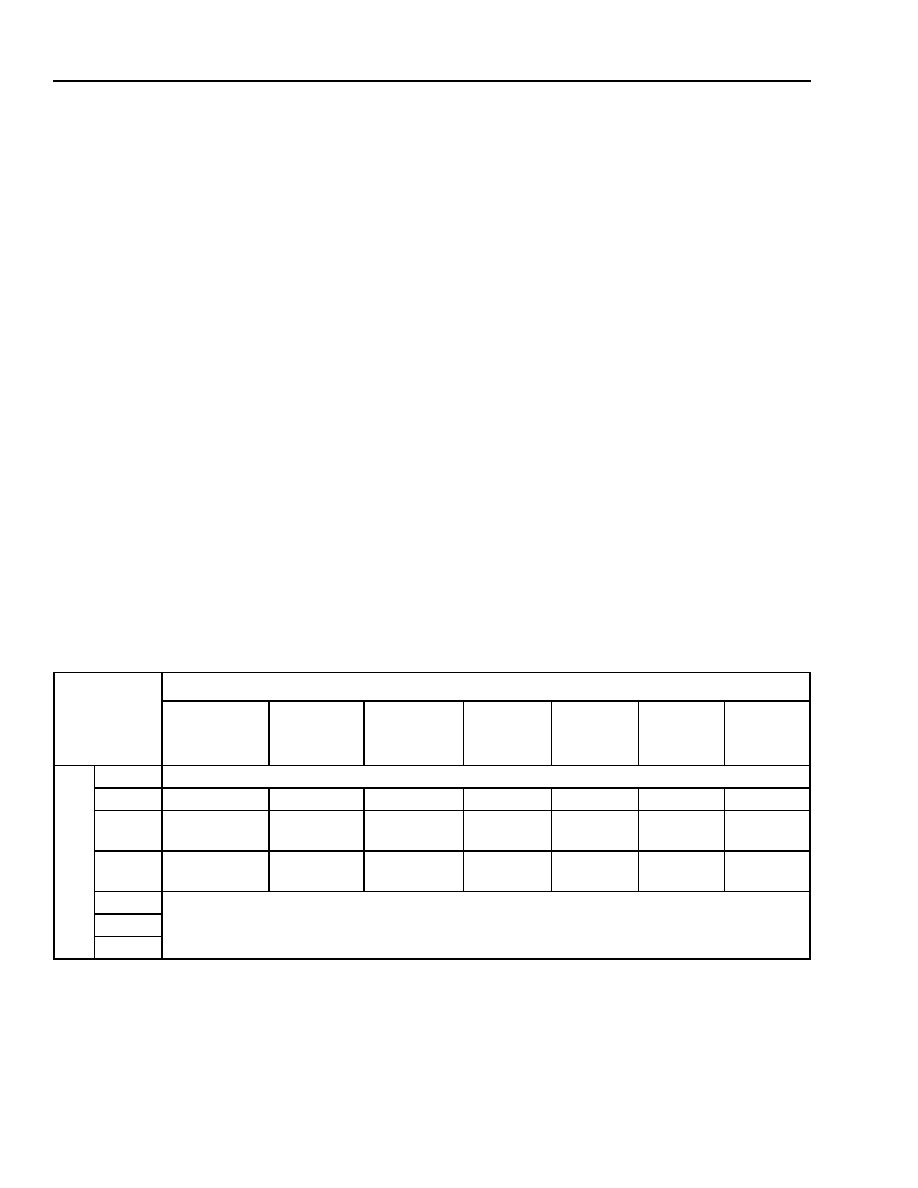

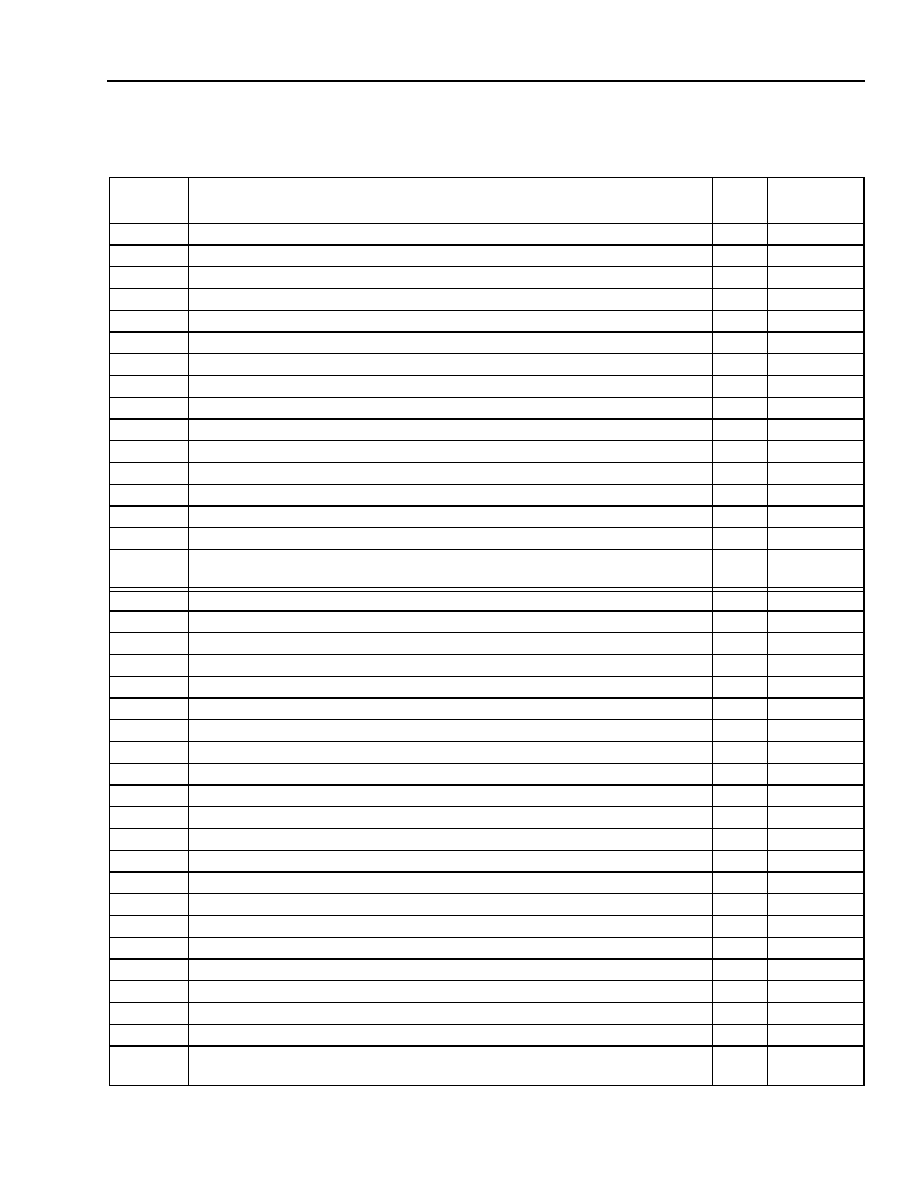

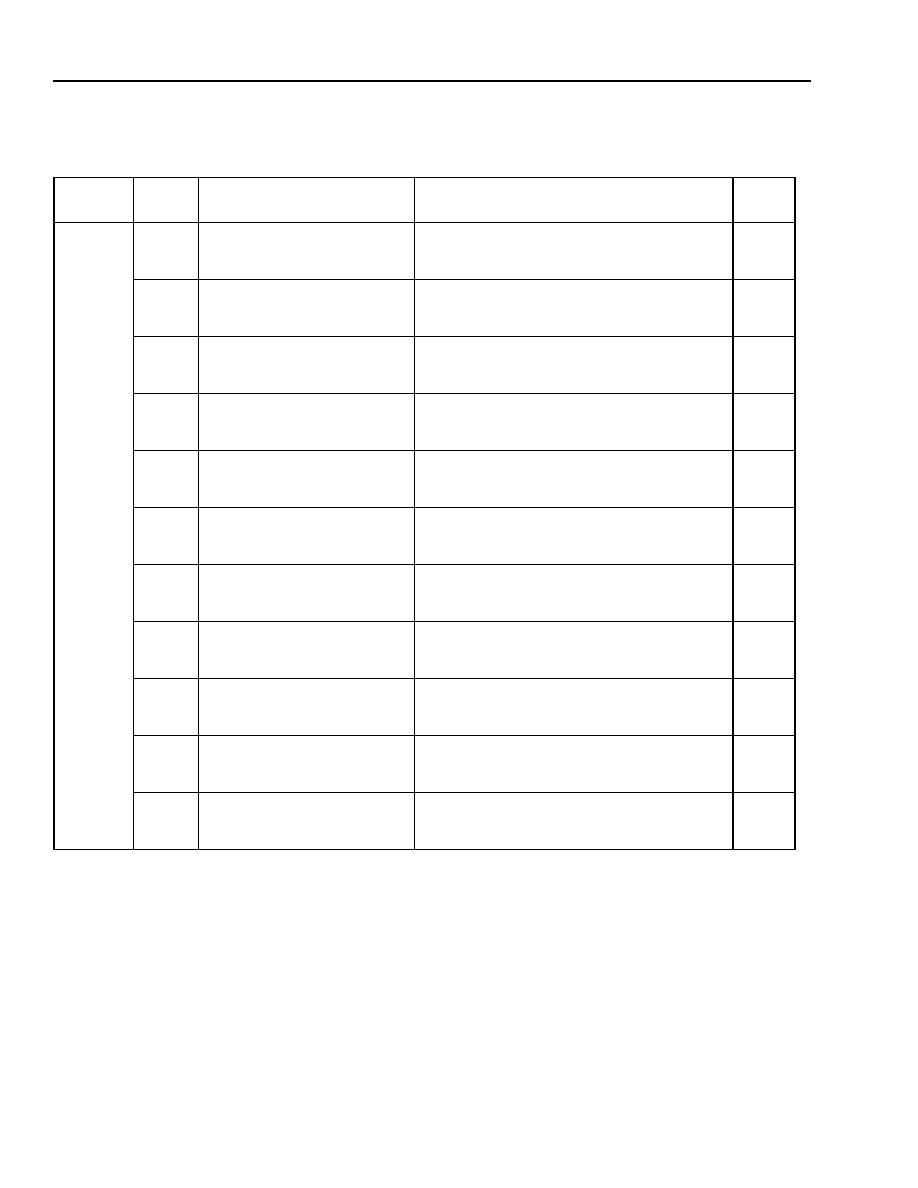

- Table 71. Register Summary��

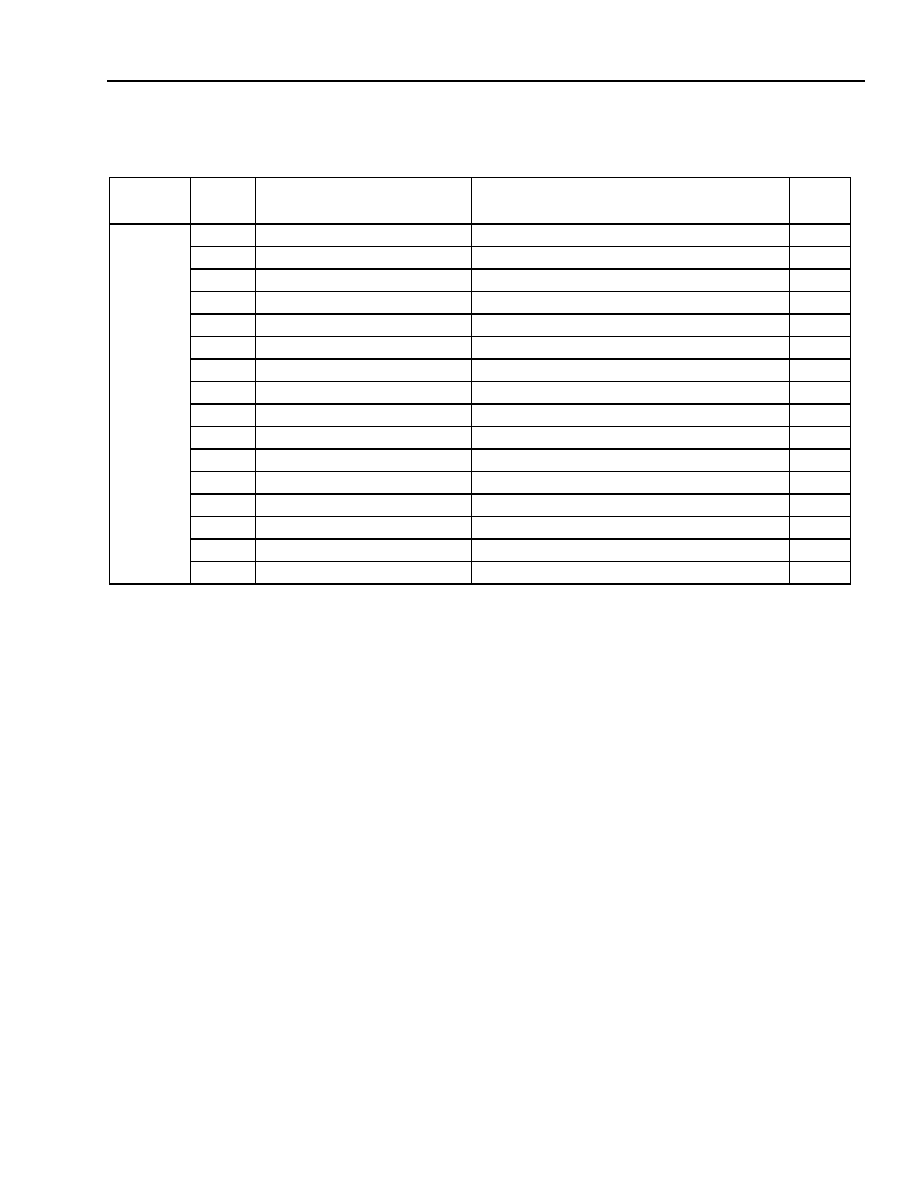

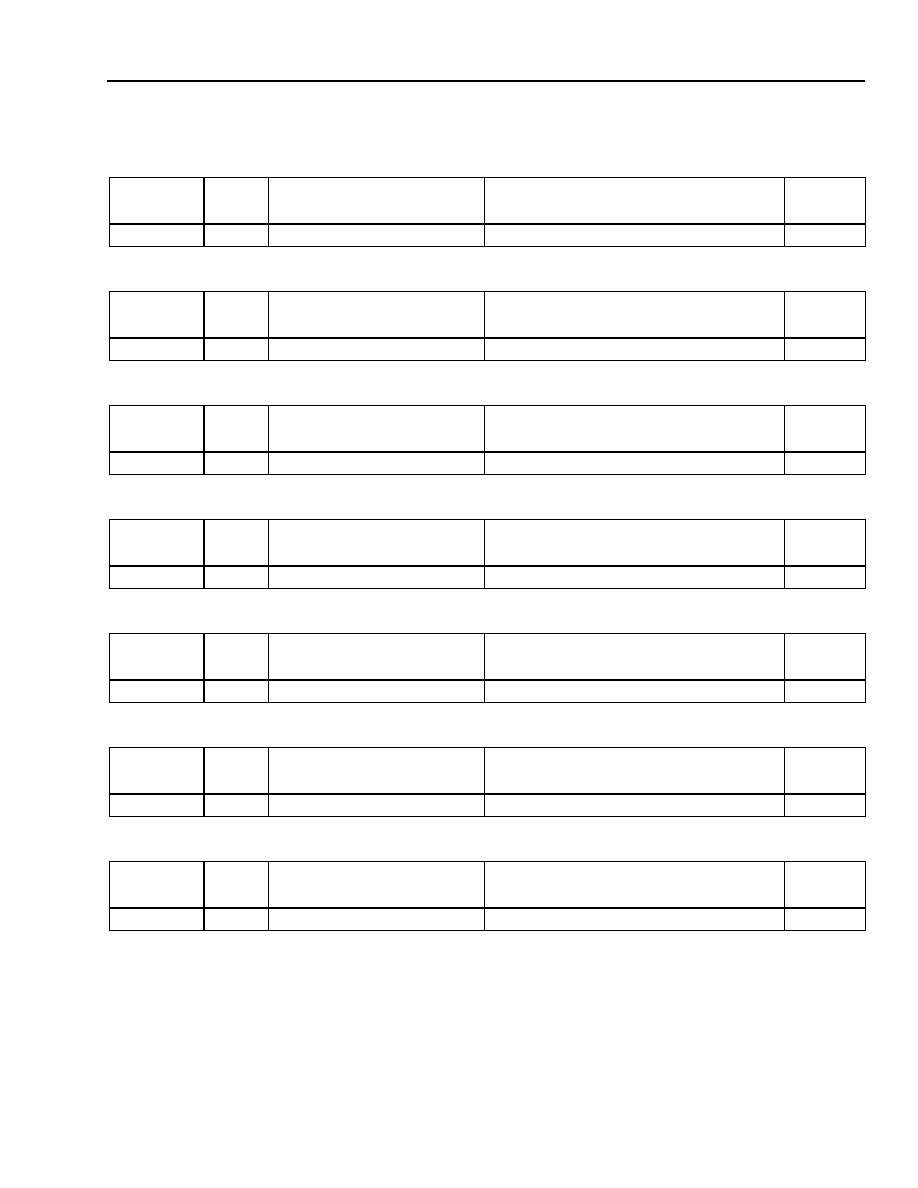

- Table 72. Interrupt Status (RO)

- Table 73. Interrupt Status Mask (R/W)

- Table 74. Chip ID (RO)

- Table 75. Chip Vintage (RO)

- Table 76. Scratch Pad, Clock Loss Alarm (R/W)

- Table 77. Chip-Level Maintenance (R/W)

- Table 78. Chip Status (RO)

- Table 79. Clock Loss Alarm/PM Clock Detection (W1C)

- Table 80. Clock Loss Alarm/PM Clock Detection Mask (R/W)

- Table 81. Software Chip Reset (WO)

- Table 82. LTE Interrupt Status (RO)

- Table 83. LTE Interrupt Status Mask (R/W)

- Table 84. Section Trace (J0) Access Maintenance (R/W)

- Table 85. J0 Access Done (W1C)

- Table 86. J0 Access Message Start (WO)

- Table 87. J0 Access Message Buffers 1Ą32 (R/W)

- Table 88. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1�x�10Ö3) (R/W)

- Table 89. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1�x�10Ö4) (R/W)

- Table 90. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1�x�10Ö5) (R/W)

- Table 91. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1�x�10Ö6) (R/W)

- Table 92. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1�x�10Ö7) (R/W)

- Table 93. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1�x�10Ö8) (R/W)

- Table 94. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1�x�10Ö9) (R/W)

- Table 95. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1�x�10Ö10) (R/W)

- Table 96. Line Signal Degrade/Signal Fail Detect Error Limit (1�x�10Ö3) (R/W)

- Table 97. Line Signal Degrade/Signal Fail Detect Error Limit (1�x�10Ö4) (R/W)

- Table 98. Line Signal Degrade/Signal Fail Detect Error Limit (1�x�10Ö5) (R/W)

- Table 99. Line Signal Degrade/Signal Fail Detect Error Limit (1�x�10Ö6) (R/W)

- Table 100. Line Signal Degrade/Signal Fail Detect Error Limit (1�x�10Ö7) (R/W)

- Table 101. Line Signal Degrade/Signal Fail Detect Error Limit (1�x�10Ö8) (R/W)

- Table 102. Line Signal Degrade/Signal Fail Detect Error Limit (1�x�10Ö9) (R/W)

- Table 103. Line Signal Degrade/Signal Fail Clear Error Limit (1�x�10Ö4) (R/W)

- Table 104. Line Signal Degrade/Signal Fail Clear Error Limit (1�x�10Ö5) (R/W)

- Table 105. Line Signal Degrade/Signal Fail Clear Error Limit (1�x�10Ö6) (R/W)

- Table 106. Line Signal Degrade/Signal Fail Clear Error Limit (1�x�10Ö7) (R/W)

- Table 107. Line Signal Degrade/Signal Fail Clear Error Limit (1�x�10Ö8) (R/W)

- Table 108. Line Signal Degrade/Signal Fail Clear Error Limit (1�x�10Ö9) (R/W)

- Table 109. Line Signal Degrade/Signal Fail Clear Error Limit (1�x�10Ö10) (R/W)

- Table 110. LTE Receive Channel 1 Provisioning (R/W)

- Table 111. LTE Receive Channel 1 Maintenance (R/W)

- Table 112. LTE Receive Channel 1 Loss-of-Signal (LOS) Threshold (R/W)

- Table 113. LTE Receive Channel 1 K Byte Status (RO)

- Table 114. LTE Receive Channel 1 S1 Byte Status (RO)

- Table 115. LTE Receive Channel 1 Service-Affecting Interrupt Alarm (W1C)

- Table 116. LTE Receive Channel 1 Service-Affecting Interrupt Alarm Mask (R/W)

- Table 117. LTE Receive Channel 1 Service-Affecting Persistency Alarm (RO)

- Table 118. LTE Receive Channel 1 Nonservice-Affecting Interrupt Alarm (W1C)

- Table 119. LTE Receive Channel 1 Nonservice-Affecting Interrupt Mask (R/W)

- Table 120. LTE Receive Channel 1 Nonservice-Affecting Persistency Alarm (RO)

- Table 121. LTE Receive Channel 1 Performance Monitoring (RO)

- Table 122. LTE Receive Channel 1 REI-L Performance Monitoring (L) (RO)

- Table 123. LTE Receive Channel 1 REI-L Performance Monitoring (U) (RO)

- Table 124. LTE Receive Channel 1 CV-L Performance Monitoring (L) (RO)

- Table 125. LTE Receive Channel 1 CV-L Performance Monitoring (U) (RO)

- Table 126. LTE Receive Channel 1 CV-S Performance Monitoring (RO)

- Table 127. LTE TransmitĄFrame Pulse Offset Count (R/W)

- Table 128. LTE TransmitĄAdd Interface Self-Sync Option (R/W)

- Table 129. LTE TransmitĄB1 Corrupt Frame Count (R/W)

- Table 130. LTE TransmitĄB2 Corrupt Frame Count (R/W)

- Table 131. LTE TransmitĄM1 Corrupt Frame Count (R/W)

- Table 132. LTE TransmitĄTFRM S1 Byte (RO)

- Table 133. LTE TransmitĄInterrupt Alarm Register (W1C)

- Table 134. LTE TransmitĄInterrupt Mask Register (R/W)

- Table 135. LTE Transmit Channel 1 Provisioning (R/W)

- Table 136. LTE Transmit Bit Assignment

- Table 137. LTE Transmit Channel 1 Maintenance (R/W)

- Table 138. LTE Transmit Channel 1 Path Unequipped (UNEQ-P) Insert Enable #1 (R/W)

- Table 139. LTE Transmit Channel 1 Path Unequipped (UNEQ-P) Insert Enable #2 (R/W)

- Table 140. LTE Transmit Channel 1 Path Unequipped (UNEQ-P) Insert Enable #3 (R/W)

- Table 141. LTE Transmit Channel 1 Path Unequipped (UNEQ-P) Insert Enable #4 (R/W)

- Table 142. LTE Transmit Channel 1 Path AIS (AIS-P) Insert Enable #1 (R/W)

- Table 143. LTE Transmit Channel 1 Path AIS (AIS-P) Insert Enable #2 (R/W)

- Table 144. LTE Transmit Channel 1 Path AIS (AIS-P) Insert Enable #3 (R/W)

- Table 145. LTE Transmit Channel 1 Path AIS (AIS-P) Insert Enable #4 (R/W)

- Table 146. LTE Transmit Channel 1 K1K2 Byte Insert Values (R/W)

- Table 147. LTE Transmit Channel 1 S1 Byte Insert Value (R/W)

- Table 148. LTE Transmit Channel 1 Interrupt Alarm (W1C)

- Table 149. LTE Transmit Channel 1 Interrupt Alarm Mask (R/W)

- Table 150. EQPT Interrupt Status (RO)

- Table 151. EQPT Interrupt Mask (R/W)

- Table 152. Receive Drop Common Service-Affecting Alarm (W1C)

- Table 153. Receive Drop Common Service-Affecting Alarm Mask (R/W)

- Table 154. Receive Drop STS-48 Channel Provisioning Register 1 (R/W)

- Table 155. J0 TraceĄSTS-12 Channel 1 (R/W)

- Table 156. J0 TraceĄSTS-12 Channel 2 (R/W)

- Table 157. J0 TraceĄSTS-12 Channel 3 (R/W)

- Table 158. J0 TraceĄSTS-12 Channel 4 (R/W)

- Table 159. Receive Drop STS-48 Channel Nonservice-Affecting Alarm (W1C)

- Table 160. Receive Drop STS-48 Channel Nonservice Affecting Alarm Mask (R/W)

- Table 161. Transmit Add STS-48 Channel Provisioning (R/W)

- Table 162. J0 Status RegisterĄ1 (RO)

- Table 163. J0 Status RegisterĄ2 (RO)

- Table 164. J0 Status RegisterĄ3 (RO)

- Table 165. J0 Status RegisterĄ4 (RO)

- Table 166. AIS Insert Status Register, STS-12 Channel #1 (RO)

- Table 167. AIS Insert Status Register, STS-12 Channel #2 (RO)

- Table 168. AIS Insert Status Register, STS-12 Channel #3 (RO)

- Table 169. AIS Insert Status Register, STS-12 Channel #4 (RO)

- Table 170. Transmit Add STS-48 Channel Alarm (W1C)

- Table 171. Transmit Add STS-48 Channel Alarm Mask (R/W)

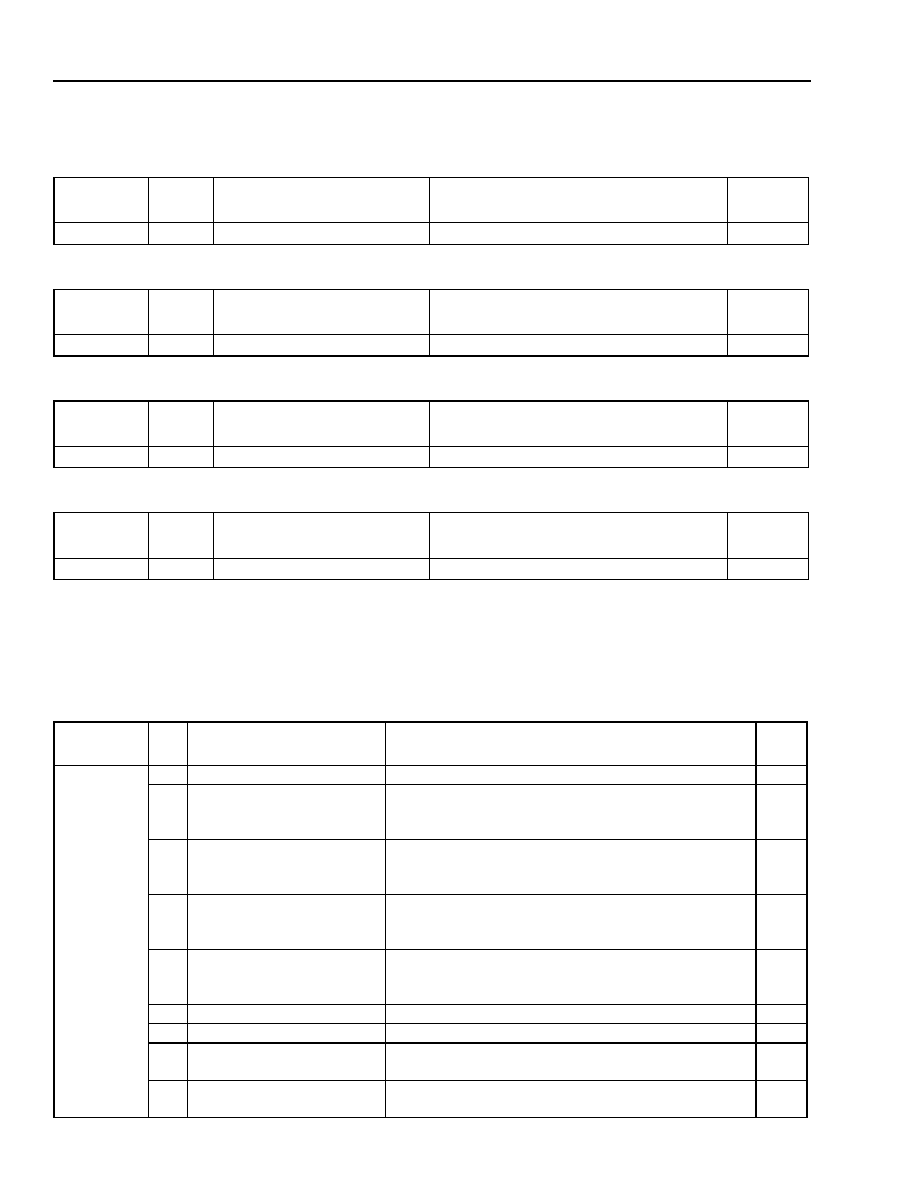

- Table 172. STS-12 Pointer Processor Provisioning, STS-1 #1 to STS-1 #12 (R/W)

- Table 173. STS-12 Pointer Processor Maintenance, STS-1 #1 to STS-1 #12 (R/W)

- Table 174. STS-12 Pointer Interpreter PM, Last Second Increments, STS-1 #1 to STS-1 #12 (RO)

- Table 175. STS-12 Pointer Interpreter PM, Last Second Decrements, STS-1 #1 to STS-1 #12 (RO)

- Table 176. STS-12 Pointer Generator PM, Last Second Increments, STS-1 #1 to STS-1 #12 (RO)

- Table 177. STS-12 Pointer Generator PM, Last Second Decrements, STS-1 #1 to STS-1 #12 (RO)

- Table 178. STS-1 #1 Path Overhead Provisioning (R/W)

- Table 179. STS-1 #1 Path Overhead Maintenance (R/W)

- Table 180. STS-1 #1 Path Overhead Status (RO)

- Table 181. STS-1 #1 Alarm Interrupt Status (W1C)

- Table 182. STS-1 #1 Alarm Interrupt Status Mask (R/W)

- Table 183. STS-1 #1 Alarm Persistency (RO)

- Table 184. STS-1 #1 PM Last Second Indicators (RO)

- Table 185. STS-1 #1 Last Second CV-P Count (RO)

- Table 186. STS-1 #1 Last Second REI-P Count (RO)

- Table 187. Path Overhead (POH) Interrupt Status (RO)

- Table 188. Path Overhead (POH) Interrupt Status Mask (R/W)

- Table 189. STS-1 Signal Fail Detect Threshold, Window Size Select 0 (R/W)

- Table 190. STS-1 Signal Fail Clear Threshold, Window Size Select 0 (R/W)

- Table 191. STS-1 Signal Fail Detect Threshold, Window Size Select 1 (R/W)

- Table 192. STS-1 Signal Fail Clear Threshold, Window Size Select 1 (R/W)

- Table 193. STS-Nc Signal Fail Detect Threshold, Window Size Select 2 (R/W)

- Table 194. STS-Nc Signal Fail Clear Threshold, Window Size Select 2 (R/W)

- Table 195. STS-Nc Signal Fail Detect Threshold, Window Size Select 3 (R/W)

- Table 196. STS-Nc Signal Fail Clear Threshold, Window Size Select 3 (R/W)

- Table 197. STS-Nc Signal Fail Detect Threshold, Window Size Select 4 (R/W)

- Table 198. STS-Nc Signal Fail Clear Threshold, Window Size Select 4 (R/W)

- Table 199. STS-Nc Signal Fail Detect Threshold, Window Size Select 5 (R/W)

- Table 200. STS-Nc Signal Fail Clear Threshold, Window Size Select 5 (R/W)

- Table 201. STS-Nc Signal Fail Detect Threshold, Window Size Select 6 (R/W)

- Table 202. STS-Nc Signal Fail Clear Threshold, Window Size Select 6 (R/W)

- Table 203. STS-Nc Signal Fail Detect Threshold, Window Size Select 7 (R/W)

- Table 204. STS-Nc Signal Fail Clear Threshold, Window Size Select 7 (R/W)

- Table 205. Signal Fail Window Size 0 (R/W)

- Table 206. Signal Fail Window Size 1 (R/W)

- Table 207. Signal Fail Window Size 2 (R/W)

- Table 208. Signal Fail Window Size 3 (R/W)

- Table 209. Path Trace Access Control (R/W)

- Table 210. Path Trace Access Complete Status (W1C)

- Table 211. Path Trace Access Start

- Table 212. Path Trace Buffer Word #1ĄWord #32

- Table 213. STS-1 Channel Interrupt Status, STS-1 #1 to STS-1 #16 (RO)

- Table 214. STS-1 Channel Interrupt Status Mask, STS-1 #1 to STS-1 #16 (R/W)

- Table 215. STS-1 Channel Interrupt Status, STS-1 #17 to STS-1 #32 (RO)

- Table 216. STS-1 Channel Interrupt Status Mask, STS-1 #17 to STS-1 #32 (R/W)

- Table 217. STS-1 Channel Interrupt Status, STS-1 #33 to STS-1 #48 (RO)

- Table 218. STS-1 Channel Interrupt Status Mask, STS-1 #33 to STS-1 #48 (R/W)

- Table 219. STS-48 Channel Path Trace Control (R/W)

- Table 220. S/W Concatenation Map STS-1 #1 to STS-1 #12 (R/W)

- Table 221. S/W Concatenation Map STS-1 #13 to STS-1 #24 (R/W)

- Table 222. S/W Concatenation Map STS-1 #25 to STS-1 #36 (R/W)

- Table 223. S/W Concatenation Map STS-1 #37 to STS-1 #48 (R/W)

- Table 224. S/W Concatenation Mask STS-1 #1 to STS-1 #12 (R/W)

- Table 225. S/W Concatenation Mask STS-1 #13 to STS-1 #24 (R/W)

- Table 226. S/W Concatenation Mask STS-1 #25 to STS-1 #36 (R/W)

- Table 227. S/W Concatenation Mask STS-1 #37 to STS-1 #48 (R/W)

- Table 228. Received Concatenation Map STS-1 #1 to STS-1 #12 (RO)

- Table 229. Received Concatenation Map STS-1 #13 to STS-1 #24 (RO)

- Table 230. Received Concatenation Map STS-1 #25 to STS-1 #36 (RO)

- Table 231. Received Concatenation Map STS-1 #37 to STS-1 #48 (RO)

- Table 232. STS-48 Channel Path Alarms 1 (W1C)

- Table 233. STS-48 Channel Path Alarms 1 Mask (W1C)

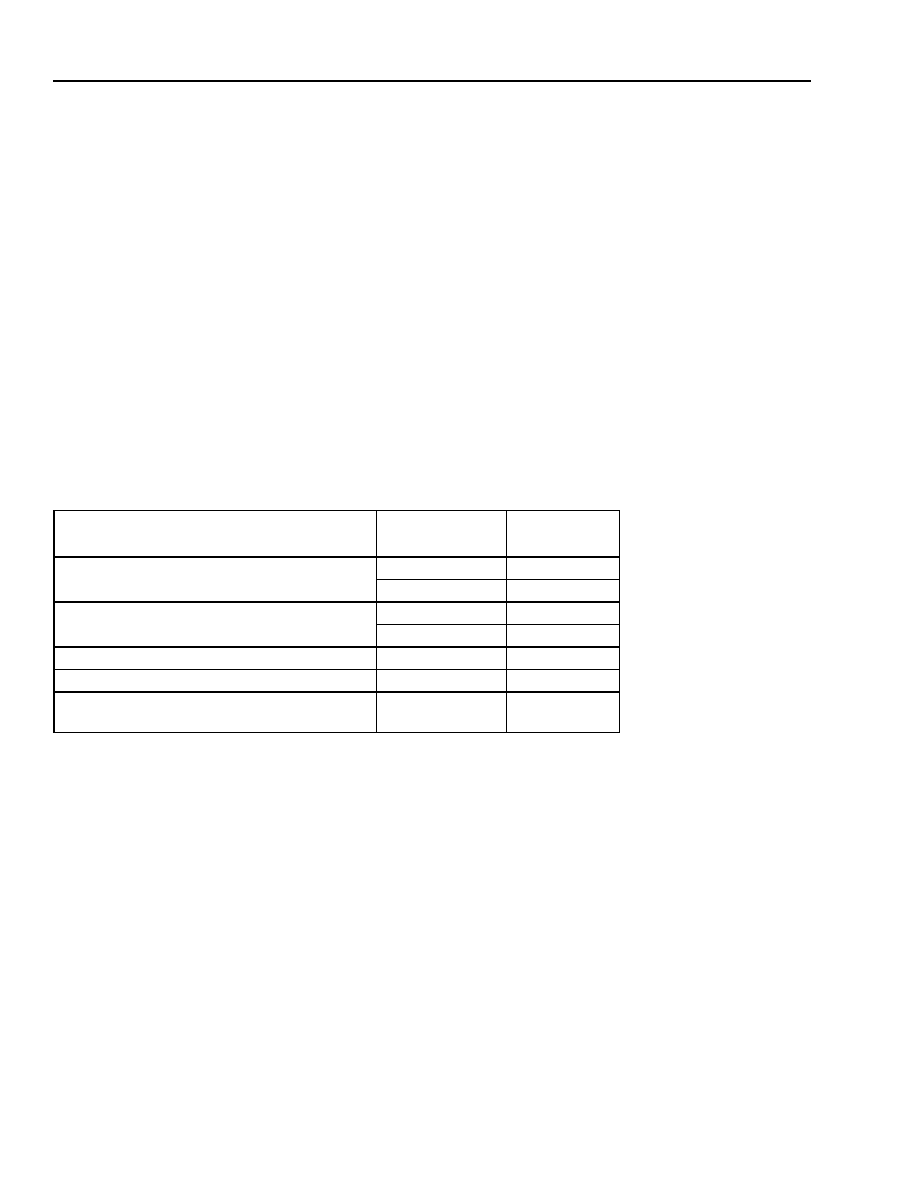

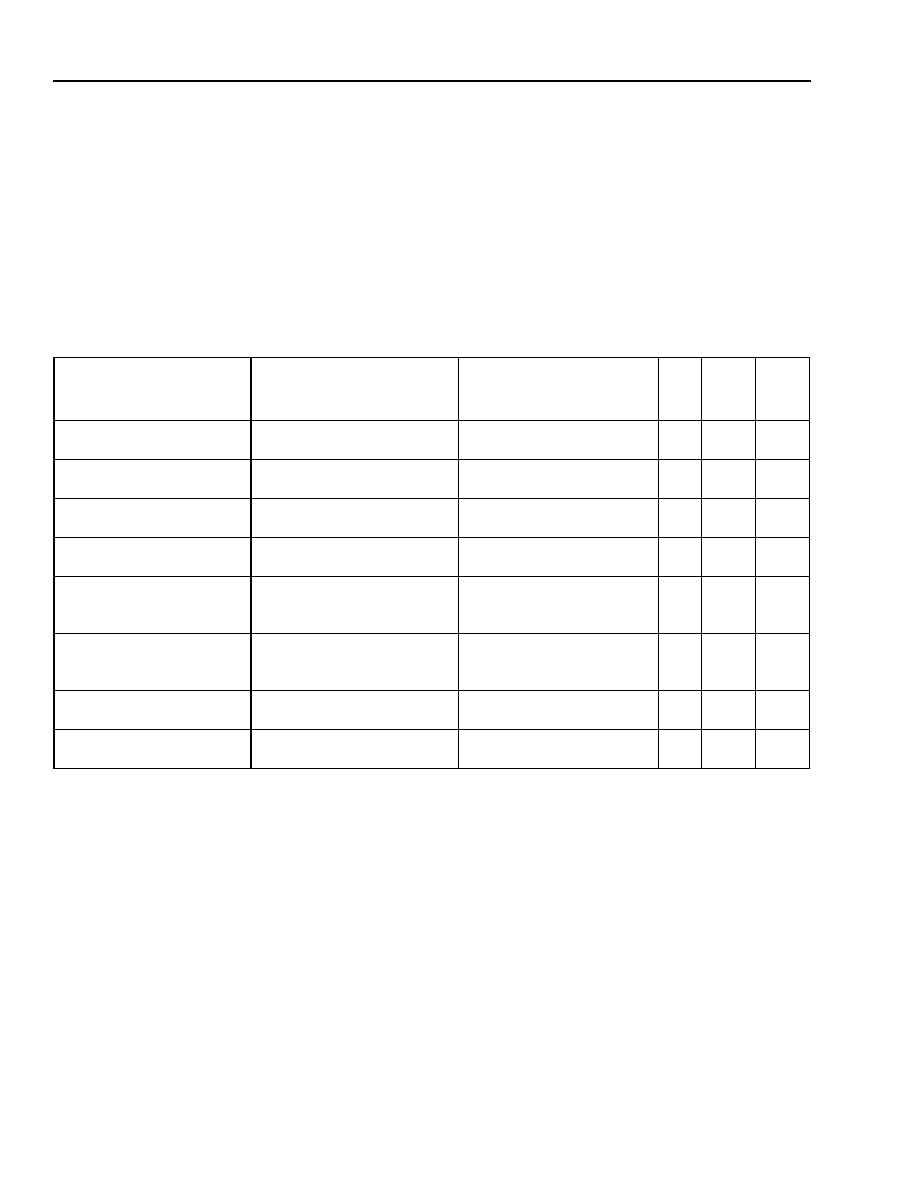

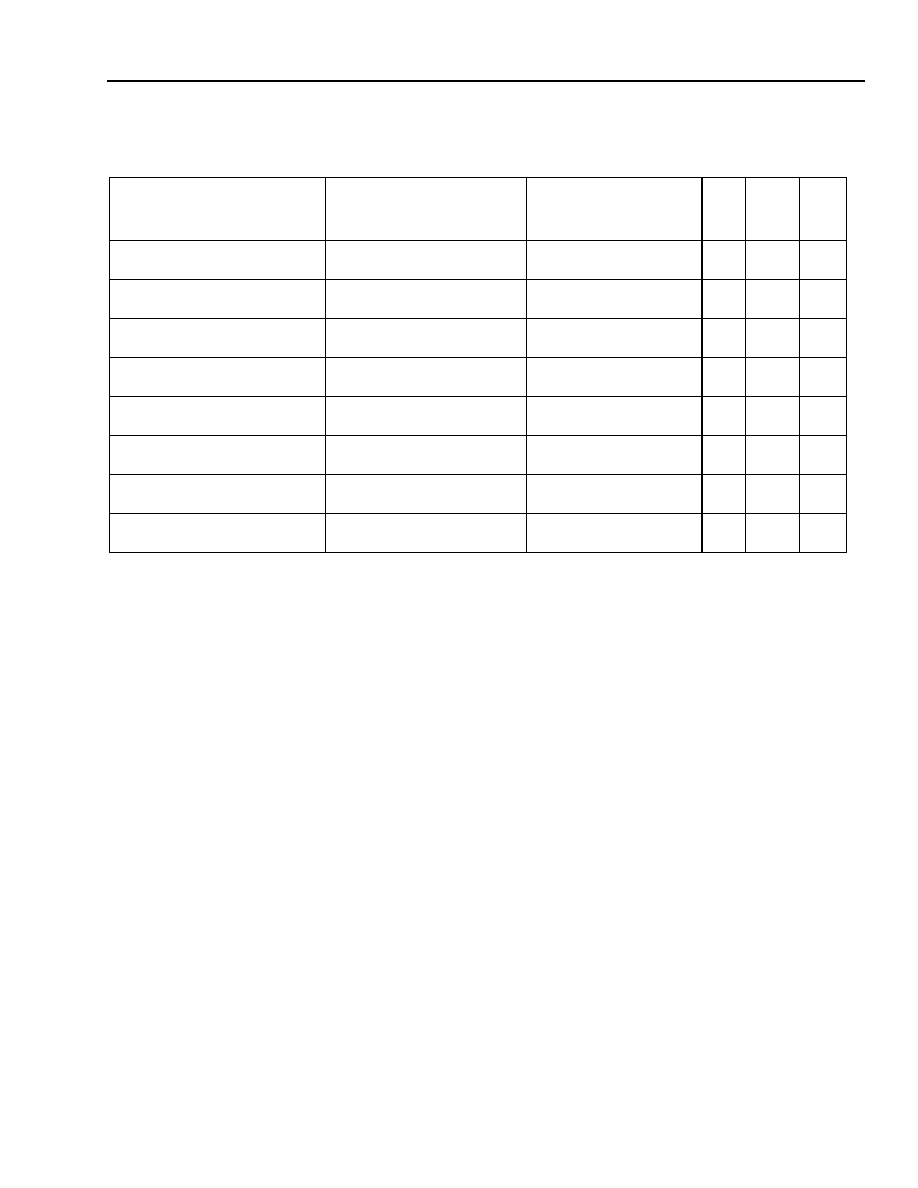

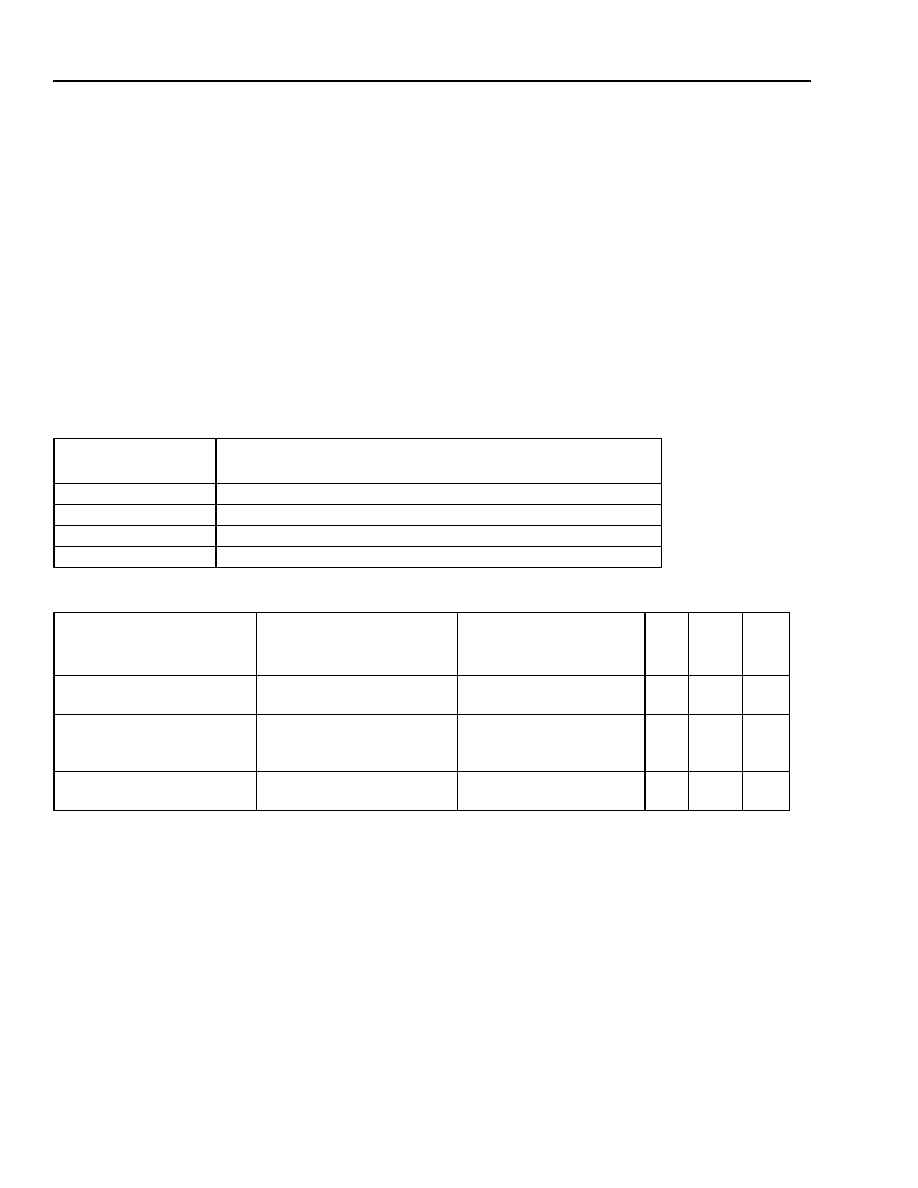

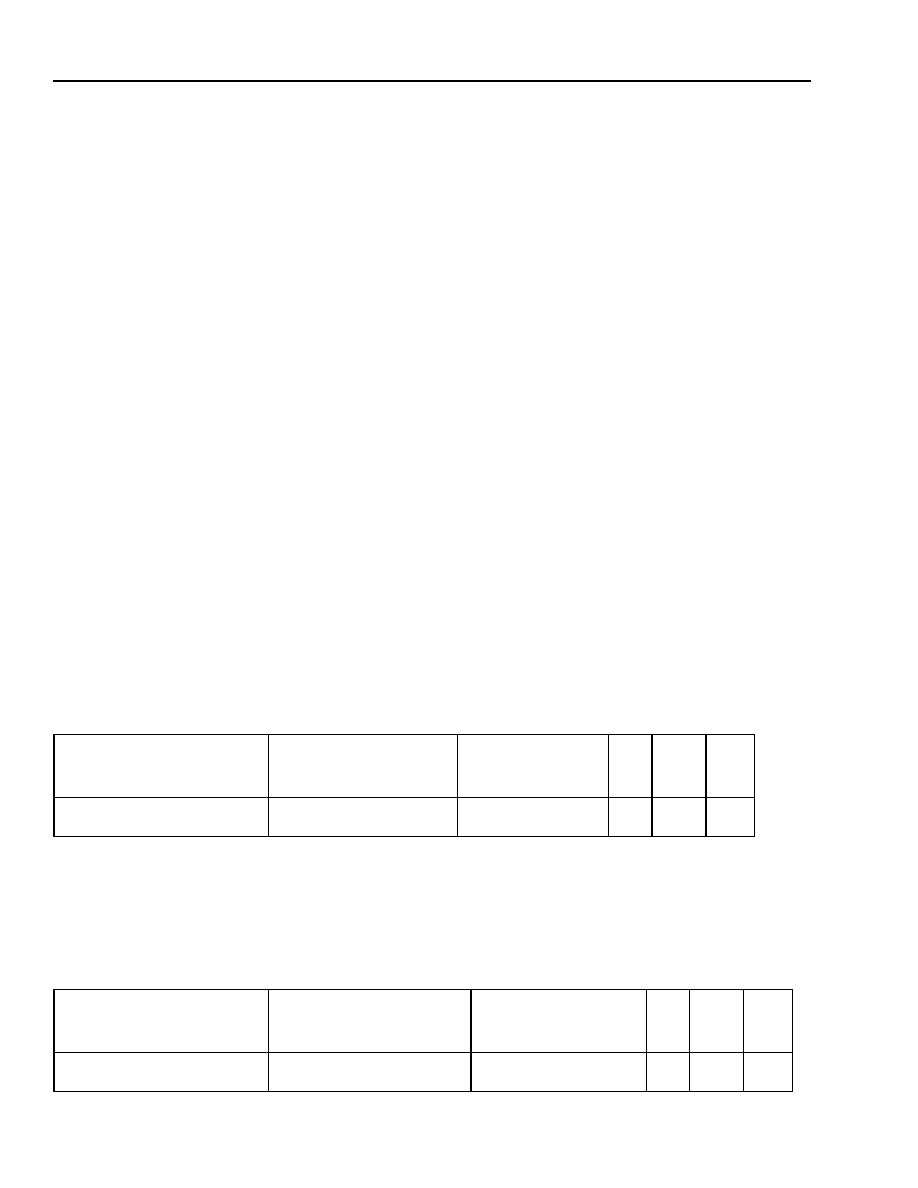

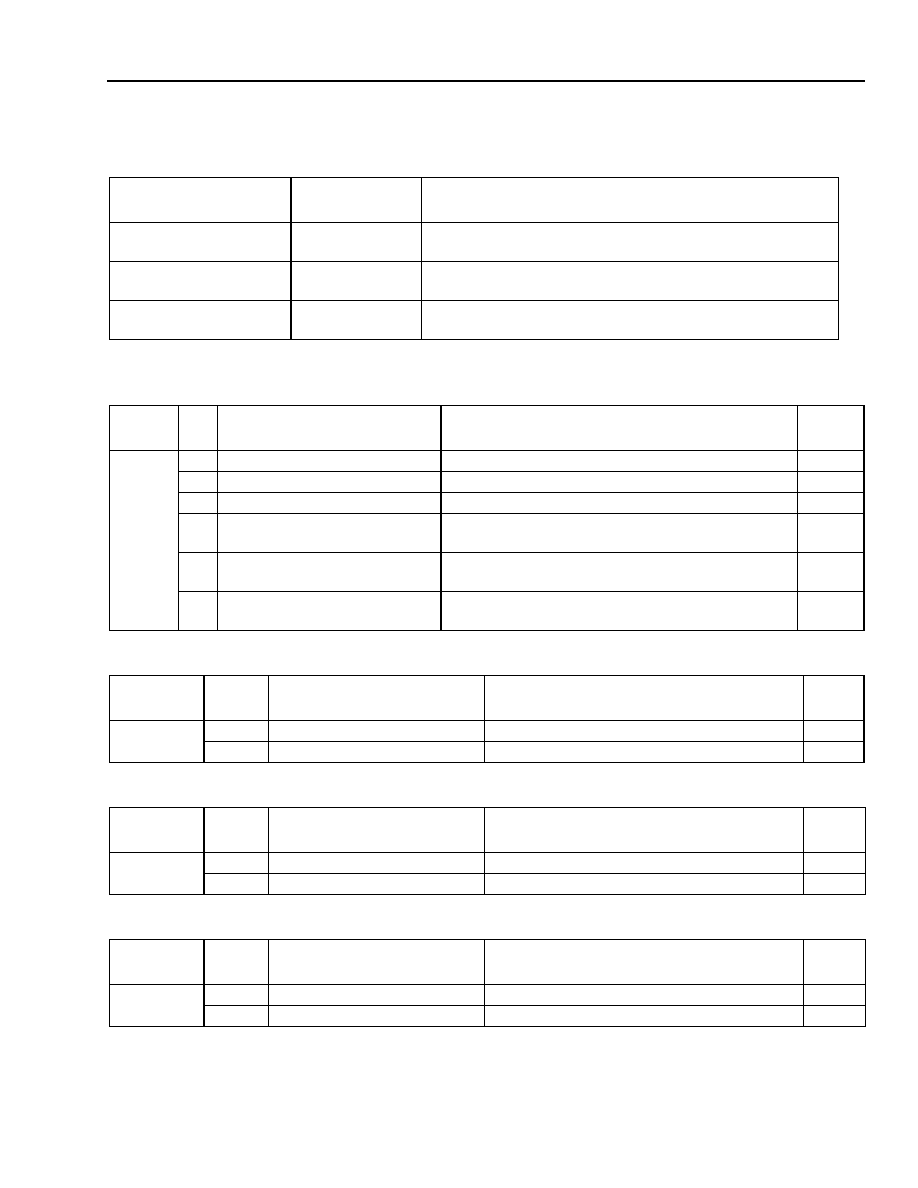

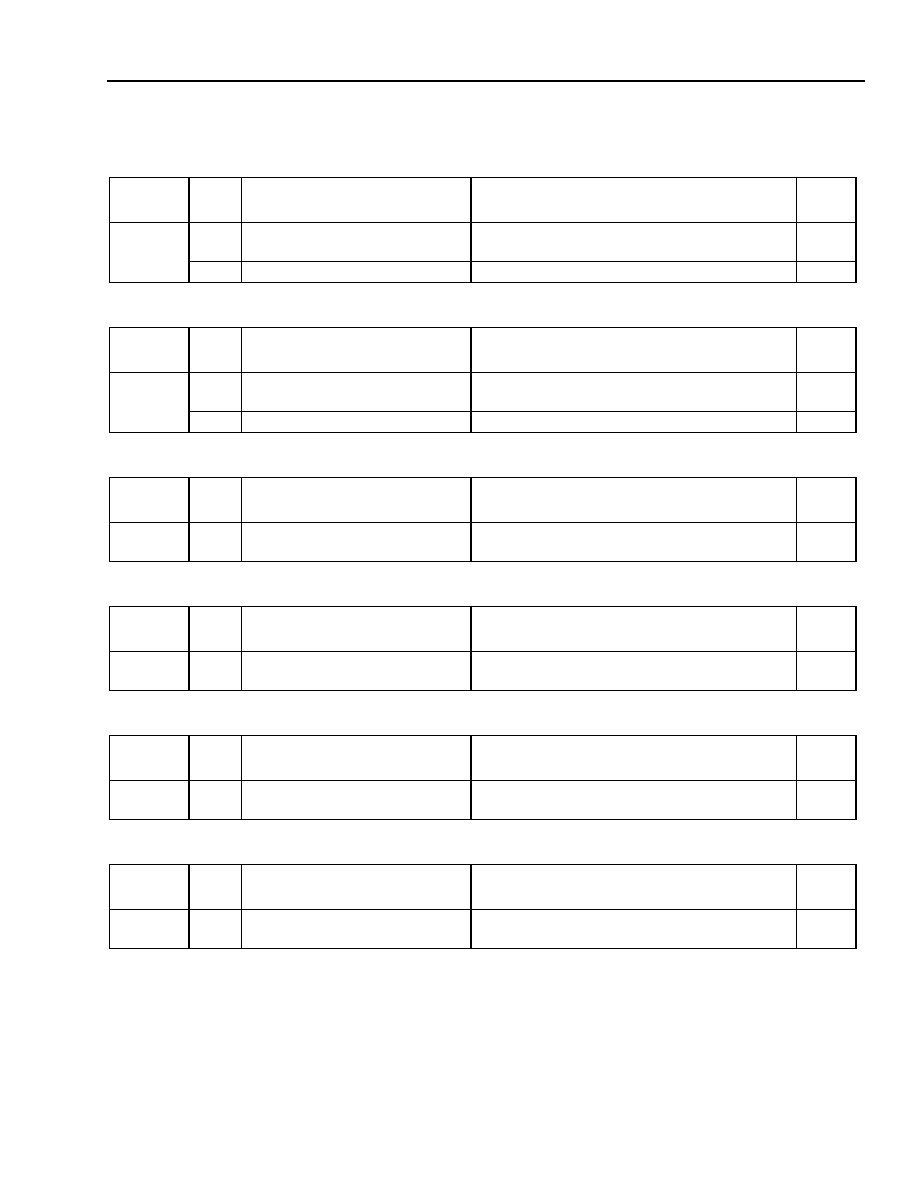

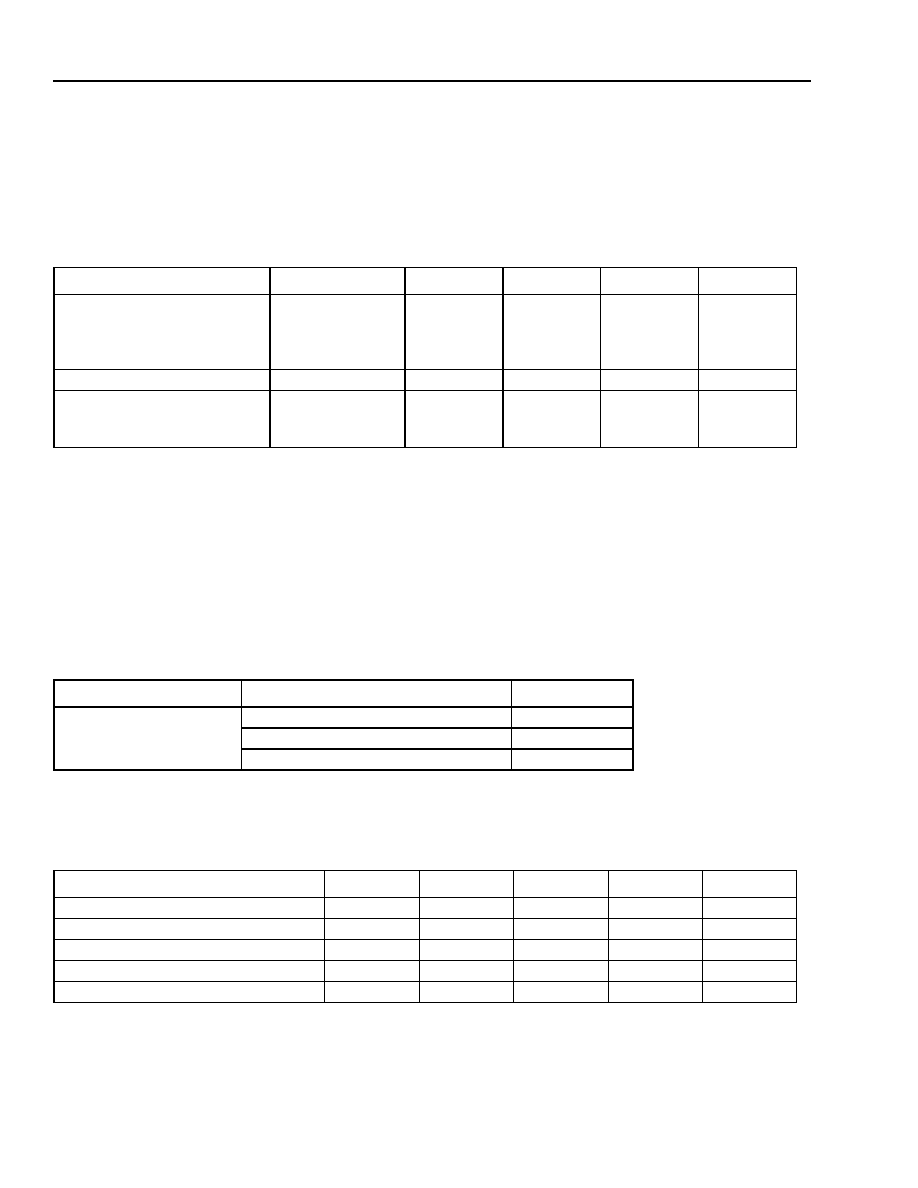

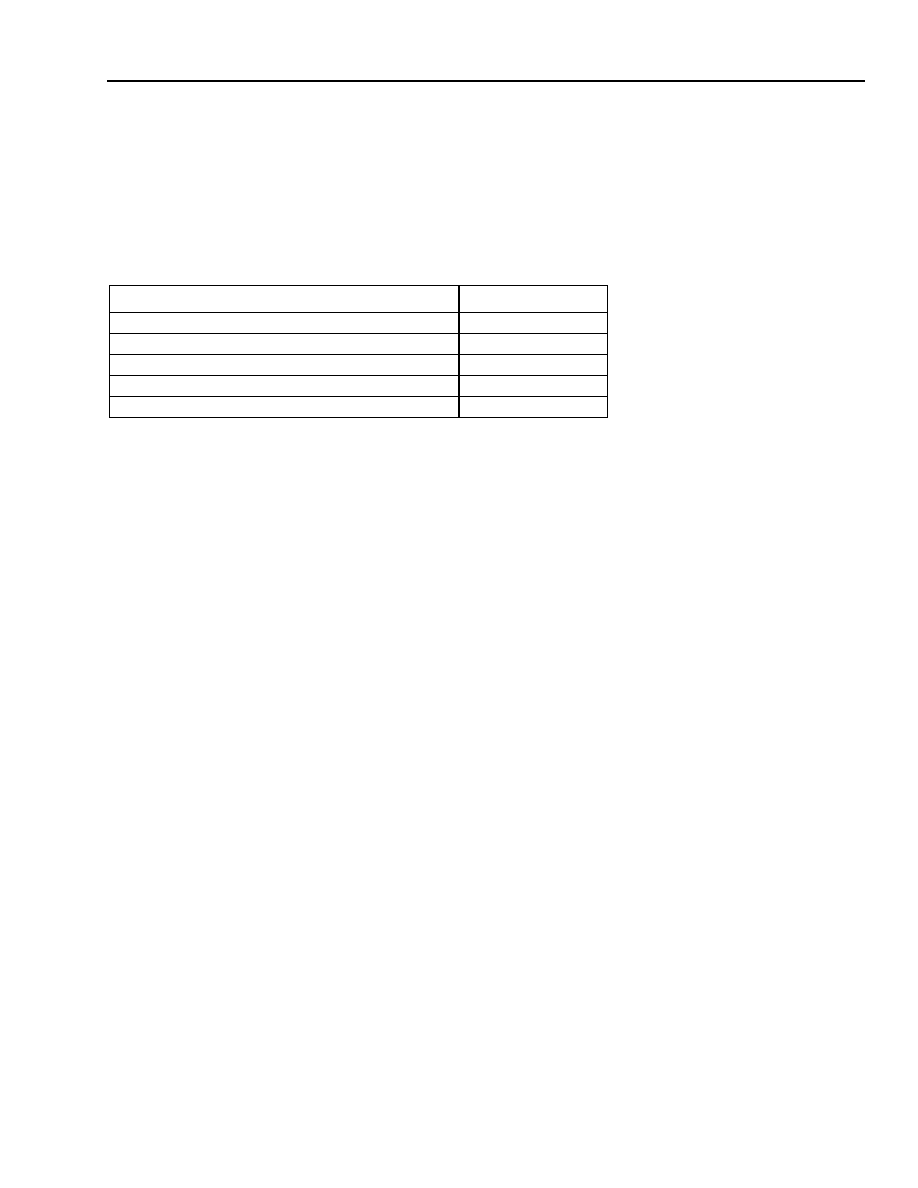

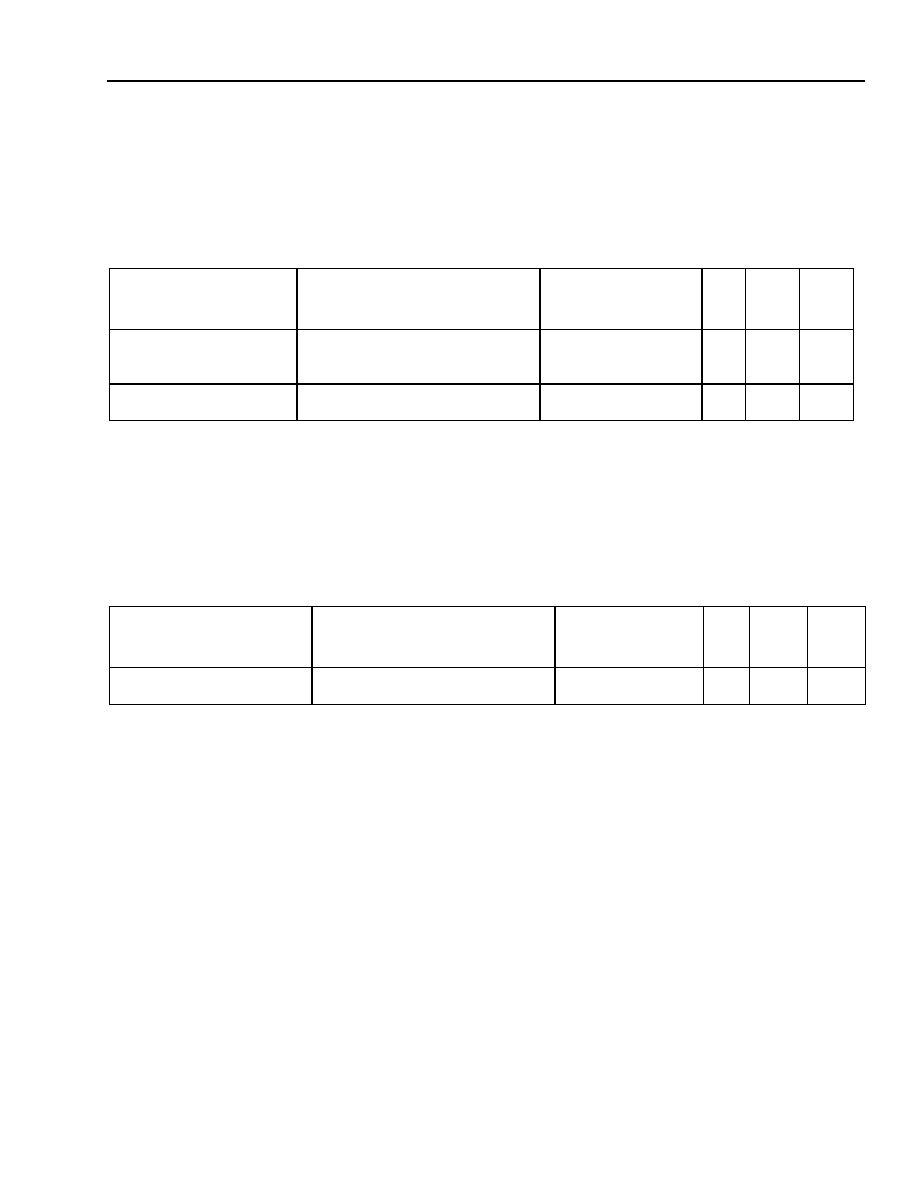

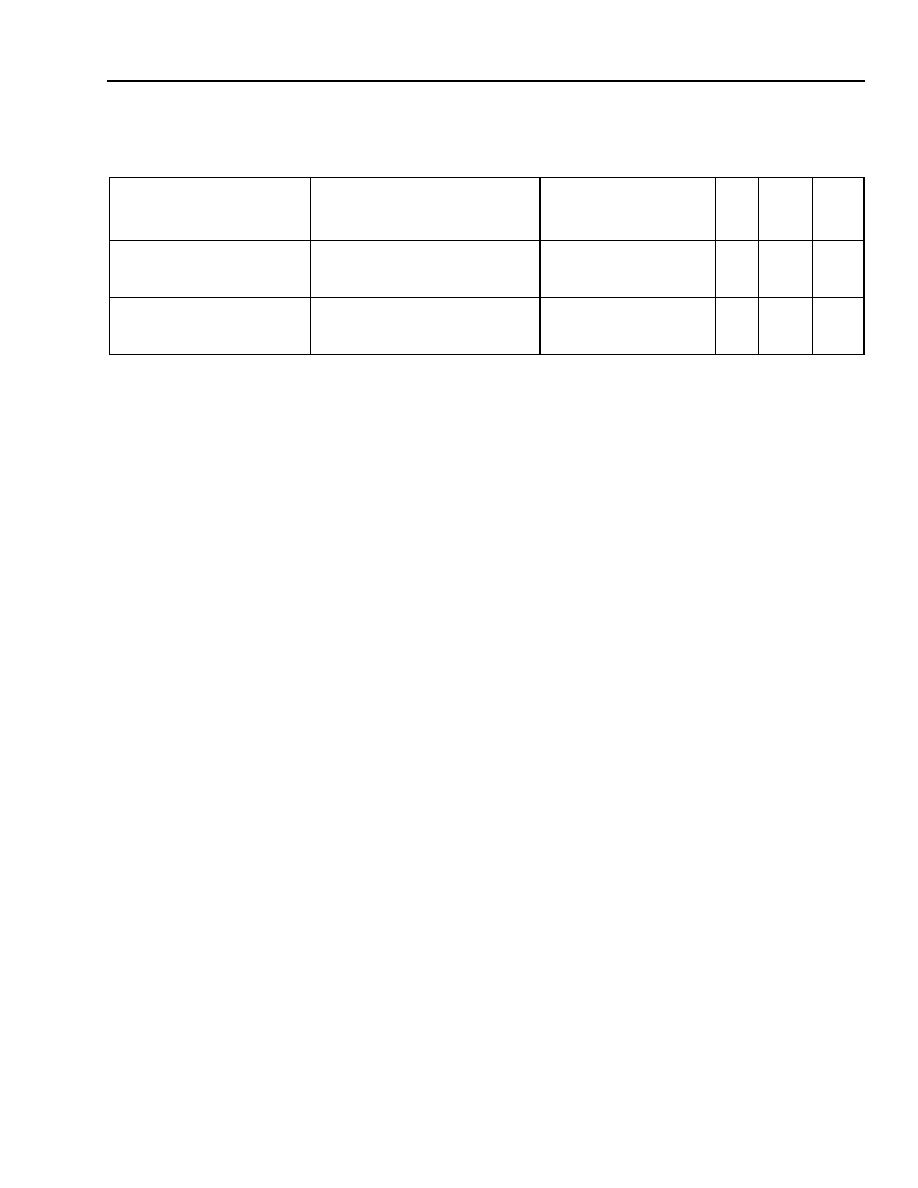

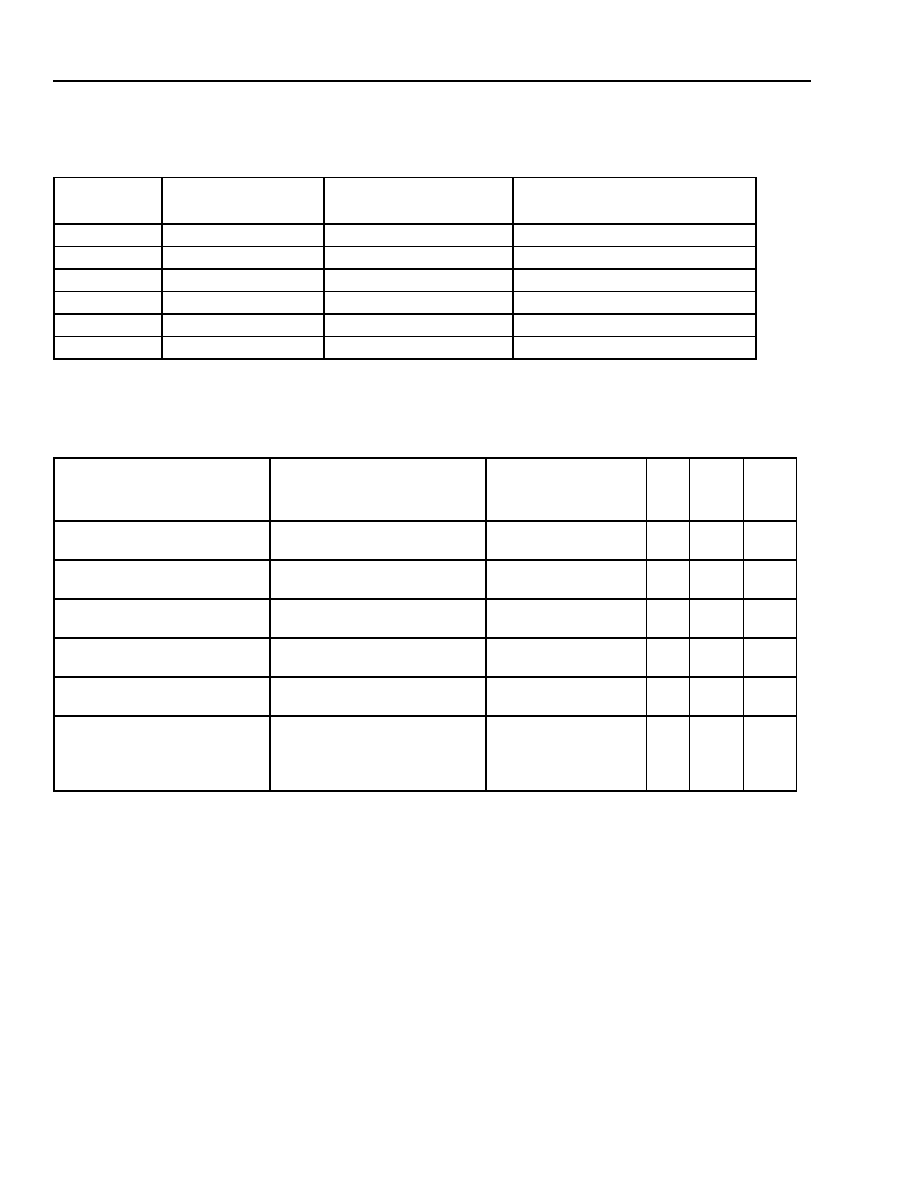

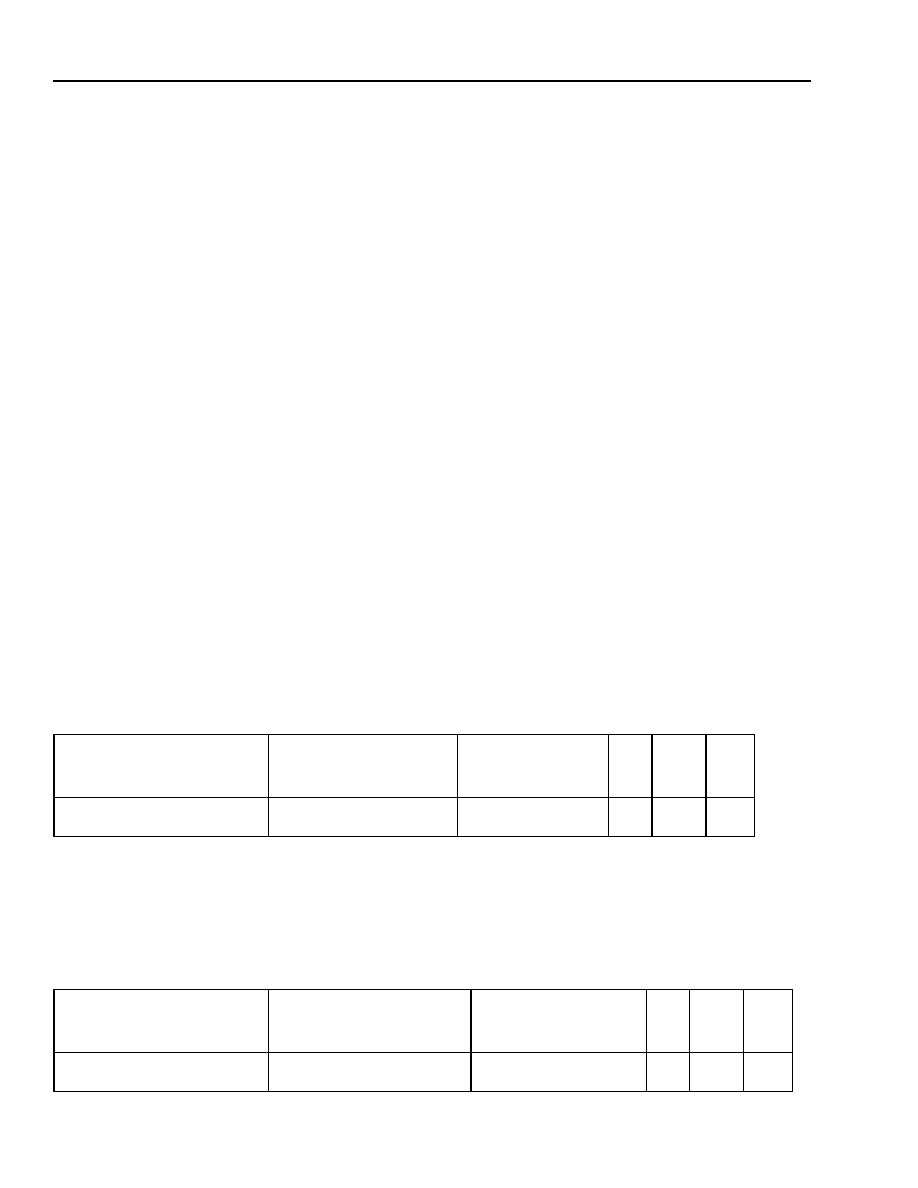

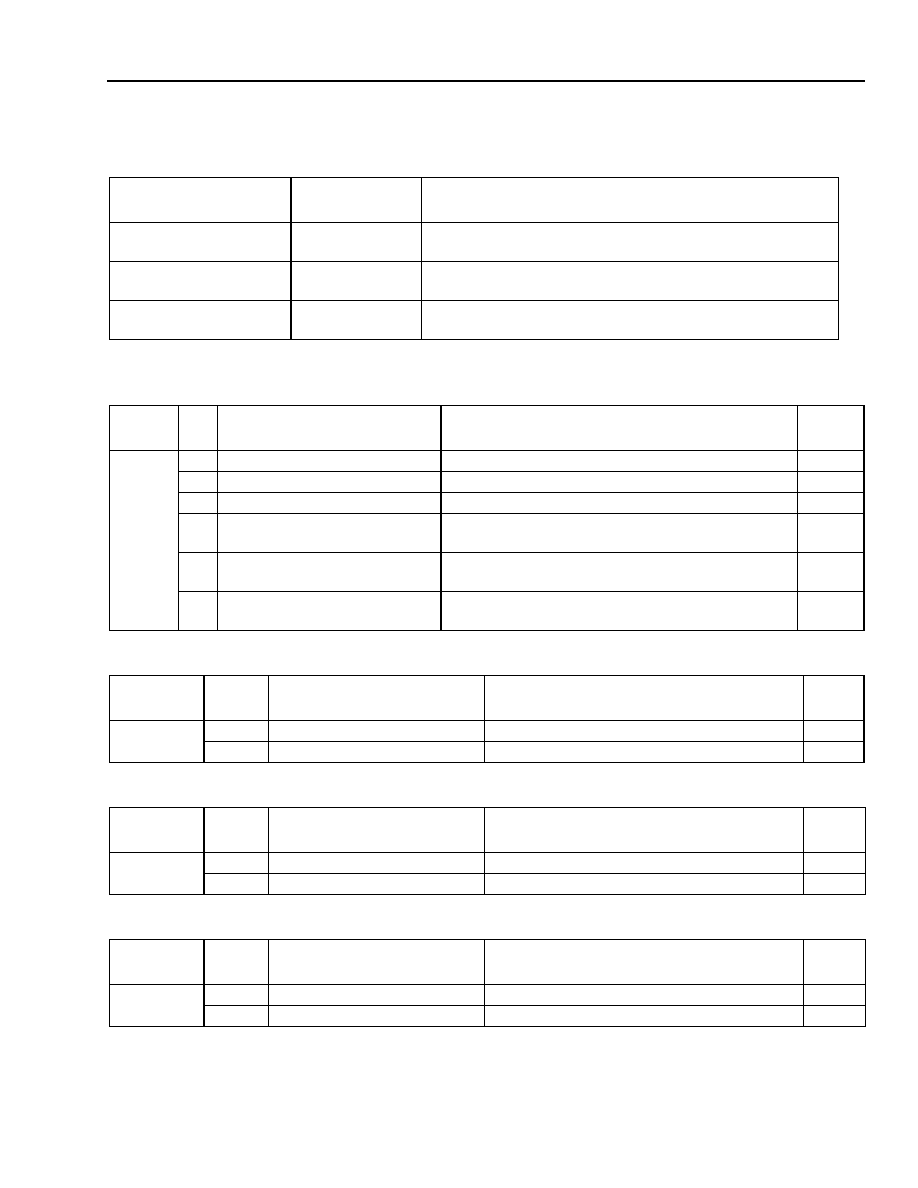

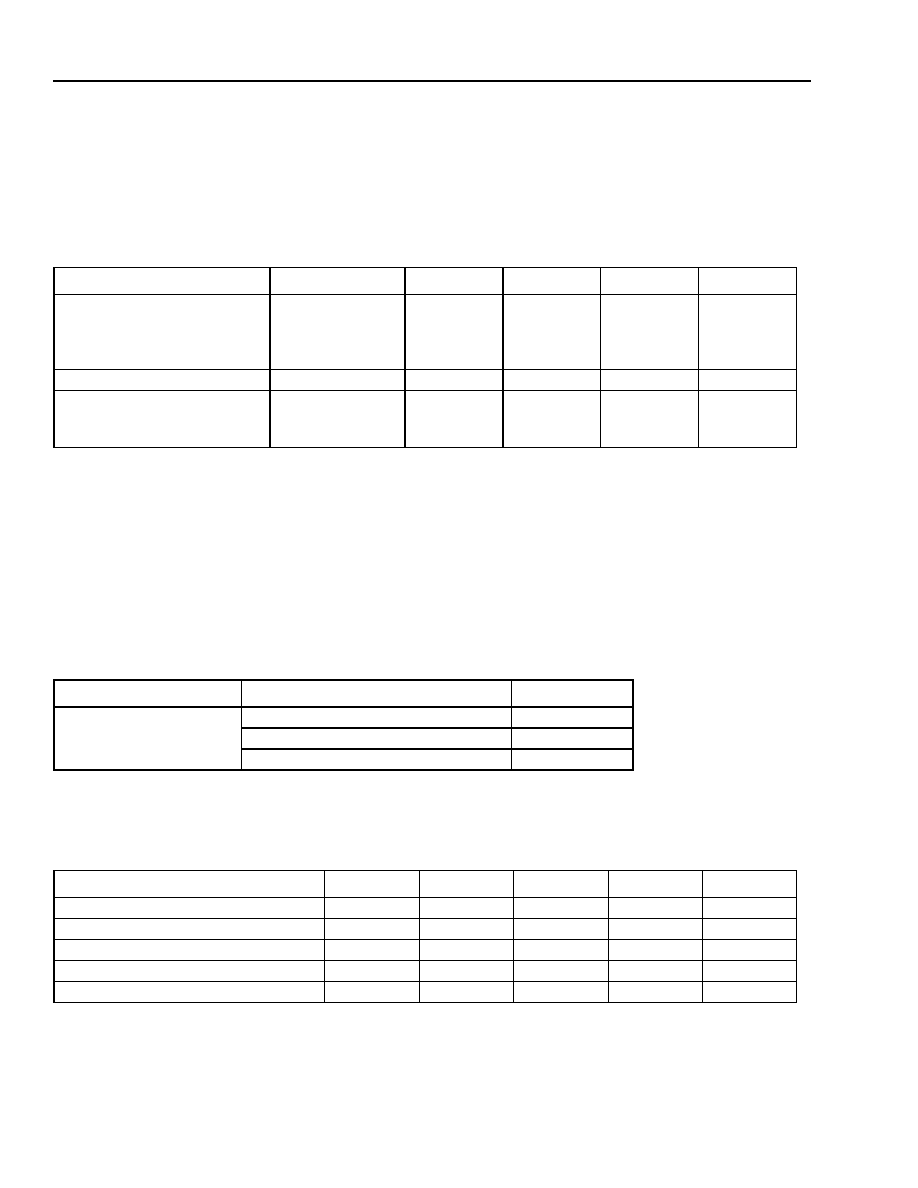

- Table 234. Absolute Maximum Ratings

- Table 235. Recommended Operating Conditions

- Table 236. Thermal ResistanceĄJunction to Ambient

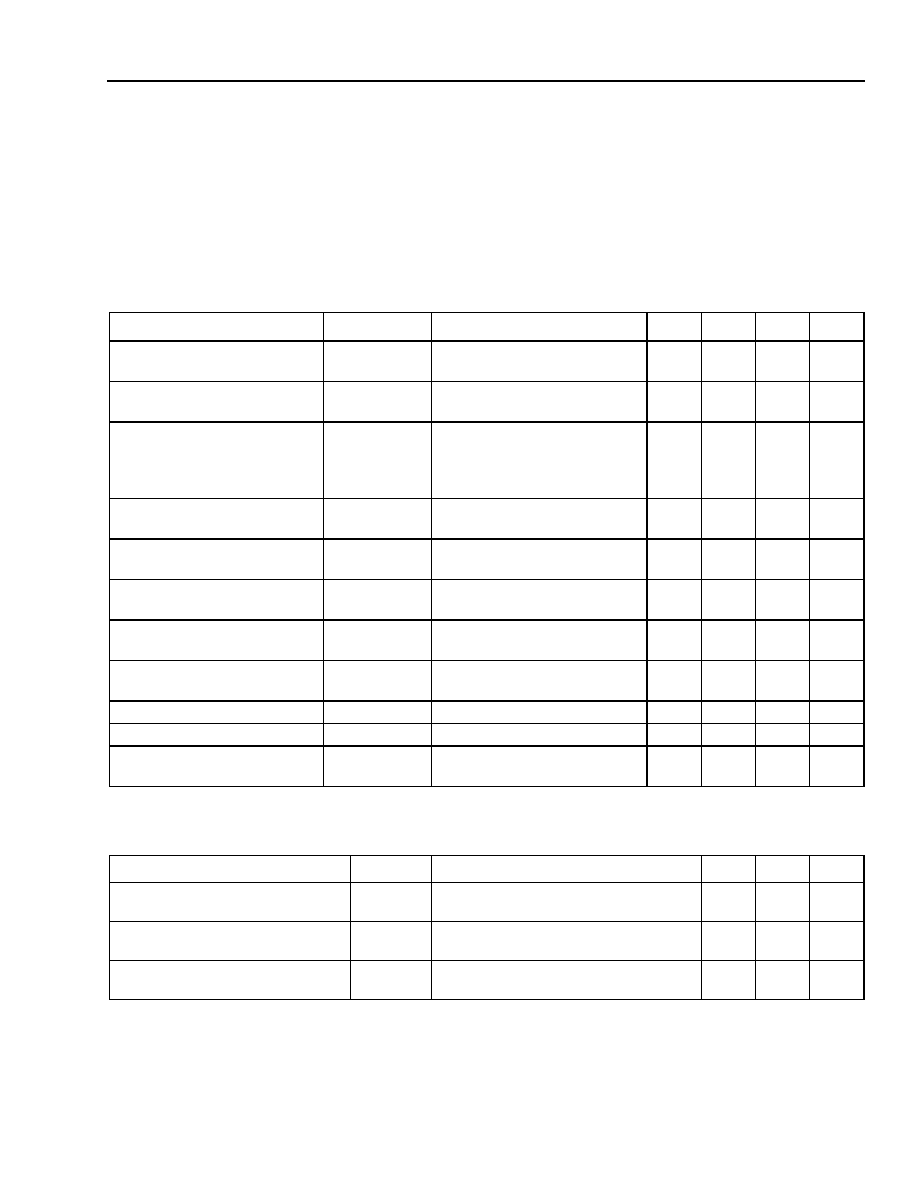

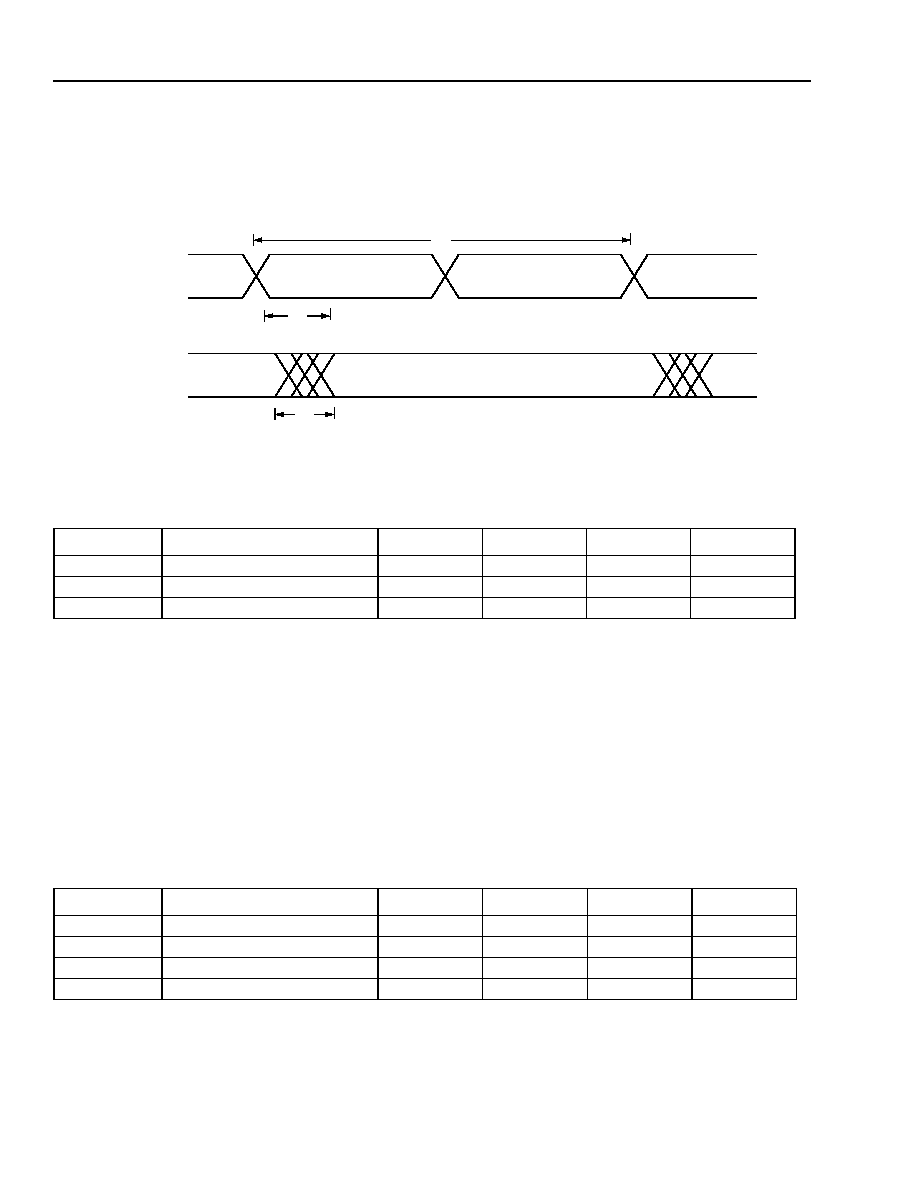

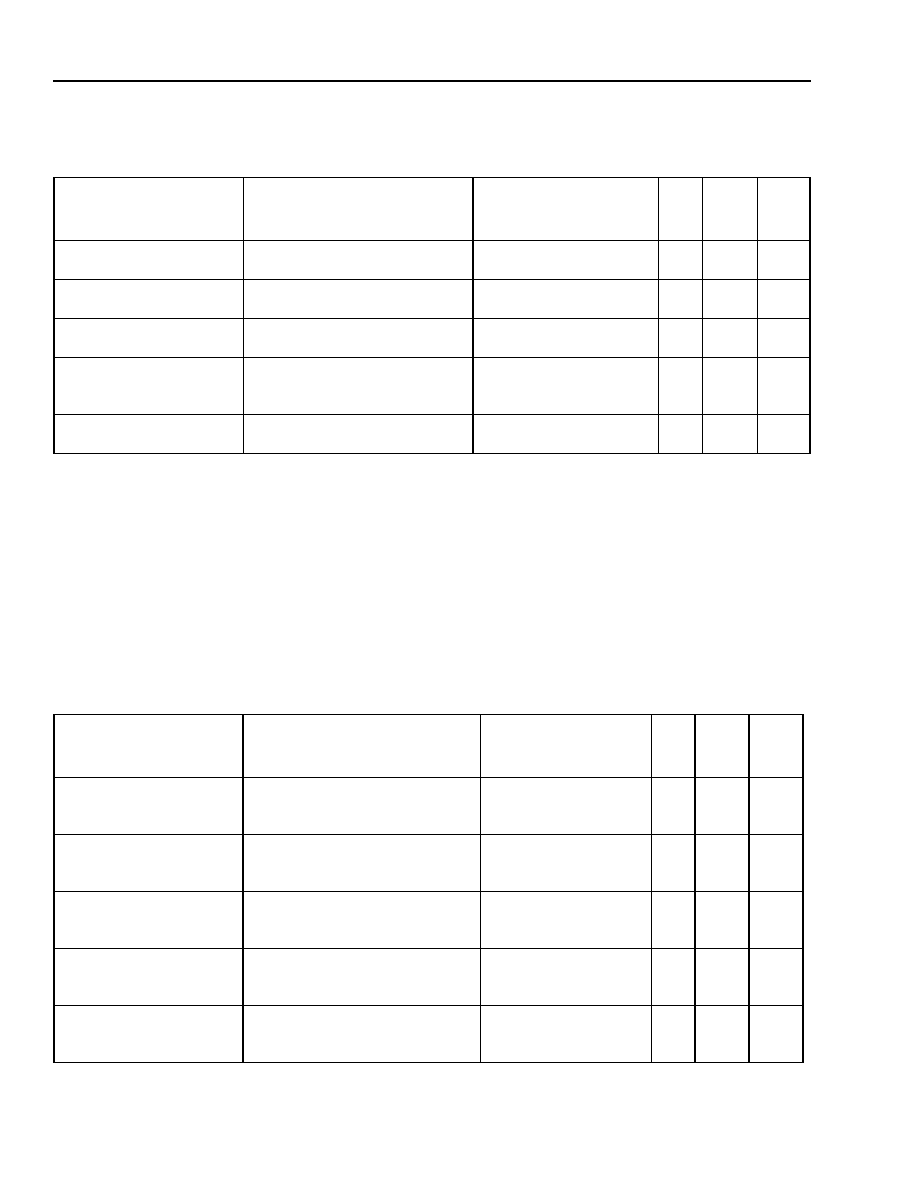

- Table 237. LVDS Driver dc Data

- Table 238. LVDS Driver ac Data

- Table 239. LVDS Driver Reference Data

- Table 240. LVDS Receiver Data

- Table 241. Receive Payload Add Interface

- Table 242. Receive Payload Drop Interface

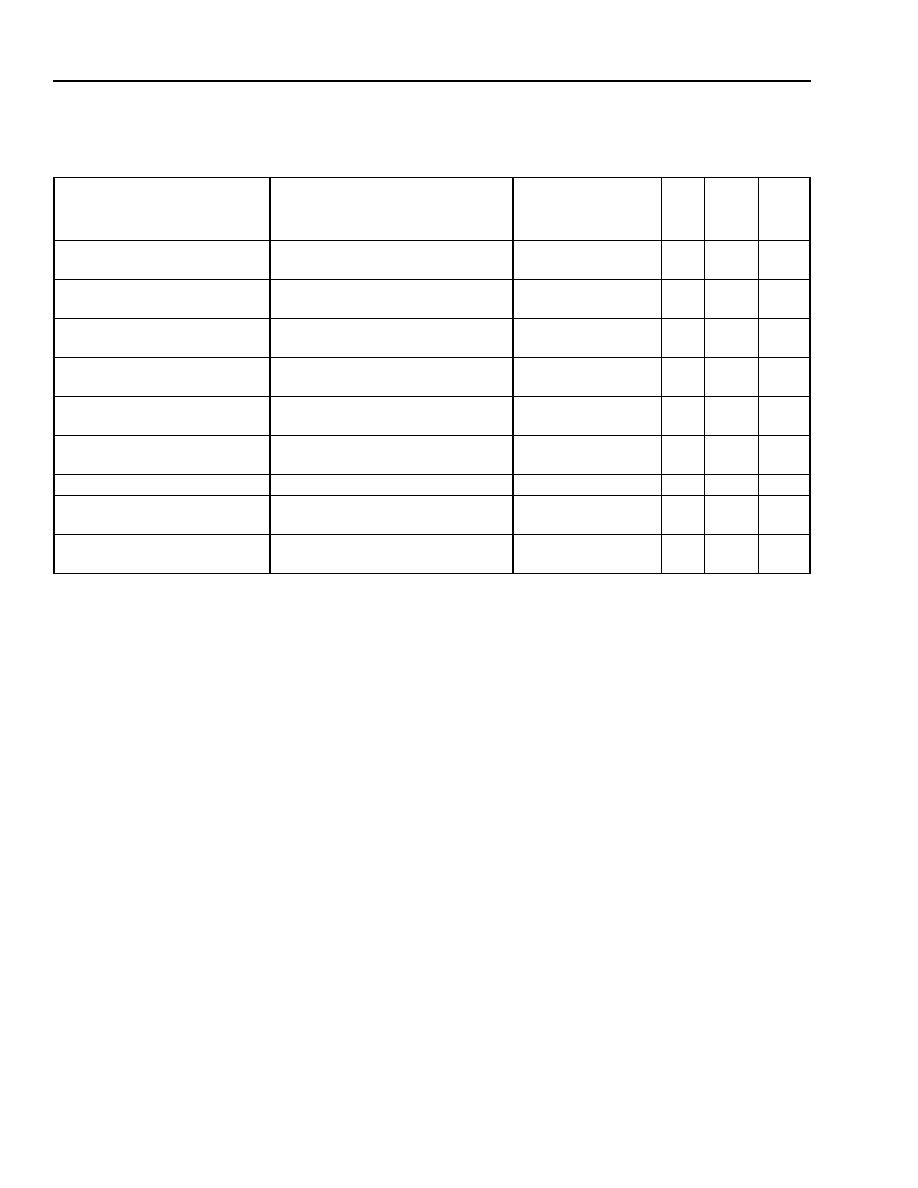

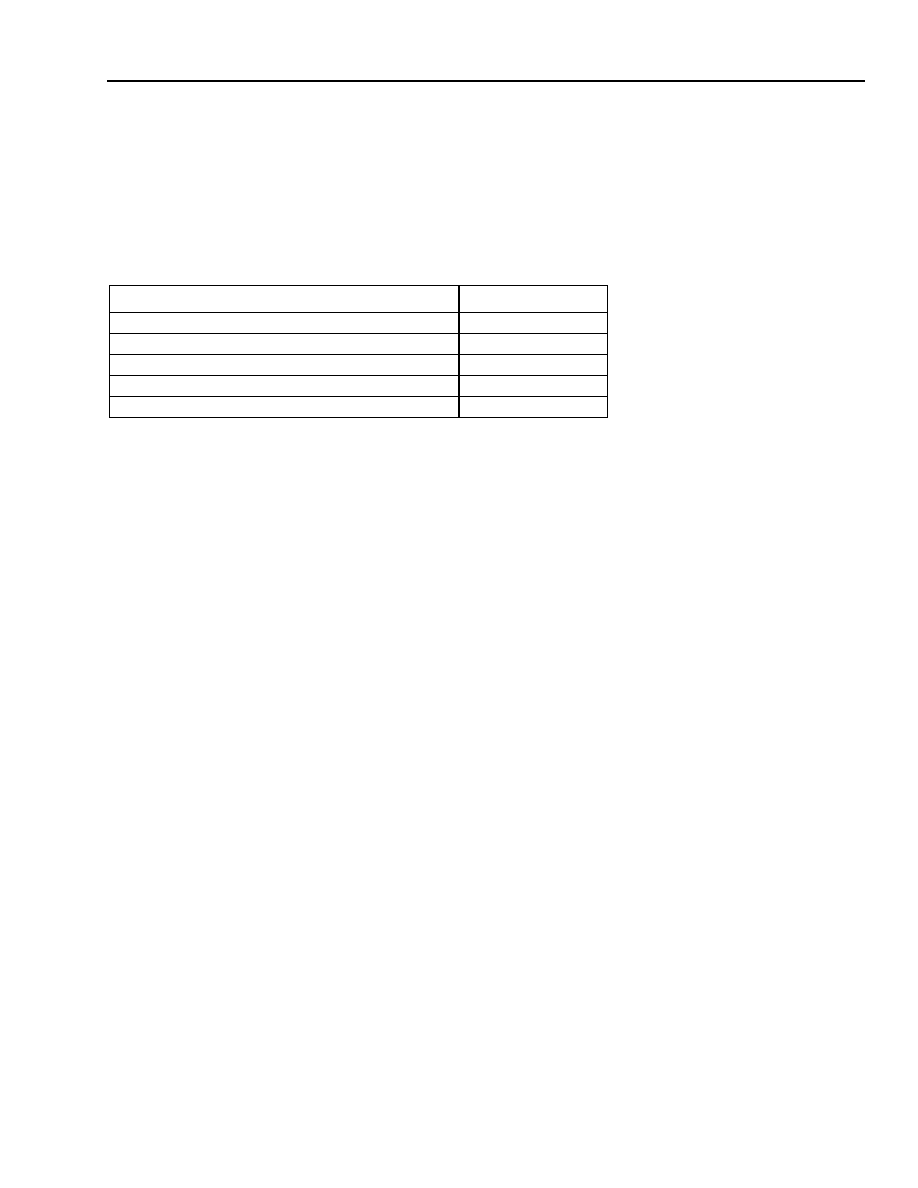

- Table 243. LVTTL 3.3�V Logic Interface Characteristics

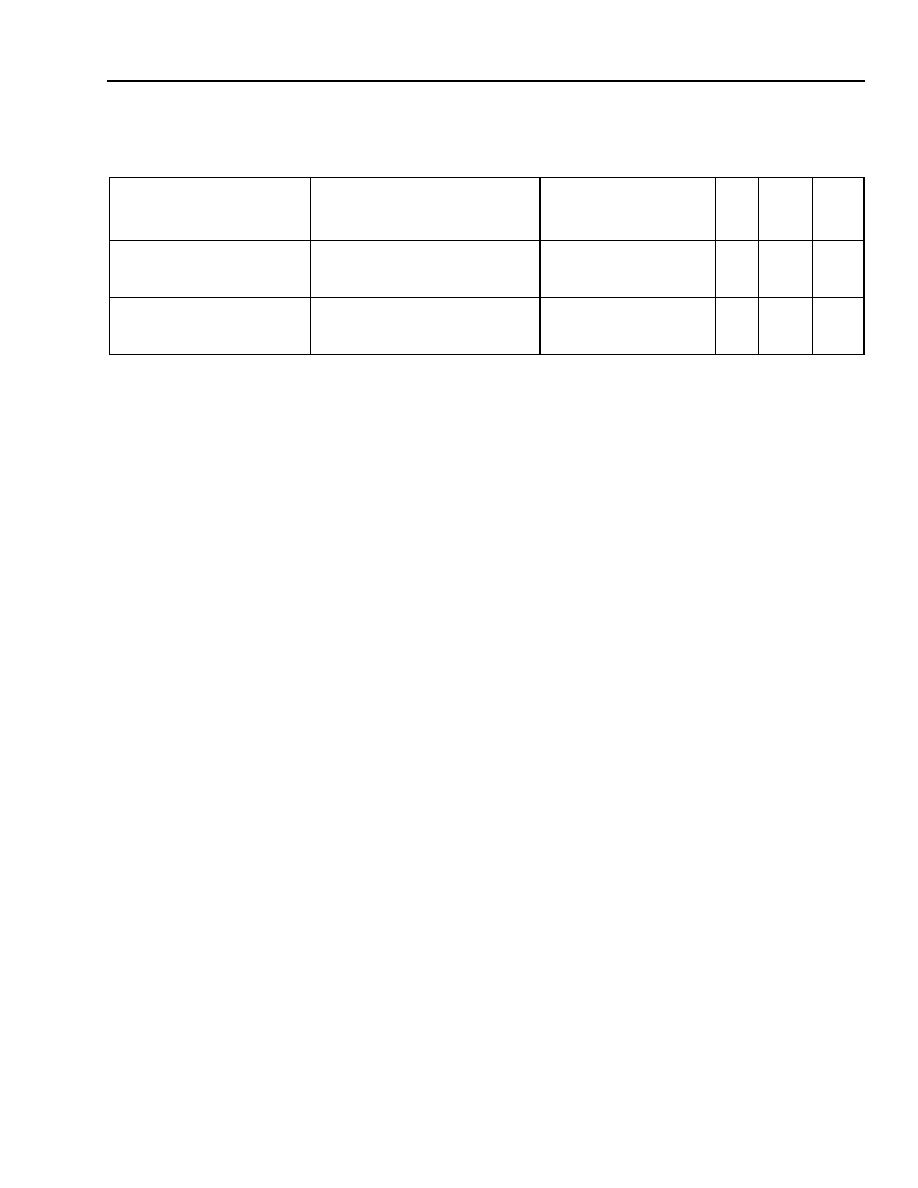

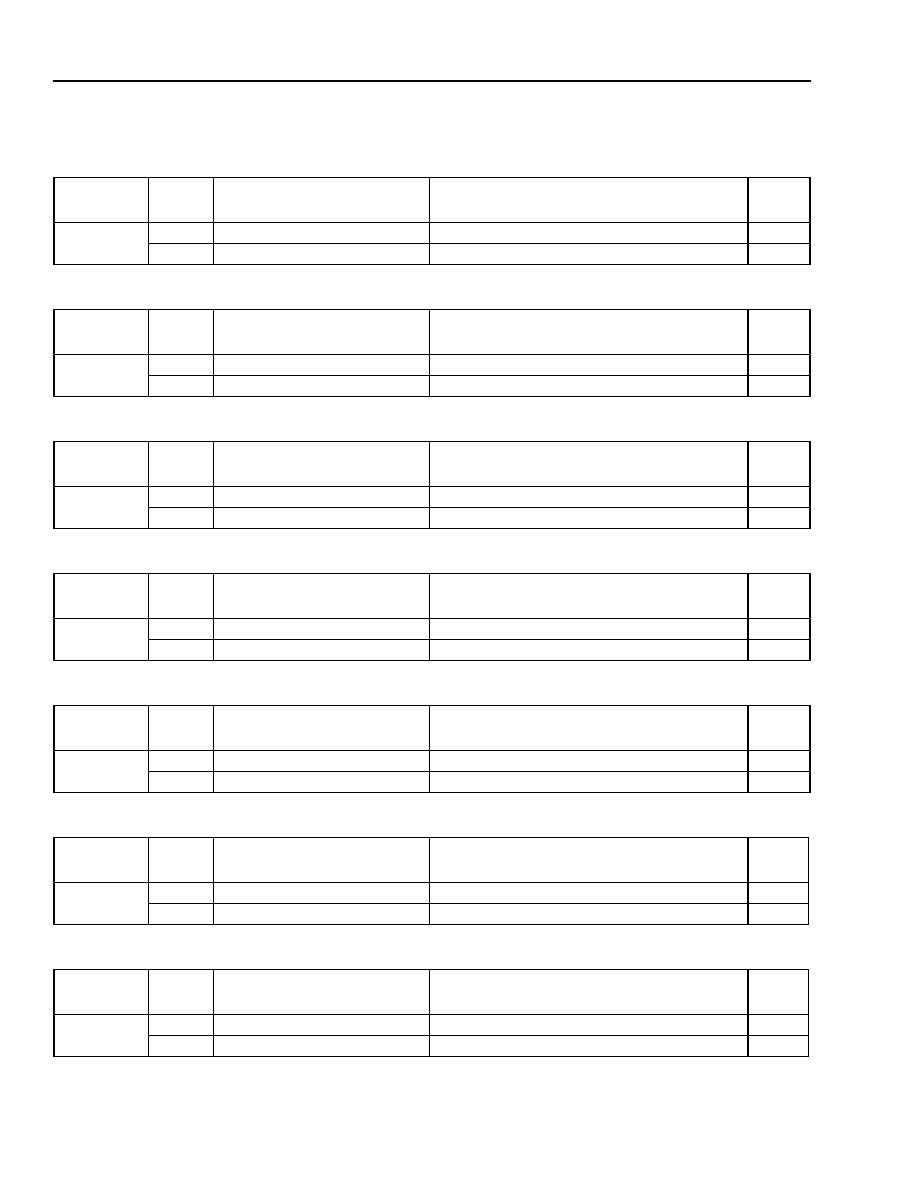

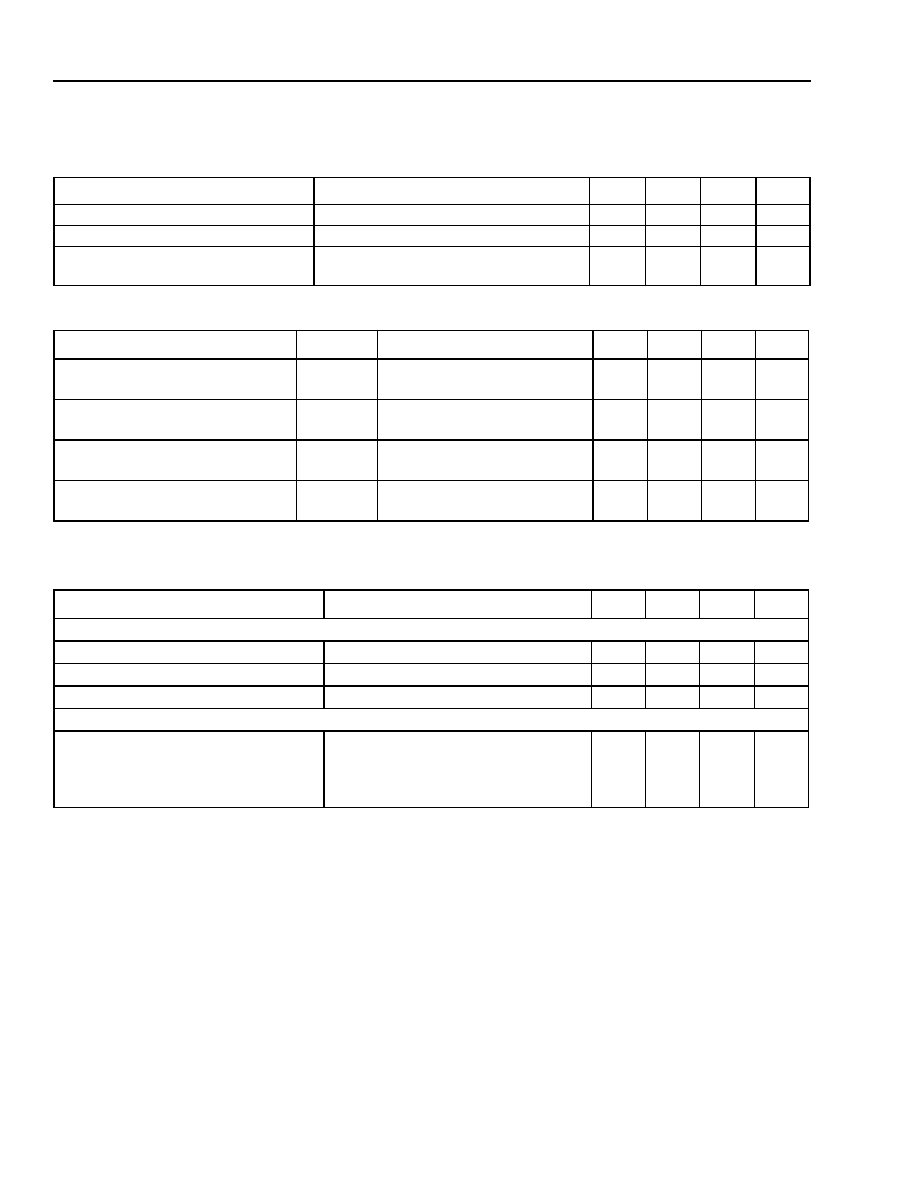

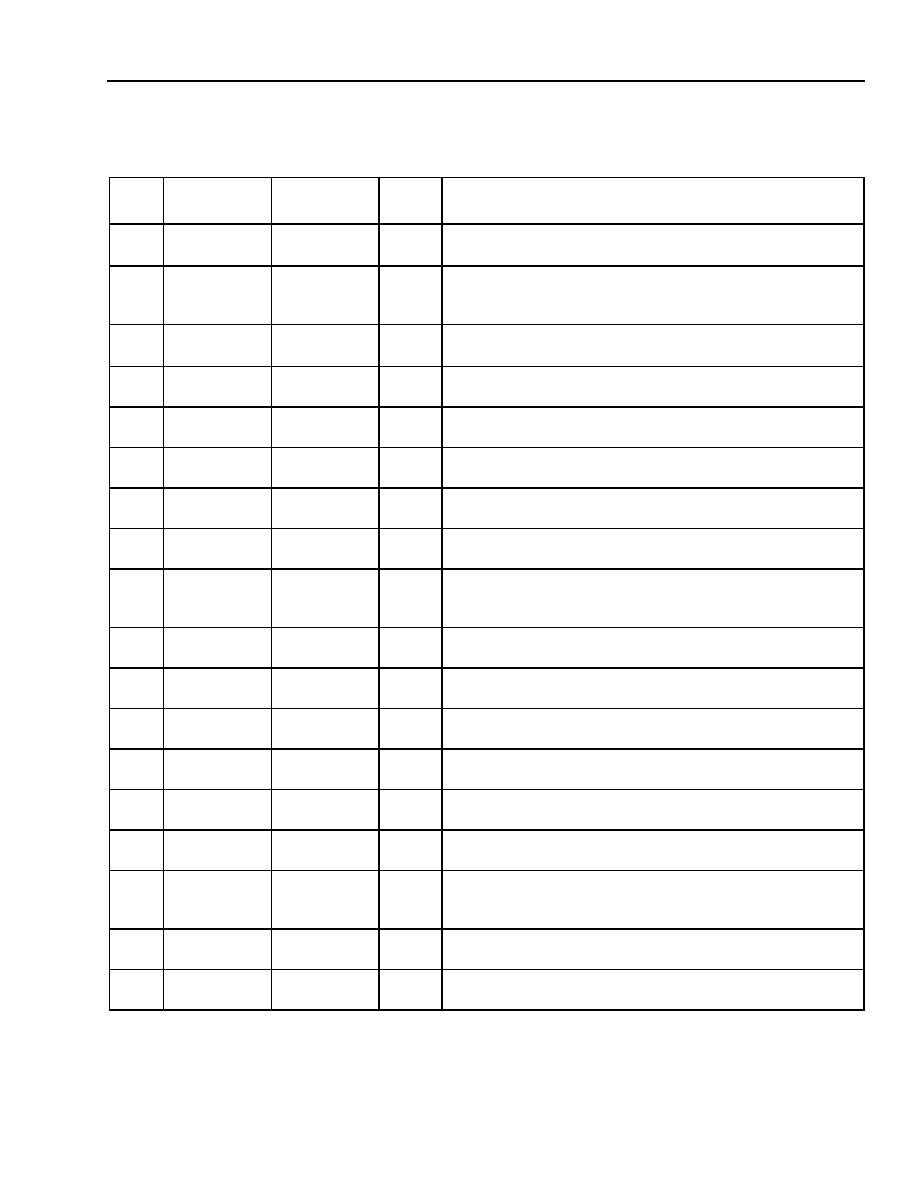

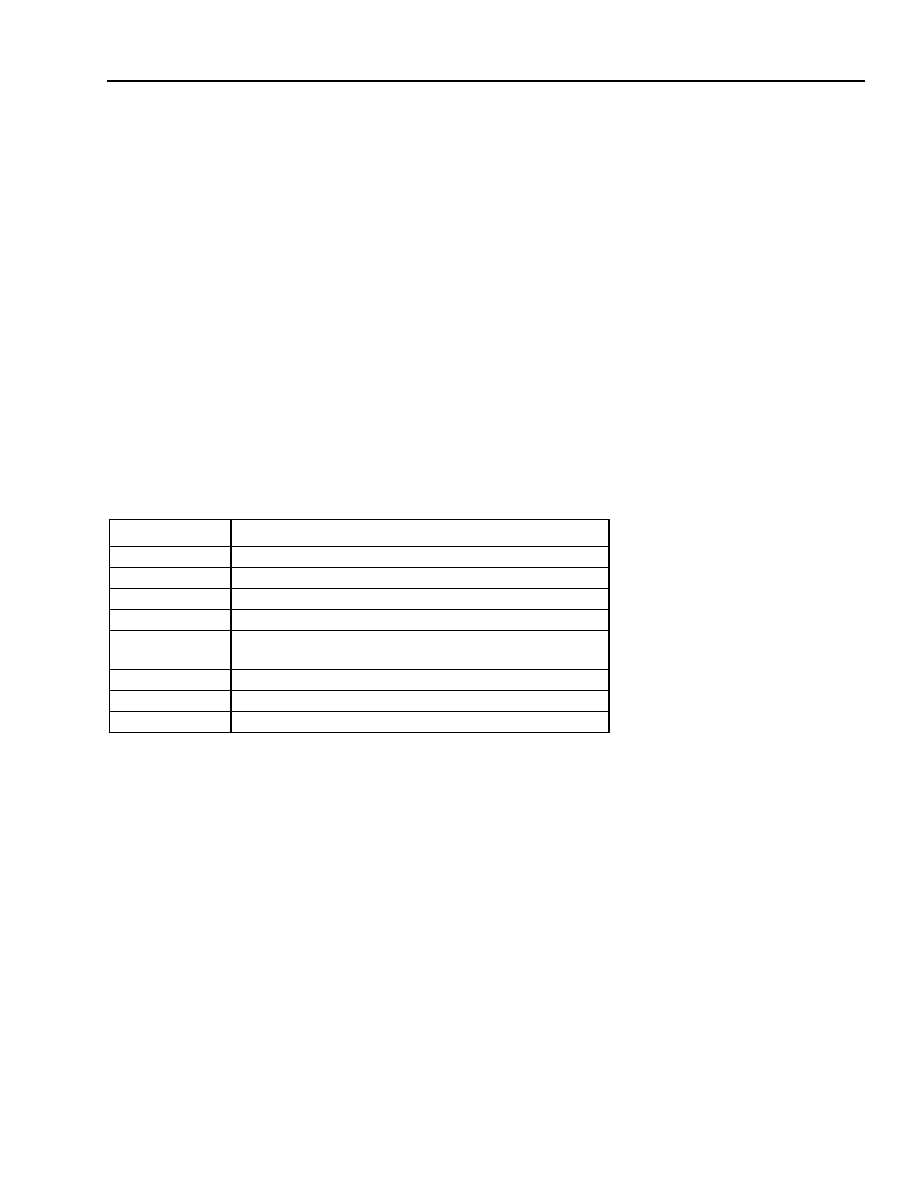

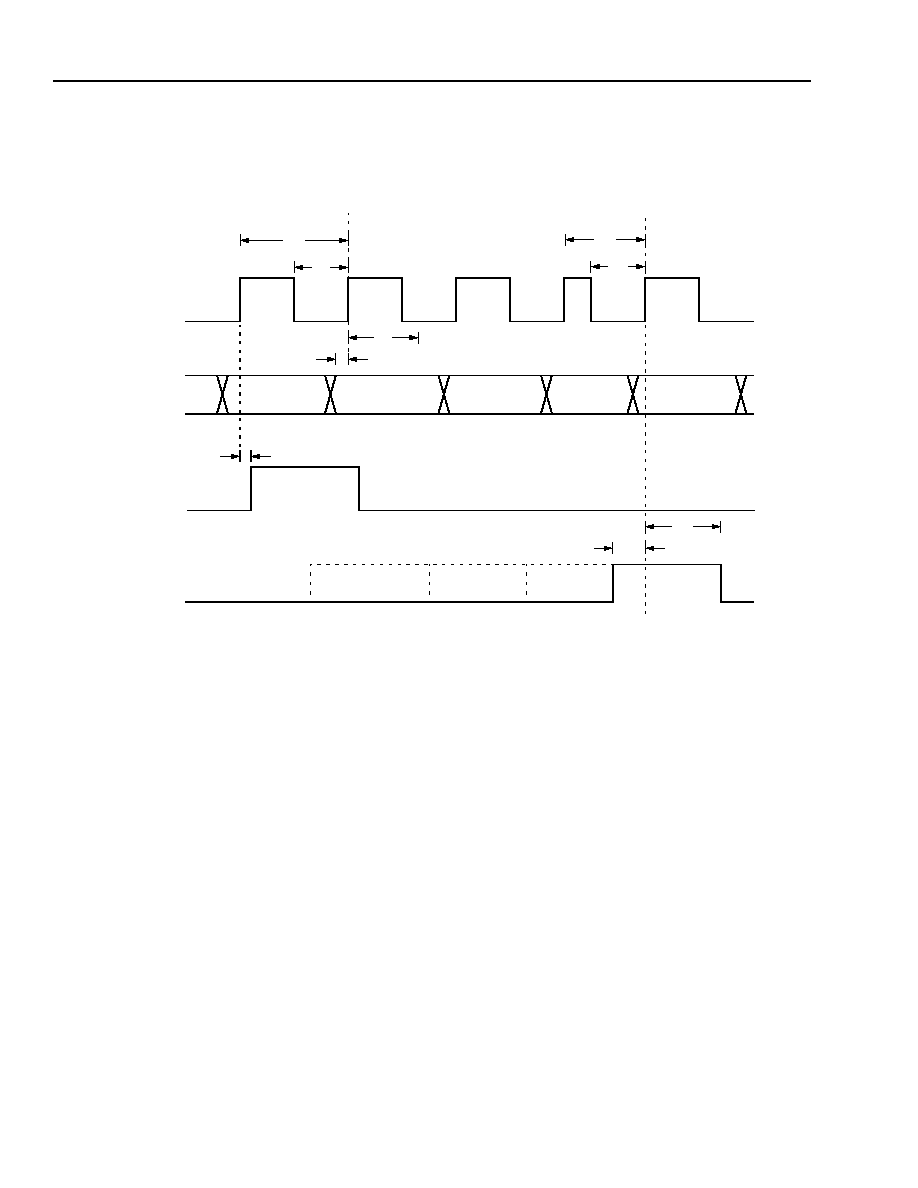

- Table 244. Receive Data Timing

- Table 245. RLCLOW/RSUSER/REXPOW Timing

- Table 246. RSDCC Timing

- Table 247. RLDCC Timing

- Table 248. Receive Overhead Serial Timing

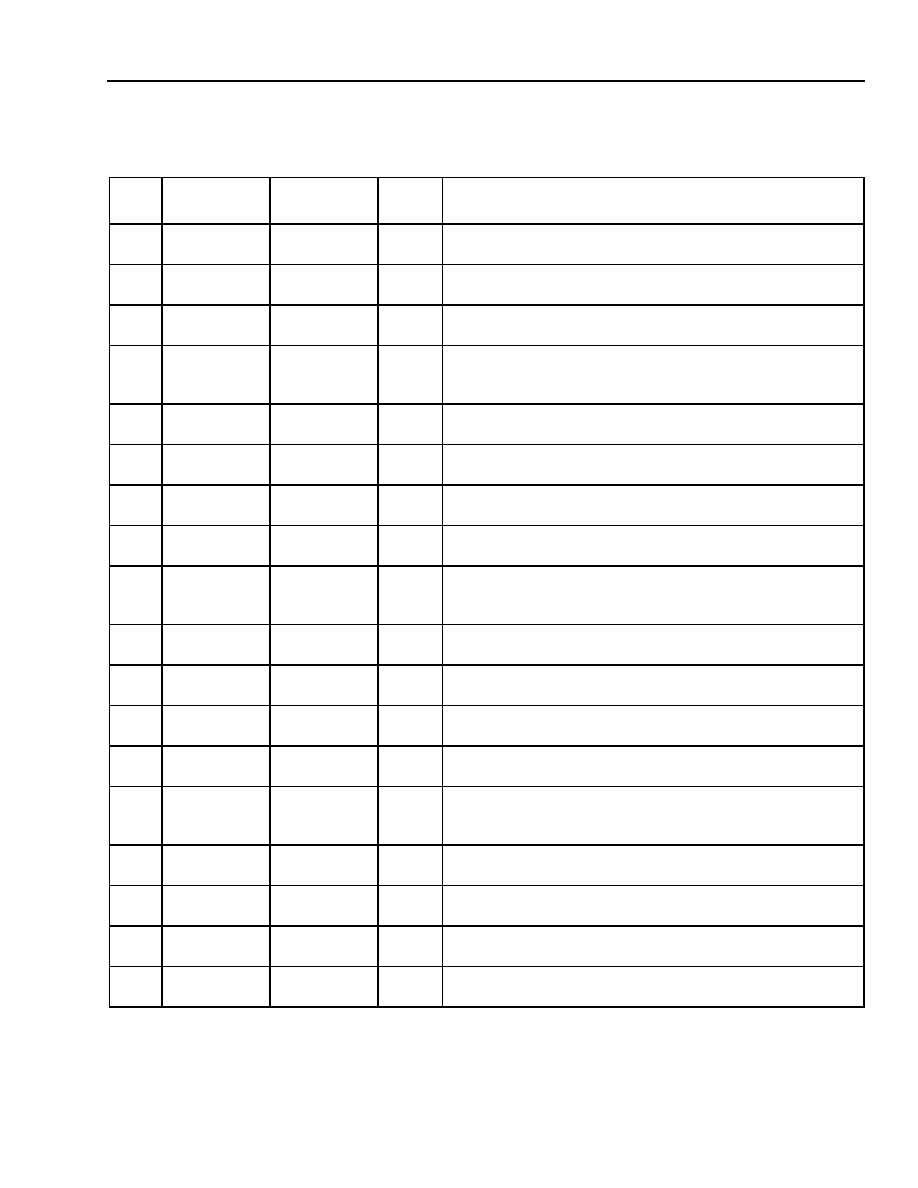

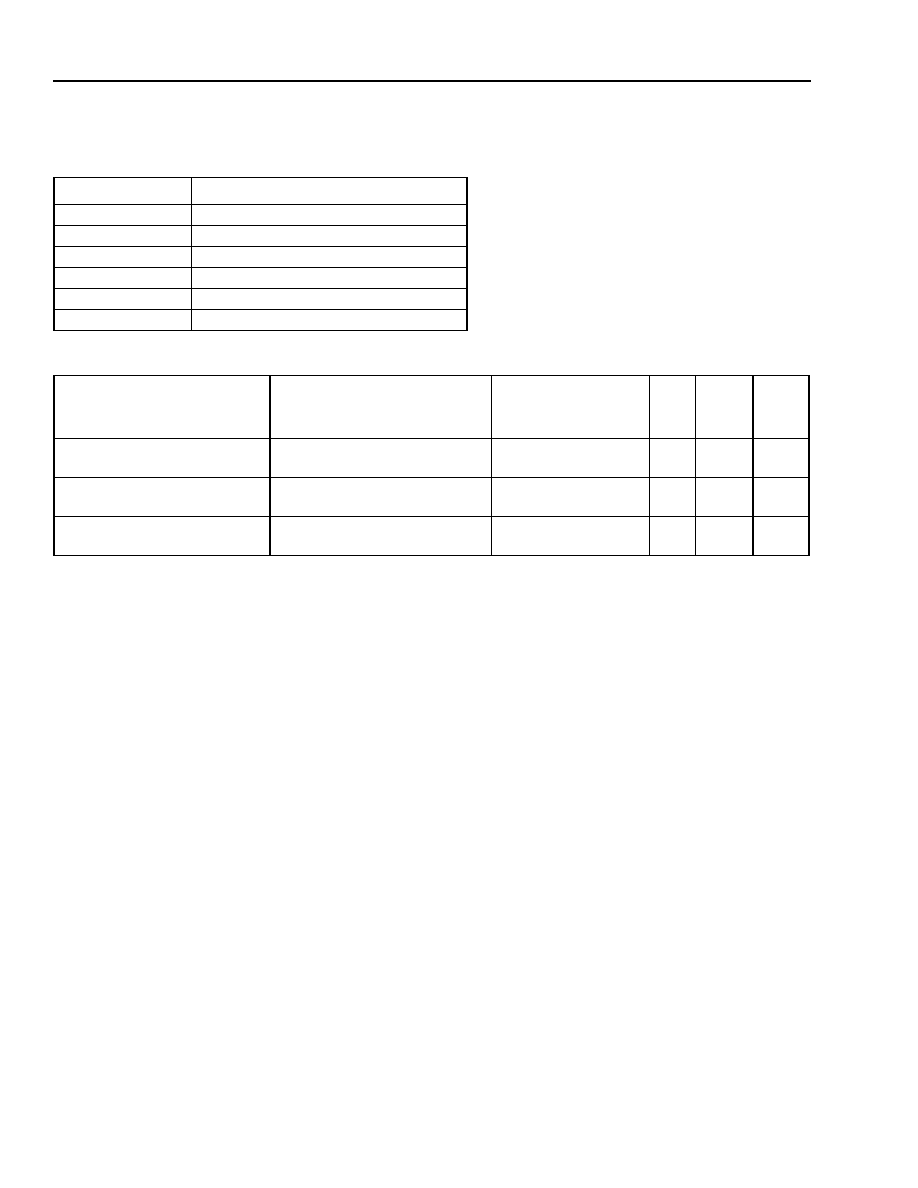

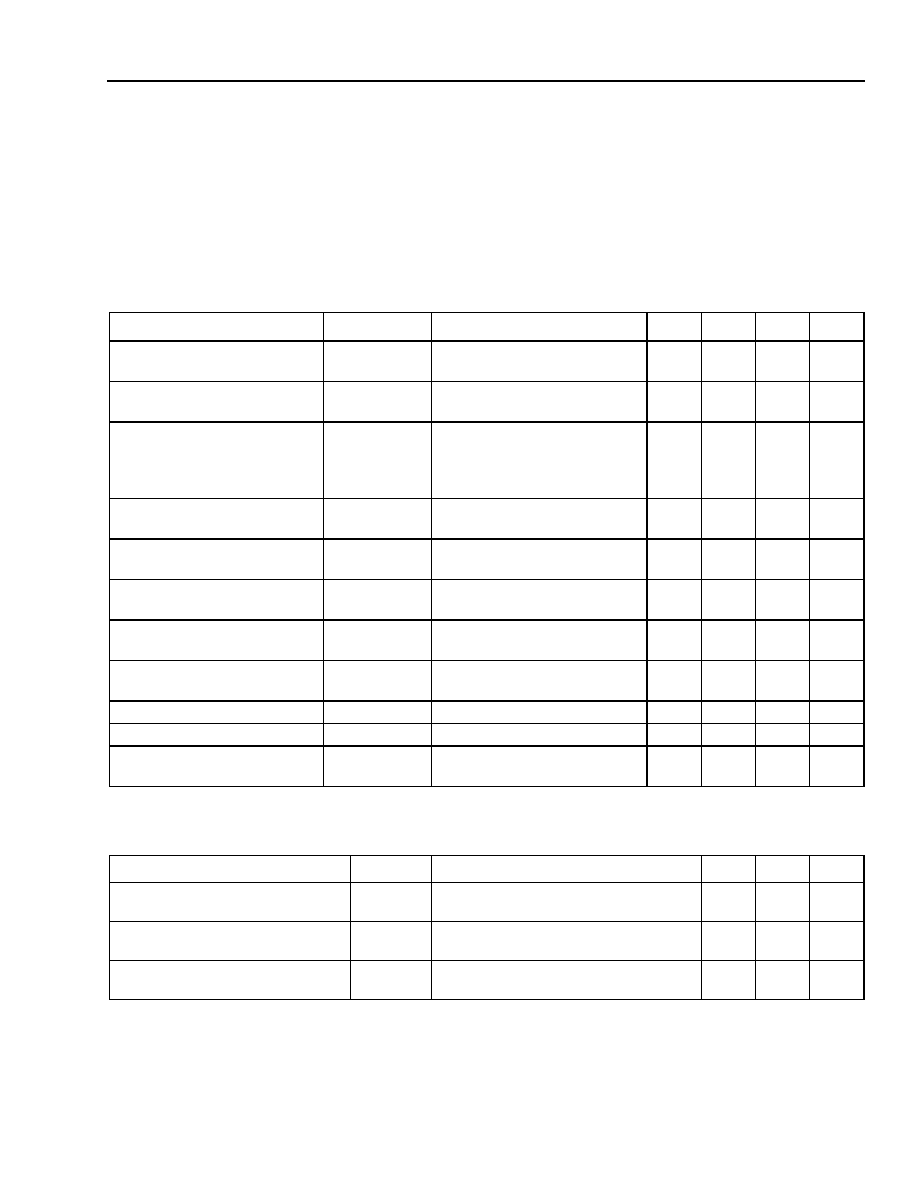

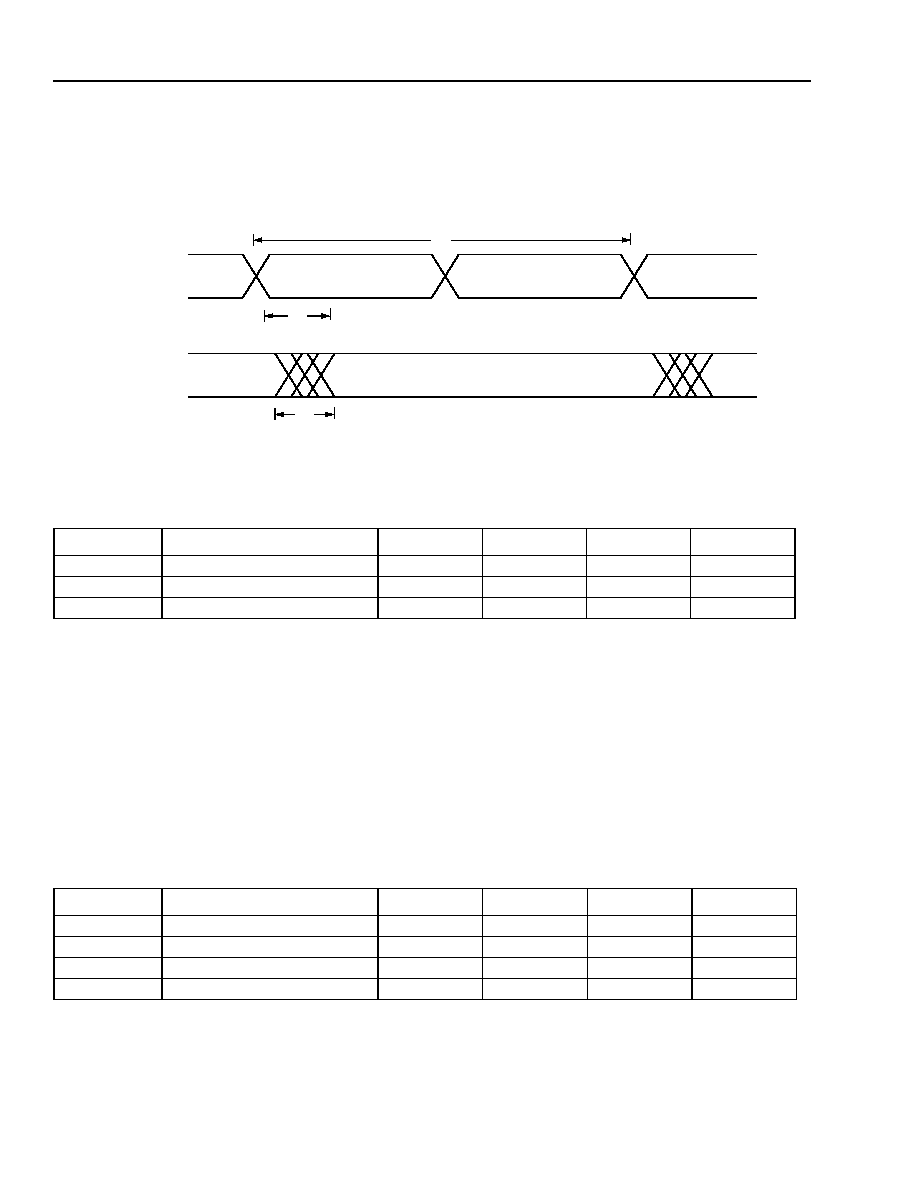

- Table 249. Transmit Data Timing

- Table 250. Transmit Frame Timing

- Table 251. TLCLOW/TSUSER/TEXPOW Timing

- Table 252. TSDCC Timing

- Table 253. TLDCC Timing

- Table 254. Transmit Overhead Serial Timing

- Table 255. Drop Frame Timing (Pointer Processor Bypassed)

- Table 256. Drop Frame Timing (Pointer Processor Active)

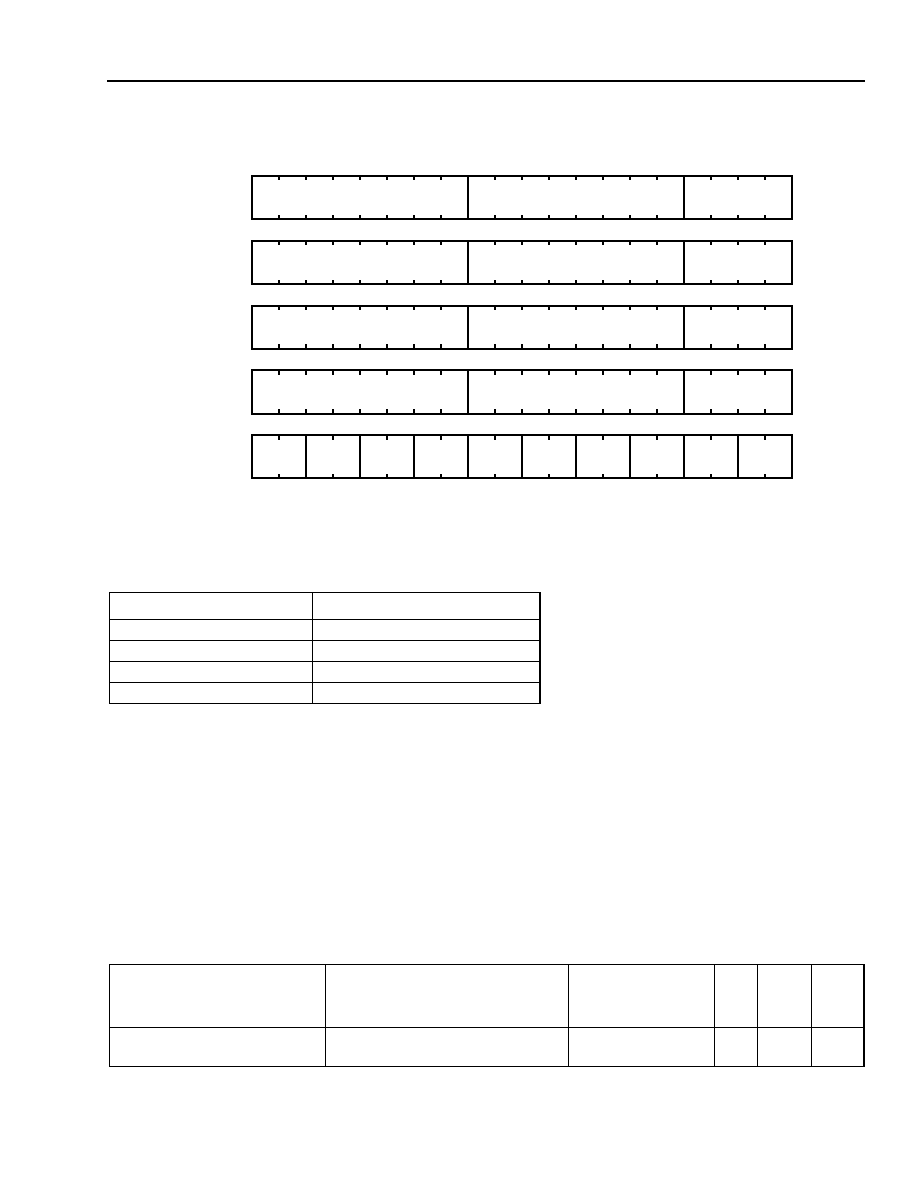

- Table 257. RDDCC Timing

- Table 258. TADCC Timing

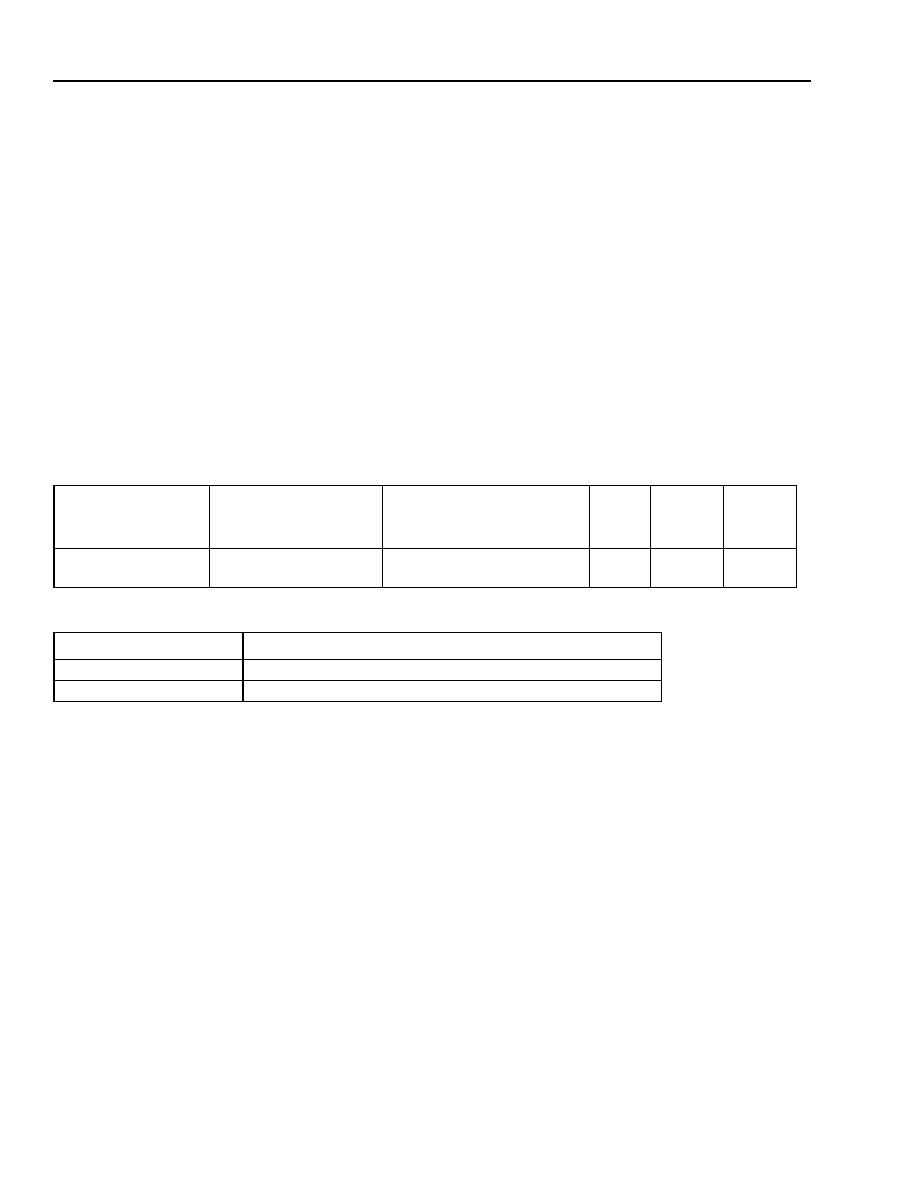

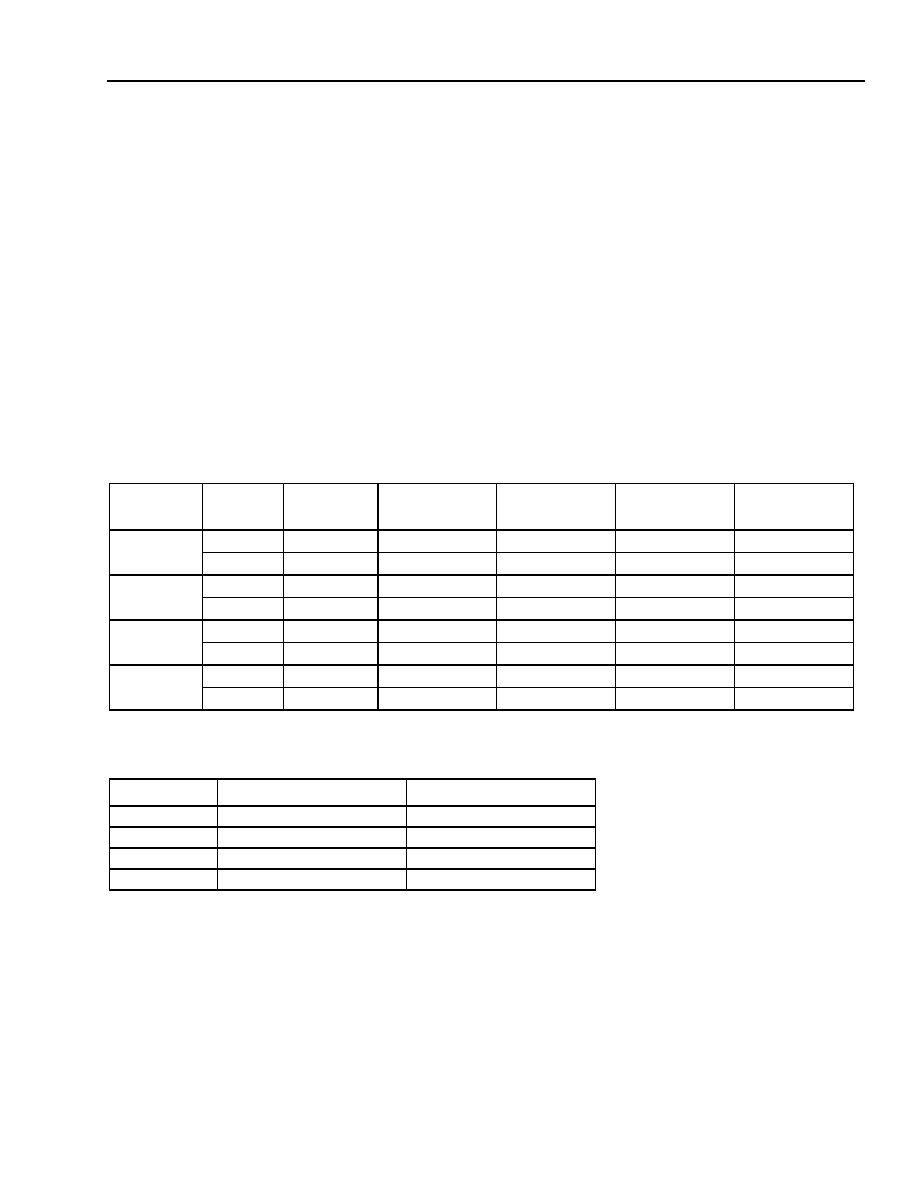

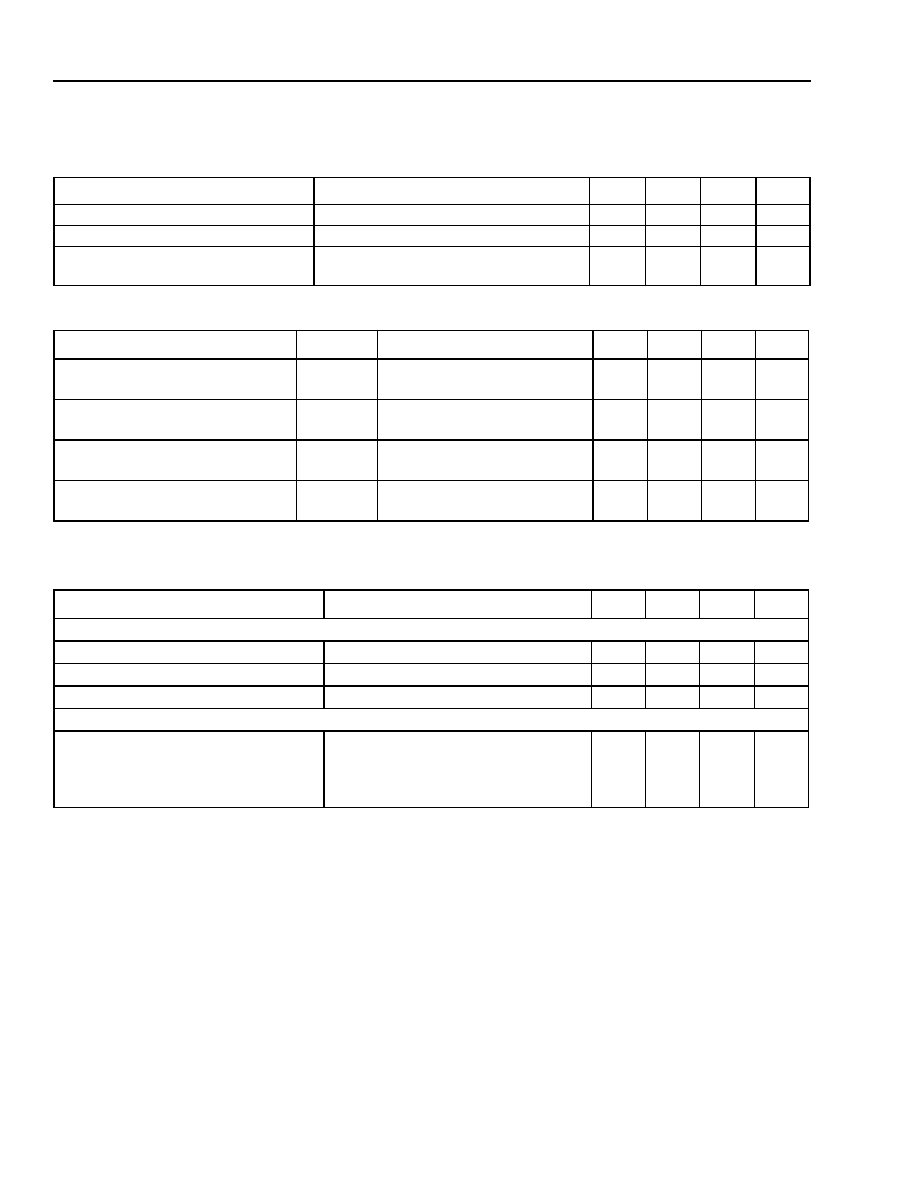

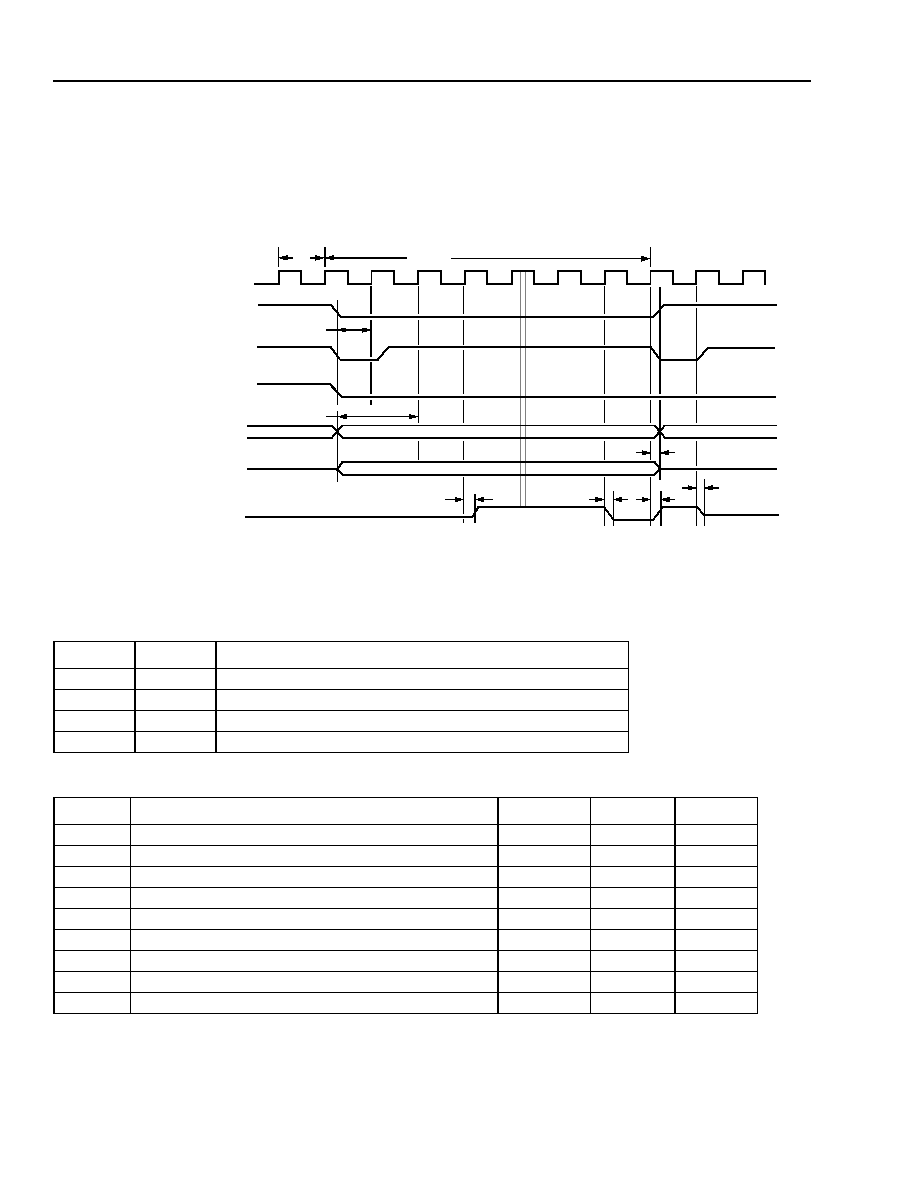

- Table 259. TA_N/TEA_N Cycle Termination for Synchronous Write Cycle

- Table 260. Microprocessor Interface Synchronous Write Cycle Specifications

- Table 261. TA_N/TEA_N Cycle Termination for Synchronous Read Cycle

- Table 262. Microprocessor Interface Synchronous Read Cycle Specifications

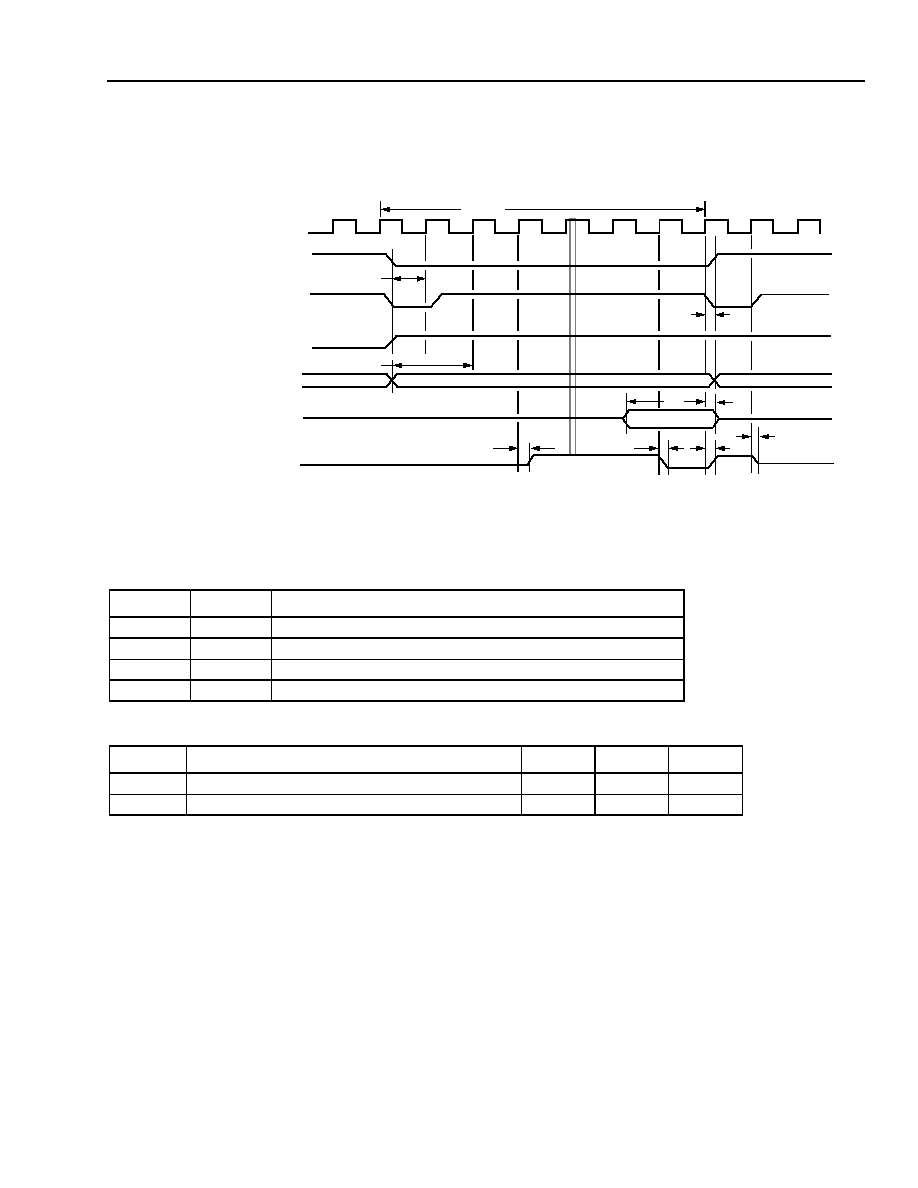

- Table 263. Microprocessor Interface Asynchronous Write Cycle Specifications

- Table 264. TA_N/TEA_N Cycle Termination for Asynchronous Write Cycle

- Table 265. TA_N/TEA_N Cycle Termination for Asynchronous Read Cycle

- Table 266. Microprocessor Interface Asynchronous Read Cycle Specifications

- Contact Us

Data Sheet

May 2003

TSOT0410G4 SONET/SDH

STS-192 Overhead and Path Processor

Features

General

s

Section overhead (RSOH) and line overhead

(MSOH) termination, and path overhead monitoring

for one SONET STS-192 (SDH STM-64) or four

STS-48 (STM-16) signals.

s

Supports any valid combination of STS-1 and

concatenated payloads from STS-3c to STS-192c.

s

Microprocessor interface configurable to operate

with most commercial microprocessors.

s

IEEE

ģ

1149.1 port with memory built-in self-test

(BIST), scan, and boundary scan (JTAG).

s

Low-power 2.5 V operation with 3.3 V (5 V tolerant)

inputs and outputs.

s

EIA

ģ

-644, IEEE 1596.3 compliant LVDS buffers*.

s

600-pin LBGA package.

s

≠40 įC to +85 įC temperature range.

STS-192/STM-64 (Line Interface)

s

Provides a 16-bit (or 4

◊

4-bit) wide, 622 MHz differ-

ential line interface.

s

Synchronizes to the receive data frames and

detects severely errored framing (SEF) and loss of

frame (LOF). Also inserts the framing bytes (A1 and

A2) in the transmit data.

s

Supports enhanced framing (A1, A1, A2, A2).

s

Performs frame-synchronous scrambling and

descrambling of the STS-192/STS-48 data, and

loss of signal (LOS) is detected.

s

Extracts the 64-byte or 16-byte section trace mes-

sage (J0) from the receive data and optionally

stores it in, or compares it to, an internal register

bank. Unstable or mismatched messages are

detected, and path alarm indication signal (AIS)

may be optionally inserted in the drop data.

s

Optionally inserts a 64-byte or 16-byte section trace

message or a fixed pattern in the J0 byte of the

transmit data.

s

Extracts and outputs, on a serial link, all transport

overhead bytes in the receive data and inserts any,

or all, transport overhead bytes in the transmit data

using a corresponding serial input.

s

Extracts and outputs, on serial links, the section

user channel (F1), orderwire channels (E1, E2),

and data communication channels (D1--D3 and

D4--D12) for the receive data. Inserts correspond-

ing serial input signals into the transmit data.

s

Extracts, integrates, and stores the automatic pro-

tection switch (APS) channel bytes (K1, K2) for the

receive data and detects protection switch failure

alarms. Inserts APS bytes in the transmit data from

internal registers or from add data overhead bytes.

s

Detects line alarm indication signal (AIS) and

remote defect indication (RDI) based on the K2

byte of the receive data. Inserts line AIS and RDI in

the transmit data. Optionally inserts line RDI auto-

matically due to LOS, LOF, or line AIS defects.

s

Extracts, integrates, and stores the synchronization

status byte (S1) for the receive data. Inserts the

synchronization status byte into the transmit data

from an internal register or from a value encoded on

the transmit frame synchronous input.

s

Calculates, detects, and counts section and line

BIP-8 errors (B1, B2) for the receive data, and

inserts BIP-8 in the transmit data. Supports either

bit or block error accumulation of B1 errors (sepa-

rately provisionable), and bit error accumulation of

B2 errors.

s

Extracts and counts line remote errors (REI) for the

receive data (M1), and inserts REI in the transmit

data based on B2 errors.

s

SS bit mode supports SONET (00) or SDH (10) val-

ues and defines the value of the SS bits for

unequipped signal insertion. In normal mode,

SS bits can be passed through or overwritten with a

provisioned value. All SS bit provisioning is done at

a STM-16 level affecting all AU-3s.

s

The B1 error mask can be extracted serially on the

ROHDAT interface, and the B2 error mask can be

extracted serially on the local orderwire, express

orderwire, and orderwire clock pins.

* Refer to LVDS Receiver Buffer Capabilities section on page 169 for additional details.

Table of Contents

Contents

Page

2

Agere Systems Inc.

Data Sheet

May 2003

STS-192 Overhead and Path Processor

TSOT0410G4 SONET/SDH

Features ................................................................................................................................................................... 1

General .................................................................................................................................................................. 1

STS-192/STM-64 (Line Interface).......................................................................................................................... 1

Add/Drop (Equipment Interface) .......................................................................................................................... 12

Applications ............................................................................................................................................................ 12

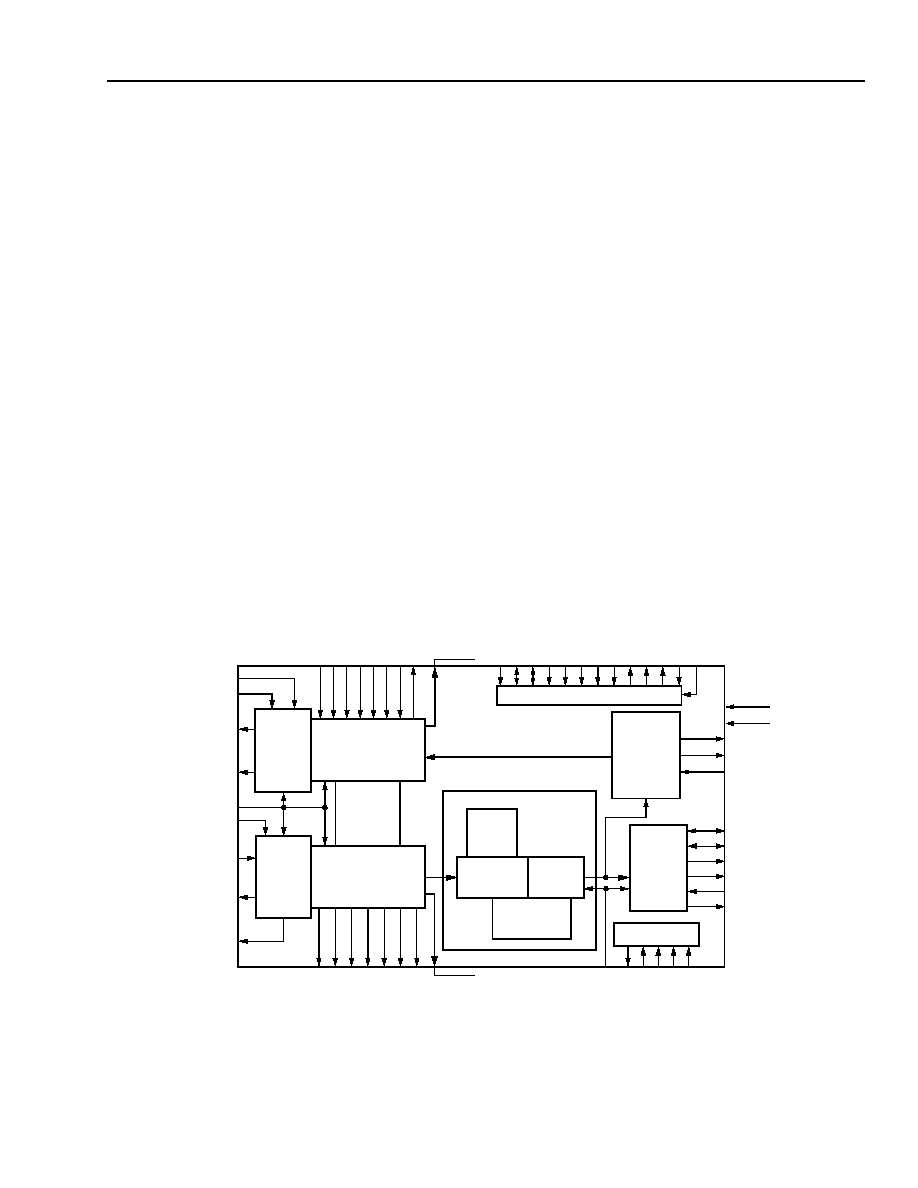

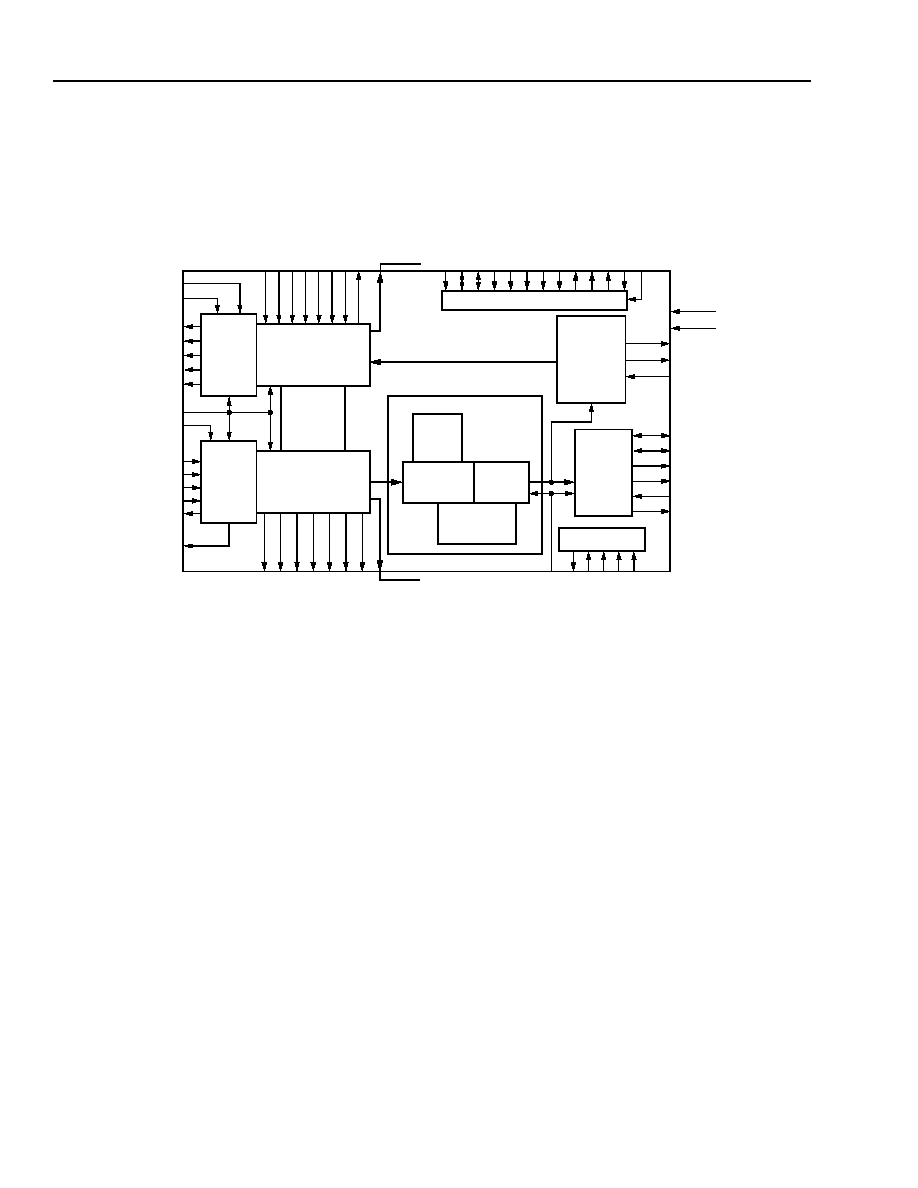

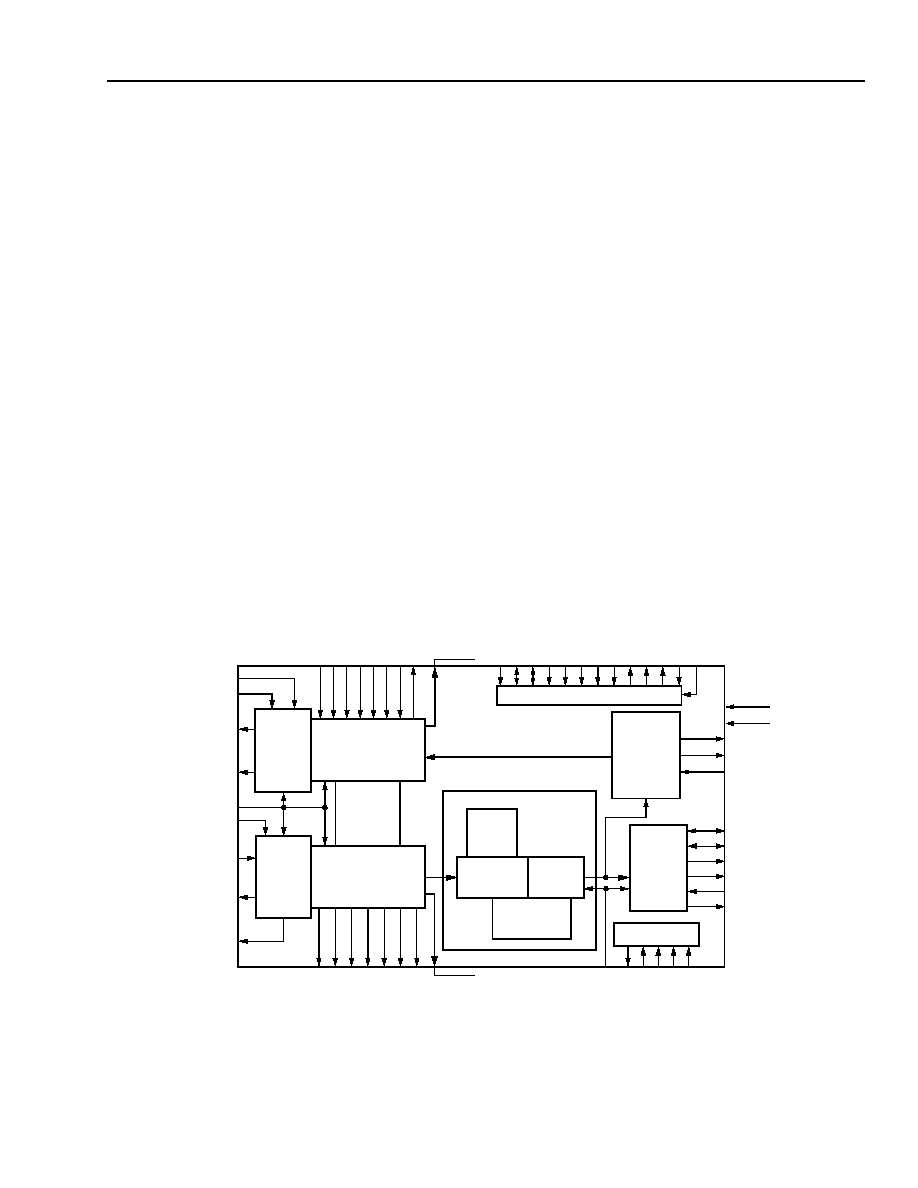

Description.............................................................................................................................................................. 13

Block Diagrams.................................................................................................................................................... 13

Glossary............................................................................................................................................................... 14

Receive Direction Overview................................................................................................................................. 15

Transmit Direction Overview................................................................................................................................ 15

STS-192 Mode Options ....................................................................................................................................... 16

TOH Transparency............................................................................................................................................ 16

Regenerator Loopback...................................................................................................................................... 16

Device Mode Setup.............................................................................................................................................. 16

Pin Information ....................................................................................................................................................... 17

Functional Description ............................................................................................................................................ 47

Receive STS-192 Line Interface.......................................................................................................................... 47

Loss-of-Signal (LOS) Detector .......................................................................................................................... 47

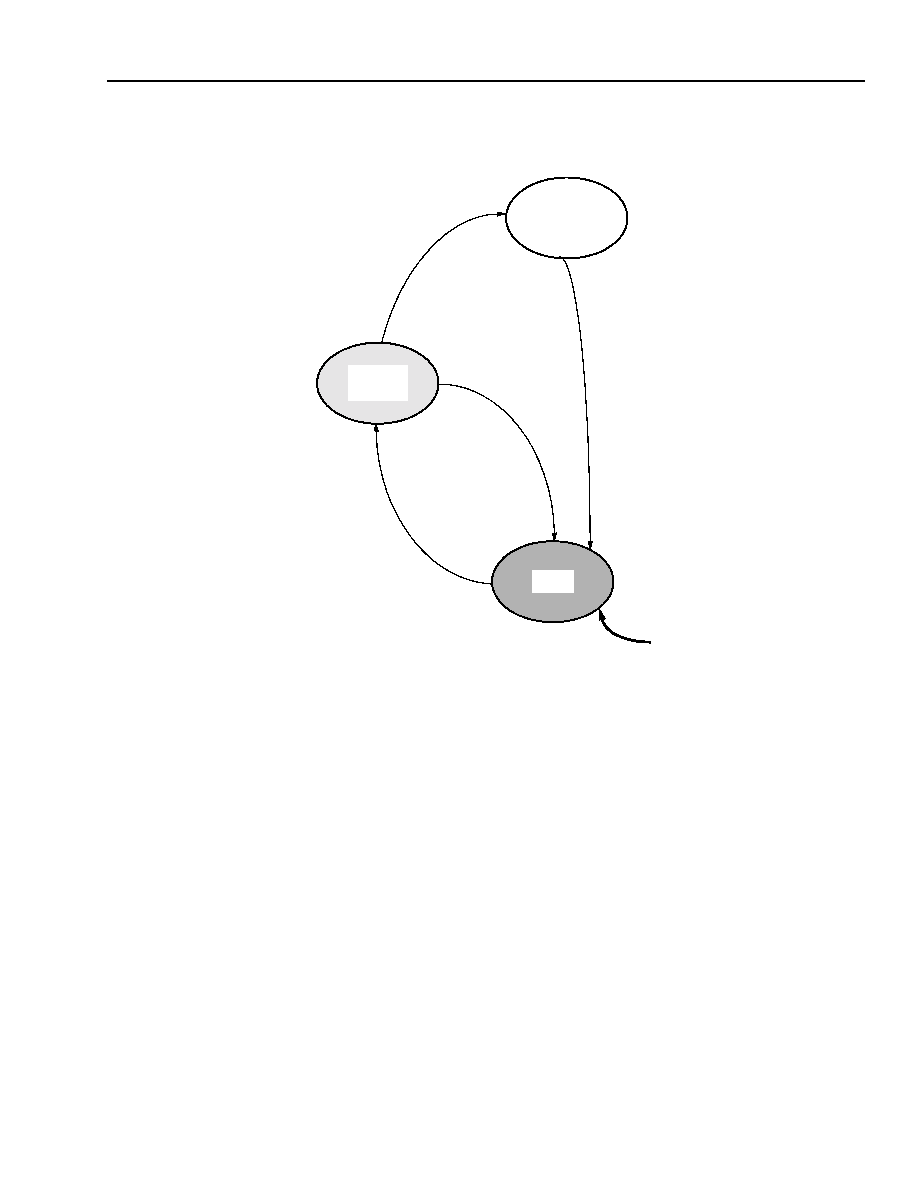

Framer (A1 and A2)........................................................................................................................................... 48

Descrambler...................................................................................................................................................... 50

Time-Slot Interchanger (TSI)............................................................................................................................. 50

Receive Transport Overhead (TOH) Processor................................................................................................... 52

Receive Overhead Serial Links......................................................................................................................... 52

Section Trace (J0)............................................................................................................................................. 53

Section Growth (Z0) .......................................................................................................................................... 54

Section BIP-8 (B1)............................................................................................................................................. 54

Section BIP-8 (B1) Errors Serial Access ........................................................................................................... 54

Local Orderwire (E1) ......................................................................................................................................... 55

Section User Channel (F1)................................................................................................................................ 55

Section Data Communications Channel (D1, D2, and D3) ............................................................................... 55

Line BIP-8 (B2).................................................................................................................................................. 56

Line BIP-8 (B2) Errors Serial Access ................................................................................................................ 58

APS Channel (K1 and K2)................................................................................................................................. 58

Line Data Communication Channel (D4--D12) ................................................................................................ 60

Synchronization Status (S1).............................................................................................................................. 60

STS-192 Line Remote Error Indication (M1) ..................................................................................................... 61

Express Orderwire (E2)..................................................................................................................................... 61

Receive STS Path Processor .............................................................................................................................. 61

1:4 Demultiplex TSI........................................................................................................................................... 62

Receive Pointer Processor................................................................................................................................ 62

Receive Path Overhead (POH) Processor........................................................................................................ 69

Receive Payload Drop Interface .......................................................................................................................... 76

STS-12 Overhead Insertion and Scrambling..................................................................................................... 77

Drop Interface Output Format ........................................................................................................................... 78

Data Path Parity ................................................................................................................................................ 79

Regenerator Loopback (STS-192 Mode Only) .................................................................................................... 80

Transmit Payload Add Interface........................................................................................................................... 80

STS-12 Framing, Descrambling, and TOH Processing..................................................................................... 81

Transmit Synchronization Buffer ....................................................................................................................... 82

Add Interface Framing (A1 and A2)................................................................................................................... 82

4:1 Time-Slot Multiplex (TSM)........................................................................................................................... 84

Table of Contents

(continued)

Contents

Page

Agere Systems Inc.

3

Data Sheet

May 2003

STS-192 Overhead and Path Processor

TSOT0410G4 SONET/SDH

Transmit Transport Overhead (TOH) Processor.................................................................................................. 84

TOH Transparency............................................................................................................................................ 85

Transmit Overhead Serial Links ........................................................................................................................ 86

Section Trace/Section Growth (J0/Z0) .............................................................................................................. 86

Section BIP-8 (B1)............................................................................................................................................. 87

Local Orderwire (E1) ......................................................................................................................................... 87

Section User Channel (F1)................................................................................................................................ 87

Section Data Communications Channel (D1, D2, and D3) ............................................................................... 88

STS Payload Pointer (H1 and H2) .................................................................................................................... 88

Line BIP-8 (B2).................................................................................................................................................. 89

APS Channel (K1 and K2)................................................................................................................................. 90

Line Data Communication Channel (D4--D12) ................................................................................................ 90

Synchronization Status (S1).............................................................................................................................. 91

STS-192 Line Remote Error Indication (M1) ..................................................................................................... 91

Express Orderwire (E2)..................................................................................................................................... 92

Transmit STS-192 Line Interface ......................................................................................................................... 92

Time-Slot Multiplexer (TSM).............................................................................................................................. 92

Scrambler .......................................................................................................................................................... 92

Data Path Parity ................................................................................................................................................ 92

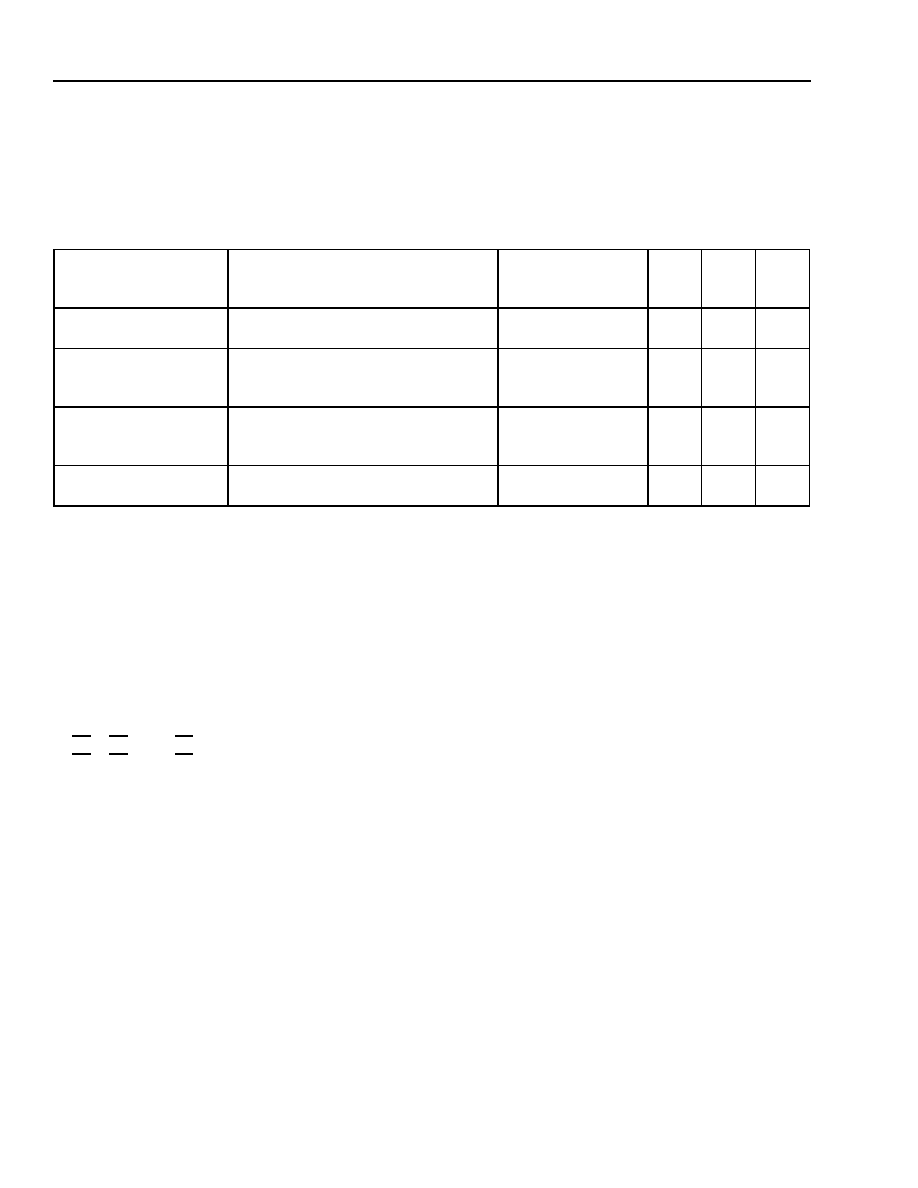

Microprocessor Interface ........................................................................................................................................ 93

Architecture.......................................................................................................................................................... 93

Transfer Error Acknowledge (TEA_N)............................................................................................................... 93

Interrupt Structure ............................................................................................................................................. 93

Parity Bits .......................................................................................................................................................... 94

Clock Domains .................................................................................................................................................. 94

Persistency Registers .......................................................................................................................................... 96

Register Description............................................................................................................................................. 96

Software Reset .................................................................................................................................................... 96

Device-Level Registers ...................................................................................................................................... 110

Line Terminating Equipment (LTE) Registers.................................................................................................... 115

LTE Common Registers .................................................................................................................................. 115

LTE J0 Access Registers ................................................................................................................................ 117

Signal Degrade/Signal Fail Registers.............................................................................................................. 119

LTE Receive Channel 1, 2, 3, and 4 Registers ............................................................................................... 122

LTE Transmit Common Registers...................................................................................................................... 128

LTE Transmit Channel Registers .................................................................................................................... 130

Equipment (EQPT) Registers ............................................................................................................................ 134

EQPT Common Registers............................................................................................................................... 134

EQPT Receive Drop STS-48 Channel Registers 1--4 ................................................................................... 137

EQPT Transmit Add STS-48 Channel Registers 1--4.................................................................................... 139

Path Overhead (POH) Registers ....................................................................................................................... 144

STS-12, STS-1 Level POH Registers ............................................................................................................. 145

STS-192 Level POH Registers........................................................................................................................ 149

STS-192 Level Path Trace Registers.............................................................................................................. 154

STS-48 Level POH Registers.......................................................................................................................... 155

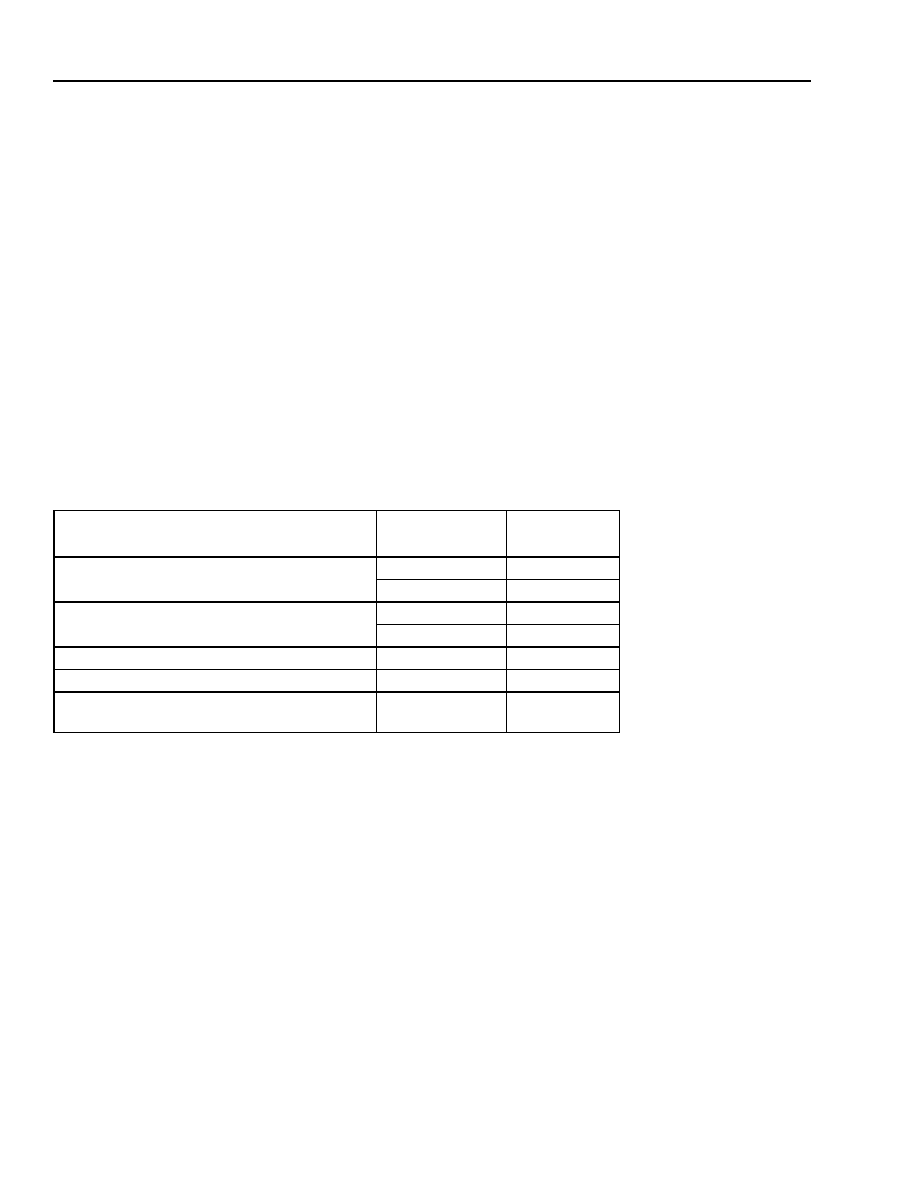

Absolute Maximum Ratings.................................................................................................................................. 166

Handling Precautions ........................................................................................................................................... 166

Recommended Operating Conditions .................................................................................................................. 166

Electrical Characteristics ...................................................................................................................................... 167

Power Sequencing............................................................................................................................................. 167

Low-Voltage Differential Signal (LVDS) Buffers................................................................................................. 167

Table of Contents

(continued)

Contents

Page

4

Agere Systems Inc.

Data Sheet

May 2003

STS-192 Overhead and Path Processor

TSOT0410G4 SONET/SDH

LVDS Receiver Buffer Capabilities.................................................................................................................. 169

Timing Characteristics .......................................................................................................................................... 172

Receive Data Interface ...................................................................................................................................... 172

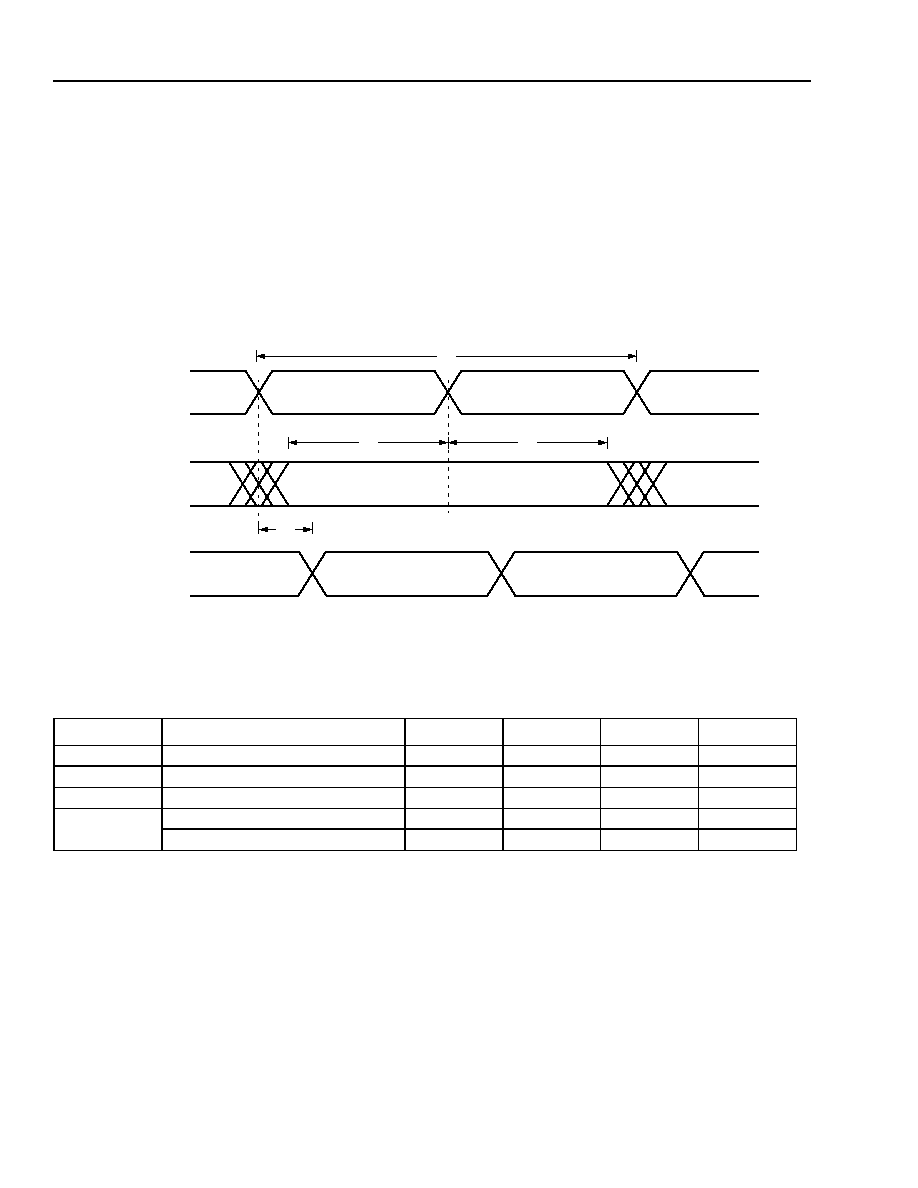

Receive STS-48/STS-192 Data ...................................................................................................................... 172

Receive Transport Overhead Interface.............................................................................................................. 173

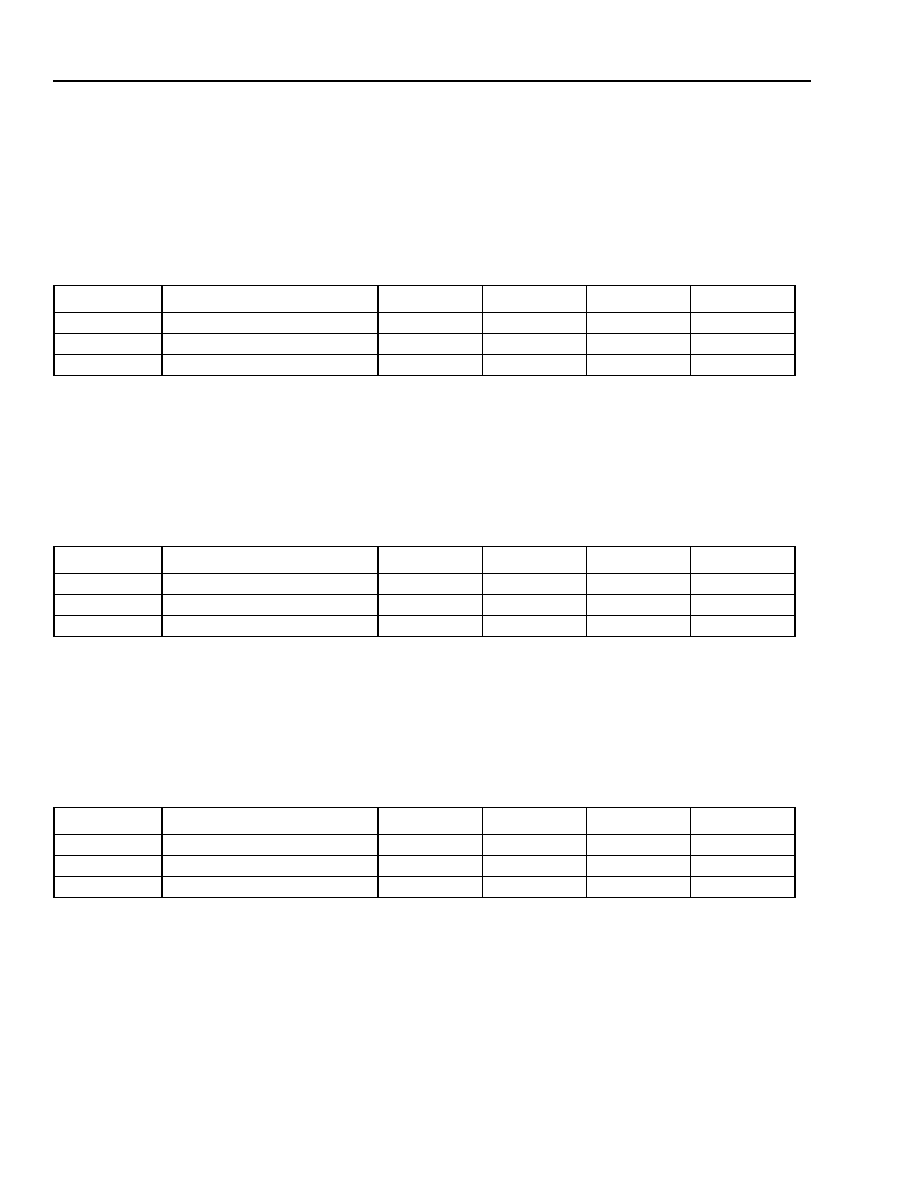

Receive Local Orderwire................................................................................................................................. 173

Receive Section User...................................................................................................................................... 173

Receive Express Orderwire............................................................................................................................. 174

Receive Section Data Com ............................................................................................................................. 174

Receive Line Data Com .................................................................................................................................. 174

Receive Overhead Serial Link......................................................................................................................... 175

Transmit Data Interface ..................................................................................................................................... 176

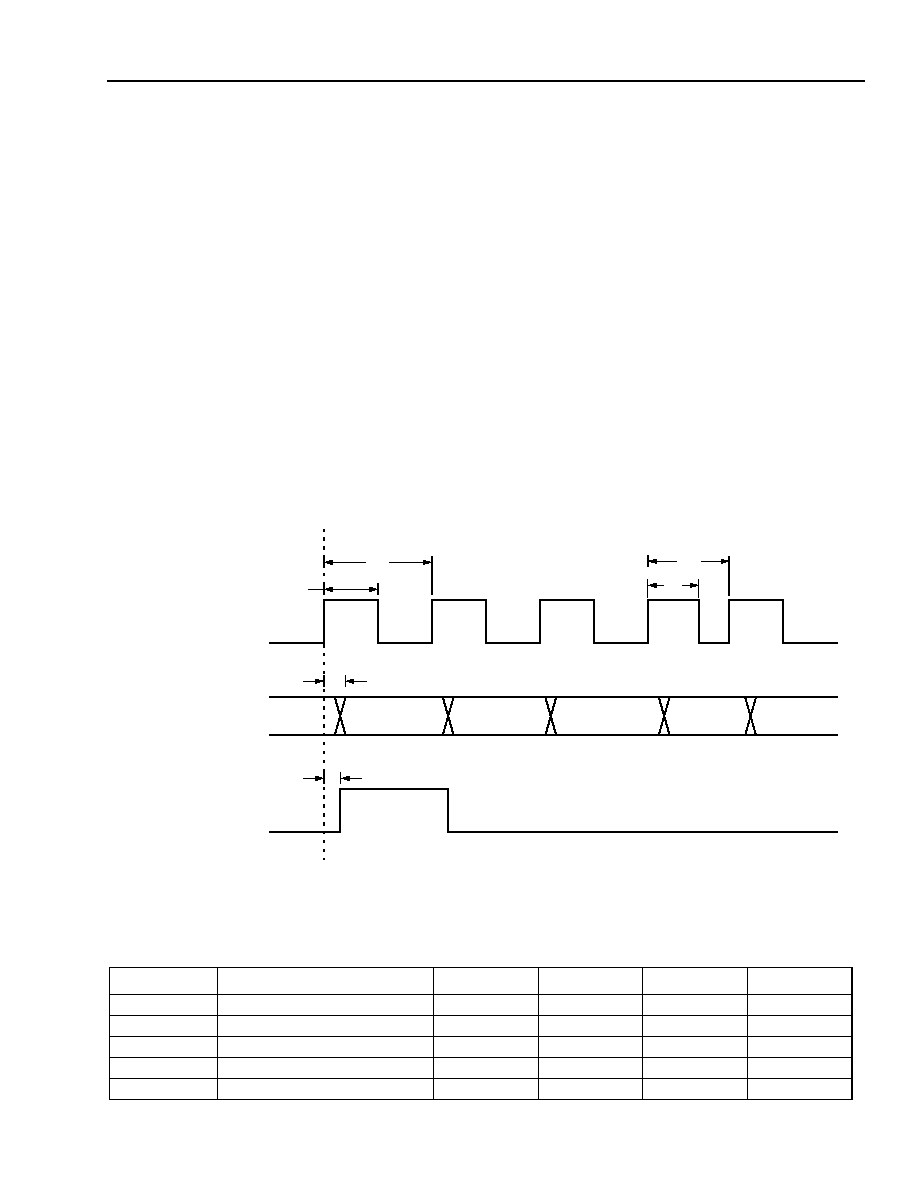

Transmit STS-48/STS-192 Data ..................................................................................................................... 176

Transmit Frame............................................................................................................................................... 177

Transmit Transport Overhead Interface............................................................................................................. 178

Transmit Local Orderwire................................................................................................................................ 178

Transmit Section User..................................................................................................................................... 178

Transmit Express Orderwire............................................................................................................................ 178

Transmit Section Data Com ............................................................................................................................ 179

Transmit Line Data Com ................................................................................................................................. 179

Transmit Overhead Serial Link........................................................................................................................ 180

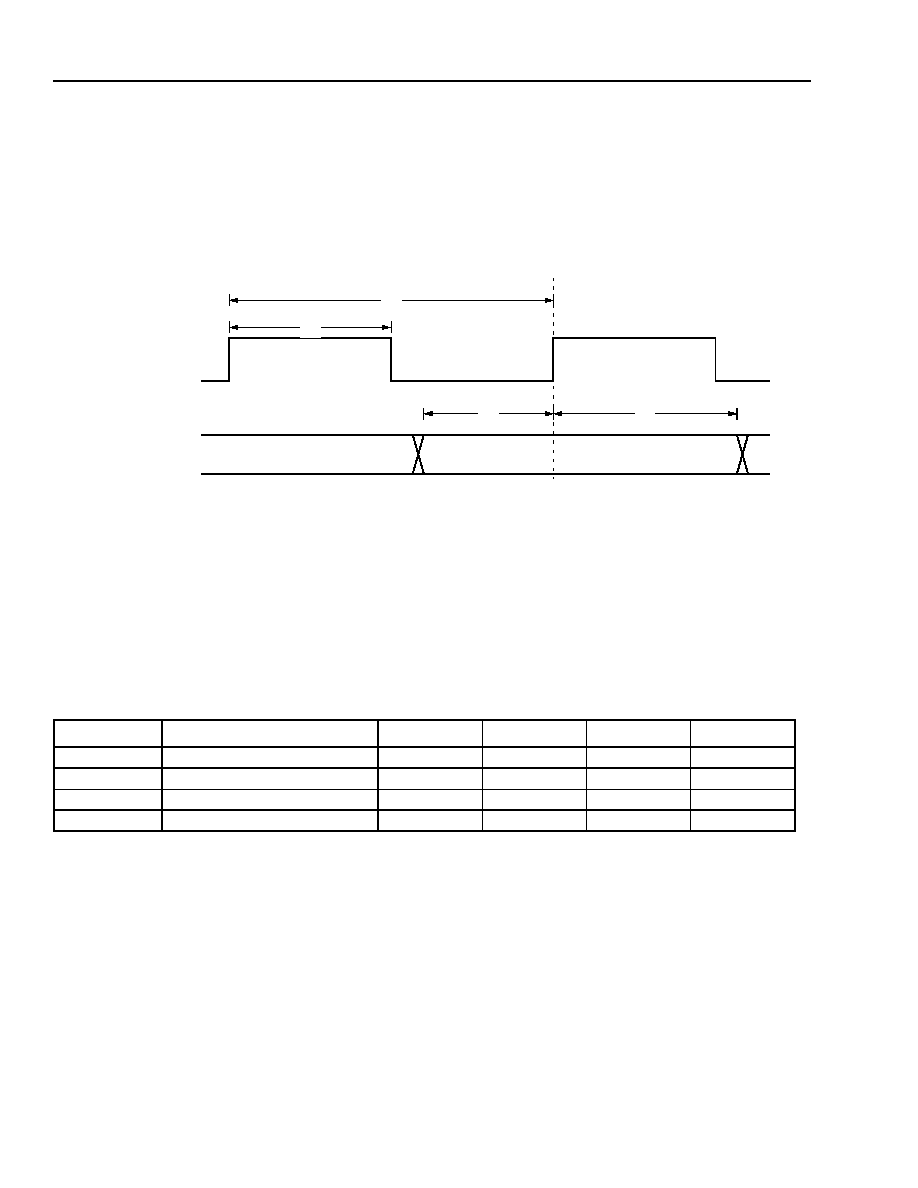

Receive Drop Interface ...................................................................................................................................... 181

Drop Clock, Drop Frame, and Drop Data........................................................................................................ 181

Receive Drop Section Data Com .................................................................................................................... 182

Transmit Add Interface....................................................................................................................................... 183

Transmit Add Data .......................................................................................................................................... 183

Transmit Add Section Data Com..................................................................................................................... 183

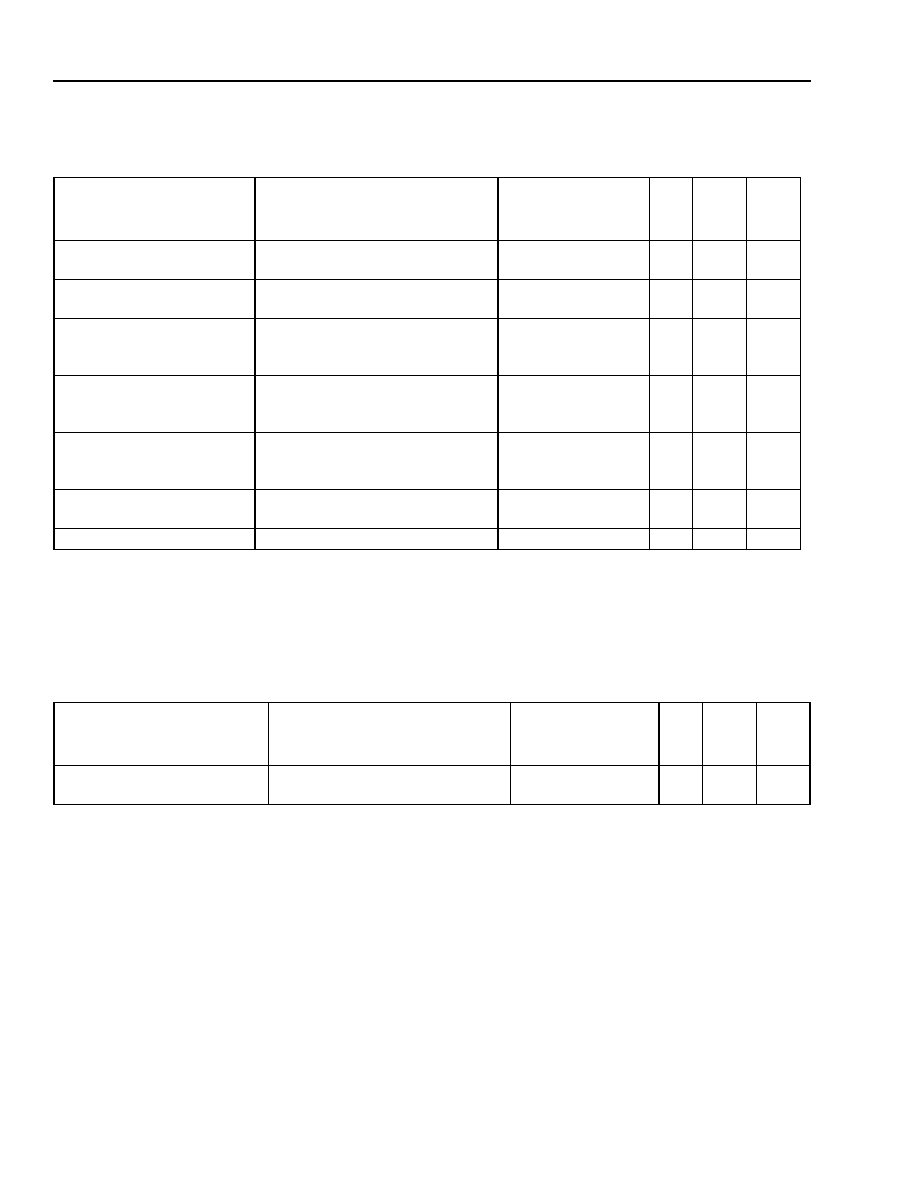

Microprocessor Interface Timing........................................................................................................................ 183

Synchronous Mode ......................................................................................................................................... 183

Asynchronous Mode........................................................................................................................................ 186

Use of a Synchronous Microprocessor with the TSOT0410G4 in Asynchronous Mode ................................. 188

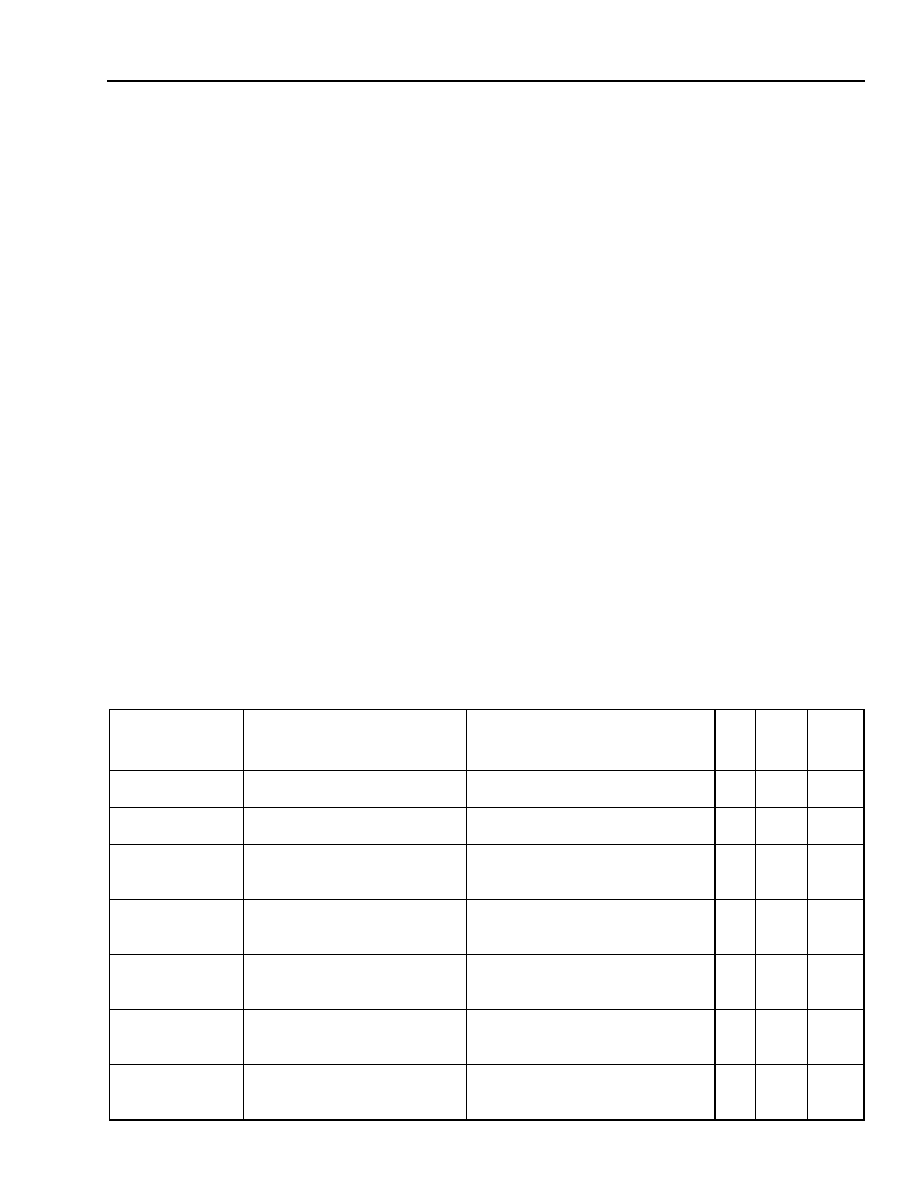

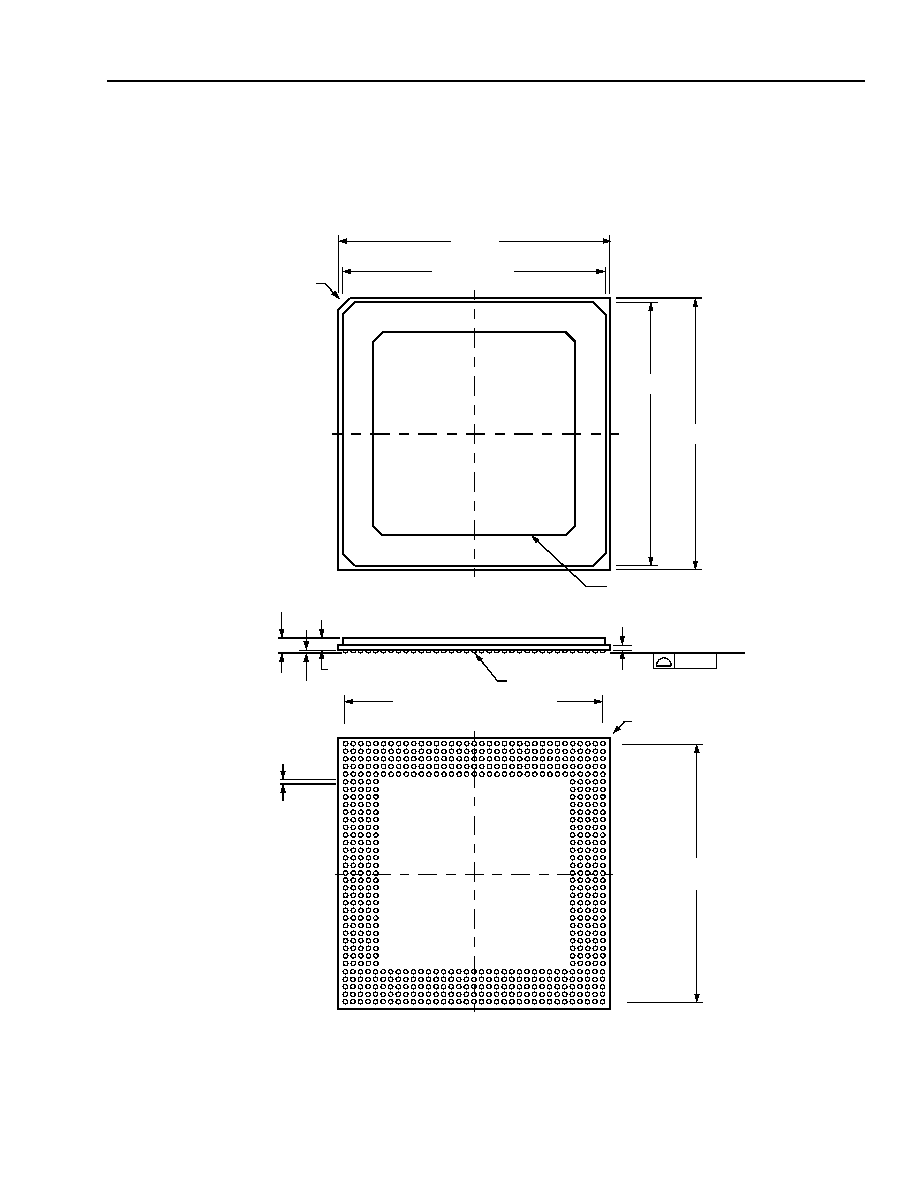

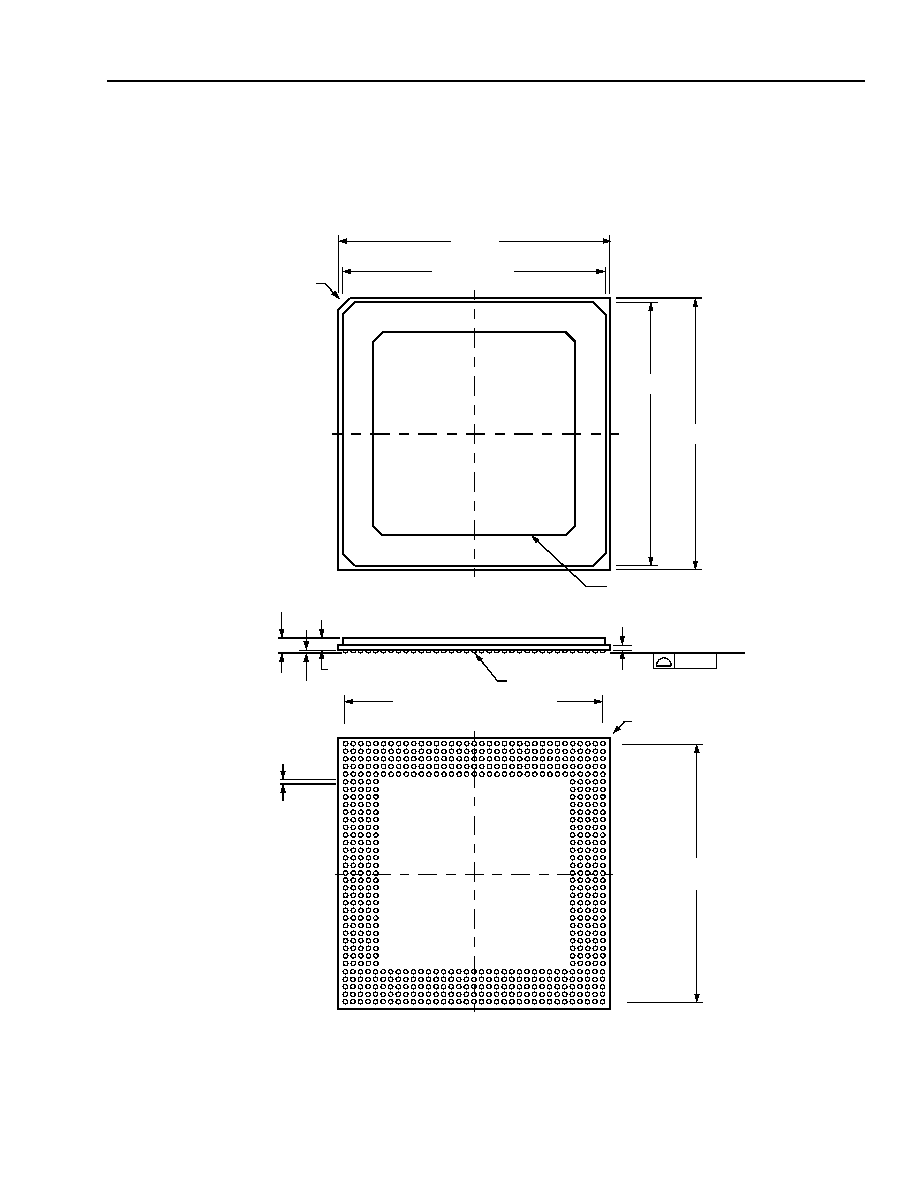

Outline Diagram.................................................................................................................................................... 189

600-Pin LBGA .................................................................................................................................................... 189

Ordering Information............................................................................................................................................. 190

List of Figures

Contents

Page

Agere Systems Inc.

5

Data Sheet

May 2003

STS-192 Overhead and Path Processor

TSOT0410G4 SONET/SDH

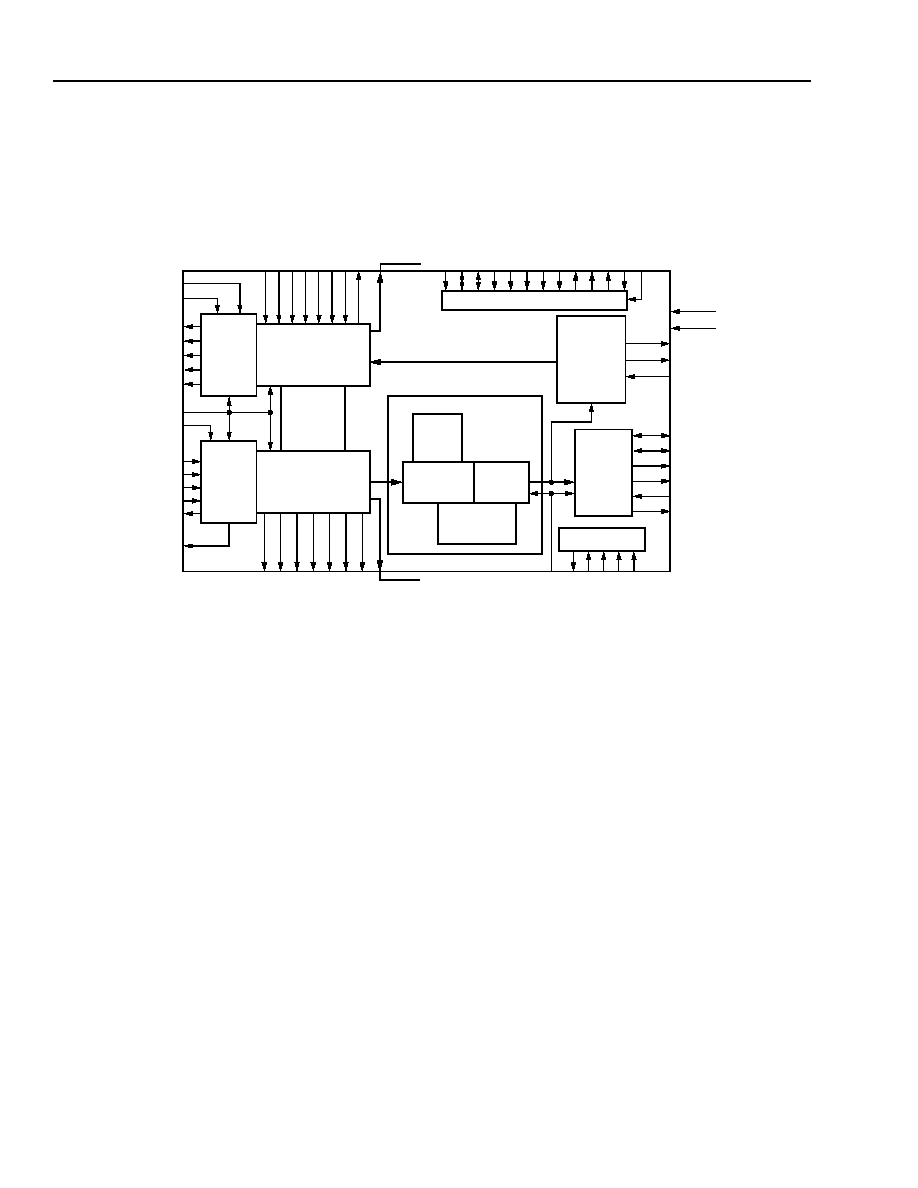

Figure 1. TSOT0410G4 Block Diagram, STS-192 Mode ...................................................................................... 13

Figure 2. TSOT0410G4 Block Diagram, STS-48 Mode ........................................................................................ 14

Figure 3. Suggested Schematic for 1.0 V and 1.4 V Reference Voltages ............................................................. 35

Figure 4. Framer FSM ........................................................................................................................................... 49

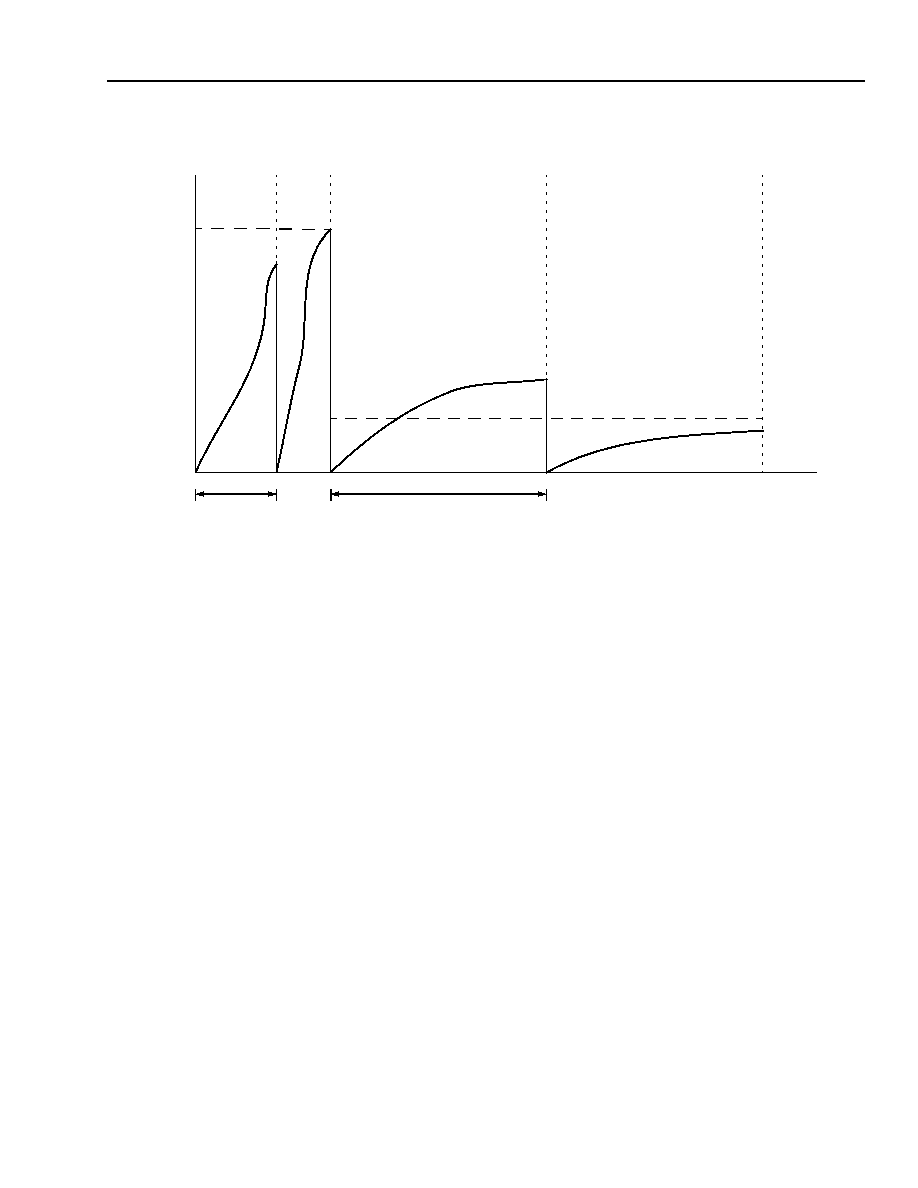

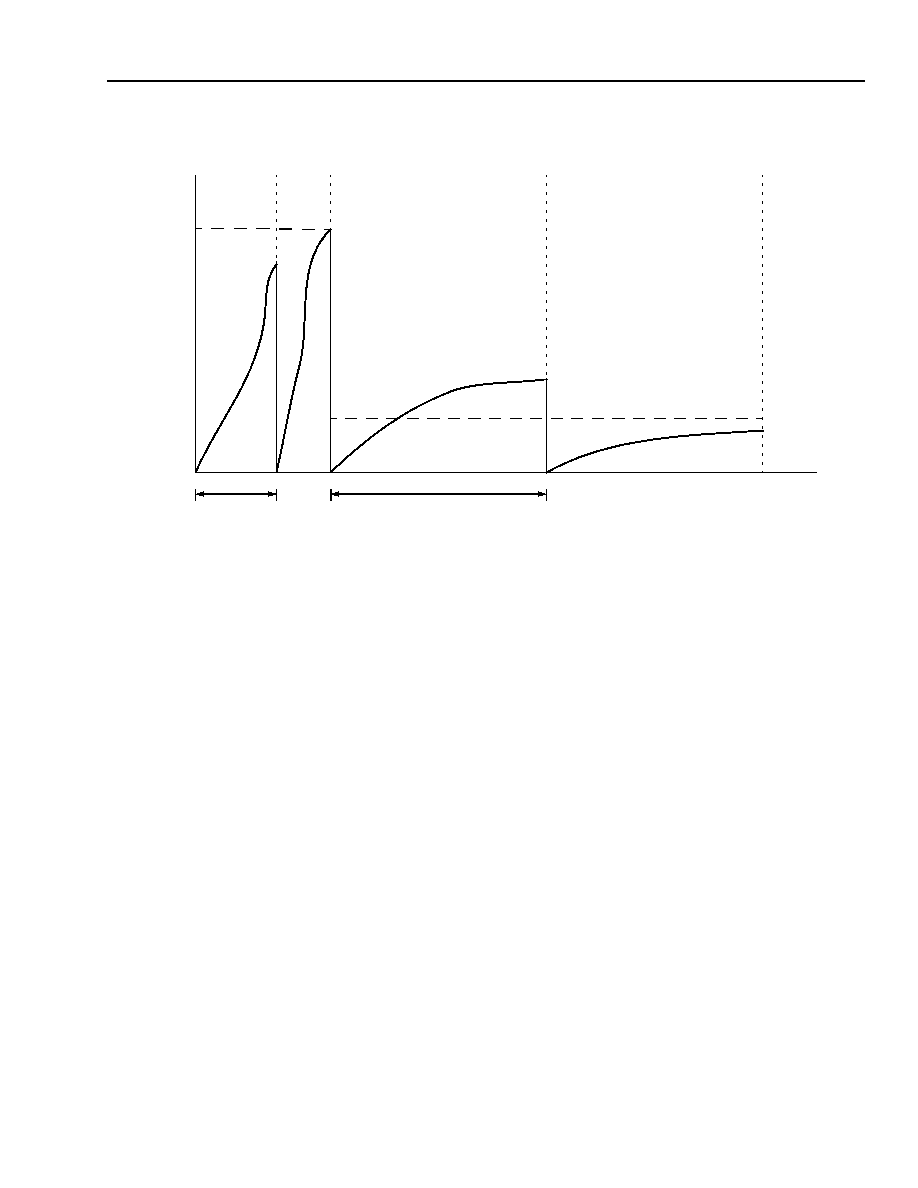

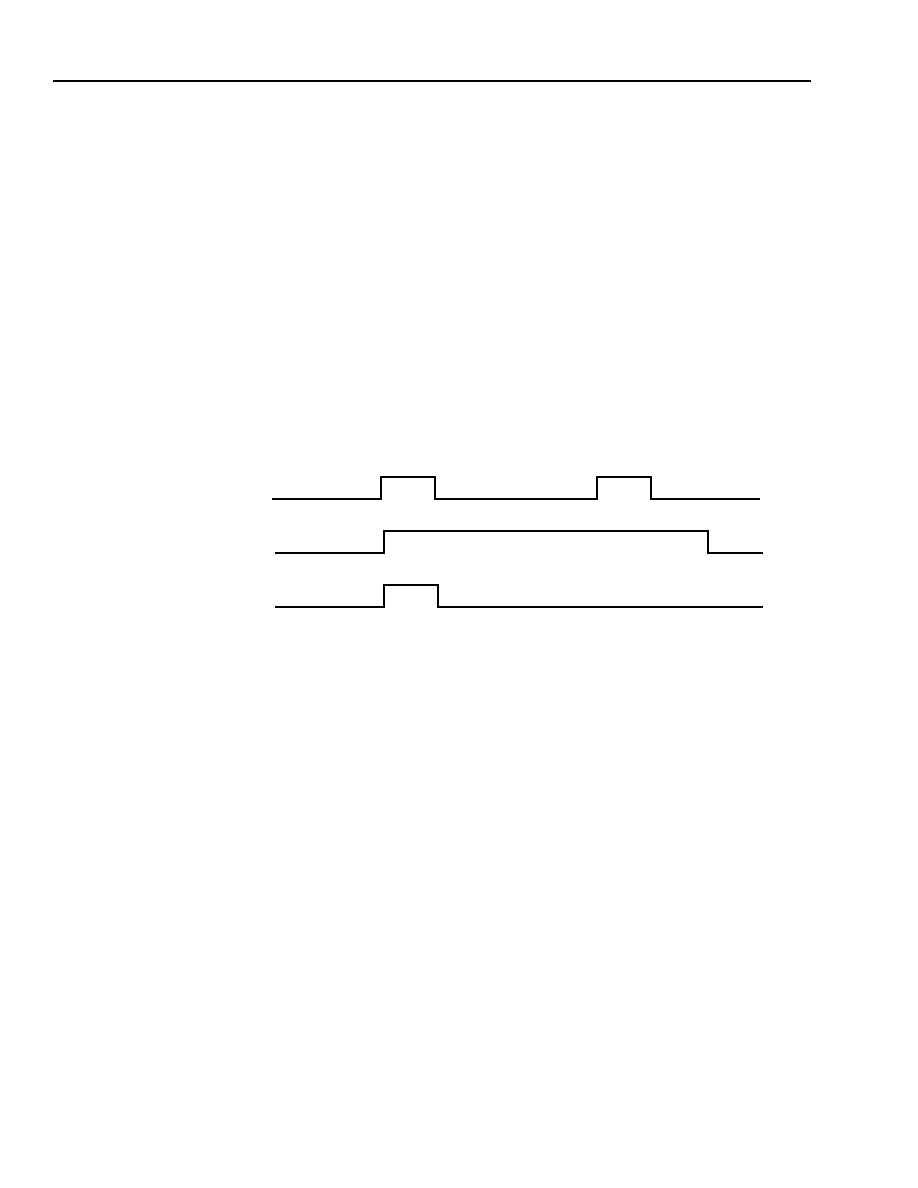

Figure 5. Example of STS-192 SD Detection (10

≠5

BER) and Clearing (10

≠6

BER) ............................................. 57

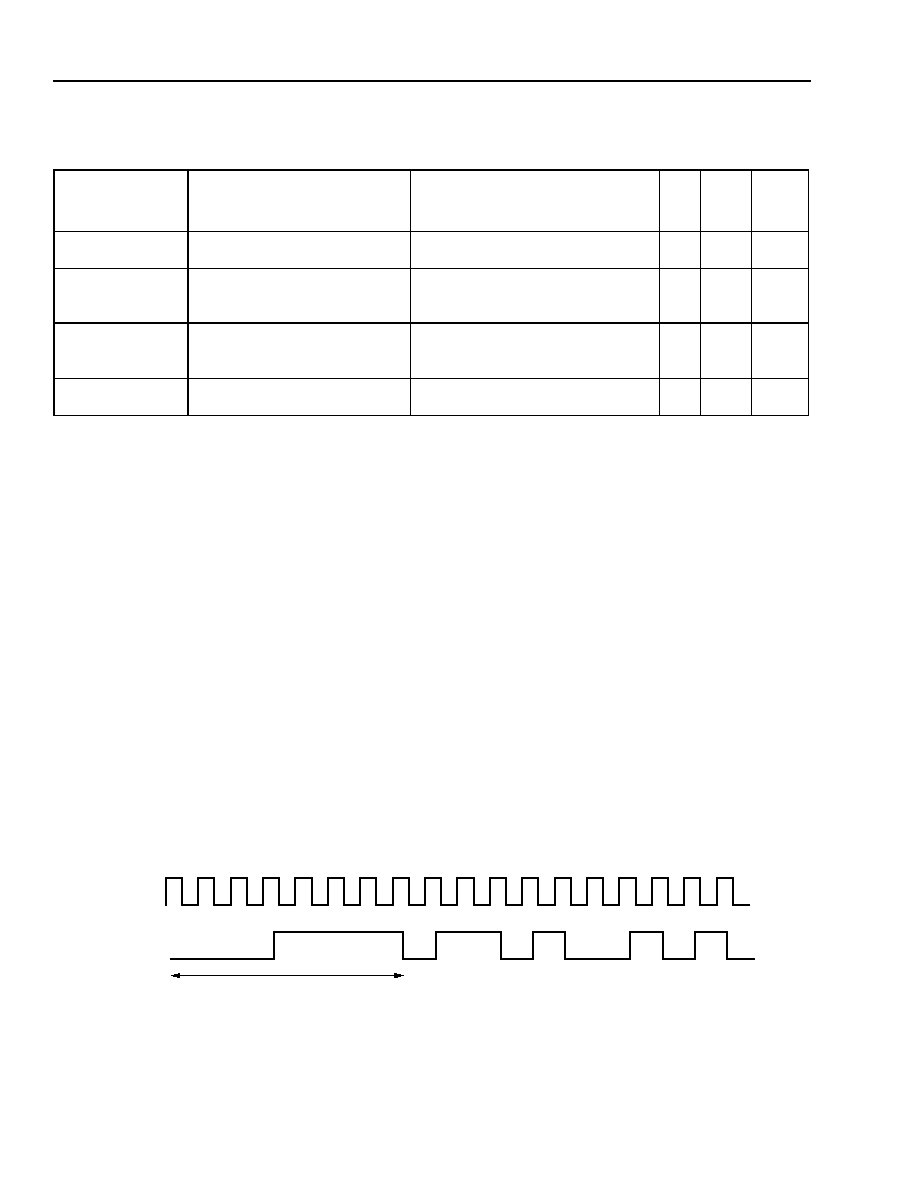

Figure 6. Timing Diagram for RFRM ..................................................................................................................... 60

Figure 7. Pointer Interpreter State Machine .......................................................................................................... 63

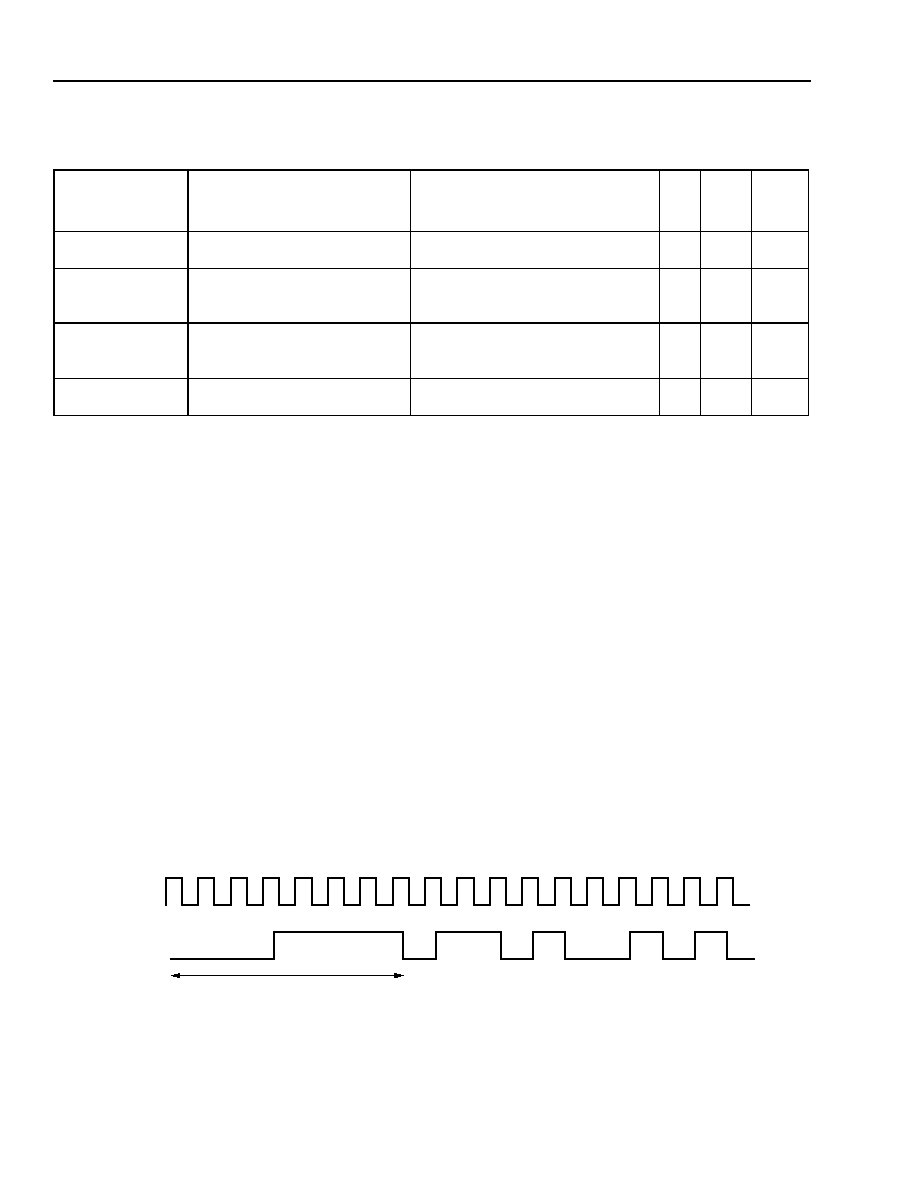

Figure 8. STS-12 Data Outputs and Timing .......................................................................................................... 79

Figure 9. TSOT0410G4 Timing Domains .............................................................................................................. 95

Figure 10. Persistency Register Operation ............................................................................................................ 96

Figure 11. Path Register Structure ...................................................................................................................... 144

Figure 12. LVDS Driver and Receiver and Associated Internal Components ..................................................... 168

Figure 13. LVDS Driver and Receiver ................................................................................................................. 168

Figure 14. LVDS Driver ....................................................................................................................................... 168

Figure 15. Receive Data Timing .......................................................................................................................... 172

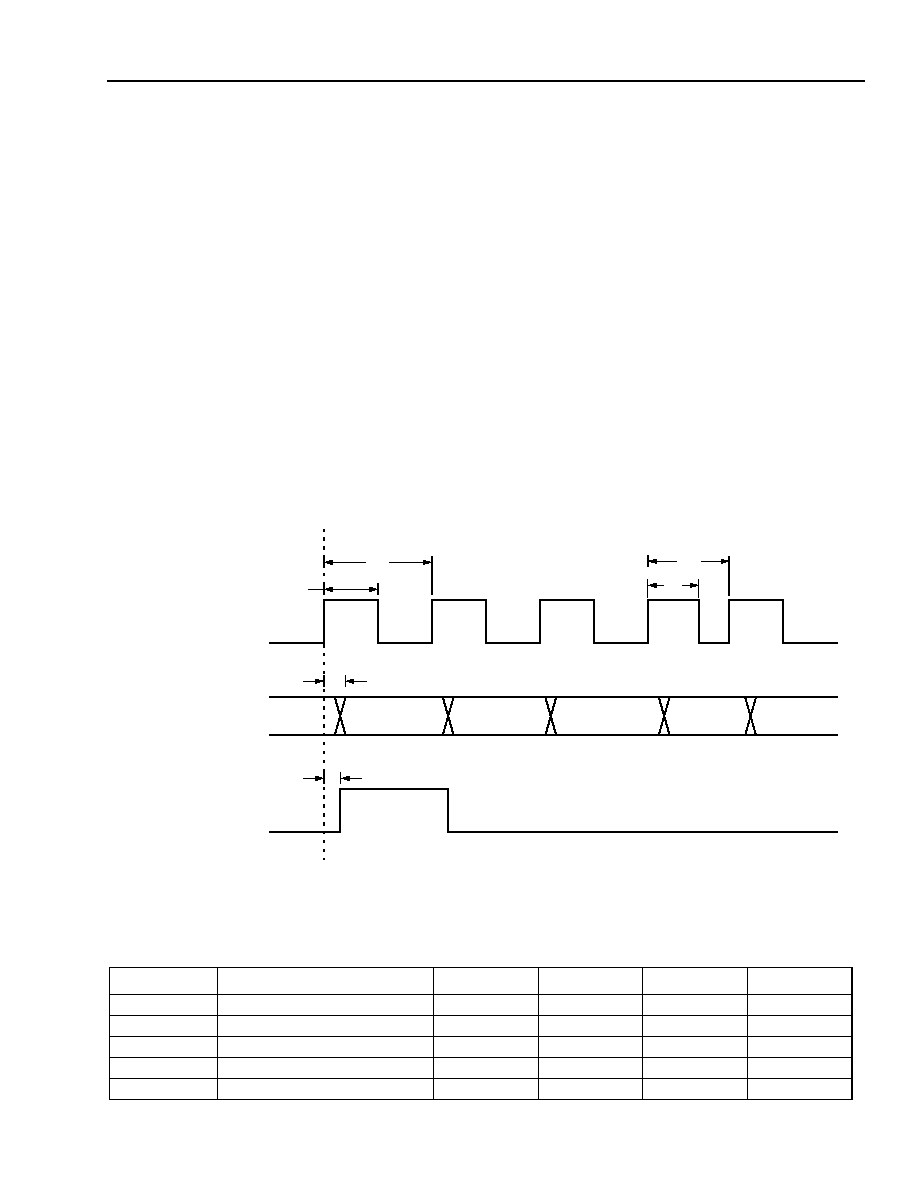

Figure 16. Receive Data Communication Channels Timing ................................................................................ 173

Figure 17. Receive Overhead Serial Timing ........................................................................................................ 175

Figure 18. Transmit Data Timing ......................................................................................................................... 176

Figure 19. Transmit Frame Timing ...................................................................................................................... 177

Figure 20. Transmit Data Communication Channels Timing ............................................................................... 178

Figure 21. Transmit Overhead Serial Timing ....................................................................................................... 180

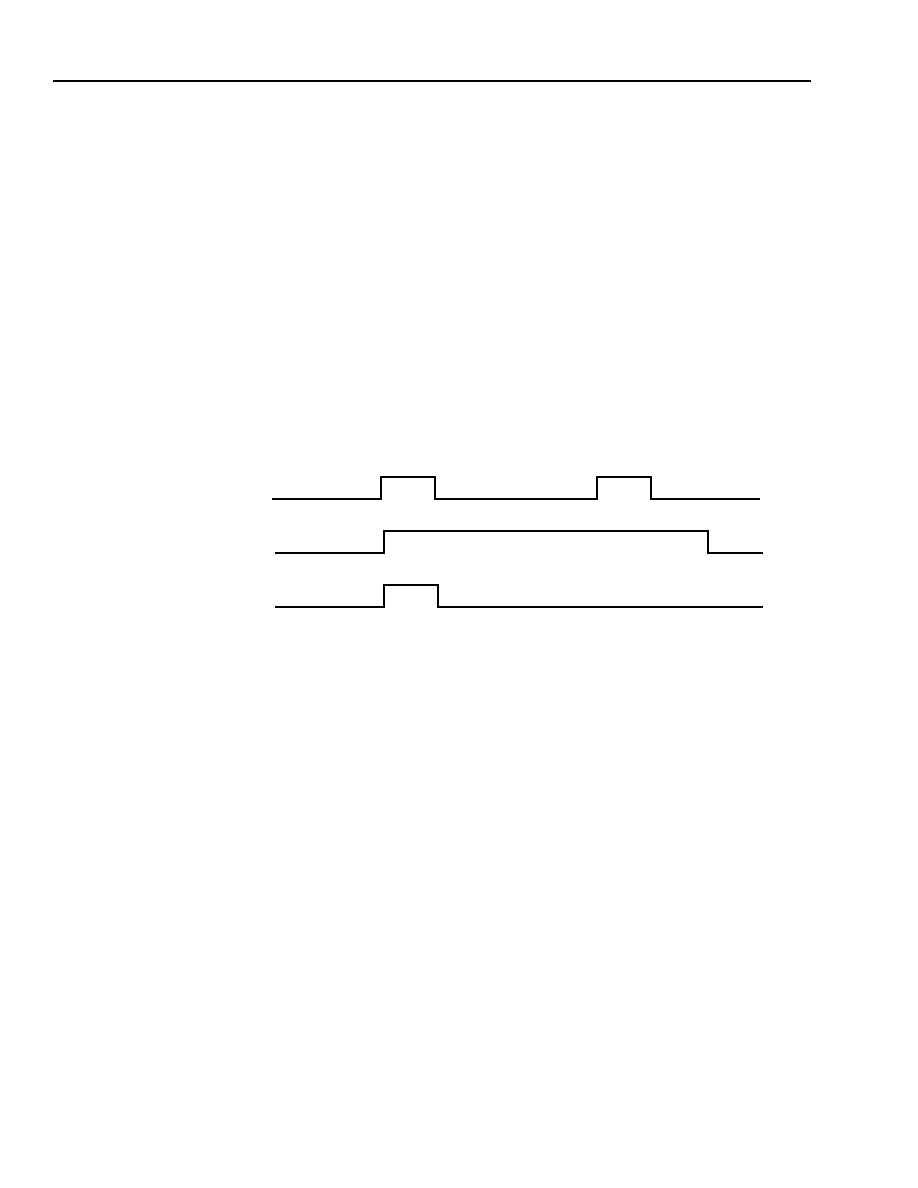

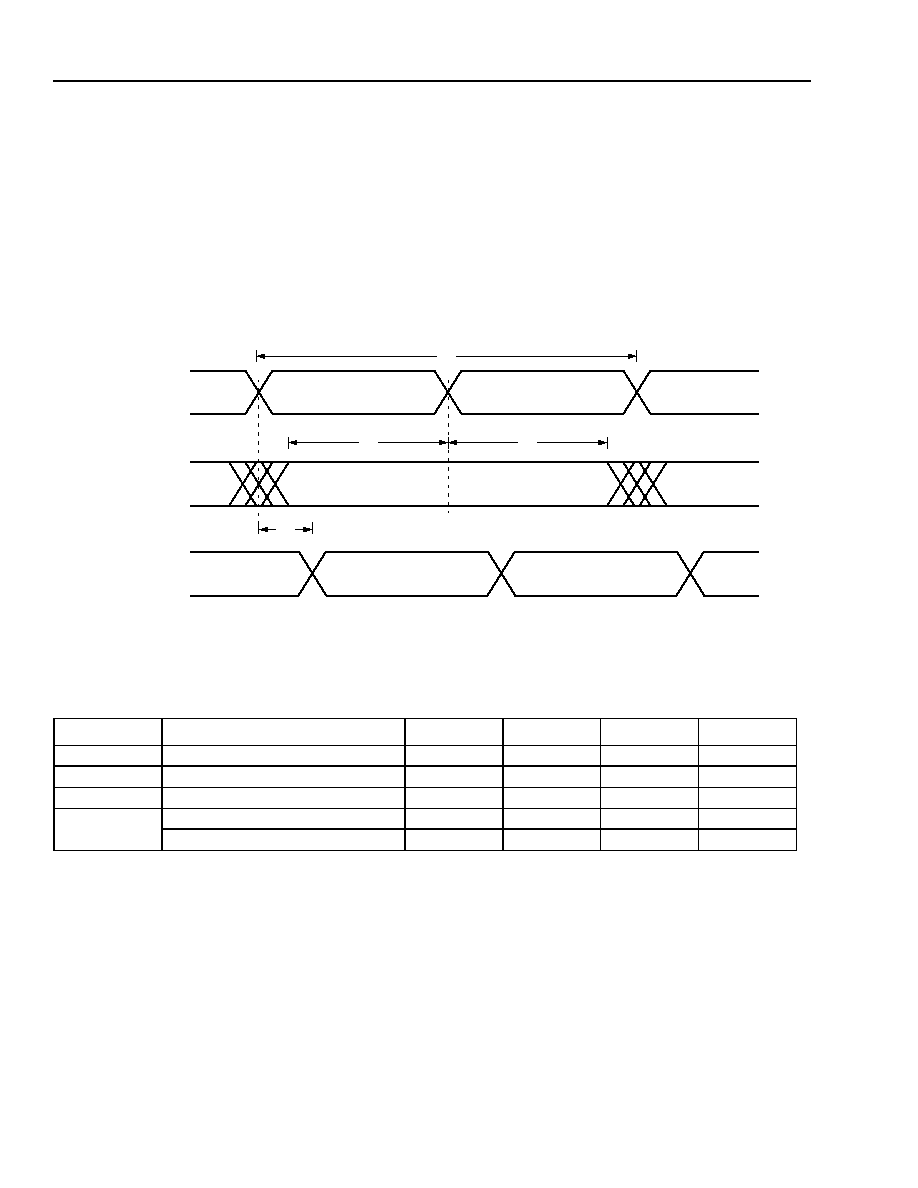

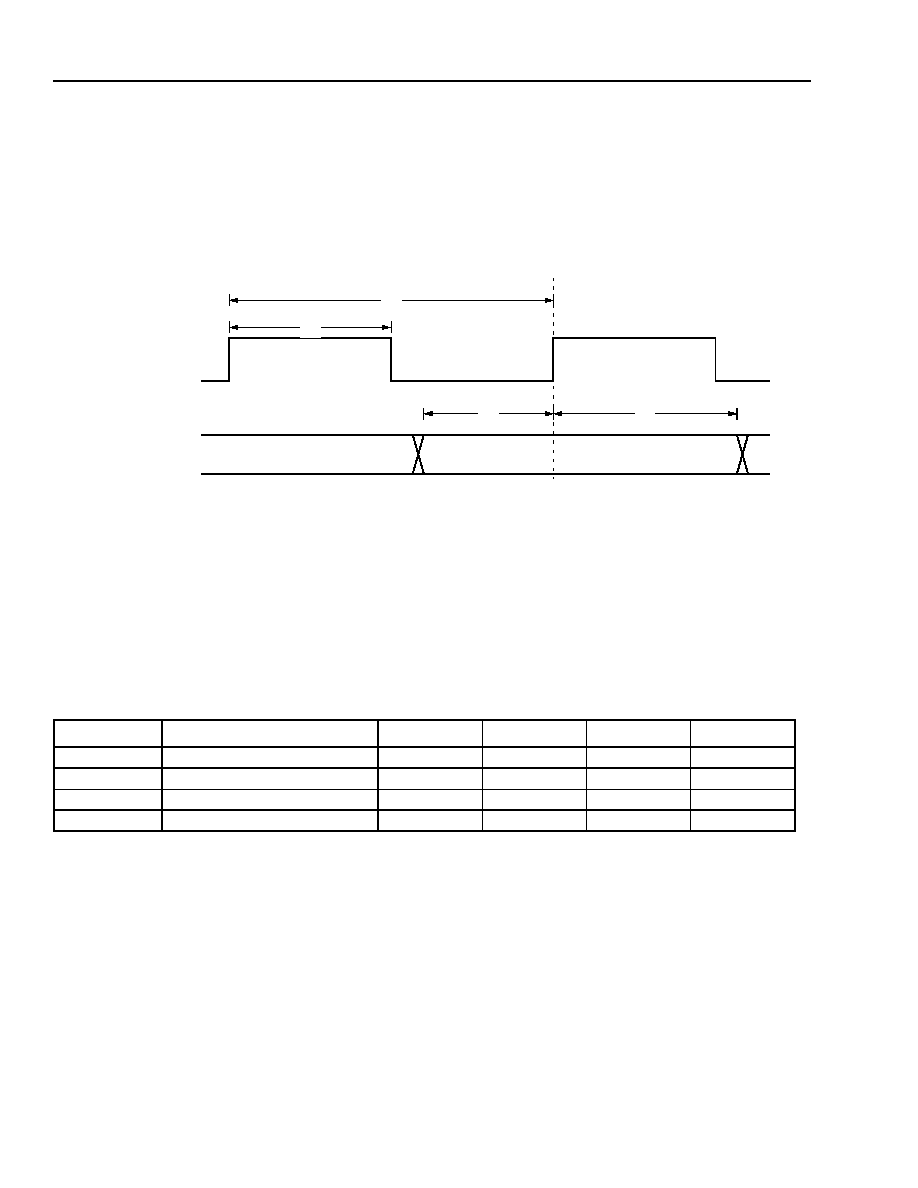

Figure 22. Receive Frame Timing (Pointer Processor Bypassed) ...................................................................... 181

Figure 23. Receive Frame Timing (Pointer Processor Active) ............................................................................ 182

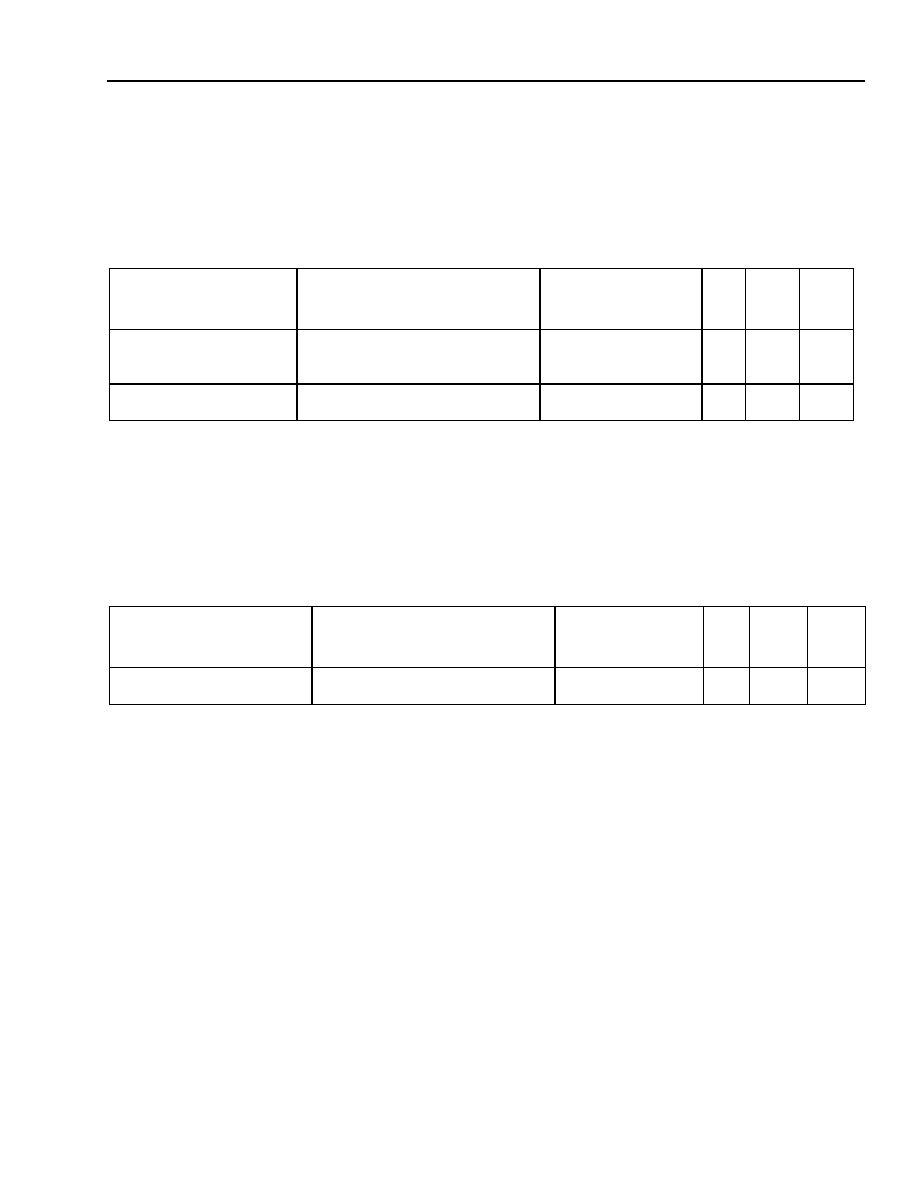

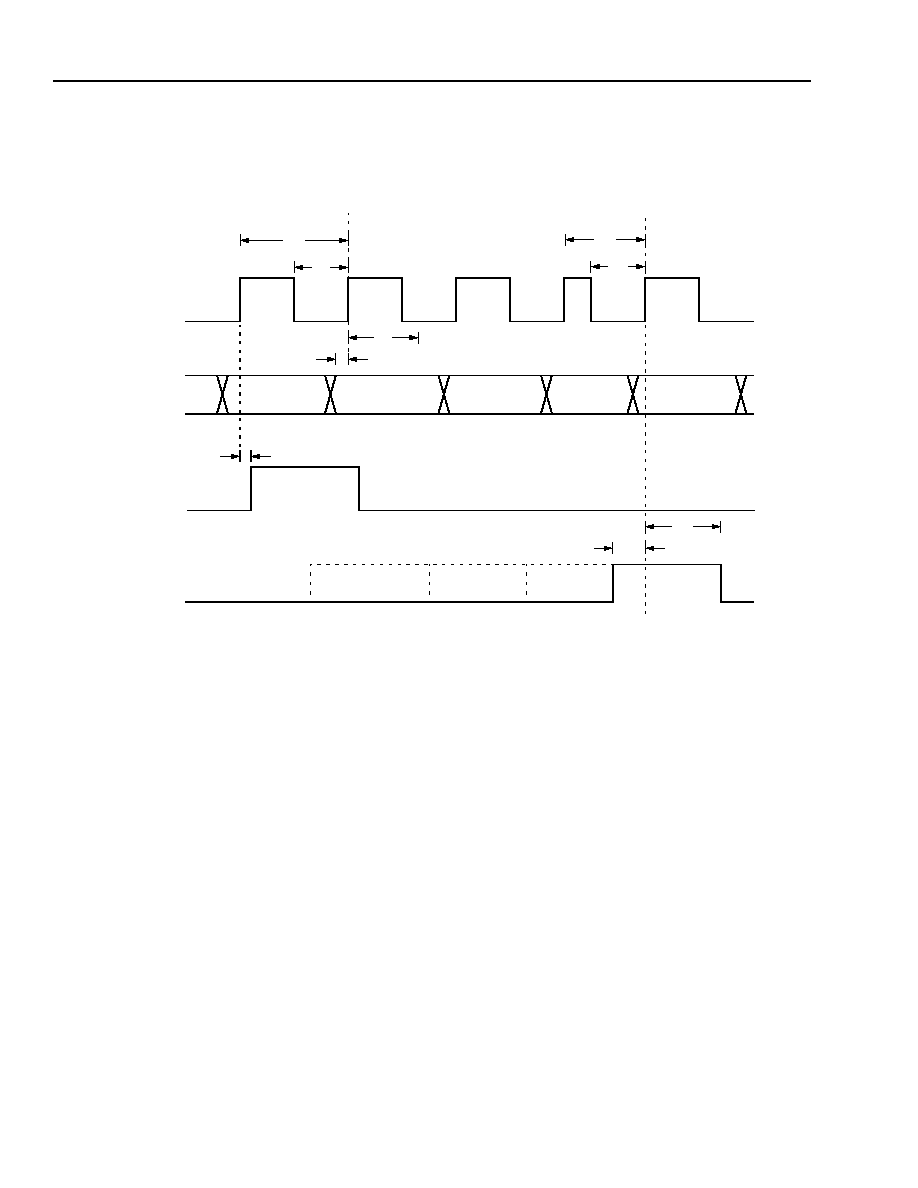

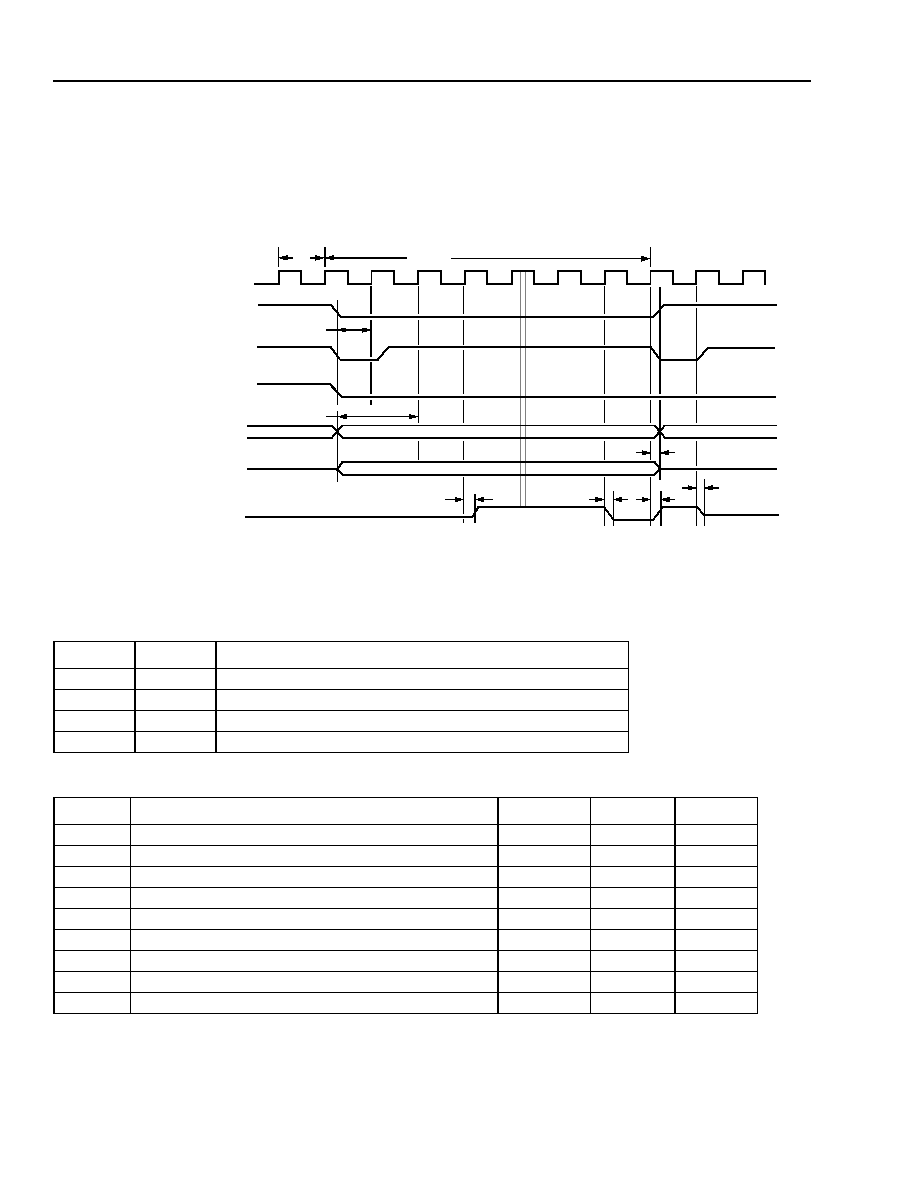

Figure 24. Microprocessor Interface Synchronous Write Cycle (MPMODE = 1) ................................................. 184

Figure 25. Microprocessor Interface Synchronous Read Cycle (MPMODE = 1) ................................................. 185

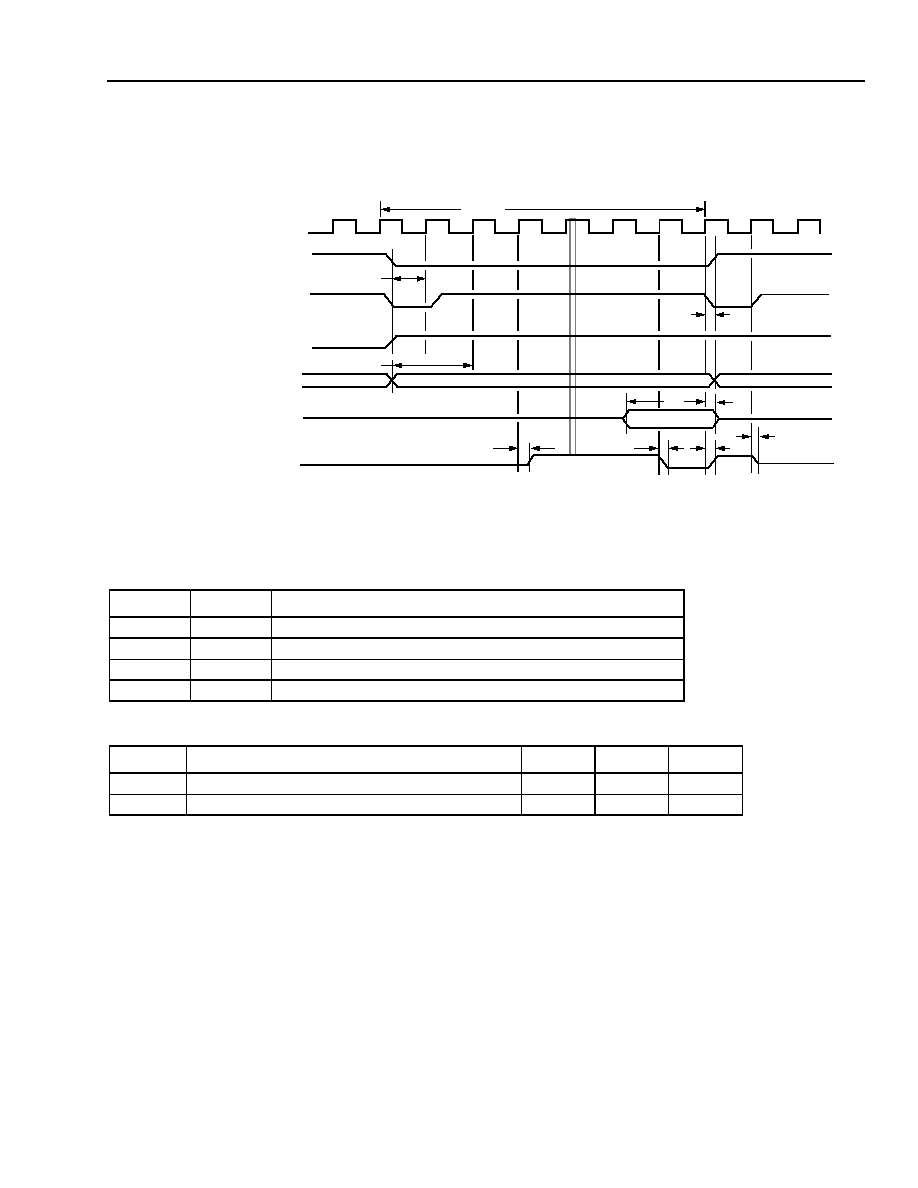

Figure 26. Microprocessor Interface Asynchronous Write Cycle (MPMODE = 0) ............................................... 186

Figure 27. Microprocessor Interface Asynchronous Read Cycle (MPMODE = 0) ............................................... 187

List of Tables

Contents

Page

6

Agere Systems Inc.

Data Sheet

May 2003

STS-192 Overhead and Path Processor

TSOT0410G4 SONET/SDH

Table 1. Pin Assignments for 600-Pin LBGA by Pin Number Order....................................................................... 17

Table 2. Pin Assignments for 600-Pin LBGA by Signal Name Order ..................................................................... 22

Table 3. Pin Descriptions--System Control ........................................................................................................... 26

Table 4. Pin Descriptions--Receive Line Interface ................................................................................................ 27

Table 5. Pin Descriptions--Transmit Line Interface ............................................................................................... 28

Table 6. Pin Descriptions--LVDS Reference, Line Interface ................................................................................. 30

Table 7. Pin Descriptions--Receive Drop Equipment Interface ............................................................................. 31

Table 8. Pin Descriptions--Transmit Add Equipment Interface ............................................................................. 33

Table 9. Pin Descriptions--LVDS Reference, Equipment Interface....................................................................... 35

Table 10. Pin Descriptions--Transport Overhead Interface................................................................................... 36

Table 11. Pin Descriptions--Microprocessor Interface .......................................................................................... 42

Table 12. Pin Descriptions--JTAG Interface.......................................................................................................... 43

Table 13. Pin Descriptions--PLL References ........................................................................................................ 44

Table 14. Pin Descriptions--Power and Ground.................................................................................................... 44

Table 15. Pin Summary .......................................................................................................................................... 46

Table 16. LOS Detector Register Summary ........................................................................................................... 48

Table 17. Framer Register Summary ..................................................................................................................... 50

Table 18. Descrambler Register Summary ............................................................................................................ 50

Table 19. STS-192 Byte Ordering .......................................................................................................................... 51

Table 20. STS-48 Byte Ordering ............................................................................................................................ 51

Table 21. Receive Overhead Serial Links Register Summary ............................................................................... 52

Table 22. J0 Register Summary ............................................................................................................................. 54

Table 23. B1 Register Summary ............................................................................................................................ 55

Table 24. BER Threshold Time and Error Limits for Line SD and SF Detection .................................................... 56

Table 25. B2 Register Summary ............................................................................................................................ 58

Table 26. APS Channel (K1 and K2) Register Summary ....................................................................................... 59

Table 27. Synchronization Status (S1) Register Summary .................................................................................... 61

Table 28. Line REI (M1) Register Summary........................................................................................................... 61

Table 29. STS-12 Byte Ordering ............................................................................................................................ 62

Table 30. Pointer Interpreter Register Summary.................................................................................................... 64

Table 31. Elastic Store Register Summary............................................................................................................. 65

Table 32. Pointer Generator Bypass Register Summary ....................................................................................... 65

Table 33. AIS-P Insertion Conditions ..................................................................................................................... 66

Table 34. Path AIS Insertion Register Summary.................................................................................................... 67

Table 35. Concatenation Register Summary.......................................................................................................... 68

Table 36. Pointer Justification Binning Register Summary..................................................................................... 68

Table 37. J1 Register Summary ............................................................................................................................. 70

Table 38. BER Threshold Time Window and Error Limits for Path SF Detection................................................... 71

Table 39. Time Window Sizes for Path SF Detection............................................................................................. 71

Table 40. B3 Register Summary ............................................................................................................................ 72

Table 41. STS Path Signal Label Assignments...................................................................................................... 73

Table 42. Path Signal Label (C2) Alarm Scenarios ................................................................................................ 74

Table 43. C2 Register Summary ............................................................................................................................ 75

Table 44. RDI-P Codes and Interpretation ............................................................................................................. 76

Table 45. G1 Register Summary ............................................................................................................................ 76

Table 46. Path Alarm Information Encoding........................................................................................................... 77

Table 47. Line Alarm Information Encoding ........................................................................................................... 78

Table 48. Drop Interface Overhead and Scrambling Register Summary ............................................................... 78

Table 49. Timing Enable Bit Definitions.................................................................................................................. 79

Table 50. Receive Data Path Parity Register Summary......................................................................................... 79

Table 51. LTE Transmit Channel Registers--Regenerator Loopback Summary................................................... 80

List of Tables

(continued)

Contents

Page

Agere Systems Inc.

7

Data Sheet

May 2003

STS-192 Overhead and Path Processor

TSOT0410G4 SONET/SDH

Table 52. Regenerator Loopback Bit Definitions .................................................................................................... 80

Table 53. Path AIS Insertion Encoding................................................................................................................... 81

Table 54. Add Interface Overhead and Scrambling Register Summary................................................................. 82

Table 55. Transmit Synchronization Buffer Register Summary.............................................................................. 82

Table 56. Frame Pulse Provisioning Bit Definitions................................................................................................ 84

Table 57. Transmit Framing Register Summary..................................................................................................... 84

Table 58. LTE Transmit Channel Registers--TOH Transparency Summary......................................................... 85

Table 59. TOH Transparency Bit Definitions .......................................................................................................... 85

Table 60. Transmit Overhead Serial Links Register Summary .............................................................................. 86

Table 61. Transmit Section Trace (J0) Register Summary .................................................................................... 87

Table 62. Transmit B1 Register Summary ............................................................................................................. 87

Table 63. Transmit STS Payload Pointer Register Summary ................................................................................ 89

Table 64. Transmit B2 Register Summary ............................................................................................................. 89

Table 65. K Byte Select Control Bits ...................................................................................................................... 90

Table 66. Transmit APS Channel (K1K2) Register Summary ................................................................................ 90

Table 67. Transmit Synchronization Status (S1) Register Summary ..................................................................... 91

Table 68. Transmit M1 Register Summary............................................................................................................. 91

Table 69. Transmit Line Scrambler Register Summary.......................................................................................... 92

Table 70. Transmit Data Path Parity Register Summary........................................................................................ 92

Table 71. Register Summary.................................................................................................................................. 97

Table 72. Interrupt Status (RO) ............................................................................................................................ 110

Table 73. Interrupt Status Mask (R/W) ................................................................................................................. 111

Table 74. Chip ID (RO)......................................................................................................................................... 111

Table 75. Chip Vintage (RO) ................................................................................................................................ 111

Table 76. Scratch Pad, Clock Loss Alarm (R/W).................................................................................................. 112

Table 77. Chip-Level Maintenance (R/W) ............................................................................................................ 112

Table 78. Chip Status (RO) .................................................................................................................................. 112

Table 79. Clock Loss Alarm/PM Clock Detection (W1C)...................................................................................... 113

Table 80. Clock Loss Alarm/PM Clock Detection Mask (R/W) ............................................................................. 114

Table 81. Software Chip Reset (WO) ................................................................................................................... 114

Table 82. LTE Interrupt Status (RO)..................................................................................................................... 115

Table 83. LTE Interrupt Status Mask (R/W) ......................................................................................................... 116

Table 84. Section Trace (J0) Access Maintenance (R/W).................................................................................... 117

Table 85. J0 Access Done (W1C) ........................................................................................................................ 118

Table 86. J0 Access Message Start (WO) ........................................................................................................... 118

Table 87. J0 Access Message Buffers 1--32 (R/W) ............................................................................................ 118

Table 88. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1 x 10

≠3

) (R/W) ................................ 119

Table 89. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1 x 10

≠4

) (R/W) ................................ 119

Table 90. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1 x 10

≠5

) (R/W) ................................ 119

Table 91. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1 x 10

≠6

) (R/W) ................................ 119

Table 92. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1 x 10

≠7

) (R/W) ................................ 119

Table 93. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1 x 10

≠8

) (R/W) ................................ 120

Table 94. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1 x 10

≠9

) (R/W) ................................ 120

Table 95. Line Signal Degrade/Signal Fail Bit Error Rate Detection Time (1 x 10

≠10

) (R/W)............................... 120

Table 96. Line Signal Degrade/Signal Fail Detect Error Limit (1 x 10

≠3

) (R/W) ................................................... 120

Table 97. Line Signal Degrade/Signal Fail Detect Error Limit (1 x 10

≠4

) (R/W) ................................................... 120

Table 98. Line Signal Degrade/Signal Fail Detect Error Limit (1 x 10

≠5

) (R/W) ................................................... 120

Table 99. Line Signal Degrade/Signal Fail Detect Error Limit (1 x 10

≠6

) (R/W) ................................................... 121

Table 100. Line Signal Degrade/Signal Fail Detect Error Limit (1 x 10

≠7

) (R/W) ................................................. 121

Table 101. Line Signal Degrade/Signal Fail Detect Error Limit (1 x 10

≠8

) (R/W) ................................................. 121

Table 102. Line Signal Degrade/Signal Fail Detect Error Limit (1 x 10

≠9

) (R/W) ................................................. 121

List of Tables

(continued)

Contents

Page

8

Agere Systems Inc.

Data Sheet

May 2003

STS-192 Overhead and Path Processor

TSOT0410G4 SONET/SDH

Table 103. Line Signal Degrade/Signal Fail Clear Error Limit (1 x 10

≠4

) (R/W) ................................................... 121

Table 104. Line Signal Degrade/Signal Fail Clear Error Limit (1 x 10

≠5

) (R/W) ................................................... 121

Table 105. Line Signal Degrade/Signal Fail Clear Error Limit (1 x 10

≠6

) (R/W) ................................................... 121

Table 106. Line Signal Degrade/Signal Fail Clear Error Limit (1 x 10

≠7

) (R/W) ................................................... 122

Table 107. Line Signal Degrade/Signal Fail Clear Error Limit (1 x 10

≠8

) (R/W) ................................................... 122

Table 108. Line Signal Degrade/Signal Fail Clear Error Limit (1 x 10

≠9

) (R/W) ................................................... 122

Table 109. Line Signal Degrade/Signal Fail Clear Error Limit (1 x 10

≠10

) (R/W).................................................. 122

Table 110. LTE Receive Channel 1 Provisioning (R/W)....................................................................................... 122

Table 111. LTE Receive Channel 1 Maintenance (R/W)...................................................................................... 123

Table 112. LTE Receive Channel 1 Loss-of-Signal (LOS) Threshold (R/W)........................................................ 123

Table 113. LTE Receive Channel 1 K Byte Status (RO) ...................................................................................... 123

Table 114. LTE Receive Channel 1 S1 Byte Status (RO) .................................................................................... 123

Table 115. LTE Receive Channel 1 Service-Affecting Interrupt Alarm (W1C) ..................................................... 124

Table 116. LTE Receive Channel 1 Service-Affecting Interrupt Alarm Mask (R/W)............................................. 124

Table 117. LTE Receive Channel 1 Service-Affecting Persistency Alarm (RO)................................................... 124

Table 118. LTE Receive Channel 1 Nonservice-Affecting Interrupt Alarm (W1C) ............................................... 125

Table 119. LTE Receive Channel 1 Nonservice-Affecting Interrupt Mask (R/W) ................................................. 126

Table 120. LTE Receive Channel 1 Nonservice-Affecting Persistency Alarm (RO)............................................. 127

Table 121. LTE Receive Channel 1 Performance Monitoring (RO) ..................................................................... 127

Table 122. LTE Receive Channel 1 REI-L Performance Monitoring (L) (RO)...................................................... 127

Table 123. LTE Receive Channel 1 REI-L Performance Monitoring (U) (RO) ..................................................... 127

Table 124. LTE Receive Channel 1 CV-L Performance Monitoring (L) (RO)....................................................... 127

Table 125. LTE Receive Channel 1 CV-L Performance Monitoring (U) (RO) ...................................................... 127

Table 126. LTE Receive Channel 1 CV-S Performance Monitoring (RO)............................................................ 128

Table 127. LTE Transmit--Frame Pulse Offset Count (R/W) .............................................................................. 128

Table 128. LTE Transmit--Add Interface Self-Sync Option (R/W)....................................................................... 128

Table 129. LTE Transmit--B1 Corrupt Frame Count (R/W)................................................................................. 128

Table 130. LTE Transmit--B2 Corrupt Frame Count (R/W)................................................................................. 128

Table 131. LTE Transmit--M1 Corrupt Frame Count (R/W) ................................................................................ 129

Table 132. LTE Transmit--TFRM S1 Byte (RO) .................................................................................................. 129

Table 133. LTE Transmit--Interrupt Alarm Register (W1C)................................................................................. 129

Table 134. LTE Transmit--Interrupt Mask Register (R/W)................................................................................... 130

Table 135. LTE Transmit Channel 1 Provisioning (R/W)...................................................................................... 130

Table 136. LTE Transmit Bit Assignment ............................................................................................................. 131

Table 137. LTE Transmit Channel 1 Maintenance (R/W)..................................................................................... 131

Table 138. LTE Transmit Channel 1 Path Unequipped (UNEQ-P) Insert Enable #1 (R/W)................................. 131

Table 139. LTE Transmit Channel 1 Path Unequipped (UNEQ-P) Insert Enable #2 (R/W)................................. 131

Table 140. LTE Transmit Channel 1 Path Unequipped (UNEQ-P) Insert Enable #3 (R/W)................................. 131

Table 141. LTE Transmit Channel 1 Path Unequipped (UNEQ-P) Insert Enable #4 (R/W)................................. 132

Table 142. LTE Transmit Channel 1 Path AIS (AIS-P) Insert Enable #1 (R/W) ................................................... 132

Table 143. LTE Transmit Channel 1 Path AIS (AIS-P) Insert Enable #2 (R/W) ................................................... 132

Table 144. LTE Transmit Channel 1 Path AIS (AIS-P) Insert Enable #3 (R/W) ................................................... 132

Table 145. LTE Transmit Channel 1 Path AIS (AIS-P) Insert Enable #4 (R/W) ................................................... 132

Table 146. LTE Transmit Channel 1 K1K2 Byte Insert Values (R/W) .................................................................. 132

Table 147. LTE Transmit Channel 1 S1 Byte Insert Value (R/W) ........................................................................ 132

Table 148. LTE Transmit Channel 1 Interrupt Alarm (W1C) ................................................................................ 133

Table 149. LTE Transmit Channel 1 Interrupt Alarm Mask (R/W)........................................................................ 133

Table 150. EQPT Interrupt Status (RO) ............................................................................................................... 134

Table 151. EQPT Interrupt Mask (R/W) ............................................................................................................... 135

Table 152. Receive Drop Common Service-Affecting Alarm (W1C) .................................................................... 136

Table 153. Receive Drop Common Service-Affecting Alarm Mask (R/W)............................................................ 136

List of Tables

(continued)

Contents

Page

Agere Systems Inc.

9

Data Sheet

May 2003

STS-192 Overhead and Path Processor

TSOT0410G4 SONET/SDH

Table 154. Receive Drop STS-48 Channel Provisioning Register 1 (R/W).......................................................... 137

Table 155. J0 Trace--STS-12 Channel 1 (R/W) .................................................................................................. 137

Table 156. J0 Trace--STS-12 Channel 2 (R/W) .................................................................................................. 137

Table 157. J0 Trace--STS-12 Channel 3 (R/W) .................................................................................................. 137

Table 158. J0 Trace--STS-12 Channel 4 (R/W) .................................................................................................. 137

Table 159. Receive Drop STS-48 Channel Nonservice-Affecting Alarm (W1C) .................................................. 138

Table 160. Receive Drop STS-48 Channel Nonservice Affecting Alarm Mask (R/W).......................................... 138

Table 161. Transmit Add STS-48 Channel Provisioning (R/W)............................................................................ 139

Table 162. J0 Status Register--1 (RO)................................................................................................................ 139

Table 163. J0 Status Register--2 (RO)................................................................................................................ 139

Table 164. J0 Status Register--3 (RO)................................................................................................................ 139

Table 165. J0 Status Register--4 (RO)................................................................................................................ 139

Table 166. AIS Insert Status Register, STS-12 Channel #1 (RO)........................................................................ 140

Table 167. AIS Insert Status Register, STS-12 Channel #2 (RO)........................................................................ 140

Table 168. AIS Insert Status Register, STS-12 Channel #3 (RO)........................................................................ 141

Table 169. AIS Insert Status Register, STS-12 Channel #4 (RO)........................................................................ 141

Table 170. Transmit Add STS-48 Channel Alarm (W1C)..................................................................................... 142

Table 171. Transmit Add STS-48 Channel Alarm Mask (R/W) ............................................................................ 143

Table 172. STS-12 Pointer Processor Provisioning, STS-1 #1 to STS-1 #12 (R/W) ........................................... 145

Table 173. STS-12 Pointer Processor Maintenance, STS-1 #1 to STS-1 #12 (R/W) .......................................... 145

Table 174. STS-12 Pointer Interpreter PM, Last Second Increments, STS-1 #1 to STS-1 #12 (RO) .................. 145

Table 175. STS-12 Pointer Interpreter PM, Last Second Decrements, STS-1 #1 to STS-1 #12 (RO) ................ 146

Table 176. STS-12 Pointer Generator PM, Last Second Increments, STS-1 #1 to STS-1 #12 (RO) .................. 146

Table 177. STS-12 Pointer Generator PM, Last Second Decrements, STS-1 #1 to STS-1 #12 (RO)................. 146

Table 178. STS-1 #1 Path Overhead Provisioning (R/W) .................................................................................... 146

Table 179. STS-1 #1 Path Overhead Maintenance (R/W) ................................................................................... 146

Table 180. STS-1 #1 Path Overhead Status (RO) ............................................................................................... 147

Table 181. STS-1 #1 Alarm Interrupt Status (W1C) ............................................................................................. 147

Table 182. STS-1 #1 Alarm Interrupt Status Mask (R/W) .................................................................................... 147

Table 183. STS-1 #1 Alarm Persistency (RO)...................................................................................................... 148

Table 184. STS-1 #1 PM Last Second Indicators (RO)........................................................................................ 148

Table 185. STS-1 #1 Last Second CV-P Count (RO) .......................................................................................... 148

Table 186. STS-1 #1 Last Second REI-P Count (RO) ......................................................................................... 148

Table 187. Path Overhead (POH) Interrupt Status (RO)...................................................................................... 149

Table 188. Path Overhead (POH) Interrupt Status Mask (R/W)........................................................................... 149

Table 189. STS-1 Signal Fail Detect Threshold, Window Size Select 0 (R/W) .................................................... 150

Table 190. STS-1 Signal Fail Clear Threshold, Window Size Select 0 (R/W)...................................................... 150

Table 191. STS-1 Signal Fail Detect Threshold, Window Size Select 1 (R/W) .................................................... 150

Table 192. STS-1 Signal Fail Clear Threshold, Window Size Select 1 (R/W)...................................................... 150

Table 193. STS-Nc Signal Fail Detect Threshold, Window Size Select 2 (R/W).................................................. 151

Table 194. STS-Nc Signal Fail Clear Threshold, Window Size Select 2 (R/W) ................................................... 151

Table 195. STS-Nc Signal Fail Detect Threshold, Window Size Select 3 (R/W).................................................. 151

Table 196. STS-Nc Signal Fail Clear Threshold, Window Size Select 3 (R/W) ................................................... 151

Table 197. STS-Nc Signal Fail Detect Threshold, Window Size Select 4 (R/W).................................................. 152

Table 198. STS-Nc Signal Fail Clear Threshold, Window Size Select 4 (R/W) ................................................... 152

Table 199. STS-Nc Signal Fail Detect Threshold, Window Size Select 5 (R/W).................................................. 152

Table 200. STS-Nc Signal Fail Clear Threshold, Window Size Select 5 (R/W) ................................................... 152

Table 201. STS-Nc Signal Fail Detect Threshold, Window Size Select 6 (R/W).................................................. 152

Table 202. STS-Nc Signal Fail Clear Threshold, Window Size Select 6 (R/W) ................................................... 152

Table 203. STS-Nc Signal Fail Detect Threshold, Window Size Select 7 (R/W).................................................. 153

Table 204. STS-Nc Signal Fail Clear Threshold, Window Size Select 7 (R/W) ................................................... 153

List of Tables

(continued)

Contents

Page

10

Agere Systems Inc.

Data Sheet

May 2003

STS-192 Overhead and Path Processor