Product Brief

October 2001

TSOT042G5 SONET/SDH

155/622/2488 Mbits/s Interface

Features

s

SONET/SDH terminal/ADM functionality for linear

and ring networks.

s

Versatile IC supports 155/622/2488 Mbits/s

SONET/SDH interface solution for overhead pro-

cessing and path monitoring.

s

Low-power 2.5 V/3.3 V operation.

s

≠40 ∞C to +85 ∞C temperature range.

s

600-pin LBGA package.

SONET/SDH Interface

s

Termination of quad STS-3/STM-1, quad STS-12/

STM-4, or single STS-48/STM-16.

s

Supports overhead processing for transport and

path overhead bytes.

s

Optional insertion and extraction of overhead bytes

via the serial overhead (TOAC) interface.

s

STS pointer processing to align the receive frame

to the system frame.

s

STS-1 granularity cross connect between receive,

mate, and STM payloads.

s

Support for 1+1 and 1:1 linear networks; UPSR

and BLSR ring networks.

s

SONET/SDH compliant condition and alarm

reporting.

s

Handles all concatenation levels of STS-3c to

STS-48c (in multiples of 3: e.g., 3c, 6c, 9c, etc.).

s

Built-in diagnostic loopback modes.

s

Compliant with

Telcordia Technologies

ˇ

,

ANSI

Æ

,

and ITU standards.

Interfaces

s

Two identical/redundant STS/STM backplane

interfaces using 622 MHz LVDS technology.

s

Mate-to-mate backplane interface using 622 MHz

LVDS technology for 1+1, 1:1, BLSR, and UPSR

network support.

s

Optional 78 MHz bus (32-bit) for STS/STM inter-

face.

s

IEEE

Æ

1149.1 port with memory built-in self-test

(BIST) scan and boundary scan (JTAG).

Microprocessor Interface

s

Up to 66 MHz synchronous.

s

16-bit address and 16-bit data interface.

s

Synchronous or asynchronous modes available.

s

Configurable to operate with most commercial

microprocessors.

Description

The TSOT042G5 SONET/SDH interface device pro-

vides a versatile solution for quad OC-3, quad

OC-12, and for single OC-48 linear and ring data-

com/telecom applications. Constructed using Agere's

state-of-the-art CMOS technology, this device incor-

porates integrated SONET/SDH framing, section/line

termination, pointer processing, and cross connect

blocks.

Communication with the TSOT device is accom-

plished through a generic microprocessor interface.

The device supports separate address and data

buses.

With the TSOT device, construction of all types of

interfaces for OC-3/OC-12/OC-48 data equipment is

simplified and cost reduced allowing extremely com-

petitive solutions to be constructed.

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Copyright © 2001 Agere Systems Inc.

All Rights Reserved

October 2001

PN00-056SONT

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET:

http://www.agere.com

E-MAIL:

docmaster@agere.com

N. AMERICA:

Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA:

Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, Kowloon

Tel. (852) 3129-2000, FAX (852) 3129-2020

CHINA: (86) 21-5047-1212 (Shanghai), (86) 10-6522-5566 (Beijing), (86) 755-695-7224 (Shenzhen)

JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 778-8833, TAIWAN: (886) 2-2725-5858 (Taipei)

EUROPE:

Tel. (44) 7000 624624, FAX (44) 1344 488 045

Product Brief

October 2001

155/622/2488 Mbits/s Interface

TSOT042G5 SONET/SDH

Description

(continued)

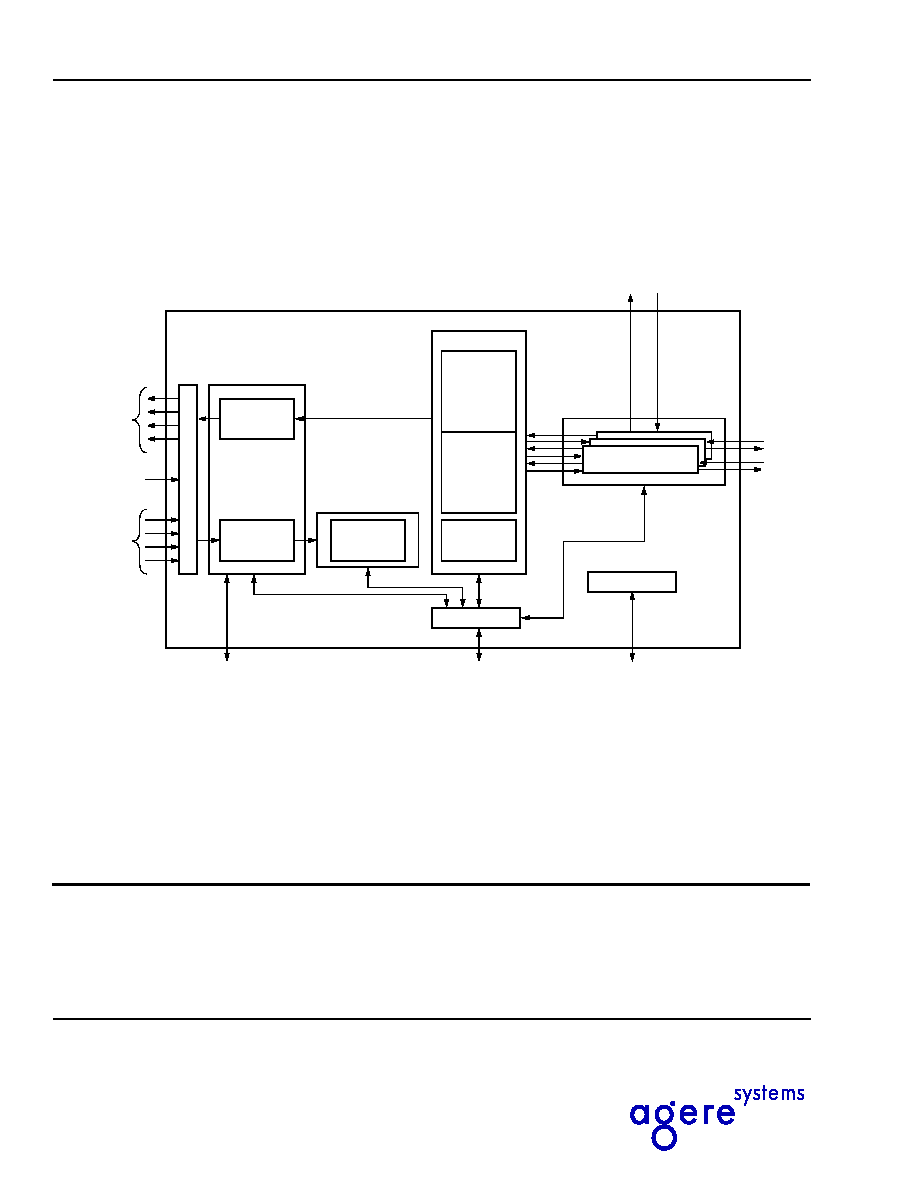

This device integrates the SONET/SDH network termination functions at the section, line, and path overhead lay-

ers. It supports STS-48/STM-16, quad STS-12/STM-4 and quad STS-3/STM-1 interface rates. The concatenation

levels supported by this device are STS-1, STS-3c, STS-6c, STS-9c, STS12c, STS-15c, . . . , STS-45c, STS-48c.

Future plans for the TSOT042G5 also call for a virtual concatenation feature with dynamic pipe-sizing

(e.g., STS-1-21V or VC-4-7V), thus enabling service providers flexibility to adjust their bandwidth on demand.*

5-9386(F)

Figure 1. Block Diagram

* Uses nomenclature only proposed in the standards.

Telcordia Technologies

is a trademark of Bell Communications Research, Inc.

ANSI

is a registered trademark of American National Standards Institute, Inc.

IEEE

is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

OVERHEAD

PROCESSOR

MONITOR

OVERHEAD

PROCESSOR

INSERT

TRANSPORT

OVERHEAD

INT

E

RF

A

C

E

B

L

O

CK

POINTER

PROCESSOR

CONNECTION

MEMORY

CONTROL

TSI

STM INTERFACE

MATE

INTERFACE

SWITCHING

STM_B

STM_A

MPU INTERFACE

SINGLE

STM-16/STS-48

OR QUAD

STM-4/STS-12

OR QUAD

STM-1/STS-3

SINGLE

STM-16/STS-48

OR QUAD

STM-4/STS-12

OR QUAD

STM-1/STS-3

MISCELLANEOUS

GPIO/STMDCC

TO GO INTERFACE

TERMINATION

TXCLK

PATH

SWITCH

LINE

SWITCH