| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: HCPL-3000 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1-329

Power Bipolar Transistor

Base Drive Optocoupler

Technical Data

Features

∑ High Output Current

I

O2

(2.0 A

Peak

, 0.6 A

Continuous)

I

O1

(1.0 A

Peak

, 0.5 A

Continuous)

∑ 1.5 kV/

µ

s Minimum Common

Mode Rejection (CMR) at

V

CM

= 600 V

∑ Wide V

CC

Range (5.4 to 13

Volts)

∑ 2

µ

s Typical Propagation

Delay

∑ Recognized under UL 1577

for Dielectric Withstand

Proof Test Voltage of 5000

Vac, 1 Minute

Applications

∑ Isolated Bipolar Transistor

Base Drive

∑ AC and DC Motor Drives

∑ General Purpose Industrial

Inverters

∑ Uninterruptable Power

Supply

Description

The HCPL-3000 consists of a

Silicon-doped GaAs LED optically

coupled to an integrated circuit

with a power output stage. This

optocoupler is suited for driving

power bipolar transistors and

power Darlington devices used in

motor control inverter applica-

tions. The high peak and steady

state current capabilities of the

output stage allow for direct

interfacing to the power device

without the need for an interme-

diate amplifier stage. With a CMR

rating of 1.5 kV/

µ

s this optocoup-

ler readily rejects transients found

in inverter applications.

The LED controls the state of the

output stage. Transistor Q2 in the

output stage is on with the LED

off, allowing the base of the

power device to be held low.

Turning on the LED turns off

transistor Q2 and switches on

transistor Q1 in the output stage

which provides current to drive

the base of a power bipolar

device.

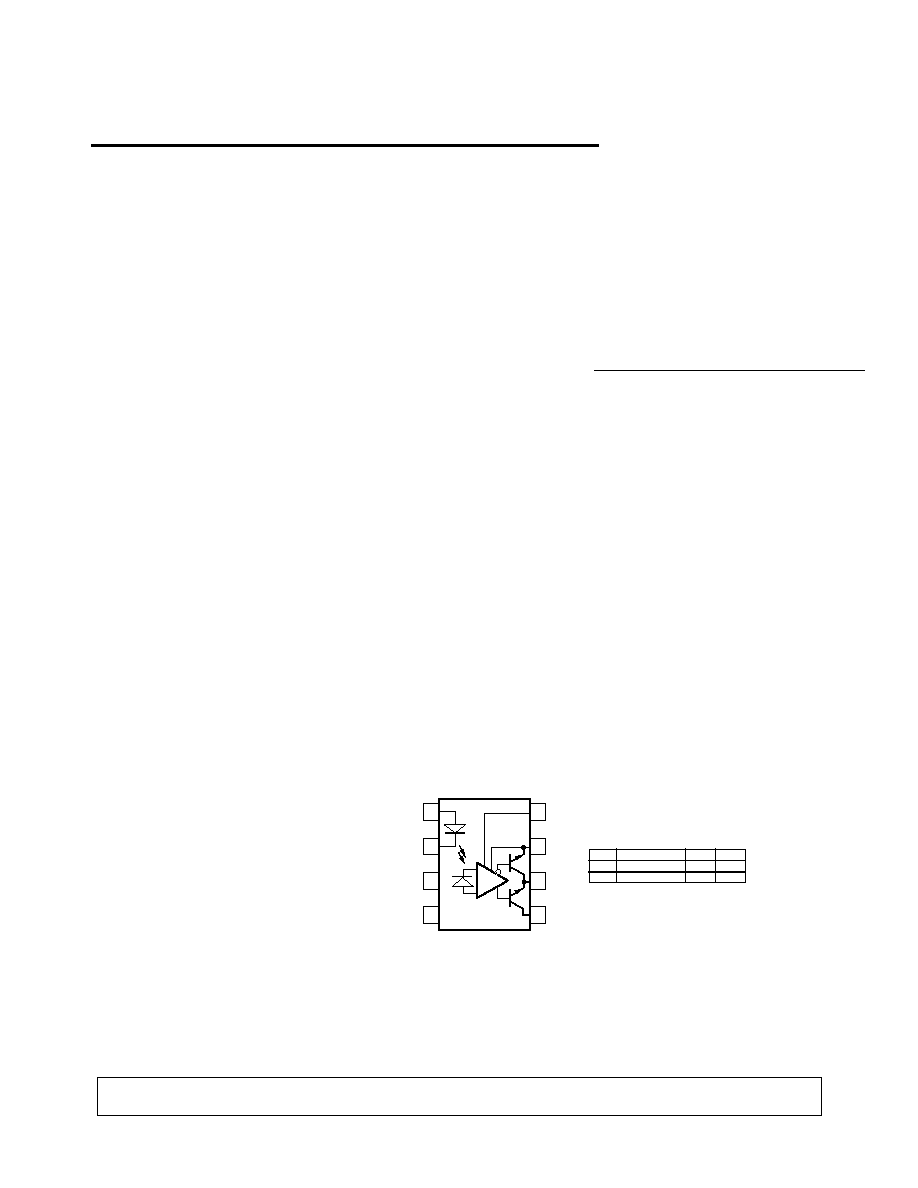

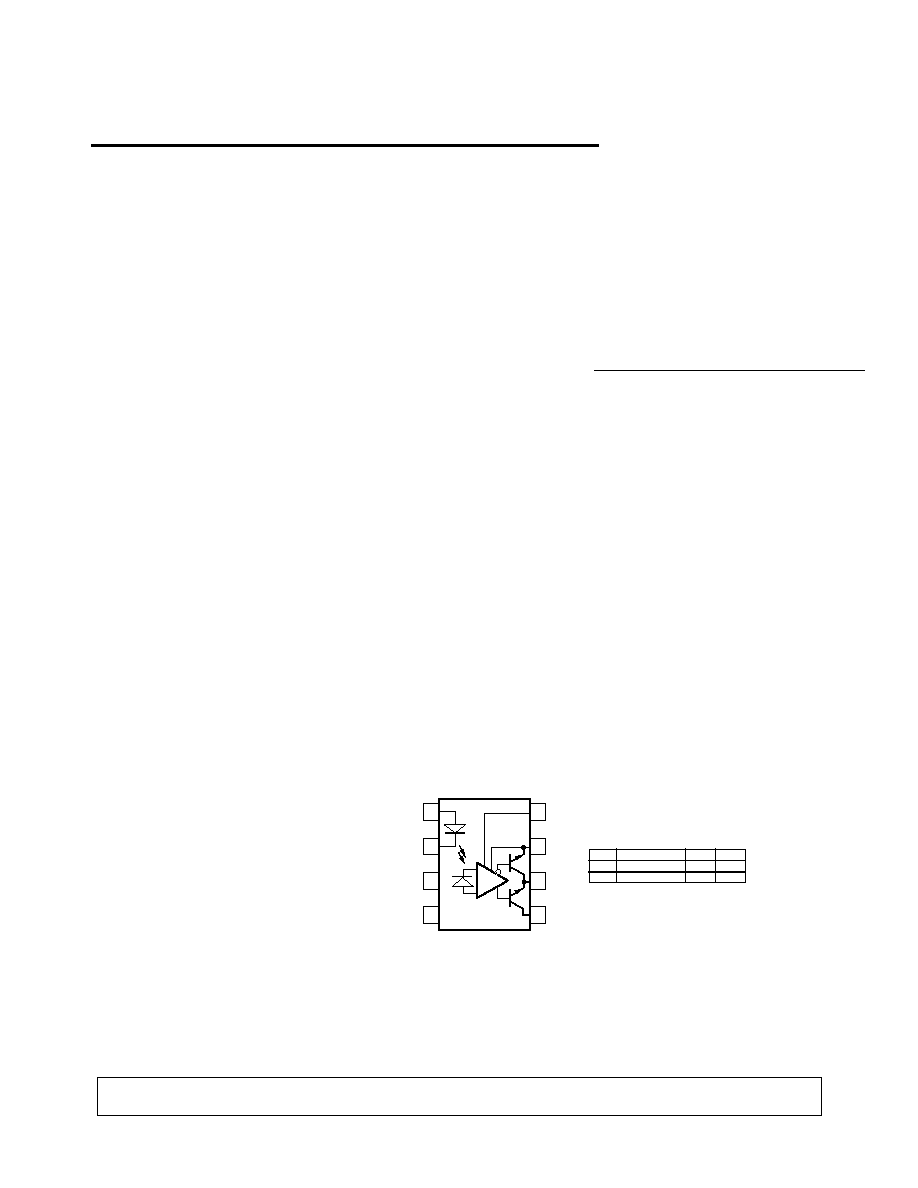

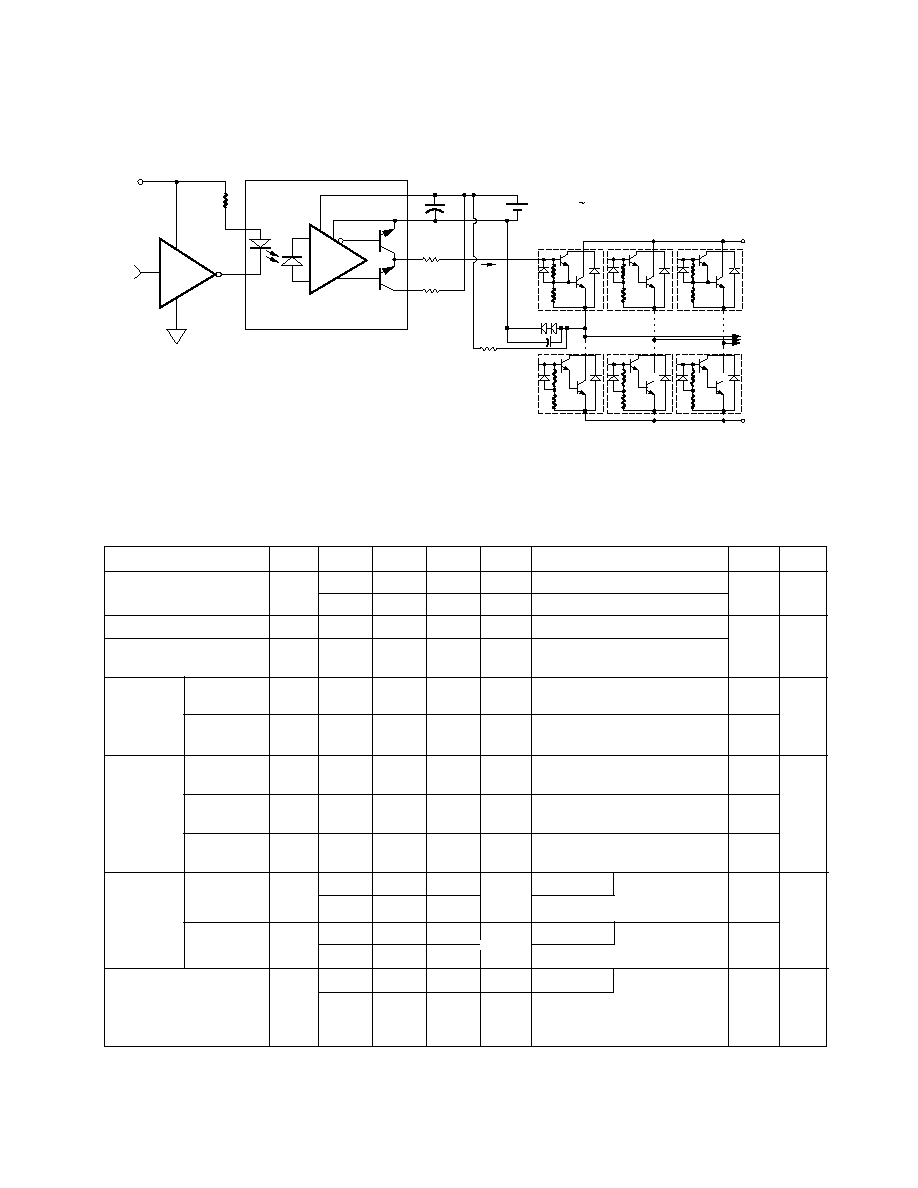

Functional Diagram

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to

prevent damage and/or degradation which may be induced by ESD.

THE USE OF A 0.1

µ

F BYPASS CAPACITOR CONNECTED BETWEEN PINS 8 AND 7 IS RECOMMENDED. ALSO, CURRENT LIMITING

RESISTORS ARE RECOMMENDED (SEE FIGURE 1, NOTE 2, AND NOTE 7).

HCPL-3000

H

GND

ANODE

CATHODE

V

O2

V

O1

V

CC

Q2

Q1

8

7

6

5

1

2

3

4

HCPL-3000

TRUTH TABLE

LED

ON

OFF

OUTPUT

HIGH LEVEL

LOW LEVEL

Q1

ON

OFF

Q2

OFF

ON

5965-3584E

1-330

Regulatory Information

The HCPL-3000 has been

approved by the following

organizations:

UL

Recognized under UL 1577,

Component Recognition Program,

File E55361.

Demonstrated ESD

Performance

Human Body Model: MIL-STD-

883 Method 3015.7: Class 2

Machine Model: EIAJ IC-121-

1988 (1988.3.28 Version 2),

Test Method 20, Condition C:

1200 V

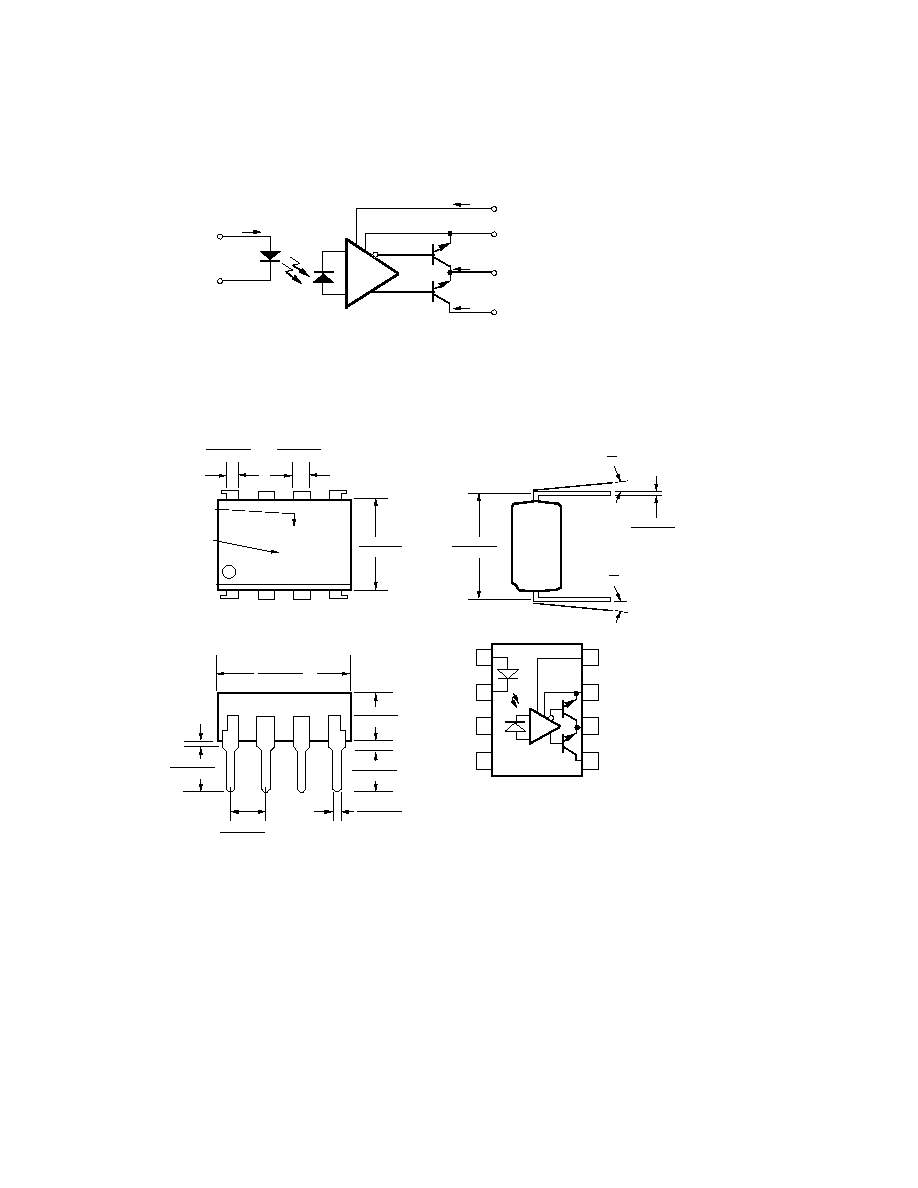

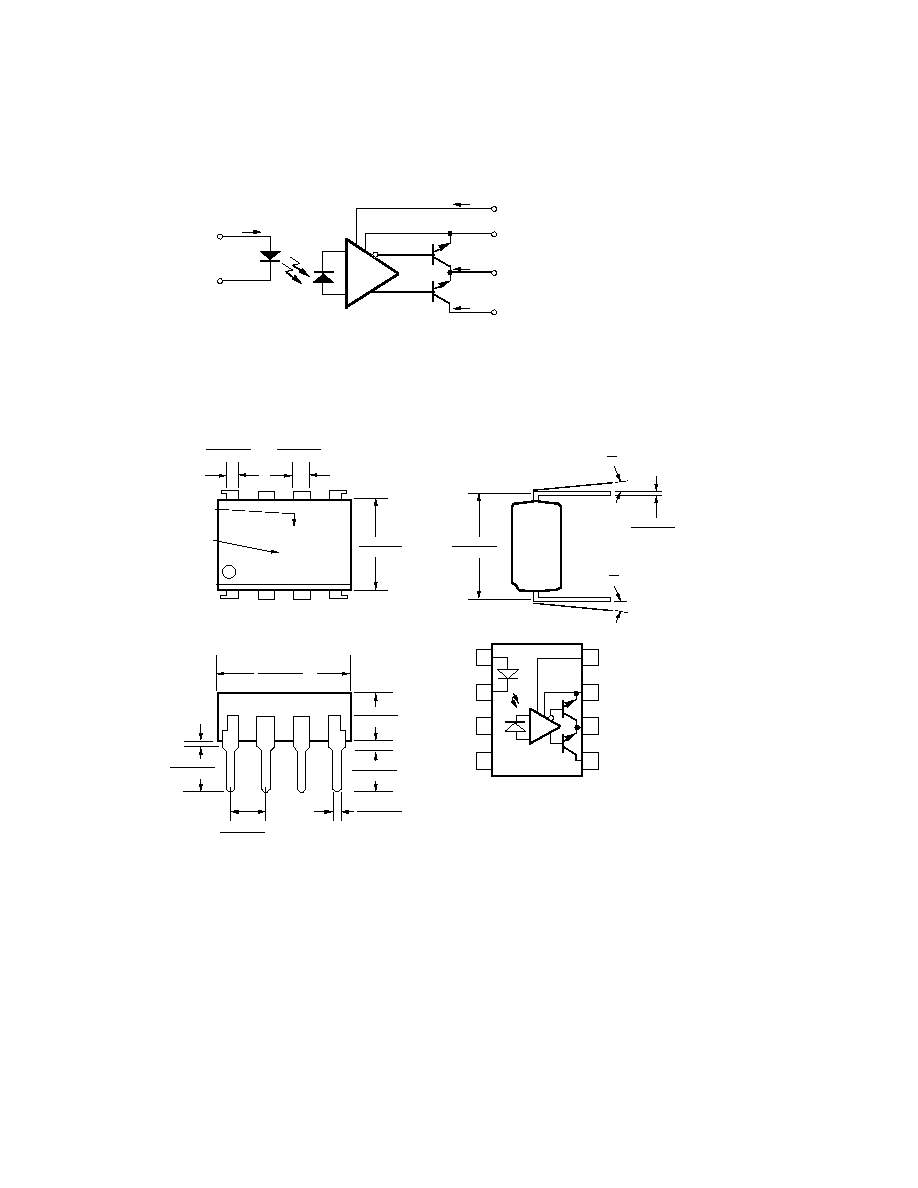

Schematic

Outline Drawing

ANODE

CATHODE

1

2

-

+

I

F

I

CC

8

7

6

5

GND

V

CC

V

O2

V

O1

I

O1

I

O2

Q2

Q1

0.16 (0.006)

0.36 (0.014)

0

∞

13

∞

7.32 (0.288)

7.92 (0.312)

0

∞

13

∞

9.16 (0.361)

10.16 (0.400)

3.00 (0.118)

4.00 (0.157)

2.90 (0.114)

3.90 (0.154)

0.40 (0.016)

0.60 (0.024)

2.29 (0.090)

2.79 (0.110)

2.55 (0.100)

3.55 (0.140)

0.50

(0.020)

TYP

0.65 (0.026)

1.05 (0.041)

0.90 (0.035)

1.50 (0.059)

6.00 (0.236)

7.00 (0.276)

HP XXXX

YYWW

DATE

CODE

TYPE

NUMBER

8

7

6

5

1

2

3

4

GND

ANODE

CATHODE

V

O2

V

O1

V

CC

Q2

Q1

8

7

6

5

1

2

3

4

HCPL-3000

1-331

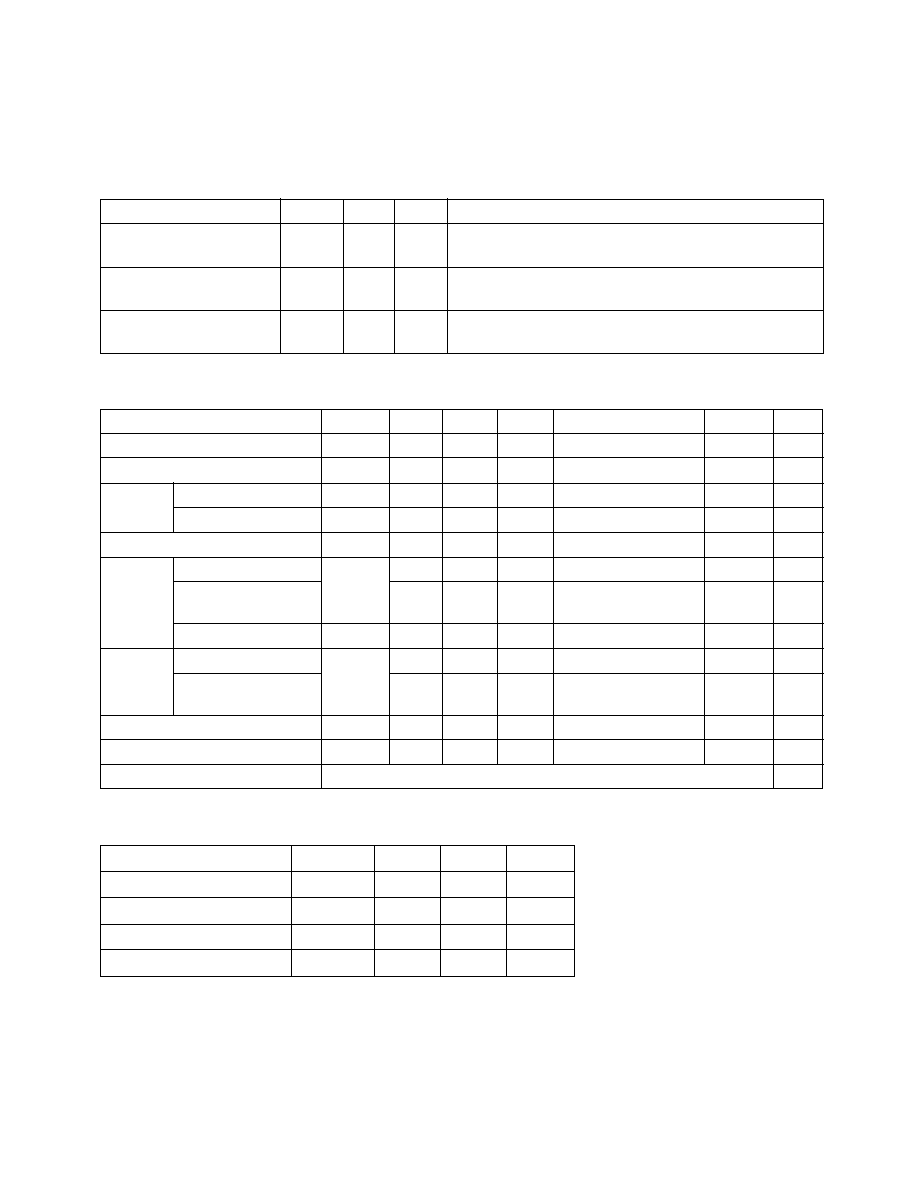

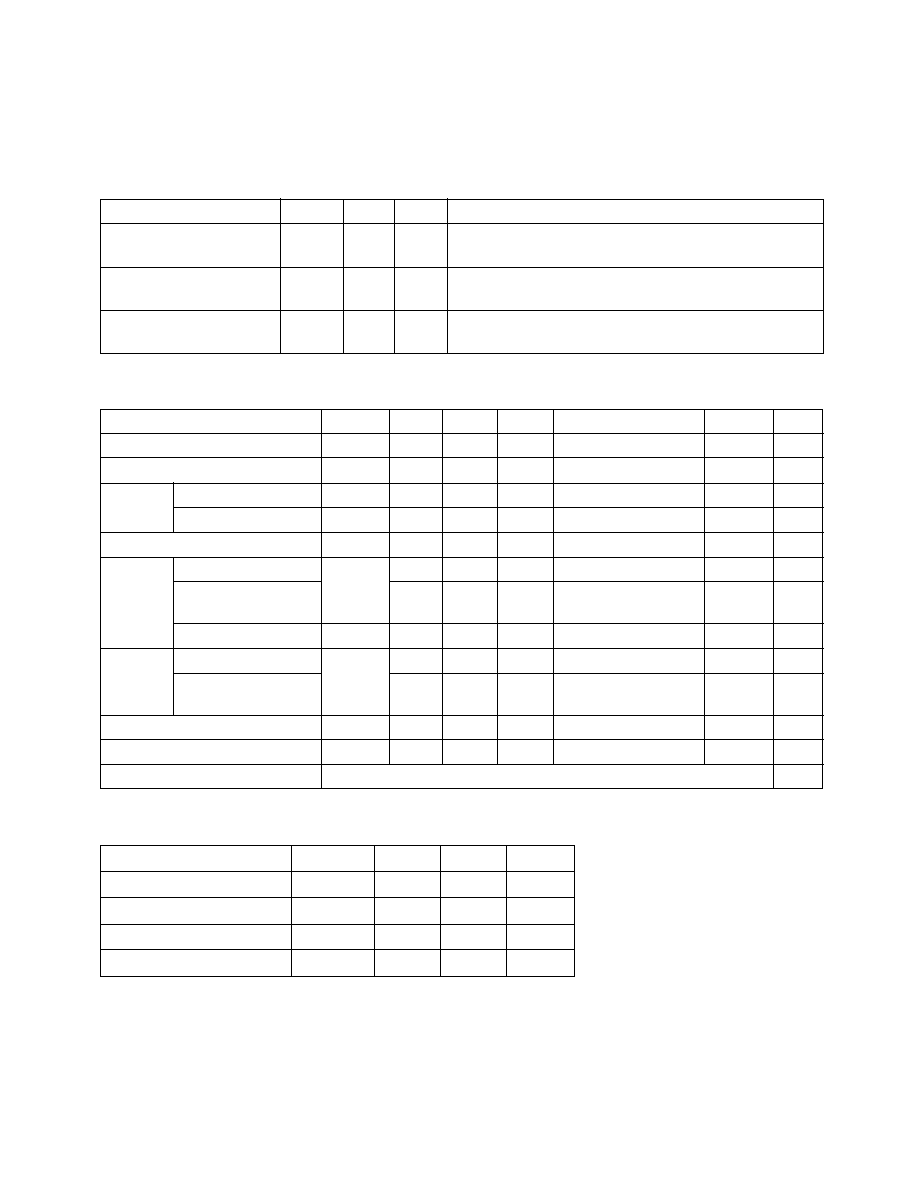

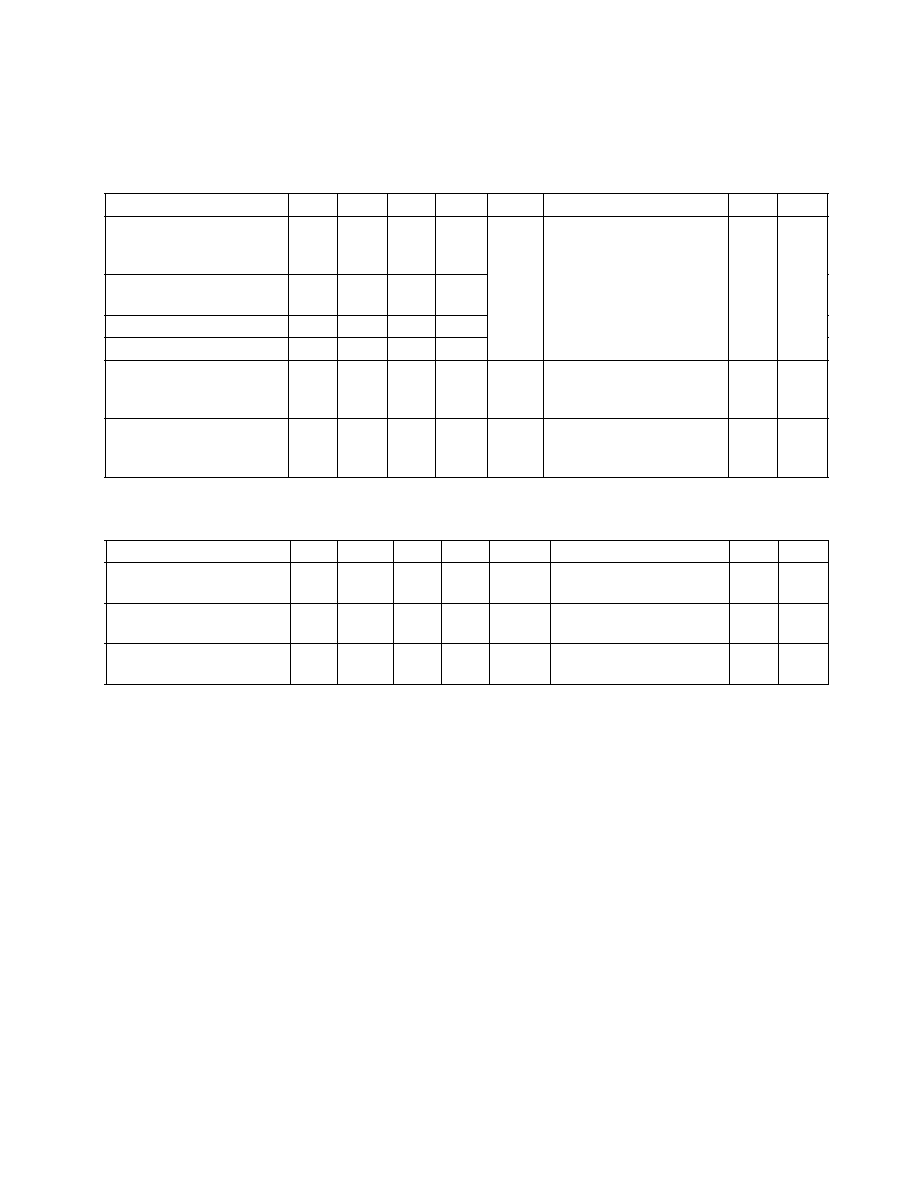

Insulation and Safety Related Specifications

Parameter

Symbol

Value Units

Conditions

Min. External Air Gap

L(IO1)

6.0

mm

Shortest distance measured through air, between

(External Clearance)

two conductive leads, input to output

Min. External Tracking

L(IO2)

6.0

mm

Shortest distance path measured along outside surface

Path (External Creepage)

of optocoupler body between the input and output leads

Min. Internal Plastic

0.15

mm

Through insulation distance conductor to conductor

Gap (Internal Clearance)

inside the optocoupler cavity

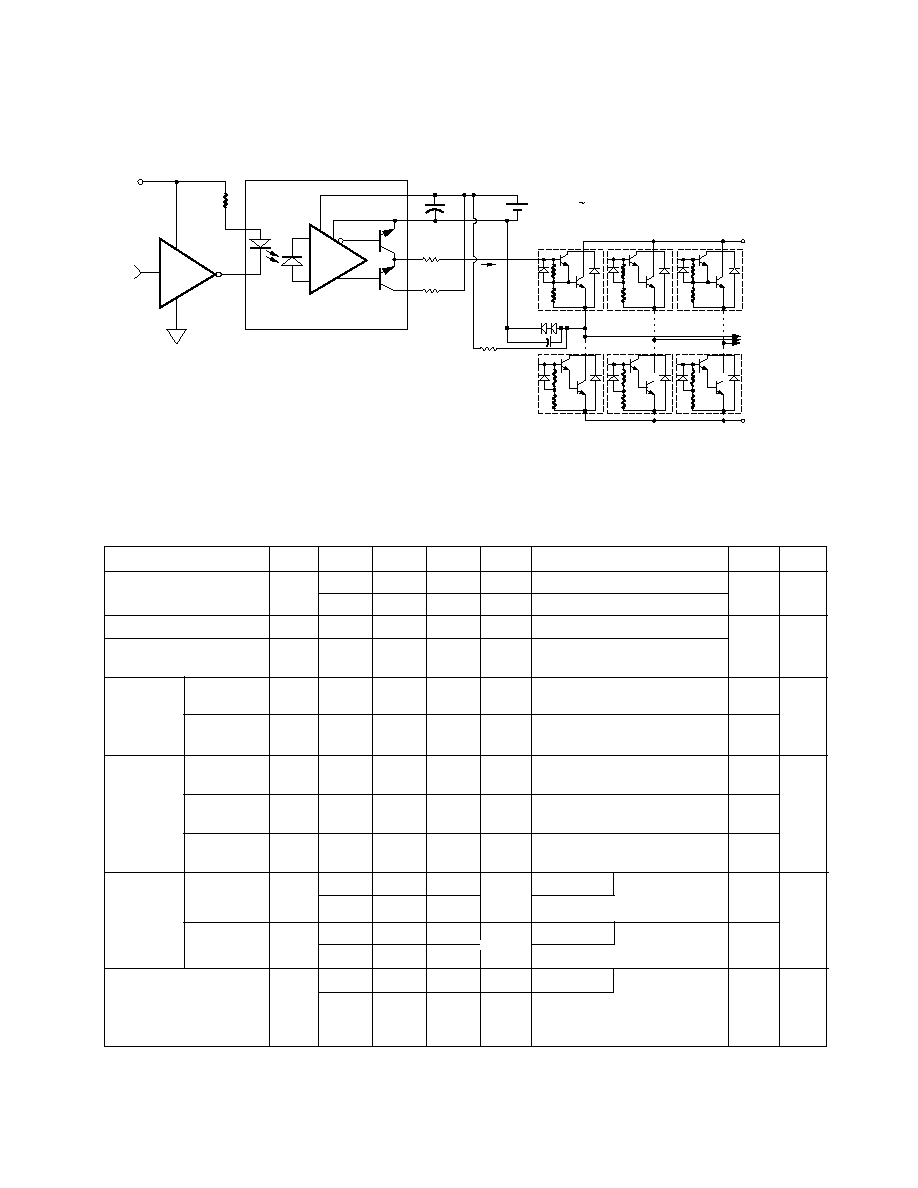

Recommended Protection

for Output Transistors

During switching transitions, the

output transistors Q1 and Q2 of

the HCPL-3000 can conduct large

Recommended Operating Conditions

Parameter

Symbol

Min.

Max.

Units

Power Supply Voltage

V

CC

5.4

13

V

Input Current (ON)

I

F(ON)

8*

20

mA

Input Current (OFF)

I

F(OFF)

-

0.2

mA

Operating Temperature

T

A

-20

80

∞

C

*The initial switching threshold is 5 mA or less.

amounts of current. Figure 1

describes a recommended circuit

design showing current limiting

resistors R

1

and R

2

which are

necessary in order to prevent

damage to the output transistors

Q1 and Q2 (see Note 7). A bypass

capacitor C

1

is also recommended

to reduce power supply noise.

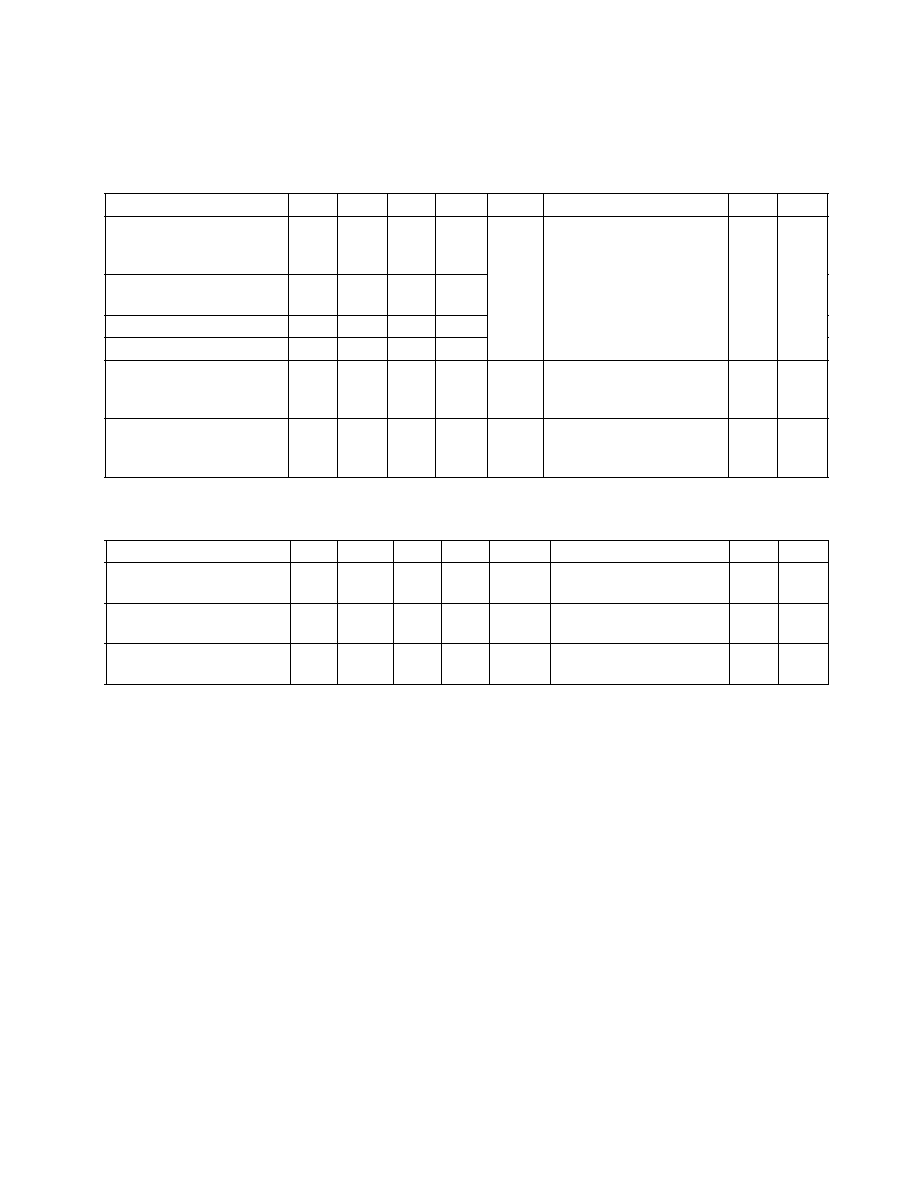

Absolute Maximum Ratings

Parameter

Symbol

Min.

Max.

Unit

Conditions

Fig.

Note

Storage Temperature

T

S

-55

125

∞

C

Operating Temperature

T

A

-20

80

∞

C

Input

Continuous Current

I

F

25

mA

9

1

Reverse Voltage

V

R

6

V

T

A

= 25

∞

C

Supply Voltage

V

CC

18

V

Output 1

Continuous Current

I

O1

0.5

A

10,11

1

Peak Current

1.0

A

Pulse Width < 5

µ

s,

1

Duty cycle = 1%

Voltage

V

O1

18

V

Output 2

Continuous Current

I

O2

0.6

A

10,11,12

1

Peak Current

2.0

A

Pulse Width < 5

µ

s,

12

1

Duty cycle = 1%

Output Power Dissipation

P

O

500

mW

10

1

Total Power Dissipation

P

T

550

mW

11

1

Lead Solder Temperature

260

∞

C for 10 s, 1.0 mm below seating plane

1-332

Electrical Specifications

Over recommended temperature (T

A

= -20

∞

C to +80

∞

C) unless otherwise specified.

Parameter

Sym.

Min.

Typ.

Max. Units

Test Conditions

Fig.

Note

Input Forward Voltage

V

F

-

1.1

1.4

V

I

F

= 5 mA, T

A

= 25

∞

C

13

0.6

0.9

-

V

I

F

= 0.2 mA, T

A

= 25

∞

C

Input Reverse Current

I

R

-

-

10

µ

A

V

R

= 3 V, T

A

= 25

∞

C

Input Capacitance

C

IN

-

30

250

pF

V

F

= 0 V, f = 1 kHz,

T

A

= 25

∞

C

Output 1

Low Level

V

O1L

-

0.2

0.4

V

V

CC

= 6 V, I

O1

= 0.4 A,

2, 16,

2

Voltage

R

L2

= 10

, I

F

= 5 mA

17

Leakage

I

O1L

-

-

200

µ

A

V

CC

= V

O1

= 13 V, V

O2

= 0 V,

4

Current

I

F

= 0 mA

Output 2

High Level

V

O2H

4.5

5.0

-

V

V

CC

= 6 V, I

O2

= -0.4 A

3, 18,

2

Voltage

I

F

= 5 mA, V

O1

= 6 V

19

Low Level

V

O2L

-

0.2

0.4

V

V

CC

= 6 V, I

O2

= 0.5 A,

20,

Voltage

I

F

= 0 mA

21

Leakage

I

O2L

-

-

200

µ

A

V

CC

= 13 V, I

F

= 5 mA,

5

Current

V

O2

= 13 V

Supply

High Level

I

CCH

-

9

13

mA

T

A

= 25

∞

C

22

2

Current

-

-

17

V

CC

= 6 V, I

F

= 5 mA

Low Level

I

CCL

-

11

15

mA

T

A

= 25

∞

C

23

-

-

20

V

CC

= 6 V, I

F

= 0 mA

Low to High

I

FLH

0.3

1.5

3.0

mA

T

A

= 25

∞

C

Threshold Input

6, 14,

3

Current

0.2

-

5.0

mA

V

CC

= 6 V, R

L1

= 5

,

15

R

L2

= 10

Figure 1. Recommended Output Transistor Protection and Typical Application Circuit.

8

7

6

5

Q2

Q1

+5 V

240

TTL

OR

LSTTL

1

2

R

2

C

+ HVDC

HCPL-3000

TOTEM

POLE

OUTPUT

GATE

CONTROL

INPUT

1

CC

V (+ 5.4 V + 13 V)

POWER TRANSISTOR

MODULE

3-PHASE

AC

- HVDC

I

O1

R

1

1

R

1

= 5 - 250

R

2

= 1 - 2

BYPASS CAPACITOR C

1

= 0.1 µF

1-333

Switching Specifications

(T

A

= 25

∞

C)

Parameter

Sym.

Min.

Typ.

Max.

Units

Test Conditions

Fig.

Note

Propagation Delay

t

PLH

-

2

5

µ

s

V

CC

= 6 V, I

F

= 5 mA,

7,

2, 6

Time to High Output

R

L1

= 5

, R

L2

= 10

24,

Level

25

Propagation Delay Time

t

PHL

-

2

5

to Low Output Level

Rise Time

t

r

-

0.2

1

Fall Time

t

f

-

0.1

1

Output High Level

|CM

H

| 1500

-

-

V/

µ

s

V

CM

= 600 V

Peak

,

8

2

Common Mode

I

F

= 5mA, R

L1

= 470

,

Transient Immunity

R

L2

= 1 k

,

V

02H

= 0.5 V

Output Low Level

|CM

L

| 1500

-

-

V/

µ

s

V

CM

= 600 V

Peak

,

Common Mode

I

F

= 0 mA, R

L1

= 470

,

Transient Immunity

R

L2

= 1 k

,

V

02L

= 0.5 V

Package Characteristics

Parameter

Sym.

Min.

Typ.

Max.

Units

Test Conditions

Fig.

Note

Input-Output Momentary

V

ISO

5000

V rms

RH = 40% to 60%,

4, 5

Withstand Voltage*

t = 1 min., T

A

= 25

∞

C

Resistance

R

I-O

5x10

10

10

11

≠

V

I-O

= 500 V, T

A

= 25

∞

C,

4

(Input-Output)

RH = 40% to 60%

Capacitance

C

I-O

≠

1.2

≠

pF

f = 1 MHz

4

(Input-Output)

*The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output

continuous voltage rating. For the continuous voltage rating refer to the VDE 0884 Insulation Characteristics Table (if applicable), your

equipment level safety specification, or HP Application Note 1074, "Optocoupler Input-Output Endurance Voltage."

Notes:

1. Derate absolute maximum ratings with ambient temperatures as shown in Figures 9, 10, and 11.

2. A bypass capacitor of 0.01

µ

F or more is needed near the device between V

CC

and GND when measuring output and transfer

characteristics.

3. I

FLH

represents the forward current when the output goes from low to high.

4. Device considered a two terminal device; pins 1-4 are shorted together and pin 5-8 are shorted together.

5. For devices with minimum V

ISO

specified at 5000 V rms, in accordance with UL1577, each optocoupler is proof-tested by applying an

insulation test voltage

6000 V rms for one second (leakage current detection limit, I

I-O

200

µ

A).

6. The t

PLH

and t

PHL

propagation delays are measured from the 50% level of the input pulse to the 50% level of the output pulse.

7. R

1

sets the base current (I

O1

in Figure 1) supplied to the power bipolar device. R

2

limits the peak current seen by Q2 when the device

is turning off. For more applications and circuit design information see Application Note "Power Transistor Gate/Base Drive

Optocouplers."