| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AIC1570CS | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

AIC1570

5-bit DAC, Synchronous PWM Power Regulator

with LDO and Linear Controller

DS-1570-00

www.analog.com.tw

1

FEATURES

Compatible with HIP6018.

Provides 3 Regulated Voltages for Micro-

processor Core, Clock and GTL Power.

Simple Voltage-Mode PWM Control.

Dual N-Channel MOSFET Synchronous Driver.

Operates from +3.3V, +5V and +12V Inputs.

Fast Transient Response.

Full 0% to 100% Duty Ratios.

±1.0% Output Voltage for VCORE and

±2.0%

Output Voltage Reference for VCLK and VGTL.

TTL Compatible 5-bit Digital-to-Analog Core

Output Voltage Selection. Range from 1.3V to

3.5V.

0.1V Steps from 2.1V to 3.5V.

0.05V Steps from 1.3V to 2.05V.

Adjustable Current Limit without External Sense

Resistor.

Microprocessor Core Voltage Protection against

Shorted MOSFET.

Power Good Output Voltage Monitor.

Over-Voltage and Over-Current Fault Monitors.

200KHz Free-Running Oscillator Programmable

up to 350KHz.

APPLICATIONS

Full Motherboard Power Regulation for

Computers.

DESCRIPTION

The AIC1570 combines a synchronous voltage

mode controller with a low dropout linear regulator

and a linear controller as well as the monitoring and

protection functions in this chip. The PWM

controller regulates the microprocessor core

voltage with a synchronous rectified buck converter.

The linear controller regulates power for the GTL

bus and the linear regulator provides power for the

clock driver circuit.

An integrated 5 bit D/A converter that adjusts the

core PWM output voltage from 2.1V to 3.5V in 0.1V

increments and from 1.3V to 2.05V in 0.05V

increments. The linear regulator uses an internal

driver device to provide 2.5V±2.5%. The linear

controller drives with an external N-channel

MOSEFET to provide 1.5V±2.5%.

This chip monitors all the output voltages. Power

Good signal is issued when the core voltage is

within ±10% of the DAC setting and the other levels

are above their under-voltage levels. Over-voltage

protection for the core output uses the lower N-

channel MOSFET to prevent output voltage above

115% of the DAC setting.

The PWM over-current function monitors the output

current by using the voltage drop across the upper

MOSFET's R

DS(on)

, eliminating the need for a

current sensing resistor.

AIC1570

2

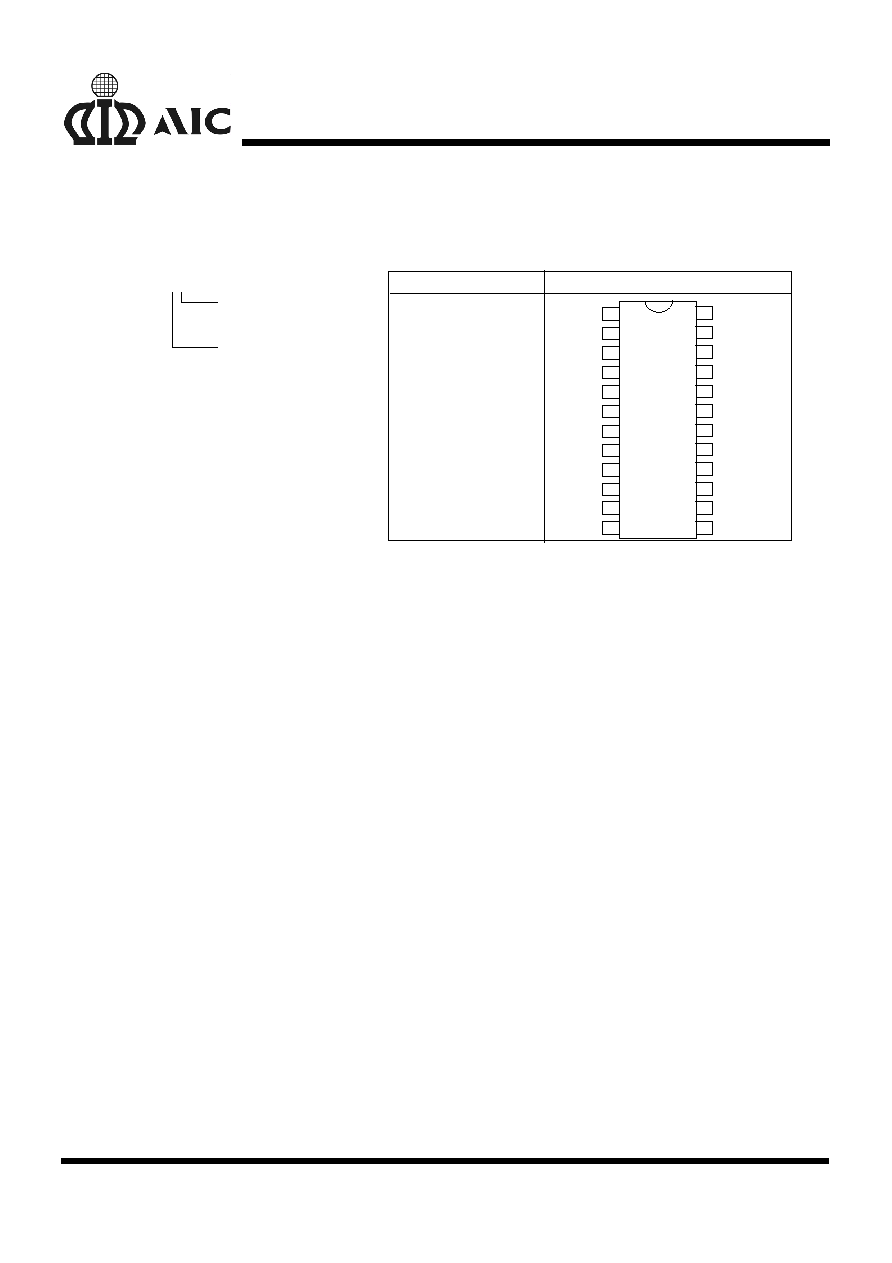

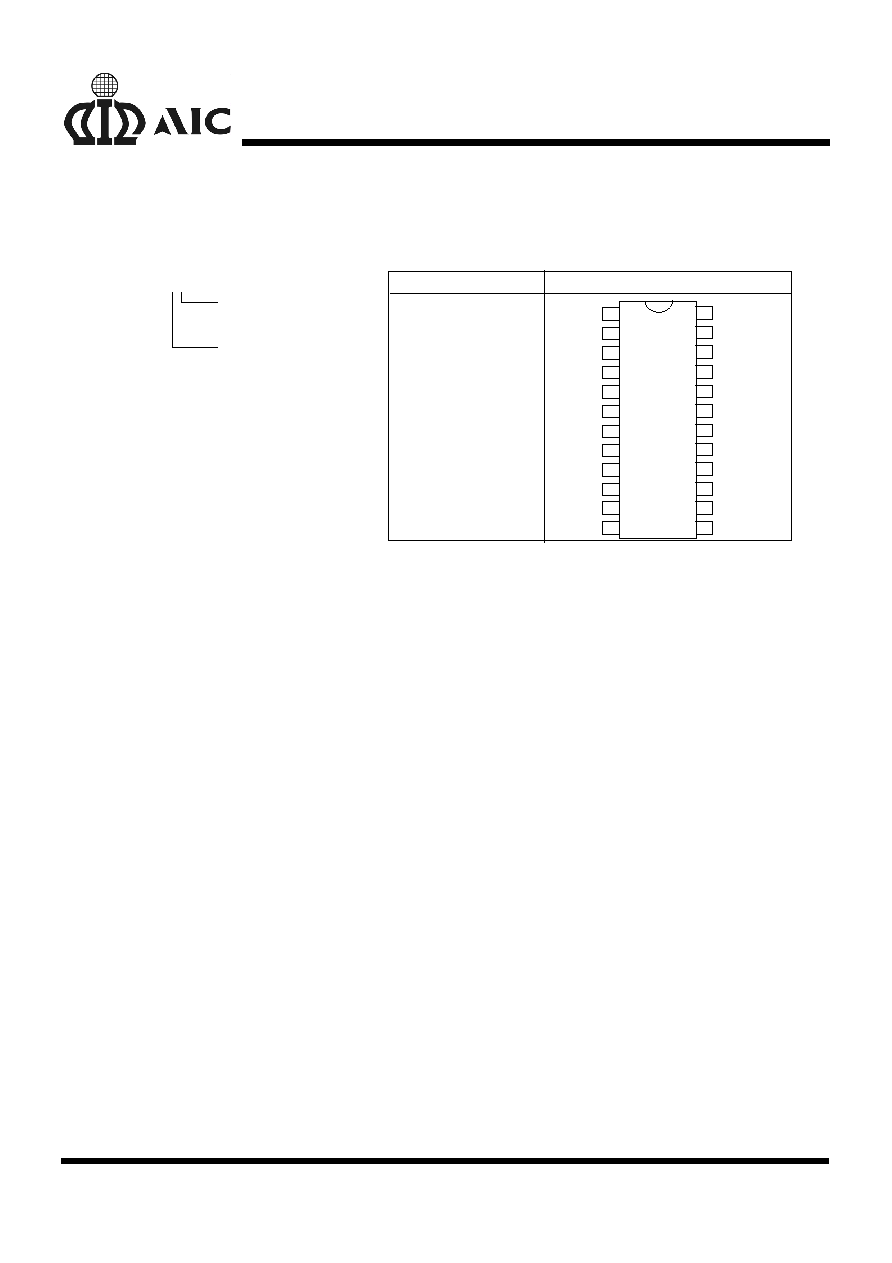

ORDERING INFORMATION

ORDER NUMBER

PIN CONFIGURATION

AIC1570-XX

AIC1570CS

(SO24)

PACKAGING TYPE

S: SMALL OUTLINE

TEMPERATURE RANGE

C: 0

∞C~+70∞C

1

3

4

2

5

7

6

8

9

10

11

12

VID0

VID4

VID3

VID2

VCC

VID1

RT

PGOOD

SS

FAULT

VIN2

FB2

16

15

24

22

23

21

20

19

17

18

14

13

LGATE

UGATE

PHASE

VSEN

PGND

OCSET

FB1

GATE3

COMP1

FB3

VOUT2

GND

ABSOLUTE MAXIMUM RATINGS

Supply Voltage, V

CC

........................................................................................ +15V

PGOOD, FAULT and GATE Voltage

.................................. GND -0.3V to V

CC

+0.3V

Input, Output , or I/O Voltage ........................................................ GND -0.3V to 7V

Recommended Operating Conditions

Supply Voltage; VCC

........................................... +12V±10%

Ambient temperature Range

........................................ 0

∞C~70∞C

Junction Temperature Range ....................................... 0

∞C~100∞C

Thermal Information

Thermal Resistance,

JA

SOIC package

........................................................... 100

∞C/W

SOIC package (with 3in

2

of copper)

.................................. 90

∞C/W

Maximum Junction Temperature (Plastic Package) ................................ 150

∞C

Maximum Storage Temperature Range ..................................... -65

∞C ~ 150∞C

Maximum Lead Temperature (Soldering 10 sec) ................................... 300

∞C

TEST CIRCUIT

Refer to APPLICATION CIRCUIT.

AIC1570

3

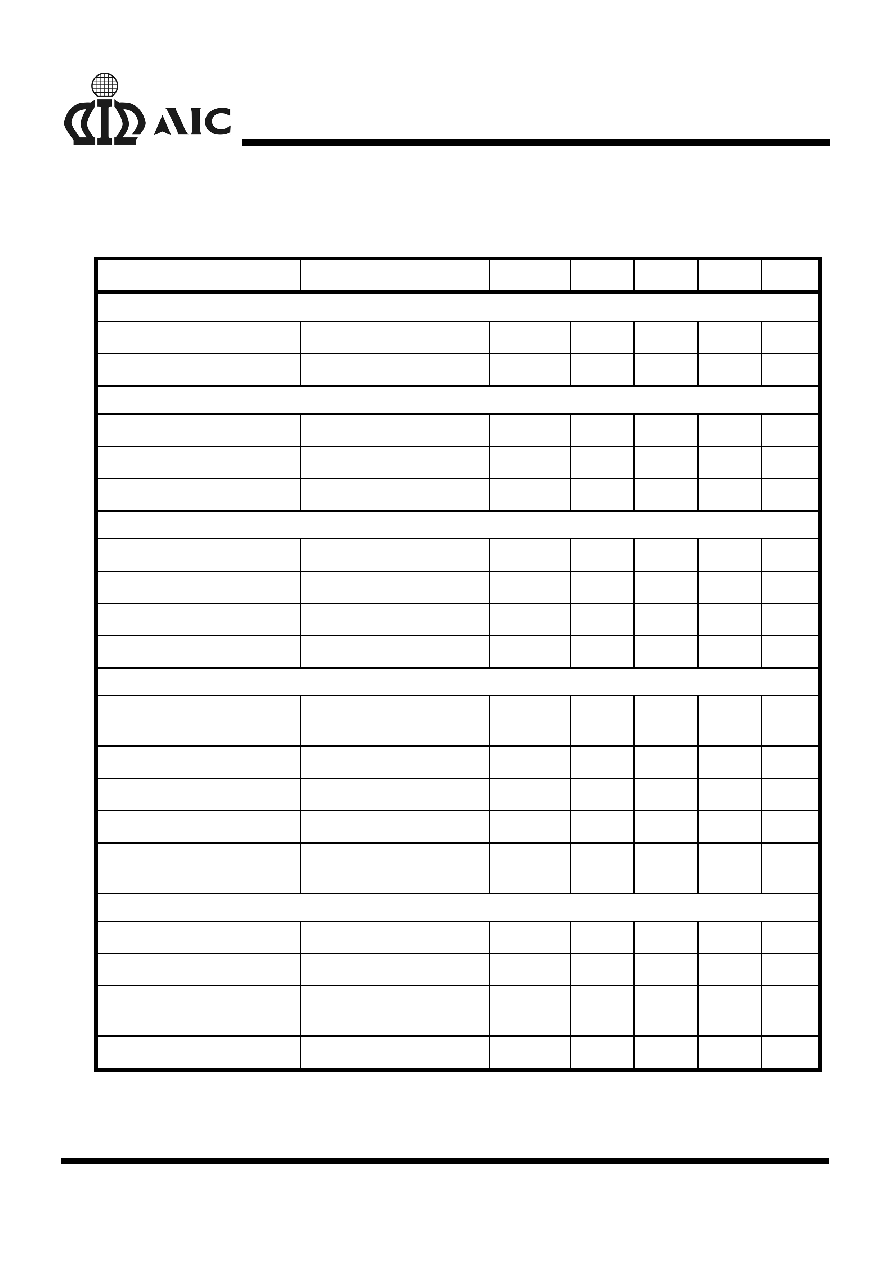

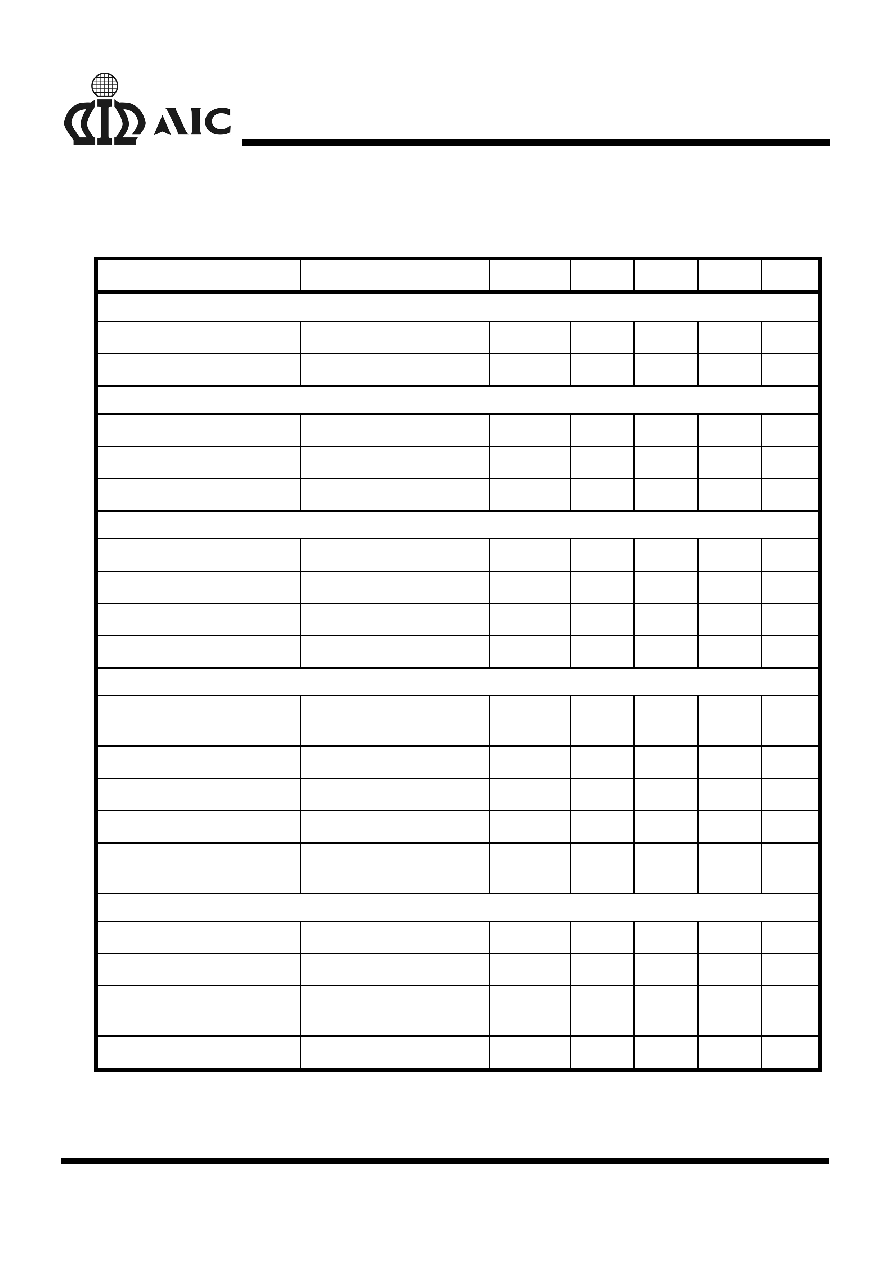

ELECTRICAL CHARACTERISTICS

(V

cc

=12V, T

J

=25

∞

∞

∞

∞C, Unless otherwise

specified)

PARAMETER

TEST CONDITIONS

SYMBOL

MIN.

TYP.

MAX.

UNIT

VCC SUPPLY CURRENT

Supply Current

UGATE, LGATE, GATE3 and

VOUT2 open

I

CC

1.8

5

mA

POWER ON RESET

Rising VCC Threshold

V

OCSET

=4.5V

VCC

THR

8.6

9.5

10.4

V

Falling VCC Threshold

V

OCSET

=4.5V

VCC

THF

8.2

9.2

10.2

V

Rising VIN2 Under-Voltage

Threshold

VIN2

THR

2.5

2.6

2.7

V

VIN2 Under-Voltage

Hysteresis

VIN2

HYS

130

mV

Rising V

OCSET1

Threshold

V

OCSETH

1.3

V

OSCILLATOR

Free Running Frequency

RT=Open

F

170

200

230

KHz

Ramp. Amplitude

RT=open

V

OSC

1.3

V

P-P

REFERENCE AND DAC

DAC (VID0~VID4) Input Low

Voltage

VID

L

0.8

V

DAC (VID0~VID4) Input

High Voltage

VID

H

2

V

DACOUT Voltage Accuracy

VDAC=1.8V~3.5V

-1.0

+1.0

%

FB2 Reference Voltage

V

REF2

1.240

1.265

1.290

V

FB3 Reference Voltage

V

REF3

1.250

1.275

1.300

V

LINEAR REGULATOR

Regulation

10mA<I

OUT2

<150mA

-1

+1

%

Under-Voltage Level

FB2 falling

FB2

UV

70

82

%

Over-Current Protection

430

570

mA

Over-Current Protection

During Start-up

750

mA

AIC1570

4

ELECTRICAL CHARACTERISTICS

(Continued)

PARAMETER

TEST CONDITIONS

SYMBOL

MIN.

TYP.

MAX.

UNIT

LINEAR CONTROLLER

Regulation

0 < I

GATE3

< 10mA

-2.5

+2.5

%

Under-Voltage Level

FB3 falling

FB3

UV

70

80

%

PWM CONTROLLER ERROR AMPLIFIER

DC GAIN

76

dB

Gain Bandwidth Product

GBWP

11

MHz

Slew Rate

COMP1=10pF

SR

6

V/

µS

PWM CONTROLLER GATE DRIVER

Upper Drive Source

VCC=12V, V

UGATE

=11V

R

UGH

5.2

6.5

Upper Drive Sink

VCC=12V, V

UGATE

=1V

R

UGL

3.3

5

Lower Drive Source

VCC=12V, V

LGATE

=11V

R

LGH

4.1

6

Lower Drive Sink

VCC=12V, V

LGATE

=1V

R

LGL

3

5

PROTECTION

V

OUT1

Voltage Over-Voltage

Trip

VSEN Rising

OVP

112

115

118

%

OCSET Current Source

V

OCSET

=4.5V

DC

I

OCSET

170

200

230

µA

FAULT Sourcing Current

V

FAULT

=10V

I

OVP

10

16

mA

Soft-Start Current

I

SS

11

µA

Chip Shutdown Soft Start

Threshold

1.0

V

POWER GOOD

V

OUT1

Upper Threshold

VSEN Rising

109

110.5

112

%

V

OUT1

Under-Voltage

VSEN Falling

90.5

92

93.5

%

V

OUT1

Hysteresis

(VSEN/DACOUT)

Upper and Lower

Threshold

3

%

P

GOOD

Voltage Low

I

PGOOD

=-4mA

V

PGOOD

0.5

V

AIC1570

5

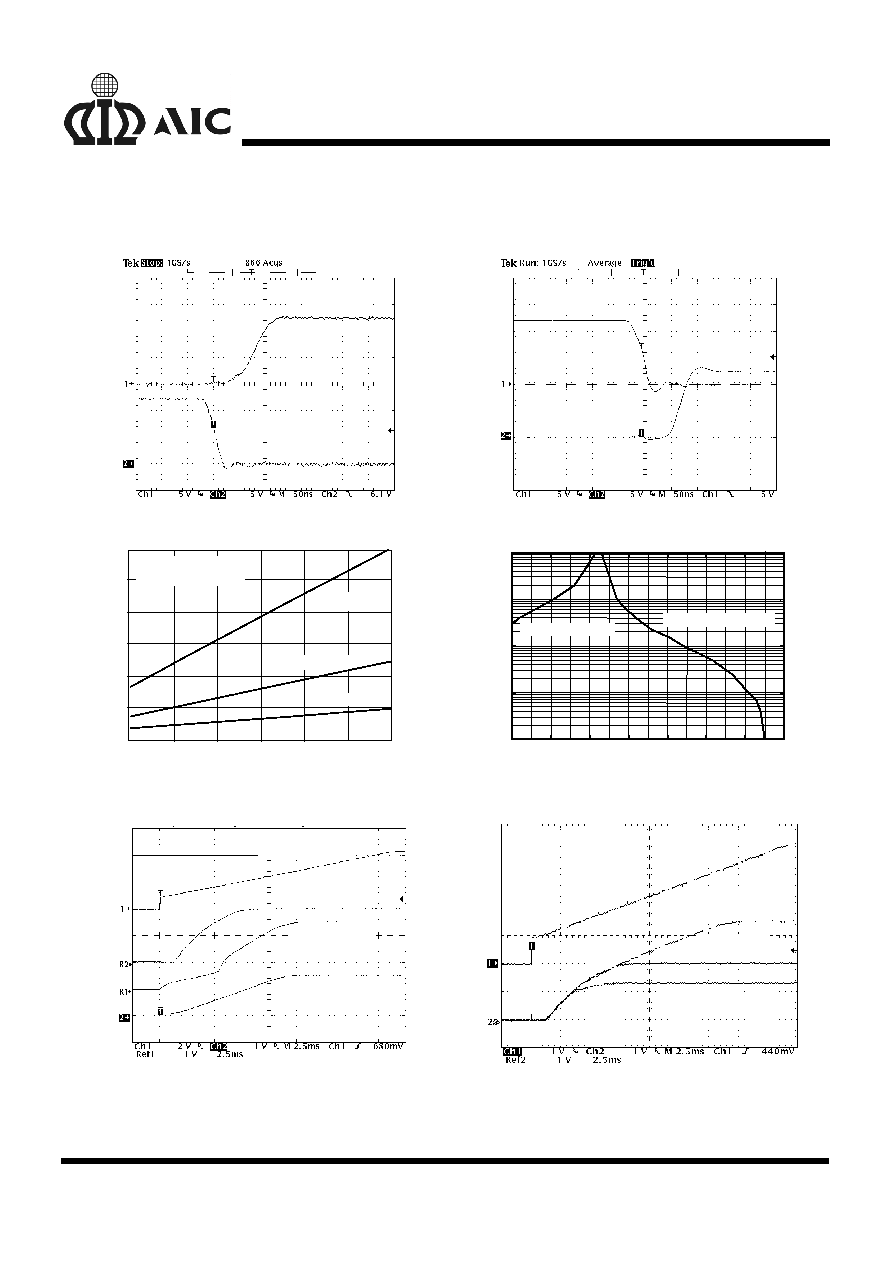

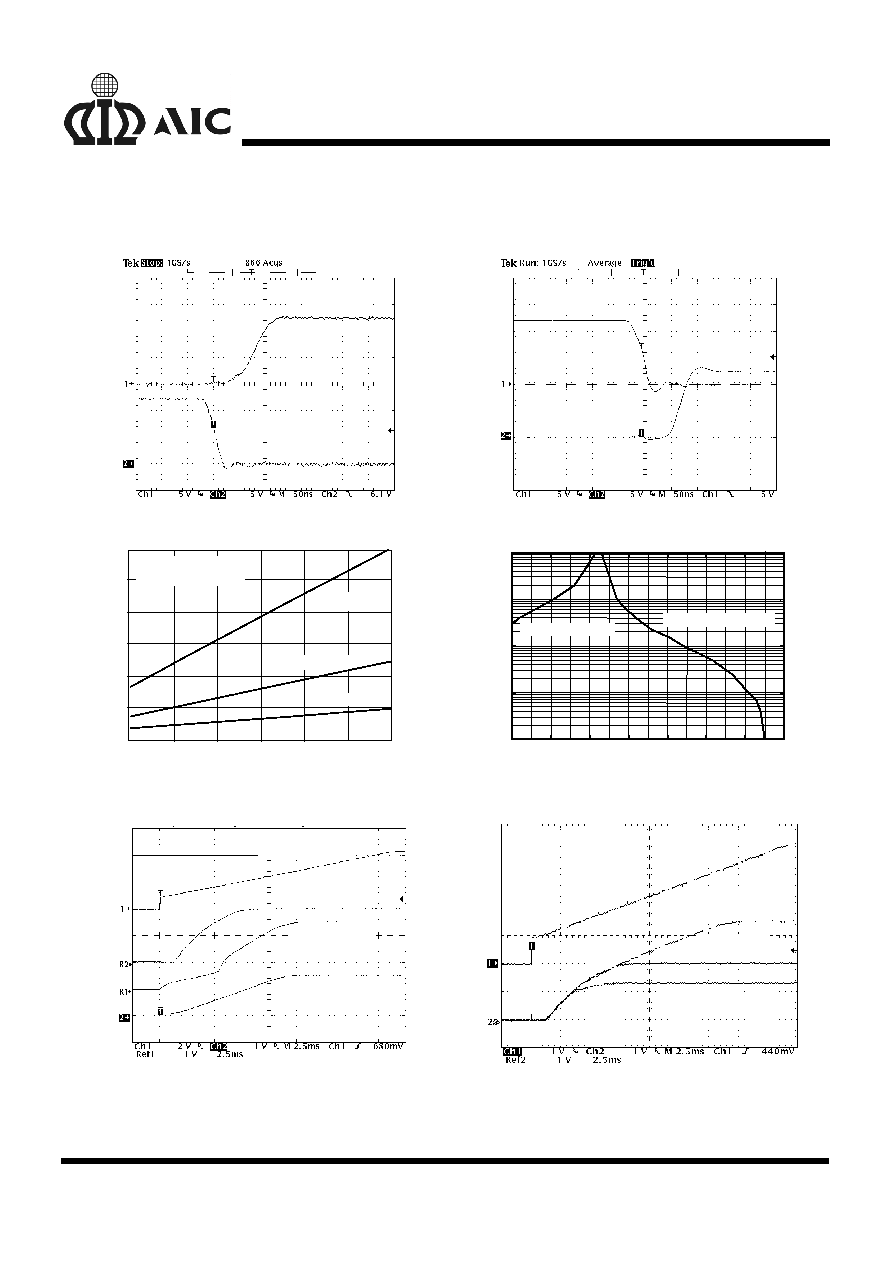

TYPICAL PERFORMANCE CHARACTERISTICS

U

GATE

L

GATE

U

GATE

L

GATE

FIG.1 The gate drive waveforms

I

CC

(mA)

Switching Frequency (KHz)

100

150

200

250

300

350

400

0

10

20

30

40

50

60

C

UGATE

=C

LGATE

=C

GATE

V

CC

=12V

C

GATE

=5000pF

C

GATE

=2000pF

C

GATE

=660pF

100

150

200

250

300

350

400

1

10

100

1000

10000

Resis

t

an

ce (

k

)

Switching Frequency (KHz)

R

T

Pull Down to GND

R

T

Pull Up to +12V

450

FIG. 2 Bias Supply Current VS. Frequency FIG. 3 R

T

Resistance VS. Frequency

SS (2V/div)

V

OUT3

(1V/div)

V

OUT2

(1V/div)

V

OUT

1

(1V/div)

PGOOD (5V/div)

VDAC=3.5V

VDAC=1.3V

VDAC=2V

SS

FIG.4 Soft Start Interval

with 3 Outputs and PGOOD FIG. 5 Soft Start Initiates PWM Output