ASAHIKASEI

[AK8813/14]

Rev.00

- 1 - 2004/Oct

AK8813/14

NTSC/PAL Digital Video Encoder

GENERAL DESCRIPTION

The AK8813/14 is low voltage, low power and small packaged Digital Video Encoder. It is suitable

for a STB or Digital TV. It converts ITU-R.BT601/656 standard 8- bit parallel data into analog

composite video signal, S-video in NTSC and PAL formats.

AK8813/14 supports Copy protection, Closed Captioning and Video Blanking ID(CGMS-A) and WSS.

These functions are controlled by high-speed I

2

C Bus interface.

FEATURES

∑ NTSC-M, PAL-B,D,G,H,I,M,N encoding.

∑ Simultaneous composite video signal and S-video signal outputs

∑ ITU-R BT.656 4:2:2 8-bit Parallel Input

- EAV Decoding

∑ Master/Slave Operation

- Digital Field Sync I/O

- Digital Vertical/Horizontal Sync I/O

∑ Y filtering 2 x over-sampling

∑ C filtering 4 x over-sampling

∑ Single 27MHz Clock (The polarity could be inverted by SYSINV pin)

∑ Triple 10-bit DACs

∑ I

2

C Bus Interface (400kHz)

∑ Closed Caption encoding (NTSC: line 21,284-SMPTE PAL: line 22,335-CCIR)

∑ Macrovision Copy Protection Rev. 7.1 * (only AK8814 )

∑ VBID, CGMS-A(EIAJ CPR-1024)

∑ WSS

∑ On-chip color bar generator

∑ Low power consumption

∑ 2.8V to 3.3V operation CMOS Monolithic

∑ 48pin LQFP Package / 57pin FBGA Package

(*Note) This device is protected by U.S. patent numbers 4,631,603, 4,577,216, and 4,819,098, and other

intellectual rights. The use of Macrovision's copy protection technology in the device must be authorized

by Macrovision and is intended for home and other limited pay-per -view use only, unless otherwise

authorized in written by Macrovision. Reverse engineering or disassembly is prohibited.

ASAHIKASEI

[AK8813/14]

Rev.00

- 4 - 2004/Oct

ORDERING GUIDE

AK8813VQ: LQFP48 Non-Macrovision (Pb Free)

AK8813VG: FBGA57 Non-Macrovision

AK8813VGP: FBGA57 Non-Macrovision (Pb Free)

AK8814VQ: LQFP48 Macrovision (Pb Free)

AK8814VG: FBGA57 Macrovision (Pb Free)

ASAHIKASEI

[AK8813/14]

Rev.00

- 6 - 2004/Oct

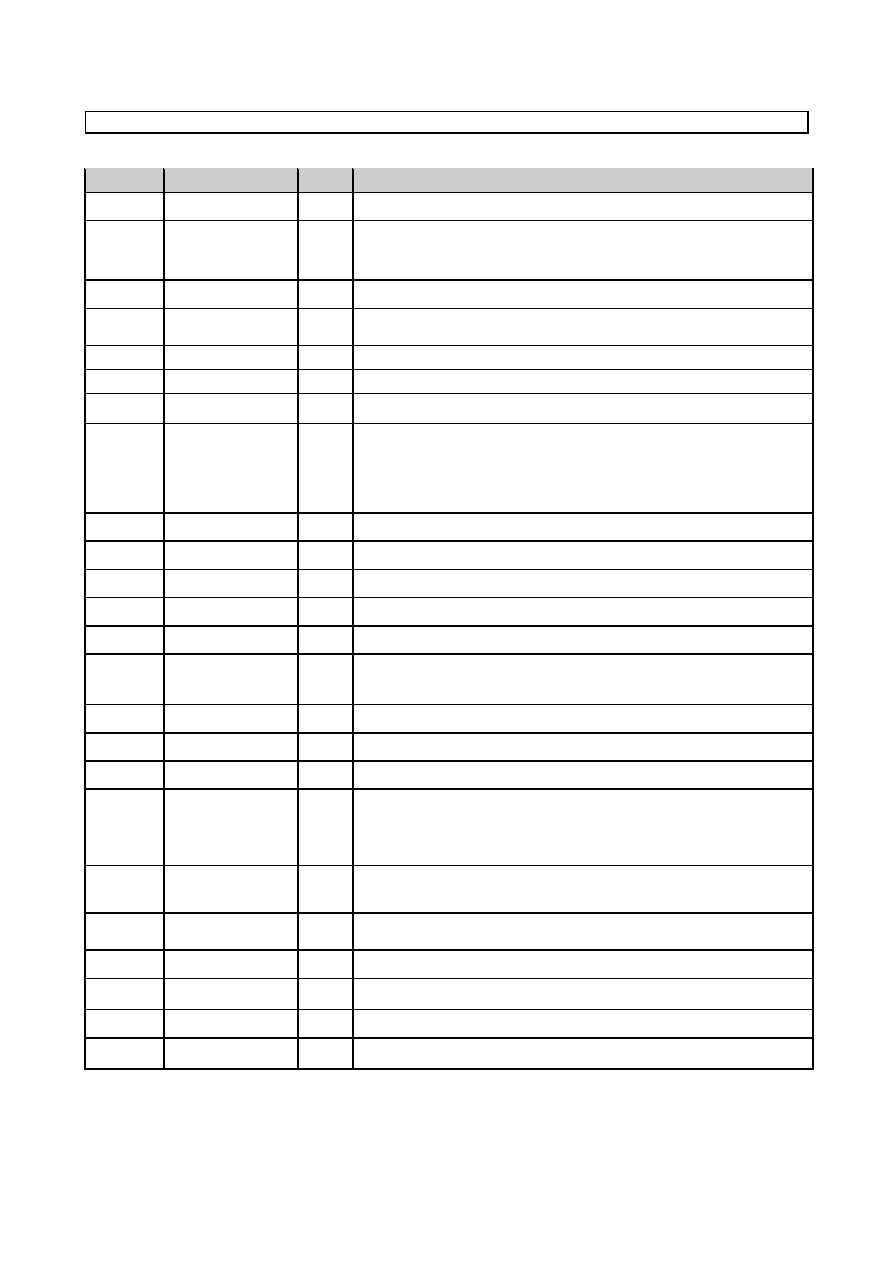

PIN/FUNCTION

48pin LQFP

No.

Pin Name

I/O

Description

1 UD9

I/O

Test pin. Open for normal operation

2-5,

8-11

D7 - D0

I

27MHz 8-Bit 4:2:2 multiplexed Y,Cb,Cr Data Input.

For Rec.656 format, AK8813/14 decodes EAV.

For non-Rec.656 format (without EAV), AK8813/14 operates in Master or

Slave mode.

12-13 TEST

I Test pin. Ground for normal operation

14 SELA

I

The slave address is set with this pin.

"L":40H "H":42H

15 SCL

I Serial interface clock

16

SDA I/O

Serial interface data

17 PD

I Power Down Pin. After returning from PD mode to normal operation,

RESET Sequence should be done to AK8813/14.

18 /RESET

I

After this pin becomes "L", AK8813/14 starts the internal initializing

sequence.

After initializing sequence, AK8813/14 is set NTSC mode, Rec.656

decoding mode. All DACs Off condition.

After power up, AK8813/14 must be initialized with this pin.

(27MHz Clock is necessary for reset sequence.)

20

Y

O

Output of Luminance Signal.

22

C

O

Output of the Chrominance signal

24

COMPOSITE

O

Output of Composite Video signal

27

VREFOUT

O

Output of the Internal Vref. Terminate with 0.1uF or more capacitor.

28

VREFIN

I

Input of the Reference Voltage

29 IREF

O

The currents flow this pin adjusts the full-scale output current of the DAC.

Connect this pin to Analog ground via a 6.8kohm resistor ( better than +/-

1% accuracy ).

32-39

UD0-UD7

I/O

Test pin. Open for normal operation

41 SYSCLK

I 27MHz Clock Input. The polarity could be inverted by SYSINV.

43

UD8

I/O

Test pin. Open for normal operation

45

FID

/VSYNC

I/O

Either of FID or VSYNC selected by the register.

Rec.656 decode mode :Output

Master mode : Output

Slave mode : Input

FID shows that "L" is odd field and "H" is even field.

46 HSYNC

I/O

Rec.656 decode mode : Output

Master mode : Output

Slave mode : Input

48 SYSINV

I

"L " : data is latched with rising edge.

"H" : data is latched with falling edge.

21,26

AVDD

P

Analog Power Supply

6,31,

42,44

DVDD P

Digital Power Supply

19,23,25

AVSS

G Analog

Ground

7,30,

40,47

DVSS G

Digital

Ground