| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AKD4383 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

ASAHI KASEI

[AK4383]

MS0090-E-00

2001/4

- 1 -

GENERAL DESCRIPTION

The AK4383 offers the perfect mix for cost and performance based audio systems. Using AKM's multi bit

architecture for its modulator the AK4383 delivers a wide dynamic range while preserving linearity for

improved THD+N performance. The AK4383 has full differential SCF outputs, removing the need for AC

coupling capacitors and increasing performance for systems with excessive clock jitter. The AK4383

accepts 192kHz PCM data and 1-Bit DSD data, ideal for a wide range of applications including DVD-

Audio and SACD. The AK4383 is offered in a space saving 20pin TSSOP package.

FEATURES

Sampling Rate Ranging from 8kHz to 192kHz

24-Bit 8 times FIR Digital Filter

On chip SCF

Digital de-emphasis for 32k, 44.1k and 48kHz sampling

Soft mute

Digital Attenuator (Linear 256 steps)

PCM I/F format: 24-Bit MSB justified, 24/20/16-Bit LSB justified or I

2

S

Master clock: 256fs, 384fs, 512fs or 768fs (PCM Normal Speed Mode)

128fs, 192fs, 256fs or 384fs (PCM Double Speed Mode)

128fs or 192fs (PCM Quad Speed Mode)

512fs or 768fs (DSD Mode)

THD+N: -94dB

Dynamic Range: 110dB

DSD Data Input Mode

High Tolerance to Clock Jitter

Power supply: 4.75 to 5.25V

Very Small Package: 20pin TSSOP (0.65mm pitch)

AK4382 Pin Compatible

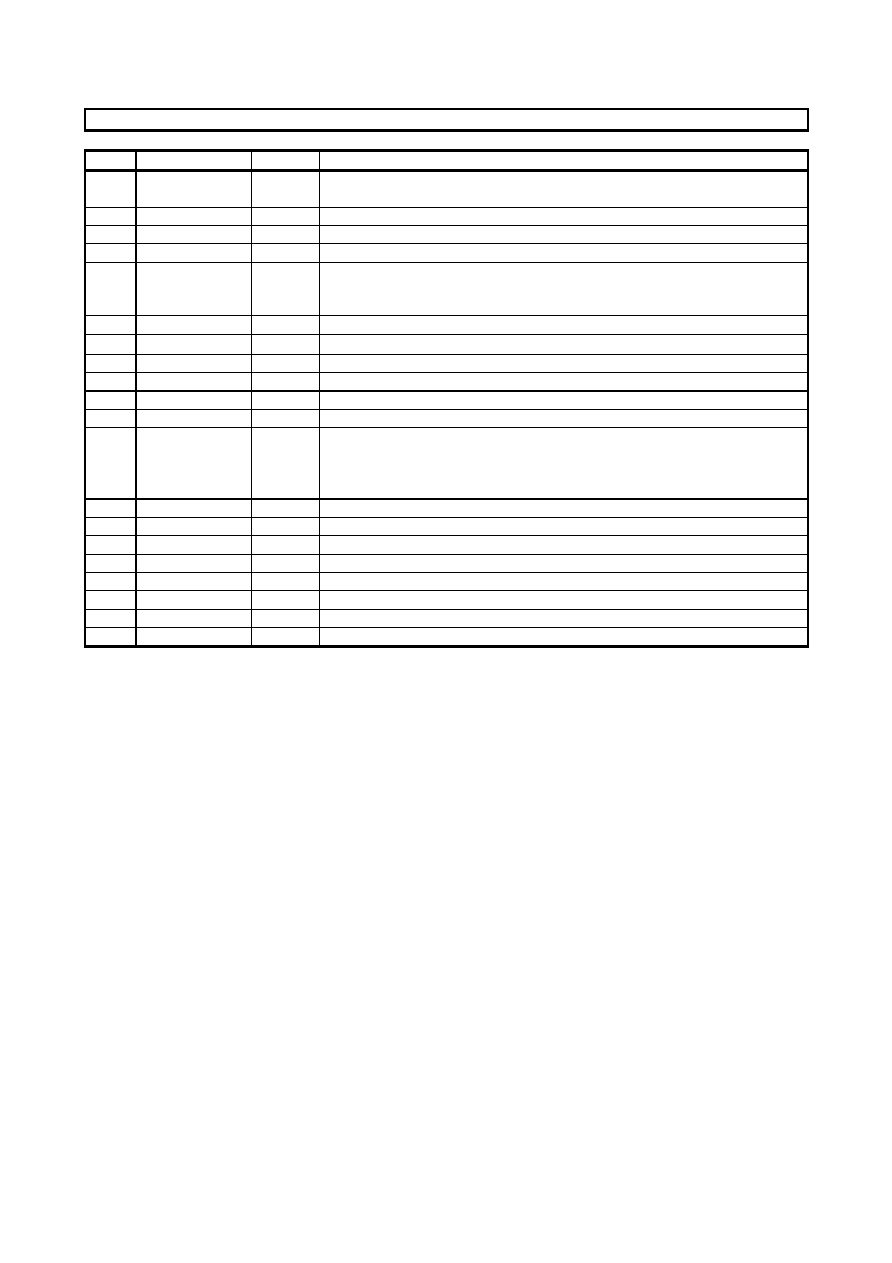

LRCK/DSDR

BICK/DCLK

SDTI/DSDL

PCM

Data

Interface

MCLK

PDN

S&H

Modulator

AOUTL+

8X

Interpolator

SCF

AOUTR+

SCF

VDD

VSS

De-emphasis

Control

µP

Interface

Clock

Divider

CSN

CCLK

CDTI

DZFR

S&H

Modulator

8X

Interpolator

AOUTL-

AOUTR-

DZFL

DSD

Data

Interface

DCLK

DSDL

DSDR

DSDM

192kHz 24-Bit 2ch

DAC with DSD input

AK4383

ASAHI KASEI

[AK4383]

MS0090-E-00

2001/4

- 2 -

Ordering Guide

AK4383VT

-40

+85

∞

C

20pin TSSOP (0.65mm pitch)

AKD4383

Evaluation Board for AK4383

Pin Layout

1

MCLK

LRCK/DSDR

BICK/DCLK

CSN

CCLK

CDTI

Top

View

2

3

4

5

6

7

8

DZFL

DZFR

VSS

VDD

AOUTL+

AOUTL-

AOUTR+

AOUTR-

20

19

18

17

16

15

14

13

PDN

SDTI/DSDL

DCLK

DSDL

9

10

DSDM

DSDR

12

11

ASAHI KASEI

[AK4383]

MS0090-E-00

2001/4

- 3 -

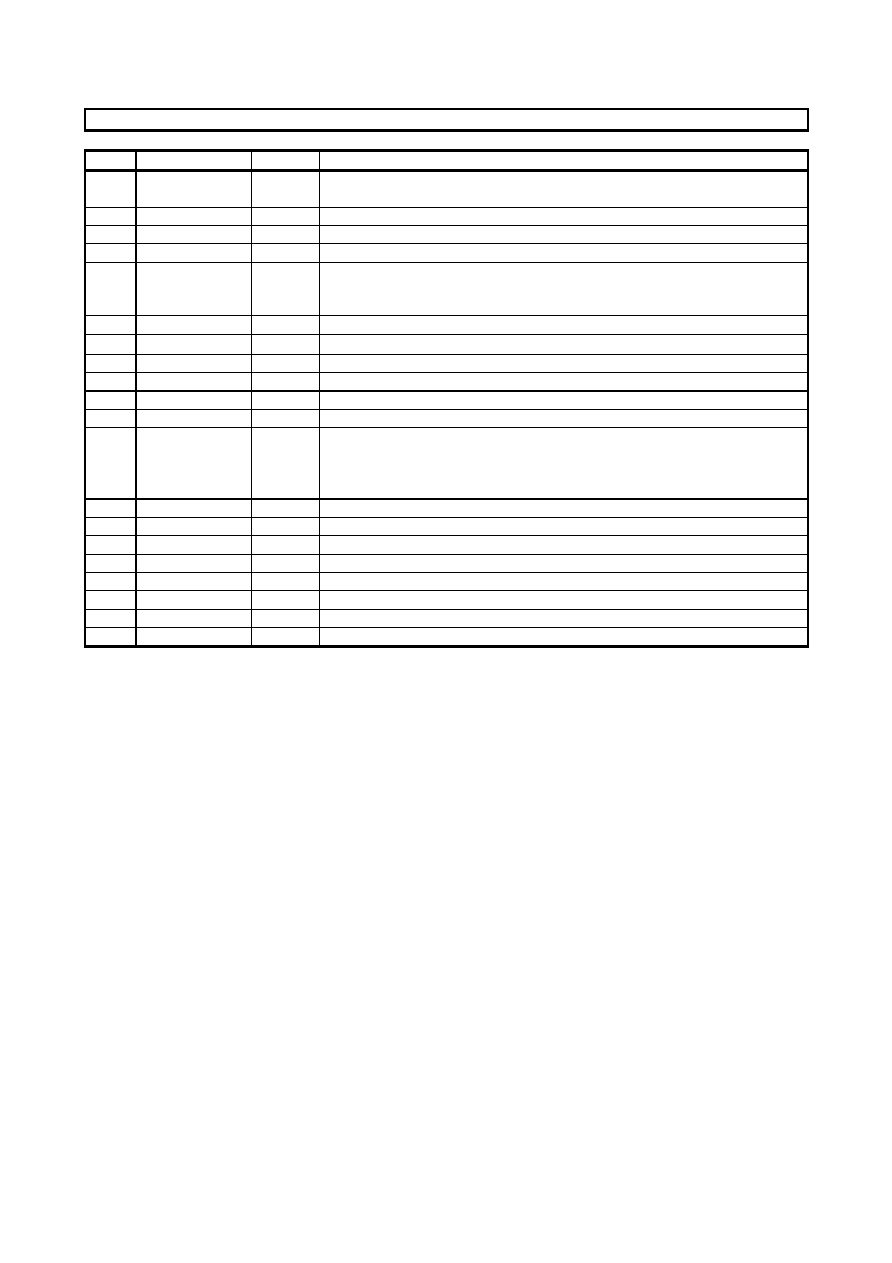

PIN/FUNCTION

No.

Pin Name

I/O

Function

1

MCLK

I

Master Clock Input Pin

An external TTL clock should be input on this pin.

2

BICK/DCLK

I

Audio Serial Data Clock Pin / DSD Clock Pin

3

SDTI/DSDL

I

Audio Serial Data Input Pin / DSD Lch Data Input Pin

4

LRCK/DSDR

I

L/R Clock Pin / DSD Rch Data Input Pin

5

PDN

I

Power-Down Mode Pin

When at "L", the AK4383 is in the power-down mode and is held in reset.

The AK4383 should always be reset upon power-up.

6

CSN

I

Chip Select Pin

7

CCLK

I

Control Data Input Pin

8

CDTI

I

Control Data Input Pin in serial mode

9

DCLK

I

DSD Clock Pin (Pull-down Pin)

10

DSDL

I

DSD Lch Data Input Pin (Pull-down Pin)

11

DSDR

I

DSD Rch Data Input Pin (Pull-down Pin)

12

DSDM

I

DSD Mode Enable Pin (Pull-down Pin)

"0": PCM data is input from Pin 2-4. And the mode can be switched between

PCM and DSD mode by register.

"1": DSD data is input from Pin 9-11.

13

AOUTR-

O

Rch Negative Analog Output Pin

14

AOUTR+

O

Rch Positive Analog Output Pin

15

AOUTL-

O

Lch Negative Analog Output Pin

16

AOUTL+

O

Lch Positive Analog Output Pin

17

VSS

-

Ground Pin

18

VDD

-

Power Supply Pin

19

DZFR

O

Rch Data Zero Input Detect Pin

20

DZFL

O

Lch Data Zero Input Detect Pin

Note: All input pins except pull-up pin should not be left floating.

ASAHI KASEI

[AK4383]

MS0090-E-00

2001/4

- 4 -

ABSOLUTE MAXIMUM RATINGS

(VSS=0V; Note 1)

Parameter

Symbol

min

max

Units

Power Supply

VDD

-0.3

6.0

V

Input Current (any pins except for supplies)

IIN

-

±

10

mA

Input Voltage

VIND

-0.3

VDD+0.3

V

Ambient Operating Temperature

Ta

-40

85

∞

C

Storage Temperature

Tstg

-65

150

∞

C

Note: 1. All voltages with respect to ground.

WARNING: Operation at or beyond these limits may results in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

RECOMMENDED OPERATING CONDITIONS

(VSS=0V; Note 1)

Parameter

Symbol

min

typ

max

Units

Power Supply

VDD

4.75

5.0

5.25

V

*AKM assumes no responsibility for the usage beyond the conditions in this datasheet.

ASAHI KASEI

[AK4383]

MS0090-E-00

2001/4

- 5 -

ANALOG CHARACTERISTICS

(Ta=25

∞

C; VDD=5.0V; fs=44.1kHz; BICK=64fs; Signal Frequency=1kHz; 24bit Input Data;

Measurement frequency=20Hz

20kHz; R

L

2k

; PCM Mode; unless otherwise specified)

Parameter

min

typ

max

Units

Resolution

24

Bits

Dynamic Characteristics (Note 3)

fs=44.1kHz

BW=20kHz

0dBFS

-60dBFS

-94

-48

-87

-

dB

dB

fs=96kHz

BW=40kHz

0dBFS

-60dBFS

-92

-45

-84

-

dB

dB

THD+N

fs=192kHz

BW=40kHz

0dBFS

-60dBFS

-92

-45

-

-

dB

dB

Dynamic Range (-60dBFS with A-weighted) (Note 4)

102

110

dB

S/N (A-weighted) (Note 5)

102

110

dB

Interchannel Isolation (1kHz)

90

110

dB

Interchannel Gain Mismatch

0.2

0.5

dB

DC Accuracy

Gain Drift

100

-

ppm/

∞

C

Output Voltage (Note 6)

±

2.3

±

2.5

±

2.7

Vpp

Load Resistance (Note 7)

2

k

Power Supplies

Power Supply Current (VDD)

Normal Operation (PDN = "H", fs

96kHz)

Normal Operation (PDN = "H", fs=192kHz)

Power-Down Mode (PDN = "L") (Note 8)

20

25

10

34

42

100

mA

mA

µA

Notes: 3. Measured by Audio Precision (System Two). Refer to the evaluation board manual.

4. 100dB at 16bit data.

5. S/N does not depend on input bit length.

6. Full-scale voltage (0dB). Output voltage scales with the voltage of VREF,

AOUT (typ.@0dB)=(AOUT+)-(AOUT-)=

±

2.5Vpp ◊ VREF/5.

7. For AC-load. 4k

for DC-load.

8. All digital inputs including clock pins (MCLK, BICK and LRCK) are held VDD or VSS.