| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 3964 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

3964

DUAL FULL-BRIDGE

PWM MOTOR DRIVER

DUAL FULL-BRIDGE PWM MOTOR DRIVER

Data Sheet

29319.28*

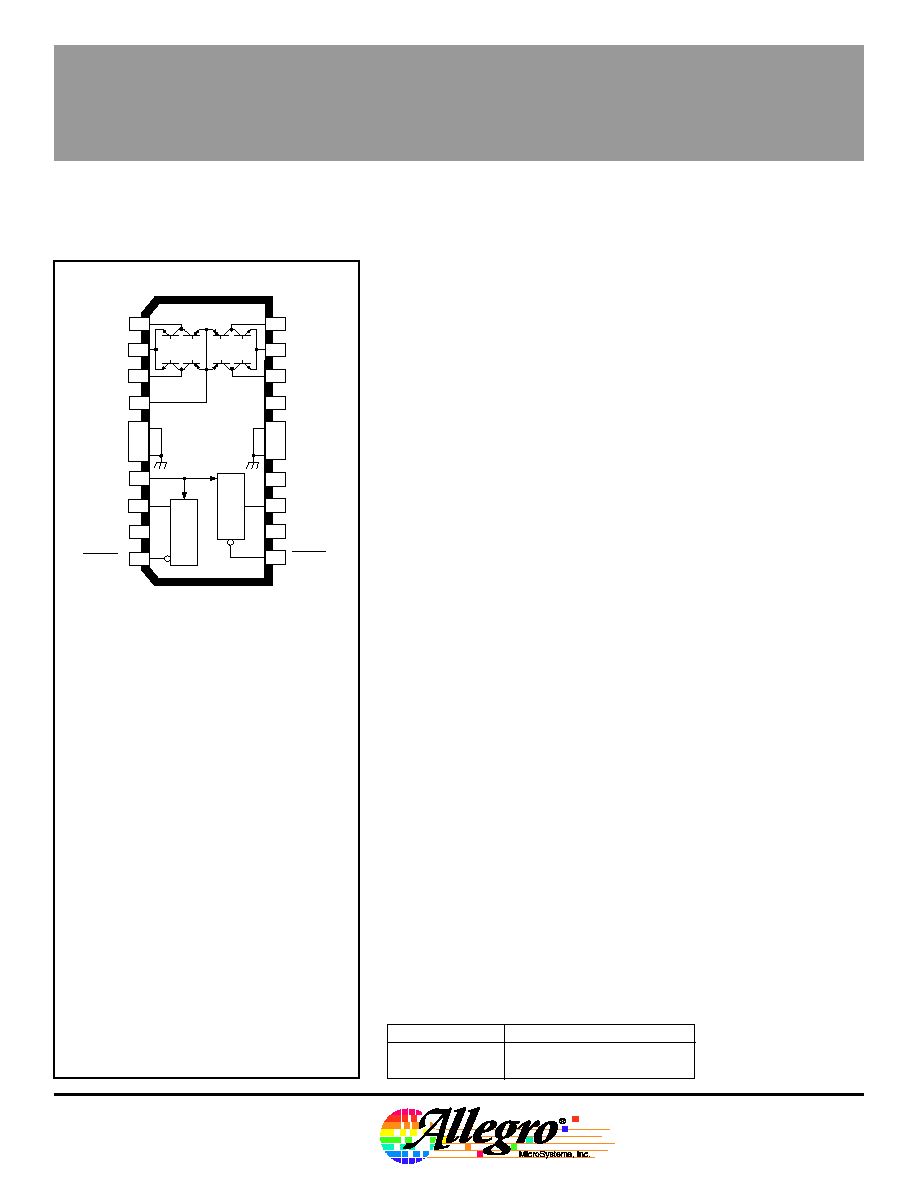

A3964SLB

Designed for pulse-width modulated (PWM) current control of

bipolar stepper motors, the A3964SB and A3964SLB are capable of

continuous output currents to

±

800 mA and operating voltages to 30 V.

Internal fixed off-time PWM current-control circuitry can be used to

regulate the maximum load current to a desired value. An internal

precision voltage reference is provided to improve motor peak-current

control accuracy. The peak load current limit is set by the user's

selection of an external resistor divider and current-sensing resistors.

The fixed off-time pulse duration is set by user-selected external

RC timing networks. The capacitor in the RC timing network also

determines a user-selectable blanking window that prevents false

triggering of the PWM current control circuitry during switching transi-

tions. This eliminates the need for two external RC filter networks on

the current-sensing comparator inputs.

For each bridge the PHASE input controls load current polarity by

selecting the appropriate source and sink driver pair. For each bridge

the ENABLE input, when held high, disables the output drivers. Spe-

cial power-up sequencing is not required. Internal circuit protection

includes thermal shutdown with hysteresis, transient-suppression

diodes, and crossover-current protection.

The A3964SB is supplied in a 24-pin plastic DIP with copper heat

sink tabs; A3964SLB is supplied in a 20-lead plastic SOIC with copper

heat sink tabs. The power tabs are at ground potential and need no

electrical isolation.

FEATURES

s

±

800 mA Continuous Output Current Rating

s

30 V Output Voltage Rating

s

Internal PWM Current Control, Saturated Sink Drivers

s

Internally Generated, Precision 2.5 V Reference

s

Internal Transient-Suppression Diodes

s

Internal Thermal-Shutdown Circuitry

s

Crossover-Current Protection, UVLO Protection

3964

1

V

BB

2

1

2

3

4

5

6

7

9

20

19

18

17

16

15

14

13

12

11

10

9

8

2

1

V

CC

PWM 1

PWM 2

GROUND

GROUND

GROUND

GROUND

PHASE

2

V

REF(OUT)

2

RC

1

RC

V

REF(IN)

PHASE

1

2B

OUT

SENSE

2

2A

OUT

1A

OUT

SENSE

1

1B

OUT

LOAD

SUPPLY

LOGIC

SUPPLY

Dwg. PP-047-1

ENABLE

1

ENABLE

2

Always order by complete part number:

Part Number

Package

A3964SB

24-Pin DIP

A3964SLB

20-Lead Wide-Body SOIC

ABSOLUTE MAXIMUM RATINGS

Load Supply Voltage, V

BB

. . . . . . . . . 33 V

Output Current, I

OUT

(10

µ

s) . . . . . .

±

1.0 A*

(continuous) . . . . . . . . . . . . .

±

800 mA*

Logic Supply Voltage, V

CC

. . . . . . . . . 7.0 V

Logic Input Voltage Range,

V

IN

. . . . . . . . . . . -0.3 V to V

CC

+ 0.3 V

Sense Voltage, V

S

. . . . . . . . . . . . . . . 1.0 V

Reference Output Current,

I

REF(OUT)

. . . . . . . . . . . . . . . . . . 1.0 mA

Package Power Dissipation,

P

D

. . . . . . . . . . . . . . . . . . . . See Graph

Operating Temperature Range,

T

A

. . . . . . . . . . . . . . . . -20∞C to +85∞C

Junction Temperature, T

J

. . . . . . . +150∞C

Storage Temperature Range,

T

S

. . . . . . . . . . . . . . . -55∞C to +150∞C

* Output current rating may be limited by duty cycle,

ambient temperature, and heat sinking. Under any set

of conditions, do not exceed the specified current rating

or a junction temperature of 150∞C.

Fault conditions that produce excessive junction

temperature will activate the device's thermal shutdown

circuitry. These conditions can be tolerated but should

be avoided.

3964

DUAL FULL-BRIDGE

PWM MOTOR DRIVER

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

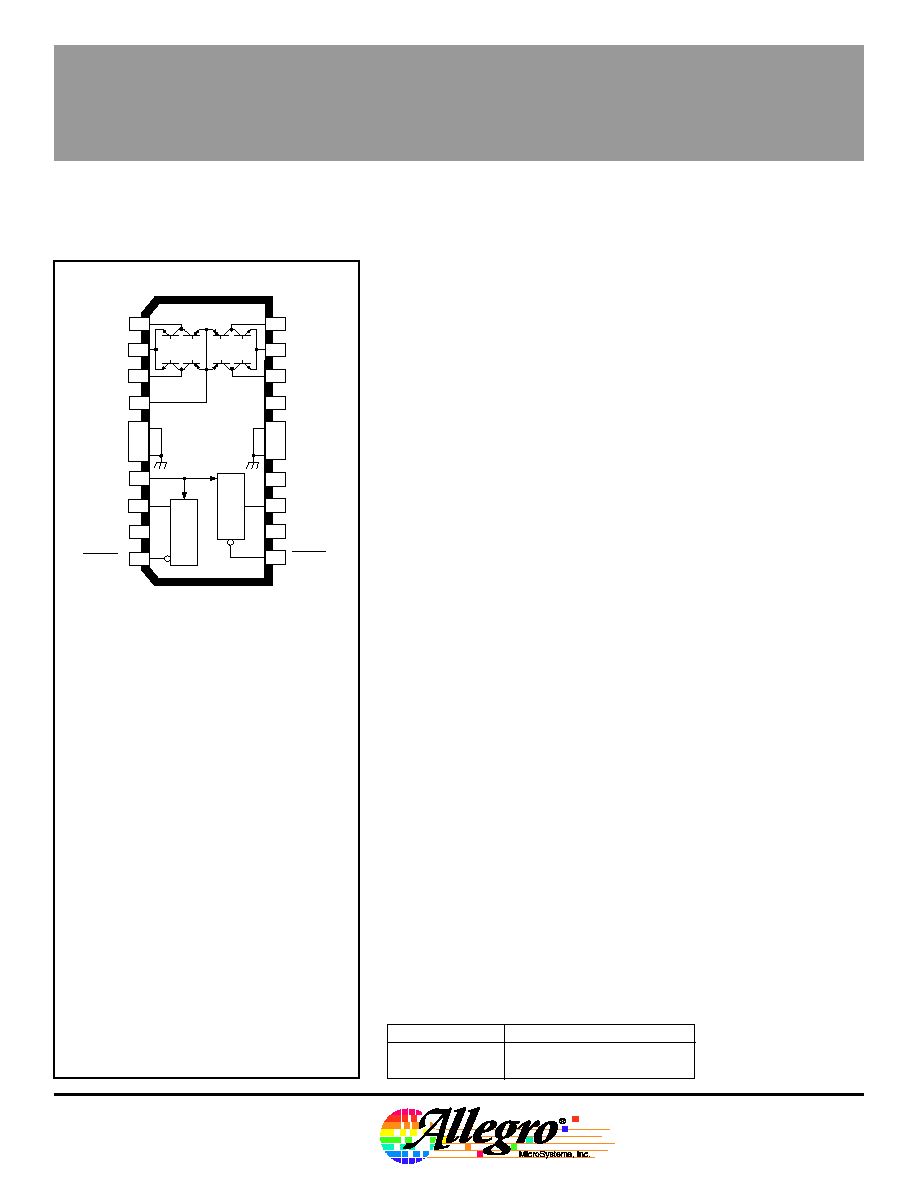

A3964SB

1

2

3

4

5

6

7

8

9

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

2

1

V

CC

PWM 1

PWM 2

1

V

BB

2

GROUND

GROUND

GROUND

GROUND

PHASE

2

V

REF(OUT)

2

RC

2B

OUT

SENSE

2

2A

OUT

LOGIC

SUPPLY

Dwg. PP-005-2

NO

CONNECT.

NO

CONNECT.

ENABLE

2

1

RC

V

REF(IN)

PHASE

1

1A

OUT

SENSE

1

1B

OUT

LOAD

SUPPLY

NO

CONNECT.

NO

CONNECT.

ENABLE

1

NC

NC

NC

NC

50

75

100

125

150

5

1

0

ALLOWABLE PACKAGE POWER DISSIPATION IN WATTS

TEMPERATURE IN

∞

C

4

3

2

25

Dwg. GP-049-4

R = 6.0

∞

C/W

JT

SUFFIX 'B', R = 40

∞

C/W

JA

SUFFIX 'LB', R = 60

∞

C/W

JA

2.5 V

REFERENCE

14

5

2

R S

19

R S

V

REF(IN)

V

CC

OUT

1A

OUT

1B

OUT

2A

OUT

2B

SENSE

1

SENSE

2

LOGIC

SUPPLY

LOAD

SUPPLY

ENABLE1

ENABLE2

RC

1

RC

2

PHASE 1

PHASE 2

V

BB

1

≠

+

ONE SHOT

SOURCE

DISABLE

≠

+

SOURCE

DISABLE

2

ONE SHOT

PWM 1

PWM 2

UVLO

& TSD

8

10

9

3

1

4

18

20

7

12

11

13

17

R T

R T

C T

C T

Dwg. FP-033-1

REF

OUT

REF

IN

6 15 16

R A

R B

FUNCTIONAL BLOCK DIAGRAM

(A3964SLB pinning shown)

Copyright © 1997 Allegro MicroSystems, Inc.

3964

DUAL FULL-BRIDGE

PWM MOTOR DRIVER

NOTES: 1. Typical Data is for design information only.

2. Negative current is defined as coming out of (sourcing) the specified device terminal.

TRUTH TABLE

ENABLE

PHASE

OUT

A

OUT

B

H

X

Off

Off

L

H

H

L

L

L

L

H

ELECTRICAL CHARACTERISTICS at T

A

= +25

∞

C, V

BB

= 30 V, V

CC

= 4.75 V to 5.25 V,

V

S

= 0 V, 30 k

& 1000 pF RC to Ground (unless noted otherwise)

Limits

Characteristic

Symbol

Test Conditions

Min.

Typ.

Max.

Units

Load Supply Voltage Range

V

BB

Operating, I

OUT

=

±

800 mA, L = 3 mH

5.0

--

30

V

Output Sustaining Voltage

V

CE(sus)

I

OUT

=

±

800 mA, L = 3 mH, V

BB

= 33 V

33

--

--

V

Output Leakage Current

I

CEX

V

OUT

= V

BB

= 33 V

--

<1.0

50

µ

A

V

OUT

= 0 V, V

BB

= 33 V

--

<1.0

-50

µ

A

Output Saturation Voltage

V

CE(SAT)

Source Driver, I

OUT

= -500 mA

--

1.0

1.2

V

Source Driver, I

OUT

= -750 mA

--

1.1

1.5

V

Source Driver, I

OUT

= -800 mA

--

--

1.7

V

Sink Driver, I

OUT

= +500 mA

--

0.3

0.6

V

Sink Driver, I

OUT

= +750 mA

--

0.5

1.2

V

Sink Driver, I

OUT

= +800 mA

--

--

1.5

V

Clamp Diode Forward Voltage

V

F

I

F

= 500 mA

--

1.1

1.4

V

(Sink or Source)

I

F

= 750 mA

--

1.3

1.6

V

I

F

= 800 mA

--

--

1.7

V

Motor Supply Current

I

BB(ON)

V

ENABLE

= 0.8 V

--

2.0

4.0

mA

(No Load)

I

BB(OFF)

V

ENABLE

= 2.4 V

--

0

500

µ

A

Output Drivers

X = Irrelevant

3964

DUAL FULL-BRIDGE

PWM MOTOR DRIVER

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Logic Supply Voltage Range

V

CC

Operating

4.75

--

5.25

V

Logic Input Voltage

V

IN(1)

2.4

--

--

V

V

IN(0)

--

--

0.8

V

Logic Input Current

I

IN(1)

V

IN

= 2.4 V

--

<1.0

20

µ

A

I

IN(0)

V

IN

= 0.8 V

--

<-2.0

-200

µ

A

Reference Output Voltage

V

REF(OUT)

V

CC

= 5.0 V, I

REF(OUT)

= 90 to 900

µ

A

2.45

2.50

2.55

V

Reference Output Current

I

REF(OUT)

3 k

R

D

= R

A

+ R

B

15 k

150

--

900

µ

A

Ref. Input Offset Current

I

OS

V

REF(IN)

= 1 V

-2.5

0

1.0

µ

A

Comparator Input Offset Volt.

V

IO

V

REF(IN)

= 0 V

-6.0

0

6.0

mV

Comparator Input Volt. Range

V

REF

Operating

-0.3

--

1.0

V

PWM RC Fixed Off-time

t

OFF RC

C

T

= 1000 pF, R

T

= 30 k

27

30

33

µ

s

PWM Propagation Delay Time

t

PWM

Comparator Trip to Source OFF

--

1.2

2.0

µ

s

PWM Minimum On Time

t

ON(min)

C

T

= 1000 pF, R

T

15 k

, V

CC

= 5 V

--

2.5

3.6

µ

s

Propagation Delay Times

t

pd

I

OUT

=

±

800 mA, 50% to 90%:

ENABLE ON to Source ON

--

3.2

--

µ

s

ENABLE OFF to Source OFF

--

1.2

--

µ

s

ENABLE ON to Sink ON

--

3.2

--

µ

s

ENABLE OFF to Sink OFF

--

0.7

--

µ

s

PHASE Change to Sink ON

--

3.2

--

µ

s

PHASE Change to Source ON

--

3.2

--

µ

s

PHASE Change to Sink OFF

--

0.7

--

µ

s

PHASE Change to Source OFF

--

1.2

--

µ

s

Thermal Shutdown Temp.

T

J

--

165

--

∞

C

Thermal Shutdown Hysteresis

T

J

--

15

--

∞

C

UVLO Disable Threshold

Decreasing V

CC

4.20

4.40

4.65

V

UVLO Hysteresis

UVLO Enable Volt. - UVLO Disable Volt.

0.075

0.125

0.175

V

UVLO Enable Threshold

Increasing V

CC

4.375

4.525

4.725

V

Logic Supply Current

I

CC(ON)

V

ENABLE 1

= V

ENABLE 2

= 0.8 V

--

60

85

mA

I

CC(OFF)

V

ENABLE 1

= V

ENABLE 2

= 2.4 V

--

13

17

mA

Logic Supply Current

I

CC(ON)

V

ENABLE 1

=

V

ENABLE 2

= 0.8 V

--

0.18

--

mA/

∞

C

Temperature Coefficient

Limits

Characteristic

Symbol

Test Conditions

Min.

Typ.

Max.

Units

ELECTRICAL CHARACTERISTICS at T

A

= +25

∞

C, V

BB

= 30 V, V

CC

= 4.75 V to 5.25 V, V

SENSE

= 0

V, 30 k

& 1000 pF RC to Ground (unless noted otherwise) (cont.)

NOTES: 1. Typical Data is for design information only.

2. Negative current is defined as coming out of (sourcing) the specified device terminal.

Control Logic

3964

DUAL FULL-BRIDGE

PWM MOTOR DRIVER

[(V

BB

≠ V

SAT(SOURCE+SINK)

) ∑ t

ON(min)

max] ≠ (1.05 (V

SAT(SINK)

+ V

F

) ∑ t

OFF

)

1.05 (t

ON(min)

max + t

OFF

) ∑ R

LOAD

I

AVG

FUNCTIONAL DESCRIPTION

Internal PWM Current Control. The A3964SB and

A3964SLB contain a fixed off-time pulse-width modulated

(PWM) current-control circuit that can be used to limit the

load current to a desired value. The peak value of the

current limiting (I

TRIP

) is set by the selection of an external

current-sensing resistor (R

S

) and reference input voltage

(V

REF(IN)

). The internal circuitry compares the voltage

across the external sense resistor to the voltage on the

reference input terminal (V

REF(IN)

) resulting in a

transconductance function approximated by:

The reference input voltage is typically set with a

resistor divider from V

REF(OUT)

. To ensure proper operation

of the voltage reference, the resistor divider should have

an impedance of 3 k

to 15 k

(R

D

= R

A

+R

B

). Within this

range, a low impedance will minimize the effect of the REF

IN input offset current.

The current-control circuitry limits the load current as

follows: when the load current reaches I

TRIP

, the compara-

tor resets a latch that turns off the selected source driver.

The load inductance causes the current to recirculate

through the sink driver and flyback diode.

For each bridge, the user selects an external resistor

(R

T

) and capacitor (C

T

) to determine the time period

(t

OFF

= R

T

C

T

) during which the source driver remains

disabled (see "RC Fixed Off-time" below). The range of

recommended values for C

T

and R

T

are 1000 pF to 1500

pF and 15 k

to 100 k

respectively. For optimal load

current regulation, C

T

is normally set to 1000 pF (see

"Load Current Regulation" below). At the end of the RC

interval, the source driver is enabled allowing the load

current to increase again. The PWM cycle repeats,

maintaining the peak load current at the desired value.

RC Blanking. In addition to determining the fixed off-time

of the PWM control circuit, the C

T

component sets the

comparator blanking time. This function blanks the output

of the comparator when the outputs are switched by the

internal current-control circuitry (or by the PHASE or

ENABLE inputs). The comparator output is blanked to

I

TRIP

V

REF(IN)

R

S

prevent false over-current detections due to reverse-

recovery currents of the clamp diodes, and/or switching

transients related to distributed capacitance in the load.

During internal PWM operation, at the end of the t

OFF

time, the comparator's output is blanked and C

T

begins to

be charged from approximately 1.1 volts by an internal

current source of approximately 1 mA. The comparator

output remains blanked until the voltage on C

T

reaches

approximately 3 volts.

When a transition of the PHASE input occurs, C

T

is discharged to near ground during the crossover delay

time (the crossover delay time is present to prevent

simultaneous conduction of the source and sink drivers).

After the crossover delay, C

T

is charged by an internal

current source of approximately 1 mA. The comparator

output remains blanked until the voltage on C

T

reaches

approximately 3 volts.

When the device is disabled, via the ENABLE input,

C

T

is discharged to near ground. When the device is

re-enabled, C

T

is charged by an internal current source of

approximately 1 mA. The comparator output remains

blanked until the voltage on C

T

reaches approximately

3 volts.

The minimum recommended value for C

T

is

1000 pF. This value ensures that the blanking time is

sufficient to avoid false trips of the comparator under

normal operating conditions. For optimal regulation of the

load current, the above value for C

T

is recommended and

the value of R

T

can be sized to determine t

OFF

. For more

information regarding load current regulation, see below.

Load Current Regulation. Because the device operates

in a slow current-decay mode (2-quadrant PWM mode),

there is a limit to the lowest level that the PWM current

control circuitry can regulate load current. The limitation is

due to the minimum PWM duty cycle, which is a function of

the user-selected value of t

OFF

and the minimum on-time

pulse t

ON(min)

max that occurs each time the PWM latch is

reset. If the motor is not rotating, as in the case of a

stepper motor in hold/detent mode, a brush dc motor when

stalled or at startup, the worst case value of current

regulation can be approximated by: