Absolute Maximum Ratings

Load Supply Voltage, V

BB

. . . . . . . . . . . . 15 V

Output Current

1

, I

OUT . . . . . . . . . . . . . . . . . . . . .

±1.4 A

Peak Output Current (Brake)

2

, I

OUT(BRK)

. ±3.0 A

Period

2

for I

OUT(BRK)

to fall from

±3.0 A to ±1.4 A . . . . . . . . . . . . . . . 800 ms

Logic Supply Voltage, V

DD

. . . . . . . . . . . 7.0 V

Logic Input Voltage Range, V

IN

(continuous) . . . . . . -0.3 V to V

DD

+ 0.3 V

(t

w

<30 ns) . . . . . . . -1.0 V to V

DD

+ 1.0 V

Package Power Dissipation, P

D

. . See Graph

Operating Temperature, T

A

. . . -20∞C to +85∞C

Junction Temperature

3

, T

J

. . . . . . . . . +150∞C

Storage Temperature,T

S

. . . . -55∞C to +150∞C

1

Output current rating may be restricted to a value

determined by system concerns and factors. These

include: system duty cycle and timing, ambient

temperature, and use of any heatsinking and/or forced

cooling. For reliable operation, the specified maximum

junction temperature should not be exceeded.

2

Peak output current is a transient condition that

occurs during braking when the motor acts as a

generator. The 3 A level is based on the maximum

peak of a sine wave that is damped. The maximum

period between the initial brake being applied and the

current through the drivers falling to 1.4 A should not

exceed 800 ms. See Braking section for more

information.

3

Fault conditions that produce excessive junction

temperature will activate device thermal shutdown

circuitry. These conditions can be tolerated, but should

be avoided.

Data Sheet

26301.5B

The A8904SLB and A8904SLP are three-phase brushless dc motor

controller/drivers designed for applications where accurate control of high-

speed motors is required. The three half-bridge outputs are low on-resistance

n-channel DMOS devices capable of driving up to 1.2 A. The A8904 provides

complete, reliable, self-contained back-EMF sensing, motor startup and

running algorithms. A programmable digital frequency-locked loop speed

control circuit together with the linear current control circuitry provides

precise motor speed regulation.

A serial port allows the user to program various features and modes of

operation, such as the speed control parameters, startup current limit, sleep

mode, direction, and diagnostic modes.

The A8904 is fabricated in Allegro's BCD (Bipolar CMOS DMOS)

process, an advanced mixed-signal technology that combines bipolar, analog

and digital CMOS, and DMOS power devices. The A8904SLB is provided in

a 24-lead wide-body SOIC batwing package. The A8904SLP is provided in a

thin (<1.2 mm), 28-lead SSOP package with an exposed thermal pad. Each

package type is available in a lead-free version (100% matte tin leadframe).

Features

Pin-for-pin replacement for A8902CLBA

Startup commutation circuitry

Sensorless commutation circuitry

Option of external sector data tachometer signal

Option of external speed control

Oscillator operation up to 20 MHz

Programmable overcurrent limit

Transconductance gain options: 500 mA/V or 250 mA/V

Programmable watchdog timer

Directional control

Serial Port Interface

TTL-compatible inputs

System diagnostics data out ported in real time

Dynamic braking through serial port or external terminal

3-PHASE BRUSHLESS DC MOTOR

CONTROLLER/DRIVER WITH BACK-EMF SENSING

8904

A8904SLB

(SOIC)

Always order by complete part number:

Part Number

Package

A8904SLB

24-pin batwing SOIC

A8904SLB-T

24-pin batwing SOIC; Lead-free

A8904SLP

28-pin SSOP with Exposed Thermal Pad

A8904SLP-T

24-pin SSOP with Exposed Thermal Pad; Lead-free

8904

3-PHASE BRUSHLESS DC

MOTOR CONTROLLER/DRIVER

www.allegromicro.com

5

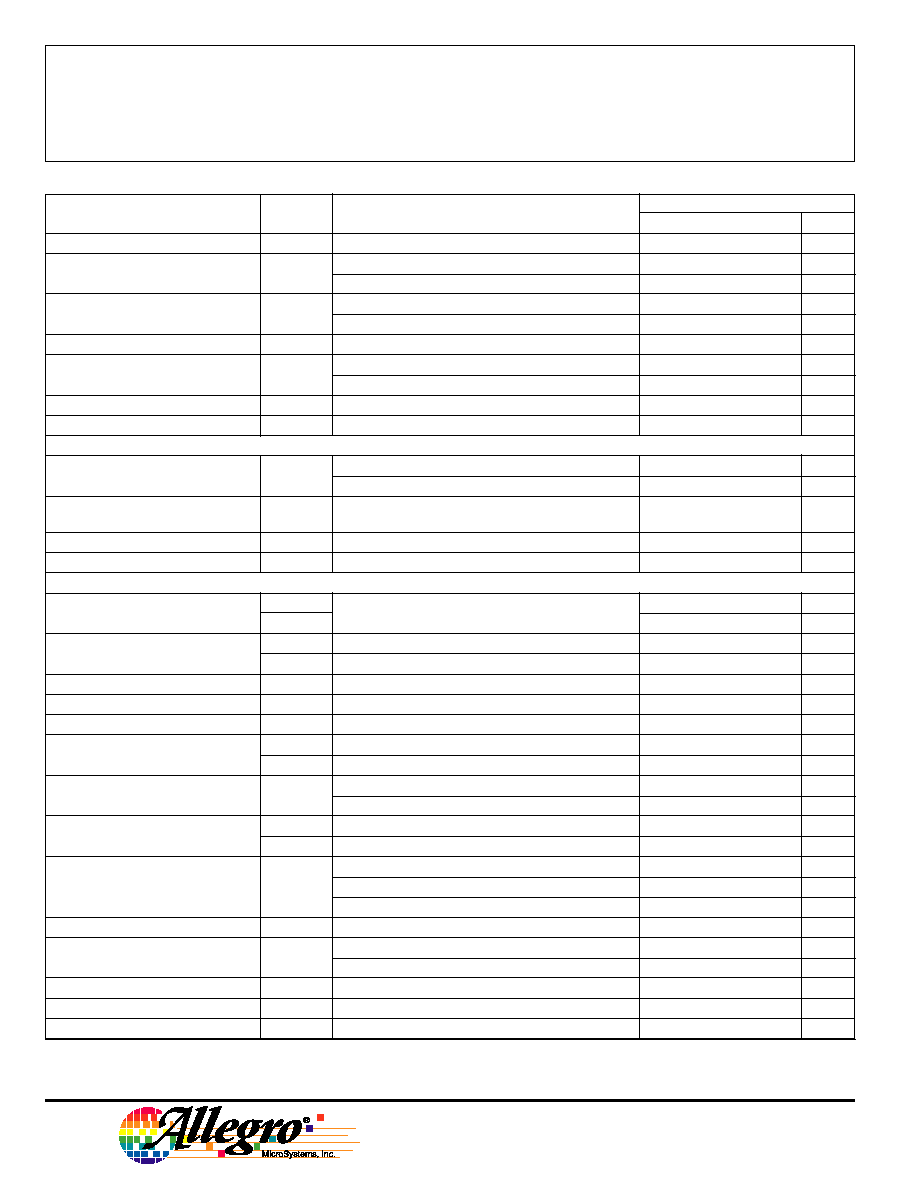

Limits

Characteristic

Symbol

Test Conditions

Min.

Typ.

Max.

Units

C

WD

Current

I

CWD

Charging, D26 = 0, D27 = 0

-9.0

-10

-11

µA

Charging, D26 = 0, D27 =1

-18

-20

-22

µA

Charging, D26 = 1 D27 = 0

-27

-30

-33

µA

Charging, D26 = 1, D27 =1

-36

-40

-44

µA

C

WD

Threshold Voltage

V

TL

0.22

0.25

0.28

V

V

TH

2.25

2.5

2.75

V

Max. FLL Oscillator Frequency

f

OSC

20*

--

--

MHz

Oscillator High Duration

ton

20

--

--

ns

Oscillator Low Duration

toff

20

--

--

ns

Maximum Output Current

I

OUT

(MAX)

D3 = 0, D4 = 0, D28 = 0

1.0

1.2

1.4

A

D3 = 0, D4 = 1, D28 = 0

0.9

1.0

1.1

A

D3 = 1, D4 = 0, D28 = 0

500

600

700

mA

D3 = 1, D4 = 1, D28 = 0

--

250

--

mA

D3 = 0, D4 = 0, D28 = 1

500

600

700

mA

D3 = 0, D4 = 1, D28 = 1

415

500

585

mA

D3 = 1, D4 = 0, D28 = 1

--

300

--

mA

D3 = 1, D4 = 1, D28 = 1

--

125

--

mA

Transconductance Gain

g

m

D28 = 1

210

250

290

mA/V

D28 = 0

420

500

580

mA/V

Centertap Resistors

R

CT

5.0

10

13

k

Back-EMF Threshold with respect

--

5.0

20

37

mV

to V

CTAP

at FCOM transition

-5.0

-20

-37

mV

ELECTRICAL CHARACTERISTICS continued

Negative current is defined as coming out of (sourcing) the specified device terminal.

* Operation at an oscillator frequency greater than the specified minimum value is possible but not waranteed.