| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: DSF10K | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- FLEX 10K Embedded Programmable Logic Family Data Sheet

Altera Corporation

1

FLEX 10K

Embedded

Programmable Logic Family

June 1999, ver. 4.01

Data Sheet

A-DS-F10K-04.01

Æ

Includes

FLEX 10KA

Features...

s

The industry's first embedded programmable logic device (PLD)

family, providing System-on-a-Programmable-Chip

TM

integration

≠

Embedded array for implementing megafunctions, such as

efficient memory and specialized logic functions

≠

Logic array for general logic functions

s

High density

≠

10,000 to 250,000 typical gates (see

Tables 1

and

2

)

≠

Up to 40,960 RAM bits; 2,048 bits per embedded array block

(EAB), all of which can be used without reducing logic capacity

s

System-level features

≠

MultiVolt

TM

I/O interface support

≠

5.0-V tolerant input pins in FLEX

Æ

10KA devices

≠

Low power consumption (typical specification less than 0.5 mA

in standby mode for most devices)

≠

FLEX 10K and FLEX 10KA devices support peripheral

component interconnect Special Interest Group (PCI SIG)

PCI

Local Bus Specification, Revision 2.2

≠

FLEX 10KA devices include pull-up clamping diode, selectable

on a pin-by-pin basis for 3.3-V PCI compliance

≠

Select FLEX 10KA devices support 5.0-V PCI buses with eight or

fewer loads

≠

Built-in Joint Test Action Group (JTAG) boundary-scan test

(BST) circuitry compliant with IEEE Std. 1149.1-1990, available

without consuming any device logic

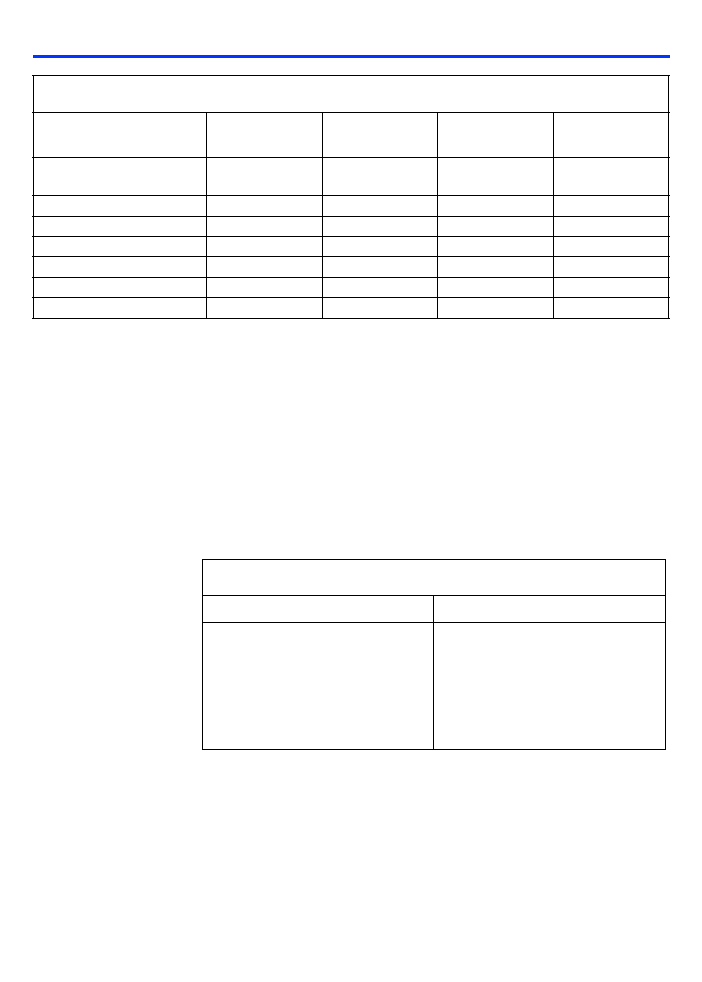

Table 1. FLEX 10K Device Features

Feature

EPF10K10

EPF10K10A

EPF10K20

EPF10K30

EPF10K30A

EPF10K40

EPF10K50

EPF10K50V

Typical gates (logic and RAM)

(1)

10,000

20,000

30,000

40,000

50,000

Maximum system gates

31,000

63,000

69,000

93,000

116,000

Logic elements (LEs)

576

1,152

1,728

2,304

2,880

Logic array blocks (LABs)

72

144

216

288

360

Embedded array blocks (EABs)

3

6

6

8

10

Total RAM bits

6,144

12,288

12,288

16,384

20,480

Maximum user I/O pins

150

189

246

189

310

2

Altera Corporation

FLEX 10K Embedded Programmable Logic Family Data Sheet

Note to tables:

(1)

The embedded IEEE Std. 1149.1 JTAG circuitry adds up to 31,250 gates in addition to the listed typical or maximum

system gates.

...and More

Features

≠

Devices are fabricated on advanced processes and operate with

a 3.3-V or 5.0-V supply voltage (see

Table 3

)

≠

In-circuit reconfigurability (ICR) via external configuration

device, intelligent controller, or JTAG port

≠

ClockLock

TM

and ClockBoost

TM

options for reduced clock

delay/skew and clock multiplication

≠

Built-in low-skew clock distribution trees

≠

100

%

functional testing of all devices; test vectors or scan chains

are not required

Table 2. FLEX 10K Device Features

Feature

EPF10K70

EPF10K100

EPF10K100A

EPF10K130V

EPF10K250A

Typical gates (logic and

RAM)

(1)

70,000

100,000

130,000

250,000

Maximum system gates

118,000

158,000

211,000

310,000

LEs

3,744

4,992

6,656

12,160

LABs

468

624

832

1,520

EABs

9

12

16

20

Total RAM bits

18,432

24,576

32,768

40,960

Maximum user I/O pins

358

406

470

470

Table 3. Supply Voltages for FLEX 10K & FLEX 10KA Devices

5.0-V Devices

3.3-V Devices

EPF10K10

EPF10K20

EPF10K30

EPF10K40

EPF10K50

EPF10K70

EPF10K100

EPF10K10A

EPF10K30A

EPF10K50V

EPF10K100A

EPF10K130V

EPF10K250A

Altera Corporation

3

FLEX 10K Embedded Programmable Logic Family Data Sheet

s

Flexible interconnect

≠

FastTrack

Æ

Interconnect continuous routing structure for fast,

predictable interconnect delays

≠

Dedicated carry chain that implements arithmetic functions such

as fast adders, counters, and comparators (automatically used by

software tools and megafunctions)

≠

Dedicated cascade chain that implements high-speed,

high-fan-in logic functions (automatically used by software tools

and megafunctions)

≠

Tri-state emulation that implements internal tri-state buses

≠

Up to six global clock signals and four global clear signals

s

Powerful I/O pins

≠

Individual tri-state output enable control for each pin

≠

Open-drain option on each I/O pin

≠

Programmable output slew-rate control to reduce switching

noise

≠

FLEX 10KA devices support hot-socketing

s

Peripheral register for fast setup and clock-to-output delay

s

Flexible package options

≠

Available in a variety of packages with 84 to 600 pins (see

Table 4

)

≠

Pin-compatibility with other FLEX 10K devices in the same

package

≠

FineLine BGA

TM

packages maximize board space efficiency

s

Software design support and automatic place-and-route provided by

Altera's MAX+PLUS

Æ

II development system for Windows-based

PCs and Sun SPARCstation, HP 9000 Series 700/800, and IBM RISC

System/6000 workstations, and Quartus

TM

development system for

Windows-based PCs and Sun SPARCstation and HP 9000 Series 700

workstations

s

Additional design entry and simulation support provided by EDIF

2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM),

DesignWare components, Verilog HDL, VHDL, and other interfaces

to popular EDA tools from manufacturers such as Cadence,

Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity,

VeriBest, and Viewlogic

4

Altera Corporation

FLEX 10K Embedded Programmable Logic Family Data Sheet

Table 4. FLEX 10K PLCC, TQFP, PQFP, RQFP & PGA Package Options & I/O Pin Count

Notes (1)

,

(2)

Device

84-Pin

PLCC

100-Pin

TQFP

144-Pin

TQFP

208-Pin

PQFP

RQFP

240-Pin

PQFP

RQFP

403-Pin

PGA

EPF10K10

59

102

134

EPF10K10A

66

102

134

EPF10K20

102

147

189

EPF10K30

147

189

EPF10K30A

102

147

189

EPF10K40

147

189

EPF10K50

189

310

EPF10K50V

189

EPF10K70

189

EPF10K100

EPF10K100A

189

EPF10K130V

EPF10K250A

Table 5. FLEX 10K BGA & FineLine BGA Package Options & I/O Pin Count

Notes (1)

,

(2)

Device

503-Pin

PGA

599-Pin

PGA

256-Pin

FineLine BGA

356-Pin

BGA

484-Pin

FineLine BGA

600-Pin

BGA

EPF10K10

EPF10K10A

150

150

(3)

EPF10K20

EPF10K30

246

EPF10K30A

191

246

246

EPF10K40

EPF10K50

274

EPF10K50V

274

291

EPF10K70

358

EPF10K100

406

EPF10K100A

274

369

406

EPF10K130V

470

470

EPF10K250A

470

470

Altera Corporation

5

FLEX 10K Embedded Programmable Logic Family Data Sheet

Notes to tables:

(1)

Contact Altera Customer Marketing for up-to-date information on package availability.

(2)

FLEX 10K and FLEX 10KA device package types include plastic J-lead chip carrier (PLCC), thin quad flat pack

(TQFP), plastic quad flat pack (PQFP), power quad flat pack (RQFP), ball-grid array (BGA), pin-grid array (PGA),

and FineLine BGA

TM

packages.

(3)

This option will be supported with a 256-pin FineLine BGA package. By using SameFrame pin migration, all

FineLine BGA packages are pin compatible. For example, a board can be designed to support both 256-pin and

484-pin FineLine BGA packages. The Quartus and MAX+PLUS II software automatically avoids conflicting pins

when future migration is set.

General

Description

Altera's FLEX 10K devices are the industry's first embedded PLDs. Based

on reconfigurable CMOS SRAM elements, the Flexible Logic Element

MatriX (FLEX) architecture incorporates all features necessary to

implement common gate array megafunctions. With up to 250,000 gates,

the FLEX 10K family provides the density, speed, and features to integrate

entire systems, including multiple 32-bit buses, into a single device.

FLEX 10K devices are reconfigurable, which allows 100

%

testing prior to

shipment. As a result, the designer is not required to generate test vectors

for fault coverage purposes. Additionally, the designer does not need to

manage inventories of different ASIC designs; FLEX 10K devices can be

configured on the board for the specific functionality required.

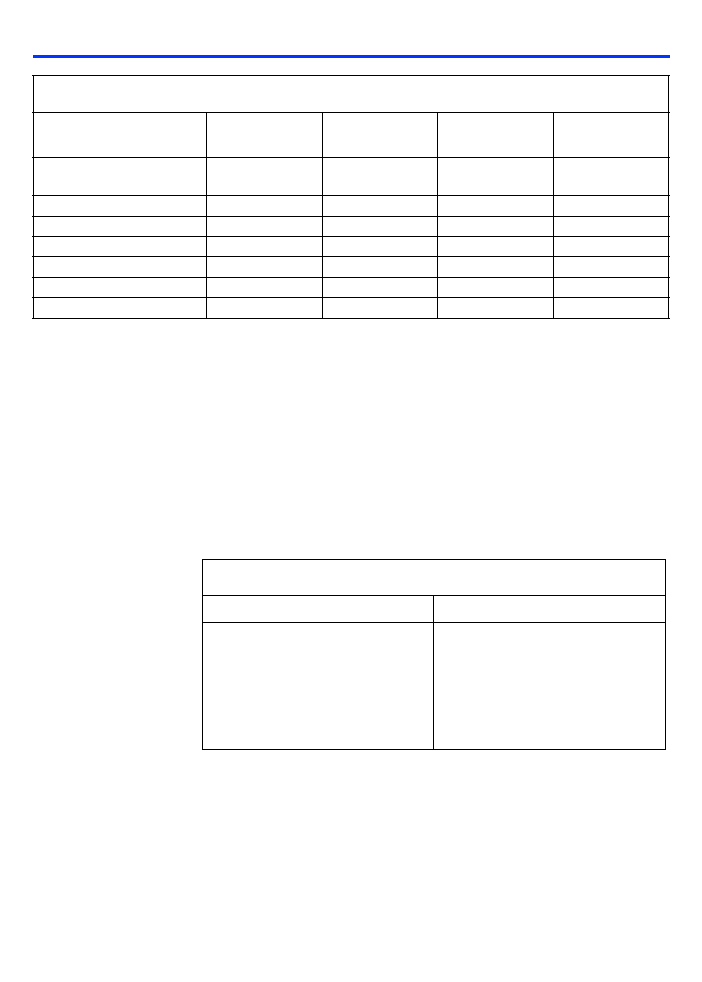

Table 6

shows FLEX 10K performance for some common designs. All

performance values were obtained with Synopsys DesignWare or LPM

functions. No special design technique was required to implement the

applications; the designer simply inferred or instantiated a function in a

Verilog HDL, VHDL, Altera Hardware Description Language (AHDL), or

schematic design file.

Notes:

(1)

The speed grade of this application is limited because of clock high and low specifications.

(2)

This application uses combinatorial inputs and outputs.

(3)

This application uses registered inputs and outputs.

Table 6. FLEX 10K & FLEX 10KA Performance

Application

Resources

Used

Performance

Units

Speed Grade

LEs

EABs

-1

-2

-3

-4

16-bit loadable

counter

(1)

16

0

204

166

125

95

MHz

16-bit accumulator

(1)

16

0

204

166

125

95

MHz

16-to-1 multiplexer

(2)

10

0

4.2

5.8

6.0

7.0

ns

256

◊

8 RAM read

cycle speed

(3)

0

1

172

145

108

84

MHz

256

◊

8 RAM write

cycle speed

(3)

0

1

106

89

68

63

MHz