Document Outline

- APEX 20K Programmable Logic Device Family Data Sheet

Æ

Altera Corporation

1

APEX 20K

Programmable Logic

Device Family

February 2002, ver. 4.3

Data Sheet

DS-APEX20K-4.3

Features...

Industry's first programmable logic device (PLD) incorporating

system-on-a-programmable-chip (SOPC) integration

≠

MultiCore

TM

architecture integrating look-up table (LUT) logic,

product-term logic, and embedded memory

≠

LUT logic used for register-intensive functions

≠

Embedded system block (ESB) used to implement memory

functions, including first-in first-out (FIFO) buffers, dual-port

RAM, and content-addressable memory (CAM)

≠

ESB implementation of product-term logic used for

combinatorial-intensive functions

High density

≠

30,000 to 1.5 million typical gates (see

Tables 1

and

2

)

≠

Up to 51,840 logic elements (LEs)

≠

Up to 442,368 RAM bits that can be used without reducing

available logic

≠

Up to 3,456 product-term-based macrocells

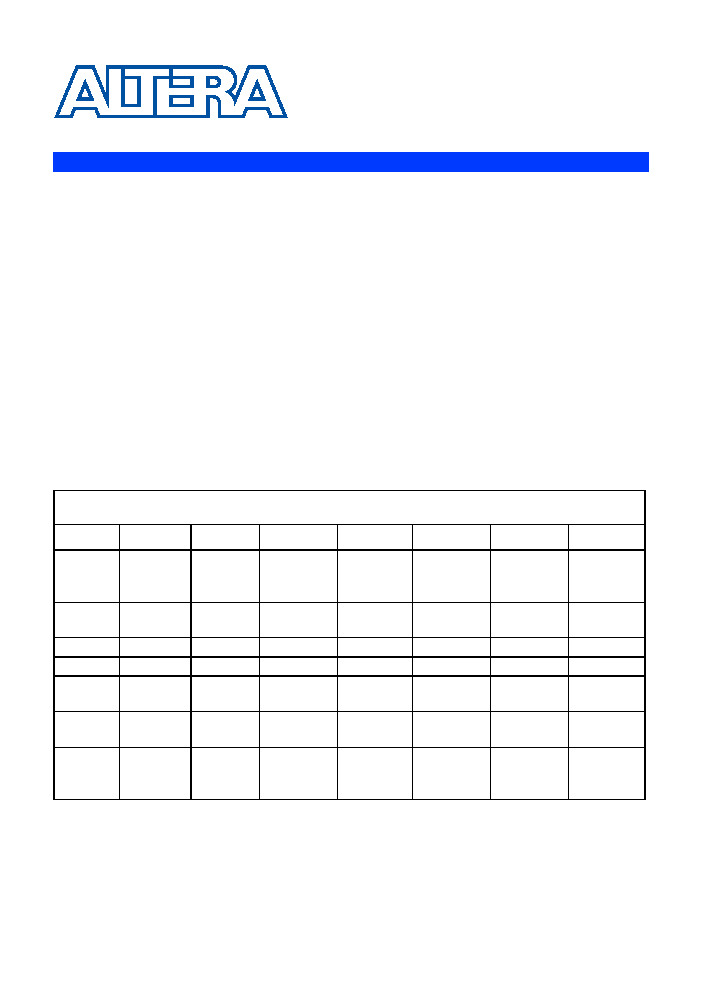

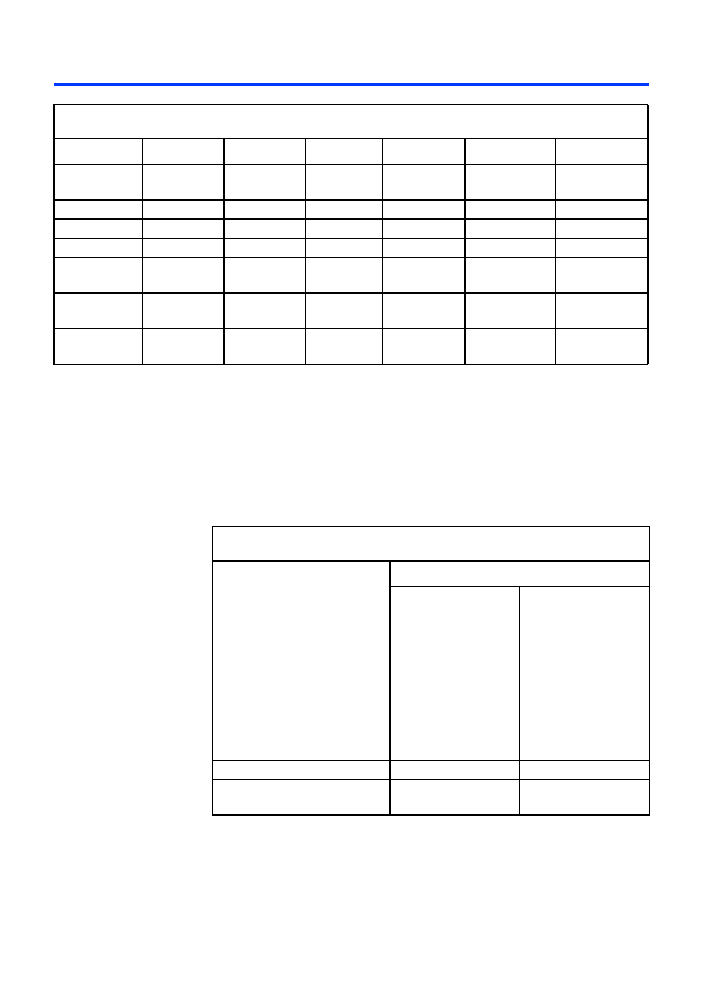

Table 1. APEX 20K Device Features

Note (1)

Feature

EP20K30E

EP20K60E

EP20K100

EP20K100E

EP20K160E

EP20K200

EP20K200E

Maximum

system

gates

113,000

162,000

263,000

263,000

404,000

526,000

526,000

Typical

gates

30,000

60,000

100,000

100,000

160,000

200,000

200,000

LEs

1,200

2,560

4,160

4,160

6,400

8,320

8,320

ESBs

12

16

26

26

40

52

52

Maximum

RAM bits

24,576

32,768

53,248

53,248

81,920

106,496

106,496

Maximum

macrocells

192

256

416

416

640

832

832

Maximum

user I/O

pins

128

196

252

246

316 382

376

2

Altera Corporation

APEX 20K Programmable Logic Device Family Data Sheet

Note to tables:

(1)

The embedded IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan circuitry contributes up to

57,000 additional gates.

...and More

Features

Designed for low-power operation

≠

1.8-V and 2.5-V supply voltage (see

Table 3

)

≠

MultiVolt

TM

I/O interface support to interface with 1.8-V, 2.5-V,

3.3-V, and 5.0-V devices (see

Table 3

)

≠

ESB offering programmable power-saving mode

Notes:

(1)

Certain APEX 20K devices are 5.0-V tolerant. See "MultiVolt I/O Interface" on page

46 for details.

(2)

APEX 20KE devices can be 5.0-V tolerant by using an external resistor.

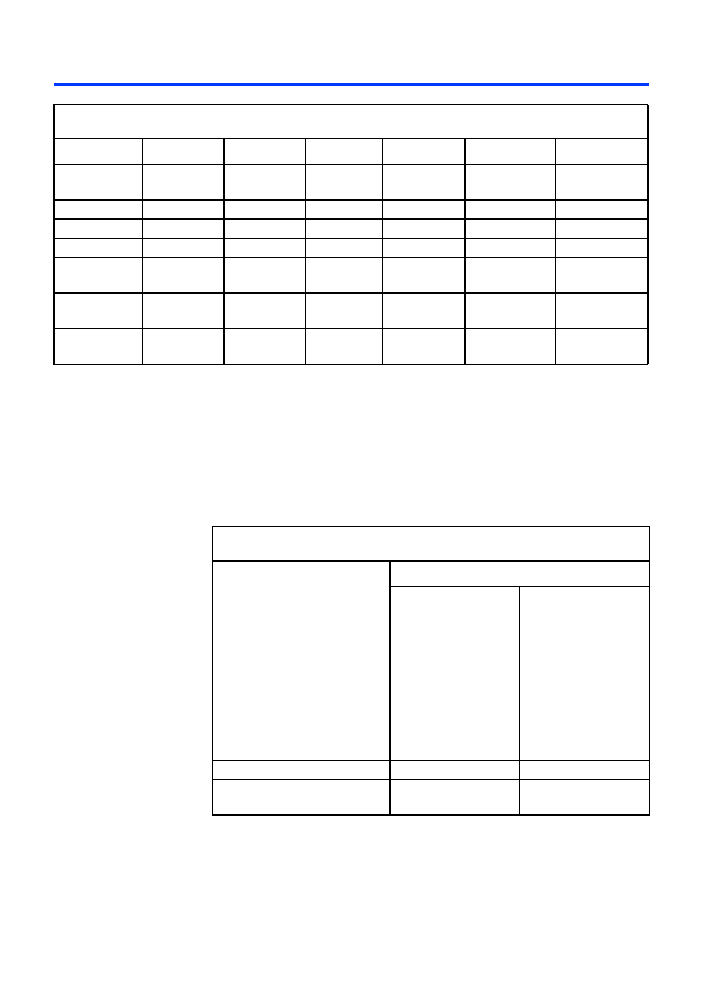

Table 2. APEX 20K Device Features

Note (1)

Feature

EP20K300E

EP20K400

EP20K400E

EP20K600E

EP20K1000E

EP20K1500E

Maximum

system gates

728,000

1,052,000

1,052,000

1,537,000

1,772,000

2,392,000

Typical gates

300,000

400,000

400,000

600,000

1,000,000

1,500,000

LEs

11,520

16,640

16,640

24,320

38,400

51,840

ESBs

72

104

104

152

160

216

Maximum

RAM bits

147,456

212,992

212,992

311,296

327,680

442,368

Maximum

macrocells

1,152

1,664

1,664

2,432

2,560

3,456

Maximum user

I/O pins

408

502

488

588

708

808

Table 3. APEX 20K Supply Voltages

Feature

Device

EP20K100

EP20K200

EP20K400

EP20K30E

EP20K60E

EP20K100E

EP20K160E

EP20K200E

EP20K300E

EP20K400E

EP20K600E

EP20K1000E

EP20K1500E

Internal supply voltage (V

CCINT

) 2.5 V

1.8 V

MultiVolt I/O interface voltage

levels (V

CCIO

)

2.5 V, 3.3 V, 5.0 V

(1)

1.8 V, 2.5 V, 3.3 V,

5.0 V

(2)

Altera Corporation

3

APEX 20K Programmable Logic Device Family Data Sheet

Flexible clock management circuitry with up to four phase-locked

loops (PLLs)

≠

Built-in low-skew clock tree

≠

Up to eight global clock signals

≠

ClockLock

TM

feature reducing clock delay and skew

≠

ClockBoost

TM

feature providing clock multiplication and

division

≠

ClockShift

TM

programmable clock phase and delay shifting

Powerful I/O features

≠

Compliant with peripheral component interconnect Special

Interest Group (PCI SIG) PCI Local Bus Specification,

Revision 2.2

for 3.3-V operation at 33 or 66 MHz and 32 or 64 bits

≠

Support for high-speed external memories, including DDR

SDRAM and ZBT SRAM (ZBT is a trademark of Integrated

Device Technology, Inc.)

≠

Bidirectional I/O performance (t

CO

+ t

SU

) up to 250 MHz

≠

LVDS performance up to 840 Mbits per channel

≠

Direct connection from I/O pins to local interconnect providing

fast t

CO

and t

SU

times for complex logic

≠

MultiVolt I/O interface support to interface with 1.8-V, 2.5-V,

3.3-V, and 5.0-V devices (see

Table 3

)

≠

Programmable clamp to V

CCIO

≠

Individual tri-state output enable control for each pin

≠

Programmable output slew-rate control to reduce switching

noise

≠

Support for advanced I/O standards, including low-voltage

differential signaling (LVDS), LVPECL, PCI-X, AGP, CTT, stub-

series terminated logic (SSTL-3 and SSTL-2), Gunning

transceiver logic plus (GTL+), and high-speed terminated logic

(HSTL Class I)

≠

Pull-up on I/O pins before and during configuration

Advanced interconnect structure

≠

Four-level hierarchical FastTrack

Æ

Interconnect structure

providing fast, predictable interconnect delays

≠

Dedicated carry chain that implements arithmetic functions such

as fast adders, counters, and comparators (automatically used by

software tools and megafunctions)

≠

Dedicated cascade chain that implements high-speed,

high-fan-in logic functions (automatically used by software tools

and megafunctions)

≠

Interleaved local interconnect allows one LE to drive 29 other

LEs through the fast local interconnect

Advanced packaging options

≠

Available in a variety of packages with 144 to 1,020 pins (see

Tables 4

through

7

)

≠

FineLine BGA

TM

packages maximize board space efficiency

Advanced software support

≠

Software design support and automatic place-and-route

provided by the Altera

Æ

Quartus

TM

II development system for

4

Altera Corporation

APEX 20K Programmable Logic Device Family Data Sheet

Windows-based PCs, Sun SPARCstations, and HP 9000

Series 700/800 workstations

≠

Altera MegaCore

Æ

functions and Altera Megafunction Partners

Program (AMPP

SM

) megafunctions

≠

NativeLink

TM

integration with popular synthesis, simulation,

and timing analysis tools

≠

Quartus II SignalTap

TM

embedded logic analyzer simplifies

in-system design evaluation by giving access to internal nodes

during device operation

≠

Supports popular revision-control software packages including

PVCS, Revision Control System (RCS), and Source Code Control

System (SCCS )

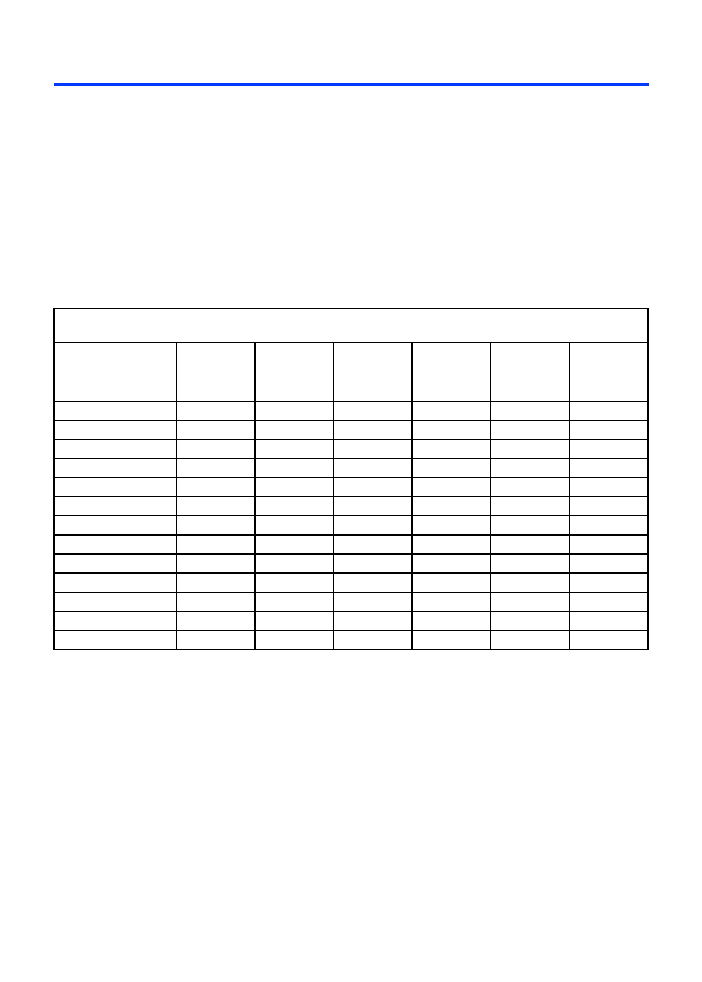

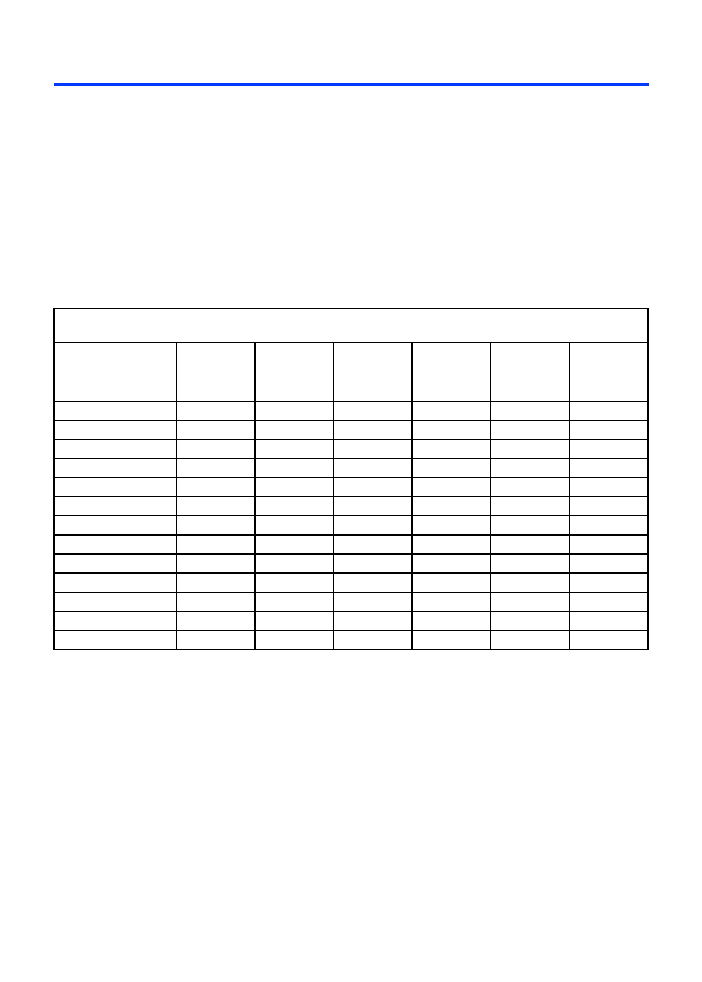

Table 4. APEX 20K QFP, BGA & PGA Package Options & I/O Count

Notes (1)

,

(2)

Device

144-Pin

TQFP

208-Pin

PQFP

RQFP

240-Pin

PQFP

RQFP

356-Pin BGA 652-Pin BGA 655-Pin PGA

EP20K30E

92

125

EP20K60E

92

148

151

196

EP20K100

101

159

189

252

EP20K100E

92

151

183

246

EP20K160E

88

143

175

271

EP20K200

144

174

277

EP20K200E

136

168

271

376

EP20K300E

152

408

EP20K400

502

502

EP20K400E

488

EP20K600E

488

EP20K1000E

488

EP20K1500E

488

Altera Corporation

5

APEX 20K Programmable Logic Device Family Data Sheet

Notes to tables:

(1)

I/O counts include dedicated input and clock pins.

(2)

APEX 20K device package types include thin quad flat pack (TQFP), plastic quad flat pack (PQFP), power quad flat

pack (RQFP), 1.27-mm pitch ball-grid array (BGA), 1.00-mm pitch FineLine BGA, and pin-grid array (PGA)

packages.

(3)

This device uses a thermally enhanced package, which is taller than the regular package. Consult the Altera Device

Package Information Data Sheet for detailed package size information.

Table 5. APEX 20K FineLine BGA Package Options & I/O Count

Notes (1)

,

(2)

Device

144 Pin

324 Pin

484 Pin

672 Pin

1,020 Pin

EP20K30E

93

128

EP20K60E

93

196

EP20K100

252

EP20K100E

93

246

EP20K160E

316

EP20K200

382

EP20K200E

376

376

EP20K300E

408

EP20K400

502

(3)

EP20K400E

488

(3)

EP20K600E

508

(3)

588

EP20K1000E

508

(3)

708

EP20K1500E

808

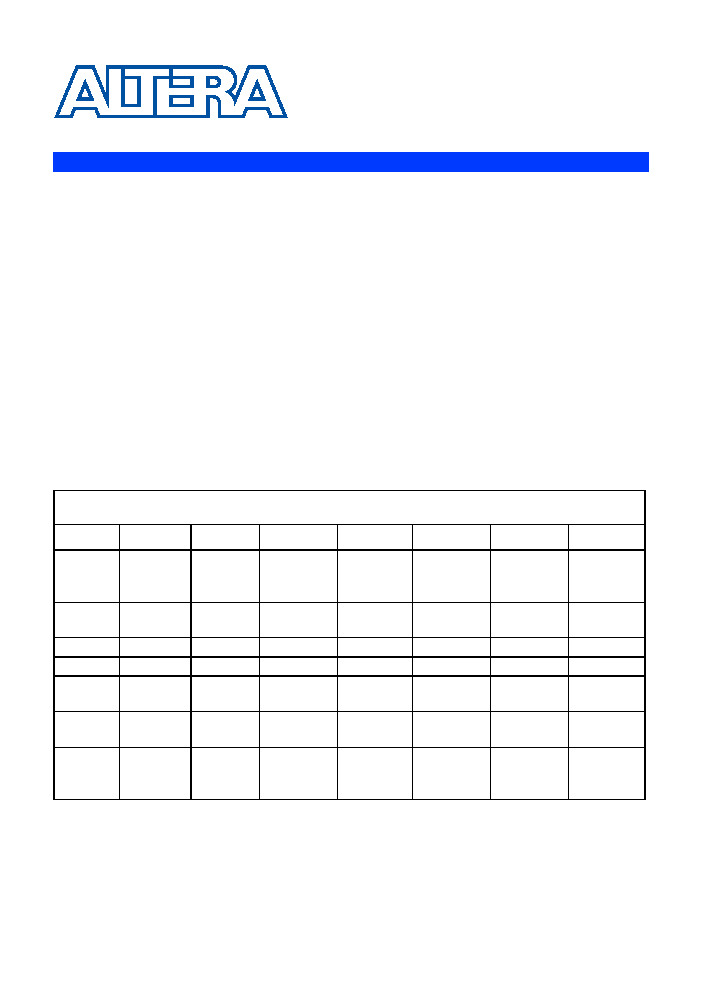

Table 6. APEX 20K QFP, BGA & PGA Package Sizes

Feature

144-Pin TQFP 208-Pin QFP 240-Pin QFP 356-Pin BGA 652-Pin BGA 655-Pin PGA

Pitch (mm)

0.50

0.50

0.50

1.27

1.27

≠

Area (mm

2

)

484

924

1,218

1,225

2,025

3,906

Length

◊

Width

(mm

◊

mm)

22

◊

22

30.4

◊

30.4

34.9

◊

34.9

35

◊

35

45

◊

45

62.5

◊

62.5

Table 7. APEX 20K FineLine BGA Package Sizes

Feature

144 Pin

324 Pin

484 Pin

672 Pin

1,020 Pin

Pitch (mm)

1.00

1.00

1.00

1.00

1.00

Area (mm

2

)

169

361

529

729

1,089

Length

◊

Width (mm

◊

mm)

13

◊

13

19

◊

19

23

◊

23

27

◊

27

33

◊

33