| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: EP224 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Æ

Altera Corporation

1

EP220 & EP224

Classic EPLDs

May 1995, ver. 1

Data Sheet

A-ds-220/224-01

Features

s

High-performance, low-power Erasable Programmable Logic

Devices (EPLDs) with 8 macrocells

≠

Combinatorial speeds as low as 7.5 ns

≠

Counter frequencies of up to 100 MHz

≠

Pipelined data rates of up to 115 MHz

≠

Maximum 5.5-ns Clock-to-output time; minimum 4.5-ns setup

time

s

Replacement or upgrade for 16V8/20V8 PAL and GAL devices

s

Up to 18 inputs (10 dedicated inputs) in EP220, 22 inputs (14

dedicated inputs) in EP224; up to 8 outputs in both EP220 and EP224

s

Macrocells independently programmable for both registered and

combinatorial logic

s

Programmable inversion control supporting active-high or active-

low outputs

s

Low power consumption

≠

Typical I

CC

= 90 mA at 25 MHz (for -7A speed grades)

≠

Quarter-power mode (I

CC

= 40 mA)

≠

Programmable zero-power mode with typical I

CC

= 50

µ

A

(for -10A and -12 speed grades)

s

Programmable Security Bit for total protection of proprietary designs

s

Low output skew for Clock driver applications

s

100

%

generically tested to provide 100

%

programming yield

s

Software and programming support from Altera and a wide range of

third-party tools

s

Available in windowed ceramic and one-time-programmable (OTP)

plastic packages

≠

20-pin plastic J-lead package (PLCC)

≠

20-pin ceramic and plastic dual in-line packages (CerDIP and

PDIP)

≠

24-pin PDIP

≠

28-pin PLCC

General

Description

The EPROM-based EP220 and EP224 devices feature a flexible I/O

architecture and implement 150 usable (300 available) gates of custom

user logic functions. EP220 and EP224 devices can be used as upgrades for

high-speed bipolar programmable logic devices (PLDs) or for 74-series LS

and CMOS (SSI and MSI) logic devices in high-performance

microcomputer systems.

2

Altera Corporation

EP220 & EP224 Classic EPLDs

Compared to bipolar devices of equivalent speed, the EP220 and

EP224 offer lower power consumption, faster input-to-non-

registered-output delay (

t

PD

) in combinatorial mode, and higher

counter frequencies in registered applications. This added

performance supports faster state machine designs compared to

bipolar devices, and provides additional timing margin for existing

designs. The EP220 and EP224 are ideal for high-volume

manufacturing of high-performance systems. These devices improve

performance and decrease system noise, power consumption, and

heat generation.

Functional

Description

Figure 1

shows block diagrams of the EP220 and EP224 device

architectures. The EP220 has 10 dedicated inputs and 8 I/O pins; the

EP224 has 14 dedicated inputs and 8 I/O pins.

Altera Corporation

3

EP220 & EP224 Classic EPLDs

Figure 1. EP220 & EP224 Block Diagram

Numbers in parentheses refer to the pin-out number.

The EP220 and EP224 architecture is based on a sum-of-products,

programmable-

AND

/fixed-

OR

structure. Each macrocell can be

individually programmed for combinatorial or registered output. An

inversion option allows each output to be configured for active-high or

active-low operation. Each I/O pin can be programmed to function as an

input, output, or bidirectional pin.

The EP220 and EP224 device architecture offers the following features:

s

Macrocells

s

High-frequency, low-skew global Clock

EP220

I/O (19)

I/O (18)

I/O (17)

I/O (16)

I/O (15)

I/O (14)

I/O (13)

I/O (12)

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Macrocell 7

Macrocell 8

Global Clock

Global

Bus

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(11)

INPUT/CLK

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

EP224

Global

Bus

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Macrocell 7

Macrocell 8

Global Clock

I/O (22)

I/O (21)

I/O (20)

I/O (19)

I/O (18)

I/O (17)

I/O (16)

I/O (15)

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

(11)

(13)

(14)

(23)

INPUT/CLK

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

4

Altera Corporation

EP220 & EP224 Classic EPLDs

Macrocells

Each macrocell includes a product-term block with 8

AND

product terms

feeding an

OR

gate. One product term is dedicated to the Output Enable

(

OE

) control of the tri-state buffer. The global logic array allows each

product term to connect to the true or complement of each input--36

inputs for the EP220, 44 inputs for the EP224--and I/O feedback signal.

See

Figure 2

.

Figure 2. EP220 & EP224 Macrocell

Macrocells can be individually configured for registered or combinatorial

operation, providing a mixed-mode operation not available in fixed-

architecture PAL devices. When registered output is selected, feedback

from the register to the logic array bypasses the output buffer. When

combinatorial output is selected, feedback comes from the I/O pin

through the output buffer, and can be used for bidirectional I/O. Unlike

PAL and GAL devices, all eight outputs on the EP220 and EP224 allow a

combinatorial feedback signal from the I/O pin to feed the logic array.

Data is clocked into the macrocell's D register on the rising edge of the

global Clock.

Feedback

Select

D

Q

CLK

Inversion

Control

Programmable

Register

Output Enable

Feedback to

Logic Array

Pin, I/O, and

Macrocell Feedback

Altera Corporation

5

EP220 & EP224 Classic EPLDs

The

XOR

gate can implement active-high or active-low logic, and can use

DeMorgan's inversion to reduce the number of product terms needed to

implement a function.

If the EP220 and EP224 register outputs do not require an

OE

signal, the

internal product term can hold the output in an enabled state; if a global

OE

signal is required, any input can be dedicated to the task, and all eight

product terms can be programmed accordingly.

High-Frequency, Low-Skew Global Clock

EP220 and EP224 devices have extremely low output-pin skew: registered

output skew (

t

OCR

) is typically less than 300 ps; combinatorial output

skew

(

t

OSC

) is typically less than 400 ps. This low output-skew rate makes

EP220 and EP224 devices ideal for high-frequency system Clock

applications, including Intel Pentium microprocessors, 486-based PCs,

and PCI bus designs.

PLD

Compatibility

The EP220 and EP224 devices are a logical superset of most high-speed,

24-pin PAL/GAL devices. Industry-standard JEDEC Files from

compatible devices can be programmed into EP220 or EP224 devices.

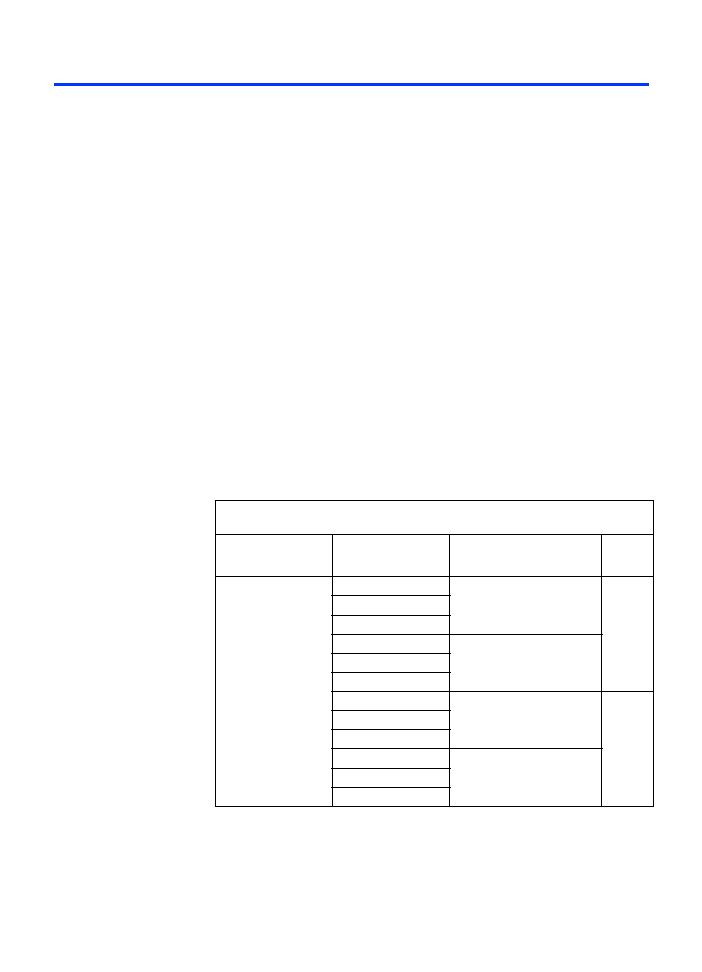

Table 1

summarizes some of the devices that can be replaced or upgraded

with EP220 and EP224 devices.

Table 1. EP220- and EP224-Compatible Devices (Part 1 of 4)

PAL/GAL Vendor

PAL/GAL Device

Altera Replacement

Device

Speed

Grade

Advanced Micro

Devices

PAL16L8

EP220-7

-7

PAL16R8

PALCE16V8

PAL20L8

EP224-7

PAL20R8

PALCE20V8

PAL16L8

EP220-10

-10

PAL16R8

PALCE16V8

PAL20L8

EP224-10

PAL20R8

PALCE20V8