Æ

Altera Corporation

265

FLASHlogic

Programmable Logic

Device Family

June 1996, ver. 2

Data Sheet

A-DS-FLSH-02

Features...

s

High-performance programmable logic device (PLD) family

≠

SRAM-based logic with shadow FLASH memory elements

fabricated on advanced CMOS technology

≠

Logic densities from 1,600 to 3,200 usable gates (see

Table 1

)

≠

Combinatorial speeds with

t

PD

as low as 10 ns

≠

Counter frequencies of up to 80 MHz

s

8 to 16 logic array blocks (LABs) linked by a 100

%

-connectable

programmable interconnect array (PIA) for improved fitting of

complex designs

s

24V10 macrocell features available

≠

Dual feedback on all I/O pins

≠

Product-term allocation matrix supporting up to 16 product

terms per macrocell

≠

Programmable registers providing D, T, SR, and JK flipflop

functionality with clear, preset, and clock controls

≠

Fast 12-bit identity compare option

s

Fully compliant with

PCI Local Bus Specification

, version 2.1

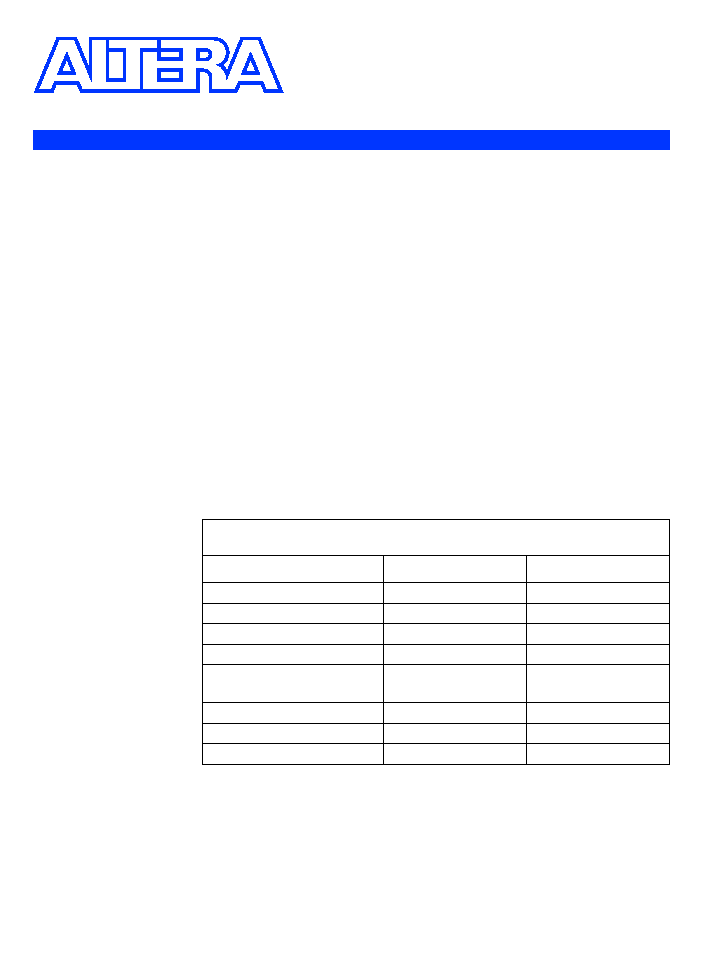

Table 1. FLASHlogic Device Features

Feature

EPX880

EPX8160

Usable gates

1,600

3,200

Maximum SRAM bits

10,240

20,480

Macrocells

80

160

Logic array blocks (LABs)

8

16

Package options

(maximum user I/O pins)

84-pin PLCC (62)

132-pin PQFP (104)

208-pin PQFP (172)

t

PD

(ns)

10

10

t

CO

(ns)

6

6

f

CNT

(MHz)

80

80

266

Altera Corporation

FLASHlogic Programmable Logic Device Family Data Sheet

... and More

Features

s

LABs can be configured as either one of the following:

≠

24V10 logic block with 10 macrocells

≠

128

◊

10 SRAM block

s

3.3-V or 5.0-V I/O on all devices (selectable in each LAB)

s

Low power consumption (1 mA/MHz in standby mode;

1.5 to 2.5 mA/MHz in active mode)

s

84 to 208 pins available in plastic J-lead (PLCC) and plastic quad flat

pack (PQFP) packages (see

Table 1

)

s

Open-drain output option

s

Joint Test Action Group (JTAG) IEEE 1149.1-compatible test port

≠

Boundary-scan testing (BST) support

≠

In-circuit reconfigurability (ICR) support

≠

In-system programmability (ISP) support

s

Programmable security bit for protection of proprietary designs

s

Supported by industry-standard design and programming tools

from Altera and other vendors

General

Description

FLASHlogic devices are SRAM-based devices with shadow FLASH

memory elements. Fabricated on advanced CMOS technology,

FLASHlogic devices provide from 1,600 to 3,200 usable gates, pin-to-pin

delays as fast as 10 ns, and counter speeds of up to 80 MHz.

Table 2

shows

the available speed grades for FLASHlogic devices.

FLASHlogic devices have a unique combination of features that is ideal

for a variety of applications, including communications and bus interface

controllers. They provide low power consumption and user-selectable

5.0-V and 3.3-V outputs, making FLASHlogic devices useful for mixed-

voltage applications such as portable and embedded systems.

The FLASHlogic device architecture supports 100

%

TTL emulation and

high-density integration of SSI, MSI, and LSI logic functions. In addition,

FLASHlogic devices easily integrate multiple programmable logic

devices ranging from PALs, GALs, and 22V10s to MACH, pLSI, and

FPGA devices. With speed, density, and I/O resources comparable to

commonly used masked gate arrays, FLASHlogic devices are ideal for

gate array prototyping and PC applications. In addition, FLASHlogic

devices in the -10 speed grade are PCI-compliant.

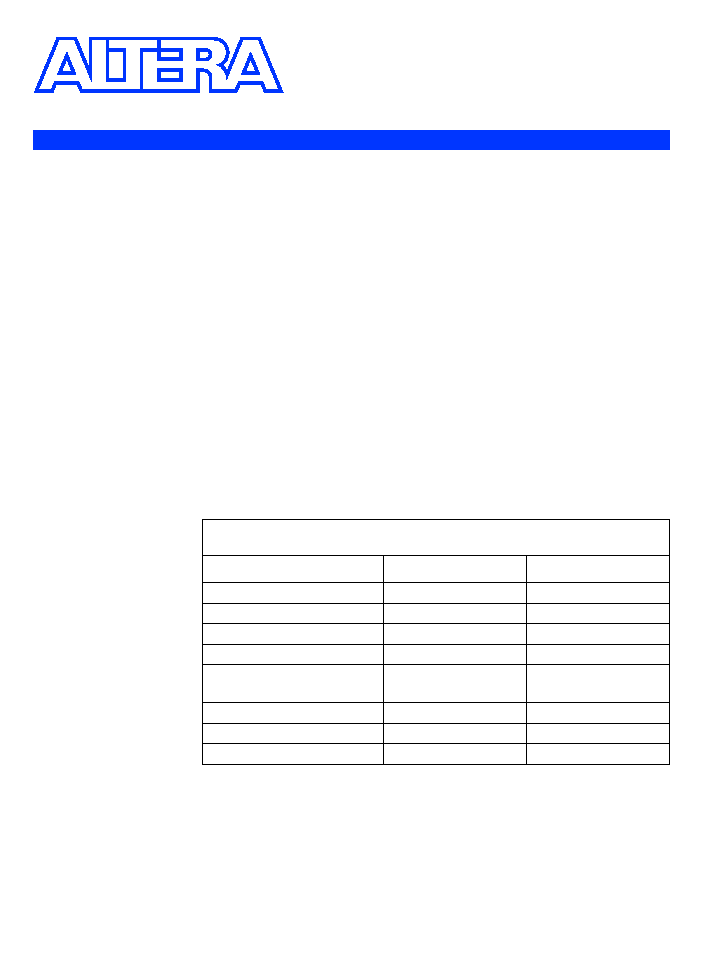

Table 2. FLASHlogic Speed Grades

Device

Available Speed Grades

-10

-12

EPX880

V

V

EPX8160

V

V

Altera Corporation

267

FLASHlogic Programmable Logic Device Family Data Sheet

FLASHlogic devices are available in plastic J-lead chip carrier (PLCC) and

plastic quad flat pack (PQFP) packages.

FLASHlogic devices contain 8 to 16 LABs linked by a PIA. Each LAB can

be defined as either a 24V10 logic block of 10 macrocells or a 128

◊

10

SRAM block. When defined as a 24V10 logic block, all 10 macrocells have

a programmable-

AND

/allocatable-

OR

array and a configurable register

with independently programmable clock, clear, and preset functions. To

build complex logic functions, product-term allocation allows up to 16

product terms for a single macrocell.

FLASHlogic devices provide dedicated pins compliant with the JTAG

IEEE 1149.1-1990 specification. The JTAG pins support BST, ICR, and ISP.

ICR and ISP offer the designer greater flexibility in prototyping new

designs. These features make FLASHlogic devices ideal for applications

in which the final configuration is not fixed.

FLASHlogic devices are supported by industry-standard PC- and

workstation-based EDA tools, including the Altera PLDshell Plus

development system. The MAX+PLUS II development software also

provides programming and configuration support for FLASHlogic

devices.

Functional

Description

The FLASHlogic device architecture includes the following elements:

s

Logic array blocks (LABs)

≠

24V10 configuration

≠

SRAM configuration

s

Programmable interconnect array (PIA)

s

I/O control blocks

Figure 1

shows the block diagram of the FLASHlogic device architecture,

which consists of LABs linked by a 100

%

-connectable PIA.

268

Altera Corporation

FLASHlogic Programmable Logic Device Family Data Sheet

Figure 1. FLASHlogic Device Block DIagram

Logic Array Blocks

The FLASHlogic device architecture is based on the linking of high-

performance, flexible logic array modules called logic array blocks

(LABs). Each LAB can be configured as a 24V10 logic block or as a 128

◊

10

SRAM block. The LABs are linked via the PIA, which is fed by all

dedicated inputs, I/O pins, and either macrocells (in 24V10 configuration)

or SRAM outputs (in SRAM configuration). Each LAB is fed by 24 signals

from the PIA and 2 global clocks.

24V10 Configuration

When a LAB is configured as a 24V10 logic block, each block contains the

following elements:

s

10 macrocells

s

A 12-bit identity comparator

s

2 global clocks

s

Control logic for array clocks, and for clear, preset and output enable

signals

10

24

5 to 10

5 to 10

10

24

5 to 10

10

5 to 10

10

24

LAB 0

Macrocells

0 to 9

LAB 1

LAB 2

LAB 3

Dedicated

Inputs

Clock

5 to 10

0 to 48

5 to 10

5 to 10

5 to 10

2 to 4

Macrocells

20 to 29

Macrocells

10 to 19

2

2

2

2

5 to 10

I/O pins

2 Output

Enables

5 to 10

I/O pins

2 Output

Enables

2 Output

Enables

5 to 10

I/O pins

2 Output

Enables

5 to 10

I/O pins

Macrocells

30 to 39

2

2

PIA

24

I/O

Control

Block

I/O

Control

Block

I/O

Control

Block

I/O

Control

Block

Altera Corporation

269

FLASHlogic Programmable Logic Device Family Data Sheet

Figure 2

shows a diagram of a LAB configured as a 24V10 logic block.

Figure 2. LAB in 24V10 Configuration

Macrocell 0

to I/O Control

Block

C/P1

C/P2

ACLK1

ACLK2

OE1

OE2

to I/O Control

Block

to PIA

to I/O Control

Block

Global Clock 1

Global Clock 2

From PIA

Delay

Delay

24

24

24

Global

Clock

Select

LAB

Identity

Comparator

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Macrocell 7

Macrocell 8

Macrocell 9

Global

Clock

Select