| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: EV2066 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Part Number EV2066

Revision 1.0 - November 16, 1999

EV2066

Quad Gigabit Ethernet Transceiver Evaluation Board

AMCC Confidential and Proprietary

1

EVALUATION BOARD

Introduction

The S2066 evaluation board provides a flexible platform for verifying the operation of the S2066 Quad Gigabit

Ethernet Transceiver. This document provides information on the evaluation board's contents. It should be used in

conjunction with the S2066 product data sheet. Contact your local AMCC field applications engineer or regional

sales manager to discuss any questions or concerns you may have.

EV2066 Kit Contents

S2066 evaluation board

EV2066 Device Specification (This document)

Four minicoax cables (To loop back clock in parallel loopback configuration)

Board Description

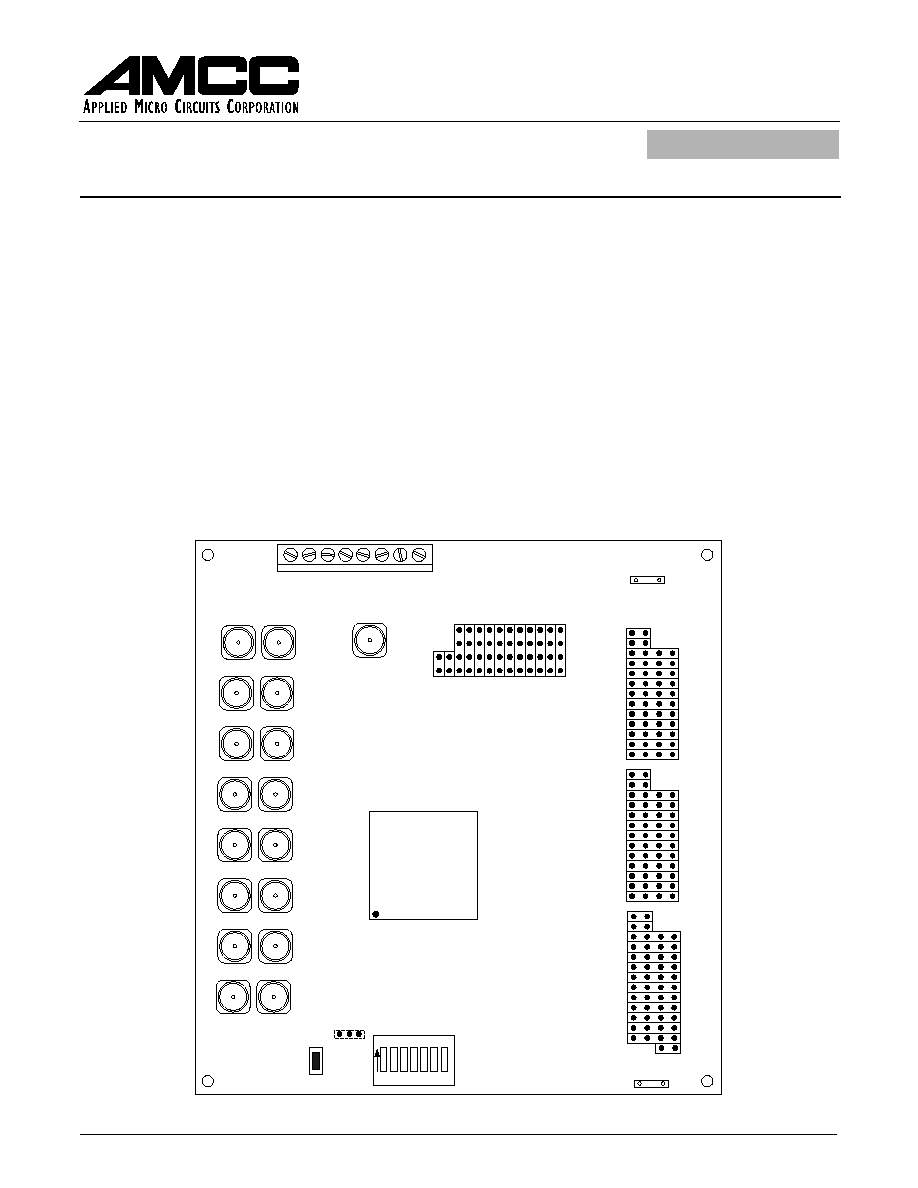

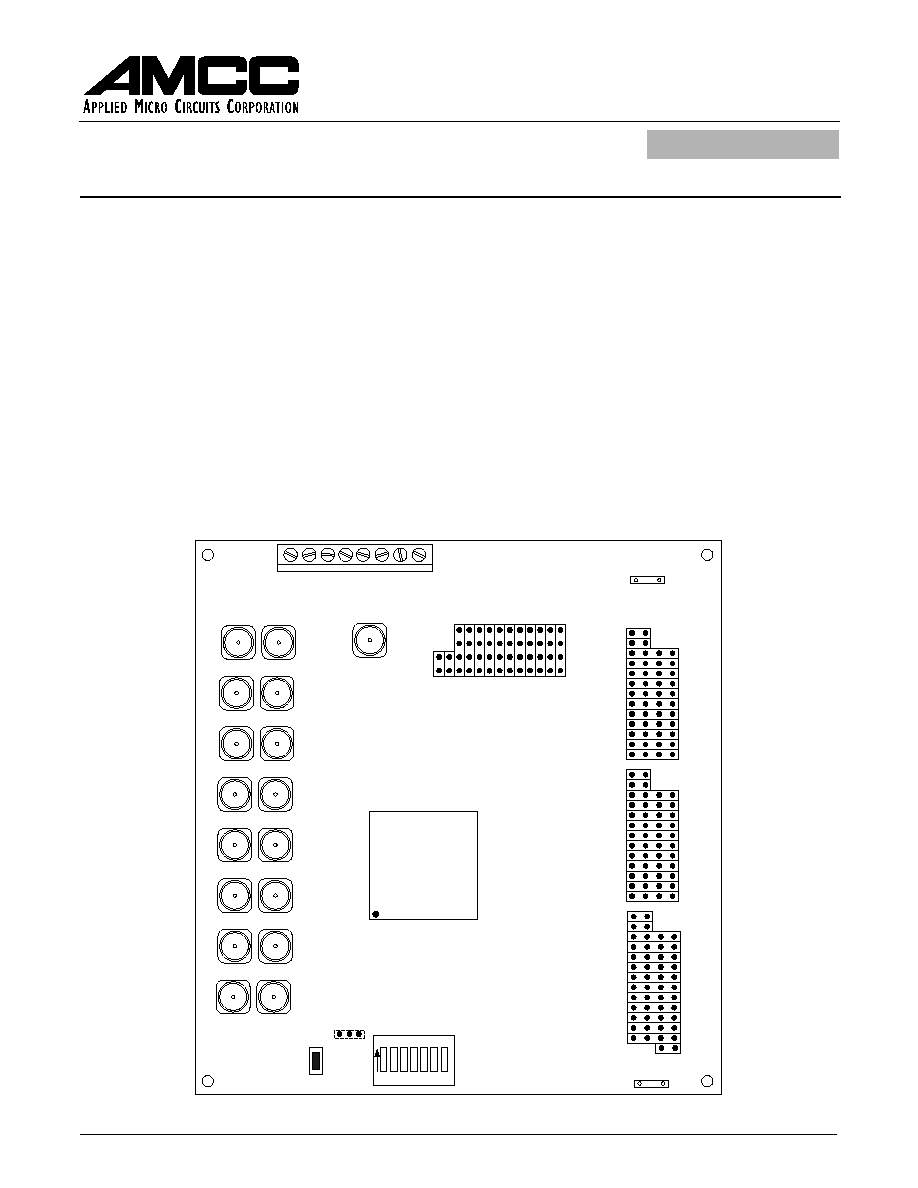

The top view of the EV2066 evaluation board is shown in Figure 1. The high speed differential LVPECL receive

RXxP/N, and transmit TXxP/N, where x = A through D, are brought in and out on the SMA connectors, as shown

on the left side of the board.

Figure 1. S2066 Evaluation Board

AMCC

S2066 Evaluation Board

1 2 3 4 5 6 7

ON

RX1AN

GND

TO DUT

FR DIPSWITCH

RX1AP

RX1BP

RX1BN

RX1CP

RX1CN

RX1DP

RX1DN

TX1AN

TX1AP

TX1BP

TX1BN

TX1CN

TX1CP

TX1DP

TX1DN

REFCLK

AMCC

S2066

GND RX TX RX PECL DIG GND TTL

VDDA VDD VDD VDD VDD VDD

GND

GND

RESET

LPEN

RATE

TMODE

CLKSEL

CMODE

CH_LOCK/TESTMODE

RESET

RCCP

RCCN

ERRC

KFLAGC

DOUTC7

DOUTC6

DOUTC5

DOUTC4

DOUTC3

DOUTC2

DOUTC1

DOUTC0

EOFC

SOFC

KGENC

DINC7

DINC6

DINC5

DINC4

DINC3

DINC2

DINC1

DINC0

TCLKC

SOFB

KGENB

DINB7

DINB6

DINB5

DINB4

DINB3

DINB2

DINB1

DINB0

TCLKB

RCBP

RCBN

ERRB

KFLAGB

DOUTB7

DOUTB6

DOUTB5

DOUTB4

DOUTB3

DOUTB2

DOUTB1

DOUTB0

EOFB

SOFA

KGENA

DINA7

DINA6

DINA5

DINA4

DINA3

DINA2

DINA1

DINA0

TCLKA

TCLK0

RCAP

RCAN

ERRA

KFLAGA

DOUTA7

DOUTA6

DOUTA5

DOUTA4

DOUTA3

DOUTA2

DOUTA1

DOUTA0

EOFA

GND

GND

INPUT

OUTPUT

RCDP

RCDN

ERRD

KFLAGD

DOUTD7

DOUTD6

DOUTD5

DOUTD4

DOUTD3

DOUTD2

DOUTD1

DOUTD0

EOFD

SOFD

KGEND

DIND7

DIND6

DIND5

DIND4

DIND3

DIND2

DIND1

DIND0

TCLKD

GND

GND

O/P

I/P

1

A

2

AMCC Confidential and Proprietary

EV2066 ≠ Quad Gigabit Ethernet Transceiver

EVALUATION BOARD

Revision 1.0 - November 16, 1999

The reference clock is brought in through the SMA connector labeled REFCLK. Power and ground are brought in

through the connector at the top of the board. The S2066 voltage is specified at 3.3V +/- 5%. Parallel I/O are

brought in and out on the connector banks on the right side of the board; there is one connector bank for each

channel (A through D). Input and output static control signals are controlled with the use of the DIP switch at the

bottom of the board. DIP switch settings are outlined in Table 1. Moving the switch to the on position creates a logic

1 (High), moving it away from the on setting creates a logic 0 (Low).

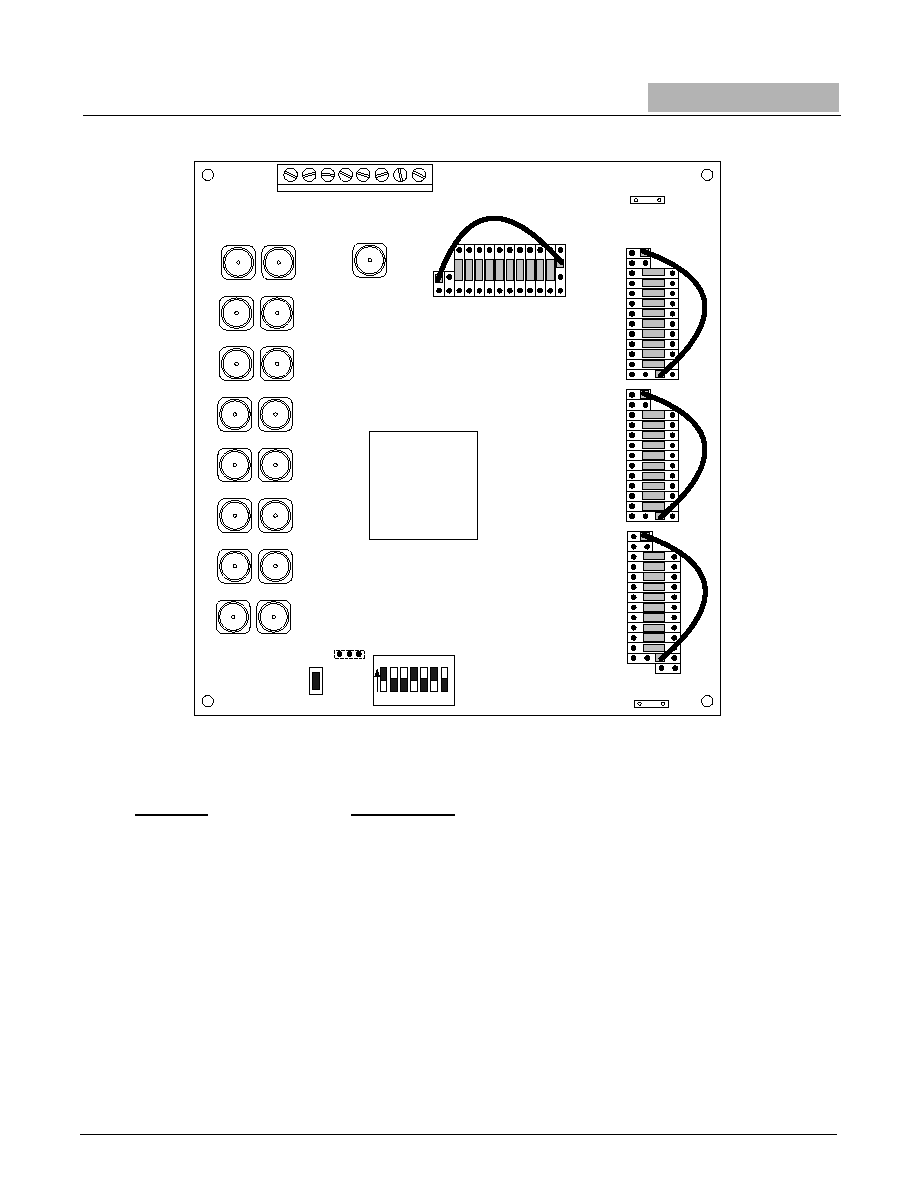

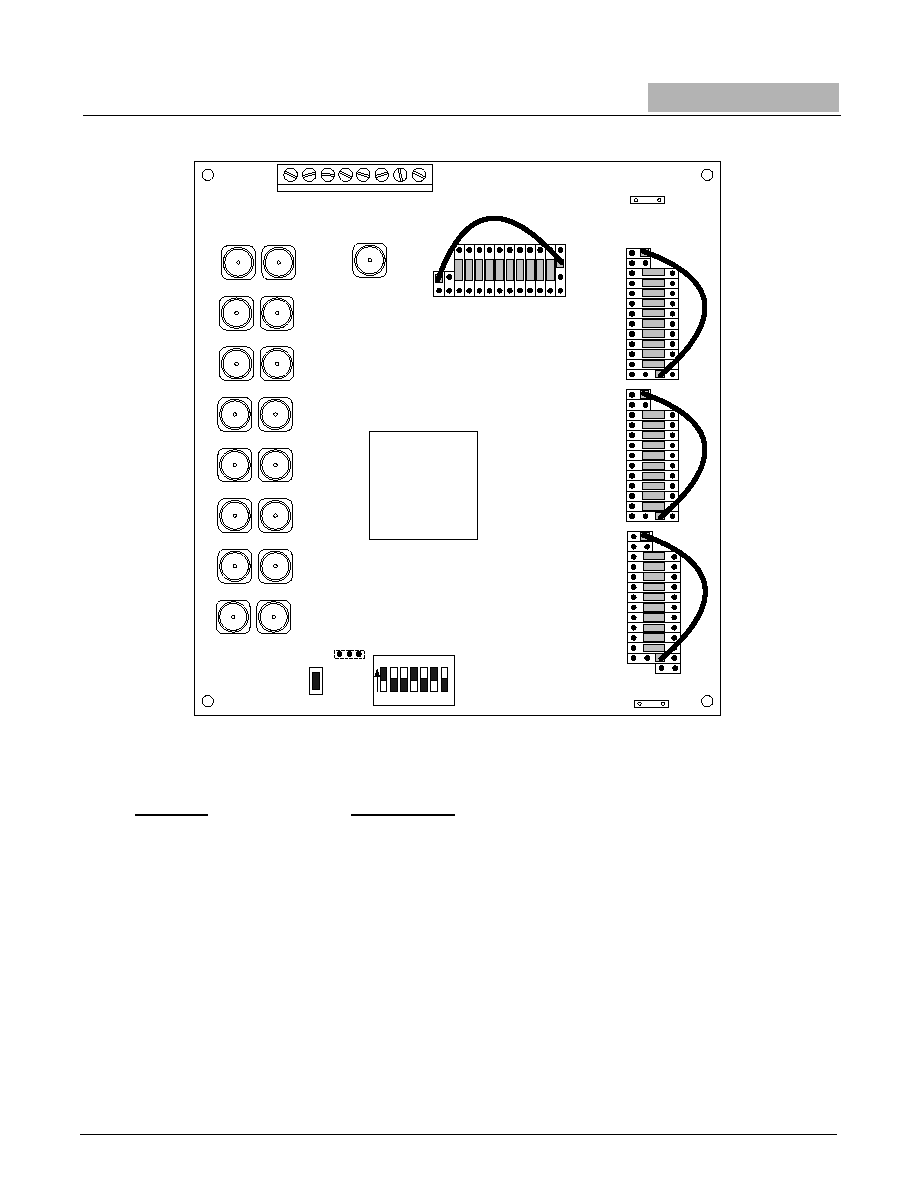

Test Setups

Typical tests performed with the S2066 evaluation board are Bit Error Rate Testing (BERT) and jitter testing. In

each case it is easiest to configure the evaluation board for serial input/output, looping back the parallel input/out-

put with jumpers. The serial input/output (parallel loopback) configuration is shown in Figure 2 and is described

below.

DIP switch settings for parallel loopback:

RESET

HIGH

LPEN

LOW

RATE

HIGH or LOW (determined by desired serial data rate)

TMODE

HIGH

CLKSEL

HIGH or LOW (determined by desired reference clock rate)

CMODE

HIGH

CH_LOCK/TEST MODE

LOW

In order to configure the board for parallel loopback, the parallel input data must be clocked into the device with the

TBCx (labled as TCLKx on the actual board) input clocks as shown in Figure 2. This clock is provided by looping

the RBCx (labled as RCxP on the actual board) output clock back into the respective TBCx (labled as TCLKx on

the actual board) input with one of the minicoax cables provided in the EV2066 Kit. These cables need only be con-

nected for the channel(s) under test.

Table 1. DIP Switch Settings

DIP Name

Description

RESET

When Low, the S2066 is held in reset. When High, the S2066 operates normally.

LPEN

Loopback Enable. When Low, the device performs normal transceiver operation. When

High the serial output for each channel is looped back to its input. The serial outputs are

squelched when LPEN = High.

RATE

When Low the S2066 operates with the serial output rate equal to the VCO frequency.

When High the S2066 operates with the VCO internally divided by 2 for all functions.

TMODE

Transmit Mode Control. When TMODE is Low, REFCLK is used to clock data on DINx

into the S2066. When TMODE is High, TBCx is used to clock data into the S2066.

CLKSEL

REFCLK Select input. This signal configures the PLL for the appropriate REFCLK fre-

quency. When CLKSEL = 0, the REFCLK frequency should equal the parallel word rate.

When CLKSEL = 1, the REFCLK frequency should be 1/2 the parallel rate.

CMODE

Clock Mode Control for receiver data stream. When Low, the rate of the parallel output

clock (RBC1/0x) is 1/2 the data rate, for ping/pong clocking. When High, the rate of the

parallel output clock (RBC1/0x) is equal to the data rate.

CH_LOCK/TESTMODE

Test Mode control. Test mode should be kept Low.

AMCC Confidential and Proprietary

3

EV2066 ≠ Quad Gigabit Ethernet Transceiver

EVALUATION BOARD

Revision 1.0 - November 16, 1999

Figure 2. Parallel Loopback Configuration

Note: The following pin names on the S2066 data sheet are labeled differently on the board:

PIN NAME

BOARD LABEL

DOUTx8

KFLAGx

DOUTx9

ERRx

DINx8

KGENx

DINx9

SOFx

TBCx

TCLKx

RBC1x

RCxP

RBC0x

RCxN

COM_DETx

EOFx

AMCC

S2066 Evaluation Board

1 2 3 4 5 6 7

ON

RX1AN

GND

TO DUT

FR DIPSWITCH

RX1AP

RX1BP

RX1BN

RX1CP

RX1CN

RX1DP

RX1DN

TX1AN

TX1AP

TX1BP

TX1BN

TX1CN

TX1CP

TX1DP

TX1DN

REFCLK

AMCC

S2066

GND RX TX RX PECL DIG GND TTL

VDDA VDD VDD VDD VDD VDD

GND

GND

RESET

LPEN

RATE

TMODE

CLKSEL

CMODE

CH_LOCK/TESTMODE

RESET

RCCP

RCCN

ERRC

KFLAGC

DOUTC7

DOUTC6

DOUTC5

DOUTC4

DOUTC3

DOUTC2

DOUTC1

DOUTC0

EOFC

SOFC

KGENC

DINC7

DINC6

DINC5

DINC4

DINC3

DINC2

DINC1

DINC0

TCLKC

SOFB

KGENB

DINB7

DINB6

DINB5

DINB4

DINB3

DINB2

DINB1

DINB0

TCLKB

RCBP

RCBN

ERRB

KFLAGB

DOUTB7

DOUTB6

DOUTB5

DOUTB4

DOUTB3

DOUTB2

DOUTB1

DOUTB0

EOFB

SOFA

KGENA

DINA7

DINA6

DINA5

DINA4

DINA3

DINA2

DINA1

DINA0

TCLKA

TCLK0

RCAP

RCAN

ERRA

KFLAGA

DOUTA7

DOUTA6

DOUTA5

DOUTA4

DOUTA3

DOUTA2

DOUTA1

DOUTA0

EOFA

GND

GND

INPUT

OUTPUT

RCDP

RCDN

ERRD

KFLAGD

DOUTD7

DOUTD6

DOUTD5

DOUTD4

DOUTD3

DOUTD2

DOUTD1

DOUTD0

EOFD

SOFD

KGEND

DIND7

DIND6

DIND5

DIND4

DIND3

DIND2

DIND1

DIND0

TCLKD

GND

GND

O/P

I/P

4

AMCC Confidential and Proprietary

EV2066 ≠ Quad Gigabit Ethernet Transceiver

EVALUATION BOARD

Revision 1.0 - November 16, 1999

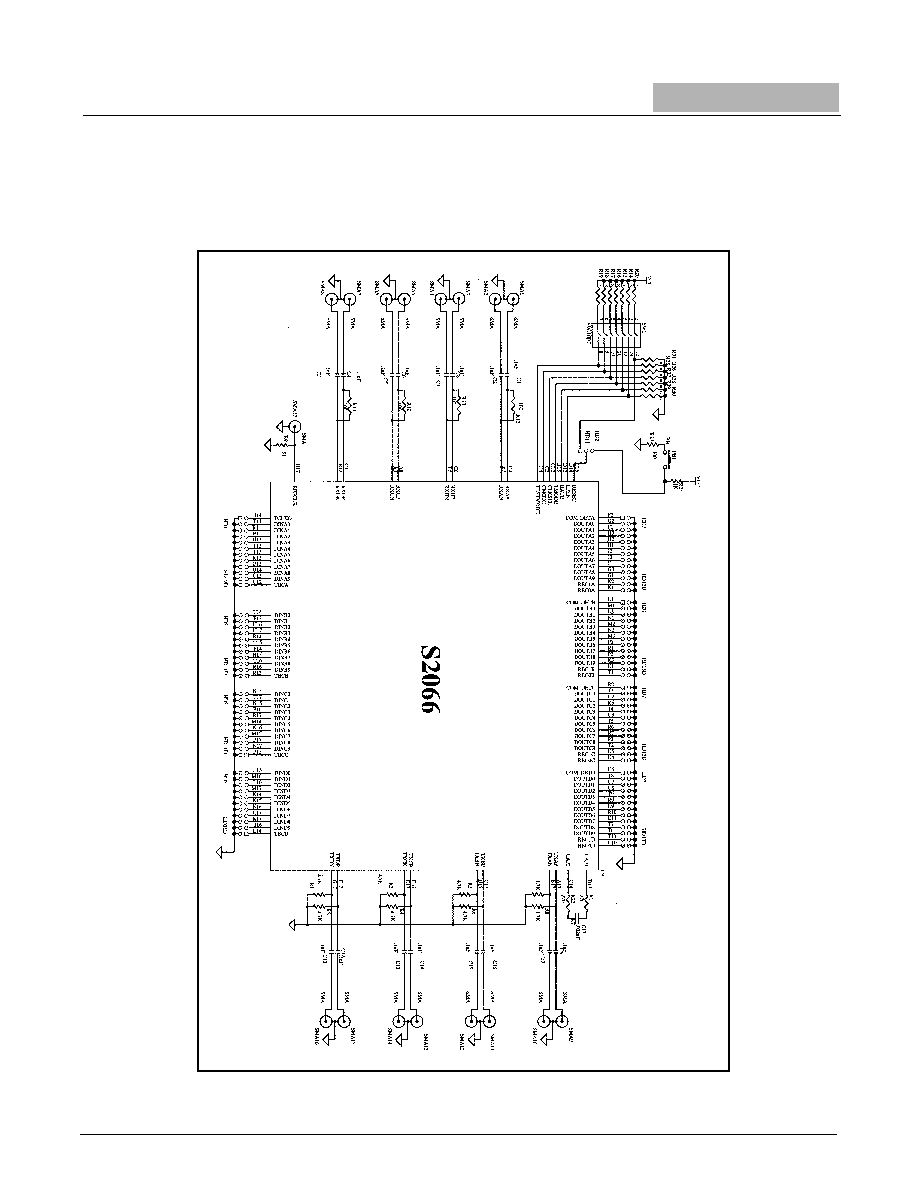

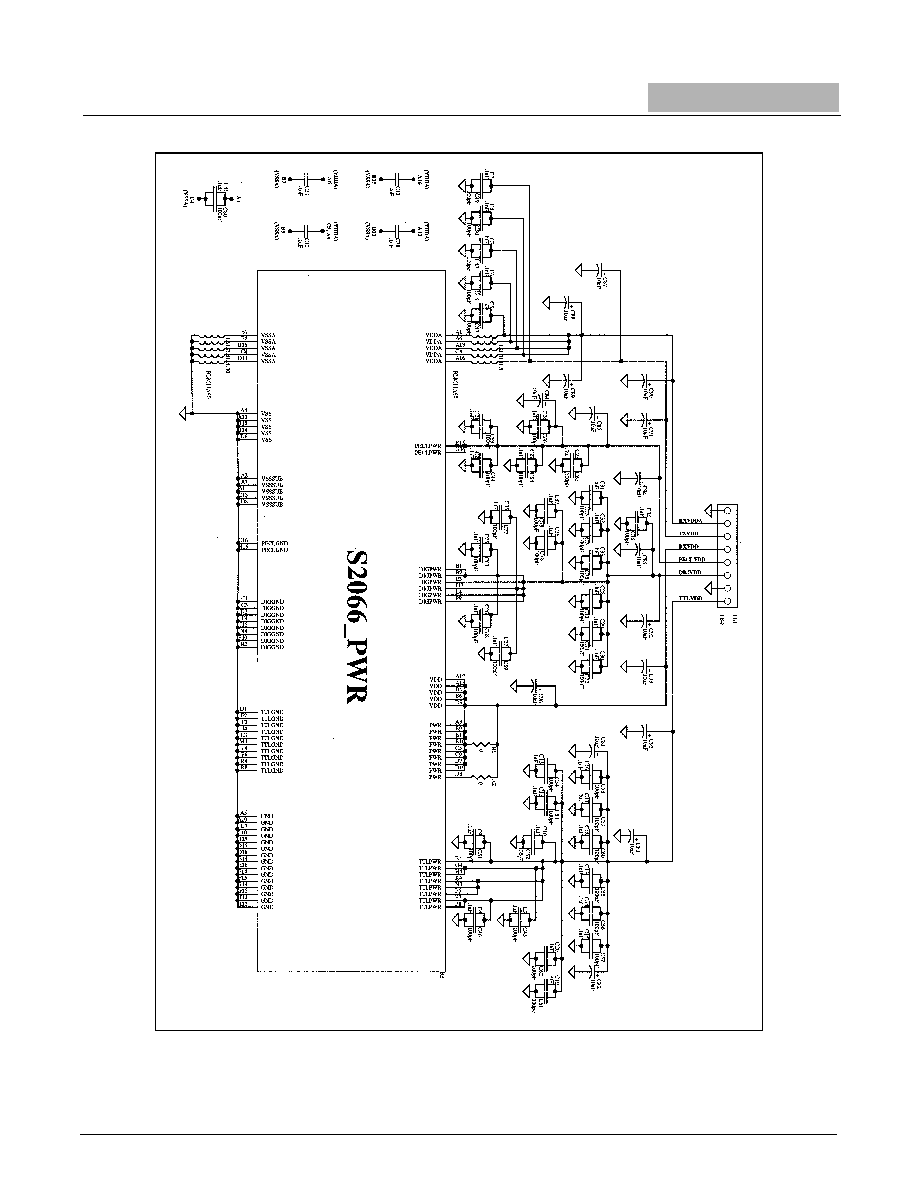

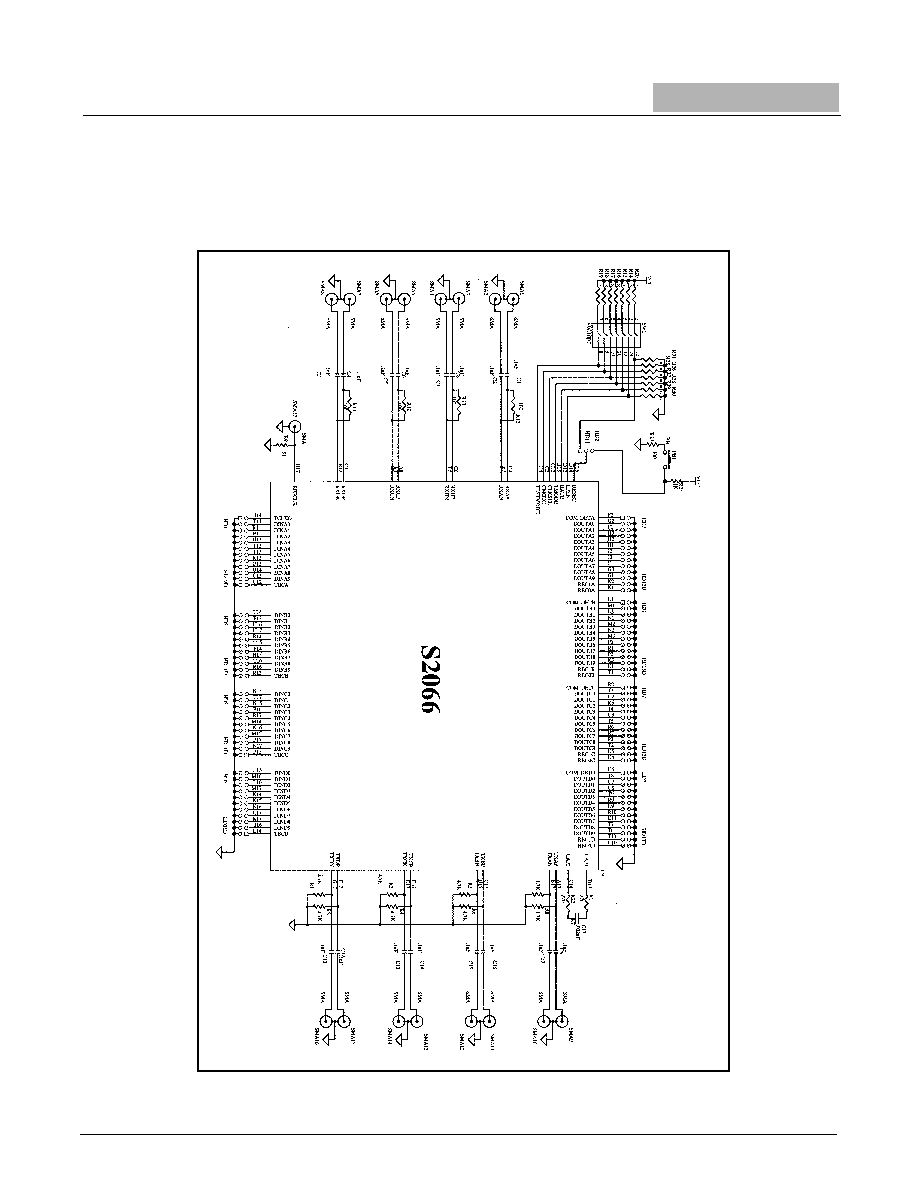

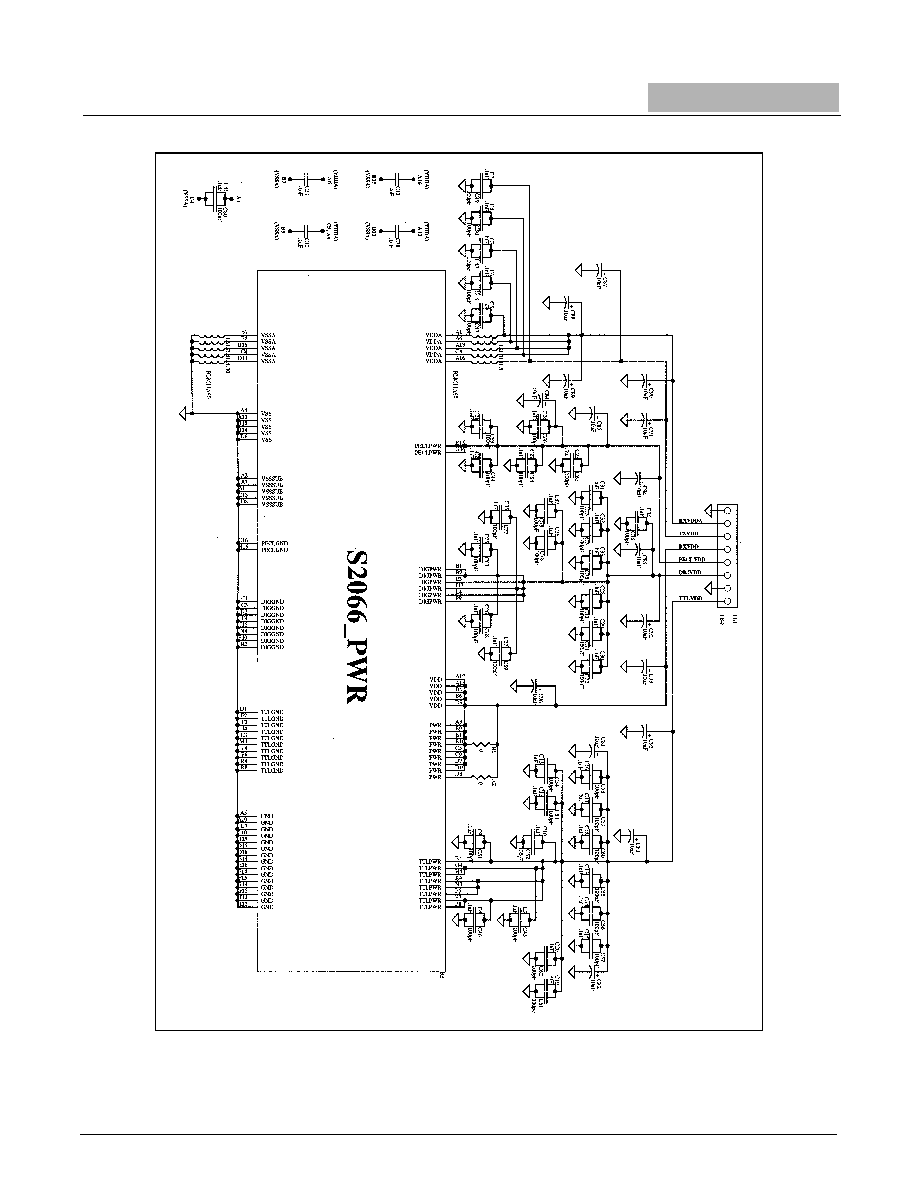

Schematic / Bill 0f Materials

Figures 3 and 4 provide a schematic representation of the S2066 evaluation board. The bill of materials are out-

lined in Tables 2 and 3.

Figure 3. EV2066 Schematic

AMCC Confidential and Proprietary

5

EV2066 ≠ Quad Gigabit Ethernet Transceiver

EVALUATION BOARD

Revision 1.0 - November 16, 1999

Figure 4. EV2066 Power and Ground Connections