| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: S2016 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

16 x 16 1.5 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

S2016

June 7, 1999 / Revision F

Æ

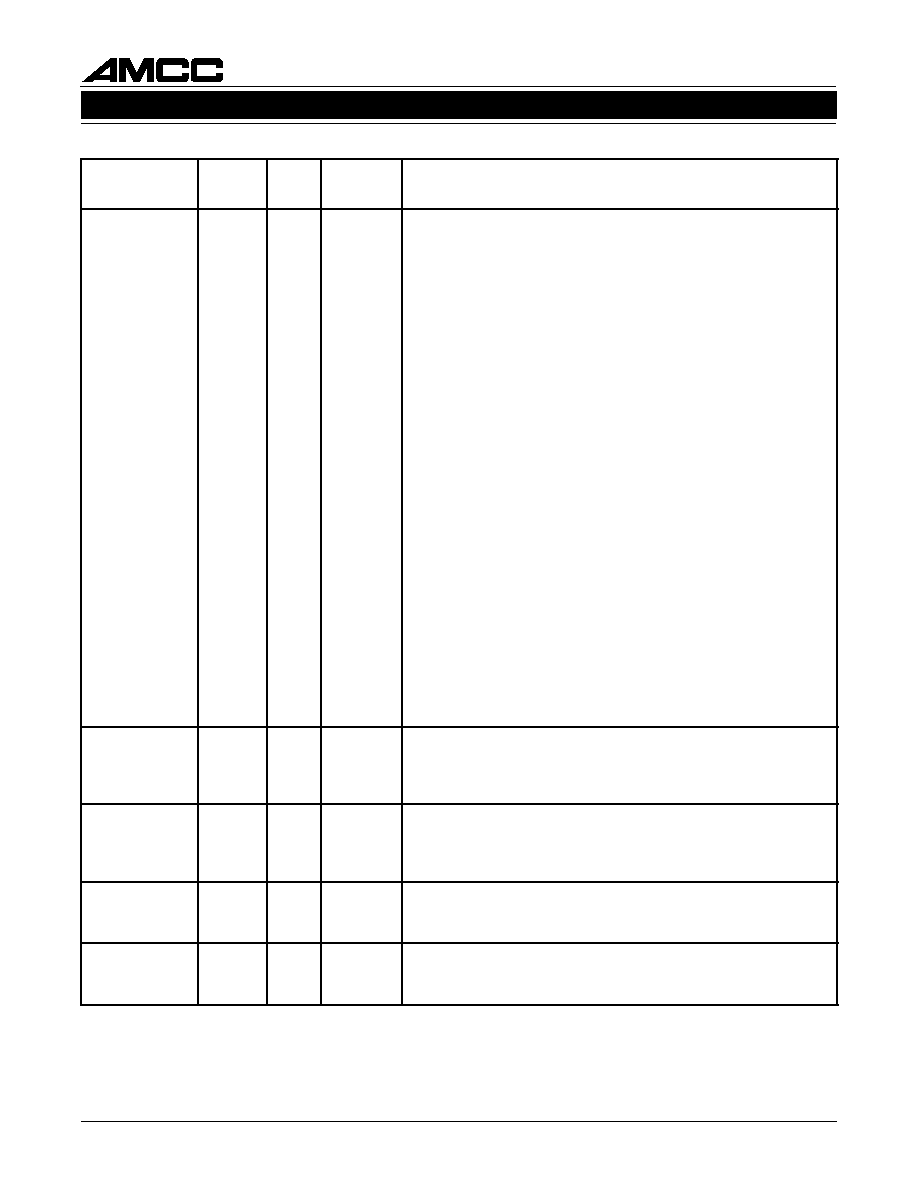

Figure 1. Functional Block Diagram

FEATURES

∑ 16 x 16 differential crosspoint switch

∑ Full broadcast switching capability

∑ Differential 10K PECL data path

∑ Up to 1.5 Gbit/s NRZ data rate

∑ TTL configuration controls

∑ Reconfigurable without disturbing operation

∑ 120-pin PQFP/TEP package

∑ +5V only power supply

APPLICATIONS

∑ Internet switches

∑ Digital video

∑ Digital demultiplexing

∑ Microwave or fiber-optic data distribution

∑ High-speed automatic test equipment

∑ Datacom or telecom switching

GENERAL DESCRIPTION

The S2016 is a very high-speed 16 x 16 differential

crosspoint switch with full broadcast capability. Any of its

16 differential PECL input signal pairs can be connected

to any or all of its 16 differential PECL output signal pairs.

The differential 10K PECL logic data path makes the

part ideal for high-speed applications. The differential

nature of the data path is retained throughout the

crosspoint structure, to minimize data distortion and to

handle NRZ data rates up to 1.5 gigabits per second.

TTL configuration controls simplify interfacing to slower

speed circuitry. Once a new configuration has been en-

tered into the configuration register file, the S2016 can be

completely reconfigured by pulsing the CONFIGN input.

16 x 16 1.5 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

S2016

PECL

Diff.

Input

Buffers

PECL

Diff.

Output

Buffers

16 x 16

Differential

Crosspoint

32

32

DIN00P

DIN15P

DOUT00P

DOUT15P

Active Configuration Latch

64

16 x 4

Configuration

Register File

64

IADDR0-3

DATA

16

4:16

Decode

EN

CONFIGN

LOADN

OADDR0-3

OADDRÿ-

4

4

4

SELECT

DOUT00N

DOUT15N

DIN00N

DIN15N

DEVICE SPECIFICATION

2

16 x 16 1.5 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

S2016

June 7, 1999 / Revision F

DATA TRANSFER

For each configured connection between a differential

input pair and an enabled output pair, any data appear-

ing at the input pair will be passed immediately through

to the output pair.

RECONFIGURATION

The S2016 can be selectively reconfigured one output

pair at a time, or any number of output pairs can be

reconfigured simultaneously. Configuration data is

stored in 16 registers, one register for each output pair.

As shown in Figure 1, the configuration data is passed

in parallel from all 16 registers to a latch which holds the

active switch configuration. This two-stage arrange-

ment allows one or more output pairs to be reconfigured

simultaneously.

To connect an output pair to a given input pair, the

output pair to be reconfigured is selected using the

OADDR0-3 (OADDR3=MSB) inputs. With the output

pair configuration register selected, the desired input

pair selection is provided on the IADDR0-3

(IADDR3=MSB) inputs. The IADDR0-3 information will

be stored into the selected output pair configuration

register by the LOADN strobe.

When the differential switch is to be reconfigured, the

S2016 minimizes the time required through the use of

an active configuration latch. While the switch is opera-

tional, and prior to the time at which it must be

reconfigured, a new configuration can be loaded into

the output pair configuration registers. Once the 16

output pair configuration registers contain the desired

connection and output pair driver enable information,

the contents of the registers are transferred in parallel

to the active configuration latch by the CONFIGN strobe.

This allows multiple connections to be simultaneously

changed.

The configuration latch can be made transparent by

driving the CONFIGN input to a logic 0. When this is

done, changes strobed into the output pair configura-

tion registers by the LOADN input pair will be passed

immediately to the switch.

Figure 2. Data Transfer Waveforms

Figure 3. Reconfiguration Waveforms

tSUIA

LDMPW

tHIA

tSULC

CFMPW

tSUOA

tHOA

OADDR0-3

IADDR0-3

LOADN

VALID

VALID

CONFIGN

tCFDO

tLDDO

tDIDO

DIMPW

DINO-15 P/N

DOUTO-15 P/N

CONFIGN

LOADN

A

A

B

C

D

E

B

C

D

E

3

16 x 16 1.5 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

S2016

June 7, 1999 / Revision F

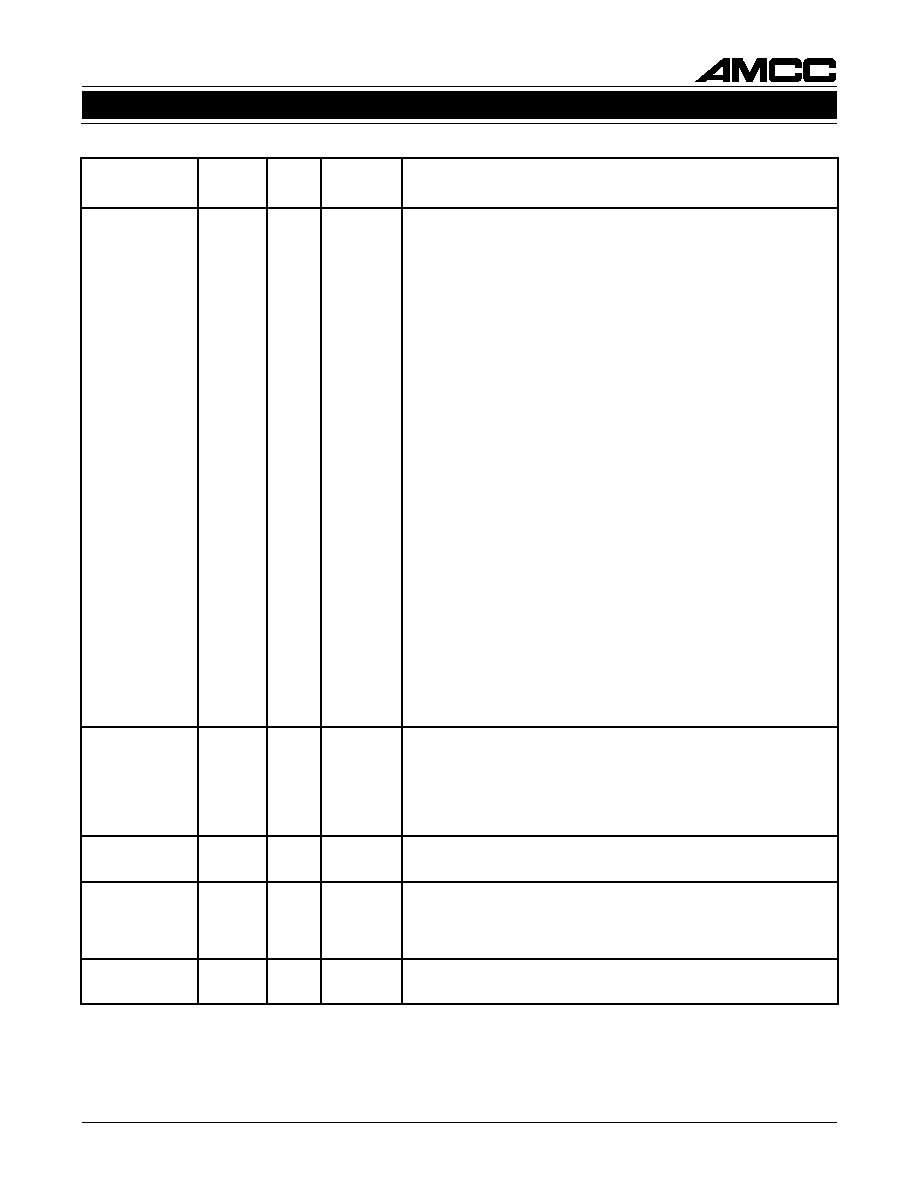

Table 1. Data Transfer Timing

1

Table 2. Reconfiguration Timing

2

Symbol

Description

Min.

Max.

Units

ps

ps

ps

ps

ps

ps

ps

1500

2000

500

1000

4200

4200

0

t

SUOA

t

HOA

t

SUIA

t

HIA

t

SULC

LD

MPW

CF

MPW

Setup time of OADDR0-3 before falling edge of LOADN

Hold time of OADDR0-3 after rising edge of LOADN

Pulse width low of LOADN

Pulse width low of CONFIGN

Setup time of IADDR0-3 before falling edge of LOADN

Hold time of IADDR0-3 after rising edge of LOADN

Setup time of LOADN to CONFIGN so that the falling edge

of CONFIGN will start reconfiguration

1. All timing measured from the V

CC

-1.3V point on the signals.

2. All timing measured from the 1.5V point on the signals.

Symbol

Description

Min.

Max.

Units

ns

ns

ns

ns

Mbit/s

0.650

3

6

7

1500

t

DIDO

t

CFDO

t

LDDO

DI

MPW

F

MAX

Propagation delay from DIN0≠15 P/N to DOUT0≠15 P/N

Propagation delay from falling edge of CONFIGN to

DOUT0≠15 P/N valid

Propagation delay from falling edge of LOADN to

DOUT0≠15 P/N valid (When CONFIGN is held low)

Pulse width of DIN0≠15 P/N

Data rate

4

16 x 16 1.5 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

S2016

June 7, 1999 / Revision F

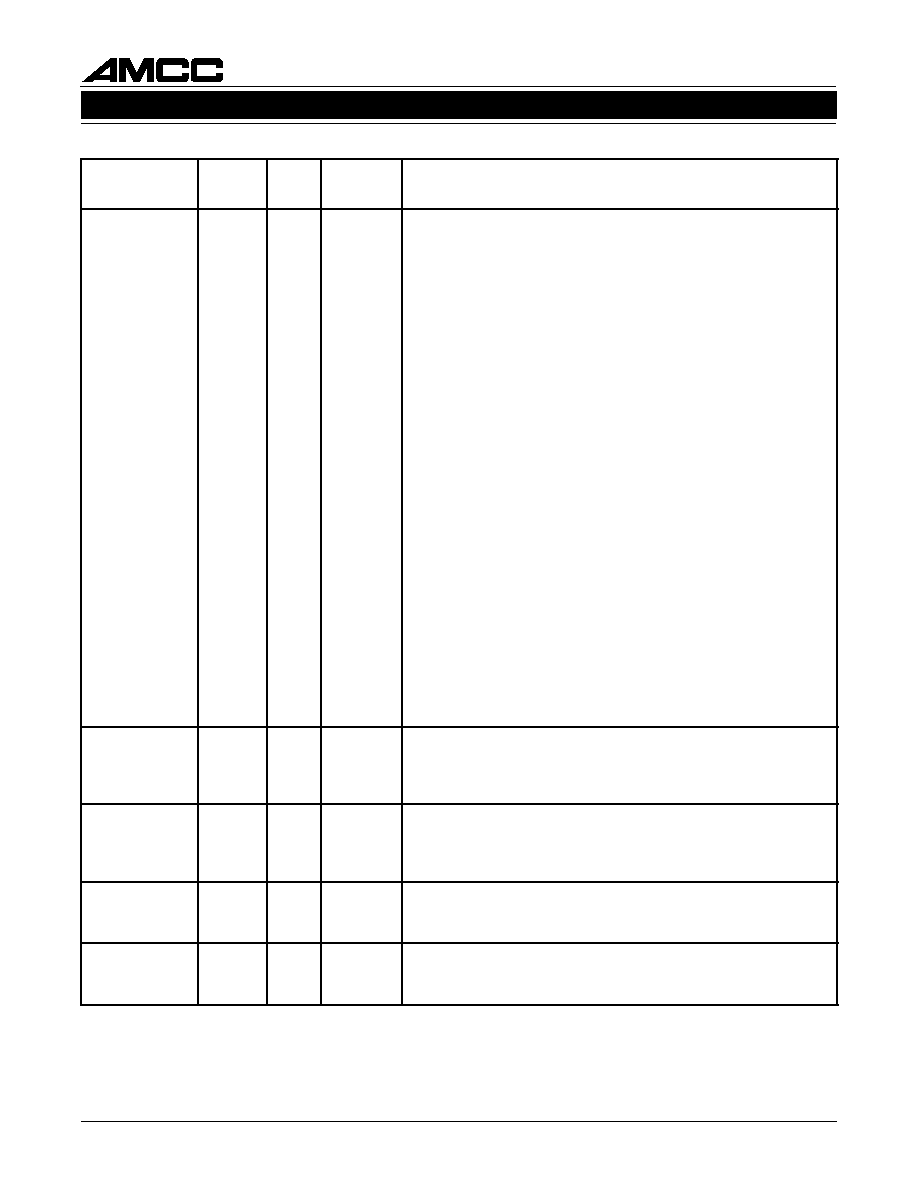

S2016 Pin Assignment and Descriptions

e

m

a

N

n

i

P

l

e

v

e

L

O

/

I

#

n

i

P

n

o

i

t

p

i

r

c

s

e

D

P

5

1

N

I

D

D N

I

N

5

1

D N

I

P

4

1

D N

I

N

4

1

D N

I

P

3

1

D N

I

N

3

1

D N

I

P

2

1

D N

I

N

2

1

D N

I

P

1

1

D N

I

N

1

1

D N

I

P

0

1

D N

I

N

0

1

D N

I

P

9

D N

I

N

9

D N

I

P

8

D N

I

N

8

P

7

N

I

D

N

7

N

I

D

P

6

N

I

D

N

6

N

I

D

P

5

N

I

D

N

5

N

I

D

P

4

N

I

D

N

4

N

I

D

P

3

N

I

D

N

3

N

I

D

P

2

N

I

D

N

2

N

I

D

P

1

N

I

D

N

1

N

I

D

P

0

N

I

D

N

0

N

I

D

.

f

f

i

D

L

C

E

P

I

5

1

1

6

1

1

6

3

5

3

1

1

1

2

1

1

0

4

9

3

9

0

1

0

1

1

2

4

1

4

7

0

1

8

0

1

4

4

3

4

3

0

1

4

0

1

8

4

7

4

1

0

1

2

0

1

0

5

9

4

9

9

0

0

1

2

5

1

5

5

9

6

9

6

5

5

5

s

t

u

p

n

i

d

e

d

n

e

-

e

l

g

n

i

s

s

a

d

e

s

u

e

b

n

a

C

.

l

a

i

t

n

e

r

e

f

f

i

D

.

a

t

a

d

t

u

p

n

I

.

r

i

a

p

t

u

p

n

i

l

a

i

t

n

e

r

e

f

f

i

d

h

c

a

e

f

o

e

d

i

s

e

n

o

o

t

d

e

i

t

B

B

V

h

t

i

w

3

R

D

D

A

O

2

R

D

D

A

O

1

R

D

D

A

O

0

R

D

D

A

O

L

T

T

I

4

6

7

5

4

3

7

2

t

u

p

t

u

o

n

a

t

c

e

l

e

s

o

t

d

e

s

U

.

h

g

i

H

e

v

i

t

c

a

,

s

s

e

r

d

d

a

t

u

p

t

u

O

.

e

li

f

r

e

t

s

i

g

e

r

n

o

i

t

a

r

u

g

i

f

n

o

c

e

h

t

n

i

r

e

t

s

i

g

e

r

n

o

i

t

a

r

u

g

i

f

n

o

c

3

R

D

D

A

I

2

R

D

D

A

I

1

R

D

D

A

I

0

R

D

D

A

I

L

T

T

I

6

8

4

9

7

1

1

5

o

t

r

i

a

p

t

u

p

n

i

e

h

t

s

t

c

e

l

e

s

0

-

3

R

D

D

A

I

.

h

g

i

H

e

v

i

t

c

a

,

s

s

e

r

d

d

a

t

u

p

n

I

.

0

-

3

R

D

D

A

O

y

b

d

e

t

c

e

l

e

s

r

i

a

p

t

u

p

t

u

o

e

h

t

o

t

t

c

e

n

n

o

c

N

D

A

O

L

L

T

T

I

6

4

n

o

i

t

a

r

u

g

i

f

n

o

c

e

h

t

s

e

r

o

t

s

,

w

o

l

n

e

h

W

.

w

o

L

e

v

i

t

c

a

,

e

b

o

r

t

s

d

a

o

L

.

e

li

f

r

e

t

s

i

g

e

r

n

o

i

t

a

r

u

g

i

f

n

o

c

e

h

t

o

t

n

i

3

-

0

R

D

D

A

I

n

o

a

t

a

d

N

G

I

F

N

O

C

L

T

T

I

5

0

1

e

h

t

s

d

a

o

l

l

e

ll

a

r

a

p

,

w

o

l

n

e

h

W

.

w

o

L

e

v

i

t

c

a

,

e

b

o

r

t

s

n

o

i

t

a

r

u

g

i

f

n

o

C

e

v

i

t

c

a

e

h

t

o

t

n

i

e

li

f

r

e

t

s

i

g

e

r

n

o

i

t

a

r

u

g

i

f

n

o

c

e

h

t

f

o

s

t

n

e

t

n

o

c

.

h

c

t

a

l

n

o

i

t

a

r

u

g

i

f

n

o

c

5

16 x 16 1.5 GBIT/S DIFFERENTIAL CROSSPOINT SWITCH

S2016

June 7, 1999 / Revision F

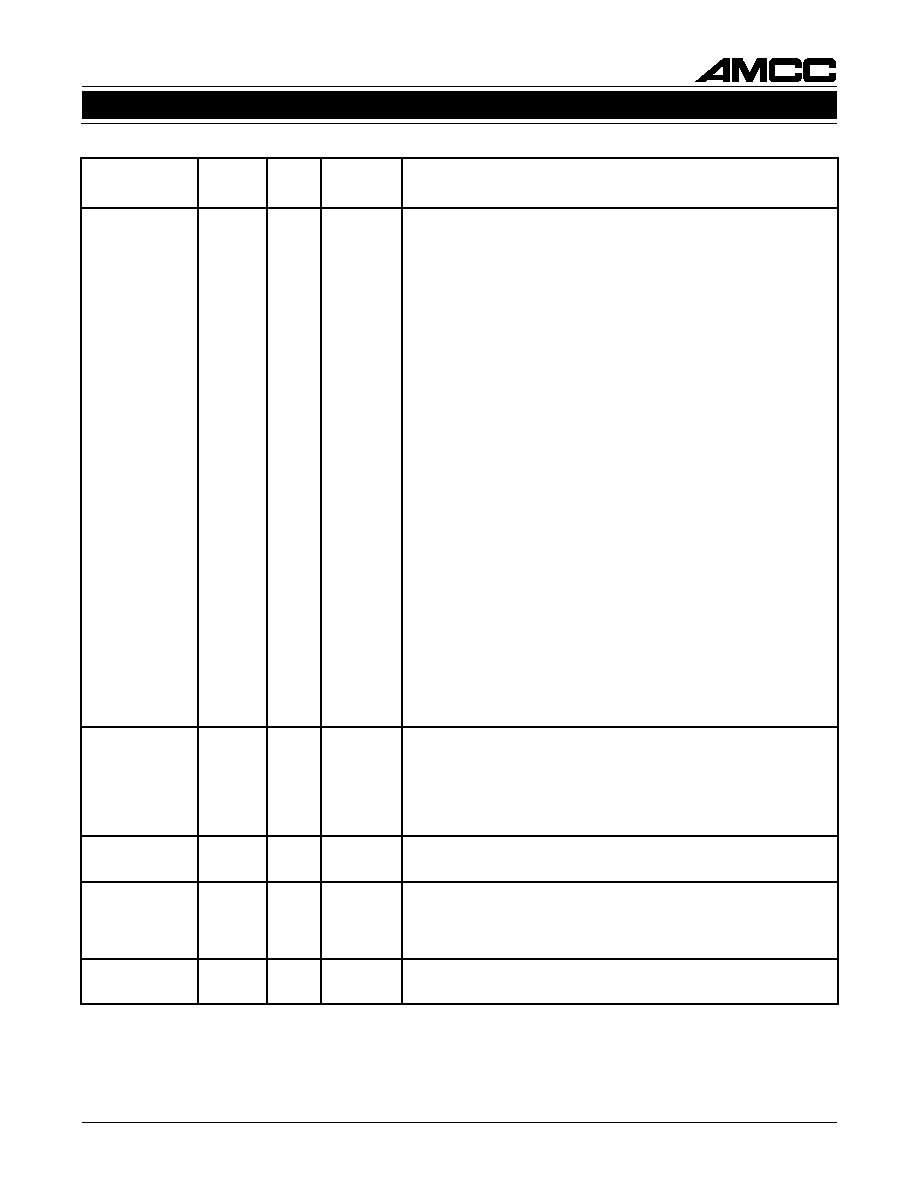

S2016 Pin Assignment and Descriptions (Continued)

e

m

a

N

n

i

P

l

e

v

e

L

O

/

I

#

n

i

P

n

o

i

t

p

i

r

c

s

e

D

P

5

1

T

U

O

D

D

T

U

O

N

5

1

D

T

U

O

P

4

1

D

T

U

O

N

4

1

D

T

U

O

P

3

1

D

T

U

O

N

3

1

D

T

U

O

P

2

1

D

T

U

O

N

2

1

D

T

U

O

P

1

1

D

T

U

O

N

1

1

D

T

U

O

P

0

1

D

T

U

O

N

0

1

D

T

U

O

P

9

D

T

U

O

N

9

D

T

U

O

P

8

D

T

U

O

N

8

P

7

T

U

O

D

N

7

T

U

O

D

P

6

T

U

O

D

N

6

T

U

O

D

P

5

T

U

O

D

N

5

T

U

O

D

P

4

T

U

O

D

N

4

T

U

O

D

P

3

T

U

O

D

N

3

T

U

O

D

P

2

T

U

O

D

N

2

T

U

O

D

P

1

T

U

O

D

N

1

T

U

O

D

P

0

T

U

O

D

N

0

T

U

O

D

.

f

f

i

D

L

C

E

P

O

6

2

5

2

2

2

1

2

0

2

9

1

8

1

7

1

5

1

4

1

3

1

2

1

1

1

0

1

7

6

5

6

6

6

9

6

0

7

1

7

2

7

3

7

4

7

6

7

7

7

8

7

9

7

0

8

1

8

4

8

5

8

.

l

a

i

t

n

e

r

e

f

f

i

D

.

a

t

a

d

t

u

p

t

u

O

C

C

V

V

5

+

≠

,

8

2

,

6

1

,

4

,

5

4

,

3

3

,

3

6

,

8

5

,

7

8

,

5

7

,

6

0

1

,

3

9

8

1

1

y

l

p

p

u

S

r

e

w

o

P

e

r

o

C

D

N

G

L

T

T

D

N

G

≠

,

2

6

,

9

2

,

3

8

8

d

n

u

o

r

G

L

T

T

C

C

V

L

C

E

V

5

+

≠

,

7

3

,

4

2

,

8

,

7

6

,

4

5

,

7

9

,

3

8

4

1

1

y

l

p

p

u

S

r

e

w

o

P

O

/

I

L

C

E

C

C

V

L

T

T

V

5

+

≠

,

9

5

,

2

3

9

1

1

,

2

9

y

l

p

p

u

S

r

e

w

o

P

L

T

T