| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: S2024B-6 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

S2024

"CROSSBOW" 32 X 32 800 MBIT/S CROSSPOINT SWITCH

June 15, 1999 / Revision B

BiCMOS PECL CLOCK GENERATOR

FEATURES

∑ Full broadcast switching capability

∑ 32 x 32 crosspoint structure, expandable to 64 x

64 with no external components

∑ ECL 10K data path and TTL I/O for configuration

control provide high speed with easy interfacing to

slower-speed circuitry

∑ Up to 800 Mbit/s NRZ data rate in transparent

mode, 400-Mbit/s operation in synchronous mode

∑ 196-pin LDCC package

∑ Reconfigurable without disturbing operation

∑ Differential or single-ended clocking

APPLICATIONS

∑ Internet switches

∑ Digital video

∑ Digital demultiplexing

∑ Microwave or fiber-optic data distribution

∑ High-speed automatic test equipment

∑ Datacom or telecom switching

GENERAL DESCRIPTION

The S2024 "Crossbow" is a high-speed 32 x 32

crosspoint switch with full broadcast capability--any of

its 32 inputs can be connected independently to any or

all of its 32 outputs. In addition, the S2024 can be

expanded, through use of its expansion data inputs

(XDIN0≠XDIN31), to a 64 x 64 crosspoint switch with

no external components. Further expansion is possible

with external addressing logic.

Two operating modes--synchronous (400 Mbit/s) and

transparent (800 Mbit/s)--provide maximum flexibility

across a range of applications. The 10K ECL logic data

path makes the part ideal for high-speed applications,

while the S2024's TTL addressing and control simplify

interfacing to slower-speed circuitry. The switch can be

completely reconfigured in only 4 ns without disturbing

switch operations.

Figure 1. Functional Block Diagram

XDINÿ≠31

DINÿ≠31

MDCLK

MDCLKN

32 x 32

CROSSPOINT

OUTPUT

LATCH

INPUT

LATCH

32

32

32

32

32

SDCLK

SDCLKN

DOUTÿ≠31

VBB2

VBB1

CNFGSTB

CONFIGURATION

LATCH

192

5:32

DECODE

EN

OUTADDÿ≠4

OAEN

CNFGCLK

RESET

INADDÿ≠5

32

6

5

192

32 X 6

REGISTER

FILE

LOAD

CLK

DATA

RST

Æ

DEVICE SPECIFICATION

S2024

"CROSSBOW" 32 X 32 800 MBIT/S CROSSPOINT SWITCH

2

S2024

"CROSSBOW" 32 X 32 800 MBIT/S CROSSPOINT SWITCH

June 15, 1999 / Revision B

OPERATING MODES

SYNCHRONOUS MODE

In synchronous mode, two clock signals, MDCLK for

data input and SDCLK for data output, provide the latch

enable strobes to allow the input data and output data

to be stored in 32-bit latches. The S2024 is capable of

400-Mbit/s operation in this mode. The data is latched

on the falling edge of SDCLK and MDCLK.

Inputs MDCLK/MDCLKN and SDCLK/SDCLKN can be

used as true differentials or as single-ended clocking

signals. Onboard voltage reference outputs VBB1 and

VBB2 allow single-ended clocking capability when con-

figured as shown in Figure 8.

TRANSPARENT MODE

In transparent, or asynchronous, mode, any data ap-

pearing at the input will be passed immediately through

to its designated output. Transparent transfer of data

through the latches takes place when both MDCLK and

SDCLK clock inputs are held high. In this mode the

S2024 is capable of up to a 800 Mbit/s NRZ data rate.

RECONFIGURATION MODE

The S2024 can be selectively reconfigured one output

at a time, or any number of outputs can be reconfigured

simultaneously. Configuration data is stored in 32 registers,

one register for each output data pin. The 6-bit content

of each register selects the input data pin which is to be

connected to that output data pin. To connect an output

to a given input, the output to reconfigure is selected

using OUTADD0≠4 and OAEN to enable the appropriate

output configuration register. With the output configura-

tion register selected, the desired input pin connection

is provided on INADD0≠5. The input pin selection on

INADD0≠5 will be stored into the selected output con-

figuration register on the rising edge of CNFGCLK.

When the switch is to be reconfigured, the S2024 mini-

mizes the time required through the use of an additional

configuration latch. While the switch is operational (and

prior to the time at which it must be reconfigured) a new

set of input addresses can be loaded into the register

file. When all registers have been updated, the contents

of the registers are parallel-transferred to the configura-

tion latch, when CNFGSTB goes high. This process

allows a switch reconfiguration in just 4 ns.

Figure 2. Synchronous Mode

DINÿ≠31

MDCLK/N

SDCLK/N

XDINÿ≠31

DOUTÿ≠31

t

SUDI

t

HDI

A

B

C

A

B

A

B

MC

MPWH

MC

MPWL

t

OVRL

t

SUXDI

t

HXDI

t

SCKDO

Figure 3. Transparent Mode

CNFGSTB

A

B

C

D

E

A

B

C

D

E

DOUTÿ≠31

DINÿ≠31

t

DIDO

t

CFDO

A

B

C

D

E

XINÿ≠31

DI

MPW

t

XIDO

XI

MPW

Figure 4. Reconfiguration Mode

OUTADDÿ≠4

OAEN

SUOA

t

t

HOA

ADDRESS VALID

t

SUOAE

t

HOAE

CC

CC

INADDÿ≠5

CNFGCLK

CNFGSTB

VALID

MPWL

MPWH

SUCFC

t

CS

MPWH

SUIA

t

t

HIA

3

S2024

"CROSSBOW" 32 X 32 800 MBIT/S CROSSPOINT SWITCH

June 15, 1999 / Revision B

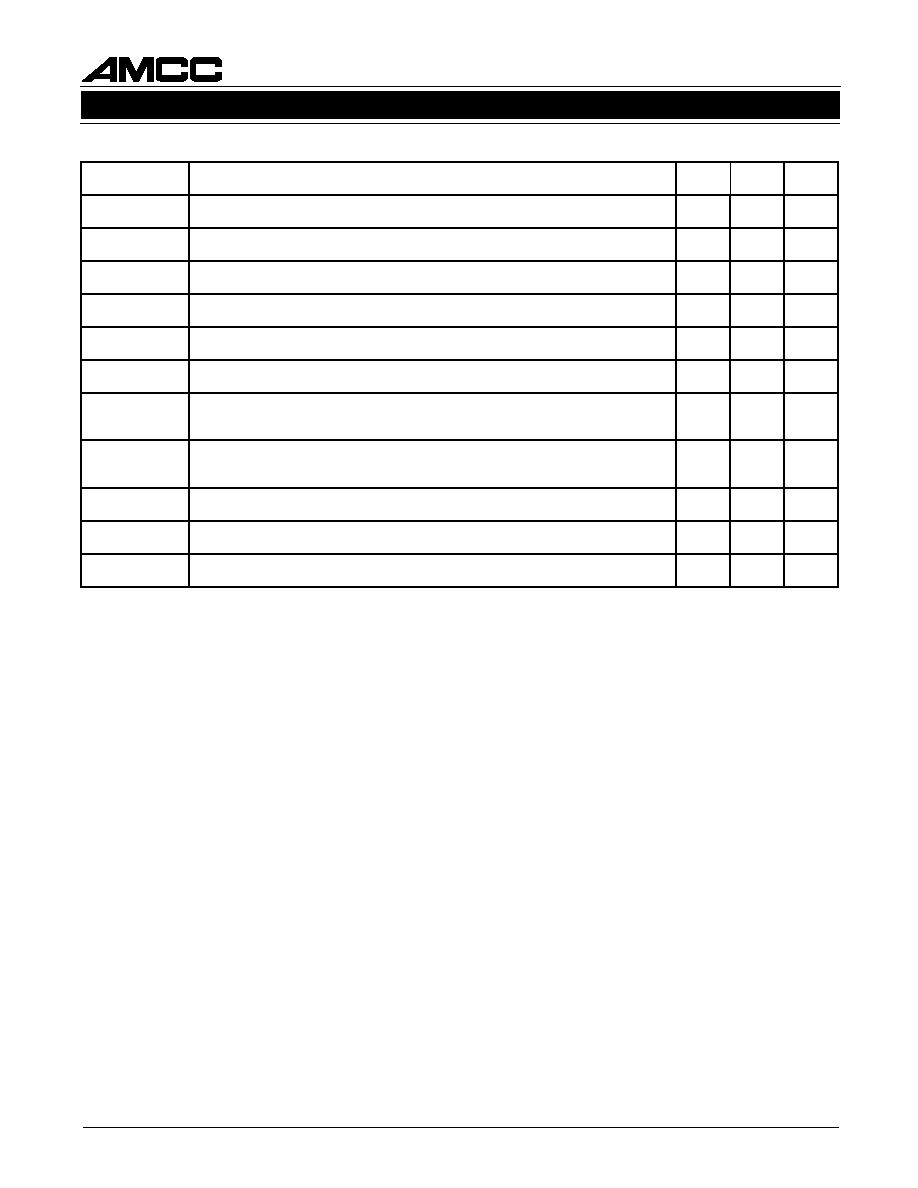

Table 1. Synchronous Mode Timing

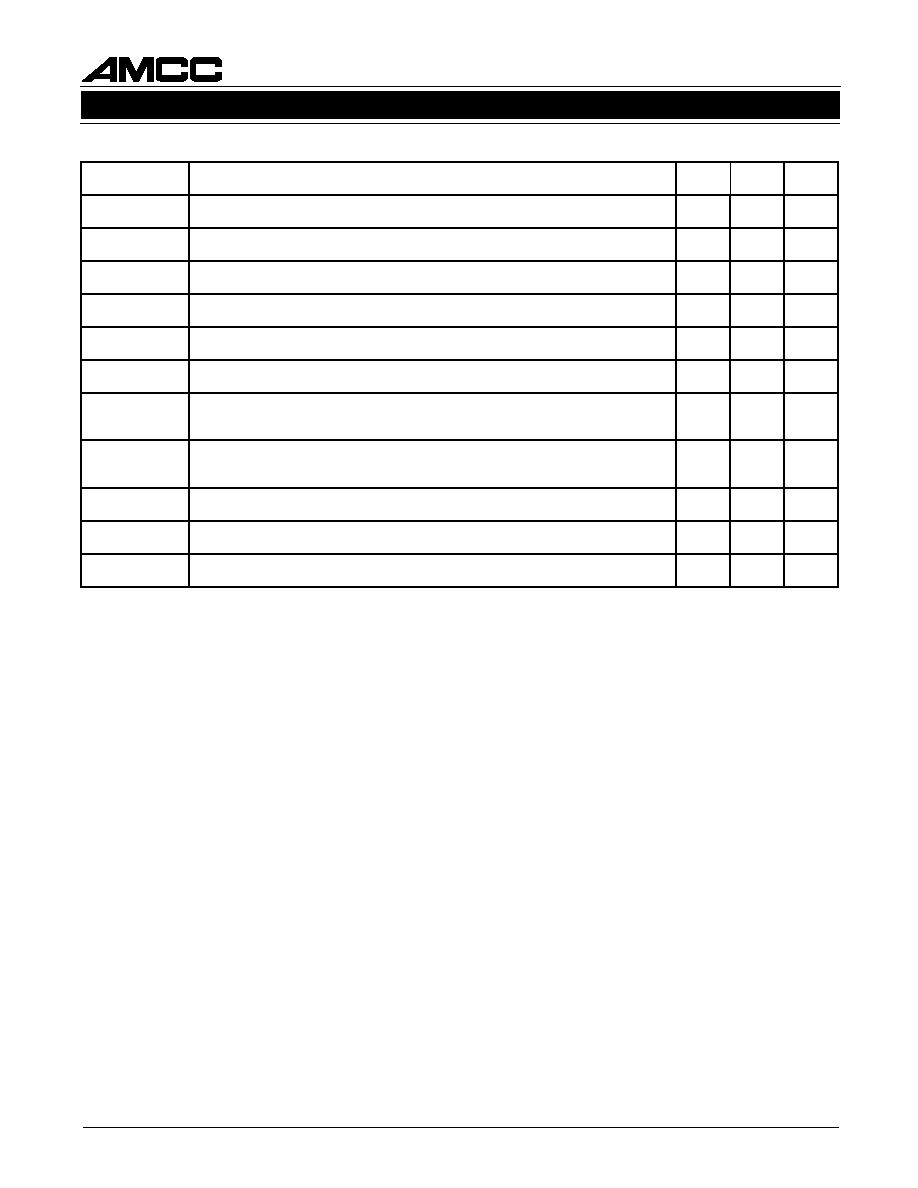

Table 2. Transparent Mode Timing

l

o

b

m

y

S

n

o

i

t

p

i

r

c

s

e

D

8

-

B

4

2

0

2

S

6

-

B

4

2

0

2

S

n

i

M

x

a

M

n

i

M

x

a

M

s

t

i

n

U

t

I

D

U

S

N

/

K

L

C

D

M

f

o

e

g

d

e

g

n

il

l

a

f

e

r

o

f

e

b

1

3

≠

0

N

I

D

f

o

e

m

i

t

p

u

t

e

S

0

6

1

1

0

8

9

s

p

t

I

D

H

f

o

e

m

i

t

d

l

o

H

1

3

≠

0

N

I

D

N

/

K

L

C

D

M

f

o

e

g

d

e

g

n

il

l

a

f

r

e

t

f

a

0

2

2

1

0

7

7

s

p

t

L

R

V

O

h

g

i

h

e

r

a

N

/

K

L

C

D

S

d

n

a

N

/

K

L

C

D

M

n

e

h

w

p

a

l

r

e

v

O

0

6

8

1

0

6

7

1

s

p

t

I

D

X

U

S

f

o

e

g

d

e

g

n

il

l

a

f

e

r

o

f

e

b

1

3

≠

0

N

I

D

X

f

o

e

m

i

t

p

u

t

e

S

N

/

K

L

C

D

S

0

6

1

1

0

4

0

1

s

p

t

I

D

X

H

f

o

e

m

i

t

d

l

o

H

1

3

≠

0

N

I

D

N

/

K

L

C

D

S

f

o

e

g

d

e

g

n

il

l

a

f

r

e

t

f

a

0

0

4

1

0

8

6

s

p

t

O

D

K

C

S

o

t

N

/

K

L

C

D

S

f

o

e

g

d

e

g

n

i

s

i

r

m

o

r

f

y

a

l

e

d

n

o

i

t

a

g

a

p

o

r

P

1

3

≠

0

T

U

O

D

0

0

4

3

0

7

7

2

s

p

C

M

H

W

P

M

N

/

K

L

C

D

S

r

o

N

/

K

L

C

D

M

f

o

h

g

i

h

h

t

d

i

w

e

s

l

u

P

0

3

6

0

9

7

s

p

C

M

L

W

P

M

N

/

K

L

C

D

S

r

o

N

/

K

L

C

D

M

f

o

w

o

l

h

t

d

i

w

e

s

l

u

P

0

0

5

0

6

6

s

p

F

X

A

M

e

t

a

R

a

t

a

D

0

0

4

0

0

3

s

/

t

i

b

M

l

o

b

m

y

S

n

o

i

t

p

i

r

c

s

e

D

8

-

B

4

2

0

2

S

6

-

B

4

2

0

2

S

n

i

M

x

a

M

n

i

M

x

a

M

s

t

i

n

U

t

O

D

I

D

m

o

r

f

y

a

l

e

d

n

o

i

t

a

g

a

p

o

r

P

o

t

1

3

≠

0

N

I

D

T

U

O

D

≠

0

1

3

0

8

1

4

5

2

1

5

s

p

t

O

D

I

X

m

o

r

f

y

a

l

e

d

n

o

i

t

a

g

a

p

o

r

P

o

t

1

3

≠

0

N

I

X

T

U

O

D

≠

0

1

3

0

4

0

3

0

0

4

3

s

p

t

O

D

F

C

o

t

B

T

S

G

F

N

C

f

o

e

g

d

e

g

n

i

s

i

r

m

o

r

f

y

a

l

e

d

n

o

i

t

a

g

a

p

o

r

P

T

U

O

D

≠

0

d

il

a

v

1

3

0

6

7

3

0

5

1

4

s

p

I

D

W

P

M

N

I

D

f

o

h

g

i

h

h

t

d

i

w

e

s

l

u

P

≠

0

1

3

0

6

8

0

3

0

1

s

p

I

X

W

P

M

N

I

D

X

f

o

h

g

i

h

h

t

d

i

w

e

s

l

u

P

≠

0

1

3

0

1

9

0

9

0

1

s

p

F

X

A

M

e

t

a

R

a

t

a

D

0

0

8

0

0

6

s

/

t

i

b

M

4

S2024

"CROSSBOW" 32 X 32 800 MBIT/S CROSSPOINT SWITCH

June 15, 1999 / Revision B

Table 3. Reconfiguration Timing (S2024B-8, S2024B-6)

l

o

b

m

y

S

n

o

i

t

p

i

r

c

s

e

D

n

i

M

x

a

M

s

t

i

n

U

t

A

O

U

S

e

r

o

f

e

b

4

≠

0

D

D

A

T

U

O

f

o

e

m

i

t

p

u

t

e

S

f

o

e

g

d

e

g

n

i

s

i

r

K

L

C

G

F

N

C

0

6

3

4

s

p

t

A

O

H

f

o

e

m

i

t

d

l

o

H

4

≠

0

D

D

A

T

U

O

f

o

e

g

d

e

g

n

i

s

i

r

r

e

t

f

a

K

L

C

G

F

N

C

0

6

5

s

p

t

E

A

O

U

S

f

o

e

m

i

t

p

u

t

e

S

N

E

A

O

e

r

o

f

e

b

f

o

e

g

d

e

g

n

i

s

i

r

K

L

C

G

F

N

C

0

6

8

3

s

p

t

E

A

O

H

N

E

A

O

f

o

e

m

i

t

d

l

o

H

e

r

o

f

e

b

f

o

e

g

d

e

g

n

i

s

i

r

K

L

C

G

F

N

C

0

4

1

≠

s

p

t

A

I

U

S

f

o

e

m

i

t

p

u

t

e

S

5

≠

0

D

D

A

N

I

e

r

o

f

e

b

f

o

e

g

d

e

g

n

i

s

i

r

K

L

C

G

F

N

C

0

6

6

2

s

p

t

A

I

H

5

≠

0

D

D

A

N

I

f

o

e

m

i

t

d

l

o

H

e

r

o

f

e

b

f

o

e

g

d

e

g

n

i

s

i

r

K

L

C

G

F

N

C

0

8

9

s

p

t

C

F

C

U

S

e

m

i

t

p

u

t

e

S

f

o

f

o

e

g

d

e

g

n

i

s

i

r

e

h

t

t

a

h

t

o

s

B

T

S

G

F

N

C

o

t

K

L

C

G

F

N

C

n

o

i

t

a

r

u

g

i

f

n

o

c

e

r

t

r

a

t

s

ll

i

w

B

T

S

G

F

N

C

0

6

7

s

p

t

G

F

C

U

S

e

m

i

t

p

u

t

e

S

f

o

f

o

e

g

d

e

g

n

i

s

i

r

e

h

t

e

r

o

f

e

b

e

g

d

e

g

n

il

l

a

f

B

T

S

G

F

N

C

K

L

C

G

F

N

C

0

6

9

1

C

C

L

W

P

M

K

L

C

G

F

N

C

f

o

w

o

l

h

t

d

i

w

e

s

l

u

P

0

0

2

4

s

p

C

C

H

W

P

M

K

L

C

G

F

N

C

f

o

h

g

i

h

h

t

d

i

w

e

s

l

u

P

0

0

2

4

s

p

S

C

H

W

P

M

B

T

S

G

F

N

C

f

o

w

o

l

h

t

d

i

w

e

s

l

u

P

0

0

2

4

s

p

5

S2024

"CROSSBOW" 32 X 32 800 MBIT/S CROSSPOINT SWITCH

June 15, 1999 / Revision B

e

m

a

N

n

i

P

l

e

v

e

L

O

/

I

#

n

i

P

n

o

i

t

p

i

r

c

s

e

D

1

3

N

I

D

0

3

N

I

D

9

2

N

I

D

8

2

N

I

D

7

2

N

I

D

6

2

N

I

D

5

2

N

I

D

4

2

N

I

D

3

2

N

I

D

2

2

N

I

D

1

2

N

I

D

0

2

N

I

D

9

1

N

I

D

8

1

N

I

D

7

1

N

I

D

6

1

N

I

D

5

1

N

I

D

4

1

N

I

D

3

1

N

I

D

2

1

N

I

D

1

1

N

I

D

0

1

N

I

D

9

N

I

D

8

N

I

D

7

N

I

D

6

N

I

D

5

N

I

D

4

N

I

D

3

N

I

D

2

N

I

D

1

N

I

D

0

N

I

D

L

C

E

I

1

8

1

0

8

1

9

7

1

7

7

1

6

7

1

5

7

1

4

7

1

9

6

1

7

6

1

6

6

1

4

6

1

1

6

1

0

6

1

9

5

1

7

5

1

6

5

1

5

5

1

4

5

1

3

5

1

2

5

1

0

5

1

5

4

1

3

4

1

2

4

1

1

4

1

0

4

1

9

3

1

7

3

1

6

3

1

4

3

1

5

3

1

1

3

1

.

h

g

i

H

e

v

i

t

c

A

.

a

t

a

d

t

u

p

t

n

I

4

D

D

A

T

U

O

3

D

D

A

T

U

O

2

D

D

A

T

U

O

1

D

D

A

T

U

O

0

D

D

A

T

U

O

L

T

T

I

3

1

5

3

2

1

t

u

p

t

u

o

e

h

t

t

c

e

l

e

s

o

t

d

e

s

U

.

s

s

e

r

d

d

a

r

e

t

s

i

g

e

r

n

o

i

t

a

r

u

g

i

f

n

o

c

t

u

p

t

u

O

.

e

li

f

r

e

t

s

i

g

e

r

e

h

t

n

i

s

r

e

t

s

i

g

e

r

n

o

i

t

a

r

u

g

i

f

n

o

c

5

D

D

A

N

I

4

D

D

A

N

I

3

D

D

A

N

I

2

D

D

A

N

I

1

D

D

A

N

I

0

D

D

A

N

I

L

T

T

I

1

2

0

2

9

1

8

1

5

1

4

1

n

i

p

a

t

a

d

t

u

p

n

i

e

h

t

t

c

e

l

e

s

o

t

d

e

s

U

.

s

e

s

s

e

r

d

d

a

a

t

a

d

t

u

p

n

I

y

b

e

li

f

r

e

t

s

i

g

e

r

o

t

n

i

d

e

r

o

t

S

.

n

i

p

a

t

a

d

t

u

p

t

u

o

h

c

a

e

o

t

d

e

t

c

e

n

n

o

c

a

t

a

d

n

o

i

s

n

a

p

x

e

e

h

t

t

c

e

l

e

s

o

t

d

e

s

u

s

i

1

=

5

D

D

A

N

I

.

K

L

C

G

F

N

C

.

s

t

u

p

n

i

N

E

A

O

L

T

T

I

0

9

1

f

o

n

o

i

t

c

e

l

e

s

e

h

t

s

e

l

b

a

n

e

,

h

g

i

h

n

e

h

W

.

e

l

b

a

n

e

s

s

e

r

d

d

a

t

u

p

t

u

O

.

r

e

t

s

i

g

e

r

n

o

i

t

a

r

u

g

i

f

n

o

c

t

u

p

t

u

o

e

t

a

i

r

p

o

r

p

p

a

K

L

C

D

M

N

K

L

C

D

M

L

C

E

I

6

6

5

6

.

s

t

u

p

n

i

l

a

i

t

n

e

r

e

f

f

i

d

e

u

r

T

.

)

a

t

a

d

t

u

p

n

i

(

s

t

u

p

n

i

k

c

o

l

c

h

c

t

a

l

r

e

t

s

a

M

.

2

B

B

V

d

n

a

1

B

B

V

h

t

i

w

d

e

d

n

e

-

e

l

g

n

i

s

d

e

s

u

e

b

n

a

C

Table 4. Pin Assignment and Descriptions