1

S2057

PORT BYPASS CIRCUIT FOR FIBRE CHANNEL AND GIGABIT ETHERNET

S2057

Æ

PORT BYPASS CIRCUIT FOR FIBRE CHANNEL AND GIGABIT ETHERNET

FEATURES

∑ Supports ANSI X3T11 1.0625 Gbit/sec FCAL

disk attach

∑ 1250 Mbps (Gigabit Ethernet) operation

∑ Fully differential for minimum deterministic

jitter accumulation (10 ps nominal)

∑ TTL Bypass Select

∑ High speed LVPECL I/O

∑ 0.2 W Typical power dissipation

∑ 3.3 V power supply

∑ 20-pin TSSOP

OUT P/N

SEL

DDI P/N

DDO P/N

IN P/N

1

0

PBC

Figure 1. S2057 Block Diagram

1

L

E

S

T

U

O

O

D

D

0

N

I

N

I

1

I

D

D

N

I

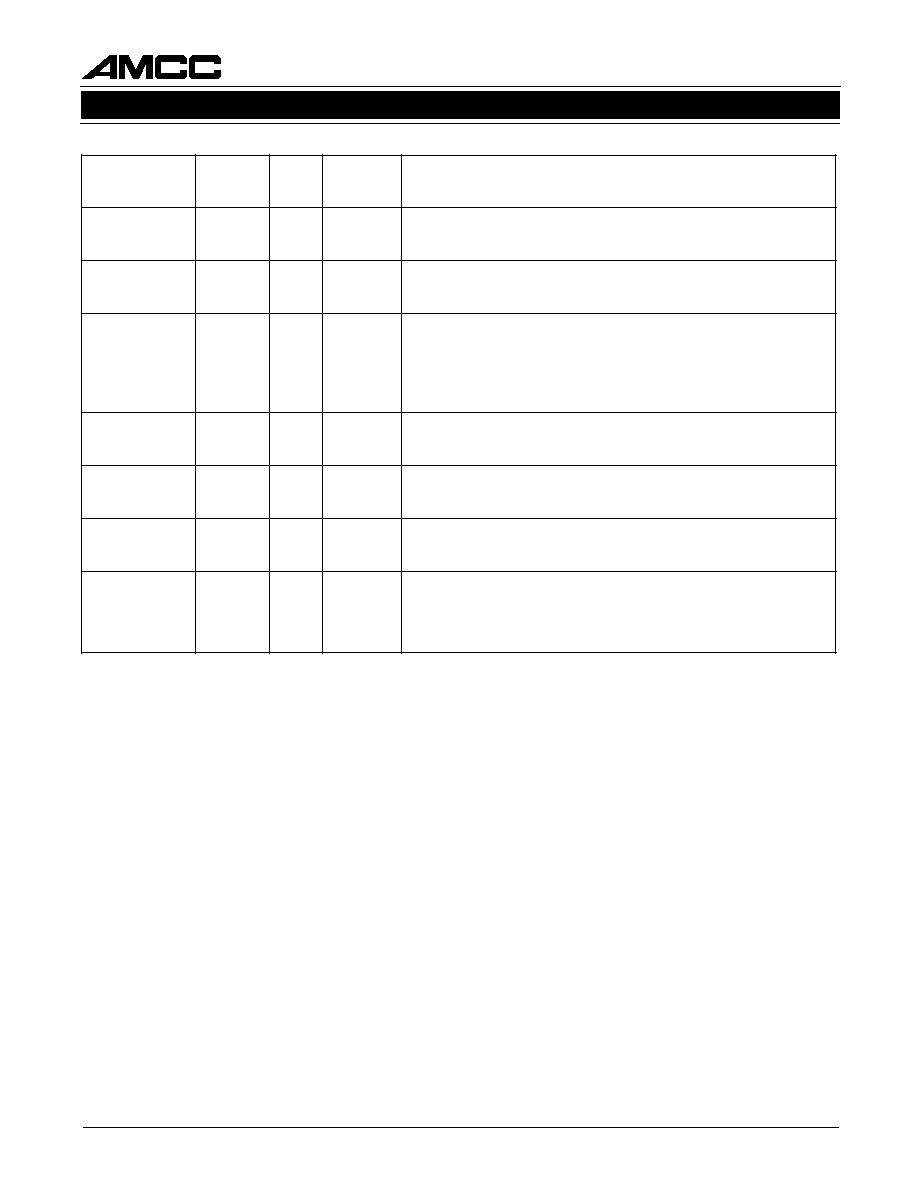

Table 1. Truth Table

DEVICE

SPECIFICATION

GENERAL DESCRIPTION

The S2057 is a single channel Port Bypass Circuit

(PBC), designed to minimize jitter accumulation by

providing a high bandwidth fully differential data path.

Primary application is in Fibre Channel Arbitrated Loop

(FC-AL) disk arrays to allow hot swapping of FC-AL

drives. The S2057 is designed to support 1.0625 Gbps

and 1.25 Gbps data rates.

The S2057 is a high speed 2:1 multiplexer with 2 modes

of operation: Normal and Bypass. A block diagram is

shown in Figure 1, and a system diagram showing the

S2057 in a single loop of a disk array is shown in Figure 2.

A disk drive connects on the Disk Drive input and output

ports (DDIP/N, DDOP/N), while the INP/N and OUTP/

N ports connect to the upstream and downstream

devices in the loop. Normal mode is enabled by setting

the SEL pin ACTIVE, which includes the disk in the loop

via the DDI/DDO ports. When the disk drive is either

absent or non-functional, Bypass mode is selected by

setting the SEL pin INACTIVE. This routes data directly

from IN to OUT, bypassing the disk ports. Direct attach

Fibre Channel Disk Drives have an "LRC Interlock"

signal designed to directly control the select function.

Table 1 is a truth table describing the data flow through

the S2057.

Jitter Performance

The primary AC parameter of importance is determinis-

tic jitter accumulation (data eye degradation) inserted

by the port bypass circuit. The S2057 utilizes high

bandwidth, low skew differential circuitry to provide

symmetric rise and fall times and excellent noise immu-

nity. This results in a nominal deterministic jitter accu-

mulation of

±

10 ps.

For arrays of disk drives greater than 4, it is recom-

mended that the S2057 be cascaded with the S2058

(Port Bypass with repeater) in a ratio of 4:1 to perform

clock and data retiming. This insures optimal jitter

performance for the disk array system.

3

S2057

PORT BYPASS CIRCUIT FOR FIBRE CHANNEL AND GIGABIT ETHERNET

Figure 3. Timing Waveforms

Figure 4. Differential Voltage

Figure 5. Input Termination

IN P/N

DDI P/N

OUT P/N

DDO P/N

T

1, 2, 3

V

P - P

= 1000mV

500mV

Single-ended swing

S2057

100

0.1

µ

F

0.1

µ

F

Biased at Vcc -0.65V

Figure 6. Output Connection

Backplane

S2057

150

150

0.1

µ

f

0.1

µ

f