1

S2091

2.5 GBIT PORT BYPASS CIRCUIT FOR FIBRE CHANNEL ARBITRATED LOOP

S2091

Æ

2.5 GBIT PORT BYPASS CIRCUIT FOR FIBRE CHANNEL ARBITRATED LOOP

FEATURES

∑ Supports 2.5 Gbps Data Rates

∑ Fully differential for minimum

jitter accumulation

∑ TTL Bypass Select

∑ High speed 50

source terminated outputs

∑ 0.4W Typical power dissipation

∑ 3.3V power supply

∑ 20 Pin TSSOP

GENERAL DESCRIPTION

The S2091 is a Port Bypass Circuit (PBC). A single

channel Fibre Channel PBC offers designers maxi-

mum flexibility in FC-AL disk architectures. The

S2091 is designed to minimize jitter accumulation by

providing a high bandwidth fully differential signal

path. Port Bypass circuits are used to provide resil-

iency in Fibre Channel Arbitrated Loop (FC-AL) ar-

chitectures. PBC's are used within FC-AL disk arrays

to allow for resiliency and hot swapping of FC-AL

drives.

A Port-by-Pass Circuit is a 2:1 Multiplexer with two

modes of operations: Normal and Bypass. In Normal

mode, the disk drive is connected to the loop. In

Bypass mode, the disk drive is either absent or non-

OUT P/N

SEL

DDI P/N

DDO P/N

IN P/N

1

0

PBC

Figure 1. S2091 Block Diagram

1

L

E

S

T

U

O

O

D

D

0

N

I

N

I

1

I

D

D

N

I

Table 1. Truth Table

functional and data bypasses to the next available disk

drive. Normal mode is enabled with a High on the SEL

pin and Bypass mode is enable by a Low on the SEL

pin. Direct Attach Fibre Channel Disk Drives have an

"LRC Interlock" signal defined to control the SEL func-

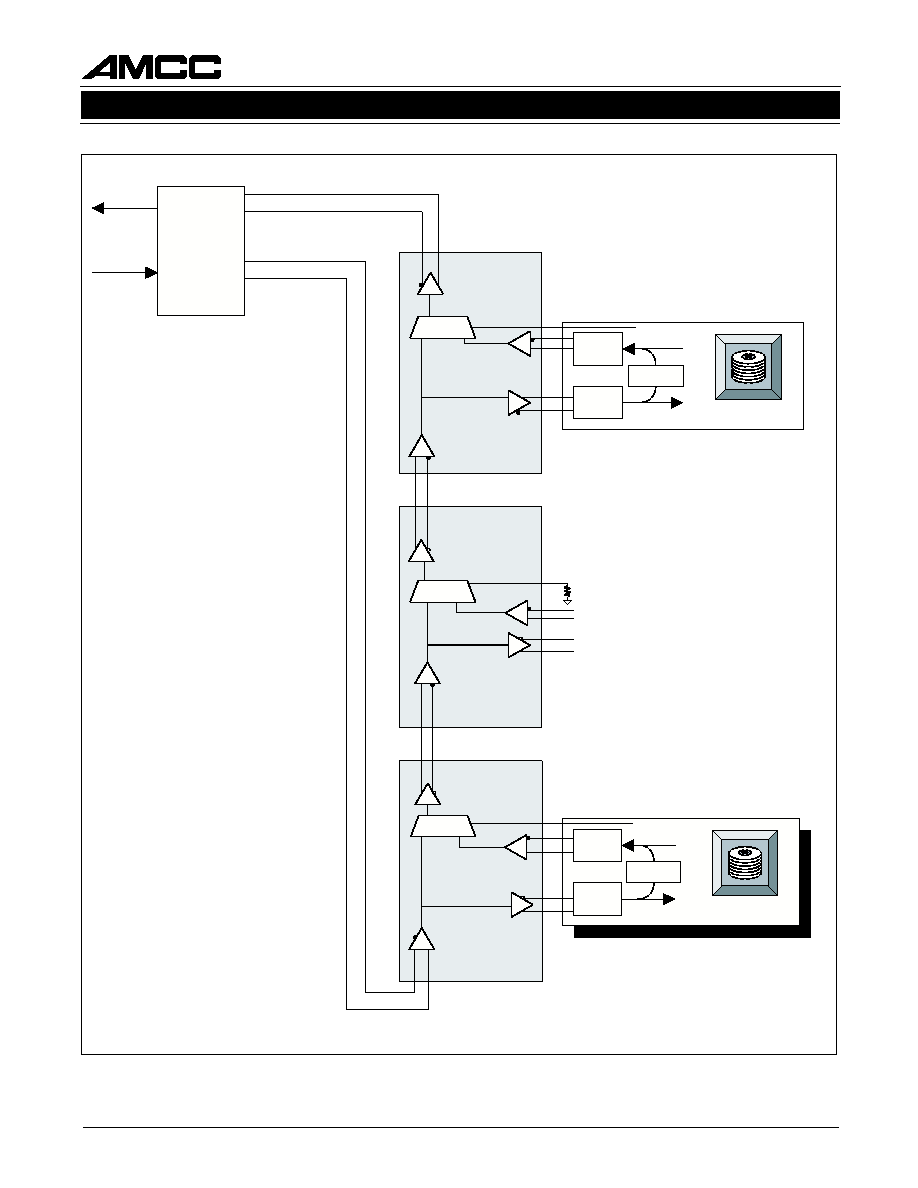

tion. A system diagram showing the S2091 in a single

loop of a disk array is illustrated in Figure 2.

The S2091 can be cascaded with the S3040 (Data

retimer) for arrays of disk drives greater than 4.

Table 1 is a truth table detailing the data flow

through the S2091. Figure 3 shows a timing diagram

of the data relationship in the S2091. The primary

AC parameter of importance is the deterministic jitter

or data eye degradation inserted by the port bypass

circuit. The design for the S2091 minimized jitter ac-

cumulation by using high bandwidth, low skew fully

differential circuits. This provides for symmetric rise

and fall delays as well as noise rejection.

DEVICE

SPECIFICATION

3

S2091

2.5 GBIT PORT BYPASS CIRCUIT FOR FIBRE CHANNEL ARBITRATED LOOP

Figure 3. Timing Waveforms

Figure 4. Differential Voltage

IN P/N

DI P/N

OUT P/N

DO P/N

T

1, 2, 3

V

P-P

= 2 x single-ended swing

Single-ended swing

4

2.5 GBIT PORT BYPASS CIRCUIT FOR FIBRE CHANNEL ARBITRATED LOOP

S2091

e

m

a

N

n

i

P

l

e

v

e

L

O

/

I

#

n

i

P

n

o

i

t

p

i

r

c

s

e

D

P

N

I

N

N

I

.

f

f

i

D

L

C

E

P

V

L

I

6

,

7

.

t

r

o

p

C

B

P

m

a

e

r

t

s

n

w

o

d

e

h

t

m

o

r

f

s

t

u

p

n

i

l

a

i

t

n

e

r

e

f

f

i

D

P

I

D

D

N

I

D

D

.

f

f

i

D

L

C

E

P

V

L

I

3

,

4

.

e

v

i

r

d

k

s

i

d

l

a

c

o

l

e

h

t

m

o

r

f

t

u

p

n

i

l

a

i

r

e

S

L

E

S

L

T

T

V

L

I

1

1

e

h

t

f

o

t

u

p

t

u

o

e

h

t

g

n

i

s

u

a

c

e

d

o

m

"

S

S

A

P

Y

B

"

e

h

t

s

t

c

e

l

e

s

w

o

L

A

,

h

g

i

H

n

e

h

W

.

T

U

O

r

o

t

r

o

p

t

x

e

n

e

h

t

o

t

e

t

a

g

a

p

o

r

p

o

t

t

r

o

p

s

u

o

i

v

e

r

p

s

u

o

i

v

e

r

p

e

h

t

s

e

t

u

o

r

h

c

i

h

w

e

d

o

m

"

L

A

M

R

O

N

"

s

t

c

e

l

e

s

l

a

n

g

i

s

s

i

h

t

e

h

t

o

t

I

D

D

,

t

u

p

n

i

l

a

c

o

l

e

h

t

s

e

t

u

o

r

d

n

a

O

D

D

,

t

u

p

t

u

o

l

a

c

o

l

e

h

t

o

t

t

r

o

p

.

T

U

O

r

o

t

r

o

p

t

x

e

n

P

O

D

D

N

O

D

D

.

f

f

i

D

L

M

C

O

8

1

,

9

1

.

e

v

i

r

d

k

s

i

d

l

a

c

o

l

e

h

t

g

n

i

v

i

r

d

t

u

p

t

u

o

l

a

i

r

e

S

P

T

U

O

N

T

U

O

.

f

f

i

D

L

M

C

O

4

1

,

5

1

.

t

r

o

p

C

B

P

m

a

e

r

t

s

p

u

e

h

t

g

n

i

v

i

r

d

t

u

p

t

u

o

l

a

i

r

e

S

C

C

V

,

0

1

,

2

,

1

0

2

,

7

1

,

2

1

.

l

a

n

i

m

o

n

V

3

.

3

.

y

l

p

p

u

S

r

e

w

o

P

D

N

G

,

9

,

8

,

5

6

1

,

3

1

g

n

i

t

n

u

o

m

e

i

d

e

h

t

o

t

d

e

h

c

a

t

t

a

y

ll

a

c

i

s

i

y

h

p

e

r

a

s

n

i

p

d

n

u

o

r

G

.

d

n

u

o

r

G

t

s

e

b

r

o

F

.

h

t

a

p

l

a

m

r

e

h

t

e

h

t

f

o

t

r

a

p

t

n

a

t

r

o

p

m

i

n

a

e

r

a

d

n

a

,

e

c

a

f

r

u

s

a

o

t

d

e

t

c

e

n

n

o

c

e

b

d

l

u

o

h

s

s

n

i

p

d

n

u

o

r

g

ll

a

,

e

c

n

a

m

r

o

f

r

e

p

l

a

m

r

e

h

t

.

e

l

b

i

s

s

o

p

f

i

s

a

i

v

e

l

p

i

t

l

u

m

g

n

i

s

u

,

e

n

a

l

p

d

n

u

o

r

g

Table 2. Pin Assignment and Descriptions

Figure 5. S2091 Pinout Package

20

VCC

19

DDOP

18

DDON

17

VCC

16

GND

15

OUTP

14

OUTN

13

GND

12

VCC

11

SEL

VCC

1

VCC

2

DDIN

3

DDIP

4

GND

5

INN

6

INP

7

GND

8

GND

9

VCC

10