PRELIMINARY

© Copyright 2001 Advanced Micro Devices, Inc. All rights reserved.

Final Draft# 22003

Rev: B Amendment/0

Issue Date: March 2001

…lanTMSC520 Microcontroller

Integrated 32-Bit Microcontroller with PC/AT-Compatible Peripherals,

PCI Host Bridge, and Synchronous DRAM Controller

DISTINCTIVE CHARACTERISTICS

s

Industry-standard Am5

x

86Æ CPU with floating

point unit (FPU) and 16-Kbyte write-back cache

≠ 100-MHz and 133-MHz operating frequencies

≠ Low-voltage operation (core V

CC

= 2.5 V)

≠ 5-V tolerant I/O (3.3-V output levels)

s

E86TM family of x86 embedded processors

≠ Part of a software-compatible family of

microprocessors and microcontrollers well

supported by a wide variety of development tools

s

Integrated PCI host bridge controller leverages

standard peripherals and software

≠ 33 MHz, 32-bit PCI bus Revision 2.2-compliant

≠ High-throughput 132-Mbyte/s peak transfer

≠ Supports up to five external PCI masters

≠ Integrated write-posting and read-buffering for

high-throughput applications

s

Synchronous DRAM (SDRAM) controller

≠ Supports 16-, 64-, 128-, and 256-Mbit SDRAM

≠ Supports 4 banks for a total of 256 Mbytes

≠ Error Correction Code provides system reliability

≠ Buffers improve read and write performance

s

AMDebugTM technology offers a low-cost

solution for the advanced debugging

capabilities required by embedded designers

≠ Allows instruction tracing during execution from

the Am5

x

86 CPU's internal cache

≠ Uses an enhanced JTAG port for low-cost debugging

≠ Parallel debug port for high-speed data exchange

during in-circuit emulation

s

General-Purpose (GP) bus with programmable

timing for 8- and 16-bit devices provides good

performance at low cost

s

ROM/Flash controller for 8-, 16-, and 32-bit devices

s

Enhanced PC/AT-compatible peripherals

provide improved performance

≠ Enhanced programmable interrupt controller

(PIC) prioritizes 22 interrupt levels (up to 15

external sources) with flexible routing

≠ Enhanced DMA controller includes double buffer

chaining, extended address and transfer counts,

and flexible channel routing

≠ Two 16550-compatible UARTs operate at baud

rates up to 1.15 Mbit/s with optional DMA interface

s

Standard PC/AT-compatible peripherals

≠ Programmable interval timer (PIT)

≠ Real-time clock (RTC) with battery backup

capability and 114 bytes of RAM

s

Additional integrated peripherals

≠ Three general-purpose 16-bit timers provide

flexible cascading for 32-bit operation

≠ Watchdog timer guards against runaway software

≠ Software timer

≠ Synchronous serial interface (SSI) offers

full-duplex or half-duplex operation

≠ Flexible address decoding for programmable

memory and I/O mapping and system addressing

configuration

s

32 programmable input/output (PIO) pins

s

Native support for pSOS, QNX, RTXC, VxWorks,

and Windows

Æ

CE operating systems

s

Industry-standard BIOS support

s

Plastic Ball Grid Array (PBGA388) package

GENERAL DESCRIPTION

The …lanTMSC520 microcontroller is a full-featured mi-

crocontroller developed for the general embedded

market. The …lanSC520 microcontroller combines a

32-bit, low-voltage Am5

x

86 CPU with a set of inte-

grated peripherals suitable for both real-time and PC/

AT-compatible embedded applications.

An integrated PCI host bridge, SDRAM controller, enhanced

PC/AT-compatible peripherals, and advanced debugging

features provide the system designer with a wide range of

on-chip resources, allowing support for legacy devices as

well as new devices available in the current PC marketplace.

Designed for medium- to high-performance applications

in the telecommunications, data communications, and

information appliance markets, the …lanSC520 micro-

controller is particularly well suited for applications re-

quiring high throughput combined with low latency. The

compact Plastic Ball Grid Array (PBGA) package pro-

vides a high degree of functionality in a very small form

factor, making it cost-effective for many applications. A

0.25-micron CMOS manufacturing process allows for

low power consumption along with high performance.

2

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

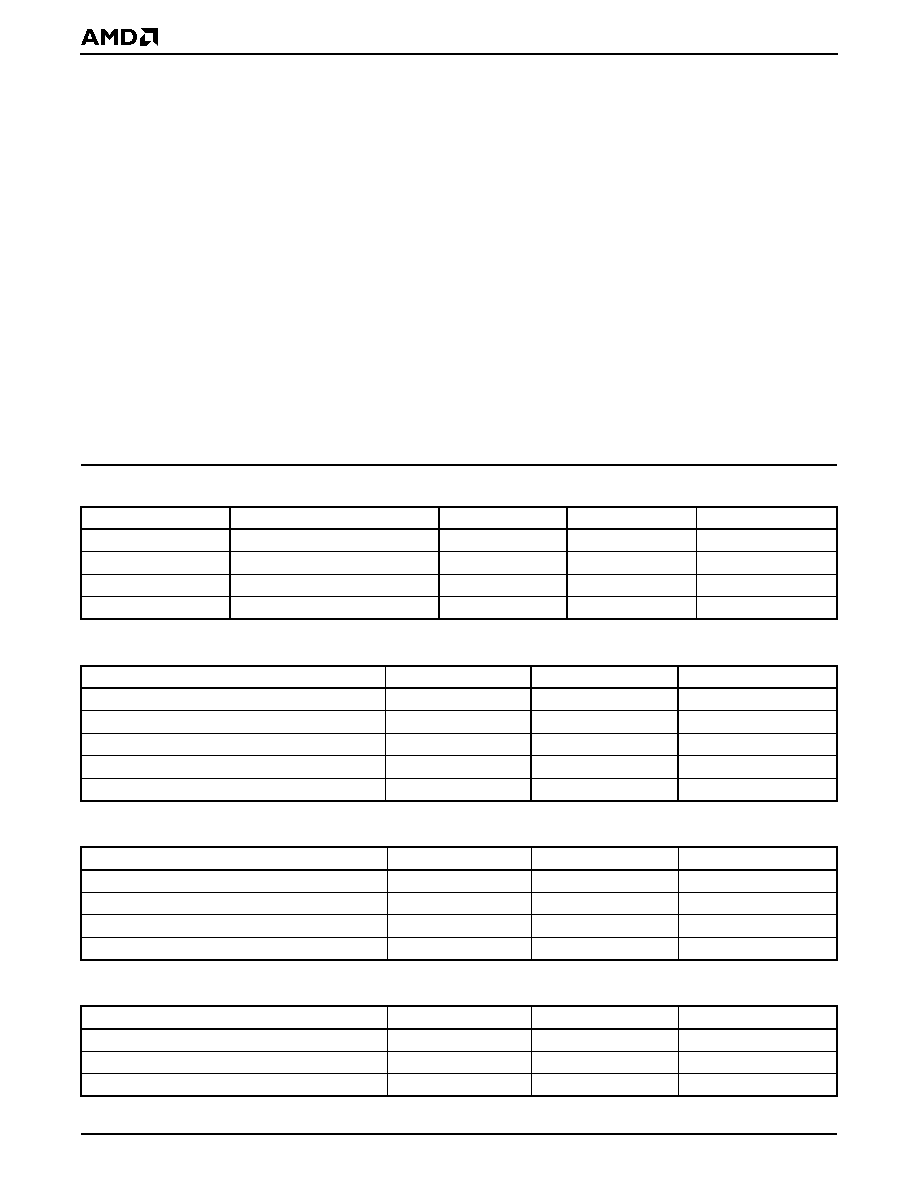

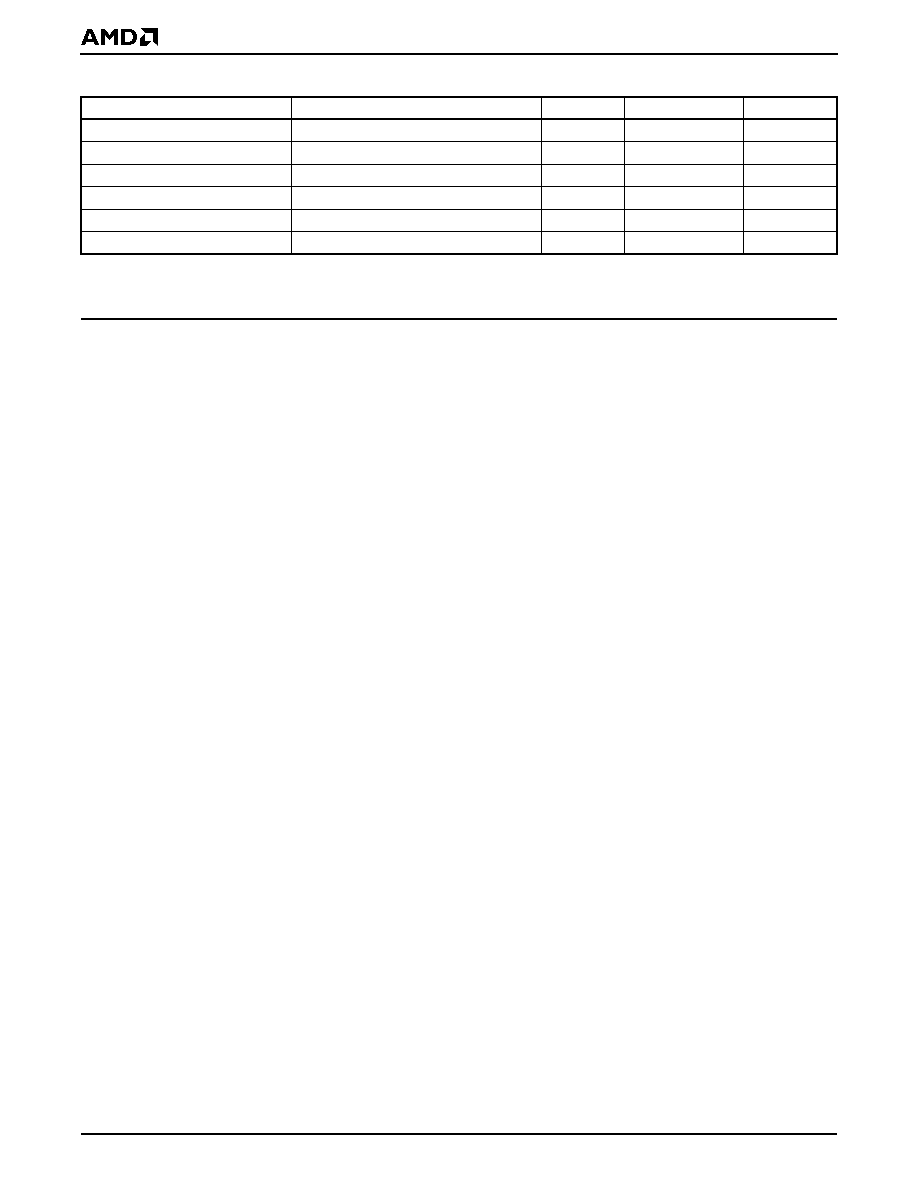

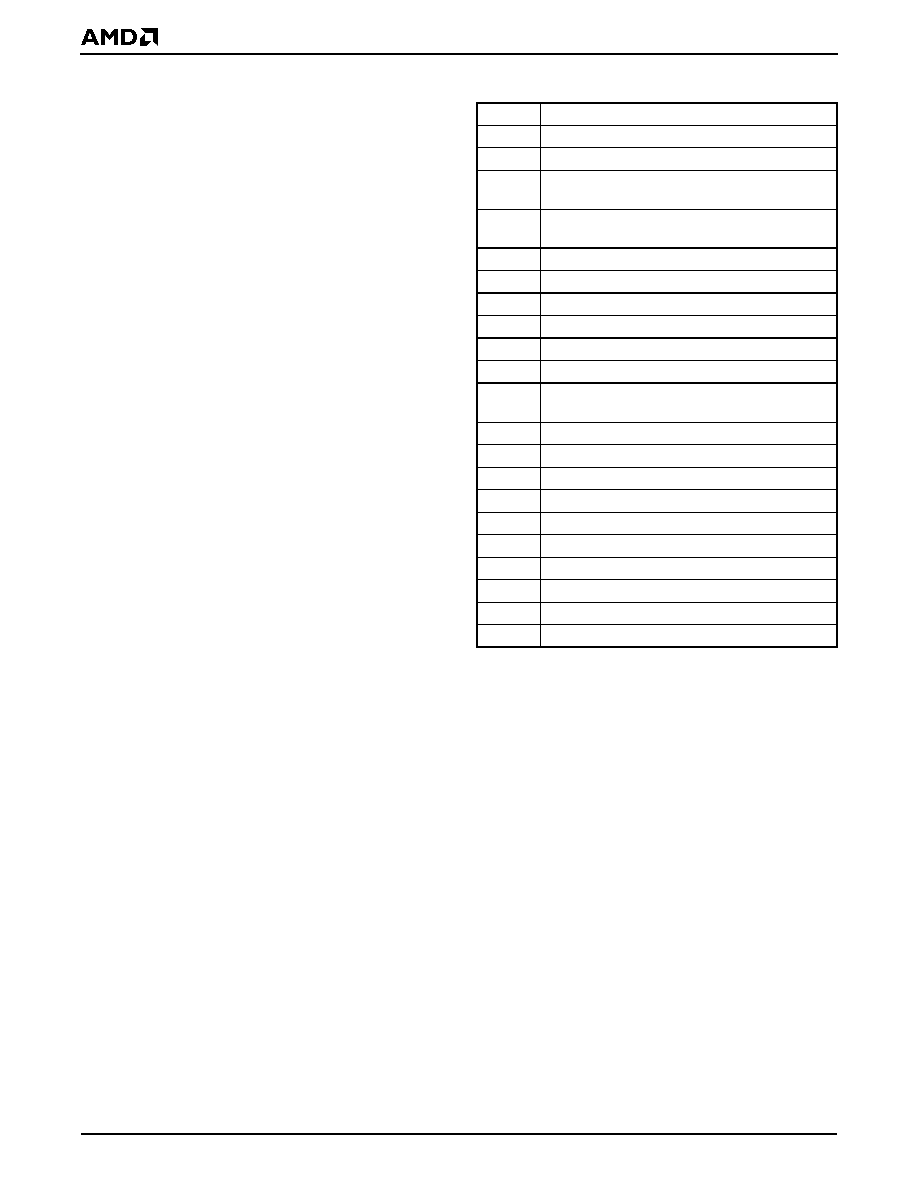

ORDERING INFORMATION

≠100 = 100 MHz

≠133 = 133 MHz

TEMPERATURE RANGE

SPEED OPTION

DEVICE NUMBER/DESCRIPTION

Valid combinations list configurations planned to be

supported in volume for this device. Consult the

local AMD sales office to confirm availability of

specific valid combinations and to check on newly

released combinations.

Valid Combinations

PACKAGE TYPE

A = 388-Pin Plastic Ball Grid Array (PBGA)

…lanSC520 integrated 32-bit microcontroller with

PC/AT-compatible peripherals, PCI host bridge,

and synchronous DRAM controller

≠133

A

C

Valid Combinations

…lanSC520≠100

…lanSC520≠133

AC

…lanSC520

C= Commercial (T

C

=0

C to +85

C)

where: T

C

= case temperature

P R E L I M I N A R Y

…lanTMSC520 Microcontroller Data Sheet

3

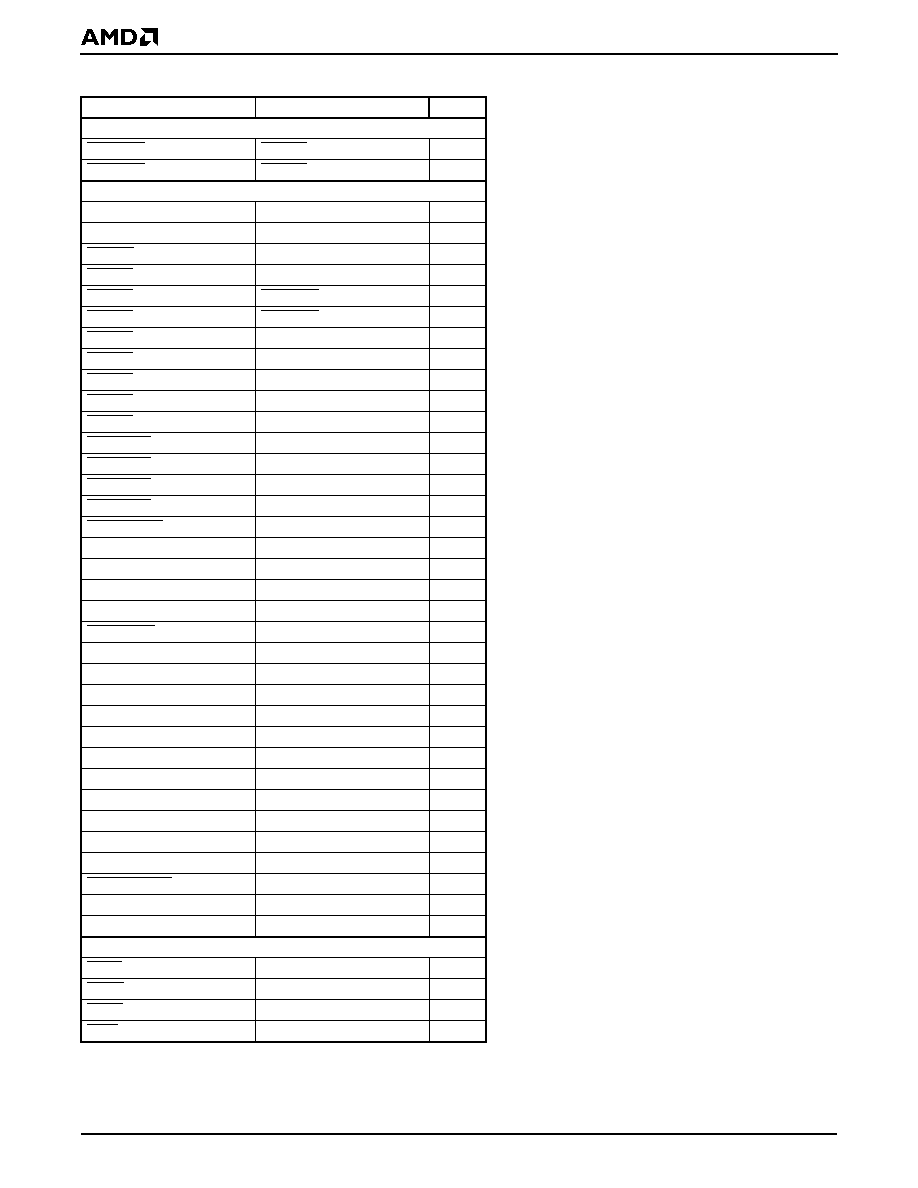

TABLE OF CONTENTS

Distinctive Characteristics ............................................................................................................ 1

General Description ..................................................................................................................... 1

Ordering Information .................................................................................................................... 2

Logic Diagram by Interface ........................................................................................................... 6

Logic Diagram by Default Pin Function ........................................................................................ 7

Connection Diagram .................................................................................................................... 8

Pin Designations ........................................................................................................................ 10

Pin Designations (Pin Number) ............................................................................................. 11

Pin Designations (Pin Name) ................................................................................................ 13

Signal Descriptions ..................................................................................................................... 16

Architectural Overview ............................................................................................................... 28

Industry-Standard x86 Architecture ....................................................................................... 30

AMDebugTM Technology for Advanced Debugging .............................................................. 30

Industry-Standard PCI Bus Interface .................................................................................... 30

High-Performance SDRAM Controller ................................................................................. 30

ROM/Flash Controller ........................................................................................................... 30

Flexible Address-Mapping Hardware .................................................................................... 31

Easy-to-Use GP Bus Interface .............................................................................................. 31

Clock Generation .................................................................................................................. 31

Integrated Peripherals ........................................................................................................... 31

JTAG Boundary Scan Test Interface .................................................................................... 32

System Test and Debug Features ........................................................................................ 32

Applications ............................................................................................................................... 33

Clock Generation and Control ................................................................................................... 38

Internal Clocks ...................................................................................................................... 39

Clock Specifications .............................................................................................................. 40

Clock Pin Loading ................................................................................................................. 40

Selecting a Crystal ................................................................................................................ 41

32.768-kHz Crystal Selection ........................................................................................... 41

33-MHz Crystal Selection................................................................................................. 42

Third Overtone Crystal Component Selection .................................................................. 42

Running the …lanTMSC520 Microcontroller at 33.333 MHz ........................................................... 43

Bypassing Internal Oscillators ............................................................................................... 44

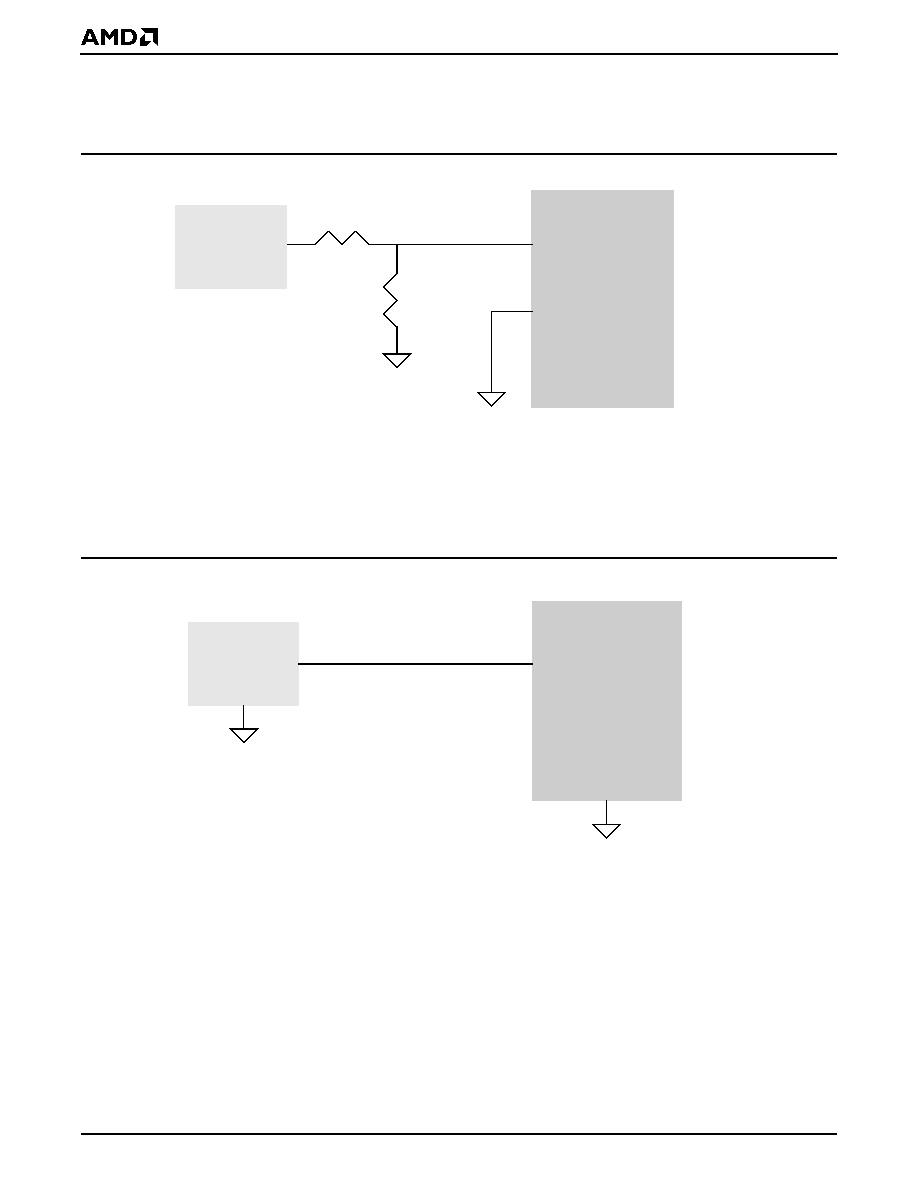

RTC Voltage Monitor ................................................................................................................. 45

Backup Battery Considerations ............................................................................................. 46

Using an External RTC Backup Battery ........................................................................... 46

Not Using an External RTC Backup Battery..................................................................... 46

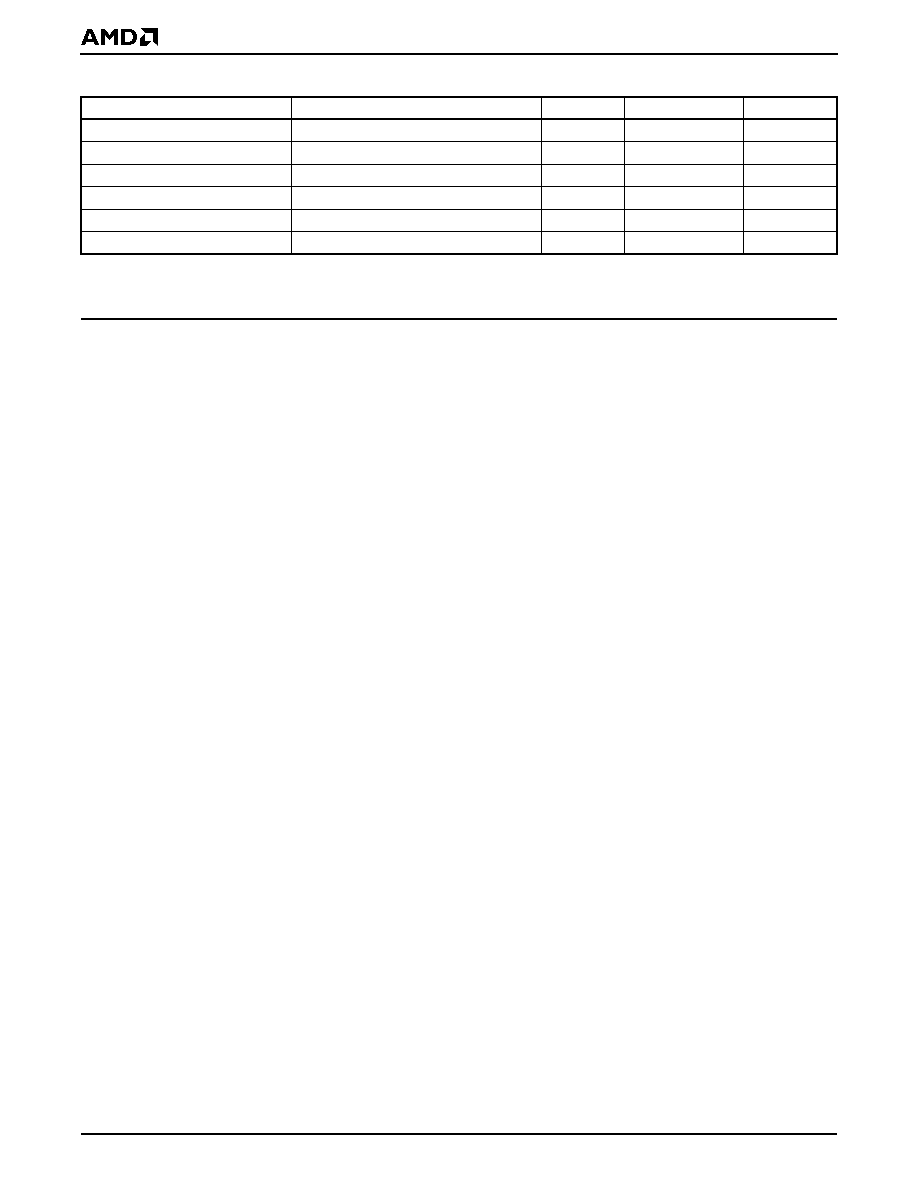

Absolute Maximum Ratings ....................................................................................................... 48

Operating Ranges at Commercial Temperatures ...................................................................... 48

Voltage Levels for Non-PCI Interface Pins ................................................................................ 49

Voltage Levels for PCI Interface Pins ........................................................................................ 49

DC Characteristics Over Commercial Operating Ranges .......................................................... 50

Capacitance ............................................................................................................................... 51

Non-PCI Interface Pin Capacitance ...................................................................................... 51

PCI Interface Pin Capacitance .............................................................................................. 51

Crystal Capacitance .............................................................................................................. 51

Derating Curves .................................................................................................................... 51

Power Characteristics ................................................................................................................ 56

Thermal Characteristics ...................................................................................................................56

388-Pin PBGA Package .............................................................................................................56

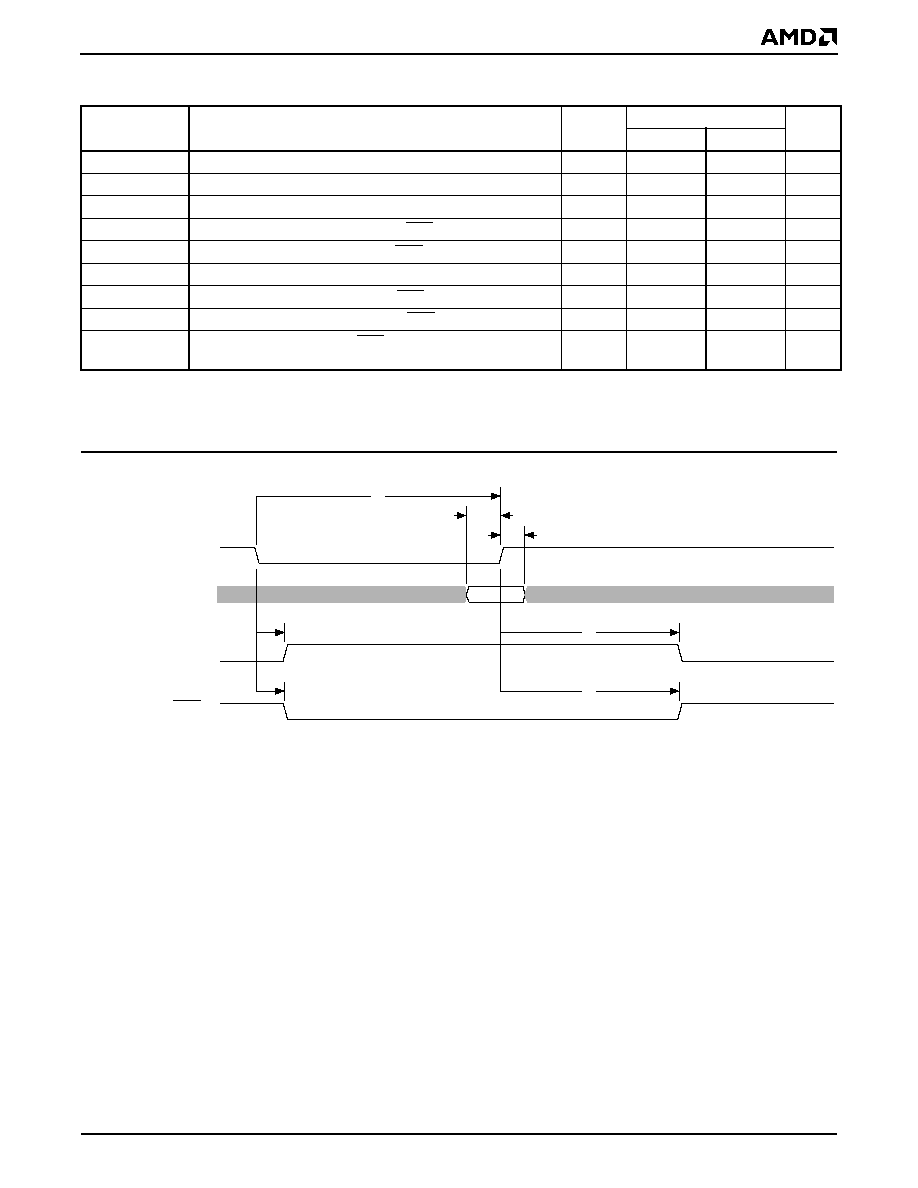

Switching Characteristics and Waveforms ................................................................................ 58

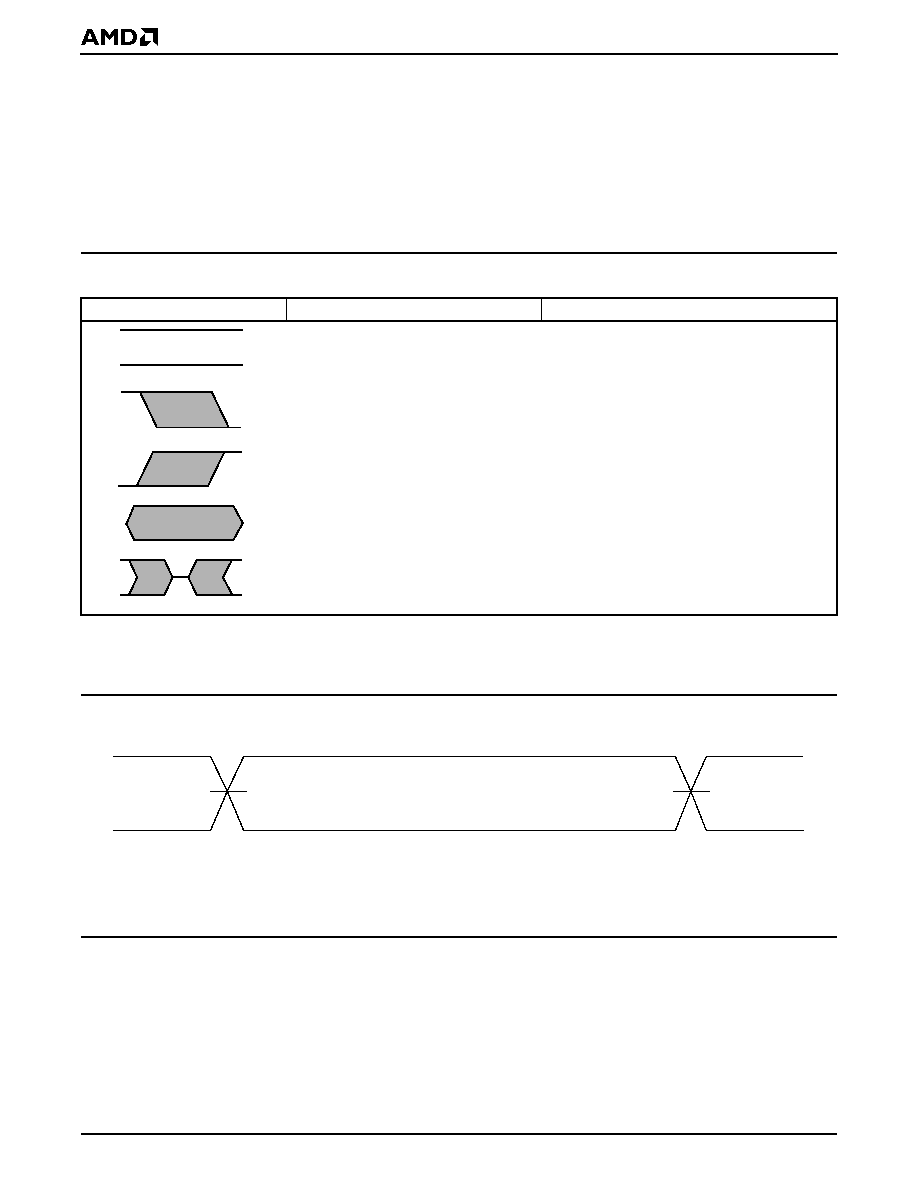

Key to Switching Waveforms ................................................................................................ 58

4

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

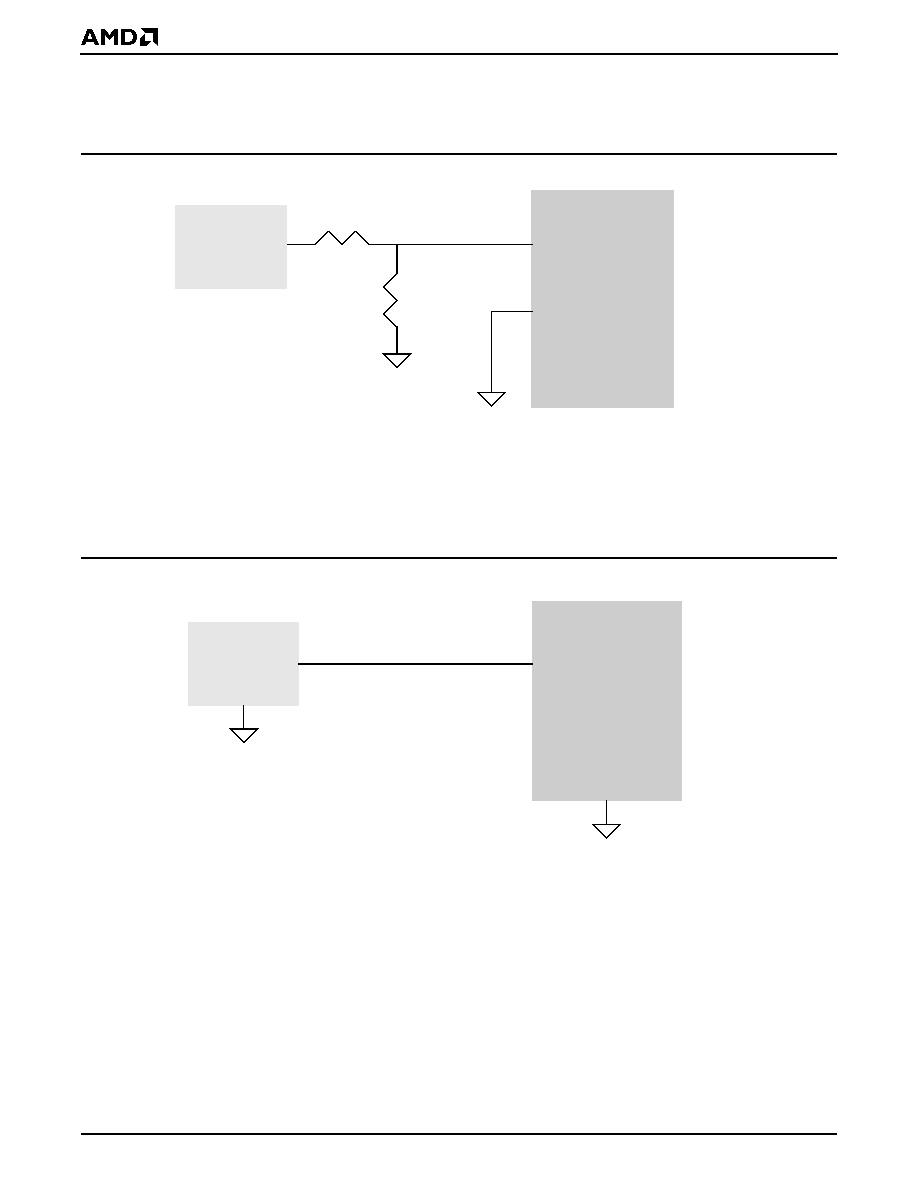

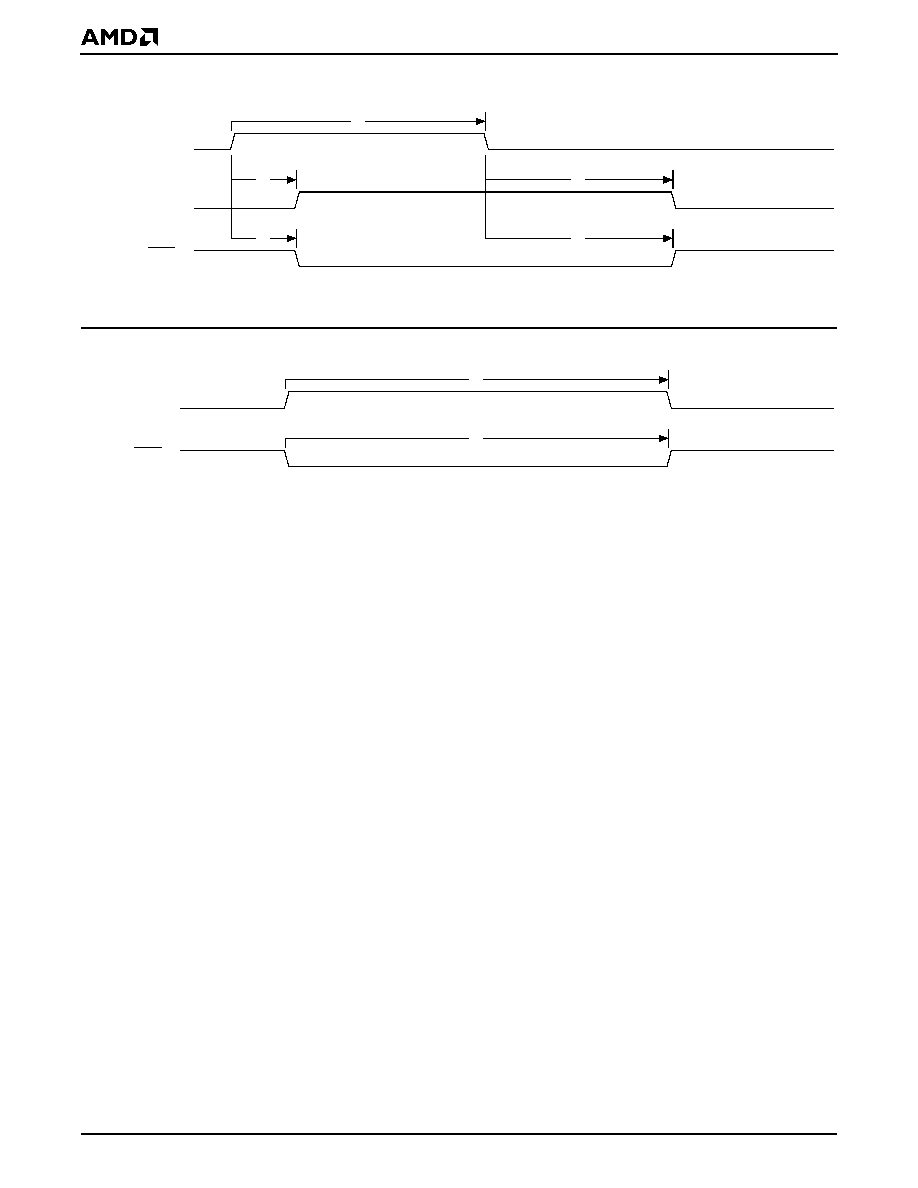

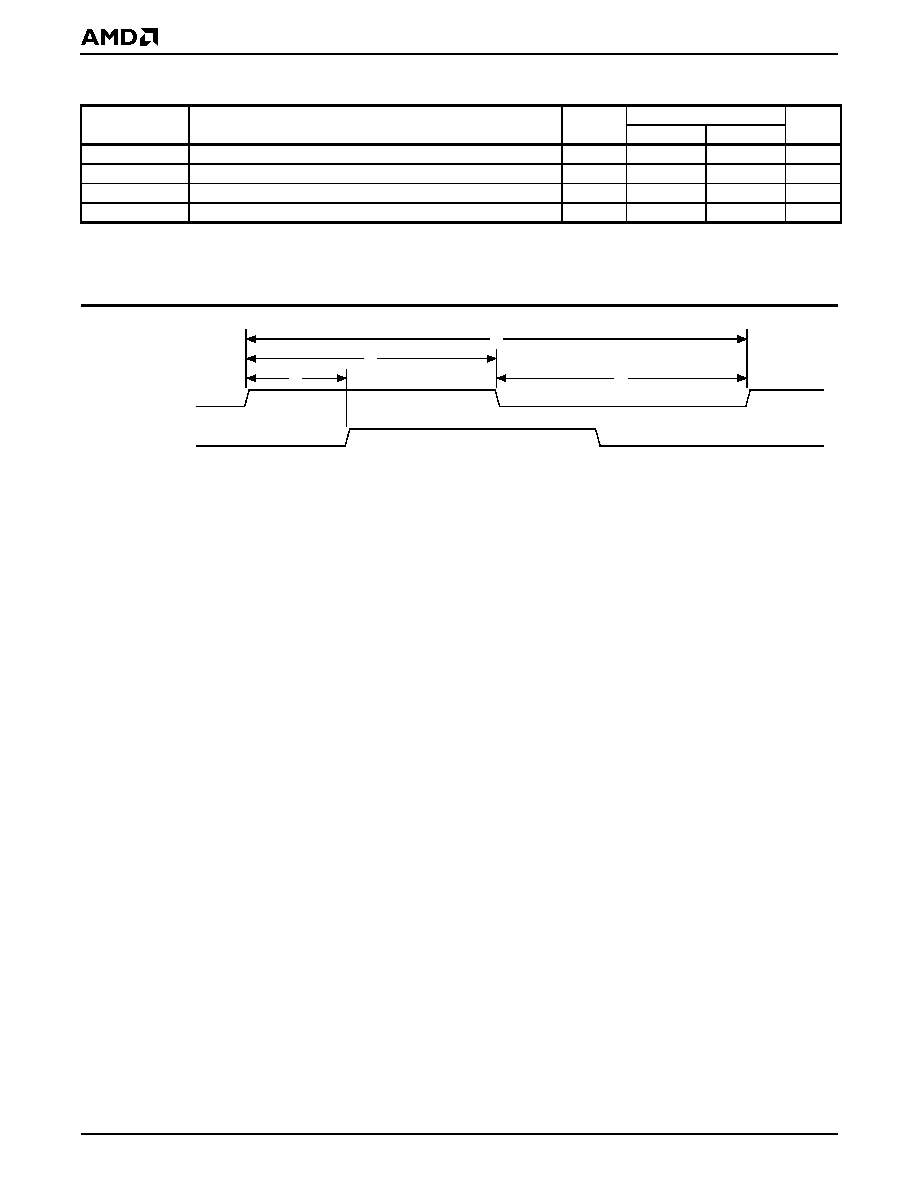

AC Switching Test Waveforms .................................................................................................. 58

Non-PCI Bus Interface Pins .................................................................................................. 58

PCI Bus Interface Pins .......................................................................................................... 58

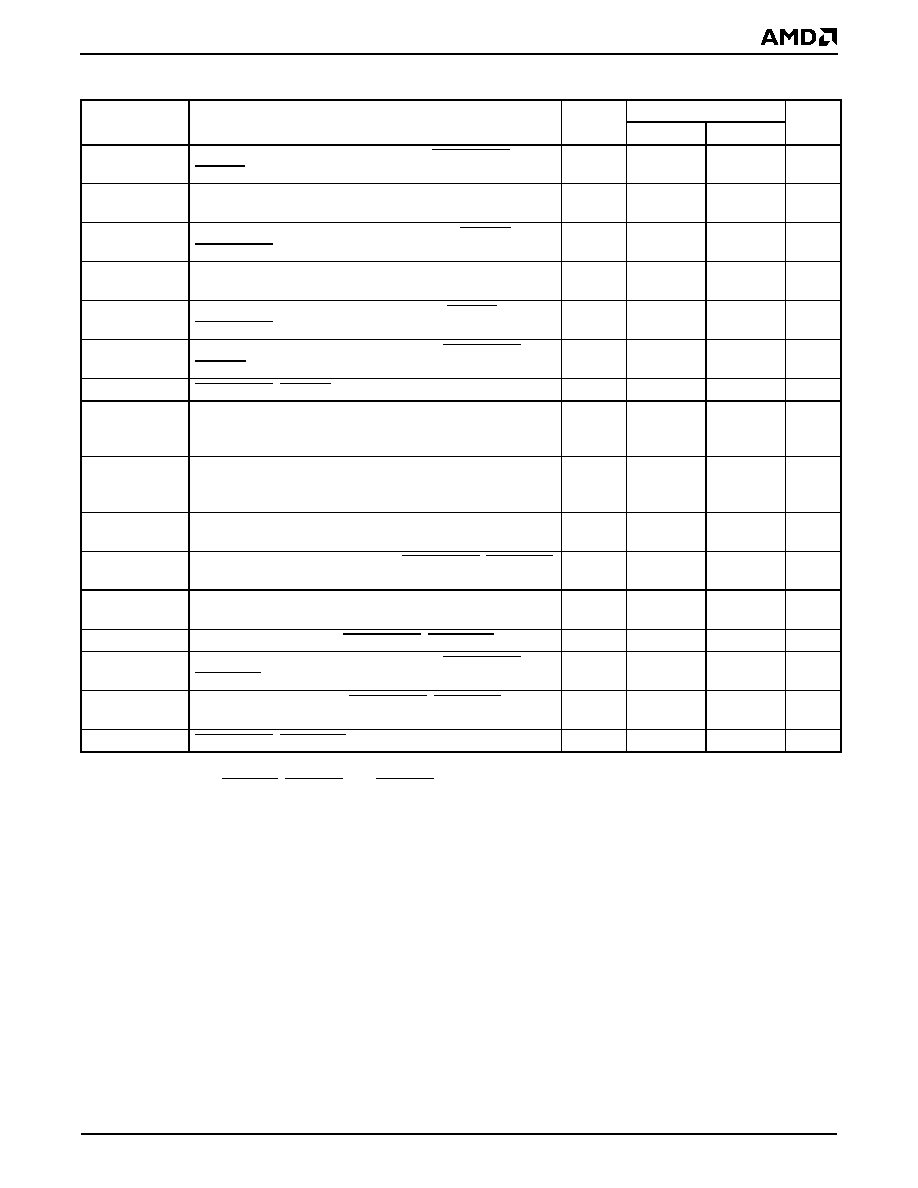

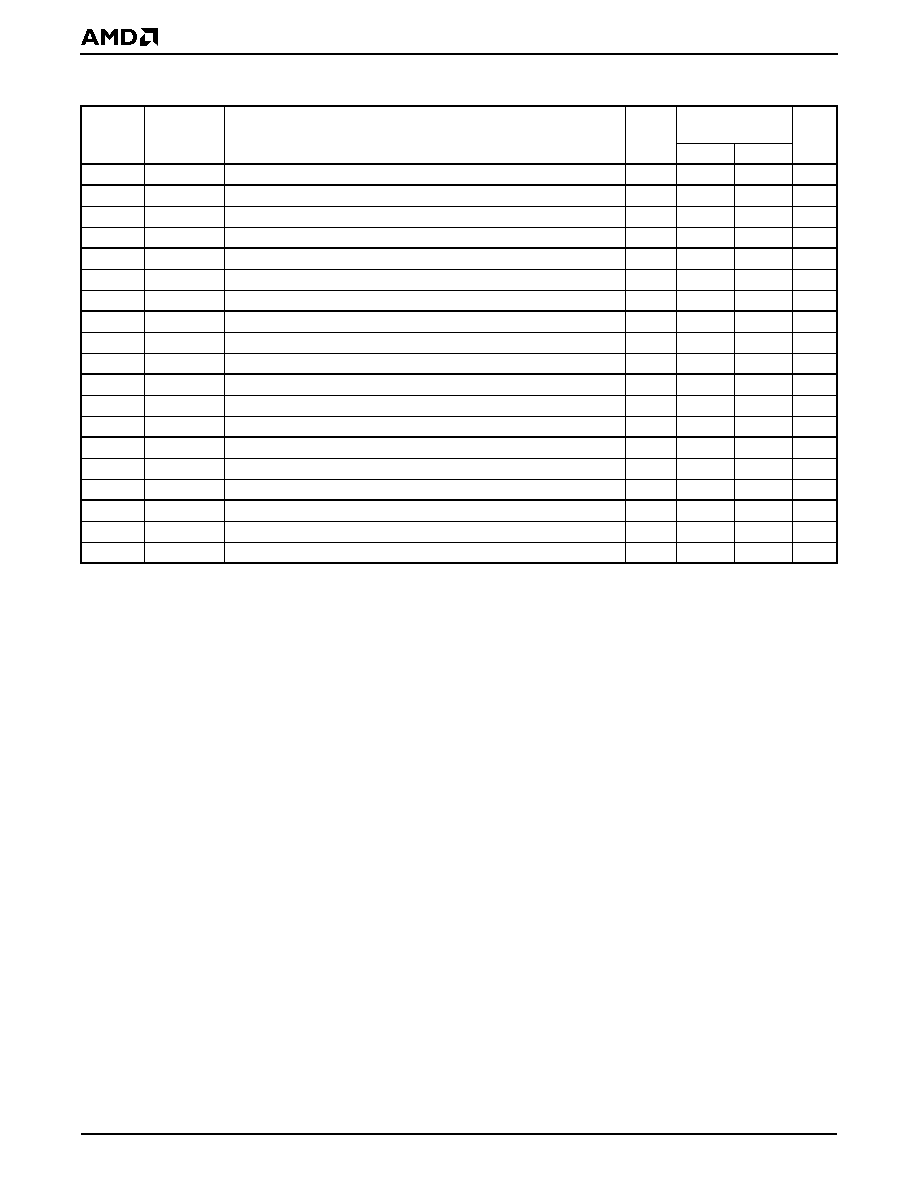

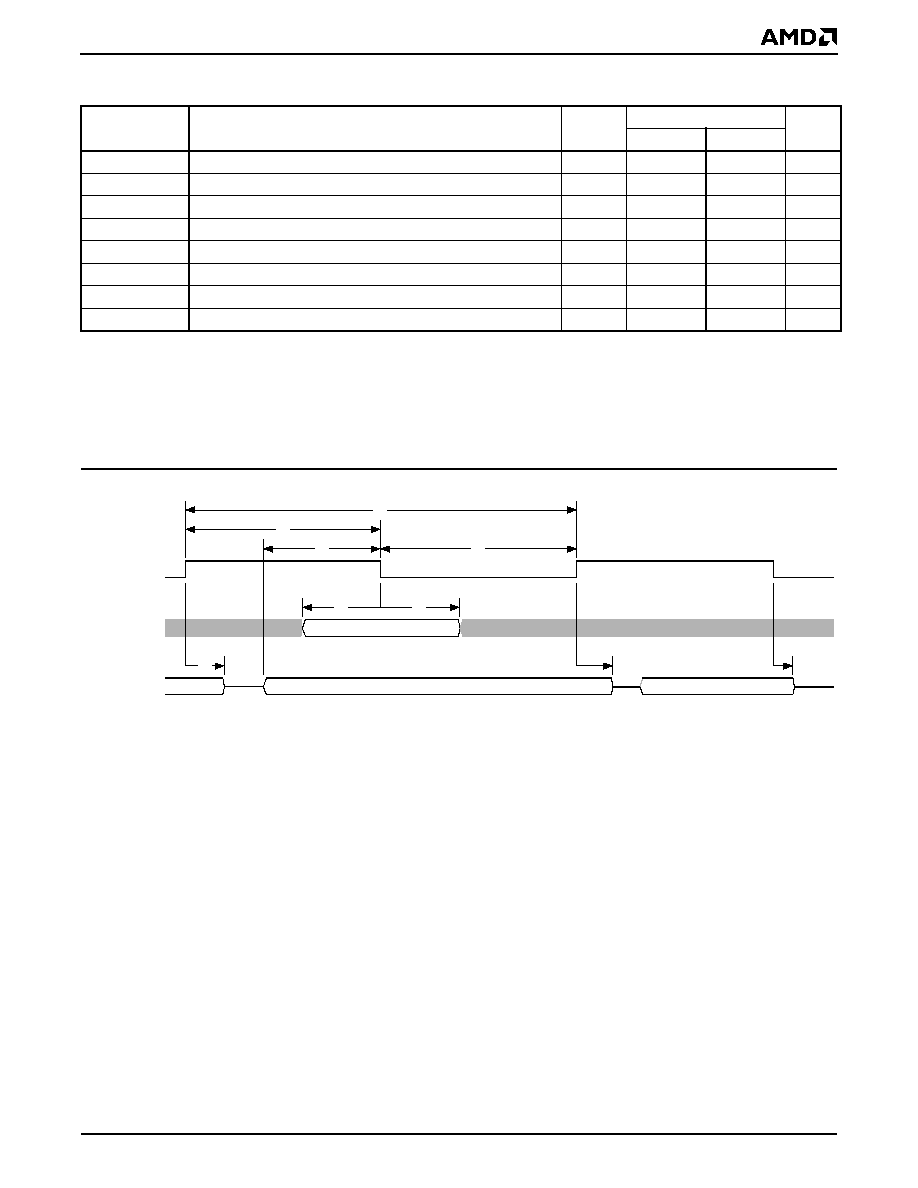

Switching Characteristics over Commercial Operating Ranges ....................................................................59

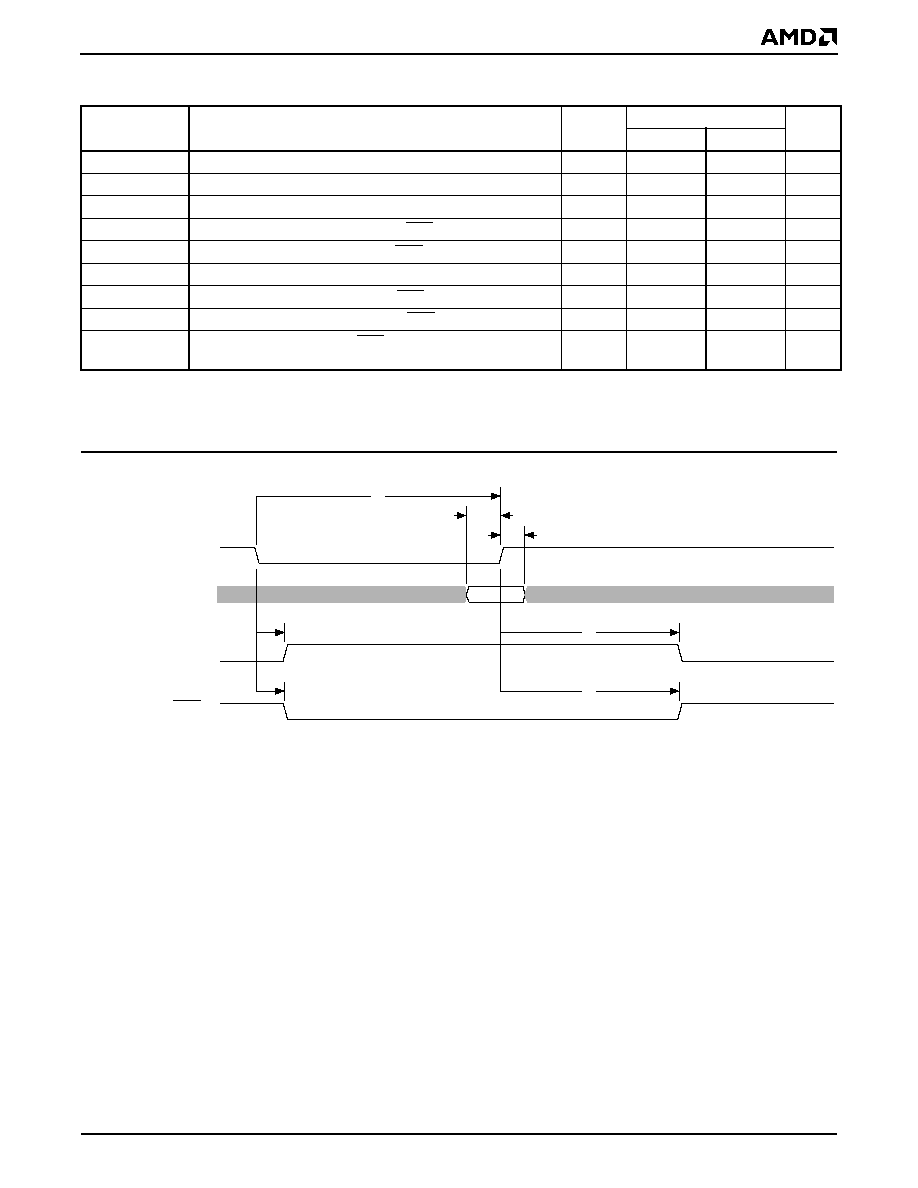

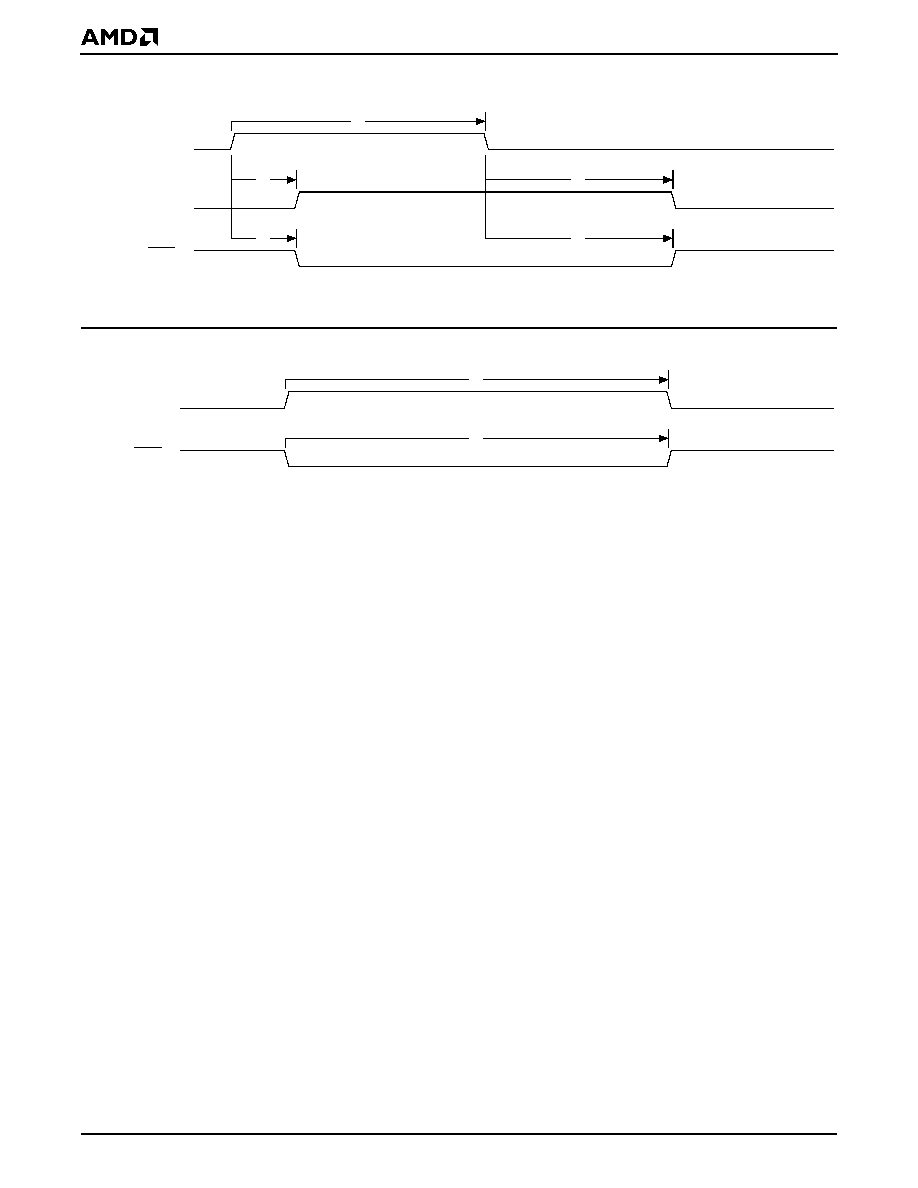

Power-On Reset Timing ........................................................................................................ 59

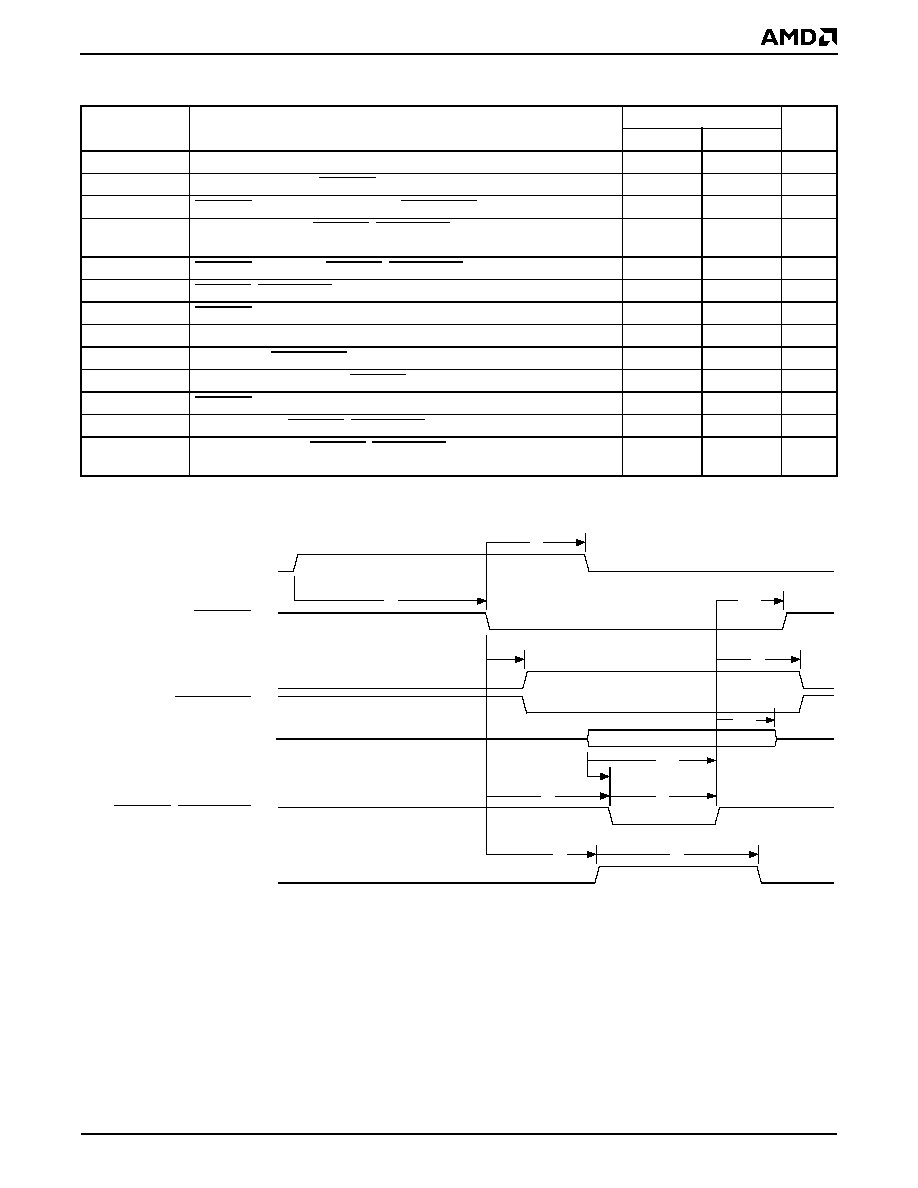

Reset Timing with Power Applied ......................................................................................... 61

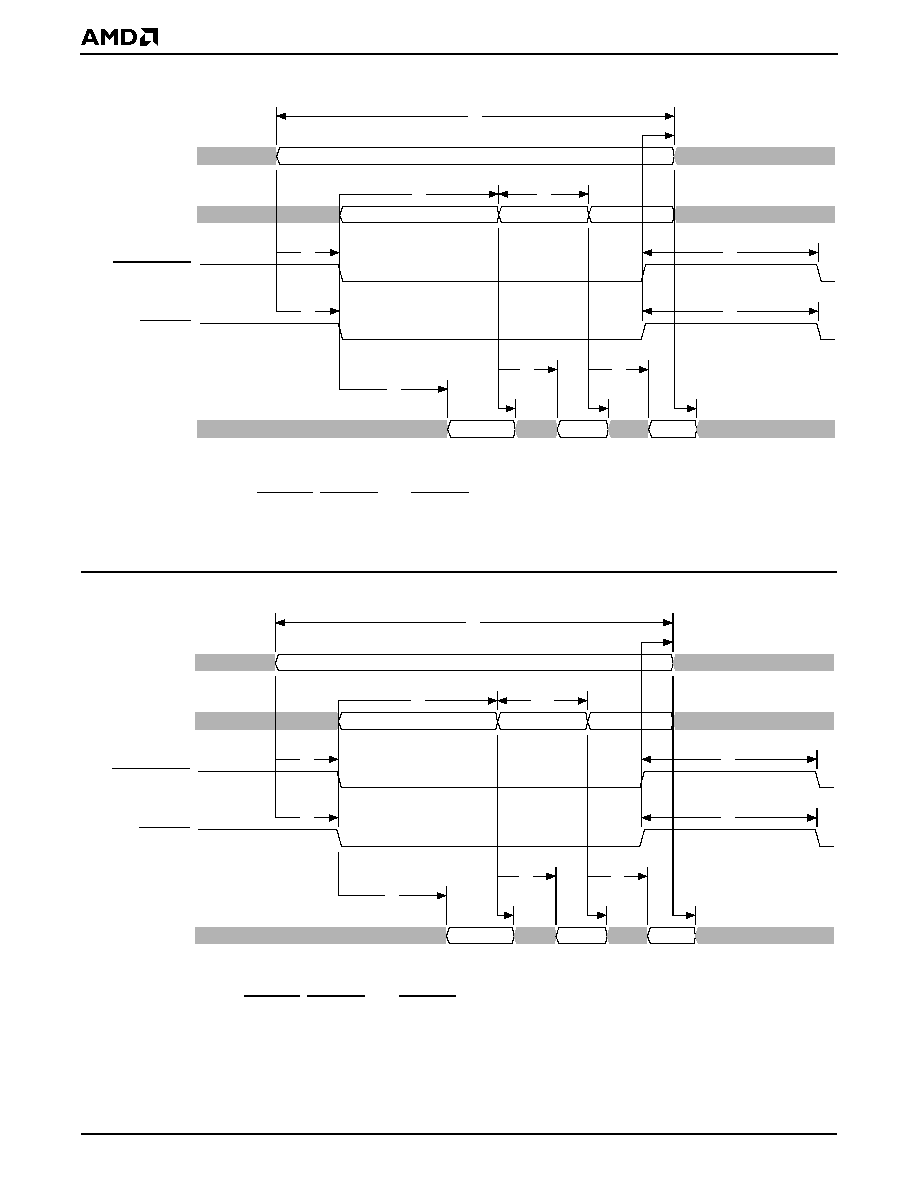

ROM Timing .......................................................................................................................... 63

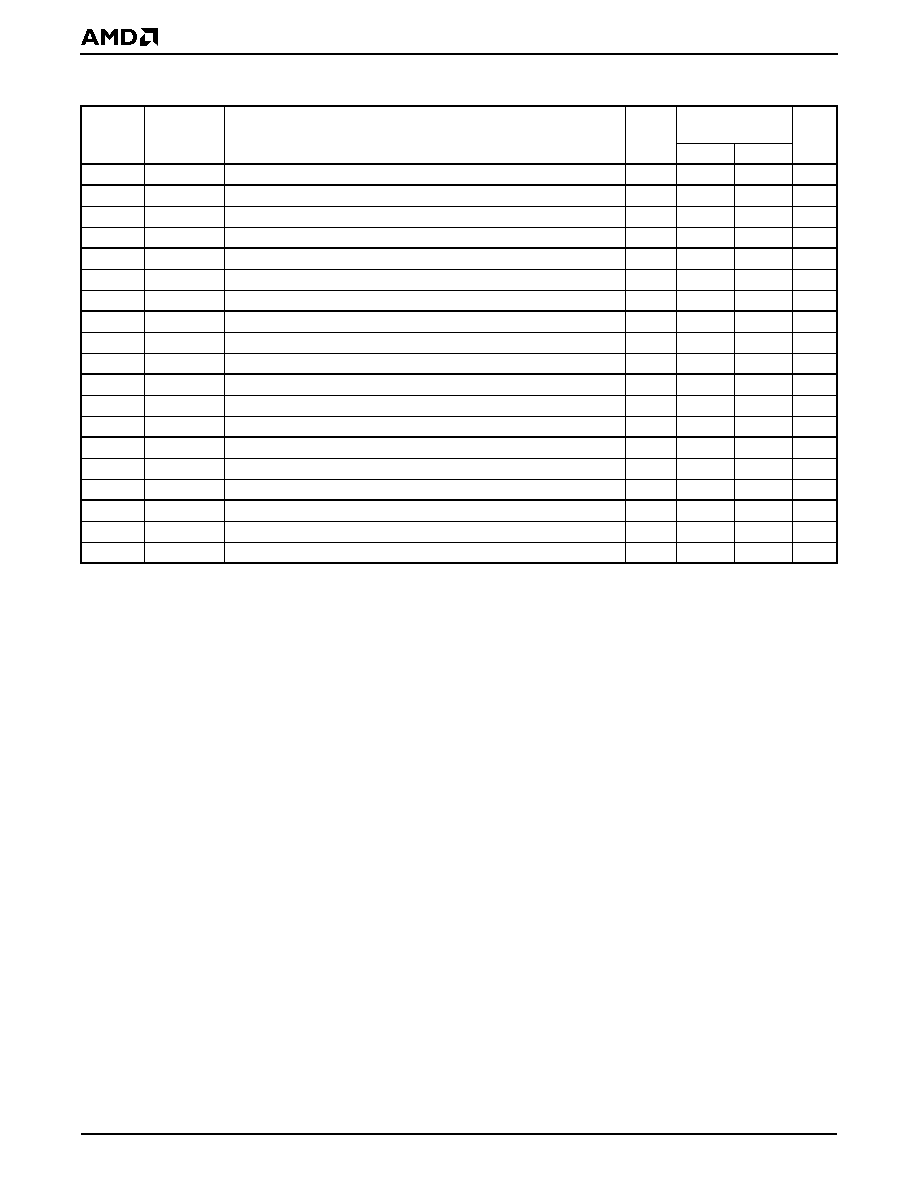

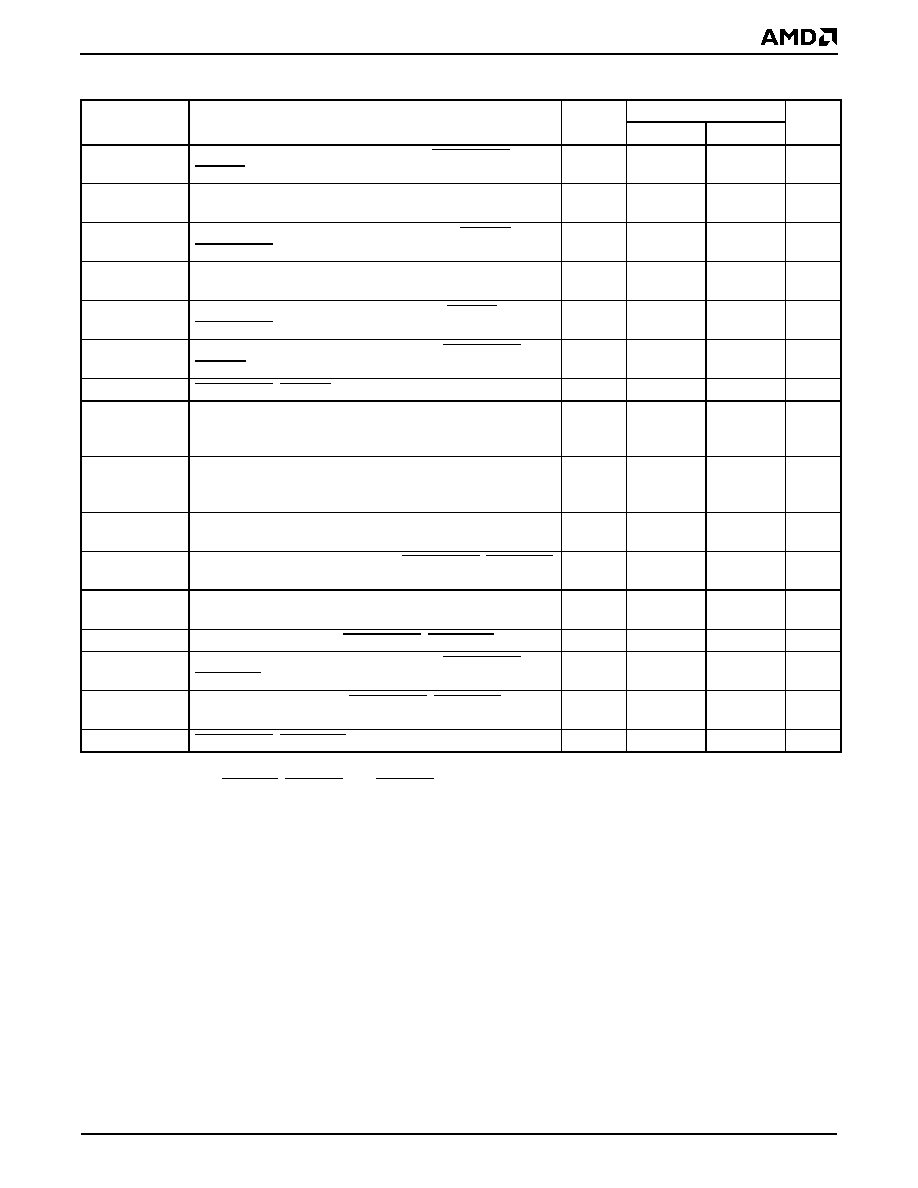

PCI Bus Timing ..................................................................................................................... 65

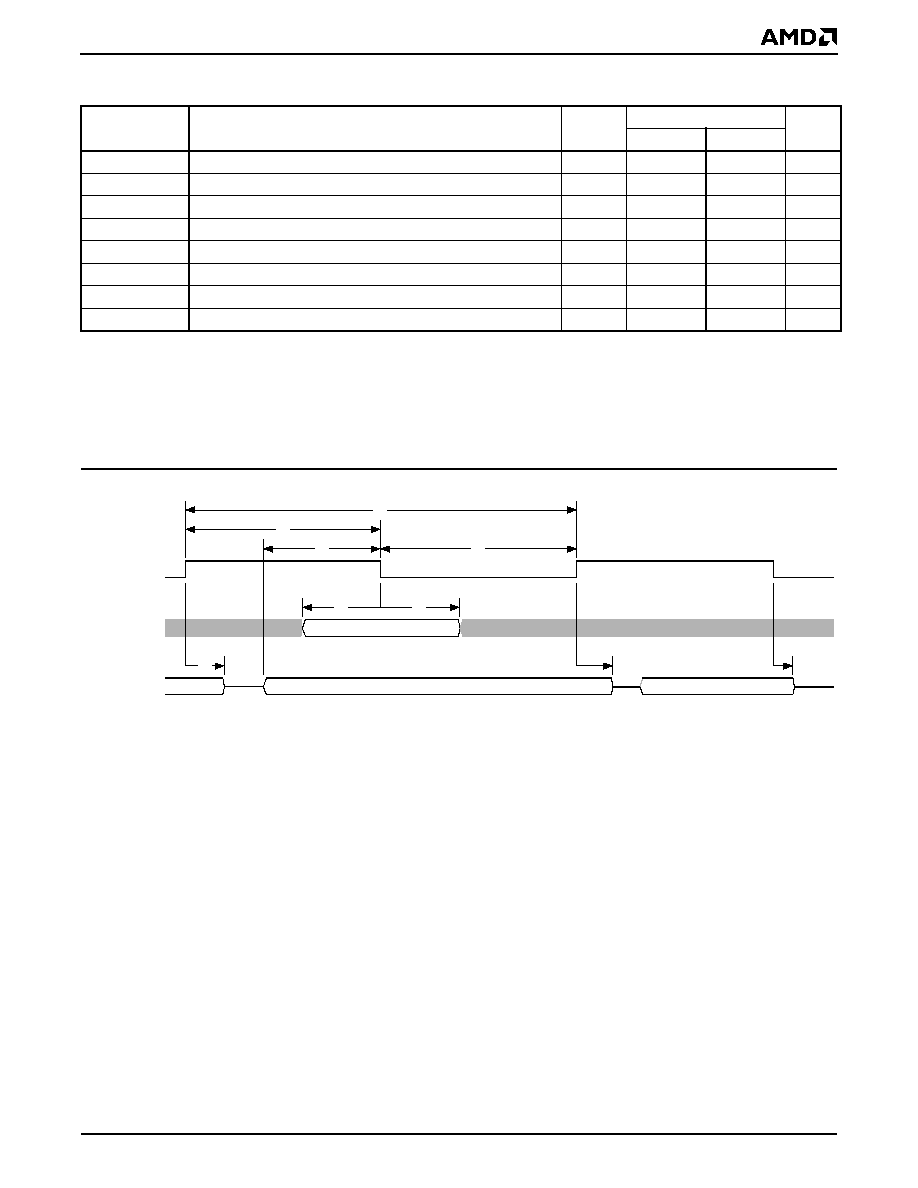

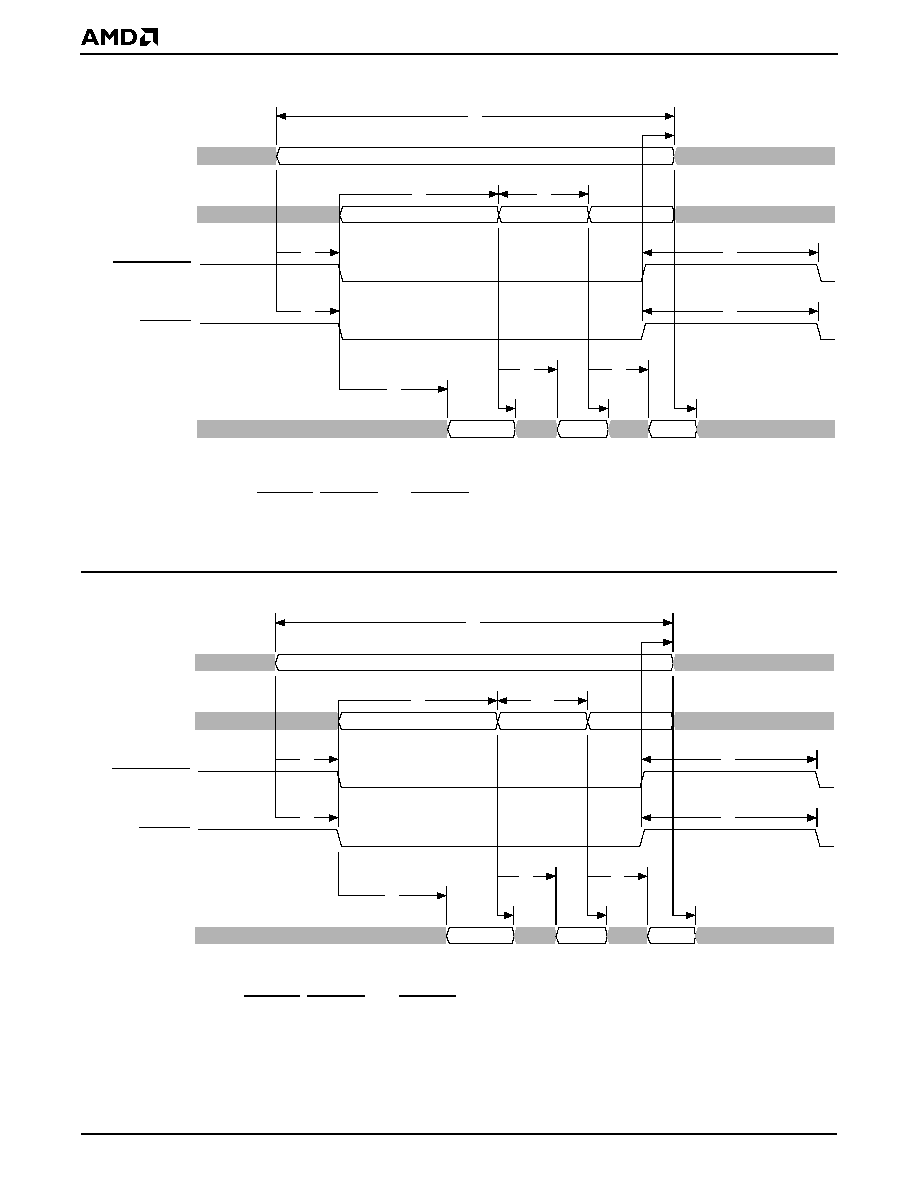

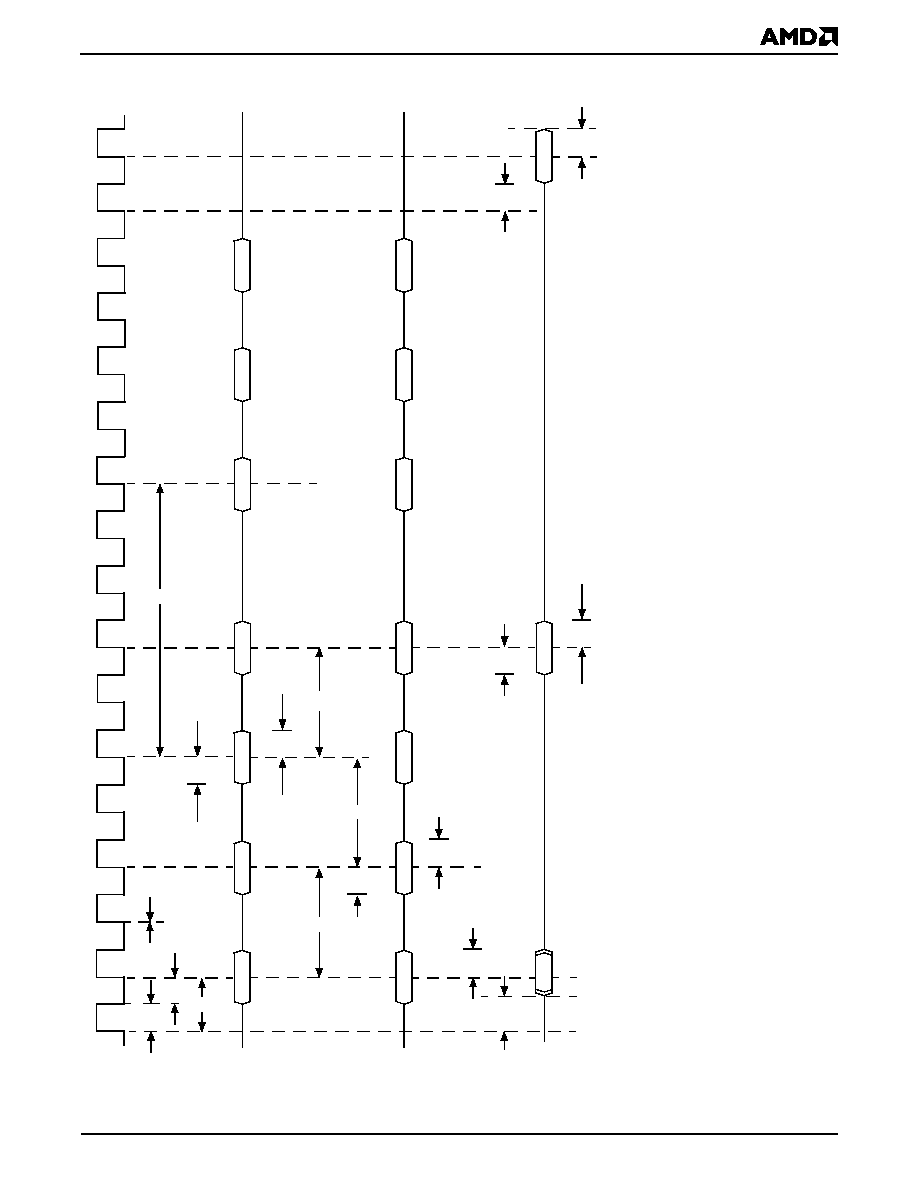

SDRAM Timing ..................................................................................................................... 66

SDRAM Clock Timing ........................................................................................................... 68

GP Bus Timing ...................................................................................................................... 69

GP Bus DMA Read Cycle Timing ......................................................................................... 71

GP Bus DMA Write Cycle Timing .......................................................................................... 72

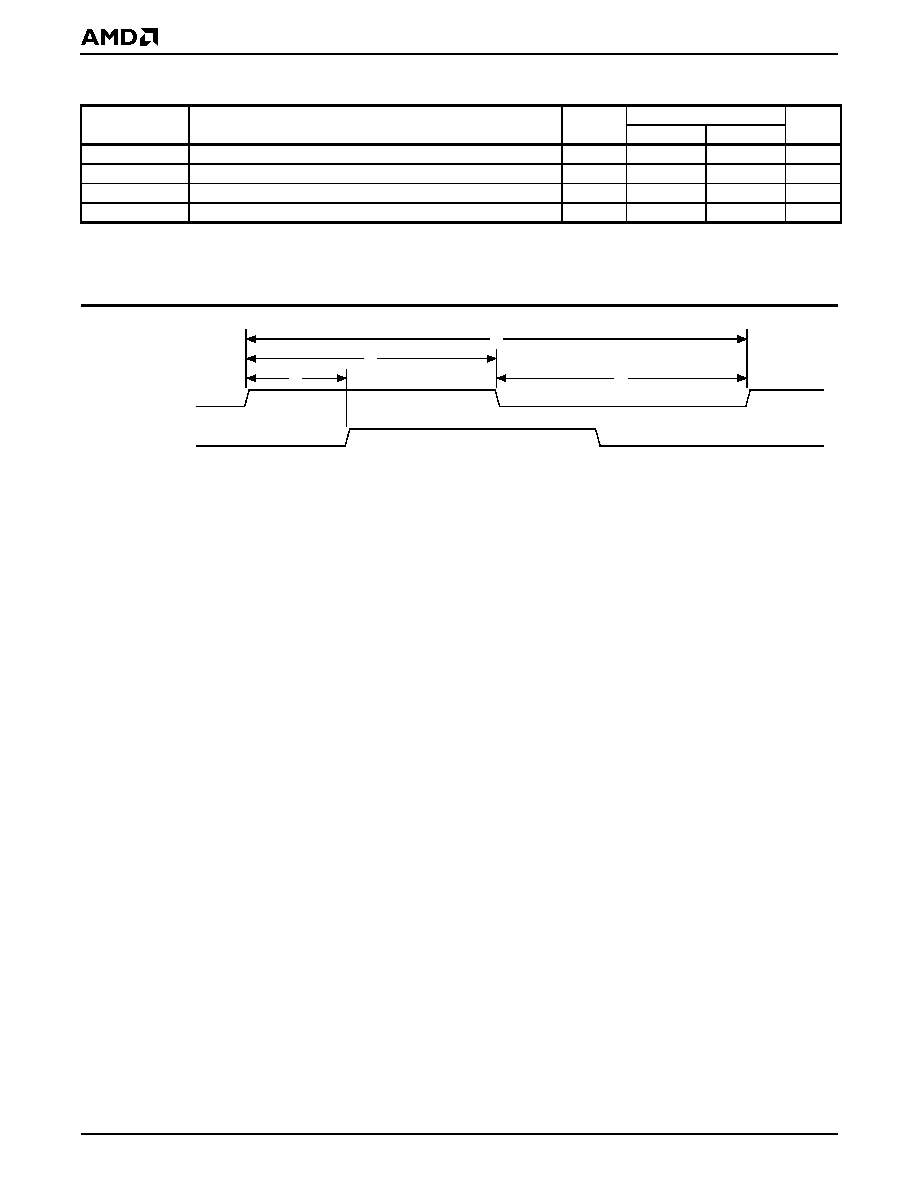

SSI Timing ............................................................................................................................. 73

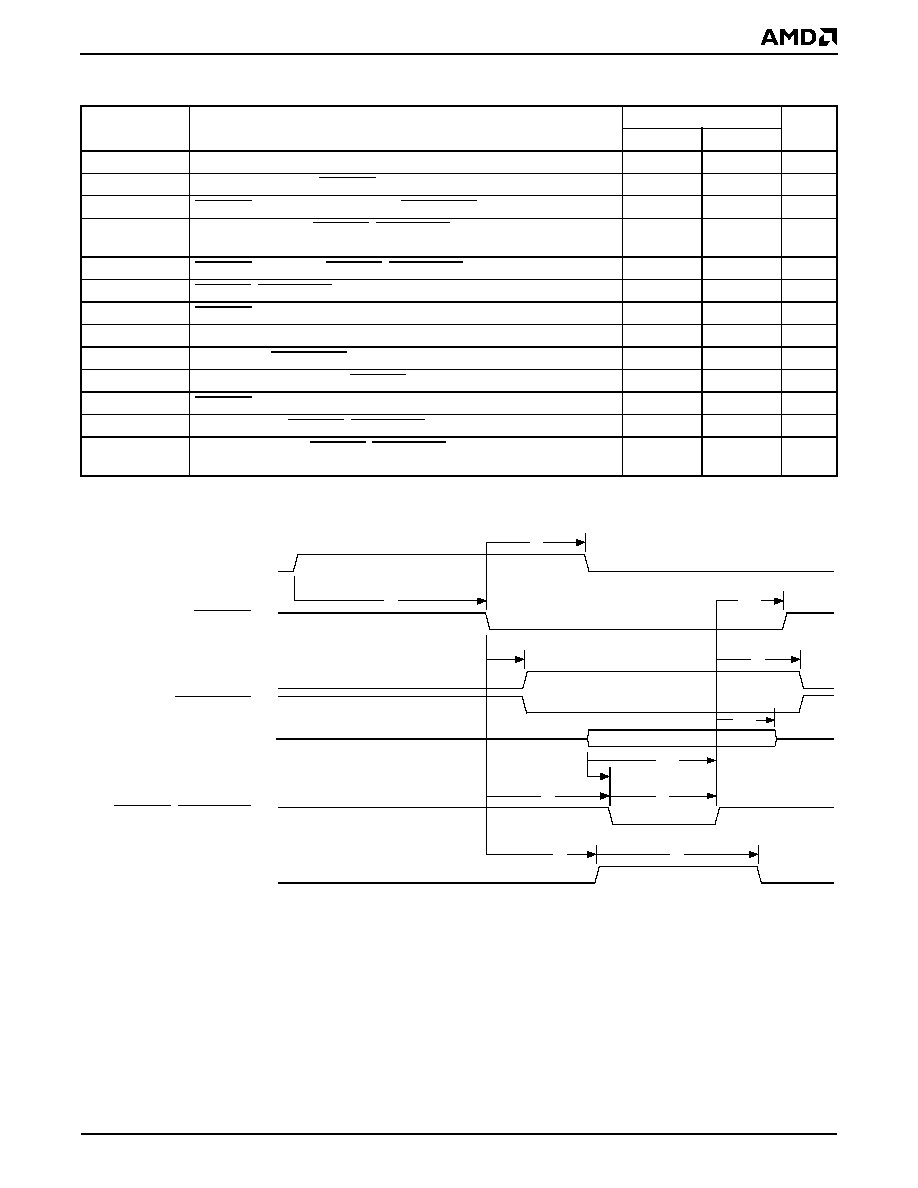

JTAG Timing ......................................................................................................................... 74

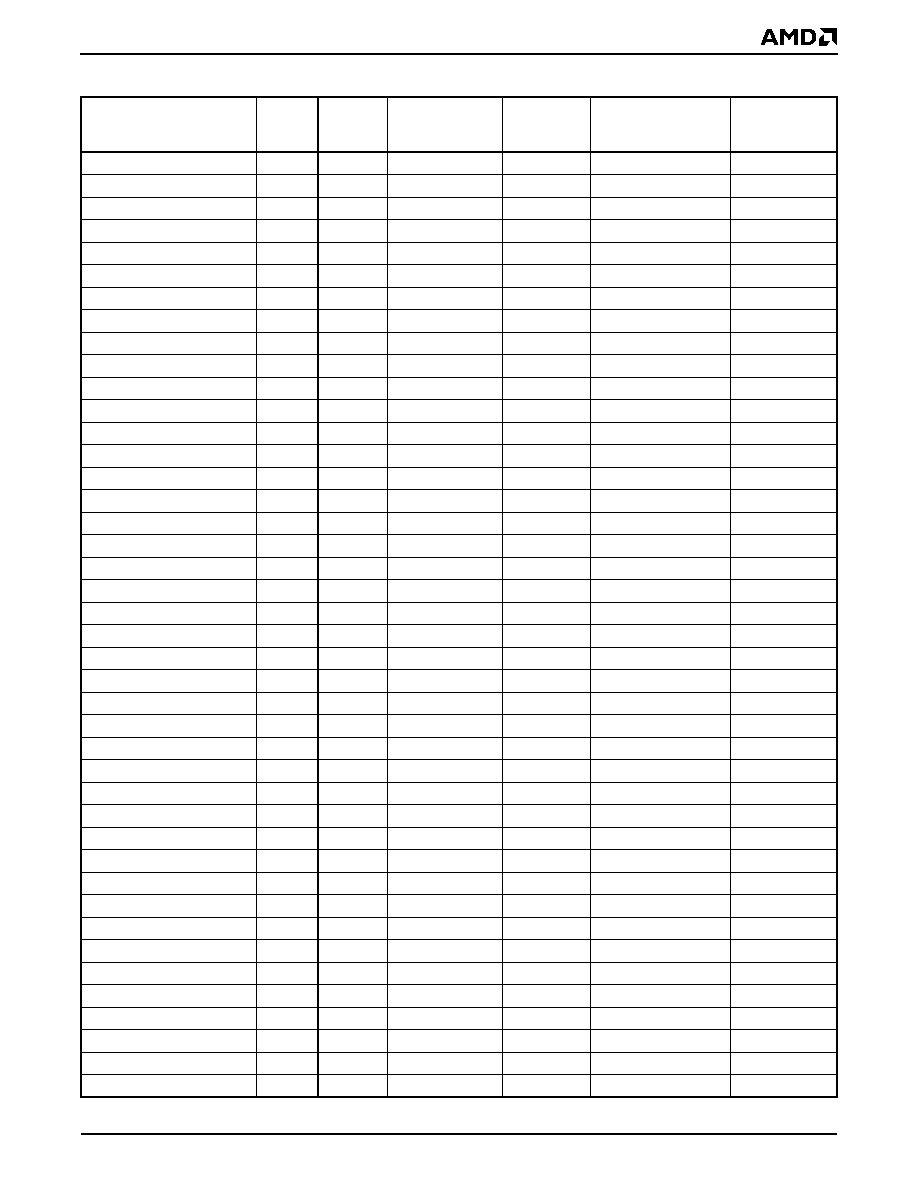

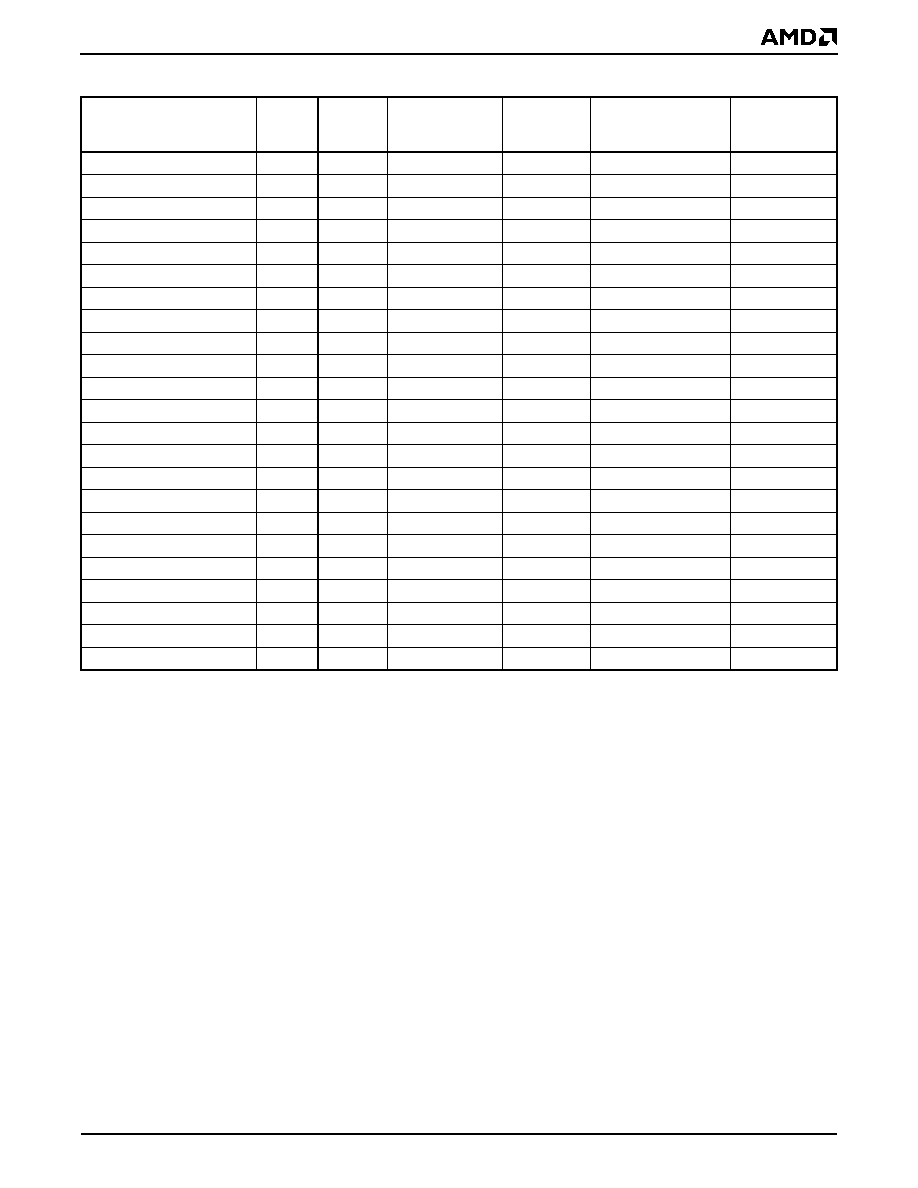

Appendix A: Pin Tables ............................................................................................................ A-1

Pin List Summary Table Column Definitions ............................................................................ A-6

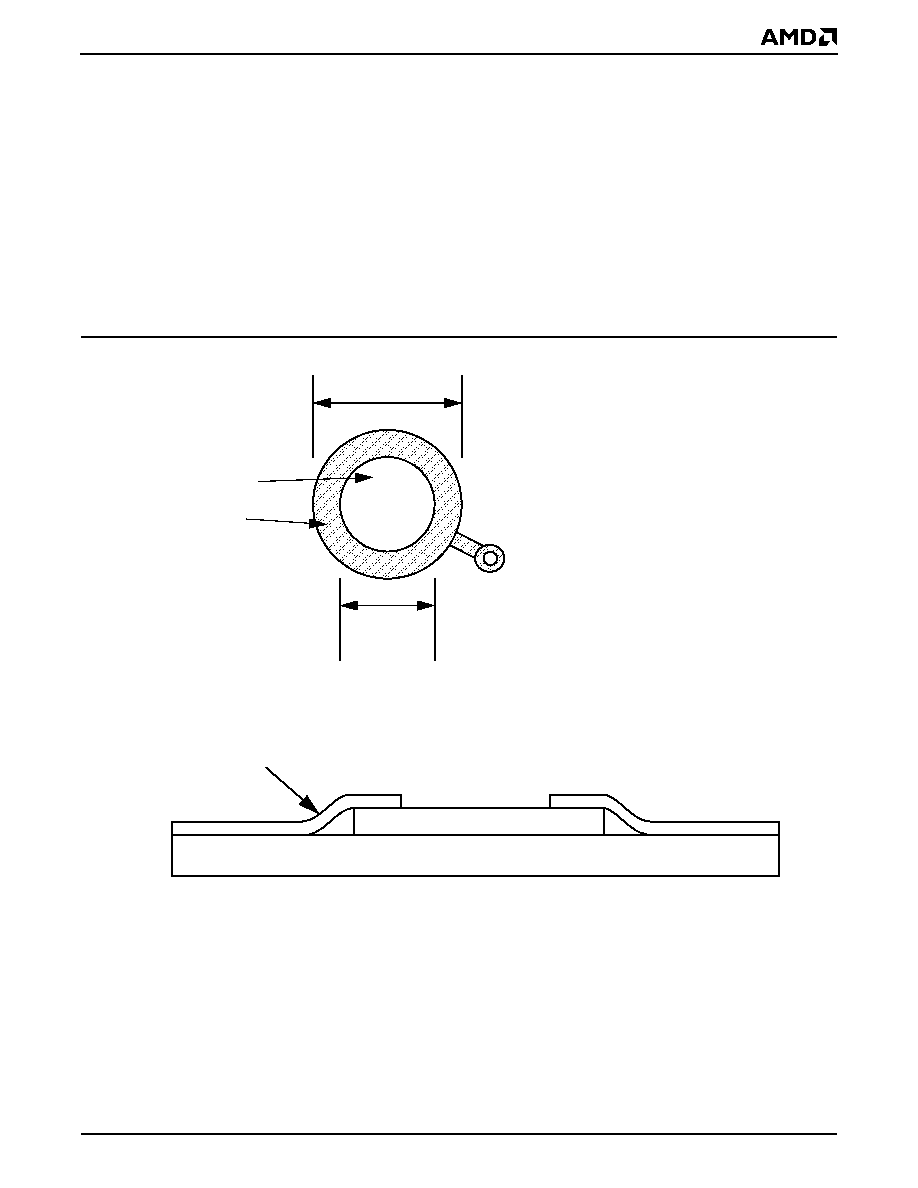

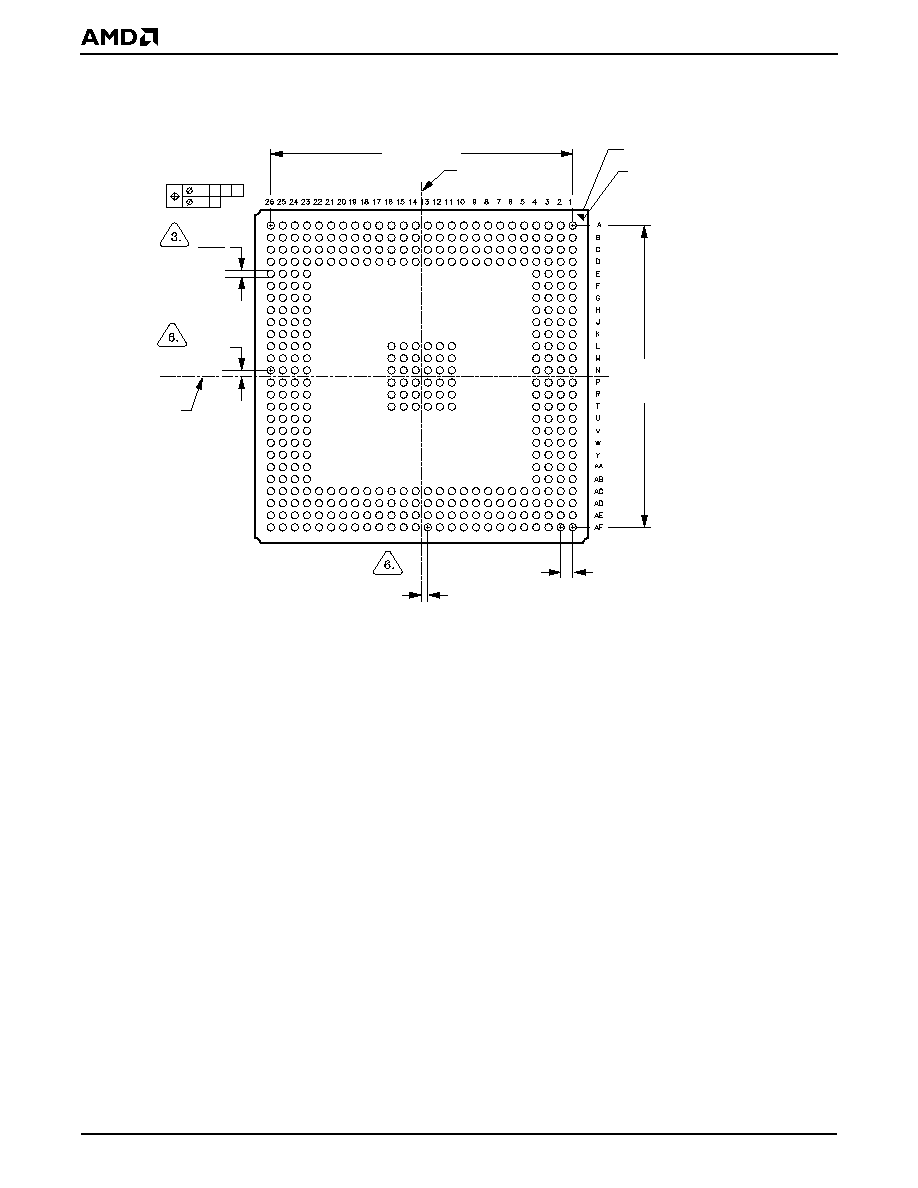

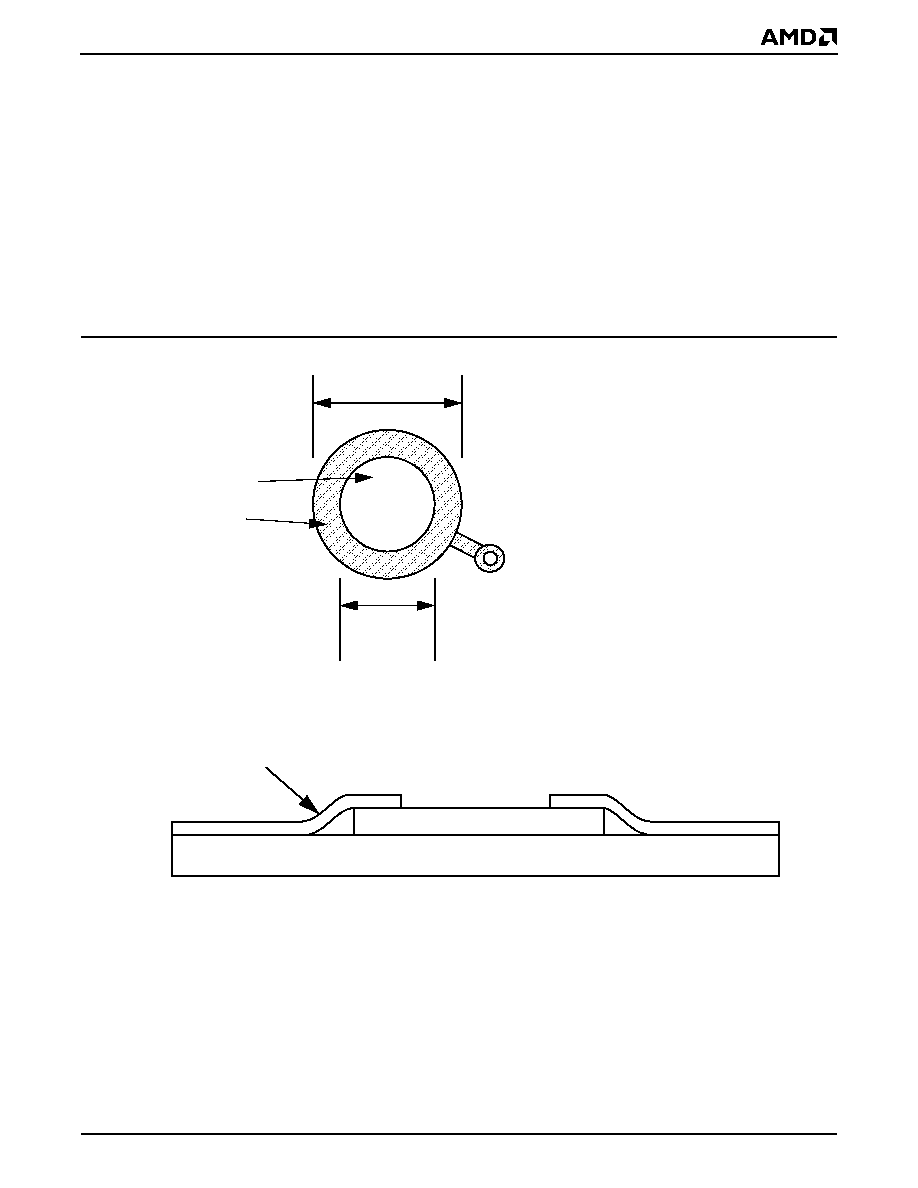

Appendix B: Physical Dimensions ............................................................................................ B-1

388-Pin Plastic BGA (PBGA) Package ................................................................................ B-1

Top View ...................................................................................................................... ........B-1

Bottom View ........................................................................................................................ B-2

Circuit Board Layout Considerations ....................................................................................B-3

Appendix C: Customer Support ................................................................................................C-1

Related Documents ..............................................................................................................C-2

Additional Information ..........................................................................................................C-2

Customer Development Platform .........................................................................................C-2

Third-Party Development Support Products .................................................................................C-2

Customer Service .................................................................................................................C-3

Hotline and World Wide Web Support............................................................................. C-3

Corporate Applications Hotline........................................................................................ C-3

World Wide Web Home Page ......................................................................................... C-3

Documentation and Literature ......................................................................................... C-3

Literature Ordering .......................................................................................................... C-3

Index ................................................................................................................................... Index-1

LIST OF FIGURES

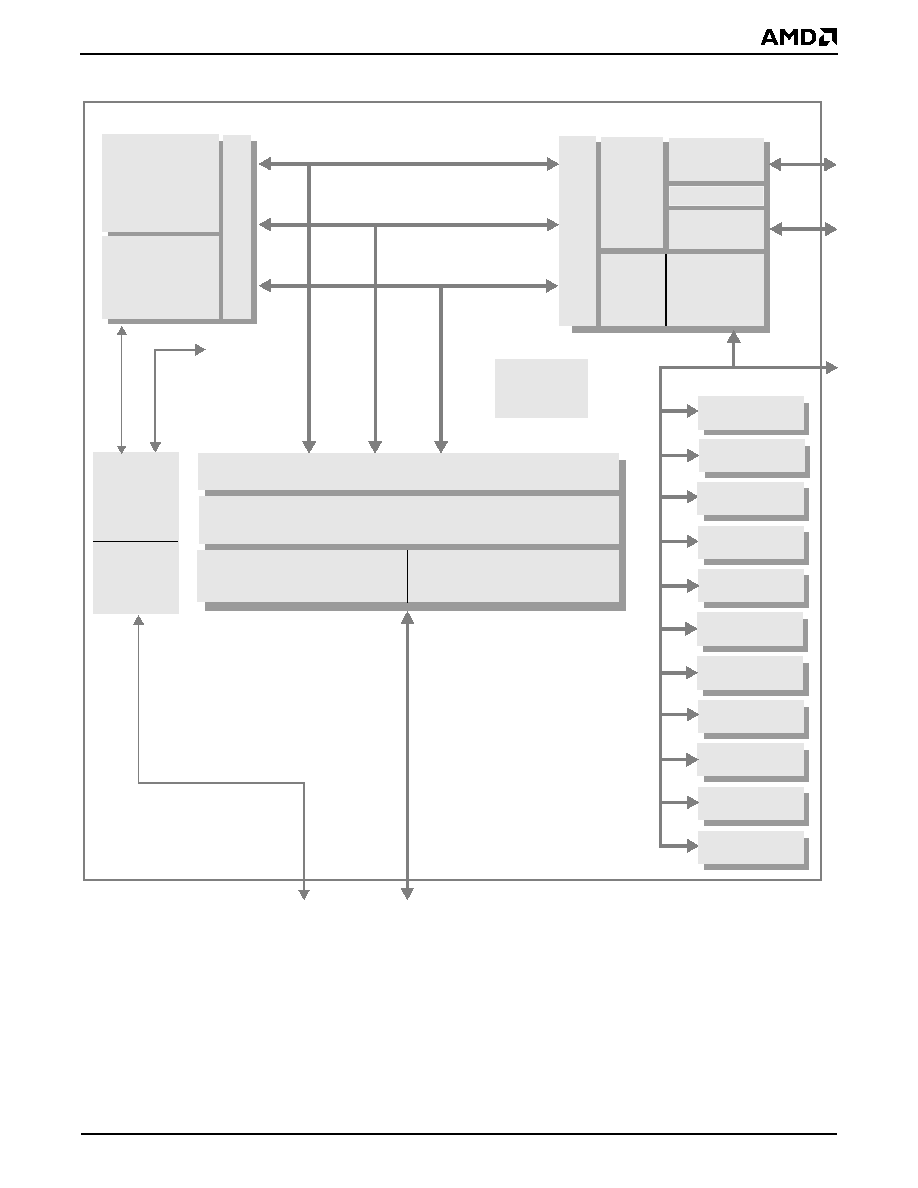

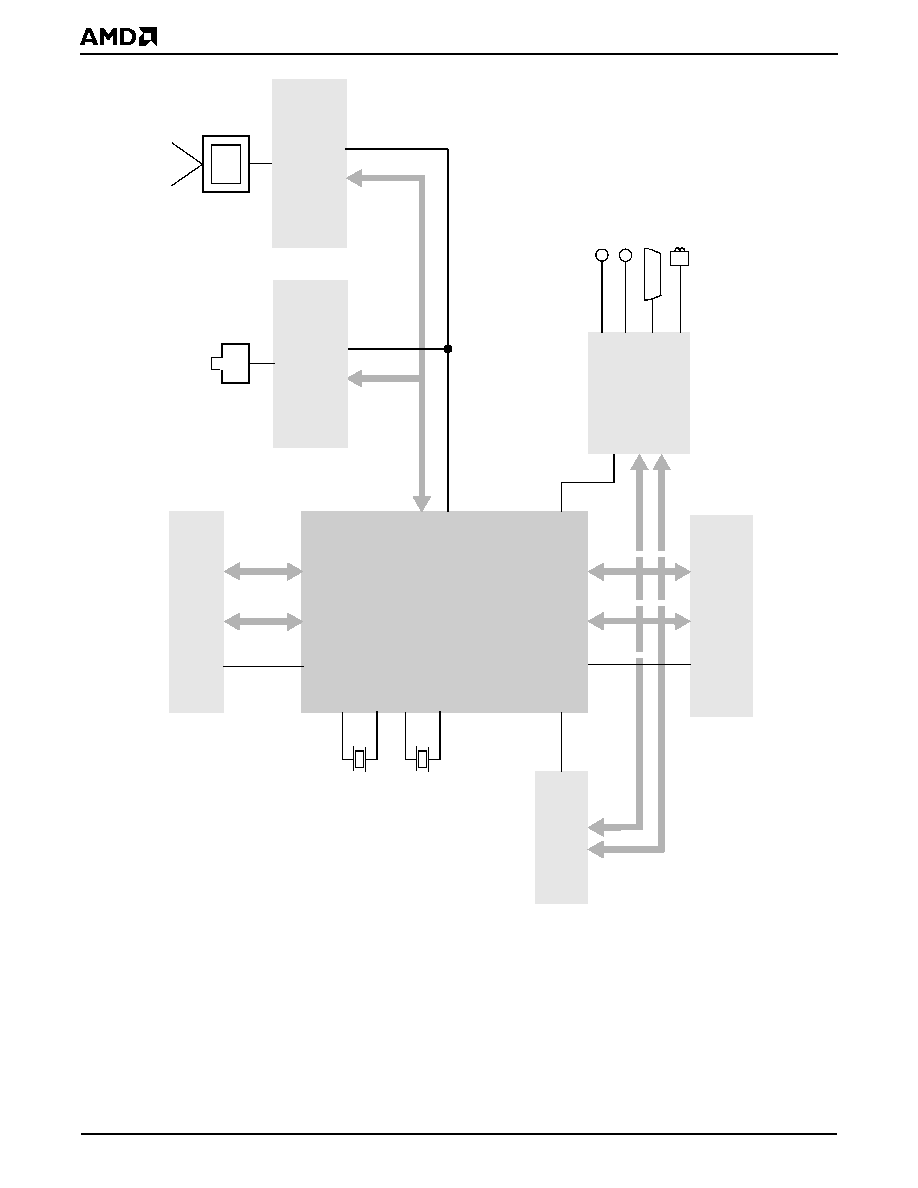

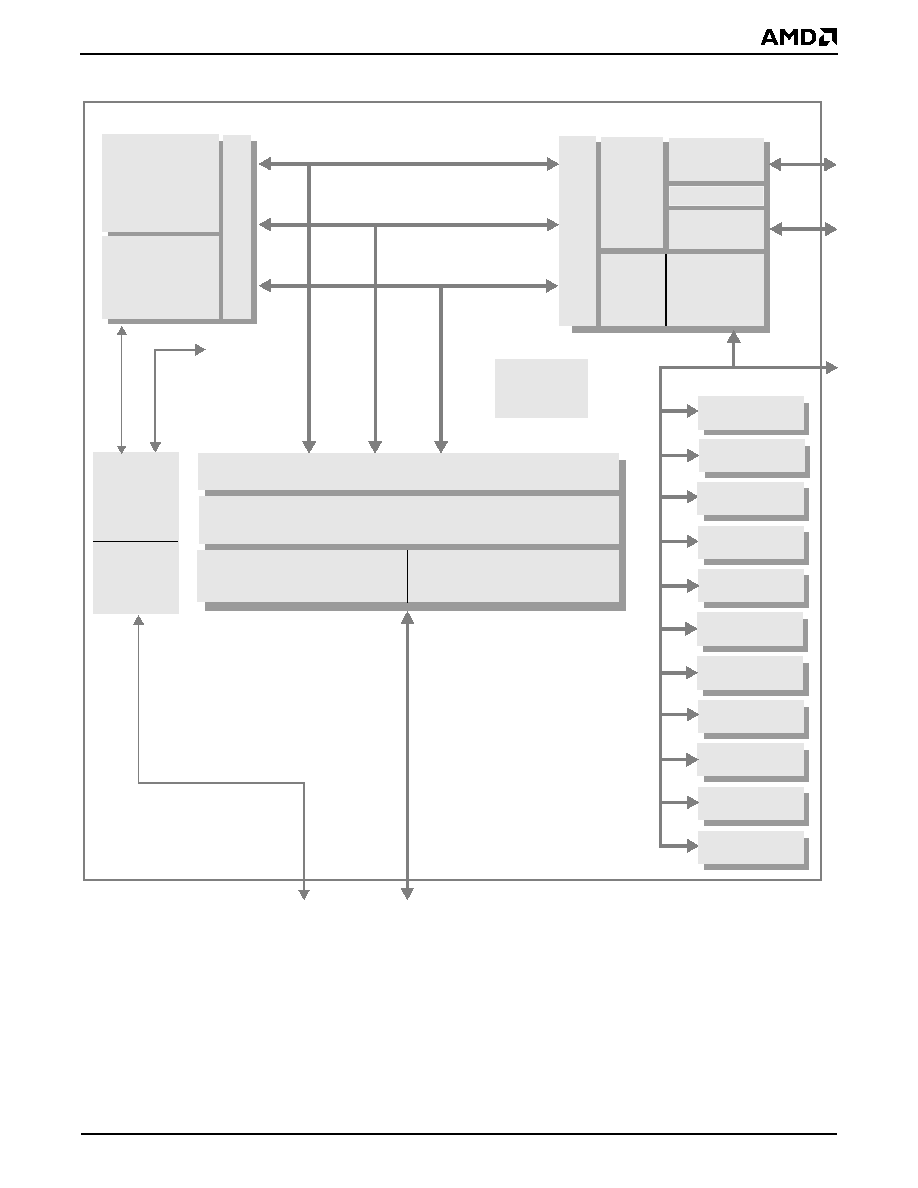

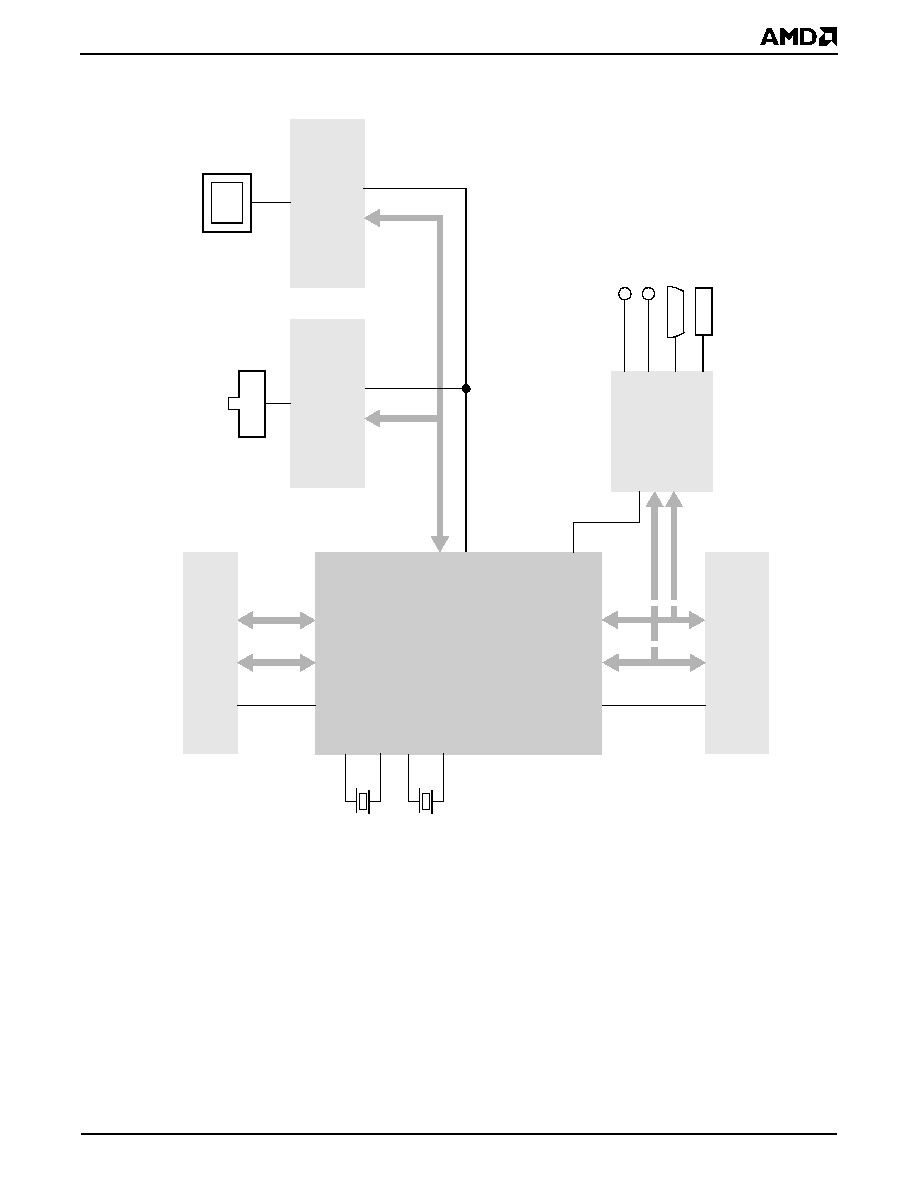

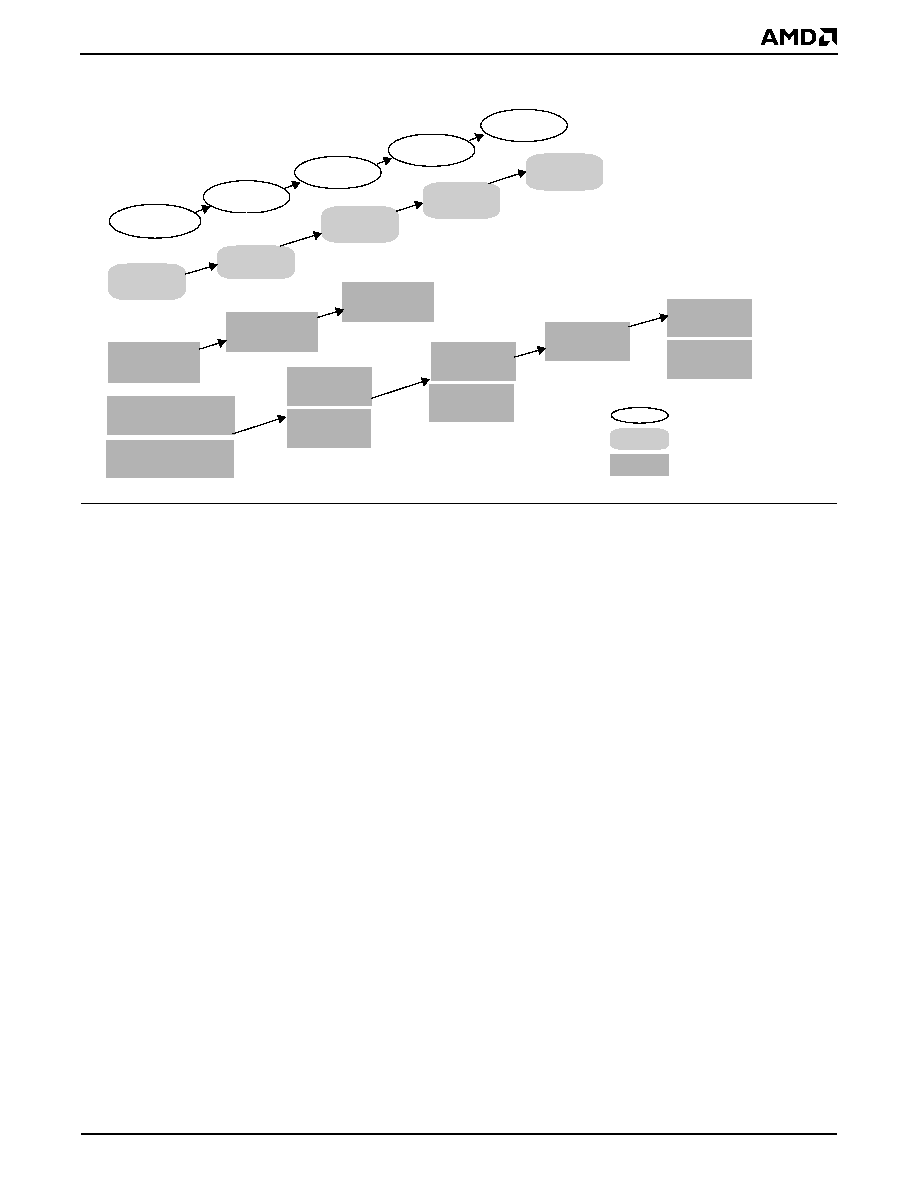

Figure 1.

…lanTMSC520 Microcontroller Block Diagram ....................................................... 29

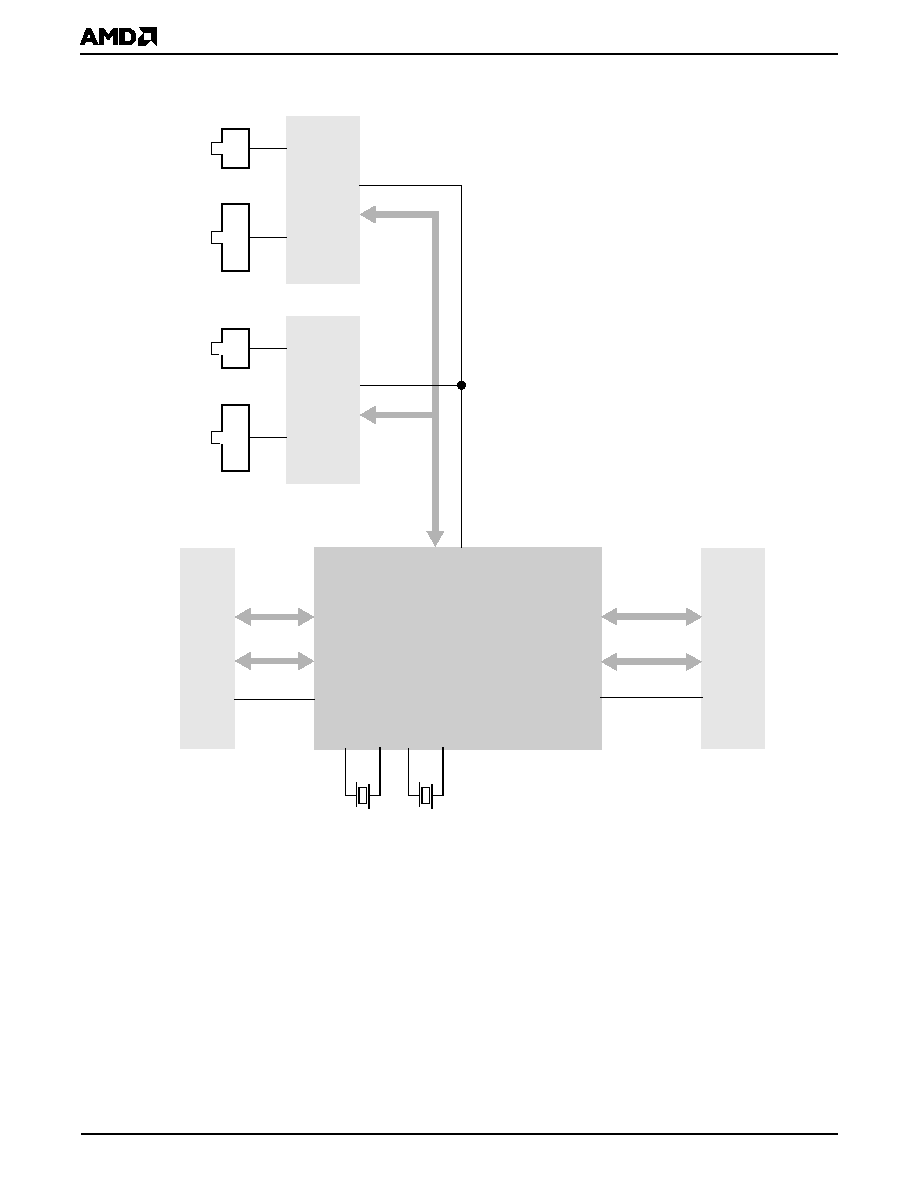

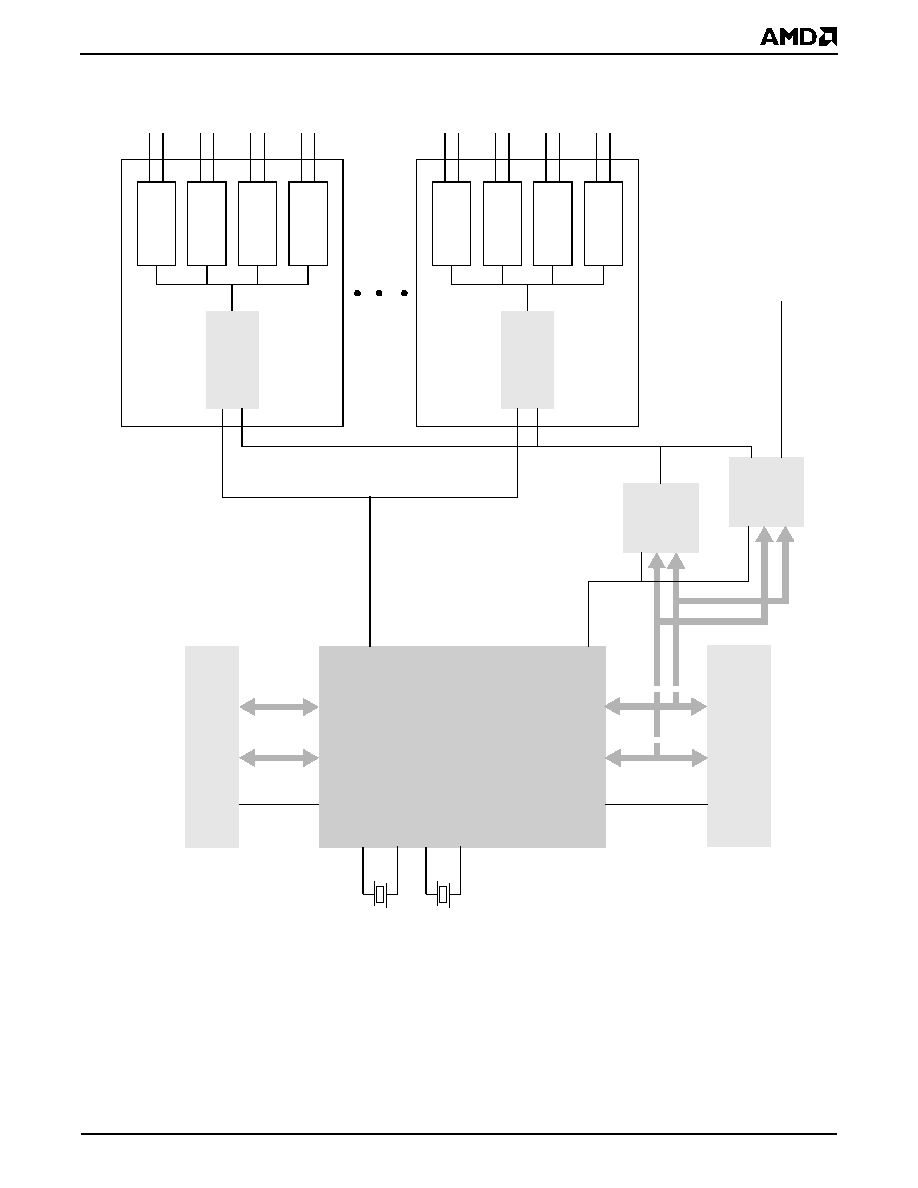

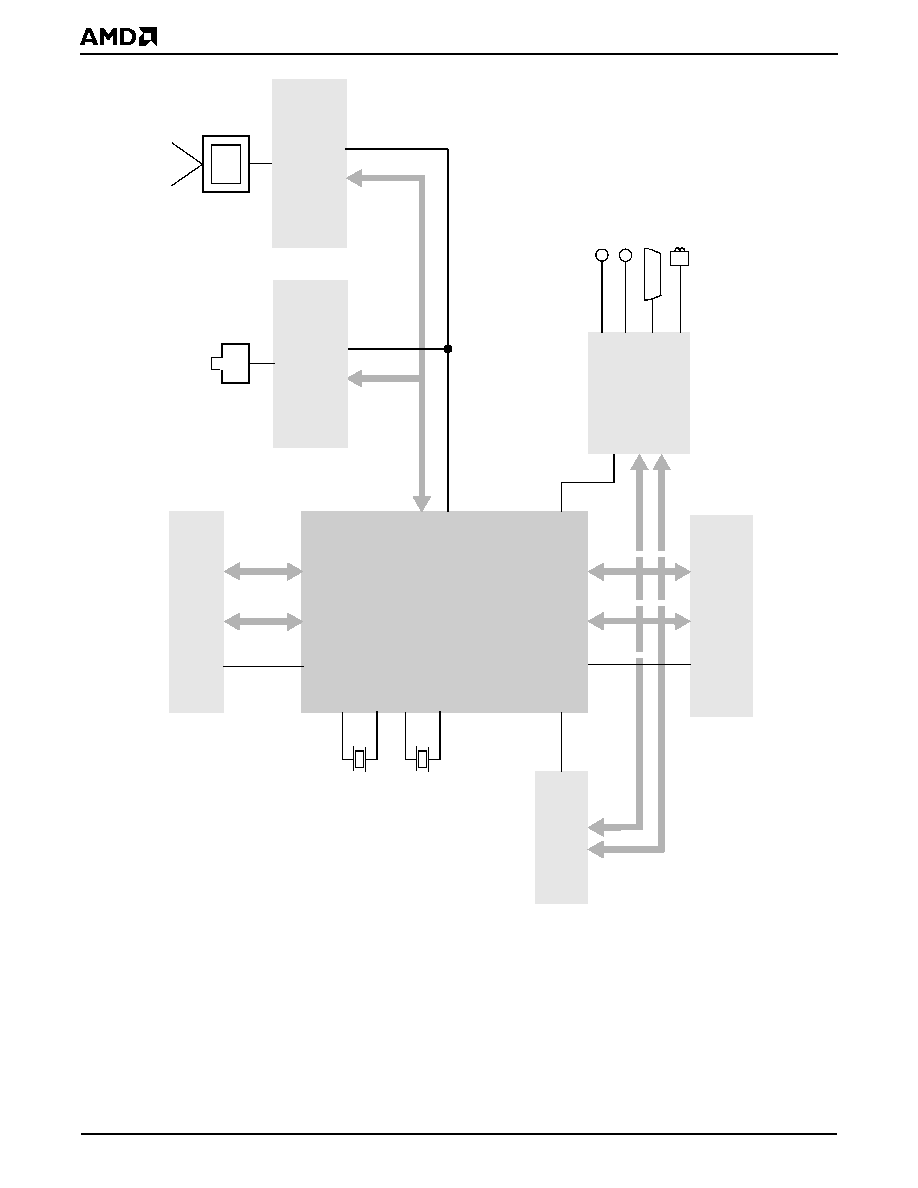

Figure 2.

…lanTMSC520 Microcontroller-Based Smart Residential Gateway

Reference Design ................................................................................................. 34

Figure 3.

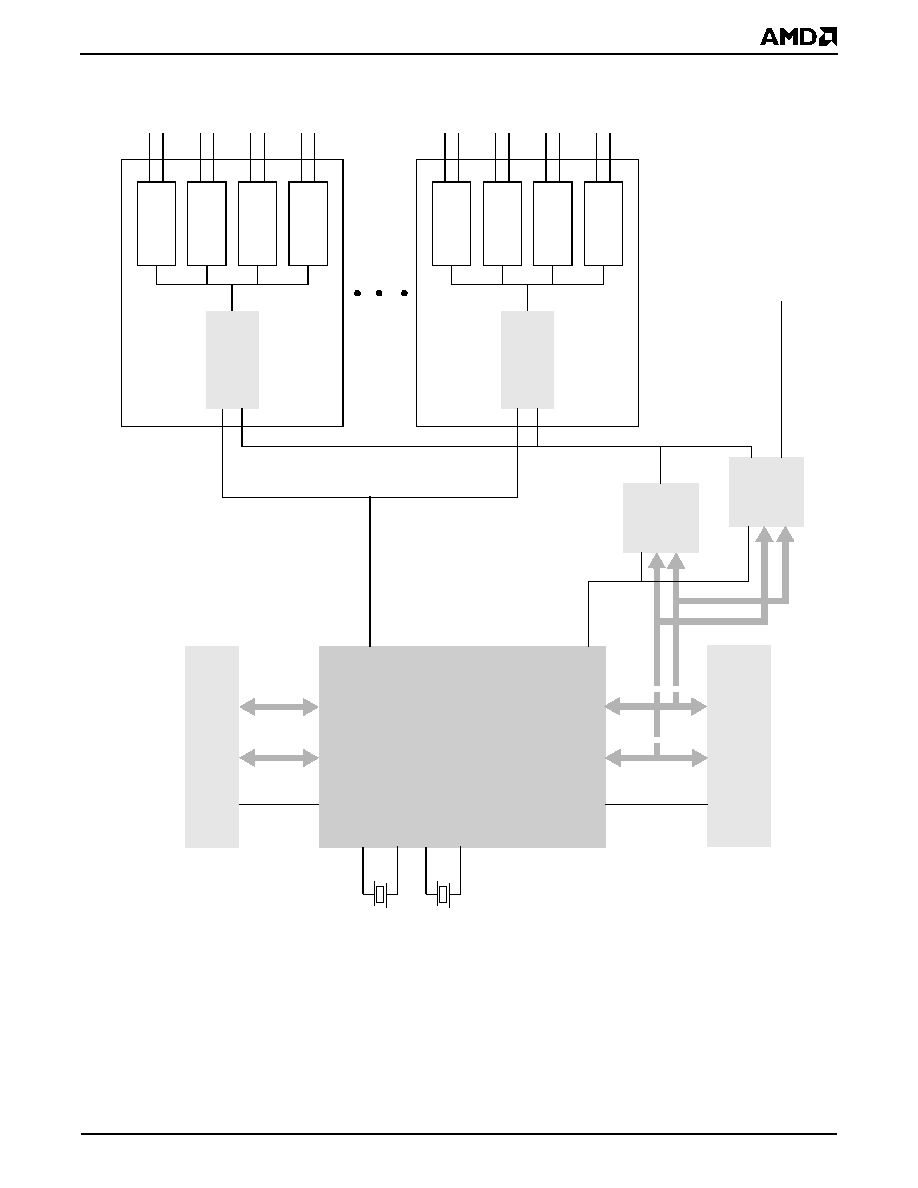

…lanTMSC520 Microcontroller-Based Thin Client Reference Design .................... 35

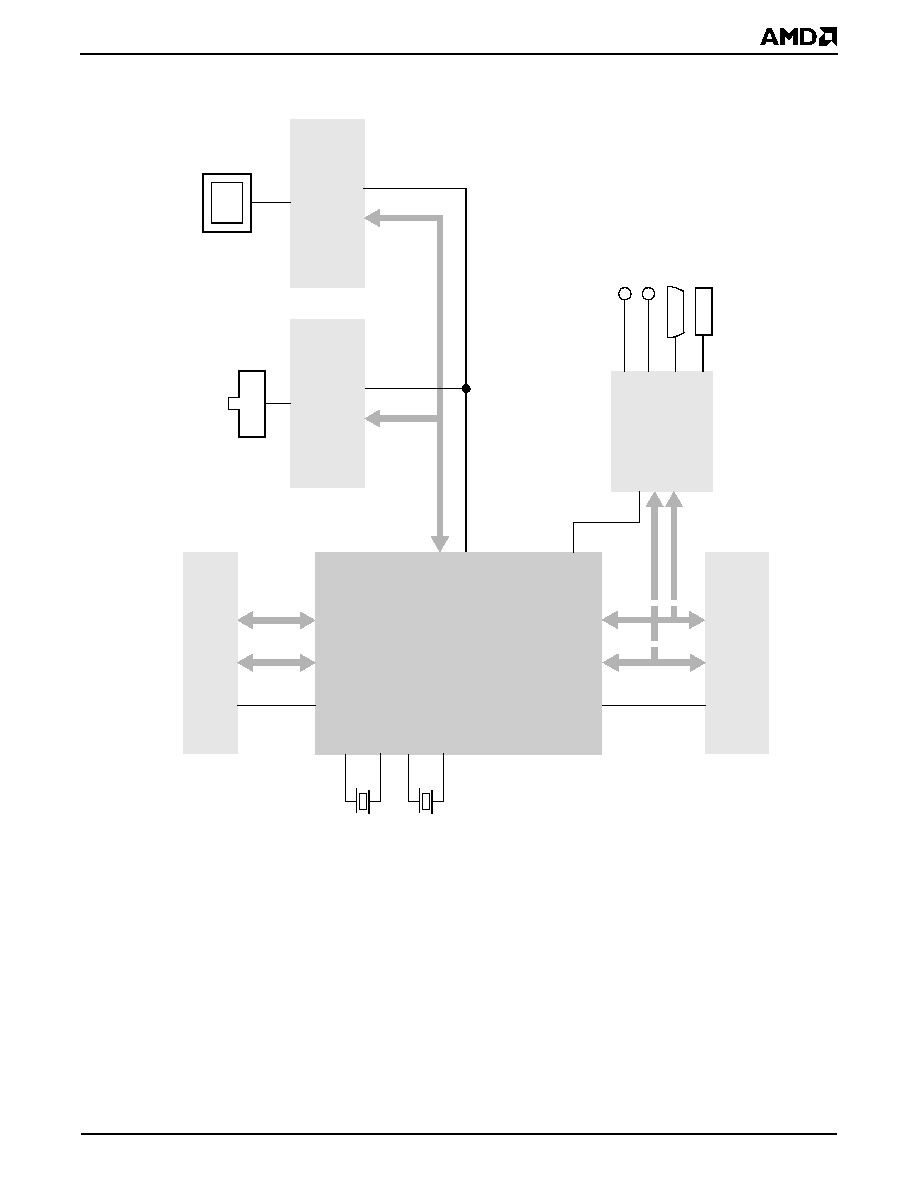

Figure 4.

…lanTMSC520 Microcontroller-Based Digital Set Top Box Reference Design ....... 36

Figure 5.

…lanTMSC520 Microcontroller-Based Telephone Line Concentrator

Reference Design ................................................................................................. 37

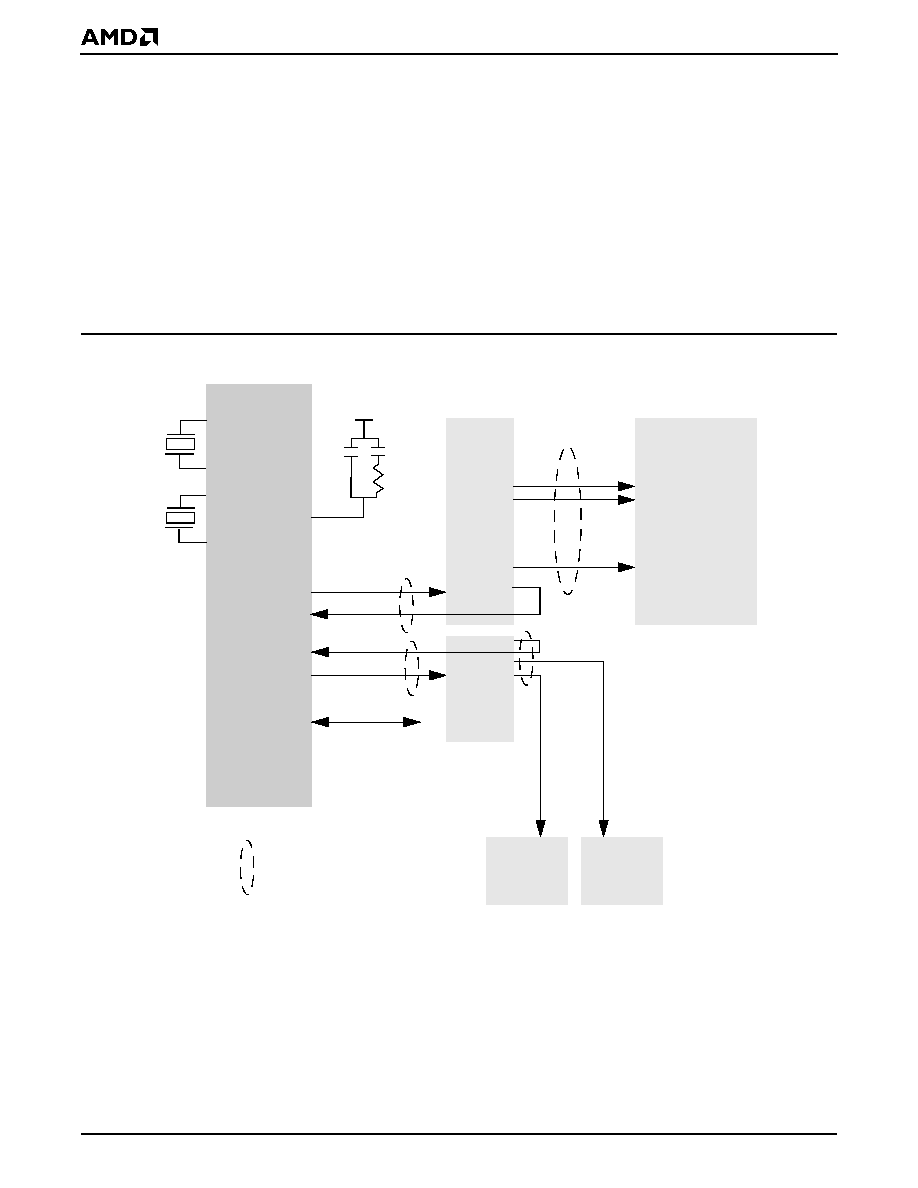

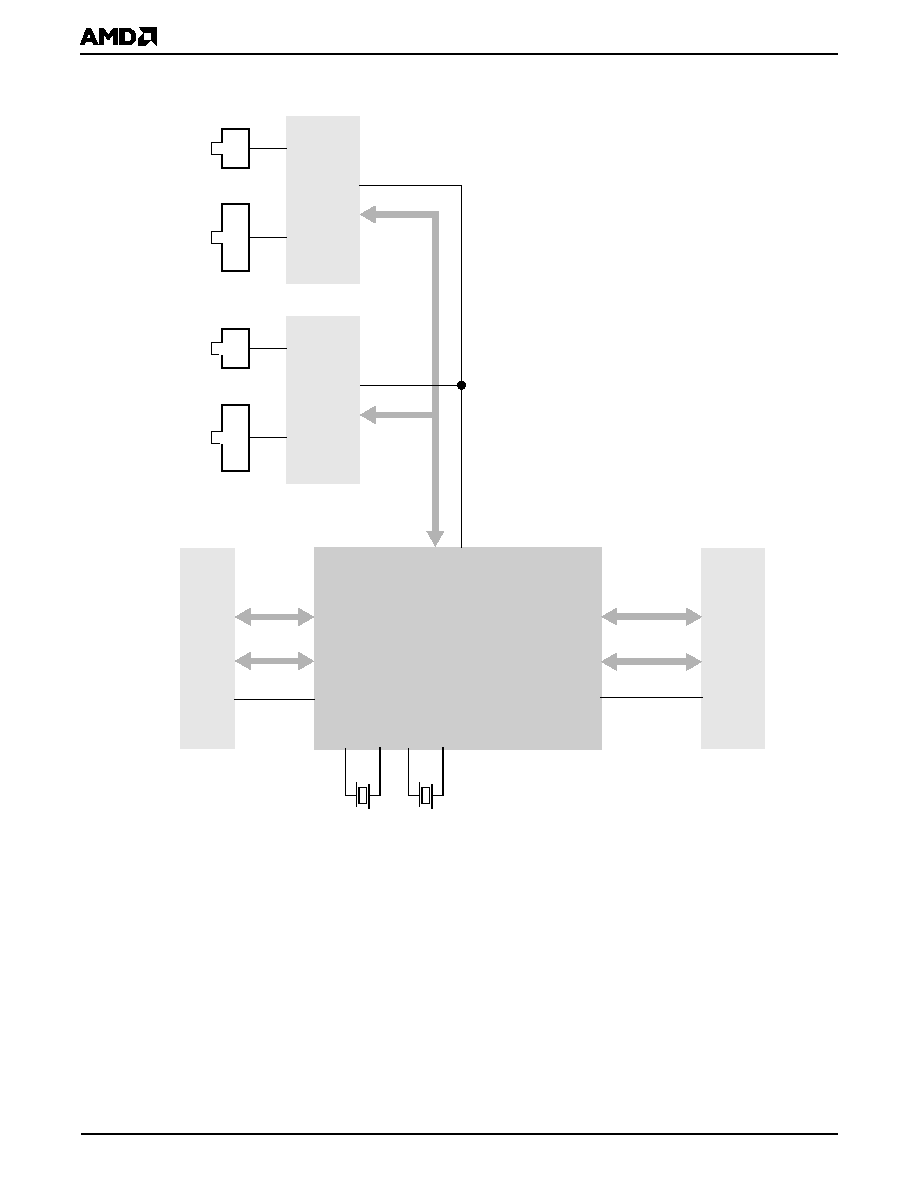

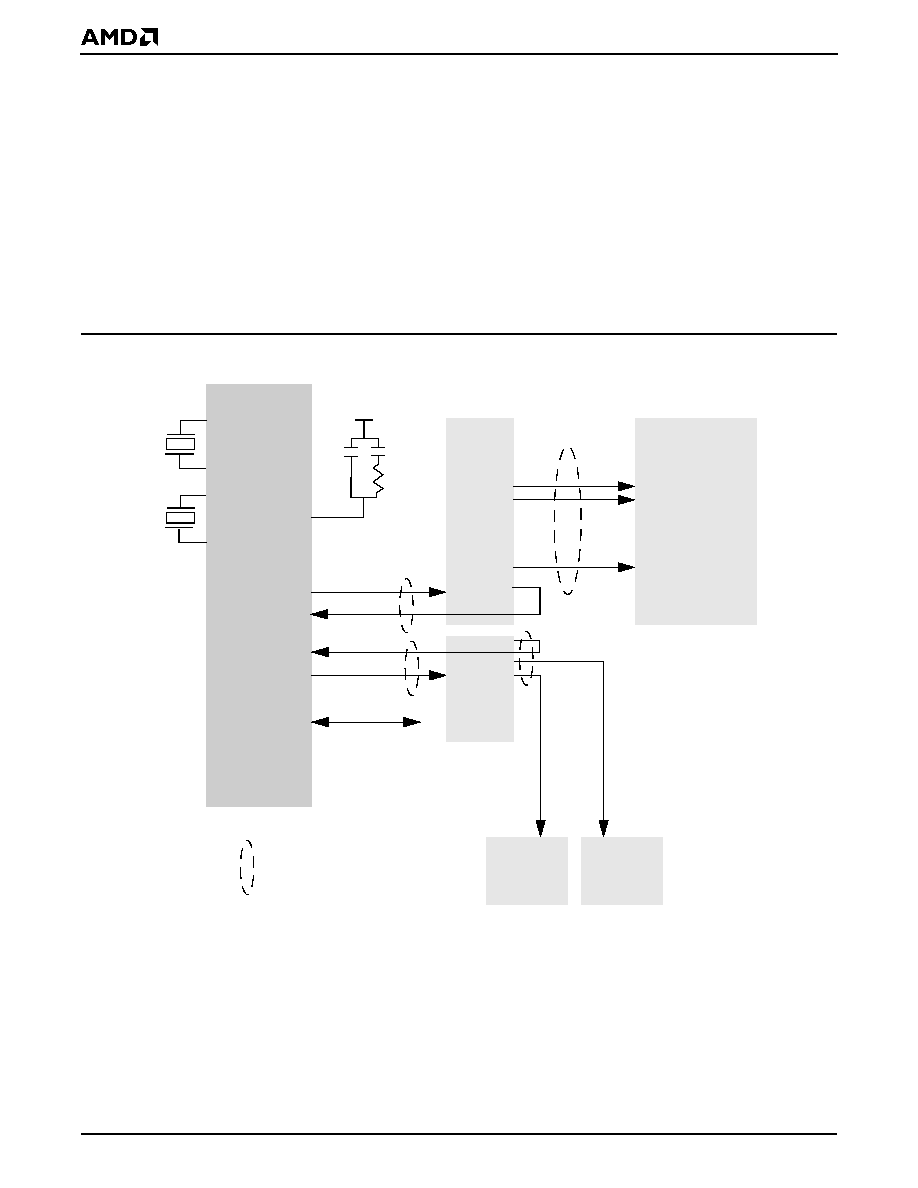

Figure 6.

System Clock Distribution Block Diagram ............................................................. 38

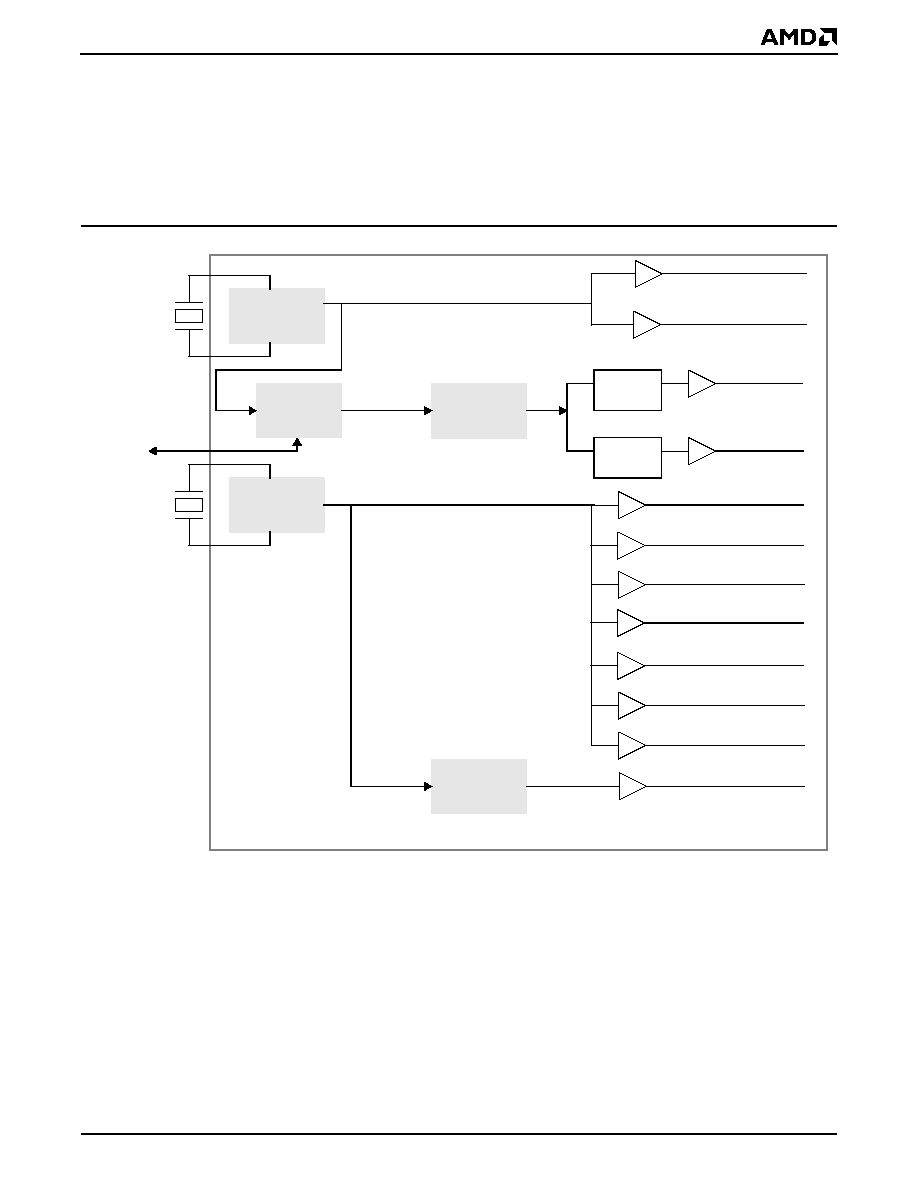

Figure 7.

Clock Source Block Diagram ................................................................................ 39

Figure 8.

32.768-kHz Crystal Circuit .................................................................................... 41

Figure 9.

33.333-MHz Third Overtone Crystal Implementation ............................................ 43

Figure 10.

Bypassing the 32.768-kHz Oscillator .................................................................... 44

Figure 11.

Bypassing the 33-MHz Oscillator .......................................................................... 44

Figure 12.

RTC Voltage Monitor Block Diagram .................................................................... 45

Figure 13.

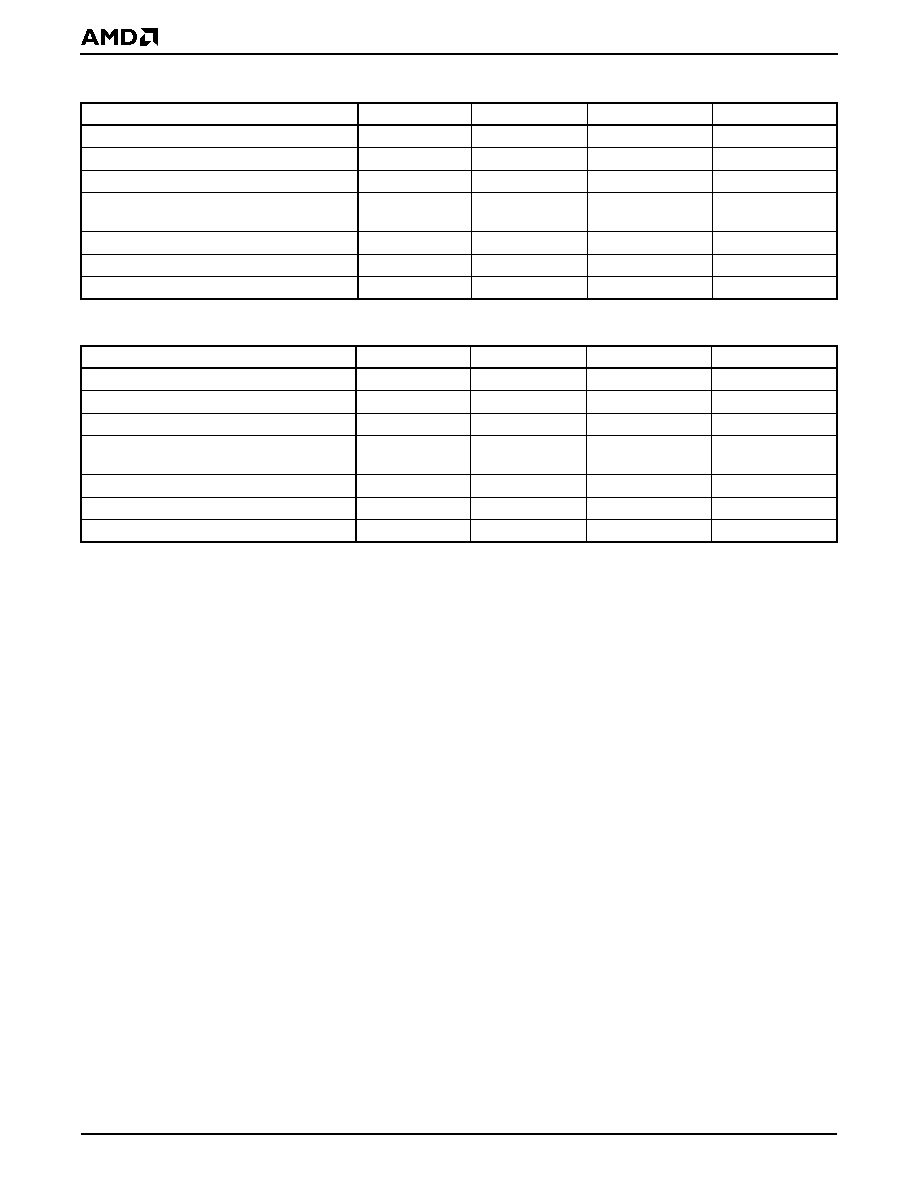

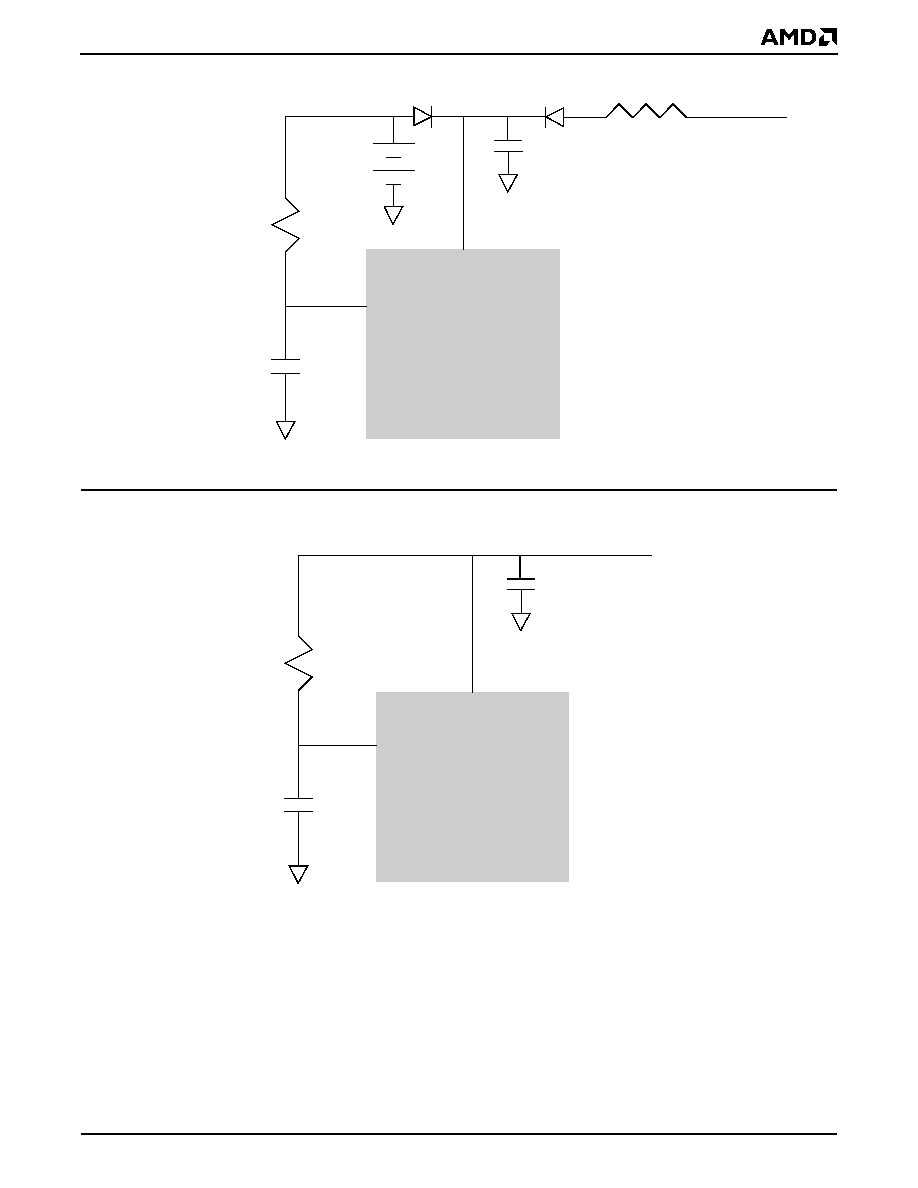

Circuit with Backup Battery ................................................................................... 47

Figure 14.

Circuit without Backup Battery .............................................................................. 47

Figure 15.

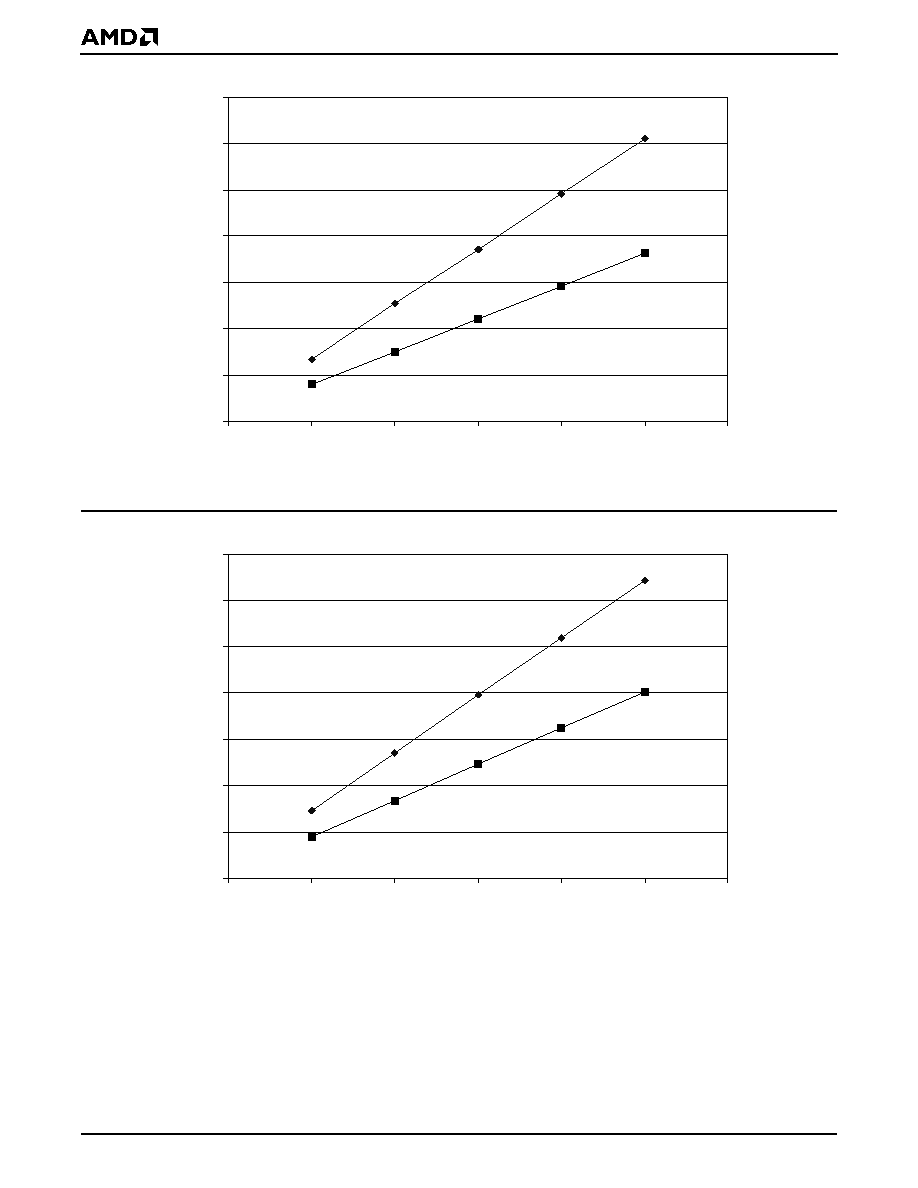

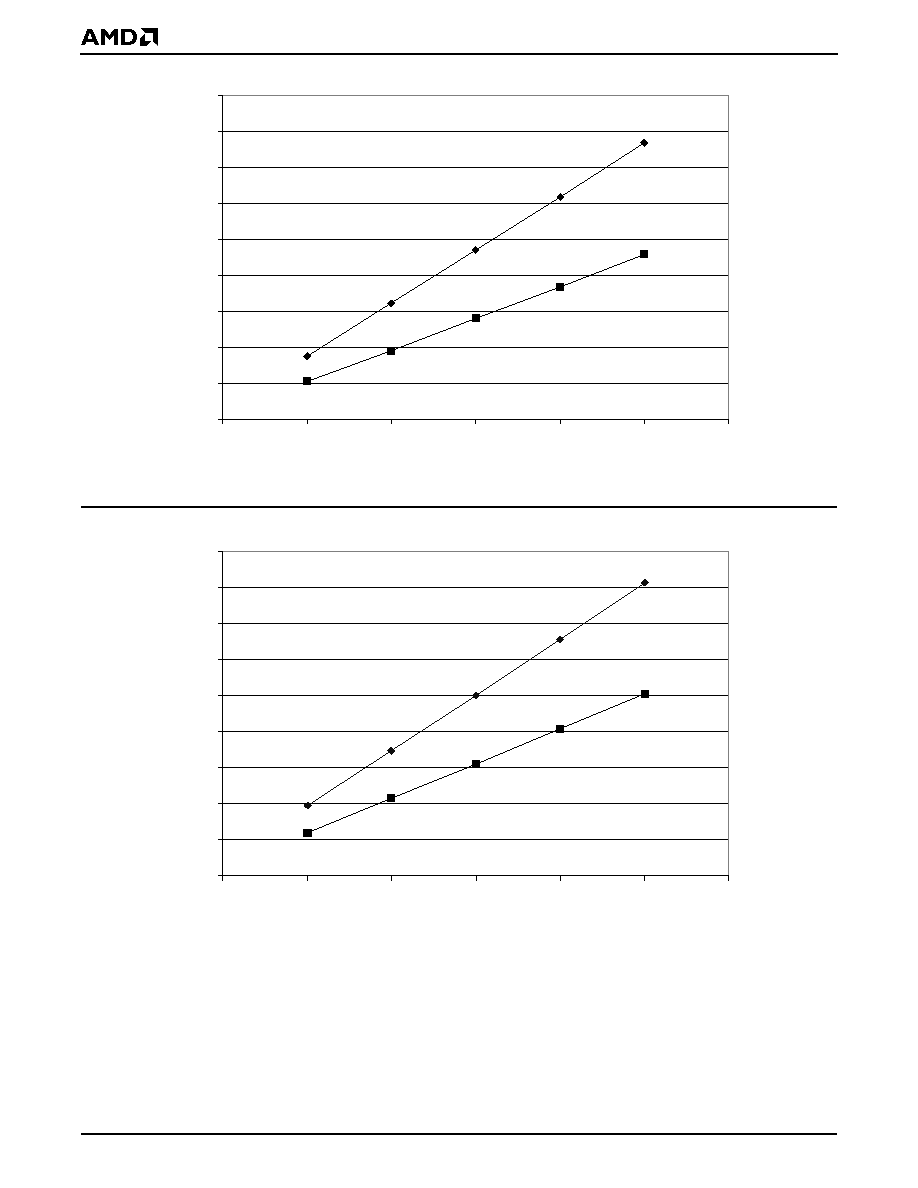

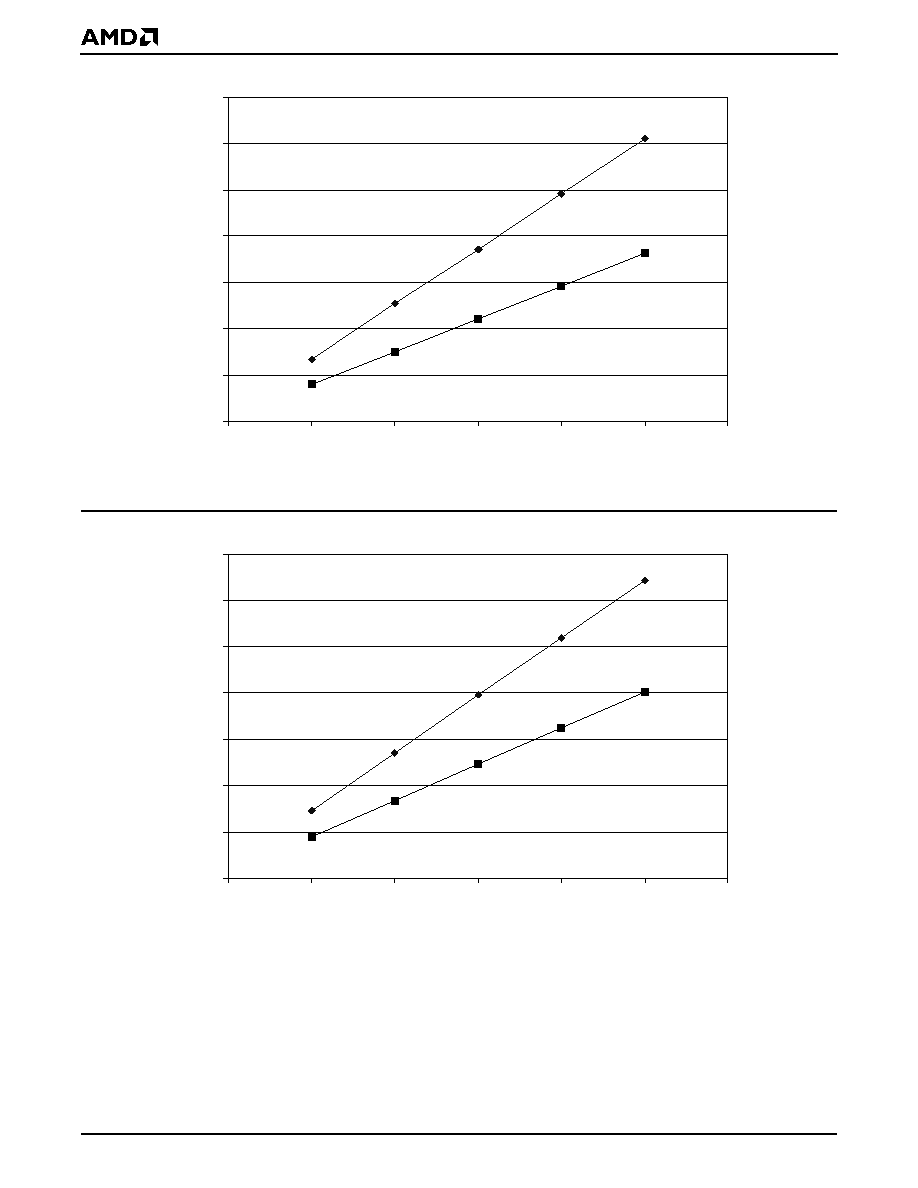

I/O Drive 6-mA Rise Time ..................................................................................... 52

P R E L I M I N A R Y

…lanTMSC520 Microcontroller Data Sheet

5

Figure 16.

I/O Drive 6-mA Fall Time ....................................................................................... 52

Figure 17.

I/O Drive 12-mA Rise Time ................................................................................... 53

Figure 18.

I/O Drive 12-mA Fall Time ..................................................................................... 53

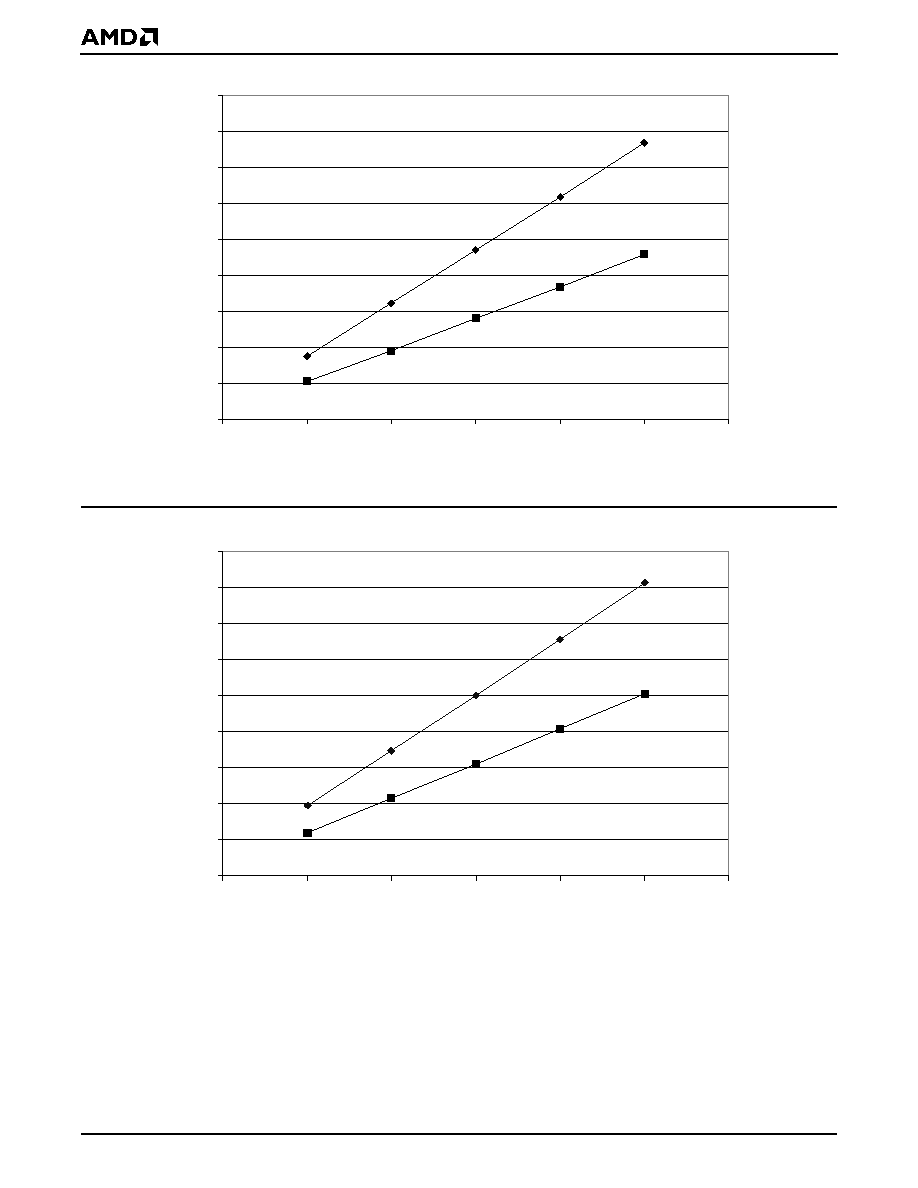

Figure 19.

I/O Drive 24-mA Rise Time ................................................................................... 54

Figure 20.

I/O Drive 24-mA Fall Time ..................................................................................... 54

Figure 21.

PCI Pads Rise Time with 1-ns Rise/Fall ............................................................... 55

Figure 22.

PCI Pads Fall Time with 1-ns Rise/Fall ................................................................. 55

Figure 23.

Thermal Resistance (

C/Watt) .............................................................................. 56

Figure 24.

Thermal Characteristics Equations ....................................................................... 57

Figure 25.

AC Switching Test Waveforms .............................................................................. 58

Figure 26.

Power-Up Timing Sequence ................................................................................. 60

Figure 27.

PWRGOOD Timing for RTC Standalone Mode .................................................... 60

Figure 28.

External System Reset Timing with Power Applied .............................................. 61

Figure 29.

PRGRESET Timing ............................................................................................... 62

Figure 30.

Internal System Reset Timing ............................................................................... 62

Figure 31.

Non-Burst ROM Read Cycle Timing ..................................................................... 64

Figure 32.

Page-Mode ROM Read Cycle Timing ................................................................... 64

Figure 33.

Flash Write Cycle Timing ...................................................................................... 65

Figure 34.

SDRAM Write and Read Timing ........................................................................... 67

Figure 35.

SDRAM Clock Timing ........................................................................................... 68

Figure 36.

GP Bus Non-DMA Cycle Timing ........................................................................... 70

Figure 37.

GP-DMA Read Cycle Timing ................................................................................ 71

Figure 38.

GP-DMA Write Cycle Timing ................................................................................. 72

Figure 39.

SSI Timing ............................................................................................................. 73

Figure 40.

JTAG Boundary Scan Timing ................................................................................ 74

Figure 41.

BGA Ball Pad Layout ........................................................................................... B-3

LIST OF TABLES

Table 1.

Signal Descriptions Table Definitions..................................................................... 16

Table 2.

Signal Descriptions ............................................................................................... 17

Table 3.

Clock Jitter Specifications ..................................................................................... 40

Table 4.

Clock Startup and Lock Times .............................................................................. 40

Table 5.

Oscillator Input Specifications ............................................................................... 40

Table 6.

Analog VCC (VCC_ANLG) Specifications ............................................................ 40

Table 7.

PLL1 Loop Filter Components .............................................................................. 41

Table 8.

Timing Error as It Translates to Clock Accuracy .................................................... 41

Table 9.

32.768-kHz Crystal Specifications ........................................................................ 42

Table 10.

33-MHz Crystal Specifications .............................................................................. 42

Table 11.

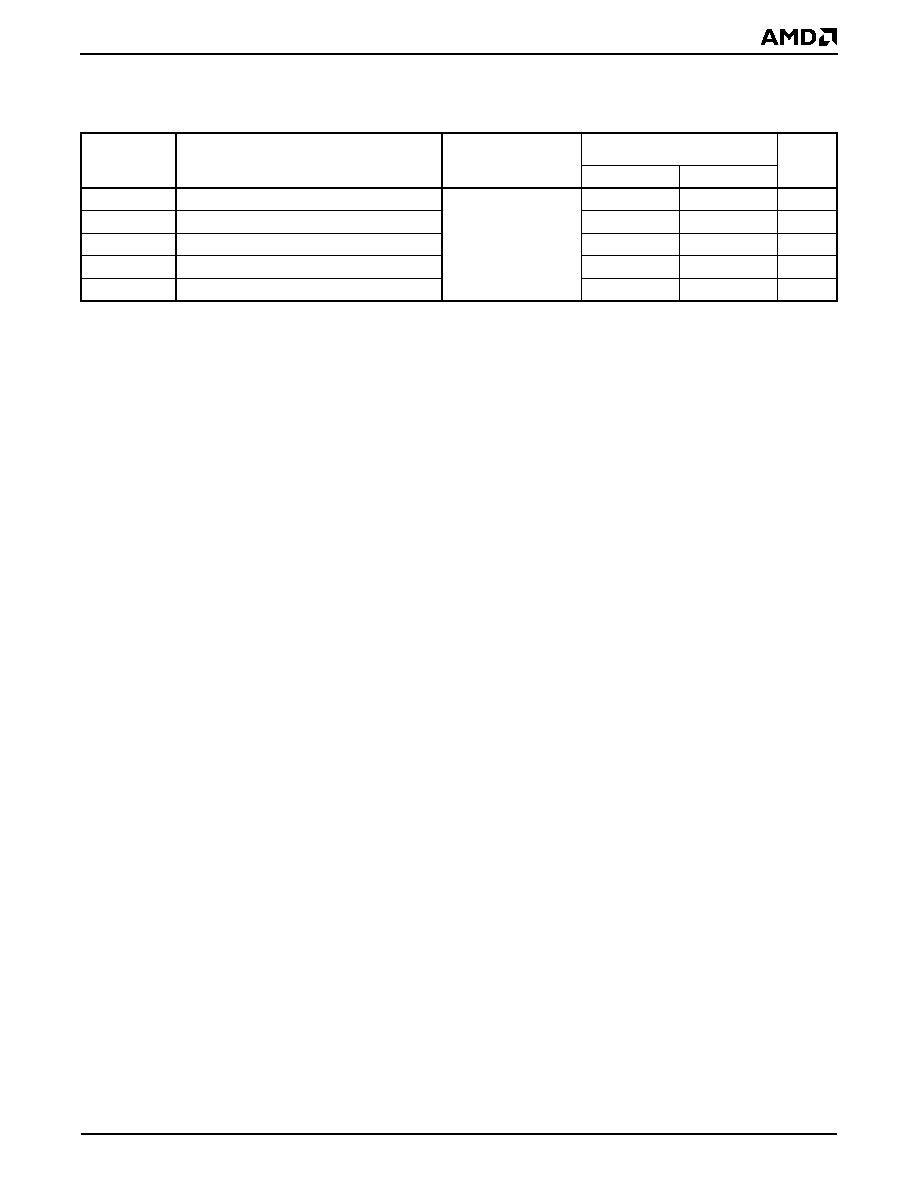

RTC Voltage Monitor Component Specifications .................................................. 46

Table 12.

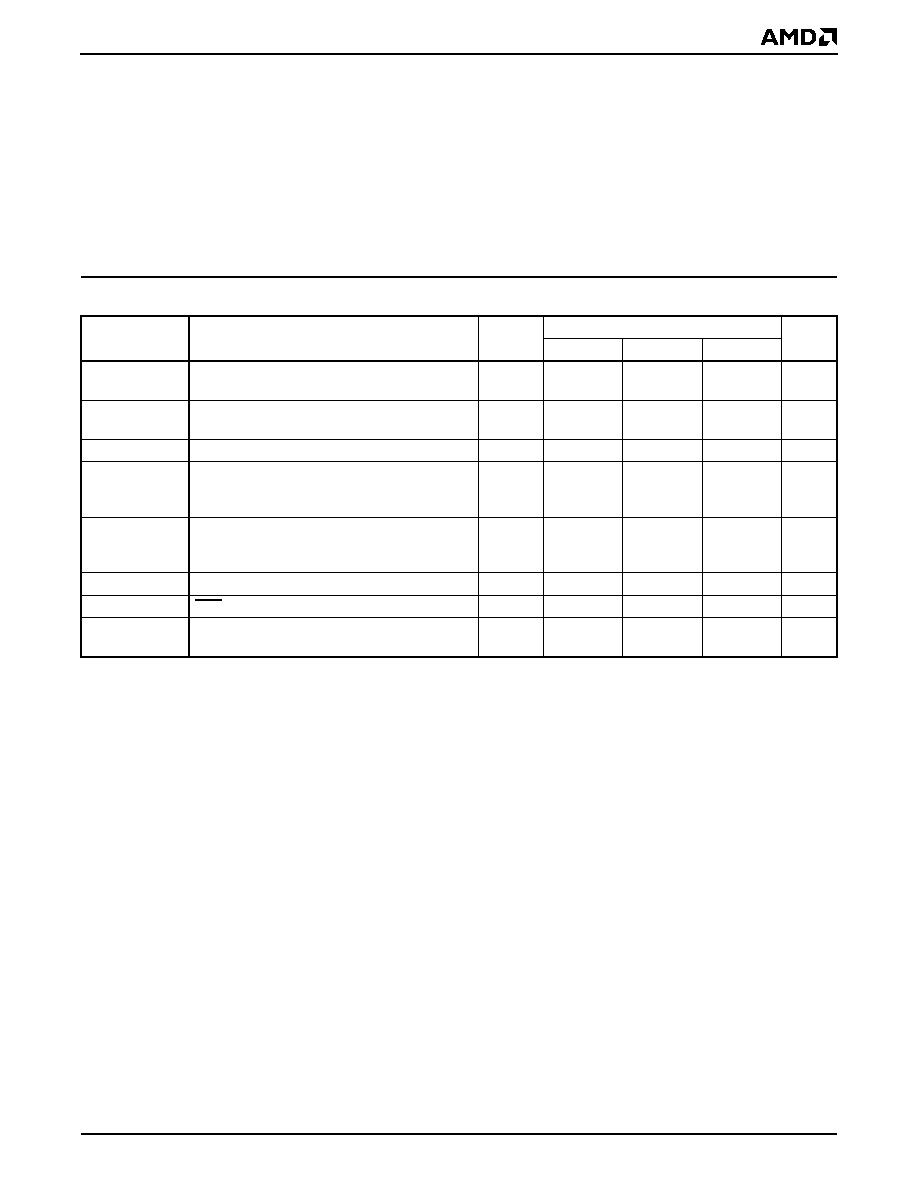

Device Power Dissipation ..................................................................................... 56

Table 13.

VCC_ANLG and VCC_RTC Power Dissipation .................................................... 56

Table 14.

Thermal Resistance (∞C/W)

q

JC

and

q

JA

for BGA Package with 6-Layer Board ... 57

Table 15.

Maximum T

A

for Plastic BGA Package with 6-Layer Board with T

CASE

= 85∞C .... 57

Table 16.

Multiplexed Signal Trade-Offs .............................................................................. A-2

Table 17.

PIOs Sorted by PIO Number ................................................................................ A-4

Table 18.

PIOs Sorted by Signal Name ............................................................................... A-5

Table 19.

Pin List Summary Table Abbreviations ................................................................. A-6

Table 20.

Pin List Summary ................................................................................................. A-7

Table 21.

Related AMD Products--E86TM Family Devices ..................................................C-1

6

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

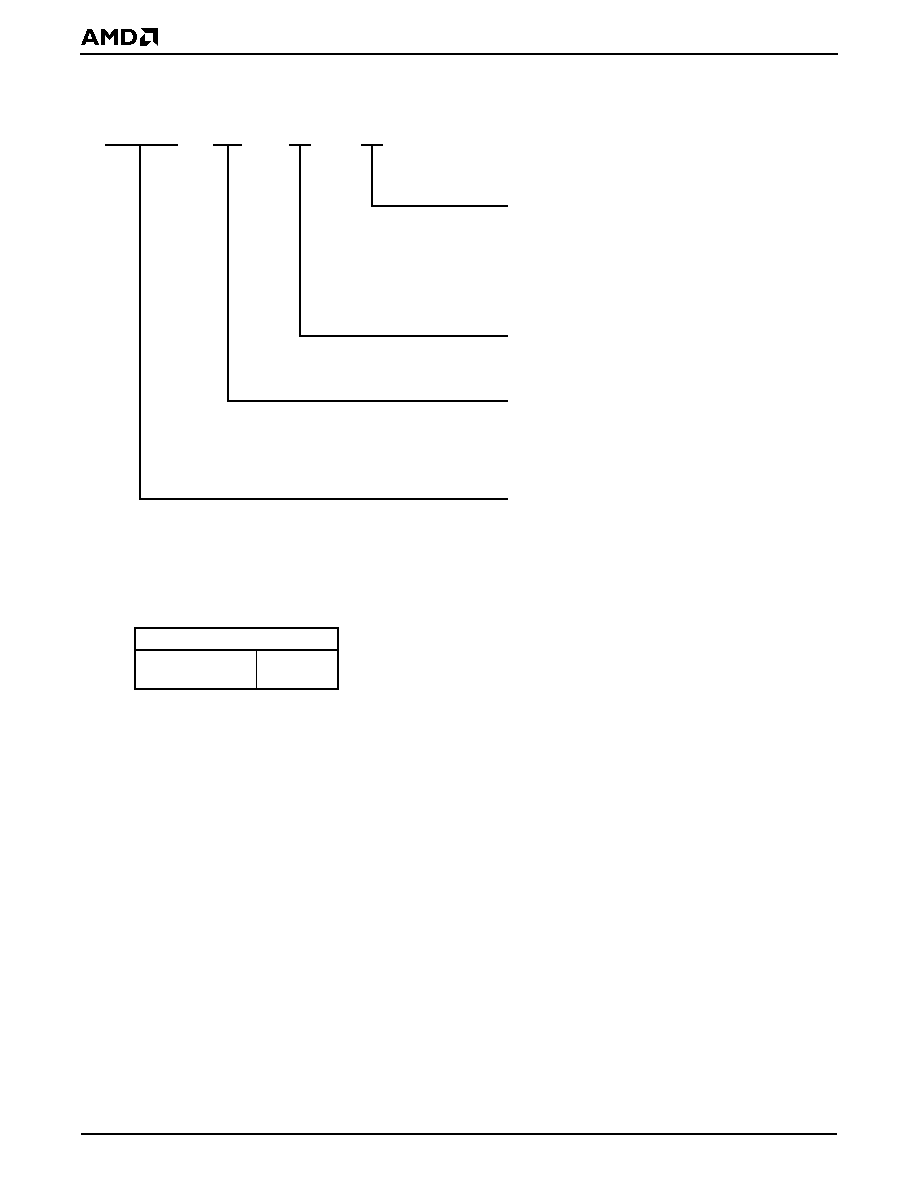

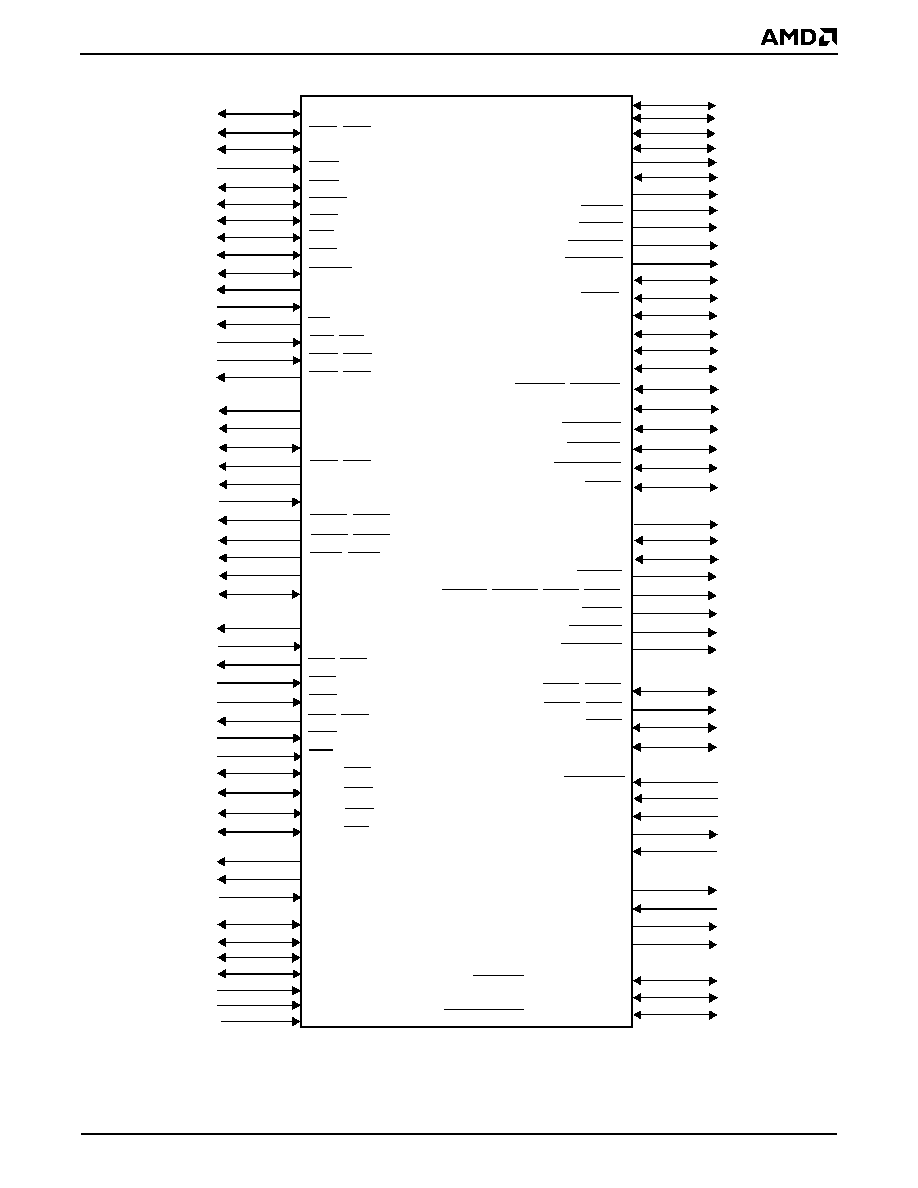

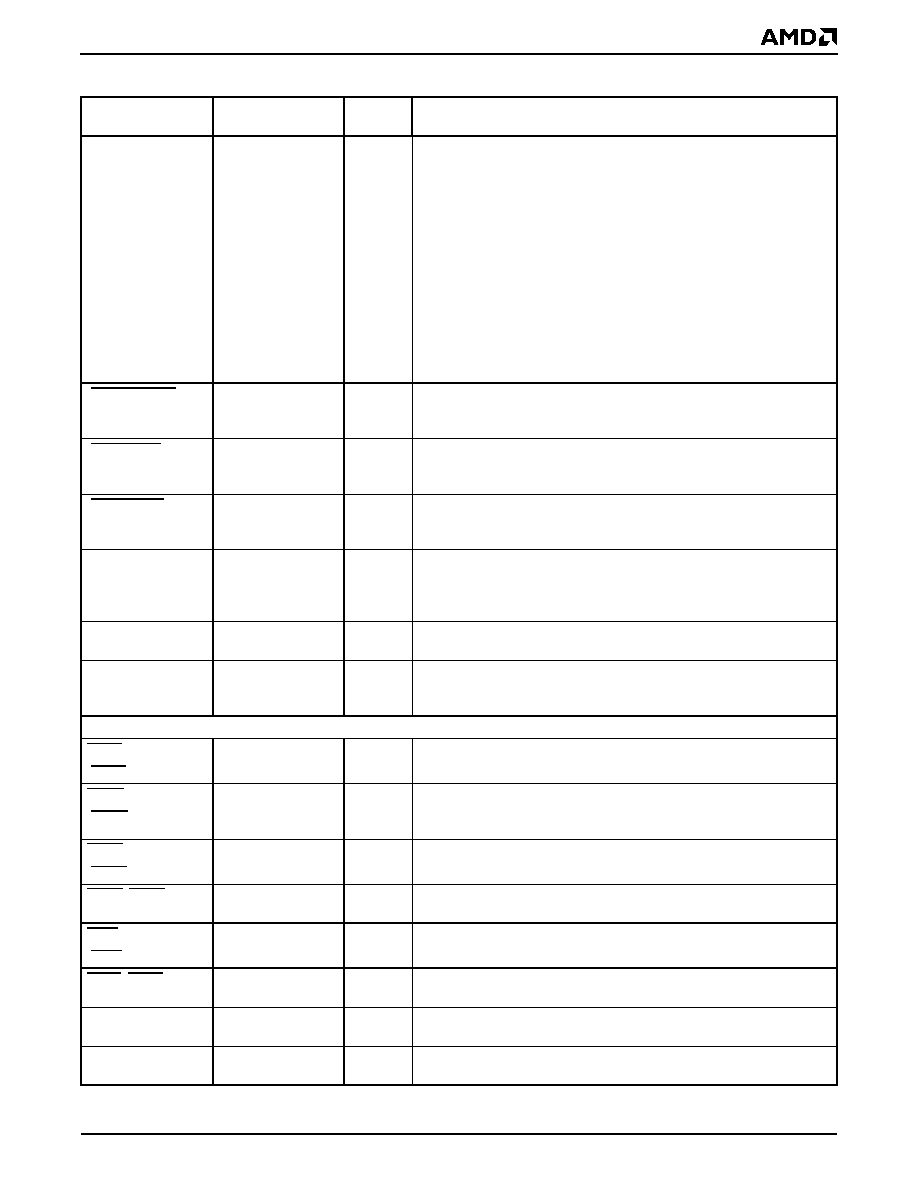

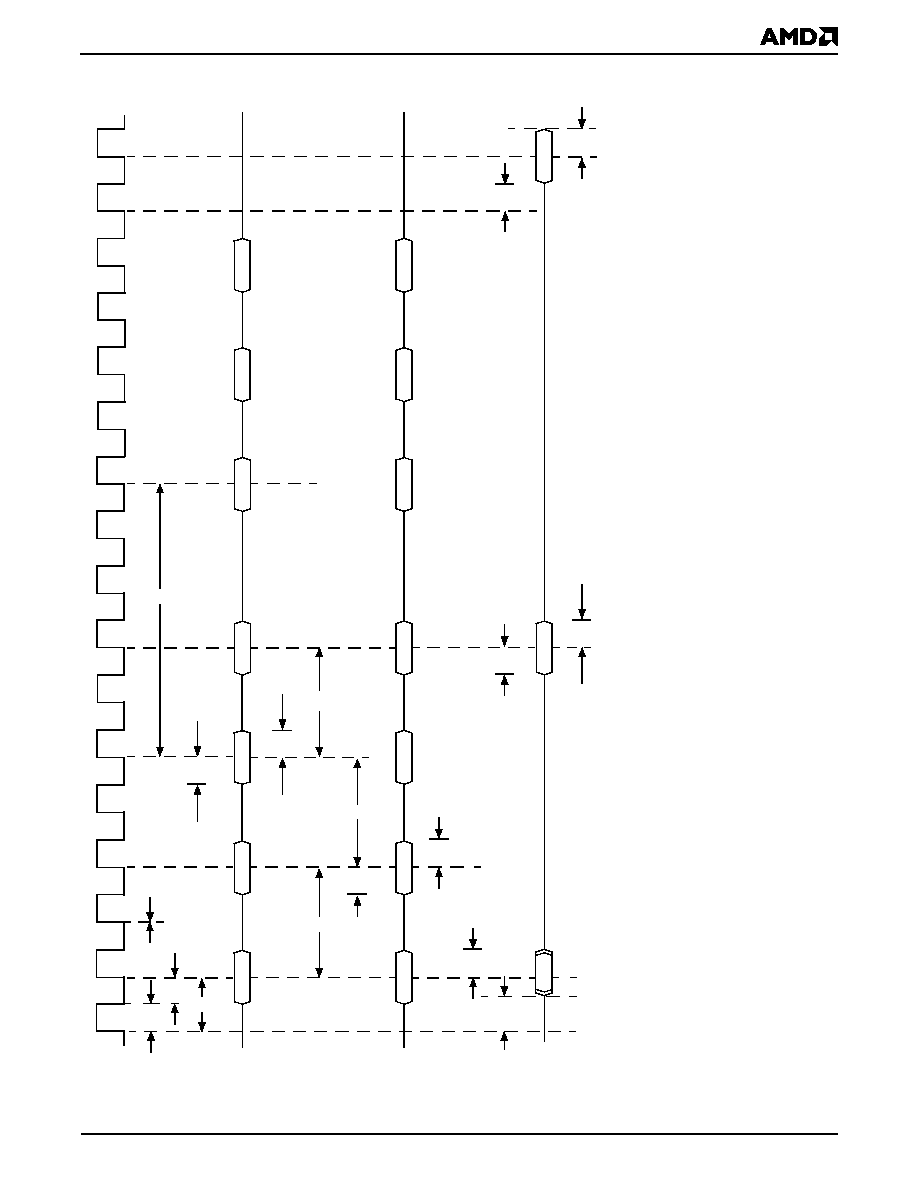

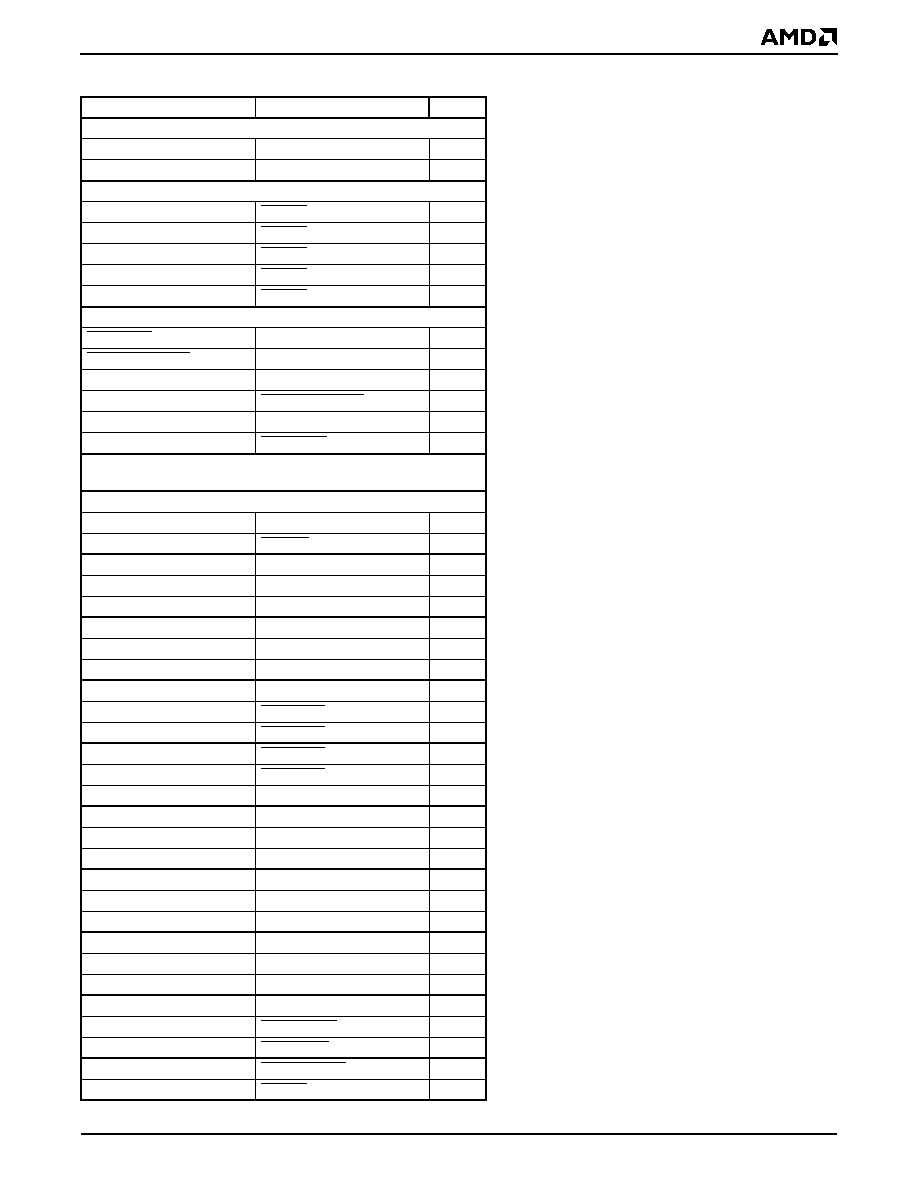

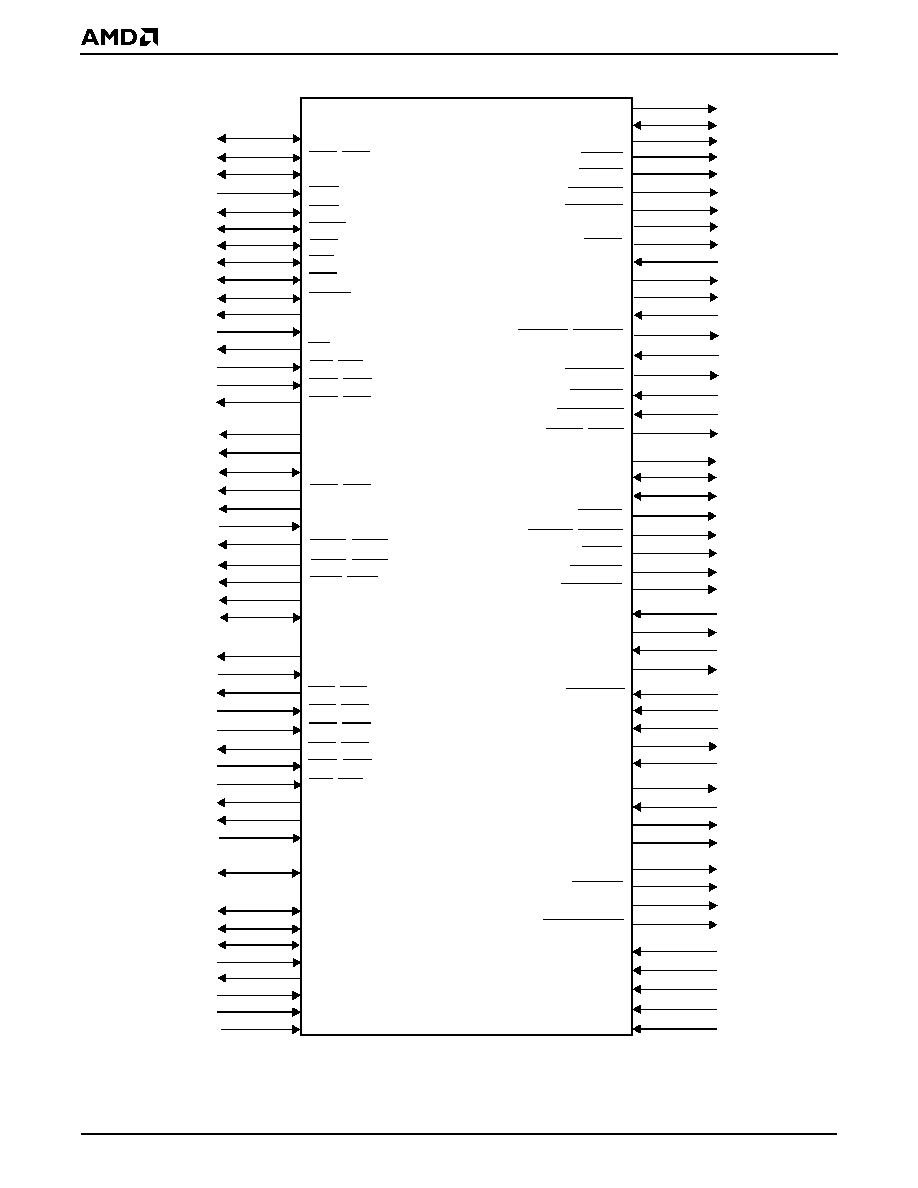

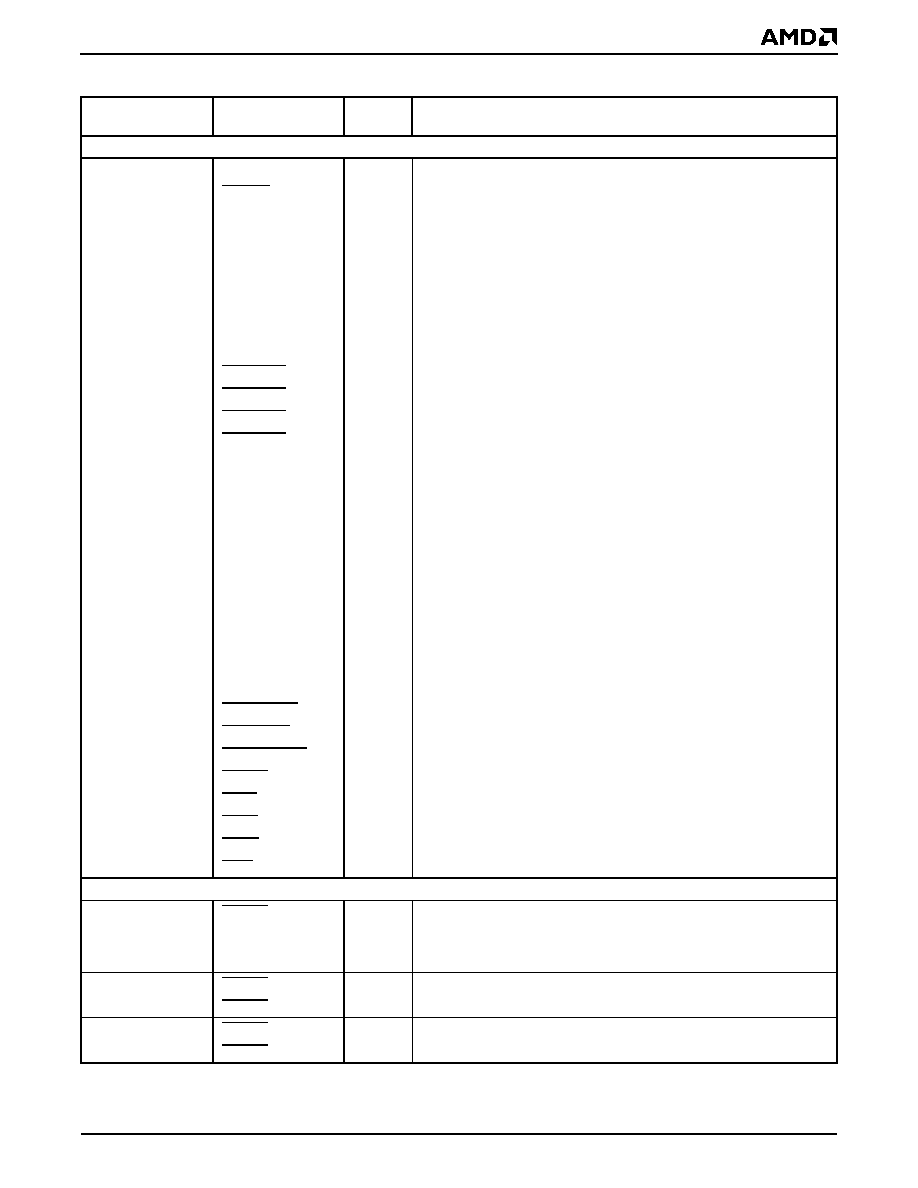

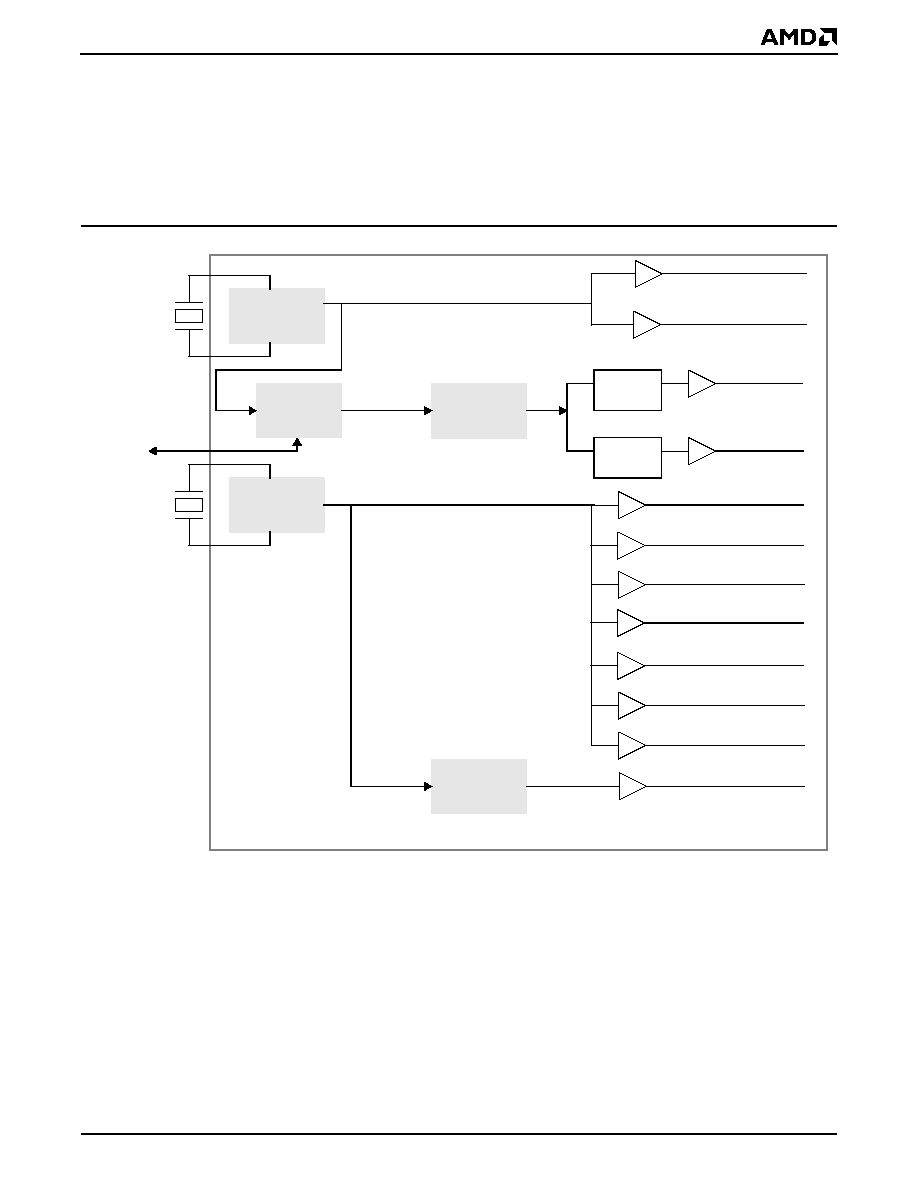

LOGIC DIAGRAM BY INTERFACE

1

Notes:

1. Pins noted with asterisks are duplicated in this diagram to clarify which signals are used for each interface.

PCI Bus

SDRAM

Serial Ports:

UART 1

UART 2

SSI

AD31≠AD0

CBE3≠CBE0

PAR

SERR

PERR

FRAME

TRDY

IRDY

STOP

DEVSEL

CLKPCIOUT

CLKPCIIN

RST

INTA≠INTD

REQ4≠REQ0

GNT4≠GNT0

BA1≠BA0

MD31≠MD0

SCS3≠SCS0

CLKMEMOUT

CLKMEMIN

SRASA≠SRASB

SCASA≠SCASB

SWEA≠SWEB

SDQM3≠SDQM0

MECC6≠MECC0

SOUT2≠SOUT1

SIN2≠SIN1

RTS2≠RTS1

CTS2≠CTS1

DSR2≠DSR1

DTR2≠DTR1

DCD2≠DCD1

RIN2≠RIN1

SSI_CLK

SSI_DO

SSI_DI

GP Bus

GPA25≠GPA0

GPD15≠GPD0

GPRESET

GPIORD

GPIOWR

GPMEMRD

GPMEMWR

GPALE

GPBHE

GPRDY

GPAEN

GPTC

GPDRQ3≠GPDRQ0

GPDACK3≠GPDACK0

GPIRQ10≠GPIRQ0

GPDBUFOE

GPIOCS16

GPMEMCS16

JTAG

AMDebug

System Test

JTAG_TRST

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

GPCS7≠GPCS0

BOOTCS

ROMCS2≠ROMCS1

ROMRD

FLASHWR

ROMBUFOE

CMDACK

BR/TC

STOP/TX

TRIG/TRACE

WBMSTR2≠WBMSTR0

CF_DRAM

DATASTRB

CF_ROM_GPCS

PIO31≠PIO0

TMRIN1≠TMRIN0

TMROUT1≠TMROUT0

Programmable

Input/Output

Timers

PITGATE2

PITOUT2

Clocks and Reset

32KXTAL2≠32KXTAL1

33MXTAL2≠33MXTAL1

CLKTIMER

CLKTEST

PWRGOOD

PRGRESET

CFG3≠CFG0

RSTLD7≠RSTLD0

Configuration

DEBUG_ENTER

INST_TRCE

AMDEBUG_DIS

BBATSEN

MD31≠MD0*

GPA25≠GPA0*

GPD15≠GPD0*

ROM/Flash

MA12≠MA0

LF_PLL1

…lanTMSC520 Microcontroller Data Sheet

7

P R E L I M I N A R Y

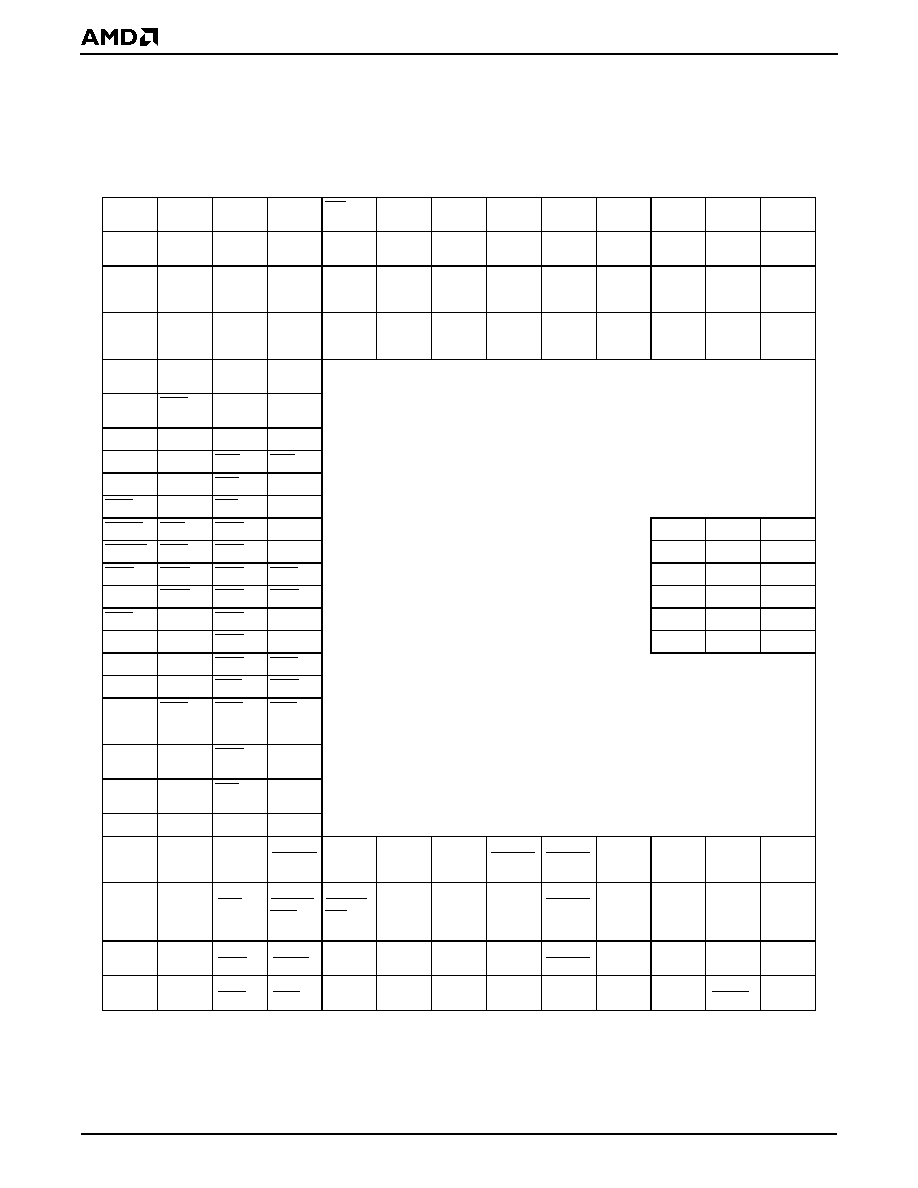

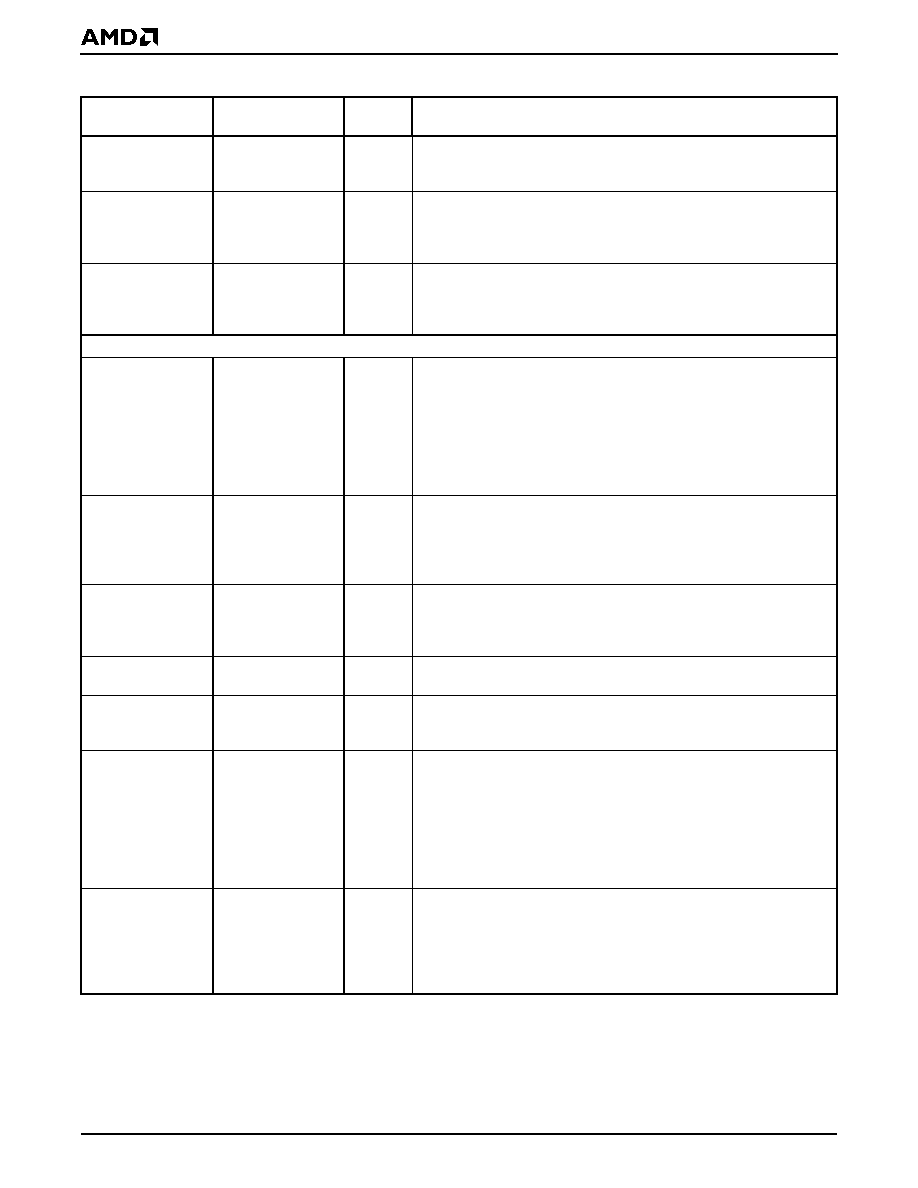

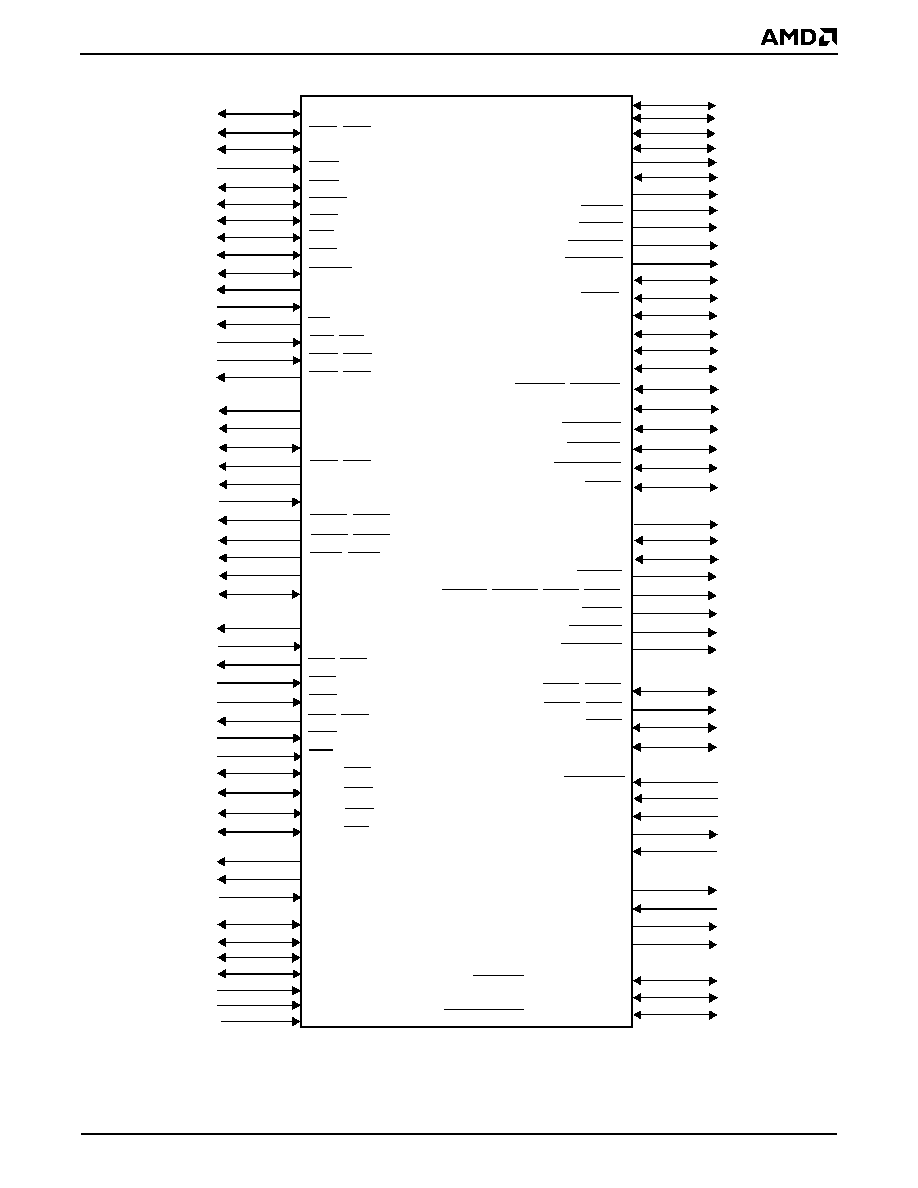

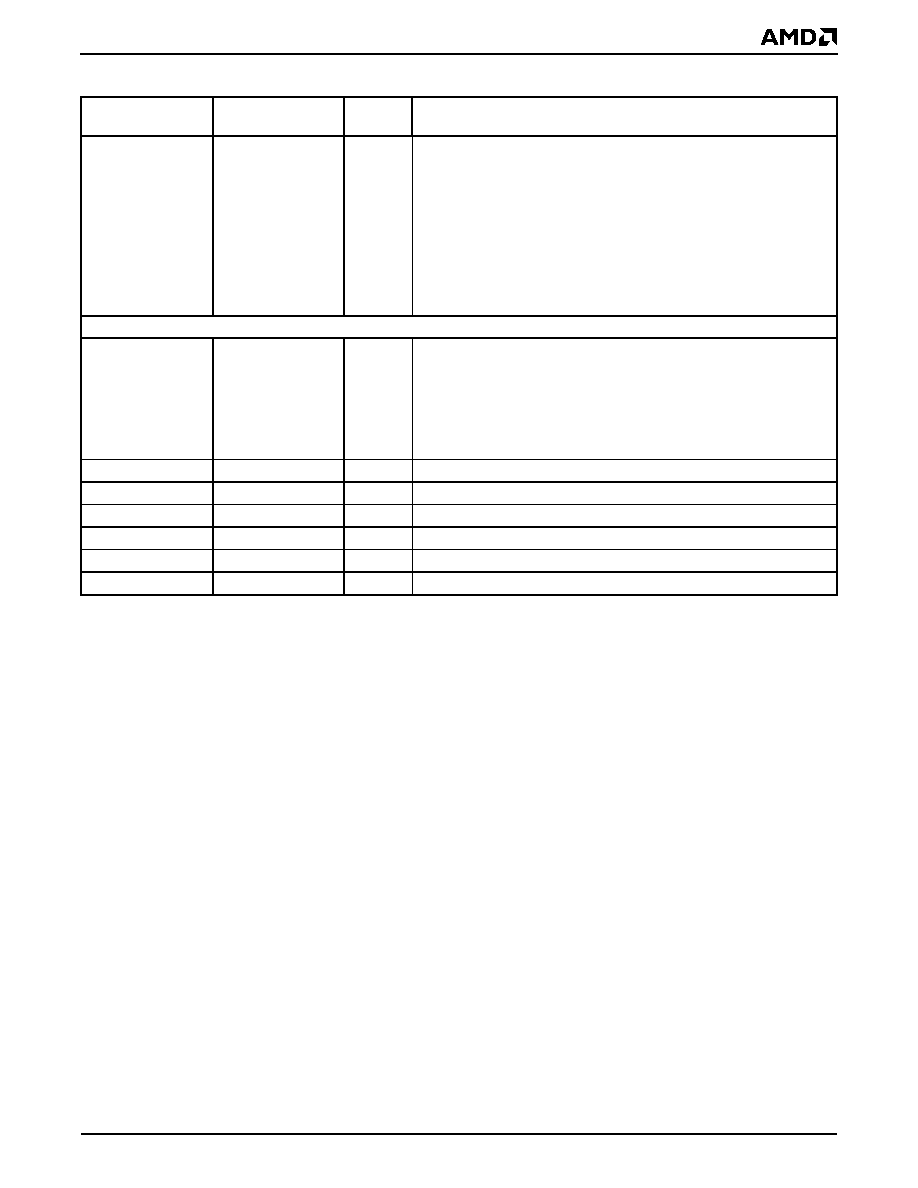

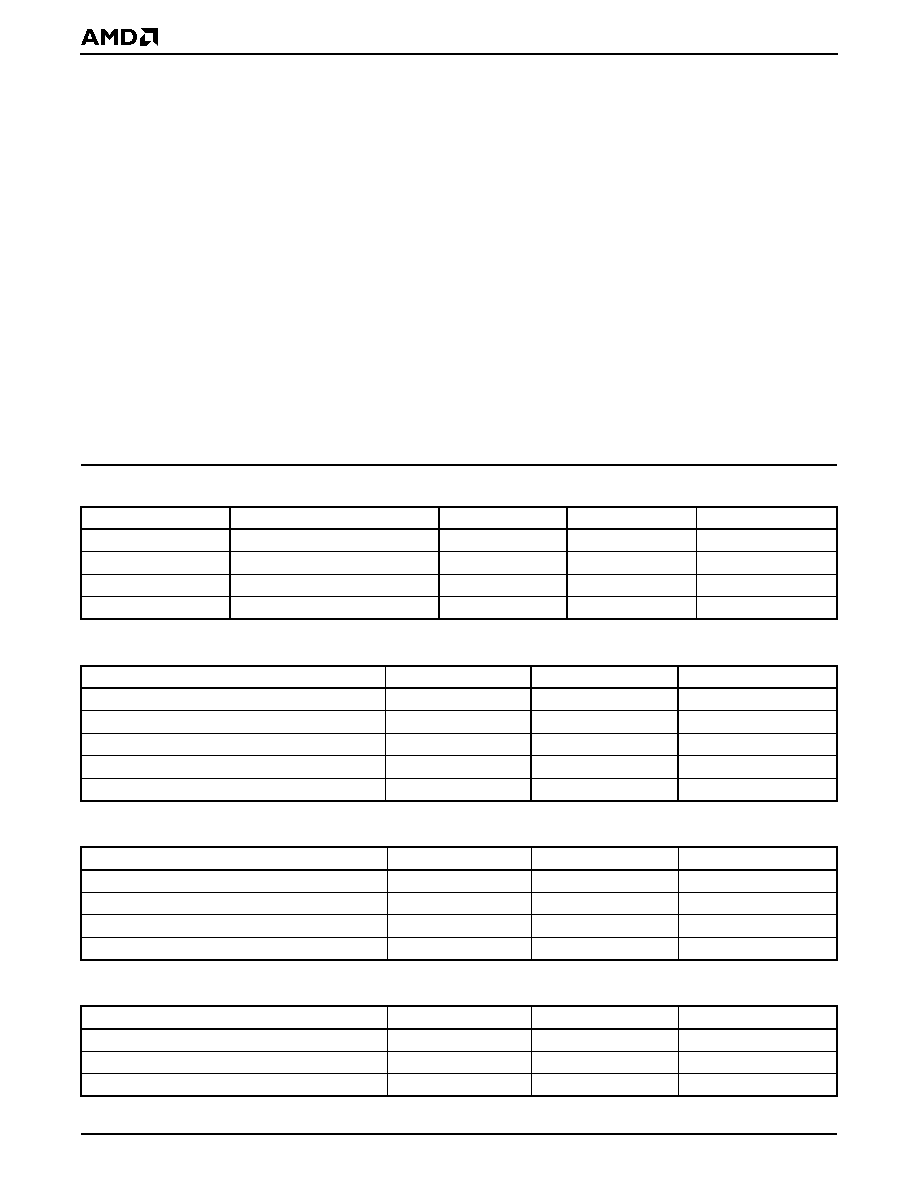

LOGIC DIAGRAM BY DEFAULT PIN FUNCTION

1

Notes:

1. Pin names in bold indicate the default pin function. Brackets, [ ], indicate alternate, multiplexed functions. Braces, { }, indicate

pinstrap pins. Pins noted with asterisks are duplicated in this diagram to clarify which signals are used for each interface.

PCI Bus

SDRAM

Serial Ports:

UART 1

UART 2

SSI

AD31≠AD0

CBE3≠CBE0

PAR

SERR

PERR

FRAME

TRDY

IRDY

STOP

DEVSEL

CLKPCIOUT

CLKPCIIN

RST

INTA≠INTD

REQ4≠REQ0

GNT4≠GNT0

BA1≠BA0

MD31≠MD0

SCS3≠SCS0

CLKMEMOUT

CLKMEMIN

SRASA≠SRASB

SCASA≠SCASB

SWEA≠SWEB

SDQM3≠SDQM0

MECC6≠MECC0

SOUT2≠SOUT1

SIN2≠SIN1

RTS2≠RTS1

CTS1

DSR1

DTR2≠DTR1

DCD1

RIN1

SSI_CLK

SSI_DO

SSI_DI

GP Bus

ROM/Flash

GPA25 {DEBUG_ENTER}

GPD15≠GPD0

GPRESET

GPIORD

GPIOWR

GPMEMRD

GPMEMWR

PIO0 [GPALE]

PIO1 [GPBHE]

PIO2 [GPRDY]

PIO3 [GPAEN]

PIO4 [GPTC]

PIO5≠PIO8 [GPDRQ3≠GPDRQ0]

PIO9≠PIO12 [GPDACK3≠GPDACK0]

PIO13≠PIO23 [GPIRQ10≠GPIRQ0]

PIO24 [GPDBUFOE]

PIO25 [GPIOCS16]

PIO26 [GPMEMCS16]

JTAG

AMDebug

System Test

JTAG_TRST

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

PIO27 [GPCS0]

BOOTCS

ROMCS2≠ROMCS1 [GPCS2≠GPCS1]

ROMRD

FLASHWR

ROMBUFOE

CMDACK

BR/TC

STOP/TX

TRIG/TRACE

CF_DRAM [WBMSTR2] {CFG2}

DATASTRB [WBMSTR1] {CFG1}

CF_ROM_GPCS [WBMSTR0] {CFG0}

TMRIN1≠TMRIN0 [GPCS4≠GPCS5]

TMROUT1≠TMROUT0 [GPCS6≠GPCS7]

Timers

PITGATE2 [GPCS3]

PITOUT2 {CFG3}

Clocks and Reset

32MXTAL2≠32MXTAL1

LF_PLL1

CLKTIMER [CLKTEST]

PWRGOOD

PRGRESET

BBATSEN

GPA22≠GPA15 {RSTLD7≠RSTLD0}

GPA13≠GPA0

GPA24 {INST_TRCE}

GPA23 {AMDEBUG_DIS}

PIO28 [CTS2]

PIO29 [DSR2]

PIO30 [DCD2]

PIO31 [RIN2]

MD31≠MD0*

GPA25≠GPA0*

GPD15≠GPD0*

MA12≠MA0

32KXTAL2≠32KXTAL1

8

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

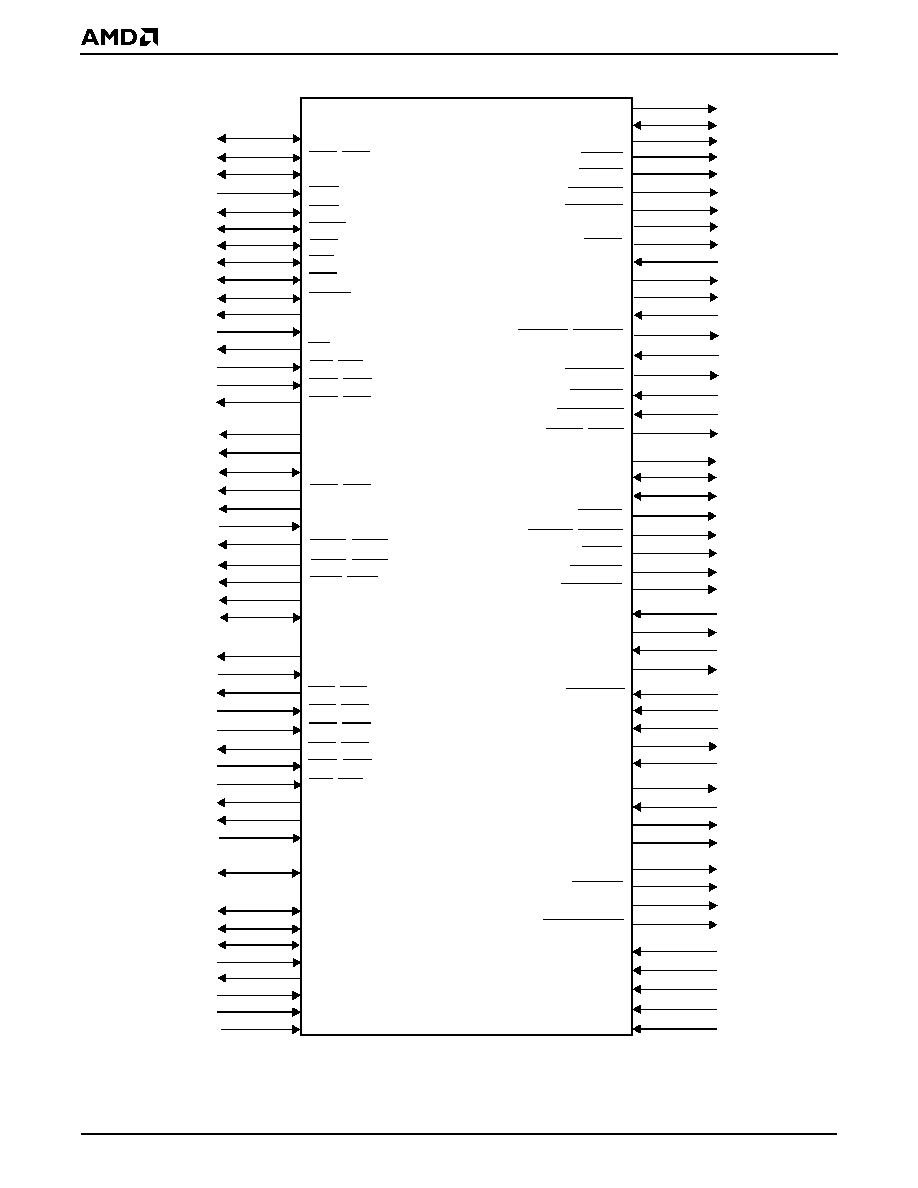

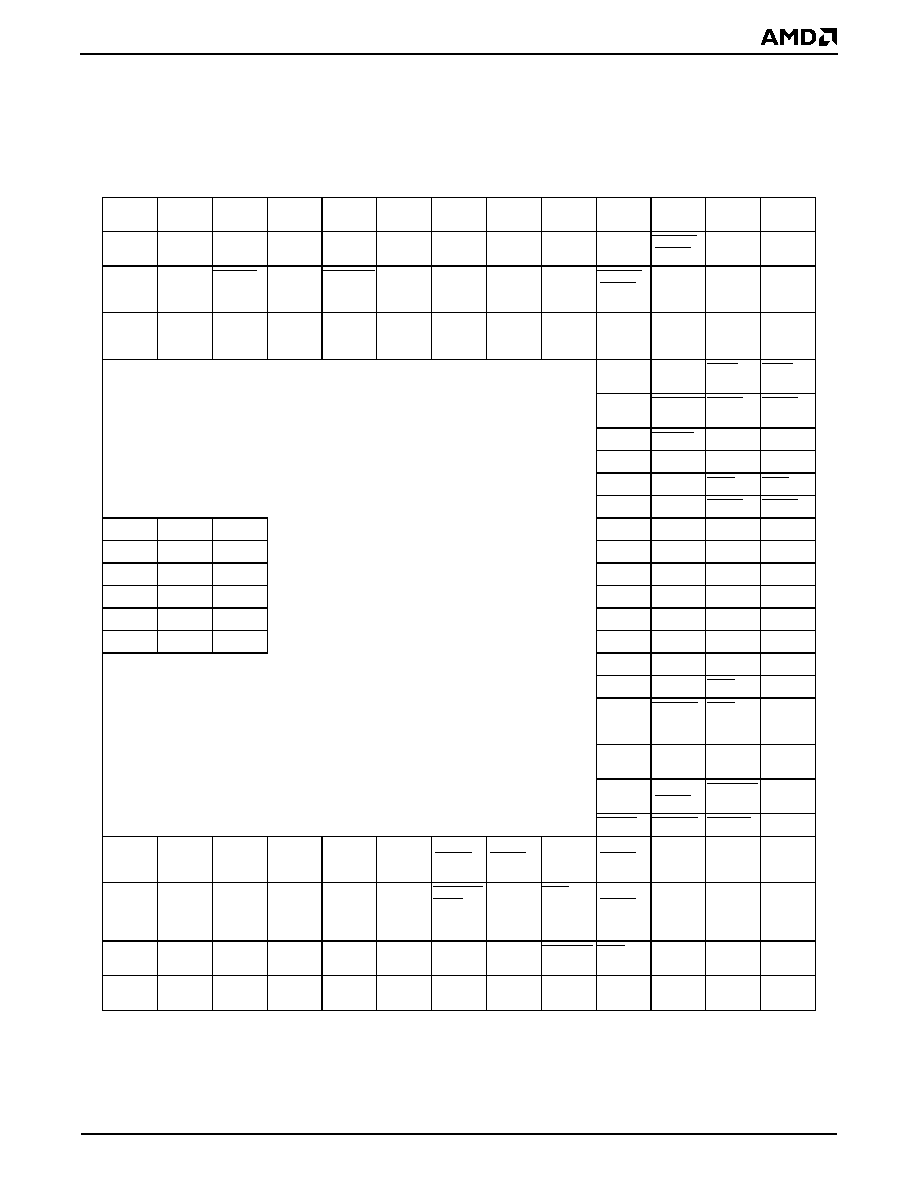

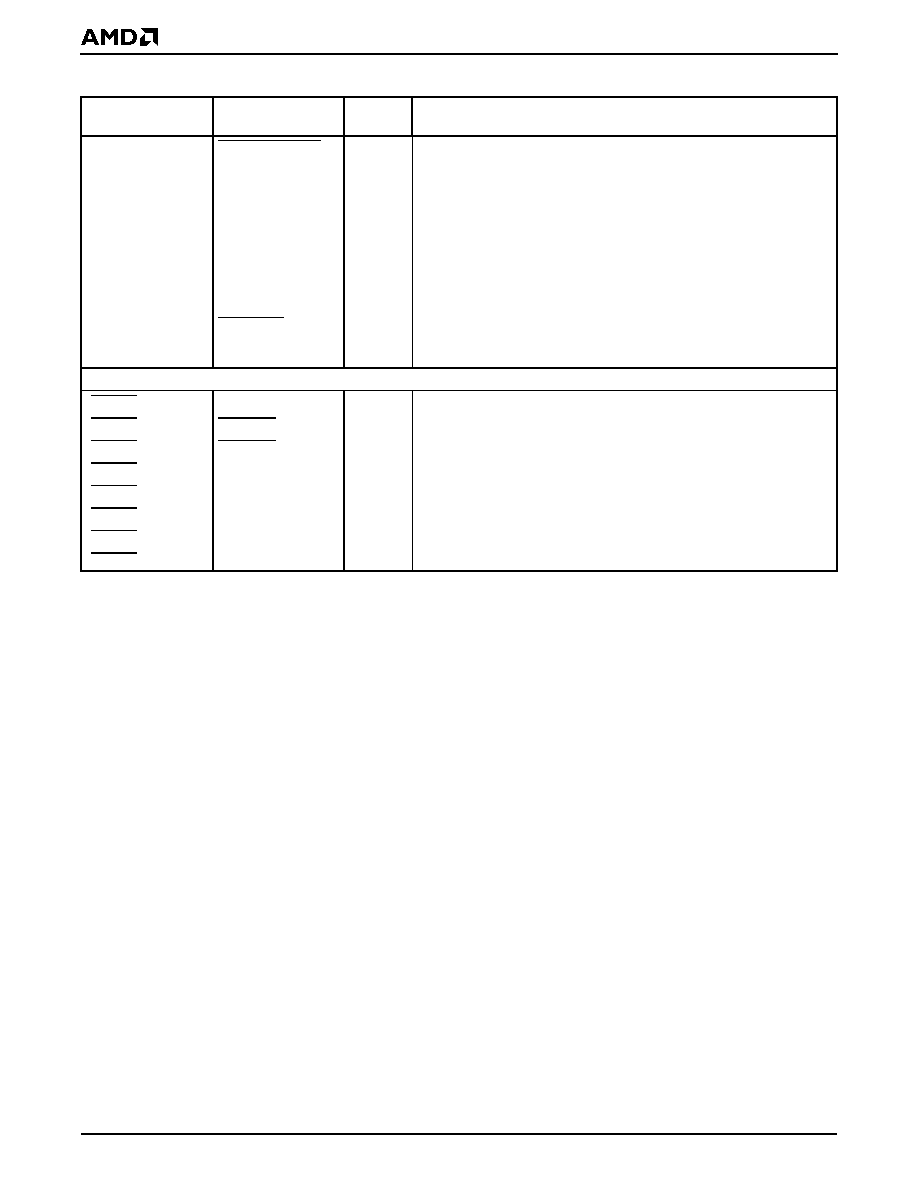

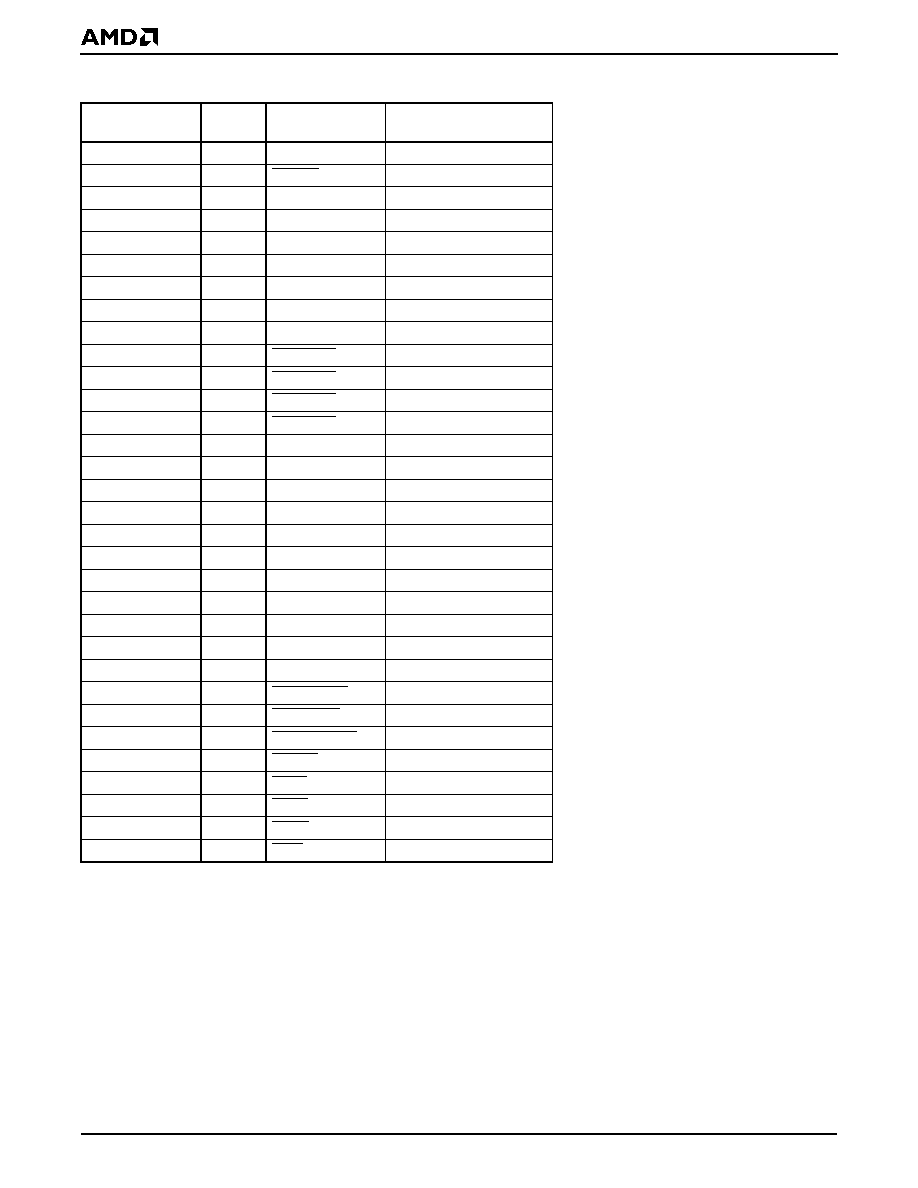

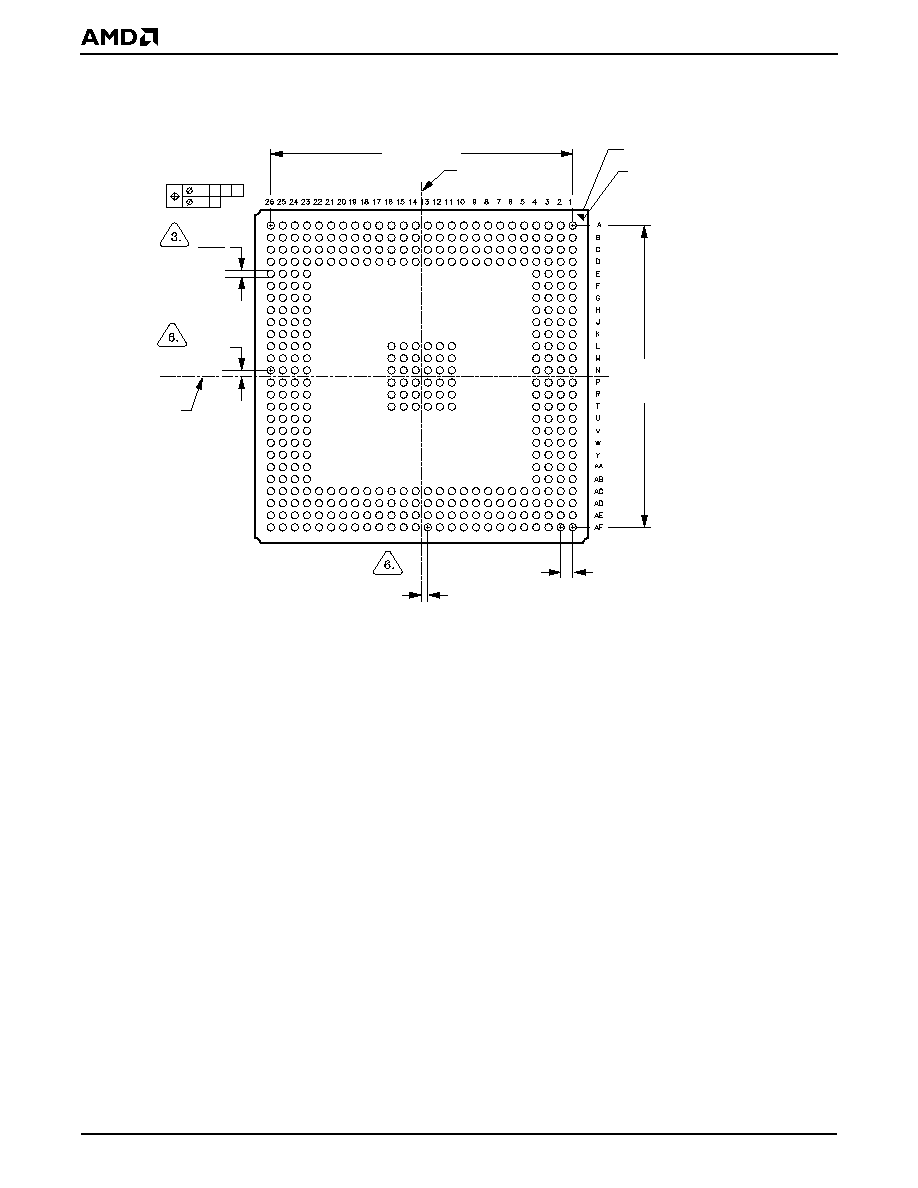

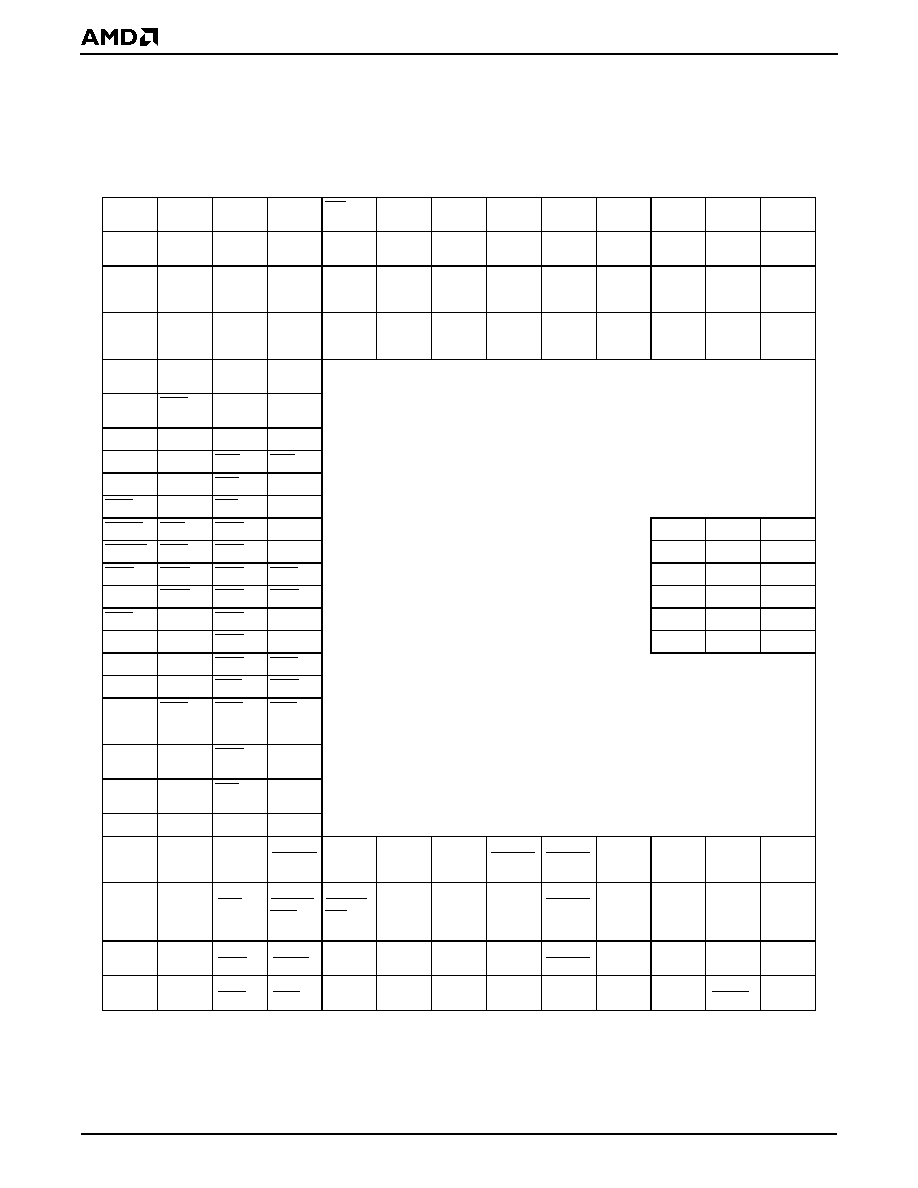

CONNECTION DIAGRAM

388-Pin Plastic BGA Package

Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

A

AD30

AD31

NC

CLKMEMIN RST

CLK-

PCIOUT

CLKTIMER

[CLKTEST]

MD1

MD17

MD3

MD19

MD5

MD21

A

B

AD29

AD28

NC

NC

GPD1

NC

MD0

MD16

MD2

MD18

MD4

MD20

MD6

B

C

GPA6

GPA9

GPA25

{DEBUG_

ENTER}

GPD0

NC

NC

GPD2

GPD3

GPD4

GPD7

GPD8

GPD9

GPD10

C

D

AD26

AD27

GPA23

{AMDEBUG

_DIS}

GPA24

{INST

_TRCE}

VCC_I/O

VCC_I/O

VCC_I/O

VCC_I/O

GPD5

GPD6

VCC_CORE VCC_CORE GPD11

D

E

AD25

AD24

NC

VCC_CORE

E

F

AD23

CBE3

GPA22

{RSTLD7}

VCC_CORE

F

G

AD22

AD21

CLKPCIIN GPA1

G

H

AD19

AD20

INTC

INTD

H

J

AD18

AD17

INTB

VCC_I/O

J

K

CBE2

AD16

INTA

VCC_I/O

K

L

FRAME

IRDY

REQ0

VCC_I/O

GND

GND

GND

L

M DEVSEL

TRDY

GNT0

VCC_I/O

GND

GND

GND

M

N

STOP

PERR

REQ1

GNT1

GND

GND

GND

N

P

PAR

SERR

GNT2

REQ2

GND

GND

GND

P

R

CBE1

AD15

REQ3

VCC_CORE

GND

GND

GND

R

T

AD13

AD14

GNT3

VCC_CORE

GND

GND

GND

T

U

AD12

AD11

REQ4

GNT4

U

V

AD9

AD10

CTS1

DCD1

V

W AD8

CBE0

DTR1

RTS1

W

Y

AD6

AD7

DSR1

VCC_I/O

Y

AA AD5

AD4

RIN1

VCC_I/O

AA

AB AD2

AD3

NC

NC

AB

AC AD1

AD0

NC

PIO25

[GPIOCS16]

VCC_CORE VCC_CORE VCC_CORE PIO12

[GPDACK0]

PIO11

[GPDACK1]

VCC_I/O

VCC_I/O

NC

TRIG/

TRACE

AC

AD NC

NC

PIO31

[RIN2]

PIO26

[GPMEM-

CS16]

PIO24

[GPDBU-

FOE]

PIO19

[GPIRQ4]

PIO18

[GPIRQ5]

PIO13

[GPIRQ10]

PIO10

[GPDACK2]

PIO5

[GPDRQ3]

PIO4

[GPTC]

NC

NC

AD

AE NC

SIN1

PIO30

[DCD2]

PIO27

[GPCS0]

PIO23

[GPIRQ0]

PIO20

[GPIRQ3]

PIO17

[GPIRQ6]

PIO14

[GPIRQ9]

PIO9

[GPDACK3]

PIO6

[GPDRQ2]

PIO3

[GPAEN]

PIO0

[GPALE]

NC

AE

AF NC

SOUT1

PIO29

[DSR2]

PIO28

[CTS2]

PIO22

[GPIRQ1]

PIO21

[GPIRQ2]

PIO16

[GPIRQ7]

PIO15

[GPIRQ8]

PIO8

[GPDRQ0]

PIO7

[GPDRQ1]

PIO2

[GPRDY]

PIO1

[GPBHE]

NC

AF

1

2

3

4

5

6

7

8

9

10

11

12

13

…lanTMSC520 Microcontroller Data Sheet

9

P R E L I M I N A R Y

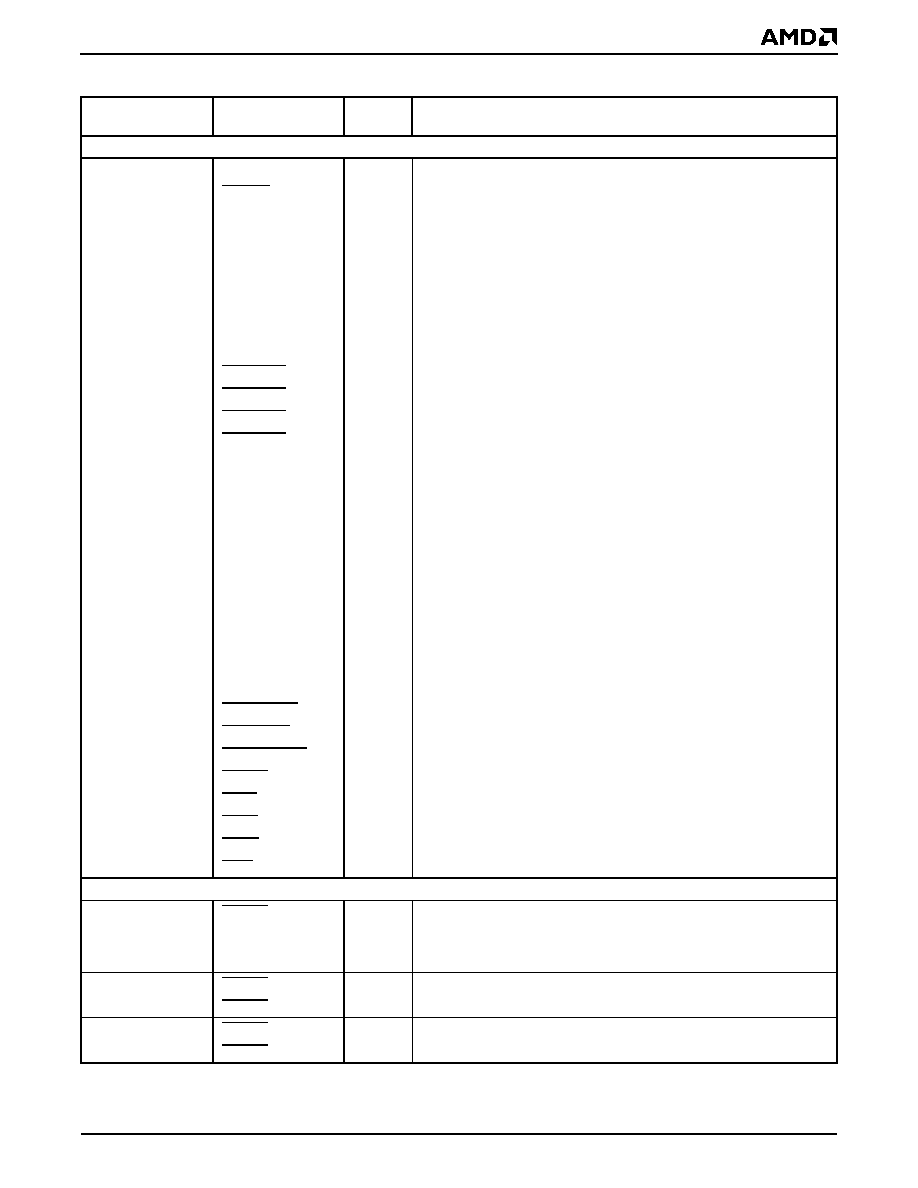

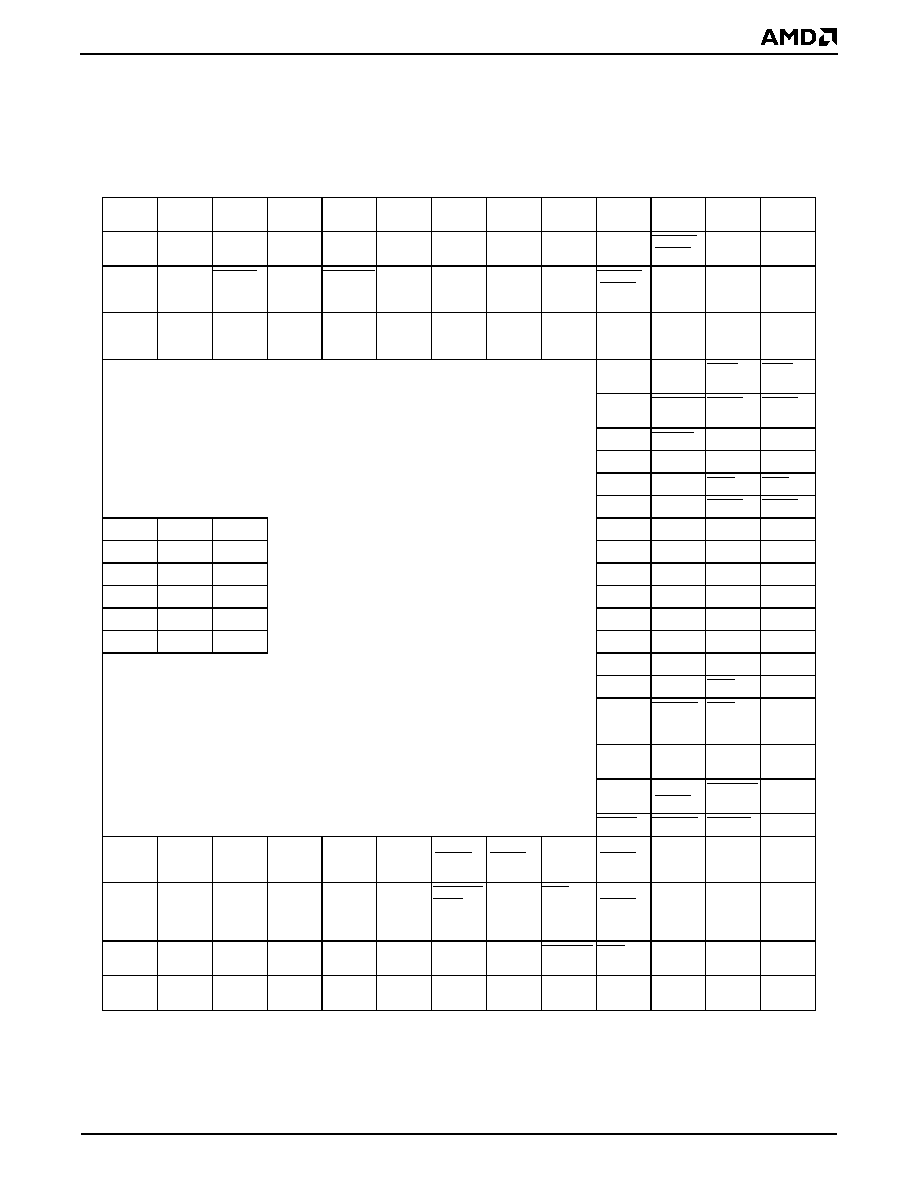

CONNECTION DIAGRAM (Continued)

388-Pin Plastic BGA Package

Top View

14

15

16

17

18

19

20

21

22

23

24

25

26

A MD7

MD23

MD9

MD25

MD11

MD27

MD28

MD13

MD14

MD30

MD31

GND_ANLG VCC_RTC

A

B MD22

MD8

MD24

MD10

MD26

CLK-

MEMOUT

MD12

MD29

GPA18

{RSTLD3}

MD15

ROMCS1

[GPCS1]

BBATSEN

VCC_ANLG B

C GPA20

{RSTLD5}

GPD13

GPIOWR

GPD14

GPMEMWR GPA21

{RSTLD6}

PWRGOOD GPA19

{RSTLD4}

NC

ROMCS2

[GPCS2]

GPA15

{RSTLD0}

MECC0

MECC4

C

D GPD12

VCC_I/O

VCC_I/O

GPD15

VCC_CORE VCC_CORE PRGRESET VCC_I/O

VCC_I/O

NC

GPA16

{RSTLD1}

MECC5

MECC1

D

E

NC

GPA17

{RSTLD2}

SWEB

SWEA

E

F

GPA7

GPMEMRD SCASA

SCASB

F

G

VCC_CORE GPIORD

SDQM0

SDQM2

G

H

VCC_CORE GPA5

SDQM3

SDQM1

H

J

GPA3

GPA0

SCS2

SCS3

J

K

VCC_I/O

GPA2

SRASA

SRASB

K

L

GND

GND

GND

VCC_I/O

GPA4

MA0

MA1

L

M

GND

GND

GND

GPA10

GPA8

MA3

MA2

M

N

GND

GND

GND

GPA11

GPA12

MA4

MA5

N

P

GND

GND

GND

VCC_CORE GPA13

MA7

MA6

P

R

GND

GND

GND

VCC_CORE GPA14

MA8

MA9

R

T

GND

GND

GND

NC

NC

BA0

MA10

T

U

SOUT2

CMDACK

BA1

MA11

U

V

VCC_I/O

SIN2

SCS0

MA12

V

W

VCC_I/O

CF_DRAM

[WBMSTR2]

{CFG2}

SCS1

MECC2

W

Y

VCC_I/O

PITOUT2

{CFG3}

MECC3

MECC6

Y

AA

VCC_I/O

TMRIN1

[GPCS4]

ROMBUFOE NC

AA

AB

ROMRD

FLASHWR BOOTCS

33MXTAL1 AB

AC VCC_CORE VCC_CORE NC

NC

VCC_I/O

VCC_I/O

TMRIN0

[GPCS5]

PITGATE2

[GPCS3]

GPRESET TMROUT1

[GPCS6]

DATASTRB

[WBMSTR1]

{CFG1}

NC

33MXTAL2 AC

AD NC

NC

NC

NC

NC

SSI_CLK

CF_ROM_

GPCS

[WBMSTR0]

{CFG0}

JTAG_TCK RTS2

TMROUT0

[GPCS7]

BR/TC

NC

NC

AD

AE NC

NC

NC

NC

NC

SSI_DI

NC

JTAG_TMS JTAG_TRST DTR2

NC

NC

32KXTAL2 AE

AF NC

NC

NC

STOP/TX

NC

SSI_DO

NC

JTAG_TDI JTAG_TDO NC

LF_PLL1

NC

32KXTAL1 AF

14

15

16

17

18

19

20

21

22

23

24

25

26

10

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

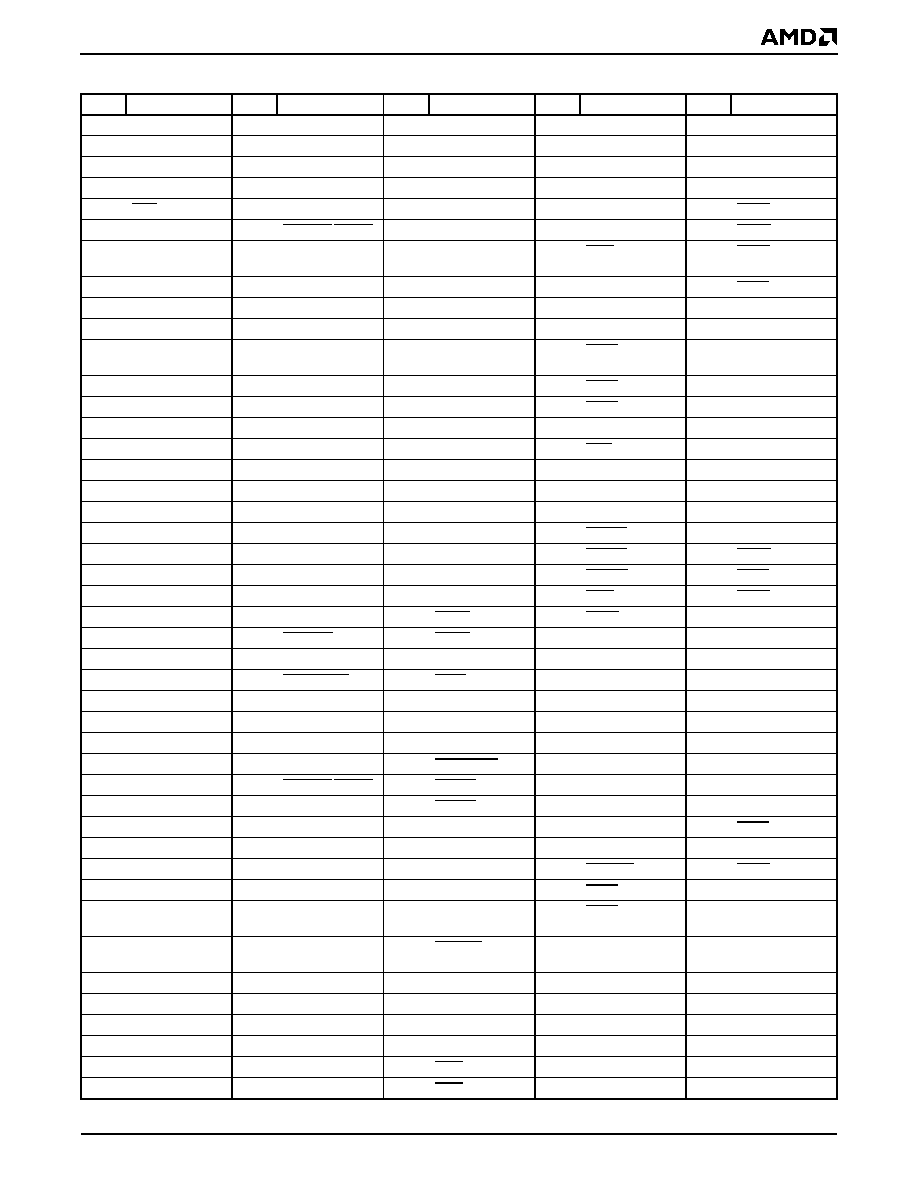

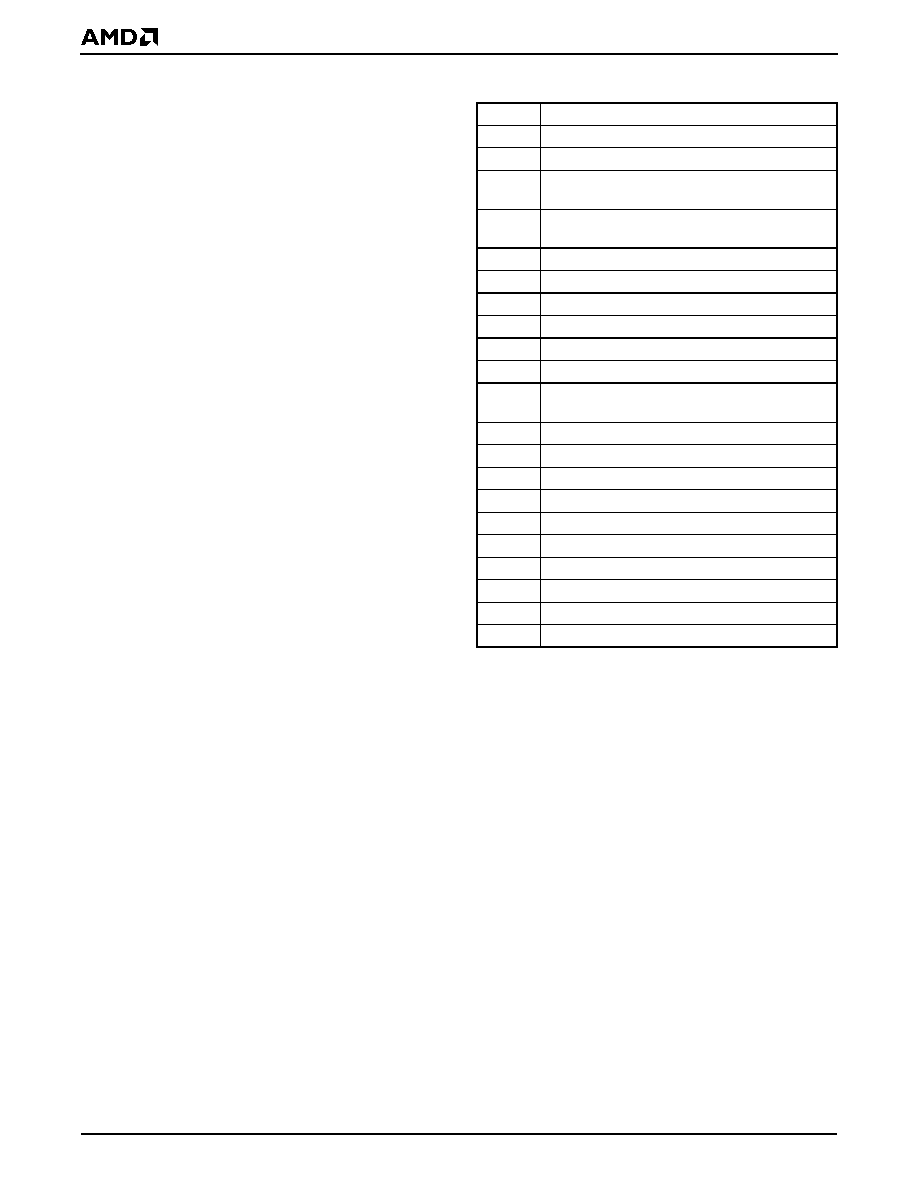

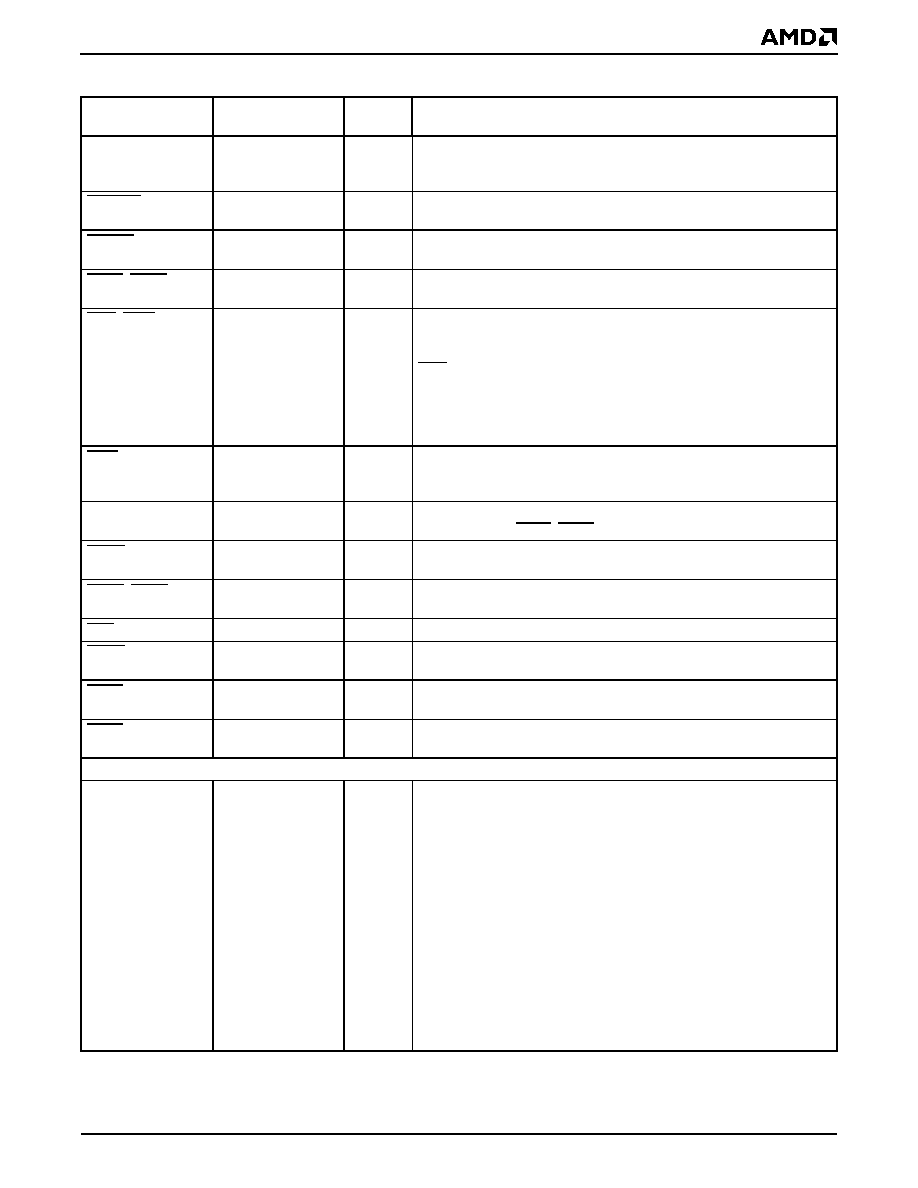

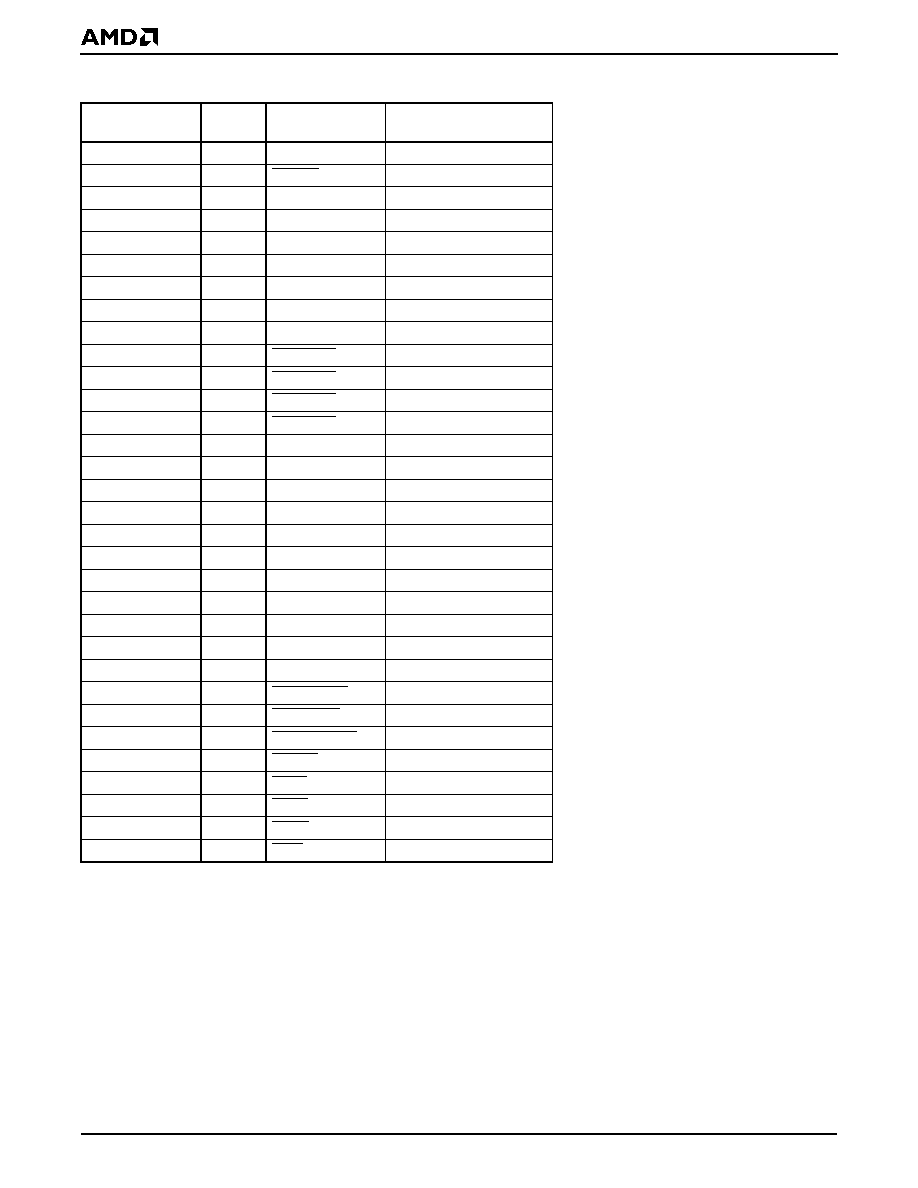

PIN DESIGNATIONS

This section identifies the pins of the …lanSC520 micro-

controller and lists the signals associated with each

pin.

In all tables the brackets, [ ], indicate alternate, multi-

plexed functions, and braces, { }, indicate reset config-

uration pins (pinstraps). The line over a pin name

indicates an active Low signal. The word pin refers to

the physical wire; the word signal refers to the electrical

signal that flows through it.

s

Pin designations are listed in the "Pin Designations

(Pin Number)" table on page 11 and the Pin

Designations (Pin Name) table on page 13.

s

Table 2, "Signal Descriptions" on page 17 contains

a descr iption of the micro controlle r signals

organized alphabetically by functional group.

Table 1 on page 16 defines terms used in Table 2.

The table includes columns listing the multiplexed

functions and I/O type.

Refer to Appendix A, "Pin Tables," on page A-1 for an

additional group of tables with the following informa-

tion:

s

Multiplexed signal tradeoffs--Table 16 on

page A-2.

s

Programmable I/O pins ordered by 1) PIO pin

n u m b e r a n d 2 ) m u l t i p l e xe d s i g n a l n a m e ,

respectively, including pin numbers, multiplexed

functions, and pin configuration following system

reset--Table 17 on page A-4 and Table 18 on

page A-5.

s

Comprehensive pin and signal summary showing

signal name and alternate function, pin number, I/O

type, maximum load values, power-on reset default

function, reset state, power-on reset default opera-

t i o n , h o l d s t a t e, a n d vo l t a g e -- Ta bl e 2 0 o n

page A-7.

…lanTMSC520 Microcontroller Data Sheet

11

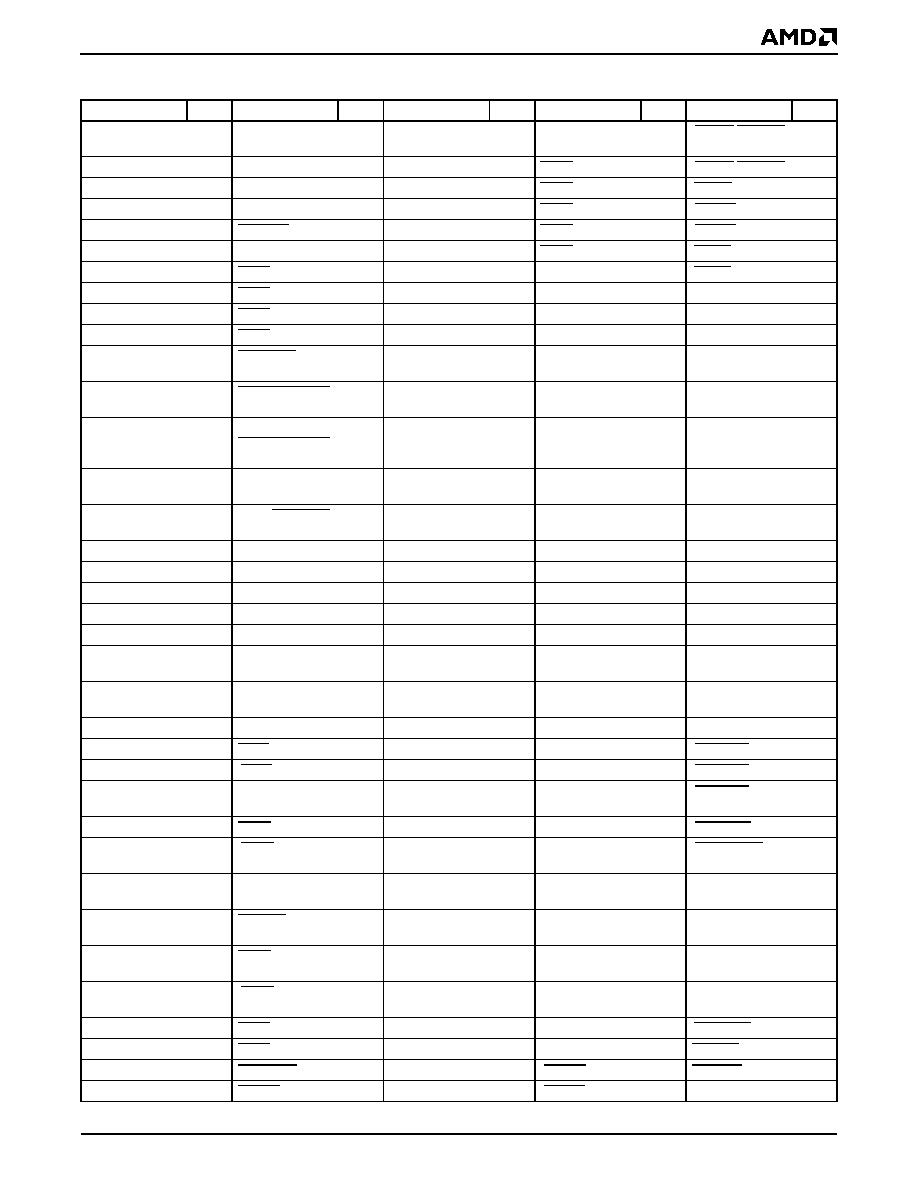

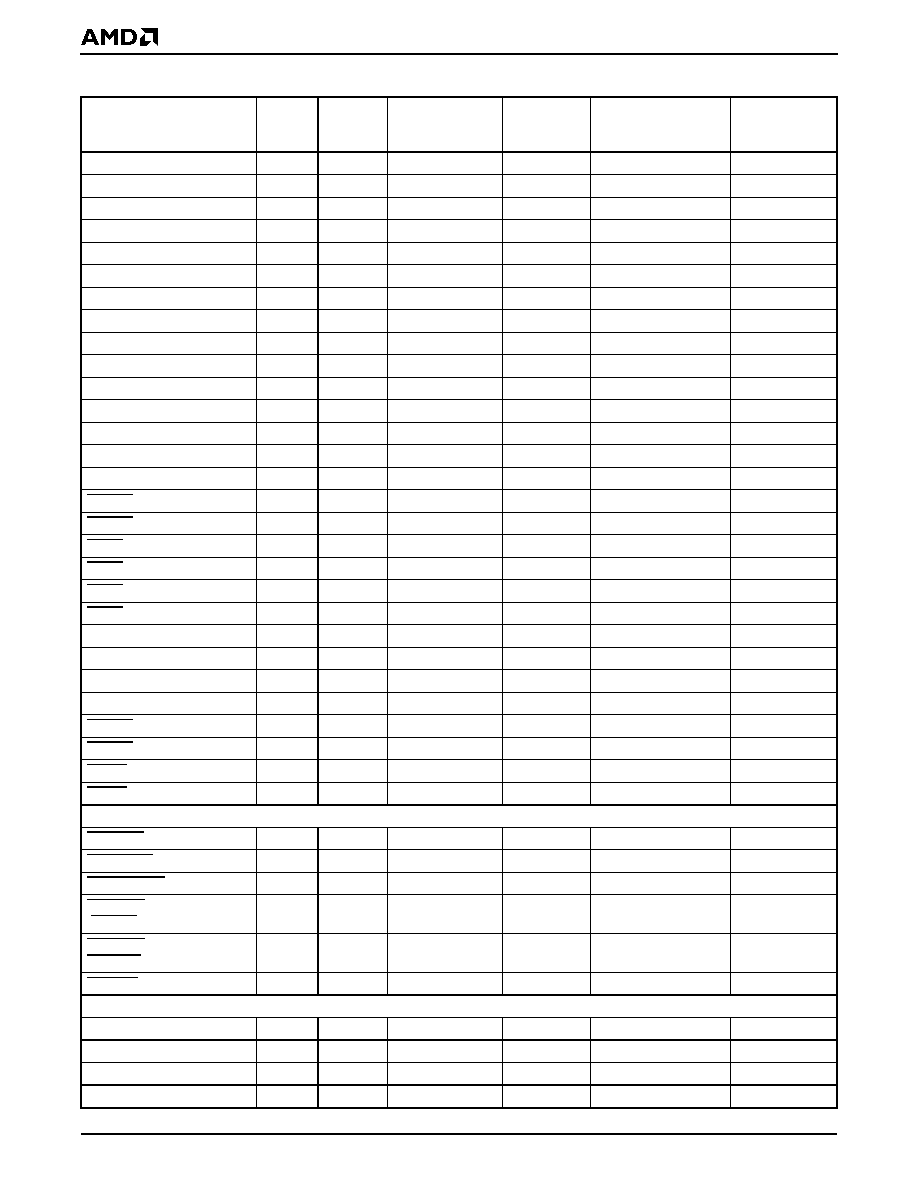

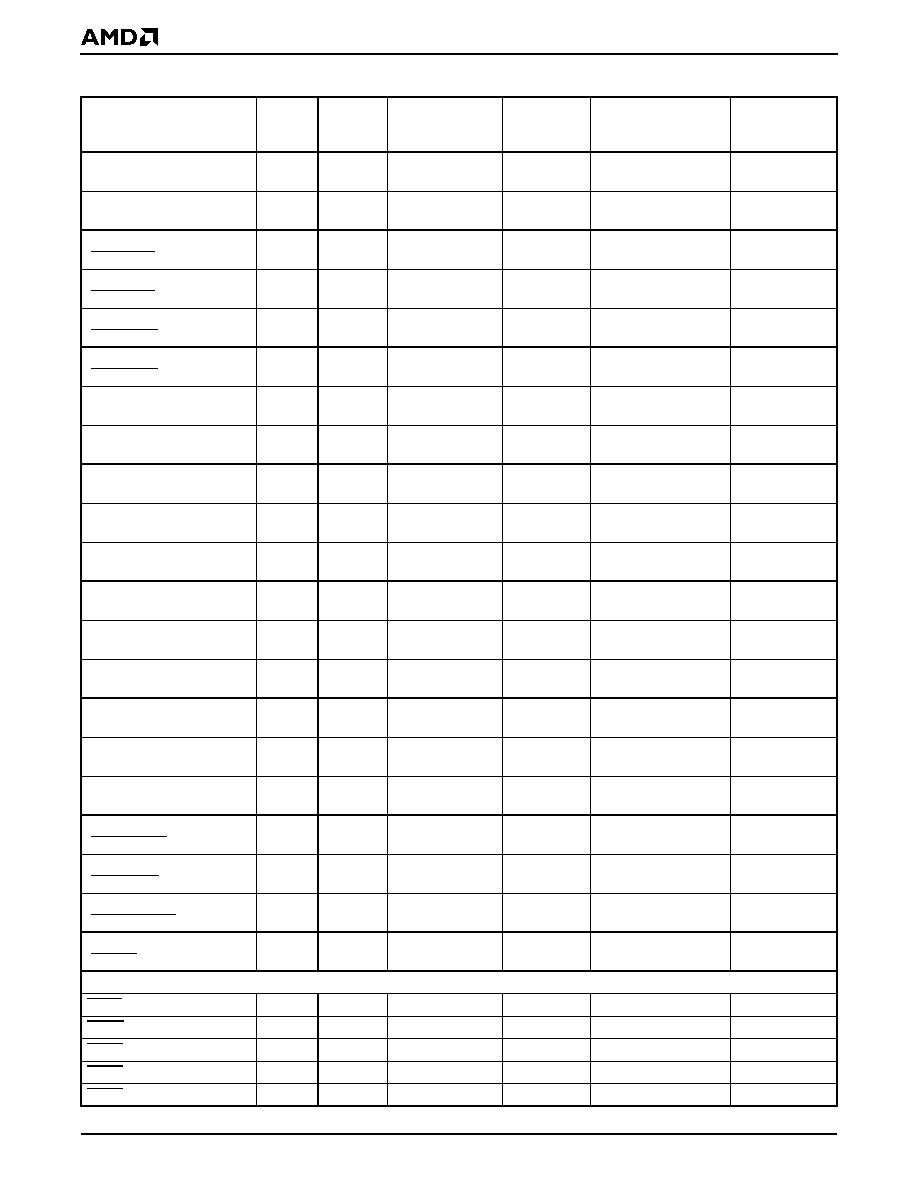

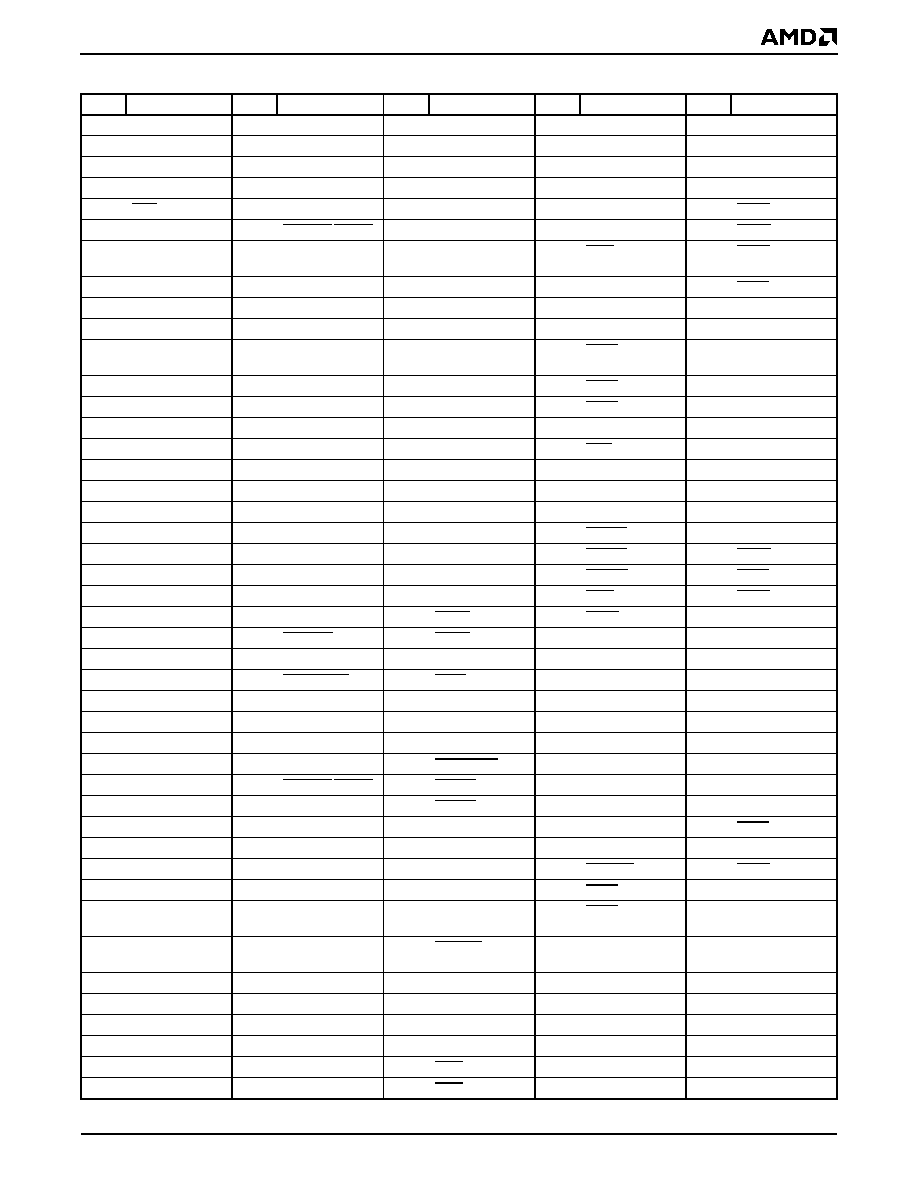

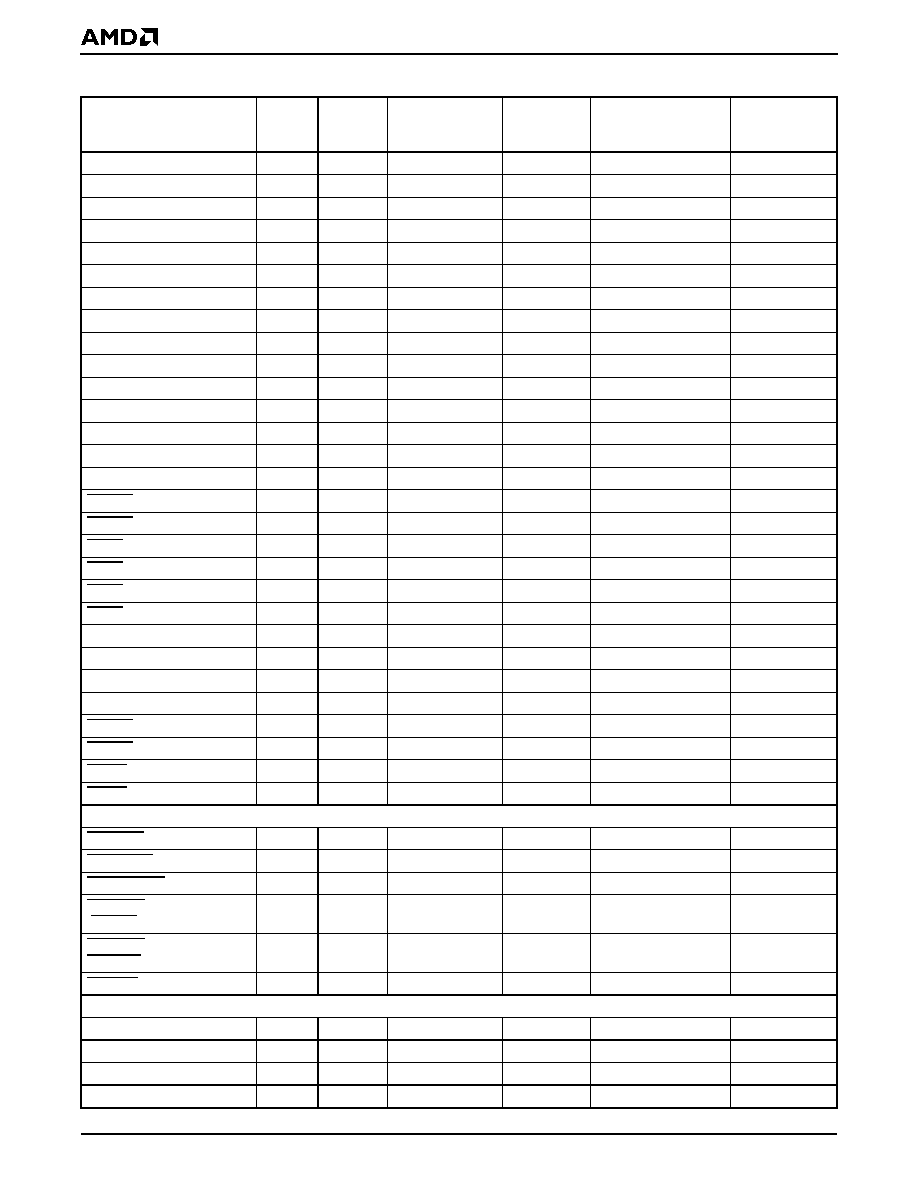

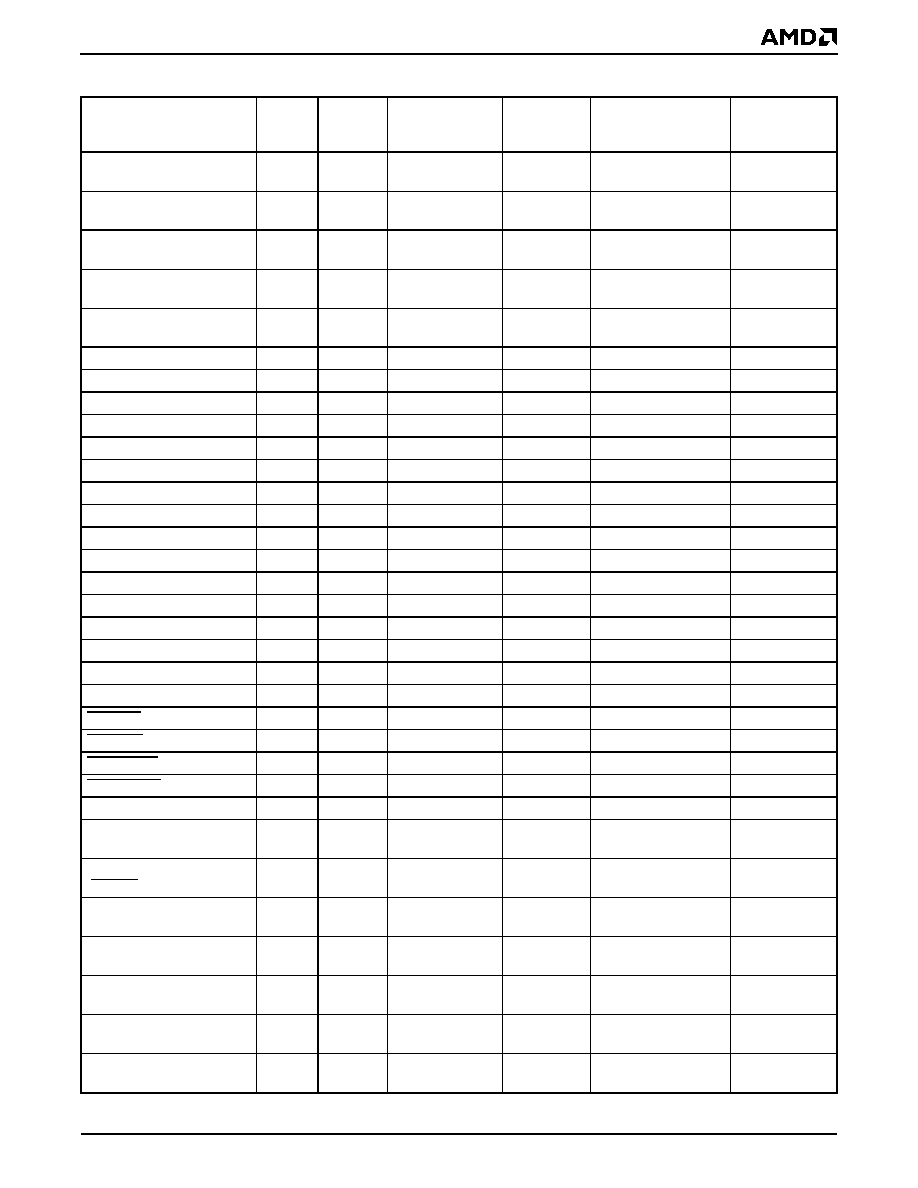

P R E L I M I N A R Y

Pin Designations (Pin Number

1

)

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

A1

AD30

B19

CLKMEMOUT

D11

VCC_CORE

H23

VCC_CORE

M23

GPA10

A2

AD31

B20

MD12

D12

VCC_CORE

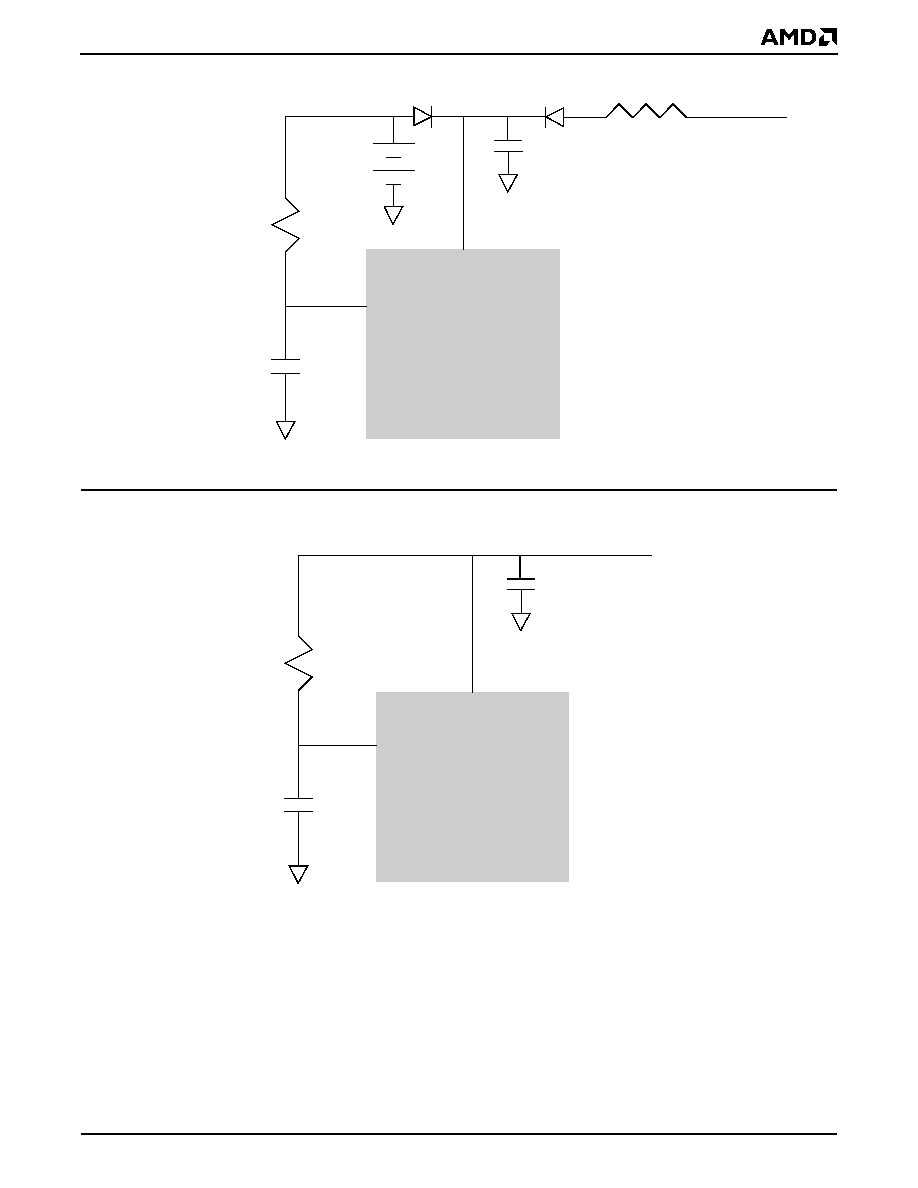

H24

GPA5

M24

GPA8

A3

NC

B21

MD29

D13

GPD11

H25

SDQM3

M25

MA3

A4

CLKMEMIN

B22

GPA18{RSTLD3}

D14

GPD12

H26

SDQM1

M26

MA2

A5

RST

B23

MD15

D15

VCC_I/O

J1

AD18

N1

STOP

A6

CLKPCIOUT

B24

ROMCS1[GPCS1]

D16

VCC_I/O

J2

AD17

N2

PERR

A7

CLKTIMER

[CLKTEST]

B25

BBATSEN

D17

GPD15

J3

INTB

N3

REQ1

A8

MD1

B26

VCC_ANLG

D18

VCC_CORE

J4

VCC_I/O

N4

GNT1

A9

MD17

C1

GPA6

D19

VCC_CORE

J23

GPA3

N11

GND

A10

MD3

C2

GPA9

D20

PRGRESET

J24

GPA0

N12

GND

A11

MD19

C3

GPA25

{DEBUG_ENTER}

D21

VCC_I/O

J25

SCS2

N13

GND

A12

MD5

C4

GPD0

D22

VCC_I/O

J26

SCS3

N14

GND

A13

MD21

C5

NC

D23

NC

K1

CBE2

N15

GND

A14

MD7

C6

NC

D24

GPA16{RSTLD1}

K2

AD16

N16

GND

A15

MD23

C7

GPD2

D25

MECC5

K3

INTA

N23

GPA11

A16

MD9

C8

GPD3

D26

MECC1

K4

VCC_I/O

N24

GPA12

A17

MD25

C9

GPD4

E1

AD25

K23

VCC_I/O

N25

MA4

A18

MD11

C10

GPD7

E2

AD24

K24

GPA2

N26

MA5

A19

MD27

C11

GPD8

E3

NC

K25

SRASA

P1

PAR

A20

MD28

C12

GPD9

E4

VCC_CORE

K26

SRASB

P2

SERR

A21

MD13

C13

GPD10

E23

NC

L1

FRAME

P3

GNT2

A22

MD14

C14

GPA20{RSTLD5}

E24

GPA17{RSTLD2}

L2

IRDY

P4

REQ2

A23

MD30

C15

GPD13

E25

SWEB

L3

REQ0

P11

GND

A24

MD31

C16

GPIOWR

E26

SWEA

L4

VCC_I/O

P12

GND

A25

GND_ANLG

C17

GPD14

F1

AD23

L11

GND

P13

GND

A26

VCC_RTC

C18

GPMEMWR

F2

CBE3

L12

GND

P14

GND

B1

AD29

C19

GPA21{RSTLD6}

F3

GPA22{RSTLD7}

L13

GND

P15

GND

B2

AD28

C20

PWRGOOD

F4

VCC_CORE

L14

GND

P16

GND

B3

NC

C21

GPA19{RSTLD4}

F23

GPA7

L15

GND

P23

VCC_CORE

B4

NC

C22

NC

F24

GPMEMRD

L16

GND

P24

GPA13

B5

GPD1

C23

ROMCS2[GPCS2]

F25

SCASA

L23

VCC_I/O

P25

MA7

B6

NC

C24

GPA15{RSTLD0}

F26

SCASB

L24

GPA4

P26

MA6

B7

MD0

C25

MECC0

G1

AD22

L25

MA0

R1

CBE1

B8

MD16

C26

MECC4

G2

AD21

L26

MA1

R2

AD15

B9

MD2

D1

AD26

G3

CLKPCIIN

M1

DEVSEL

R3

REQ3

B10

MD18

D2

AD27

G4

GPA1

M2

TRDY

R4

VCC_CORE

B11

MD4

D3

GPA23

{AMDEBUG_DIS}

G23

VCC_CORE

M3

GNT0

R11

GND

B12

MD20

D4

GPA24

{INST_TRCE}

G24

GPIORD

M4

VCC_I/O

R12

GND

B13

MD6

D5

VCC_I/O

G25

SDQM0

M11

GND

R13

GND

B14

MD22

D6

VCC_I/O

G26

SDQM2

M12

GND

R14

GND

B15

MD8

D7

VCC_I/O

H1

AD19

M13

GND

R15

GND

B16

MD24

D8

VCC_I/O

H2

AD20

M14

GND

R16

GND

B17

MD10

D9

GPD5

H3

INTC

M15

GND

R23

VCC_CORE

B18

MD26

D10

GPD6

H4

INTD

M16

GND

R24

GPA14

12

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

R25

MA8

W3

DTR1

AC5

VCC_CORE

AD13

NC

AE21

JTAG_TMS

R26

MA9

W4

RTS1

AC6

VCC_CORE

AD14

NC

AE22

JTAG_TRST

T1

AD13

W23

VCC_I/O

AC7

VCC_CORE

AD15

NC

AE23

DTR2

T2

AD14

W24

CF_DRAM

[WBMSTR2]{CFG2}

AC8

PIO12

[GPDACK0]

AD16

NC

AE24

NC

T3

GNT3

W25

SCS1

AC9

PIO11[GPDACK1]

AD17

NC

AE25

NC

T4

VCC_CORE

W26

MECC2

AC10

VCC_I/O

AD18

NC

AE26

32KXTAL2

T11

GND

Y1

AD6

AC11

VCC_I/O

AD19

SSI_CLK

AF1

NC

T12

GND

Y2

AD7

AC12

NC

AD20

CF_ROM_GPCS

[WBMSTR0]{CFG0}

AF2

SOUT1

T13

GND

Y3

DSR1

AC13

TRIG/TRACE

AD21

JTAG_TCK

AF3

PIO29[DSR2]

T14

GND

Y4

VCC_I/O

AC14

VCC_CORE

AD22

RTS2

AF4

PIO28[CTS2]

T15

GND

Y23

VCC_I/O

AC15

VCC_CORE

AD23

TMROUT0

[GPCS7]

AF5

PIO22[GPIRQ1]

T16

GND

Y24

PITOUT2{CFG3}

AC16

NC

AD24

BR/TC

AF6

PIO21[GPIRQ2]

T23

NC

Y25

MECC3

AC17

NC

AD25

NC

AF7

PIO16[GPIRQ7]

T24

NC

Y26

MECC6

AC18

VCC_I/O

AD26

NC

AF8

PIO15[GPIRQ8]

T25

BA0

AA1

AD5

AC19

VCC_I/O

AE1

NC

AF9

PIO8[GPDRQ0]

T26

MA10

AA2

AD4

AC20

TMRIN0[GPCS5]

AE2

SIN1

AF10

PIO7[GPDRQ1]

U1

AD12

AA3

RIN1

AC21

PITGATE2[GPCS3]

AE3

PIO30[DCD2]

AF11

PIO2[GPRDY]

U2

AD11

AA4

VCC_I/O

AC22

GPRESET

AE4

PIO27[GPCS0]

AF12

PIO1[GPBHE]

U3

REQ4

AA23

VCC_I/O

AC23

TMROUT1[GPCS6]

AE5

PIO23[GPIRQ0]

AF13

NC

U4

GNT4

AA24

TMRIN1[GPCS4]

AC24

DATASTRB

[WBMSTR1]{CFG1}

AE6

PIO20[GPIRQ3]

AF14

NC

U23

SOUT2

AA25

ROMBUFOE

AC25

NC

AE7

PIO17[GPIRQ6]

AF15

NC

U24

CMDACK

AA26

NC

AC26

33MXTAL2

AE8

PIO14[GPIRQ9]

AF16

NC

U25

BA1

AB1

AD2

AD1

NC

AE9

PIO9[GPDACK3]

AF17

STOP/TX

U26

MA11

AB2

AD3

AD2

NC

AE10

PIO6[GPDRQ2]

AF18

NC

V1

AD9

AB3

NC

AD3

PIO31[RIN2]

AE11

PIO3[GPAEN]

AF19

SSI_DO

V2

AD10

AB4

NC

AD4

PIO26

[GPMEMCS16]

AE12

PIO0[GPALE]

AF20

NC

V3

CTS1

AB23

ROMRD

AD5

PIO24[GPDBUFOE]

AE13

NC

AF21

JTAG_TDI

V4

DCD1

AB24

FLASHWR

AD6

PIO19[GPIRQ4]

AE14

NC

AF22

JTAG_TDO

V23

VCC_I/O

AB25

BOOTCS

AD7

PIO18[GPIRQ5]

AE15

NC

AF23

NC

V24

SIN2

AB26

33MXTAL1

AD8

PIO13[GPIRQ10]

AE16

NC

AF24

LF_PLL1

V25

SCS0

AC1

AD1

AD9

PIO10[GPDACK2]

AE17

NC

AF25

NC

V26

MA12

AC2

AD0

AD10

PIO5[GPDRQ3]

AE18

NC

AF26

32KXTAL1

W1

AD8

AC3

NC

AD11

PIO4[GPTC]

AE19

SSI_DI

W2

CBE0

AC4

PIO25 [GPIOCS16]

AD12

NC

AE20

NC

Notes:

1. See Table 17 on page A-4 for PIOs sorted by pin number.

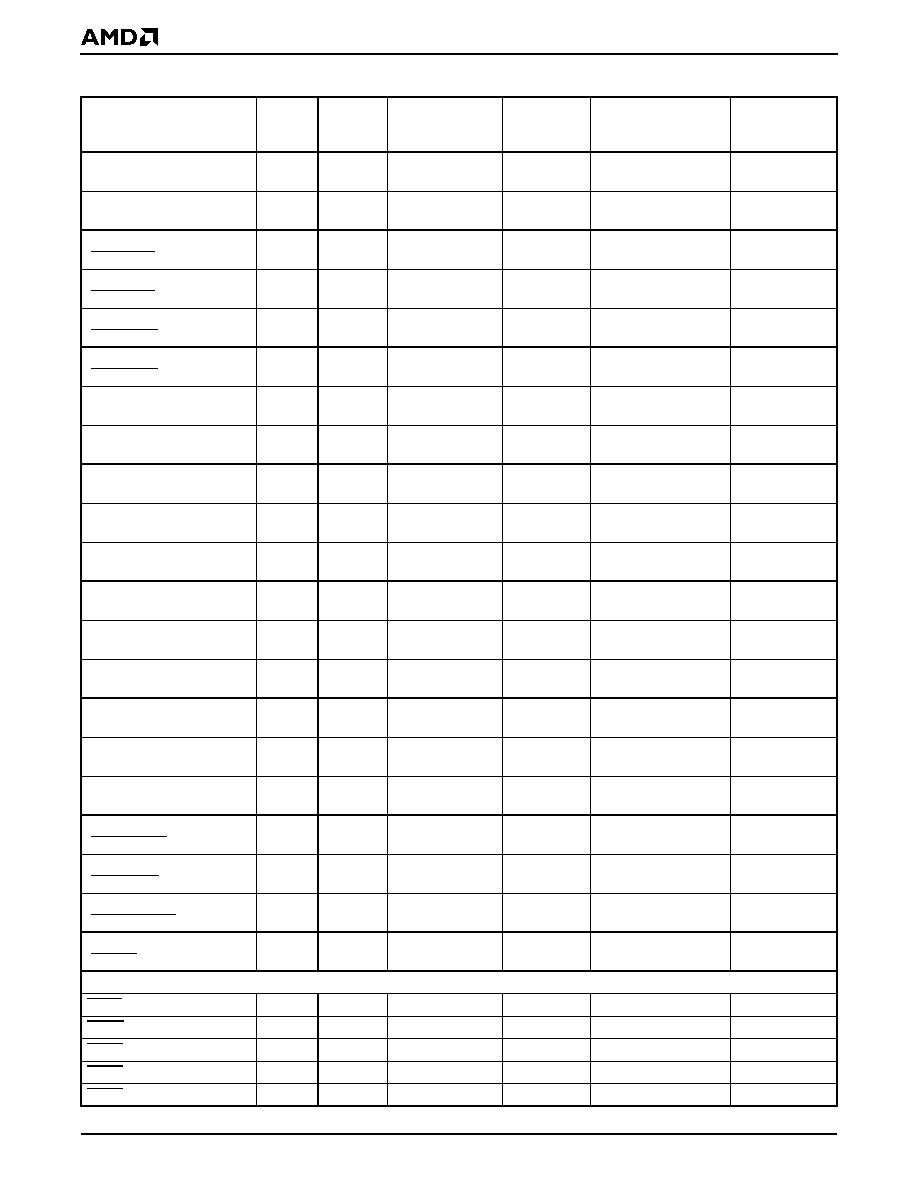

Pin Designations (Pin Number

1

) (Continued)

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

…lanTMSC520 Microcontroller Data Sheet

13

P R E L I M I N A R Y

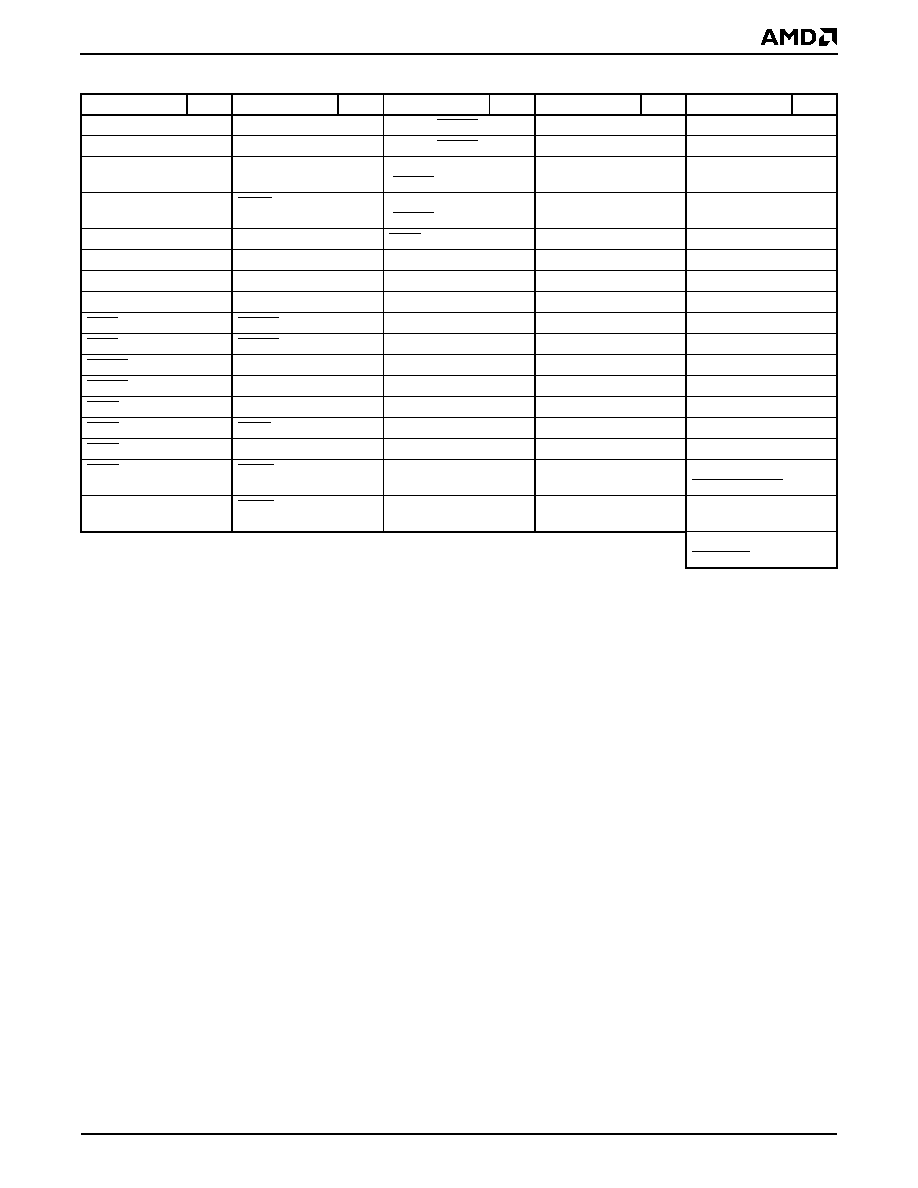

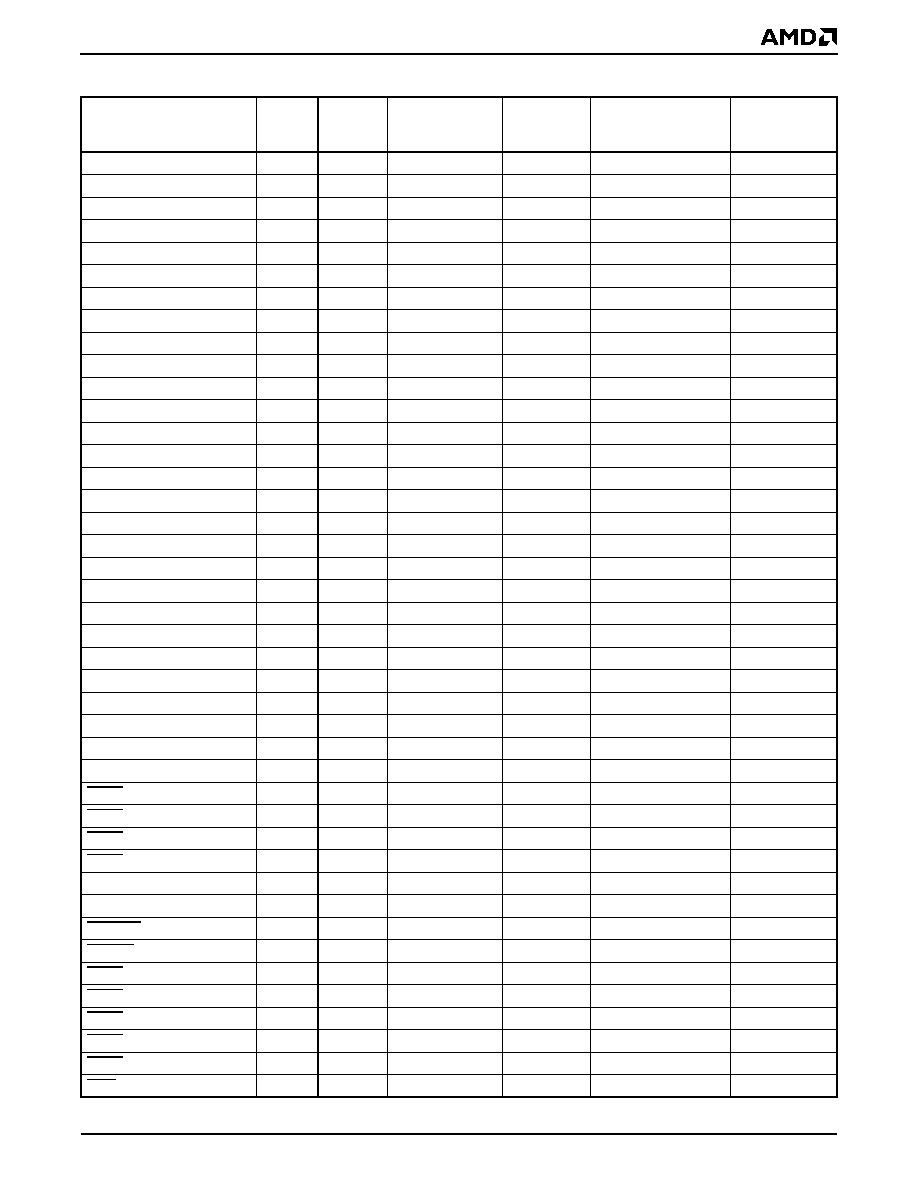

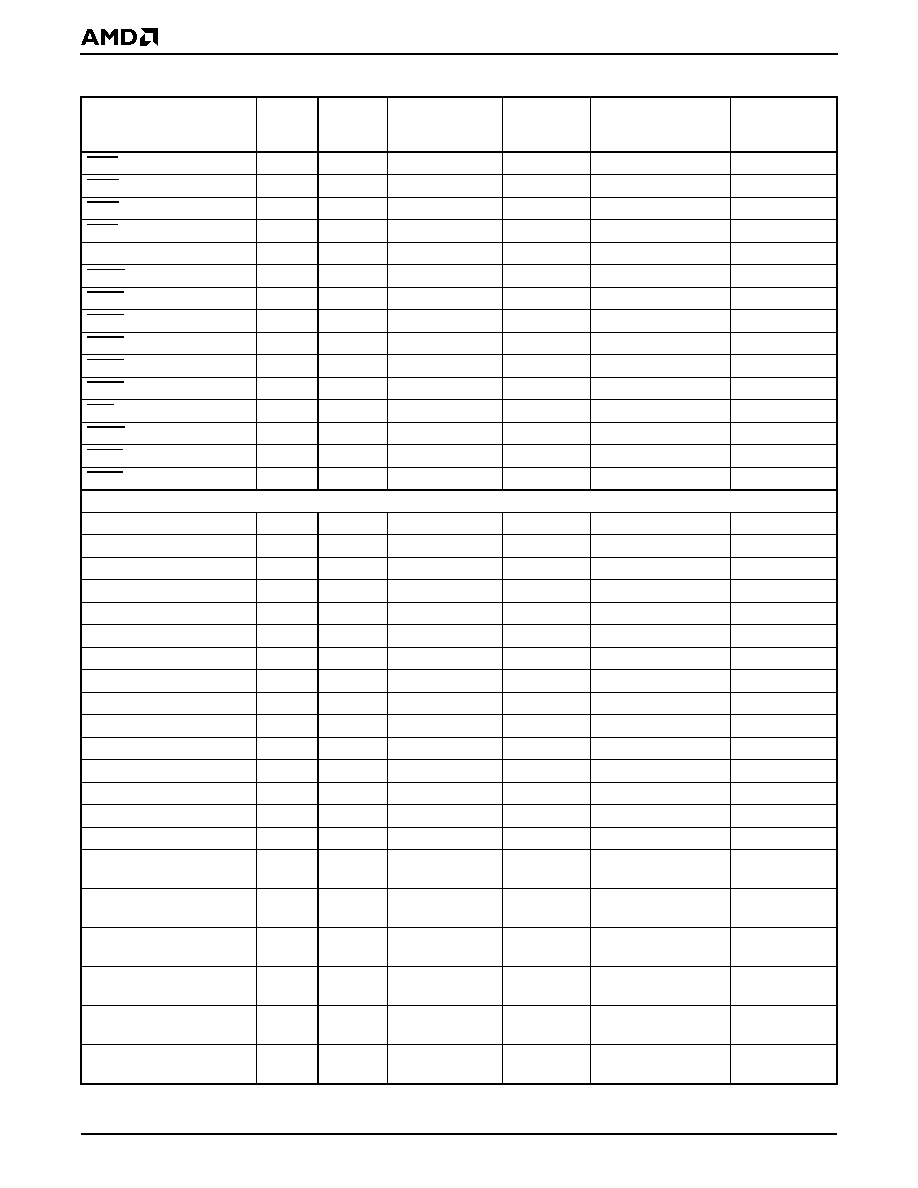

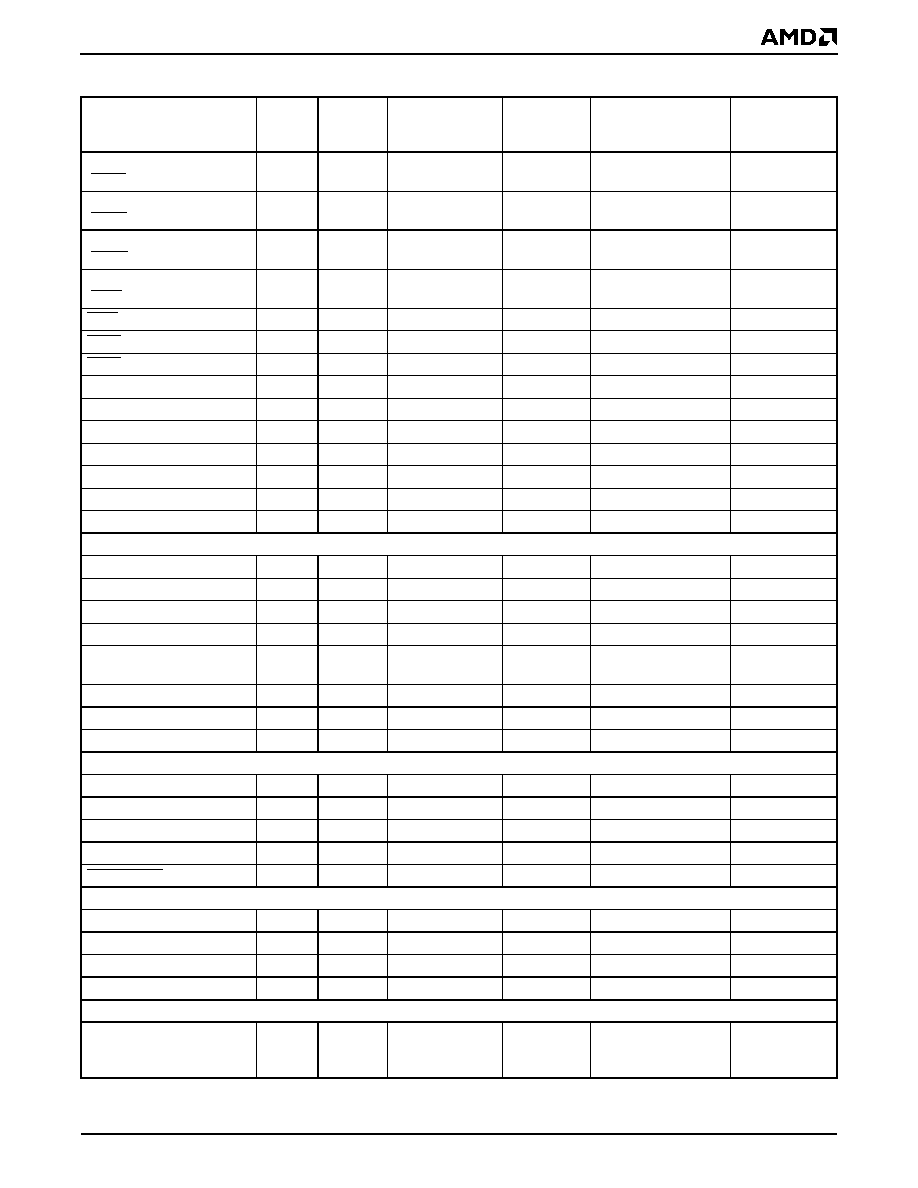

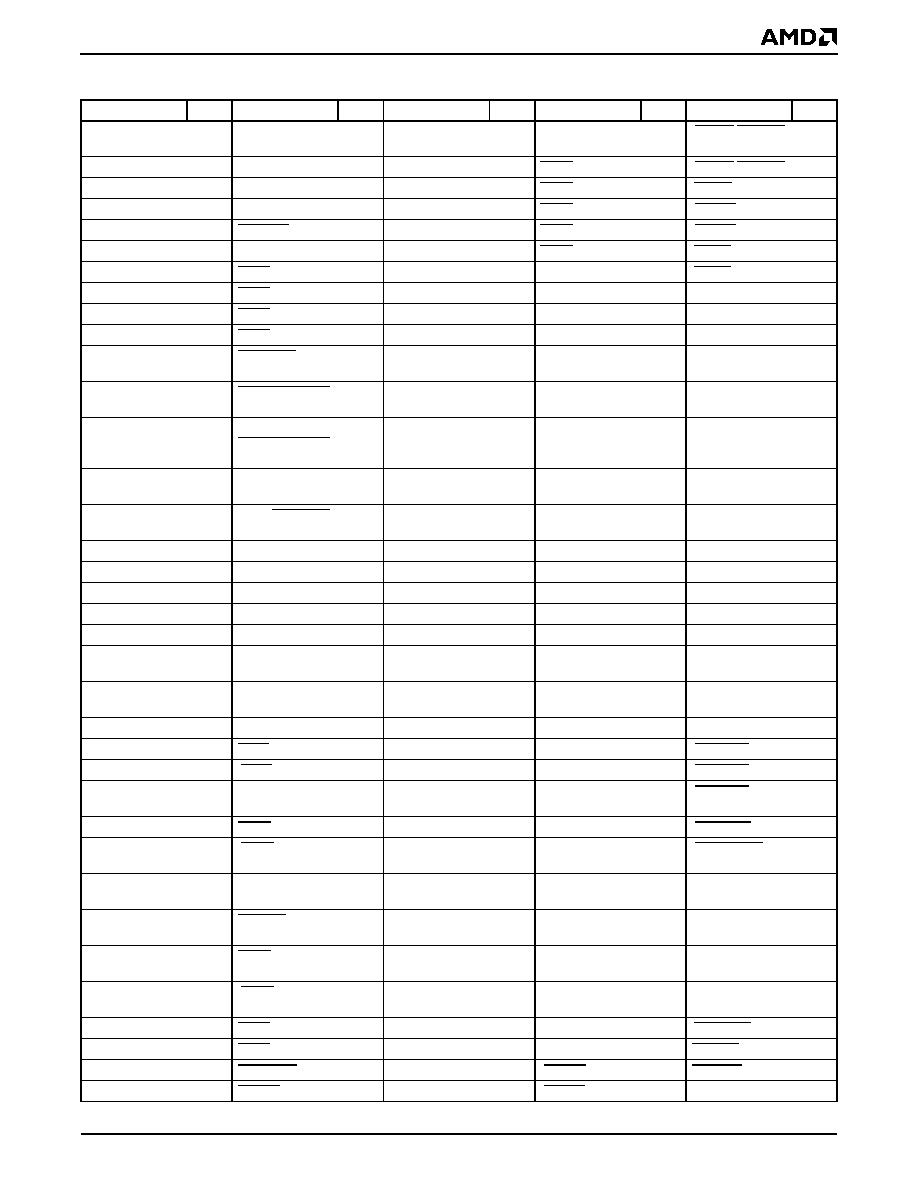

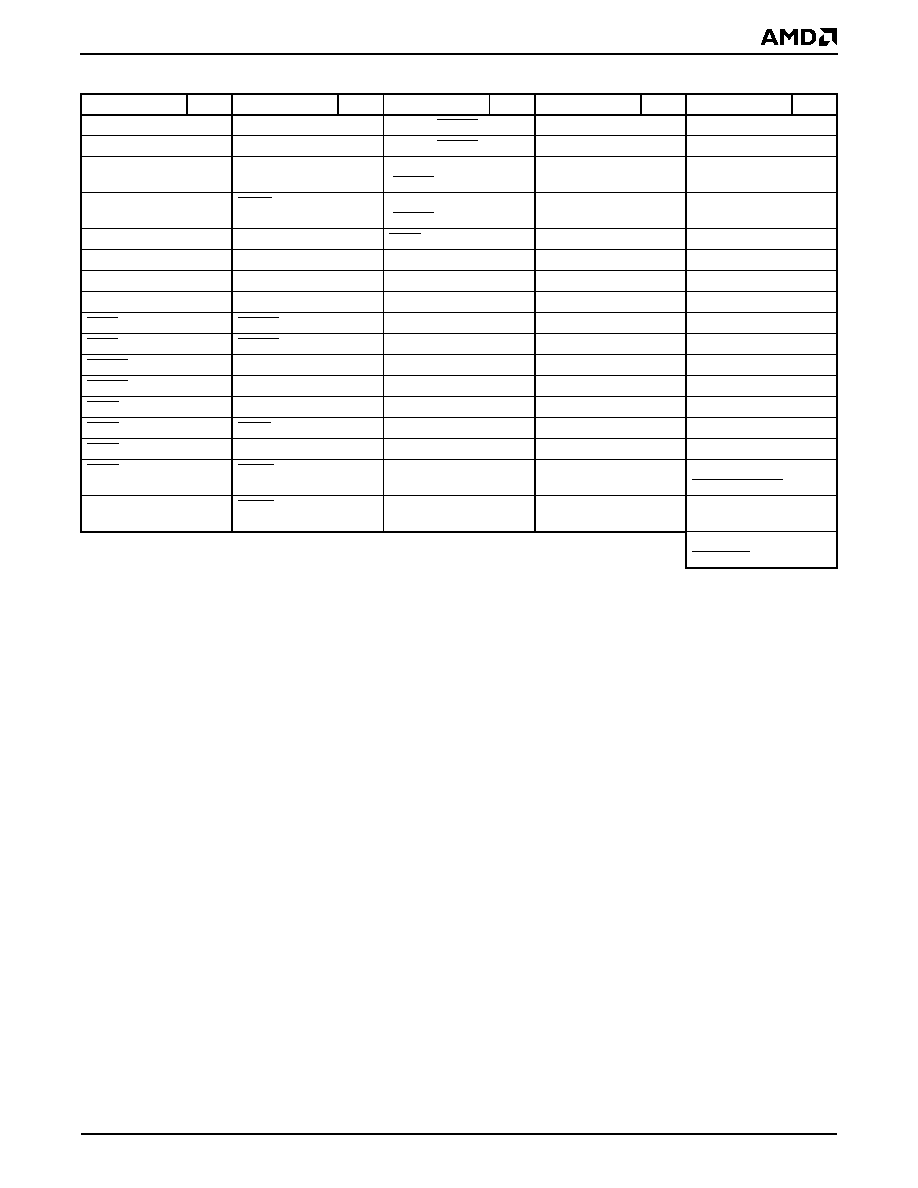

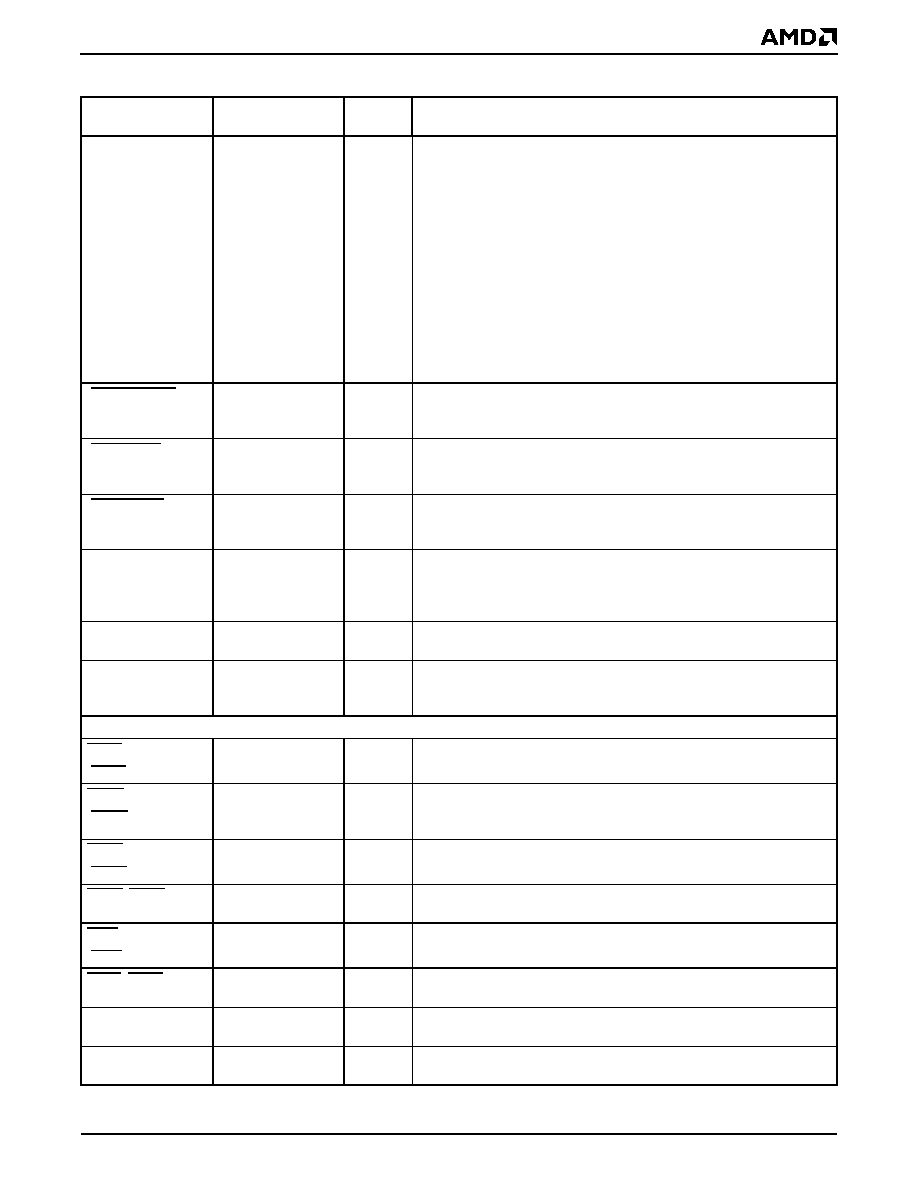

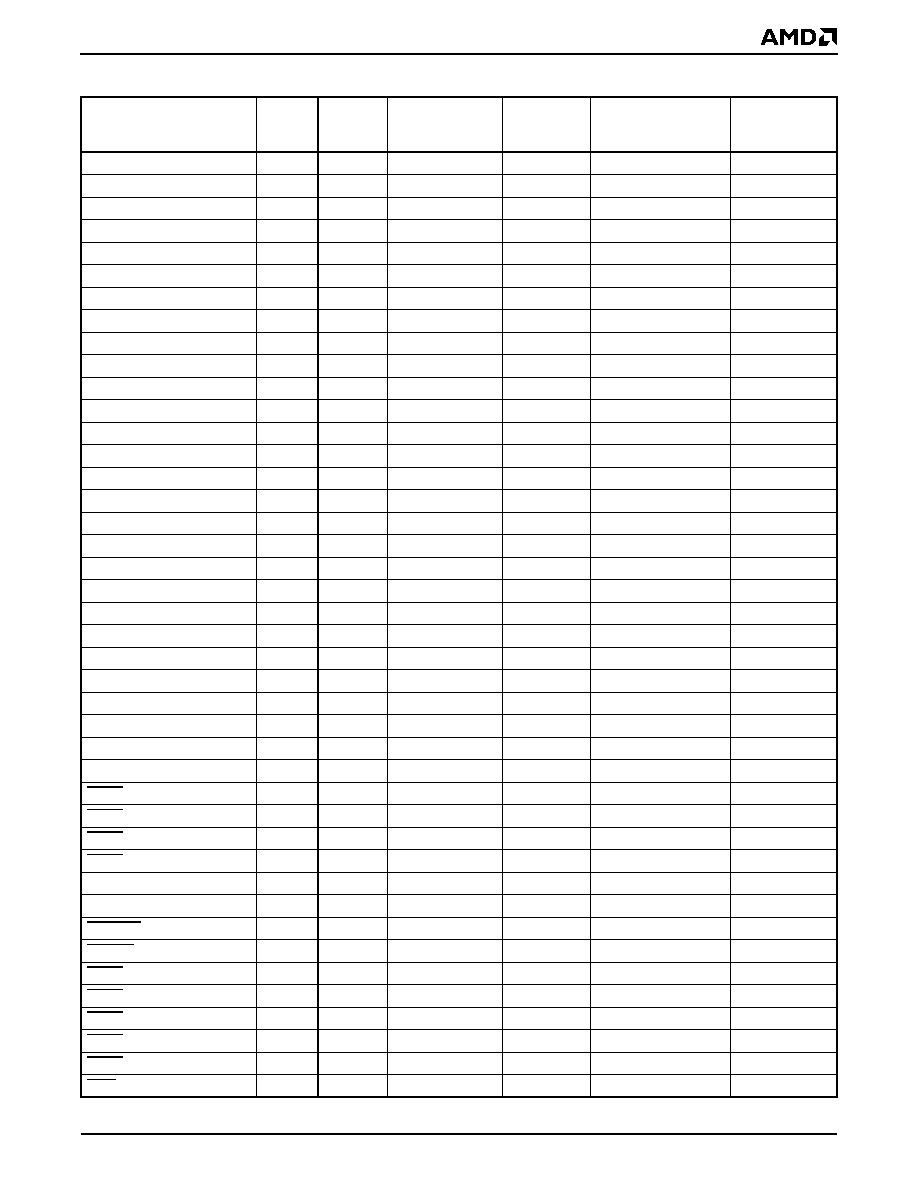

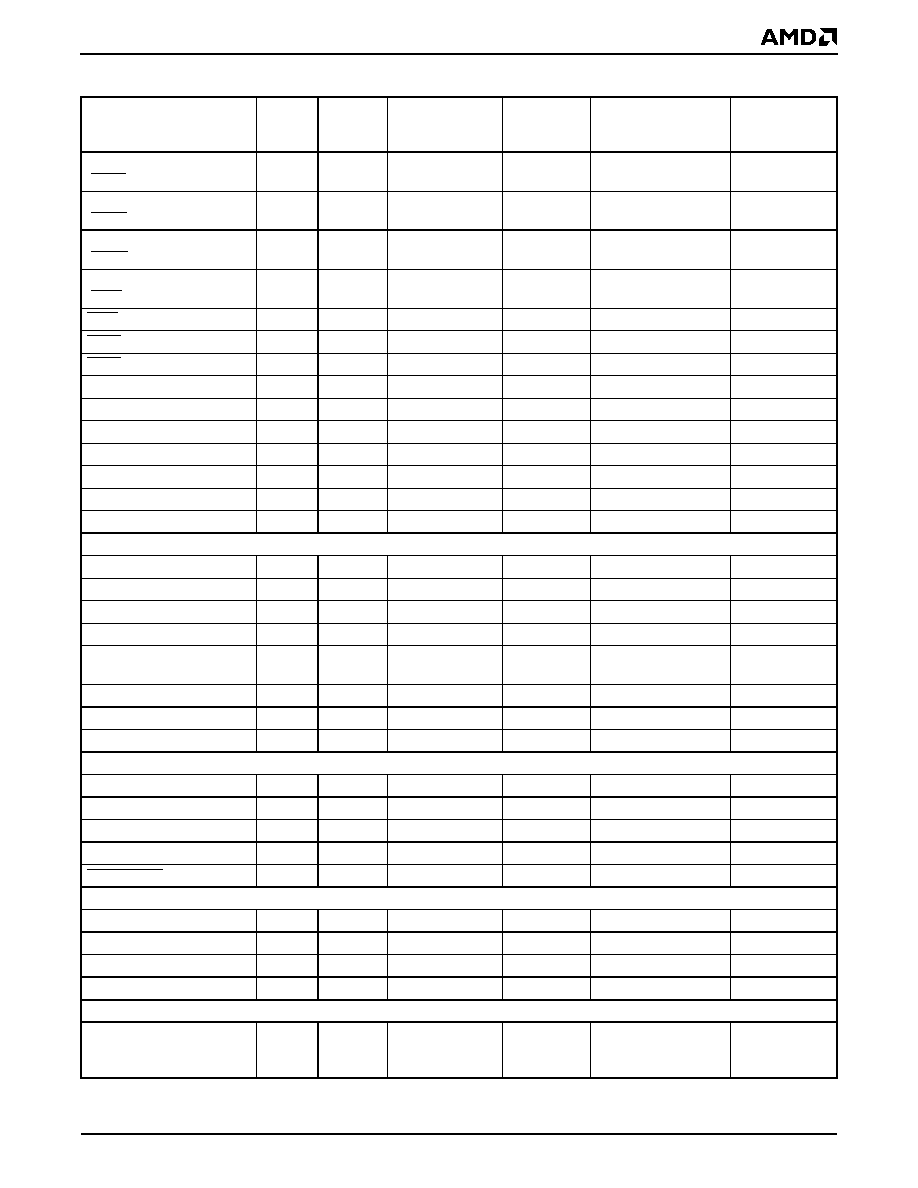

Pin Designations (Pin Name

1

)

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

32KXTAL1

AF26

{AMDEBUG_DIS}

GPA23

D3

GND

L11

GND_ANLG

A25

[GPCS1]ROMCS1

B24

32KXTAL2

AE26 BA0

T25

GND

L12

GNT0

M3

[GPCS2]ROMCS2

C23

33MXTAL1

AB26 BA1

U25

GND

L13

GNT1

N4

[GPCS3]PITGATE2

AC21

33MXTAL2

AC26 BBATSEN

B25

GND

L14

GNT2

P3 [GPCS4]TMRIN1

AA24

AD0

AC2

BOOTCS

AB25

GND

L15

GNT3

T3

[GPCS5]TMRIN0

AC20

AD1

AC1

BR/TC

AD24

GND

L16

GNT4

U4

[GPCS6]TMROUT1

AC23

AD2

AB1

CBE0

W2

GND

M11

GPA0

J24

[GPCS7]TMROUT0

AD23

AD3

AB2

CBE1

R1

GND

M12

GPA1

G4

GPD0

C4

AD4

AA2

CBE2

K1

GND

M13

GPA2

K24

GPD1

B5

AD5

AA1

CBE3

F2

GND

M14

GPA3

J23

GPD2

C7

AD6

Y1

CF_DRAM

[WBMSTR2]{CFG2}

W24

GND

M15

GPA4

L24

GPD3

C8

AD7

Y2

CF_ROM_GPCS

[WBMSTR0]{CFG0}

AD20

GND

M16

GPA5

H24

GPD4

C9

AD8

W1

{CFG0}

CF_ROM_GPCS

[WBMSTR0]

AD20

GND

N11

GPA6

C1

GPD5

D9

AD9

V1

{CFG1}DATASTRB

[WBMSTR1]

AC24

GND

N12

GPA7

F23

GPD6

D10

AD10

V2

{CFG2]CF_DRAM

[WBMSTR2}

W24

GND

N13

GPA8

M24

GPD7

C10

AD11

U2

{CFG3}PITOUT2

Y24

GND

N14

GPA9

C2

GPD8

C11

AD12

U1

CLKMEMIN

A4

GND

N15

GPA10

M23

GPD9

C12

AD13

T1

CLKMEMOUT

B19

GND

N16

GPA11

N23

GPD10

C13

AD14

T2

CLKPCIIN

G3

GND

P11

GPA12

N24

GPD11

D13

AD15

R2

CLKPCIOUT

A6

GND

P12

GPA13

P24

GPD12

D14

AD16

K2

CLKTEST

[CLKTIMER]

A7

GND

P13

GPA14

R24

GPD13

C15

AD17

J2

[CLKTIMER]

CLKTEST

A7

GND

P14

GPA15{RSTLD0} C24

GPD14

C17

AD18

J1

CMDACK

U24

GND

P15

GPA16{RSTLD1} D24

GPD15

D17

AD19

H1

CTS1

V3

GND

P16

GPA17{RSTLD2} E24

[GPDACK0]PIO12

AC8

AD20

H2

[CTS2]PIO28

AF4

GND

R11

GPA18{RSTLD3} B22

[GPDACK1]PIO11

AC9

AD21

G2

DATASTRB

[WBMSTR1]{CFG1}

AC24

GND

R12

GPA19{RSTLD4] C21

[GPDACK2]PIO10

AD9

AD22

G1

DCD1

V4

GND

R13

GPA20{RSTLD5} C14

[GPDACK3]PIO9

AE9

AD23

F1

[DCD2]PIO30

AE3

GND

R14

GPA21[RSTLD6} C19

[GPDBUFOE]

PIO24

AD5

AD24

E2

{DEBUG_ENTER}

GPA25

C3

GND

R15

GPA22{RSTLD7} F3

[GPDRQ0]PIO8

AF9

AD25

E1

DEVSEL

M1

GND

R16

GPA23

{AMDEBUG_DIS}

D3

[GPDRQ1]PIO7

AF10

AD26

D1

DSR1

Y3

GND

T11

GPA24

{INST_TRCE]

D4

[GPDRQ2]PIO6

AE10

AD27

D2

[DSR2]PIO29

AF3

GND

T12

GPA25

{DEBUG_ENTER]

C3

[GPDRQ3]PIO5

AD10

AD28

B2

DTR1

W3

GND

T13

[GPAEN]PIO3

AE11

[GPIOCS16]PIO25

AC4

AD29

B1

DTR2

AE23

GND

T14

[GPALE]PIO0

AE12

GPIORD

G24

AD30

A1

FLASHWR

AB24

GND

T15

[GPBHE]PIO1

AF12

GPIOWR

C16

AD31

A2

FRAME

L1

GND

T16

[GPCS0]PIO27

AE4

[GPIRQ0]PIO23

AE5

14

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

[GPIRQ1]PIO22

AF5

MA8

R25

MD31

A24

NC

AE24

PIO12[GPDACK0] AC8

[GPIRQ2]PIO21

AF6

MA9

R26

MECC0

C25

NC

AE25

PIO13[GPIRQ10] AD8

[GPIRQ3]PIO20

AE6

MA10

T26

MECC1

D26 NC

AF1

PIO14[GPIRQ9] AE8

[GPIRQ4]PIO19

AD6

MA11

U26

MECC2

W26 NC

AF13

PIO15[GPIRQ8] AF8

[GPIRQ5]PIO18

AD7

MA12

V26

MECC3

Y25

NC

AF14

PIO16[GPIRQ7] AF7

[GPIRQ6]PIO17

AE7

MD0

B7

MECC4

C26

NC

AF15

PIO17[GPIRQ6] AE7

[GPIRQ7]PIO16

AF7

MD1

A8

MECC5

D25

NC

AF16

PIO18[GPIRQ5] AD7

[GPIRQ8]PIO15

AF8

MD2

B9

MECC6

Y26

NC

AF18

PIO19[GPIRQ4] AD6

[GPIRQ9]PIO14

AE8

MD3

A10

NC

A3

NC

AF20

PIO20[GPIRQ3] AE6

[GPIRQ10]PIO13

AD8

MD4

B11

NC

AA26

NC

AF23

PIO21[GPIRQ2] AF6

[GPMEMCS16]

PIO26

AD4

MD5

A12

NC

AB3

NC

AF25

PIO22[GPIRQ1] AF5

GPMEMRD

F24

MD6

B13

NC

AB4

NC

B3

PIO23[GPIRQ0] AE5

GPMEMWR

C18

MD7

A14

NC

AC3

NC

B4

PIO24

[GPDBUFOE]

AD5

[GPRDY]PIO2

AF11

MD8

B15

NC

AC12

NC

B6

PIO25

[GPIOCS16]

AC4

GPRESET

AC22

MD9

A16

NC

AC16

NC

C5

PIO26

[GPMEMCS16]

AD4

[GPTC]PIO4

AD11

MD10

B17

NC

AC17

NC

C6

PIO27[GPCS0] AE4

{INST_TRCE}

GPA24

D4

MD11

A18

NC

AC25

NC

C22

PIO28[CTS2] AF4

INTA

K3 MD12

B20

NC

AD1

NC

D23

PIO29[DSR2] AF3

INTB

J3

MD13

A21

NC

AD2

NC

E3

PIO30[DCD2] AE3

INTC

H3

MD14

A22

NC

AD12

NC

E23

PIO31[RIN2] AD3

INTD

H4

MD15

B23

NC

AD13

NC

T23

PITGATE2

[GPCS3]

AC21

IRDY

L2

MD16

B8

NC

AD14

NC

T24

PITOUT2{CFG3} Y24

JTAG_TCK

AD21

MD17

A9

NC

AD15

PAR

P1

PRGRESET

D20

JTAG_TDI

AF21

MD18

B10

NC

AD16

PERR

N2

PWRGOOD

C20

JTAG_TDO

AF22

MD19

A11

NC

AD17

PIO0[GPALE] AE12

REQ0

L3

JTAG_TMS

AE21

MD20

B12

NC

AD18

PIO1[GPBHE] AF12

REQ1

N3

JTAG_TRST

AE22

MD21

A13

NC

AD25

PIO2[GPRDY] AF11

REQ2

P4

LF_PLL1

AF24

MD22

B14

NC

AD26 PIO3[GPAEN]

AE11

REQ3

R3

MA0

L25

MD23

A15

NC

AE1

PIO4[GPTC] AD11

REQ4

U3

MA1

L26

MD24

B16

NC

AE13

PIO5[GPDRQ3] AD10

RIN1

AA3

MA2

M26

MD25

A17

NC

AE14

PIO6[GPDRQ2] AE10

[RIN2]PIO31

AD3

MA3

M25

MD26

B18 NC

AE15

PIO7[GPDRQ1] AF10

ROMBUFOE

AA25

MA4

N25

MD27

A19

NC

AE16

PIO8[GPDRQ0] AF9

ROMCS1[GPCS1]

B24

MA5

N26

MD28

A20

NC

AE17

PIO9[GPDACK3]

AE9

ROMCS2

[GPCS2 ]

C23

MA6

P26 MD29

B21

NC

AE18

PIO10[GPDACK2]

AD9

ROMRD

AB23

MA7

P25

MD30

A23

NC

AE20

PIO11[GPDACK1]

AC9

RST

A5

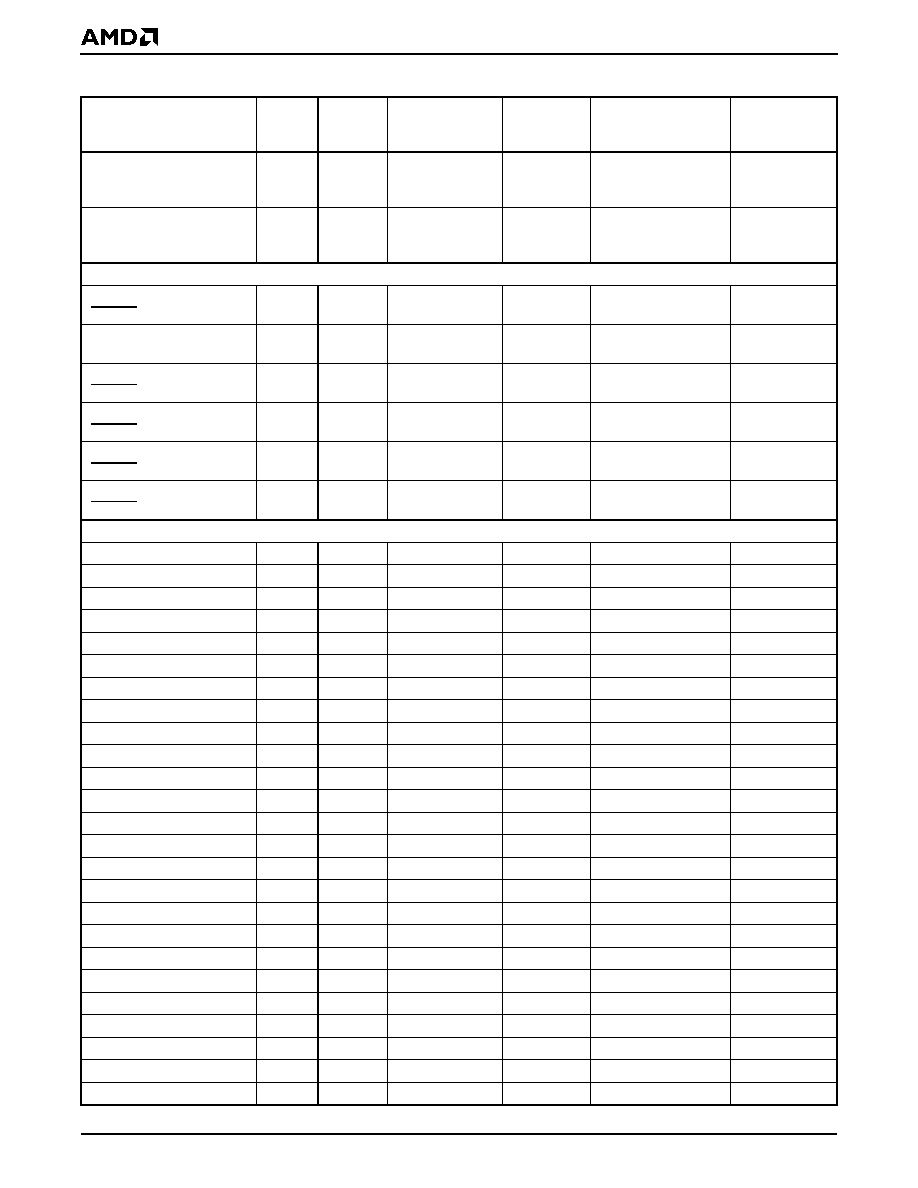

Pin Designations (Pin Name

1

) (Continued)

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

…lanTMSC520 Microcontroller Data Sheet

15

P R E L I M I N A R Y

{RSTLD0}GPA15

C24

SDQM1

H26

TMRIN0[GPCS5]

AC20

VCC_CORE

F4

VCC_I/O

D15

{RSTLD1}GPA16

D24

SDQM2

G26

TMRIN1[GPCS4] AA24

VCC_CORE

G23

VCC_I/O

D16

{RSTLD2}GPA17

E24

SDQM3

H25

TMROUT0

[GPCS7]

AD23

VCC_CORE

H23

VCC_I/O

D21

{RSTLD3}GPA18

B22

SERR

P2

TMROUT1

[GPCS6]

AC23

VCC_CORE

P23

VCC_I/O

D22

{RSTLD4}GPA19

C21

SIN1

AE2

TRDY

M2

VCC_CORE

R23

VCC_I/O

J4

{RSTLD5}GPA20

C14

SIN2

V24

TRIG/TRACE

AC13

VCC_CORE

R4

VCC_I/O

K23

{RSTLD6}GPA21

C19

SOUT1

AF2

VCC_ANLG

B26 VCC_CORE

T4

VCC_I/O

K4

{RSTLD7}GPA22

F3

SOUT2

U23

VCC_CORE

AC5

VCC_I/O

AA23

VCC_I/O

L4

RTS1

W4

SRASA

K25

VCC_CORE

AC6

VCC_I/O

AA4

VCC_I/O

L23

RTS2

AD22

SRASB

K26

VCC_CORE

AC7

VCC_I/O

AC10

VCC_I/O

M4

SCASA

F25

SSI_CLK

AD19

VCC_CORE

AC14

VCC_I/O

AC11

VCC_I/O

V23

SCASB

F26

SSI_DI

AE19

VCC_CORE

AC15

VCC_I/O

AC18

VCC_I/O

W23

SCS0

V25

SSI_DO

AF19

VCC_CORE

D11

VCC_I/O

AC19

VCC_I/O

Y4

SCS1

W25

STOP

N1

VCC_CORE

D12

VCC_I/O

D5

VCC_I/O

Y23

SCS2

J25

STOP/TX

AF17

VCC_CORE

D18

VCC_I/O

D6

VCC_RTC

A26

SCS3

J26

SWEA

E26

VCC_CORE

D19

VCC_I/O

D7

[WBMSTR0]{CFG0}

CF_ROM_GPCS

AD20

SDQM0

G25

SWEB

E25

VCC_CORE

E4

VCC_I/O

D8

[WBMSTR1]{CFG1}

DATASTRB

AC24

[WBMSTR2]{CFG2}

CF_DRAM

W24

Notes:

1. See Table 17 on page A-4 for PIOs sorted by pin number.

Pin Designations (Pin Name

1

) (Continued)

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

Signal Name

Pin #

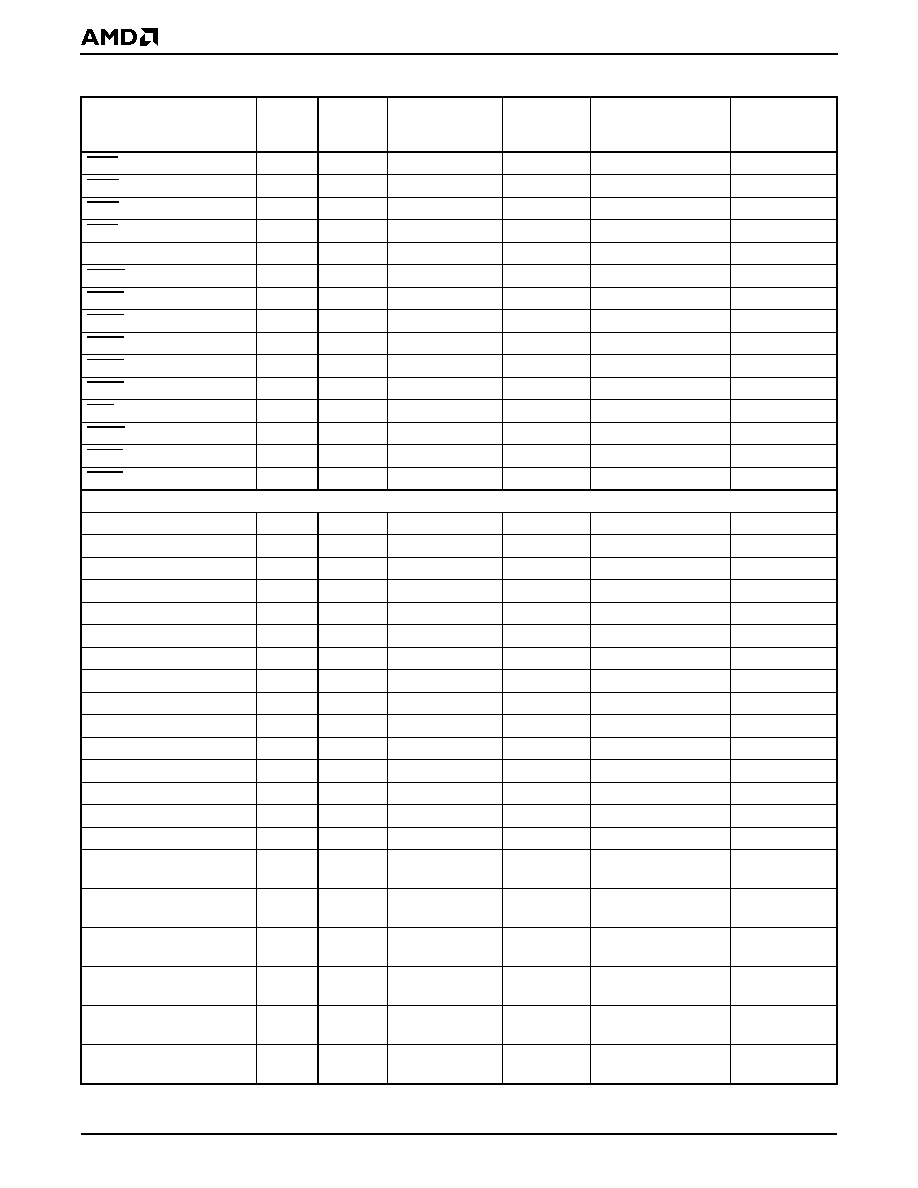

16

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

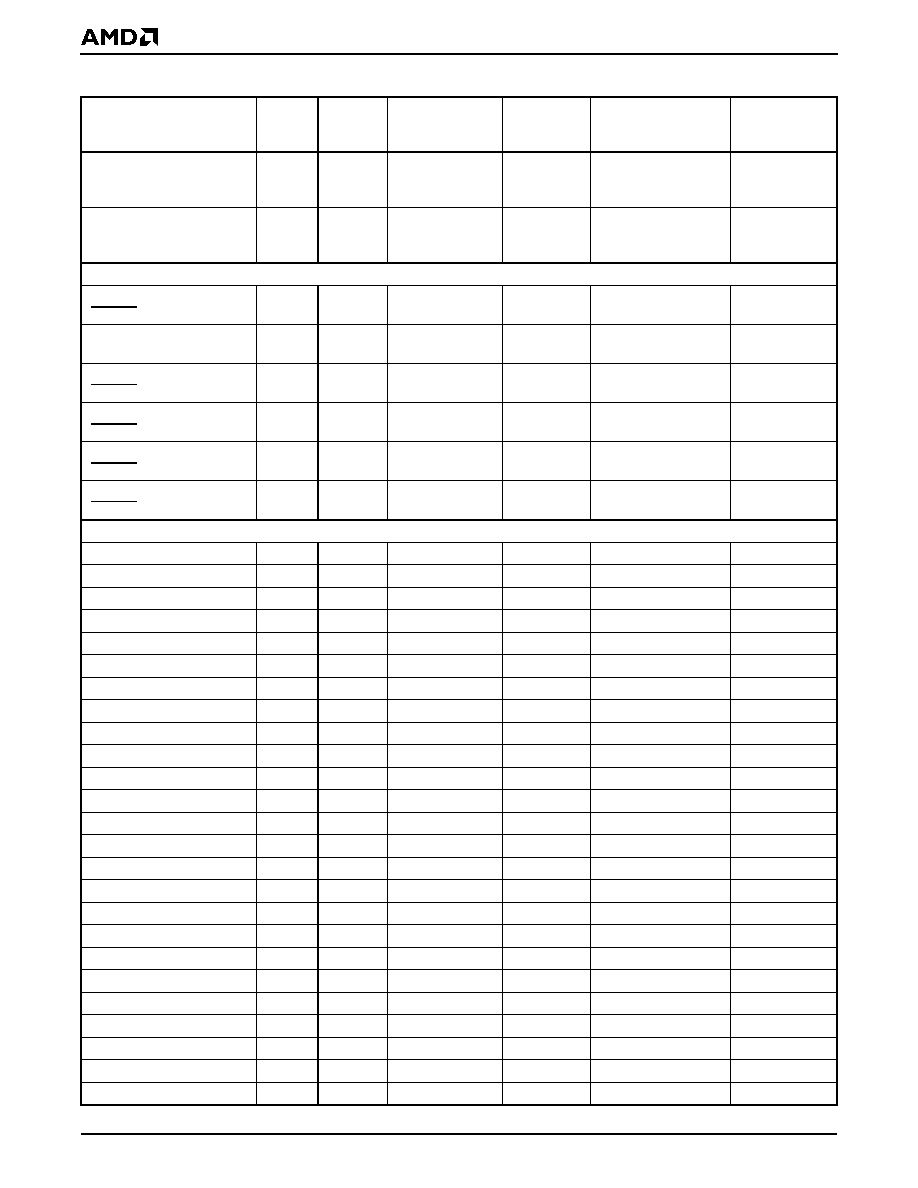

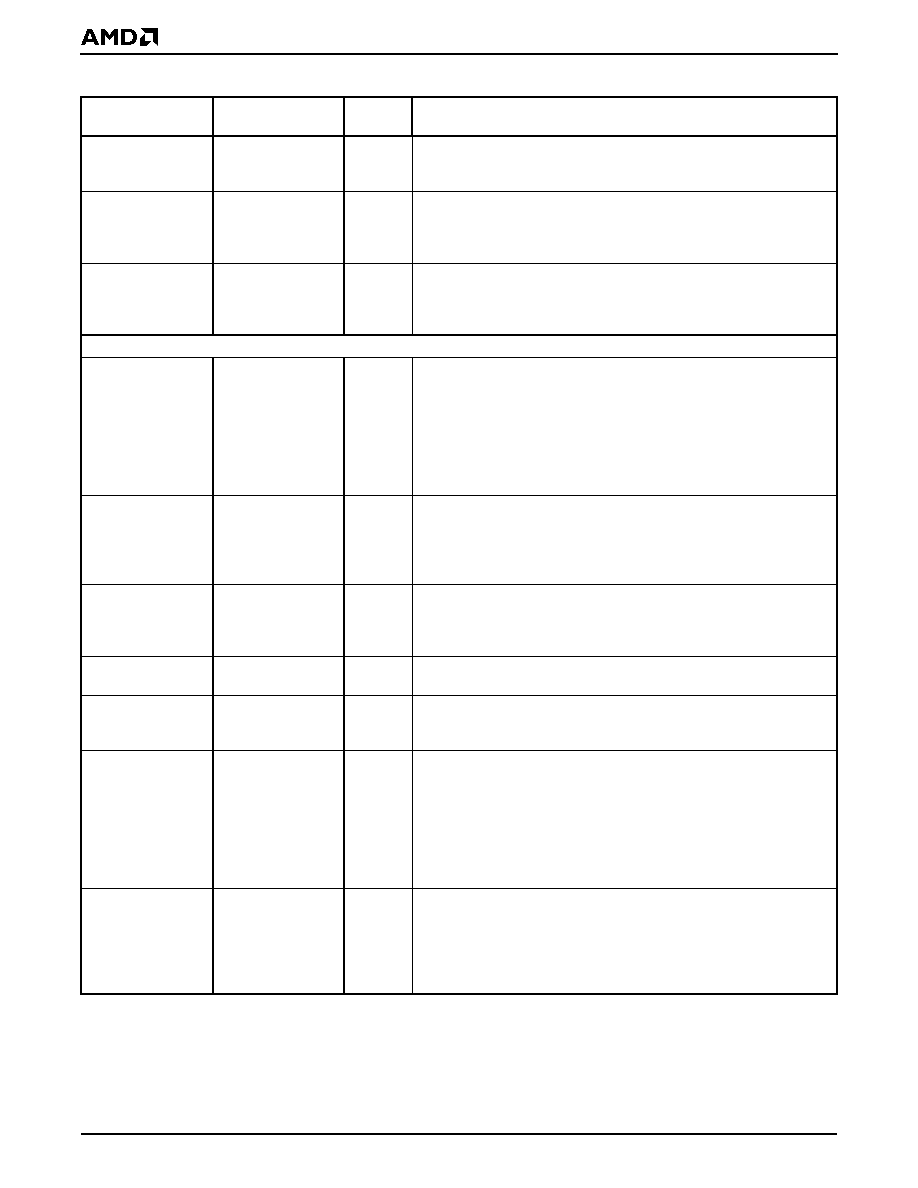

SIGNAL DESCRIPTIONS

Table 2, "Signal Descriptions" on page 17 contains a

description of the …lanSC520 microcontroller signals.

The microcontroller contains 258 signal pins in addition

to power and ground pins in a Plastic Ball Grid Array

(PBGA) package.

Table 1 describes the terms used in the signal descrip-

tion table. The signals are organized alphabetically

within the following functional groups:

s

Synchronous DRAM (page 17)

s

ROM/Flash (page 18)

s

PCI bus (page 18)

s

GP bus (page 19)

s

Serial ports (page 21)

s

Clocks and reset (page 22)

s

JTAG (page 23)

s

AMDebugTM Interface (page 23)

s

System test (page 23)

s

Chip selects (page 24)

s

Programmable I/O (PIO) (page 25)

s

Timers (page 25)

s

Configuration (page 26)

s

Power (page 27)

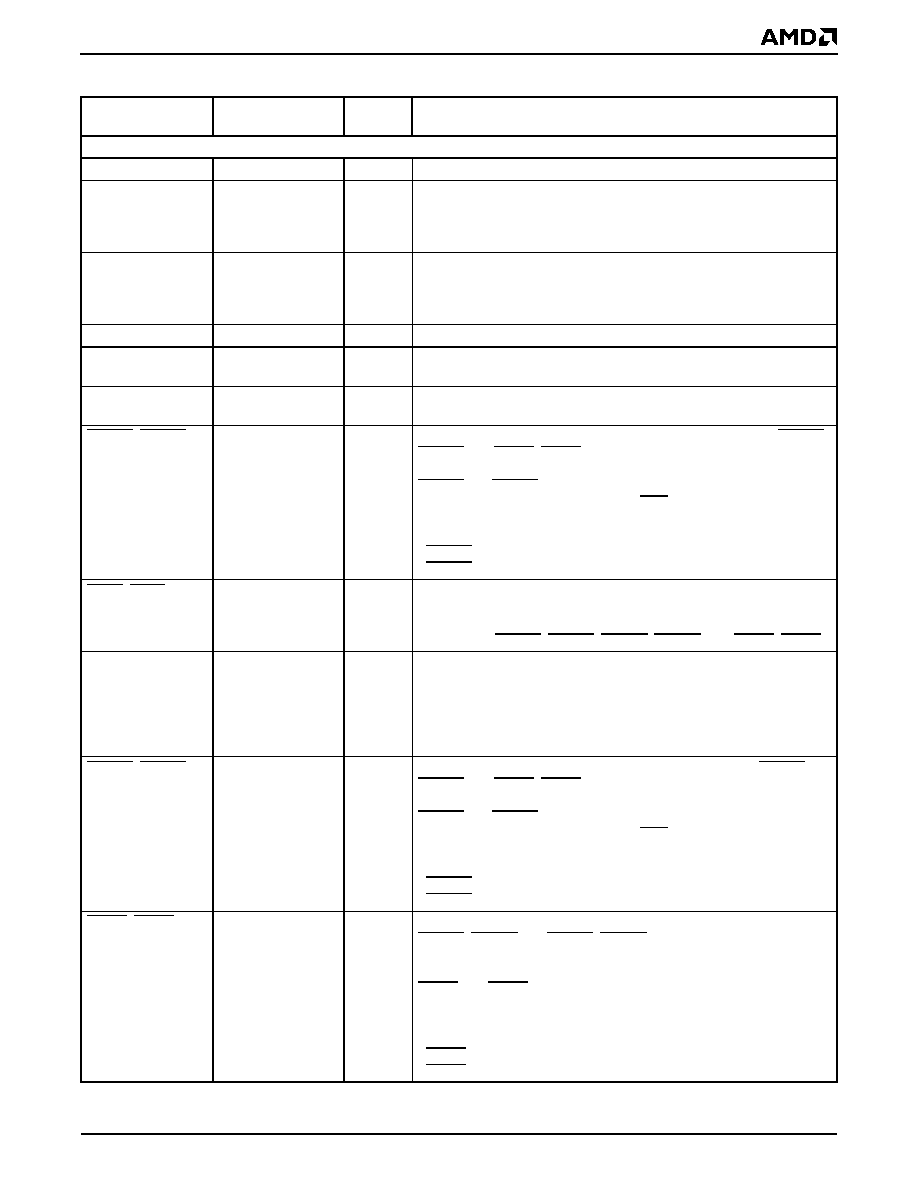

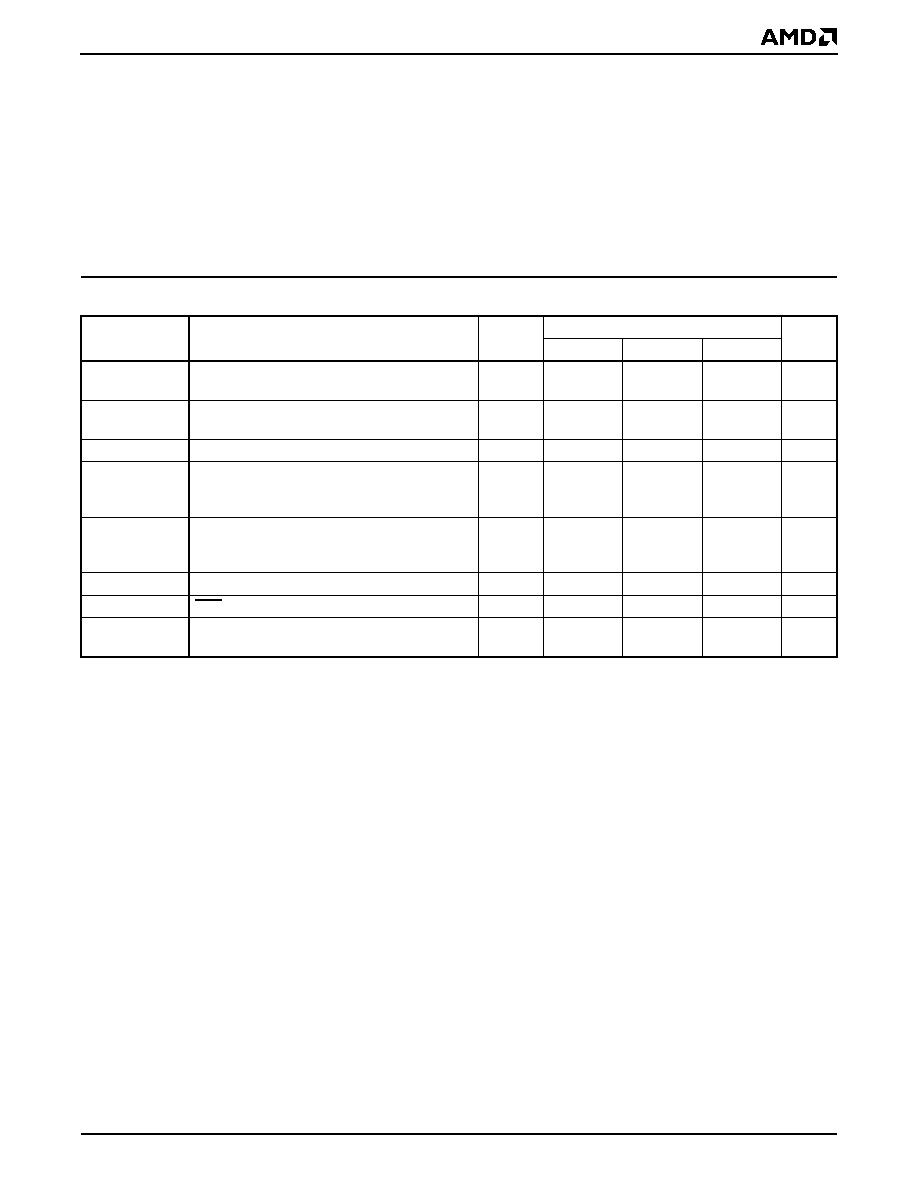

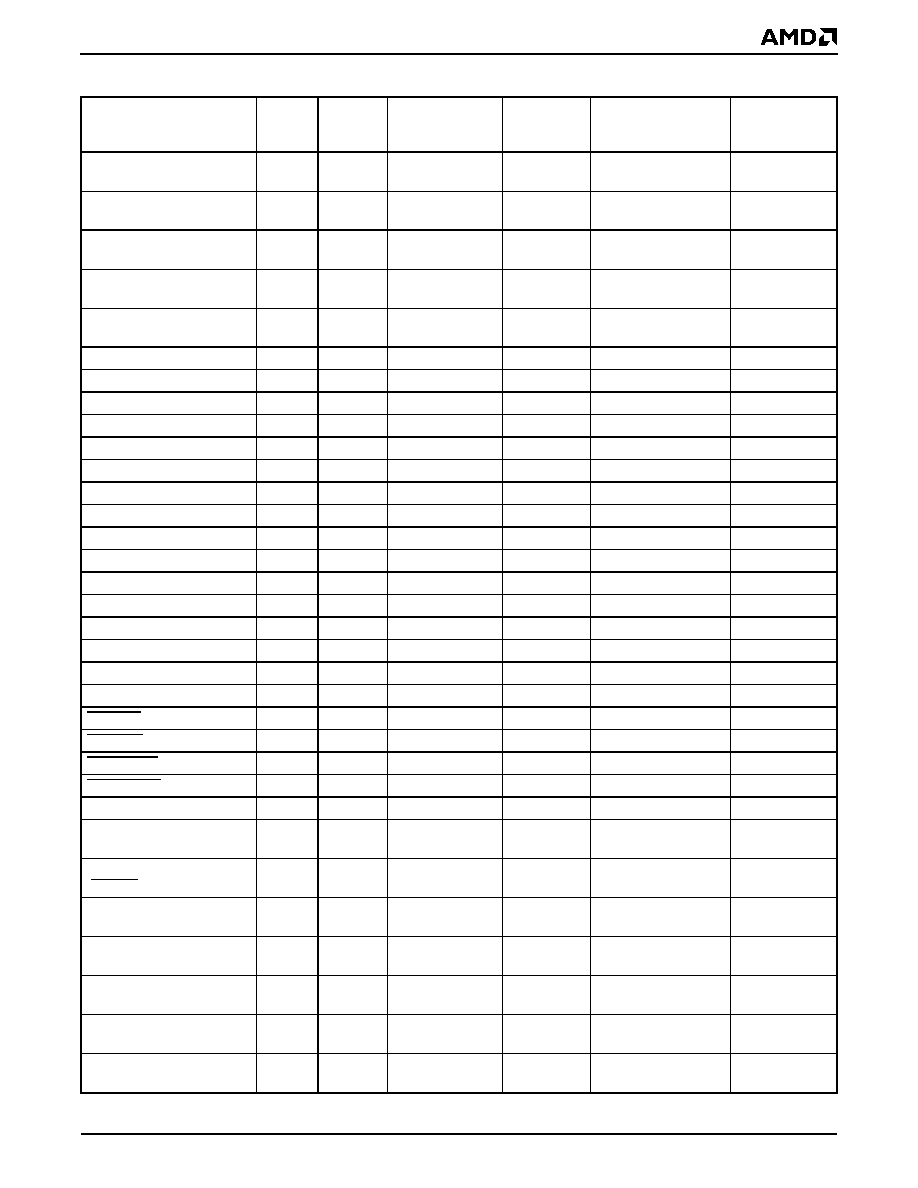

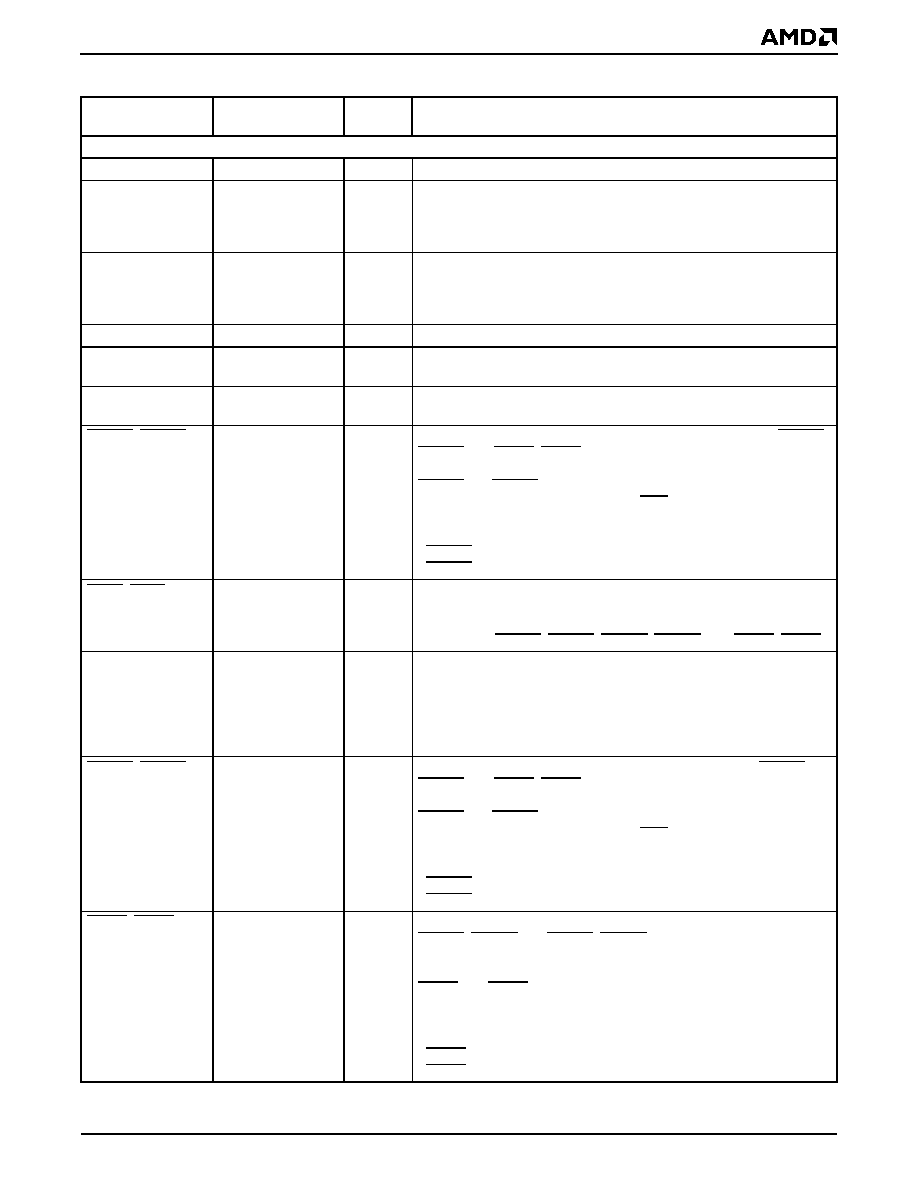

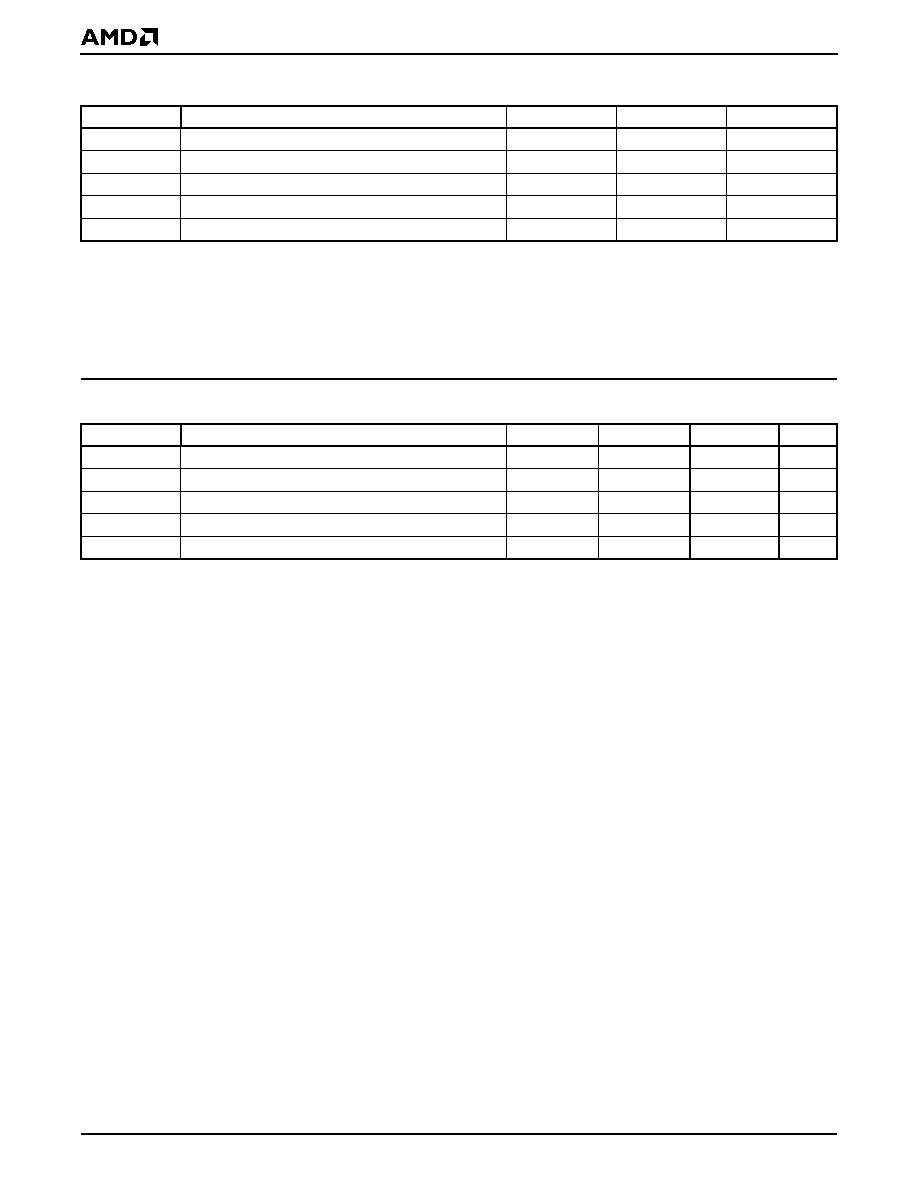

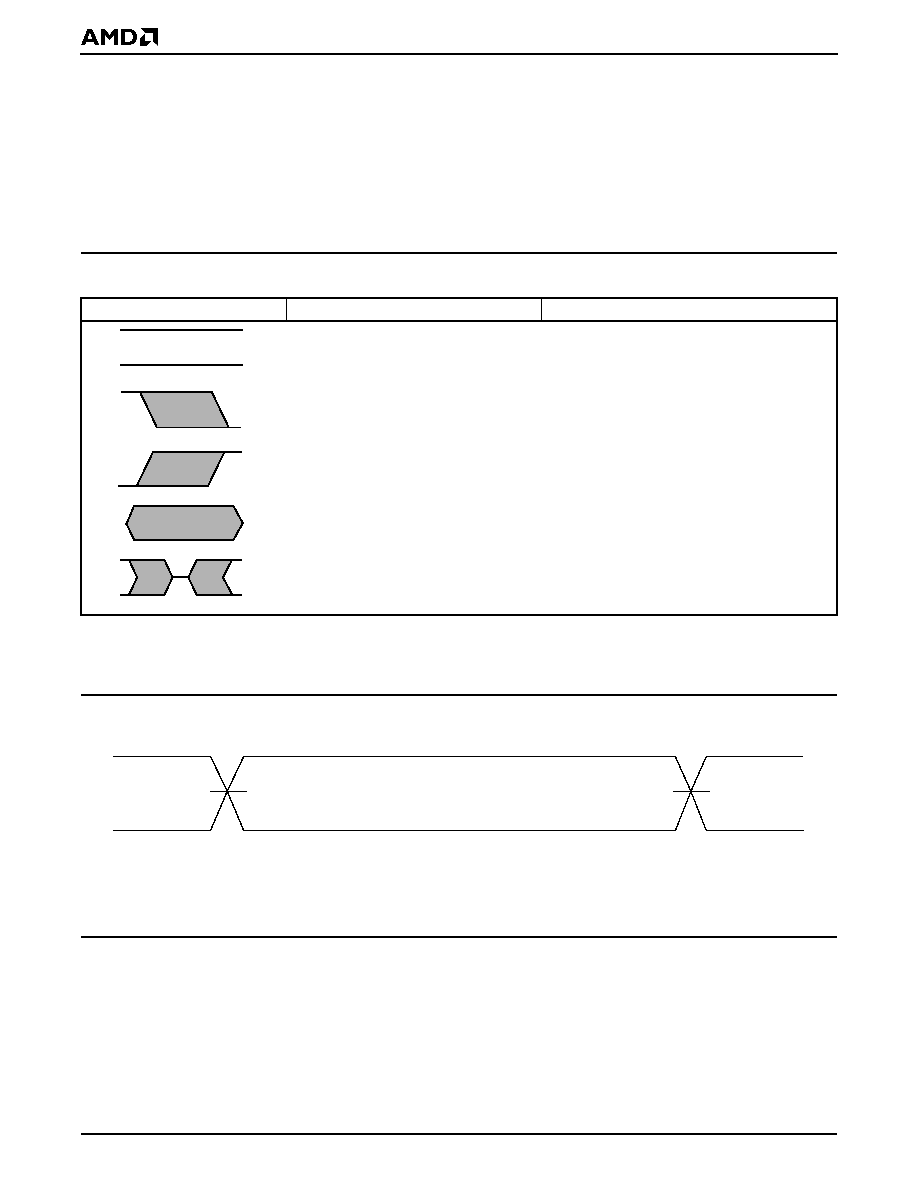

Table 1.

Signal Descriptions Table Definitions

Term

Definition

General Terms

[ ]

Indicates the pin alternate function; a pin

defaults to the signal named without the

brackets.

{ }

Indicates the reset configuration pin (pinstrap).

pin

Refers to the physical wire.

signal

Refers to the electrical signal that flows across

a pin.

SIGNAL

A line over a signal name indicates that the

signal is active Low; a signal name without a

line is active High.

Signal Types

Analog

Analog voltage

B

Bidirectional

H

High

I

Input

LS

Programmable to hold last state of pin

O

Totem pole output

O/TS

Totem pole output/three-state output

OD

Open-drain output

OD-O

Open-drain output or totem pole output

Osc

Oscillator

PD

Internal pulldown resistor (~100≠150 k

W)

Power

Power pins

PU

Internal pullup resistor (~100≠150 k

W)

STI

Schmitt trigger input

STI-OD

Schmitt trigger input or open-drain output

TS

Three-state output

…lanTMSC520 Microcontroller Data Sheet

17

P R E L I M I N A R Y

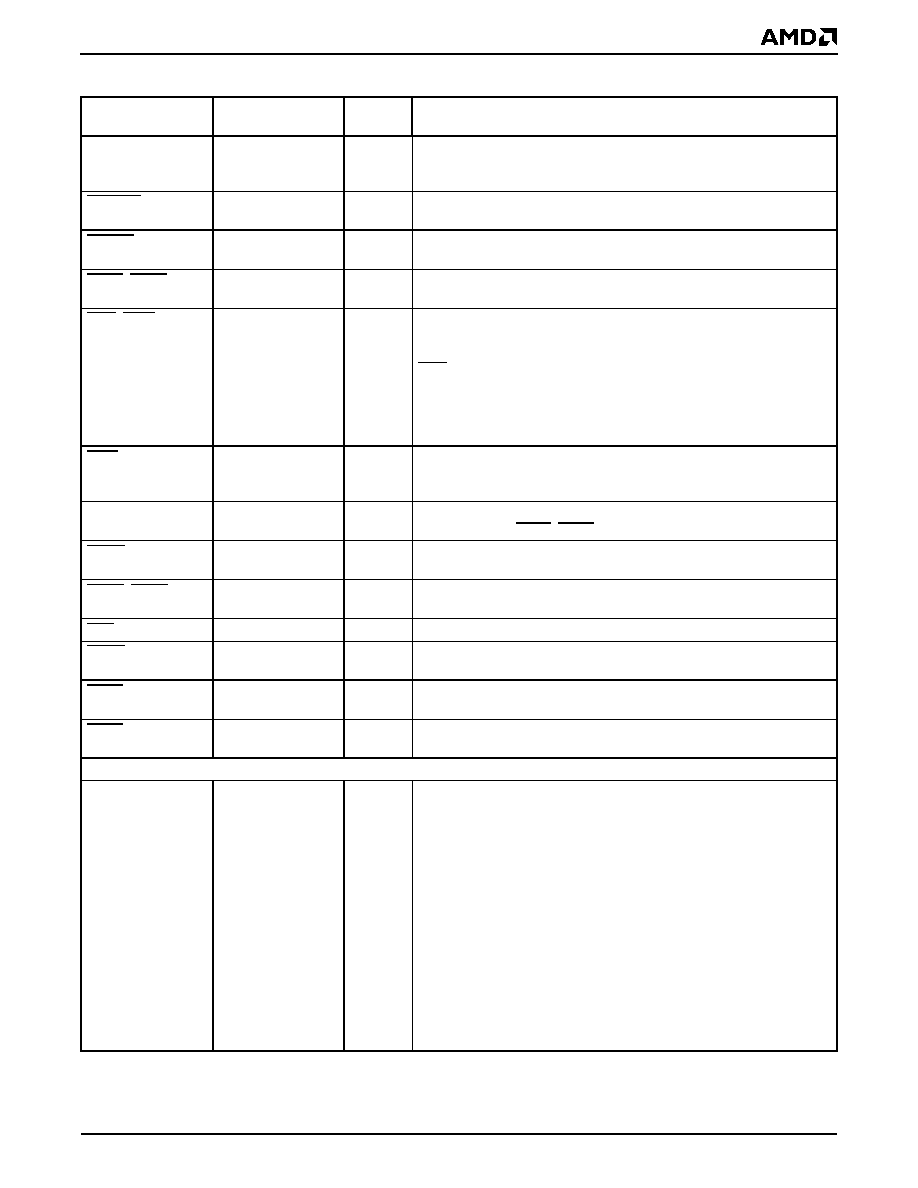

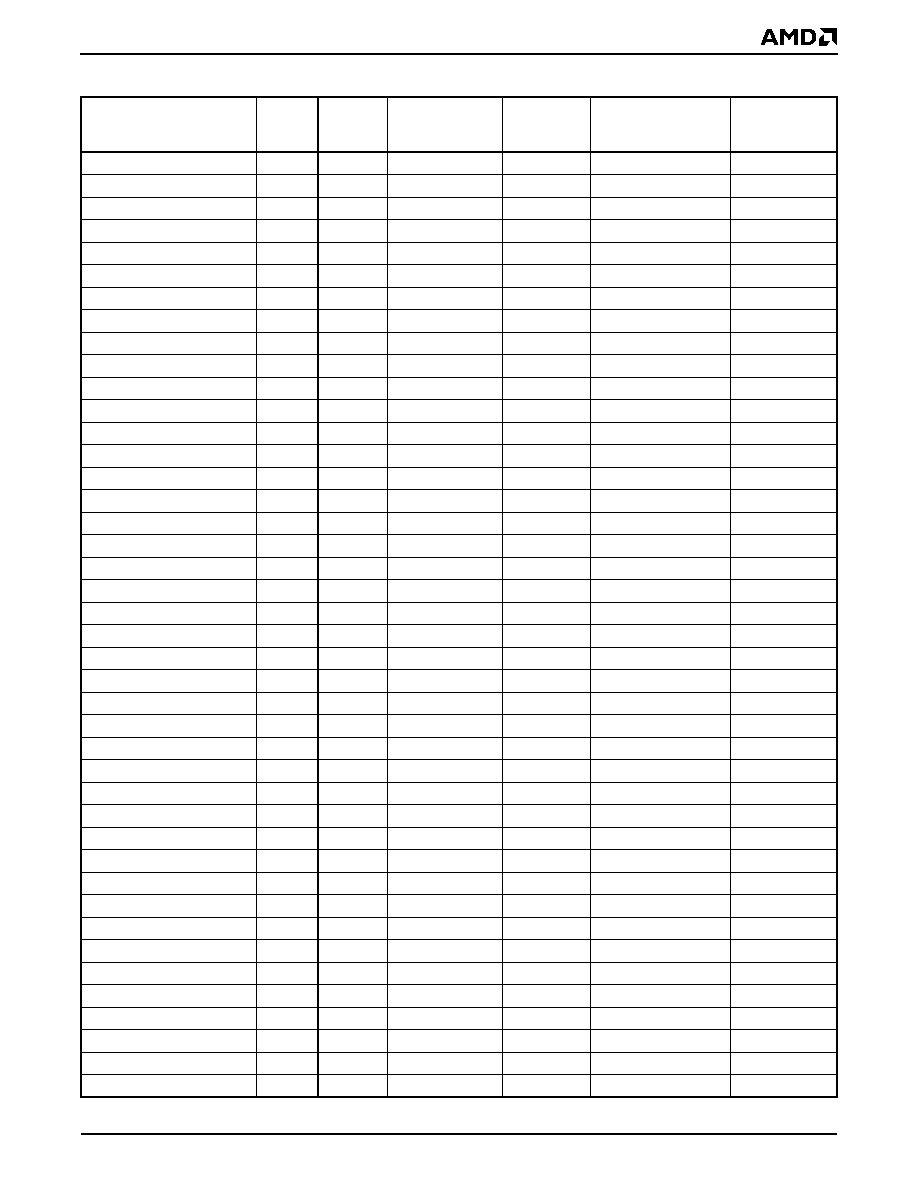

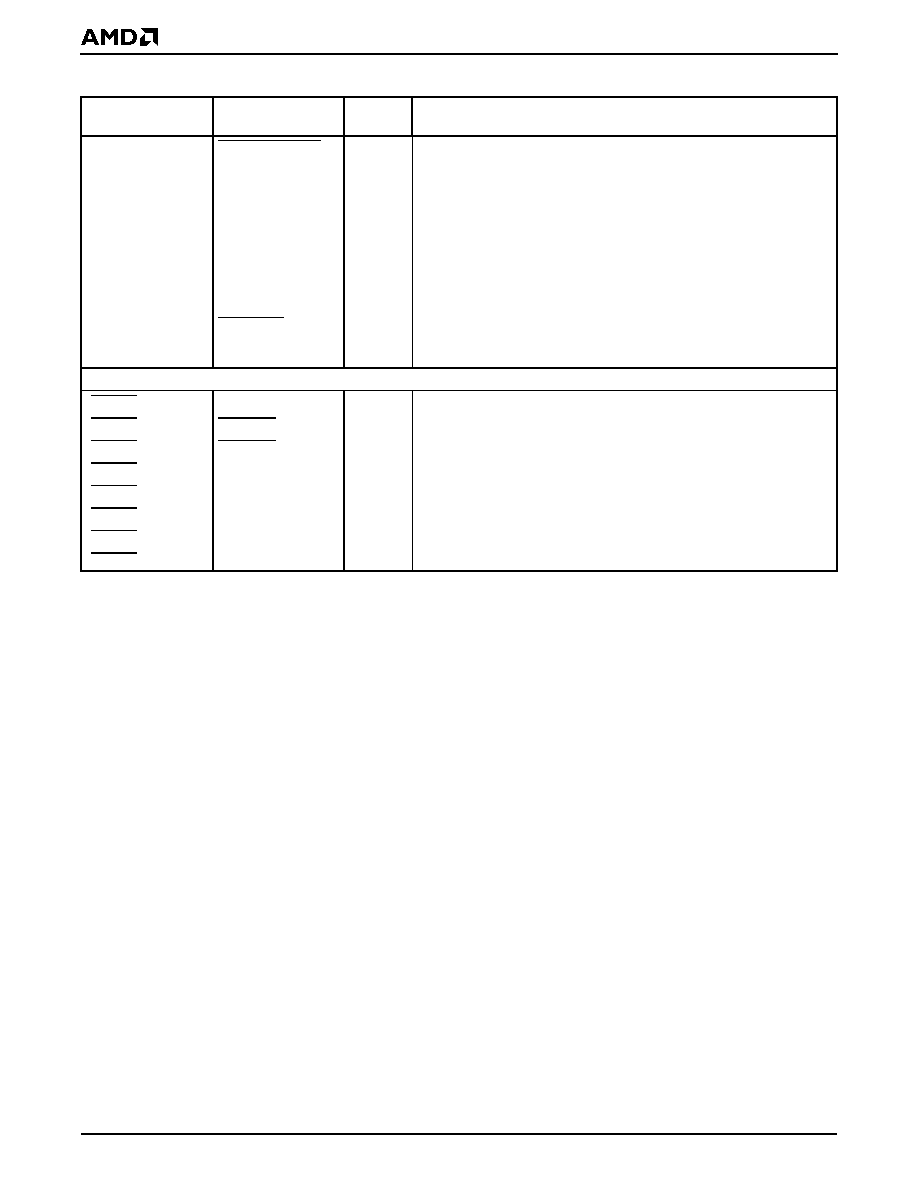

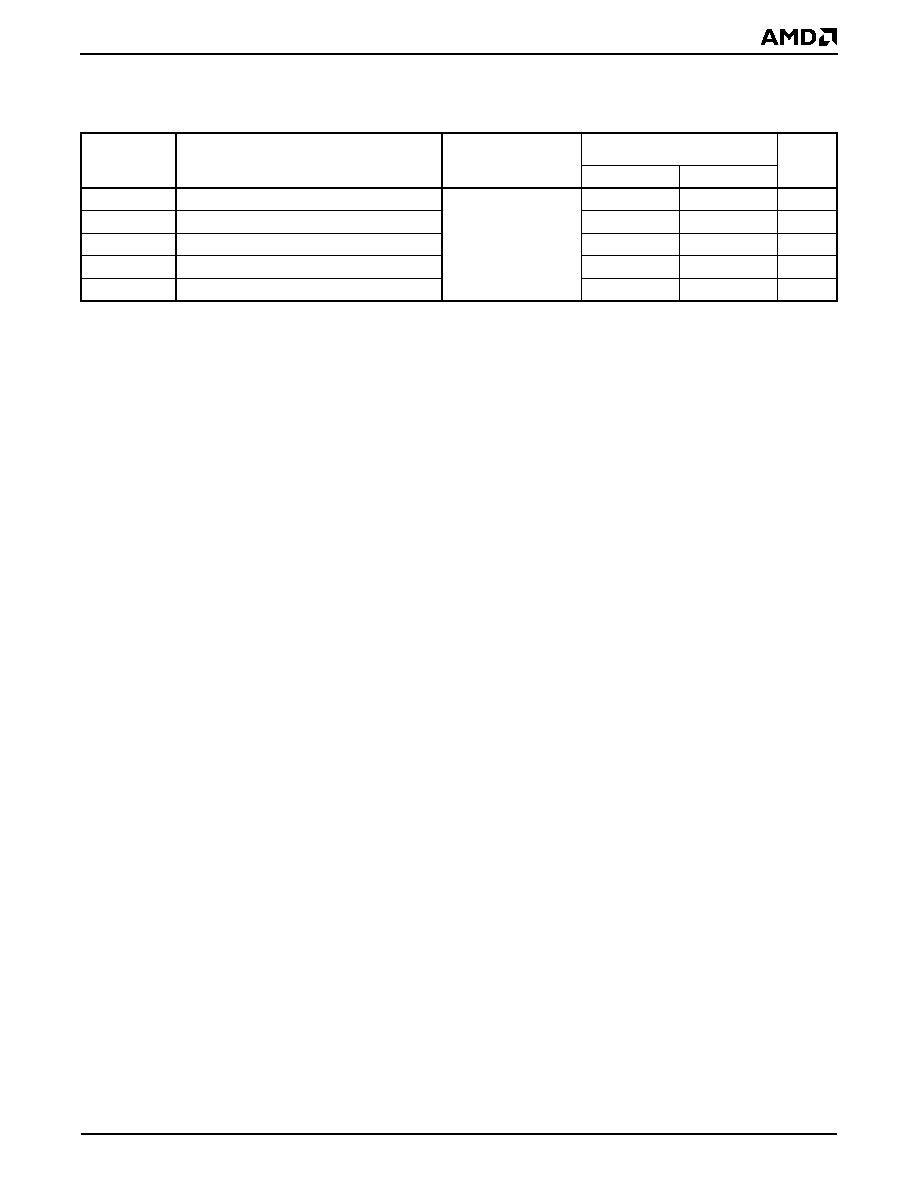

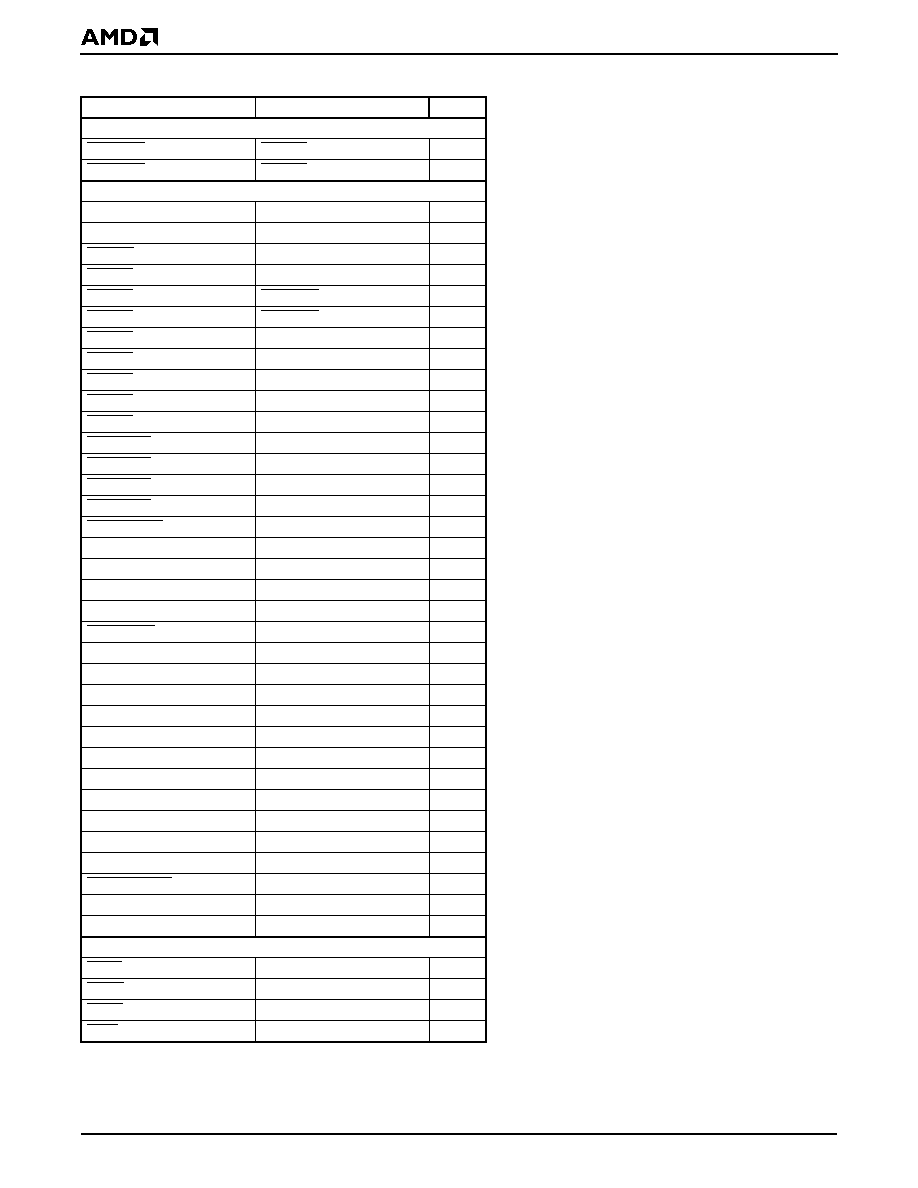

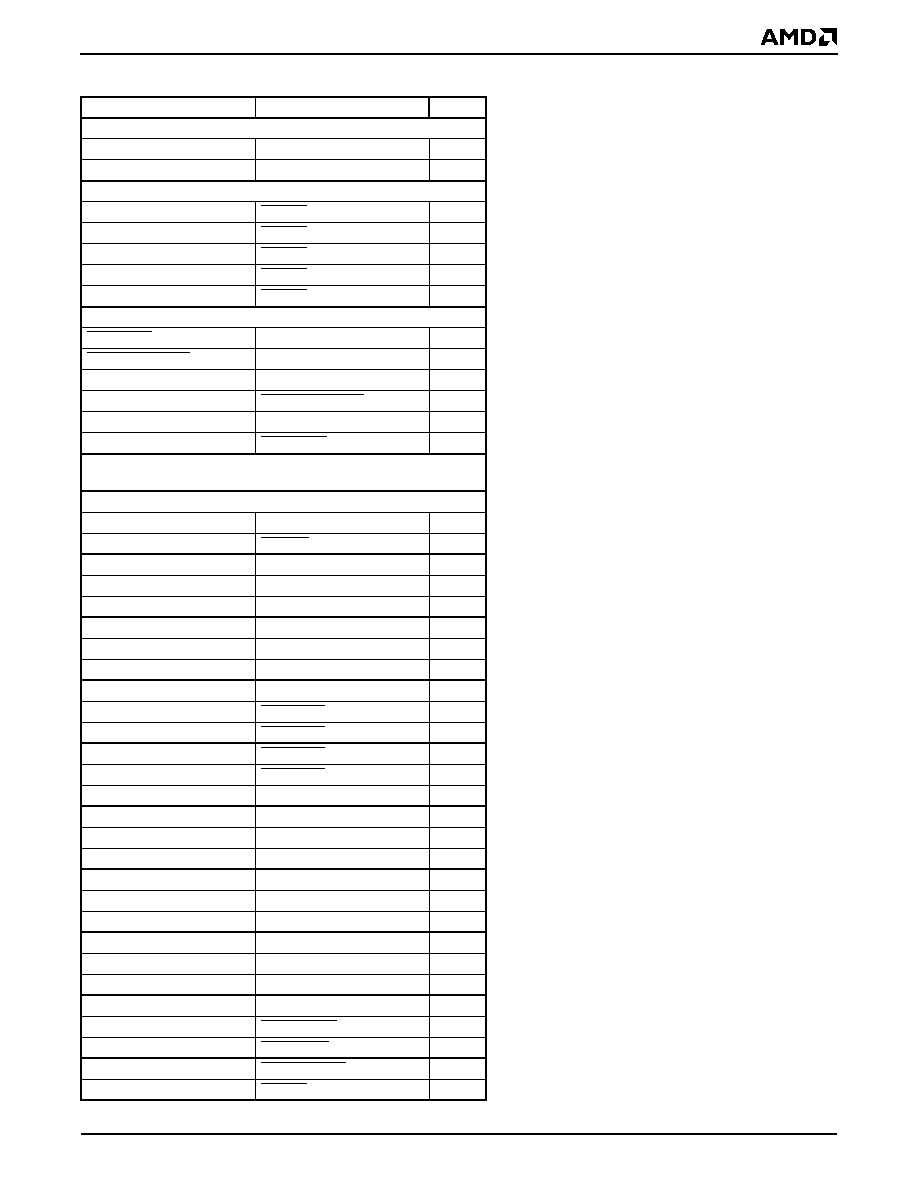

Table 2.

Signal Descriptions

Signal

Multiplexed

Signal

Type

Description

Synchronous DRAM

BA1≠BA0

--

O

Bank Address is the SDRAM bank address bus.

CLKMEMIN

--

I

SDRAM Clock Input is the SDRAM clock return signal used to

minimize skew between the internal SDRAM clock and the

CLKMEMOUT signal provided to the SDRAM devices. This signal

compensates for buffer and load delays introduced by the board design.

CLKMEMOUT

--

O

SDRAM Clock Output is the 66-MHz clock that provides clock

signaling for the synchronous DRAM devices. This clock may require

an external Low skew buffer for system implementations that result in

heavy loading on the SDRAM clock signal.

MA12≠MA0

--

O

SDRAM Address is the SDRAM multiplexed address bus.

MD31≠MD0

--

B

SDRAM Data Bus inputs data during SDRAM read cycles and outputs

data during SDRAM write cycles.

MECC6≠MECC0

--

B

Memory Error Correction Code contains the ECC checksum

(syndrome) bits used to validate and correct data errors.

SCASA≠SCASB

--

O

Column Address Strobes are used in combination with the SRASA≠

SRASB and SWEA≠SWEB to encode the SDRAM command type.

SCASA and SCASB are the same signal provided on two different pins

to reduce the total load connected to CAS.

Suggested system connection:

SCASA for SDRAM banks 0 and 1

SCASB for SDRAM banks 2 and 3

SCS3≠SCS0

--

O

SDRAM Chip Selects are the SDRAM chip-select outputs. These

signals are asserted to select a bank of SDRAM devices. The chip-

select signals enable the SDRAM devices to decode the commands

asserted via SRASA≠SRASB, SCASA≠SCASB, and SWEA≠SWEB.

SDQM3≠SDQM0

--

O

Data Input/Output Masks make SDRAM data output high-impedance

and blocks data input on SDRAM while active. Each of the four

SDQM3≠SDQM0 signals is associated with one byte of four

throughout the array. Each SDQMx signal provides an input mask

signal for write accesses and an output enable signal for read

accesses.

SRASA≠SRASB

--

O

Row Address Strobes are used in combination with the SCASA≠

SCASB and SWEA≠SWEB to encode the SDRAM command type.

SRASA and SRASB are the same signal provided on two different pins

to reduce the total load connected to RAS.

Suggested system connection:

SRASA for SDRAM banks 0 and 1

SRASB for SDRAM banks 2 and 3

SWEA≠SWEB

--

O

SDRAM Memory Write Enables are used in combination with the

SRASA≠SRASB and SCASA≠SCASB to encode the SDRAM

command type.

SWEA and SWEB are the same signal provided on two different pins

to reduce the total load connected to WE.

Suggested system connection:

SWEA for SDRAM banks 0 and 1

SWEB for SDRAM banks 2 and 3

18

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

ROM/Flash

BOOTCS

--

O

ROM/Flash Boot Chip Select is an active Low output that provides

the chip select for the startup ROM and/or the ROM/Flash array (BIOS,

HAL, O/S, etc.). The BOOTCS signal asserts for accesses made to the

64-Kbyte segment that contains the Am5

x

86 CPU boot vector:

addresses 3FF0000h≠3FFFFFFh. In addition to this linear decode

region, BOOTCS asserts in response to accesses to user-

programmable address regions.

FLASHWR

--

O

Flash Write indicates that the current cycle is a write of the selected

Flash device. When this signal is asserted, the selected Flash device

can latch data from the data bus.

GPA25≠GPA0

--

O

General-Purpose Address Bus provides the address to the system's

ROM/Flash devices. It is also the address bus for the GP bus devices.

Twenty-six address lines provide a maximum addressable space of 64

Mbytes for each ROM chip select.

GPD15≠GPD0

--

B

General-Purpose Data Bus inputs data during memory and I/O read

cycles and outputs data during memory and I/O write cycles.

A reset configuration pin (CFG2) allows the GP bus to be used for the

boot chip-select ROM interface. Configuration registers are used to

select whether ROMCS2 and ROMCS1 use the GP bus data bus or

the MD data bus. The GP data bus supports 16-bit or 8-bit ROM

interfaces. Two data buses are selectable to facilitate the use of ROM

in a mixed voltage system.

MD31≠MD0

--

B

Memory Data Bus inputs data during SDRAM read cycles and

outputs data during SDRAM write cycles. Configuration registers are

used to select whether ROMCS2 and ROMCS1 use the GP bus data

bus or the MD data bus. A reset configuration pin (CFG2) allows the

GP data bus to be used for BOOTCS. The memory data bus supports

an 8-, 16-, or 32-bit ROM interface.

ROMBUFOE

--

O

ROM Buffer Output Enable is an optional signal used to enable a

buffer to the ROM/Flash devices if they need to be isolated from the

…lanSC520 microcontroller, other GP bus devices, or SDRAM system

for voltage or loading considerations. This signal asserts for all

accesses through the ROM controller. The buffer direction is controlled

by the ROMRD or FLASHWR signal.

ROMCS2

[GPCS2]

O

ROM/Flash Chip Selects are signals that can be programmed to be

asserted for accesses to user-programmable address regions.

ROMCS1

[GPCS1]

O

ROMRD

--

O

ROM/Flash Read indicates that the current cycle is a read of the

selected ROM/Flash device. When this signal is asserted, the selected

ROM device can drive data onto the data bus.

Peripheral Component Interconnect (PCI) Bus

AD31≠AD0

--

B

PCI Address Data Bus is the PCI time-multiplexed address/data bus.

CBE3≠CBE0

--

B

Command or Byte-Enable Bus functions 1) as a time-multiplexed

bus command that defines the type of transaction on the AD bus,

or 2) as byte enables:

CBE0 for AD7≠AD0

CBE1 for AD15≠AD8

CBE2 for AD23≠AD16

CBE3 for AD31≠AD24

CLKPCIIN

--

I

PCI Bus Clock Input is the 33-MHz PCI bus clock. This pin can be

connected to the CLKPCIOUT pin for systems where the …lanSC520

microcontroller is the source of the PCI bus clock.

Table 2.

Signal Descriptions (Continued)

Signal

Multiplexed

Signal

Type

Description

…lanTMSC520 Microcontroller Data Sheet

19

P R E L I M I N A R Y

CLKPCIOUT

--

O

PCI Bus Clock Output is a 33-MHz clock output for the PCI bus

devices. This signal is derived from the 33MXTAL1/33MXTAL2

interface.

DEVSEL

--

B

Device Select is asserted by the target when it has decoded its

address as the target of the current transaction.

FRAME

--

B

Frame is driven by the transaction initiator to indicate the start and

duration of the transaction.

GNT4≠GNT0

--

O

Bus Grants are asserted by the …lanSC520 microcontroller to grant

access to the bus.

INTA≠INTD

--

I

Interrupt Requests are asserted to request an interrupt. These four

interrupts are the same type of interrupt as the GPIRQ10≠GPIRQ0

signals, and they go to the same interrupt controller. They are named

INTx to match the common PCI interrupt naming convention.

Configuration registers allow inversion of these interrupt requests to

recognize active low interrupt requests. These interrupt requests can

be routed to generate NMI.

IRDY

--

B

Initiator Ready is asserted by the current bus master to indicate that

data is ready on the bus (write) or that the master is ready to accept

data (read).

PAR

--

B

PCI Parity is driven by the initiator or target to indicate parity on the

AD31≠AD0 and CBE3≠CBE0 buses.

PERR

--

B

Parity Error is asserted to indicate a PCI bus data parity error in the

previous clock cycle.

REQ4≠REQ0

--

I

Bus Requests are asserted by the master to request access to the

bus.

RST

--

O

Reset is asserted to reset the PCI devices.

SERR

--

I

System Error is used for reporting address parity errors or any other

system error where the result is catastrophic.

STOP

--

B

Stop is asserted by the target to request that the current bus

transaction be stopped.

TRDY

--

B

Target Ready is asserted by the currently addressed target to indicate

its ability to complete the current data phase of a transaction.

General-Purpose Bus (GP Bus)

GPA14≠GPA0

--

O

General-Purpose Address Bus outputs the physical memory or I/O

port address. Twenty-six address lines provide a maximum

addressable space of 64 Mbytes. This bus also provides the address

to the system's ROM/Flash devices.

GPA15

{RSTLD0}

O{I}

GPA16

{RSTLD1}

O{I}

GPA17

{RSTLD2}

O{I}

GPA18

{RSTLD3}

O{I}

GPA19

{RSTLD4}

O{I}

GPA20

{RSTLD5}

O{I}

GPA21

{RSTLD6}

O{I}

GPA22

{RSTLD7}

O{I}

GPA23

{AMDEBUG_DIS}

O{I}

GPA24

{INST_TRCE}

O{I}

GPA25

{DEBUG_ENTER}

O{I}

Table 2.

Signal Descriptions (Continued)

Signal

Multiplexed

Signal

Type

Description

20

…lanTMSC520 Microcontroller Data Sheet

P R E L I M I N A R Y

[GPAEN]

PIO3

O

GP Bus Address Enable indicates that the current address on the

GPA25≠GPA0 address bus is a memory address, and that the current

cycle is a DMA cycle. All I/O devices should use this signal in decoding

their I/O addresses and should not respond when this signal is

asserted. When GPAEN is asserted, the GPDACKx signals are used

to select the appropriate I/O device for the DMA transfer. GPAEN also

asserts when a DMA cycle is occurring internally.

[GPALE]

PIO0

O

GP Bus Address Latch Enable is driven at the beginning of a GP bus

cycle with valid address. This signal can be used by external devices

to latch the GP address for the current cycle.

[GPBHE]

PIO1

O

GP Bus Byte High Enable is driven active when data is to be

transferred on the upper 8 bits of the GP data bus.

GPD15≠GPD0

--

B

General-Purpose Data Bus inputs data during memory and I/O read

cycles, and outputs data during memory and I/O write cycles.

[GPDACK0]

PIO12

O

GP Bus DMA Acknowledge can each be mapped to one of the seven

available DMA channels. They are asserted active Low to

acknowledge the corresponding DMA requests.

[GPDACK1]

PIO11

O

[GPDACK2]

PIO10

O

[GPDACK3]

PIO9

O

[GPDBUFOE]

PIO24

O

GP Bus Data Bus Buffer Output Enable is used to control the output

enable on an external transceiver that may be on the GP data bus.

Using this transceiver is optional in the system design and is

necessary only to alleviate loading or voltage issues. This pin is

asserted for all external GP bus accesses. It is not asserted during

accesses to the internal peripherals even if GP bus echo mode is

enabled.

Note that if the ROM is configured to use the GP data bus, then its

bytes are not controlled by this buffer enable; they are controlled by the

ROMBUFOE signal.

[GPDRQ0]

PIO8

I

GP Bus DMA Request can each be mapped to one of the seven

available DMA channels. They are asserted active High to request

DMA service.

[GPDRQ1]

PIO7

I

[GPDRQ2]

PIO6

I

[GPDRQ3]

PIO5

I

[GPIOCS16]

PIO25

STI

GP Bus I/O Chip-Select 16 is driven active early in the cycle by the

targeted I/O device on the GP bus to request a 16-bit I/O transfer.

GPIORD

--

O

GP Bus I/O Read indicates that the current cycle is a read of the

currently addressed I/O device on the GP bus. When this signal is

asserted, the selected I/O device can drive data onto the data bus.

GPIOWR

--

O

GP Bus I/O Write indicates that the current cycle is a write of the

currently addressed I/O device on the GP bus. When this signal is

asserted, the selected I/O device can latch data from the data bus.

Table 2.

Signal Descriptions (Continued)

Signal

Multiplexed

Signal

Type

Description

…lanTMSC520 Microcontroller Data Sheet

21

P R E L I M I N A R Y

[GPIRQ0]

PIO23

I

GP Bus Interrupt Request can each be mapped to one of the

available interrupt channels or NMI. They are asserted when a

peripheral requires interrupt service.

Configuration registers allow inversion of these interrupt requests to

recognize active low interrupt requests. These interrupt requests can

be routed to generate NMI.

[GPIRQ1]

PIO22

I

[GPIRQ2]

PIO21

I

[GPIRQ3]

PIO20

I

[GPIRQ4]

PIO19

I

[GPIRQ5]

PIO18

I

[GPIRQ6]

PIO17

I

[GPIRQ7]

PIO16

I

[GPIRQ8]

PIO15

I

[GPIRQ9]

PIO14

I

[GPIRQ10]

PIO13

I

[GPMEMCS16]

PIO26

STI

GP Bus Memory Chip-Select 16 is driven active early in the cycle by

the targeted memory device on the GP bus to request a 16-bit memory

transfer.

[GPMEMRD]

--

O

GP Bus Memory Read indicates that the current GP bus cycle is a

read of the selected memory device. When this signal is asserted, the

selected memory device can drive data onto the data bus.

[GPMEMWR]

--

O

GP Bus Memory Write indicates that the current GP bus cycle is a

write of the selected memory device. When this signal is asserted, the

selected memory device can latch data from the data bus.

[GPRDY]

PIO2

STI

GP Bus Ready can be driven by open-drain devices. When pulled

Low during a GP bus access, wait states are inserted in the current

cycle. This pin has an internal weak pullup that should be

supplemented by a stronger external pullup for faster rise time.

GPRESET

--

O

GP Bus Reset, when asserted, re-initializes to reset state all devices

connected to the GP bus.

[GPTC]