A617308 Series

Preliminary

128K X 8 BIT HIGH SPEED CMOS SRAM

PRELIMINARY

(January, 2000, Version 0.2)

AMIC Technology, Inc.

Document Title

128K X 8 BIT HIGH SPEED CMOS SRAM

Revision History

Rev. No. History

Issue Date

Remark

0.0

Initial issue

September 17, 1999

Preliminary

0.1

Change V

DR

(Max.) from 3.6V to 5.5V

November 30, 1999

Add 32-pin SOP package

Modify 32-pin SOJ package outline drawing and

Dimensions

0.2

Add 15ns part

January 19, 2000

Change operating current from 180mA to 150mA (Max.)

Change V

DR

(Min.) from 2V to 3V

Remove 32-pin SOP package

A617308 Series

Preliminary

128K X 8 BIT HIGH SPEED CMOS SRAM

PRELIMINARY

(January, 2000, Version 0.2)

1

AMIC Technology, Inc.

Features

n

Single + 5V power supply

n

Access times: 10/12/15 ns (max.)

n

Current: Operating: 150mA (max.)

Standby:

12mA (max.)

n

Full static operation, no clock or refreshing required

n

All inputs and outputs are directly TTL compatible

n

Common I/O using three-state output

n

Data retention voltage: 3V (min.)

n

Available in 32-pin SOJ and TSOP packages

General Description

The A617308 is a high-speed, low-power 1,048,576-bit

static random access memory organized as 131,072

words by 8 bits and operates on a single 5V power

supply. It is built using high performance CMOS process.

Inputs and three-state outputs are TTL compatible and

allow for direct interfacing with common system bus

structures.

Minimum standby power is drawn by this device when

chip enable is disable, independent of the other input

levels.

Data retention is guaranteed at a power supply voltage

as low as 3V.

Pin Configurations

n

SOJ

n

n

TSOP

A10

7

6

5

4

3

GND

OE

CE1

2

1

0

1

9

32

24

A11

A9

2

3

4

5

6

7

8

10

11

12

13

14

15

16

A8

A13

VCC

NC

A14

A12

A7

A6

A5

A4

31

30

29

28

27

26

25

23

22

21

20

19

18

17

I/O

I/O

I/O

I/O

I/O

A0

A1

A2

A3

A15

WE

CE2

I/O

I/O

I/O

~~

~~

A16

A617308V

NC

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O

0

I/O

1

I/O

2

I/O

3

GND

I/O

4

I/O

5

I/O

6

I/O

7

A10

A9

A8

A13

CE2

A15

VCC

A11

A617308S

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

OE

CE1

WE

A16

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

2

AMIC Technology, Inc.

Block Diagram

Pin Descriptions ≠ SOJ

Pin No.

Symbol

Description

2 - 12, 23,

25 - 28, 31

A0 - A16

Address Inputs

13 - 15,

17 - 21

I/O

0

- I/O

7

Data Inputs/Outputs

22

CE1

Chip Enable 1

30

CE2

Chip Enable 2

24

OE

Output Enable

29

WE

Write Enable

32

VCC

Power Supply

16

GND

Ground

1

NC

No Connection

Pin Description - TSOP

Pin No.

Symbol

Description

1 - 4, 7,

10 - 20, 31

A0 - A16

Address Inputs

21 - 23,

25 - 29

I/O

0

- I/O

7

Data Inputs/Outputs

30

CE1

Chip Enable 1

6

CE2

Chip Enable 2

32

OE

Output Enable

5

WE

Write Enable

8

VCC

Power Supply

24

GND

Ground

9

NC

No Connection

ADDRESS

DECODER

1,048,576-BIT

MEMORY ARRAY

I/O CONTROL

CONTROL

LOGIC

CE1

A16

A0

OE

WE

8

8

8

I/O

0

- I/O

7

CE2

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

3

AMIC Technology, Inc.

Recommended DC Operating Conditions

(T

A

= 0

∞

C to + 70

∞

C)

Symbol

Parameter

Min.

Typ.

Max.

Unit

VCC

Supply Voltage

4.5

5.0

5.5

V

GND

Ground

0

0

0

V

V

IH

Input High Voltage

2.2

-

VCC + 0.5

V

V

IL

Input Low (1) Voltage

-0.5

0

+0.8

V

C

L

Output Load

-

-

30

pF

Absolute Maximum Ratings*

VCC to GND . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +7V

IN, IN/OUT Volt to GND . . . . . . . . . . -0.5V to VCC +0.5V

Operating Temperature, Topr . . . . . . . . . . . 0

∞

C to +70

∞

C

Storage Temperature, Tstg . . . . . . . . . . -55

∞

C to +125

∞

C

Temperature Under Bias, Tbias . . . . . . . . -10

∞

C to +85

∞

C

Power Dissipation, P

T

. . . . . . . . . . . . . . . . . . . . . . . 1.0W

*Comments

Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage to this device.

These are stress ratings only. Functional operation of this

device at these or any other conditions above those

indicated in the operational sections of this specification is

not implied or intended. Exposure to the absolute maximum

rating conditions for extended periods may affect device

reliability.

DC Electrical Characteristics

(T

A

= 0

∞

C to + 70

∞

C, VCC = 5V

±

10%, GND = 0V)

Symbol

Parameter

A617308-10/12/15

Unit

Conditions

Min.

Max.

I

LI

Input Leakage

-

5

µ

A

V

IN

= GND to VCC

I

LO

Output Leakage

-

5

µ

A

1

CE = V

IH

, CE2= V

IL

or OE = V

IH

V

I/O

= GND to VCC

I

CC1

(2)

Dynamic Operating Current

-

150

mA

1

CE = V

IL

, CE2 = V

IH

, I

I/O

= 0 mA

Min. Cycle, Duty = 100%

I

SB

-

35

mA

1

CE = V

IH

or CE2 = V

IL

I

SB1

Standby Power

Supply Current

-

12

mA

1

CE

VCC - 0.2V, CE2

0.2V

V

IN

VCC -0.2V or V

IN

0.2V

V

OL

Output Low Voltage

-

0.4

V

I

OL

= 8 mA

V

OH

Output High Voltage

2.4

-

V

I

OH

= -4 mA

Notes: 1. V

IL

= -3.0V for pulses less than 20 ns.

2. I

CC1

is dependent on output loading, cycle rates, and Read/Write patterns.

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

4

AMIC Technology, Inc.

Truth Table

Mode

1

CE

CE2

OE

WE

I/O Operation

Supply Current

H

X

X

X

High Z

I

SB

, I

SB1

Standby

X

L

X

X

High Z

I

SB

, I

SB1

Output Disable

L

H

H

H

High Z

I

CC1

Read

L

H

L

H

D

OUT

I

CC1

Write

L

H

X

L

D

IN

I

CC1

Note: X = H or L

Capacitance

(T

A

= 25

∞

C, f = 1.0MHz)

Symbol

Parameter

Min.

Max.

Unit

Conditions

C

IN

*

Input Capacitance

-

8

pF

V

IN

= 0V

C

I/O

*

Input/Output Capacitance

-

8

pF

V

I/O

= 0V

* These parameters are sampled and not 100% tested.

AC Characteristics

(T

A

= 0

∞

C to +70

∞

C, VCC = 5V

±

10%)

Symbol

Parameter

A617308-10

A617308-12

A617308-15

Unit

Min.

Max.

Min.

Max.

Min.

Max.

Read Cycle

t

RC

Read Cycle Time

10

-

12

-

15

-

ns

t

AA

Address Access Time

-

10

-

12

-

15

ns

t

ACE

Chip Enable Access Time

-

10

-

12

-

15

ns

t

OE

Output Enable to Output Valid

-

5

-

6

-

8

ns

t

CLZ

Chip Enable to Output in Low Z

3

-

3

-

3

-

ns

t

OLZ

Output Enable to Output in Low Z

0

-

0

-

0

-

ns

t

CHZ

Chip Disable Output in High Z

0

5

0

6

-

8

ns

t

OHZ

Output Disable to Output in High Z

0

5

0

6

0

8

ns

t

OH

Output Hold from Address Change

3

-

3

-

3

-

ns

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

5

AMIC Technology, Inc.

AC Characteristics (continued)

Symbol

Parameter

A617308-10

A617308-12

A617308-15

Unit

Min.

Max.

Min.

Max.

Min.

Max.

Write Cycle

t

WC

Write Cycle Time

10

-

12

-

15

-

ns

t

CW

Chip Enable to End of Write

9

-

10

-

12

-

ns

t

AS

Address Setup Time of Write

0

-

0

-

0

-

ns

t

AW

Address Valid to End of Write

9

-

10

-

12

-

ns

t

WP

Write Pulse Width

9

-

10

-

12

-

ns

t

WR

Write Recovery Time

0

-

0

-

0

-

ns

t

WHZ

Write to Output in High Z

0

5

0

6

0

8

ns

t

DW

Data to Write Time Overlap

5

-

6

-

7

-

ns

t

DH

Data Hold from Write Time

0

-

0

-

0

-

ns

t

OW

Output Active from End of Write

3

-

3

-

3

-

ns

Notes: t

CHZ

, t

OHZ

and t

WHZ

are defined as the time at which the outputs achieve the open circuit condition and are not

referred to output voltage levels.

Timing Waveforms

Read Cycle 1

(1)

t

RC

Address

CE2

D

OUT

t

AA

t

OE

t

OLZ5

t

ACE

t

CHZ5

t

OHZ5

t

OH

OE

CE1

t

CLZ5

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

6

AMIC Technology, Inc.

Timing Waveforms (continued)

Read Cycle 2

(1, 2, 4)

t

RC

t

OH

t

AA

t

OH

Address

D

OUT

Read Cycle 3

(1, 3, 4, 6)

t

CLZ5

t

ACE

t

CHZ5

D

OUT

CE1

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

7

AMIC Technology, Inc.

Timing Waveforms (continued)

Read Cycle 4

(1, 4, 7, 8)

t

CLZ5

t

ACE

t

CHZ5

D

OUT

CE2

Notes: 1.

WE

is high for Read Cycle.

2. Device is continuously enabled, CE1= V

IL

and CE2= V

IH

3. Address valid prior to or coincident with CE1 transition low.

4. OE = V

IL

.

5. Transition is measured

±

200mV from steady state. This parameter is sampled and not 100% tested.

6. CE2 is high.

7. CE1 is low.

8. Address valid prior to or coincident with CE2 transition high.

Write Cycle 1

(6)

(Write Enable Controlled)

t

WC

Address

CE1

CE2

D

IN

t

DH

t

DW

t

WP2

t

AS1

(4)

t

CW5

t

AW

t

WR3

WE

D

OUT

(4)

t

OW7

t

WHZ7

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

8

AMIC Technology, Inc.

Timing Waveforms (continued)

Write Cycle 2

(Chip Enable Controlled)

t

WC

Address

CE1

CE2

D

IN

t

DH

t

DW

(4)

t

CW5

t

AW

t

WR3

WE

D

OUT

t

WHZ7

t

WP2

t

AS1

(4)

Notes: 1. t

AS

is measured from the address valid to the beginning of Write.

2. A Write occurs during the overlap (t

WP

) of a low CE1, a high CE2 and a low WE .

3. t

WR

is measured from the earliest of CE1 or WE going high or CE2 going low to the end of the Write cycle.

4. If the CE1 low transition or the CE2 high transition occurs simultaneously with the WE low transition or after

the WE transition, outputs remain in a high impedance state.

5. t

CW

is measured from the later of CE1 going low or CE2 going high to the end of Write.

6. OE is continuously low. ( OE = V

IL

)

7. Transition is measured

±

200mV from steady state. This parameter is sampled and not 100% tested.

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

9

AMIC Technology, Inc.

AC Test Conditions

Input Pulse Levels

0V to 3.0V

Input Rise and Fall Time

2 ns

Input and Output Timing Reference Levels

1.5V

Output Load

See Figures 1 and 2

* Including scope and jig.

5V

DATA

OUT

30pF

480

255

5V

DATA

OUT

5pF*

480

255

Figure 1. Output Load

Figure 2. Output Load for t

CLZ

, t

OLZ

,

t

CHZ

, t

OHZ

, t

WHZ

, and t

OW

Data Retention Characteristics

(T

A

= 0

∞

C to 70

∞

C)

Symbol

Parameter

Min.

Max.

Unit

Conditions

V

DR

VCC for Data Retention

3

5.5

V

CE1

VCC - 0.2V

I

CCDR

Data Retention Current

-

1

mA

VCC = 3.0V

CE1

VCC - 0.2V

CE2

0.2V

V

IN

VCC - 0.2V or

V

IN

0.2V

t

CDR

Chip Disable to Data Retention

Time

0

-

ns

See Retention Waveform

t

R

Operation Recovery Time

T

RC

*

-

ms

t

RC

= Read Cycle Time

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

10

AMIC Technology, Inc.

Low VCC Data Retention Waveform (1) (

CE1 controlled)

VCC

CE1

t

CDR

V

IH

4.5V

t

R

V

IH

4.5V

DATA RETENTION MODE

V

DR

> 3.0V

CE1 > V

DR

- 0.2V

Low VCC Data Retention Waveform (2) (CE2 controlled)

VCC

CE2

t

CDR

V

IL

4.5V

t

R

V

IL

4.5V

DATA RETENTION MODE

V

DR

> 3.0V

CE2 < 0.2V

Ordering Information

Part No.

Access Time (ns)

Operating Current

Max. (mA)

Standby Current

Max. (mA)

Package

A617308S-10

10

150

12

32L SOJ

A617308S-12

12

150

12

32L SOJ

A617308S-15

15

150

12

32L SOJ

A617308V-10

10

150

12

32L TSOP

A617308V-12

12

150

12

32L TSOP

A617308V-15

15

150

12

32L TSOP

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

11

AMIC Technology, Inc.

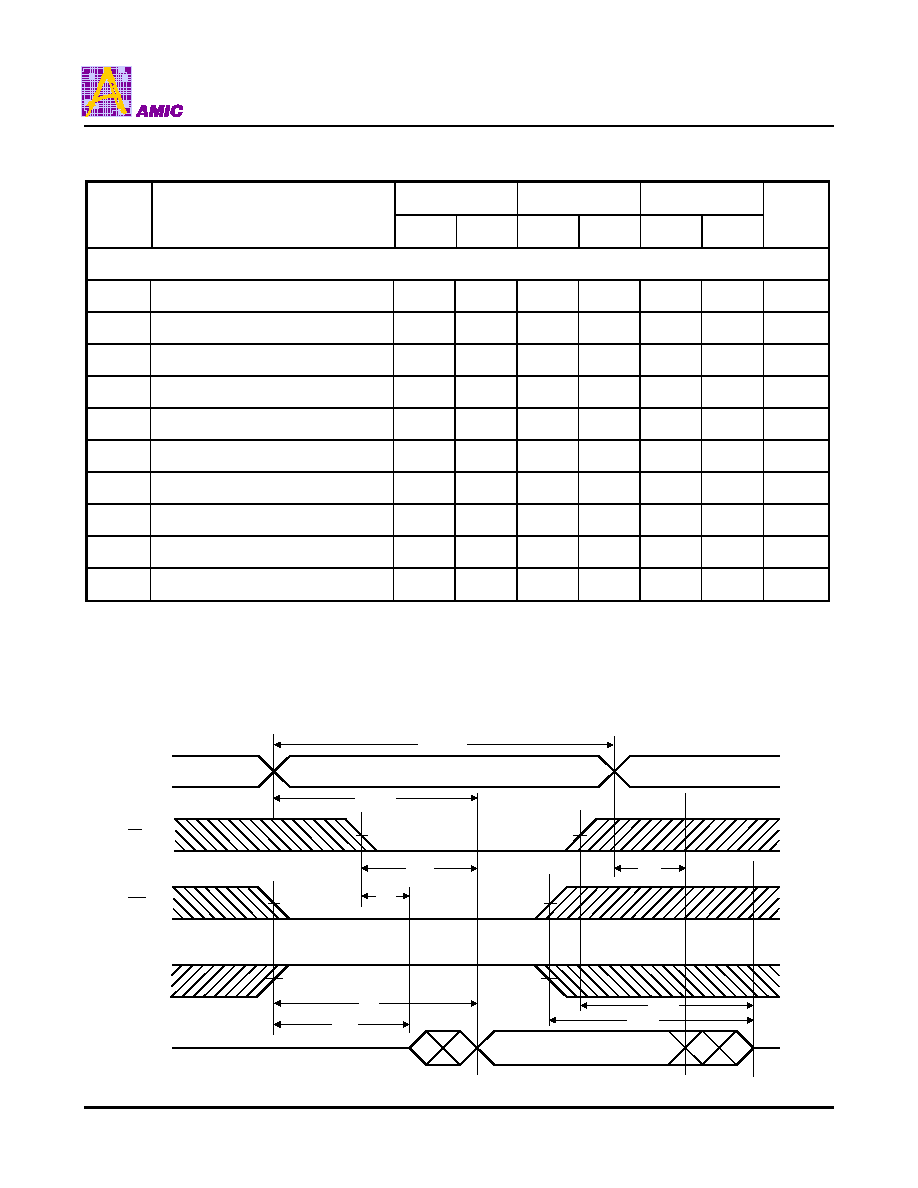

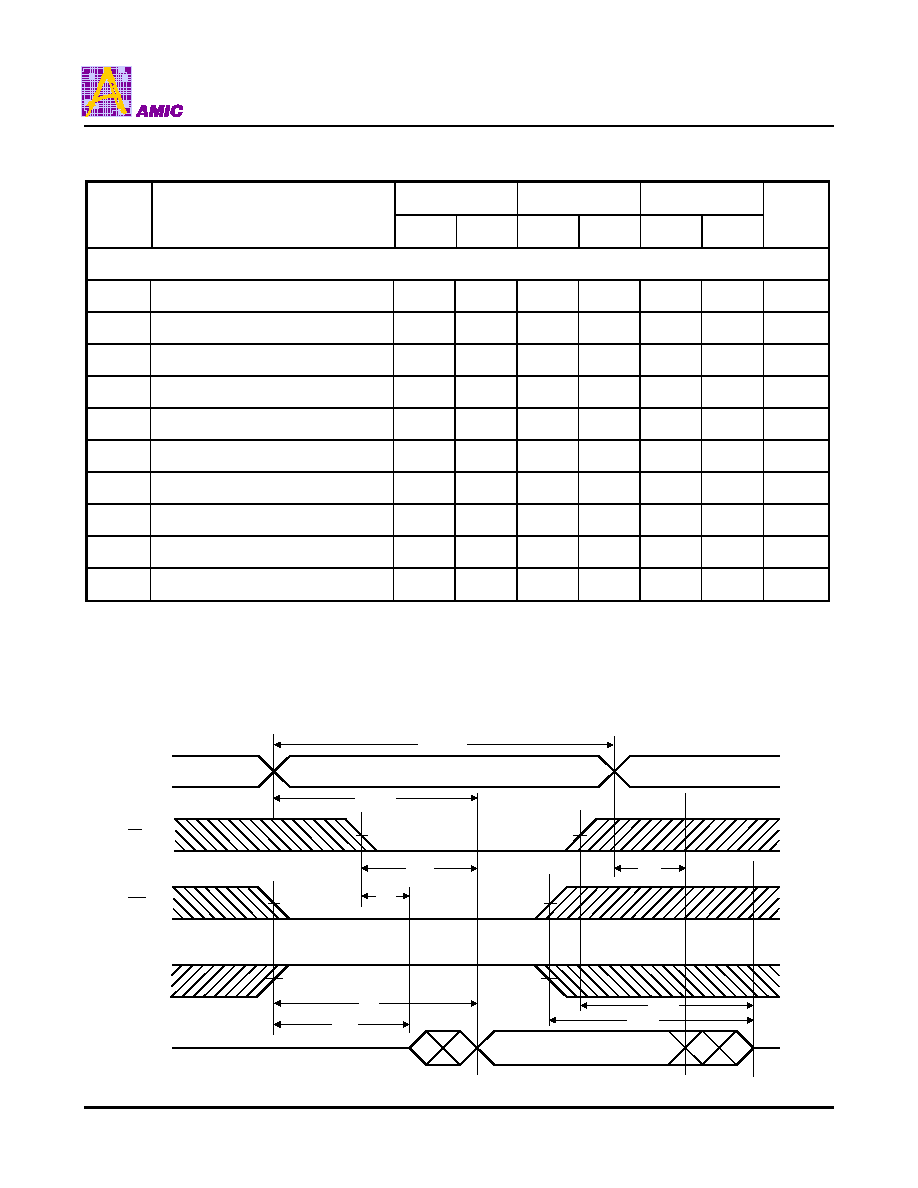

Package Information

SOJ 32L Outline Dimensions

unit: inches/mm

Dimensions in inches

Dimensions in mm

Symbol

Min

Nom

Max

Min

Nom

Max

A

0.128

0.132

0.140

3.25

3.35

3.56

A

1

0.052

-

-

2.08

-

-

A

2

0.095

0.100

0.105

2.41

2.54

2.67

b

0.016

0.018

0.020

0.41

0.46

0.51

b

1

0.026

0.028

0.032

0.66

0.71

0.81

C

0.006

0.008

0.012

0.15

0.20

0.30

D

0.820

0.825

0.830

20.83

20.96

21.08

E

0.330

0.335

0.340

8.39

8.51

8.63

E

1

0.295

0.300

0.305

7.49

7.62

7.75

E

2

0.260

0.267

0.274

6.61

6.78

6.96

e

-

0.050

-

-

1.27

-

S

-

-

0.048

-

-

1.22

y

-

-

0.004

-

-

0.10

Notes:

1. The maximum value of dimension D includes end flash.

2. Dimension E does not include resin fins.

3. Dimension E

1

is for PC Board surface mount pad pitch design

reference only.

4. Dimension S includes end flash.

1

A

1

A

2

A

e

E

2

C

16

17

32

S

Seating Plane

D

y

b

1

b

E

1

D

Min

0.025"

0.004

E

y

y

A617308 Series

PRELIMINARY

(January, 2000, Version 0.2)

12

AMIC Technology, Inc.

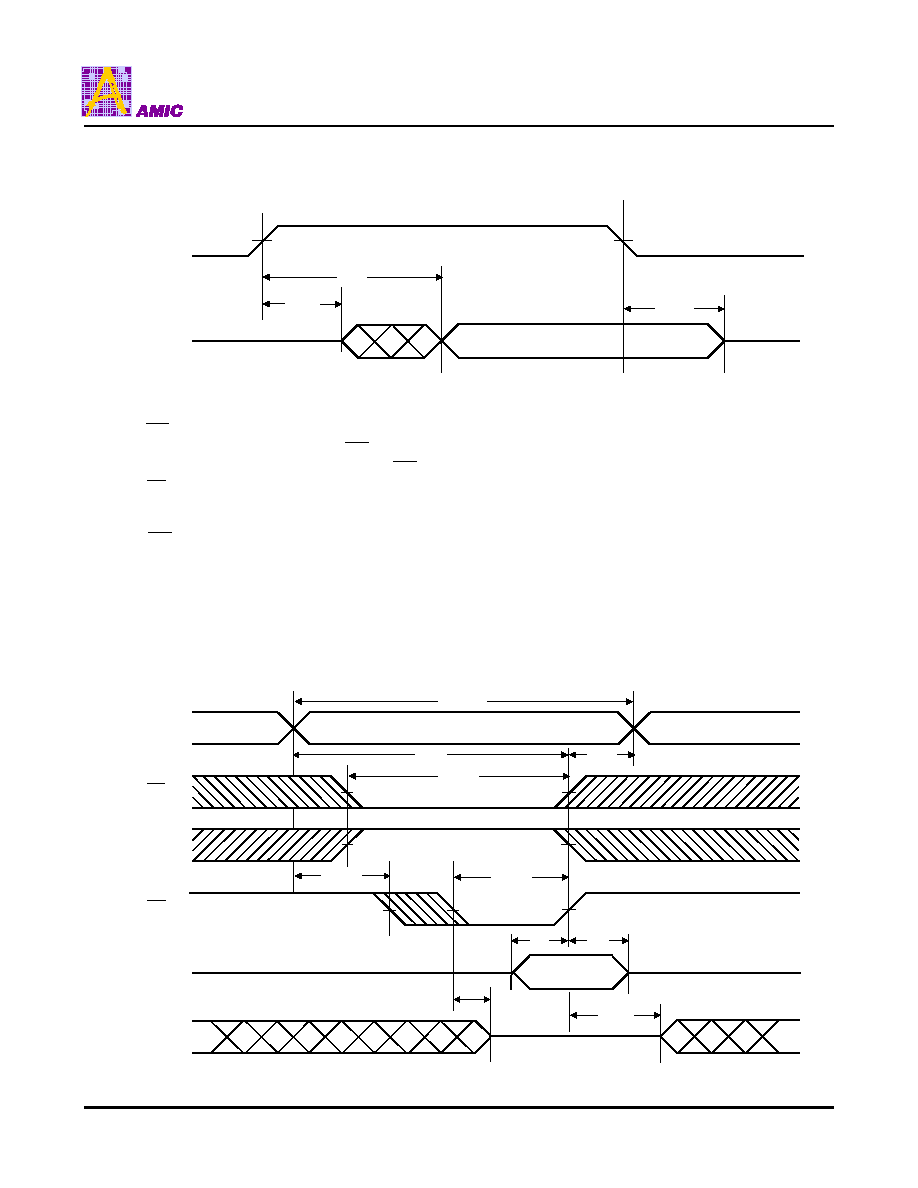

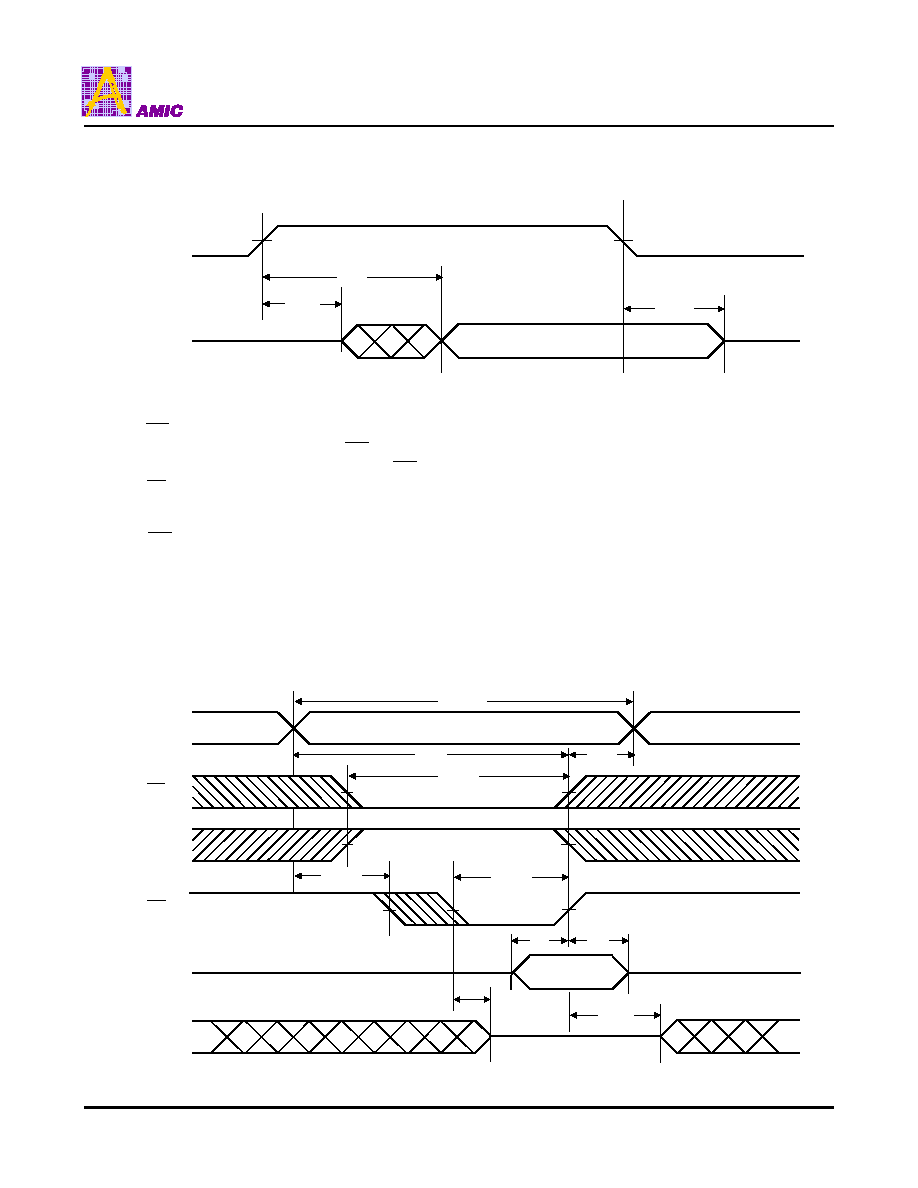

Package Information

TSOP 32L TYPE I (8 X 20mm) Outline Dimensions

unit: inches/mm

e

L

E

L

A

A

2

c

D

y

Detail "A"

S

A

1

b

H

D

D

E

Detail "A"

Dimensions in inches

Dimensions in mm

Symbol

Min

Nom

Max

Min

Nom

Max

A

-

-

0.047

-

-

1.20

A

1

0.002

-

0.006

0.05

-

0.15

A

2

0.037

0.039

0.041

0.95

1.00

1.05

b

0.007

0.009

0.011

0.18

0.22

0.27

c

0.004

-

0.008

0.11

-

0.20

D

0.720

0.724

0.728

18.30

18.40

18.50

E

-

0.315

0.319

-

8.00

8.10

e

0.020 BSC

0.50 BSC

H

D

0.779

0.787

0.795

19.80

20.00

20.20

L

0.016

0.020

0.024

0.40

0.50

0.60

L

E

-

0.032

-

-

0.80

-

S

-

-

0.020

-

-

0.50

y

-

-

0.003

-

-

0.08

0

∞

-

5

∞

0

∞

-

5

∞

Notes:

1. The maximum value of dimension D

includes end flash.

2. Dimension E does not include resin fins.

3. Dimension S includes end flash.