A67P9318/A67P8336

Preliminary

512K X 18, 256K X 36 LVTTL, Pipelined ZeBL

TM

SRAM

PRELIMINARY (July, 2005, Version 0.0)

2

AMIC Technology, Corp.

Features

Fast access time:

2.6/2.8/3.2/3.5/3.8/4.2 (250/227/200/166/150/133MHz)

Zero Bus Latency between READ and WRITE cycles

allows 100% bus utilization

Signal +2.5V

±

5% power supply

Individual Byte Write control capability

Clock enable (

CEN

) pin to enable clock and suspend

operations

Clock-controlled and registered address, data and

control signals

Registered output for pipelined applications

Three separate chip enables allow wide range of

options for CE control, address pipelining

Internally self-timed write cycle

Selectable BURST mode (Linear or Interleaved)

SLEEP mode (ZZ pin) provided

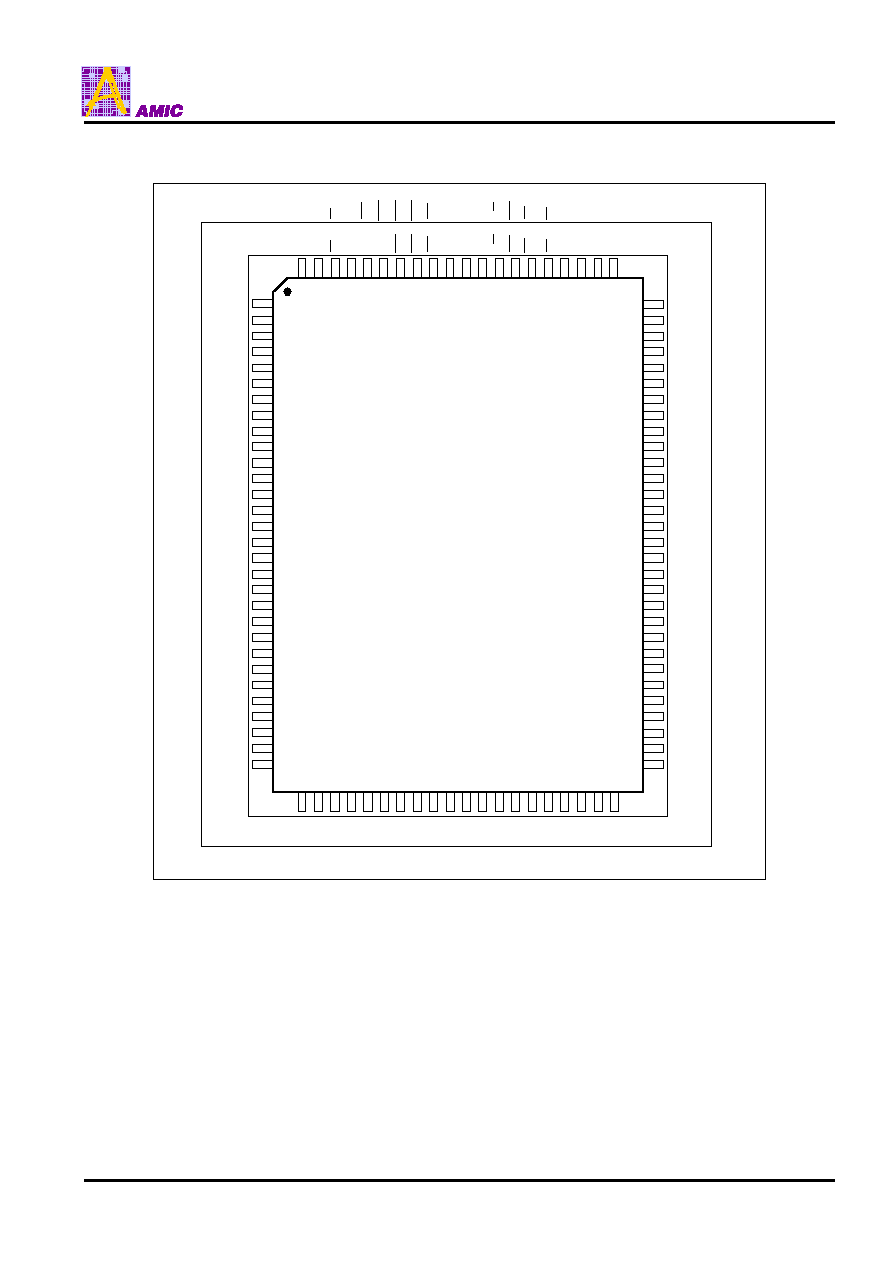

Available in 100 pin LQFP package

General Description

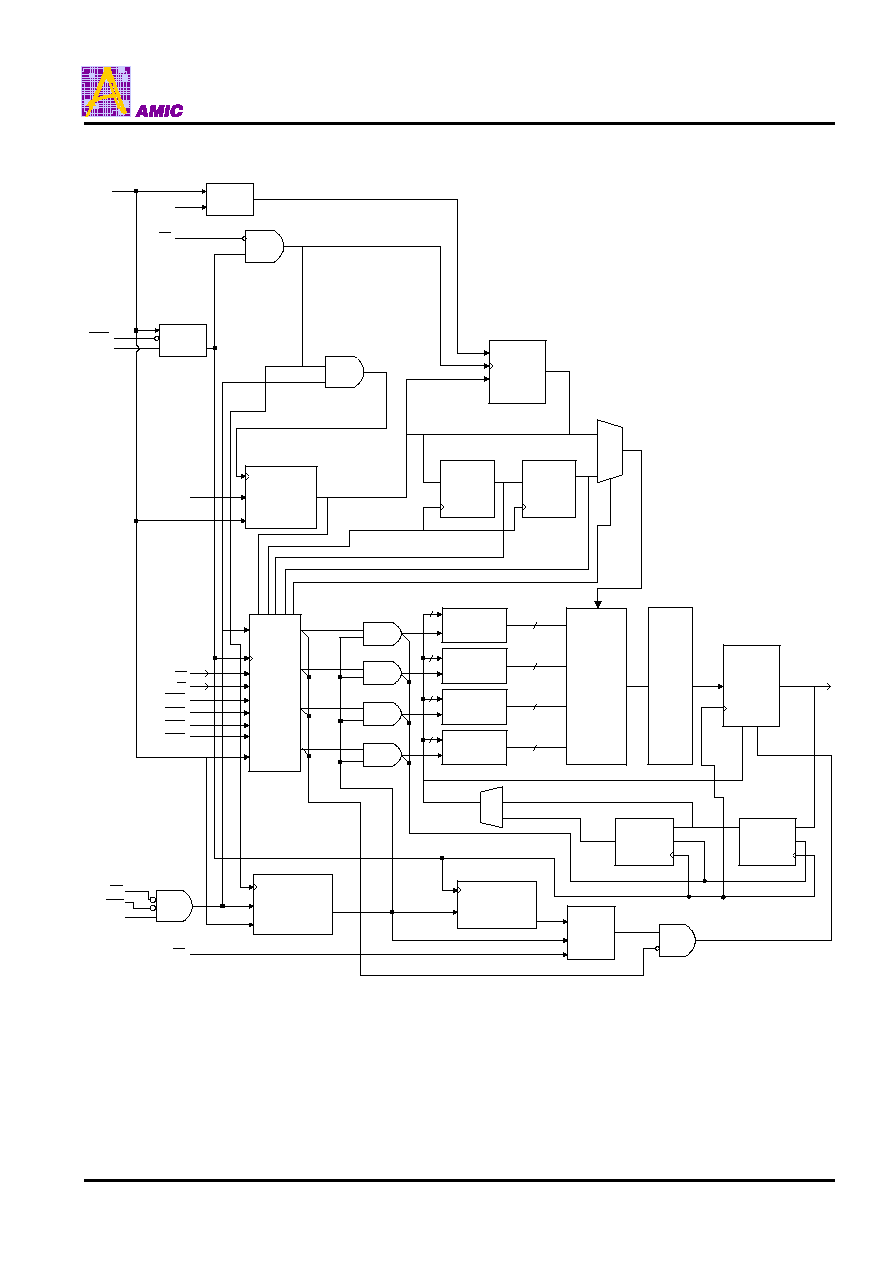

The AMIC Zero Bus Latency (ZeBL

TM

) SRAM family

employs high-speed, low-power CMOS designs using an

advanced CMOS process.

The A67P9318, A67P8336 SRAMs integrate a 512K X 18,

256K X 36 SRAM core with advanced synchronous

peripheral circuitry and a 2-bit burst counter. These SRAMs

are optimized for 100 percent bus utilization without the

insertion of any wait cycles during Write-Read alternation.

The positive edge triggered single clock input (CLK) controls

all synchronous inputs passing through the registers. The

synchronous inputs include all address, all data inputs,

active low chip enable (

CE

), two additional chip enables for

easy depth expansion (CE2,

CE2

), cycle start input

(ADV/ LD ), synchronous clock enable (

CEN

), byte write

enables (

BW1

,

BW2

,

BW3

,

BW4

) and read/write (R/

W

).

Asynchronous inputs include the output enable (

OE

), clock

(CLK), SLEEP mode (ZZ, tied LOW if unused) and burst

mode (MODE). Burst Mode can provide either interleaved or

linear operation, burst operation can be initiated by

synchronous address Advance/Load (ADV/LD ) pin in Low

state. Subsequent burst address can be internally

generated by the chip and controlled by the same input pin

ADV/LD in High state.

Write cycles are internally self-time and synchronous with

the rising edge of the clock input and when R/

W

is Low.

The feature simplified the write interface. Individual Byte

enables allow individual bytes to be written.

BW1

controls

I/Oa pins;

BW2

controls I/Ob pins;

BW3

controls I/Oc pins;

and

BW4

controls I/Od pins. Cycle types can only be

defined when an address is loaded.

The SRAM operates from a +2.5V power supply, and all

inputs and outputs are LVTTL-compatible. The device is

ideally suited for high bandwidth utilization systems.