08/2001

ACA0861 - A, B, C, D

750/860 MHz CATV Line Amplifier MMIC

Data Sheet - Rev 2.0

The ACA0861 family of surface mount monolithic

GaAs RF Linear Amplifiers has been developed to

replace, in new designs, the standard CATV Hybrid

amplifiers currently in use. The MMICs consist of

two parallel amplifiers, each with 12 dB gain. The

Amplifiers are optimized for exceptionally low

distortion and noise figure while providing flat gain

and excellent input and output return loss. There are

four differently specified amplifiers available: two

input stages and two output stages. The ACA0861A

and the ACA0861C are input stages and are

specified at +34 dBmV flat output. The ACA0861B

and ACA0861D are output stages and are specified

at +44 dBmV flat output. A Hybrid equivalent is formed

when one input stage ACA0861 is cascaded with an

ACA0861 output stage between two transmission

line baluns. For low gain applications a single

ACA0861 can be used between baluns, for higher

gain applications more than two ACA0861 can be

cascaded between baluns. See ACA0861

application note for more information.

PRODUCT DESCRIPTION

FEATURES

� Flat Gain

� Very Low Distortion

� Excellent Input/Output Match

� Low DC Power Consumption

� Good RF Stability with High VSWR Load

Conditions

� Surface Mount Package Compatible with

Automatic Assembly

� Low Cost

� Repeatability of Monolithic Fabrication

� Meets Cenelec Standard

S7 Package

16 Pin Wide Body SOIC

with Heat Slug

Figure 1: Hybrid Application Diagram

RF Input

12dB

12dB

ACA0861A/C

12dB

12dB

ACA0861B/D

RF Output

2

ACA0861 - A, B, C, D

Data Sheet - Rev 2.0

08/2001

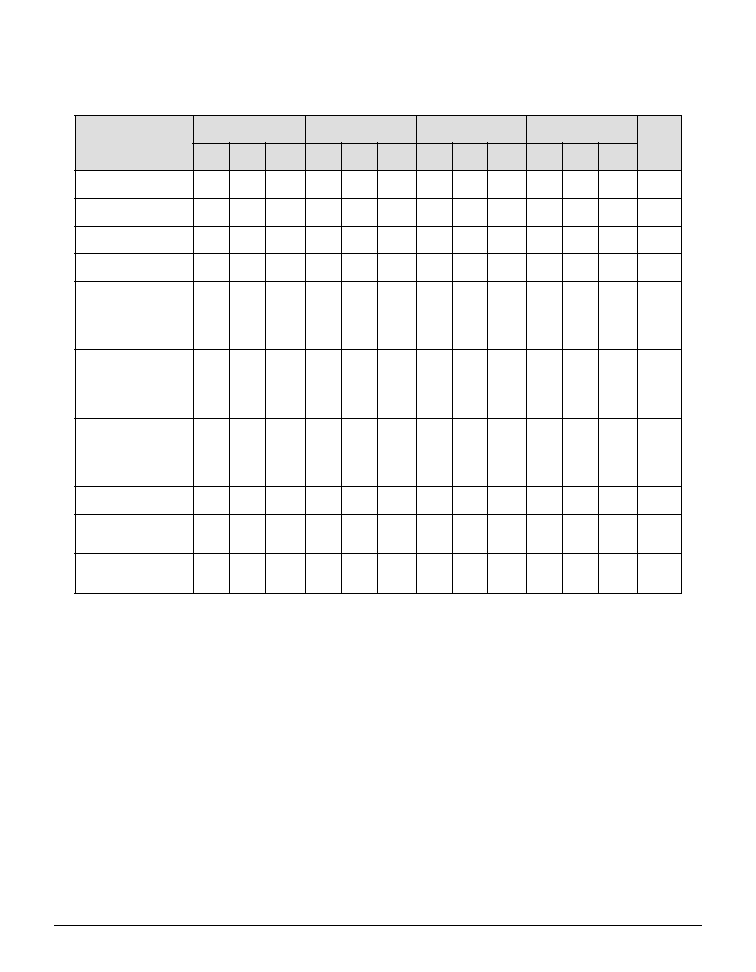

Figure 2: Pin Out

N

I

P

E

M

A

N

N

O

I

T

P

I

R

C

S

E

D

N

I

P

E

M

A

N

N

O

I

T

P

I

R

C

S

E

D

1

D

N

G

d

n

u

o

r

G

9

D

N

G

d

n

u

o

r

G

2

C

/

N

n

o

it

c

e

n

n

o

C

o

N

0

1

V

B

B

r

e

if

il

p

m

A

r

o

f

y

l

p

p

u

S

3

F

R

A

N

I

A

r

e

if

il

p

m

A

o

t

t

u

p

n

I

1

1

F

R

B

T

U

O

B

r

e

if

il

p

m

A

m

o

rf

t

u

p

t

u

O

4

D

N

G

d

n

u

o

r

G

2

1

D

N

G

d

n

u

o

r

G

5

D

N

G

d

n

u

o

r

G

3

1

D

N

G

d

n

u

o

r

G

6

F

R

B

N

I

B

r

e

if

il

p

m

A

o

t

t

u

p

n

I

4

1

F

R

A

T

U

O

A

r

e

if

il

p

m

A

m

o

rf

t

u

p

t

u

O

7

I

J

D

A

t

s

u

j

d

A

t

n

e

rr

u

C

5

1

V

A

A

r

e

if

il

p

m

A

r

o

f

y

l

p

p

u

S

8

D

N

G

d

n

u

o

r

G

6

1

D

N

G

d

n

u

o

r

G

Table 1: Pin Description

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

GND

GND

I

ADJ

RF

INA

GND

GND

GND

RF

OUTA

V

B

N/C

GND

RF

INB

GND

GND

RF

OUTB

V

A

Input Stages

The ACA0861A and the ACA0861C are designed as

input stages and are specified at +34 dBmV flat

output. These parts can be used alone for low gain,

low output level applications or can be cascaded

with one of the ACA0861 output stages for higher

gain and output signal drive level. The ACA0861A is

a low power dissipation part designed to drive the

ACA0861B output stage. The ACA0861C is a slightly

higher power dissipation part and provides the

needed distortion parameters to drive the ACA0861D

output stage.

Output Stages

The ACA0861B and ACA0861D are designed as

output stages and are specified at +44 dBmV flat

output. These parts can be used alone for low gain,

high output level applications or can be cascaded

with one of the ACA0861 input stages for higher gain.

The ACA0861B is a low power dissipation part

designed as the output stage with an ACA0861A input

stage. The ACA0861D is a higher power dissipation

part designed as the output stage with an ACA0861C

input stage. Cascaded, an ACA0861A and ACA0861B

provide exceptional push-pull hybrid equivalent

performance; an ACA0861C and an ACA0861D

cascaded provide exceptional power doubling hybrid

equivalent performance.

Data Sheet - Rev 2.0

08/2001

3

ACA0861 - A, B, C, D

ELECTRICAL CHARACTERISTICS

Table 2: Absolute Minimum and Maximum Ratings

Stresses in excess of the absolute ratings may cause permanent

damage. Functional operation is not implied under these conditions.

Exposure to absolute ratings for extended periods of time may

adversely affect reliability.

R

E

T

E

M

A

R

A

P

N

I

M

X

A

M

T

I

N

U

)

5

1

,

4

1

,

1

1

,

0

1

s

n

i

p

(

s

e

il

p

p

u

S

r

e

if

il

p

m

A

0

5

1

+

C

D

V

)

6

,

3

s

n

i

p

(

r

e

w

o

P

t

u

p

n

I

F

R

-

0

7

+

V

m

B

d

e

r

u

t

a

r

e

p

m

e

T

e

g

a

r

o

t

S

5

6

-

0

5

1

+

C

�

e

r

u

t

a

r

e

p

m

e

T

g

n

ir

e

d

l

o

S

-

0

6

2

+

C

�

e

m

i

T

g

n

ir

e

d

l

o

S

-

0

.

5

c

e

s

Table 3: Operating Ranges

The device may be operated safely over these conditions; however, parametric

performance is guaranteed only over the conditions defined in the electrical

specifications.

R

E

T

E

M

A

R

A

P

N

I

M

P

Y

T

X

A

M

T

I

N

U

y

c

n

e

u

q

e

r

F

F

R

0

4

-

0

6

8

z

H

M

V

:

y

l

p

p

u

S

D

)

5

1

,

4

1

,

1

1

,

0

1

s

n

i

p

(

-

2

1

+

-

C

D

V

T

:

e

r

u

t

a

r

e

p

m

e

T

g

n

it

a

r

e

p

O

A

0

4

-

-

0

1

1

+

C

�

Notes:

1. Pins 3 and 6 should be AC-coupled. No external DC bias should be applied.

2. Pin 7 should be pulled to ground through a resistor or left open-circuited . No

external DC bias should be applied.

4

ACA0861 - A, B, C, D

Data Sheet - Rev 2.0

08/2001

Notes:

1. Measured performance of MMIC alone. Balun effects de-imbedded from measurement.

2. Measured with a balun on input and output of the device. See Figure 3 for test setup.

3. All parts measured with 110 channel flat input. Parts A and C measured at +34 dBmV output (per channel).

Parts B and D measured at +44 dBmV output (per channel).

4. A fixed resistor is needed for parts A through C; part D does not need an external resistor (see Table 6.)

These resistors set the devices current draw. Bias voltage is +12 VDC.

Table 4: Electrical Specifications

(T

A

= +25 �C, V

D

= +12 VDC)

R

E

T

E

M

A

R

A

P

A

1

6

8

0

A

C

A

B

1

6

8

0

A

C

A

C

1

6

8

0

A

C

A

D

1

6

8

0

A

C

A

T

I

N

U

N

I

M

P

Y

T

X

A

M

N

I

M

P

Y

T

X

A

M

N

I

M

P

Y

T

X

A

M

N

I

M

P

Y

T

X

A

M

h

t

d

i

w

d

n

a

B

1

0

4

-

0

6

8

0

4

-

0

6

8

0

4

-

0

6

8

0

4

-

0

6

8

z

H

M

n

i

a

G

1

4

.

1

1

9

.

1

1

4

.

2

1

5

.

1

1

2

1

5

.

2

1

5

.

1

1

2

1

5

.

2

1

6

.

1

1

1

.

2

1

6

.

2

1

B

d

s

s

e

n

t

a

l

F

n

i

a

G

1

-

-

3

.

0

-

-

3

.

0

-

-

3

.

0

-

-

3

.

0

B

d

e

r

u

g

i

F

e

s

i

o

N

2

-

3

5

-

3

5

-

3

5

-

3

6

B

d

B

T

C

3

,

2

s

l

e

n

n

a

h

C

7

7

s

l

e

n

n

a

h

C

0

1

1

s

l

e

n

n

a

h

C

8

2

1

-

-

-

0

7

-

8

6

-

5

6

-

-

4

6

-

-

-

-

-

2

6

-

0

6

-

8

5

-

-

7

5

-

-

-

-

-

7

7

-

5

7

-

1

7

-

-

8

6

-

-

-

-

-

0

7

-

8

6

-

7

6

-

-

4

6

-

-

c

B

d

c

B

d

c

B

d

O

S

C

3

,

2

s

l

e

n

n

a

h

C

7

7

s

l

e

n

n

a

h

C

0

1

1

s

l

e

n

n

a

h

C

8

2

1

-

-

-

1

7

-

1

7

-

0

7

-

-

6

6

-

-

-

-

-

6

6

-

6

6

-

4

6

-

-

0

6

-

-

-

-

-

5

7

-

5

7

-

3

7

-

-

8

6

-

-

-

-

-

2

7

-

2

7

-

0

7

-

-

8

6

-

-

c

B

d

c

B

d

c

B

d

D

O

M

X

3

,

2

s

l

e

n

n

a

h

C

7

7

s

l

e

n

n

a

h

C

0

1

1

s

l

e

n

n

a

h

C

8

2

1

-

-

-

7

6

-

3

6

-

9

5

-

-

6

5

-

-

-

-

-

2

6

-

6

5

-

5

5

-

-

0

5

-

-

-

-

-

4

7

-

1

7

-

7

6

-

-

2

6

-

-

-

-

-

1

7

-

8

6

-

6

6

-

-

1

6

-

-

c

B

d

c

B

d

c

B

d

t

n

e

rr

u

C

y

l

p

p

u

S

4

-

0

8

1

0

0

2

-

0

1

3

0

3

3

-

0

6

2

5

7

2

-

5

7

4

5

1

5

A

m

t

n

e

l

a

v

i

u

q

E

e

l

b

a

C

e

p

o

l

S

1

5

.

0

-

-

0

.

1

5

.

0

-

-

0

.

1

5

.

0

-

-

0

.

1

5

.

0

-

-

0

.

1

B

d

s

s

o

L

n

r

u

t

e

R

)t

u

p

t

u

O

/t

u

p

n

I(

1

8

1

2

2

-

8

1

2

2

-

8

1

2

2

-

8

1

2

2

-

B

d

�

�

�

�

Data Sheet - Rev 2.0

08/2001

5

ACA0861 - A, B, C, D

Note: Apply voltage to both V

D

lines simultaneously

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

N/C

R

1

+VD

L2

+ VD

F In

RF Out

L1

T

1

T

2

C

1

C

2

C

4

C

3

C

6

A

C

A

0

8

6

1

C

5

R

E

B

M

U

N

T

R

A

P

E

U

L

A

V

1

R

A

1

6

8

0

A

C

A

s

m

h

O

5

.

1

2

B

1

6

8

0

A

C

A

s

m

h

O

4

7

2

C

1

6

8

0

A

C

A

s

m

h

O

1

2

1

D

1

6

8

0

A

C

A

)

n

e

p

o

(

F

E

R

N

O

I

T

P

I

R

C

S

E

D

Y

T

Q

R

O

D

N

E

V

.

O

N

T

R

A

P

R

O

D

N

E

V

6

C

,

5

C

,

2

C

,

1

C

r

o

ti

c

a

p

a

c

p

i

h

c

F

u

1

0

.

0

4

a

t

a

r

u

M

V

5

2

K

3

0

1

1

R

7

X

9

3

M

R

G

4

C

,

3

C

r

o

ti

c

a

p

a

c

p

i

h

c

F

p

0

0

3

2

a

t

a

r

u

M

V

5

2

K

1

0

3

R

7

X

9

3

M

R

G

2

L

,

1

L

r

o

t

c

u

d

n

i

p

i

h

c

d

n

u

o

w

-r

i

a

H

n

0

9

3

2

tf

a

r

c

li

o

C

1

9

3

-

S

C

8

0

0

1

1

R

)

6

e

l

b

a

T

e

e

s

(

1

2

T

,

1

T

)

1

(

e

r

o

c

e

ti

rr

e

f

2

s

p

il

i

h

P

3

D

3

-

3

.

1

/

8

.

1

/

4

.

3

C

T

e

ri

w

s

e

ir

t

s

u

d

n

i

e

ri

W

S

W

M

1

1

6

8

3

2

B

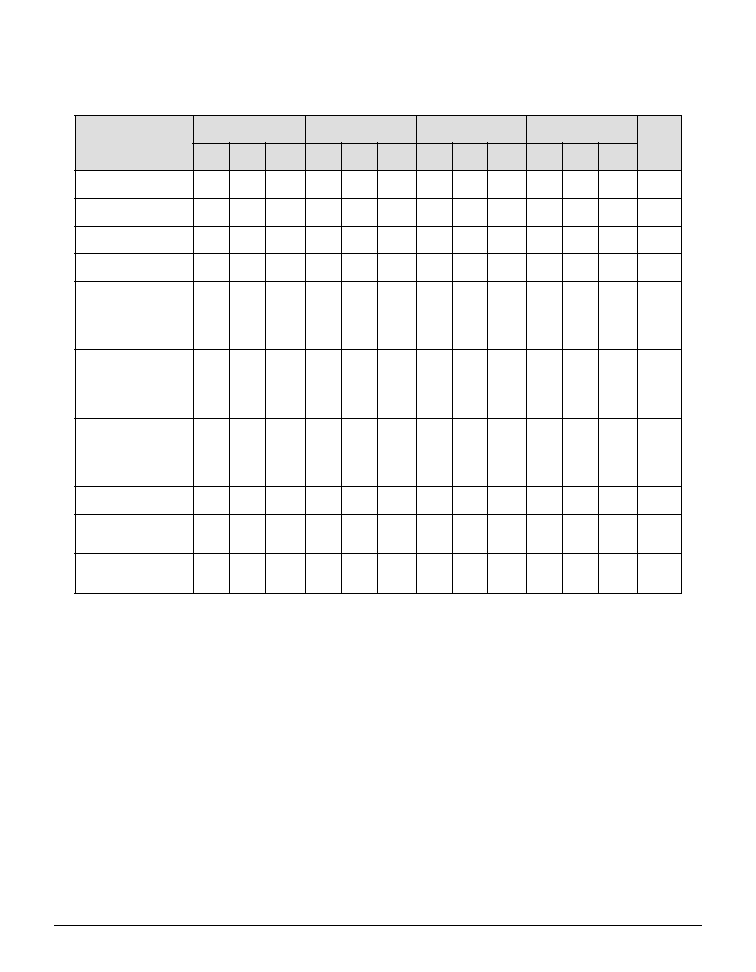

Figure 3: Test Circuit

Table 5: Parts List for Test Circuit

Table 6: R1 Resistor Value

Figure 4: Balun Drawing (4 Turns)

Note:

(1) T1, T2 (balun) wind 4 turns thru core, as shown in Figure 4.