| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ARM10200 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Product Overview

Æ

ARM10200

Reference Device Product

Overview

Applications

∑

© Copyright ARM Limited. All rights reserved.

ARM DVI 0015A

∑

Next-generation hand-held

products:

- Communicators

- Smartphones

- Subnotebook computers

∑

Digital consumer

appliances featuring:

- 3D graphics

- Web content

- Voice recognition and

synthesis

- Digital video

- High-speed connectivity

Benefits

∑

Multi-sourced high-perfor-

mance, low-power

processor macrocells

∑

High-performance vector

floating point delivers 3D

graphics and floating point

DSP

∑

Access to existing ARM

architecture, tools, OS,

and code-base

∑

Low system cost via

excellent code density

∑

High performance allows

cost saving via migration of

hardware features to soft-

ware implementations

∑

System-on-a-chip ready

allowing rapid integration

with short time to market

∑

Designed to run sophisti-

cated OS such as Linux,

EPOC, and WindowsCE

The ARM10200TM Reference Device

The ARM10

TM

ThumbÆ Family of processors will deliver 400 Dhrystone 2.1

MIPS at 300MHz, and 600 MFLOPS for 3D graphics and floating point DSP.

Process portable to high performance 0.25 micron and 0.18 micron CMOS

fabrication processes, the ARM10 processor units will be licensed to multiple

semiconductor partners, offering OEMs guaranteed continuity of supply. The

ARM10 Thumb Family maintains traditional ARM values of low system cost,

low power consumption, and use within larger system-on-chip designs. The

Thumb 16-bit compressed instruction set gives a reduction in the required

memory size and bandwidth, which directly reduces system cost.The

ARM10TDMI

TM

integer unit features the ARM 32-bit RISC instruction set, and

Thumb compressed 16-bit instruction set. The ARM10TDMI unit employs par-

allel instruction execution, branch prediction, and a non-blocking data cache

interface to achieve high performance on real applications.The ARM1020T

TM

cached processor macrocell is built around the ARM10TDMI unit, and also

features large on-chip instruction and data caches, an MMU with demand

paged virtual memory support, a write buffer, and a new high-bandwidth

AMBA

TM

Advanced High-Speed Bus (AHB) system-on-a-chip bus interface.

The ARM10200 Reference Device is a packaged chip containing an

ARM1020T core with the VFP10

TM

coprocessor, a high performance SDRAM

memory interface and an on-chip Phase Locked Loop (PLL). The ARM10200

can be used for all types of evaluation, especially benchmarking and system

prototyping.

System-on-a-chip Ready

The ARM10 processors feature EmbeddedICETM JTAG software debug, and

the AMBA AHB multi-master on-chip bus architecture that provides for periph-

eral design reuse and efficient production test. ARM and its partners provide

ASIC simulation models, and co-simulation tools to enable the design pro-

cess.

ARM7TDMITM, ARM9TDMITM and StrongARMÆ Compatible

The ARM10 Thumb Processor Family is backwards compatible with the ARM7

Thumb Family, the ARM9 Thumb Family, and StrongARM processor families,

giving designers software-compatible processors with a range of price/perfor-

mance points from 60 MIPS to 400 MIPS. Support for the ARM architecture

today includes the WindowsCE, EPOC, JavaOS, and Linux operating sys-

tems, more than 25 Real Time Operating Systems, Co-simulation tools from

leading EDA vendors, and a variety of software development tools.

This document refers to the ARM 10200TM and is subject to change.

ARM1020T

ARM DVI 0015A © Copyright ARM Limited 2000. All rights reserved. Page 2

ARM1020T

The ARM1020T includes cache and

memory management functions to

support a full demand-paged virtual

memory operating system and sup-

port for real-time embedded operat-

ing systems.

MMUs

Twin 64-entry Translation Lookaside

Buffers (TLBs) provide fast access to

the most recent address transla-

tions. ARM1020T also provides TLB

lock-down. This allows critical trans-

lations to remain in the TLB to

ensure predictable access to real-

time code.

Caches

Two 32KB caches are implemented,

one for instructions, the other for

data, both with an eight-word line

size. These caches connect to the

integer unit via 64-bit buses, to allow

two instructions to be passed into

the instruction prefetch unit every

cycle, and to allow load and store

multiple instructions to transfer two

32-bit registers every cycle.

Cache lock-down

Cache lock-down is provided to

allow critical code sequences to be

locked into the cache to ensure pre-

dictability for real-time code. The

cache replacement policy can be

selected by the operating system as

either fully random or round-robin.

Both caches are 64-way set-associa-

tive.

Data cache features

The data cache supports nonblock-

ing hit-under-miss operation. Non-

blocking operation allows instructions

that occur after a data cache miss to

continue execution before the data is

returned. The hit-under-miss opera-

tion allows subsequent load or store

instructions after a cache miss to

access the data cache. Together

these mechanisms can provide sig-

nificantly higher performance for

applications that incur high data

cache miss rates.

Write buffer

ARM1020T also incorporates a dou-

ble word 8-entry write buffer, to avoid

stalling the processor when writes to

external memory are performed.

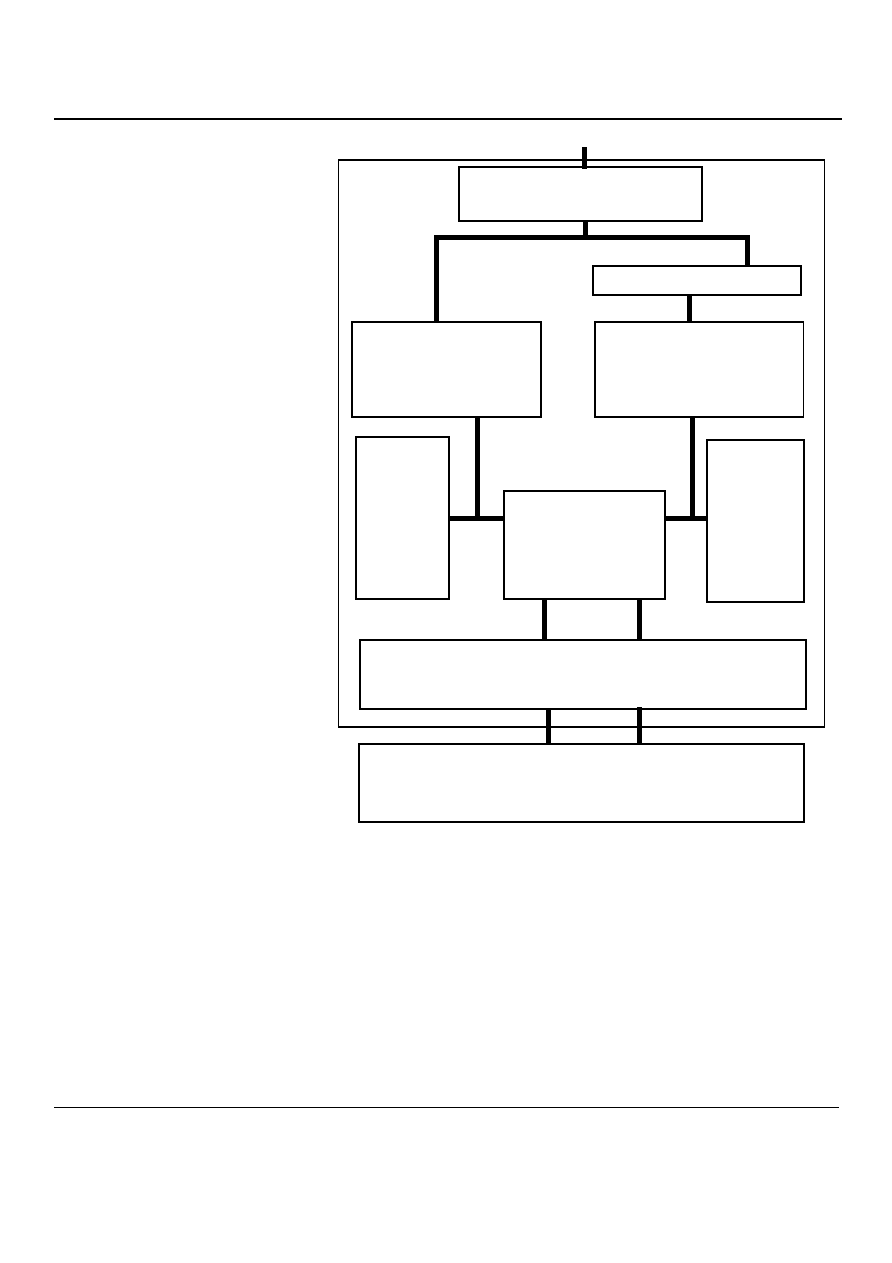

32KByte data

cache

32KByte instruction

cache

AMBA Bus Interface

Instruction

MMU and

TLB

ARM10TDMI

Integer Unit

Data

MMU and

TLB

Debug and System Control coprocessor

VFP10 Floating-point coprocessor

ARM1020T

Write buffer

The ARMv5T Architecture

ARM DVI 0015A © Copyright ARM Limited 2000. All rights reserved. Page 3

ARM10TDMI integer unit

The ARM10TDMI integer unit is an

implementation of the ARM Architec-

ture Version 5T, the latest implemen-

tation of the ARM Architecture.

ARMv5T is a superset of the ARMv4

ISA implemented by the StrongARM

processors and the ARMv4T ISA

implemented by the ARM7 Thumb

and ARM9 Thumb Family proces-

sors.

Performance and code

density

ARM10TDMI executes two instruc-

tion sets, the 32-bit ARM instruction

set, and the 16-bit Thumb instruction

set. The ARM instruction set allows a

program to achieve maximum perfor-

mance with the minimum number of

instructions. The simpler Thumb

instruction set offers much increased

code density for code that does not

require maximum performance. Code

can switch between the ARM and

Thumb instruction sets on any proce-

dure call.

Registers

The Integer Unit consists of a 32-bit

datapath and associated control

logic. The datapath contains 31 gen-

eral-purpose registers, coupled to a

full shifter, Arithmetic Logic Unit, and

multiplier. At any one time 16 regis-

ters are visible to the user. The

remainder are banked registers used

to speed up exception processing.

Register 15 is the Program Counter

(PC) and can be used in memory

access instructions to reference data

relative to the current instruction

address. R14 holds the return

address after a subroutine call. R13

is used (by software convention) as a

stack pointer.

Modes and exception

handling

All exceptions have banked registers

for R14 and R13. After an exception

R14 holds the return address for

exception processing. This address

is used both to return after the excep-

tion is processed and to address the

instruction that caused the exception.

R13 is banked across exception

modes to provide each exception

handler with a private stack pointer.

The fast interrupt mode also banks

registers 8 to 12 so that interrupt pro-

cessing can begin without the need

to save or restore these registers. A

seventh processing mode, System

mode, does not have any banked

registers. It uses the User mode reg-

isters. System mode runs tasks that

require a privileged processor mode

and allows them to invoke all classes

of exceptions.

Status registers

All other processor states are held in

status registers. The current operat-

ing processor status is in the Current

Program Status Register (CPSR).

The CPSR holds 4 ALU flags (Nega-

tive, Zero, Carry and Overflow), two

interrupt disable bits (one for each

type of interrupt), a bit to indicate

ARM or Thumb execution, and 5 bits

to encode the current processor

mode. All 5 exception modes also

have a Saved Program Status Regis-

ter (SPSR) which holds the CPSR of

the task immediately before the

exception occurred.

Exception types

ARM10TDMI supports 5 types of

exception, and a privileged process-

ing mode for each type. The 5 types

of exceptions are:

∑

fast interrupt (FIQ)

∑

normal interrupt (IRQ)

∑

memory aborts (used to imple-

ment memory protection or vir-

tual memory)

∑

attempted execution of an unde-

fined instruction

∑

software interrupts (SWIs).

Conditional execution

All ARM instructions (with the excep-

tion of BLX) are conditionally exe-

cuted. Instructions optionally update

the four condition code flags (Nega-

tive, Zero, Carry and Overflow)

according to their result. Subsequent

instructions are conditionally exe-

cuted according to the status of flags.

Fifteen conditions are implemented.

4 classes of instructions

The ARM and Thumb instruction sets

can be divided into four broad

classes of instruction

∑

data processing instructions

∑

load, store and swap instructions

∑

branch instructions

∑

coprocessor instructions.

Data processing

The data processing instructions

operate on data held in general pur-

pose registers. Of the two source

operands, one is always a register.

The other has two basic forms, an

immediate value or a register value

optionally shifted. If the operand is a

shifted register the shift amount may

have an immediate value or the value

of another register. Four types of shift

can be specified. Most data process-

ing instructions can perform a shift

followed by a logical or arithmetic

operation. Multiply instructions come

in two classes, (normal) 32-bit result

and (long) 64-bit result variants. Both

The ARMv5T Architecture

ARM DVI 0015A © Copyright ARM Limited 2000. All rights reserved. Page 4

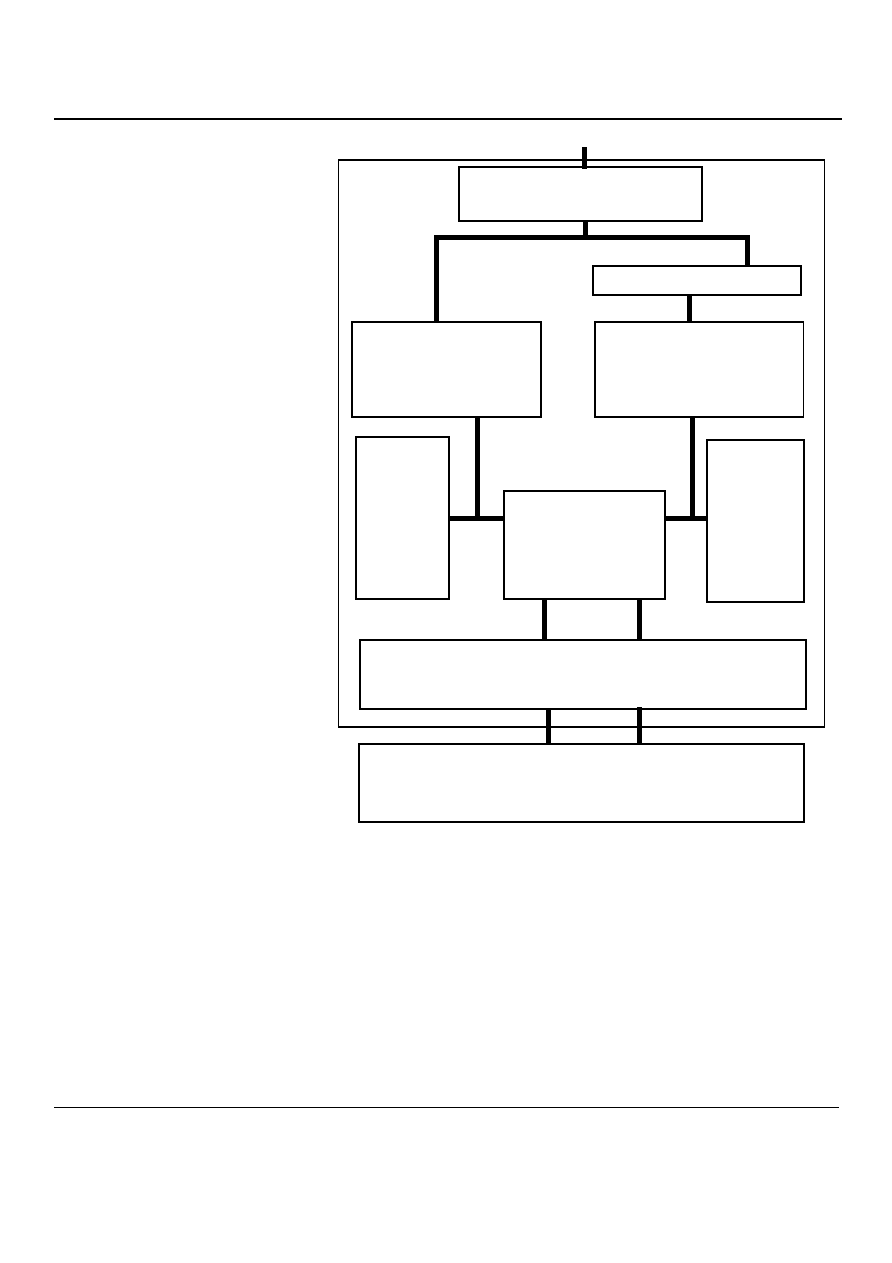

Modes and Registers

User and

System Mode

Supervisor

Mode

Abort Mode

Undefined

Mode

Interrupt Mode

Fast Interrupt

Mode

R0

R0

R0

R0

R0

R0

R1

R1

R1

R1

R1

R1

R2

R2

R2

R2

R2

R2

R3

R3

R3

R3

R3

R3

R4

R4

R4

R4

R4

R4

R5

R5

R5

R5

R5

R5

R6

R6

R6

R6

R6

R6

R7

R7

R7

R7

R7

R7

R8

R8

R8

R8

R8

R8_FIQ

R9

R9

R9

R9

R9

R9_FIQ

R10

R10

R10

R10

R10

R10_FIQ

R11

R11

R11

R11

R11

R11_FIQ

R12

R12

R12

R12

R12

R12_FIQ

R13

R13_SVC

R13_ABORT

R13_UNDEF

R13_IRQ

R13_FIQ

R14

R14_SVC

R14_ABORT

R14_UNDEF

R14_IRQ

R14_FIQ

PC

PC

PC

PC

PC

PC

CPSR

CPSR

CPSR

CPSR

CPSR

CPSR

-

SPSR_SVC

SPSR_ABORT

SPSR_UNDEF

SPSR_IRQ

SPSR_FIQ

types of multiply instruction can

optionally perform an accumulate

operation.

Load and store

The second class of instruction is

load and store instructions. These

instructions come in two main types:

∑

load or store the value of a single

register

∑

load and store multiple register

values.

Load and store single register

instructions can transfer a 32-bit

word, a 16-bit halfword and an 8-bit

byte between memory and a register.

Byte and halfword loads may be

automatically zero or sign extended

as they are loaded. Swap instructions

perform an atomic load and store as

a synchronization primitive.

Mode-specific banked registers

The ARMv5T Architecture

ARM DVI 0015A © Copyright ARM Limited 2000. All rights reserved. Page 5

Addressing modes

Load and store instructions have

three primary addressing modes

∑

offset

∑

pre-indexed

∑

post-indexed.

They are formed by adding or sub-

tracting an immediate or register

based offset to or from a base regis-

ter. Register based offsets can also

be scaled with shift operations. Pre-

indexed and post-indexed addressing

modes update the base register with

the base plus offset calculation. As

the PC is a general purpose register,

a 32-bit value can be loaded directly

into the PC to perform a jump to any

address in the 4Gigabyte memory

space.

Block transfers

Load and store multiple instructions

perform a block transfer of any num-

ber of the general purpose registers

to or from memory. Four addressing

modes are provided:

∑

pre-increment addressing

∑

post-increment addressing

∑

pre-decrement addressing

∑

post-decrement addressing.

The base address is specified by a

register value (which may be option-

ally updated after the transfer). As

the subroutine return address and

the PC values are in general purpose

registers, very efficient subroutine

calls and returns can be constructed.

Branch

The third class of instructions is

branch instructions. As well as allow-

ing any data processing or load

instruction to change control flow (by

writing the Program Counter) a stan-

dard branch instruction is provided

with 24-bit signed offset, allowing for-

ward and backward branches of up to

32Megabytes.

Branch with Link

The Branch with Link (BL) instruction

allows efficient subroutine calls. BL

preserves the address of the instruc-

tion after the branch in R14 (the Link

Register or LR). This allows a move

instruction to copy the LR into the PC

to return to the instruction after the

branch.

The third type of branch (BX and

BLX) is used to switch between ARM

and Thumb instruction sets, option-

ally with the return address preserv-

ing "link" option.

Coprocessor

The fourth class of instructions is

coprocessor instructions. There are

three types of coprocessor instruc-

tions:

∑

coprocessor data processing

instructions

These are used to invoke a copro-

cessor specific internal operation.

∑

coprocessor register transfer

instructions

These allow a coprocessor value to

be transferred to or from an ARM

register.

∑

coprocessor data transfer

instructions.

These transfer coprocessor data to

or from memory, where the ARM cal-

culates the address of the transfer.