1

Features

∑

Links an Embedded ARM7TDMI

TM

Core to the Atmel AMBA

TM

Bus

∑

Bus Master Granted State Machine

∑

Bus Interface State Machine

∑

Fully Scan Testable (up to 96% Fault Coverage)

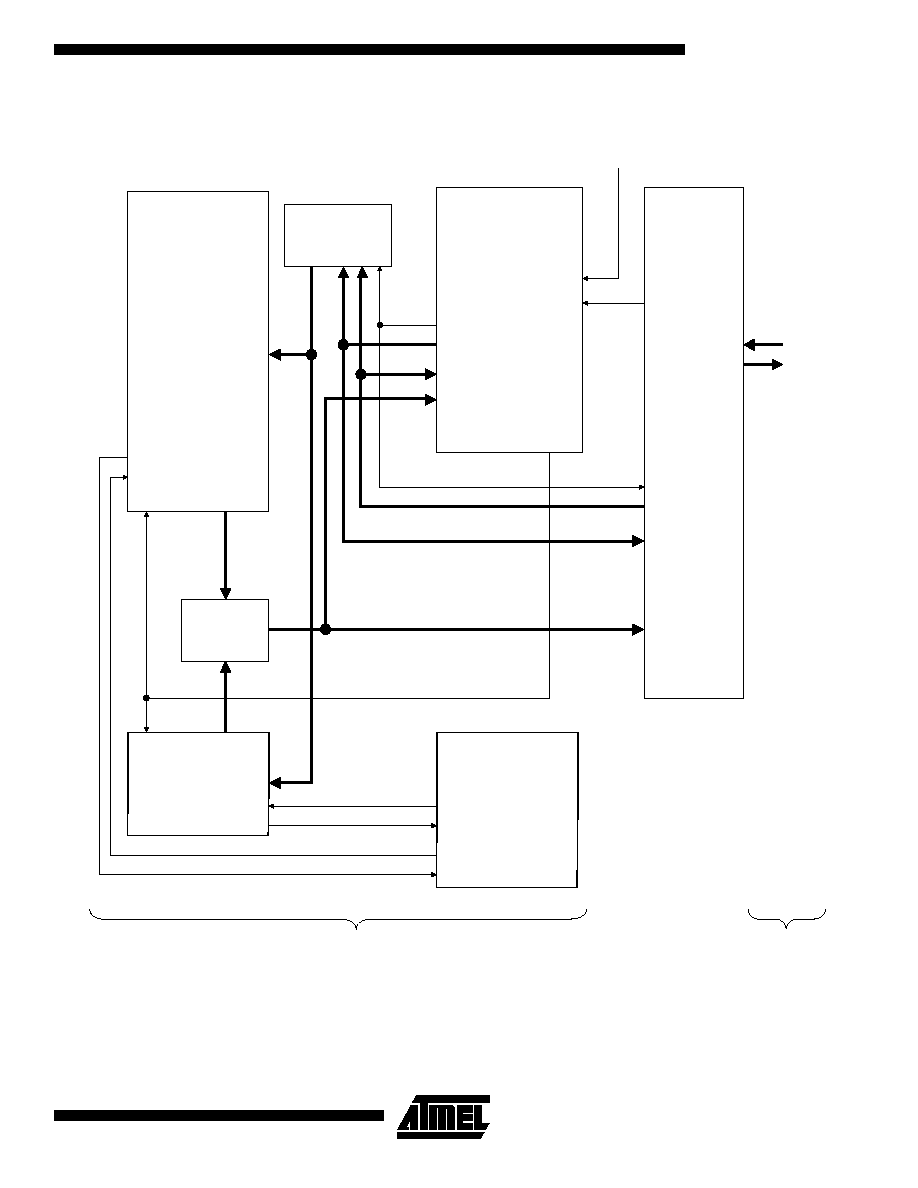

Description

Designed for the Atmel implementation of the AMBA Bus, the ARM7TDMI Bus Inter-

face module enables an ARM7TDMI embedded core to become an AMBA bus

master.

The bus interface is designed to link the embedded ARM7TDMI core signals to the

AMBA Bus. It includes two state machines. The first state machine determines if the

master is currently granted the bus, and the second, more complex, state machine is

used to control the bus interface of the master.

This peripheral can only be used with an embedded ARM7TDMI core.

There are no user-programmable registers in this block.

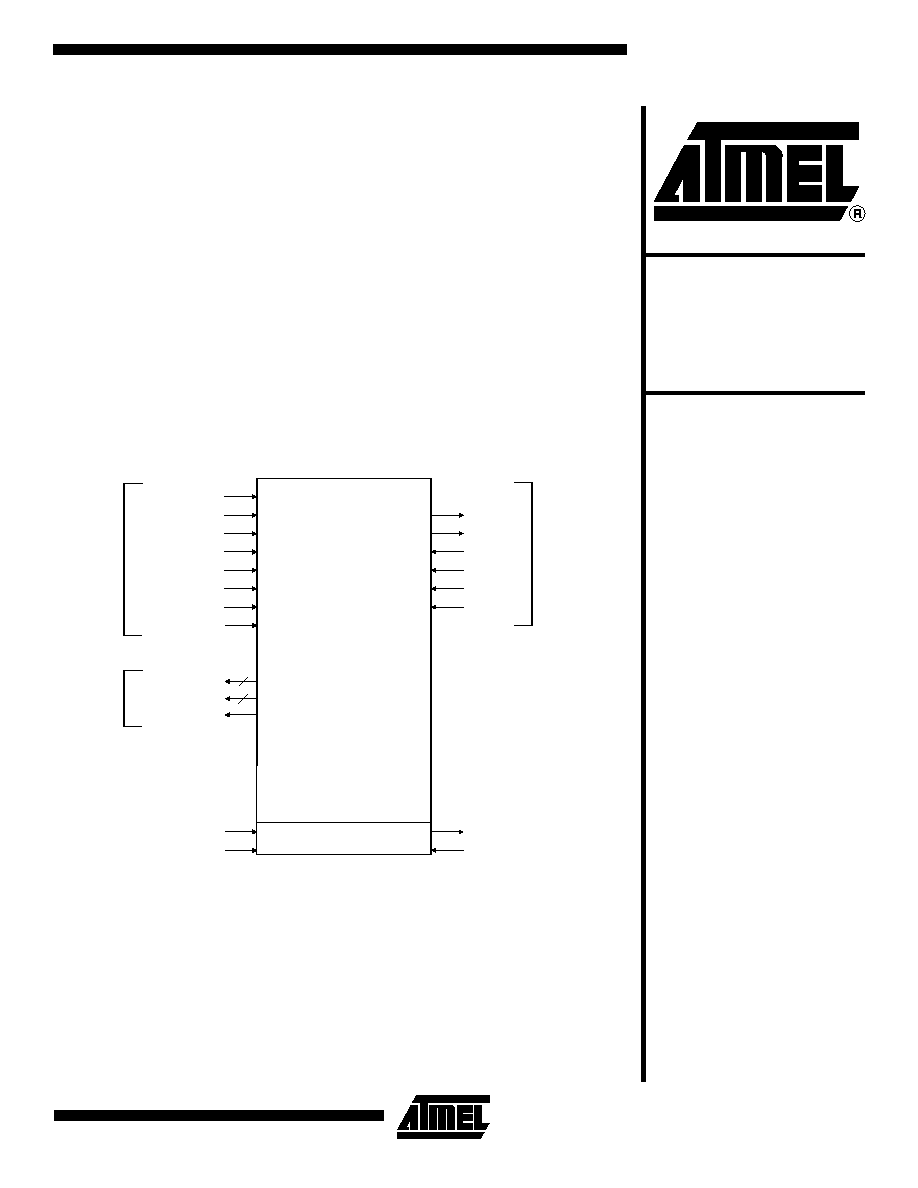

Figure 1. ARM7TDMI Bus Interface Pin Configuration

blast_in

nreset_r

berror_in

agnt

nreset_f

nwait

abort

ARM7TDMI

Bus Interface

(AMBA Wrapper)

AMBA Bus

Inputs

ARM7TDMI

AMBA Related

Signals

system clock_n

bwait_in

system clock

btran[1:0]

bprot[1:0]

nmreq

seq

nopc

ntrans

mabe

scan_test_mode

test_se

AMBA Bus

Outputs

test_so

test_si

Scan Interface

32-bit

Embedded Core

Interface

ARM7TDMI

TM

Bus Interface

Rev. 1283D≠03/01

2

Bus Interface

1283D≠03/01

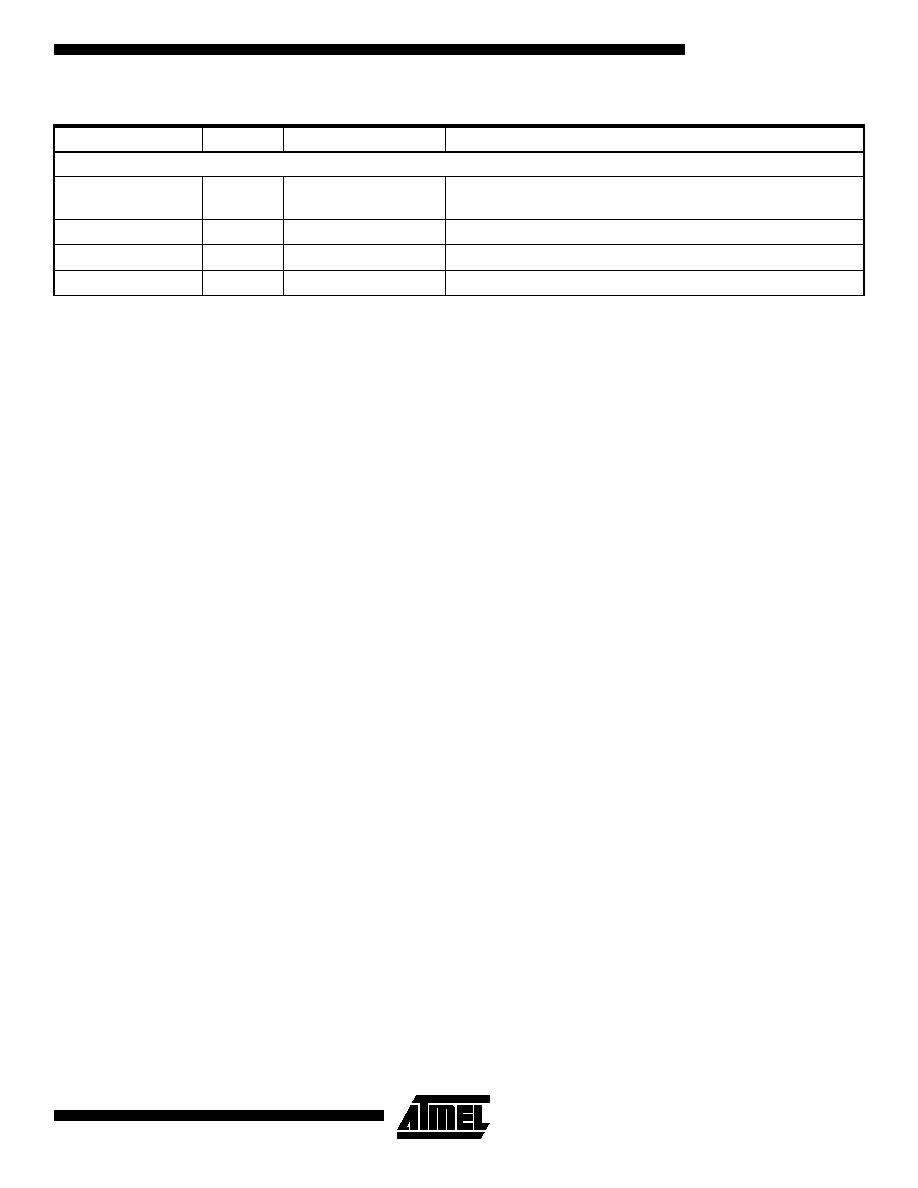

Table 1. Bus Interface Pin Description

Name

Direction

Source/Destination

Description

AMBA Bus Inputs

nreset_r

Input

Reset Controller

System reset for flip-flop working on the rising edge of the System

Clock (nreset_r synchronous to nclock). Active low.

nreset_f

Input

Reset Controller

System reset for flip-flop working on the rising edge of the inverted

System Clock (nreset_f synchronous to clock). Active low.

clock

Input

System Clock

nclock

Input

Inverted System Clock

bwait_in

Input

Slaves + decoder

Multiplexed BWAIT response from all the peripherals. Active high.

berror_in

Input

Slaves + decoder

Multiplexed BERROR response from all the peripherals. Active

high.

blast_in

Input

Slaves + decoder

Multiplexed BLAST response from all the peripherals. Active high.

agnt

Input

Arbiter

Bus Grant: indicates that the bus master (ARM7TDMI) will be

granted the bus when BWAIT is low.

AMBA Bus Outputs

btran[1:0]

Output

Current bus

master/decoder, slaves

Transfer type: type of the next transaction (Address-only, Non-

sequential or Sequential). To be connected to the tri-state bus

BTRAN[1:0] of the ASB.

bprot[1:0]

Output

Current bus master

Protection control: indicates if the transfer is an opcode fetch or

data access, as well as if the transfer is a supervisor mode access

or a user mode access. To be connected to the tri-state bus

BPROT[1:0] of the ASB.

mabe

Output

Master address bus enable: indicates when BA bus can be taken

into account. Active high.

ARM7TDMI AMBA Related Signals

nwait

Output

ARM7TDMI

Not wait: used when accessing slow peripherals to make the

processor wait. Active Low.

abort

Output

ARM7TDMI

Memory abort: tells the processor that a requested access is not

allowed. Active High.

nmreq

Input

ARM7TDMI

Not memory request: memory access requested by the processor.

Active Low.

seq

Input

ARM7TDMI

Sequential address: next address (memory access) will be related

to the last memory access. Active High.

nopc

Input

ARM7TDMI

Not op-code fetch: indicates that the processor is fetching an

instruction from the memory. Active Low.

ntrans

Input

ARM7TDMI

Not memory translate: indicates that the processor is in user mode.

Active Low.

3

Bus Interface

1283D≠03/01

Note:

1. The scan chain uses the clock BCLK.

Scan Test

Configuration

The coverage is maximum if all non-scan inputs can be controlled and all non-scan outputs

can be observed. In order to achieve this, the ATPG vectors must be generated on the entire

circuit (top level) which includes the ARM7TDMI Bus Interface or all ARM7TDMI Bus Interface

I/Os must have a top level access and ATPG vectors must be applied to these pins.

Scan Test

scan_test_mode

Input

Must be tied to 1 during scan test

Must be tied to 0 in functional mode

test_se

Input

Test scan shift enabled when tied to 1

test_si

(1)

Input

Test scan input (input of the scan chain)

test_so

(1)

Output

Test scan output (output of the scan chain)

Table 1. Bus Interface Pin Description (Continued)

Name

Direction

Source/Destination

Description