Rev. 4190A�8051�11/02

Features

�

80C51 Compatible

� Three I/O Ports

� Two 16-bit Timer/Counters

� 256 Bytes RAM

�

4K Bytes ROM/OTP Program Memory with 64 Bytes Encryption Array and 3 Security

Levels

�

High-Speed Architecture

� 33 MHz at 5V (66 MHz Equivalent)

� 20 MHz at 3V (40 MHz Equivalent)

� X2 Speed Improvement Capability (6 Clocks/Machine Cycle)

�

10-bit, 8 Channels A/D Converter

�

Hardware Watchdog Timer

�

Programmable I/O Mode: Standard C51, Input Only, Push-pull, Open Drain

�

Asynchronous Port Reset

�

Full Duplex Enhanced UART with Baud Rate Generator

�

SPI, Master Mode

�

Dual System Clock

� Crystal or Ceramic Oscillator (33/40 MHz)

� Internal RC Oscillator (12 MHz)

� Programmable Prescaler

�

Programmable Counter Array with High-speed Output, Compare/Capture, Pulse Width

Modulation and Watchdog Timer Capabilities

�

Interrupt Structure

� 8 Interrupt Sources

� 4 Interrupt Priority Levels

�

Power Control Modes

� Idle Mode

� Power-down Mode

� Power-off Flag

�

Power Supply: 2.7 - 5.5V

�

Temperature Range: Industrial (-40 to 85

o

C)

�

Package: SO24, DIL24, SSOP24

Description

The AT8xC5111 is a high-performance ROM/OTP version of the 80C51 8-bit micro-

controller in low pin count package.

The AT8xC5111 retains all the features of the standard 80C51 with 4K Bytes

ROM/OTP program memory, 256 bytes of internal RAM, an 8-source, 4-level interrupt

system, an on-chip oscillator and two timer/counters.

The AT8xC5111 is dedicated for analog interfacing applications. For this, it has a 10-

bit, 8 channels A/D converter and a five-channel Programmable Counter Array.

In addition, the AT8xC5111 has a Hardware Watchdog Timer, a versatile serial chan-

nel that facilitates multiprocessor communication (EUART) with an independent baud

rate generator, an SPI serial bus controller and a X2 speed improvement mechanism.

The X2 feature permits keeping the same CPU power at an oscillator frequency

divided by two. The prescaler allows to decrease CPU and peripherals clock

frequency.

The fully static design of the AT8xC5111 can reduce system power consumption by

bringing the clock frequency down to any value, even DC, without loss of data.

The AT8xC5111 has 3 software-selectable modes of reduced activity for further reduc-

tion in power consumption. In the idle mode, the CPU is frozen while the peripherals

are still operating. In the quiet mode, only the A/D converter is operating.

Low Pin Count

8-bit

Microcontroller

with A/D

Converter

AT83C5111

AT87C5111

2

AT8xC5111

4190A�8051�11/02

In the power-down mode, the RAM is saved and all other functions are inoperative. Two

oscillator sources, crystal and RC, provide a versatile power management.

The AT8xC5111 is proposed in low-pin count packages. Port 0 and Port 2 (address/data

buses) are not available .

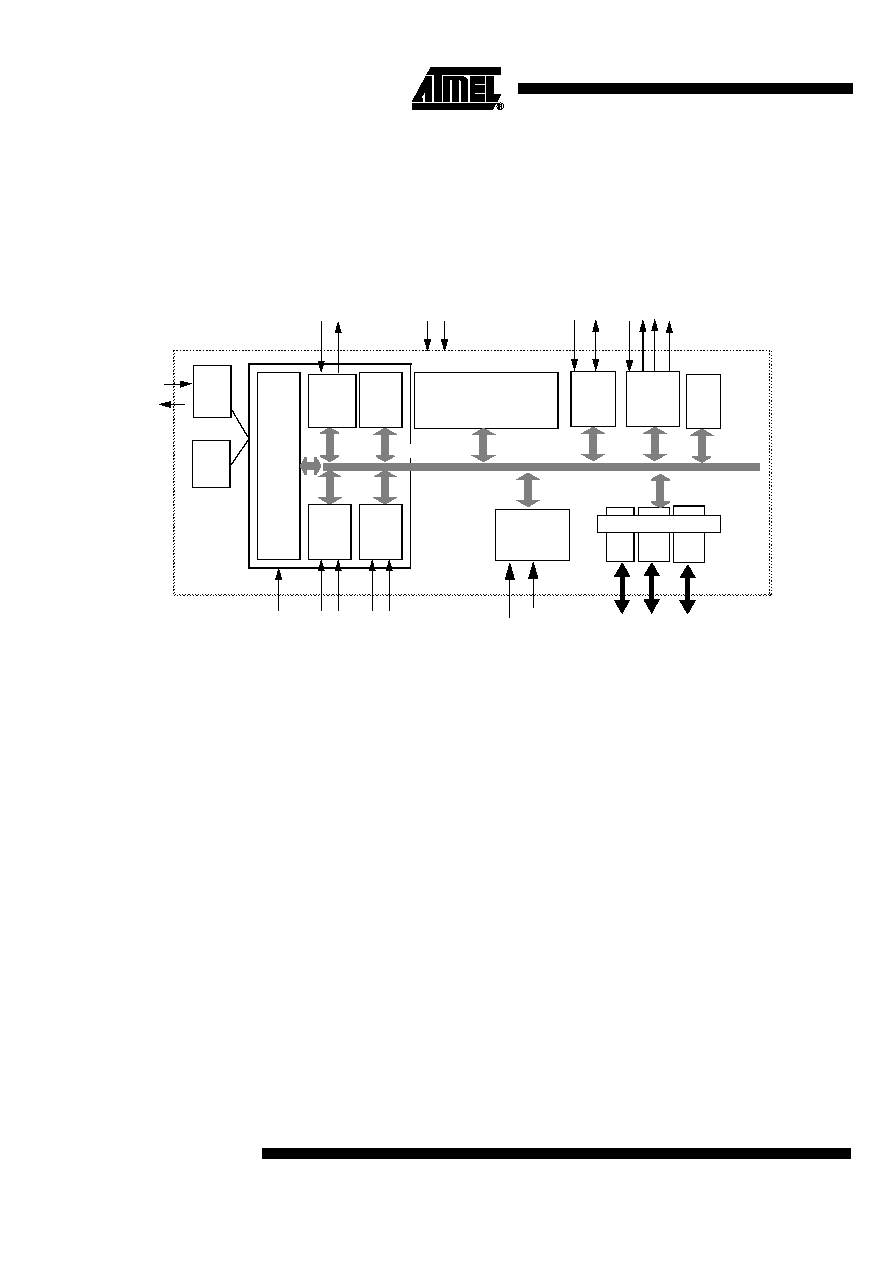

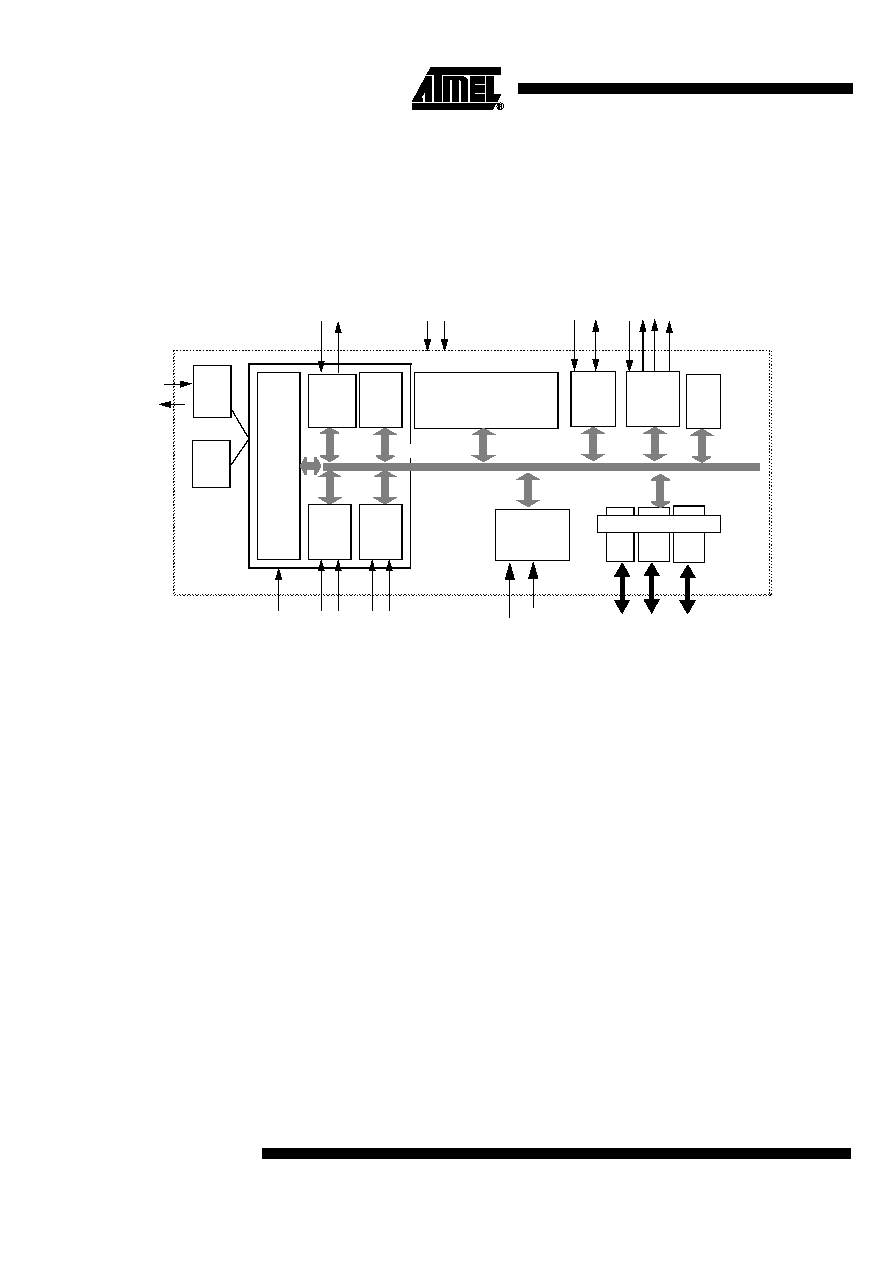

Block Diagram

Notes:

1. Alternate function of Port 1.

2. Alternate function of Port 3.

3. Alternate function of Port 4.

Timer 0

INT

RAM

256

T0

T1

Rx

D

Tx

D

XTAL2

XTAL1

EUART

CPU

Timer 1

IN

T

1

Ctrl

IN

T

0

C51

CORE

(2) (3)

(2) (3)

Port 1 Port 3

P1

P4

IB-bus

Watch

Dog

Vs

s

Vc

c

(2)

(2)

ROM /OTP

4K *8

x8

ECI

CEX0

-

4

Xtal

Osc

RC

Osc

(1)

(1)

Port 4

P3

(2)

(2)

(2)

PCA

MIS

O

(3)

MO

S

I

(3)

SPS

CK

(3)

SPI

BRG

SS

(3)

RST

/

V

PP

A/D

Converter

V

RE

F

AIN

0

-

7

(3)

Parallel I/O Ports

3

AT8xC5111

4190A�8051�11/02

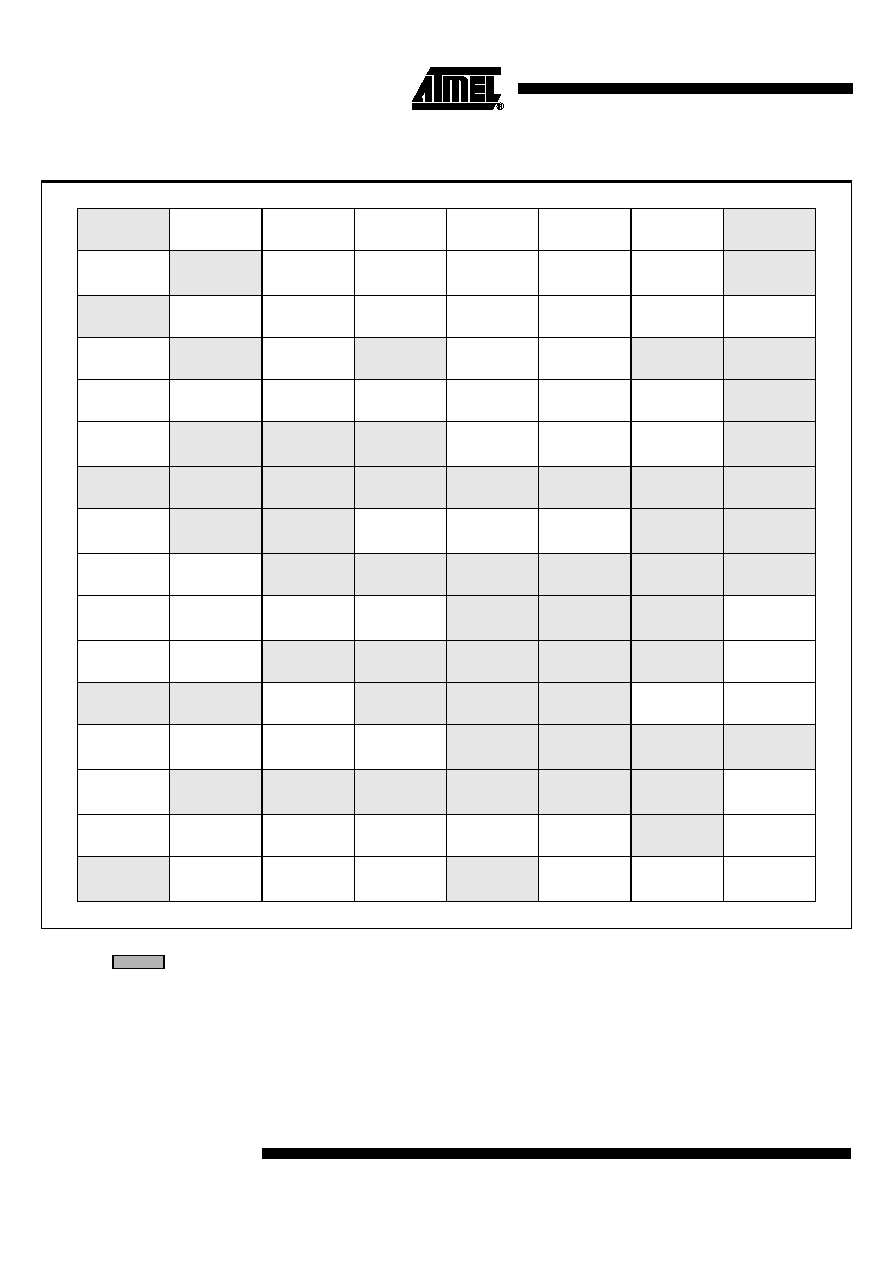

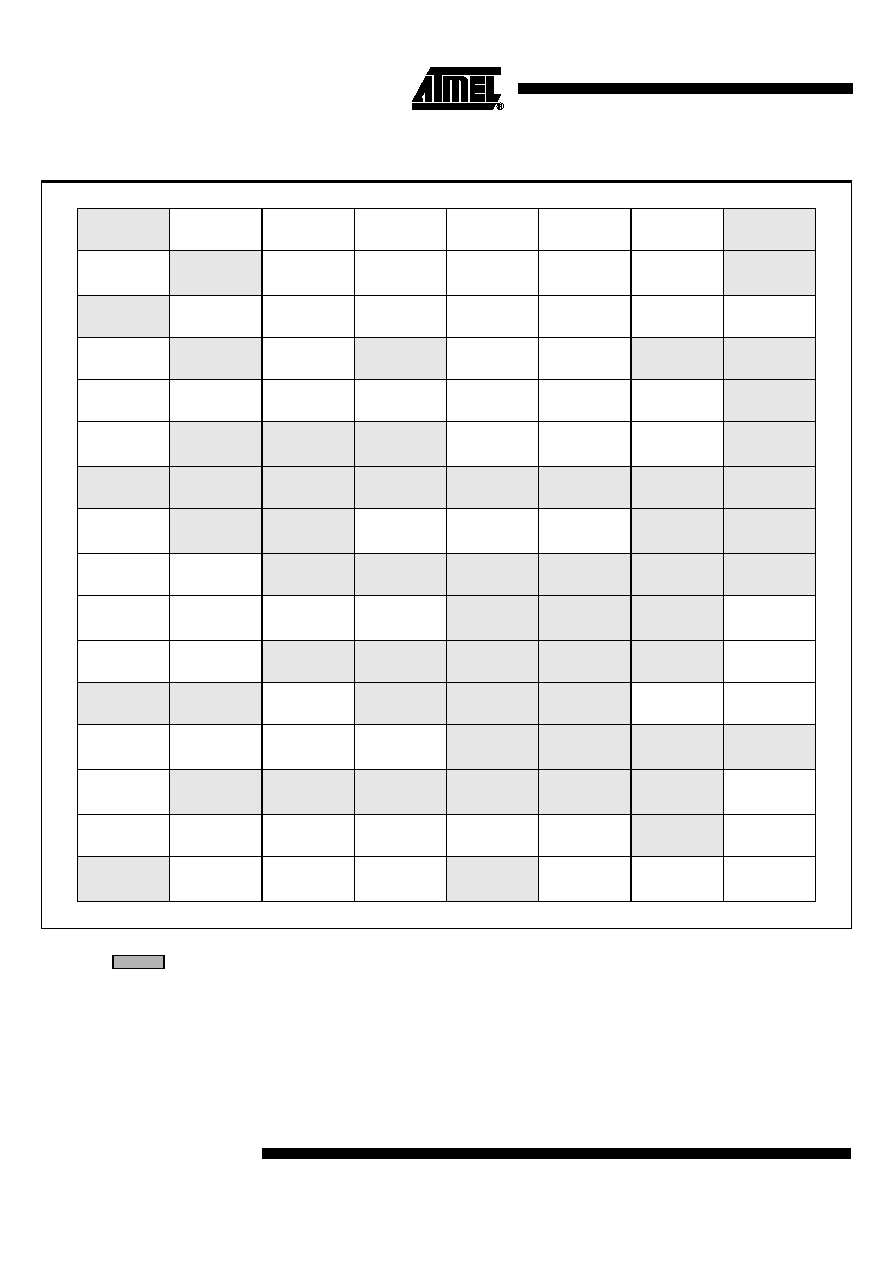

SFR Mapping

The Special Function Registers (SFRs) of the AT8xC5111 belong to the following

categories:

�

C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

�

I/O port registers: P1, P3, P4, P1M1, P1M2, P3M1, P3M2, P4M1, P4M2

�

Timer registers: TCON, TH0, TH1, TMOD, TL0, TL1

�

Serial I/O port registers: SADDR, SADEN, SBUF, SCON, BRL, BDRCON

�

Power and clock control registers: CKCON0, CKCON1, OSCCON, CKSEL, PCON,

CKRL

�

Interrupt system registers: IE, IE1, IPL0, IPL1, IPH0, IPH1

�

Watchdog Timer: WDTRST, WDTPRG

�

SPI: SPCON, SPSTA, SPDAT

�

PCA: CCAP0L, CCAP1L, CCAP2L, CCAP3L, CCAP4L, CCAP0H, CCAP1H,

CCAP2H, CCAP3H, CCAP4H, CCAPM0, CCAPM1, CCAPM2, CCAPM3,

CCAPM4, CL, CH, CMOD, CCON

�

ADC: ADCCON, ADCCLK, ADCDATH, ADCDATL, ADCF

4

AT8xC5111

4190A�8051�11/02

Reserved

Table 1. SFR Addresses and Reset Values

0/8

1/9

72/A

3/B

4/C

5/D

6/E

7/F

F8h

CH

0000 0000

CCAP0H

XXXX XXXX

CCAP1H

XXXX XXXX

CCAP2H

XXXX XXXX

CCAP3H

XXXX XXXX

CCAP4H

XXXX XXXX

FFh

F0h

B

0000 0000

ADCLK

0000 0000

ADCON

0000 0000

ADDL

XXXXXX00

ADDH

0000 0000

ADCF

0000 0000

F7h

E8h

CL

0000 0000

CCAP0L

XXXX XXXX

CCAP1L

XXXX XXXX

CCAP2L

XXXX XXXX

CCAP3L

XXXX XXXX

CCAP4L

XXXX XXXX

CONF

EFh

E0h

ACC

0000 0000

P1M2

0000 0000

P3M2

0000 0000

P4M2

0000 0000

E7h

D8h

CCON

00X0 0000

CMOD

X000 0000

CCAPM0

00XX X000

CCAPM1

X000 0000

CCAPM2

X000 0000

CCAPM3

X000 0000

CCAPM4

X000 0000

DFh

D0h

PSW

0000 0000

P1M1

0000 0000

P3M1

0000 0000

P4M1

0000 0000

D7h

C8h

CFh

C0h

P4

1111 1111

SPCON

0001 0100

SPSTA

XXXXXXXX

SPDAT

XXXX XXXX

C7h

B8h

IPL0

0000 0000

SADEN

0000 0000

BFh

B0h

P3

1111 1111

IE1

0000 0000

IPL1

0000 0000

IPH1

0000 0000

IPH0

X000 0000

B7h

A8h

IE0

0000 0000

SADDR

0000 0000

CKCON1

XXXX XXX0

AFh

A0h

AUXR1

XXXXXXX0

WDRST

0000 0000

WDTPRG

0000 0000

A7h

98h

SCON

0000 0000

SBUF

XXXX XXXX

BRL

0000 0000

BDRCON

0000 0000

9Fh

90h

P1

1111 1111

CKRL

1111 1111

97h

88h

TCON

0000 0000

TMOD

0000 0000

TL0

0000 0000

TL1

0000 0000

TH0

0000 0000

TH1

0000 0000

CKCON0

X000X000

8Fh

80h

SP

0000 0111

DPL

0000 0000

DPH

0000 0000

CKSEL

XXXX XXX1

OSCCON

XXXX XX01

PCON

00X1 0000

87h

0/8

1/9

2/A

3/B

4/C

5/D

6/E

7/F

5

AT8xC5111

4190A�8051�11/02

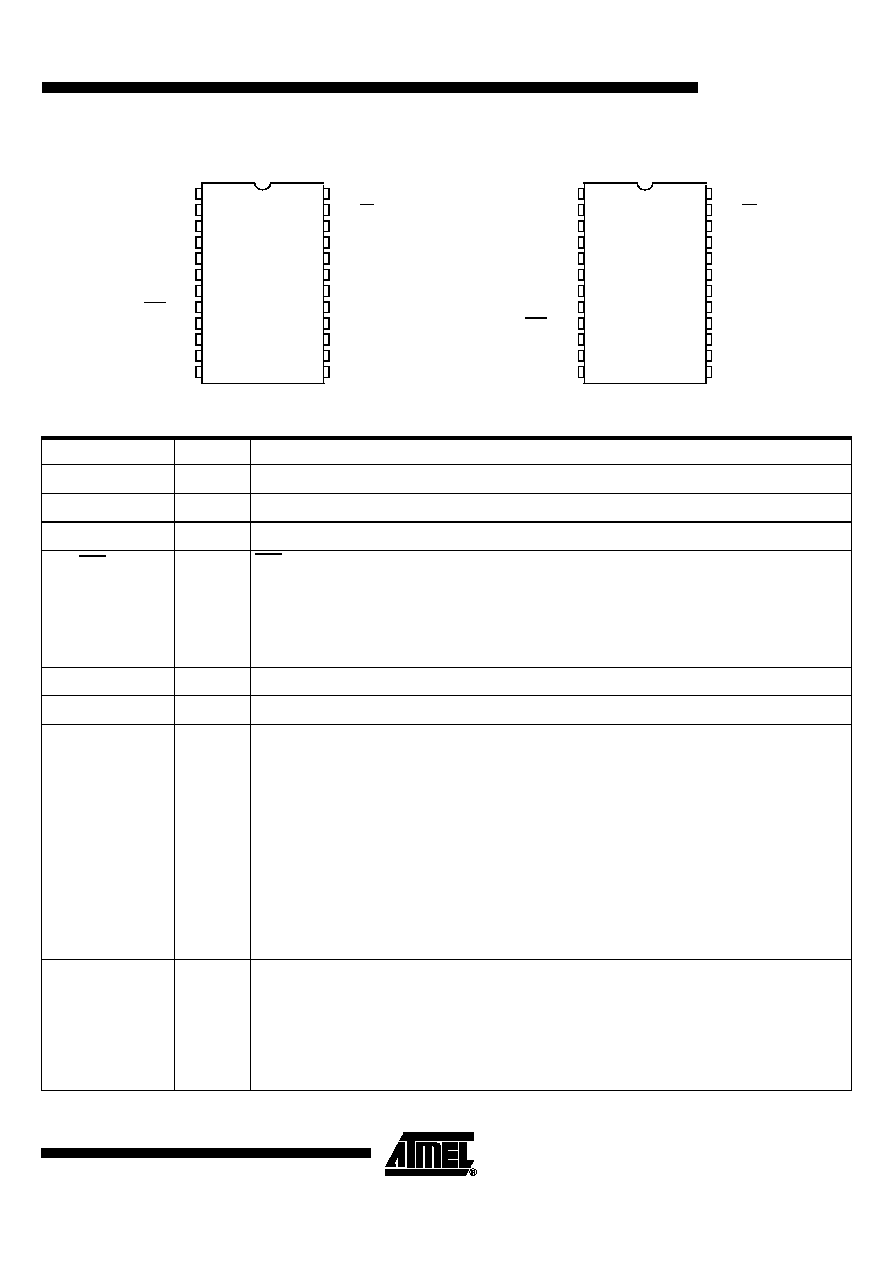

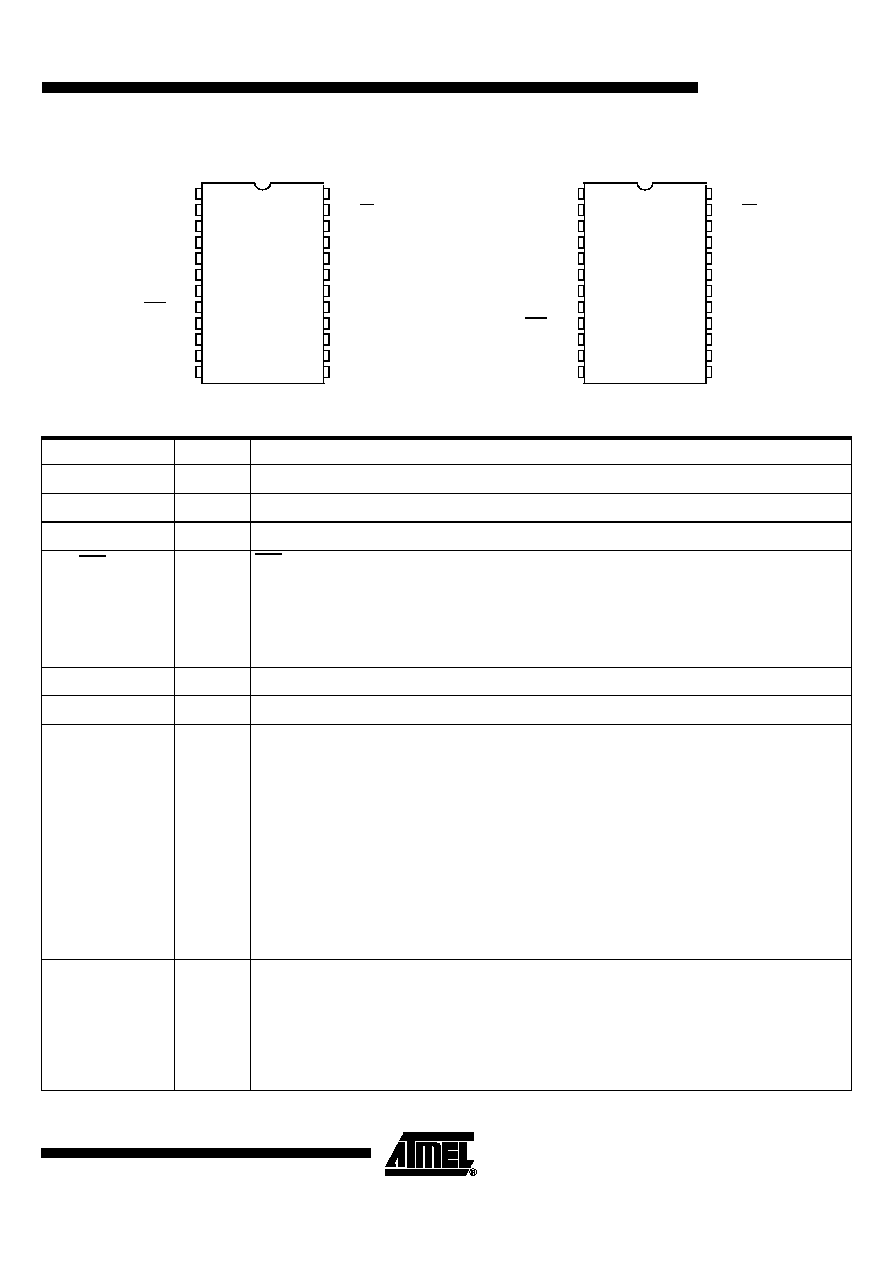

Pin Configuration

Pin Descriptions

XTAL1

P1.7/CEX4

P4.7/AIN7

1

VCC

P1.6/CEX3

P3.1/TxD

P1.3/CEX0

P1.2/ECI

P1.4/CEX1

P4.4/MISO/AIN4

P4.6/SPSCK/AIN6

P4.5/MOSI/AIN5

P4.3/INT1/AIN3

P4.2/SS/AIN2

P4.1/AIN1/T1

P4.0/AIN0

P3.0/RxD

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

P1.5/CEX2

P3.3/T0

P3.2/INT0

SO24

DIL24

VREF

VSS

RST/VPP

XTAL2

XTAL2

XTAL1

VREF

1

AVCC

P1.6/CEX3

P3.1/TxD

P1.3/CEX0

P1.2/ECI

P1.4/CEX1

P4.4/MISO/AIN4

P4.6/SPSCK/AIN6

P4.5/MOSI/AIN5

P4.3/INT1/AIN3

P4.2/SS/AIN2

P4.1/AIN1/T1

P4.0/AIN0

P3.0/RxD

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

P1.5/CEX2

P3.3/T0

P3.2/INT0

SSOP24

VSS

AVSS

VCC

RST/VPP

Mnemonic

Type

Name and Function

V

SS

I

Ground: 0V reference

V

CC

I

Power Supply: This is the power supply voltage for normal, idle and power-down operation.

VREF

I

VREF: A/D converter positive reference input

RST/VPP

I

RST/V

PP

: Reset/Programming Supply Voltage:

A low on this pin for two machine cycles while the oscillator is running, resets the device. This pin

has no pull-up. In order to use the internal power-on reset, an external pull-up resistor must be

connected.

This pin also receives the 12V programming pulse which will start the EPROM programming and the

manufacturer test modes.

XTAL1

I

XTAL1 : Input to the inverting oscillator amplifier and input to the internal clock generator circuits

XTAL2

O

XTAL2 : Output from the inverting oscillator amplifier

P1.2 - P1.7

I/O

Port 1: Port 1 is an 6-bit programmable I/O port . See Section "Ports", page 18 for a description of

I/O ports.

Alternate functions for Port 1 include:

I/O

ECI (P1.2): External Clock for the PCA

I/O

CEX0 (P1.3): Capture/Compare External I/O for PCA module 0

I/O

CEX1 (P1.4): Capture/Compare External I/O for PCA module 1

I/O

CEX2 (P1.5): Capture/Compare External I/O for PCA module 2

I/O

CEX3 (P1.6): Capture/Compare External I/O for PCA module 3

I/O

CEX4 (P1.7): Capture/Compare External I/O for PCA module 4

P3.0 - P3.3

I/O

Port 3: Port 3 is an 6-bit programmable I/O port with internal pull-ups. See Section "Ports", page 18

for a description of I/O ports.

Port 3 also serves the special features of the 80C51 family, as listed below.

I/O

RXD (P3.0): Serial input port

I/O

TXD (P3.1): Serial output port