Rev. 4779F≠ISM≠09/04

Features

∑

Fully Integrated Low IF Receiver

∑

Fully Integrated GFSK Modulator for 72, 144, 288, 576 and 1152 kBit/s

∑

High Sensitivity of Typically -93 dBm Due to Integrated LNA

∑

High Output Power of Typically +4 dBm

∑

Multi-channel Operation

≠ 95 Channels

≠ Support Frequency Hopping (ETSI) and Digital Modulation (FCC)

∑

Supply-voltage Range 2.9 V to 3.6 V (Unregulated)

∑

Auxiliary-voltage Regulator on Chip (3.2 V to 4.6 V)

∑

Low Current Consumption

∑

Few Low Cost External Components

∑

Integrated Ramp-signal Generator and Power Control for an Additional

Power Amplifier

∑

Low Profile Lead-free Plastic Package QFN32 (5

◊

5

◊

0.9 mm)

Applications

∑

Hightech Multi-user Toys

∑

Wireless Game Controllers

∑

Telemetry

∑

Wireless Audio/Video

∑

Electronic Point of Sales

∑

Wireless Head Set

∑

FCC CFR47, Part 15, ETSI EN 300 328 and ARIB STD-T-66 Compliant Radio Links

Electrostatic sensitive device.

Observe precautions for handling.

Description

The ATR2406 is a single chip RF-transceiver intended for applications in the 2.4 GHz

ISM band. The QFN32 packaged IC is a complete transceiver including image rejec-

tion mixer, low IF filter, FM demodulator, RSSI, TX preamplifier, power-ramping

generator for external power amplifier, integrated synthesizer, and a fully integrated

VCO and TX filter. No mechanical adjustment is necessary in production.

The RF-transceiver offers a clock recovery function on-chip.

Low IF 2.4 GHz

ISM Transceiver

ATR2406

Preliminary

2

ATR2406 [Preliminary]

4779F≠ISM≠09/04

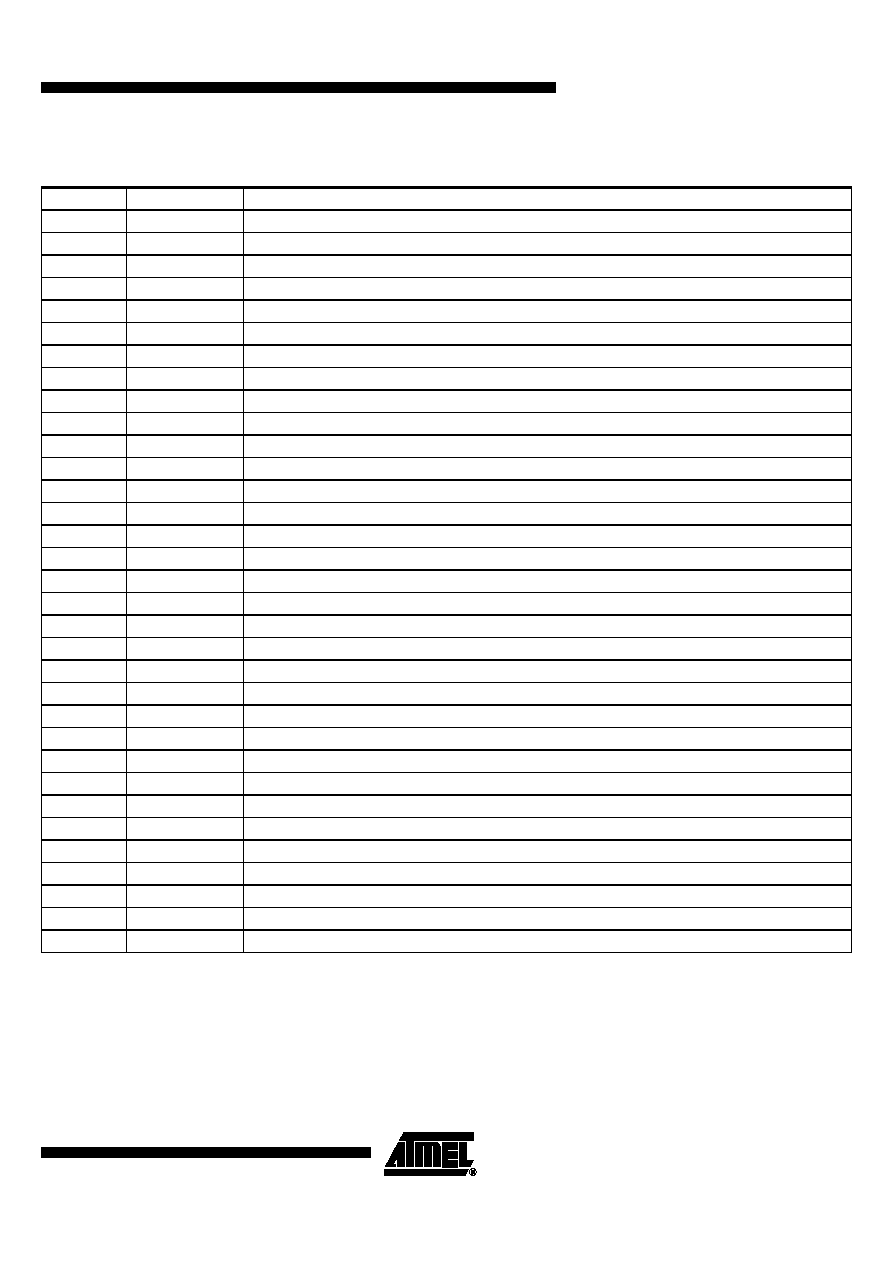

Figure 1. Block Diagram

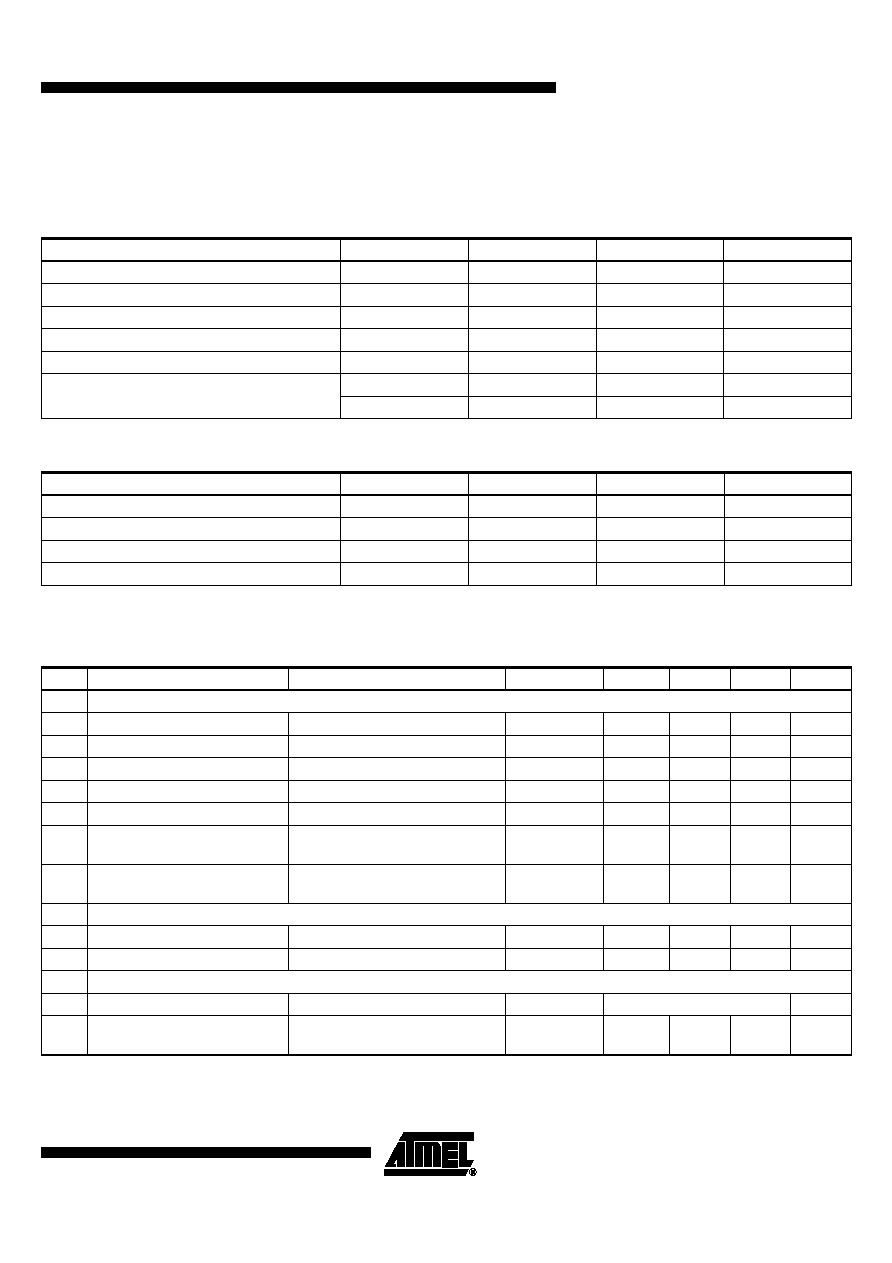

Pin Configuration

Figure 2. Pinning QFN32 - 5

◊

5

LNA

IR-MIXER

BP

VTUNE

VREG_VCO

VREG REG_CTRL VS_REG IREF

RX_IN

VS_SYN

RX-CLOCK

RX_DATA

RSSI

CLOCK

DATA

VS_IFA

VS_IFD

REG_DEC

DEMOD

LIMITER

RSSI

ENABLE

VS_RX/TX

RAMP_OUT

PA

TX_OUT

nOLE

PLL

REF_CLK

VCO

CP

TX_DATA

VCO

REG

AUX

REG

VREF

BUS

GAUSSIAN

FILTER

CTRL

LOGIC

PU_TRX

TX_ON

PU_REG

RX_ON

RAMP

GEN

32 31 30 29 28 27 26 25

9 10 11 12 13 14 15 16

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

ATR2406

PU_REG

REF_CLK

RSSI

VS_IFD

VS_IFA

RX-CLOCK

IC

IREF

RX_ON

RAMP_OUT

TX_OUT

RX_IN1

RX_IN2

VS_TRX

EN

ABL

E

DA

T

A

CLOCK

TX_D

ATA

RX

_DA

T

A

PU

_

T

R

X

nOLE

TX_ON

RE

G_CT

RL

VR

EG

VS_

R

E

G

RE

G_DE

C

VR

EG

_

V

C

O

V

T

UNE

CP

VS_

SYN

IC

IC

3

ATR2406 [Preliminary]

4779F≠ISM≠09/04

Pin Description

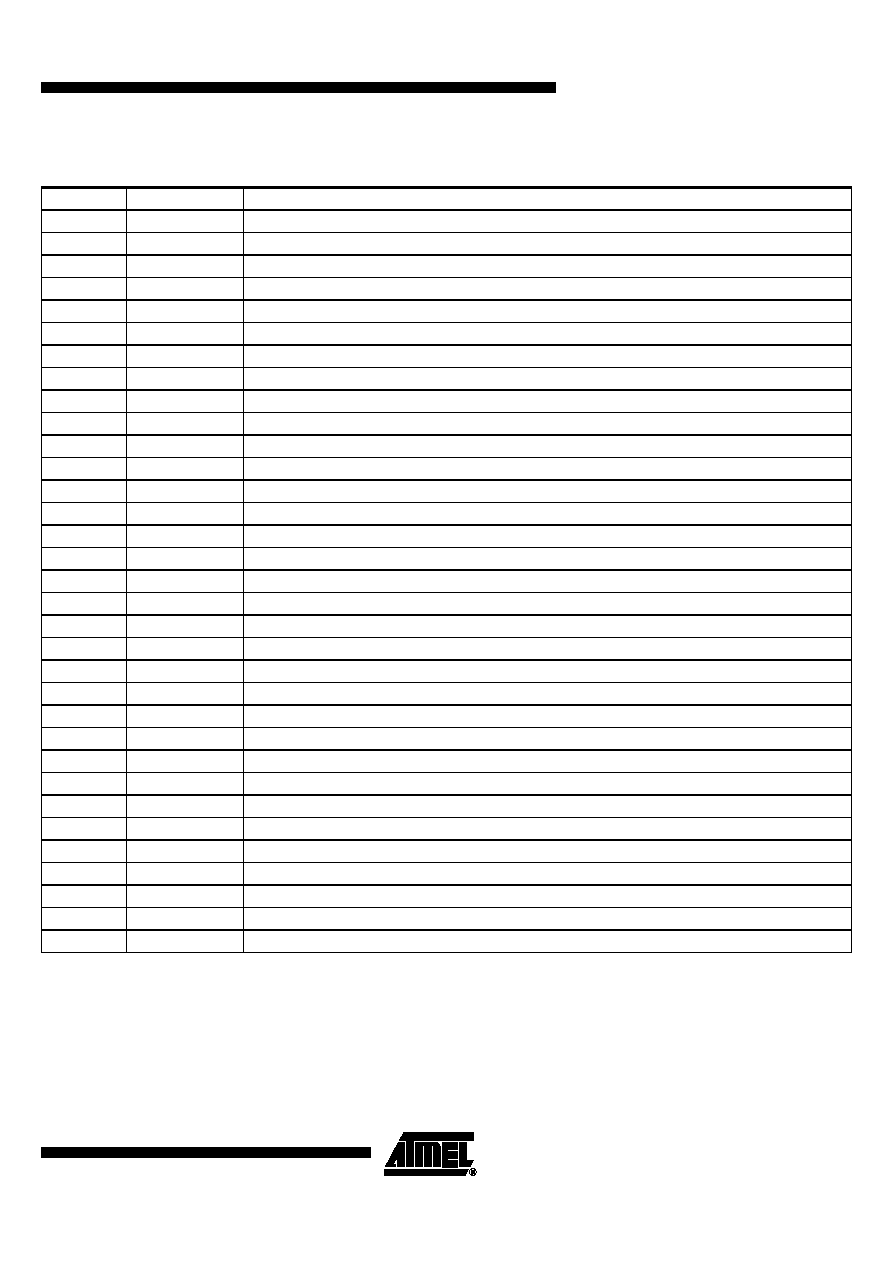

Pin

Symbol

Function

1

PU_REG

Power-up input for auxiliary regulator

2

REF_CLK

Reference frequency input

3

RSSI

Received signal strength indicator output

4

VS_IFD

Digital supply voltage

5

VS_IFA

Analog supply voltage for IF circuits

6

RX-CLOCK

RX-CLOCK, if RX mode with clock recovery is active

7

IC

Internal connected, do not connect on PCB

8

IREF

External resistor for band-gap reference

9

REG_CTRL

Auxiliary voltage regulator control output

10

VREG

Auxiliary voltage regulator output

11

VS_REG

Auxiliary voltage regulator supply voltage

12

REG_DEC

Decoupling pin for VCO_REG

13

VREG_VCO

VCO voltage regulator

14

VTUNE

VCO tuning voltage input

15

CP

Charge-pump output

16

VS_SYN

Synchronous supply voltage

17

VS_TRX

Transmitter receiver supply voltage

18

RX_IN2

Differential receiver input 2

19

RX_IN1

Differential receiver input 1

20

TX_OUT

TX driver amplifier output

21

RAMP_OUT

Ramp generator output for PA power ramping

22

IC

Internal connected, do not connect on PCB

23

IC

Internal connected, do not connect on PCB

24

RX_ON

RX control input

25

TX_ON

TX control input

26

nOLE

Open loop enable input

27

PU_TRX

RX/TX/PLL/VCO power-up input

28

RX_DATA

RX data output

29

TX_DATA

TX data input

30

CLOCK

3-wire-bus: Clock input

31

DATA

3-wire-bus: Data input

32

ENABLE

3-wire-bus: Enable input

Paddle

GND

Ground

4

ATR2406 [Preliminary]

4779F≠ISM≠09/04

Functional Description

Receiver

The RF signal at RF_IN is differently fed through the LNA to the image rejection mixer

IR_MIXER driving the integrated LowIF bandpass filter. The IF frequency is

864 kHz.The limiting IF_AMP with an integrated RSSI function feeds the signal to the

digital demodulator DEMOD. No tuning is required. Datasling is handled internally.

Clock Recovery

For 1152 kBit/s data rate the receiver has a clock recovery function on-chip.

The receiver includes a clock recovery circuit which regenerates the clock out of the

received data. The advantage is that this recovered clock is synchronous to the clock of

the transmitting device (and thus to the transmitted data) which allows to reduce the

load of the processing microcontroller significantly.

The falling edge of the clock gives the optimal sampling position for the RX_Data signal

so at this event the data must be sampled by the microcontroller. The recovered clock is

available at pin 6.

Transmitter

The transmit data at TX_DATA is filtered by an integrated Gaussian Filter GF and fed to

the fully integrated VCO operating at twice the output frequency. After modulation the

signal is frequency-divided by 2 and fed to the internal preamplifier PA. This preamplifier

supplies typically +4 dBm output power at TX_OUT.

A ramp-signal generator RAMP_GEN, providing a ramp signal at RAMP_OUT for the

external power amplifier, is integrated. The slope of the ramp signal is controlled inter-

nally so that spurious requirements are fulfilled.

Synthesizer

The IR_MIXER, the PA and the programmable counter PC are driven by the fully inte-

grated VCO, using on-chip inductors and varactors. The output signal is frequency

divided to supply the desired frequency to the TX_DRIVER, 0/90 degree phase shifter

f o r t h e I R _ M I X E R a n d t o b e u s e d b y t h e P C f o r t h e p h a s e d e t e c t o r P D

(f

PD

= 1.728 MHz). Open loop modulation is supported.

Power Supply

An integrated bandgap-stabilized voltage regulator for use with an external low-cost

PNP transistor is implemented. Multiple power-down and current saving modes are

provided.

5

ATR2406 [Preliminary]

4779F≠ISM≠09/04

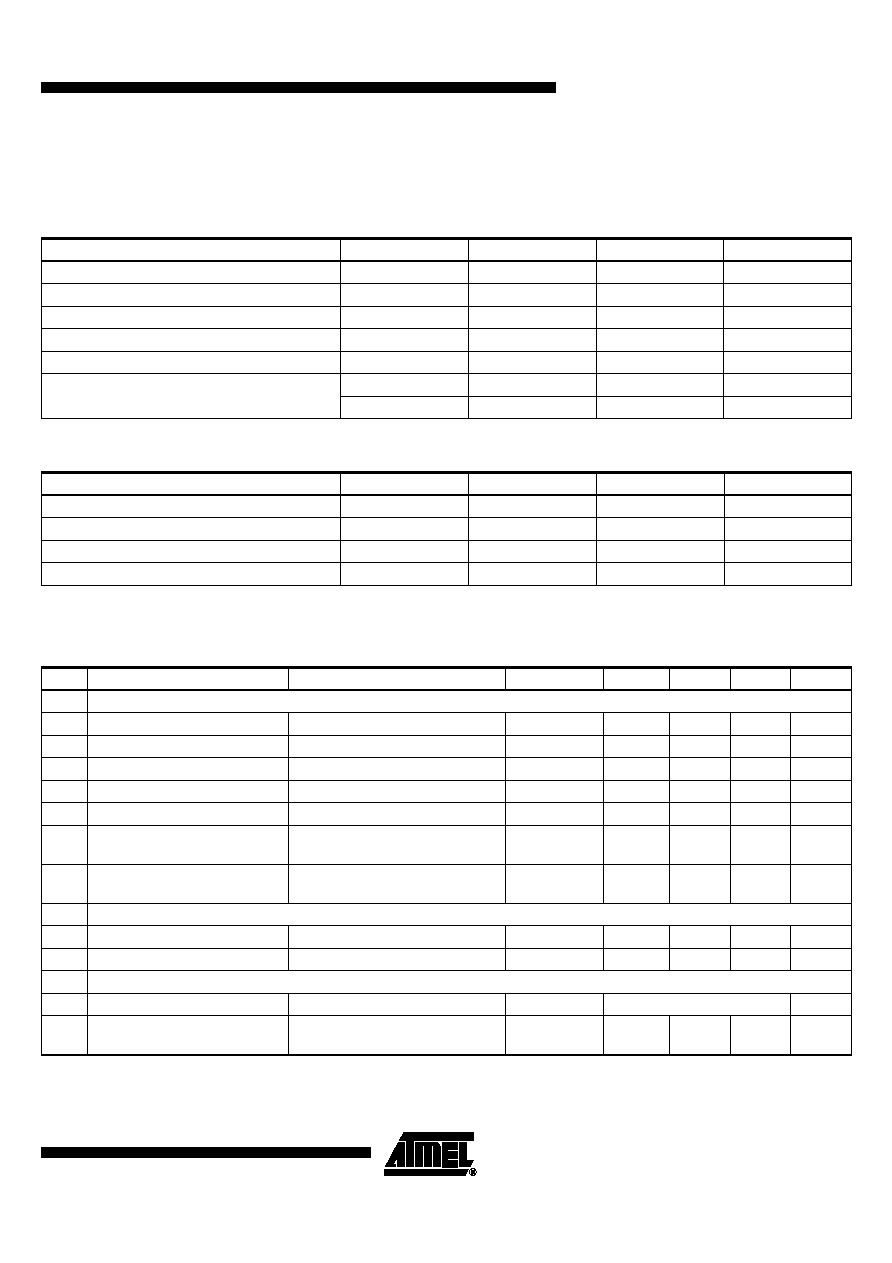

Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Parameters

Symbol

Min.

Max.

Unit

Supply voltage auxiliary regulator

V

S

-0.3

+4.7

V

Supply voltage

V

S

-0.3

+3.6

V

Control voltages

V

contr

-0.3

V

S

V

Storage temperature

T

stg

-40

+125

∞C

Input RF level

P

RF

+10

dBm

ESD protection

V

ESD_anal

TBD

V

V

ESD_dig

TBD

V

Operating Range

Parameters

Symbol

Min.

Max.

Unit

Supply voltage

V

S

2.9

3.6

V

Auxiliary regulator supply voltage

V

S_BATT

3.2

4.6

V

Temperature ambient

T

amb

-10

+60

∞C

Input frequency range

f

RX

2400

2483

MHz

Electrical Characteristics

V

S

= 3.6 V with AUX regulator, T

amb

= 25∞C, unless otherwise specified

No.

Parameters

Test Conditions

Symbol

Min.

Typ.

Max.

Unit

1

Supply

1.1

Supply voltage

With AUX regulator

V

S

3.2

3.6

4.6

V

1.2

Supply voltage

w/o AUX regulator

V

S

2.9

3.0

3.6

V

1.3

RX supply current

CW-mode

I

S

31

mA

1.4

TX supply current

CW-mode

I

S

16

mA

1.5

Synthesizer supply current

I

S

26

mA

1.6

Supply current in power-down

mode

With AUX regulator

PU_TRX = 0; PU_REG = 0

I

S

< 1

µA

1.7

Supply current in power-down

mode

w/o AUX regulator

PU_TRX = 0; PU_REG = 0

I

S

< 1

µA

2

Voltage Regulator

2.1

AUX regulator

VREG

3.0

V

2.2

VCO regulator

VREG_VCO

2.7

V

3

Transmitter Part

3.1

TX data rate

72/144/288/576/1152

kBit/s

3.2

Output power

Over full temperature range, from

2400 MHz to 2483 MHz

(1)

PTX

0

4

dBm

Notes:

1. Measured and guaranteed only on the Atmel evaluation board, including PCB and balun filter.

2. Timing is determined by external loop filter characteristics. Faster timing can be achieved by modification of loop filter. For

further information refer to Application Note.