| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: T7024-TRS | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

4533D≠BLURF≠01/04

Features

∑

Single 3-V Supply Voltage

∑

High Power-added Efficient Power Amplifier (P

out

Typically 23 dBm)

∑

Ramp-controlled Output Power

∑

Low-noise Preamplifier (NF Typically 2.1 dB)

∑

Biasing for External PIN Diode T/R Switch

∑

Current-saving Standby Mode

∑

Few External Components

∑

Packages:

≠ PSSO20

≠ QFN20 with Extended Performance

Electrostatic sensitive device.

Observe precautions for handling.

Description

The T7024 is a monolithic SiGe transmit/receive front-end IC with power amplifier,

low-noise amplifier and T/R switch driver. It is especially designed for operation in

TDMA systems like Bluetooth

TM

and WDCT.

Due to the ramp-control feature and a very low quiescent current, an external switch

transistor for V

S

is not required.

Figure 1. Block Diagram

PA

PA_IN

V3_PA_OUT

RAMP

V2_PA

V1_PA

LNA

LNA_OUT

LNA_IN

TX/RX/

standby

Control

PU

RX_ON

VS_LNA

SWITCH_OUT

R_SWITCH

TX

RX

Bluetooth

TM

/ISM

2.4-GHz Front-

End IC

T7024

2

T7024

4533D≠BLURF≠01/04

Pin Configuration

Figure 2. Pinning PSSO20

Figure 3. Pinning QFN20

1

2

3

4

5

6

7

8

10

9

19

18

17

16

14

15

13

12

11

20

LNA_IN

VS_LNA

GND

V3_PA_OUT

V3_PA_OUT

V3_PA_OUT

SWITCH_OUT

GND

GND

PA_IN

V1_PA

GND

V2_PA

V2_PA

RX_ON

LNA_OUT

GND

RAMP

R_SWITCH

PU

T7024

1

2

3

4

5

15

14

13

12

11

10

6

7

8

9

16

20

19

18

17

LNA_OUT

RX_ON

PU

R_SWITCH

SWITCH_OUT

G

N

D

V

S

_

L

N

A

G

N

D

L

N

A

_

I

N

G

N

D

V3_PA_OUT

V3_PA_OUT

V3_PA_OUT

GND

RAMP

V

2

_

P

A

V

2

_

P

A

G

N

D

V

1

_

P

A

P

A

_

I

N

T7024

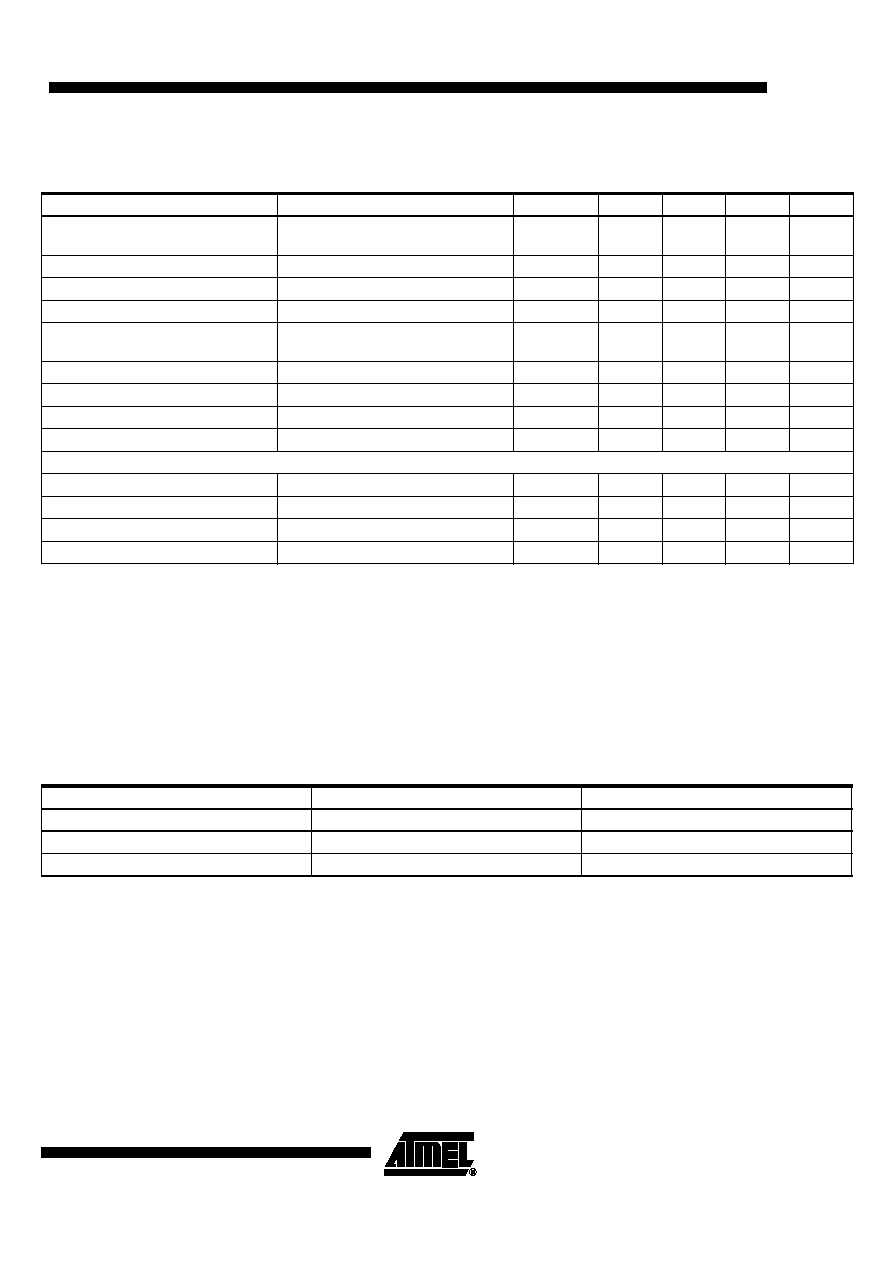

Pin Description

Pins PSSO20

Pins QFN20

Symbol

Function

1

4

R_SWITCH

Resistor to GND sets the PIN diode current

2

5

SWITCH_OUT

Switched current output for PIN diode

3

6

GND

Ground

4

7

LNA_IN

Low-noise amplifier input

5

9

VS_LNA

Supply voltage input for low-noise amplifier

6

8

GND

Ground

7

11

V3_PA_OUT

Inductor to power supply and matching network for power amplifier output

8

12

V3_PA_OUT

Inductor to power supply and matching network for power amplifier output

9

13

V3_PA_OUT

Inductor to power supply and matching network for power amplifier output

10

10

GND

Ground

11

15

RAMP

Power ramping control input

12

16

V2_PA

Inductor to power supply for power amplifier

13

17

V2_PA

Inductor to power supply for power amplifier

14

14

GND

Ground

15

19

V1_PA

Supply voltage for power amplifier

16

20

PA_IN

Power amplifier input

17

18

GND

Ground

18

1

LNA_OUT

Low-noise amplifier output

19

2

RX_ON

RX active high

20

3

PU

Power-up active high

Slug

Slug

GND

Ground

3

T7024

4533D≠BLURF≠01/04

Handling

Do not operate this part near strong electrostatic fields. This IC meets class 1 ESD test

requirement (HBM in accordance to EIA/JESD22-A114-A (October 97) and class A ESD

test requirement (MM) in accordance to EIA/JESD22-A115A.

Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Parameters

Symbol

Value

Unit

Supply voltage

Pins VS_LNA, V1_PA, V2_PA, V3_PA_OUT

V

S

6

V

Junction temperature

T

j

150

∞

C

Storage temperature

T

stg

-40 to +125

∞

C

RF input power LNA

P

inLNA

5

dBm

RF input power PA

P

inPA

10

dBm

Thermal Resistance

Parameters

Symbol

Value

Unit

Junction ambient PSSOP20, slug soldered on PCB

R

thJA

19

K/W

Junction ambient QFN20, slug soldered on PCB

R

thJA

27

K/W

Operating Range

All voltages are referred to ground (pins GND and slug). Power supply points are VS_LNA, V1_PA, V2_PA, V3_PA_OUT.

The table represents the sum of all supply currents depending on the TX/RX mode.

Parameters

Symbol

Min.

Typ.

Max.

Unit

Supply voltage

Pins V1_PA, V2_PA and V3_PA_OUT

V

S

2.7

3.0

4.6

V

Supply voltage

Pin VS_LNA

V

S

2.7

3.0

5.5

V

Supply current TX

PSSO20

QFN20

Supply current RX

I

S

I

S

I

S

190

165

8

mA

mA

mA

Standby current

PU = 0

I

S_standby

10

µA

Ambient temperature

T

amb

-25

+25

+85

∞

C

4

T7024

4533D≠BLURF≠01/04

Electrical Characteristics

Test conditions (unless otherwise specified): V

S

= 3.0 V, T

amb

= 25∞C

Parameters

Test Conditions

Symbol

Min.

Typ.

Max.

Unit

Power Amplifier

(1)

Supply voltage

Pins V1_PA, V2_PA, V3_PA_OUT

V

S

2.7

3.0

4.6

V

Supply current

TX

PSSO20

TX

QFN20

I

S_TX

I

S_TX

190

165

mA

mA

RX (PA off), V

RAMP

0.1 V

I

S_RX

10

µA

Standby current

Standby

I

S_standby

10

µA

Frequency range

TX

f

2.4

2.5

GHz

Gain-control range

TX

Gp

60

42

dB

Power gain maximum

TX, Pin PA_IN to V3_PA_OUT

Gp

28

30

33

dB

Power gain minimum

TX, Pin PA_IN to V3_PA_OUT

Gp

-40

-17

dB

Ramping voltage maximum

TX, power gain (maximum)

Pin RAMP

V

RAMP max

1.7

1.75

1.83

V

Ramping voltage minimum

TX, power gain (minimum)

Pin RAMP

V

RAMP min

0.1

V

Ramping current maximum

TX, V

RAMP

= 1.75 V, Pin RAMP

I

RAMP max

0.5

mA

Power-added efficiency

TX

PSSO20

TX

QFN20

PAE

PAE

30

35

35

40

%

%

Saturated output power

TX, input power = 0 dBm referred to

Pins V3_PA_OUT

P

sat

22

23

24

dBm

Input matching

(2)

TX, Pin PA_IN

Load

VSWR

<1.5:1

Output matching

(2)

TX, Pins V3_PA_OUT

Load

VSWR

<1.5:1

Harmonics at P

sat

= 23 dBm

TX, Pins V3_PA_OUT

2 fo

-30

dBc

TX, Pins V3_PA_OUT

3 fo

-30

dBc

T/R Switch Driver (Current Programming by External Resistor from R_SWITCH to GND)

Switch-out current output

Standby, Pin SWITCH_OUT

I

S_O_standby

1

µA

RX

I

S_O_RX

1

µA

TX at 100

I

S_O_100

1.7

mA

TX at 1.2 k

I

S_O_1k2

7

mA

TX at 33 k

I

S_O_33k

17

mA

TX at

I

S_O_

R

19

mA

Low-noise Amplifier

(3)

Supply voltage

All, Pin VS_LNA

V

S

2.7

3.0

5.5

V

Supply current

RX

I

S

8

9

mA

Notes:

1. Power amplifier shall be unconditionally stable, maximum duty cycle 100%, true CW operation, maximum load mismatch

and duration: load VSWR = 10:1 (all phases) 10 s, Z

G

= 50

.

2. With external matching network, load impedance 50

.

3. Low-noise amplifier shall be unconditionally stable.

4. With external matching components.

5. LNA gain can be adjusted with RX_ON voltage according to Figure 19 on page 11. Please note, that for RX_ON below

1.4 V the T/R switch driver switches to TX mode.

5

T7024

4533D≠BLURF≠01/04

Control Logic for LNA and T/R Switch Driver

Supply current

(LNA and control logic)

TX (control logic active)

Pin VS_LNA

I

S

0.5

mA

Standby current

Standby, Pin VS_LNA

I

S_standby

1

10

µA

Frequency range

RX

f

2.4

2.5

GHz

Power gain

(5)

RX, Pin LNA_IN to LNA_OUT

Gp

15

16

19

dB

Noise figure

RX,

PSSO20

RX

QFN20

NF

NF

2.5

2.1

2.8

2.3

dB

dB

Gain compression

RX, referred to Pin LNA_OUT

O1dB

-9

-7

-6

dBm

3

rd

-order input interception point

RX

IIP3

-16

-14

-13

dBm

Input matching

(4)

RX, Pin LNA_IN

VSWRin

2:1

Output matching

(4)

RX Pin LNA_OUT

VSWRout

2:1

Logic Input Levels (RX_ON, PU)

(5)

High input level

= `1' Pins RX_ON and PU

V

iH

2.4

V

S, LNA

V

Low input level

= `0'

V

iL

0

0.5

V

High input current

= `1' V

iH

= 2.4 V

I

iH

40

60

µA

Low input current

= `0'

I

iL

0.2

µA

Electrical Characteristics (Continued)

Test conditions (unless otherwise specified): V

S

= 3.0 V, T

amb

= 25∞C

Parameters

Test Conditions

Symbol

Min.

Typ.

Max.

Unit

Notes:

1. Power amplifier shall be unconditionally stable, maximum duty cycle 100%, true CW operation, maximum load mismatch

and duration: load VSWR = 10:1 (all phases) 10 s, Z

G

= 50

.

2. With external matching network, load impedance 50

.

3. Low-noise amplifier shall be unconditionally stable.

4. With external matching components.

5. LNA gain can be adjusted with RX_ON voltage according to Figure 19 on page 11. Please note, that for RX_ON below

1.4 V the T/R switch driver switches to TX mode.

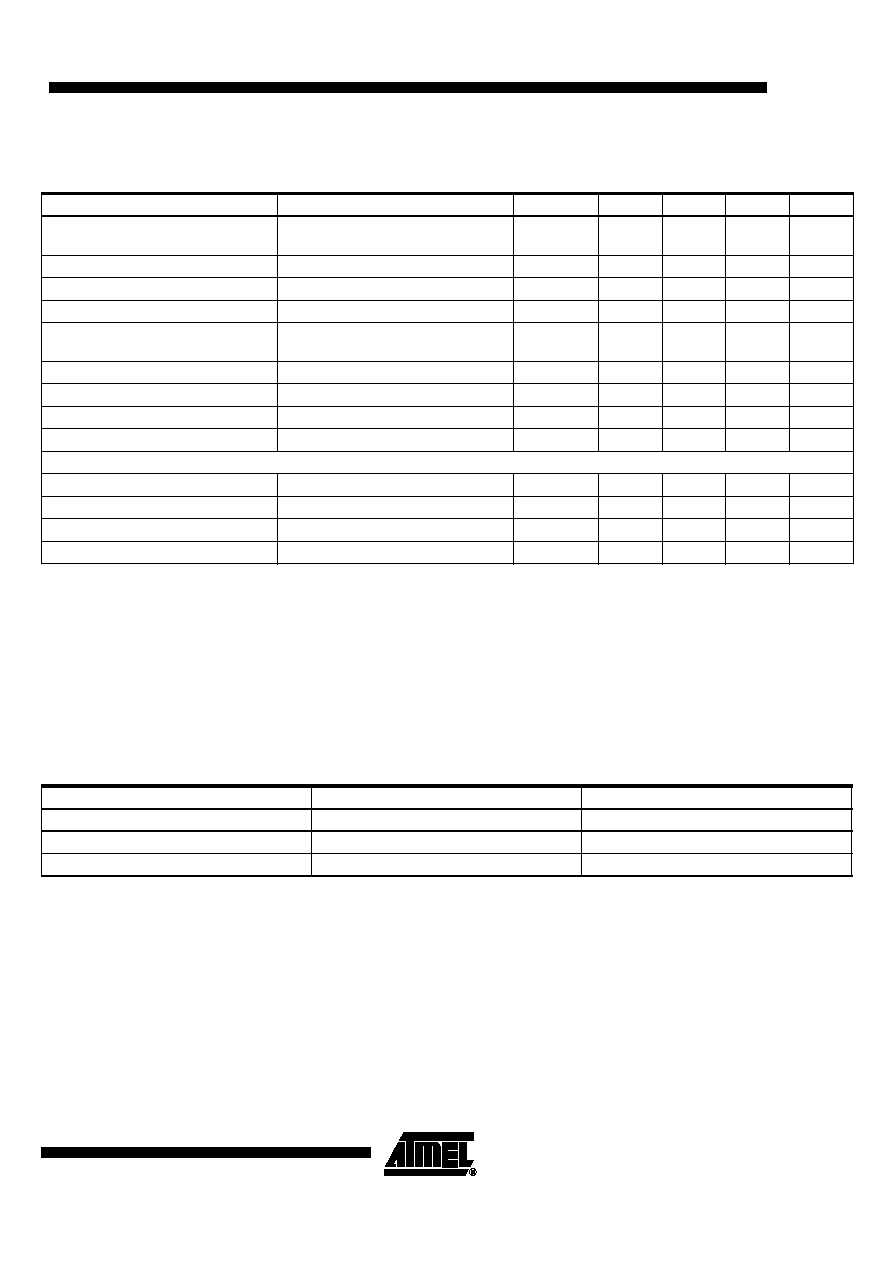

Operation Mode

PU

RX_ON

Standby

0

0

TX

1

0

RX

1

1