| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: U2794B | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

Features

∑

Supply Voltage 5 V

∑

Very Low Power Consumption 125 mW

∑

Very Good Image Rejection By Means of Phase Control Loop for Precise 90∞ Phase

Shifting

∑

Duty-cycle Regeneration for Single-ended LO Input Signal

∑

Low LO Input Level -10 dBm

∑

LO Frequency from 70 MHz to 1 GHz

∑

Power-down Mode

∑

25 dB Gain Control

∑

Very Low I/Q Output DC Offset Voltage Typically < 5 mV

Benefits

∑

Low Current Consumption

∑

Easy to Implement

∑

Perfect Performance for Large Variety of Wireless Applications

Electrostatic sensitive device.

Observe precautions for handling.

Description

The silicon monolithic integrated circuit U2794B is a quadrature demodulator manu-

factured using Atmel's advanced UHF technology. This demodulator features a

frequency range from 70 MHz to 1000 MHz, low current consumption, selectable gain,

power-down mode and adjustment-free handling. The IC is suitable for direct conver-

sion and image rejection applications in digital radio systems up to 1 GHz such as

cellular radios, cordless telephones, cable TV and satellite TV systems.

1000-MHz

Quadrature

Demodulator

U2794B

Rev. 4653C≠CELL≠06/03

2

U2794B

4653C≠CELL≠06/03

Figure 1. Block Diagram

Pin Configuration

Figure 2. Pinning SSO20

90∞Control

loop

90∞

0∞

Frequency

doubler

Duty cycle

regenerator

Power

down

14

5,6

V

S

PU

4

3

17

1

2

19

20

10

9

16,18

11

GC

GND

7

8

RF

in

IIX

II

OUTPUT

IX

I

LO

12

13

PC

PCX

OUTPUT

Q

QX

QQ

QQX

15

1

2

3

4

5

6

7

8

10

9

19

18

17

16

14

15

13

12

11

20

IX

I

II

V

S

V

S

QQ

QQX

IIX

QX

Q

GND

LO

in

GND

PU

PC

PCX

GC

RF

in

RFX

in

LOX

in

3

U2794B

4653C≠CELL≠06/03

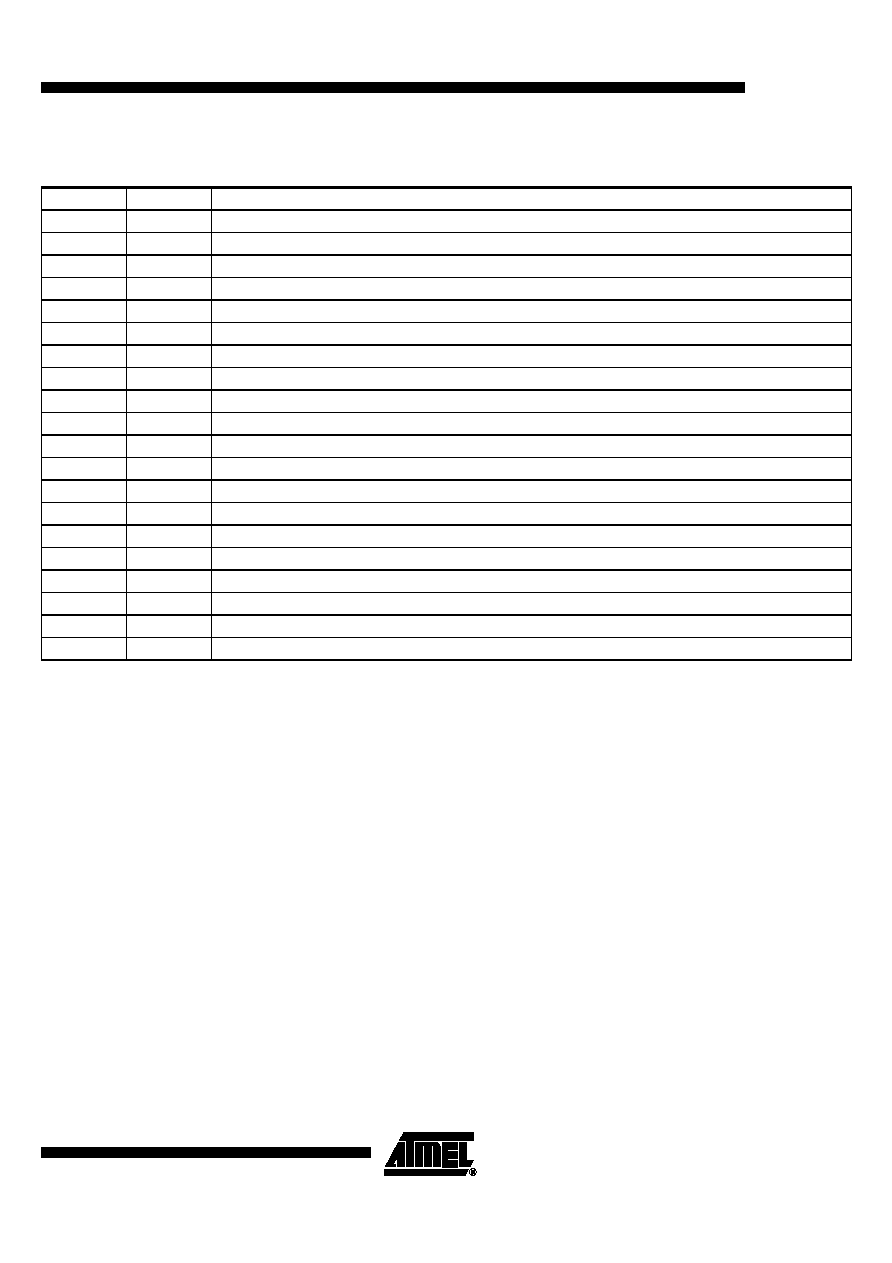

Pin Description

Pin

Symbol

Function

1

IX

IX output

2

I

I output

3

II

II lowpass filter I

4

IIX

IIX lowpass filter I

5

V

S

Supply voltage

6

V

S

Supply voltage

7

RF

in

RF input

8

RFX

in

RFX input

9

QQ

QQ lowpass filter Q

10

QQX

QQX lowpass filter Q

11

GC

GC gain control

12

PCX

PCX phase control

13

PC

PC phase control

14

PU

PU power up

15

LOX

in

LOX input

16

GND

Ground

17

LO

in

LO input

18

GND

Ground

19

Q

Q output

20

QX

QX output

4

U2794B

4653C≠CELL≠06/03

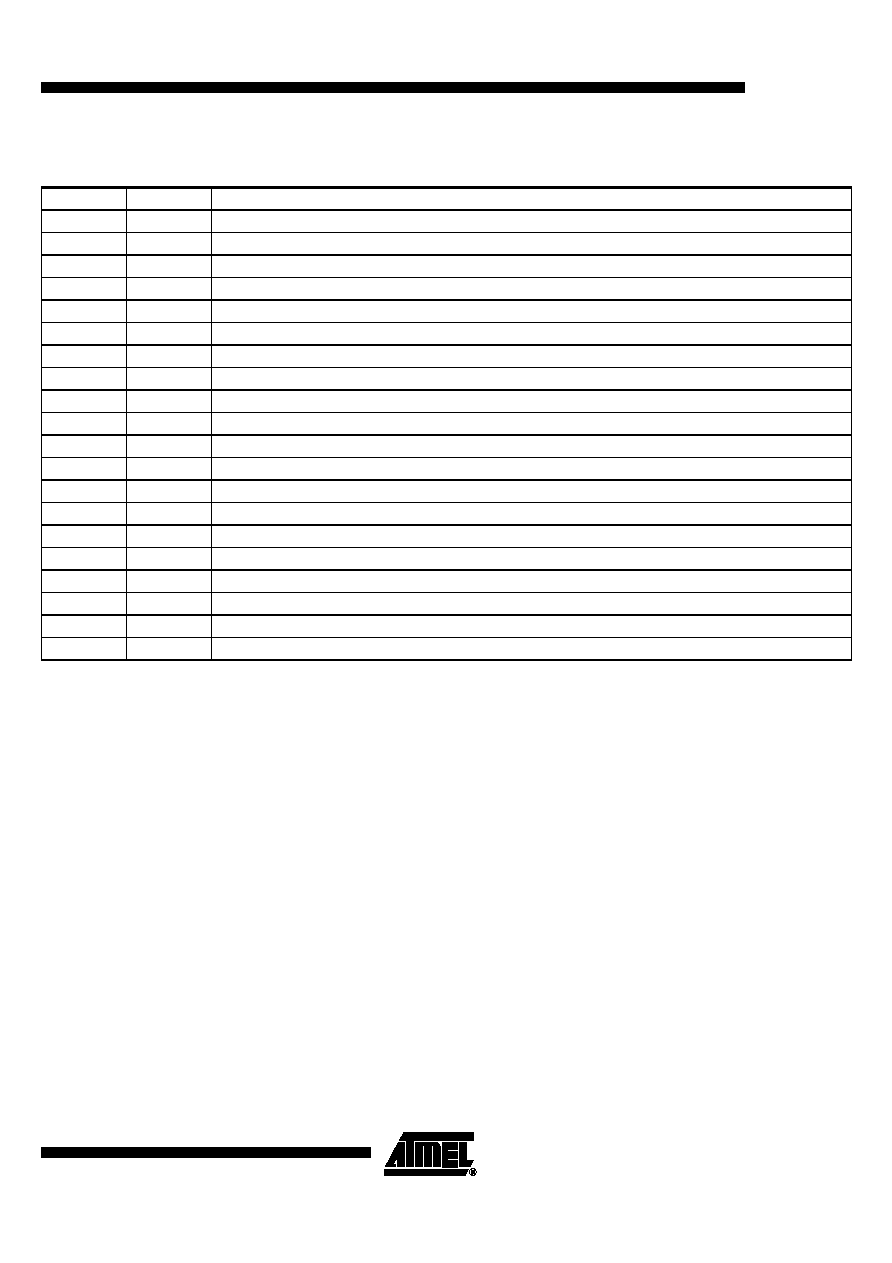

Absolute Maximum Ratings

Parameters

Symbol

Value

Unit

Supply voltage

V

S

6

V

Input voltage

V

i

0 to V

S

V

Junction temperature

T

j

+125

∞

C

Storage-temperature range

T

stg

-40 to +125

∞

C

Thermal Resistance

Parameters

Symbol

Value

Unit

Junction ambient SSO20

R

thJA

140

K/W

Operating Range

Parameters

Symbol

Value

Unit

Supply-voltage range

V

S

4.75 to 5.25

V

Ambient-temperature range

T

amb

-40 to +85

∞

C

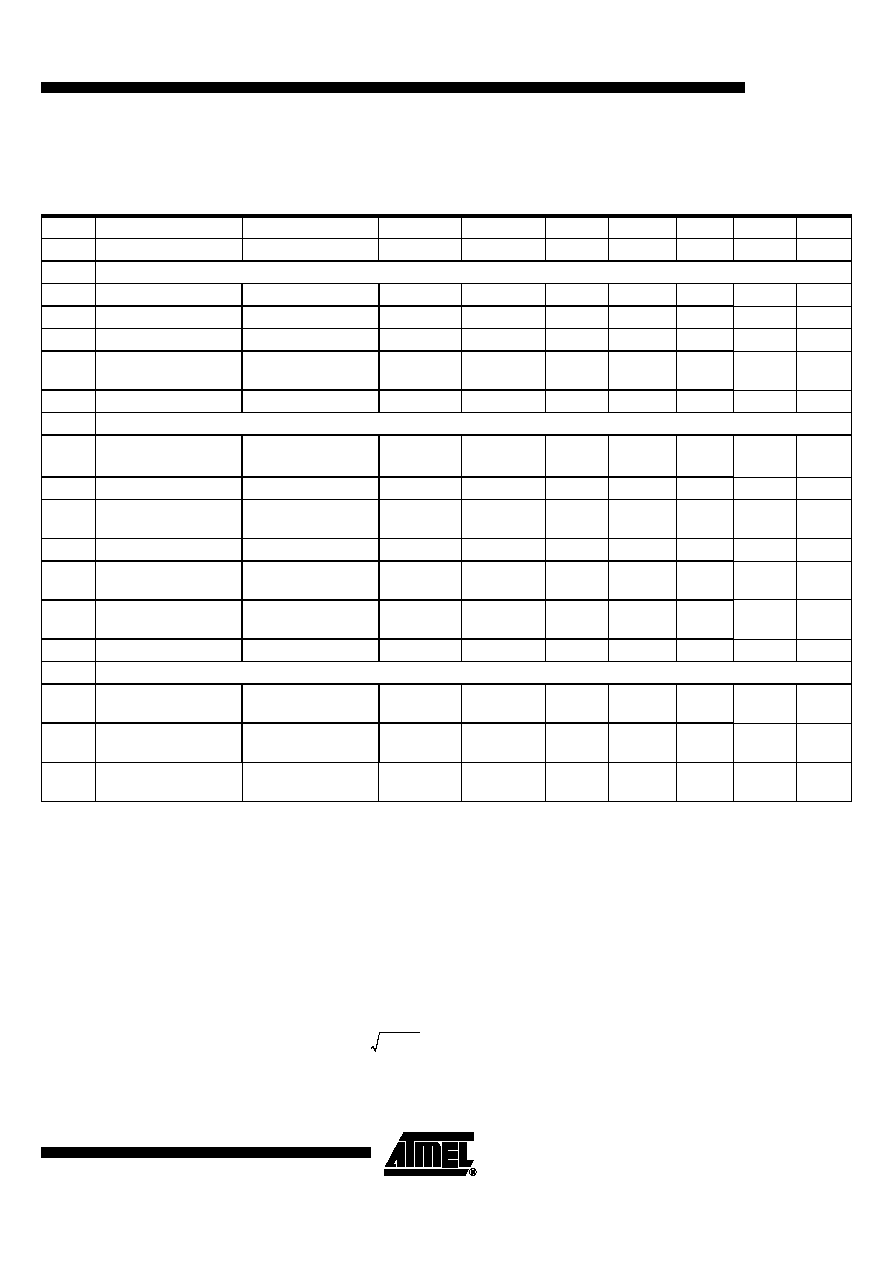

Electrical Characteristics

Test conditions (unless otherwise specified); V

S

= 5 V, T

amb

= 25∞C, referred to test circuit

System impedance Z

O

= 50

W

, fiLO = 950 MHz, PiLO = -10 dBm

No.

Parameters

Test Conditions

Pin

Symbol

Min.

Typ.

Max.

Unit

Type*

1.1

Supply-voltage range

5, 6

V

S

4.75

5.25

V

A

1.2

Supply current

5, 6

I

S

22

30

35

mA

A

2

Power-down Mode

2.1

"OFF" mode supply

current

V

PU

£

0.5 V

V

PU

= 1.0 V

(1)

14, 5

6

I

SPU

£ 1

20

µA

µA

B

D

3

Switch Voltage

3.1

"Power ON"

14

V

PON

4

V

D

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes:

1. During power-down status a load circuitry with DC-isolation to GND is assumed, otherwise a current of I

ª

(VS -0.8 V)/RI

has to be added to the above power-down current for each output I, IX, Q, QX.

2. The required LO-Level is a function of the LO frequency (see Figure 8).

3. Measured with input matching. For 950 MHz, the optional transmission line T3 at the RF input may be used for this pur-

pose. Noise figure measurements without using the differential output signal result in a worse noise figure.

4. Using Pins 7 and 8 as a symmetric RF input, the second-order IIP can be improved.

5. Due to test board parasitics, this bandwidth may be reduced and not be equal for I, IX, Q, QX. If symmetry and full band-

width is required, the lowpass Pins 3, 4 and 9, 10 should be isolated from the board. the bandwidth of the I/Q outputs can

be increased further by using a resistor between Pins 3, 4, 9 and 10. These resistors shunt the internal loads of

RI ~ 5.4 k

W

. The decrease in gain here has to be considered.

6. The internal current of the output emitter followers is 0.6 mA. This reduces the undistorted output voltage swing at a 50

W

load to approsimately 30 mV. For low signal distortion the load impedance should be RI

≥

5 k

W

.

7. Referred to the level of the output vector

8. The low-gain status is achieved with an open or high-ohmic Pin 11. A recommended application circuit for switching

between high and low gain status is hown in Figure 3.

I

2

Q

2

+

5

U2794B

4653C≠CELL≠06/03

3.2

"Power DOWN"

14

V

POFF

1

V

D

4

LO Input, LO

in

4.1

Frequency range

17

f

iLO

70

1000

MHz

D

4.2

Input level

(2)

17

P

iLO

-12

-10

-5

dBm

D

4.3

Input impedance

See Figure 12

17

Z

iLO

50

W

D

4.4

Voltage standing

wave ratio

See Figure 5

17

VSWR

LO

1.2

2

D

4.5

Duty-cycle range

17

DCR

LO

0.4

0.6

D

5

RF Input, RF

in

5.1

Noise figure (DSB)

symmetrical output

at 950 MHz

(3)

at 100 MHz

7, 8

NF

12

10

dB

D

5.2

Frequency range

f

iRF

= Fi

LO

±

BW

YQ

7, 8

f

iRF

40

1030

MHz

D

5.3

-1 dB input

compression point

High gain

Low gain

7, 8

P

1dBHG

P

1dBLG

-8

+3.5

dBm

D

5.4

Second order IIP

(4)

7, 8

IIP

2HG

35

dBm

D

5.5

Third order IIP

High gain

Low gain

7, 8

IIP

3HG

IIP

3LG

+3

+13

dBm

D

5.6

LO leakage

Symmetric input

Asymmetric input

7, 8

L

OL

£

-60

£

-55

dBm

D

5.7

Input impedance

see Figure 12

7, 8

Z

iRF

500II0.8

W

IIpF

D

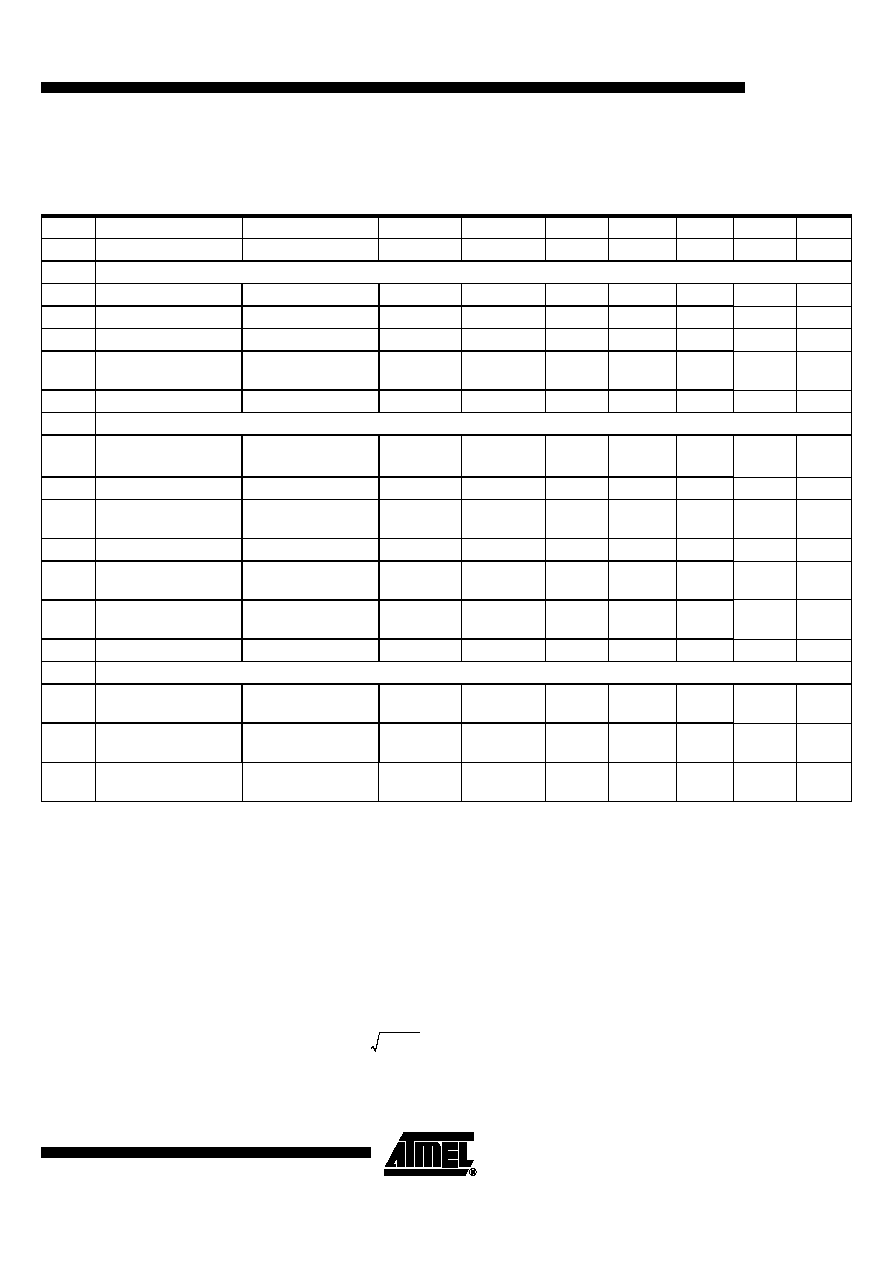

6

I/Q Outputs (I, IX, Q, QX) Emitter Follower I = 0.6 mA

6.1

3≠dB bandwidth

w/o external C

1, 2, 19,

20

BWI/Q

≥

30

MHz

D

6.2

I/Q amplitude error

1, 2, 19,

20

Ae

-0.5

£ ±

0.2

+0.5

dB

B

6.3

I/Q phase error

1, 2, 19,

20

Pe

-3

£ ±

1.5

+3

Deg

B

Electrical Characteristics (Continued)

Test conditions (unless otherwise specified); V

S

= 5 V, T

amb

= 25∞C, referred to test circuit

System impedance Z

O

= 50

W

, fiLO = 950 MHz, PiLO = -10 dBm

No.

Parameters

Test Conditions

Pin

Symbol

Min.

Typ.

Max.

Unit

Type*

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes:

1. During power-down status a load circuitry with DC-isolation to GND is assumed, otherwise a current of I

ª

(VS -0.8 V)/RI

has to be added to the above power-down current for each output I, IX, Q, QX.

2. The required LO-Level is a function of the LO frequency (see Figure 8).

3. Measured with input matching. For 950 MHz, the optional transmission line T3 at the RF input may be used for this pur-

pose. Noise figure measurements without using the differential output signal result in a worse noise figure.

4. Using Pins 7 and 8 as a symmetric RF input, the second-order IIP can be improved.

5. Due to test board parasitics, this bandwidth may be reduced and not be equal for I, IX, Q, QX. If symmetry and full band-

width is required, the lowpass Pins 3, 4 and 9, 10 should be isolated from the board. the bandwidth of the I/Q outputs can

be increased further by using a resistor between Pins 3, 4, 9 and 10. These resistors shunt the internal loads of

RI ~ 5.4 k

W

. The decrease in gain here has to be considered.

6. The internal current of the output emitter followers is 0.6 mA. This reduces the undistorted output voltage swing at a 50

W

load to approsimately 30 mV. For low signal distortion the load impedance should be RI

≥

5 k

W

.

7. Referred to the level of the output vector

8. The low-gain status is achieved with an open or high-ohmic Pin 11. A recommended application circuit for switching

between high and low gain status is hown in Figure 3.

I

2

Q

2

+