| ÐлекÑÑоннÑй компоненÑ: ADS8370IB | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

Burr Brown Products

from Texas Instruments

FEATURES

APPLICATIONS

DESCRIPTION

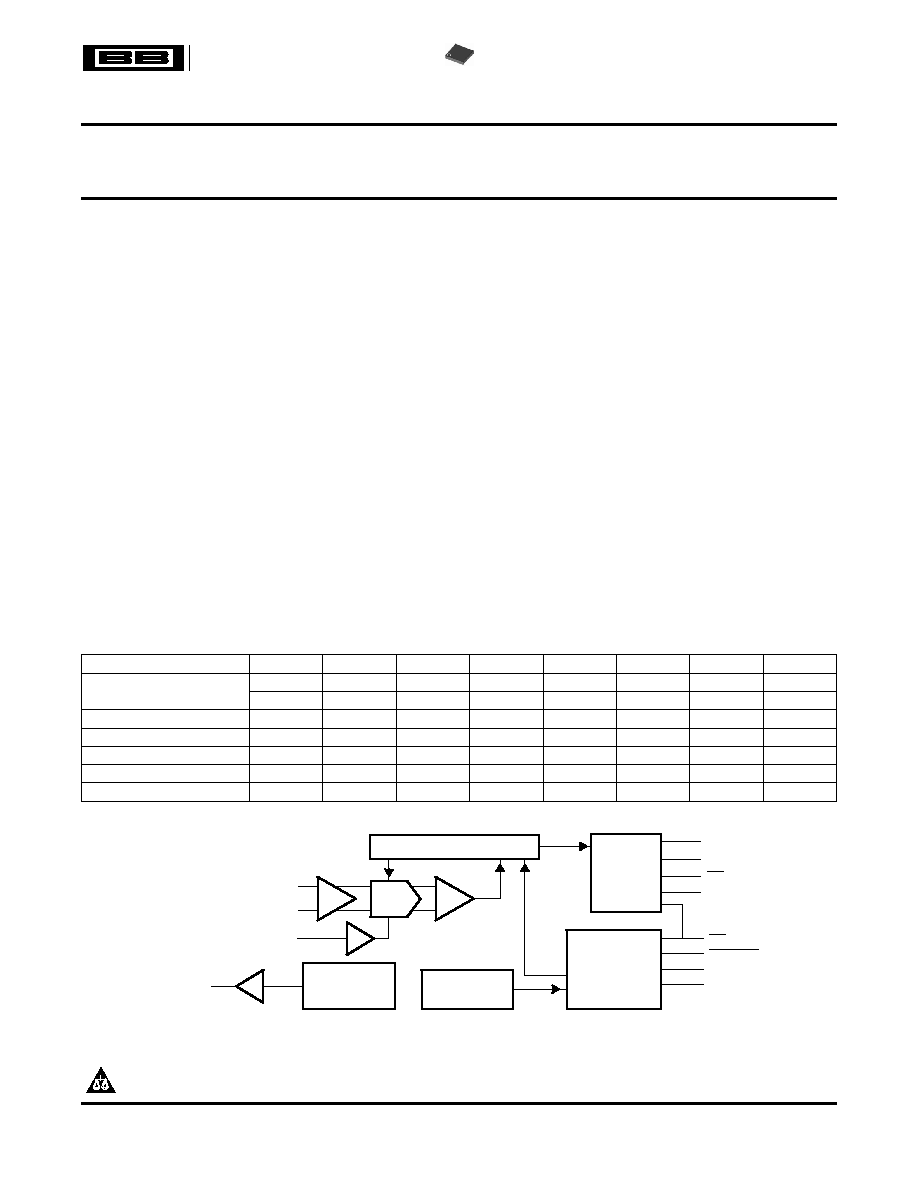

CDAC

_

+

Output

Latches

and

3-State

Drivers

FS

SAR

Conversion

and

Control Logic

Comparator

Clock

+IN

-IN

REFIN

CONVST

BUSY

CS

PD

4.096-V

Internal

Reference

REFOUT

SCLK

SDO

SB/2C

ADS8370

SLAS450 JUNE 2005

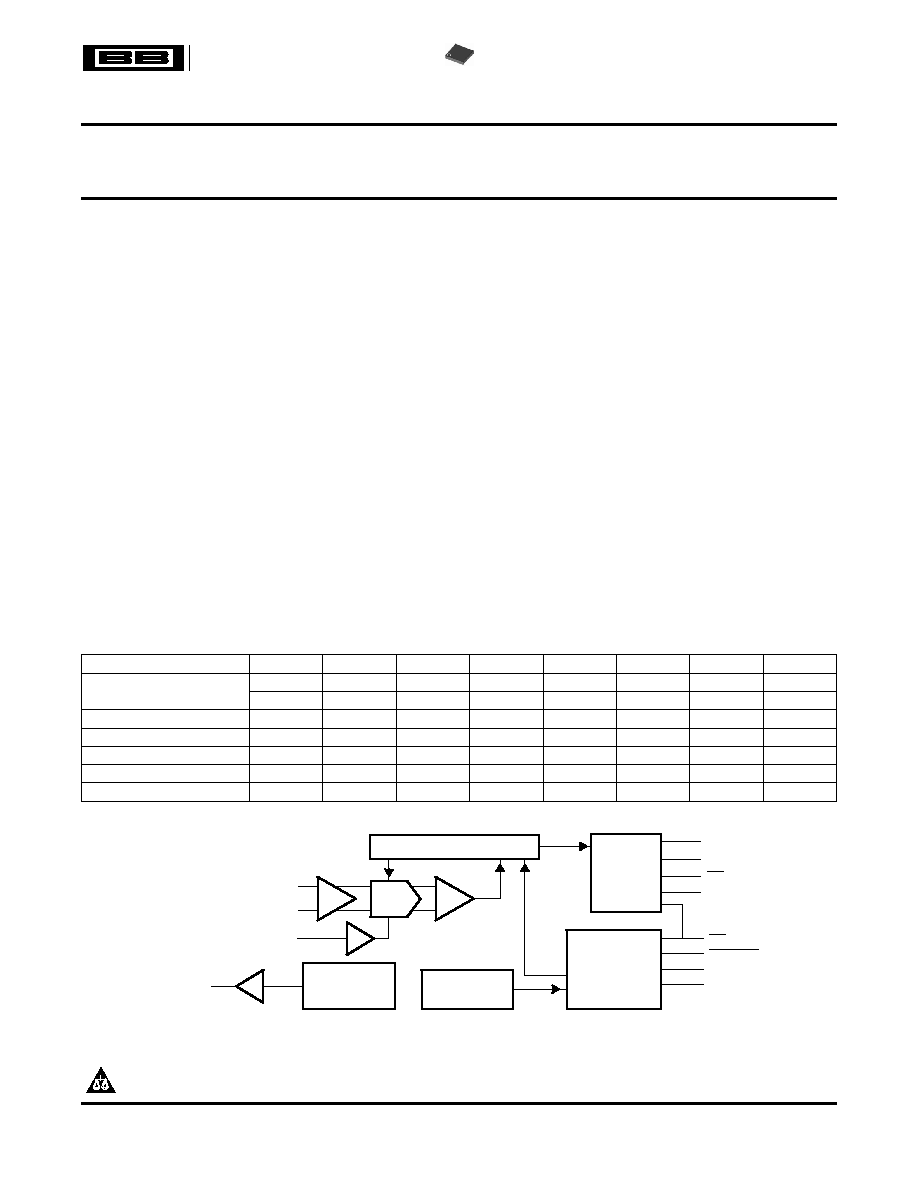

16-BIT, 600-kHz, PSEUDO-DIFFERENTIAL INPUT, MICROPOWER SAMPLING

ANALOG-TO-DIGITAL CONVERTER WITH SERIAL INTERFACE AND REFERENCE

·

Pin compatible With 18-Bit ADS8380

·

600-kHz Sample Rate

·

±0.5 LSB Typ, ±1.25 LSB Max INL

·

Medical Instruments

·

±0.4 LSB Typ, ±0.75 LSB Max DNL

·

Optical Networking

·

16-Bit NMC

·

Transducer Interface

·

SINAD 89.5 dB, SFDR 119 dB at f

i

= 1 kHz

·

High Accuracy Data Acquisition Systems

·

High-Speed Serial Interface up to 40 MHz

·

Magnetometers

·

Onboard Reference Buffer

·

Onboard 4.096-V Reference

·

Pseudo-Differential Input, 0 V to 4.2 V

The ADS8370 is a high performance 16-bit, 600-kHz

·

Onboard Conversion Clock

A/D converter with single-ended (pseudo-differential)

·

Selectable Output Format, 2's Complement or

input. The device includes an 16-bit capacitor-based

Straight Binary

SAR A/D converter with inherent sample and hold.

The ADS8370 offers a high-speed CMOS serial

·

Zero Latency

interface with clock speeds up to 40 MHz.

·

Wide Digital Supply

·

Low Power:

The ADS8370 is available in a 28 lead 6 × 6 QFN

package and is characterized over the industrial

110 mW at 600 kHz

40°C to 85°C temperature range.

15 mW During Nap Mode

10

µ

W During Power Down

·

28-Pin 6 x 6 QFN Package

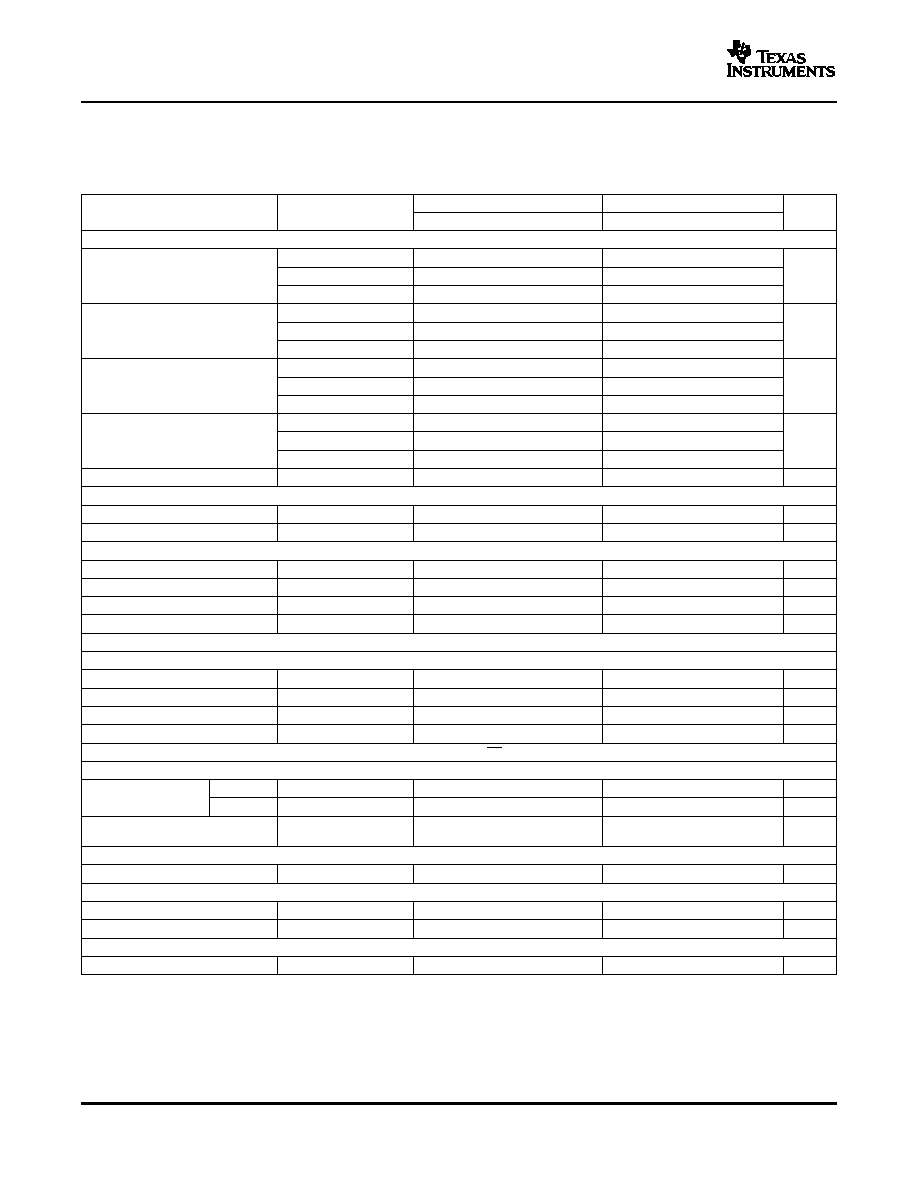

High Speed SAR Converter Family

Type/Speed

500 kHz

~ 600 kHz

750 kHZ

1 MHz

1.25 MHz

2 MHz

3 MHz

4 MHz

ADS8383

ADS8381

18-Bit Pseudo-Diff

ADS8380 (S)

18-Bit Pseudo-Bipolar, Fully Diff

ADS8382 (S)

16-Bit Pseudo-Diff

ADS8370 (S)

ADS8371

ADS8401/05

ADS8411

16-Bit Pseudo-Bipolar, Fully Diff

ADS8372 (S)

ADS8402/06

ADS8412

14-Bit Pseudo-Diff

ADS7890 (S)

ADS7891

12-Bit Pseudo-Diff

ADS7886

ADS7881

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Copyright © 2005, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

www.ti.com

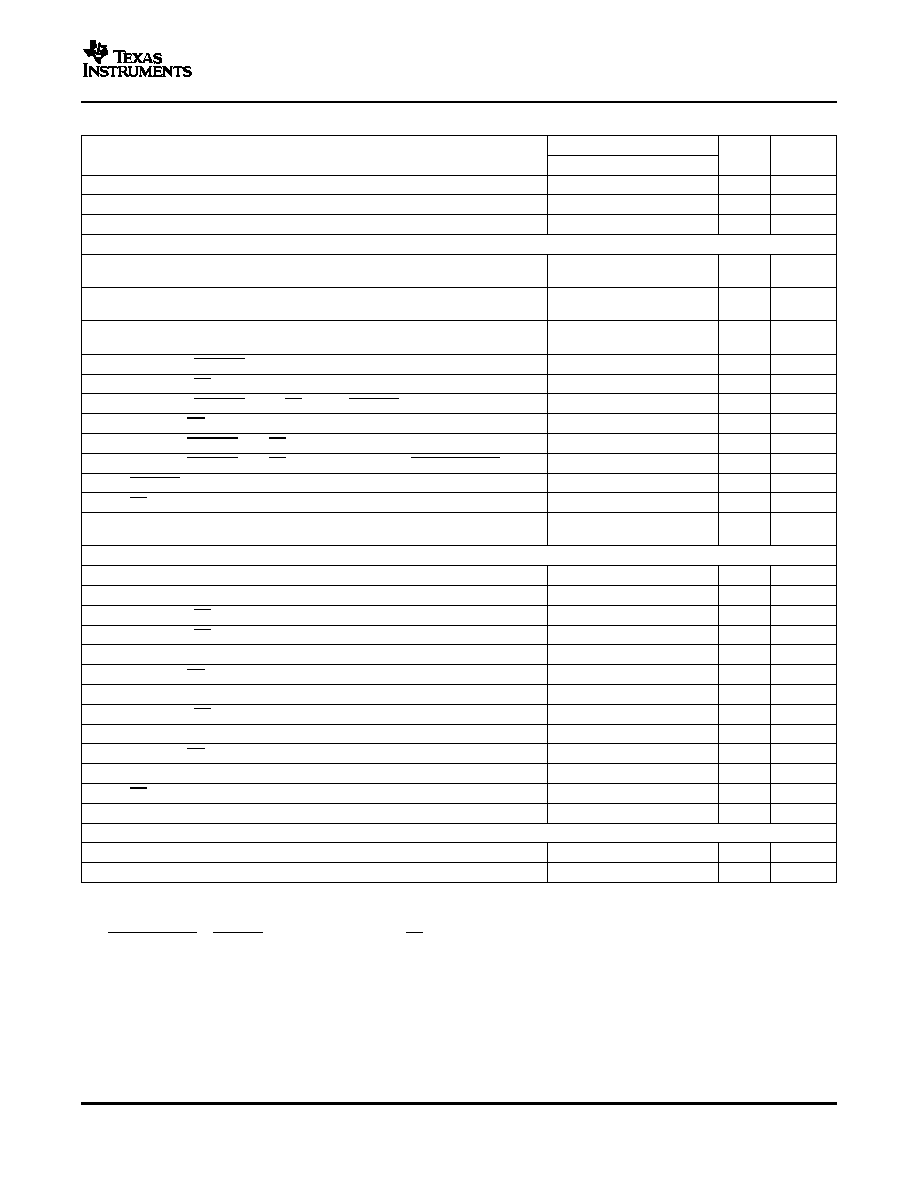

ABSOLUTE MAXIMUM RATINGS

ADS8370

SLAS450 JUNE 2005

These devices have limited built-in ESD protection. The leads should be shorted together or the device

placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

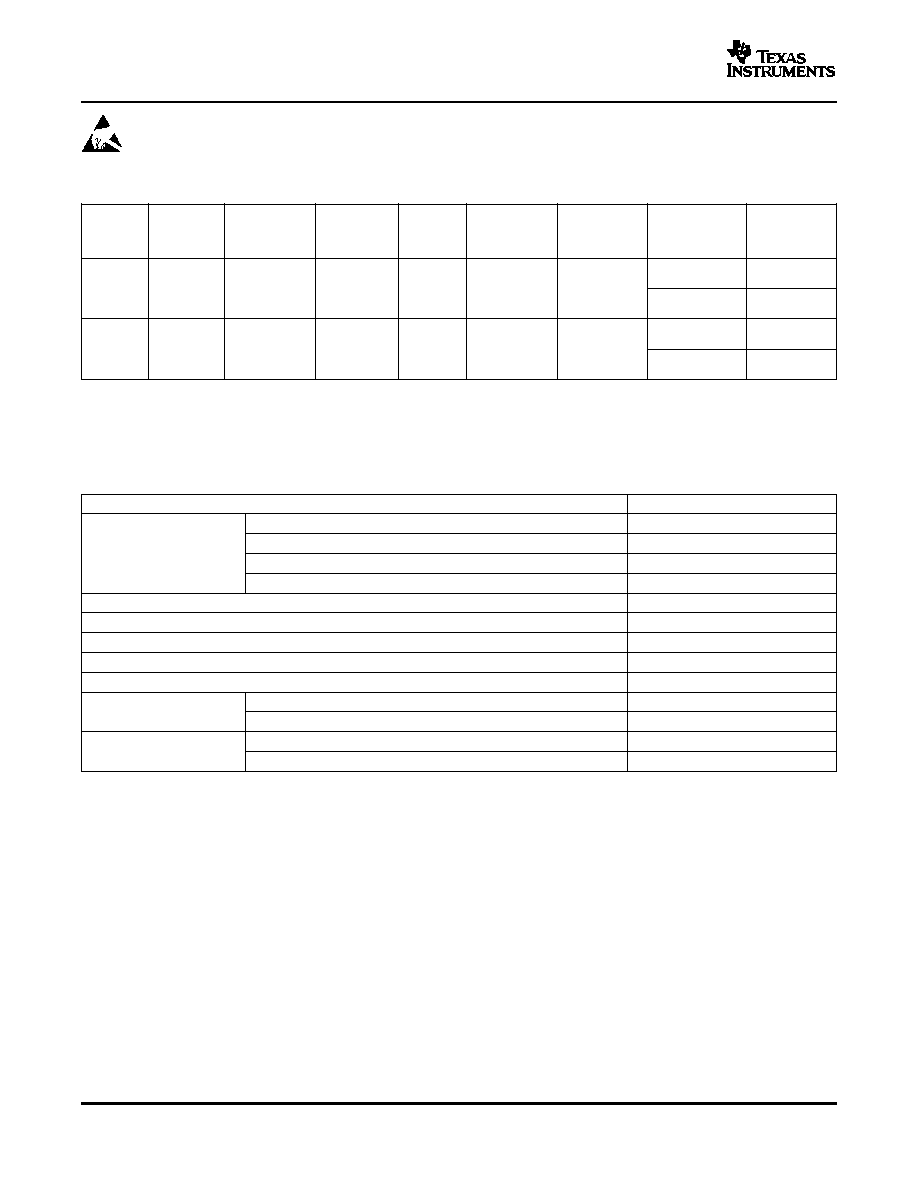

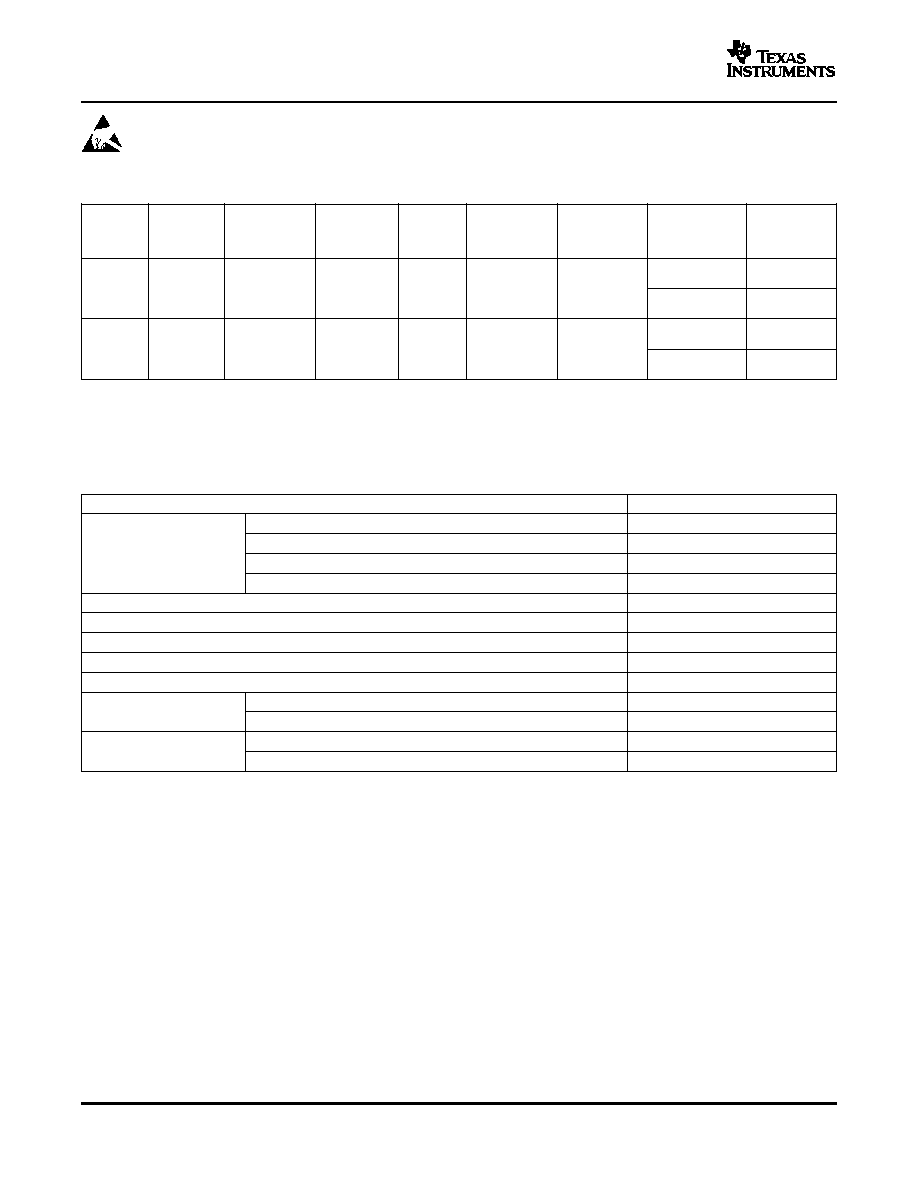

ORDERING INFORMATION

(1)

MAXIMUM

MAXIMUM

NO MISSING

TRANSPORT

INTEGRAL

DIFFERENTIAL

CODES

PACKAGE

PACKAGE

TEMPERATURE

ORDERING

MODEL

MEDIA

LINEARITY

LINEARITY

RESOLUTION

TYPE

DESIGNATOR

RANGE

INFORMATION

QUANTITY

(LSB)

(LSB)

(BIT)

Small Tape and

ADS8370IRHPT

reel 250

28 Pin

ADS8370I

±2

1/1.5

16

RHP

40°C to 85°C

6×6 QFN

Tape and reel

ADS8370IRHPR

2500

Small Tape and

ADS8370IBRHPT

reel 250

28 Pin

ADS8370IB

±1.25

±0.75

16

RHP

40°C to 85°C

6×6 QFN

Tape and reel

ADS8370IBRHPR

2500

(1)

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

website at www.ti.com.

over operating free-air temperature range unless otherwise noted

(1)

UNIT

+IN to AGND

0.3 V to +VA + 0.3 V

IN to AGND

0.3 V to +VA + 0.3 V

Voltage

+VA to AGND

0.3 V to 6 V

+VBD to BDGND

0.3 V to 6 V

Digital input voltage to BDGND

0.3 V to +VBD + 0.3 V

Digital input voltage to +VA

+0.3 V

Operating free-air temperature range, T

A

40°C to 85°C

Storage temperature range, T

stg

65°C to 150°C

Junction temperature (T

J

max)

150°C

Power dissipation

(T

J

max T

A

)/

JA

QFN package

JA

thermal impedance

86°C/W

Vapor phase (60 sec)

215°C

Lead temperature, soldering

Infrared (15 sec)

220°C

(1)

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating

conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2

www.ti.com

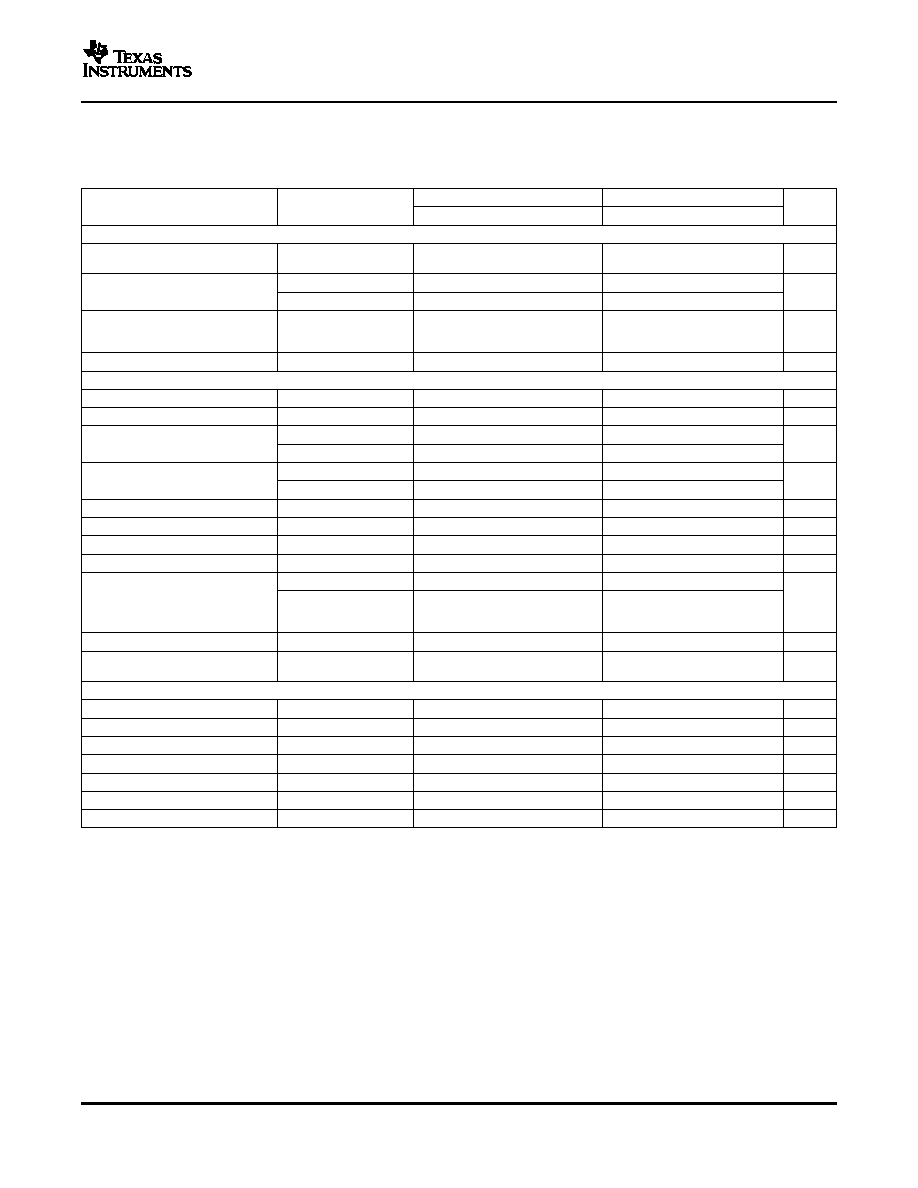

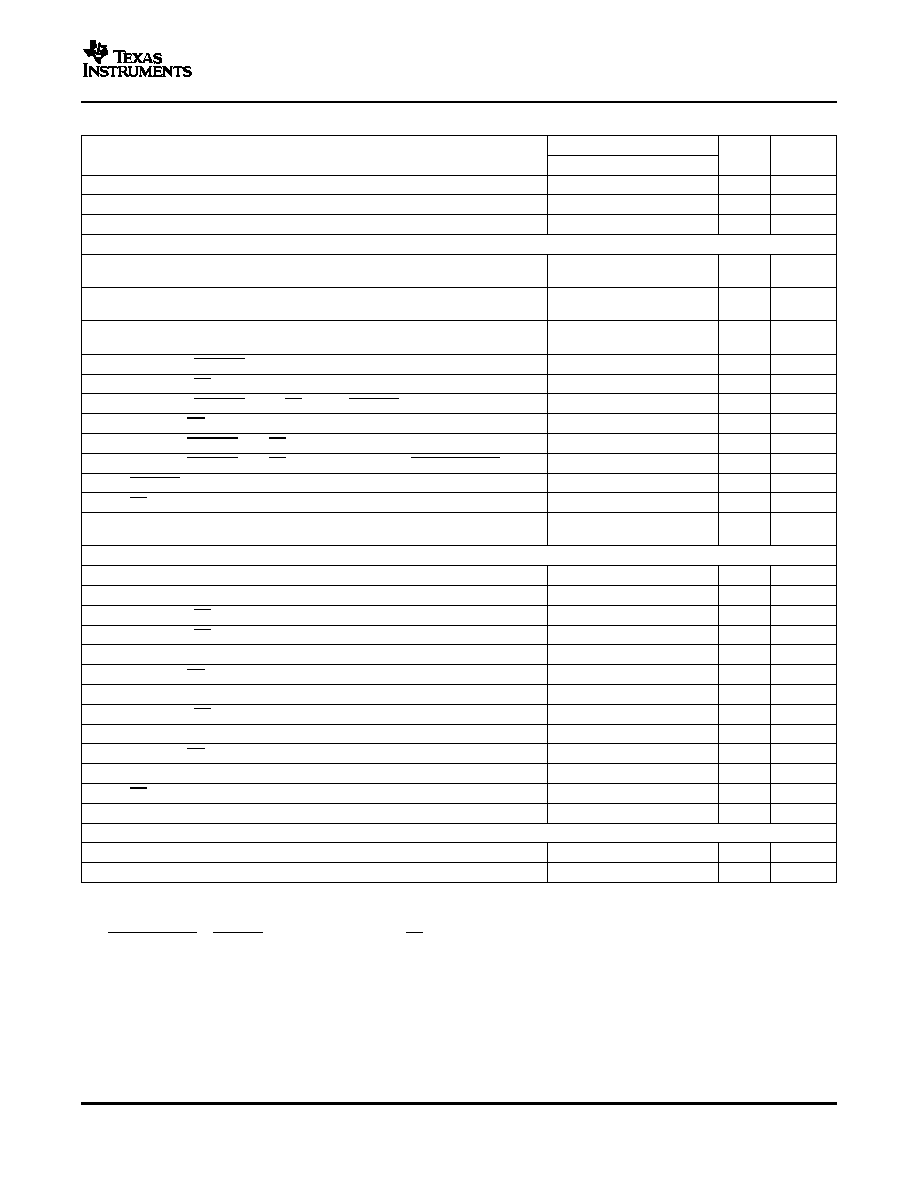

SPECIFICATIONS

ADS8370

SLAS450 JUNE 2005

At 40°C to 85°C, +VA = +5 V, +VBD = +5 V or +VBD = +2.7 V, using internal or external reference, f

SAMPLE

= 600 kHz,

unless otherwise noted. (All performance parameters are valid only after device has properly resumed from power down, see

Table 2

.)

ADS8370IB

ADS8370I

PARAMETER

TEST CONDITIONS

UNIT

MIN

TYP

MAX

MIN

TYP

MAX

ANALOG INPUT

Full-scale

+IN (IN)

0

V

ref

0

V

ref

V

input voltage

(1)

+IN

0.2

V

ref

+ 0.2

0.2

V

ref

+ 0.2

Absolute input voltage

V

IN

0.2

0.2

0.2

0.2

Sampling capacitance

(measured from ±IN to

40

40

pF

AGND)

Input leakage current

1

1

nA

SYSTEM PERFORMANCE

Resolution

16

16

Bits

No missing codes

16

16

Bits

Quiet zones observed

1.25

±0.5

1.25

2

2

LSB

INL

Integral linearity

(2) (3) (4)

(16 bit)

Quiet zones not observed

±0.8

Quiet zones observed

0.75

±0.4

0.75

1

1.5

LSB

DNL

Differential linearity

(3)

(16 bit)

Quiet zones not observed

±0.75

E

O

Offset error

(3)

0.75

±0.4

0.75

1.5

1.5

mV

Offset temperature drift

(3)

±0.4

±0.4

ppm/°C

E

G

Gain error

(3) (5)

0.075

0.075

0.15

0.15

%FS

Gain temperature drift

(3) (5)

±1.25

±1.25

ppm/°C

At DC

80

80

[+IN (IN)] = V

ref

/2 with

CMRR

Common-mode rejection ratio

dB

50 mV

p-p

common mode

55

55

signal at 1 MHz

Noise

At 0 V analog input

40

40

µ

V RMS

DC Power supply rejection

PSRR

At full scale analog input

55

55

dB

ratio

SAMPLING DYNAMICS

Conversion time

1.0

1.16

1.0

1.16

µ

s

Acquisition time

0.50

0.50

µ

s

Throughput rate

600

600

kHz

Aperture delay

10

10

ns

Aperture jitter

12

12

ps RMS

Step response

(6)

400

400

ns

Overvoltage recovery

400

400

ns

(1)

Ideal input span; does not include gain or offset error.

(2)

LSB means least significant bit.

(3)

Measured using analog input circuit in

Figure 51

and digital stimulus in

Figure 56

and

Figure 57

and reference voltage of 4.096 V.

(4)

This is endpoint INL, not best fit.

(5)

Measured using external reference source so does not include internal reference voltage error or drift.

(6)

Defined as sampling time necessary to settle an initial error of Vref on the sampling capacitor to a final error of 1 LSB at 16-bit level.

Measured using the input circuit in

Figure 51

.

3

www.ti.com

ADS8370

SLAS450 JUNE 2005

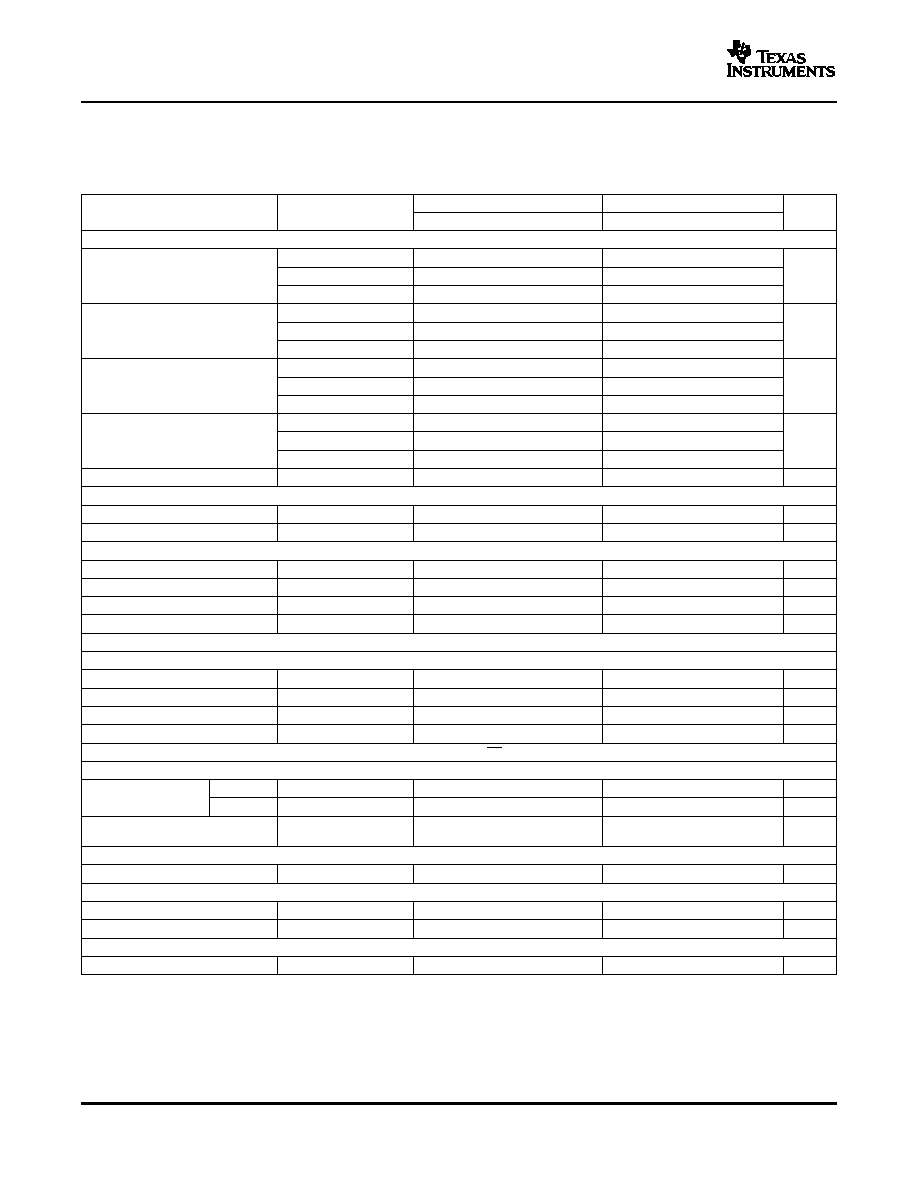

SPECIFICATIONS (continued)

At 40°C to 85°C, +VA = +5 V, +VBD = +5 V or +VBD = +2.7 V, using internal or external reference, f

SAMPLE

= 600 kHz,

unless otherwise noted. (All performance parameters are valid only after device has properly resumed from power down, see

Table 2

.)

ADS8370IB

ADS8370I

PARAMETER

TEST CONDITIONS

UNIT

MIN

TYP

MAX

MIN

TYP

MAX

DYNAMIC CHARACTERISTICS

VIN = 4 V

p-p

at 1 kHz

112

111

Total harmonic

THD

VIN = 4 V

p-p

at 10 kHz

111

111

dB

distortion

(7) (8)

VIN = 4 V

p-p

at 100 kHz

92

92

VIN = 4 V

p-p

at 1 kHz

89.5

89.5

SNR

Signal-to-noise ratio

(7)

VIN = 4 V

p-p

at 10 kHz

89.5

89

dB

VIN = 4 V

p-p

at 100 kHz

89.5

88.5

VIN = 4 V

p-p

at 1 kHz

89.5

89.5

Signal-to-noise

SINAD

VIN = 4 V

p-p

at 10 kHz

89.5

89

dB

+ distortion

(7) (8)

VIN = 4 V

p-p

at 100 kHz

87.5

87

VIN = 4 V

p-p

at 1 kHz

119

119

Spurious free dynamic

SFDR

VIN = 4 V

p-p

at 10 kHz

117

117

dB

range

(7)

VIN = 4 V

p-p

at 100 kHz

92

92

3dB Small signal bandwidth

75

75

MHz

REFERENCE INPUT

V

ref

Reference voltage input range

2.5

4.096

4.2

2.5

4.096

4.2

V

Resistance

(9)

10

10

M

INTERNAL REFERENCE OUTPUT

V

ref

Reference voltage range

IOUT = 0 A, T

A

= 30°C

4.088

4.096

4.104

4.088

4.096

4.104

V

Source current

Static load

10

10

µ

A

Line regulation

+VA = 4.75 V to 5.25 V

2.5

2.5

mV

Drift

IOUT = 0 A

25

25

ppm/°C

DIGITAL INPUT/OUTPUT

Logic family CMOS

V

IH

High level input voltage

+VBD 1

+VBD + 0.3

+VBD 1

+VBD + 0.3

V

V

IL

Low level input voltage

0.3

0.8

0.3

0.8

V

V

OH

High level output voltage

I

OH

= 2 TTL loads

+VBD 0.6

+VBD 0.6

V

V

OL

Low level output voltage

I

OL

= 2 TTL loads

0.4

0.4

V

Data format: MSB first, 2's complement or straight binary (selectable via the SB/2C pin)

POWER SUPPLY REQUIREMENTS

+VA

4.75

5

5.25

4.75

5

5.25

V

Power supply

voltage

+VBD

2.7

3.3

5.25

2.7

3.3

5.25

V

Supply current, 600-kHz

I

CC

+VA = 5 V

22

25

22

25

mA

sample rate

(10)

POWER DOWN

I

CC(PD)

Supply current, power down

2

2

µ

A

NAP MODE

I

CC(NAP)

Supply current, nap mode

3

3

mA

Power-up time from nap

300

300

ns

TEMPERATURE RANGE

Specified performance

40

85

40

85

°C

(7)

Measured using analog input circuit in

Figure 51

and digital stimulus in

Figure 56

and

Figure 57

and reference voltage of 4.096 V.

(8)

Calculated on the first nine harmonics of the input frequency.

(9)

Can vary +/-30%.

(10) This includes only +VA current. With +VBD = 5 V, +VBD current is typically 1 mA with a 10-pF load capacitance on the digital output

pins.

4

www.ti.com

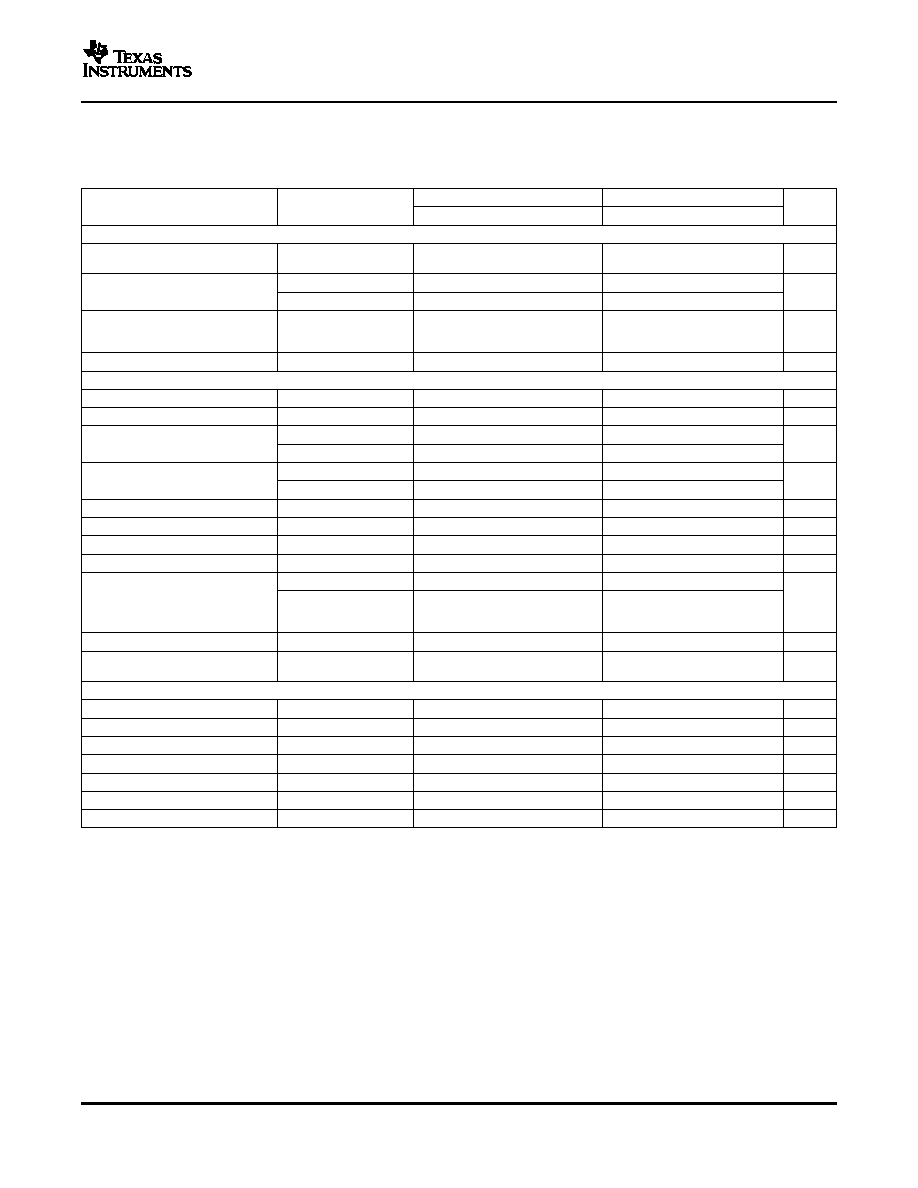

TIMING REQUIREMENTS

(1) (2) (3) (4) (5) (6)

ADS8370

SLAS450 JUNE 2005

ADS8370I/ADS8370IB

REF

PARAMETER

UNIT

FIGURE

MIN

TYP

MAX

t

conv

Conversion time

1000

1160

ns

41 44

t

acq1

Acquisition time in normal mode

0.5

µs

41,42,44

t

acq2

Acquisition time in nap mode (t

acq2

= t

acq1

+ t

d18

)

0.8

µs

43

CONVERSION AND SAMPLING

Quite sampling time (last toggle of interface signals to convert start

40 43,

t

quiet1

30

ns

command)

(6)

45 47

Quite sampling time (convert start command to first toggle of interface

40 43,

t

quiet2

10

ns

signals)

(6)

45 47

Quite conversion time (last toggle of interface signals to fall of BUSY)

(6)

40 43,

t

quiet3

600

ns

45,47

t

su1

Setup time, CONVST before BUSY fall

15

ns

41

t

su2

Setup time, CS before BUSY fall (only for conversion/sampling control)

20

ns

40,41

t

su4

Setup time, CONVST before CS rise (so CONVST can be recognized)

5

ns

41,43,44

t

h1

Hold time, CS after BUSY fall (only for conversion/sampling control)

0

ns

41

t

h3

Hold time, CONVST after CS rise

7

ns

43

t

h4

Hold time, CONVST after CS fall (to ensure width of CONVST_QUAL)

(4)

20

ns

42

t

w1

CONVST pulse duration

20

ns

43

t

w2

CS pulse duration

10

ns

41,42

Pulse duration, time between conversion start command and conversion

t

w5

1000

ns

44

abort command to successfully abort the ongoing conversion

DATA READ OPERATION

t

cyc

SCLK period

25

ns

45 47

SCLK duty cycle

40%

60%

t

su5

Setup time, CS fall before first SCLK fall

10

ns

45

t

su6

Setup time, CS fall before FS rise

7

ns

46,47

t

su7

Setup time, FS fall before first SCLK fall

7

ns

46,47

t

h5

Hold time, CS fall after SCLK fall

3

ns

45

t

h6

Hold time, FS fall after SCLK fall

7

ns

46,47

t

su2

Setup time, CS fall before BUSY fall (only for read control)

20

ns

40,45

t

su3

Setup time, FS fall before BUSY fall (only for read control)

20

ns

40,47

t

h2

Hold time, CS fall after BUSY fall (only for read control)

15

ns

40,45

t

h8

Hold time, FS fall after BUSY fall (only for read control)

15

ns

40,47

t

w2

CS pulse duration

10

ns

45

t

w3

FS pulse duration

10

ns

46,47

MISCELLANEOUS

t

w4

PD pulse duration for reset and power down

60

ns

53,54

All unspecified pulse durations

10

ns

(1)

All input signals are specified with t

r

= t

f

= 5 ns (10% to 90% of V

DD

) and timed from a voltage level of (V

IL

+ V

IH

)/2.

(2)

All specifications typical at 40°C to 85°C, +VA = +4.75 V to +5.25 V, +VBD = +2.7 V to +5.25 V.

(3)

All digital output signals loaded with 10-pF capacitors.

(4)

CONVST_QUAL is CONVST latched by a low value on CS (see

Figure 39

).

(5)

Reference figure indicated is only a representative of where the timing is applicable and is not exhaustive.

(6)

Quiet time zones are for meeting performance and not functionality.

5

Document Outline