ADS8401

SLAS376B ≠ DECEMBER 2002 ≠ REVISED APRIL 2003

16-BIT, 1.25 MSPS, UNIPOLAR INPUT, MICRO POWER SAMPLING ANALOG-TO-

DIGITAL CONVERTER WITH PARALLEL INTERFACE AND REFERENCE

FEATURES

D

1.25-MHz Sample Rate

D

16-Bit NMC Ensured Over Temperature

D

Zero Latency

D

Unipolar Single-Ended Input Range: 0 V to

V

ref

D

Onboard Reference

D

Onboard Reference Buffer

D

High-Speed Parallel Interface

D

Power Dissipation: 155 mW at 1.25 MHz Typ

D

Wide Digital Supply

D

8-/16-Bit Bus Transfer

D

48-Pin TQFP Package

APPLICATIONS

D

DWDM

D

Instrumentation

D

High-Speed, High-Resolution, Zero Latency

Data Acquisition Systems

D

Transducer Interface

D

Medical Instruments

D

Communication

DESCRIPTION

The ADS8401 is a 16-bit, 1.25 MHz A/D converter with an

internal 4.096-V reference. The device includes a 16-bit

capacitor-based SAR A/D converter with inherent sample

and hold. The ADS8401 offers a full 16-bit interface and an

8-bit option where data is read using two 8-bit read cycles.

The ADS8401 has a unipolar single-ended input. It is

available in a 48-lead TQFP package and is characterized

over the industrial ≠40

∞

C to 85

∞

C temperature range.

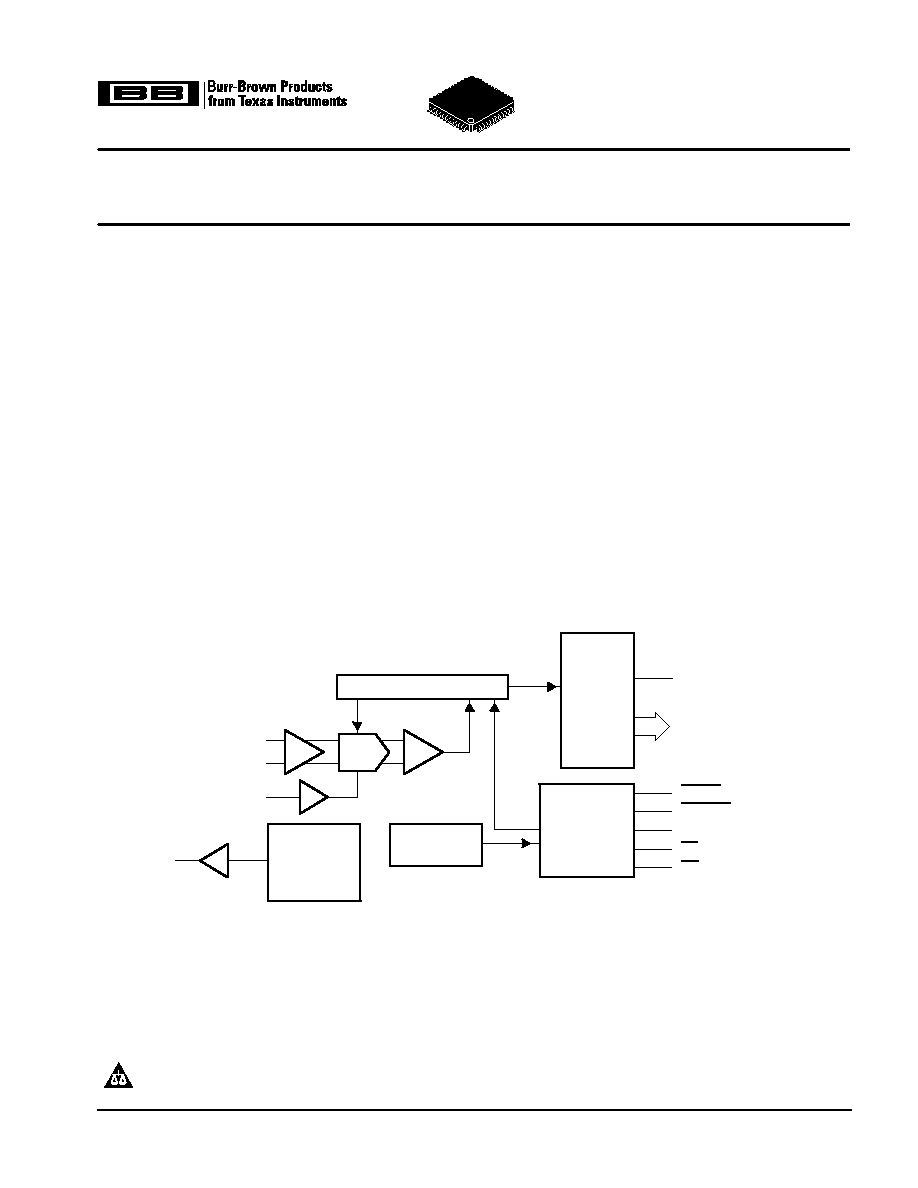

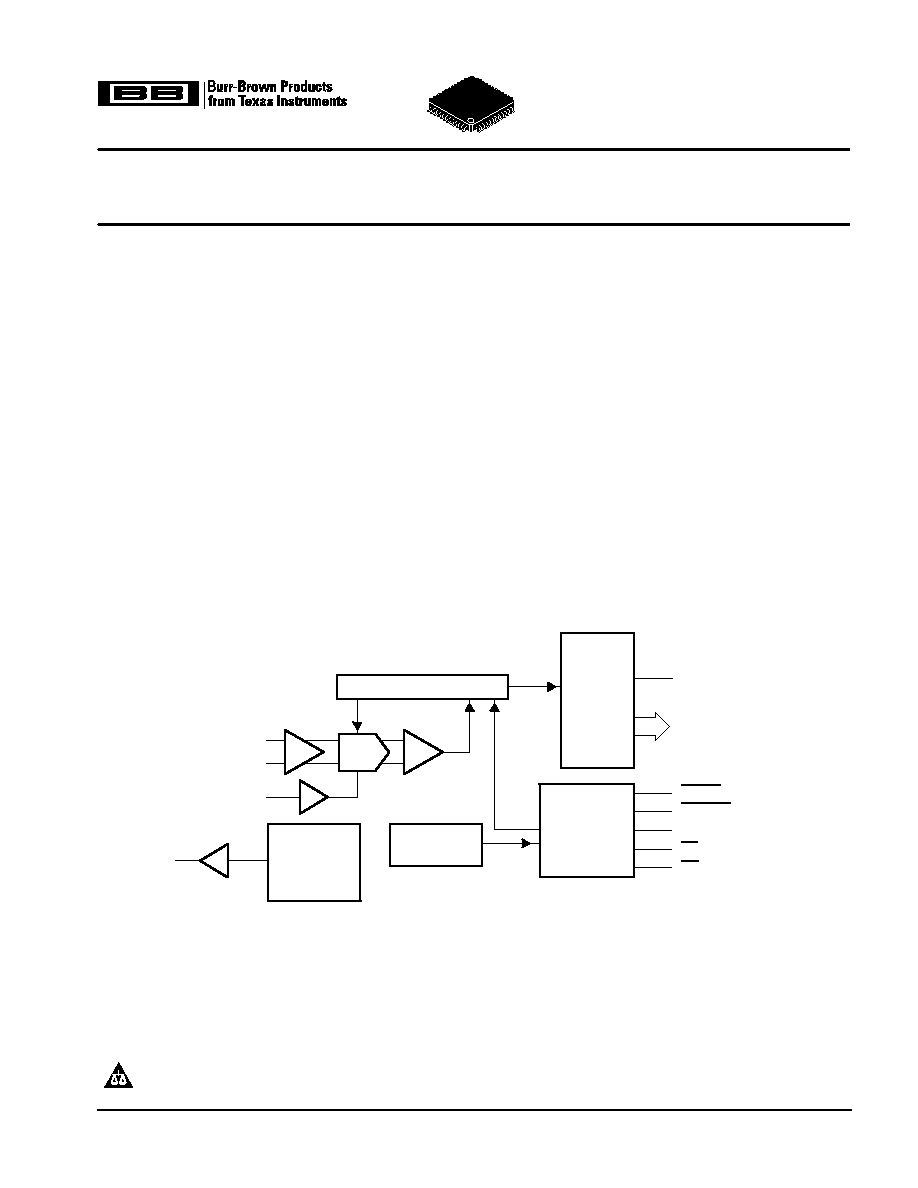

CDAC

_

+

Output

Latches

and

3-State

Drivers

BYTE

16-/8-Bit

Parallel DATA

Output Bus

SAR

Conversion

and

Control Logic

Comparator

Clock

+IN

≠IN

REFIN

CONVST

BUSY

CS

RD

RESET

4.096-V

Internal

Reference

REFOUT

PRODUCTION DATA information is current as of publication date. Products

conform to specifications per the terms of Texas Instruments standard warranty.

Production processing does not necessarily include testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments

semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright

2002≠2003, Texas Instruments Incorporated

ADS8401

SLAS376B ≠ DECEMBER 2002 ≠ REVISED APRIL 2003

www.ti.com

2

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during

storage or handling to prevent electrostatic damage to the MOS gates.

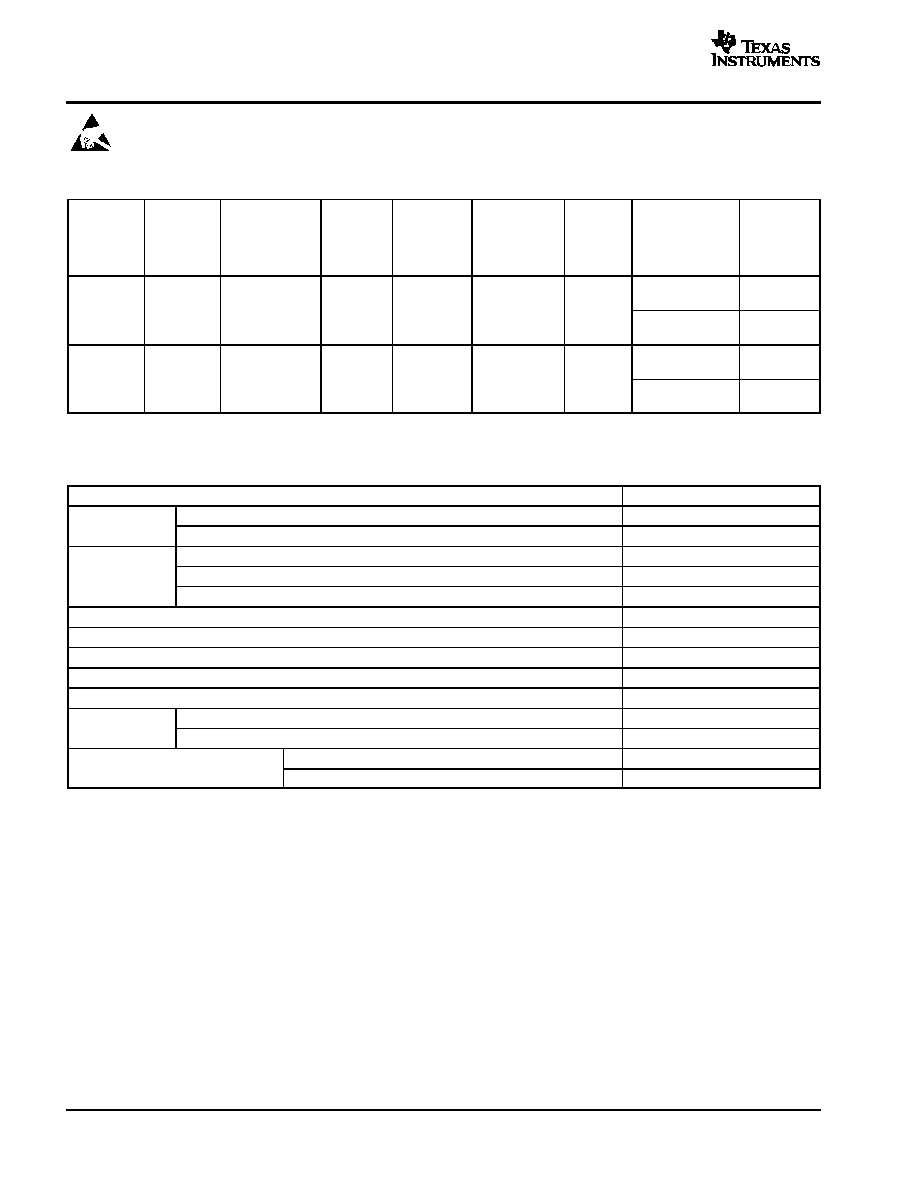

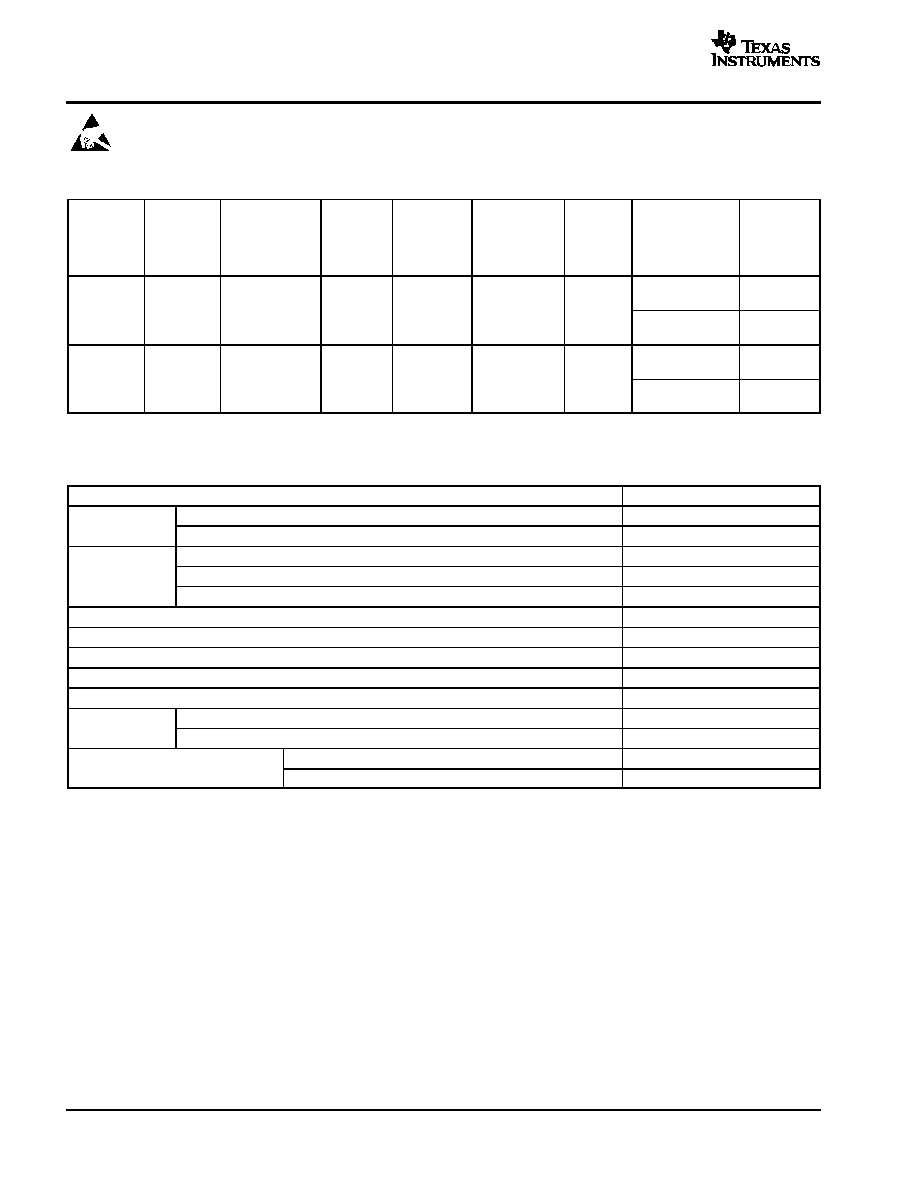

ORDERING INFORMATION

MODEL

MAXIMUM

INTEGRAL

LINEARITY

(LSB)

MAXIMUM

DIFFERENTIAL

LINEARITY

(LSB)

NO

MISSING

CODES

RESOLU-

TION (BIT)

PACKAGE

TYPE

PACKAGE

DESIGNATOR

TEMPER-

ATURE

RANGE

ORDERING

INFORMATION

TRANS-

PORT

MEDIA

QUANTITY

ADS8401I

±

6

2 3

15

48 Pin

PFB

≠40

∞

C to

ADS8401IPFBT

Tape and

reel 250

ADS8401I

±

6

≠2~3

15

48 Pin

TQFP

PFB

≠40 C to

85

∞

C

ADS8401IPFBR

Tape and

reel 1000

ADS8401IB

±

3 5

1 2

16

48 Pin

PFB

≠40

∞

C to

ADS8401IBPFBT

Tape and

reel 250

ADS8401IB

±

3.5

≠1~2

16

48 Pin

TQFP

PFB

≠40 C to

85

∞

C

ADS8401IBPFBR

Tape and

reel 1000

NOTE: For the most current specifications and package information, refer to our website at www.ti.com.

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted(1)

UNIT

Voltage

+IN to AGND

+VA + 0.1 V

Voltage

≠IN to AGND

0.5 V

+VA to AGND

≠0.3 V to 7 V

Voltage range

+VBD to BDGND

≠0.3 V to 7 V

Voltage range

+VA to +VBD

≠0.3 V to 2.5 V

Digital input voltage to BDGND

≠0.3 V to +VBD + 0.3 V

Digital output voltage to BDGND

≠0.3 V to +VBD + 0.3 V

Operating free-air temperature range, TA

≠40

∞

C to 85

∞

C

Storage temperature range, Tstg

≠65

∞

C to 150

∞

C

Junction temperature (TJ max)

150

∞

C

TQFP package

Power dissipation

(TJMax ≠ TA)/

JA

TQFP package

JA thermal impedance

86

∞

C/W

Lead temperature soldering

Vapor phase (60 sec)

215

∞

C

Lead temperature, soldering

Infrared (15 sec)

220

∞

C

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

ADS8401

SLAS376B ≠ DECEMBER 2002 ≠ REVISED APRIL 2003

www.ti.com

3

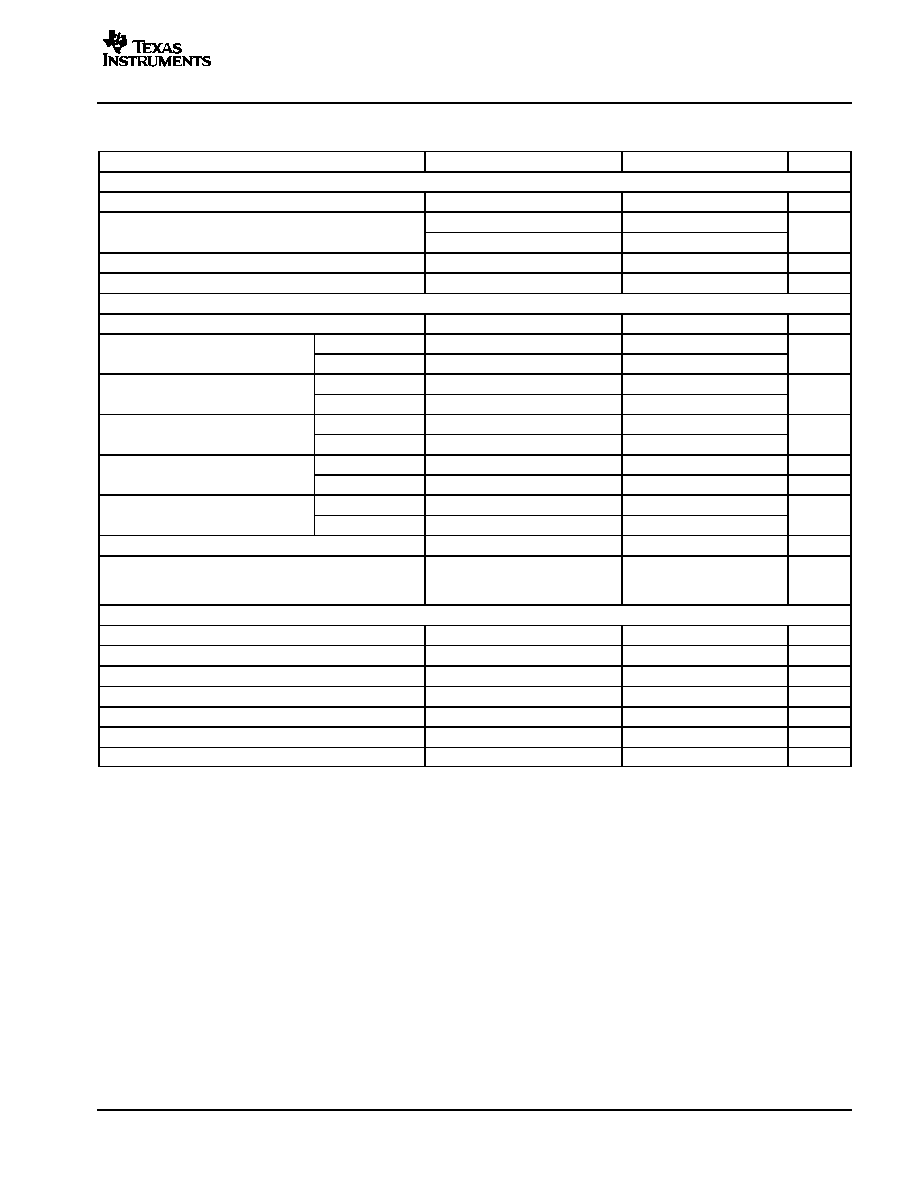

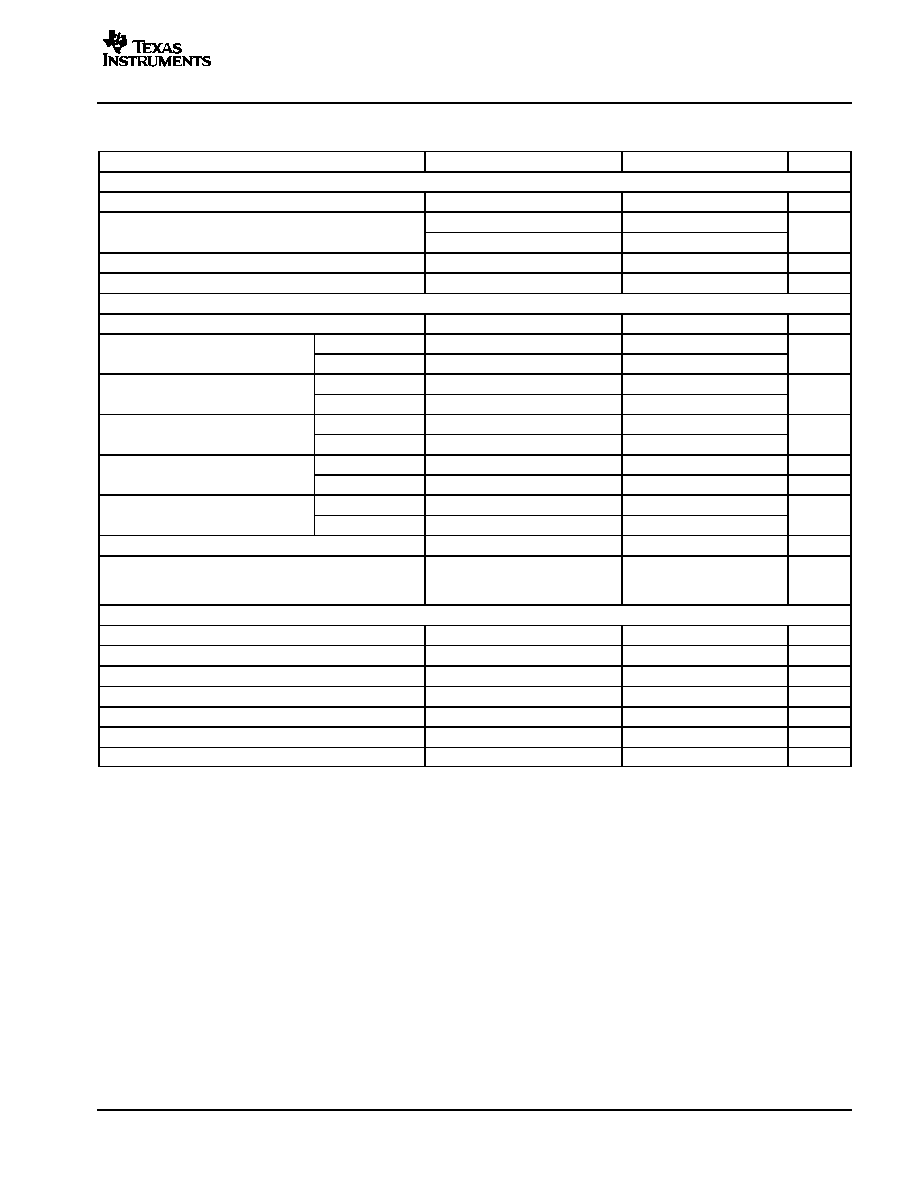

SPECIFICATIONS

TA = ≠40

∞

C to 85

∞

C, +VA = 5 V, +VBD = 3 V or 5 V, Vref = 4.096 V, fSAMPLE = 1.25 MHz (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Analog Input

Full-scale input voltage (see Note 1)

+IN ≠ ≠IN

0

Vref

V

Absolute input voltage

+IN

≠0.2

Vref + 0.2

V

Absolute input voltage

≠IN

≠0.2

0.2

V

Input capacitance

25

pF

Input leakage current

0.5

nA

System Performance

Resolution

16

Bits

No missing codes

ADS8401I

15

Bits

No missing codes

ADS8401IB

16

Bits

Integral linearity (see Notes 2 and 3)

ADS8401I

≠6

±

2.5

6

LSB

Integral linearity (see Notes 2 and 3)

ADS8401IB

≠3.5

±

2

3.5

LSB

Differentiallinearity

ADS8401I

≠2

±

1

3

LSB

Differential linearity

ADS8401IB

≠1

±

0.75

2

LSB

Offset error (see Note 4)

ADS8401I

≠1.5

±

0.5

1.5

mV

Offset error (see Note 4)

ADS8401IB

≠0.75

±

0.25

0.75

mV

Gain error (see Notes 4 and 5)

ADS8401I

≠0.15

0.15

%FS

Gain error (see Notes 4 and 5)

ADS8401IB

≠0.098

0.098

%FS

Noise

60

µ

V RMS

DC Power supply rejection ratio

At FFFFh output code,

+VA = 4.75 V to 5.25 V,

Vref = 4.096 V, See Note 4

2

LSB

Sampling Dynamics

Conversion time

610

ns

Acquisition time

150

ns

Throughput rate

1.25

MHz

Aperture delay

2

ns

Aperture jitter

25

ps

Step response

100

ns

Overvoltage recovery

100

ns

(1) Ideal input span, does not include gain or offset error.

(2) LSB means least significant bit

(3) This is endpoint INL, not best fit.

(4) Measured relative to an ideal full-scale input (+IN ≠ ≠IN) of 4.096 V

(5) This specification does not include the internal reference voltage error and drift.

ADS8401

SLAS376B ≠ DECEMBER 2002 ≠ REVISED APRIL 2003

www.ti.com

4

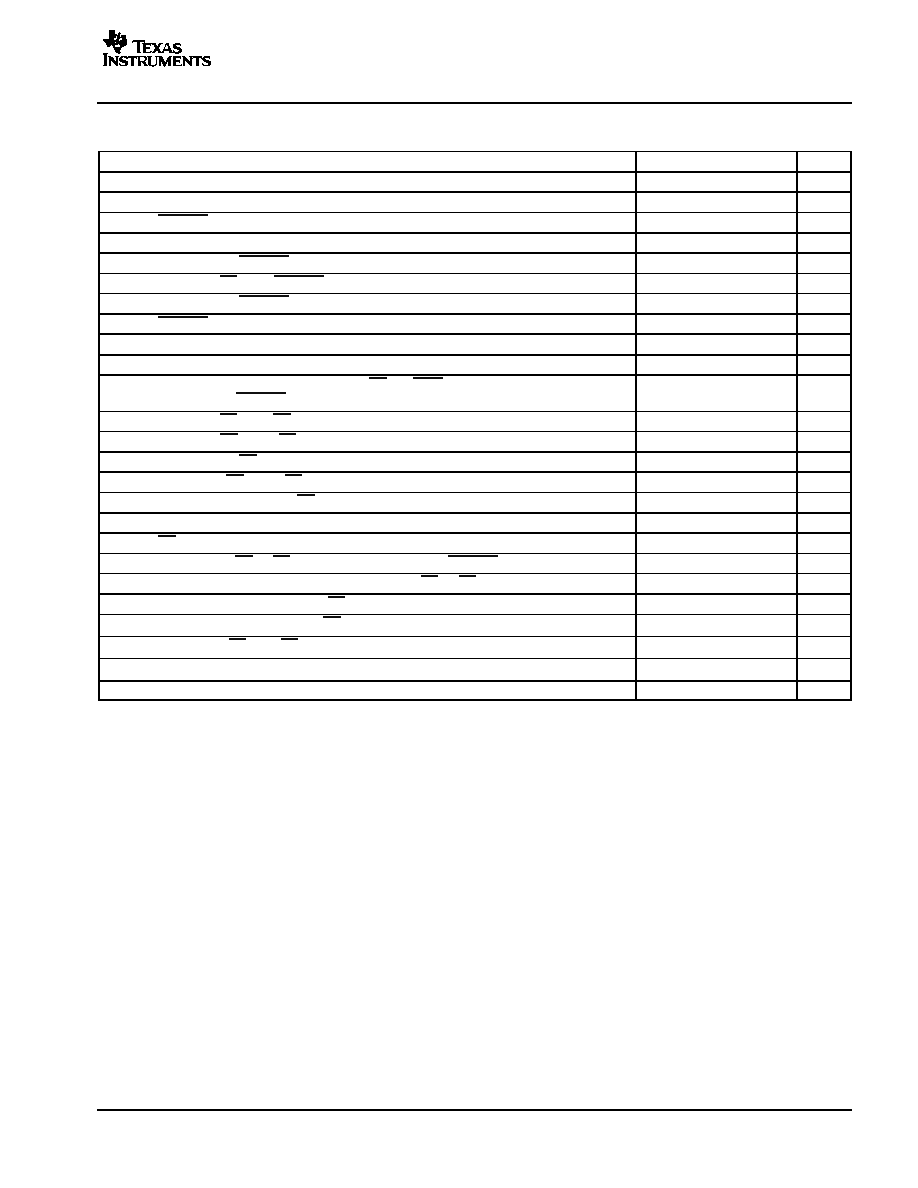

SPECIFICATIONS (CONTINUED)

TA = ≠40

∞

C to 85

∞

C, +VA = +5 V, +VBD = 3 V or 5 V, Vref = 4.096 V, fSAMPLE = 1.25 MHz (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Dynamic Characteristics

Total harmonic distortion (THD) (see Note 1)

VIN = 4 Vpp at 100 kHz

≠93

dB

Signal-to-noise ratio (SNR)

VIN = 4 Vpp at 100 kHz

86

dB

Signal-to-noise + distortion (SINAD)

VIN = 4 Vpp at 100 kHz

85

dB

Spurious free dynamic range (SFDR)

VIN = 4 Vpp at 100 kHz

93

dB

≠3dB Small signal bandwidth

5

MHz

External Voltage Reference Input

Reference voltage at REFIN, Vref

2.5

4.096

4.2

V

Reference resistance (see Note 2)

500

k

Internal Reference Output

Internal reference start-up time

from 95% (+VA), with 1

µ

F storage

capacitor

120

ms

Vref range

IOUT = 0

4.065

4.096

4.13

V

Source Current

Static load

10

µ

A

Line Regulation

+VA = 4.75 ~ 5.25 V

0.6

mV

Drift

IOUT = 0

36

PPM/C

Digital Input/Output

Logic family

CMOS

VIH

IIH = 5

µ

A

+VBD≠1

+VBD + 0.3

L

i l

l

VIL

IIL = 5

µ

A

≠0.3

0.8

V

Logic level

VOH

IOH = 2 TTL loads

+VBD ≠ 0.6

+VBD

V

VOL

IOL = 2 TTL loads

0

0.4

Data format

Straight

Binary

Power Supply Requirements

Power supply

+VBD (see Notes 3 and 4)

2.95

3.3

5.25

V

Power su

ly

voltage

+VA (see Note 4)

4.75

5

5.25

V

+VA Supply current (see Note 5)

fs = 1.25 MHz

31

34

mA

Power dissipation (see Note 5)

fs = 1.25 MHz

155

mW

Temperature Range

Operating free-air

≠40

85

∞

C

(1) Calculated on the first nine harmonics of the input frequency

(2) Can vary

±

20%

(3) The difference between +VA and +VBD should not be less than 2.3 V, i.e., if +VA is 5.25 V, +VBD should be minimum of 2.95 V.

(4) +VBD

+VA ≠ 2.3 V

(5) This includes only VA+ current. +VBD current is typically 1 mA with 5 pF load capacitance on output pins.

ADS8401

SLAS376B ≠ DECEMBER 2002 ≠ REVISED APRIL 2003

www.ti.com

5

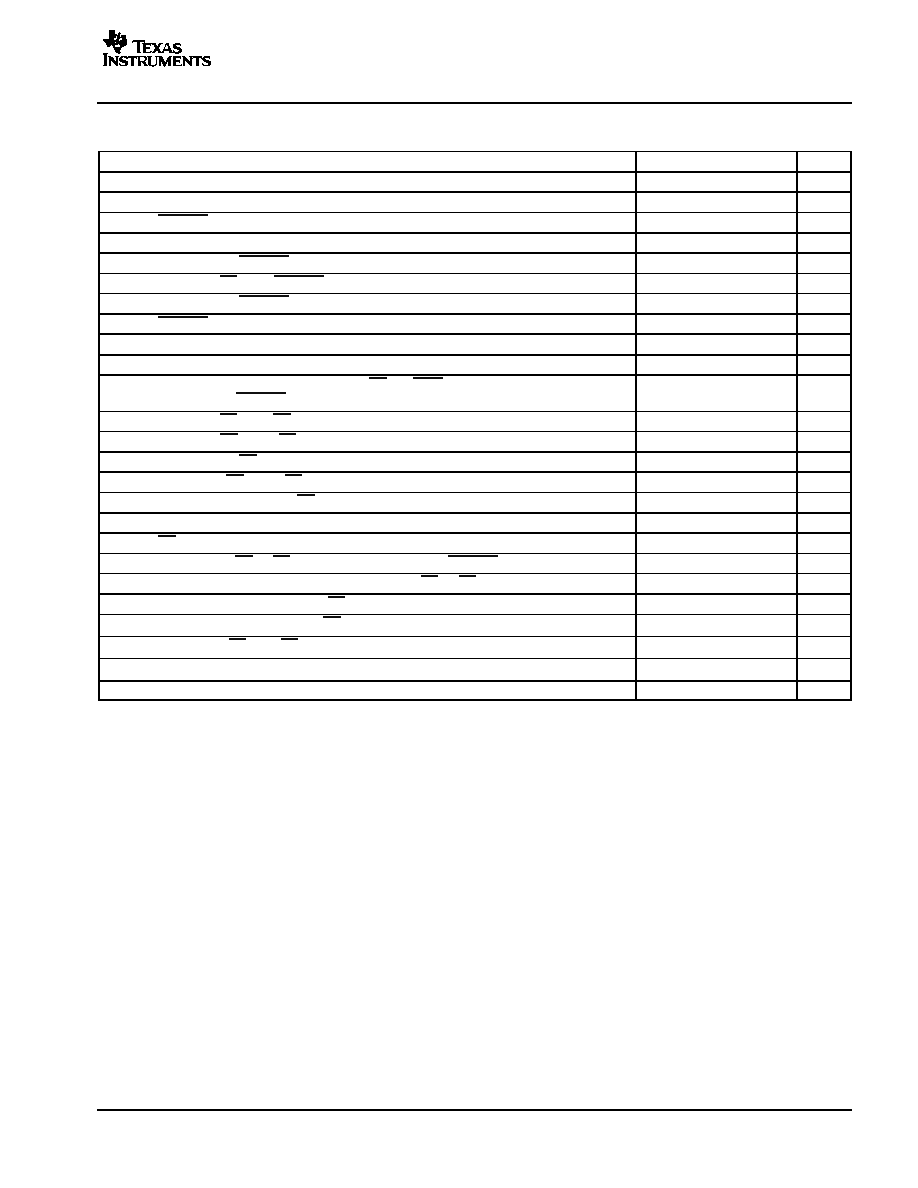

TIMING CHARACTERISTICS

All specifications typical at ≠40

∞

C to 85

∞

C, +VA = +VBD = 5 V (see Notes 1, 2, and 3)

PARAMETER

MIN

TYP

MAX

UNIT

tCONV

Conversion time

600

610

ns

tACQ

Acquisition time

150

ns

tpd1

CONVST low to conversion started (BUSY high)

35

ns

tpd2

Propagation delay time, End of conversion to BUSY low

20

ns

tw1

Pulse duration, CONVST low

20

ns

tsu1

Setup time, CS low to CONVST low

0

ns

tw2

Pulse duration, CONVST high

20

ns

CONVST falling edge jitter

10

ps

tw3

Pulse duration, BUSY signal low

Min(tACQ)

ns

tw4

Pulse duration, BUSY signal high

630

ns

th1

Hold time, First data bus data transition (RD low, or CS low for read cycle, or BYTE input

changes) after CONVST low

40

ns

td1

Delay time, CS low to RD low

0

ns

tsu2

Setup time, RD high to CS high

0

ns

tw5

Pulse duration, RD low time

50

ns

ten

Enable time, RD low (or CS low for read cycle) to data valid

20

ns

td2

Delay time, data hold from RD high

0

ns

td3

Delay time, BYTE rising edge

or falling edge to data valid

2

20

ns

tw6

RD high

20

ns

th2

Hold time, last RD (or CS for read cycle ) rising edge to CONVST falling edge

50

ns

tpd4

Propagation delay time, BUSY falling edge to next RD (or CS for read cycle) falling edge

Max(td5)

ns

tsu3

Setup time, BYTE rising edge to RD falling edge

0

ns

th3

Hold time, BYTE falling edge to RD falling edge

0

ns

tdis

Disable time, RD High (CS high for read cycle) to 3-stated data bus

20

ns

td5

Delay time, BUSY low to MSB data valid

0

ns

tsu4

Setup time, BYTE change before BUSY falling edge

2

20

ns

(1) All input signals are specified with tr = tf = 5 ns (10% to 90% of +VBD) and timed from a voltage level of (VIL + VIH)/2.

(2) See timing diagrams.

(3) All timings are measured with 20 pF equivalent loads on all data bits and BUSY pins.