| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: OPA177GS | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

©

1990 Burr-Brown Corporation

PDS-1081E

Printed in U.S.A. August, 1997

OPA177

FEATURES

q

LOW OFFSET VOLTAGE: 25

µ

V max

q

LOW DRIFT: 0.3

µ

V/

∞

C

q

HIGH OPEN-LOOP GAIN: 130dB min

q

LOW QUIESCENT CURRENT: 1.5mA typ

q

REPLACES INDUSTRY-STANDARD OP

AMPS: OP-07, OP-77, OP-177, AD707,

ETC.

APPLICATIONS

q

PRECISION INSTRUMENTATION

q

DATA ACQUISITION

q

TEST EQUIPMENT

q

BRIDGE AMPLIFIER

q

THERMOCOUPLE AMPLIFIER

Precision

OPERATIONAL AMPLIFIER

14k

500

Trim

8

V+

7

Trim

1

+In

3

≠In

2

V≠

4

25

30

V

6

O

20µA

500

DESCRIPTION

The OPA177 precision bipolar op amp feature very

low offset voltage and drift. Laser-trimmed offset,

drift and input bias current virtually eliminate the need

for costly external trimming. The high performance

and low cost make them ideally suited to a wide range

of precision instrumentation.

The low quiescent current of the OPA177 dramati-

cally reduce warm-up drift and errors due to thermo-

electric effects in input interconnections. It provides

an effective alternative to chopper-stabilized amplifi-

ers. The low noise of the OPA177 maintains accuracy.

OPA177 performance gradeouts are available. Pack-

aging options include 8-pin plastic DIP

and SO-8 surface-mount packages.

Æ

International Airport Industrial Park ∑ Mailing Address: PO Box 11400, Tucson, AZ 85734 ∑ Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 ∑ Tel: (520) 746-1111 ∑ Twx: 910-952-1111

Internet: http://www.burr-brown.com/ ∑ FAXLine: (800) 548-6133 (US/Canada Only) ∑ Cable: BBRCORP ∑ Telex: 066-6491 ∑ FAX: (520) 889-1510 ∑ Immediate Product Info: (800) 548-6132

OPA177

OPA177

2

Æ

OPA177

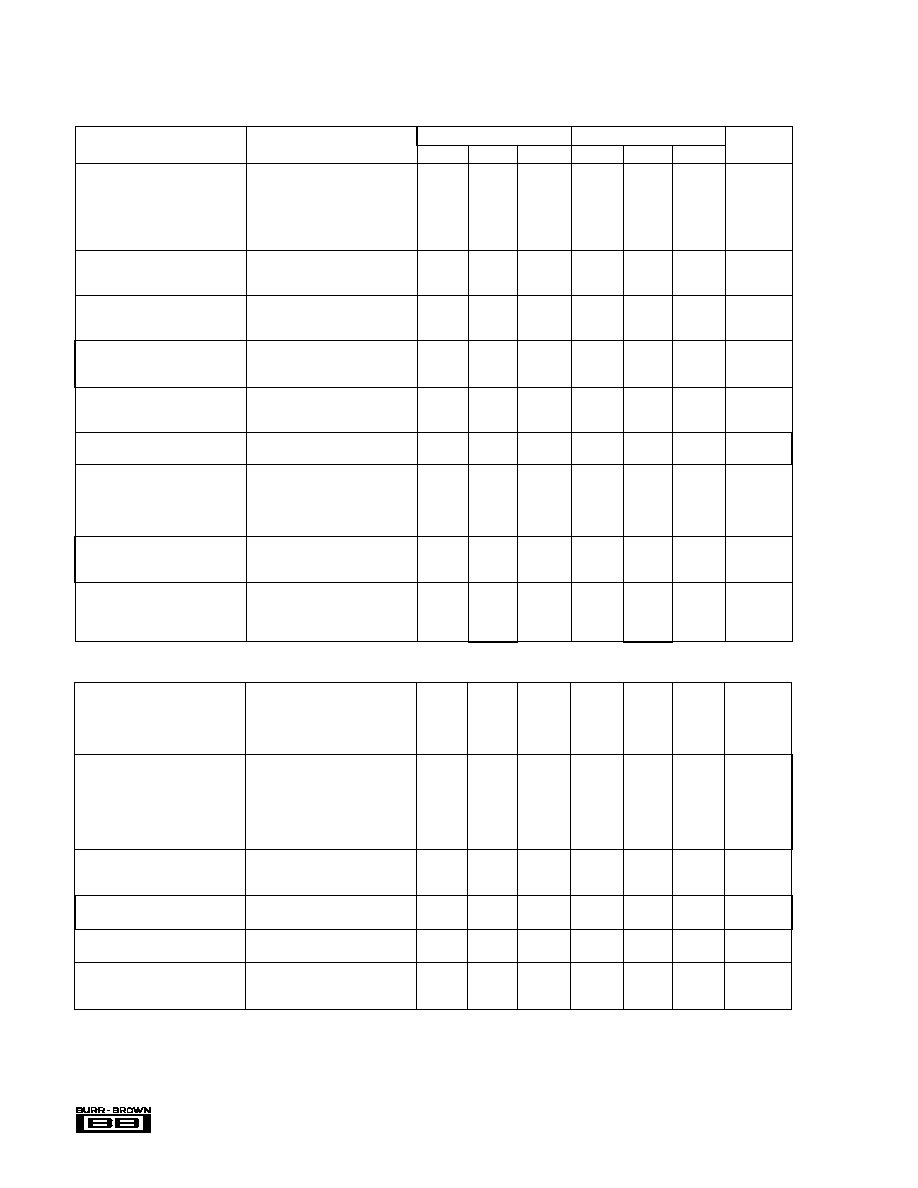

OPA177 SPECIFICATIONS

At V

S

=

±

15V, T

A

= +25

∞

C, unless otherwise noted.

OPA177F

OPA177G

PARAMETER

CONDITION

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

OFFSET VOLTAGE

Input Offset Voltage

10

25

20

60

µ

V

Long-Term Input Offset

(1)

0.3

0.4

µ

V/Mo

Voltage Stability

Offset Adjustment Range

R

P

= 20k

±

3

T

mV

Power Supply Rejection Ratio

V

S

=

±

3V to

±

18V

115

125

110

120

dB

INPUT BIAS CURRENT

Input Offset Current

0.3

1.5

T

2.8

nA

Input Bias Current

0.5

±

2

T

±

2.8

nA

NOISE

Input Noise Voltage

1Hz to 100Hz

(2)

85

150

T

T

nVrms

Input Noise Current

1Hz to 100Hz

4.5

T

pArms

INPUT IMPEDANCE

Input Resistance

Differential Mode

(3)

26

45

18.5

T

M

Common-Mode

200

T

G

INPUT VOLTAGE RANGE

Common-Mode Input Range

(4)

±

13

±

14

T

T

V

Common-Mode Rejection

V

CM

=

±

13V

130

140

115

T

dB

OPEN-LOOP GAIN

R

L

2k

Large Signal Voltage Gain

V

O

=

±

10V

(5)

5110

12,000

2000

6000

V/mV

OUTPUT

Output Voltage Swing

R

L

10k

±

13.5

±

14

T

T

V

R

L

2k

±

12.5

±

13

T

T

V

R

L

1k

±

12

±

12.5

T

T

V

Open-Loop Output Resistance

60

T

FREQUENCY RESPONSE

Slew Rate

R

L

2k

0.1

0.3

T

T

V/

µ

s

Closed-Loop Bandwidth

G = +1

0.4

0.6

T

T

MHz

POWER SUPPLY

Power Consumption

V

S

=

±

15V, No Load

40

60

T

T

mW

V

S

=

±

3V, No Load

3.5

4.5

T

T

mW

Supply Current

V

S

=

±

15V, No Load

1.3

2

T

T

mA

At V

S

=

±

15V, ≠40

∞

C

T

A

+85

∞

C, unless otherwise noted.

OFFSET VOLTAGE

Input Offset Voltage

15

40

20

100

µ

V

Average Input Offset

0.1

0.3

0.7

1.2

µ

V/

∞

C

Voltage Drift

Power Supply Rejection Ratio

V

S

=

±

3V to

±

18V

110

120

106

115

dB

INPUT BIAS CURRENT

Input Offset Current

0.5

2.2

T

4.5

nA

Average Input Offset Current

1.5

40

T

85

pA/

∞

C

Drift

(6)

Input Bias Current

0.5

±

4

T

±

6

nA

Average Input Bias Current

8

40

15

60

pA/

∞

C

Drift

(6)

INPUT VOLTAGE RANGE

Common-Mode Input Range

±

13

±

13.5

T

T

V

Common-Mode Rejection

V

CM

=

±

13V

120

140

110

T

dB

OPEN-LOOP GAIN

Large Signal Voltage Gain

R

L

2k

, V

O

=

±

10V

2000

6000

1000

4000

V/mV

OUTPUT

Output Voltage Swing

R

L

2k

±

12

±

13

T

T

V

POWER SUPPLY

Power Consumption

V

S

=

±

15V, No Load

60

75

T

T

mW

Supply Current

V

S

=

±

15V, No Load

2

25

T

T

mA

T

Same as specification for product to left.

NOTES: (1) Long-Term Input Offset Voltage Stability refers to the averaged trend line of V

OS

vs time over extended periods after the first 30 days of operation. Excluding

the initial hour of operation, changes in V

OS

during the first 30 operating days are typically less than 2

µ

V. (2) Sample tested. (3) Guaranteed by design. (4) Guaranteed

by CMRR test condition. (5) To insure high open-loop gain throughout the

±

10V output range, A

OL

is tested at ≠10V

V

O

0V, 0V

V

O

+10V, and ≠10V

V

O

+10V.

(6) Guaranteed by end-point limits.

3

Æ

OPA177

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

PIN CONFIGURATION

Top View

DIP/SOIC

ABSOLUTE MAXIMUM RATINGS

ELECTROSTATIC

DISCHARGE SENSITIVITY

Any integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with

appropriate precautions. ESD can cause damage ranging

from subtle performance degradation to complete device

failure. Precision integrated circuits may be more suscep-

tible to damage because very small parametric changes

could cause the device not to meet published specifications.

Burr-Brown's standard ESD test method consists of five

1000V positive and negative discharges (100pF in series

with 1.5k

) applied to each pin.

Failure to observe proper handling procedures could result

in small changes to the OPA177's input bias current.

1

2

3

4

8

7

6

5

Offset Trim

≠In

+In

V≠

Offset Trim

V+

V

No Internal Connection

O

Power Supply Voltage .......................................................................

±

22V

Differential Input Voltage ...................................................................

±

30V

Input Voltage .......................................................................................

±

V

S

Output Short Circuit ................................................................. Continuous

Operating Temperature:

Plastic DIP (P), SO-8 (S) .............................................. ≠40

∞

C to +85

∞

C

JA

(PDIP) ................................................................................. 100

∞

C/W

JA

(SOIC) ................................................................................. 160

∞

C/W

Storage Temperature:

Plastic DIP (P), SO-8 (S) ............................................ ≠65

∞

C to +125

∞

C

Junction Temperature .................................................................... +150

∞

C

Lead Temperature (soldering, 10s) P packages ........................... +300

∞

C

(soldering, 3s) S package ............................... +260

∞

C

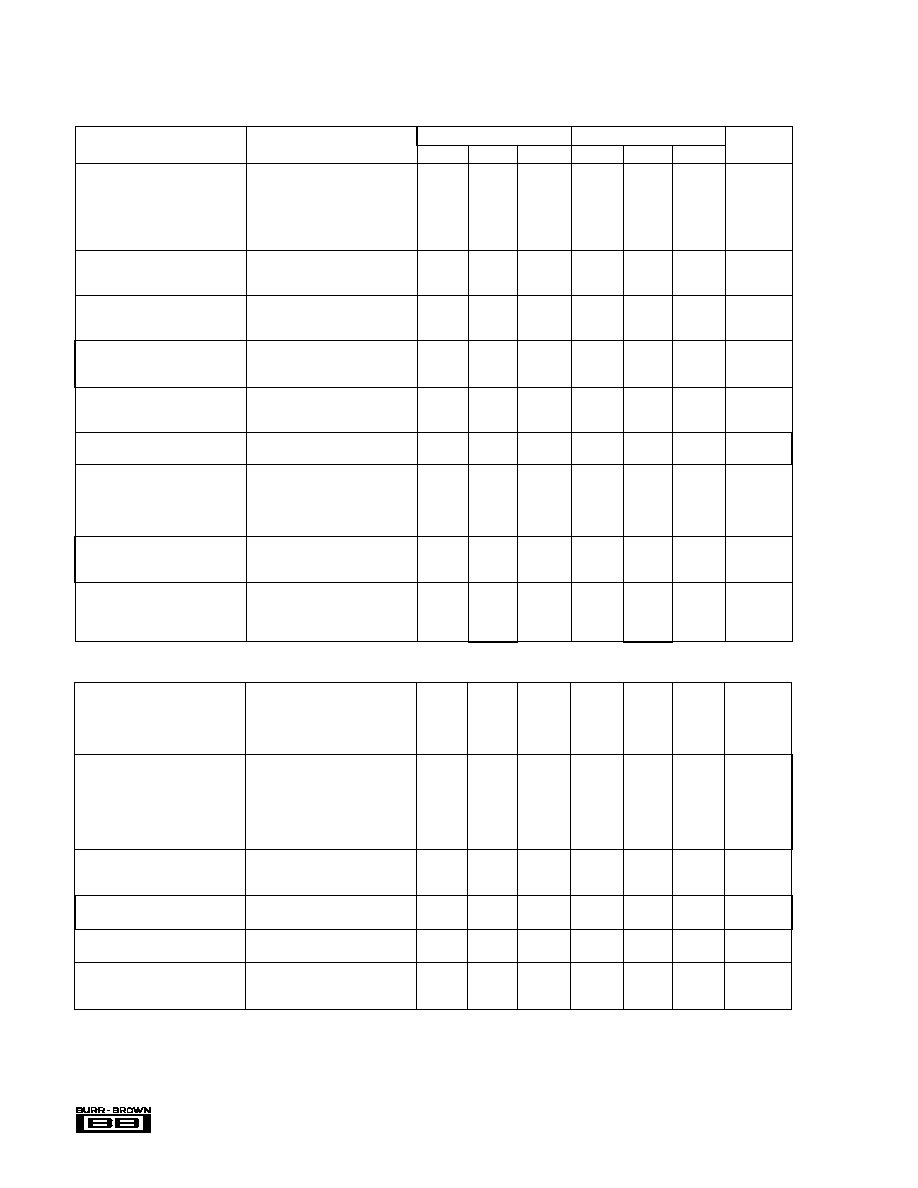

PACKAGE

DRAWING

TEMPERATURE

PRODUCT

PACKAGE

NUMBER

(1)

RANGE

OPA177FP

8-Pin Plastic DIP

006

≠40

∞

C to +85

∞

C

OPA177GP

8-Pin Plastic DIP

006

≠40

∞

C to +85

∞

C

OPA177GS

SO-8 Surface-Mount

182

≠40

∞

C to +85

∞

C

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix C of Burr-Brown IC Data Book.

PACKAGE/ORDERING INFORMATION

4

Æ

OPA177

TYPICAL PERFORMANCE CURVES

At T

A

= +25

∞

C, V

S

=

±

15V, unless otherwise noted.

10

30

50

70

0

20

40

60

30

25

20

15

10

5

0

Absolute Change in Input

Offset Voltage (µV)

Time (s)

OFFSET VOLTAGE CHANGE

DUE TO THERMAL SHOCK

80

Device Immersed in 70∞C Inert Liquid

Plastic DIP

CLOSED-LOOP RESPONSE vs FREQUENCY

100

80

60

40

20

0

≠20

10

100

1k

10k

100k

1M

10M

Closed-Loop Gain (dB)

Frequency (Hz)

3

2

1

0

≠1

≠2

≠3

Offset Voltage Change (µV)

0

30

60

90

120

Time from Power Supply Turn-On (s)

WARM-UP OFFSET VOLTAGE DRIFT

15

45

75

105

17.5

15

12.5

10

7.5

5

2.5

0

V

OUT

(V)

0

6

12

18

24

30

36

I

OUT

(mA)

MAXIMUM V

OUT

vs I

OUT

(Positive Swing)

V

S

= ±18V

V

S

= ±15V

V

S

= ±12V

V

S

= ±15V

≠17.5

≠15

≠12.5

≠10

≠7.5

≠5

≠2.5

0

V

OUT

(V)

0

≠2

≠4

≠6

≠8

≠10

≠12

≠I

OUT

(mA)

MAXIMUM V

OUT

vs I

OUT

(Negative Swing)

V

S

= ±18V

V

S

= ±15V

V

S

= ±12V

V

S

= ±15V

1

0.1

0.01

0.001

THD + N (%)

1k

10k

100k

Frequency (Hz)

TOTAL HARMONIC DISTORTION AND NOISE

vs FREQUENCY

A = 20dB, 3Vrms, 10k

load

30kHz low pass filtered

Inverting

Noninverting

5

Æ

OPA177

TYPICAL PERFORMANCE CURVES

(CONT)

At T

A

= +25

∞

C, V

S

=

±

15V, unless otherwise noted.

150

140

130

120

110

100

90

80

CMRR (dB)

1

10

100

1k

10k

100k

Frequency (Hz)

CMRR vs FREQUENCY

OPEN-LOOP GAIN/PHASE vs FREQUENCY

160

140

120

100

80

60

40

20

0

Open-Loop Gain (dB)

0.01

1

10

100

1k

10k

100k

1M

0.1

Frequency (Hz)

0

45

90

135

180

Phase Shift (Degrees)

Phase

Gain

2

1

0

≠1

≠2

≠40

≠15

10

35

60

85

Temperature (∞C)

INPUT BIAS AND INPUT OFFSET CURRENT

vs TEMPERATURE

Input Bias and Input Offset Current (nA)

I

B

I

OS

150

130

110

90

70

50

Power Supply Rejection (dB)

1

10

100

1k

10k

0.1

Frequency (Hz)

POWER SUPPLY REJECTION

vs FREQUENCY

1k

100

10

1

Input Noise Voltage (nV/

Hz)

1

Frequency (Hz)

INPUT NOISE VOLTAGE DENSITY vs FREQUENCY

10

100

1k

10k

R = 0

S

R = R = 200k

Thermal noise of

source resistors

included.

S1

S2

10

1

0.1

0.01

RMS Noise (µV)

100

1k

10k

100k

Bandwidth (Hz)

TOTAL NOISE vs BANDWIDTH

(0.1Hz to Frequency Indicated)

6

Æ

OPA177

TYPICAL PERFORMANCE CURVES

(CONT)

At T

A

= +25

∞

C, V

S

=

±

15V, unless otherwise noted.

40

35

30

25

20

15

Output Short-Circuit Current (mA)

0

1

2

3

4

Time from Output Being Shorted (min)

OUTPUT SHORT-CIRCUIT CURRENT vs TIME

SC

I ≠

SC

I +

20

15

10

5

0

Maximum Output (V)

100

10k

Load Resistance to Ground ( )

MAXIMUM OUTPUT VOLTAGE vs LOAD RESISTANCE

1k

Negative

Output

Positive

Output

32

28

24

20

16

12

8

4

0

Peak-to-Peak Amplitude (V)

1k

10k

100k

1M

Frequency (Hz)

MAXIMUM OUTPUT SWING vs FREQUENCY

G = +1

R = 2k

L

100

10

1

Power Consumption (mW)

0

10

20

30

40

Total Supply Voltage (V)

POWER CONSUMPTION vs POWER SUPPLY

7

Æ

OPA177

APPLICATIONS INFORMATION

The OPA177 is unity-gain stable, making it easy to use and

free from oscillations in the widest range of circuitry. Ap-

plications with noisy or high impedance power supply lines

may require decoupling capacitors close to the device pins.

In most cases 0.1

µ

F ceramic capacitors are adequate.

The OPA177 has very low offset voltage and drift. To

achieve highest performance, circuit layout and mechanical

conditions must be optimized. Offset voltage and drift can

be degraded by small thermoelectric potentials at the op amp

inputs. Connections of dissimilar metals will generate ther-

mal potential which can mask the ultimate performance of

the OPA177. These thermal potentials can be made to cancel

by assuring that they are equal in both input terminals.

1. Keep connections made to the two input terminals close

together.

2. Locate heat sources as far as possible from the critical

input circuitry.

3. Shield the op amp and input circuitry from air currents

such as cooling fans.

OFFSET VOLTAGE ADJUSTMENT

The OPA177 has been laser-trimmed for low offset voltage

and drift so most circuits will not require external adjust-

ment. Figure 1 shows the optional connection of an external

potentiometer to adjust offset voltage. This adjustment should

not be used to compensate for offsets created elsewhere in a

system since this can introduce excessive temperature drift.

INPUT PROTECTION

The inputs of the OPA177 are protected with 500

series

input resistors and diode clamps as shown in the simplified

circuit diagram. The inputs can withstand

±

30V differential

inputs without damage. The protection diodes will, of course,

conduct current when the inputs are overdriven. This may

disturb the slewing behavior of unity-gain follower applica-

tions, but will not damage the op amp.

NOISE PERFORMANCE

The noise performance of the OPA177 is optimized for

circuit impedances in the range of 2k

to 50k

. Total noise

in an application is a combination of the op amp's input

voltage noise and input bias current noise reacting with

circuit impedances. For applications with higher source

impedance, the OPA627 FET-input op amp will generally

provide lower noise. For very low impedance applications,

the OPA27 will provide lower noise.

INPUT BIAS CURRENT CANCELLATION

The input stage base current of the OPA177 is internally

compensated with an equal and opposite cancellation cur-

rent. The resulting input bias current is the difference

between the input stage base current and the cancellation

current. This residual input bias current can be positive or

negative.

When the bias current is cancelled in this manner, the input

bias current and input offset current are approximately the

same magnitude. As a result, it is not necessary to balance

the DC resistance seen at the two input terminals (Figure 2).

A resistor added to balance the input resistances may actu-

ally increase offset and noise.

FIGURE 1. Optional Offset Nulling Circuit.

OPA177

V

2

3

1

8

Trim Range is approximately ±3.0mV

V+

20k

OUT

V

IN

Op Amp

(a)

R

B

OPA177

(b)

No bias current

cancellation resistor needed

Conventional op amp with

external bias current

cancellation resistor.

OPA177 with no external

bias current cancellation

resistor.

= R

2

|| R

1

R

2

R

1

R

2

R

1

FIGURE 2. Input Bias Current Cancellation.