Central

Semiconductor Corp.

TM

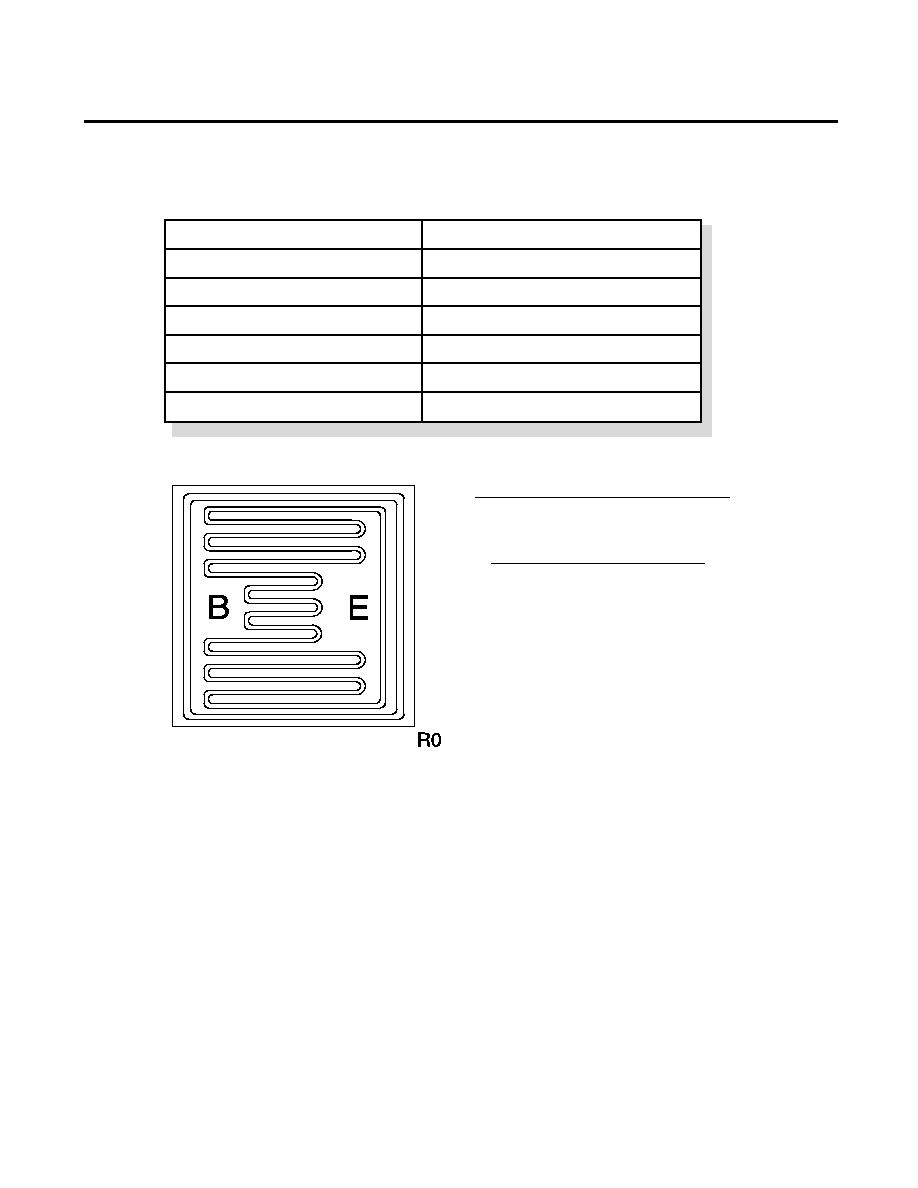

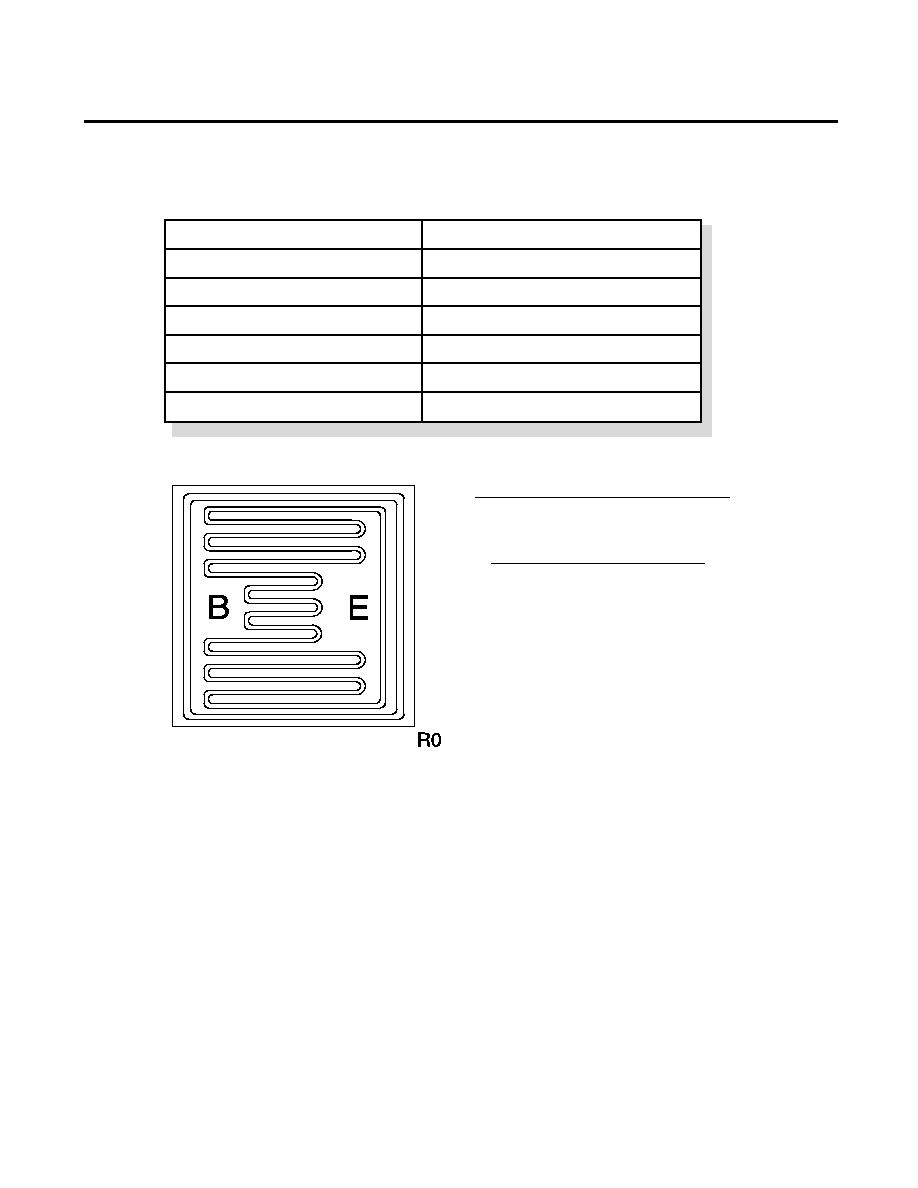

PROCESS

CP714

Small Signal Transistor

PNP - High Current Transistor Chip

PRINCIPAL DEVICE TYPES

CBCP69

CBCX69

CZT751

MPS750

MPS751

Process

EPITAXIAL PLANAR

Die Size

40 x 40 MILS

Die Thickness

9.0 MILS

Base Bonding Pad Area

7.9 x 8.7 MILS

Emitter Bonding Pad Area

9.0 x 14 MILS

Top Side Metalization

Al - 30,000≈

Back Side Metalization

Au - 18,000≈

PROCESS DETAILS

145 Adams Avenue

Hauppauge, NY 11788 USA

Tel: (631) 435-1110

Fax: (631) 435-1824

www.centralsemi.com

BACKSIDE COLLECTOR

GEOMETRY

R2 (1-August 2002)

GROSS DIE PER 4 INCH WAFER

7,070

Central

Semiconductor Corp.

TM

PROCESS

CP714

Typical Electrical Characteristics

145 Adams Avenue

Hauppauge, NY 11788 USA

Tel: (631) 435-1110

Fax: (631) 435-1824

www.centralsemi.com

R2 (1-August 2002)