30

N-Channel Logic Level Enhancement Mode Field Effect Transistor

FEATURES

30V , 55A , R

DS(ON)

=11.5m

@V

GS

=10V.

Super high dense cell design for extremely low R

DS(ON)

.

High power and current handling capability.

TO-252 & TO-251 package.

ABSOLUTE MAXIMUM RATINGS (Tc=25 C unless otherwise noted)

Parameter

Symbol

Limit

Unit

Drain-Source Voltage

V

DS

V

Gate-Source Voltage

V

GS

20

V

-Pulsed

I

D

55

A

I

DM

165

A

Drain-Source Diode Forward Current

I

S

55

A

Maximum Power Dissipation

P

D

W

Operating and Storage Temperature Range

T

J

, T

STG

-55 to 175

C

THERMAL CHARACTERISTICS

Thermal Resistance, Junction-to-Case

Thermal Resistance, Junction-to-Ambient

R

JC

R

JA

2.5

40

/W

C

/W

C

R

DS(ON)

=16m

@V

GS

=4.5V.

CED62A3/CEU62A3

@Tc=25 C

Derate above 25 C

60

0.4

W/ C

Drain Current-Continuous

S

G

D

6

Feb. 2003

CEU SERIES

TO-252AA(D-PAK)

CED SERIES

TO-251(l-PAK)

G

G

S

S

D

D

6-147

CED62A3/CEU62A3

ELECTRICAL CHARACTERISTICS (T

C

=25 C unless otherwise noted)

Parameter

Symbol

Condition

Min Typ Max Unit

OFF CHARACTERISTICS

Drain-Source Breakdown Voltage

BV

DSS

V

GS

= 0V, I

D

= 250

�

A

30

V

Zero Gate Voltage Drain Current

I

DSS

V

DS

= 30V, V

GS

= 0V

1

�

A

Gate-Body Leakage

I

GSS

V

GS

= 20V, V

DS

= 0V

100 nA

ON CHARACTERISTICS

a

Gate Threshold Voltage

V

GS(th)

V

DS

= V

GS

, I

D

= 250

�

A

1

3

V

Drain-Source On-State Resistance

R

DS(ON)

V

GS

= 10V, I

D

= 14A

9.5

11.5

m

V

GS

= 4.5V, I

D

= 11A

13

16

m

On-State Drain Current

I

D(ON)

V

GS

= 10V, V

DS

= 5V

55

26

A

S

Forward Transconductance

FS

g

V

DS

= 5V, I

D

= 12A

DYNAMIC CHARACTERISTICS

b

Input Capacitance

C

ISS

C

RSS

C

OSS

Output Capacitance

Reverse Transfer Capacitance

V

DS

=15V, V

GS

= 0V

f =1.0MH

Z

1100

P

F

600

P

F

P

F

180

SWITCHING CHARACTERISTICS

b

Turn-On Delay Time

Rise Time

Turn-Off Delay Time

t

D(ON)

t

r

t

D(OFF)

t

f

V

DD

= 15V,

I

D

=14A,

V

GS

= 10V,

R

GEN

=6

19

48

ns

ns

ns

ns

36

72

97

175

68

135

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

Q

g

Q

gs

Q

gd

V

DS

=10V, I

D

= 14A,

V

GS

=10V

35

42

nC

nC

nC

6

11

Fall Time

6

6-148

Parameter

Symbol

Condition

Min Typ Max Unit

ELECTRICAL CHARACTERISTICS (T

C

=25 C unless otherwise noted)

DRAIN-SOURCE DIODE CHARACTERISTICS

Diode Forward Voltage

V

SD

V

GS

= 0V, Is = 2.3A

1.3

V

a

Notes

b.Guaranteed by design, not subject to production testing.

a.Pulse Test:Pulse Width 300 s, Duty Cycle 2%.

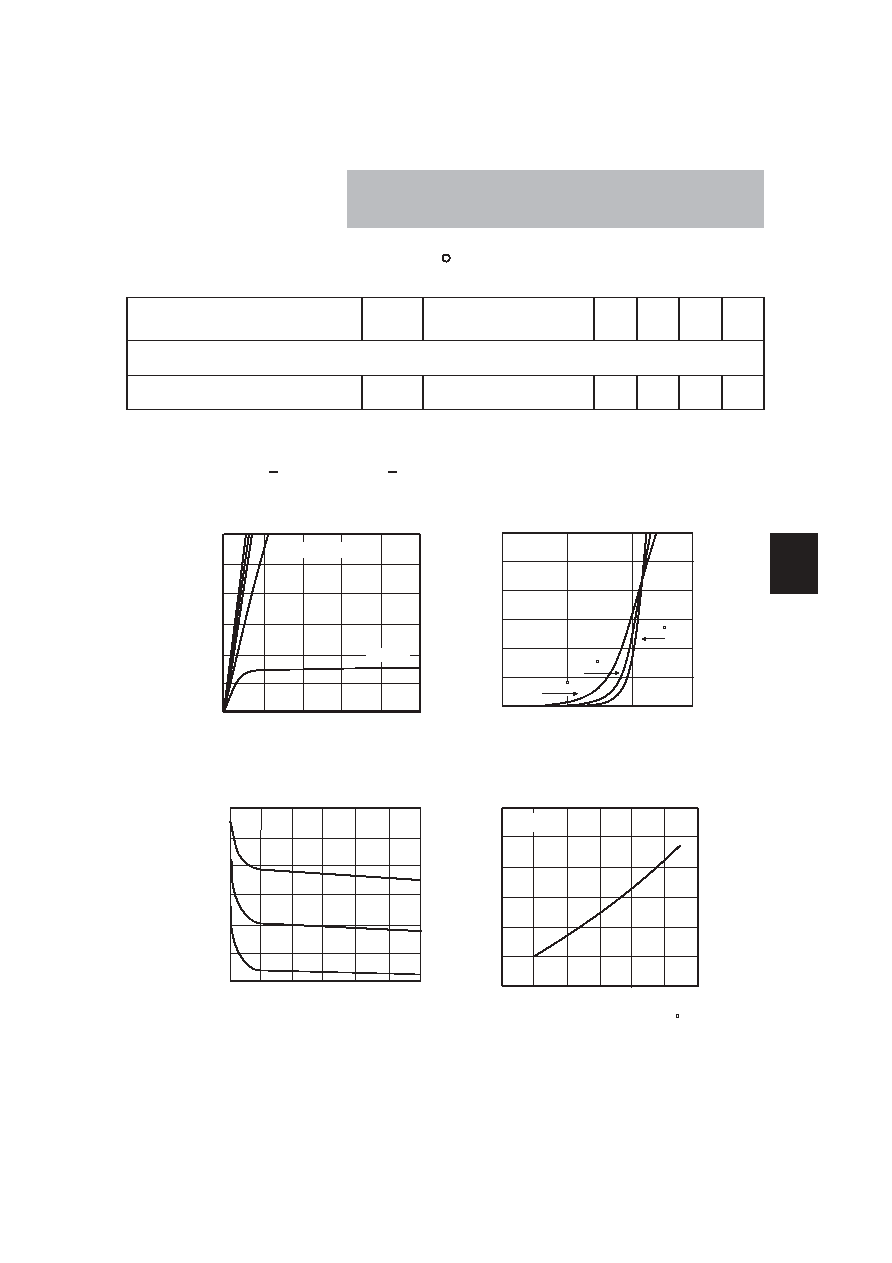

Figure 1. Output Characteristics

Figure 2. Transfer Characteristics

Figure 3. Capacitance

V

DS

, Drain-to Source Voltage (V)

V

GS

, Gate-to-Source Voltage (V)

V

DS

, Drain-to-Source Voltage (V)

C

,

Capacitance

(pF)

I

D

,

D

r

a

in

Current

(A)

I

D

,

D

r

a

in

Current

(A)

6-149

CED62A3/CEU62A3

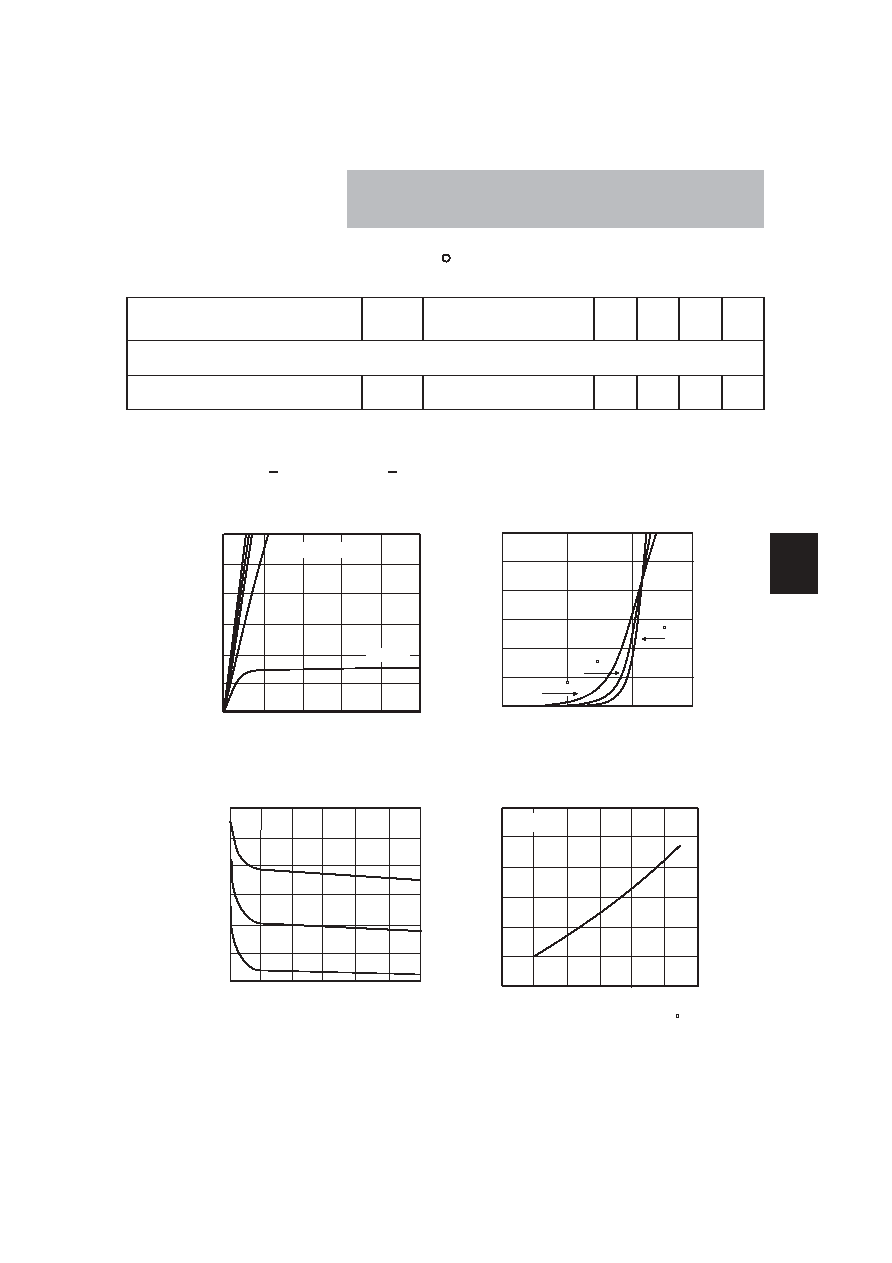

Figure 4. On-Resistance Variation with

Temperature

T

J

, Junction Temperature( C)

On-Resistance(Ohms)

R

DS(ON)

,

R

DS(ON)

,

N

or

maliz

e

d

0

1

2

3

4

25 C

Tj=125 C

-55 C

20

30

40

50

60

10

60

50

40

30

20

10

0

0

1

2

3

4

5

V

GS

=3V

V

GS

=10,8,6,4V

1800

1500

1200

900

600

300

0

5

10

15

20

25

30

Ciss

Coss

Crss

0

-100

-50

0

50

100

200

2.2

1.9

1.6

1.3

1.0

0.7

0.4

V

GS

=10V

I

D

=14A

150

6

CED62A3/CEU62A3

with Temperature

Figure 6. Breakdown Voltage Variation

Figure 5. Gate Threshold Variation

with Temperature

Vth,

Normalized

Gate-Source

Threshold

Voltage

g

FS

,

Transconductance

(S)

V

GS

,

Gate

t

o

Source

Voltage

(V)

BV

DSS

,

Normalized

Drain-Source

Breakdown

Voltage

Is,

Source-drain

c

urrent

(A)

Figure 7. Transconductance Variation

with Drain Current

I

DS

, Drain-Source Current (A)

Figure 9. Gate Charge

Qg, Total Gate Charge (nC)

Figure 10. Maximum Safe

Operating Area

V

DS

, Drain-Source Voltage (V)

Figure 8. Body Diode Forward Voltage

Variation with Source Current

V

SD

, Body Diode Forward Voltage (V)

Tj, Junction Temperature ( C)

Tj, Junction Temperature ( C)

I

D

,

D

rain

Current

(A)

6-150

1.30

1.20

1.10

1.00

0.90

0.80

0.70

0.60

-50 -25

0

25

50

75

100 125 150

V

DS

=V

GS

I

D

=250 A

10

10

-2

10

10

1

0

-1

10

1

10

-2

10

0

10

-1

10

2

10

2

RDS(O

N)

Limit

DC

1s

100

ms

10m

s

1ms

T

A

=25 C

Single Pulse

R

JA

=

40 C/W

-50

-25

0

25

50

75 100 125 150

1.15

1.10

1.05

1.00

0.95

0.90

0.85

I

D

=250 A

10

0

2

4

6

8

0

10

20

30

40

V

DS

=15V

I

D

=14A

50

10

1.0

0.1

0.4

0.6

0.8

1.0

1.2

1.4

50

40

30

20

10

0

0

10

20

30

40

V

DS

=10V

6

Figure 11. Switching Test Circuit

Figure 12. Switching Waveforms

CED62A3/CEU62A3

t

V

V

t

t

d(on)

OUT

IN

on

r

10%

t

d(off)

90%

10%

10%

50%

50%

90%

t

off

t

f

90%

PULSE WIDTH

6-151

4

INVERTED

Transient

Thermal

Impedance

Square Wave Pulse Duration (sec)

Figure 13. Normalized Thermal Transient Impedance Curve

r(t),Normalized

Effective

V

DD

R

D

V

V

R

S

V

G

GS

IN

GEN

OUT

L

10

-4

10

-3

10

-2

10

-1

10

0

P

DM

t

1

t

2

1. R

JA

(t)=r (t) * R

JA

2. R

JA

=See Datasheet

3. T

JM-

T

A

= P* R

JA

(t)

4. Duty Cycle, D=t1/t2

10

-3

10

-2

10

-1

10

0

10

2

10

1

Single Pulse

0.01

0.02

0.05

0.1

0.2

D=0.5

6