| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: Pm37LV512 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

FEATURES

∑

Low Voltage Operation

- Dual read V

CC

ranges: 2.7 V to 3.6 V or 4.5 V to

5.5 V

- Program/Erase voltage: V

CC

- 2.7 V to 3.6 V and

V

PP

- 11.5 V to 12.5 V

∑ High Performance Read

- 70 ns access time

∑ Electrical Chip Erase and Byte Program

Using EPROM Programmer

- Maximum 20 µs/byte programming

- Maximum 100 ms chip erase

- Do not require UV erase

∑ Low Power Consumption

- Typical 5 mA active read current

- Typical 18 µA CMOS standby current

∑ Excellent Product Reliablity

- Guarantee minimum 1,000 program/erase cycles

- Minimum 20 years data retention

∑ JEDEC Standard Byte-wide Flash Memory

Pin-out

∑ Industrial Standard Packaging

- 32-pin PLCC

- 32-pin PDIP

- 32-pin VSOP

GENERAL DESCRIPTION

The Pm37LV512 is a 512 Kbit, Multiple-Cycle-Programmable Read-Only-Memory (MCP ROM) organized as 65,563

bytes of 8 bits each. The program and erase operation of device can be done on EPROM programmers by applying

3.0 Volt V

CC

and 12.0 Volt V

PP

to A9 and/or OE# pin. This eliminates the need of a UV-Source for erase operation

such as EPROM device. The read operation of device can be in 2.7 Volt to 3.6 Volt or 4.5 Volt - 5.5 Volt range

compatible to either 3.0 Volt or 5.0 Volt systems. The dual read operation ranges can greatly increase application

flexibility for users.

The device has a standard microprocessor interface as well as JEDEC single-power-supply Flash compatible pin-

out. For applications that do not require in-system-programming (ISP) function for firmwire upgrade, the Pm37LV512

offers a direct cost reduction path for Flash memory, i.e. Pm39LV512, without modifying the schematic and board

layout of system.

The Pm37LV512 is manufactured on PMC's advanced nonvolatile CMOS technology, P-FLASHTM. The device is

offered in 32-pin PLCC, VSOP and PDIP packages with access time of 70 ns.

PMC

512 Kbit (64K X 8) Dual-Voltage Multiple-Cycle-Programmable ROM

Programmable Microelectronics Corp.

Issue Date: Dec, 2002 Rev:1.3

Pm37LV512

1

Programmable Microelectronics Corp.

Issue Date: Dec, 2002 Rev: 1.3

PMC

Pm37LV512

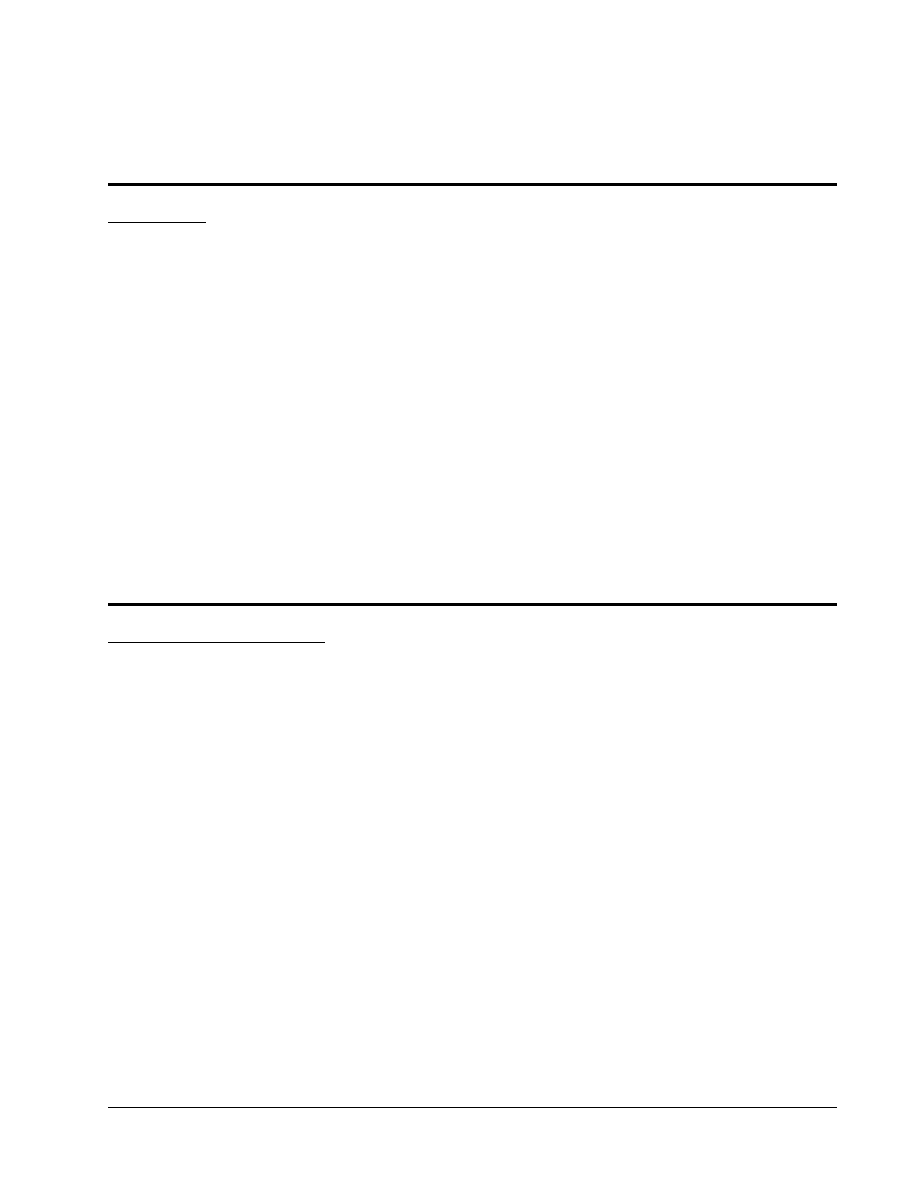

CONNECTION DIAGRAMS

LOGIC SYMBOL

2

1 6

8

A 0 - A 1 5

I/O0-I/O7

C E #

O E #

W E #

32-Pin PLCC

2 0

1 9

1 8

1 7

1 6

1 5

1 4

5

6

7

8

9

1 0

1 1

1 2

1 3

1

2

3

4

3 2

3 1

3 0

A12

A15

NC

V

CC

WE#

NC

I/O1

GND

I/O2

I/O3

I/O4

I/O5

I/O6

I/O0

A 0

A 1

A 2

A 3

A 4

A 5

A 6

A 7

2 9

2 8

2 7

2 6

2 5

2 4

2 3

2 2

2 1

A 1 4

A 1 3

A 8

A 9

A 1 1

O E #

A 1 0

C E #

I/O7

NC

32-Pin PDIP

3 2

3 1

3 0

2 9

2 8

2 7

2 6

2 5

2 4

2 3

2 2

2 1

2 0

1 9

1 8

1 7

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

N C

N C

A 1 5

A 1 2

A 7

A 6

A 5

A 4

A 3

A 2

I/O0

I/O1

A 1

A 0

I/O2

G N D

V

C C

W E #

N C

A 1 4

A 1 3

A 8

A 9

O E #

A 1 0

A 1 1

C E #

I/O7

I/O6

I/O5

I/O4

I/O3

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

3 2

3 1

3 0

2 9

2 8

2 7

2 6

2 5

2 4

2 3

2 2

2 1

2 0

1 9

1 8

1 7

A 1 1

A 9

A 8

A 1 3

A 1 4

N C

W E #

V

C C

N C

N C

A 1 5

A 1 2

A 7

A 6

A 5

A 4

32-Pin VSOP

I/O4

O E #

A 1 0

C E #

I/O7

I/O6

I/O5

I/O3

G N D

I/O2

I/O1

I/O0

A 0

A 1

A 2

A 3

Programmable Microelectronics Corp.

Issue Date: Dec, 2002 Rev: 1.3

PMC

Pm37LV512

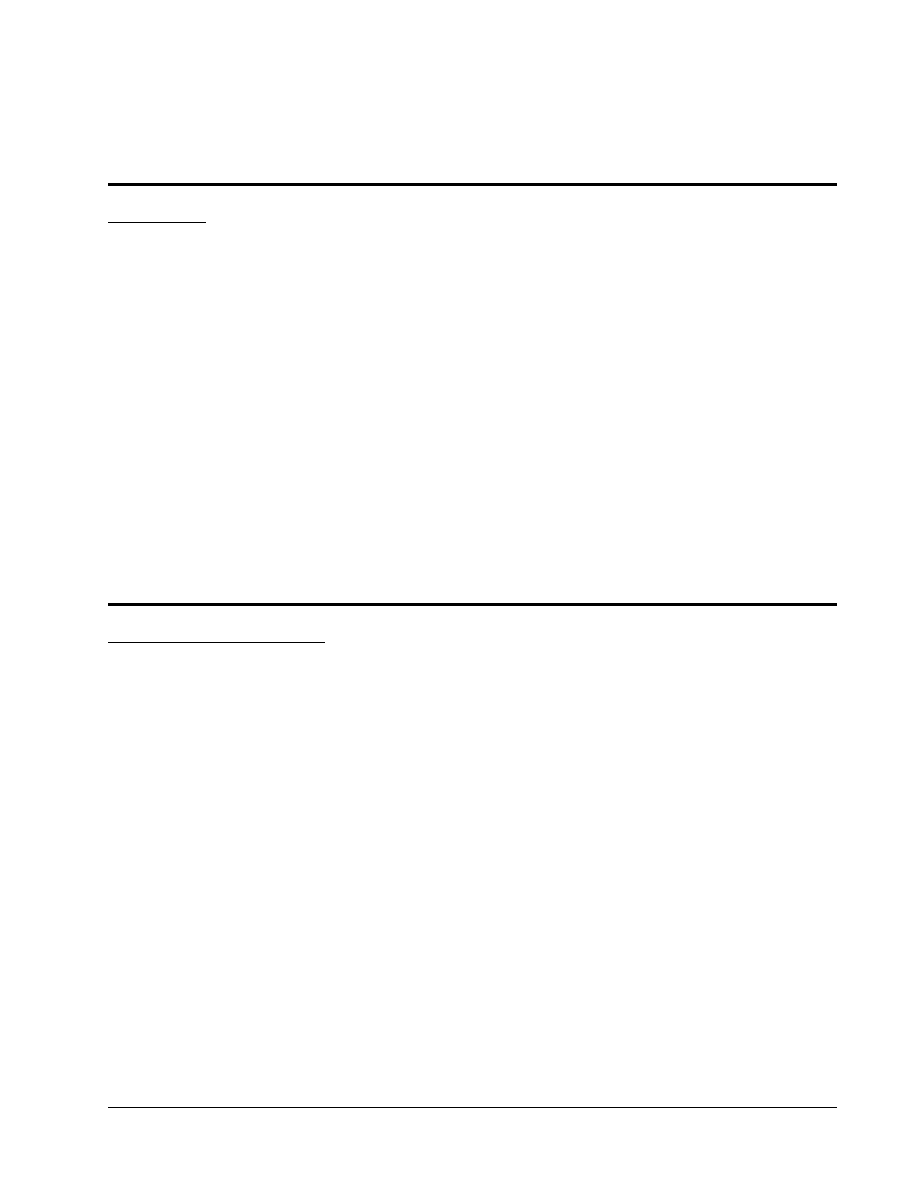

PRODUCT ORDERING INFORMATION

3

Pm37LV512 -70 J C

Temperature Range

C = Commercial (0∞C to +70∞C)

Package Type

J = 32-pin Plastic J-Leaded Chip Carrier (32J)

P = 32-pin Plastic DIP (32P)

V = 32-pin Thin Small Outline Package (32V)

Speed Option

PMC Device Number

r

e

b

m

u

N

t

r

a

P

t

C

C

A

)

s

n

(

e

g

a

k

c

a

P

e

g

n

a

R

e

r

u

t

a

r

e

p

m

e

T

C

J

0

7

-

2

1

5

V

L

7

3

m

P

0

7

J

2

3

l

a

i

c

r

e

m

m

o

C

)

C

∞

0

7

+

o

t

C

∞

0

(

C

P

0

7

-

2

1

5

V

L

7

3

m

P

P

2

3

l

a

i

c

r

e

m

m

o

C

)

C

∞

0

7

+

o

t

C

∞

0

(

C

V

0

7

-

2

1

5

V

L

7

3

m

P

V

2

3

l

a

i

c

r

e

m

m

o

C

)

C

∞

0

7

+

o

t

C

∞

0

(

Programmable Microelectronics Corp.

Issue Date: Dec, 2002 Rev: 1.3

PMC

Pm37LV512

PIN DESCRIPTIONS

4

L

O

B

M

Y

S

E

P

Y

T

N

O

I

T

P

I

R

C

S

E

D

5

1

A

-

0

A

T

U

P

N

I

y

ll

a

n

r

e

t

n

i

e

r

a

s

e

s

s

e

r

d

d

A

.

t

u

p

n

i

s

e

s

s

e

r

d

d

a

y

r

o

m

e

m

r

o

F

:

s

t

u

p

n

I

s

s

e

r

d

d

A

.

e

l

c

y

c

e

t

i

r

w

a

g

n

i

r

u

d

#

E

W

f

o

e

g

d

e

g

n

il

l

a

f

e

h

t

n

o

d

e

h

c

t

a

l

#

E

C

T

U

P

N

I

r

o

f

s

e

i

r

t

i

u

c

r

i

c

l

a

n

r

e

t

n

i

s

'

e

c

i

v

e

d

e

h

t

s

e

t

a

v

i

t

c

a

w

o

l

s

e

o

g

#

E

C

:

e

l

b

a

n

E

p

i

h

C

o

t

n

i

s

e

h

c

t

i

w

s

d

n

a

e

c

i

v

e

d

e

h

t

s

t

c

e

l

e

s

e

d

h

g

i

h

s

e

o

g

#

E

C

.

n

o

i

t

a

r

e

p

o

e

c

i

v

e

d

.

n

o

i

t

p

m

u

s

n

o

c

r

e

w

o

p

e

h

t

e

c

u

d

e

r

o

t

e

d

o

m

y

b

d

n

a

t

s

#

E

W

T

U

P

N

I

.

w

o

l

e

v

i

t

c

a

s

i

#

E

W

.

n

o

i

t

a

r

e

p

o

e

t

i

r

w

r

o

f

e

c

i

v

e

d

e

h

t

e

t

a

v

i

t

c

A

:

e

l

b

a

n

E

e

t

i

r

W

#

E

O

T

U

P

N

I

#

E

O

.

e

l

c

y

c

d

a

e

r

a

g

n

i

r

u

d

s

r

e

f

f

u

b

t

u

p

t

u

o

s

'

e

c

i

v

e

d

e

h

t

l

o

r

t

n

o

C

:

e

l

b

a

n

E

t

u

p

t

u

O

.

w

o

l

e

v

i

t

c

a

s

i

7

O

/

I

-

0

O

/

I

/

T

U

P

N

I

T

U

P

T

U

O

a

t

a

d

t

u

p

t

u

o

r

o

e

l

c

y

c

e

t

i

r

w

a

g

n

i

r

u

d

a

t

a

d

/

d

n

a

m

m

o

c

t

u

p

n

I

:

s

t

u

p

t

u

O

/

s

t

u

p

n

I

a

t

a

D

.

d

e

l

b

a

s

i

d

e

r

a

#

E

O

n

e

h

w

e

t

a

t

s

-

i

r

t

o

t

t

a

o

l

f

s

n

i

p

O

/

I

e

h

T

.

e

l

c

y

c

d

a

e

r

a

g

n

i

r

u

d

V

C

C

y

l

p

p

u

S

r

e

w

o

P

e

c

i

v

e

D

D

N

G

d

n

u

o

r

G

C

N

n

o

i

t

c

e

n

n

o

C

o

N

Programmable Microelectronics Corp.

Issue Date: Dec, 2002 Rev: 1.3

PMC

Pm37LV512

BLOCK DIAGRAM

PRODUCT IDENTIFICATION

The hardware product identification mode can be used

by an EPROM programmer to identify the device and

manufacturer for selecting the right programming algo-

rithm

for the device. The product identification mode is

activated by applying 12.0 Volt on A9 pin. For details,

please see Bus Operation Modes in Table 1.

5

W E #

C E #

O E #

C O M M A N D

R E G I S T E R

C E , O E L O G I C

A 0 - A 1 5

I/O0-I/O7

I / O B U F F E R S

D A T A

L A T C H

S E N S E

A M P

Y - G A T I N G

M E M O R Y

A R R A Y

ADDRESS

LATCH

Y - D E C O D E R

X - D E C O D E R

BYTE PROGRAMMING

The Pm37LV512 is programmed by using an external

EPROM programmer. The programming mode is acti-

vated by applying 12.0 Volt on OE# pin and V

IL

on CE#

pin. The byte program operation is completed by assert-

ing WE# to low for 20 µs. A chip erase operation is

required prior to program due to a data "0" can not be

programmed back to a "1" and only erase operation can

convert "0"s to "1"s. The entire chip can be programmed

byte-by-byte by using the byte program algorithmm. Re-

fer to Chart 1. Byte Programming Flowchart and Byte

Program Operations AC Waveforms.

DEVICE OPERATION

READ OPERATION

The access of Pm37LV512 is similar as that of EPROM

or Flash Memory. To obtain data at the outputs, three

control functions must be satisfied:

∑ CE# is the chip enable and should be pulled low

( V

IL

).

∑ OE# is the output enable and should be pulled

low ( V

IL

).

∑ WE# is the write enable and should remains high

( V

IH

)

.

CHIP ERASE

The entire memory array can be erased through a chip

erase operation on an external EPROM programmer.

Pre-program the "1"s cells in the device is not required

prior to chip erase operation. The chip erase operation

is activated by applying 12.0 Volt to OE# and A9 pins

while CE# pin is low. All other address and data pins

are "don't care". Chip erase is completed by asserting

WE# pin to low for 100 ms. The falling edge of WE# will

start the chip erase operation. The device will return back

to standby mode after the completion of chip erase. Refer

to Chart 2. Chip Erase Flowchart and Chip Erase

Operations AC Waveforms.