TM

Virtual Components for the Converging World

Amphion continues to expand its family of application-specific cores

1

See http://www.amphion.com for a current list of products

CS5250-80

High Performance AES Decryption Cores

The CS5250-80 series of decryption cores

1

are designed to achieve data privacy and authenticity in digital

broadband, wireless, and multimedia systems. These high performance application specific silicon cores support

the AES (Rijndael) algorithm as described in the NIST Federal Information Processing Standard. They can be

used in conjunction with the CS5210-40 series of Amphion AES encryption cores to rapidly construct complete

security solutions. The CS5200 family of cores are available in both ASIC and programmable logic versions that

have been hand crafted by Amphion to deliver high performance while minimizing power consumption and

silicon area.

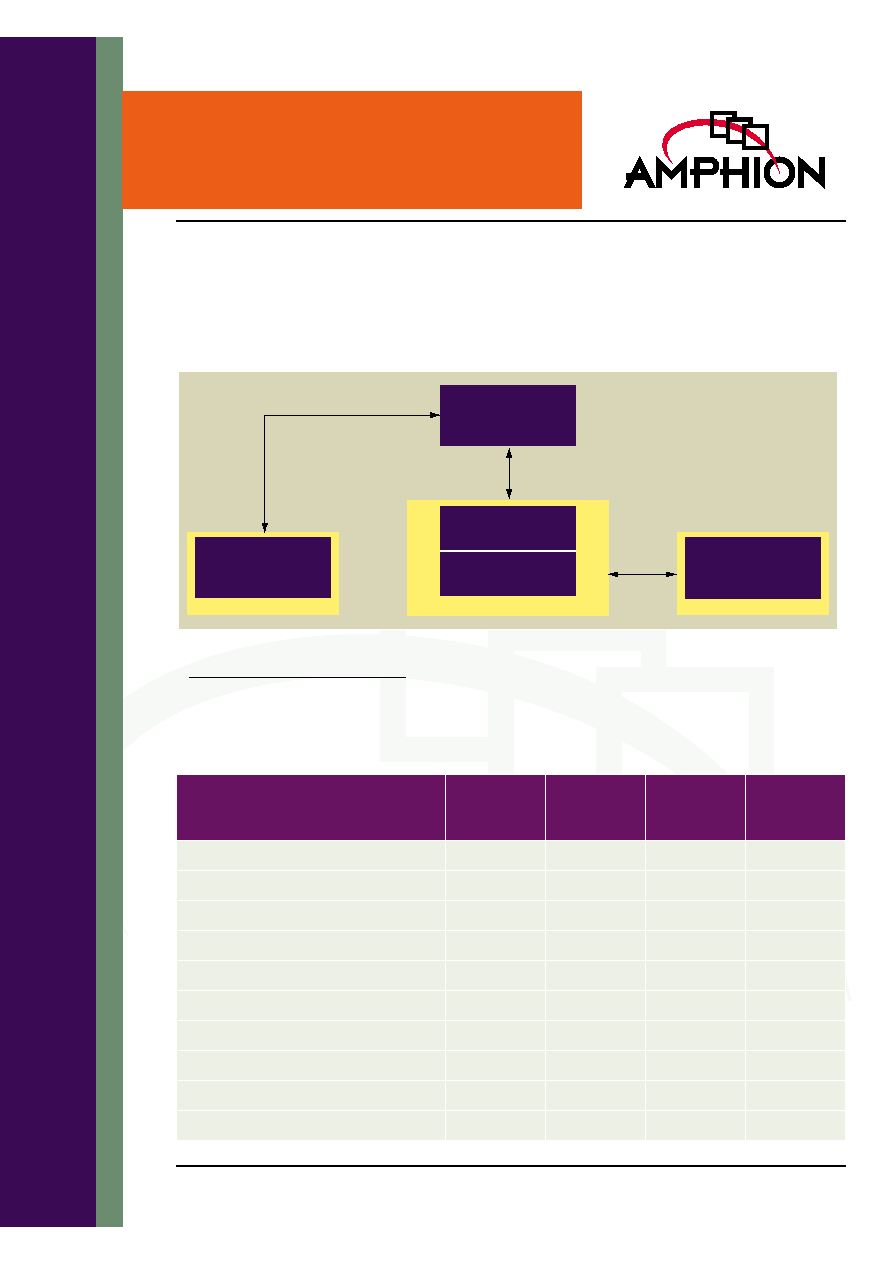

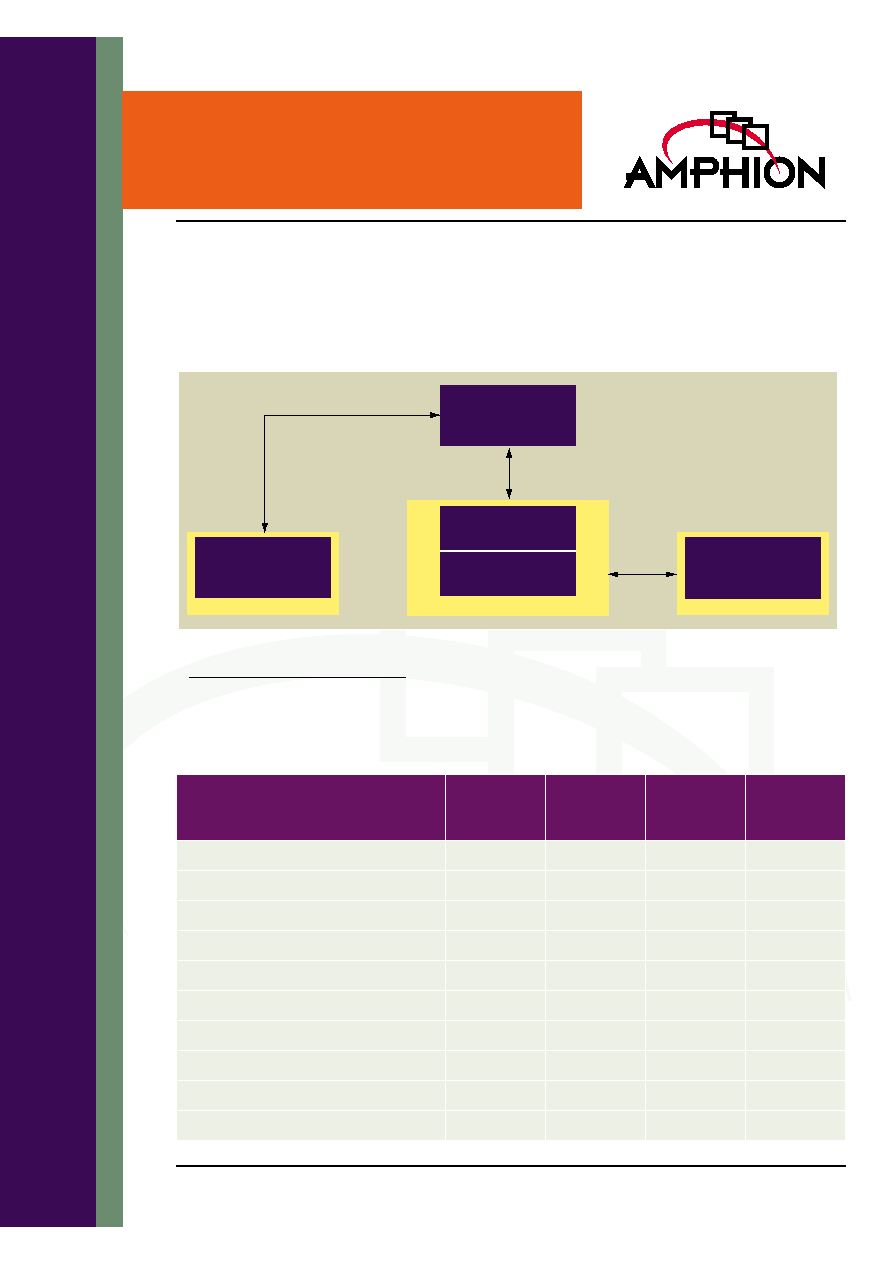

Figure 1: Example of a Satellite and Point-to-Point Secure Communication Scheme Using AES

1. Patent pending

Long Distance Location

Ground Station Uplink

Ultra High Speed AES

Location #1

Ground Station Uplink

Ultra High Speed AES

Metropolitan Link

High Speed AES

Location #2

Metropolitan Link

High Speed AES

Satellite Downlink

Ultra High Speed AES

DECRYPTION CORE FEATURES

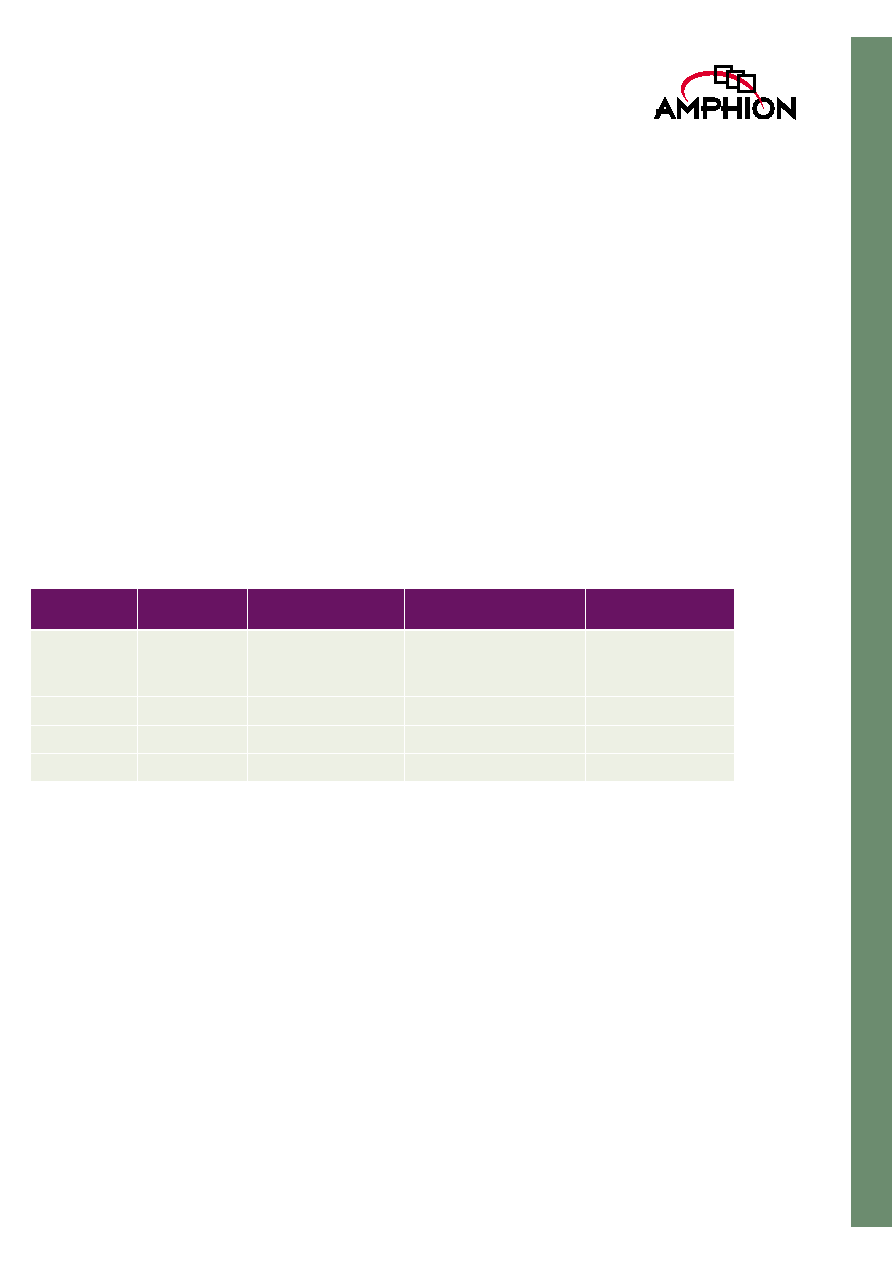

Table 1: CS5250-80 Features at a Glance

CS5250

Standard

CS5260

Compact

CS5270

High Speed

CS5280

Ultra High

Speed

Fully compliant with AES NIST FIPS

�

�

�

�

128-bit data block

�

�

�

�

128-, 192-, 256-bit keys on-line selectable

�

128-bit keys only

�

�

�

32-bit I/O

�

�

�

128-bit I/O

�

Electronic Codebook mode (ECB)

�

�

�

�

Output Feedback mode (OFB)

�

�

�

�

Cipher Block Chaining mode (CBC)

�

�

�

Cipher Feedback mode (CFB)

�

�

�

2

CS5250-80

High Performance AES Decryption Cores

APPLICATIONS

Electronic financial transactions

-

eCommerce

-

Banking

-

Securities exchange

-

Point-of-Sale

Secure corporate communications

-

Storage Area Networks (SAN)

-

Virtual private networks (VPN)

-

Video conferencing

-

Voice services

Personal mobile communications

-

Video phones

-

PDA

-

Point-to-Point Wireless

-

Wearable computers

Secure environments

-

Satellite communications

-

Surveillance systems

-

Network appliances

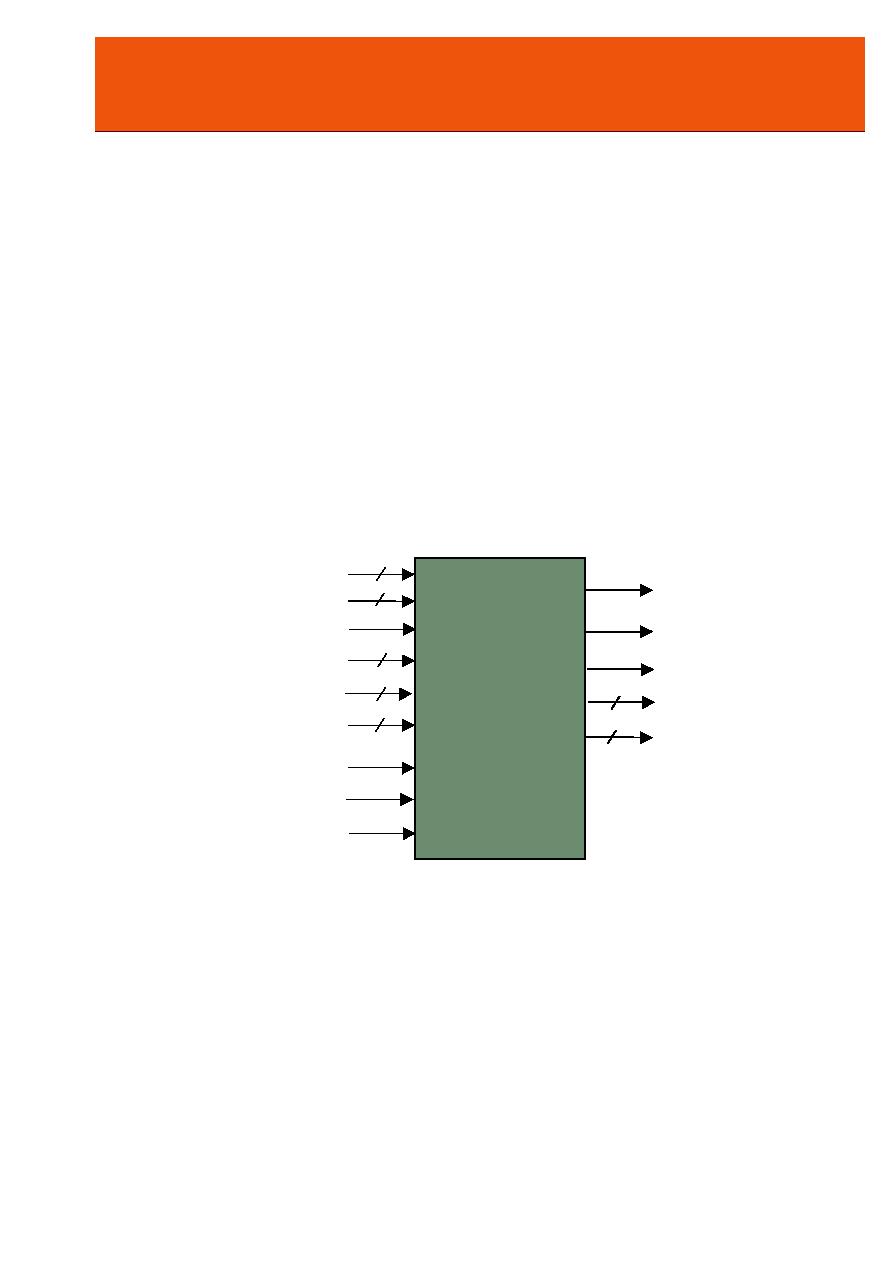

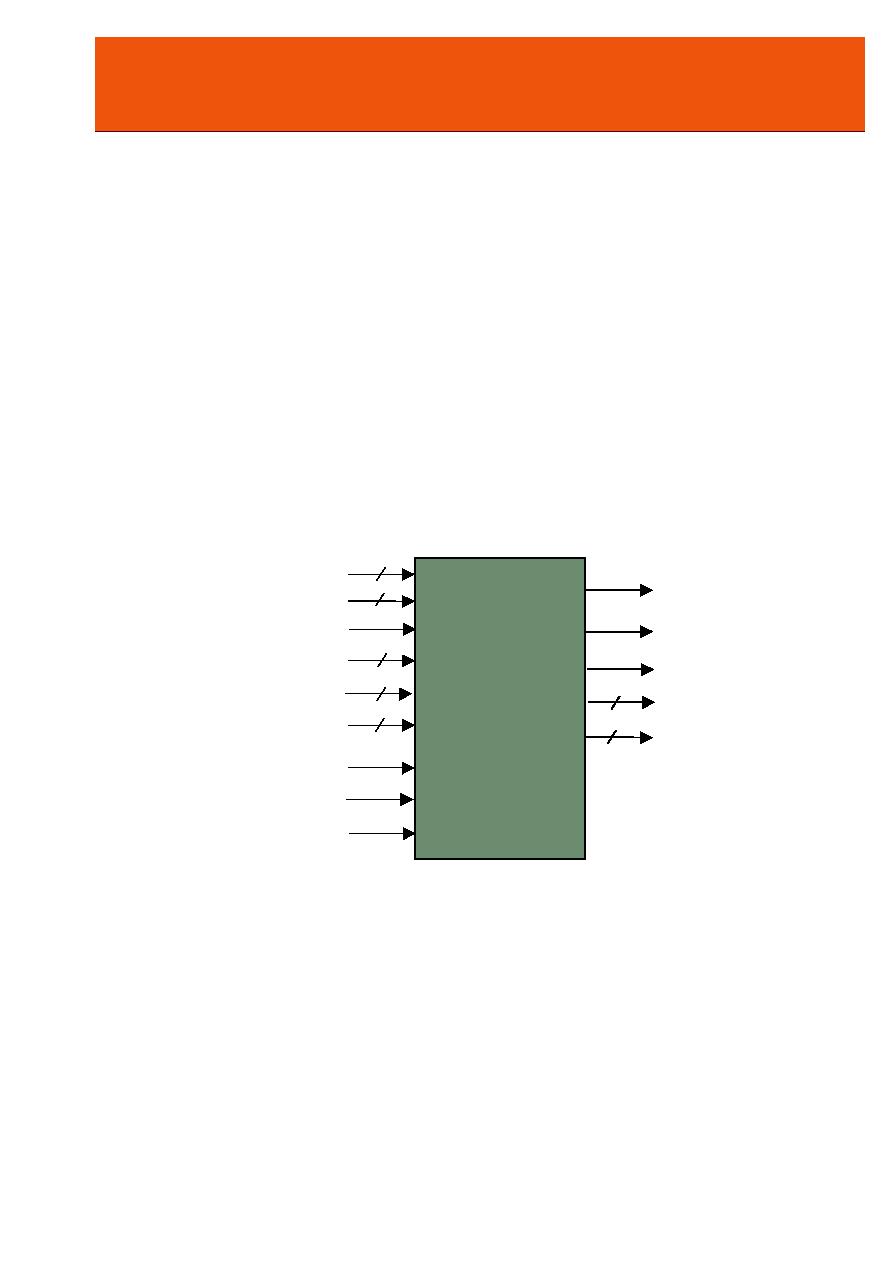

CS5250-80 SYMBOL AND

PIN DESCRIPTION

Table 2 gives the descriptions of the input and output ports

(shown graphically in Figure 2) of the CS5250-80 series of AES

decryption cores. Unless otherwise stated, all signals are

active high and bit(0) is the least significant bit.

Figure 2: CS5250-80 Symbol

CS5250-80

CLK

RST

NKS

(CS5250 only)

LDKY

KADDR

IKEY

LOAD

DAADR

D

KSTAT

DSTAT

QSTRB

QADDR

Q

3

TM

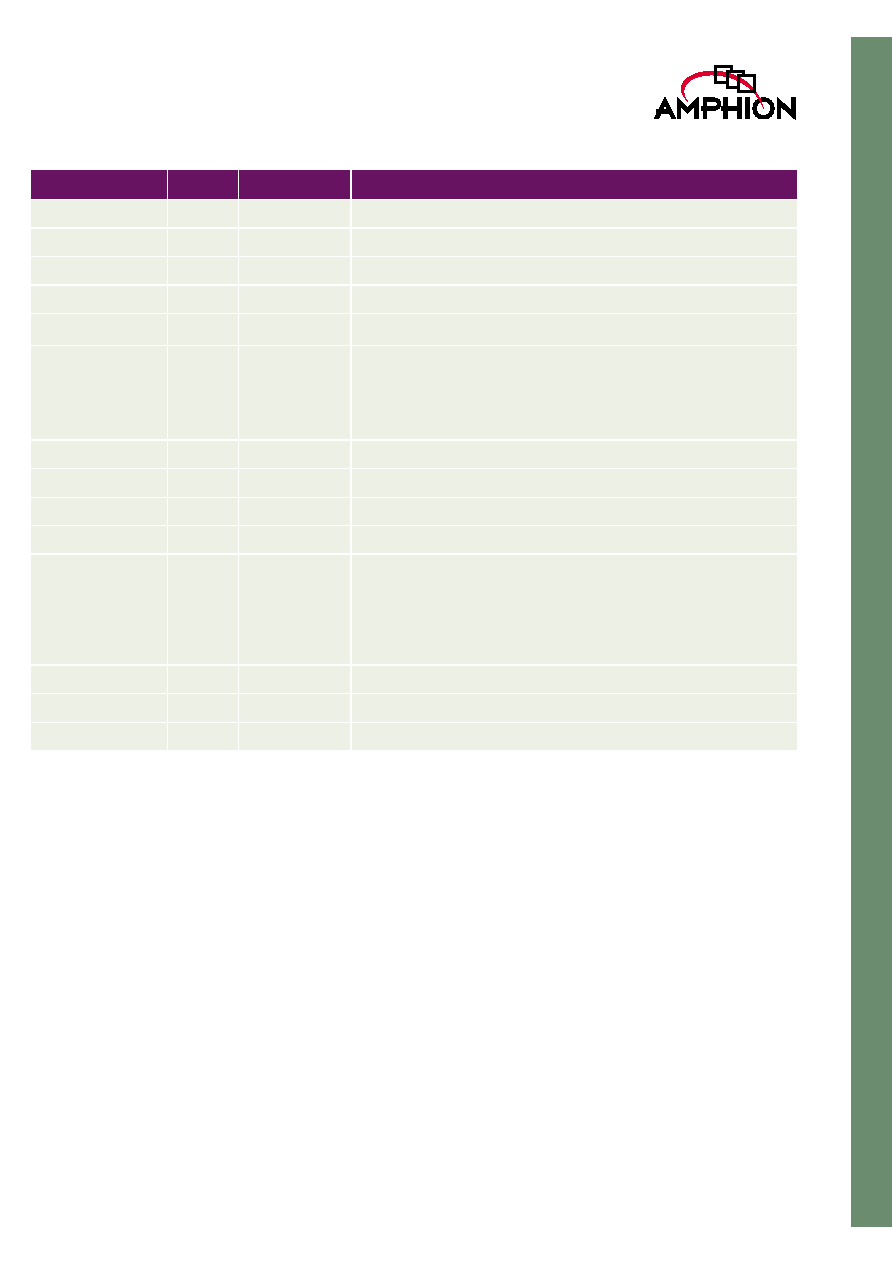

Table 2: CS5250-80 Standard Rijndael Decryption Interface Signal Definitions

Signal

I/O

Width (Bits)

Description

D

I

32 (128)

Cipher text data (128-bit width for CS5280)

DADDR

I

2

Cipher text data address, 0: the lowest 32-bit word

LDKEY

I

1

Load inverse cipher key

IKEY

I

32 (128)

Inverse cipher key (128-bit width for CS5280)

KADDR

I

3

a

Inverse cipher key address, 0: the lowest 32-bit word

NKS

I

2

Inverse cipher key size select

(CS5250 only)

When 00: Selects a 128-bit Key

When 01: Selects a 192-bit Key

When 1X: Selects a 256-bit Key

LOAD

I

1

Load ciphertext enable

CLK

I

1

System clock, rising edge active

RST

I

1

Asynchronous reset

KSTAT

O

1

Key port status, when Asserted, loading of cipher keys is not allowed

DSTAT

O

1

Input port status

The next cycle after text D[3] (the highest word of 128-bit clock) is

loaded, DSTAT will be De-asserted to indicate decryption is in progress.

It will be Asserted when the core is ready for loading the highest word of

the next 128-bit text. The lower three words can be loaded at anytime in

the period when DSTAT is LOW depending on the key-size selection.

QSTRB

O

1

Output strobe indicating the Plaintext word Q is valid

QADDR

O

2

Plaintext data address, 0: the lowest 32-bit word

Q

O

32 (128)

Plaintext data (128-bit width for CS5280)

a. 3 bits wide for the standard; 2 bits wide for compact/high speed cores; not applicable for ultra high speed core

4

CS5250-80

High Performance AES Decryption Cores

FUNCTIONAL DESCRIPTION

The Rijndael algorithm is an iterated block cipher that

encrypts and decrypts data in 128-bit data blocks using a

128-bit, 192-bit, or 256-bit key. The algorithm consists of:

�

An initial data/key addition

�

Nine, eleven or thirteen rounds when the length is

128-bits, 192-bits, or 256-bits respectively

�

A final round which is a variation of the typical round

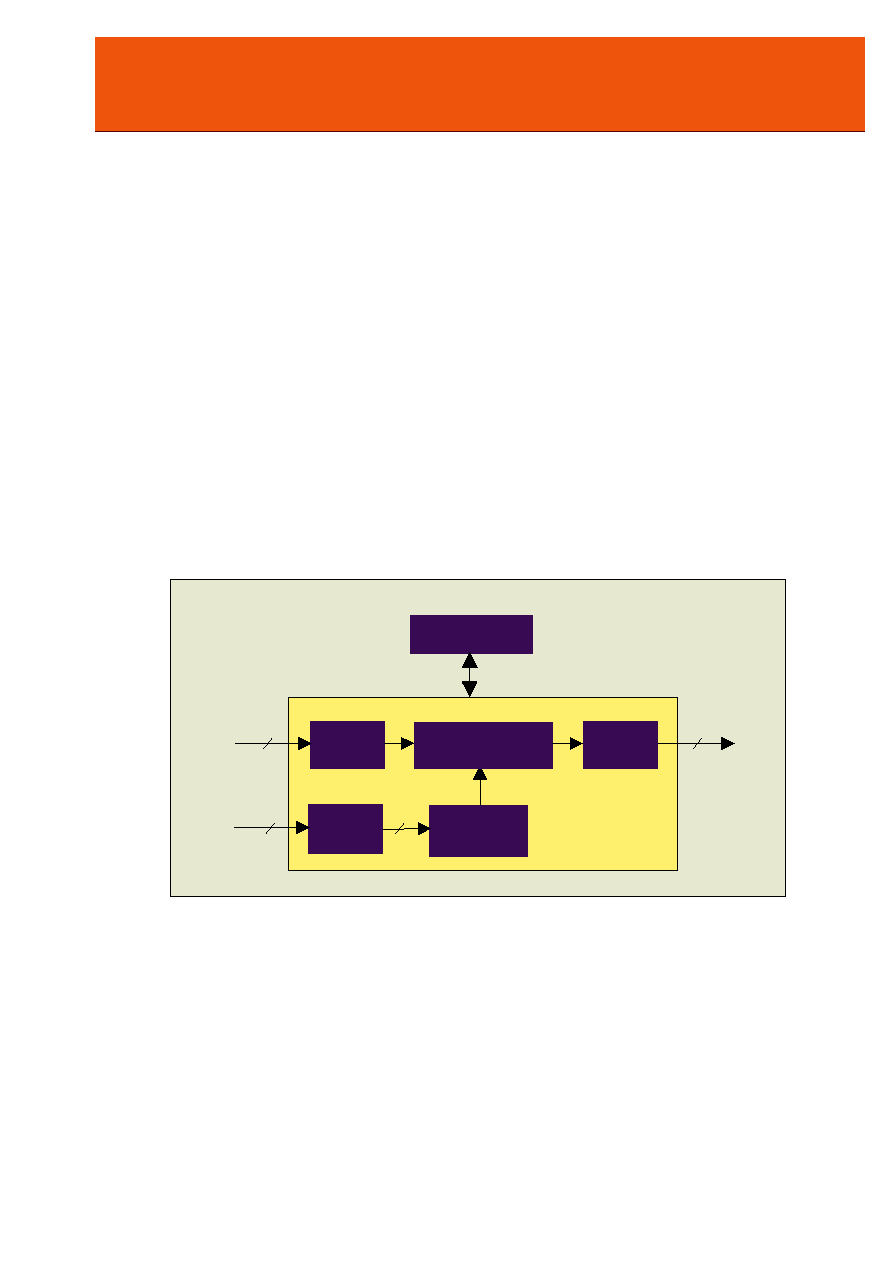

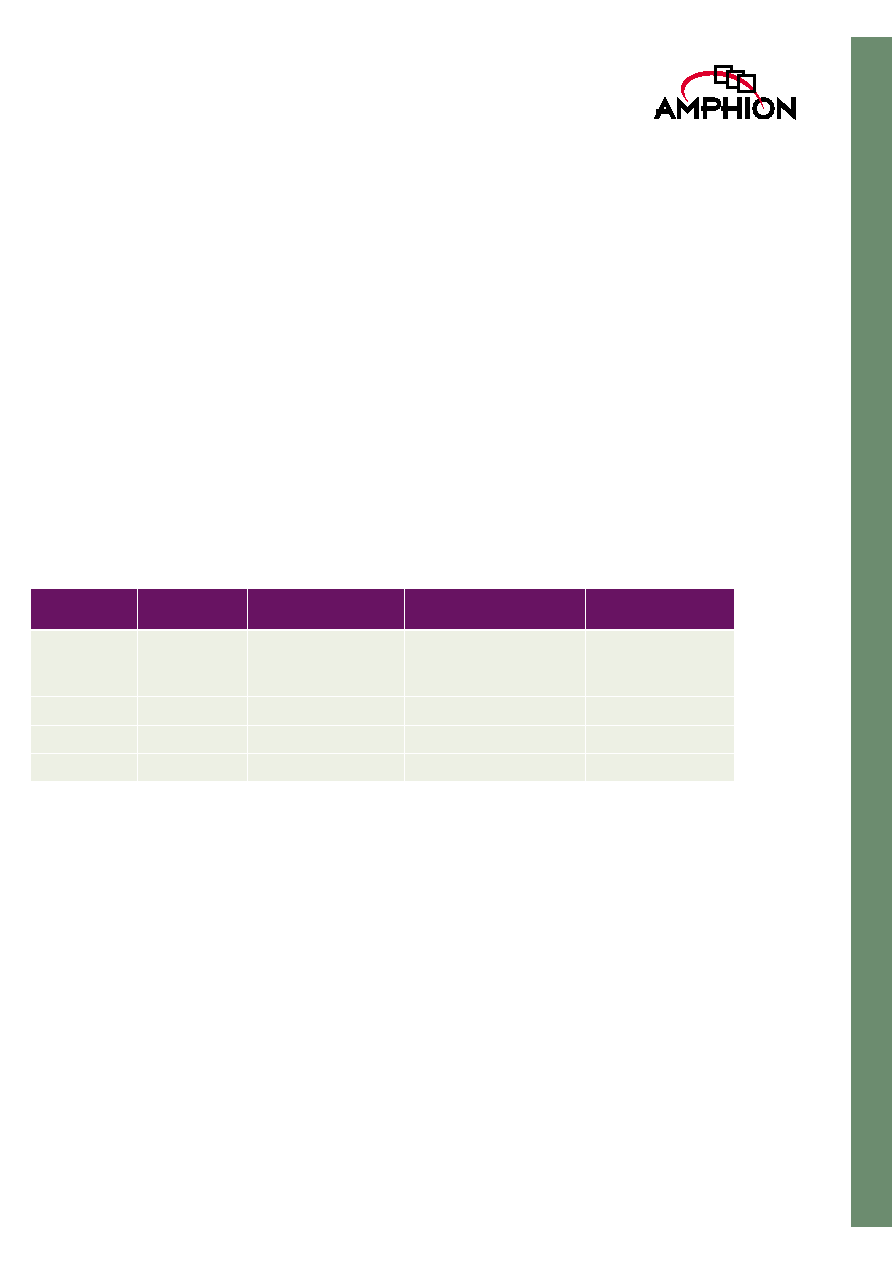

Figure 3 represents a block diagram of the Rijndael decryption

algorithm. A Rijndael round transforms the data using

permutations, non-linear substitutions, additions and Galois

field multiplications. The Rijndael key schedule consists of

two parts:

1.

Key Expansion - expands the cipher key into a linear

array of 4-byte words

2.

Round Key Selection - selection of the required number of

Round Keys from the expanded key array

All four versions of the Amphion AES decryption cores follow

the block diagram shown in Figure 3.

The CS5200 AES decryption cores are outstanding matches

with other Amphion cores. For instance they can be combined

with the CS6650 MPEG2 Decoder to easily provide a secure

high definition closed-circuit TV system, and they can be

combined with the CS3252 FEC Codec as part of a secure

wireless access point.

The Amphion encryption/decryption cores are also an

excellent choice for VPN security ICs incorporated into

broadband switches, routers, firewalls and remote access

concentrators. Likewise, the cores are an ideal fit for the

Secure Socket Layer (SSL) channel ICs used in Web servers,

WAP gateways and other access applications requiring a high

number of parallel SSL channels to carry out eCommerce.

Figure 3: Block Diagram of CS5250-80 Series of Decryption Cores

Ciphertext

Control Logic

Input

Buffer

Key

Scheduler

Key

Buffer

Inverse Key

Plaintext

Round

Transformations

Output

Buffer

5

TM

AVAILABILITY AND IMPLEMENTATION INFORMATION

Hardware accelerated AES technology is governed internationally by export regulations. The Amphion AES cores listed in this

datasheet have been officially reviewed and classified by the UK Department of Trade and Industry and US Bureau of Export

Administration. These cores are licensed for immediate export to the following countries:

Austria

Australia

Belgium

Canada

Czech Republic

Denmark

Finland

France

Germany

Greece

Hungary

Ireland

Italy

Japan

Luxembourg

New Zealand

The Netherlands

Norway

Poland

Portugal

Spain

Sweden

Switzerland

United Kingdom

United States

For delivery to other destinations, please contact Amphion. Approval is subject to applicable export regulations. Licensees of the

Amphion AES cores are responsible for complying with applicable requirements for the re-export of electronics containing AES

technology.

ASIC CORES

For applications that require the high performance, low cost and high integration of an ASIC, Amphion delivers the application

specific silicon cores that are pre-optimized to a targeted ASIC technology by Amphion experts.

Consult your local Amphion representative for product specific performance information, current availability of individual

products, and lead times on ASIC core porting.

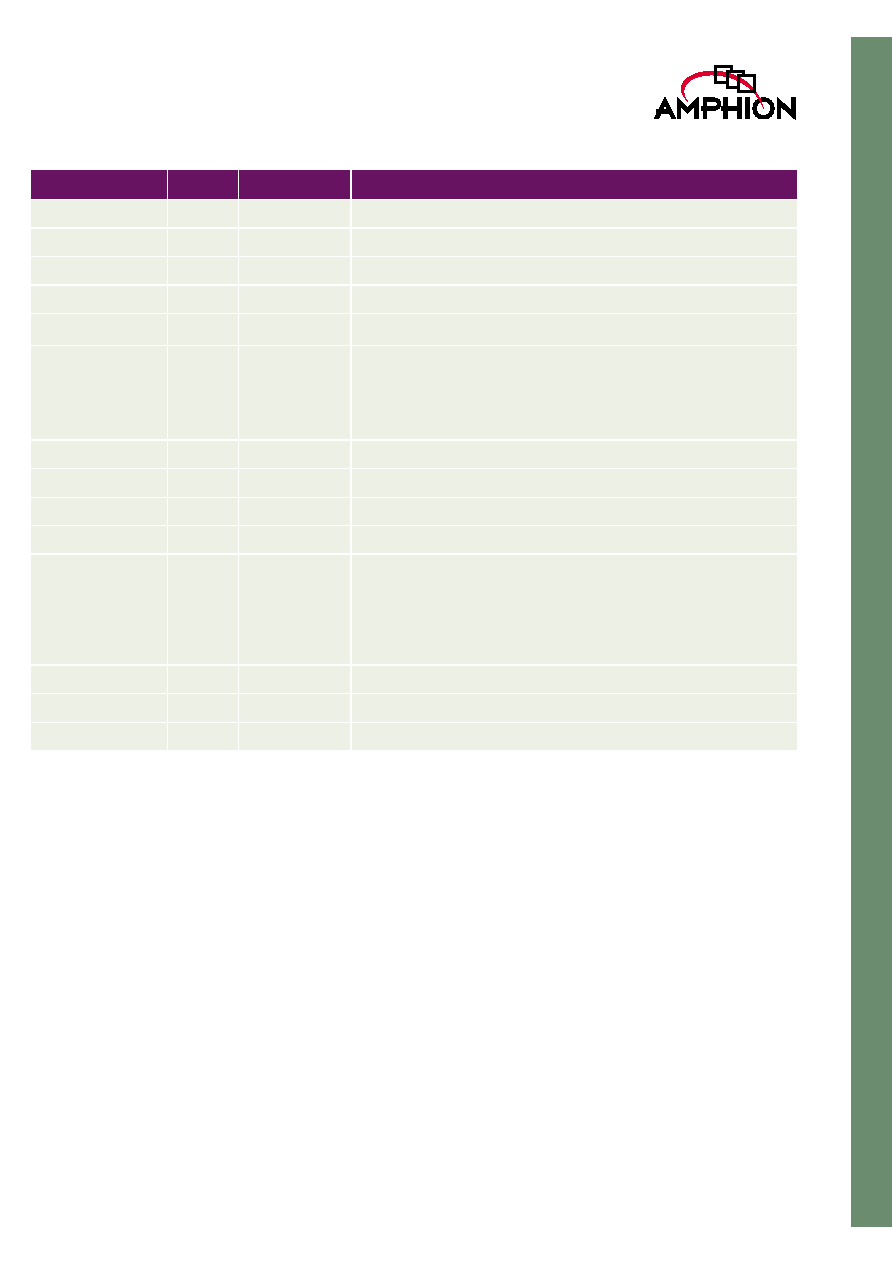

Table 3: CS5250-80 Family of ASIC Cores using TSMC 180nm Process and Standard Cell Libraries

PRODUCT ID

LOGIC

GATES

CYCLES PER

OPERATION

TIMING CONSTRAINT (MHz)

DATA RATE

(MBITS/Sec)

CS5250TK

19.2K

44

a

52

b

60

c

a. Implementation of 128-bit key length

b. Implementation of 192-bit key length

c. Implementation of 256-bit key length

200

581

a

492

b

426

c

CS5260TK

16.4K

44

200

581

CS5270TK

34K

11

200

2,327

CS5280TK

283K

1

200

25,600